MAX15159

## オプト・カプラを使わずにフィードバックする 高電圧マルチフェーズ昇圧／ フライバック・コントローラ

### 製品のハイライト

- 広い動作範囲

- 入力電圧範囲 : 8V～120V（昇圧およびフライバック構成）、-8V～-120V（反転昇降圧構成）

- シングル／デュアル／トリプル／クワッドフェーズ動作

- スイッチング周波数範囲 : 120kHz～1MHz

- 温度範囲 : -40°C～+125°C

- 集積化により設計フットプリントを削減

- フィードバックのサンプル&ホールドにより、絶縁型フライバック・コンバータでオプト・カプラを使わないフィードバックに対応

- ローサイド MOSFET ドライバを内蔵

- マルチフェーズ同期とインターリーブ動作

- フェーズ間の電流バランスをアクティブに制御

- 堅固なフォルト保護により信頼性を向上

- 調整可能な入力低電圧ロックアウト（UVLO）

- 調整可能なサイクル単位のピーク電流制限と高速過電流保護（OCP）

- サーマル・シャットダウン

### 主なアプリケーション

- 通信

- 産業用機器

- マルチフェーズ・フライバック

- IEEE802.3btに基づいて電力供給を受けるデバイス

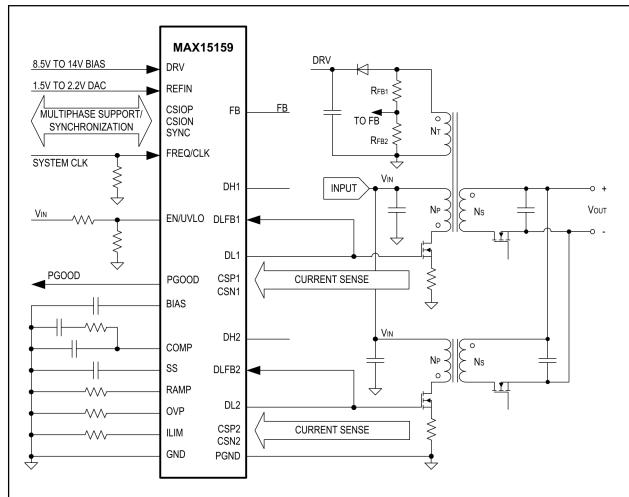

### 簡略アプリケーション回路図

### ピン配置

型番はデータシート末尾に記載されています。

# オプト・カプラを使わずにフィードバックする 高電圧マルチフェーズ昇圧／ フライバック・コントローラ

MAX15159

## 絶対最大定格

|                      |                                |

|----------------------|--------------------------------|

| CSP_、CSN_～GND        | -0.3V～+0.3V                    |

| CSP_～CSN_            | -0.3V～+0.3V                    |

| DH_～GND              | -0.3V～V <sub>BIAS</sub> + 0.3V |

| DL_～PGND             | -0.3V～V <sub>DRV</sub> + 0.3V  |

| DLFB_～GND            | -0.3V～V <sub>DRV</sub> + 0.3V  |

| DRV～GND              | -0.3V～+16V                     |

| BIAS～GND             | -0.3V～+6V                      |

| DRV～BIAS             | -0.3V～+16V                     |

| FB～GND               | -6V～+6V                        |

| PGOOD、REFIN～GND      | -0.3V～+6V                      |

| EN/UVLO、FREQ/CLK～GND | -0.3V～+6V                      |

|                                                                            |                                |

|----------------------------------------------------------------------------|--------------------------------|

| COMP、SS、ILIM～GND                                                           | -0.3V～V <sub>BIAS</sub> + 0.3V |

| OVP、RAMP、SYNC～GND                                                          | -0.3V～V <sub>BIAS</sub> + 0.3V |

| CSIOP、CSION～GND                                                            | -0.3V～V <sub>BIAS</sub> + 0.3V |

| PGND～GND                                                                   | -0.3V～+0.3V                    |

| BIAS からの最大電流                                                               | 100mA                          |

| 動作温度範囲                                                                     | -40°C～+125°C                   |

| 連続消費電力 (T <sub>A</sub> = +70°C) TQFN (+70°C を超えた場合は<br>34.5mW/C でディレーティング) | 2.76W                          |

| ジャンクション温度                                                                  | +150°C                         |

| 保存温度範囲                                                                     | -40°C～+150°C                   |

| リード温度 (はんだ処理、10 秒)                                                         | +300°C                         |

| はんだ処理温度                                                                    | +240°C                         |

上記の**絶対最大定格**を超えるストレスを加えるとデバイスに恒久的な損傷を与えることがあります。これらの規定はストレス定格のみを定めたものであり、この仕様の動作セクションに記載する規定値以上でデバイスが正常に動作することを意味するものではありません。デバイスを長時間絶対最大定格状態に置くとデバイスの信頼性に影響を与えます。

## パッケージ情報

|                                                       |          |

|-------------------------------------------------------|----------|

| Package Code                                          | T3255+4C |

| Outline Number                                        | 21-0140  |

| Land Pattern Number                                   | 90-0012  |

| <b>THERMAL RESISTANCE, FOUR-LAYER BOARD</b>           |          |

| Junction-to-Ambient ( $\theta_{JA}$ )                 | 29 °C/W  |

| Junction-to-Case Thermal Resistance ( $\theta_{JC}$ ) | 1.7 °C/W |

# オプト・カプラを使わずにフィードバックする 高電圧マルチフェーズ昇圧／ フライバック・コントローラ

MAX15159

## 電気的特性

(特に指定のない限り、 $V_{DRV} = 9V$ 、 $V_{EN/UVLO} = 1.5V$ 、 $REFIN = BIAS$ 、 $C_{BIAS} = 2.2\mu F$ 、 $C_{SS} = 10nF$ 、 $R_{FREQ} = 100k\Omega$  (600kHz) 、 $T_A = T_J = -40^\circ C \sim +125^\circ C$ 。) (Note 1)

| PARAMETER                                         | SYMBOL                 | CONDITIONS                                       | MIN   | TYP  | MAX   | UNITS   |

|---------------------------------------------------|------------------------|--------------------------------------------------|-------|------|-------|---------|

| <b>INPUT SUPPLIES</b>                             |                        |                                                  |       |      |       |         |

| DRV Operating Range                               | $V_{DRV}$              |                                                  | 8.5   | 14   |       | V       |

| DRV Quiescent Current                             | $I_{DRV}$              | Device switching, 2 phases, DH_ and DL_ unloaded | 20    | 29   |       | mA      |

| DRV Shutdown Current                              | $I_{DRV\_SHDN}$        | $EN/UVLO = GND$                                  | 4.5   | 7    |       | mA      |

| DRV Undervoltage Lockout Threshold                | $V_{DRV(UVLO)}$        | $V_{DRV}$ rising                                 | 8.1   | 8.25 | 8.4   | V       |

|                                                   |                        | $V_{DRV}$ falling                                | 8     | 8.12 | 8.25  |         |

| <b>BIAS LINEAR REGULATOR</b>                      |                        |                                                  |       |      |       |         |

| BIAS LDO Output Voltage                           | $V_{BIAS}$             | $I_{BIAS} = 5mA$                                 | 4.9   | 5    | 5.1   | V       |

| BIAS LDO Current Limit                            | $I_{BIAS}$             | $V_{BIAS} = 3V$                                  | 35    | 56   | 80    | mA      |

| BIAS Undervoltage Lockout Threshold               | $V_{BIAS(UVLO)}$       | $V_{BIAS}$ rising, 230mV hysteresis              | 4.4   | 4.5  | 4.7   | V       |

| <b>CONTROLLER ENABLE</b>                          |                        |                                                  |       |      |       |         |

| EN/UVLO Adjustable Undervoltage Lockout Threshold | $V_{UVLO}$             | $V_{UVLO}$ rising                                | 0.98  | 1    | 1.03  | V       |

|                                                   |                        | $V_{UVLO}$ falling                               | 0.88  | 0.9  | 0.93  |         |

| EN/UVLO Input Leakage Current                     | $I_{UVLO}$             | $V_{UVLO} = 0V$ to $V_{BIAS}$                    | -1    |      | +1    | $\mu A$ |

| <b>CONTROLLER LOOP</b>                            |                        |                                                  |       |      |       |         |

| FB Regulation Threshold (Preset Mode)             | $V_{FB}$               | $REFIN = BIAS$                                   | 1.985 | 2    | 2.015 | V       |

| FB-to-REFIN Offset Voltage (Tracking Mode)        | $V_{FB\_OFS}$          | $V_{REFIN} = 1.5V$ to $2.2V$                     | -5    |      | +5    | mV      |

| REFIN Input Voltage Range                         | $V_{REFIN}$            | (Note 2)                                         | 1.5   |      | 2.2   | V       |

| Preset Mode REFIN Threshold Rising                |                        | 100mV hysteresis (typ)                           | 2.33  | 2.36 | 2.4   | V       |

| FB Input Leakage Current                          | $I_{FB}$               | $V_{FB} = 0V$ to $2.2V$                          | -1.5  |      | +1.5  | $\mu A$ |

| REFIN Input Leakage Current                       | $I_{REFIN}$            | $V_{REFIN} = 1.5V$ to $2.2V$                     | -1    |      | +1    | $\mu A$ |

| FB S/H Time                                       | $T_{SH}$               | FB sample time starts on the DLFB1 falling edge  | 210   | 320  |       | ns      |

| CSP_ to CSN_ Differential Voltage Range           | $D_{VCS\_}$            | $V_{CSP\_} - V_{CSN\_}$                          | -200  |      | +200  | mV      |

| Current-Sense Common-Mode Voltage Range           | $V_{CSP\_}, V_{CSN\_}$ | With respect to GND (Note 3)                     | -300  |      | +300  | mV      |

オプト・カプラを使わずにフィードバックする

高電圧マルチフェーズ昇圧／

フライバック・コントローラ

MAX15159

(特に指定のない限り、 $V_{DRV} = 9V$ 、 $V_{EN/UVLO} = 1.5V$ 、 $REFIN = BIAS$ 、 $C_{BIAS} = 2.2\mu F$ 、 $C_{SS} = 10nF$ 、 $R_{FREQ} = 100k\Omega$  (600kHz) 、 $T_A = T_J = -40^\circ C \sim +125^\circ C$ 。) (Note 1)

| PARAMETER                                                    | SYMBOL                 | CONDITIONS                                             | MIN              | TYP  | MAX  | UNITS   |

|--------------------------------------------------------------|------------------------|--------------------------------------------------------|------------------|------|------|---------|

| CSP_-, CSN_ Current-Sense Amplifier Gain                     | $A_{CS\_}$             |                                                        | 4.1              | 4.4  | 4.7  | V/V     |

| CSP_-, CSN_ Input Leakage Current                            | $I_{CSP\_}, I_{CSN\_}$ | $V_{CSP\_}, V_{CSN\_} = \pm 300mV$ with respect to GND | -3               |      | +3   | $\mu A$ |

| Error Amplifier Transconductance                             | $G_{MEA}$              |                                                        | 0.8              | 1.15 | 1.5  | mS      |

| RAMP Pin Amplitude Adjustable Range                          | $V_{RAMP}$             |                                                        | 130              |      | 730  | mV      |

| Internal Slope Compensation Ramp Voltage to $V_{RAMP}$ Ratio |                        | $V_{RAMP} = 0.3V$                                      |                  | 2    |      | V/V     |

| RAMP Bias Current                                            | $I_{RAMP}$             | $V_{RAMP} = 0V$                                        | 9.7              | 10   | 10.3 | $\mu A$ |

| <b>SWITCHING FREQUENCY</b>                                   |                        |                                                        |                  |      |      |         |

| Preset PWM Switching Frequency                               | $f_{SW}$               | $R_{FREQ} = OPEN, V_{OVP} = 0V$                        | 293              | 300  | 307  | kHz     |

| Adjustable PWM Switching Frequency                           | $f_{SW}$               | $R_{FREQ} = 20k\Omega, V_{OVP} = 0V$                   | 108              | 115  | 123  | kHz     |

|                                                              |                        | $R_{FREQ} = 25k\Omega, V_{OVP} = 0V$                   | 138              | 145  | 153  |         |

|                                                              |                        | $R_{FREQ} = 100k\Omega, V_{OVP} = 0V$                  | 580              | 602  | 622  |         |

| PWM Switching Frequency Range                                | $f_{SW}$               | FREQ/CLK externally applied                            | 120              |      | 1000 | kHz     |

| FREQ/CLK Frequency Detection Range                           | $f_{CLK}$              |                                                        | 0.48             |      | 4    | MHz     |

| FREQ/CLK Logic Level                                         | $V_{CLK}$              | Logic-high (rising)                                    |                  | 1.8  | 1.9  | V       |

|                                                              |                        | Logic-low (falling)                                    |                  | 1.5  | 1.6  |         |

| FREQ/CLK Input Bias Current                                  | $I_{CLK}$              | $V_{FREQ/CLK} = GND$                                   | -10.2            | -10  | -9.8 | $\mu A$ |

| FREQ/CLK to PWM Switching Frequency Ratio                    | $f_{CLK}/f_{SW}$       | 1-/2-/4-phase operation                                |                  | 4    |      | kHz/kHz |

|                                                              |                        | 3-phase operation                                      |                  | 3    |      |         |

| <b>SYNCHRONIZATION</b>                                       |                        |                                                        |                  |      |      |         |

| SYNC Logic Threshold                                         | $V_{SYNC}$             | Logic-high (rising)                                    |                  | 1.6  | 1.95 | V       |

|                                                              |                        | Logic-low (falling)                                    | 0.9              | 1.2  |      |         |

| SYNC Input Leakage Current                                   | $I_{SYNC}$             | $V_{SYNC} = 0V$ to 4.6V, internal 5MΩ pulldown         | -2               |      | +2   | $\mu A$ |

| SYNC Frequency Range                                         | $f_{SYNC}$             |                                                        | 200              |      | 2000 | kHz     |

| SYNC Output Voltage Level                                    | $V_{SYNC}$             | Logic-high, $I_{SOURCE} = 10mA$                        | $V_{BIAS} - 0.4$ |      |      | V       |

|                                                              |                        | Logic-low, $I_{SINK} = 10mA$                           |                  |      | 0.4  |         |

| <b>OUTPUT FAULT PROTECTION</b>                               |                        |                                                        |                  |      |      |         |

| ILIM Source Current                                          |                        |                                                        | 9.6              | 10   | 10.4 | $\mu A$ |

# オプト・カプラを使わずにフィードバックする 高電圧マルチフェーズ昇圧／ フライバック・コントローラ

MAX15159

(特に指定のない限り、 $V_{DRV} = 9V$ 、 $V_{EN/UVLO} = 1.5V$ 、 $REFIN = BIAS$ 、 $C_{BIAS} = 2.2\mu F$ 、 $C_{SS} = 10nF$ 、 $R_{FREQ} = 100k\Omega$  (600kHz) 、 $T_A = T_J = -40^{\circ}C \sim +125^{\circ}C$ 。) (Note 1)

| PARAMETER                                                                                  | SYMBOL | CONDITIONS                                                                                   | MIN | TYP | MAX  | UNITS |

|--------------------------------------------------------------------------------------------|--------|----------------------------------------------------------------------------------------------|-----|-----|------|-------|

| $V_{ILIM}$ to  CSP_- - CSN_ <br>Cycle-by-Cycle Positive Peak Current-Limit Threshold Ratio |        |                                                                                              |     | 10  |      | V/V   |

| CSP_to CSN_<br>Minimum Threshold for Cycle-by-Cycle Positive Peak Current Limit            |        | $V_{ILIM} = 0V$                                                                              | 17  | 20  | 23   | mV    |

| CSP_to CSN_<br>Maximum Threshold for Cycle-by-Cycle Positive Peak Current Limit            |        | $V_{ILIM} > 1.25V$                                                                           | 94  | 100 | 106  | mV    |

| CSP_to CSN_<br>Minimum Threshold for Cycle-by-Cycle Negative Peak Current Limit            |        | $V_{ILIM} > 1.25V$                                                                           | -90 | -80 | -68  | mV    |

| CSP_to CSN_<br>Maximum Threshold for Cycle-by-Cycle Negative Peak Current Limit            |        | $V_{ILIM} = 0V$                                                                              | -22 | -16 | -10  | mV    |

| CSP_to CSN_<br>Minimum Threshold for Fast Positive Overcurrent Protection                  |        | $V_{ILIM} = 0V$                                                                              | 21  | 26  | 31   | mV    |

| CSP_to CSN_<br>Maximum Threshold for Fast Positive Overcurrent Protection                  |        | $V_{ILIM} > 1.25V$                                                                           | 121 | 133 | 145  | mV    |

| CSP_to CSN_ Cycle-by-Cycle Positive Peak Current-Limit Threshold Accuracy                  |        | $0.25V < V_{ILIM} < 0.95V$                                                                   | -10 | +10 |      | %     |

|                                                                                            |        | $V_{ILIM} = 500mV$                                                                           | -3  | +3  |      |       |

| CSP_to CSN_ Negative Overcurrent Protection Threshold Accuracy                             |        | $V_{ILIM} = 500mV$                                                                           | -18 | +18 |      | %     |

| FB Overvoltage Default Threshold (Preset Mode)                                             | FB OV  | Measured with respect to target voltage ( $REFIN = BIAS$ )<br>$V_{FB}$ rising, 3% hysteresis | 9   | 10  | 11   | %     |

| FB Overvoltage Threshold (Tracking Mode)                                                   | FB OV  | Measured with respect to target voltage ( $REFIN = 2V$ )<br>$V_{FB}$ rising, 3% hysteresis   | 9   | 10  | 11   | %     |

| OVP Selector Output Source Current                                                         |        | Resistor connected to GND                                                                    | 9.6 | 10  | 10.4 | µA    |

|                                                                                            |        | EN/UVLO rising to SS rising                                                                  | 32  |     |      | µs    |

オプト・カプラを使わずにフィードバックする

高電圧マルチフェーズ昇圧／

フライバック・コントローラ

MAX15159

(特に指定のない限り、 $V_{DRV} = 9V$ 、 $V_{EN/UVLO} = 1.5V$ 、 $REFIN = BIAS$ 、 $C_{BIAS} = 2.2\mu F$ 、 $C_{SS} = 10nF$ 、 $R_{FREQ} = 100k\Omega$  (600kHz) 、 $T_A = T_J = -40^\circ C \sim +125^\circ C$ 。) (Note 1)

| PARAMETER                                             | SYMBOL           | CONDITIONS                                                                                        | MIN              | TYP    | MAX  | UNITS          |

|-------------------------------------------------------|------------------|---------------------------------------------------------------------------------------------------|------------------|--------|------|----------------|

| EN/UVLO Propagation Delay                             |                  | EN/UVLO falling to SS falling                                                                     | 7                | 13     | 21   |                |

| Fault Propagation Delay                               |                  | Cumulative cycle-by-cycle peak current limit or negative overcurrent protection events for hiccup |                  | 32     |      | events         |

|                                                       |                  | FB OV                                                                                             |                  | 128    |      | PWM CLK cycles |

| Hiccup Timeout Duration                               |                  |                                                                                                   |                  | 32,768 |      | PWM CLK cycles |

| Thermal Shutdown                                      | $T_{SHDN}$       | 15°C hysteresis (Note 3)                                                                          |                  | 165    |      | °C             |

| <b>PGOOD</b>                                          |                  |                                                                                                   |                  |        |      |                |

| PGOOD Threshold                                       |                  | PGOOD rising ( $REFIN = BIAS$ )                                                                   | 1.86             | 1.88   | 1.9  | V              |

|                                                       |                  | PGOOD falling ( $REFIN = BIAS$ )                                                                  | 1.8              | 1.82   | 1.84 |                |

| PGOOD Falling and Rising Delay                        |                  |                                                                                                   |                  | 64     |      | PWM CLK cycles |

| PGOOD Output Low Voltage                              | $V_{PGOOD}$      | $I_{SINK} = 3mA$                                                                                  |                  | 20     | 40   | mV             |

| PGOOD Leakage Current                                 | $I_{PGOOD}$      | $FB = REFIN, V_{PGOOD} = 5V$                                                                      |                  | 1      |      | µA             |

| <b>SOFT-START (SS)</b>                                |                  |                                                                                                   |                  |        |      |                |

| SS Pull-Up Current                                    | $I_{SS}$         | Source                                                                                            | 9.6              | 10     | 10.4 | µA             |

| SS Pull-Down Resistance                               | $R_{SS}$         | Discharge                                                                                         |                  | 5.5    | 10   | Ω              |

| <b>PWM OUTPUT</b>                                     |                  |                                                                                                   |                  |        |      |                |

| DH_Output Voltage Level                               | $V_{DH\_}$       | Logic-high, $I_{SOURCE} = 10mA$                                                                   | $V_{BIAS} - 0.3$ |        |      | V              |

|                                                       |                  | Logic-low, $I_{SINK} = 10mA$                                                                      | 0.15             |        |      |                |

| DL_Output Voltage Level                               | $V_{DL\_}$       | Logic-high, $I_{SOURCE} = 20mA$                                                                   | $V_{DRV} - 0.4$  |        |      | V              |

|                                                       |                  | Logic-low, $I_{SINK} = 20mA$                                                                      | 0.1              |        |      |                |

| DL_Driver Peak Current                                | $I_{DL\_SOURCE}$ | Source current                                                                                    |                  | 1      |      | A              |

|                                                       | $I_{DL\_SINK}$   | Sink current                                                                                      |                  | 2      |      |                |

| DH_Minimum Off-Time                                   | $T_{OFF\_DH\_}$  |                                                                                                   |                  | 85     | 125  | ns             |

| DL_Minimum On-Time                                    | $T_{ON\_DL\_}$   |                                                                                                   |                  | 52     | 90   | ns             |

| DLFB_Leakage Current                                  | $I_{LK}$         | $V_{DLFB\_} = 9V$                                                                                 | -1               | +1     |      | µA             |

| DLFB_Logic Threshold                                  | $V_{DLFB\_}$     | Logic-high (rising)                                                                               | 0.75             | 0.8    | 0.85 | V              |

|                                                       |                  | Logic-low (falling)                                                                               | 0.45             | 0.5    | 0.55 |                |

| <b>CURRENT SHARING (MULTIPHASE APPLICATIONS ONLY)</b> |                  |                                                                                                   |                  |        |      |                |

# オプト・カプラを使わずにフィードバックする 高電圧マルチフェーズ昇圧／ フライバック・コントローラ

MAX15159

(特に指定のない限り、 $V_{DRV} = 9V$ 、 $V_{EN/UVLO} = 1.5V$ 、 $REFIN = BIAS$ 、 $C_{BIAS} = 2.2\mu F$ 、 $C_{SS} = 10nF$ 、 $R_{FREQ} = 100k\Omega$  (600kHz) 、 $T_A = T_J = -40^\circ C \sim +125^\circ C$ 。) (Note 1)

| PARAMETER                           | SYMBOL       | CONDITIONS          | MIN | TYP  | MAX | UNITS      |

|-------------------------------------|--------------|---------------------|-----|------|-----|------------|

| CSION Output Voltage                | $V_{CSION}$  | With respect to GND |     | 1.24 |     | V          |

| CSIO_ Differential Input Resistance | $R_{CSIO\_}$ |                     |     | 3.8  |     | k $\Omega$ |

**Note 1 :** 限界値は  $T_A = +25^\circ C$  ですべてテストされています。動作温度範囲および関連する電源電圧範囲全体にわたる限界値は、設計と特性評価によって裏付けられています。

**Note 2 :** 1.5V 未満の  $REFIN$  で動作させることはできません。 $REFIN < 1.47V$  の場合、PWM がディスエーブルになります。

**Note 3 :** 設計により裏付けられていますが、製品テストは行っていません。

# オプト・カプラを使わずにフィードバックする 高電圧マルチフェーズ昇圧／ フライバック・コントローラ

MAX15159

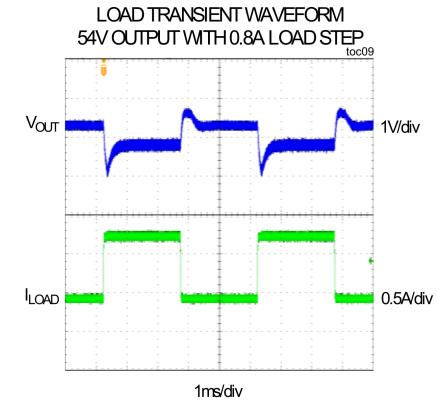

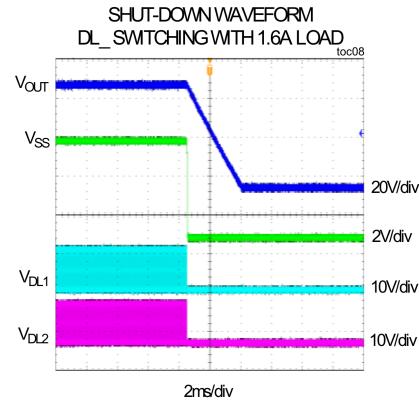

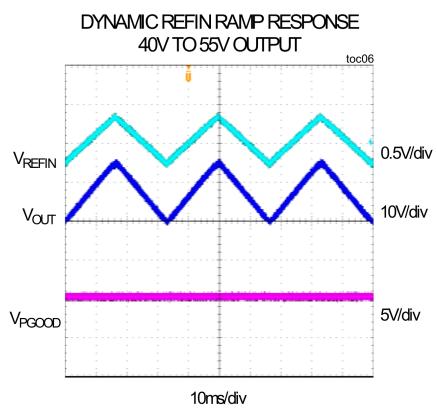

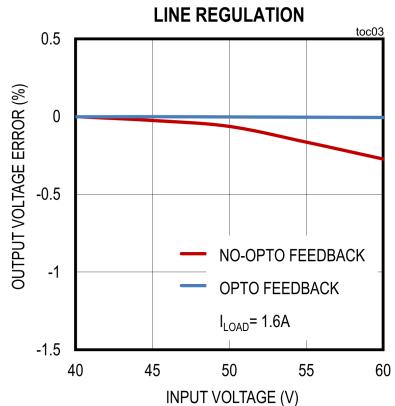

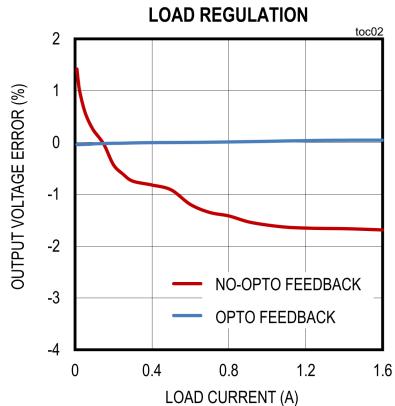

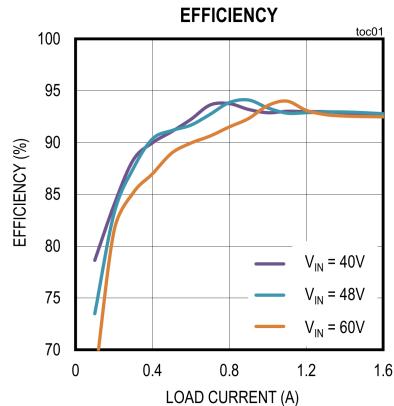

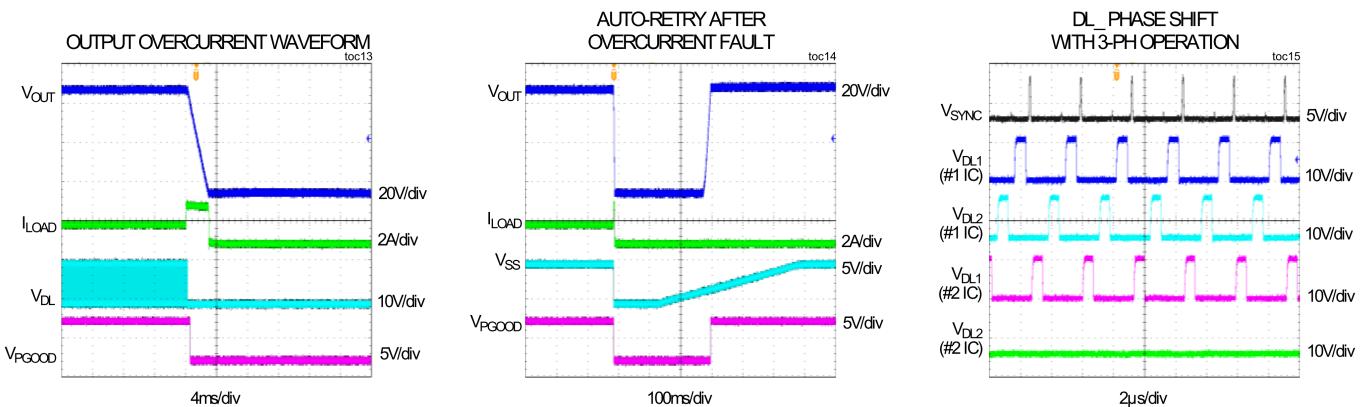

## 標準動作特性

(特に指定のない限り、 $T_A = +25^\circ\text{C}$ 、 $V_{IN} = 48\text{V}$ 、 $V_{OUT} = 54\text{V}$ 。標準アプリケーション回路を参照してください。)

# オプト・カプラを使わずにフィードバックする 高電圧マルチフェーズ昇圧／ フライバック・コントローラ

MAX15159

(特に指定のない限り、 $T_A = +25^\circ\text{C}$ 、 $V_{IN} = 48\text{V}$ 、 $V_{OUT} = 54\text{V}$ 。標準アプリケーション回路を参照してください。)

# オプト・カプラを使わずにフィードバックする 高電圧マルチフェーズ昇圧／ フライバック・コントローラ

MAX15159

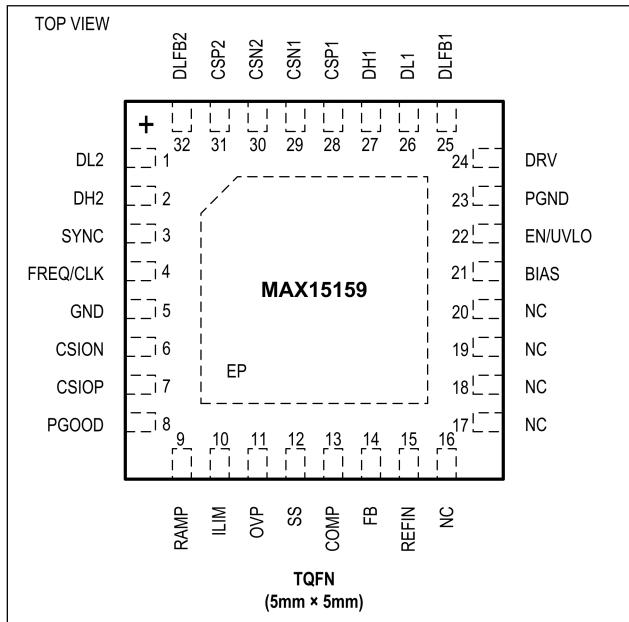

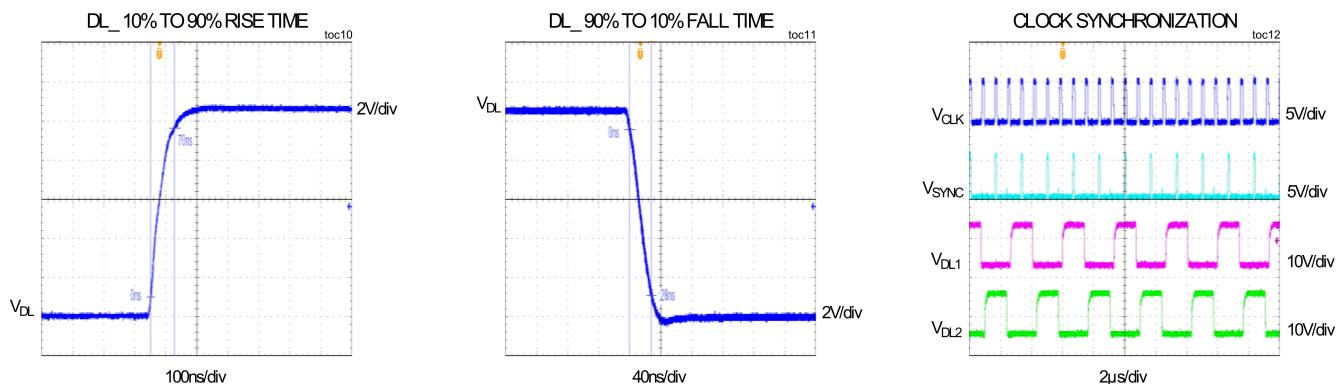

## ピン配置

## 端子説明

| ピン | 名称       | 説明                                                                                                                                                                                                                                                                                        |

|----|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1  | DL2      | 第2フェーズに関するローサイドMOSFETのゲート・ドライバ出力。DL2でDRVとPGNDを切り替えます。                                                                                                                                                                                                                                     |

| 2  | DH2      | 第2フェーズに関するハイサイドMOSFETゲート・ドライバのロジック出力。DH2は第2フェーズの外付けMOSFETドライバのハイサイド入力ピンに接続します。DH2でBIASとGNDを切り替えます。                                                                                                                                                                                        |

| 3  | SYNC     | マルチフェーズ同期ピン。単一IC動作の場合は、このピンを無接続のままにしておきます。2つのICをコントローラ／ターゲット動作モードでスタックアップする場合は、このピン同士を接続します。                                                                                                                                                                                              |

| 4  | FREQ/CLK | 周波数選択／クロック同期入力。MAX15159は、120kHz～1MHzのスイッチング周波数に対応しています。内蔵の発振器周波数を使用するために適切な外付け抵抗を選択するか、またはレギュレータを外部システム・クロックに同期させることにより、スイッチング周波数を設定します（表2参照）。FREQ/CLKピンを無接続のままにして、ブリセッテされた300kHzのスイッチング周波数を選択するか、またはFREQ/CLKとGNDの間に抵抗を配置して、 $f_{SW} = (R_{FREQ}/100k\Omega) \times 600kHz$ に従う周波数を設定します。 |

| 5  | GND      | アナログ・グランド。                                                                                                                                                                                                                                                                                |

| 6  | CSION    | コントローラ／ターゲット電流検出信号の負入力。MAX15159は、MAX15159のICをコントローラ／ターゲット動作モードで2つスタックアップするアプリケーションにおいて、差動電流検出信号を使用して適切なスタートアップと電流バランス特性を確保します。                                                                                                                                                            |

| 7  | CSIOP    | コントローラ／ターゲット電流検出信号の正入力。MAX15159は、MAX15159のICをコントローラ／ターゲット動作モードで2つスタックアップするアプリケーションにおいて、差動電流検出信号を使用して適切なスタートアップと電流バランス特性を確保します。                                                                                                                                                            |

| 8  | PGOOD    | オープンドレインのパワーグッド出力。MAX15159は、ソフトスタート時やシャットダウン時に出力電圧がOVPスレッショルドを超えた場合、PGOODをローに引き下げます（EN/UVLOがローに引き下げられます）。PGOOD出力は、コントローラがソフトスタートを完了してレギュレーション状態を保っているときに、ハイインピーダンスになります。コントローラ／ターゲット動作モードではターゲットICのPGOODを無接続のままにしておきます。                                                                   |

| 9  | RAMP     | 勾配補償入力。RAMPとGNDの間に接続された抵抗で、勾配補償の程度をプログラムします。選択可能な勾配補償（RAMP）のセクションを参照してください。                                                                                                                                                                                                               |

| 10 | ILIM     | CSPとCSNの間のサイクル単位／ヒップの電流制限スレッショルドの選択。ILIMとGNDの間に抵抗を接続して保護値を選択します。                                                                                                                                                                                                                          |

| 11 | OVP      | プログラム・ピン。OVPとGNDの間に抵抗を接続して、FB過電圧保護を設定し、マルチフェーズ構成を選択します（表1参照）。                                                                                                                                                                                                                             |

| 12 | SS       | ソフトスタート制御。SSとGNDの間の容量（ $C_{SS}$ ）でスタートアップ期間を設定します。コントローラがスタートアップ・シーケンスを開始するまで、内蔵のプルダウンMOSFETがSSをローに保持します。                                                                                                                                                                                 |

# オプト・カプラを使わずにフィードバックする 高電圧マルチフェーズ昇圧／ フライバック・コントローラ

MAX15159

|                    |         |                                                                                                                                                                              |

|--------------------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 13                 | COMP    | 補償アンプの出力。COMP は、内蔵のトランスコンダクタンス誤差アンプの出力です。 <a href="#">標準アプリケーション回路</a> に示すように、タイプII補償ネットワークを接続します（ <a href="#">補償設計ガイドライン</a> のセクションも参照してください）。                              |

| 14                 | FB      | フィードバック入力。オプト・カプラを使わずにフィードバックするために、フライバック・コンバータの3次巻線の両端につながる抵抗分圧器の中央に FB を接続します。MAX15159 の IC を 2つ使用してコントローラ／ターゲット動作モードでスタックアップする場合、ターゲット IC の FB は BIAS に接続します。             |

| 15                 | REFIN   | 外部リファレンス入力。REFIN は、1.5V～2.2V の電圧が供給される場合の FB レギュレーション電圧を設定します。REFIN ピンを BIAS に接続すると、2.0V の内部リファレンス電圧が選択されます。REFIN ピンの立下がリスレッショルドが 1.45V（標準）を下回ると、IC がディスエーブルになり、PWM動作が停止します。 |

| 16, 17, 18, 19, 20 | NC      | 無接続。                                                                                                                                                                         |

| 21                 | BIAS    | 5V リニア・レギュレータの出力とコントローラのバイアス電源。2.2μF 以上のセラミック・キャパシタで GND にバイパスします。                                                                                                           |

| 22                 | EN/UVLO | スタートアップ／シャットダウン時のパワー・シーケンスに関するイネーブル制御／調整可能な低電圧ロックアウト入力。 <a href="#">標準アプリケーション回路</a> に示すように、入力と GND の間にある抵抗分圧器の中央に EN/UVLO を接続して、低電圧ロックアウト電圧レベルを調整します。                       |

| 23                 | PGND    | 電源グランド。PGND は、DL_ゲート・ドライバのスイッチング電流のリターン・パスです。これをシステムのグランド・プレーンに直接接続します。                                                                                                      |

| 24                 | DRV     | 電源電圧入力。内部バイアス生成のために、8.5V～14V の電源を供給します。                                                                                                                                      |

| 25                 | DLFB1   | 第 1 フェーズに関する外付け MOSFET のステータス・フィードバック・ピン第 1 フェーズのローサイド MOSFET のゲートと GND の間にある抵抗分圧器の中央に DLFB1 を接続します。 <a href="#">MOSFET ゲート制御</a> のセクションを参照してください。                           |

| 26                 | DL1     | 第 1 フェーズに関するローサイド MOSFET のゲート・ドライバ出力。DL1 で DRV と PGND を切り替えます。                                                                                                               |

| 27                 | DH1     | 第 1 フェーズに関するハイサイド MOSFET ゲート・ドライバのロジック出力。DH1 を第 1 フェーズの外付け MOSFET ドライバのハイサイド入力ピンに接続します。DH1 で BIAS と GND を切り替えます。                                                             |

| 28                 | CSP1    | 第 1 フェーズに関するローサイド差動電流検出の正入力。MAX15159 は、電流モード制御ループとマルチフェーズ電流分担に差動電流検出信号を使用します。CSP1 を電流センス抵抗の MOSFET 側に接続します。                                                                  |

| 29                 | CSN1    | 第 1 フェーズに関するローサイド差動電流検出の負入力。MAX15159 は、電流モード制御ループとマルチフェーズ電流分担に差動電流検出信号を使用します。CSN1 を電流センス抵抗のグランド側に接続します。                                                                      |

| 30                 | CSN2    | 第 2 フェーズに関するローサイド差動電流検出の負入力。MAX15159 は、電流モード制御ループとマルチフェーズ電流分担に差動電流検出信号を使用します。CSN2 を電流センス抵抗のグラウンド側に接続します。                                                                     |

| 31                 | CSP2    | 第 2 フェーズに関するローサイド差動電流検出の正入力。MAX15159 は、電流モード制御ループとマルチフェーズ電流分担に差動電流検出信号を使用します。CSP2 を電流センス抵抗の MOSFET 側に接続します。                                                                  |

| 32                 | DLFB2   | 第 2 フェーズに関する外付け MOSFET のステータス・フィードバック・ピン。第 2 フェーズのローサイド MOSFET のゲートと GND の間にある抵抗分圧器の中央に DLFB2 を接続します。 <a href="#">MOSFET ゲート制御</a> のセクションを参照してください。                          |

| -                  | EP      | 露出パッド。GND に接続します。                                                                                                                                                            |

オプト・カプラを使わずにフィードバックする

高電圧マルチフェーズ昇圧／

フライバック・コントローラ

MAX15159

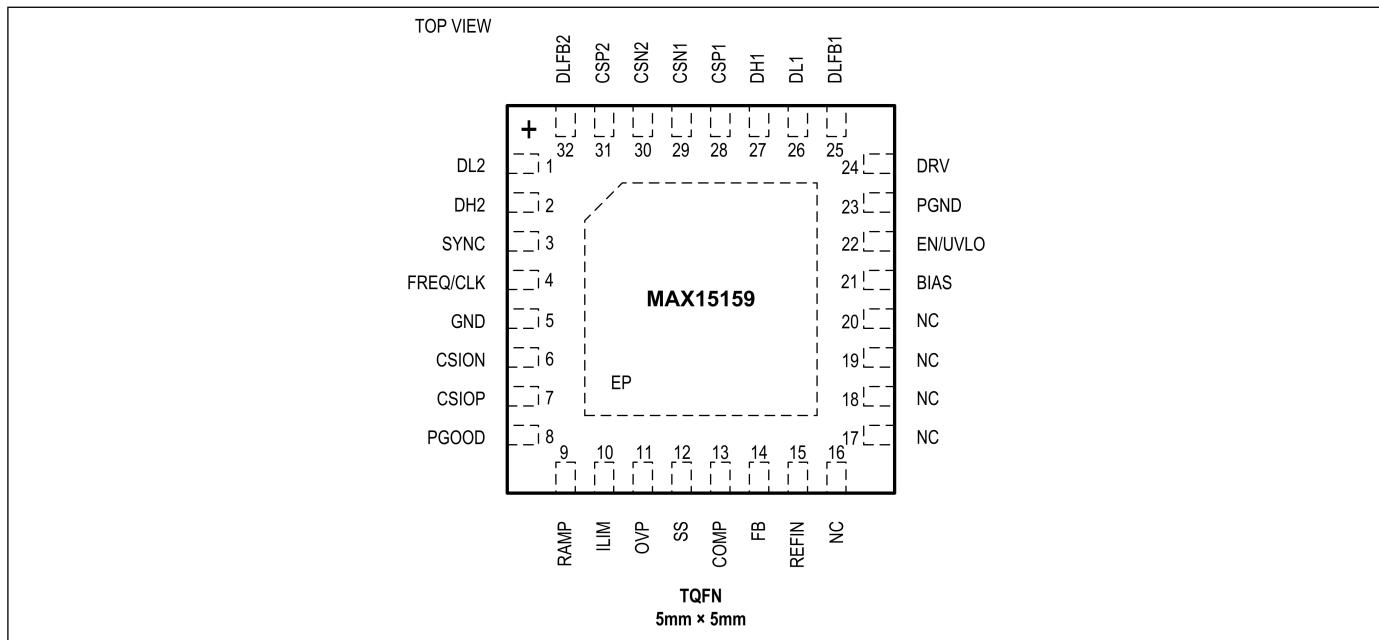

機能図

## 詳細

**MAX15159** は高電圧マルチフェーズ昇圧／フライバック・コントローラで、強化されたローサイド MOSFET ゲート・ドライバ機能を備え、シングルフェーズまたはデュアルフェーズの昇圧／フライバック構成に対応するように設計されています。トリプルフェーズまたはクワッドフェーズで動作させるために、2 つのデバイスをスタックアップすることができます。出力電圧は、モジュラー・デザインに対応するために、1.5V～2.2V のリファレンス入力 (REFIN) で動的に設定できます。

スイッチング周波数の制御は、内蔵発振器を設定する外付け抵抗によって、またはレギュレータを外部クロックに同期させることによって行います。デバイスは、120kHz～1MHz のスイッチング周波数に対応するように設計されています。トリプルフェーズまたはクワッドフェーズで動作させるために 2 つのデバイスをコントローラ／ターゲットとしてスタックアップする場合、両デバイスの SYNC ピン同士を接続して、クロック同期とフェーズ・インターリーブを確保します。コントローラは、柔軟なパワー・シーケンス設定を行う専用のイネーブル／入力低電圧ロックアウト (EN/UVLO) ピンを備えています。

MAX15159 は、内部勾配補償を調整する専用の RAMP ピンを備えています。また、このデバイスは、専用の ILIM ピンによる調整可能な過電流保護機能を備えています。デバイスには、正確なフェーズ電流分担を実行するために、外付けセンス抵抗の両端で各フェーズの電流を正確に測定する電流センス・アンプが内蔵されています。コントローラは、出力過電圧、入力低電圧、サーマル・シャットダウンからも保護されています。

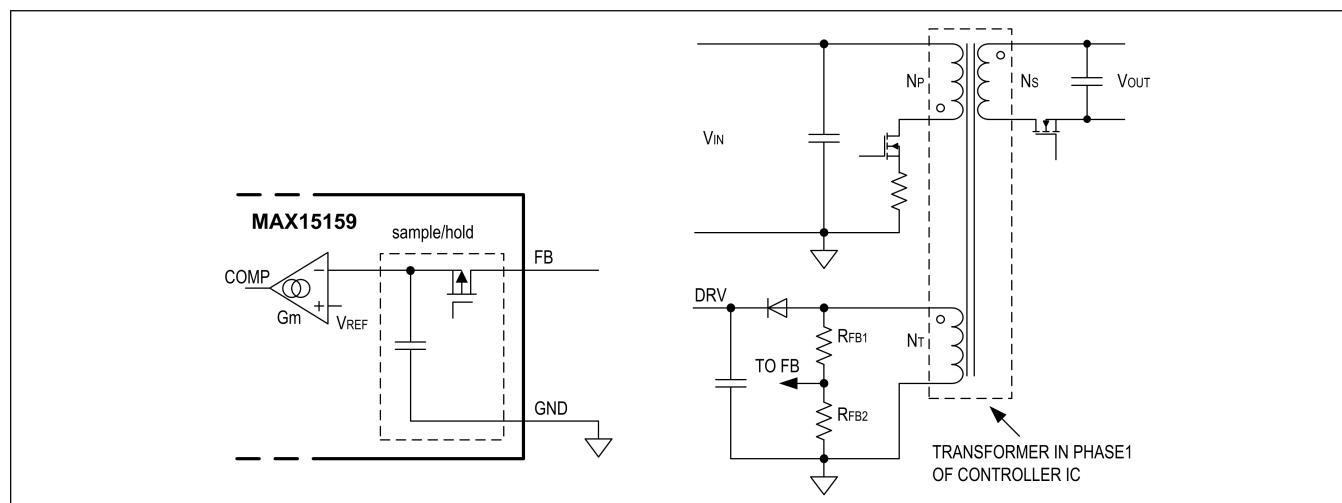

## オプト・カプラを使わないフィードバック

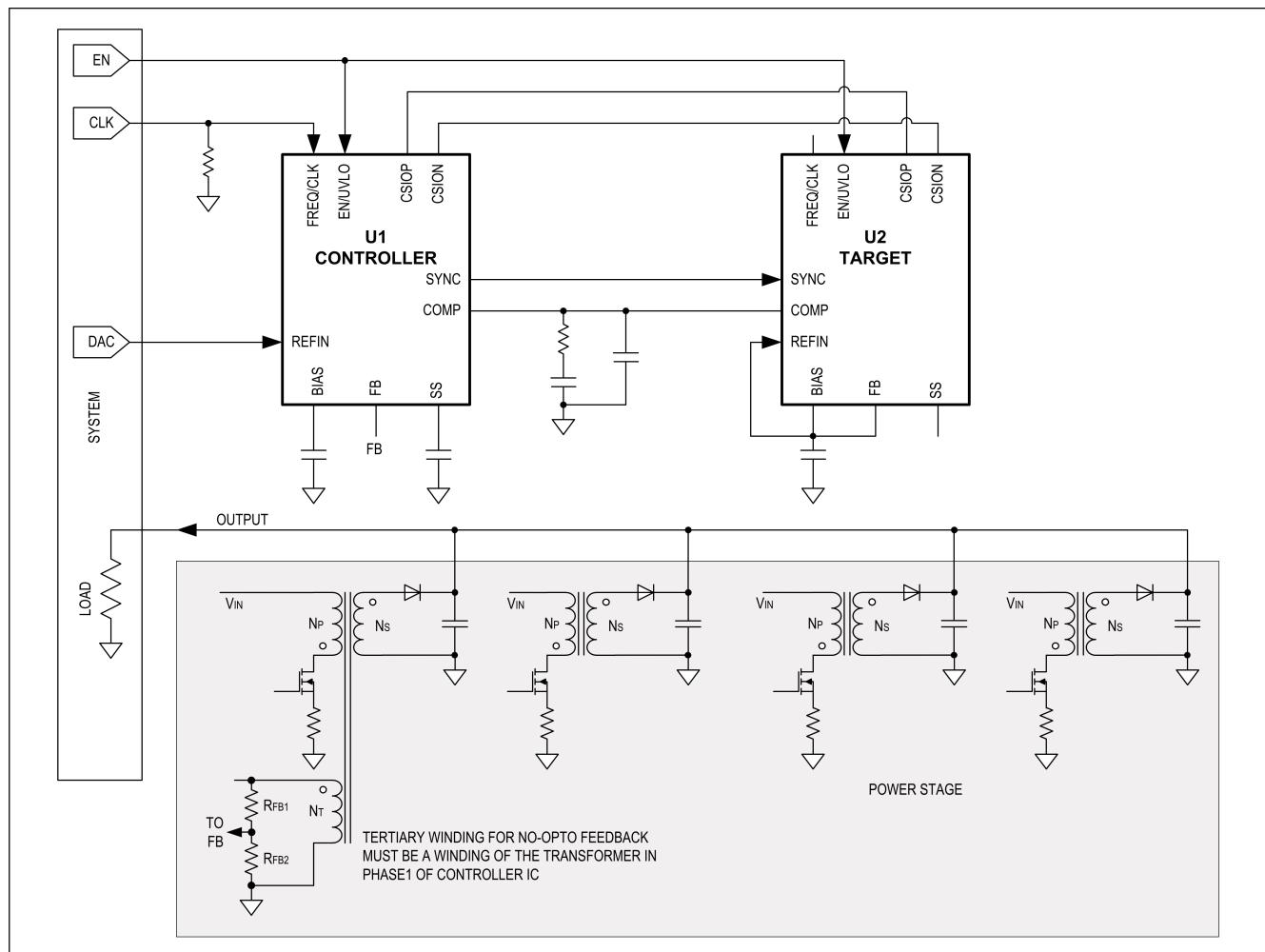

FB ピンには内蔵のサンプル＆ホールド回路があるため、MAX15159 は、絶縁型フライバック構成での動作時にオプト・カプラを使わないフィードバックに対応しており、オプト・カプラや 2 次フィードバック回路を使わずに済ますことが可能になります。FB ピンは、3 次巻線の両端につながる抵抗分圧器の中央に接続されます。マルチフェーズ動作の場合、この 3 次巻線は、図 1 に示すように、コントローラ IC のフェーズ 1 におけるトランス巻線でなければなりません。

図 1. フライバック・コンバータにおけるオプト・カプラを使わないフィードバック

出力電圧は次式で与えられます。

$$V_{OUT} = (1 + R_{FB1}/R_{FB2}) \times V_{REF} \times N_S/N_T$$

$V_{REF}$  には、REFIN ピンで 1.5V～2.2V の電圧を外部から供給できます。REFIN ピンを BIAS に接続することで、デフォルトの内部リファレンス電圧 2.0V が選択されます。

オンタイム時には、FB ピンの負電圧が次式で与えられます。

$$V_{FB-ON} = -[R_{FB2}/(R_{FB1} + R_{FB2})] \times V_{IN} \times N_T/N_P$$

FB ピンのこの負電圧は、その絶対最大定格を超えないように注意しなければなりません。

ここで、

$V_{IN}$  = 入力電圧

$N_S/N_T$  = トランスの 2 次側対 3 次側の巻数比

$N_T/N_P$  = トランスの 3 次側対 1 次側の巻数比

# オプト・カプラを使わずにフィードバックする 高電圧マルチフェーズ昇圧／ フライバック・コントローラ

MAX15159

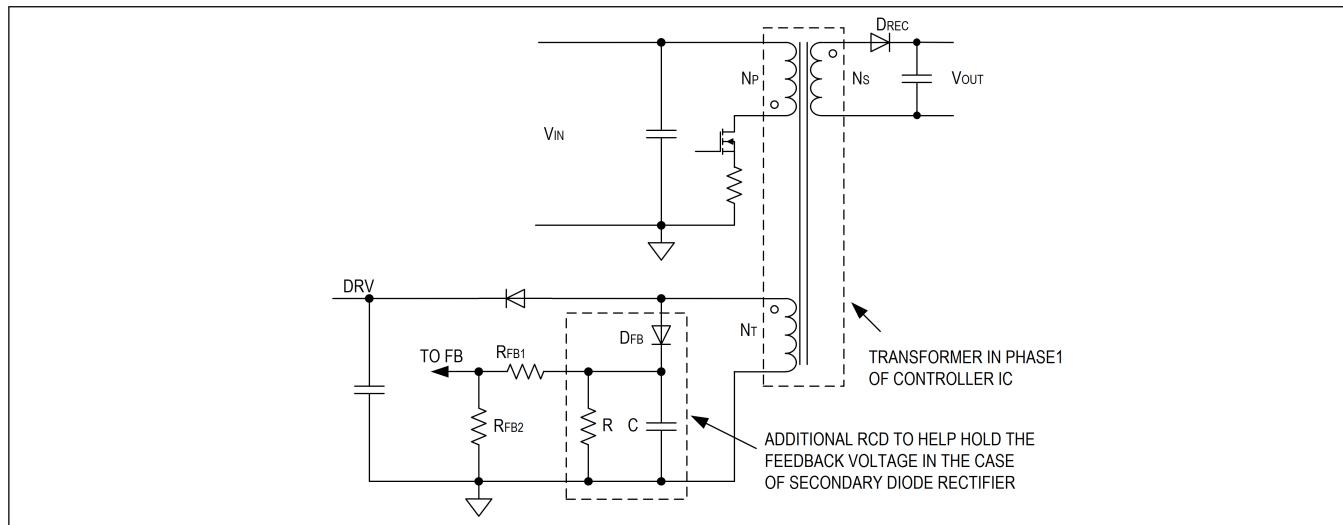

特に、2次側に整流ダイオードを使用したフライバック・コンバータが軽出力負荷状態にあると、2次側巻線電流の放電期間が最短になり、2次側巻線のエネルギーが完全に減衰した後に内蔵のサンプル&ホールドが終了した場合、サンプリングされた  $V_{OUT}$  電圧に大きな誤差が生じるおそれがあります。その場合には、RCD回路の追加を推奨します。これにより、3次巻線の両端でサンプリングされた電圧を保持しやすくなります（図2を参照）。その出力電圧は次式で与えられます。

$$V_{OUT} = [(1 + R_{FB1}/R_{FB2}) \times V_{REF} + V_{D\_FB}] \times N_s/N_t - V_{D\_REC}$$

ここで、

$V_{D\_FB}$  = ダイオード  $D_{FB}$ （図2）の順方向電圧

$V_{D\_REC}$  = 出力整流ダイオード  $D_{REC}$ （図2）の順方向電圧

図2. 3次巻線の両端にRCD回路を追加したオプト・カプラを使わないフィードバック

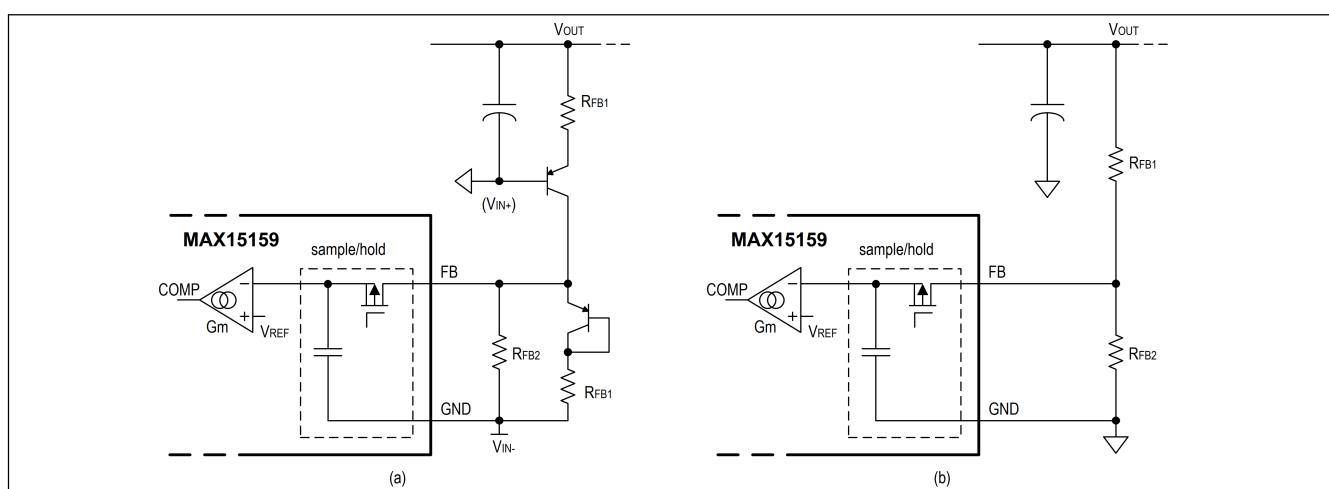

## 昇圧／反転昇降圧アプリケーション

MAX15159は、昇圧と反転昇降圧の両方のアプリケーションに対応可能です。

反転昇降圧動作で構成される場合、デバイスのGNDピンは負入力電圧端子 ( $V_{IN-}$ ) に接続しなければならず、その結果、ICのグランドは出力キャパシタおよび負荷のグランドと異なることになります。出力電圧の制御は簡単な抵抗分圧器ではできないので、図3(a)に示すように、外付けのFBレベル・シフタをマッチングした2つのPNPトランジスタで構成します。

図3. FBピンの接続：(a) 外付けのFBレベル・シフタを備えた反転昇降圧アプリケーション、(b) 昇圧アプリケーション

# オプト・カプラを使わずにフィードバックする 高電圧マルチフェーズ昇圧／ フライバック・コントローラ

MAX15159

昇圧および反転昇降圧の出力電圧は次式で与えられます。

$$V_{OUT} = (1 + R_{FB1}/R_{FB2}) \times V_{REF}$$

ここで、

$V_{REF}$  = FB レギュレーションのリファレンス電圧 (REFIN ピンで設定されます)

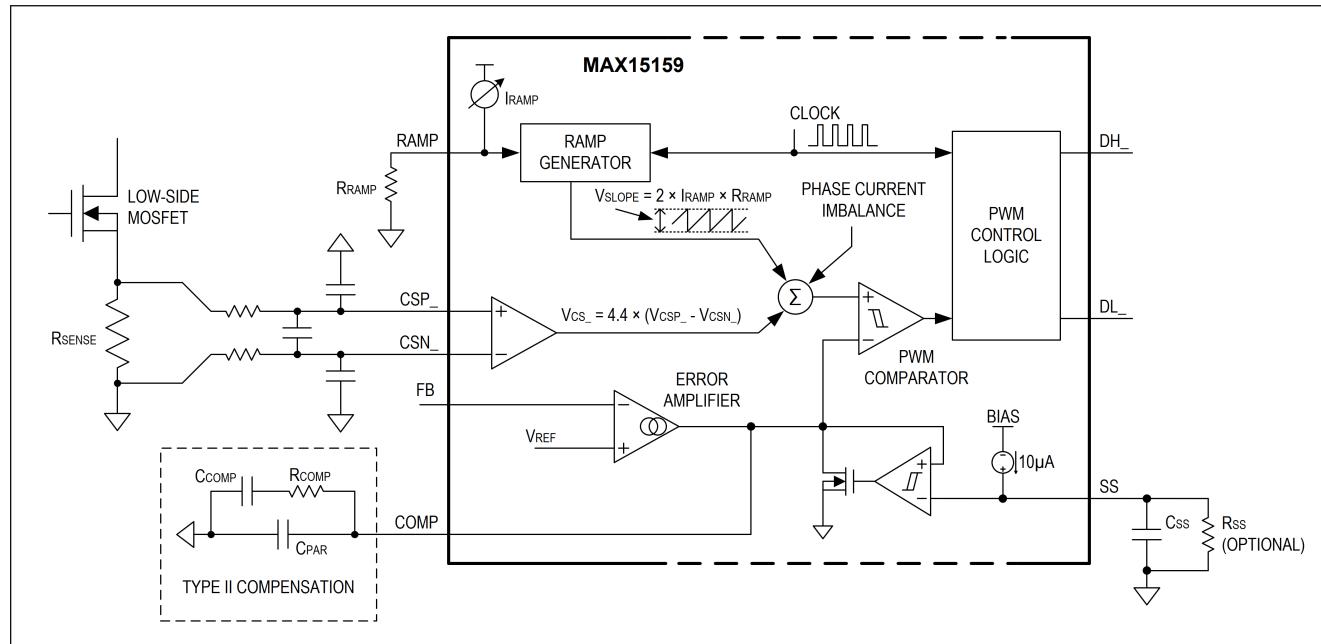

## ピーク電流モードの制御ループ

コントローラは、固定周波数のピーク電流モード・アーキテクチャを利用して出力を安定化します。制御ループの詳細なブロック図を図 4 に示します。電流を検出するには、ローサイド MOSFET のソースと GND の間にセンス抵抗が必要です。センス抵抗は、CSP\_ と CSN\_ の両端にかかる最大差動電圧がサイクル単位のピーク電流制限スレッショルドを超えないように選択する必要があります (過電流保護のセクションを参照)。CSP\_ と CSN\_ の両端にかかる差動電圧は、内蔵の電流センス・アンプで 4.4 倍に増幅され、内部の PWM 勾配補償ランプに足し合わされた上で、コントローラの PWM 出力を生成するのに使用されます。センス抵抗の両端には RC による高周波ノイズ・フィルタを設けることを推奨します。

出力フィードバック電圧 ( $V_{FB}$ ) とリファレンス電圧 ( $V_{REFIN}$  または内蔵 2V) の間の誤差は誤差アンプの入力に供給されます。誤差アンプの出力 (COMP) は、制御ループの安定化のために、タイプ II 補償ネットワークに接続する必要があります (補償設計ガイドラインのセクションを参照)。特に、COMP 電圧は SS 電圧でも制御されます。スタートアップ時に、MAX15159 が SS キャパシタ (図 4 の  $C_{SS}$ ) を  $10\mu A$  の定電流源で充電すると、SS 電圧が直線的に上昇します。これにより、レートを制御して COMP 電圧を直線的にランプアップさせることができます。この場合、出力電圧は、そのレギュレーション・セットポイントに達するまで、単調にランプアップします。SS と GND の間に抵抗 (図 4 の  $R_{SS}$ ) を接続すると SS に最大電圧を設定でき、その結果、COMP 電圧がクランプされて、最大デューティ・サイクルと最大ピーク電流が設定されます。

勾配補償ランプの発生器も使用します。補償ランプの勾配は、RAMP と GND の間に抵抗を接続することで調整できます (選択可能な勾配補償 (RAMP) のセクションを参照)。

コントローラは、クロックの立上がり毎にローサイド MOSFET を駆動します ( $DL_-$  がハイに駆動されます)。コントローラが  $DL_-$  をローに引き下げ、 $DH_-$  をハイに駆動するのは、電流センス・アンプ出力 ( $V_{CS}$ ) 、勾配補償ランプ、フェーズ電流アンバランス信号の合計が COMP 電圧を超えたことを PWM コンパレータが検出したときです。

図 4. ピーク電流モードの制御ループ

## 補償設計ガイドライン

MAX15159 は、固定周波数のピーク電流モード制御方式を利用して、容易な補償と高速過渡応答を実現します。これは、昇圧／反転昇降圧／フライバック・コンバータがその制御側から出力側への小信号伝達関数に右半平面（RHP）ゼロを持つように設計することで行われます。

昇圧コンバータの場合、RHP ゼロの位置は次式で計算されます。

$$f_{RHP} = \frac{V_{OUT} \times (1-D)^2}{2 \times \pi \times I_{OUT(MAX)} \times L}$$

ここで、

$I_{OUT(MAX)}$  = フェーズごとの最大負荷電流

$D$  = デューティ・サイクル =  $1 - V_{IN}/V_{OUT}$

$L$  = インダクタの値

反転昇降圧／フライバック・コンバータの場合、RHP ゼロの位置は次式で計算されます。

$$f_{RHP} = \frac{V_{OUT} \times (1-D)^2 \times (N_p/N_s)^2}{2 \times \pi \times I_{OUT(MAX)} \times L \times D}$$

ここで、

$D$  = デューティ・サイクル =  $(N_p/N_s \times V_{OUT}) / [|V_{IN}| + (N_p/N_s \times V_{OUT})]$

$N_p/N_s$  = フライバック・コンバータにおけるトランジスの 1 次側対 2 次側の巻数比（反転昇降圧コンバータでは、 $N_p/N_s = 1$  を選択）

安定した動作のために、制御ループの帯域幅（BW）は次式に示すように、 $f_{RHP}$  およびスイッチング周波数（ $f_{SW}$ ）より十分低くする必要があります。

$$BW \leq \min(f_{RHP}/7, f_{SW}/10)$$

COMP と GND の間にはタイプII補償ネットワーク（図4の  $R_{COMP}$ 、 $C_{COMP}$ 、 $C_{PAR}$ ）を接続して、制御ループに対する十分なフェーズ・マージンおよびゲイン・マージンを確保する必要があります。昇圧コンバータの  $R_{COMP}$  は次式で選択できます。

$$R_{COMP} = \frac{2 \times \pi \times BW \times C_{OUT} \times A_{CS} \times R_{SENSE} \times V_{OUT}}{N \times G_{MEA} \times V_{REF} \times (1 - D)}$$

ここで、

$R_{SENSE}$  = センス抵抗の値

$C_{OUT}$  = 出力キャパシタの値

$N$  = フェーズ数

$G_{MEA}$  = 誤差アンプのトランジスコンダクタンス（代表値：1.15mS）

$A_{CS}$  = 電流センス・アンプのゲイン（代表値：4.4V/V）

反転昇降圧／フライバック・コンバータの  $R_{COMP}$  は次式で選択できます。

$$R_{COMP} = \frac{2 \times \pi \times BW \times C_{OUT} \times A_{CS} \times R_{SENSE} \times V_{OUT}^2}{N \times G_{MEA} \times V_{REF} \times D \times V_{IN}}$$

$C_{COMP}$  および  $C_{PAR}$  は次式で選択できます。

$$C_{COMP} = \frac{5}{\pi \times R_{COMP} \times BW}$$

$$C_{PAR} = \frac{1}{2 \times \pi \times R_{COMP} \times f_{SW}}$$

### 選択可能な勾配補償 (RAMP)

MAX15159 が 50%を超えるデューティ・サイクルで動作する場合、安定性を確保しつつ、連続導通モード (CCM) で動作するピーク電流モード制御コンバータでは自然に発生する分数調波振動を防ぐために、別の勾配補償が必要になります。MAX15159 は、内部勾配補償ランプを 260mV～1500mV の範囲内で選択するための RAMP 入力を備えています。不連続導通モード (DCM) の設計でも、良好なノイズ耐性とジッタのない動作を実現するために、この最小限の勾配補償を使用することを推奨します。

図 4 に示すように、RAMP と GND の間に抵抗 ( $R_{RAMP}$ ) を接続することで、勾配補償ランプの振幅は次のように計算されます。

$$V_{SLOPE} = 2 \times V_{RAMP} = 2 \times I_{RAMP} \times R_{RAMP}$$

ここで、

$I_{RAMP}$  = RAMP から GND へ供給される電流 (代表値 : 10μA)

安定かつジッタのない動作を確保するために、RAMP 抵抗を次のように選択することを推奨します。

$$R_{RAMP} \geq \frac{5 \times (V_{OUT(MAX)} - V_{IN(MIN)}) \times R_{SENSE}}{I_{RAMP} \times f_{SW} \times L}$$

ここで、

$V_{OUT(MAX)}$  = 最大出力電圧

$V_{IN(MIN)}$  = 最小入力電圧

$R_{SENSE}$  = センス抵抗の値

$f_{SW}$  = スイッチング周波数

$L$  = インダクタの値

### DRV 電源とバイアス・レギュレータ (BIAS)

コントローラには 8.5V～14V の外部 DRV 電源が必要です。DRV 電源は、安定化された 5V バイアス電源を生成する内蔵のリニア・レギュレータに電力を供給して、機能図に示す内蔵のアナログ/デジタル制御回路に電力を供給します。BIAS ピンを 2.2μF 以上のセラミック・キャパシタでバイパスして、ノイズ耐性と安定性を維持します。BIAS レギュレータは最大 35mA の負荷電流を供給します。

コントローラの DRV には UVLO スレッショルドが設けられています。低電圧保護回路は、DRV が 8.25V (代表値) を超えるまでスイッチングを抑制します。

DRV がその低電圧スレッショルド未満に低下した場合、コントローラは、有効な制御決定を行うには電源電圧が不足していると判断します。レギュレータと出力を保護するために、コントローラは直ちに PGOOD をローに引き下げ、ドライバをディスエーブルにして (すべてのドライバ出力をローに引き下げて)、内蔵の 5.5Ω 放電 MOSFET を介して SS キャパシタを放電します。これにより、レギュレータはハイインピーダンス出力状態に置かれるので、出力キャパシタは負荷電流を通じて受動的に放電ていきます。

BIAS のリニア・レギュレータは、DRV がその UVLO スレッショルドを超えている限り起動します。

### EN/UVLO とソフトスタート/シャットダウン

EN/UVLO ピンによって、入力電圧動作範囲をパワー・シーケンス制御のために外部から調整できるようになります。入力と GND の間にある抵抗分圧器の中央に EN/UVLO を接続して、UVLO 電圧レベルを調整します (標準アプリケーション回路を参照)。外付け MOSFET ドライバの DRV 電圧スレッショルドが DRV ピンの UVLO スレッショルドより高い場合には、外付け MOSFET ドライバがイネーブルになる前に、EN/UVLO ピンも GND に引き下げる必要があります。

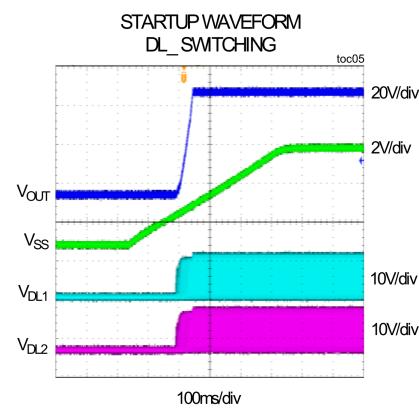

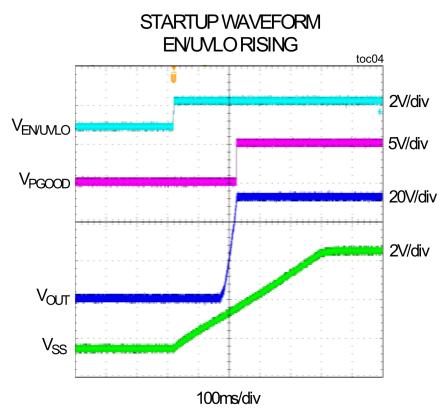

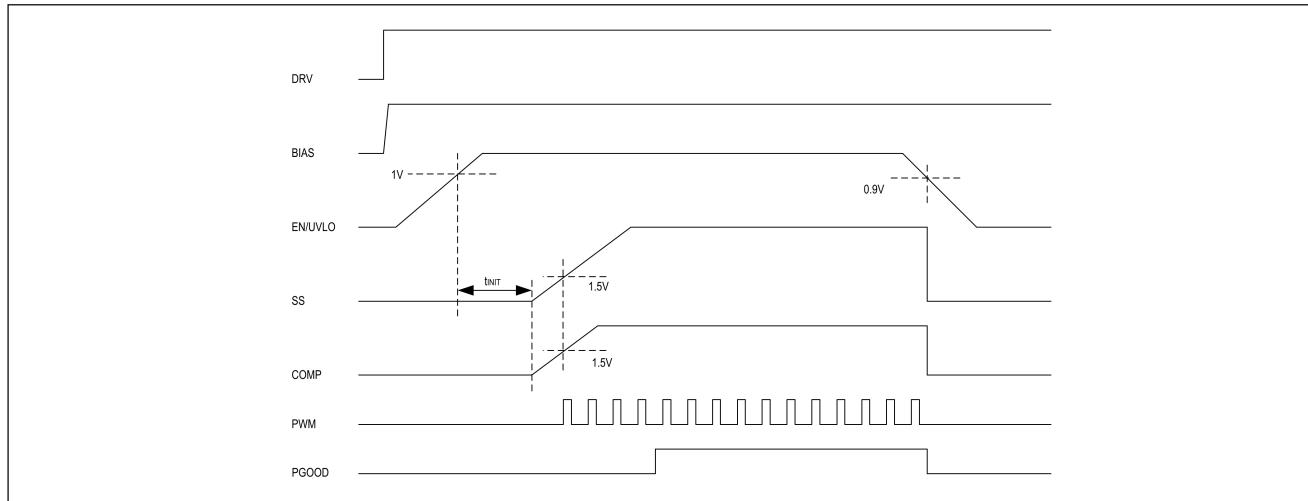

起動時に、EN/UVLO の電圧が 1V (代表値) より高くなっていると、内部リファレンスが安定すると、コントローラは初期化期間を開始し OVP ピン配置を確認します。この初期化期間に、コントローラは 5.5Ω の放電 MOSFET を介して SS をローに引き下げます。初期化が完了して、 $1.5V < V_{REFIN} < 2.2V$  を満たしているか、または REFIN が BIAS に短絡されている限り、コントローラは、10μA の定電流源で SS キャパシタを充電することにより、ソフトスタート・シーケンスを開始します。COMP 電圧は、SS 電圧で制御されたスルーレートで増加します。PWM は COMP と SS が 1.5V (標準) に達すると始動し、プリセットされたレギュレーション・セットポイントまで FB をランプアップします。

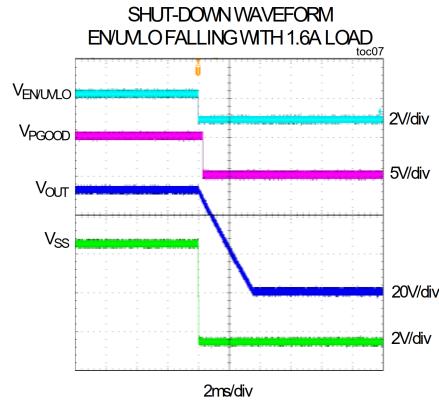

パワーダウン時に、EN/UVLO の電圧が 0.9V (代表値) 未満になると、または  $V_{REFIN}$  が 1.4V (代表値) 未満になると、コントローラは直ちに PGOOD、CSION、DH\_、DL\_ をローに引き下げて、SS キャパシタと COMP を急速に GND に放電します (図 5 参照)。

図 5. EN/UVLO を使用したソフトスタートとシャットダウン・シーケンス

## 過電流保護

ローサイド MOSFET のソースと GND の間に電流センス抵抗を接続します。MAX15159 は、電流センス信号 (CSP\_ と CSN\_ の間) を検出して、それをローサイドのオン時間の間にサイクル単位のピーク電流制限スレッショルドと比較します。電流がサイクル単位のピーク電流制限スレッショルドを超えると、デバイスは、そのスイッチング・サイクルの終了まで、ローサイド MOSFET をオフにしてハイサイド MOSFET をオンにします。各フェーズは、連続して起こるピーク電流制限事象の件数を累積するための独立したアップ／ダウン・カウンタを備えています。カウンタが 32 を超えた場合、デバイスはドライバをディスエーブルにして（すべてのドライバ出力をローに引き下げて）、SS キャパシタを放電します。32,768 回のクロック・サイクル後に、デバイスはソフトスタート・シーケンスを使用して自動的に再起動しようとします。

二次的な高速正過電流保護 (FPOCP) スレッショルドが設けられており、このスレッショルドはサイクル単位のピーク電流制限スレッショルドより 33% 高くなっています。インダクタのピーク電流が FPOCP スレッショルドを超えた場合、デバイスはドライバをディスエーブルにして（すべてのドライバ出力をローに引き下げて）SS キャパシタを放電します。32,768 回のクロック・サイクル後に、デバイスはソフトスタート・シーケンスを使用して自動的に再起動しようとします。

サイクル単位のピーク電流制限スレッショルドは、ILIM ピンの抵抗で設定されます。この抵抗には  $10\mu\text{A}$  のソース電流が流れ込み、これにより電圧レベルが生成されます。この電圧レベルは、サイクル単位のピーク電流制限スレッショルドを設定するために、0.1 倍に内部スケーリングされます。設定可能な最小および最大の電流制限レベル ( $V_{OCP}$ ) はそれぞれ、 $20\text{mV}$  と  $100\text{mV}$  です。サイクル単位のピーク電流制限レベルは次式で与えられます。

$$V_{OCP} = 0.1 \times 10\mu\text{A} \times R_{ILIM}$$

最大のピーク・インダクタ電流は、 $V_{OCP}$  と電流センス抵抗 ( $R_{SENSE}$ ) の両方で設定されます。

$$I_{PEAK(MAX)} = V_{OCP}/R_{SENSE}$$

デバイスには、負過電流保護 (NOCP) スレッショルドもあり、このスレッショルドはサイクル単位のピーク電流制限スレッショルドの -80% です。ローサイド MOSFET がオンになり、インダクタ電流が NOCP スレッショルドを下回ると、デバイスはローサイド MOSFET をオンに保つよう命令して、そのスイッチング・サイクルの終了まで、入力電圧によってインダクタ電流を充電できるようにします。各フェーズは、連続して起こる NOCP 事象の件数を累積するための独立したアップ／ダウン・カウンタを備えています。カウンタが 32 を超えた場合、デバイスはドライバをディスエーブルにして（すべてのドライバ出力をローに引き下げて）、SS キャパシタを放電します。32,768 回のクロック・サイクル後に、デバイスはソフトスタート・シーケンスを使用して自動的に再起動しようとします。

## 過電圧保護

MAX15159 は、FB 電圧を監視する OVP コンパレータを備えています。デバイスは、OVP ピンと GND の間に抵抗を接続することにより、OVP をディスエーブルにするか、または OVP スレッショルドを 110% に選択するように構成できます。

OVP がイネーブルになると、ドライバはスイッチングを開始し、 $V_{REF}$  は  $1.5\text{V}$ ～ $2.2\text{V}$  の範囲内になります。FB 過電圧コンパレータは、フィードバック電圧が 128 回を超える PWM クロック・サイクルにわたって  $V_{REF}$  電圧を 110% 上回った場合にトリップし、MAX15159 は PGOOD、CSION、SS、COMP ピンを強制的にローにしてドライバをディスエーブルにします。コントローラは、フォルト状態が取り除かれると直ちに再起動します。OVP がディスエーブルになると、FB 電圧が  $V_{REF}$  電圧より 10% 高いときに PGOOD はハイのままになります。

# オプト・カプラを使わずにフィードバックする 高電圧マルチフェーズ昇圧／ フライバック・コントローラ

MAX15159

OVP ピンと GND の間にある抵抗は、シングル、デュアル／クワッド、またはトリプルフェーズ動作の選択にも使用されます。詳細は表 1 を参照してください。

表 1. FB の OVP 設定とフェーズ構成

| R <sub>OVP</sub> (1% RESISTOR) | FB OVP THRESHOLD | PHASE CONFIGURATION                |

|--------------------------------|------------------|------------------------------------|

| GND                            | 110%             | Dual-phase or quad-phase operation |

| 51.1kΩ                         | Disabled         |                                    |

| 95.3kΩ                         | 110%             | Single-phase operation             |

| 140kΩ                          | Disabled         |                                    |

| 182kΩ                          | 110%             | Triple-phase operation             |

| 226kΩ                          | Disabled         |                                    |

## スイッチング周波数 (FREQ/CLK)

コントローラは、120kHz～1MHz のスイッチング周波数に対応しています。FREQ/CLK を無接続のままにすると、プリセットされた 300kHz のスイッチング周波数が選択されます。スイッチング周波数を調整するには、FREQ/CLK と GND の間に外付け抵抗を置くか、または外部システム・クロックで FREQ/CLK を駆動します（表 2 参照）。抵抗でプログラム可能なスイッチング周波数は次式で決定します。

$$f_{SW} = \frac{R_{FREQ}}{100k\Omega} \times 600kHz$$

表 2. フェーズとコントローラ／ターゲット構成

| NUMBER OF PHASES | NUMBER OF MAX15159 DEVICES | FB OF TARGET IC CONNECTED TO BIAS | CLK FREQUENCY       |

|------------------|----------------------------|-----------------------------------|---------------------|

| 1                | 1                          | N/A                               | 4 × f <sub>SW</sub> |

| 2                | 1                          | N/A                               | 4 × f <sub>SW</sub> |

| 3                | 2                          | Yes                               | 3 × f <sub>SW</sub> |

| 4                | 2                          | Yes                               | 4 × f <sub>SW</sub> |

## フェーズとコントローラ／ターゲット構成

MAX15159 は、シングルフェーズ、デュアルフェーズ、トリプルフェーズ、またはクワッドフェーズ動作モードに構成可能です。トリプルフェーズまたはクワッドフェーズ動作に対応する場合、コントローラおよびターゲットとして、MAX15159 の IC を 2 つ使用します。コントローラは、フェーズ数を識別するのに OVP ピンの抵抗を使います（コントローラ IC およびターゲット IC に必要な同じ R<sub>OVP</sub>を選択します）。この識別結果を使用して、コントローラが第 1 フェーズで生成されたマルチフェーズ・クロック信号にどう応答するかを判断します。

2 つのデバイス同士を適切に同期させるために、コントローラとターゲット・デバイスの SYNC、COMP、CSIOP、CSION をそれぞれ一緒に接続します。ターゲット・デバイスの FB ピンと REFIN ピンをその BIAS ピンに接続します（図 10 参照）。

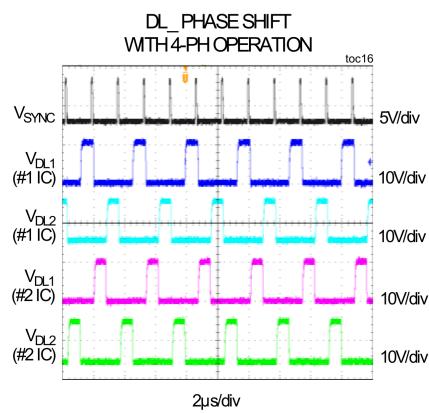

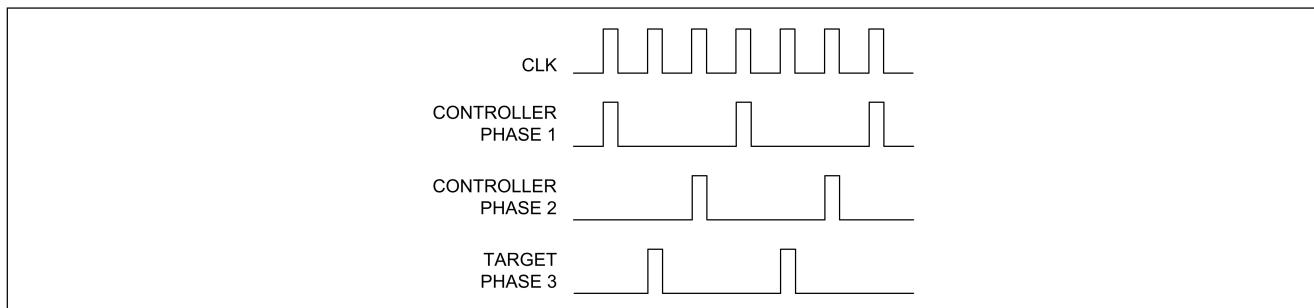

トリプルフェーズ・コンバータでは、MAX15159 によるコントローラの 2 つのフェーズは 240° インターリープしており、MAX15159 によるターゲットのフェーズ 1 はコントローラと比べて 120° 位相シフトして動作します。ターゲットの第 2 フェーズは使わないままで（図 6）。

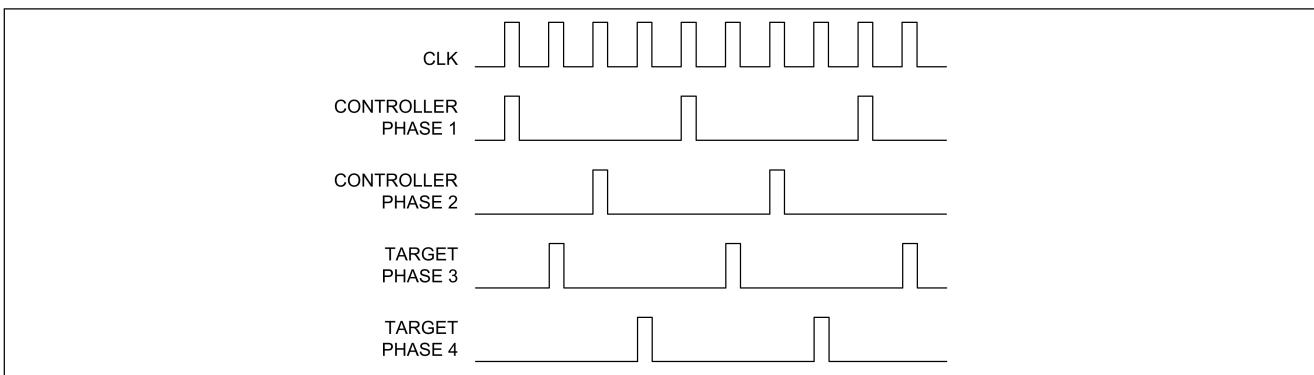

クワッドフェーズ・コンバータでは、MAX15159 によるコントローラまたはターゲットの 2 つのフェーズは 180° インターリープしており、コントローラとターゲットは 90° 位相シフトして動作します（図 7）。

図 6. トリプルフェーズの同期（コントローラ／ターゲット）

図 7. クワッドフェーズの同期（コントローラ／ターゲット）

## マルチフェーズでの電流バランス

MAX15159は、マルチフェーズ動作においてアクティブにフェーズ間の電流バランスを保つよう、各フェーズのローサイド MOSFET 電流を監視します。電流のアンバランスはサイクル単位の電流検出回路にフィードバックとして反映されるので、負荷電流が 2 つのフェーズ間で均一に分担されるよう安定化するのに役立ちます（[機能図](#)を参照）。

トリプルフェーズまたはクワッドフェーズで動作させる場合、デバイスは CSIO\_ の差動接続を使用して、コントローラとターゲットの間でチップごとの平均電流を伝達します。電流モードのコントローラおよびターゲット・デバイスは、すべてのフェーズが均等に負荷電流を分担するようにそれぞれの電流を安定化します。

## MOSFET ゲート制御

フライバックの非同期式昇圧／反転昇降圧アプリケーションでは、MAX15159 の DL\_ 出力で MOSFET を直接駆動できます。

同期式昇圧／反転昇降圧アプリケーションの場合、MAX15159 は、パワーMOSFET を駆動する外付け MOSFET ドライバと一緒に使わなければなりません。デバイスは、ローサイド MOSFET のゲート電圧を検出する専用の DLFB\_ ピンを備えており、これを使用して、外付け MOSFET ドライバによって引き起こされる遅延のミスマッチによりハイサイドとローサイドの MOSFET 間に発生するシートスルーがないようにしています。DLFB\_ ピンの立上がりリセットショルドは 0.8V（代表値）、立下がリセットショルドは 0.5V（代表値）です。ローサイド MOSFET のゲートと DLFB\_ ピンの間に抵抗分圧器を用いると、MOSFET のゲート・リセットショルド電圧と DLFB\_ リセットショルドを整合させることができます（[標準アプリケーション回路](#)を参照）、様々な MOSFET との堅固な動作が可能になると同時にデッド・タイムによる電力損失を最小限に抑えることができます。

## サーマル・シャットダウン

コントローラは、サーマル・フォルト保護回路を備えています。ジャンクション温度が +165°C を超えるまで上昇すると、内蔵のサーマル・センサーがフォルト保護をトリガし、ドライバをディスエーブルにして、SS キャパシタを放電します。コントローラは、ジャンクション温度が 15°C 下がるまでディスエーブルのままでです。デバイスが冷えると、コントローラはソフトスタート・シーケンスを使用して自動的に再起動します。

## トランス／インダクタの選択

トランスは、フライバック・コンバータにとって重要な役割を果たします。その磁化インダクタンスによって、DCM または CCM でのフライバック・コンバータの働きが決まります。磁化インダクタンスを大きくすると、リップル電流が低くなり、コア損失が低減することになります。しかし、磁化インダクタンスを大きくすると、物理的サイズが大きくなるか、または飽和電流定格が下がることになります。磁化インダクタンス ( $L_M$ 、1 次側巻線の開放回路インダクタンス) は次式で推定できます。

# オプト・カプラを使わずにフィードバックする 高電圧マルチフェーズ昇圧／ フライバック・コントローラ

MAX15159

$$L_M = \frac{\eta \times (D \times V_{IN})^2}{2 \times f_{SW} \times V_{OUT} \times I_{OUT\_BOUNDARY}}$$

ここで、

$\eta$  = ターゲット効率

$I_{OUT\_BOUNDARY}$  = フライバック・コンバータが DCM と CCM の間の境界モードで動作する場合の目的の出力電流。DCM が入出力範囲にわたって動作する場合は、 $V_{IN} = V_{IN(MIN)}$ 、 $I_{OUT\_BOUNDARY} = I_{OUT(MAX)}$  を選択します。

トランジスの 1 次側対 2 次側の巻数比 ( $N_p/N_s$ ) は次式で推定できます。

$$\frac{N_p}{N_s} = \frac{D_{MAX} \times V_{IN(MIN)}}{(1 - D_{MAX}) \times V_{OUT}}$$

ここで、

$D_{MAX}$  = フライバック・コンバータにおける目的の最大デューティ・サイクル (通常、 $D_{MAX} = 0.45$  を選択)

昇圧／反転昇降圧コンバータでは、インダクタンス値を大きくすると、インダクタのリップル電流が抑制されて、インダクタのコア損失が低減することになります。しかし、インダクタの値を大きくすると、物理的サイズが大きくなるか、または直列抵抗 (DCR) が高くなり飽和電流定格が下がることになります。通常、インダクタの値は電流リップル ( $\Delta I_L$ ) が平均インダクタ電流の約 50%になるように選択します。平均インダクタ電流は次のように計算できます。

$$I_L(AVE) = \frac{I_{OUT(MAX)}}{(1 - D) \times N}$$

ここで、

$N$  = フェーズ数

インダクタは次式を使って選択できます。

$$L = \frac{D \times V_{IN}}{f_{SW} \times \Delta I_L}$$

## 出力コンデンサの選択

出力キャパシタは、安定性、出力電圧リップル、負荷過渡応答性能を向上させるように選択します。出力電圧リップル ( $V_{RIPPLE}$ ) の要件を満たすために、出力キャパシタは次式で選択できます。

$$C_{OUT(RIPPLE)} = \frac{D \times I_{OUT(MAX)}}{N \times f_{SW} \times V_{RIPPLE}}$$

一部のアプリケーションでは、負荷過渡応答時に出力電圧のオーバーシュートおよびアンダーシュートを制限することが必要となります。負荷過渡応答の要件を満たすために、出力キャパシタは次式で選択できます。

$$C_{OUT(TRANSIENT)} = \frac{\Delta I_{OUT}}{3 \times BW \times \Delta V_{OUT}}$$

ここで、

$\Delta I_{OUT}$  = 負荷電流ステップ

$BW$  = 制御ループの帯域幅 (補償設計ガイドラインのセクションを参照)

$\Delta V_{OUT}$  = 目的の出力電圧オーバーシュートまたはアンダーシュート

最終的な出力容量は次のように選択する必要があります。

$$C_{OUT} \geq \text{maximum}(C_{OUT(RIPPLE)}, C_{OUT(TRANSIENT)})$$

## 入力コンデンサの選択

入力キャパシタは、入力電圧リップル ( $V_{IN\_RIPPLE}$ ) の低減に役立つように選択します。

昇圧コンバータの場合、入力電流は連続的です。入力キャパシタの ESR と ESL を無視すると、入力キャパシタは次式で選択できます。

$$C_{IN} = \frac{\Delta I_L}{8 \times N \times f_{SW} \times V_{IN\_RIPPLE}}$$

反転昇降圧／フライバック・コンバータの場合、入力電流は不連続です。入力キャパシタは次式で選択できます。

$$C_{IN} = \frac{D \times I_{OUT(MAX)} \times N_S/N_P}{N \times f_{SW} \times V_{IN\_RIPPLE}}$$

ここで、

$N_S/N_P$  = フライバック・コンバータのトランスの2次側対1次側の巻数比（反転昇降圧コンバータでは、 $N_S/N_P = 1$  を選択）。

## PCB レイアウトのガイドライン

PCB レイアウトは、出力コンバータの性能に著しい影響を与える可能性があります。ボードの設計が良くないと、効率、熱性能、ノイズ制御、そして制御ループの安定性さえ低下する可能性があります。スイッチング周波数が高くなると、レイアウトの問題は特に重大になります。

一般的なガイドラインとしては、入力キャパシタ、インダクタまたはトランス、MOSFET、センス抵抗、出力キャパシタを互いにすぐ近くに配置して、高周波電流経路をできるだけ短くする必要があります。MOSFET ドライバは、MOSFET とスイッチング・ノード (SW) の近くに配置して、ゲート・ドライブ、BST、SW の配線パターンを短くする必要があります。MAX15159 は、高 dv/dt の SW、BST、ゲート・ドライブの配線パターンからある程度の距離を置く必要があります。周辺部の RC 部品は、できるだけコントローラの近くに配置する必要があります。優先的に対応する必要があるのは、ノイズに影響されやすいピン (COMP、SS、REFIN、FB など) です。差動モード・フィルタおよびコモン・モード・フィルタを両方とも、CSP\_ピンと CSN\_ピンとセンス抵抗の間に配置することを推奨します（[標準アプリケーション回路](#)を参照）。

高電力アプリケーションでは、電力配線パターンである  $V_{IN}$ 、 $V_{OUT}$ 、GND にプレーンを使用することを推奨します。十分な数のビアを設けて、異なるレイヤの電力プレーンを接続することが重要です。信号グランドと電力グランドは分離しなければなりません。すべての電力部品、例えば、入出力キャパシタ、MOSFET、センス抵抗、MOSFET ドライバは、電力グランドに接続する必要があります。MAX15159 およびその周辺部にある RC 部品は、信号グランドに接続しなければなりません。コントローラの下にある最も近い内部レイヤに信号グランドの島を設けることを推奨します。複数のビアを使用して、信号グランドの島をコントローラの露出パッドとノイズに影響されやすい信号 (COMP、SS、REFIN、FB など) のグランド・ノードに接続できます。信号グランドは、センス抵抗および入力キャパシタの電力グランド・ノードに近接している短い配線パターンまたは  $0\Omega$  抵抗を介して、電力グランドに接続する必要があります。

センス抵抗から CSP\_および CSN\_までの電流検出ラインは別個に配線する必要があります。コントローラがマルチフェーズ動作用に構成されている場合、異なるフェーズの電流検出ラインは信号カップリングを避けるために離しておく必要があります。すべての検出ラインとノイズに影響されやすい他の信号 (CSIO\_、COMP、SS、REFIN、FB など) は、ノイズが多い配線パターン (SW、BST、ゲート・ドライブ、FREQ/CLK、SYNC など) から離しておきます。

オプト・カプラを使わずにフィードバックする

高電圧マルチフェーズ昇圧／

フライバック・コントローラ

MAX15159

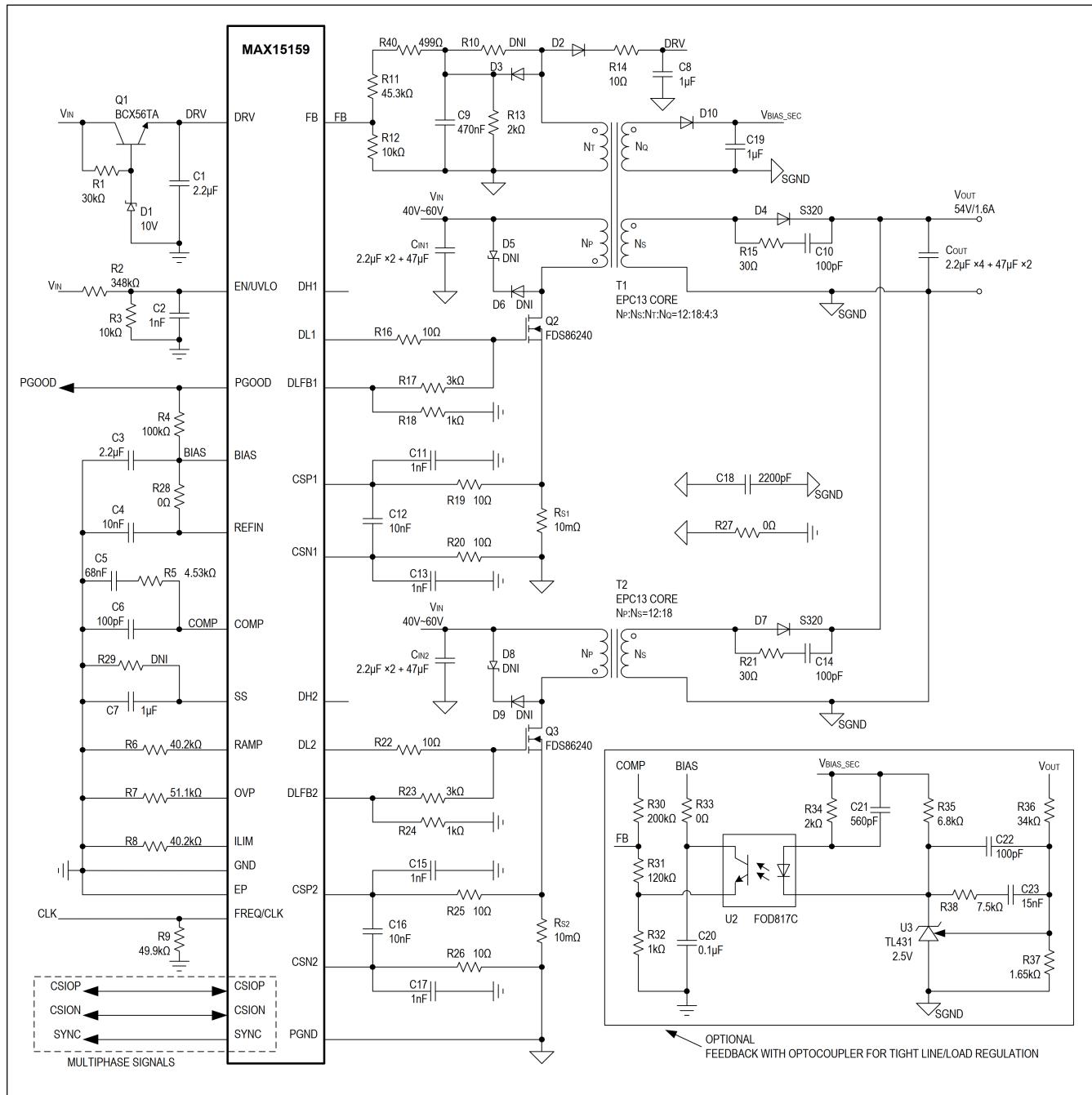

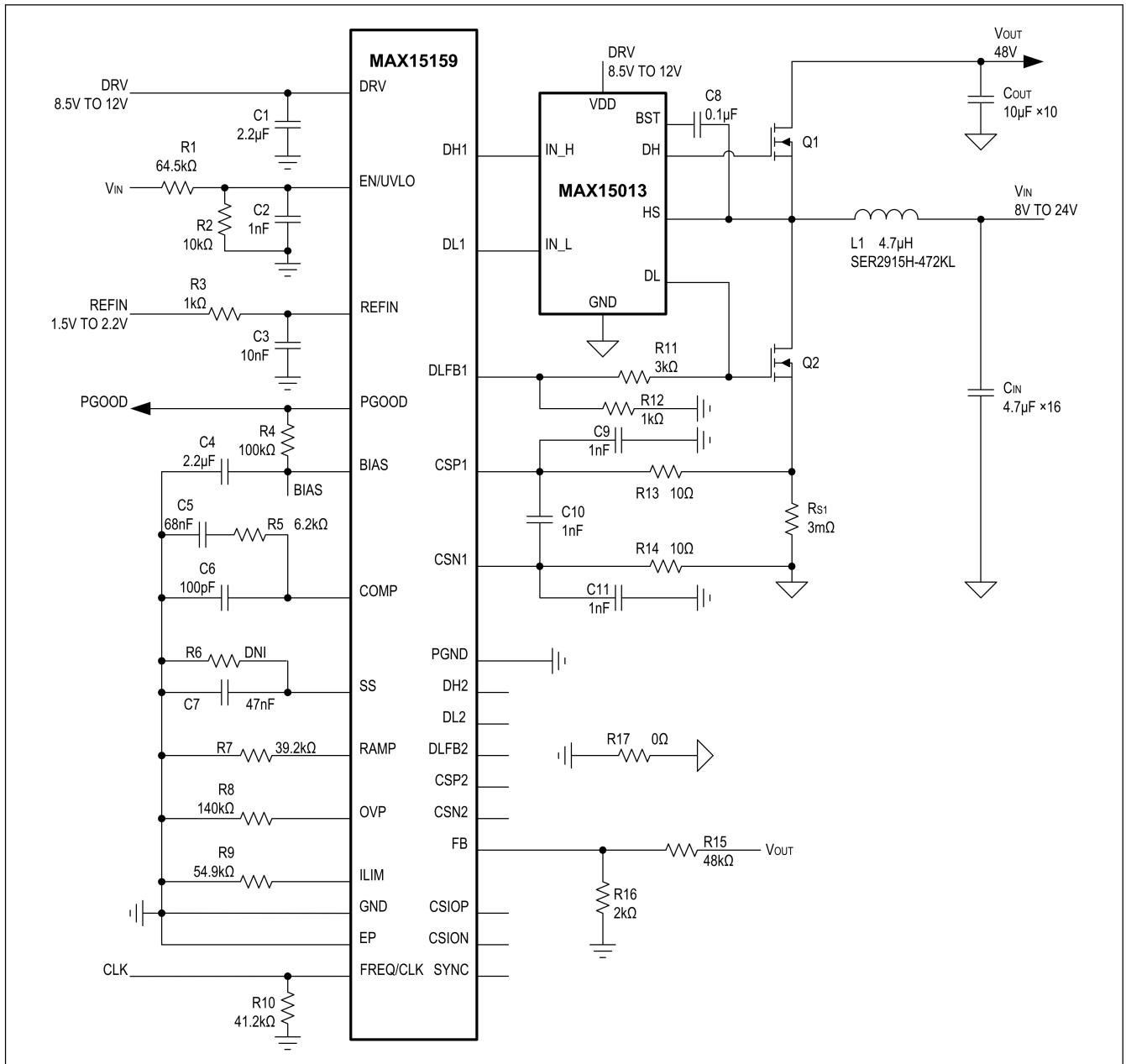

標準アプリケーション回路

図 8. デュアルフェーズのフライバック・コンバータ

オプト・カプラを使わずにフィードバックする

高電圧マルチフェーズ昇圧／

フライバック・コントローラ

MAX15159

図 9. シングルフェーズの同期式昇圧コンバータ

図 10. クワッド フェーズの相互接続（フライバック・コンバータ）

## 型番

| PART NUMBER   | TEMP RANGE      | PIN-PACKAGE |

|---------------|-----------------|-------------|

| MAX15159ATJ+  | -40°C to +125°C | 32 TQFN-EP* |

| MAX15159ATJ+T | -40°C to +125°C | 32 TQFN-EP* |

\*は鉛 (Pb) フリー／RoHS 準拠のパッケージであることを示します。

T = テープ & リール。

\*EP = 露出パッド。

# オプト・カプラを使わずにフィードバックする 高電圧マルチフェーズ昇圧／ フライバック・コントローラ

MAX15159

## 改訂履歴

| 版数 | 改訂日   | 説明           | 改訂ページ |

|----|-------|--------------|-------|

| 0  | 05/23 | 市場投入のためのリリース | -     |

アナログ・デバイセズ社は、提供する情報が正確で信頼できるものであることを期していますが、その情報の利用に関して、あるいは利用によって生じる第三者の特許やその他の権利の侵害に関して一切の責任を負いません。また、アナログ・デバイセズ社の特許または特許の権利の使用を明示的または暗示的に許諾するものでもありません。仕様は、予告なく変更される場合があります。本紙記載の商標および登録商標は、各社の所有に属します。※日本語版資料は REVISION が古い場合があります。最新の内容については、英語版をご参照ください。