## 20V<sub>IN</sub>、20A の降圧 DC/DC μModule レギュレータ

### 特長

- ▶ 1cm<sup>2</sup> (片面 PCB) または 0.5cm<sup>2</sup> (両面 PCB) 未満のフル機能ソリューション

- ▶ 広い入力電圧範囲 : 3.1V~20V

- ▶ 出力電圧 : 0.6V~3.3V

- ▶ 出力電流 : 最大 20A DC

- ▶ 最大総合 DC 出力電圧誤差 : ±1.5%

- ▶ リモート検出差動アンプ

- ▶ 高速過渡応答

- ▶ 外部周波数同期

- ▶ 最大 4 個の LTM4640 による多相並列電流分担

- ▶ パワー・グッド・インジケータ

- ▶ 過電圧保護と過熱保護

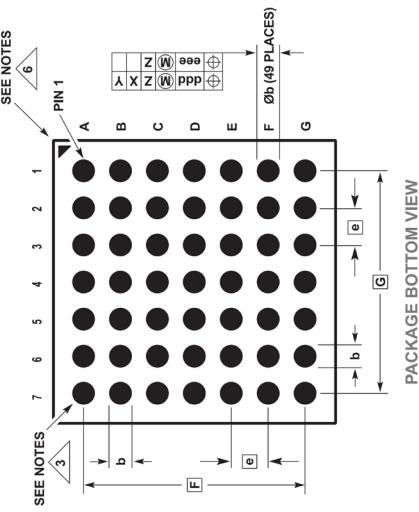

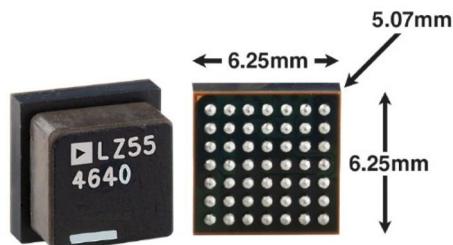

- ▶ 49 ピン、6.25mm × 6.25mm × 5.07mm、BGA パッケージ

- ▶ LTM4626、LTM4638、LTM4657 とピン互換

### 概要

LTM4640 は、6.25mm × 6.25mm × 5.07mm の小型 BGA パッケージに収容されたフル機能の 20A 降圧スイッチング・モード・パワーμModule®（マイクロモジュール）レギュレータです。このパッケージには、スイッチング・コントローラ、パワー MOSFET、インダクタ、および補助部品が内蔵されています。LTM4640 は、3.1V~20V の入力電圧範囲で動作し、1 個の外付け抵抗による設定で、0.6V~3.3V の範囲の電圧を出力します。高効率設計により、最大 20A の連続出力電流を供給します。必要なのは、バルク入力コンデンサとバルク出力コンデンサだけです。

LTM4640 は、選択可能な不連続導通モード (DCM) 動作と電源レール・シーケンシング用の出力電圧トラッキングをサポートしています。高いスイッチング周波数とオン時間制御式の谷電流モード・アーキテクチャにより、安定性を損なうことなく、ラインと負荷の変化に対して非常に高速の過渡応答を実現します。フォルト保護機能として、過電圧保護と過熱保護を備えています。

LTM4640 は、RoHS に適合した端子仕上げで提供されます。

### アプリケーション

- ▶ テレコム、データ通信、ネットワーク、産業用機器

- ▶ 医療用診断機器

- ▶ データ・ストレージ・ラック装置およびカード

- ▶ テストおよびデバッグ・システム

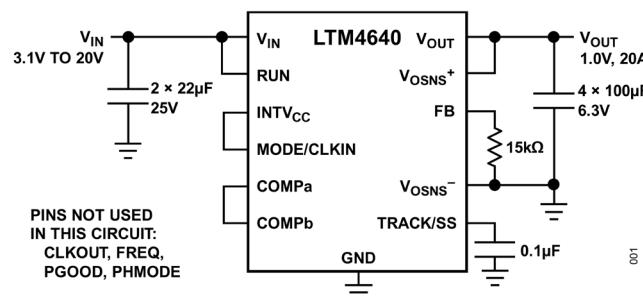

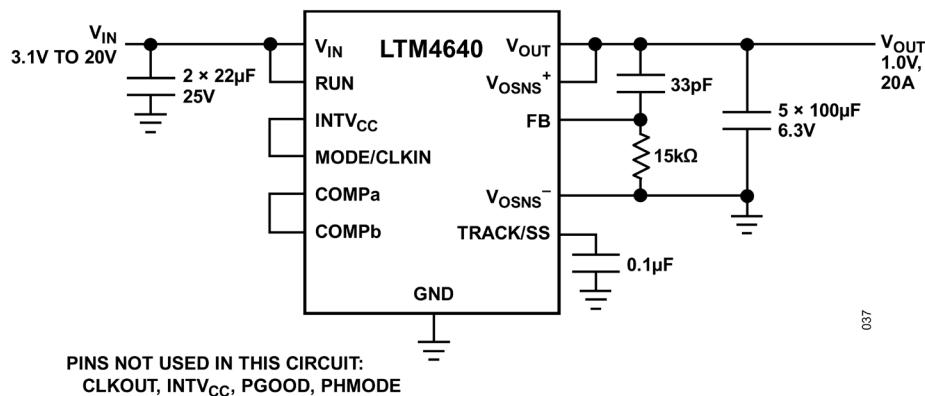

### 代表的なアプリケーション回路

図 1. 20A、1V<sub>OUT</sub> DC/DC 降圧 μModule レギュレータ

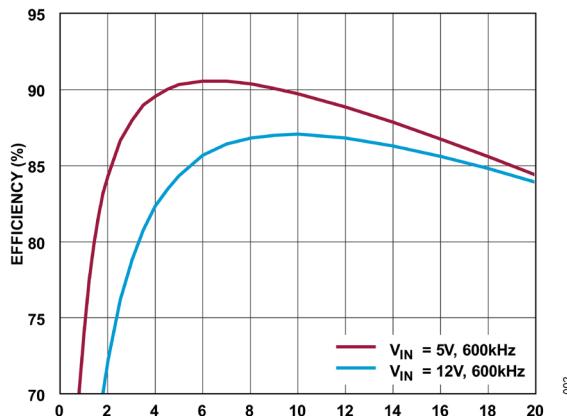

図 2. 1V<sub>OUT</sub> 時の効率と負荷電流の関係

※こちらのデータシートには正誤表が付属しています。当該資料の最終ページ以降をご参照ください。

Rev. 0

アナログ・デバイセズ社は、提供する情報が正確で信頼できるものであることを期していますが、その情報の利用に関して、あるいは利用によって生じる第三者の特許やその他の権利の侵害に関して一切の責任を負いません。また、アナログ・デバイセズ社の特許または特許の権利の使用を明示的または暗示的に許諾するものではありません。仕様は、予告なく変更される場合があります。本紙記載の商標および登録商標は、各社の所有に属します。※日本語版資料は REVISION が古い場合があります。最新の内容については、英語版をご参照ください。

## 目次

|                             |    |

|-----------------------------|----|

| 特長                          | 1  |

| アプリケーション                    | 1  |

| 概要                          | 1  |

| 代表的なアプリケーション回路              | 1  |

| 改訂履歴                        | 3  |

| 仕様                          | 4  |

| 絶対最大定格                      | 6  |

| 熱抵抗                         | 7  |

| 静電放電 (ESD)                  | 7  |

| ESD 定格                      | 7  |

| ESD に関する注意                  | 7  |

| ピン配置およびピン機能の説明              | 8  |

| 端子説明                        | 8  |

| 代表的な性能特性                    | 11 |

| 動作原理                        | 13 |

| LTM4640 の概要                 | 13 |

| 簡略化したブロック図                  | 14 |

| デカップリング条件                   | 14 |

| アプリケーション情報                  | 15 |

| $V_{IN}$ から $V_{OUT}$ への降圧比 | 15 |

| 出力電圧の設定                     | 15 |

| 入力デカップリング・コンデンサ             | 16 |

| 出力デカップリング・コンデンサ             | 16 |

| 不連続導通モード                    | 16 |

| 連続強制モード                     | 17 |

| 動作周波数                       | 17 |

| 周波数同期とクロック入力                | 17 |

| マルチフェーズ動作                   | 17 |

| 入力実効値リップル電流の相殺              | 18 |

| ソフトスタートおよび出力電圧トラッキング        | 19 |

| パワー・グッド                     | 21 |

| RUN イネーブル                   | 21 |

| プライバיאス出力に向けた起動             | 21 |

| SW ピンとオプションのスナバ回路           | 21 |

---

|                               |    |

|-------------------------------|----|

| 安定性補償.....                    | 22 |

| 差動リモート検出アンプ .....             | 22 |

| 入力過電圧保護.....                  | 22 |

| 出力電流制限.....                   | 22 |

| 温度モニタリング .....                | 23 |

| 熱に関する考慮事項と出力電流のディレーティング ..... | 24 |

| 空気流とヒート・シンク .....             | 25 |

| 安全に関する考慮事項 .....              | 30 |

| レイアウト・チェックリスト／レイアウト例.....     | 31 |

| 標準的応用例.....                   | 32 |

| 関連製品.....                     | 34 |

| 外形寸法.....                     | 35 |

| オーダー・ガイド .....                | 36 |

| 選択ガイド .....                   | 37 |

| パッケージ写真.....                  | 37 |

| 設計リソース .....                  | 37 |

## 改訂履歴

10/2024 - Rev. 0: Initial Release.

## 仕様

表 1. 電気的特性

(特に指定のない限り、 $T_A = 25^\circ\text{C}$ 、 $V_{IN} = 12\text{V}$ 、図 1 に示す代表的なアプリケーションを使用)

| PARAMETER                                                   | SYMBOL                             | CONDITIONS                                                                                                                                                                        | COMMENTS                                            | MIN   | TYP  | MAX   | UNITS         |

|-------------------------------------------------------------|------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|-------|------|-------|---------------|

| <b>Switching Regulator Section (per Channel)</b>            |                                    |                                                                                                                                                                                   |                                                     |       |      |       |               |

| Input DC voltage                                            | $V_{IN}$                           |                                                                                                                                                                                   | $-40^\circ\text{C} \leq T_J \leq 125^\circ\text{C}$ | 3.1   |      | 20    | V             |

| Output voltage range                                        | $V_{OUT}$                          |                                                                                                                                                                                   | $-40^\circ\text{C} \leq T_J \leq 125^\circ\text{C}$ | 0.6   |      | 3.3   | V             |

| Output voltage, total variation with line and load          | $V_{OUT(DC)}$                      | $R_{FB} = 6.65\text{k}\Omega$ , MODE = INTV <sub>CC</sub> , $I_{OUT} = 0\text{A}$ to $15\text{A}$ <sup>2</sup>                                                                    | $-40^\circ\text{C} \leq T_J \leq 125^\circ\text{C}$ | 1.477 | 1.50 | 1.523 | V             |

|                                                             |                                    | $R_{FB} = 6.65\text{k}\Omega$ , MODE = INTV <sub>CC</sub> , $I_{OUT} = 0\text{A}$ to $20\text{A}$                                                                                 |                                                     | 1.477 | 1.50 | 1.523 | V             |

| RUN pin ON threshold                                        | $V_{RUN}$                          | $V_{RUN}$ rising                                                                                                                                                                  |                                                     | 1.15  | 1.25 | 1.35  | V             |

| Input supply bias current                                   | $I_{Q(VIN)}$                       | $V_{IN} = 12\text{V}$ , $V_{OUT} = 1.5\text{V}$ , MODE = INTV <sub>CC</sub> , $I_{OUT} = 0\text{A}$                                                                               |                                                     |       | 100  |       | mA            |

|                                                             |                                    | $V_{IN} = 12\text{V}$ , $V_{OUT} = 1.5\text{V}$ , MODE = GND, $I_{OUT} = 0.1\text{A}$                                                                                             |                                                     |       | 18   |       | mA            |

|                                                             |                                    | Shutdown, RUN = 0, $V_{IN} = 12\text{V}$                                                                                                                                          |                                                     |       | 20   |       | $\mu\text{A}$ |

| Input supply current                                        | $I_{S(VIN)}$                       | $V_{IN} = 12\text{V}$ , $V_{OUT} = 1.5\text{V}$ , $I_{OUT} = 20\text{A}$                                                                                                          |                                                     |       | 3.25 |       | A             |

| Output continuous current range                             | $I_{OUT(DC)}$                      | $V_{IN} = 12\text{V}$ , $V_{OUT} = 1.5\text{V}$                                                                                                                                   |                                                     | 0     |      | 20    | A             |

| Line regulation accuracy                                    | $\Delta V_{OUT}$ (Line)/ $V_{OUT}$ | $V_{OUT} = 1.5\text{V}$ , $V_{IN} = 3.1\text{V}$ to $20\text{V}$ , $I_{OUT} = 0\text{A}$                                                                                          | $-40^\circ\text{C} \leq T_J \leq 125^\circ\text{C}$ |       | 0.01 | 0.1   | %/V           |

| Load regulation accuracy                                    | $\Delta V_{OUT}$ (Load)/ $V_{OUT}$ | $V_{OUT} = 1.5\text{V}$ , $I_{OUT} = 0\text{A}$ to $15\text{A}$                                                                                                                   | $-40^\circ\text{C} \leq T_J \leq 125^\circ\text{C}$ |       | 0.1  | 0.5   | %             |

|                                                             |                                    | $V_{OUT} = 1.5\text{V}$ , $I_{OUT} = 0\text{A}$ to $20\text{A}$                                                                                                                   |                                                     |       | 0.1  | 0.5   | %             |

| Turn-on overshoot                                           | $\Delta V_{OUT(START)}$            | $I_{OUT} = 0\text{A}$ , $C_{OUT} = 4 \times 220\mu\text{F}$ ceramic, $V_{IN} = 12\text{V}$ , $V_{OUT} = 1.5\text{V}$ <sup>5</sup>                                                 |                                                     |       | 30   |       | mV            |

| Turn-on time                                                | $t_{START}$                        | No load, TRACK/SS = $0.01\mu\text{F}$ , $V_{IN} = 12\text{V}$ , $V_{OUT} = 1.5\text{V}$                                                                                           |                                                     |       | 1    |       | ms            |

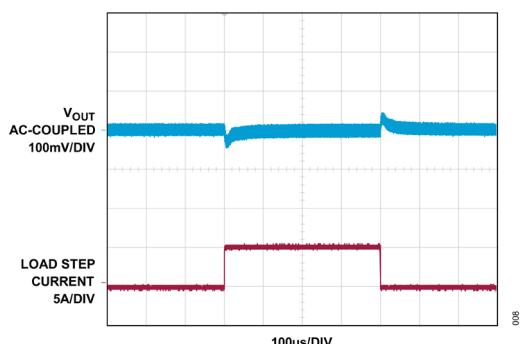

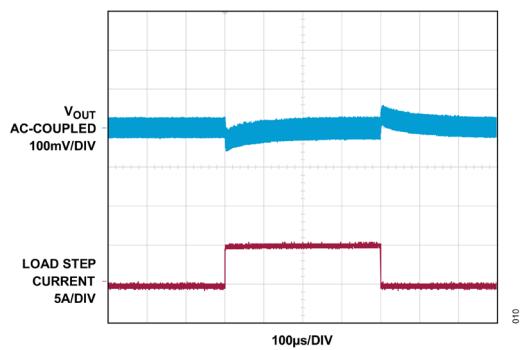

| Peak-to-peak output voltage deviation for dynamic load step | $\Delta V_{OUTLS}$                 | Load: 0% to 50% to 0% of full load, $10\text{A}/\mu\text{s}$ slew rate, $C_{OUT} = 4 \times 220\mu\text{F}$ ceramic, $V_{IN} = 12\text{V}$ , $V_{OUT} = 1.5\text{V}$ <sup>5</sup> |                                                     |       | 160  |       | mV            |

| Settling time for dynamic load step                         | $t_{SETTLE}$                       | Load: 0% to 50% to 0% of full load, $10\text{A}/\mu\text{s}$ slew rate, $C_{OUT} = 4 \times 220\mu\text{F}$ ceramic, $V_{IN} = 12\text{V}$ , $V_{OUT} = 1.5\text{V}$ <sup>5</sup> |                                                     |       | 60   |       | $\mu\text{s}$ |

(特に指定のない限り、 $T_A = 25^\circ\text{C}$ 、 $V_{IN} = 12\text{V}$ 、図1に示す代表的なアプリケーションを使用)

| PARAMETER                                 | SYMBOL         | CONDITIONS                                                       | COMMENTS                                            | MIN   | TYP  | MAX      | UNITS         |   |

|-------------------------------------------|----------------|------------------------------------------------------------------|-----------------------------------------------------|-------|------|----------|---------------|---|

| Output current limit                      | $I_{OUTPK}$    | $V_{IN} = 12\text{V}, V_{OUT} = 1.5\text{V}$                     |                                                     |       | 26   |          | A             |   |

| Voltage at FB pin                         | $V_{FB}$       | $I_{OUT} = 0\text{A}, V_{OUT} = 1.5\text{V}$                     | $-40^\circ\text{C} \leq T_J \leq 125^\circ\text{C}$ | 0.594 | 0.60 | 0.606    | V             |   |

| Current at FB pin                         | $I_{FB}$       | <sup>3</sup>                                                     |                                                     |       |      | $\pm 30$ | nA            |   |

| Resistor between $V_{OSNS^+}$ and FB pins | $R_{FBHI}$     |                                                                  |                                                     |       | 10   |          | k $\Omega$    |   |

| Track pin soft start pull-up current      | $I_{TRACK/SS}$ | $TRACK/SS = 0\text{V}$                                           |                                                     |       | 6    | 10       | $\mu\text{A}$ |   |

| $V_{IN}$ Undervoltage lockout             | $V_{IN(UVLO)}$ | $V_{IN}$ falling                                                 |                                                     | 2.45  | 2.6  | 2.75     | V             |   |

|                                           |                | $V_{IN}$ hysteresis                                              |                                                     | 350   |      |          | mV            |   |

| Minimum on-time                           | $t_{ON(MIN)}$  | <sup>3</sup>                                                     |                                                     |       | 25   |          | ns            |   |

| Minimum off-time                          | $t_{OFF(MIN)}$ | <sup>3</sup>                                                     |                                                     |       | 50   |          | ns            |   |

| PGOOD trip level                          | $V_{PGOOD}$    | $V_{FB}$ with respect to set output<br>$V_{FB}$ ramping negative |                                                     |       | -12  | -8       | -5            | % |

|                                           |                | $V_{FB}$ with respect to set output<br>$V_{FB}$ ramping positive |                                                     |       | 5    | 8        | 12            | % |

| PGOOD leakage                             | $I_{PGOOD}$    | $V_{PGOOD} = INTV_{CC}, V_{FB} = 0.6\text{V}$                    |                                                     |       |      | 2        | $\mu\text{A}$ |   |

| PGOOD voltage low                         | $V_{PGL}$      | $I_{PGOOD} = 1\text{mA}$                                         |                                                     |       | 0.02 | 0.1      | V             |   |

| Internal $V_{CC}$ voltage                 | $V_{INTVCC}$   | $V_{IN} = 4\text{V}$ to $20\text{V}$                             |                                                     | 3.2   | 3.3  | 3.4      | V             |   |

| Oscillator frequency                      | $f_{osc}$      |                                                                  |                                                     |       | 600  |          | kHz           |   |

<sup>1</sup> LTM4640は、EグレードとIグレードのデバイスを含め（表14を参照）、 $T_J \approx T_A$ となるようなパルス負荷条件でテストされています。LTM4640Eは、 $0^\circ\text{C}$ ～ $125^\circ\text{C}$ の内部動作温度範囲内で性能仕様を満たすよう設計されています。 $-40^\circ\text{C}$ ～ $125^\circ\text{C}$ の内部動作温度範囲全体における仕様は、設計、特性評価、および統計的プロセス制御との相関付けによって裏付けられています。LTM4640Iは $-40^\circ\text{C}$ ～ $125^\circ\text{C}$ の内部動作温度範囲全域で仕様を満たすよう設計されています。ここに示した仕様を満たす最高周囲温度は、基板レイアウト、パッケージの定格熱抵抗、および他の環境要因に加え、個々の動作条件によって決定されることに留意してください。

<sup>2</sup> 様々な  $V_{IN}$ 、 $V_{OUT}$ 、 $T_A$  の条件については、[熱に関する考慮事項と出力電流のディレーティング](#)のセクションを参照してください。

<sup>3</sup> ウエハ・レベルで 100% テストしています。

<sup>4</sup> LTM4640は、一時的な過負荷状態からデバイスを保護することを目的とした過熱保護機能を備えています。過熱保護機能が作動した場合、ジャンクション温度は  $125^\circ\text{C}$  を超えています。仕様規定された最高動作ジャンクション温度を超える温度での連続動作は、デバイスの信頼性を損なう可能性があります。

<sup>5</sup> 設計により性能を確保しています。ベンチ測定で検証しています。

**絶対最大定格**

特に指定のない限り、 $T_A = 25^\circ\text{C}$ 。

表 2. 絶対最大定格

| PARAMETER                                              | RATING               |

|--------------------------------------------------------|----------------------|

| $V_{IN}$                                               | -0.3V to 22V         |

| $V_{OUT}$                                              | -0.3V to 3.6V        |

| $INTV_{CC}$                                            | -0.3V to 3.6V        |

| RUN                                                    | -0.3V to 20V         |

| PGOOD, FREQ, COMPa, COMPb,<br>PHMODE, CLKOUT, FB       | -0.3V to 3.6V        |

| MODE/CLKIN, TRACK/SS                                   | -0.3V to $INTV_{CC}$ |

| $V_{OSNS}^+$                                           | -0.3V to 3.6V        |

| $V_{OSNS}^-$                                           | -0.3V to 0.3V        |

| Internal operating temperature<br>range <sup>1,2</sup> | -40°C to 125°C       |

| Storage temperature range                              | -55°C to 125°C       |

| Peak solder reflow body<br>temperature                 | 250°C                |

- <sup>1</sup> LTM4640 は、E グレードと I グレードのデバイスを含め（表 14 を参照）、 $T_J \approx T_A$ となるようなパルス負荷条件でテストされています。LTM4640E は、0°C～125°C の内部動作温度範囲内で性能仕様を満たすよう設計されています。-40°C～125°C の内部動作温度範囲全体における仕様は、設計、特性評価、および統計的プロセス制御との相関付けによって裏付けられています。LTM4640I は-40°C～125°C の内部動作温度範囲全域で仕様を満たすよう設計されています。ここに示した仕様を満たす最高周囲温度は、基板レイアウト、パッケージの定格熱抵抗、および他の環境要因に加え、個々の動作条件によって決定されることに留意してください。

- <sup>2</sup> LTM4640 は、一時的な過負荷状態からデバイスを保護することを目的とした過熱保護機能を備えています。過熱保護機能が作動した場合、ジャンクション温度は 125°C を超えています。仕様規定された最高動作ジャンクション温度を超える温度での連続動作は、デバイスの信頼性を損なう可能性があります。

上記の絶対最大定格を超えるストレスを加えるとデバイスに恒久的な損傷を与えることがあります。これらはストレス定格のみを定めたものであり、この仕様の動作のセクションに記載する規定値以上でデバイスが正常に動作することを示唆するものではありません。デバイスを長時間にわたり絶対最大定格状態に置くと、デバイスの信頼性に影響を与えることがあります。

## 熱抵抗

熱性能は、プリント回路基板（PCB）の設計と動作環境に直接関連しています。PCB の熱設計には細心の注意が必要です。

## 静電放電（ESD）

以下の ESD 情報は、ESD に敏感なデバイスを取り扱うために示したものですが、対象は ESD 保護区域内だけに限られます。ANSI/ESDA/JEDEC JS-001 準拠の人体モデル（HBM）。ANSI/ESDA/JEDEC JS-002 準拠の電界誘起帯電デバイス・モデル（FICDM）と帯電デバイスモデル（CDM）。

## ESD 定格

表 3. LTM4640 の ESD 定格

| ESD MODEL | WITHSTAND THRESHOLD (V) | CLASS |

|-----------|-------------------------|-------|

| HBM       | $\pm 2500$              | 3A    |

| CDM       | $\pm 1250$              | C3    |

## ESD に関する注意

ESD（静電放電）の影響を受けやすいデバイスです。

電荷を帯びたデバイスや回路ボードは、検知されないまま放電することがあります。本製品は当社独自の特許技術である ESD 保護回路を内蔵していますが、デバイスが高エネルギーの静電放電を被った場合、損傷を生じる可能性があります。したがって、性能劣化や機能低下を防止するため、ESD に対する適切な予防措置を講じることをお勧めします。

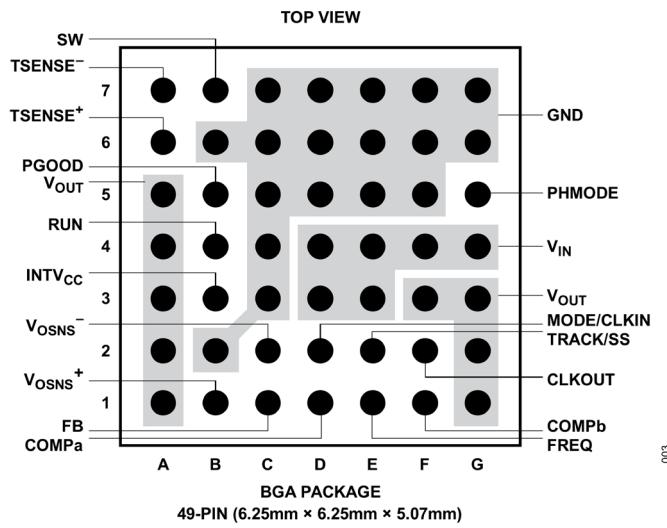

## ピン配置およびピン機能の説明

$T_{JMAX} = 125^{\circ}\text{C}$ ,  $\theta_{JCTop} = 10.1^{\circ}\text{C/W}$ ,  $\theta_{JCBottom} = 3.9^{\circ}\text{C/W}$ ,  $\theta_{JA} = 16^{\circ}\text{C/W}$

θ VALUES ARE DETERMINED BY SIMULATION PER JESD51 CONDITIONS,

WEIGHT 660mg.

θ<sub>JA</sub> VALUE IS OBTAINED WITH DEMO BOARD.

SEE THE APPLICATIONS INFORMATION SECTION FOR LAB MEASUREMENT

AND DERATING INFORMATION.

図 3. ピン配列構成

μModule 製品では、パッケージの行と列のラベル表示が製品ごとに異なることがあります。各パッケージのレイアウトをよくご確認ください。

## 端子説明

表 4. 端子説明

| 端子                                        | 名称                             | 説明                                                                                                                                                      |

|-------------------------------------------|--------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| CFG 1                                     |                                |                                                                                                                                                         |

| A1–A5, F3, G1–G3                          | V <sub>OUT</sub>               | スイッチング・モード・レギュレータの電力出力ピン。これらのピンと GND の間に出力負荷を加えます。これらのピンと GND ピンの間に、出力デカップリング容量を直接接続することを推奨します。出力の並列化については、 <a href="#">アプリケーション情報</a> のセクションを参照してください。 |

| A6                                        | TSENSE <sup>+</sup>            | 温度モニタ・ピン。内蔵の NPN トランジスタがダイオード接続で TSENSE <sup>+</sup> ピンと TSENSE <sup>-</sup> ピンの間に配置されています。詳細については、 <a href="#">アプリケーション情報</a> のセクションを参照してください。         |

| A7                                        | TSENSE <sup>-</sup>            | 内蔵温度モニタの低電圧側。                                                                                                                                           |

| B1                                        | V <sub>OSNS</sub> <sup>+</sup> | 差動リモート検出アンプの正側入力。このピンは、 $10\text{k}\Omega \pm 0.5\%$ の高精度抵抗を介して FB ピンに内部で接続されています。詳細については、 <a href="#">アプリケーション情報</a> のセクションを参照してください。                  |

| B2, B6, C3–C7, D5–D7, E5–E7, F5–F7, G6–G7 | GND                            | 入出力リターン用電源グラウンド・ピン。PCB の大面積銅領域を使用して GND ピンを相互に接続してください。                                                                                                 |

| 端子                   | 名称                 | 説明                                                                                                                                                                                                                                                                                                                                                |

|----------------------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CFG 1                |                    |                                                                                                                                                                                                                                                                                                                                                   |

| B3                   | INTV <sub>CC</sub> | スイッチング・モード・レギュレータ・チャンネルの内部 3.3V レギュレータ出力。内部パワー・ドライバおよび制御回路には、この電圧から給電されます。LTM4640 には 2.2μF のデカップリング・コンデンサが内蔵されています。外付けのデカップリング・コンデンサは必要ありません。                                                                                                                                                                                                     |

| B4                   | RUN                | RUN 制御入力ピン。1.35V を超える電圧に RUN ピンを接続するとレギュレータの動作がイネーブルされます。1.1V 未満の電圧に接続すると、対応するレギュレータ・チャンネルはシャットダウンされます。                                                                                                                                                                                                                                           |

| B5                   | PGOOD              | オープン・ドレイン・ロジックの出力パワー・グッド・ピン。FB ピンの電圧が内部 0.6V リファレンスの ±8% から外れると、PGOOD ピンはグラウンドに引き下げられます。                                                                                                                                                                                                                                                          |

| B7                   | SW                 | テスト目的に使用する各チャンネルのスイッチング・ノード。また、R-C スナバ回路ネットワークを適用してスイッチ・ノードのリンクを低減または除去することもできます。それ以外の場合はフロート状態のままにします。詳細については、 <a href="#">アプリケーション情報</a> のセクションを参照してください。                                                                                                                                                                                       |

| C1                   | FB                 | スイッチング・モード・レギュレータのエラー・アンプの負側入力。このピンは、10kΩ の高精度抵抗を介して V <sub>OSNS+</sub> に内部接続されています。FB ピンと V <sub>OSNS-</sub> ピンの間に抵抗を追加することで、出力電圧を設定できます。PolyPhase®動作では、FB ピンを互いに接続することで並列動作させることができます。詳細については、 <a href="#">アプリケーション情報</a> のセクションを参照してください。                                                                                                      |

| C2                   | V <sub>OSNS-</sub> | 差動リモート検出アンプの負側入力。チャンネルの出力電圧を設定するには、FB ピンと V <sub>OSNS-</sub> ピンの間に外部抵抗を接続します。詳細については、 <a href="#">アプリケーション情報</a> のセクションを参照してください。                                                                                                                                                                                                                 |

| D1                   | COMP <sub>a</sub>  | スイッチング・モード・レギュレータ・チャンネルの電流制御閾値およびエラー・アンプ補償点。内部電流コンパレータの閾値はこの電圧に正比例します。並列動作させる場合は、各チャンネルの COMP <sub>a</sub> ピンを互いに接続してください。このデバイスは内部補償機能を備えています。内部補償機能を使用する場合は、COMP <sub>b</sub> ピンに接続します。また、カスタマイズした補償を使用する場合は、タイプ II の C-R-C ネットワークに接続します。                                                                                                       |

| D2                   | MODE/CLKIN         | 不連続モード選択ピンおよび位相検出器への外部同期入力。不連続導通モード (DCM) 動作を行う場合は、MODE/CLKIN を GND に接続します。MODE/CLKIN をフロート状態にするか 1V を超える電圧に接続すると、強制連続モード (FCM) が選択されます。また、MODE/CLKIN を外部クロックに接続すると、システム・クロックが外部クロックに同期し、デバイスは FCM で動作します。詳細については、 <a href="#">アプリケーション情報</a> のセクションを参照してください。                                                                                    |

| D3–D4, E3–E4, F4, G4 | V <sub>IN</sub>    | 内部の上側 MOSFET のドレインに接続されている電源入力ピンであり、各スイッチング・モード・レギュレータ・チャンネルの制御回路用 3.3V 内部レギュレータに接続されている V <sub>IN</sub> 信号もあります。これらのピンと GND ピンの間に入力電圧を印加します。各 V <sub>IN</sub> ピンと GND ピンの間には、入力デカップリング・コンデンサを直接接続することを推奨します。                                                                                                                                     |

| E1                   | FREQ               | スイッチング周波数設定ピン。周波数は内部で 600kHz に設定されています。外付け抵抗をこのピンと GND の間に配置すると周波数が増加し、また、このピンと INTV <sub>CC</sub> の間に配置すると周波数が減少します。周波数の調整については、 <a href="#">アプリケーション情報</a> のセクションを参照してください。                                                                                                                                                                     |

| E2                   | TRACK/SS           | スイッチング・モード・レギュレータの出力トラッキングおよびソフトスタート・ピン。TRACK/SS ピンを使用して出力電圧の立ち上がり時間を制御できます。このピンの電圧を 0.6V 未満にすると、エラー・アンプの内部リファレンス入力をバイパスし、TRACK の電圧を目標に FB ピンをサーボ制御します。0.6V を超えると、トラッキング機能は停止し、内部リファレンスによるエラー・アンプの制御が再開されます。このピンには INTV <sub>CC</sub> からの内部 6μA ブルアップ電流があるため、コンデンサを配置することによりソフトスタート機能を実施できます。詳細については、 <a href="#">アプリケーション情報</a> のセクションを参照してください。 |

| 端子    | 名称     | 説明                                                                                                                                                                                                                                 |

|-------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CFG 1 |        |                                                                                                                                                                                                                                    |

| F1    | COMPb  | 内部ループ補償ネットワーク。大多数のアプリケーションでは、COMPa ピンに接続して内部補償を使用します。                                                                                                                                                                              |

| F2    | CLKOUT | PolyPhase 動作用のクロック信号出力。CLKIN を基準とする CLKOUT の位相は、対応する PHMODE ピンの状態によって決まります。CLKOUT のピーク to ピーク振幅は $\text{INTV}_{\text{CC}} \sim \text{GND}$ です。詳細については、 <a href="#">アプリケーション情報</a> のセクションを参照してください。                                 |

| G5    | PHMODE | スイッチング・モード・レギュレータの位相セレクタへの制御入力。内部発振器と CLKOUT の間の位相関係を決定します。2 相動作の場合はこのピンを $\text{INTV}_{\text{CC}}$ に接続してください。3 相動作の場合は GND に接続し、4 相動作の場合は $\text{INTV}_{\text{CC}}/2$ に接続します。詳細については、 <a href="#">アプリケーション情報</a> のセクションを参照してください。 |

表 5. LTM4640 の BGA ピン配置

| PIN ID       | FUNCTION            | PIN ID | FUNCTION            | PIN ID | FUNCTION                  | PIN ID | FUNCTION         |

|--------------|---------------------|--------|---------------------|--------|---------------------------|--------|------------------|

| <b>A1-G4</b> |                     |        |                     |        |                           |        |                  |

| A1           | $V_{\text{OUT}}$    | A2     | $V_{\text{OUT}}$    | A3     | $V_{\text{OUT}}$          | A4     | $V_{\text{OUT}}$ |

| B1           | $V_{\text{OSNS}^+}$ | B2     | GND                 | B3     | $\text{INTV}_{\text{CC}}$ | B4     | RUN              |

| C1           | FB                  | C2     | $V_{\text{OSNS}^-}$ | C3     | GND                       | C4     | GND              |

| D1           | COMPa               | D2     | MODE/CLKIN          | D3     | $V_{\text{IN}}$           | D4     | $V_{\text{IN}}$  |

| E1           | FREQ                | E2     | TRACK/SS            | E3     | $V_{\text{IN}}$           | E4     | $V_{\text{IN}}$  |

| F1           | COMPb               | F2     | CLKOUT              | F3     | $V_{\text{OUT}}$          | F4     | $V_{\text{IN}}$  |

| G1           | $V_{\text{OUT}}$    | G2     | $V_{\text{OUT}}$    | G3     | $V_{\text{OUT}}$          | G4     | $V_{\text{IN}}$  |

| <b>A5-G7</b> |                     |        |                     |        |                           |        |                  |

| A5           | $V_{\text{OUT}}$    | A6     | TSENSE <sup>+</sup> | A7     | TSENSE <sup>-</sup>       |        |                  |

| B5           | PGOOD               | B6     | GND                 | B7     | SW                        |        |                  |

| C5           | GND                 | C6     | GND                 | C7     | GND                       |        |                  |

| D5           | GND                 | D6     | GND                 | D7     | GND                       |        |                  |

| E5           | GND                 | E6     | GND                 | E7     | GND                       |        |                  |

| F5           | GND                 | F6     | GND                 | F7     | GND                       |        |                  |

| G5           | PHMODE              | G6     | GND                 | G7     | GND                       |        |                  |

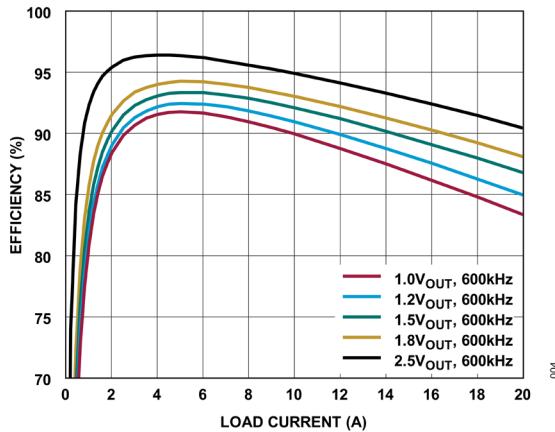

## 代表的な性能特性

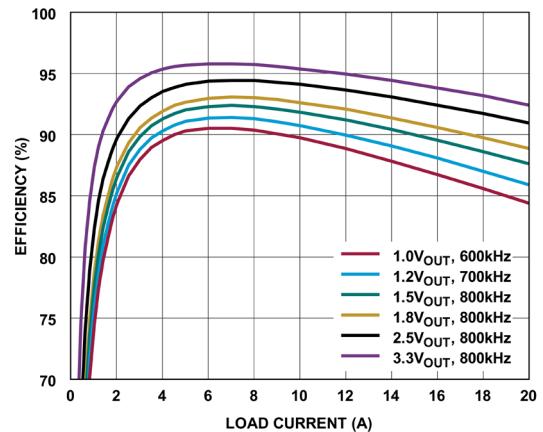

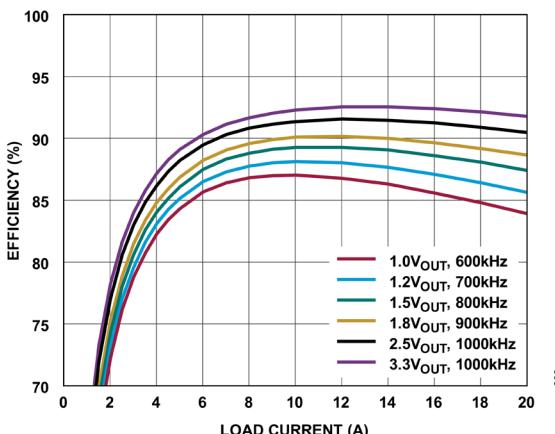

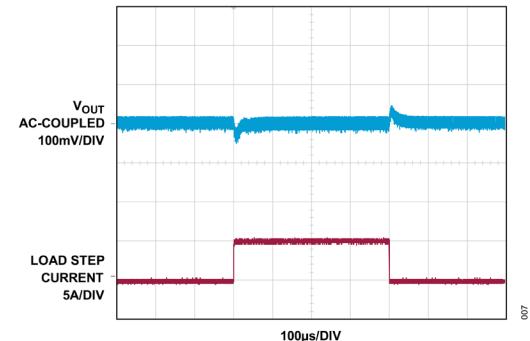

図 4.  $3.3V_{IN}$  での効率と負荷電流の関係図 5.  $5V_{IN}$  での効率と負荷電流の関係図 6.  $12V_{IN}$  での効率と負荷電流の関係図 7.  $1V_{OUT}$  時の過渡応答

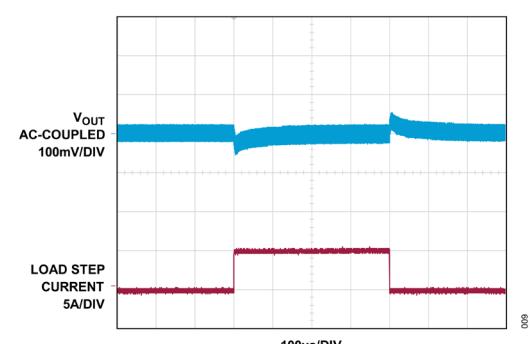

図 10. 3.3V<sub>OUT</sub>時の過渡応答

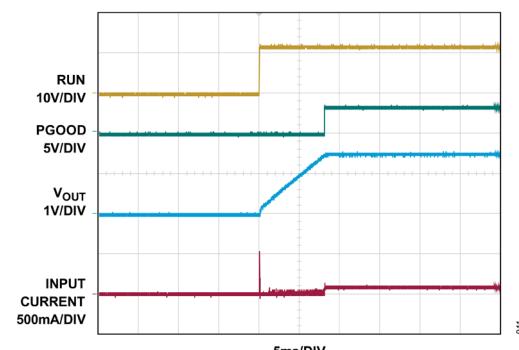

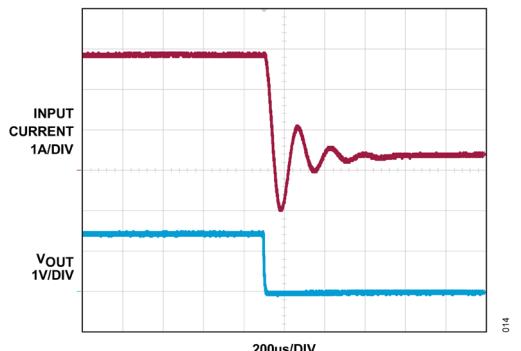

図 11. 無負荷電流における起動時の波形

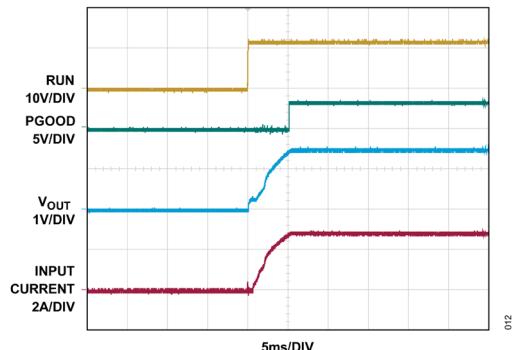

図 12. 20A 負荷電流における起動時の波形

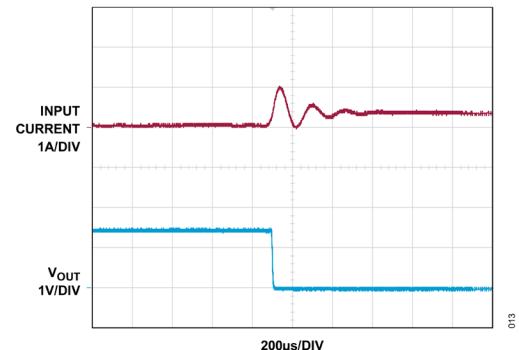

図 13. 無負荷電流状態での出力短絡時の波形

図 14. 20A 負荷電流印加状態での出力短絡時の波形

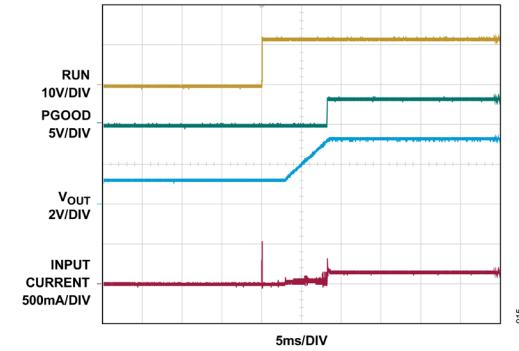

図 15. プリバイアス出力への起動

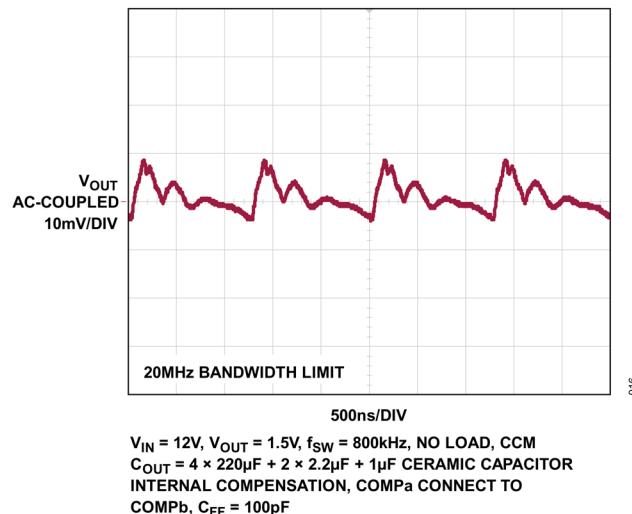

図 16. 定常状態の出力電圧リップル

## 動作原理

### LTM4640 の概要

LTM4640 は、スタンダードアロンで動作する非絶縁型スイッチ・モード DC/DC 電源です。LTM4640 は、わずかな外付け入出力コンデンサの使用で最大 20A の DC 出力電流を供給できます。この μModule は、3.1V~20V の入力電圧範囲にわたり、1 つの外付け抵抗を使用して正確に安定化された出力電圧を供給し、その電圧は 0.6V~3.3V の範囲で調整可能です。代表的なアプリケーション回路図を図 37 に示します。

LTM4640 は、オン時間制御式の谷電流モード・コントローラ、パワーMOSFET、インダクタ、その他のサポート用ディスクリート部品を内蔵しています。デフォルトのスイッチング周波数は 600kHz です。ノイズの影響を受けやすいアプリケーションのために、スイッチング周波数を外付け抵抗で調整でき、μModule レギュレータを設定周波数の±30%以内のクロックに外部同期させることも可能です。詳細については、[アプリケーション情報](#)のセクションを参照してください。

電流モード制御と内部帰還ループ補償を使用することにより、LTM4640 では、使用する出力コンデンサがすべてセラミック・コンデンサである場合を含め、様々な出力コンデンサで十分な安定性マージンと良好な高速トランジエント性能が得られます。

電流モード制御は、サイクルごとに高速の電流制限を行います。出力帰還電圧がレギュレーション・ポイントの±8%のウインドウから外れると、内蔵の出力過電圧コンパレータまたは低電圧コンパレータがオープンドレインの PGOOD 出力をローにします。過電圧および低電圧状態でも連続動作が強制されますが、TRACK ピンが 0.6V に向けて増加している起動時は例外です。

更に、内蔵のパワーMOSFET デバイスを過渡的な電圧スパイクから保護するために、LTM4640 は V<sub>IN</sub> ピンを継続的にモニタし、過電圧状態に備えています。V<sub>IN</sub> が 24.5V を上回ると、レギュレータは両方のパワーMOSFET をオフすることにより動作を一時停止します。V<sub>IN</sub> が 21.5V 未満になると、レギュレータは直ちに通常動作を再開します。過電圧状態が解消されたときには、レギュレータはソフトスタート機能を実行しません。

マルチフェーズ動作は、同期および位相モード制御を用いて容易に設定できます。PHMODE ピンを様々なレベルに設定することによって、最大 4 フェーズを互いにカスケードさせて同時に動作させることができます。LTM4640 は MODE/CLKIN ピンと CLKOUT ピンを備えており、複数デバイスの PolyPhase 動作や周波数同期に使用できます。

RUN ピンを GND に引き下げるとき、コントローラは強制的にシャットダウン状態になり、両方のパワーMOSFET とほとんどの内部制御回路がオフになります。軽負荷電流時には、MODE/CLKIN ピンを GND にプルダウンすることにより、不連続導通モード (DCM) 動作を有効にし、連続導通モード (CCM) に比べて高い効率を達成できます。電源のトラッキングとソフトスタートのプログラミングには、TRACK/SS ピンを使用します。詳細については、[アプリケーション情報](#)のセクションを参照してください。

## 簡略化したブロック図

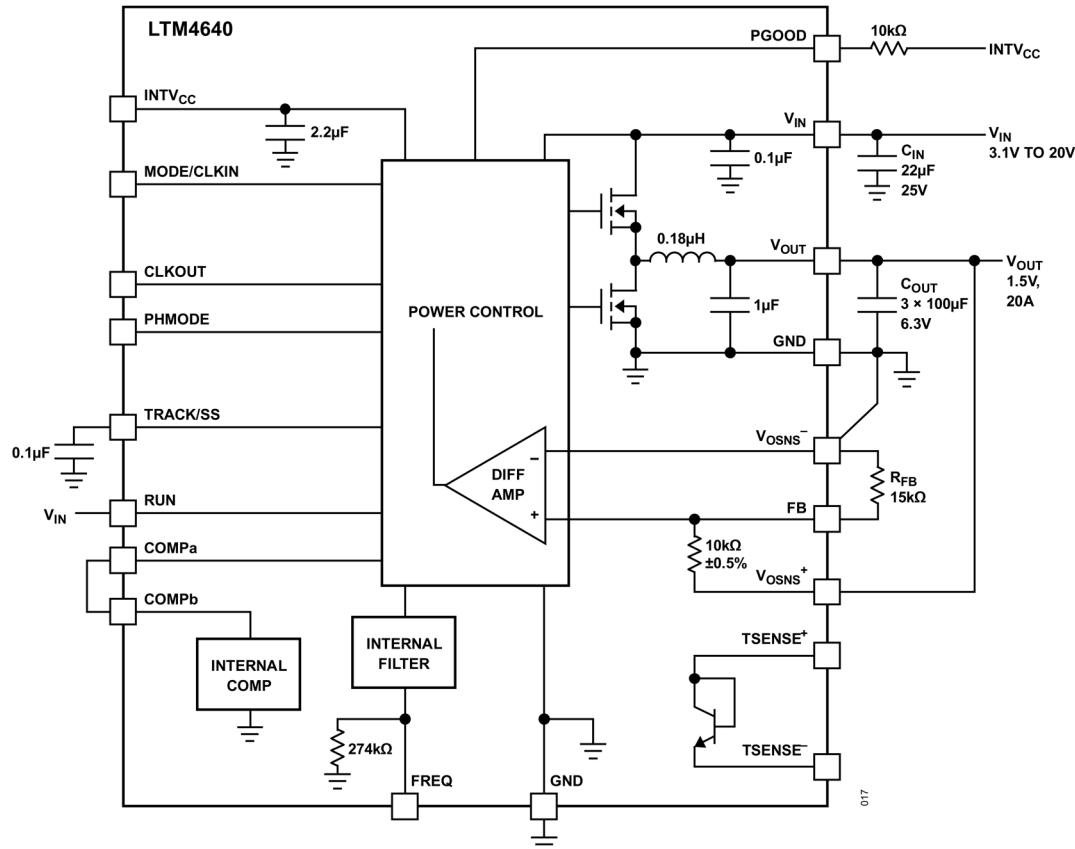

図 17. LTM4640 の簡略化したブロック図

## デカップリング条件

表 6. デカップリング条件

| SYMBOL    | PARAMETER                                                                                | CONDITIONS      | MIN              | TYP              | MAX | UNITS |

|-----------|------------------------------------------------------------------------------------------|-----------------|------------------|------------------|-----|-------|

| $C_{IN}$  | External input capacitor requirement<br>( $V_{IN} = 3.1V$ to $20V$ , $V_{OUT} = 1.5V$ )  | $I_{OUT} = 20A$ | 33               | 44               |     | μF    |

| $C_{OUT}$ | External output capacitor requirement<br>( $V_{IN} = 3.1V$ to $20V$ , $V_{OUT} = 1.5V$ ) | $I_{OUT} = 20A$ | 330 <sup>1</sup> | 470 <sup>1</sup> |     | μF    |

<sup>1</sup> 極端な温度条件やコンデンサのバイパス電圧条件、あるいはその両方が存在する場合、バイアス電圧と温度の範囲にわたる実容量の変動により、容量の追加が必要となる場合があります。

## アプリケーション情報

LTM4640 の代表的なアプリケーション回路を図 37 に示します。外付け部品は、主に入力電圧、出力電圧、負荷変動、最大負荷電流に基づいて選定します。特定のアプリケーションに対する外付けコンデンサの具体的な要件については、表 12 を参照してください。

### V<sub>IN</sub> から V<sub>OUT</sub>への降圧比

レギュレータの最小オフ時間および最小オン時間の制限により、V<sub>IN</sub> から V<sub>OUT</sub>への最大降圧比は、与えられた入力電圧に応じて実現可能な値に制限されます。最小オフ時間制限によってデューティ・サイクルの最大値が決まり、式 1 を使用して計算できます。

$$D_{MAX} = 1 - (t_{OFF(MIN)} \times f_{SW}) \quad (1)$$

ここで、t<sub>OFF(MIN)</sub>は最小オフ時間であり、LTM4640 の代表値は 50ns です。また、f<sub>SW</sub> (Hz) はスイッチング周波数です。逆に、最小オン時間の制限によってコンバータの最小デューティ・サイクルが決まり、式 2 を使用して計算できます。

$$D_{MIN} = t_{ON(MIN)} \times f_{SW} \quad (2)$$

ここで、t<sub>ON(MIN)</sub>は最小オン時間で、LTM4640 の代表値は 25ns です。デューティ・サイクルの最小値を超えるまれなケースでは、出力電圧はレギュレーション状態を維持し、スイッチング周波数は設定値より低くなります。熱によるディレーティングが追加されることにも注意してください。熱に関する考慮事項と出力電流のディレーティングのセクションを参照してください。

### 出力電圧の設定

パルス幅変調 (PWM) コントローラは、0.6V のリファレンス電圧を内蔵しています。図 17 (簡略化したブロック図) に示すように、10kΩ の内部帰還抵抗で V<sub>OSNS<sup>+</sup></sub>ピンと FB ピンが接続されています。FB ピンと V<sub>OSNS<sup>-</sup></sub>ピンの間に抵抗 R<sub>FB</sub>を追加することで、出力電圧を式 3 に従って設定します。

$$R_{FB} = \frac{0.6V}{V_{OUT} - 0.6V} \times 10k\Omega \quad (3)$$

表 7 には、いくつかの代表的な出力電圧のアプリケーションについて求められる R<sub>FB</sub>の値をまとめています。

表 7. 様々な出力電圧に対する R<sub>FB</sub> 抵抗の表

| V <sub>OUT</sub> (V) | 0.6  | 1.0 | 1.2 | 1.5  | 1.8  | 2.5  | 3.3  |

|----------------------|------|-----|-----|------|------|------|------|

| R <sub>FB</sub> (kΩ) | OPEN | 15  | 10  | 6.65 | 4.99 | 3.16 | 2.21 |

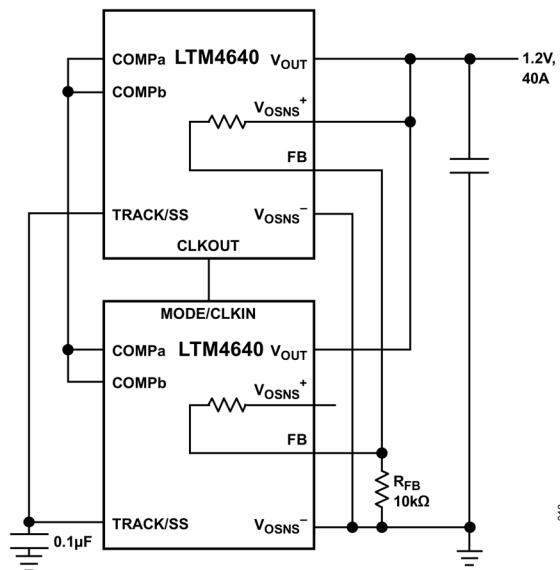

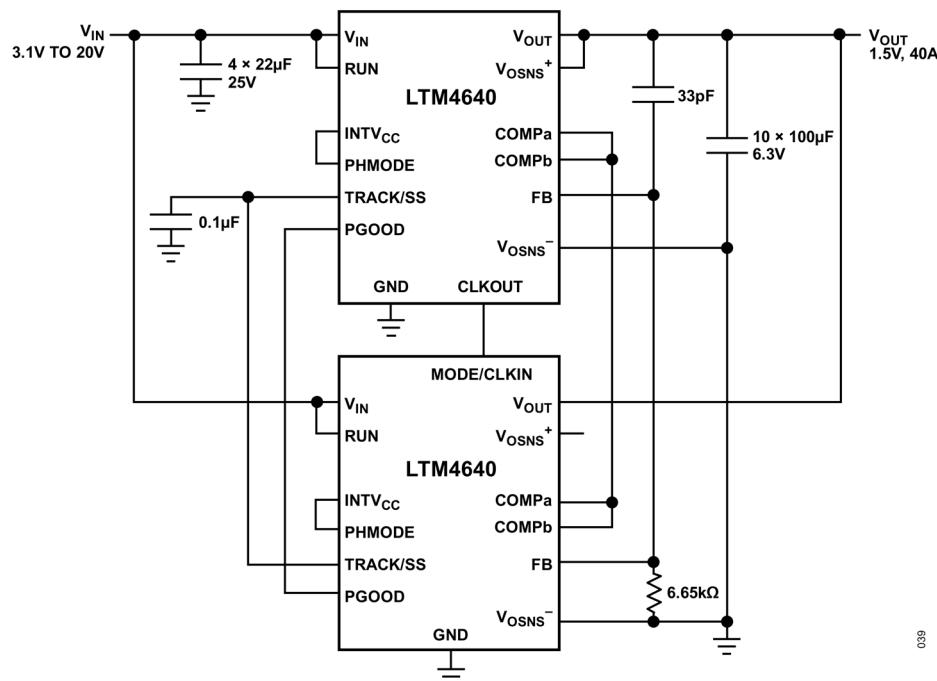

複数のチャンネルを並列に動作させる並列化設計では、同一の帰還設定抵抗を使用します。並列化を行うには、図 18 に示すように、V<sub>OSNS<sup>+</sup></sub>と出力を接続して、内蔵の 10kΩ 抵抗の 1つを出力に接続します。図 18 に示すように、すべての V<sub>FB</sub>ピンをまとめて 1つの設定抵抗に接続します。並列動作の例については、図 39 を参照してください。

図 18.2 相並列構成

## 入力デカップリング・コンデンサ

LTM4640 は、低 AC インピーダンスの DC 電源に接続する必要があります。二乗平均平方根（実効値）リップル電流をデカップリングするため、レギュレータには  $22\mu\text{F}$  の入力セラミック・コンデンサを使用することを推奨します。バルク入力コンデンサが必要になるのは、長い誘導性のリード線やパターン、または電源の容量不足によって入力ソース・インピーダンスが損なわれる場合に限られます。バルク・コンデンサには、アルミ電解コンデンサやポリマー・コンデンサを使用します。

インダクタ電流リップルを考慮に入れなければ、入力コンデンサの実効値電流は式 4 で概算できます。

$$I_{CIN(RMS)} = \frac{I_{OUT(MAX)}}{\eta\%} \times \sqrt{\frac{V_{OUT} \times (V_{IN} - V_{OUT})}{V_{IN}^2}} \quad (4)$$

ここで、 $\eta\%$  はパワー  $\mu\text{Module}$  レギュレータの推定効率です。

## 出力デカップリング・コンデンサ

最適化された高周波・広帯域幅の設計では、LTM4640 の出力に低等価直列抵抗 (ESR) 出力のセラミック・コンデンサを 1 個追加するだけで、低出力電圧リップルと優れた過渡応答を実現できます。極端な低温または高温の条件、あるいは高出力電圧条件では、バイアス電圧と温度の範囲にわたり実容量の変動があるため、セラミック・コンデンサまたはタンタル・ポリマー・コンデンサの追加が必要です。

表 12 には、5A の負荷ステップ遷移時に電圧ドループとオーバーシュートを最小限に抑えるための、様々な出力電圧と出力コンデンサの組み合わせを示しています。出力リップルまたは動的トランジエント・スペイクを更に低減する必要がある場合、システム設計において追加の出力フィルタリングが必要になる場合があります。アナログ・デバイセズの LTpowerCAD® 設計ツールは、オンラインでダウンロードでき、出力リップル、安定性、過渡応答を解析して更なる最適化を実施できます。

## 不連続導通モード

中程度の電流に対して低出力リップルと高効率が求められるアプリケーションでは、MODE/CLKIN ピンを GND に接続して不連続導通モード (DCM) を使用します。軽負荷時には、内蔵の電流コンパレータが数サイクルの間作動したままになり、上側 MOSFET を数サイクルの間オフに保つことにより、サイクルがスキップされます。このモードではインダクタ電流は反転しません。

## 連続強制モード

低電流での効率よりも固定周波数の動作が重要なアプリケーション、および出力リップルを最小限に抑える必要があるアプリケーションでは、FCM動作を使用します。FCM動作は、MODE/CLKINピンをINTV<sub>CC</sub>に接続することでイネーブルされます。このモードでは、低出力負荷の状態ではインダクタ電流が反転する場合があり、COMP電圧が終始電流コンパレータの閾値を制御し、上側MOSFETは発振器のパルスごとに必ずオンになります。スタートアップ時にはFCMは無効になっており、LTM4640の出力電圧がレギュレーション状態になるまではインダクタ電流が反転することはありません。

## 動作周波数

LTM4640の動作周波数は、小型パッケージ・サイズと最小の出力リップル電圧を実現しながらも高効率を維持できるよう最適化されています。デフォルトの動作周波数は600kHzです。ほとんどのアプリケーションでは、周波数を調整する必要はありません。

アプリケーションで600kHz以外の動作周波数が必要である場合には、図38に示すように抵抗RFSETをFREQピンとGNDの間に配置すると動作周波数が増加し、FREQピンとINTVCCの間に抵抗を配置すると減少します。RFSETの抵抗値は式5で計算されます。

$$R_{FSET} = \begin{cases} \frac{1.67 \times 10^{11} \Omega \times Hz}{f - 600kHz} & (f > 600kHz) \\ \frac{2.72 \times 10^{11} \Omega \times Hz}{600kHz - f} & (f < 600kHz) \end{cases} \quad (5)$$

設定可能な動作周波数範囲は400kHz～3MHzです。

## 周波数同期とクロック入力

LTM4640は、内蔵電圧制御発振器と位相検出器で構成されるフェーズ・ロック・ループを備えています。これにより、内部の上側MOSFETのターンオンを外部クロックの立上がりエッジに同期させることができます。外部クロックの周波数は、RFSET抵抗で設定された周波数の±30%の範囲内であることが必要です。パルス検出回路がCLKINピンのクロックを検出し、フェーズ・ロック・ループをオンします。クロックのパルス幅は100ns以上であることが必要です。クロックのハイ・レベルは1Vより高く、ロー・レベルは0.3Vより低いことが必要です。レギュレータの起動中は、フェーズ・ロック・ループ機能は無効になっています。

## マルチフェーズ動作

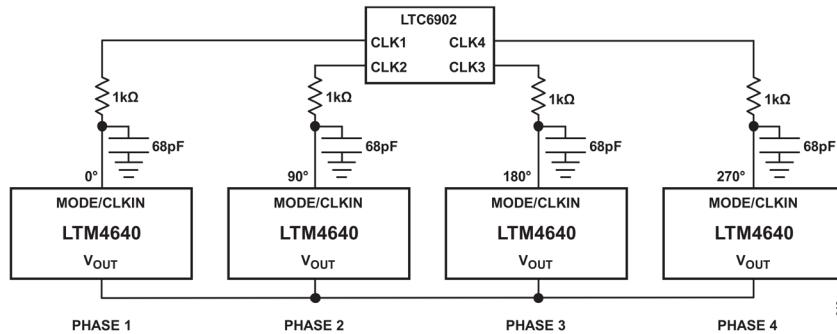

出力負荷が20Aを超える電流を必要とする場合、複数のLTM4640を並列に接続し、位相をずらして動作させることで、入出力の電圧リップルを増やさずに出力電流を増やすことができます。

CLKOUT信号を後続段のLTM4640のCLKINピンに接続することにより、システム全体の周波数と位相の両方を揃えることができます。PHMODEピンをINTV<sub>CC</sub>ピンに接続すると180°、GNDピンに接続すると120°、フロート状態にすると90°の位相差がそれぞれCLKINとCLKOUTの間に生じ、これらは2相動作、3相動作、4相動作に相当します。図39に2相の設計を示します。3相動作または4相動作で最高の性能を実現するためには、外付けのクロック集積回路(IC)を使用して、各LTM4640に必要な位相差を与えることを推奨します。各外部クロック信号に、LTM4640に供給される手前にオプションのローパス・フィルタを追加することもできます。図19にそのような4相の設計を示します。4相より多い相の間でのインターリーブは推奨されません。

表 8. PHMODE ピンの状態と対応する位相関係（CLKIN 基準）

| PHMODE | INTV <sub>CC</sub> | GND  | FLOAT |

|--------|--------------------|------|-------|

| CLKOUT | 180°               | 120° | 90°   |

図 19. 外部クロック IC とローパス・フィルタを使用した 4 相動作

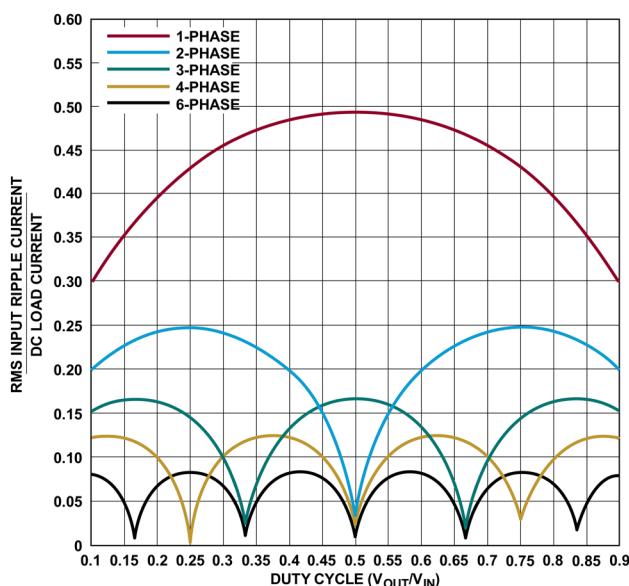

マルチフェーズ電源では、入力コンデンサと出力コンデンサのリップル電流の量が大幅に低減します。実効値入力リップル電流は使用した位相の数に応じて小さくなり、実効リップル周波数は位相数を乗じた値になります（入力電圧が、出力電圧と使用している位相数を乗じた値より大きい場合）。また、すべての出力を 1 つに接続して单一の高出力電流を得る設計にした場合、出力リップルの振幅も、使用する位相数に応じて小さくなります。

LTM4640 は本質的に電流モード・コントローラ・デバイスであるので、並列動作では良好な電流分担が確保されます。設計上の熱バランスが保たれます。並列に配置された各チャンネルの RUN ピン、TRACK/SS ピン、FB ピン、COMPa ピンを相互に接続してください。図 39 に並列動作とピン接続の例を示します。

### 入力実効値リップル電流の相殺

アナログ・デバイセズのアプリケーション・ノート 77 には、マルチフェーズ動作が詳細に説明されています。入力実効値リップル電流の相殺に関する数学的導出が提示されており、インターリープ相数の関数として実効値リップル電流が減少する様子がグラフに示されています。図 20 に、このグラフを示します。

図 20. デューティ・サイクルの関数としての DC 負荷電流に対する入力実効値電流の比

## ソフトスタートおよび出力電圧トラッキング

TRACK/SS ピンを使用して、レギュレータのソフトスタート、または異なる電源とのトラッキングが可能です。TRACK/SS ピンにコンデンサを接続して、出力電圧の上昇率を設定します。6 $\mu$ A の内部電流源が、外付けのソフトスタート・コンデンサを INTV<sub>CC</sub> 電圧まで充電します。TRACK/SS の電圧が 0.6V 未満の間は、0.6V の内部リファレンス電圧の代わりに TRACK/SS が出力電圧を制御します。合計ソフトスタート時間は、式 6 で計算されます。

$$t_{ss} = 0.6V \times \frac{C_{ss}}{6\mu A} \quad (6)$$

ここで、 $C_{ss}$  は TRACK/SS ピンの容量です。ソフトスタート・プロセスの間は、電流フォールドバックと FCM は無効になります。

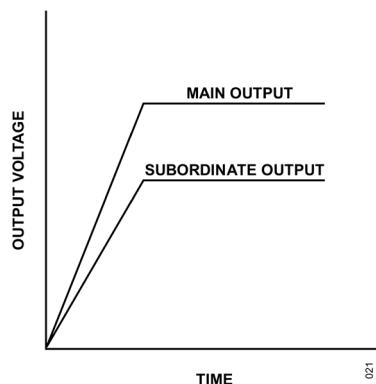

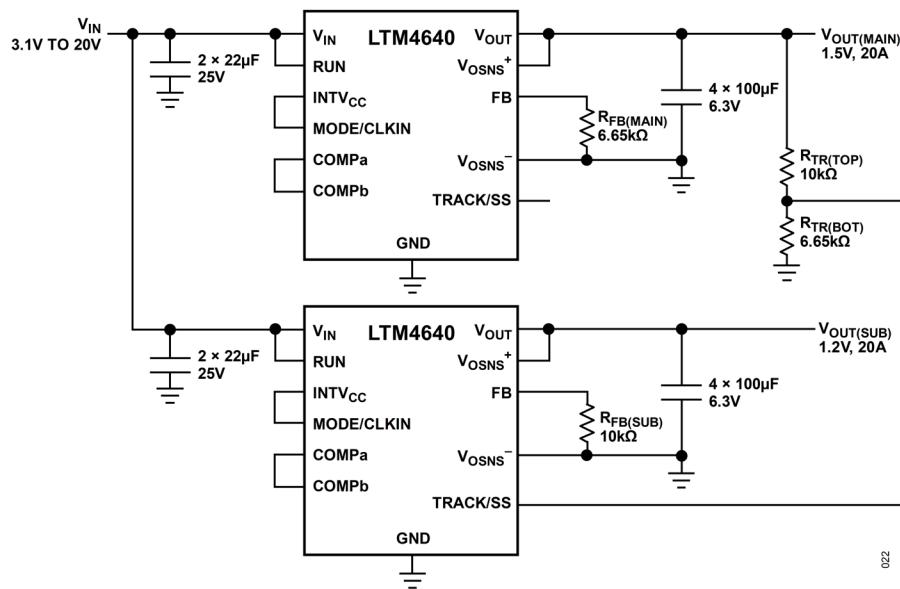

TRACK/SS ピンを使用して、出力電圧のトラッキングを外部で設定することもできます。出力は、他のレギュレータに合わせて上昇および下降するようトラッキングされます。図 21 と図 22 は比例トラッキングの波形と回路図の例を示しており、下位レギュレータの出力スルーレートはメイン・デバイスに比例しています。

図 21. 出力比例トラッキングの波形

図 22. 比例出力電圧トラッキングの回路図の例

下位レギュレータの TRACK/SS は抵抗分圧器  $R_{TR(TOP)}/R_{TR(BOT)}$  を介してメイン・デバイスの出力に接続されており、TRACK/SS 電圧が 0.6V より低いときはこの電圧が下位デバイスの出力電圧を安定化するため、スタートアップ中の下位デバイスの出力電圧とメイン・デバイスの出力電圧は式 7 を満足します。

$$\begin{aligned} & V_{OUT(SUB)} \times \frac{R_{FB(SUB)}}{R_{FB(SUB)} + 10k\Omega} \\ & = V_{OUT(MAIN)} \times \frac{R_{TR(BOT)}}{R_{TR(TOP)} + R_{TR(BOT)}} \end{aligned} \quad (7)$$

$R_{FB(SUB)}$  は帰還抵抗、 $R_{TR(TOP)}/R_{TR(BOT)}$  は下位レギュレータの TRACK/SS ピンに接続された抵抗分圧器です（図 22 参照）。

式 7 により、メイン・デバイスの出力スルーレート (MR) と下位デバイスの出力スルーレート (SR) の比は式 8 に示すようになります。

$$\frac{MR}{SR} = \frac{\frac{R_{FB(SUB)}}{R_{FB(SUB)} + 10k\Omega}}{\frac{R_{TR(BOT)}}{R_{TR(TOP)} + R_{TR(BOT)}}} \quad (8)$$

例えば、 $V_{OUT(MAIN)} = 1.5V$ 、 $MR = 1.5V/1ms$ 、 $V_{OUT(SUB)} = 1.2V$ 、 $SR = 1.2V/1ms$  とします。式 8 から、 $R_{TR(TOP)} = 10k\Omega$ 、 $R_{TR(BOT)} = 6.65k\Omega$  の組み合わせがこの比例トラッキングに適切であると求められます。

抵抗分圧器を使用して下位レギュレータをトラッキングしている場合、TRACK/SS ピンには  $6\mu A$  の電流源が存在します。これにより、TRACK/SS ピンの入力にオフセットが発生します。このような影響を緩和するために、式 8 で計算した抵抗値と同じ比率で、より小さな値の抵抗を使用することを推奨します。例えば、 $10k\Omega$  を使用していたところに  $5k\Omega$  を使用することで TRACK/SS ピンのオフセットを無視できる値まで低減することができます。

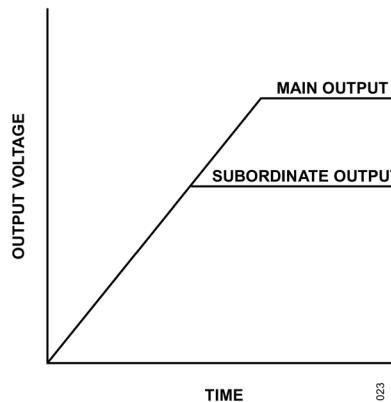

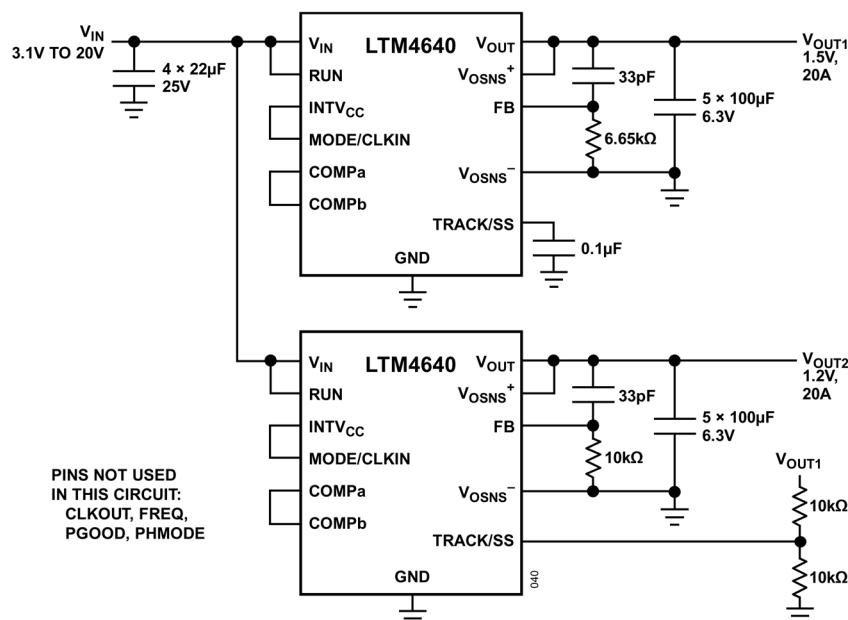

同時出力トラッキングは、比例出力トラッキングにおいてメイン・デバイスの出力スルーレート (MR) と下位デバイスの出力スルーレート (SR) が等しい特別な場合と見なすことができ、波形は図 23 に示すようになります。

図 23. 出力同時トラッキングの波形

式 8 から、同時トラッキングでは下位レギュレータの TRACK/SS ピンの抵抗分圧器は常に帰還分圧器と等しいことが容易に分かります（式 9）。

$$\frac{R_{FB(SUB)}}{R_{FB(SUB)} + 10k\Omega} = \frac{R_{TR(BOT)}}{R_{TR(TOP)} + R_{TR(BOT)}} \quad (9)$$

例えば、 $V_{OUT(MAIN)}=1.5V$  および  $V_{OUT(SUB)}=1.2V$  のアプリケーションにおける同時トラッキングには、 $R_{TR(TOP)}=10k\Omega$  および  $R_{TR(BOT)}=10k\Omega$  の組み合わせが良いことが分かります。

## パワー・グッド

PGOOD ピンはオープン・ドレイン・ピンで、出力電圧が有効にレギュレーションされているかどうかをモニタするために使用します。出力電圧がレギュレーション・ポイントの±8%のウインドウから外れると、このピンはローにプルダウンされます。トランジエント時または VOUT の動的変化時に不要な PGOOD のグリッチが生じるのを防ぐため、LTM4640 の PGOOD の立下がりエッジには、約 25 スイッチング・サイクルのブランкиング遅延が与えられています。

## RUN イネーブル

RUN ピンをグラウンドに引き下げると LTM4640 は強制的にシャットダウン状態となり、両方のパワーMOSFET とほとんどの内部制御回路がオフになります。RUN ピンが 0.6V より高くなると、内部リファレンスのみがオンになり、パワーMOSFET はオフの状態を保ちます。RUN ピンの電圧が 1.35V を超える値まで上昇すると、デバイス全体がオンになります。

## プライバイス出力に向けた起動

状況によっては、出力コンデンサに電荷がある状態で電源を起動することが必要になります。LTM4640 は、出力コンデンサを放電せずに、プライバイスされた出力に向けて安全に起動できます。

LTM4640 では、TRACK/SS ピンが 0.6V のリファレンス電圧に達するまで強制的に不連続モード (DCM) で動作することにより、この動作が実現されます。プライバイスされた出力での起動中に下側 FET がオンして出力を放電してしまうことを防ぎます。

## SW ピンとオプションのスナバ回路

SW ピンは一般的にテスト目的で使用します。SW ピンを使用して、スイッチング電流経路内の LC 寄生成分によるスイッチ・ノードのリングを、直列 RC スナバ回路を使用して減衰させることもできます。抵抗が共振を減衰するため、コンデンサは、抵抗両端に生じる高周波のリングをのみ影響するよう選択します。LTM4640 は PCB レイアウトが適切であれば良好に動作し得るため、スナバ回路はオプションです。必要な場合のため、以下にスナバ回路の設計に関する推奨を示します。

浮遊インダクタンスまたは浮遊容量を測定または概算できる場合は、解析的手法を用いてスナバ回路の各値を選択できます。通常、予測しやすいのはインダクタンスの方です。このインダクタンスは、電源経路のインダクタンスと MOSFET 接続用ボンディング・ワイヤのインダクタンスが組み合わさったものです。

最初に SW ピンを、高周波プローブを用い広帯域オシロスコープでモニタします。その値に対するリング周波数が測定できます。インピーダンス  $Z_L$  は式 10 で計算されます。

$$Z_L = 2\pi \times f \times L \quad (10)$$

ここで、f はリングの共振周波数、L はスイッチ経路の総寄生インダクタンスです。 $Z_L$  に等しい抵抗を選択すれば、リングが減衰するはずです。スナバ回路のキャパシタの値は、リング周波数でインピーダンスが抵抗と等しくなるよう選択します。これは式 11 によって計算します。

$$Z_C = \frac{1}{2\pi \times f \times C} \quad (11)$$

これらの値が良い開始点となります。これらの部品値は、電力損失を最小限に抑えながらリングを減衰させるように変更する必要があります。

## 安定性補償

LTM4640 では、COMP<sub>b</sub> と COMP<sub>a</sub> を接続した場合には、すべてセラミック・コンデンサを用いるアプリケーションを含み、出力電圧とコンデンサのあらゆる組み合わせに対して既に内部補償が行われています。出力コンデンサがすべてセラミック・コンデンサであるアプリケーションで、十分な位相マージンを確保し広帯域幅の制御ループ補償を実現するためには、V<sub>OUT</sub> と V<sub>FB</sub> の間に 22pF~100pF のフィードフォワード・コンデンサ (C<sub>FF</sub>) の接続が必要です。表 12 は、この最適化された内部補償を使用するほとんどのアプリケーション条件を示しています。

特定の最適化条件がある場合は、COMP<sub>b</sub> を COMP<sub>a</sub> から切り離し、タイプ II の補償ネットワークを COMP<sub>a</sub> と GND の間に適用して、外部補償を行います。ライン変動や負荷変動に対して必要な出力応答や、帰還ループの位相マージンやゲイン・マージンなどのループ安定性パラメータに応じて、タイプ II ネットワークの部品を選定してください。一般的に、COMP<sub>a</sub> ピンのタイプ II ネットワークに対しては、低容量および高抵抗を選択すると、高速過渡応答が実現できますが、ループ安定性パラメータには悪影響を及ぼす可能性があります。

LTpowerCAD 設計ツールは、オンラインでダウンロードでき、特定の制御ループの最適化や、制御安定性と負荷過渡応答性能の分析が可能です。

## 差動リモート検出アンプ

LTM4640 は高精度の差動リモート検出アンプを備えており、リモートの負荷ポイントの出力電圧を正確に測定できます。大電流負荷の場合には特に正確なものとなります。V<sub>OSNS<sup>+</sup></sub> ピンと V<sub>OSNS<sup>-</sup></sub> ピンをリモート出力検出ポイントに適切に接続し、帰還抵抗 R<sub>FB</sub> を V<sub>FB</sub> ピンと V<sub>OSNS<sup>-</sup></sub> ピンの間に接続することが重要です (図 37 参照)。

マルチフェーズ単一出力アプリケーションでは、1組の差動検出アンプと1組の帰還抵抗のみが必要で、各チャンネルの RUN、TRACK/SS、V<sub>OUT</sub>、V<sub>FB</sub>、COMP<sub>a</sub> はまとめて接続します。並列アプリケーションの例については、図 39 を参照してください。

## 入力過電圧保護

内蔵のパワーMOSFET デバイスをトランジエント電圧スパイクから保護するために、LTM4640 は、V<sub>IN</sub> ピンを定的にモニタし、過電圧状態に備えています。V<sub>IN</sub> が 24.5V を上回ると、レギュレータは、上回ったチャンネルのパワーMOSFET を両方ともオフして動作を一時停止します。V<sub>IN</sub> が 21.5V 未満になると、レギュレータは直ちに通常動作を再開します。過電圧状態が解消されると、レギュレータはソフトスタート機能を実行します。

## 出力電流制限

過電圧状態と短絡状態でも、出力電流は規定の出力電流制限値より高くはなりません。LTM4640 がスイッチングを継続していても、出力電圧レギュレーションは確保されず、そのような状況での負荷抵抗に依存します。このような条件での連続動作は推奨されません。最大動作ジャンクション温度を超過し、デバイスの信頼性を損ねる可能性があるためです。

## 温度モニタリング

式 12 の標準的なダイオードの式で表される電流、電圧、温度の関係により、ダイオードの絶対温度を測定することができます。

$$I_D = I_S \times e^{\frac{V_D}{\eta \times V_T}}$$

または

$$V_D = \eta \times V_T \times \ln \frac{I_D}{I_S} \quad (12)$$

ここで、 $I_D$  はダイオード電流、 $V_D$  はダイオード電圧、 $\eta$  は理想係数（通常 1 に近い値）、 $I_S$ （飽和電流）はプロセス依存のパラメータです。 $V_T$  は式 13 により導出されます。

$$V_T = \frac{K \times T}{q} \quad (13)$$

ここで、 $T$  はダイオードのジャンクション温度（単位：ケルビン）、 $q$  は電荷、 $K$  はボルツマン定数です。 $V_T$  は室温（298K）では約 26mV で、ケルビン温度に比例して増加します。ダイオードが温度センサーに適している理由は、この直線的な温度依存性にあります。式 13 の  $I_S$  の項は、ダイオード接合を通じて流れる電流をダイオードの端子間電圧が 0V の場合にまで外挿した値です。この  $I_S$  項は、プロセスによっても温度によっても異なりますが、常に  $I_D$  よりは小さい値となります。すべての定数を 1 つの項にまとめます（式 14 を参照）。

$$K_D = \frac{\eta \times k}{q} \quad (14)$$

ここで  $K_D = 8.62 \times 10^{-5}$  V/K であり、理想係数が 1 であると仮定し、 $I_D$  が常に  $I_S$  より大きいため  $\ln(I_D/I_S)$  は常に正であると分かっているので、式 15 の結果が得られます。

$$V_D = T_{(KELVIN)} \times K_D \times \ln \frac{I_D}{I_S} \quad (15)$$

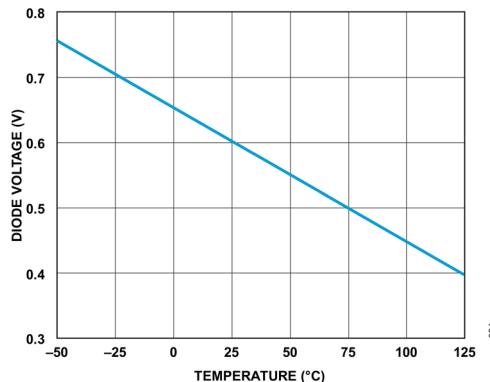

温度の上昇に伴って、 $I_S$  項はより早く増加するため、 $\ln(I_D/I_S)$  の絶対値は早く減少し、ダイオード電圧と温度の間の係数は負になって、図 24 に示すように約 -2mV/°C の温度関係となります。

図 24. ダイオード電圧  $V_D$  と温度  $T$  (°C) の関係

電圧の温度に対する直線的な関係を得るために、自然対数項の  $I_S$  変数を打ち消して式 15 の  $I_S$  依存性をなくします。これを行うには、2つの電流でダイオード電圧を計測します。即ち  $I_1 = 10 \times I_2$  となるような  $I_1$  と  $I_2$  で式 16 に示すように減算します。

$$\Delta V_D = T_{(KELVIN)} \times K_D \times \ln \frac{I_1}{I_S} - T_{(KELVIN)} \times K_D \times \ln \frac{I_2}{I_S} \quad (16)$$

共通項をまとめて自然対数部を簡素化すると式 17 になります。

$$\Delta V_D = T_{(KELVIN)} \times K_D \times \ln(10) \quad (17)$$

式 18 のように定数を再定義します。

$$K'_D = K_D \times \ln(10) = \frac{198\mu V}{K} \quad (18)$$

これにより式 19 が得られます。

$$\Delta V_D = K'_D \times T_{(KELVIN)} \quad (19)$$

式 20 により温度が得られます。

$$T_{(KELVIN)} = \frac{\Delta V_D}{K'_D}$$

$$T_{(^\circ CELSIUS)} = T_{(KELVIN)} - 273.15 \quad (20)$$

ここで例えば  $300.15K = 27^\circ C$  となります。

10 倍異なる 2 つの電流値で測定したダイオード両端の電圧の差分をとると、その結果はジャンクション電圧が 1 ケルビンあたり  $198\mu V$  となり、0 ケルビンでの切片はゼロになります。

TSENSE<sup>+</sup>ピンと TSENSE<sup>-</sup>ピンの間にダイオード接続された内蔵NPN ランジスタを用いることで、LTM4640 の内部温度をモニタできます。

## 熱に関する考慮事項と出力電流のディレーティング

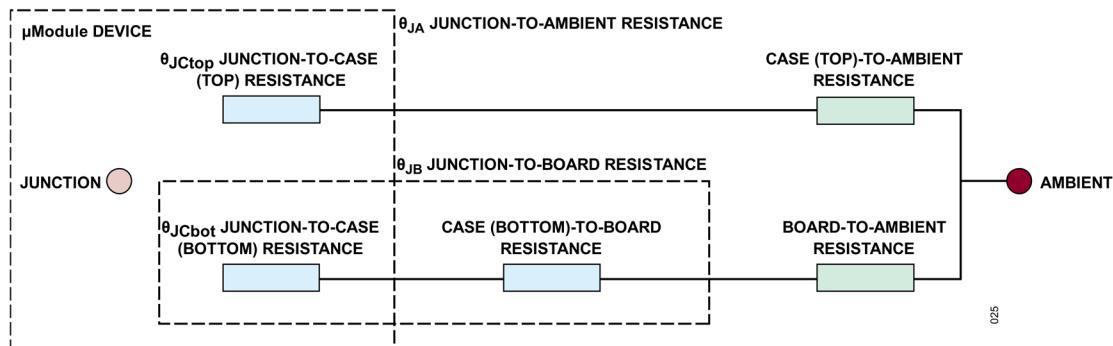

ピン配置およびピン機能の説明のセクションに記載されている熱抵抗は、JESD5112 で定義されているパラメータと整合しており、有限要素法による解析（FEA）ソフトウェアのモデリング・ツールで使用することを目的としています。このツールでは、熱モデリング、シミュレーション、およびハードウェア・テスト基板に実装された μModule パッケージで実行されたハードウェア評価との相關の結果を活用します。これらの熱係数を提供する理由は、JESD5112（Guidelines for Reporting and Using Electronic Package Thermal Information）に記載されています。

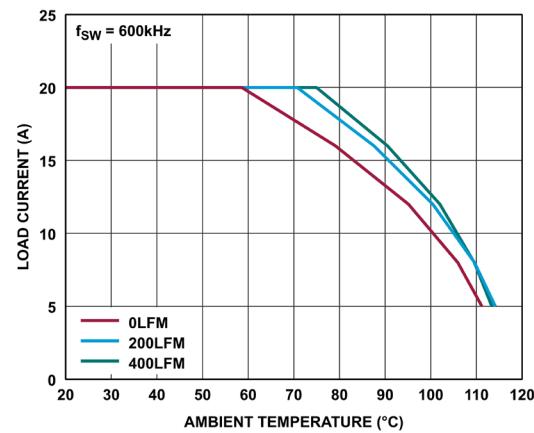

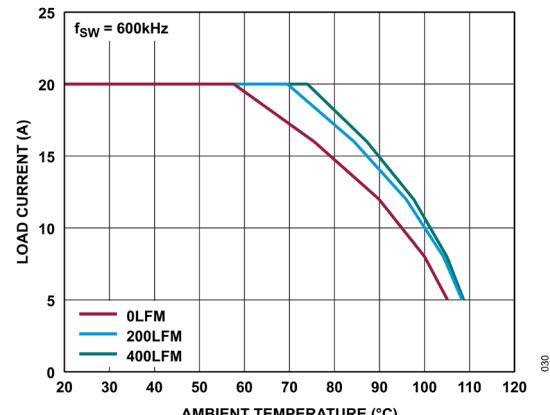

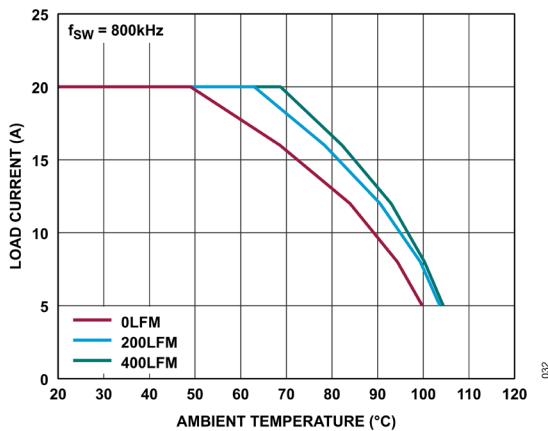

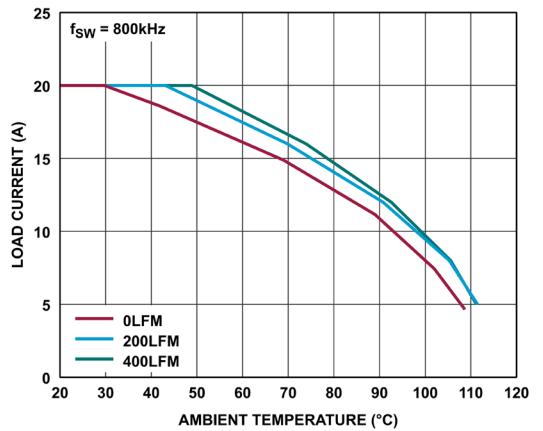

多くの設計者は、実験装置および評価（デモ）用ボードなどのテスト媒体を使用し、自身のアプリケーションにおける μModule レギュレータの熱性能を様々な電気的および環境的な動作条件で予測して、FEA 結果を補完することができます。FEA ソフトウェアを使用しない場合、ピン配置およびピン機能の説明のセクションに記載されている熱抵抗は、それ自体では、熱性能のガイダンスの提供には関係ありません。むしろ、ディレーティング曲線（図 29～図 34）が、ユーザのアプリケーションに関する洞察とガイダンスが得られるような方法で使用でき、これを適宜変更して熱性能とユーザのアプリケーションを関連付けることができます。

ピン配置およびピン機能の説明のセクションには、JESD5112に明示的に定義された3つの熱抵抗が記載されています。これらの係数を、以下に引用または解説します。

- $\theta_{JA}$ はジャンクションと周囲空気の間の熱抵抗であり、1立方フィートの密閉エンクロージャ内で測定された、自然対流によるジャンクションと周囲空気の間の熱抵抗です。この環境は「静止状態の空気」と呼ばれることもありますが、実際には自然対流により空気の動きが生じます。この値は、95mm × 76mm の4層 PCB に実装された部品を使用して決定します。

- $\theta_{JCbottom}$ はジャンクションと製品ケース底部の間の熱抵抗であり、素子の消費電力がすべてパッケージの底部を通るものとして求められます。標準的な μModule レギュレータでは熱の大半がパッケージの底面から放出されますが、周囲環境への熱の放出も必ず発生します。結果として、この熱抵抗の値はパッケージの比較には有用な場合がありますが、テストの条件は一般にはユーザのアプリケーションに即したものとはなりません。

- $\theta_{JCtop}$ はジャンクションから製品ケース上面への熱抵抗であり、部品からの熱放散のはばすべてがパッケージ上面を通じて行われるものとして決定されます。標準的な μModule レギュレータの電気的接続はパッケージの底面で行われるので、熱の大半がジャンクションからデバイス上面へ流れるような形でアプリケーションが動作することは稀です。 $\theta_{JCbottom}$ の場合と同じく、この値はパッケージの比較には有用な場合がありますが、テストの条件は一般的にユーザのアプリケーションに即したものとはなりません。

熱抵抗を視覚的に表したもののが図25です。青色の部分が μModule レギュレータ内部の熱抵抗で、緑色の部分は μModule 外部の熱抵抗です。

図 25. JESD51-12 の熱係数の図解

実際には、JESD5112の定義による、[ピン配置およびピン機能の説明](#)のセクションに示したこれら3つの熱抵抗パラメータは、個別でも、あるいはいくつかを組み合わせた場合でも、μModule レギュレータの通常の動作条件を反映または表現するものではありません。例えば、通常の基板実装アプリケーションでは、デバイスの総電力損失(熱)の100%が、μModule パッケージの上部のみを通して、または底部のみを通して(規格でそれぞれ  $\theta_{JCtop}$  と  $\theta_{JCbottom}$  として定義しているように)熱伝導することは決してありません。実際には、電力損失は、パッケージから両方向に熱として放散されます。ただし、ヒート・シンクと空気流がない場合、熱流の大部分は基板の方へ流れます。

## 空気流とヒート・シンク

LTM4640 内部には電力を消費する電力デバイスやコンポーネントが複数存在し、したがってコンポーネントやダイの様々な接合部での熱抵抗はパッケージ全体の電力損失とは完全には正比例しないことに留意してください。この複雑な問題を、モデリングの簡潔性を犠牲にすることなく、同時に現実的な実用性を無視することもなく解決するために、このデータシートに記載されている熱抵抗値は、実験室での恒温槽を使ったテストと FEA ソフトウェア・モデリングを併用する方法を採用して合理的に定義し、相関付けを行っています。(1) 最初に、FEA ソフトウェアが、適切な材料係数と正確な電力損失源定義と共に、LTM4640 と指定の PCB の正確な機械的形状モデルを作成します。(2) このモデルが、JESD5112 に適合するソフトウェア定義の JEDEC 環境をシミュレーションして、様々な接合面における電力損失による熱の流れと温度値を予測します。これで、JEDEC 定義の熱抵抗値を計算することができます。(3) このモデルと FEA ソフトウェアが、ヒート・シンクと空気流がある場合の LTM4640 の熱性能を評価します。(4) これらの熱抵抗値を計算して分析し、ソフトウェア・モデルで様々な動作条件によるシミュレーションを行った上で、徹底した実験室評価を実施してシミュレーションで得た状態を再現します。具体的には恒温槽を使い、シミュレーションと同じ電力損失でデバイスを動作させながら、熱電対を使用して温度を測定します。このプロセスと適切な評価により、図 29~図 34 に示す一連のディレーティング曲線が得られます。このような実験室でのテストを実施し、LTM4640 との関連付けを行った後、 $\theta_{JB}$  と  $\theta_{BA}$  を合計すると、 $\theta_{JA}$  にほぼ等しい値が求められます。これは、空気流や上部に実装されたヒート・シンクがない状態では、電力損失のほぼ 100%が、ジャンクションから基板を抜けて周囲環境に流れることによるものです。

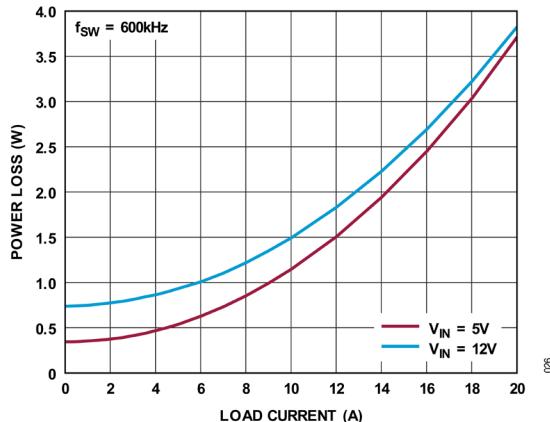

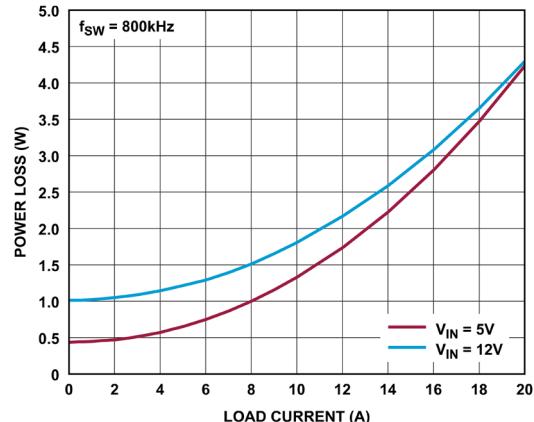

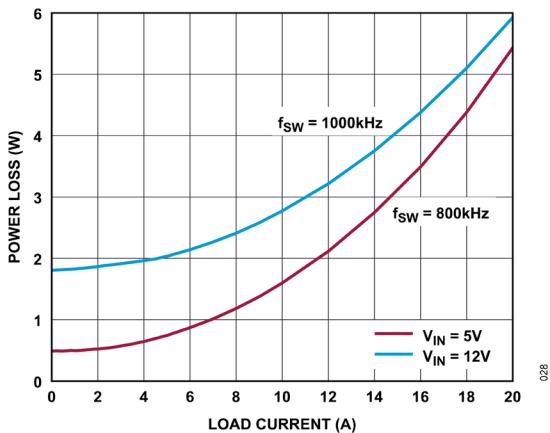

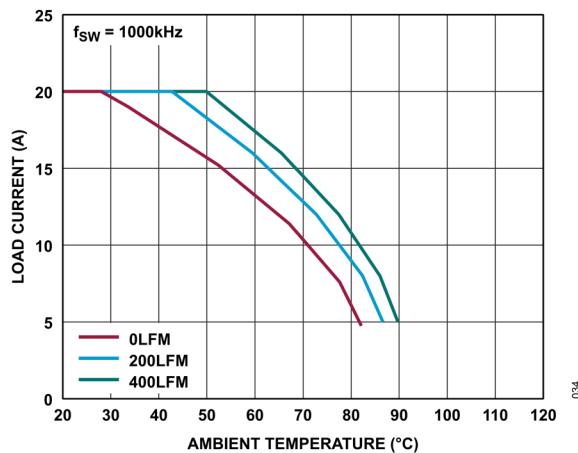

図 26～図 28 に示す 1V、1.5V、3.3V の電力損失曲線を、図 29～図 34 の負荷電流ディレーティング曲線を組み合わせて使用すると、様々な空気流条件下における LTM4640 の熱抵抗  $\theta_{JA}$  の概算値を求めることができます。電力損失曲線は室温で得られたものであり、周囲温度に応じて乗算的に増加します。この近似係数はジャンクション温度が 120°C のときに 1.2 です。ジャンクション温度が 120°C (125°C の最大ジャンクション温度から 5°C の安全領域を見込んだ値) 未満であれば、周囲温度が増加している間も最大負荷電流は実現可能です。ジャンクション温度が 120°C となるような周囲温度に達した場合、周囲温度が 120°C まで増加する間、負荷電流は 120°C のジャンクション温度を維持するよう低下します。ディレーティング曲線は、電流値 20A で周囲温度 30°C からの出力電流についてプロットされています。出力電圧は 1V、1.5V、3.3V です。これらは熱抵抗との相関を検証するため、低めの出力電圧範囲と高めの出力電圧範囲を含めるよう選択されています。熱モデルは、恒温槽におけるいくつかの温度測定と熱モデリング解析から導出されます。ジャンクション温度は、空気流がある場合とない場合について周囲温度を上げながらモニタします。ディレーティング曲線には、周囲温度の変化に伴う電力損失の増加が加味されます。周囲温度が上昇すると、出力電流または出力電力を減少させて、ジャンクション温度を最大 120°C に維持します。この出力電流の低下により、周囲温度が上昇すると共に μModule 内部の損失が低下します。モニタされた 120°C のジャンクション温度から周囲動作温度を差し引いた値により、どれだけの μModule 溫度の上昇を許容できるかを規定できます。例えば図 30 に示すように、約 95°C で空気流もヒート・シンクもなしの条件では、負荷電流が約 10A にディレーティングされ、12V 入力で 10A の 1V 出力時の電力損失は約 1.8W になります。1.8W の損失は、12V 入力 1V 出力時の電力損失曲線の 10A 時の値から得られる室温での損失約 1.5W に、ジャンクション温度 120°C での倍率係数 1.2 を乗算して得られます。周囲温度 95°C をジャンクション温度の 120°C から差し引き、その差の 25°C を 1.8W で除算すると、熱抵抗  $\theta_{JA}$  は 13.9°C/W になります。表 9 には、この値に非常に近い 14°C/W が示されています。表 10 と表 11 は、空気流とヒート・シンクがある場合とない条件における、出力が 1.5V と 3.3V の場合の等価熱抵抗を示しています。表 9、表 10、表 11 に示す様々な条件での算出熱抵抗に、周囲温度の関数として算出した電力損失を乗じると、周囲温度からの温度上昇値が得られ、これから最大ジャンクション温度が得られます。室温での電力損失は [代表的な性能特性](#) のセクションに示す効率曲線から求め、更に前述の周囲温度の倍率係数で調整して求めることができます。プリント回路基板は 1.6mm 厚の 6 層基板で、この 6 層すべてに 2 オンスの銅を使用しています。PCB の寸法は 90mm × 90mm です。

特に指定のない限り、 $T_A = 25^\circ\text{C}$ 。

図 26. 1V 出力での電力損失

図 27. 1.5V 出力での電力損失

図 28. 3.3V 出力での電力損失

図 29. 5V 入力、1V 出力でのディレーティング曲線

(ヒート・シンクなし)

図 30. 12V 入力、1V 出力でのディレーティング曲線

(ヒート・シンクなし)

図 31. 5V 入力、1.5V 出力でのディレーティング曲線

(ヒート・シンクなし)

図 32. 12V 入力、1.5V 出力でのディレーティング曲線

(ヒート・シンクなし)

図 33. 5V 入力、3.3V 出力でのディレーティング曲線

(ヒート・シンクなし)

図 34. 12V 入力、3.3V 出力でのディレーティング曲線

(ヒート・シンクなし)

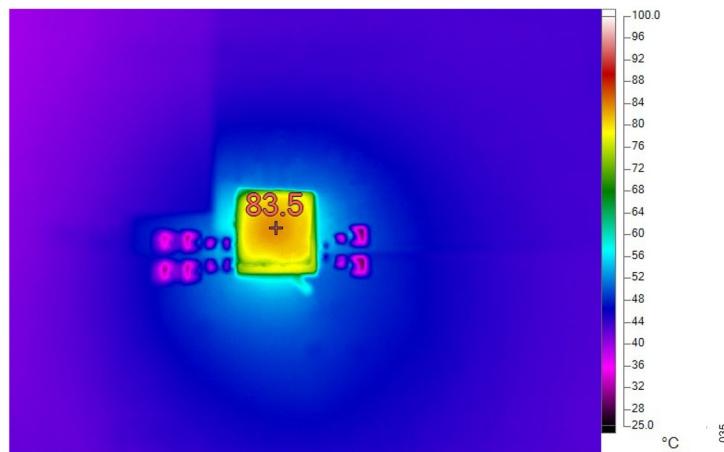

図 35 は LTM4640 の熱画像で、12V 入力、1V 20A 出力、600kHz、周囲温度 21°C、空気流とヒート・シンクなしの条件です。

図 35. 12V<sub>IN</sub>、1V<sub>OUT</sub> で 20A、600kHz、周囲温度 21°C、空気流とヒート・シンクなしでの熱画像

表 9. 1V 出力

| DERATING CURVE                       | V <sub>IN</sub> (V) | POWER LOSS CURVE          | AIRFLOW (LFM) | HEAT SINK | θ <sub>JA</sub> (°C/W) |

|--------------------------------------|---------------------|---------------------------|---------------|-----------|------------------------|

| <a href="#">Figure 29, Figure 30</a> | 5, 12               | <a href="#">Figure 26</a> | 0             | None      | 14                     |

| <a href="#">Figure 29, Figure 30</a> | 5, 12               | <a href="#">Figure 26</a> | 200           | None      | 11                     |

| <a href="#">Figure 29, Figure 30</a> | 5, 12               | <a href="#">Figure 26</a> | 400           | None      | 10                     |

表 10. 1.5V 出力

| DERATING CURVE                       | V <sub>IN</sub> (V) | POWER LOSS CURVE          | AIRFLOW (LFM) | HEAT SINK | θ <sub>JA</sub> (°C/W) |

|--------------------------------------|---------------------|---------------------------|---------------|-----------|------------------------|

| <a href="#">Figure 31, Figure 32</a> | 5, 12               | <a href="#">Figure 27</a> | 0             | None      | 14                     |

| <a href="#">Figure 31, Figure 32</a> | 5, 12               | <a href="#">Figure 27</a> | 200           | None      | 11                     |

| <a href="#">Figure 31, Figure 32</a> | 5, 12               | <a href="#">Figure 27</a> | 400           | None      | 10                     |

表 11. 3.3V 出力

| DERATING CURVE                       | V <sub>IN</sub> (V) | POWER LOSS CURVE          | AIRFLOW (LFM) | HEAT SINK | θ <sub>JA</sub> (°C/W) |

|--------------------------------------|---------------------|---------------------------|---------------|-----------|------------------------|

| <a href="#">Figure 33, Figure 34</a> | 5, 12               | <a href="#">Figure 28</a> | 0             | None      | 15                     |

| <a href="#">Figure 33, Figure 34</a> | 5, 12               | <a href="#">Figure 28</a> | 200           | None      | 12                     |

| <a href="#">Figure 33, Figure 34</a> | 5, 12               | <a href="#">Figure 28</a> | 400           | None      | 11                     |

表 12. 出力電圧応答と部品の組み合わせ（図 37 参照）

| <b>C<sub>OUT1</sub><br/>VENDORS</b> | <b>PART NUMBER</b>  | <b>DESCRIPTION</b>     | <b>C<sub>OUT2</sub><br/>VENDORS</b> | <b>PART NUMBER</b> | <b>DESCRIPTION</b> |

|-------------------------------------|---------------------|------------------------|-------------------------------------|--------------------|--------------------|

| Murata                              | GRM32EC70J107ME15L  | 100μF, 6.3V, X7S, 1210 | Panasonic                           | EEF-GX0E471L       | 470μF, 2.5V, 3mΩ   |

| Taiyo Yuden                         | JMK325AC7107MM      | 100μF, 6.3V, X7S, 1210 |                                     |                    |                    |

| TDK                                 | C3225X6S0J107M250AC | 100μF, 6.3V, X6S, 1210 |                                     |                    |                    |

| Murata                              | GRM31CR60J227ME11L  | 220μF, 6.3V, X5R, 1206 |                                     |                    |                    |

## 全セラミック出力コンデンサ

| <b>V<sub>OUT</sub><br/>(V)</b> | <b>V<sub>IN</sub><br/>(V)</b> | <b>R<sub>FB</sub><br/>(kΩ)</b> | <b>f<sub>SW</sub><br/>(kHz)</b> | <b>C<sub>OUT1</sub><br/>(CERAMIC<br/>CAP)</b> | <b>C<sub>OUT2</sub><br/>(BULK<br/>CAP)</b> | <b>COMP<sub>a</sub><br/>(pF)</b> | <b>R<sub>TH</sub> ON<br/>COMP<sub>a</sub><br/>(kΩ)</b> | <b>C<sub>TH</sub> ON<br/>COMP<sub>a</sub><br/>(pF)</b> | <b>LOAD<br/>STEP<br/>(A)</b> | <b>PK-PK<br/>DEVIATION<br/>(mV)</b> | <b>RECOVERY<br/>TIME<br/>(μs)</b> |

|--------------------------------|-------------------------------|--------------------------------|---------------------------------|-----------------------------------------------|--------------------------------------------|----------------------------------|--------------------------------------------------------|--------------------------------------------------------|------------------------------|-------------------------------------|-----------------------------------|

| 1                              | 5                             | 15                             | 600                             | 4 × 220μF                                     | None                                       | Short to<br>COMP <sub>b</sub>    | None                                                   | None                                                   | 5                            | 90                                  | 40                                |

| 1                              | 12                            | 15                             | 600                             | 4 × 220μF                                     | None                                       | Short to<br>COMP <sub>b</sub>    | None                                                   | None                                                   | 5                            | 100                                 | 40                                |

| 1.5                            | 5                             | 6.65                           | 800                             | 4 × 220μF                                     | None                                       | Short to<br>COMP <sub>b</sub>    | None                                                   | None                                                   | 5                            | 97                                  | 60                                |

| 1.5                            | 12                            | 6.65                           | 800                             | 4 × 220μF                                     | None                                       | Short to<br>COMP <sub>b</sub>    | None                                                   | None                                                   | 5                            | 97                                  | 60                                |

| 2.5                            | 5                             | 3.16                           | 800                             | 4 × 220μF                                     | None                                       | Short to<br>COMP <sub>b</sub>    | None                                                   | None                                                   | 5                            | 110                                 | 80                                |

| 2.5                            | 12                            | 3.16                           | 1000                            | 4 × 220μF                                     | None                                       | Short to<br>COMP <sub>b</sub>    | None                                                   | None                                                   | 5                            | 114                                 | 80                                |

| 3.3                            | 5                             | 2.21                           | 800                             | 4 × 220μF                                     | None                                       | Short to<br>COMP <sub>b</sub>    | None                                                   | None                                                   | 5                            | 121                                 | 80                                |

| 3.3                            | 12                            | 2.21                           | 1000                            | 4 × 220μF                                     | None                                       | Short to<br>COMP <sub>b</sub>    | None                                                   | None                                                   | 5                            | 124                                 | 80                                |

## 安全に関する考慮事項

LTM4640 モジュールの V<sub>IN</sub> と V<sub>OUT</sub> は、ガルバニック絶縁されていません。また、内部ヒューズもありません。必要に応じて、最大入力電流の 2 倍の定格値を持つ低速溶断ヒューズを使って、ユニットを致命的損傷から保護してください。デバイスは、サーマル・シャットダウンをサポートしています。

## レイアウト・チェックリスト/レイアウト例

LTM4640 は高度に集積化されているので、プリント回路基板（PCB）のレイアウトはシンプルで容易に導入可能なものになります。ただし、電気的性能と熱的性能を最適化するには、レイアウト上の配慮がある程度必要になります。

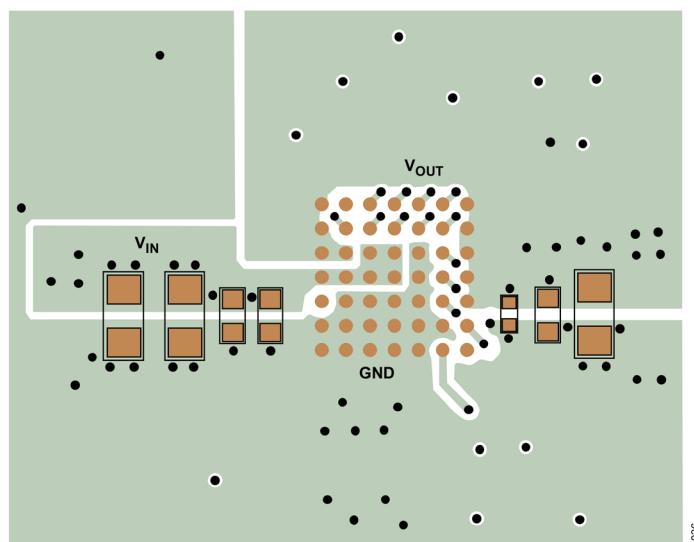

1.  $V_{IN}$ 、GND、 $V_{OUT}$  を含む大電流バスでは、PCB の銅箔面積を広くします。これは、PCB の導通損失と熱ストレスを最小限に抑える助けとなります。

2. 出力でのノイズ結合を最小化するため、 $V_{IN}$  と  $V_{OUT}$  の銅領域の境界を短くし、それらを GND の銅領域から離してください。

3. 高周波ノイズを最小限に抑えるため、高周波の入出力セラミック・コンデンサを  $V_{IN}$  ピン、PGND ピン、 $V_{OUT}$  ピンの近くに配置します。

4. ユニットの下には専用の電源グラウンド層を配置します。

5. ビアの伝導損失を最小限に抑え、μModule の熱ストレスを低減するため、最上層と他の電源層の接続には複数のビアを使用します。

6. ビアは、キャップされているか、メッキされている場合を除いて、パッド上に直接配置してはいけません。

7. モニタリングのため、信号ピンからテスト・ポイントを引き出します。

8. CLKIN ピン、CLKOUT ピン、FREQ ピンのパターン間の分離を確保し、これらの信号の間のクロストークによるノイズの可能性を最小限に抑えます。

推奨 PCB レイアウトの例を図 36 に示します。

図 36. 推奨 PCB レイアウト

## 標準的応用例

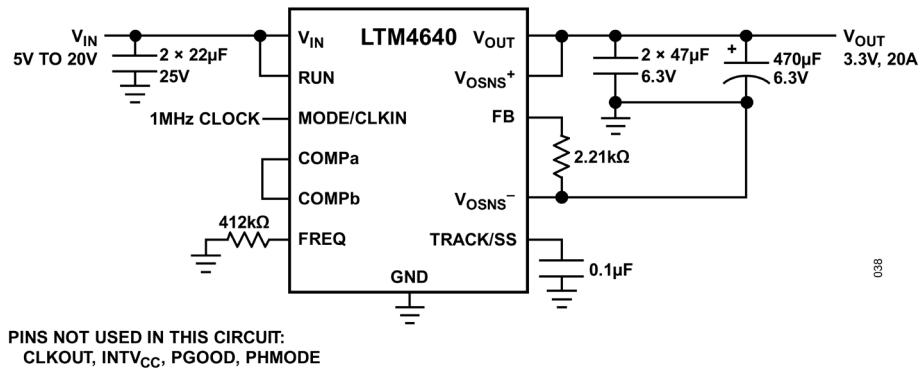

図 37. 3.1V<sub>IN</sub>~20V<sub>IN</sub>、1V 20A 出力の設計図 38. 5V<sub>IN</sub>~20V<sub>IN</sub>、3.3V 出力、1MHz 外部クロックを使用

図 39. 3.1V<sub>IN</sub>~20V<sub>IN</sub>、2相、1.5V 40A 出力の設計図 40. 3.1V<sub>IN</sub>~20V<sub>IN</sub>、1.2V と 1.5V の同時トラッキング

## 関連製品

表 13. 関連製品

| 製品番号                 | 説明                                                         | 注釈                                                                                                                                                           |

|----------------------|------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LTM4657              | 8A μModuleレギュレータ、LTM4626、LTM4638、LTM4640とピン互換              | $3.1V \leq V_{IN} \leq 20V$ 、 $0.6V \leq V_{OUT} \leq 5.5V$ 、 $6.25mm \times 6.25mm \times 3.87mm$ BGA                                                       |

| LTM4626              | 12A μModuleレギュレータ、LTM4657、LTM4638、LTM4640とピン互換             | $3.1V \leq V_{IN} \leq 20V$ 、 $0.6V \leq V_{OUT} \leq 5.5V$ 、 $6.25mm \times 6.25mm \times 3.87mm$ BGA                                                       |

| LTM4638              | 15A μModuleレギュレータ、LTM4657、LTM4626、LTM4640とピン互換             | $3.1V \leq V_{IN} \leq 20V$ 、 $0.6V \leq V_{OUT} \leq 5.5V$ 、 $6.25mm \times 6.25mm \times 5.02mm$ BGA                                                       |

| LTM4702              | 10A Silent Switcher 3 μModuleレギュレータ、LTM4703およびLTM4707とピン互換 | $3V \leq V_{IN} \leq 16V$ 、 $0.3V \leq V_{OUT} \leq 6V$ 、 $6.25mm \times 6.25mm \times 5.07mm$ BGA                                                           |

| LTM4703              | 12A Silent Switcher 3 μModuleレギュレータ、LTM4702およびLTM4707とピン互換 | $3V \leq V_{IN} \leq 16V$ 、 $0.3V \leq V_{OUT} \leq 6V$ 、 $6.25mm \times 6.25mm \times 5.07mm$ BGA                                                           |

| LTM4707              | 15A Silent Switcher 3 μModuleレギュレータ、LTM4702およびLTM4703とピン互換 | $3V \leq V_{IN} \leq 16V$ 、 $0.3V \leq V_{OUT} \leq 6V$ 、 $6.25mm \times 6.25mm \times 5.07mm$ BGA                                                           |

| LTM4622              | デュアル2.5Aまたはシングル5AのμModuleレギュレータ                            | $3.6V \leq V_{IN} \leq 20V$ 、 $0.6V \leq V_{OUT} \leq 5.5V$ 、 $6.25mm \times 6.25mm \times 1.82mm$ (LGA) または $2.42mm$ (BGA)                                  |

| LTM4705              | デュアル5Aまたはシングル10AのμModuleレギュレータ                             | $3.1V \leq V_{IN} \leq 20V$ 、 $0.6V \leq V_{OUT} \leq 5.5V$ 、 $6.25mm \times 7.5mm \times 3.22mm$ BGA                                                        |

| LTM4646              | デュアル10Aまたはシングル20AのμModuleレギュレータ                            | $4.5V \leq V_{IN} \leq 20V$ 、 $0.6V \leq V_{OUT} \leq 5.5V$ 、 $11.25mm \times 15mm \times 5.01mm$ BGA                                                        |

| LTM4630/<br>LTM4630A | デュアル18Aまたはシングル36A μModuleレギュレータ、LTM4650とピン互換               | $4.5V \leq V_{IN} \leq 15V$ (LTM4630Aは $18V$ )、 $0.6V \leq V_{OUT} \leq 1.8V$ (LTM4630Aは $8V$ )、 $16mm \times 16mm \times 4.41mm$ (LGA) または $5.01mm$ (BGA)   |

| LTM4650/<br>LTM4650A | デュアル25Aまたはシングル50A μModuleレギュレータ、LTM4630とピン互換               | $4.5V \leq V_{IN} \leq 15V$ (LTM4650Aは $16V$ )、 $0.6V \leq V_{OUT} \leq 1.8V$ (LTM4650Aは $5.5V$ )、 $16mm \times 16mm \times 4.41mm$ (LGA) または $5.01mm$ (BGA) |

| LTM4668/<br>LTM4668A | 構成可能な1.2AクワッドμModuleレギュレータ                                 | $2.7V \leq V_{IN} \leq 17V$ 、 $0.6V \leq V_{OUT} \leq 1.8V$ (LTM4668Aは $5.5V$ )、 $6.25mm \times 2.1mm$ BGA                                                   |

| LTM4643              | 設定可変なクワッド3A μModuleレギュレータ、LTM4644とピン互換                     | $4V \leq V_{IN} \leq 20V$ 、 $0.6V \leq V_{OUT} \leq 3.3V$ 、 $9mm \times 15mm \times 1.82mm$ LGA、 $2.42mm$ BGA                                                |

| LTM4644              | 構成可能なクワッド4A μModuleレギュレータ、LTM4643とピン互換                     | $4V \leq V_{IN} \leq 14V$ 、 $0.6V \leq V_{OUT} \leq 5.5V$ 、 $9mm \times 15mm \times 5.01mm$ BGA                                                              |

## 外形寸法

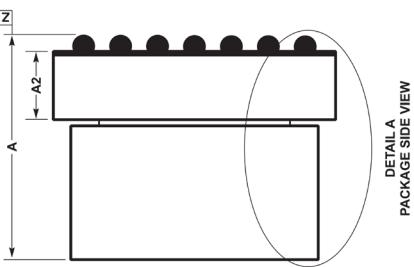

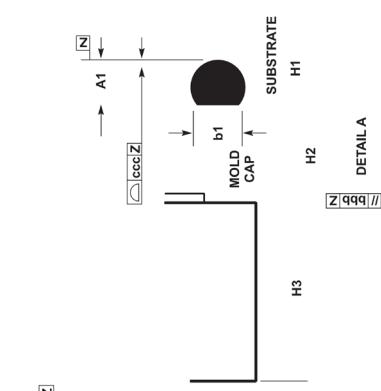

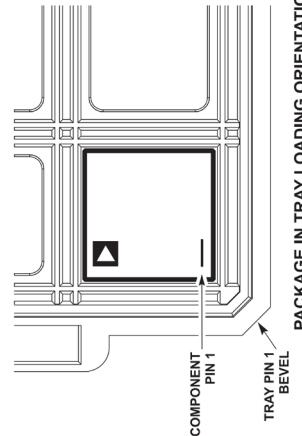

**49-Ball Chip Scale Package Ball Grid Array [CSP\_BGA]**

6.25mm × 6.25mm × 5.07mm

(Reference DWG # BC-49-9)

## NOTES:

1. DIMENSIONING AND TOLERANCING PER ASME Y14.5M-1994

2. ALL DIMENSIONS ARE IN MILLIMETERS

3. BALL DESIGNATION PER JEP95

4. DETAILS OF PIN 1 IDENTIFIER ARE OPTIONAL,

BUT MUST BE LOCATED WITHIN THE ZONE INDICATED.

THE PIN 1 IDENTIFIER MAY BE EITHER A MOLD OR

MARKED FEATURE

5. PRIMARY DATUM Z - IS SEATING PLANE

6. ! AMONG μModule PRODUCTS, REVIEW EACH PACKAGE

LAYOUT CAREFULLY

| DIMENSIONS                |          |      |      | NOTES          |

|---------------------------|----------|------|------|----------------|

| SYMBOL                    | MIN      | NOM  | MAX  |                |

| A                         | 4.76     | 5.07 | 5.39 | BALL HT        |

| A1                        | 0.30     | 0.40 | 0.50 |                |

| A2                        | 1.43     | 1.52 | 1.61 |                |

| b                         | 0.45     | 0.50 | 0.55 | BALL DIMENSION |

| b1                        | 0.37     | 0.40 | 0.43 | PAD DIMENSION  |

| D                         | 6.25     |      |      |                |

| E                         | 6.25     |      |      |                |

| e                         | 0.80     |      |      |                |

| F                         | 4.80     |      |      |                |

| G                         | 4.80     |      |      |                |

| H1                        | 0.32 REF |      |      | SUBSTRATE THK  |

| H2                        | 1.20 REF |      |      | MOLD CAP HT    |

| H3                        |          | 3.28 |      | INDUCTOR HT    |

| aaa                       |          |      | 0.15 |                |

| bbb                       |          |      | 0.10 |                |

| ccc                       |          |      | 0.20 |                |

| ddd                       |          |      | 0.20 |                |

| eee                       |          |      | 0.08 |                |

| TOTAL NUMBER OF BALLS: 49 |          |      |      |                |

SUGGESTED PCB LAYOUT

TOP VIEW

06-16-2022-C

## オーダー・ガイド

表 14. オーダー・ガイド

| MODEL         | TEMPERATURE RANGE <sup>1</sup> | PACKAGE DESCRIPTION*                                                                                            | PACKAGE OPTION                                 |

|---------------|--------------------------------|-----------------------------------------------------------------------------------------------------------------|------------------------------------------------|

| LTM4640EY#PBF | -40°C to 125°C                 | Part marking: 4640, SAC305 (RoHS) ball finish, e1 finish code, moisture sensitivity level (MSL 4) rated device. | 49-Pin, 6.25mm × 6.25mm × 5.07mm, BGA package. |

| LTM4640IY#PBF | -40°C to 125°C                 | Part marking: 4640, SAC305 (RoHS) ball finish, e1 finish code, moisture sensitivity level (MSL 4) rated device. | 49-Pin, 6.25mm × 6.25mm × 5.07mm, BGA package. |

<sup>1</sup> LTM4640 は、E グレードと I グレードのデバイスを含め（表 14 を参照）、 $T_J \approx T_A$ となるようなパルス負荷条件でテストされています。LTM4640E は、0°C～125°C の内部動作温度範囲内で性能仕様を満たすよう設計されています。-40°C～125°C の内部動作温度範囲全体における仕様は、設計、特性評価、および統計的プロセス制御との相關付けによって裏付けられています。LTM4640I は-40°C～125°C の内部動作温度範囲全域で仕様を満たすよう設計されています。ここに示した仕様を満たす最高周囲温度は、基板レイアウト、パッケージの定格熱抵抗、および他の環境要因に加え、個々の動作条件によって決定されることに留意してください。

更に広い動作温度範囲仕様のデバイスについては、弊社または弊社代理店までお問い合わせください。\*ポールの仕上げコードは IPC/JEDEC J-STD-609 によります。温度グレードは出荷時のコンテナのラベルに示されています。

推奨される LGA および BGA PCB のアセンブリおよび製造手順。

LGA および BGA のパッケージ図面とトレイ図面。

表 15. 評価用ボード

| PART NUMBER | DESCRIPTION                                                                           |

|-------------|---------------------------------------------------------------------------------------|

| DC3107A     | 20V <sub>IN</sub> , 20A Step-Down DC-to-DC μModule Regulator evaluation (demo) board. |

## 選択ガイド

## パッケージ写真

(製品マーキングはレーザ・マーキング)

## 設計リソース

表 16. 設計リソース

|                      | 項目                                                                                                                                           | 説明                                                                                                                                                |

|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| μModuleの設計と製造リソース    | <b>設計 :</b> <ul style="list-style-type: none"> <li>▶ 選択ガイド</li> <li>▶ 評価（デモ）用ボードとガーバーファイル</li> <li>▶ 無償シミュレーション・ツール</li> </ul>               | <b>製造 :</b> <ul style="list-style-type: none"> <li>▶ クイック・スタート・ガイド</li> <li>▶ PCB設計、アセンブリ、製造のガイドライン</li> <li>▶ パッケージ・レベルおよびボード・レベルの信頼性</li> </ul> |

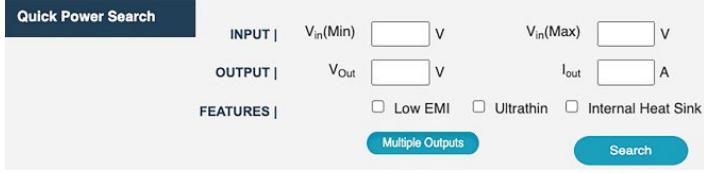

| μModuleレギュレータ製品検索    | <ul style="list-style-type: none"> <li>▶ パラメータによって製品表をソートし、結果をスプレッドシートとしてダウンロードします。</li> <li>▶ Quick Power Searchパラメータ表を使って検索します。</li> </ul> |                                                               |

| デジタルパワー・システム・マネージメント | <p>アナログ・デバイセズのデジタル電源管理ICファミリは、電源モニタリング、監視、マージニング、シーケンシングなどの必須機能と、ユーザ設定および�ト・ログ記録の保存のためのEEPROMを備えた、高度に集積化されたソリューションです。</p>                    |                                                                                                                                                   |

ここに含まれるすべての情報は、現状のまま提供されるものであり、アナログ・デバイセズはそれに関するいかなる種類の保証または表明も行いません。アナログ・デバイセズは、その情報の利用に関して、また利用によって生じる第三者の特許またはその他の権利の侵害に関して、一切の責任を負いません。仕様は予告なく変更されることがあります。明示か默示かを問わず、アナログ・デバイセズ製品またはサービスが使用される組み合わせ、機械、またはプロセスに関するアナログ・デバイセズの特許権、著作権、マスクワーク権、またはその他のアナログ・デバイセズの知的財産権に基づくライセンスは付与されません。商標および登録商標は、各社の所有に属します。

## 正誤表

この製品のデータシートに間違いがありましたので、お詫びして訂正いたします。

この正誤表は、2025年5月14日現在、アナログ・デバイセズ株式会社で確認した誤りを記したものです。

なお、英語のデータシート改版時に、これらの誤りが訂正される場合があります。

正誤表作成年月日：2025年5月14日

製品名：LTM4640

対象となるデータシートのリビジョン(Rev)：Rev.0

訂正箇所：10頁、表4の最後、G5 PHMODE の説明欄

### 【誤】

「3相動作の場合はGNDに接続し、4相動作の場合はINTVCC/2に接続します。」

### 【正】

「3相動作の場合はGNDに接続し、4相動作の場合はINTVCC/2に接続あるいはフロント状態にします。ノイズ耐性最適化のためINTVCC/2を推奨します。」

アナログ・デバイセズ株式会社

本社／〒105-7323 東京都港区東新橋1-9-1

東京汐留ビルディング 23F

大阪営業所／〒532-0003 大阪府大阪市淀川区宮原3-5-36

新大阪トラストタワー 10F

名古屋営業所／〒451-6038 愛知県名古屋市西区牛島6-1

名古屋ルーセントタワー 40F

## 正誤表

この製品のデータシートに間違いがありましたので、お詫びして訂正いたします。

この正誤表は、2025年5月14日現在、アナログ・デバイセズ株式会社で確認した誤りを記したものです。

なお、英語のデータシート改版時に、これらの誤りが訂正される場合があります。

正誤表作成年月日：2025年5月14日

製品名：LTM4640

対象となるデータシートのリビジョン(Rev)：Rev.0

訂正箇所：P13、下から5行目

### 【誤】

「過電圧状態が解消されたときには、レギュレータはソフトスタート機能を実行しません。」

### 【正】

「過電圧状態が解消されたときには、レギュレータはソフトスタート機能を実行します。」

アナログ・デバイセズ株式会社

本社／〒105-7323 東京都港区東新橋1-9-1

東京汐留ビルディング 23F

大阪営業所／〒532-0003 大阪府大阪市淀川区宮原3-5-36

新大阪トラストタワー 10F

名古屋営業所／〒451-6038 愛知県名古屋市西区牛島6-1

名古屋ルーセントタワー 40F

## 正誤表

この製品のデータシートに間違いがありましたので、お詫びして訂正いたします。

この正誤表は、2025年5月14日現在、アナログ・デバイセズ株式会社で確認した誤りを記したものです。

なお、英語のデータシート改版時に、これらの誤りが訂正される場合があります。

正誤表作成年月日：2025年5月14日

製品名：LTM4640

対象となるデータシートのリビジョン(Rev)：Rev.0

訂正箇所：P17、下から5行目

### 【誤】

「…フロート状態にすると 90° の位相差がそれぞれ CLKIN と CLKOUT の間に生じ…」

### 【正】

「…フロート状態あるいは INTVCC/2 にすると 90° の位相差がそれぞれ CLKIN と CLKOUT の間に生じ…」

**【注意】** PHMODE ピンはフロート状態あるいは INTVCC/2 のどちらでも同じ動作をします。ノイズ耐性最適化のため、INTVCC/2 接続を推奨します。

アナログ・デバイセズ株式会社

本 社／〒105-7323 東京都港区東新橋1-9-1

東京汐留ビルディング 23F

大 阪営業所／〒532-0003 大阪府大阪市淀川区宮原3-5-36

新大阪トラストタワー 10F

名古屋営業所／〒451-6038 愛知県名古屋市西区牛島6-1

名古屋ルーセントタワー 40F

## 正誤表

この製品のデータシートに間違いがありましたので、お詫びして訂正いたします。

この正誤表は、2025年5月14日現在、アナログ・デバイセズ株式会社で確認した誤りを記したものです。

なお、英語のデータシート改版時に、これらの誤りが訂正される場合があります。

正誤表作成年月日：2025年5月14日

製品名：LTM4640

対象となるデータシートのリビジョン(Rev)：Rev.0

訂正箇所：P18、表 8. PHMODE ピンの状態と対応する位相関係 (CLKIN 基準)、最初の行、

### 【誤】

| PHMODE | INTV <sub>cc</sub> | GND  | FLOAT |

|--------|--------------------|------|-------|

| CLKOUT | 180°               | 120° | 90°   |

### 【正】

| PHMODE | INTV <sub>cc</sub> | GND  | FLOAT or INTV <sub>cc</sub> /2 *1 |

|--------|--------------------|------|-----------------------------------|

| CLKOUT | 180°               | 120° | 90°                               |

\*1 どちらでも 90° 位相とできますが、ノイズ耐性最適化のため INTV<sub>cc</sub>/2 接続を推奨します。

アナログ・デバイセズ株式会社

本社／〒105-7323 東京都港区東新橋1-9-1

東京汐留ビルディング 23F

大阪営業所／〒532-0003 大阪府大阪市淀川区宮原3-5-36

新大阪トラストタワー 10F

名古屋営業所／〒451-6038 愛知県名古屋市西区牛島6-1

名古屋ルーセントタワー 40F