## 24/48 ポート IEEE 802.3bt PoE PSE コントローラ

### 特長

- ▶ IEEE 802.3bt に完全に適合したタイプ 3 の 2 ペア PSE

- ▶ 最大 48 個の PSE ポート（1 ポートあたり 1 個の電源チャンネル）

- ▶ +80V/-20V に対応可能なポート対向ピン

- ▶ ECC で保護された eFlash とデータ RAM

- ▶ 業界をリードする電力経路効率

- ▶ 検出抵抗 : 100mΩ

- ▶ 30mΩ 以下の MOSFET  $R_{DS(ON)}$

- ▶ チップセット構成時の電気的絶縁

- ▶ フォトカプラおよび 3.3V 絶縁型電源が不要

- ▶ 非常に信頼性の高いマルチポイント PD 検出

- ▶ 電圧、温度、電流を継続的に監視

- ▶ 1MHz I<sup>2</sup>C 対応のシリアル制御インターフェース

- ▶ ピンまたは I<sup>2</sup>C により PD 電力を設定可能

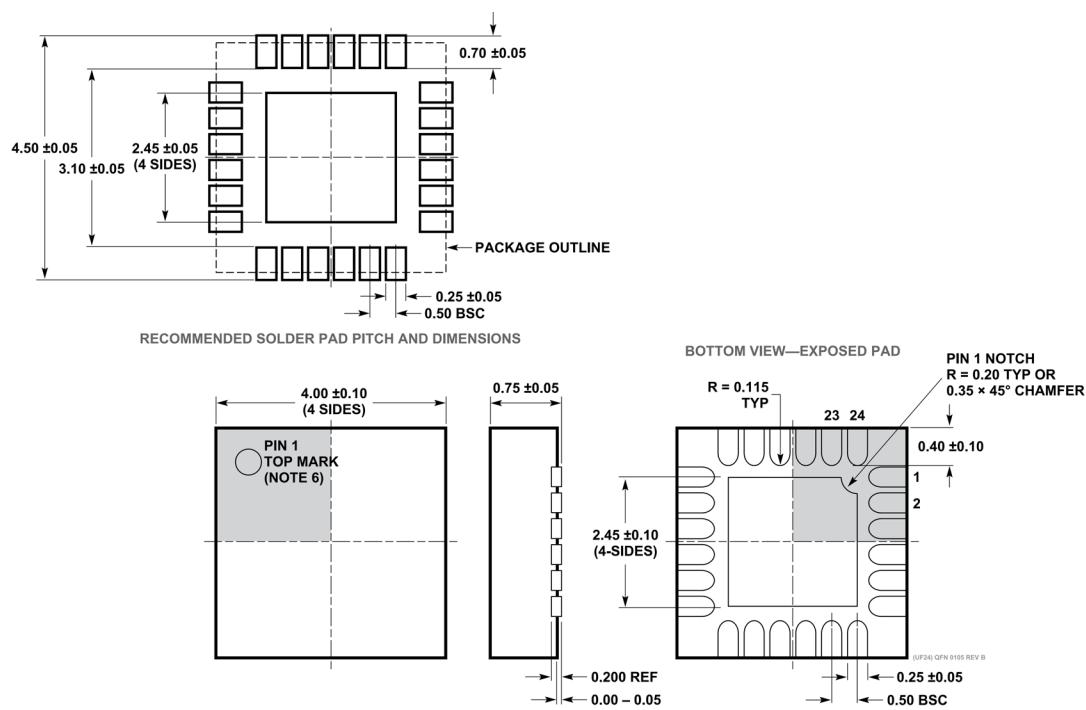

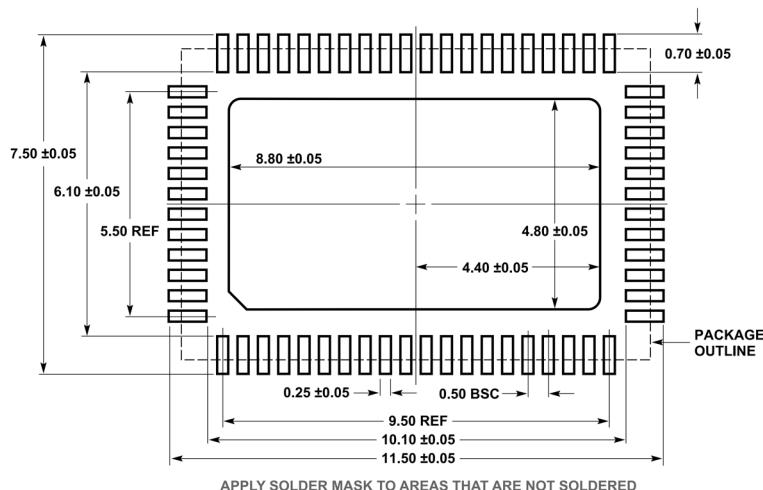

- ▶ 24 ピン 4mm × 4mm QFN パッケージ (LTC9101-2B)

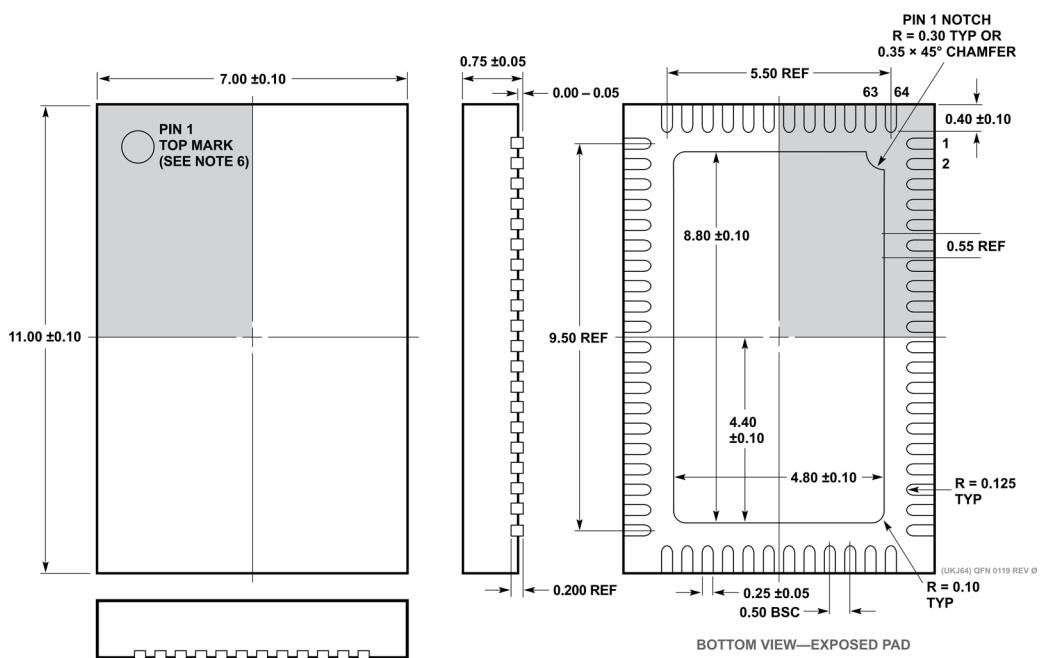

および 64 ピン 7mm × 11mm QFN パッケージ (LTC9102)

で供給

### アプリケーション

- ▶ PoE PSE スイッチ／ルータおよびミッドスパン

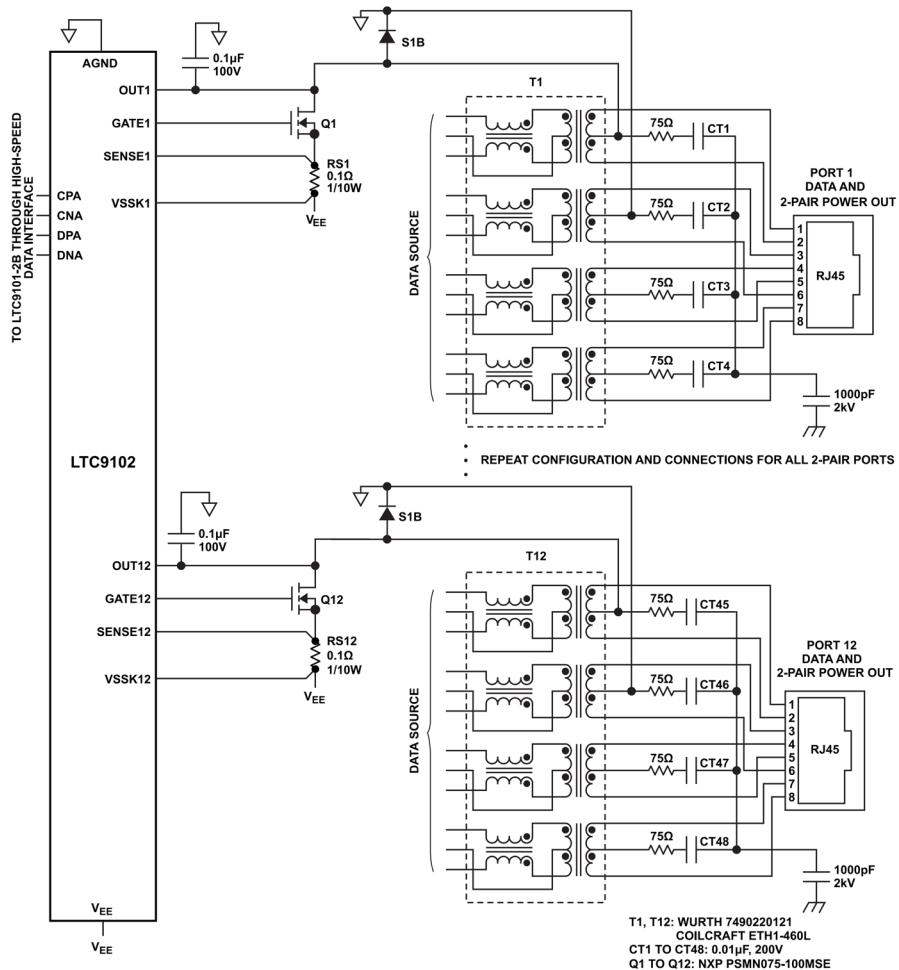

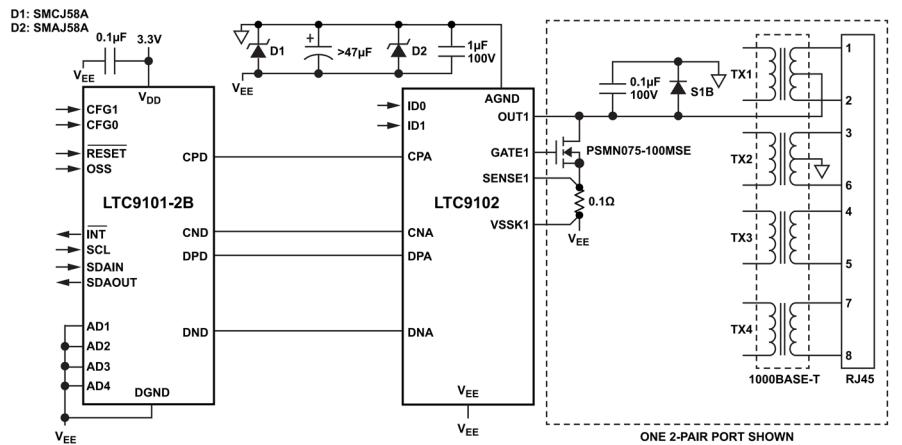

### 標準的応用例

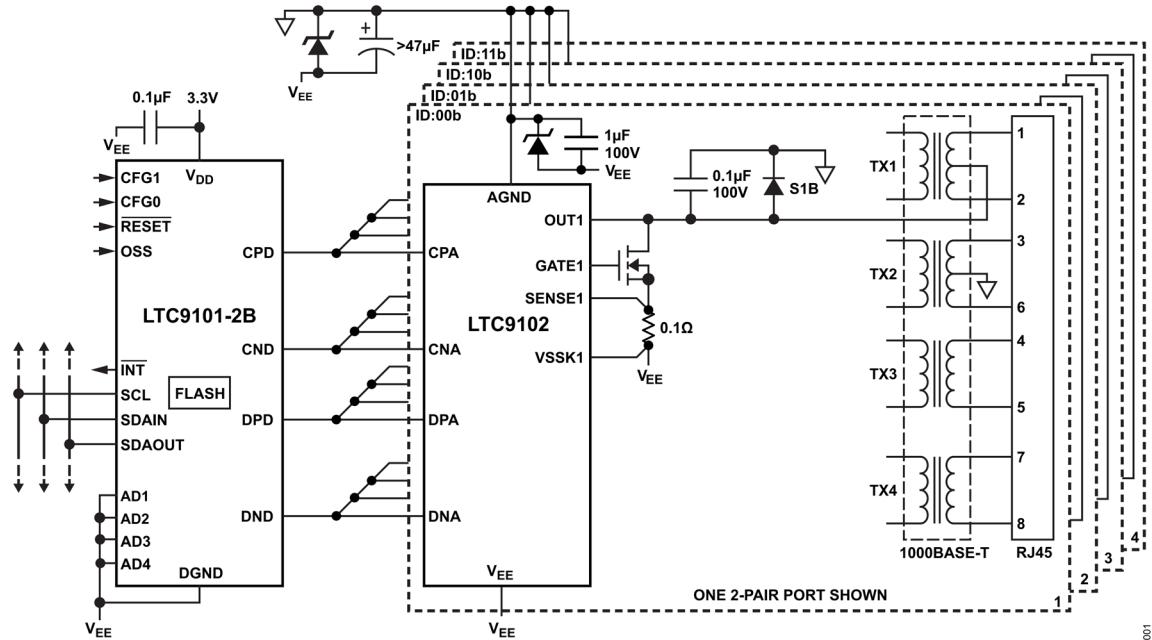

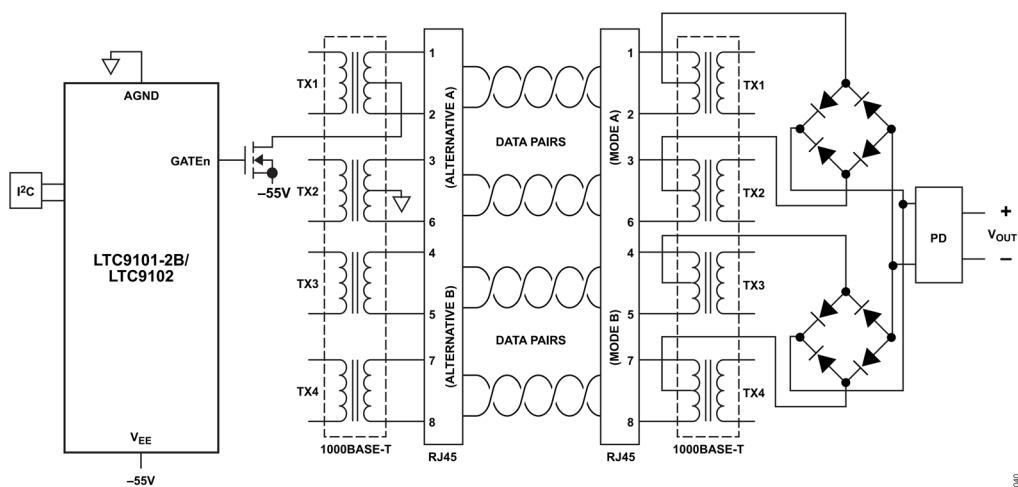

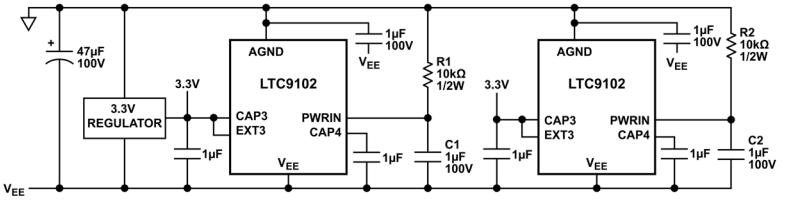

図 1. 802.3bt 2 ペア・アプリケーション（図は 1 ポートを示す）

アナログ・デバイセズでは、文化的に適切な用語および言語を提供するよう、技術資料の更新を行っております。これは広い範囲にわたるプロセスですが、できるだけ早期に段階的に導入して行く予定です。完了までしばらくお待ちいただけますようお願いします。

## 目次

|                         |    |                    |    |

|-------------------------|----|--------------------|----|

| 特長                      | 1  | 802.3bt 2 ペア動作     | 18 |

| アプリケーション                | 1  | PoE の基本            | 20 |

| 概要                      | 1  | デバイスの設定            | 21 |

| 標準的応用例                  | 1  | 動作モード              | 22 |

| 絶対最大定格                  | 3  | 接続チェック             | 22 |

| LTC9101-2B              | 3  | 検出                 | 22 |

| LTC9102                 | 3  | 分類                 | 24 |

| ESD に関する注意              | 3  | 電力の制御              | 26 |

| ピン配置                    | 4  | シリアル・デジタル・インターフェース | 30 |

| オーダー情報                  | 5  | 絶縁条件               | 30 |

| 電気的特性                   | 6  | 外付け部品の選択           | 31 |

| 代表的な性能特性                | 10 | レイアウト条件            | 35 |

| テスト・タイミング図              | 14 | 代表的なアプリケーション       | 36 |

| I <sup>2</sup> C タイミング図 | 15 | パッケージの説明           | 37 |

| ピン機能                    | 16 | 標準的応用例             | 39 |

| アプリケーション情報              | 18 | 関連製品               | 39 |

| 概要                      | 18 |                    |    |

## 改訂履歴

11/2024—Revision 0: Initial Version

## 絶対最大定格

## LTC9101-2B

表 1. (Notes 1、4)

| PARAMETER                                      | RATING                          |

|------------------------------------------------|---------------------------------|

| Supply Voltages (with respect to DGND)         |                                 |

| V <sub>DD</sub>                                | -0.3V to 3.6V                   |

| CAP1, CAP2                                     | -0.3V to 1.32V                  |

| Digital Pins                                   |                                 |

| ADn, CFGn, OSS, SDAIN, SDAOUT, SCL, RESET, INT | -0.3V to V <sub>DD</sub> + 0.3V |

| Analog Pins                                    |                                 |

| CPD, CND, DPD, DND                             | -0.3V to V <sub>DD</sub> + 0.3V |

| Operating Ambient Temperature Range            | -40°C to 85°C                   |

| Operating Junction Temperature Range (Note 2)  | -40°C to 125°C                  |

| Storage Temperature Range                      | -65°C to 150°C                  |

## LTC9102

表 2. (Note 1)

| PARAMETER                                          | RATING               |

|----------------------------------------------------|----------------------|

| Supply Voltages (with respect to V <sub>EE</sub> ) |                      |

| AGND                                               | -0.3V to 80V         |

| PWRIN                                              | -0.3V to 80V         |

| CAP3, CAP4                                         | -0.3V to 5V          |

| VSSKn                                              | -0.3V to 0.3V        |

| Analog Pins                                        |                      |

| SENSEn, OUTn                                       | -20V to 80V          |

| GATEn, IDn, PWRMDn                                 | -0.3V to 80V         |

| CPA, CNA, DPA, DNA                                 | -0.3V to CAP3 + 0.3V |

| EXT3                                               | -0.3V to 30V         |

| Operating Ambient Temperature Range                | -40°C to 85°C        |

| Operating Junction Temperature Range (Note 2)      | -40°C to 125°C       |

| Storage Temperature                                | -65°C to 150°C       |

## ESD に関する注意

ESD（静電放電）の影響を受けやすいデバイスです。電荷を帯びたデバイスや回路ボードは、検知されないまま放電することができます。本製品は当社独自の特許技術であるESD保護回路を内蔵していますが、デバイスが高エネルギーの静電放電を被った場合、損傷を生じる可能性があります。したがって、性能劣化や機能低下を防止するため、ESDに対する適切な予防措置を講じることをお勧めします。

## ピン配置

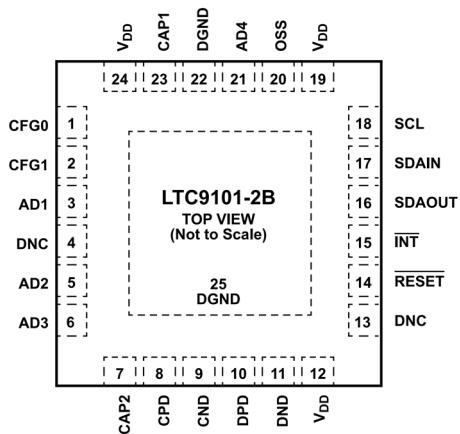

図 2. LTC9101-2B

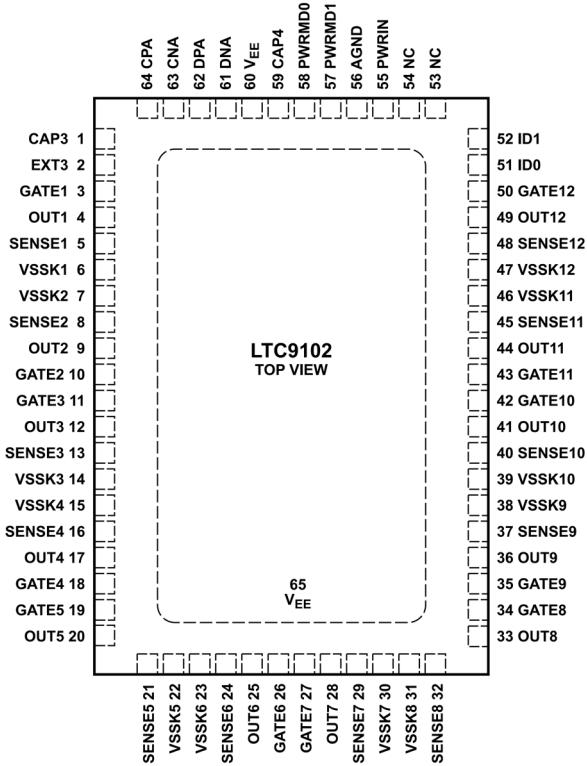

図 3. LTC9102

## オーダー情報

表 3.

| LEAD FREE FINISH  | TAPE AND REEL       | PART MARKING | PACKAGE DESCRIPTION              | TEMPERATURE RANGE |

|-------------------|---------------------|--------------|----------------------------------|-------------------|

| LTC9101AUF-2B#PBF | LTC9101AUF-2B#TRPBF | 9101B        | 24-Lead (4mm × 4mm) Plastic QFN  | -40°C to 85°C     |

| LTC9102AUKJ#PBF   | LTC9102AUKJ#TRPBF   | LTC9102      | 64-Lead (7mm × 11mm) Plastic QFN | -40°C to 85°C     |

更に広い動作温度範囲仕様のデバイスについては、弊社または弊社代理店までお問い合わせください。[テープ & リールの仕様](#)。一部のパッケージは指定された販売チャネルを通じて 500 個単位のリールで供給され、製品番号末尾に「#TRMPBF」という記号が付いています。

## 電気的特性

\*は全動作温度範囲に適用される仕様であることを示します。それ以外は、 $T_A = 25^\circ\text{C}$  での仕様です。また、特に指定のない限り、 $\text{AGND} - V_{EE} = 55\text{V}$ 、 $V_{DD} - \text{DGND} = 3.3\text{V}$  です。 (Notes 3, 4)

表 4.

| SYMBOL                      | PARAMETER                              | CONDITIONS                                                             | MIN | TYP  | MAX  | UNITS                   |                        |             |

|-----------------------------|----------------------------------------|------------------------------------------------------------------------|-----|------|------|-------------------------|------------------------|-------------|

|                             | Main PoE Supply Voltage                | $\text{AGND} - V_{EE}$                                                 |     |      |      |                         |                        |             |

|                             | Type 3 Compliant Output                |                                                                        | *   | 51   |      | 57                      | V                      |             |

|                             | LTC9102 Undervoltage Lockout           | $\text{AGND} - V_{EE}$                                                 | *   |      | 8.2  | 9                       | V                      |             |

| $V_{DD}$                    | $V_{DD}$ Supply Voltage                | $V_{DD} - \text{DGND}$                                                 | *   | 3    | 3.3  | 3.6                     | V                      |             |

|                             | Undervoltage Warning                   |                                                                        |     |      | 2.8  |                         | V                      |             |

|                             | Undervoltage Lockout                   |                                                                        |     |      | 2.6  |                         |                        |             |

|                             | $V_{DD}$ Slew Rate, Falling            | $2.4 \leq V_{DD} - \text{DGND} \leq 3.0$ (Note 7)                      |     |      | 20   | $\text{mV}/\mu\text{s}$ |                        |             |

| $V_{CAP1}, V_{CAP2}$        | Internal Regulator Supply Voltage      | $V_{CAP1} - \text{DGND}, V_{CAP2} - \text{DGND}$ (Note 13)             |     | 1.2  |      | V                       |                        |             |

| $V_{CAP3}$                  | Internal 3.3V Regulator Supply Voltage | $CAP3 - V_{EE}$ (Note 13)                                              | *   | 3    | 3.3  | 3.6                     | V                      |             |

| $t_{CAP3EXT}$               | CAP3 External Supply Rise Time         | $0.5\text{V} < CAP3 < CAP3(\text{Min}), EXT3 Tied to CAP3$ (Note 7)    | *   |      | 1    | ms                      |                        |             |

| $V_{CAP4}$                  | Internal 4.3V Regulator Supply Voltage | $CAP4 - V_{EE}$ (Note 13)                                              | *   |      | 4.3  |                         | V                      |             |

| $I_{EE}$                    | $V_{EE}$ Supply Current                | PWRIN Pin Connected to AGND, EXT3 LOW, All Gates Fully Enhanced        |     | 7.7  | 11   | 14                      | mA                     |             |

|                             | 3.3V Rail Supply Current               | From CAP3 = 3.3V (EXT3 HIGH)                                           |     | 4.2  | 5.4  | 6.6                     | mA                     |             |

| $I_{DD}$                    | $V_{DD}$ Supply Current                | $(V_{DD} - \text{DGND}) = 3.3\text{V}$                                 | *   |      | 40   | 60                      | mA                     |             |

| <b>Detection</b>            |                                        |                                                                        |     |      |      |                         |                        |             |

|                             | Forced Current                         | Load Resistance 15.5k to 32k                                           | *   | 220  | 240  | 260                     | $\mu\text{A}$          |             |

|                             |                                        |                                                                        | *   | 143  | 160  | 180                     | $\mu\text{A}$          |             |

|                             | Forced Voltage                         | Load Resistance 18.5k to 27.5k                                         | *   | 7    | 8    | 9                       | V                      |             |

|                             |                                        |                                                                        | *   | 3    | 4    | 5                       | V                      |             |

|                             | Detection Current Compliance           | $\text{AGND} - \text{OUTn} = 0\text{V}$                                | *   |      | 0.8  | 0.9                     | mA                     |             |

| $V_{OC}$                    | Detection Voltage Compliance           | $\text{AGND} - \text{OUTn}$ , Open Port                                | *   |      | 10.4 | 12                      | V                      |             |

|                             | Detection Voltage Slew Rate            | $\text{AGND} - \text{OUTn}, C_{PORT} = 150\text{nF}$ (Note 7)          |     |      |      | 0.01                    | $\text{V}/\mu\text{s}$ |             |

|                             | Min. Valid Signature Resistance        |                                                                        | *   | 15.5 | 17   | 18.5                    | $\text{k}\Omega$       |             |

|                             | Max. Valid Signature Resistance        |                                                                        | *   | 27.5 | 29.7 | 32                      | $\text{k}\Omega$       |             |

| <b>Classification</b>       |                                        |                                                                        |     |      |      |                         |                        |             |

| $V_{CLASS}$                 | Classification Voltage                 | $\text{AGND} - \text{OUTn}, \text{SENSEn} - \text{VSSKn} < 5\text{mV}$ | *   | 16   |      | 20.5                    | V                      |             |

|                             | Classification Current Compliance      | $\text{SENSEn} - \text{VSSKn}, \text{OUTn} = \text{AGND}$ (Note 14)    | *   | 7    | 8    | 9                       | $\text{mV}$            |             |

|                             | Classification Threshold               | $\text{SENSEn} - \text{VSSKn}$ (Note 14)                               |     |      |      |                         |                        |             |

|                             |                                        | Class Signature 0 – 1                                                  |     | *    | 0.5  | 0.65                    | 0.8                    | $\text{mV}$ |

|                             |                                        | Class Signature 1 – 2                                                  |     | *    | 1.3  | 1.45                    | 1.6                    | $\text{mV}$ |

|                             |                                        | Class Signature 2 – 3                                                  |     | *    | 2.1  | 2.3                     | 2.5                    | $\text{mV}$ |

|                             |                                        | Class Signature 3 – 4                                                  |     | *    | 3.1  | 3.3                     | 3.5                    | $\text{mV}$ |

|                             |                                        | Class Signature 4 – Overcurrent                                        |     | *    | 4.5  | 4.8                     | 5.1                    | $\text{mV}$ |

| $V_{MARK}$                  | Classification Mark State Voltage      | $\text{AGND} - \text{OUTn}, \text{SENSEn} - \text{VSSKn} < 5\text{mV}$ | *   | 7.5  | 9    | 10                      | V                      |             |

|                             | Mark State Current Compliance          | $\text{OUTn} = \text{AGND}$                                            | *   | 7    | 8    | 9                       | $\text{mV}$            |             |

| <b>Gate Driver</b>          |                                        |                                                                        |     |      |      |                         |                        |             |

|                             | GATE Pin Pull-Down Current             | Port Off, $\text{GATEn} = V_{EE} + 5\text{V}$                          |     |      | 1    |                         | mA                     |             |

|                             | GATE Pin Fast Pull-Down Current        | $\text{GATEn} = V_{EE} + 5\text{V}$                                    |     |      | 65   |                         | mA                     |             |

|                             | GATE Pin On Voltage                    | $\text{GATEn} - V_{EE}, I_{GATEn} = 1\mu\text{A}$                      | *   | 11   |      | 14                      | V                      |             |

| <b>Output Voltage Sense</b> |                                        |                                                                        |     |      |      |                         |                        |             |

| $V_{PG}$                    | Power Good Threshold Voltage           | $\text{OUTn} - V_{EE}$                                                 | *   | 2    | 2.4  | 2.8                     | V                      |             |

|                             | OUT Pin Pull-Up Resistance to AGND     | Port On                                                                |     |      | 2500 |                         | $\text{k}\Omega$       |             |

|                             |                                        | Port Off                                                               | *   | 300  | 500  | 700                     | $\text{k}\Omega$       |             |

## 電気的特性

表 4. (続き)

| SYMBOL                                                                            | PARAMETER                                              | CONDITIONS                                                     | MIN | TYP  | MAX   | UNITS  |

|-----------------------------------------------------------------------------------|--------------------------------------------------------|----------------------------------------------------------------|-----|------|-------|--------|

| <b>Current Sense</b>                                                              |                                                        |                                                                |     |      |       |        |

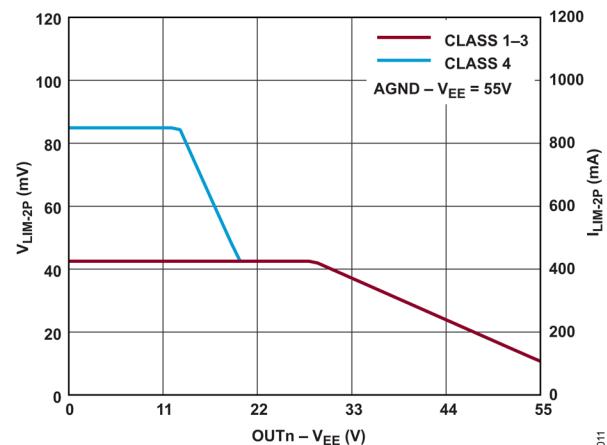

| V <sub>LIM-2P</sub>                                                               | Active Current Limit                                   | OUTn – V <sub>EE</sub> < 10V                                   |     |      |       |        |

|                                                                                   |                                                        | Class 1 to Class 3                                             | *   | 40   | 42.5  | 45     |

|                                                                                   |                                                        | Class 4                                                        | *   | 80   | 85    | 90     |

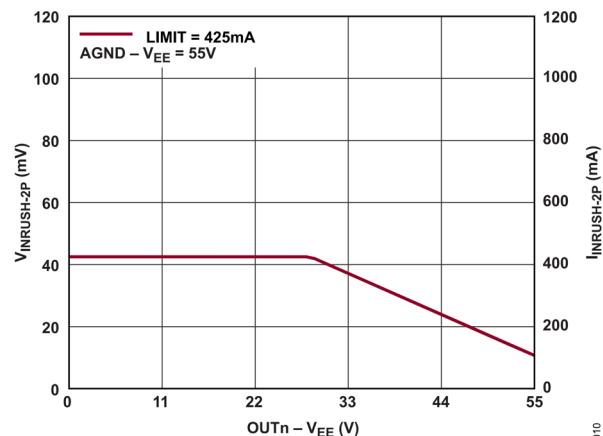

| V <sub>INRUSH-2P</sub>                                                            | Active Current Limit, Inrush                           | OUTn – V <sub>EE</sub> < 30V (Note 15)                         | *   | 40   | 42.5  | 45     |

| V <sub>HOLD-2P</sub>                                                              | DC Disconnect Sense Voltage                            | SENSEn – VSSKn                                                 | *   | 500  | 700   | 900    |

| V <sub>SC</sub>                                                                   | Short-Circuit Sense                                    | SENSEn – VSSKn – V <sub>LIM-2P</sub>                           |     |      | 60    | mV     |

| <b>Port Current Readback</b> (See Typical Performance Characteristics, Note 16)   |                                                        |                                                                |     |      |       |        |

|                                                                                   | Full-Scale Range                                       | (Notes 7, 15)                                                  |     |      | 204.6 | mV     |

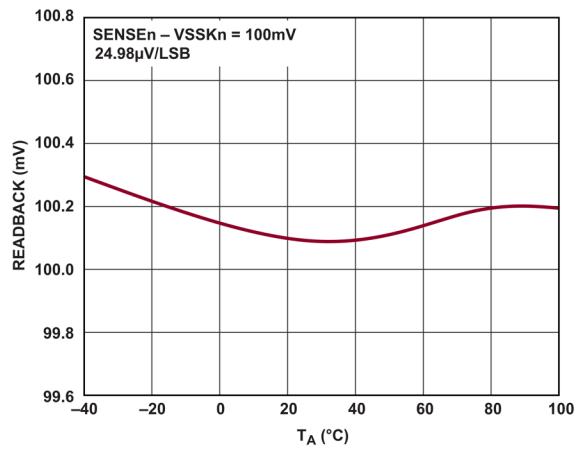

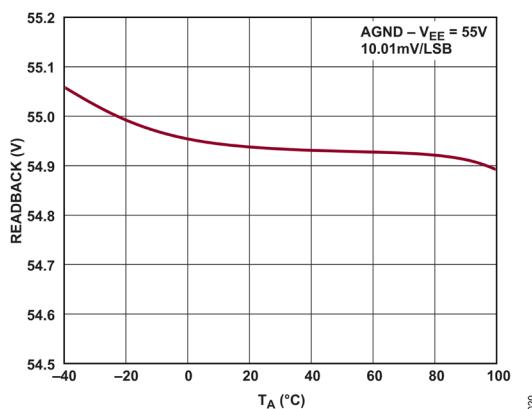

|                                                                                   | LSB Weight                                             | SENSEn – VSSKn , VSSKn = V <sub>EE</sub> (Note 14)             |     |      | 24.98 | μV/LSB |

|                                                                                   | Conversion Period                                      |                                                                |     |      | 1.967 | ms     |

| <b>V<sub>EE</sub> Readback</b> (See Typical Performance Characteristics, Note 16) |                                                        |                                                                |     |      |       |        |

|                                                                                   | Full-Scale Range                                       | (Note 7)                                                       |     |      | 82    | V      |

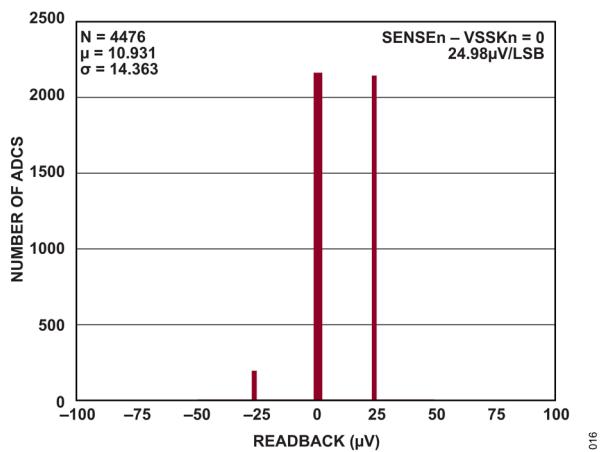

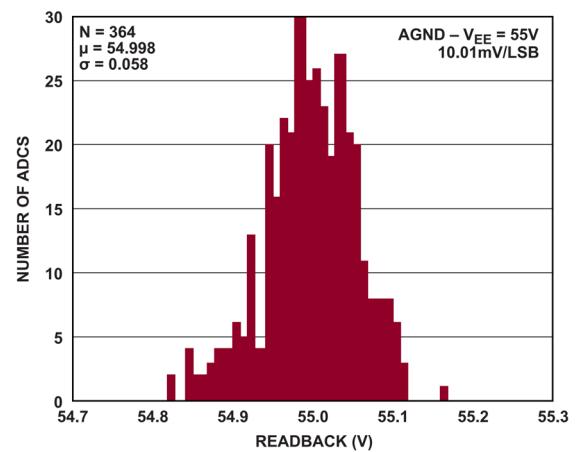

|                                                                                   | LSB Weight                                             | AGND – V <sub>EE</sub>                                         |     |      | 10.01 | mV/LSB |

|                                                                                   | Conversion Period                                      |                                                                |     |      | 1.967 | ms     |

| <b>Digital Interface</b>                                                          |                                                        |                                                                |     |      |       |        |

| V <sub>ILD</sub>                                                                  | Digital Input Low Voltage                              | ADn, RESET, OSS, CFGn (Note 6)                                 | *   |      |       | 0.8    |

|                                                                                   | I <sup>2</sup> C Input Low Voltage                     | SCL, SDAIN (Note 6)                                            | *   |      |       | 1      |

| V <sub>IHD</sub>                                                                  | Digital Input High Voltage                             |                                                                | *   | 2.2  |       | V      |

|                                                                                   | Digital Output Low Voltage                             | I <sub>SDAOUT</sub> = 3mA, I <sub>INT</sub> = 3mA              | *   |      |       | 0.4    |

|                                                                                   |                                                        | I <sub>SDAOUT</sub> = 5mA, I <sub>INT</sub> = 5mA              | *   |      |       | 0.7    |

|                                                                                   | Internal Pull-Up to V <sub>DD</sub>                    | ADn, RESET, OSS                                                |     |      | 50    | kΩ     |

|                                                                                   | Internal Pull-Down to DGND                             | CFG0                                                           |     |      | 50    | kΩ     |

|                                                                                   | EXT3 Pull-Down to V <sub>EE</sub>                      |                                                                |     |      | 50    | kΩ     |

|                                                                                   | IDn Internal Pull-Up to CAP4                           | IDn = 0V                                                       |     |      | 5     | μA     |

| <b>PSE Timing Characteristics</b> (Note 7)                                        |                                                        |                                                                |     |      |       |        |

| t <sub>DET</sub>                                                                  | Detection Time                                         | Beginning to End of Detection                                  | *   |      | 380   | 500    |

| t <sub>CLASS_RESET</sub>                                                          | Classification Reset Duration                          |                                                                | *   | 15   |       | ms     |

| t <sub>CEV</sub>                                                                  | Class Event Duration                                   |                                                                | *   | 6    | 15    | 20     |

| t <sub>CEVON</sub>                                                                | Class Event Turn On Duration                           | C <sub>PORT</sub> = 0.6μF                                      | *   |      |       | 0.1    |

| t <sub>LCE</sub>                                                                  | Long Class Event Duration                              |                                                                | *   | 88   |       | 105    |

| t <sub>CLASS</sub>                                                                | Class Event I <sub>CLASS</sub> Measurement Timing      |                                                                | *   | 6    |       | ms     |

| t <sub>CLASS_LCE</sub>                                                            | Long Class Event I <sub>CLASS</sub> Measurement Timing |                                                                | *   | 6    |       | 75     |

| t <sub>CLASS_ACS</sub>                                                            | Autoclass I <sub>CLASS</sub> Measurement Timing        |                                                                | *   | 88   |       | 105    |

| t <sub>ME1</sub>                                                                  | Mark Event Duration (Except Last Mark Event)           | (Note 11)                                                      | *   | 6    | 9.6   | 12     |

| t <sub>ME2</sub>                                                                  | Last Mark Event Duration                               | (Note 11)                                                      | *   | 6    | 20    | ms     |

| t <sub>PON</sub>                                                                  | Power On Delay, Auto Mode                              | From End of Valid Detect to End of Valid Inrush                | *   |      |       | 400    |

| t <sub>AUTO_PSE1</sub>                                                            | Autoclass Power Measurement Start                      | From End of Inrush to Beginning of Autoclass Power Measurement | *   | 1.4  |       | 1.6    |

| t <sub>AUTO_PSE2</sub>                                                            | Autoclass Power Measurement End                        | From End of Inrush to End of Autoclass Power Measurement       | *   | 3.1  |       | 3.5    |

| t <sub>AUTO_WINDOW</sub>                                                          | Autoclass Average Power Sliding Window                 |                                                                | *   | 0.15 | 0.23  | 0.3    |

| t <sub>ED</sub>                                                                   | Fault Delay                                            | From Power On Fault to Next Detect                             | *   | 1.0  | 1.3   | 1.8    |

| t <sub>START</sub>                                                                | Maximum Current Limit Duration During Inrush           |                                                                | *   | 50   | 60    | 75     |

| t <sub>LIM</sub>                                                                  | Maximum Current Limit Duration After Inrush            | (Note 12)                                                      |     |      |       |        |

|                                                                                   |                                                        | t <sub>LIMn</sub> = 0x0                                        |     |      | 50    | ms     |

|                                                                                   |                                                        | t <sub>LIMn</sub> = 0x1                                        |     |      | 15    | ms     |

|                                                                                   |                                                        | t <sub>LIMn</sub> = 0x2                                        |     |      | 10    | 15     |

|                                                                                   |                                                        |                                                                |     |      | 22    | ms     |

## 電気的特性

表 4. (続き)

| SYMBOL         | PARAMETER                                              | CONDITIONS                                                                 | MIN | TYP | MAX | UNITS |         |

|----------------|--------------------------------------------------------|----------------------------------------------------------------------------|-----|-----|-----|-------|---------|

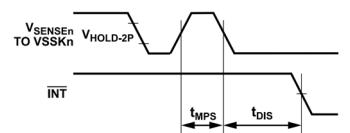

| $t_{MPS}$      | Maintain Power Signature (MPS) Pulse Width Sensitivity | $t_{LIMn} = 0x3$<br>Current Pulse Width to Reset Disconnect Timer (Note 8) | *   | 6   | 11  | 17    | ms      |

| $t_{DIS}$      | Maintain Power Signature (MPS) Dropout Time            | (Note 5)                                                                   | *   | 320 | 370 | 400   | ms      |

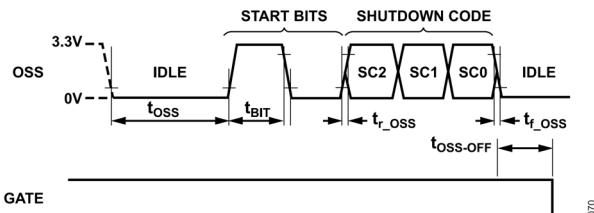

| $t_{BIT}$      | Bit Duration                                           |                                                                            | *   | 24  | 25  | 26    | $\mu s$ |

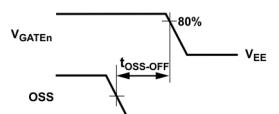

| $t_{OSS-OFF}$  | Shutdown Priority Delay                                |                                                                            | *   |     | 6.5 | 10    | $\mu s$ |

| $t_{r\_OSS}$   | OSS Rise Time                                          |                                                                            | *   | 1   |     | 300   | ns      |

| $t_{f\_OSS}$   | OSS Fall Time                                          |                                                                            | *   | 1   |     | 300   | ns      |

| $t_{OSS\_IDL}$ | OSS Idle Time                                          |                                                                            |     |     | 50  |       | $\mu s$ |

|                | $I^2C$ Watchdog Timer Duration                         |                                                                            | *   | 1.5 | 2   | 3     | s       |

|                | Minimum Pulse Width for Masked Shutdown                |                                                                            | *   | 3   |     |       | $\mu s$ |

|                | Minimum Pulse Width for RESET                          |                                                                            | *   | 4.5 |     |       | $\mu s$ |

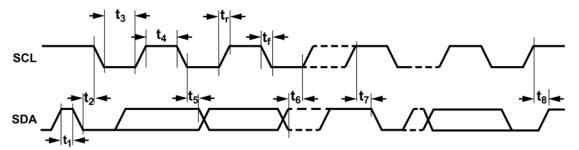

$I^2C$  Timing (Note 7)

|            |                               |                    |   |     |     |         |

|------------|-------------------------------|--------------------|---|-----|-----|---------|

| $f_{SCLK}$ | Clock Frequency               |                    | * |     | 1   | MHz     |

| $t_1$      | Bus Free Time                 | Figure 31 (Note 9) | * | 480 |     | ns      |

| $t_2$      | Start Hold Time               | Figure 31 (Note 9) | * | 240 |     | ns      |

| $t_3$      | SCL Low Time                  | Figure 31 (Note 9) | * | 480 |     | ns      |

| $t_4$      | SCL High Time                 | Figure 31 (Note 9) | * | 240 |     | ns      |

| $t_5$      | SDAIN Data Hold Time          | Figure 31 (Note 9) | * | 60  |     | ns      |

|            | Data Clock to SDAOUT Valid    | Figure 31 (Note 9) | * |     | 250 | ns      |

| $t_6$      | Data Set-Up Time              | Figure 31 (Note 9) | * | 80  |     | ns      |

| $t_7$      | Start Set-Up Time             | Figure 31 (Note 9) | * | 240 |     | ns      |

| $t_8$      | Stop Set-Up Time              | Figure 31 (Note 9) | * | 240 |     | ns      |

| $t_r$      | SCL, SDAIN Rise Time          | Figure 31 (Note 9) | * |     | 120 | ns      |

| $t_f$      | SCL, SDAIN Fall Time          | Figure 31 (Note 9) | * |     | 60  | ns      |

|            | Fault Present to INT Pin Low  | (Notes 9, 10)      | * |     | 150 | ns      |

|            | Stop Condition to INT Pin Low | (Notes 9, 10)      | * |     | 1.5 | $\mu s$ |

|            | ARA to INT Pin High Time      | (Note 9)           | * |     | 1.5 | $\mu s$ |

|            | SCL Fall to ACK Low           | (Note 9)           | * |     | 250 | ns      |

**Note 1 :** 上記の絶対最大定格を超えるストレスを加えるとデバイスに恒久的な損傷を与えることがあります。デバイスを長時間絶対最大定格状態に置くと、デバイスの信頼性と寿命に影響を与えます。

**Note 2 :** このチップセットは、一時的な過負荷状態からデバイスを保護することを目的とした過熱保護機能を備えています。過熱保護機能が作動した場合、ジャンクション温度は 140°C を超過しています。仕様規定された最高動作ジャンクション温度より上での連続動作はデバイスの信頼性を損なう可能性があります。

**Note 3 :** デバイスのピンに流れ込む電流はすべて正です。デバイスのピンから流れ出す電流はすべて負です。

**Note 4 :** LTC9102 は負の電源電圧 (AGND 基準) で動作します。混乱を避けるために、このデータシートの電圧は絶対値で示されています。

**Note 5 :**  $t_{DIS}$  は、IEEE 802.3 に定める  $t_{MPD}$  と同じです。

**Note 6 :** LTC9101-2B のデジタル・インターフェースは DGND 基準で動作します。すべてのロジック・レベルは DGND 基準で測定されます。

**Note 7 :** 設計上の性能は確保していますが、テストの対象外です。

**Note 8 :** IEEE 802.3 は、電力維持のための最小 PSE および PD 入力電流条件のセットとして MPS を定義しています。LTC9101-2B/LTC9102 のポートは、 $V_{SENSEn} - V_{SSKn} \geq V_{HOLD-2P}$  の状態が  $t_{MPS}$  に達するとその MPS タイマーをリセットし、 $V_{SENSEn} - V_{SSKn} \geq V_{HOLD-2P}$  の状態が  $t_{DIS}$  を超えるとポートの電力供給を停止します。切断のセクションを参照してください。

**Note 9 :**  $V_{IHD}$  で測定した値。

## 電気的特性

**Note 10 :** I<sup>2</sup>C トランザクション中にフォルト状態が生じた場合でも、I<sup>2</sup>C バスの停止条件が満たされるまで $\overline{\text{INT}}$ ピンはプルダウンされません。

**Note 11 :** マーク時の LTC9102 の負荷特性 :  $7V < (\text{AGND} - \text{V}_{\text{OUTH}}) < 10V$

**Note 12 :** シリアル・バスの使用法、デバイスの設定、およびステータス・レジスタについては、LTC9101-2B ソフトウェア・インターフェース・ガイドを参照してください。

**Note 13 :** CAPI1、CAPI2、CAPI3、CAPI4 から電流のソースやシンクはしないでください。

**Note 14 :** ポート電流とポート電力の測定値は、検出抵抗の値（代表値 :  $0.1\Omega$ ）によって異なります。詳細については、[外付け部品の選択](#)のセクションを参照してください。

**Note 15 :** 突入電流閾値の選択については、[突入電流の制御](#)のセクションを参照してください。

**Note 16 :** ADC の特性と代表的性能値は、LTC9102 のハードウェア能力に関するものです。LTC9102 での測定値は LTC9101-2B で処理と合成が行われます。レジスタの説明とユーザに提示される LSB の重み付け（ポート電流、ポート電圧、 $V_{EE}$  電圧、およびシステム温度）については、LTC9101-2B ソフトウェア・インターフェース・ガイドを参照してください。

## 代表的な性能特性

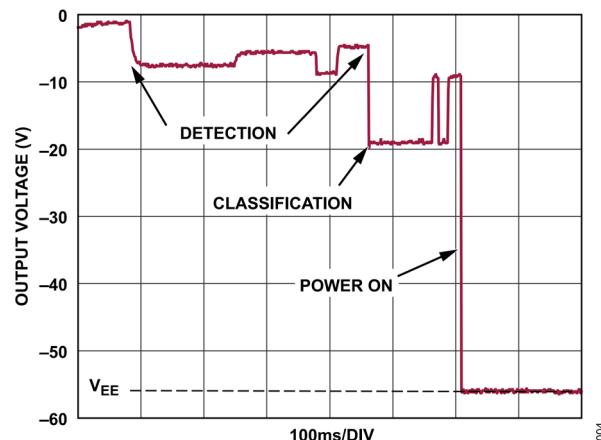

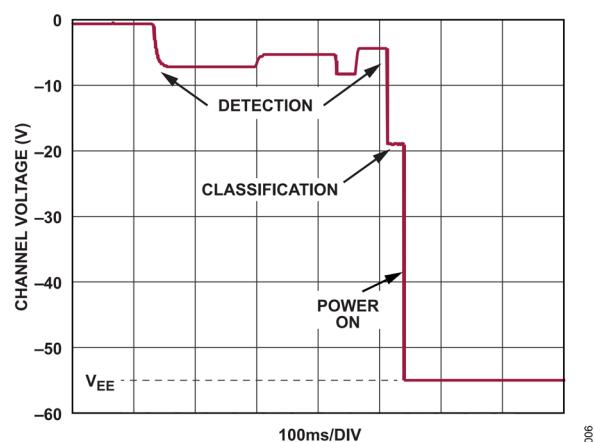

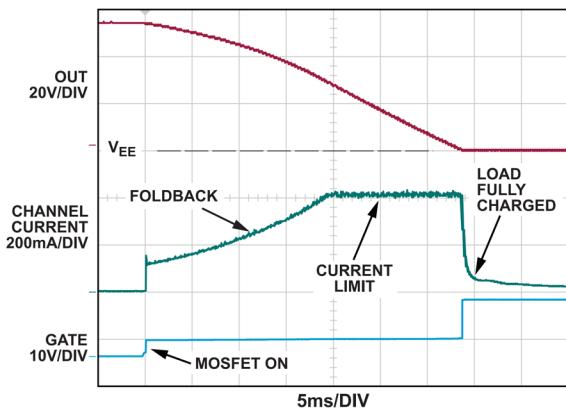

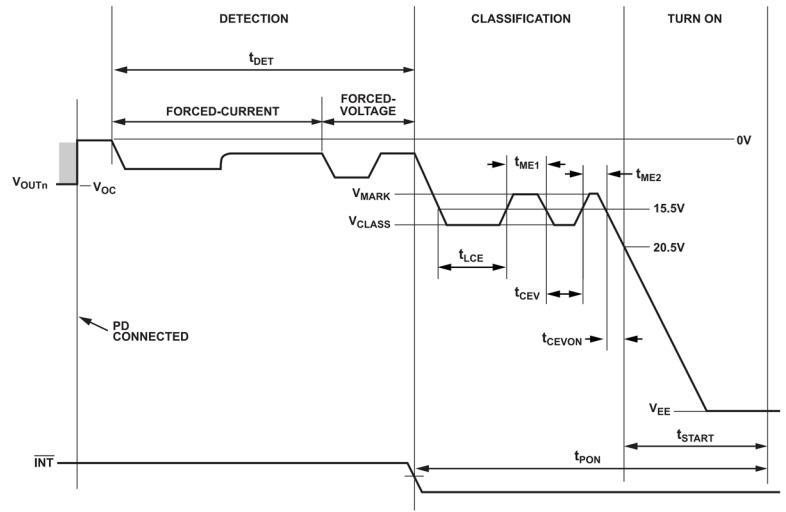

図 4. パワー・オン・シーケンス、802.3bt 2 ペア

図 7. 突入電流制限 (Note 15)

図 5. パワー・オン・シーケンス、タイプ 1 モード

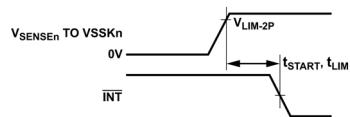

図 8. パワー・オン電流制限

図 6. オープン・サーキット検出

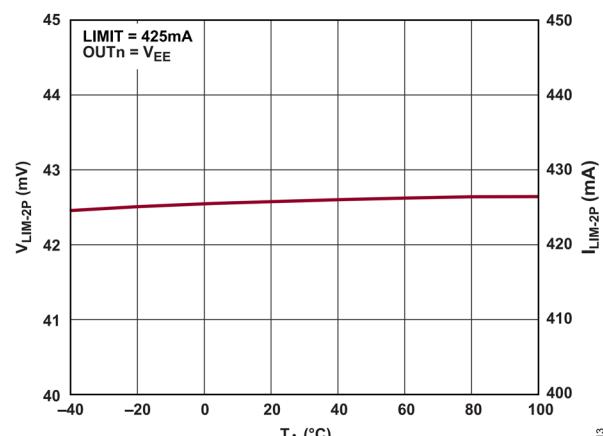

図 9. I\_LIM-2P と温度の関係

## 代表的な性能特性

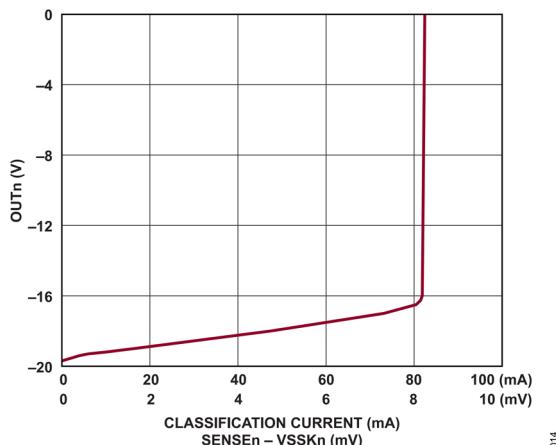

図 10. 分類電流コンプライアンス

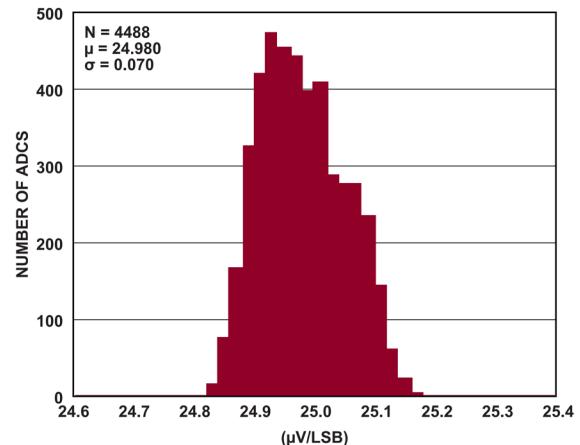

図 13. ポート電流リードバック LSB

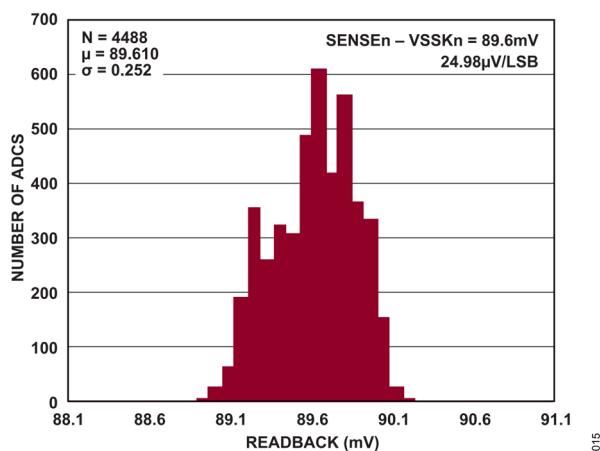

図 11. ポート電流のリードバック

図 14. ポート電流リードバックと温度の関係

図 12. ポート電流リードバック · オフセット

図 15. V<sub>EE</sub> のリードバック

## 代表的な性能特性

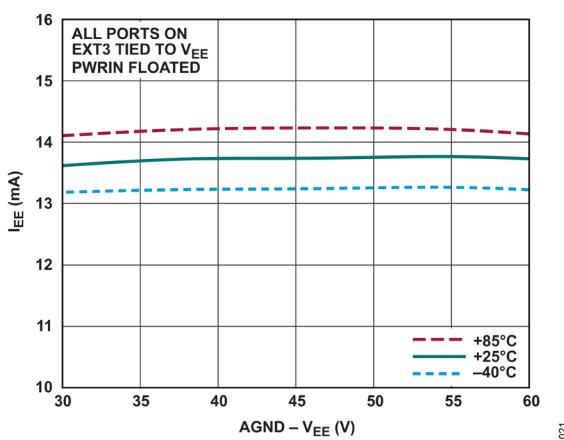

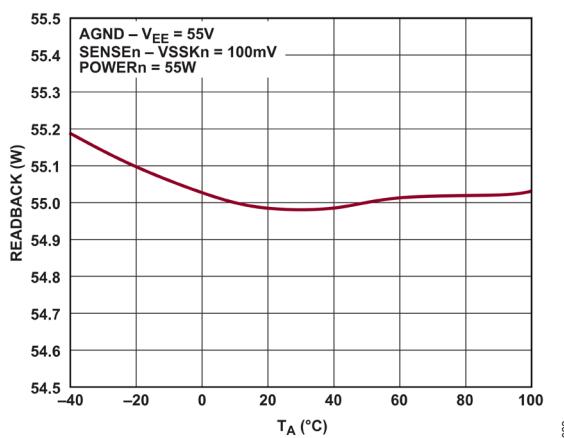

図 16.  $V_{EE}$  リードバックと温度の関係図 19.  $180\mu F$  負荷への給電図 17.  $V_{EE}$  電源電流 ( $I_{EE}$ ) と電圧および温度の関係

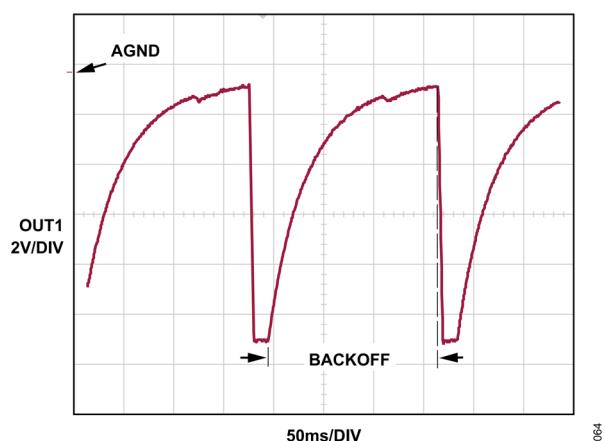

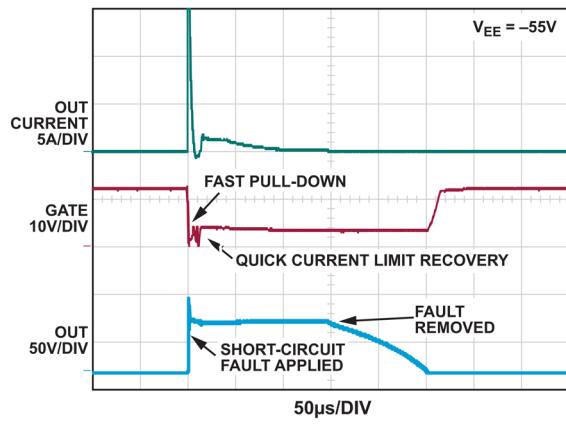

図 20. 短絡からの回復

図 18. ポート電力モニタ精度と温度の関係

図 21. クロックとデータ書き込みのアイ・ダイアグラム

## 代表的な性能特性

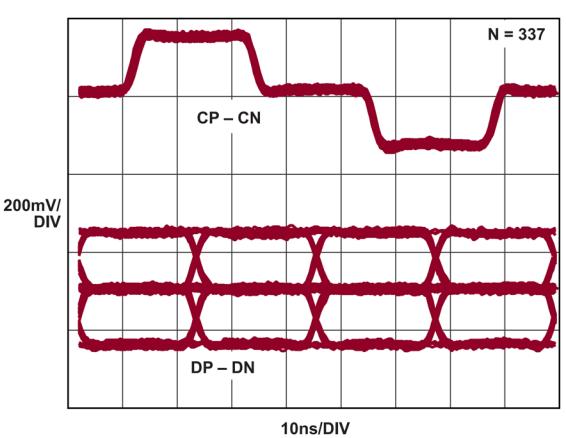

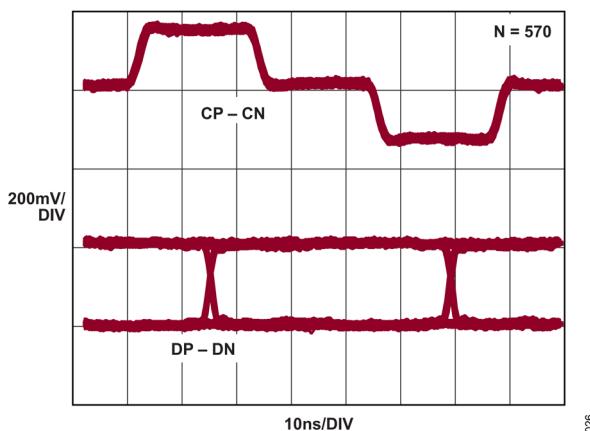

図 22. クロックとデータ読み出しのアイ・ダイアグラム

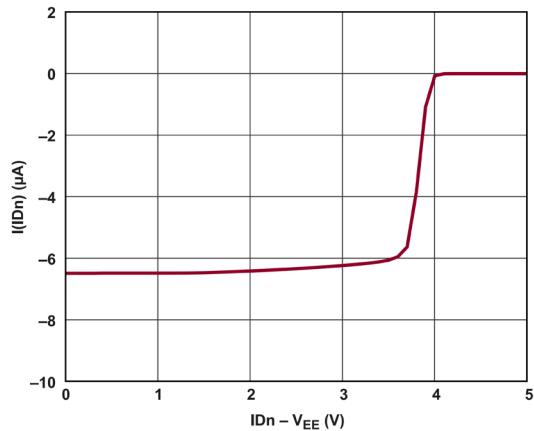

図 25. IDn ピン電流と電圧の関係

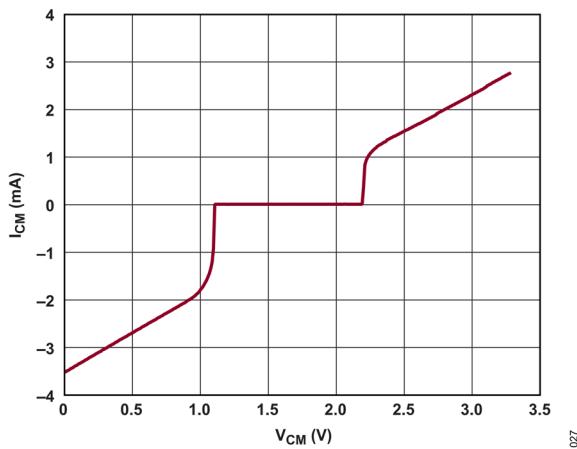

図 23. LTC9102 の CP/CN および DP/DN コモンモード補正電流

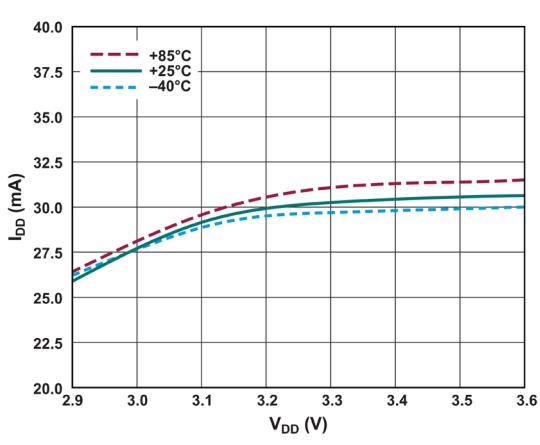

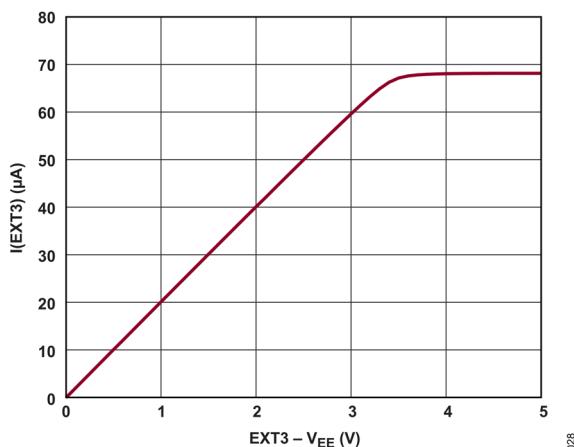

図 26. V<sub>DD</sub> 電源電流 (I<sub>DD</sub>) と電圧および温度の関係

図 24. EXT3 ピン電流と電圧の関係

## テスト・タイミング図

図 27. 検出、分類、およびターン・オンのタイミング（自動または半自動モード）

図 28. 電流制限タイミング

図 29. DC 切断タイミング

図 30. 1ビット・シャットダウン優先度のタイミング

## テスト・タイミング図

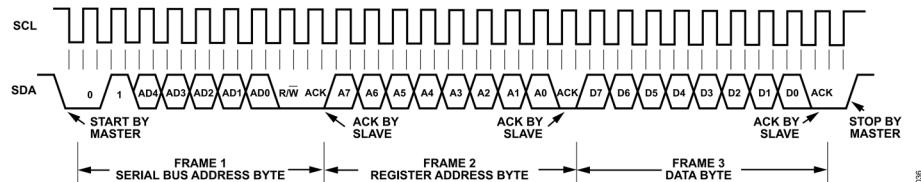

I<sup>2</sup>C タイミング図図 31. I<sup>2</sup>C インターフェースのタイミング

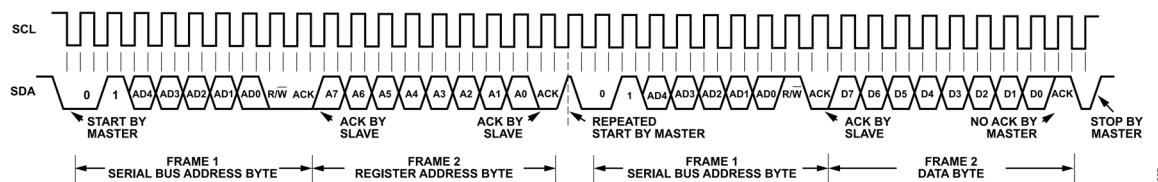

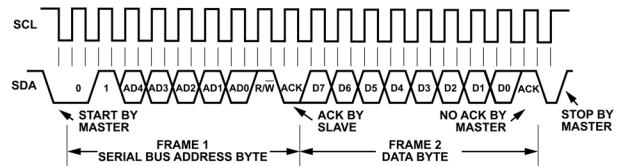

図 32. レジスタへの書き込み

図 33. レジスタからの読み出し

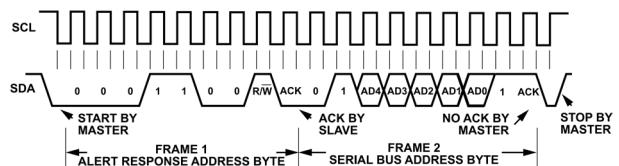

図 34. 割込みレジスタの読み出し（ショート・フォーム）

図 35. アラート応答アドレスからの読み出し

## ピン機能

| ピン番号                       | 記号              | 説明                                                                                                                                                                                                                                                                                                                                                                  |

|----------------------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>LTC9101-2B</b>          |                 |                                                                                                                                                                                                                                                                                                                                                                     |

| Pins 2, 1<br>Respectively  | CFG[1:0]        | デバイス設定入力。接続する LTC9102 デバイスの数を設定するには、これらの設定ピンをハイまたはローに接続します。詳細については <a href="#">デバイスの設定</a> のセクションを参照してください。                                                                                                                                                                                                                                                         |

| Pins 7, 23<br>Respectively | CAP[2:1]        | コア電源バイパス・コンデンサ。これらのピンは、内部 1.2V レギュレータのバイパス用に 1μF のコンデンサを介して DGND に接続します。コンデンサの容量は必ず 1μF としてください。また、このピンからは電流のソースやシンクをしないでください。                                                                                                                                                                                                                                      |

| Pin 8                      | CPD             | クロック・トランシーバの正の出入力（デジタル）。データ・トランスを介して CPA に接続します。                                                                                                                                                                                                                                                                                                                    |

| Pin 9                      | CND             | クロック・トランシーバの負の出入力（デジタル）。データ・トランスを介して CNA に接続します。                                                                                                                                                                                                                                                                                                                    |

| Pin 10                     | DPD             | データ・トランシーバの正の出入力（デジタル）。データ・トランスを介して DPA に接続します。                                                                                                                                                                                                                                                                                                                     |

| Pin 11                     | DND             | データ・トランシーバの負の出入力（デジタル）。データ・トランスを介して DNA に接続します。                                                                                                                                                                                                                                                                                                                     |

| Pins 12, 19, 24            | V <sub>DD</sub> | V <sub>DD</sub> IO 電源。DGND 基準の 3.3V 電源に接続します。それぞれの V <sub>DD</sub> ピンは、0.1μF 以上のコンデンサを使いローカルでバイパスする必要があります。サージ耐性を向上させるには、V <sub>DD</sub> に 10μF のパルク・コンデンサを接続する必要があります。                                                                                                                                                                                             |

| Pin 14                     | RESET           | リセット入力、アクティブ・ロー。 <u>RESET</u> がローになると LTC9101-2B/LTC9102 は非アクティブになります、すべてのポートがオフになって内部レジスタもすべてリセットされます。 <u>RESET</u> がハイになると、LTC9101-2B/LTC9102 は通常動作を開始します。 <u>RESET</u> を外付けのコンデンサまたは RC 回路に接続すると、パワー・オン遅延を設定することができます。 <u>RESET</u> には内部フィルタリングがあるため、幅 1μs 未満のグリッチによって LTC9101-2B/LTC9102 がリセットされることはありません。内部で V <sub>DD</sub> にプルアップされます。                       |

| Pin 15                     | INT             | 割込み出力、オープン・ドライン。いくつかのイベントのいずれか 1 つが LTC9101-2B 内で発生すると、 <u>INT</u> はローになります。このピンは、Reset レジスタのビット 6 または 7 がセットされると高インピーダンス状態に戻ります。 <u>INT</u> 信号を使用すればホスト・プロセッサへの割込みを生成できるので、継続的にソフトウェア・ポーリングを行う必要がなくなります。 <u>INT</u> イベントは、Int Mask レジスタを使って個別にディスエーブルできます詳細については LTC9101-2B のソフトウェア・インターフェース・ガイドを参照してください。 <u>INT</u> は 2 つの I <sup>2</sup> C トランザクションの間にのみ更新されます。 |

| ピン番号                             | 記号      | 説明                                                                                                                                                                                                                                                                                                       |

|----------------------------------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin 16                           | SDAOUT  | シリアル・データ出力、つまり I <sup>2</sup> C シリアル・インターフェース・バスのオープン・ドライン・データ出力。LTC9101-2B は、2 つのピンを使って双方向 SDA 機能を実現し、I <sup>2</sup> C バスの光絶縁を簡略化します。標準的な双方向 SDA ピンを実装するには、SDAOUT と SDAIN を互いに接続します。詳細については <a href="#">アプリケーション情報</a> のセクションを参照してください。                                                                 |

| Pin 17                           | SDAIN   | シリアル・データ入力。I <sup>2</sup> C シリアル・インターフェース・バスの高インピーダンス・データ入力。LTC9101-2B は、2 つのピンを使って双方 SDA 機能を実現し、I <sup>2</sup> C バスの光絶縁を簡略化します。標準的な双方向 SDA ピンを実装するには、SDAOUT と SDAIN を互いに接続します。詳細については <a href="#">アプリケーション情報</a> のセクションを参照してください。                                                                       |

| Pin 18                           | SCL     | シリアル・クロック入力。I <sup>2</sup> C シリアル・インターフェース・バスの高インピーダンス・クロック入力。SCL ピンは、I <sup>2</sup> C SCL バス・ラインに直接接続する必要があります。I <sup>2</sup> C シリアル・インターフェース・バスを使用しない場合は、SCL をハイに接続してください。                                                                                                                             |

| Pin 20                           | OSS     | マスク可能なシャットダウン入力、アクティブ・ハイ。1 ビット・シャットダウン優先度と 3 ビット・シャットダウン優先度の両方がサポートされています。詳細については <a href="#">過電流シャットダウン (OSS)</a> のセクションを参照してください。内部で DGND にプルダウンされます。                                                                                                                                                  |

| Pins 21, 6, 5, 3<br>Respectively | AD[4:1] | I <sup>2</sup> C アドレス・ビット 4~1。ベース I <sup>2</sup> C シリアル・アドレスを設定するには、これらのアドレス・ピンをハイまたはローに接続します。ベース・アドレスは (01A <sub>4</sub> A <sub>3</sub> A <sub>2</sub> A <sub>1</sub> 0b) になり、内部で V <sub>DD</sub> にプルアップされます。詳細については <a href="#">バス・アドレスの指定</a> のセクションを参照してください。                                        |

| Pins 22, 25                      | DGND    | デジタル・グラウンド。DGND は、V <sub>DD</sub> 電源からのリターンに接続する必要があります。                                                                                                                                                                                                                                                 |

| <b>LTC9102</b>                   |         |                                                                                                                                                                                                                                                                                                          |

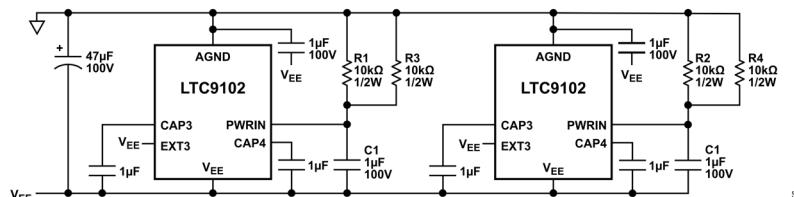

| Pin 1                            | CAP3    | 3.3V 内部アナログ電源のバイパス・コンデンサ。V <sub>EE</sub> との間に 1μF のセラミック・コンデンサを接続してください。3.3V 電源をこのピンに接続すれば電源効率を改善できます。外部電源使用時に内部 3.3V レギュレータをシャットオフするには、EXT3 ピンを CAP3 と同じ電圧にする必要があります。また、このピンからは電流のソースやシンクをしないでください。アナログ・デバイセズのマニュアルに明示されている場合（例えば、LTC9102 のピンをストラップ配線する場合やシリアル・インターフェースを終端する場合）を除き、CAP3 には何も接続しないでください。 |

## ピン機能

| ピン番号                                                            | 記号          | 説明                                                                                                                                                                                                                                                                                    |

|-----------------------------------------------------------------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin 2                                                           | EXT3        | 外部 3.3V イネーブル。外部電源使用時に内部 3.3V レギュレータをシャットオフするには、EXT3 ピンを CAP3 に接続します。内部レギュレータを作動させるには、フロート状態にするか V <sub>EE</sub> に接続してください。                                                                                                                                                           |

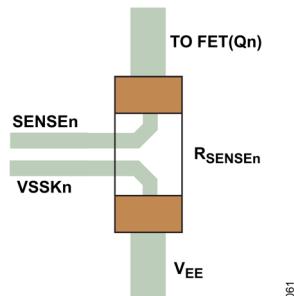

| Pins 47, 46, 39, 38, 31, 30, 23, 22, 15, 14, 7, 6 Respectively  | VSSK[12:1]  | V <sub>EE</sub> へのケルビン検出接続。0.1Ωの抵抗を介して、チャンネル n 用検出抵抗の V <sub>EE</sub> 側へ接続します。V <sub>EE</sub> プレーンに直接接続することはしないでください。要件については <a href="#">ケルビン検出</a> のセクションを参照してください。                                                                                                                  |

| Pins 48, 45, 40, 37, 32, 29, 24, 21, 16, 13, 8, 5 Respectively  | SENSE[12:1] | チャンネル n の電流検出入力。SENSEn は、SENSEn と VSSKn の間にある 0.1Ω の検出抵抗を介して外部 MOSFET の電流をモニタします。検出抵抗の電圧が電流制限閾値 I <sub>LIM-2P</sub> に達すると、外部 MOSFET の電流を一定に保つために GATEn ピン電圧が下げられます。詳細については <a href="#">アプリケーション情報</a> のセクションを参照してください。そのチャンネルを使わない場合は、SENSEn を V <sub>EE</sub> に接続します。                |

| Pins 49, 44, 41, 36, 33, 28, 25, 20, 17, 12, 9, 4 Respectively  | OUT[12:1]   | チャンネル n の出力電圧モニタ。OUTn を出力チャンネルに接続してください。ドレインとソース間の電圧が 10V を超えた場合は、電流制限閾値を下げることによって、電流制限回路が外部 MOSFET の消費電力を制限します。OUTn と V <sub>EE</sub> 間の電圧が 2.4V (代表値) 未満になると、ポート・パワーグッド・イベントが生成されます。チャンネルがアイドル状態のときは、OUTn と AGND 間に 500k 的抵抗が内部で接続されます。そのチャンネルを使用しない場合は、OUTn ピンをフロート状態にしてください。      |

| Pins 50, 43, 42, 35, 34, 27, 26, 19, 18, 11, 10, 3 Respectively | GATE[12:1]  | チャンネル n のゲート駆動。GATEn をチャンネル n の外部 MOSFET のゲートに接続してください。MOSFET をオンすると、ゲート電圧が V <sub>EE</sub> より 12V (代表値) 高い値に駆動されます。電流制限状態では、外部 MOSFET に流れれる電流を一定に保つために GATEn の電圧が下げられます。フォルト・タイマーが終了すると GATEn がブルダウントされて MOSFET がオフになり、ポート・フォルト・イベントが生成されます。そのチャンネルを使用しない場合は、GATEn ピンをフロート状態にしてください。 |

| Pins 52, 51 Respectively                                        | ID[1:0]     | トランシーバ ID。マルチドロップ高速データ・インターフェース上で LTC9102 のアドレスを設定します。ID の値は 00b から始めてください。CAP3 に接続することによってハイにし、V <sub>EE</sub> に接続することによってローにします。詳細については <a href="#">デバイスの設定</a> のセクションを参照してください。                                                                                                    |

| ピン番号                                       | 記号              | 説明                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|--------------------------------------------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin 55                                     | PWRIN           | スタートアップ・レギュレータ・バイパスおよび外部低電圧電源入力。内部 4.3V および 3.3V 電源用の電力。内部レギュレータが、このピンの電圧を 6V より高い値に維持します。このノードに外付けの抵抗または電源を接続すれば、LTC9102 の電力効率を改善することができます。このピンと V <sub>EE</sub> の間には 1μF のコンデンサを接続してください。                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Pin 56                                     | AGND            | アナログ・グラウンド。                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Pins 57, 58 Respectively                   | PWRMD[1:0]      | 最大電力モード入力。ID[1:0] = 00b として、設定抵抗 R <sub>PWRMD</sub> を使用 LTC9102 の PWRMD0 を V <sub>EE</sub> に接続します。LTC9101-2B をリセットすると、R <sub>PWRMD</sub> がチップセット内のすべてのポートの初期最大電力割当値を選択します。システム電源のサイズは、R <sub>PWRMD</sub> までの電力を出力するすべてのポートに対応できるように決定する必要があります。自動モードをイネーブルすると、チップセットは PoE PSE として独立して動作します。チップセットはすべてのポートの検出と分類を行い、R <sub>PWRMD</sub> で設定された値までの電力を各ポートに供給できるようにします。ID ピンが 01b、10b、および 11b に設定された LTC9102 の PWRMD0 ピンは、フロート状態のままにしておく必要があります。すべての LTC9102 の PWRMD1 ピンもフロート状態のままにしてください。R <sub>PWRMD</sub> オプションとその詳細については、 <a href="#">自動モードでの最大 PSE 電力</a> のセクションを参照してください。カスタム設定パッケージが存在する場合、PWRMD ピンは無視されます。詳細については <a href="#">保存されている設定</a> のセクションを参照してください。 |

| Pin 59                                     | CAP4            | 4.3V 内部アナログ電源のバイパス・コンデンサ。V <sub>EE</sub> との間に 1μF のセラミック・コンデンサを接続してください。また、このピンからは電流のソースやシンクをしないでください。                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Pins 60, 65                                | V <sub>EE</sub> | PoE 主電源入力。AGND を基準として、-51V~ -57V の電源に接続します。電圧は PSE のタイプ (タイプ 3 または 4) によって異なります。                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Pin 61                                     | DNA             | データ・トランシーバの負の出入力 (アナログ)。データ・トランスを介して DND に接続します。                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Pin 62                                     | DPA             | データ・トランシーバの正の出入力 (アナログ)。データ・トランスを介して DPD に接続します。                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Pin 63                                     | CAN             | クロック・トランシーバの負の出入力 (アナログ)。データ・トランスを介して CND に接続します。                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Pin 64                                     | CPA             | クロック・トランシーバの正の出入力 (アナログ)。データ・トランスを介して CPD に接続します。                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| <b>Common Pins</b>                         |                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| LTC9101-2B Pins 4, 13; LTC9102 Pins 53, 54 | NC, DNC         | 「NC」または「DNC」で識別されるピンは、すべて未接続のままになります。                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

## アプリケーション情報

### 概要

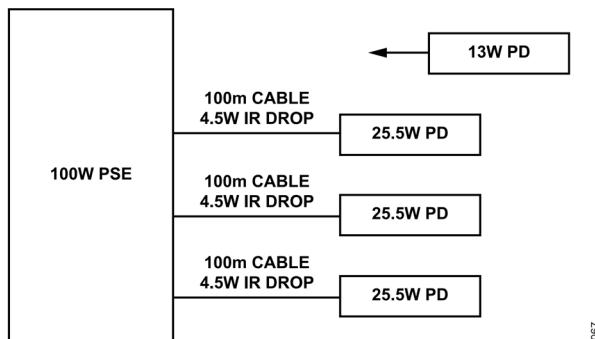

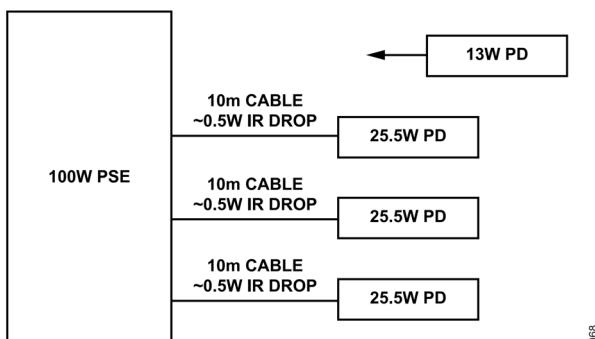

PoE (Power over Ethernet) は、銅製のイーサネット用データ配線を使って DC 電力を供給するための標準プロトコルです。802.3 イーサネット・データ規格を管理する IEEE グループは、PoE 給電機能を 2003 年に追加しました。802.3af と呼ばれる最初の PoE 規格は、最大 13W で 48V の DC 電力を供給できました。802.3af は広く普及していましたが、アプリケーションによっては 13W の電力では不十分でした。2009 年、IEEE は 802.3at (PoE+) として知られる新規格を公開し、電圧と電流の条件を上げて 25.5W の電力を供給できるよう規定しました。IEEE 802.3af と 802.3at は PoE 1 として広く認知されています。更に 2018 年、IEEE は 802.3bt (PoE 2) と呼ばれる最新の PoE 規格を公開しました。802.3bt では PD の最大供給電力が 71.3W まで上げられています。

IEEE 規格は PoE の用語も定義しています。ネットワークに電力を供給するデバイスは PSE (Power Sourcing Equipment) と呼ばれ、ネットワークから電力を取り込むデバイスは PD (Powered Device) と呼ばれます。PSE には 2 つのタイプがあります。データと電力を供給するエンドポイント（代表的なものとしてはネットワーク・スイッチやルータ）と、電力を供給する一方でデータはバス・スルーするミッドスパンです。ミッドスパンは、主に PoE 非対応の既存ネットワークに PoE 機能を追加するためを使われます。PD の代表的なものは、IP 電話、ワイヤレス・アクセス・ポイント、防犯カメラなどです。

### PoE++の進化

IEEE 802.3at (PoE 1) の 25.5W 規格の策定中でさえ 25.5W を超える供給電力を求める声は大きく、その声が更に高まるであろうことは明らかでした。2013 年には、増大する PD 供給電力に対応できる規格を策定するために 802.3bt 作業部会が設置されました。

この作業部会の主な目標は、802.3at で利用されている 2 ペアの電源ではなく、4 ペアのイーサネット・ケーブルすべてを使用することでした。4 ペアすべてを使用すれば、既存のイーサネット・ケーブルに対して少なくとも 2 倍の電力を供給することができます。更に、イーサネットのデータ信号の完全性を維持しながら、(ペアセットと呼ばれる) 2 ペアあたりの電流量も増加しました。802.3bt では PD 供給電力が 25.5W から 71.3W に増加し、IEEE 準拠の大電力 PD アプリケーションを実現することが可能になります。

LTC9101-2B/LTC9102 は 2 ペアのデバイスで、1 つのペアセットを介して各ポートに電力を供給します。各ペアは、専用のパワー・チャンネルによって駆動されます。このデータシートでは、チャンネルという語は対応するペアセットに割り当てられた PSE 回路のことを指します。したがって、このデータシートにおいては、「チャンネル」と「ペアセット」という語は同義と見なすことができます。

加えて、IEEE 802.3bt では電力維持シグネチャ (Maintain Power Signature: MPS) 電流を大幅に低減できるので、待機時の消費電力も大幅に減ります。これにより、標準的な PoE 部品を使って、政府や業界の新たな待機電力規制を満たすことができます。

### LTC9101-2B/LTC9102 の製品概要

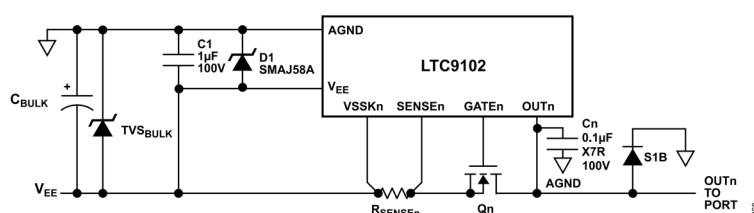

LTC9101-2B/LTC9102 は第 6 世代の PSE コントローラで、エンドポイント・アプリケーションまたはミッドスパン・アプリケーションにおいて、最大 48 個 (25.5W) の 2 ペア PSE ポートに対応できます。IEEE 802.3bt 準拠の PSE 設計を実現するために必要な回路を実質的にすべて内蔵しており、必要なのは 1 ポートにつき 1 つの外付けパワー MOSFET とポートごとの検出抵抗だけです。これにより、MOSFET を内蔵する同様のデバイスと比較して電力損失が最小限に抑えられ、システムの信頼性が向上します。

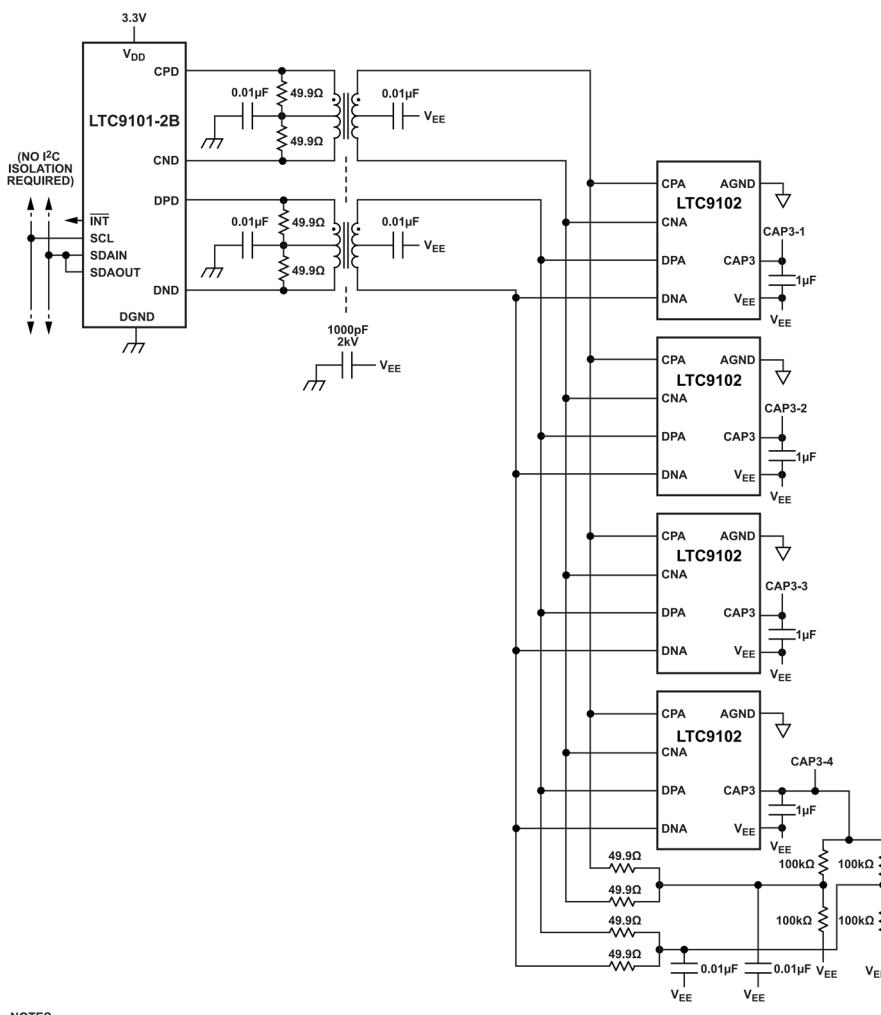

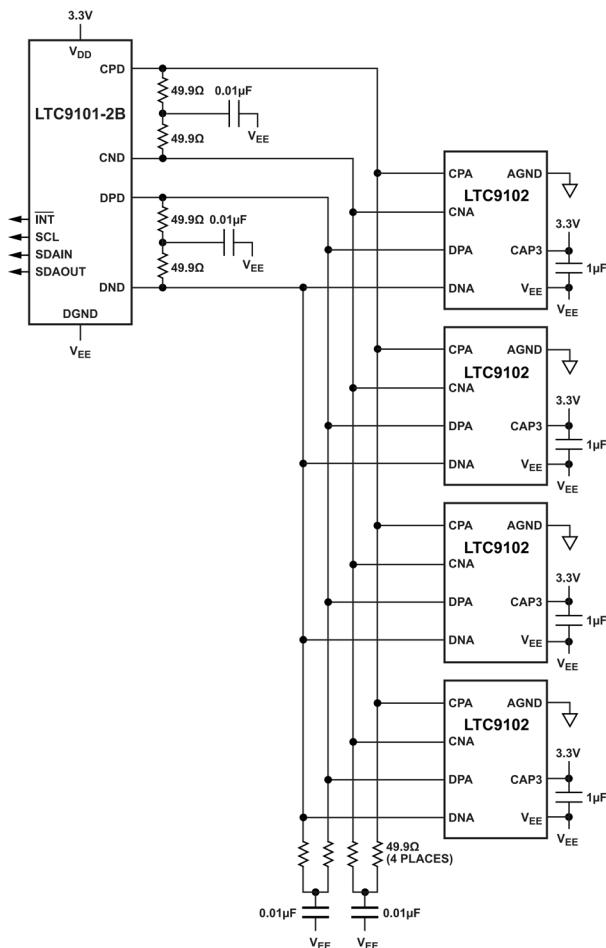

LTC9101-2B/LTC9102 チップセットは、チップ間通信用に独自の絶縁方式を実装しています。このアーキテクチャは、高価な光アイソレータや絶縁型電源を 1 個の低価格トランジスで置き換えることによって、部品コストを大幅に削減します。1 個の LTC9101-2B は、このトランジス絶縁されたインターフェースを介して最大 4 個の LTC9102 のバスを制御することができます。LTC9101-2B と、対応する LTC9102 を直接接続することも可能です。

LTC9101-2B/LTC9102 は、ポートごとのイベントでトリガされる設定可能な割込み信号、チャンネルごとのパワー・オン制御とフォルト・レメトリ、チャンネルごとの電流モニタリング、 $V_{EE}$  モニタリング、電流および電圧の 100ms の移動平均などの機能を備えています。

LTC9101-2B/LTC9102 は高度な第 6 世代 PSE 機能も備えており、これには、ファームウェア・アップデートやカスタム・ユーザ構成パッケージを保存する内蔵 eFlash、802.3at/bt 対応モードの選択、クワッド・ベースの IC ドライバとの完全な後方互換性を確保する I<sup>2</sup>C クワッド・バーチャライゼーション、100mΩ の極小検出抵抗、+80V/-20V 対応のポート対向ピン、ケーブル・サージ・ライドスルーの改善などが含まれています。

LTC9102 の各パワー・チャンネルには専用の検出および分類ハードウェアが含まれています。これは、すべてのポートとチャンネルの検出、分類、パワー・オンを同時にを行うことを可能にして、スイッチを介したパワー・オン遅延を大幅に短縮します。それほど高度な機能を持たない他の PSE では、例えば LED ライトなどの PD へポートごとに給電する際に、目立った遅延が生じます。

$V_{EE}$  とポート電流の測定は同時に行われるので、ポートごとに一貫した高精度の電力モニタリングを行うことができます。

### 802.3bt 2 ペア動作

LTC9101-2B には、4 個の同じチャンネルで構成されるグループが最大 12 個含まれています。4 個のポートからなるそれぞれのグループは、「クワッド」と呼ばれます。LTC9101-2B のアーキテクチャでは、各クワッドにレジスタ設定とちょうど 4 個のチャンネルのステータスがあり、4 つの 2 ペア 802.3bt ポートを制御できます。

2 ペア・モードでは、IEEE 802.3bt 規格は最大 25.5W の供給電力をサポートし、クラス 4 以下の電力を必要とする PD をサポートします。ハイパワー・シングルシグネチャ PD (クラス 5 以上) およびデュアルシグネチャ PD はクラス 4 (25.5W) の電力に格下げされ、1 つのペアセットを介して電力を受け取ります。

## アプリケーション情報

### 802.3at タイプ 1 モード

表 5 に示すように、802.3bt 適合のすべての PSE は、既存の 802.3at タイプ 1 およびタイプ 2 の PD と後方互換です。

802.3bt PSE では、この完全互換性に加えて、低待機電力、電流制限タイミング機能の強化、ダイナミック・パワー・マネージメントなどのサポートがすべての PD タイプに拡張されています（PD アプリケーションでサポートされているのと同様）。

LTC9101-2B は更に 802.3af 準拠のポート動作もサポートしています。802.3af PD が 802.3bt 動作に対応できないというまれなケースに備え、cfg2p4p レジスタには 15W で CC なしのモードがサポートされています。

なお、802.3at PSE は 802.3bt PSE のコンプライアンス・テストに適合せず、802.3bt PSE は 802.3at PSE のコンプライアンス・テストに適合しません。これは、それぞれの規格の設計によるものです。802.3at と 802.3bt のデバイスは相互運用が可能なように設計されています。802.3at 規格と 802.3bt 規格の主な特性の対比を表 6 に示します。

表 5. PSE の最大供給電力（ポートごと）<sup>1</sup>

| DEVICE |         | PSE      |                  |                    |                    |                  |       |

|--------|---------|----------|------------------|--------------------|--------------------|------------------|-------|

|        |         | STANDARD |                  | 802.3at            |                    | 802.3bt          |       |

| PD     | 802.3at | Type     | 1                | 2                  | 3 (2-Pair)         | 3 (4-Pair)       | 4     |

|        |         | 1        | 13W              | 13W                | 13W                | 13W              | 13W   |

| PD     | 802.3bt | 2        | 13W <sup>1</sup> | 25.5W              | 25.5W              | 25.5W            | 25.5W |

|        |         | 3        | 13W <sup>1</sup> | 25.5W <sup>1</sup> | 25.5W <sup>1</sup> | 51W              | 51W   |

|        |         | 4        | 13W <sup>1</sup> | 25.5W <sup>1</sup> | 25.5W <sup>1</sup> | 51W <sup>1</sup> | 71.3W |

<sup>1</sup> PD には要求値より少ない電力を割り当てられる（格下げできる）ことを示します。

表 6. 802.3at タイプ 1 と 802.3bt の特性

| FEATURE                     | 802.3at (Type 1)       | 802.3bt                            |

|-----------------------------|------------------------|------------------------------------|

| First Class Event           | Short                  | Long                               |

| First Mark Event (15W Mode) | No                     | Yes                                |

| Limit Timer                 | No (Uses Cutoff Timer) | Yes                                |

| Connection Check            | No                     | 2-Pair: No<br>4-Pair: Yes          |

| Active Alternative(s)       | A or B                 | 2-Pair: A or B<br>4-Pair: A and B  |

| Maximum Class Events        | 1                      | 2-Pair: 2<br>4-Pair: 5             |

| Maximum Available Power     | Class 3                | 2-Pair: Class 4<br>4-Pair: Class 8 |

| Short MPS                   | No                     | Yes                                |

| Autoclass                   | No                     | Yes                                |

## アプリケーション情報

## PoE の基本

一般的なイーサネット・データ接続は 2 本または 4 本のツイスト・ペア銅線（通称イーサネット・ケーブル）で構成され、それぞれの端をトランスで結合してグラウンド・ループを防止しています。PoE システムはこの結合配置の利点を生かし、データ・トランスのセンタータップ間に電圧を加えることによって、データ伝送に影響することなく PSE から PD へ電力を送ります。PoE システムの回路図の概要を図 36 に示します。

DC 電圧が加わることを想定していない旧式のデータ装置を損傷させないように、PoE 規格では、PSE による電力の供給および停止が可能かどうかを判定するプロトコルを規定しています。有

効な PD には、その入力に 25k の固有コモンモード抵抗が必要です。このような PD をケーブルに接続すると、PSE はこのシグネチャ抵抗を検出して電力を供給します。その後に PD を切り離すと、PSE はオープン・サーキットを検出して電力の供給を停止します。PSE は、電流フォルトや短絡が発生した場合も電力の供給を停止します。

PD が検出されると、PSE は、PD で消費する最大電力を PSE に知らせる分類シグネチャを探します。PSE はこの情報を使って、いくつかのポートに電力を割り振る、PD の消費電力を監視する、あるいは PSE が供給できる電力以上の電力を消費する PD を拒否する、といった対応を取ることができます。

図 36. 802.3bt システムの構成図 – 2 ペア PSE とシングルシグネチャ PD

## アプリケーション情報

### 802.3bt の新機能

- 802.3bt仕様では、いくつかの新機能が導入されています。

- ▶ タイプ3のPSEは、2ペアまたは4ペア・デバイスとして構成できます。タイプ4のPSEは4ペア・デバイスとして構成できます。

- ▶ タイプ3およびタイプ4のPSEは、PSEの構成および接続されているPDの特性に応じて、4ペアすべて（両方のペアセット）を介して電力を供給できます。

- ▶ タイプ3およびタイプ4のPDは、4ペアすべて（両方のペアセット）を介して電力を受け取ることができなければなりません。

- ▶ タイプ3およびタイプ4のPDは、シングルシグネチャPDまたはデュアルシグネチャPDとして構成できます。シングルシグネチャPDは、両方のペアセットに対して有効な同じシグネチャ抵抗を同時に示します（図36を参照）。デュアルシグネチャPDは、完全に独立した2つの有効な検出シグネチャを、各ペアセットに対して1つずつ示します。

- ▶ タイプ3のシングルシグネチャPDは、6種類の電力レベル（3.84W、6.49W、13W、25.5W、40W、51W）のいずれか1つを要求します。

- ▶ タイプ3のデュアルシグネチャPDは、4種類の電力レベル（3.84W、6.49W、13W、25.5W）のいずれか1つを各ペアセットに要求します。PDの合計要求電力は、両方のペアセットが要求する電力の合計です。

- ▶ タイプ3のPDクラスは、より低い電力レベルでタイプ3の追加機能セットを提供するために、タイプ1およびタイプ2クラスとオーバーラップしています。

- ▶ タイプ4のシングルシグネチャPDは、2種類の電力レベル（62W、71.3W）のいずれか1つを要求します。

- ▶ タイプ4のデュアルシグネチャPDは、少なくとも一方のペアセットで35.6Wの電力を要求し、もう一方のペアセットで5種類の電力レベル（3.84W、6.49W、13W、25.5W、35.6W）のいずれか1つを要求します。PDの合計要求電力は、両方のペアセットが要求する電力の合計です。

- ▶ 分類は、最大で5つのクラス・イベントに拡張されます。追加イベントは、既存のPDクラスと新しいPDクラスを一意に識別できます。

- ▶ タイプ3と4のPSEは、長い最初のクラス・イベントを発行して、タイプ3と4の機能をサポートしていることを接続先のPDに通知します。

- ▶ 低待機電力機能は、電力維持シグネチャ・パルスの長さを短縮する（短縮MPS）ことによって有効になります。PDのデューティ・サイクルは約23%から約2%に低下します。PSEが長い最初のクラス・イベントを発行した場合、PDは短縮MPSを出力できます。

- ▶ パワー・マネージメント機能は、Autoclass（802.3btのPSEおよびPDのオプション機能）によって強化されています。Autoclassシステムでは、PDの最大電力が測定されてPSEホストに報告され、PDアプリケーションで使われなかつた出力電力とイーサネット・ケーブル配線の損失をPSEに回収することができます（表7）。詳細については、Autoclassのセクションと、LTC9101-2Bのソフトウェア・インターフェース・ガイドを参照してください。

表7. IEEEが仕様規定した電力割当て

(シングルシグネチャPD)

| PD CLASS | PSE OUTPUT POWER | ALLOCATED CABLING LOSS | PD INPUT POWER |

|----------|------------------|------------------------|----------------|

| 1        | 4W               | 0.16W                  | 3.84W          |

| 2        | 6.7W             | 0.21W                  | 6.49W          |

| 3        | 14W              | 1W                     | 13W            |

| 4        | 30W              | 4.5W                   | 25.5W          |

| 5        | 45W              | 5W                     | 40W            |

| 6        | 60W              | 9W                     | 51W            |

| 7        | 75W              | 13W                    | 62W            |

| 8        | 90W              | 18.7W                  | 71.3W          |

### デバイスの設定

1個のLTC9101-2Bは、1個から4個までのLTC9102を制御できます。それぞれのLTC9102は12個のパワー・チャンネルを制御します。したがって、各LTC9101-2Bは最大48個のパワー・チャンネルを制御できます。

[バス・アドレスの指定](#)のセクションに述べるように、4チャンネルからなる各グループが1個のI<sup>2</sup>Cアドレスを使用します。

表8. デバイスの設定オプション

| CFG[1:0] | NUMBER OF PORTS | NUM 9102s | I <sup>2</sup> C ADDRS | I <sup>2</sup> C ADDRESS OFFSET |   |   |   |   |   |   |   |   |   |    |    |

|----------|-----------------|-----------|------------------------|---------------------------------|---|---|---|---|---|---|---|---|---|----|----|

|          |                 |           |                        | 0                               | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 |

| 0(00b)   | 12              | 1         | 3                      | ✓                               | ✓ | ✓ |   |   |   |   |   |   |   |    |    |

| 1(01b)   | 24              | 2         | 6                      | ✓                               | ✓ | ✓ | ✓ | ✓ | ✓ |   |   |   |   |    |    |

| 2(10b)   | 36              | 3         | 9                      | ✓                               | ✓ | ✓ | ✓ | ✓ | ✓ | ✓ | ✓ | ✓ | ✓ |    |    |

| 3(11b)   | 48              | 4         | 12                     | ✓                               | ✓ | ✓ | ✓ | ✓ | ✓ | ✓ | ✓ | ✓ | ✓ | ✓  | ✓  |

## アプリケーション情報

### 動作モード

LTC9101-2B/LTC9102 は最大で 48 個の独立したチャンネルを制御し、それを 3 つのモード（手動、半自動、自動）のいずれかで動作させることができます。4 つ目のモードはシャットダウン・モードで、ポートをディスエーブルします（表 9 を参照）。

表 9. 動作モード

|           | AUTO MODE | PORT MODE | Detect/Class      | Power-up      | Automatic Threshold Assignment |

|-----------|-----------|-----------|-------------------|---------------|--------------------------------|

| Auto      | 1         | 11b       | Enabled at Reset  | Automatically | Yes                            |

|           | 0         | 11b       | Host Enabled      | Automatically | Yes                            |

| Semi-Auto | 0         | 10b       | Host Enabled      | Upon Request  | Yes                            |

| Manual    | 0         | 01b       | Once Upon Request | Upon Request  | Yes                            |

| Shutdown  | 0         | 00b       | Disabled          | Disabled      | No                             |

手動モードでは、ポートはホスト・システムからの命令を待ってから動作します。ポートは、ホストによって命令されると検出サイクルまたは分類サイクルを 1 回実行して、その結果をポート・ステータス・レジスタで報告します。ホスト・システムは、いつでも電力の供給または停止をポートに命令できます。

半自動モードでは、ポートは、接続されたすべての PD の検出と分類を繰り返し試みます。ポートはこれらの試行のステータスをホストに報告し、ホストからの命令を待ってポートに電力を供給します。ホストは、検出と分類をイネーブルする必要があります。検出および分類の結果は、供給される電力に対して有効なものでなければなりません。

自動モードは半自動モードと同様に動作しますが、検出と分類の結果が有効だった場合は自動的にポートへ電力が供給される点が異なります。自動モードでは、2P Police と  $I_{LIM-2P}$  の値が PSE 割当てクラスに基づいて自律的に設定されます。この動作モードにするには、表 14 に示すように PWRMD0 ピンを抵抗経由で  $V_{EE}$  に接続するか、動作モード・レジスタを自動モードに設定します。自動モードでの最大 PSE 電力のセクションを参照してください。

シャットダウン・モードではポートがディスエーブルされて PD の検出も分類も行われず、電力も供給されません。

LTC9101-2B/LTC9102 は、現在どのモードにあるのかに関係なく、フォルトが発生したポートへの電力供給を自動的に停止します。切断検出がイネーブルされた場合は、切断イベントが発生したすべてのポートへの電力供給が自動的に停止します。ホスト・コントローラも、いつでも電力供給停止をポートに命令できます。

### リセットと PWRMD

LTC9101-2B/LTC9102 の初期設定は、リセット時の PWRMD0 の状態によって異なります。リセットは、パワーアップ時、RESET がローになったとき、またはグローバルの Reset All ビットがセットされたときに行われます。

パワーアップ後に PWRMD0 の状態を変更しても、リセットされるまで LTC9101-2B/LTC9102 のポート動作は変わりません。PWRMD1 ピンは予備です。

R\_PWRMD を介して自動モードがイネーブルされた場合は、PD が見つかるまで各ポートが検出と分類を繰り返します。PD が見つかると、そのポートは PSE が割り当てたクラスに従い 2P Police をセットして有効な PD に電力を供給し、フォルトが検出されると電力の供給を停止します。

PSE が割り当てたクラスに基づいて自動モードで自動的に設定される 2P Police の値を、表 10 に示します。DC Disconnect の閾値はすべての PSE 割当てクラスで 7.0mA（代表値）です。4P Police の値は無視されます。

表 10. 自動モードでのパワー・オン閾値（代表値）

| PSE ASSIGNED CLASS       | 2P POLICE (W) |

|--------------------------|---------------|

| 0                        | 15.5          |

| 1                        | 4             |

| 2                        | 7             |

| 3                        | 15.5          |

| 4                        | 30            |

| CLASS 4+, TYPE 1 LIMITED | 15.5          |

## 接続チェック

### 接続チェックの概要

IEEE 802.3bt は接続チェックを導入しています。これは、4ペア PSE が PD のシグネチャ設定、つまりシングルシグネチャ、デュアルシグネチャ、または無効な結果（PD 以外）を検出するためのメカニズムです。接続チェックの結果は、4ペア対応の PSE が 4 ペア電力を供給すべきかどうかと、供給する場合の方法を決定します。

802.3at で記述されていた PD 構成は 1 つだけで、これはシングルシグネチャ PD と呼ばれます。その構成を図 36 に示します。シングル・シグネチャ PD は、両方のペアセットに対して同じ 25k 検出抵抗を並列に示します。

802.3bt ではデュアルシグネチャ PD が新たに加わりました。デュアルシグネチャ PD では、完全に独立した 2 つの 25k 検出シグネチャ抵抗が各ペアセットに対して 1 つずつあります。

802.3bt 2 ペア PSE (LTC9101-2B/LTC9102 を含む) は接続チェックを行いません。シングルシグネチャ PD とデュアルシグネチャ PD は同様に扱われます。つまり、PSE が検出と分類を行って、1 つのペアセットに電力を供給します。ハイパワーPD は、PSE によってより低い割当てクラスに格下げされます。デュアルシグネチャ PD では、1 つのペアセットだけに電力が割り当てられます。

## 検出

### 検出の概要

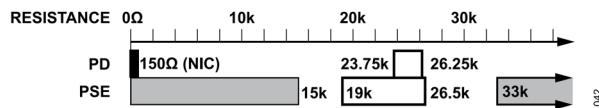

DC 電圧に耐えられるように設計されていないネットワーク・デバイスを損傷させてしまうことがないように、PSE は、電力を供給する前に、接続されたデバイスが有効な PD であるかどうかを確認する必要があります。IEEE802.3 規格では、有効な PD は、すべてのチャンネル電圧が 10V 未満のときに  $25k \pm 5\%$  のコモンモード抵抗を内蔵していることが求められます。PSE は  $19k \sim 26.5k$  の抵抗を合格とし、 $33k$  を超える抵抗または  $15k$  未満の抵抗（図 37 の網掛け領域）を不合格とする必要があります。必須

## アプリケーション情報

合格範囲と必須不合格範囲の間の未定義領域の抵抗を合格にするか不合格にするかは、PSE が選択できます。特に、PSE はコンピュータの標準的なネットワーク・インターフェース・カード (NIC) を不合格にする必要があります。これらのカードの多くは  $150\Omega$  のコモンモード終端抵抗を使用しており、電力を供給すると損傷させてしまうことになります (図 37 の左側に黒で示された領域)。

図 37. IEEE 802.3 のシグネチャ抵抗範囲

## マルチポイント検出

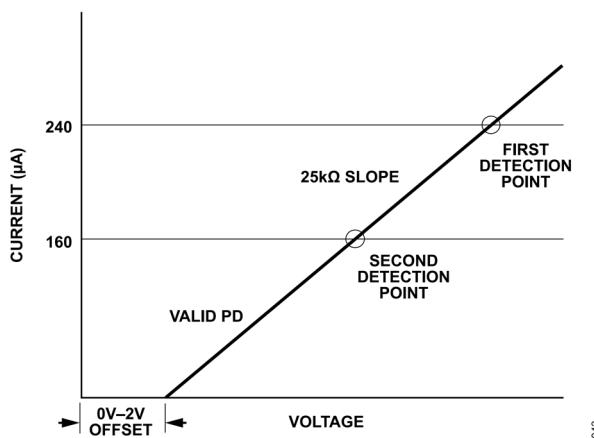

LTC9101-2B/LTC9102 はマルチポイント方式を使って PD を検出します。強制電流測定と強制電圧測定を併用してシグネチャ抵抗をチェックすることにより、誤検出が最小限に抑えられます。最初は 2 種類のテスト電流を (OUTn ピンを介して) そのチャンネルに強制的に流し、それによって得られる電圧を測定します。検出回路は 2 つの V-I ポイントの差を取って抵抗の傾きを求める一方、ポートのリーク電流や直列ダイオードによって生じるオフセットを除去します (図 38 参照)。強制電流検出によって有効なシグネチャ抵抗が得られた場合は、2 種類のテスト電圧をチャンネルに加え、それによって得られる電流を測定して差を取ります。有効な検出をレポートするには、両方の方法で有効な抵抗がレポートされなければなりません。PD シグネチャ抵抗が  $17k\Omega$ ~ $29k\Omega$  (代表値) の範囲内であれば有効として検出され、対応する検出ステータス・レジスタで、有効な検出 (Detect Valid) として報告されます。また、オープン・サーキットや短絡を含めて、この範囲外の値も報告されます。強制電流テスト時にチャンネルの測定値が  $1V$  未満の値を示した場合、検出サイクルは中断されて短絡 (Short Circuit) がレポートされます。考えられる検出結果を表 11 に示します。

図 38. PD 検出

表 11. 検出ステータス

| MEASURED PD SIGNATURE (TYPICAL)       | DETECTION RESULT                   |

|---------------------------------------|------------------------------------|

| Incomplete or Not Yet Tested          | Detect Status Unknown              |

| $V_{PD} < 1V$                         | Short Circuit                      |

| $C_{PD} > 2.7\mu F$ or $V_{PD} > 10V$ | $C_{PD}$ Too High                  |

| $R_{PD} < 17k\Omega$                  | $R_{SIG}$ Too Low                  |

| $17k\Omega < R_{PD} < 29k\Omega$      | Detect Valid                       |

| $R_{PD} > 29k\Omega$                  | $R_{SIG}$ Too High                 |

| $R_{PD} > 50k\Omega$                  | Open Circuit                       |

| PSE Detected                          | PSE Detected or Port is Precharged |

| MOSFET Fault                          | MOSFET Fault Detected              |

## 動作モードに関するその他の情報

LTC9101-2B/LTC9102 が検出サイクルを実行するタイミングは、ポートの動作モードによって決まります。手動モードでは、ホストが検出サイクルを命令するまでポートはアイドル状態になります。その後ポートは検出を実行し、結果をレポートしてアイドル状態に戻り、次のコマンドを待ちます。

半自動モードでは、LTC9101-2B/LTC9102 はポートを自律的にポーリングして PD を探しますが、ホストが命令するまで電力は供給しません。ポート・ステータス・レジスタとチャンネル・ステータス・レジスタは各検出／分類サイクルの最後に更新されます。

半自動モードでは、有効なシグネチャ抵抗が検出されて分類がイネーブルされると、ポートが PD を分類してその結果もレポートします。その後ポートは少なくとも  $100ms$  待機してから検出サイクルを繰り返し、検出／分類ステータス・レジスタ内のデータを更新します。電流検出の結果が有効 (Detect Valid) でない限り、ポートがパワー・オン・コマンドに応じてターン・オンされることはありません。検出結果がそれ以外の場合にパワー・オン・コマンドを受け取ると、 $t_{START}$  フォルトが発生します。

自動モードでの動作は半自動モードと同様です。ただし、有効な検出 (Detect Valid) が報告されてポートの分類が完了すると、ポートはホストの介入なしで自動的にパワー・オンされます。自動モードでは、2P Police と DC Disconnect が自動的に設定されます。詳細についてはリセットと PWRMD のセクションを参照してください。

ポートがシャットダウン・モードにある場合、または対応する検出イネーブル (Detect Enable) ビットがクリアされている場合は、ポートの検出がディスエーブルされます。

## レガシーPD の検出

最初の IEEE 802.3af 規格以前から存在する独自設計の PD は、現在では一般にレガシーPD と呼ばれています。ある種のレガシー PD は、大容量のコモンモード容量 ( $>10\mu F$ ) を検出シグネチャとして使用します。

レガシーPD は検出結果によって推定できます。レガシーPD は自動モードでは自動的には電力供給されません。

## アプリケーション情報

### 分類

#### 802.3af (タイプ1) の分類

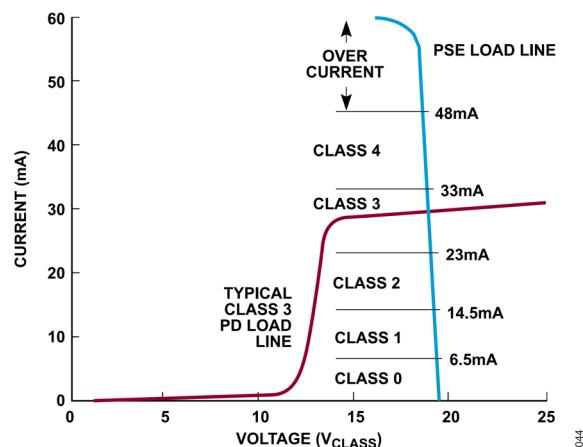

PD は、オプションで分類シグネチャを PSE に示して、動作時に消費する最大電力を知らせることができます。図 40 に示すように、IEEE 仕様ではこのシグネチャを、PSE ポートの電圧が  $V_{CLASS}$  の範囲 (15.5V~20.5V) 内にあるときに流れる定電流として規定しています。5 種類ある PD シグネチャのどれになるかは、この電流レベルによって示されます。PD の代表的な負荷曲線を図 39 に示します。10V 以下の 25k シグネチャ抵抗による勾配に始まり、 $V_{CLASS}$  の範囲で分類シグネチャ電流（この場合はクラス 3）に遷移します。考えられる分類値を表 12 に示します。

図 39. PD 分類

図 40. タイプ1またはタイプ2 PSE

(1イベント・クラス・シーケンス)

表 12. タイプ1およびタイプ2 PD の分類値

| CLASS   | RESULT                                         |

|---------|------------------------------------------------|

| Class 0 | No Class Signature Present; Treat Like Class 3 |

| Class 1 | 3.84W                                          |

| Class 2 | 6.49W                                          |

| Class 3 | 13W                                            |

| Class 4 | 25.5W (802.3at, Type 2)                        |

分類がイネーブルされると、PSE は検出サイクルが正常に終了した直後に PD を分類します。PSE は、OUTn を介してポートに  $V_{CLASS}$  電圧を加え、それにより流れる電流を測定して PD 分類シグネチャを測定します。その後、PD が要求したクラスを該当

ポート・ステータス・レジスタでレポートします。自動モードの場合、LTC9101-2B/LTC9102 は、それに応じて 2P Police、Current Limit、および DC Disconnect の各閾値を設定します。

ポートがシャットダウン・モードにある場合、または対応する分類イネーブル (Class Enable) ビットがクリアされている場合は、ポートの分類がディスエーブルされます。

### LLDP 分類

PoE におけるリンク層検出プロトコル (LLDP) は、802.3at で導入され、802.3bt で拡張された PoE 仕様によって分類方式が規定されています。LLDP 方式では、イーサネット LLDP データ・プロトコルに特別なフィールドを追加します。

LTC9101-2B/LTC9102 はこの分類方式に対応していますが、データ・パスへのアクセス権がないため、LLDP 分類を直接実行することはできません。LLDP 分類では、ホストが PD と LLDP 通信を行って、PD の電力割当てを更新できます。LTC9101-2B/LTC9102 は 2P Police レベルを動的に変更でき、システムレベルで LLDP をサポート可能です。

### 802.3at の2イベント分類

802.3at では、802.3af の分類をタイプ1分類と呼んでいます。802.3at 規格は、タイプ1分類の拡張版であるタイプ2(2イベント)分類を導入しています。タイプ2のPSEには分類の実行が求められます。

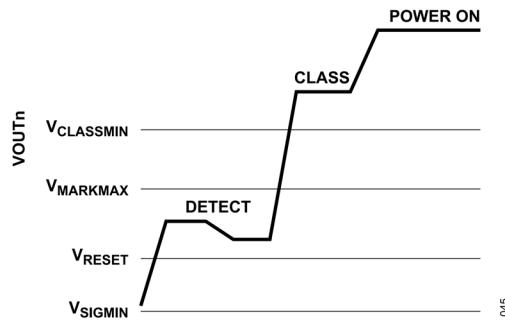

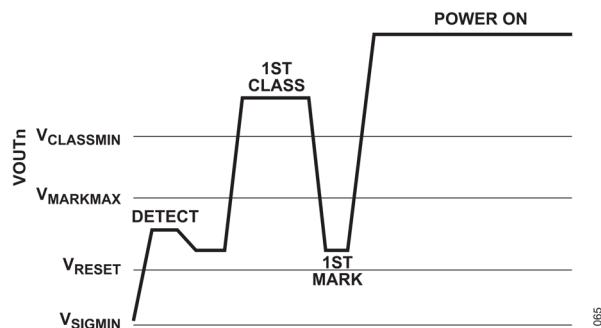

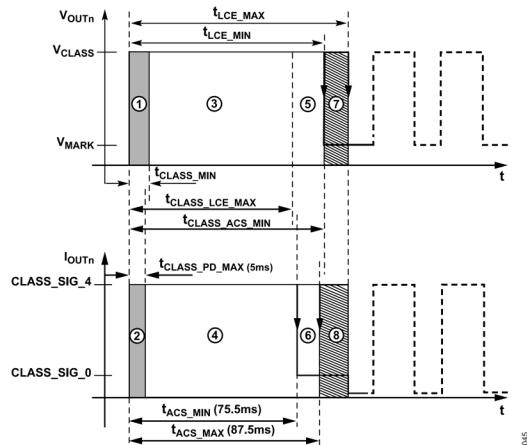

25.5W を要求するタイプ2PD は、すべてのクラス・イベント時にクラス・シグネチャ4を示します。供給可能電力が 25.5W のタイプ2PSE は、図 41 に示すように、最初のクラス・イベント時にクラス・シグネチャ4を認識すると、PD に  $V_{MARK}$  (代表値 9V) を供給し、少し間を置いてから 2番目のクラス・イベントを発行します。2番目のクラス・イベントは、PSE が 25.5W を割り当てたことを PD に知らせます。

図 41. タイプ2 PSE (2イベント・クラス・シーケンス)

2番目の分類イベントが実行されるのは、IEEE 分類手順で必要とされる場合に限られます。例えば、クラス 0~3 の PD に発行されるのは、図 40 に示すようなシングル・クラス・イベントに限られます。

802.3at では格下げの概念が導入されています。タイプ2のPDは、パワー・マネージメント上の制限などのため供給能力が13Wに限られるPSEにも接続できます。この場合、PSEは図40に示すようなシングル分類イベントを実行しますが、要求されるのは 25.5W です。供給できる電力が限られているので、PSEは2番目のイベントを発行することなく、そのまま PD に電力を供給する段階に進みます。シングル・クラス・イベントが存在するという事実により、タイプ2PDが13Wに格下げされたことがそのPDに通知されます。格下げされたPDは電力制限を受け、低減電力モードで動作します。

## アプリケーション情報

### 802.3bt のマルチイベント分類

802.3bt はタイプ 3 およびタイプ 4 の分類を導入しています。タイプ 2 (802.3at) 分類はタイプ 1 (802.3af) 分類を拡張したもので、タイプ 3 およびタイプ 4 分類はタイプ 1 分類とタイプ 2 分類に代わるものであります。これまでのセクションで示したタイプ 1 分類とタイプ 2 分類に関する説明は、従来規格に関する参考情報として示したものであります。また、電力の格下げ、クラス・イベント、マーク・イベント、電気的パラメータといった共通用語の定義を示すことも目的であります。

802.3bt は、表 13 に示すように、シングルシグネチャ PD に対して 8 つの PD クラスを規定し、デュアルシグネチャ PD に対して 5 つの PD クラスを規定であります。

表 13. PD 構成によるタイプ 3 およびタイプ 4 PD の分類

| SINGLE-SIGNATURE PDs |                    | DUAL-SIGNATURE PDs |                                      |

|----------------------|--------------------|--------------------|--------------------------------------|

| CLASS                | PD AVAILABLE POWER | CLASS              | CHANNEL AVAILABLE POWER <sup>1</sup> |

| Class 1              | 3.84W              | Class 1            | 3.84W                                |

| Class 2              | 6.49W              | Class 2            | 6.49W                                |

| Class 3              | 13W                | Class 3            | 13W                                  |

| Class 4              | 25.5W              | Class 4            | 25.5W                                |

| Class 5              | 40W                | Class 5            | 35.6W                                |

| Class 6              | 51W                |                    |                                      |

| Class 7              | 62W                |                    |                                      |

| Class 8              | 71.3W              |                    |                                      |

<sup>1</sup> デュアルシグネチャ PD が受給できる全電力は、両方のチャンネルが受給できる電力の合計です。クラス・シグネチャはポートのチャンネル間で異なる場合があります。例えば、クラス 3 + クラス 4 = 13W + 25.5W = 38.5W となります。

LTC9101-2B/LTC9102 はタイプ 3 の 2 ペア PSE として 802.3bt の分類を満たしています。

802.3bt 2 ペア PSE の割当てクラスは、クラス 4 までに制限されています。クラス 4 を超える電力を要求する PD は、LTC9101-2B/LTC9102 ポートの最大電力設定に応じて、クラス 4 またはクラス 3 に格下げされます。

802.3bt 2 ペア PSE は、シングルシグネチャ PD とデュアルシグネチャ PD を区別しません。検出、分類、および電力供給は、1 つのペアセット（通常はオルタナティブ A）で行われます。シングルシグネチャ PD はクラス 4 までの要求電力を受け取り、デュアルシグネチャ PD は 1 つのペアセットのみでクラス 4 までの電力を受け取ります。詳細については接続チェックの概要のセクションを参照してください。

### 802.3bt 2 ペアの分類

802.3bt 2 ペア PSE は、クラス 0 からクラス 3 までの PD にシングル分類イベントを発行します。クラス 0~3 の PD はそのクラ

ス・シグネチャを PSE に提示し、十分な電力が得られる場合はパワー・オンされます。また、電力制限された 802.3bt PSE は、クラス 4 以上の PD にもシングル分類イベントを発行して、それらの PD をクラス 3 (13W) に格下げすることができます。図 42 を参照してください。

十分な電力を利用できる場合、802.3bt の 2 ペア PSE はクラス 4 以上を要求する PD に 2 つの分類イベントを発行します。クラス 4 以上を要求する PD は、両方の分類イベントに対してクラス・シグネチャ 4 を示します。クラス 5 以上を要求する PD はクラス 4 (25.5W) に格下げされます。図 43 を参照してください。

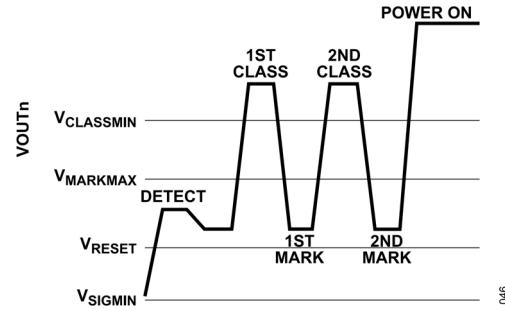

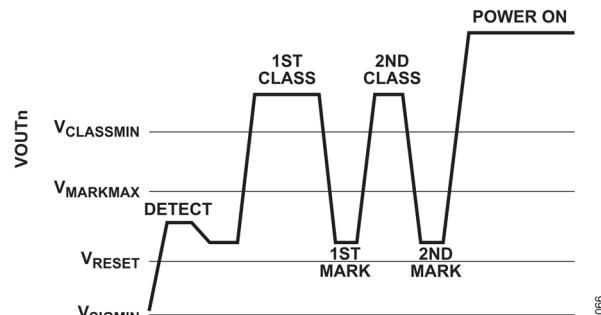

図 42. タイプ 3 2 ペア PSE (1 イベント・クラス・シーケンス)

図 43. タイプ 3 2 ペア PSE (2 イベント・クラス・シーケンス)

### 無効なマルチイベント分類の組み合わせ

802.3bt 規格は、一連の有効なクラス・シグネチャの組み合わせを規定しています。すべての PD は、最初の 2 回のクラス・イベントで同じ分類シグネチャを返します。タイプ 3 とタイプ 4 の PD は、その後のすべてのクラス・イベントで分類シグネチャを変更します。例えば、シングル・シグネチャのクラス 5 PD は、クラス・シグネチャ 4、4、0、0 を使って、それぞれクラス・イベント 1、2、3、4 に応答します。

クラス電流制限値を超える個々のクラス・シグネチャは、無効な分類結果としてフラグされます。PD の設定に基づく正しいシーケンスを表さないクラス・シグネチャのシーケンスも、同様に無効な分類結果としてフラグされます。

## アプリケーション情報

### 自動モードでの最大 PSE 電力

自動モードでは、接続されているすべての有効 PD の検出、分類、電力供給を LTC9101-2B/LTC9102 が自動的に行います。そのためには、最大電力を割り当てるように各ポートを設定する必要があります。システムのポートごとの最大電力供給能力を反映する抵抗  $R_{PWRMD}$  を、表 14 から選択してください。

ID アドレス 00b にある LTC9102 の PWRMD0 ピンを、 $R_{PWRMD}$  を介して  $V_{EE}$  に接続します。ID アドレス 01b、10b、11b にある LTC9102 の PWRMD0 ピンは、フロート状態のままにしておく必要があります。それぞれの LTC9102 の PWRMD1 ピンもフロート状態のままにしてください。 $PWRMD0$  抵抗はリセット時に測定されます。

最大電力割当ては、電源と電力バスの能力を反映するものです。 $PWRMD0$  抵抗による設定は、すべてのクワッドと IC を通じ、このチップセット内のすべてのポートに適用されます。したがって、 $PWRMD0$  抵抗の設定は、各ポートの電力バスの能力とシステムの電力供給能力を考慮して行う必要があります。

LTC9101-2B の内部フラッシュ・ストレージにカスタム設定を保存することによって、最大電力設定およびその他のポート制御をポートごとに指定することもできます。詳細については [保存されている設定](#) のセクションを参照してください。

表 14. PWRMD0 ピンの  $R_{PWRMD0}$  設定

| MODE         | $R_{PWRMD}$ (kΩ) | PORT MODE<br>0x12 | DETECT/<br>CLASS | 2P/4P CONFIG<br>0x14 | 2P/4P CONFIG<br>0x29 |

|--------------|------------------|-------------------|------------------|----------------------|----------------------|