## 窒化ガリウム (GaN) FET 向け低 $I_Q$ 、 デュアル 2 相同期整流式昇圧コントローラ

### 特長

- ▶ GaN FET 向けに全面的に最適化された GaN 駆動テクノロジ

- ▶ 出力電圧 : 最大 100V

- ▶ 広い  $V_{IN}$  範囲 : 4V~60V、起動後は 1V の低電圧で動作

- ▶ キャッチ／クランプ／ブーストストラップ・ダイオード不要

- ▶ 内蔵のスマート・ブーストストラップ・スイッチにより、ハイサイド・ドライバ用電源の過充電を防止

- ▶ 抵抗により調整可能なデッド・タイム

- ▶ 分割出力ゲート・ドライバにより、オン／オフ時のドライバ強度が調整可能

- ▶ 調整可能で正確なドライバ電圧と UVLO

- ▶ 低い動作  $I_Q$  : 15µA

- ▶ プログラム可能な周波数 (100kHz~3MHz)

- ▶ 同期可能な周波数 (100kHz~3MHz)

- ▶ スペクトラム拡散周波数変調

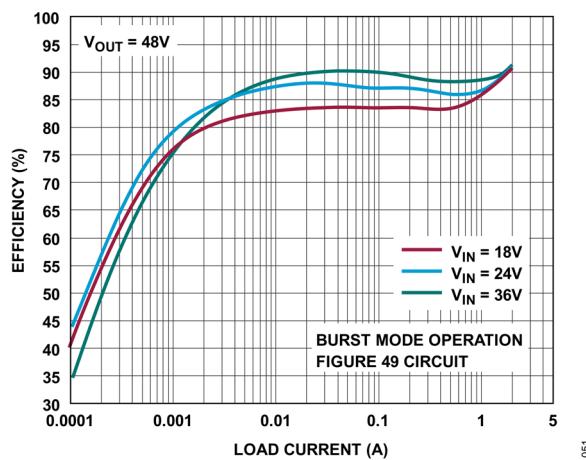

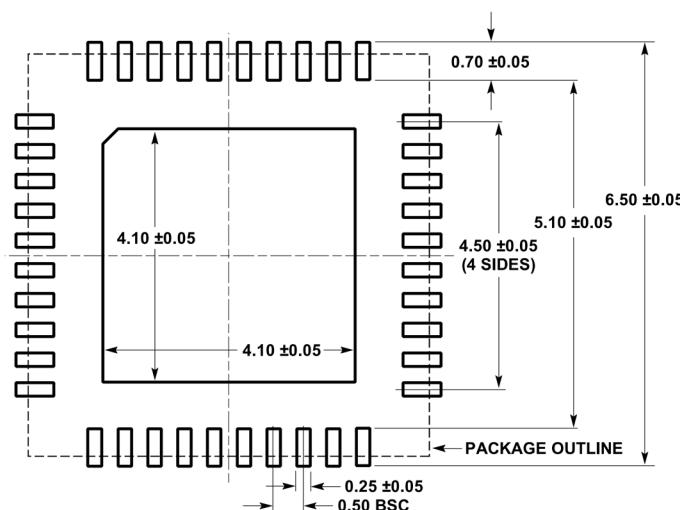

- ▶ 40 ピン (6mm × 6mm)、サイド・ウェッタブル、QFN パッケージ

- ▶ オートモーティブ・アプリケーション向けの AEC-Q100 に適合

### アプリケーション

- ▶ オートモーティブ用および工業用電源システム

- ▶ 防衛アビオニクス（航空電子機器）および医療用システム

- ▶ 電気通信用電源システム

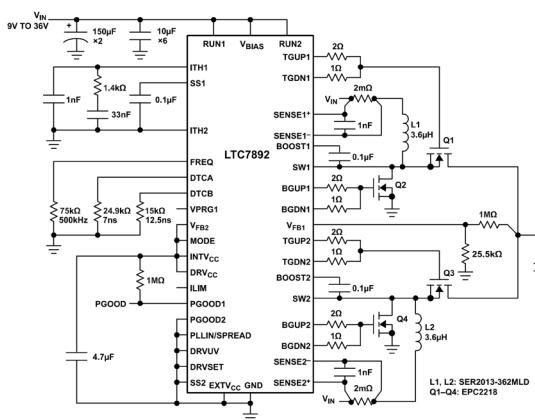

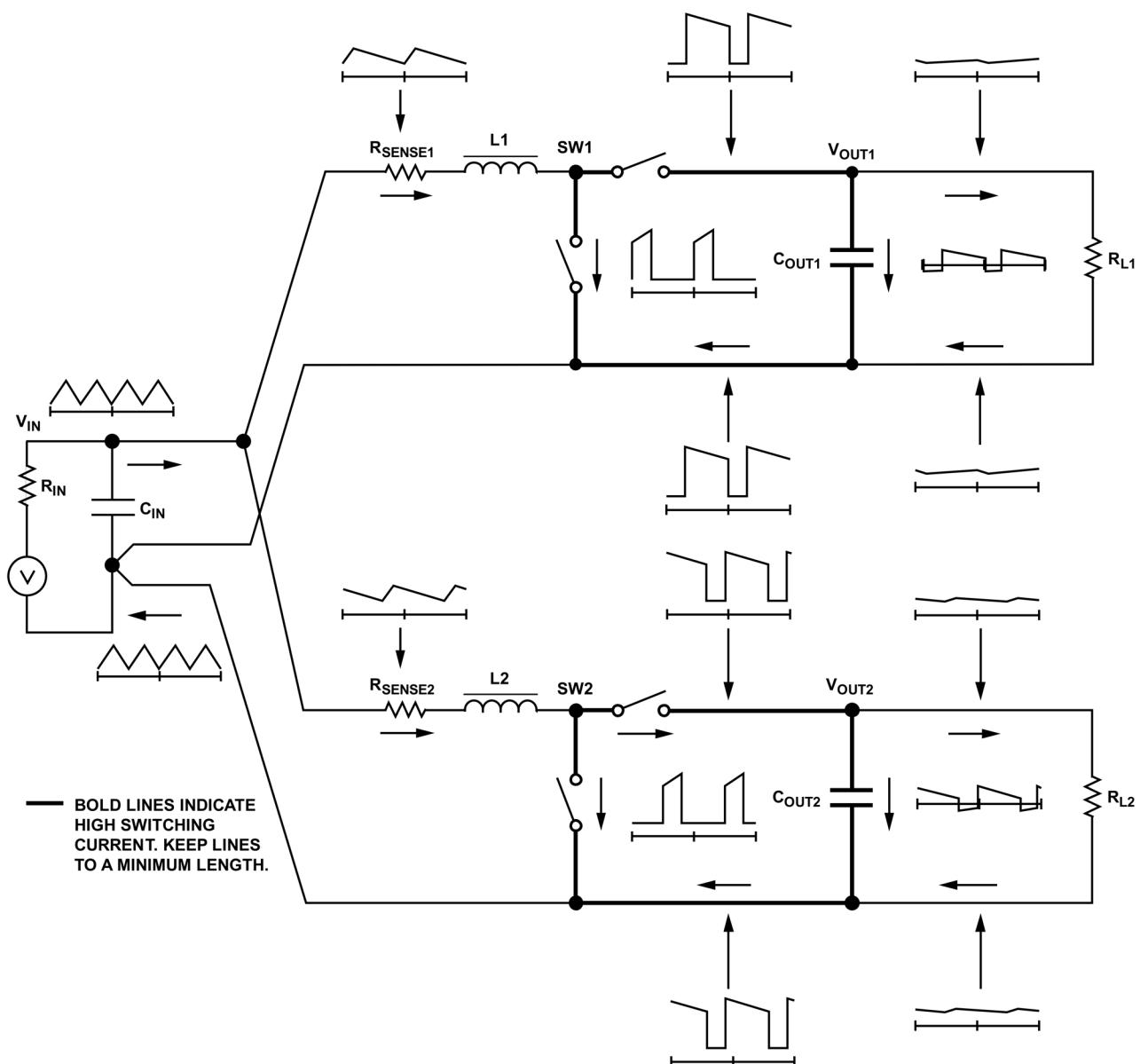

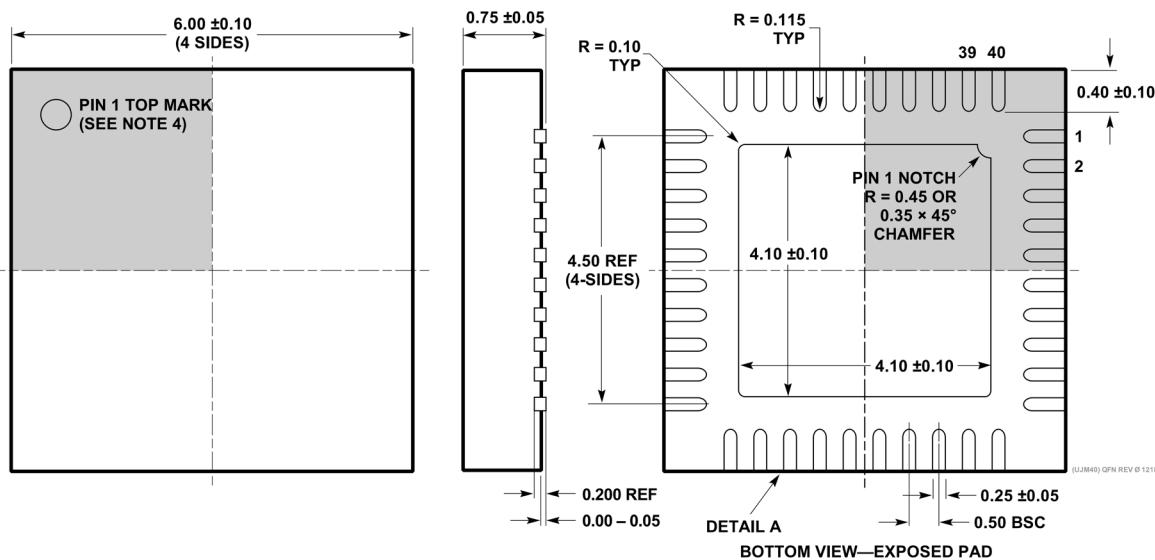

### 代表的なアプリケーション回路

図 1. ハイ・パワー、48V 出力の昇圧コンバータ

### 概要

高性能のデュアル昇圧 DC/DC スイッチング・レギュレータ・コントローラ LTC<sup>®</sup>7892 は、あらゆる N チャンネル同期窒化ガリウム (GaN) 電界効果トランジスタ (FET) のパワー段を最大 100V の出力電圧で駆動できます。LTC7892 は、これまで GaN FET を使用する際に直面していた多くの課題を解決します。LTC7892 を使用すると、シリコン金属酸化膜半導体電界効果トランジスタ (MOSFET) ソリューションと比べてアプリケーション設計が簡素化すると同時に、保護ダイオードやその他の外付け部品の追加が不要になります。

内蔵のスマート・ブーストストラップ・スイッチにより、デッド・タイム時の BOOSTx ピンから SWx ピンのハイサイド・ドライバ電源への過充電を防止して、上側 GaN FET のゲートを保護できます。外部抵抗を使用して LTC7892 のデッド・タイムを最適化することで、マージンを確保したり、アプリケーションをカスタマイズして効率を高め、高周波動作を可能にしたりすることもできます。

LTC7892 のゲート駆動電圧を 4V~5.5V の間で正確に調節できるため、性能の最適化や、様々な GaN FET あるいはロジック・レベル MOSFET の使用が可能です。LTC7892 を昇圧コンバータ・レギュレータの出力からバイアスする場合、起動後であれば入力電源電圧が 1V という低い値でも動作できます。

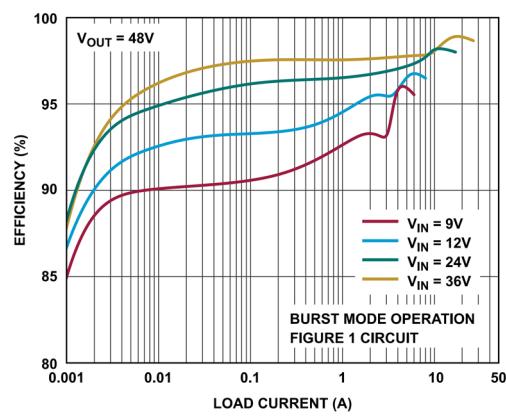

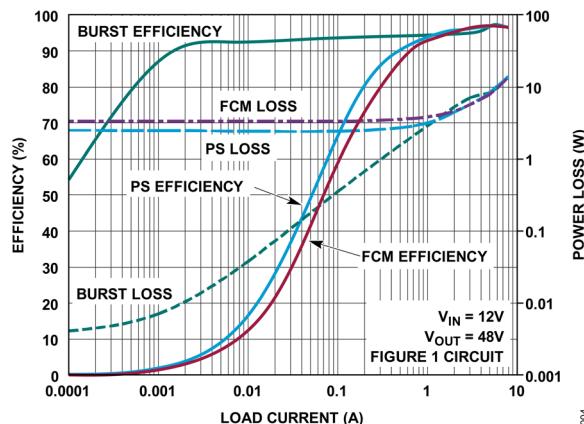

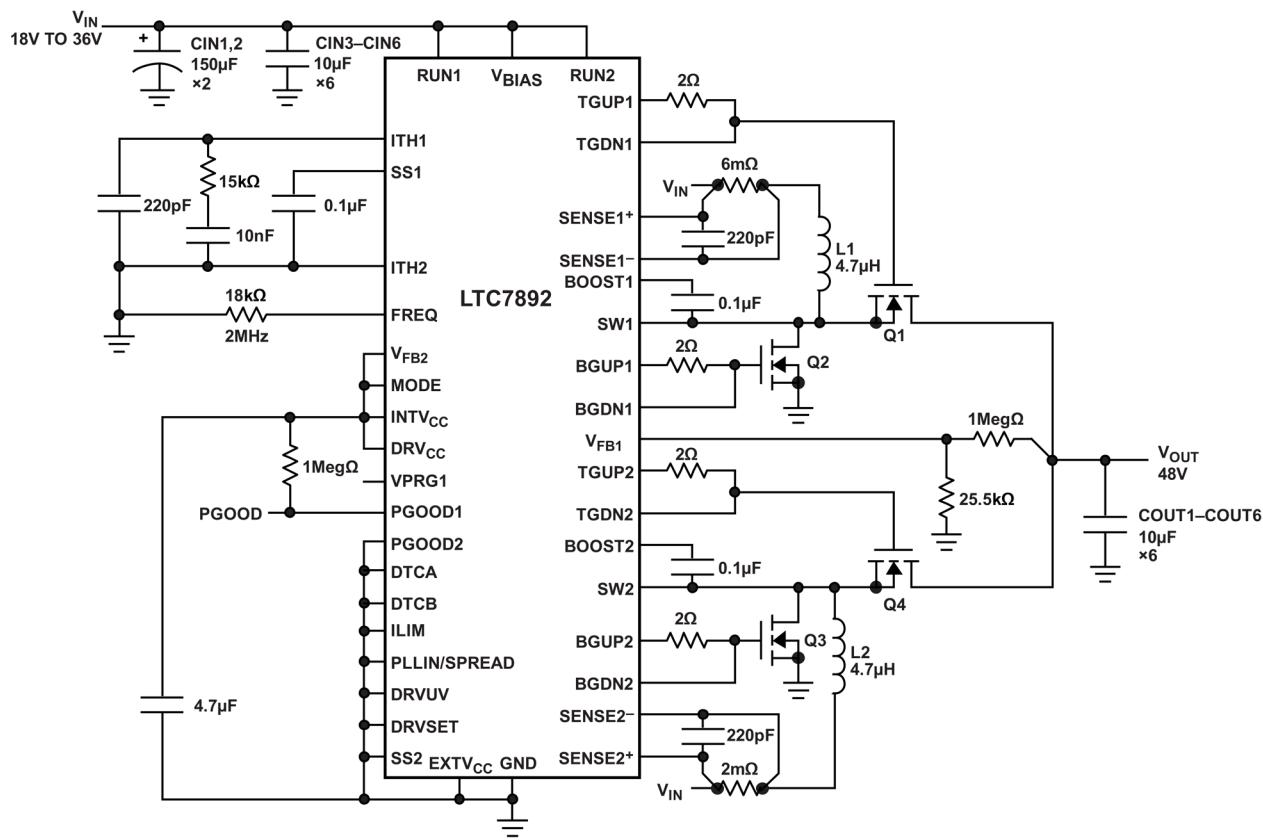

図 2. 効率および電力損失

※こちらのデータシートには正誤表が付属しています。当該資料の最終ページ以降をご参照ください。

Rev. 0

アナログ・デバイセズ社は、提供する情報が正確で信頼できるものであることを期していますが、その情報の利用に関して、あるいは利用によって生じる第三者の特許やその他の権利の侵害に関して一切の責任を負いません。また、アナログ・デバイセズ社の特許または特許の権利の使用を明示的または暗示的に許諾するものではありません。仕様は、予告なく変更される場合があります。本紙記載の商標および登録商標は、各社の所有に属します。※日本語版資料は REVISION が古い場合があります。最新の内容については、英語版をご参照ください。

## 目次

|                                                                                               |    |

|-----------------------------------------------------------------------------------------------|----|

| 特長                                                                                            | 1  |

| アプリケーション                                                                                      | 1  |

| 概要                                                                                            | 1  |

| 代表的なアプリケーション回路                                                                                | 1  |

| 改訂履歴                                                                                          | 3  |

| 仕様                                                                                            | 4  |

| 絶対最大定格                                                                                        | 9  |

| ピン配置およびピン機能の説明                                                                                | 10 |

| 代表的な性能特性                                                                                      | 14 |

| 機能図                                                                                           | 19 |

| 動作原理                                                                                          | 20 |

| メイン制御ループ                                                                                      | 20 |

| 電力およびバイアスの供給 (V <sub>BIAIS</sub> 、EXTV <sub>CC</sub> 、DRV <sub>CC</sub> 、INTV <sub>CC</sub> ) | 20 |

| ハイ・サイド・ブートストラップ・コンデンサ                                                                         | 20 |

| デッド・タイム制御 (DTCA ピンおよび DTCB ピン)                                                                | 21 |

| スタートアップとシャットダウン (RUN ピンおよび SS ピン)                                                             | 21 |

| 軽負荷時の動作 : Burst Mode 動作、パルススキッピング・モード、または強制連続モード (MODE ピン)                                    | 21 |

| 周波数の選択、スペクトラム拡散、フェーズ・ロック・ループ (FREQ ピンおよび PLLIN/SPREAD ピン)                                     | 22 |

| 出力過電圧保護                                                                                       | 23 |

| パワー・グッド                                                                                       | 23 |

| アプリケーション情報                                                                                    | 24 |

| インダクタ値の計算                                                                                     | 24 |

| インダクタ・コアの選択                                                                                   | 24 |

| 電流検出方式の選択                                                                                     | 25 |

| 値の小さな抵抗による電流検出                                                                                | 25 |

| インダクタの DCR による電流検出                                                                            | 26 |

| 動作周波数の設定                                                                                      | 28 |

| 軽負荷時動作モードの選択                                                                                  | 29 |

| デッド・タイム制御 (DTCA ピンおよび DTCB ピン)                                                                | 30 |

| DTCx ピンをグラウンドに接続 (適応型デッド・タイム制御)                                                               | 31 |

| DTCx ピンを抵抗を介して GND に接続                                                                        | 31 |

| パワーFET の選択                                                                                    | 32 |

| C <sub>IN</sub> と C <sub>OUT</sub> の選択                                                        | 33 |

| 单一出力 2 相動作                                                                                    | 34 |

|                                  |    |

|----------------------------------|----|

| 出力電圧の設定 .....                    | 35 |

| RUNx ピンと低電圧ロックアウト .....          | 36 |

| ソフトスタート (SSx ピン) .....           | 36 |

| INTVcc レギュレータ (OPTI-DRIVE) ..... | 36 |

| 上側 FET ドライバの電源 ( $C_B$ ) .....   | 38 |

| 最小オン時間に関する考慮事項 .....             | 39 |

| フォルト状態：過熱保護 .....                | 39 |

| フェーズ・ロック・ループと周波数同期 .....         | 39 |

| 効率に関する考慮事項 .....                 | 39 |

| 過渡応答のチェック .....                  | 40 |

| 設計例 .....                        | 41 |

| PCB ボード・レイアウト時のチェックリスト .....     | 43 |

| PCB レイアウトのデバッグ .....             | 45 |

| 代表的なアプリケーション .....               | 46 |

| 関連製品 .....                       | 47 |

| 外形寸法 .....                       | 48 |

| オーダー・ガイド .....                   | 49 |

## 改訂履歴

| 版数 | 改訂日   | 説明   | 改訂ページ |

|----|-------|------|-------|

| 0  | 12/24 | 初版発行 | -     |

## 仕様

表 1. 電気的特性

(特に指定のない限り、各仕様は  $T_J = -40^{\circ}\text{C} \sim +125^{\circ}\text{C}$  (最小値および最大値)、 $T_A = 25^{\circ}\text{C}$  (代表値)、 $V_{\text{BIAS}} = 12\text{V}$ 、RUN1 および RUN2 = 5V、VPRG1 = フロート、EXTV<sub>CC</sub> = 0V、DRVSET = 0V、DRVUV = 0V、DTCA および DTCB = 0V における値です。)

| PARAMETER                                         | SYMBOL                         | CONDITIONS/COMMENTS                                                                                                                                                                            | MIN                              | TYP                    | MAX                              | UNITS               |

|---------------------------------------------------|--------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|------------------------|----------------------------------|---------------------|

| <b>Input Supply</b>                               |                                |                                                                                                                                                                                                |                                  |                        |                                  |                     |

| Bias Input Supply Operating Range                 | $V_{\text{BIAS}}$              |                                                                                                                                                                                                | 4                                |                        | 100                              | V                   |

| Boost Converter Input Supply Operating Range      | $V_{\text{IN}}$                | $V_{\text{BIAS}} \geq 4\text{V}$                                                                                                                                                               | 1                                |                        | 60                               | V                   |

| Output Voltage Operating Range                    | $V_{\text{OUT1,OUT2}}$         |                                                                                                                                                                                                | 1.2                              |                        | 100                              | V                   |

| <b>Controller Operation</b>                       |                                |                                                                                                                                                                                                |                                  |                        |                                  |                     |

| Channel 1 Regulated Feedback Voltage              | $V_{\text{FB1}}$               | $V_{\text{BIAS}} = 4\text{V to } 100\text{V}$ ,<br>ITH1 Voltage = 0.6V to 1.2V<br>VPRG1 = floating, $T_A = 25^{\circ}\text{C}$<br>VPRG1 = floating<br>VPRG1 = 0V<br>VPRG1 = INTV <sub>CC</sub> | 1.188<br>1.182<br>23.45<br>27.38 | 1.2<br>1.2<br>24<br>28 | 1.212<br>1.218<br>24.55<br>28.62 | V                   |

| Channel 2 Regulated Feedback Voltage <sup>1</sup> | $V_{\text{FB2}}$               | $V_{\text{BIAS}} = 4\text{V to } 100\text{V}$ ,<br>ITH2 Voltage = 0.6V to 1.2V<br>$T_A = 25^{\circ}\text{C}$                                                                                   | 1.188<br>1.182                   | 1.2<br>1.2             | 1.212<br>1.218                   | V                   |

| Channel 1 Feedback Current <sup>1</sup>           |                                | VPRG1 = floating, $T_A = 25^{\circ}\text{C}$<br>VPRG1 = 0V or INTV <sub>CC</sub>                                                                                                               | -50                              | 0<br>2                 | +50                              | nA<br>$\mu\text{A}$ |

| Channel 2 Feedback Current <sup>1</sup>           |                                | $T_A = 25^{\circ}\text{C}$                                                                                                                                                                     | -50                              | 0                      | +50                              | nA                  |

| Feedback Overvoltage Threshold                    |                                | Relative to $V_{\text{FBx}}$ , $T_A = 25^{\circ}\text{C}$                                                                                                                                      | 7                                | 10                     | 13                               | %                   |

| Transconductance Amplifier <sup>1</sup>           | $g_{\text{m}1}, g_{\text{m}2}$ | ITH1 and ITH2 = 1.2V,<br>Sink and Source = 5 $\mu\text{A}$                                                                                                                                     |                                  | 1.8                    |                                  | mmho                |

| Maximum Current Sense Threshold                   | $V_{\text{SENSE(MAX)}}$        | $V_{\text{FBx}} = 1.1\text{V}$ , SENSE <sup>+</sup> = 12V<br>ILIM = 0V<br>ILIM = floating<br>ILIM = INTV <sub>CC</sub>                                                                         | 21<br>45<br>67                   | 25<br>50<br>75         | 31<br>55<br>83                   | mV                  |

(特に指定のない限り、各仕様は  $T_J = -40^\circ\text{C} \sim +125^\circ\text{C}$  (最小値および最大値)、 $T_A = 25^\circ\text{C}$  (代表値)、 $V_{BIAS} = 12\text{V}$ 、RUN1 および RUN2 = 5V、VPRG1 = フロート、EXTV<sub>CC</sub> = 0V、DRVSET = 0V、DRVUV = 0V、DTCA および DTCB = 0V における値です。)

| PARAMETER                                               | SYMBOL                          | CONDITIONS/COMMENTS                                                                                                                   | MIN            | TYP  | MAX  | UNITS          |

|---------------------------------------------------------|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|----------------|------|------|----------------|

| Current Sense Threshold Matching between Channels       |                                 | $V_{FBx} = 1.1\text{V}$ , SENSE <sub>x</sub> <sup>+</sup> = 12V, ILIM = floating, $T_A = 25^\circ\text{C}$                            | -3.5           | 0    | 3.5  | mV             |

| SENSE1 <sup>-</sup> and SENSE2 <sup>-</sup> Pin Current | $I_{SENSE1^-}$ , $I_{SENSE2^-}$ | SENSE1 <sup>-</sup> and SENSE2 <sup>-</sup> = 12V, $T_A = 25^\circ\text{C}$                                                           | -1             |      | +1   | μA             |

| SENSE1 <sup>+</sup> Pin Current                         | $I_{SENSE1^+}$                  | SENSE1 <sup>+</sup> < 3V<br>3.3V ≤ SENSE1 <sup>+</sup> < INTV <sub>CC</sub> - 0.5V<br>SENSE1 <sup>+</sup> > INTV <sub>CC</sub> + 0.5V | 1<br>75<br>725 |      |      | μA<br>μA<br>μA |

| SENSE2 <sup>+</sup> Pin Current                         | $I_{SENSE2^+}$                  | SENSE2 <sup>+</sup> < INTV <sub>CC</sub> - 0.5V, $T_A = 25^\circ\text{C}$<br>SENSE2 <sup>+</sup> > INTV <sub>CC</sub> + 0.5V          | -2<br>650      |      | +2   | μA<br>μA       |

| Soft-Start Charge Current                               |                                 | SS1 and SS2 = 0V                                                                                                                      | 9.5            | 12   | 14.5 | μA             |

| RUN Pin ON Threshold                                    |                                 | RUNx rising                                                                                                                           | 1.15           | 1.20 | 1.25 | V              |

| RUN Pin Hysteresis                                      |                                 |                                                                                                                                       |                | 120  |      | mV             |

#### DC Supply Current

|                                                     |  |                                                                                     |          |          |

|-----------------------------------------------------|--|-------------------------------------------------------------------------------------|----------|----------|

| $V_{BIAS}$ Shutdown Current                         |  | RUN1 and RUN2 = 0V                                                                  | 1        | μA       |

| $V_{BIAS}$ Sleep Mode Current                       |  | SENSE1 <sup>+</sup> < 3.2V, EXT $V_{CC}$ = 0V<br>One Channel On<br>Both Channels On | 15<br>19 | μA<br>μA |

| Sleep Mode Current <sup>2</sup> , Only Channel 1 On |  |                                                                                     |          |          |

| $V_{BIAS}$ Current                                  |  | SENSE1 <sup>+</sup> ≥ 3.2V, EXT $V_{CC}$ = 0V                                       | 5        | μA       |

| $V_{BIAS}$ Current                                  |  | SENSE1 <sup>+</sup> ≥ 3.2V, EXT $V_{CC}$ ≥ 4.8V                                     | 1        | μA       |

| EXT $V_{CC}$ Current                                |  | SENSE1 <sup>+</sup> ≥ 3.2V, EXT $V_{CC}$ ≥ 4.8V                                     | 6        | μA       |

| SENSE1 <sup>+</sup> Current                         |  | SENSE1 <sup>+</sup> ≥ 3.2V                                                          | 10       | μA       |

| Sleep Mode Current <sup>2</sup> , Both Channels On  |  | SENSE1 <sup>+</sup> ≥ 3.2V, EXT $V_{CC}$ ≥ 4.8V                                     |          |          |

| $V_{BIAS}$ Current                                  |  |                                                                                     | 1        | μA       |

| EXT $V_{CC}$ Current                                |  |                                                                                     | 7        | μA       |

| SENSE1 <sup>+</sup> Current                         |  |                                                                                     | 12       | μA       |

(特に指定のない限り、各仕様は  $T_J = -40^\circ\text{C} \sim +125^\circ\text{C}$  (最小値および最大値)、 $T_A = 25^\circ\text{C}$  (代表値)、 $V_{BIAS} = 12\text{V}$ 、RUN1 および RUN2 = 5V、VPRG1 = フロート、EXTV<sub>CC</sub> = 0V、DRVSET = 0V、DRVUV = 0V、DTCA および DTCB = 0V における値です。)

| PARAMETER                                                                                                            | SYMBOL        | CONDITIONS/COMMENTS                                                                         | MIN           | TYP | MAX | UNITS                |

|----------------------------------------------------------------------------------------------------------------------|---------------|---------------------------------------------------------------------------------------------|---------------|-----|-----|----------------------|

| Pulse-Skipping (PS)<br>Mode or Forced<br>Continuous Mode<br>(FCM), $V_{BIAS}$ or $EXTV_{CC}$<br>Current <sup>2</sup> |               | One Channel On<br>Both Channels On                                                          | 2             | 3   |     | mA<br>mA             |

| <b>Gate Drivers</b>                                                                                                  |               |                                                                                             |               |     |     |                      |

| TGxxx or BGxxx On<br>Resistance                                                                                      |               | DRVSET = $INTV_{CC}$<br>Pull-Up<br>Pull-Down                                                | 1.0           | 1.0 |     | $\Omega$<br>$\Omega$ |

| BOOSTx to DRV <sub>CC</sub><br>Switch on Resistance                                                                  |               | DRVSET = $INTV_{CC}$                                                                        | 6             |     |     | $\Omega$             |

| TGxxx or BGxxx<br>Transition Time <sup>3</sup>                                                                       |               | Rise Time<br>Fall Time                                                                      | 25            | 15  |     | ns<br>ns             |

| BGxxx Off to TGxxx<br>on Adaptive Delay<br>Time <sup>4</sup>                                                         |               | DTCA = 0V                                                                                   | 15            |     |     | ns                   |

| TGxxx Off to BGxxx<br>on Adaptive Delay<br>Time <sup>4</sup>                                                         |               | DTCB = 0V                                                                                   | 15            |     |     | ns                   |

| BGxxx Off to TGxxx<br>on Open-Loop Delay <sup>4</sup>                                                                |               | DTCA = 10k $\Omega$<br>DTCA = 50k $\Omega$<br>DTCA = 100k $\Omega$                          | 7<br>25<br>40 |     |     | ns<br>ns<br>ns       |

| TGxxx Off to BGxxx<br>on Open-Loop Delay <sup>4</sup>                                                                |               | DTCB = 10k $\Omega$<br>DTCB = 50k $\Omega$<br>DTCB = 100k $\Omega$                          | 7<br>25<br>40 |     |     | ns<br>ns<br>ns       |

| BGxxx Minimum<br>On-Time <sup>5</sup>                                                                                | $t_{ON(MIN)}$ |                                                                                             | 100           |     |     | ns                   |

| Maximum Duty Factor<br>for BGxxx                                                                                     |               | $V_{FREQ} = 0\text{V}$                                                                      | 93            |     |     | %                    |

| <b><math>INTV_{CC}</math> Low Dropout (LDO) Linear Regulators</b>                                                    |               |                                                                                             |               |     |     |                      |

| $INTV_{CC}$ Voltage for $V_{BIAS}$<br>and $EXTV_{CC}$ LDOs                                                           |               | $EXTV_{CC} = 0\text{V}$ for $V_{BIAS}$ LDO,<br>$EXTV_{CC} = 12\text{V}$ for $EXTV_{CC}$ LDO |               |     |     |                      |

(特に指定のない限り、各仕様は  $T_J = -40^\circ\text{C} \sim +125^\circ\text{C}$  (最小値および最大値)、 $T_A = 25^\circ\text{C}$  (代表値)、 $V_{BIAS} = 12\text{V}$ 、RUN1 および RUN2 = 5V、VPRG1 = フロート、EXTV<sub>CC</sub> = 0V、DRVSET = 0V、DRVUV = 0V、DTCA および DTCB = 0V における値です。)

| PARAMETER                                                                     | SYMBOL | CONDITIONS/COMMENTS                                                                                                                                                                   | MIN                                     | TYP                                      | MAX                                     | UNITS    |

|-------------------------------------------------------------------------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|------------------------------------------|-----------------------------------------|----------|

|                                                                               |        | DRVSET = INTV <sub>CC</sub><br>DRVSET = 0V<br>DRVSET = 64.9kΩ                                                                                                                         | 5.2<br>4.8<br>4.5                       | 5.5<br>5.0<br>4.75                       | 5.7<br>5.2<br>5.0                       | V        |

| DRV <sub>CC</sub> Load Regulation                                             |        | DRV <sub>CC</sub> load current = 0mA to 100mA,<br>$T_A = 25^\circ\text{C}$                                                                                                            |                                         | 1                                        | 3                                       | %        |

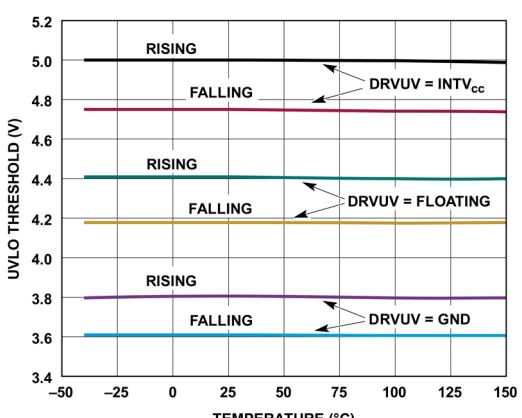

| Undervoltage Lockout                                                          | UVLO   | DRV <sub>CC</sub> Rising<br>DRVUV = INTV <sub>CC</sub><br>DRVUV = 0V<br>DRVUV = floating<br>DRV <sub>CC</sub> Falling<br>DRVUV = INTV <sub>CC</sub><br>DRVUV = 0V<br>DRVUV = floating | 4.8<br>3.6<br>4.2<br>4.55<br>3.4<br>4.0 | 5.0<br>3.8<br>4.4<br>4.75<br>3.6<br>4.18 | 5.2<br>4.0<br>4.6<br>4.95<br>3.8<br>4.4 | V        |

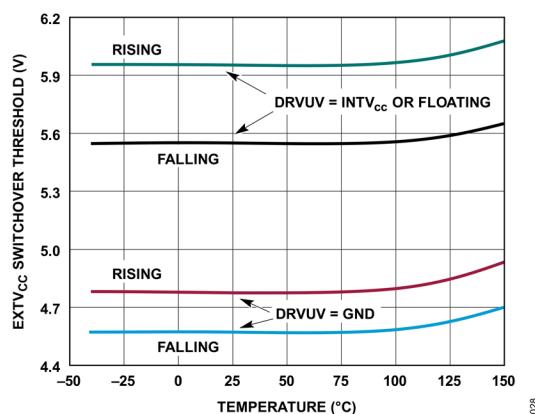

| EXTV <sub>CC</sub> LDO<br>Switchover Voltage<br>EXTV <sub>CC</sub> Rising     |        | DRVUV = INTV <sub>CC</sub> or floating, $T_A = 25^\circ\text{C}$<br>DRVUV = 0V, $T_A = 25^\circ\text{C}$                                                                              | 5.75<br>4.6                             | 5.95<br>4.76                             | 6.15<br>4.9                             | V        |

| EXTV <sub>CC</sub> LDO<br>Switchover Hysteresis<br>EXTV <sub>CC</sub> Falling |        | DRVUV = INTV <sub>CC</sub> or floating<br>DRVUV = 0V                                                                                                                                  |                                         | 390<br>220                               |                                         | mV<br>mV |

#### Spread Spectrum Oscillator and Phase-Locked Loop (PLL)

|                                                          |            |                                                                                                                                                                 |                               |                           |                   |                                 |

|----------------------------------------------------------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|---------------------------|-------------------|---------------------------------|

| Fixed Frequencies                                        | $f_{osc}$  | PLLIN/SPREAD = 0V<br>FREQ = 0V, $T_A = 25^\circ\text{C}$<br>FREQ = INTV <sub>CC</sub><br>FREQ = 374kΩ<br>FREQ = 75kΩ, $T_A = 25^\circ\text{C}$<br>FREQ = 12.4kΩ | 320<br>2.0<br>100<br>450<br>3 | 370<br>2.25<br>500<br>550 | 420<br>2.5<br>550 | kHz<br>MHz<br>kHz<br>kHz<br>MHz |

| Synchronizable Frequency Range                           | $f_{SYNC}$ | PLLIN/SPREAD = External Clock                                                                                                                                   | 0.1                           | 3                         |                   | MHz                             |

| PLLIN Input High-Level                                   |            |                                                                                                                                                                 | 2.2                           |                           |                   | V                               |

| PLLIN Input Low-Level                                    |            |                                                                                                                                                                 |                               | 0.5                       |                   | V                               |

| Spread Spectrum Frequency Range (Relative to $f_{osc}$ ) |            | PLLIN/SPREAD = INTV <sub>CC</sub><br>Minimum Frequency<br>Maximum Frequency                                                                                     |                               | 0<br>20                   |                   | %                               |

(特に指定のない限り、各仕様は  $T_J = -40^{\circ}\text{C} \sim +125^{\circ}\text{C}$  (最小値および最大値)、 $T_A = 25^{\circ}\text{C}$  (代表値)、 $V_{\text{BIAS}} = 12\text{V}$ 、RUN1 および RUN2 = 5V、VPRG1 = フロート、EXTV<sub>CC</sub> = 0V、DRVSET = 0V、DRVUV = 0V、DTCA および DTCB = 0V における値です。)

| PARAMETER                                                                      | SYMBOL | CONDITIONS/COMMENTS                                                                                           | MIN      | TYP                     | MAX                | UNITS         |

|--------------------------------------------------------------------------------|--------|---------------------------------------------------------------------------------------------------------------|----------|-------------------------|--------------------|---------------|

| <b>PGOODx Outputs</b>                                                          |        |                                                                                                               |          |                         |                    |               |

| PGOODx Voltage Low                                                             |        | PGOODx = 2mA, $T_A = 25^{\circ}\text{C}$                                                                      |          | 0.2                     | 0.4                | V             |

| PGOODx Leakage Current                                                         |        | PGOODx = 5V, $T_A = 25^{\circ}\text{C}$                                                                       | -1       | 0                       | +1                 | $\mu\text{A}$ |

| PGOODx Trip Level<br>( $V_{\text{FBX}}$ with respect to Set Regulated Voltage) |        | $T_A = 25^{\circ}\text{C}$<br>$V_{\text{FBX}}$ Rising<br>Hysteresis<br>$V_{\text{FBX}}$ Falling<br>Hysteresis | 7<br>-13 | 10<br>1.6<br>-10<br>1.6 | 13<br>%<br>-7<br>% | %             |

| PGOODx Delay for Reporting a Fault                                             |        |                                                                                                               |          | 25                      |                    | $\mu\text{s}$ |

<sup>1</sup> LTC7892 は帰還ループでテストされています。このループでは ITHx 電圧 ( $V_{\text{ITHx}}$ ) を仕様規定された電圧にサーボ制御して、得られた帰還電圧 ( $V_{\text{FBX}}$ ) を測定しています。

<sup>2</sup> SENSE1+のバイアス電流は、 $I_{\text{VBIAS}} = I_{\text{SENSE1+}} \times V_{\text{BIAS}} / (V_{\text{OUT1}} \times \eta)$  ( $\eta$  は効率) の式に従ってバイアス電源に反映されます。

<sup>3</sup> 立上がり時間と立下がり時間は、10%と 90%のレベルで測定しています。特に指定のない限り、遅延時間は 50%のレベルで測定しています。

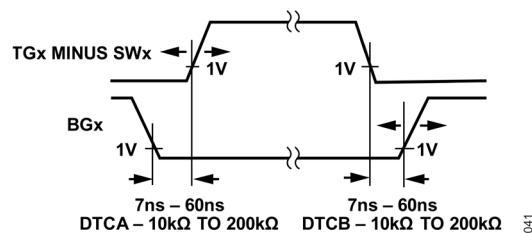

<sup>4</sup> TGxxx の立下がりから BGxxx の立上がりまで、および BGxxx の立下がりから TGxxx の立上がりまでの遅延時間は、TGxxx と BGxxx の立上がり閾値と立下がり閾値が約 1V のときに測定しています。詳細については、[図 40](#) および [図 41](#) を参照してください。

<sup>5</sup> インダクタのピーク to ピーク・リップル電流に対して仕様規定される最小オン時間条件は、最大負荷電流 ( $I_{\text{MAX}}$ ) の 40%以上です。詳細については[最小オン時間に関する考慮事項](#)を参照してください。

**絶対最大定格**

特に指定のない限り、 $T_A = 25^\circ\text{C}$ 。

表 2. 絶対最大定格

| PARAMETER                                                                                            | RATING           |

|------------------------------------------------------------------------------------------------------|------------------|

| Bias Input Supply ( $V_{BIAS}$ )                                                                     | -0.3V to 100V    |

| RUN1 and RUN2                                                                                        | -0.3V to 100V    |

| BOOST1 and BOOST2                                                                                    | -0.3V to 106V    |

| SW1 and SW2                                                                                          | -5V to 100V      |

| BOOST1 to SW1 and BOOST2 to SW2                                                                      | -0.3V to 6V      |

| TGUP1, TGUP2, TGDN1, TGDN2 <sup>1</sup>                                                              | Not applicable   |

| BGUP1, BGUP2, BGDN1, BGDN2 <sup>1</sup>                                                              | Not applicable   |

| EXTV <sub>CC</sub>                                                                                   | -0.3V to 30V     |

| DRV <sub>CC</sub> and INTV <sub>CC</sub>                                                             | -0.3V to 6V      |

| $V_{FB1}$                                                                                            | -0.3V to 65V     |

| PLLIN/SPREAD FREQ and $V_{FB2}$                                                                      | -0.3V to 6V      |

| SS1, SS2, ITH1, and ITH2                                                                             | -0.3V to 6V      |

| DRVSET and DRVUV                                                                                     | -0.3V to 6V      |

| MODE, ILIM, and VPRG1                                                                                | -0.3V to 6V      |

| PGOOD1 and PGOOD2                                                                                    | -0.3V to 6V      |

| DTCA and DTCB                                                                                        | -0.3V to 6V      |

| SENSE1 <sup>+</sup> , SENSE2 <sup>+</sup> , SENSE1 <sup>-</sup> , and SENSE2 <sup>-</sup>            | -0.3V to 65V     |

| SENSE1 <sup>+</sup> to SENSE1 <sup>-</sup> and SENSE2 <sup>+</sup> to SENSE2 <sup>-</sup> Continuous | -0.3V to +0.3V   |

| SENSE1 <sup>+</sup> to SENSE1 <sup>-</sup> and SENSE2 <sup>+</sup> to SENSE2 <sup>-</sup> < 1ms      | -100mA to +100mA |

| Operating Junction Temperature Range <sup>2</sup>                                                    | -40°C to 125°C   |

| Storage Temperature Range                                                                            | -65°C to 150°C   |

<sup>1</sup> これらのピンには電圧も電流も印加しないでください。容量性負荷にのみ接続する必要があります。これを行わない場合、恒久的な損傷が生じるおそれがあります。

<sup>2</sup> LTC7892 は、-40°C~125°C の動作ジャンクション温度範囲で仕様規定されています。ジャンクション温度が高い場合は動作寿命が低下します。ここに示す仕様に見合った最大周囲温度は、具体的な動作条件と、ボード・レイアウト、パッケージの熱抵抗定格値、およびその他の環境条件の組み合わせによって決まります。ジャンクション温度 ( $T_J$ , °C) は、次式を使って周囲温度 ( $T_A$ , °C) と消費電力 ( $P_D$ , ワット) から計算します： $T_J = T_A + (P_D \times \theta_{JA})$ 。ここで、 $\theta_{JA}$ はパッケージの熱抵抗で、40 ピン (6mm × 6mm)、サイド・ウェッタブル、クワッド・フラット・ノード・リード (QFN) パッケージの場合、33°C/W に相当します。

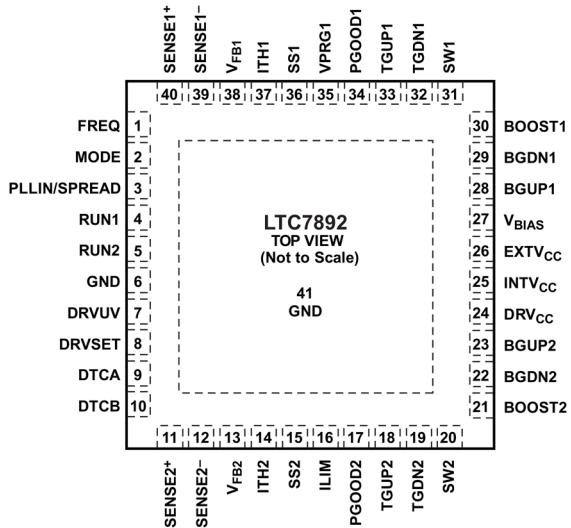

## ピン配置およびピン機能の説明

## NOTES

1. THE EXPOSED PAD (PIN 41) MUST BE SOLDERED TO PCB GROUND FOR RATED ELECTRICAL AND THERMAL PERFORMANCE.

003

図 3. ピン配置

表 3. 端子説明

| 端子 | 名称           | 説明                                                                                                                                                                                                                                                               |

|----|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1  | FREQ         | 内部電圧制御発振器（VCO）の周波数制御ピン。FREQ を GND に接続すると、370kHz の周波数に固定されます。FREQ を INTV <sub>CC</sub> に接続すると、2.25MHz の周波数に固定されます。FREQ と GND の間に抵抗を接続すると、100kHz～3MHz の範囲で周波数を設定できます。FREQ の容量は最小限に抑えてください。                                                                         |

| 2  | MODE         | モード・セレクト入力。この入力により、LTC7892 の軽負荷時の動作が決まります。MODE を GND に接続すると、Burst Mode®動作が選択されます。MODE がフロート状態の場合も、GND に接続された 100kΩ の内部抵抗によって、Burst Mode 動作が選択されます。MODE を INTV <sub>CC</sub> に接続すると、連続インダクタ電流動作になります。MODE を 100kΩ の抵抗を介して INTV <sub>CC</sub> に接続すると、PS 動作が選択されます。 |

| 3  | PLLIN/SPREAD | 位相検出器／スペクトラム拡散への外部同期入力イネーブル。外部クロックを PLLIN/SPREAD に印加すると、PLL は BGxx1 信号の立上がりを外部クロックの立上がりエッジに強制的に同期させます。外部クロックに同期させない場合、この入力を INTV <sub>CC</sub> に接続すると、発振器のスペクトラム拡散ディザリングが有効になり、GND に接続すると、スペクトラム拡散ディザリングが無効になります。                                                |

| 4  | RUN1         | チャンネル 1 の実行制御入力。RUN1 を 1.08V 未満にすると、コントローラのスイッチングが無効化されます。RUN1 と RUN2 を 0.7V 未満にすると、LTC7892 がシャットダウンし、I <sub>Q</sub> が約 1μA に低下します。常時動作しているようにするには、RUN1 ピンを V <sub>BIA</sub> S に接続します。                                                                           |

|    |                     |                                                                                                                                                                                                                                                                                                                                                                                                              |

|----|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5  | RUN2                | チャンネル 2 の実行制御入力。RUN2 を 1.08V 未満にすると、コントローラのスイッチングが無効化されます。RUN1 と RUN2 を 0.7V 未満にすると、LTC7892 がシャットダウンし、 $I_{\text{Q}}$ が約 1 $\mu\text{A}$ に低下します。常時動作しているようにするには、RUN2 ピンを $V_{\text{BIAS}}$ に接続します。                                                                                                                                                                                                           |

| 6  | GND                 | グラウンド。定格の電気的および熱的性能を得るには、GND ピンと露出パッドを PCB のグラウンドにハンダ付けする必要があります。                                                                                                                                                                                                                                                                                                                                            |

| 7  | DRVUV               | DRV <sub>CC</sub> UVLO および EXTV <sub>CC</sub> の切替え設定ピン。DRVUV は、表 1 に示すように、INTV <sub>CC</sub> UVLO および EXTV <sub>CC</sub> の立上がりおよび立下がりの切替え閾値を指定します。                                                                                                                                                                                                                                                           |

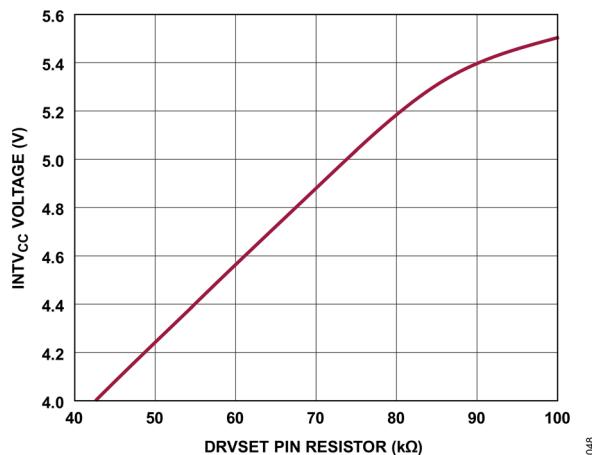

| 8  | DRVSET              | INTV <sub>CC</sub> のレギュレーション設定ピン。DRVSET は、INTV <sub>CC</sub> LDO リニア・レギュレータのレギュレーション・ポイントを設定します。DRVSET を GND に接続すると INTV <sub>CC</sub> は 5V に設定されます。DRVSET を INTV <sub>CC</sub> に接続すると INTV <sub>CC</sub> は 5.5V に設定されます。DRVSET と GND の間に抵抗 (43k $\Omega$ ~110k $\Omega$ ) を接続すると、4V~5.5V の範囲で電圧を設定できます。この抵抗と 20 $\mu\text{A}$ の内部ソース電流により、INTV <sub>CC</sub> LDO レギュレータがレギュレーション・ポイントを設定するために使用する電圧が生成されます。 |

| 9  | DTCA                | 下側 FET のオフから上側 FET のオンまでの遅延用デッド・タイム制御ピン。DTCA を GND に接続すると、約 15ns の適応型デッド・タイム遅延が設定されます。DTCA と GND の間に抵抗を接続すると、7ns~60ns の範囲で非適応型（オープンループ）デッド・タイム遅延が設定されます。                                                                                                                                                                                                                                                     |

| 10 | DTCB                | 上側 FET のオフから下側 FET のオンまでの遅延用デッド・タイム制御ピン。GND に接続すると、TG オフから BG オンまでの適応型デッド・タイム遅延が約 15ns に設定されます。DTCB と GND の間に抵抗を接続すると、TG オフから BG オンまでの非適応型（オープンループ）デッド・タイムが 7ns~60ns の範囲で設定されます。                                                                                                                                                                                                                             |

| 11 | SENSE2 <sup>+</sup> | チャンネル 2 の差動電流コンパレータへの正入力。SENSE2 <sup>+</sup> ピンは、SENSE2 <sup>+</sup> が INTV <sub>CC</sub> より大きいときに、チャンネル 2 の電流コンパレータに電流を供給します。                                                                                                                                                                                                                                                                               |

| 12 | SENSE2 <sup>-</sup> | チャンネル 2 の差動電流コンパレータへの負入力。ITH2 ピンの電圧および SENSE2 <sup>+</sup> ピンと SENSE2 <sup>-</sup> ピンの間の制御されたオフセットは、電流センス抵抗 ( $R_{\text{SENSE}}$ ) と組み合わせて電流トリップ閾値を設定します。                                                                                                                                                                                                                                                    |

| 13 | $V_{\text{FB}2}$    | チャンネル 2 のエラー・アンプ帰還入力。 $V_{\text{FB}2}$ は、リモート・センシングされたチャンネル 2 の帰還電圧を、出力両端に接続された外付け抵抗分圧器から受け取ります。両チャンネルが $V_{\text{FB}1}$ 、ITH1、SS1 を共用する 2 相単出力アプリケーションの場合は、 $V_{\text{FB}2}$ を INTV <sub>CC</sub> に接続します。                                                                                                                                                                                                   |

| 14 | ITH2                | チャンネル 2 のエラー・アンプ出力とスイッチング・レギュレータの補償ポイント。電流コンパレータの作動閾値は、この制御電圧に応じて増加します。                                                                                                                                                                                                                                                                                                                                      |

| 15 | SS2                 | チャンネル 2 の外部ソフトスタート入力。SS2 は、 $V_{\text{FB}2}$ 電圧を 1.2V または SS2 ピンの電圧のいずれか低い方に安定化します。SS2 には 12 $\mu\text{A}$ の内部プルアップ電流源が接続されています。SS2 と GND の間に接続するコンデンサにより、最終の安定化出力電圧までのランプ上昇時間が設定されます。ランプ上昇時間は、10nF の静電容量ごとに 1ms です。                                                                                                                                                                                         |

| 16 | ILIM                | 電流コンパレータの検出電圧範囲入力。ILIM を GND または INTV <sub>CC</sub> に接続するか、ILIM をフロート状態にすることで、最大電流検出閾値を 3 つのレベル (25mV、75mV、50mV) のいずれかに設定できます。                                                                                                                                                                                                                                                                               |

| 17 | PGOOD2              | チャンネル 2 のパワーグッド・オープン・ドライン・ロジック出力。PGOOD2 は、 $V_{\text{FB}2}$ 電圧が設定値の ±10% 以内にないとき、グラウンドにプルダウンされます。                                                                                                                                                                                                                                                                                                            |

|    |                    |                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|----|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 18 | TGUP2              | チャンネル 2 の上側 FET 用高電流ゲート・ドライバ・プルアップ。TGUP2 は BOOST2 にプルアップします。TGUP2 を上側 FET のゲートに直接接続すると、ゲートの立上がりエッジでゲート駆動の遷移速度が最大になります。TGUP2 と上側 FET ゲートの間に抵抗を接続すると、ゲートの立上がりリスルー・レートを調整できます。                                                                                                                                                                                                                                                         |

| 19 | TGDN2              | チャンネル 2 の上側 FET 用大電流ゲート・ドライバ・プルダウン。TGDN2 は SW にプルダウンします。TGDN2 を上側 FET のゲートに直接接続すると、ゲートの立下がりエッジでゲート駆動の遷移速度が最大になります。TGDN2 と上側 FET ゲートの間に抵抗を接続すると、ゲートの立下がリスルー・レートを調整できます。                                                                                                                                                                                                                                                              |

| 20 | SW2                | チャンネル 2 のインダクタへのスイッチ・ノード接続。                                                                                                                                                                                                                                                                                                                                                                                                         |

| 21 | BOOST2             | チャンネル 2 の上側フローティング・ドライバへのブーストストラップ電源。BOOST2 ピンと SW2 ピンの間にコンデンサを接続します。下側 FET がオンになると、内部スイッチが DRV <sub>CC</sub> から BOOST2 ピンに電力を供給します。BOOST2 ピンの電圧振幅は DRV <sub>CC</sub> から ( $V_{OUT2} + DRV_{CC}$ ) までです。                                                                                                                                                                                                                            |

| 22 | BGDN2              | チャンネル 2 の下側 FET 用高電流ゲート・ドライバ・プルダウン。BGDN2 は GND にプルダウンします。BGDN2 を下側 FET のゲートに直接接続すると、ゲートの立下がりエッジでゲート駆動の遷移速度が最大になります。BGDN2 と下側 FET ゲートの間に抵抗を接続すると、ゲートの立下がリスルー・レートを調整できます。BGDN2 は、ターンオン時における下側 FET ゲートのケルビン検出としても機能します。                                                                                                                                                                                                                |

| 23 | BGUP2              | チャンネル 2 の下側 FET 用大電流ゲート・ドライバ・プルアップ。BGUP2 は DRV <sub>CC</sub> にプルアップします。BGUP2 を下側 FET のゲートに直接接続すると、ゲートの立上がりエッジでゲート駆動の遷移速度が最大になります。BGUP2 と下側 FET ゲートの間に抵抗を接続すると、ゲートの立下がリスルー・レートを調整できます。BGUP2 は、ターンオフ時における下側 FET ゲートのケルビン検出としても機能します。                                                                                                                                                                                                  |

| 24 | DRV <sub>CC</sub>  | ゲート・ドライバ電源ピン。ゲート・ドライバは DRV <sub>CC</sub> から給電されます。DRV <sub>CC</sub> を INTV <sub>CC</sub> まで、INTV <sub>CC</sub> バイパス・コンデンサへの配線パターンとは別の配線パターンで接続します。                                                                                                                                                                                                                                                                                  |

| 25 | INTV <sub>CC</sub> | 内部低ドロップアウト・レギュレータの出力。INTV <sub>CC</sub> の電圧レギュレーション・ポイントは DRVSET ピンで設定します。INTV <sub>CC</sub> は、4.7μF~10μF のセラミック・コンデンサまたは他の等価直列抵抗 (ESR) の低いコンデンサでグラウンドとデカッピングする必要があります。                                                                                                                                                                                                                                                             |

| 26 | EXTV <sub>CC</sub> | DRV <sub>CC</sub> に接続された内蔵 LDO への外部電源入力。この LDO は INTV <sub>CC</sub> に電力を供給し、EXTV <sub>CC</sub> が EXTV <sub>CC</sub> 切替え電圧より高いときは常に内部の V <sub>BIAS</sub> LDO をバイパスします。EXTV <sub>CC</sub> の接続については、 <a href="#">電力およびバイアスの供給 (V<sub>BIAS</sub>, EXTV<sub>CC</sub>, DRV<sub>CC</sub>, INTV<sub>CC</sub>)</a> のセクションを参照してください。EXTV <sub>CC</sub> は 30V を超えないようにしてください。EXTV <sub>CC</sub> LDO を使用しない場合は、EXTV <sub>CC</sub> をグラウンドに接続します。 |

| 27 | V <sub>BIAS</sub>  | 主電源ピン。V <sub>BIAS</sub> と GND の間にバイパス・コンデンサを接続する必要があります。                                                                                                                                                                                                                                                                                                                                                                            |

| 28 | BGUP1              | チャンネル 1 の下側 FET 用高電流ゲート・ドライバ・プルアップ。BGUP1 は DRV <sub>CC</sub> にプルアップします。BGUP1 を下側 FET のゲートに直接接続すると、ゲートの立上がりエッジでゲート駆動の遷移速度が最大になります。BGUP1 と下側 FET ゲートの間に抵抗を接続すると、ゲートの立下がリスルー・レートを調整できます。BGUP1 は、ターンオフ時における下側 FET ゲートのケルビン検出としても機能します。                                                                                                                                                                                                  |

| 29 | BGDN1              | チャンネル 1 の下側 FET 用高電流ゲート・ドライバ・プルダウン。BGDN1 は GND にプルダウンします。BGDN1 を下側 FET のゲートに直接接続すると、ゲートの立下がりエッジでゲート駆動の遷移速度が最大になります。BGDN1 と下側 FET ゲートの間に抵抗を接続すると、ゲートの立下がリスルー・レートを調整できます。BGDN1 は、ターンオン時における下側 FET ゲートのケルビン検出としても機能します。                                                                                                                                                                                                                |

|    |                      |                                                                                                                                                                                                                                                                  |

|----|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 30 | BOOST1               | チャンネル 1 の上側フローティング・ドライバへのブーストストラップ電源。BOOST1 ピンと SW1 ピンの間にコンデンサを接続します。下側 FET がオンになると、内部スイッチが DRV <sub>CC</sub> から BOOST1 ピンに電源を供給します。BOOST1 ピンの電圧振幅は DRV <sub>CC</sub> から ( $V_{OUT1} + DRV_{CC}$ ) までです。                                                         |

| 31 | SW1                  | チャンネル 1 のインダクタへのスイッチ・ノード接続。                                                                                                                                                                                                                                      |

| 32 | TGDN1                | チャンネル 1 の上側 FET 用高電流ゲート・ドライバ・プルダウン。TGDN1 は SW にプルダウンします。TGDN1 を上側 FET のゲートに直接接続すると、ゲートの立下がりエッジでゲート駆動の遷移速度が最大になります。TGDN1 と上側 FET ゲートの間に抵抗を接続すると、ゲートの立下がリスルー・レートを調整できます。                                                                                           |

| 33 | TGUP1                | チャンネル 1 の上側 FET 用高電流ゲート・ドライバ・プルアップ。TGUP1 は BOOST1 にプルアップします。TGUP1 を上側 FET のゲートに直接接続すると、ゲートの立上がりエッジでゲート駆動の遷移速度が最大になります。TGUP1 と上側 FET ゲートの間に抵抗を接続すると、ゲートの立上がりリスルー・レートを調整できます。                                                                                      |

| 34 | PGOOD1               | チャンネル 1 のパワーグッド・オープン・ドレイン・ロジック出力。PGOOD1 は、 $V_{FB1}$ 電圧が設定値の $\pm 10\%$ 以内にない場合、グラウンドにプルダウンされます。                                                                                                                                                                 |

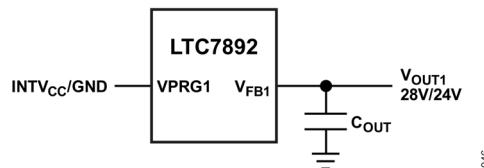

| 35 | VPRG1                | チャンネル 1 の出力電圧制御ピン。VPRG1 は、チャンネル 1 を外付け帰還抵抗で調整可能な出力モードにするか、28V/24V の固定出力モードにするかを設定します。VPRG1 をフロート状態にすると、外付けの抵抗分圧器を用いて出力を 1.2V~100V に設定でき、 $V_{FB1}$ は 1.2V に安定化されます。VPRG1 を INTV <sub>CC</sub> または GND に接続すると、 $V_{FB1}$ の内部抵抗分圧器を通じてそれぞれ、28V または 24V に出力が設定されます。 |

| 36 | SS1                  | チャンネル 1 の外部ソフトスタート入力。SS1 は、 $V_{FB1}$ 電圧を 1.2V または SS1 ピンの電圧のいずれか低い方に安定化します。SS1 には 12µA の内部プルアップ電流源が接続されています。SS1 と GND の間に接続するコンデンサにより、最終の安定化出力電圧までのランプ上昇時間が設定されます。ランプ上昇時間は、10nF の静電容量ごとに 1ms です。                                                                |

| 37 | ITH1                 | チャンネル 1 のエラー・アンプ出力とスイッチング・レギュレータの補償ポイント。電流コンパレータの作動閾値は、この制御電圧に応じて増加します。                                                                                                                                                                                          |

| 38 | $V_{FB1}$            | チャンネル 1 のエラー・アンプ帰還入力。VPRG1 ピンがフロート状態の場合、 $V_{FB1}$ は、リモート・センシングされたチャンネル 1 の帰還電圧を、出力端子間に接続された外付け抵抗分圧器から受け取ります。VPRG1 を INTV <sub>CC</sub> または GND に接続した場合、 $V_{FB1}$ ピンはリモート・センシングされた出力電圧を直接受け取ります。                                                                |

| 39 | SENSE1 <sup>-</sup>  | チャンネル 1 の差動電流コンパレータへの負入力。ITH1 ピンの電圧および SENSE1 <sup>+</sup> ピンと SENSE1 <sup>-</sup> ピンの間の制御されたオフセットは、電流センス抵抗 ( $R_{SENSE}$ ) と組み合わせて電流トリップ閾値を設定します。                                                                                                               |

| 40 | SENSE1 <sup>+</sup>  | チャンネル 1 の差動電流コンパレータへの正入力。SENSE1 <sup>+</sup> ピンは、SENSE1 <sup>+</sup> が INTV <sub>CC</sub> より大きいときに、チャンネル 1 の電流コンパレータに電流を供給します。                                                                                                                                   |

| 41 | GND<br>(Exposed Pad) | グラウンド（露出パッド）。定格の電気的性能および熱性能を得るため、露出パッドは PCB のグラウンドにハンダ付け処理する必要があります。                                                                                                                                                                                             |

## 代表的な性能特性

特に指定のない限り、 $T_A = 25^\circ\text{C}$ 。

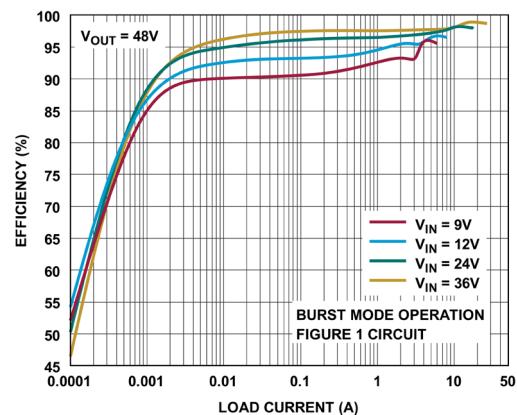

図 4. 効率および電力損失と負荷電流の関係

図 5. 効率と負荷電流の関係

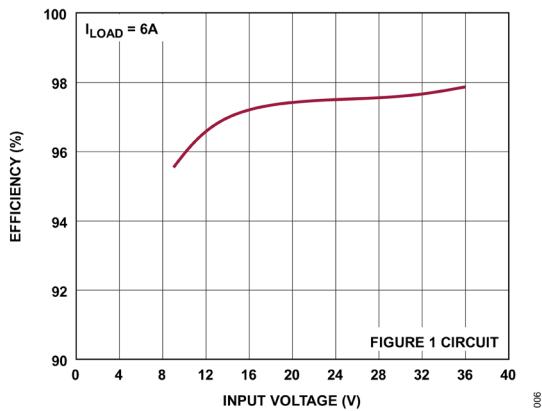

図 6. 効率と入力電圧の関係

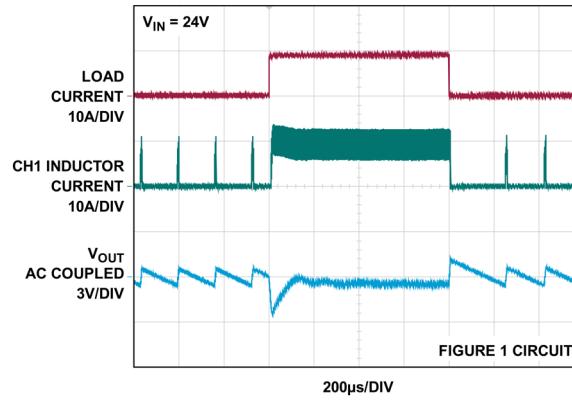

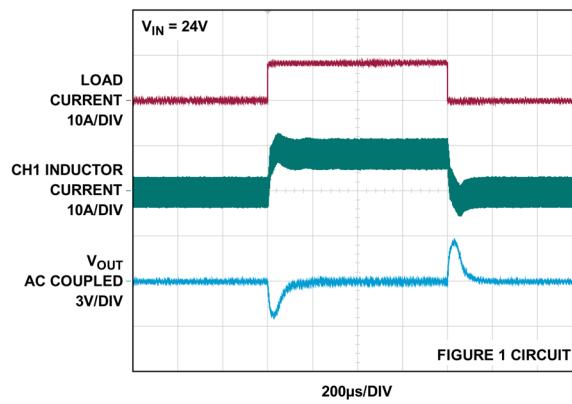

図 7. 負荷ステップ (Burst Mode®動作)

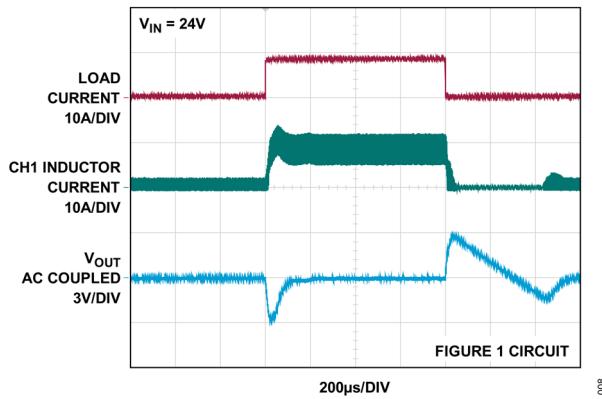

図 8. 負荷ステップ (PS モード)

図 9. 負荷ステップ (FCM)

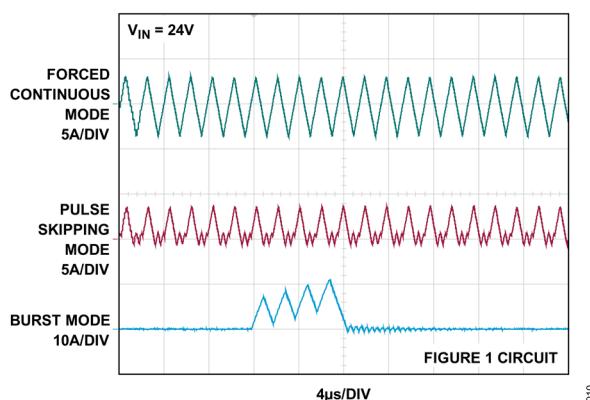

図 10. 軽負荷時のインダクタ電流

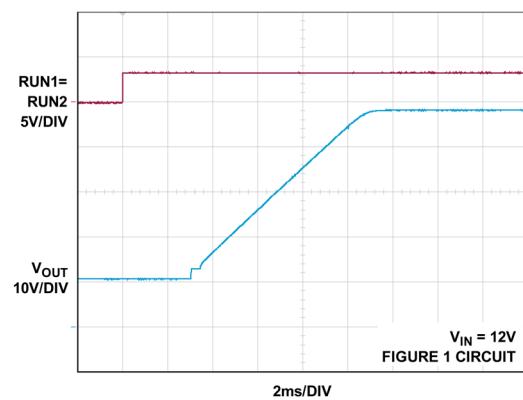

図 11. ソフト・スタートアップ

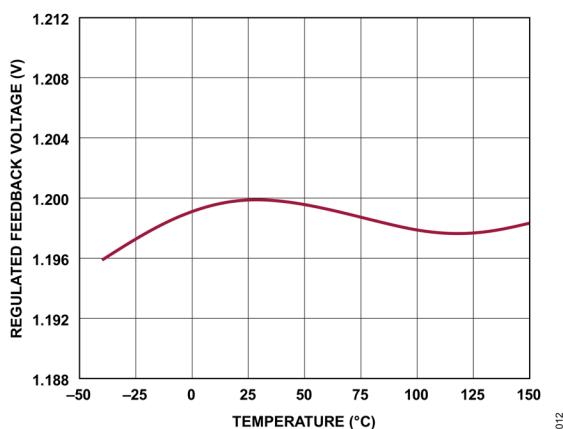

図 12. 安定化帰還電圧の温度特性

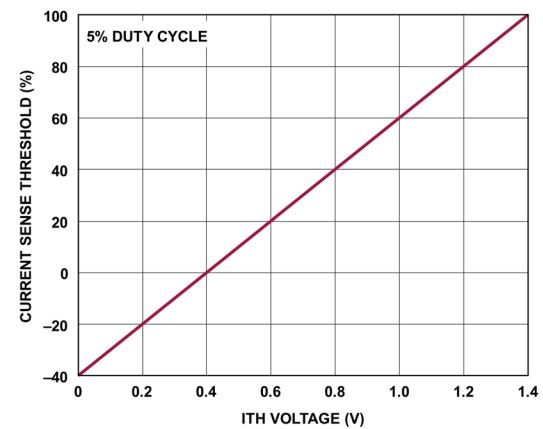

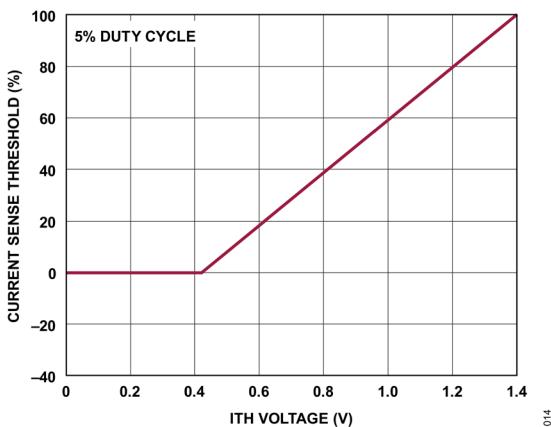

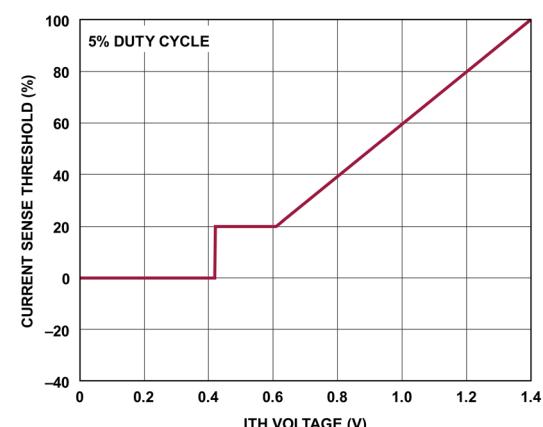

図 13. FCM での  $V_{SENSE(MAX)}$  基準の最大電流検出閾値と  $V_{ITHx}$  の関係図 14. PS モードでの  $V_{SENSE(MAX)}$  基準の最大電流検出閾値と  $V_{ITHx}$  電圧の関係図 15. Burst Mode での  $V_{SENSE(MAX)}$  基準の最大電流検出閾値と  $V_{ITHx}$  電圧の関係

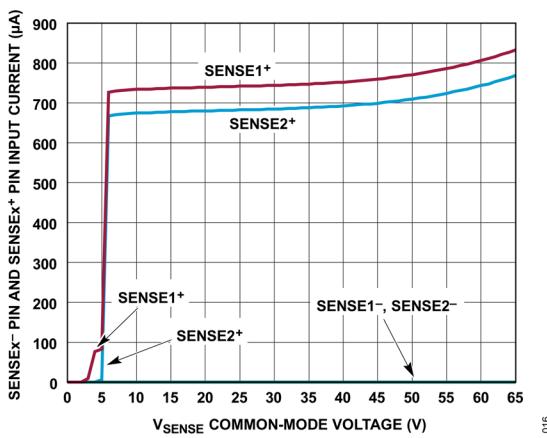

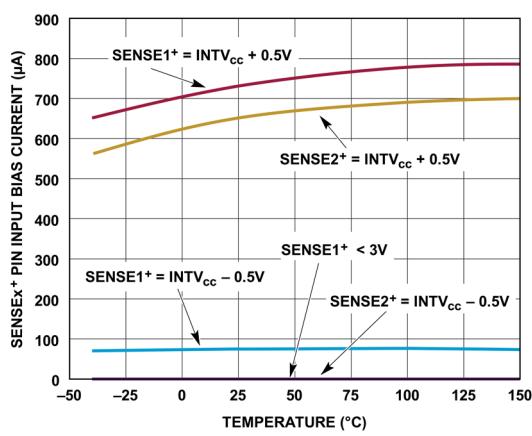

図 16. SENSE<sub>x</sub><sup>+</sup>ピンおよび SENSE<sub>x</sub><sup>-</sup>ピンの入力バイアス電流と V<sub>SENSE</sub> コモンモード電圧の関係

図 17. SENSE<sub>x</sub><sup>-</sup>ピンの入力電流と温度の関係

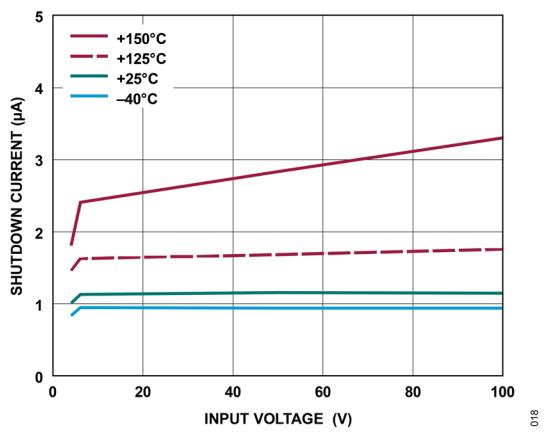

図 18. シャットダウン電流と入力電圧の関係

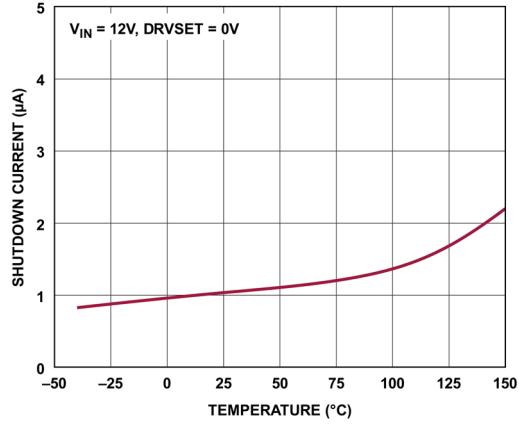

図 19. シャットダウン電流と温度の関係

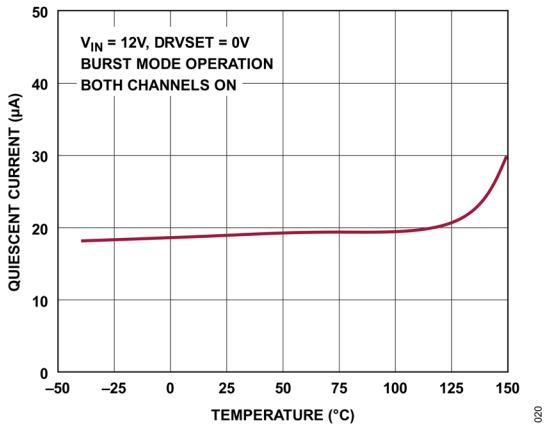

図 20. 自己消費電流と温度の関係

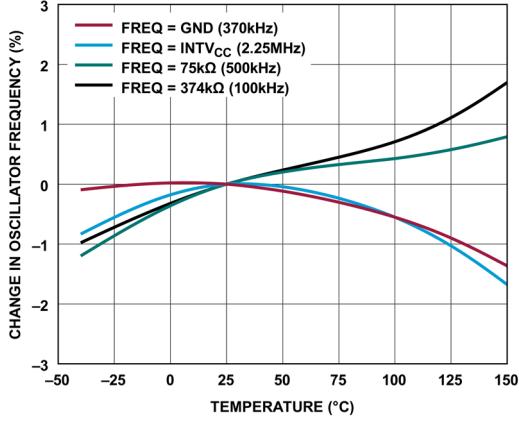

図 21. 発振器周波数と温度の関係

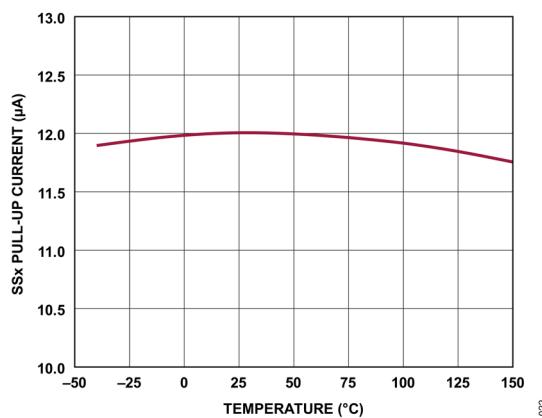

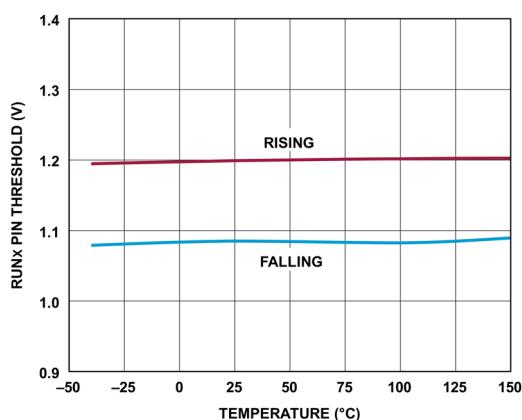

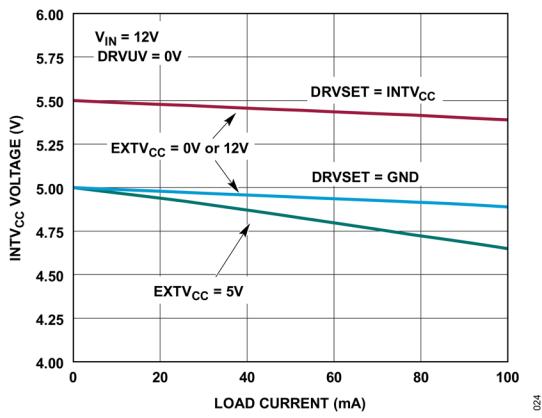

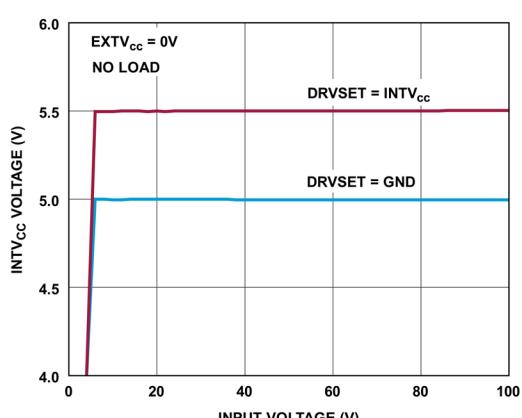

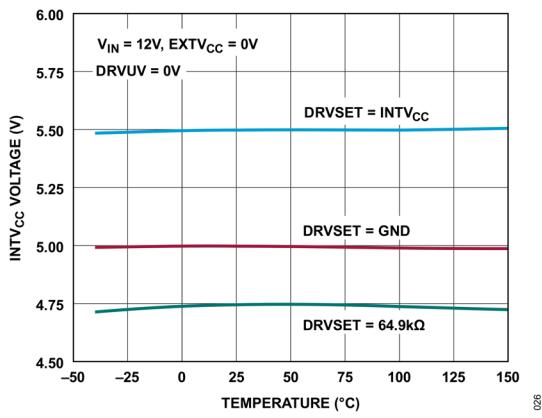

図 22. SS<sub>x</sub> のプルアップ電流と温度の関係図 23. RUN<sub>x</sub> ピンの閾値と温度の関係図 24. INTV<sub>cc</sub> 電圧と負荷電流の関係図 25. INTV<sub>cc</sub> 電圧と入力電圧の関係図 26. INTV<sub>cc</sub> 電圧と温度の関係

図 27. UVLO の閾値と温度の関係

図 28. EXTV<sub>CC</sub> の切替え閾値と温度の関係

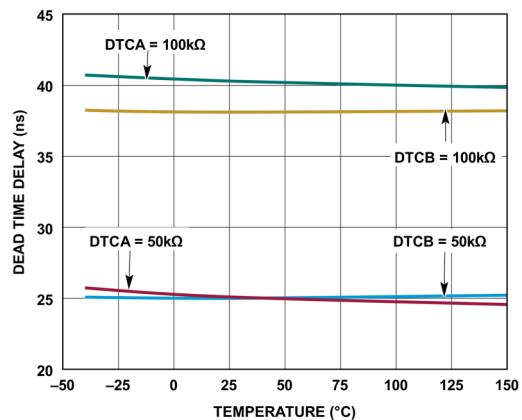

図 29. デッド・タイム遅延と温度の関係

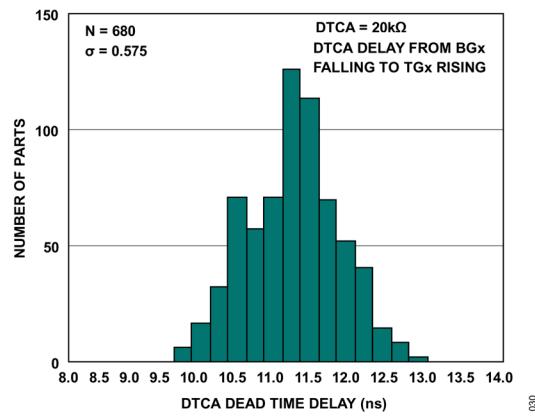

図 30. DTCA = 20kΩ でのデッド・タイム遅延のヒストグラム

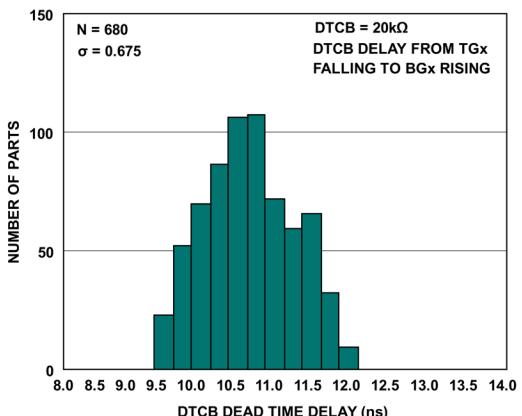

図 31. DTCB = 20kΩ でのデッド・タイム遅延のヒストグラム

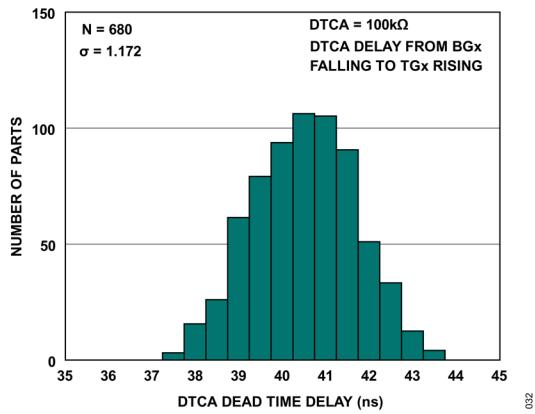

図 32. DTCA = 100kΩ でのデッド・タイム遅延のヒストグラム

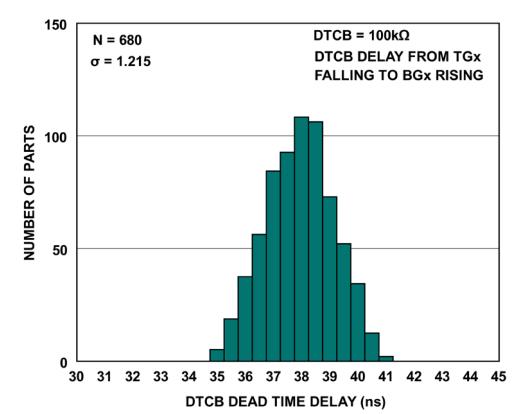

図 33. DTCB = 100kΩ でのデッド・タイム遅延のヒストグラム

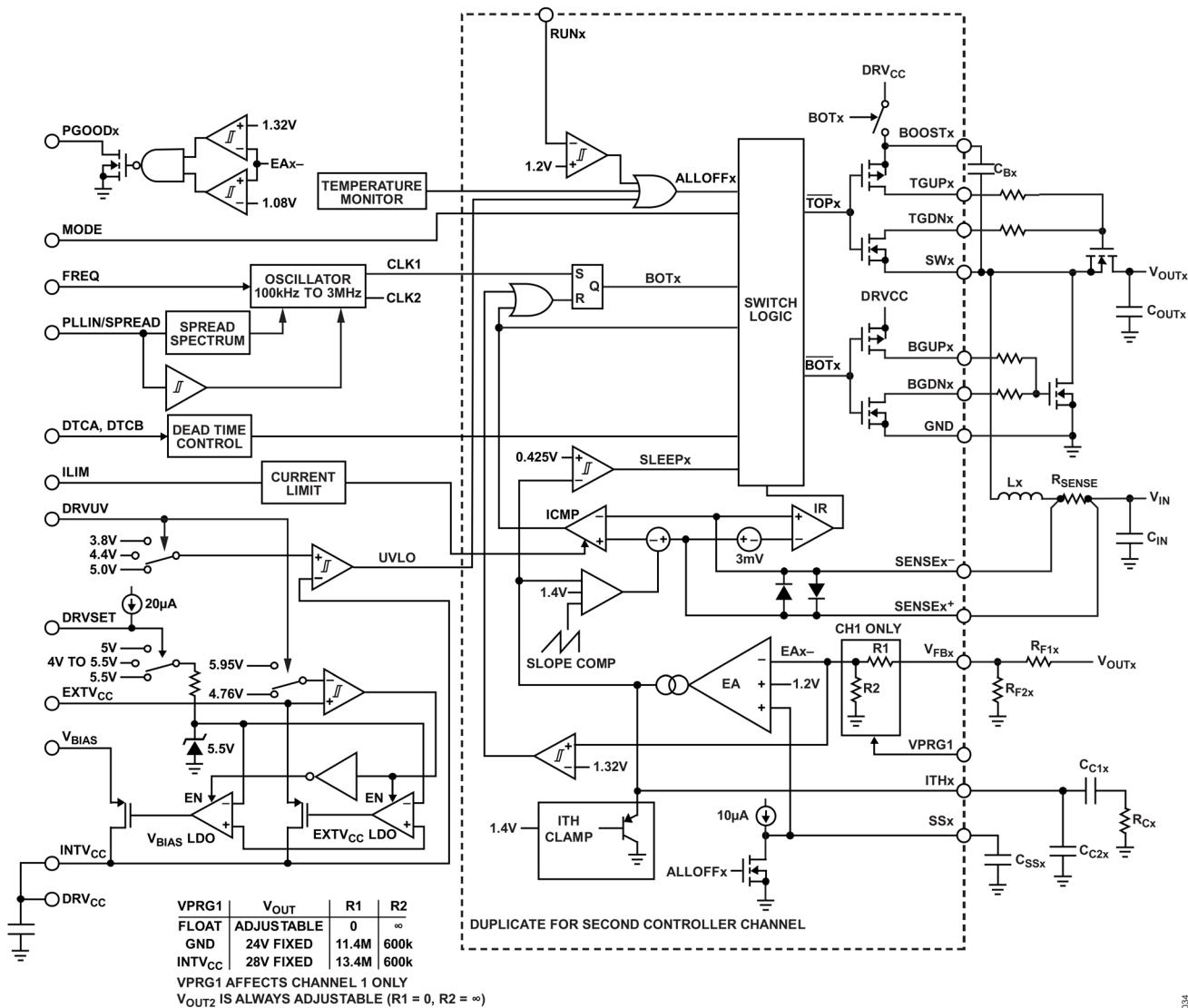

## 機能図

図 34. 機能図

## 動作原理

### メイン制御ループ

LTC7892 はデュアル同期整流式昇圧コントローラで、固定周波数のピーク電流モード・アーキテクチャを採用しています。2つのコントローラ・チャンネルは  $180^\circ$  位相がずれて動作するため、必要な入力静電容量と電源に起因するノイズが減少します。通常動作時には、クロックがセット／リセット (SR) ラッチをセットすると外付けの下側 FET がオンになり、インダクタ電流が増加します。メイン・スイッチは、メインの電流コンパレータ (ICMP) が SR ラッチをリセットするとオフになります。サイクルごとに下側 FET がオフになった後、インダクタ電流が反転し始めて電流コンパレータ IR がそれを検出するか、または次のクロック・サイクルが始まるまで、上側 FET がオンになってインダクタ電流が減少します。

ICMP が作動してラッチをリセットするピーク・インダクタ電流は、エラー・アンプの出力である  $ITH_x$  ピンの電圧によって制御されます。エラー・アンプは、 $V_{FBx}$  ピンの出力電圧帰還信号（出力電圧  $V_{OUTx}$  と GND の間に接続した外付け抵抗分圧器で生成）を  $1.2V$  の内部リファレンス電圧と比較します。負荷電流が増加するとリファレンス電圧に対して  $V_{FBx}$  がわずかに低くなるので、平均インダクタ電流が新しい負荷電流に見合った値となるまで、エラー・アンプが  $ITH_x$  電圧を上昇させます。

### 電力およびバイアスの供給 ( $V_{BIAS}$ 、 $EXTV_{CC}$ 、 $DRV_{CC}$ 、 $INTV_{CC}$ )

$INTV_{CC}$  ピンは、上側と下側の FET ドライバおよびほとんどの内部回路に電力を供給する役割を果たします。FET ドライバ用の電源は  $DRV_{CC}$  ピンから供給されます。このピンはゲート・ドライバに電源を供給するために  $INTV_{CC}$  ピンに接続する必要があります。LDO（低ドロップアウト・リニア・レギュレータ）は  $V_{BIAS}$  ピンと  $EXTV_{CC}$  ピンの両方から利用可能で、 $INTV_{CC}$  に電力を供給します。これは、 $DRVSET$  ピンの制御により  $4V$ ~ $5.5V$  の範囲で設定できます。 $EXTV_{CC}$  ピンをその切替え電圧より低い電圧に接続した場合、 $V_{BIAS}$  LDO が  $INTV_{CC}$  に電力を供給します。 $EXTV_{CC}$  がその切替え電圧を超えると、 $V_{BIAS}$  LDO レギュレータがオフになり、 $EXTV_{CC}$  LDO がオンになります。 $EXTV_{CC}$  LDO レギュレータは、イネーブルにした場合に  $INTV_{CC}$  に電力を供給します。 $EXTV_{CC}$  ピンを使用すると、高効率の外部電源から  $INTV_{CC}$  に電力を供給できます。

### ハイ・サイド・ブートストラップ・コンデンサ

各上側 FET ドライバは、フローティング・ブートストラップ・コンデンサ ( $C_B$ ) からバイアスされます。このコンデンサは通常、下側 FET がオンになるたびに、 $BOOST_x$  と  $DRV_{CC}$  の間の内部スイッチを介して再充電されます。この内部スイッチは、下側 FET がオフのときは常時高インピーダンスであり、デッド・タイム中に  $SW_x$  が GND より低い値を示すときは常に、ブートストラップ・コンデンサの過充電を防止します。

入力電圧がその出力に近い電圧まで増加すると、ループがドロップアウト状態に入り、上側 FET を連続的にオンにしようとする可能性があります。下側 FET がブートストラップ・コンデンサを再充電できるだけの頻度でオンにならない場合、上側 FET は完全なエンハンスマント・モードにはならず、場合によっては、コントローラが上側 FET をオンにしようとしても完全にオフになる可能性さえあります。

## デッド・タイム制御 (DTCA ピンおよび DTCB ピン)

LTC7892 のデッド・タイム遅延は、DTCA ピンと DTCB ピンを設定することで、7ns～60ns の範囲で設定できます。DTCA ピンは、下側 FET のターンオフと上側 FET のターンオン (SWx がローからハイに遷移) に関するデッド・タイムを設定します。DTCB ピンは、上側 FET のターンオフと下側 FET のターンオン (SWx がハイからローに遷移) に関するデッド・タイムを設定します。

DTCA ピンをグラウンドに接続すると、適応型デッド・タイム制御が設定され、ドライバ・ロジックは、下側 FET がターンオフするのを待ってから上側 FET をターンオンします。適応型デッド・タイム制御により、BGx の立下がりから TGx の立上がりまでのデッド・タイムは約 15ns となります。DTCA ピンとグラウンドの間に抵抗を接続すると、下側 FET のターンオフと上側 FET のターンオンの間のオープンループ遅延が設定されます。この遅延は 7ns～60ns の範囲で設定できます。詳細については、[デッド・タイム制御 \(DTCA ピンおよび DTCB ピン\)](#) のセクションを参照してください。

DTCB ピンをグラウンドに接続すると、適応型デッド・タイム制御が設定され、ドライバ・ロジックは、上側 FET がターンオフするのを待ってから下側 FET をターンオンします。適応型デッド・タイム制御により、TGx の立下がりから BGx の立上がりまでのデッド・タイムは約 15ns となります。DTCB ピンとグラウンドの間に抵抗を接続すると、上側 FET のターンオフと下側 FET のターンオンの間のオープンループ遅延が設定されます。この遅延は 7ns～60ns の範囲で設定できます。詳細については、[デッド・タイム制御 \(DTCA ピンおよび DTCB ピン\)](#) のセクションを参照してください。

## スタートアップとシャットダウン (RUN ピンおよび SS ピン)

LTC7892 の 2 つのチャンネルは、RUN1 ピンと RUN2 ピンを用いて個別にシャットダウンできます。RUNx ピンを 1.1V 未満にすると、そのチャンネルのメイン制御ループがシャットダウンします。両方の RUNx ピンを 0.7V 未満にすると、両方のコントローラと、INTVcc LDO レギュレータを含むほとんどの内部回路が無効化されます。このシャットダウン状態では、V<sub>BIAS</sub> から LTC7892 に流れる電流はわずか 1μA です。

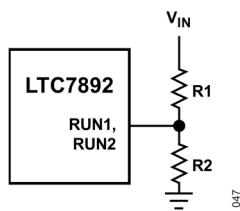

RUNx ピンは外部からプルアップするか、ロジックで直接駆動する必要があります。各 RUNx ピンは最大 100V まで許容できます。詳細については、[絶対最大定格](#) のセクションを参照してください。したがって、一方または両方のコントローラが連続的に有効化されて、シャットダウンされることのない常時オンのアプリケーションでは、RUNx ピンを V<sub>IN</sub> または V<sub>BIAS</sub> に接続でき便利です。更に、V<sub>IN</sub> ピンと RUNx ピンの間に抵抗分圧器を接続すれば、高精度の入力低電圧ロックアウトを設定し、調整可能なレベル未満で電源が動作しないようになります。

各チャンネルの出力電圧 V<sub>OUTx</sub> のスタートアップは、対応する SSx ピンの電圧によって制御します。SSx ピンの電圧が 1.2V の内部リファレンス電圧よりも低い場合、LTC7892 は V<sub>FBx</sub> 電圧を 1.2V のリファレンス電圧ではなく SSx ピンの電圧に安定化します。これにより、スタートアップ時に出力電圧を滑らかに上昇させるソフトスタートとして SSx ピンを使用できます。SSx ピンと GND の間の外付けコンデンサは 12μA の内部プルアップ電流で充電され、これによって SSx ピンに電圧ランプが発生します。SSx ピンの電圧が 0V から 1.2V (以上) まで直線的に上昇するにつれて、出力電圧 V<sub>OUTx</sub> も、その最終値まで滑らかに上昇します。

## 軽負荷時の動作 : Burst Mode 動作、パルススキッピング・モード、または強制連続モード (MODE ピン)

LTC7892 は、低負荷電流時に、高効率の Burst Mode 動作、固定周波数 PS モード、または強制連続導通モードになるように設定できます。

Burst Mode 動作を選択するには、MODE ピンを GND に接続します。強制連続動作を選択するには、MODE ピンを INTVcc に接続します。PS モードを選択するには、MODE ピンを 1.2V より大きく INTVcc - 1.3V より小さい DC 電圧に接続します。MODE ピンがフロート状態のときは、接地された 100kΩ の内部抵抗によって Burst Mode 動作が起動し、MODE ピンを 100kΩ の外付け抵抗を介して INTVcc に接続すると、PS モードになります。

コントローラで Burst Mode 動作が有効化されている場合、ITHx ピンの電圧が低い値を示している場合でも、インダクタの最小ピーク電流は最大値の約 25% に設定されます。平均インダクタ電流が負荷電流より大きい場合、エラー・アンプが ITHx ピンの電圧を低下させます。ITHx 電圧が 0.425V より低くなると、内部のスリープ信号がハイになり (スリープ・モードが有効化され)、両方の外付け FET がオフになります。すると、ITHx ピンがエラー・アンプの出力から遮断され、0.45V を維持します。

スリープ・モードでは内部回路のはほとんどがオフになるため、LTC7892 に流れる自己消費電流 ( $I_Q$ ) が減少します。一方のチャンネルがスリープ・モードで、もう一方のチャンネルがシャットダウンされている場合、LTC7892 に流れる  $I_Q$  はわずか  $15\mu A$  です。両方のチャンネルがスリープ・モードの場合、LTC7892 に流れる  $I_Q$  はわずか  $20\mu A$  です。

スリープ・モードでは、負荷電流が出力コンデンサから供給されます。出力電圧が低下するにつれて、エラー・アンプの出力が上昇します。出力電圧が十分に低下すると、 $ITH_x$  ピンがエラー・アンプの出力に再接続され、スリープ信号がローになり、コントローラは内部発振器の次のサイクルで下側 FET をオンにして通常動作を再開します。

コントローラの **Burst Mode** 動作が有効化されると、インダクタ電流は反転することができません。インダクタ電流がゼロに達する直前に、逆電流コンパレータ (IR) が上側 FET をオフにし、インダクタ電流が反転して負になるのを防ぎます。したがって、コントローラは不連続動作状態で動作します。

強制連続動作の場合、軽負荷時または大きなトランジエント状態時にはインダクタ電流を反転させることができます。ピーク・インダクタ電流は、通常動作時と同様に  $ITH_x$  ピンの電圧によって決まります。このモードでは、軽負荷での効率が **Burst Mode** 動作の場合よりも低下します。ただし、連続動作には出力電圧リップルが小さく、オーディオ回路への干渉が少ないという利点があります。強制連続モードでは、出力リップルは負荷電流に依存しません。

パルススキッピング・モードになるように MODE ピンを接続すると、LTC7892 は軽負荷時にパルス幅変調 (PWM) のパルススキッピング・モードで動作します。このモードでは、出力電流が最大設計値の約 1%に低下するまで固定周波数動作が維持されます。負荷が非常に軽い場合には、ICMP は数サイクルの間トリップ状態を維持し、同じサイクル数の間下側 FET をオフしたままにする（つまり、パルスをスキップする）ことがあります。インダクタ電流は反転できません（不連続動作）。強制連続動作と同様、このモードでは、**Burst Mode** 動作に比べて出力リップルとオーディオ・ノイズが小さくなり、RF 干渉が減ります。PS モードでは、低電流での効率が FCM より高くなりますが、**Burst Mode** 動作ほど高くはありません。

FCM やパルススキッピング・モードとは異なり、**Burst Mode** は外部クロックに同期することができません。そのため、**Burst Mode** 動作を選択し、スイッチング周波数が PLLIN/SPREAD ピンに印加された外部クロックに同期している場合、LTC7892 は **Burst Mode** から FCM に切り替わります。

## 周波数の選択、スペクトラム拡散、フェーズ・ロック・ループ (FREQ ピンおよび PLLIN/SPREAD ピン)

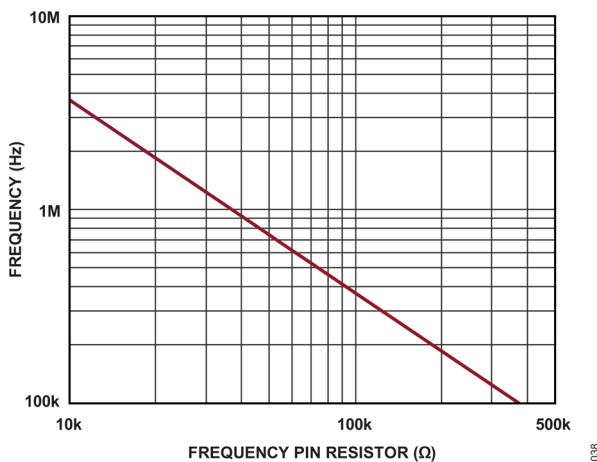

LTC7892 のコントローラの自走スイッチング周波数は、FREQ ピンを使って選択します。FREQ を GND に接続すると  $370\text{kHz}$  が選択され、FREQ を  $INTV_{CC}$  に接続すると  $2.25\text{MHz}$  が選択されます。FREQ と GND の間に抵抗を接続すると、周波数を  $100\text{kHz} \sim 3\text{MHz}$  の範囲で設定できます。

スイッチング・レギュレータは、電磁干渉 (EMI) が懸念されるアプリケーションでは特に問題を生じことがあります。EMI 性能を向上するために、LTC7892 はスペクトラム拡散モードで動作できます。このモードは、PLLIN/SPREAD ピンを  $INTV_{CC}$  に接続することで有効化できます。この機能により、スイッチング周波数は FREQ ピンで設定した周波数  $\sim +20\%$ （代表値）の範囲内で変化します。

LTC7892 では PLL が使用可能で、PLLIN/SPREAD ピンに接続された外部クロック信号源に内部発振器を同期させることができます。LTC7892 の PLL は、チャンネル 1 の外付け下側 FET のターンオンを同期信号の立上がりエッジに一致させます。チャンネル 2 の外付け下側 FET のターンオンは、外部クロック源の立上がりエッジに対して  $180^\circ$  位相がずれます。

PLL の周波数は、外部クロックが入力される前に、FREQ ピンで設定した自走周波数にプリバイアスされます。PLL を外部クロックの周波数の近くにプリバイアスしておくと、わずかに変化させるだけで、外部クロックの立上がりエッジを BG1 の立上がりエッジに同期させることができます。より高速に外部クロックにロックインするには、FREQ ピンを使用して、内部発振器の周波数を外部クロックの周波数前後の値に設定します LTC7892 の PLL は、周波数が 100kHz~3MHz の外部クロック源に確実にロックするよう設計されています。

PLLIN/SPREAD ピンはトランジスタ・トランジスタ・ロジック (TTL) に対応しており、閾値が 1.6V (立上がり) および 1.1V (立下がり) であるため、0.5V~2.2V のクロック信号振幅での動作が確保されています。

## 出力過電圧保護

LTC7892 は各チャンネルに過電圧コンパレータを備えており、トランジエント・オーバーシュートや、出力過電圧の原因となるその他の深刻な状態から保護します。V<sub>FBx</sub> ピンがレギュレーション・ポイントである 1.2V を 10%以上超えると、下側 FET がオフになり、インダクタ電流は逆転できなくなります。

## パワー・グッド

LTC7892 には各チャンネルに PGOODx ピンがあり、内部 N チャンネル MOSFET のオープン・ドレインに接続されています。V<sub>FBx</sub> 電圧が 1.2V リファレンスの±10%以内にない場合、MOSFET がオンになり、PGOODx ピンがローになります。PGOODx ピンは、RUNx ピンがロー（シャットダウン）のときにもローになります。V<sub>FBx</sub> 電圧が±10%の条件になると、MOSFET がオフになるため、PGOODx ピンを外付け抵抗によって INTV<sub>cc</sub> などの 6V を超えない電源にプルアップできます。

LTC7892 が 2 相単出力構成で動作している場合、出力電圧は、V<sub>FBI</sub> ピンでのみ検出されます。V<sub>FBI</sub> 電圧が 1.2V リファレンスの±10%以内にない場合、PGOOD1 ピンがローになります。PGOOD2 はフロート状態のままになります。

## アプリケーション情報

図 50 は、LTC7892 の基本的なアプリケーション回路を示しています。外付け部品の選択は主に負荷条件によって決まり、まずインダクタ、電流検出部品、動作周波数、軽負荷時の動作モードの選択から始めます。その後、入出力コンデンサおよびパワーFET で構成される残りのパワーワンコンポーネントを選択します。次に、帰還抵抗を選択して、目的の出力電圧を設定します。その後に、ソフトスタート、バイアス、ループ補償などに使用する、残りの外付け部品を選択します。

## インダクタ値の計算

動作周波数が高いほど小さな値のインダクタとコンデンサを使用できるという意味で、動作周波数とインダクタの選択には相関関係があります。FET のスイッチング損失とゲート電荷損失のために、一般に周波数が高いほど効率が低下します。このトレードオフに加えて、リップル電流と低電流動作に対するインダクタ値の影響も考慮しなければなりません。インダクタの値は、リップル電流に直接影響します。

連続導通モードでの最大平均インダクタ電流 ( $I_{L(MAX)}$ ) は、最大平均出力電流 ( $I_{OUT(MAX)}$ ) に  $V_{OUT}/V_{IN}$  を乗じた値に等しくなります。つまり、 $I_{L(MAX)} = I_{OUT(MAX)} \cdot V_{OUT}/V_{IN}$  です。最大出力電流は、 $V_{IN}$  が低下するにつれて減少することに注意してください。したがって、 $I_{L(MAX)}$  をどう選択するかは、最小通常動作電圧  $V_{IN}$  におけるレギュレーション電圧  $V_{OUT}$  の最大負荷電流により異なります。したがって、 $I_{L(MAX)}$  をどう選択するかは、最小通常動作電圧  $V_{IN}$  におけるレギュレーション電圧  $V_{OUT}$  の最大負荷電流により異なります。所定の  $V_{IN}$  に対する負荷電流を超えた場合は、 $I_{L(MAX)} = I_{OUT(MAX)} \cdot V_{OUT}/V_{IN}$  の式が満たされるまで  $V_{OUT}$  は低下します。

昇圧コンバータのインダクタのリップル電流 ( $\Delta I_L$ ) は、式 1 で与えられます。

$$\Delta I_L = \frac{1}{f \cdot L} V_{IN} \left( 1 - \frac{V_{IN}}{V_{OUT}} \right) \quad (1)$$

$\Delta I_L$  が大きな値でもよければ、低い値のインダクタンスを使用できますが、出力電圧リップルが大きくなり、コア損失が大きくなります。リップル電流を設定するための妥当な出発点は  $\Delta I_L = 0.3 \cdot I_{L(MAX)}$  です。昇圧コンバータの最大  $\Delta I_L$  は、 $V_{IN} = 1/2 V_{OUT}$  のときに発生します。インダクタの値は、2 次的な影響も与えます。必要な平均インダクタ電流が減少すると、ピーク電流が  $R_{SENSE}$  によって決定される電流制限の 25%未満になった時点で Burst Mode 動作への移行が開始されます。インダクタ値を低くする ( $\Delta I_L$  を高くする) と、低い負荷電流で Burst Mode 動作に移行するので、低電流動作の値の高い範囲での効率が低下する可能性があります。Burst Mode 動作では、インダクタンス値が小さくなるとバースト周波数が低下します。

## インダクタ・コアの選択

$L$  の値が定まつたら、インダクタの種類を選択する必要があります。高効率レギュレータは、通常、低価格の鉄粉コアに見られるコア損失を許容できないので、より高価なフェライトまたはモリバーマロイのコアを使わざるを得ません。実際のコア損失は、インダクタ値が同じであればコア・サイズには依存しませんが、選択するインダクタンス値には大きく依存します。インダクタンスが大きくなると、コア損失は減少します。しかし、インダクタンスを増加させるには巻き線数を増やす必要があるため、銅損失が増加します。

フェライトを使った設計ではコア損失が非常に小さくなるので、スイッチング周波数が高い場合に適しています。したがって、設計目標を銅損失と飽和防止に集中できます。フェライト・コア材料の飽和は「ハード」です。つまり、ピーク設計電流を超えると急激にインダクタンスが低下します。その結果、インダクタのリップル電流が急激に増加し、それに伴い出力電圧リップルも増加します。コアは飽和させないようにしてください。

## 電流検出方式の選択

LTC7892 はインダクタの DC 抵抗 (DCR) による検出または値の低い抵抗による検出のいずれかを使うように構成できます。2 つの電流検出方式のどちらを選択するかは、設計においてコスト、消費電力、精度のいずれを主に重視するかで決まります。DCR による検出が普及したのは、高価な電流センス抵抗が不要で、特に大電流のアプリケーションで電力効率が向上するためです。一方、電流センス抵抗を使用すると、コントローラの非常に正確な電流制限値が得られます。他の外付け部品の選択は、 $R_{SENSE}$  ( $R_{SENSE}$  を使用する場合) とインダクタの値の選択から始めます。

$SENSEx^+$  ピンと  $SENSEx^-$  ピンは、電流コンパレータへの入力となります。これらのピンのコモンモード電圧範囲は 0V ~ 65V で（詳細については [絶対最大定格](#) のセクションを参照）、LTC7892 はこの全範囲の入力で動作できます。 $SENSEx^-$  ピンは高インピーダンスであり、流れる電流は約 1 $\mu$ A 未満です。このようにインピーダンスが高いため、電流コンパレータをインダクタの DCR による検出に使うことができます。

$SENSEx^+$  ピンのインピーダンスは、コモンモード電圧に応じて変化します。INTV<sub>CC</sub> - 0.5V 未満のとき、 $SENSEx^+$  ピンは比較的の高インピーダンスとなり、 $SENSE1^+$  には約 75 $\mu$ A、 $SENSE2^+$  には約 1 $\mu$ A の電流が流れます。 $SENSEx^+$  ピンが INTV<sub>CC</sub> + 0.5V を超えると、各ピンにはより大きな電流（約 700 $\mu$ A）が流れます。INTV<sub>CC</sub> - 0.5V と INTV<sub>CC</sub> + 0.5V の間の場合は、電流は小電流から大電流に変化します。 $SENSE1^+$  ピンの電圧が 3.2V を超えると、 $V_{BIAS}$  ではなく  $V_{IN}$  から内部回路にバイアスがかかるため、 $SENSE1^+$  ピンには更に約 75 $\mu$ A の電流が流れ、入力換算電源電流が減少します。

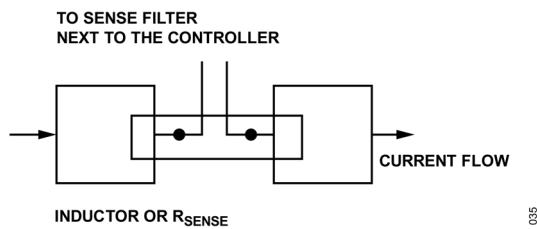

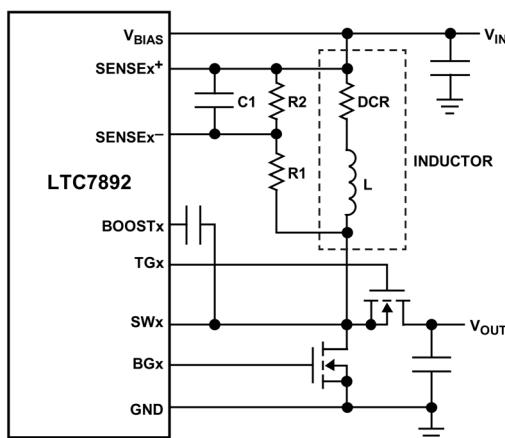

検出ラインに共通するフィルタ部品は LTC7892 の近くに配置し、検出ラインは電流検出素子の下のケルビン接続点まで互いに近付けて配線します（[図 35](#) を参照）。他の場所で電流を検出すると、寄生インダクタンスと容量が電流検出素子に実質的に追加され、検出端子の情報が劣化して、電流制限の設定値が予測不能になることがあります。DCR による検出を使用する場合は（[図 37](#) を参照）、 $R1$  抵抗をスイッチング・ノードの近くに配置して、高感度の小信号ノードにノイズが結合しないようにする必要があります。

図 35. インダクタまたはセンス抵抗を使用した検出ラインの配置

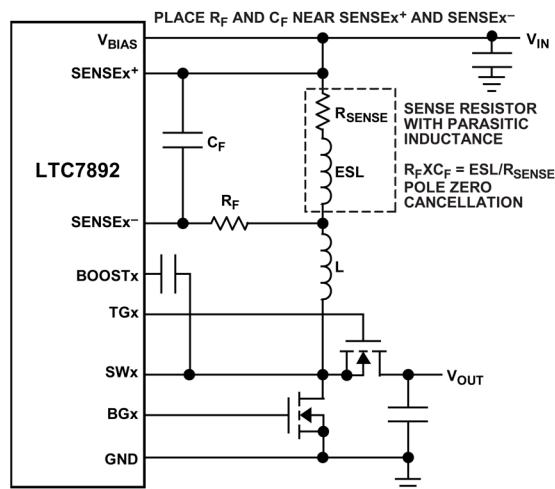

## 値の小さな抵抗による電流検出

[図 36](#) に、ディスクリート抵抗を使用した代表的な検出回路を示します。 $R_{SENSE}$  は必要な出力電流に基づいて選択します。電流コンパレータの最大閾値  $V_{SENSE(MAX)}$  は 50mV、25mV、または 75mV で、これは ILIM ピンの状態によって決まります。電流コンパレータの閾値電圧により、インダクタのピーク電流が設定されます。

最大インダクタ電流 ( $I_{L(MAX)}$ ) およびリップル電流 ( $\Delta I_L$ ) を用いると（[インダクタ値の計算](#) のセクションを参照）、目標とするセンス抵抗値は式 2 で与えられます。

$$R_{SENSE} = \frac{V_{SENSE(MAX)}}{I_{L(MAX)} + \frac{\Delta I_L}{2}} \quad (2)$$

アプリケーションが全動作温度範囲にわたって確実に最大負荷電流を供給するようにするには、[表 1](#)（電気的特性の表）に示す  $V_{SENSE(MAX)}$  の最小値を選択します。

センス抵抗に寄生インダクタンス（ESL）があると、インダクタ値が小さめ ( $< 3\mu\text{H}$ ) のアプリケーションや電流が大きめ ( $> 5\text{A}$ ) のアプリケーションでは、電流検出信号に大きな誤差が生じます。この誤差は入力電圧に比例し、ライン・レギュレーションを劣化させたり、ループを不安定化させたりする可能性があります。図 36 に示すように、RC フィルタ（フィルタ抵抗  $R_F$  とフィルタ・コンデンサ  $C_F$ ）を  $\text{SENSE}^+$  ピンと  $\text{SENSE}^-$  ピンの間に配置することで、この誤差を補正できます。ESL を最も適切に抑えるには、RC フィルタの時定数を  $R_F \times C_F = \text{ESL}/R_{\text{SENSE}}$  となるように設定します。一般に、 $1\text{nF} \sim 10\text{nF}$  の範囲内になるように  $C_F$  を選択し、それに応じて  $R_F$  を計算します。この誤差を最小限に抑えるため、低 ESL で footprint の広い形状の表面実装型センス抵抗を推奨します。ESL がメーカーのデータシートに仕様規定されていない場合、1206 フットプリントの抵抗では  $0.4\text{nH}$ 、1225 フットプリントの抵抗では  $0.2\text{nH}$  として ESL を概算できます。

図 36. 抵抗を使用した電流検出

## インダクタの DCR による電流検出

大負荷電流時に可能な限り高い効率を必要とするアプリケーションの場合、図 37 に示すように、LTC7892 はインダクタの直流抵抗 (DCR) 両端の電圧降下を検出できます。インダクタの DCR とは、銅巻線の小さな DC 抵抗値を表し、値の小さい大電流インダクタでは  $1\text{m}\Omega$  未満にもなり得ます。このようなインダクタを必要とする大電流アプリケーションでは、センス抵抗による電力損失は、インダクタの DCR による検出に比べると数ポイントの効率低下になると考えられます。

図 37. インダクタの DCR を用いた電流検出 (R<sub>SENSE(EQUIV)</sub>は等価検出抵抗)

外部の( $R_1 \parallel R_2$ ) •  $C_1$  の時定数が  $L/DCR$  の時定数に厳密に等しくなるように選択すると、外付けコンデンサ両端の電圧降下はインダクタの  $DCR$  両端の電圧降下に  $R_2/(R_1 + R_2)$  を乗じたものに等しくなります。 $R_2$  は、目標とするセンス抵抗よりも  $DCR$  が大きいアプリケーションに対して、検出端子両端の電圧を調整する抵抗です。外付けフィルタ部品を適切な大きさにするには、インダクタの  $DCR$  を知る必要があります。インダクタの  $DCR$  はインダクタンス、容量、抵抗 (LCR) メータを使って測定することができますが、 $DCR$  の許容誤差は常に一定ではなく、温度によって変化します。詳細については、メーカーのデータシートを参照してください。

$I_{L(MAX)}$  および  $\Delta I_L$  を用いて ([インダクタ値の計算](#) のセクションを参照)、目標とするセンス抵抗値は式 3 で与えられます。

$$R_{SENSE(EQUIV)} = \frac{V_{SENSE(MAX)}}{I_{L(MAX)} + \frac{\Delta I_L}{2}} \quad (3)$$

アプリケーションが全動作温度範囲にわたって確実に最大負荷電流を供給するようにするには、表 1 (電気的特性の表) に示す  $V_{SENSE(MAX)}$  の最小値を選択します。

次に、インダクタの  $DCR$  を決めます。メーカーから仕様が提供されている場合は、通常は  $20^\circ\text{C}$  で規定されている最大値を使用します。銅抵抗の温度係数 (約  $0.4\%/\text{C}$ ) を考慮して、この値を増加させます。インダクタ温度 ( $T_{L(MAX)}$ ) の値は控え目に見て  $100^\circ\text{C}$  です。最大インダクタ  $DCR$  ( $DCR_{MAX}$ ) をセンス抵抗の目標値 ( $R_D$ ) に調整するには、式 4 で与えられる分圧比を使用します。

$$R_D = \frac{R_{SENSE(EQUIV)}}{DCR_{MAX} \text{ at } T_{L(MAX)}} \quad (4)$$

$C_1$  は通常、 $0.1\mu\text{F} \sim 0.47\mu\text{F}$  の範囲に入るように選択します。この範囲では、等価抵抗 ( $R_1 \parallel R_2$ ) が約  $2\text{k}\Omega$  になるため、SENSE-ピンの約  $1\mu\text{A}$  の電流に起因する誤差が低減します。

$R_1 \parallel R_2$  は、室温のインダクタンスに比例し、最大  $DCR$  は式 5 で求められます。

$$R_1 \parallel R_2 = \frac{L}{(DCR \text{ at } 20^\circ\text{C}) \cdot C_1} \quad (5)$$

センス抵抗値は、以下に示す式 6 および式 7 で与えられます。

$$R_1 = \frac{R_1 \parallel R_2}{R_D} \quad (6)$$

$$R_2 = \frac{R_1 \cdot R_D}{1 - R_D} \quad (7)$$

$R_1$  の最大電力損失 (PLOSS) はデューティ・サイクルに関連して、連続モード時の  $V_{IN} = 1/2 V_{OUT}$  で発生し、式 8 で与えられます。

$$P_{LOSS \text{ in } R1} = \frac{(V_{OUT} - V_{IN}) \cdot V_{IN}}{R1} \quad (8)$$

$R_1$  の電力定格は  $R_1$  の  $P_{LOSS}$  より大きくなるようにします。軽負荷時に高い効率が必要な場合、 $DCR$  検出とセンス抵抗のどちらを使用するかを決定するときには、この電力損失を検討します。軽負荷での電力損失は、 $R_1$  によって余分のスイッチング損失が生じるため、センス抵抗の場合より  $DCR$  ネットワークの方がわずかに大きくなることがあります。ただし、 $DCR$  による検出ではセンス抵抗がないので、導通損失が減少し、重負荷時の効率が高くなります。ピーク効率はどちらの方法でもほぼ同じです。

## 動作周波数の設定

動作周波数の選択では、効率と部品サイズの間にトレードオフがあります。動作周波数が高いと、小型のインダクタと値の小さいコンデンサを使用することができます。低い周波数で動作させるとゲート電荷と遷移損失が減るので効率が改善されますが、出力リップル電圧を低く維持するには、インダクタンスの値や出力容量を大きくする必要があります。

高電圧アプリケーションでは、遷移損失が電力損失により大きく影響し、スイッチング周波数が 300kHz~900kHz の場合にサイズと効率の間で良好なバランスをとることができます。低電圧アプリケーションは、スイッチング損失が低いという利点があるため、必要に応じて最大 3MHz のスイッチング周波数で動作させることができます。スイッチング周波数は、表 4 に示すように、FREQ ピンと PLLIN/SPREAD ピンで設定します。

表 4. FREQ と PLLIN/SPREAD を用いたスイッチング周波数の設定

| FREQ PIN           | PLLIN/SPREAD PIN              | FREQUENCY                                             |

|--------------------|-------------------------------|-------------------------------------------------------|

| 0V                 | 0V                            | 370kHz                                                |

| INTV <sub>CC</sub> | 0V                            | 2.25MHz                                               |

| Resistor to GND    | 0V                            | 100kHz to 3MHz                                        |

| Any of the Above   | External Clock 100kHz to 3MHz | Phase-Locked to External Clock                        |

| Any of the Above   | INTV <sub>CC</sub>            | Spread Spectrum f <sub>osc</sub> modulated 0% to +20% |

FREQ ピンをグラウンドに接続すると 370kHz が選択され、FREQ を INTV<sub>CC</sub> に接続すると 2.25MHz が選択されます。FREQ とグラウンドの間に抵抗を接続すると、100kHz~3MHz の範囲内で任意の周波数に設定できます。FREQ ピンの抵抗 ( $R_{FREQ}$ ) は、図 38 または式 9 により選択します。

$$R_{FREQ} (\text{in } k\Omega) = \frac{37\text{MHz}}{f_{osc}} \quad (9)$$

図 38. 発振器周波数と FREQ ピンの抵抗値の関係

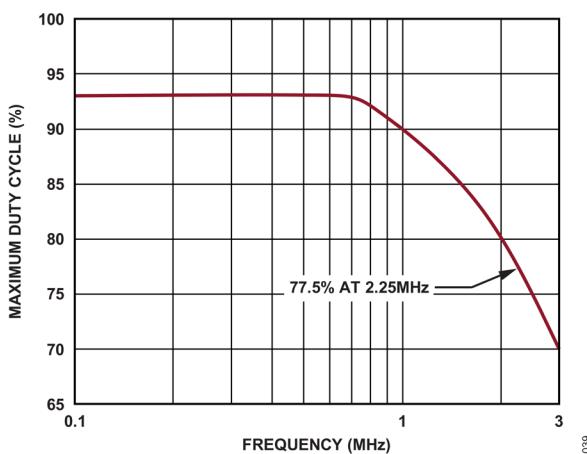

図 39. 最大デューティ・サイクルと動作周波数の関係

動作周波数に関する更なる制約条件は、昇圧コンバータの最大デューティ・サイクルです。最大デューティ・サイクル ( $DC_{MAX}$ ) には図 39 に示すように限界があり、その限界値は、 $DC_{MAX} = (1 - V_{IN(MIN)}/V_{OUT}) \cdot 100\%$ で近似できます。デューティ・サイクルが  $DC_{MAX}$  より大きい場合、出力を安定化できなくなり、固定周波数動作が維持されなくなる可能性があります。動作周波数は、昇圧コンバータのデューティ・サイクルが  $DC_{MAX}$  未満となるように選択する必要があります。

EMI 性能を向上させるため、PLLIN/SPREAD ピンを INTV<sub>cc</sub> に接続してスペクトラム拡散モードを選択することもできます。スペクトラム拡散機能を有効化した場合、スイッチング周波数は、FREQ ピンで選択した周波数から+20%までの範囲内で調整されます。スペクトラム拡散モードは、MODE ピンで選択した任意の動作モード (Burst Mode、PS モード、または FCM) で使用できます。

また、LTC7892 では PLL が使用可能で、PLLIN/SPREAD ピンに接続された外部クロック信号源に内部発振器を同期させることができます。PLL がロックした後、BGxx1 は外部クロック信号の立上がりエッジに同期し、BGxx2 は位相が BGxx1 から 180° ずれます。詳細については、[フェーズ・ロック・ループと周波数同期](#)のセクションを参照してください。

## 軽負荷時動作モードの選択

LTC7892 は、軽負荷電流時に、高効率の Burst Mode 動作、固定周波数 PS モード、または強制連続導通モードになるように設定できます。Burst Mode 動作を選択するには、MODE ピンを GND に接続します。強制連続動作を選択するには、MODE ピンを INTV<sub>cc</sub> に接続します。PS モードを選択するには、MODE ピンを 100kΩ の抵抗を介して INTV<sub>cc</sub> に接続します。MODE ピンとグラウンドの間にある 100kΩ の内部抵抗により、MODE ピンがフロート状態の場合は Burst Mode が選択されます。PLLIN/SPREAD ピンを介して外部クロックに同期させた場合、PS モードが選択されていれば、LTC7892 はそのモードで動作します。それ以外の場合、LTC7892 は FCM で動作します。MODE ピンを用いて軽負荷時動作モードを選択する方法を表 5 に示します。

表 5. MODE ピンを使用した軽負荷時動作モードの選択

| MODE PIN                    | LIGHT-LOAD OPERATING MODE | MODE WHEN SYNCHRONIZED |

|-----------------------------|---------------------------|------------------------|

| 0V or Floating              | Burst Mode                | FCM                    |

| 100kΩ to INTV <sub>cc</sub> | PS Mode                   | PS Mode                |

| INTV <sub>cc</sub>          | FCM                       | FCM                    |

どの軽負荷時動作モードを選択するのが適切かは、それぞれのアプリケーションの条件によって決まります。Burst Mode 動作では、インダクタ電流は反転できません。インダクタ電流がゼロに達する直前に、逆電流コンパレータが上側 FET をオフにし、インダクタ電流が反転して負になるのを防ぎます。したがって、レギュレータは不連続動作状態で動作します。更に、負荷電流が少ないと、インダクタ電流はスイッチング周波数より低い周波数でバースト動作を開始し、スイッチングが停止している場合は低消費電流のスリープ・モードに入ります。結果として、軽負荷時に可能な限りの最も高い効率が得られるのは Burst Mode 動作です。

FCM では、インダクタ電流は軽負荷で反転し、負荷に関係なく同じ周波数でスイッチングします。このモードでは、軽負荷での効率が Burst Mode 動作の場合よりも顕著に低下します。ただし、連続動作には出力電圧リップルが小さく、オーディオ回路への干渉が少ないという利点があります。FCM では、出力リップルは負荷電流に依存しません。

PS モードでは、出力電流が最大設計値の約 1%に低下するまで固定周波数動作が維持されます。非常に軽い負荷の場合には、PWM コンパレータは数サイクル間トリップ状態を維持し、同じサイクル数の間下側 FET をオフにしたままにする（つまり、パルスをスキップする）ことがあります。インダクタ電流は反転できません（不連続動作）。強制連続動作と同様、このモードでは、Burst Mode 動作に比べて出力リップルとオーディオ・ノイズが小さくなり、RF 干渉が減ります。PS モードでは、軽負荷時の効率が FCM より高くなりますが、Burst Mode 動作ほど高くはありません。したがって、PS モードは軽負荷時の効率、出力リップル、および EMI の間での妥協点となります。

アプリケーションによっては、システム内の条件に応じて軽負荷時の動作モードを変更することが望ましい場合があります。例えば、システムが動作していない場合は、MODE ピンを 0V に維持することによって、高効率の Burst Mode 動作を選択することが考えられます。システムが起動したら、外部クロックを PLLIN/SPREAD に送信するか、MODE を INTV<sub>CC</sub> に接続して、低ノイズの強制連続モードに切り替えることができます。このような変更を行うと、個々のアプリケーションでそれぞれの軽負荷時動作モードの利点が得られます。

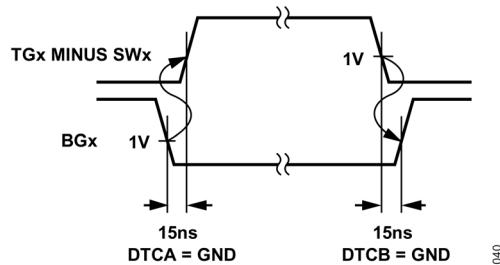

## デッド・タイム制御 (DTCA ピンおよび DTCB ピン)

LTC7892 のデッド・タイム遅延は、DTCA ピンと DTCB ピンの設定により、7ns～60ns の範囲で調整できます。図 40 および図 41 に、各 DTCx ピンの設定に対する TG<sub>x</sub> - SW<sub>x</sub> および BG<sub>x</sub> の各波形とそのタイミング図を示します。DTCx ピンをグラウンドに接続（適応型デッド・タイム制御）および DTCx ピンを抵抗を介して GND に接続の各セクションでは、TG<sub>x</sub> は上側 FET ゲートで検出される電圧 (TG<sub>x</sub> の立上がり閾値は TGUP<sub>x</sub> ピンで検出) を、BG<sub>x</sub> は下側 FET で検出される電圧 (BG<sub>x</sub> の立上がり閾値は BGDN<sub>x</sub> ピンで、立下がり閾値は BGUP<sub>x</sub> ピンで検出) を表します。DTCA ピンは、下側 FET のターンオフと上側 FET のターンオン (SW<sub>x</sub> がローからハイに遷移) に関するデッド・タイムを設定します。DTCB ピンは、上側 FET のターンオフと下側 FET のターンオン (SW<sub>x</sub> がハイからローに遷移) に関するデッド・タイムを設定します。

### DTCx ピンをグラウンドに接続（適応型デッド・タイム制御）

DTCA ピンと DTCB ピンを GND に接続すると、適応型デッド・タイム制御が設定されます。適応型制御（図 40 を参照）では、一方の FET がオフになってから他方の FET がオンになるまでのデッド・タイムが測定されます。DTCA ピンを GND に接続すると、BGx の立下がりから TGx - SWx の立上がりまでの遅延が約 15ns に固定されます。DTCB ピンを GND に接続すると、TGx - SWx の立下がりから BGx の立上がりまでの遅延が約 15ns に固定されます。

図 40. DTC ピンを GND に接続 - 適応型デッド・タイム制御

### DTCx ピンを抵抗を介して GND に接続

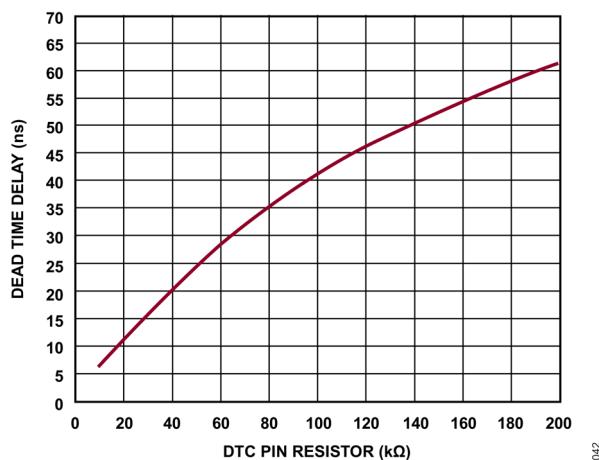

DTCx ピンと GND の間に抵抗を接続すると、TGx - SWx のエッジと BGx のエッジ間に 7ns~60ns のオープンループ・デッド・タイム遅延が設定されます（図 41 を参照）。DTCA ピンに抵抗を接続すると、BGx の立下がりから TGx - SWx の立上がりまでの間にオープンループ遅延が設定されます。DTCB ピンに抵抗を接続すると、TGx - SWx の立下がりから BGx の立上がりまでの間にオープンループ遅延が設定されます。図 42 は、DTCx ピンの抵抗値と TGx - SWx のエッジと BGx のエッジの間に設定される遅延の関係を示しています。この抵抗は 10kΩ 以上 200kΩ 以下にする必要があります。

図 41. DTCx ピンを抵抗を介して GND に接続 - 調整可能デッド・タイム制御

図 42. デッド・タイム遅延と DTCx ピン抵抗値の関係

DTCx ピンの一方を抵抗で設定している場合、もう一方の DTCx ピンを抵抗で設定していなければ、適切なデッド・タイム制御動作はできません。一方の DTCx ピンを抵抗で設定し、もう一方の DTCx ピンを GND に接続すると、予期しないデッド・タイム遅延が発生する可能性があります。これらの DTCx ピンは、GND に接続するか、抵抗を介して GND に接続するかのいずれかでなくてはなりません。

## パワーFET の選択

LTC7892 のコントローラごとに 2 つの外付けパワーFET を選択する必要があります。1 つは下側（メイン）スイッチ用の N チャンネル FET、もう 1 つは上側（同期）スイッチ用の N チャンネル FET です。ピーク to ピークのゲート駆動レベルは、INTVCC のレギュレーション・ポイント (4V~5.5V) によって設定されます。ほとんどの GaN FET は、この INTVCC レギュレーション・ウィンドウ内で十分に駆動できます。シリコン MOSFET を使用する場合、ほとんどのアプリケーションでは、ロジック・レベル閾値の MOSFET を使用する必要があります。FET の  $BVD_{SS}$  の仕様にも十分注意を払ってください。

パワーFET の選択基準には、オン抵抗 ( $R_{DS(ON)}$ )、ミラー容量 ( $C_{MILLER}$ )、入力電圧、および最大出力電流などがあります。 $C_{MILLER}$  は、FET メーカーのデータシートに一般に記載されているゲート電荷曲線から概算できます。 $C_{MILLER}$  は、曲線がほぼ平らな区間の水平軸に沿ったゲート電荷の増分を、FET のドレイン端子とソース端子間の電圧差 ( $V_{DS}$ ) の仕様規定されている変化量で割ったものに等しくなります。次に、この結果に、アプリケーションで印加される  $V_{DS}$  とゲート電荷曲線で規定されている  $V_{DS}$  との比を乗じます。連続モードで動作している場合の上側 FET と下側 FET のデューティ・サイクルは、式 10 および式 11 で与えられます。

$$\text{Main Switch Duty Cycle} = \frac{V_{OUT} - V_{IN}}{V_{OUT}} \quad (10)$$

$$\text{Synchronous Switch Duty Cycle} = \frac{V_{IN}}{V_{OUT}} \quad (11)$$

最大出力電流時における FET の消費電力は、式 12 と式 13 で与えられます。

$$P_{MAIN} = \frac{(V_{OUT}-V_{IN})V_{OUT}}{V_{IN}^2} (I_{OUT(MAX)})^2 \cdot (1 + \delta)R_{DS(ON)} + \left( \frac{V_{OUT}^3}{V_{IN}} \right) \left( \frac{I_{OUT(MAX)}}{2} \right) \cdot (R_{DR})(C_{MILLER}) \cdot \left| \frac{1}{V_{INTVCC}-V_{THMIN}} + \frac{1}{V_{THMIN}} \right| (f) \quad (12)$$

$$P_{SYNC} = \frac{V_{OUT}}{V_{IN}} (I_{OUT(MAX)})^2 (1 + \delta)R_{DS(ON)} \quad (13)$$

ここで、

$P_{MAIN}$  はメイン・スイッチの消費電力。

$\delta$  は  $R_{DS(ON)}$  の温度依存性 ( $\delta \approx 0.005/\text{°C}$ )。

$R_{DR}$  は FET のミラー閾値電圧における実効ドライバ抵抗 ( $R_{DR} \approx 2\Omega$ )。

$V_{INTVCC}$  は INTVCC 電圧。

$V_{THMIN}$  は FET の最小閾値電圧の代表値。

$P_{SYNC}$  は同期スイッチの消費電力。

どちらの FET にも  $I^2R$  損失 ( $I^2R$  は定常状態でオン時における FET の電力損失式) が生じますが、メインの N チャンネル式には、低入力電圧で最も高くなる遷移損失の追加項が含まれます。高入力電圧の場合、大電流時の効率は一般に FET が大きいほど向上します。しかし、低入力電圧の場合は、遷移損失は急速に増加し、 $C_{MILLER}$  が低く  $R_{DS(ON)}$  が高いデバイスを使用した方が、効率が高くなる点まで達します。同期 FET の損失は、下側スイッチのデューティ比が低い場合には、入力電圧が高いときに最も大きくなります。

## C<sub>IN</sub> と C<sub>OUT</sub> の選択

昇圧コンバータの入力電流は連続しているので、入力リップル電流は（出力リップル電流と比較して）相対的に小さくなります。昇圧コンバータの入力コンデンサ（C<sub>IN</sub>）の電圧定格は、最大入力電圧より高い値であることが必要です。セラミック・コンデンサは過電圧状態に対して耐性がありますが、アルミニウム電解コンデンサにはこの耐性がありません。入力コンデンサに過度のストレスを与え得るあらゆる過電圧トランジェントの可能性について、入力電圧の特性を評価するようにしてください。

C<sub>IN</sub>の値はソース・インピーダンスの関数であり、一般にソース・インピーダンスが高いほど必要な入力容量も大きくなります。必要な入力容量の大きさはデューティ・サイクルによっても大きく影響されます。高いデューティ・サイクルでの動作も行う大出力電流アプリケーションは、DC電流とリップル電流の両方の点で、入力電源に大きな負担を負わせることができます。

出力容量（C<sub>OUT</sub>）の選択は出力電圧リップル（V<sub>RIPPLE</sub>）の要件によって決まります。昇圧コンバータの出力電流は不連続です。そのため、C<sub>OUT</sub>の選択時には、ESRの影響とバルク容量の影響の両方を考慮する必要があります。C<sub>OUT</sub>のバルク容量の充放電による V<sub>RIPPLE</sub>は、式 14 を用いて次のように与えられます。

$$V_{\text{RIPPLE}} = \frac{I_{\text{OUT}(\text{MAX})} \cdot (V_{\text{OUT}} - V_{\text{IN}(\text{MIN})})}{C_{\text{OUT}} \cdot V_{\text{OUT}} \cdot f} \quad (14)$$

C<sub>OUT</sub>のESRでの電圧降下によるリップル（ΔV<sub>ESR</sub>）は、式 12 を用いて次のように与えられます。

$$\Delta V_{\text{ESR}} = \left( I_{\text{L}(\text{MAX})} + \frac{1}{2} \Delta I_{\text{L}} \right) \cdot \text{ESR} \quad (15)$$

ここで、

Δ<sub>L</sub>はインダクタのリップル電流。

I<sub>L(MAX)</sub>は最大平均インダクタ電流。

I<sub>OUT(MAX)</sub>は最大平均出力電流。

fは動作周波数。

ESRと RMS 電流処理の条件を満たすために、複数のコンデンサを並列に配置しなければならない場合があります。乾式タンタル、特殊ポリマー、アルミ電解、セラミックの各コンデンサは、いずれも表面実装パッケージで入手できます。セラミック・コンデンサは優れた低 ESR 特性を備えていますが、電圧係数が高いことがあります。低 ESR で高リップル電流定格のコンデンサ（OS-CON や POSCAP など）を使用できます。

## 单一出力 2 相動作

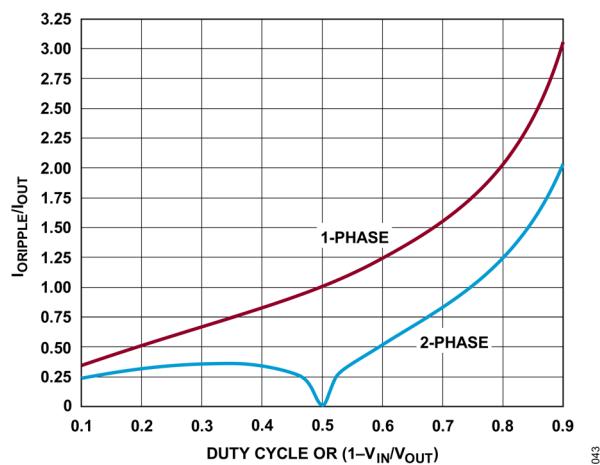

大電力アプリケーションでは、2つのチャンネルを2相の单一出力構成で動作させることができます。2相動作の場合、2つのチャンネルは位相が $180^\circ$ ずれて動作し、出力電流パルスを効率的にインターリーブします。電流パルスをインターリーブすることで、最大出力電流を2倍にできると同時に、出力コンデンサのリップル電流を減少できます。出力コンデンサのリップル電流が減少することで、所定の出力リップル電圧要件を満たす高周波数出力コンデンサの容量およびESRの要件が低減されます。

2相構成の場合、式14に示す出力コンデンサのリップル電流要件は、図43に示すように低減できます。図43は、正規化された出力コンデンサ・リップル電流を、2相構成のデューティ・サイクルの関数として表したもので、比較のため単相構成の場合についても示しています。2相構成での出力コンデンサのリップル電流定格を選択するには、次の手順に従います。

1. 出力電圧および入力電圧範囲に応じたデューティ・サイクル範囲を計算します。

2. 図43に示すように、最も厳しい最大正規化リップル電流を最大負荷電流のパーセンテージとして選択します。

図43. 昇圧コンバータの正規化された出力コンデンサ・リップル電流（実効値）

LTC7892を2相動作に構成するには、 $V_{FB2}$ をINTV<sub>CC</sub>に、ITH2をグラウンドに、SS2をグラウンドに、PGOOD2をグラウンド（またはフロート状態のまま）に、RUN2をRUN1に接続します。

RUN1、 $V_{FB1}$ 、ITH1、およびSS1ピンが両チャンネルの制御に使用されますが、各チャンネルは独自のICMPおよびIRコンパレータを用いてそれぞれのインダクタ電流をモニタします。

図44に单一出力2相動作の構成を示します。また、図50に单一出力2相動作に構成された代表的なアプリケーションを示します。

図44. 単一出力 2 相動作の構成

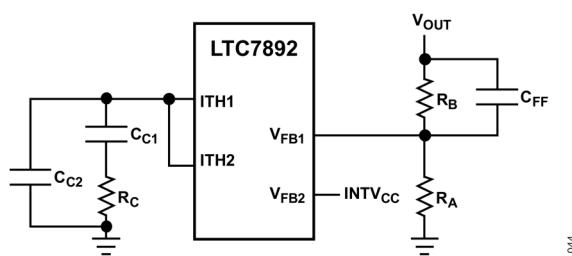

## 出力電圧の設定

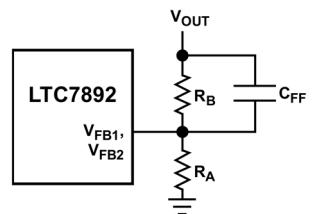

LTC7892 の出力電圧は、図 45 および図 46 に示すように、それぞれ出力の両端に注意深く配置された外付けの帰還抵抗分圧器によって設定します。安定化出力電圧は式 16 により求めます。

$$V_{OUT} = 1.2V \left(1 + \frac{R_B}{R_A}\right) \quad (16)$$