## 5mm × 8mm LQFNで実現する SilentMOSスマート電力段

### 特長

- 140Aのピーク出力電流

- SilentMOS™スマート電力段

- 低EMI/EMCのSilent Switcher®2アーキテクチャを採用

- 超低SW電圧オーバーシュート

- 最大2MHzの周波数

- $V_{IN}$  = 最大16V

- 1MHz、1.8V $V_{OUT}$ で最大94%の効率

- 昇圧ダイオードおよびコンデンサとパワー・スイッチを内蔵

- 正確なスイッチ電流モニタリング

- パワーMOSFET過電流保護

- 入力過電圧およびバイアス低電圧保護

- 過熱フラグによる熱監視

- 3.3V/5V互換3ステートPWM入力

- 5mm × 8mm LQFNパッケージ

### アプリケーション

- 大電流サーバーおよびワークステーション

- ネットワーク/テレコム・マイクロプロセッサ電源

- 小型フォーム・ファクタのPOLコンバータ

### 概要

LTC®7051-1 モノリシック電力段は、低抵抗ハーフブリッジ・パワー・スイッチを備えた高速ドライバと包括的なモニタリングおよび保護回路を、電気的および熱的に最適化されたパッケージに全て内蔵しています。この電力段は、適切な高周波数コントローラを使用して、最高水準の効率と過渡応答を備えた、コンパクトな高電流電圧レギュレータ・システムを形成します。

SilentMOS技術は、第2世代のSilent Switcher 2アーキテクチャを利用しており、高いスイッチング周波数で効率を最大化すると同時にEMIおよびスイッチ・ノード電圧オーバーシュートの両方を低減しています。

高速電流検出によりスイッチ電流情報が低遅延で提供されるため、厳しい電流バランスと即時過電流保護が可能です。

熱強化型パッケージを通じて、65A定格の電流出力能力が実現されています。

全ての登録商標および商標の所有権は、それぞれの所有者に帰属します。第9525351号を含む米国特許により保護されています。

### 標準的応用例

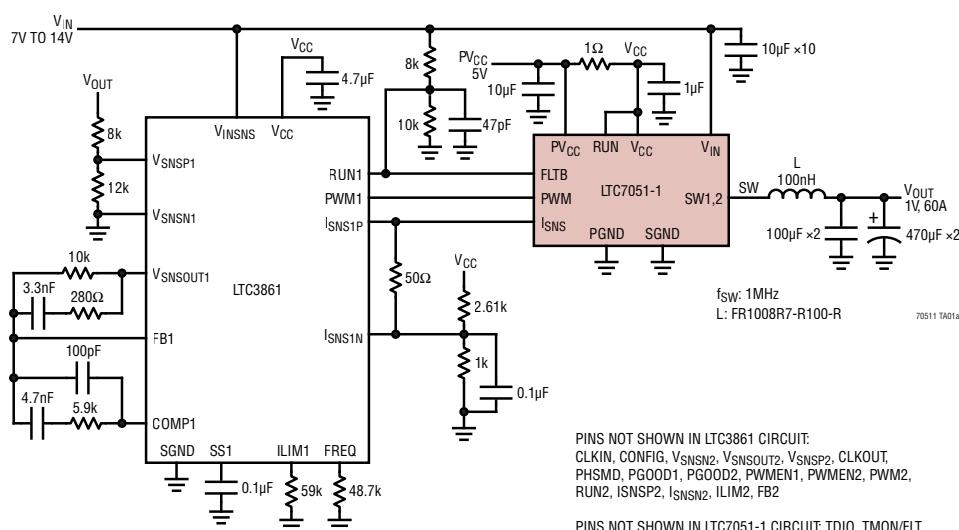

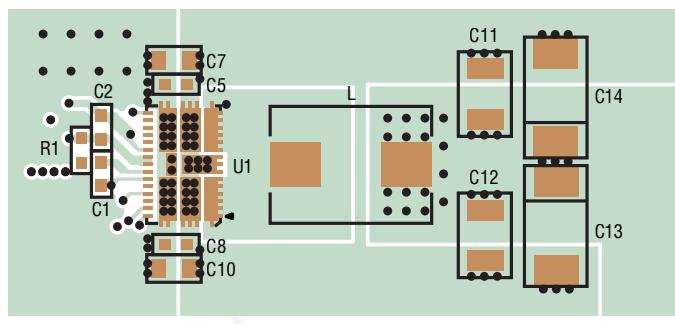

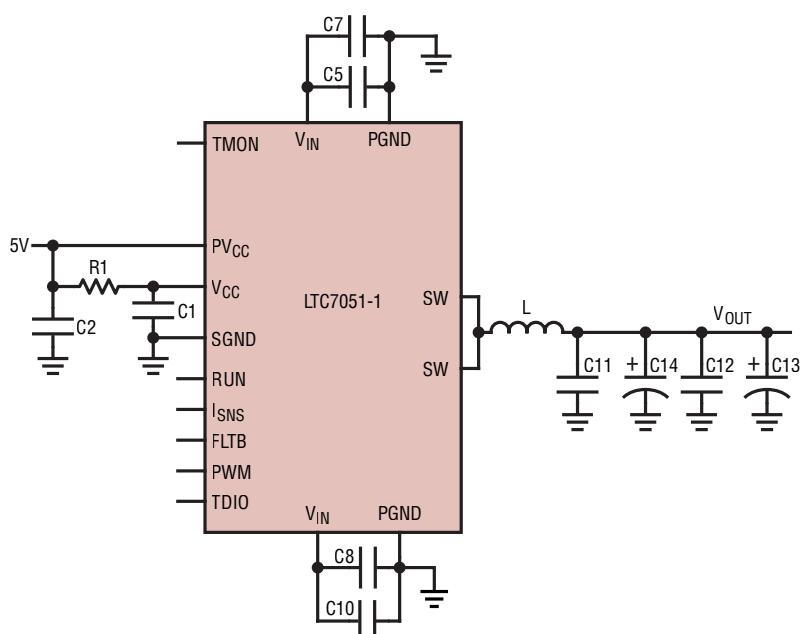

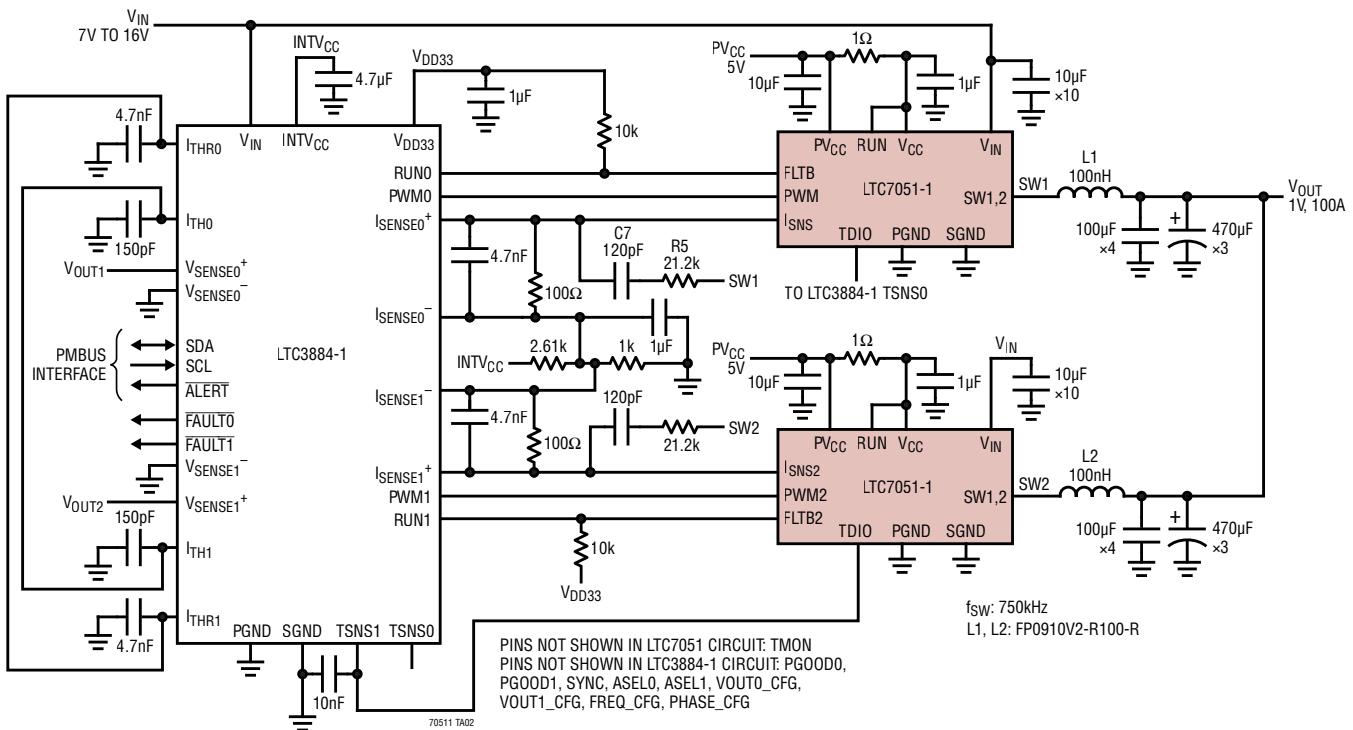

#### 12V $V_{IN}$ 、1V/60A $V_{OUT}$ 、1MHzのデュアルフェーズPOLコンバータ

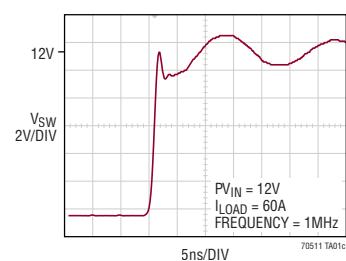

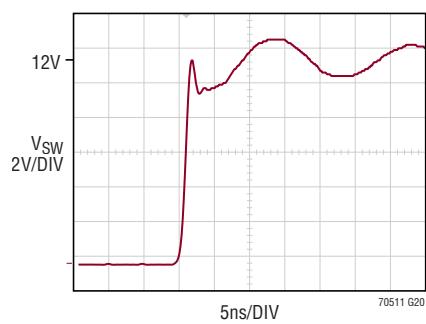

#### 1MHz時の $V_{SW}$ 波形

## 絶対最大定格 (Note 1)

|                                       |                                |

|---------------------------------------|--------------------------------|

| V <sub>IN</sub> DC電圧                  | -0.3V～19V                      |

| V <sub>IN</sub> トランジエント電圧             | -0.3V～25V                      |

| SWの電圧                                 | -0.3V～25V DC                   |

| SWの電圧(20ns)                           | -2V～25V                        |

| PV <sub>CC</sub> 、V <sub>CC</sub> の電圧 | -0.3V～6V                       |

| RUN                                   | -0.3V～(V <sub>CC</sub> + 0.3V) |

| PWM                                   | -0.3V～(V <sub>CC</sub> + 0.3V) |

| I <sub>SNS</sub>                      | -0.3V～(V <sub>CC</sub> + 0.3V) |

| FLTB                                  | -0.3V～(V <sub>CC</sub> + 0.3V) |

| TDIO電圧／電流                             | -0.3V～-5mA                     |

| 絶対最大ジャンクション温度                         | 125°C                          |

| 保管温度                                  | -55°C～150°C                    |

| 最大リフロー(パッケージ・ボディ)温度                   | 260°C                          |

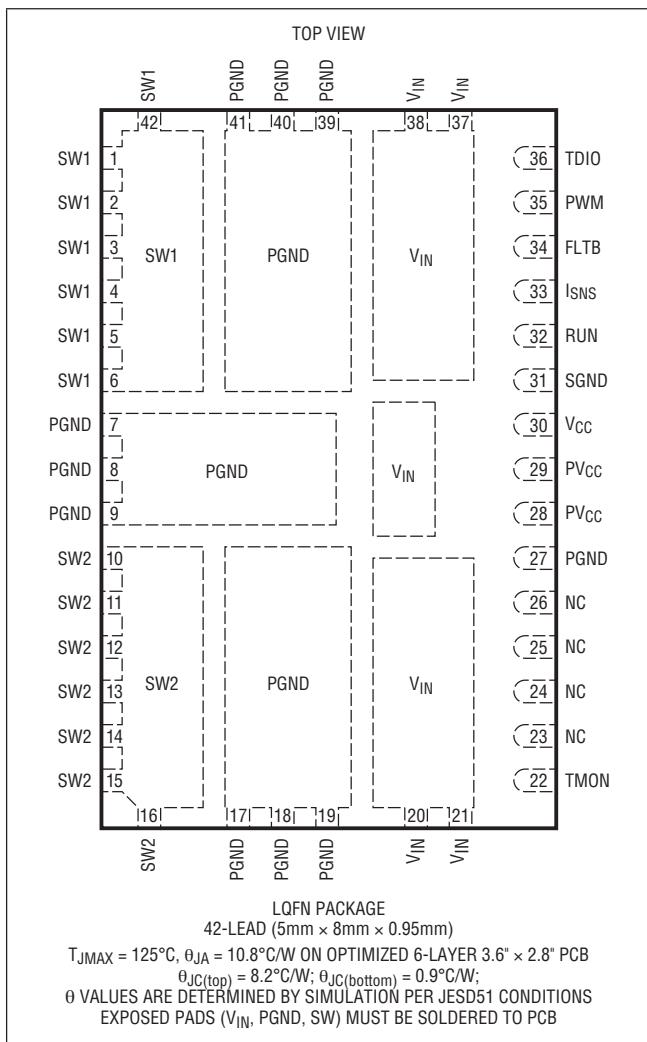

## ピン配置

## 発注情報

| 製品番号            | 部品マーキング | 仕上げコード | パッド仕上げ    | パッケージ・タイプ                      | MSL<br>レーティング | 温度範囲        |

|-----------------|---------|--------|-----------|--------------------------------|---------------|-------------|

| LTC7051AV-1#PBF | 70511   | e4     | Au (RoHS) | LQFN (QFN フットプリント<br>の積層パッケージ) | 3             | -40°C～125°C |

- 更に広い動作温度範囲で規定されたデバイスについては、弊社または弊社代理店にお問い合わせください。

- \*パッドまたはポールの仕上げコードは IPC/JEDEC J-STD-609 によります。

製品番号末尾がPBFとなっている製品はRoHSおよびWEEEに準拠しています。

## 電気的特性

●は、仕様規定された温度範囲に適用される仕様を示しています。それ以外の場合、特に指定のない限り、 $T_A = 25^\circ\text{C}$ 、 $V_{IN} = 12\text{V}$ 、 $P_{VCC} = V_{CC} = 5\text{V}$ です。

| SYMBOL               | PARAMETER                                                              | CONDITIONS                                                 |   | MIN  | TYP  | MAX  | UNITS            |

|----------------------|------------------------------------------------------------------------|------------------------------------------------------------|---|------|------|------|------------------|

| $V_{IN}$             | Power Input Supply Range                                               |                                                            | ● |      |      | 16   | V                |

|                      | $V_{IN}$ Overvoltage Lockout Threshold                                 | $V_{IN}$ Rising                                            | ● | 17.7 |      | 18.7 | V                |

|                      | $V_{IN}$ Overvoltage Lockout Hysteresis                                |                                                            |   |      | 1    |      | V                |

|                      | $V_{IN}$ Overvoltage Lockout Delay                                     | (Note 3)                                                   |   |      | 1    |      | $\mu\text{s}$    |

|                      | $V_{IN}$ Shutdown Current                                              | $V_{IN} = 12\text{V}$ , RUN = 0                            |   |      | 25   |      | $\mu\text{A}$    |

| $V_{CC}$             | $V_{CC}$ Input Supply Range                                            |                                                            | ● | 4.5  | 5    | 5.5  | V                |

| $V_{CC(UVLO)}$       | $V_{CC}$ Undervoltage Lockout Threshold                                | $V_{CC}$ Rising                                            | ● | 4.05 | 4.15 | 4.25 | V                |

| $V_{UVLO\_HYST}$     | $V_{CC}$ Undervoltage Lockout Hysteresis                               |                                                            |   |      | 0.2  |      | V                |

| $I_{VCC(SD)}$        | $V_{CC}$ Supply Current in Shutdown                                    | RUN = 0                                                    |   |      | 14   |      | $\mu\text{A}$    |

| $I_{VCC\_active}$    | $V_{CC}$ Supply Current in Active                                      | RUN = 5V, PWM = Float                                      |   |      | 2.5  |      | mA               |

| $P_{VCC}$            | Driver Input Supply Range                                              |                                                            | ● | 4.5  | 5    | 5.5  | V                |

| $P_{VCC(UVLO)}$      | $P_{VCC}$ Undervoltage Lockout Threshold                               | $P_{VCC}$ Rising                                           | ● | 3.9  | 4.0  | 4.1  | V                |

| $P_{VUVLO\_HYST}$    | $P_{VCC}$ Undervoltage Lockout Hysteresis                              |                                                            |   |      | 0.35 |      | V                |

| $I_{PVCC(SD)}$       | $P_{VCC}$ Supply Current in Shutdown                                   | RUN = 0                                                    |   |      | 300  |      | $\mu\text{A}$    |

| $I_{PVCC\_active}$   | $P_{VCC}$ and $V_{CC}$ Supply Current in Active                        | RUN = 5V, PWM = Float                                      |   |      | 2.5  |      | mA               |

| $t_{UVLO}$           | Undervoltage Time Lockout Delay, from $V_{CC}$ and $P_{VCC}$ to SW Low | $P_{VCC}, V_{CC}$ Rising<br>RUN = 5V PWM = 0 (Note 3)      |   |      | 1    |      | $\mu\text{s}$    |

| <b>RUN Input</b>     |                                                                        |                                                            |   |      |      |      |                  |

| $V_{IH\_RUN}$        | RUN High Threshold                                                     | RUN Rising                                                 | ● | 2.2  | 2.45 | 2.7  | V                |

| $V_{RUN\_HYS}$       | RUN Hysteresis                                                         |                                                            |   |      | 0.2  |      | V                |

| $R_{PD\_RUN}$        | EN Pull-Down Resistor                                                  |                                                            |   |      | 30   |      | $\text{k}\Omega$ |

| $T_d\_RUNH$          | Propagation Delay for RUN Low to High                                  | From RUN Low $\geq$ High to SW = 0, PWM = 0<br>(Note 3)    |   |      | 12   |      | $\mu\text{s}$    |

| $T_d\_RUNL$          | Propagation Delay for RUN High to Low                                  | From RUN High $\geq$ Low to SW High Z,<br>PWM = 0 (Note 3) |   |      | 0.1  |      | $\mu\text{s}$    |

| <b>PWM Input</b>     |                                                                        |                                                            |   |      |      |      |                  |

| $V_{IH\_PWM}$        | PWM High Threshold                                                     |                                                            | ● |      |      | 2.7  | V                |

| $V_{IL\_PWM}$        | PWM Low Threshold                                                      |                                                            | ● | 0.8  |      |      | V                |

| $V_{TR\_PWM}$        | PWM Tri-State Range                                                    |                                                            | ● | 1.5  |      | 2.1  | V                |

| $V_{PWM\_HYS}$       | PWM Hysteresis                                                         | Active to Tri-State or Tri-State to Active                 |   |      | 300  |      | mV               |

| $R_{PD\_PWM}$        | PWM Pull-Down Resistor                                                 | To SGND                                                    |   |      | 9.6  |      | $\text{k}\Omega$ |

| $R_{PU\_PWM}$        | PWM Pull-Up Resistor                                                   | To $V_{CC}$                                                |   |      | 18.8 |      | $\text{k}\Omega$ |

| $t_{PWMHI-SW}$       | Delay Time, PWM High to SW High                                        | No Fault Condition (Note 3)                                |   |      | 10   |      | ns               |

| $t_{PWMLO-SW}$       | Delay Time, PWM Low to SW Low                                          | No Fault Condition (Note 3)                                |   |      | 10   |      | ns               |

| $t_{Tri\_Lo\_Delay}$ | Tri-State to Low Propagation Delay                                     | PWM Going Low to SW Going Low                              |   |      | 20   |      | ns               |

| $t_{Tri\_Hi\_Delay}$ | Tri-State to High Propagation Delay                                    | PWM Going High to SW Going High                            |   |      | 30   |      | ns               |

| $t_{Tri\_Hold}$      | Active to Tri-State Delay Time                                         | PWM Going to High Z to SW High Z (Note 3)                  |   |      | 20   |      | ns               |

| $t_{PWM\_MINON}$     | PWM Minimum ON-Time                                                    |                                                            |   |      | 20   |      | ns               |

| $V_{PWM\_FLOAT}$     | PWM Floating Voltage                                                   |                                                            | ● | 1.6  | 1.7  | 1.8  | V                |

## 電気的特性

●は、仕様規定された温度範囲に適用される仕様を示しています。それ以外の場合、特に指定のない限り、 $T_A = 25^\circ\text{C}$ 、 $V_{IN} = 12\text{V}$ 、 $P_{VCC} = V_{CC} = 5\text{V}$ です。

| SYMBOL                        | PARAMETER                                   | CONDITIONS                                                                                                                                             | MIN | TYP          | MAX | UNITS                      |                        |

|-------------------------------|---------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--------------|-----|----------------------------|------------------------|

| <b>I<sub>SNS</sub> Output</b> |                                             |                                                                                                                                                        |     |              |     |                            |                        |

| A <sub>IMON</sub>             | Current Sense Gain ( $I_{MON}/I_{OUT}$ )    | $V_{ISNS} = 1.5\text{V}$<br>$I_{OUT} = 5\text{A}$ to $25\text{A}$ , PWM = 0                                                                            |     | 8.5          | 10  | 11.5                       | $\mu\text{A}/\text{A}$ |

| I <sub>SNS</sub>              | Overall Accuracy                            | $I_{OUT} = 50\text{A}$ , $V_{ISNS} = 1.5\text{V}$ , PWM = 0, Accuracy at Trim<br>$I_{OUT} = -10\text{A}$ , $V_{ISNS} = 1.5\text{V}$ , PWM = 0 (Note 3) |     | $500 \pm 40$ |     |                            | $\mu\text{A}$          |

| V <sub>IMON</sub>             | IMON Operational Voltage Range              |                                                                                                                                                        | ●   | 1.2          | 2.0 | V                          |                        |

| <b>FLTB Output</b>            |                                             |                                                                                                                                                        |     |              |     |                            |                        |

| R <sub>FLTB-PD</sub>          | Fault Bar Open-Drain Pull-Down Resistance   | FLTB Low                                                                                                                                               |     |              | 1   | $\text{k}\Omega$           |                        |

| <b>TMON/FLT Output</b>        |                                             |                                                                                                                                                        |     |              |     |                            |                        |

| A <sub>TMON</sub>             | Thermal Monitor Gain                        | $0^\circ\text{C} < T_J < 150^\circ\text{C}$ (Note 3)                                                                                                   |     | 8            |     | $\text{mV}/^\circ\text{C}$ |                        |

| V <sub>TMON</sub>             | Thermal Monitor Voltage                     | $T_J = 0^\circ\text{C}$ (Note 3)<br>$T_J = 25^\circ\text{C}$<br>$T_J = 125^\circ\text{C}$ (Note 3)                                                     |     | 0.6          | 780 | 800                        | $\text{mV}$            |

| OTP                           | Overttemperature Protection Accuracy        | (Note 3)                                                                                                                                               |     | 150          |     | $^\circ\text{C}$           |                        |

| OTP_Hys                       | Overttemperature Hysteresis                 | (Note 3)                                                                                                                                               |     | 40           |     | $^\circ\text{C}$           |                        |

| I <sub>SOURCE_TMON</sub>      | Thermal Monitor Maximum Source Current      | $T_J = 25^\circ\text{C}$ , T <sub>MON</sub> Forced at 0V                                                                                               |     | 650          |     | $\mu\text{A}$              |                        |

| I <sub>SINK_TMON</sub>        | Thermal Monitor Maximum Sink Current        | $T_J = 25^\circ\text{C}$ , T <sub>MON</sub> Forced at 1.28V                                                                                            |     | 45           |     | $\mu\text{A}$              |                        |

| V <sub>Tdiode</sub>           | Tdiode Forward Voltage Drop                 | $T_J = 25^\circ\text{C}$ , $I_F = 0.1\text{mA}$                                                                                                        |     | 678          |     | $\text{mV}$                |                        |

|                               | Tdiode Voltage Drop Temperature Coefficient | $I_F = 0.1\text{mA}$ (Note 3)                                                                                                                          |     | -1.8         |     | $\text{mV}/^\circ\text{C}$ |                        |

| <b>SW Node</b>                |                                             |                                                                                                                                                        |     |              |     |                            |                        |

| V <sub>SW_Float</sub>         | SW Floating Voltage                         | $V_{IN} = 12\text{V}$ , RUN = 5V                                                                                                                       |     | 0.7          |     | V                          |                        |

| R <sub>SW-PGND</sub>          | SW Pull-Down Resistance                     |                                                                                                                                                        |     | 0.6          |     | $\text{k}\Omega$           |                        |

| <b>Overcurrent Limits</b>     |                                             |                                                                                                                                                        |     |              |     |                            |                        |

| I <sub>OCP</sub>              | Positive Overcurrent Threshold              | PWM = H                                                                                                                                                | 160 | 180          | 200 | A                          |                        |

| I <sub>NCP</sub>              | Negative Overcurrent Threshold              | PWM = L                                                                                                                                                |     | -90          |     | A                          |                        |

| t <sub>Blank_OC</sub>         | Positive Overcurrent Blanking Time          | PWM = H (Note 3)                                                                                                                                       |     | 22           |     | ns                         |                        |

| t <sub>Blank_NC</sub>         | Negative Overcurrent Blanking Time          | PWM = L (Note 3)                                                                                                                                       |     | 55           |     | ns                         |                        |

| I <sub>ZCP</sub>              | Positive Zero Current Threshold             |                                                                                                                                                        |     | 10           |     | A                          |                        |

| I <sub>ZCN</sub>              | Negative Zero Current Threshold             |                                                                                                                                                        |     | -16          |     | A                          |                        |

Note 1: 上記の絶対最大定格を超えるストレスを加えるとデバイスに恒久的な損傷を与えることがあります。デバイスを長時間絶対最大定格状態に置くと、デバイスの信頼性と寿命に影響を与えることがあります。

Note 2:LTC7051A-1は、 $-40^\circ\text{C}$ ～ $125^\circ\text{C}$ の動作ジャンクション温度範囲で仕様規定されています。ジャンクション温度が高い場合は動作寿命が低下します。ここに示す仕様に見合った最大周囲温度は、具体的な動作条件と、ボード・レイアウト、パッケージの熱インピーダンス定格値、およびその他の環境条件の組み合わせによって決まります。ジャンクション温度( $T_J$ ,  $^\circ\text{C}$ )は、次式を使って周囲温度( $T_A$ ,  $^\circ\text{C}$ )と消費電力( $P_D$ , ワット)から計算します。

$$T_J = T_A + (P_D \cdot \theta_{JA})$$

ここで、 $\theta_{JA}$ ( $^\circ\text{C/W}$ )はパッケージの熱抵抗です。

Note 3: このパラメータについてはテストは行われていませんが、設計により性能が確保されています。

Note 4: デバイスのピンに流れ込む電流はすべて正です。デバイスのピンから流れ出す電流はすべて負です。特に指定のない限り、全ての電圧はグラウンド基準です。

Note 5:LTC7051A-1は、一時的な過負荷状態からデバイスを保護することを目的とした過熱保護機能を内蔵しています。過熱保護機能が作動した場合、ジャンクション温度は $125^\circ\text{C}$ を超えていきます。仕様規定の最大動作ジャンクション温度より上の連続動作はデバイスの信頼性を損なう可能性があります。

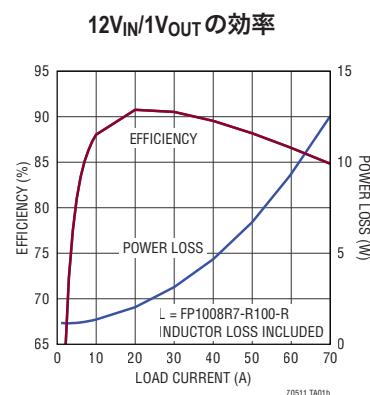

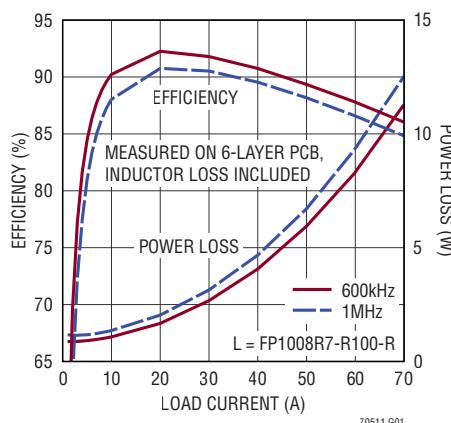

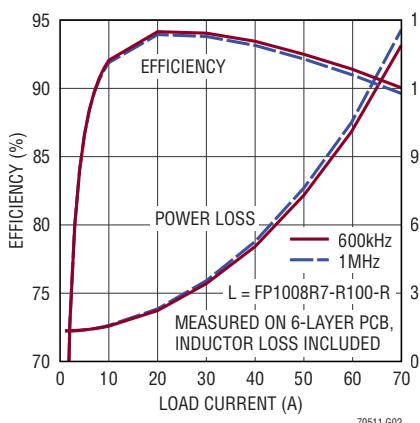

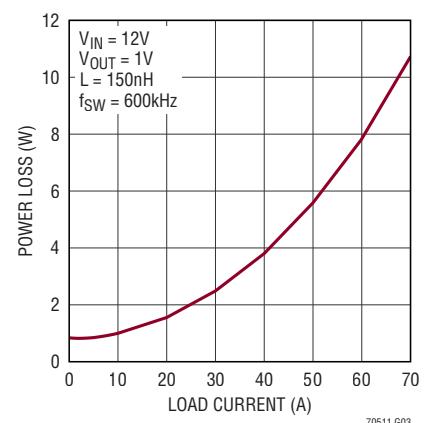

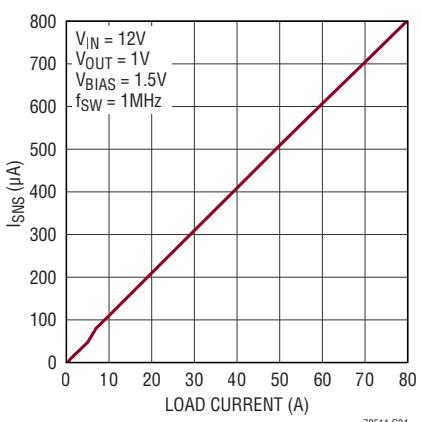

## 代表的な性能特性

特に指定のない限り、 $T_A = 25^\circ\text{C}$ 、 $V_{IN} = 12\text{V}$ 、 $P_{VCC} = V_{CC} = 5\text{V}$ 。12V<sub>IN</sub>/1V<sub>OUT</sub>の効率12V<sub>IN</sub>/1.8V<sub>OUT</sub>の効率

LTC7051-1の消費電力と負荷の関係

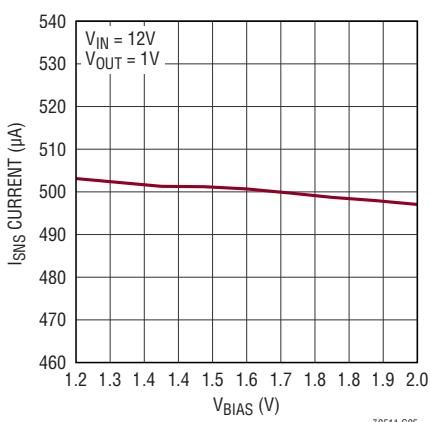

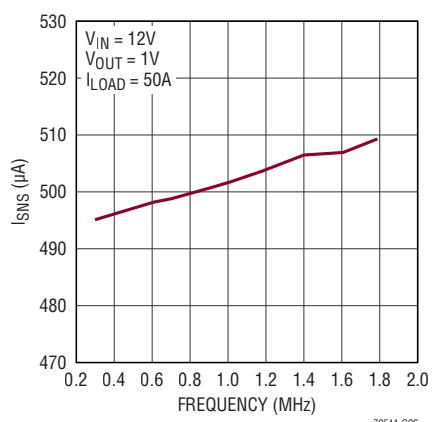

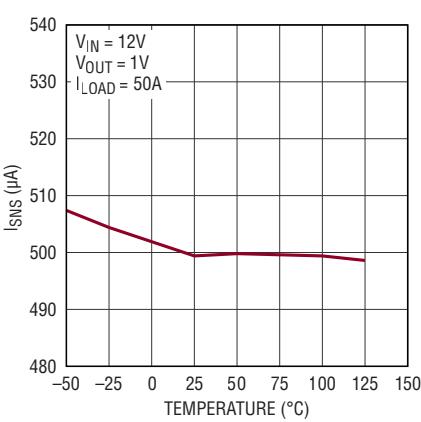

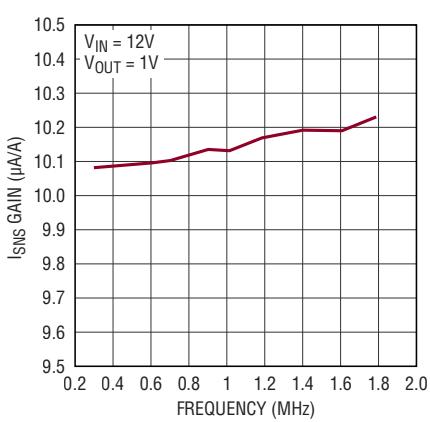

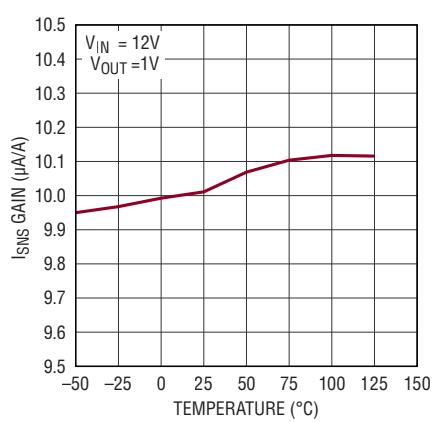

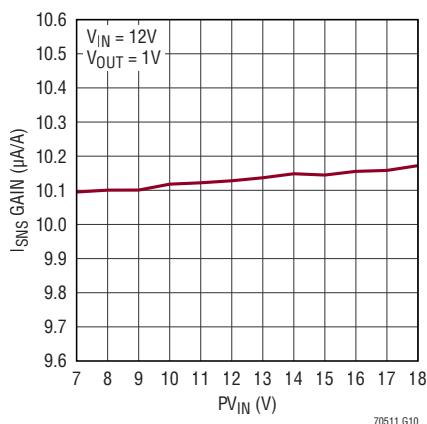

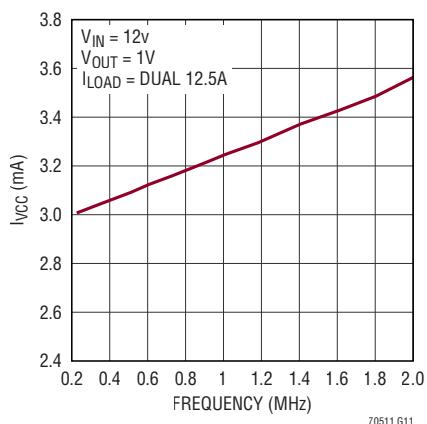

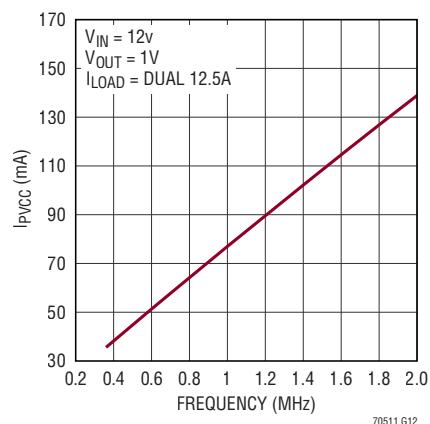

I<sub>SNS</sub>と負荷の関係I<sub>SNS</sub>電流とV<sub>BIAS</sub>の関係I<sub>SNS</sub>と周波数の関係I<sub>SNS</sub>と温度の関係I<sub>SNS</sub>ゲインと周波数の関係I<sub>SNS</sub>ゲインと温度の関係

## 代表的な性能特性

特に指定のない限り、 $T_A = 25^\circ\text{C}$ 、 $V_{IN} = 12\text{V}$ 、 $P_{VCC} = V_{CC} = 5\text{V}$ 。

$I_{SNS}$  ゲインと  $P_{VIN}$  の関係

$I_{VCC}$  と周波数の関係

$I_{PVCC}$  と周波数の関係

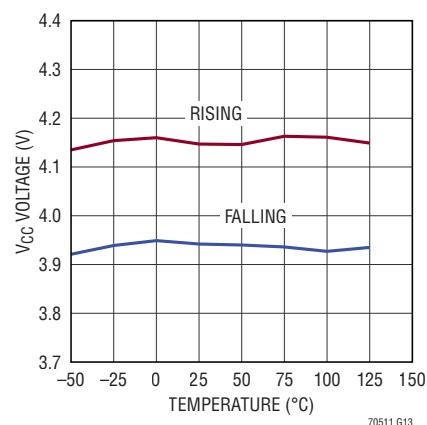

$V_{CC}$  UVLO と温度の関係

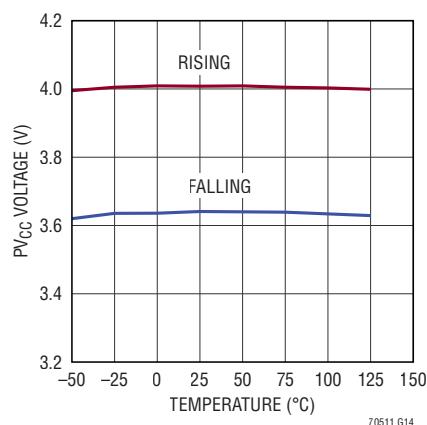

$P_{VCC}$  UVLO と温度の関係

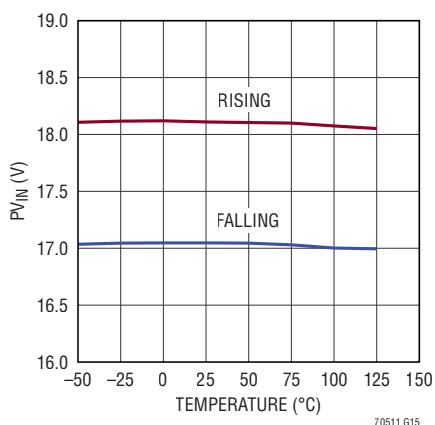

$P_{VIN}$  OVLO と温度の関係

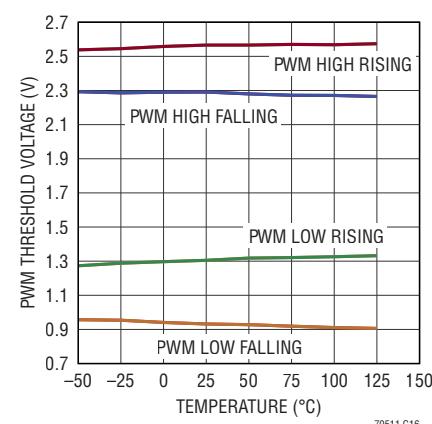

PWM 閾値と温度の関係

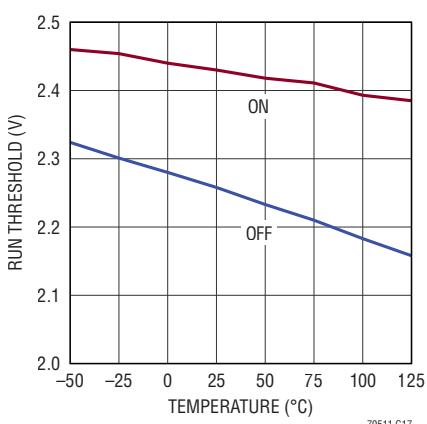

RUN 閾値と温度の関係

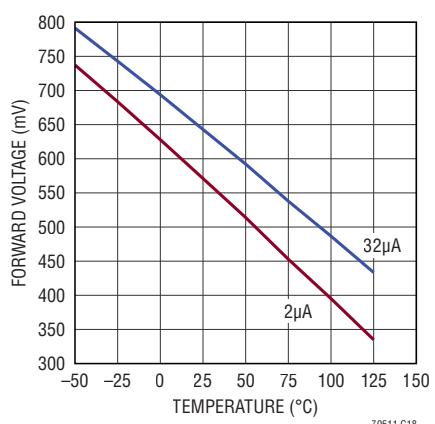

$I_{DIODE}$  順電圧と温度の関係

## 代表的な性能特性

特に指定のない限り、 $T_A = 25^\circ\text{C}$ 、 $V_{IN} = 12\text{V}$ 、 $PV_{CC} = V_{CC} = 5\text{V}$ 。

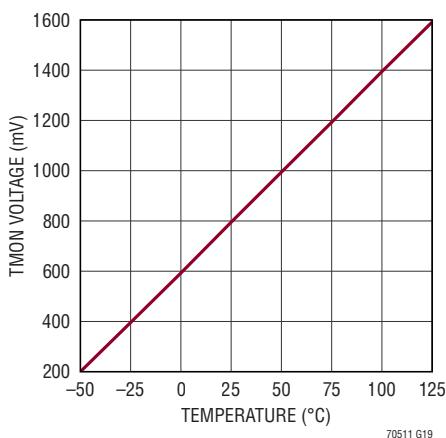

TMONと温度の関係

スイッチング時の立上がりエッジ

$PV_{IN} = 12\text{V}$

$I_{LOAD} = 60\text{A}$

FREQUENCY = 1MHz

## ピン機能

**FLT<sub>B</sub>**: フォルト・バー・ピン。このオープンドレイン・ピンは、チップやチャンネルがOCやOCNなどのフォルト状態になった場合に、プルダウンされます。

**I<sub>SNS</sub>**: 電流検出ピン。このピンは、SWノードの電流の1/100,000に相当する瞬時電流をソース(正の場合)またはシンク(負の場合)します。

**PGND**: 出力段グラウンド。このピンは、ロー・サイドNチャンネルFETを通じてSWに接続されています。ドライバへの給電も行います。

**PV<sub>CC</sub>**: 5Vドライバ電源。このピンは、ロー・サイドのゲート・ドライバに直接給電し、ハイ・サイドのゲート・ドライバには、SWを基準電圧とする内蔵ブートストラップ電源を介して給電します。このピンは、10μFのセラミック・コンデンサを使用しチップのできる限り近くでPGNDにバイパスします。

**PWM**: PWM入力ピン。RUNがハイに駆動されている場合、SWの公称動作はこのピンのハイ、ロー、高インピーダンスの各状態に追随します。公称3VのCMOSロジック・レベルは3V～5VのCMOS信号で駆動できます。高インピーダンス状態の場合、抵抗分圧器により電圧が1.7Vに維持されます。

**RUN**: 動作ピン。このピンがハイに駆動されるとチャンネルがイネーブルされます。RUNがローの場合はSWノードが高インピーダンス状態になります。

**SGND**: 回路のグラウンド。

**SW1、SW2**: 電力段スイッチ・ノード。電力段の出力であるこのノードは、ハイ・サイドNチャンネルFETを通じてV<sub>IN</sub>に接続され、ロー・サイドNチャンネルFETを通じてPGNDに接続されています。これらのSWピンはPCBで接続する必要があります。

**TDIO**: 温度ダイオード・ピン。このピンは、ダイ温度を測定するために使用するリファレンス・ダイオードを介してSGNDに接続されています。

**TMON/FLT**: 温度モニタ／フォルト・ピン。このピンは、SGNDを基準として、8mV/°Cのゲインで0°C～150°Cのダイ温度に対応して0.6V～1.8Vの電圧を発生します。150°Cを超える場合は、このピンはハイにプルアップされ、過熱(OT)フォルトを指示します。このピンの電流シンク能力は限定されています。そのため、複数の同様のピンを連結し、最高温度もしくは単一のOTフォルトを検出することができます。

**V<sub>CC</sub>**: 5V電源。このピンは、1μFのセラミック・コンデンサを使用しチップのできる限り近くでSGNDにバイパスします。

**V<sub>IN</sub>**: 出力段電源。このピンは、ハイ・サイドNチャンネルFETを通じてSWに接続されています。

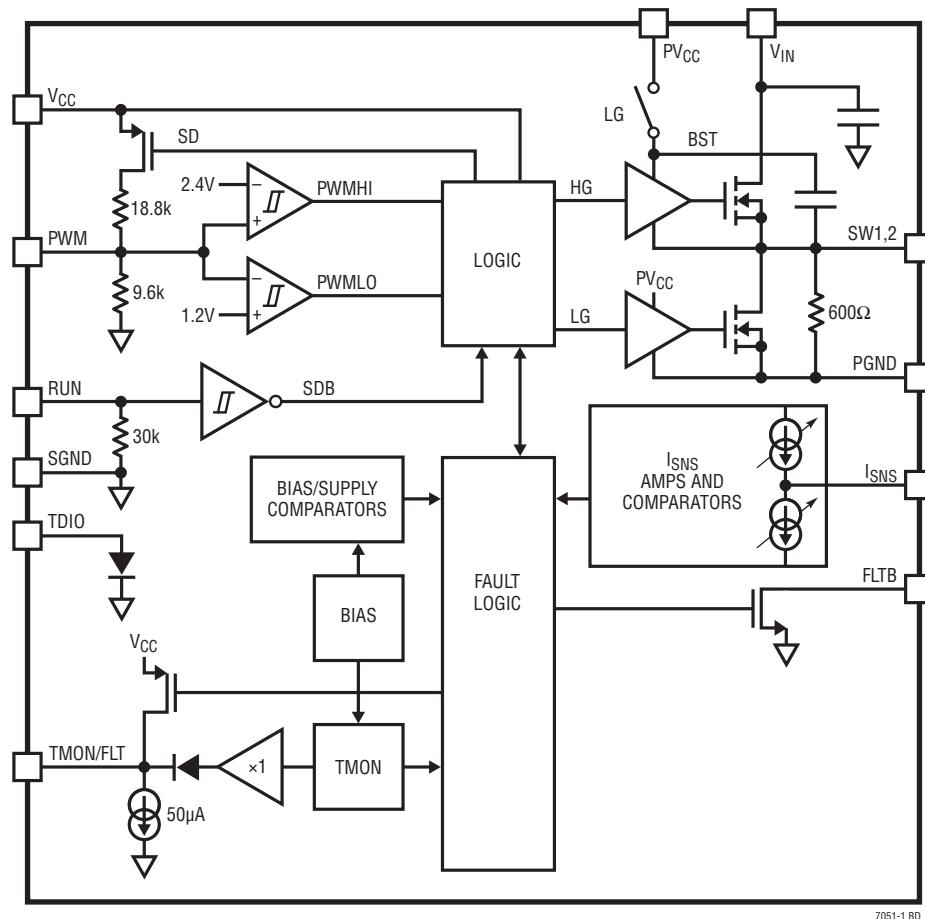

## ブロック図

7051-1 BD

## 動作

### メイン制御アーキテクチャ

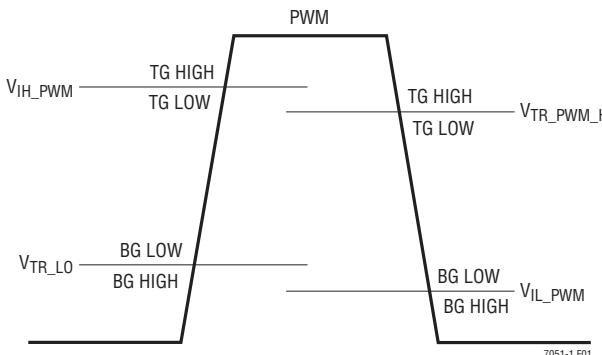

LTC7051-1は、DC/DC降圧アプリケーションを目的とした、シングル・チャンネルのドライバ内蔵ハーフブリッジ・パワーMOSFET段です。3.3Vまたは5VのPWM 3ステート出力を利用するコントローラと同期スイッチング・アーキテクチャで使用されるよう、設計されています。LTC7051-1の遷移閾値と3入力状態の間の関係を図1に示します。

図1.3ステート入力動作

通常動作の場合、PWMHIがハイ・サイドFETをオンにし、PWMLOがロー・サイドFETをオンにします。SWノードは通常10nsの遅延でPWMピンに追随します。SWがPGNDからV<sub>IN</sub>に増加するまで1ns未満のデッド・タイムがあり、SWの立ち下がり後は通常3nsのデッド・タイムがあります。

ハイ・サイドFETドライバは、内蔵のスイッチおよびコンデンサを介して内部BSTノードとSW間の電位で給電されます。これにより、通常のダイオードで実現できるよりも低いドロップアウトと高周波数動作が可能となります。

### 電流検出

リアルタイム電流検出アンプは、SW電流をスケールダウンした電流を供給します。PWMHIまたはPWMLOの間、I<sub>SNS</sub>ピンはその時のSW電流の1/100,000に相当する電流を、SWの電流方向に従いソースまたはシンクします。

関連する電流コンパレータは、ハイ・サイドFETの正の過電流(OC)状態およびロー・サイドFETの負の過電流(OCN)状態を示すフラグを発します。両FETのゼロ電流も関連する電流コンパレータで検出されます。

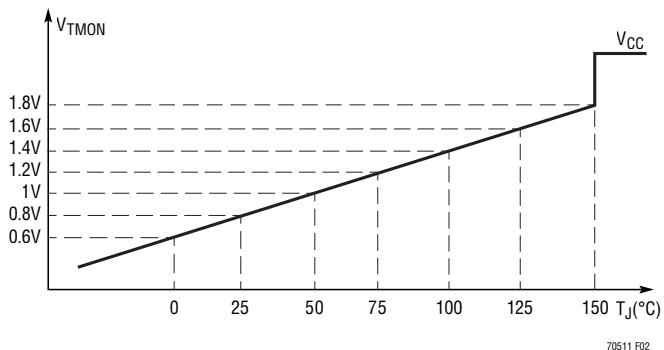

### 温度モニタと過熱フォルト

通常、TMONは0°C～150°Cのダイ温度に対応して0.6V～1.8Vの電圧を出力します。TMONの電圧は次式で計算されます。

$$V_{TMON} (V) = 800mV + (T_J (°C) - 25°C) \cdot (8mV/°C)$$

図2に、V<sub>TMON</sub>とダイ温度の関係を示します。

図2.V<sub>TMON</sub>とダイ温度の関係

TMONは、電流をソース可能でありながらシンク能力には制限があるようなアンプによって駆動されています。そのため、最高温度がレポートされる状態で複数のTMONピンを並列化することができます。過熱は150°C(代表値)でトリガれます。これによってTMONピンはハイにプルアップされ、V<sub>CC</sub>の値となります。過熱フォルトは、内部温度が閾値より40°C(代表値)低下するとクリアされます。

TDIOピンは内部でP/Nジャンクション・ダイオードのアノードに接続されており、ダイオードのカソードはSGNDに接続されています。これは、LTC3884-1などのコントローラのダイ温度の代替測定法を提供するもので、直接V<sub>BE</sub>法またはΔV<sub>BE</sub>法を使用してダイ温度を測定できます。

### 電圧フォルト状態

V<sub>CC</sub>またはPV<sub>CC</sub>がUVLOの場合、あるいは、V<sub>IN</sub>がOVLOの場合、SWはPWMに応答せず、トップFETとボトムFETのいずれもオフになります。

BSTとSW間の電圧がUVLOの場合は、PWMLOが供給されBSTとSW間の電圧が十分に再充電されるまで、SWはPWMHIに応答しません。

## 動作

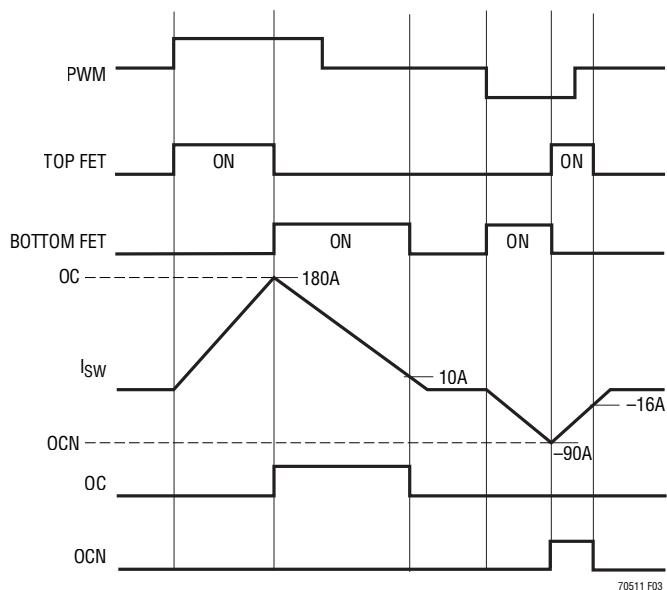

### 過電流フォルト状態

ハイ・サイドFETがオンの場合、その時点のSW電流(SWから供給される正味電流)が180Aを超えると、過電流(OC)コンパレータが動作し、内部OC状態をセットします。これが生じると、PWMのピン状態に関係なく、ハイ・サイドFETがオフになり、ロー・サイドFETがオンになります。これはSW電流が10Aに減少するまで続き、その時点でOC状態がリセットされます。通常のPWMHIとハイ・サイドFETの動作およびPWMLOとロー・サイドFETの動作は再開します。

ロー・サイドFETがオンの場合、その時点のSW電流(SWに供給される正味電流)が-90A未満になると、OCNコンパレータが動作します。これが生じると、PWMのピン状態に関係なく、ロー・サイドFETがオフになり、ハイ・サイドFETがオンになります。これはSW電流が-16Aに増加するまで続き、その時点でOCN状態がリセットされます。通常のPWMIとハイ・サイドFETの動作およびPWMLOとロー・サイドFETの動作は再開します。過電流状態のトリガとリセットの様子を図3に示します。

OCとOCNのいずれの状態でも、FLTBはプルダウンされます。

図3. 過電流状態

### アクティブ・ダイオード・モード

大電流(>10A)がV<sub>IN</sub>からSWに向けてトップFETを流れている状態でPWMがハイから高インピーダンス状態になると、トップFETがオフ、ボトムFETがオンになり、電流が徐々に低下し終わるまでこの状態を続けます。大電流( $\geq 16A$ )がSWからV<sub>IN</sub>に向けてトップFETを流れている状態でPWMがハイから高インピーダンス状態になると、トップFETは電流が徐々に低下し終わるまでオフにはなりません。

同様に、大電流( $\geq 16A$ )がSWからPGNDに向けてボトムFETを流れている状態でPWMがローから高インピーダンス状態になると、ボトムFETがオフ、トップFETがオンになり、電流が徐々に低下し終わるまで自由に流れます。大電流(>10A)がPGNDからSWに向けてボトムFETを流れている状態でPWMがハイから高インピーダンス状態になると、ボトムFETは電流が徐々に低下し終わるまでオフにはなりません。

## アプリケーション情報

### 電源シーケンス

LTC7051-1のV<sub>CC</sub>とPV<sub>CC</sub>は、V<sub>IN</sub>が加えられる前にバイアスしておき、V<sub>IN</sub>が消失してからパワーダウンする必要があります。RUNピンの電圧はV<sub>CC</sub>の電圧を超えることのないようにしてください。LTC7051-1のバイアスを正しく行い、LTC7051-1のRUNピンをプルアップしてからPWMコントローラをイネーブルするようにしてください。

### �ルト管理

LTC7051-1の�ルト管理とシャットダウン・モードを表1に示します。オープンドレイン出力FLTBピンをコントローラのRUNピンに接続すれば、BST・SW間低電圧�ルトの場合を除き、LTC7051-1が�ルト状態になった場合にコントローラが起動してコンバータを再始動させることのないようにできます。

表1. フォルト管理とシャットダウン・モードの概要

|                       | FLTB | RESPOND TO PWM                                 | TMON                         |

|-----------------------|------|------------------------------------------------|------------------------------|

| V <sub>IN</sub> OVLO  | Low  | No, Both FETs Off<br>When I <sub>SW</sub> = 0  | Report Temperature           |

| V <sub>CC</sub> UVLO  | Low  | No, Both FETs<br>Immediate Off                 | Floating                     |

| PV <sub>CC</sub> UVLO | Low  | No, Both FETs Off<br>When I <sub>SW</sub> = 0. | Report Temperature           |

| Positive OC           | Low  | No, Top FET<br>Immediate Off                   | Report Temperature           |

| Negative OC           | Low  | No, Bottom FET<br>Immediate Off                | Report Temperature           |

| Overtemperature       | Low  | Yes                                            | Pull Up to V <sub>CC</sub> . |

| BST-to-SW UV          | High | Ignore PWMHI                                   | Report Temperature           |

| RUN Shutdown          | Low  | No, Both FETs<br>Immediate Off                 | Floating                     |

### 電流検出および電流制限

I<sub>SNS</sub>では、SW電流の1/100,000の電流が流入／流出します。I<sub>SNS</sub>電流をリアルタイムのSW電流を反映する差動電圧信号に変換できるよう、コントローラの最大電流検出信号範囲に応じて適切な抵抗を選択してください。この抵抗は、電流シンク／ソース能力のある低インピーダンスのコモンモード電圧でバイアスする必要があります。最大の正電流および負電流時にI<sub>SNS</sub>ピンの電圧が仕様規定された範囲にあり、ゲイン(I<sub>SNS</sub>/I<sub>SW</sub>)が一定となるようにしてください。

LTC7051-1の一般的なアプリケーション回路の1つを、このデータシートの最初のページに示します。LTC7051-1は、高周波数で高電流電圧のレギュレータ・アプリケーション用に最適化されています。外付け部品の選択は負荷条件によって大きく左右されますが、最初にスイッチング周波数f<sub>SW</sub>とインダクタLを選択します。インダクタが決まれば、入力コンデンサ、C<sub>IN</sub>、出力コンデンサ、C<sub>OUT</sub>を選択することができます。I<sub>SNS</sub>の抵抗は、電流制限値を設定するために選択します。

### 周波数の選択

スイッチング周波数の選択は、効率と部品サイズの間の兼ね合いで決まります。低い周波数で動作させるとFETのスイッチング損失が減るので効率が改善されますが、出力リップル電圧を低く保つには、インダクタンスや容量の値を大きくする必要があります。スイッチング周波数を選択する場合、最大入力電圧時のハイ・サイドのオン時間がLTC7051-1の最小オン時間t<sub>ON(MIN)</sub>(LTC7051-1がトップFETをオンにできる最小の時間間隔)より長くなるようにしてください。この時間は、内部タイミング遅延、パワー段のタイミング遅延、トップFETをオンにするのに必要なゲート電荷によって決まります。デューティ・サイクルの低いアプリケーションではこの最小オン時間制限に近付く可能性があります(式1参照)。

$$t_{ON(MIN)} < \frac{V_{OUT}}{V_{IN} \cdot f_{SW}} \quad (1)$$

### 入力コンデンサ

LTC7051-1は、低インピーダンスの電源プレーンを介してV<sub>IN</sub>電源に接続する必要があります。セラミック入力コンデンサをパッケージのできるだけ近くに配置します。コンデンサのサイズと数は、以下のように計算されるリップル電流に伴う温度上昇に適したものにしてください。

降圧コンバータの場合、スイッチングのデューティ・サイクルは式2によって見積もることができます。

$$D = \frac{V_{OUT}}{V_{IN}} \quad (2)$$

## アプリケーション情報

各出力のインダクタのリップル電流を考えなければ、入力コンデンサのRMS電流は式3で概算できます。

$$I_{CIN(RMS)} = \frac{I_{OUT(MAX)}}{\eta} \cdot \sqrt{D \cdot (1-D)} \quad (3)$$

ここで $\eta$ は電源セクションの推定効率です。

### インダクタの選択

必要な入力電圧と出力電圧が与えられると、インダクタ値と動作周波数f<sub>Osc</sub>から直接、インダクタのピークtoピーク・リップル電流が決まります(式4)。

$$I_{RIPPLE} = \frac{V_{OUT}}{V_{IN}} \left( \frac{V_{IN} - V_{OUT}}{f_{SW} \cdot L} \right) \quad (4)$$

リップル電流が小さくなると、インダクタのコア損失、出力コンデンサのESR損失、および出力電圧リップルが減少します。このように、周波数が低くリップル電流が小さい場合に最も効率の高い動作が得られます。ただし、これを達成するには大きなインダクタが必要になります。妥当な出発点は、I<sub>OUT(MAX)</sub>の約40%のリップル電流を選択することです。最大リップル電流は、入力の電圧が最大のときに発生することに注意してください。リップル電流が仕様規定された最大値を超えることがないようにするために、インダクタは式5に従って選択します。

$$L \geq \left( \frac{V_{IN} - V_{OUT}}{f_{SW} \cdot I_{RIPPLE}} \right) \cdot \frac{V_{OUT}}{V_{IN}} \quad (5)$$

インダクタンスの値が定まつたら、インダクタの種類を選択する必要があります。インダクタ値が同じ場合、コア損失はコア・サイズではなく、選択したインダクタンスに大きく依存します。インダクタンスが増加すると、コア損失は減少します。しかし、インダクタンスを増加させるには巻き線数を増やす必要があるため、銅損失が増加します。フェライトを使用した設計ではコア損失が極めて小さく、高いスイッチング周波数に適しているため、設計目標を銅損失と飽和の防止に集中することができます。フェライト・コア材料の飽和はハードです。つまり、ピーク設計電流を超えるとインダクタンスが急激に低下します。その結果、インダクタのリップル電流が急

激に増加し、それに伴い出力電圧リップルも増加します。コアは決して飽和させないでください。

### 出力コンデンサ

LTC7051-1は、高周波数スイッチングおよび低出力電圧リップル・ノイズに適した設計となっています。C<sub>OUT</sub>で定義されるバルク出力コンデンサは、出力電圧リップルとトランジエントに関する条件を満たすために、等価直列抵抗(ESR)が十分に小さいものを選択します。C<sub>OUT</sub>には、低ESRのタンタル・コンデンサ、低ESRのポリマー・コンデンサ、またはセラミック・コンデンサを使用できます。1MHzの場合、出力容量の代表的な範囲は500μF～1000μFです。出力リップルまたは動的トランジエント・スパイクを更に削減する必要がある場合、設計時に出力フィルタの追加が必要となる場合があります。

### バイパス処理とグラウンディング

LTC7051-1では、スイッチングが高速(ナノ秒の単位)でAC電流が大量(アンペアの単位)のため、PV<sub>CC</sub>およびV<sub>CC</sub>の各電源に対してバイパス処理を適切に行うことが必要です。部品配置とPCBパターン配線に慎重さを欠くと、過度なリングやアンダーシュート／オーバーシュートが生じるおそれがあります。LTC7051-1から最高の性能を引き出すためには次の手順を実行します。

- V<sub>CC</sub>ピンとSGNDピンの間、および、PV<sub>CC</sub>ピンとPGNDピンの間にバイパス・コンデンサができるだけ近付けて取り付けます。パターンはできるだけ短くして、リード線のインダクタンスを低減します。

- 低インダクタンス、低インピーダンスのグランド・プレーンを使用して、グラウンドの電圧降下や浮遊容量を低減します。グラウンドの電圧降下があると信号の完全性が損なわれます。

- 電源／グラウンドの配線は慎重に設計します。大量の負荷スイッチング電流がどこから流れ、どこに流れていくかを把握します。入力ピンと出力パワー段のグラウンドのリターン・パスは別々にしてください。

- LTC7051-1のパッケージ裏面にある露出パッドを基板にハンダ処理してください。裏面の露出パッドと銅箔基板との間で熱的に十分な接触を確保できないと、熱抵抗がはるかに大きくなります。

## アプリケーション情報

### PCBレイアウト

LTC7051-1は電力密度が大きく、高速高周波数動作であるため、性能を最大限に発揮するには、PCBのレイアウトと構成が適切であることが重要です。

最低限、PCBは4層構造とし、少なくともトップ層とボトム層には2オンスの銅を使用してください。トップ層とボトム層では、V<sub>IN</sub>領域とPGND領域ができるだけ大きな連続面であることが必要です。少なくとも1つの内部層(できれば2番目の層)は、連続したPGND面である必要があります。

パッケージの露出パッド下には銅の充填ビアを使用し、トップPCB層とボトムPCB層を接続します。 $\theta_{JCbottom}$ は1°C/W未満です。銅充填ビア以外の場合、 $\theta_{JA}$ は大きく悪化します。

インダクタのパッドはパッケージにできるだけ近付けて配置してください。パターンはできるだけ短く幅広にします。可能ならば、SWのパターンは敏感なパターンに影響しないよう、2番目の層を共用します。

推奨PCBレイアウトを図4bに示します。

(b) Example PCB Layout

図4.

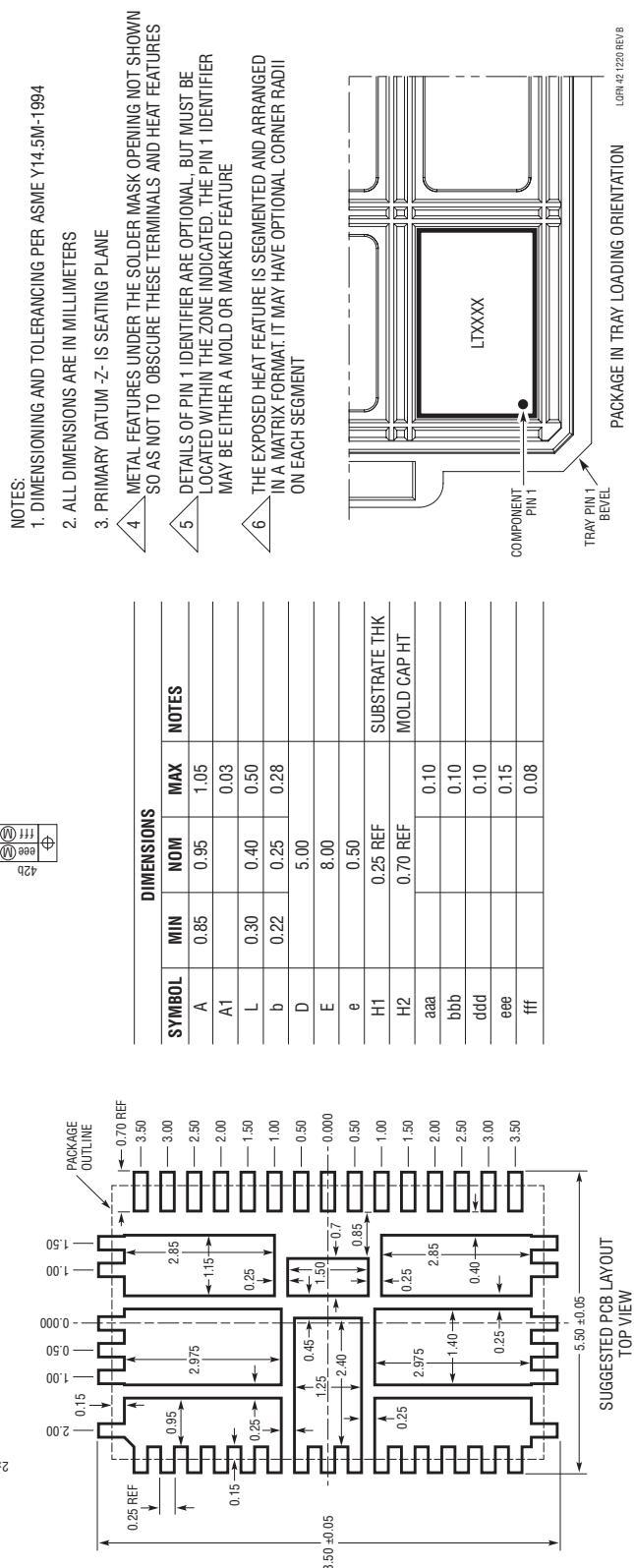

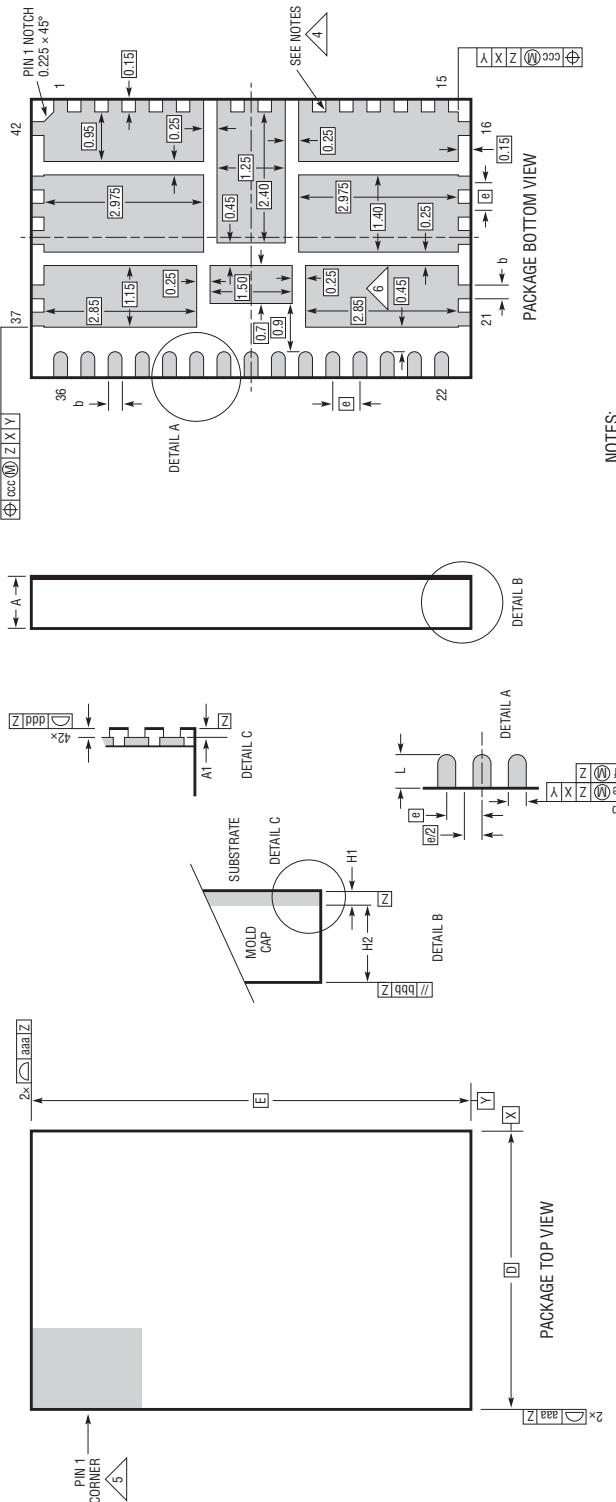

## パッケージの説明

**LQFN Package

42-Lead (5mm × 8mm × 0.95mm)**

(Reference LTC DWG # 05-08-1571 Rev B)

LTC7051-1

## 標準的應用例

関連製品

| 製品番号                  | 概要                                                               | 注釈                                                                                                                                                  |

|-----------------------|------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| LTC7051               | 5mm × 8mm LQFNで実現するSilentMOSスマート電力段                              | 140Aのピーク電流、Silent Switcher 2アーキテクチャ、最大14VのVIN、5mm × 8mm LQFNパッケージ                                                                                   |

| LTC7050               | 5mm × 8mm LQFNで実現するデュアルSilentMOSスマート電力段                          | チャンネルあたり70Aのピーク電流、Silent Switcher 2アーキテクチャ、最大14VのVIN、5mm × 8mm LQFNパッケージ                                                                            |

| LTC7050-1             | 5mm × 8mm LQFNで実現するデュアルSilentMOSスマート電力段                          | チャンネルあたり70Aのピーク電流、Silent Switcher 2アーキテクチャ、最大16VのVIN、5mm × 8mm LQFNパッケージ                                                                            |

| LTC3888/<br>LTC3888-1 | デジタル・パワー・システム・マネージメントを搭載したデュアル出力8相降圧DC/DCコントローラ                  | $4.5V \leq V_{IN} \leq 26.5V$ 、 $0.3V \leq V_{OUT} \leq 3.45V$ 、I <sup>2</sup> C/PMBus、プログラマブルなループ補償、5mm × 8mm QFN-52                               |

| LTC3884/<br>LTC3884-1 | サブmΩ DCR検出機能とデジタル・パワー・システム・マネージメント機能を搭載したデュアル出力PolyPhase降圧コントローラ | $4.5V \leq V_{IN} \leq 38V$ 、 $0.5V \leq V_{OUT} \leq 5.5V$ 、I <sup>2</sup> C/PMBus、プログラマブルなループ補償、5mm × 8mm QFN-52                                  |

| LTC7851               | 高精度の電流分担機能を備えたクワッド出力、マルチフェーズ、降圧電圧モードのDC/DCコントローラ                 | DrMOS、パワー・ブロック、または外付けドライバおよびMOSFETで動作、VIN範囲は外付け部品に依存、 $4.5V \leq V_{CC} \leq 5.5V$ 、 $0.6V \leq V_{OUT} \leq V_{CC} - 0.5V$                         |

| LTC7852/<br>LTC7852-1 | 電流モニタリング機能付きデュアル出力6相電流モード同期整流式降圧コントローラ                           | DrMOS、パワー・ブロックで動作、 $0.5V \leq V_{OUT} \leq 2V$ 、ヒップ・モード過電流保護、柔軟な位相構成                                                                                |

| LTC3861               | 高精度の電流分担機能を備えたデュアル出力、マルチフェーズ、降圧電圧モードのDC/DCコントローラ                 | パワー・ブロック、DrMOS、または外付けドライバ/MOSFETを組み合わせて動作、 $3V \leq V_{IN} \leq 24V$                                                                                |

| LTC3882/<br>LTC3882-1 | デジタル・パワー・システム・マネージメント機能を備えたデュアル出力マルチフェーズ降圧DC/DC電圧モード・コントローラ      | $3V \leq V_{IN} \leq 38V$ 、 $0.5V \leq V_{OUT1,2} \leq 5.25V$ 、 $\pm 0.5\%$ のV <sub>OUT</sub> 精度、I <sup>2</sup> C/PMBusインターフェース、DrMOSまたはパワー・ブロックを使用 |

| LTC3887/<br>LTC3887-1 | デジタル・パワー・システム・マネージメント機能を搭載したデュアル出力マルチフェーズ降圧DC/DCコントローラ、70ms起動    | $4.5V \leq V_{IN} \leq 24V$ 、 $0.5V \leq V_{OUT0,1} (\pm 0.5\%) \leq 5.5V$ 、70ms起動、I <sup>2</sup> C/PMBusインターフェース、-1バージョンではDrMOSまたはパワー・ブロックを使用      |