## 正誤表

この製品のデータシートに間違いがありましたので、お詫びして訂正いたします。

この正誤表は、2020年12月9日現在、アナログ・デバイセズ株式会社で確認した誤りを記したものです。

なお、英語のデータシート改版時に、これらの誤りが訂正される場合があります。

正誤表作成年月日：2020年12月9日

製品名：LTC4372/LTC4373

対象となるデータシートのリビジョン(Rev)：Rev.0

訂正箇所：P.13 右の段

文章中の製品名に関し3か所の表記が「LTC4372/LTC4372」となっておりますが、正しくは「LTC4372/LTC4373」となります。

**アナログ・デバイセズ株式会社**

|                                                                         |                                                                          |

|-------------------------------------------------------------------------|--------------------------------------------------------------------------|

| 本社／〒105-6891 東京都港区海岸1-16-1<br>ニュービア竹芝サウスタワービル 10F<br>電話 03 (5402) 8200  | 大阪営業所／〒532-0003 大阪府大阪市淀川区宮原3-5-36<br>新大阪トラストタワー 10F<br>電話 06 (6350) 6868 |

| 名古屋営業所／〒451-6038 愛知県名古屋市西区牛島6-1<br>名古屋ルーセントタワー 40F<br>電話 052 (569) 6300 |                                                                          |

# 自己消費電流の少ない理想ダイオード・コントローラ

## 特長

- パワー・ショットキー・ダイオードを置き換えることにより消費電力を低減

- 低自己消費電流:動作時5 $\mu$ A、シャットダウン時0.5 $\mu$ A

- 広い動作電圧範囲:2.5V ~ 80V

- -28Vまでの逆電源保護

- ハイサイド外付けNチャンネルMOSFETの駆動

- バックツーバックMOSFETを駆動して突入電流の制御と負荷の切替えに対応

- 1.5 $\mu$ s以内の高速逆電流ターンオフ

- 8ピンMSOPパッケージおよび3mm×3mm DFNパッケージ

## アプリケーション

- 自動車のバッテリ保護

- 冗長電源

- 携帯型計測器

- 太陽光電池式システム

- 環境発電(エナジー・ハーベスト)アプリケーション

- 電源電圧の保持

## 概要

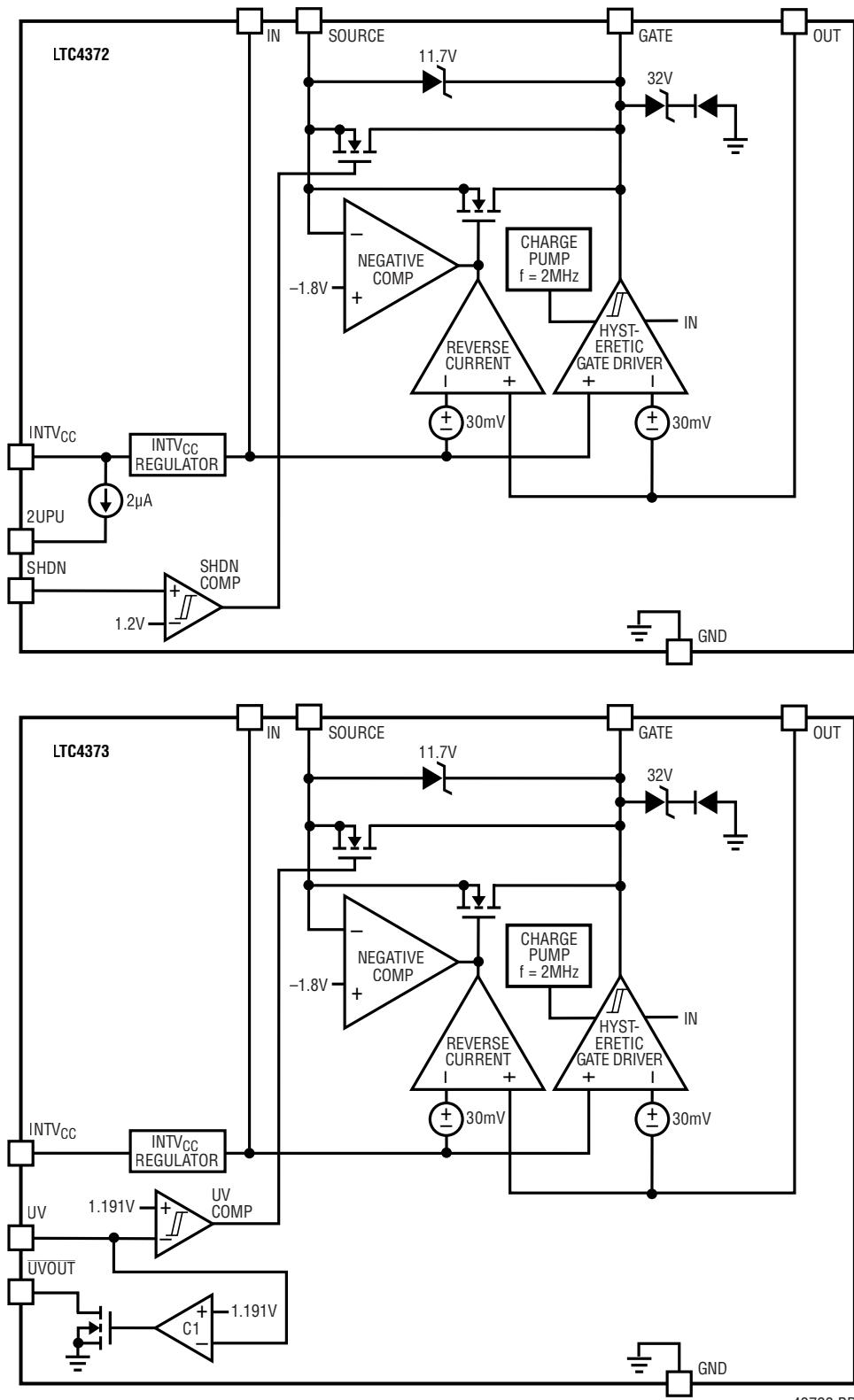

LTC<sup>®</sup>4372/LTC4373は、外付けのNチャンネルMOSFETを駆動してショットキー・ダイオードを置き換える正の高電圧理想ダイオード・コントローラです。MOSFET両端の順方向電圧降下を制御して、軽負荷時であっても、ある経路から別の経路へ電流を確実に供給または転送します。

5 $\mu$ Aの動作電流により、断続的負荷のアプリケーションや常時オンのバックアップ電源に対して高い効率を実現します。電源が故障した場合や短絡した場合は、高速ターンオフによって逆方向電流トランジエントが最小限に抑えられます。LTC4372/LTC4373は、バックツーバックのNチャンネルMOSFETを制御して、突入電流制御や負荷の切替えに対応します。

LTC4372のシャットダウン機能により、自己消費電流は0.5 $\mu$ Aまで減少します。LTC4373のUVピンは低電圧モニタリング機能を備えているのに対して、UVOUTピンにはヒステリシスの調整機能やステータス情報の出力機能があります。低電圧時に、バックツーバックMOSFETは遮断され、自己消費電流は0.5 $\mu$ Aまで減少します。

全ての登録商標および商標の所有権は、それぞれの所有者に帰属します。

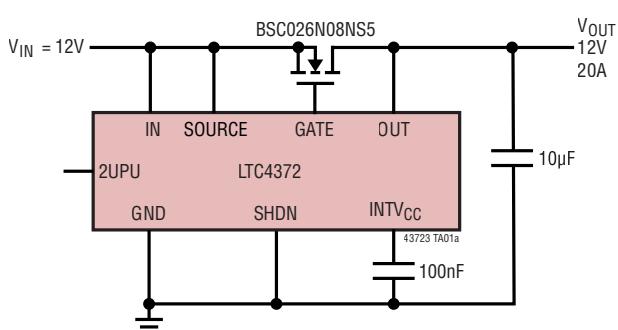

## 標準的応用例

### 12V、20Aバッテリ逆接続保護

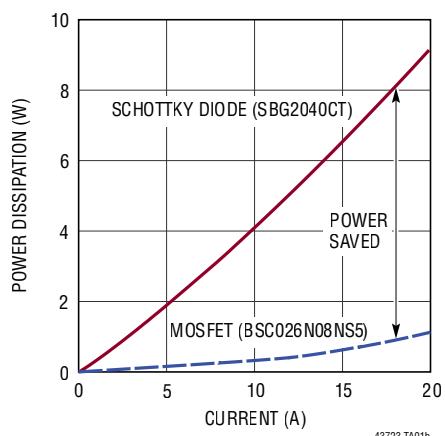

### 消費電力と負荷電流

## 絶対最大定格

(Note 1, 2)

|                                    |              |

|------------------------------------|--------------|

| IN, SOURCE                         | -28V ~ 100V  |

| OUT                                | -2V ~ 100V   |

| IN - OUT 間                         | -100V ~ 100V |

| IN - SOURCE 間                      | -1V ~ 100V   |

| SOURCE - OUT 間                     | -100V ~ 100V |

| GATE - SOURCE 間 (Note 3)           | -0.3V ~ 10V  |

| SHDN, UV, 2UPU, $\overline{UVOUT}$ | -0.3V ~ 100V |

| INTV <sub>CC</sub>                 | -0.3V ~ 6V   |

## 動作周囲温度範囲

|                    |               |

|--------------------|---------------|

| LTC4372C, LTC4373C | 0°C ~ 70°C    |

| LTC4372I, LTC4373I | -40°C ~ 85°C  |

| LTC4372H, LTC4373H | -40°C ~ 125°C |

| 保存温度範囲             | -65°C ~ 150°C |

| ピン温度 (ハンダ処理、10秒)   |               |

| MSOP パッケージ         | 300°C         |

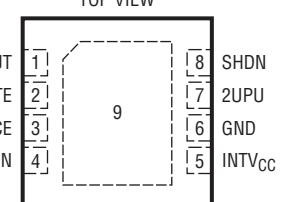

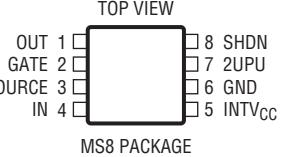

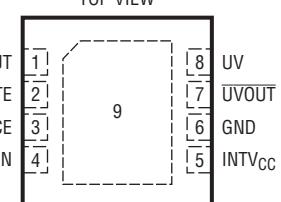

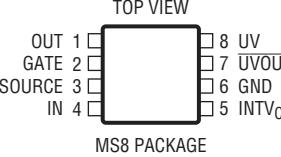

## ピン配置

|                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                               |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LTC4372                                                                                                                                                                                                                                                                                                                                                                                                                        | LTC4372                                                                                                                                                                                                                                                                                                                                                       |

|  <p>TOP VIEW</p> <p>OUT 1<br/>GATE 2<br/>SOURCE 3<br/>IN 4<br/>INTV<sub>CC</sub> 5<br/>GND 6<br/>2UPU 7<br/>SHDN 8<br/>PIN 9</p> <p>DD PACKAGE<br/>8-LEAD (3mm x 3mm) PLASTIC DFN<br/><math>T_{JMAX} = 150^\circ\text{C}</math>, <math>\theta_{JA} = 43^\circ\text{C/W}</math><br/>EXPOSED PAD (PIN 9) PCB CONNECTION TO GND IS OPTIONAL</p> |  <p>TOP VIEW</p> <p>OUT 1<br/>GATE 2<br/>SOURCE 3<br/>IN 4<br/>INTV<sub>CC</sub> 5<br/>GND 6<br/>2UPU 7<br/>SHDN 8<br/>PIN 9</p> <p>MS8 PACKAGE<br/>8-LEAD PLASTIC MSOP<br/><math>T_{JMAX} = 150^\circ\text{C}</math>, <math>\theta_{JA} = 163^\circ\text{C/W}</math></p> |

| LTC4373                                                                                                                                                                                                                                                                                                                                                                                                                        | LTC4373                                                                                                                                                                                                                                                                                                                                                       |

|  <p>TOP VIEW</p> <p>OUT 1<br/>GATE 2<br/>SOURCE 3<br/>IN 4<br/>INTV<sub>CC</sub> 5<br/>GND 6<br/>UVOUT 7<br/>UV 8<br/>PIN 9</p> <p>DD PACKAGE<br/>8-LEAD (3mm x 3mm) PLASTIC DFN<br/><math>T_{JMAX} = 150^\circ\text{C}</math>, <math>\theta_{JA} = 43^\circ\text{C/W}</math><br/>EXPOSED PAD (PIN 9) PCB CONNECTION TO GND IS OPTIONAL</p> |  <p>TOP VIEW</p> <p>OUT 1<br/>GATE 2<br/>SOURCE 3<br/>IN 4<br/>INTV<sub>CC</sub> 5<br/>GND 6<br/>UVOUT 7<br/>UV 8<br/>PIN 9</p> <p>MS8 PACKAGE<br/>8-LEAD PLASTIC MSOP<br/><math>T_{JMAX} = 150^\circ\text{C}</math>, <math>\theta_{JA} = 163^\circ\text{C/W}</math></p>  |

## 発注情報

| チューブ            | テープ&リール           | 製品マーキング* | パッケージ                          | 温度範囲           |

|-----------------|-------------------|----------|--------------------------------|----------------|

| LTC4372CDD#PBF  | LTC4372CDD#TRPBF  | LHGR     | 8-Lead (3mm × 3mm) Plastic DFN | 0°C to 70°C    |

| LTC4372IDD#PBF  | LTC4372IDD#TRPBF  | LHGR     | 8-Lead (3mm × 3mm) Plastic DFN | -40°C to 85°C  |

| LTC4372HDD#PBF  | LTC4372HDD#TRPBF  | LHGR     | 8-Lead (3mm × 3mm) Plastic DFN | -40°C to 125°C |

| LTC4372CMS8#PBF | LTC4372CMS8#TRPBF | LTHGS    | 8-Lead Plastic MSOP            | 0°C to 70°C    |

| LTC4372IMS8#PBF | LTC4372IMS8#TRPBF | LTHGS    | 8-Lead Plastic MSOP            | -40°C to 85°C  |

| LTC4372HMS8#PBF | LTC4372HMS8#TRPBF | LTHGS    | 8-Lead Plastic MSOP            | -40°C to 125°C |

| LTC4373CDD#PBF  | LTC4373CDD#TRPBF  | LHMQ     | 8-Lead (3mm × 3mm) Plastic DFN | 0°C to 70°C    |

| LTC4373IDD#PBF  | LTC4373IDD#TRPBF  | LHMQ     | 8-Lead (3mm × 3mm) Plastic DFN | -40°C to 85°C  |

| LTC4373HDD#PBF  | LTC4373HDD#TRPBF  | LHMQ     | 8-Lead (3mm × 3mm) Plastic DFN | -40°C to 125°C |

| LTC4373CMS8#PBF | LTC4373CMS8#TRPBF | LTHMR    | 8-Lead Plastic MSOP            | 0°C to 70°C    |

| LTC4373IMS8#PBF | LTC4373IMS8#TRPBF | LTHMR    | 8-Lead Plastic MSOP            | -40°C to 85°C  |

| LTC4373HMS8#PBF | LTC4373HMS8#TRPBF | LTHMR    | 8-Lead Plastic MSOP            | -40°C to 125°C |

更に広い動作温度範囲で規定されるデバイスについては、弊社または弊社代理店にお問い合わせください。

テープ&リールの仕様。一部のパッケージは、指定された販売経路を通じて、#TRMPBFの接尾辞を付けた500個入りリールで提供しています。

## 電気的特性

●は全動作温度範囲での規格値を意味する。それ以外は  $T_A = 25^\circ\text{C}$  での値。注記がない限り、IN = SOURCE = 12V、SHDN = 0V、UV = 2V。

| SYMBOL                | PARAMETER                                    | CONDITIONS                                                                                                                                                              | MIN | TYP  | MAX  | UNITS         |               |

|-----------------------|----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|------|---------------|---------------|

| $V_{IN}$              | Input Supply Voltage Range                   |                                                                                                                                                                         | ●   | 2.5  | 80   | V             |               |

| $V_{IN(UVL)}$         | Input Supply Undervoltage Lockout            | IN Rising                                                                                                                                                               | ●   | 1.9  | 2.1  | 2.45          | V             |

| $\Delta V_{IN(HYST)}$ | Input Supply Undervoltage Lockout Hysteresis |                                                                                                                                                                         |     | 80   |      | mV            |               |

| $V_{INTVCC}$          | Internal Regulator Voltage                   | $ V_{INTVCC}  = 0 \text{ to } -10\mu\text{A}$                                                                                                                           | ●   | 2.5  | 3.5  | 4.5           | V             |

| $I_Q$                 | Total Supply Current                         | Diode Control: $I_{GATE} = -0.1\mu\text{A}$<br>Single or Back-to-Back MOSFETs (Note 4)<br>(C-Grade, I-Grade)<br>(H-Grade)                                               | ●   | 5    | 10   | $\mu\text{A}$ |               |

|                       |                                              |                                                                                                                                                                         | ●   | 5    | 20   | $\mu\text{A}$ |               |

|                       |                                              | Shutdown: SHDN = 2V, UV = 0V<br>Single MOSFET<br>Back-to-Back MOSFETs                                                                                                   | ●   | 3.5  | 10   | $\mu\text{A}$ |               |

|                       |                                              |                                                                                                                                                                         | ●   | 0.5  | 2.5  | $\mu\text{A}$ |               |

|                       |                                              | Reverse Current: $\Delta V_{SD} = -0.1\text{V}$ , IN = 12V<br>Single MOSFET<br>Back-to-Back MOSFETs                                                                     | ●   | 20   | 30   | $\mu\text{A}$ |               |

|                       |                                              |                                                                                                                                                                         | ●   | 10   | 20   | $\mu\text{A}$ |               |

| $I_{OUT}$             | OUT Current                                  | $ IN - OUT  = 4\text{V}$<br>$ IN - OUT  = -4\text{V}$                                                                                                                   | ●   | -0.5 | -10  | $\mu\text{A}$ |               |

| $I_{NEG}$             | IN + SOURCE Current During Reverse Battery   | IN = SOURCE = -24V, OUT = 24V                                                                                                                                           | ●   | -1   | -5   | mA            |               |

|                       | OUT Current During Reverse Battery           | IN = SOURCE = -24V, OUT = 24V                                                                                                                                           | ●   | 0.3  | 0.5  | mA            |               |

| $\Delta V_{SD(T)}$    | Source-Drain Threshold (IN-OUT)              | Low to High. Activates $I_{GATE(UP)}$                                                                                                                                   | ●   | 20   | 30   | 45            | mV            |

| $\Delta V_{GATE(H)}$  | Maximum GATE Drive (GATE-SOURCE)             | $IN \leq 5\text{V}$ , $\Delta V_{SD} = 0.1\text{V}$ , $I_{GATE} = 0, -1\mu\text{A}$<br>$IN > 5\text{V}$ , $\Delta V_{SD} = 0.1\text{V}$ , $I_{GATE} = 0, -1\mu\text{A}$ | ●   | 4.5  | 6.5  | 10            | V             |

|                       |                                              |                                                                                                                                                                         | ●   | 10   | 11.7 | 16            | V             |

| $I_{GATE(UP)}$        | GATE Pull-Up Current                         | $GATE = IN$ , $\Delta V_{SD} = 0.1\text{V}$                                                                                                                             | ●   | -15  | -20  | -25           | $\mu\text{A}$ |

## 電気的特性

●は全動作温度範囲での規格値を意味する。それ以外は  $T_A = 25^\circ\text{C}$  での値。注記がない限り、IN = SOURCE = 12V、SHDN = 0V、UV = 2V。

| SYMBOL                  | PARAMETER                             | CONDITIONS                                                                                                                                                                                                            | MIN         | TYP             | MAX             | UNITS           |               |

|-------------------------|---------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-----------------|-----------------|-----------------|---------------|

| $I_{\text{GATE(DOWN)}}$ | GATE Pull-Down Current                | Shutdown: SHDN = 2V, UV = 0V, $\Delta V_{\text{GATE}} = 5\text{V}$<br>Reverse Current: $\Delta V_{\text{SD}} = -0.1\text{V}$ , $\Delta V_{\text{GATE}} = 5\text{V}$<br>Reverse Battery: IN = SOURCE = -7V, GATE = -3V | ●<br>●<br>● | 0.5<br>70<br>70 | 1<br>130<br>130 | 3<br>230<br>230 | mA            |

| $V_{\text{GATE(NEG)}}$  | GND-GATE clamp                        | $I_{\text{GATE}} = 10\text{mA}$ (Note 3)                                                                                                                                                                              | ●           | -28             | -32             | -35             | V             |

| $V_{\text{SOURCE(TH)}}$ | Reverse SOURCE Threshold for GATE Off | GATE = 0V (Note 5)                                                                                                                                                                                                    | ●           | -0.9            | -1.8            | -2.7            | V             |

| $t_{\text{OFF}}$        | Gate Turn-Off Delay Time              | $\Delta V_{\text{SD}} = \text{Step } 0.1\text{V to } -0.8\text{V}$ , $C_{\text{GATE}} = 0\text{pF}$ , $\Delta V_{\text{GATE}} < 1\text{V}$                                                                            | ●           |                 | 0.5             | 1.5             | $\mu\text{s}$ |

| $t_{\text{ON}}$         | Gate Turn-On Delay Time               | IN = 12V, SOURCE = OUT = 0V, $\Delta V_{\text{GATE}} > 4.5\text{V}$ , $C_{\text{GATE}} = 0\text{pF}$ , SHDN = 2V to 0V, UV = 0V to 1.25V                                                                              | ●           | 100             | 500             | 1200            | $\mu\text{s}$ |

### LTC4372

|                         |                           |              |   |    |         |          |               |

|-------------------------|---------------------------|--------------|---|----|---------|----------|---------------|

| $I_{\text{2UPU}}$       | 2UPU Pull-Up Current      |              | ● | -1 | -2      | -3       | $\mu\text{A}$ |

| $V_{\text{SHDN}}$       | SHDN Threshold            | SHDN Falling | ● | 1  | 1.2     | 1.4      | V             |

| $V_{\text{SHDN(HYST)}}$ | SHDN Threshold Hysteresis |              | ● | 2  | 15      | 40       | mV            |

| $I_{\text{SHDN}}$       | SHDN Leakage Current      | SHDN = 1.2V  | ● |    | $\pm 1$ | $\pm 50$ | nA            |

### LTC4373

|                        |                                                              |                                                                                     |        |       |                    |                       |               |

|------------------------|--------------------------------------------------------------|-------------------------------------------------------------------------------------|--------|-------|--------------------|-----------------------|---------------|

| $V_{\text{UV}}$        | UV Threshold                                                 | UV Falling                                                                          | ●      | 1.174 | 1.191              | 1.208                 | V             |

| $V_{\text{UV(HYST)}}$  | UV Threshold Hysteresis                                      |                                                                                     | ●      | 2     | 15                 | 40                    | mV            |

| $I_{\text{UV(LK)}}$    | UV Leakage Current                                           | UV = 1.2V                                                                           | ●      |       | $\pm 1$            | $\pm 50$              | nA            |

| $I_{\text{UVOUT(LK)}}$ | $\text{UVOUT}^{\text{T}}$ Leakage Current                    | UV = 2V, $\text{UVOUT}^{\text{T}} = 1.2\text{V}$<br>(C-Grade, I-Grade)<br>(H-Grade) | ●<br>● |       | $\pm 1$<br>$\pm 1$ | $\pm 50$<br>$\pm 200$ | nA<br>nA      |

| $R_{\text{UVOUT}\#}$   | $\text{UVOUT}^{\text{T}}$ Output Low Resistance              | $I = 2\text{mA}$                                                                    | ●      |       | 140                | 500                   | $\Omega$      |

| $t_{\text{UV}}$        | Under Voltage Detect to $\text{UVOUT}^{\text{T}}$ Assert Low | UV = Step 1.25V to 1.1V                                                             | ●      | 10    | 50                 | 300                   | $\mu\text{s}$ |

**Note 1:** 絶対最大定格に記載された値を超えるストレスはデバイスに永続的損傷を与える可能性がある。また、長期にわたって絶対最大定格条件に曝すと、デバイスの信頼性と寿命に悪影響を与える可能性がある。

**Note 2:** デバイスのピンに流れ込む電流は全て正。デバイスのピンから流れ出す電流は全て負。注記がない限り、全ての電圧は GND を基準にしている。

**Note 3:** 内部クランプにより、GATE ピンは最小でも SOURCE ピンより 10V 高い電圧または GND ピンより 100V 高い電圧に制限される。もう 1 つの内部クランプにより、GATE ピンは最小でも GND より 28V 低い電圧に制限される。このピンをクランプ電圧より高い電圧に駆動すると、デバイスを損傷する恐れがある。

**Note 4:** 単一の MOSFET 構成をテストする場合、IN は SOURCE に接続される。バックツーバック MOSFET 構成をテストする場合、SOURCE は未接続のままになっている。

**Note 5:** SOURCE  $\leq -1.8\text{V}$  の条件を満たすと、GATE から SOURCE に 130mA のブルダウン電流が流れれる。内部クランプにより、GATE ピンは GND より最小でも 28V 低い電圧に制限される。SOURCE をクランプより高い電圧に駆動するとデバイスを損傷する恐れがある。

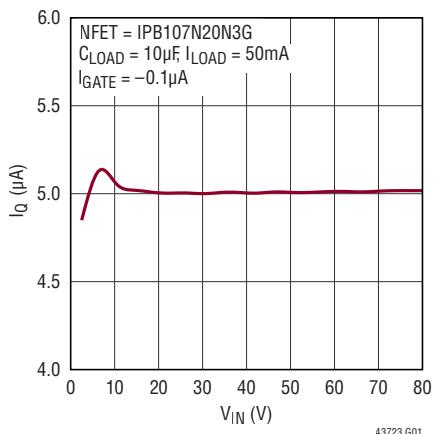

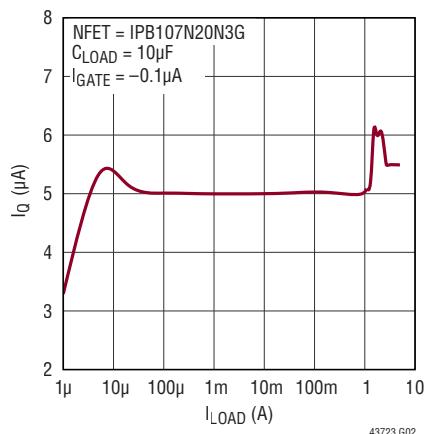

## 代表的な性能特性

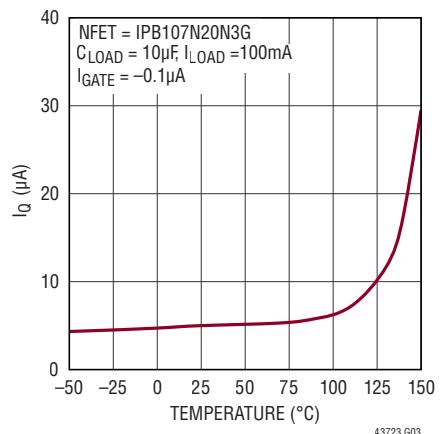

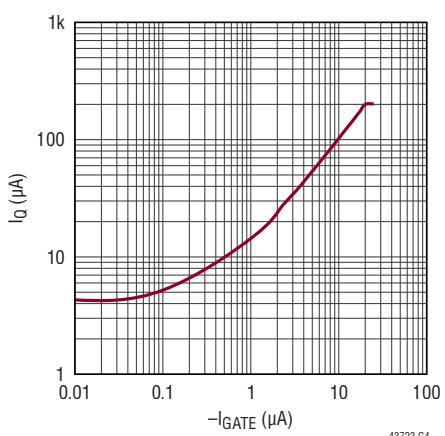

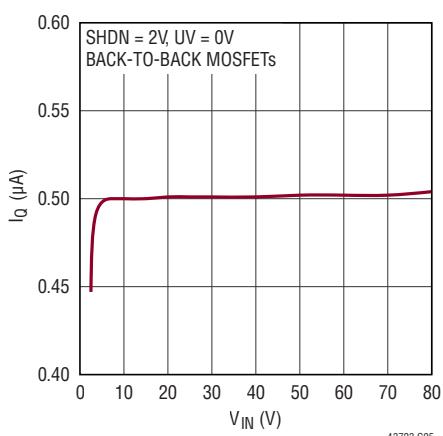

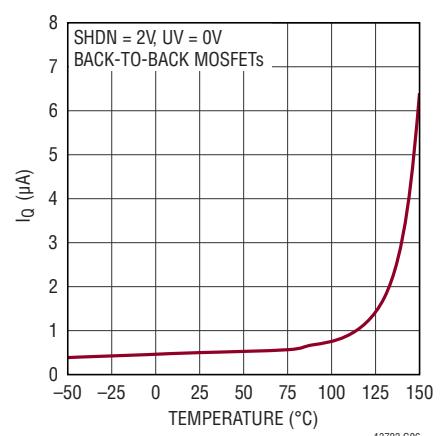

注記がない限り、 $T_A = 25^\circ\text{C}$ 、IN = SOURCE = 12V、SHDN = 0V、UV = 2V。

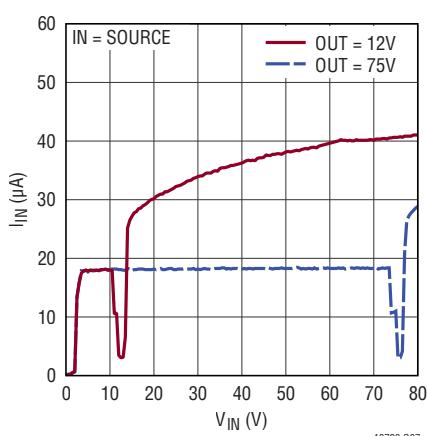

全電源電流と $V_{IN}$

全電源電流と負荷電流

全電源電流と温度

全電源電流と

GATEピンのリーク電流

全電源電流(シャットダウン)と $V_{IN}$

全電源電流(シャットダウン)と

温度

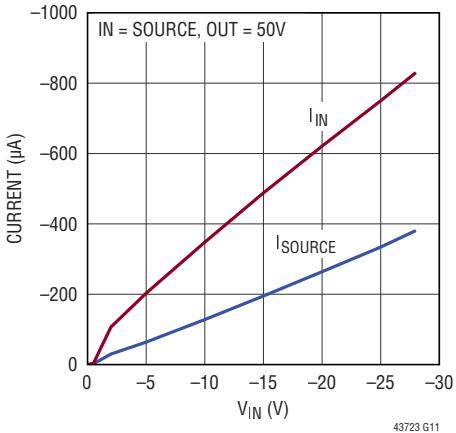

INピンの電流

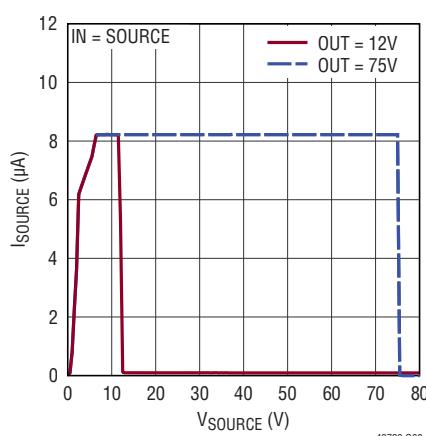

SOURCEピンの電流

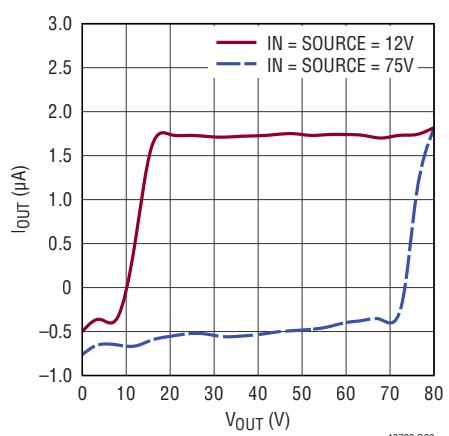

OUTピンの電流

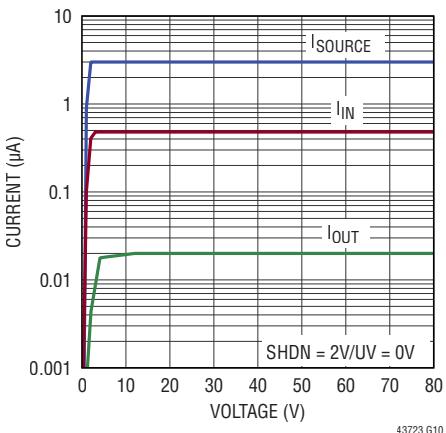

## 代表的な性能特性

注記がない限り、 $T_A = 25^\circ\text{C}$ 、 $\text{IN} = \text{SOURCE} = 12\text{V}$ 、 $\text{SHDN} = 0\text{V}$ 、 $\text{UV} = 2\text{V}$ 。

シャットダウン時のピン電流

負入力時のピン電流

負入力時のOUTピンの電流

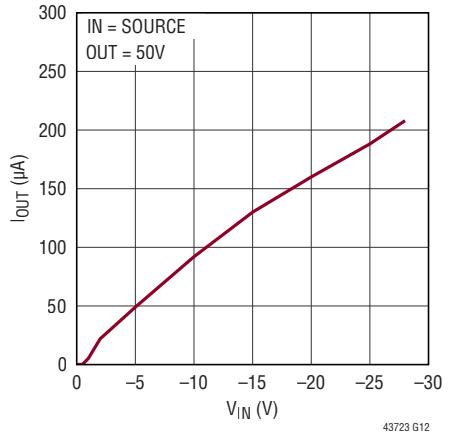

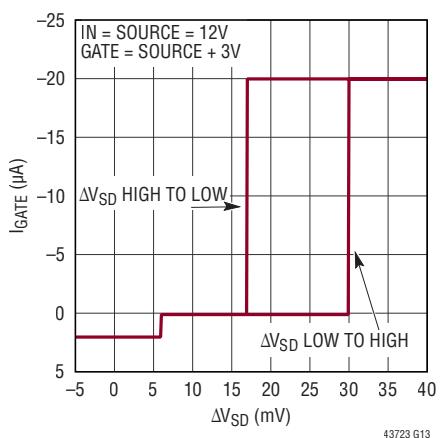

GATEピンの電流と

順方向電圧降下

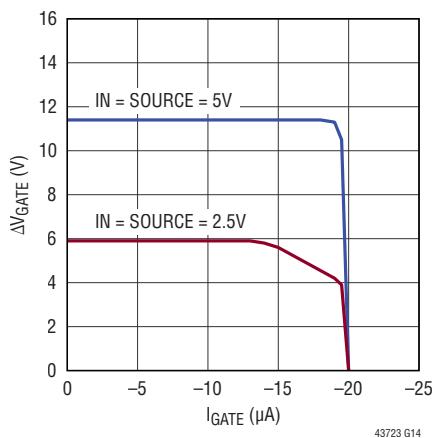

$\Delta V_{GATE}$ (平均値)と

GATEピンのリーク電流

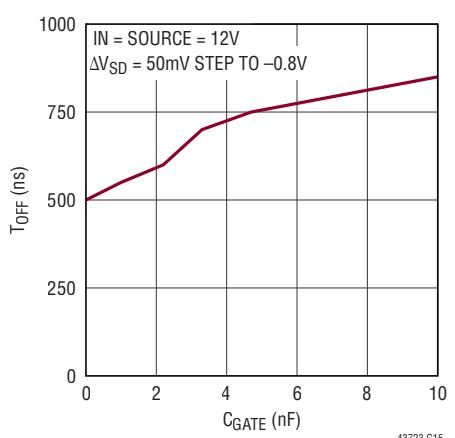

GATEピンのターンオフ時間と

GATEピンの容量

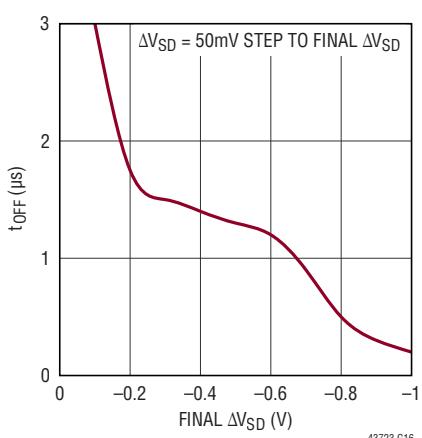

GATEピンのターンオフ時間と

順方向オーバードライブ

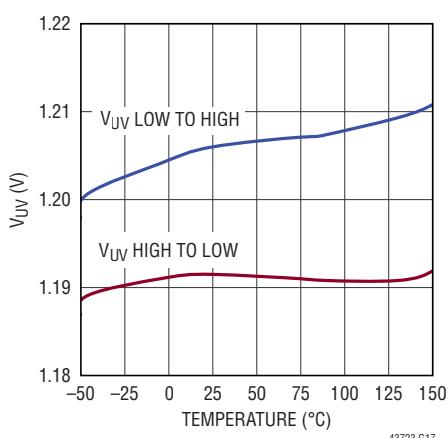

UVの閾値と温度

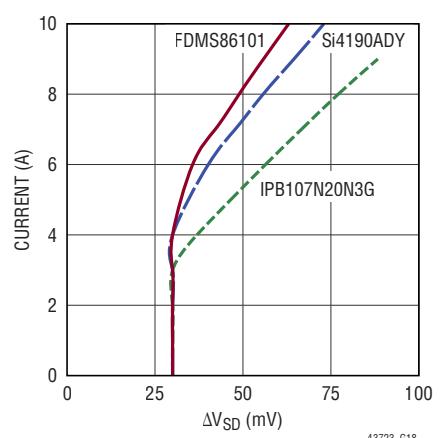

負荷電流とV<sub>FWD</sub>

## ピン機能

**露出パッド(DDパッケージのみ)**：露出パッドは開放のままにするか、デバイスのグラウンドに接続することができます。

**GATE**：MOSFETのゲート駆動出力。LTC4372/LTC4373は、パルス制御方式を使用してMOSFETのゲートを制御し、電圧降下を0mV～30mVの範囲に維持します。逆方向電流が流れると、高速プルダウン回路により、GATEピンは0.5μs以内にSOURCEピンに接続され、MOSFETはオフになります。

**GND**：デバイスのグラウンド。

**IN**：電圧検出ピンおよび電源電圧ピン。INピンは理想ダイオードのアノードです。このピンで検出された電圧を使用してMOSFETのゲートを制御し、順方向電圧のレギュレーションと逆電流のターンオフを行います。正電源の入力電圧範囲は、通常動作では2.5V～80Vです。また、逆バッテリ状態のときにGND電位より最大で28V低い電圧になっても、デバイスは損傷せずに済みます。

**INTV<sub>CC</sub>**：内部3V電源のデカップリング出力。このピンには0.1μF(以上)のコンデンサを接続します。このピンに接続できる外部負荷は10μA未満です。

**OUT**：MOSFETのドレイン電圧検出。OUTは理想ダイオードのカソードであり、複数のLTC4372/LTC4373を理想ダイオードORとして構成する場合の共通の出力です。NチャネルMOSFETのドレインに接続します。このピンで検出された電圧を使用してMOSFETのゲートを制御し、順方向

電圧のレギュレーションと逆電流のターンオフを行います。OUTは、INを使用できない(電圧がUVLOより低い)ときにMOSFETをオフに維持するための電源として使用します。このピンには10μF(以上)のコンデンサを接続します。

**SHDN (LTC4372)**：シャットダウン制御入力。SHDNピンの電圧を1.215Vより高くすることにより、LTC4372をシャットダウンして低電流モードにすることができます。使用しない場合はGNDに接続します。

**SOURCE**：MOSFETのソース接続。SOURCEピンはGATEの高速プルダウン回路の帰路です。このピンは外付けNチャネルMOSFETのソースにできるだけ近づけて接続してください。

**2UPU (LTC4372)**：2μAのプルアップ出力。このピンはINTV<sub>CC</sub>に接続する2μAのプルアップ電流出力を備えています。このピンをSHDNピンに接続して、マイクロコントローラのオープンドレイン出力によるLTC4372のオン／オフ制御を容易にすることができます。使用しない場合は、オープンのままにするか、INTV<sub>CC</sub>に接続してください。

**UVOUT (LTC4373)**：UVステータス出力。UVピンの電圧が1.191V(V<sub>UV</sub>)より低くなるとローになり、UVピンの電圧が1.191Vを超えると高インピーダンスになるオープンドレイン出力。UVOUTを使用してUVモニタのヒステリシスを調整できます。このピンは、使用しない場合、オープンのままにしてもGNDに接続してもかまいません。

**UV (LTC4373)**：低電圧検出入力。UVピンの電圧が1.191Vより低くなると、LTC4373は低電流のシャットダウン・モードになります。使用しない場合、INTV<sub>CC</sub>に接続します。

# LTC4372/LTC4373

## ブロック図

43723 BD

Rev.0

## 動作

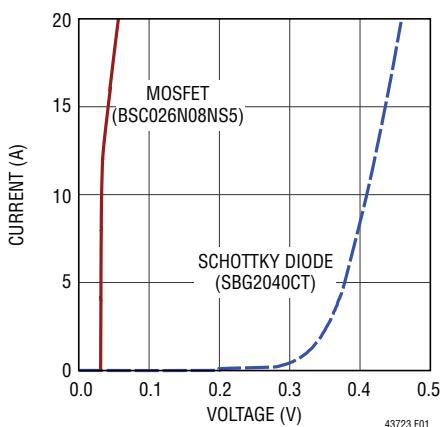

冗長電源をOR接続して電源の極性反転から保護するため、ブロッキング・ダイオードは一般に電源入力と直列に配置されます。LTC4372/LTC4373は、携帯機器やオートモーティブ・アプリケーションなどに組み込まれているダイオードを、理想ダイオードとして動作するNチャンネルMOSFETに置き換えます。順方向電圧降下は図1に示すように減少します。これは、ヘッドルームの狭い低入力電圧ですぐに評価される特長です。

図1. MOSFETとショットキー・ダイオードとの順方向電圧降下の比較

この低い順方向電圧降下の結果、1ページの標準的応用例の曲線で示すように、電力損失の劇的な減少が実用的なアプリケーションで達成されました。これは、パス・デバイスでの放熱条件を大きく低減することによる基板面積の大変な節減を表しています。これら2つの望ましい特性に加えて、LTC4372/LTC4373には低動作電流(5 $\mu$ A)や低シャットダウン電流(0.5 $\mu$ A)といった特長もあります。これにより、断続的な負荷や常時オンのスタンバイ・チャンネルに理想ダイオードを使用するアプリケーションで効率が向上するので、LTC4372/LTC4373は、携帯型計測器、オートモーティブ、および再生可能エネルギーの分野でのバッテリ駆動アプリケーションに適しています。

外付けMOSFETのソースはINピンとSOURCEピンに接続しますが、ドレインはOUTピンに接続します。LTC4372/LTC4373は、MOSFETのゲートを制御して、パス・トランジスタ両端の電圧降下を30mV未満に調整します。

入力短絡障害や負方向への電圧スパイクなど、入力電圧の急速な降下が発生した場合は、MOSFETに一時的に逆電流が流れます。この電流の供給源は、負荷容量と、ダイオードORアプリケーションで出力に電源を供給する他の電源またはバッテリです。逆電流コンパレータは、MOSFETを500ns以内にオフすることにより、この状態に対して素早く応答します。この高速ターンオフにより、逆電流が損傷を及ぼすレベルまで増加せずに済むため、出力バスに対する外乱が最小限に抑えられます。

IN、SOURCE、およびGATEは、-28Vまでの逆入力から保護されます。負電圧コンパレータは、SOURCEピンで負の入力電位を検出し、GATEピンをSOURCEピンに素早く接続してMOSFETをオフし、負荷を負入力から分離します。

LTC4372では、SHDNピンをハイにすると、MOSFETのゲート電圧は、1mAのプレダウン電流によりSOURCEピンの電圧まで低下します。バックツーバックMOSFET構成の場合は $I_Q$ が0.5 $\mu$ Aに減少し、3 $\mu$ Aのプレダウン電流がGNDに流れることにより、GATEピンはローに保持されます。SHDNピンがローになると、LTC4372はGATEピンの電圧を高くして外付けMOSFETをオンします。2UPUは、INTVCCに接続する2 $\mu$ Aのプルアップ電流出力を備えており、SHDNに接続して、マイクロコントローラのオープンドレイン出力によるオン/オフ制御を容易にすることができます。

LTC4373は、抵抗分圧器をUVピンに外付けすることにより、入力電圧をモニタできます。UVの電圧が1.191Vより低くなると、GATEは1mAのプレダウン電流によってSOURCEの電圧まで低下し、UVOUTはローになります。バックツーバックMOSFET構成の場合は $I_Q$ が0.5 $\mu$ Aに減少し、3 $\mu$ Aのプレダウン電流がGNDに流れることにより、GATEピンはローに保持されます。UVの電圧が回復して $V_{UV} + V_{UV(HYST)}$ より高くなると、LTC4373はGATEの電圧を高くして外付けMOSFETをオンします。UVとUVOUTの間にオプションの抵抗を接続して、 $V_{UV(HYST)}$ をオーバーライドする外部ヒステリシスを設定できます。

## アプリケーション情報

LTC4372/LTC4373は2.5V～80Vの範囲で動作し、-28V～100Vの絶対最大定格範囲に耐えられ、損傷は生じません。オートモーティブ・アプリケーションでは、LTC4372/LTC4373は負荷ダンプ、コールド・クランク、2バッテリ・ジャンプ・スタートの状況で動作可能であり、逆バッテリ接続に耐えられる上に負荷も保護します。

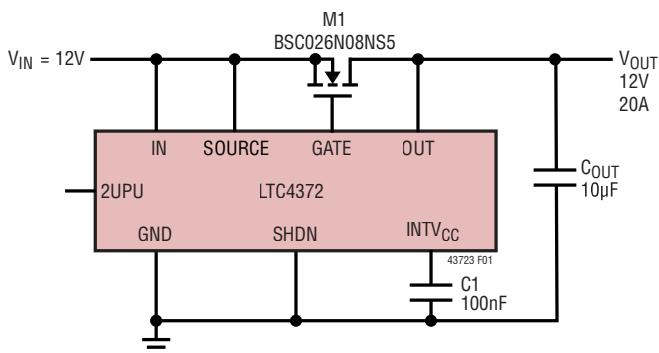

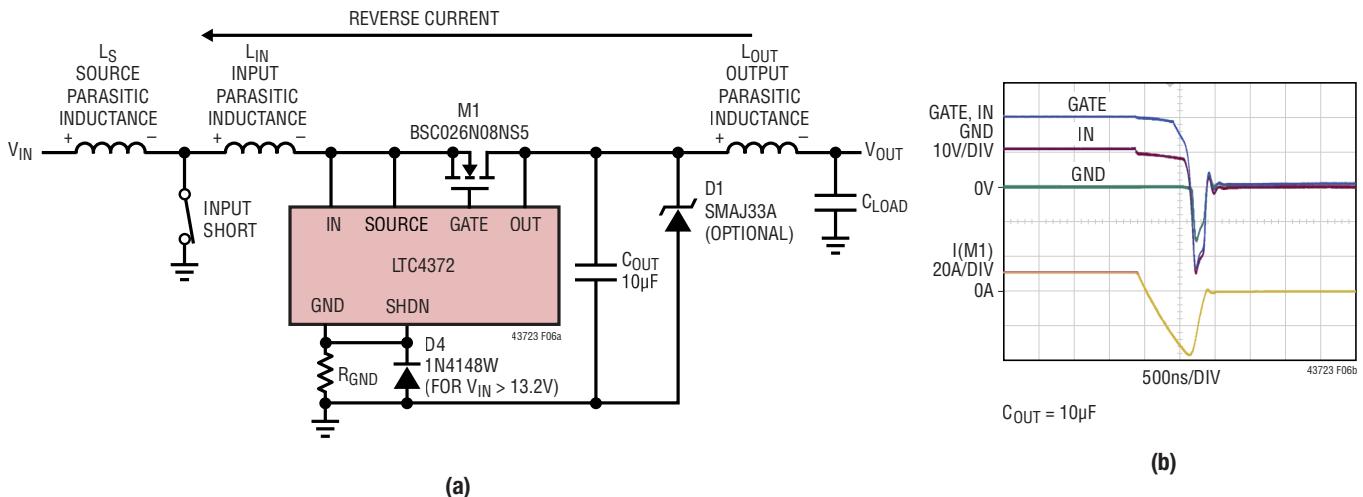

12V/20Aの理想ダイオード・アプリケーションを図2に示します。以降のセクションでは、電源投入、理想ダイオード動作、シャットダウンと、LTC4372/LTC4373が検出して対処する各種の障害について説明します。

図2. 逆入力保護を備えた12V/20A理想ダイオード

### 電源投入と理想ダイオードの動作

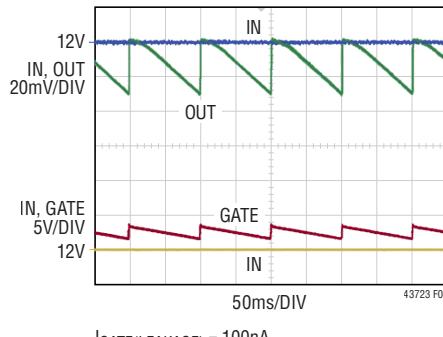

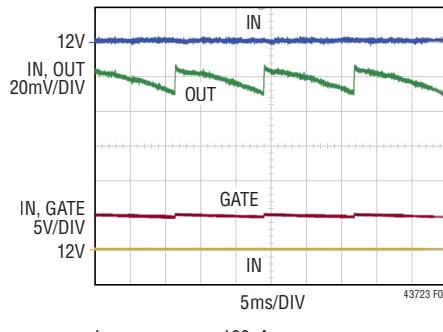

電源が投入されると、最初の負荷電流はMOSFET M1のボディ・ダイオードを流れます。INの電圧がUVLOレベルである2.1Vを超えるか、かつSHDNがローであるかUVがハイの場合、LTC4372/LTC4373は動作を開始します。内部チャージ・ポンプはGATEでの20µAのプルアップ電流をアサートして、MOSFETを導通させます。低電源電流を実現するため、LTC4372/LTC4373は、内部チャージ・ポンプが必ずしも常時オンではないパルス制御動作方式を採用しています。代わりに、チャージ・ポンプはリークによる電圧低下後、周期的に起動してGATEピンを再充電し、 $\Delta V_{SD}$ を30mV以下に維持します。このパルス制御により、安定したDC負荷の場合でもOUTに電圧リップルが発生します。このリップルの振幅は、ゲートのリーク、GATEピンの容量、負荷条件、およびOUTでのバイパス容量の大きさにより異なります。低負荷または無負荷の条件では、このリップルが30mV<sub>PK-PK</sub>まで増加することがあります。図2に示す回路の場合、超軽負荷条件( $I_{LOAD} = 1\mu A$ )でのOUTの代表的なリップルを図3に示します。

中程度のDC負荷では、リップル振幅は約10mV<sub>pk-pk</sub>です。図2に示す回路の場合、中程度の負荷条件( $I_{LOAD} = 2A$ )でのOUTの代表的なリップルを図4に示します。

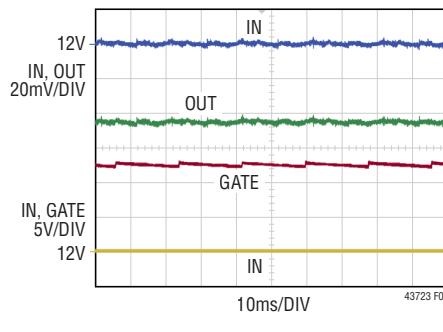

図2に示す回路の場合、 $I_{LOAD} = 16A$ でのOUTの代表的なリップルを図5に示します。

図3. 少量の $I_{LOAD} = 1\mu A$ での $\Delta V_{SD}$ のレギュレーション

図4. 中程度の $I_{LOAD} = 2A$ での $\Delta V_{SD}$ のレギュレーション

図5. 大量の $I_{LOAD} = 16A$ での $\Delta V_{GATE}$ のレギュレーション

## アプリケーション情報

負荷電流が増えるにつれて、GATEはますます高い電圧に駆動されるようになります。この状況は、 $\Delta V_{GATE}$ が、内部チャージ・ポンプが対応できる最大オーバードライブ電圧( $\Delta V_{GATE(H)}$ )に達するまで続きますが、 $\Delta V_{SD}$ は30mVより高いままであります。この状況では、内部チャージ・ポンプが周期的にオンして、GATEを必要に応じて再充電し、 $\Delta V_{GATE}$ を $\Delta V_{GATE(H)} \sim \Delta V_{GATE(H)} - 0.7V$ の範囲内に維持します。その結果、 $\Delta V_{SD}$ は $R_{DS(ON)} \cdot I_{LOAD}$ と等しくなります。 $\Delta V_{GATE}$ 上の0.7Vpk-pkのリップルはMOSFETの $R_{ON}$ にほとんど影響しないので、OUT上のリップルは小さくて済みます。

### 低い $I_Q$ 平均値の実現

GATEがハイのときダイオード制御モードでの $I_Q$ 平均値を低く抑えるため、LTC4372/LTC4373はチャージ・ポンプを周期的にオンすることによって動作します。チャージ・ポンプがスリープ・モードのとき、 $I_Q$ は3.5 $\mu A$ です。いったんチャージ・ポンプがオンして電流パルスをGATEに供給すると、 $I_Q$ は300 $\mu A$ まで増加します。 $I_Q$ の平均値はチャージ・ポンプがオンする頻度に依存し、このことはGATEのリーク電流、GATEの容量、OUTのバイパス容量、および $I_{LOAD}$ に影響されます。可能な最小の $I_Q$ 平均値を達成するには、GATEのリーク電流を最小限に抑えて、GATEの容量が中程度(>1nF)になるようにします。MOSFETのCGSがこの値を超えていない場合は、GATEとSOURCEの間に1nFのコンデンサを追加します。 $C_{LOAD}$ は負荷の近くに配置してもかまいませんが、OUTのバイパス容量は10 $\mu F$ 以上でESRとESLの小さい電解コンデンサまたはセラミック・コンデンサにして、MOSFET M1のドレイン・ピンの近くに配置することが必要です(図6a参照)。ダイオード制御モードでの $I_Q$ の平均値は、式1により概算できます。

$$\text{AVERAGE } I_Q = 3.5 + \frac{I_{GATE(LEAKAGE)}}{I_{GATE(UP)}} \cdot 300 \mu A \quad (1)$$

代表的な性能特性のセクションに、 $I_Q$ と $I_{GATE(LEAKAGE)}$ および $I_{LOAD}$ との関係を示します。

### MOSFETの選択

LTC4372/LTC4373は、NチャンネルMOSFETを駆動して負荷電流を導通させます。MOSFETの重要な特性は、ゲートの閾値電圧( $V_{GS(TH)}$ )、ドレイン-ソース間の最大電圧( $BV_{DSS}$ )、およびオン抵抗( $R_{DS(ON)}$ )です。

ゲート駆動回路は、2.5V～80Vの全動作電圧範囲で4.5Vロジック・レベルのMOSFETと互換性があります。電源電圧が5Vを超えるアプリケーションでは、閾値が10Vの標準的なMOSFETを使用できます。内部のクランプ回路により、ゲート駆動電圧はGATEとSOURCEの間の最大電圧である16Vに制限されます。

ドレイン-ソース間の許容最大電圧( $BV_{DSS}$ )は、電源電圧より高くなればなりません。入力が接地されると、MOSFETの両端(ドレイン-ソース間)に全電源電圧が加わります。逆バッテリが生じる可能性があり、充電済みコンデンサ、バッテリ、または電源によって出力電圧が保持される場合は、入力電圧と出力電圧の合計がMOSFETの両端に加わるため、 $BV_{DSS}$ は $V_{OUT} + |V_{IN}|$ より高い必要があります。

MOSFETのオン抵抗( $R_{DS(ON)}$ )は、重負荷時には順方向電圧降下および消費電力に直接影響します。目的の順方向電圧降下( $V_{FWD}$ )は、消費電力を低減するため、ダイオードの順方向電圧降下より小さくします。50mVが適切な初期値です。LTC4372/LTC4373では、MOSFETの両端で30mV以上降下するので、費やすことができる $R_{DS(ON)}$ は非常に小さくなります。式2を使用してMOSFETを選択します。

$$R_{DS(ON)} < \frac{V_{FWD}}{I_{LOAD}} \quad (2)$$

得られる消費電力を式3に示します。

$$P_d = I_{LOAD}^2 \cdot R_{DS(ON)} \quad (3)$$

### 入力短絡障害

逆電流が流れる原因となる入力短絡が発生する状況は様々です。いくつか例を挙げると、PCBのパターンが誤って短絡した例や、上流の電源のバイパス・コンデンサが故障して短絡した例などがあります。LTC4372/LTC4373は、外付けのMOSFETを使用して堅牢な入力短絡保護機能を追加しますが、その際、大型のTVSクランプやコンデンサは使用しません。

図6aは、低インピーダンスの入力短絡をスイッチによってモデル化したものです。短絡スイッチが閉じると、 $L_{IN}$ 、 $L_{OUT}$ 、およびM1を表示の方向に流れる逆電流が発生します。LTC4372/LTC4373は逆電流を迅速に検出し、130mAの内部プルダウン電流をGATEとSOURCEの間に導通させてM1をオフにします。 $L_{IN}$ と $L_{OUT}$ を流れる逆電流が遮断され

## アプリケーション情報

図6. 逆回復により、IN、SOURCE、およびOUTに誘導性スパイクが発生する。寄生インダクタンスの両端には誘導性スパイクの極性を示す

ることにより、INには負のスパイクが、OUTには正のスパイクが発生します。OUTでは、 $L_{OUT}$ に起因する正方向スパイクを $C_{OUT}$ がクランプして、 $I(L_{OUT})$ をゼロまで整流します。INでは、GND – GATE間の内部クランプがアサートしてGATEをGNDより32V低い電圧に保持することにより、IN/SOURCEの電圧がGATEの電圧より低くなるとM1はオフに戻ります。 $L_{IN}$ を流れる電流はM1によって $C_{OUT}$ に分流され、図6bの短絡過渡応答で示すように、ゼロになるまで安全に整流されます。これらの過渡電流によってOUTに生じた $\Delta V$ が大きすぎる場合は、 $C_{OUT}$ の容量を増やすか、TVS D1を追加します。

信号源抵抗の低い電源で $V_{IN}$ を駆動した場合、短絡時には $L_S$ に大量の電流が流れます。短絡が解消されると、 $I(L_S)$ がM1のボディ・ダイオードによって $C_{OUT}$ に達して保持されるまで、この電流によってINとSOURCEに正のスパイクが発生します。SOURCEでのこの高速のスルーレートにより、大量のシートスルーレートによって SOURCEからGNDへ流れ込むため、損傷が生じる可能性があります。外付けの $R_{GND}$ を追加すると、この電流は安全なレベルに制限されます。

INの電圧が13.2V以下のアプリケーションでは、 $R_{GND}$ として0805サイズの100Ωを使用すれば十分です。INの電圧が13.2Vより高いアプリケーションでは、より大きな値の $R_{GND}$ (1k)が必要です。GND – GATE間のクランプがオンしたときにGNDの電位が過剰に負にならないように、1N4148Wのような高速回復ダイオードを1kの $R_{GND}$ と並列に接続します。

SOURCEを $V_{IN}$ で駆動しないバックツーバックMOSFETアプリケーションでは、 $R_{GND}$ は必要ありません。信号源インピーダンスの大きい電源で駆動するシングルMOSFETア

リケーションでは、 $R_{GND}$ を省略してもかまいません。短絡時は $V_{IN}$ の電圧が低下するため、 $L_S$ に電流を流すことができません。短絡が解消されたとき、SOURCEでは高速スルーレートを確認できません。

33Vまでの入力電圧では、外付けのMOSFETを使用して、入力短絡時の寄生インダクタ電流を整流することができます。これにより、過渡電圧の発生時に、IN – OUT間の絶対最大定格である±100Vを超えないようにすることができます。短絡過渡電圧の発生時に、MOSFETの $V_{DS}$ は $|V_{GND}| + |V_{GATE(NEG)}| + V_{TH(M1)} + V_{OUT}$ になります。これに応じてMOSFETの $BV_{DSS}$ を選択します。入力短絡時にLTC4372/LTC4373を保護する他の方法については、[設計例](#)のセクションを参照してください。

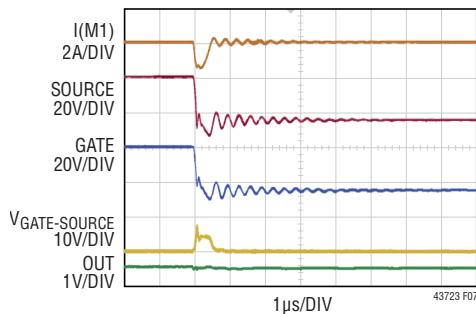

### 逆入力保護

バッテリを逆向きに差し込むか、誤って負電源を接続した場合には、INに負電圧も発生します。図2のアプリケーション回路を-24Vに活線挿抜したときの波形を図7に示します。入力とIN/SOURCEピンの間の寄生インダクタンスが原因で、これらのピンは-24Vより低い電圧まで大きくリギングすることができます。入力短絡の状況と同様に、GND – GATE間のクランプにより、M1は寄生インダクタンスを流れる電流を $C_{OUT}$ に分流します。GND – GATE間のクランプ回路は、図2のアプリケーションで対応できるDC負電圧の最大値を-28Vに制限します。

## アプリケーション情報

図7. LTC4372/LTC4373による逆入力の処理

(a)

(b)

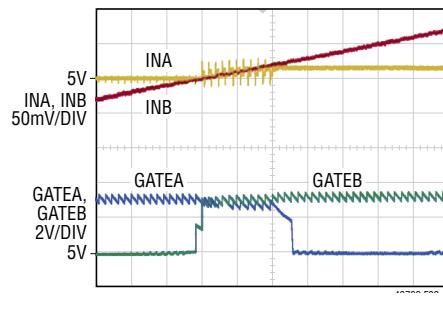

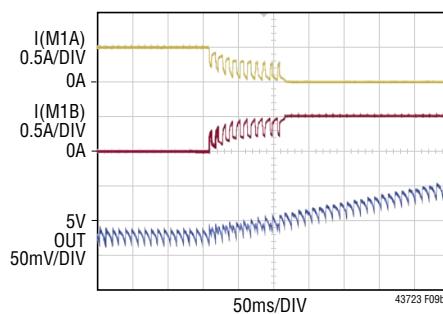

図9. 冗長電源の負荷遷移

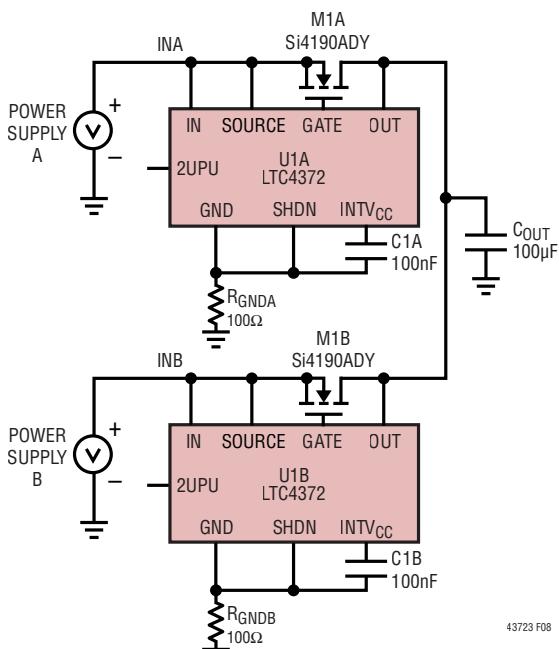

図8. 冗長電源

LTC4372/LTC4373はこの逆電流を検出し、高速プルダウン回路を作動させてMOSFETを素早くオフにします。

全ての負荷電流を短絡発生チャンネルが供給していた場合は、出力が低下し、次のMOSFETのボディ・ダイオードが導通するまで低下したままです。その間、LTC4372/LTC4373は、順方向電圧降下が30mVに低下するまでMOSFETのゲートを20μAで充電します。この電源が障害発生時点で負荷電流を分担していた場合、この電源に対応付けられているOR接続のMOSFETは、既に30mV未満の電圧降下量にサーボ制御されています。この場合、LTC4372/LTC4373は、MOSFETのゲートを単に高くして、最大負荷時に30mVの電圧降下を維持します。

電源の出力電圧と信号源インピーダンスの両方がほぼ等しい場合には、負荷分担を実現できます。30mVのレギュレーション技法により、複数の出力間で負荷を分担できます。分担の程度は、MOSFETのRDS(ON)、電源の信号源インピーダンス、および電源の初期出力電圧に応じて変わります。

## アプリケーション情報

### LTC4372のSHDNおよび2UPUの使用

SHDNがハイになると、LTC4372はシャットダウン・モードになります。GATEとSOURCEの間に1mAのプルダウン電流をアサートして、外付けMOSFETをオフにします。また、ほとんどの内部回路がオフして、 $I_{IN}$ は0.5μAまで減少します。GATEはGNDへの3μAのプルダウン電流により、ローに保持されます。INとSOURCEを互いに接続した場合は、 $I_Q = 3.0\mu A + 0.5\mu A = 3.5\mu A$ となります。

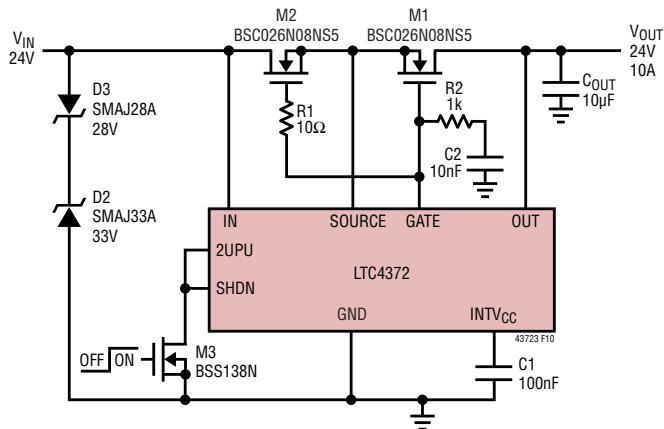

電流経路はM1のボディ・ダイオードを介して引き続き存在するので、デバイスをシャットダウンしても順方向電流の流れは遮断されません。別のMOSFETを追加して順方向の電流経路を遮断することができます(図10参照)。この場合、GATEとSOURCEはシャットダウン中GND電位に引き下げられます。GATEでの3μAのプルダウン電流はピンチオフされ、 $I_Q = 0.5\mu A$ となります。バックツーバックMOSFETでは、SHDNが順方向電流経路のオン/オフ制御ピンとして機能するだけでなく、ダイオード機能をイネーブルする役割も果たします。SHDNをローにすると、LTC4372はシャットダウン状態を終了して、理想ダイオード動作に戻ります。

SHDNが必要ない場合は、GNDに接続してください。SHDNは3.3Vまたは5Vのロジック信号で駆動できます。また、SHDNを2UPUに接続して、オープンドレイン出力またはコレクタ出力で駆動することもできます。2UPUは、2μAの内部プ

図10. 突入電流制御と逆入力保護を備えた24V負荷スイッチおよび理想ダイオード

ルアップ電流をINTVCCに供給します。ルアップ電流を増やす場合は、SHDNとINTVCC(最大10μAを供給可能)との間またはINとの間に抵抗を接続してください。

### 負荷の切替えと突入電流の制御

図10に示すように、別のMOSFETを追加することにより、LTC4372/LTC4373を使用して、順方向では電力の流れを制御するのに対して、逆方向では理想ダイオードの動作を保持することができます。M1およびM2のボディ・ダイオードは、MOSFETがオフのときに電流の流れを遮断します。M1は理想ダイオードとして機能するのに対して、M2は順方向の電力の流れを制御するスイッチとして機能します。オン/オフ制御はSHDNまたはUVにより実行できます。C2とR2を追加して、突入電流を更に低減できます。一方で、ソフトスタート動作が必要ない場合は、C2とR2を省略してもかまいません。R1はMOSFETの寄生発振を防止するために必要があり、M2の近くに配置する必要があります。

SHDNをローにするか、UVをハイにすると、 $\Delta V_{DS} > 30mV$ が成立している場合は、GATEピンから20μAが流れ出してC2を徐々に充電し、2つのMOSFETのゲート電位を両方とも上昇させます。式4に示すように、M2はソース・フォロワとして動作します。

$$I_{INRUSH} = \frac{C_{OUT}}{C_2} \cdot 20\mu A \quad (4)$$

$\Delta V_{DS} \leq 30mV$ の場合、LTC4372/LTC4373は動作状態のままでありますが、M1とM2は、入力電圧が出力電圧より30mV高くなるまでオフ状態を維持します。このようにして回路の通常のダイオード動作は維持されますが、ダイオードが導通するとソフトスタート動作を伴います。

SHDNをハイに駆動するかUVをローに駆動すると、GATEは1mAのプルダウン電流により、MOSFETのゲート電圧をSOURCEまで素早く引き下げます。順方向と逆方向の両方の経路が遮断され、 $I_Q$ は0.5μAまで減少します。

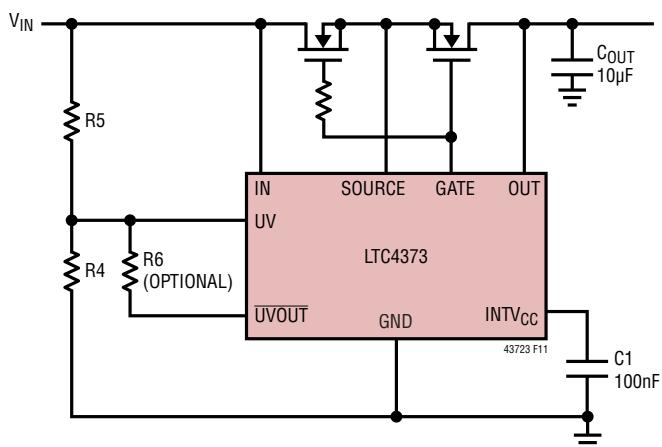

### 電圧モニタリングに対応したLTC4373のUVおよびUVOUTの構成

バックツーバックMOSFETを使用することにより、LTC4373はINピンでの電圧モニタリングを実装できます。INとグラウンドの間に抵抗分圧器を接続して、UVにバイアスを加えます。UVのハイからローへの閾値は1.191Vで、15mVのヒステリシスがあります。UVのヒステリシスは、 $V_{UV}$ を基準にして約1.3%です。

UVがハイからローに低下していくと、LTC4373は低電圧モードになり、GATEとSOURCEの間に1mAのプルダウン電流をアサートして、外付けMOSFETをオフにします。また、ほとんどの内部回路がオフして、 $I_Q$ は0.5μAまで減少します。UVがローからハイに上昇していくと、LTC4373は低電圧モードを終了して、理想ダイオード動作に戻ります。

## アプリケーション情報

図11に、UVを使用してINをモニタするための回路を示します。UVピンでの入力リーク電流は最大50nAです。リーク電流による誤差が最大で1%の場合は、抵抗分圧器の電流 $I_{RVD}$ は、リーク電流の合計の少なくとも100倍、すなわち5μA以上になります。INの低電圧閾値( $V_{H2L}$ )は、式5に示すように、R4、R5、および低電圧回復閾値( $V_{L2H}$ )の値を計算するのに使用します。

$$V_{H2L} = V_{UV} \cdot \frac{R4 + R5}{R5} \quad (5)$$

$$V_{L2H} = (V_{UV} + V_{UV(HYST)}) \cdot \frac{R4 + R5}{R5}$$

ヒステリシスの大きさと精度を高めることが要求されるアプリケーションでは、UVOUTを使用して外部ヒステリシスを設定し、デフォルトのヒステリシスをオーバーライドすることができます。ブロック図のコンパレータC1は、140Ωの内部スイッチがUVOUTでプルダウンするのを制御します。UVの電圧が1.191Vより低くなつてC1が作動すると、スイッチは

図11. INのモニタリングに対応した構成

UVOUTをローにします。UVの電圧が1.191Vより高くなつてC1の動作が停止すると、スイッチはオフになります。UVとUVOUTの間にR6を接続すると、R4およびR5によって $V_{H2L}$ と $V_{L2H}$ が実装されます。式5からR4とR5を求め、式6を使用してR6を計算します。

$$V_{H2L} = V_{UV} \cdot \frac{R4 + R5}{R5} \quad (6)$$

$$V_{L2H} = V_{UV} \cdot \frac{R4 + Rpa}{Rpa}$$

where  $Rpa = R5//R6 = \frac{R5 \cdot R6}{R5 + R6}$

実装する外部ヒステリシスが $V_{H2L}$ の5%を超える限り、式6は、精度に影響を及ぼすことなくデフォルトのUVヒステリシスを無視できます。

UVOUTに抵抗分圧器を接続する場合は、リーク電流の誤差を再検討する必要があります。UVOUTピンでの入力リーク電流は、85°C未満では最大50nAです。INがハイからローに低下していく間、抵抗分圧器にはUVとUVOUTの両方からリーク電流が流れます。このため、リーク電流は合計で100nAになります。R4とR5には5μAが流れるので、リーク電流によって $V_{H2L}$ の精度は2%低下します。INがローからハイに上昇していく間に、UVOUTはローになります。UVから抵抗分圧器に流れるリーク電流は、わずか50nAです。R4とR5には5μAが流れるので、リーク電流によって $V_{L2H}$ の精度は1%低下します。リーク電流による誤差を低減するには、 $I_{RVD}$ を増やしてください。

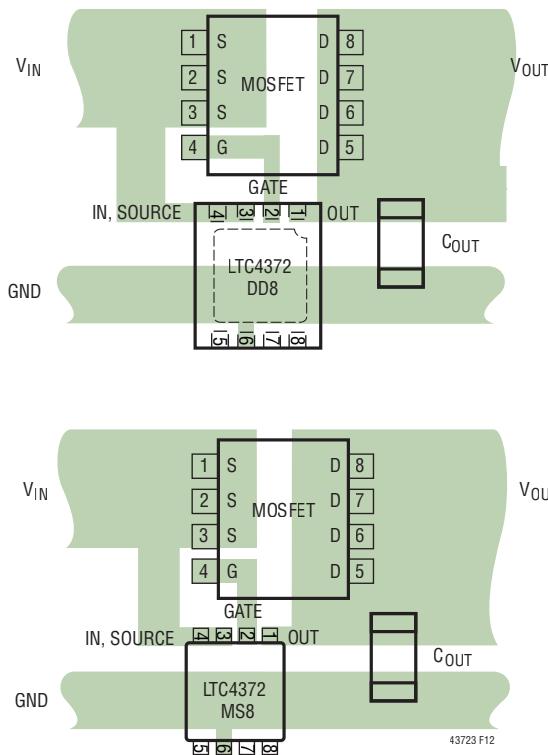

## レイアウトに関する検討事項

IN、SOURCE、およびOUTピンは、MOSFETのソース・ピンおよびドレイン・ピンにできるだけ近づけて接続します。ドレインおよびソースからMOSFETへのパターンは、図12に示すように幅を広く、長さを短くして抵抗性の損失を最小限に抑えてください。 $C_{OUT}$ はMOSFETのドレイン・ピンに近づけて配置し、LTC4372/LTC4373のGATEピンからMOSFETのゲートまでのパターンを短くかつ薄くして、寄生インダクタンスおよび寄生容量を最小限に抑えてください。これにより、MOSFETの寄生発振が生じる確率が下がります。サージ・サプレッサおよび必要なトランジエント保護部品は、リード長を短くしてLTC4372/LTC4373の近くに配置します。

DFNパッケージでは、30Vより高い電圧のときピン間隔が問題になる可能性があります。沿面距離と間隙のガイドラインを確認して、これが問題になるかどうか判断します。高圧ピンとグラウンド・ピンの間の有効なピン間隔を広げるため、露出パッドの接続はオープンのままにします。無洗浄フックスを使用してPCBの汚れを最小限に抑えます。

## アプリケーション情報

図12. レイアウト、MS8パッケージとDD8パッケージ

## 設計例

以下の設計例では、最大負荷電流が20Aの12Vシステムの部品を選択するのに必要な検討事項を示します(図2参照)。まず、NチャンネルMOSFETを選択します。80VのBSC026N08NS5と $R_{DS(ON)} = 2.6\text{m}\Omega$ (最大)を組み合わせると優れた解決策が得られます。両端の最大電圧降下は次のとおりです。

$$\Delta V_{SD} = 20\text{A} \cdot 2.6\text{m}\Omega = 52\text{mV}$$

MOSFETでの最大消費電力は次のとおりです。

$$P = 20\text{A} \cdot 52\text{mV} = 1.04\text{W}$$

入力短絡過渡電圧の発生時には、GND - GATE間クランプを使用し、GATEの電圧を保持して、IN、SOURCE、GATE、およびOUTの電圧を**絶対最大定格**の範囲内に維持します。入力短絡時にSOURCEからGNDへのショートスルーレ電流による問題が発生した場合は、 $100\Omega$ のRGNDを追加します。

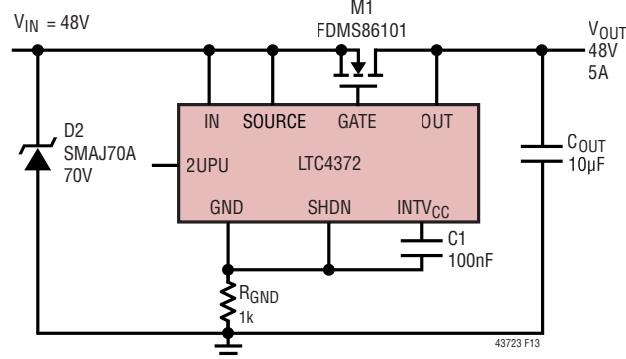

図13に、高電圧アプリケーションを示します。48Vシステムでは、入力短絡過渡電圧の発生時にGND - GATE間のクランプを使用してGATEの電圧を保持すると、IN - OUT間の**絶対最大定格**である-100Vを超える可能性があります。INとグ

ラウンドの間にD2を追加して、INとSOURCEに負のスパイクが発生したらこれらのピンをクランプします。入力短絡過渡電圧の発生時に、D2は入力寄生インダクタンスでの逆回復電流をグラウンドに分流するのに対して、COUTは出力寄生インダクタンスに対して同じ動作を行います。 $R_{DS(ON)} = 8\text{m}\Omega$ (最大)で100V耐圧のFDMS86101は、5Aの負荷電流ならびに入力短絡過渡電圧の両方に対処できます。

図13. 逆入力保護のない48V理想ダイオード

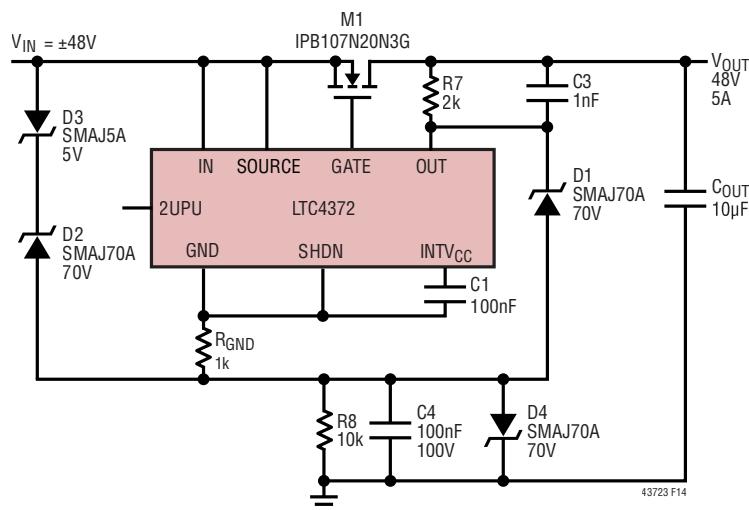

図14に、逆バッテリ保護機能を備えた高電圧アプリケーションを示します。入力側が-48Vで出力側が48Vという考え得る最も厳しい状況に対処するため、外付けMOSFETのBV<sub>DSS</sub>は、余裕を見て $48\text{V} + 48\text{V} = 96\text{V}$ より大きい必要があります。200V耐圧のIPB107N20N3Gを選択します。TO-263パッケージに収容されており、 $R_{DS(ON)} = 10.7\text{m}\Omega$ (最大)です。

INの電圧が-48VでOUTの電圧が48Vのときは、D3がブレークダウンしてIN - GND間を約-6Vでクランプします。MOSFETはオフのままとなり、負荷は負入力から分離されます。D1とR7により、OUT - GND間は約70Vでクランプされます。D1、D2、D3、R7の組み合わせにより、IN - OUT間は約76Vでクランプされます。

入力短絡時に、M1のドレインには正のスパイクが、INには負のスパイクが発生します。D2、D3、およびD4は入力寄生インダクタンスでの逆回復電流を整流するのに対して、COUTは出力寄生インダクタンスに対して同じ動作を行います。D1、D2、D3、D4、R7、およびR8は、IN、SOURCE、OUT、およびGNDの電圧を各ピンの**絶対最大定格**の範囲内にクランプします。

GATEをハイにした通常の理想ダイオード動作時に、D4、C3、およびC4は、300μA(GATEの充電)と3.5μA(チャージ・ポンプのスリープ・モード)との間での $I_Q$ のパルス動作を処理するのに役立つのに対して、D1、D2、およびD3には電流が流れません。

## アプリケーション情報

図14. 逆入力保護を備えた48V理想ダイオード

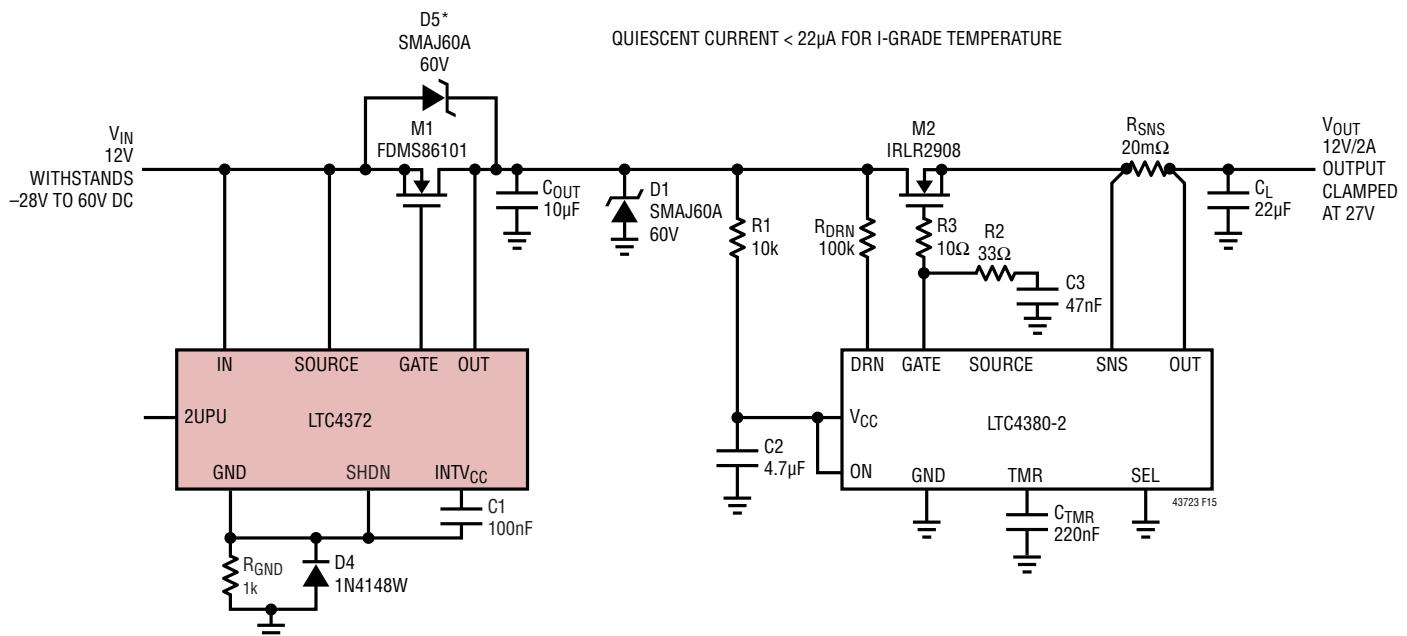

\*D5 IS NEEDED TO CLAMP TRANSIENTS IN CASE INPUT SHORT-CIRCUIT OCCURS AT  $V_{IN} > 33V$

図15. 理想ダイオードを備えたマイクロパワー12Vサージ・ストップ

## パッケージ

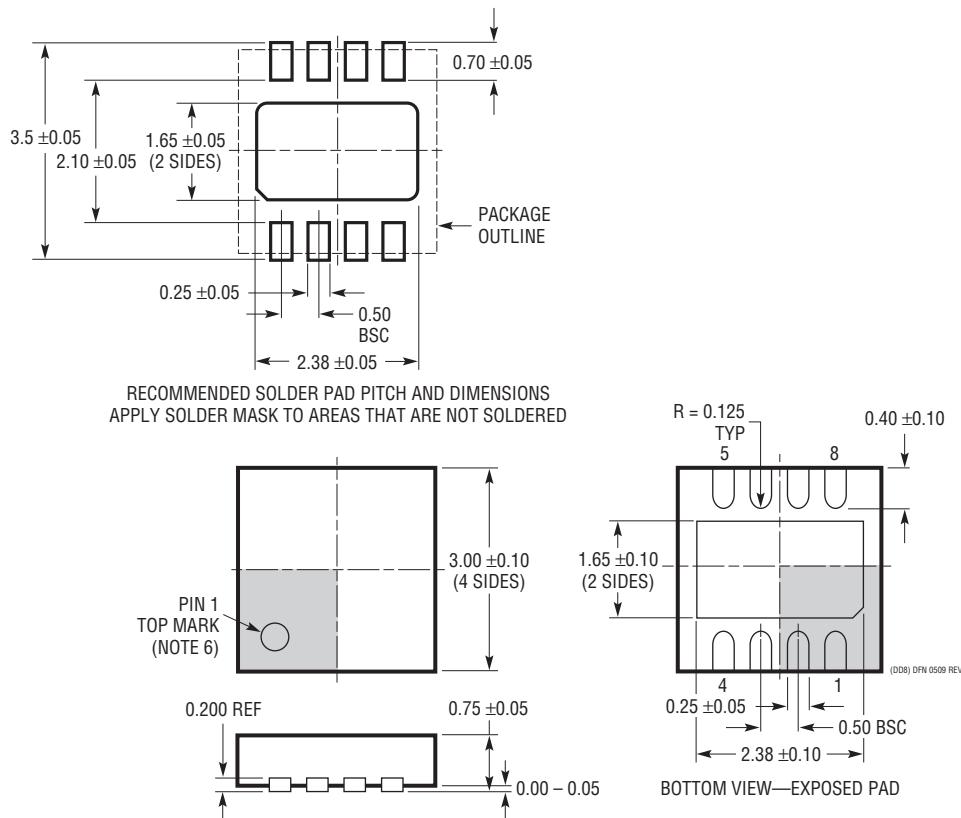

**DD Package**

**8-Lead Plastic DFN (3mm × 3mm)**

(Reference LTC DWG # 05-08-1698 Rev C)

注記 :

1. 図は JEDEC のパッケージ外形 MO-229 のバリエーション (WEED-1) に含めるよう提案されている

2. 図は実寸とは異なる

3. 全ての寸法の単位はミリメートル

4. パッケージ底面の露出パッドの寸法にはモールドのバリを含まない。

モールドのバリ(存在する場合)はどの側でも 0.15mm を超えない

5. 露出パッドはハンダ・メッキとする

6. 灰色の部分はパッケージの上面と底面の 1 番ピンの位置の参考にすぎない

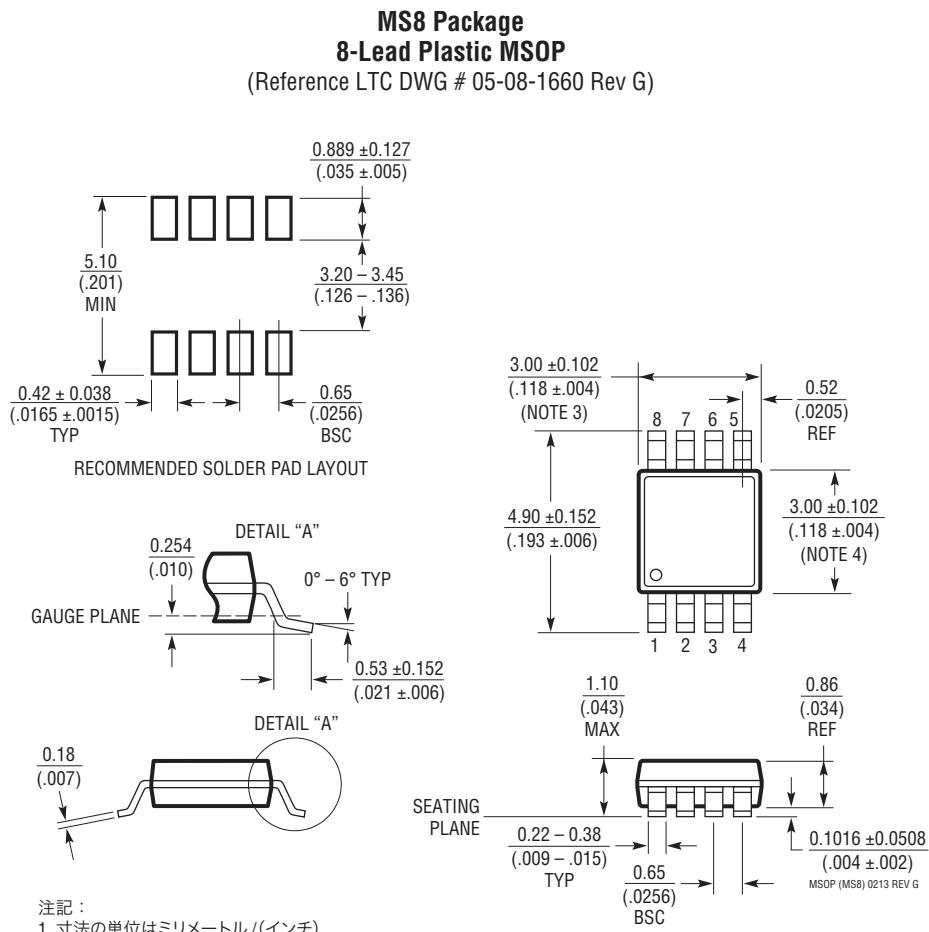

## パッケージ

## 注記 :

- 寸法の単位はミリメートル/(インチ)

- 図は実寸とは異なる

- 寸法にはモールドのバリ、突出部、ゲートのバリを含まない。

モールドのバリ、突出部、ゲートのバリは、各サイドで  $0.152$  mm ( $0.006$  in) を超えない

- 寸法には、リード間のバリまたは突出部を含まない。

- リード間のバリと突出部は、各サイドで  $0.152$  mm ( $0.006$  in) を超えない

- リードの平坦度(整形後のリードの底面)は最大  $0.102$  mm ( $0.004$  in) である

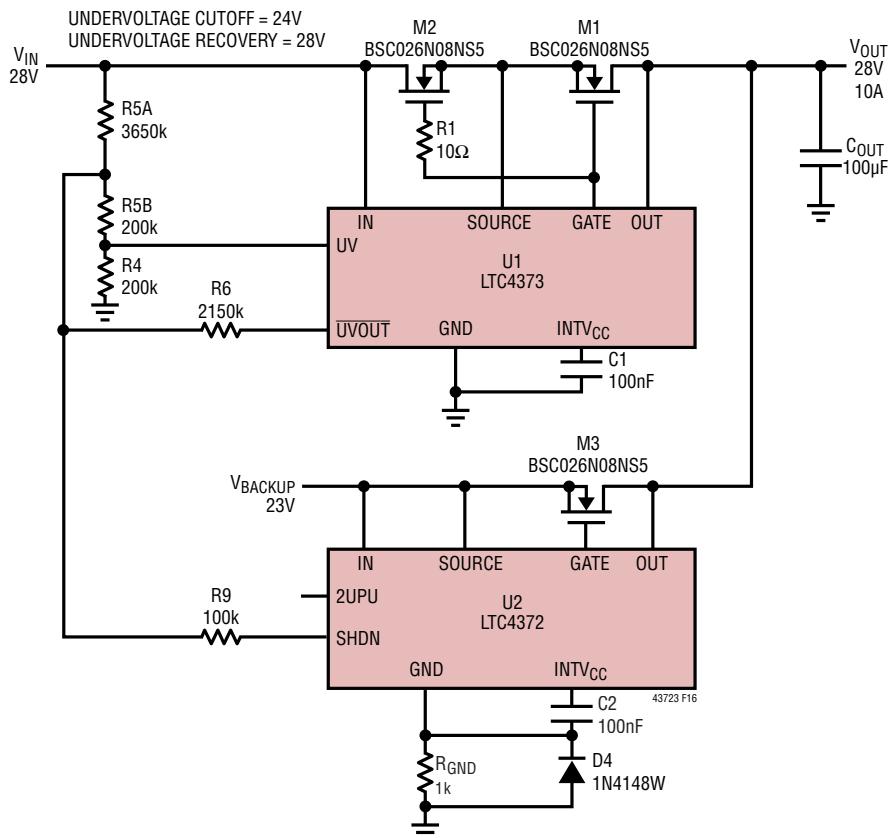

## 標準的応用例

図16. 電圧モニタリングとバックアップ・チャンネルを備えた28V電源

## 関連製品

| 製品番号    | 説明                           | 注釈                                           |

|---------|------------------------------|----------------------------------------------|

| LTC4352 | 理想ダイオード・コントローラ               | NチャンネルMOSFETを制御、動作電圧:0V ~ 18V                |

| LTC4353 | デュアル理想ダイオード・コントローラ           | 2個のNチャンネルMOSFETを制御、動作電圧:0V ~ 18V             |

| LTC4355 | 高電圧ダイオードORコントローラおよびモニタ       | 2個のNチャンネルMOSFETを制御、0.4μsのターンオフ時間、80V動作       |

| LTC4357 | 高電圧理想ダイオード・コントローラ            | NチャンネルMOSFETを制御、0.5μsのターンオフ時間、80V動作          |

| LTC4358 | 5A理想ダイオード                    | NチャンネルMOSFET内蔵、動作電圧:9V ~ 26.5V               |

| LTC4359 | 逆入力保護回路を備えた理想ダイオード・コントローラ    | NチャンネルMOSFETを制御、動作電圧:4V ~ 80V、逆入力保護:-40V     |

| LTC4364 | 理想ダイオードを備えたサージ・ストップ          | 動作電圧:4V ~ 80V、逆入力:-40V、逆出力:-20V              |

| LTC4371 | デュアル負電圧理想ダイオードORコントローラおよびモニタ | 2個のMOSFETを制御、ターンオフ時間:220ns、トランジエント耐電圧:>±300V |

| LTC4376 | 逆入力保護を備えた7A理想ダイオード           | NチャンネルMOSFET内蔵、動作電圧:4V ~ 40V、逆入力保護:-40V      |