## 8V、12A、2相、低IQの同期整流式昇降圧コンバータ

## 特長

- ▶ 入力電圧範囲 : 2.5V~5.5V

- ▶ 出力電圧 : 最大8Vまでプログラム可能

- ▶ 2相動作により、必要入力/出力容量と電源誘導ノイズを低減

- ▶ 同期動作によって高い効率と熱損失の低減を実現

- ▶ 軽負荷時に高効率を実現するStage Sheding<sup>TM</sup>およびBurst Mode<sup>®</sup>動作

- ▶ 低V<sub>IN</sub>ピン静止電流 :

- ▶ シャットダウン時0.5µA

- ▶ Burst Mode動作時15µA

- ▶ 8V/6Aの同期整流式パワー・スイッチを内蔵

- ▶ 調整と同期が可能 : 300kHz~4MHz

- ▶ 軽負荷時はBurst Mode動作または強制連続動作

- ▶ 高精度のイネーブル・ピン閾値 : 1V

- ▶ 1.9mm × 2.6mm WLCSPパッケージ

## アプリケーション

- #### ▶ ハンドヘルド用および工業用電源

## 概要

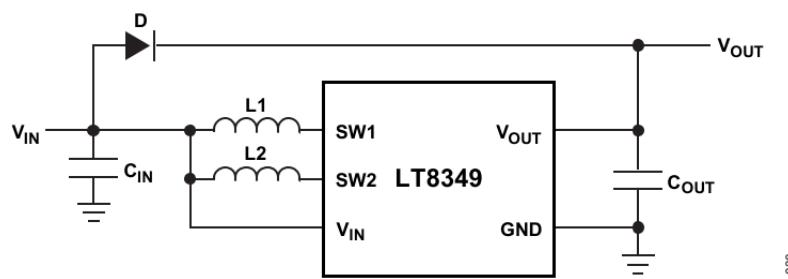

LT8349は、2つのNチャンネル・パワーMOSFET段を異なる位相で駆動する、2相シングル出力の同期整流式昇圧コンバータです。多相動作により入力および出力用コンデンサの条件が緩和され、単相の同等デバイスより小型のインダクタを使用できます。同期整流方式により効率が向上して電力損失が減少し、熱条件が緩和されるため、高電力の昇圧アプリケーションを実現可能です。

軽負荷時はStage Sheddingと選択可能なBurst Mode動作を使用することができ、広い負荷範囲にわたって高い効率を実現します。また、EMI放射を最小限に抑えるためにスペクトラム拡散周波数変調（SSFM）機能を備えています。

8V/6Aのパワー・スイッチを内蔵しており、300kHz～4MHzの範囲にプログラム可能な固定スイッチング周波数で動作し、外部クロックに同期することも可能です。さらに、出力ソフトスタート機能と出力過電圧ロックアウト機能を備えています。

## 代表的なアプリケーション

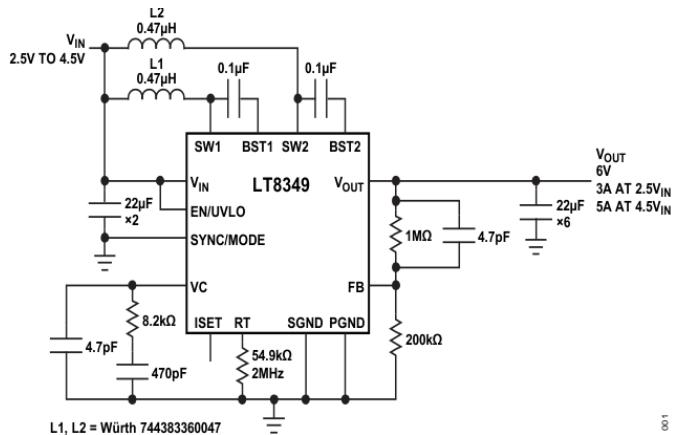

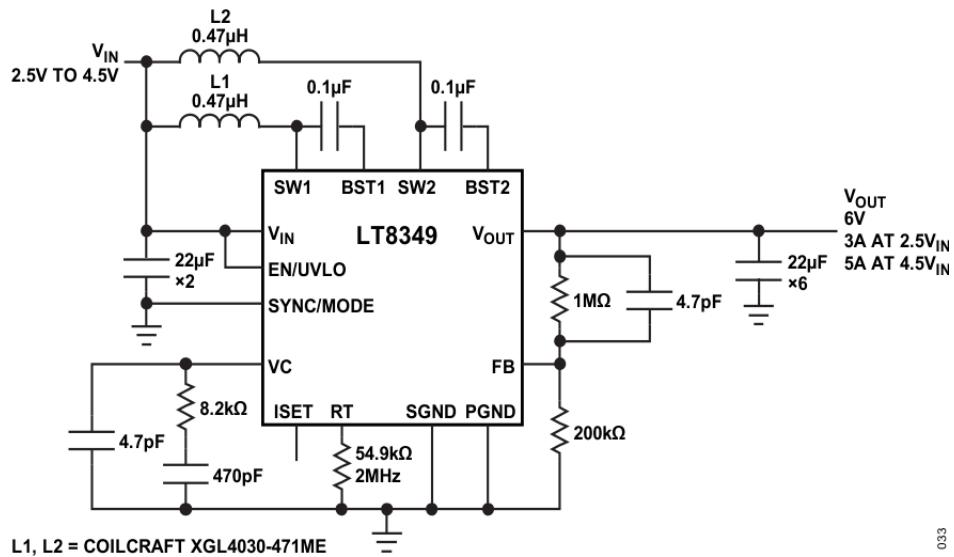

図1. 2.5V～4.5V入力、6V出力の昇圧コンバータ

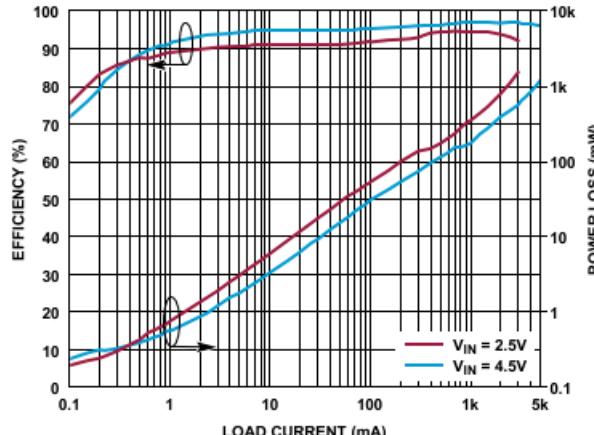

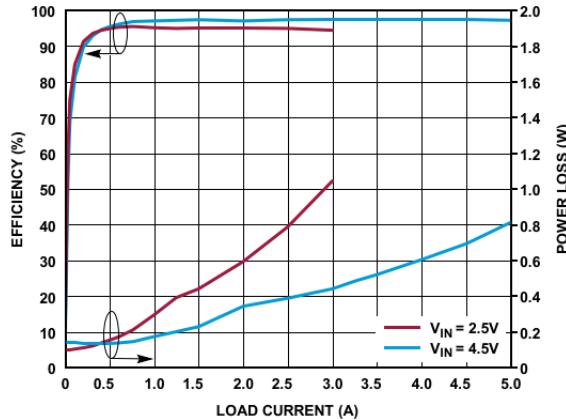

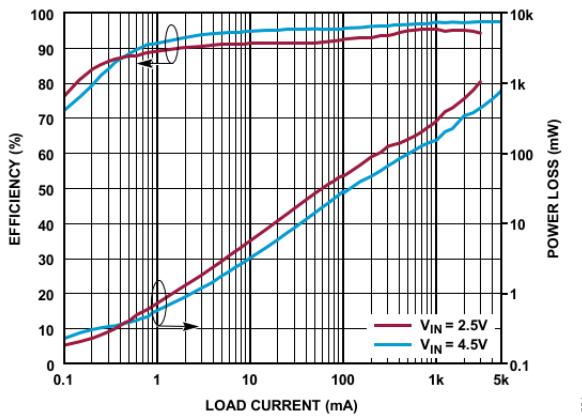

図2. 効率と電力損失 (Burst Mode時)

## 改訂履歴

| 変更内容                                     | ページ番号 |

|------------------------------------------|-------|

| 2023/10 - Rev Sp0                        | -     |

| 2024/1 - Rev A、公開                        | -     |

| 2024/2 - 電気的特性の表を更新、<br>$V_{IN}$ 静止電流の単位 | 4     |

## 目次

|                                             |    |

|---------------------------------------------|----|

| 特長                                          | 1  |

| アプリケーション                                    | 1  |

| 概要                                          | 1  |

| 代表的なアプリケーション                                | 1  |

| 改訂履歴                                        | 2  |

| 仕様                                          | 4  |

| 絶対最大定格                                      | 6  |

| ピン配置およびピン機能の説明                              | 7  |

| 代表的な性能特性                                    | 9  |

| ブロック図                                       | 12 |

| 動作原理                                        | 13 |

| 多相動作                                        | 13 |

| アプリケーション情報                                  | 15 |

| EN/UVLOピンによるV <sub>IN</sub> オン／オフ閾値のプログラミング | 15 |

| 軽負荷電流動作                                     | 15 |

| スイッチング周波数同期                                 | 17 |

| スペクトラム拡散周波数変調                               | 19 |

| FB抵抗ネットワークと無負荷時の静止電流                        | 19 |

| 過電圧ロックアウト                                   | 20 |

| スタートアップ                                     | 20 |

| インダクタの選択                                    | 21 |

| 入力コンデンサの選択                                  | 21 |

| 出力コンデンサの選択                                  | 22 |

| 周波数補償                                       | 22 |

| 基板レイアウト                                     | 23 |

| 熱に関する考慮事項                                   | 24 |

| 代表的なアプリケーション                                | 26 |

| パッケージの説明                                    | 27 |

| 関連製品                                        | 28 |

| オーダー・ガイド                                    | 28 |

## 仕様

表1. 電気仕様

(特に指定のない限り、仕様は $T_A = 25^\circ\text{C}$ 、 $V_{IN} = 3.6\text{V}$ 、 $V_{EN/UVLO} = 1.5\text{V}$ での値<sup>1)</sup>)

| パラメータ                                             | 記号                 | 条件/コメント                                                                          |                                                     | 最小値   | 代表値  | 最大値   | 単位            |

|---------------------------------------------------|--------------------|----------------------------------------------------------------------------------|-----------------------------------------------------|-------|------|-------|---------------|

| $V_{IN}$ Operating Voltage Range                  | $V_{IN}$           | $-40^\circ\text{C} \leq T_J \leq 125^\circ\text{C}$                              |                                                     | 2.5   | 5.5  |       | V             |

| $V_{IN}$ Undervoltage Lockout Threshold           | $V_{IN\_UVLO\_R}$  | 立上がり                                                                             |                                                     | 2.36  | 2.5  |       | V             |

|                                                   | $V_{IN\_UVLO\_F}$  | 立下がり                                                                             |                                                     | 2.1   | 2.3  |       |               |

| $V_{IN}$ Quiescent Current in Shutdown            | $I_{Q\_SD}$        | $V_{EN/UVLO} \leq 0.3\text{V}$                                                   |                                                     | 0.5   | 3    |       | $\mu\text{A}$ |

|                                                   |                    |                                                                                  | $-40^\circ\text{C} \leq T_J \leq 125^\circ\text{C}$ | 0.5   | 10   |       |               |

| $V_{IN}$ Quiescent Current                        | $I_Q$              | SYNC/MODE = 0V、スイッチングなし                                                          |                                                     | 15    | 30   |       | $\mu\text{A}$ |

|                                                   |                    | SYNC/MODE = オープン、FB = 1.5V、 $R_T = 54.9\text{k}\Omega$                           |                                                     | 11.2  | 15   |       |               |

| $V_{OUT}$ Operating Voltage                       | $V_{OUT}$          | $-40^\circ\text{C} \leq T_J \leq 125^\circ\text{C}$                              |                                                     |       | 8    |       | V             |

| $V_{OUT}$ Quiescent Current                       | $I_{Q-OUT}$        | SYNC/MODE = 0V、 $V_{OUT} = 5.5\text{V}$ 、スイッチングなし                                |                                                     | 1     | 2    |       | $\mu\text{A}$ |

|                                                   |                    | SYNC/MODE = オープン、 $V_{OUT} = 2.5\text{V}$ 、FB = 1.5V、 $R_T = 54.9\text{k}\Omega$ |                                                     | 7.6   | 12   |       |               |

| $V_{OUT}$ Over Voltage Protection Threshold       | $V_{OUT\_OV\_R}$   | 立上がり                                                                             |                                                     | 8.12  | 9    | 9.8   | V             |

|                                                   | $V_{OUT\_OV\_HYS}$ | ヒステリシス                                                                           |                                                     |       | 0.1  |       |               |

| FB Regulation Voltage3                            | $V_{FB\_REG}$      | $VC = 1.25\text{V}$                                                              | $-40^\circ\text{C} \leq T_J \leq 125^\circ\text{C}$ | 0.985 | 1.00 | 1.015 | V             |

| FB Line Regulation3                               |                    | $2.5\text{V} < V_{IN} < 5.5\text{V}$                                             |                                                     | 0.2   | 0.35 |       | %/V           |

| FB Pin Input Current                              | $I_{FB}$           | FB = 1.0V                                                                        |                                                     | -20   | 20   |       | nA            |

| Error Amp Transconductance3                       | $g_m$              | $VC = 1.25\text{V}$                                                              |                                                     |       | 0.4  |       | $\text{mS}$   |

| Error Amp Gain3                                   | $G_v$              |                                                                                  |                                                     |       | 400  |       | V/V           |

| VC Source Current                                 | $I_{VC}$           | FB = 0.8V、 $VC = 1.25\text{V}$                                                   |                                                     | -80   |      |       | $\mu\text{A}$ |

| VC Sink Current                                   | $I_{VC}$           | FB = 1.2V、 $VC = 1.25\text{V}$                                                   |                                                     |       | 73   |       | $\mu\text{A}$ |

| VC to Switch Current Gain, per phase, no shedding |                    |                                                                                  |                                                     |       | 6.0  |       | A/V           |

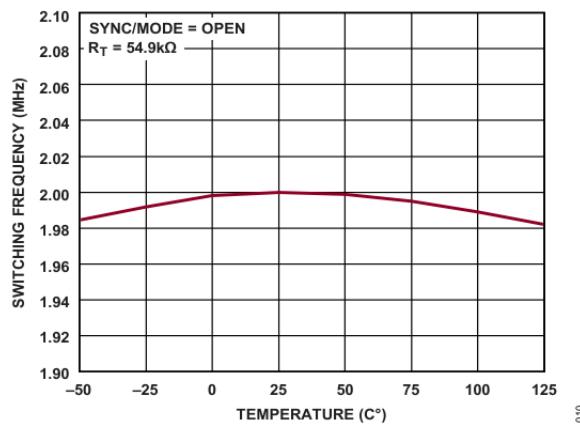

| Switching Frequency                               | $f_{SW}$           | $R_T = 464\text{k}\Omega$                                                        |                                                     | 0.25  | 0.3  | 0.36  | MHz           |

|                                                   |                    | $R_T = 127\text{k}\Omega$                                                        |                                                     | 0.82  | 1    | 1.2   |               |

|                                                   |                    | $R_T = 54.9\text{k}\Omega$                                                       |                                                     | 1.83  | 2    | 2.2   |               |

|                                                   |                    | $R_T = 18.7\text{k}\Omega$                                                       |                                                     | 3.6   | 4    | 4.67  |               |

(特に指定のない限り、仕様は $T_A = 25^\circ\text{C}$ 、 $V_{IN} = 3.6\text{V}$ 、 $V_{EN/UVLO} = 1.5\text{V}$ での値<sup>1)</sup>)

| パラメータ                                                                | 記号                | 条件/コメント                                                    | 最小値                         | 代表値  | 最大値 | 単位   |    |

|----------------------------------------------------------------------|-------------------|------------------------------------------------------------|-----------------------------|------|-----|------|----|

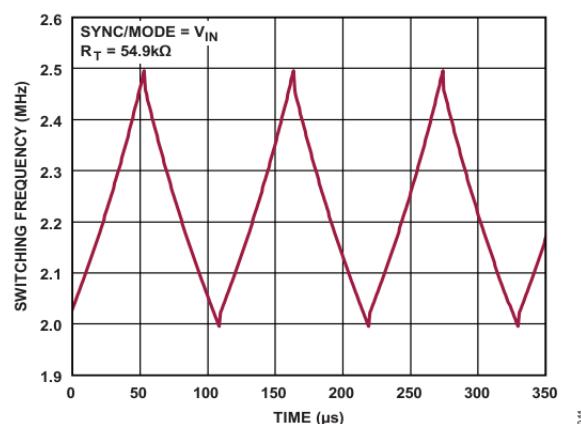

| Spread Spectrum Modulation Frequency as Percentage of $f_{SW}$       |                   | $R_T = 54.9\text{k}\Omega$                                 | 0.45                        |      |     | %    |    |

| Spread Spectrum Modulation Frequency Range as Percentage of $f_{SW}$ |                   | $R_T = 54.9\text{k}\Omega$                                 | 25                          |      |     | %    |    |

| Synchronizable Frequency                                             | $f_{SYNC}$        | SYNC/MODE = 外部クロック                                         | 0.3                         | 4    |     | MHz  |    |

| SYNC/MODE Pin Input Logic Level for Frequency Synchronization        | $V_{SYNC\_HIGH}$  | SYNCロジック・ロー                                                |                             | 0.4  |     | V    |    |

|                                                                      | $V_{SYNC\_LOW}$   | SYNCロジック・ハイ                                                | 1.8                         |      |     |      |    |

| Soft-Start Time                                                      | SS                | $R_T = 54.9\text{k}\Omega$                                 | 1.2                         |      |     | ms   |    |

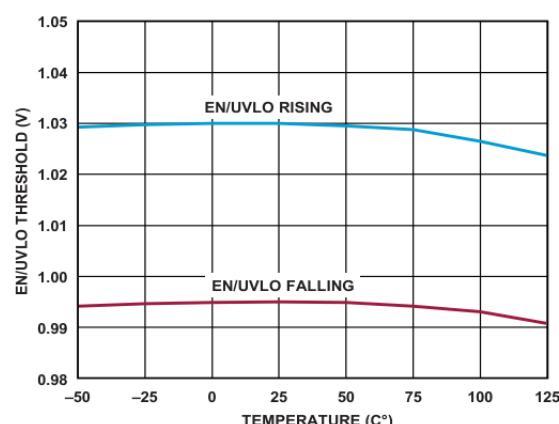

| EN/UVLO Threshold Voltage                                            | $V_{EN\_F}$       | 立下がり                                                       | -40°C $\leq T_J \leq$ 125°C | 0.94 | 1.0 | 1.06 | V  |

|                                                                      | $V_{EN\_HYS}$     | ヒステリシス                                                     |                             | 35   |     |      | ms |

| EN/UVLO Input Bias Current                                           | $I_{EN}$          | EN/UVLO = 2V                                               | -40                         | 40   |     | nA   |    |

| Bottom Switch On-Resistance per Phase                                |                   | $I_{SW} = 1\text{A}$                                       | 12                          |      |     | mΩ   |    |

| Top Switch On-Resistance per Phase                                   | $R_{DS\_ON\_BOT}$ | $I_{SW} = 1\text{A}$                                       | 13                          |      |     | mΩ   |    |

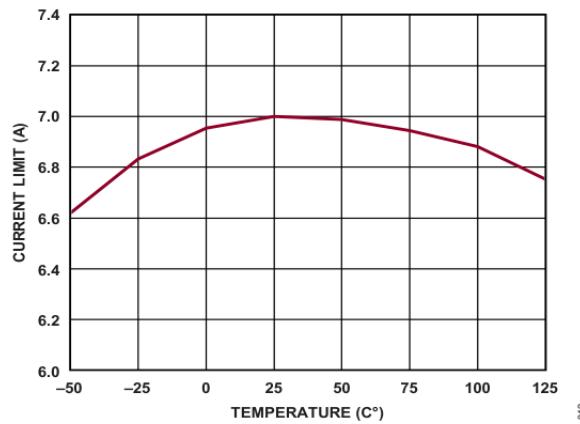

| Bottom Switch Current Limit per Phase                                | $I_{SW\_LIM}$     | -40°C $\leq T_J \leq$ 125°C                                | 6                           | 7    | 8   | A    |    |

| Channel 1 Burst Mode Bottom Switch Minimum Peak Current              | $I_{PK\_BURST}$   | ISET = $V_{IN}$                                            |                             | 1.7  |     | A    |    |

|                                                                      |                   | ISET = オープン                                                |                             | 1.47 |     |      |    |

|                                                                      |                   | ISET = 0V                                                  |                             | 1.23 |     |      |    |

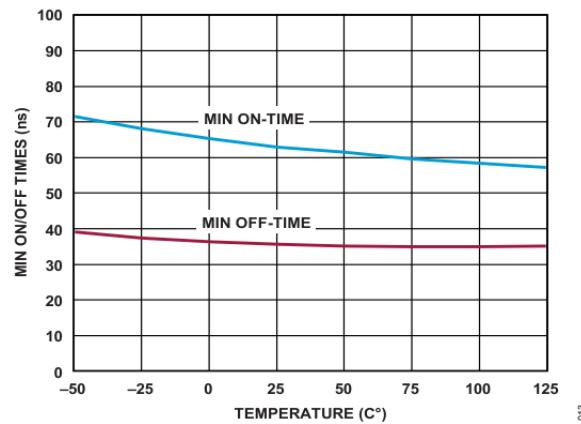

| Bottom Switch Minimum Off-time                                       | $t_{OFF-MIN}$     |                                                            | 20                          | 36   | 60  | ns   |    |

| Bottom Switch Minimum On-time                                        | $t_{ON-MIN}$      |                                                            | 20                          | 61   | 90  | ns   |    |

| SW Leakage Current per Phase                                         | $I_{SW\_LKG}$     | $V_{OUT} = 6.1\text{V}$ 、 $SW = 0\text{V}$ 、 $6.1\text{V}$ | -1.5                        |      | 1.5 | μA   |    |

## 絶対最大定格

表2. 絶対最大定格

| PARAMETER                                            | RATING         |

|------------------------------------------------------|----------------|

| $V_{IN}$ , EN/UVLO, SYNC/MODE, FB, ISET              | -0.3V to 6V    |

| $V_{OUT}$                                            | -0.3V to 10V   |

| $VC$                                                 | -0.3V to 3V    |

| Operating Junction Temperature Range <sup>1, 2</sup> | -40°C to 125°C |

| Storage Temperature Range                            | -65°C to 150°C |

<sup>1</sup> LT8349は-40°C～125°Cの動作ジャンクション温度範囲で仕様規定されています。ジャンクション温度が高い場合は動作寿命が低下します。なお、ここに示す仕様に見合った最大周囲温度は、具体的な動作条件と、ボード・レイアウト、パッケージの熱抵抗定格値、およびその他の環境条件の組み合わせによって決まります。

<sup>2</sup> LT8349は一時的な過負荷状態からデバイスを保護することを目的とした過熱保護機能を備えています。過熱保護機能が作動した場合、ジャンクション温度は150°Cを超えていません。仕様規定された絶対最大動作ジャンクション温度より上での動作は、デバイスの信頼性を損なう可能性があります。

<sup>3</sup> LT8349は帰還ループでテスト済みです。このループはVCピン電圧を仕様規定された電圧にサーボ制御して、得られたFBピン電圧を測定します。

上記の絶対最大定格を超えるストレスを加えると、デバイスに恒久的な損傷を与えることがあります。これはストレス定格のみを定めたものであり、本仕様の動作セクションに記載する規定値以上でデバイスが正常に動作することを示唆するものではありません。デバイスを長時間にわたり絶対最大定格状態に置くと、デバイスの信頼性に影響を与えることがあります。

## ピン配置およびピン機能の説明

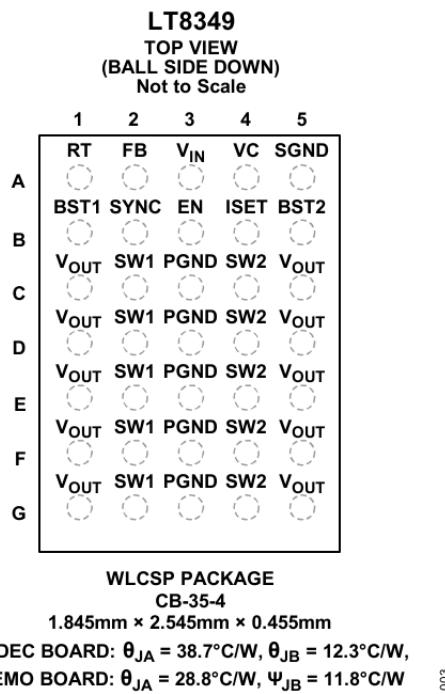

図3. ピン配置

表3. ピンの説明

| ピン | 名称              | 説明                                                                                                                                                           |

|----|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A1 | RT              | RTとSGNDの間に抵抗を接続すると、スイッチング周波数を設定できます。                                                                                                                         |

| A2 | FB              | フィードバック入力ピン。このピンには、V <sub>OUT</sub> とSGNDの間にある外部抵抗分圧器からの帰還電圧を入力します。FBピンは、出力電圧制御ループのエラー・アンプへの入力の1つです。                                                         |

| A3 | V <sub>IN</sub> | 入力電源ピン。このピンは、内部ドライバ回路と制御回路に電源を供給します。このピンは、1μF以上の低ESRセラミック・コンデンサを使って、グランド・プレーンに対してデカップリングする必要があります。V <sub>IN</sub> バイパス・コンデンサはV <sub>IN</sub> ピンの近くに配置してください。 |

| A4 | VC              | エラー・アンプ出力およびスイッチング・レギュレータの補償ピン。このピンは、レギュレータのループ周波数応答を補償するために適切な外付け部品に接続します。                                                                                  |

| A5 | SGND            | 信号グラウンド。SGNDは、PCB上のPGNDに低インピーダンスで接続します。                                                                                                                      |

| B1 | BST1            | このピンは、チャンネル1のトップサイド・パワー・スイッチにゲート駆動電圧を供給するために使用します。BST1ピンとSW1ピンの間のできるだけICに近い位置に、0.1μFのブーストストラップ・コンデンサを配置してください。                                               |

| B2 | SYNC/MODE       | 外部同期入力およびモード選択ピン。このピンを使用すると、5つのモードを選択して性能を最適化することができます。<br>選択可能な動作モードは以下の通りです。<br>Burst Mode = 軽負荷時の低I <sub>Q</sub> 、低出力リップル動作。                              |

| ピン                                     | 名称                                     | 説明                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |               |                                        |               |            |                   |                   |               |       |          |             |        |               |

|----------------------------------------|----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|----------------------------------------|---------------|------------|-------------------|-------------------|---------------|-------|----------|-------------|--------|---------------|

|                                        |                                        | <p>強制連続 = 負のインダクタ電流が可能。パルススキッピングを行わず（クロックに同期）、スイッチング周波数は固定。</p> <p>同期 = スイッチング周波数をSYNCクロック周波数の半分に同期。SSFM = 低EMIを目的としたスペクトラム拡散周波数変調。</p> <table border="1"> <thead> <tr> <th>SYNC/MODEピン入力</th><th>選択可能な動作モード</th></tr> </thead> <tbody> <tr> <td>SGNDまたは0.1V未満</td><td>Burst Mode</td></tr> <tr> <td>SGNDとの間に50kΩ抵抗を接続</td><td>Burst Mode + SSFM</td></tr> <tr> <td>フロート（ピン・オープン）</td><td>強制連続</td></tr> <tr> <td><math>V_{IN}</math></td><td>強制連続 + SSFM</td></tr> <tr> <td>外部クロック</td><td>強制連続 + 同期クロック</td></tr> </tbody> </table> | SYNC/MODEピン入力 | 選択可能な動作モード                             | SGNDまたは0.1V未満 | Burst Mode | SGNDとの間に50kΩ抵抗を接続 | Burst Mode + SSFM | フロート（ピン・オープン） | 強制連続  | $V_{IN}$ | 強制連続 + SSFM | 外部クロック | 強制連続 + 同期クロック |

| SYNC/MODEピン入力                          | 選択可能な動作モード                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |               |                                        |               |            |                   |                   |               |       |          |             |        |               |

| SGNDまたは0.1V未満                          | Burst Mode                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |               |                                        |               |            |                   |                   |               |       |          |             |        |               |

| SGNDとの間に50kΩ抵抗を接続                      | Burst Mode + SSFM                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |               |                                        |               |            |                   |                   |               |       |          |             |        |               |

| フロート（ピン・オープン）                          | 強制連続                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |               |                                        |               |            |                   |                   |               |       |          |             |        |               |

| $V_{IN}$                               | 強制連続 + SSFM                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |               |                                        |               |            |                   |                   |               |       |          |             |        |               |

| 外部クロック                                 | 強制連続 + 同期クロック                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |               |                                        |               |            |                   |                   |               |       |          |             |        |               |

| B3                                     | EN/UVLO                                | イネーブルおよび入力低電圧ロックアウト・ピン。このピンが1V（代表値）未満になると、ICはシャットダウンします。このピンが0.15V未満になると、ICに流れる $V_{IN}$ 電流が0.5μA（代表値）に減少します。このピンが1.035V（代表値）を超えるとICがイネーブルされます。 $V_{IN}$ とSGNDの間に置いた抵抗分圧器を使用すれば、 $V_{IN}$ の閾値をプログラムして、その閾値未満になるとICがシャットダウンするようにすることができます。シャットダウン機能とUVLO機能を使わない場合は、EN/UVLOを $V_{IN}$ に接続してください。                                                                                                                                                                                                                                        |               |                                        |               |            |                   |                   |               |       |          |             |        |               |

| B4                                     | ISET                                   | <p>チャンネル1のBurst Modeボトム・スイッチの最小ピーク電流調整入力。このピンにより、3つのBurst Modeピーク電流（<math>I_{PK\_BURST}</math>）レベルを選択できるようにして、性能を最適化できます。</p> <table border="1"> <thead> <tr> <th>ISETピンの設定</th><th>Burst Modeピーク電流（<math>I_{PK\_BURST}</math>、代表値）</th></tr> </thead> <tbody> <tr> <td><math>V_{IN}</math></td><td>1.7A</td></tr> <tr> <td>フロート（ピン・オープン）</td><td>1.47A</td></tr> <tr> <td>SGNDまたは0.4V未満</td><td>1.23A</td></tr> </tbody> </table>                                                                                                    | ISETピンの設定     | Burst Modeピーク電流（ $I_{PK\_BURST}$ 、代表値） | $V_{IN}$      | 1.7A       | フロート（ピン・オープン）     | 1.47A             | SGNDまたは0.4V未満 | 1.23A |          |             |        |               |

| ISETピンの設定                              | Burst Modeピーク電流（ $I_{PK\_BURST}$ 、代表値） |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |               |                                        |               |            |                   |                   |               |       |          |             |        |               |

| $V_{IN}$                               | 1.7A                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |               |                                        |               |            |                   |                   |               |       |          |             |        |               |

| フロート（ピン・オープン）                          | 1.47A                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |               |                                        |               |            |                   |                   |               |       |          |             |        |               |

| SGNDまたは0.4V未満                          | 1.23A                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |               |                                        |               |            |                   |                   |               |       |          |             |        |               |

| B5                                     | BST2                                   | このピンは、チャンネル2のトップサイド・パワー・スイッチにゲート駆動電流を供給するために使用します。BST2ピンとSW2ピンの間のできるだけICに近い位置に、0.1μFのブートストラップ・コンデンサを配置してください。                                                                                                                                                                                                                                                                                                                                                                                                                         |               |                                        |               |            |                   |                   |               |       |          |             |        |               |

| C1, D1, E1, F1, G1, C5, D5, E5, F5, G5 | $V_{OUT}$                              | 昇圧コンバータの出力ピン。両方の列の $V_{OUT}$ をまとめてPCB上に接続します。このピンは、低ESRのセラミック・コンデンサを使ってグランド・プレーンにバイパスしてください。コンデンサはできる限りピンに近付けて配置します。レイアウト例については、アプリケーション情報のセクションを参照してください。                                                                                                                                                                                                                                                                                                                                                                            |               |                                        |               |            |                   |                   |               |       |          |             |        |               |

| C2, D2, E2, F2, G2                     | SW1                                    | SW1ピンは、位相1の内部パワー・スイッチのスイッチング・ノードです。これらのピンは互いにまとめて、位相1のインダクタとブートストラップ・コンデンサに接続します。良好なEMI性能を得るには、PCB上でこれらのノードの面積をできるだけ小さくする必要があります。                                                                                                                                                                                                                                                                                                                                                                                                     |               |                                        |               |            |                   |                   |               |       |          |             |        |               |

| C3, D3, E3, F3, G3                     | PGND                                   | 電源グラウンド。                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |               |                                        |               |            |                   |                   |               |       |          |             |        |               |

| C4, D4, E4, F4, G4                     | SW2                                    | SW2ピンは、位相2の内部パワー・スイッチのスイッチング・ノードです。これらのピンは互いにまとめて、位相2のインダクタとブートストラップ・コンデンサに接続します。良好なEMI性能を得るには、PCB上でこれらのノードの面積をできるだけ小さくする必要があります。                                                                                                                                                                                                                                                                                                                                                                                                     |               |                                        |               |            |                   |                   |               |       |          |             |        |               |

## 代表的な性能特性

特に指定のない限り、 $T_A = 25^\circ\text{C}$ 。

図4. 効率および電力損失と出力電流の関係

(Burst Mode、26ページの回路を参照)

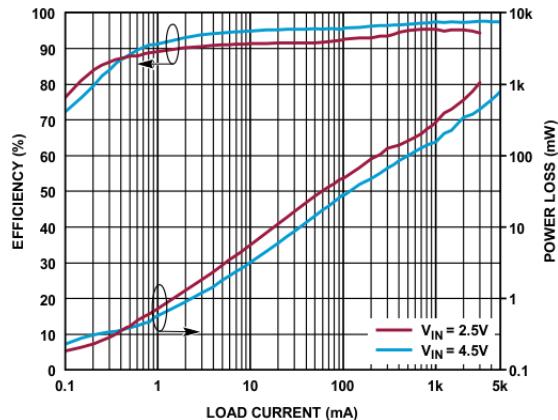

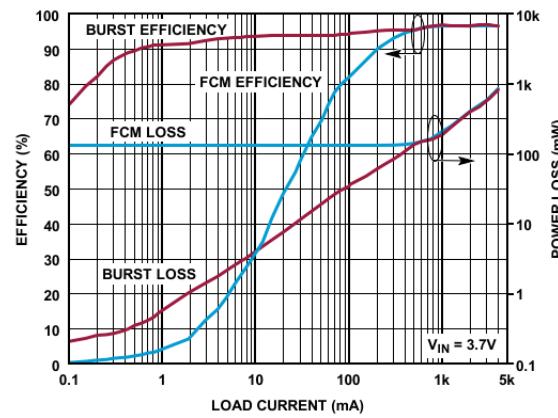

図5. 効率および電力損失と出力電流の関係

(FCMモード、26ページの回路を参照)

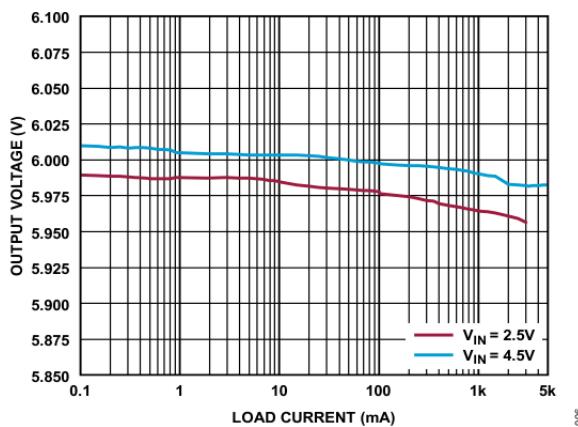

図6. 出力電圧と出力電流の関係 (Burst Mode、

26ページの回路を参照)

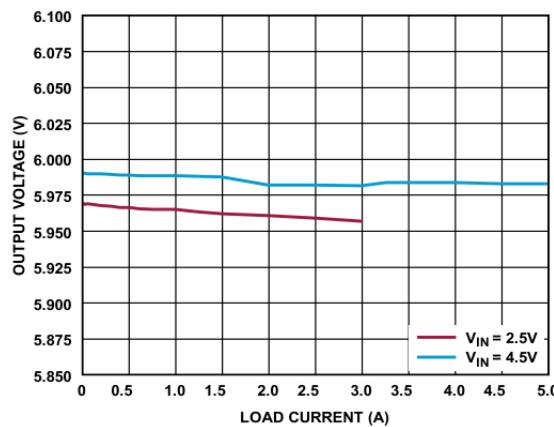

図7. 出力電圧と出力電流の関係 (FCMモード、

26ページの回路を参照)

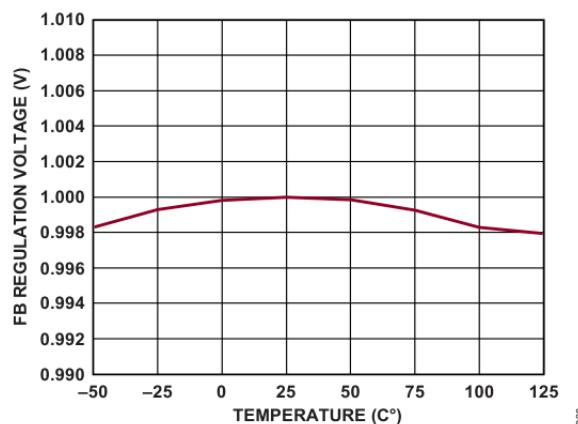

図8. FBレギュレーション電圧と温度の関係

図9. EN/UVLO閾値と温度の関係

図10. スイッチング周波数と温度の関係

図11. スペクトラム拡散変調時のスイッチング周波数

図12. ポトム・スイッチの電流制限と温度の関係

(両方のチャンネル)図13. ポトム・スイッチの最小オン／オフ時間と温度の関係

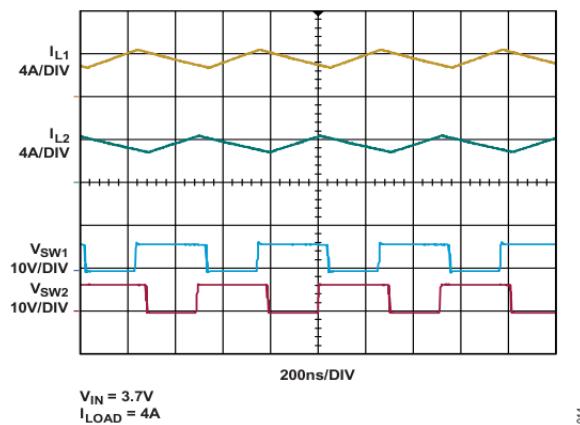

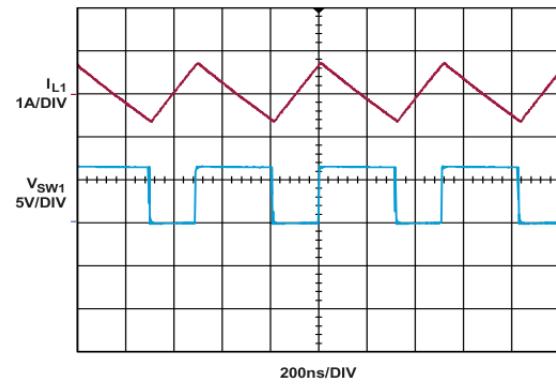

(両方のチャンネル)図14. スイッチング波形（重負荷時の2相動作、

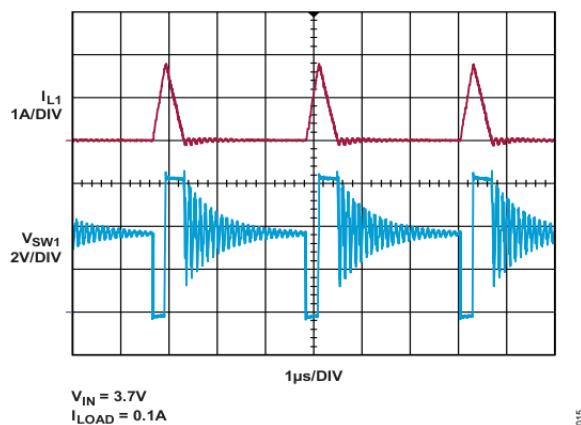

26ページの回路を参照）図15. スイッチング波形（軽負荷時の1相Burst Mode動作、

26ページの回路を参照）

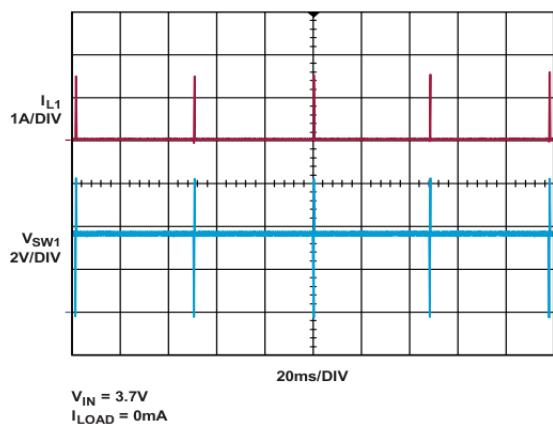

図16. スイッチング波形（ゼロ負荷時の1相Burst Mode動作、

26ページの回路を参照）

図17. スイッチング波形（ゼロ負荷時の1相FCM動作、

26ページの回路を参照）

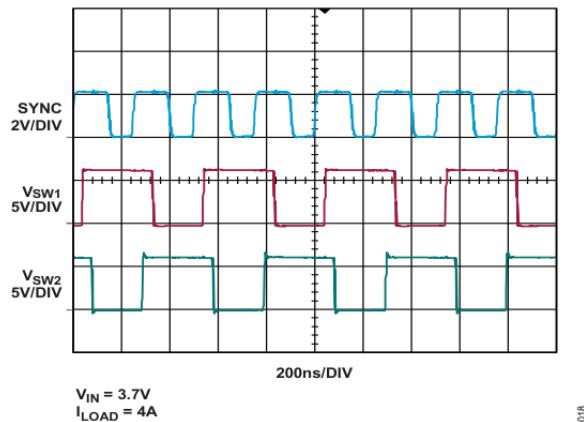

図18. スイッチング波形（同期動作における重負荷時の2相動作、

26ページの回路を参照）

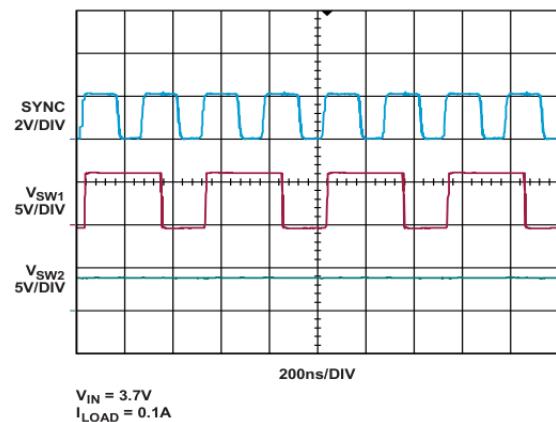

図19. スイッチング波形（同期動作における軽負荷時の1相動作、

26ページの回路を参照）

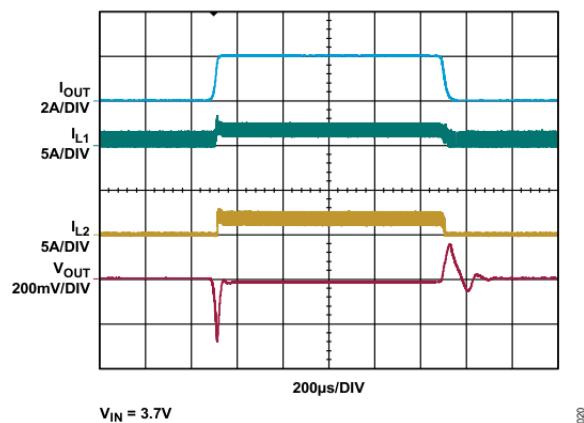

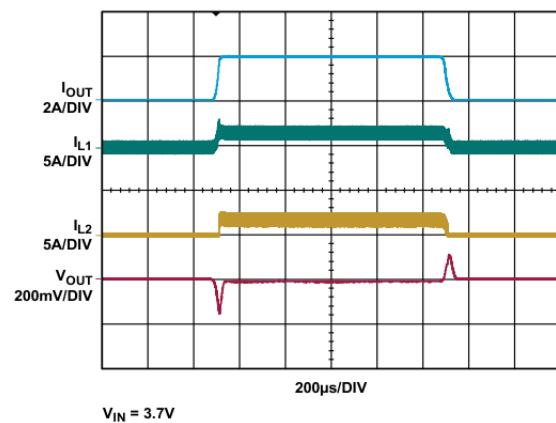

図20. 負荷過渡応答（Burst Mode動作、

26ページの回路を参照）

図21. 負荷過渡応答（FCMモード動作、

26ページの回路を参照）

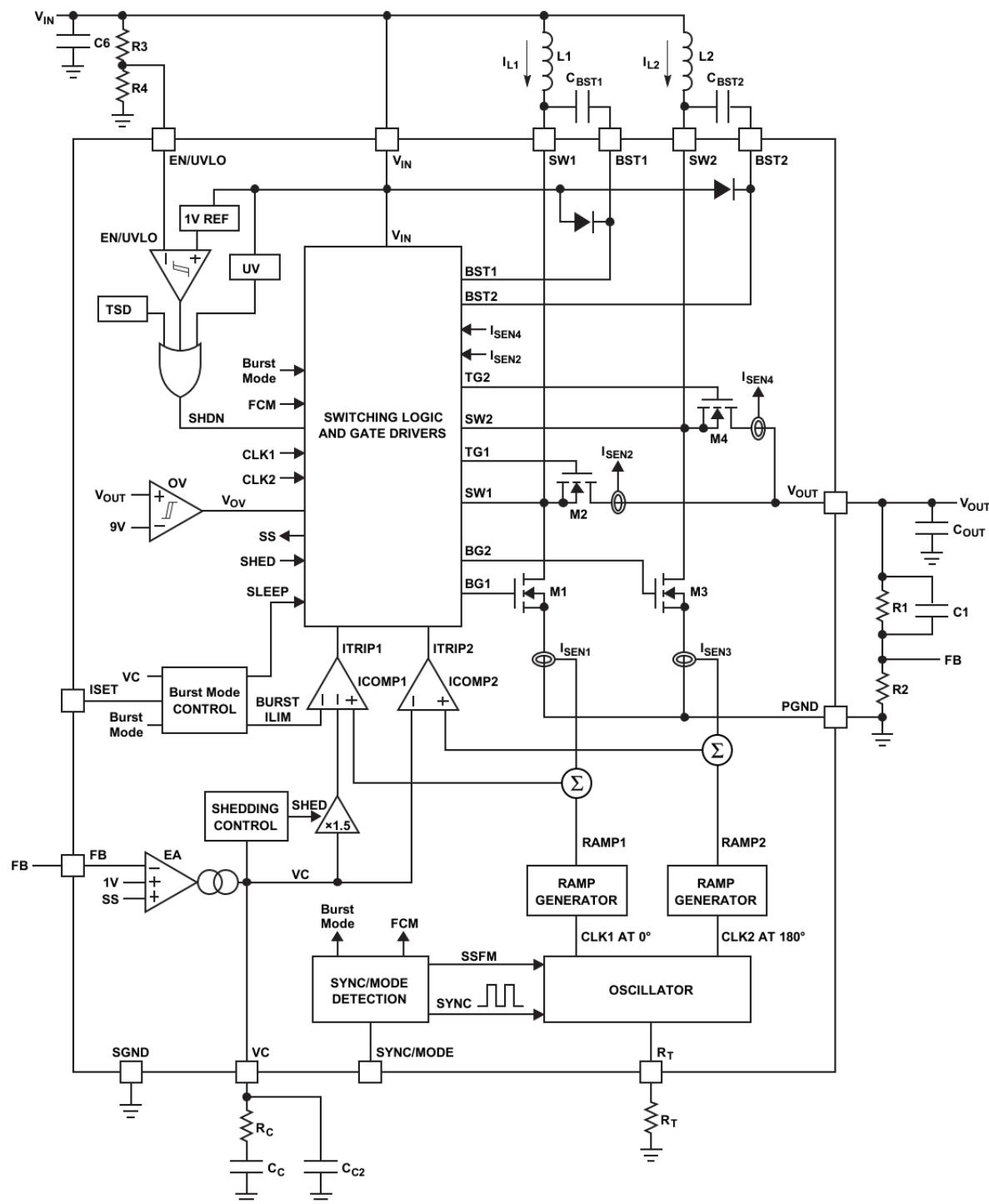

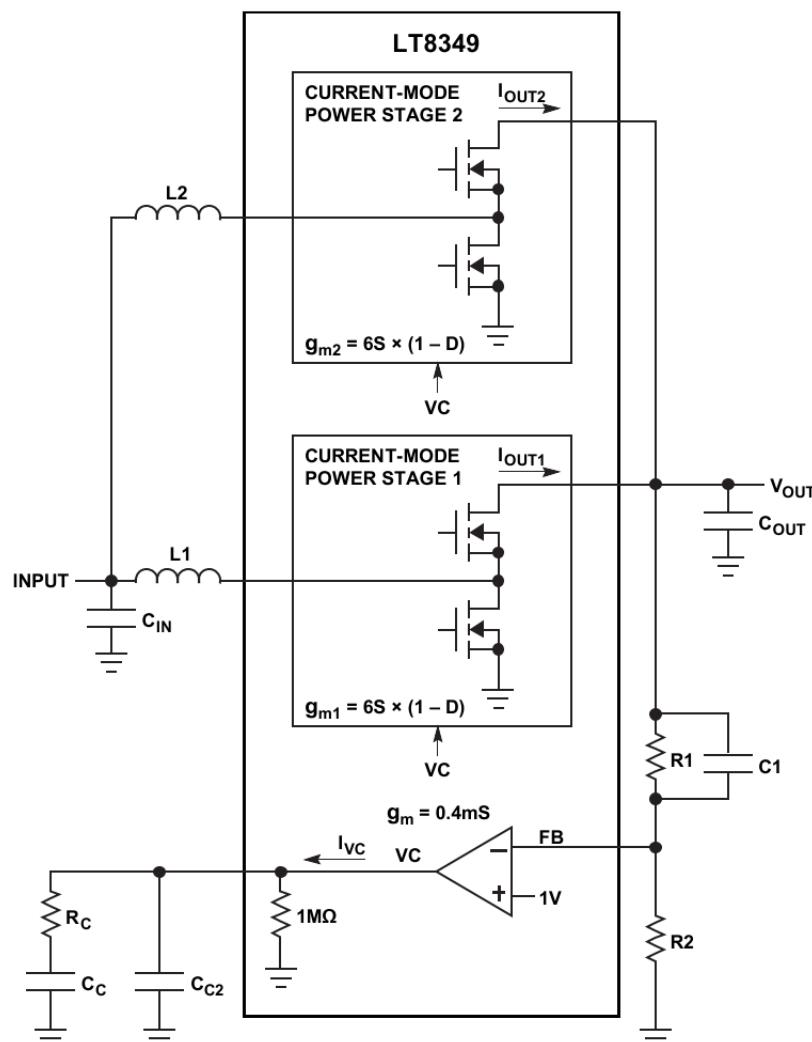

## ブロック図

図22. ブロック図

## 動作原理

LT8349は周波数の調整が可能な2相の同期整流式昇降圧コンバータで、ブロック図に示すように、固定周波数の電流モード制御方式を使用して、優れたライン・レギュレーションと負荷レギュレーションを行います。スイッチング・ロジックおよびゲート・ドライバのブロックは、CLK1サイクルの開始ごとにチャンネル1のパワースイッチM1をオンにし、CLK2サイクルの開始ごとにチャンネル2のパワースイッチM3をオンにします。CLK1とCLK2は位相差が180°で、発振器によって生成されます。M1スイッチがオンになっている間は、M1にインダクタ電流 $I_{L1}$ が流れます。M1スイッチ電流に比例した信号 $I_{SEN1}$ が安定化スロープ補償ランプRAMP1に加えられて、その合計値がPWMコンパレータICOMP1の正端子に供給されます。「VC」で示されるICOMP1の負入力電圧はエラー・アンプEAによって設定されますが、これは帰還電圧FBとリファレンス電圧(1V)の差を増幅したものです。M1がオンになっている間は、 $I_{L1}$ が増加します。ICOMP1の正入力信号がVCを超えると、ICOMP1はスイッチング・ロジックおよびゲート・ドライバのブロックに信号ITRIP1を送信して、M1をオフにします。M1がオフになると、次のCLK1サイクルが始まるまで、あるいはインダクタ電流 $I_{L1}$ が減少して0になるまで、同期電源スイッチM2がオンになります(Burst Mode動作時のみ)。M1がオフになっている間とM2がオンになっている間は、 $I_{L1}$ が減少します。チャンネル2はチャンネル1に従って動作します。また、 $I_{L1}$ と $I_{L2}$ は互いに一致するように設計されています(位相が180°異なる点を除く)。この繰り返し動作を通じ、EAは $I_{L1}$ と $I_{L2}$ の正しいピーク電流レベルを設定して $V_{OUT}$ のレギュレーションを維持します。

## 多相動作

LT8349は、他の昇圧コンバータに使われている従来の単相アーキテクチャと異なり、2つの位相を180°の差で等間隔に配置する2相アーキテクチャを使用しています。このアーキテクチャには、従来方式では1つで済んでいたインダクタが2つ必要ですが、重要な利点がいくつあります。

- ▶ ピーク・インダクタ電流が大幅に減るので、使用するインダクタを小さくできます。

- ▶ 出力リップル電流が大幅に減るので、出力容量の要件を最小限に抑えることができます。

- ▶ 低ノイズ・アプリケーションで高周波出力リップルをフィルタで容易に除去できます。

- ▶ 入力リップル電流を減らして $V_{IN}$ のノイズを低減できます。

ピーク・インダクタ電流は、単相昇圧コンバータと比較して1/2近くまで減少します。その値は次式で与えられます。

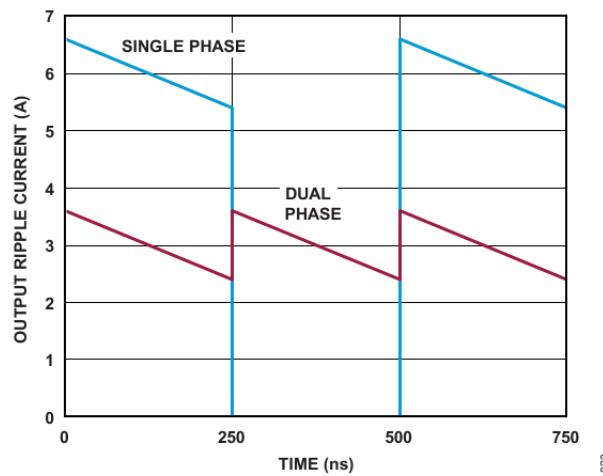

$$I_{LPEAK} \cong \frac{1}{2} \cdot \frac{I_0}{1 - D} + \frac{\Delta I_L}{2}$$

ここで、 $I_0$ は平均負荷電流、 $D$ はPWMのデューティ・サイクル、 $\Delta I_L$ はインダクタのリップル電流です。2相動作では、 $V_{IN}$ が $V_{OUT}$ の1/2を超えている限り(デューティ・サイクルが50%未満)、一方の位相が負荷に対して常時電流を供給します。デューティ・サイクルがさらに低下すると2つの位相間で負荷電流の供給が重なり始め、デューティ・サイクルがゼロに近づくにつれて各位相で負荷電流供給が同時に発生する部分が増えていきます。単相コンバータと比較した場合、これは各インダクタの出力リップル電流とピーク電流の両方を大幅に減らします。50%デューティ・サイクルで動作する単相昇圧コンバータと2相昇圧コンバータの出力リップル電流を比較したグラフを図23に示します。

図23. 3A負荷アプリケーションにおいて50%デューティ・サイクルで動作する単相昇圧コンバータと2相昇圧コンバータの出カリップル電流の比較

## アプリケーション情報

### EN/UVLOピンによるV<sub>IN</sub>オン／オフ閾値のプログラミング

EN/UVLOピンは、LT8349をイネーブル状態にするかシャットダウン状態にするかを制御します。1.0Vのリファレンスと、35mVのヒステリシスを持つコンパレータEN（ブロック図）を使用すれば、ICがオン／オフする電源電圧を正確にプログラムできます。V<sub>IN</sub>ピンの立下がり閾値電圧と立上がりヒステリシス電圧は次式で計算できます。

$$V_{V_{IN},FALLING} = 1V \cdot \frac{(R3 + R4)}{R4}$$

$$V_{V_{IN},RISING} = 35mV \cdot \frac{(R3 + R4)}{R4} + V_{V_{IN},FALLING}$$

軽負荷電流でのBurst Mode動作時は、抵抗ネットワークR3とR4に流れる電流が、ICの消費する電源電流を簡単に超えてしまう可能性があります。したがって、軽負荷時の効率に与える影響を最小限に抑えるために、R3とR4には大きい抵抗を使用することができます。シャットダウン機能を使わない場合は、EN/UVLOピンをV<sub>IN</sub>に接続できます。また、シャットダウン制御が必要な場合は、このピンをロジック・レベルに接続することもできます。EN/UVLOピンが0.15V未満になると、ICに流れるV<sub>IN</sub>静止電流が0.5μA（代表値）に減少します。

### 軽負荷電流動作

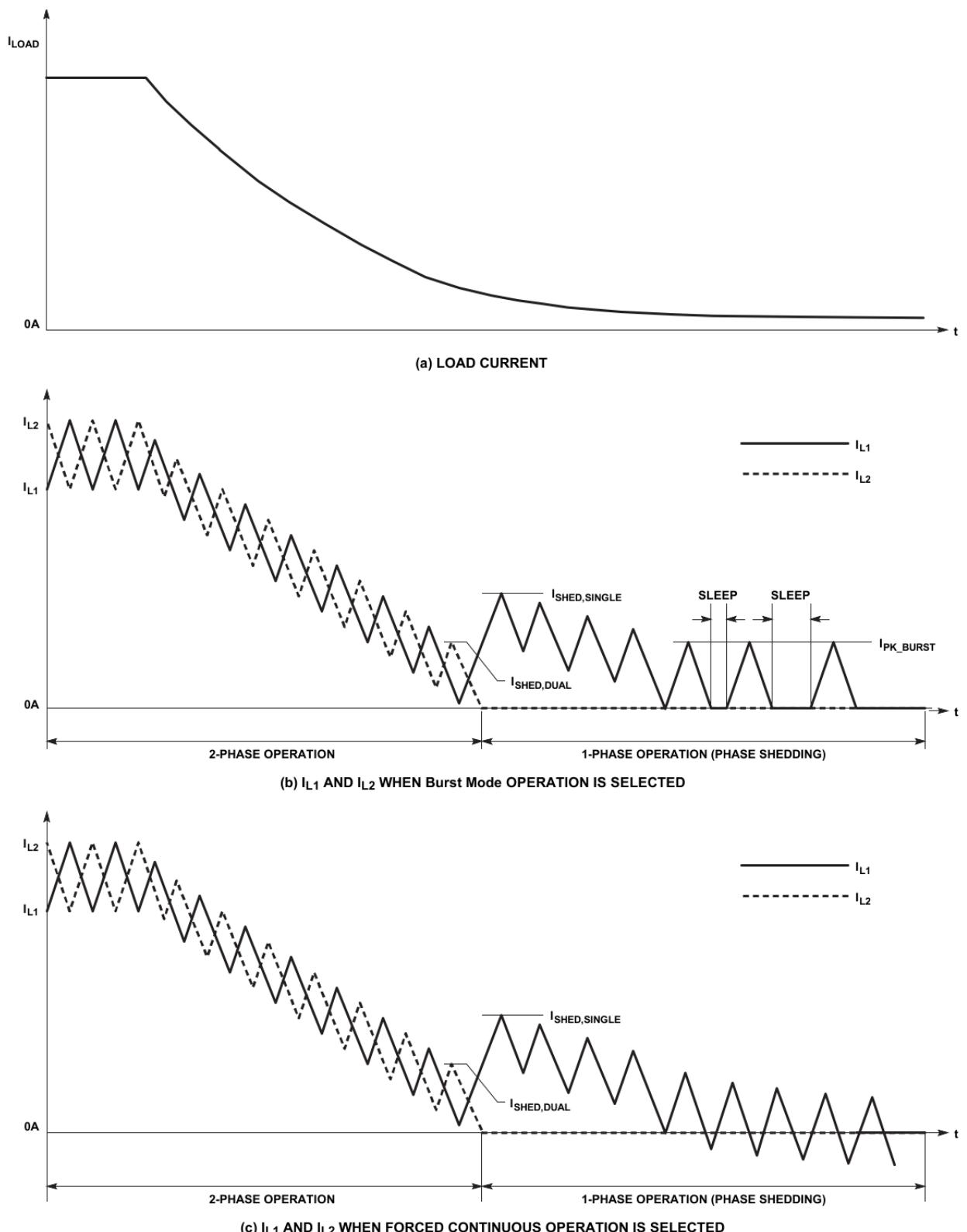

LT8349は重負荷時に位相差180°の2相で動作しますが、軽負荷時は効率を上げるために単相で動作します（Stage Sheding動作）。負荷が非常に軽い場合、LT8349では単相の低リップルBurst Mode動作または単相の強制連続動作のどちらかを選択できます。図24は、負荷電流を非常に大きい値から非常に小さい値へと徐々に減少させた場合のLT8349の動作を示す簡略図です。図24aは負荷電流を示し、図24bはSYNC/MODEピンでBurst Mode動作を選択した場合のI<sub>L1</sub>電流とI<sub>L2</sub>電流を示しています。図24bに示すように、重負荷時のLT8349は2相動作をします。2相動作時は、各チャンネルのインダクタのピーク電流が互いに一致します。2相動作時に各インダクタのピーク電流が位相シェディング閾値I<sub>SHED,DUAL</sub>（約1.7A）まで低下すると、チャンネル2がオフになって（I<sub>L2</sub>を0Aに維持）LT8349は単相で動作します。同時に、遷移を円滑するためにチャンネル1の電流ゲインが約1.5倍に増やされ、その結果、単相動作時におけるチャンネル1インダクタのピーク電流の位相シェディング閾値（I<sub>SHED,SINGLE</sub>）も1.5倍（+代表値0.35Aのヒステリシス）になります。

$$I_{SHED,SINGLE} \approx (I_{SHED,DUAL} + 0.35A) \cdot 1.5$$

負荷電流がさらに減少すると、チャンネル1ボトム・スイッチの最小ピーク電流（インダクタの最小ピーク電流と同じ）がISETピンによって設定される値I<sub>BURST</sub>にセットされます。これは、VCノード（ブロック図）がこれより低い値を示していたとしても同じです。この状態で、LT8349はインダクタのピーク電流を減らすのではなく、スイッチング周波数を下げることによって出力レギュレーション電圧を維持します。LT8349は单一パルス分の電流を出力コンデンサへ送り、その後はスリープ期間（図24b）とします。スリープ期間中は内部回路の大半がオフになり、出力電力は出力コンデンサによって供給されます。この低リップルのBurst Mode動作は、入力静止電流と出力電圧リップルを最小限に抑えます。出力負荷が低下するにつれて单一電流パルスの繰り返し頻度は減少し、LT8349がスリープ・モードになっている時間のパーセンテージは増加します。この結果、軽負荷時の効率は標準的なコンバータよりもはるかに高くなります。パルスの間隔を最大にすると、出力負荷がない代表的なアプリケーションでは、コンバータのV<sub>IN</sub>ピン静止電流が15μAに近付きます。軽負荷時の静止電流性能を最適化するには、負荷電流として出力に現れる帰還抵抗分圧器の電流を最小限に抑える必要があります。

図24. 負荷電流を大きい値から非常に小さい値へと減少させた場合のLT8349の動作を示す簡略図

より高い軽負荷時効率を実現するには、Burst Mode動作時の単一パルスでより多くのエネルギーを出力に供給し、各パルス間でLT8349がより長くスリープ・モードに止まれるようにする必要があります。これは、ISETピンを使ってIBURST電流をより高い値に設定することで実現できます（[ピン機能](#)のセクションを参照）。軽負荷時の効率は、インダクタの値を大きくすることによってさらに向上させることができます。この場合のトレードオフは、単一パルスでより大きなエネルギーを供給すると、軽負荷時の出力電圧リップルが大きくなることです。しかし、出力電圧リップルは出力容量を大きくすることによって減らすことができ、その減少量は容量値に比例します。インダクタや出力コンデンサの値を調整するときは、十分な設計マージンを確保するためにシステムの安定性を慎重に評価する必要があります。インダクタや出力コンデンサを大きくすれば、コストやソリューション・サイズも増大します。

図24cはSYNC/MODEピンで強制連続動作（FCM）を選択した場合のIL1電流とIL2電流を示しています。図24cに示すように、軽負荷時にはIL2が0Aに維持され、IL1は負の値とすることもできるので、レギュレータは出力電流がゼロになるまで設定周波数でスイッチングできます。このモードには負荷の全範囲にわたって設定スイッチング周波数を維持できるという利点があるのでスイッチの高調波とEMIが安定し、予測が可能です。FCMの欠点は、Burst Mode動作と比較して軽負荷時の効率が低くなることです。

## スイッチング周波数と同期

スイッチング周波数の選択は、効率と部品サイズのトレードオフです。低周波数動作では、パワー・スイッチのスイッチング損失とゲート駆動電流を減らすことができるため効率が向上します。しかし、低周波数動作には物理的サイズの大きいインダクタが必要です。

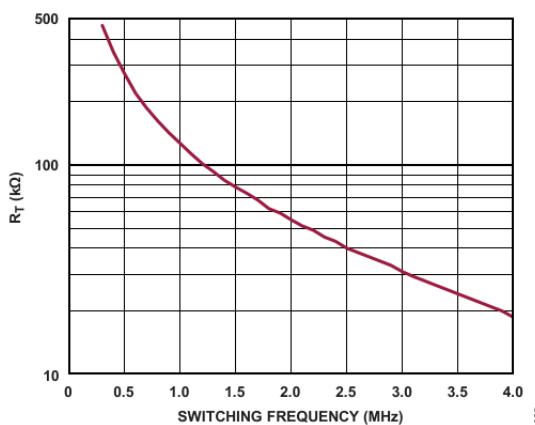

LT8349は固定周波数アーキテクチャを使用しています。このアーキテクチャでは、ブロック図に示すように、RTピンとグラウンドの間に抵抗を1個外付けすることによって、周波数を300kHz～4MHzの範囲でプログラムすることができます。所定のスイッチング周波数に対応するRTの値を選択するための一覧を表4に示します。また、RTの値とスイッチング周波数の関係を示すグラフを図25に示します。

図25. R<sub>T</sub>値とスイッチング周波数の関係

表4. SW周波数 (f<sub>sw</sub>) とR<sub>T</sub>値の関係

| f <sub>sw</sub> (MHz) | R <sub>T</sub> (kΩ) | f <sub>sw</sub> (MHz) | R <sub>T</sub> (kΩ) |

|-----------------------|---------------------|-----------------------|---------------------|

| 0.3                   | 464                 | 2.2                   | 48.7                |

| 0.4                   | 348                 | 2.3                   | 45.2                |

| 0.5                   | 274                 | 2.4                   | 43.2                |

| 0.6                   | 221                 | 2.5                   | 40.2                |

| 0.7                   | 187                 | 2.6                   | 38.3                |

| 0.8                   | 162                 | 2.7                   | 36.5                |

| 0.9                   | 143                 | 2.8                   | 34.8                |

| $f_{SW}$ (MHz) | $R_T$ (kΩ) | $f_{SW}$ (MHz) | $R_T$ (kΩ) |

|----------------|------------|----------------|------------|

| 1.0            | 127        | 2.9            | 33.2       |

| 1.1            | 113        | 3.0            | 30.9       |

| 1.2            | 102        | 3.1            | 29.4       |

| 1.3            | 93.1       | 3.2            | 28.0       |

| 1.4            | 84.5       | 3.3            | 26.7       |

| 1.5            | 78.7       | 3.4            | 25.5       |

| 1.6            | 73.2       | 3.5            | 24.3       |

| 1.7            | 68.1       | 3.6            | 23.2       |

| 1.8            | 61.9       | 3.7            | 22.1       |

| 1.9            | 59.0       | 3.8            | 21.0       |

| 2.0            | 54.9       | 3.9            | 20.0       |

| 2.1            | 51.1       | 4.0            | 18.7       |

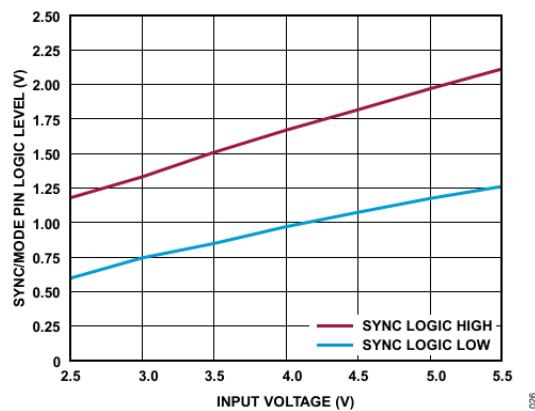

LT8349の動作周波数は、最小パルス幅100nsの外部クロック・ソースに同期させることができます。同期時にSYNCピンで必要になる外部クロック閾値（代表値）を図26に示します。

図26. SYNC/MODEピンのロジック・レベル（代表値）と入力電圧の関係

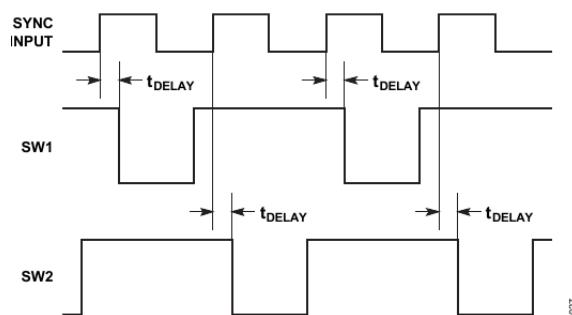

SYNC/MODEピンにデジタル・クロック信号を入力することによって、ICはSYNCクロック周波数の半分で動作し、軽負荷時には自動的にFCM動作になります。FCMでは発振器が連続して動作し、SW1とSW2の立下がり遷移は、遅延時間80ns（代表値）でクロックの立上がりエッジに交互に同期します（位相差180°）。図27に、SYNC/MODEピン入力クロックと、SW1遷移およびSW2遷移の同期の様子を示します。この機能を使用するときは、できるだけSYNCパルス周波数に近いスイッチング周波数をプログラムできる $R_T$ 抵抗を選ぶ必要があります。

図27. SYNC/MODEピン入力クロックとSW1およびSW2遷移の同期

## スペクトラム拡散周波数変調

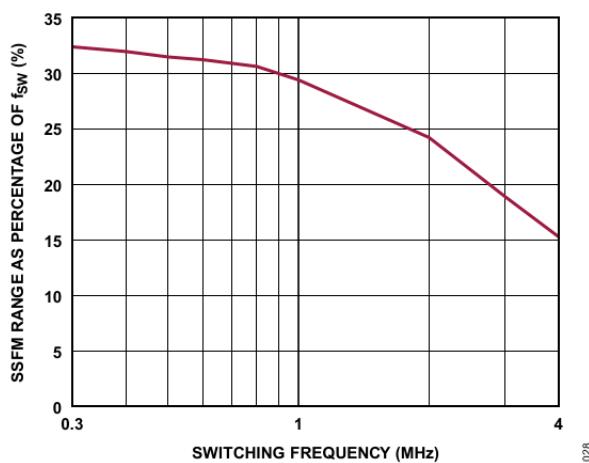

LT8349は、EMI放射を更に減らすためにスペクトラム拡散周波数変調機能を備えています。50kの抵抗を介してSYNC/MODEピンをグラウンドに接続すれば、Burst Mode動作でスペクトラム拡散周波数変調を選択できます。あるいは、SYNC/MODEピンをV<sub>IN</sub>ピンに接続すれば、FCM動作でスペクトラム拡散周波数変調を選択できます。スペクトラム周波数変調選択時は、ステップ三角波周波数変調を使用して、R<sub>T</sub>抵抗でプログラムされた値と、その値より約25% (F<sub>sw\_set</sub> = 2MHz時) 高い値の間で、内部発振器周波数を変化させます。スイッチング周波数に伴うスペクトラム拡散の深度（代表値）の変化を図28に示します。変調周波数はスイッチング周波数の約0.45%です。例えば、LT8349を2MHzにプログラムしてスペクトラム拡散周波数変調を選択した場合、発振器周波数は9kHzきざみで2MHzから2.5MHzまで変化します（代表的な性能特性セクションに示すスペクトラム拡散変調時の発振器周波数の曲線を参照）。軽負荷時の動作では、スペクトラム拡散周波数変調は、Burst Mode動作よりFCMモード動作で使用した方が効果的です。これは、FCM動作では、プログラムされたスイッチング周波数が負荷電流範囲全体にわたって維持されるからです。

図28. F<sub>sw</sub>（代表値）のパーセンテージで示したSSFM範囲とスイッチング周波数の関係

## FB抵抗ネットワークと無負荷時の静止電流

出力電圧は、出力とFBピンの間にある抵抗分圧器でプログラムされます。抵抗値は以下の式に従って選択します。

$$R1 = R2 \cdot \left( \frac{V_{OUT}}{1V} - 1 \right)$$

式に使われている記号についてはブロック図を参照してください。出力電圧の精度を維持するには、1%抵抗を使用することを推奨します。入力静止電流を低く抑え、良好な軽負荷時効率を得る必要がある場合は、FB抵抗分圧器に大きい抵抗値を使用してください。分圧器に流れる電流は負荷電流として働き、コンバータへの無負荷時入力電流を増大させます。LT8349の無負荷時Burst Mode静止電流は、次式を使って予測できます。

$$I_Q \approx 15\mu A + \left( \frac{V_{OUT}}{R1 + R2} + 1\mu A \right) \cdot \frac{V_{OUT}}{V_{IN}} \cdot 3$$

ここで、15μAはLT8349のV<sub>IN</sub>ピン静止電流です。第2項は帰還分圧器とV<sub>OUT</sub>ピン（1μA）に流れる電流で、昇圧動作の入力に反映されます。3.7V入力、6V出力、R1 = 1MΩ、R2 = 200kΩの昇圧コンバータの場合、LT8349コンバータには無負荷時に電源から約45μAの電流が流れると計算できます。

大きいFB抵抗を使用するときは、V<sub>OUT</sub>とFBの間に4.7pF～22pFの進相コンデンサを接続すると共に、十分な設計マージンを確保するためにはシステムの安定性を慎重に評価する必要があります。

## 過電圧ロックアウト

V<sub>OUT</sub>ピンの電圧は、LT8349によって常にモニタされます。V<sub>OUT</sub>ピンの電圧が約9Vを超えると、過電圧状態となります。過電圧状態になるとスイッチングは停止します。V<sub>OUT</sub>ピンの電圧が8.9V以下に戻ると、通常のスイッチングが再開されます。

## スタートアップ

スタートアップ時のピーク・スイッチ電流とV<sub>OUT</sub>のオーバーシュートを制限するために、LT8349はソフトスタート動作を行う回路を内蔵しています（ブロック図のエラー・アンプEAを参照）。スタートアップ時には、内蔵のソフトスタート回路が内部SS信号をゼロから1Vまでゆっくりとランプ・アップします。SS電圧がFB初期電圧と1Vの間の値に低下すると、LT8349はFBピン電圧を1VではなくSS電圧にレギュレーションします。このようにして、スタートアップ時のピーク・スイッチ電流を制限しながら、出力コンデンサが徐々に最終値まで充電されます。

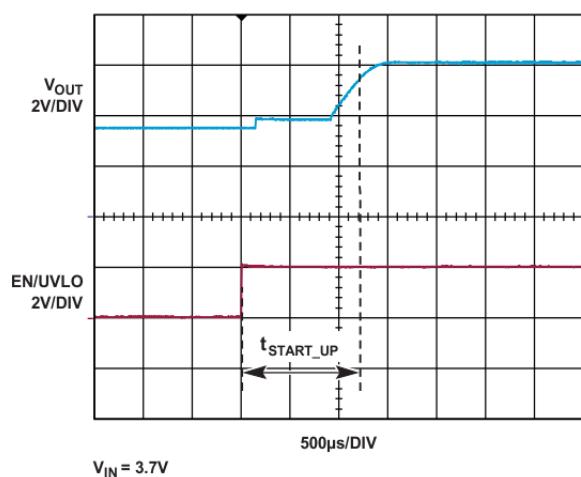

図29に示すように、スタートアップ時間T<sub>START\_UP</sub>は、EN/UVLOがハイに遷移してから、V<sub>OUT</sub>がFB抵抗ネットワークによってプログラムされたレギュレーション電圧の90%に達するまでの時間です。T<sub>START\_UP</sub>の概算値は次式で得られます。

$$T_{\text{START\_UP}} \approx 0.15\text{ms} + \frac{3.6\text{V}}{V_{\text{IN}} - 0.1\text{V}} \cdot \frac{2100}{f_{\text{SW}}}$$

LT8349は、スタートアップ時にはスペクトラム拡散周波数変調なしの固定周波数動作を選択し、SYNC/MODEピン設定は無視されます。

図29. 代表的なスタートアップ波形

LT8349昇圧コンバータを通電状態の電源にそのまま接続すると、L1、L2、C<sub>OUT</sub>、およびM2とM4のボディ・ダイオードで構成される共振回路（ブロック図を参照）によって、V<sub>OUT</sub>がV<sub>IN</sub>の2倍の電圧でリニングを起こすことがあります。このようなオーバーシュートがV<sub>OUT</sub>の定格を超ってしまう場合は、負荷およびコンバータを保護するために制限を加える必要があります。このような状況では、図30に示すようにV<sub>IN</sub>とV<sub>OUT</sub>の間に小さいショットキー・ダイオードやシリコン・ダイオードを接続することで共振回路を無効化し、V<sub>OUT</sub>のオーバーシュートを制限することができます。このようなダイオードの接続は、出力短絡や過負荷といった出力故障状態に対して、昇圧機能の堅牢性を向上させることになります。これは、ダイオードが出力電流の大部分をICから迂回させるためです。Dの定格値は、V<sub>IN</sub>電源の短絡電流に合わせる必要があります。例えば、入力側バッテリまたは電圧源の電流制限値です。

図30.  $V_{IN}$ と $V_{OUT}$ の間にダイオードを追加したLT8349電力段の簡略図

## インダクタの選択

連続導通モード (CCM) での動作時は、出力電圧 ( $V_{OUT}$ ) と入力電圧 ( $V_{IN}$ ) に基づいてデューティ・サイクルを計算できます。デューティ・サイクルが最大 ( $D_{MAX}$ ) になるのは、コンバータの入力電圧が最小のときです。

$$D_{MAX} = \frac{V_{OUT} - V_{IN(MIN)}}{V_{OUT}}$$

不連続導通モード (DCM) では特定の周波数で変換比が向上しますが、効率は低下してスイッチング電流値も大きくなります。

各インダクタのリップル電流 $\Delta I_{sw}$ は、インダクタ値の選択、コンバータの最大出力電流能力、およびBurst Mode動作における軽負荷時の効率に直接影響します。より小さい $\Delta I_{sw}$ 値を選択すれば出力電流能力とBurst Mode動作における軽負荷時の効率は向上しますが、大きいインダクタンス値が必要となり、電流ループ・ゲインも低下します。より大きい $\Delta I_{sw}$ 値を選択すれば高速の過渡応答が得られ、低インダクタンス値の使用も可能になりますが、入力電流リップルやコア損失の増大、Burst Mode動作における軽負荷時効率の低下、出力電流能力の低下といった欠点が生じます。高デューティ・サイクル動作時に $\Delta I_{sw}$ の値を大きくすると、低調波振動を起こす可能性があります。一般的には $\Delta I_{sw} = 1.2A \sim 2A$ の範囲が多くのアプリケーションにとって適切な開始値ですが、十分な設計マージンを確保するためにシステムの安定性を慎重に評価する必要があります。

動作入力電圧範囲が決まって、動作周波数と各インダクタのリップル電流を選択したら、次式を使って昇圧コンバータの各インダクタの値を決定することができます。

$$L1 = L2 = \frac{V_{IN(MIN)}}{\Delta I_{sw} \cdot f_{sw}} \cdot D_{MAX}$$

各インダクタのピーク電流値は、電気的特性の表に示すように、LT8349のボトム・スイッチ電流制限値と同じです。インダクタは、インダクタのピーク電流に対処するために、十分な飽和定格とRMS電流定格のものを選ぶ必要があります。

## 入力コンデンサの選択

昇圧コンバータの入力リップル電流は連続的なものなので、（出力リップル電流と比較して）比較的低い値に止まります。 $C_{IN}$ の値はソース・インピーダンスの関数であり、一般にソース・インピーダンスが高いほど必要な入力容量も大きくなります。 $C_{IN}$ リップル電流の実効値は次式で予測できます。

$$I_{RMS(CIN)} = 0.3 \cdot \Delta I_L$$

## 出力コンデンサの選択

出力コンデンサには2つの重要な役割があります。1つめが、LT8349の不連続トップ・スイッチ電流のフィルタリングを行って、DC出力を生成することです。この役割では、出力コンデンサが出力リップルを決定するので、スイッチング周波数でのインピーダンスを小さくすることが重要です。2つめの役割は、過渡負荷を吸収してICの制御ループを安定させるためにエネルギーを保存することです。X5RおよびX7Rタイプのセラミック・コンデンサは等価直列抵抗 (ESR) が非常に小さく、出力リップルを緩和して良好な過渡応答を実現します。過渡応答性能は、出力容量を大きくしてV<sub>OUT</sub>とFBの間にフィードフォワード・コンデンサを追加することによって改善できます。フィードフォワード・コンデンサを使用したり出力容量を調整したりする場合は、十分な設計マージンを確保するためにシステムの安定性を慎重に評価する必要があります。また、出力容量を大きくすると、出力電圧リップルが小さくなります。スペースとコストを節約するために出力容量を小さくすることができますが、過渡応答性能が低下してループも不安定になります。

また、ワイヤやケーブルが長いため負荷に対するインダクタンスがかなり大きくなる場合は、更に大きい容量が必要になります。これには電界コンデンサを使用できます。コンデンサを選択するときは、コンデンサのデータシートを十分に吟味し、電圧バイアスや温度などの関係する動作条件に基づいて、効果的な容量を計算する必要があります。

## 周波数補償

LT8349には、ループ補償の最適化に使用できるVCピンがあります。補償ネットワークの設計は少々複雑で、最適値はアプリケーション、特に出力コンデンサのタイプによって異なります。実用的な方法は、このデータシートの回路の中から目的のアプリケーションに似た回路を探して出発点とし、補償ネットワークを調整して性能を最適化することです。このプロセスにはLTspice®シミュレーションが役に立つ場合があります。その後負荷電流、入力電圧、温度など、全動作条件について安定性を確認します。

LT8349の制御ループの簡略回路図を図31に示します。エラー・アンプは、FBピンの電圧に比例する出力電流I<sub>VC</sub>を生成するトランスクタンス・アンプ ( $g_m$ ) です。それぞれが電力段とインダクタで構成される2つのパワー・セクションは、VCピンの電圧に比例する出力電流 ( $I_{OUT1}$ または $I_{OUT2}$ ) を生成するトランスクタンス・アンプ ( $gm1$ または $gm2$ ) としてモデル化されています。出力コンデンサC<sub>OUT</sub>は $I_{OUT1}$ と $I_{OUT2}$ を積分し、VCピンのコンデンサ ( $C_c$ ) はエラー・アンプの出力電流I<sub>VC</sub>を積分するので、ループには2つの極が存在します。ゼロが必要ですが、これはC<sub>c</sub>と直列に接続した抵抗R<sub>C</sub>によって得られます。この簡単なモデルは、インダクタの値が大きすぎず、ループのクロスオーバー周波数がスイッチング周波数よりはるかに低いという条件が満たされている限り、良好に機能します。小さいコンデンサC<sub>c2</sub>を追加すると、VCピンにカップリングしたスイッチング・ノイズをフィルタリングできます。また、帰還抵抗分圧器のR<sub>1</sub>と並列に進相コンデンサ (C<sub>1</sub>) を接続すれば、過渡応答を改善できます。このコンデンサは、帰還ノードとグラウンドの間の容量によって生じる寄生極を相殺するためにも必要です。

図31. ループ応答の簡略モデル

031

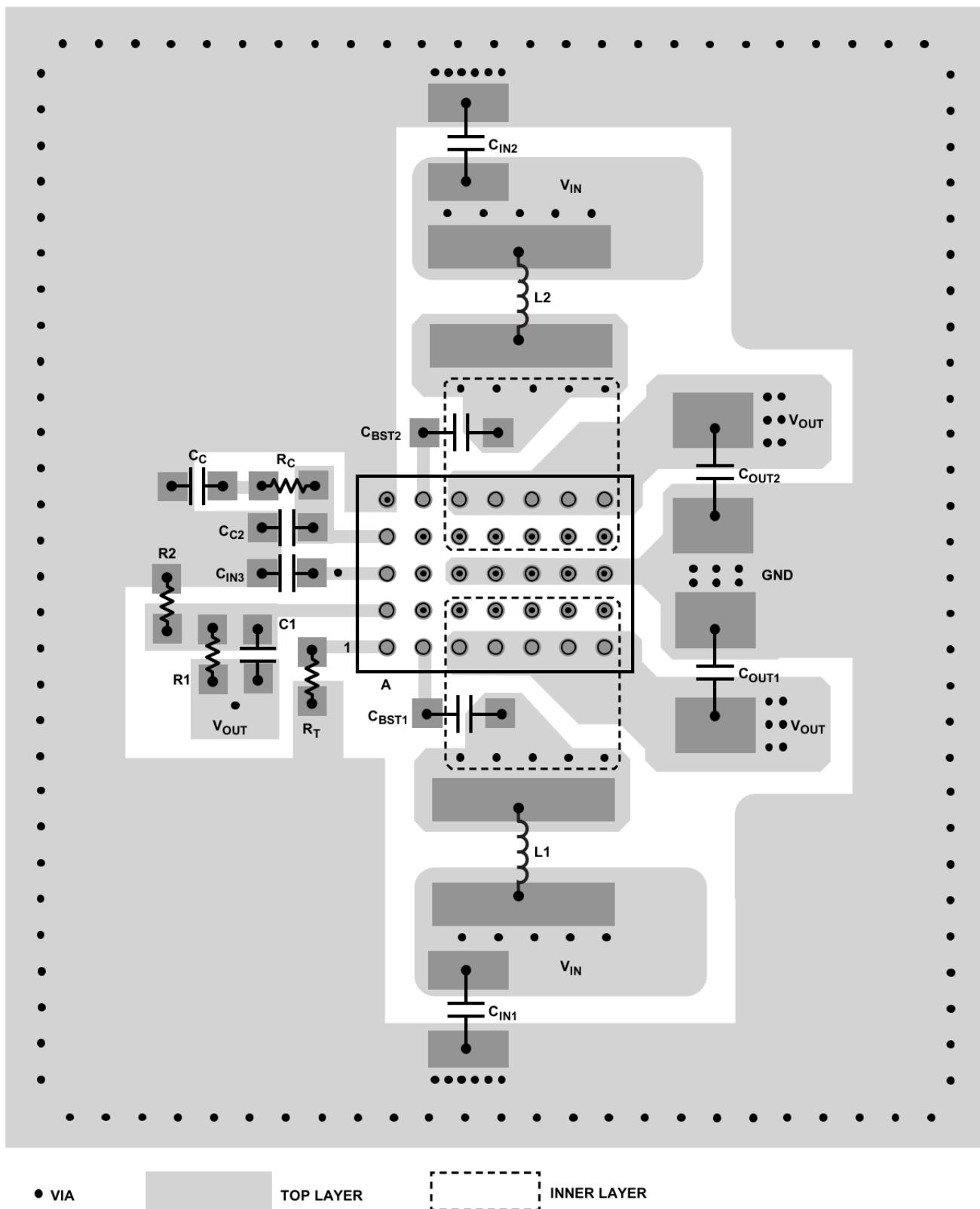

## 基板レイアウト

LT8349は、電磁干渉(EMI)の放出を最小限に抑えて、高周波数でのスイッチング時に最大限の効率が得られるよう特に設計されています。LT8349用の推奨PCBレイアウト(簡略図)を図32に示します(SYNC、EN、ISETを接続した回路は示されていません)。PCBレイアウトに関する詳細とPCB設計ファイルについては、LT8349の評価用ボードのユーザ・ガイドを参照してください。

放射と高周波共振の問題を防止するには、コンポーネントを正しいレイアウトでICに接続することが極めて重要であり、高di/dtの電力経路については特に注意が必要です。図32を参照してください。以下の高di/dtループは、誘導性のリンクギングとEMIの放出を減らすために、互いにできるだけ近付ける必要があります。

- ▶ チャンネル1の高di/dtループは、C<sub>OUT1</sub>の正端子、LT8349の(C-G)1ピン、LT8349のPGNDピン、およびC<sub>OUT1</sub>の負端子によって形成されます。

- ▶ チャンネル2の高di/dtループは、C<sub>OUT2</sub>の正端子、LT8349の(C-G)4ピン、LT8349のPGNDピン、およびC<sub>OUT2</sub>の負端子によって形成されます。

出力コンデンサは、インダクタや入力コンデンサと共に回路基板の同じ側に配置し、その接続も同じ層上で行います。電流分担を改善するため、2つのチャンネルのレイアウトを同じにすることを推奨します（[図32](#)を参照）。

局部的な切れ目のない電源グランド・プレーンを、表面層に最も近い層にあるアプリケーション回路の下に配置してください。SW1、SW2、BST1、およびBST2ノードは、できるだけ小さくする必要があります。また、FBノードとRTノードも小さく保ち、これらのノードが、SW1、SW2、BST1、およびBST2ノードによって生じるノイズから、グラウンド・パターンで遮蔽されるようにします。

更に、熱抵抗を小さく保つためにグランド・プレーンをできるだけ広くし、回路基板内の広くなった電源グランド・プレーンに多数のサーマル・ビアを追加します。

## 熱に関する考慮事項

LT8349から効率よく放熱するには、PCBのレイアウトに細心の注意を払う必要があります。電源グランド・プレーンは、サーマル・ビアを配置した広い銅層で構成する必要があります。これらの層は、ICが放出する熱を拡散します。ビアを追加すれば、熱抵抗を更に小さくすることができます。最大負荷電流は、ジャンクション温度がその最大温度定格値に近付くに従ってディレーティングする必要があります。IC内での消費電力は、効率測定値から合計電力損失を計算して、そこからインダクタ損失を減じることによって予測できます。ジャンクション温度は、ICの合計消費電力にジャンクションから周囲への熱抵抗を乗じ、その値に周囲温度を加えることによって計算できます。LT8349は、一時的な過負荷状態からデバイスを保護することを目的とした過熱保護機能を内蔵しています。この過熱保護機能により、ジャンクション温度が170°C（代表値）を超えるとICがシャットダウンします。ジャンクション温度が165°C（代表値）未満に下がると、内部ソフトスタートがトリガされます。この保護機能が作動するときは、ジャンクション温度が最大定格値を超えていません。仕様に規定された絶対最大動作ジャンクション温度（絶対最大定格のセクションを参照）を超える温度での連続動作は、デバイスの信頼性を損なったり、デバイスに恒久的な損傷を生じさせたりする可能性があります。

図32. LT8349の推奨PCBレイアウト

## 代表的なアプリケーション

図33. 2.5V~4.5V入力、6V出力の昇圧コンバータ

図34.効率および電力損失と出力電流の関係

図35.効率および電力損失と出力電流の関係

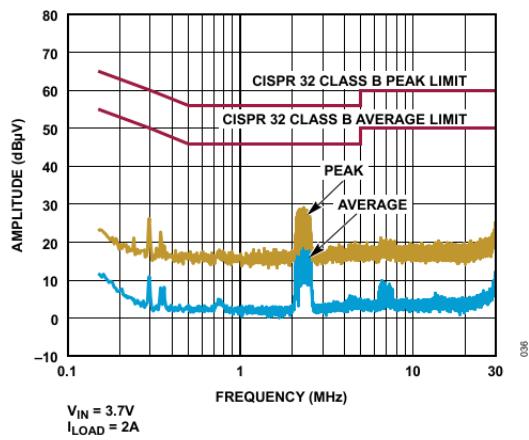

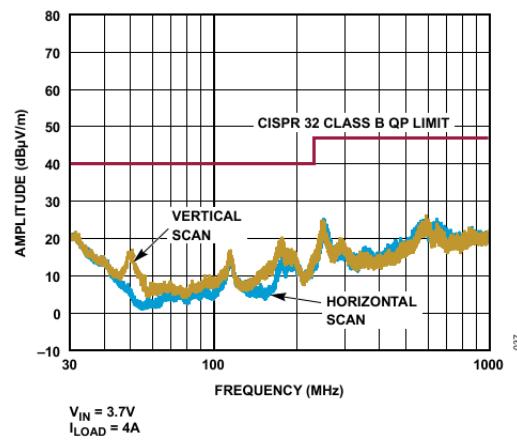

図36.EVAL-LT8349-BZを使いSSFMモードで測定した CISPR32による伝導EMI

図37.EVAL-LT8349-BZを使いSSFMモードで測定した CISPR32による放射EMI

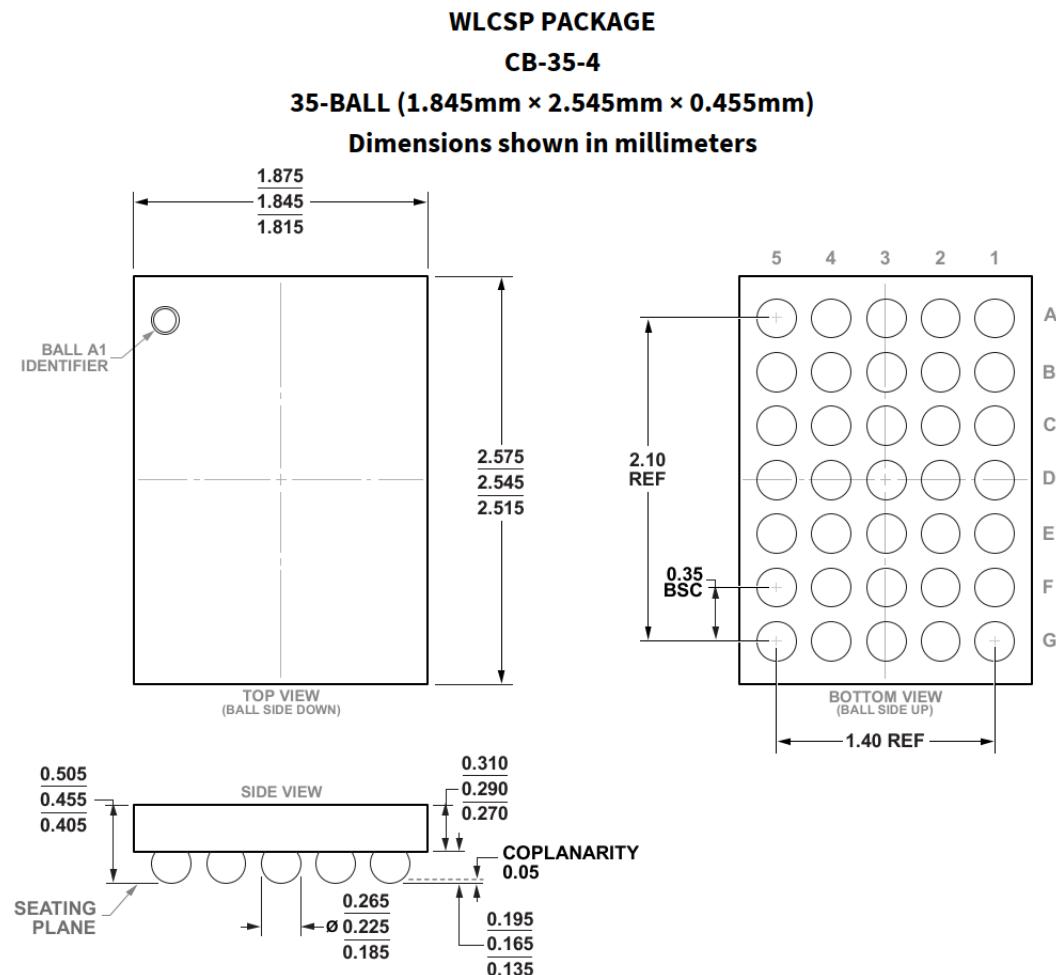

## パッケージの説明

02-11-2022A

## 関連製品

| 製品番号            | 説明                                          | 注釈                                                                                                                |

|-----------------|---------------------------------------------|-------------------------------------------------------------------------------------------------------------------|

| LT8336          | 40V、2.5A、低IQの同期整流式昇圧Silent Switcher         | $V_{IN} = 2.7V \sim 40V$ 、 $V_{OUT(MAX)} = 40V$ 、 $I_Q = 4\mu A$ (Burst Mode動作) 、<br>3mm × 3mm LQFNパッケージ          |

| LT8337/LT8337-1 | 28V、5A、低IQの同期整流式昇圧Silent Switcher           | $V_{IN} = 2.7V \sim 28V$ 、 $V_{OUT(MAX)} = 28V$ 、 $I_Q = 4\mu A$ (Burst Mode動作) 、<br>3mm × 3mm LQFNパッケージ          |

| LTC3421         | 出力切断機能を備えた3A、3MHzの同期整流式昇圧DC/DCコンバータ         | 効率95%、 $V_{IN} = 0.5V \sim 4.5V$ 、 $V_{OUT(MAX)} = 5.25V$ 、 $I_Q = 12\mu A$ 、<br>$I_{SD} < 1\mu A$ 、QFN24パッケージ    |

| LTC3428         | 4A、2MHz (1MHzスイッチング) の2相昇圧DC/DCコンバータ        | 効率92%、 $V_{IN} = 1.6V \sim 4.5V$ 、 $V_{OUT(MAX)} = 5.25V$ 、 $I_{SD} < 1\mu A$ 、<br>3mm × 3mm DFNパッケージ             |

| LTC3425         | 出力切断機能を備えた5A、8MHz、低リップルの4相同期整流式昇圧DC/DCコンバータ | 効率95%、 $V_{IN} = 0.5V \sim 4.5V$ 、 $V_{OUT(MAX)} = 5.25V$ 、 $I_Q = 12\mu A$ 、<br>$I_{SD} < 1\mu A$ 、QFN32パッケージ    |

| LTC3124         | 出力切断機能を備えた15V、5Aの2相同期整流式昇圧DC/DCコンバータ        | $V_{IN} = 1.8V \sim 5.5V$ 、 $V_{OUT(MAX)} = 15V$ 、 $I_Q = 25\mu A$ (Burst Mode動作) 、<br>3mm × 5mm DFNおよびTSSOPパッケージ |

## オーダー・ガイド

表5. オーダー・ガイド

| テープ&リール       | 製品マーキング* | パッケージの説明                        | 温度範囲          |

|---------------|----------|---------------------------------|---------------|

| LT8349ACBZ-R7 | 8349     | 35ポール (1.845mm × 2.545mm) WLCSP | -40°C ~ 125°C |

更に広い動作温度範囲で規定されたデバイスについては、弊社または弊社代理店にお問い合わせください。\*温度グレードは出荷容器のラベルに表示されています。

テープ&リールの仕様。

ここに含まれるすべての情報は現状のまま提供されるものであり、アナログ・デバイセズはそれに関するいかなる種類の保証または表明も行いません。アナログ・デバイセズ社は、その情報の利用に関して、あるいはその利用によって生じる第三者の特許やその他の権利の侵害に関して一切の責任を負いません。仕様は予告なく変更される場合があります。明示か黙示かを問わず、アナログ・デバイセズ製品またはサービスが使用される組み合わせ、機械、またはプロセスに関するアナログ・デバイセズの特許権、著作権、マスクワーク権、またはその他のアナログ・デバイセズの知的財産権に基づくライセンスは付与されません。商標および登録商標は、各社の所有に属します。ここに記載されているすべてのアナログ・デバイセズ製品は、出荷および在庫状況に依存します。