## 超低ノイズ・リファレンス内蔵 42V、1A/2.5A 降圧 Silent Switcher® (サイレント・スイッチャ) 3

### 特長

- ▶ **Silent Switcher® 3 アーキテクチャ**

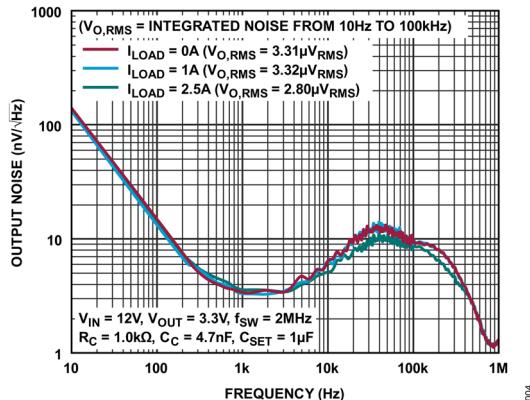

- ▶ 超低実効値ノイズ (10Hz~100kHz) :  $2.8\mu V_{RMS}$

- ▶ 超低スポット・ノイズ :  $4nV/\sqrt{Hz}$  (10kHz 時)

- ▶ 超低 EMI 放射

- ▶ **超高速過渡応答**

- ▶ 出力容量を最小化

- ▶ **高周波数で高い効率**

- ▶ 2MHz で最大 92.4% の効率 (12V<sub>IN</sub>、5V<sub>OUT</sub>)

- ▶ **入力電圧範囲 : 2.8V~42V**

- ▶ **出力電圧範囲 : 0V~(V<sub>IN</sub> - 1V)**

- ▶ 最大 15V<sub>OUT</sub> のユニティ・ゲイン構成

- ▶ **高速最小スイッチ・オン時間 : 22ns**

- ▶ **高精度リファレンス : リモート検出を使用して全温度範囲で±0.8%**

- ▶ 強制連続モード機能

- ▶ 調整と同期が可能 : 300kHz~6MHz

- ▶ プログラマブルなパワー・グッド

- ▶ **小型の 15 ピン 3mm × 2mm LFCSP パッケージ**

- ▶ ピン互換ファミリ : LT83201 (18V, 1A)、LT83203 (18V, 3A)、LT83205 (18V, 5A)

- ▶ AEC-Q100 認定を申請中

### 概要

LT®83401/LT®83402 同期整流式降圧レギュレータは、超低ノイズ・リファレンスと Silent Switcher アーキテクチャを組み合わせた独自の設計により、高い効率と優れた広帯域ノイズ性能の両方を実現します。

革新的な超低ノイズ・アーキテクチャにより、低周波数 (0.1Hz~100kHz) で優れた出力ノイズ性能がスイッチング・レギュレータで得られます。出力電圧を单一の抵抗で設定できるため、出力電圧に関係なく出力ノイズがほぼ一定になります。

Silent Switcher アーキテクチャは、高スイッチング周波数で高い効率を実現しながら、電磁干渉 (EMI) 放射を最小限に抑えます。

LT83401/LT83402 は、同期整流式スイッチング・レギュレータの高い効率によるメリットが得られる、ノイズの影響を受けやすい大電流アプリケーションに適しています。

### アプリケーション

- ▶ 自動車用および工業用電源

- ▶ 医療用アプリケーション : イメージングおよび診断

- ▶ 高速かつ高精度のデータ・コンバータ

- ▶ バイポーラ超低ノイズ電源

- ▶ 低ノイズの計測器およびディスプレイ

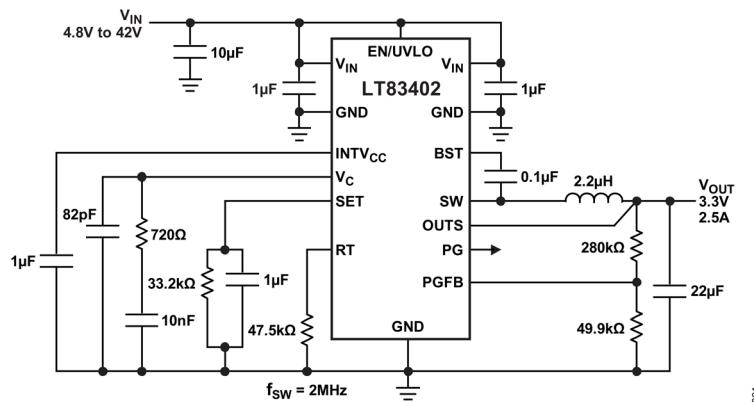

### 代表的なアプリケーション

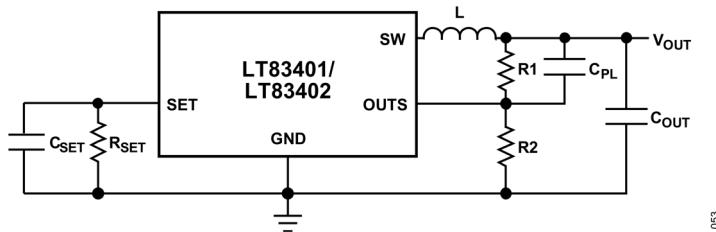

図 1. 簡略アプリケーション回路図

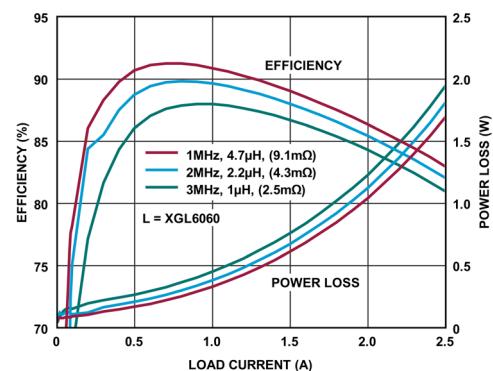

図 2. 12V 入力、3.3V 出力時の効率

## 目次

|                             |    |

|-----------------------------|----|

| 特長                          | 1  |

| 概要                          | 1  |

| アプリケーション                    | 1  |

| 代表的なアプリケーション                | 1  |

| 改訂履歴                        | 3  |

| 仕様                          | 4  |

| 絶対最大定格                      | 8  |

| ピン配置およびピン機能の説明              | 9  |

| 代表的な性能特性                    | 12 |

| ブロック図                       | 19 |

| 動作原理                        | 20 |

| アプリケーション情報                  | 21 |

| 低周波出力ノイズ                    | 21 |

| スイッチング・リップルと高周波ノイズのフィルタリング  | 21 |

| PCB レイアウトに関する推奨事項           | 22 |

| 強制連続モード (FCM)               | 24 |

| パルススキッピング・モード               | 24 |

| 同期                          | 24 |

| スイッチング周波数の設定                | 25 |

| 動作周波数の選択とトレードオフ             | 25 |

| インダクタの選択と最大出力電流             | 26 |

| 過電流保護 (OCP)                 | 28 |

| 入力コンデンサ                     | 28 |

| 出力コンデンサと出力リップル              | 28 |

| 出力電圧                        | 29 |

| 15V を超える出力電圧                | 31 |

| 高 V <sub>OUT</sub> に関する考慮事項 | 31 |

| 0.5V を下回る出力電圧               | 31 |

| 出力検出とその安定性                  | 31 |

| 周波数補償                       | 32 |

| EN/UVLO ピン                  | 33 |

| INTV <sub>CC</sub> レギュレータ   | 33 |

| SET ピン・コンデンサ：ノイズとソフトスタート    | 33 |

| 高速スタートアップ                   | 36 |

| プログラマブルなパワー・グッド             | 36 |

|                    |    |

|--------------------|----|

| 短絡保護と逆入力保護 .....   | 37 |

| 熱に関する考慮事項 .....    | 38 |

| 代表的なアプリケーション ..... | 39 |

| 外形寸法 .....         | 41 |

| オーダー・ガイド .....     | 42 |

| 関連製品 .....         | 43 |

### 改訂履歴

| 版数 | 改訂日   | 説明   | 改訂ページ |

|----|-------|------|-------|

| 0  | 10/25 | 初版発行 | -     |

## 仕様

表 1. 電気的特性

(特に指定のない限り、 $T_J = -40^{\circ}\text{C} \sim +150^{\circ}\text{C}$ 。代表値は  $T_A = +25^{\circ}\text{C}$  での値。特に指定のない限り、電圧はすべて GND を基準。)

| PARAMETER                                                          | SYMBOL                    | CONDITIONS/COMMENTS                                                                                                                                                                                                                                   | MIN  | TYP   | MAX   | UNITS                  |

|--------------------------------------------------------------------|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|-------|------------------------|

| Minimum $V_{IN}$                                                   | $V_{IN}$                  | $V_{SET} = 1\text{V}$                                                                                                                                                                                                                                 |      | 2.5   | 2.8   | V                      |

| OUTS, SET Operating Voltage                                        | $V_{OUTS}, V_{SET}$       |                                                                                                                                                                                                                                                       | 0    |       | 15    | V                      |

| SET Pin Current ( $I_{SET}$ )                                      | $I_{SET}$                 | $V_{SET} = V_{OUTS} = 1\text{V}$                                                                                                                                                                                                                      | 99.2 | 100   | 100.8 | $\mu\text{A}$          |

| Fast Start-Up Set Pin Current                                      | $I_{FAST\_STARTUP}$       | $V_{IN} = 12\text{V}, V_{SET} = 1\text{V}, T_A = +25^{\circ}\text{C}$                                                                                                                                                                                 | 1.9  | 2.5   | 3.1   | mA                     |

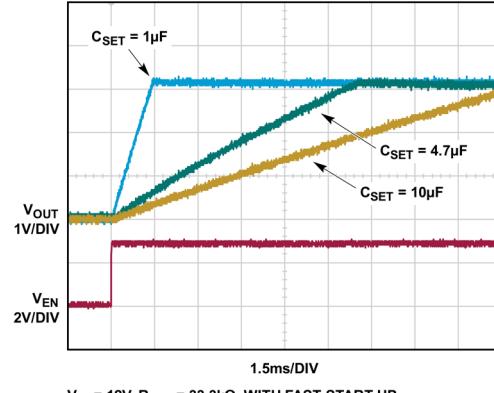

| Start-Up Time Without Fast Start-Up <sup>1,2</sup>                 | $t_{STARTUP}$             | $V_{OUT} = 1\text{V}, C_{SET} = 1\mu\text{F}, V_{IN} = 12\text{V}, V_{PGFB} = 0.5\text{V}$                                                                                                                                                            |      | 29.4  |       | ms                     |

|                                                                    |                           | $V_{OUT} = 1\text{V}, C_{SET} = 4.7\mu\text{F}, V_{IN} = 12\text{V}, V_{PGFB} = 0.5\text{V}$                                                                                                                                                          |      | 127.8 |       |                        |

| Start-Up Time With Fast Start-Up <sup>1,2</sup>                    | $t_{STARTUP}$             | $V_{OUT} = 1\text{V}, C_{SET} = 1\mu\text{F}, V_{IN} = 12\text{V}, R_{PGFB(TOP)} = 49.9\text{k}\Omega, R_{PGFB(BOT)} = 49.9\text{k}\Omega$                                                                                                            |      | 0.5   |       | ms                     |

|                                                                    |                           | $V_{OUT} = 1\text{V}, C_{SET} = 4.7\mu\text{F}, V_{IN} = 12\text{V}, R_{PGFB(TOP)} = 49.9\text{k}\Omega, R_{PGFB(BOT)} = 49.9\text{k}\Omega$                                                                                                          |      | 2     |       |                        |

| Output Noise Spectral Density (10kHz) <sup>1,3,4</sup>             | $V_{O,NSD(10\text{kHz})}$ | $V_{IN} = 12\text{V}, V_{OUT} = 3.3\text{V}, C_{OUT} = 88\mu\text{F}, L = 2.2\mu\text{H}, R_{SET} = 33.2\text{k}\Omega, C_{SET} = 4.7\mu\text{F}, f_{SW} = 6\text{MHz}, R_C = 2.7\text{k}\Omega, C_C = 1\text{nF}$                                    |      | 4     |       | nV/ $\sqrt{\text{Hz}}$ |

| Output Root Mean Square (RMS) Noise (10Hz–100kHz) <sup>1,3,4</sup> | $V_{O,RMS}$               | $V_{IN} = 12\text{V}, V_{OUT} = 3.3\text{V}, BW = 10\text{Hz to } 100\text{kHz}, C_{OUT} = 88\mu\text{F}, L = 2.2\mu\text{H}, R_{SET} = 3.3\text{k}\Omega, C_{SET} = 4.7\mu\text{F}, f_{SW} = 6\text{MHz}, R_C = 2.7\text{k}\Omega, C_C = 1\text{nF}$ |      | 2.8   |       | $\mu\text{V}_{RMS}$    |

| $V_{IN}$ Quiescent Current                                         | $I_Q$                     | $V_{EN/UVLO} = 2\text{V}$ , not switching, $T_A = +25^{\circ}\text{C}$                                                                                                                                                                                |      | 3     | 3.6   | mA                     |

|                                                                    |                           | $V_{EN/UVLO} = 0.2\text{V}$ , shutdown, $T_A = +25^{\circ}\text{C}$                                                                                                                                                                                   |      | 45    | 70    | $\mu\text{A}$          |

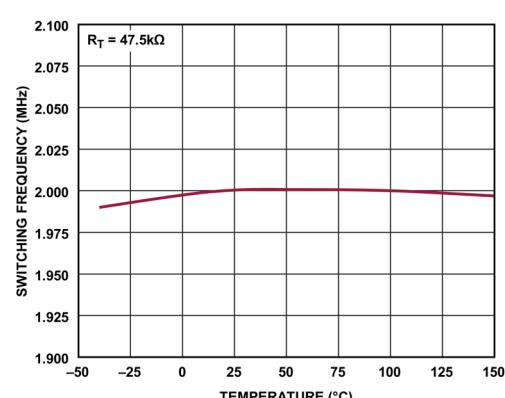

| Oscillator Frequency                                               | $f_{SW}$                  | $R_T = 392\text{k}\Omega$                                                                                                                                                                                                                             | 285  | 315   | 345   | kHz                    |

|                                                                    |                           | $R_T = 47.5\text{k}\Omega$                                                                                                                                                                                                                            | 1.95 | 2     | 2.05  | MHz                    |

|                                                                    |                           | $R_T = 9.76\text{k}\Omega$                                                                                                                                                                                                                            | 5.04 | 5.6   | 6.16  |                        |

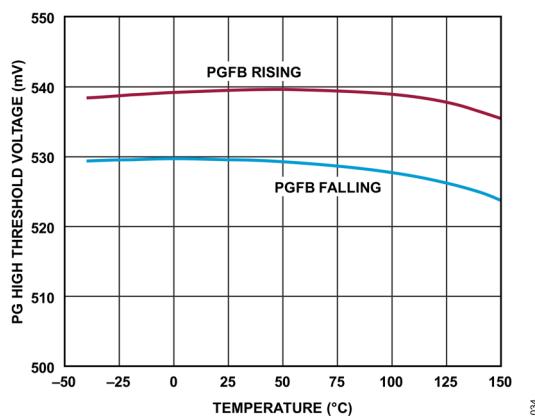

| Power Good Feedback (PGFB) Upper Threshold                         | $V_{PGH}$                 | $V_{PGFB}$ rising                                                                                                                                                                                                                                     | 529  | 537.5 | 546   | mV                     |

| PGFB Upper Threshold Hysteresis                                    | $V_{PGH\_HYS}$            |                                                                                                                                                                                                                                                       |      | 10    |       | mV                     |

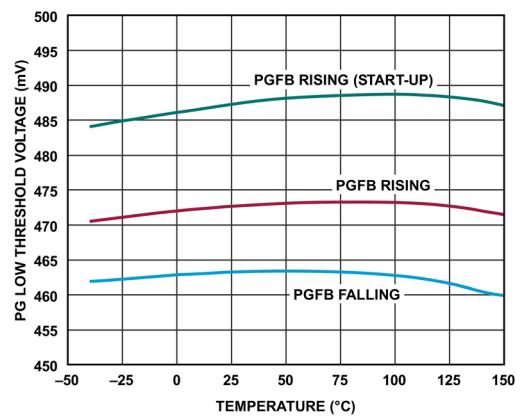

| PGFB Lower Threshold                                               | $V_{PGL}$                 | $V_{PGFB}$ falling                                                                                                                                                                                                                                    | 455  | 462.5 | 470   | mV                     |

(特に指定のない限り、 $T_J = -40^{\circ}\text{C} \sim +150^{\circ}\text{C}$ 。代表値は  $T_A = +25^{\circ}\text{C}$  での値。特に指定のない限り、電圧はすべて GND を基準。)

| PARAMETER                                   | SYMBOL                 | CONDITIONS/COMMENTS                                                                                                       | MIN  | TYP   | MAX  | UNITS         |

|---------------------------------------------|------------------------|---------------------------------------------------------------------------------------------------------------------------|------|-------|------|---------------|

| PGFB Lower Threshold Hysteresis             | $V_{PGL\_HYS}$         |                                                                                                                           |      | 10    |      | mV            |

| PGFB Lower Threshold (Start-Up Only)        | $V_{PGL\_STARTUP}$     | $V_{PGFB}$ rising                                                                                                         | 480  | 487.5 | 495  | mV            |

| PGFB Pin Current                            | $I_{PGFB}$             | $V_{IN} = 12\text{V}$ , $V_{EN/UVLO} = 2\text{V}$ , $V_{PGFB} = 0.5\text{V}$                                              |      | 13    |      | nA            |

| Power Good (PG) Leakage                     | $I_{PG\_LKG}$          | $V_{PG} = 3.3\text{V}$ , $T_A = +25^{\circ}\text{C}$                                                                      | -40  |       | +40  | nA            |

| PG Pull-Down Resistance                     | $R_{PG}$               | $V_{PG} = 0.5\text{V}$                                                                                                    | 380  | 1200  |      | $\Omega$      |

| SYNC/MODE Threshold                         | $V_{IL}$               | SYNC/MODE DC and clock low- level voltage                                                                                 | 0.7  |       |      | V             |

|                                             | $V_{IH}$               | SYNC/MODE DC and clock high- level voltage                                                                                |      |       | 1.5  |               |

| OUTS Pin Output Current                     | $I_{OUTS}$             | $V_{OUTS} = 1\text{V}$ , $T_A = +25^{\circ}\text{C}$                                                                      | 110  | 170   | 230  | nA            |

| Output Voltage Line Regulation <sup>5</sup> | $\Delta V_{OUT(LINE)}$ | $V_{IN} = 4\text{V}$ to $42\text{V}$ , $T_A = +25^{\circ}\text{C}$                                                        |      | 0.001 | 0.01 | %/V           |

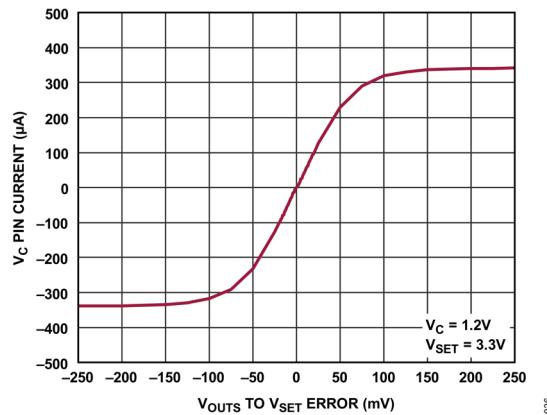

| Error Amp Offset <sup>5,6</sup>             | $V_{EA, OFFSET}$       | $V_C = 1.2\text{V}$ , $V_{SET} = 3\text{V}$ , $V_{IN} = 12\text{V}$ , positive-negative-positive (PNP)- based input pair  | -2   |       | +2   | mV            |

|                                             |                        | $V_C = 1.2\text{V}$ , $V_{SET} = 5\text{V}$ , $V_{IN} = 5.7\text{V}$ , negative-positive-negative (NPN)- based input pair | -2   |       | +2   |               |

| Error Amp Transconductance <sup>6</sup>     | $g_m(EA)$              | $V_C = 1.2\text{V}$ , $V_{SET} = 3\text{V}$ , $V_{IN} = 12\text{V}$ , PNP-based input pair, $T_A = +25^{\circ}\text{C}$   | 9.5  | 12    | 14.5 | mS            |

|                                             | $g_m(EA)$              | $V_C = 1.2\text{V}$ , $V_{SET} = 5\text{V}$ , $V_{IN} = 5.7\text{V}$ , NPN-based input pair, $T_A = +25^{\circ}\text{C}$  | 8.3  | 10.5  | 12.7 |               |

| Error Amp Gain                              | $A_V$                  | $V_C = 1.2\text{V}$ , $V_{SET} = 1\text{V}$ , $V_{IN} = 6\text{V}$ , LT83401                                              | 2400 |       |      | V/V           |

|                                             |                        | $V_C = 1.2\text{V}$ , $V_{SET} = 1\text{V}$ , $V_{IN} = 6\text{V}$ , LT83402                                              | 2000 |       |      |               |

| $V_C$ Source Current <sup>5</sup>           | $I_{VC-SRC}$           | $V_C = 1.2\text{V}$ , $V_{SET} = 3\text{V}$ , $V_{IN} = 12\text{V}$ , PNP- based input pair                               | 340  |       |      | $\mu\text{A}$ |

|                                             |                        | $V_C = 1.2\text{V}$ , $V_{SET} = 3\text{V}$ , $V_{IN} = 12\text{V}$ , NPN- based input pair                               | 340  |       |      |               |

| $V_C$ Sink Current <sup>5</sup>             | $I_{VC-SNK}$           | $V_C = 1.2\text{V}$ , $V_{SET} = 3\text{V}$ , $V_{IN} = 12\text{V}$ , PNP- based input pair                               | 340  |       |      | $\mu\text{A}$ |

|                                             |                        | $V_C = 1.2\text{V}$ , $V_{SET} = 3\text{V}$ , $V_{IN} = 12\text{V}$ , NPN- based input pair                               | 340  |       |      |               |

| $V_C$ Pin-to-Switch Current Gain            | $G_M$                  | LT83401                                                                                                                   | 2.3  |       |      | A/V           |

|                                             |                        | LT83402                                                                                                                   | 3.6  |       |      |               |

| $V_C$ Clamp Voltage                         | $V_{C\_CLAMP}$         |                                                                                                                           | 2    |       |      | V             |

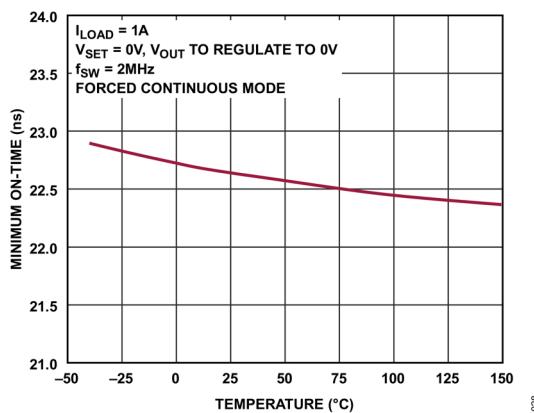

| Minimum On-Time                             | $t_{ON(MIN)}$          | $I_{LOAD} = 1\text{A}$                                                                                                    | 22   | 27    |      | ns            |

(特に指定のない限り、 $T_J = -40^{\circ}\text{C} \sim +150^{\circ}\text{C}$ 。代表値は  $T_A = +25^{\circ}\text{C}$  での値。特に指定のない限り、電圧はすべて GND を基準。)

| PARAMETER                                              | SYMBOL                    | CONDITIONS/COMMENTS                                                                                  | MIN  | TYP  | MAX  | UNITS            |

|--------------------------------------------------------|---------------------------|------------------------------------------------------------------------------------------------------|------|------|------|------------------|

| Minimum Off-Time                                       | $t_{\text{OFF(MIN)}}$     | $I_{\text{LOAD}} = 0.5\text{A}$ , LT83401<br>$I_{\text{LOAD}} = 1\text{A}$ , LT83402                 |      | 80   | 100  | ns               |

| Top Power N-Channel MOSFET Current Limit               | $I_{\text{PEAK-LIMIT}}$   | LT83401                                                                                              | 1.96 | 2.2  | 2.44 | A                |

|                                                        |                           | LT83402                                                                                              | 3.4  | 4.0  | 4.4  |                  |

| Bottom Power N-Channel MOSFET Current Limit            | $I_{\text{VALLEY-LIMIT}}$ | LT83401                                                                                              | 1.28 | 1.5  | 1.72 | A                |

|                                                        |                           | LT83402                                                                                              | 1.95 | 2.4  | 2.85 |                  |

| SW Leakage Current                                     | $I_{\text{SW\_LKG}}$      | $V_{\text{IN}} = 42\text{V}$ , $V_{\text{SW}} = 0\text{V}, 42\text{V}$ , $T_A = +25^{\circ}\text{C}$ | -1   |      | +1   | $\mu\text{A}$    |

| Power MOSFET On-Resistance Main Switch (Top)           | $R_{\text{DS-ONH}}$       |                                                                                                      |      | 280  |      | $\text{m}\Omega$ |

| Power MOSFET On-Resistance Synchronous Switch (Bottom) | $R_{\text{DS-ONL}}$       |                                                                                                      |      | 135  |      | $\text{m}\Omega$ |

| SET Pull-Down Resistance                               | $R_{\text{SET-PULLDOWN}}$ | $V_{\text{SET}} = 0.5\text{V}$                                                                       | 540  | 865  |      | $\Omega$         |

| EN/UVLO Threshold                                      | $V_{\text{ENR}}$          | EN/UVLO rising                                                                                       | 0.7  | 0.75 | 0.8  | V                |

| EN/UVLO Hysteresis                                     | $V_{\text{EN_HYS}}$       |                                                                                                      |      | 55   |      | $\text{mV}$      |

| EN/UVLO Input Current                                  | $I_{\text{EN}}$           | $V_{\text{EN/UVLO}} = 2\text{V}$ , $T_A = +25^{\circ}\text{C}$                                       | -40  |      | +40  | $\text{nA}$      |

<sup>1</sup> 製品テストの対象外です。

<sup>2</sup> スタートアップ時間は、EN/UVLO ピンの立ち上がりが EN/UVLO 閾値を超えてから  $V_{\text{OUT}}$  が最終値の 95%に達するまでに要する時間として定義されます。

<sup>3</sup> OUTS は直接  $V_{\text{OUT}}$  に接続されています。

<sup>4</sup> SET ピンの抵抗にコンデンサを追加すると、出力電圧ノイズが減少します。このコンデンサの追加により、SET ピンの抵抗の熱ノイズとリファレンス電流のノイズがバイパスされます。SET ピンにバイパス・コンデンサを使用することは、スタートアップ時間の増加にもつながります。

<sup>5</sup> LT83401/LT83402 は帰還ループでテストされています。このループでは  $V_c$  を仕様規定された電圧にサーボ制御して、得られた  $V_{\text{OUTS}}$  を測定します。

<sup>6</sup>  $V_{\text{IN}}$  が  $V_{\text{SET}}$  より 1.4V 以上高い間は、エラー・アンプに対して PNP ベースの入力ペアが動作します。 $V_{\text{IN}}$  が  $V_{\text{SET}} + 1.4\text{V}$  を下回ると、デバイスは徐々に NPN ベースの入力ペアによる動作に遷移します。

<sup>7</sup> 熱抵抗 ( $\theta$ ) 値は JEDEC 51-7、51-12 に従って決定されます。熱抵抗の改善と、代表的な動作条件におけるデモ・ボードの実際の温度測定値については、[アプリケーション情報](#) のセクションを参照してください。

<sup>8</sup> この IC は、過負荷状態からデバイスを保護することを目的とした過熱保護機能を備えています。過熱保護機能が作動した場合、ジャンクション温度は 150°C を超えています。仕様規定された最大動作ジャンクション温度を超えてデバイスを連続動作させると、寿命が短くなります。

**絶対最大定格**

特に指定のない限り、 $T_A = 25^\circ\text{C}$ 。

表 2. 絶対最大定格

| PARAMETER                      | RATING          |

|--------------------------------|-----------------|

| $V_{IN}$ , EN/UVLO, PG         | -0.3V to 42V    |

| OUTS, SET                      | -0.3V to 16.5V  |

| SYNC, PGFB                     | -0.3V to 6V     |

| Operating Junction Temperature | -40°C to +150°C |

| Storage Temperature Range      | -65°C to +150°C |

| Peak Package Body Temperature  | 260°C           |

上記の**絶対最大定格**を超えるストレスを加えるとデバイスに恒久的な損傷を与えることがあります。これらはストレス定格のみを定めたものであり、この仕様の動作のセクションに記載する規定値以上でデバイスが正常に動作することを示唆するものではありません。デバイスを長時間にわたり絶対最大定格状態に置くと、デバイスの信頼性に影響を与えることがあります。

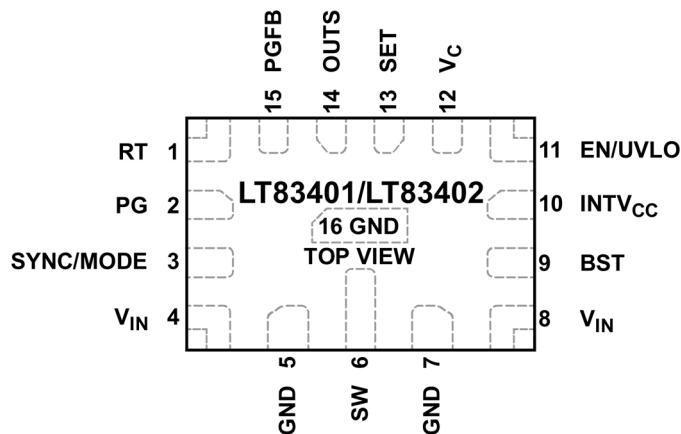

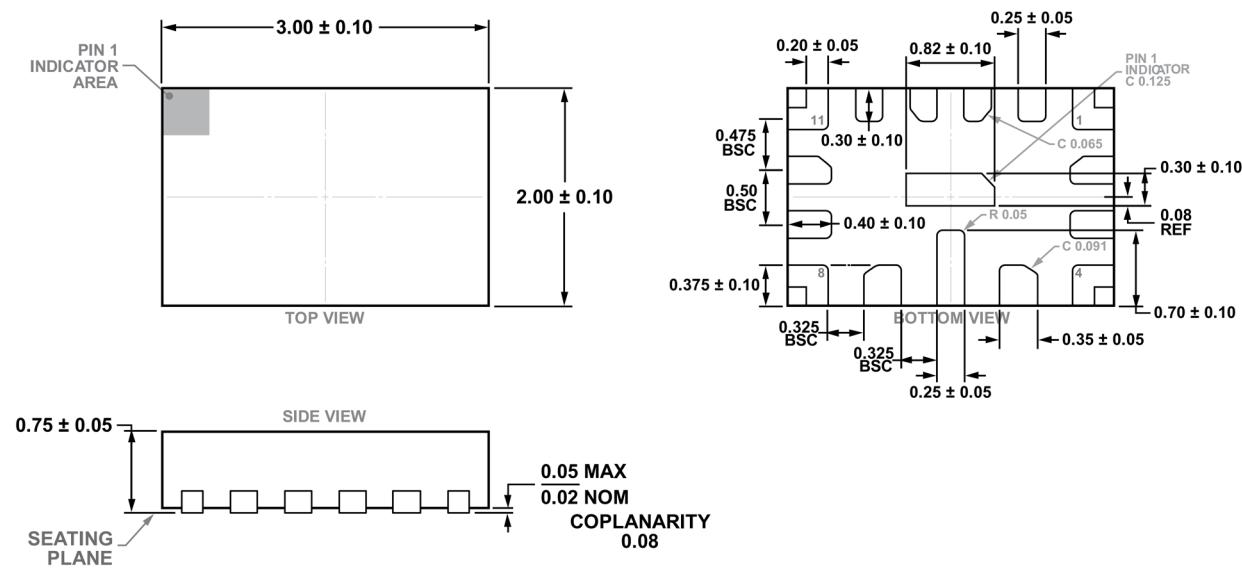

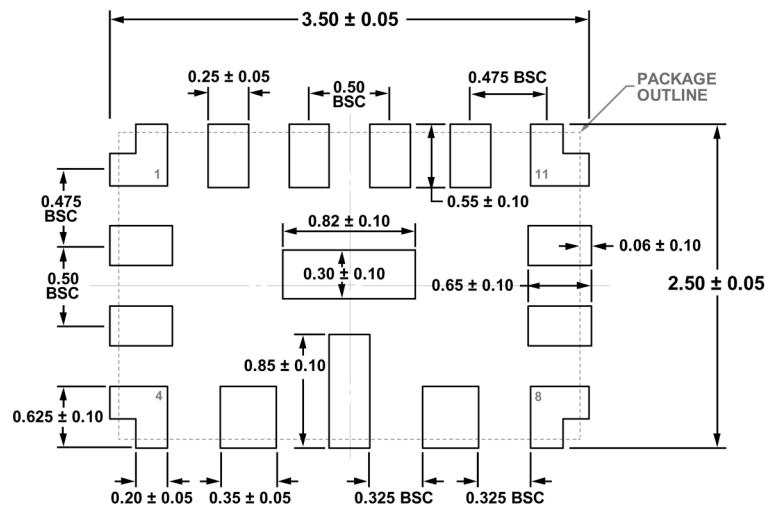

## ピン配置およびピン機能の説明

LFCSP PACKAGE

15-LEAD (3mm × 2mm × 0.75mm)

JEDEC BOARD  $\theta_{JA} = 50^{\circ}\text{C/W}$ ,  $\theta_{JC(\text{TOP})} = 67.1^{\circ}\text{C/W}$ ,  $\theta_{JC(\text{PAD})} = 10.4^{\circ}\text{C/W}$

DEMO BOARD  $\theta_{JA} = 33^{\circ}\text{C/W}$ ,  $\psi_{JT} = 1.7^{\circ}\text{C/W}$

EXPOSED PAD IS GND AND SHOULD BE SOLDERED TO PCB

003

図 3. ピン配置

表 3. 端子説明

| 端子 | 名称        | 説明                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|----|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1  | RT        | RT とグラウンドの間に抵抗を接続することで、スイッチング周波数を設定します。                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 2  | PG        | PG ピンは内部コンパレータのオープン・ドレイン出力です。PG は、PGFB ピンが 0.5V の±7.5%以内になり、かつフォルト状態がなくなるまでの間、ハイ・インピーダンスを維持します。EN/UVLO が 0.75V 未満になった場合、INTV <sub>CC</sub> が低くなりすぎた場合、あるいはサーマル・シャットダウンが発生している間、PG はローになります。PG は、V <sub>IN</sub> が 2.8V より高い場合に有効です。                                                                                                                                                                                                                                                                                                                                                                                        |

| 3  | SYNC/MODE | LT83401/LT83402 では、このピンで次の 3 種類の動作モードを設定します。1) パルススキッピング・モード：このピンを GND に接続するとパルススキッピング・モードが有効になり、軽負荷時の効率を向上させることができます。2) 強制連続モード (FCM)：このモードでは、広い負荷範囲にわたって高速過渡応答が得られると共に、最大周波数での動作が可能になります。このピンを INTV <sub>CC</sub> (約 3.4V) または 1.5V より高い外部電源に接続してハイ状態にすると FCM が有効になります。このピンをフロート状態のままですると、デバイスはデフォルトでこのモードで動作します。3) 同期モード：このピンをクロック信号源で駆動することで、外部周波数に同期させることができます。同期動作中、デバイスは強制連続モードで動作します。SYNC/MODE ピンを動作中にトグルすることで、動作モードを変更できます。このデバイスの SYNC/MODE ピンを CLKOUT ピンに置き換えたバージョンについては、アナログ・デバイセズにお問い合わせください。CLKOUT ピンには、スイッチング周波数の 50% デューティ・サイクルの矩形波が、デバイスの内部クロックと 180° の位相差で、INTV <sub>CC</sub> ～GND のピーク to ピーク振幅で出力されます。 |

|                           |                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|---------------------------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4, 8                      | V <sub>IN</sub>    | V <sub>IN</sub> ピンは LT83401/LT83402 の内部回路と上側パワー・スイッチに電流を供給します。0.1μF 以上の 0402 コンデンサを 2 個配置して、V <sub>IN</sub> ピンの両方をバイパスしてください。その際、入力コンデンサの正端子は V <sub>IN</sub> ピンにできるだけ近付けて接続し、負端子は GND ピンにできるだけ近付けて接続してください。また、V <sub>IN</sub> ピンには、追加で 4.7μF 以上のローカル・バイパス・コンデンサを接続する必要があります。電流リファレンスに十分なヘッドルームを持たせるため、SET ピンで設定するレギュレーション設定値より V <sub>IN</sub> を 900mV 以上高くする必要があります。例えば、目標のレギュレーション設定値が 3.3V の場合、V <sub>IN</sub> は、少なくとも 3.3V + 900mV = 4.2V 以上であることが必要です。                                                                                                                                                                       |

| 5, 7, 16<br>(Exposed Pad) | GND                | グラウンド。入力コンデンサの負端子は、できるだけ GND ピンに近付けて接続してください。良好な熱的性能を実現するには、露出パッドを PCB に半田付けする必要があります。製造上の制約によって必要になる場合は、露出パッドを未接続のままにできますが、性能は低下します。                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 6                         | SW                 | SW ピンは内部パワー・スイッチの出力です。このピンをインダクタに接続します。優れた性能と低い EMI を実現するため、PCB 上でのこのノードの面積をできるだけ小さくしてください。                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 9                         | BST                | このピンは、入力電圧より高い駆動電圧を上側パワー・スイッチに供給するために使用します。デバイスのできるだけ近くに 0.1μF の昇圧コンデンサを配置してください。                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 10                        | INTV <sub>CC</sub> | 内部 3.4V レギュレータのバイパス・ピン。内部パワー・ドライバおよび制御回路には、この電圧から給電されます。INTV <sub>CC</sub> ピンには外部回路からの負荷をかけないでください。INTV <sub>CC</sub> の電流は V <sub>IN</sub> から供給されます。このピンは、等価直列抵抗 (ESR) が低い 1μF 以上のセラミック・コンデンサを IC の近くに接続してグラウンドとデカッピングします。                                                                                                                                                                                                                                                                                                                                                                                                         |

| 11                        | EN/UVLO            | このピンの電圧が 0.75V を超えるとスイッチングが有効化され、電圧が 200mV 未満になると内部電流バイアスとサブレギュレータがシャットダウンされます。閾値電圧にはヒステリシスがあります。上昇時は 0.75V、下降時は 0.7V です。シャットダウン機能を使わない場合は、V <sub>IN</sub> に接続してください。V <sub>IN</sub> との間に抵抗分圧器を外付けすることで、V <sub>IN</sub> の閾値を設定して、その閾値未満では LT83401/LT83402 をシャットダウンさせることができます。                                                                                                                                                                                                                                                                                                                                                      |

| 12                        | V <sub>c</sub>     | V <sub>c</sub> ピンは内部エラー・アンプの出力です。このピンの電圧はピーク・スイッチ電流を制御します。制御ループの補償を行うには、このピンとグラウンドの間に RC 回路を接続します。                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 13                        | SET                | このピンは、エラー・アンプの非反転入力で、LT83401/LT83402 のレギュレーション設定値となります。SET は 100μA の高精度電流を供給し、この電流は SET と GND の間を接続する外付け抵抗に流れます。LT83401/LT83402 の出力電圧は、デフォルトのユニティ・ゲイン構成で使用する場合、 $V_{SET} = I_{SET} \times R_{SET}$ で決まります。SET ピンの電圧範囲は 0V~15V です。15V を超える出力電圧が必要なアプリケーションについては、 <a href="#">15V を超える出力電圧</a> のセクションを参照してください。最良のノイズ性能を実現するには、SET と GND の間にコンデンサを追加してください。このコンデンサを追加することでノイズは改善されますが、スタートアップ時間が長くなります。このコンデンサの選択方法に関する重要な情報については、 <a href="#">SET ピン・コンデンサ：ノイズとソフトスタート</a> のセクションを参照してください。最適な負荷レギュレーションを実現するため、SET ピンの抵抗のグラウンド側を負荷に直接ケルビン接続します。シャットダウンおよびフォルト状態時には、このピンは 520Ω の MOSFET ( $R_{SET-PULLDOWN}$ ) によってグラウンドにプルダウンされます。 |

|    |      |                                                                                                                                                                                                                                                                                                                                                                                    |

|----|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 14 | OUTS | 出力検出。このピンは、エラー・アンプへの反転入力です。最適なトランジエント性能と負荷レギュレーションを実現するため、OUTS は出力コンデンサと負荷に直接ケルビン接続します。                                                                                                                                                                                                                                                                                            |

| 15 | PGFB | パワー・グッド・フィードバック。PGFB が 537.5mV を超えるか 462.5mV 未満になると、PG ピンはローに引き下げられます。V <sub>OUT</sub> 、PGFB、GND の間に外付けの抵抗分圧器を接続することにより、次の伝達関数によりプログラマブルなパワー・グッド閾値が設定されます。 $0.5V(\pm7.5\%) \times (1 + R_{PGFB(TOP)}/R_{PGFB(BOT)})$ 。また、 <a href="#">アプリケーション情報</a> のセクションで説明するように、PGFB を使用して高速スタートアップ回路を起動することもできます。パワー・グッド機能と高速スタートアップ機能が不要な場合は、PGFB ピンを INTV <sub>CC</sub> または 0.5V に接続してください。 |

## 代表的な性能特性

特に指定のない限り、 $T_A = 25^\circ\text{C}$ 。

図 4. ノイズ・スペクトル密度と負荷の関係

標準アプリケーション回路（図 59）を参照

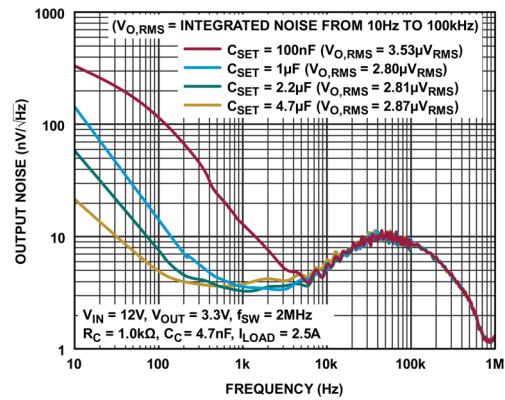

図 5. ノイズ・スペクトル密度と C<sub>SET</sub> の関係

標準アプリケーション回路（図 59）を参照

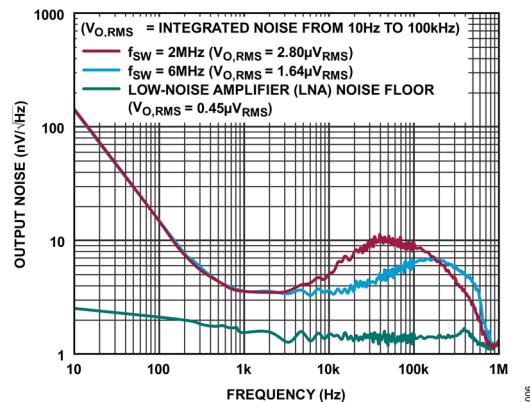

図 6. ノイズ・スペクトル密度と f<sub>SW</sub> の関係

標準アプリケーション回路（図 59）を参照

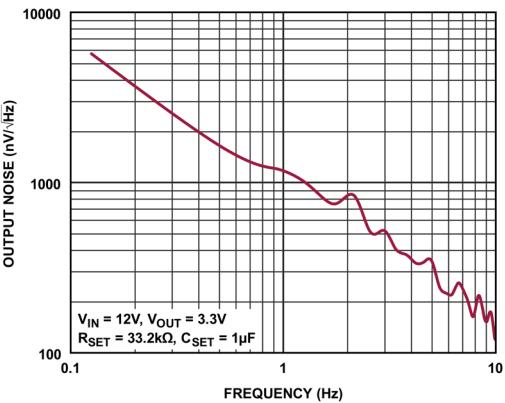

図 7. ノイズ・スペクトル密度（0.1Hz～10Hz）

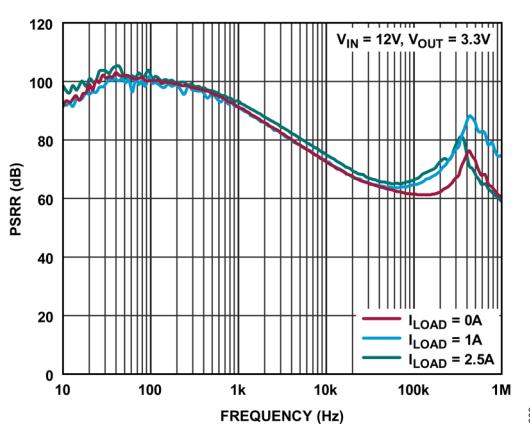

図 8. 電源電圧リップル除去

標準アプリケーション回路（図 59）を参照

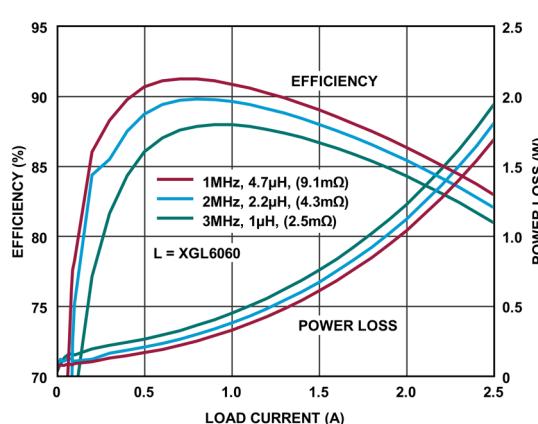

図 9. 12V<sub>IN</sub>/3.3V<sub>OUT</sub> の効率

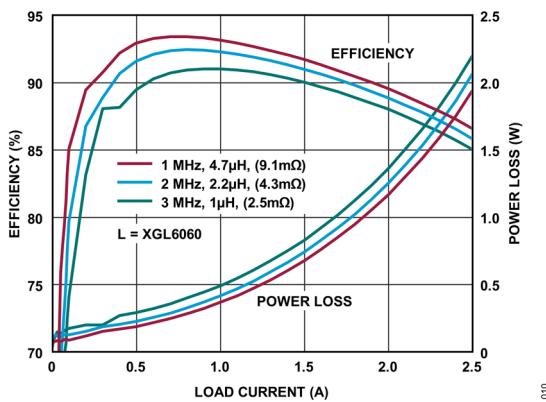

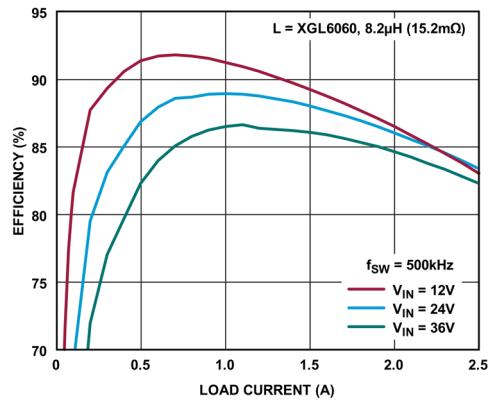

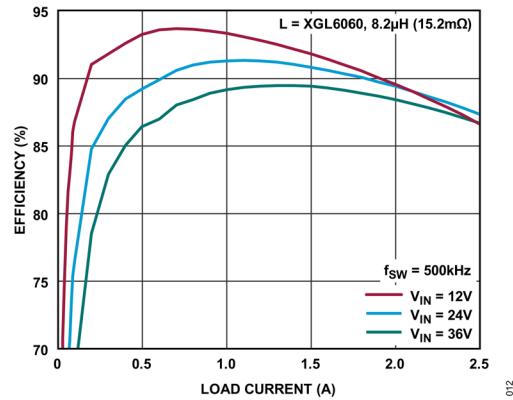

図 10. 12V<sub>IN</sub>/5V<sub>OUT</sub> の効率図 11. 3.3V<sub>OUT</sub> 時の効率図 12. 5V<sub>OUT</sub> 時の効率

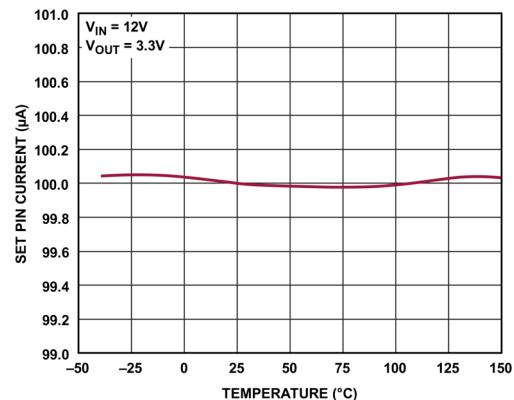

図 13. SET ピン電流と温度の関係

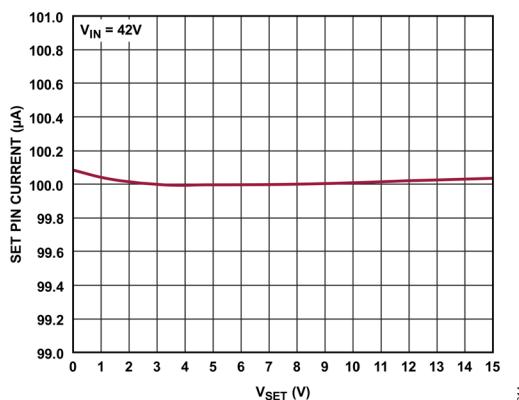

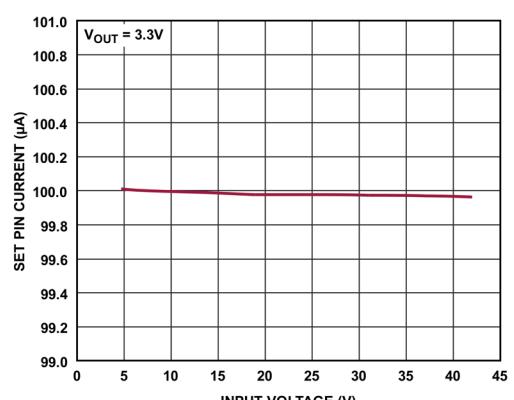

図 14. SET ピン電流と  $V_{SET}$  の関係図 15. SET ピン電流と  $V_{IN}$  の関係

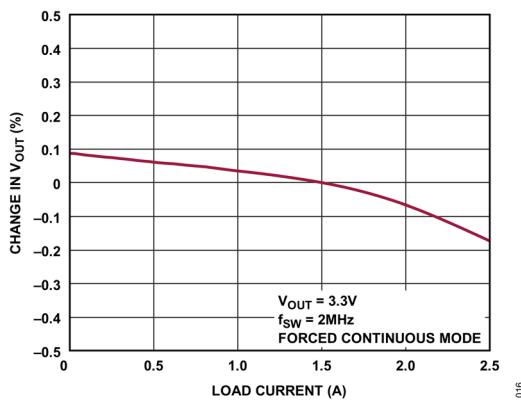

図 16. 負荷レギュレーション

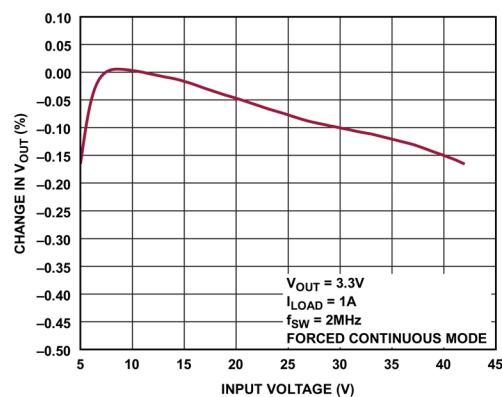

図 17. ライン・レギュレーション

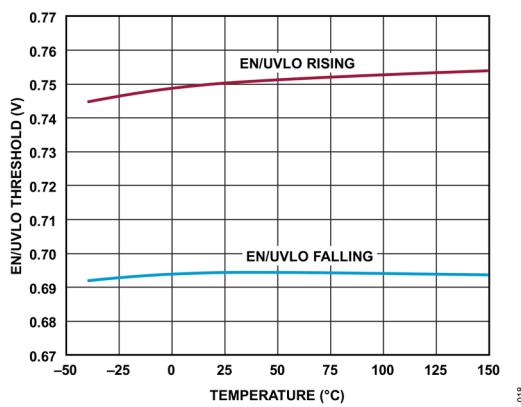

図 18. EN/UVLO ピンの閾値

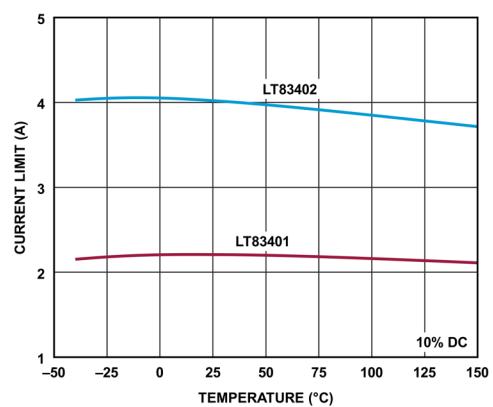

図 19. 上側 MOSFET の電流制限値と温度の関係

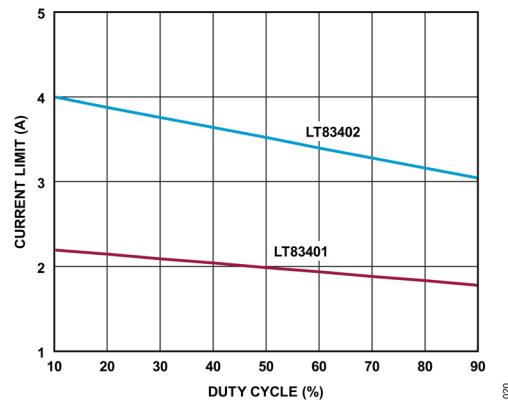

図 20. 上側 MOSFET 電流制限値とデューティサイクルの関係

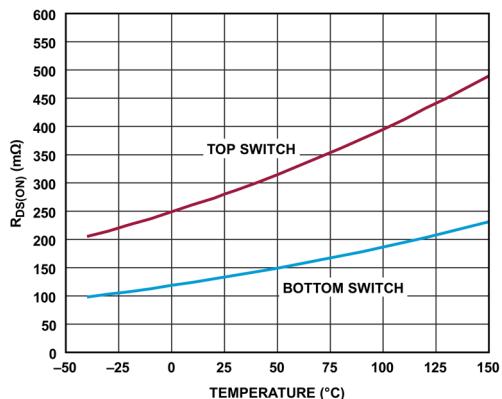

図 21. スイッチの  $R_{DS(ON)}$  と温度の関係

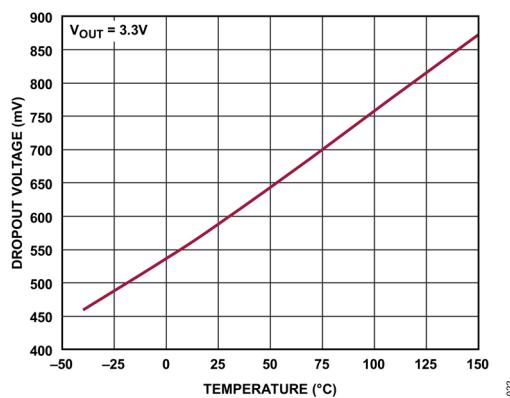

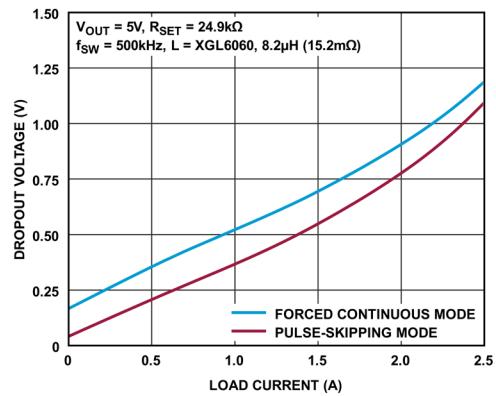

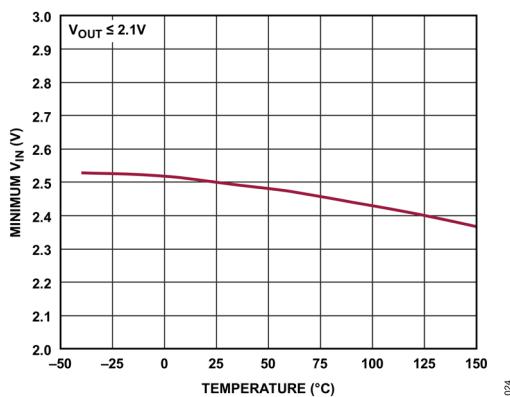

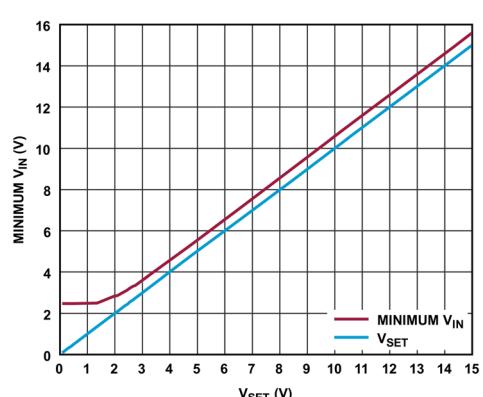

図 22.  $V_{IN} \sim V_{SET}$  のドロップアウト電圧と温度の関係図 23.  $V_{IN} \sim V_{OUT}$  のドロップアウト電圧と  $I_{LOAD}$  の関係図 24. 最低  $V_{IN}$  と温度の関係図 25. 最低  $V_{IN}$  と  $V_{SET}$  の関係

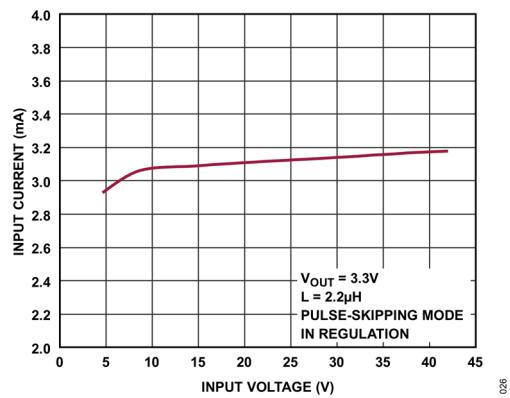

図 26. 無負荷時の電源電流

図 27. スイッチング周波数と温度の関係

図 28. 最小オン時間と温度の関係

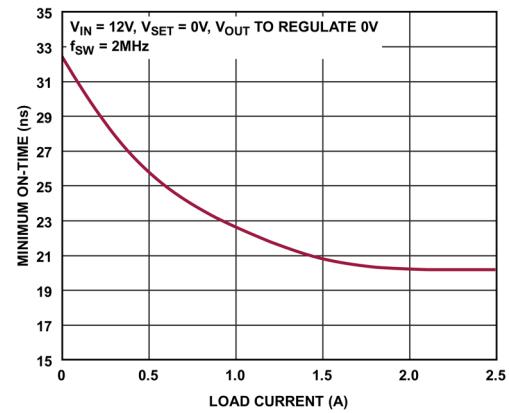

図 29. 最小オン時間と負荷の関係

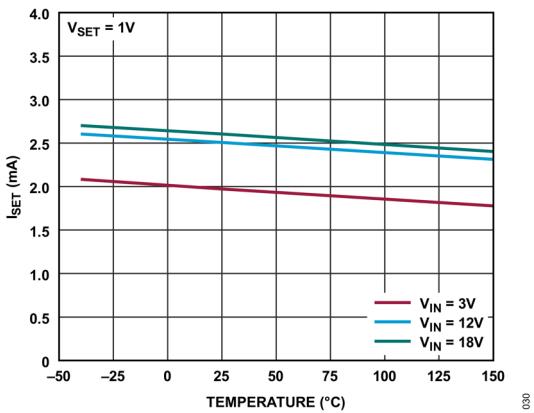

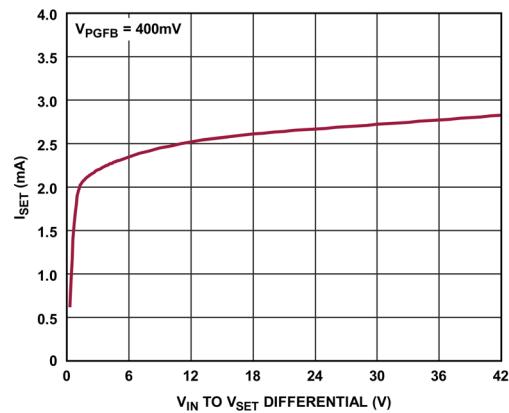

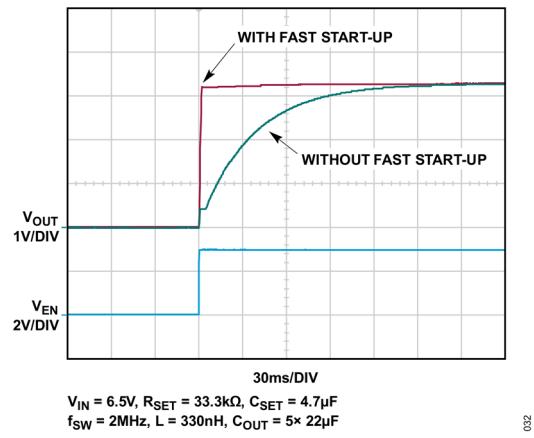

図 30. 高速スタートアップ有効時の起動中の  $I_{SET}$  と温度の関係図 31. 高速スタートアップ有効時の起動中の  $I_{SET}$  と  $V_{IN}$ ～ $V_{SET}$  間差分の関係図 32.  $C_{SET}$  が大きいときの高速スタートアップ回路有効時と無効時のスタートアップ時間

図 33. ソフトスタート波形

図 34. PG 上限閾値

図 35. PG 下限閾値

図 36. エラー・アンプ出力電流

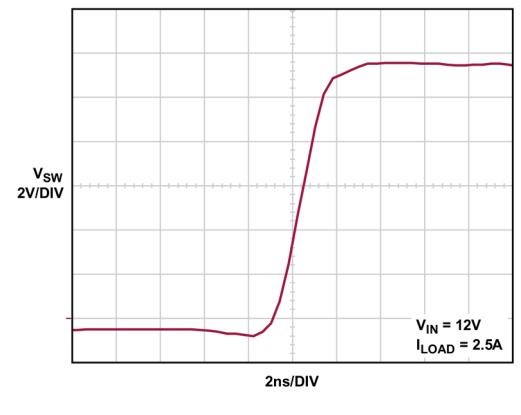

図 37. スイッチの立上がりエッジ

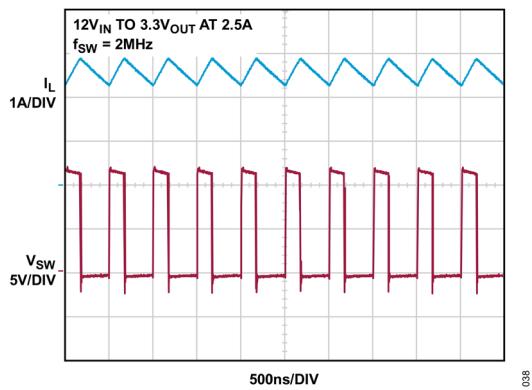

図 38. 最大周波数連続動作時のスイッチング波形

図 39. 最大周波数パルススキッピング動作時のスイッチング波形

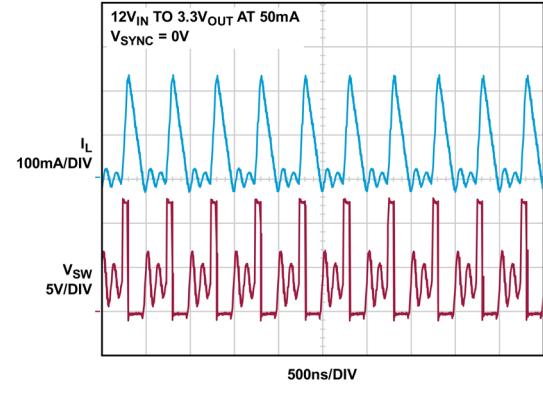

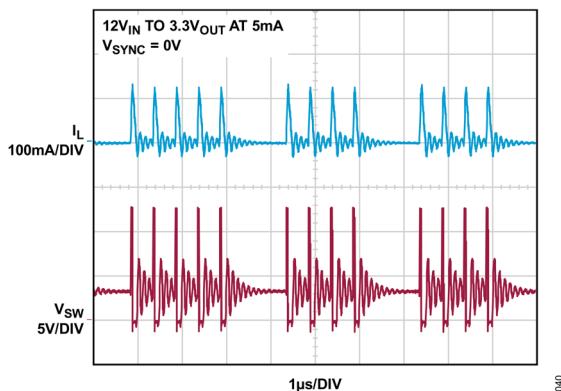

図 40. パルススキッピング動作時のスイッチング波形

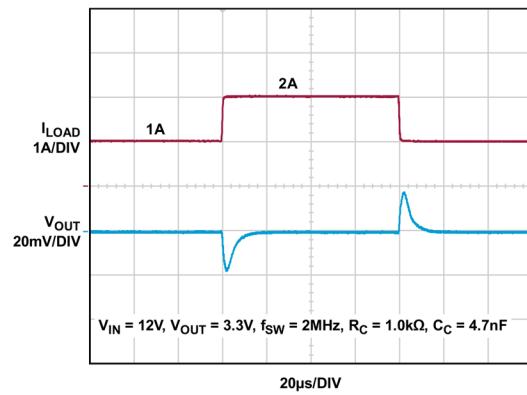

図 41. 過渡応答：1A から 2A への負荷電流ステップ

標準アプリケーション回路（図 59）を参照

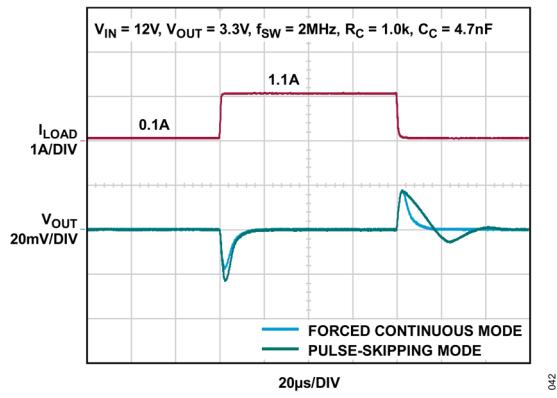

図 42. 過渡応答：0.1A から 1.1A への負荷電流ステップ

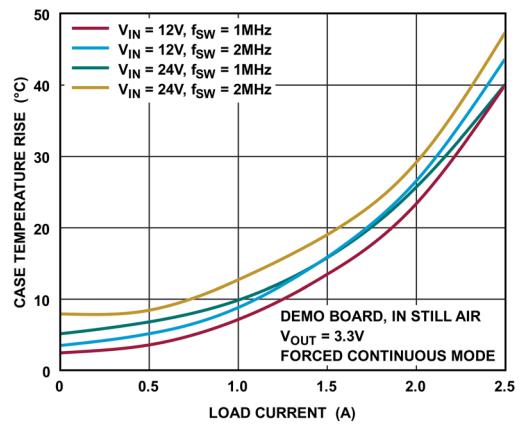

図 43. ケース温度の上昇

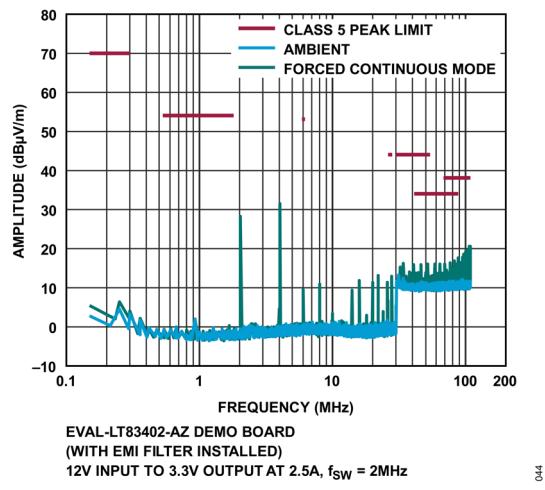

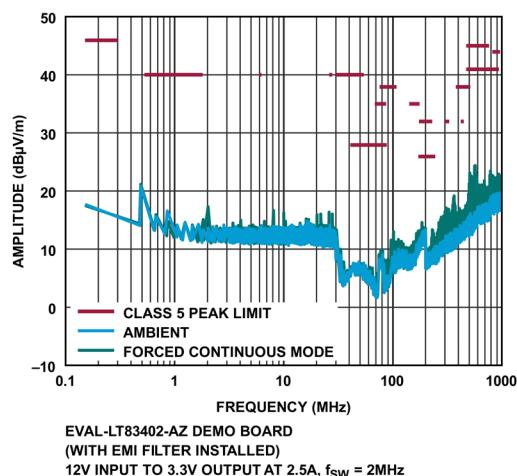

図 44. 伝導 EMI 性能 (Class 5 ピーク限界値での CISPR 伝導エミッション・テスト)

図 45. 放射 EMI 性能 (Class 5 ピーク限界値での CISPR25 放射エミッション・テスト)

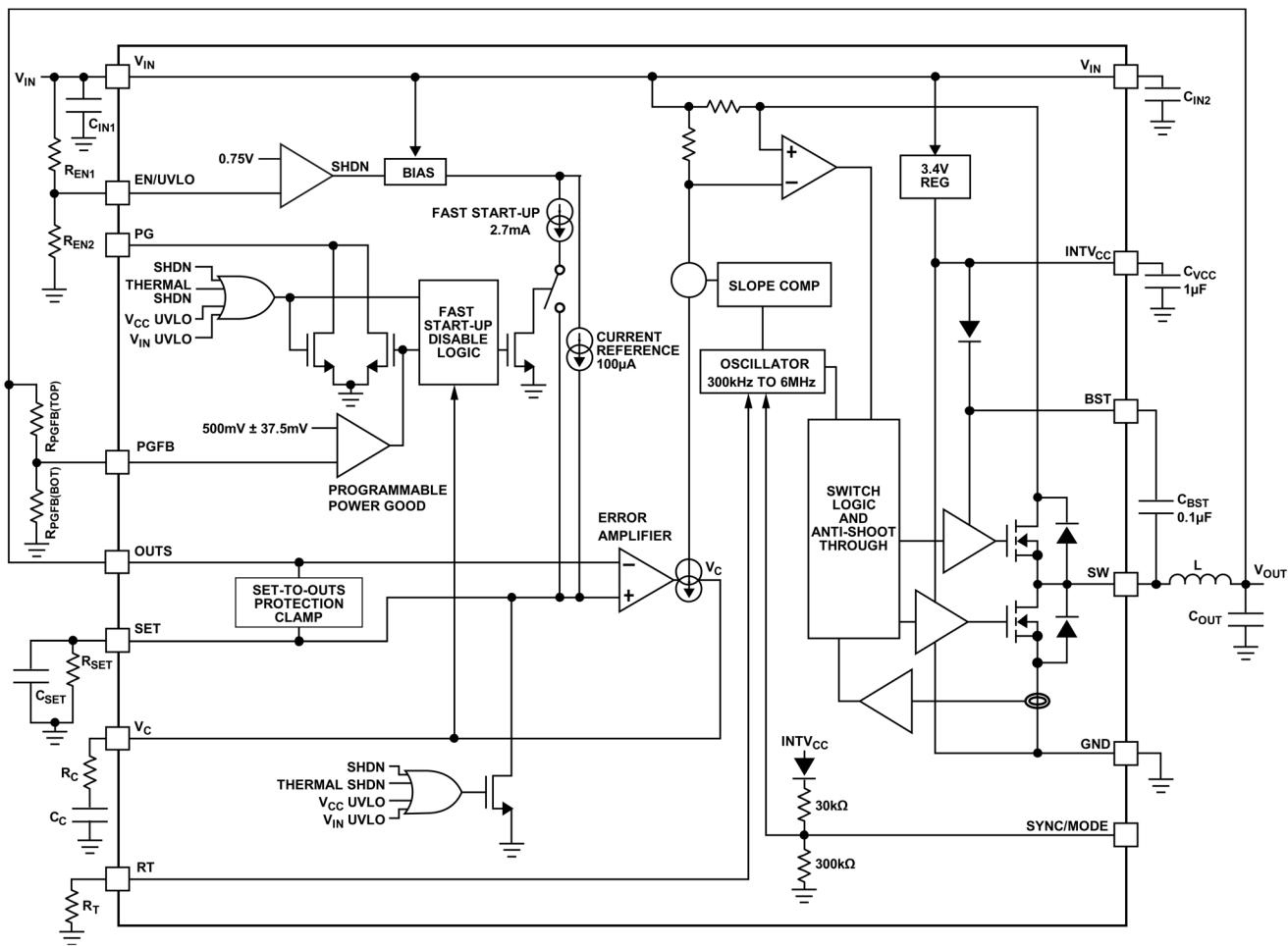

## ブロック図

図 46. ブロック図

046

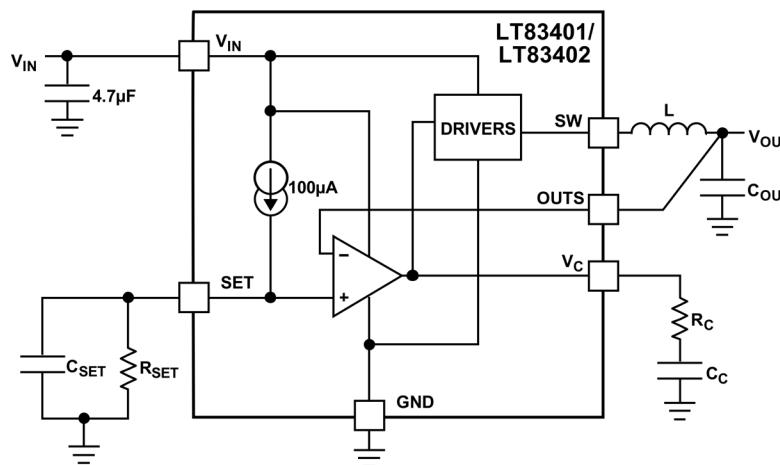

## 動作原理

LT83401/LT83402 は、固定周波数、電流モードのモノリシック降圧レギュレータです。電流リファレンスに基づくアーキテクチャを使用して動作し、ユニティ・ゲインを採用することで出力電圧の全範囲において出力ノイズを最小限に抑えます。RT ピンに接続した抵抗で周波数が設定された発振器により、各クロック・サイクルの開始時に内蔵の上側パワー・スイッチがオンします。インダクタを流れる電流は、上側スイッチの電流コンパレータがトリップするまで増加し、トリップすると上側パワー・スイッチがオフになります。上側スイッチがオフになるピーク・インダクタ電流値は、 $V_C$  ピンの電圧によって制御されます。エラー・アンプは、OUTS ピンの電圧と SET ピンのリファレンス電圧を比較することで  $V_C$  ノードをサーボ制御します。このリファレンス電圧は、SET ピンとグラウンドの間に抵抗を接続することで設定します。負荷電流が増加すると、OUTS 電圧はリファレンスと比較して低くなるので、平均インダクタ電流が新たな負荷電流と釣り合うまで、エラー・アンプが  $V_C$  電圧を上昇させます。上側パワー・スイッチがオフになると、次のクロック・サイクルが始まるまで、あるいはインダクタ電流がゼロに低下するまで（これはパルススキッピング・モードの場合のみ）、同期パワー・スイッチがオンになります。過負荷状態となって下側スイッチに流れる電流が 1.5A (LT83401) / 2.4A (LT83402) を超えると、スイッチ電流が安全なレベルに戻るまで次のクロック・サイクルの開始が遅延されます。

LT83401/LT83402 は、従来世代の Silent Switcher 技術に超低ノイズの電流リファレンスを組み合わせた、第 3 世代の Silent Switcher 技術を採用しています。出力電圧は、1 つの抵抗で設定でき、出力範囲全域でユニティ・ゲイン動作が可能です。これにより、出力電圧とは無関係に、実質的に一定の出力ノイズを維持できます。

EN/UVLO ピンが 0.2V を下回ると、LT83401/LT83402 はシャットダウンし、入力から流れ込む電流は 45 $\mu$ A になります。EN/UVLO ピンが 0.75V を超えると、スイッチング・レギュレータがアクティブになります。

軽負荷時の効率を改善するため、LT83401/LT83402 は軽負荷状態ではパルススキッピング・モードで動作します。パルススキッピング動作を使用するには、SYNC/MODE ピンをグラウンドに接続します。また、FCM を使用するには、INTV<sub>CC</sub> や 1.5V より高い電圧に接続するか、フローティング状態にします。SYNC ピンにクロックを入力すると、デバイスは外部クロック周波数に同期して FCM で動作します。

LT83401/LT83402 を FCM で動作させると、広い負荷範囲にわたって高速過渡応答を得ることができ、最大周波数での動作が可能です。FCM では発振器が連続的に動作し、正の SW 遷移がクロックに同期されます。負のインダクタ電流も許容されます。このモードでは、LT83401/LT83402 が output から電流をシンクしてその電荷を入力に戻せるので、負荷ステップ過渡応答が改善されます。

$V_C$  ピンを使用すれば、事前に設定されたスイッチング周波数に基づいてスイッチング・レギュレータのループ補償を最適化できるので、高速過渡応答に対応することができます。

## アプリケーション情報

### 低周波出力ノイズ

LT83401/LT83402 には、低周波数範囲（100kHz 未満）におけるノイズ性能に関して多くの利点があります。従来の降圧レギュレータには、低周波数のノイズ源がいくつかありました。従来型レギュレータの最も決定的なノイズ源は、そのリファレンス、エラー・アンプ、出力電圧の設定に使用される抵抗分圧ネットワークからのノイズ、そしてこの抵抗分圧器が生成するノイズ・ゲインです。

一般的な降圧レギュレータと異なり、LT83401/LT83402 は電圧リファレンスを使用しません。その代わりに、 $100\mu\text{A}$  の電流リファレンスを使用します。従来の降圧レギュレータに存在する問題の 1 つは、出力電圧を設定する抵抗分圧器によってリファレンスのノイズのゲインが増加することです。これに対して、LT83401/LT83402 が採用している電流リファレンスのアーキテクチャは、ユニティ・ゲイン動作によってリファレンスと出力の間におけるノイズの増加を防ぐことができます。このため、コンデンサで SET ピンの抵抗をバイパスした場合、出力ノイズは出力電圧の設定値に依存しません。

結果として生じる出力ノイズは主としてエラー・アンプのノイズによって決まり、その値は通常、 $10\text{kHz} \sim 1\text{MHz}$  で  $4\text{nV}/\sqrt{\text{Hz}}$  です。エラー・アンプがそのような低ノイズ・レベルで動作している場合、降圧レギュレータの駆動段ノイズが出力ノイズに対して無視できない要因になる可能性があります。レギュレータのループ・ゲインは駆動段ノイズを低下させます。そのため、補償ネットワークの選択によって駆動段ノイズがどの程度寄与するかが決まります。

一般に、良好なトランジエント性能を実現する補償ネットワークを用いれば、駆動段ノイズの寄与を確実に抑えることができます。[周波数補償](#)のセクションに、適切な補償を選択するためのガイドラインが記載されています。補償を選択する場合、クローズド・ループ応答でのピーキングを防ぐために、ループが良好な位相マージンを持つよう徹底することが必須です。クローズド・ループ応答のピーキングは、ノイズを増加させるため、避ける必要があります。

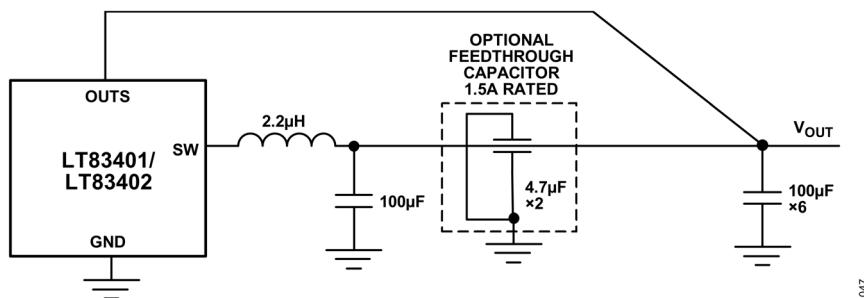

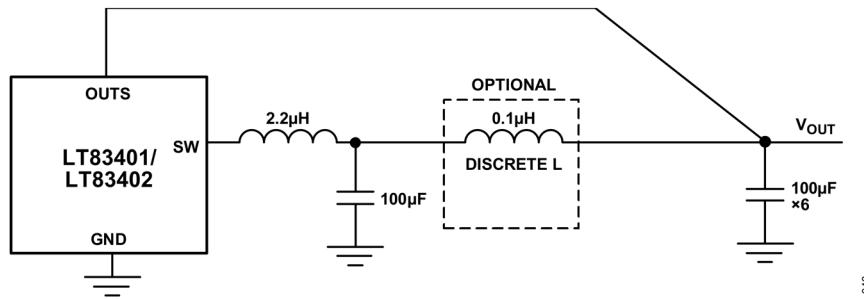

### スイッチング・リップルと高周波ノイズのフィルタリング

LT83401/LT83402 はスイッチング・レギュレータであり、出力にはスイッチング・レギュレータ特有のアーチファクトが発生します。すなわち、スイッチング周波数の基本波成分のリップルと高速スイッチング・エッジによる高周波スパイクです。出力コンデンサがこれらのスパイクをある程度は吸収するものの、コンデンサの等価直列インダクタンス (ESL) により、高周波数ではその能力が制限されます。フィードスルー・コンデンサ、フェライト・ビーズ、または LC フィルタ段を追加のフィルタリングとして出力に使用することを推奨します。これにより、高周波スパイクを取り除き、スイッチング・リップルを大幅に低減します。

高速の過渡応答を維持しながらスイッチング・リップルを更に低減することが必要であれば、フェライト・ビーズ、プリント回路基板 (PCB) パターン、またはフィードスルー・コンデンサを使用できます。フィードスルー・コンデンサを使用する場合は、必要な負荷電流を流せるように十分な数のフィードスルー・コンデンサを並列に接続してください。[図 47](#)に示す例では、1.5A 定格のフィードスルー・コンデンサを 2 個使用してスイッチング・リップルの追加抑制を行い、最大 3A の出力を提供しています。実際には、出力電流は LT83401 が 1A、LT83402 が 2.5A に制限されています。

図 47. フィードスルー・コンデンサを使用した追加の出力リップル・フィルタリング

トランジエント性能が重要でない場合、大きな第 2 の L として物理的なインダクタと、第 2 の C として出力コンデンサを追加することで受動部品によるフィルタ処理を実現できます（図 48 を参照）。

図 48. 第 2 の LC フィルタを使用した追加の出力リップル・フィルタリング

スイッチング・リップルを更に減衰するための追加フィルタを設計する場合は、LTpowerCAD®を使用して設計することを強く推奨します。これにより、十分な位相マージンを備え安定した設計ができると共に、対象となるスイッチング周波数で優れた減衰性能を実現できます。Silent Switcher 3 アーキテクチャにより、受動部品によるフィルタリングを使用するだけで、LT83401/LT83402 の出力で低周波から高周波までの優れたノイズ性能を可能にします。

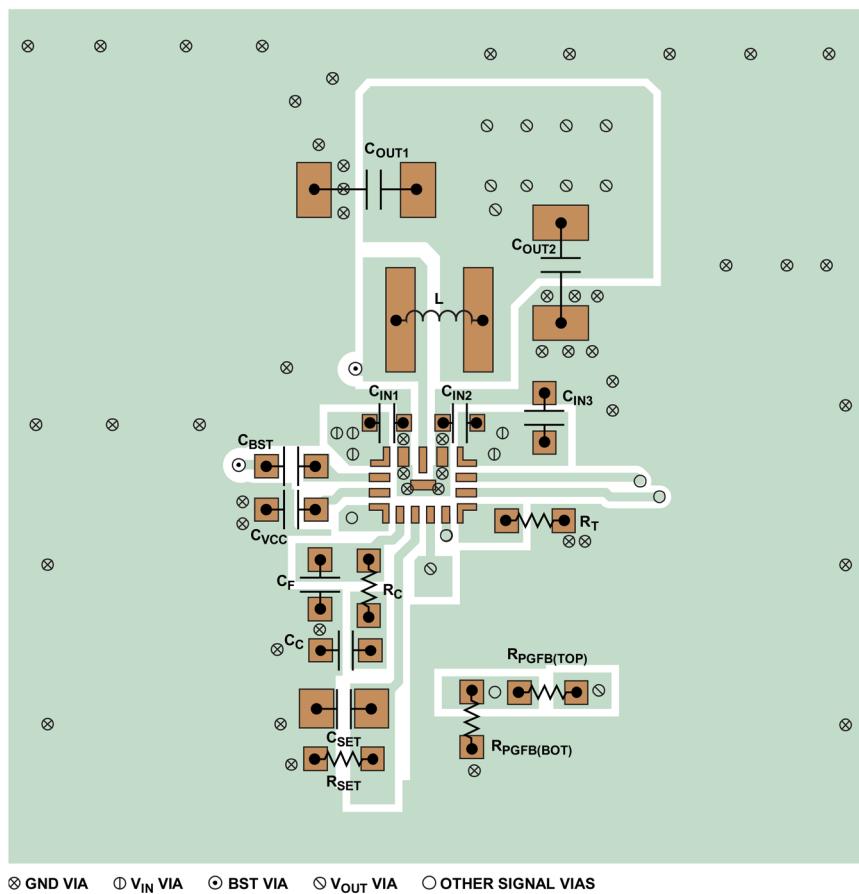

## PCB レイアウトに関する推奨事項

LT83401/LT83402 は低周波ノイズ（10Hz～100kHz）と EMI 放射を最小限に抑えて、高周波数でのスイッチング時に最大限の効率が得られるよう特別に設計されています。LT83401/LT83402 の性能を最大限に引き出すために、複数の V<sub>IN</sub> バイパス・コンデンサを使用することができます。

小さいコンデンサを 2 個、LT83401/LT83402 の V<sub>IN</sub> ピンのできるだけ近くに配置します。より大きな値の（4.7μF 以上）3 つ目のコンデンサを、これら 2 つのコンデンサの近くに置いてください。推奨の PCB レイアウトについては、図 49 を参照してください。

詳細および PCB 設計ファイルについては、[EVAL-LT83401/EVAL-LT83402 ユーザ・ガイド](#)を参照してください。LT83401/LT83402 の V<sub>IN</sub> ピンと GND ピン、および入力コンデンサには大きいスイッチ電流が流れる点に注意してください。また、V<sub>IN</sub> ピンと GND ピンに隣接させてコンデンサを配置することにより、入力コンデンサによって形成されるループをできるだけ小さくする必要があります。0402 や 0603 といったケース・サイズの小さいコンデンサは寄生インダクタンスが小さいので、この用途に最適です。入力コンデンサが IC グラウンドへの低インピーダンスのリターン経路を確保できるよう、特に注意を払う必要があります。これを実現するため、入力コンデンサの GND 側に複数のグラウンド接続を配置し、グランド・プレーンを最大限に活用します。これは、切れ目のないグランド・プレーンと IC の露出パッドを強固に接続することで実現できます（図 49 を参照）。

図 49. LT83401/LT83402 の推奨レイアウト

メイン・インダクタと出力コンデンサは、回路基板の IC と同じ側に配置し、その接続も同じ層上で行います。また、バルク出力コンデンサの IC グラウンドへのリターン経路のインピーダンスも、グラウンド・ビアを多数使用して最小限に抑える必要があります。グラウンドのレイアウトに注意を払うことで、スイッチング電流が入力コンデンサからグラウンドを通じて出力に結合するのを防ぎ、OUTS ピンに意図しない変動が生じるのを抑えられます。必要に応じて、小型のコンデンサを近くに配置することで OUTS ピンをデカップリングできます。

追加で LC フィルタを使用する場合、回路基板の反対側に配置することで EMI 性能を最適化できますが、必須ではありません。局部的な切れ目のないグランド・プレーンを、表面層に最も近い層でアプリケーション回路の下に配置します。SW ノードと BST ノードは、できるだけ小さくする必要があります。最後に、OUTS、PGFB、および RT ノードを小さくしておくことで、グラウンド・パターンがそれらのノードをシールドして、SW ノードと BST ノードからの影響を受けないようにします。OUTS、PGFB、RT の配線パターンはメイン・インダクタの下を通してください。また、インダクタのビアから離して配置してください。

パッケージから周囲への熱抵抗を減らすために、パッケージ底面にある露出パッドを PCB に半田付けする必要があります。熱抵抗を小さく保つには、GND からのグランド・プレーンをできるだけ広くして、回路基板内と底面側の広くなったグランド・プレーンにサーマル・ビアを追加します。

LT83401/LT83402 の電流リファレンス・アーキテクチャでは、負荷の正端子だけでなく負端子のリモート検出が可能です。R<sub>SET</sub> と C<sub>SET</sub> のグラウンド側のビアが C<sub>OUT</sub> のグラウンド側に接続されており、これにより離れた位置にある負荷の負端子のリモート検出を構成できます。LT83401/LT83402 で行っているリモート検出の詳細については、[出力検出とその安定性](#)のセクションを参照してください。

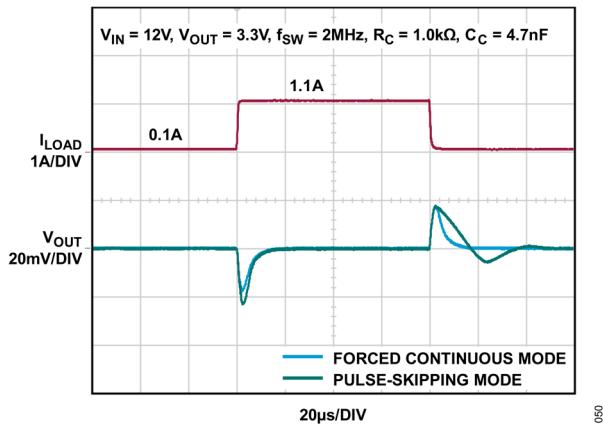

## 強制連続モード (FCM)

LT83401/LT83402 を FCM で動作させると、広い負荷範囲にわたって高速過渡応答を得ることができ、最大周波数での動作が可能です。FCM では発振器が連続的に動作し、正の SW 遷移がクロックに同期されます。軽負荷時や大きなトランジエント状態時には、負のインダクタ電流が許容されます。このモードでは、LT83401/LT83402 が出力から電流をシンクしてその電荷を入力に戻せるので、負荷ステップ過渡応答が改善されます（パルススキッピング・モードと FCM の比較については、図 50 を参照してください）。軽負荷時には FCM 橋接の方がパルススキッピング・モード動作より効率が低下しますが、スイッチング高調波が信号帯域内に入らないようにする必要のあるアプリケーションでは、FCM の方が適している場合があります。出力に電流をシンクさせる必要がある場合は FCM を使用してください。FCM を有効化するには、ピンを INTV<sub>CC</sub> または 1.5V より高い電圧に接続するか、フロート状態にします。

図 50. FCM 使用時と不使用時の負荷ステップ過渡応答

標準アプリケーション回路（図 59）を参照

$V_{IN}$  の過電圧状態 ( $V_{IN}$  ピンが 42V より高い電圧)、 $V_{OUT}$  が高すぎる (PGFB ピンが 537.5mV より高い) 場合、および、スタートアップ時の  $V_{OUT}$  の電圧がその最終値の約 97.5%まで充電されるまで (PGFB ピンが 487.5mV まで上昇したこと示される) は、FCM は無効化されています。この最後の 2 つの状態については、PGFB ピンが適切な抵抗により出力電圧に接続されていることが前提となります。このような形で FCM が無効化された場合は、負のインダクタ電流が許容されず、LT83401/LT83402 はパルススキッピング・モードで動作します。

## パルススキッピング・モード

FCM で動作していない場合、LT83401/LT83402 はパルススキッピング・モードで動作します。パルススキッピング・モードでは発振器が連続的に動作し、全スイッチング・サイクルがクロックに同期されます。このモードでは負のインダクタ電流は許容されません。そのため、軽負荷時には LT83401/LT83402 は不連続モードで動作する場合があります。また、パルススキッピング・モードでは、LT83401/LT83402 は、負荷が非常に軽い場合に効率を向上させたり、非常に高いデューティサイクル時にドロップアウトを改善させたりするために、スイッチング・サイクルをスキップする場合もあります。パルススキッピング・モードを有効化するには、SYNC/MODE ピンを GND に接続します。

## 同期

LT83401/LT83402 の発振器を外部周波数に同期させるには、SYNC/MODE ピンに矩形波を接続します。この矩形波は、最小オン時間と最小オフ時間が 50ns で、振幅の谷が 0.7V 未満、山が 1.5V を超える (最大 6V) ものとする必要があります。

外部クロックに同期している間、デバイスは FCM で動作してレギュレーションを維持します。LT83401/LT83402 は 300kHz~6MHz の範囲で同期できます。 $R_T$  抵抗は、LT83401/LT83402 のスイッチング周波数が最低同期入力未満となるように選ぶ必要があります。スロープ補償は  $R_T$  値によって設定されますが、低調波振動を避けるために必要な最小のスロープ補償は、インダクタ・サイズ、入力電圧、出力電圧によって確定します。同期周波数によってインダクタ電流波形の勾配が変化するわけではないため、インダクタが  $R_T$  で設定された周波数での低調波振動を回避できるだけの大きさであれば、スロープ補償はすべての同期周波数に対して十分なものになります。

## スイッチング周波数の設定

LT83401/LT83402 は固定周波数のパルス幅変調 (PWM) アーキテクチャを採用しており、 $R_T$  ピンと GND の間に抵抗を接続することによって、300kHz～6MHz の範囲でスイッチング周波数を設定できます。

目的のスイッチング周波数を得るために必要な  $R_T$  抵抗の値は、式 1 を使って計算できます。

$$R_T = \frac{118.41}{f_{SW}} - 11.7 \quad (1)$$

ここで  $R_T$  の単位は kΩ です。また、 $f_{SW}$  は目的のスイッチング周波数であり、単位は MHz です。目的のスイッチング周波数に必要な  $R_T$  の値を表 4 に示します。

表 4. スイッチング周波数と  $R_T$  値の関係

| $f_{SW}$ (MHz) | $R_T$ (kΩ) |

|----------------|------------|

| 0.3            | 412        |

| 0.4            | 301        |

| 0.5            | 237        |

| 0.6            | 191        |

| 0.7            | 162        |

| 0.8            | 140        |

| 0.9            | 121        |

| 1.0            | 107        |

| 1.2            | 88.7       |

| 1.4            | 73.2       |

| 1.6            | 61.9       |

| 1.8            | 53.6       |

| 2              | 47.5       |

| 2.5            | 35.7       |

| 3              | 27.4       |

| 3.5            | 22.1       |

| 4              | 17.8       |

| 6              | 8.25       |

## 動作周波数の選択とトレードオフ

動作周波数の選択は、効率、部品サイズ、および入力電圧範囲のトレードオフになります。高周波数動作の利点はインダクタとコンデンサの値を小さくできることで、欠点は効率が低く入力電圧範囲が狭いことです。アプリケーションの最大スイッチング周波数 ( $f_{SW(MAX)}$ ) は式 2 で計算できます。

$$f_{SW(MAX)} = \frac{V_{OUT} + V_{SW(BOT)}}{t_{ON(MIN)}(V_{IN} - V_{SW(TOP)} + V_{SW(BOT)})} \quad (2)$$

ここで、 $V_{IN}$ は入力電圧（代表値）、 $V_{OUT}$ は出力電圧、 $V_{SW(TOP)}$ と $V_{SW(BOT)}$ は内蔵スイッチの電圧降下（最大負荷時でそれぞれ約0.28Vと約0.14V）、 $t_{ON(MIN)}$ は上側スイッチの最小オン時間です（電気的特性の表を参照）。この式から、高い $V_{IN}/V_{OUT}$ 比に対応するためには、スイッチング周波数を下げる必要があります。

トランジエント動作では、 $R_T$ の値によらず $V_{IN}$ が絶対最大定格の42Vにまで達する可能性があります。しかし、LT83401/LT83402は必要に応じてスイッチング周波数を下げてインダクタ電流の制御を維持し、安全な動作を確保します。

パルススキッピング・モードでは、LT83401/LT83402は約98%の最大デューティサイクルに対応でき、 $V_{IN} \sim V_{OUT}$ 間のドロップアウト電圧は上側スイッチの $R_{DS(ON)}$ によって制限されます。これにより、 $V_{IN}$ と $V_{SET}$ の間に電流リファレンス回路を正常に機能させるために十分なヘッドルーム（約0.9V）が確保されます。このモードでは、LT83401/LT83402はスイッチ・オフ時間のサイクルをスキップするため、スイッチング周波数は $R_T$ で設定した周波数よりも低くなります。LT83401/LT83402は、昇圧コンデンサのリフレッシュに必要な周波数でスイッチングを行い、最小スイッチング周波数は約80kHzです。スイッチング周波数が高くなると、最小入力電圧の値も高くなることに注意してください。入力電圧が最小値未満になると、デューティ・サイクルを上げるためにサイクル数が減少します。約0.9Vという電流リファレンスのヘッドルーム要件に依存しない良好なドロップアウト性能を実現するには、外部抵抗分圧器を介して $OUTS$ を $V_{OUT}$ に接続します（図53参照）。例えば、12V $OUT$ のアプリケーションでは、2:1の分圧器により出力で6Vが生じ、動作範囲全体において $V_{IN}$ と $V_{SET}$ の差が0.9Vを確実に超えることができます。詳細は、図23を参照してください。

FCMでは、LT83401/LT83402はサイクルをスキップしません。そのため、最大デューティ・サイクルは最小オフ時間と選択したスイッチング周波数によって制限されます。 $V_{IN}/V_{OUT}$ 比が低い場合に設定スイッチング周波数からの偏差を許容できず、FCMでの動作が必要なアプリケーションでは、式3を使ってスイッチング周波数を設定します。

$$V_{IN(MIN)} = \frac{V_{OUT} + V_{SW(BOT)}}{1 - f_{SW} \times t_{OFF(MIN)}} - V_{SW(BOT)} + V_{SW(TOP)} \quad (3)$$

ここで $V_{IN(MIN)}$ はサイクルをスキップしない場合の最小入力電圧、 $V_{OUT}$ は出力電圧、 $V_{SW(TOP)}$ と $V_{SW(BOT)}$ は内部スイッチの電圧降下（最大負荷時でそれぞれ約0.28V/0.7Vと約0.14V/0.34V）、 $f_{SW}$ は（ $R_T$ によって設定された）スイッチング周波数、 $t_{OFF(MIN)}$ は最小スイッチ・オフ時間です。

## インダクタの選択と最大出力電流

LT83401/LT83402は、アプリケーションの出力負荷条件に基づいてインダクタを選択できるようにすることで、ソリューション・サイズを最小限に抑えるように設計されています。LT83401/LT83402は、高速ピーク電流モード・アーキテクチャの採用により、過負荷時や短絡時にインダクタが飽和した状態になっても安全な動作を確保できます。

インダクタ値の初期値として妥当な値は、式4で得られます。

$$L = \left( \frac{V_{OUT} + V_{SW(BOT)}}{f_{SW}} \right) \times 1.2 \quad (4)$$

ここで、 $f_{SW}$ はスイッチング周波数（MHz）、 $V_{OUT}$ は出力電圧、 $V_{SW(BOT)}$ は下側スイッチの電圧降下（約0.14V/0.34V）、 $L$ はインダクタの値（ $\mu$ H）です。

過熱と効率の低下を回避するには、アプリケーションで予想される最大出力負荷よりも大きいRMS電流定格のインダクタを選択します。更に、（通常は $I_{SAT}$ と表示される）インダクタの飽和電流定格は、負荷電流にインダクタのリップル電流の%を加算した値よりも大きくする必要があります。式5を参照してください。

$$I_{L(PEAK)} = I_{LOAD(MAX)} + \frac{1}{2} \Delta I_L \quad (5)$$

ここで  $\Delta I_L$  は式 7 で計算されるインダクタのリップル電流、 $I_{LOAD(MAX)}$  はアプリケーションの最大出力負荷です。

簡単な例を挙げると、1A の出力を必要とするアプリケーションでは、実効電流定格値が 1A より大きく、 $I_{SAT}$  が 2A より大きいインダクタを使用します。過負荷状態または短絡状態が長時間に及ぶ場合は、インダクタの過熱を防ぐために、インダクタの実効電流定格の要求値が大きくなります。高い効率を保つには、直列抵抗 (DCR) を 135mΩ より小さくし、コア材を高周波アプリケーション向けのものにする必要があります。

LT83401/LT83402 は、スイッチとシステムを過負荷によるフォルトから保護するために、ピーク・スイッチ電流を制限します。

上側スイッチの電流制限値 ( $I_{PEAK-LIMIT}$ ) は低デューティサイクルでは 2.2A (LT83401) / 4A (LT83402) ですが、そこから直線的に減少して、デューティサイクル = 80% では 1.8A (LT83401) / 3.2A (LT83402) になります。

インダクタの値は目的の最大出力電流 ( $I_{OUT(MAX)}$ ) を供給するのに十分な大きさにする必要があります。この電流は、上側スイッチの電流制限値 ( $I_{PEAK-LIMIT}$ ) とリップル電流の関数です (式 6 を参照)。

$$I_{OUT(MAX)} = I_{PEAK-LIMIT} - \frac{\Delta I_L}{2} \quad (6)$$

インダクタのピーク to ピーク・リップル電流は、式 7 を使って計算できます。

$$\Delta I_L = \frac{V_{OUT}}{L \times f_{SW}} \times \left(1 - \frac{V_{OUT}}{V_{IN(MAX)}}\right) \quad (7)$$

ここで、 $f_{SW}$  は LT83201 のスイッチング周波数、 $L$  はインダクタの値です。したがって、LT83401/LT83402 が供給できる最大出力電流は、スイッチ電流制限値、インダクタの値、および入力電圧と出力電圧に依存します。目的のアプリケーションで使用するスイッチング周波数と最大入力電圧が決まっている場合で、インダクタのリップル電流が最大出力電流 ( $I_{OUT(MAX)}$ ) に対して不十分な場合は、インダクタの値を大きくしなければならないことがあります。

特定のアプリケーションに最適なインダクタは、この設計ガイドに示すものと異なる場合があります。インダクタの値が大きければ最大負荷電流は増加し、出力電圧リップルは減少します。必要な負荷電流が小さいアプリケーションではインダクタの値を小さくすることができます、LT83401/LT83402 を大きいリップル電流で動作させることができます。したがって、物理的に小さいインダクタを使用するか DCR の小さいものを使用して、効率を高めることができます。ただし、インダクタンスが小さいとパルススキッピング・モードで不連続動作が生じることがあり、最大負荷電流が更に減少するので注意が必要です。

最大出力電流と不連続動作の詳細については、アプリケーション・ノート 44 : LT1074/LT1076 デザイン・マニュアルを参照してください。

デューティサイクルが 50% を超える場合 ( $V_{OUT}/V_{IN} > 0.5$ ) は、低調波発振を防ぐためにインダクタンスを最小限に抑える必要があります。詳細については、アプリケーション・ノート 19 : LT1070 デザイン・マニュアルを参照してください。式 8 を使用して最小インダクタンスを計算します。ここで、 $I_{SC}$  はスロープ補償係数です。 $I_{SC}$  は、LT83401 の場合 0.4、LT83402 の場合 0.8 です。

$$L_{MIN} = \frac{V_{IN}(2 \times DC - 1)}{I_{SC} \times f_{SW}} \quad (8)$$

ここで、DC はデューティサイクル比 ( $V_{OUT}/V_{IN}$ )、 $f_{SW}$  はスイッチング周波数です。

## 過電流保護 (OCP)

LT83401/LT83402 は、上側スイッチと下側スイッチを流れる電流の両方にサイクルごとの電流制限を行うことにより、過負荷状態および出力短絡状態から保護します。

上側スイッチがオンになると、電流検出が行われます。上側スイッチで電流制限値 ( $I_{PEAK-LIMIT}$ ) が検出されると、上側スイッチは直ちにオフになり、下側スイッチがオンになります。下側スイッチのオンによっても電流検出が行われ、下側スイッチの電流が制限値 ( $I_{VALLEY-LIMIT}$ ) を下回るまで、上側スイッチは再度オンになることができません。下側スイッチの電流が  $I_{VALLEY-LIMIT}$  を下回るまで上側スイッチが発振器のクロック・エッジでオンにならないことで、保護が必要とされる間は、効率的にスイッチング周期を長くして、周波数を低下させます。これにより、出力短絡状態の間、平均電流を  $I_{PEAK-LIMIT}$  と  $I_{VALLEY-LIMIT}$  の RMS 平均に制限します。

## 入力コンデンサ

最大限の性能を得るには、LT83401/LT83402 の  $V_{IN}$  を、少なくとも 3 個のセラミック・コンデンサでバイパスする必要があります。小型セラミック・コンデンサ 2 個 ( $C_{IN1}$ 、 $C_{IN2}$ ) をデバイスに近付けて配置してください。これらのコンデンサのサイズは 0402 とします。

スイッチング周波数が低いほど、より大きな入力容量が必要になることに注意してください。入力電源のインピーダンスが高い場合、あるいは長い配線やケーブルによって大きなインダクタンスが存在する場合は、更に大きい容量が必要になることがあります。これには性能の高くない電解コンデンサを使用できます。

セラミック入力コンデンサにパターンまたはケーブルのインダクタンスが組み合わさることにより、高品質の（不足減衰の）タンク回路が構成されます。LT83401/LT83402 を通電状態の電源に接続すると、入力電圧に公称値の 2 倍のリングングが生じて LT83401/LT83402 の電圧定格値を超えてしまうおそれがありますが、この状況は容易に回避できます。詳細については、アプリケーション・ノート 88：セラミック入力コンデンサによって生じる過電圧トランジェントを参照してください。

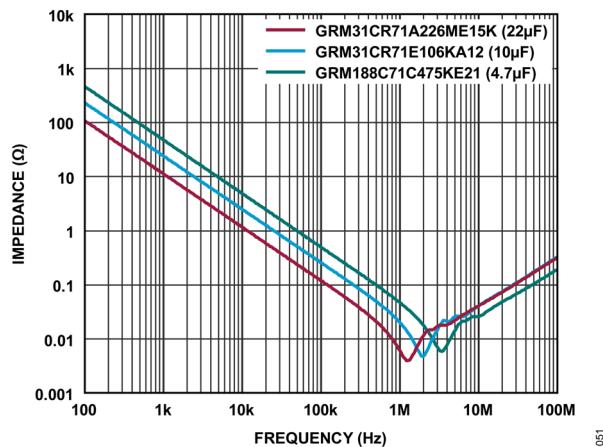

## 出力コンデンサと出力リップル

出力コンデンサには 2 つの重要な役割があります。まず、インダクタと併用して、LT83401/LT83402 によって生成される矩形波をフィルタ処理することで DC 出力を発生させます。この役割は出力リップルを決定するものなので、スイッチング周波数におけるインピーダンスを小さくすることが重要です。2 つ目の役割は、トランジェントな負荷に対応できるようエネルギーを保存し、LT83401/LT83402 の制御ループを安定させることです。セラミック・コンデンサは ESR が非常に低く、最高のリップル性能を提供します。妥当な初期値については、[代表的なアプリケーション](#) のセクションを参照してください。

コンデンサは X5R または X7R タイプを使用してください。これらのコンデンサは、低出力リップルで良好な過渡応答を実現します。出力コンデンサを大きくするとトランジェント性能を向上できます。出力容量を大きくしても出力電圧リップルを低減できます。値の小さい出力コンデンサを使用するとスペースとコストが節約できますが、トランジェント性能が悪化し、ループが不安定になります。コンデンサの推奨値については、[代表的なアプリケーション](#) のセクションを参照してください。

コンデンサを選ぶときは、そのデータシートを十分に吟味し、関係する電圧バイアスと温度での動作条件に基づいて、効果的な容量を計算する必要があります。物理的に大きいコンデンサや、より高い電圧定格のコンデンサが必要になる場合があります。

LT83401/LT83402 は通常、2MHz のスイッチング周波数で動作します。[表 5](#) に、約 2MHz のスイッチング周波数で動作する場合の、理想的な周波数特性を備えた出力コンデンサの例を示します。[図 51](#) に、これらのコンデンサの周波数特性を示します。これらのコンデンサの組み合わせでは、出力におけるスイッチング周波数でのインピーダンスが最小化され、スイッチング周波数近辺においてより高い周波数の高調波を抑制するのに十分な低いインピーダンスを保ち、非常に低い出力リップルが実現されることが分かります。

表 5. 2MHz 動作に要求される周波数特性を備えた出力コンデンサの例

| PART DESCRIPTION          | MANUFACTURER/PART NUMBER   |

|---------------------------|----------------------------|

| 22μF, X7R, 10V, 20% 1206  | MURATA, GRM31CR71A226ME15K |

| 10μF, X7R, 25V, 10% 1206  | MURATA, GRM31CR71E106KA12  |

| 4.7μF, X7S, 16V, 10% 0603 | MURATA, GRM188C71C475KE21  |

図 51. 例に示した出力コンデンサの 2MHz 動作における周波数特性

## 出力電圧

LT83401/LT83402 は、SET ピンに電流を流す  $100\mu\text{A}$  の高精度電流源を内蔵しており、この電流源はエラー・アンプの非反転入力にも接続されています。図 52 に、SET と GND の間に抵抗を接続して、エラー・アンプ用のリファレンス電圧を生成する構成を示します。このリファレンス電圧は、SET ピン電流と SET ピンの抵抗を掛け合わせたものです。エラー・アンプはユニティ・ゲイン構成になっているので、この電圧を低インピーダンスにしたもののが反転入力、すなわち外部で回路の出力電圧に接続される OUTS ピンに出力されます。

図 52. 調整可能なエラー・アンプのリファレンス

LT83401/LT83402 のエラー・アンプと電流リファレンスにより、 $0\text{V}$  ( $0\Omega$  抵抗を使用) から  $15\text{V}$ までの広い出力電圧に対応します。 $V_{\text{OUT}}$  が  $0\text{V}$  から  $V_{\text{IN}} - 1.4\text{V}$  の範囲では PNP ベースの入力ペアがアクティブになります、 $V_{\text{OUT}}$  が  $V_{\text{IN}} - V_{\text{OUT}} < 1\text{V}$  の範囲では NPN ベースの入力ペアがアクティブになります。そして、これらの範囲間における 2 つの入力ペアの遷移はスムーズに行われます。PNP ベースの入力ペアは、アプリケーションの大部分においてアクティブになるため、全体性能が最高になるように設計されています。オフセット電圧、SET ピン電流、出力ノイズの詳細については、電気的特性の表を参照してください。表 6 に、いくつかの一般的な出力電圧と、それに対応する 1% 精度の  $R_{\text{SET}}$  抵抗の値を示します。出力電圧に必要な抵抗値を正確に得られない場合は、2 個の抵抗を並列に使用することで必要な値を得ることができます。例えば、 $0.8\text{V}$  の出力電圧を得るには  $8\text{k}\Omega$  ちょうどどの抵抗値が必要です。1% 抵抗 1 個で最も近い値は  $8.06\text{k}\Omega$  ですが、2 個の抵抗、 $8.25\text{k}\Omega$  と  $267\text{k}\Omega$  を並列に使用することで（ほぼ）正確に  $8\text{k}\Omega$  が得られます。0.1% 抵抗を使用すると、更に高い精度が得られます。

表 6. 一般的な出力電圧に対する 1%抵抗値

| V <sub>OUT</sub> (V) | R <sub>SET</sub> (kΩ) |

|----------------------|-----------------------|

| 0.8                  | 8.06                  |

| 1                    | 10                    |

| 1.8                  | 18                    |

| 2.5                  | 24.9                  |

| 3.3                  | 33.2                  |

| 5                    | 49.9                  |

| 6                    | 60.4                  |

| 9                    | 90.9                  |

| 12                   | 120                   |

一般的なレギュレータで用いられる電圧リファレンスと比較して、電流リファレンスを使用するメリットは、設定出力電圧に関わらずレギュレータが常にユニティ・ゲイン構成で動作することです。これにより、LT83401/LT83402 では、出力電圧に依存しないループ・ゲイン、周波数応答、帯域幅が得られます。更に、SET ピンの電圧をより高い出力電圧まで増幅するようなエラー・アンプのゲインが不要なため、出力の負荷レギュレーションをより厳密に規定できます。

電流源は T<sub>C</sub> がゼロで非常に精度が高いため、高精度を実現する上で SET ピンの抵抗が制限要因になり得ます。したがって、高精度の抵抗を使用する必要があります。更に、SET ピンに入り出す漏れ電流の経路があると、出力電圧の誤差につながります。必要に応じて、高品質の絶縁体（例えばテフロンや Kel-F）を使用してください。また、絶縁部の表面を洗浄し、フラックスなどの残留物を除去することも必要です。湿度の高い環境では、SET ピンに対して表面にコーティングを施し、防湿バリアを形成しなければならない場合もあります。

SET ピンは高インピーダンス・ノードのため、不要な信号が混入して不正な動作を招くことがあります。これは、出力コンデンサが最小限で負荷電流が高いときの動作で最も顕著になります。この問題は、SET ピンを小さな容量で GND にバイパスすることで解決できます。容量は 100nF で十分ですが、この値は推奨される容量の最小値です。一般には、もっと大きな容量が推奨されます。詳細については、[SET ピン・コンデンサ：ノイズとソフトスタート](#) のセクションを参照してください。

より高い精度が必要なアプリケーションや可変出力電圧が必要なアプリケーションでは、SET ピンを 100μA のシンクが可能な外部電圧源でアクティブに駆動することができます。SET ピンに高精度の電圧リファレンスを接続すると、リファレンス電流と SET ピン抵抗の許容誤差に起因する出力電圧の誤差を除去できます。

## 15V を超える出力電圧

SET ピン電圧が最大 15V に制限されている場合でも、図 53 に示すような従来型の抵抗分圧器を V<sub>OUT</sub> と OUTS の間に使用することにより、LT83401/LT83402 でも 15V を超える出力電圧に設定できます。SET ピン電圧は 15V に設定することを推奨します。この場合、抵抗値は式 9 に従って選択できます。

$$R1 = R2f(x) = (x + a)^n = \left( \frac{V_{OUT} - 15V}{15V + R_2 \times I_{OUTS}} \right) \quad (9)$$

電気的特性の表から、OUTS ピン電流は  $170\text{nA} \pm 60\text{nA}$  です。分圧器の R1 と R2 の値は、この OUTS ピン電流の変動による出力電圧レギュレーションの誤差が 0.1% 未満になるように選択します。抵抗分圧器の抵抗の熱ノイズも、出力ノイズに寄与します。ノイズの寄与がデバイス自体のノイズへの寄与に比べて低くなるように、抵抗値は SET ピンから見たインピーダンス ( $R1||R2$ ) が  $5\text{k}\Omega$  より低くなるように選択することを推奨します。

053

図 53. 15V を超える出力電圧に対応した LT83401/LT83402 の構成

15V を超える出力電圧では、低周波ノイズが出力電圧の影響を受けるようになります。SET 電圧が 15V になるように構成すると、この依存性を最小化できます。例えば、18V<sub>OUT</sub> の場合の 15V リファレンスからのノイズ・ゲインは、従来の 0.5V 電圧リファレンスから 18V<sub>OUT</sub>へのゲインに比べて 1/30 になります。

## 高 V<sub>OUT</sub>に関する考慮事項

出力電圧が 20V より高いアプリケーションでは、アプリケーション・ノート AN-2582 の逆電流に関する考慮事項のセクションを参照してください。

## 0.5V を下回る出力電圧

LT83401/LT83402 は、電流リファレンス・アーキテクチャを採用しているため、0.5V 未満から 0V までの出力電圧を設定できます。0.5V 未満の出力電圧では、パワー・グッド機能と高速スタートアップ機能は使用できないので注意してください。また、PGFB を INTV<sub>CC</sub> または 0.5V に接続してこれらの機能を無効化する必要があります。

## 出力検出とその安定性

LT83401/LT83402 の OUTS ピンは出力にケルビン検出接続します。SET ピン抵抗の GND 側は、負荷の GND 側にケルビン検出接続します。

LT83401/LT83402 の内部エラー・アンプは、約 2400/2000 という比較的高い電圧ゲインを備えています。これにより、大きな寄生成分とノイズの混入が組み合わされるとシステムが不安定になる可能性があるため、フィードバック・ループに更に追加のインピーダンス (ESR および ESL) を加えないようにし、OUTS ピンに混入するノイズを最小限に抑えることがとても重要です。そのため、OUTS ピンを C<sub>OUT</sub> に直接接続し、C<sub>SET</sub> の GND 側を C<sub>OUT</sub> の GND 側に直接接続することによって、PCB パターンと半田処理によるインダクタンスの影響を最小化します。例えばリモート検出が必要となる設計などにより、これができない場合は、OUTS ピンの近くに 150pF 以下の小型コンデンサを追加することで OUTS ピンのノイズをデカップリングできます。これらの条件を満たす推奨レイアウトの詳細については、LT83401/LT83402 のデモ・ボード・マニュアルを参照してください。

LT83401/LT83402 は外部補償されたデバイスです。そのため、推奨レイアウトに従っていない場合でも（アプリケーション固有の制限により従うことが不可能な場合があります）、動作中の安定性を維持するため、より低いゲインや帯域幅を使用してより安全な補償を選択することができます。ただし、これにより過渡応答性能が低下します。良好なレイアウトであれば、補償値の選定においても過渡応答、位相マージン、出力ノイズ性能の間のトレードオフを改善できます。

## 周波数補償

ループ補償は安定性とトランジエント性能を決定し、 $V_C$  ピンに接続する部品によって行われます。一般的には、グラウンドに直列に接続したコンデンサ ( $C_C$ ) と抵抗 ( $R_C$ ) が使われます。補償回路の設計は複雑で、最適値はアプリケーションによって異なります。実用的な方法は、このデータシートの回路の中から目的のアプリケーションに似た回路を探して出発点とし、補償回路を調整して性能を最適化することです。このプロセスには LTpowerCAD シミュレーションが役に立ちます。その後負荷電流、入力電圧、温度など、全動作条件について安定性を確認します。LT1375 のデータシートには、ループ補償に関する詳細な説明が記載されており、トランジエント負荷を使用した安定性のテスト方法も説明されています。

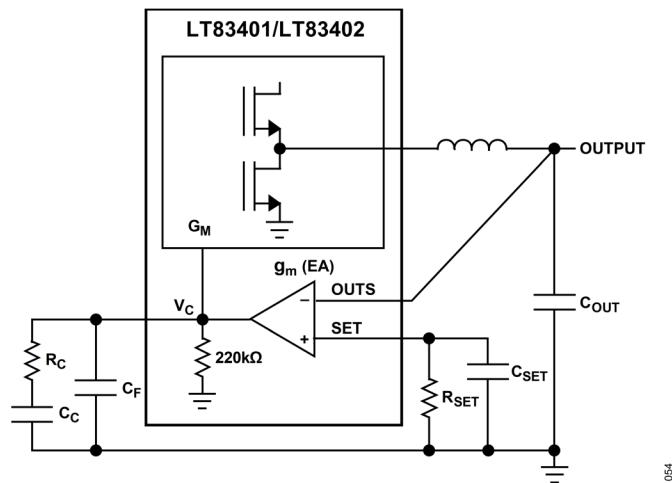

LT83401/LT83402 の制御ループの等価回路を図 54 に示します。エラー・アンプは、出力インピーダンスが有限で、トランスコンダクタンス  $g_{m(EA)} = 12\text{mS}$  のトランスコンダクタンス・アンプです。変調器、パワー・スイッチ、およびインダクタで構成される電源セクションは、 $G_M = 2.3\text{A/V}$  (LT83401) /  $3.6\text{A/V}$  (LT83402) のトランスコンダクタンスを持つトランスコンダクタンス・アンプとしてモデル化され、 $V_C$  ピンの電圧に比例した出力電流を生成します。出力コンデンサはこの電流を積分し、 $V_C$  ピンのコンデンサ ( $C_C$ ) はエラー・アンプの出力電流を積分するので、ループには 2 つのポールが生じる点に注意してください。ゼロが必要ですが、これは  $C_C$  と直列に接続した抵抗  $R_C$  によって得られます。この単純なモデルは、インダクタの値が大きすぎず、ループのクロスオーバー周波数がスイッチング周波数よりはるかに低いという条件が満たされている限り、機能します。スイッチング・モードの電源における補償の詳細については、アプリケーション・ノート 149 : Modeling and Loop Compensation Design of Switching Mode Power Supplies を参照してください。

図 54. ループ応答のモデル

## EN/UVLO ピン

LT83401/LT83402 は、EN/UVLO ピンがローになるとシャットダウンされ、ハイになるとアクティブになります。EN/UVLO コンパレータの立上がり閾値は 0.75V で、50mV のヒステリシスがあります。シャットダウン機能を使わない場合は、EN/UVLO ピンを V<sub>IN</sub> に接続します。また、シャットダウン制御が必要な場合は、このピンをロジック・レベルに接続します。EN/UVLO ピンをデジタル信号で駆動せず、V<sub>IN</sub> に接続する場合、適切な UVLO 閾値を設定するために、抵抗分圧器を介して EN/UVLO を V<sub>IN</sub> に接続することを推奨します。これにより、電源の急なオン／オフが繰り返された場合でも正確に起動とシャットダウンを行うことができます。

イネーブル・ピンが 0.7V を下回るとデバイスはスイッチングを停止しますが、INTV<sub>CC</sub> のレギュレータは動作しているので内部回路の電流は流れ続けます。イネーブル・ピンの電圧が 200mV を下回ると、完全にシャットダウンします。完全にシャットダウンすると、INTV<sub>CC</sub> レギュレータは無効化され、デバイスに流れる電流は 70µA 未満になります。

V<sub>IN</sub> と EN/UVLO の間に抵抗分圧器を追加すると、V<sub>IN</sub> が目的の電圧より高くなった場合にのみ出力を安定化するように、LT83401/LT83402 を設定できます（[プロック図](#)を参照）。この閾値（V<sub>IN(EN)</sub>）は通常、入力電源の電流が制限されている場合や入力電源のソース抵抗が比較的高い場合に使われます。スイッチング・レギュレータは電源から一定の電力を引き出すため、電源電圧が低下するにつれて電源電流が増加します。これは電源からは負の抵抗負荷のように見えるため、電源電圧が低い条件下では電源が電流制限されるか、ローにラッピングされます。V<sub>IN(EN)</sub> 閾値は、この問題が生じる可能性があるような電源電圧でレギュレータが動作するのを防ぎます。この閾値は、[式 10](#) を満たすように R<sub>EN1</sub> と R<sub>EN2</sub> の値を設定することによって調整できます。

$$V_{IN(EN)} = \left( \frac{R_{EN1}}{R_{EN2}} + 1 \right) \times 0.75V \quad (10)$$

この場合、LT83401/LT83402 は V<sub>IN</sub> が V<sub>IN(EN)</sub> より大きくなるまでオフのままになります。コンパレータにはヒステリシスがあるので、入力が V<sub>IN(EN)</sub> よりわずかに低くなるまでスイッチングは停止しません。

## INTV<sub>CC</sub> レギュレータ

内蔵低ドロップアウト（LDO）レギュレータは、V<sub>IN</sub> から 3.4V の電源を生成し、ドライバと内部バイアス回路に電力を供給します。INTV<sub>CC</sub> は LT83401/LT83402 の回路に十分な電流を供給します。V<sub>IN</sub> が 2.8V～3.5V の場合、INTV<sub>CC</sub> ピンの電圧は 2.7V～3.4V の範囲で変化します。INTV<sub>CC</sub> ピンには外部負荷を接続しないでください。

## SET ピン・コンデンサ：ノイズとソフトスタート

SET ピンのバイパス・コンデンサを用いると、出力ノイズを減らす他に、SET ピンに加わる電圧スパイクの寄生カッピングに対する感度を減らすこともできます。バイパス・コンデンサに漏れ電流があると、LT83401/LT83402 の DC レギュレーション性能は低下します。コンデンサのリークが 100nA の場合でも 0.1% の DC 誤差が生じます。そのため、高品質で低リークのセラミック・コンデンサの使用を推奨します。

また、SET ピンのバイパス・コンデンサは、出力のソフトスタートと突入電流の制限にも使用できます。出力のソフトスタートは、入力電源の電流サーボを防ぎます。SET ピンのコンデンサと抵抗の値により、リファレンス電圧のランプアップ時間が設定され、出力電圧はこの電圧に追従します。SET ピンの抵抗のサイズは、アプリケーションに必要な出力電圧によって決まりますが、コンデンサのサイズは必要なランプアップ時間を実現するように選択できます。SET ピンのコンデンサのサイズはノイズ性能にも影響を及ぼす点を考慮することが重要です。これは通常、このコンデンサのサイズを決める上でより重要な要素です。

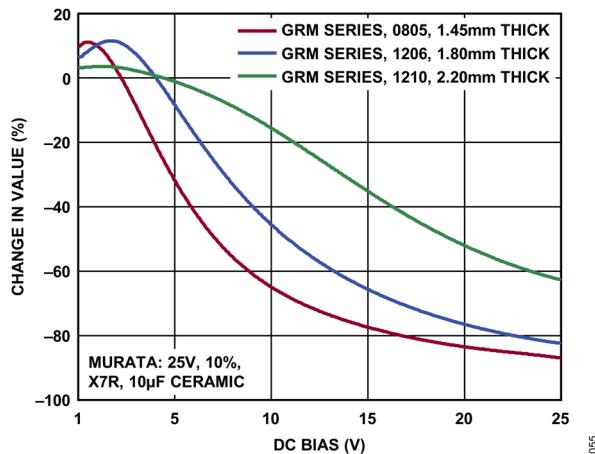

セラミック・コンデンサは様々な誘電体を使って作られており、温度や印加電圧に対する動作がそれぞれ異なります。SET ピンをバイパスするためのセラミック・コンデンサは重要な部品のため、この選択には注意を払う必要があります。温度と DC 電圧バイアスに対する優れた安定性から、X7R（もしくはそれ以上の）セラミック・コンデンサを強く推奨します。また、優れた DC バイアスと AC 電圧特性を得るために、大きなケース・サイズのものを推奨します。

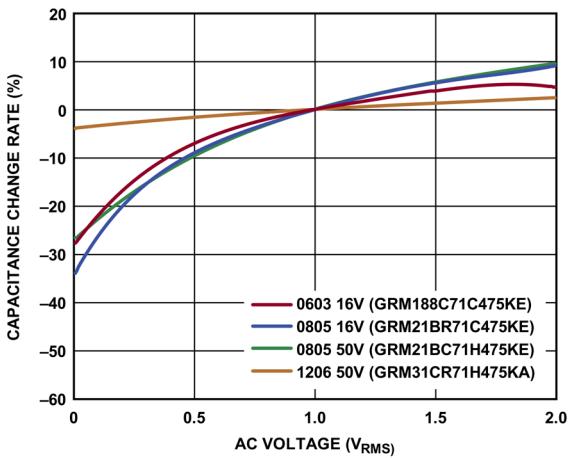

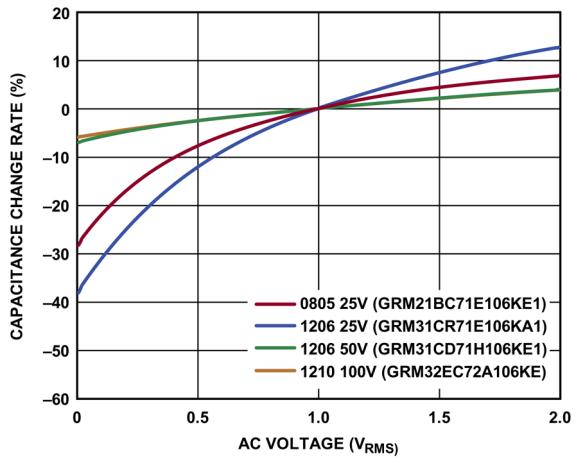

図 55 に示すように、コンデンサの DC バイアス特性は部品のケース・サイズが大きいほど良い傾向があります。

図 55. 様々なケース・サイズのコンデンサの電圧係数

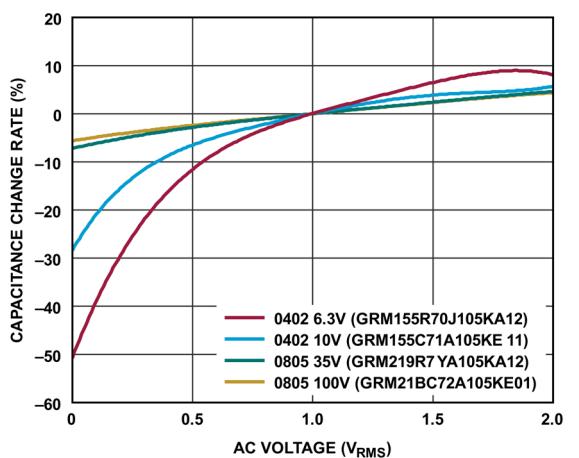

大きなケース・サイズは、AC 電圧特性の向上に対しても有利です。コンデンサの値は  $1V_{RMS}$  の AC 電圧で定格が定められますが、バイパス・コンデンサの動作条件である  $0V_{RMS}$  付近で動作する場合、大幅に低下することがあります。

図 56 に示すように、 $0V_{RMS}$  付近で動作する場合、大きなケース・サイズのものの容量低下は小さい傾向があります。したがって、最高の性能を実現するため、SET ピンのバイパス・コンデンサには 0805 以上のサイズのセラミック・コンデンサを使用してください。より大きな容量値ではより大きなケース・サイズが必要となる場合があります。例えば、 $4.7\mu F$  の容量値では 1206 以上のサイズを使用してください。

表 7 に推奨の SET ピン・コンデンサを示します。

表 7. 推奨される SET コンデンサの部品番号

| PART DESCRIPTION      | MANUFACTURER/PART NUMBER  |

|-----------------------|---------------------------|

| 1μF, X7R, 35V, 0805   | MURATA, GRM219R7YA105KA12 |

| 4.7μF, X7R, 50V, 1206 | MURATA, GRM31CR71H475MA12 |

| 10μF, X7R, 100V, 1210 | MURATA, GRM32EC72A106KE05 |

振動の大きい環境では、最適な性能を得るために圧電応答を示さないコンデンサを使用する必要があります。圧電特性を持つセラミック・コンデンサは、機械的振動や温度変動によって機械的ストレスがかかると端子間に電圧を発生します。フィルム・コンデンサは推奨される選択肢です。セラミック・コンデンサを使用する必要がある場合は、樹脂電極を採用したセラミック・コンデンサが使用できます。これにより、圧電効果に対する感度を低減できます。

(a) 定格容量 = 1  $\mu$ F

056

(b) 定格容量 = 4.7  $\mu$ F

057

(c) 定格容量 = 10  $\mu$ F

058

図 56. 様々なコンデンサ・ケース・サイズでの AC 電圧特性

高速スタートアップを有効化していない場合は、SET ピンの抵抗とコンデンサで形成される  $R_C$  時定数によってソフトスタート時間を制御します。PGFB ピンを INTV<sub>CC</sub> または 0.5V に接続すると高速スタートアップを無効化できます。公称 V<sub>OUT</sub> の 0%から 90%への上昇率は式 11 で得られます。

$$t_{\text{START\_NO\_FAST\_START-UP}} = 2.3 \times R_{\text{SET}} \times C_{\text{SET}} \quad (11)$$

高速スタートアップを有効化している場合は、式 12 で得られる公称 V<sub>OUT</sub> の 0%から 90%に達するまでの立上がり時間に従い、スタートアップ時間は大幅に短縮されます。2.5mA の高速スタートアップ電流の温度と V<sub>IN</sub> - V<sub>SET</sub> 電圧差による変動については、[代表的な性能特性](#) のセクションを参照してください。

$$t_{\text{START\_FAST\_START-UP}} = \frac{100\mu\text{A} \times R_{\text{SET}} \times C_{\text{SET}}}{2.5\text{mA}} \quad (12)$$

ほとんどのアプリケーションでは、高速スタートアップを有効化できます。その場合、リファレンス電圧の過充電を防ぐと共に良好なノイズ性能を確保するため、1μF 以上の SET コンデンサ・サイズを推奨します。

SET ピンは、シャットダウン、サーマル・シャットダウン、V<sub>CC</sub> UVLO、および V<sub>IN</sub> UVLO の間、520Ω の MOSFET (R<sub>SET-PULLDOWN</sub>) でグラウンドにプルダウンされます。これらの状態から抜けるときに確実にソフトスタートを実行するため、SET ピンには、スタートアップ前にグラウンド付近までプルダウンできるだけの十分な時間が必要です。この時間は、選択した SET ピン・コンデンサと R<sub>SET-PULLDOWN</sub> の関数となります。

## 高速スタートアップ

(100Hz 以下での) 1/f ノイズの低減が必要な超低ノイズのアプリケーションでは、SET ピンのコンデンサには最大 22μF に至る大きな値のものが必要となります。これより大きな値のコンデンサも使用できますが、リークに関して注意が必要です。大きな値のコンデンサを使用すると通常、レギュレータの起動時間が大幅に増加しますが、LT83401/LT83402 には、起動中に SET ピン電流を約 2.5mA まで増加させる高速スタートアップ回路が組み込まれています。

スタートアップ時、PGFB が 487.5mV のパワー・グッド・スタートアップ閾値 (V<sub>PGL\_STARTUP</sub>) 未満である限り、2.5mA の電流源は動作します。ただし、レギュレータがサーマル・シャットダウン状態にある、V<sub>IN</sub> が低すぎる場合、INTV<sub>CC</sub> が低下しすぎている場合を除きます。

PGFB が V<sub>PGL\_STARTUP</sub> を超えると、高速スタートアップ回路は無効化され、デバイスがパワー・ダウンするか、EN/UVLO ピンが 0.75V 未満まで引き下げられてデバイスがシャットダウン状態になるまで、無効化状態が続きます。

スタートアップ時に 2.5mA の電流源が無効化される条件はもう 1つあります。この条件の目的は、V<sub>SET</sub> が過充電になるのを防ぐことです。デバイスでは、PGFB ピンが SET ピンの電圧を正確に示していることを前提としているため、V<sub>OUTS</sub> が V<sub>SET</sub> に厳格に追従するものとしています。ただし、これが常に当てはまるとは限りません。例えば、出力容量が非常に大きい場合、あるいは何らかの理由で出力が GND に一時的に短絡している場合です。したがって、V<sub>OUTS</sub> が V<sub>SET</sub> から 30mV 以上遅れた場合は必ず、高速充電が無効化されます。これにより、V<sub>SET</sub> がその想定された最終値を超えた場合でも 2.5mA の電流源がオン状態を維持するというような、不適切な動作を防ぐことができます。プログラマブルなパワー・グッド機能および高速スタートアップ機能が不要な場合、PGFB ピンを INTV<sub>CC</sub> または 0.5V に接続してください。

## プログラマブルなパワー・グッド

ブロック図に示すように、パワー・グッド閾値は 2 つの外付け抵抗 R<sub>PGFB(BOT)</sub> と R<sub>PGFB(TOP)</sub> の比率によってユーザ設定可能です (式 13 を参照)。

$$V_{\text{OUT(PG_THRESHOLD)}} = 0.5V \times (x + a)^n = \left(1 + \frac{R_{\text{PGFB(TOP)}}}{R_{\text{PGFB(BOT)}}}\right) + I_{\text{PGFB}} \times R_{\text{PGFB(TOP)}} \quad (13)$$

PGFB ピンの電圧が 537.5mV より高くなるか 462.5mV 未満になると、オープン・ドレインの PG ピンがアサートされ、低インピーダンスになります。これにより、電源に問題があることを示します。パワー・グッド・コンパレータには 10mV のヒステリシスがあります。抵抗分圧ネットワークの値を決める際には、[電気的特性](#) の表より、PGFB ピンの電流 (I<sub>PGFB</sub>) を考慮する必要があります。なお、プログラマブルなパワー・グッド機能と高速スタートアップ機能は、PGFB が 0.5V に接続されている場合、またはデバイスがシャットダウン状態にある場合は、無効化される点に注意してください。

$R_{PGFB(BOT)}$ が  $50\text{k}\Omega$  未満の場合は、PGFB ピンの電流 ( $I_{PGFB}$ ) を無視できます。一般的な  $V_{OUT}$  構成に対する 1% PGFB 抵抗分圧器の値を表 8 に示します。

表 8. 推奨される PGFB 抵抗分圧器の値

| $V_{OUT}$ (V) | $R_{PGFB(TOP)}$ (kΩ) | $R_{PGFB(BOT)}$ (kΩ) |

|---------------|----------------------|----------------------|

| 0.8           | 29.4                 | 48.7                 |

| 0.9           | 39.2                 | 48.7                 |

| 1             | 49.9                 | 49.9                 |

| 1.2           | 69.8                 | 49.9                 |

| 1.8           | 130                  | 49.9                 |

| 3.3           | 280                  | 49.9                 |

| 5             | 453                  | 49.9                 |

## 短絡保護と逆入力保護

LT83401/LT83402 は出力短絡に耐えることができます。下側スイッチの電流がモニタされており、インダクタ電流が安全なレベルを超えた場合は、インダクタ電流が安全なレベルに減少するまで上側スイッチのスイッチングを遅らせます。

LT83401/LT83402 への入力がない場合に出力が高い電圧に保たれるシステムでは、考慮すべき状況がもう 1 つあります。この状況が発生するのは、バッテリ充電アプリケーションやバッテリ・バックアップ・システムなど、バッテリや他の電源が LT83401/LT83402 の出力とダイオード OR 接続されている場合です。 $V_{IN}$  ピンをフロート状態にできる場合に、EN/UVLO ピンがハイに保持されていると、LT83401/LT83402 の内部回路には SW ピンを通じて静止電流が流れます。システムがこの状態で電流流出を許容できる場合は、このことが問題になることはありません。EN/UVLO ピンを接地している場合、SW ピンの電流は約  $50\mu\text{A}$  まで減少します。

ただし、出力を高く保持した状態で  $V_{IN}$  ピンを接地すると、EN/UVLO ピンの状態に関係なく、出力から SW ピンと  $V_{IN}$  ピンを通って、LT83401/LT83402 内部の寄生ボディ・ダイオードに電流が流れ込む可能性があります。

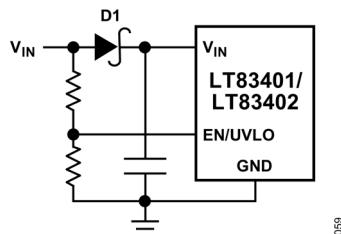

図 57 に示すように  $V_{IN}$  ピンと EN/UVLO ピンを接続すれば、LT83401/LT83402 は入力電圧が加わっているときにのみ動作し、短絡入力や逆入力に対して保護されます。

図 57. 逆  $V_{IN}$  保護

## 熱に関する考慮事項

周囲温度が高い場合は、PCB のレイアウトに注意を払い、LT83401/LT83402 が十分放熱できるようにします。パッケージ底面にある露出パッドは、グランド・プレーンに半田付け処理する必要があります。このグランド・プレーンは、その下にある広い銅層にサーマル・ビアで接続してください。これらの層は LT83401/LT83402 が発生する熱を拡散します。ビアを追加すれば、熱抵抗を更に小さくすることができます。周囲温度が最大ジャンクション温度の定格値に近付くにつれて、最大負荷電流をディレーティングする必要があります。LT83401/LT83402 内での消費電力は、効率測定値から合計電力損失を計算して、そこからインダクタ損失を減じることによって予測できます。ダイ温度は、LT83401/LT83402 の消費電力に、ジャンクションから周囲への熱抵抗を乗じることによって計算できます。

内蔵の過熱保護機能が、LT83401/LT83402 のジャンクション温度をモニタします。ジャンクション温度が約 165°C に達すると LT83401/LT83402 はスイッチング動作を停止し、温度が約 5°C 低下するまでフォルト状態を示します。

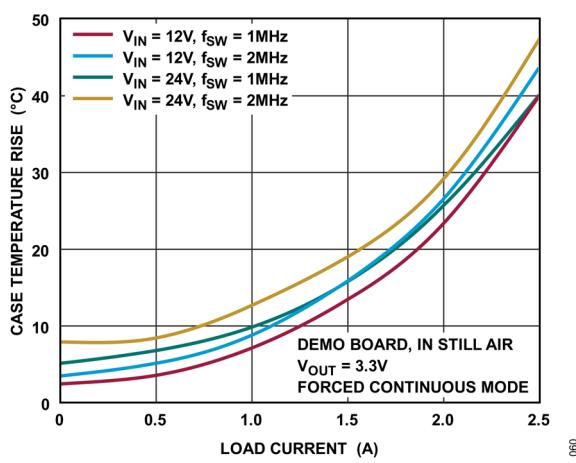

LT83401/LT83402 の温度上昇が最も大きくなるのは、高負荷、高  $V_{IN}$ 、高スイッチング周波数の状態で動作させた場合です。与えられたアプリケーションにおけるケース温度が高すぎる場合は、 $V_{IN}$ 、スイッチング周波数、負荷電流のいずれかを減らせば、温度を適切なレベルまで下げることができます。図 58 の例は、負荷を減らすことでケース温度の上昇をどのように管理できるかを示しています。

LT83401/LT83402 の上側スイッチ電流制限は、スロープ補償のために、デューティ・サイクルが高くなるにつれて減少します。このことによっても、特定のアプリケーションでは LT83401/LT83402 が供給できる出力電流が制限されます。代表的な性能特性の図 20 を参照してください。

図 58. LT83401/LT83402 のケースの温度上昇

## 代表的なアプリケーション

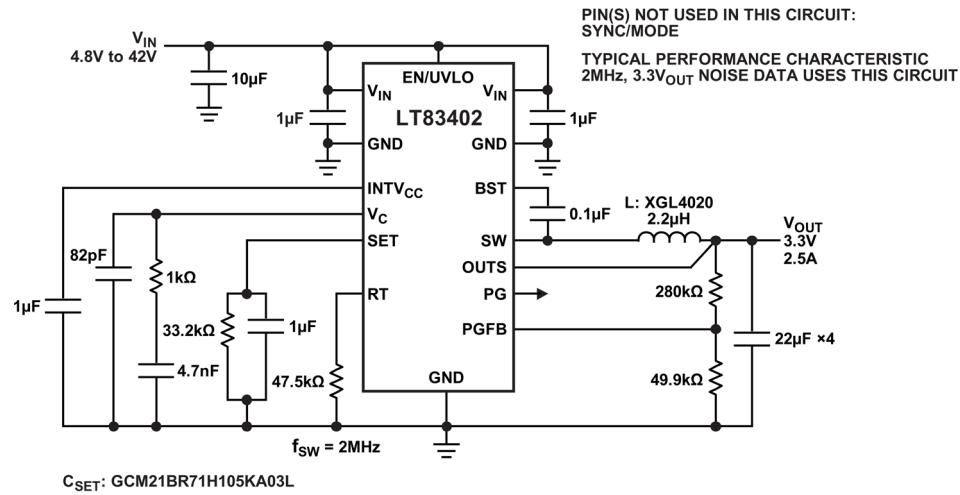

図 59. ソフトスタート、高速スタートアップ、およびパワー・ゲット機能を備えた、3.3V、2.5A、2MHz 降圧コンバータ

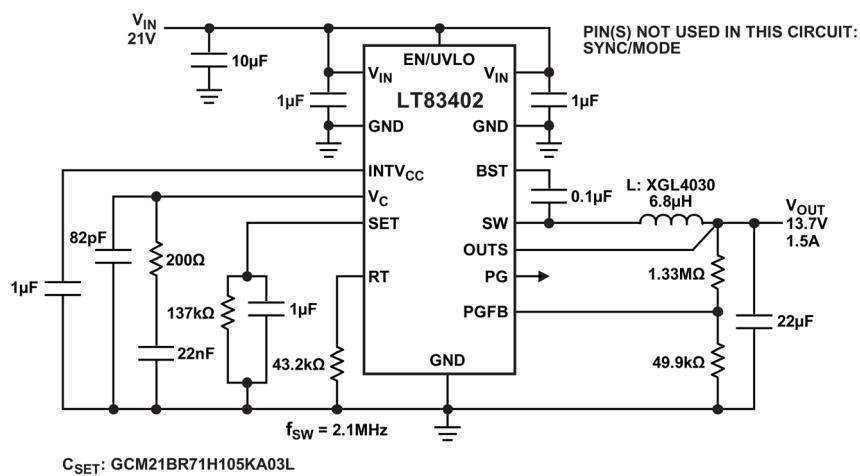

図 60. 高速スタートアップおよびパワー・グッド機能を備えた、13.7V、1.5A、2.1MHz 降圧コンバータ

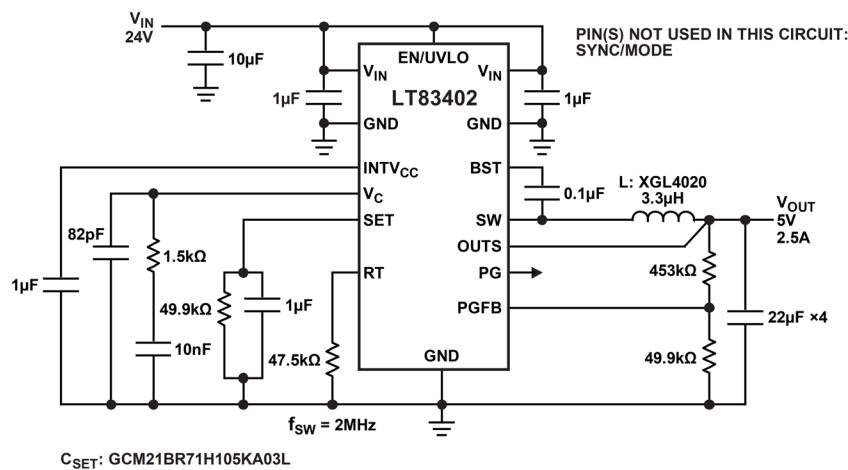

図 61. 高速スタートアップおよびパワー・ゲッド機能を備えた、5V、2.5A、2MHz 降圧コンバータ

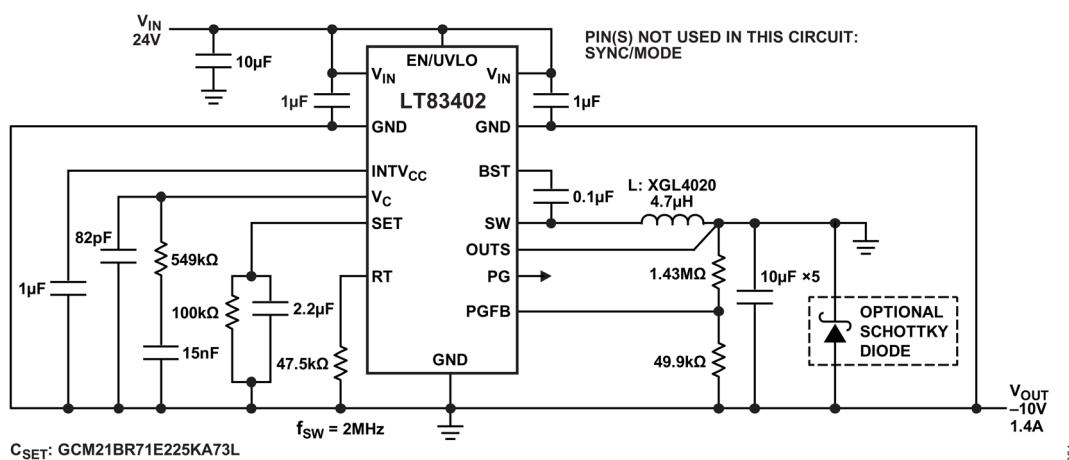

図 62. 高速スタートアップおよびパワー・グッド機能を備えた、-10V、1.4A、2MHz 降圧コンバータ

## 外形寸法

15-Lead Lead Frame Chip Scale Package [LFCSP]

3mm x 2mm Body and 0.75mm Package Height

(CP-15-1)

Dimensions shown in millimeters

PHG-0037875

09-20-2024-A

RECOMMENDED SOLDER PAD LAYOUT

(TOP VIEW)

図 63. 小型 15 ピン 3mm × 2mm LFCSP

## オーダー・ガイド

表 9. オーダー・ガイド

| PART NUMBER <sup>1</sup>               | TAPE AND REEL <sup>2</sup> | PAD OR BALL FINISH <sup>3</sup> | PART MARKING <sup>4</sup> |             | PACKAGE TYPE <sup>5</sup>                | MSL RATING | TEMPERATURE RANGE <sup>6</sup> |

|----------------------------------------|----------------------------|---------------------------------|---------------------------|-------------|------------------------------------------|------------|--------------------------------|

|                                        |                            |                                 | DEVICE                    | FINISH CODE |                                          |            |                                |

| LT83401RUDB#PBF                        | LT83401RUDB#TRPBF          | Au (RoHS)                       | LHWS                      | e4          | LFCSP<br>(Lead Frame Chip Scale Package) | 1          | -40°C to 150°C                 |

| LT83402RUDB#PBF                        | LT83402RUDB#TRPBF          |                                 | LHWR                      |             |                                          |            |                                |

| <b>AUTOMOTIVE PRODUCTS<sup>7</sup></b> |                            |                                 |                           |             |                                          |            |                                |

| LT83401RUDB#WPBF                       | LT83401RUDB#WTRPBF         | Au (RoHS)                       | LHWS                      | e4          | LFCSP<br>(Lead Frame Chip Scale Package) | 1          | -40°C to 150°C                 |

| LT83402RUDB#WPBF                       | LT83402RUDB#WTRPBF         |                                 | LHWR                      |             |                                          |            |                                |

1. 製品番号末尾が PBF となっている製品は RoHS および WEEE に対応しています。

2. **テープ & リールの仕様**。一部のパッケージは指定された販売チャネルを通じて 500 個単位のリールで供給され、製品番号末尾に '#TRMPBF' という記号が付いています。

3. パッドまたはボールの仕上げコードは IPC/JEDEC J-STD-609 に準拠しています。

4. 温度グレードは出荷容器のラベルに示されています。

5. LT83401/LT83402 のパッケージ寸法は、標準の 3mm × 2mm LFCSP パッケージと同じです。

6. LT83401/LT83402 は -40°C ~ 150°C の動作ジャンクション温度範囲で仕様規定されています。ジャンクション温度が高い場合は動作寿命が低下します。ジャンクション温度 ( $T_J$ , °C) は、次式を使って周囲温度 ( $T_A$ , °C) と消費電力 ( $P_D$ , ワット) から計算します。 $T_J = T_A + (P_D \times \theta_{JA})$ 。ここで、 $\theta_{JA}$  (°C/W) はパッケージの熱抵抗です。

7. このデバイスの各バージョンは、オートモーティブ・アプリケーションの品質と信頼性の要件に対応するよう管理された製造工程により提供されます。これらのモデルは '#W' という末尾記号で指定されます。オートモーティブ・アプリケーション向けには、上記のオートモーティブ・グレード製品のみを提供しています。特定製品のオーダー情報や、これらのモデルの具体的な自動車信頼性レポートについては、アナログ・デバイセズの販売代理店にご相談ください。

8. 更に広い動作温度範囲で規定されたデバイスについては、アナログ・デバイセズまでお問い合わせください。

9. 推奨される LGA および BGA PCB のアッセンブリおよび製造手順の詳細については、[μModule 電源技術](#)のページを参照してください。

10. LGA および BGA のパッケージ図面とトレイ図面の詳細については、[パッケージング、クオリティ、シンボルおよびフットプリント](#)のページを参照してください。

## 関連製品

表 10. 関連製品

| 製品番号                    | 説明                                                                      | 注釈                                                                                                                                                    |

|-------------------------|-------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| LT83203/<br>LT83205     | 超低ノイズ・リファレンス内蔵 18V、4A 降圧 Silent Switcher 3                              | $4\mu V_{RMS}$ のノイズ、 $V_{IN} = 2.8V \sim 18V$ 、 $V_{OUT(MIN)} = 0V$ 、 $I_Q = 2.7mA$ 、 $3mm \times 2mm$ LFCSP-15                                       |

| LT8622S/<br>LT8624S     | 超低ノイズ・リファレンス内蔵 18V、2A/4A 同期整流式降圧 Silent Switcher 3                      | $4\mu V_{RMS}$ のノイズ、 $V_{IN} = 2.7V \sim 18V$ 、 $V_{OUT(MIN)} = 0V$ 、 $I_Q = 2.8mA$ 、 $4mm \times 3mm$ LQFN-20                                        |

| LT8625S                 | 超低ノイズ・リファレンス内蔵 18V/8A 同期整流式降圧 Silent Switcher 3                         | $4\mu V_{RMS}$ のノイズ、 $V_{IN} = 2.7V \sim 18V$ 、 $V_{OUT(MIN)} = 0V$ 、 $I_Q = 2.8mA$ 、 $4mm \times 3mm$ LQFN-20                                        |

| LT8625SP/<br>LT8625SP-1 | 超低ノイズ・リファレンス内蔵 18V/8A 同期整流式降圧 Silent Switcher 3                         | $4\mu V_{RMS}$ のノイズ、 $V_{IN} = 2.7V \sim 18V$ 、 $V_{OUT(MIN)} = 0V$ 、 $I_Q = 2.8\mu A$ 、 $4mm \times 3mm$ LQFN-20、または $4mm \times 4mm$ LQFN-24        |

| LT8627SP                | 超低ノイズ・リファレンス内蔵 18V/16A 同期整流式降圧 Silent Switcher 3                        | $4\mu V_{RMS}$ のノイズ、 $V_{IN} = 2.8V \sim 18V$ 、 $V_{OUT(MIN)} = 0V$ 、 $I_Q = 3.2\mu A$ 、 $4mm \times 4mm$ LQFN-24                                     |

| LT8640A                 | 42V、5A 同期整流式降圧 Silent Switcher                                          | $V_{IN} = 3.4V \sim 42V$ 、 $V_{OUT(MIN)} = 0.97V$ 、 $I_Q = 2.5\mu A$ 、 $I_{SD} < 1\mu A$ 、 $3mm \times 4mm$ QFN-18                                    |

| LT3042                  | 20V、200mA、超低ノイズ、超高 PSRR のリニア・レギュレータ                                     | $0.8\mu V_{RMS}$ のノイズおよび 79dB の PSRR (1MHz 時)、 $V_{IN} = 1.8V \sim 20V$ 、350mV のドロップアウト電圧、プログラマブルな電流制限およびパワー・グッド、 $3mm \times 3mm$ DFN および MSOP パッケージ |

| LT3045                  | 20V、500mA、超低ノイズ、超高 PSRR のリニア・レギュレータ                                     | $0.8\mu V_{RMS}$ のノイズおよび 75dB の PSRR (1MHz 時)、 $V_{IN} = 1.8V \sim 20V$ 、260mV のドロップアウト電圧、 $3mm \times 3mm$ DFN および MSOP パッケージ                        |

| LT8640S/<br>LT8643S     | $I_Q = 2.5\mu A$ の 42V、6A 同期整流式降圧 Silent Switcher 2                     | $V_{IN(MIN)} = 3.4V$ 、 $V_{IN(MAX)} = 42V$ 、 $V_{OUT(MIN)} = 0.97V$ 、 $I_Q = 2.5\mu A$ 、 $I_{SD} < 1\mu A$ 、 $4mm \times 4mm$ LQFN-24                 |

| LT8609/<br>LT8609A      | $I_Q = 2.5\mu A$ の 42V、2A、効率 94%、2.2MHz 同期整流式 MicroPower 降圧 DC/DC コンバータ | $V_{IN(MIN)} = 3V$ 、 $V_{IN(MAX)} = 42V$ 、 $V_{OUT(MIN)} = 0.8V$ 、 $I_Q = 2.5\mu A$ 、 $I_{SD} < 1\mu A$ 、MSOP-10E                                     |

ここに含まれるすべての情報は現状のまま提供されるものであり、アナログ・デバイセズはそれに関するいかなる種類の保証または表明も行いません。アナログ・デバイセズ社は、その情報の利用に関して、あるいはその利用によって生じる第三者の特許やその他の権利の侵害に関して一切の責任を負いません。仕様は予告なく変更される場合があります。明示か默示かを問わず、アナログ・デバイセズの製品またはサービスが使用される組み合わせ、マシン、またはプロセスに関連するアナログ・デバイセズの特許権、著作権、マスク・ワーク権、またはその他のアナログ・デバイセズの知的所有権に基づいてライセンスが付与されるわけではありません。本紙記載の商標および登録商標は、各社の所有に属します。ここに記載のすべてのアナログ・デバイセズ製品は、販売状況および在庫状況に依存します。