## 40V USB Type-C Power Delivery 昇降圧コントローラ

### 特長

- 独自の低EMI昇降圧アーキテクチャ

- 広い入力電圧範囲: 4V~40V

- 同期スイッチング: 最大効率98%

- 出力電圧レギュレーション:  $\pm 1.5\%$

- 単一出力で1つのType-Cポートを最大100Wまでサポート

- 出力チャンネルのイネーブル機能

- 設定可能なスイッチング周波数

(外部同期およびスペクトラム拡散機能あり)

- 過電流保護、過電圧保護、短絡保護

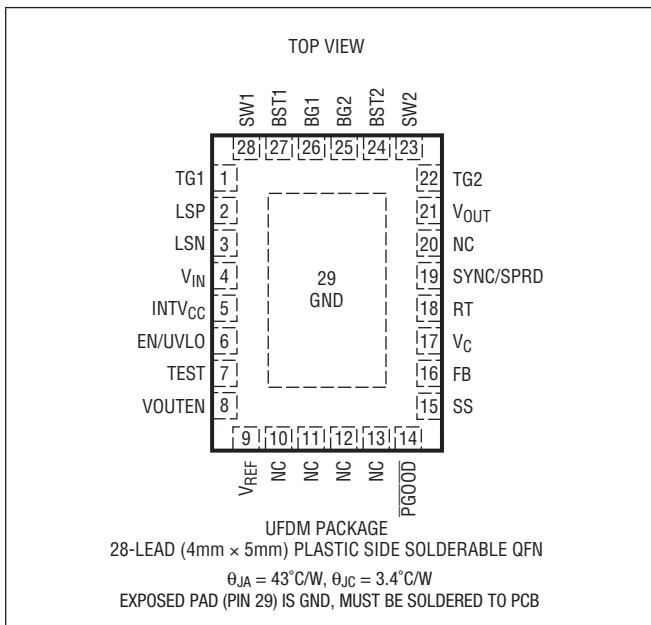

- 側面からハンダ処理可能な28ピンQFNパッケージで供給

- AEC-Q100認定進行中

### アプリケーション

- 車載用USB-C給電

- 汎用の電圧レギュレータ

### 概要

LT<sup>®</sup>8253/LT8253Aは、車載用のUSB-C給電向けに最適化された同期整流式4スイッチ昇降圧コントローラです。LT8253/8253Aは、USB Type-CコントローラまたはPDポート・コントローラと併用した場合、USB Power Delivery(PD)規格に完全に準拠しています。出力電圧のスルーレートはFBピンを介して制御できます。LT8253は、AM帯域より低い帯域で動作する場合、最大100Wの出力電力を98%のピーク効率で供給できます。LT8253Aは、AM帯域より高い帯域で動作する場合、最大60Wの出力電力を95%のピーク効率で供給できます。

LT8253/8253Aは、1つのType-Cポート用にシングル昇降圧出力をサポートしており、パワーグッド・フラグを備えています。また、過電流、過電圧、短絡保護回路も内蔵しています。

全ての登録商標および商標の所有権は、それぞれの所有者に帰属します。

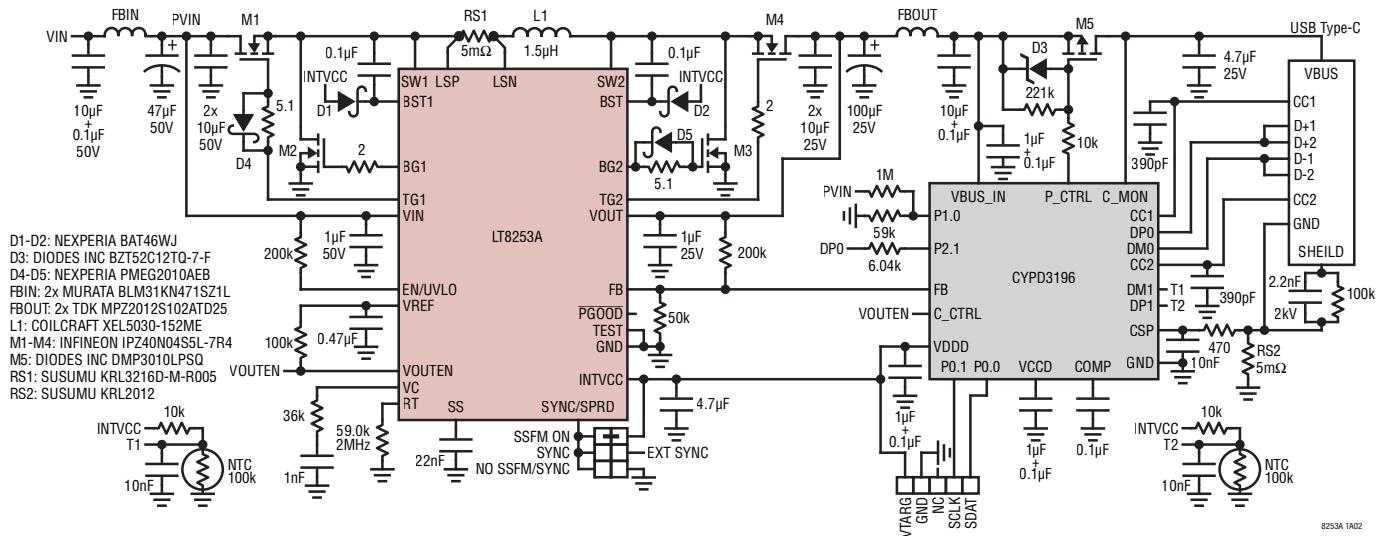

### 標準的応用例

車載用60W USB-C Power Deliveryチャージャ(400kHz)

LT8253A TA01

# LT8253/LT8253A

## 絶対最大定格

### (Note 1)

|                                             |             |

|---------------------------------------------|-------------|

| $V_{IN}$ 、EN/UVLO                           | 42V         |

| $V_{OUT}$                                   | 30V         |

| BST1                                        | 48V         |

| BST2                                        | 36V         |

| SW1、LSP、LSN                                 | -6V~42V     |

| SW2                                         | -6V~30V     |

| INTV <sub>CC</sub> 、(BST1-SW1間)、(BST2-SW2間) | 6V          |

| (BST1-LSP間)、(BST1-LSN間)                     | 6V          |

| FB、VOUTEN、SYNC/SPRD、 $\overline{PGOOD}$     | 6V          |

| 動作ジャンクション温度範囲 (Note 2, Note 3)              |             |

| LT8253E、LT8253AE                            | -40°C~125°C |

| LT8253J、LT8253AJ                            | -40°C~150°C |

| LT8253H、LT8353AH                            | -40°C~150°C |

| 保存温度範囲                                      | -65°C~150°C |

## ピン配置

## 発注情報

| 鉛フリー仕上げ             | テープ&リール             | 製品マーキング* | パッケージ                                           | 温度範囲           |

|---------------------|---------------------|----------|-------------------------------------------------|----------------|

| LT8253EUFDM#PBF     | LT8253EUFDM#TRPBF   | 8253     | 28-Lead (4mm x 5mm) Plastic Side Solderable QFN | -40°C to 125°C |

| LT8253JUFDM#PBF     | LT8253JUFDM#TRPBF   | 8253     | 28-Lead (4mm x 5mm) Plastic Side Solderable QFN | -40°C to 150°C |

| LT8253HUFDM#PBF     | LT8253HUFDM#TRPBF   | 8253     | 28-Lead (4mm x 5mm) Plastic Side Solderable QFN | -40°C to 150°C |

| LT8253AEUFDM#PBF    | LT8253AEUFDM#TRPBF  | 8253A    | 28-Lead (4mm x 5mm) Plastic Side Solderable QFN | -40°C to 125°C |

| LT8253AJUFDM#PBF    | LT8253AJUFDM#TRPBF  | 8253A    | 28-Lead (4mm x 5mm) Plastic Side Solderable QFN | -40°C to 150°C |

| LT8253AHUFDM#PBF    | LT8253AHUFDM#TRPBF  | 8253A    | 28-Lead (4mm x 5mm) Plastic Side Solderable QFN | -40°C to 150°C |

| <b>オートモーティブ製品**</b> |                     |          |                                                 |                |

| LT8253JUFDM#WPBF    | LT8253JUFDM#WTRPBF  | 8253     | 28-Lead (4mm x 5mm) Plastic Side Solderable QFN | -40°C to 150°C |

| LT8253HUFDM#WPBF    | LT8253HUFDM#WTRPBF  | 8253     | 28-Lead (4mm x 5mm) Plastic Side Solderable QFN | -40°C to 150°C |

| LT8253AJUFDM#WPBF   | LT8253AJUFDM#WTRPBF | 8253A    | 28-Lead (4mm x 5mm) Plastic Side Solderable QFN | -40°C to 150°C |

| LT8253AHUFDM#WPBF   | LT8253AHUFDM#WTRPBF | 8253A    | 28-Lead (4mm x 5mm) Plastic Side Solderable QFN | -40°C to 150°C |

更に広い動作温度範囲で規定されるデバイスについては、弊社または弊社代理店にお問い合わせください。\*温度グレードは出荷時のコンテナのラベルで識別されます。

**テープ&リールの仕様。**一部のパッケージは、指定された販売経路を通じて、#TRMPBFの接尾辞を付けた500個入りリールで提供しています。

\*\* このデバイス・バージョンは、オートモーティブ・アプリケーションの品質と信頼性の条件に対応するため、管理の行き届いた製造工程により供給されます。これらのモデルは#W接尾部により指定されます。オートモーティブ・アプリケーション向けには、上記のオートモーティブ・グレード製品のみを提供しています。特定製品のオーダー情報とこれらのモデルに特有の車載信頼性レポートについては、最寄りのアナログ・デバイセズ代理店までお問い合わせください。

## 電気的特性

●は全動作温度範囲での規格値を意味する。それ以外は  $T_A = 25^\circ\text{C}$  での値。注記がない限り、 $V_{IN} = 12\text{V}$ 、 $V_{EN/UVLO} = 1.5\text{V}$ 。

| SYMBOL      | PARAMETER                                       | CONDITIONS                                                                                                                           | MIN    | TYP         | MAX         | UNITS                        |                                |

|-------------|-------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|--------|-------------|-------------|------------------------------|--------------------------------|

| 電源          |                                                 |                                                                                                                                      |        |             |             |                              |                                |

|             | $V_{IN}$ Operating Voltage Range                |                                                                                                                                      | ●      | 4           | 40          | V                            |                                |

|             | $V_{IN}$ Quiescent Current                      | $V_{EN/UVLO} = 0.3\text{V}$<br>$V_{EN/UVLO} = 1.5\text{V}$                                                                           |        | 1<br>2.1    | 2<br>3      | $\mu\text{A}$<br>$\text{mA}$ |                                |

|             | $V_{OUT}$ Voltage Range                         |                                                                                                                                      | ●      | 1           | 25          | V                            |                                |

| リニア電圧レギュレータ |                                                 |                                                                                                                                      |        |             |             |                              |                                |

|             | INTVcc Regulation Voltage                       | $I_{INTVCC} = 20\text{mA}$                                                                                                           |        | 4.8         | 5           | 5.2                          | V                              |

|             | INTVcc Current Limit                            | $V_{INTVCC} = 4.5\text{V}$ (LT8253)<br>$V_{INTVCC} = 4.5\text{V}$ (LT8253A)                                                          |        | 80<br>110   | 110<br>145  | 160<br>190                   | $\text{mA}$                    |

|             | INTVcc Undervoltage Lockout Threshold           | Falling                                                                                                                              |        | 3.44        | 3.54        | 3.64                         | V                              |

|             | INTVcc Undervoltage Lockout Hysteresis          |                                                                                                                                      |        | 0.24        |             |                              | V                              |

|             | $V_{REF}$ Regulation Voltage                    | $I_{VREF} = 100\mu\text{A}$                                                                                                          |        | 1.96        | 2           | 2.04                         | V                              |

|             | $V_{REF}$ Current Limit                         | $V_{REF} = 1.8\text{V}$                                                                                                              |        | 2           | 2.5         | 3.2                          | $\text{mA}$                    |

| 制御入力        |                                                 |                                                                                                                                      |        |             |             |                              |                                |

|             | EN/UVLO Shutdown Threshold                      |                                                                                                                                      |        | 0.3         | 0.6         | 1                            | V                              |

|             | EN/UVLO Enable Threshold                        | Falling                                                                                                                              |        | 1.196       | 1.22        | 1.244                        | V                              |

|             | EN/UVLO Enable Hysteresis                       |                                                                                                                                      |        | 13          |             |                              | $\text{mV}$                    |

|             | EN/UVLO Hysteresis Current                      | $V_{EN/UVLO} = 1.1\text{V}$<br>$V_{EN/UVLO} = 1.3\text{V}$                                                                           |        | 2<br>-0.1   | 2.5<br>0    | 3<br>0.1                     | $\mu\text{A}$<br>$\mu\text{A}$ |

|             | VOUTEN Threshold                                |                                                                                                                                      |        | 1           | 1.6         |                              | V                              |

| エラーアンプ      |                                                 |                                                                                                                                      |        |             |             |                              |                                |

|             | FB Regulation Voltage                           |                                                                                                                                      | ●      | 0.985       | 1           | 1.015                        | V                              |

|             | FB Voltage Regulation Amplifier $g_m$           |                                                                                                                                      |        | 660         |             |                              | $\mu\text{S}$                  |

| 電流コンパレータ    |                                                 |                                                                                                                                      |        |             |             |                              |                                |

|             | Maximum Current Sense Threshold $V_{(LSP-LSN)}$ | Buck, $V_{FB} = 0.8\text{V}$<br>Boost, $V_{FB} = 0.8\text{V}$                                                                        |        | 35<br>35    | 50<br>50    | 65<br>65                     | $\text{mV}$                    |

| 障害          |                                                 |                                                                                                                                      |        |             |             |                              |                                |

|             | FB Short Threshold                              | Falling                                                                                                                              |        | 0.2         | 0.25        | 0.3                          | V                              |

|             | FB Short Hysteresis                             |                                                                                                                                      |        | 30          | 50          | 70                           | $\text{mV}$                    |

|             | PGOOD Upper Threshold from $V_{FB}$             | Rising                                                                                                                               |        | 8           | 10          | 12                           | %                              |

|             | PGOOD Lower Threshold from $V_{FB}$             | Falling                                                                                                                              |        | -12         | -10         | -8                           | %                              |

|             | PGOOD Pull-Down Resistance                      |                                                                                                                                      |        | 100         | 200         |                              | $\Omega$                       |

|             | SS Hard Pull-Down Resistance                    | $V_{EN/UVLO} = 1.1\text{V}$                                                                                                          |        | 100         | 200         |                              | $\Omega$                       |

|             | SS Pull-Up Current                              | $V_{FB} = 0.4\text{V}$ , $V_{SS} = 0\text{V}$                                                                                        |        | 12.5        |             |                              | $\mu\text{A}$                  |

|             | SS Pull-Down Current                            | $V_{FB} = 0.1\text{V}$ , $V_{SS} = 2\text{V}$                                                                                        |        | 1.25        |             |                              | $\mu\text{A}$                  |

|             | SS Fault High Threshold                         |                                                                                                                                      |        | 1.7         |             |                              | V                              |

|             | SS Fault Low Threshold                          |                                                                                                                                      |        | 0.2         |             |                              | V                              |

| 発振器         |                                                 |                                                                                                                                      |        |             |             |                              |                                |

|             | Oscillator Frequency                            | $V_{SYNC/SPRD} = 0\text{V}$ , $RT = 100\text{k}\Omega$ (LT8253)<br>$V_{SYNC/SPRD} = 0\text{V}$ , $RT = 59.0\text{k}\Omega$ (LT8253A) | ●<br>● | 380<br>1900 | 400<br>2000 | 420<br>2100                  | kHz<br>kHz                     |

|             | SYNC/SPRD Clock SYNC Frequency                  | (LT8253)<br>(LT8253A)                                                                                                                |        | 150<br>600  | 650<br>2000 |                              | kHz<br>kHz                     |

## 電気的特性

●は全動作温度範囲での規格値を意味する。それ以外は  $T_A = 25^\circ\text{C}$  での値。注記がない限り、 $V_{IN} = 12\text{V}$ 、 $V_{EN/UVLO} = 1.5\text{V}$ 。

| SYMBOL | PARAMETER                      | CONDITIONS | MIN | TYP | MAX | UNITS |

|--------|--------------------------------|------------|-----|-----|-----|-------|

|        | SYNC/SPRD Clock SYNC Threshold |            | 0.4 | 1.5 |     | V     |

### NMOS ドライバ

|                                                                      |                            |  |            |  |                      |

|----------------------------------------------------------------------|----------------------------|--|------------|--|----------------------|

| TG1, TG2 Gate Driver On-Resistance<br>Gate Pull-Up<br>Gate Pull-Down | $V_{(BST-SW)} = 5\text{V}$ |  | 2.6<br>1.7 |  | $\Omega$<br>$\Omega$ |

| BG1, BG2 Gate Driver On-Resistance<br>Gate Pull-Up<br>Gate Pull-Down | $V_{(INTVCC)} = 5\text{V}$ |  | 3<br>1.2   |  | $\Omega$<br>$\Omega$ |

| TG Off to BG On Delay Time                                           | LT8253<br>LT8253A          |  | 60<br>25   |  | ns<br>ns             |

| BG Off to TG On Delay Time                                           | LT8253<br>LT8253A          |  | 60<br>25   |  | ns<br>ns             |

**Note 1 :** 絶対最大定格に記載された値を超えるストレスはデバイスに永続的損傷を与える可能性がある。また、長期にわたって絶対最大定格条件に曝すと、デバイスの信頼性と寿命に悪影響を与える恐れがある。

**Note 2 :** LT8253E/LT8253AEは $0^\circ\text{C} \sim 125^\circ\text{C}$ の動作ジャンクション温度で性能仕様に適合することが確認されている。 $-40^\circ\text{C} \sim 125^\circ\text{C}$ の動作ジャンクション温度範囲での仕様は、設計、特性評価および統計学的なプロセス・コントロールとの関連で確認されている。LT8253J/LT8253AJおよびLT8253H/LT8253AHは、 $-40^\circ\text{C} \sim 150^\circ\text{C}$ の動作ジャンクション温度範囲で動作することが確認されている。ジャンクション温度が高いと、動作寿命は短くなる。 $125^\circ\text{C}$ を超えるジャンクション温度では動作寿命がディレーティングされる。

**Note 3 :** LT8253/LT8253Aは、瞬間的な過負荷状態時にデバイスを保護するための過熱保護機能を備えている。過熱保護機能がアクティブなときジャンクション温度は $150^\circ\text{C}$ を超える。規定された絶対最大動作ジャンクション温度を超えた動作が継続すると、デバイスの信頼性を損なう恐れがある。

## ピン機能

**TG1**：降圧側の上側ゲート駆動端子。SW1からBST1までの電圧振幅で降圧側の上側NチャンネルMOSFETのゲートを駆動します。

**LSP**：降圧側のインダクタ電流検出抵抗の正端子。ケルビン接続を使って、電流が正確に検出されるようにします。

**LSN**：降圧側のインダクタ電流検出抵抗の負端子。ケルビン接続を使って、電流が正確に検出されるようにします。

**V<sub>IN</sub>**：入力電源。V<sub>IN</sub>ピンは、動作領域を決定するために電源入力に接続する必要があります。このピンは0.1 μF以上のセラミック・コンデンサでデバイス近くのグラウンドにバイパスします。

**INTV<sub>CC</sub>**：内蔵の5Vリニア電圧レギュレータの出力。INTV<sub>CC</sub>リニア電圧レギュレータはV<sub>IN</sub>ピンから電源供給を受けており、内部制御回路およびゲート・ドライバに電力を供給します。このピンは4.7 μF以上のセラミック・コンデンサでデバイス近くのグラウンドにバイパスします。

**EN/UVLO**：イネーブルおよび低電圧ロックアウト。デバイスをシャットダウンする場合は、このピンの電圧を強制的に0.3Vより低くします。通常動作の場合は、このピンの電圧を強制的に1.23Vより高くなります。1.22Vの立下がり閾値と2.5 μAのプルダウン電流を使用して、ヒステリシスありのV<sub>IN</sub> UVLOを設定できます。どちらの機能も使用しない場合、このピンはV<sub>IN</sub>に直接接続します。

**TEST**：工場テスト。このピンは出荷時テスト専用であり、正常な動作のためにはグラウンドに直接接続する必要があります。

**VOUTEN**：出力イネーブル。VOUTENピンは、昇降圧スイッチングをイネーブルして出力電力を供給するために使用します。

**V<sub>REF</sub>**：電圧リファレンス出力。V<sub>REF</sub>ピンは、1mAの電流を供給できる高精度の2Vリファレンスを提供します。このピンは0.47 μFのセラミック・コンデンサでデバイス近くのグラウンドにバイパスします。

**PGOOD**：パワーグッド・オーブンドレイン出力。FBピンの電圧がレギュレーション電圧の±10%以内に入ると、PGOODピンはローになります。このピンを機能させるには、外付けのプルアップ抵抗が必要です。

**SS**：ソフトスタート・タイマー設定。SSピンは、コンデンサを接地することで、ソフトスタート・タイマーの設定に使用します。

12.5 μAの内部プルアップ電流がSSピンの外付けコンデンサを充電することにより、FBピンのレギュレーション電圧が徐々に上昇します。

**FB**：電圧ループの帰還入力。FBピンは出力電圧のレギュレーションと出力障害保護のために使用します。

**VC**：エラー・アンプの出力。VCピンは、外付けRC回路網を使用して制御ループを補償するために使用します。

**RT**：スイッチング周波数の設定、このピンとグラウンドの間に抵抗を接続して、内部発振周波数を設定します。

**SYNC/SPRD**：外部クロックの周波数同期またはスペクトラム拡散。内部発振周波数でスイッチングする場合は、このピンを接地します。外部周波数同期を行う場合は、クロック信号をこのピンに供給します。スペクトラム拡散周波数変調を行う場合は、INTV<sub>CC</sub>に接続します。

**V<sub>OUT</sub>**：出力ピン。V<sub>OUT</sub>ピンは、動作領域を決定するために電源出力に接続する必要があります。このピンは0.1 μF以上のセラミック・コンデンサでデバイス近くのグラウンドにバイパスします。

**TG2**：昇圧側の上側ゲート駆動端子。昇圧側上側NチャンネルMOSFETのゲートを、SW2からBST2までの電圧振幅で駆動します。

**SW2**：昇圧側スイッチ・ノード。

**BST2**：昇圧側のブートストラップ・フローティング・ドライバの電源。BST2ピンには、INTV<sub>CC</sub>ピンからのブートストラップ・ダイオードが内蔵されており、SW2ピンとの間に外付けブートストラップ・コンデンサが必要です。

**BG2**：昇圧側の下側ゲート駆動端子。グラウンドからINTV<sub>CC</sub>までの電圧振幅で昇圧側の下側NチャンネルMOSFETのゲートを駆動します。

**BG1**：降圧側の下側ゲート駆動端子。グラウンドからINTV<sub>CC</sub>までの電圧振幅で降圧側の下側NチャンネルMOSFETのゲートを駆動します。

**BST1**：降圧側のブートストラップ・フローティング・ドライバの電源。BST1ピンには、INTV<sub>CC</sub>ピンからのブートストラップ・ダイオードが内蔵されており、SW1ピンとの間に外付けブートストラップ・コンデンサが必要です。

**SW1**：降圧側スイッチ・ノード。

**GND(露出パッド)**：グラウンド。この露出パッドは、直接グラウンド・プレーンにハンダ処理してください。

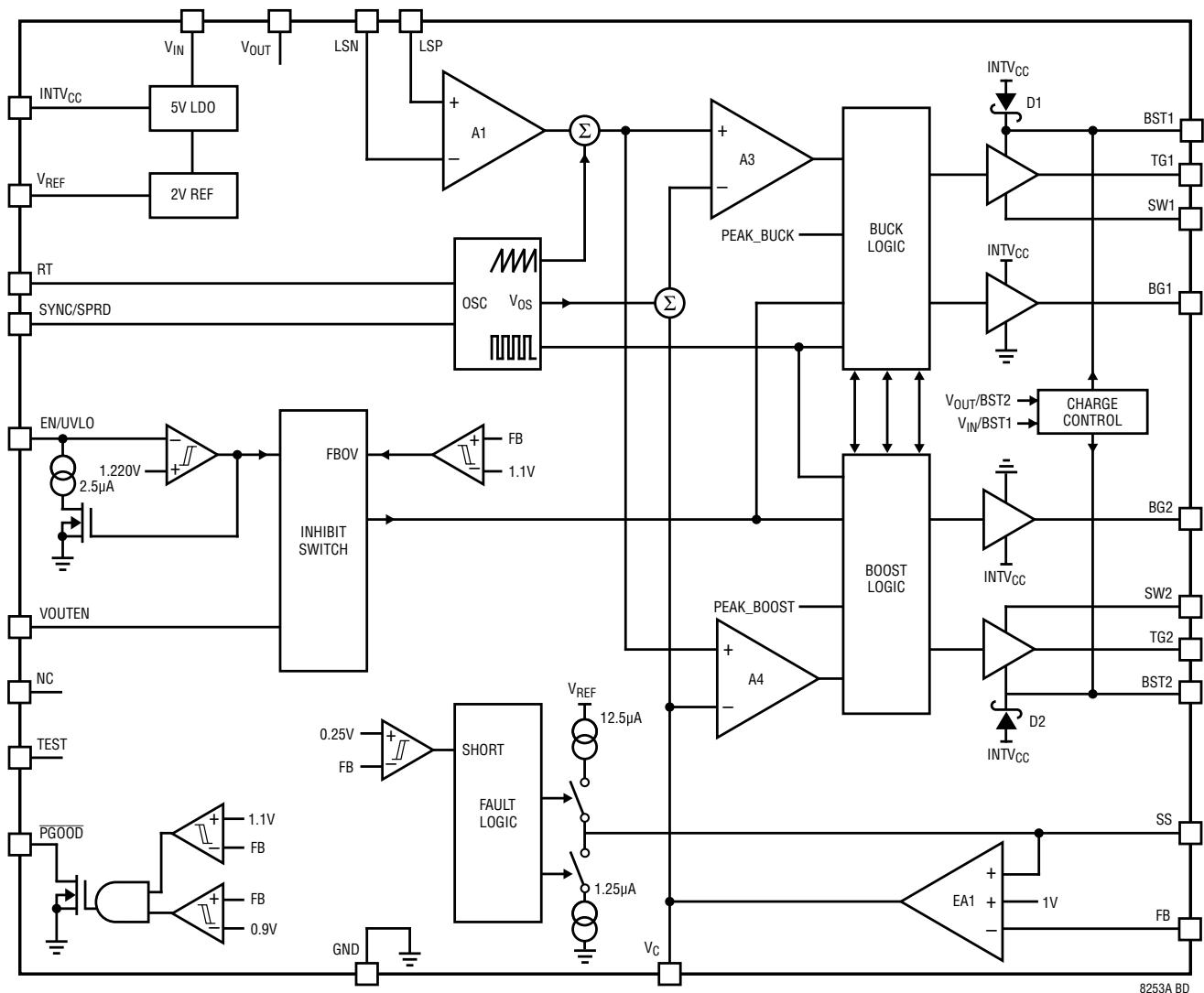

## ブロック図

## 動作

LT8253/LT8253Aは、出力電圧より高い、低い、または等しい入力電圧から出力電圧を安定化できる電流モードDC/DCコントローラです。独自のピーク降圧ピーク昇圧電流モード制御方式では、1個の電流検出抵抗を使用して、降圧領域、昇降圧領域、および昇圧領域の間を滑らかに遷移します。その動作は、ブロック図を参照するとよく理解できます。

### パワー・スイッチの制御

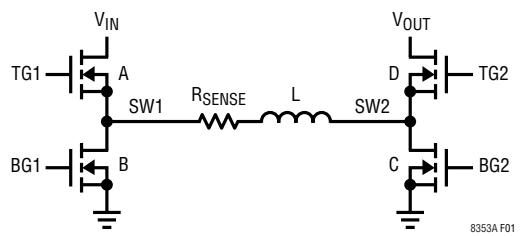

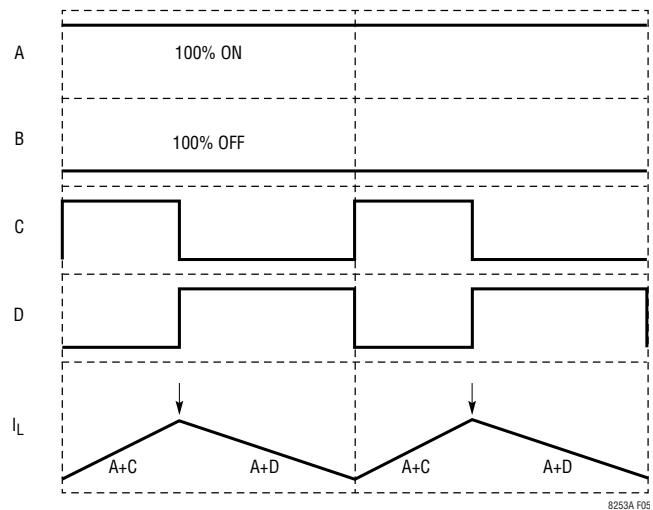

図1に、4つのパワー・スイッチA、B、C、およびDを、インダクタL、電流検出抵抗RSENSE、電源入力VIN、電源出力VOUT、およびグラウンドに接続する方法の簡略図を示します。LSPピンおよびLSNピンに接続された検出抵抗RSENSEは、降圧領域、昇降圧領域、および昇圧領域におけるピーク電流モード制御および逆電流検出の両方に関するインダクタ電流情報を提供します。

全部で次の4つの状態があります。(1) 降圧領域でのピーク降圧電流モード制御、(2) 昇降圧領域でのピーク降圧電流モード制御、(3) 昇降圧領域でのピーク昇圧電流モード制御、(4) 昇圧領域でのピーク昇圧電流モード制御。以下のセクションでは、波形を用いて各状態について詳細に説明します。説明を簡単にするために、スイッチAとBの間、スイッチCとDの間のショートスルーパrotectのデッド・タイムは無視されます。

図1. パワー・スイッチの簡略図

## 動作

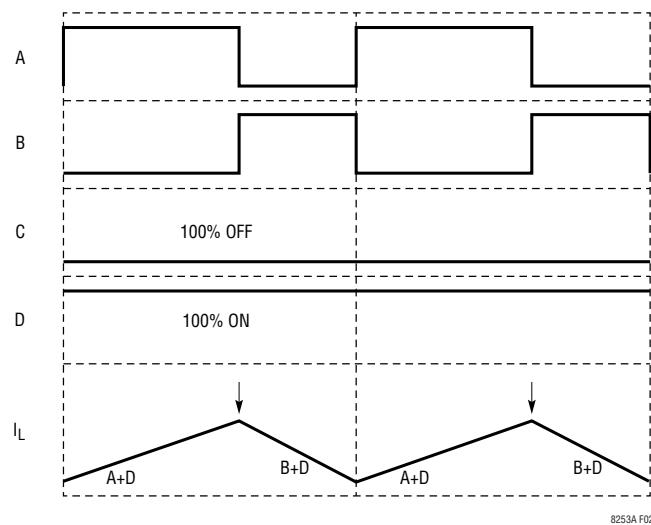

### (1) 降圧領域でのピーク降圧 ( $V_{IN}$ が $V_{OUT}$ より非常に高い)

$V_{IN}$  が  $V_{OUT}$  よりもはるかに高い場合、LT8253/LT8253A は、降圧領域においてピーク降圧電流モード制御を使用します(図2)。スイッチCは常にオフになり、スイッチDは常にオンになります。各サイクルの開始時に、スイッチAがオンになります。インダクタ電流が増加します。インダクタ電流が、(A+D)フェーズの間に降圧電流コンパレータA3での $V_C$ 電圧で指定されたピーク降圧電流閾値に達すると、サイクルの残りの期間、スイッチAがオフになり、スイッチBがオンになります。スイッチAとスイッチBは交互に動作し、典型的な同期整流式降圧レギュレータと同様に動作します。

図2. 降圧領域でのピーク降圧 ( $V_{IN}$  が  $V_{OUT}$  より非常に高い)

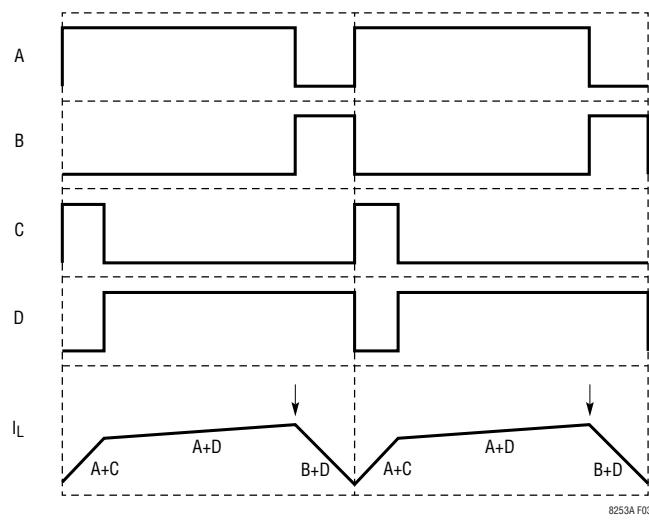

### (2) 昇降圧領域でのピーク降圧 ( $V_{IN}$ が $V_{OUT}$ よりわずかに高い)

$V_{IN}$  が  $V_{OUT}$  よりもわずかに高い場合、LT8253/LT8253A は、昇降圧領域においてピーク降圧電流モード制御を使用します(図3)。最初のプリセット・サイクルの間はスイッチCが常にONになります。残りのサイクルの間はスイッチDが常にONになります。各サイクルの開始時に、スイッチAおよびCがONになります。インダクタ電流が増加します。プリセット・サイクル経過後はスイッチCがオフになり、スイッチDがONになります。インダクタ電流が増加し続けます。インダクタ電流が、(A+D)フェーズの間に降圧電流コンパレータA3での $V_C$ 電圧で指定されたピーク降圧電流閾値に達すると、サイクルの残りの期間、スイッチAがオフになり、スイッチBがONになります。

図3. 昇降圧領域でのピーク降圧 ( $V_{IN}$  が  $V_{OUT}$  よりわずかに高い)

## 動作

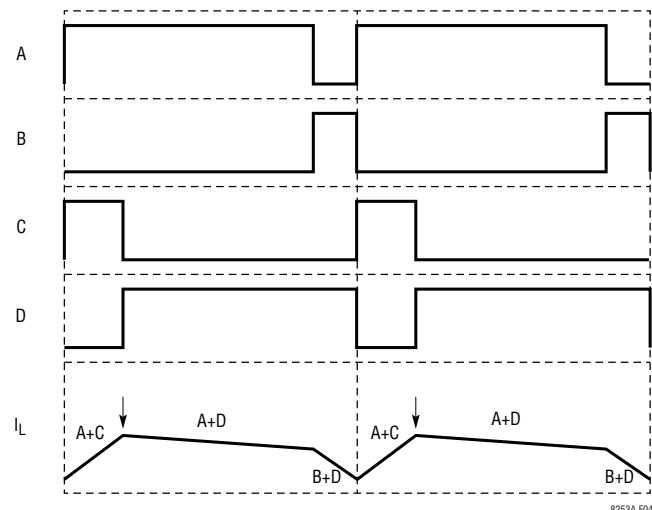

### (3) 昇降圧領域でのピーク昇圧( $V_{IN}$ が $V_{OUT}$ よりわずかに低い)

$V_{IN}$ が $V_{OUT}$ よりもわずかに低い場合、LT8253/LT8253Aは、昇降圧領域においてピーク昇圧電流モード制御を使用します(図4)。最初のプリセット・サイクルの間はスイッチAが常にオンになり、残りのサイクルの間はスイッチBが常にオンになります。各サイクルの開始時に、スイッチAおよびCがオンになり、インダクタ電流が増加します。インダクタ電流が、(A+C)フェーズの間に昇圧電流コンパレータA4での $V_C$ 電圧で指定されたピーク昇圧電流閾値に達すると、サイクルの残りの期間、スイッチCがオフになり、スイッチDがオンになります。プリセット・サイクル経過後、サイクルの残りの間はスイッチAがオフになり、スイッチBがオンになります。

図4. 昇降圧領域でのピーク昇圧( $V_{IN}$ が $V_{OUT}$ よりわずかに低い)

### (4) 昇圧領域でのピーク昇圧( $V_{IN}$ が $V_{OUT}$ より非常に低い)

$V_{IN}$ が $V_{OUT}$ よりもはるかに低い場合、LT8253/LT8253Aは、昇圧領域においてピーク昇圧電流モード制御を使用します(図5)。スイッチAは常にONになります。スイッチBは常にOFFになります。各サイクルの開始時に、スイッチCがONになります。インダクタ電流が増加します。インダクタ電流が、(A+C)フェーズの間に昇圧電流コンパレータA4での $V_C$ 電圧で指定されたピーク昇圧電流閾値に達すると、サイクルの残りの期間、スイッチCがOFFになります。スイッチDがONになります。スイッチCとスイッチDは交互に動作し、典型的な同期整流式昇圧レギュレータと同様に動作します。

図5. 昇圧領域でのピーク昇圧( $V_{IN}$ が $V_{OUT}$ より非常に低い)

## 動作

### メイン制御ループ

LT8253/LT8253Aは固定周波数の電流モード・コントローラです。インダクタ電流は、LSPピンとLSNピンの間のインダクタ検出抵抗を介して検出されます。電流検出電圧は、アンプA1によって増幅されて、内部発振器からのスロープ補償ランプ信号に加えられます。その後、この加算信号が降圧電流コンパレータA3および昇圧電流コンパレータA4の正端子に供給されます。A3およびA4の負端子は、エラー・アンプEA1の出力である $V_C$ ピンの電圧によって制御されます。

ピーク降圧ピーク昇圧電流モード制御の状態に応じて、降圧ロジックと昇圧ロジックのいずれかが4つのパワー・スイッチを制御するので、FBピンの電圧は1Vに安定化されます。

### 軽負荷電流動作

軽負荷に、LT8253/LT8253Aは、通常は不連続導通モードで動作し、レギュレーションを維持して効率を向上させます。

### シャットダウンおよびパワー・オン・リセット

EN/UVLOピンの電圧がシャットダウン閾値(最小0.3V)よりも低くなると、LT8253/LT8253Aはシャットダウン・モードになります。自己消費電流は2 $\mu$ A未満になります。EN/UVLOピンの電圧がシャットダウン閾値(最大1V)を超えると、LT8253/LT8253Aは起動回路を起動してバンドギャップ・リファレンスを生成し、内部INTV<sub>CC</sub> LDOに電力を供給します。INTV<sub>CC</sub> LDOは、内部制御回路およびゲート・ドライバに電力を供給します。その後、LT8253/LT8253Aは低電圧ロックアウト(UVLO)モードに移行して、ヒステリシス電流(代表値2.5 $\mu$ A)がEN/UVLOピンに流れ込みます。INTV<sub>CC</sub>ピンが充電されて上昇時UVLO閾値(代表値3.78V)よりも高くなり、EN/UVLOピンが上昇時イネーブル閾値(代表値1.233V)を超え、ジャンクション温度がサーマル・シャットダウン温度(代表値165°C)よりも低くなると、LT8253/LT8253Aはイネーブル・モードに移行します。イネーブル・モードでは、EN/UVLOヒステリシス電流がオフになり、電圧リファレンス $V_{REF}$ がグラウンドから充電されます。イネーブル・モードに移行してから、 $V_{REF}$ が上昇時UVLO閾値(代表値1.89V)を超えるまで、LT8253/LT8253Aはパワーオン・リセット(POR)を経て、内部制御回路全体を起動し、適切な初期状態に安定化します。POR後に、LT8253/LT8253Aはスイッチングを開始します。

## 動作

### 起動および障害保護

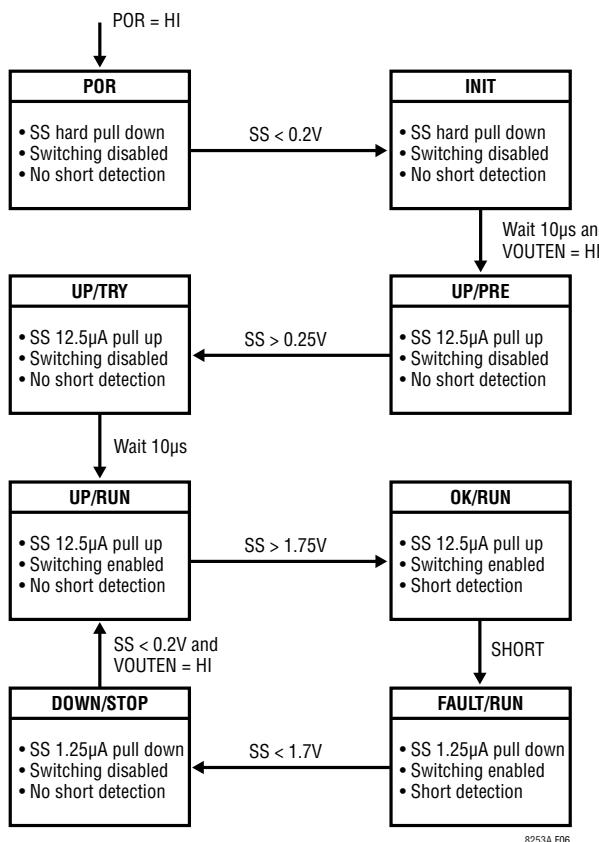

図6に、LT8253/LT8253Aの起動および障害のシーケンスを示します。POR状態の間、SSピンは100Ωでグラウンドに強く引き下げられます。プリバイアスされた状態では、SSピンを0.2V未満に引き下げて、INIT状態に移行する必要があります。INIT状態では、LT8253/LT8253Aは、SSピンが完全にグラウンドに放電できるように10μs待機します。10μs後に、VOUTEN信号がハイになると、LT8253/LT8253AはUP/PRE状態に移行します。

UP/PRE状態の間、SSピンは12.5μAのプルアップ電流によって充電される一方で、スイッチング動作はディスエーブルされます。SSピンが0.25Vを超えて充電されると、LT8253/LT8253AはUP/TRY状態に移行します。UP/TRY状態で10μs経過した後に、LT8253/LT8253AはUP/RUN状態に移行します。

図6. 起動シーケンスと障害シーケンス

UP/RUN状態の間、スイッチング動作がイネーブルされ、出力電圧VOUTの起動は、SSピンの電圧によって制御されます。SSピンの電圧が1Vより低いと、LT8253/LT8253AはFBピンの電圧を1Vのリファレンス電圧ではなく、SSピンの電圧に安定化します。このため、SSピンとGNDの間に外付けコンデンサを接続することにより、SSピンでソフトスタートを設定することができます。12.5μAの内部プルアップ電流がこのコンデンサを充電して、SSピンに電圧ランプを生成します。SSピンの電圧が0.25Vから1V(以上)に直線的に上昇するにつれて、出力電圧VOUTも最終的なレギュレーション電圧まで滑らかに上昇します。

SSピンが充電されて1.75Vを超えると、LT8253/LT8253AはOK/RUN状態に移行します。この状態では、出力短絡検出が動作状態になります。出力短絡とは、VFBが0.25Vより低い状態のことです。出力短絡が発生すると、LT8253/LT8253AはFAULT/RUN状態に移行します。この状態では、1.25μAのプルダウン電流がSSピンをゆっくりと放電し、その他の条件はOK/RUN状態と同じです。SSピンが放電されて1.7Vより低くなると、LT8253/LT8253AはDOWN/STOP状態に移行します。DOWN/STOP状態では、スイッチング動作がディスエーブルされ、短絡検出が非アクティブになり、前の障害がラッチされます。SSピンが放電されて0.2Vより低くなり、VOUTEN信号がハイのままの場合、LT8253/LT8253AはUP/RUN状態に戻ります。

出力短絡状態では、SSピンとVREFピンの間に抵抗を接続して、LT8253/LT8253Aをヒップ、ラッチオフ、または動作維持のいずれかの障害保護モードに設定できます。この抵抗を使用しない場合、LT8253/LT8253Aは0.2V～1.75Vの間ヒップ・モードで動作し、障害状態が解消されるまで、UP/RUN状態、OK/RUN状態、FAULT/RUN状態、およびDOWN/STOP状態を循環します。499kΩの抵抗を使用すると、LT8253/LT8253AはEN/UVLOが切り替わるまでラッチオフします。100kΩの抵抗を使用すると、LT8253/LT8253Aは、障害の有無にかかわらず動作を維持します。最初のページにLT8253/LT8253Aの代表的応用例を示します。このアプリケーション情報セクションは、標準的なアプリケーションで外付け部品を選択する場合のガイドラインとして役立ちます。このセクションの例および式では、特に規定されない限り、連続導通モードを前提とします。

### スイッチング周波数の選択

LT8253/LT8253Aは固定周波数制御方式を採用しており、周波数範囲はLT8253では150kHz～650kHz、LT8253Aで

## アプリケーション情報

は600kHz～2MHzです。スイッチング周波数の選択は効率と部品サイズの間のトレードオフになります。低周波数動作ではMOSFETのスイッチング損失が減ることで効率が高まりますが、値の大きいインダクタおよびコンデンサが必要になります。大電力アプリケーションでは、スイッチング損失によるMOSFETの発熱を最小限に抑えるため、低周波数での動作を検討してください。低消費電力アプリケーションでは、ソリューション・サイズ全体を最小限に抑えるため、高周波数での動作を検討してください。

加えて、スイッチング周波数の選択に際しては、特定のアプリケーションも重要な役割を果たします。ノイズに敏感なシステムでは、通常は、スイッチング・ノイズが敏感な周波数帯の内側にこないようにスイッチング周波数を選択します。

### スイッチング周波数の設定

LT8253/LT8253Aのスイッチング周波数は、内部発振器によって設定できます。SYNC/SPRDピンをグラウンドに引き下げるとき、スイッチング周波数は、RTピンから接地した抵抗によって設定されます。表1および表2に、LT8253およびLT8253Aの一般的なスイッチング周波数のRT抵抗値をそれぞれ示します。

表1. LT8253のスイッチング周波数とRTの値

(許容誤差1%の抵抗)

| fosc (kHz) | RT (k) |

|------------|--------|

| 150        | 309    |

| 200        | 226    |

| 300        | 140    |

| 400        | 100    |

| 500        | 75     |

| 600        | 59     |

| 650        | 51.1   |

表2. LT8253Aのスイッチング周波数とRTの値

(許容誤差1%の抵抗)

| fosc (MHz) | RT (k) |

|------------|--------|

| 0.6        | 267    |

| 0.8        | 191    |

| 1.0        | 147    |

| 1.2        | 118    |

| 1.4        | 97.6   |

| 1.6        | 82.5   |

| 1.8        | 66.5   |

| 2.0        | 59.0   |

### スペクトラム拡散周波数変調

スイッチング・レギュレータは、電磁干渉(EMI)が懸念されるアプリケーションで特に手間がかかることがあります。EMI性能を改善するため、LT8253/LT8253Aには三角波スペクトラム拡散周波数変調方式が実装されています。SYNC/SPRDピンをINTVCCに接続すると、LT8253は±15%の範囲で自身のスイッチング周波数を拡散し、LT8253Aは内部発振器の周波数より25%高い周波数まで自身のスイッチング周波数を拡散します。

### 周波数同期

LT8253/LT8253Aのスイッチング周波数は、SYNC/SPRDピンを使用して外部クロックに同期させることができます。SYNC/SPRDピンを50%のデューティ・サイクル波形でドライブするのは常に良い選択ですが、それ以外の場合はデューティ・サイクルを10%から90%の間に保ってください。

### インダクタの選択

スイッチング周波数が高いほど小さい値のインダクタとコンデンサを使用できるという意味で、スイッチング周波数とインダクタの選択には相関関係があります。インダクタの値は、リップル電流に直接影響を与えます。最大電流リップル $\Delta I_L\%$ は、降圧領域において $V_{IN(MAX)}$ で発生し、最小電流リップル $\Delta I_L\%$ は、昇圧領域において $V_{IN(MIN)}$ で発生します。顧客が設定した特定のリップル許容量に対して、最小インダクタンスを次のように計算できます。

$$L_{BUCK} > \frac{V_{OUT} \cdot (V_{IN(MAX)} - V_{OUT})}{f \cdot I_{OUT(MAX)} \cdot \Delta I_L \% \cdot V_{IN(MAX)}}$$

$$L_{BOOST} > \frac{V_{IN(MIN)}^2 \cdot (V_{OUT} - V_{IN(MIN)})}{f \cdot I_{OUT(MAX)} \cdot \Delta I_L \% \cdot V_{OUT}^2}$$

ここで、

$$\Delta I_L \% = \frac{\Delta I_L}{I_L(AVG)}$$

fはスイッチング周波数

$V_{IN(MIN)}$ は最小入力電圧

$V_{IN(MAX)}$ は最大入力電圧

$V_{OUT}$ は出力電圧

$I_{OUT(MAX)}$ は最大出力電流

## アプリケーション情報

スロープ補償を行うと、特定のデューティ・サイクルでの低調波発振を防止することにより、固定周波数電流モード制御での安定性が得られます。デューティ・サイクルが50%より大きい場合の安定性に必要な最小インダクタンスは、次のように計算できます。

$$L > \frac{10 \cdot V_{OUT} \cdot R_{SENSE}}{f}$$

高効率を実現するには、フェライトなど、コア損失の小さなインダクタを選択します。また、 $I^2R$  損失を減らすため、インダクタはDC抵抗が低く、飽和せずにピーク・インダクタ電流を扱えるものにします。放射ノイズを抑えるには、シールドされたインダクタを使用します。

### R<sub>SENSE</sub>の選択と最大出力電流

R<sub>SENSE</sub>は必要な出力電流に基づいて選択します。デューティ・サイクルに無関係な最大電流検出閾値(ピーク降圧で50mV、ピーク昇圧で50mV)は、降圧領域、昇降圧領域、および昇圧領域での最大インダクタ・ピーク電流を設定します。

昇圧領域において、最も低い最大平均負荷電流はV<sub>IN(MIN)</sub>で発生し、次のように計算できます。

$$I_{OUT(MAX\_BOOST)} = \left( \frac{50mV}{R_{SENSE}} - \frac{\Delta I_{L(BOOST)}}{2} \right) \cdot \frac{V_{IN(MIN)}}{V_{OUT}}$$

ここで、 $\Delta I_{L(BOOST)}$ は昇圧領域でのインダクタのピークtoピーク・リップル電流であり、次のように計算できます。

$$\Delta I_{L(BOOST)} = \frac{V_{IN(MIN)} \cdot (V_{OUT} - V_{IN(MIN)})}{f \cdot L \cdot V_{OUT}}$$

降圧領域において、最も低い最大平均負荷電流はV<sub>IN(MAX)</sub>で発生し、次のように計算できます。

$$I_{OUT(MAX\_BUCK)} = \left( \frac{50mV}{R_{SENSE}} - \frac{\Delta I_{L(BUCK)}}{2} \right)$$

ここで、 $\Delta I_{L(BUCK)}$ は降圧領域でのインダクタのピークtoピーク・リップル電流であり、次のように計算できます。

$$\Delta I_{L(BUCK)} = \frac{V_{OUT} \cdot (V_{IN(MAX)} - V_{OUT})}{f \cdot L \cdot V_{IN(MAX)}}$$

昇圧領域での電流検出抵抗R<sub>SENSE</sub>の最大値は次のとおりです。

$$R_{SENSE(BOOST)} = \frac{2 \cdot 50mV \cdot V_{IN(MIN)}}{2 \cdot I_{OUT(MAX)} \cdot V_{OUT} + \Delta I_{L(BOOST)} \cdot V_{IN(MIN)}}$$

降圧領域での電流検出抵抗R<sub>SENSE</sub>の最大値は次のとおりです。

$$R_{SENSE(BUCK)} = \frac{2 \cdot 50mV}{2 \cdot I_{OUT(MAX)} + \Delta I_{L(BUCK)}}$$

降圧と昇圧のどちらの領域でも、最終的なR<sub>SENSE</sub>の値は、算出されるR<sub>SENSE</sub>よりも小さくする必要があります。通常は20%~30%のマージンを推奨します。低ESL電流検出抵抗を必ず選択します。

### パワー MOSFET の選択

LT8253/LT8253Aには4つの外付けNチャンネル・パワーMOSFETが必要です。内訳は上側スイッチが2つ(図1に示すスイッチAおよびD)と下側スイッチが2つ(図1に示すスイッチBおよびC)です。パワーMOSFETの重要なパラメータは、ブレーカダウン電圧V<sub>BR(DSS)</sub>、スレッショルド電圧V<sub>GS(TH)</sub>、オン抵抗R<sub>DS(ON)</sub>、逆伝達容量C<sub>RSS</sub>、および最大電流I<sub>DS(MAX)</sub>です。

2MHzの動作を実現するには、パワーMOSFETの選択が極めて重要になります。標準25nsのショートスルーパrot保護のデッド・タイムの場合、低いQ<sub>g</sub>および低いR<sub>DS(ON)</sub>を備える高性能なパワーMOSFETを使用する必要があります。

ゲート駆動電圧は5VのINTV<sub>CC</sub>電源によって設定されるため、LT8253/LT8253Aのアプリケーションでは、ロジックレベル閾値のMOSFETを使用する必要があります。2MHzのような高い周波数で4つのMOSFETをスイッチングする場合、INTV<sub>CC</sub>からの大きなゲート充電電流は次のように概算できます。

$$I_{INTVCC} = f \cdot (Q_{gA} + Q_{gB} + Q_{gC} + Q_{gD})$$

ここで、

fはスイッチング周波数です。

Q<sub>gA</sub>、Q<sub>gB</sub>、Q<sub>gC</sub>、Q<sub>gD</sub>は、MOSFET A、B、C、Dの合計ゲート電荷です。

必要なINTV<sub>CC</sub>電流の合計がデータシートのINTV<sub>CC</sub>電流制限を超えないことを確認してください。通常は、Q<sub>g</sub>が10nC未満のMOSFETを推奨します。

## アプリケーション情報

LT8253/LT8253Aは、 $V_{IN}/V_{OUT}$ の比を使用して、モード間および領域間を遷移します。MOSFETとインダクタの不適切な選択が原因で電力経路でのIR電圧降下が大きくなると、LT8253/LT8253Aが滑らかに遷移できないことがあります。降圧動作モード、昇降圧動作モード、および昇圧動作モードの間での遷移を確実に滑らかにするには、以下の式を満足するように低  $R_{DS(ON)}$  のMOSFETおよび低 DCR のインダクタを選択します。

$$I_{OUT(MAX)} \leq \frac{0.025 \cdot V_{OUT}}{R_{A,B} + R_{C,D} + R_{SENSE} + R_L}$$

ここで、

$R_{A,B}$ は25°CでのMOSFET AまたはBの最大  $R_{DS(ON)}$

$R_{C,D}$ は25°CでのMOSFET CまたはDの最大  $R_{DS(ON)}$

$R_L$ は25°Cでのインダクタの最大 DCR 抵抗

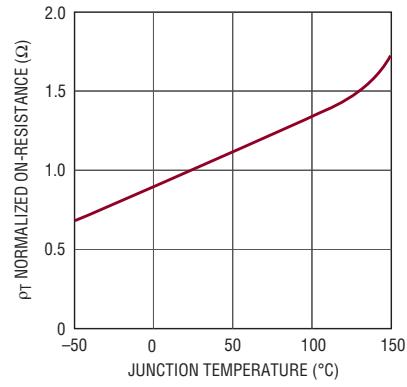

ジャンクション温度が高くなると  $R_{DS(ON)}$  および DCR が増加し、上の計算にはプロセス変動が含まれています。

パワーMOSFETを選択するには、デバイスによって消費される電力を知る必要があります。スイッチAの場合、最大消費電力は(スイッチAが常にオン状態に留まる)昇圧領域で生じます。最大出力電流での最大消費電力は次式で与えられます。

$$P_{A(BOOST)} = \left( \frac{I_{OUT(MAX)} \cdot V_{OUT}}{V_{IN}} \right)^2 \cdot \rho_T \cdot R_{DS(ON)}$$

$\rho_T$ は正規化係数(25°Cで1)で、温度によるオン抵抗の大きな変化を表し、図7に示されているように標準で0.4%/°Cです。125°Cの最大ジャンクション温度の場合は、 $\rho_T = 1.5$ の値を使うのが妥当です。

スイッチBは、降圧領域では同期整流器として動作します。最大出力電流での消費電力は次式で与えられます。

$$P_{B(BUCK)} = \frac{V_{IN} - V_{OUT}}{V_{IN}} \cdot I_{OUT(MAX)}^2 \cdot \rho_T \cdot R_{DS(ON)}$$

スイッチCは、昇圧領域では制御スイッチとして動作します。最大電流での消費電力は次式で与えられます。

$$P_{C(BOOST)} = \frac{(V_{OUT} - V_{IN}) \cdot V_{OUT}}{V_{IN}^2} \cdot I_{OUT(MAX)}^2 \cdot \rho_T \cdot R_{DS(ON)} + k \cdot V_{OUT}^3 \cdot \frac{I_{OUT(MAX)}}{V_{IN}} \cdot C_{RSS} \cdot f$$

図7. 正規化された  $R_{DS(ON)}$  と温度

ここで、 $C_{RSS}$ は通常MOSFETの製造メーカーにより規定されています。逆回復電流によって生じる損失を反映する定数  $k$  は、ゲート駆動電流に反比例し、その経験値は1.7です。

スイッチDの場合、最大消費電力は昇圧領域で生じ、そのときのデューティ・サイクルは50%を超えます。最大出力電流での最大消費電力は次式で与えられます。

$$P_{D(BOOST)} = \frac{V_{OUT}}{V_{IN}} \cdot I_{OUT(MAX)}^2 \cdot \rho_T \cdot R_{DS(ON)}$$

同じ出力電圧と出力電流では、出力に短絡が生じない限り、スイッチAの消費電力が最大になり、スイッチBの消費電力が最小になります。

パワーMOSFETで消費される既知の電力から、次式を使ってジャンクション温度を求めることができます。

$$T_J = T_A + P \cdot R_{TH(JA)}$$

接合部-周囲間熱抵抗  $R_{TH(JA)}$  には、接合部-ケース間熱抵抗  $R_{TH(JC)}$  およびケース-周囲間熱抵抗  $R_{TH(CA)}$  が含まれます。次に  $T_J$  のこの値を反復計算に使用された元の仮定値と比べることができます。

## アプリケーション情報

### **C<sub>IN</sub>とC<sub>OUT</sub>の選択**

入力容量と出力容量は、レギュレータとの間を出入りする不連続な電流によって生じる電圧リップルを抑えるために必要です。通常はコンデンサを並列に組み合わせて使用することで大容量と低等価直列抵抗(ESR)を実現します。乾式タンタル、特殊ポリマー、アルミ電解およびセラミックの各コンデンサは、全て表面実装パッケージで入手できます。OS-CONやPOSCAPなど、低ESRで高リップル電流定格のコンデンサも入手できます。

セラミック・コンデンサをレギュレータの入力と出力の近くに配置して、高周波のスイッチング・スパイクを抑えてください。1μF以上のセラミック・コンデンサもLT8253/LT8253Aのピンにできるだけ近づけてV<sub>IN</sub>とGNDの間およびV<sub>OUT</sub>とGNDの間に配置してください。セラミック・コンデンサは優れた低ESR特性を備えているので、入力リップル電圧を大幅に低減することが可能であり、ESRの高いバルク・コンデンサでの電力損失を抑えるのに役立ちます。X5RやX7Rの誘電体材料は広い電圧範囲と温度範囲にわたって容量を保持するので推奨されます。多くのセラミック・コンデンサ(特にケース・サイズが0805または0603のものは)は、目的の動作電圧での容量が大きく減少します。

**入力容量 C<sub>IN</sub>:**スイッチAのオンとオフが切り替わることが原因で、降圧領域では不連続な入力電流が最も大きくなります。C<sub>IN</sub>コンデンサ回路網のESRが十分に低く、最大RMS電流を扱うのに十分な大きさであることを確認してください。降圧領域では、入力RMS電流は次式で与えられます。

$$I_{RMS} \approx I_{OUT(MAX)} \cdot \frac{V_{OUT}}{V_{IN}} \cdot \sqrt{\frac{V_{IN}}{V_{OUT}} - 1}$$

この式はV<sub>IN</sub> = 2V<sub>OUT</sub>のときに最大値となります。ここで、I<sub>RMS</sub> = I<sub>OUT(MAX)</sub>/2です。設計ではこの単純で最も厳しい条件がよく使用されます。条件を大きく変化させても状況がそれほど改善されないからです。

**出力容量 C<sub>OUT</sub>:**昇圧領域において、不連続電流が入力から出力に移動します。C<sub>OUT</sub>コンデンサ回路網が出力電圧リップルを低減できることを確認してください。与えられた出力リップル電圧に対する適切なコンデンサを選択するには、ESRとバルク容量の影響について検討する必要があります。

バルク容量の充放電による定常状態の最大リップルは次式で与えられます。

$$\Delta V_{CAP(BOOST)} = \frac{I_{OUT(MAX)} \cdot (V_{OUT} - V_{IN(MIN)})}{C_{OUT} \cdot V_{OUT} \cdot f}$$

$$\Delta V_{CAP(BUCK)} = \frac{V_{OUT} \cdot \left(1 - \frac{V_{OUT}}{V_{IN(MAX)}}\right)}{8 \cdot L \cdot f^2 \cdot C_{OUT}}$$

ESR両端の電圧降下による最大定常リップルは次式で与えられます。

$$\Delta V_{ESR(BOOST)} = \frac{V_{OUT} \cdot I_{OUT(MAX)} \cdot ESR}{V_{IN(MIN)}}$$

$$\Delta V_{ESR(BUCK)} = \frac{V_{OUT} \cdot \left(1 - \frac{V_{OUT}}{V_{IN(MAX)}}\right) \cdot ESR}{L \cdot f}$$

### **INTV<sub>CC</sub>レギュレータ**

内部Pチャンネル低損失レギュレータは、V<sub>IN</sub>電源ピンからINTV<sub>CC</sub>ピンに5Vを発生します。INTV<sub>CC</sub>は、LT8253/LT8253Aの内部回路およびゲート・ドライバに電力を供給します。INTV<sub>CC</sub>レギュレータは4.7μF以上のセラミック・コンデンサを使用してグラウンドにバイパスする必要があります。MOSFETゲート・ドライバが必要とする大きな過渡電流を供給するには、適切な短距離のバイパスが必要です。

大きなMOSFETを高いスイッチング周波数で駆動する高入力電圧のアプリケーションでは、LT8253/LT8253Aの最大ジャンクション温度定格を超える恐れがあります。システムの電源電流は、通常、ゲート充電電流によって支配されます。消費電力を計算する際には、INTV<sub>CC</sub>の追加的な外付け負荷も考慮に入れる必要があります。この場合のLT8253/LT8253Aの全消費電力はV<sub>IN</sub> • I<sub>INTVCC</sub>で、全体的な効率は低下します。ジャンクション温度は次の式を使って推算することができます。

$$T_J = T_A + P_D \cdot \theta_{JA}$$

ここで、θ<sub>JA</sub>(°C/W)はパッケージの熱抵抗です。

## アプリケーション情報

最大ジャンクション温度を超えないようにするには、連続モード動作時の入力電源電流を最大  $V_{IN}$  で検査する必要があります。

### 上側ゲートMOSFETドライバ電源( $C_{BST1}$ 、 $C_{BST2}$ )

上側MOSFETドライバ(TG1およびTG2)は、それぞれのSWピンの電圧とBSTピンの電圧の間で駆動されます。昇圧電圧はフロート状態のブートストラップ・コンデンサ  $C_{BST1}$  および  $C_{BST2}$  によってバイアスされますが、これらは通常、それぞれの上側MOSFETがオフすると、内部ブートストラップ・ダイオードを介して再充電されます。両方のコンデンサは、 $INTV_{CC}$  と同じ電圧に充電されます。ブートストラップ・コンデンサ  $C_{BST1}$  および  $C_{BST2}$  は、上側スイッチAおよびDが必要とするゲート電荷の約100倍の電荷を保存する必要があります。ほとんどのアプリケーションでは、 $0.1\mu F$ ～ $0.47\mu F$  のX5RまたはX7R誘電体コンデンサで十分です。

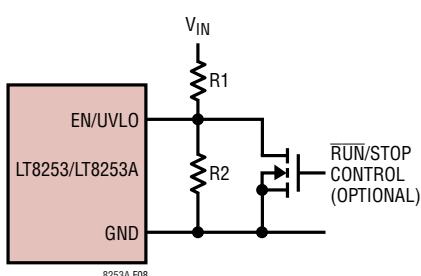

### $V_{IN}$ UVLOの設定

$V_{IN}$ ピンとEN/UVLOピンの間に抵抗分圧器を接続することにより、 $V_{IN}$ の低電圧ロックアウト(UVLO)を実装できます。EN/UVLOのイネーブル立下がり閾値は1.220Vに設定されており、13mVのヒステリシスがあります。また、EN/UVLOピンの電圧が1.220Vより低いと、このピンに $2.5\mu A$ のシンク電流が流れます。この電流により、R1の値に基づいてプログラマブルなヒステリシスが得られます。プログラマブルなUVLO閾値は次のようにになります。

$$V_{IN(UVLO+)} = 1.233V \cdot \frac{R1+R2}{R2} + 2.5\mu A \cdot R1$$

$$V_{IN(UVLO-)} = 1.220V \cdot \frac{R1+R2}{R2}$$

図8は、外部シャットダウン制御を実施しつつ、一方でUVLO機能を使用する回路を示しています。NMOSがオンするとEN/UVLOピンが接地され、LT8253/LT8253Aは自己消費電流が $2\mu A$ 未満のシャットダウン状態になります。

図8.  $V_{IN}$ の低電圧ロックアウト(UVLO)

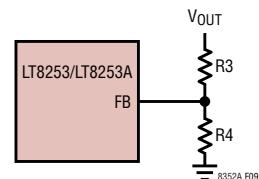

### 出力電圧および閾値の設定

LT8253/LT8253Aには電圧帰還ピンFBがあり、R3とR4(図9)を次式に従って使用することで出力電圧を設定できます。

$$V_{OUT} = 1V \cdot \frac{R3+R4}{R4}$$

加えて、FBピンは、出力過電圧閾値、出力パワーグッド閾値、出力短絡閾値も設定します。小さい出力コンデンサを備えるアプリケーションの場合、負荷過渡応答の発生時に、出力電圧が大きくオーバーシュートすることがあります。FBピンの電圧が過電圧閾値の1.1Vに達すると、LT8253/LT8253Aはオフになります。

図9. 帰還抵抗の接続

LT8253AはTG1、BG1、TG2、およびBG2をオフすることによってスイッチングを停止します。出力過電圧閾値は、次のように設定できます。

$$V_{OUT(OVP)} = 1.1V \cdot \frac{R3+R4}{R4}$$

出力短絡の検出および保護を提供するために、出力短絡下降時閾値を次のように設定できます。

$$V_{OUT(SHORT)} = 0.25V \cdot \frac{R3+R4}{R4}$$

### パワーグッド( $\overline{PGOOD}$ )ピン

LT8253/LT8253Aはオープンドレインのステータス・ピン( $\overline{PGOOD}$ )を備えていますが、このピンは、 $V_{FB}$ がレギュレーション電圧1.00Vの $\pm 10\%$ 以内に入るとローになります。 $\overline{PGOOD}$ ピンは、外付け抵抗によって $INTV_{CC}$ または最大6Vの外部電源にプルアップすることができます。

## アプリケーション情報

### ソフトスタートおよび短絡保護

図6に示され、動作セクションで説明されているように、SSピンを使用し、外付けコンデンサをSSピンから接地することによって、出力電圧のソフトスタートを設定できます。12.5μAの内部プルアップ電流がこのコンデンサを充電して、SSピンに電圧ランプを生成します。SSピンの電圧が0.25Vから1V(更にそれより上)に直線的に上昇するにつれて、出力電圧がその最終的なレギュレーション電圧に滑らかに上昇します。ソフトスタート時間は次のように計算できます。

$$t_{SS} = 1V \cdot \frac{C_{SS}}{12.5\mu A}$$

$C_{SS}$ は $V_C$ ピンの補償コンデンサの少なくとも5倍~10倍にして、出力電圧のソフトスタートを十分に制御されたものにします。

SSピンは障害タイマーとしても使われます。出力短絡障害が検出されると、1.25μAのプルダウン電流源がアクティブになります。SSピンと $V_{REF}$ ピンの間に1つの抵抗を使用して、LT8253/LT8253Aを、ヒップ(抵抗なし)、ラッチオフ(499k)、および動作維持(100k)という3種類の障害保護モードに設定できます。

動作維持モードで100k抵抗を使用すると、LT8253/LT8253Aは正常にスイッチング動作を継続し、グラウンドに流れ込む電流を安定化します。ラッチオフ・モードで499kの抵抗を使用すると、LT8253/LT8253Aは、EN/UVLOピンがローに引き下げられてからハイに引き上げられて再起動されるまで、スイッチング動作を停止します。ヒップ・モードで抵抗を使用しない場合、LT8253/LT8253Aは低デューティ・サイクルの自動再試行動作に移行します。1.25μAのプルダウン電流がSSピンを0.2Vに放電し、その後、12.5μAのプルアップ電流がSSピンを充電します。SSが1.75Vに達したときに出力短絡状態が解消されていない場合は、1.25μAのプルダウン電流が再びオンして新しいヒップ・サイクルを開始します。これは、障害状態が解消されるまで続きます。出力短絡状態が解消されると、ソフトスタートによって出力が短絡から滑らかに回復します。

### ループ補償

LT8253/LT8253Aは内部のトランスコンダクタンス・エラーアンプを使用しており、その出力 $V_C$ によって制御ループが補償されます。外部インダクタ、出力コンデンサ、および補償抵抗とコンデンサにより、ループの安定性が決まります。

インダクタと出力コンデンサは、性能、サイズおよびコストに基づいて選択します。 $V_C$ ピンの補償抵抗とコンデンサは、制御ループの応答性と安定性を最適化するように設定されます。

### 効率に関する検討事項

スイッチング・レギュレータの電力効率は、出力電力を入力電力で割って100%を掛けた値に等しくなります。多くの場合、個々の損失を分析して、効率を制限する要素が何であり、また何が変化すれば最も効率が改善されるかを判断することが有益です。回路内の電力を消費する全ての素子で損失が生じますが、LT8253/LT8253Aの回路での損失の大部分は主に次の4つの要因によって生じます。

1. DCの $I^2R$ 損失。これは、MOSFET、検出抵抗、インダクタ、およびプリント回路基板のパターンの各抵抗成分によって発生し、大きな出力電流が流れるときに効率低下の原因になります。

2. 遷移損失。この損失は、スイッチ・ノードが遷移するとき、スイッチAまたはスイッチCが短時間飽和領域に留まることから生じます。これは、入力電圧、負荷電流、ドライバ強度、MOSFET容量などの要因に依存します。

3. INT $V_{CC}$ 電流。これはMOSFETドライバ電流と制御電流の和です。

4.  $C_{IN}$ と $C_{OUT}$ の損失。入力コンデンサは、降圧領域でレギュレータに流れる大きなRMS入力電流をフィルタリングするという困難な役目を担っています。出力コンデンサも、昇圧領域で大きなRMS出力電流をフィルタリングするという困難な役目を担っています。 $C_{IN}$ と $C_{OUT}$ は両方とも、ACの $I^2R$ 損失を最小にするためにESRを小さくして、RMS電流が上流でヒューズやバッテリ内の追加損失を生じないように十分な容量にすることが必要です。

## アプリケーション情報

5. 他の損失。ショットキー・ダイオード  $D_B$  と  $D_D$  により、デッド・タイムと軽負荷導通期間に導通損失が生じます。インダクタのコア損失は主に軽負荷で生じます。降圧領域ではスイッチAによって逆回復電流損失が発生し、昇圧領域ではスイッチCによって逆回復電流損失が発生します。

効率を改善するための調整を行う場合、入力電流は効率の変化を示す最良のインジケータです。変更を加えて入力電流が減少すれば、効率は向上しています。入力電流に変化がなければ効率にも変化はありません。

### プリント回路基板レイアウトのチェックリスト

基本的なPC基板のレイアウトには専用のグラウンド・プレーン層が必要です。また、大電流では、多層基板がパワー部品を放熱する役割を果たします。

- グラウンド・プレーン層にはパターンがあつてはならず、パワーMOSFETの置かれている層にできるだけ近くします。

- $C_{IN}$ 、スイッチA、スイッチB、および $D_B$ も一箇所に密集させて配置します。 $C_{OUT}$ 、スイッチC、スイッチD、および $D_D$ も一箇所に密集させて配置します。

- すぐ近くでビアを使用して、各部品をグラウンド・プレーンに接続します。各パワー部品には大きなビアを複数使います。

- 十分な電圧フィルタリングを維持し、電力損失を低く抑えるため、 $V_{IN}$ と $V_{OUT}$ にはプレーンを使用します。

- 全ての層の全ての未使用領域を銅で覆います。銅箔で覆うことにより、電源部品の温度上昇を抑えることができます。これらの銅領域はDCネットのどれか( $V_{IN}$ または $GND$ )に接続します。

- 信号グラウンドと電源グラウンドを分離します。全ての小信号部品は、底面から $GND$ 露出パッドに戻します。この $GND$ 露出パッドは、スイッチBとスイッチCのソースに近づけてパワー $GND$ に接続します。

- スイッチAとスイッチCはできるだけコントローラに近づけて配置し、 $PGND$ 、 $BG$ 、および $SW$ のパターンを短くします。

- $dV/dT$ の高い $SW1$ 、 $SW2$ 、 $BST1$ 、 $BST2$ 、 $TG1$ 、および $TG2$ の各ノードは敏感な小信号ノードから離します。

- スイッチA、スイッチB、 $D_B$ 、および $C_{IN}$ コンデンサで形成される経路のリード長とPCBパターン長を短くします。また、スイッチC、スイッチD、 $D_D$ および $C_{OUT}$ コンデンサで形成される経路のリード長とPCBパターン長も短くします。

- 出力コンデンサの(-)端子は入力コンデンサの(-)端子にできるだけ近づけて接続します。

- 上側ドライバのブートストラップ・コンデンサ $C_{BST1}$ は、 $BST1$ ピンと $SW1$ ピンに近づけて接続します。上側ドライバのブートストラップ・コンデンサ $C_{BST2}$ は、 $BST2$ ピンと $SW2$ ピンに近づけて接続します。

- 入力コンデンサ $C_{IN}$ と出力コンデンサ $C_{OUT}$ はパワーMOSFETに近づけて接続します。これらのコンデンサはMOSFETのAC電流を供給します。

- LSPとLSNのパターンは、PCBパターンの間隔を最小にして一緒に配線します。検出ラインが、スイッチ・ノードなどのノイズの大きい領域を通過しないようにしてください。LSPとLSNの間のフィルタ・コンデンサは、できるだけデバイスに近づけて配置します。RSENSE抵抗では、ケルビン接続を使用して高精度の電流検出を確実に行ってください。低ESLの検出抵抗を推奨します。

- $V_C$ ピンの補償ネットワークはデバイスに近づけて、 $V_C$ と信号グラウンドの間に接続します。コンデンサはPCBノイズと出力電圧のリップル電圧の影響を補償ループから除去するのに役立ちます。

- $INTV_{CC}$ のバイパス・コンデンサ( $C_{INTVCC}$ )はデバイスの近くで $INTV_{CC}$ と電源グラウンドの間に接続します。このコンデンサはMOSFETドライバのピーク電流を供給します。

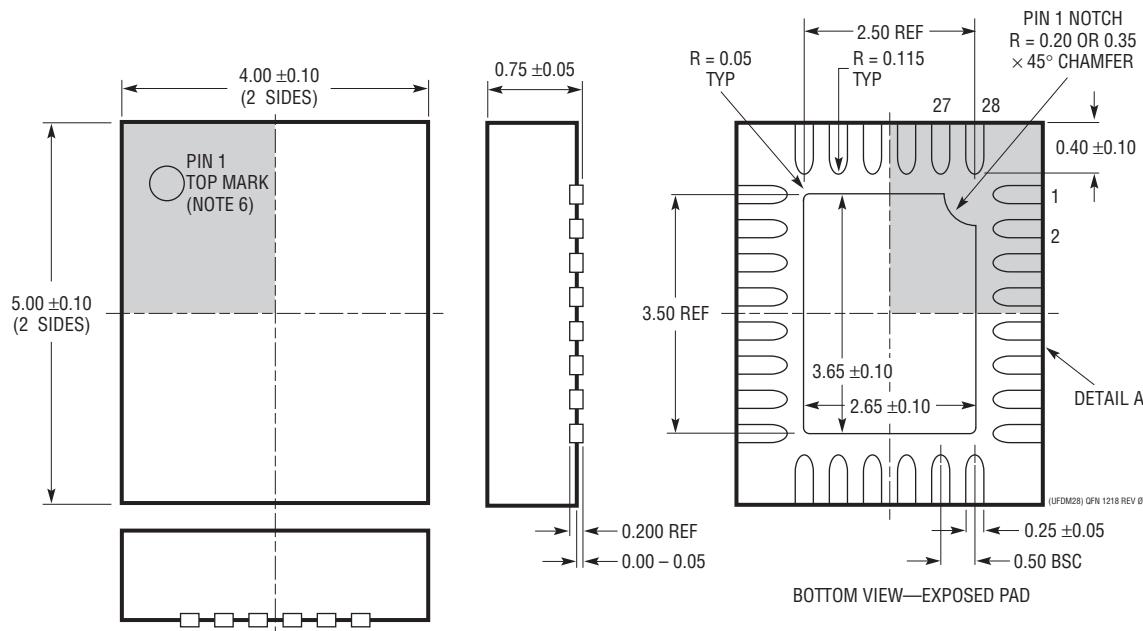

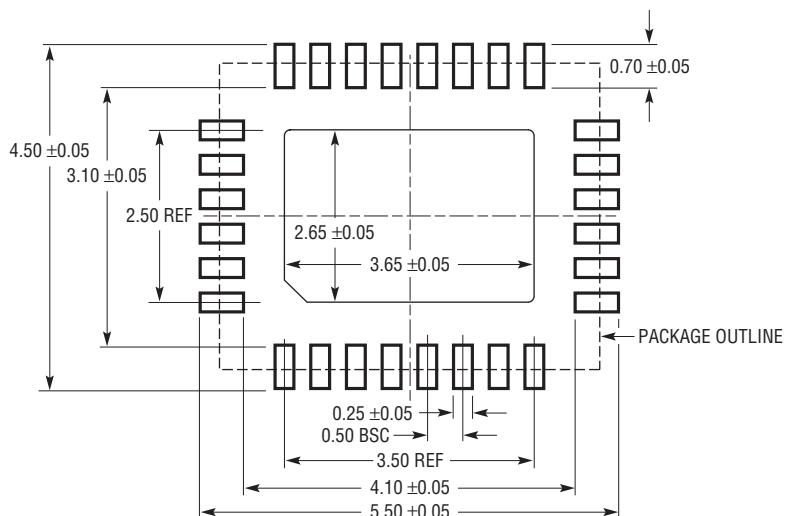

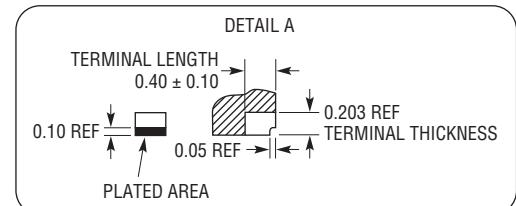

## パッケージ

**UFDM Package**

**28-Lead Plastic Side Wettable QFN (4mm × 5mm)**

(Reference LTC DWG # 05-08-1682 Rev Ø)

## 注記：

1. 図は実寸とは異なる

2. 全ての寸法の単位はミリメートル

3. パッケージ底面の露出パッドの寸法にはモールドのバリを含まない

モールドのバリ(存在する場合)はどの側でも 0.15mm を超えない

4. 灰色の部分はパッケージの上面と底面の 1 番ピンの位置の参考にすぎない

RECOMMENDED SOLDER PAD PITCH AND DIMENSIONS

APPLY SOLDER MASK TO AREAS THAT ARE NOT SOLDERED

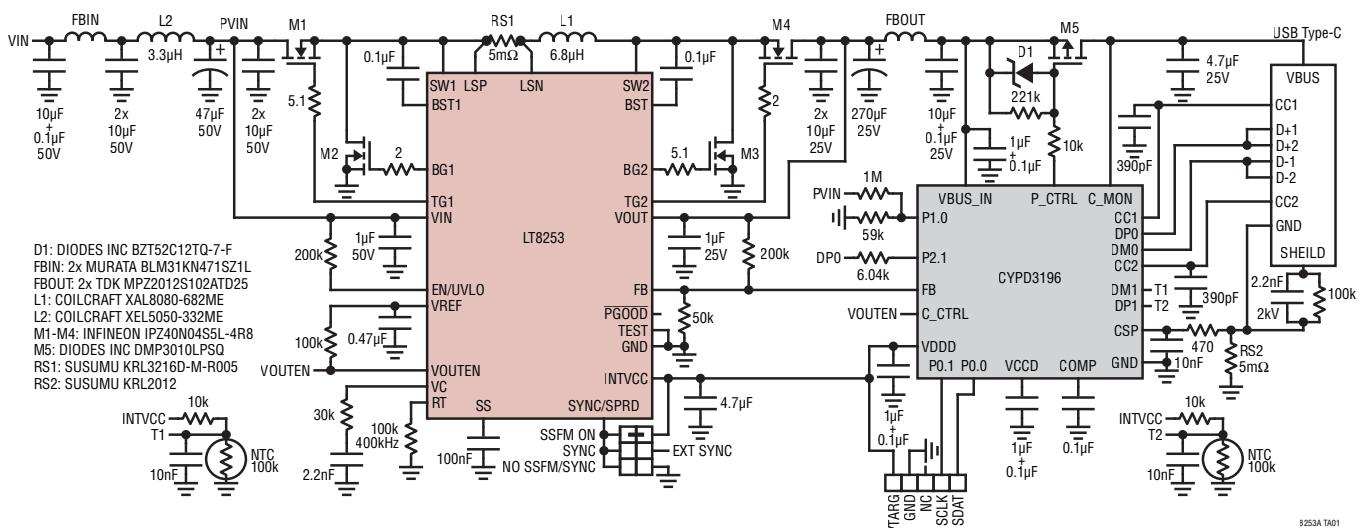

## 標準的応用例

### 車載用 45W USB-C Power Delivery チャージャ (2MHz)