# デジタル・パワー・システム・マネージメント機能を備えた 6A/20V デュアル・チャンネル PolyPhase 同期整流式降圧 Silent Switcher 2

## 特長

- Silent Switcher®2アーキテクチャ: コンパクトで効率的な低EMIのソリューションを実現

- PMBus/I<sup>2</sup>Cシリアル・インターフェース

- V<sub>OUT</sub>、I<sub>OUT</sub>、V<sub>IN</sub>、ダイ温度、障害検出を含むテレメトリ・リードバック

- 電圧、電流リミット、デジタル・ソフトスタート/ストップ、シーケンシング、UV/OV、位相、周波数(最大4MHz)、ループ補償をプログラム可能

- 障害イベント・ログ機能を備えたEEPROMを内蔵

- 設定抵抗によって重要パラメータを設定し、プログラムを行うことなくデバイスを動作させることができます

- 0.6V~1.375Vでの出力電圧精度: 全温度範囲で±0.25%

- 最大8相でのPolyPhase負荷分担

- 広いV<sub>IN</sub>範囲: 最小2.9V、またはEXTV<sub>CC</sub>使用時で1.5V

- 1MHz、12V<sub>IN</sub>、3.3V<sub>OUT</sub>で最大95%の効率

- V<sub>OUT</sub>範囲: 0.4V~5.5V(最大0.85·V<sub>IN</sub>)

- V<sub>OUT</sub>の差動リモート検出

- 外部周波数同期

- 40ピン(5mm × 7mm)LQFNパッケージ

## アプリケーション

- 通信、ストレージ、および産業システム

- データ・センターおよびソリッドステート駆動電源

## 概要

LT<sup>®</sup>7182Sはデュアル出力のモノリシックPolyPhase DC/DC同期整流式降圧レギュレータで、両方のチャンネルから最大6Aの連続電流を同時に供給可能で、どちらのチャンネルも最大8Aの負荷に対応できます。LT7182Sは第2世代のSilent Switcher®アーキテクチャが特長で、スイッチング・エッジを高速かつクリーンなものにしてオーバーシュートを小さくするV<sub>IN</sub>バイパス・コンデンサを内蔵しており、高スイッチング周波数と高効率を実現しながら、EMI放射を最小限に抑えます。

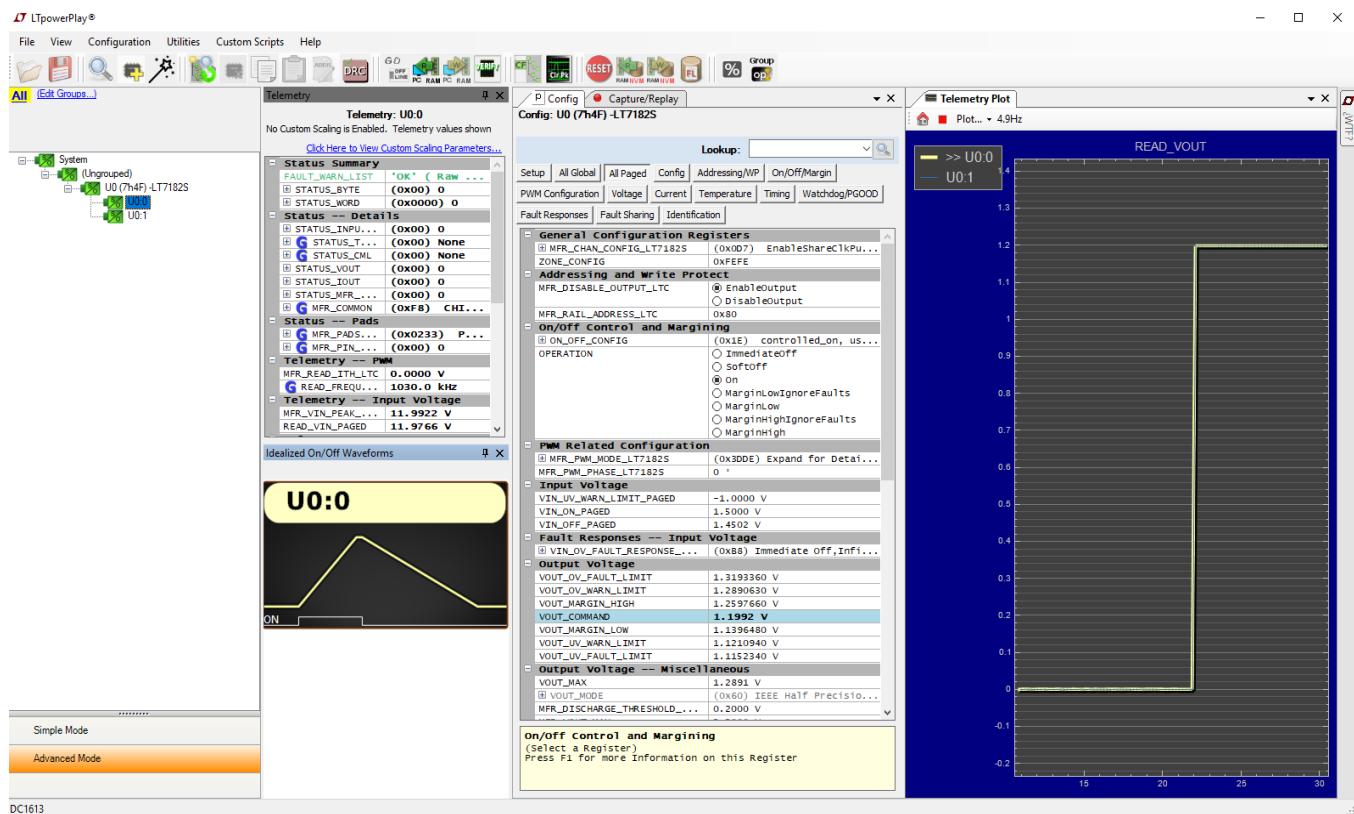

I<sup>2</sup>CをベースとするPMBus 1.3準拠のシリアル・インターフェースは、デバイス機能を制御したり、システム・モニタリング用のテレメトリ情報を探したりすることを可能にします。LT7182Sには、LTpowerPlay<sup>®</sup>グラフィカル・ユーザ・インターフェース・ツールを使用できます。

出力電圧、周波数、位相、およびデバイス・アドレスは抵抗を使って設定できるので、プログラムを行うことなくデバイスを動作させることができます。設定内容は、シリアル・インターフェースを介してEEPROMに書き込んだり保存したりすることができます。

最小オン時間が20ns(代表値)のオン時間制御式谷電流モード制御アーキテクチャが、低出力電圧時の高スイッチング周波数動作を可能にし、優れた過渡応答を実現すると共に、全体的なソリューション・サイズを小さく抑えます。

全ての登録商標および商標の所有権は、それぞれの所有者に帰属します。第8823345号を含む米国特許により保護されています。

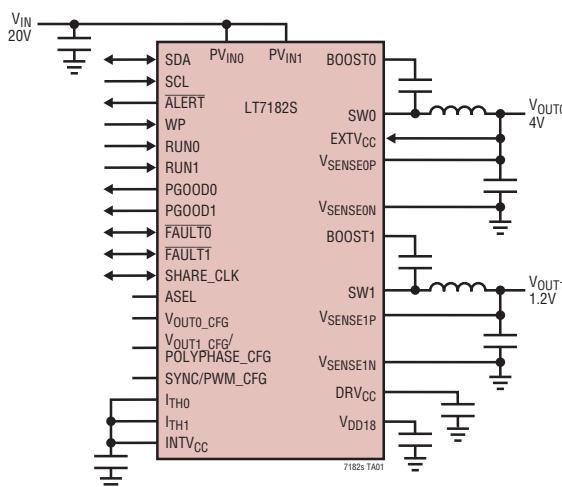

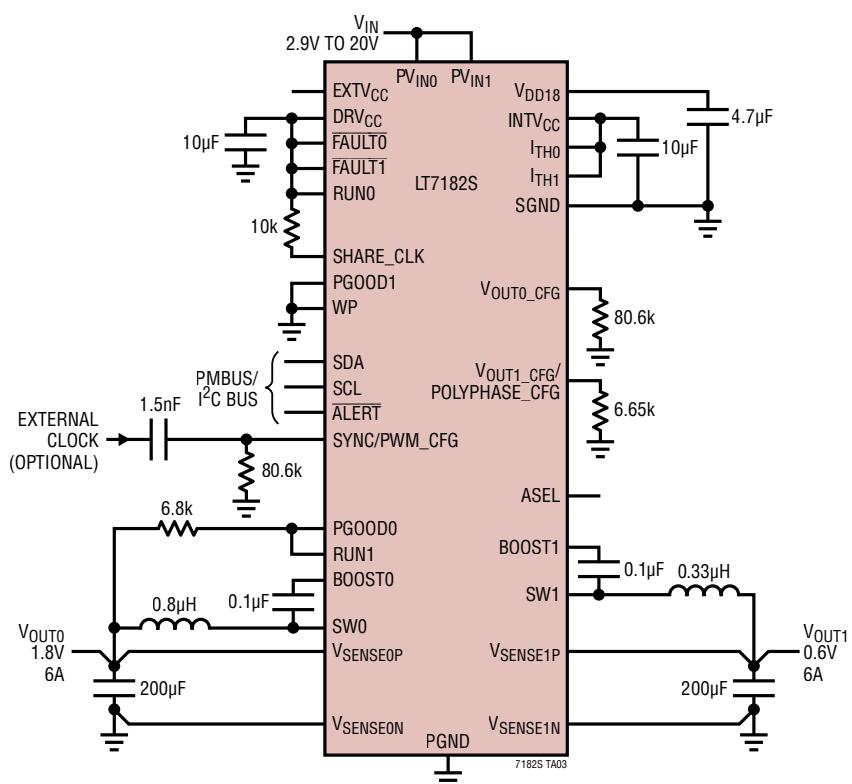

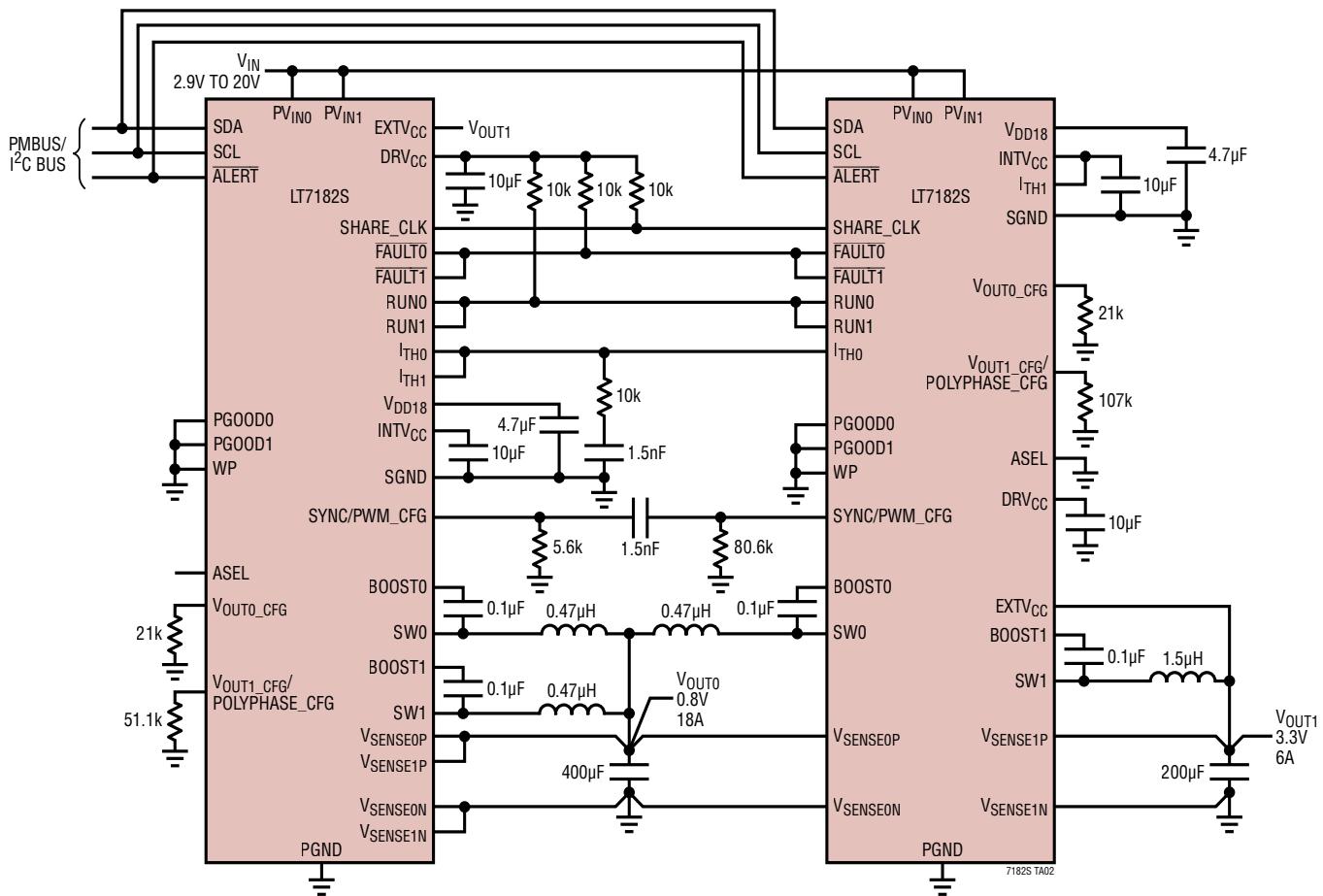

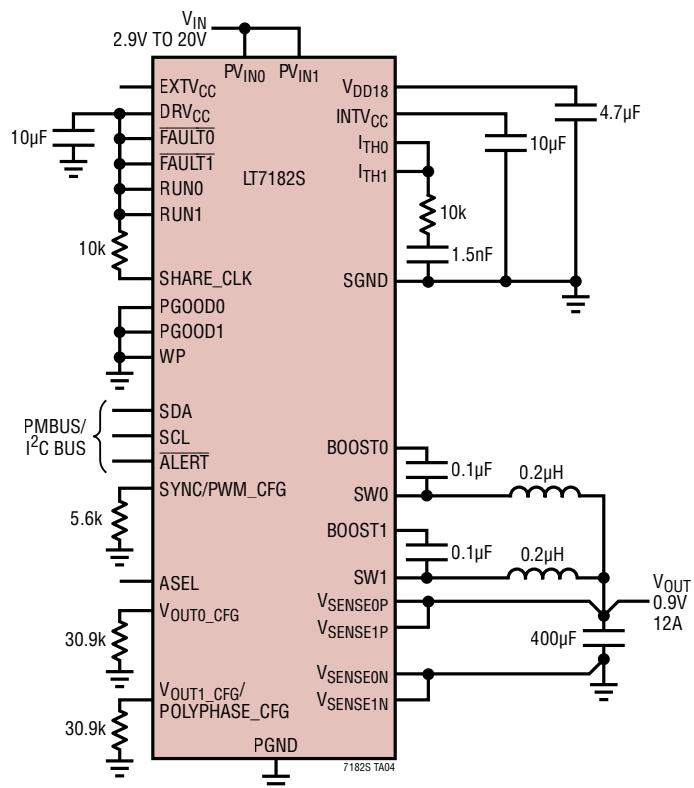

## 標準的応用例

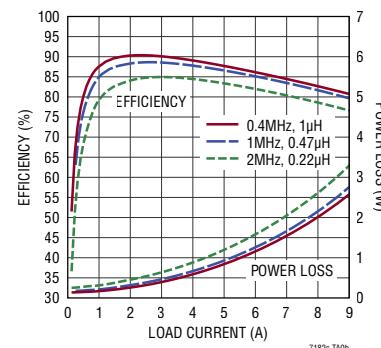

12V<sub>IN</sub>、1.2V<sub>OUT</sub>時の効率

## 目次

|                                         |    |

|-----------------------------------------|----|

| 特長                                      | 1  |

| アプリケーション                                | 1  |

| 標準的応用例                                  | 1  |

| 概要                                      | 1  |

| 絶対最大定格                                  | 3  |

| 発注情報                                    | 3  |

| ピン配置                                    | 3  |

| 電気的特性                                   | 4  |

| 代表的な性能特性                                | 8  |

| ピン機能                                    | 11 |

| ブロック図                                   | 14 |

| 動作                                      | 15 |

| 概要                                      | 15 |

| スイッチング・レギュレータの制御ループ                     | 15 |

| 軽負荷電流動作                                 | 16 |

| EEPROM                                  | 16 |

| パワーアップと初期化                              | 16 |

| ソフトスタート                                 | 17 |

| シャットダウン                                 | 17 |

| 警告と障害の処理                                | 17 |

| アプリケーション情報                              | 20 |

| 抵抗設定ピンの使用法                              | 20 |

| 出力電圧の設定                                 | 20 |

| スイッチング周波数と位相                            | 21 |

| プログラマブルな電流リミット                          | 25 |

| インダクタの選択                                | 26 |

| 入力コンデンサと出力コンデンサ                         | 27 |

| プログラマブルな PWM 制御ループ補償                    | 27 |

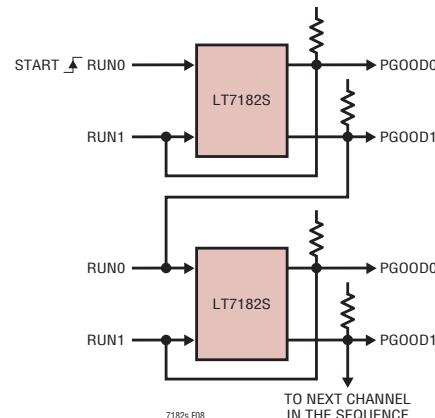

| ソフトウェアによる設定が可能なシーケンシング                  | 28 |

| イベントベースのシーケンシング                         | 28 |

| LTpowerPlay GUI                         | 28 |

| PMBus コマンドの概要                           | 29 |

| PMBus/I <sup>2</sup> C シリアル・インターフェースの概要 | 29 |

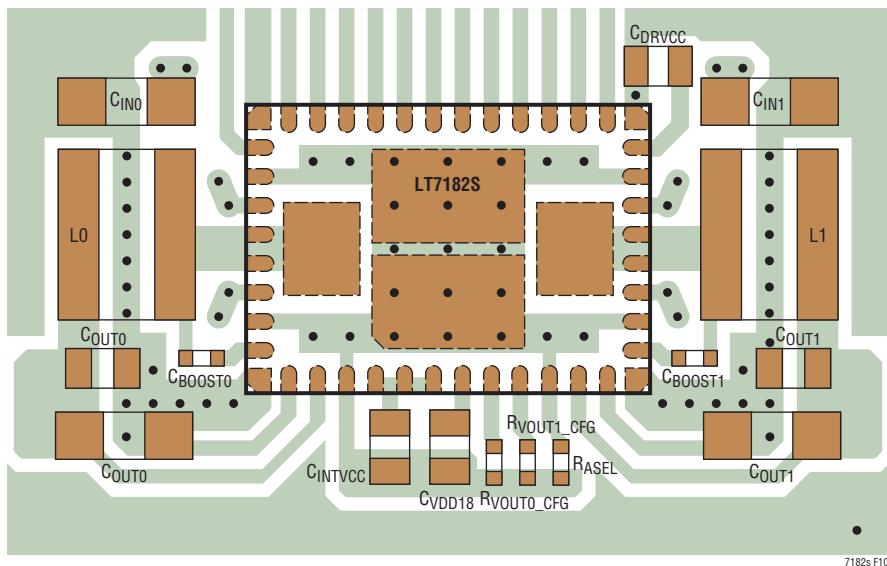

| ボード・レイアウト時の考慮事項                         | 34 |

| レイアウト時の考慮事項                             | 34 |

| 熱に対する考慮事項                               | 34 |

| 標準的応用例                                  | 35 |

| パッケージの説明                                | 37 |

| 標準的応用例                                  | 38 |

| 関連製品                                    | 38 |

関連文書の LT7182S PMBus/I<sup>2</sup>C リファレンス・マニュアルも合わせて参照してください。このリファレンス・マニュアルには、PMBus コマンド、シリアル・デバイス・アドレスの選択、物理インターフェースの詳細を含むデジタル機能の詳しい説明が記載されています。

## 絶対最大定格 (Note 1)

|                                                                                                |             |

|------------------------------------------------------------------------------------------------|-------------|

| PVIN0, PVIN1                                                                                   | -0.3V~25V   |

| EXTV <sub>CC</sub>                                                                             | -0.3V~6V    |

| V <sub>SENSE0P</sub> , V <sub>SENSE1P</sub>                                                    | -0.3V~6V    |

| V <sub>SENSE0N</sub> , V <sub>SENSE1N</sub>                                                    | -0.3V~0.3V  |

| I <sub>TH0</sub> , I <sub>TH1</sub>                                                            | -0.3V~6V    |

| SYNC/PWM_CFG, WP, SHARE_CLK,<br>ALERT, SDA, SCL, FAULT0, FAULT1, RUN0,<br>RUN1, PGOOD0, PGOOD1 | -0.3V~6V    |

| 動作ジャンクション温度 (Note 2)                                                                           |             |

| LT7182SR                                                                                       | -40°C~150°C |

| ABSMAX T <sub>J</sub>                                                                          | 150°C       |

| 保存温度範囲                                                                                         | -65°C~150°C |

| 最大ピーク・リフロー (パッケージ・ボディ)                                                                         |             |

| 温度                                                                                             | 260°C       |

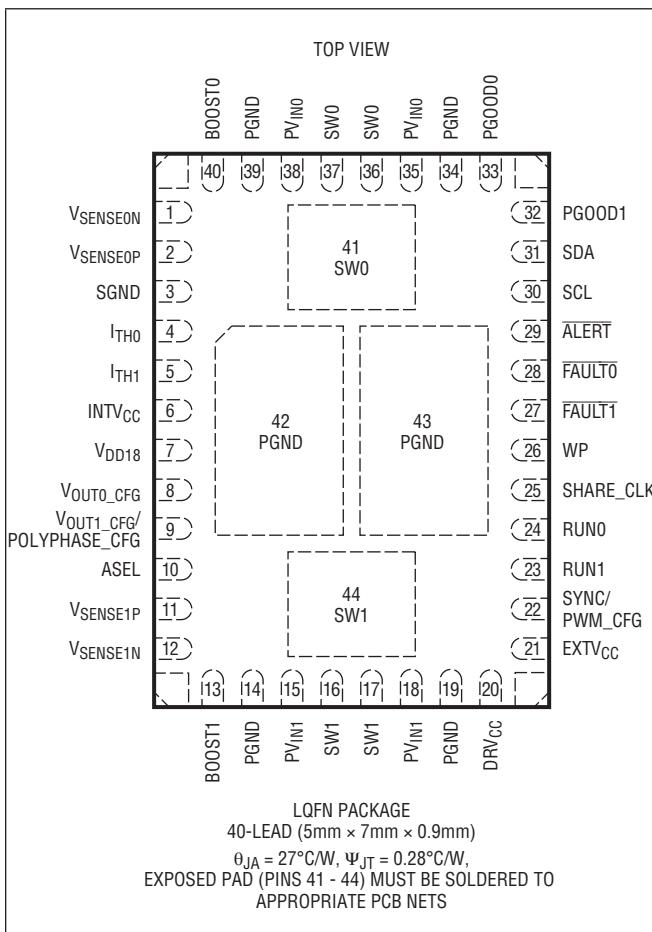

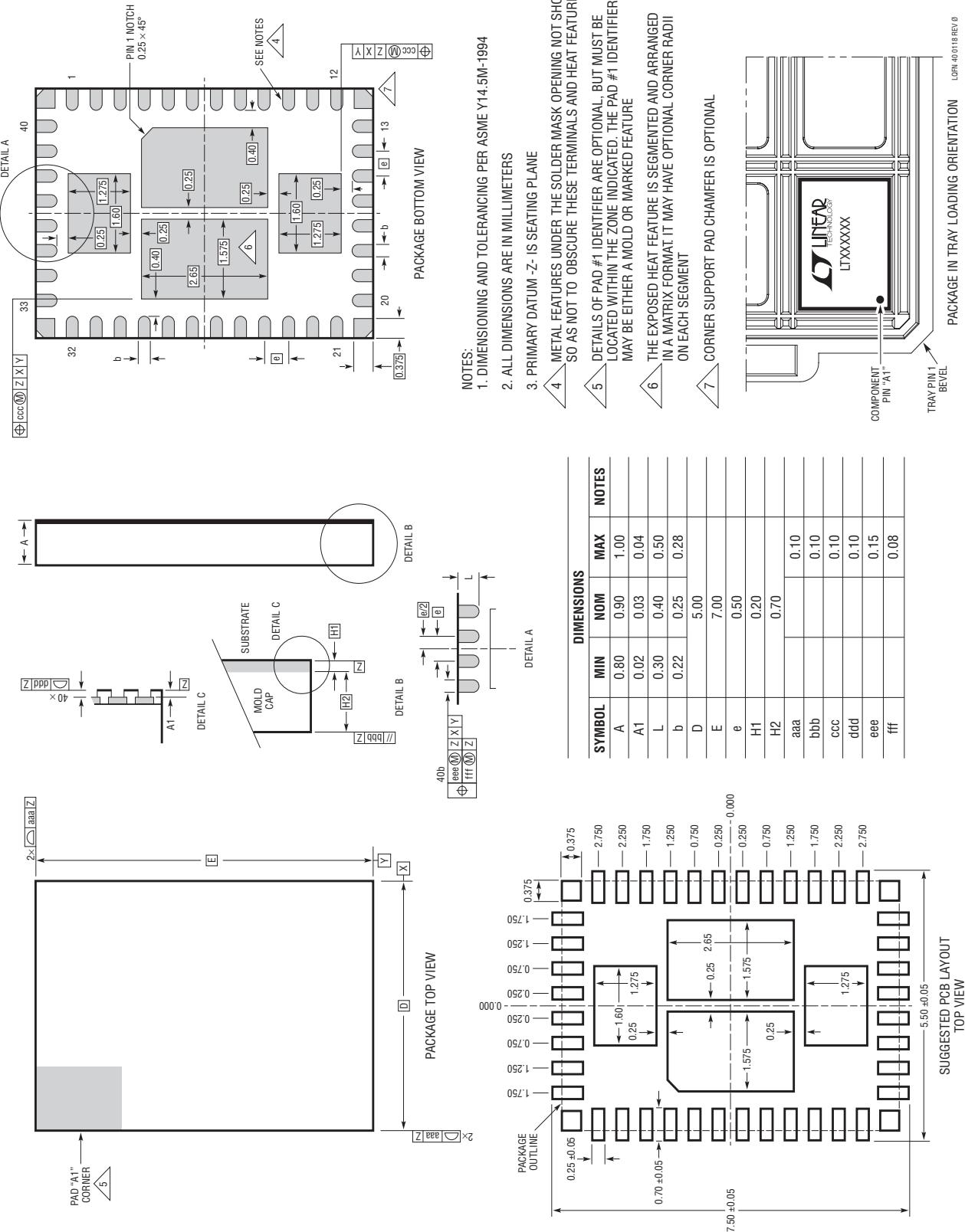

## ピン配置

## 発注情報

| 部品番号          | パッドまたはポール<br>仕上げ | 部品マーキング* |        | パッケージ<br>タイプ | MSL<br>レーティング | 温度範囲 (Note 2) |

|---------------|------------------|----------|--------|--------------|---------------|---------------|

|               |                  | デバイス     | 仕上げコード |              |               |               |

| LT7182SRV#PBF | Au (RoHS)        | 7182S    | e4     | LQFN         | 3             | -40°C~150°C   |

\* パッドまたはポールの仕上げコードは IPC/JEDEC J-STD-609 によります。温度グレードは出荷時のコンデンサのラベルに示されています。

- 推薦されるLGAおよびBGAPCBのアセンブリおよび製造手順

- LGAおよびBGAのパッケージ図面とトレイ図面

\*\* LQFNはQFNフットプリントの積層パッケージを表します。LT7182SパッケージのXY寸法は、標準の5mm x 7mm QFNパッケージと同じです。

## 電気的特性

- は、全動作温度範囲に適用される仕様であることを示します。それ以外の仕様は  $T_A = 25^\circ\text{C}$  での値です。

| PARAMETER                                                                                                                                                 | CONDITIONS                                                                                                                                  | MIN    | TYP           | MAX                                 | UNITS      |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|--------|---------------|-------------------------------------|------------|

| <b>Input Supply</b>                                                                                                                                       |                                                                                                                                             |        |               |                                     |            |

| Channel 0 Input Supply Range                                                                                                                              | EXTV <sub>CC</sub> = 0V                                                                                                                     | ●      | 2.9           | 20                                  | V          |

| Channel 0 Input Supply Range with EXTV <sub>CC</sub>                                                                                                      | 3V $\leq$ EXTV <sub>CC</sub> $\leq$ 5.5V                                                                                                    | ●      | 1.5           | 20                                  | V          |

| Channel 1 Input Supply Range                                                                                                                              | PV <sub>IN0</sub> $\geq$ 2.9V or EXTV <sub>CC</sub> $\geq$ 3V                                                                               | ●      | 1.5           | 20                                  | V          |

| Optional EXTV <sub>CC</sub> Input Supply Range                                                                                                            |                                                                                                                                             | ●      | 3             | 5.5                                 | V          |

| EXTV <sub>CC</sub> + PV <sub>IN0</sub> + PV <sub>IN1</sub> Quiescent Current<br>Both channels switching                                                   | f <sub>SW</sub> = 1MHz, Forced Continuous Mode, V <sub>IN</sub> = 12V, No Load                                                              |        |               | 21                                  | mA         |

| Sleep (Pulse Skip Mode) or Shutdown                                                                                                                       |                                                                                                                                             |        |               | 7                                   | mA         |

| Initialization Time (Delay from RESTORE_USER_ALL, MFR_RESET, or Application of PV <sub>IN0</sub> or EXTV <sub>CC</sub> , Until TON_DELAY Timer Can Begin) | With CFG Pins Enabled (Default)<br>CFG Pins Ignored                                                                                         |        |               | 13<br>10                            | ms<br>ms   |

| <b>Switching Regulator</b>                                                                                                                                |                                                                                                                                             |        |               |                                     |            |

| V <sub>OUT</sub> Range                                                                                                                                    | PV <sub>IN</sub> > 6.1V<br>PV <sub>IN</sub> $\leq$ 6.1V                                                                                     | ●<br>● | 0.4<br>0.4    | 5.5<br>0.85 $\cdot$ V <sub>IN</sub> | V<br>V     |

| V <sub>OUT</sub> Set Point Accuracy                                                                                                                       | High-Performance Low-V <sub>OUT</sub> Mode, 0.6V $\leq$ V <sub>OUT</sub> $\leq$ 1.375V<br>0.4V $\leq$ V <sub>OUT</sub> $\leq$ 5.5V          | ●<br>● | -0.25<br>-0.5 | 0.25<br>0.5                         | %<br>%     |

| V <sub>OUT</sub> Set-Point Resolution                                                                                                                     |                                                                                                                                             |        |               | 1                                   | mA         |

| V <sub>SENSE0P</sub> , V <sub>SENSE1P</sub> Input Resistance                                                                                              | V <sub>SENSE0N</sub> = V <sub>SENSE1N</sub> = 0V                                                                                            |        |               | 30                                  | k $\Omega$ |

| Error Amplifier Transconductance Programming Resolution                                                                                                   |                                                                                                                                             |        |               | 3                                   | bits       |

| Error Amplifier Transconductance g <sub>m</sub> (MAX)                                                                                                     | Full V <sub>OUT</sub> Range Mode, 0.4V $\leq$ V <sub>OUT</sub> $\leq$ 5.5V. Includes Internal V <sub>OUT</sub> Feedback Divider             |        |               | 300                                 | $\mu$ s    |

| Error Amplifier Transconductance g <sub>m</sub> (MIN)                                                                                                     | Full V <sub>OUT</sub> Range Mode, 0.4V $\leq$ V <sub>OUT</sub> $\leq$ 5.5V. Includes Internal V <sub>OUT</sub> Feedback Divider             |        |               | 37.5                                | $\mu$ s    |

| Error Amplifier Transconductance g <sub>m</sub> Step Size                                                                                                 | Full V <sub>OUT</sub> Range Mode, 0.4V $\leq$ V <sub>OUT</sub> $\leq$ 5.5V. Includes Internal V <sub>OUT</sub> Feedback Divider             |        |               | 37.5                                | $\mu$ s    |

| Error Amplifier Transconductance g <sub>m</sub> (MAX)                                                                                                     | High-Performance Low-V <sub>OUT</sub> Mode, 0.4V $\leq$ V <sub>OUT</sub> $\leq$ 1.375V, Includes Internal V <sub>OUT</sub> Feedback Divider |        |               | 1.2                                 | $\mu$ s    |

| Error Amplifier Transconductance g <sub>m</sub> (MIN)                                                                                                     | High-Performance Low-V <sub>OUT</sub> Mode, 0.4V $\leq$ V <sub>OUT</sub> $\leq$ 1.375V, Includes Internal V <sub>OUT</sub> Feedback Divider |        |               | 150                                 | $\mu$ s    |

| Error Amplifier Transconductance g <sub>m</sub> Step Size                                                                                                 | High-Performance Low-V <sub>OUT</sub> Mode, 0.4V $\leq$ V <sub>OUT</sub> $\leq$ 1.375V, Includes Internal V <sub>OUT</sub> Feedback Divider |        |               | 150                                 | $\mu$ s    |

| Max Programmable Internal Compensation Resistor R <sub>ITH</sub> (MAX)                                                                                    | Internal Compensation (I <sub>TH</sub> Tied to INTV <sub>CC</sub> ) (Note 5)                                                                |        |               | 120                                 | k $\Omega$ |

| Min Programmable Internal Compensation Resistor R <sub>ITH</sub> (MIN)                                                                                    | Internal Compensation (I <sub>TH</sub> Tied to INTV <sub>CC</sub> ) (Note 5)                                                                |        |               | 5                                   | k $\Omega$ |

| Internal Compensation Capacitor Programming Resolution                                                                                                    | Internal Compensation (I <sub>TH</sub> Tied to INTV <sub>CC</sub> )                                                                         |        |               | 3                                   | bits       |

| Internal Compensation Capacitor C <sub>ITH</sub> (MAX)                                                                                                    | Internal Compensation (I <sub>TH</sub> Tied to INTV <sub>CC</sub> )                                                                         |        |               | 80                                  | pF         |

| Internal Compensation Capacitor C <sub>ITH</sub> (MIN)                                                                                                    | Internal Compensation (I <sub>TH</sub> Tied to INTV <sub>CC</sub> )                                                                         |        |               | 10                                  | pF         |

| Internal Compensation Capacitor C <sub>ITH</sub> Step Size                                                                                                | Internal Compensation (I <sub>TH</sub> Tied to INTV <sub>CC</sub> )                                                                         |        |               | 10                                  | pF         |

## 電気的特性

●は、全動作温度範囲に適用される仕様であることを示します。それ以外の仕様は  $T_A = 25^\circ\text{C}$  での値です。

| PARAMETER                                                                             | CONDITIONS                                                                    | MIN | TYP      | MAX          | UNITS   |

|---------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|-----|----------|--------------|---------|

| Positive Inductor Valley Current Limit ILIM-POS (Note 6)<br>(Sourcing Output Current) | ILIM Range 0                                                                  | ●   | 2.3      | 3            | 3.7 A   |

|                                                                                       | ILIM Range 1                                                                  | ●   | 3.5      | 4.5          | 5.5 A   |

|                                                                                       | ILIM Range 2                                                                  | ●   | 5        | 6.5          | 8 A     |

|                                                                                       | ILIM Range 3                                                                  | ●   | 6.5      | 8.5          | 10.5 A  |

| Negative Inductor Valley Current Limit ILIM-NEG (Note 6)<br>(Sinking Output Current)  | ILIM Range 0                                                                  | ●   | -3       | -2.3         | -1.6 A  |

|                                                                                       | ILIM Range 1                                                                  | ●   | -4.4     | -3.4         | -2.4 A  |

|                                                                                       | ILIM Range 2                                                                  | ●   | -5       | -4           | -3 A    |

|                                                                                       | ILIM Range 3                                                                  | ●   | -5.5     | -4.25        | -3 A    |

| Power FET On-Resistance<br>Main Switch (Top)<br>Synchronous Switch (Bottom)           |                                                                               |     | 48<br>17 |              | mΩ      |

| SW Leakage                                                                            | $V_{IN} = 20\text{V}$ , $V_{SW} = 0\text{V}, 20\text{V}$                      |     | -120     | 120          | μA      |

| Minimum On-Time                                                                       | $I_{LOAD} = 1\text{A}$                                                        | ●   | 20       | 40           | ns      |

| Minimum Off-Time                                                                      |                                                                               | ●   | 60       | 100          | ns      |

| <b>Output Voltage Supervisors</b>                                                     |                                                                               |     |          |              |         |

| $V_{OUT}$ Undervoltage (UV) Fault/Warning Programming Range                           |                                                                               |     | 0.36     | 5.5          | V       |

| $V_{OUT}$ Overvoltage (OV) Fault/Warning Programming Range                            |                                                                               |     | 0.4      | 6            | V       |

| $V_{OUT}$ UV/OV Fault/Warning Threshold Accuracy                                      | $V_{OUT}$ UV/OV Threshold $< 0.6\text{V}$                                     | ●   | -12      | 12           | mV      |

|                                                                                       | $V_{OUT}$ UV/OV Threshold $\geq 0.6\text{V}$                                  | ●   | -2       | 2            | %       |

| $V_{OUT}$ UV/OV Fault/Warning Programming Step Size                                   |                                                                               |     | 4        |              | mV      |

| $V_{OUT}$ UV/OV Fault/Warning Time                                                    | $V_{OUT} = 10\text{mV}$ Beyond Threshold                                      | ●   |          | 25           | μs      |

| <b>Input Voltage Supervisors</b>                                                      |                                                                               |     |          |              |         |

| ON Threshold Programming Range                                                        |                                                                               |     | 1.4      | 20           | V       |

| OFF Threshold Programming Range                                                       |                                                                               |     | 1.35     | 20           | V       |

| ON/OFF Threshold Programming Step Size                                                |                                                                               |     | 25       |              | mV      |

| ON/OFF Threshold Set Point Accuracy                                                   | $V_{IN\_ON/OFF} \leq 5\text{V}$                                               | ●   | -100     | 100          | mV      |

| ON/OFF Threshold Set Point Accuracy                                                   | $5\text{V} \leq V_{IN\_ON/OFF} \leq 20\text{V}$                               | ●   | -2       | 2            | %       |

| $V_{IN}$ Overvoltage Lockout Threshold                                                | $V_{IN}$ Rising<br>$V_{IN}$ Falling                                           | ●   | 22<br>21 | 23.3<br>22.3 | V       |

| <b>Oscillator and Phase Locked Loop</b>                                               |                                                                               |     |          |              |         |

| SYNC/PWM_CFG Pin Input Frequency Range                                                |                                                                               | ●   | 0.4      | 4            | MHz     |

| Switching Frequency Programming Range                                                 |                                                                               |     | 0.4      | 4            | MHz     |

| Switching Frequency Set Point Accuracy                                                |                                                                               | ●   | -7.5     | 7.5          | %       |

| Switching Phase Programming Range                                                     |                                                                               |     | 0        | 345          | degrees |

| Switching Phase Programming Resolution                                                |                                                                               |     | 15       |              | degrees |

| <b>Telemetry Readback</b>                                                             |                                                                               |     |          |              |         |

| Telemetry Measurement Period, All Except Die Temperature                              |                                                                               |     | 6.5      |              | ms      |

| Telemetry Measurement Period, Die Temperature                                         |                                                                               |     | 26       |              | ms      |

| <b>Output Voltage Readback</b>                                                        |                                                                               |     |          |              |         |

| READ_VOUT Accuracy                                                                    | High-Performance Low-VOUT Mode, $0.6\text{V} \leq V_{OUT} \leq 1.375\text{V}$ | ●   | -0.15    | 0.15         | %       |

| READ_VOUT Accuracy                                                                    | $0.4\text{V} < V_{OUT} < 5.5\text{V}$                                         | ●   | -0.35    | 0.35         | %       |

## 電気的特性

●は、全動作温度範囲に適用される仕様であることを示します。それ以外の仕様は  $T_A = 25^\circ\text{C}$  での値です。

| PARAMETER                                                                                        | CONDITIONS                                                                                                                                                                                                                                                                                               | MIN              | TYP                       | MAX                   | UNITS              |

|--------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|---------------------------|-----------------------|--------------------|

| <b>PV<sub>IN0</sub>, PV<sub>IN1</sub> Input Voltage Readback</b>                                 |                                                                                                                                                                                                                                                                                                          |                  |                           |                       |                    |

| READ_VIN Accuracy                                                                                | V <sub>IN</sub> = 1.5V to 2.5V<br>V <sub>IN</sub> = 2.5V to 20V                                                                                                                                                                                                                                          | ●<br>●           | -25<br>-1                 | 25<br>1               | mV<br>%            |

| <b>Output Current Readback</b>                                                                   |                                                                                                                                                                                                                                                                                                          |                  |                           |                       |                    |

| READ_IOUT Accuracy                                                                               | I <sub>OUT</sub> = 0A to 4A, (V <sub>OUT</sub> /V <sub>IN</sub> ) ≤ 0.5<br>I <sub>OUT</sub> = 4A to 8A, (V <sub>OUT</sub> /V <sub>IN</sub> ) ≤ 0.5<br>I <sub>OUT</sub> = 0A to 4A, (V <sub>OUT</sub> /V <sub>IN</sub> ) > 0.5<br>I <sub>OUT</sub> = 4A to 8A, (V <sub>OUT</sub> /V <sub>IN</sub> ) > 0.5 | ●<br>●<br>●<br>● | -200<br>-5<br>-600<br>-15 | 200<br>5<br>600<br>15 | mA<br>%<br>mA<br>% |

| <b>Input Current Readback</b>                                                                    |                                                                                                                                                                                                                                                                                                          |                  |                           |                       |                    |

| READ_IIN Accuracy                                                                                | I <sub>IIN</sub> = 0A to 1A,<br>I <sub>IIN</sub> = 1A to 5A                                                                                                                                                                                                                                              | ●<br>●           | -250<br>-25               | 250<br>25             | mA<br>%            |

| <b>Frequency Readback</b>                                                                        |                                                                                                                                                                                                                                                                                                          |                  |                           |                       |                    |

| READ_FREQUENCY Accuracy                                                                          | f <sub>SW</sub> ≤ 400kHz<br>f <sub>SW</sub> ≥ 400kHz                                                                                                                                                                                                                                                     |                  | -20<br>-5                 | 20<br>5               | kHz<br>%           |

| <b>EEPROM Characteristics</b>                                                                    |                                                                                                                                                                                                                                                                                                          |                  |                           |                       |                    |

| Retention                                                                                        | (Note 4)                                                                                                                                                                                                                                                                                                 | ●                | 10                        |                       | years              |

| Endurance                                                                                        | (Note 4)                                                                                                                                                                                                                                                                                                 | ●                | 10,000                    |                       | writes             |

| Mass Write Time (STORE_USER_ALL)                                                                 |                                                                                                                                                                                                                                                                                                          | ●                |                           | 250<br>500            | ms                 |

| <b>Digital Inputs RUN0, RUN1, FAULT0, FAULT1, PGOOD0, PGOOD1, SHARE_CLK, SCL, SDA, ALERT, WP</b> |                                                                                                                                                                                                                                                                                                          |                  |                           |                       |                    |

| Input High Threshold (V <sub>IH</sub> )                                                          |                                                                                                                                                                                                                                                                                                          | ●                |                           | 1.1<br>1.35           | V                  |

| Input Low Threshold (V <sub>IL</sub> )                                                           |                                                                                                                                                                                                                                                                                                          | ●                | 0.8<br>0.9                |                       | V                  |

| Hysteresis (V <sub>HYS</sub> )                                                                   |                                                                                                                                                                                                                                                                                                          |                  | 50<br>200<br>400          |                       | mV                 |

| Leakage Current                                                                                  | Applied Voltage = 0V, 5.5V                                                                                                                                                                                                                                                                               |                  |                           | ±10                   | µA                 |

| Input Capacitance                                                                                |                                                                                                                                                                                                                                                                                                          |                  |                           | 10                    | pF                 |

| <b>Digital Clock Input SYNC/PWM_CFG</b>                                                          |                                                                                                                                                                                                                                                                                                          |                  |                           |                       |                    |

| Peak-to-Peak Input Voltage Swing                                                                 | SYNC Input Mode                                                                                                                                                                                                                                                                                          | ●                | 1.6                       | 5.5                   | V                  |

| Rise Time                                                                                        | SYNC Input Mode                                                                                                                                                                                                                                                                                          |                  |                           | 25                    | ns                 |

| Duty Cycle                                                                                       | SYNC Input Mode                                                                                                                                                                                                                                                                                          |                  | 30                        | 70                    | %                  |

| <b>Digital Clock Output SYNC/PWM_CFG</b>                                                         |                                                                                                                                                                                                                                                                                                          |                  |                           |                       |                    |

| Output High Voltage                                                                              | SYNC Output Mode                                                                                                                                                                                                                                                                                         | ●                | 1.6<br>1.88<br>1.98       |                       | V                  |

| Output Low Voltage                                                                               | SYNC Output Mode                                                                                                                                                                                                                                                                                         | ●                | 0<br>0.1                  |                       | V                  |

| <b>Current-Limited Open-Drain Output RUN0, RUN1, FAULT0, FAULT1</b>                              |                                                                                                                                                                                                                                                                                                          |                  |                           |                       |                    |

| Pulldown Current                                                                                 | Applied Voltage = 0.4V to 5.5V                                                                                                                                                                                                                                                                           | ●                | 1<br>1.5<br>2             |                       | mA                 |

| <b>Open-Drain Outputs PGOOD0, PGOOD1, SHARE_CLK</b>                                              |                                                                                                                                                                                                                                                                                                          |                  |                           |                       |                    |

| Output Low Voltage                                                                               | I = 6mA                                                                                                                                                                                                                                                                                                  | ●                |                           | 0.4                   | V                  |

| <b>Digital I/O SCL, SDA, ALERT</b>                                                               |                                                                                                                                                                                                                                                                                                          |                  |                           |                       |                    |

| Output Low Voltage                                                                               | I = 20mA                                                                                                                                                                                                                                                                                                 | ●                |                           | 0.4                   | V                  |

## 電気的特性

- は、全動作温度範囲に適用される仕様であることを示します。それ以外の仕様は  $T_A = 25^\circ\text{C}$  での値です。

| SYMBOL                                                     | PARAMETER                                | CONDITIONS | MIN | TYP | MAX  | UNITS         |

|------------------------------------------------------------|------------------------------------------|------------|-----|-----|------|---------------|

| <b><math>\text{I}^2\text{C}/\text{PMBus}</math> Timing</b> |                                          |            |     |     |      |               |

| $t_{SCL}$                                                  | Serial Bus Operating Frequency           |            | ●   | 10  | 1000 | kHz           |

| $t_{BUF}$                                                  | Bus Free Time Between Stop and Start     |            | ●   | 500 |      | ns            |

| $t_{HD:STA}$                                               | Hold Time After repeated Start Condition |            | ●   | 260 |      | ns            |

| $t_{SU:STA}$                                               | Repeated Start Condition Setup Time      |            | ●   | 260 |      | ns            |

| $t_{SU:STO}$                                               | Stop Condition Setup Time                |            | ●   | 260 |      | ns            |

| $t_{SU:DAT}$                                               | Data Input Setup Time                    |            | ●   | 50  |      | ns            |

| $t_{HD:DAT}$                                               | Data Input Hold Time                     |            | ●   | 0   |      | ns            |

|                                                            | Data Output Hold Time                    |            | ●   | 0   | 450  | ns            |

| $t_{TIMEOUT}$                                              | Bus Timeout                              |            | ●   | 25  | 35   | ms            |

| $t_{LOW}$                                                  | Serial Clock Low Period                  |            | ●   | 0.5 |      | $\mu\text{s}$ |

| $t_{HIGH}$                                                 | Serial Clock High Period                 |            | ●   | 260 |      | ns            |

**Note 1:** 上記の**絶対最大定格**を超えるストレスを加えるとデバイスに恒久的な損傷を与えることがあります。デバイスを長時間絶対最大定格状態に置くと、デバイスの信頼性と寿命に影響を与えることがあります。

**Note 2:** LT7182SRは-40°C～150°Cの動作ジャンクション温度範囲での動作が仕様規定されています。ジャンクション温度が高い場合は動作寿命が低下し、このような寿命の低下はジャンクション温度が125°Cを超えると始まります。ここに示す仕様に見合った最大周囲温度は、具体的な動作条件と、ボード・レイアウト、パッケージの熱抵抗定格値、およびその他の環境条件との組み合わせによって決まります。

**Note 3:** LT7182Sは、一時的な過負荷状態からデバイスを保護することを目的とした過熱保護機能を内蔵しています。この保護機能が動作するのは、ジャンクション温度が最大定格値を超えるおそれがある場合です。仕様に規定された最大動作ジャンクション温度を超えてデバイスを連続動作させると、寿命が短くなります。

**Note 4:** EEPROMの書換え回数は、設計、特性評価、および統計的プロセス制御との相関付けによって確認されています。データ保持寿命は、ウェーハ・レベルでの高温ベーキによって出荷テストされています。最小データ保持時間仕様は、EEPROMのサイクル回数が最小書換え回数仕様値未満のデバイスに適用されます。

**Note 5:** 内部補償を選択した場合は( $I_{TH}$ をINTV<sub>CC</sub>に接続)、非直線的なインクリメントで8つの内部抵抗値を使用できます。LT7182S PMBus/ $\text{I}^2\text{C}$ リファレンス・マニュアルに記載されているMFR\_PWM\_MODE\_LT7182Sコマンドの説明を参照してください。

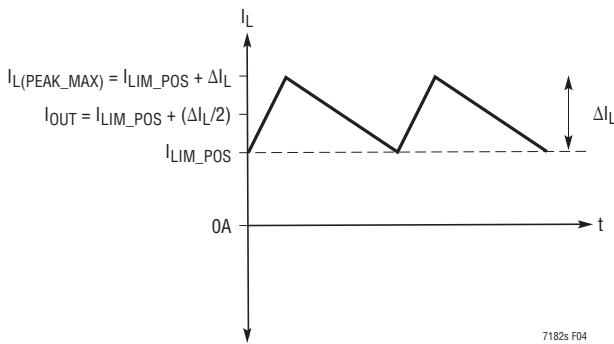

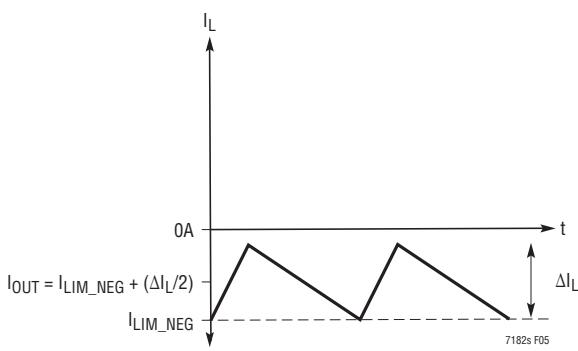

**Note 6:** LT7182Sスイッチング・レギュレータは谷電流モード制御を使用するので、仕様に規定された電流リミットは、インダクタ電流波形の谷部分に対応します。最大負荷電流はこれより大きく、谷電流リミットにインダクタ・リップル電流の1/2を加えた値に等しくなります。詳細については、[アプリケーション情報](#)のセクションを参照してください。

## 代表的な性能特性

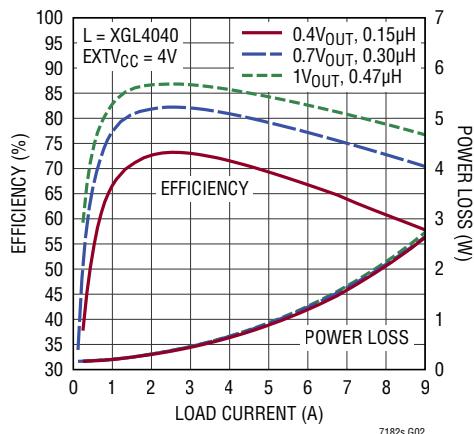

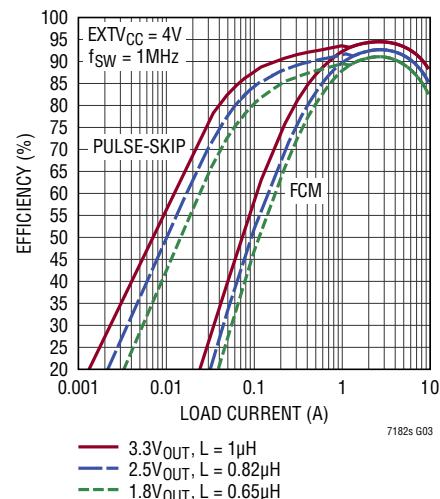

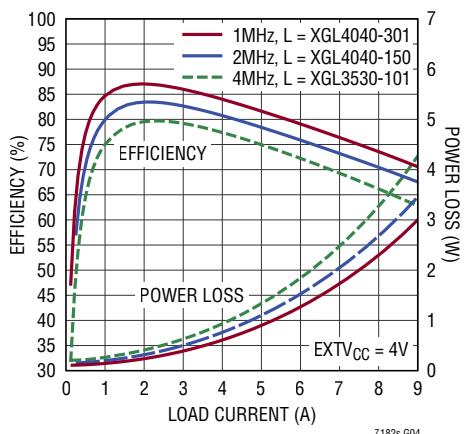

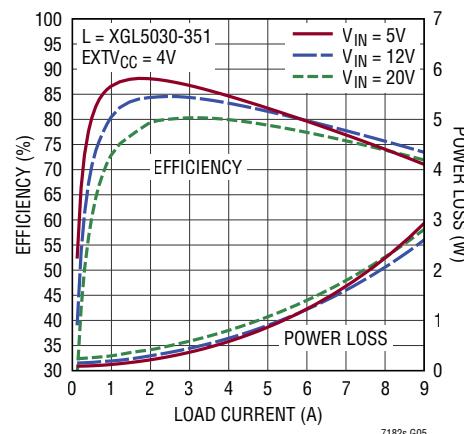

12V<sub>IN</sub>での効率 (f<sub>SW</sub> = 1MHz、異なるV<sub>OUT</sub>)

12V<sub>IN</sub>でV<sub>OUT</sub>を変化させた場合の低負荷時効率

5V<sub>IN</sub>、0.8V<sub>OUT</sub>での効率(異なるf<sub>SW</sub>)

0.8V<sub>OUT</sub>での効率(f<sub>SW</sub> = 1MHz、様々なV<sub>IN</sub>)

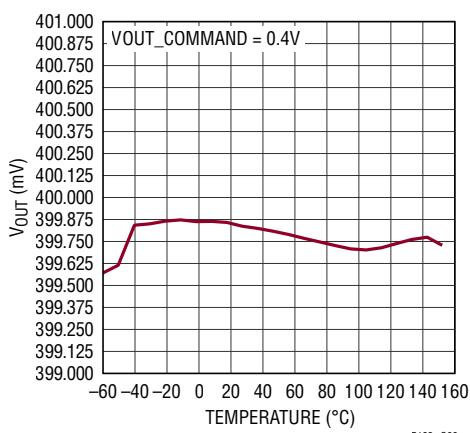

V<sub>OUT</sub>と温度の関係

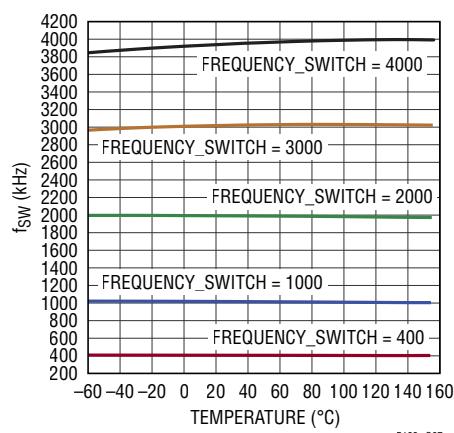

f<sub>SW</sub>と温度の関係

## 代表的な性能特性

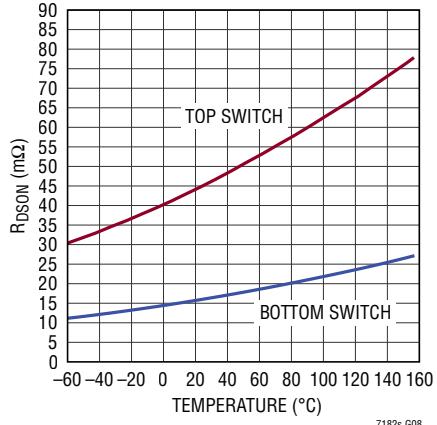

スイッチの  $R_{DS(ON)}$  と温度の関係

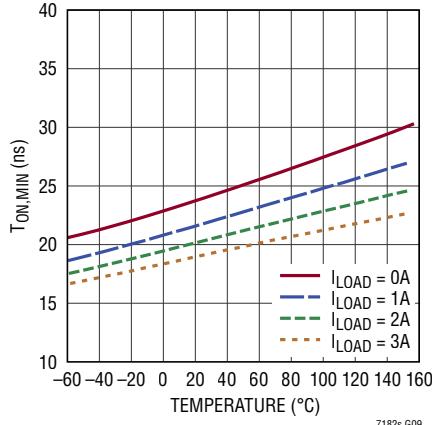

最小オン時間

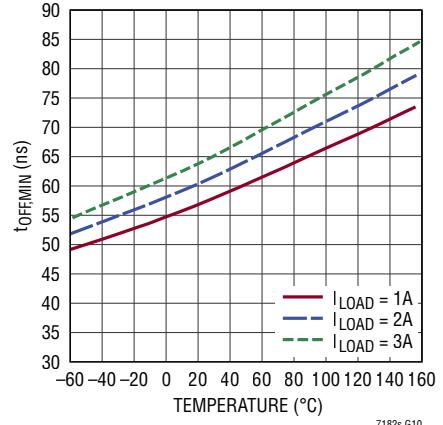

最小オフ時間

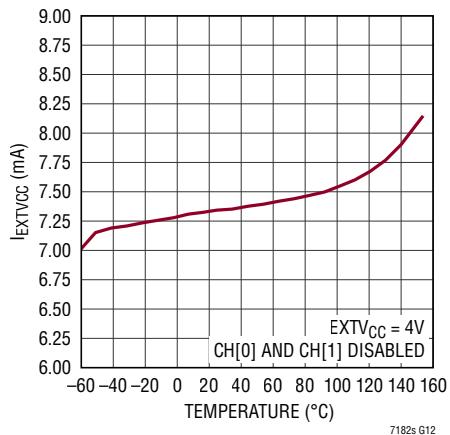

EXTV<sub>CC</sub> アイドル電流と温度の関係

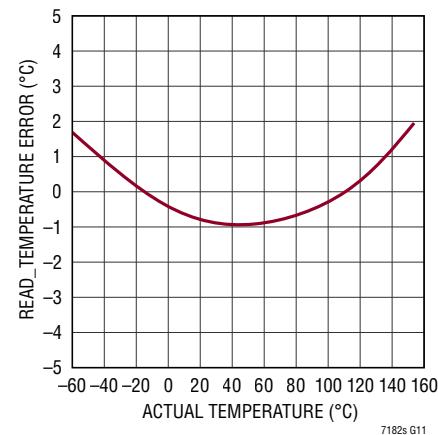

READ\_TEMPERATURE 誤差と温度の関係

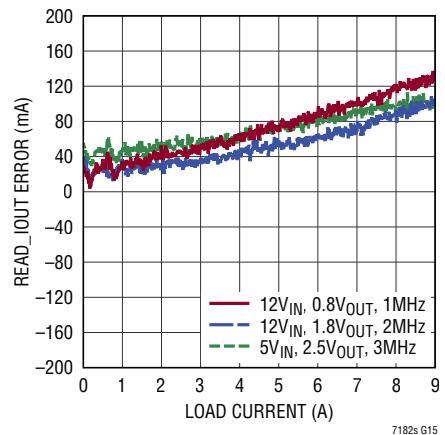

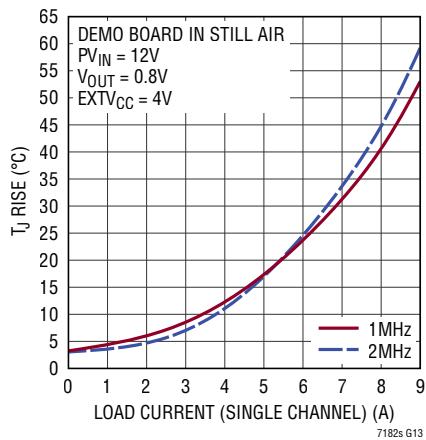

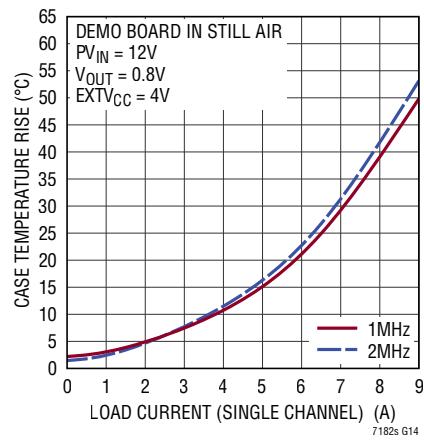

READ\_I<sub>OUT</sub> 誤差と I<sub>OUT</sub> の関係T<sub>J</sub> の上昇と負荷の関係

ケース温度の上昇

## 代表的な性能特性

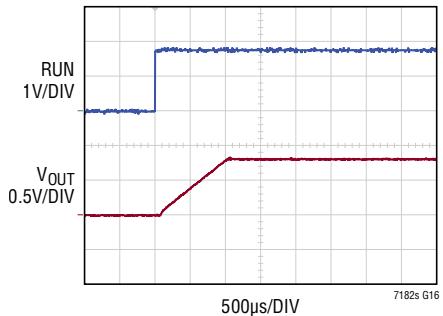

### ソフトスタート・ランプ

TON\_RISE = 1ms

TON\_DELAY = 0ms

VOUT\_COMMAND = 0.8V

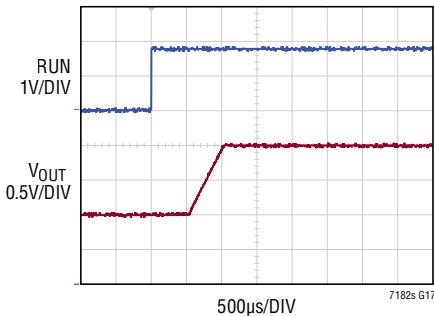

### 負荷をプリバイアスした場合の起動

TON\_RISE = 1ms

TON\_DELAY = 0ms

VOUT\_COMMAND = 2V

PREBIASED AT 1V

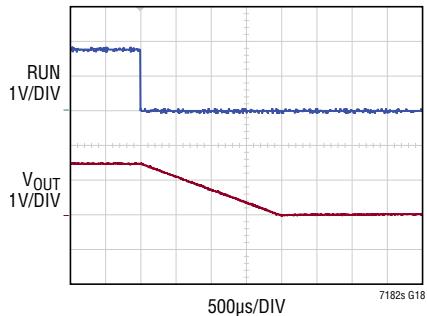

### ソフトオフ・ランプ

TOFF\_FALL = 2ms

TOFF\_DELAY = 0ms

VOUT\_COMMAND = 1.5V

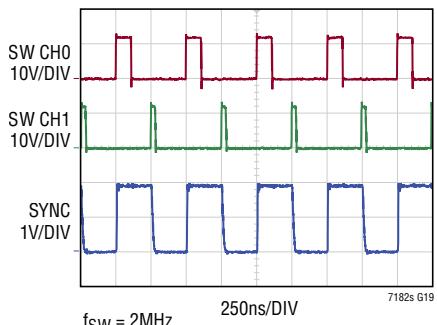

### SW ノードと SYNC 出力

f<sub>SW</sub> = 2MHz

CH1 MFR\_PWM\_PHASE = 180

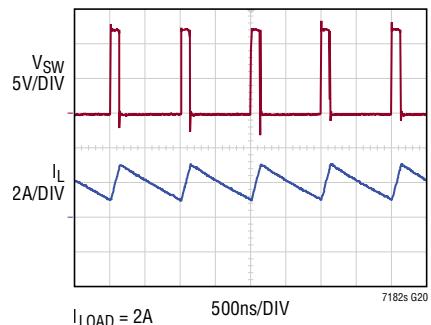

### 連続導通モード時のスイッチング波形

I<sub>LOAD</sub> = 2A

V<sub>IN</sub> = 12V

V<sub>OUT</sub> = 1.5V

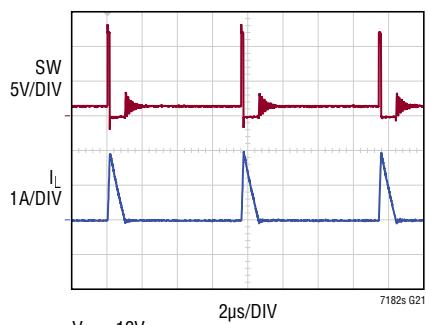

### パルススキップ・モード時のスイッチング波形

V<sub>IN</sub> = 12V

V<sub>OUT</sub> = 1.5V

I<sub>LOAD</sub> = 100mA

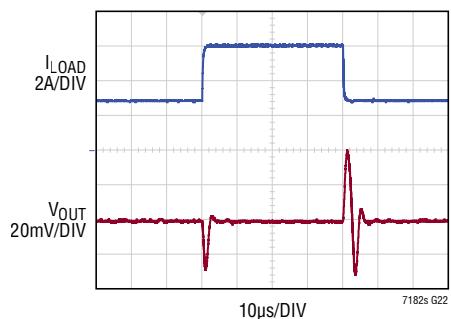

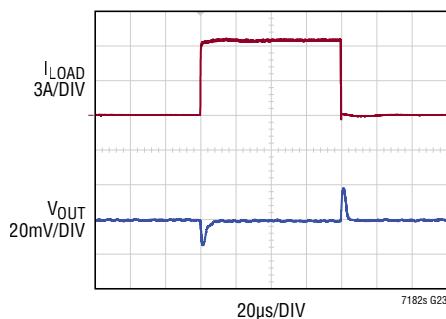

### 過渡応答: 負荷電流ステップ変化 3A～6A、内部補償

V<sub>IN</sub> = 12V, V<sub>OUT</sub> = 0.8V, C<sub>OUT</sub> = 47µF x2

FCM, f<sub>SW</sub> = 2MHz

R<sub>COMP</sub> = 10k, C<sub>COMP</sub> = 80pF, g<sub>MEA</sub> = 750µS

### 過渡応答: デュアル位相ステップ変化 0A～6A、外部補償

V<sub>IN</sub> = 12V, V<sub>OUT</sub> = 1.2V, C<sub>OUT</sub> = 100µF x4

FCM, f<sub>SW</sub> = 1MHz

R<sub>COMP</sub> = 7k, C<sub>COMP</sub> = 470pF, g<sub>MEA</sub> = 1.2mS

## ピン機能

**VSENSE0N、VSENSE1N(ピン1、ピン12)**：出力電圧の負の検出入力。これらのピンは出力電圧のグラウンド検出ポイントに接続します。

**VSENSE0P、VSENSE1P(ピン2、ピン11)**：出力電圧の正の検出入力。これらのピンは出力電圧の検出ポイントに接続します。

**SGND(ピン3)**：信号グラウンド。このピンは、LT7182S直下の基板のグラウンドに1箇所だけで接続する必要があります。

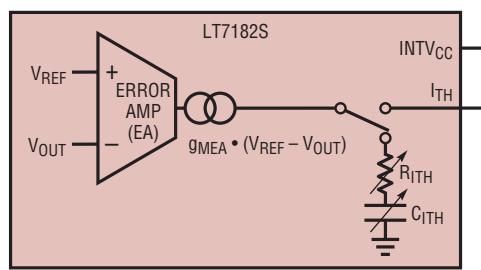

**I<sub>TH0</sub>、I<sub>TH1</sub>(ピン4、ピン5)**：エラー・アンプ出力とスイッチング・レギュレータの補償ポイント。レギュレータ・ループの周波数応答を補償するには、これらのピンとSGNDの間に適切な外付け部品を接続します。チャンネルの内部補償を選択する場合は、I<sub>TH</sub>ピンをINTV<sub>CC</sub>に接続してください。

**INTV<sub>CC</sub>(ピン6)**：内部3V LDOレギュレータのバイパス。このレギュレータは内部回路に電源電流を供給します。このピンは、デバイスのできるだけ近くに10 $\mu$ F以上の低ESRセラミック・コンデンサを接続して、SGNDにバイパスする必要があります。INTV<sub>CC</sub>ピンには外部回路から負荷をかけないでください。

**V<sub>DD18</sub>(ピン7)**：内部1.8Vレギュレータのバイパス。このピンは、4.7 $\mu$ F以上の低ESRセラミック・コンデンサを使って、グラウンド(SGNDまたはPGND)にバイパスする必要があります。V<sub>DD18</sub>ピンには外部回路から負荷をかけないでください。

**V<sub>OUT0\_CFG</sub>(ピン8)**：チャンネル0の出力電圧設定。16個ある出力電圧設定点の中から1つを選択するには、[アプリケーション情報のセクションの表2](#)に従ってV<sub>OUT0\_CFG</sub>とグラウンド(SGNDまたはPGND)の間に1%抵抗を接続します。フロート状態のままにするかV<sub>DD18</sub>に接続すると、LT7182Sは、EEPROM内にプログラムされたV<sub>OUT\_COMMAND</sub>の値を使用します。V<sub>OUT0\_CFG</sub>ピンは、LT7182Sの起動時またはリセット時に読み出されます。

**V<sub>OUT1\_CFG/POLYPHASE\_CFG</sub>(ピン9)**：チャンネル1の出力電圧設定、またはPolyPhase設定。SYNC/PWM\_CFGピンがPolyPhase用に設定されていない場合は、V<sub>OUT1\_CFG/POLYPHASE\_CFG</sub>とグラウンド(SGNDまたはPGND)の間にある1%抵抗が、[アプリケーション情報のセクションの表2](#)に従って電圧設定点を選択します。SYNC/PWM\_CFGピンがPolyPhase用に設定されている場合は、V<sub>OUT0\_CFG</sub>に基づいてチャンネル1の出力がチャンネル0と同じ値に設定され、V<sub>OUT1\_CFG/POLYPHASE\_CFG</sub>とSGNDの間にある1%抵抗が、[アプリケーション情報のセクションの表4](#)に従ってPolyPhase構成を選択します。V<sub>OUT1\_CFG/POLYPHASE\_CFG</sub>ピンは、LT7182Sの起動時またはリセット時に読み出されます。

**ASEL(ピン10)**：シリアル・バスのアドレス設定。16個あるシリアル・バス・インターフェース・アドレスの中から1つを選択するには、ASELとグラウンド(SGNDまたはPGND)の間に1%抵抗を接続します。LT7182S PMBus/I<sup>2</sup>Cリファレンス・マニュアルに記載されているMFR\_ADDRESSの説明を参照してください。ASELピンは、LT7182Sの起動時またはリセット時に読み出されます。ASELピンがフロート状態のままになっている場合、工場出荷時のデフォルトの7ビット・デバイス・アドレスは0x4Fです。ASELピンが接地されている場合、工場出荷時のデフォルトのデバイス・アドレスは0x40です。

**BOOST1(ピン13)**：昇圧されたフローティング・ドライバ電源。PCBの最上層を使い、BOOST1とSW1の間のできるだけICに近い位置に、0.1 $\mu$ Fの昇圧コンデンサを接続します。このピンの通常動作時の電圧振幅は、DRV<sub>CC</sub>からPVIN1+DRV<sub>CC</sub>までです。

**PGND(ピン14、19、34、39、露出パッド・ピン42、43)**：電源グラウンド。PVIN0およびPVIN1入力バイパス・コンデンサの(-)端子と、出力コンデンサCOUT0およびCOUT1の(-)端子を、低インピーダンスの接続でこれらのピンに接続してください。PCBは、電源グラウンドへの接続の電気的インピーダンスと熱的インピーダンスが小さくなるように設計する必要があります。

## ピン機能

**P<sub>VIN1</sub> (ピン15、18)** : チャンネル1の電源入力。これらのピンは互いに接続し、4.7 $\mu$ F以上の低ESRコンデンサを使って、LT7182Sにできるだけ近い位置でバイパスする必要があります。

**SW1 (ピン16、17、露出パッド・ピン44)** : チャンネル1内部電源スイッチの出力。これらのピンは互いにまとめて、チャンネル1のインダクタとBOOST1コンデンサに接続してください。優れた性能を実現するには、PCB上でのこのノードの面積をできるだけ小さくする必要があります。

**DRV<sub>CC</sub> (ピン20)** : 内部3.5V LDOレギュレータのバイパス。このレギュレータはパワーFETドライバの電源電流を供給します。このピンは、PCBの最上層を使い、デバイスのできるだけ近くに10 $\mu$ F以上の低ESRセラミック・コンデンサを接続して、PGNDにバイパスする必要があります。DRV<sub>CC</sub>ピンには外部回路から負荷をかけないでください。ただし、SHARE\_CLKピンのプルアップ抵抗、またはRUN0ピン、RUN1ピン、FAULT0ピンあるいはFAULT1ピンのプルアップ抵抗、もしくはその両方については、必ずしもこの限りではありません。

**EXTV<sub>CC</sub> (ピン21)** : オプションの電源入力。3V～5.5Vの電圧源に接続した場合、このピンはDRV<sub>CC</sub>、INTV<sub>CC</sub>、およびV<sub>DD18</sub>の各電源を使用するために使われます。レギュレータ出力の1つが3V以上のV<sub>OUT</sub>に設定されている場合は、電力損失を小さくするために、そのV<sub>OUT</sub>をEXTV<sub>CC</sub>に接続することができます。このピンをレギュレータ出力に接続しない場合は、LT7182Sにできるだけ近い位置に0.1 $\mu$ F以上のロード・バイパス・セラミック・コンデンサを接続します。

**SYNC/PWM\_CFG (ピン22)** : 外部クロック同期入出力またはPWM設定、もしくはその両方。外部クロックを使って駆動した場合、内部フェーズ・ロック・ループ(PLL)は外部クロックの立上がりエッジでスイッチング・レギュレータ出力に同期します。このピンをクロック入力として使用する場合は、設定抵抗を無視するようにEEPROMがプログラムされていない限り(MFR\_CONFIG\_ALL\_LT7182Sのビット6をセット)、クロック源と直列に1.5nFのACカップリング・コンデンサを挿入する必要があります。設定抵抗を無視するようにEEPROMがプログラムされている場合は、クロック

源を直接接続できます。出力として設定した場合(MFR\_SYNC\_CONFIG\_LT7182Sのビット0をセット)、LT7182Sは、FREQUENCY\_SWITCHによって設定されたスイッチング・クロック周波数でSYNC/POWM\_CFGピン出力を駆動します。この場合の電圧振幅は0V～1.88Vです(代表値)。周波数、位相、およびモードの設定を選択するには、[アプリケーション情報](#)のセクションの表3に従って、SYNC/PWM\_CFGとグラウンド(PGNDまたはSGND)の間に1%抵抗を接続します。SYNC/PWM\_CFGピンは、LT7182Sの起動時またはリセット時に読み出されます。詳細については、[アプリケーション情報](#)を参照してください。

**RUN0、RUN1 (ピン24、ピン23)** : レギュレータ・イネーブル入力。ロジック・ハイでレギュレータをイネーブルします。RUN0ピンとRUN1ピンは、他のレギュレータとのシーケンシングを容易にするために、POR時とリセット時に1.5mA(代表値)の電流でプルダウンされますが、別のデバイスのデジタル出力によってハイにオーバードライブできます。入力電源が存在する場合、これらのピンは、レギュレータをイネーブルするためにDRV<sub>CC</sub>に直接接続できます。

**SHARE\_CLK (ピン25)** : 双方向オーブンドレイン・シーケンスの時間ベース共有クロック。公称100kHz。PolyPhaseまたは時間ベースのシーケンシングが採用されている場合に、複数のアナログ・デバイセズ製品間でレギュレータ出力の起動とシャットダウンを揃えるために使用します。SHARE\_CLK機能を使用する場合は、1.6Vから5.5Vへのプルアップ抵抗が必要です。PolyPhaseも時間ベースのシーケンシングも必要ない場合は、両方のチャンネルでMFR\_CHAN\_CONFIG\_LT7182Sのビット2がゼロに設定されなければ(SHARE\_CLKを無視)、SHARE\_CLKをグラウンドに接続することができます。

**WP (ピン26)** : 書込み保護入力。このピンがハイのときは、PAGE、OPERATION、MFR\_EE\_UNLOCK、およびCLEAR\_FAULTSコマンドだけを書き込むことができます。STATUSコマンドのそれぞれのビットに1を書き込むことによって、個々の障害ビットをクリアしてください。

## ピン機能

**FAULT0、FAULT1(ピン28、ピン27)**：障害入力／オープンドレイン出力。LT7182Sは、マスクされていない障害がレギュレータに発生すると、1.5mA(代表値)でこのピンをプルダウンします。別のデバイスがFAULTピンをプルダウンすると、LT7182Sレギュレータは直ちにオフになります。PolyPhase構成が使われている場合は、すべてのPloyPhaseチャンネルのFAULTピンを互いに接続してください。PolyPhase構成が使われている場合、あるいはFAULTピンのレポートまたは共有が求められる場合は、6.8k以上のプルアップ抵抗を使って1.6Vから5.5Vへプルアップする必要があります。FAULTピン機能が必要ない場合は、FAULTピンを直接DRVCCに接続することができます。

**ALERT(ピン29)**：オープンドレイン・アラート出力。ALERTピン機能を使用する場合は、1.6Vから5.5Vへのプルアップ抵抗が必要です。ALERTピン機能が必要ない場合、このピンはグラウンドに接続できます。

**SCL(ピン30)**：シリアル・バス・クロック入出力。クロック・ストレッ칭をイネーブルした場合は、LT7182SのSCLをローに保持することができます(PMBus速度が400kHz～1MHzの場合のみ)。PMBus/I<sup>2</sup>Cを動作させるには、1.6Vから5.5Vへのプルアップ抵抗が必要です。シリアル・バス動作の必要がない場合はSCLをグラウンドに接続できます。

**SDA(ピン31)**：シリアル・バス・データ入出力。PMBus/I<sup>2</sup>Cを動作させるには、1.6Vから5.5Vへのプルアップ抵抗が必要です。シリアル・バス動作が必要ない場合はSDAをグラウンドに接続できます。

**PGOOD0、PGOOD1(ピン33、ピン32)**：パワーグッド・インジケータのオープンドレイン出力。レギュレータ出力がOV/UV閾値範囲外にある場合、チャンネルがディスエーブルされた場合、およびオン／オフ・シーケンシング中の場合は、PGOODがローにプルダウンされます。PGOOD出力は内部設定タイマーによってデグリッチされます。PGOODピン機能を使用する場合は、1.6Vから5.5Vへのプルアップ抵抗が必要です。PGOODピン機能を使わない場合、これらのピンはPGNDに接続できます。

**PV<sub>IN0</sub>(ピン35、38)**：チャンネル0および内部LDOレギュレータの電源入力。これらのピンは互いにまとめ、4.7μF以上の低ESRコンデンサを使って、LT7182Sにできるだけ近い位置でPGNDにバイパスする必要があります。EXTV<sub>CC</sub> < 3Vの場合、内部LDOレギュレータ(DRV<sub>CC</sub>、INTV<sub>CC</sub>、およびV<sub>DD18</sub>用)の電源はPV<sub>IN0</sub>から供給されます。

**SW0(ピン36、37、露出パッド・ピン41)**：チャンネル0内部電源スイッチの出力。これらのピンは互いにまとめて、チャンネル0のインダクタとBOOST0コンデンサに接続してください。優れた性能を実現するには、PCB上でのこのノードの面積をできるだけ小さくする必要があります。

**BOOST0(ピン40)**：昇圧されたフローティング・ドライバ電源。PCBの最上層を使い、BOOST0とSW0の間のできるだけICに近い位置に、0.1μFの昇圧コンデンサを接続します。このピンの通常動作時の電圧振幅は、DRV<sub>CC</sub>からPV<sub>IN0</sub>+DRV<sub>CC</sub>までです。

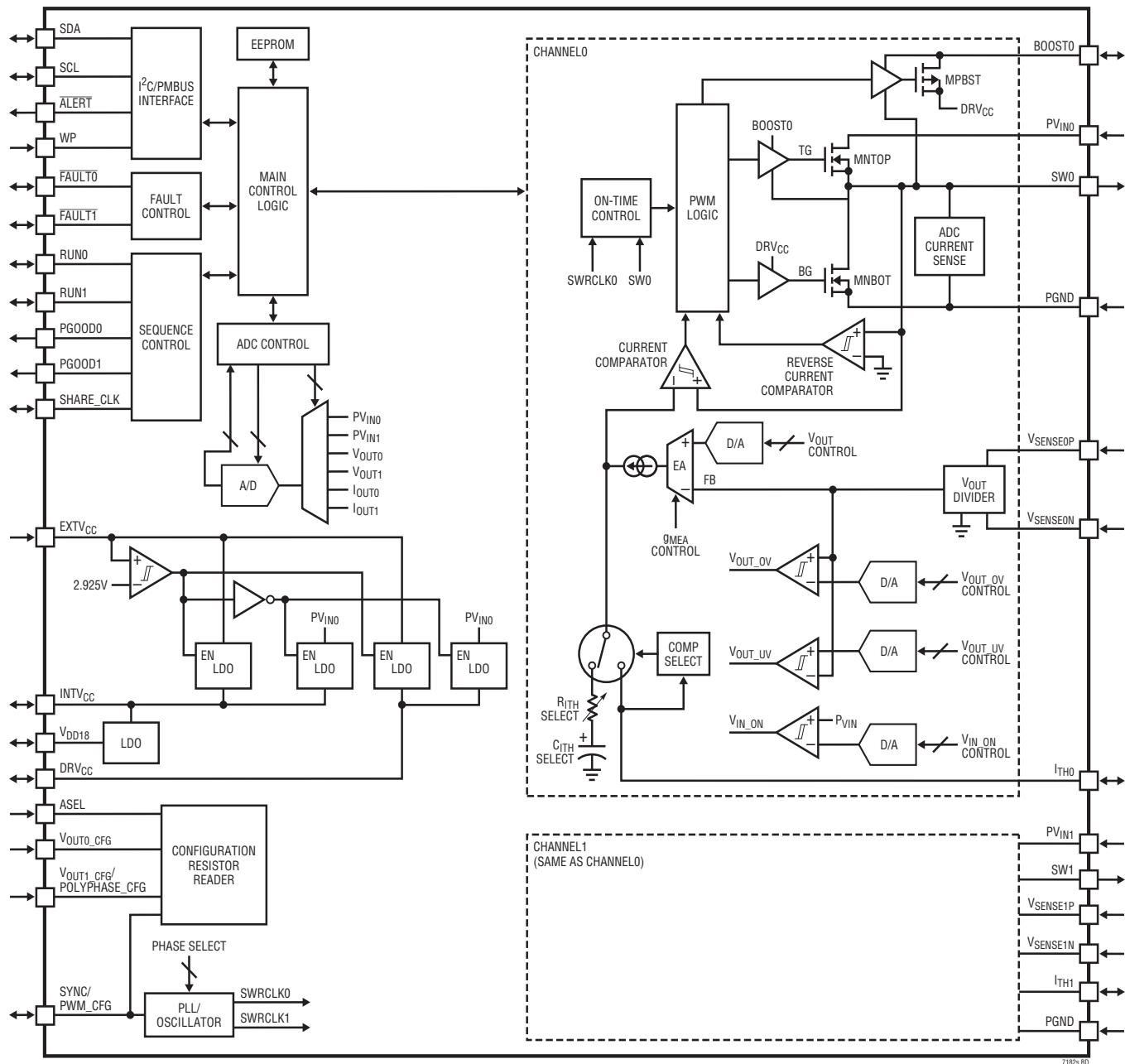

## ブロック図

## 動作

### 概要

LT7182Sは、デュアル出力のモノリシック PolyPhase DC/DC 同期整流式降圧レギュレータです。LT7182Sの「S」は、第2世代のSilent Switcher技術が採用されていることを表しています。この技術は高速でクリーンなスイッチング・エッジを実現し、全体的なソリューション・サイズを小さくして効率を改善すると共に、EMI放射を最小限に抑えます。 $I^2C$ ベースのシリアル・インターフェースは、最大1MHzのバス速度をサポートするPMBus 1.3と互換です。

主な機能には以下が含まれます。

- プログラマブルな出力電圧

- プログラマブルな電流リミット

- プログラマブルなスイッチング周波数

- プログラマブルな出力過電圧／低電圧障害閾値および警告閾値

- プログラマブルなオン／オフ遅延時間

- プログラマブルな出力立上がり／立下がり時間

- プログラマブルな制御ループ補償

- プログラマブルな入力低電圧閾値

- 各チャンネル専用のパワーグッド・ピン

- 同期PolyPhase動作用のフェーズ・ロック・ループ(2,3,4,6、または8相)

- 入力および出力電圧／電流、およびダイ温度テレメトリ

- V<sub>OUT</sub>の完全差動リモート検出

- ECC機能付きの不揮発性構成メモリ

- 不揮発性のイベントベース障害ログ

- 重要動作パラメータ用の外付け設定抵抗(オプション)

- 複数のデバイスを同期する時間ベース・インターフェクト(オプション)

- 内部設定を書き込みから保護するWPピン

- 設定抵抗または不揮発性構成メモリを使用するスタンドアロン動作

障害および警告を処理するための様々なメカニズムが使用できます。障害および警告の検出機能には以下が含まれています。

- 出力低電圧／過電圧障害および警告

- 内部過熱障害および警告

- 通信、メモリ、またはロジック(CML)障害

- 入力過電圧障害および低電圧警告

- 出力過電圧障害および警告

- 平均入力過電流警告

- 内部リファレンス障害

- 双方向FAULTピンを介した外部障害検出

障害または警告が発生したことを示すために、専用のALERTピンを備えています。

また、個々のステータス・コマンドを使用して障害と警告をレポートし、特定のイベントを確認することができます。

LT7182SのFAULTピンは、チャンネル間や、LTC3880、LTC2974、LTC2978、LTC4676 μModule®などを含む他のアナログ・デバイセズ製パワー・システム・マネージメント製品との間で、障害情報を共有することを可能にします。

障害のレポートとシャットダウンの動作は、FAULTピンとMFR\_FAULT\_PROPAGATE\_LT7182Sコマンドを使って自由に設定できます。障害は個別にマスク可能で、レギュレータ出力を再試行(ラッチ解除)するかラッチオフするように障害応答をプログラムできます。

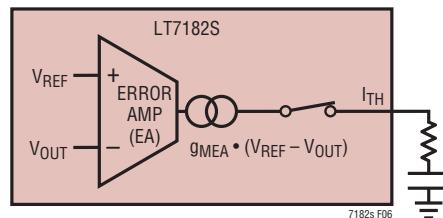

### スイッチング・レギュレータの制御ループ

LT7182Sは、オン時間制御式の谷電流アーキテクチャを採用しています。通常動作時には、オン時間制御回路によって決定される時間だけ、内蔵の上側パワーMOSFETがオンになります。上側パワーMOSFETがオフになると、谷電流コンパレータがトリップしてオン時間制御回路が動作を再開することにより次のサイクルが開始されるまで、下側パワーMOSFETがオンになります。インダクタ電流は、下側パワーMOSFETがオフになっているときにMOSFETでの電圧低下を検出することによって決定されます。I<sub>TH</sub>ピンの電圧は、インダクタの谷電流に対応するコンパレータ閾値を設定します。エラー・アンプ(EA)は、出力電圧と内部リファレンス

## 動作

DAC出力を比較することによって $I_{TH}$ 電圧を調整します。負荷電流が増大すると内部リファレンスに対する出力電圧が低下し、それにより、平均インダクタ電流と平均負荷電流が一致するまで $I_{TH}$ 電圧が上昇します。

SYNC/PWM\_CFGピン上に外部クロック信号が存在する場合、内部フェーズ・ロック・ループ(PLL)は、発振器周波数をその外部クロック信号に同期します。外部クロックが供給されていない場合、スイッチング周波数はFREQUENCY\_SWITCHコマンドによって設定されます。このコマンドは、設定レジスタを使って初期化できます(詳細については[アプリケーション情報](#)のセクションを参照)。

### 軽負荷電流動作

LT7182Sには2つのPWM動作モード、つまりパルススキップ・モードと連続導通モードがあります。PWM動作モードはMFR\_PWM\_MODE\_LT7182Sコマンドのビット0によって選択しますが、このコマンドは、表3と表4に示すように設定レジスタを使って初期化できます。ソフトスタート時には常にパルススキップ・モードが使われます。

一方のチャンネルでパルススキップ・モードをイネーブルした場合、インダクタ電流を反転することはできません。逆電流コンパレータは、インダクタ電流が0になる直前に下側スイッチをオフにし、電流が反転して負になるのを防ぎます。両方のパワーMOSFETはオフのままになり、 $I_{TH}$ 電圧がゼロ電流閾値を超えて次のサイクルが開始されるまで、出力コンデンサが負荷電流を供給します。

強制連続モード(FCM)では、軽負荷時または過渡状態時にインダクタ電流を反転できます。インダクタの谷電流は $I_{TH}$ ピンの電圧によって決まります。このモードでは、軽負荷時の効率がパルススキップ・モードより低下します。しかし、連続導通モードでは出力リップルが小さくなっています。周波数が一定に保たれ、過渡応答も速くなります。

### EEPROM

LT7182Sは、ユーザ構成設定と障害ログ情報を保存するためのEEPROMを内蔵しています。

内蔵EEPROMの完全性は誤り訂正符号(ECC)によって保護され、パワーオン・リセット後やRESTORE\_USER\_ALLコマンド実行後はCRC計算を使ってチェックされます。無効なCRCが検出された場合はALERTピン、SHARE\_CLKピン、PGOODピン、およびRUNピンがローになり、問題が解消さ

れるまで両方の出力チャンネルがディスエーブルされたままになります。

効率的なバルクEEPROMプログラミングを含む効率的なシステム内EEPROMプログラミングの詳細については、LT7182S PMBus/I<sup>2</sup>Cリファレンスマニュアルを参照するか、アナログ・デバイセズへお問い合わせください。

### パワーアップと初期化

LT7182Sは、スタンダードアロンの電源シーケンシングと、制御されたターンオンおよびターンオフ動作が可能で、1つの入力電源または2つの独立した入力電源( $PV_{IN0}$ と $PV_{IN1}$ )で動作します。LT7182Sの消費電力を減らすために、EXTV<sub>CC</sub>は外部の3V～5.5V電源を使って駆動するか、3V～5.5Vを供給するLT7182Sの出力に接続することができます。EXTV<sub>CC</sub>を3V～5.5Vに接続した場合に使用できる $PV_{IN0}$ の入力範囲は1.5V～20Vで、EXTV<sub>CC</sub>を使用しない場合の $PV_{IN0}$ の動作範囲は2.9V～20Vです。 $PV_{IN1}$ の動作範囲は1.5V～20Vです。チャンネル1を動作させるには、 $PV_{IN1}$ と、EXTV<sub>CC</sub>または $PV_{IN0}$ のどちらかに電源を供給する必要があります。EXTV<sub>CC</sub>、 $PV_{IN0}$ 、 $PV_{IN1}$ は、LT7182Sの電源シーケンシングを気にすることなく、任意の順番で供給することができます。

LT7182Sは、 $PV_{IN0}$ またはEXTV<sub>CC</sub>に電源を供給した時点、もしくはMFR\_RESETまたはRESTORE\_USER\_ALLコマンドが送信された時点で初期化されます。初期化ステップにおいて、LT7182SはEEPROMの設定や抵抗設定ピンを読み出して、PMBusコマンドの構成初期状態を設定します。

初期化中、PGOODピンとSHARE\_CLKはローに保持され、RUNピンが1.5mA(代表値)でプルダウンされて、FAULTピンは高インピーダンス状態になります。

CFG抵抗設定ピンがイネーブルされている場合、LT7182Sは設定レジスタの値に基づいて一定のコマンドを初期化します。これはEEPROMの設定より優先されます。抵抗設定ピンは、工場出荷時のデフォルトによってイネーブルされます。CFGピンをディスエーブルするには、EEPROM内のMFR\_CONFIG\_ALL\_LT7182Sのビット6をクリアします。詳細については、[アプリケーション情報](#)のセクションの抵抗設定ピンの使用法を参照してください。設定抵抗に基づいて初期化されないコマンドについては、EEPROMまたは工場出荷時のデフォルトによって初期値が決定されます。

## 動作

LT7182Sの初期化には13ms(代表値)を要します。CFGビンがディスエーブルされている場合(EEPROM内のMFR\_CONFIG\_ALL\_LT7182Sのビット6が1に設定されている場合)、初期化時間は10ms(代表値)に短縮されます。

初期化が完了すると、コンパレータがPV<sub>IN0</sub>とPV<sub>IN1</sub>をモニタします。チャンネルを動作させるには、PV<sub>IN</sub>電圧が、プログラム可能なV<sub>IN\_ON</sub>閾値を超えていなければなりません。デフォルトでは、PV<sub>IN0</sub>がPAGE 0のV<sub>IN\_ON</sub>を超えるまで、あるいはPV<sub>IN0</sub>がV<sub>IN\_OFF</sub>未満に低下するまで、SHARE\_CLKがローに保持されます。デフォルトでは、PV<sub>IN1</sub>はSHARE\_CLKに影響しません。デフォルト動作では、SHARE\_CLKがローになると両方のチャンネルがオフになり、その状態が保持されます。この動作の設定方法については、LT7182S PMBus/I<sup>2</sup>Cリファレンス・マニュアルに記載されているMFR\_CHAN\_CONFIG\_LT7182Sコマンドの説明を参照してください。

PORの初期化が完了してそのチャンネルのPV<sub>IN</sub>電位がV<sub>IN\_ON</sub>閾値を最初に超えた時点で、LT7182SはRUNピンのプルダウン電流(代表値1.5mA)を停止します。

### ソフトスタート

起動に必要なすべての条件が満たされてチャンネルがイネーブルされると、LT7182Sは、コマンドで指定されたターンオン遅延が経過するまで待機してから、コマンド指定電圧設定点まで対象出力電圧をランプアップします。ソフトスタートの立上がり時間はTON\_RISEコマンドで設定し、デフォルトは1msです。ターンオン遅延はTON\_DELAYによって設定し、工場出荷時のデフォルトは0msです。LT7182SのPWMは、ソフトスタート時には常にパルススキップ・モードを使用します。これにより、レギュレータはプリバイアスされた負荷状態で起動できるようになります。強制連続導通モードを選択した場合(MFR\_PWM\_MODE\_LT7182Sのビット0を0にクリア)、そのチャンネルは、コマンドで指定された電圧設定点に達した後で連続導通モードへ遷移します。

### シャットダウン

LT7182Sは、直ちにターンオフするようにプログラムするか、シーケンス・オフするようにプログラムできます。

シーケンス・オフする場合、LT7182Sは、ターンオフ遅延が経過するまで待機してからソフトストップ・ランプを実行し、この過程でレギュレーション対象電圧がゼロまでランプダウンします。ターンオフ遅延はTOFF\_DELAYコマンドによって設定し、デフォルトはゼロです。対象電圧ランプダウン時間はTOFF\_FALLによって設定し、デフォルトは2msで

す。デフォルトでは、チャンネルは強制連続導通モードでランプダウンします。ランプオフ動作はMFR\_PWM\_MODE\_LT7182Sを使って設定できます。

シーケンス・オフは、OPERATIONを0x40に設定した場合、もしくはRUNピンをデアサートしてON\_OFF\_CONFIGのビット0を0に、ビット2を1に設定した場合に実行されます。

直ちにターンオフする場合は、レギュレータがインダクタ電流をできるだけ速やかに0までランプダウンして、その後にスイッチングを停止します。この場合の出力電圧は、負荷電流とオプションの内部250Ωプルダウンだけに基づいて低下します。内部250Ωプルダウンは、MFR\_CHAN\_CONFIG\_LT7182Sのビット6をクリアすることによってディスエーブルできます。以下の場合、デバイスは直ちにシャットダウンされます。

- PV<sub>IN</sub>がV<sub>IN\_OFF</sub>閾値未満に低下した場合

- OPERATIONコマンドをクリアして0x00にし、ON\_OFF\_CONFIGのビット3を1に設定した場合

- 障害状態が発生したことによって出力がオフになった場合

- RUNピンがデアサートされた場合で、なおかつRUNピンがデアサートされた場合は直ちにデバイスがシャットダウンされるようにON\_OFF\_CONFIGが設定されている場合(ON\_OFF\_CONFIGのビット0と2が共に1にセット)

- そのチャンネルのFAULTピンが外部的にローにプルダウンされた場合(MFR\_FAULT\_RESPONSEが0x00にクリアされた場合を除く)

- SHARE\_CLKが失われた場合(MFR\_CHAN\_CONFIG\_LT7182Sのビット2がクリアされた場合を除く)

### 警告と障害の処理

LT7182Sは、障害状態と警告状態の有無について継続的にシステムをモニタします。

障害応答は、VOUT\_UV\_FAULT\_RESPONSEやVOUT\_OV\_FAULT\_RESPONSEなどの該当するFAULT\_RESPONSEコマンドを使って設定します。設定可能な障害応答は以下のとおりです。

- 動作を続行(無視)

- 直ちにシャットダウンし、障害状態が解消された場合は再試行

## 動作

- 直ちにシャットダウンしてラッチオフ

このセクションの残りの部分では、工場出荷時のデフォルトの警告および障害動作を説明します。表1を参照してください。

障害および警告動作設定の詳細については、LT7182S PMBus/I<sup>2</sup>Cリファレンス・マニュアルを参照してください。

すべての障害と警告は、PMBusのSTATUSコマンドで示されます。

出力電圧、出力電流、または温度に関する警告が発生した場合は、LT7182SはALERTピンをローにプルダウンし、該当するSTATUSコマンドの対応ビットをセットしますが、そのチャンネルは動作を継続します。

出力電圧がVOUT\_UV\_FAULT\_LIMIT未満に低下した場合、LT7182Sは以下のように応答します。

- そのチャンネルのPGOODピンをローにプルダウン

- ALERTピンをローにプルダウン

- STATUS\_VOUT、STATUS\_BYTE、およびSTATUS\_WORDコマンドのVOUT\_UV障害ビットをセット

- 最大谷電流を制限しながらチャンネルの動作を継続

出力過電圧または入力過電圧による障害が発生した場合、LT7182Sは以下のように応答します。

- 障害が発生したチャンネルを直ちにシャットダウン

- そのチャンネルのFAULTピンとPGOODピンをローにプルダウン

- ALERTピンをローにプルダウン

- 該当するSTATUSコマンドの対応インジケータ・ビットをセット

- 10ms (MFR\_RETRY\_DELAYによって定義される時間) 経過後に障害状態が解消されている場合は、チャンネルが再スタートを試行

過熱による障害が発生した場合、LT7182Sは以下のように応答します。

- 両方のチャンネルを直ちにシャットダウン

- 両方のチャンネルのFAULTピンとPGOODピンをローにプルダウン

- ALERTピンをローにプルダウン

- 該当するSTATUSコマンドの過熱(OT)ビットをセット

- ADCの測定した温度が過熱閾値未満だった場合は、チャンネルの再スタートを試行

LT7182Sは、ADCを使い、プライマリ内部電圧リファレンスとセカンダリ内部電圧リファレンスの比較を周期的に行います。異常が検出された場合、LT7182Sは以下のように応答します。

- 両方のチャンネルを直ちにシャットダウン

- FAULTピン、PGOODピン、ALERTピンをローにプルダウン

- STATUSコマンドの内部リファレンス障害ビットをセット

- リファレンスが回復した場合(例えば温度ドリフトによって)、RESTORE\_USER\_ALLまたはMFR\_RESETコマンドを受信した場合、もしくはPV<sub>IN0</sub>とEXTV<sub>CC</sub>両方の入力電源が遮断された場合を除いて、両方のチャンネルをオフ状態に保持

### FAULTピン

対応するFAULT\_RESPONSEコマンドがレギュレータ出力をシャットダウンするようにプログラムされ、なおかつMFR\_FAULT\_PROPAGATE\_LT7182SコマンドがオーブンドラインFAULTピンに障害を伝搬するようにプログラムされている場合は、障害が発生するとFAULTピンがローにプルダウンされます。

LT7182SがFAULTピンをプルダウンすると、このピンは、以下のいずれかが発生するまでローに保持されます

- 再試行を行うように設定された障害の場合、チャンネルは再試行を行う

- 障害発生チャンネルを一度ディスエーブルしてから再びイネーブルする

- RESTORE\_USER\_ALL、またはMFR\_RESETコマンドを受信する

- PV<sub>IN0</sub>とEXTV<sub>CC</sub>両方の入力電源を遮断する

FAULTピンは、LT7182Sによる外部障害への応答方法を提供するための入力として使用することもできます。チャンネルのFAULTピンを外部からローにプルダウンすると、そのチャンネルは直ちにターンオフされます。これは、複数のパワー・システム・マネージメント製品間で障害を連携させることを可能にします。

## 動作

### PGOOD ピン

ソフトスタートおよびソフトストップ時に何らかの理由でチャンネルがオフになるか、出力電圧がVOUT\_UV\_FAULT\_LIMIT未満になると、対応するオープンドレインPGOODピンがそれぞれローにプルダウンされます。

### ALERT ピン

SMBALERT\_MASKコマンドは、LT7182Sがどの警告インジケータと障害インジケータによってオープンドレインALERTピンをプルダウンするかを設定します

LT7182SがALERTピンをプルダウンすると、このピンは以下のいずれかが発生するまでローに保持されます。

- 障害発生チャンネルを一度ディスエーブルしてから再びイネーブルする

- CLEAR\_FAULTS、RESTORE\_USER\_ALL、またはMFR\_RESETコマンドを受信する

- マスクされていないすべてのステータス・ビットが、各ビットに1を書き込むことによってクリアされる

- LT7182SがPMBus ARAのときに、そのアドレスを正常に送信する

- PV<sub>IN0</sub>とEXTV<sub>CC</sub>両方の入力電源を遮断する

### 障害イベント・ログ

レギュレータ出力をオフするように設定された障害状態が発生した場合は、EEPROMの障害ログにイベントが書き込まれます。その障害に先行する警告や障害で、出力をオフするように設定されていないものは、イベント書き込み時にすべてサブイベントとして書き込まれます。それぞれのイベントとサブイベントは、タイムスタンプと共に書き込まれます。障害ログには、最大3個の障害オフ・イベントが保存されます。障害ログは、MFR\_FAULT\_LOGコマンドによって読み込むことができます。また、MFR\_FAULT\_LOG\_CLEARコマンドを書き込むことによってEEPROMからクリアできます。障害ログ機能はデフォルトでイネーブルされていますが、MFR\_CONFIG\_ALLのビット7をクリアすることによってディスエーブルできます。

詳細については、LT7182S PMBus/I<sup>2</sup>Cリファレンス・マニュアルに記載されているMFR\_FAULT\_LOGコマンドの説明を参照してください。

表1. 出荷時デフォルトの警告および障害動作 (Note 1)

| WARNING OR FAULT TYPE                                       | DETECTION METHOD      | DEFAULT THRESHOLD                                     | DEFAULT REGULATOR RESPONSE | DEFAULT PIN RESPONSE |          |          |

|-------------------------------------------------------------|-----------------------|-------------------------------------------------------|----------------------------|----------------------|----------|----------|

|                                                             |                       |                                                       |                            | PGOOD                | FAULT    | ALERT    |

| V <sub>OUT</sub> UV Warning                                 | Comparator            | V <sub>OUT_COMMAND</sub> -6.5%                        | Continue Operation         |                      |          | Pull Low |

| V <sub>OUT</sub> OV Warning                                 | Comparator            | V <sub>OUT_COMMAND</sub> +7.5%                        | Continue Operation         |                      |          | Pull Low |

| V <sub>OUT</sub> UV Fault                                   | Comparator            | V <sub>OUT_COMMAND</sub> -7%                          | Continue Operation         | Pull Low             |          | Pull Low |

| V <sub>OUT</sub> OV Fault                                   | Comparator            | V <sub>OUT_COMMAND</sub> +10%                         | Shutdown and Retry         | Pull Low             | Pull Low | Pull Low |

| V <sub>IN</sub> OV Fault                                    | Comparator            | 23.3V                                                 | Shutdown and Retry         | Pull Low             | Pull Low | Pull Low |

| V <sub>IN</sub> UV Warning                                  | ADC                   | -1.0V (Disabled)                                      | Continue Operation         |                      |          | Pull Low |

| Overtemperature (OT) Warning                                | ADC                   | 140°C                                                 | Continue Operation         |                      |          | Pull Low |

| OT Fault                                                    | ADC                   | 160°C                                                 | Shutdown and Retry         | Pull Low             | Pull Low | Pull Low |

| I <sub>OUT</sub> Overcurrent (I <sub>OUT_OC</sub> ) Warning | ADC                   | I <sub>Avg</sub> > 8A                                 | Continue Operation         |                      |          | Pull Low |

| I <sub>OUT</sub> OC Fault                                   | Valley Comparator     | I <sub>Valley</sub> > 6.5A (Note 2)                   | Continue Operation         |                      |          |          |

| Turn-On Time (t <sub>ON_MAX</sub> ) Fault                   | Comparator and Timer  | 5ms without Exceeding V <sub>OUT_UV_FAULT_LIMIT</sub> | Continue Operation         | Pull Low             |          | Pull Low |

| Turn-Off Time (t <sub>OFF_MAX</sub> ) Warning               | ADC and Timer         | 0 (Disabled)                                          | N/A                        |                      |          |          |

| Pin Configuration Error (Note 3)                            | I/O                   | N/A                                                   | Lock Off Until Next Reset  | Pull Low             | Pull Low | Pull Low |

| EEPROM Error                                                | CRC, ECC              | N/A                                                   | Lock Off Until Next Reset  | Pull Low             |          | Pull Low |

| Internal Reference Fault                                    | ADC and 2nd Reference | ±5%                                                   | Shutdown and Retry         | Pull Low             | Pull Low | Pull Low |

| PMBus/I <sup>2</sup> C Communication Error (CML)            | Logic                 | N/A                                                   | N/A                        |                      |          | Pull Low |

Note 1. 閾値と応答の設定を含む詳細については、LT7182S PMBus/I<sup>2</sup>Cリファレンス・マニュアルを参照してください。

Note 2. I<sub>OUT\_OC</sub>\_FAULT谷電流閾値は、MFR\_PWM\_MODE\_LT7182Sのビット[10:9]で制御します。

Note 3. 初期化中にピン設定エラーが検出された場合、デバイスは以下のピンをローにプルダウンします:FAULT0、FAULT1、RUN0、RUN1、SHARE\_CLK、PGOOD0、PGOOD1、およびALERT。

## アプリケーション情報

## 抵抗設定ピンの使用法

LT7182Sには4個の抵抗設定ピンがあり、それぞれが $\pm 1\%$ 抵抗1個を使って重要な動作パラメータを選択します。抵抗設定ピンは、ASEL、VOUT0\_CFG、VOUT1\_CFG/POLYPHASE\_CFG、およびSYNC/PWM\_CFGです。抵抗設定ピンは、パワーアップ時と、RESTORE\_USER\_ALLまたはMFR\_RESETコマンドの実行時に測定されます。それぞれの抵抗設定ピンの機能を以下に示します。

EEPROMでMFR\_CONFIG\_ALL\_LT7182Sコマンドのビット6が1に設定されている場合、CFGピン(VOUT0\_CFG、VOUT1\_CFG/POLYPHASE\_CFG、およびSYNC/PWM\_CFG)の設定抵抗は無視されますが、ASELの抵抗は常に有効です。

ASEL設定抵抗の選択を含むシリアル・インターフェース・デバイス・アドレスの設定については、LT7182S PMBus/I<sup>2</sup>Cリ

ファレンス・マニュアルに記載されているMFR\_ADDRESSコマンドの説明を参照してください。

## 出力電圧の設定

チャンネルがイネーブルされている場合は、PMBusコマンドVOUT\_COMMANDが出力電圧を指定します。

VOUT\_COMMANDコマンドは、表2の値に基づき、VOUT0\_CFGピンとVOUT1\_CFG/POLYPHASE\_CFGピンの抵抗を使って初期化することができます。VOUT0\_CFGとSGNDの間にある抵抗が、チャンネル0を設定します。チャンネル1がチャンネル0からの独立出力として設定されている場合は、VOUT1\_CFG/POLYPHASE\_CFGピンとSGNDの間にある抵抗がチャンネル1を設定します。PolyPhase構成が選択されている場合(SYNC/PWM\_CFGとグラウンドの間に5.6k $\pm 10\%$ の抵抗を1個接続)、VOUT0\_CFGはチャンネル0と1の両方を設定します。

表2. VOUTn\_CFGピン設定抵抗の選択(Note 1)

| RESISTOR VALUE ( $\pm 1\%$ ) | OUTPUT VOLTAGE SET POINT (V) (Note 2) | VOUT RANGE MODE (Note 3)                                | REGULATOR ENABLE (Note 4)                                                                                                                                        |

|------------------------------|---------------------------------------|---------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Floating or VDD18            | Initialized from NVM (Default 0.5V)   | Initialized from NVM (Default full VOUT range).         | Initialized from NVM (By default, regulator is enabled if RUN pin is asserted high.)                                                                             |

| 124k $\Omega$                | 5                                     | Full VOUT range. Supports 0.4V $\leq$ VOUT $\leq$ 5.5V. | Regulator is enabled if RUN is asserted high.<br>(OPERATION = 0x80. ON_OFF_CONFIG initialized from NVM, default requires OPERATION = 0x80 and RUN pin asserted.) |

| 107k $\Omega$                | 3.3                                   |                                                         |                                                                                                                                                                  |

| 93.1k $\Omega$               | 2.5                                   |                                                         |                                                                                                                                                                  |

| 80.6k $\Omega$               | 1.8                                   |                                                         |                                                                                                                                                                  |

| 69.8k $\Omega$               | 1.5                                   |                                                         |                                                                                                                                                                  |

| 60.4k $\Omega$               | 1.35                                  |                                                         |                                                                                                                                                                  |

| 51.1k $\Omega$               | 1.2                                   |                                                         |                                                                                                                                                                  |

| 43.2k $\Omega$               | 1.1                                   |                                                         |                                                                                                                                                                  |

| 36.5k $\Omega$               | 1                                     |                                                         |                                                                                                                                                                  |

| 30.9k $\Omega$               | 0.9                                   |                                                         |                                                                                                                                                                  |

| 25.5k $\Omega$               | 0.85                                  |                                                         |                                                                                                                                                                  |

| 21k $\Omega$                 | 0.8                                   |                                                         |                                                                                                                                                                  |

| 16.5k $\Omega$               | 0.75                                  |                                                         |                                                                                                                                                                  |

| 11.8k $\Omega$               | 0.7                                   |                                                         |                                                                                                                                                                  |

| 6.65k $\Omega$               | 0.6                                   |                                                         |                                                                                                                                                                  |

| 0 (SGND)                     | Initialized from NVM (Default 0.5V)   | Initialized from NVM (default full VOUT range)          | Regulator disabled and RUN pin ignored.                                                                                                                          |

Note 1. 表3に従ってSYNC/PWM\_CFGピンを5.6k $\Omega \pm 10\%$ の抵抗に接続してPolyPhase動作を選択した場合は、表4に従い、VOUT1\_CFG/POLYPHASE\_CFG設定抵抗が周波数と位相を含むPWM設定を制御します。

Note 2. 出力電圧設定点はVOUT\_COMMANDで制御します。

Note 3. VOUT範囲モードの選択は、MFR\_PWM\_MODE\_LT7182Sのビット1で制御します。値を1にすると、高性能低VOUTモードが選択されます。

Note 4. PMBus ON\_OFF\_CONFIGコマンドは、RUNピンとPMBus OPERATIONコマンドのどちらでレギュレータをイネーブルするかを選択します。

## アプリケーション情報

$V_{OUTn\_CFG}$ ピンがオープンになっている場合または $V_{DD18}$ に接続されている場合は、EEPROMから $VOUT\_COMMAND$ コマンドがロードされて出力電圧を決定します。デフォルトのEEPROM設定では、電圧設定抵抗が取り付けられている場合を除き、レギュレータをディスエーブルした状態で初期化が行われます。

出力電圧の初期化に抵抗設定ピンが使われている場合は、 $VOUT\_COMMAND$ のパーセンテージに基づいて以下のコマンドが初期化されます。

|                            |       |

|----------------------------|-------|

| • $VOUT\_OV\_FAULT\_LIMIT$ | +10%  |

| • $VOUT\_OV\_WARN\_LIMIT$  | +7.5% |

| • $VOUT\_MAX$              | +7.5% |

| • $VOUT\_MARGIN\_HIGH$     | +5%   |

| • $VOUT\_MARGIN\_LOW$      | -5%   |

| • $VOUT\_UV\_WARN\_LIMIT$  | -6.5% |

| • $VOUT\_UV\_FAULT\_LIMIT$ | -7%   |

### スイッチング周波数と位相

PWMスイッチング周波数は、内部発振器を使用するか、 $SYNC/PWM\_CFG$ ピンに外部クロックを加えることによって設定できます。内部フェーズ・ロック・ループ(PLL)は、クロックが内部供給か外部供給かにかかわらず、このタイミング・リファレンスにPWM制御を同期します。内部発振器の周波数は、 $FREQUENCY\_SWITCH$ コマンドによって設定します。 $MFR\_PWM\_PHASE\_LT7182S$ コマンドは、各チャンネルの位相を設定します。

$SYNC/PWM\_CFG$ ピンは柔軟な多目的入出力ピンで、設定抵抗入力として、あるいはクロック入力または出力として使用することができます。

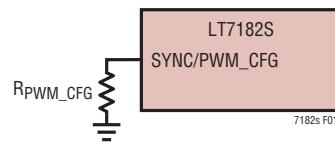

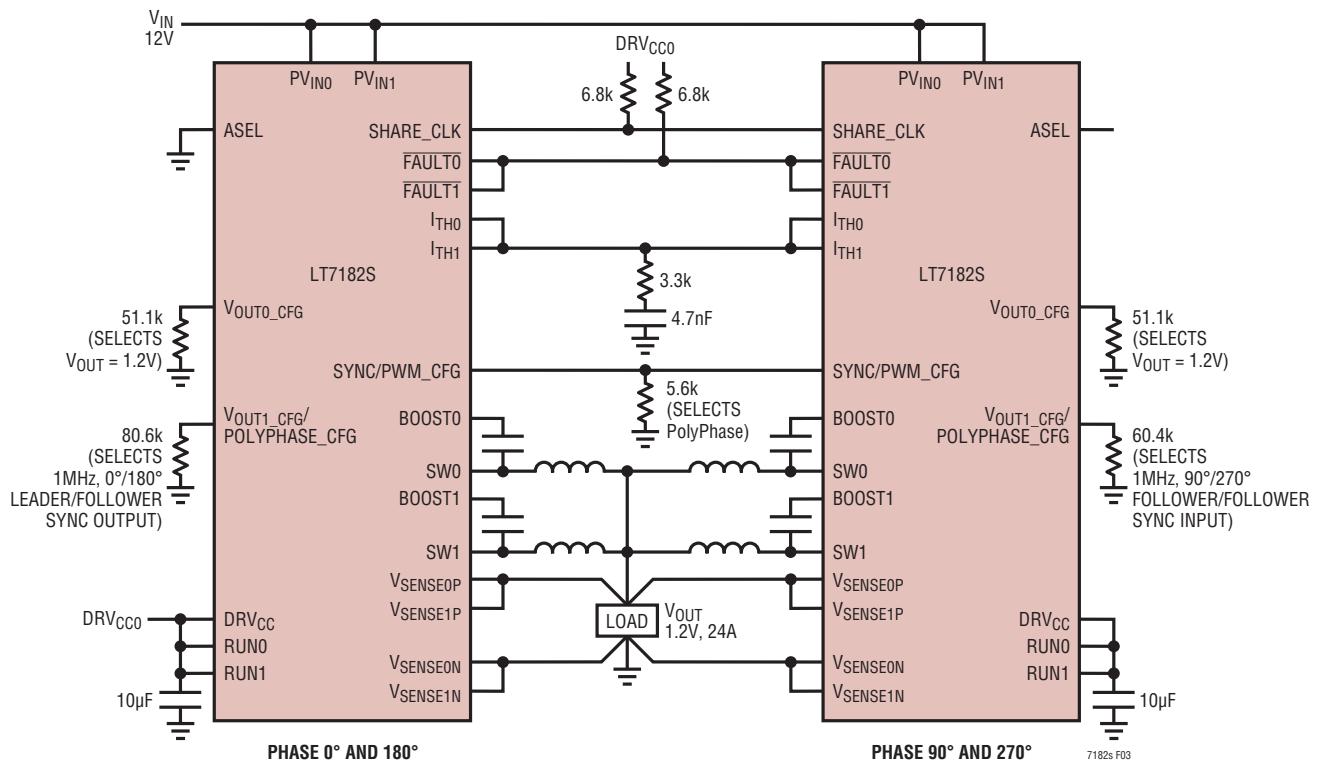

$SYNC/PWM\_CFG$ とグラウンド(PGNDまたはSGND)の間に接続した抵抗は、表3に従ってPWM設定(周波数、位相、および動作モードを含む)を初期化するために使用できます。単相および2相アプリケーションにおけるPWM設定抵抗接続の例については、図1を参照してください。これらの例では、外部同期入力や出力のクロックは不要です。 $PWM\_CFG$ 抵抗の選択肢については表2を参照してください。

図1. 外部クロックを使わないPWM抵抗設定

LT7182Sは、出力ドライバとして設定されている場合や、入力クロックを無視するようにプログラムされている場合を除き、自動的にPWMスイッチングを $SYNC/PWM\_CFG$ の外部クロック入力に同期します。 $SYNC/PWM\_CFG$ ピンに外部同期クロックが使われている場合、LT7182Sは両方のチャンネルで自動的に強制連続モードを使用します。外部クロック信号が失われた場合、LT7182Sは内部発振器を使ってPWM動作を続行します。外部同期クロックを使用する場合は、 $FREQUENCY\_SWITCH$ コマンドをプログラムするか、設定抵抗を使って内部発振器周波数を外部クロック周波数と同様の周波数値に設定することを推奨します。これにより、外部クロックが失われた場合でも、PWMスイッチング周波数を適切な値に維持することができます。LT7182Sは、 $MFR\_SYNC\_CONFIG\_LT7182S$ のビット1に1を書き込むことによって、外部クロックを無視するようにプログラムできます。

LT7182Sは、 $MFR\_SYNC\_CONFIG\_LT7182S$ のビット0を1に設定することによって、 $SYNC/PWM\_CFG$ ピンから他のデバイスへ同期クロック出力を供給するように設定できます。

$SYNC/PWM\_CFG$ 出力クロックをイネーブルすると、LT7182Sは、 $SYNC/PWM\_CFG$ ピンを、 $FREQUENCY\_SWITCH$ でプログラムされた周波数と0~1.88V(代表値)の振幅を持つ矩形波として駆動します。 $SYNC$ の位相は、PWM出力の位相より、 $MFR\_PWM\_PHASE\_LT7182S$ で設定された値だけ進んだ位相となります。出力として設定できるのは、 $SYNC/PWM\_CFG$ に接続された1つのデバイスだけです。

$SYNC/PWM\_CFG$ のクロックがアクティブになっているときは、 $MFR\_PWM\_PHASE\_LT7182S$ コマンドが、 $SYNC/PWM\_CFG$ の立上がりエッジと、そのチャンネルのSWの立上がりエッジ間の位相関係を指定します。

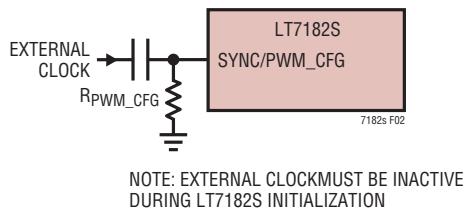

$SYNC/PWM\_CFG$ 設定抵抗と同期クロック入力機能の両方を使用する場合は、図2に示すようにクロック源とLT7182Sの間に1.5nFのコンデンサを配置して、クロック信号をACカップリングする必要があります。この場合は、クロック信号が抵抗設定機能に干渉しないようにするために、LT7182Sの初期化時にクロック信号を非アクティブにしてください。ACカップリングしたクロック源出力のインピーダンスが50Ω未満の場合は、クロック源と直列に50Ωの抵抗を追加する必要があります。 $PWM\_CFG$ 抵抗の選択については表2を参照してください。

## アプリケーション情報

表3. SYNC/PWM\_CFG ピン設定抵抗の選択

| RESISTOR<br>VALUE<br>( $\pm 1\%$ )             | PWM<br>FREQUENCY<br>(Notes 1, 2)                                                                                                                                                                                                                                                 | PWM PHASE<br>(Note 3)                   |                                           | PWM MODE<br>(Note 4)                     | PolyPhase<br>FOLLOWER/<br>LEADER<br>(Note 5)      | INTERNAL COMPENSATION<br>(Note 6)         |                                                    |                                     | SYNC/PWM<br>CFG CLOCK<br>OUTPUT OR<br>INPUT<br>(Note 8) |  |

|------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|-------------------------------------------|------------------------------------------|---------------------------------------------------|-------------------------------------------|----------------------------------------------------|-------------------------------------|---------------------------------------------------------|--|