# 5V、±25A 高効率 Silent Switcher® (サイレント・スイッチャ) 2 降圧レギュレータ

## 特長

- ▶ Silent Switcher®2 アーキテクチャ

- ▶ 超低 EMI

- ▶ PCB レイアウト感度の影響を排除

- ▶ 内蔵バイパス・コンデンサが放射 EMI を低減

- ▶  $V_{IN}$  : 2.7V~5V,  $P_{VIN}$  : 1.5V~5V

- ▶  $V_{OUT}$  : 0.5V~0.9· $V_{IN}$

- ▶ 正確なリファレンス: 全温度範囲で  $0.5V \pm 0.8\%$

- ▶ 内蔵 N-MOSFET :  $1.8m\Omega/0.7m\Omega$

- ▶ 15ns の最小オン時間: 低デューティサイクル動作

- ▶ 差動  $V_{OUT}$  リモート検出

- ▶ 設定可能な固定出力オプション

- ▶ プログラマブルな負荷ライン (3つの設定)

- ▶ プログラマブルな電流制限 (3つの設定)

- ▶ プログラマブル、同期可能: 400kHz~5MHz

- ▶ Discontinuous Mode® (不連続モード、DCM) または強制連續モード (FCM) 動作を選択可能

- ▶ 制御 TON、電流モード: 優れた過渡特性

- ▶ パワー・グッド・ステータス、出力トラッキング、クロック出力

- ▶ スペクトラム拡散動作をサポート

- ▶ PolyPhase 動作: 2, 3, 4, 6, 8, 12 相

- ▶ 36 ピン (4mm × 7mm) 背面露出 LQFN パッケージ

## 概要

LT®7153SP は、負荷に±25A を供給できる高効率モノリシック同期整流式 Silent Switcher® (サイレント・スイッチャ) 2 降圧レギュレータです。独自の固定周波数、オン時間制御、電流モードのアーキテクチャは、高周波数で動作し、高速過渡応答を必要とする高降圧比アプリケーションに最適です。PolyPhase 動作により、複数の LT7153SP レギュレータを位相をずらして動作させることができます。必要な入力コンデンサと出力コンデンサの量が削減されると共に、並列接続によってより高い出力電流が得られます。動作電源電圧範囲は 2.7V~5V です。

動作周波数は、400kHz~5MHz の範囲で外部抵抗を用いてプログラム可能であり、また、外部クロック信号への同期もできます。高周波機能により、物理的に小さいインダクタとコンデンサを使用できます。

LT7153SP パッケージは、第 2 世代の Silent Switcher アーキテクチャを採用しており、高いスイッチング周波数で高い効率を実現しながら EMI 放出を最小限に抑えることができます。このデバイスには、高周波電流ループを最適化するためのバイパス・コンデンサが内蔵されており、レイアウト感度を低減することで、規定された EMI 性能の実現を容易にしています。また、ヒート・シンクの取り付け用に背面が露出しており、これにより熱性能を大幅に向上させることができます。

## アプリケーション

- ▶ 光学モジュール・アプリケーション

- ▶ 分散型電源システム、サーバー電源

- ▶ ポイントオブロード電源 (ASIC、FPGA、DSP、μP)

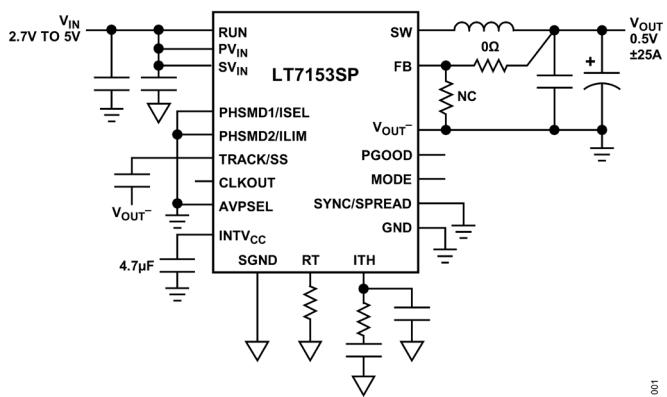

## 代表的なアプリケーション回路

図 1. 0.5V、±25A 降圧レギュレータ

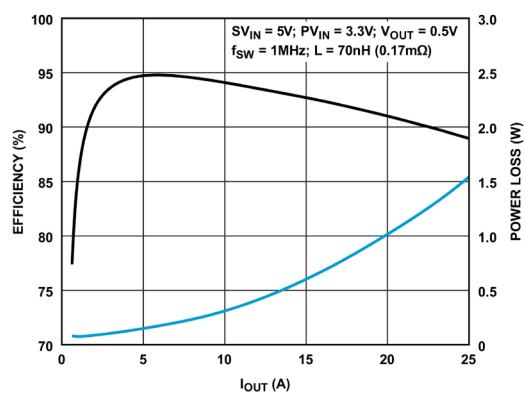

図 2. 効率と電力損失 (1MHz)

※こちらのデータシートには正誤表が付属しています。当該資料の最終ページ以降をご参照ください。

Rev. A

アナログ・デバイセズ社は、提供する情報が正確で信頼できるものであることを期していますが、その情報の利用に関して、あるいは利用によって生じる第三者の特許やその他の権利の侵害に関して一切の責任を負いません。また、アナログ・デバイセズ社の特許または特許の権利の使用を明示的または暗示的に許諾するものではありません。仕様は、予告なく変更される場合があります。本紙記載の商標および登録商標は、各社の所有に属します。※日本語版資料は REVISION が古い場合があります。最新の内容については、英語版をご参照ください。

## 目次

|                                      |    |

|--------------------------------------|----|

| 特長                                   | 1  |

| アプリケーション                             | 1  |

| 概要                                   | 1  |

| 代表的なアプリケーション回路                       | 1  |

| 改訂履歴                                 | 3  |

| 仕様                                   | 4  |

| 絶対最大定格                               | 7  |

| ピン配置およびピン機能の説明                       | 8  |

| 代表的な性能特性                             | 11 |

| ブロック図                                | 15 |

| 動作原理                                 | 16 |

| メイン制御ループ                             | 16 |

| 低 $I_Q$ シャットダウン (RUN)                | 16 |

| INTV <sub>CC</sub> レギュレータとバイパス・コンデンサ | 16 |

| 調整可能な電流制限                            | 17 |

| 過電流保護と短絡保護                           | 17 |

| マルチフェーズ動作                            | 17 |

| パワー・グッド・ステータス出力                      | 17 |

| V <sub>IN</sub> 過電圧保護                | 17 |

| 選択可能な負荷ライン (AVPSEL)                  | 17 |

| MODE、SYNC、スペクトラム拡散動作                 | 17 |

| アプリケーション情報                           | 18 |

| Silent Switcher アーキテクチャ              | 18 |

| スイッチング周波数の設定                         | 18 |

| 出力電圧の設定                              | 18 |

| ソフトスタートおよび出力電圧 TRACK                 | 19 |

| インダクタの選択                             | 19 |

| 入力コンデンサ ( $C_{IN}$ ) の選択             | 20 |

| 出力コンデンサ ( $C_{OUT}$ ) の選択            | 20 |

| 入出力セラミック・コンデンサの使用                    | 21 |

| 最小オフ時間と最小オン時間に関する考慮事項                | 21 |

| マルチフェーズ構成                            | 22 |

| ITH 補償                               | 23 |

| 過渡応答のチェック                            | 23 |

|                      |    |

|----------------------|----|

| 熱的条件.....            | 24 |

| 効率に関する考慮事項.....      | 24 |

| 設計例.....             | 25 |

| ボード・レイアウト時の考慮事項..... | 26 |

| 代表的なアプリケーション.....    | 27 |

| 外形寸法.....            | 28 |

| オーダー・ガイド.....        | 29 |

| 関連製品.....            | 30 |

## 改訂履歴

| 版数 | 改訂日   | 説明                  | 改訂ページ |

|----|-------|---------------------|-------|

| 0  | 05/25 | 初版発行                | -     |

| A  | 07/25 | 図番号を図 31 から図 24 に更新 | 24    |

## 仕様

表 1. 電気的特性

(特に指定のない限り、各仕様は  $T_A = 25^\circ\text{C}$ 、 $V_{IN} = 5\text{V}$  における値。)

| PARAMETER                             | SYMBOL             | CONDITIONS/COMMENTS                                             | MIN  | TYP  | MAX         | UNITS         |

|---------------------------------------|--------------------|-----------------------------------------------------------------|------|------|-------------|---------------|

| Supply Voltage Range                  | $SV_{IN}$          | $-40^\circ\text{C} \leq T_J \leq 125^\circ\text{C}$             | 2.7  | 5    |             | V             |

|                                       | $PV_{IN}$          |                                                                 | 1.5  | 5    |             |               |

| $V_{OUT}$ Operating Voltage           | $V_{OUT}$          | $R_{RT} = 100\text{k}\Omega$                                    | 0.5  |      | $0.9V_{IN}$ | V             |

| Supply Operating Current <sup>2</sup> | $I_Q(\text{ACT})$  | Active, No-Load<br>$R_{RT} = 100\text{k}\Omega$ , MODE/SYNC = 0 |      | 1.5  | 3           | mA            |

| Supply Shutdown Current <sup>2</sup>  | $I_Q(\text{SHDN})$ | $V_{RUN} = 0\text{V}$                                           |      |      | 5           | $\mu\text{A}$ |

| $V_{IN}$ OV Threshold                 | $V_{IN-OV}$        | Rising                                                          |      | 8.0  |             | V             |

|                                       |                    | Falling                                                         |      | 7.5  |             |               |

| RUN Threshold                         | $V_{RUN}$          | Rising                                                          | 1.13 | 1.18 | 1.23        | V             |

|                                       | $V_{RUN\_Hys}$     | Hysteresis                                                      |      | 80   |             | mV            |

| INTV <sub>cc</sub> Regulated Voltage  | $V_{INTVCC}$       | $SV_{IN} > 4\text{V}$                                           | 3.45 | 3.6  | 3.75        | V             |

| INTV <sub>cc</sub> UVLO               | $V_{UVLO}$         | Rising                                                          |      | 2.55 | 2.65        | V             |

|                                       |                    | Falling                                                         |      | 2.4  |             |               |

## BUCK Regulator Loop

|                                                     |                                   |                                                     |                                                     |      |      |      |                  |

|-----------------------------------------------------|-----------------------------------|-----------------------------------------------------|-----------------------------------------------------|------|------|------|------------------|

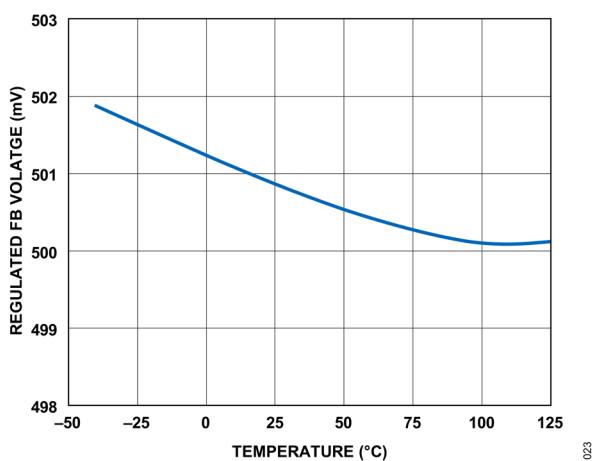

| FB regulation Voltage <sup>3</sup>                  | $V_{FB}$                          | ITH = 1V                                            | $-40^\circ\text{C} \leq T_J \leq 125^\circ\text{C}$ | 496  | 500  | 504  | mV               |

| FB Line and Load Regulation <sup>3</sup>            | $\Delta V_{FB(\text{LINE+LOAD})}$ | AVPSEL = 0V                                         | $-40^\circ\text{C} \leq T_J \leq 125^\circ\text{C}$ |      | 0.05 | 0.3  | %<br>%           |

|                                                     |                                   | AVPSEL = Float, ITH > 1V                            |                                                     |      | 1    |      |                  |

|                                                     |                                   | AVPSEL = INTV <sub>cc</sub> , ITH > 1V              |                                                     |      | 1.5  |      |                  |

| FB Pin Input Current                                | $I_{FB}$                          | $-40^\circ\text{C} \leq T_J \leq 125^\circ\text{C}$ |                                                     | -50  | 50   |      | nA               |

| Error Amplifier gm                                  | $GM_{(EA)}$                       | ITH = 1V                                            |                                                     | 0.85 | 1    | 1.15 | mS               |

| Minimum On-Time                                     | $t_{ON(\text{MIN})}$              | $-40^\circ\text{C} \leq T_J \leq 125^\circ\text{C}$ |                                                     |      | 15   | 25   | ns               |

| Minimum Off-Time                                    | $t_{OFF(\text{MIN})}$             |                                                     |                                                     |      | 30   |      | ns               |

| Positive Inductor Valley Current Limit <sup>4</sup> | $I_{LIM-POS}$                     | FB = 0.48V                                          |                                                     | 20   | 25   | 30   | A                |

| Current Threshold vs. ITH Voltage                   | $I_{LIM-ITH}$                     | ITH = 1.3V                                          |                                                     |      | 25   |      | A                |

|                                                     |                                   | ITH = 1.0V                                          |                                                     |      | 0    |      |                  |

|                                                     |                                   | ITH = 0.7V                                          |                                                     |      | -25  |      |                  |

| Negative Inductor Valley Current Limit              | $I_{LIM-NEG}$                     | FB = 0.52V                                          |                                                     |      | -60  |      | A                |

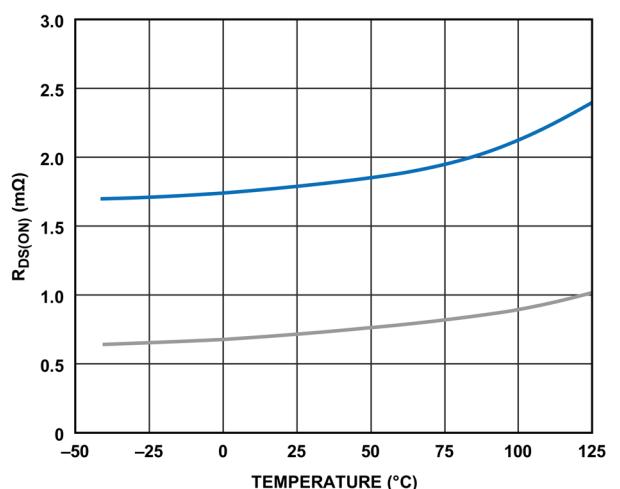

| Top Power NMOS On Resistance                        | $R_{ON-TOP}$                      | INTV <sub>cc</sub> = 3.6V                           |                                                     |      | 1.8  |      | $\text{m}\Omega$ |

| Bottom Power NMOS On Resistance                     | $R_{ON-BOT}$                      | INTV <sub>cc</sub> = 3.6V                           |                                                     |      | 0.7  |      | $\text{m}\Omega$ |

| Top Switch Leakage                                  | $I_{SW-TOP}$                      | $V_{IN} = 5\text{V}, V_{SW} = 0\text{V}$            |                                                     |      | 0.5  |      | $\mu\text{A}$    |

| Bottom Switch Leakage                               | $I_{BOT-TOP}$                     | $V_{IN} = 5\text{V}, V_{SW} = 5\text{V}$            |                                                     |      | 1    |      | $\mu\text{A}$    |

(特に指定のない限り、各仕様は  $T_A = 25^\circ\text{C}$ 、 $V_{IN} = 5\text{V}$  における値。)

| PARAMETER                         | SYMBOL                            | CONDITIONS/COMMENTS                                          | MIN                | TYP      | MAX  | UNITS         |

|-----------------------------------|-----------------------------------|--------------------------------------------------------------|--------------------|----------|------|---------------|

| <b>Oscillator</b>                 |                                   |                                                              |                    |          |      |               |

| Oscillator Frequency              | $f_{osc}$                         | $R_{RT} = 232\text{k}\Omega$                                 |                    | 0.4      |      | MHz           |

|                                   |                                   | $R_{RT} = 100\text{k}\Omega$                                 | 0.85               | 1        | 1.15 |               |

|                                   |                                   | $R_{RT} = 20\text{k}\Omega$                                  |                    | 5        |      |               |

| SYNC Input Range                  | $f_{SYNC}$                        | % of programmed frequency                                    |                    | $\pm 30$ |      | %             |

| MODE, SYNC/SPREAD Threshold       | $V_{IL(MODE)}$                    | MODE or SYNC/SPREAD LOW                                      |                    |          | 0.3  | V             |

|                                   | $V_{IH(SYNC/SPREAD)}$             | MODE or SYNC/SPREAD HIGH                                     | 1.0                |          |      |               |

| MODE, SYNC/SPREAD Currents        | $I_{MODE}$<br>$I_{SYNC/SPREAD}$   | MODE = 0,<br>SYNC = 0V                                       | 6                  | 14       |      | $\mu\text{A}$ |

| CLKOUT Threshold                  | $V_{IL(CLKOUT)}$                  | CLKOUT High                                                  | $V_{INTVCC} - 0.2$ |          |      | V             |

|                                   | $V_{IH(CLKOUT)}$                  | CLKOUT Low                                                   | 0                  | 0.2      |      |               |

| <b>Phasing</b>                    |                                   |                                                              |                    |          |      |               |

| SYNC to Oscillator                | $\phi_{(SYNC \text{ to } OSC)}$   | PHSMD1 = 0, PHSMD2 = 0                                       |                    | 0        |      | Degree        |

|                                   |                                   | PHSMD1 = INTV <sub>cc</sub> , PHSMD2 = 0                     |                    | 0        |      |               |

|                                   |                                   | PHSMD1 = 0, PHSMD2 = INTV <sub>cc</sub> /2                   | -30                |          |      |               |

|                                   |                                   | PHSMD1 = INTV <sub>cc</sub> , PHSMD2 = INTV <sub>cc</sub> /2 | -45                |          |      |               |

|                                   |                                   | PHSMD1 = 0, PHSMD2 = INTV <sub>cc</sub>                      | -60                |          |      |               |

|                                   |                                   | PHSMD1 = INTV <sub>cc</sub> , PHSMD2 = INTV <sub>cc</sub>    | -90                |          |      |               |

| Oscillator to CLKOUT              | $\phi_{(OSC \text{ to } CLKOUT)}$ | PHSMD1 = 0, PHSMD2 = 0                                       | 180                |          |      | Degree        |

|                                   |                                   | PHSMD1 = INTV <sub>cc</sub> , PHSMD2 = 0                     | 120                |          |      |               |

|                                   |                                   | PHSMD1 = 0, PHSMD2 = INTV <sub>cc</sub> /2                   | 180                |          |      |               |

|                                   |                                   | PHSMD1 = INTV <sub>cc</sub> , PHSMD2 = INTV <sub>cc</sub> /2 | 180                |          |      |               |

|                                   |                                   | PHSMD1 = 0, PHSMD2 = INTV <sub>cc</sub>                      | 120                |          |      |               |

|                                   |                                   | PHSMD1 = INTV <sub>cc</sub> , PHSMD2 = INTV <sub>cc</sub>    | 180                |          |      |               |

| AVPSEL, PHSMD1, PHSMD2, Threshold | $V_{IH}$                          | AVPSEL, PHSMD1, PHSMD2 High                                  | $V_{INTVCC} - 0.2$ |          |      | V             |

| AVPSEL, PHSMD1, PHSMD2 Threshold  | $V_{IL}$                          | AVPSEL, PHSMD1, PHSMD2 Low                                   |                    | 0.2      |      | V             |

| <b>ILIM</b>                       |                                   |                                                              |                    |          |      |               |

| Reduced Max Current Limit         | $I_{LIM55}$                       | PHSMD1 = INTV <sub>cc</sub> /2, PHSMD2 = 0                   |                    | 14       |      | A             |

|                                   | $I_{LIM70}$                       | PHSMD1 = INTV <sub>cc</sub> /2, PHSMD2 = INTV <sub>cc</sub>  |                    | 18       |      |               |

| <b>Power Good</b>                 |                                   |                                                              |                    |          |      |               |

| PGOOD Over Voltage Threshold      | OV                                | $V_{FB}$ Rising                                              | 4                  | 6.5      | 9    | %             |

|                                   |                                   | $V_{FB}$ Hysteresis (Falling)                                |                    | 1.5      |      |               |

| PGOOD Under Voltage Threshold     | UV                                | $V_{FB}$ Falling                                             | -9                 | -6.5     | -4   | %             |

|                                   |                                   | $V_{FB}$ Hysteresis (Rising)                                 |                    | 1.5      |      |               |

(特に指定のない限り、各仕様は  $T_A = 25^\circ\text{C}$ 、 $V_{IN} = 5\text{V}$  における値。)

| PARAMETER                  | SYMBOL                | CONDITIONS/COMMENTS    | MIN | TYP | MAX | UNITS         |

|----------------------------|-----------------------|------------------------|-----|-----|-----|---------------|

| PGOOD Leakage Current      | $I_{PGOOD}$           |                        |     |     | 0.5 | $\mu\text{A}$ |

| PGOOD Pull-Down Resistance | $R_{PGOOD}$           | $V_{PG} = 0.1\text{V}$ |     | 5   |     | $\Omega$      |

| PGOOD Delay                | $PG_{(\text{Delay})}$ | PGOOD Low to High      |     | 6   |     | Cycles        |

|                            |                       | PGOOD High to Low      |     | 25  |     |               |

### Track/Soft-Start

|                      |                |                              |      |    |               |

|----------------------|----------------|------------------------------|------|----|---------------|

| Source Current       | $I_{TRACK/SS}$ | $V_{TRACK/SS} = 0\text{V}$   | 10   | 15 | $\mu\text{A}$ |

| Pull-Down Resistance | $R_{TRACK/SS}$ | $V_{TRACK/SS} = 0.1\text{V}$ | 2500 |    | $\Omega$      |

<sup>1</sup> LT7153SP は  $T_J \approx T_A$  となるようなパルス負荷条件下でテストされています。 $-40^\circ\text{C} \sim 125^\circ\text{C}$  の動作ジャンクション温度範囲における仕様は、設計、特性評価、および統計的プロセス制御との相關付けによって確認されています。LT7153SP の動作は、 $-40^\circ\text{C} \sim 125^\circ\text{C}$  の動作ジャンクション温度範囲全体にわたって確保されています。ここに示す仕様に見合った最大周囲温度は、具体的な動作条件と、ボード・レイアウト、パッケージの熱抵抗定格値、およびその他の環境条件の組み合わせによって決まります。ジャンクション温度 ( $T_J$ 、 $^\circ\text{C}$ ) は、次式を使って周囲温度 ( $T_A$ 、 $^\circ\text{C}$ ) と消費電力 ( $P_D$ 、ワット) から計算します。

$$T_J = T_A + (P_D \cdot \theta_{JA}) \quad \text{ここで、} \theta_{JA} \quad (\text{C/W}) \quad \text{はパッケージの熱抵抗です。}$$

<sup>2</sup> 不連続モード時の静止電流には、パワーFETのスイッチング損失は含まれていません。

<sup>3</sup>  $V_{FB}$  は、仕様規定されている電圧に  $V_{ITH}$  をサーボ制御する帰還ループ内で測定されます。

<sup>4</sup> インダクタは、アプリケーションにおいてピーク・インダクタ電流が 39A を超過しないように選択する必要があります。

**絶対最大定格**

表 2. 絶対最大定格

| PARAMETER                                | RATING                             |

|------------------------------------------|------------------------------------|

| SV <sub>IN</sub> , PV <sub>IN</sub> , SW | -0.3V to 5.5V                      |

| RUN, PGOOD, TRACK                        | -0.3V to 5.5V                      |

| MODE, SYNC/SPREAD                        | -0.3V to INTV <sub>cc</sub> + 0.3V |

| FB, ITH, RT                              | -0.3V to INTV <sub>cc</sub> + 0.3V |

| PHSMD1/ISEL, PHSMD2/ILIM, CLKOUT, AVPSEL | -0.3V to INTV <sub>cc</sub> + 0.3V |

| VOUT-                                    | -0.3V to 0.3V                      |

| Operating Junction Temperature Range     | -40°C to 125°C                     |

| Storage Temperature Range                | -65°C to 150°C                     |

| Maximum Internal Temperature             | 125°C                              |

| Peak Reflow Solder Body temperature      | 260°C                              |

上記の絶対最大定格を超えるストレスを加えると、デバイスに恒久的な損傷を与えることがあります。この規定はストレス定格のみを指定するものであり、この仕様の動作のセクションに記載する規定値以上でのデバイス動作を定めたものではありません。デバイスを長時間にわたり絶対最大定格状態に置くと、デバイスの信頼性に影響を与えることがあります。

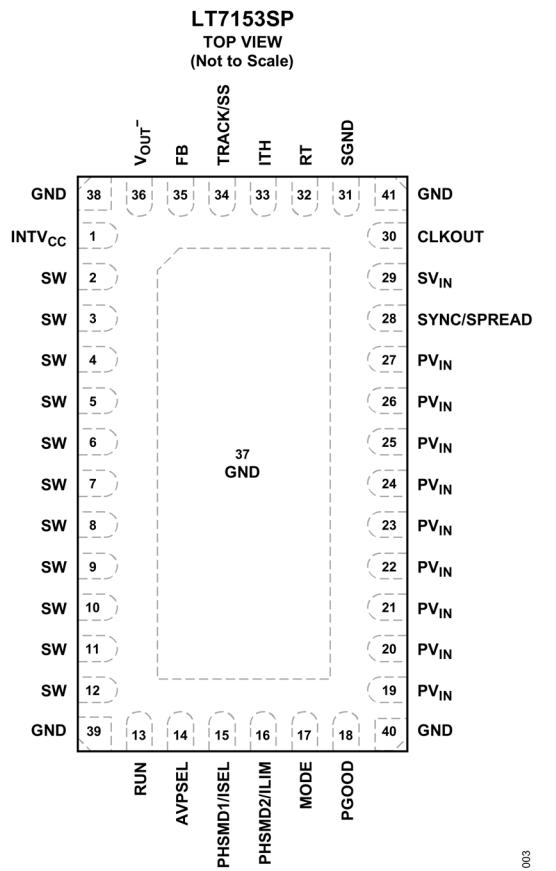

## ピン配置およびピン機能の説明

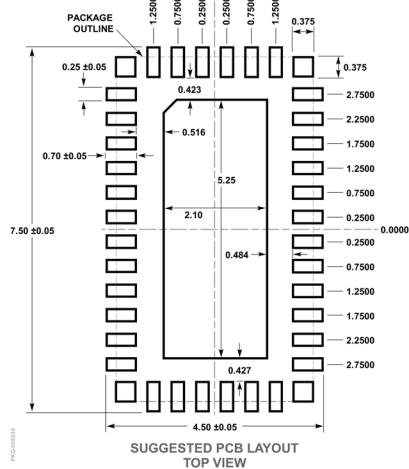

LQFN PACKAGE

36-LEAD (4mm x 7mm x 1.02mm)

T<sub>JMAX</sub> = 125 °C, θ<sub>JA</sub> = 15.8°C/W (BASED ON DEMOBOARD), θ<sub>JCTop</sub> = 0.4°C/W, θ<sub>JCbot</sub> = 3.4°C/W

EXPOSED PAD (PIN 37) AND CORNER PINS (38~41) ARE GND, MUST BE SOLDERED TO PCB

図 3. ピン配置

表 3. 端子説明

| 端子    | 名称                 | 説明                                                                                                                                                                                                                |

|-------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | INTV <sub>cc</sub> | 内部 3.6V レギュレータ出力。内部パワー・ドライバおよび制御回路には、この電圧から給電されます。このピンは、4.7μF 以上の低 ESR セラミック・コンデンサを用いて電源グラウンドとデカップリングします。                                                                                                         |

| 2-12  | SW                 | 外付けインダクタへのスイッチ・ノードの接続。SW の電圧振幅は、グラウンドからダイオード電圧を差し引いた電圧から PV <sub>IN</sub> よりダイオード電圧分だけ高い電圧までです。                                                                                                                   |

| 13    | RUN                | ロジック制御の RUN 入力。このピンはフロート状態のままにしないでください。ロジック・ハイで降圧レギュレータが起動します。                                                                                                                                                    |

| 14    | AVPSEL             | このピンを使用して 3 通りの負荷ラインから選択します。GND に接続 : 0.2%、フローティング : 1%、INTV <sub>cc</sub> : 1.5%                                                                                                                                 |

| 15    | PHSMD1/<br>ISEL    | 位相セレクタと ILIM オプションの制御入力。このピンがハイまたはローである場合は、PHSMD2/ILIM ピンの状態との組み合わせで、SYNC と内部発振器の間の位相関係、内部発振器と CLKOUT の位相関係が決定します。このピンを中間レール (1/2 INTV <sub>cc</sub> ) にフロートすると、PHSMD2/ILIM を使用して 3 つの低い ILIM 設定の中から選択できます。       |

| 16    | PHSMD2/<br>ILIM    | 位相セレクタと ILIM 設定の制御入力。PHSMD1/ISEL をハイまたはローである場合は、このピンと PHSMD1/ILIM との組み合わせで、SYNC と内部発振器の間の位相関係、内部発振器と CLKOUT の位相関係が決定します。PHSMD1/ISEL を中間レール (1/2 INTV <sub>cc</sub> ) にフロートすると、このピンを使用して 3 つの低い ILIM 設定の中から選択できます。 |

| 17    | MODE               | モード選択ピン。MODE を GND に接続すると、不連続モードで動作します。MODE をフロート状態にするか 1V を超える電圧に接続すると、強制連続モードが選択されます。                                                                                                                           |

| 18    | PGOOD              | オープン・ドレイン・ロジックの出力パワー・グッド。FB ピンの電圧が内部 0.5V リファレンスの ±6.5% から外れると、PGOOD はグラウンドに引き下げられます。                                                                                                                             |

| 19-27 | PV <sub>IN</sub>   | 電源 V <sub>IN</sub> 。内蔵パワーMOSFETへの入力電圧。                                                                                                                                                                            |

| 28    | SYNC/ SPREAD       | スペクトラム拡散選択と発振器同期ピン。SYNC/SPREAD を GND に接続するとスペクトラム拡散動作がディスエーブルされ、INTV <sub>cc</sub> に接続するかフローティングにするとスペクトラム拡散が開始します。外部クロックに接続すると、システム・クロックが外部クロックに同期し、デバイスは強制連続モードになります。                                           |

| 29    | SV <sub>IN</sub>   | 信号 V <sub>IN</sub> 。3.6V 内蔵レギュレータへのフィルタ処理された入力電圧。2.2Ω の抵抗と 10μF のセラミック・コンデンサの直列接続を介して SV <sub>IN</sub> ピンに信号をバイパス接続します。                                                                                           |

| 30    | CLKOUT             | PolyPhase 動作用のクロック信号出力。SYNC を基準とする CLKOUT の位相は、PHSMD1 ピンと PHSMD2 ピンの状態によって決まります。CLKOUT のピーク to ピーク振幅は INTV <sub>cc</sub> ～GND です。位相誤差を低減するため、このピンの寄生容量は最小限にします。RUN がローのとき、このピンはデフォルトでハイになります。                     |

| 31    | SGND               | 信号グラウンド用のグラウンド。                                                                                                                                                                                                   |

| 32    | RT                 | スイッティング周波数の設定ピン。このピンと GND の間に外付け抵抗を接続すると、周波数を 400kHz～5MHz の範囲で設定できます。                                                                                                                                             |

|       |            |                                                                                                                                                                                                                                          |

|-------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 33    | ITH        | エラー・アンプの出力およびスイッチング・レギュレータの補償ポイント。電流コンパレータのトリップ閾値は、この電圧と線形に比例します。この電圧の通常の範囲は 0.3V~1.3V です。                                                                                                                                               |

| 34    | TRACK/SS   | 出力トラッキングおよびソフトスタート・ピン。出力電圧の立ち上がり時間を制御できます。 $V_{OUT-}$ を基準に 0V~0.5V の範囲の電圧をこのピンに接続すると、内部リファレンス入力をエラー・アンプにバイパスします。それ以外の場合、 $V_{OUT-}$ 電圧を基準としてこの電圧に FB ピンがサーボ制御されます。INTV <sub>CC</sub> ピンからこのピンに 10µA の内部プルアップ電流が流れることによりソフトスタート機能を実現できます。 |

| 35    | FB         | 降圧レギュレータのエラー・アンプへの帰還入力。帰還抵抗分圧器の中点のタップをこのピンに接続します。出力は 0.5V~4.5V の範囲で調節可能です。                                                                                                                                                               |

| 36    | $V_{OUT-}$ | 出力レールの負側リターン。PCB の金属パターンでの電圧降下による誤差を最小化するため、負荷の近くに配置したリモート出力コンデンサの下側端子に直接接続します。                                                                                                                                                          |

| 37    | GND        | 露出パッド (EP)。                                                                                                                                                                                                                              |

| 38-41 |            | コーナー・グラウンド・ピン。                                                                                                                                                                                                                           |

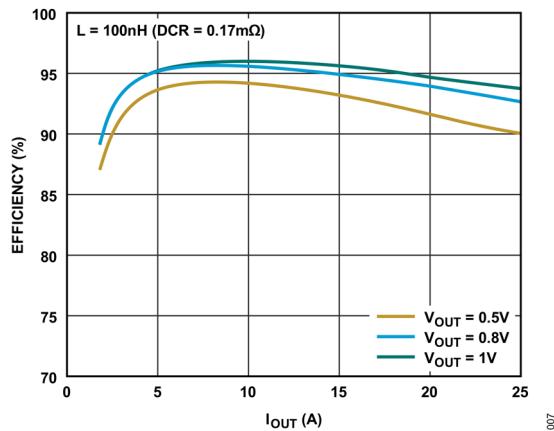

## 代表的な性能特性

特に指定のない限り、 $T_A = 25^\circ\text{C}$ 、 $V_{IN} = 3.3\text{V}$ 、 $V_{OUT} = 0.5\text{V}$ 。

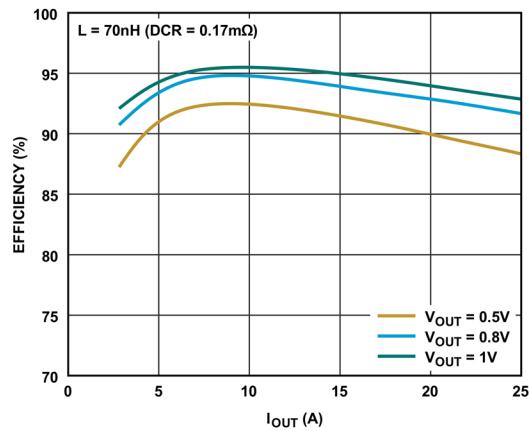

図 4. 効率と負荷電流の関係 (500kHz)

図 5. 効率と負荷電流の関係 (1MHz)

図 6. 効率と負荷電流の関係 (2MHz)

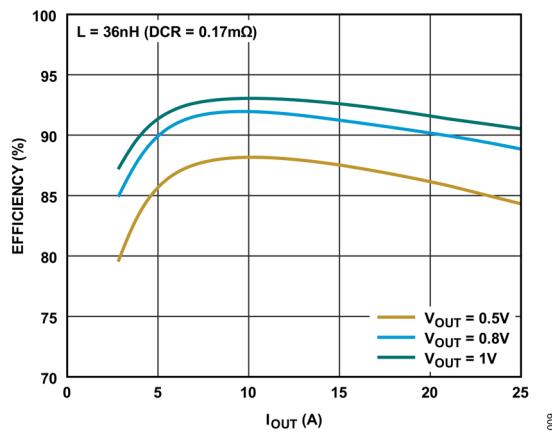

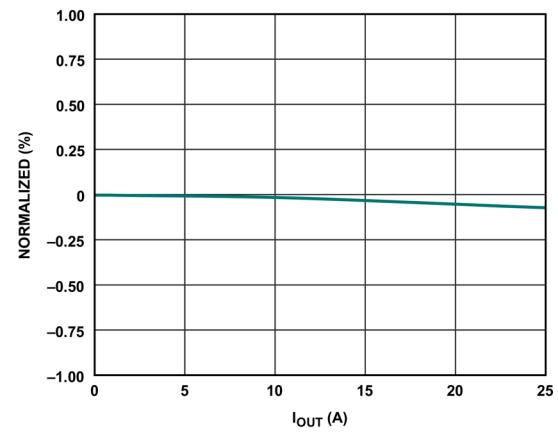

図 7. 負荷レギュレーションと負荷電流の関係

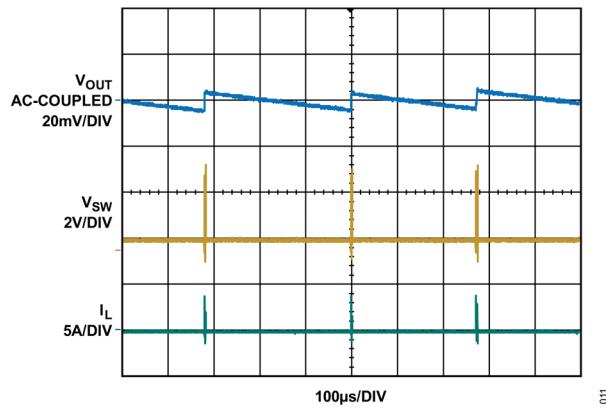

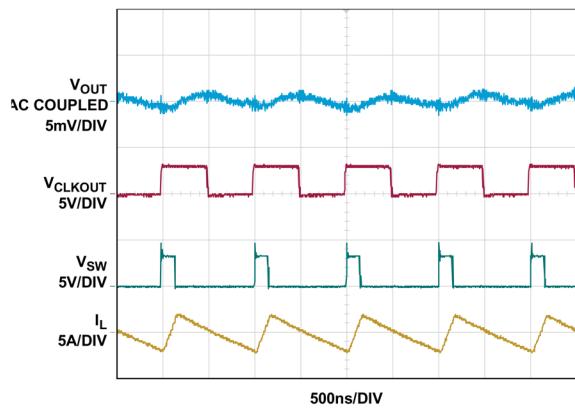

図 8. 不連続モード (DCM) 動作

$V_{IN} = 3.3\text{V}$ 、 $V_{OUT} = 0.5\text{V}$ 、 $I_{OUT} = 0\text{A}$ 、 $f_{sw} = 1\text{MHz}$

$L = 70\text{nH}$ 、 $C_{OUT} = 5 \times 100\mu\text{F}$ 、 $R_{ITH} = 2\text{k}\Omega$ 、 $C_{ITH} = 10\text{nF}$

図 9. 強制連続モード (FCM) 動作

$V_{IN} = 3.3\text{V}$ 、 $V_{OUT} = 0.5\text{V}$ 、 $I_{OUT} = 0\text{A}$ 、 $f_{sw} = 1\text{MHz}$

$L = 70\text{nH}$ 、 $C_{OUT} = 5 \times 100\mu\text{F}$ 、 $R_{ITH} = 2\text{k}\Omega$ 、 $C_{ITH} = 10\text{nF}$

013

014

015

016

017

018

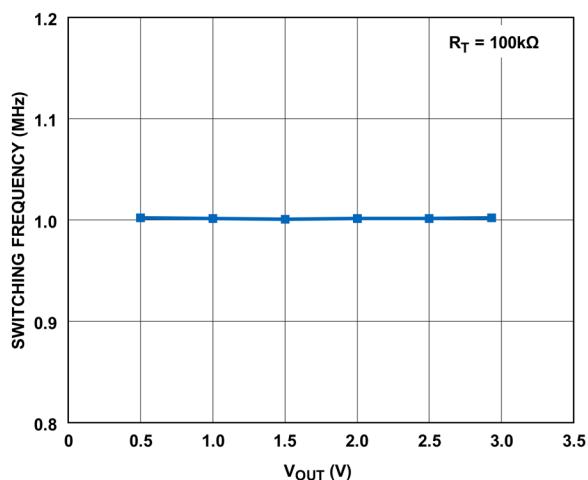

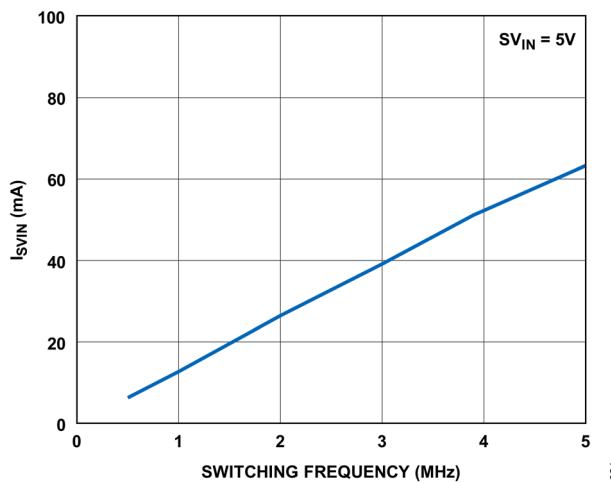

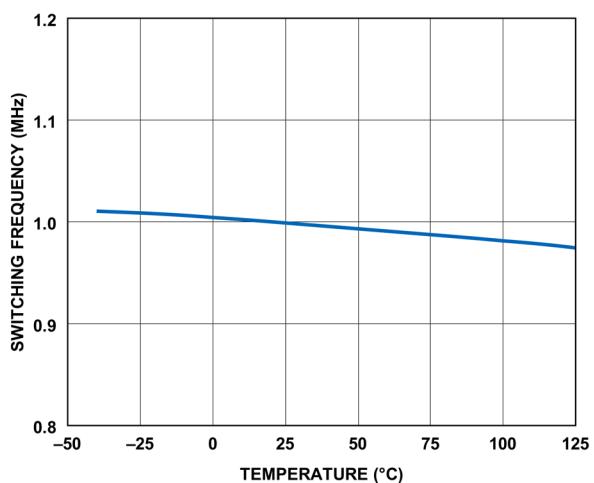

図 16. スイッチング周波数と  $R_T$  の関係図 17. スイッチング周波数と  $V_{OUT}$  の関係図 18.  $SV_{IN}$  電流とスイッチング周波数の関係、CCM

図 19. スイッチング周波数と温度の関係

図 20. 安定化 FB 電圧と温度の関係

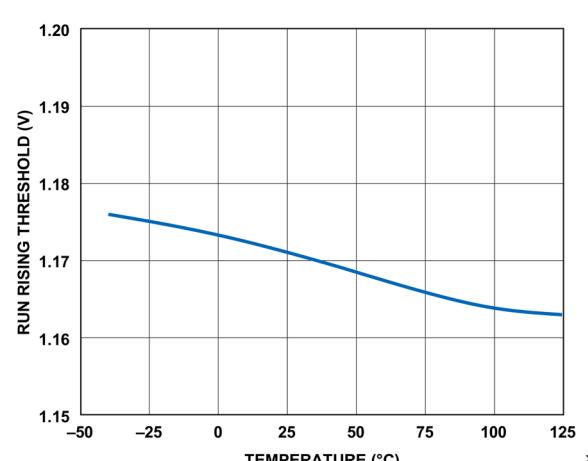

図 21. RUN の立上がり閾値と温度の関係

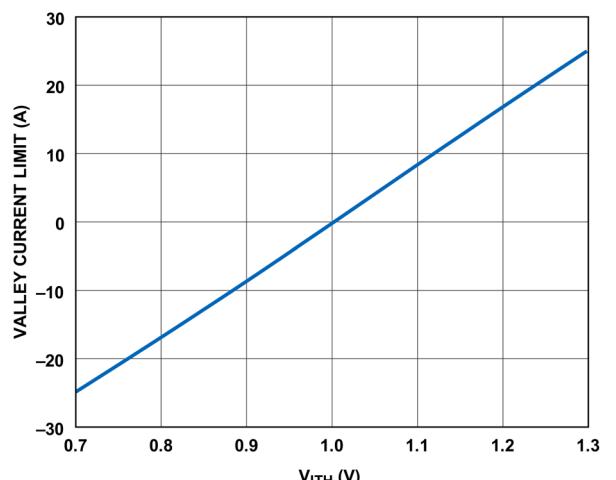

図 22. バレー電流制限値と  $V_{ITH}$  の関係

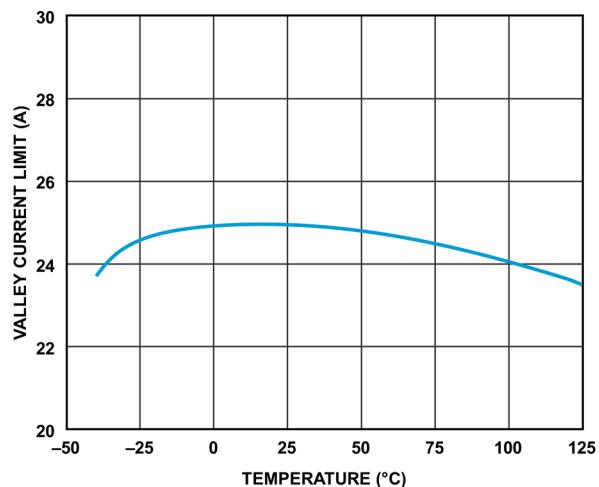

図 23. バレー電流制限値と温度の関係

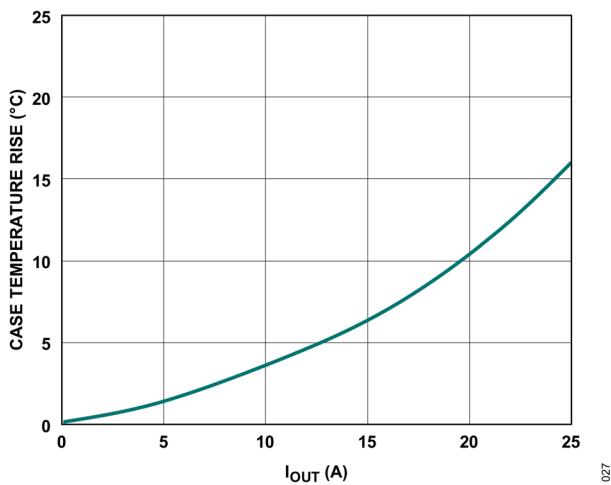

図 24. ケース温度と負荷の関係

図 25.  $R_{DS(ON)}$  と温度の関係

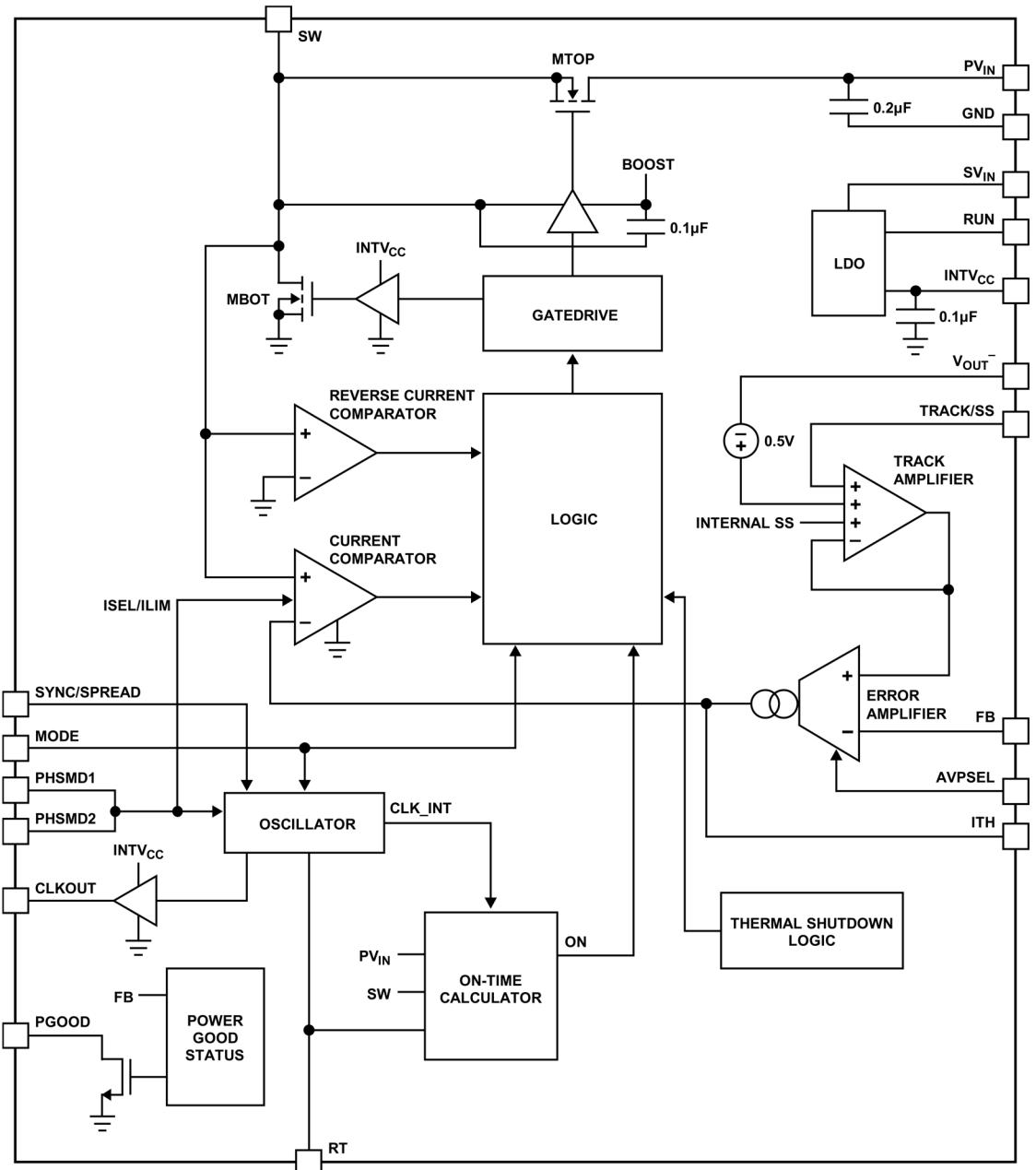

## ブロック図

図 26. ブロック図

032

## 動作原理

### メイン制御ループ

LT7153SP は、單一チャンネルの電流モード・モノリシック降圧レギュレータで、 $\pm 25A$  の出力電流を供給可能です。通常動作では内蔵の上側パワーMOSFET はワンショット・タイマーによって定められた時間だけオンになります（図 26 のブロック図の「ON」信号）。上側パワーMOSFET がオフになると、電流コンパレータ  $I_{CMP}$  がトリップし、ワンショット・タイマーを再開して次のサイクルを開始するまで、下側パワーMOSFET がオンになります。インダクタ電流は、下側パワーMOSFET がオンになっているときの MOSFET の SW ノードと GND ノードの電圧降下を検出することによって決定されます。ITH ピンの電圧は、インダクタの谷電流に対応するコンパレータ閾値を設定します。エラー・アンプ EA は、帰還信号  $V_{FB}$  と  $0.5V$  内部リファレンスを比較することによって、この ITH 電圧を調整します。負荷電流が増加すると、内部リファレンスに対する帰還電圧が低下し、それに伴って平均インダクタ電流が平均負荷電流と一致するまで ITH 電圧が増加します。

負荷電流が小さい場合、インダクタ電流がゼロや負になる場合があります。Burst Mode動作時には、これは電流反転コンパレータ ( $I_{REV}$ ) によって検出され、それにより下側パワーMOSFET がシャットオフされます。両方のパワーMOSFET はオフのままになり、ITH 電圧がゼロ電流レベル値を超えて次のサイクルが開始されるまで、出力コンデンサが負荷電流を供給します。連続動作モードが必要な場合は、単に MODE ピンをフロート状態にするか、INTV<sub>CC</sub> に接続します。

動作周波数は、内部発振器の電流を設定する  $R_{RT}$  の値によって決定されます。内部フェーズロック・ループにより、スイッチング・レギュレータのオン時間を内部発振器に追従するようにサーボ制御して、スイッチング周波数を一定に保ちます。クロック信号を SYNC/SPREAD ピンに印加すると、スイッチング周波数を外部クロックに同期させることができます。クロック信号がある場合、レギュレータのデフォルト動作は強制連続動作です。

LT7153SP の「S」は、第 2 世代 Silent Switcher 技術が使われていることを表しています。この IC には、 $V_{IN}$ 、INTV<sub>CC</sub>、BOOST 用にセラミック・コンデンサが集積されており、全ての高速 AC 電流ループが小型に維持されるため、EMI 性能が向上します。更に、スイッチング・エッジの速度を増加できるため、高スイッチング周波数での効率が大きく改善します。

### 低 $I_Q$ シャットダウン (RUN)

RUN ピンをグラウンドにプルダウンすると、LT7153SP は強制的にシャットダウン状態になり、流れる電流が極めて低くなります。RUN が  $0.6V$  より高くなると、内部リファレンスがオンになり、MOSFET はオフの状態を保ちます。更に RUN の電圧を高めて RUN の立上がり閾値である  $1.2V$  (定格値) を超えると、チップ全体がオンになります。正確な  $1.2V$  の RUN 閾値により、SVIN の低電圧ロックアウト閾値を外部の抵抗分圧器で設定できます。

### INTV<sub>CC</sub> レギュレータとバイパス・コンデンサ

内蔵の低ドロップアウト・レギュレータは、 $3.6V$  の電源を生成し、ドライバと内部バイアス回路に電力を供給します。 $10\mu F$  のセラミック・コンデンサを使用して INTV<sub>CC</sub> をグラウンドにバイパスします。推奨される最小値は  $4.7\mu F$  です。MOSFET ドライバに必要な大きい過渡電流を供給するには、良好なバイパスが必要です。

高周波数および高出力電流で動作するアプリケーションでは、スイッチング電流を増加させると、LDO 部での消費電力が高くなり、ダイ温度が高くなる可能性があります。このような場合には、INTV<sub>CC</sub> を SV<sub>IN</sub> と短絡することを検討してください。SV<sub>IN</sub> は  $3.3V$  または  $5V$  のレールとすることができますが、 $5V$  動作ではスイッチング損失が高くなり、スイッチング周波数が高い場合にはこれが問題になることに留意してください。PV<sub>IN</sub> と SV<sub>IN</sub> は同じ電位に接続する必要はないため、外部  $3.3V$  電源が使用できる場合にはそれを SV<sub>IN</sub> の給電に使用できます。SV<sub>IN</sub> と PV<sub>IN</sub> を別々の電位からバイアスするときには、PV<sub>IN</sub> より早く SV<sub>IN</sub> に給電され、パワーダウンは PV<sub>IN</sub> が先になるように 2 つの電源をシーケンス処理することが必要です。

## 調整可能な電流制限

LT7153SPの電流制限設定は、フル容量の25Aを必要としないアプリケーションでは、フルの値の70%または55%に低減できます。2つの位相モード・ピン（PHSMD1/ISEL、PHSMD2/ILIM）の状態により、電流制限設定が決定されます。詳細は表1を参照してください。

## 過電流保護と短絡保護

LT7153SPには、インダクタの谷電流検出によるサイクルごとの過電流保護機能があります。電流制限値に達すると、出力が低下し始め、上側パワーMOSFETのオン時間が減少します。短絡状態が続きオン時間がその最小値に達すると、オフ時間が長くなり、スイッチング周波数が低下して、 $V_{IN}$ から過度な電流が流れるのを防止します。過電流または短絡状態が解消すると、レギュレータは、出力電圧がオーバーシュートしないよう、ソフトスタート機能を実行します。

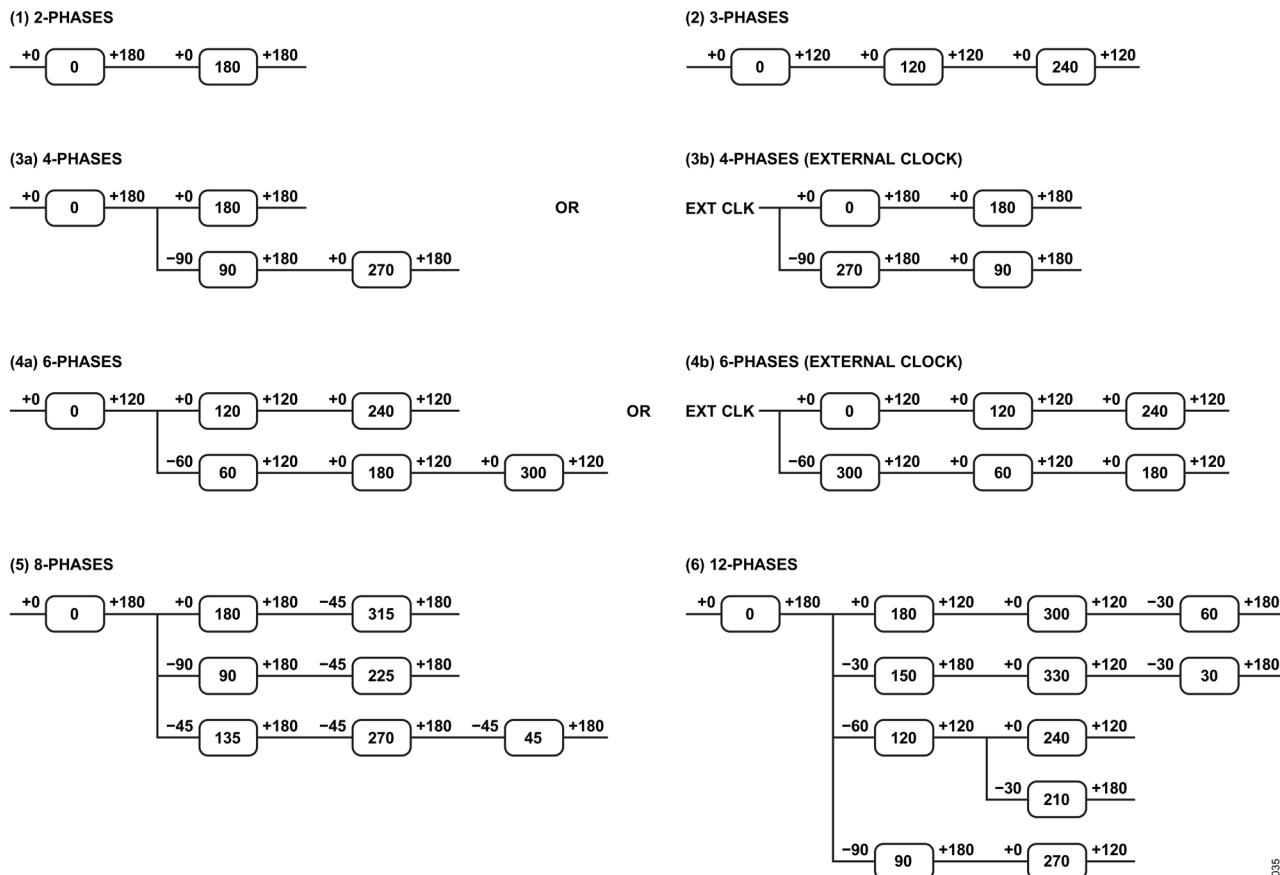

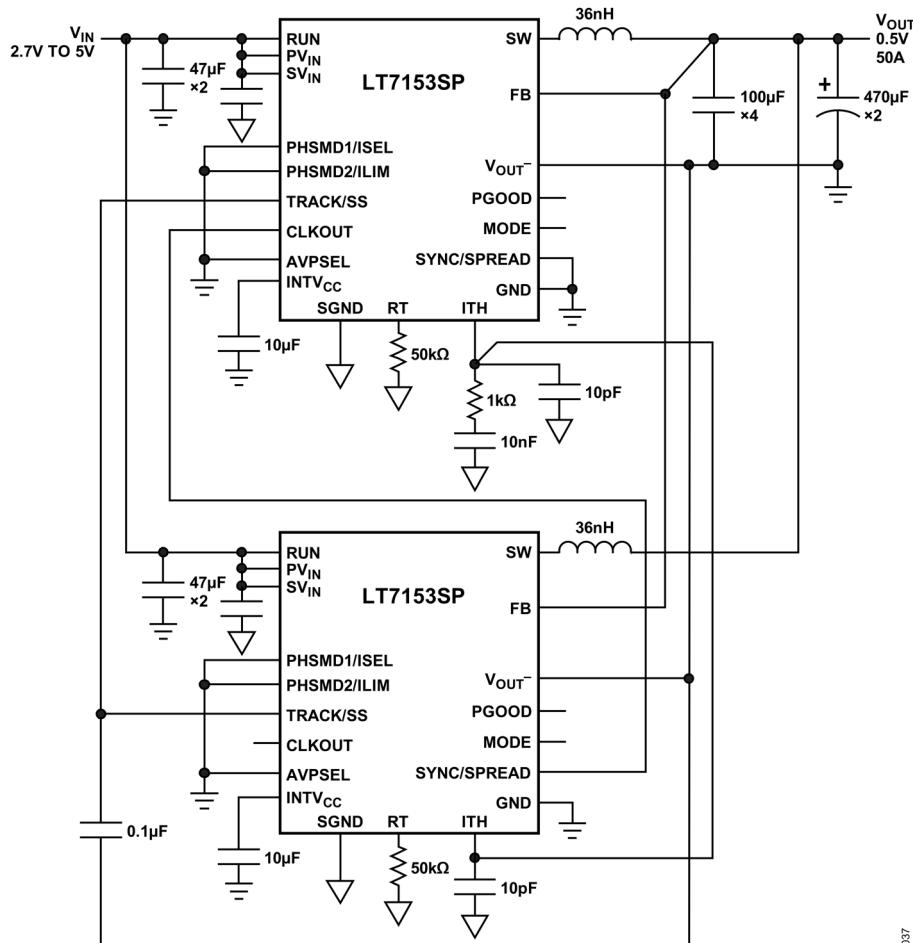

## マルチフェーズ動作

出力負荷が25Aを超える電流を必要とする場合、複数のLT7153SPの出力を相互に接続し、位相をずらして動作させることで、出力電流を増加できます。詳細については、表1と図28を参照してください。LT7153SPは内部発振器とCLKOUTの間の位相を変化させるだけではなく、外部クロックと内部発振器の位相も変化させるので、シグナル・チェーンが短くなり、累積的なクロック・ジッタが最小限に抑えられます。

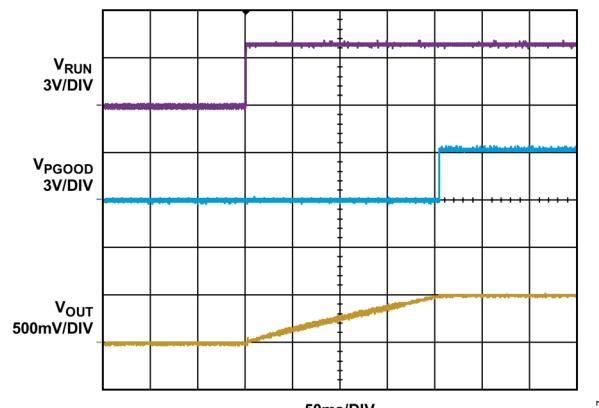

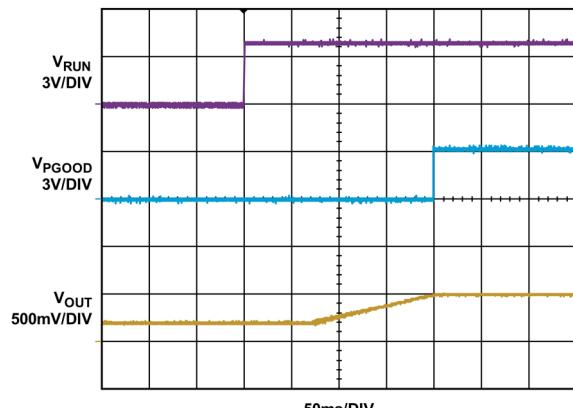

## パワー・グッド・ステータス出力

過電圧(OV)または低電圧(UV)コンパレータがトリップしているとき、レギュレータの出力帰還電圧 $V_{FB}$ がレギュレーション・ポイントを中心にして±6.5%の範囲を外れている場合、PGOODオープン・ドレイン出力がローに引き下げられます。この状態は、レギュレーションが±6.5%の範囲に復帰すると解除されます。

TRACK/SSピンが0.5Vに向けて増加するスタートアップ時を除き、OVおよびUV状態では連続動作が強制されます。

## VIN過電圧保護

内蔵のパワーMOSFETをトランジエント電圧スパイクから保護するために、LT7153SPは、 $PV_{IN}$ ピンを継続的にモニタし、過電圧状態に備えています。 $PV_{IN}$ が8Vを上回ると、レギュレータは両方のパワーMOSFETをオフすることで動作を一時停止します。 $PV_{IN}$ が7.5V未満になると、レギュレータは直ちに通常動作を再開します。過電圧イベント時、内蔵ソフトスタート電圧は帰還電圧よりわずかに高い電圧にクランプされます。したがって、過電圧状態の終了時には、ソフトスタート機能が存在します。

## 選択可能な負荷ライン(AVPSEL)

必要な出力コンデンサの量を最小化するため、LT7153SPではフラットな負荷ライン設定に加えて2つの異なる負荷ライン設定を選択できます。負荷ライン設定はAVPSELピンの状態により指定し、このピンがグラウンドに接続されているときには負荷ラインがフラット、フローティング時には1%、INTVccへの接続時には1.5%になります。

## MODE、SYNC、スペクトラム拡散動作

MODEピンをグラウンドに接続すると、Burst Mode動作が可能となり、低負荷電流時に優れた効率を実現できますが、出力電圧リップルはわずかに増加します。MODEピンをINTVccに接続するかフロート状態にすると、強制連続モードが選択され、出力リップルは最小限の一定値になりますが、軽負荷時の効率は低下します。

SYNC/SPREADピンはデュアル機能ピンです。このピンにより、LT7153SPを外部クロック信号に同期させることと、スペクトラム拡散機能の有効化／無効化が可能です。LT7153SPは、外部クロックがSYNC/SPREADピンに入力されるとこれを検出し、入力されたクロックの周波数に内部発振器を同期させます。SYNC入力と内部発振器の位相は2つの位相モード・ピン（PHSMD1/ISEL、PHSMD2/ILIM）の状態により決定します。SYNC/SPREADピンがINTVccに接続されているかフローティング状態のとき、スペクトラム拡散がイネーブルされます。LT7153SPは、プリセット周波数とそのプリセット値より20%高い値との間で周波数を変動させます。SYNC/SPREADピンがグラウンドに接続されているときには、周波数拡散はディスエーブルされます。

## アプリケーション情報

LT7153SP の簡略化したアプリケーション回路を、データシートの最初のページに示しています。外付け部品の選択は、目標とする電流リップル、負荷条件、スイッチング周波数によって大きく異なります。部品の選択は、通常、インダクタ L と抵抗 R<sub>RT</sub> の選択から始まります。インダクタを選択した後は、入力コンデンサ C<sub>IN</sub> および出力コンデンサ C<sub>OUT</sub> を選択します。次に、目的の出力電圧を設定する帰還抵抗を選択します。最後に、外部ループ補償、トラッキング／ソフトスタート、入力 UVLO、PGOOD 等の機能のため、その他の外付け部品をオプションで選択します。

## Silent Switcher アーキテクチャ

LT7153SP はコンデンサを内蔵しているため、高いスイッチング周波数において効率的に動作できます。内蔵の V<sub>IN</sub> バイパス・コンデンサにより、SW エッジを極めて高速で切り替えることができ、遷移損失を効果的に低減できます。また、このコンデンサは、上側 FET がオンになるときの SW オーバーシュートを大幅に抑制するため、時間変化に伴うデバイスの堅牢性を向上できます。

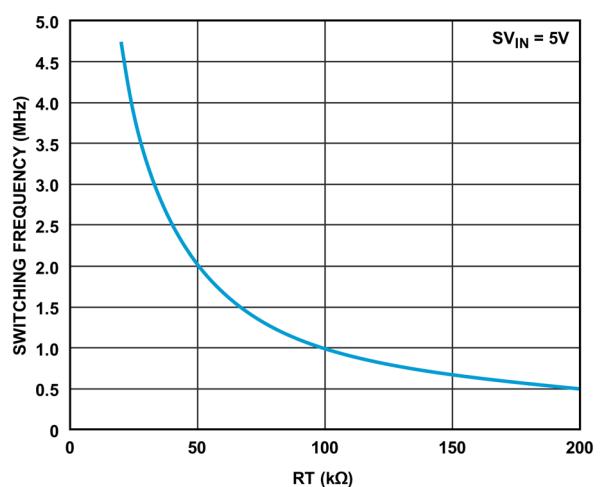

## スイッチング周波数の設定

スイッチング周波数の選択は、効率と部品サイズのトレードオフです。動作周波数が高い場合、小型のインダクタとコンデンサを使用できます。低周波数での動作は、内部ゲート電荷損失が減少するので効率が改善されますが、出力リップル電圧を低く維持するには、インダクタンスや容量を大きくする必要があります。

抵抗 R<sub>RT</sub> を RT ピンと SGND の間に接続すると、スイッチング周波数 f<sub>sw</sub> を次式に従って 400kHz～5MHz の範囲で設定できます。

$$f_{sw}(\text{Hz}) = \frac{1e^{11}}{R_{RT}(\Omega)}$$

内部 PLL の同期範囲は設定された周波数を中心に±30%です。したがって、外部クロック同期時には、外部クロック周波数がこの R<sub>RT</sub> で設定した周波数の±30%の範囲内にあることを確認してください。

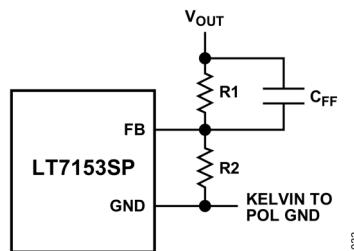

## 出力電圧の設定

レギュレータの出力電圧は、次式に従い外付け抵抗分圧器を使って設定されます。

$$V_{OUT} = 0.5V \cdot \left( 1 + \frac{R1}{R2} \right)$$

必要な出力電圧は、抵抗 R1 および R2 を適切に選択することで設定され、これらの抵抗によって、図 27 に示すように、V<sub>FB</sub> ピンで出力電圧の一定の割合を検出することができます。R1 および R2 に大きな値を選択すると、ゼロ負荷時や軽負荷時の効率が向上しますが、V<sub>FB</sub> ノードの寄生容量により、不要なノイズ・カップリングや位相マージンの減少が生じる可能性があります。V<sub>FB</sub> のパターンは、SW パターンなどのノイズ源から離すよう注意してください。フィードフォワード補償コンデンサ C<sub>FF</sub> を V<sub>OUT</sub> と FB の間に配置して、トランジエント性能を向上することもできます。

図 27. 出力電圧の設定

出力電圧が  $V_{ON}$  の検出範囲 (0.5V~4V) から外れている場合、出力電圧はレギュレーション状態にあるものの、スイッチング周波数は設定周波数とは異なる可能性があります。

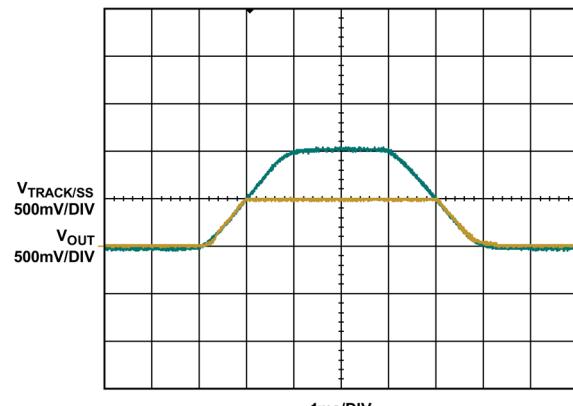

## ソフトスタートおよび出力電圧 TRACK

TRACK ピンは 10 $\mu$ A の内部電流で INTV<sub>CC</sub> にプルアップされています。TRACK ピンとグラウンドの間にコンデンサ  $C_{SS}$  を外付けすると、出力をソフトスタートして入力電源の電流サージを防ぐことができます。出力立ち上がり時間  $T_{SS}$  とソフトスタート容量  $C_{SS}$  の間には次式の関係があります。

$$T_{SS} = 0.5e^5 \cdot C_{SS}$$

起動時、LT7153SP は、トラック電圧が 0.5V を超えるまで不連続モードで動作します。その後、出力が UV 閾値を超える ( $V_{FB} > 0.475V$ ) まで、レギュレータは強制連続モードで動作します。出力がこの電圧に達すると、レギュレータの動作モードは前述のように MODE ピンで選択したモードに切り替わります。

LT7153SP では、TRACK ピンを用いて出力電圧の上昇率をプログラムすることができます。0V から 0.5V までは、TRACK 電圧がエラー・アンプへの 0.5V の内部リファレンス入力より優先されるので、フィードバック電圧は TRACK ピンの電圧にレギュレーションされます。TRACK が 0.5V を超えると、トランкиングはディスエーブルされ、帰還電圧は内部リファレンス電圧にレギュレーションされます。

## インダクタの選択

与えられた入力電圧  $V_{IN}$  に対し、出力電圧  $V_{OUT}$ 、インダクタ値  $L$ 、動作周波数  $f$  によって、次式のようにリップル電流が決まります。

$$\Delta I_L = \frac{V_{OUT}}{f_{SW} \cdot L} \cdot \left(1 - \frac{V_{OUT}}{V_{IN}}\right)$$

インダクタのリップル電流は、インダクタ値が高いほど、また、動作周波数が高いほど、小さくなります。リップル電流が小さくなると、インダクタのコア損失、出力コンデンサの ESR 損失、および出力電圧リップルが減少します。最大効率の動作は、低周波数でリップル電流が小さいときに得られます。しかし、これを実現するには大きいインダクタが必要です。部品サイズ、効率、動作周波数は互いにトレードオフの関係にあります。

妥当な出発点は、 $I_{OUT(MAX)}$  の約 40% のリップル電流を選択することです。 $I_{OUT(MAX)}$  の 60% を超えることは推奨できません。最大電圧リップルは、 $V_{IN}$  が最大のときに発生することに注意してください。リップル電流が仕様規定された最大値を超えないようにするには、次式に従ってインダクタンスを選択する必要があります。

$$L = \frac{V_{OUT}}{f_{SW} \cdot \Delta I_{(MAX)}} \cdot \left(1 - \frac{V_{OUT}}{V_{IN(MAX)}}\right)$$

$L$  の値が定まったら、インダクタの種類を選択する必要があります。インダクタ値が固定の場合、実際のコア損失はコア・サイズには無関係ですが、選択したインダクタンスには大きく依存します。インダクタンスまたは周波数が増加すると、コア損失は減少します。しかし、インダクタンスを大きくするには、より多くの巻数を必要とするため、DCR と銅損が大きくなってしまいます。

フェライトを使用した設計ではコア損失は非常に小さく、高いスイッチング周波数に適しています。そのため、設計目標を銅損と飽和の防止に集中させることができます。フェライト・コア材料の飽和は「ハード」です。つまり、ピーク設計電流を超えると急激にインダクタンスが低下します。その結果、インダクタのリップル電流が急激に増加し、それに伴い出力電圧リップルも増加します。コアは飽和させないようにしてください。

過熱と効率の低下を回避するには、アプリケーションで予想される最大出力負荷よりも大きい RMS 電流定格のインダクタを選択します。更に、インダクタの飽和電流定格値（通常は  $I_{SAT}$  で表します）は、負荷電流にインダクタ・リップル電流の 1/2 を加えた値（次式）よりも大きくなればなりません。

$$I_{L(Peak)} = I_{OUT(MAX)} + \frac{\Delta I_L}{2}$$

コアの材料や形状を変えると、インダクタのサイズ／電流および価格／電流の関係も変わります。フェライトやパーマロイを使用したトロイド・コアやシールド・ポット・コアは小型で、それほど多くのエネルギーを放出することはありませんが、一般的には、同様の特性を持つ鉄粉コアのインダクタよりも高コストです。どのタイプのインダクタを使用するかの選択は、価格とサイズの条件や放射フィルード／EMI 条件によって異なります。

## 入力コンデンサ ( $C_{IN}$ ) の選択

入力容量  $C_{IN}$  は、上側パワーMOSFET のドレインに流れる矩形波電流をフィルタ処理するために必要です。大きな電圧トランジエントが生じるのを防ぐために、最大実効値電流に見合ったサイズで低 ESR の入力コンデンサを使用してください。最大実効値電流は次式で与えられます。

$$I_{RMS} \cong I_{OUT(MAX)} \cdot \frac{V_{OUT}}{V_{IN}} \cdot \sqrt{\frac{V_{IN}}{V_{OUT}} - 1}$$

この式は  $V_{IN} = 2V_{OUT}$  で最大値を取ります。ここで、

$$I_{RMS} \cong \frac{I_{OUT}}{2}$$

設計ではこの単純で最も厳しい条件がよく使用されます。条件を大きく変化させても状況はそれほど改善されないからです。なお、コンデンサ・メーカーのリップル電流定格は、多くの場合わずか 2000 時間程度の寿命を基本としています。そのため、コンデンサを更にディレーティングするか、必要とするよりも高い温度で規定された定格のコンデンサを選択することを推奨します。設計におけるサイズや高さの条件を満たすために、数個のコンデンサを並列に接続することもできます。低入力電圧のアプリケーションでは、出力負荷が変化した際のトランジエント効果を打ち消すために、十分なバルク入力容量が必要です。

## 出力コンデンサ ( $C_{OUT}$ ) の選択

$C_{OUT}$  の選択は、電圧リップルや負荷ステップに対する過渡応答を最小化するために必要な等価直列抵抗 (ESR) と、制御ループの安定性を確保するために必要なバルク容量によって決定されます。ループの安定性は負荷の過渡応答を見ることで確認できます。出力リップル  $\Delta V_{OUT}$  は次式で求めます。

$$\Delta V_{OUT} < \Delta I_L \cdot \left( \frac{1}{8 \cdot f_{SW} \cdot C_{OUT}} + ESR \right)$$

$\Delta I_L$  は入力電圧に応じて増加するので、出力リップルは入力電圧が最大のとき最大になります。ESR と RMS 電流処理の条件を満たすために、複数のコンデンサを並列に配置しなければならない場合があります。

乾式タンタル、特殊ポリマー、アルミ電解、セラミックの各コンデンサは、いずれも表面実装パッケージで入手できます。特殊な高分子コンデンサの ESR は非常に低いものになっていますが、他のタイプより容量密度は小さめです。タンタル・コンデンサは静電容量密度が最も高いものになっていますが、スイッチング電源用としてサージ・テストされたものののみを使用することが重要です。アルミ電解コンデンサは ESR がかなり高いものになっていますが、リップル電流定格と長期信頼性を考慮すれば、コスト重視のアプリケーションに使用できます。セラミック・コンデンサは、低 ESR 特性に優れ、実装面積も小さくできます。

セラミック・コンデンサの ESR は非常に低いため、電荷蓄積の条件を満たす出力コンデンサ値を選択する方がより有用です。負荷ステップでは、帰還ループがスイッチ電流を十分に増加させて負荷に対応できるようになるまで、出力コンデンサが即座に電流を供給して負荷に対応する必要があります。帰還ループの応答を要する時間は、補償および出力のコンデンサのサイズに依存します。負荷ステップへの応答には通常 5 サイクルを要しますが、出力電圧が直線的に低下するのは最初のサイクルのみです。出力のループ  $V_{DROOP}$  は通常、最初のサイクルの直線的な電圧低下量の 3 倍程度になります。したがって、次式で得られる出力コンデンサの値が、およそその出発点として適した値です。

$$C_{OUT} = 3 \cdot \left( \frac{\Delta I_{OUT}}{f_o \cdot V_{DROOP}} \right)$$

## 入出力セラミック・コンデンサの使用

セラミック・コンデンサは、より大容量で安価なものが小型ケースで入手できるようになりました。高リップル電流、高電圧定格、低ESRという特長は、スイッチング・レギュレータ用途に最適です。ただし、セラミック・コンデンサの種類によっては自己共振や高Q特性があるため、これらのコンデンサを入出力に使用する場合は注意が必要です。入力にセラミック・コンデンサを使用し、壁コンセントから長い電線を介して電源を供給する場合、出力の負荷ステップによって  $V_{IN}$  入力にリングが誘起することがあります。最善の場合でも、このリングが出力に結合して、ループが不安定になったと誤解されることがあります。最もひどい場合、長い配線を介した電流突入により、部品を損傷するのに十分な大きさの電圧スパイクを  $V_{IN}$  に生じさせる可能性があります。詳細な説明は、アプリケーション・ノート 88 を参照してください。

入出力のセラミック・コンデンサには、誘電体が X5R や X7R のものを選択します。これらの誘電体は、与えられた値とサイズに対して、全てのセラミックの中で最も優れた温度および電圧特性を示します。150°C のアプリケーションには X8R を選択します。デューティ・サイクルや負荷ステップの条件によっては、より多くの容量が必要になる場合があります。ほとんどのアプリケーションでは、電源に対するインピーダンスが非常に低いため、入力コンデンサは単に高周波のバイパス用としてのみ必要とされます。このような条件下では、通常 47μF のセラミック・コンデンサで十分です。この入力コンデンサは PV<sub>IN</sub> ピンおよび GND ピンのできるだけ近くに配置します。

## 最小オフ時間と最小オン時間に関する考慮事項

最小オフ時間  $t_{OFF(MIN)}$  は、LT7153SP がボトム・パワーMOSFET をターンオンして電流コンパレータをトリップさせてから、ボトム・パワーMOSFET を再びオフに戻すことができるまでの最小時間です。この時間は一般的に約 30ns です。最小オフ時間の制限によって、最大デューティ・サイクルは  $t_{ON}/(t_{ON} + t_{OFF(MIN)})$  となります。入力電圧の低下などにより最大デューティ・サイクルに達した場合、出力はレギュレーション範囲を外れます。ドロップアウトを回避するための最小入力電圧は次式のとおりです。

$$V_{IN(MIN)} = V_{OUT} \cdot \frac{t_{ON} + t_{OFF(MIN)}}{t_{ON}}$$

これに対して、最小オン時間とは、上側パワーMOSFET をオン状態する時間の最小値です。この時間は 15ns（代表値）です。連続モード動作の場合、最小オン時間の制限により、最小デューティ・サイクルは次式で与えられます。

$$DC_{(MIN)} = f_{SW} \cdot t_{ON(MIN)}$$

ここで、 $t_{ON(MIN)}$  は最小オン時間です。動作周波数を下げると、最小デューティ・サイクルの制約を緩和できます。

デューティ・サイクルの最小値を超えるまれなケースでは、出力電圧はレギュレーション状態を維持し、スイッチング周波数は設定値より低くなります。これは多くのアプリケーションで許容可能な結果です。そのため、この制約はほとんどの場合、極めて重要というわけではありません。高いスイッチング周波数は、出力過電圧を招くおそれがなく、設計に使用できます。インダクタとコンデンサの選択のセクションで示したように、スイッチング周波数が高いほど小さな基板部品を使用できるため、アプリケーション回路のサイズを小さくできます。

## マルチフェーズ構成

PolyPhase動作により、複数のLT7153SPレギュレータを位相をずらして動作させることができます（相数は2、3、4、6、8、12、図28参照）、必要な入力コンデンサと出力コンデンサの量が低減し、並列接続によってより高い出力電流が得られます。PHASE1/SELピンとPHSMD2/ILIMピンを設定することにより（表4を参照）、内部発振器とCLKOUTの間、内部発振器とSYNCの間の位相関係が決定します。

図28. 2、3、4、6、8、12相のマルチフェーズ構成

表4. マルチフェーズのピン設定

|                      |                                 |                                                              |     |        |

|----------------------|---------------------------------|--------------------------------------------------------------|-----|--------|

| SYNC to Oscillator   | $\phi_{(\text{SYNC to OSC})}$   | PHSMD1 = 0, PHSMD2 = 0                                       | 0   | Degree |

|                      |                                 | PHSMD1 = INTV <sub>CC</sub> , PHSMD2 = 0                     | 0   |        |

|                      |                                 | PHSMD1 = 0, PHSMD2 = INTV <sub>CC</sub> /2                   | -30 |        |

|                      |                                 | PHSMD1 = INTV <sub>CC</sub> , PHSMD2 = INTV <sub>CC</sub> /2 | -45 |        |

|                      |                                 | PHSMD1 = 0, PHSMD2 = INTV <sub>CC</sub>                      | -60 |        |

|                      |                                 | PHSMD1 = INTV <sub>CC</sub> , PHSMD2 = INTV <sub>CC</sub>    | -90 |        |

| Oscillator to CLKOUT | $\phi_{(\text{OSC to CLKOUT})}$ | PHSMD1 = 0, PHSMD2 = 0                                       | 180 | Degree |

|                      |                                 | PHSMD1 = INTV <sub>CC</sub> , PHSMD2 = 0                     | 120 |        |

|                      |                                 | PHSMD1 = 0, PHSMD2 = INTV <sub>CC</sub> /2                   | 180 |        |

|                      |                                 | PHSMD1 = INTV <sub>CC</sub> , PHSMD2 = INTV <sub>CC</sub> /2 | 180 |        |

|                      |                                 | PHSMD1 = 0, PHSMD2 = INTV <sub>CC</sub>                      | 120 |        |

|                      |                                 | PHSMD1 = INTV <sub>CC</sub> , PHSMD2 = INTV <sub>CC</sub>    | 180 |        |

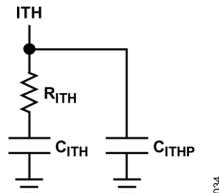

**ITH 補償**

OPTI-LOOP®の最適化のため、適切な ITH 部品を選択する必要があります。補償ネットワークを図 29 に示します。RC フィルタにより、支配的なポールゼロ・ループ補償が設定されます。ループのゲインは  $R_{ITH}$  と共に増加し、ループの帯域幅は  $C_{ITH}$  を減少させると増加します。 $C_{ITH}$  が減少するのと同じ比率で  $R_{ITH}$  が増加しても、ゼロ周波数は同じに保たれるため、位相も、帰還ループの最も重要な周波数範囲で同じに保たれます。

図 29. 外部補償ネットワーク

1MHz のアプリケーションでは、 $4.7nF$  と  $2k\Omega$  の R-C ネットワークが良い出発点となります。基板の浮遊容量による高周波結合をフィルタリングするために、ITH ピンに  $4.7pF$  のバイパス・コンデンサ  $C_{ITHP}$  を使用することを推奨します。表 5 に、デバイスの与えられた周波数に対して使用すべき補償値の基本的なガイドラインを示します。アプリケーションで必要な出力容量によっては、これらの値の微調整が必要になることもあります。

表 5. 补償値

| Frequency | $R_{ITH}$ | $C_{ITH}$ | $C_{THP}$ |

|-----------|-----------|-----------|-----------|

| 1MHz      | 2k        | $4.7nF$   | $4.7pF$   |

| 2MHz      | 2k        | $2.2nF$   | $4.7pF$   |

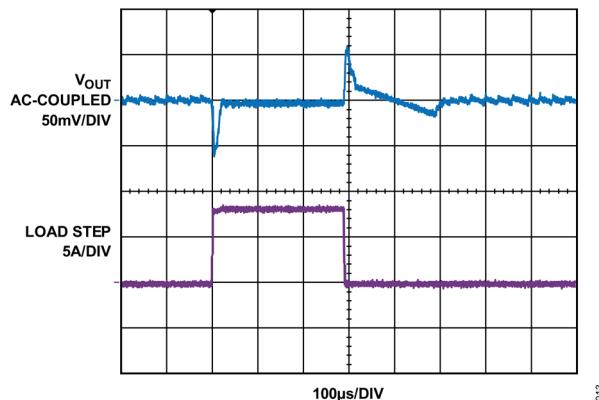

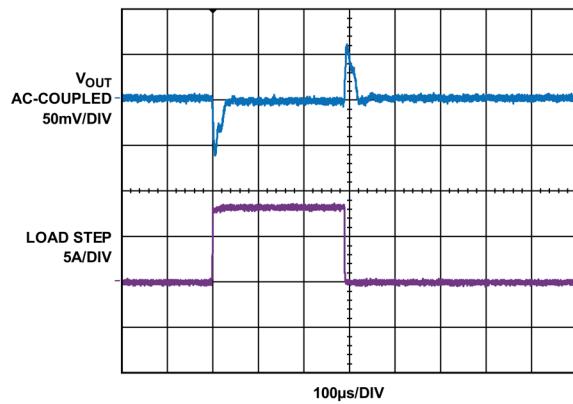

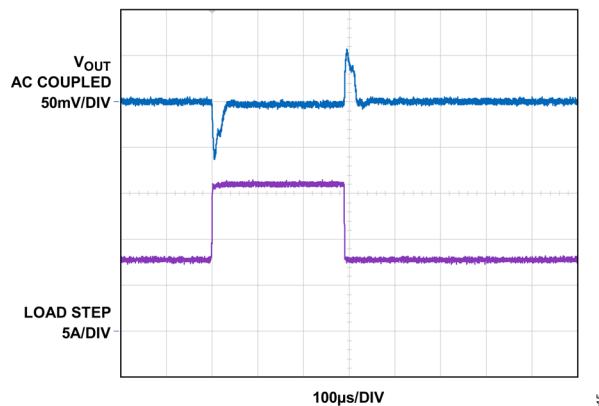

**過渡応答のチェック**

OPTI-LOOP 補償が備わっているため、幅広い範囲の負荷および出力キャパシタ値にわたって過渡応答を最適化できます。ITH ピンを使用すれば、この制御ループの動作を最適化できるだけでなく、DC 結合された AC フィルタ付きクローズドループ応答のテスト・ポイントとして利用することもできます。このテスト・ポイントでの DC ステップ、立上がり時間、およびセトリングは、クローズドループ応答を正確に反映します。2 次特性が支配的なシステムの場合は、このピンに現れるオーバーシュートのパーセンテージを使って位相マージンや減衰係数を予想できます。

表 5 の回路に示す ITH ピンの外付け部品は、ほとんどのアプリケーションにおいて妥当な出発点となります。RC フィルタにより、支配的なポールゼロ・ループ補償が設定されます。これらの値は、最終的なプリント回路基板のレイアウトを完了し、出力コンデンサの種類と容量値を決定したら、過渡応答を最適化するために多少（推奨値の 0.5~2 倍）変更することができます。出力コンデンサの種類と値によって、ループの帰還係数、ゲイン、位相が決まるため、出力コンデンサを選択する必要があります。また、高周波応答を改善するために、図 29 に示すように、フィードフォワード・コンデンサ  $C_{FF}$  を追加することも可能です。コンデンサ  $C_{FF}$  は、R2 で高周波のゼロを生成することで位相進みをもたらし、位相マージンを改善します。

立上がり時間が約  $1\mu s$  である、全負荷電流の 20%~100% の出力電流パルスを流すと、帰還ループを壊すことなくループ全体が安定するような出力電圧と ITH ピンの波形が得られます。スイッチング・レギュレータは、負荷電流のステップに応答するために数サイクルを要する場合があります。負荷ステップが発生すると、 $V_{OUT}$  は  $\Delta I_{LOAD} \times ESR$  に等しい大きさだけ直ちにシフトします。ここで、ESR は  $C_{OUT}$  の等価直列抵抗です。更に、 $\Delta I_{LOAD}$  により  $C_{OUT}$  の充放電も開始されて帰還誤差信号が発生し、レギュレータはこれを用いて  $V_{OUT}$  を定常値に回復させます。この回復期間に、 $V_{OUT}$  をモニタして、安定性に問題があることを示す過度のオーバーシュートやリンギングが発生していないかをチェックできます。

最初の出力電圧ステップはフィードバック・ループの帯域幅内にない可能性があるため、標準の2次オーバーシュート/DC比を用いて位相マージンを決定することはできません。出力電圧のセトリングの挙動はクローズド・ループ・システムの安定性に関係しており、実際の全体的電源性能を表します。制御ループ理論のレビューなど、補償部品の最適化の詳細な説明については、アナログ・デバイセズのアプリケーション・ノート76を参照してください。

アプリケーションによっては、大容量の( $>47\mu F$ )入力コンデンサを接続している場合、負荷のスイッチングによって深刻なトランジエント現象が発生することがあります。放電する入力コンデンサは実質的に $C_{OUT}$ と並列になり、 $V_{OUT}$ の急降下を引き起します。負荷に接続されたスイッチが低抵抗で高速駆動される場合、どのレギュレータもこの問題を防ぐのに十分な電流を供給することができません。その解決策として、負荷スイッチ・ドライバのターンオン速度を制限することが挙げられます。ホット・スワップ・コントローラは、この目的に特化して設計されたもので、通常は電流制限、短絡保護、ソフトスタートが組み込まれています。

## 熱的条件

高周囲温度、高スイッチング周波数、高 $V_{IN}$ 、高出力負荷が組み合わさった状態でLT7153SPが動作するようなアプリケーションでは、必要な消費電力により、デバイスが最大ジャンクション温度を越えてしまう場合があります。LT7153SPが最大ジャンクション温度を超えることのないよう、動作条件に応じて、最大電流定格はディレーティングされます。デバイスの温度上昇は、PCB基板の銅の厚さ、基板の層数、銅パターンの形状によって異なります。一般的に、SWピンおよびGNDピンにはPCBの最上層で厚い切れ目がない銅を用いると、デバイスの熱性能を大きく向上できます。

LT7153SPには、ヒート・シンク搭載の目的でパッケージ上面に露出ダイ・パッドを設けています。このオプションにより、適切なサイズのヒート・シンクを正しくパッケージに実装すると、同等の負荷に対して熱性能を改善することが可能になります。**図24**に、1層あたり2オンスの銅を用いた標準的な6層PCB基板(標準デモ・ボード)上にLT7153SPを実装した場合のケース温度の上昇を示します。

## 効率に関する考慮事項

スイッチング・レギュレータの効率(パーセント)は、出力電力を入力電力で割った値に100%を乗じたものです。効率を制限しているのは何か、何を変更すれば最も効率が向上するかを判定するには、多くの場合、個々の損失を分析することが有益です。パーセント表示の効率は次式で表せます。

$$\%Efficiency = 100\% - (L_1 + L_2 + L_3 + \dots)$$

ここで、 $L_1$ 、 $L_2$ 、などは、個々の損失を入力電力に対するパーセンテージで表したものです。

回路内の電力を消費する全ての要素で損失が生じますが、LT7153SPの回路の損失の大部分は、次の主な3つの損失要因によって生じます：1)  $I^2R$ 損失、2) スイッチングおよびバイアス損失、3) その他の損失、が3大要因です。

1.  $I^2R$ 損失は、内部スイッチのDC抵抗値 $R_{SW}$ と外付けインダクタのDC抵抗値 $R_L$ から計算できます。連続モードでは、平均出力電流はインダクタ $L$ を流れますが、この電流は内蔵の上側と下側のパワーMOSFETの間で細かく切り替えられます。したがって、SWピンへの直列抵抗は、次式のように、上側および下側MOSFET両方の $R_{DS(ON)}$ とデューティ・サイクル(DC)の関数となります。

$$R_{SW} = (R_{DS(ON)TOP})(DC) + (R_{DS(ON)BOT})(1 - DC)$$

上側および下側のMOSFETのどちらの $R_{DS(ON)}$ も、代表的な性能特性のグラフから求めることができます。したがって、次式から $I^2R$ 損失を求めることができます。

$$I^2R \text{ losses} = I_{OUT}^2(R_{SW} + R_L)$$

2. スイッチング電流は、MOSFET のドライバ電流と制御電流の和です。パワーMOSFET のドライバ電流は、パワーMOSFET のゲート容量が切り替わることにより発生します。パワーMOSFET のゲートがローからハイ、そして再度ローに切り替わるたびに、ある量の電荷  $dQ$  が  $P_{V_{IN}}$  からグラウンドに移動します。その結果生じる  $dQ/dt$  が IN から流出する電流であり、通常は、DC 制御バイアス電流よりもはるかに大きくなります。連続モードでは、 $I_{GATECHG} = f(Q_T + Q_B)$  となります。ここで、 $Q_T$  と  $Q_B$  は上側および下側の内部パワーMOSFET のゲート電荷、 $f$  はスイッチング周波数です。したがって、電力損失は次式のようになります。

$$\text{Switching Loss} = I_{GATECHG} \cdot P_{V_{IN}}$$

ゲート電荷損失は、 $INTV_{CC}$  ピンの電流として、周波数に伴って発生します。したがって、これらの影響は、入力電圧と周波数が高いアプリケーションにおいてより顕著なものとなります。

3. 遷移損失や銅パターンの抵抗および内部負荷抵抗などの「隠れた」損失が、電源システム全体の効率を更に低下させる原因となることがあります。これらのシステム・レベルの損失をシステム設計段階で盛り込むことが非常に重要です。遷移損失は、スイッチ・ノードの遷移中に上側パワーMOSFET が飽和領域で費やすわずかな時間によって生じます。LT7153SP の内蔵パワー・デバイスは十分速く切り替わるため、これらの損失は他の損失に比べてそれほど大きくはありません。デッド・タイム時のダイオード伝導損失やインダクタのコア損失など、その他の損失は一般的に総損失の 2%未満です。

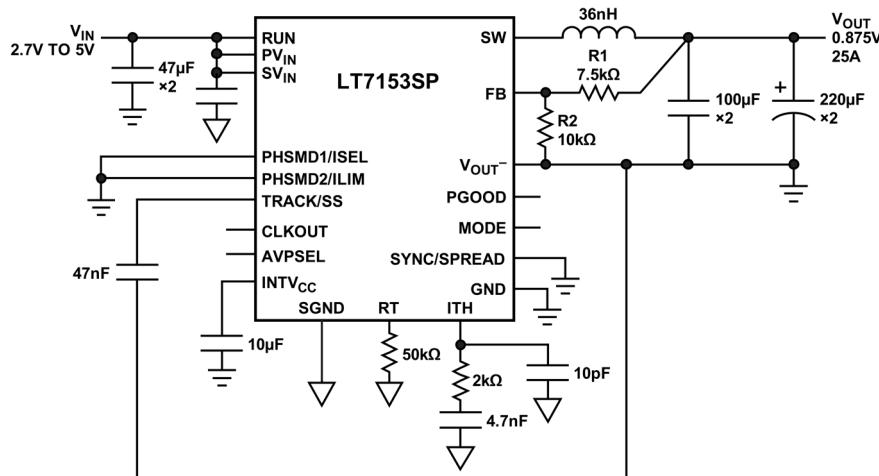

## 設計例

設計例として、次の仕様のアプリケーションで LT7153SP を使用する場合を考えてみます。

$$V_{IN} = 3.3V \text{ to } 5V$$

$$V_{OUT} = 0.875V$$

$$I_{OUT(MAX)} = 25A$$

$$f_{SW} = 2MHz$$

まず、図 27 に従い、 $R_2$  を  $10k\Omega$ 、 $R_1$  を  $7.5k\Omega$  に設定して出力を  $0.875V$  に設定します。最高の精度を実現するため、0.1%の抵抗を用います。

標準的なソフトスタート時間（最終的な  $V_{OUT}$  値の 0%から 100%までの時間）を  $4ms$  にするためには、 $C_{SS}$  を以下の式のようにします。

$$10\mu A = C_{SS} \cdot \frac{0.875V}{4ms}$$

$$C_{SS} = 46nF$$

$C_{SS}$  には標準的な  $47nF$  のコンデンサを用います。

負荷電流が大きい場合も小さい場合も効率は重要なことで、不連続モード動作を採用します。2MHz のスイッチング周波数に適した  $R_T$  抵抗を特性曲線から選択します。これに基づき、 $R_T$  を  $50k\Omega$  とします。次に、電流リップルが最大  $V_{IN}$  での最大ピーク電流制限値（25A）の約 40%となるようにするインダクタ値を計算します。

$$L = \frac{V_{OUT}}{f_{SW} \cdot \Delta L_{(MAX)}} \cdot \left( 1 - \frac{V_{OUT}}{V_{IN(MAX)}} \right)$$

$$L = \frac{0.875V}{2MHz \cdot 10A} \cdot \left( 1 - \frac{0.875V}{5V} \right) = 36nH$$

これに最も近い標準値は  $36nH$  です。

$C_{OUT}$ は、出力のリップル条件を満たすために必要なESRと、ループ安定性を確保するために必要なバルク容量に基づいて選択します。この設計では、 $100\mu F$ と $220\mu F$ のセラミック・コンデンサを2個ずつ使用します。

$$\Delta V_{OUT} < \Delta I_L \cdot \left( \frac{1}{8 \cdot f_{SW} \cdot C_{OUT}} + ESR \right)$$

$C_{IN}$ の大きさは、以下の最大電流定格に見合うものとなるようにします。

$$I_{RMS} \cong I_{OUT(MAX)} \cdot \frac{V_{OUT}}{V_{IN}} \cdot \text{Sqrt}\left(\frac{V_{IN}}{V_{OUT}} - 1\right)$$

$$I_{RMS} = 25A \cdot (0.875V/5V) \cdot ((5V/0.875V) - 1)^{1/2} = 9.5A$$

ほとんどのアプリケーションでは、図30に示すように、 $47\mu F$ のセラミック・コンデンサ2個を用いて $V_{IN}$ をデカップリングするのが適当です。

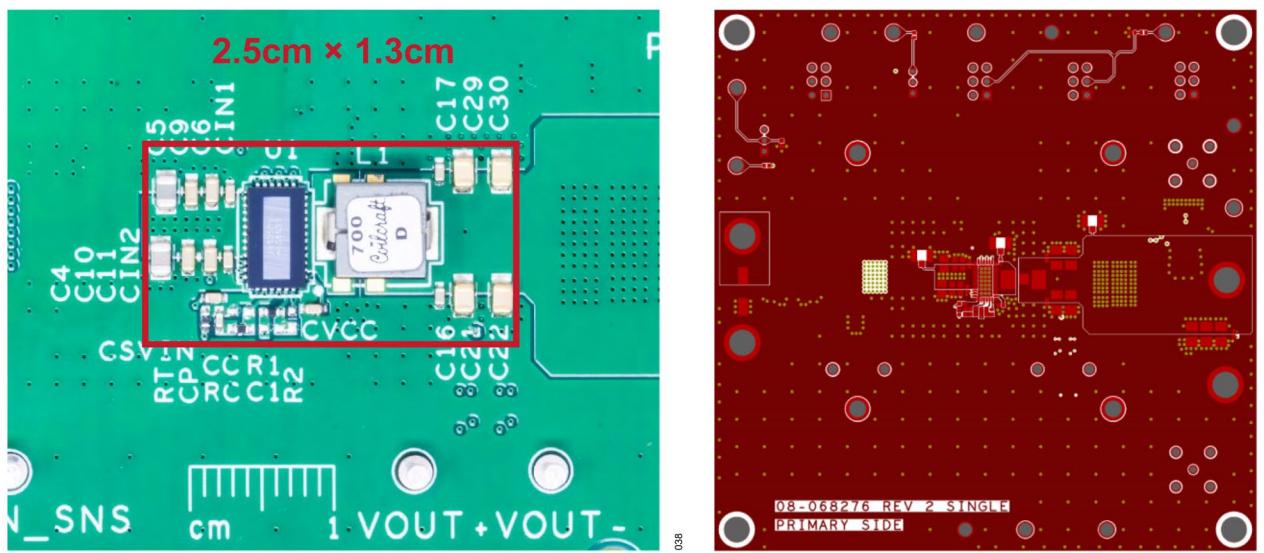

## ボード・レイアウト時の考慮事項

プリント回路基板のレイアウト時には、次のチェックリストを使用して、LT7153SPが正しく動作するようにしてください（図30を参照）。レイアウト時のチェック項目は次のとおりです。

1. コンデンサ  $C_{IN}$ を、 $P_{VIN}$ と GND にできるだけ近づけて接続します。これらのコンデンサは、内蔵のパワーMOSFETおよびそのドライバにAC電流を供給します。

2.  $C_{OUT}$ と L は近づけて接続されていますか？ $C_{OUT}$ の (-) プレートは、電流を GND と  $C_{IN}$ の (-) プレートに戻します。

3. FB 分圧器はデバイスの近くに配置し、ポイント・オブ・ロードで  $V_{OUT}$ と GND にケルビン接続します。

4. ノイズの影響を受けやすい部品は SW ピンから離して配置します。FB 抵抗、RT 抵抗、補償部品、INTVcc バイパス・コンデンサは、SW パターンやインダクタから離して配線します。

5. グランド・プレーンの使用が望されます。

6. 使用しない領域は全て銅で覆ってください。これにより電力部品の温度上昇が抑制されます。これらの銅領域は GND に接続します。

図30. 最上層のPCB設計の例

## 代表的なアプリケーション

036

図 31. 0.875V/25A、2MHz、降圧コンバータ (1%負荷ライン)

037

図 32. 高効率、デュアル・フェーズ 0.5V/50A、2MHz、降圧コンバータ

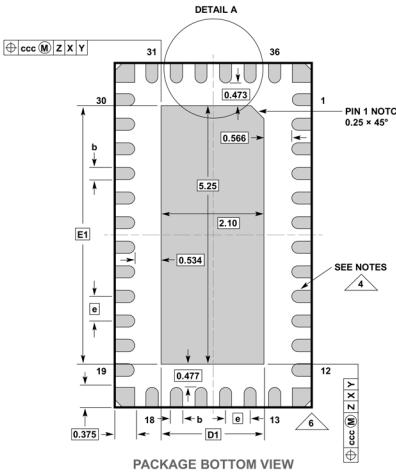

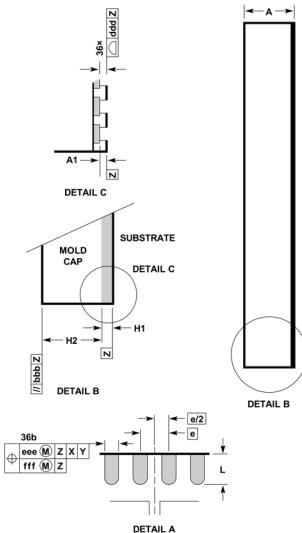

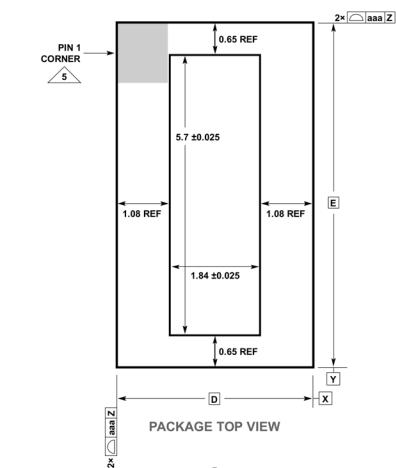

## 外形寸法

**36-Terminal Land Grid Array [LGA]**

**(7mm x 4mm x 1.02mm)**

**(Reference DWG # CC-36-3)**

| DIMENSIONS |          |      |               |

|------------|----------|------|---------------|

| SYMBOL     | MIN      | NOM  | MAX           |

| A          | 0.92     | 1.02 | 1.12          |

| A1         |          | 0.03 |               |

| L          | 0.30     | 0.40 | 0.50          |

| b          | 0.22     | 0.25 | 0.28          |

| D          |          | 4.00 |               |

| E          |          | 7.00 |               |

| D1         |          | 2.10 |               |

| E1         |          | 5.25 |               |

| e          |          | 0.50 |               |

| H1         | 0.32 REF |      | SUBSTRATE THK |

| H2         | 0.70 REF |      | MOLD CAP HT   |

| aaa        |          | 0.10 |               |

| bbb        |          | 0.10 |               |

| ccc        |          | 0.10 |               |

| ddd        |          | 0.10 |               |

| eee        |          | 0.15 |               |

| fff        |          | 0.08 |               |

- NOTES:**

1. DIMENSIONING AND TOLERANCING PER ASME Y14.5M-1994

2. ALL DIMENSIONS ARE IN MILLIMETERS

3. PRIMARY DATUM -Z- IS SEATING PLANE

4. METAL FEATURES UNDER THE SOLDER MASK OPENING NOT SHOWN SO AS NOT TO OBSCURE THESE TERMINALS AND HEAT FEATURES

5. DETAILS OF PIN 1 IDENTIFIER ARE OPTIONAL, BUT MUST BE LOCATED WITHIN THE ZONE INDICATED. THE PIN 1 IDENTIFIER MAY BE EITHER A MOLD OR MARKED FEATURE

6. CORNER SUPPORT PAD CHAMFER IS OPTIONAL

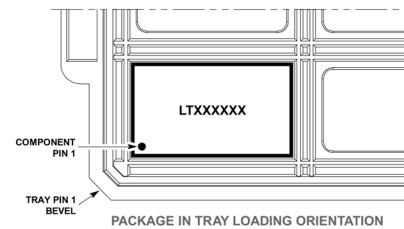

## オーダー・ガイド

| TAPE AND REEL<br>(MINI) | TAPE AND REEL    | PART<br>MARKING | FINISH<br>CODE | PAD<br>FINISH | PACKAGE<br>TYPE                                        | MSL<br>RATING | TEMPERATURE<br>RANGE |

|-------------------------|------------------|-----------------|----------------|---------------|--------------------------------------------------------|---------------|----------------------|

| LT7153SPAV#TRMPBF       | LT7153SPAV#TRPBF | 7153SPV         | E4             | Au<br>(RoHS)  | LQFN<br>(Laminate<br>Package<br>with QFN<br>Footprint) | 3             | -40°C to 125°C       |

- 製品番号末尾が PBF となっている製品は RoHS および WEEE に準拠しています。

- パッドとボールの仕上げコードは IPC/JEDEC J-STD-609 によります。

- 温度グレードは出荷容器のラベルで識別されます。更に広い動作温度範囲仕様のデバイスについては、弊社または弊社代理店までお問い合わせください。

- TRM = 500 個。

- [推奨される PCB のアセンブリと製造の手順](#)。

- パッケージ図面とトレイ図面。

## 関連製品

| 製品番号                    | 説明                                            | 注釈                                                                                                                                    |

|-------------------------|-----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|

| LT7200S                 | 18V、クワッド±5A/4相±20A Silent Switcher®2 降圧レギュレータ | $2.9V < V_{IN} < 18V$ 、 $0.5V < V_{OUT} < 0.9V_{IN}$ 、最大効率96%、<br>5mm × 6mm LQFN-48パッケージ                                              |

| LTC7150S                | 20V、20A 同期整流式降圧レギュレータ                         | $3.1V \leq V_{IN} \leq 20V$ 、 $0.6V \leq V_{OUT} \leq 5.5V$ 、最大効率96%、<br>5mm × 6mm BGAパッケージ                                           |

| LTC3605/<br>LTC3605A    | 20V、5A 同期整流式降圧レギュレータ                          | $4V < V_{IN} < 20V$ 、 $0.6V < V_{OUT} < 20V$ 、最大効率：96%、<br>4mm × 4mm QFN-24パッケージ                                                      |

| LTC3613                 | 差動出力検出機能を備えた 24V、15A モノリシック降圧レギュレータ           | $4.5V < V_{IN} < 24V$ 、 $0.6V < V_{OUT} < 5.5V$ 、出力電圧精度：<br>0.67%、谷電流モード、200kHz～1MHzでプログラマブル、<br>電流検出、7mm × 9mm QFN-56パッケージ           |

| LTC3622                 | 超低静止電流の17V、デュアル1A同期整流式降圧レギュレータ                | $2.7V < V_{IN} < 17V$ 、 $0.6V < V_{OUT} < V_{IN}$ 、最大効率：95%、<br>3mm × 4mm DFN-14 および MSOP-16 パッケージ                                    |

| LTC3623                 | 15V、±5A レール to レールの同期整流式降圧レギュレータ              | $4V \leq V_{IN} \leq 15V$ 、最大効率96%、3mm × 5mm QFNパッケージ                                                                                 |

| LTC3624                 | 静止電流が 3.5μA の 17V、2A 同期整流式降圧レギュレータ            | $2.7V < V_{IN} < 17V$ 、 $0.6V < V_{OUT} < V_{IN}$ 、最大効率95%、3.5μAの<br>$I_Q$ 、ゼロ電流シャットダウン、3mm × 3mm DFN-8パッケージ                          |

| LTC3633A/<br>LTC3633A-1 | デュアル・チャンネル 3A、20V モノリシック同期整流式降圧レギュレータ         | $3.6V < V_{IN} < 20V$ 、 $0.6V < V_{OUT} < V_{IN}$ 、最大効率：95%、<br>4mm × 5mm QFN-28およびTSSOP-28パッケージ                                      |

| LTM4639                 | 低 $V_{IN}$ 20A DC/DC μModule 降圧レギュレータ         | 完全な20Aスイッチ・モード電源、 $2.375V < V_{IN} < 7V$ 、<br>$0.6V < V_{OUT} < 5.5V$ 、最大合計DC出力電圧誤差1.5%、差動リモート・センス・アンプ、15mm × 15mm BGAパッケージ           |

| LTM4637                 | 20A DC/DC μModule 降圧レギュレータ                    | 完全な20Aスイッチ・モード電源、 $4.5V < V_{IN} < 20V$ 、<br>$0.6V < V_{OUT} < 5.5V$ 、最大合計DC出力電圧誤差：1.5%、差動リモート・センス・アンプ、15mm × 15mm BGAまたはLGA<br>パッケージ |

| LTC7130                 | 超低 DCR 検出機能を備えた 20V、20A モノリシック降圧コンバータ         | $4.5V < V_{IN} < 20V$ 、最大効率：95%、低デューティ・サイクル・アプリケーション向けに最適化、6.25mm × 7.5mm BGA<br>パッケージ                                                |

| LT8642S                 | 18V、10A 同期整流式降圧 Silent Switcher 2             | $2.8V < V_{IN} < 18V$ 、 $0.6V < V_{OUT} < V_{IN}$ 、最大効率96%、<br>4mm × 4mm 0.94mm LQFNパッケージ                                             |

ここに含まれるすべての情報は、現状のまま提供されるものであり、アナログ・デバイセズはそれに関するいかなる種類の保証または表明も行いません。アナログ・デバイセズは、その情報の利用に関して、また利用によって生じる第三者の特許またはその他の権利の侵害に関して、一切の責任を負いません。仕様は予告なく変更されることがあります。明示か默示かを問わず、アナログ・デバイセズ製品またはサービスが使用される組み合わせ、機械、またはプロセスに関するアナログ・デバイセズの特許権、著作権、マスクワーク権、またはその他のアナログ・デバイセズの知的財産権に基づくライセンスは付与されません。商標および登録商標は、各社の所有に属します。

## 正誤表

この製品のデータシートに間違いがありましたので、お詫びして訂正いたします。

この正誤表は、2025年10月7日現在、アナログ・デバイセズ株式会社で確認した誤りを記したものです。

なお、英語のデータシート改版時に、これらの誤りが訂正される場合があります。

正誤表作成年月日：2025年10月7日

製品名：LT7153SP

対象となるデータシートのリビジョン(Rev)：Rev.A

訂正箇所：22頁、「マルチフェーズ構成」の項、上から2行目

### 【誤】

「PHASE1/SEL ピンと PHSMD2/ILIM ピンを設定することにより」

### 【正】

「PHSMD1/ISEL ピンと PHSMD2/ILIM ピンを設定することにより」

アナログ・デバイセズ株式会社

本 社／〒105-7323 東京都港区東新橋1-9-1

東京汐留ビルディング 23F

大 阪営業所／〒532-0003 大阪府大阪市淀川区宮原3-5-36

新大阪トラストタワー 10F

名古屋営業所／〒451-6038 愛知県名古屋市西区牛島6-1

名古屋ルーセントタワー 40F

## 正誤表

この製品のデータシートに間違いがありましたので、お詫びして訂正いたします。

この正誤表は、2025年10月7日現在、アナログ・デバイセズ株式会社で確認した誤りを記したものです。

なお、英語のデータシート改版時に、これらの誤りが訂正される場合があります。

正誤表作成年月日：2025年10月7日

製品名：LT7153SP

対象となるデータシートのリビジョン(Rev)：Rev.A

訂正箇所：24頁、「熱的条件」の項、上から6行目

### 【誤】

「LT7153SPには、ヒートシンク搭載の目的でパッケージ上面に露出ダイ・パッドを設けています。」

### 【正】

「LT7153SPのダイ背面は、パッケージ上面の露出パッド接続されヒートシンクとなっています。」

アナログ・デバイセズ株式会社

本 社／〒105-7323 東京都港区東新橋1-9-1

東京汐留ビルディング 23F

大 阪営業所／〒532-0003 大阪府大阪市淀川区宮原3-5-36

新大阪トラストタワー 10F

名古屋営業所／〒451-6038 愛知県名古屋市西区牛島6-1

名古屋ルーセントタワー 40F