## 特長

- デュアル14ビット高速ADC、パッシブ・フィルタ、固定利得差動アンプを内蔵

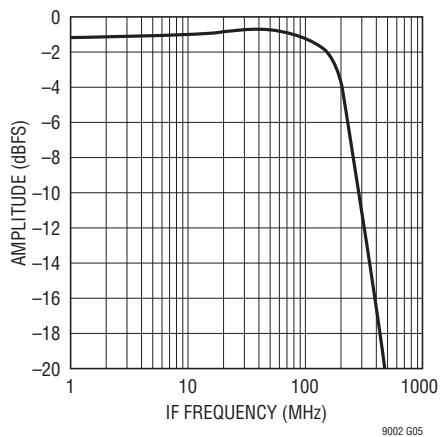

- 最大300MHzのIF範囲

ローパスおよびバンドパス・フィルタ・バージョン

- 低ノイズ、低歪みアンプを内蔵

固定利得: 8dB、14dB、20dB、26dB

入力インピーダンス: 50Ω、200Ωまたは400Ω

- バイパス容量を内蔵、外付け部品不要

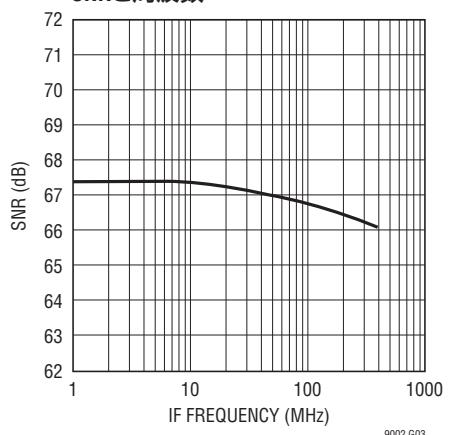

- 140MHzまでの入力でSNR: 66dB (LTM9002-AA)

- 140MHzまでの入力でSFDR: 76dB (LTM9002-AA)

- 利得調整用の補助12ビットDAC

- クロック・デューティ・サイクル・スタビライザ

- 3V~3.3Vの単一電源

- 低消費電力: 1.3W (665mW/チャネル)

- シャットダウン・モードとナップ・モード

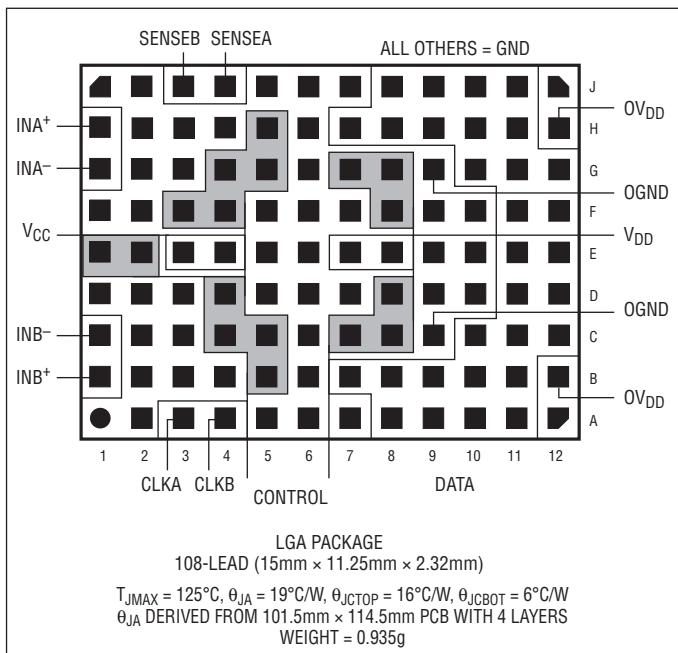

- 15mm × 11.25mm LGAパッケージ

## アプリケーション

- 通信機器

- ダイレクトコンバージョン・レシーバ

- メインおよびダイバーシティ・レシーバ

- セルラー基地局

## 概要

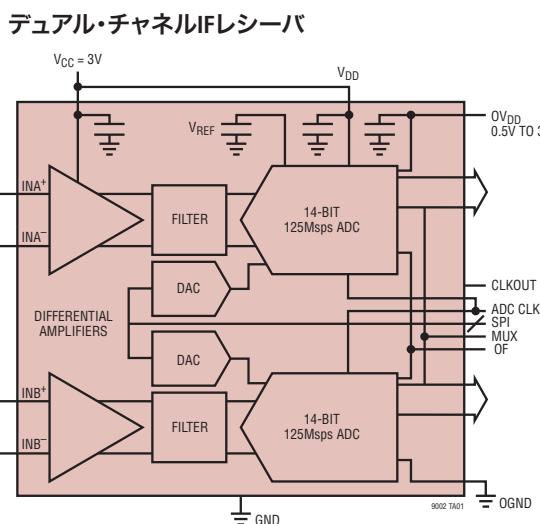

LTM<sup>®</sup>9002は14ビット、デュアルチャネルIFレシーバ・サブシステムです。集積化SiP(System in a Package)技術を利用し、デュアル高速14ビットA/Dコンバータ、整合ネットワーク、アンチエイリアシング・フィルタ、2個の低ノイズ差動アンプを内蔵しています。このデバイスは、中間周波数(IF)が300MHzまでの高ダイナミックレンジ信号をデジタル化するために設計されています。アンプはACまたはDC結合入力をドライブできます。ローパスまたはバンドパス・フィルタ・ネットワークは、多様な周波数に対応できます。カスタム対応については、弊社にお問い合わせください。

LTM9002は、SNRが66dB、SFDRが76dBというAC特性を備えているので、要求の厳しい通信アプリケーションに最適です。補助DACにより、チャネル間で利得のバランスをとることができます。

単一3V電源で動作するため、低消費電力動作が可能です。個別の出力電源により、出力が0.5V~3.3Vのロジックをドライブできます。また、オプションのマルチプレクサにより、両チャネルが1本のデジタル出力バスを共用できます。2つのシングルエンドCLK入力は一緒に、もしくは個別にドライブ可能です。また、オプションのクロック・デューティ・サイクル・スタビライザにより、広範なクロック・デューティ・サイクルにおいてフルスピードで高性能を実現できます。

、LT、LTC、LTM、Linear Technologyおよびリニアのロゴはリニアテクノロジー社の登録商標です。

他の全ての商標はそれぞれの所有者に所有権があります。

## 標準的応用例

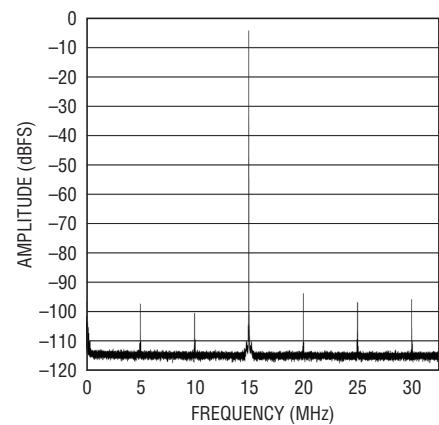

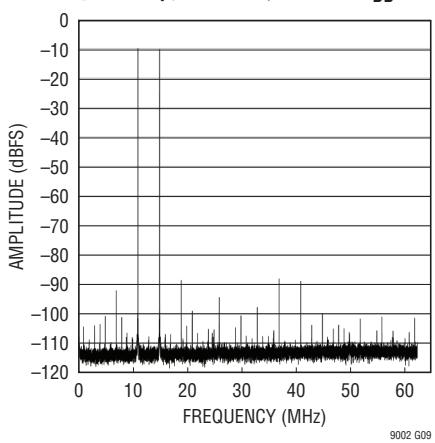

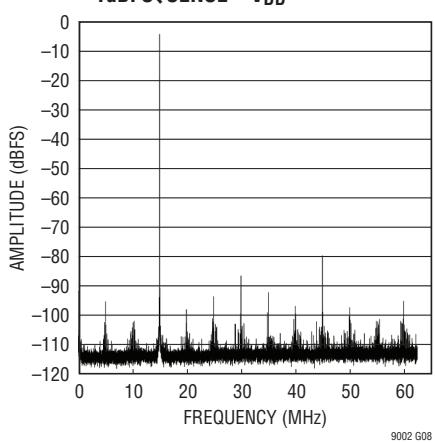

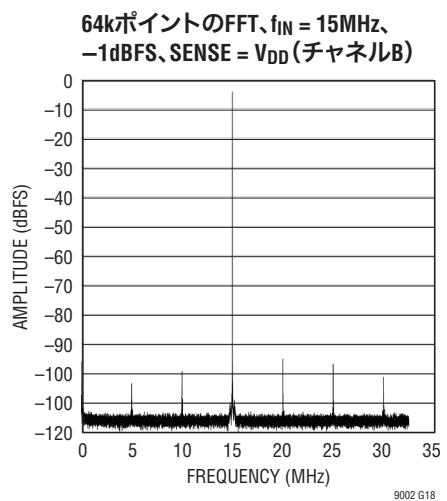

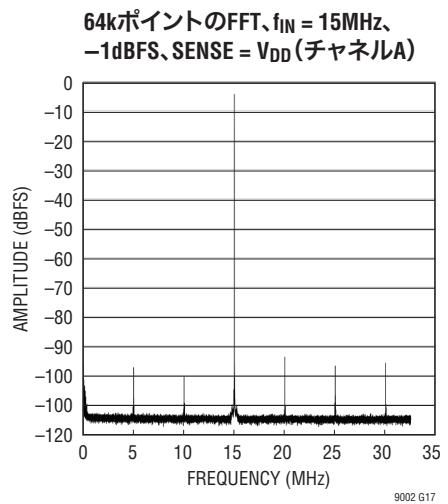

64kポイントのFFT、f<sub>IN</sub> = 15MHz、-1dBFS、

SENSE = V<sub>DD</sub>、チャネルA (LTM9002-LA)

# LTM9002

## 絶対最大定格

(Note 1,2)

|                                  |                                 |

|----------------------------------|---------------------------------|

| 電源電圧 ( $V_{CC}$ )                | -0.3V~3.6V                      |

| 電源電圧 ( $V_{DD}, 0V_{DD}$ )       | -0.3V~4V                        |

| デジタル出力のグランド電圧 (OGND)             | -0.3V~1V                        |

| 入力電流 ( $IN^+, IN^-$ )            | $\pm 10\text{mA}$               |

| DACのデジタル入力電圧                     |                                 |

| ( $\overline{CS}/LD, SDI, SCK$ ) | -0.3V~6V                        |

| デジタル入力電圧                         |                                 |

| ( $AMPSHDN$ を除く)                 | -0.3V~( $V_{DD}+0.3\text{V}$ )  |

| デジタル入力電圧                         |                                 |

| ( $AMPSHDN$ )                    | -0.3V~( $V_{CC}+0.3\text{V}$ )  |

| デジタル出力電圧                         | -0.3V~( $0V_{DD}+0.3\text{V}$ ) |

| 動作温度範囲                           |                                 |

| LTM9002C                         | 0°C~70°C                        |

| LTM9002I                         | -40°C~85°C                      |

| 保存温度範囲                           | -65°C~125°C                     |

## ピン配置

## 発注情報

| 鉛フリー仕様           | トレイ              | 製品マーキング*   | パッケージ                                 | 温度範囲          |

|------------------|------------------|------------|---------------------------------------|---------------|

| LTM9002CV-AA#PBF | LTM9002CV-AA#PBF | LTM9002VAA | 108-Lead (15mm x 11.25mm x 2.3mm) LGA | 0°C to 70°C   |

| LTM9002CV-LA#PBF | LTM9002CV-LA#PBF | LTM9002VLA | 108-Lead (15mm x 11.25mm x 2.3mm) LGA | 0°C to 70°C   |

| LTM9002IV-AA#PBF | LTM9002IV-AA#PBF | LTM9002VAA | 108-Lead (15mm x 11.25mm x 2.3mm) LGA | -40°C to 85°C |

| LTM9002IV-LA#PBF | LTM9002IV-LA#PBF | LTM9002VLA | 108-Lead (15mm x 11.25mm x 2.3mm) LGA | -40°C to 85°C |

より広い動作温度範囲で規定されるデバイスについては、弊社へお問い合わせください。\*温度等級は出荷時のコンテナのラベルで識別されます。

鉛フリー製品のマーキングの詳細については、<http://www.linear-tech.co.jp/leadfree/> をご覧ください。

この製品はトレイでのみ供給されます。詳細については、<http://www.linear-tech.co.jp/packaging/> をご覧下さい。

## 電気的特性

●は全動作温度範囲の規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。(Note 3)

| SYMBOL              | PARAMETER                                     | CONDITIONS                                                   | MIN | TYP  | MAX      | UNITS                        |

|---------------------|-----------------------------------------------|--------------------------------------------------------------|-----|------|----------|------------------------------|

| $G_{\text{DIFF}}$   | Gain                                          | DC, LTM9002-AA<br>$f_{\text{IN}} = 140\text{MHz}$            | ●   | 25   | 26       | 27                           |

|                     |                                               | Channel A, DC (LTM9002-LA)<br>$f_{\text{IN}} = 15\text{MHz}$ | ●   | 19.4 | 20       | 20.6                         |

|                     |                                               | Channel B, DC (LTM9002-LA)<br>$f_{\text{IN}} = 15\text{MHz}$ | ●   | 7.5  | 8        | 8.5                          |

| $G_{\text{TEMP}}$   | Gain Temperature Drift                        | $V_{\text{IN}} = \text{MAX}$ , (Note 3)                      |     |      | 1.5      | $\text{mV}/^\circ\text{C}$   |

|                     | Gain Matching                                 | External Reference                                           |     |      | 5        | $\text{mV}$                  |

| $V_{\text{IN}}$     | Input Voltage Range for $-1\text{dBFS}$       | Both Channels, $f_{\text{IN}} = 140\text{MHz}$ (LTM9002-AA)  |     |      | 100      | $\text{mV}_{\text{P-P}}$     |

|                     |                                               | Channel A, $f_{\text{IN}} = 15\text{MHz}$ (LTM9002-LA)       |     |      | 200      | $\text{mV}_{\text{P-P}}$     |

|                     |                                               | Channel B, $f_{\text{IN}} = 15\text{MHz}$ (LTM9002-LA)       |     |      | 800      | $\text{mV}_{\text{P-P}}$     |

| $V_{\text{INCM}}$   | Input Common Mode Voltage Range               |                                                              |     | 1    | 1.5      | V                            |

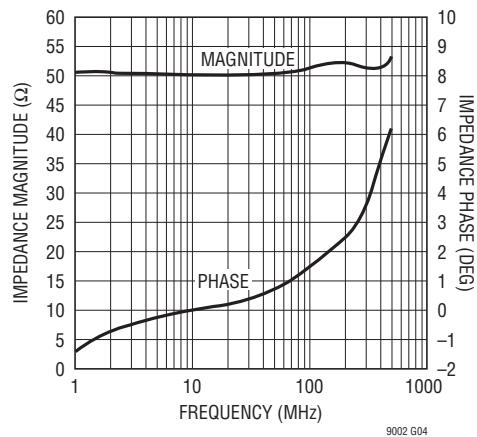

| $R_{\text{INDIFF}}$ | Differential Input Impedance                  | Both Channels (LTM9002-AA)                                   |     |      | 50       | $\Omega$                     |

|                     |                                               | Channel A (LTM9002-LA)                                       |     |      | 200      | $\Omega$                     |

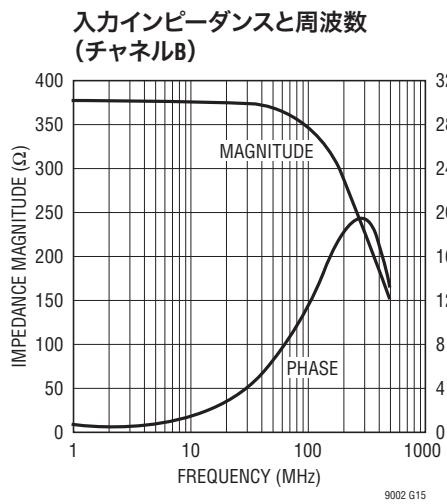

|                     |                                               | Channel B (LTM9002-LA)                                       |     |      | 400      | $\Omega$                     |

| $C_{\text{INDIFF}}$ | Differential Input Capacitance                | Includes Parasitic                                           |     |      | 1        | $\text{pF}$                  |

| $V_{\text{OS}}$     | Offset Error (Note 5)                         | Including Amplifier and ADC                                  | ●   | -5   | 0.3      | 5                            |

|                     | Offset Matching                               |                                                              |     |      | 0.3      | $\text{mV}$                  |

|                     | Offset Drift                                  | Including Amplifier and ADC                                  |     |      | $\pm 10$ | $\mu\text{V}/^\circ\text{C}$ |

| CMRR                | Common Mode Rejection Ratio                   |                                                              |     |      | 50       | $\text{dB}$                  |

| $I_{\text{SENSE}}$  | SENSE Input Leakage                           | $0\text{V} < \text{SENSE} < 1\text{V}$                       | ●   | -3   | 3        | $\mu\text{A}$                |

| $I_{\text{MODE}}$   | MODE Input Leakage                            | $0\text{V} < \text{MODE} < V_{\text{DD}}$                    | ●   | -3   | 3        | $\mu\text{A}$                |

| $t_{\text{AP}}$     | Sample and Hold Acquisition Delay Time        |                                                              |     |      | 0        | ns                           |

| $t_{\text{JITTER}}$ | Sample-and-Hold Acquisition Delay Time Jitter |                                                              |     |      | 0.2      | $\text{ps}_{\text{RMS}}$     |

## コンバータの特性

●は全動作温度範囲の規格値を示す。それ以外は $T_A = 25^\circ\text{C}$ での値。(Note 3)

| SYMBOL        | PARAMETER                         | CONDITIONS | MIN | TYP | MAX       | UNITS |

|---------------|-----------------------------------|------------|-----|-----|-----------|-------|

| <b>ADCの特性</b> |                                   |            |     |     |           |       |

|               | Resolution (No Missing Codes)     | LTM9002-AA | ●   | 14  |           | Bits  |

|               |                                   | LTM9002-LA | ●   | 12  |           | Bits  |

| INL           | Integral Linearity Error (Note 4) | LTM9002-AA |     |     | $\pm 1.5$ | LSB   |

|               |                                   | LTM9002-LA |     |     | $\pm 0.3$ | LSB   |

| DNL           | Differential Linearity Error      | LTM9002-AA | ●   | -1  | $\pm 0.6$ | 1     |

|               |                                   | LTM9002-LA | ●   | -1  | $\pm 0.2$ | 1     |

# LTM9002

## ダイナミック精度

●は全動作温度範囲の規格値を示す。それ以外は $T_A = 25^\circ\text{C}$ での値。入力 =  $-1\text{dBFS}$ 。(Note 3)

| SYMBOL    | PARAMETER                                                                             | CONDITIONS                               | MIN | TYP  | MAX  | UNITS |

|-----------|---------------------------------------------------------------------------------------|------------------------------------------|-----|------|------|-------|

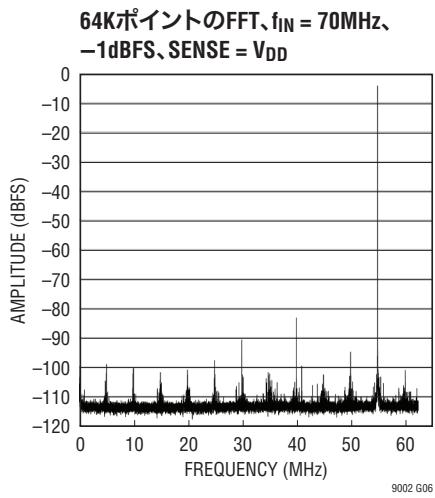

| SNR       | Signal-to-Noise Ratio                                                                 | 70MHz Input (Both Channels), LTM9002-AA  |     | 66   |      | dBFS  |

|           |                                                                                       | 140MHz Input (Both Channels), LTM9002-AA | ●   | 61.5 | 66   | dBFS  |

| SFDR      | Spurious Free Dynamic Range, 2nd or 3rd Harmonic                                      | 15MHz Input (Channel A), LTM9002-LA      | ●   | 67.7 | 69.9 | dBFS  |

|           |                                                                                       | 15MHz Input (Channel B), LTM9002-LA      | ●   | 68.5 | 71.1 | dBFS  |

| SFDR      | Spurious Free Dynamic Range 4th or Higher                                             | 70MHz Input (Both Channels), LTM9002-AA  |     | 82   |      | dBc   |

|           |                                                                                       | 140MHz Input (Both Channels), LTM9002-AA | ●   | 67.5 | 76   | dBc   |

| S/(N+D)   | Signal-to-Noise Plus Distortion Ratio                                                 | 15MHz Input (Channel A), LTM9002-LA      | ●   | 75   | 86.2 | dBc   |

|           |                                                                                       | 15MHz Input (Channel B), LTM9002-LA      | ●   | 72.7 | 85.5 | dBc   |

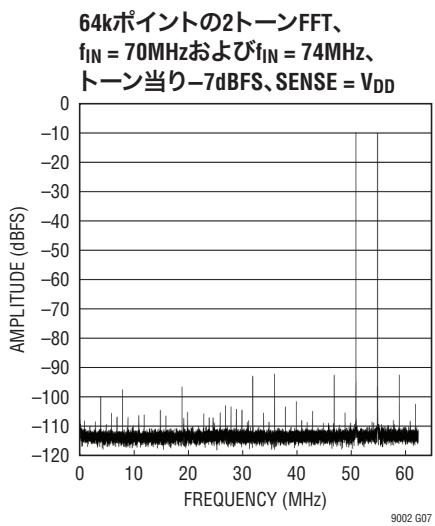

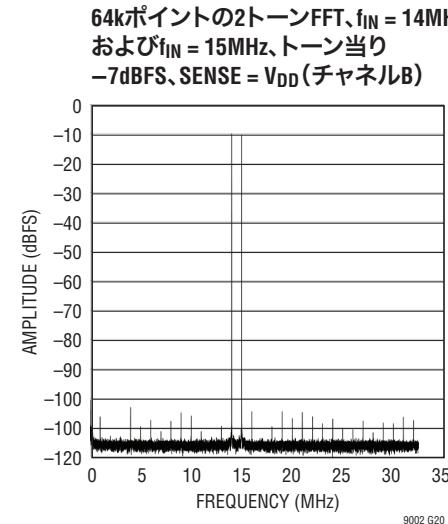

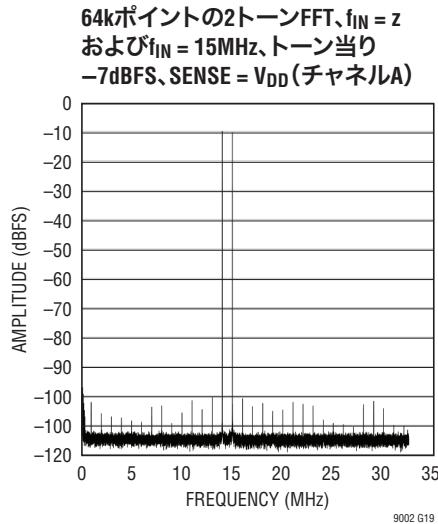

| IMD3      | Third Order Inter-Modulation Distortion; 1MHz Tone Spacing, Two Tones $-7\text{dBFS}$ | 70MHz Input, LTM9002-AA                  |     | 90   |      | dBc   |

|           |                                                                                       | 140MHz Input, LTM9002-AA                 | ●   | 74.2 | 90   | dBc   |

| Crosstalk |                                                                                       | 15MHz Input, LTM9002-LA                  | ●   | 78.8 | 88.5 | dBc   |

|           |                                                                                       | 15MHz Input, LTM9002-LA                  | ●   | 79.8 | 90.7 | dBc   |

## 補助DACの特性

●は全動作温度範囲の規格値を示す。それ以外は $T_A = 25^\circ\text{C}$ での値。(LTM9002-LAには適用されない) (Note 3)

| PARAMETER        | CONDITIONS                                                                    | MIN | TYP | MAX  | UNITS         |

|------------------|-------------------------------------------------------------------------------|-----|-----|------|---------------|

| Resolution       |                                                                               | ●   | 12  |      | Bits          |

| Monotonicity     |                                                                               | ●   | 12  |      | Bits          |

| Full-Scale Range | Internal Reference                                                            |     |     | 1.5  | V             |

| Settling Time    | $\pm 0.024\%$ ( $\pm 1\text{LSB}$ at 12 Bits),<br>No External Sense Capacitor |     |     | 83.5 | $\mu\text{s}$ |

## デジタル入力とデジタル出力

●は全動作温度範囲の規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。

| SYMBOL                                                 | PARAMETER                | CONDITIONS                       | MIN | TYP | MAX | UNITS         |

|--------------------------------------------------------|--------------------------|----------------------------------|-----|-----|-----|---------------|

| <b>ロジック入力 (CLK, OE, ADCSHDN, MUX, CS/LD, SCK, SDI)</b> |                          |                                  |     |     |     |               |

| $V_{IH}$                                               | High Level Input Voltage | $V_{DD} = 3\text{V}$             | ●   | 2   |     | V             |

| $V_{IL}$                                               | Low Level Input Voltage  | $V_{DD} = 3\text{V}$             | ●   |     | 0.8 | V             |

| $I_{IN}$                                               | Input Current            | $V_{IN} = 0\text{V}$ to $V_{DD}$ | ●   | -10 | 10  | $\mu\text{A}$ |

| $C_{IN}$                                               | Input Capacitance        | (Note 6)                         |     |     | 3   | $\text{pF}$   |

## デジタル入力とデジタル出力

●は全動作温度範囲の規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。

| SYMBOL                                    | PARAMETER                 | CONDITIONS                                        | MIN | TYP           | MAX | UNITS         |

|-------------------------------------------|---------------------------|---------------------------------------------------|-----|---------------|-----|---------------|

| <b>ロジック入力(AMPSHDN)</b>                    |                           |                                                   |     |               |     |               |

| $V_{IL}$                                  | Low Level Input Voltage   |                                                   |     |               | 0.8 | V             |

| $V_{IH}$                                  | High Level Input Voltage  |                                                   |     | 2.4           |     | V             |

| $I_{IL}$                                  | Input Low Current         | AMPSHDN = 0.8V                                    |     |               | 0.5 | $\mu\text{A}$ |

| $I_{IH}$                                  | Input High Current        | AMPSHDN = 2.4V                                    |     | 1.4           | 3   | $\mu\text{A}$ |

| <b>ロジック出力</b>                             |                           |                                                   |     |               |     |               |

| <b><math>OV_{DD} = 3\text{V}</math></b>   |                           |                                                   |     |               |     |               |

| $C_{OZ}$                                  | Hi-Z Output Capacitance   | $\overline{OE} = 3\text{V}$ (Note 6)              |     |               | 3   | $\text{pF}$   |

| $I_{SOURCE}$                              | Output Source Current     | $V_{OUT} = 0\text{V}$                             |     | 50            |     | $\text{mA}$   |

| $I_{SINK}$                                | Output Sink Current       | $V_{OUT} = 3\text{V}$                             |     | 50            |     | $\text{mA}$   |

| $V_{OH}$                                  | High Level Output Voltage | $I_0 = -10\mu\text{A}$<br>$I_0 = -200\mu\text{A}$ |     | 2.995<br>2.99 |     | V<br>V        |

| $V_{OL}$                                  | Low Level Output Voltage  | $I_0 = 10\mu\text{A}$<br>$I_0 = 1.6\text{mA}$     |     | 0.005<br>0.09 | 0.4 | V<br>V        |

| <b><math>OV_{DD} = 2.5\text{V}</math></b> |                           |                                                   |     |               |     |               |

| $V_{OH}$                                  | High Level Output Voltage | $I_0 = -200\mu\text{A}$                           |     | 2.49          |     | V             |

| $V_{OL}$                                  | Low Level Output Voltage  | $I_0 = 1.6\text{mA}$                              |     | 0.09          |     | V             |

| <b><math>OV_{DD} = 1.8\text{V}</math></b> |                           |                                                   |     |               |     |               |

| $V_{OH}$                                  | High Level Output Voltage | $I_0 = -200\mu\text{A}$                           |     | 1.79          |     | V             |

| $V_{OL}$                                  | Low Level Output Voltage  | $I_0 = 1.6\text{mA}$                              |     | 0.1           |     | V             |

## 電源条件

●は全動作温度範囲の規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。(Note 7)

| SYMBOL         | PARAMETER                                          | CONDITIONS                                                                       | MIN | TYP         | MAX | UNITS                      |

|----------------|----------------------------------------------------|----------------------------------------------------------------------------------|-----|-------------|-----|----------------------------|

| $V_{CC}$       | Amplifier and Auxiliary DAC Operating Supply Range |                                                                                  |     | 2.85        | 3.0 | 3.4                        |

| $V_{DD}$       | ADC Analog Supply Voltage                          |                                                                                  |     | 2.85        | 3.0 | 3.5                        |

| $OV_{DD}$      | Output Supply Voltage                              |                                                                                  |     | 0.5         | 3.0 | 3.6                        |

| $I_{CC}$       | Amplifier                                          | DAC Powered Up, Both Amplifiers Enabled, LTM9002-AA                              |     | 180         | 207 | $\text{mA}$                |

|                |                                                    | Both Amplifiers Enabled, LTM9002-LA                                              |     | 90          | 120 | $\text{mA}$                |

| $I_{CC(SHDN)}$ | Amplifier Shutdown Supply Current                  | AMPSHDN = 3V, DAC Powered Down                                                   |     | 0.7         |     | $\text{mA}$                |

| $I_{DD(ADC)}$  | ADC Supply Current                                 | LTM9002-AA                                                                       |     | 263         | 313 | $\text{mA}$                |

|                |                                                    | LTM9002-LA                                                                       |     | 140         | 159 | $\text{mA}$                |

| $P_{D(SHDN)}$  | ADC Shutdown Power (Each Channel)                  | ADCSHDN = AMPSHDN = 3V, $\overline{OE} = 3\text{V}$ , No CLK                     |     | 2           |     | $\text{mW}$                |

| $P_{D(NAP)}$   | ADC Nap Mode Power (Each Channel)                  | ADCSHDN = AMPSHDN = 3V, $\overline{OE} = 0\text{V}$ , No CLK                     |     | 15          |     | $\text{mW}$                |

| $P_{D(AMP)}$   | Amplifier Power Dissipation                        | DAC Powered Up, LTM9002-AA                                                       |     | 540         |     | $\text{mW}$                |

|                |                                                    | LTM9002-LA                                                                       |     | 270         |     | $\text{mW}$                |

| $P_{D(ADC)}$   | ADC Power Dissipation                              | LTM9002-AA                                                                       |     | 790         | 939 | $\text{mW}$                |

|                |                                                    | LTM9002-LA                                                                       |     | 420         | 477 | $\text{mW}$                |

| $P_{D(TOTAL)}$ | Total Power Dissipation                            | $f_{SAMPLE} = \text{MAX}$ , LTM9002-AA<br>$f_{SAMPLE} = \text{MAX}$ , LTM9002-LA |     | 1329<br>690 |     | $\text{mW}$<br>$\text{mW}$ |

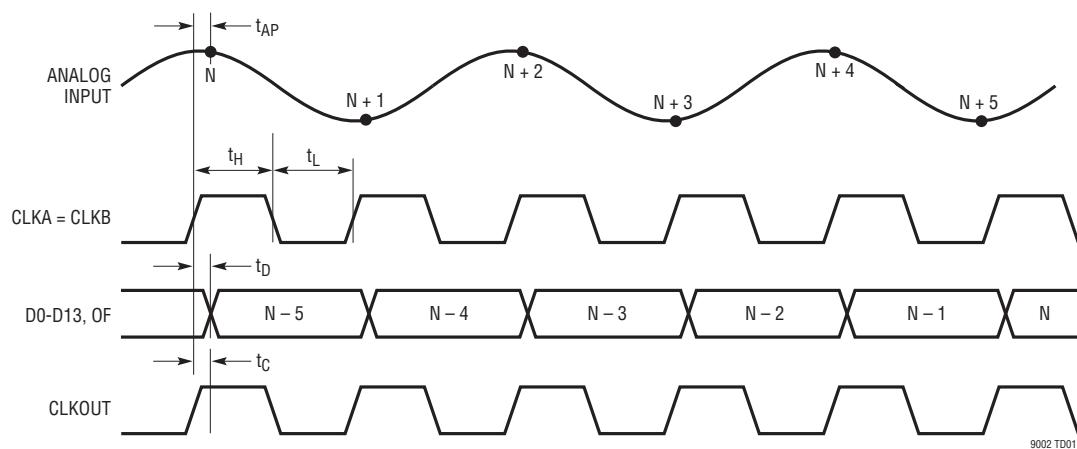

## タイミング特性

●は全動作温度範囲の規格値を表す。それ以外は $T_A = 25^\circ\text{C}$ での値。(Note 6) (LTM9002-LAには適用されない)

| SYMBOL           | PARAMETER                              | CONDITIONS                                     | MIN | TYP  | MAX | UNITS  |

|------------------|----------------------------------------|------------------------------------------------|-----|------|-----|--------|

| $f_S$            | Sampling Frequency                     | LTM9002-AA                                     | ●   | 1    | 125 | MHz    |

|                  |                                        | LTM9002-LA                                     | ●   | 1    | 65  | MHz    |

| $t_L$            | CLK Low Time                           | Duty Cycle Stabilizer Off (Note 6), LTM9002-AA | ●   | 3.8  | 4   | 500    |

|                  |                                        | Duty Cycle Stabilizer On (Note 6), LTM9002-AA  | ●   | 3    | 4   | 500    |

| $t_H$            | CLK High Time                          | Duty Cycle Stabilizer Off (Note 6), LTM9002-AA | ●   | 3.8  | 4   | 500    |

|                  |                                        | Duty Cycle Stabilizer On (Note 6), LTM9002-AA  | ●   | 3    | 4   | 500    |

| $t_L$            | CLK Low Time                           | Duty Cycle Stabilizer Off (Note 6), LTM9002-LA | ●   | 7.3  | 7.7 | 500    |

|                  |                                        | Duty Cycle Stabilizer On (Note 6), LTM9002-LA  | ●   | 5    | 7.7 | 500    |

| $t_H$            | CLK High Time                          | Duty Cycle Stabilizer Off (Note 6), LTM9002-LA | ●   | 7.3  | 7.7 | 500    |

|                  |                                        | Duty Cycle Stabilizer On (Note 6), LTM9002-LA  | ●   | 5    | 7.7 | 500    |

| $t_{AP}$         | Absolute Aperture Delay                |                                                |     | 0    |     | ns     |

| $t_D$            | CLK to DATA Delay                      | $C_L = 5\text{pF}$ (Note 6)                    | ●   | 1.4  | 2.7 | 5.4    |

| $t_C$            | CLK to CLKOUT Delay                    | $C_L = 5\text{pF}$ (Note 6)                    | ●   | 1.4  | 2.7 | 5.4    |

|                  | DATA to CLKOUT Skew                    | $(t_D - t_C)$ (Note 6)                         | ●   | -0.6 | 0   | 0.6    |

| $t_{MD}$         | MUX to DATA Delay                      | $C_L = 5\text{pF}$ (Note 6)                    | ●   | 1.4  | 2.7 | 5.4    |

|                  | DATA Access Time After $\overline{OE}$ | $C_L = 5\text{pF}$ (Note 6)                    | ●   |      | 4.3 | 10     |

|                  | BUS Relinquish Time                    | (Note 6)                                       | ●   |      | 3.3 | 8.5    |

| Pipeline Latency |                                        |                                                |     | 5    |     | Cycles |

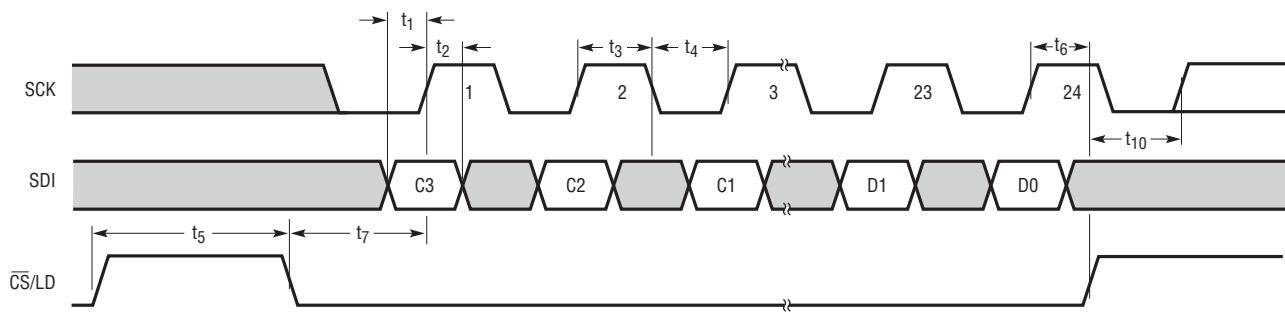

補助DACのSPIインターフェース、 $V_{DD} = 2.7\text{V} \sim 3.6\text{V}$

|          |                                              |  |    |    |     |

|----------|----------------------------------------------|--|----|----|-----|

| $t_1$    | SDI Valid to SCK Setup                       |  | 4  |    | ns  |

| $t_2$    | SDI Valid to SCK Hold                        |  | 4  |    | ns  |

| $t_3$    | SCK High Time                                |  | 9  |    | ns  |

| $t_4$    | SCK Low Time                                 |  | 9  |    | ns  |

| $t_5$    | $\overline{CS}/LD$ Pulse Width               |  | 10 |    | ns  |

| $t_6$    | LSB SCK High to $\overline{CS}/LD$           |  | 7  |    | ns  |

| $t_7$    | $\overline{CS}/LD$ Low to SCK High           |  | 7  |    | ns  |

| $t_{10}$ | $\overline{CS}/LD$ High to SCK Positive Edge |  | 7  |    | ns  |

|          | SCK Frequency 50% Duty Cycle                 |  |    | 50 | MHz |

**Note 1:**絶対最大定格に記載された値を超えるストレスはデバイスに永続的損傷を与える可能性がある。長期にわたって絶対最大定格条件に曝すと、デバイスの信頼性と寿命に悪影響を与える可能性がある。

**Note 2:**全ての電圧値は(注記がない限り)GNDとOGNDを結線したグランドを基準にしている。

**Note 3:**注記がない限り、 $0V_{DD} = V_{CC} = V_{DD} = 3\text{V}$ 、 $f_{SAMPLE} = \text{MAX}$ 、入力レンジ = 差動ドライブで $V_{IN}$ 、 $CLK_A = CLK_B$ 、 $V_{INCM} = 1.25\text{V}$ 、 $\text{AMPSHDN} = \text{ADCSHDN} = 0\text{V}$ 。

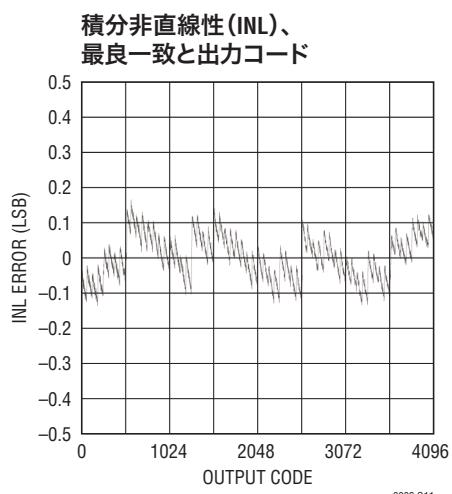

**Note 4:**積分非直線性は、実際の伝達曲線のエンドポイントを通る直線からのコードの偏差として定義されている。偏差は量子化幅の中心から測定される。

**Note 5:**オフセット誤差は、入力が相互に短絡された状態で生じる出力コードである。出力コードはミリボルトに変換される。

**Note 6:**設計によって保証されているが、テストされない。

**Note 7:** $V_{DD} = 3\text{V}$ 、 $f_{SAMPLE} = \text{MAX}$ 、入力レンジ = 差動ドライブで $V_{IN}$ 。消費電流と電力損失は両チャネルがアクティブなときの両チャネルの合計である。

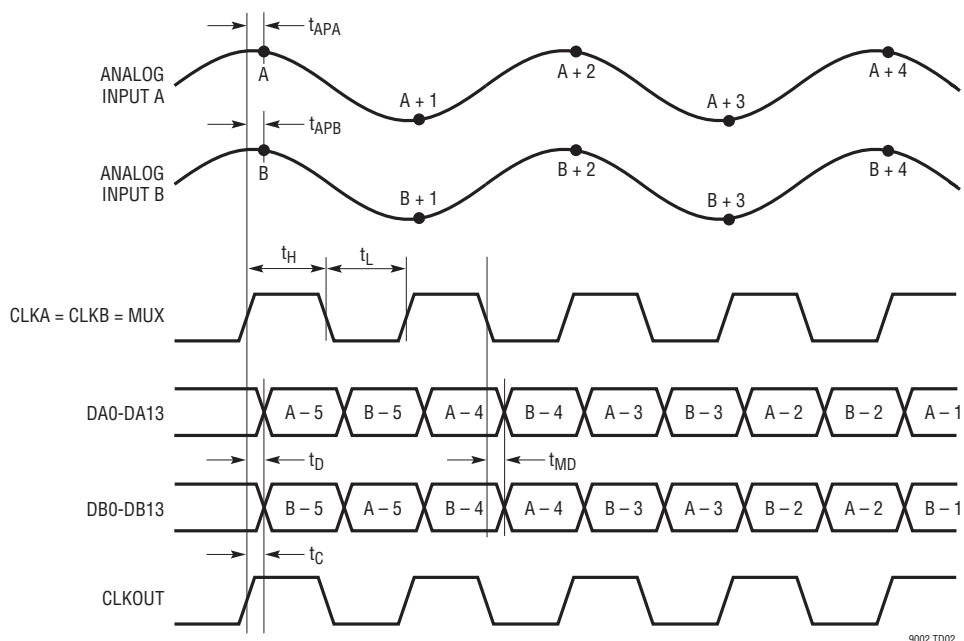

## タイミング図

デュアル・デジタル出力バスのタイミング

多重化されたデジタル出力バスのタイミング

# LTM9002

## タイミング図

### 補助DACのタイミング

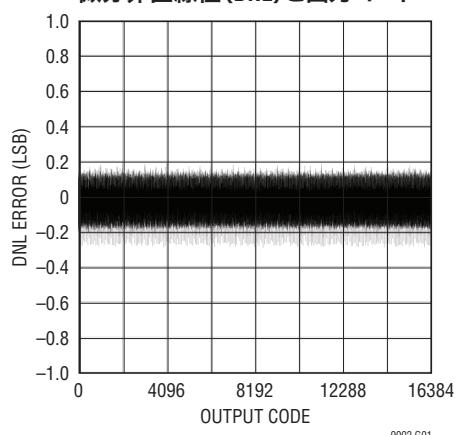

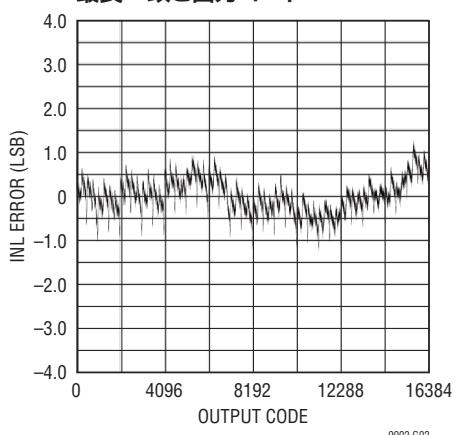

## 標準的性能特性

(LTM9002-AA)

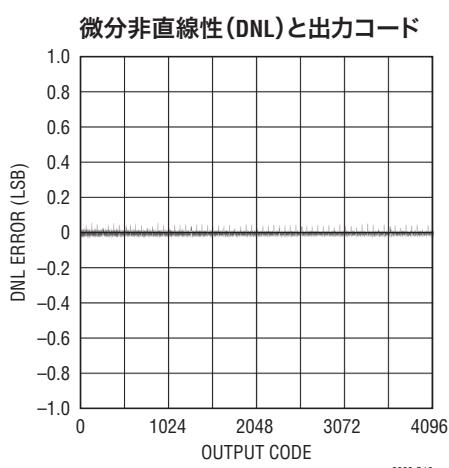

### 微分非直線性(DNL)と出力コード

### 積分非直線性(INL)、最良一致と出力コード

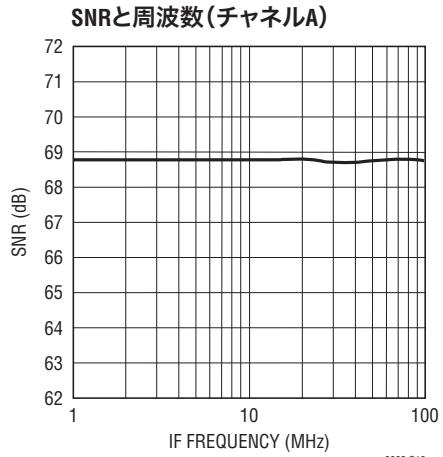

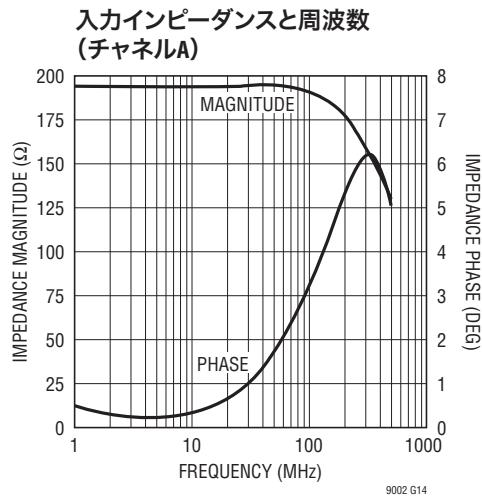

### SNRと周波数

### 入力インピーダンスと周波数

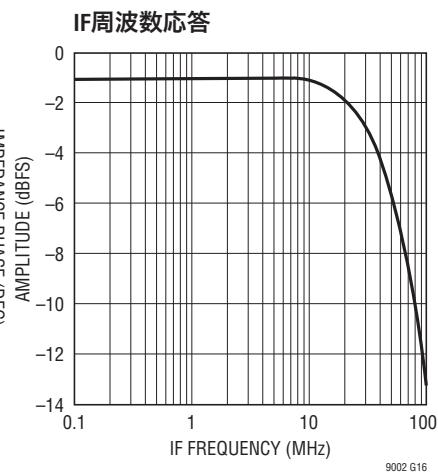

### IF周波数応答

## 標準的性能特性

(LTM9002-AA)

(LTM9002-LA)

## 標準的性能特性 (LTM9002-LA)

## ピン機能

### 電源ピン

**GND(ピンA1-2、A5-7、B2-4、B6、C2-3、C6、D1-3、D5-7、D9-10、E5-6、E9-10、F1-2、F5-7、F9-10、G2-3、G6、H2-4、H6、J1-2、J5-7) :** ADCの電源グランド。

**OGND(ピンA12、C9、G9、J12) :** 出力ドライバのグランド。

**OV<sub>DD</sub>(ピンB12、H12) :** ADCの出力ドライバの正電源。既定動作範囲は0.5V～3.6Vです。OV<sub>DD</sub>は内部でOGNDにバイパスされています。

**V<sub>CC</sub>(ピンE3、E4) :** アンプおよび補助DACの電源。規定動作範囲は2.85V～3.465Vです。このピンの電圧はアンプ段および補助DACにだけ電力を供給し、内部でGNDにバイパスされています。LTM9002-LAには補助DACがないことに注意してください。

**V<sub>DD</sub>(ピンE7、E8) :** ADC用アナログ3V電源。規定動作範囲は2.7V～3.6Vです。V<sub>DD</sub>は内部でGNDにバイパスされています。

### アナログ入力

**CLKA(ピンA3) :** チャネルAのADCクロック入力。立上りエッジで入力のサンプリングが開始されます。

**CLKB(ピンA4) :** チャネルBのADCクロック入力。立上りエッジで入力のサンプリングが開始されます。

**DNC1(ピンH5) :** 接続しないでください。これらのピンはテストに使われ、PCB上では接続しません。それらは接続されていないパッドに半田付けし、十分絶縁します。DNCピンはADC入力の前の信号経路に接続されているので、他の信号をこれらの敏感なノードから遠ざけるように注意します。DNC1はチャネルAの正差動アナログ入力の近くに接続されています。

**DNC2(ピンG5) :** 接続しないでください。これらのピンはテストに使われ、PCB上では接続しません。それらは接続されていないパッドに半田付けし、十分絶縁します。DNCピンはADC入力の前の信号経路に接続されているので、他の信号をこれらの敏感なノードから遠ざけるように注意します。DNC2はチャネルAの負差動アナログ入力の近くに接続されています。

**DNC3(ピンC5) :** 接続しないでください。これらのピンはテストに使われ、PCB上では接続しません。それらは接続されていないパッドに半田付けし、十分絶縁します。DNCピンはADC入力の前の信号経路に接続されているので、他の信号をこれらの敏感なノードから遠ざけるように注意します。DNC3はチャネルBの正差動アナログ入力の近くに接続されています。

**DNC4(ピンB5) :** 接続しないでください。これらのピンはテストに使われ、PCB上では接続しません。それらは接続されていないパッドに半田付けし、十分絶縁します。DNCピンはADC入力の前の信号経路に接続されているので、他の信号をこれらの敏感なノードから遠ざけるように注意します。DNC4はチャネルBの負差動アナログ入力の近くに接続されています。

**DNC5(ピンG4) :** 接続しないでください。このピンはテストに使われ、PCB上では接続しません。接続されていないパッドに半田付けし、十分絶縁します。これは補助DACのチャネルAの電圧出力のテスト・ポイントです。

**DNC6(ピンC4) :** 接続しないでください。このピンはテストに使われ、PCB上では接続しません。接続されていないパッドに半田付けし、十分絶縁します。これは補助DACのチャネルBの電圧出力のテスト・ポイントです。

**INA<sup>-</sup>(ピンG1) :** チャネルAの負(反転)アンプ入力。

**INA<sup>+</sup>(ピンH1) :** チャネルAの正(非反転)アンプ入力。

**INB<sup>-</sup>(ピンC1) :** チャネルBの負(反転)アンプ入力。

**INB<sup>+</sup>(ピンB1) :** チャネルBの正(非反転)アンプ入力。

## ピン機能

### 制御ピン

**ADCSHDNA (ピンG7)**: チャネルAのシャットダウン・モード選択ピン。ADCSHDNAと $\overline{OEA}$ をGNDに接続すると通常動作になり、出力がイネーブルされます。ADCSHDNAをGNDに接続し、 $\overline{OEA}$ をV<sub>DD</sub>に接続すると通常動作になり、出力が高インピーダンスになります。ADCSHDNAをV<sub>DD</sub>に接続し、 $\overline{OEA}$ をGNDに接続するとナップ・モードになり、出力が高インピーダンスになります。ADCSHDNAと $\overline{OEA}$ をV<sub>DD</sub>に接続するとスリープ・モードになり、出力が高インピーダンスになります。

**ADCSHDNB (ピンC7)**: チャネルBのシャットダウン・モード選択ピン。ADCSHDNBと $\overline{OEB}$ をGNDに接続すると通常動作になり、出力がイネーブルされます。ADCSHDNBをGNDに接続し、 $\overline{OEB}$ をV<sub>DD</sub>に接続すると通常動作になり、出力が高インピーダンスになります。ADCSHDNBをV<sub>DD</sub>に接続し、 $\overline{OEB}$ をGNDに接続するとナップ・モードになり、出力が高インピーダンスになります。ADCSHDNBと $\overline{OEB}$ をV<sub>DD</sub>に接続するとスリープ・モードになり、出力が高インピーダンスになります。

**AMPSHDNA (ピンE1)**: チャネルAのアンプの電源シャットダウン・ピン。このピンはアナログ・グランドを基準にしたロジック入力です。AMPSHDNを“L”にすると通常動作になります。AMPSHDNを“H”にするとアンプがパワーダウンし、アンプの消費電流が<1mAになります。

**AMPSHDNB (ピンE2)**: チャネルBのアンプの電源シャットダウン・ピン。このピンはアナログ・グランドを基準にしたロジック入力です。AMPSHDNを“L”にすると通常動作になります。AMPSHDNを“H”にするとアンプがパワーダウンし、アンプの消費電流が<1mAになります。

**MODE (ピンG8)**: 出力のフォーマットとクロック・デューティ・サイクル・スタビライザの選択ピン。MODEは両方のチャネルをコントロールすることに注意してください。MODEをGNDに接続すると、ストレート・バイナリの出力フォーマットが選択され、クロック・デューティ・サイクル・スタビライザがオフします。1/3V<sub>DD</sub>に接続すると、ストレート・バイナリの出力フォーマットが選択され、クロック・デューティ・サイクル・スタビライザがオンします。2/3V<sub>DD</sub>に接続すると、2の補数の出力フォーマットが選択され、クロック・デューティ・サイクル・スタビライザがオンします。V<sub>DD</sub>に接続すると、2の補数の出力フォーマットが選択され、クロック・デューティ・サイクル・スタビライザがオフします。

**MUX (ピンC8)**: デジタル出力のマルチプレクサ・コントロール。MUXが“H”だと、チャネルAはDA<sub>x</sub>から出力し、チャネルBはDB<sub>x</sub>から出力します。MUXが“L”だと出力バスが入れ替わり、チャネルAはDB<sub>x</sub>から出力し、チャネルBはDA<sub>x</sub>から出力します。両方のチャネルを1つの出力バスに多重化するにはMUX、CLKAおよびCLKBを一緒に結合します。

**$\overline{OEA}$  (ピンF8)**: チャネルAの出力イネーブル・ピン。ADCSHDNAピンの機能を参照してください。

**$\overline{OEB}$  (ピンD8)**: チャネルBの出力イネーブル・ピン。ADCSHDNBピンの機能を参照してください。

**SENSEA (ピンJ4)**: チャネルAのリファレンス・プログラミング・ピン。SENSEAをV<sub>DD</sub>に接続すると、内部リファレンスと高い方の入力レンジが選択されます。1.5Vに接続すると低い方のレンジが選択されます。0.5Vより大きく1Vより小さい外部リファレンスをSENSEAに印加すると、 $\pm V_{SENSEA}$ /利得の入力レンジが選択されます。「SENSEピンの動作」のセクションを参照してください。

**SENSEB (ピンJ3)**: チャネルBのリファレンス・プログラミング・ピン。SENSEBをV<sub>DD</sub>に接続すると、内部リファレンスと高い方の入力レンジが選択されます。1.5Vに接続すると低い方のレンジが選択されます。0.5Vより大きく1Vより小さい外部リファレンスをSENSEBに印加すると、 $\pm V_{SENSEB}$ /利得の入力レンジが選択されます。「SENSEピンの動作」のセクションを参照してください。

### デジタル入力 (LTM9002-LAでは接続されていない)

**$\overline{CS/LD}$  (ピンF3)**: シリアル・インターフェースの補助DACのチップ・セレクト/ロード入力。 $\overline{CS/LD}$ が“L”的とき、SCKがイネーブルされ、SDIのデータをレジスタにシフトします。 $\overline{CS/LD}$ が“H”に引き上げられると、SCKはディスエーブルされ、指定されたコマンド(表3を参照)が実行されます。

**SCK (ピンF4)**: 補助DACのシリアル・インターフェース・クロック入力。CMOSとTTLに対して互換性があります。

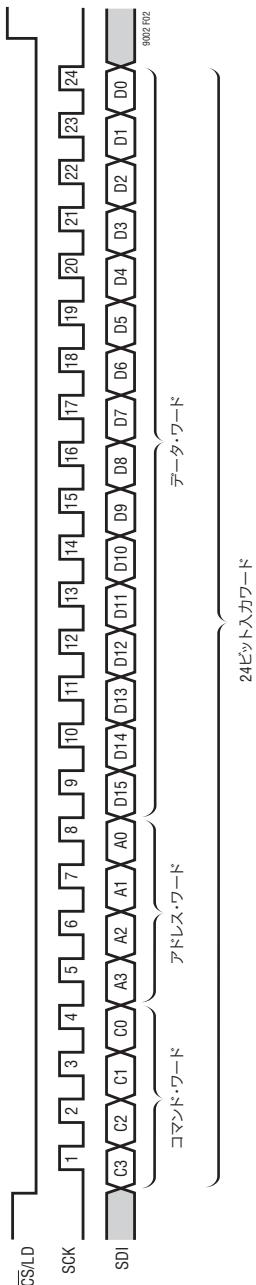

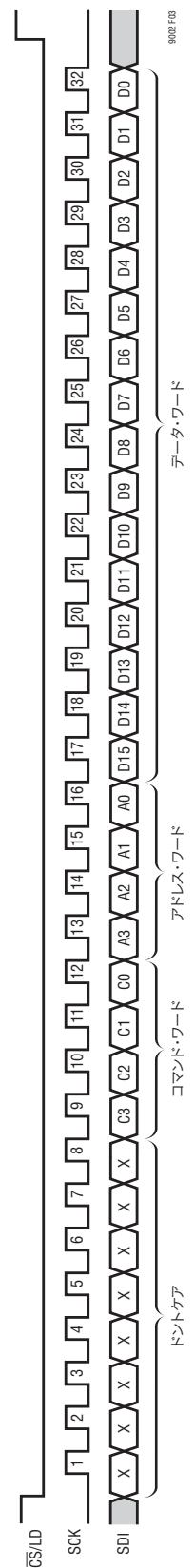

**SDI (ピンD4)**: 補助DACのシリアル・インターフェース・データ入力。データはSDIに与えられ、SCKの立上りエッジでデバイスに転送されます。補助DACは24ビットまたは32ビットの入力ワード長を受け入れます。

## ピン機能

### デジタル出力

**CLKOUT(ピンE12、LTM9002-AA)**: ADCのデータ・レディ・クロック出力。CLKOUTの立下りエッジでデータをラッチします。CLKOUTはCLKBから得られます。同時動作ではCLKAをCLKBに接続します。

**OFB(ピンE12、LTM9002-LA)**: オーバーフロー/アンダーフロー出力。チャネルBにオーバーフローまたはアンダーフローが生じると”H”になります。

**DA0～DA13(ピン配置の表を参照)**: チャネルAのADCのデジタル出力。DA13はLTM9002-AAのMSB；DA11はLTM9002-LAのMSB。

**DB0～DB13(ピン配置の表を参照)**: チャネルBのADCのデジタル出力。DB13はLTM9002-AAのMSB；DB11はLTM9002-LAのMSB。

**OF(ピンH7、LTM9002-AA)**: オーバーフロー/アンダーフロー出力。チャネルAまたはチャネルBにオーバーフローまたはアンダーフローが生じると”H”になります。

**OFA(ピンH7、LTM9002-LA)**: オーバーフロー/アンダーフロー出力。チャネルAにオーバーフローまたはアンダーフローが生じると”H”になります。

### ピン配置(LTM9002-AA)

|   | 1                | 2         | 3               | 4               | 5    | 6   | 7               | 8               | 9    | 10   | 11   | 12               |

|---|------------------|-----------|-----------------|-----------------|------|-----|-----------------|-----------------|------|------|------|------------------|

| J | GND              | GND       | SENSEB          | SENSEA          | GND  | GND | GND             | DA8             | DA5  | DA6  | DA7  | OGND             |

| H | INA <sup>+</sup> | GND       | GND             | GND             | DNC1 | GND | OF              | DA10            | DA12 | DA11 | DA9  | 0V <sub>DD</sub> |

| G | INA <sup>-</sup> | GND       | GND             | DNC5            | DNC2 | GND | ADC SHDNA       | MODE            | OGND | DA13 | DA4  | DA3              |

| F | GND              | GND       | CS/LD           | SCK             | GND  | GND | GND             | OE <sub>A</sub> | GND  | GND  | DA2  | DA1              |

| E | AMP SHDNA        | AMP SHDNB | V <sub>CC</sub> | V <sub>CC</sub> | GND  | GND | V <sub>DD</sub> | V <sub>DD</sub> | GND  | GND  | DAO  | CLKOUT           |

| D | GND              | GND       | GND             | SDI             | GND  | GND | GND             | OE <sub>B</sub> | GND  | GND  | DB13 | DB12             |

| C | INB <sup>-</sup> | GND       | GND             | DNC6            | DNC3 | GND | ADC SHDNB       | MUX             | OGND | DB1  | DB11 | DB10             |

| B | INB <sup>+</sup> | GND       | GND             | GND             | DNC4 | GND | DB0             | DB4             | DB2  | DB3  | DB5  | 0V <sub>DD</sub> |

| A | GND              | GND       | CLKA            | CLKB            | GND  | GND | GND             | DB6             | DB9  | DB8  | DB7  | OGND             |

### ピン配置(LTM9002-LA)

|   | 1                | 2         | 3               | 4               | 5    | 6   | 7               | 8               | 9    | 10   | 11   | 12               |

|---|------------------|-----------|-----------------|-----------------|------|-----|-----------------|-----------------|------|------|------|------------------|

| J | GND              | GND       | SENSEB          | SENSEA          | GND  | GND | GND             | DA6             | DA3  | DA4  | DA5  | OGND             |

| H | INA <sup>+</sup> | GND       | GND             | GND             | DNC1 | GND | OFA             | DA8             | DA10 | DA9  | DA7  | 0V <sub>DD</sub> |

| G | INA <sup>-</sup> | GND       | GND             | DNC5            | DNC2 | GND | ADC SHDNA       | MODE            | OGND | DA11 | DA2  | DA1              |

| F | GND              | GND       | NC              | NC              | GND  | GND | GND             | OE <sub>A</sub> | GND  | GND  | DAO  | NC               |

| E | AMP SHDNA        | AMP SHDNB | V <sub>CC</sub> | V <sub>CC</sub> | GND  | GND | V <sub>DD</sub> | V <sub>DD</sub> | GND  | GND  | NC   | OFB              |

| D | GND              | GND       | GND             | NC              | GND  | GND | GND             | OE <sub>B</sub> | GND  | GND  | DB11 | DB10             |

| C | INB <sup>-</sup> | GND       | GND             | DNC6            | DNC3 | GND | ADC SHDNB       | MUX             | OGND | NC   | DB9  | DB8              |

| B | INB <sup>+</sup> | GND       | GND             | GND             | DNC4 | GND | NC              | DB2             | DB0  | DB1  | DB3  | 0V <sub>DD</sub> |

| A | GND              | GND       | CLKA            | CLKB            | GND  | GND | GND             | DB4             | DB7  | DB6  | DB5  | OGND             |

# LTM9002

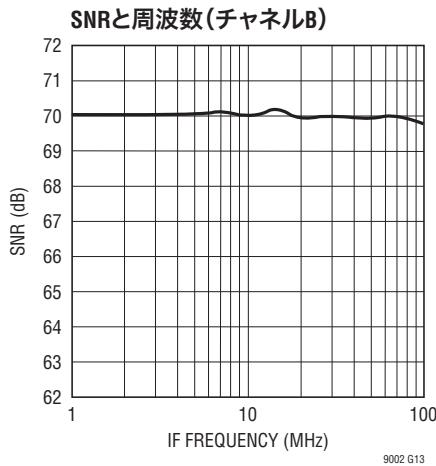

## ブロック図

機能ブロック図(1チャネルだけ示されている)

9002f

## 動作

### 動的性能の定義

#### 信号と雑音+歪みの比

信号と雑音+歪みの比S/(N+D)は、ADCの出力での基本入力周波数のRMS振幅と他の全ての周波数成分のRMS振幅の比です。出力の帯域はDCからサンプリング周波数の半分より低い周波数に制限されます。

#### 信号対雑音比

信号対雑音比(SNR)は基本入力周波数のRMS振幅と、最初の5つの高調波およびDCを除く他の全ての周波数成分のRMS振幅の比です。

#### 全高調波歪み

全高調波歪みは入力信号の全高調波のRMS和の基本周波数に対する比です。帯域外高調波はDCとサンプリング周波数の半分の間の周波数帯域でエイリアスを生じます。THDは次のように表されます。

$$THD = 20 \log \sqrt{(V2^2 + V3^2 + V4^2 + \dots + Vn^2)} / V1$$

ここで、V1は基本周波数のRMS振幅で、V2～Vnは2次～n次の高調波の振幅です。このデータシートで計算されているTHDには5次までの高調波が全て使われています。

#### 混変調歪み

ADCの入力信号に複数のスペクトル成分が含まれていると、ADCの伝達関数の非直線性により、THDに加えて混変調歪み(IMD)が生じことがあります。IMDは周波数の異なる別の正弦波入力が存在するためにある正弦波入力に生じる変化です。

周波数がfaとfbの2つの純粋な正弦波がADCの入力に与えられると、ADCの伝達関数の非直線性によりmfa ± nfbの和と差の周波数で歪み積を生じことがあります。ここで、mとnは0、1、2、3などです。3次の混変調歪み積は2fa+fb、2fb+fa、2fa-fbおよび2fb-faです。混変調歪みは、最大の3次混変調積のRMS値に対する、どちらかの入力トーンのRMS値の比として定義されます。

#### スプリアスフリー・ダイナミックレンジ(SFDR)

スプリアスフリー・ダイナミックレンジは、入力信号とDCを除いた最大のスペクトル成分であるピーク高調波またはスプリアス・ノイズです。この値はフルスケール入力信号のRMS値を基準にしたデシベル値で表されます。

#### アパー・チャ・遅延時間

CLKが電源電圧の中点に達したときから、入力信号がサンプル&ホールド回路によってホールドされる瞬間までの時間。

#### アパー・チャ・遅延ジッタ

変換ごとのアパー・チャ・遅延時間の変動。このランダムな変動により、AC入力のサンプリング時にノイズが生じます。ジッタだけによる信号対雑音比は次のようになります。

$$SNRJITTER = -20 \log (2\pi) \cdot f_{IN} \cdot t_{JITTER}$$

#### クロストーク

一方のチャネルから他方のチャネルに結合する信号の大きさ。これは、チャネルAにフルスケール正弦波入力を与え、チャネルBの入力を短絡して、信号電力の比をFFTで測定します。

## 動作

### 概要

LTM9002は集積化SiP(System in a Package)であり、2個の高速14ビットA/Dコンバータ、整合ネットワーク、アンチエイリアシング・フィルタ、2個の固定利得の低ノイズ差動アンプを内蔵しています。これらのアンプは同じである必要はないので、2つのチャネルの利得と入力インピーダンスは異なります。1対の補助DACも内蔵されているので、各チャネルのフルスケールをデジタルで調節することができます。LTM9002は、入力周波数が最大300MHzまでの高周波数のダイナミックレンジの広い信号をデジタル化するように設計されています。標準的応用例には、基地局アプリケーションの同相チャネルと直交チャネルまたはメイン・チャネルとダイバーシティ・チャネルのデジタル化が含まれます。

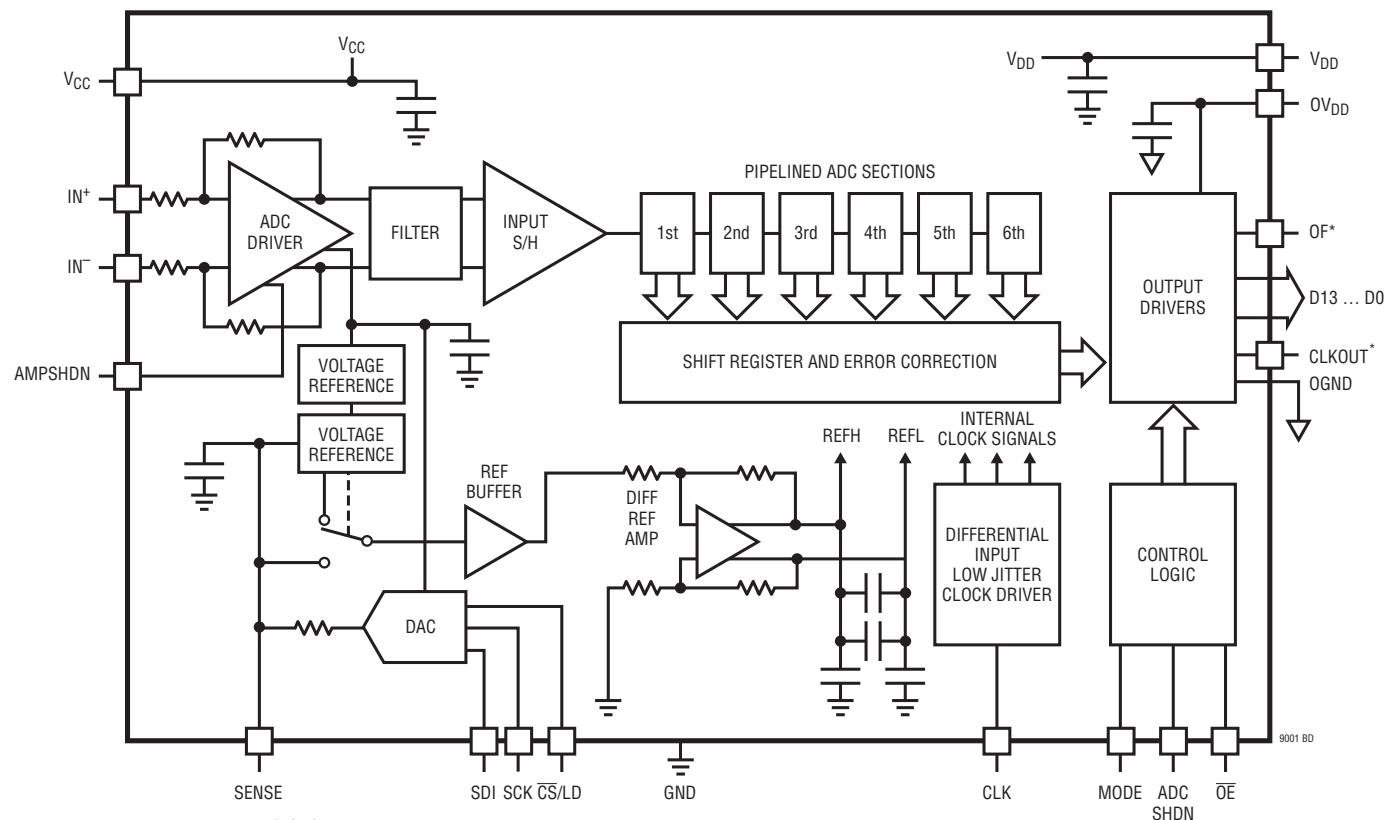

以下のセクションでは各部分の動作を詳細に説明します。SiPテクノロジーによりLTM9002はカスタム化が可能で、それについて最初のセクションで説明します。残りのセクションのアウトラインは図1に示されている基本機能要素に従います。

図1. 基本機能要素

表1. セミカスタム・オプション

| アンプのIF範囲 | アンプの入力インピーダンス                        | アンプの利得                              | フィルタ       | ADCのサンプルレート | ADCの分解能 | 補助DAC       | 製品番号       |

|----------|--------------------------------------|-------------------------------------|------------|-------------|---------|-------------|------------|

| 300MHz   | 50Ω                                  | 26dB                                | 170MHz LPF | 125Msps     | 14-Bit  | 12-Bit, SPI | LTM9002-AA |

| 140MHz   | 200Ω (Channel A)<br>400Ω (Channel B) | 20dB (Channel A)<br>8dB (Channel B) | 25MHz LPF  | 65Msps      | 12-Bit  | None        | LTM9002-LA |

以下の列からオプションの組合せを選択する

|           |      |      |     |         |        |                          |  |

|-----------|------|------|-----|---------|--------|--------------------------|--|

| DC-300MHz | 50Ω  | 26dB | TBD | 125Msps | 14-Bit | 12-Bit, I <sup>2</sup> C |  |

| DC-140MHz | 200Ω | 20dB |     | 105Msps | 12-Bit | None                     |  |

| DC-70MHz  | 200Ω | 14dB |     | 80Msps  | 10-Bit |                          |  |

| DC-35MHz  | 400Ω | 8dB  |     | 65Msps  |        |                          |  |

|           |      |      |     | 40Msps  |        |                          |  |

|           |      |      |     | 25Msps  |        |                          |  |

|           |      |      |     | 10Msps  |        |                          |  |

### セミカスタム・オプション

μModule構造は、アプリケーション固有の標準製品に新しいレベルの柔軟性を可能にしました。特定のアプリケーション向けに、標準的ADCとアンプの部品を(それらのプロセス・テクノロジーに関係なく)一体化し、受動部品に適合させることができます。最初の例として、LTM9002-AAは最高125MHzのレートでサンプリングするデュアル14ビットADCを使って構成されています。アンプの利得は26dB、入力インピーダンスは50Ω、入力範囲は100mV<sub>P-P</sub>(-16dBm)です。整合ネットワークはこれらの条件でアンプの出力とADCのインターフェースを最適化するように設計されています。さらに、カットオフ周波数が170MHzの3次ローパス・フィルタがあります。補助DACにより、12ビットの分解能でフルスケールを調節することもできます。

ただし、リニアテクノロジーのセミカスタム開発プログラムを通して他のオプションも可能です。リニアテクノロジーは、ほとんどどんなアプリケーションにも対応する、他の速度、分解能、IF範囲、利得およびフィルタ構成を提供するプログラムを用意しています。これらのセミカスタム・デザインは、適切に変更を加えた整合ネットワークと組み合わせた既存のADCとアンプを基礎にします。次いで、アプリケーションで定義された精確なパラメータに対して最終サブシステムがテストされます。最終的には、同じパッケージに完全に一体化され、精確にテストされ、最適化されたソリューションになります。セミカスタムのレシーバ・サブシステム・プログラムの詳細については、弊社にお問い合わせください。

## 動作

表1の全ての組合せが現時点では可能なわけではなく、規定性能が既存の値と大きく異なることがあることに注意してください。

### アンプの動作

LTM9002に使われているアンプは低ノイズ、低歪みの完全差動オペアンプ/ADCドライバで、DCから2GHzまで動作します（-3dB帯域幅）。アンプは内蔵帰還付き完全差動アンプと出力同相電圧制御回路で構成されています。差動利得と入力インピーダンスは帰還ネットワーク内の内部抵抗によって設定されます。

表2. アンプの利得と入力インピーダンス

| 利得(dB) | 利得(V/V) | $Z_{IN}$ (差動) |

|--------|---------|---------------|

| 8      | 2.5     | 400Ω          |

| 14     | 5       | 200Ω          |

| 20     | 10      | 200Ω          |

| 26     | 20      | 50Ω           |

アンプはI/Oのカップリングの点で非常に柔軟性があります。それらの入力はAC結合またはDC結合することができます。入力と出力の間の内部接続により、ユーザーが適切な動作のために入力同相範囲を1V～1.7Vに保つことを推奨します。入力をAC結合すると、入力の同相電圧は自動的にADCの入力同相電圧の近くにバイアスされますので、バイアスのための外部回路は不要です。入力信号はシングルエンドでも差動でもよく、歪み性能がいくらか違います。

### ADCの入力ネットワーク

アンプの出力段とADCの入力段の間のパッシブ・ネットワークは、バンドパスまたはローパス応答を異なるカットオフ周波数および帯域幅で構成設定できる3次トポロジーを与えます。たとえば、LTM9002-AAは170MHzに設定されたローパス・フィルタを実現します。

### コンバータの動作

ブロック図に示されているように、A/Dコンバータ(ADC)はデュアルCMOSパイプライン・マルチステップ・コンバータです。パイプライン構成の6つのADC段を備えており、サンプリングされたアナログ入力は6サイクル後にデジタル値になります（タイミング図を参照）。CLK入力はシングルエンドです。ADCはCLK入力ピンの状態で定まる2つのフェーズで動作します。

ブロック図に示されているパイプライン構成の各段は、1個のADC、再構成DAC、および段間残余アンプを備えています。動作時、ADCは各段の入力を量子化し、量子化された値はDACによって入力から差し引かれ、残余を生じます。残余は残余アンプによって増幅されて出力されます。奇数段がその残余を出力しているとき偶数段がその残余を取得するように、またその逆になるように、後に続く段は位相がずれて動作します。

CLKが“L”的とき、アナログ入力はブロック図に示されている「入力S/H」内部の入力サンプル&ホールド・コンデンサに差動で直接サンプリングされます。CLKが“L”から“H”に遷移する瞬間、サンプリングされた入力がホールドされます。CLKが“H”的間、ホールドされた入力電圧はS/Hアンプによってバッファされます。このS/Hアンプはパイプライン構成の最初のADC段をドライブします。初段はCLKのこの“H”フェーズの間にS/Hの出力を取得します。CLKが“L”に戻ると初段はその残余を出力し、この残余が2番目の段によって取得されます。同時に、入力のS/Hは再度アナログ入力を取得します。CLKが“H”に戻ると2番目の段はその残余を出力し、この残余が3番目の段によって取得されます。同様の過程が3番目、4番目、さらに5番目の段で繰り返され、5番目の段の残余は最終評価のために6番目の段のADCに送られます。

初段に続く各ADC段にはフラッシュ誤差とアンプのオフセット誤差を調節するための追加範囲があります。ADCの全段からの結果は、出力バッファに送る前に、それらの結果を補正ロジックで適切に結合できるようにデジタル動作で同期させます。

### 補助DACの動作

各ADCのフルスケール電圧スパンはSENSEに接続された補助電圧出力DACによって制御されます。DACの出力の直列抵抗により、外部電圧がDACをオーバーライドすることができます。

内部リファレンスが両方の補助DACを1.5Vのフルスケール範囲に設定します。外部リファレンスより大きい、または小さい内部電圧を発生するようにDACをプログラムすると、それに比例してADCのスパンが調整されます（「フルスケール入力範囲の調節」を参照）。

## 動作

補助DACをパワーダウンするとADCスパンのトリム制御がディスエーブルされます。補助DACをパワーダウンするときは、SENSEをV<sub>DD</sub>または外部リファレンスに接続します。

### パワーオン・リセット

補助DACは電源が最初に入れられたとき出力をゼロスケールにクリアして、システムの初期状態を一定に保ち、反復可能にします。

### 伝達関数

デジタルからアナログへの伝達関数は次のとおりです。

$$V_{\text{OUT}(\text{IDEAL})} = (k/2^N) V_{\text{REF}}$$

ここで、kはDACの2進数の入力コードに相当する10進数、Nは分解能、V<sub>REF</sub>は1.5V(ADCの内部リファレンス電圧)です。

### シリアル・インターフェース

全てのシリアル・インターフェース・ピン( CS/LD、SCK および SDI)はTTL入力レベルで、5Vに耐えます。CS/LD入力はレベル・トリガれます。この入力が“L”に引き下げられるとチップ・セレクト信号として機能し、SDIとSCKのバッファが作動状態になり、入力のシフト・レジスタをイネーブルします。データ(SDI入力)は次に続く24のSCKの立上りエッジで転送されます。最初に4ビットのコマンド(C3~C0)、次に4ビットのDACアドレス(A3~A0)、そして最後に16ビットのデータ・ワードがロードされます。データ・ワードは12ビットの入力コードで構成され、MSBからLSBに向かって並び、4つのドントケア・ビットが続きます。データはCS/LD信号が“L”的きだけデバイスに転送することができます。CS/LDの立上りエッジでデータの転送が終了し、24ビットの入力ワードで指定されたアクションがデバイスによって実行されます。完全なシーケンスを図3に示します。

コマンド(C3~C0)とアドレス(A3~A0)の割当てを表3に示します。表の中の最初の4つのコマンドは書き込みと更新の操作です。書き込み操作は、32ビットのシフト・レジスタから16ビットのデータ・ワードを、選択されたDAC(*n*)の入力レジスタにロードします。更新操作はデータ・ワードを入力レジスタからDACレジスタにコピーします。DACレジスタにコピーされると、データ・ワードはアクティブな12ビットの入力コードになります。DAC出力でアナログ電圧に変換されます。また、パワーダ

ウン・モードであれば、更新操作により、選択されたDACがパワーアップされます。データ・パスとレジスタをブロック図に示します。

最小入力ワードは24ビットですが、16ビット(2バイト)の最小ワード幅のマイクロプロセッサに適合させるために32ビットに拡張することができます。32ビットのワード幅を利用するには、ドントケア(対象外)の8ビットが最初にデバイスに転送され、続いて上で説明した24ビットのワードが転送されます。32ビットのシーケンスを図3bに示します。

### パワーダウン・モード

コマンド0100bを適切なDACアドレス(*n*)と組み合わせて使って、一方または両方のDACチャネルをパワーダウン・モードにすることができます。16ビットのデータ・ワードは無視されます。

表3に示されているように、DACの更新を含むどのコマンドを実行しても、通常の動作を再開することができます。選択されたDACはその電圧出力が更新されるとパワーアップされます。両方のDACがパワーダウンされると、個々のDACのアンプやリファレンス入力に加えて、主バイアス発生回路ブロックが自動的にシャットダウンされます。この場合、パワーアップ遅延時間は(V<sub>CC</sub> = 3Vでは)700μsです。

表3. 補助DACのコマンド

#### コマンド\*

| C3 | C2 | C1 | C0 |                                                  |

|----|----|----|----|--------------------------------------------------|

| 0  | 0  | 0  | 0  | 入力レジスタ <i>n</i> に書き込む                            |

| 0  | 0  | 0  | 1  | DACのレジスタ <i>n</i> を更新(パワーアップ)する                  |

| 0  | 0  | 1  | 0  | 入力レジスタ <i>n</i> に書き込み、全ての <i>n</i> を更新(パワーアップ)する |

| 0  | 0  | 1  | 1  | <i>n</i> に書き込み、更新(パワーアップ)する                      |

| 0  | 1  | 0  | 0  | <i>n</i> をパワーダウン                                 |

| 1  | 1  | 1  | 1  | 動作なし                                             |

#### アドレス(*n*)\*

| A3 | A2 | A1 | A0 |        |

|----|----|----|----|--------|

| 0  | 0  | 0  | 0  | DAC A  |

| 0  | 0  | 0  | 1  | DAC B  |

| 1  | 1  | 1  | 1  | 全てのDAC |

\*示されていないコマンドとアドレス・コードは予備であり、使用してはならない。

## 動作

図2. 補助DACの24ビットのロード・シーケンス(最小入力ワード)

図3. 補助DACの32ビット・ロード・シーケンス

## アプリケーション情報

### 入力スパン

LTM9002は一定の入力スパンと入力インピーダンスで構成設定されます。LTM9002-AAに関して上で説明されたアンプの利得とADCの入力ネットワークを使うと、ドライバ回路のフルスケール入力範囲は0.1V<sub>P-P</sub>です。推奨ADC入力スパンはSENSEピンをV<sub>DD</sub>に接続することにより実現されます。ただし、ADCの入力スパンはアプリケーションで必要なら変更することができます。その結果得られるIN<sup>+</sup>/IN<sup>-</sup>ピンの入力スパンは、ADCの入力スパンを利得で割ったものです。

LTM9002はIN<sup>+</sup>ピンおよびIN<sup>-</sup>ピンを通してドライブされることが意図されています。DNCピンはテストに使われ、アプリケーションで使うことは意図されていません。これらはADCの入力フィルタ・ネットワーク内のテスト・ポイントです。ただし、これらは内部の信号経路に直接接続されているので、これらのピンには注意してください。それらは接続されていないパッドに半田付けし、十分絶縁します。

### 入力インピーダンスと整合

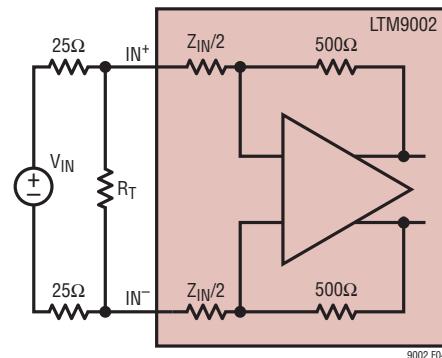

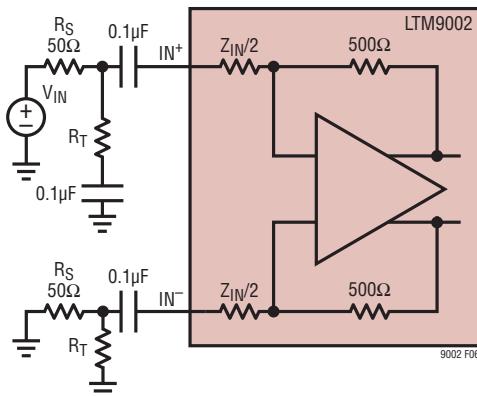

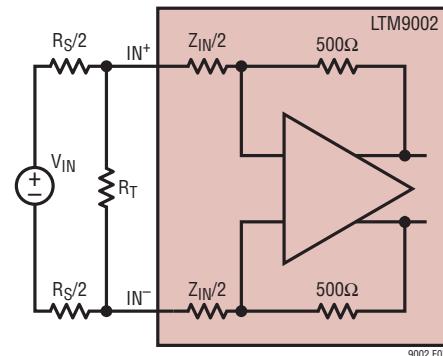

アンプの入力インピーダンスは、アンプの利得に依存して、50Ω、200Ωまたは400Ωです。ソースとインピーダンスを整合させるため、アプリケーションによっては、差動入力をもっと低い値のインピーダンス（たとえば、50Ω）に終端する必要があるかもしれません。いくつかの選択肢があります。

1つの方法は差動シャント抵抗を使います（図4）。別の方法は広帯域トランスとシャント抵抗を使います（図5）。どちらの方法も広帯域整合を与えます。終端抵抗またはトランスは、入力の不整合による反射を最小に抑えるため、入力ピンの近くに配置する必要があります。

代わりに、周波数選択やノイズ削減のために狭帯域インピーダンス整合を入力に与えることができます。

図4. シャント抵抗を使った50Ω

差動入力インピーダンスの入力の終端

図5. バランを使った50Ω

差動入力インピーダンスの入力の終端

図6を参照して、バランを使わずに、アンプ入力をシングルエンド入力に簡単に構成することができます。信号は整合ネットワークを通して一方の入力に与えられ、他方の入力は同じ整合ネットワークとソース抵抗に接続されます。2つの帰還経路のリターン比は等しいので、2つの出力は利得が同じであり、振幅が対称になります。一般に、シングルエンド入力のインピーダンスと終端抵抗R<sub>T</sub>は、R<sub>S</sub>、R<sub>G</sub>およびR<sub>F</sub>の組合せで決まります（表5を参照）。

表4. 差動アンプの入力終端値

| GAIN (dB) | Z <sub>IN</sub> /2 | R <sub>T</sub> FIGURE 4 | R <sub>T</sub> FIGURE 5 |

|-----------|--------------------|-------------------------|-------------------------|

| 8         | 200Ω               | 57Ω                     | 400Ω                    |

| 14        | 100Ω               | 66.5Ω                   | None                    |

| 20        | 100Ω               | 66.5Ω                   | None                    |

| 26        | 25Ω                | None                    | None                    |

表5. シングルエンドのアンプの入力終端値

| GAIN (dB) | Z <sub>IN</sub> /2 | R <sub>T</sub> FIGURE 6 |

|-----------|--------------------|-------------------------|

| 8         | 200Ω               | 59Ω                     |

| 14        | 100Ω               | 68.5Ω                   |

| 20        | 100Ω               | 66.5Ω                   |

| 26        | 25Ω                | 150Ω                    |

## アプリケーション情報

図6. シヤント抵抗を使った50Ω

差動入力インピーダンスの入力の終端

図7. 差動利得の計算

アンプは無条件に安定しています。つまり、差動安定係数  $K_f > 1$  であり、安定度  $B_1 > 0$  です。ただし、全体の差動利得は図7のソース・インピーダンスによって影響を受けます。

$$AV = |V_{\text{OUT}}/V_{\text{IN}}| = (500/(R_S + Z_{\text{IN}}/2))$$

アンプのノイズ性能はソースのインピーダンスと終端にも依存します。たとえば、図5の入力の1:4のトランジスタは入力の利得を6dB増やしてノイズフィギュアを改善します。一定のノイズフィギュアの円と一定の利得の円を同じ入力スミスチャート内に描くと、利得とノイズのトレードオフは明らかです。それに基づいて、ユーザーは一定の利得とノイズの要件に対して最適なソース・インピーダンスを選択することができます。

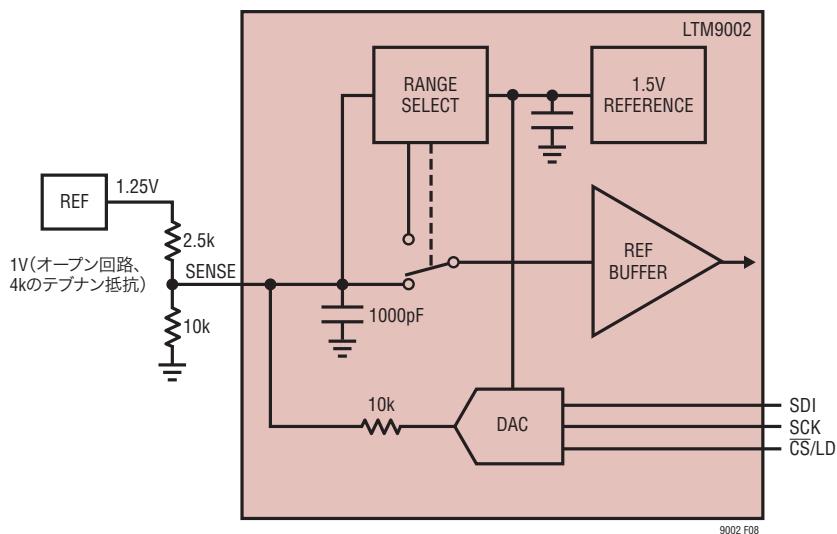

## SENSEピンの動作

LTM9002-AAの内部電圧リファレンスは、ピンで選択可能な0.1V(差動±50mV)または0.5V(差動±0.25mV)の2つの入力レンジに設定することができます。SENSEピンをV<sub>DD</sub>に接続すると高いレンジが選択され、SENSEピンを1.5Vに接続すると低いレンジが選択されます。LTM9002の他のバージョンでは、入力スパンは2V<sub>P-P</sub>を利得で割った値か、1V<sub>P-P</sub>を利得で割った値かのどちらかです。

外部リファレンスを使って、その出力を直接または抵抗分割器を通してSENSEに与えることができます。ロジック・デバイスを使ってSENSEピンをドライブすることは推奨しません。SENSEピンはできるだけコンバータの近くで適切なレベルに接続します。SENSEピンは、1μFセラミック・コンデンサを使って内部でグランドにバイパスしてあります。

## 入力レンジ

入力レンジはアプリケーションに基づいて設定することができます。0.1V入力レンジ(LTM9002-AA)では、優れたSFDRを保ったまま最良のSNRが得られます。もっと低い入力レンジのSFDR性能はわずかに良くなります。SNRは5dBほど低下します。「標準的性能特性」のセクションを参照してください。

## フルスケール入力レンジの調節

一方のチャネルのフルスケール・レンジを調整して、他方のチャネルのそれに一致させるには、図8に示されているように、まず外部リファレンスをSENSEAとSENSEBに与えて、両方のチャネルの望みのレンジを設定します。DACコードを外部リファレンス電圧にほぼ一致するように設定します。フルスケール電圧を各チャネルの入力に与えます。両方のチャネルの出力を読み取り、望みのチャネル整合が達成されるまで一方のチャネルのDACの設定を調整します。

調整範囲とステップの大きさは、外部リファレンス回路のために選択された抵抗値または外部リファレンス回路のソース抵抗に依存します。外部リファレンスはSENSEピンに接続され、このピンは内部DAC電圧に対して10k(±1%)の直列インピーダンスを備えています。図8に示されている回路では、ステップの大きさは76μV、1Vを表すコードは0xAAB(10進数で0.666748)です。この例では、SENSE電圧の調整範囲は、オフセットと利得誤差を含めて約0.79Vから1.1Vです。したがって、実効入力スパンは3.8μVのステップで±39.6mV～55.2mVの範囲で調整することができます。ただし、±50mVを超えることは推奨しません。

## アプリケーション情報

内部1000pFのコンデンサは、2.5kの外部抵抗と一緒に使うと64kHzのコーナー周波数を与えます。追加の0.1 $\mu$ Fのバイパス・コンデンサがSENSEピンに必要になることがあります。

CCDイメージングや低振幅信号のオーバーサンプリングのような同相に近いノイズに敏感ではないアプリケーションでは、補助DACを外部リファレンスなしで使うことができます。外部リファレンスなしでは、DACのステップの大きさはSENSEピンで366 $\mu$ Vであり、入力スパンでは18 $\mu$ Vのステップになります。この場合、SENSEピンは0.1 $\mu$ Fのコンデンサでバイパスすることができます。

補助DACはその後LTM9002がパワーアップする度に設定する必要があります。

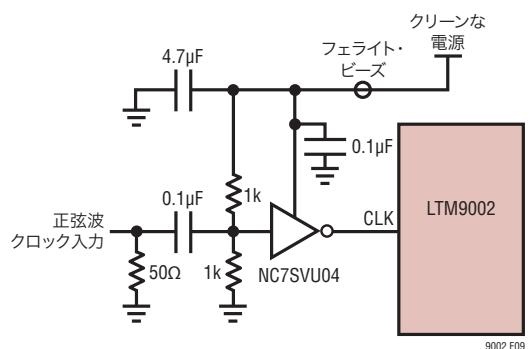

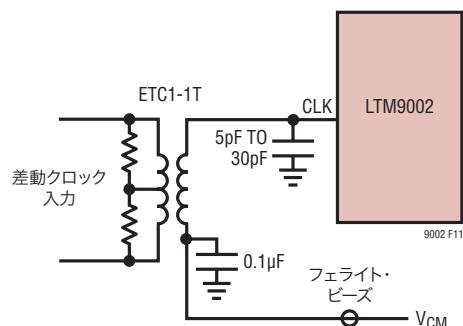

### クロック入力のドライブ

CLK入力はCMOSまたはTTLレベルの信号で直接ドライブすることができます。CLKピンの前にジッタの小さな方形波発生回路を置いて正弦波のクロックを使うこともできます(図9)。

ADCのノイズ特性はアナログ入力に依存するのと同程度にクロック信号の質の良し悪しに依存することがあります。CLK信号に含まれるどんなノイズも新たなアーチャ・ジッタを生じ、このジッタは本来のADCアーチャ・ジッタにRMSとして追加されます。高い入力周波数をデジタル変換する場合など、ジッタに対する要求が厳しいアプリケーションではできるだけ大きな振幅を使います。または、正弦波信号でADCをクロック駆動する場合は、クロック信号をフィルタに通して広帯域ノイズとソースによって生じた歪み積を減らします。

図8. 外部リファレンスの使用

図9. 正弦波のシングルエンドCLKドライバ

## アプリケーション情報

CLKAとCLKBを短絡して同じクロック・ソースでドライブすることを推奨します。2つのチャネルがアナログ入力をサンプリングするタイミングの間に小さな遅延時間を持つのが望ましい場合、CLKAとCLKBを2つの異なる信号でドライブすることができます。この遅延時間が1nsを超えると、デバイスの性能が低下することがあります。CLKAとCLKBは非同期信号でドライブしないでください。

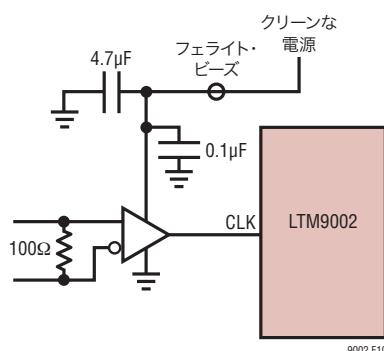

差動クロックをシングルエンドCLK入力に変換する別の方法を図10と図11に示します。トランスを使うと位相ノイズの増加はありません。LVDSまたはPECLからCMOSへの変換器は70MHz以下ではSNRがほとんど劣化しませんが、140MHzではトランスのソリューションに比べてSNRが劣化します。受信した信号の性質もSNRがどれだけ劣化するかに大きく関係します。WCDMAやOFDMなどの波高率の高い信号では（この場合、公称電力レベルがフルスケールより少なくとも6dB～8dB小さくなければなりません）、これらの変換器の使用の影響は小さくなります。

この例のトランスは使用される信号に適切な終端で終端することができます。低い電圧の差動信号が考えられる場合は、1:4のインピーダンス比のトランスの使用が望ましいでしょう。差動信号が別のプレーンから来る場合、センタータップをADCに近いコンデンサを介してグランドにバイパスすることができます。コンデンサを入力に使用するとピーキングが生じることがあり、伝送ラインの長さに依存して、近傍のデジタル信号によってクロック・ラインに誘起されることがある高周波ノイズに対するローパス・フィルタおよび反射に対する減衰メカニズムの両方として機能する10Ω～20Ωの直列抵抗が必要になることがあります。

### 最大変換レートと最小変換レート

LTM9002-AAの最大変換レートは125Msps、LTM9002-LAの場合は65Mspsです。サンプリング・レートの下限はサンプル&ホールド回路の垂下によって決まります。このADCのパイプライン・アーキテクチャでは、アナログ信号を小容量のコンデンサに保存します。接合部のリーク電流によりコンデンサが放電します。LTM9002の規定最小動作周波数は1Mspsです。

LVDSの場合、FIN1002またはFIN1018を使用。

PECLの場合、AZ1000ELT21または同等品を使用

図10. LVDSまたはPECLからCMOSへの変換器を使ったCLKドライバ

図11. トランスを使ったLVDSまたはPECLのCLKドライバ

## アプリケーション情報

### クロック・デューティ・サイクル・スタビライザ

入力クロックのデューティ・サイクルが50%でなくても、オプションのクロック・デューティ・サイクル・スタビライザ回路が確実に高性能を与えます。ほとんどのアプリケーションにはクロック・デューティ・サイクル・スタビライザの使用を推奨します。クロック・デューティ・サイクル・スタビライザを使うには、外付け抵抗を使ってMODEピンを1/3V<sub>DD</sub>または2/3V<sub>DD</sub>に接続します。

この回路はCLKピンの立上りエッジを使ってアナログ入力をサンプリングします。CLKの立下りエッジは無視され、フェーズロック・ループにより内部で立下りエッジが作られます。入力クロックのデューティ・サイクルは40%～60%の範囲で変化することができ、クロック・デューティ・サイクル・スタビライザは内部デューティ・サイクルを50%に保ちます。クロックが長時間オフすると、デューティ・サイクル・スタビライザ回路のPLLが入力クロックにロックするのに100クロック・サイクル必要です。

サンプル・レートを即座に変更する必要のあるアプリケーションでは、クロック・デューティ・サイクル・スタビライザをディスエーブルすることができます。デューティ・サイクル・スタビライザをディスエーブルする場合、サンプリング・クロックのデューティ・サイクルが50%( $\pm 5\%$ )になるように注意してください。

### デジタル出力

アナログ入力電圧、デジタル・データ・ビット、およびオーバーフロー・ビットの相互関係を表6に示します。チャネルAまたはチャネルBにオーバーフローまたはアンダーフローが生じるとOFが“H”になることに注意してください。

表6. 出力コードと入力電圧(100mVの入力スパン)

| IN <sup>+</sup> - IN <sup>-</sup><br>(SENSE = V <sub>DD</sub> ) | OF | D13～D0<br>(オフセット・バイナリ) | D13～D0<br>(2の補数)  |

|-----------------------------------------------------------------|----|------------------------|-------------------|

| ≥ 50mV                                                          | 1  | 11 1111 1111 1111      | 01 1111 1111 1111 |

|                                                                 | 0  | 11 1111 1111 1111      | 01 1111 1111 1111 |

|                                                                 | 0  | 11 1111 1111 1110      | 01 1111 1111 1110 |

| 0.000000V                                                       | 0  | 10 0000 0000 0001      | 00 0000 0000 0001 |

|                                                                 | 0  | 10 0000 0000 0000      | 00 0000 0000 0000 |

|                                                                 | 0  | 01 1111 1111 1111      | 11 1111 1111 1111 |

|                                                                 | 0  | 01 1111 1111 1110      | 11 1111 1111 1110 |

| ≤ -50mV                                                         | 0  | 00 0000 0000 0001      | 10 0000 0000 0001 |

|                                                                 | 0  | 00 0000 0000 0000      | 10 0000 0000 0000 |

|                                                                 | 1  | 00 0000 0000 0000      | 10 0000 0000 0000 |

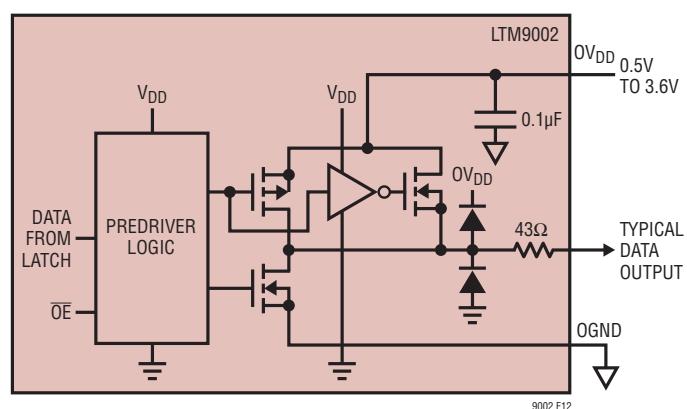

### デジタル出力モード

1個の出力バッファの等価回路を図12に示します。各バッファはOV<sub>DD</sub>とOGNDから給電され、ADCの電源とグランドからは分離されています。出力ドライバにNチャネル・トランジスタが追加されているので低電圧まで動作可能です。出力に直列接続された内部抵抗により、外部回路から見ると出力は50Ωに見えるので、外部の減衰抵抗を必要としないこともあります。

全ての高速高分解能コンバータの場合と同様、デジタル出力負荷が性能に影響を与えることがあります。デジタル出力と敏感な入力回路の間に生じるおそれのある相互反応を抑えるため、ADCのデジタル出力はできるだけ小さな容量性負荷をドライブするようにします。全速動作では負荷の容量は10pF以下に抑えます。

OV<sub>DD</sub>電圧を低くすることも、デジタル出力からの干渉を減らすのに役立ちます。

図12. デジタル出力のバッファ

## アプリケーション情報

### データのフォーマット

ADCのパラレル・デジタル出力は、MODEピンを使って、オフセット・バイナリ形式または2の補数形式に設定できます。MODEはチャネルAとチャネルBの両方をコントロールすることに注意してください。MODEをGNDまたは1/3V<sub>DD</sub>に接続するとストレート・バイナリの出力フォーマットが選択されます。MODEを2/3V<sub>DD</sub>またはV<sub>DD</sub>に接続すると2の補数の出力フォーマットが選択されます。外部抵抗分割器を使って1/3V<sub>DD</sub>または2/3V<sub>DD</sub>のロジック値を設定することができます。MODEピンのロジック状態を表7に示します。

表7. MODEピンの機能

| MODEピン             | 出力フォーマット   | クロック・デューティ・サイクル・スタビライザ |

|--------------------|------------|------------------------|

| 0                  | ストレート・バイナリ | オフ                     |

| 1/3V <sub>DD</sub> | ストレート・バイナリ | オン                     |

| 2/3V <sub>DD</sub> | 2の補数       | オン                     |

| V <sub>DD</sub>    | 2の補数       | オフ                     |

### オーバーフロー・ビット

LTM9002-AAの場合、OF出力がロジック“H”的とき、コンバータはチャネルAまたはチャネルBにオーバーレンジまたはアンダーレンジが生じています。両方のチャネルが共通のOFピンを共有していることに注意してください。チャネルAがスリープ・モードまたはナップ・モードのとき、OFはディスエーブルされます。LTM9002-LAの場合、OFAおよびOFBがそれぞれのチャネルのどちらかの状態を表示します。

### 出力クロック

LTM9002-AAにはCLKB入力を遅延させた信号がデジタル出力(CLKOUT)として備わっています。CLKOUTピンの立下りエッジを使ってデジタル出力データをラッチすることができます。チャネルBがスリープ・モードまたはナップ・モードのとき、CLKOUTはディスエーブルされます。

### 出力ドライバの電源

出力専用の電源ピンとグランド・ピンが備わっているので、出力ドライバをアナログ回路から分離することができます。デジタル出力バッファの電源(OV<sub>DD</sub>)は、ドライブされるロジックに給電しているのと同じ電源に接続します。たとえば、1.8V電源から給電されているDSPをコンバータがドライブする場合、OV<sub>DD</sub>を同じ1.8V電源に接続します。

OV<sub>DD</sub>は、V<sub>DD</sub>から独立して、500mVから3.6Vまでの任意の電圧で電力供給を受けることができます。OGNDはGND～1Vの任意の電圧で電力供給を受けることができ、OV<sub>DD</sub>より低くなければなりません。ロジック出力はOGNDとOV<sub>DD</sub>の間で振幅します。

### 出力イネーブル

出力イネーブル・ピン( $\overline{OE}$ )を使って出力をディスエーブルすることができます。 $\overline{OE}$ を“H”にすると、OFを含む全てのデータ出力がディスエーブルされます。データのアクセス時間やバスの解放時間は、全速動作時に出力のイネーブルやディスエーブルをするには遅すぎます。出力のHi-Z状態はテストや初期化のときに使うことを意図しています。チャネルAとチャネルBには独立した出力イネーブル・ピン( $\overline{OEA}$ 、 $\overline{OEB}$ )が備わっています。

### スリープ・モードとナップ・モード

節電のため、コンバータをシャットダウン・モードまたはナップ・モードにすることができます。ADCSHDNをGNDに接続すると正常動作になります。ADCSHDNをV<sub>DD</sub>に接続し、 $\overline{OE}$ をV<sub>DD</sub>に接続するとスリープ・モードになり、リファレンスを含む全ての回路がパワーダウンし、ADCの電力損失は標準で1mWになります。スリープ・モードを抜け出すとき、リファレンスのコンデンサを再充電して安定化する必要があるので、出力データが有効になるまで700μs～1msかかります。ADCSHDNをV<sub>DD</sub>に接続し、 $\overline{OE}$ をGNDに接続するとナップ・モードになり、ADCの電力損失は標準で30mWになります。ナップ・モードでは内蔵リファレンス回路はオンしたままなので、ナップ・モードからの回復はスリープ・モードからの回復よりも速く、標準で100クロック・サイクルかかります。スリープとナップの両方のモードで全てのデジタル出力はディスエーブルされ、Hi-Z状態になります。

チャネルAとチャネルBには独立したADCSHDNピン(ADCSHDNA、ADCSHDNB)が備わっています。チャネルAはADCSHDNAと $\overline{OEA}$ によってコントロールされ、チャネルBはADCSHDNBと $\overline{OEB}$ によってコントロールされます。2つのチャネルのナップ・モード、スリープ・モードおよび出力イネーブル・モードは完全に独立しているので、一方のチャネルを動作させながら、他方のチャネルをナップ・モードまたはスリープ・モードにすることができます。

### デジタル出力のマルチプレクサ

ADCのデジタル出力は1本のデータバスに多重化することができます。MUXピンは2本のデータバスを交換するデジタル入力です。MUXが“H”だと、チャネルAはDAxから出力し、チャネルBはDBxから出力します。

## アプリケーション情報

MUXが“L”だと出力バスを入れ替わり、チャネルAはDB<sub>x</sub>から出力し、チャネルBはDA<sub>x</sub>から出力します。両方のチャネルを1つの出力バスに多重化するにはMUX、CLKAおよびCLKBと一緒に結合します(多重モードの「タイミング図」を参照)。多重化されたデータはどちらのデータバスでも利用できます(使用しないデータバスは対応する $\overline{OE}$ ピンを使ってディスエーブルすることができます)。

### 電源シーケンシング

V<sub>CC</sub>ピンは電源をアンプと補助DACに供給し、V<sub>DD</sub>ピンはADCに電源を供給します。アンプ、ADCおよびDACはLTM9002内の別個の集積回路です。ただし、標準的なやり方以外の電源シーケンシングは考慮されていません。アンプ、ADCおよびDACが全て同じ低ノイズの3.0V電源を使うことを推奨しますが、そうしたければ、V<sub>CC</sub>を別の電圧レベルで動作させることができます。両方のレールを同じ3.0Vのリニア・レギュレータで動作させることができますが、V<sub>CC</sub>ピンとV<sub>DD</sub>ピンの間にフェライト・ビーズを置きます。別々のリニア・レギュレータが共通の入力電源を持っていれば、追加の電源シーケンシング回路なしに、それらを使うことができます。

### 接地とバイパス

LTM9002には全く切れ目の無いグランド・プレーンを備えたプリント基板が必要です。内部グランド・プレーンを備えた多層基板を推奨します。LTM9002のピン配置はフロースルー・レイアウトに最適化されているので、入力とデジタル出力間の相互反応が最小に抑えられます。一列に連続したグランド・パッドによりレイアウトが簡単になり、デジタル信号ラインとアナログ信号ラインをできるだけ分離することができます。

LTM9002は内部でバイパスされており、ADC(V<sub>DD</sub>)とアンプおよびDAC(V<sub>CC</sub>)の電源は共通グランド(GND)に戻ります。デジタル出力電源(OV<sub>DD</sub>)はOGNDに戻ります。追加のバイパス・コンデンサはオプションで、電源ノイズが大きいと必要になることがあります。

差動入力は互いに並行にできるだけ近づけて配線します。入力トレースはできるだけ短くして容量を小さくし、ノイズを拾わないようにします。

### 熱伝達

LTM9002が発生する熱の大部分は底面のグランド・パッドを通して伝わります。電気的および熱的性能を良くするには、全てのグランド・ピンを面積が十分大きなグランド・プレーンにできるだけ多くのビアを使って接続することが重要です。

### 推奨レイアウト

LTM9002は高度に一体化されていますので、PCボードのレイアウトが非常に簡単で容易です。ただし、電気的性能と熱的性能を最適化するにはいくつかのレイアウト上の配慮が依然として必要です。

- グランドにはPCBの大きな銅領域を使用します。これにより基板を通してパッケージ内部の熱が放散するのが助けられ、基板上の敏感なアナログ信号をシールドするのにも役立ちます。共通グランド(GND)と出力グランド(OGND)はLTM9002では電気的に絶縁されていますが、PCB上でデバイスの下で接続して共通リターン経路を与えることができます。

- 複数のグランド・ビアを使います。できるだけ多くのビアを使うと、基板の熱性能を改善するのに役立ち、基板上のアナログ・トレースとデジタル・トレースを高周波数で分離するのに必要なバリヤを形成します。

- ビアを使って高周波バリヤを作り、アナログ・トレースとデジタル・トレースをできるだけ分離します。これにより、LTM9002の信号対雑音比(SNR)とダイナミックレンジを下げる可能性のあるデジタル・フィードバックが減少します。

ペースト印刷の品質は、高歩留りアセンブリにとって重要な要素です。タイプ3またはタイプ4を使って無洗浄半田ペーストを印刷することを推奨します。半田ステンシルは「アプリケーションノート100」で説明されているガイドラインに従ってデザインします。

LTM9002は鉛ベースまたは錫ベースの半田ペーストで使えるように金仕上げのパッドを採用しています。内部は鉛フリーで、JEDEC(e4)標準規格に適合しています。材料表は[http://www.linear.com/leadfree/mat\\_dec.jsp](http://www.linear.com/leadfree/mat_dec.jsp)からオンラインで入手できます。

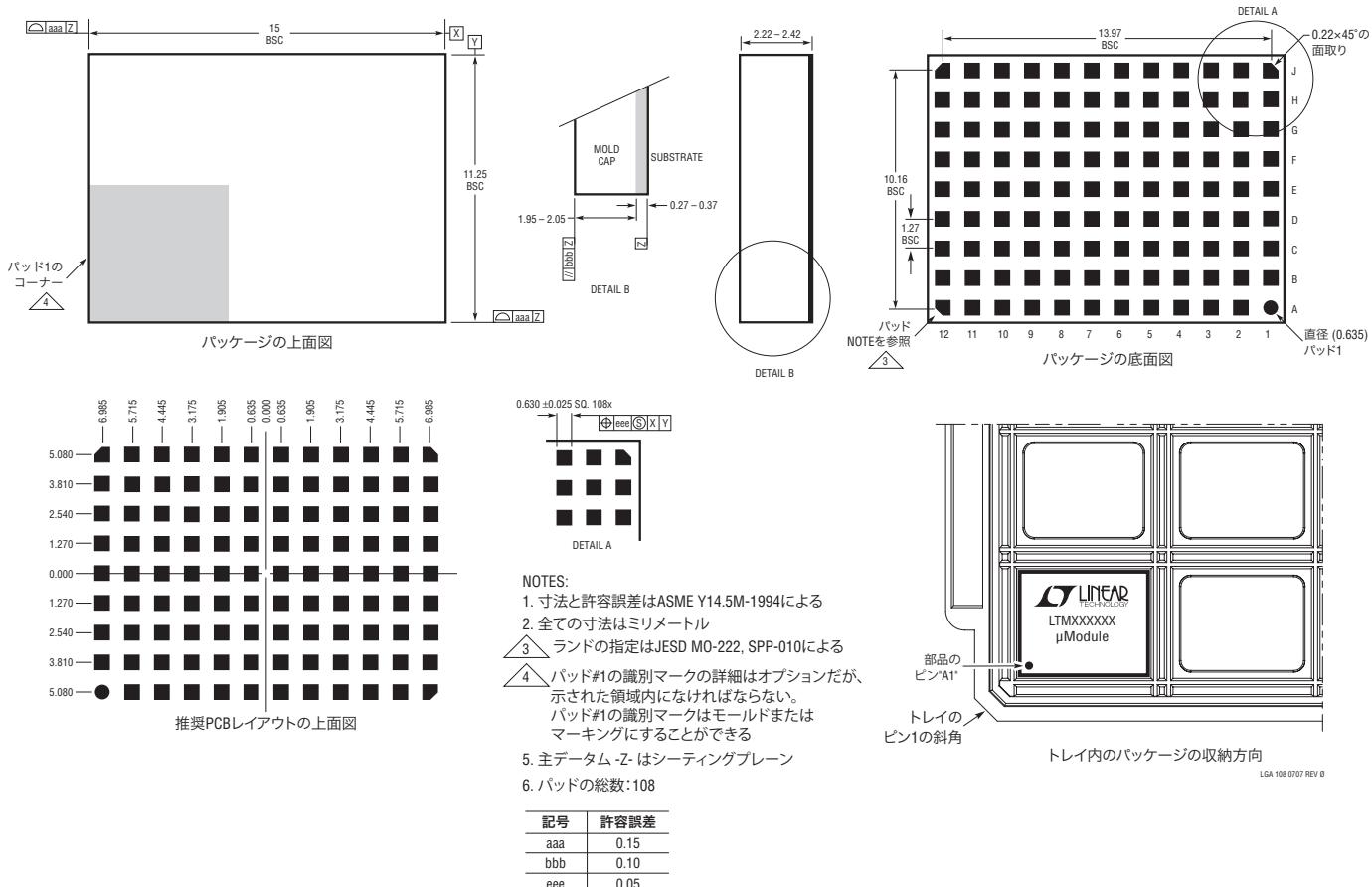

## パッケージ

**LGA/パッケージ**

**108ピン (15mm×11.25mm×2.32mm)**

(Relation LTC DWG # 05-08-1757 Rev 0)

## 関連製品

| 製品番号                                           | 説明                                                     | 注釈                                                           |

|------------------------------------------------|--------------------------------------------------------|--------------------------------------------------------------|

| LT1994                                         | 低ノイズ、低歪みの完全差動入出力アンプ/ドライバ                               | 低歪み:-94dBc(1MHz)                                             |

| LTC2205                                        | 16ビット、65Msps ADC                                       | 530mW、SNR:79dB、SFDR:100dB                                    |

| LTC2206                                        | 16ビット、80Msps ADC                                       | 725mW、SNR:77.9dB、SFDR:100dB                                  |

| LTC2207                                        | 16ビット、105Msps ADC                                      | 900mW、SNR:77.9dB、SFDR:100dB                                  |

| LTC2208                                        | 16ビット、130Msps ADC                                      | 1250mW、SNR:77.7dB、SFDR:100dB                                 |

| LTC2240-12                                     | 12ビット、170Msps、2.5V ADC、LVDS出力                          | 445mW、SNR:65.6dB、SFDR:80dB、64ピンQFN                           |

| LTC2241-12                                     | 12ビット、210Msps、2.5V ADC、LVDS出力                          | 585mW、SNR:65.6dB、SFDR:80dB、64ピンQFN                           |

| LTC2242-12                                     | 12ビット、250Msps、2.5V ADC、LVDS出力                          | 745mW、SNR:65.6dB、SFDR:80dB、64ピンQFN                           |

| LTC2248                                        | 14ビット、65Msps ADC                                       | 210mW、SNR:74dB、5mm×5mm QFN                                   |

| LTC2249                                        | 14ビット、80Msps ADC                                       | 230mW、SNR:73dB、5mm×5mm QFN                                   |

| LTC2254                                        | 14ビット、105Msps ADC                                      | 320mW、SNR:72.5dB、SFDR:88dB、5mm×5mm QFN                       |

| LTC2255                                        | 14ビット、125Msps ADC                                      | 395mW、SNR:72.4dB、SFDR:88dB、5mm×5mm QFN                       |

| LTC2282                                        | デュアルの12ビット、105Msps ADC                                 | 540mW、SNR:70.1dB、SFDR:88dB、64ピンQFN                           |

| LTC2283                                        | デュアルの12ビット、125Msps ADC                                 | 790mW、SNR:70.2dB、SFDR:88dB、64ピンQFN                           |

| LTC2284                                        | デュアルの4ビット、105Msps ADC                                  | 540mW、SNR:72.4dB、SFDR:88dB、64ピンQFN                           |

| LTC2285                                        | デュアルの14ビット、125Msps ADC                                 | 790mW、SNR:72.4dB、SFDR:88dB、64ピンQFN                           |

| LTC2293                                        | デュアルの12ビット、65Msps ADC                                  | 410mW、SNR:71dB、9mm×9mm QFN                                   |

| LTC2294                                        | デュアルの12ビット、80Msps ADC                                  | 445mW、SNR:70.6dB、9mm×9mm QFN                                 |

| LTC2295                                        | デュアルの14ビット、10Msps ADC                                  | 120mW、SNR:74.4dB、9mm×9mm QFN                                 |

| LTC2296                                        | デュアルの14ビット、25Msps ADC                                  | 150mW、SNR:74dB、9mm×9mm QFN                                   |

| LTC2297                                        | デュアルの14ビット、40Msps ADC                                  | 240mW、SNR:74dB、9mm×9mm QFN                                   |

| LTC2298                                        | デュアルの14ビット、65Msps ADC                                  | 410mW、SNR:74dB、9mm×9mm QFN                                   |

| LTC2299                                        | デュアルの14ビット、80Msps ADC                                  | 445mW、SNR:73dB、9mm×9mm QFN                                   |

| LT557                                          | 400MHz～3.8GHzの3.3V<br>高直線性ダウンコンバーティングRFミキサ             | IIP3:1.9GHzで24.7dBm、NF:11.7dB、<br>シングルエンドのRFポートとLOポート、3.3V電源 |

| LT5575                                         | 800MHz～2.7GHz高直線性直接変換直交復調器                             | IIP2:1.9GHzで60dBm、NF:12.7dB、低いDCオフセット                        |

| LTC6400-8/LTC6400-14/<br>LTC6400-20/LTC6400-26 | 300MHz IF向け低ノイズ、低歪み差動アンプ、<br>8dB、14dB、20dBまたは26dBの固定利得 | 3V、90mA、OIP3:300MHzで39.5dBm、NF:6dB                           |

| LTC6401-8/LTC6401-14/<br>LTC6401-20/LTC6401-26 | 140MHz IF向け低ノイズ、低歪み差動アンプ、<br>8dB、14dB、20dBまたは26dBの固定利得 | 3V、45mA、OIP3:140MHzで45.5dBm、NF:6dB                           |