## 特長

- 直列接続された最多12個のリチウムイオン・セルを測定（最大60V）

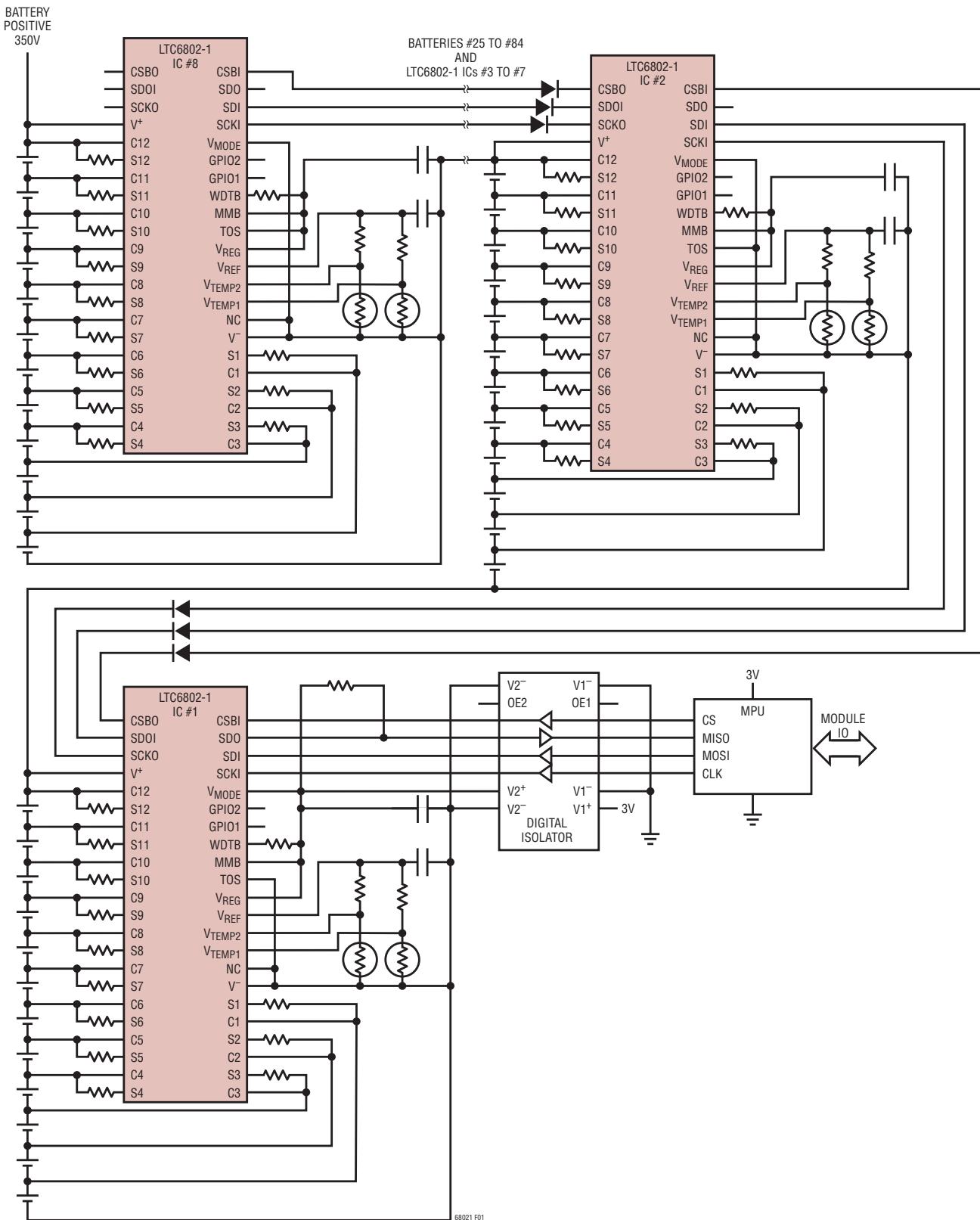

- スタック可能なアーキテクチャにより、1000Vを超えるシステムが可能

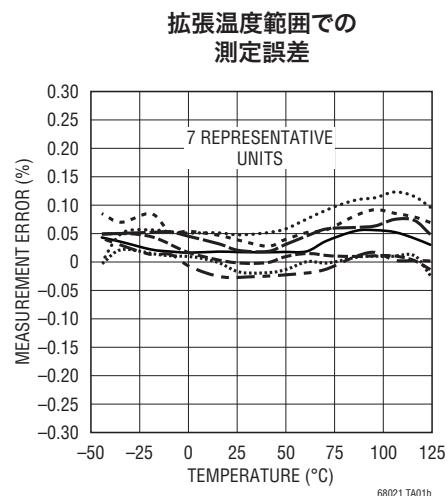

- 全測定誤差:0.25%（最大）

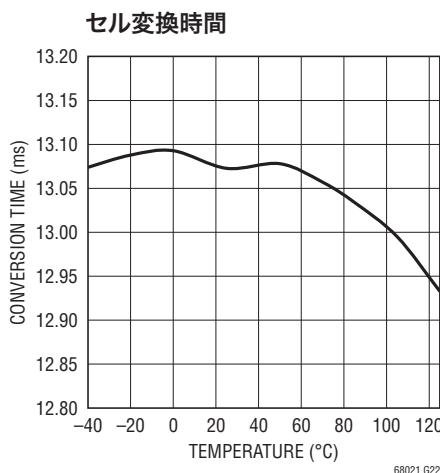

- 13ms以内でシステム内の全てのセルを測定

- セル・バランシング:

- 受動セル・バランシング・スイッチを内蔵

- オフチップ受動バランシング用機能

- 2つのサーミスタ入力と内部温度センサ

- デイジーチェーン接続が可能な1MHzシリアル・インターフェース

- 高いEMI耐性

- ノイズ・フィルタを備えたデルタシグマ・コンバータ

- オープンワイヤ接続フォールト検出

- 低消費電力モード

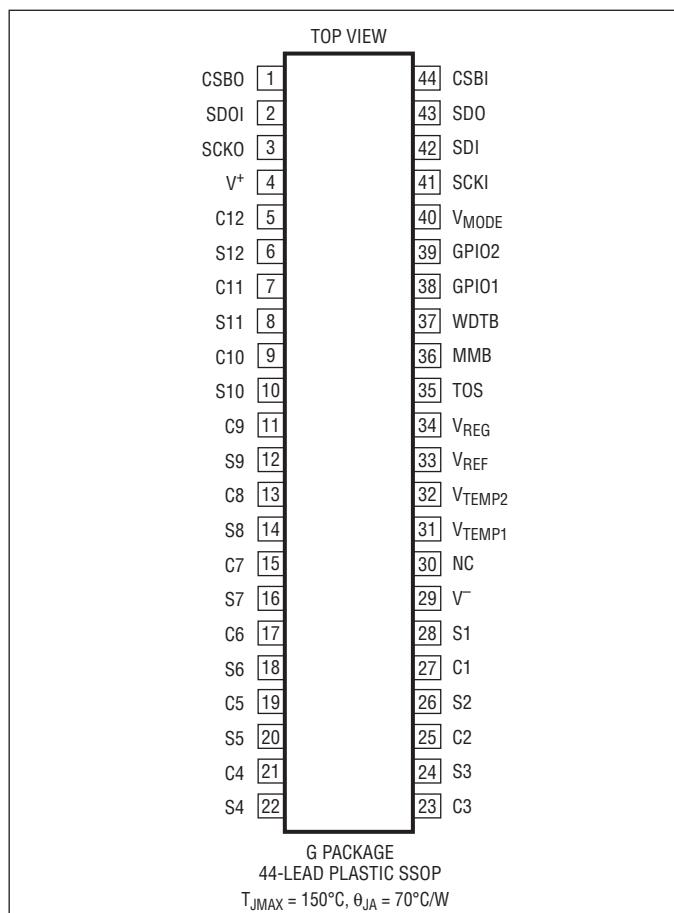

- 44ピンSSOPパッケージ

## アプリケーション

- 電気自動車やハイブリッド電気自動車

- 高電力携帯機器

- バックアップ・バッテリ・システム

- 高電圧データ収集システム

△、LT、LTC、LTM、Linear TechnologyおよびLinearのロゴはリニアテクノロジー社の登録商標です。他の全ての商標はそれぞれの所有者に所有権があります。

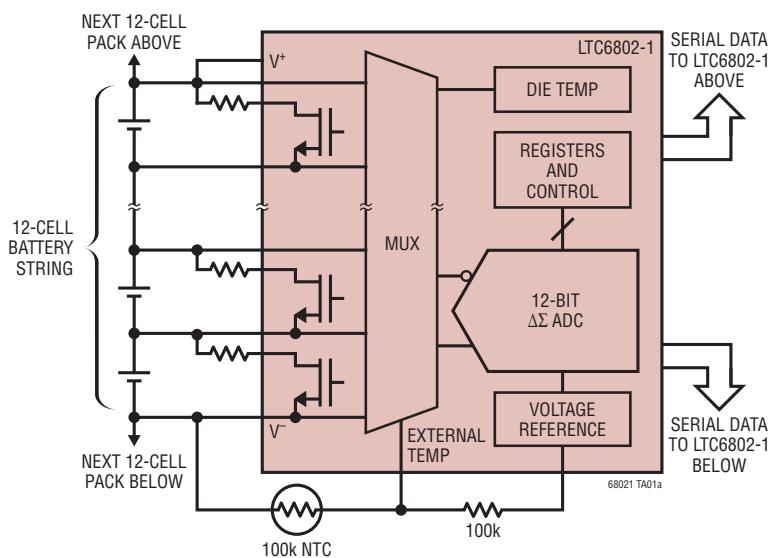

## 標準的応用例

## 概要

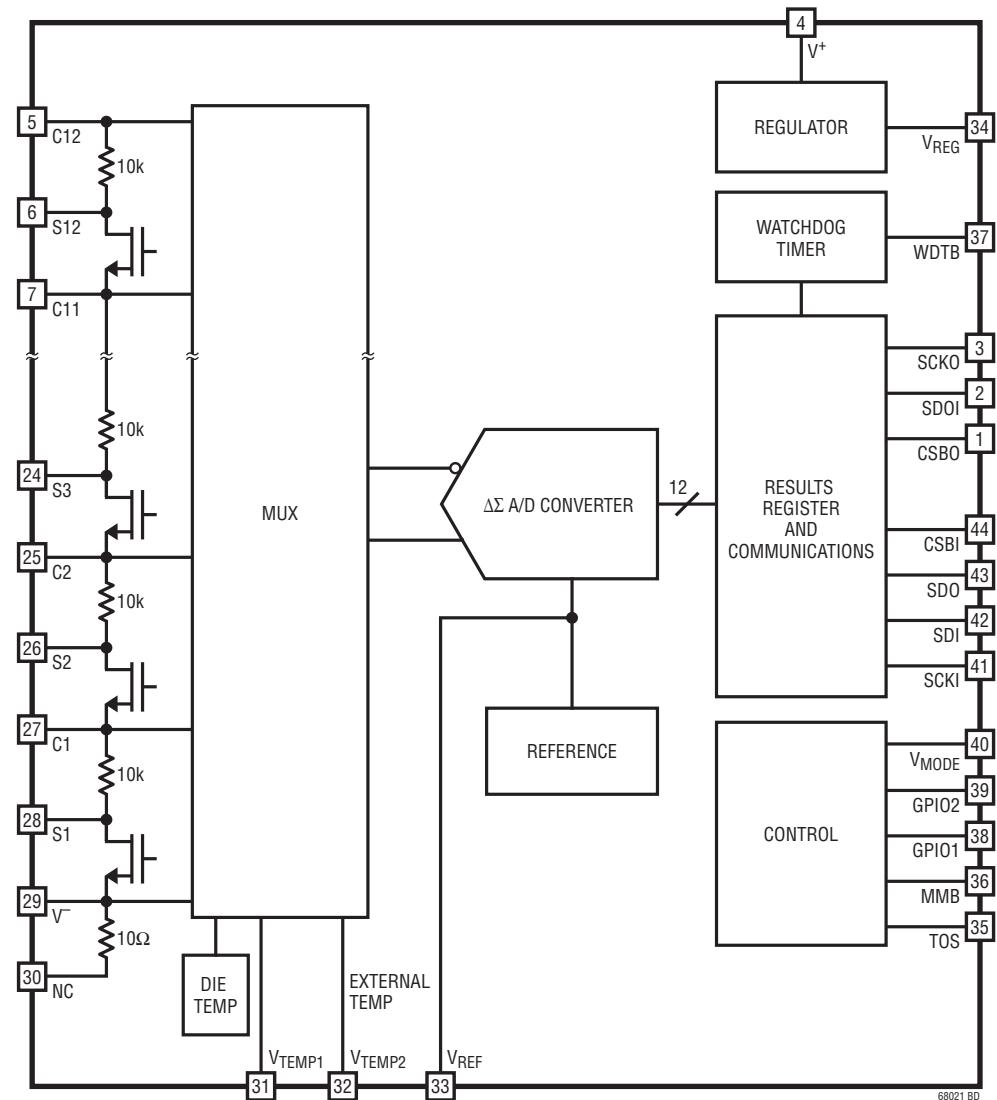

LTC<sup>®</sup>6802-1は、12ビットADC、高精度電圧リファレンス、高電圧入力マルチプレクサ、シリアル・インターフェースを内蔵した完全なバッテリ・モニタICです。各LTC6802-1は、最大60Vの入力同相電圧で直列に接続された最大12個のバッテリ・セルを測定できます。さらに、複数のLTC6802-1を直列に接続できるので、長いバッテリ・ストリングの1つのセルごとにモニタリングを実施できます。さらに、独自のレベルシフト・シリアル・インターフェースにより、オプトカプラやアイソレータを使わずに、これらのデバイスのシリアル・ポートをデイジーチェーン接続することができます。

複数のLTC6802-1が直列に接続されていると、これらのデバイスは同時に動作可能なので、バッテリ・スタック内の全てのセルの電圧を13ms以内で測定できます。

LTC6802-1は消費電力を最小限に抑えるために、セルごとに過電圧状態と低電圧状態を簡単にモニタする測定モードを備えています。スタンバイ・モードもあります。

各セル入力は、対応する内部MOSFETスイッチを使用して過充電されたセルを放電することができます。

個々にアドレス指定可能なシリアル通信を必要とする大きなバッテリ・スタック・アプリケーションに関しては、LTC6802-2を参照してください。

## 絶対最大定格

(Note 1)

全電源電圧( $V^+$ から $V^-$ ) ..... 60V

入力電圧( $V^-$ を基準)

C1 ..... -0.3V~9V

C12 ..... ( $V^+ - 0.6V$ )~( $V^+ + 0.3V$ )

Cn (Note 5) ..... -0.3V~min (9 • n, 60V)

Sn (Note 5) ..... -0.3V~min (9 • n, 60V)

CSBO, SCKO, SDOI ..... ( $V^+ - 0.6V$ )~( $V^+ + 0.3V$ )

他の全てのピン ..... -0.3V~7V

入力間の電圧

CnとCn-1間 ..... -0.3V~9V

SnとCn-1間 ..... -0.3V~9V

C12とC8間 ..... -0.3V~25V

C8とC4間 ..... -0.3V~25V

C4と $V^-$ 間 ..... -0.3V~25V

動作温度範囲 ..... -40°C~85°C

規定温度範囲 ..... -40°C~85°C

接合部温度 ..... 150°C

保存温度範囲 ..... -65°C~150°C

\*n = 1~12

## ピン配置

## 発注情報

| 鉛フリー仕様          | テープアンドリール         | 製品マーキング    | パッケージ                | 温度範囲          |

|-----------------|-------------------|------------|----------------------|---------------|

| LTC6802IG-1#PBF | LTC6802IG-1#TRPBF | LTC6802G-1 | 44-Lead Plastic SSOP | -40°C to 85°C |

さらに広い動作温度範囲で規定されるデバイスについては、弊社または弊社代理店にお問い合わせください。

非標準の鉛ベース仕様の製品の詳細については、弊社または弊社代理店にお問い合わせください。

鉛フリー仕様の製品マーキングの詳細については、<http://www.linear-tech.co.jp/leadfree/> をご覧ください。

テープアンドリールの仕様の詳細については、<http://www.linear-tech.co.jp/tapeandreel/> をご覧ください。

## 電気的特性

●は全動作温度範囲の規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。注記がない限り、 $V^+ = 43.2\text{V}$ 、 $V^- = 0\text{V}$ 。

| SYMBOL            | PARAMETER                                            | CONDITIONS                                                                                                                                                                                                                                                                                                                                                                                              | MIN              | TYP                                                                             | MAX                                                                                                          | UNITS                                                            |        |

|-------------------|------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|---------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|--------|

| <b>DC仕様</b>       |                                                      |                                                                                                                                                                                                                                                                                                                                                                                                         |                  |                                                                                 |                                                                                                              |                                                                  |        |

| $V_{\text{ACC}}$  | Measurement Resolution                               | Quantization of the ADC                                                                                                                                                                                                                                                                                                                                                                                 | ●                | 1.5                                                                             |                                                                                                              | mV/Bit                                                           |        |

|                   | ADC Offset Voltage                                   | (Note 2)                                                                                                                                                                                                                                                                                                                                                                                                | ●                | -0.5                                                                            | 0.5                                                                                                          | mV                                                               |        |

|                   | ADC Gain Error                                       | (Note 2)                                                                                                                                                                                                                                                                                                                                                                                                | ●                | -0.12                                                                           | 0.12                                                                                                         | %                                                                |        |

|                   |                                                      |                                                                                                                                                                                                                                                                                                                                                                                                         | ●                | -0.22                                                                           | 0.22                                                                                                         | %                                                                |        |

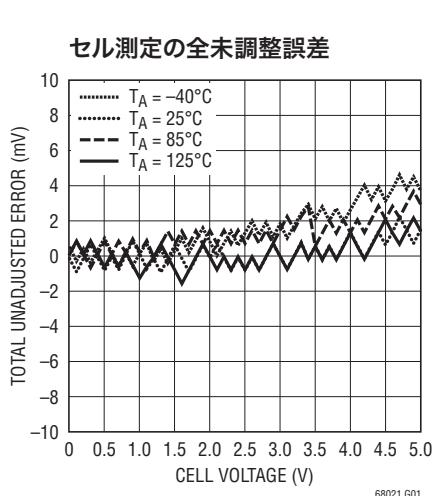

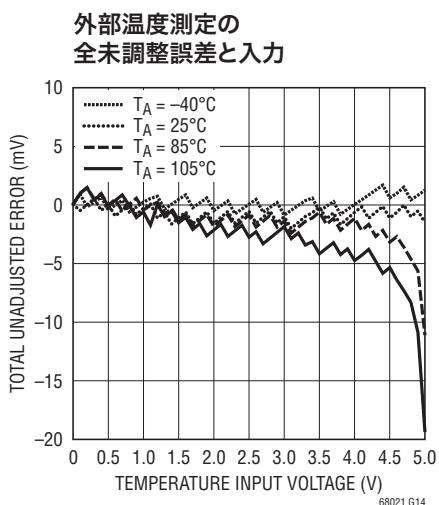

| $V_{\text{ERR}}$  | Total Measurement Error                              | (Note 4)<br>$V_{\text{CELL}} = 0\text{V}$<br>$V_{\text{CELL}} = 2.3\text{V}$<br>$V_{\text{CELL}} = 2.3\text{V}$<br>$V_{\text{CELL}} = 3.6\text{V}$<br>$V_{\text{CELL}} = 3.6\text{V}$<br>$V_{\text{CELL}} = 4.2\text{V}$<br>$V_{\text{CELL}} = 4.2\text{V}$<br>$V_{\text{CELL}} = 4.6\text{V}$<br>$V_{\text{TEMP}} = 2.3\text{V}$<br>$V_{\text{TEMP}} = 3.6\text{V}$<br>$V_{\text{TEMP}} = 4.2\text{V}$ | ●                | 0.8<br>-2.8<br>-5.1<br>-4.3<br>-7.9<br>-5<br>-9.2<br>±8<br>-5.1<br>-7.9<br>-9.2 | 2.8<br>5.1<br>4.3<br>7.9<br>5<br>9.2<br>mV<br>mV<br>mV<br>mV<br>mV<br>mV<br>mV<br>mV<br>mV<br>mV<br>mV<br>mV | mV                                                               |        |

| $V_{\text{CELL}}$ | Cell Voltage Range                                   | Full Scale Voltage Range                                                                                                                                                                                                                                                                                                                                                                                |                  | 5                                                                               |                                                                                                              | V                                                                |        |

| $V_{\text{CM}}$   | Common Mode Voltage Range Measured Relative to $V^-$ | Range of Inputs CN for $<0.25\%$ Gain Error, $N = 3$ to 11<br>Range of Input C3 for $<1\%$ Gain Error<br>Range of Input C2 for $<0.25\%$ Gain Error<br>Range of Input C1 for $<0.25\%$ Gain Error                                                                                                                                                                                                       | ●<br>●<br>●<br>● | 3.7<br>1.8<br>1.2<br>0                                                          | 5 • N<br>15<br>10<br>5                                                                                       | V<br>V<br>V<br>V                                                 |        |

|                   | Overvoltage (OV) Detection Level                     | Programmed for 4.2V                                                                                                                                                                                                                                                                                                                                                                                     | ●                | 4.182                                                                           | 4.200                                                                                                        | 4.218                                                            | V      |

|                   | Undervoltage (UV) Detection Level                    | Programmed for 2.3V                                                                                                                                                                                                                                                                                                                                                                                     | ●                | 2.290                                                                           | 2.300                                                                                                        | 2.310                                                            | V      |

|                   | Die Temperature Measurement Error                    | Error in Measurement at $125^\circ\text{C}$                                                                                                                                                                                                                                                                                                                                                             |                  |                                                                                 | 3                                                                                                            | $^\circ\text{C}$                                                 |        |

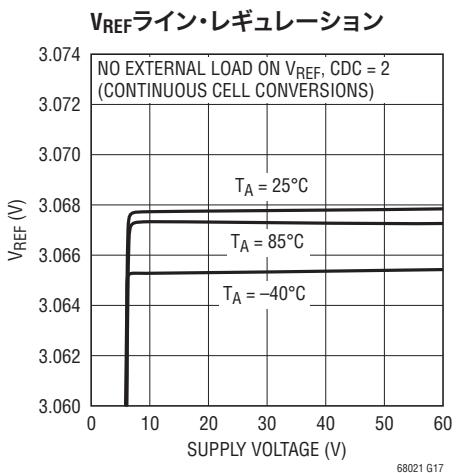

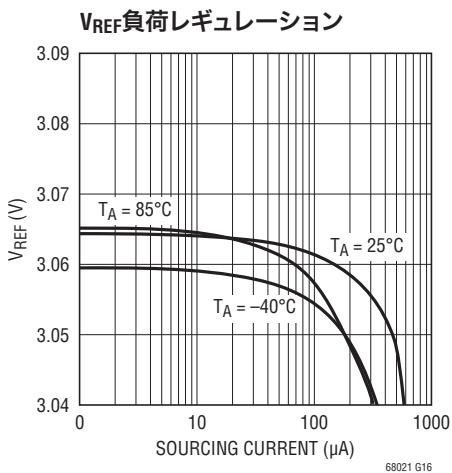

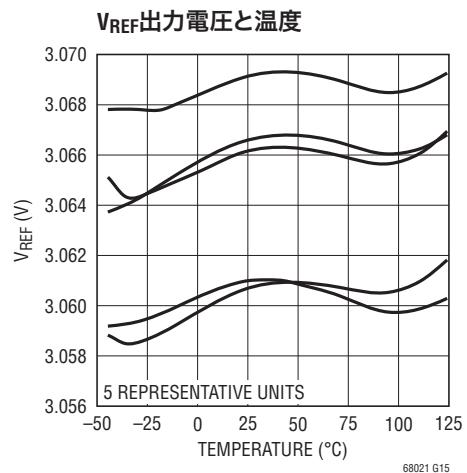

| $V_{\text{REF}}$  | Reference Pin Voltage                                | $R_{\text{LOAD}} = 100\text{k}$ to $V^-$                                                                                                                                                                                                                                                                                                                                                                | ●<br>●           | 3.020<br>3.015                                                                  | 3.065<br>3.065                                                                                               | 3.110<br>3.115                                                   | V<br>V |

|                   | Reference Voltage Temperature Coefficient            |                                                                                                                                                                                                                                                                                                                                                                                                         |                  |                                                                                 | 8                                                                                                            | ppm/ $^\circ\text{C}$                                            |        |

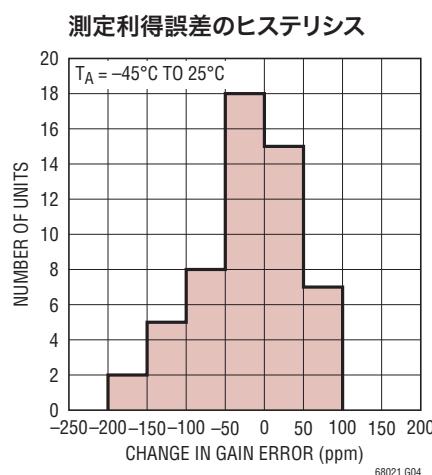

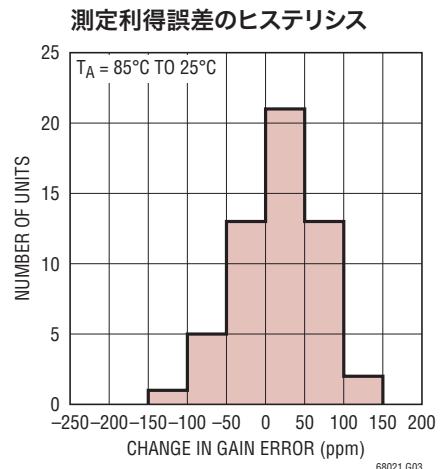

|                   | Reference Voltage Thermal Hysteresis                 | 25°C to 85°C and 25°C to -40°C                                                                                                                                                                                                                                                                                                                                                                          |                  |                                                                                 | 100                                                                                                          | ppm                                                              |        |

|                   | Reference Voltage Long Term Drift                    |                                                                                                                                                                                                                                                                                                                                                                                                         |                  |                                                                                 | 60                                                                                                           | ppm/ $\sqrt{\text{kh}}$                                          |        |

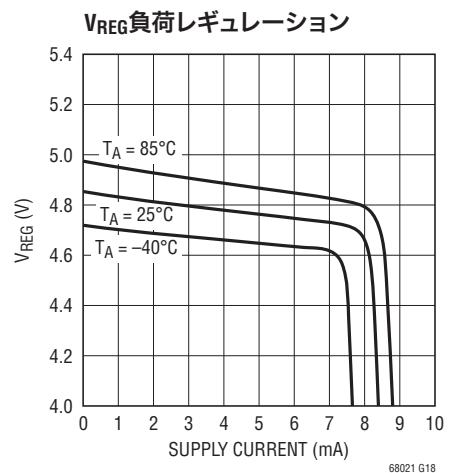

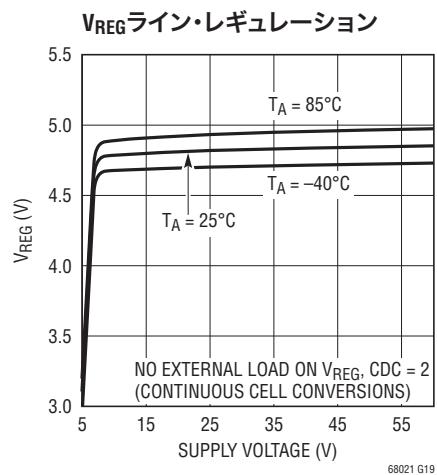

| $V_{\text{REG}}$  | Regulator Pin Voltage                                | 10 < $V^+ < 50$ , No Load<br>$I_{\text{LOAD}} = 4\text{mA}$                                                                                                                                                                                                                                                                                                                                             | ●<br>●           | 4.5<br>4.1                                                                      | 5.0<br>4.8                                                                                                   | 5.5                                                              | V<br>V |

|                   | Regulator Pin Short Circuit Current Limit            |                                                                                                                                                                                                                                                                                                                                                                                                         | ●                | 5                                                                               | 8                                                                                                            | mA                                                               |        |

| $V_S$             | Supply Voltage, $V^+$ Relative to $V^-$              | $V_{\text{ERR}}$ Specifications Met<br>Timing Specifications Met                                                                                                                                                                                                                                                                                                                                        | ●<br>●           | 10<br>4                                                                         | 50<br>50                                                                                                     | V<br>V                                                           |        |

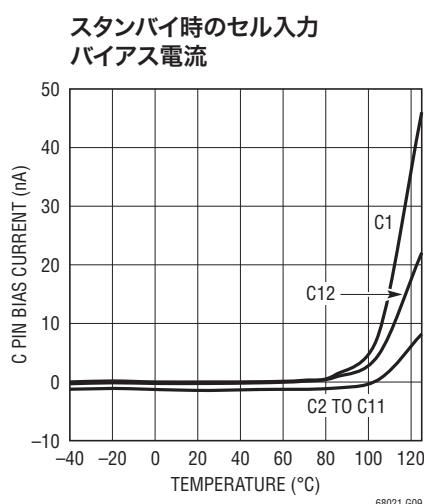

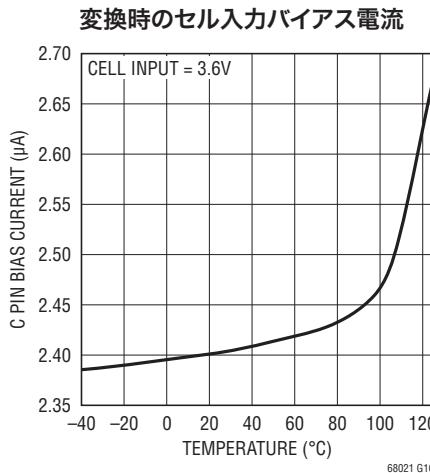

| $I_B$             | Input Bias Current                                   | In/Out of Pins C1 Thru C12<br>When Measuring Cells<br>When Not Measuring Cells                                                                                                                                                                                                                                                                                                                          | ●                | -10<br>1                                                                        | 10                                                                                                           | $\mu\text{A}$<br>$\text{nA}$                                     |        |

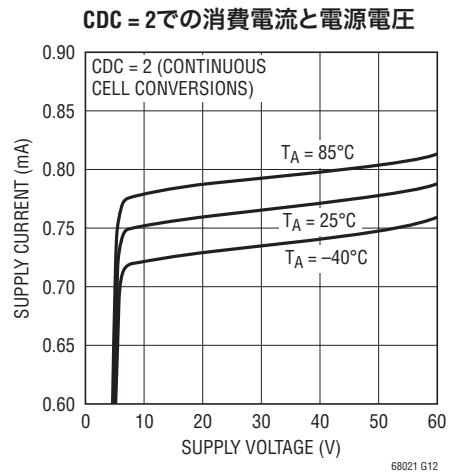

| $I_S$             | Supply Current, Active                               | Current Into the $V^+$ Pin when Measuring Voltages with the ADC                                                                                                                                                                                                                                                                                                                                         | ●                |                                                                                 | 0.8<br>1.1<br>1.2                                                                                            | mA<br>mA                                                         |        |

| $I_M$             | Supply Current, Monitor Mode                         | Average Current Into the $V^+$ Pin While Monitoring for UV and OV Conditions<br>Continuous Monitoring (CDC = 2)<br>Monitor Every 130ms (CDC = 5)<br>Monitor Every 500ms (CDC = 6)<br>Monitor Every 2s (CDC = 7)                                                                                                                                                                                         |                  |                                                                                 | 800<br>225<br>150<br>100                                                                                     | $\mu\text{A}$<br>$\mu\text{A}$<br>$\mu\text{A}$<br>$\mu\text{A}$ |        |

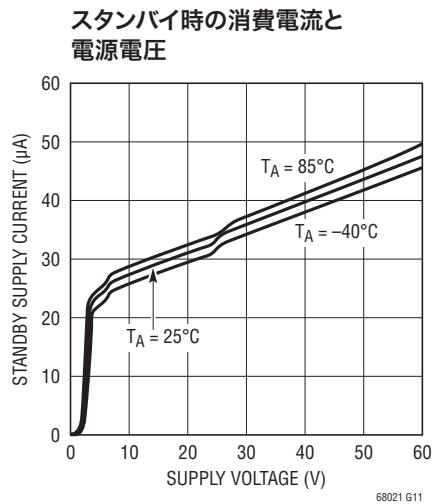

| $I_{\text{QS}}$   | Supply Current, Idle                                 | Current into the $V^+$ Pin When Idle<br>All Serial Port Pins at Logic '1'                                                                                                                                                                                                                                                                                                                               | ●                | 35<br>30                                                                        | 60<br>85                                                                                                     | $\mu\text{A}$<br>$\mu\text{A}$                                   |        |

| $I_{\text{CS}}$   | Supply Current, Serial I/O                           | All Serial Port Pins at Logic '0' $V_{\text{MODE}} = 0$ , This Current is Added to $I_S$ or $I_{\text{QS}}$                                                                                                                                                                                                                                                                                             | ●                | 3                                                                               | 4.5                                                                                                          | mA                                                               |        |

## 電気的特性

●は全動作温度範囲の規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。注記がない限り、 $V^+ = 43.2\text{V}$ 、 $V^- = 0\text{V}$ 。

| SYMBOL | PARAMETER                      | CONDITIONS                             | MIN | TYP | MAX | UNITS            |

|--------|--------------------------------|----------------------------------------|-----|-----|-----|------------------|

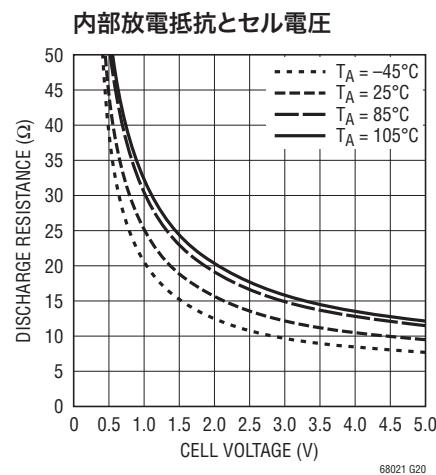

|        | Discharge Switch On-Resistance | $V_{\text{CELL}} > 3\text{V}$ (Note 3) | ●   | 10  | 20  | $\Omega$         |

|        | Temperature Range              |                                        | ●   | -40 | 85  | $^\circ\text{C}$ |

|        | Thermal Shutdown Temperature   |                                        |     | 145 |     | $^\circ\text{C}$ |

|        | Thermal Shutdown Hysteresis    |                                        |     | 5   |     | $^\circ\text{C}$ |

## 電圧モードのタイミング仕様

|                    |                                |                                                                                                                       |             |                |                 |                   |                |

|--------------------|--------------------------------|-----------------------------------------------------------------------------------------------------------------------|-------------|----------------|-----------------|-------------------|----------------|

| $t_{\text{CYCLE}}$ | Measurement Cycle Time         | Time Required to Measure 11 or 12 Cells<br>Time Required to Measure Up to 10 Cells<br>Time Required to Measure 1 Cell | ●<br>●<br>● | 11<br>9.2<br>1 | 13<br>11<br>1.2 | 16<br>13.5<br>1.5 | ms<br>ms<br>ms |

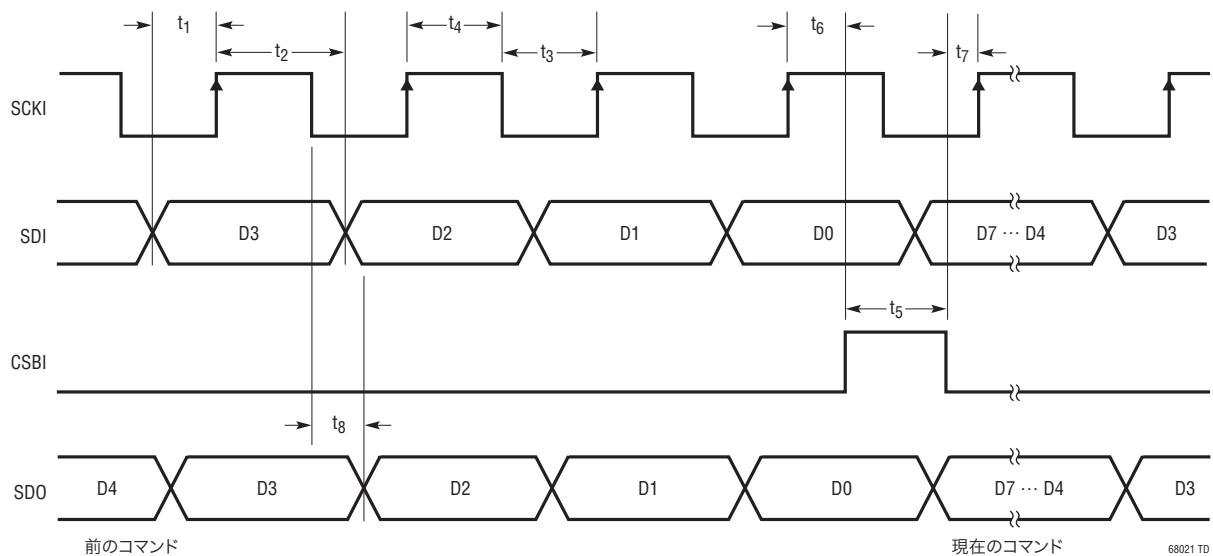

| $t_1$              | SDI Valid to SCKI Rising Setup |                                                                                                                       | ●           | 10             |                 |                   | ns             |

| $t_2$              | SDI Valid to SCKI Rising Hold  |                                                                                                                       | ●           | 250            |                 |                   | ns             |

| $t_3$              | SCKI Low                       |                                                                                                                       | ●           | 400            |                 |                   | ns             |

| $t_4$              | SCKI High                      |                                                                                                                       | ●           | 400            |                 |                   | ns             |

| $t_5$              | CSBI Pulse Width               |                                                                                                                       | ●           | 400            |                 |                   | ns             |

| $t_6$              | SCKI Rising to CSBI Rising     |                                                                                                                       | ●           | 100            |                 |                   | ns             |

| $t_7$              | CSBI Falling to SCKI Rising    |                                                                                                                       | ●           | 100            |                 |                   | ns             |

| $t_8$              | SCKI Falling to SDO Valid      |                                                                                                                       | ●           |                | 250             |                   | ns             |

|                    | Clock Frequency                |                                                                                                                       | ●           |                | 1               |                   | MHz            |

|                    | Watchdog Timer Time Out Period |                                                                                                                       | ●           | 1              | 2.5             |                   | s              |

## タイミング仕様

|                  |                         |                                  |   |     |  |    |

|------------------|-------------------------|----------------------------------|---|-----|--|----|

| $t_{\text{PD1}}$ | CSBI to CSBO            | $C_{\text{CSBO}} = 150\text{pF}$ | ● | 600 |  | ns |

| $t_{\text{PD2}}$ | SCKI to SCKO            | $C_{\text{SCKO}} = 150\text{pF}$ | ● | 300 |  | ns |

| $t_{\text{PD3}}$ | SDI to SDOI Write Delay | $C_{\text{SDOI}} = 150\text{pF}$ | ● | 300 |  | ns |

| $t_{\text{PD4}}$ | SDOI to SDI Read Delay  | $C_{\text{SDO}} = 150\text{pF}$  | ● | 300 |  | ns |

## 電圧モードのデジタルI/Oの仕様

|                 |                            |                                    |   |   |     |   |

|-----------------|----------------------------|------------------------------------|---|---|-----|---|

| $V_{\text{IH}}$ | Digital Input Voltage High | Pins SCKI, SDI, and CSBI           | ● | 2 |     | V |

| $V_{\text{IL}}$ | Digital Input Voltage Low  | Pins SCKI, SDI, and CSBI           | ● |   | 0.8 | V |

| $V_{\text{OL}}$ | Digital Output Voltage Low | Pin SDO; Sinking 500 $\mu\text{A}$ | ● |   | 0.3 | V |

## 電流モードのデジタルI/Oの仕様

|                  |                             |                                   |   |       |       |               |

|------------------|-----------------------------|-----------------------------------|---|-------|-------|---------------|

| $I_{\text{IH1}}$ | Digital Input Current High  | Pins CSBI, SCKI, and SDI (Write)  | ● | 10    |       | $\mu\text{A}$ |

| $I_{\text{IL1}}$ | Digital Input Current Low   | Pins CSBI, SCKI, and SDI (Write)  | ● | 1000  |       | $\mu\text{A}$ |

| $I_{\text{IH2}}$ | Digital Input Current High  | Pin SDOI (Read)                   | ● |       | -1000 | $\mu\text{A}$ |

| $I_{\text{IL2}}$ | Digital Input Current Low   | Pin SDOI (Read)                   | ● | -10   |       | $\mu\text{A}$ |

| $I_{\text{OH1}}$ | Digital Output Current High | Pins CSBO, SCKO, and SDOI (Write) | ● | 3     | 10    | $\mu\text{A}$ |

| $I_{\text{OL1}}$ | Digital Output Current Low  | Pins CSBO, SCKO, and SDOI (Write) | ● | 1000  | 1200  | 1650          |

| $I_{\text{OH2}}$ | Digital Output Current High | Pin SDI (Read)                    | ● | -1650 | -1200 | -1000         |

| $I_{\text{OL2}}$ | Digital Output Current Low  | Pin SDI (Read)                    | ● | -10   | -3    | 0             |

**Note 1:**絶対最大定格に記載された値を超えるストレスはデバイスに永続的損傷を与える可能性がある。長期にわたって絶対最大定格条件に曝すと、デバイスの信頼性と寿命に悪影響を与える可能性がある。

**Note 2:**ADCの仕様は全測定誤差( $V_{\text{ERR}}$ )仕様によって保証される。

**Note 3:**製造ラインのテスターの接触抵抗により、この仕様は緩和されたリミット値に対してテストされる。 $20\Omega$ のリミットは設計により保証されている。

**Note 4:** $V_{\text{CELL}}$ は以下のピンの組合せの両端に加えられる電圧を指す。 $C_n$ から $C_{n-1}$ ( $n = 2 \sim 12$ )、 $C_1$ から $V^-$ 。 $V_{\text{TEMP}}$ は $V_{\text{TEMP1}}$ または $V_{\text{TEMP2}}$ から $V^-$ に加えられる電圧を指す。

**Note 5:**これらの絶対最大定格は、入力間の電圧がそれらの絶対最大定格を超えない限り適用される。

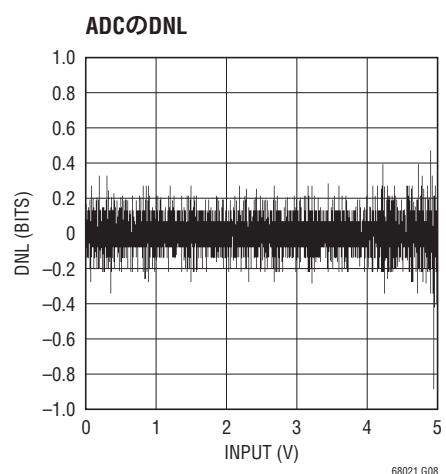

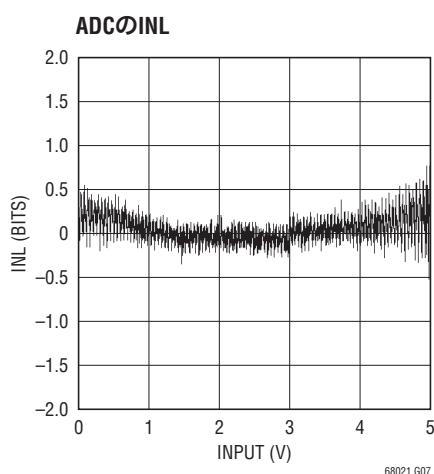

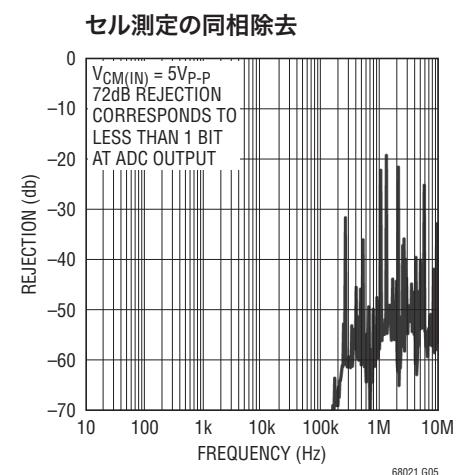

## 標準的性能特性

## 標準的性能特性

## 標準的性能特性

## ピン機能

**CSBO(ピン1)**:チップ・セレクト出力(アクティブ“L”)。CSBOはチップ・セレクト入力(CSBI)のバッファされたバージョンです。CSBOはデイジーチェーン接続された次のデバイスをドライブします。「アプリケーション情報」のセクションの「シリアル・ポート」を参照してください。

**SDOI(ピン2)**:シリアル・データI/Oピン。SDOIはデイジーチェーン接続された次のデバイスとの間でデータをやり取りします。「アプリケーション情報」のセクションの「シリアル・ポート」を参照してください。

**SCKO(ピン3)**:シリアル・クロック出力。SCKOはSCKIのバッファされたバージョンです。SCKOはデイジーチェーン接続された次のデバイスをドライブします。「アプリケーション情報」のセクションの「シリアル・ポート」を参照してください。

**V<sup>+</sup>(ピン4)**:ピン4はバッテリ・スタックの最も高い正電位に接続します。一般にV<sup>+</sup>はC12と同じ電位です。

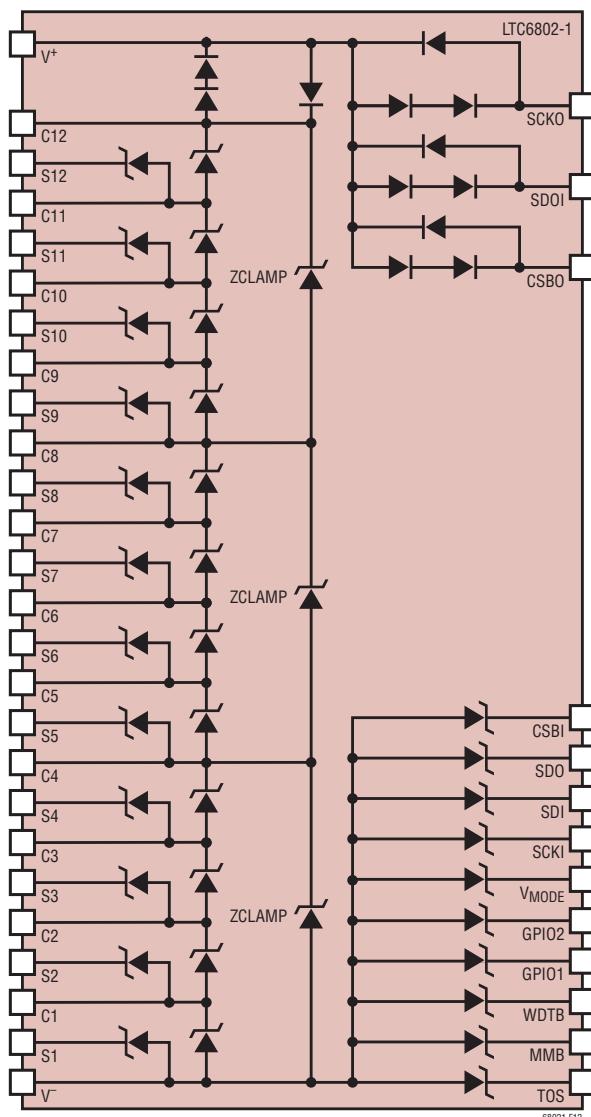

**C12、C11、C10、C9、C8、C7、C6、C5、C4、C3、C2、C1(ピン5、7、9、11、13、15、17、19、21、23、25、27)**:C1～C12はバッテリのセル電圧のモニタ用入力です。12セルまでモニタすることができます。最も低い電位はV<sup>-</sup>ピンに接続します。次に低い電位はC1に接続し、以下同様にします。LTC6802-1へのバッテリの接続の詳細については、「アプリケーション情報」のセクションの図を参照してください。

LTC6802-1は12セルまでの直列接続をモニタすることができます。直列接続の各セルの同相電圧は、その下方にあるセルの同相電圧と同じ、もしくは、それより高くなればなりません。

**S12、S11、S10、S9、S8、S7、S6、S5、S4、S3、S2、S1(ピン6、8、10、12、14、16、18、20、22、24、26、28)**:S1～S12の各ピンはバッテリ・セルをバランスするために使います。一連のセルの1つが過充電状態になると、S出力を使ってそのセルを放電することができます。各S出力には放電用に内部NチャネルMOSFETが備わっています。ブロック図を参照してください。このNMOSの最大オン抵抗は20Ωです。外部抵抗をNMOSに直列に接続して、LTC6802-1パッケージの外部で熱を放散します。内部MOSFETを使ってセルを放電するとき、ダイ温度をモニタします。「アプリケーション情報」セクションの「電力損失とサーマル・シャットダウン」を参照してください。

Sピンは内部10kプルアップ抵抗も備えています。これにより、Sピンを使って外部PチャネルMOSFETのゲートをドライブして放電能力を高めることができます。

**V<sup>-</sup>(ピン29)**:V<sup>-</sup>を一連のセルの最も大きな負電位に接続します。

**NC(ピン30)**:ピン30は内部で10Ωを介してV<sup>-</sup>に接続されています。ピン30は未接続のままにするか、PCB上でピン29に接続することができます。

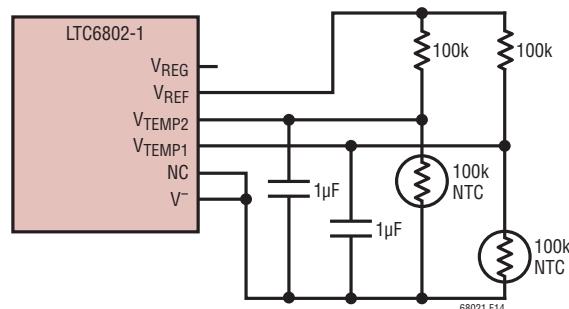

**V<sub>TEMP1</sub>、V<sub>TEMP2</sub>(ピン31、32)**:温度センサ入力。このADCはV<sup>-</sup>を基準にしてV<sub>TEMPx</sub>の電圧を測定し、結果をTMPレジスタに保存します。ADCの測定値はV<sub>REF</sub>ピンの電圧を基準にしています。したがって、V<sub>REF</sub>ピンに接続した簡単なサーミスタと抵抗の組合せを使って温度をモニタすることができます。V<sub>TEMP</sub>入力は汎用のADC入力にすることもできます。

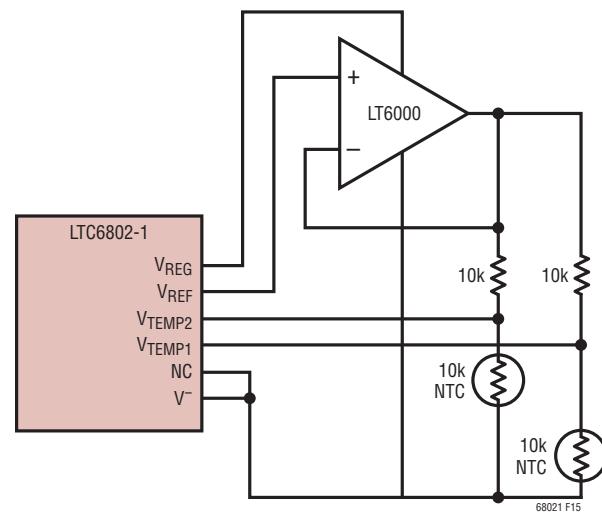

**V<sub>REF</sub>(ピン33)**:3.075V電圧リファレンスの出力。このピンは1μFのコンデンサを使ってバイパスします。V<sub>REF</sub>ピンはV<sup>-</sup>に接続された100kの抵抗性負荷をドライブすることができます。もっと大きな負荷はLT6003オペアンプまたは同様のデバイスでバッファします。

**V<sub>REG</sub>(ピン34)**:リニア電圧レギュレータの出力。このピンは1μFのコンデンサを使ってバイパスします。V<sub>REG</sub>ピンは最大4mAを外部負荷に供給する能力があります。V<sub>REG</sub>ピンは電流をシンクしません。

**TOS(ピン35)**:スタック入力のトップ。LTC6802-1がデイジーチェーンのトップ・デバイスのとき、TOSをV<sub>REG</sub>に接続します。LTC6802-1がデイジーチェーンの他のどのデバイスであっても、TOSをV<sup>-</sup>に接続します。TOSがV<sub>REG</sub>に接続されていると、LTC6802-1はSDOI入力を無視します。TOSがV<sup>-</sup>に接続されていると、LTC6802-1はSDOIピンを介してデータがやり取りされると期待します。

**MMB(ピン36)**:モニタ・モード(アクティブ“L”)入力。MMBが“L”的とき(V<sup>-</sup>と同じ電位)、LTC6802-1はモニタ・モードになります。「アプリケーション情報」セクションの「動作モード」を参照してください。

**WDTB(ピン37)**:ウォッチドッグ・タイマ出力(アクティブ“L”)。SCKIピンに2.5秒間何も活動がないと、WDTB出力がアサートされます。WDTBピンはオープン・ドレインのNMOS出力です。アサートされると、それは出力をV<sup>-</sup>に引き下げ、構成設定レジスタを既定状態にリセットします。「アプリケーション情報」セクションの「ウォッチドッグ・タイマ回路」を参照してください。

## ピン機能

**GPIO1、GPIO2(ピン38、39)**:汎用入力/出力。これらのピンの動作はMMBピンの状態に依存します。

MMBが“H”的とき、ピンは従来のGPIOとして振る舞います。構成設定レジスタのGPIOビットに0を書き込むと、オープン・ドレイン出力がアクティブになります。ピンはV<sup>-</sup>に引き下げられます。構成設定レジスタのビットにロジック1を書き込むと、対応するGPIOピンが高インピーダンスになります。ピンをV<sub>REG</sub>に引き上げるには外部抵抗が必要です。

構成設定レジスタのGPIO1とGPIO2のロケーションを読み出すことにより、ピンの状態を決定することができます。たとえば、レジスタのビットGPIO1に0を書き込むと、出力のNMOSFETがピン38をV<sup>-</sup>に引き下げる所以常に0が読み出されます。レジスタのビットGPIO1に1が書き込まれると、ピンは高インピーダンスになります。ピン38に存在する電圧に依存して1または0のどちらかが読み出されます。GPIOはLTC6802-1の周りの回路をオン/オフしたり、LTC6802-1の周りの回路からロジック値を読み取ることを可能にします。

MMBピンが“L”的とき、GPIOピンとWDTBピンはモニタされるセルの個数を設定する入力として扱われます。「アプリケーション情報」セクションの「モニタ・モード」を参照してください。

**V<sub>MODE</sub>(ピン40)**:電圧モード入力。V<sub>MODE</sub>がV<sub>REG</sub>に接続されると、SCKI、SDI、SDOおよびCSBIの各ピンは電圧入力および電圧出力として構成設定されます。つまり、これらのピンは標準TTLレベルを受け入れます。LTC6802-1がデイジーチェーンのボトム・デバイスのとき、V<sub>MODE</sub>をV<sub>REG</sub>に接続します。

V<sub>MODE</sub>がV<sup>-</sup>に接続されると、SCKI、SDIおよびCSBIの各ピンは電流入力および電流出力として構成設定され、SDOは使用されません。LTC6802-1がデイジーチェーン内で別のLTC6802-1によってドライブされる場合、V<sub>MODE</sub>をV<sup>-</sup>に接続します。

**SCKI(ピン41)**:シリアル・クロック入力。SCKIピンはV<sub>MODE</sub>がV<sub>REG</sub>に接続されているとロジック・ゲート(TTLレベル)とインターフェースします。V<sub>MODE</sub>がV<sup>-</sup>に接続されているとSCKIは別のLTC6802-1のSCKOピンによってドライブする必要があります。「アプリケーション情報」のセクションの「シリアル・ポート」を参照してください。

**SDI(ピン42)**:シリアル・データ入力。SDIピンはV<sub>MODE</sub>がV<sub>REG</sub>に接続されているとロジック・ゲート(TTLレベル)とインターフェースします。V<sub>MODE</sub>がV<sup>-</sup>に接続されているとSDIは別のLTC6802-1のSDOピンによってドライブする必要があります。「アプリケーション情報」のセクションの「シリアル・ポート」を参照してください。

**SDO(ピン43)**:シリアル・データ出力。V<sub>MODE</sub>がV<sub>REG</sub>に接続されるとSDOピンはオープン・ドレインのNMOS出力です。V<sub>MODE</sub>がV<sup>-</sup>に接続されるとSDOは使用されません。「アプリケーション情報」のセクションの「シリアル・ポート」を参照してください。

**CSBI(ピン44)**:チップ選択(アクティブ“L”)入力。CSBIピンはV<sub>MODE</sub>がV<sub>REG</sub>に接続されているとロジック・ゲート(TTLレベル)とインターフェースします。V<sub>MODE</sub>がV<sup>-</sup>に接続されているとCSBIは別のLTC6802-1のCSBOピンによってドライブする必要があります。「アプリケーション情報」のセクションの「シリアル・ポート」を参照してください。

## ブロック図

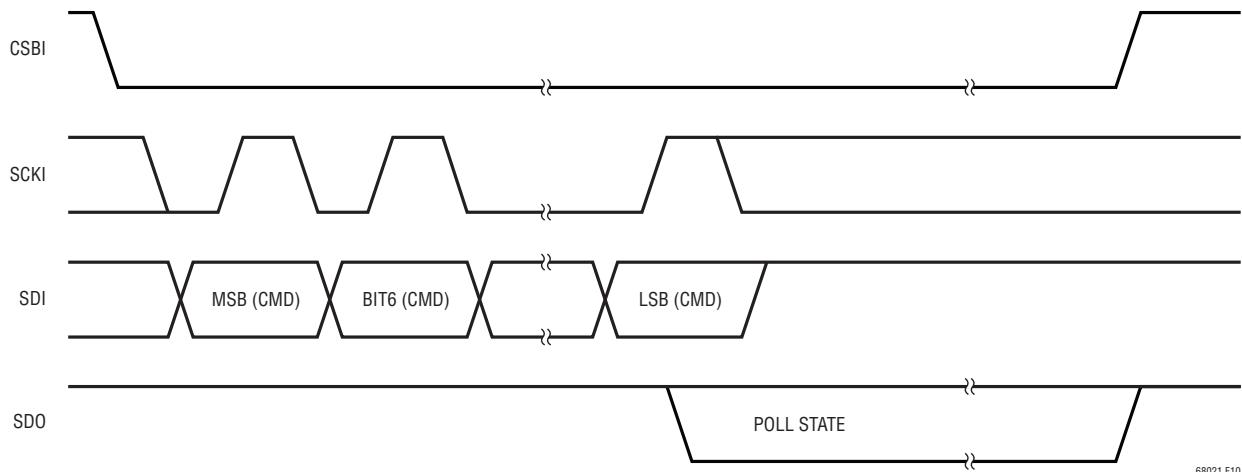

## タイミング図

シリアル・インターフェースのタイミング図

## 動作

### 動作原理

LTC6802-1はデータ収集ICで、直列接続された12個のバッテリ・セルの電圧を測定することができます。入力のマルチプレクサはバッテリを12ビット・デルタシグマA/Dコンバータ(ADC)に接続します。ADCと組み合わされた内部の10ppm電圧リファレンスがLTC6802-1に並外れた測定精度を与えます。他のタイプのADC(たとえば、逐次近似)に比べたデルタシグマADCの本質的利点については、「アプリケーション情報」のセクションの「デルタシグマADCの利点」で説明されています。

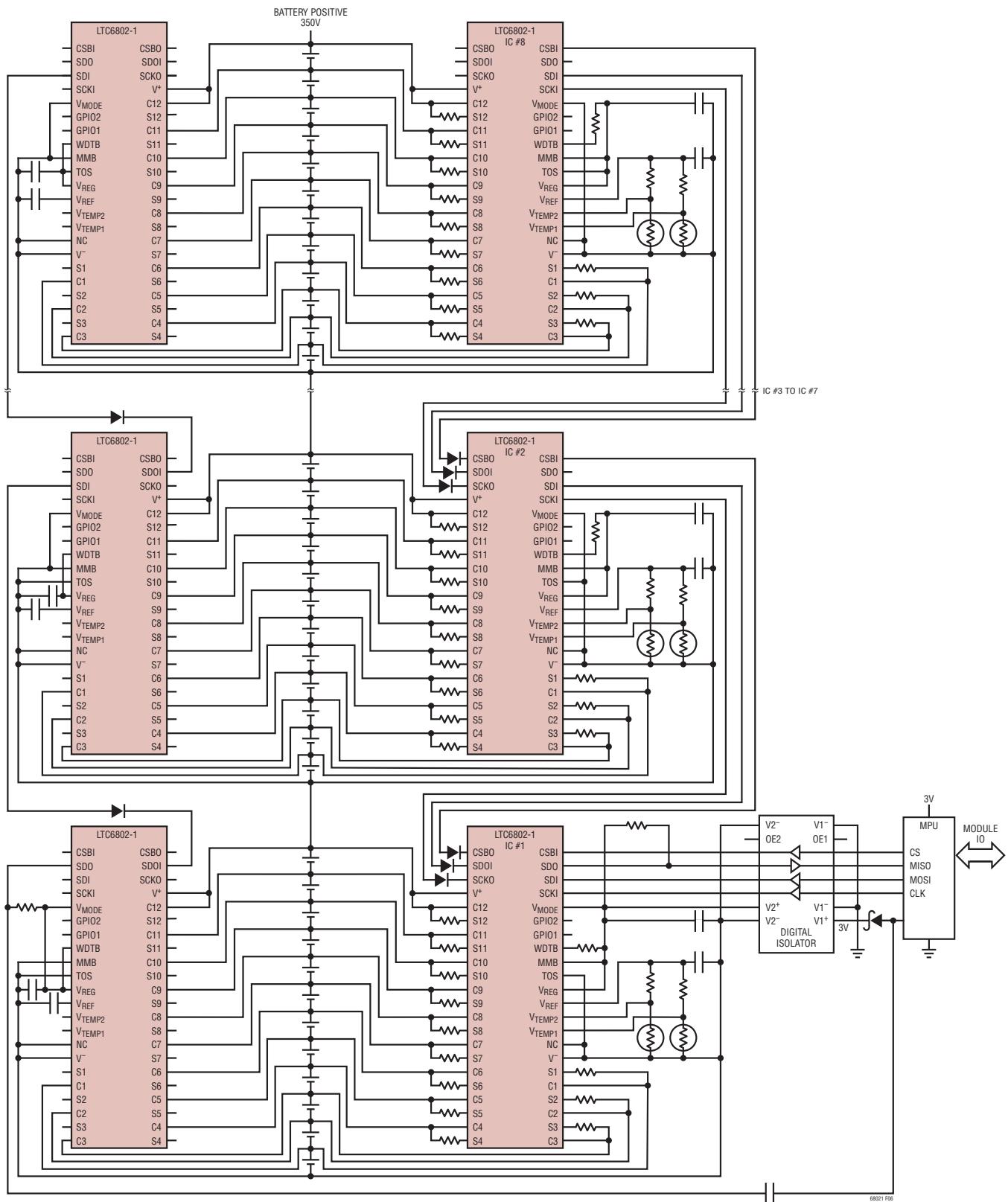

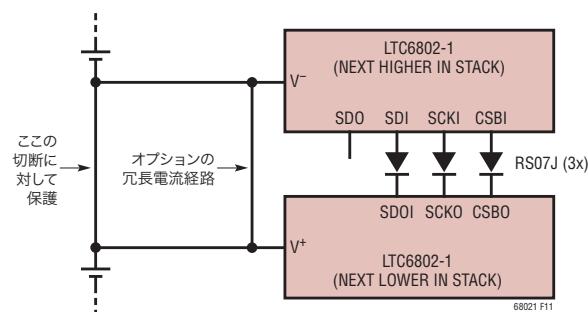

LTC6802-1とホストプロセッサの間の通信はSPI互換のシリアル・インターフェースによって扱われます。図1に示されているように、絶縁のための簡単なダイオードを使って、LTC6802-1はスタッツに構成されたデバイスの間で上にも下にもデータを渡すことができます。この動作は「アプリケーション情報」のセクションの「シリアル・ポート」で説明されています。

LTC6802-1はセルの電圧をバランスさせる回路も備えています。内蔵MOSFETを使ってセルを放電させることができます。これらの内部MOSFETは外部のバランス回路を制御す

るのにも使うことができます。内部放電によるセル・バランスを図1に示します。図4は外部バランス回路を制御するSピンを示しています。LTC6802-1は内部MOSFETのオン/オフの決定は行わないことに注意することが重要です。これは完全にホストプロセッサによって制御されます。ホストプロセッサはLTC6802-1内部の構成設定レジスタに値を書き込んでスイッチを制御します。ホストプロセッサとの通信が中断したら、LTC6802-1のウォッチドッグ・タイマを使って放電スイッチをオフします。

### オープンワイヤの検出

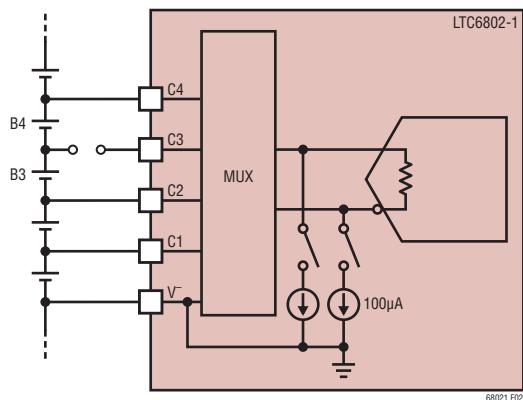

セル入力(Cピン)がオープンになっていると、2つのセルの測定値に影響します。図2は、Cピンとセルの間に外部フィルタを使用しないアプリケーションにおける、C3のオープンワイヤを示しています。通常のADC変換(STCVADコマンドを使用)時は、C3がオープンになっていると、B3とB4の測定値がゼロになります。B3の測定時はADCの入力抵抗によってC3がC2の電位になるので、B3の測定値はゼロになります。同様に、B4の測定時は、ADCの入力抵抗によってC3がC4の電位になります。

## 動作

図1. 96セル・バッテリ・スタックのデイジーチェーン・インターフェース。これは、基本的なマルチICアーキテクチャを示す簡略回路図です。

68021 FA

## 動作

図2. オープンワイヤ

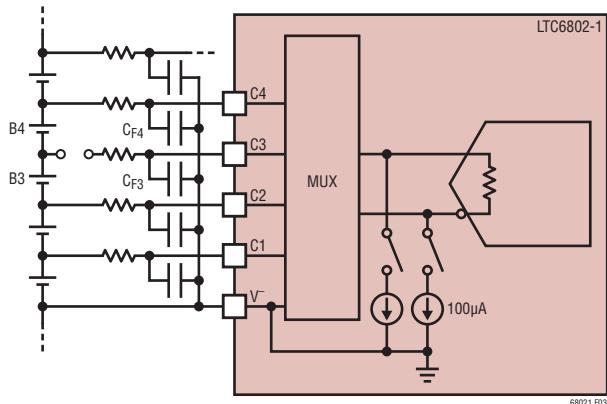

図3. RCフィルタ付きオープンワイヤ

図3では、図2と同じセルスタック内のポイントで接続がオープンになっていますが、外部フィルタ・ネットワークがC3に接続されています。C3ピンは真にオープンではないため、C3に接続されたままのコンデンサの値によっては、B3とB4の通常の測定値がゼロに近づかないことがあります。実際には、C3に大きな外部容量が接続されていると、B3とB4のセルを数回測定した後、C3の電圧はC2とC4の中間あたりに充電されます。このため、B3とB4の測定値は、B3とB4の正確な状態が実際には不明なときに有効なセル電圧を示すことがあります。

オープンワイヤを確実に検出するために、STOWADコマンドがあります。このコマンドを使うと、すべてのセルの変換時に2つの100µA電流源がADC入力に接続され、オンされます。図3からわかるように、STOWADコマンドを使用すると、C3ピンはB3セルの測定時とB4セルの測定時に100µA電流源によって

プルダウンされます。これにより、通常のSTCVADコマンドと比べて、B3の測定値が減少し、B4の測定値が増加します。変化が最も大きいのは、C3がオープン状態のときのB4の測定値です。このため、C3入力におけるオープンワイヤを検出する最良の方法は、C3とC4の入力の間に接続されたセル（セルB4）の測定値の増加を調べることです。

したがって、以下のアルゴリズムを使用して、セル・ピンCNのオープンワイヤを検出することができます。

(1) STCVADコマンドを発行(100µAの電流源を使用せずにADC変換)

(2) RDCVコマンドを発行し、すべてのセルの測定値をアレイCELLA(N)に格納

(3) STOWADコマンドを発行(100µAの電流源を使ってADC変換)

(4) RDCVコマンドを発行し、すべてのセルの測定値をアレイCELLB(N)に格納

(5) 1から11までの各N値に対し

$CELLB(N+1) - CELLA(N+1) \geq +200mV$ であれば、CNはオープン、それ以外の場合はオープンでない。

+200mVのスレッショルドは、100µA電流源を接続したときの測定誤差に対してゆとりを持たせるために選択されます。MUXスイッチの有限抵抗の両端にIR降下が生じるため、オープンワイヤが生じていない場合でも、100µAの電流源を接続した場合と接続しない場合とで、測定されるセルの間に常にある程度の差が生じます。一方、Cピンがオープンしてはいるが0.1µFよりも大きなコンデンサが接続されたままの場合は、1回のSTOWADコマンドでオープン状態のCピンの電圧を200mV変化させるには、100µA電流源では不十分かもしれません。STOWADコマンドを数回繰り返すと、大きな外部コンデンサが十分に放電するので、セルの測定値に200mVの変化が生じます。ピンに0.1µFよりも大きなコンデンサが接続されたままの状態でオープンワイヤを検出するためには、上記のステップ(4)に進む前に、ステップ(3)を数回繰り返す必要があります。

上記のアルゴリズムは、N+1セルの測定値に基づいて、CNピンがオープンかどうかを決定します。例えば12セル・システムの場合、アルゴリズムはセルB2～B12の測定値を調べるこ

## 動作

とにより、ピンC1～C11のオープンワイヤを検出します。そのため、このアルゴリズムは、トップのCピンがオープンかどうかを決定するためには使用できません。幸い、バッテリからトップのCピンまでのオープンワイヤは通常、V<sup>+</sup>ピンもまたフロート状態であることを意味します。これが生じると、トップのバッテリ・セルの測定値は常に0Vとなり、不良であることを示します。トップのCピンがオープン状態であるのにV<sup>+</sup>は接続されたままの場合、トップのCピンのオープンワイヤを検出する最良の方法は、STCVADコマンドを使った全てのセルの測定値の合計と、図18に示すのと同じような方法で行った、すべてのセルの合計の補助的測定値を比較することです。12セルすべてを計算した合計が著しく低い値である場合は、他のCピンがオープンでないことが既に確定していれば、トップのCピンがオープン状態であることを示します。

## セル測定中の放電

主セル電圧のA/D測定コマンド(STCVADとSTOWAD)は、セル電圧を測定する間、自動的にセルの放電スイッチをオフします。上のセルと下のセルの放電スイッチも測定中オフします。たとえば、セル5が測定されている間、放電スイッチのS4、S5およびS6がディスエーブルされます。

システムによっては、セル電圧の測定中に放電の継続を許すことがあります。セル電圧のA/D変換コマンドのSTCVDCとSTOWDCは、イネーブルされたどの放電スイッチもセル電圧の測定中にオンに留まることを許します。この機能により、システムは自己テストを行い、放電機能とマルチプレクサ動作を検証することができます。

OVとUVの比較測定の間、全ての放電スイッチが自動的にディスエーブルされます。

## A/Dコンバータのデジタル自己テスト

自己テストの2つのコマンドを使って、ADCのデジタル部分の機能を検証することができます。自己テストはセル電圧レジスタと温度モニタ・レジスタも検証します。これらの自己テストの間、テスト信号がADCに与えられます。回路が正しく動作していると、全てのセル電圧レジスタと温度レジスタに同一のコードが格納されます。自己テスト1ではレジスタに0x555が格納されます。自己テスト2ではレジスタに0xAAAが格納されます。自己テスト機能に要する時間は、全てのセル電圧または全ての温度センサを測定するのに要する時間と同じです。構成設定レジスタのCDC[2:0]が1にセットされた状態で自己テスト機能を実行します。

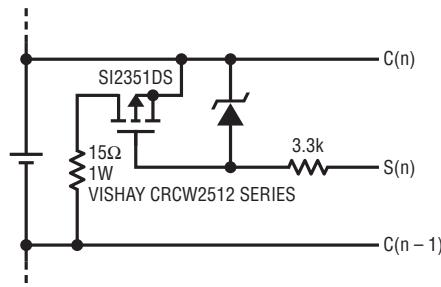

## デジタル出力またはゲート・ドライバとしてのSピンの利用

S出力は内部10kプルアップ抵抗を備えています。したがって、高インピーダンスの負荷(たとえば、外部MOSFETのゲート)を与えられると、Sピンはデジタル出力として振る舞います。高いバッテリ放電電流を必要とするアプリケーションでは、図4に示されているように、ディスクリートPMOSスイッチ・デバイスと適当な放電抵抗をセルに接続し、ゲート端子をS出力ピンに接続します。

図4. 外部の放電用FETの接続(1個のセルが示されている)

## 動作

### 電力損失とサーマル・シャットダウン

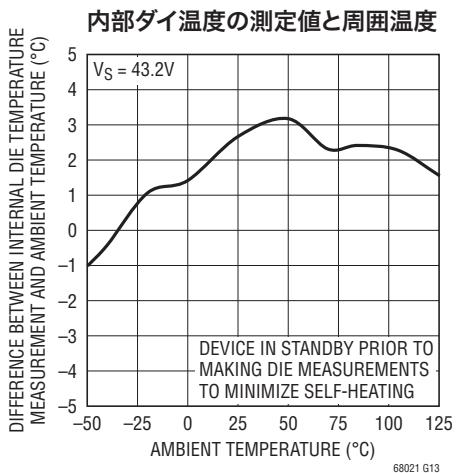

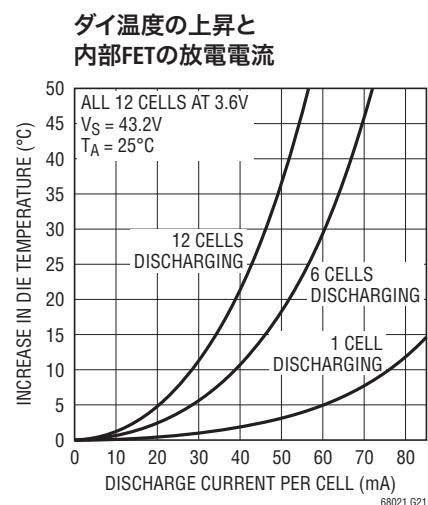

ピンS1～S12に接続されたMOSFETを使ってバッテリ・セルを放電することができます。外部抵抗を使ってMOSFETの消費する電力を制限します。MOSFETの最大電力損失はLTC6802-1が許容可能な熱量によって制限されます。過度の熱はダイ温度を上昇させます。85°Cまでのダイ温度に対して電気的特性が保証されています。105°Cまでのダイ温度では測定精度の低下はわずかしか、または全く見られません。150°C近くではダメージが生じることがあるので、推奨最大ダイ温度は125°Cです。

過熱によるダメージからLTC6802-1を保護するため、サーマル・シャットダウン回路が備わっています。セル放電用スイッチで大きな電力が消費されるとき、または電流モード・シリアル・インターフェースを使ってデバイスに頻繁に通信するときデバイスの過熱が生じることがあります。V<sup>+</sup>とV<sup>-</sup>の間の電圧が大きいとき、またはシステムの熱伝導性が良くない状態で動作すると問題が悪化します。

デバイスの検出された温度が約145°Cを超えると、構成設定レジスタが既定の状態にリセットし、全ての放電スイッチをオフし、A/D変換をディスエーブルします。サーマル・シャットダウンが起きると、温度レジスタ・グループのTHSDビットが”H”になります。このビットは温度レジスタを読み出すとクリアされます(RDTMPコマンド)。

シャットダウンは通常動作を中断するので、内部温度モニタを使ってデバイスの温度が許容できないレベルに近づいているか判断します。

## アプリケーション情報

### 12セルより少ないセルでのLTC6802-1の使用

LTC6802-1はわずか4セルでも使うことができます。セルの最少数はLTC6802-1の電源電圧の要件によって支配されます。全ての電気的仕様が満たされることを保証するには、セル電圧の和が10Vである必要があります。

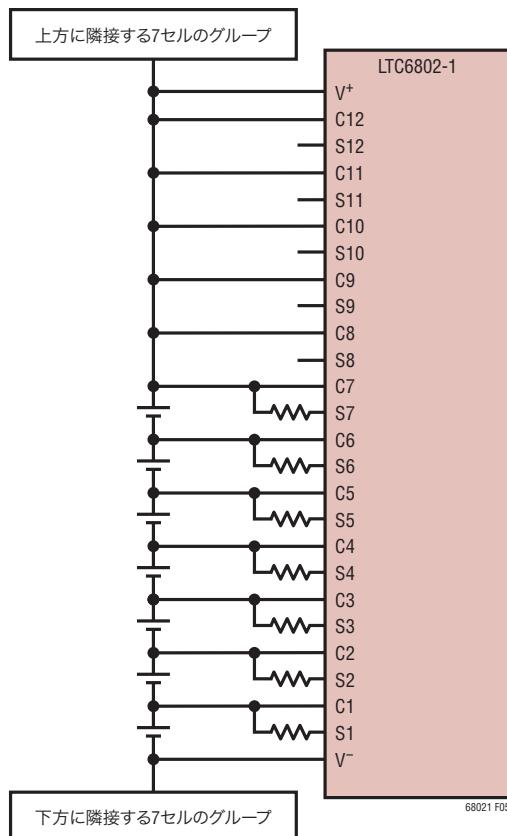

7個のセルをモニタするのに使われたLTC6802-1の例を図5に示します。下の方のC入力は7個のセルに接続し、上方のC入力はV<sup>+</sup>に接続します。他の構成設定(たとえば、9個のセル)は同様に構成設定することができます。下の方のC入力はバッテリ・セルに接続し、使用されないC入力はV<sup>+</sup>に接続します。使用されない入力のチャネルは0Vの測定値になります。

制御レジスタのCELL10ビットの状態に依存して、10回または12回の測定を行うことによりセルのスタックを測定するようにADCに命令することができます。10回または12回の全ての測定からのデータは、変換結果を読み出すときダウンロードする必要があります。ADCに命令して、どの個別セルの電圧でも測定することができます。

図5. LTC6802-1による7セルのモニタ

### 汎用入力/出力の利用(GPIO1, GPIO2)

LTC6802-1には2つの汎用デジタル入力/出力が備わっています。GPIO構成設定レジスタ・ビットにロジック“L”を書き込むことにより、オープン・ドレイン出力をアクティブにすることができます。ユーザーはGPIOを使ってLTC6802-1の周りの回路をオン/オフすることができます。一例として、システムの動作を検証する回路があります。

GPIO構成設定ビットにロジック“H”を書き込むと、対応するGPIOピンを入力として使うことができます。そのビットの読み出された値は、GPIOピンに現れるロジック・レベルになります。

MMBピンが“L”的とき、GPIOピンとWDTBピンはモニタされるセルの個数を設定する入力として扱われます。「モニタ・モード」のセクションを参照してください。

### ウォッチドッグ・タイマ回路

LTC6802-1にはウォッチドッグ・タイマ回路が備わっています。SCKIピンに2.5秒間何の活動も検出されないと、WDTBオープン・ドレイン出力が“L”にアサートされます。WDTBピンはSCKIピンにエッジが検出されるまで“L”に留まります。

ウォッチドッグ・タイマ回路がタイムアウトすると、構成設定ビットはそれらの既定(パワーアップ)状態にリセットします。

パワーアップ状態では、S出力はオフしています。したがって、ウォッチドッグ・タイマは、MPUへの通信が中断したときセルの放電をオフする手段を与えます。タイムアウト後、デバイスは最小消費電力のスタンバイ・モードになります。外部からWDTBピンを”L”に引き下げても構成設定ビットはリセットされないことに注意してください。

ウォッチドッグ・タイマの動作はMMBが”L”的ディスエールされます。

構成設定レジスタを読み出すとき、バイトCFG0のビット7は、WDTBピンの状態を反映します。

### リビジョン・コード

温度レジスタ・グループには3ビットのリビジョン・コードが含まれています。ソフトウェアでデバイスのリビジョンを検出する必要があれば、詳細に関しては弊社までお問い合わせください。そうでなければ、コードは無視してかまいません。ただし、全ての場合に、データ読み出し時にパケット・エラー・コード(PEC)のCRCバイトを計算するときは全ビットの値を使う必要があります。

## アプリケーション情報

### 動作モード

LTC6802-1には、スタンバイ、測定およびモニタの3つの動作モードが備わっています。スタンバイ・モードは省電力状態で、シリアル・インターフェース以外の全回路がオフします。測定モードでは、LTC6802-1はセル電圧を測定して結果をメモリに保存するのに使われます。測定モードでは、過電圧(OV)および低電圧(UV)状態の各セル電圧もモニタします。モニタ・モードでは、デバイスはUV状態およびOV状態のセルだけをモニタします。信号がSDOピンに出力されてUV/OV状態を示します。シリアル・インターフェースはディスエーブルされます。

### スタンバイ・モード

LTC6802-1は既定で(パワーアップ時に)スタンバイ・モードになります。スタンバイ・モードは消費電流が最小の状態です。シリアル・インターフェースと電圧レギュレータ以外の全回路がオフします。スタンバイ時の電流消費をできるだけ下げるため、全てのSPIロジック入力をロジック1のレベルに設定します。コンバーティのデューティ・サイクル構成ビット(CDC[2:0])を0に設定することにより、LTC6802-1をスタンバイ・モードにプログラムすることができます。ADCの測定が進行中にデバイスをスタンバイ・モードにすると、測定は中断され、セル電圧レジスタは不定の状態になります。スタンバイ・モードを終了するには、CDCビットに0以外の値を書き込む必要があります。

### 測定モード

1~7の値でCDCピンをプログラムするとLTC6802-1は測定モードになります。デバイスは各セル電圧をモニタし、SDOピンに割込み信号を発生して、全てのセル電圧がUVリミットおよびOVリミットの範囲内であることを示します。UV/OV割込み状態を示す2つの方法があります。(1kHzの出力信号を使った)トグル・ポーリングおよび("H"または"L"の出力信号を使った)レベル・ポーリングです。ポーリング方法は「シリアル・ポート」のセクションで説明します。

UV/OVのリミットは構成設定レジスタのVUVとVOVの値によって設定されます。セル電圧がUV/OVのリミットを超えると、フラグ・レジスタのビットがセットされます。各セルのUVとOVのフラグの状態はフラグ読み出しレジスタ・グループを使って決定することができます。

12個より少ないセルがLTC6802-1に接続されている場合、使用されない入力チャネルをマスクする必要があります。構成設定レジスタのMCxIビットを使ってチャネルをマスクします。CELL10ビットが“H”であると、セル11とセル12の入力は自動的にマスクされます。

LTC6802-1はUVとOVの状態を連続してモニタすることができます。代わりに、全体の電力消費を下げるため、UVとOVの比較のデューティ・サイクルを減らす、またはオフすることができます。CDCビットを使ってデューティ・サイクルを制御します。

測定モードでセル電圧の測定を開始するには、**A/D変換開始および状態ポーリング**のコマンドを送る必要があります。コマンドが送られた後、「シリアル・ポート」のセクションで説明されているように、LTC6802-1はトグル・ポーリングまたはレベル・ポーリングのどちらかの方法を使ってA/Dコンバータの状態を送ります。CELL10ビットが“H”であれば、下から10セルの電圧だけが測定されるので、電力消費と測定時間が減少します。既定では、CELL10ビットは“L”であり、全12セルの電圧測定がイネーブルされます。セル電圧測定コマンドの間、フラグ・レジスタ・グループに反映されているUVとOVのフラグ状態も更新されます。測定が完了すると、デバイスはCDCビットで指定されたレートでUVとOVの状態のモニタに戻ります。

### モニタ・モード

MMBピンを“L”に引き下げることにより、シリアル・インターフェースなしの単純なモニタ回路としてLTC6802-1を使用することができます。このモードでは、「シリアル・ポート」のセクションで説明されているトグル・ポーリング・モードを使って、割込み状態がSDOピンに示されます。ただし、シリアル・ポートのポーリング・コマンドとは異なり、トグル機能はCSBIピンの状態には依存しません。図6を参照してください。

MMBピンが“L”的とき、デバイスの構成設定の全ての値が表12に示されている既定状態にリセットします。MMBが“L”に保持されていると、VUV、VOVおよびCDDのレジスタの値は無視されます。代わりに、VUVとVOVは製造時にプログラムされた設定を使います。CDCは状態5に設定されます。モニタされるセルの個数は、表1に示されているように、WDTBピンとGPIOピンのロジックレベルによって設定されます。

## アプリケーション情報

図6. 疎解冗長モニタ回路。これは、一般的なアーキテクチャを示す簡略回路図である。

68021fa

## アプリケーション情報

表1 モニタ・モードのセル選択

| WDTB | GPIO2 | GPIO1 | モニタされるセル入力 |

|------|-------|-------|------------|

| 0    | 0     | 0     | セル1～5      |

| 0    | 0     | 1     | セル1～6      |

| 0    | 1     | 0     | セル1～7      |

| 0    | 1     | 1     | セル1～8      |

| 1    | 0     | 0     | セル1～9      |

| 1    | 0     | 1     | セル1～10     |

| 1    | 1     | 0     | セル1～11     |

| 1    | 1     | 1     | セル1～12     |

MMBが“L”から“H”に引き上げられると、VUV、VOVおよびCDCの各構成設定ビットを含む、デバイスの全ての構成設定値が既定状態にリセットされます。

## シリアル・ポート

概要

LTC6802-1はSPIバス互換のシリアル・ポートを備えています。いくつかのデバイスを直列にデイジーチェーン接続することができます。

ローサイドおよびハイサイドと名付けられた2組のシリアル・ポートのピンがあります。ローサイドとハイサイドのポートにより、デバイスが異なる電源電位で動作するときでも、それらをデイジーチェーン接続することが可能です。標準的構成設定では、図1に示されているように、最初のボトム・デバイスの正電源は2番目の(トップ・デバイス)負電源に接続されます。デバイスがこのようにスタックに構成されていると、ボトム・デバイスのハイサイド・ポートをトップ・デバイスのローサイド・ポートに接続することにより、それらをデイジーチェーン接続することができます。このような構成法では、マスターは、カスケード接続されたデバイスに対して、それらが1つの長いシフトレジスタを形成しているかのように、書き込んだり、読み出したりします。LTC6802-1はローサイド・ポートとハイサイド・ポートの間の信号の電圧レベルを変換し、データをバッテリ・スタックの上下方向に沿って渡します。

## 物理層

LTC6802-1では、7つのピンがローサイドとハイサイドのポートを構成しています。ローサイドのピンはCSBI、SCKI、SDIおよびSDOです。ハイサイドのピンはCSBO、SCKOおよびSDOIです。CSBIとSCKIは常に入力で、マスタによって、またはスタックの中のすぐ下のデバイスによってドライブされます。CSBOとSCKOは常に出力で、スタックの中のすぐ上に位置するデバイスをドライ

するすることができます。SDIはスタックに構成したデバイスに書き込むときのデータ入力です。スタックのボトムではないデバイスでは、スタックから読み出すときSDIはデータ出力です。SDOIはスタックに構成したデバイスに書き込むときはデータ出力で、スタックから読み出すときはデータ入力です。SDOはオープン・ドレイン出力で、スタックのボトム・デバイスでだけ使われます。ここでは、望むなら、それをSDIと接続して1つの双方向ポートを形成することができます。スタックのボトム・デバイスのSDOピンにはプルアップ抵抗が必要です。スタックの上方のデバイスでは、SDOをローカルV<sup>-</sup>に接続するか、フロート状態のままにします。

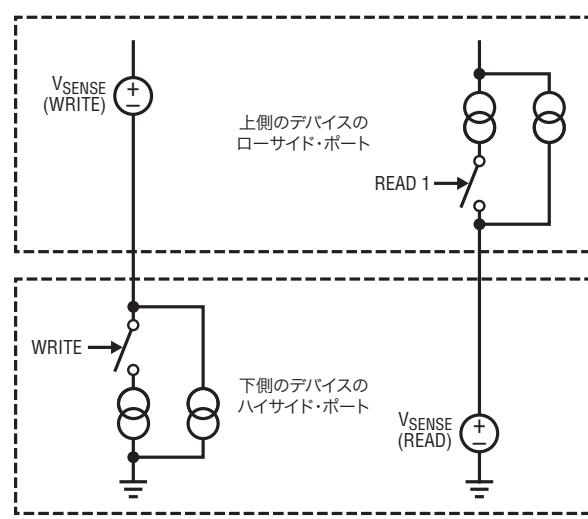

デイジーチェーン接続されたデバイスの間で通信するため、下側のデバイスのハイサイド・ポート・ピン(CSBO、SCKOおよびSDOI)を、PN接合ダイオードを通して、すぐ上のデバイスのそれぞれのローサイド・ポート・ピン(CSBI、SCKIおよびSDI)に接続する必要があります。この構成設定では、デバイスは電圧ではなく電流を使って通信します。下側のデバイスから上側のデバイスにロジック“H”的信号を送るには、下側のデバイスは上側のデバイスのピンから小さな電流をシンクします。ロジック“L”的信号を送るには、下側のデバイスは大きな電流をシンクします。同様に上側のデバイスから下側のデバイスにロジック“H”的信号を送るには、上側のデバイスは下側のデバイスのピンに大きな電流をソースします。ロジック“L”的信号を送るには、上側のデバイスは小さな電流をソースします。図7を参照してください。

電流モード・シリアル・インターフェースで消費されるスタンバイ電流は、CSBI、SCKIおよびSDIが全て“H”的とき最小化されます。

図7 電流モード・インターフェース

## アプリケーション情報

電圧モード・ピン(V MODE)は、ローサイド・シリアル・ポートが電圧モードで構成設定されるか電流モードで構成設定されるかを決定します。デイジーチェーン・スタックのボトム・デバイスでは、このピンを“H”に引き上げる(V REGに接続する)必要があります。デイジーチェーンの他のデバイスでは、このピンを“L”に引き下げて(V-に接続して)、電流モード通信を指定する必要があります。ポーリング・コマンドのトップオブスタック(スタック最上位)デバイスを指定するには、デイジーチェーンのトップ・デバイスのTOSピンを“H”に接続する必要があります。スタック内の他のデバイスはTOSを“L”にする必要があります。図1を参照してください。

### データリンク層

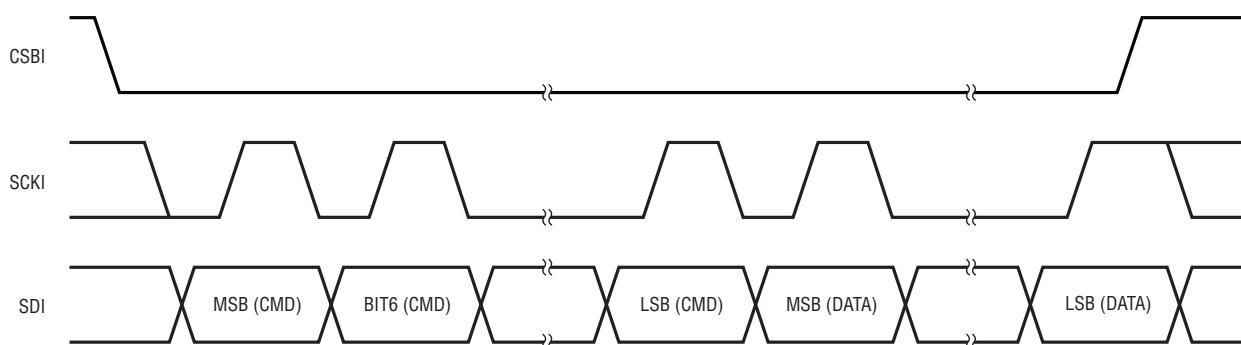

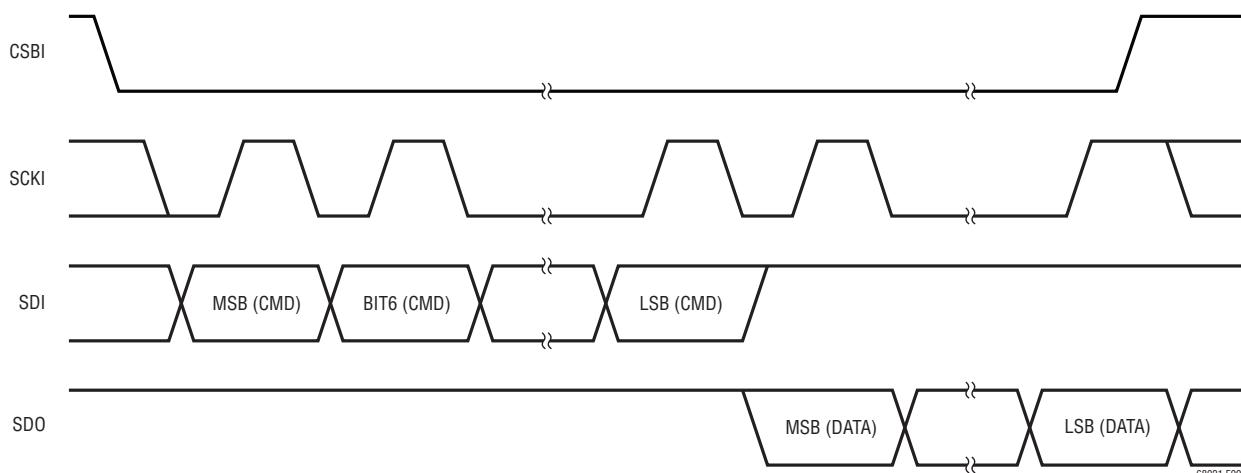

**クロックの位相と極性:** LTC6802-1のSPI互換インターフェースは、CPHA=1およびCPOL=1を使ったシステムで動作するように構成設定されます。したがって、SDIのデータはSCKIの立上がりエッジの間安定している必要があります。

**データ転送:** 各バイトは8ビットで構成されます。バイトは最上位ビット(MSB)から先に送られます。書込みでは、SDIのデータの値がSCKIの立上がりエッジでデバイスにラッチされます(図8を参照)。同様に、読み出しがSDOに出力されるデータの値はSCKIの立上がりエッジの間有効で、SCKIの立下りエッジで遷移します(図9を参照)。

CSBIはコマンド・バイトとそれに続くデータの間を含むコマンド・シーケンスの全期間“L”に留まる必要があります。書込みコマンドでは、データはCSBIの立上がりエッジでラッチされます。

ポーリング・コマンドが与えられた後、SDO出力は直ちにポーリング状態によってドライブされ、SCKI入力は無視されます(図10を参照)。「トグル・ポーリング」と「レベル・ポーリング」のセクションを参照してください。

図8. 転送形式(書き込み)

図9. 転送形式(読み出し)

68021fa

## アプリケーション情報

図10. 転送形式(ポーリング)

### ネットワーク層

**ブロードキャスト・コマンド:**ブロードキャスト・コマンドは、バス上の全デバイスが応答するコマンドです。「バス・プロトコルとコマンド」のセクションを参照してください。

デイジーチェーン接続された構成設定では、チェーン内の全デバイスがコマンド・バイトを同時に受け取ります。たとえば、スタック構成のデバイスでA/D変換を開始するには、1つのSTCVADコマンド・バイトを送ると、全デバイスが同時に変換を開始します。読み出しと書き込みのコマンドでは、1つのコマンド・バイトが送られ、次いでスタック構成のデバイスが実効的にカスケード接続されたシフトレジスタになり、データが各デバイスを通してスタック内で上に隣接する(書き込みの場合)または下に隣接する(読み出しの場合)デバイスにシフトされます。「シリアル・コマンドの例」のセクションを参照してください。

**PECバイト:**パケット・エラー・コード(PEC)バイトは、レジスタ・グループ内の全ビットに対して、それらが読み出される順に、次の特性多項式を使って計算されたCRC値です。

$$x^8 + x^2 + x + 1$$

読み出しこマンドでは、レジスタ・グループの最後のバイトが送られた後、デバイスは計算されたPECを、MSBを先頭にしてシフトして出力します。デイジーチェーン接続されたデバイスでは、PECが最初のデバイスから読み出された後、デイジーチェーン接続されたどのデバイスからのデータも同じ順序で続きます。たとえば、2個のスタック構成のデバイス(ボトム・デバイスAとトップ・デバイスB)からのフラグ・レジスタを読み出すとき、データは次の順序で出力されます。

FLGR0(A)、FLGR1(A)、FLGR2(A)、PEC(A)、FLGR0(B)、

FLGR1(B)、FLGR2(B)、PEC(B)

**トグル・ポーリング:**トグル・ポーリングにより、デバイスの状態とスタック内のデバイス間の接続状態の両方を確実に決定することができます。トグル・ポーリングはLVLPLビットが“L”的ときイネーブルされます。ポーリング・コマンドが与えられた後、データ出力ラインはそれらの状態に基づいてスレーブ・デバイスによりドライブされます。A/Dコンバータの状態についてポーリングすると、デバイスのどれかがA/D変換の実行中でビジーのときはデータ出力が“L”になり、どのデバイスも実行中でなくビジーでないときは1kHzでトグルします。同様に、割込み状態についてポーリングすると、デバイスのどれかが割込み状態のときは出力が“L”になり、どれも割込み状態でないときは1kHzでトグルします。

**トグル・ポーリング-デイジーチェーン接続されたブロードキャスト・ポーリング:**SDOピン(ボトム・デバイス)またはSDIピン(スタック構成されたデバイス)は、デバイスがビジー/割込み状態であれば“L”になります。ビジーでもなく、割込み状態でもない場合、デバイスはSDOI入力からの信号をデータ出力に渡すか(スタックのトップのデバイスではない場合)、またはデータ出力ラインを1kHzでトグルします(スタックのトップのデバイスの場合)。

マスターはCSBIを“H”に引き上げてポーリングを終了します。

**レベル・ポーリング:**レベル・ポーリングはLVLPLビットが“H”的ときイネーブルされます。ポーリング・コマンドが与えられた後、データ出力ラインはそれらの状態に基づいてスレーブ・デバイスによりドライブされます。

## アプリケーション情報

A/Dコンバータの状態についてポーリングすると、デバイスのどれかがA/D変換の実行中でビジーのときはデータ出力が“L”になり、どのデバイスも実行中でなくビジーでないときは“H”になります。同様に、割込み状態についてポーリングすると、デバイスのどれかが割込み状態のときは出力が“L”になり、どれも割込み状態でないときは“H”になります。

**レベル・ポーリング・デイジーチェーン接続されたブロードキャスト・ポーリング:** SDOピン(ボトム・デバイス)またはSDIピン(スタック構成されたデバイス)は、デバイスがビジー/割込み状態であれば“L”になります。ビジーでもなく、割込み状態でもない場合、デバイスはSDOI入力からのレベルをデータ出力に渡すか(スタックのトップのデバイスではない場合)、またはデータ出力ラインを“H”に保持します(スタックのトップのデバイスの場合)。したがって、チェーン内のデバイスのどれかがビジーまたは割込み状態だと、スタックのボトムのSDO信号は“L”になります。全デバイスがビジー状態でもなく、割込み状態でもないと、スタックのボトムのSDO信号は“H”になります。

マスタはCSBIを“H”に引き上げてポーリングを終了します。

表2. プロトコルのキー

|          |                     |  |            |

|----------|---------------------|--|------------|

| PEC      | パケット・エラー・コード(CRC-8) |  | マスタ/スレーブ動作 |

| <i>N</i> | ビット数                |  | スレーブからマスタ  |

| ...      | プロトコルの続き            |  | データの完全なバイト |

表3. ブロードキャスト・ポーリング・コマンド

|   |      |           |

|---|------|-----------|

| 8 | コマンド | ポーリング・データ |

|---|------|-----------|

表4. ブロードキャスト読み取り

|      |            |     |            |     |          |     |                  |

|------|------------|-----|------------|-----|----------|-----|------------------|

| 8    | 8          | ... | 8          | 8   | 8        | ... | 8                |

| コマンド | データ・バイト・ロー | ... | データ・バイト・ハイ | PEC | シフト・バイト1 | ... | シフト・バイト <i>N</i> |

表5. ブロードキャスト書き込み

|      |            |     |            |          |     |                  |

|------|------------|-----|------------|----------|-----|------------------|

| 8    | 8          | ... | 8          | 8        | ... | 8                |

| コマンド | データ・バイト・ロー | ... | データ・バイト・ハイ | シフト・バイト1 | ... | シフト・バイト <i>N</i> |

## アプリケーション情報

## コマンド

表6. コマンドのコード

|                                 |         |                                                                                                                                                                                                                 |

|---------------------------------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 構成設定レジスタ・グループへの書込み              | WRCFG   | 0x01                                                                                                                                                                                                            |

| 構成設定レジスタ・グループからの読み出し            | RDCFG   | 0x02                                                                                                                                                                                                            |

| セル電圧レジスタ・グループからの読み出し            | RDCV    | 0x04                                                                                                                                                                                                            |

| フラグ・レジスタ・グループからの読み出し            | RDFLG   | 0x06                                                                                                                                                                                                            |

| 温度レジスタ・グループからの読み出し              | RDTMP   | 0x08                                                                                                                                                                                                            |

| セル電圧のA/D変換の開始と状態のポーリング          | STCVAD  | 0x10(全てのセル電圧入力)<br>0x11(セル1のみ)<br>0x12(セル2のみ)<br>...<br>0x1A(セル10のみ)<br>0x1B(セル11のみ、CELL10ビット=0の場合)<br>0x1C(セル12のみ、CELL10ビット=0の場合)<br>0x1D(未使用)<br>0x1E(セルの自己テスト1; 全てCV=0x555)<br>0x1F(セルの自己テスト2; 全てCV=0xAAA)   |

| オープンワイヤのA/D変換の開始と状態のポーリング       | STOWAD  | 0x20(全てのセル電圧入力)<br>0x21(セル1のみ)<br>0x22(セル2のみ)<br>...<br>0x2A(セル10のみ)<br>0x2B(セル11のみ、CELL10ビット=0の場合)<br>0x2C(セル12のみ、CELL10ビット=0の場合)<br>0x2D(未使用)<br>0x2E(セルの自己テスト1; 全てCV=0x555)<br>0x2F(セルの自己テスト2; 全てCV=0xAAA)   |

| 温度のA/D変換の開始と状態のポーリング            | STTMPAD | 0x30(全ての温度入力)<br>0x31(外部温度1のみ)<br>0x32(外部温度2のみ)<br>0x33(内部温度のみ)<br>0x34—0x3D(未使用)<br>0x3E(温度の自己テスト1; 全てのTMP=0x555)<br>0x3F(温度の自己テスト2; 全てのTMP=0xAAA)                                                             |

| A/D コンバータの状態のポーリング              | PLADC   | 0x40                                                                                                                                                                                                            |

| 割込み状態のポーリング                     | PLINT   | 0x50                                                                                                                                                                                                            |

| セル電圧のA/D変換の開始と状態のポーリング、放電を許可    | STCVDC  | 0x60(全てのセル電圧入力)<br>0x61(セル1のみ)<br>0x62(セル2のみ)<br>...<br>0x6A(セル10のみ)<br>0x6B(セル11のみ、CELL10ビット=0の場合)<br>0x6C(セル12のみ、CELL10ビット=0の場合)<br>0x6D(未使用)<br>0x6E(セルの自己テスト1; 全てCV=0x555)<br>0x6F(セルの自己テスト2; 全てCV=0xAAA)   |

| オープンワイヤのA/D変換の開始と状態のポーリング、放電を許可 | STOWDC  | 0x70(全てのセル電圧入力)<br>0x71(セル1のみ)<br>0x72(セル2のみ)<br>...<br>0x7A(セル10のみ)<br>0x7B(セル11のみ、CELL10ビット=0の場合)<br>0x7C(セル12のみ、CELL10ビット=0の場合)<br>0x7D(未使用)<br>0x7E(セルの自己テスト1; 全てのCV=0x555)<br>0x7F(セルの自己テスト2; 全てのCV=0xAAA) |

## アプリケーション情報

### メモリ・マップ

LTC6802-1のメモリ・マップを表7～表12に示します。表12にはビットの説明が与えられています。

表7. 構成設定(CFG)レジスタ・グループ

| REGISTER | RD/WR | BIT 7  | BIT 6  | BIT 5  | BIT 4  | BIT 3  | BIT 2  | BIT 1  | BIT 0  |

|----------|-------|--------|--------|--------|--------|--------|--------|--------|--------|

| CFGRO    | RD/WR | WDT    | GPIO2  | GPIO1  | LVLPL  | CELL10 | CDC[2] | CDC[1] | CDC[0] |

| CFGRI    | RD/WR | DCC8   | DCC7   | DCC6   | DCC5   | DCC4   | DCC3   | DCC2   | DCC1   |

| CFGRII   | RD/WR | MC4I   | MC3I   | MC2I   | MC1I   | DCC12  | DCC11  | DCC10  | DCC9   |

| CFGRIII  | RD/WR | MC12I  | MC11I  | MC10I  | MC9I   | MC8I   | MC7I   | MC6I   | MC5I   |

| CFGRIV   | RD/WR | VUV[7] | VUV[6] | VUV[5] | VUV[4] | VUV[3] | VUV[2] | VUV[1] | VUV[0] |

| CFGRIV   | RD/WR | VOV[7] | VOV[6] | VOV[5] | VOV[4] | VOV[3] | VOV[2] | VOV[1] | VOV[0] |

表8. セル電圧(CV)レジスタ・グループ

| REGISTER | RD/WR | BIT 7    | BIT 6    | BIT 5   | BIT 4   | BIT 3    | BIT 2    | BIT 1   | BIT 0   |

|----------|-------|----------|----------|---------|---------|----------|----------|---------|---------|

| CVR00    | RD    | C1V[7]   | C1V[6]   | C1V[5]  | C1V[4]  | C1V[3]   | C1V[2]   | C1V[1]  | C1V[0]  |

| CVR01    | RD    | C2V[3]   | C2V[2]   | C2V[1]  | C2V[0]  | C1V[11]  | C1V[10]  | C1V[9]  | C1V[8]  |

| CVR02    | RD    | C2V[11]  | C2V[10]  | C2V[9]  | C2V[8]  | C2V[7]   | C2V[6]   | C2V[5]  | C2V[4]  |

| CVR03    | RD    | C3V[7]   | C3V[6]   | C3V[5]  | C3V[4]  | C3V[3]   | C3V[2]   | C3V[1]  | C3V[0]  |

| CVR04    | RD    | C4V[3]   | C4V[2]   | C4V[1]  | C4V[0]  | C3V[11]  | C3V[10]  | C3V[9]  | C3V[8]  |

| CVR05    | RD    | C4V[11]  | C4V[10]  | C4V[9]  | C4V[8]  | C4V[7]   | C4V[6]   | C4V[5]  | C4V[4]  |

| CVR06    | RD    | C5V[7]   | C5V[6]   | C5V[5]  | C5V[4]  | C5V[3]   | C5V[2]   | C5V[1]  | C5V[0]  |

| CVR07    | RD    | C6V[3]   | C6V[2]   | C6V[1]  | C6V[0]  | C5V[11]  | C5V[10]  | C5V[9]  | C5V[8]  |

| CVR08    | RD    | C6V[11]  | C6V[10]  | C6V[9]  | C6V[8]  | C6V[7]   | C6V[6]   | C6V[5]  | C6V[4]  |

| CVR09    | RD    | C7V[7]   | C7V[6]   | C7V[5]  | C7V[4]  | C7V[3]   | C7V[2]   | C7V[1]  | C7V[0]  |

| CVR10    | RD    | C8V[3]   | C8V[2]   | C8V[1]  | C8V[0]  | C7V[11]  | C7V[10]  | C7V[9]  | C7V[8]  |

| CVR11    | RD    | C8V[11]  | C8V[10]  | C8V[9]  | C8V[8]  | C8V[7]   | C8V[6]   | C8V[5]  | C8V[4]  |

| CVR12    | RD    | C9V[7]   | C9V[6]   | C9V[5]  | C9V[4]  | C9V[3]   | C9V[2]   | C9V[1]  | C9V[0]  |

| CVR13    | RD    | C10V[3]  | C10V[2]  | C10V[1] | C10V[0] | C9V[11]  | C9V[10]  | C9V[9]  | C9V[8]  |

| CVR14    | RD    | C10V[11] | C10V[10] | C10V[9] | C10V[8] | C10V[7]  | C10V[6]  | C10V[5] | C10V[4] |

| CVR15*   | RD    | C11V[7]  | C11V[6]  | C11V[5] | C11V[4] | C11V[3]  | C11V[2]  | C11V[1] | C11V[0] |

| CVR16*   | RD    | C12V[3]  | C12V[2]  | C12V[1] | C12V[0] | C11V[11] | C11V[10] | C11V[9] | C11V[8] |

| CVR17*   | RD    | C12V[11] | C12V[10] | C12V[9] | C12V[8] | C12V[7]  | C12V[6]  | C12V[5] | C12V[4] |

\*レジスタCVR15、CVR16およびCVR17は、レジスタCFGROのCELL10ビットが”L”の場合だけ読み出すことができます。

## アプリケーション情報

表9. フラグ(FLG)レジスタ・グループ

| REGISTER | RD/WR | BIT 7  | BIT 6  | BIT 5  | BIT 4  | BIT 3 | BIT 2 | BIT 1 | BIT 0 |

|----------|-------|--------|--------|--------|--------|-------|-------|-------|-------|

| FLGR0    | RD    | C40V   | C4UV   | C30V   | C3UV   | C20V  | C2UV  | C10V  | C1UV  |

| FLGR1    | RD    | C80V   | C8UV   | C70V   | C7UV   | C60V  | C6UV  | C50V  | C5UV  |

| FLGR2    | RD    | C120V* | C12UV* | C110V* | C11UV* | C100V | C10UV | C90V  | C9UV  |

\*レジスタCFGROのCELL10ビットが”H”だと、ビットC11UV、C12UV、C110VおよびC120Vは常に”L”です。

表10. 温度(TMP)レジスタ・グループ

| REGISTER | RD/WR | BIT 7     | BIT 6     | BIT 5    | BIT 4    | BIT 3     | BIT 2     | BIT 1    | BIT 0    |

|----------|-------|-----------|-----------|----------|----------|-----------|-----------|----------|----------|

| TMPR0    | RD    | ETMP1[7]  | ETMP1[6]  | ETMP1[5] | ETMP1[4] | ETMP1[3]  | ETMP1[2]  | ETMP1[1] | ETMP1[0] |

| TMPR1    | RD    | ETMP2[3]  | ETMP2[2]  | ETMP2[1] | ETMP2[0] | ETMP2[11] | ETMP2[10] | ETMP2[9] | ETMP2[8] |

| TMPR2    | RD    | ETMP2[11] | ETMP2[10] | ETMP2[9] | ETMP2[8] | ETMP2[7]  | ETMP2[6]  | ETMP2[5] | ETMP2[4] |

| TMPR3    | RD    | ITMP[7]   | ITMP[6]   | ITMP[5]  | ITMP[4]  | ITMP[3]   | ITMP[2]   | ITMP[1]  | ITMP[0]  |

| TMPR4    | RD    | REV[2]    | REV[1]    | REV[0]   | THSD     | ITMP[11]  | ITMP[10]  | ITMP[9]  | ITMP[8]  |

表11. パケット・エラー・コード(PEC)

| REGISTER | RD/WR | BIT 7  | BIT 6  | BIT 5  | BIT 4  | BIT 3  | BIT 2  | BIT 1  | BIT 0  |

|----------|-------|--------|--------|--------|--------|--------|--------|--------|--------|

| PEC      | RD    | PEC[7] | PEC[6] | PEC[5] | PEC[4] | PEC[3] | PEC[2] | PEC[1] | PEC[0] |

## アプリケーション情報

表12. メモリ・ビットの説明

| 名称                          | 説明                | 値                                                                                             |                             |                               |          |

|-----------------------------|-------------------|-----------------------------------------------------------------------------------------------|-----------------------------|-------------------------------|----------|

| CDC                         | コンパレータのデューティ・サイクル | CDC                                                                                           | UV/OVコンパレータ時間               | 測定と測定との間<br>$V_{REF}$ はパワーダウン | セル電圧測定時間 |

|                             |                   | 0<br>(default)                                                                                | N/A(コンパレータはオフ)<br>スタンバイ・モード | Yes                           | N/A      |

|                             |                   | 1                                                                                             | N/A(コンパレータはオフ)              | No                            | 13ms     |

|                             |                   | 2                                                                                             | 13ms                        | No                            | 13ms     |

|                             |                   | 3                                                                                             | 130ms                       | No                            | 13ms     |

|                             |                   | 4                                                                                             | 500ms                       | No                            | 13ms     |

|                             |                   | 5*                                                                                            | 130ms                       | Yes                           | 21ms     |

|                             |                   | 6                                                                                             | 500ms                       | Yes                           | 21ms     |

|                             |                   | 7                                                                                             | 2000ms                      | Yes                           | 21ms     |

| *MMBピンが“L”的とき、CDCの値は5に設定される |                   |                                                                                               |                             |                               |          |

| CELL10                      | 10セル・モード          | 0=12セル・モード(既定); 1=10セル・モード                                                                    |                             |                               |          |

| LVLPL                       | レベル・ポーリング・モード     | 0=トグル・ポーリング(既定); 1=レベル・ポーリング                                                                  |                             |                               |          |

| GPIO1                       | GPIO1ピンの制御        | 書込み: 0=GPIO1ピンのプルダウンをオン; 1=GPIO1ピンのプルダウンをオフ(既定)<br>読み出し: 0=GPIO1ピンをロジック'0'; 1=GPIO1ピンをロジック'1' |                             |                               |          |

| GPIO2                       | GPIO2ピンの制御        | 書込み: 0=GPIO2ピンのプルダウンをオン; 1=GPIO2ピンのプルダウンをオフ(既定)<br>読み出し: 0=GPIO2ピンをロジック'0'; 1=GPIO2ピンをロジック'1' |                             |                               |          |

| WDT                         | ウォッチドッグ・タイマ       | 読み出しのみ: 0=WDTBピンをロジック'0'; 1=WDTBピンをロジック'1'                                                    |                             |                               |          |

| DCCx                        | Cell xの放電         | x=1..12 0=セル'x'の短絡スイッチをオフ(既定); 1=短絡スイッチをオン                                                    |                             |                               |          |

| VUV                         | 低電圧比較電圧*          | 比較電圧 = VUV * 16 * 1.5mV<br>(既定でVUV=0。MMBピンが“L”的とき、製造時にプログラムされた比較電圧が使われる)                      |                             |                               |          |

| VOV                         | 過電圧比較電圧*          | 比較電圧 = VOV * 16 * 1.5mV<br>(既定でVOV=0。MMBピンが“L”的とき、製造時にプログラムされた比較電圧が使われる)                      |                             |                               |          |

| MCxI                        | Cell xの割込みのマスク    | x=1..12 0=セル'x'の割込みをイネーブル(既定)<br>1=セル'x'の割込みをオフし、フラグをクリアする                                    |                             |                               |          |

| CxV                         | Cell xの電圧*        | x=1..12 セル'x'の12ビットADCの測定値<br>セル'x'のセル電圧 = CxV * 1.5mV<br>A/D変換の進行中に0xFFFFとして読み出し             |                             |                               |          |

| CxUV                        | Cell xの低電圧フラグ     | x=1..12 VUV比較電圧と比較されたセル電圧<br>0=セル'x'は低電圧状態のフラグが発生しない; 1=セル'x'はフラグが発生                          |                             |                               |          |

| CxOV                        | Cell xの過電圧フラグ     | x=1..12 VOV比較電圧と比較されたセル電圧<br>0=セル'x'は過電圧状態のフラグが発生しない; 1=セル'x'はフラグが発生                          |                             |                               |          |

| ETMPx                       | 外部温度測定*           | 温度測定電圧 = ETMPx * 1.5mV                                                                        |                             |                               |          |

| THSD                        | サーマル・シャットダウン状態    | 0= サーマル・シャットダウンは起きていない; 1= サーマル・シャットダウンが起きている<br>サーマル・レジスタ・グループの読み出しで状態が'0'にクリア               |                             |                               |          |

| REV                         | リビジョン・コード         | デバイスのリビジョン・コード                                                                                |                             |                               |          |

| ITMP                        | 内部温度測定*           | 温度測定電圧 = ITMP * 1.5mV = 8mV * T(°K)                                                           |                             |                               |          |

| PEC                         | パケット・エラー・コード      | 読み出しのCRCの値                                                                                    |                             |                               |          |

\*電圧の決定にはレジスタの10進数(12ビットでは0~4095、8ビット・レジスタでは0~255)を使う

## アプリケーション情報

### シリアル・コマンドの例

#### LTC6802-1(デイジーチェーン構成設定)

以下の例ではスタック構成された3つのデバイスの構成設定を使います。ボトム(B)、ミドル(M)およびトップ(T)です。

##### 構成設定レジスタへの書き込み

1. CSBIを“L”に引き下げる

2. WRCFGコマンド・バイトを送る

3. トップ・デバイスのCFGR0バイトを送ってから、CFGR1 (T)、CFGR2 (T)、… CFGR5 (T)を送る

4. ミドル・デバイスのCFGR0バイトを送ってから、CFGR1 (M)、CFGR2 (M)、… CFGR5 (M)を送る

5. ボトム・デバイスのCFGR0バイトを送ってから、CFGR1 (B)、CFGR2 (B)、… CFGR5 (B)を送る

6. CSBIを“H”に引き上げる；データはCSBIの立上りエッジで全デバイスにラッピングされる

上のシーケンスのシリアル・インターフェースの時間の計算：

スタック内のデバイスの個数=N

シーケンスのバイト数=B=1コマンド・バイトとデバイス当たり6データ・バイト=1+6\*N

ビット当たりのシリアル・ポートの周波数=F

時間=(1/F)\*B\*8ビット/バイト=(1/F)\*(1+6\*N)\*8

3セル・スタックの上の例の1MHzシリアル・ポートの時間=(1/1000000)\*(1+6\*3)\*8=152us

##### セル電圧レジスタからの読み出し(12セル・モード)

1. CSBIを“L”に引き下げる

2. RDCVコマンド・バイトを送る

3. ボトム・デバイスのCVR00バイトを読み出してから、CVR01 (B)、CVR02 (B)、… CVR17 (B)、次いでPEC (B)

4. ミドル・デバイスのCVR00バイトを読み出してから、CVR01 (M)、CVR02 (M)、… CVR17 (M)、次いでPEC (M)

5. トップ・デバイスのCVR00バイトを読み出してから、CVR01 (T)、CVR02 (T)、… CVR17 (T)、次いでPEC (T)

6. CSBIを“H”に引き下げる

上のシーケンスのシリアル・インターフェースの時間の計算：

スタック内のデバイスの個数=N

シーケンスのバイト数=B=1コマンド・バイトとデバイス当たり18データ・バイトおよび1PEC=1+19\*N

ビット当たりのシリアル・ポートの周波数=F

時間=(1/F)\*B\*8ビット/バイト=(1/F)\*(1+19\*N)\*8

上の3セルの例の1MHzシリアル・ポートの時間=(1/1000000)\*(1+19\*3)\*8=464us

##### セル電圧のA/D変換の開始と状態のポーリング(トグル・ポーリング)

1. CSBIを“L”に引き下げる

2. STCVADコマンド・バイトを送る(スタック内の全デバイスが同時にA/D変換を開始)

3. ボトム・デバイスからのSDO出力は約12msの間“L”に引き下げられる

4. SDO出力は1kHzのレートでトグルし、デイジーチェーン内の全デバイスで変換が完了したことを示す

5. CSBIを“H”に引き上げてポーリングを終了

## アプリケーション情報

### 割込み状態のポーリング(レベル・ポーリング)

1. CSBIを“L”に引き下げる

2. PLINTコマンド・バイトを送る

3. デバイスのどれかが割込み状態であればボトム・デバイスからのSDOは“L”に引き下げられる;それ以外、SDOは“H”

4. CSBIを“H”に引き上げてポーリングを終了

## フォールト保護

### 概要

バッテリなど高エネルギー源を使う場合は常に注意を要します。システムが「誤って」構成され、バッテリ・システムの動作寿命期間を通じてバッテリ・システムに影響を与える可能性があるような様々な状況が存在します。保護回路を立案する際に検討すべき様々な状況を表13に示します。最初の5つのシナリ

オは製造時に予想されるケースで、適切な保護がLTC6802-1デバイス自体に組み込まれています。保護回路を計画するとき検討すべき様々な状況を表13に示します。最初の5つのシナリオは製造時に予想され、適切な保護がLTC6802-1のデバイス自体に内蔵されています。

表13. LTC6802-1の故障メカニズムの影響分析

| 状況                                           | 影響                                                                                                    | 設計による緩和                                                                                                                                      |

|----------------------------------------------|-------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| セル入力のオープン回路(偶発)                              | IC入力のパワーアップ・シーケンス                                                                                     | 各ピンからV <sup>+</sup> およびV <sup>-</sup> へのクランプ・ダイオード(IC内部)が代わりの電力経路を与える。                                                                       |

| セル入力のオープン回路(偶発)                              | 差動入力電圧のオーバーストレス                                                                                       | 各セル電圧入力対のツェナー・ダイオード(IC内部)がストレスを制限する。                                                                                                         |

| トップ・セル入力接続なし(V <sup>+</sup> )                | 電力は最上位に接続されたセルの入力からまたはデータ・ポートのフォールト電流を介して与えられる                                                        | 各ピンからV <sup>+</sup> およびV <sup>-</sup> へのクランプ・ダイオード(IC内部)が代わりの電力経路を与える。データ・ポートでのダイオードの導通は電位がもっと高いユニットとの通信を阻害する。                               |

| ボトム・セル入力接続なし(V <sup>-</sup> )                | 電力は最下位に接続されたセルの入力からまたはデータ・ポートのフォールト電流を介して与えられる                                                        | 各ピンからV <sup>+</sup> およびV <sup>-</sup> へのクランプ・ダイオード(IC内部)が代わりの電力経路を与える。データ・ポートでのダイオードの導通は電位がもっと高いユニットとの通信を阻害する。                               |

| バッテリ・セル・グループとICの間のハーネスの切断(スタック構成のグループのシステム内) | ICへの電源接続の喪失                                                                                           | LTC6802-1に接続された(電力を供給できる)他のデバイスがあると、各ピンからV <sup>+</sup> およびV <sup>-</sup> へのクランプ・ダイオードが代わりの電源経路を与える。データ・ポートでのダイオードの導通は電位がもっと高いユニットとの通信を阻害する。 |

| スタック構成のLTC6802-1ユニット間のデータリンクの切断              | 「デイジーチェーン」通信の途絶(ICへのストレスなし)。切断箇所より上のデバイスへの通信が途絶える。切断箇所より下のデバイスは依然通信可能で、全機能が実行されるが、ポーリング機能がディスエーブルされる。 | ウォッチドッグ・タイマがイネーブルされていると、切断箇所より上の全ユニットが切断から2秒以内にスタンバイ・モードに入る。スタンバイ・モードでは放電スイッチはディスエーブルされる。                                                    |

| セル・パックの完全性、スタック構成のユニット間の切断                   | パック放電時にデイジーチェーン電圧が最大スタック電位に反転                                                                         | 直列保護ダイオードをトップ・ポートI/O整合と一緒に使う(600VまではRS07J)。最下位のデータ・ポートには絶縁されたデータリンクを使う。                                                                      |

| セル・パックの完全性、スタック構成のユニット間の切断                   | 充電時にデイジーチェーンの正オーバーストレス                                                                                | 冗長電流経路接続を追加する。                                                                                                                               |

| セル・パックの完全性、スタック・ユニット内の切断                     | 放電時にセル入力の反転オーバーストレス                                                                                   | 負荷経路の冗長性のため各セル両端に並列ショットキー・ダイオードを追加する。ダイオードと接続はスタックの最大動作電流を扱う必要があり、ICへのストレスを制限する。                                                             |

| セル・パックの完全性、スタック・ユニット内の切断                     | 充電時にセル入力の正オーバーストレス                                                                                    | 充電経路の冗長性のため各セル両端にSCRを追加する。SCRと接続はスタックの最大充電電流を扱う必要があり、トリガ・ツェナー・ダイオードの選択によりICへのストレスを制限する。                                                      |

## アプリケーション情報

### バッテリの相互配線の完全性

最も損傷を与える可能性のあるFMEAのシナリオは、スタック構成のバッテリ・セルの切断を含むものです。LTC6802-1デバイスによってモニタされるセルのグループ間に切断があるバッテリ・スタックの場合、どんな負荷も大きな逆電位をデイジーチェーン接続に強制します。この状況はバッテリ・モジュール・システムの最初のインストールまたはサービス作業中に起きる可能性があります。このシナリオでは、図11に示されているように、上方ポートのデータ接続に必要な外部直列高電圧ダイオードによって、デイジーチェーンのポートは逆電位から保護されます。

充電フェーズの動作の間、このフォールトによりデイジーチェーンのESDクランプが順方向にバイアスされ、これによりデバイスの損傷が生じます。このシナリオの間電流を流す代替接続は、このストレスが加わるのを防ぎます(図11)。

図11. デイジーチェーンの逆電圧保護

(1つのリンク接続が示されている)

### 内部保護ダイオード

LTC6802-1の各ピンは保護ダイオードを備えており、図12に示されているように、電源レールを超える電圧の外部からの印加によって生じる内部デバイス構造への損傷を防ぐのに役立ちます。

示されているダイオードは、順方向ブレークダウン電圧が0.5Vの通常のシリコン・ダイオードです。ラベルの付いていないツェナー・ダイオード構造は、最初12Vでブレークダウンし、次いで7Vのクランプ電位にスナップバックする逆ブレークダウン特

性を有しています。ZCLAMPとラベルが付けてあるツェナー・ダイオードはもっと高い電圧のデバイスで、最初の逆ブレークダウンが30Vで、25Vにスナップバックします。全てのツェナー・ダイオードの順方向電圧降下は0.5Vです。予測できない電圧クランプや電流が生じた場合、この図を参照してください。どのピンの電流も±10mAに制限するとICへの損傷を防ぎます。

図12. 内部保護ダイオード

## アプリケーション情報

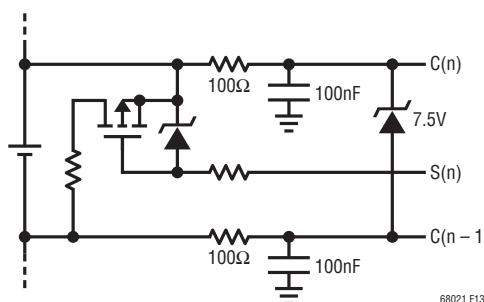

### セル電圧のフィルタ処理

LTC6802-1はA/D変換を行うサンプリング・システムを採用しており、512kHzのデルタシグマ変調器を基準にしたノイズ・エイリアシングがない限り、基本的に0.5msの変換ウィンドウの平均である変換結果を与えます。これは、500kHzで有効に減衰するローパスフィルタが役立つことを示しています。デルタシグマ積分帯域幅は約1kHzなので、精確な変換を確実にするためにフィルタのコーナー周波数をこれより低くする必要はありません。

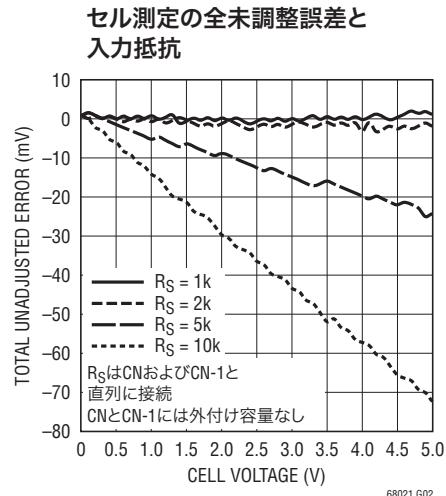

外部放電スイッチ用FETだけを使用する限り、有意味な測定誤差を生じることなく100Ωの直列抵抗を入力経路に挿入することができます。図13に示されているように、シャント・コンデンサをセル入力からV-に追加して、RCフィルタを作ることができます。このフィルタ方式は、ケルビン・モードのセル検出のためどのアクティブなスイッチも一時にオープンするので、変換時にセトリング誤差を生じるため、電流を担う内部放電スイッチの使用に適応しないことに注意してください。放電スイッチが開くとき、セル配線抵抗も小さな電圧ステップを生じるので、(小さなIR電圧降下からの回復)、フィルタのカットオフ周波数を比較的高く保つと、実際の変換の前に適当なセトリングが可能になります。約60μsのガード時間がADCのタイミングに与えられているので、16kHzのLPは最適で、約30dBのノイズ除去を与えます。

V-ピンには直列に抵抗を接続しません。消費電流はV-ピンから流れるので、このピンのどんな抵抗もCELL1にかなりの変換誤差を生じます。

図13. セル入力へのRCフィルタの追加

(1セルの接続が示されている)

V<sup>+</sup>ピンには、モニタされるセル群のトップのセルの電位から電力が供給されます。20Ω/100nFのデカップリング・ネットワークが推奨されます。

### 外部温度プローブの読み取り

### 専用入力の利用

LTC6802-1は2チャネルのADC入力(VTEMP1とVTEMP2)を備えており、セル・アレイ内に配置されたサーミスタ(温度係数が一般に-4%/°C)またはダイオード(標準-2.2mV/°C)をモニタすることを意図しています。図14に示されているように、センサーには直接V<sub>REF</sub>から給電することができます(最大60μA)。

高いドライブ電流を必要とするセンサーには、図15に示されているように、バッファ・オペアンプを使うことができます。この場合、センサーの電力は実際にはV<sub>REG</sub>ピンから間接的にソースされます。

図14. サーミスタをV<sub>REF</sub>から直接ドライブ

図15. 高電流センサーのためにV<sub>REF</sub>をバッファ

## アプリケーション情報

プローブの最大約1mAの負荷はこの構成設定でサポートされます。LTC6802-1のアイドル・モードとシャットダウン・モードの間V<sub>REF</sub>はシャットダウンするので、サーミスタのドライブもオフし、電力損失が最小になります。V<sub>REG</sub>は常にオンのままなので、電力消費が極めて低い(10 $\mu$ A)バッファ・オペアンプ(LT6000が示されています)が選択されています。

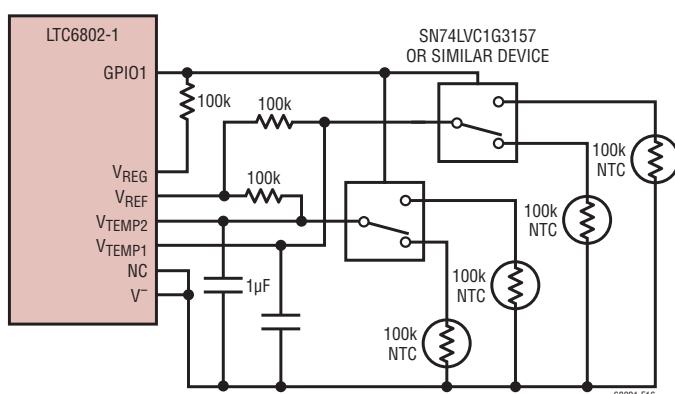

### プローブの個数の拡張

LTC6802-1は汎用I/Oピン(GPIO1とGPIO2)を備えており、複数の温度プローブの多重化を制御するのに使うことができます。図16に示されているように、1つのGPIOピンだけを使って、センサーの個数を倍の4個に増やすことができます。両方のGPIOピンを使って、最大8つのセンサー入力をサポートすることができます。

### 複数箇所で温度をモニタするためのダイオードの利用

どのGPIOピンも使わずに複数のセンサーをサポートする別の方法が可能です。センサーがPNダイオードであり、複数個が並列に使われていると、最も温度の高いダイオードの順方向電圧が最も低くなり、実効的にV<sub>TEMP</sub>入力への入力信号となります。したがって、それらのダイオードが接続されている

V<sub>TEMP</sub>入力からの読み取り値を支配するのは最も温度の高いダイオードです、このシナリオでは、熱分布の具体的な場所は分りませんが、このような情報は実際には重要ではないことがあります。基本概念を図17に示します。

示されているセンサーのどの構成設定でも、フルスケールの低温の読み取り値は、LTC6802-1へのセンサーの接続がオープンしてしまっていることを示しています。

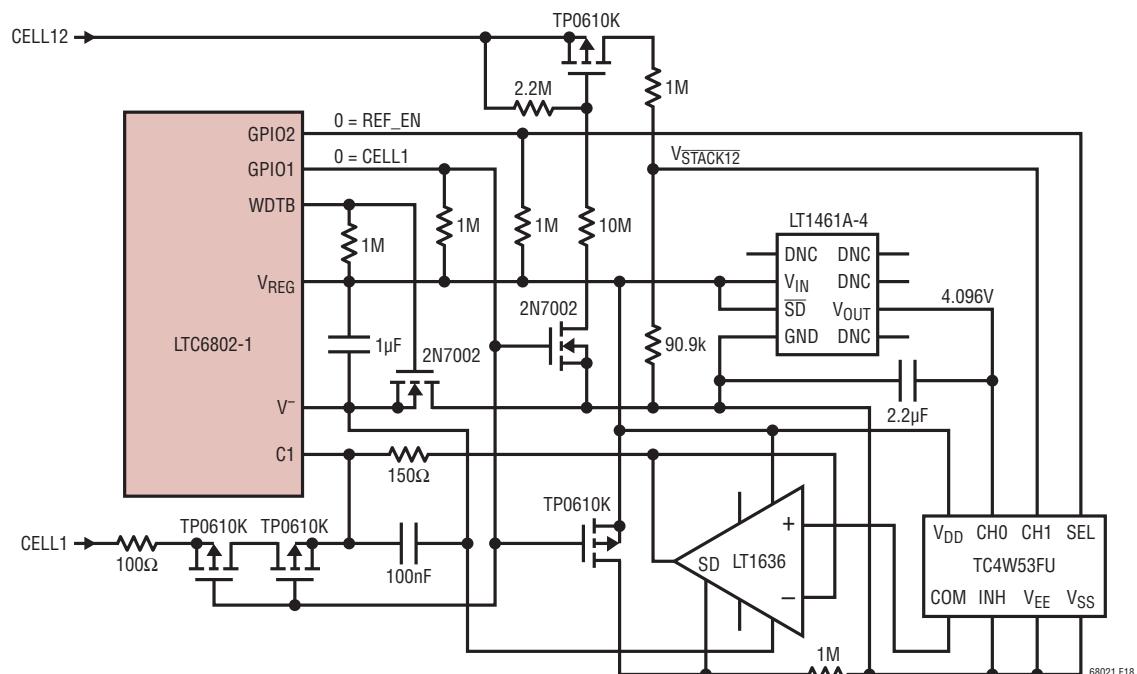

### 較正の追加とスタック全体の測定

多重化用ハードウェアの追加により、CELL1 ADCチャネルによって追加信号をデジタル化することができます。与えるべき有用な信号の1つは(LT1461A-4が与えるような)高精度電圧リファレンスです。この信号の周期的読み取りにより、ホスト・ソフトウェアはLTC6802-1の読み取り値を補正して、LTC6802-1の内部リファレンスよりも精度を改善し、ADCの動作を確認することができます。別の有用な信号は全スタック電位の測定値です。これは、通常のデータ収集過程の動作不良の発生時に、またはスタック全体の電位をもっと速くモニタする手段として、セル動作の冗長測定を与えます。これら両方の機能を与える手段を図18に示します。

図16. 多重化によるセンサーの個数の拡張

図17. ホットスポット検出器としてのダイオード・センサーの利用

## アプリケーション情報

最大スタック電位(C12からC0の電圧)を低電圧で表すために抵抗分割器が使われており、不要なときは分割器の電流を遮断するためのMOSFETを備えています。シャットダウン・モードを備えたオペアンプと組み合わされた他のMOSFETが電圧セレクタを形成しており、(GPIO1が“L”的ときの)通常のセル1の電位またはバッファされたMUX信号の測定を可能にします。MUXがアクティブなとき(GPIO1が“H”)、リファレンス

(4.096V)または最大スタック電圧分割器のどちらかを選択することができます(GPIO2が“L”に設定されるとリファレンスを選択します)。LTC6802-1のWTB信号が“L”になるアイドル・タイムの間、外部回路はパワーダウン状態になり、バッテリの流出を最小に抑えます。アクティブに測定を行っていないとき、GPIO1を“L”に設定し、GPIO2を“H”に設定して、示されている構成設定の最も低い電力状態を達成します。

図18. CELL1ポートを通した較正リファレンスと最大スタック電圧の測定

## アプリケーション情報

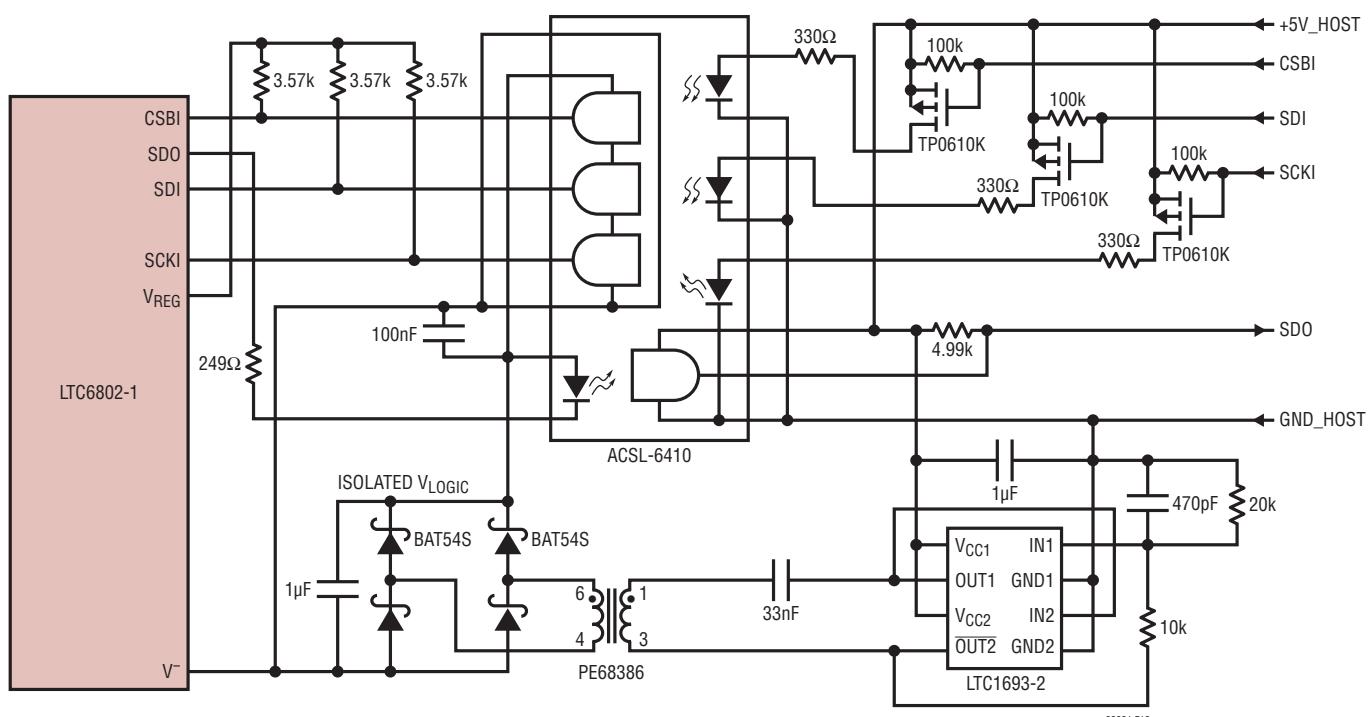

## SPIデータ・ポートの高速オプトアイソレーションの実現

LTC6802-1の1Mbpsのデータ・レートをサポートできるアイソレーション技法では、LTC6802-1のV<sub>REG</sub>出力で供給可能な電力より大きな電力を、絶縁される側(バッテリ側)で必要とします。このことは、バッテリの流出を最小に抑えるため、図19に示されているように、適当なデータ・アイソレーション回路とともにDC/DC機能を実装する必要があることを意味します。ここでは、最適なAvagoの4チャネル(3/1双方向)オプトカプラが使

われており、200kHz発振器として構成設定されたLTC1693-2によって簡単な絶縁型電源を発生しています。DC/DC機能は、ホストが供給する5Vのエネルギーから、安定化されていないロジック電圧(約4V)をオプトカプラの絶縁された側に与えます。この回路はバッテリとホストプロセッサの間に完全な電気的絶縁を与え、絶縁定格は連続で560V、過渡で2500Vです。

図19 絶縁された高速データ・インターフェースの実現

## アプリケーション情報

### PCBレイアウトの検討事項

最良の性能を得るには、V<sub>REG</sub>ピンとV<sub>REF</sub>ピンを1μFのコンデンサを使ってバイパスします。

LTC6802-1はV<sup>+</sup>とV<sup>-</sup>の間が最大60Vで動作することができます。PCBのレイアウトに注意して、電位の異なるトレースの物理的間隔を維持するようにします。LTC6802-1のピン配置はこの物理的間隔を取り易いように選択されています。12個の3.6Vバッテリ・セルをLTC6802-1に接続したときのV<sup>-</sup>を基準にした各ピンのDC電圧を図20に示します。どの隣接する2つのピンの間も5.5Vを超ません。パッケージのボディーが最高電圧(43.5V)を最低電圧(0V)から遠ざけるのに使われています。

| LTC6802-1 |                |                              |

|-----------|----------------|------------------------------|

| 42.5V     | CSB0           | CSBI 0V TO 5.5V              |

| 42.5V     | SD0I           | SD0 0V TO 5.5V               |

| 42.5V     | SCK0           | SDI 0V TO 5.5V               |

| 43.2V     | V <sup>+</sup> | SCKI 0V TO 5.5V              |

| 43.2V     | C12            | V <sub>MODE</sub> 0V TO 5.5V |

| 43.2V     | S12            | GPIO2 0V TO 5.5V             |

| 39.6V     | C11            | GPIO1 0V TO 5.5V             |

| 39.6V     | S11            | WDTB 0V TO 5.5V              |

| 36V       | C10            | MMB 0V TO 5.5V               |

| 36V       | S10            | TOS 0V TO 5.5V               |

| 32.4V     | C9             | V <sub>REG</sub> 5.5V        |

| 32.4V     | S9             | V <sub>REF</sub> 3.1V        |

| 28.8V     | C8             | V <sub>TEMP2</sub> 1.5V      |

| 28.8V     | S8             | V <sub>TEMP1</sub> 1.5V      |

| 25.2V     | C7             | NC 0V                        |

| 25.2V     | S7             | V <sup>-</sup> 0V            |

| 21.6V     | C6             | S1 3.6V                      |

| 21.6V     | S6             | C1 3.6V                      |

| 18V       | C5             | S2 7.2V                      |

| 18V       | S5             | C2 7.2V                      |

| 14.4V     | C4             | S3 10.8V                     |

| 14.4V     | S4             | C3 10.8V                     |

図20. 12個の3.6Vセルの標準的ピン電圧

### デルタシグマADCの利点

LTC6802-1は電圧測定にデルタシグマA/Dコンバータを採用しています。デルタシグマ・コンバータのアーキテクチャは大きく異なることがあります、共通の特徴は、変換過程にわたって入力が何回もサンプルされ、次いでフィルタされ、または平均化されてデジタル出力コードを発生することです。対照的に、SARコンバータは入力電圧を1回サンプルし、次いでこの1個のサンプルに対して変換を行います。ノイズの多い環境での測定では、デルタシグマ・コンバータにはSARコンバータに比べて明らかな利点があります。

SARコンバータはサンプル・レートを高くでき、SARのフルパワー帯域幅は多くの場合1MHzを超えます。これは、コンバータがこの周波数までのノイズに敏感であることを意味します。また、多くのSARコンバータは50MHzを超えるはるかに高い帯域幅を有します。入力をフィルタすることは可能ですが、コンバータが複数の入力チャネルを測定するため多重化されると、それぞれのチャネルに別個のフィルタが必要になります。低周波数のフィルタはマルチプレクサとADCの間に置くことができず、複数チャネルにわたって高いスキャン・レートを達成することはできません。SAR ADCのフィルタ処理の別の結果は、フィルタがセトリングするのに多くの変換サイクルを必要とするため、入力のフィルタ処理によって得られるノイズの削減が、高いサンプル・レートの恩恵を相殺してしまうことです。

与えられたサンプル・レートで、デルタシグマ・コンバータは優れたノイズ除去を実現し、1回の変換で完全にセトリングします。これはフィルタ付きSARコンバータのなしえないことです。ノイズ除去は、高電圧スイッチング・コントローラでは得に重要です。この場合、測定された電圧の中に常にスイッチング・ノイズが存在します。デルタシグマ・コンバータの他の利点は、それらが本質的に単調であることです。つまり、ミッシング・コードがなく、DC仕様が優れています。

## アプリケーション情報

### コンバータの詳細

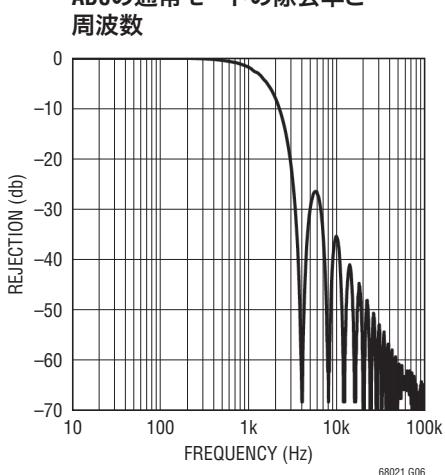

LTC6802-1のADCは、2次デルタシグマ変調器とそれに続くSinc2の有限インパルス応答(FIR)デジタル・フィルタを備えています。フロントエンドのサンプル・レートは512kspsで、入力のフィルタ要件を大きく緩和します。各入力の100Ω抵抗と0.1μFコンデンサで構成される簡単な16kHz、1ポールのフィルタがほとんどのアプリケーションで適切なフィルタ機能を与えます。これらの部品の値はADCのDC精度を低下させません。

各変換は2フェーズ(オートゼロ・フェーズおよび測定フェーズ)で構成されています。ADCは各変換ごとにオートゼロ調整され、CMRRを大幅に改善します。変換の後半は実際の測定です。

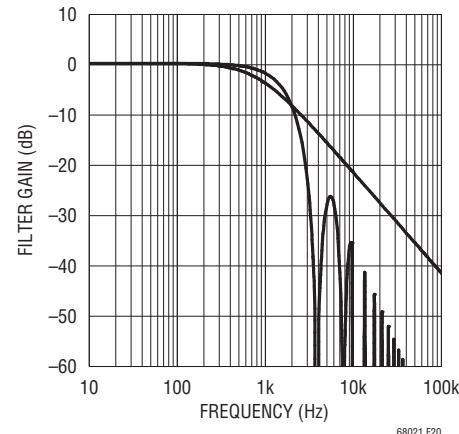

### ノイズの除去

ADCの周波数応答を図21に示します。ロールオフがSinc2応答に続き、最初のノッチは4kHzです。1ポール、850Hzフィルタ(187μs時定数)の応答も示されており、LTC6802-1の約1350HzのADCと同じ広帯域ノイズに対する積分応答を示します。つまり、LTC6802-1の入力に広帯域ノイズが与えられると、デジタル出力で見られるノイズの増加は、完全な1350Hzローパス・フィルタ付きの(SARのような)広帯域幅ADCと同じになります。

したがって、LTC6802-1のADCと同じノイズ除去を達成するためアナログ・フィルタをSARコンバータの前に置くと、SARは入力信号に対する応答が遅くなります。

図21. LTC6802-1のADCのノイズ・フィルタ

たとえば、850Hzのフィルタの入力にステップ入力を与えると、12ビットの精度にセトリングするには1.55msかかりますが、LTC6802-1のADCは1回の1msの変換サイクルでセトリングします。これは、アナログ・フィルタが周波数応答を制限するため、非常に速いサンプル・レートが何らの追加情報も与えないことも意味します。

高次のアクティブ・フィルタはいくらかの改善をもたらす可能性がありますが、それらは複雑であり、各入力に1個のフィルタが必要なので、多チャネル測定では実際的ではなくなります。

Sinc2応答には2次のロールオフ・エンベロープがあり、1ポールのアナログ・フィルタに比べて追加の利点があることにも注意してください。

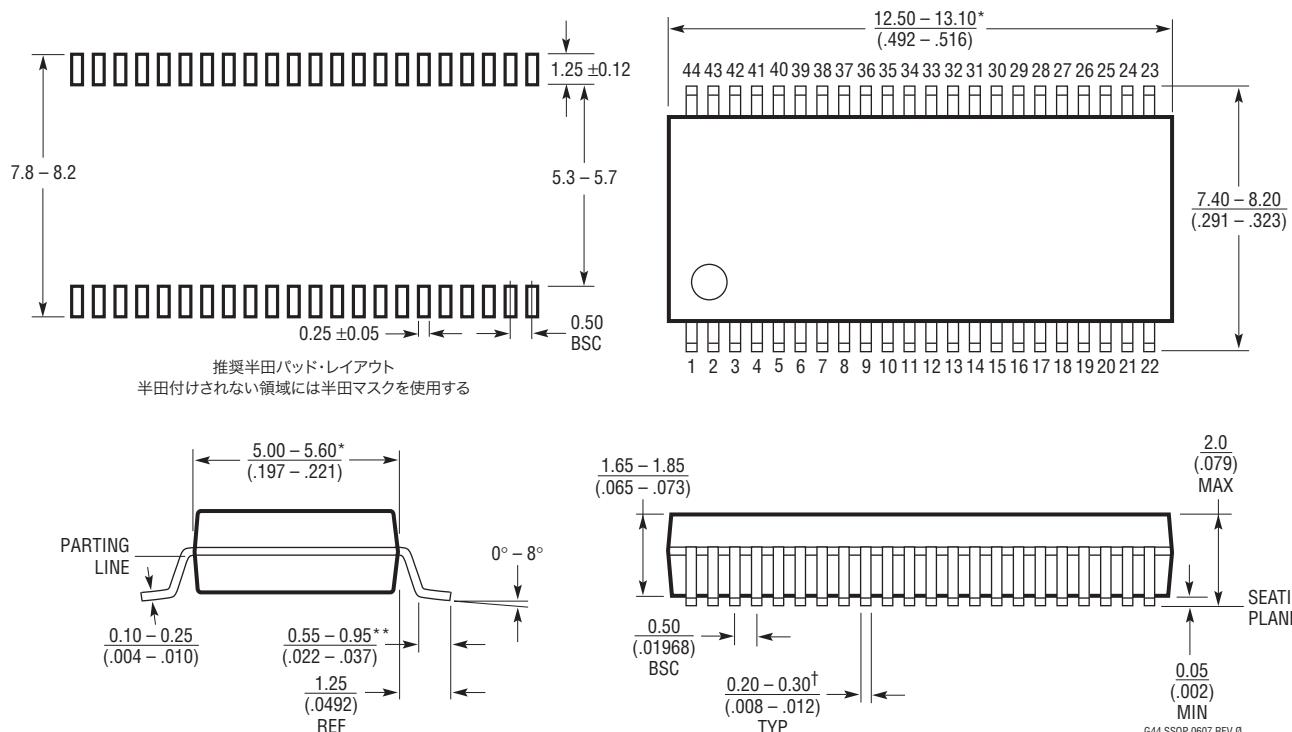

## パッケージ

**G/パッケージ**

**44ピン・プラスチックSSOP(5.3mm)**

(Reference LTC DWG # 05-08-1754 Rev Ø)

NOTE:

1. 図はJEDECの外形ではない

2. 標準寸法:ミリメートル

3. 寸法は ミリメートル

(インチ)

4. 図は実寸とは異なる

5. 整形されたリードはシーティング面で

相互に0.08mm以内に平坦であること

\* 寸法にはモールドのバリまたは突出部を含まないが、

モールドの不整合を含み、分割線で測定される。

モールドのバリは各サイドで0.15mmを超えないこと

\*\* サブストレートに半田付けするためのリードの長さ

† 最大寸法にはダムバーの突出部を含まない。

ダムバーの突出部は各サイドで0.13mmを超えない

G44 SSOP 0607 REV Ø

## 改訂履歴 (Rev Aよりスタート)

| REV | 日付    | 概要                   | ページ番号          |

|-----|-------|----------------------|----------------|

| A   | 01/10 | 概要の変更                | 1              |

|     |       | 絶対最大定格の追加            | 2              |

|     |       | 電気的特性の変更             | 3、4            |

|     |       | グラフG02の変更            | 5              |

|     |       | ピン機能の説明の変更           | 8              |

|     |       | オープンワイヤ検出の説明の書き換え    | 11、13          |

|     |       | 「動作」セクションの変更         | 11、13、14       |

|     |       | 図1、6のタイトルの変更         | 12、18          |

|     |       | 「アプリケーション情報」セクションの変更 | 16、28、29、30、31 |

|     |       | 表6、7、12、13の改訂        | 23、24、26、28    |

|     |       | 図12の改訂               | 29             |

|     |       | 標準的応用例の改訂            | 38             |

# LTC6802-1

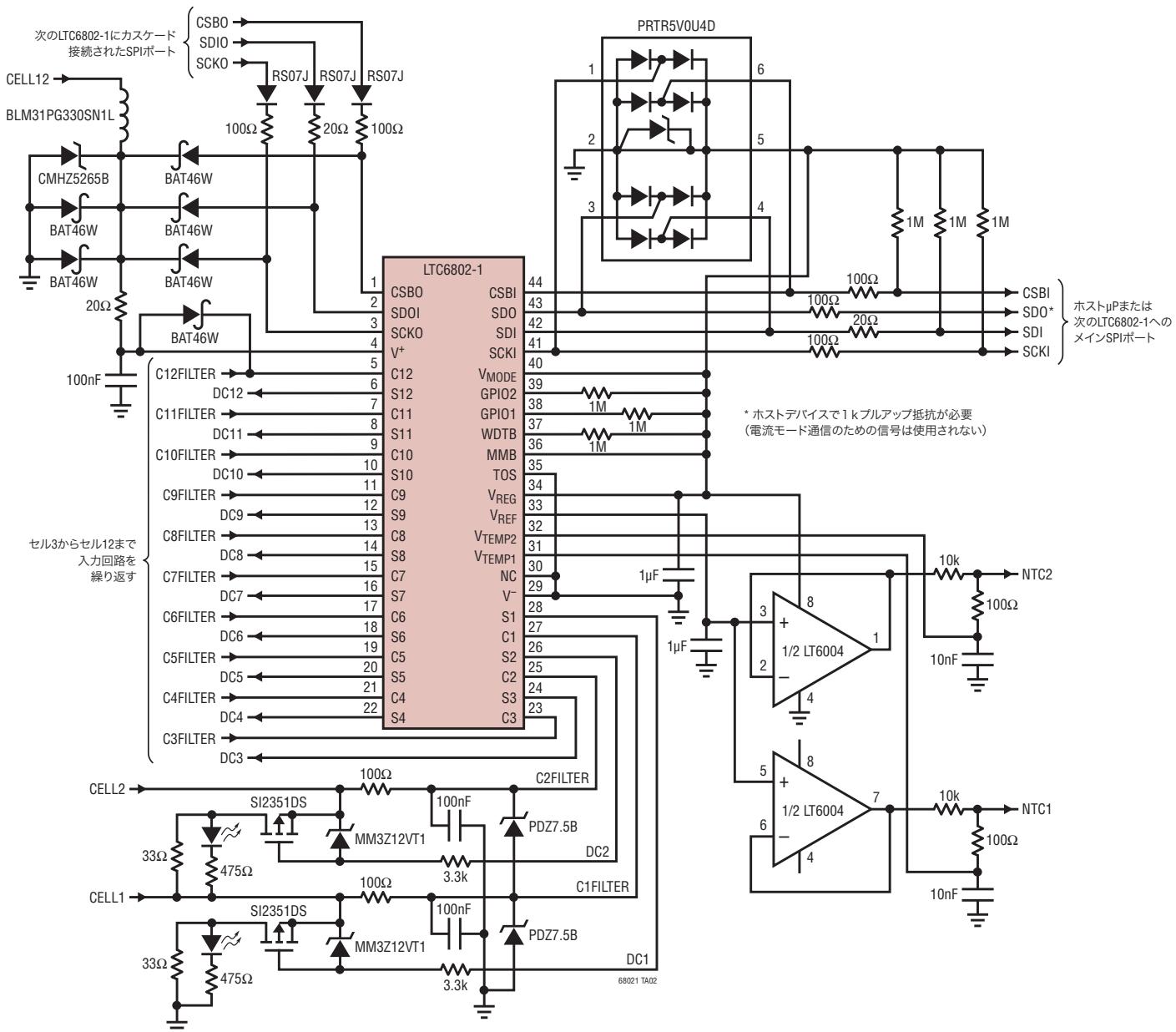

## 標準的応用例

### カスケード接続可能な12セル・リチウムイオン・バッテリ・モニタ

## 関連製品