高精度、低消費電力の

レール・トゥー・レール差動入力/差動出力

オペアンプ/SAR ADC ドライバ

## 特長

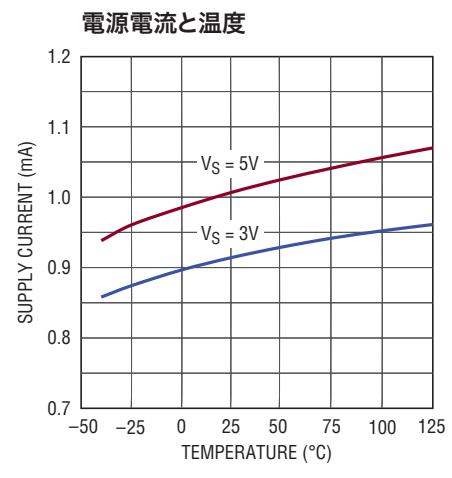

- 電源電流: 1mA

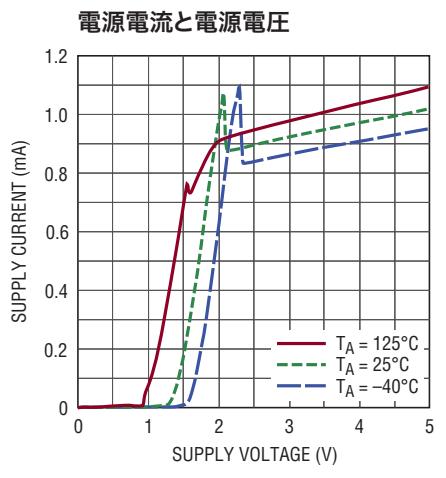

- 単一電源: 2.8V ~ 5.25V

- 完全な差動入力および差動出力

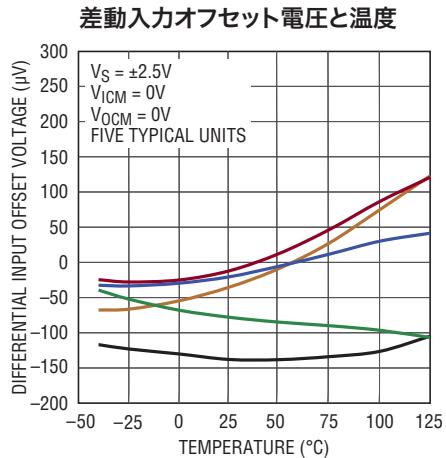

- 最大オフセット電圧: 200µV

- 最大入力バイアス電流: 260nA

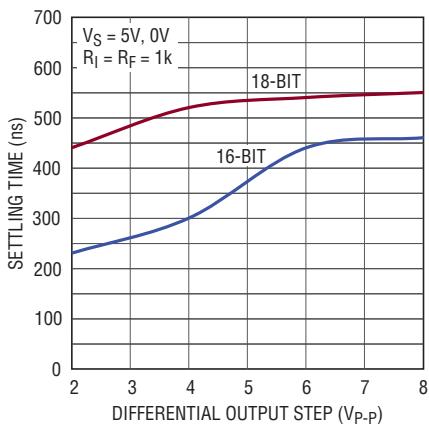

- 高速セトリング時間: 550ns (18ビット、8V<sub>P-P</sub>出力)

- 低歪み: -116dBc (1kHz、8V<sub>P-P</sub>)

- レール・トゥ・レールの入力および出力

- 入力換算ノイズ: 3.9nV/√Hz

- 利得帯域幅積: 180MHz

- -3dB 帯域幅: 34MHz

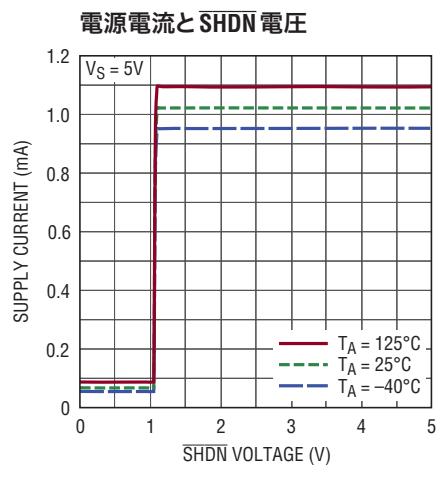

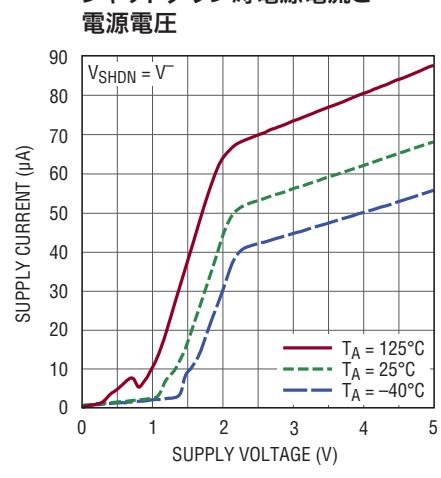

- 低消費電力のシャットダウン時電流: 70µA

- 8ピン MSOP パッケージおよび

3mm×3mm の 8ピン DFN パッケージ

## アプリケーション

- 16ビットおよび18ビットのSAR ADC ドライバ

- シングルエンドから差動への変換

- 低消費電力のパイプライン型ADC ドライバ

- 差動ライン・ドライバ

- 電池駆動の計測装置

## 概要

LTC<sup>®</sup>6362は、入力および出力の振幅をレール・トゥー・レールにすることが可能な低消費電力、低ノイズの差動オペアンプで、低消費電力の逐次比較型(SAR) ADCを駆動するためには最適化されています。動作時に流れる電源電流はわずか1mAであり、消費電流が70µAに減少するシャットダウン・モードを備えています。

このアンプは、シングルエンドの入力信号を差動出力信号に変換するように構成することが可能で、反転構成または非反転構成のいずれでも動作可能です。

LTC6362は、低オフセット電圧、低入力バイアス電流、および安定した高インピーダンス構成により、ADC ドライバとして使用するのに適している以外に、高精度のセンサ信号を平衡型(差動)信号に変換してノイズの多い産業環境で処理するために、シグナルチェーン内の前方に使用するのにも適しています。

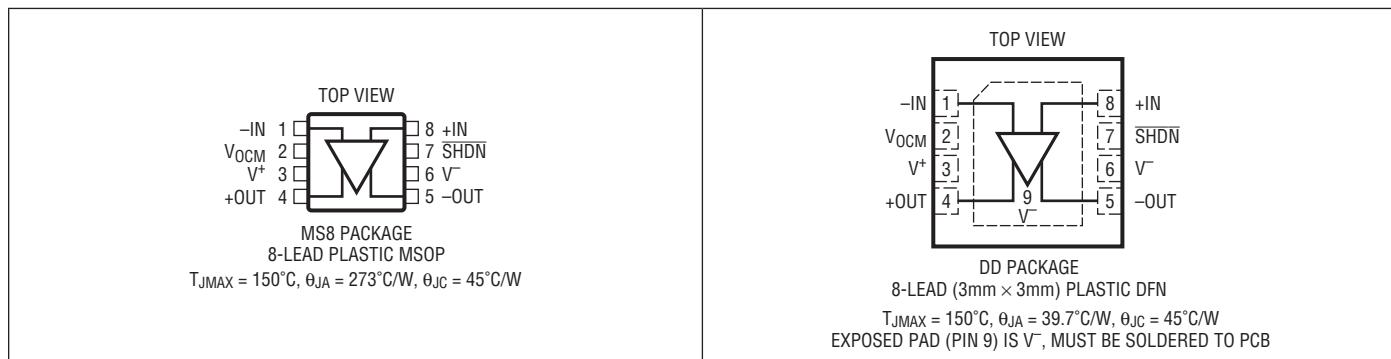

LTC6362は8ピンのMSOPパッケージと、リード線のない小型の3mm×3mm 8ピンDFNパッケージで供給され、-40°C ~ 125°Cの温度範囲で動作し、その範囲で規格値も保証されています。

△、LT、LTC、LTM、Linear Technology およびLinear のロゴは、リニアテクノロジー社の登録商標です。その他すべての商標の所有権は、それぞれの所有者に帰属します。

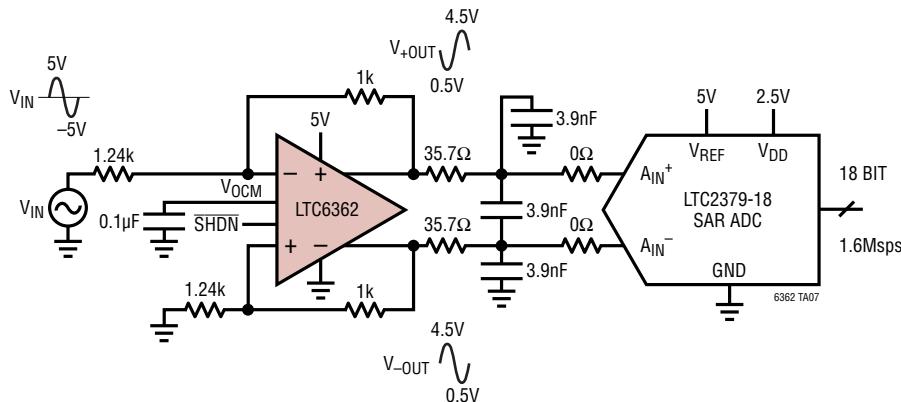

## 標準的応用例

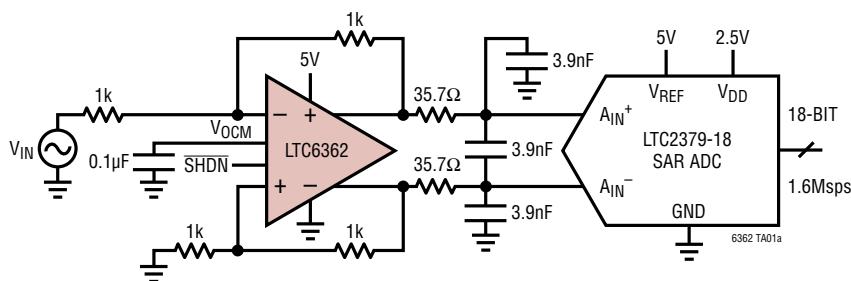

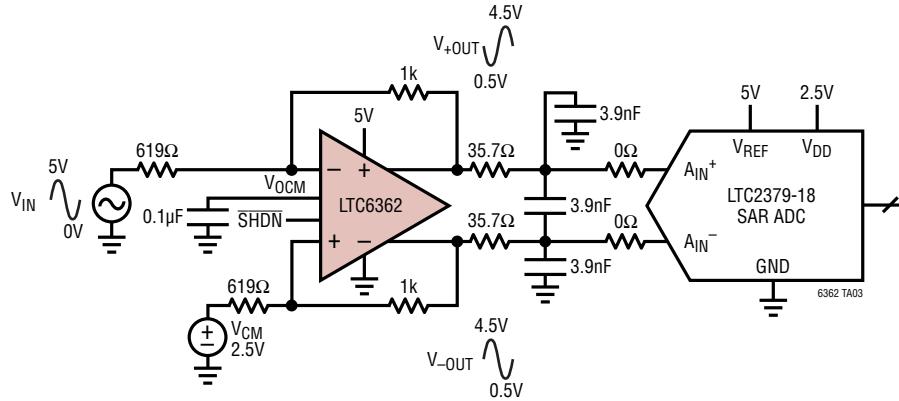

### グランドを基準にしたシングルエンド入力から LTC2379-18 SAR ADCまでのDC結合インターフェース

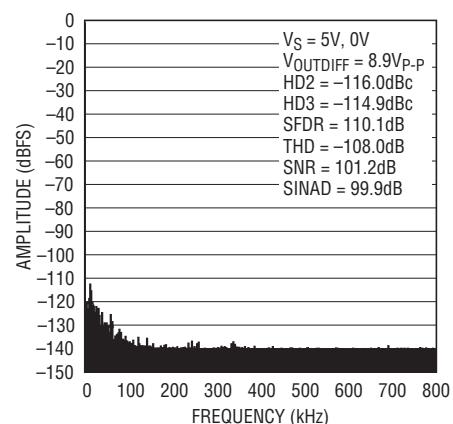

### LTC2379-18を駆動するLTC6362 f<sub>IN</sub> = 2kHz、-1dBFS、16384 ポイントの FFT

6362 TA01b

6362fa

## 絶対最大定格

(Note 1)

|                                                         |                                            |                 |                                            |

|---------------------------------------------------------|--------------------------------------------|-----------------|--------------------------------------------|

| 全電源電圧( $V^+ \sim V^-$ )                                 | 5.5V                                       | 規定温度範囲 (Note 5) |                                            |

| 入力電流(+IN, -IN, $V_{OCM}$ , $\overline{SHDN}$ ) (Note 2) | $\pm 10\text{mA}$                          | LTC6362C        | $0^\circ\text{C} \sim 70^\circ\text{C}$    |

| 出力短絡時間 (Note 3)                                         | 無期限                                        | LTC6362I        | $-40^\circ\text{C} \sim 85^\circ\text{C}$  |

| 動作温度範囲 (Note 4)                                         |                                            | LTC6362H        | $-40^\circ\text{C} \sim 125^\circ\text{C}$ |

| LTC6362C/LTC6362I                                       | $-40^\circ\text{C} \sim 85^\circ\text{C}$  | 最大接合部温度         | $150^\circ\text{C}$                        |

| LTC6362H                                                | $-40^\circ\text{C} \sim 125^\circ\text{C}$ | 保存温度範囲          | $-65^\circ\text{C} \sim 150^\circ\text{C}$ |

## ピン配置

## 発注情報

| 無鉛仕上げ           | テープアンドリール         | 製品マーキング* | パッケージ                          | 規定温度範囲                                            |

|-----------------|-------------------|----------|--------------------------------|---------------------------------------------------|

| LTC6362CMS8#PBF | LTC6362CMS8#TRPBF | LTGCN    | 8-Lead Plastic MSOP            | $0^\circ\text{C} \text{ to } 70^\circ\text{C}$    |

| LTC6362IMS8#PBF | LTC6362IMS8#TRPBF | LTGCN    | 8-Lead Plastic MSOP            | $-40^\circ\text{C} \text{ to } 85^\circ\text{C}$  |

| LTC6362HMS8#PBF | LTC6362HMS8#TRPBF | LTGCN    | 8-Lead Plastic MSOP            | $-40^\circ\text{C} \text{ to } 125^\circ\text{C}$ |

| LTC6362CDD#PBF  | LTC6362CDD#TRPBF  | LGCM     | 8-Lead (3mm x 3mm) Plastic DFN | $0^\circ\text{C} \text{ to } 70^\circ\text{C}$    |

| LTC6362IDD#PBF  | LTC6362IDD#TRPBF  | LGCM     | 8-Lead (3mm x 3mm) Plastic DFN | $-40^\circ\text{C} \text{ to } 85^\circ\text{C}$  |

| LTC6362HDD#PBF  | LTC6362HDD#TRPBF  | LGCM     | 8-Lead (3mm x 3mm) Plastic DFN | $-40^\circ\text{C} \text{ to } 125^\circ\text{C}$ |

さらに広い動作温度範囲で規定されるデバイスについては、弊社または弊社代理店にお問い合わせください。\* 温度グレードは出荷時のコンテナのラベルで識別されます。

非標準の鉛仕上げの製品の詳細については、弊社または弊社代理店にお問い合わせください。

無鉛仕上げの製品マーキングの詳細については、<http://www.linear-tech.co.jp/leadfree/> をご覧ください。

テープアンドリールの仕様の詳細については、<http://www.linear-tech.co.jp/tapeandreel/> をご覧ください。

**電気的特性** ●は全動作温度範囲の規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。 $V^+ = 5\text{V}$ 、 $V^- = 0\text{V}$ 、 $V_{\text{CM}} = V_{\text{OCM}} = V_{\text{ICM}} = 2.5\text{V}$ 、 $V_{\text{SHDN}} = \text{開放}$ 。 $V_S$ は $(V^+ - V^-)$ として定義されている。 $V_{\text{OUTCM}}$ は $(V_{+,\text{OUT}} + V_{-,\text{OUT}})/2$ として定義されている。 $V_{\text{ICM}}$ は $(V_{+,\text{IN}} + V_{-,\text{IN}})/2$ として定義されている。 $V_{\text{OUTDIFF}}$ は $(V_{+,\text{OUT}} - V_{-,\text{OUT}})$ として定義されている。

| SYMBOL                                       | PARAMETER                                                                                            | CONDITIONS                                                            | MIN | TYP        | MAX       | UNITS                        |

|----------------------------------------------|------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|-----|------------|-----------|------------------------------|

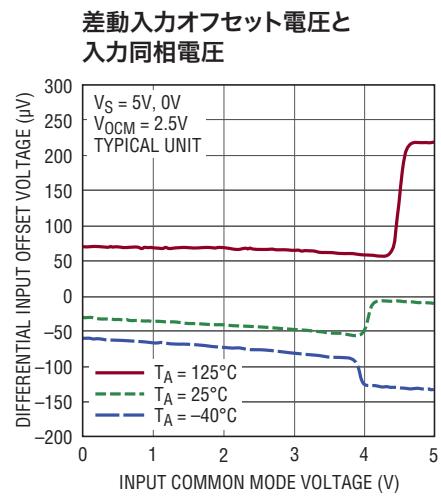

| $V_{\text{OSDIFF}}$ (Note 6)                 | Differential Offset Voltage (Input Referred)                                                         | $V_S = 3\text{V}$<br>$V_{\text{ICM}} = 1.5\text{V}$                   |     | 50         | 200       | $\mu\text{V}$                |

|                                              |                                                                                                      |                                                                       | ●   | 350        |           | $\mu\text{V}$                |

|                                              |                                                                                                      | $V_{\text{ICM}} = 2.75\text{V}$                                       |     | 65         | 250       | $\mu\text{V}$                |

|                                              |                                                                                                      |                                                                       | ●   | 600        |           | $\mu\text{V}$                |

|                                              |                                                                                                      | $V_S = 5\text{V}$<br>$V_{\text{ICM}} = 2.5\text{V}$                   |     | 50         | 200       | $\mu\text{V}$                |

|                                              |                                                                                                      |                                                                       | ●   | 350        |           | $\mu\text{V}$                |

| $\Delta V_{\text{OSDIFF}}/\Delta T$ (Note 7) | Differential Offset Voltage Drift (Input Referred)                                                   | $V_S = 3\text{V}$<br>$V_S = 5\text{V}$                                | ●   | 0.9        | 2.5       | $\mu\text{V}/^\circ\text{C}$ |

|                                              |                                                                                                      |                                                                       | ●   | 0.9        | 2.5       | $\mu\text{V}/^\circ\text{C}$ |

|                                              |                                                                                                      | $V_S = 3\text{V}$<br>$V_{\text{ICM}} = 1.5\text{V}$                   |     | $\pm 100$  | $\pm 350$ | $\text{nA}$                  |

|                                              |                                                                                                      |                                                                       | ●   | $\pm 500$  |           | $\text{nA}$                  |

|                                              |                                                                                                      | $V_{\text{ICM}} = 2.5\text{V}$                                        |     | $\pm 75$   | $\pm 350$ | $\text{nA}$                  |

|                                              |                                                                                                      |                                                                       | ●   | $\pm 850$  |           | $\text{nA}$                  |

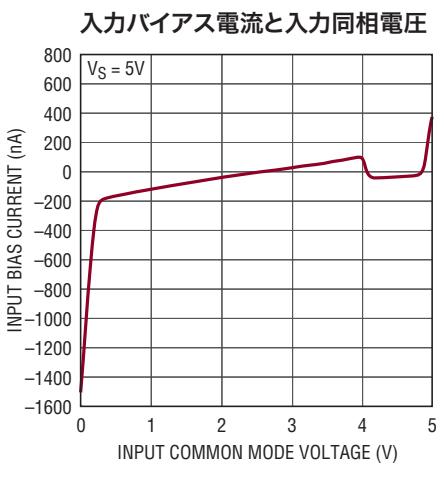

| $I_B$ (Note 8)                               | Input Bias Current                                                                                   | $V_S = 5\text{V}$<br>$V_{\text{ICM}} = 2.5\text{V}$                   |     | $\pm 75$   | $\pm 260$ | $\text{nA}$                  |

|                                              |                                                                                                      |                                                                       | ●   | $\pm 460$  |           | $\text{nA}$                  |

|                                              |                                                                                                      | $V_{\text{ICM}} = 4.5\text{V}$                                        |     | $\pm 75$   | $\pm 350$ | $\text{nA}$                  |

|                                              |                                                                                                      |                                                                       | ●   | $\pm 850$  |           | $\text{nA}$                  |

|                                              |                                                                                                      | $V_S = 3\text{V}$<br>$V_S = 5\text{V}$                                | ●   | 1.1        |           | $\text{nA}/^\circ\text{C}$   |

|                                              |                                                                                                      |                                                                       | ●   | 0.9        |           | $\text{nA}/^\circ\text{C}$   |

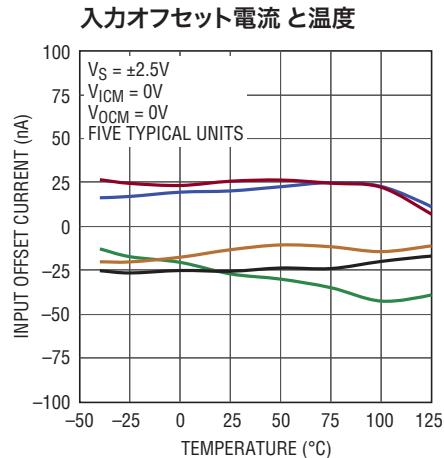

| $I_{\text{OS}}$ (Note 8)                     | Input Offset Current                                                                                 | $V_S = 3\text{V}$<br>$V_{\text{ICM}} = 1.5\text{V}$                   |     | $\pm 75$   | $\pm 325$ | $\text{nA}$                  |

|                                              |                                                                                                      |                                                                       | ●   | $\pm 650$  |           | $\text{nA}$                  |

|                                              |                                                                                                      | $V_{\text{ICM}} = 2.5\text{V}$                                        |     | $\pm 125$  | $\pm 425$ | $\text{nA}$                  |

|                                              |                                                                                                      |                                                                       | ●   | $\pm 1200$ |           | $\text{nA}$                  |

|                                              |                                                                                                      | $V_S = 5\text{V}$<br>$V_{\text{ICM}} = 2.5\text{V}$                   |     | $\pm 75$   | $\pm 325$ | $\text{nA}$                  |

|                                              |                                                                                                      |                                                                       | ●   | $\pm 500$  |           | $\text{nA}$                  |

| $R_{\text{IN}}$                              | Input Resistance                                                                                     | $V_{\text{ICM}} = 4.5\text{V}$                                        |     | $\pm 125$  | $\pm 425$ | $\text{nA}$                  |

|                                              |                                                                                                      |                                                                       | ●   | $\pm 1200$ |           | $\text{nA}$                  |

|                                              |                                                                                                      | Common Mode                                                           |     | 14         |           | $\text{M}\Omega$             |

|                                              |                                                                                                      | Differential Mode                                                     |     | 32         |           | $\text{k}\Omega$             |

|                                              |                                                                                                      |                                                                       |     |            |           |                              |

|                                              |                                                                                                      |                                                                       |     | 2          |           | $\text{pF}$                  |

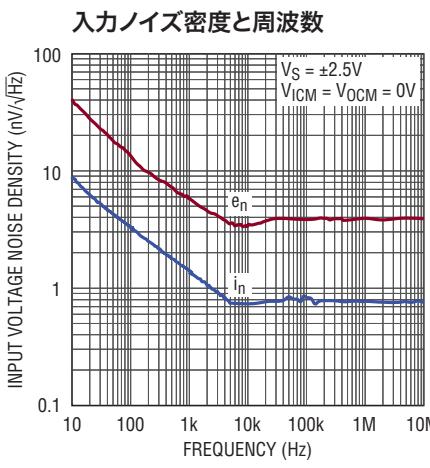

| $e_n$                                        | Differential Input Noise Voltage Density                                                             | $f = 100\text{kHz}$ , Not Including $R_{\text{I}}/R_{\text{F}}$ Noise |     | 3.9        |           | $\text{nV}/\sqrt{\text{Hz}}$ |

| $i_n$                                        | Input Noise Current Density                                                                          | $f = 100\text{kHz}$ , Not Including $R_{\text{I}}/R_{\text{F}}$ Noise |     | 0.8        |           | $\text{pA}/\sqrt{\text{Hz}}$ |

| $e_{\text{envocm}}$                          | Common Mode Noise Voltage Density                                                                    | $f = 100\text{kHz}$                                                   |     | 14.3       |           | $\text{nV}/\sqrt{\text{Hz}}$ |

| $V_{\text{ICMR}}$ (Note 9)                   | Input Common Mode Range                                                                              | $V_S = 3\text{V}$<br>$V_S = 5\text{V}$                                | ●   | 0          | 3         | $\text{V}$                   |

|                                              |                                                                                                      |                                                                       | ●   | 0          | 5         | $\text{V}$                   |

| CMRR (Note 10)                               | Input Common Mode Rejection Ratio (Input Referred) $\Delta V_{\text{ICM}}/\Delta V_{\text{OSDIFF}}$  | $V_S = 3\text{V}$ , $V_{\text{ICM}}$ from 0V to 3V                    | ●   | 70         | 95        | $\text{dB}$                  |

|                                              |                                                                                                      | $V_S = 5\text{V}$ , $V_{\text{ICM}}$ from 0V to 5V                    | ●   | 73         | 98        | $\text{dB}$                  |

| CMRRIO (Note 10)                             | Output Common Mode Rejection Ratio (Input Referred) $\Delta V_{\text{OCM}}/\Delta V_{\text{OSDIFF}}$ | $V_S = 3\text{V}$ , $V_{\text{OCM}}$ from 0.5V to 2.5V                | ●   | 75         | 100       | $\text{dB}$                  |

|                                              |                                                                                                      | $V_S = 5\text{V}$ , $V_{\text{OCM}}$ from 0.5V to 4.5V                | ●   | 55         | 90        | $\text{dB}$                  |

| PSRR (Note 11)                               | Differential Power Supply Rejection ( $\Delta V_S/\Delta V_{\text{OSDIFF}}$ )                        | $V_S = 2.8\text{V}$ to $5.25\text{V}$                                 | ●   | 80         | 105       | $\text{dB}$                  |

| PSRR <sub>CM</sub> (Note 11)                 | Output Common Mode Power Supply Rejection ( $\Delta V_S/\Delta V_{\text{OSCM}}$ )                    | $V_S = 2.8\text{V}$ to $5.25\text{V}$                                 | ●   | 58         | 72        | $\text{dB}$                  |

**電気的特性** ●は全動作温度範囲の規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。 $V^+ = 5\text{V}$ 、 $V^- = 0\text{V}$ 、 $V_{\text{CM}} = V_{\text{OCM}} = V_{\text{ICM}} = 2.5\text{V}$ 、 $V_{\text{SHDN}} = \text{開放}$ 。 $V_S$ は $(V^+ - V^-)$ として定義されている。 $V_{\text{OUTCM}}$ は $(V_{+,\text{OUT}} + V_{-,\text{OUT}})/2$ として定義されている。 $V_{\text{ICM}}$ は $(V_{+,\text{IN}} + V_{-,\text{IN}})/2$ として定義されている。 $V_{\text{OUTDIFF}}$ は $(V_{+,\text{OUT}} - V_{-,\text{OUT}})$ として定義されている。

| SYMBOL                            | PARAMETER                                                                    | CONDITIONS                                                                                                                                                                                      | MIN    | TYP                      | MAX                               | UNITS                        |                                              |

|-----------------------------------|------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|--------------------------|-----------------------------------|------------------------------|----------------------------------------------|

| GCM                               | Common Mode Gain ( $\Delta V_{\text{OUTCM}}/\Delta V_{\text{OCM}}$ )         | $V_S = 3\text{V}$ , $V_{\text{OCM}}$ from 0.5V to 2.5V<br>$V_S = 5\text{V}$ , $V_{\text{OCM}}$ from 0.5V to 4.5V                                                                                | ●<br>● | 1<br>1                   |                                   | V/V<br>V/V                   |                                              |

| $\Delta G_{\text{CM}}$            | Common Mode Gain Error $100 \cdot (G_{\text{CM}} - 1)$                       | $V_S = 3\text{V}$ , $V_{\text{OCM}}$ from 0.5V to 2.5V<br>$V_S = 5\text{V}$ , $V_{\text{OCM}}$ from 0.5V to 4.5V                                                                                | ●<br>● | $\pm 0.07$<br>$\pm 0.07$ | $\pm 0.16$<br>$\pm 0.4$           | %<br>%                       |                                              |

| BAL                               | Output Balance ( $\Delta V_{\text{OUTCM}}/\Delta V_{\text{OUTDIFF}}$ )       | $\Delta V_{\text{OUTDIFF}} = 2\text{V}$<br>Single-Ended Input<br>Differential Input                                                                                                             | ●<br>● | -57<br>-57               | -35<br>-35                        | dB<br>dB                     |                                              |

| AVOL                              | Open-Loop Voltage Gain                                                       |                                                                                                                                                                                                 |        | 95                       |                                   | dB                           |                                              |

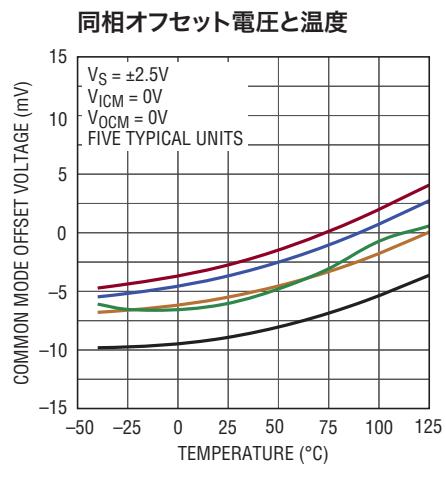

| $V_{\text{OSCM}}$                 | Common Mode Offset Voltage ( $V_{\text{OUTCM}} - V_{\text{OCM}}$ )           | $V_S = 3\text{V}$<br>$V_S = 5\text{V}$                                                                                                                                                          | ●<br>● | $\pm 6$<br>$\pm 6$       | $\pm 30$<br>$\pm 30$              | mV<br>mV                     |                                              |

| $\Delta V_{\text{OSCM}}/\Delta T$ | Common Mode Offset Voltage Drift                                             |                                                                                                                                                                                                 | ●      | 45                       |                                   | $\mu\text{V}/^\circ\text{C}$ |                                              |

| $V_{\text{OUTCMR}}$ (Note 9)      | Output Signal Common Mode Range (Voltage Range for the $V_{\text{OCM}}$ Pin) | $V_{\text{OCM}}$ Driven Externally, $V_S = 3\text{V}$<br>$V_{\text{OCM}}$ Driven Externally, $V_S = 5\text{V}$                                                                                  | ●<br>● | 0.5<br>0.5               | 2.5<br>4.5                        | V<br>V                       |                                              |

| $V_{\text{OCM}}$                  | Self-Biased Voltage at the $V_{\text{OCM}}$ Pin                              | $V_{\text{OCM}}$ Not Connected, $V_S = 3\text{V}$<br>$V_{\text{OCM}}$ Not Connected, $V_S = 5\text{V}$                                                                                          | ●<br>● | 1.475<br>2.475           | 1.5<br>2.5                        | 1.525<br>2.525               | V<br>V                                       |

| $R_{\text{INVOCM}}$               | Input Resistance, $V_{\text{OCM}}$ Pin                                       |                                                                                                                                                                                                 | ●      | 110                      | 170                               | 230                          | $\text{k}\Omega$                             |

| $V_{\text{OUT}}$                  | Output Voltage, High, Either Output Pin                                      | $I_L = 0\text{mA}$ , $V_S = 3\text{V}$<br>$I_L = -5\text{mA}$ , $V_S = 3\text{V}$                                                                                                               | ●<br>● | 2.85<br>2.75             | 2.93<br>2.85                      |                              | V<br>V                                       |

|                                   |                                                                              | $I_L = 0\text{mA}$ , $V_S = 5\text{V}$<br>$I_L = -5\text{mA}$ , $V_S = 5\text{V}$                                                                                                               | ●<br>● | 4.8<br>4.7               | 4.93<br>4.85                      |                              | V<br>V                                       |

|                                   | Output Voltage, Low, Either Output Pin                                       | $I_L = 0\text{mA}$ , $V_S = 3\text{V}$<br>$I_L = 5\text{mA}$ , $V_S = 3\text{V}$                                                                                                                | ●<br>● | 0.05<br>0.13             | 0.15<br>0.3                       |                              | V<br>V                                       |

|                                   |                                                                              | $I_L = 0\text{mA}$ , $V_S = 5\text{V}$<br>$I_L = 5\text{mA}$ , $V_S = 5\text{V}$                                                                                                                | ●<br>● | 0.05<br>0.13             | 0.2<br>0.4                        |                              | V<br>V                                       |

| $I_{\text{SC}}$                   | Output Short-Circuit Current, Either Output Pin                              | $V_S = 3\text{V}$<br>$V_S = 5\text{V}$                                                                                                                                                          | ●<br>● | 13<br>15                 | 25<br>35                          |                              | $\text{mA}$<br>$\text{mA}$                   |

| SR                                | Slew Rate                                                                    | Differential 8V <sub>P-P</sub> Output                                                                                                                                                           |        |                          | 45                                |                              | V/ $\mu\text{s}$                             |

| GBWP                              | Gain-Bandwidth Product                                                       | $f_{\text{TEST}} = 200\text{kHz}$                                                                                                                                                               | ●      | 145<br>90                | 180                               |                              | MHz<br>MHz                                   |

| $f_{-3\text{dB}}$                 | -3dB Bandwidth                                                               | $R_I = R_F = 1\text{k}\Omega$                                                                                                                                                                   |        |                          | 34                                |                              | MHz                                          |

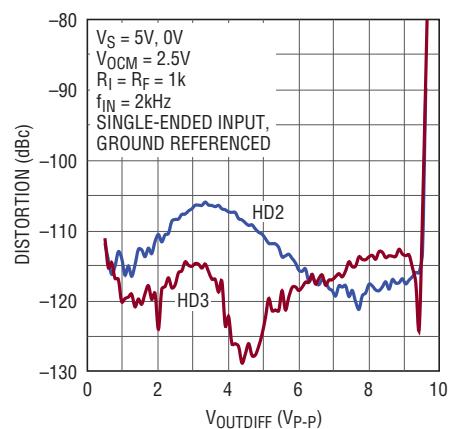

| HD2/HD3                           | 2nd/3rd Order Harmonic Distortion Single-Ended Input                         | $f = 1\text{kHz}$ , $V_{\text{OUT}} = 8\text{V}_P\text{-}_P$<br>$f = 10\text{kHz}$ , $V_{\text{OUT}} = 8\text{V}_P\text{-}_P$<br>$f = 100\text{kHz}$ , $V_{\text{OUT}} = 8\text{V}_P\text{-}_P$ |        |                          | -120/-116<br>-106/-103<br>-84/-76 |                              | $\text{dBc}$<br>$\text{dBc}$<br>$\text{dBc}$ |

| $t_s$                             | Settling Time to a 2V <sub>P-P</sub> Output Step                             | 0.1%<br>0.01%<br>0.0015% (16-Bit)<br>4ppm (18-Bit)                                                                                                                                              |        |                          | 160<br>180<br>230<br>440          |                              | ns<br>ns<br>ns<br>ns                         |

|                                   |                                                                              | 0.1%<br>0.01%<br>0.0015% (16-Bit)<br>4ppm (18-Bit)                                                                                                                                              |        |                          | 230<br>300<br>460<br>550          |                              | ns<br>ns<br>ns<br>ns                         |

|                                   | Settling Time to a 8V <sub>P-P</sub> Output Step                             | 0.1%<br>0.01%<br>0.0015% (16-Bit)<br>4ppm (18-Bit)                                                                                                                                              |        |                          |                                   |                              |                                              |

|                                   |                                                                              | 0.1%<br>0.01%<br>0.0015% (16-Bit)<br>4ppm (18-Bit)                                                                                                                                              |        |                          |                                   |                              |                                              |

| $V_S$ (Note 12)                   | Supply Voltage Range                                                         |                                                                                                                                                                                                 | ●      | 2.8                      | 5.25                              |                              | V                                            |

| $I_S$                             | Supply Current                                                               | $V_S = 3\text{V}$ , Active                                                                                                                                                                      | ●      |                          | 0.9<br>1.05                       |                              | $\text{mA}$<br>$\text{mA}$                   |

|                                   |                                                                              | $V_S = 3\text{V}$ , Shutdown                                                                                                                                                                    | ●      |                          | 55<br>130                         |                              | $\mu\text{A}$                                |

|                                   |                                                                              | $V_S = 5\text{V}$ , Active                                                                                                                                                                      | ●      |                          | 1<br>1.06<br>1.18                 |                              | $\text{mA}$                                  |

|                                   |                                                                              | $V_S = 5\text{V}$ , Shutdown                                                                                                                                                                    | ●      |                          | 70<br>140                         |                              | $\mu\text{A}$                                |

6362fa

**電気的特性** ●は全動作温度範囲の規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。 $V^+ = 5\text{V}$ 、 $V^- = 0\text{V}$ 、 $V_{\text{CM}} = V_{\text{OCM}} = V_{\text{ICM}} = 2.5\text{V}$ 、 $V_{\text{SHDN}} = \text{開放}$ 。 $V_S$ は $(V^+ - V^-)$ として定義されている。 $V_{\text{OUTCM}}$ は $(V_{+,\text{OUT}} + V_{-,\text{OUT}})/2$ として定義されている。 $V_{\text{ICM}}$ は $(V_{+,\text{IN}} + V_{-,\text{IN}})/2$ として定義されている。 $V_{\text{OUTDIFF}}$ は $(V_{+,\text{OUT}} - V_{-,\text{OUT}})$ として定義されている。

| SYMBOL           | PARAMETER             | CONDITIONS | MIN | TYP | MAX | UNITS         |

|------------------|-----------------------|------------|-----|-----|-----|---------------|

| $V_{\text{IL}}$  | SHDN Input Logic Low  |            | ●   |     | 0.8 | V             |

| $V_{\text{IH}}$  | SHDN Input Logic High |            | ●   | 2   |     | V             |

| $t_{\text{ON}}$  | Turn-On Time          |            |     |     | 2   | $\mu\text{s}$ |

| $t_{\text{OFF}}$ | Turn-Off Time         |            |     |     | 2   | $\mu\text{s}$ |

**Note 1:** 絶対最大定格に記載された値を超えるストレスはデバイスに永続的損傷を与える可能性がある。長期にわたって絶対最大定格条件に曝すと、デバイスの信頼性と寿命に悪影響を与える恐れがある。

**Note 2:** 入力ピン $(+ \text{IN}, -\text{IN}, V_{\text{OCM}}$ 、および $\text{SHDN}$ )は正負両方の電源に対してステアリング・ダイオードで保護されている。入力電圧がいずれか一方の電源電圧を超える場合は、入力電流を $10\text{mA}$ 未満に制限する必要がある。さらに、入力 $(+ \text{IN}, -\text{IN})$ は一对の逆並列接続ダイオードで保護されている。差動入力電圧が $1.4\text{V}$ を超える場合は、入力電流を $10\text{mA}$ 未満に制限する必要がある。

**Note 3:** 出力が無期限に短絡されるときは、接合部温度を絶対最大定格より低く抑えるためにヒートシンクが必要になることがある。

**Note 4:** LTC6362C および LTC6362I は、 $-40^\circ\text{C} \sim 85^\circ\text{C}$  の動作温度範囲で機能することが保証されている。LTC6362H は、 $-40^\circ\text{C} \sim 125^\circ\text{C}$  の動作温度範囲で機能することが保証されている。

**Note 5:** LTC6362C は、 $0^\circ\text{C} \sim 70^\circ\text{C}$  で性能仕様に適合することが保証されている。LTC6362I は、 $-40^\circ\text{C} \sim 85^\circ\text{C}$  で性能仕様に適合することが保証されている。LTC6362C は $-40^\circ\text{C} \sim 85^\circ\text{C}$  で性能仕様に適合するように設計され、特性が評価されており、性能仕様に適合すると予想されるが、これらの温度ではテストされず、QAサンプリングも行われない。LTC6362H は、 $-40^\circ\text{C} \sim 125^\circ\text{C}$  で性能仕様に適合することが保証されている。

**Note 6:** 差動入力換算オフセット電圧には、 $1\text{k}$ のソース抵抗を流れる入力オフセット電流に起因するオフセットが含まれる。

**Note 7:** 差動入力換算オフセット電圧ドリフトの最大値は、標準的デバイスのサンプリングを大量に行うことによって決定される。ドリフトがこの値でのテストまたはQAサンプリングによって保証されることはない。

**Note 8:** 入力バイアス電流は、一方の入力ピン $(-\text{IN}$  および $+ \text{IN})$ に流れる入力電流の最大値として定義される。入力オフセット電流は、入力電流の差として定義される $(I_{\text{OS}} = I_{\text{g}^+} - I_{\text{g}^-})$ 。

**Note 9:** 入力同相電圧範囲のテストでは、「電気的特性」の表に記載されている制限値で、差動オフセット $(V_{\text{OSDIFF}})$ と同相オフセット $(V_{\text{OSCM}})$ が、 $V_{\text{CM}} = 2.5\text{V}$  ( $V_S = 5\text{V}$ ) および  $V_{\text{CM}} = 1.5\text{V}$  ( $V_S = 3\text{V}$ ) の場合と比較して、それぞれ $\pm 1\text{mV}$ 以内および $\pm 35\text{mV}$ 以内になっていることを検査する。

出力同相電圧範囲のテストでは、「電気的特性」の表に記載されている制限値で、同相オフセット $(V_{\text{OSCM}})$ が、 $V_{\text{OCM}} = 2.5\text{V}$  ( $V_S = 5\text{V}$ ) および  $V_{\text{OCM}} = 1.5\text{V}$  ( $V_S = 3\text{V}$ ) の場合と比較して、 $\pm 15\text{mV}$ 以内になっていることを検査する。

**Note 10:** 入力 CMRR は、 $+ \text{IN}$  ピンまたは $-\text{IN}$  ピンでの入力同相電圧の変化と差動入力換算オフセット電圧の変化の比として定義される。出力 CMRR は、 $V_{\text{OCM}}$  ピンの電圧の変化と差動入力換算オフセット電圧の変化の比として定義される。この規格は 2 つの出力とそれぞれの入力の間の帰還比の整合に大きく依存し、実際のアンプ性能を測定するのは困難である(「アプリケーション情報」のセクションの「抵抗対の不整合による影響」を参照)。帰還部品の整合に依存しない実際のアンプ性能を示すより優れた指標については、PSRR の規格を参照。

**Note 11:** 差動電源電圧除去比(PSRR)は、電源電圧の変化と差動入力換算オフセット電圧の変化の比として定義される。同相電源電圧除去比(PSRRCM)は、電源電圧の変化と同相オフセット電圧の変化の比として定義される。

**Note 12:** 電源電圧範囲は電源電圧除去比のテストによって保証される。

## 標準的性能特性

6362 G01

6362 G02

6362 G03

6362 G04

6362 G05

6362 G06

6362 G07

6362 G08

6362 G09

## 標準的性能特性

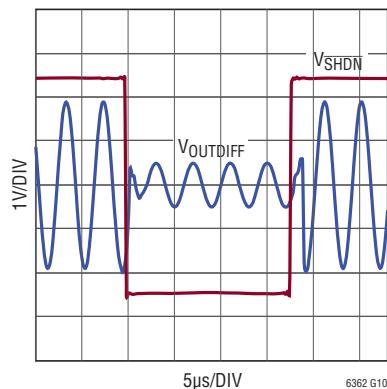

ターンオンおよびターンオフ時の過渡応答

6362 G10

6362 G11

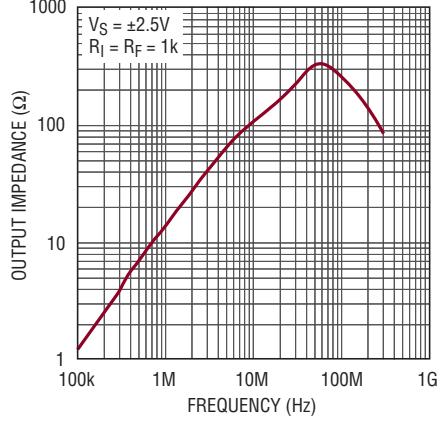

差動出力インピーダンスと周波数

6362 G12

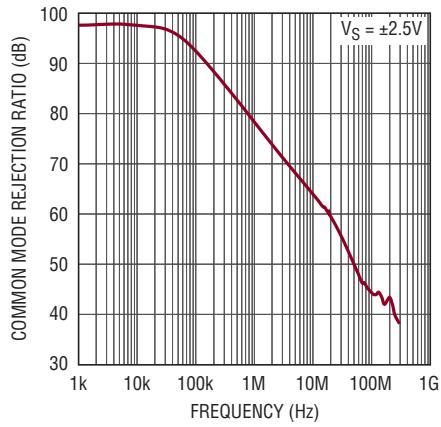

同相除去比と周波数

6362 G13

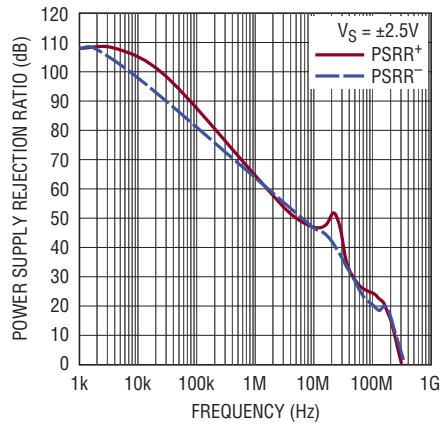

差動電源電圧除去比と周波数

6362 G14

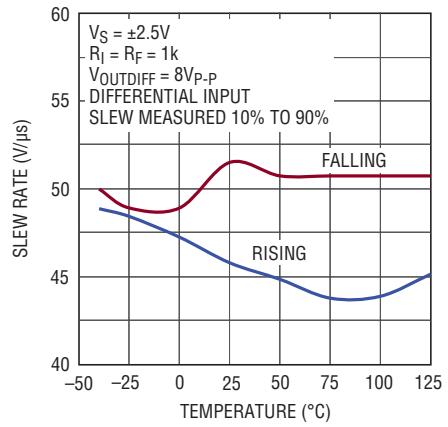

スルーレートと温度

6362 G15

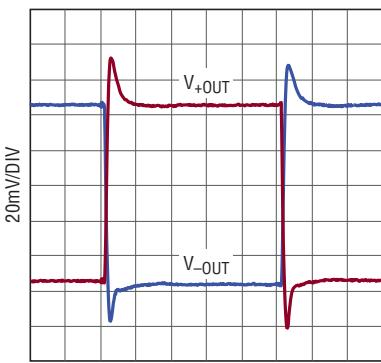

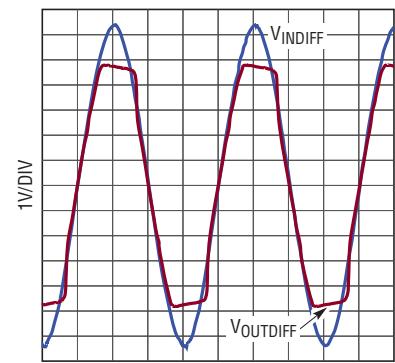

小信号ステップ応答

$V_S = \pm 2.5V$

$V_{INDIFF} = 200mV_{P-P}$

$R_I = R_F = 1k$

$R_{LOAD} = 1k$

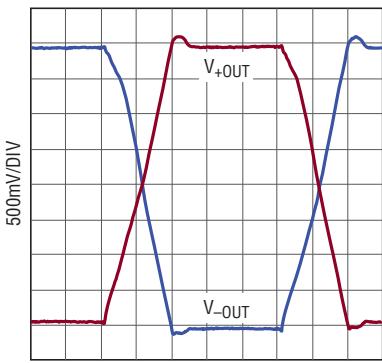

大信号ステップ応答

$V_S = \pm 2.5V$

$V_{INDIFF} = 8V_{P-P}$

$R_{LOAD} = 1k$

オーバードライブされた出力の過渡応答

$V_S = \pm 2.5V$

$V_{INDIFF} = 13V_{P-P}$

$R_{LOAD} = 1k$

## 標準的性能特性

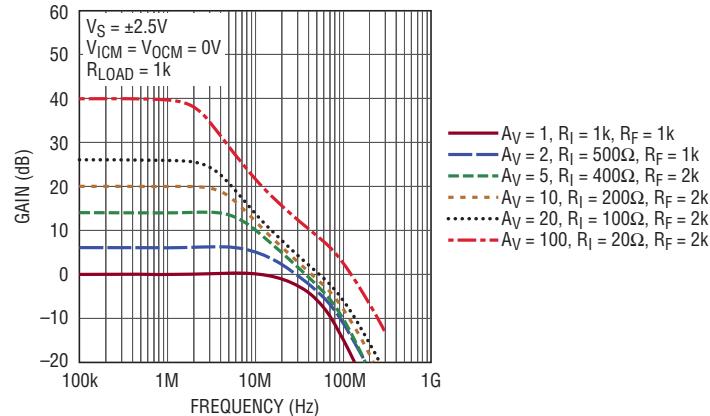

周波数応答と閉ループ利得

6362 G19

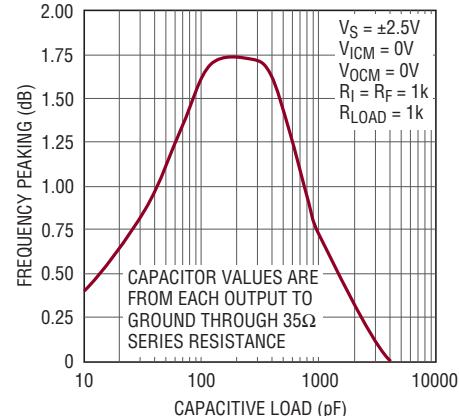

周波数のピーキングと負荷容量

6362 G20

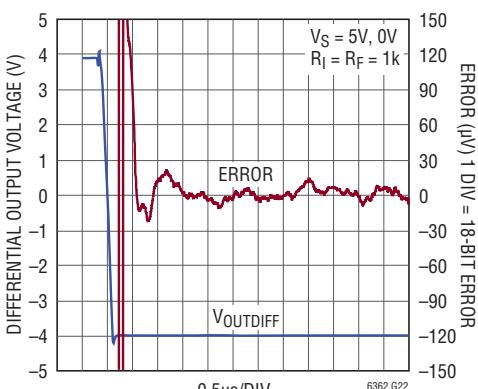

セッティング時間と出力ステップ

6362 G21

8V<sub>P-P</sub>の出力ステップに対する

セッティング時間

6362 G22

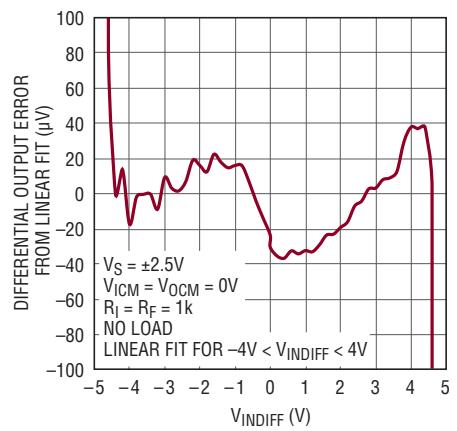

DC直線性

6362 G23

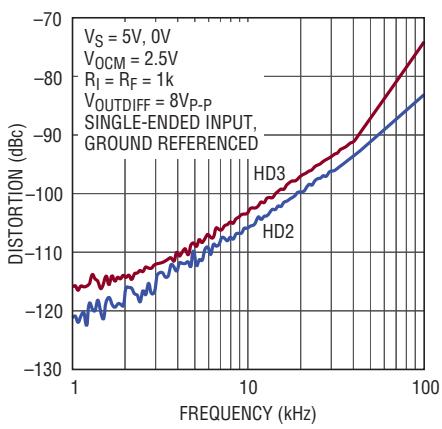

高調波歪みと周波数

6362 G24

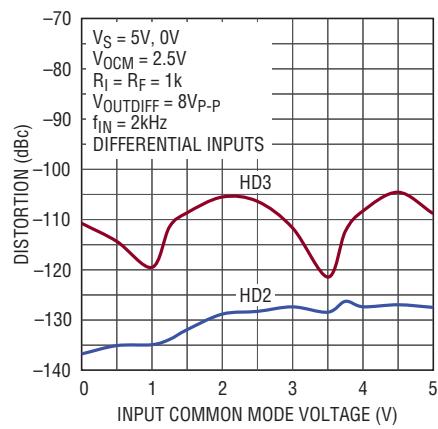

高調波歪みと入力同相電圧

6362 G25

高調波歪みと出力振幅

6362 G26

6362fa

## ピン機能

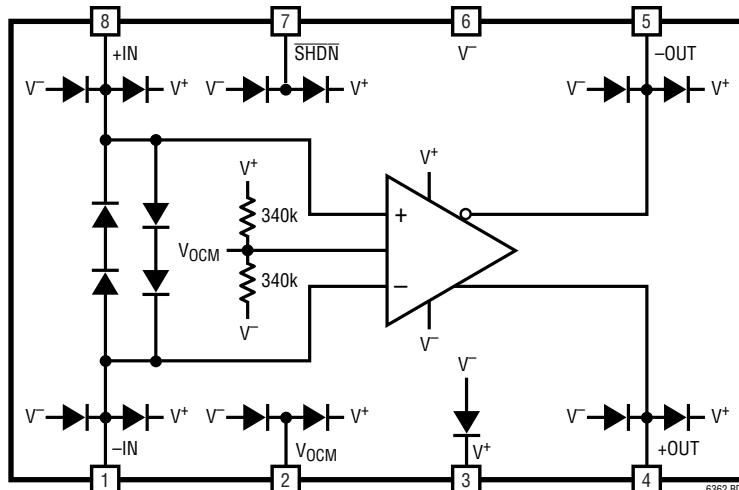

**-IN(ピン1)** : アンプの反転入力。有効な入力範囲は  $V^-$  から  $V^+$  までです。

**$V_{OCM}$ (ピン2)** : 出力同相リファレンス電圧。このピンの電圧は出力同相電圧のレベルを設定します。フロートのままにすると、内部の抵抗分割器によってデフォルトの電圧である 2.5V が発生します(5V 電源の場合)。

**$V^+$ (ピン3)** : 正電源。動作電源範囲は  $V^- = 0V$  の場合、2.8V ~ 5.25V です。

**+OUT(ピン4)** : 正の出力ピン。出力はレール・トゥ・レールの振幅が可能です。

**-OUT(ピン5)** : 負の出力ピン。出力はレール・トゥ・レールの振幅が可能です。

**$V^-$ (ピン6、露出パッド・ピン9)** : 負電源。通常は 0V です。負電源は  $2.8V \leq (V^+ - V^-) \leq 5.25V$  の条件を維持する限り負の電圧にすることができます。

**SHDN(ピン7)** : SHDN をフロート状態にするか  $V^+$  に直接接続すると、LTC6362 は通常の(アクティブな)動作モードに入ります。SHDN ピンを  $V^-$  に接続するとデバイスはディスエーブルされ、流れる電源電流は約  $70\mu A$  になります。

**+IN(ピン8)** : アンプの非反転入力。有効な入力範囲は  $V^-$  から  $V^+$  までです。

## ブロック図

## アプリケーション情報

### 機能の説明

LTC6362は、低消費電力、低ノイズ、高DC精度の完全差動オペアンプ/ADCドライバです。このアンプは、完全な差動信号またはシングルエンド信号を、高性能、低消費電力の差動逐次比較型(SAR)A/Dコンバータに適した低インピーダンスの平衡差動出力に変換するように最適化されています。このアンプの平衡差動特性により、偶数次高調波歪みが取り除かれ、(電源ノイズのような)同相ノイズの影響を受けにくくなります。

LTC6362の出力はレール・トゥ・レールの振幅が可能で、最大35mAの電流を流し出すことや流し込むことができます。LTC6362は帯域幅が広く低消費電力のアプリケーション向けに最適化されています。対グランドでは10pF、差動では5pFを超える負荷容量がある場合は、10Ω～100Ωの直列抵抗を各出力から接続してデカップリングし、発振やリンギングを防ぐ必要があります。帰還はアンプの出力から直接とるようにしてください。電圧利得が高い構成は電圧利得が低い構成に比べて閉ループ帯域幅が低いので、容量性負荷の駆動能力が高くなる傾向があります。

### 入力ピンの保護

LTC6362の入力段は、+INと-INの間に逆並列接続された2対の直列ダイオードによって、1.4Vを超える差動入力電圧から保護されます。さらに、すべてのピンには正負両方の電源に対してクランピング・ダイオードが接続されています。任意のピンがいざれか一方の電源電圧を超える電圧まで駆動されると、デバイスの損傷を防ぐために電流は10mA以下に制限されます。

### SHDNピン

LTC6362はSHDNピンを備えています。このピンは、負の電源電圧の上0.8V以内の電圧に駆動すると、電源から流れる電流がわずか70μAになるようにアンプの動作を停止する機能を備えています。すべての条件で完全なシャットダウンを保証するため、プルダウン回路には4μA以上のシンク電流能力が必要です。通常動作のためには、SHDNピンをフロート状態のままにするか、正の電源に接続する必要があります。

### 一般的なアンプのアプリケーション

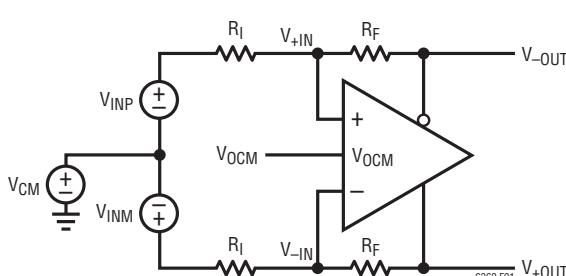

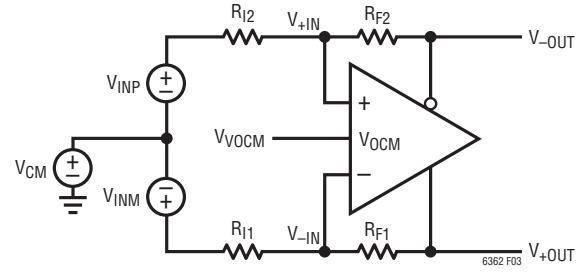

図1では、V<sub>INP</sub>およびV<sub>INM</sub>から得られるV<sub>OUTDIFF</sub>に対する利得は次式で表されます。

$$V_{\text{OUTDIFF}} = V_{+\text{OUT}} - V_{-\text{OUT}} \approx \left( \frac{R_F}{R_I} \right) \cdot (V_{\text{INP}} - V_{\text{INM}})$$

この式では、差動出力電圧(V<sub>+</sub>OUT - V<sub>-</sub>OUT)が入力と出力の同相電圧、つまり同相ピンの電圧とはまったく無関係であることに注意してください。このためLTC6362は、シングルエンド信号の前置増幅、レベルシフト、差動出力信号への変換を行って、差動入力のA/Dコンバータを駆動するのに最適です。

### 出力同相電圧とV<sub>OCM</sub>ピン

出力同相電圧は2つの出力の平均として定義されます。

$$V_{\text{OUTCM}} = V_{\text{OCM}} = \left( \frac{V_{+\text{OUT}} + V_{-\text{OUT}}}{2} \right)$$

この式が示すように、出力同相電圧は入力同相電圧とは無関係であり、同相帰還ループが内蔵されているために、むしろV<sub>OCM</sub>ピンの電圧によって決まります。

V<sub>OCM</sub>ピンを開放のままにすると、内部の抵抗分割器によってデフォルトの電圧である2.5Vが発生します(5V電源の場合)。V<sub>OCM</sub>ピンは必要に応じて別の電圧にオーバードライブすることができます。たとえば、A/Dコンバータを駆動するときに、同相電圧を設定するためのリファレンスがA/Dコンバータから得られる場合は、V<sub>OCM</sub>ピンによって示される170kの入力抵抗を駆動する能力がA/Dコンバータにある限り、リファレンスをV<sub>OCM</sub>ピンに直接接続することができます。V<sub>OCM</sub>ピンに入力できる電圧の有効な範囲(V<sub>OUTCMR</sub>)は、「電気的特性」の表に規定されています。

## アプリケーション情報

### 入力同相電圧範囲

LTC6362の入力同相電圧( $V_{ICM}$ )は、2つの入力ピン $V_{+IN}$ と $V_{-IN}$ の電圧の平均として定義されます。LTC6362の入力はレール・トゥ・レールの振幅が可能なので、 $V_{ICM}$ として使用できる有効な範囲は $V^- \sim V^+$ となります。ただし、利得設定用抵抗および帰還抵抗の外付け抵抗分割器動作により、処理できる信号の有効な範囲はさらに広くなります。オペアンプ入力での入力同相電圧範囲は、回路構成(利得)、 $V_{OCM}$ 、および $V_{CM}$ により異なります(図1を参照)。完全な差動入力アプリケーションの場合、つまり $V_{INP} = -V_{INM}$ である場合、同相入力電圧はおよそ次のようになります。

$$V_{ICM} = \frac{V_{+IN} + V_{-IN}}{2} \approx V_{OCM} \cdot \frac{R_I}{R_I + R_E} + V_{CM} \cdot \frac{R_F}{R_I + R_E}$$

シングルエンド入力の場合は、入力同相電圧に対する入力信号成分があります。 $(V_{INM}を0に設定して)$   $V_{INP}$ のみを入力すると、入力同相電圧はおよそ次のようにになります。

$$V_{\text{ICM}} = \frac{V_{+\text{IN}} + V_{-\text{IN}}}{2}$$

$$\approx V_{\text{OCM}} \cdot \frac{R_I}{R_I + R_E} + V_{\text{CM}} \cdot \frac{R_F}{R_I + R_E} + \frac{V_{\text{INP}}}{2} \cdot \frac{R_F}{R_I + R_E}$$

この意味は、たとえば入力信号( $V_{INP}$ )が正弦波の場合は、その正弦波信号が減衰した信号もオペアンプの入力に現れるということです。

図1. 定義と用語

### 入力バイアス電流

入力バイアス電流は $V_{ICM}$ に応じて変化します。負電源より0.2V高い電圧から正電源より1.1V低い電圧までを範囲とする同相電圧の場合、入力バイアス電流は $\Delta I_B/\Delta V_{ICM} = 75\text{nA/V}$ に従

います。ここで、 $V_{ICM} = 2.5V$ での $I_B$ は、5V電源では標準で75nA未満です。正電源より1.1V低い電圧から正電源より0.2V低い電圧までを範囲とする同相電圧の場合、入力バイアス電流は $\Delta I_B / \Delta V_{ICM} = 25nA/V$ に従います。ここで、 $V_{ICM} = 4.5V$ での $I_B$ は、5V電源では標準で75nA未満です。これらの範囲内での動作では、電圧降下による誤差を最小限に抑える必要があるソース抵抗の高いアプリケーションでアンプを使用できます。 $V_{ICM}$ が正負両電源電圧の0.2V以内にあるアプリケーションでは、入力バイアス電流が1 $\mu A$ より高い値に達することができます。

## 入力インピーダンスと負荷の影響

図1のV<sub>INP</sub>入力またはV<sub>INM</sub>入力に対する低周波数での入力インピーダンスは、入力の駆動方法によって異なります。完全な差動入力信号源の場合(V<sub>INP</sub>=-V<sub>INM</sub>)、一方の入力から見た入力インピーダンスは単純に次のようになります。

$$R_{INP} = R_{INM} = R_I$$

シングルエンド入力の場合は、入力での信号の不均衡により、均衡のとれた差動の場合よりも入力インピーダンスが実際に増加します。入力インピーダンスはどちらの入力の場合も次式で表されます。

$$R_{INP} = R_{INM} = \frac{R_I}{1 - \left( \frac{1}{2} \right) \cdot \left( \frac{R_F}{R_I + R_F} \right)}$$

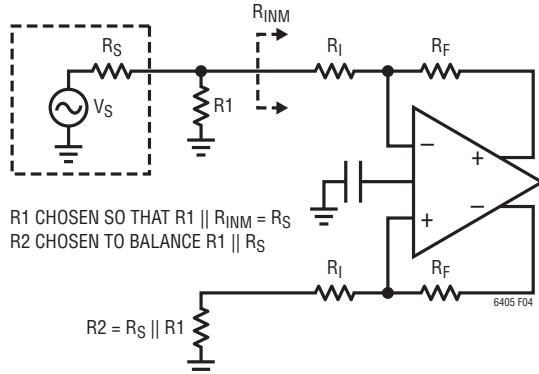

出力インピーダンスが0ではない入力信号源は、帰還回路網の対の間で帰還の不均衡を生じることもあります。最良の性能を発揮するには、入力信号源の出力インピーダンスを補償することを推奨します。信号源によって入力インピーダンスの整合が要求される場合は、次式に当てはまるように終端抵抗  $R_1$  を選択してください(図2を参照)。

$$R1 = \frac{R_{INM} \cdot R_S}{R_{INM} - R_S}$$

図2によると、上の式で示すように、差動アンプへの入力インピーダンス( $R_{INM}$ )は、シングルエンドの信号源の場合を反映しています。また、 $R_2$ は次式に従って選択します。

$$R_2 = R_1 \parallel R_S = \frac{R_1 \cdot R_S}{R_1 + R_S}$$

## アプリケーション情報

図2. 信号源インピーダンスの最適な補償

### 抵抗対の不整合による影響

実際の抵抗が完全には整合しないことを考慮に入れた回路図を図3に示します。開ループ利得が無限であると仮定すると、差動出力の関係は次式によって表されます。

$$\begin{aligned} V_{\text{OUT(DIFF)}} &= V_{+\text{OUT}} - V_{-\text{OUT}} \\ &\approx V_{\text{INDIFF}} \cdot \frac{R_F}{R_I} + V_{\text{CM}} \cdot \frac{\Delta\beta}{\beta_{\text{AVG}}} - V_{\text{OCM}} \cdot \frac{\Delta\beta}{\beta_{\text{AVG}}} \end{aligned}$$

ここで、 $R_F$ は $R_{F1}$ と $R_{F2}$ の平均、 $R_I$ は $R_{I1}$ と $R_{I2}$ の平均です。

$\beta_{\text{AVG}}$ は、出力からそれぞれの入力への平均帰還率として定義されます。

$$\beta_{\text{AVG}} = \frac{1}{2} \cdot \left( \frac{R_{I1}}{R_{I1} + R_{F1}} + \frac{R_{I2}}{R_{I2} + R_{F2}} \right)$$

$\Delta\beta$ は帰還率の差として定義されます。

$$\Delta\beta = \frac{R_{I2}}{R_{I2} + R_{F2}} - \frac{R_{I1}}{R_{I1} + R_{F1}}$$

ここで、 $V_{\text{CM}}$ および $V_{\text{INDIFF}}$ は、それぞれ2つの入力電圧 $V_{\text{INP}}$ および $V_{\text{INM}}$ の平均および差として定義されます。

$$V_{\text{CM}} = \frac{V_{\text{INP}} + V_{\text{INM}}}{2}$$

$$V_{\text{INDIFF}} = V_{\text{INP}} - V_{\text{INM}}$$

図3. 帰還抵抗対の不整合がある場合の実際のアプリケーション

帰還率に不整合( $\Delta\beta$ )があると、同相から差動への変換が行われます。差動入力を0に設定( $V_{\text{INDIFF}} = 0$ )すると、同相から差動への変換の程度は次式によって得られます。

$$V_{\text{OUTDIFF}} \approx (V_{\text{CM}} - V_{\text{OCM}}) \cdot \Delta\beta / \beta_{\text{AVG}}$$

一般に、帰還対の不整合は2つの信号およびノイズが同相から差動に変換される原因の1つです。0.1%以上の精度の抵抗を使用すれば、大半の問題は軽減されます。入力信号源と $V_{\text{OCM}}$ ピンの両方のリファレンスとして、低インピーダンスのグランド・プレーンを使用する必要があります。

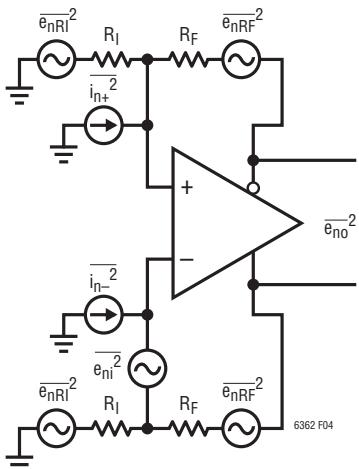

### ノイズ

LTC6362の差動入力換算の電圧ノイズ密度および電流ノイズ密度は、それぞれ $3.9\text{nV}/\sqrt{\text{Hz}}$ および $0.8\text{pA}/\sqrt{\text{Hz}}$ です。アンプで発生するノイズの他に、周辺の帰還抵抗もノイズの発生源になります。簡素化されたノイズのモデルを図4に示します。アンプと帰還部品の双方から発生する出力ノイズは次式によって求められます。

$$e_{\text{no}} = \sqrt{\left[ e_{\text{ni}} \cdot \left( 1 + \frac{R_F}{R_I} \right) \right]^2 + 2 \cdot (i_n \cdot R_F)^2 + 2 \cdot \left[ e_{\text{nRI}} \cdot \frac{R_F}{R_I} \right]^2 + 2 \cdot e_{\text{nRF}}^2}$$

たとえば、 $R_F = R_I = 1\text{k}$ の場合、回路の出力ノイズは $e_{\text{no}} = 12\text{nV}/\sqrt{\text{Hz}}$ となります。

アンプ周辺の回路が十分に均衡がとれている場合、上に示す差動出力ノイズの式には同相ノイズ( $e_{\text{nvocm}}$ )が現れません。

## アプリケーション情報

図4. 簡素化したノイズ・モデル

LTC6362の入力換算電圧ノイズは、920Ωの抵抗によって発生するノイズと等価です。これより値が大きい抵抗で帰還回路網が構成されている場合、出力ノイズの中心となるのは抵抗ノイズとアンプの電流ノイズです。920Ωより小さい値の抵抗で構成される帰還回路網の場合、出力ノイズの中心となるのは電圧ノイズです。

抵抗値を低くするとノイズは必ず小さくなります。出力の帰還回路網の負荷が重くなるために歪みが大きくなるというマイナス面があります。抵抗値を高くすると出力ノイズが大きくなりますが、出力の負荷が軽くなるので通常は歪み特性が改善されます。この理由から、差動利得を1にしてLTC6362を構成した場合は、1k以上の帰還抵抗を使用することを推奨します。

### 利得帯域幅積と $f_{-3dB}$

利得帯域幅積(GBW)および $-3dB$ 周波数( $f_{-3dB}$ )は、LTC6362の速度を表す2つの異なる測定基準として「電気的特性」に規定されています。GBWは、特定の周波数( $f_{TEST}$ )でアンプの開ループ利得を測定し、その後「利得 $\times f_{TEST}$ 」を計算することによって求められます。GBWはアンプの内部設計と補償のみに依存するパラメータで、アンプ固有の速度性能を規定するのに適した測定基準です。

他方、 $f_{-3dB}$ はさまざまなアプリケーションでより実用的な目的のあるパラメータで、定義によると開ループ利得が低周波数での値より3dB低くなる周波数です。 $f_{-3dB}$ の値はアンプの速

度と帰還率に依存します。LTC6362は差動信号利得が1の場合(その場合は $R_I = R_F$ つまり $\beta = 1/2$ )に安定するよう設計されているので、「電気的特性」の表に示すように、最大の $f_{-3dB}$ はこの利得設定で得られ、実測されます。

大半のアンプでは、ユニティ・ゲインのクロスオーバー周波数より低いほとんどの周波数領域で、開ループ利得の応答が従来の単一ポール減衰を示し、GBWとユニティ・ゲイン周波数は互いに近い値になります。しかし、LTC6362では、GBWが $f_{-3dB}$ より大幅に大きくなるように意図的に補償されています。これは、通常アンプの入力が動作する低い周波数領域では、アンプの利得が大きくなり、したがって帰還ループ利得が大きくなることを意味します。これには、アンプをさらに線形化して該当の周波数領域での歪み特性を改善するという重要な利点があります。

### 帰還コンデンサ

反転入力での寄生容量の結合(デバイス+プリント回路基板)によって、アンプの閉ループ帯域幅の範囲内に周波数が入るポールが形成されるようにLTC6362を接続する場合には、帰還抵抗( $R_F$ )と並列にコンデンサ( $C_F$ )を追加して、安定性の低下を打ち消すことができます。 $C_F$ はポールの周波数に近い周波数でゼロを生成するように選ぶ必要があります。

通常は $C_F$ の値を大きくすると周波数と時間領域の両方でアンプのピーキング(オーバーシュート)が減りますが、閉ループ帯域幅( $f_{-3dB}$ )も減少します。

### 基板のレイアウトとバイパス・コンデンサ

単電源アプリケーションでは、高品質の0.1μFセラミック・バイパス・コンデンサをV<sup>+</sup>ピンとV<sup>-</sup>ピンの間に短い配線で直接配置することを推奨します。V<sup>-</sup>ピン(DD8パッケージの露出パッドを含む)は配線を極力短くして低インピーダンスのグランド・プレーンに直接接続してください。両(分割)電源の場合は、V<sup>+</sup>とグランドの間、およびV<sup>-</sup>とグランドの間に、やはり最短の配線長で高品質の0.1μFセラミック・バイパス・コンデンサを追加して使用することを推奨します。寸法の小さい(たとえば0603サイズの)表面実装セラミック・コンデンサは、リード付きコンデンサよりもはるかに自己共振周波数が高く、LTC6362に最適です。

## アプリケーション情報

安定性応答の低下を防ぐには、プリント回路基板の接続配線を可能な限り短くすることにより、入力ピン(+INおよび-IN)での浮遊容量を徹底的に小さくすることを推奨します。

出力では、LTC6362の差動特性を常に念頭においてください。両方の出力に存在する負荷インピーダンス(浮遊インピーダンスまたは意図的なインピーダンス)ができるだけ均衡させ対称にすることが非常に重要であるからです。このことは、偶数次高調波歪みの発生を最小限に抑えて同相信号および同相ノイズを最大限に除去するLTC6362のバランスのとれた動作を維持するのに役立ちます。

V<sub>OCM</sub>ピンは高品質の0.1μFセラミック・コンデンサを使用してグランド・プレーンにバイパスする必要があります。こうすると、インピーダンスの不整合により、このピンの同相信号および同相ノイズが誤って差動信号および差動ノイズに変換されるのをデバイスの外部と内部の両方で防ぐことができます。

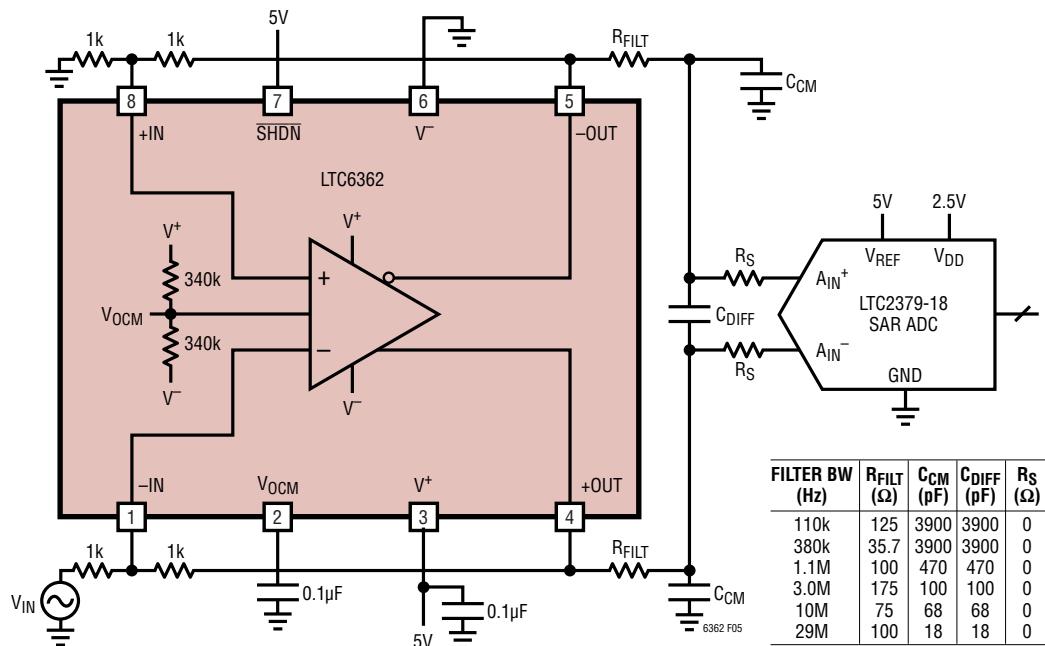

### A/Dコンバータとのインターフェース

A/Dコンバータを駆動するときは、LTC6362の出力とA/Dコンバータの入力の間に受動フィルタを追加してください。アプリケーションによっては、単一ポールのRCフィルタで十分なことがあります。A/Dコンバータのサンプリング過程では、A/Dコンバータのサンプリング・コンデンサのスイッチングに起因する電荷の過渡現象が発生します。これにより、アンプとサンプリング・コンデンサの間を電荷が移動するときに、アンプの出力が瞬間的に「短絡」します。入力信号の有効な表現を得るには、収集期間が終了する前にアンプがこの負荷トランジエントから回復して安定状態に戻る必要があります。ドライバの出力とA/Dコンバータの入力の間に接続されたRC回路網は、A/Dコンバータのサンプリング時過渡電圧を減結合します(図5を参照)。この容量はサンプリング過程中に大量の電荷を供給する役割を果たし、LTC6362の出力に取り付けた2本の抵抗は、A/Dコンバータから注入された電荷を抑制して減衰させるために使用されます。RCフィルタには、広帯域出力ノイズの帯域を制限するという付加的な利点もあります。

適切なフィルタの選択は個別のA/Dコンバータによって異なりますが、フィルタ部品の値を選択する場合には以下の手順を推奨します。入力信号に対して適切なRC時定数を選択することから始めます。一般に、時定数を長くするとSNRは改善されますが、セトリング時間が長くなります。出力の過渡状態を18ビット精度まで安定化するには、通常RC時定数の12倍を超える時間がかかります。抵抗値を選択するときは、デカッピング回路網の抵抗を10Ω以上にする必要があることを忘れないでください。これらの抵抗はLTC6362の出力を負荷容量から減結合する役割も果たしていることに注意してください。抵抗値が大きすぎるとセトリング時間が不十分になります。抵抗値が小さすぎるとサンプリング過程の負荷トランジエントを十分に抑制できず、セトリングに要する時間が長くなります。歪みを最小限に抑えるには、C0G積層セラミック・コンデンサなど、誘電吸収の小さいコンデンサを選択してください。一般に、コンデンサの値が大きいと固定非線形充電のキックバックが減衰しますが、コンデンサの値が非常に大きいと目的の入力周波数でドライバに重い負荷がかかるので、ドライバで歪みが発生します。入力振幅が小さいと、ドライバでの負荷処理の要求が減少するので、通常はフィルタ・コンデンサの値を大きくすることができます。ただし、この特性は、使用される特定のA/Dコンバータに対する微分非線形充電のキックバックが特定の入力振幅に依存することによって制限される場合があります。

アプリケーションによっては、A/Dコンバータの入力に直列抵抗を配置すると歪み性能がさらに改善することができます。これらの直列抵抗はA/Dコンバータのサンプリング・コンデンサとの組み合わせにより、潜在的なグランド・バウンスなど、高速サンプリングによる外乱を減衰させる役割を果たします。さらに、これらの抵抗は、ドライバ出力まで伝播してしまう残留フィルタ・グリッチの立ち上がり時間を制限します。可能性があるグリッチ伝播の立ち上がり時間をドライバの小信号帯域幅の範囲内に制限すると、外乱の少ない出力セトリングが可能になります。

LTC2379-18 SAR A/Dコンバータを利得がA<sub>V</sub>=-1の構成で駆動するLTC6362の特定のアプリケーションについて、可変フィルタ帯域幅でのRCフィルタの部品推奨値を図5に示します。これらの部品の値は最適な歪み性能が得られるように選択されています。広帯域の出力ノイズはフィルタの帯域幅によって異なります。

## アプリケーション情報

図5. LTC2379-18 SAR ADCを駆動するための推奨インターフェース解決策

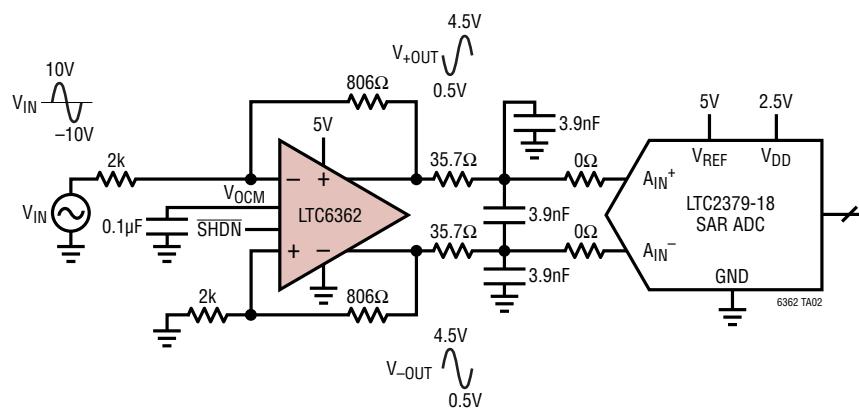

## 標準的応用例

グランドを基準にした20V<sub>P-P</sub>の入力を  $A_V = -0.4$  の利得でシングルエンドから差動に変換してA/Dコンバータを駆動

# LTC6362

## 標準的応用例

2.5Vを基準にした5V<sub>P-P</sub>の入力を $A_V = -1.6$ の利得でシングルエンドから差動に変換してA/Dコンバータを駆動

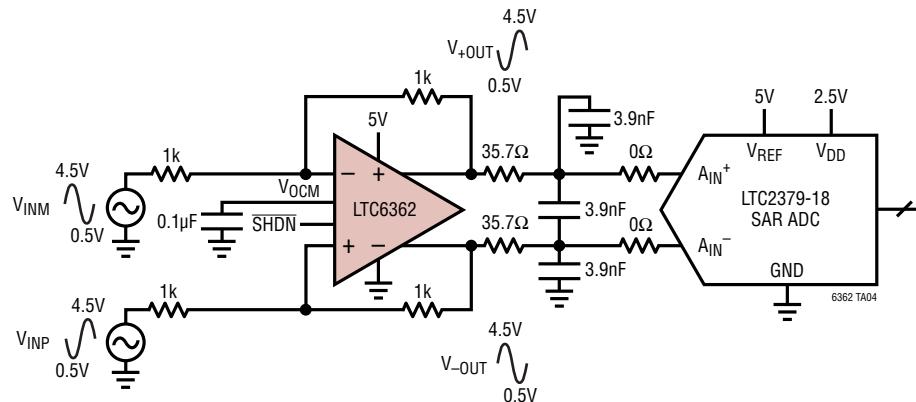

$\Delta V_{IN} = 8V_{P-P}$ および $A_V = 1$ という利得でA/Dコンバータを差動で駆動

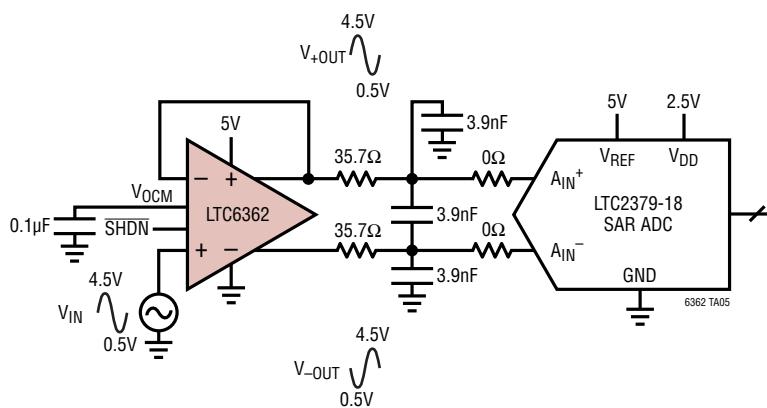

4V<sub>P-P</sub>の入力を $A_V = 2$ の利得でシングルエンドから差動に変換してA/Dコンバータを駆動するアプリケーション。

入力インピーダンスが高いことが重要であるため、歪み、ノイズ、およびDC精度がある程度悪化するのは構わない。

入力は真の高インピーダンスだが、出力には同相ノイズと同相オフセットが存在する。さらに、入力信号が2.8V<sub>P-P</sub>を超えると、入力オフセットに段差が生じて歪み性能が低下する。

6362fa

## 標準的應用例

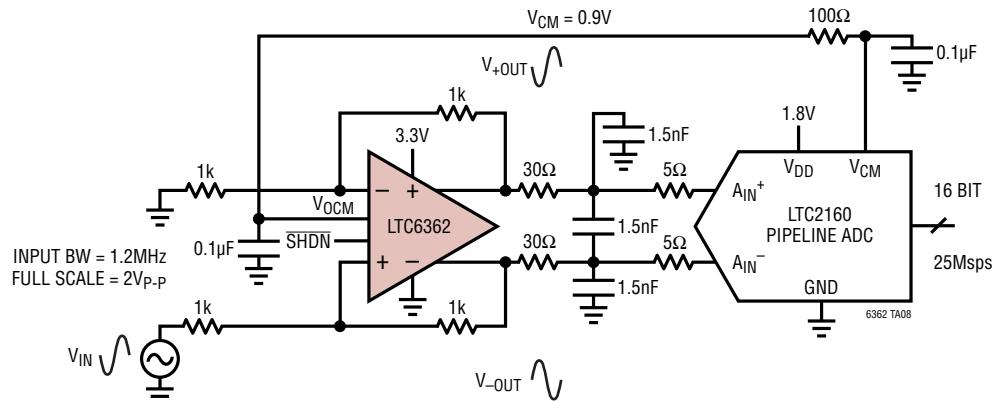

$A_V = 1$  でパイプライン型 A/D コンバータを差動で駆動

#### MEASURED PERFORMANCE FOR LTC6362 DRIVING LTC2160:

INPUT:  $f_{IN} = 2\text{kHz}$ ,  $-1\text{dBFS}$

SNR: 77.0dB

HD2: -98.9dBc

HD3: -102.3dB

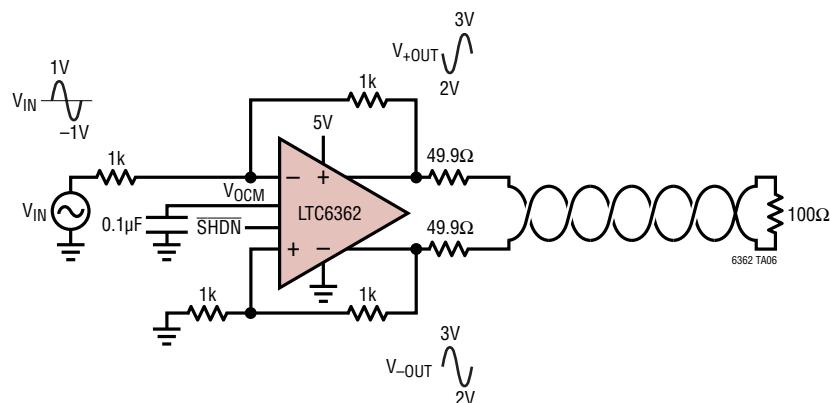

$A_V = -1$ の利得で接続された差動ライン・ドライバ

LTC6362

## 標準的應用例

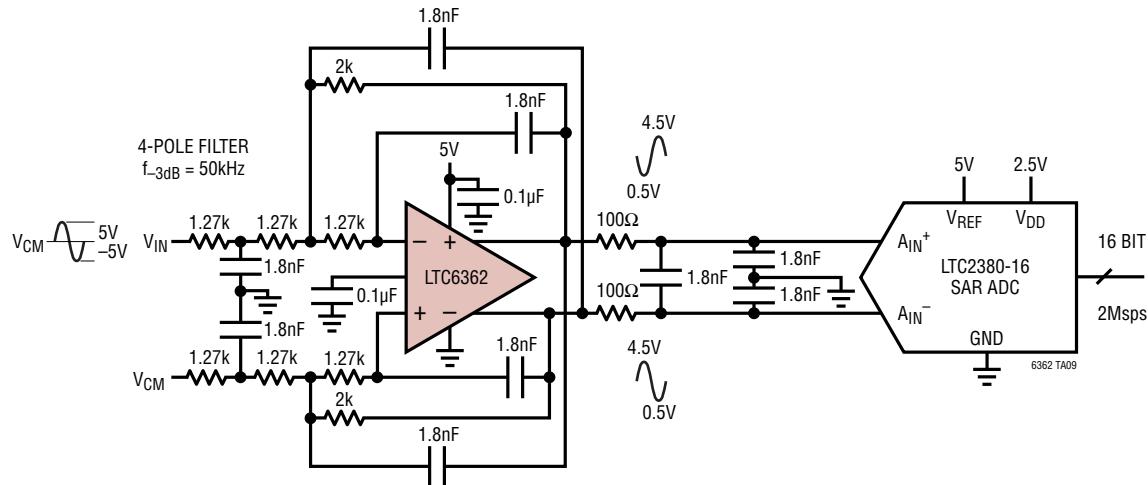

ローパス・フィルタ/ドライバとして使用する LTC6362。10V<sub>P-P</sub> のシングルエンド入力、SAR A/D コンバータを駆動

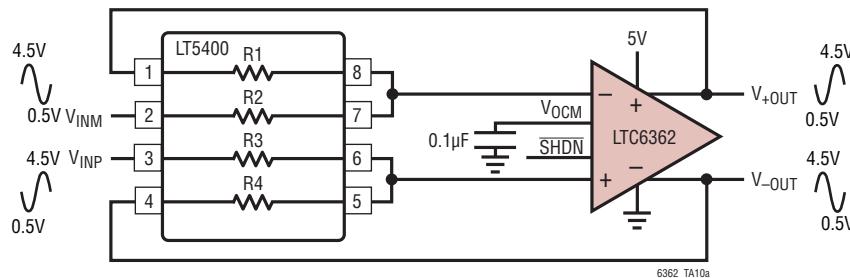

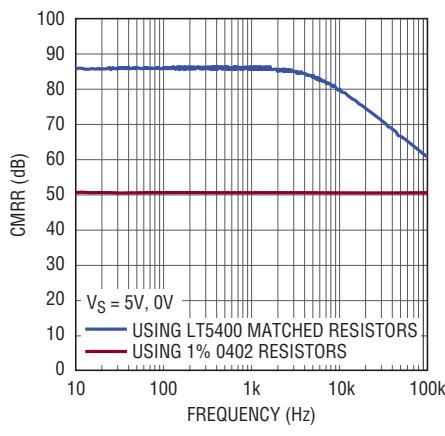

4回路入りの整合した抵抗回路網であるLT<sup>®</sup>5400を使用した $A_V = 1$ の差動構成

## LT5400 使用時と 1% 精度の 0402 抵抗使用時の CMRR の比較

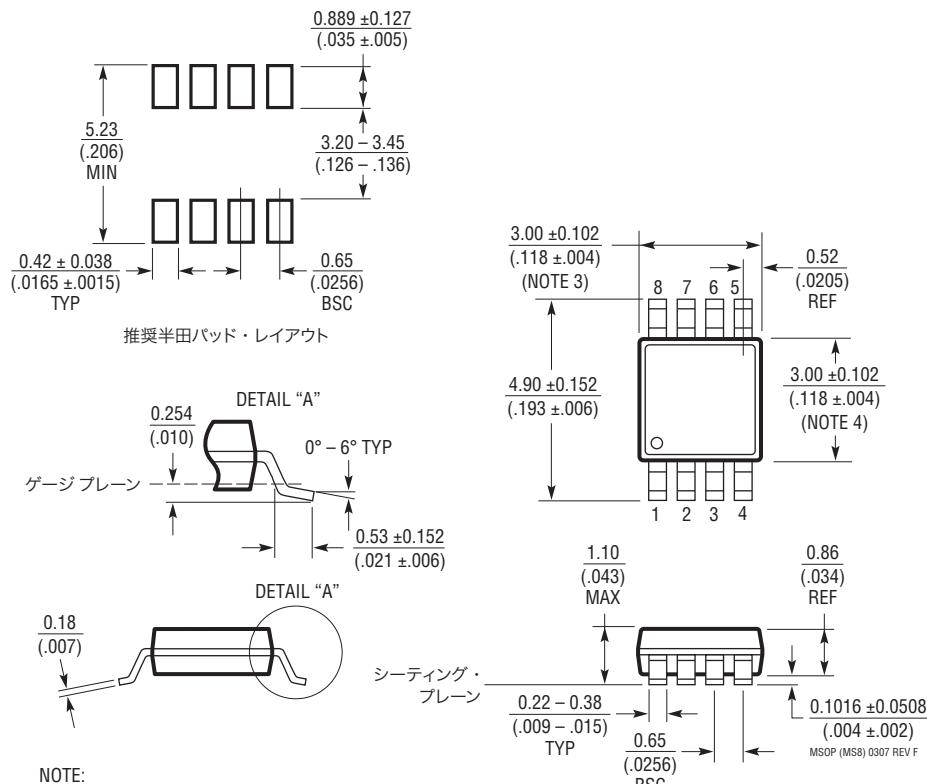

## パッケージ

最新のパッケージ図については、<http://www.linear-tech.co.jp/designtools/packaging/>を参照してください。

**MS8 Package**

**8-Lead Plastic MSOP**

(Reference LTC DWG # 05-08-1660 Rev F)

## NOTE:

- 寸法はミリメートル / (インチ)

- 図は実寸とは異なる

- 寸法にはモールドのバリ、突出部、またはゲートのバリを含まない

モールドのバリ、突出部、またはゲートのバリは、各サイドで 0.152mm (0.006") を超えないこと

- 寸法にはリード間のバリまたは突出部を含まない

リード間のバリまたは突出部は各サイドで 0.152mm (0.006") を超えないこと

- リードの平坦度(成形後のリードの底面)は最大 0.102mm (0.004") であること

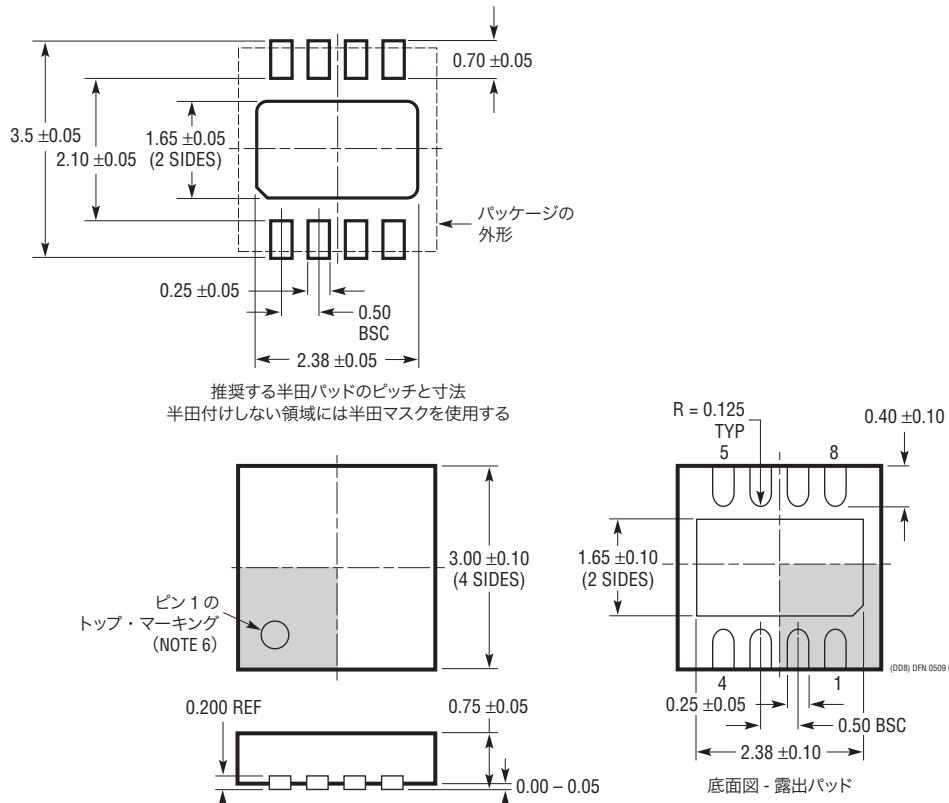

## パッケージ

最新のパッケージ図については、<http://www.linear-tech.co.jp/designtools/packaging>を参照してください。

DDパッケージ

8ピン・プラスチック DFN(3mm×3mm)

(Reference LTC DWG #05-08-1698 Rev C)

NOTE:

1. 図はJEDECのパッケージ外形 MO-229 のバリエーション(WEED-1)になる予定

2. 図は実寸とは異なる

3. 全ての寸法はミリメートル

4. パッケージの底面の露出パッドの寸法にはモールドのバリを含まない

モールドのバリは(もしあれば)各サイドで 0.15mm を超えないこと

5. 露出パッドは半田メッキとする

6. 灰色の部分はパッケージの上面と底面のピン1の位置の参考に過ぎない

## 改訂履歴

| REV | 日付   | 概要                                                       | ページ番号            |

|-----|------|----------------------------------------------------------|------------------|

| A   | 5/12 | DFNパッケージを追加<br>2V <sub>P-P</sub> t <sub>S</sub> の標準仕様を追加 | 1、2、9、13、20<br>4 |

# LTC6362

## 標準的応用例

グランドを基準にした10V<sub>P-P</sub>の入力を $A_V = -0.8$ の利得でシングルエンドから差動に変換して

5VリファレンスのSAR A/Dコンバータを駆動

## 関連製品

| 製品番号                                           | 説明                                                   | 注釈                                                                                         |

|------------------------------------------------|------------------------------------------------------|--------------------------------------------------------------------------------------------|

| <b>オペアンプ</b>                                   |                                                      |                                                                                            |

| LT6350                                         | 低ノイズ、シングルエンドから差動へのコンバータ/ADCドライバ                      | 4.8mA、100kHzでの歪み:-97dBc、4V <sub>P-P</sub> 出力                                               |

| LTC6246/LTC6247/<br>LTC6248                    | シングル/デュアル/クワッド 180MHz、<br>レール・トゥ・レール低消費電力オペアンプ       | アンプ1回路あたりの静止電流:1mA、4.2nV/ $\sqrt{\text{Hz}}$                                               |

| LTC6360                                        | 真のゼロ出力を備えた超低ノイズの<br>1GHzシングルエンドSAR ADCドライバ           | 13.6mA、HD2/HD3 = -103dBc/-109dBc(40kHz)、4V <sub>P-P</sub> 出力                               |

| LTC1992/LTC1992-X                              | 3MHz～4MHzの完全差動入出力アンプ                                 | 帰還抵抗を内蔵(利得=1、2、5、10)                                                                       |

| LT1994                                         | 低ノイズ、低歪みの70MHz完全差動<br>入出力アンプ/ドライバ                    | 13mA、1MHzでの歪み:-94dBc、2V <sub>P-P</sub> 出力                                                  |

| <b>A/Dコンバータ</b>                                |                                                      |                                                                                            |

| LTC2379-18/LTC2378-18<br>LTC2377-18/LTC2376-18 | 18ビット、1.6Msps/1Msps/500ksps/250ksps<br>シリアル、低消費電力ADC | 2.5V電源、差動入力、SNR:101.2dB、入力範囲: $\pm 5V$ 、DGC、<br>MSOP-16および4mm×3mm DFN-16パッケージの<br>ピン互換ファミリ |

| LTC2380-16/LTC2378-16<br>LTC2377-16/LTC2376-16 | 16ビット、2Msps/1Msps/500ksps/250ksps<br>シリアル、低消費電力ADC   | 2.5V電源、差動入力、SNR:96.2dB、入力範囲: $\pm 5V$ 、DGC、<br>MSOP-16および4mm×3mm DFN-16パッケージの<br>ピン互換ファミリ  |

| LTC2383-16/LTC2382-16/<br>LTC2381-16           | 16ビット、1Msps/500ksps/250kspsシリアル、<br>低消費電力ADC         | 2.5V電源、差動入力、SNR:92dB、入力範囲: $\pm 2.5V$ 、<br>MSOP-16および4mm×3mm DFN-16パッケージの<br>ピン互換ファミリ      |

| LTC2393-16/LTC2392-16/<br>LTC2391-16           | 16ビット、1Msps/500ksps/250kspsパラレル/<br>シリアルADC          | 5V電源、差動入力、SNR:94dB、入力範囲: $\pm 4.096V$ 、<br>7mm×7mm LQFP-48およびQFN-48パッケージのピン互換ファミリ          |

| LTC2355-14/LTC2356-14                          | 14ビット、3.5MspsシリアルADC                                 | 3.3V電源、1チャネル、ユニポーラ/バイポーラ、18mW、<br>MSOP-10パッケージ                                             |

| LTC2366                                        | 12ビット、3MspsシリアルADC                                   | 2.35V～3.6V電源、6ピンおよび8ピンTSOT-23パッケージ                                                         |

| LTC2162/LTC2161/<br>LTC2160                    | 16ビット、65/40/25Msps低消費電力ADC                           | 1.8V電源、差動入力、SNR:77dB、入力範囲:2V <sub>P-P</sub> 、<br>7mm×7mm QFN-48パッケージのパイプライン型A/Dコンバータ       |

6362fa