SmartMesh IP ノード 2.4GHz 802.15.4e

ワイヤレス・モート・モジュール

## ネットワークの特長

- 自己回復メッシュ・ネットワークを形成するための完全な無線トランシーバ、組み込みプロセッサ、およびネットワーク・ソフトウェア

- SmartMesh® ネットワークが実装する機能:

- ネットワーク規模の時間同期式スケジューリング

- 伝送周波数ホッピング単位

- 空間冗長性のある多様なトポロジー

- ネットワーク規模の信頼性と電力の最適化

- NIST認証済みのセキュリティ

- SmartMesh ネットワークが実現する性能:

- 最も困難なRF環境でも99.999%を超えるデータ信頼性を実現

- ルーティング・ノードの電流が50µA未満

- 6LoWPANインターネット・プロトコル(IP)およびIEEE 802.15.4e規格に準拠

## LTP5901-IPM/LTP5902-IPMの特長

- 業界最高レベルの低消費電力無線技術

- パケット受信時:4.5mA

- 0dBmでの送信時:5.4mA

- 8dBmでの送信時:9.7mA

- 米国、カナダ、EU、日本、台湾、韓国、インド、オーストラリア、ニュージーランドを含むRFモジュール認証

- PCBアセンブリにチップ・アンテナ(LTP5901-IPM)またはMMCXアンテナ・コネクタ(LTP5902-IPM)を内蔵

- QFNバージョン(LTC®5800-IPM)あり

## 概要

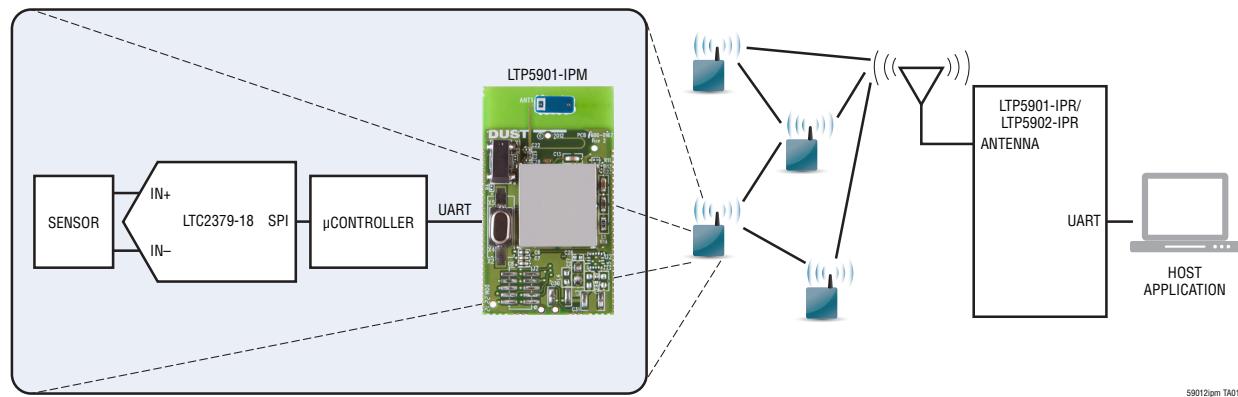

SmartMesh IP™ワイヤレス・センサ・ネットワークは、モートと呼ばれるワイヤレス・ノードから構築された自己管理式で低消費電力のインターネット・プロトコル(IP)ネットワークです。LTP™5901-IPM/LTP5902-IPMは、IEEE 802.15.4eプリント回路基板アセンブリ・ソリューションのEterna®\*ファミリにおけるIPモート製品で、Dust Networks®社による集積度の高い低消費電力無線設計とともに、Dust社の組み込みSmartMesh IPネットワーク・ソフトウェアが動作するARM Cortex-M3 32ビット・マイクロプロセッサを特長としています。24mm×42mmのLTP5901-IPM(チップ・アンテナ内蔵)と24mm×37mmのLTP5902-IPM(MMCXコネクタ内蔵)はいずれも表面実装組み立て用に設計されています。

Dust社の時間同期SmartMesh IPネットワークでは、ネットワーク内のすべてのモートがデータのルーティング、送信、または終了処理を実行しながら、バッテリ電源で何年も動作できます。LTP5901-IPM/LTP5902-IPMに付属のIPソフトウェアは、テストと検証が完全に行われており、ソフトウェアのアプリケーション・プログラミング・インターフェース(API)を介して簡単に設定できます。

SmartMesh IPモートは信頼性の実績がある柔軟性の高いネットワークを実現し、組み込みが容易なプラットフォームで低消費電力性能を示します。

LT、LT、LTC、LTM、Linear Technology、Linearのロゴ、Dust、Dust Networks、SmartMeshおよびEternaはリニアテクノロジー社の登録商標です。LTP、Dust Networksのロゴ、およびSmartMesh IPはリニアテクノロジー社の商標です。その他すべての商標の所有権は、それぞれの所有者に帰属します。7375594、7420980、7529217、7791419、7881239、7898322、8222965を含む米国特許によって保護されています。

\* EternaはDust Networksの低消費電力無線SoCアーキテクチャです。

## 標準的応用例

59012ipm TA01

59012ipmf

## 目次

|                                   |    |                        |    |

|-----------------------------------|----|------------------------|----|

| ネットワークの特長 .....                   | 1  | ピン機能 .....             | 18 |

| LTP5901-IPM/LTP5902-IPM の特長 ..... | 1  | 動作 .....               | 22 |

| 標準的応用例 .....                      | 1  | 電源 .....               | 22 |

| 概要 .....                          | 1  | 電源モニタリセット .....        | 23 |

| 目次 .....                          | 2  | 高精度のタイミング .....        | 23 |

| SmartMesh ネットワークの概要 .....         | 3  | アプリケーションの時間同期 .....    | 23 |

| 絶対最大定格 .....                      | 4  | 時間基準 .....             | 23 |

| ピン配置 .....                        | 4  | 無線 .....               | 24 |

| 発注情報 .....                        | 5  | UART .....             | 24 |

| 推奨動作条件 .....                      | 5  | 自律 MAC .....           | 25 |

| DC 特性 .....                       | 5  | セキュリティ .....           | 25 |

| 無線規格 .....                        | 6  | 温度センサ .....            | 25 |

| 無線レシーバ特性 .....                    | 6  | 無線禁止 .....             | 25 |

| 無線トランスマッタ特性 .....                 | 7  | 工場インストール済みソフトウェア ..... | 25 |

| デジタル I/O 特性 .....                 | 7  | フラッシュのデータ保持 .....      | 25 |

| 温度センサ特性 .....                     | 8  | 状態図 .....              | 26 |

| アナログ入力チェーン特性 .....                | 8  | アプリケーション情報 .....       | 28 |

| システム特性 .....                      | 8  | 信号/データの取得と制御 .....     | 28 |

| UART の AC 特性 .....                | 9  | 法規制と標準規格の順守 .....      | 28 |

| TIMEn の AC 特性 .....               | 10 | 半田付け情報 .....           | 28 |

| Radio_Inhibit の AC 特性 .....       | 10 | 関連資料 .....             | 29 |

| フラッシュの AC 特性 .....                | 11 | パッケージ .....            | 30 |

| フラッシュ SPI スレーブの AC 特性 .....       | 11 | 標準的応用例 .....           | 32 |

| 標準的性能特性 .....                     | 13 | 関連製品 .....             | 32 |

## SmartMesh ネットワークの概要

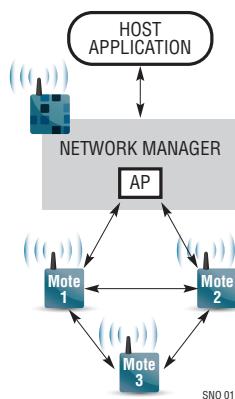

SmartMesh ネットワークは、データを収集して中継する自己形成型マルチホップ・メッシュ・ノード(モートと呼ばれるもの)と、ネットワークの性能およびセキュリティをモニタして管理し、ホスト・アプリケーションとデータを交換するネットワーク・マネージャで構成されます。

SmartMesh ネットワークは、Dust Networks が開発したタイムスロット・チャネル・ホッピング(TSCH)リンク層を使用して通信します。TSCH ネットワークでは、ネットワーク内のすべてのモートが 1 ミリ秒以内に同期しています。ネットワーク内の時間は複数のタイムスロットに編成されるので、衝突のないパケット交換と伝送単位のチャネル・ホッピングが可能になります。SmartMesh ネットワークでは、すべてのデバイスに 1 つ以上の親(上位ノード)があります(たとえば、モート 3 には親としてモート 1 およびモート 2 があります)、干渉、物理的妨害、または多経路フェージングに起因する通信の遮断を克服するための冗長経路を実現します。ある経路でパケット传送が失敗した場合は、次の再传送を別の経路および別の RF チャネルで試行できます。

ネットワーク・マネージャがその内蔵アクセス・ポイント(AP)に指示してアドバタイズメントの送信を開始すると、ネットワークが形成され始めます。アドバタイズメントとは、デバイスがネットワークに同期して参加を要求できるようにする情報が入っているパケットのことです。このメッセージ交換は、マネージャまたはアプリケーションとモートの間の暗号化通信を確立するセキュリティ・ハンドシェイクの一部です。モートはネットワークに参加すると、パケットのアクノリッジを受け取ったときの時間補正によって同期を維持します。

進行中のディスカバリ処理により、RFの状態が変化するのに応じてネットワークが新しい経路を絶えず検出することが保証されます。さらに、ネットワーク内の各モート性能の統計情報(例: 使用した経路の品質や潜在的経路のリスト)を追跡し、その情報を健全性レポートと呼ばれるパケットでネットワーク・マネージャに

定期的に送信します。ネットワーク・マネージャは健全性レポートを使用してネットワークを絶えず最適化し、最も困難な RF 環境でも 99.999% を超えるデータ信頼性を維持します。

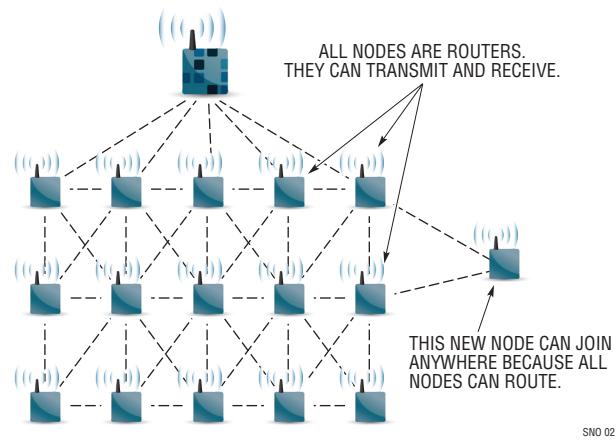

TSCH を使用すると、SmartMesh デバイスを予定の通信間にスリープ状態にすることができますので、この状態では電力をほとんど消費せずに済みます。モートがアクティブ状態になるのは、モートによる送信または受信を予定しているタイムスロット内に限られるので、通常はデューティ・サイクルが 1% 未満になります。ネットワーク・マネージャ内の最適化ソフトウェアにより、この予定は自動的に調整されます。低消費電力の無線システムである Eterna と組み合わせると、SmartMesh ネットワーク内のすべてのモートは、ルーティングが混雑したモートであっても、数年間はバッテリで動作を継続できます。デフォルトでは、ネットワーク内のすべてのモートは他のモートからのトライフィックのルーティングが可能なので、別個のルータと非ルーティング・エンド・ノードという複雑な構造を回避することにより設置を簡素化しています。モートを非ルーティング・ノードとして構成し、その特定のモートの消費電力をさらに低減して、多種多様なネットワーク・トポロジーに対応できます。

SmartMesh モートとネットワーク・マネージャの中核をなすのは、Eterna IEEE 802.15.4e システムオンチップ(SoC)であり、Dust Networks 社の集積度の高い低消費電力無線設計に加えて、SmartMesh ネットワーク・ソフトウェアが動作する ARM Cortex-M3 32 ビット・マイクロプロセッサを特長としています。SmartMesh ネットワーク・ソフトウェアは完全にコンパイルされた状態で付属していますが、豊富な一連のアプリケーション・プログラミング・インターフェース(API)を介して構成可能です。これらの API により、ホスト・アプリケーションがネットワークと対話して(たとえば、情報をデバイスに転送して)、1 つ以上のモートのデータ発行レートを設定したり、ネットワークの状態や性能測定基準をモニタすることができます。データの発行は均一でもデバイスごとに異なってもかまいません。モートによる発行頻度は、必要に応じて低頻度にするか 1 秒に 1 回より頻繁にすることができます。

59012ipm

## LTP5901-IPM/LTP5902-IPM

## 絶対最大定格

(Note 1)

|                     |                        |

|---------------------|------------------------|

| VSUPPLYでの電源電圧       | 3.76V                  |

| AI_0/1/2/3 入力での入力電圧 | 1.80V                  |

| すべてのデジタルI/Oピンでの電圧   | -0.3V ~ VSUPPLY + 0.3V |

| 入力RFレベル             | +10dBm                 |

| 保存温度範囲 (Note 3)     | -55°C ~ 105°C          |

| 動作温度範囲              |                        |

| TTP5901I / PT5902I  | -40°C ~ 85°C           |

注意:このデバイスは、静電放電(ESD)の影響を受けやすい。LTP5901-IPM/LTP5902-IPMを取り扱う場合は、適切なESD予防策に従うことが非常に重要である。

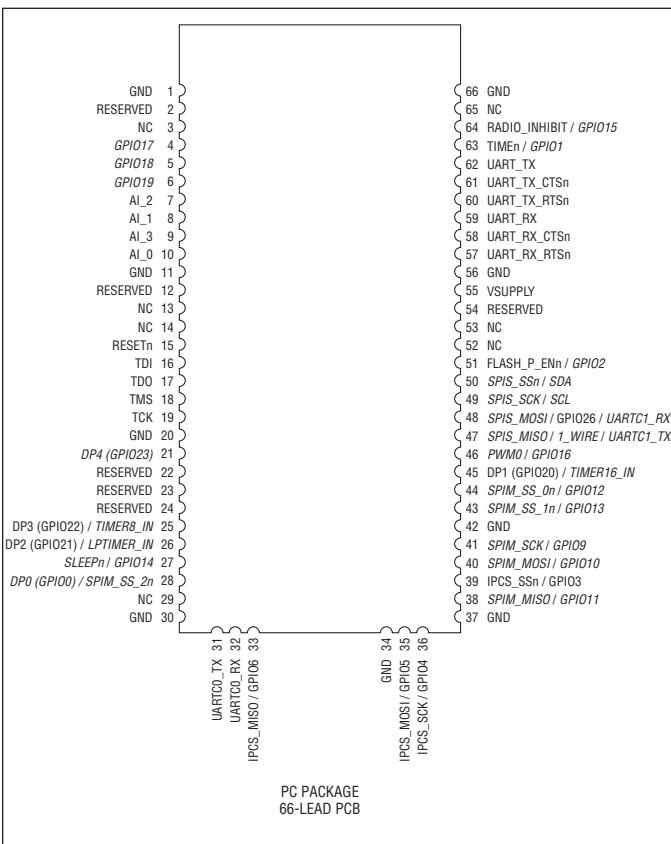

## ピン配置

イタリック体で表示しているピン機能は、現時点ではソフトウェアでサポートされていません。

## 発注情報

| 無鉛仕上げ                  | 製品マーキング                | パッケージ                                               | 温度範囲          |

|------------------------|------------------------|-----------------------------------------------------|---------------|

| LTP5901IPC-IPMA???#PBF | LTP5901IPC-IPMA???#PBF | 66-Lead (42mm×24mm×5.5mm) PCB with Chip Antenna     | -40°C to 85°C |

| LTP5902IPC-IPMA???#PBF | LTP5902IPC-IPMA???#PBF | 66-Lead (37.5mm×24mm×5.5mm) PCB with MMCX Connector | -40°C to 85°C |

\* ソフトウェア・バージョンは???としています。

それぞれの発注情報については、<http://www.linear-tech.co.jp/product/LTP5901-IPM#orderinfo> または <http://www.linear-tech.co.jp/product/LTP5902-IPM#orderinfo> をご覧ください。

無鉛仕上げの製品マーキングの詳細については、<http://www.linear-tech.co.jp/leadfree/> をご覧ください。

テープ・アンド・リールの仕様の詳細については、<http://www.linear-tech.co.jp/tapeandree/> をご覧ください。

## 推奨動作条件

●は全動作温度範囲での規格値を意味する。それ以外は  $T_A = 25^\circ\text{C}$  での値。注記がない限り、VSUPPLY = 3.6V。

| SYMBOL  | PARAMETER                                        | CONDITIONS                          | MIN | TYP | MAX  | UNITS  |

|---------|--------------------------------------------------|-------------------------------------|-----|-----|------|--------|

| VSUPPLY | Supply Voltage                                   | Including Noise and Load Regulation | ●   | 2.1 | 3.76 | V      |

|         | Supply Noise                                     | 50Hz to 2MHz                        | ●   |     | 250  | mV     |

|         | Operating Relative Humidity                      | Non-Condensing                      | ●   | 10  | 90   | % RH   |

|         | Temperature Ramp Rate While Operating in Network |                                     | ●   | -8  | +8   | °C/min |

## DC 特性

●は全動作温度範囲での規格値を意味する。それ以外は  $T_A = 25^\circ\text{C}$  での値。注記がない限り、VSUPPLY = 3.6V。

| OPERATION/STATE                          | CONDITIONS                                                                                                                                         | MIN | TYP | MAX        | UNITS    |

|------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|------------|----------|

| Power-on Reset                           | During Power-On Reset, Maximum 750μs + VSUPPLY Rise Time from 1V to 1.9V                                                                           |     |     | 12         | mA       |

| Doze                                     | RAM on, ARM Cortex-M3, Flash, Radio, and Peripherals Off, All Data and State Retained, 32.768kHz Reference Active                                  |     |     | 1.2        | μA       |

| Deep Sleep                               | RAM on, ARM Cortex-M3, Flash, Radio, and Peripherals Off, All Data and State Retained, 32.768kHz Reference Inactive                                |     |     | 0.8        | μA       |

| In-Circuit Programming                   | RESETn and FLASH_P_ENn Asserted, IPCS_SCK at 8MHz                                                                                                  |     |     | 20         | mA       |

| Peak Operating Current<br>+8dBm<br>+0dBm | System Operating at 14.7MHz, Radio Transmitting, During Flash Write. Maximum Duration 4.33 ms.                                                     |     |     | 30<br>26   | mA<br>mA |

| Active                                   | ARM Cortex M3, RAM and Flash Operating, Radio and All Other Peripherals Off. Clock Frequency of CPU and Peripherals Set to 7.3728MHz, VCORE = 1.2V |     |     | 1.3        | mA       |

| Flash Write                              | Single Bank Flash Write                                                                                                                            |     |     | 3.7        | mA       |

| Flash Erase                              | Single Bank Page or Mass Erase                                                                                                                     |     |     | 2.5        | mA       |

| Radio Tx<br>+0dBm<br>+8dBm               | Current with Autonomous MAC Managing Radio Operation, CPU Inactive. Clock Frequency of CPU and Peripherals Set to 7.3728MHz.                       |     |     | 5.4<br>9.7 | mA<br>mA |

| Radio Rx                                 | Current with Autonomous MAC Managing Radio Operation, CPU Inactive. Clock Frequency of CPU and Peripherals Set to 7.3728MHz.                       |     |     | 4.5        | mA       |

# LTP5901-IPM/LTP5902-IPM

## 無線規格

● は全動作温度範囲での規格値を意味する。それ以外は  $T_A = 25^\circ\text{C}$  での値。注記がない限り、 $\text{VSUPPLY} = 3.6\text{V}$ 。

| PARAMETER                  | CONDITIONS                                                            | MIN               | TYP | MAX                | UNITS       |

|----------------------------|-----------------------------------------------------------------------|-------------------|-----|--------------------|-------------|

| Frequency Band             |                                                                       | ● 2.4000          |     | 2.4835             | GHz         |

| Number of Channels         |                                                                       | ● 15              |     |                    |             |

| Channel Separation         |                                                                       | ● 5               |     |                    | MHz         |

| Channel Center Frequency   | Where $k = 11$ to 25, as Defined by IEEE 802.4.15                     | ● 2405 + 5•(k-11) |     |                    | MHz         |

| Modulation                 | IEEE 802.15.4 Direct Sequence Spread Spectrum (DSSS)                  |                   |     |                    |             |

| Raw Data Rate              |                                                                       | ● 250             |     |                    | kbps        |

| Antenna Pin ESD Protection | HBM per JEDEC JESD22-A114F (Note 2)                                   |                   |     | ±6000              | V           |

| Range (Note 4)             | 25°C, 50% RH, +2dBi Omni-Directional Antenna, Antenna 2m Above Ground |                   |     | 100<br>300<br>1200 | m<br>m<br>m |

| Indoor                     |                                                                       |                   |     |                    |             |

| Outdoor                    |                                                                       |                   |     |                    |             |

| Free Space                 |                                                                       |                   |     |                    |             |

## 無線レシーバ特性

● は全動作温度範囲での規格値を意味する。それ以外は  $T_A = 25^\circ\text{C}$  での値。注記がない限り、 $\text{VSUPPLY} = 3.6\text{V}$ 。

| PARAMETER                                             | CONDITIONS                                                                                                  | MIN | TYP | MAX        | UNITS |

|-------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|-----|-----|------------|-------|

| Receiver Sensitivity                                  | Packet Error Rate (PER) = 1% (Note 5)                                                                       |     |     | -93        | dBm   |

| Receiver Sensitivity                                  | PER = 50%                                                                                                   |     |     | -95        | dBm   |

| Saturation                                            | Maximum Input Level the Receiver Will Properly Receive Packets                                              |     |     | 0          | dBm   |

| Adjacent Channel Rejection (High Side)                | Desired Signal at -82dBm, Adjacent Modulated Channel 5MHz Above the Desired Signal, PER = 1% (Note 5)       |     |     | 22         | dBc   |

| Adjacent Channel Rejection (Low Side)                 | Desired Signal at -82dBm, Adjacent Modulated Channel 5MHz Below the Desired Signal, PER = 1% (Note 5)       |     |     | 19         | dBc   |

| Alternate Channel Rejection (High Side)               | Desired Signal at -82dBm, Alternate Modulated Channel 10MHz Above the Desired Signal, PER = 1% (Note 5)     |     |     | 40         | dBc   |

| Alternate Channel Rejection (Low Side)                | Desired Signal at -82dBm, Alternate Modulated Channel 10MHz Below the Desired Signal, PER = 1% (Note 5)     |     |     | 36         | dBc   |

| Second Alternate Channel Rejection                    | Desired Signal at -82dBm, Second Alternate Modulated Channel Either 15MHz Above or Below, PER = 1% (Note 5) |     |     | 42         | dBc   |

| Co-Channel Rejection                                  | Desired Signal at -82dBm, Undesired Signal is an 802.15.4 Modulated Signal at the Same Frequency, PER = 1%  |     |     | -6         | dBc   |

| LO Feed Through                                       |                                                                                                             |     |     | -55        | dBm   |

| Frequency Error Tolerance (Note 6)                    |                                                                                                             |     |     | ±50        | ppm   |

| Symbol Error Tolerance                                |                                                                                                             |     |     | ±50        | ppm   |

| Received Signal Strength Indicator (RSSI) Input Range |                                                                                                             |     |     | -90 to -10 | dBm   |

| RSSI Accuracy                                         |                                                                                                             |     |     | ±6         | dB    |

| RSSI Resolution                                       |                                                                                                             |     |     | 1          | dB    |

## 無線トランスマッタ特性

●は全動作温度範囲での規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。注記がない限り、 $\text{VSUPPLY} = 3.6\text{V}$ 。

| PARAMETER                            | CONDITIONS                                                                                                          | MIN  | TYP | MAX | UNITS        |

|--------------------------------------|---------------------------------------------------------------------------------------------------------------------|------|-----|-----|--------------|

| Output Power                         | Delivered to a $50\Omega$ load                                                                                      |      |     |     |              |

| High Calibrated Setting              |                                                                                                                     | 8    |     |     | $\text{dBm}$ |

| Low Calibrated Setting               |                                                                                                                     | 0    |     |     | $\text{dBm}$ |

| Spurious Emissions                   | Conducted Measurement with a $50\Omega$ Single-Ended Load, +8dBm Output Power. All Measurements Made with Max Hold. |      |     |     |              |

| 30MHz to 1000MHz                     | $\text{RBW} = 120\text{kHz}, \text{V}_{\text{BW}} = 100\text{Hz}$                                                   | <-70 |     |     | $\text{dBm}$ |

| 1GHz to 12.75GHz                     | $\text{RBW} = 1\text{MHz}, \text{V}_{\text{BW}} = 3\text{MHz}$                                                      | -45  |     |     | $\text{dBm}$ |

| 2.4GHz ISM Upper Band Edge (Peak)    | $\text{RBW} = 1\text{MHz}, \text{V}_{\text{BW}} = 3\text{MHz}$                                                      | -37  |     |     | $\text{dBm}$ |

| 2.4GHz ISM Upper Band Edge (Average) | $\text{RBW} = 1\text{MHz}, \text{V}_{\text{BW}} = 10\text{Hz}$                                                      | -49  |     |     | $\text{dBm}$ |

| 2.4GHz ISM Lower Band Edge           | $\text{RBW} = 100\text{kHz}, \text{V}_{\text{BW}} = 100\text{kHz}$                                                  | -45  |     |     | $\text{dBc}$ |

| Harmonic Emissions                   | Conducted Measurement Delivered to a $50\Omega$ Load, Resolution Bandwidth = 1MHz, Video Bandwidth = 1MHz           |      |     |     |              |

| 2nd Harmonic                         |                                                                                                                     | -50  |     |     | $\text{dBm}$ |

| 3rd Harmonic                         |                                                                                                                     | -45  |     |     | $\text{dBm}$ |

## デジタルI/O特性

●は全動作温度範囲での規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。注記がない限り、 $\text{VSUPPLY} = 3.6\text{V}$ 。

| SYMBOL   | PARAMETER                    | CONDITIONS (Note 7)                                      | MIN             | TYP | MAX           | UNITS      |

|----------|------------------------------|----------------------------------------------------------|-----------------|-----|---------------|------------|

| $V_{IL}$ | Low Level Input Voltage      |                                                          | ● -0.3          |     | 0.6           | V          |

| $V_{IH}$ | High Level Input Voltage     | (Note 8)                                                 | ● VSUPPLY - 0.3 |     | VSUPPLY + 0.3 | V          |

| $V_{OL}$ | Low Level Output Voltage     | Type 1, $I_{OL(\text{MAX})} = 1.2\text{mA}$              | ●               |     | 0.4           | V          |

|          |                              | Type 2, Low Drive, $I_{OL(\text{MAX})} = 2.2\text{mA}$   | ●               |     | 0.4           | V          |

|          |                              | Type 2, High Drive, $I_{OL(\text{MAX})} = 4.5\text{mA}$  | ●               |     | 0.4           | V          |

| $V_{OH}$ | High Level Output Voltage    | Type 1, $I_{OH(\text{MAX})} = -0.8\text{mA}$             | ● VSUPPLY - 0.3 |     | VSUPPLY + 0.3 | V          |

|          |                              | Type 2, Low Drive, $I_{OH(\text{MAX})} = -1.6\text{mA}$  | ● VSUPPLY - 0.3 |     | VSUPPLY + 0.3 | V          |

|          |                              | Type 2, High Drive, $I_{OH(\text{MAX})} = -3.2\text{mA}$ | ● VSUPPLY - 0.3 |     | VSUPPLY + 0.3 | V          |

|          | Input Leakage Current        | Input Driven to VSUPPLY or GND                           |                 |     | 50            | nA         |

|          | Pull-Up/Pull-Down Resistance |                                                          |                 |     | 50            | k $\Omega$ |

# LTP5901-IPM/LTP5902-IPM

## 温度センサ特性

● は全動作温度範囲での規格値を意味する。それ以外は  $T_A = 25^\circ\text{C}$  での値。注記がない限り、 $\text{VSUPPLY} = 3.6\text{V}$ 。

| PARAMETER   | CONDITIONS                                     | MIN | TYP | MAX         | UNITS                           |

|-------------|------------------------------------------------|-----|-----|-------------|---------------------------------|

| Offset      | Temperature Offset Error at $25^\circ\text{C}$ |     |     | $\pm 0.25$  | $^\circ\text{C}$                |

| Slope Error |                                                |     |     | $\pm 0.033$ | $^\circ\text{C}/^\circ\text{C}$ |

## アナログ入力チェーン特性

● は全動作温度範囲での規格値を意味する。それ以外は  $T_A = 25^\circ\text{C}$  での値。注記がない限り、 $\text{VSUPPLY} = 3.6\text{V}$ 。

| SYMBOL     | PARAMETER                                                                                                                                                                                          | CONDITIONS                                 | MIN                                            | TYP                                                                         | MAX                                            | UNITS                                                                                             |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|------------------------------------------------|-----------------------------------------------------------------------------|------------------------------------------------|---------------------------------------------------------------------------------------------------|

|            | Variable Gain Amplifier<br>Gain<br>Gain Error                                                                                                                                                      |                                            |                                                | 1                                                                           | 8<br>2                                         | %                                                                                                 |

| DNL        | Offset-Digital to Analog Converter (DAC)<br>Full-Scale<br>Resolution<br>Differential Non-Linearity                                                                                                 |                                            |                                                | 1.80<br>4                                                                   | 2.7                                            | $\text{V}$<br>Bits<br>$\text{mV}$                                                                 |

| DNL<br>INL | Analog to Digital Converter (ADC)<br>Full-Scale, Signal<br>Resolution<br>Offset<br>Differential Non-Linearity<br>Integral Non-Linearity<br>Settling Time<br>Conversion Time<br>Current Consumption | Mid-Scale<br>10k $\Omega$ Source Impedance | 1.80<br>1.8<br>1.4<br>1<br>1<br>10<br>20<br>40 | 12<br>1<br>1<br>10<br>20<br>$\mu\text{s}$<br>$\mu\text{s}$<br>$\mu\text{A}$ | 1.80<br>1.8<br>1.4<br>1<br>1<br>10<br>20<br>40 | $\text{V}$<br>$\text{mV}$<br>LSB<br>LSB<br>LSB<br>$\mu\text{s}$<br>$\mu\text{s}$<br>$\mu\text{A}$ |

|            | Analog Inputs (Note 9)<br>Load<br>Series Input Resistance                                                                                                                                          |                                            |                                                | 20<br>1                                                                     | 20                                             | $\text{pF}$<br>$\text{k}\Omega$                                                                   |

## システム特性

● は全動作温度範囲での規格値を意味する。それ以外は  $T_A = 25^\circ\text{C}$  での値。注記がない限り、 $\text{VSUPPLY} = 3.6\text{V}$ 。

| SYMBOL           | PARAMETER                        | CONDITIONS                                                                  | MIN | TYP | MAX | UNITS         |

|------------------|----------------------------------|-----------------------------------------------------------------------------|-----|-----|-----|---------------|

|                  | Doze to Active State Transition  |                                                                             |     | 5   |     | $\mu\text{s}$ |

|                  | Doze to Radio Tx or Rx           |                                                                             |     | 1.2 |     | ms            |

| QCCA             | Charge to Sample RF Channel RSSI | Charge Consumed Starting from Doze State and Completing an RSSI Measurement |     | 4   |     | $\mu\text{C}$ |

| Q <sub>MAX</sub> | Largest Atomic Charge Operation  | Flash Erase, 21ms Max Duration                                              | ●   |     | 200 | $\mu\text{C}$ |

|                  | RESET <sub>n</sub> Pulse Width   |                                                                             | ●   | 125 |     | $\mu\text{s}$ |

|                  | Total Capacitance                |                                                                             |     |     | 6   | $\mu\text{F}$ |

|                  | Total Inductance                 |                                                                             |     |     | 3   | $\mu\text{H}$ |

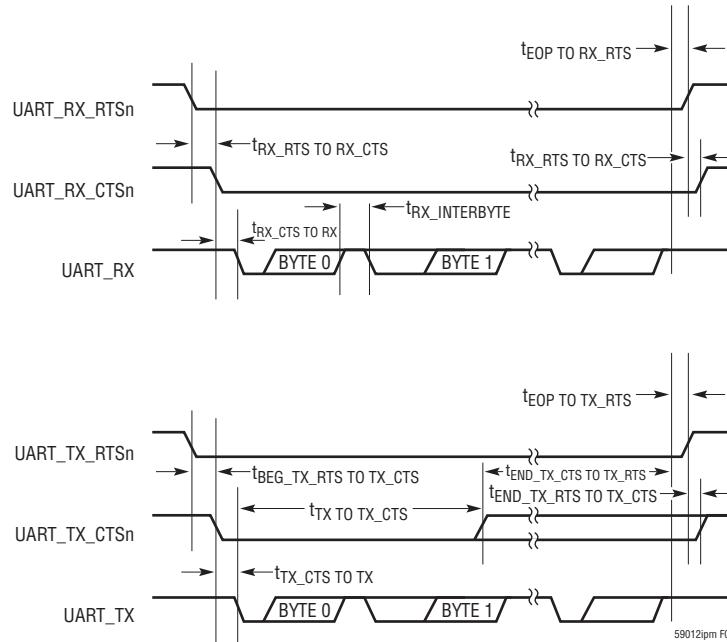

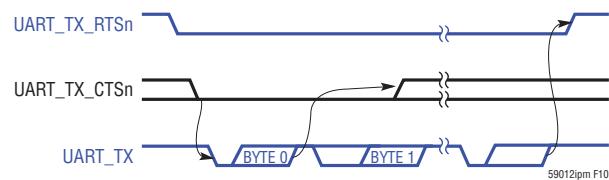

## UARTのAC特性

●は全動作温度範囲での規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。注記がない限り、 $\text{VSUPPLY} = 3.6\text{V}$ 。(Note 13)

| SYMBOL                                 | PARAMETER                                                                                                                                                        | CONDITIONS                                                                          | MIN | TYP | MAX | UNITS      |

|----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|-----|-----|-----|------------|

|                                        | Permitted Rx Baud Rate Error                                                                                                                                     | Both Application Programming Interface (API) and Command Line Interface (CLI) UARTs | ●   | -2  | 2   | %          |

|                                        | Generated Tx Baud Rate Error                                                                                                                                     | Both API and CLI UARTs                                                              | ●   | -1  | 1   | %          |

| $t_{RX\_RTS \text{ to } RX\_CTS}$      | Assertion of $\text{UART\_RX\_RTS}_n$ to Assertion of $\text{UART\_RX\_CTS}_n$ , or Negation of $\text{UART\_RX\_RTS}_n$ to Negation of $\text{UART\_RX\_CTS}_n$ |                                                                                     | ●   | 0   | 2   | ms         |

| $t_{CTS\_R \text{ to } RX}$            | Assertion of $\text{UART\_RX\_CTS}_n$ to Start of Byte                                                                                                           |                                                                                     | ●   | 0   | 20  | ms         |

| $t_{EOP \text{ to } RX\_RTS}$          | End of Packet (End of the Last Stop Bit) to Negation of $\text{UART\_RX\_RTS}_n$                                                                                 |                                                                                     | ●   | 0   | 22  | ms         |

| $t_{BEG\_TX\_RTS \text{ to } TX\_CTS}$ | Assertion of $\text{UART\_TX\_RTS}_n$ to Assertion of $\text{UART\_TX\_CTS}_n$                                                                                   |                                                                                     | ●   | 0   | 22  | ms         |

| $t_{END\_TX\_CTS \text{ to } TX\_RTS}$ | Negation of $\text{UART\_TX\_CTS}_n$ to Negation of $\text{UART\_TX\_RTS}_n$                                                                                     |                                                                                     |     | 2   |     | Bit Period |

| $t_{TX\_CTS \text{ to } TX}$           | Assertion of $\text{UART\_TX\_CTS}_n$ to Start of Byte                                                                                                           |                                                                                     | ●   | 0   | 2   | Bit Period |

| $t_{EOP \text{ to } TX\_RTS}$          | End of Packet (End of the Last Stop Bit) to Negation of $\text{UART\_TX\_RTS}_n$                                                                                 |                                                                                     | ●   | 0   | 1   | Bit Period |

| $t_{RX\_INTERBYTE}$                    | Receive Inter-Byte Delay                                                                                                                                         |                                                                                     | ●   |     | 100 | ms         |

| $t_{TX \text{ to } TX\_CTS}$           | Start of Byte to Negation of $\text{UART\_TX\_CTS}_n$                                                                                                            |                                                                                     | ●   | 0   |     | ns         |

図1. API UARTのタイミング

# LTP5901-IPM/LTP5902-IPM

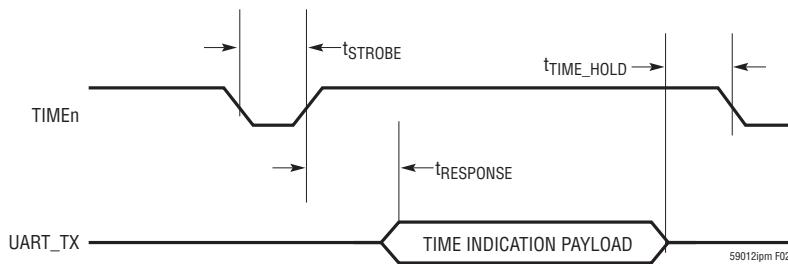

## TIMEn の AC 特性

● は全動作温度範囲での規格値を意味する。それ以外は  $T_A = 25^\circ\text{C}$  での値。注記がない限り、 $\text{VSUPPLY} = 3.6\text{V}$ 。 (Note 13)

| SYMBOL                  | PARAMETER                                                                     | CONDITIONS | MIN | TYP     | MAX | UNITS         |

|-------------------------|-------------------------------------------------------------------------------|------------|-----|---------|-----|---------------|

| $t_{\text{STROBE}}$     | TIMEn Signal Strobe Width                                                     |            | ●   | 125     |     | $\mu\text{s}$ |

| $t_{\text{RESPONSE}}$   | Delay from Rising Edge of TIMEn to the Start of Time Packet on API UART       |            | ●   | 0       | 100 | ms            |

| $t_{\text{TIME\_HOLD}}$ | Delay from End of Time Packet on API UART to Falling Edge of Subsequent TIMEn |            | ●   | 0       |     | ns            |

|                         | Timestamp Resolution (Note 10)                                                |            | ●   | 1       |     | $\mu\text{s}$ |

|                         | Network-Wide Time Accuracy (Note 11)                                          |            | ●   | $\pm 5$ |     | $\mu\text{s}$ |

図2. タイムスタンプのタイミング

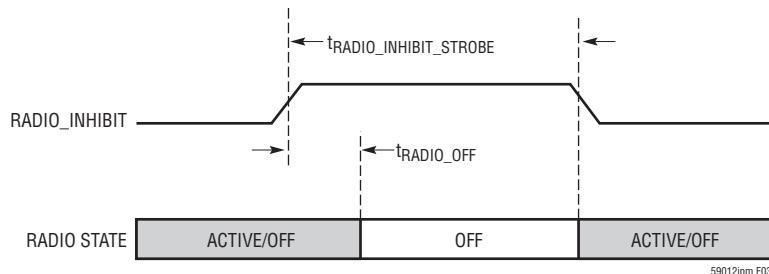

## Radio\_Inhibit の AC 特性

● は全動作温度範囲での規格値を意味する。それ以外は  $T_A = 25^\circ\text{C}$  での値。注記がない限り、 $\text{VSUPPLY} = 3.6\text{V}$ 。 (Note 13)

| SYMBOL                              | PARAMETER                                                 | CONDITIONS | MIN | TYP | MAX | UNITS |

|-------------------------------------|-----------------------------------------------------------|------------|-----|-----|-----|-------|

| $t_{\text{RADIO\_OFF}}$             | Delay from Rising Edge of RADIO_INHIBIT to Radio Disabled |            | ●   | 20  |     | ms    |

| $t_{\text{RADIO\_INHIBIT\_STROBE}}$ | Maximum RADIO_INHIBIT Strobe Width                        |            | ●   | 2   |     | s     |

図3. RADIO\_INHIBIT のタイミング

## フラッシュのAC特性

●は全動作温度範囲での規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。注記がない限り、 $\text{VSUPPLY} = 3.6\text{V}$ 。(Note 13)

| SYMBOL                   | PARAMETER                                | CONDITIONS            | MIN | TYP            | MAX | UNITS                   |

|--------------------------|------------------------------------------|-----------------------|-----|----------------|-----|-------------------------|

| $t_{\text{WRITE}}$       | Time to Write a 32-Bit Word (Note 12)    |                       | ●   |                | 21  | $\mu\text{s}$           |

| $t_{\text{PAGE\_ERASE}}$ | Time to Erase a 2kB Page (Note 12)       |                       | ●   |                | 21  | ms                      |

| $t_{\text{MASS\_ERASE}}$ | Time to Erase 256kB Flash Bank (Note 12) |                       | ●   |                | 21  | ms                      |

|                          | Data Retention                           | 25°C<br>85°C<br>105°C |     | 100<br>20<br>8 |     | Years<br>Years<br>Years |

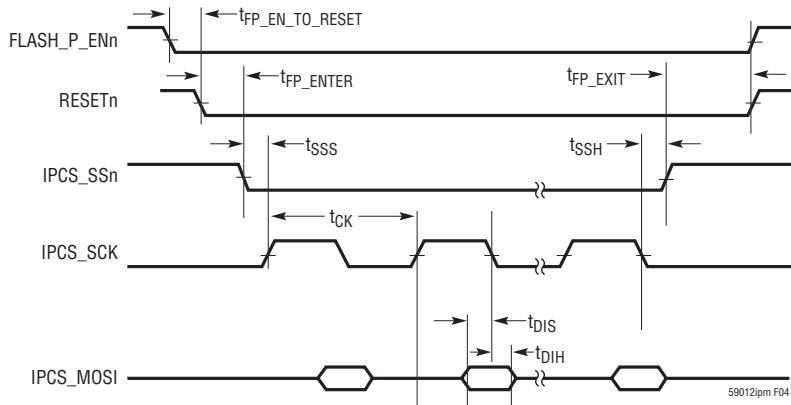

## フラッシュSPIスレーブのAC特性

●は全動作温度範囲での規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。注記がない限り、 $\text{VSUPPLY} = 3.6\text{V}$ 。(Note 13)

| SYMBOL                         | PARAMETER                                                                                                   | CONDITIONS | MIN | TYP | MAX | UNITS         |

|--------------------------------|-------------------------------------------------------------------------------------------------------------|------------|-----|-----|-----|---------------|

| $t_{\text{FP\_EN\_to\_RESET}}$ | Setup from Assertion of FLASH_P_ENn to Assertion of RESETn                                                  |            | ●   | 0   |     | ns            |

| $t_{\text{FP\_ENTER}}$         | Delay from the Assertion RESETn to the First Falling Edge of IPCS_SS <sub>n</sub>                           |            | ●   | 125 |     | $\mu\text{s}$ |

| $t_{\text{FP\_EXIT}}$          | Delay from the Completion of the Last Flash SPI Slave Transaction to the Negation of RESETn and FLASH_P_ENn |            | ●   | 10  |     | $\mu\text{s}$ |

| $t_{\text{SS}}$                | IPCS_SS <sub>n</sub> Setup to the Leading Edge of IPCS_SCK                                                  |            | ●   | 15  |     | ns            |

| $t_{\text{SSH}}$               | IPCS_SS <sub>n</sub> Hold from Trailing Edge of IPCS_SCK                                                    |            | ●   | 15  |     | ns            |

| $t_{\text{CK}}$                | IPCS_SCK Period                                                                                             |            | ●   | 50  |     | ns            |

| $t_{\text{DIS}}$               | IPCS_MOSI Data Setup                                                                                        |            | ●   | 15  |     | ns            |

| $t_{\text{DIH}}$               | IPCS_MOSI Data Hold                                                                                         |            | ●   | 5   |     | ns            |

| $t_{\text{DOV}}$               | IPCS_MISO Data Valid                                                                                        |            | ●   | 3   |     | ns            |

| $t_{\text{OFF}}$               | IPCS_MISO Data Tri-State                                                                                    |            | ●   | 0   | 30  | ns            |

## フラッシュSPIスレーブのAC特性

図4. フラッシュのプログラミング・インターフェースのタイミング

**Note 1:** 絶対最大定格に記載された値を超えるストレスはデバイスに永続的損傷を与える可能性がある。長期にわたって絶対最大定格条件に曝すと、デバイスの信頼性と寿命に悪影響を与える恐れがある。

**Note 2:** ESD(静電気放電)の影響を受けやすいデバイス。ESD保護デバイスはEternaの内部に広範囲にわたって使用されている。ただし、高電圧の静電気放電はデバイスを損傷または劣化させる可能性がある。ESD取り扱いの適切な予防策を講じること。

**Note 3:** Eternaの校正データのデータ保持に悪影響を及ぼすので、高温での長期保存は避けること。詳細は「フラッシュのデータ保持」セクションを参照。

**Note 4:** 実際のRF範囲は設置に固有の変数の数によって異なる。変数には、周囲温度、相対湿度、活動状態の干渉源の存在、見通し線の遮断障害物、多経路フェージングを誘発する可能性がある物体(樹木、壁面、看板など)が近くに存在するかどうかを含むが、それに限定されない。このため、範囲は変化する。

**Note 5:** IEEE Std.802.15.4-2006:Wireless Medium Access Control (MAC) and Physical Layer (PHY) Specifications for Low-Rate Wireless Personal Area Networks (LR-WPANs) <http://standards.ieee.org/findstds/standard/802.15.4-2011.html>での規定に基づく。

**Note 6:** IEEE Std.802.15.4-2006では、トランスマッタが±40ppmより優れた周波数の許容範囲を維持することを要求している。

**Note 7:** ピンごとのI/Oタイプは「ピン機能」セクションに示す。

**Note 8:** VIHの最大入力電圧はVSUPPLYの最大電圧規格を基準にする必要がある。

**Note 9:** A/Dコンバータのアナログ入力はコンデンサに直列接続した抵抗としてモデル化できる。最低でも、アナログ入力を駆動する信号の信号源インピーダンスを含む回路全体をサンプリング期間内に1/4 LSB以内に安定化するよう設計して、A/Dコンバータの性能に適合させる必要がある。

**Note 10:** 時間指示の通知定義については、『SmartMesh IP Mote API Guide』を参照。

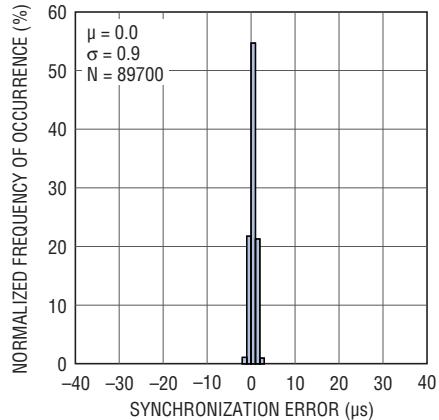

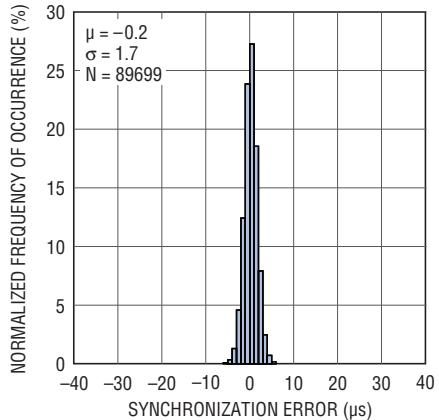

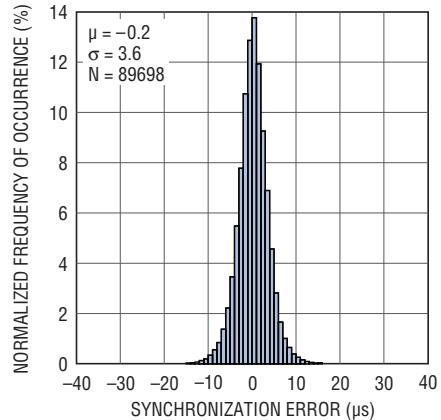

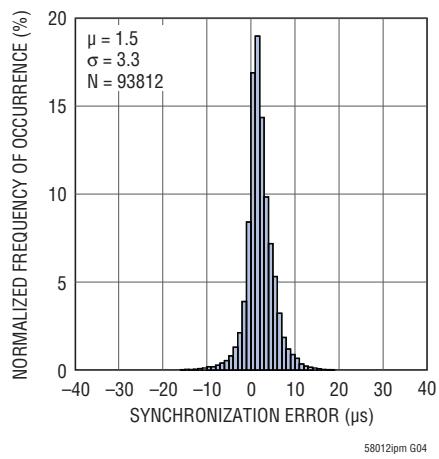

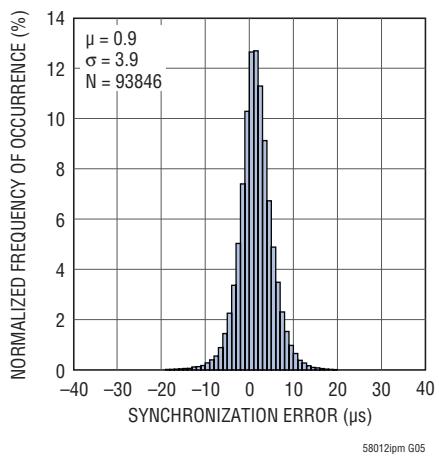

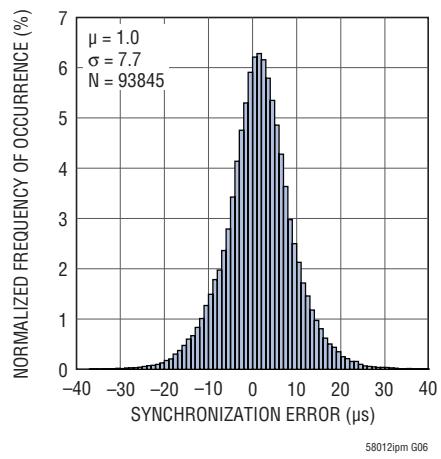

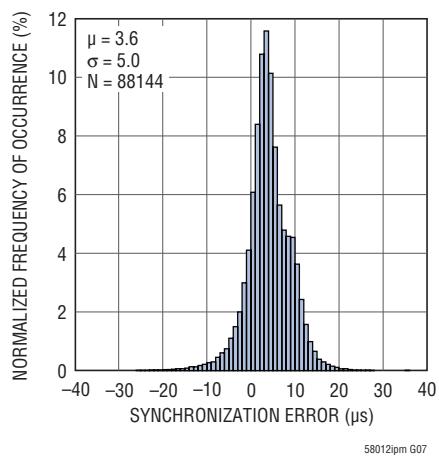

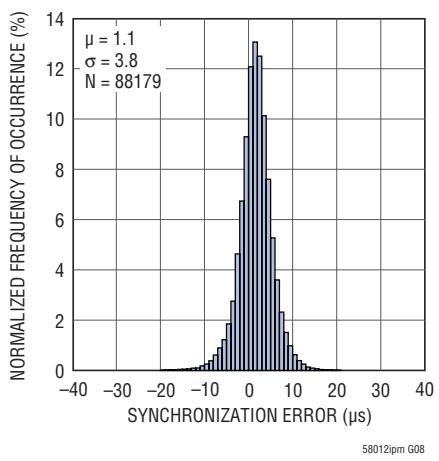

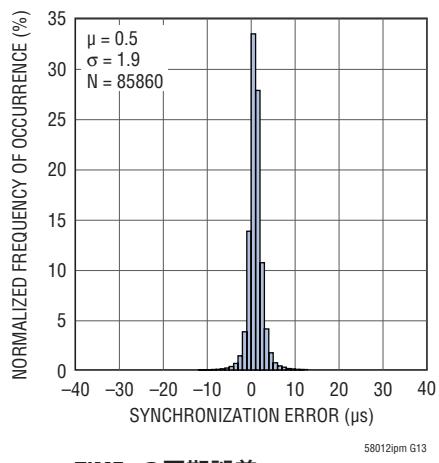

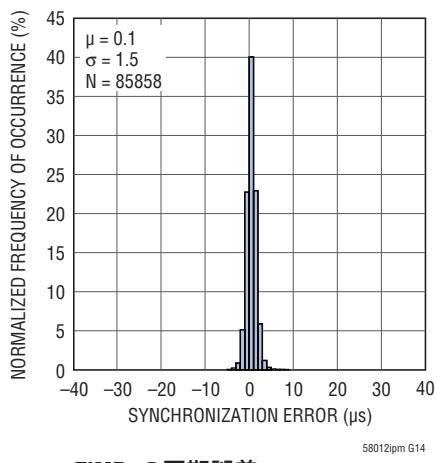

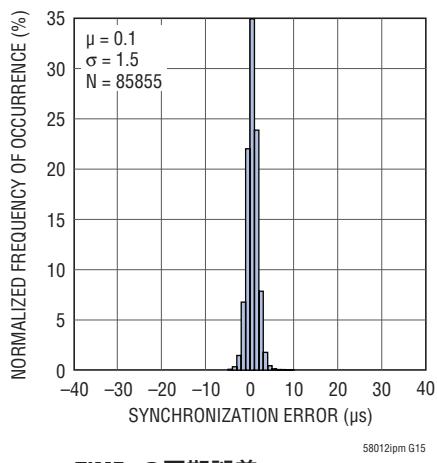

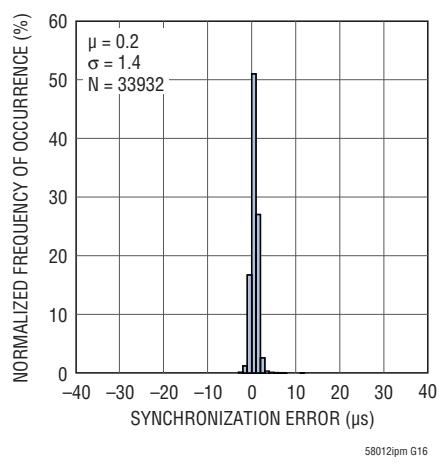

**Note 11:** ネットワーク時間の精度は統計上の基準であり、全温度範囲で変化し、ネットワーク内でのマネージャを基準にしたデバイスの位置およびレートを通知する。詳細な説明については、「標準的性能特性」セクションを参照。

**Note 12:** 書き込みまたは消去対象コードのフラッシュ・バンクからの実行は、フラッシュ動作が完了するまで一時停止する。

**Note 13:** 設計により保証されている。量産時にはテストされない。

## 標準的性能特性

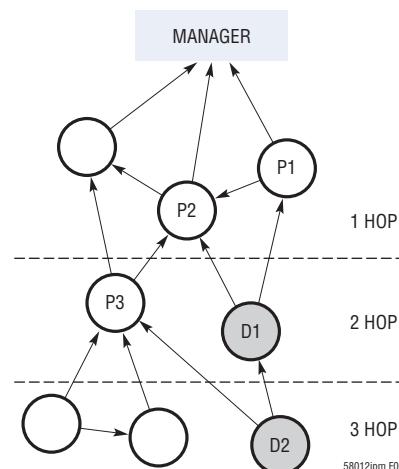

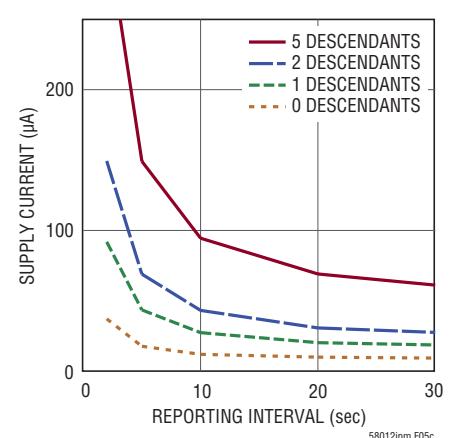

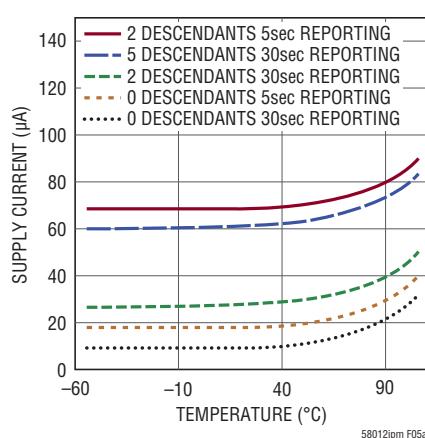

ネットワーク・モートは、通常、マネージャを送信先とするトライックを2つ以上の親を経由して送ります。図5に示す電源電流のグラフには、子孫(下位ノード)と呼ばれるパラメータが記載されています。これらのグラフでは、子孫という用語はトライックで重み付けされた子孫の省略形であり、すべてのネットワーク・トライックが該当モートに送信されたと仮定した場合、子孫の数と等価な活動量を指します。通常、1つの親の子孫の数は、トライックで重み付けされた子孫の数より多数(通常は2倍以上)です。たとえば、図6を参照すると、ネットワーク・グラフ・モートP1のトライックで重み付けされた子孫の数は0.75です。この値を得るには、モートD1はそのパケットの半分をモートP1を経由して転送するので、トライックで重み付けされた子孫の値に0.5が加算されることに注意してください。D1の残りの半分のトライックは別の親(P2)を経由して転送されます。モートD2はそのパケットの半分をモートD1を経由して(残りの半分は親P3を経由して)転送するので、そのパケットの半分はモートP1に転送されることが分かり、トライックで重み付けされた子孫の値にさらに0.25を加算して、トライックで重み付けされた子孫の合計値は0.75になります。

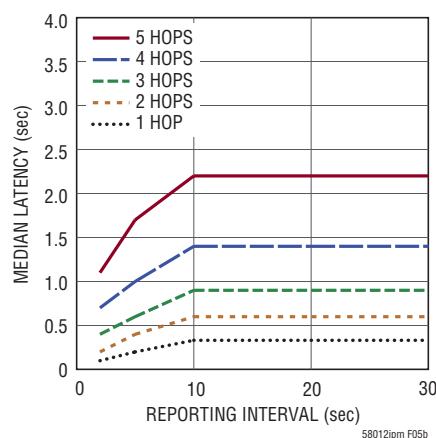

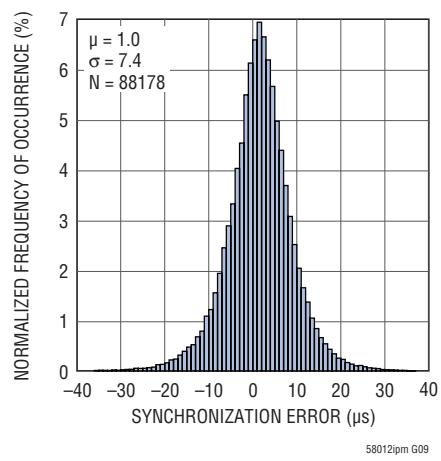

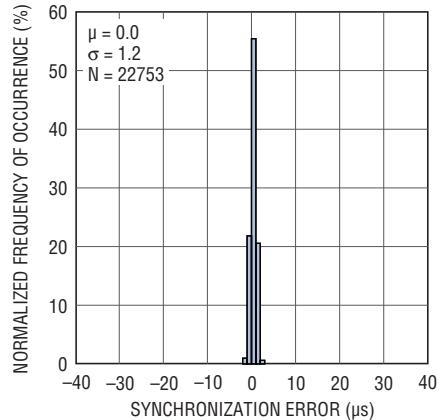

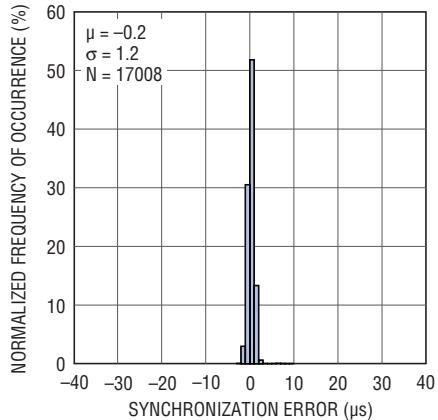

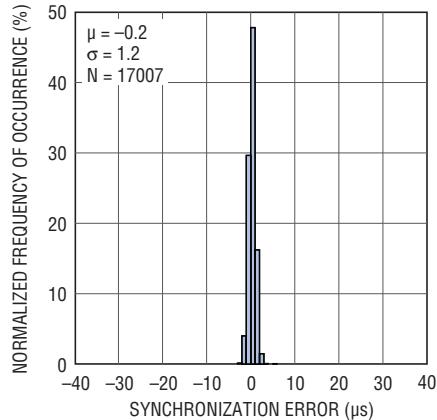

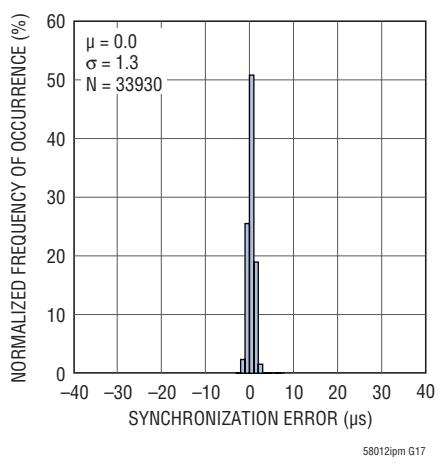

「[アプリケーションの時間同期](#)」セクションで説明したように、Eternaは、アプリケーションがネットワーク全体にわたって時間基準を維持するための2つの仕組みを備えています。以下に示す同期性能のグラフは、より高精度のTIMEn入力を使用して作成されました。発行レートは、モート・アプリケーションが上流のデータを送信する速度です。発行レートが高くなるにつれて同期は改善されます。基準線となる同期性能は、発行レートがゼロで動作するネットワークに対して与えられます。ネットワークでのアプリケーションの実際の性能は、発行レートが高くなるにつれて向

上します。すべての同期テストは、恒温槽の内部で1ホップのモートを使って行われました。したがって、ネットワーク・マネージャとこのモートの間、およびこのモートとその子孫の間の両方の温度変化と温度差に起因するタイミング誤差は、ネットワークを通じて伝播します。このため、3ホップと5ホップのモートとマネージャとの同期は、モートが室温であっても温度の傾斜に影響されました。2°C/分のテストでは、恒温槽の温度が-40°C～85°Cの間を24時間にわたってこのレートで循環しました。8°C/分のテストでは、恒温槽の温度が85°C～45°Cの間を8時間にわたって急速に循環し、その後-5°C～45°Cの間を8時間、最後に-40°C～15°Cの間を8時間急速に循環しました。

図6. ネットワーク例のグラフ

図5

## 標準的性能特性

TIMEn の同期誤差、

0パケット/秒の発行レート、

1ホップ、室温

TIMEn の同期誤差、

0パケット/秒の発行レート、

3ホップ、室温

TIMEn の同期誤差、

0パケット/秒の発行レート、

5ホップ、室温

TIMEn の同期誤差、

0パケット/秒の発行レート、

1ホップ、2°C/分

TIMEn の同期誤差、

0パケット/秒の発行レート、

3ホップ、2°C/分

TIMEn の同期誤差、

0パケット/秒の発行レート、

5ホップ、2°C/分

TIMEn の同期誤差、

0パケット/秒の発行レート、

1ホップ、8°C/分

TIMEn の同期誤差、

0パケット/秒の発行レート、

3ホップ、8°C/分

TIMEn の同期誤差、

0パケット/秒の発行レート、

5ホップ、8°C/分

59012ipm

## 標準的性能特性

TIMEn の同期誤差、

1パケット/秒の発行レート、

1ホップ、室温

TIMEn の同期誤差、

1パケット/秒の発行レート、

3ホップ、室温

TIMEn の同期誤差、

1パケット/秒の発行レート、

5ホップ、室温

TIMEn の同期誤差、

1パケット/秒の発行レート、

1ホップ、2°C/分

TIMEn の同期誤差、

1パケット/秒の発行レート、

3ホップ、2°C/分

TIMEn の同期誤差、

1パケット/秒の発行レート、

5ホップ、2°C/分

TIMEn の同期誤差、

1パケット/秒の発行レート、

1ホップ、8°C/分

TIMEn の同期誤差、

1パケット/秒の発行レート、

3ホップ、8°C/分

TIMEn の同期誤差、

1パケット/秒の発行レート、

5ホップ、8°C/分

## 標準的性能特性

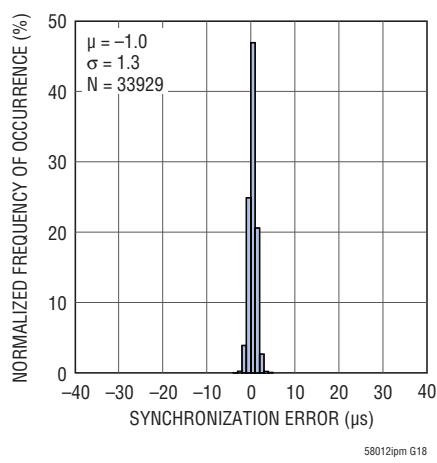

「SmartMesh ネットワークの概要」セクションで説明したように、ネットワーク内のデバイスはその大半の時間を消費電力が最も低い非活動状態(ドーズ状態)で費やします。同期スケジュールでは、モートが起動して他のモートと通信します。起動、機能の実行、スリープ状態へ戻る定常的な一連の動作はアトミック(不可分)とみなされます。有効な機能を実行している間、一連のイベントをそれより小さなイベントに分割できないので、これらの動作はアトミックとみなされます。たとえば、無線を介したパケットの伝送はアトミック動作です。アトミック動作は電荷またはエネルギーで特性が評価できます。モートがパケットを正常に送信したタイムスロットでは、メッセージ送信前の準備、メッセージの送信、アクノリッジの受信、およびメッセージの送信結果として必要な後処理がアトミック送信に含まれます。同様に、モートがパケットを正常に受信したタイムスロットでは、リスニング前の準備、パケット伝送開始までのリスニング、パケットの受信、アクノリッジの送信、およびパケットの到着によって必要になった後処理がアトミック受信に含まれます。

信頼性を確保するため、ネットワーク内の各モートは、形式上モートが送信して転送するパケットごとに複数のタイムスロットに用意されます。タイムスロットは、2つ以上の異なるモートと上流で通信するために割り当てられます。周波数ホッピングと組み合わせた場合、一時的、空間的、およびスペクトルの冗長性が得られます。送信側のモートはタイムスロットを使用しないので、このアプローチを想定すると、モートは決して受信しないメッセージを対象にリスニングすることが多くなります。このモートは既にパケットを正常に転送しています。通常は送信または転送される1つのパケットごとに3つのタイムスロットが予定されるので、モートがこれらのアトミック「アイドル・リスニング」を実行する回数は、アトミック送信シーケンスまたはアトミック受信シーケンスの回数より多くなります。送信、受信、およびアイドル・リスニング・アトミック動作の例を図7に示します。

## 標準的性能特性

図7

# LTP5901-IPM/LTP5902-IPM

## ピン機能 イタリック体で表示しているピン機能は、現時点ではソフトウェアでサポートされていません。

以下の表では、ピンを機能グループごとに整理しています。複数の機能を持つI/Oピンの場合、代替機能を該当列の2行目と3行目に示しています。「番号」列はピン番号を示します。2番目の列は機能を示します。「タイプ」列はI/Oタイプを示します。

「I/O」列は、Eternaに対する信号の向きを示します。「プル」列は、信号の固定受動回路がプルアップまたはプルダウンのどちらであるかを示します。「説明」列は、信号の簡単な説明を示します。

| 番号 | 電源      | タイプ | I/O | プル | 説明           |

|----|---------|-----|-----|----|--------------|

| 1  | GND     | 電源  | -   | -  | グランド接続       |

| 11 | GND     | 電源  | -   | -  | グランド接続       |

| 20 | GND     | 電源  | -   | -  | グランド接続       |

| 30 | GND     | 電源  | -   | -  | グランド接続       |

| 34 | GND     | 電源  | -   | -  | グランド接続       |

| 37 | GND     | 電源  | -   | -  | グランド接続       |

| 42 | GND     | 電源  | -   | -  | グランド接続       |

| 56 | GND     | 電源  | -   | -  | グランド接続       |

| 66 | GND     | 電源  | -   | -  | グランド接続       |

| 55 | VSUPPLY | 電源  | -   | -  | Eternaへの電源入力 |

| 番号 | 無線                      | タイプ         | I/O      | プル | 説明                                    |

|----|-------------------------|-------------|----------|----|---------------------------------------|

| 64 | RADIO_INHIBIT<br>GPIO15 | 1 (Note 14) | I<br>I/O | -  | 無線禁止<br>汎用デジタルI/O                     |

| 4  | GPIO17                  | 1           | I/O      | -  | 汎用デジタルI/O                             |

| 5  | GPIO18                  | 1           | I/O      | -  | 汎用デジタルI/O                             |

| 6  | GPIO19                  | 1           | I/O      | -  | 汎用デジタルI/O                             |

| -  | ANTENNA                 | N/A         | N/A      | -  | チップ・アンテナ(LTP5901)またはMMCXコネクタ(LTP5902) |

| 番号 | アナログ | タイプ  | I/O | プル | 説明      |

|----|------|------|-----|----|---------|

| 7  | AI_2 | アナログ | I   | -  | アナログ入力2 |

| 8  | AI_1 | アナログ | I   | -  | アナログ入力1 |

| 9  | AI_3 | アナログ | I   | -  | アナログ入力3 |

| 10 | AI_0 | アナログ | I   | -  | アナログ入力0 |

| 番号 | リセット   | タイプ | I/O | プル  | 説明              |

|----|--------|-----|-----|-----|-----------------|

| 15 | RESETn | 1   | I   | アップ | リセット入力、アクティブ“L” |

| 番号 | JTAG | タイプ | I/O | プル  | 説明            |

|----|------|-----|-----|-----|---------------|

| 16 | TDI  | 1   | I   | アップ | JTAGテストのデータ入力 |

| 17 | TDO  | 1   | 0   | -   | JTAGテストのデータ出力 |

| 18 | TMS  | 1   | I   | アップ | JTAGテストのモード選択 |

| 19 | TCK  | 1   | I   | ダウン | JTAGテストのクロック  |

**ピン機能** イタリック体で表示しているピン機能は、現時点ではソフトウェアでサポートされていません。

| 番号 | GPIO (NOTE 14)                    | タイプ | I/O      | ブル | 説明                                    |

|----|-----------------------------------|-----|----------|----|---------------------------------------|

| 21 | DP4(GPIO23)                       | 1   | I/O      | -  | 汎用デジタルI/O                             |

| 25 | DP3(GPIO22)<br><i>TIMER8_EXT</i>  | 1   | I/O<br>/ | -  | 汎用デジタルI/O<br>8ビット・タイマ/カウンタへの外部入力      |

| 26 | DP2(GPIO21)<br><i>LPTIMER_EXT</i> | 1   | I/O<br>/ | -  | 汎用デジタルI/O<br>低消費電力タイマ/カウンタへの外部入力      |

| 28 | DP0(GPIO0)<br><i>SPIM_SS_2n</i>   | 1   | I/O<br>0 | -  | 汎用デジタルI/O<br>SPIマスターのスレーブ選択2、アクティブ“L” |

| 45 | DP1(GPIO20)<br><i>TIMER16_EXT</i> | 1   | I/O<br>/ | -  | 汎用デジタルI/O<br>16ビット・タイマ/カウンタへの外部入力     |

| 番号 | 特殊用途                                 | タイプ         | I/O           | ブル | 説明                                                   |

|----|--------------------------------------|-------------|---------------|----|------------------------------------------------------|

| 27 | SLEEPn<br>GPIO14                     | 1 (Note 14) | /<br>I/O      | -  | 深いスリープ状態、アクティブ“L”<br>汎用デジタルI/O                       |

| 46 | PWM0<br><i>TIMER16_OUT</i><br>GPIO16 | 2           | 0<br>0<br>I/O | -  | パルス幅変調器0<br>16ビット・タイマ/カウンタ突き合わせ出力/PWM出力<br>汎用デジタルI/O |

| 63 | TIMEn<br>GPIO1                       | 1 (Note 14) | /<br>I/O      | -  | 時刻取り込み要求、アクティブ“L”<br>汎用デジタルI/O                       |

| 番号 | CLI       | タイプ | I/O | ブル  | 説明            |

|----|-----------|-----|-----|-----|---------------|

| 31 | UARTCO_TX | 2   | 0   | -   | CLI UART 0送信側 |

| 32 | UARTCO_RX | 1   | /   | アップ | CLI UART 0受信側 |

| 番号 | SPIマスター              | タイプ | I/O      | ブル | 説明                                         |

|----|----------------------|-----|----------|----|--------------------------------------------|

| 38 | SPIM_MISO<br>GPIO11  | 1   | /<br>I/O | -  | SPIマスターの(MISO)マスター入力スレーブ出力ポート<br>汎用デジタルI/O |

| 40 | SPIM_MOSI<br>GPIO10  | 2   | 0<br>I/O | -  | SPIマスターの(MOSI)マスター出力スレーブ入力ポート<br>汎用デジタルI/O |

| 41 | SPIM_SCK<br>GPIO9    | 2   | 0<br>I/O | -  | SPIマスターの(SCK)シリアル・クロック・ポート<br>汎用デジタルI/O    |

| 43 | SPIM_SS_1n<br>GPIO13 | 1   | 0<br>I/O | -  | SPIマスターのスレーブ選択1、アクティブ“L”<br>汎用デジタルI/O      |

| 44 | SPIM_SS_0n<br>GPIO12 | 1   | 0<br>I/O | -  | SPIマスターのスレーブ選択0、アクティブ“L”<br>汎用デジタルI/O      |

# LTP5901-IPM/LTP5902-IPM

**ピン機能** イタリック体で表示しているピン機能は、現時点ではソフトウェアでサポートされていません。

| 番号 | IPCS SPI/フラッシュのプログラミング(NOTE 16)                           | タイプ | I/O           | ブル          | 説明                                                                                  |

|----|-----------------------------------------------------------|-----|---------------|-------------|-------------------------------------------------------------------------------------|

| 33 | <i>IPCS_MISO</i><br><i>TIMER16_OUT</i><br>GPIO6           | 2   | I<br>0<br>I/O | -<br>-<br>- | SPI フラッシュ・エミュレーションの(MISO)マスタ入力スレーブ出力ポート<br>16ビット・タイマ/カウンタ突き合わせ出力/PWM出力<br>汎用デジタルI/O |

| 35 | <i>IPCS_MOSI</i><br><i>TIMER16_EXT</i><br>GPIO5           | 1   | I<br>/<br>I/O | -<br>-<br>- | SPI フラッシュ・エミュレーションの(MOSI)マスタ出力スレーブ入力ポート<br>16ビット・タイマ/カウンタへの外部入力<br>汎用デジタルI/O        |

| 36 | <i>IPCS_SCK</i><br><i>TIMER8_EXT</i><br>GPIO4             | 1   | I<br>/<br>I/O | -<br>-<br>- | SPI フラッシュ・エミュレーションの(SCK)シリアル・クロック・ポート<br>8ビット・タイマ/カウンタへの外部入力<br>汎用デジタルI/O           |

| 39 | <i>IPCS_SS<sub>n</sub></i><br><i>LPTIMER_EXT</i><br>GPIO3 | 1   | I<br>/<br>I/O | -<br>-<br>- | SPI フラッシュ・エミュレーションのスレーブ選択、アクティブ“L”<br>低消費電力タイマ/カウンタへの外部入力<br>汎用デジタルI/O              |

| 51 | FLASH_P_EN <sub>n</sub>                                   | 1   | I             | アップ         | フラッシュ・プログラムのイネーブル、アクティブ“L”                                                          |

| 番号 | I <sup>2</sup> C/単線式/SPIスレーブ                          | タイプ | I/O           | ブル          | 説明                                                        |

|----|-------------------------------------------------------|-----|---------------|-------------|-----------------------------------------------------------|

| 47 | <i>SPIS_MISO</i><br><i>UARTC1_TX</i><br><i>1_WIRE</i> | 2   | 0<br>0<br>I/O | -<br>-<br>- | SPIスレーブの(MISO)マスタ入力スレーブ出力ポート<br>CLI UART1送信側<br>単線式マスタ    |

| 48 | <i>SPIS_MOSI</i><br><i>UARTC1_RX</i><br>GPIO26        | 1   | /<br>/<br>I/O | -<br>-<br>- | SPIスレーブの(MOSI)マスタ出力スレーブ入力ポート<br>CLI UART1受信側<br>汎用デジタルI/O |

| 49 | <i>SPIS_SCK</i><br><i>SCL</i>                         | 2   | /<br>I/O      | -<br>-      | SPIスレーブの(SCK)シリアル・クロック・ポート<br>I <sup>2</sup> Cシリアル・クロック   |

| 50 | <i>SPIS_SS<sub>n</sub></i><br><i>SDA</i>              | 2   | /<br>I/O      | -<br>-      | SPIスレーブ選択、アクティブ“L”<br>I <sup>2</sup> Cシリアル・データ            |

| 番号 | API UART                 | タイプ         | I/O | ブル | 説明                        |

|----|--------------------------|-------------|-----|----|---------------------------|

| 57 | UART_RX_RTS <sub>n</sub> | 1 (Note 14) | I   | -  | UART受信側(RTS)送信要求、アクティブ“L” |

| 58 | UART_RX_CTS <sub>n</sub> | 1           | 0   | -  | UART受信側(CTS)送信可、アクティブ“L”  |

| 59 | UART_RX                  | 1 (Note 14) | I   | -  | UART受信側                   |

| 60 | UART_TX_RTS <sub>n</sub> | 1           | 0   | -  | UART送信側(RTS)送信要求、アクティブ“L” |

| 61 | UART_TX_CTS <sub>n</sub> | 1 (Note 14) | I   | -  | UART送信側(CTS)送信可、アクティブ“L”  |

| 62 | UART_TX                  | 2           | 0   | -  | UART送信側                   |

**Note 14:**これらの入力は常にイネーブルされており、有効な状態に駆動するかブルアップ/ブルダウンして漏れを防止する必要がある。

**Note 15:**他のGPIOポートについては、ピン40、42、44、および45も参照。

**Note 16:**RESET<sub>n</sub>がアサートされている場合は、IPCS SPIバスを介した組み込みプログラミングのみが使用可能。

## ピン機能

**VSUPPLY**: システムおよび入出力の電源。モジュールに電力を供給します。デジタル・インターフェースのI/O電圧もこの電圧によって設定されます。

**ANTENNA**: レシーバ入力とトランスマッタ出力の多重化ピン。MMCXコネクタに現れるインピーダンスは、グランドを基準にしたシングルエンドで $50\Omega$ になります。

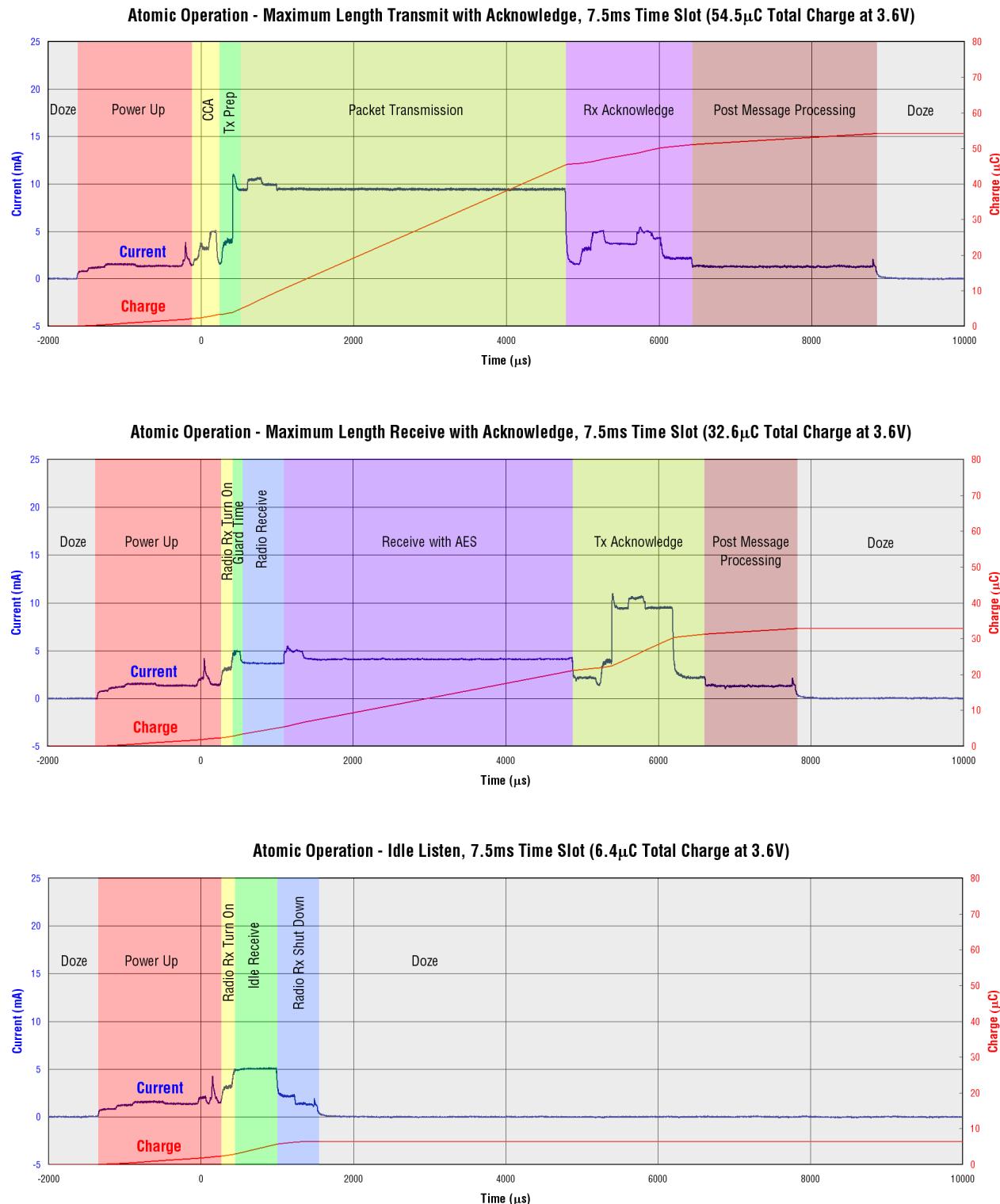

**AI\_0, AI\_1, AI\_2, AI\_3**: アナログ入力。これらのピンはアナログ入力チェーンに多重化されています。図8に示すように、アナログ入力チェーンはソフトウェアで設定可能であり、可変利得アンプ、入力範囲調整用のオフセットD/Aコンバータ、および10ビットA/Dコンバータを内蔵しています。有効な入力範囲は0V～1.8Vです。アナログ入力は、「信号/データの取得と制御」セクションに説明する方法でサンプリングできます。

図8. アナログ入力チェーン

**RESETn**: 非同期のリセット信号は内部でプルアップされています。EternaをリセットするとARM Cortex M3が再起動し、ネットワーク接続が失われます。電源投入時とインサーキット・プログラミング時を除いて、Eternaをリセットするためにこの信号を使用することは推奨しません。

**RADIO\_INHIBIT**: RADIO\_INHIBITは、外部デバイスが無線動作を一時的にディスエーブルするための仕組みを確保します。「Radio\_InhibitのAC特性」セクションに規定されているタイミング要件に従うことができないと、信頼できないネットワーク動作になる可能性があります。RADIO\_INHIBIT機能が必要ない設計では、入力を“L”に接続するか、プルダウンするか、またはアクティブに駆動して、過剰な漏れを防止する必要があります。

**TMS, TCK, TDI, TDO**: JTAGポート対応ソフトウェアのデバッグおよびバウンダリ・スキャン。

**SLEEPn**: SLEEPn機能は、現時点ではソフトウェアでサポートされていません。SLEEPn入力は“H”に接続するか、プルアップするか、またはアクティブに駆動して、過剰な漏れを防止する必要があります。

**UART\_RX, UART\_RX\_RTn, UART\_RX\_CTSn, UART\_TX, UART\_TX\_RTn, UART\_TX\_CTSn**: API UARTインターフェースには、双方向の起動制御およびフロー制御機能が組み込まれています。未使用的入力信号は信号の非アクティブ状態に駆動するかプルアップ/プルダウンで非アクティブ状態にする必要があります。

**TIMEn**: Eternaによって保持されているネットワーク時間を取り込む最も正確な方法は、TIMEn入力にストローブ信号を入力する方法です。Eternaは、TIMEn信号の立ち上がりエッジでミリ秒未満の分解能でネットワーク・タイムスタンプをラッチし、タイミング情報を記録したパケットをAPIシリアル・ポートで生成します。

**UARTCO\_RX, UARTCO\_TX**: CLI UARTは、動作中にEternaのモニタ、構成、および制御を行うための仕組みを確保します。サポートされているコマンドの詳細な記述については、『SmartMesh IP Mote CLI Guide』を参照してください。

**GPIO3, GPIO4, GPIO5, GPIO6, GPIO20, GPIO21, GPIO22, GPIO23, GPIO26**: 「信号/データの取得と制御」セクションに説明する方法でサンプリングまたは駆動できる汎用I/Oです。

**FLASH\_P\_ENn, IPCS\_SSn, IPCS\_SCK, IPCS\_MISO, IPCS\_SS**: インサーキット・プログラミング制御システム(IPCS)バスにより、Eternaのフラッシュ・メモリのインサーキット・プログラミングが可能になります。IPCS\_SCKはクロックであり、オーバーシュートやリンギングを防ぐための駆動源として適切に終端する必要があります。

## 動作

LTP5901-IPM/LTP5902-IPMは、世界で最もエネルギー効率の高いIEEE 802.15.4準拠のプラットフォームであり、バッテリ駆動アプリケーションや環境発電(エナジーハーベスト)アプリケーションを使用可能にします。強力な32ビットのARM Cortex-M3、クラス最高の無線機能、フラッシュ、RAMおよび特定用途向け周辺機器により、Eternaは、最も困難なRF環境であっても最小限のエネルギー消費とデータ信頼性が要求されるアプリケーションに対して、柔軟でスケーラブルかつ堅牢なネットワーク・ソリューションを実現します。

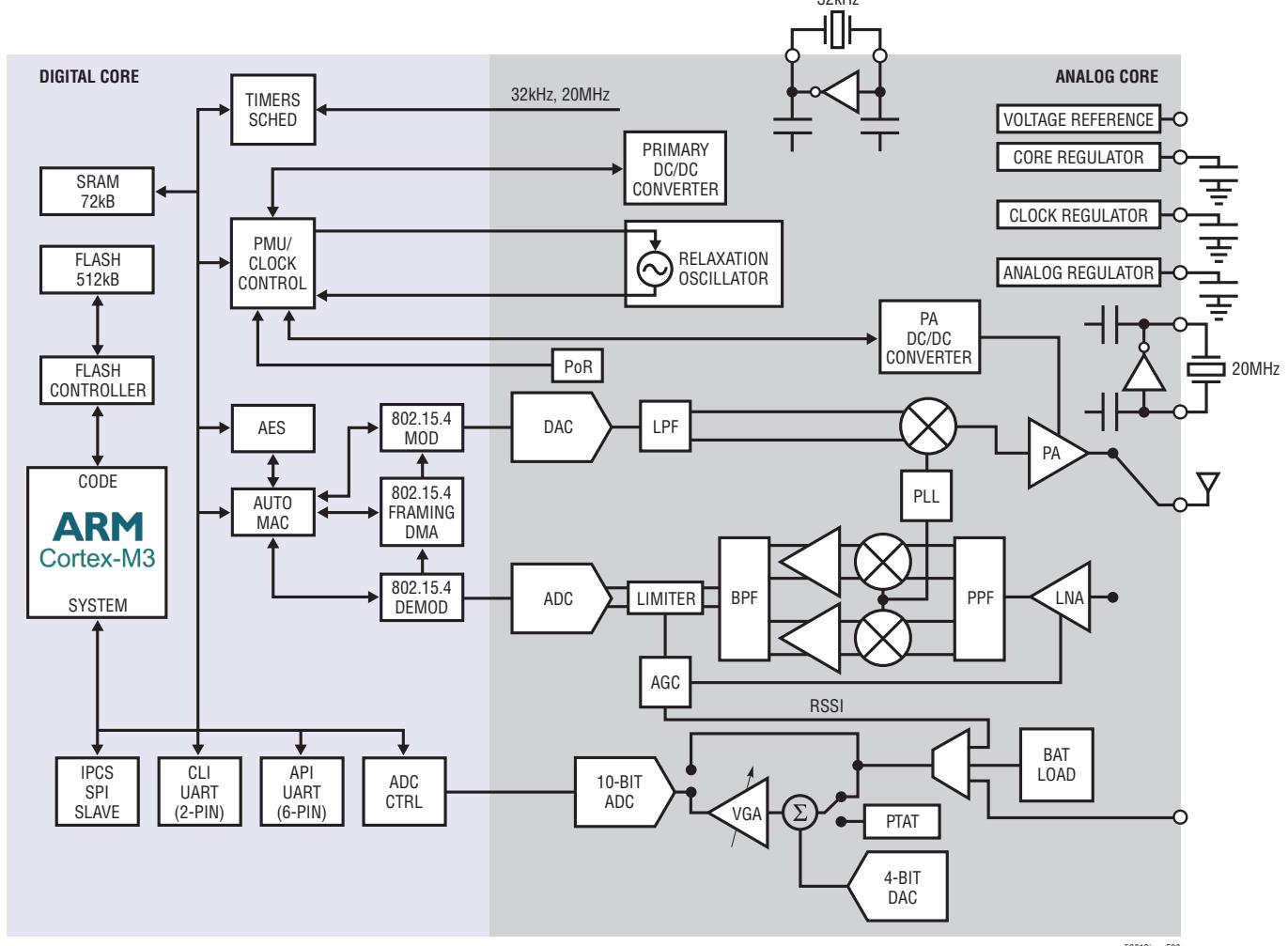

図9に示すように、Eternaは、低動作エネルギー消費面と、動作状態と低消費電力状態の間を迅速かつ高精度に循環する能力面の両方で優れている特定用途向けの周辺機器を一体化しています。Analog Coreとラベル付けされた灰色の網掛け領域内の品目がアナログ/RF部品に相当します。

## 電源

Eternaは1つのピン(VSUPPLY)から電力供給を受けます。このピンはI/Oセルに電力を供給し、内部電源を発生する目的にも使用されます。Eternaの2つの内蔵DC/DCコンバータは、デバイスが起動している間、Eternaのエネルギー消費量を最小限に抑えます。消費電力を節減するため、デバイスが低消費電力状態のとき、DC/DCコンバータはディスエーブルされます。2つの内蔵DC/DCコンバータと3つの内蔵低ドロップアウト・レギュレータを含むEternaの電源調整アーキテクチャにより、電源ノイズの優れた除去性能を実現します。Eternaの動作電源電圧範囲は、塩化チオニルリチウム(Li-SOCl<sub>2</sub>)電池への直接接続をサポートするのに十分な高さであり、広い温度範囲にわたってバッテリ動作をサポートするのに十分な広さです。

図9. Eternaのブロック図

59012ipmf

## 動作

### 電源モニタとリセット

Eternaはパワーオン・リセット(PoR)回路を内蔵しています。RESETn入力ピンは、公称では内部プレアップ抵抗で構成されているので、接続の必要はありません。シャットダウンを正常に行うため、ソフトウェアとネットワーク層はRESETnピンのアサーションの前にAPIコマンドを介して明確に停止している必要があります。切断コマンドおよびリセット・コマンドの詳細については、『SmartMesh IP Mote API Guide』を参照してください。Eternaは、フラッシュへの書き込み中に電源が取り外された場合、フラッシュが損傷しないよう完全に保護するソフト電圧低下モニタを内蔵しています。内蔵のフラッシュ監視機能と耐フォルト型のファイル・システムの組み合わせにより、堅牢な不揮発性メモリ・ソリューションが得られます。

### 高精度のタイミング

競合する802.15.4製品に勝るEternaの主な特長は、低消費電力専用タイミング・ハードウェアおよびタイミング・アルゴリズムです。この機能により、本データシートの発行時点で入手可能な他の低消費電力ソリューションより2、3桁精度の高いタイミング精度が得られます。タイミング精度の向上により、パケットの受信を保証するために必要な無線リスニング時間の長さをモートが最小限に抑えることができるので、その結果、SmartMeshネットワークの消費電力はさらに低下します。Eternaの特許取得済みのタイミング・ハードウェアおよびタイミング・アルゴリズムにより、温度が急速に変化したときに優れた性能が発揮され、他のワイヤレス製品と比較した場合にEternaの信頼性がいっそう際立ちます。さらに、高精度のタイミングにより、ネットワークがスペクトルのデッドタイムを低減して、ネットワークの総スループットを高めることができます。

### アプリケーションの時間同期

ユーザーには意識されない、ネットワーク全体にわたるタイムスロットの調整の他に、Eternaのタイミング管理機能を使用して、ネットワーク時間を共有する2つの仕組みをサポートします。高精度で共有された、ネットワーク規模の時間基準があることにより、イベントにタイムスタンプを正確に刻むことや、作業をネットワーク全体にわたって同期方式で実行することができます。次のいずれかが行われると、Eternaはそのシリアル・インターフェースを介して時間パケットを送信します。

- Eternaが時刻を読み取るAPI要求を受信する

- TIMEn信号がアサートされる

TIMEnを使用する利点は精度の向上です。タイムスタンプの値は、TIMEnの立ち上がりエッジを基準にしてハードウェアに取り込まれます。API要求を使用した場合は、パケット処理が原因で、タイムスタンプの値がパケットの受信後数ミリ秒後に取り込まれることがあります。時間機能の定義および仕様については、「TIMEnのAC特性」セクションを参照してください。

### 時間基準

Eternaは3つのクロック信号源を内蔵しています。それは、内部弛張発振器、32.768kHz水晶発振器用に設計された低消費電力の発振器、および20MHz水晶発振器用に設計された無線基準発振器です。

### 弛張発振器

弛張発振器はEternaの主なクロック信号源であり、CPU、メモリ・サブシステム、およびすべての周辺機器にクロックを供給します。内部弛張発振器は、7.3728MHzに動的に校正されます。内部弛張発振器は、通常は数 $\mu$ s以内に起動し、アクティブ状態と低消費電力状態とを繰り返す好都合で低エネルギーの方法を実現します。ドーズ状態(「状態図」セクションで定義)から急速に起動すると、該当信号の動きを検出するだけで、Eternaを起動してUARTおよびSPIインターフェースを介してデータを受信することができます。

### 32.768kHz水晶発振器

Eternaの電源が投入されて32.768kHz水晶発振器信号源が発振を開始すると、32.768kHz水晶発振器はアクティブ状態時も動作状態が維持され、ドーズ状態時にはタイミングの基準として使用されます。Eternaの動作状態の説明については、「状態図」セクションを参照してください。

### 20MHz水晶発振器

20MHz水晶発振器信号源は無線部の周波数リファレンスを供給し、またEternaにより、必要に応じて自動的にイネーブルまたはディスエーブルされます。

## 動作

### 無線

Eternaは、商品化されている低消費電力の2.4GHz IEEE 802.15.4e無線部を相当な余裕をもって内蔵しています。(電力消費量の数値については、「無線規格」セクションを参照してください)。Eternaに内蔵されているパワーアンプは、世界規模の無線認証規格に適合した制限値内で電力を着実に供給するよう校正され、温度補償されています。さらにEternaは、トランシミッタ、レシーバ、高度暗号化標準(AES)周辺機器などの周辺機器の高精度シーケンス制御を処理するハードウェア・ベースの自律MACを独自に内蔵しています。ハードウェア・ベースの自律メディア・アクセス・コントローラ(MAC)により、CPUの動作が最小限に抑えられるので、電力消費量はいつも低減されます。

### UART

主要なネットワーク・インターフェースは、アプリケーション・プログラミング・インターフェース(API)UARTを介しています。テスト機能およびデバッグ機能をサポートするため、コマンドライン・インターフェース(CLI)も用意されています。2種類のUARTは両方とも動作を絶えず検出し、データがポートを介して転送されるまで実質的に電力を消費せず、転送終了後その最も低消費電力の状態に自動的に戻ります。API UARTインターフェースでのパケット・コード化の定義は『SmartMesh IP Mote API Guide』に記載されており、CLIコマンド定義は『SmartMesh IP Mote CLI Guide』に記載されています。

### API UARTのプロトコル

API UARTプロトコルは、システムの電力消費量を低減しながら、広範なコンピュオン多点制御装置(MCU)をサポートすることを目標に作成されました。API UARTプロトコルの受信側の半分には、UART\_RXの他に2つの付加的な信号があります。それは、UART\_RX\_RTsnとUART\_RX\_CTSnです。API UARTプロトコルの送信側の半分には、UART\_TXの他に2つの付加的な信号があります。それは、UART\_TX\_RTsnとUART\_TX\_CTSnです。API UARTプロトコルはモード4と呼ばれます。

プロトコルの説明を示す図では、コンピュオン・プロセッサが駆動する信号を黒で表記し、Eternaが駆動する信号を青で表記しています。

### UARTモード4

UARTモード4はレベル感度の高いフロー制御をTXチャネルで実装しており、RXチャネルではフロー制御が不要で、115200ボーレートをサポートしています。レベル感度の高いフロー制御信号を使用すると、短縮した一連のフロー制御信号を使用するオプションにより、高いデータ・レートが可能になります。ただし、コンピュオン・プロセッサはパケットの終わりに達する前にUART\_TX\_CTSnを否定しておく必要があり、パケット送信の間で少なくともtRX\_RTS to RX\_CTSは待機する必要があります。完全なタイミング仕様については、「UARTのAC特性」セクションを参照してください。パケットはHDLCでコード化され、ストップ・ビットが1ビットでパリティ・ビットはありません。モード4におけるRXフロー制御信号(UART\_RX\_RTsnおよびUART\_RX\_CTSn)の使用はオプションです。TXチャネルのフロー制御信号を図10に示します。UARTモード4の送信フロー制御UART\_TX\_RTsnをアサートしているEternaによって転送が開始されます。パケットの受信準備が完了したら、UART\_TX\_CTSn信号をコンピュオン・プロセッサでアクティブに駆動できます。あるいは、コンピュオン・プロセッサのパケット受信準備が常時整っている場合は、UART\_TX\_CTSnを「L」に接続することができます。UART\_TX\_CTSnでロジック「0」を検出後、Eternaは全パケットを送信します。Eternaはパケットの最終バイトの送信後、UART\_TX\_RTsnを否定し、「UARTのAC特性」セクションで定義されている最短期間の待機後、UART\_TX\_RTsnを再度アサートします。

図10. UARTモード4の送信フロー制御

UARTプロトコルのタイミングの詳細については、「UARTのAC特性」セクションを参照してください。

### CLI UART

コマンドライン・インターフェース(CLI)UARTポートは、固定の9600ボーレートで動作し、ストップ・ビットが1ビットでパリティ・ビットのない2線式プロトコル(TXおよびRX)です。CLI UARTインターフェースは、コマンドラインの命令および応答動作をサポートすることを目的としています。

## 動作

### 自律 MAC

Eternaは、信頼性が高く、超低消費電力で安全なネットワークを実現するシステム・ソリューションとして設計されました。変化する環境で動作を動的に最適化できる高信頼ネットワークでは、複雑過ぎてハードウェアによる加速化だけでは完全にはサポートできないソリューションが要求されます。「高精度のタイミング」セクションで説明しているように、低消費電力かつ高信頼性のソリューションを最適化するには、適切な時間管理が不可欠です。これらの要求に対応するため、Eternaは自律MACを備えており、自律MACには、時間が肝要なすべての無線動作を制御するためのコプロセッサが組み込まれています。自律MACには利点が2つあります。まず、変わりやすいソフトウェア待ち時間がネットワークのタイミングに影響するのを防止します。次に、大半の無線動作時にCPUを非アクティブ状態に維持できることにより、システムの電力消費量が大幅に減少します。自律MACは無線および無線関連機能のソフトウェアに依存しないタイミング制御を実現するので、優れた信頼性と並外れた低消費電力が得られます。

### セキュリティ

ネットワーク・セキュリティは、包括的なネットワーク・ソリューションで見過ごされがちな要素です。セキュリティ・プロトコルを適切に実装することは、技術的な労力とOEM製品の市場価値の両方の観点から重要です。Eternaシステム・ソリューションは、MACおよびネットワーク層での認証および暗号化をモートごとに異なる鍵を使用して組み込んだFIPS-197検証済みの暗号化方式を実現します。これにより、終端間のセキュリティが確保できるだけでなく、モートが何らかの形で危険にさらされている場合でも、他のモートからの通信は引き続き安全です。安全な鍵交換のメカニズムにより、鍵を新規の状態に保持できます。物理的な攻撃を阻止するため、Eternaにはデバイスを電子的にロックするハードウェア・サポートが組み込まれています。これにより、Eternaのフラッシュ・メモリとRAMメモリ、さらにそこに保存されている鍵とコードにアクセスできないようにしています。

### 温度センサ

Eternaは、校正された温度センサをチップ上に組み込んでいます。温度測定値はEternaのシリアルAPIを介してローカルに読み取る以外に、ネットワーク・マネージャ経由で得ることもできます。温度センサの性能特性は「温度センサ特性」セクションに記載されています。

### 無線禁止

RADIO\_INHIBIT入力を使用すると、外部コントローラが無線ソフトウェア・ドライバを一時的にディスエーブルすることができます(たとえば、無線妨害の影響を受けやすいセンサ値の読み取り時)。RADIO\_INHIBITがアサートされると、ソフトウェア無線ドライバはクリア・チャネル評価、パケット送信、パケット受信などの無線動作を禁止します。RADIO\_INHIBITがアサートされたとき現行のタイムスロットで無線がアクティブである場合、無線がディスエーブルされるのは現在の動作完了後となります。RADIO\_INHIBITに関連したタイミングの詳細については、「Radio\_InhibitのAC特性」セクションを参照してください。

### 工場インストール済みソフトウェア

この製品は、ソフトウェアをデバイス内にプログラミングした状態で供給されます。デバイスは、CLIまたはAPIポートのいずれかを通して構成できます。構成コマンドと設定は、『SmartMesh IP Mote API Guide』および『SmartMesh IP Mote CLI Guide』に定義されています。

### フラッシュのデータ保持

Eternaは、校正結果、固有ID、構成設定、およびソフトウェア・イメージを格納するフラッシュ(不揮発性メモリ)を内蔵しています。フラッシュは全動作温度範囲でデータを保持します。「電気的特性」と「絶対最大定格」のセクションを参照してください。

-40°C～85°Cの動作温度範囲外での非破壊記憶が可能です。ただし、保持特性が劣化する可能性があります。

85°Cを超える温度でのフラッシュの保持特性の劣化は、次式を使って無次元の加速係数を計算することにより、近似することができます。

$$AF = e^{\left[ \left( \frac{Ea}{k} \right) \left( \frac{1}{T_{USE} + 273} - \frac{1}{T_{STRESS} + 273} \right) \right]}$$

ここで、

AF = 加速係数

Ea = 活性化エネルギー = 0.6eV

k = 8.625 · 10<sup>-5</sup> eV/K

T<sub>USE</sub> = 規定の保持温度(°C)

T<sub>STRESS</sub> = 実際の保存温度(°C)

## 動作

例: 温度 105°C で保存した場合の保持特性への影響を計算します。

$T_{STRESS} = 105^\circ\text{C}$

$T_{USE} = 85^\circ\text{C}$

$AF = 2.8$

したがって、フラッシュの総合的な保持特性は係数 2.8 で劣化し、データ保持性能は 85°C 時の 20 年から 105°C 時の 7.1 年に低下します。

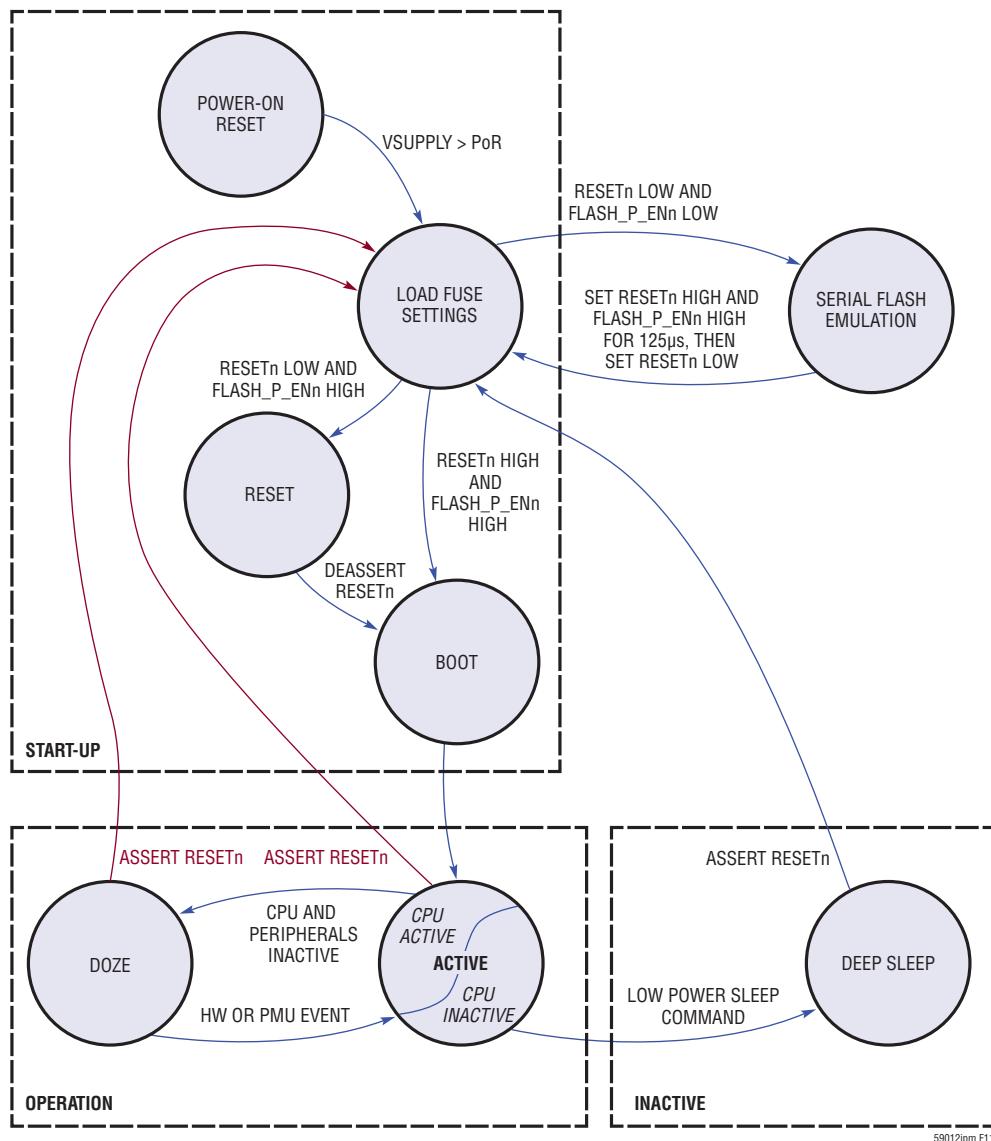

## 状態図

超低消費電力の他に能力と柔軟性を発揮するため、図 11 に示すように、Eterna はさまざまな状態で動作します。このセクションに Eterna の状態図を示します。赤で示す状態遷移は非推奨です。

図 11. Eterna の状態図

## 動作

### 起動

起動はパワーオン・リセットしきい値を超えた結果またはRESETnをアサートした結果として行われます。パワーオン・リセットの完了後または内部で同期したRESETnの立ち下がりエッジ後に、Eternaはそのヒューズ・テーブルを読み込みます。前のセクションで説明したように、ヒューズ・テーブルにはI/O方向の設定情報が組み込まれています。この状態で、EternaはFLASH\_P\_ENnとRESETnの状態を調べ、信号が両方ともアサートされている場合、シリアル・フラッシュ・エミュレーション・モードに入ります。FLASH\_P\_ENnピンはアサートされていないがRESETnピンはアサートされた場合、EternaはRESETnが解放されるまで、そのエネルギー消費量を自動的に最小限に抑えます。RESETnが解除されると、Eternaは起動シーケンスを経てアクティブ状態に移行します。

### シリアル・フラッシュのエミュレーション

RESETnとFLASH\_P\_ENnが両方ともアサートされると、Eternaは通常動作をディスエーブルして、シリアル・フラッシュの動作をエミュレートするモードに入ります。このモードでは、そのフラッシュをプログラムできます。

### 動作

Eternaは、起動が完了すると動作状態群(アクティブ/CPUアクティブ、アクティブ/CPU非アクティブ、およびドーズ)に移行します。そこで、Eternaはさまざまな状態間を循環し、起こり得る最も低い消費電力の状態を自動的に選択すると同時に、ネットワーク動作の要求を実現します。

### アクティブ状態

アクティブ状態では、Eternaの弛張発振器が動作しており、必要に応じて周辺機器がイネーブルされます。ARM Cortex-M3はCPUアクティブ状態とCPU非アクティブ状態との間を循環します(ARM Cortex-M3の技術資料では、スリープ・ナウ・モードと呼ばれています)。EternaがDMAを大量に使用することと、アクティブ状態とドーズ状態との間でEternaの状態を独自に移すインテリジェント周辺機器により、CPUがアクティブな時間が最小限に抑えられるので、Eternaのエネルギー消費量は大幅に減少します。

### ドーズ状態

ドーズ状態での消費電流はアクティブ状態より数桁少なく、ドーズ状態になるのは、すべての周辺機器とCPUが非アクティブ状態になったときです。ドーズ状態では、Eternaの全状態が保持され、タイミングが維持され、さらに(UART信号やTIMEnピンなど)I/Oでの動作を検出してEternaを起動し、迅速に応答するようEternaが構成されます。ドーズ状態では、32.768kHzの発振器と関連のタイマがアクティブ状態です。

## アプリケーション情報

### 信号/データの取得と制御

SmartMesh IP ソフトウェアには、温度、Eterna の ADC 入力および GPIO 入力をサンプリングするための組み込みアプリケーション・サポートと、GPIO 出力を操作するためのサポートが含まれます。これらの機能は、オンチップ・アプリケーション・プロトコル(OAP)により、ネットワーク・マネージャを介して無線送信されたデータ・パケットを介して有効化できます。そのため、モートにマイクロプロセッサを接続したり、Eterna 上での組み込みソフトウェアを開発する必要はありません。オンチップ・アプリケーション・プロトコル(OAP) の詳細については、『SmartMesh IP Tools Guide』を参照してください。

### 法規制と標準規格の順守

#### 無線認証

LTP5901 と LTP5902 は、ETERNA2 というモジュール名にて、1つのモジュール型認証の下で認証されています。『ETERNA2 User's Guide』に記載されている規制要件に従うと、完成品に対して非意図的放射機器スキャンを実施するだけで、お客様はサポート対象の地域で製品を出荷可能です。『ETERNA2 User's Guide』には、モジュール型認証をサポートを(まだ)していない地域において、お客様がモジュールまたはモジュールに基づく製品のいずれかを認証するために必要な技術情報も記載されています。

#### 有害物質の制限(RoHS)の順守

RoHS 2(有害物質に関する制限2)は、電子・電気機器における特定の有害物質の使用に対する最高濃度制限を定義する指令です。リニアテクノロジーは、欧州共同体(EC)指令 2011/65/EU の要件に適合するよう取り組んでいます。

本製品は、RoHS に準拠した原料を使用することと、規制物質の使用を排除または削減して 2011/65/EU に適合することを目的として設計されています。

RoHS に準拠した設計の特長は以下のとおりです。

- RoHS に準拠した半田による半田接合

- RoHS に準拠した卑金属合金

- RoHS に準拠した貴金属めっき

- RoHS に準拠したケーブル・アセンブリおよびコネクタ選択

- RoHS に準拠し、245°C のリフロー互換

注記: お客様は、欧州共同体(EC) 指令 2011/65/EU に従って、特定の種類の無鉛半田合金を選んで使用することができます。選択した半田ペーストの種類によっては、リフロー温度を最適化するために、それに対応する工程変更が必要になる可能性があります。

#### 半田付け情報

LTP5901 と LTP5902 は共晶 PbSn リフローと RoHS-6 リフローの両方に適しています。最大リフロー半田付け温度は 260°C です。レイアウトの推奨事項、組み立て手順、および設計上の検討事項の詳細については、『LTP5901 and LTP5902 Hardware Integration Guide』に記載されています。

## 関連資料

| 資料名                                            | URL                                                                                           | 概要                                                                                                    |

|------------------------------------------------|-----------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|

| SmartMesh IP Users Guide                       | <a href="http://www.linear-tech.co.jp/docs/41880">http://www.linear-tech.co.jp/docs/41880</a> | SmartMesh IP ネットワークおよびモードの動作原理                                                                        |

| SmartMesh IP Mote API Guide                    | <a href="http://www.linear-tech.co.jp/docs/41886">http://www.linear-tech.co.jp/docs/41886</a> | API UARTで使用できるアプリケーション・インターフェース・コマンドの定義                                                               |

| SmartMesh IP Mote CLI Guide                    | <a href="http://www.linear-tech.co.jp/docs/41885">http://www.linear-tech.co.jp/docs/41885</a> | CLI UARTで使用できるコマンドライン・インターフェース・コマンドの定義                                                                |

| LTP5901 and LTP5902 Hardware Integration Guide | <a href="http://www.linear-tech.co.jp/docs/41877">http://www.linear-tech.co.jp/docs/41877</a> | LTP5901 および LTP5902 を使用して設計するための推奨の手法                                                                 |

| ETERNA2 User's Guide                           | <a href="http://www.linear-tech.co.jp/docs/42916">http://www.linear-tech.co.jp/docs/42916</a> | ETERNA2 モジュールのユーザー・ガイドには、認証済み地域に適用される認証要件と、LTP5901 および LTP5902 についてお客様がその他の地域の認証を可能にするサポート文書が含まれています。 |

| SmartMesh IP Tools Guide                       | <a href="http://www.linear-tech.co.jp/docs/42453">http://www.linear-tech.co.jp/docs/42453</a> | すべての IP 関連のツール、および特にオンチップ・アプリケーション・プロトコル (OAP) の定義に関するユーザー・ガイド                                        |

# LTP5901-IPM/LTP5902-IPM

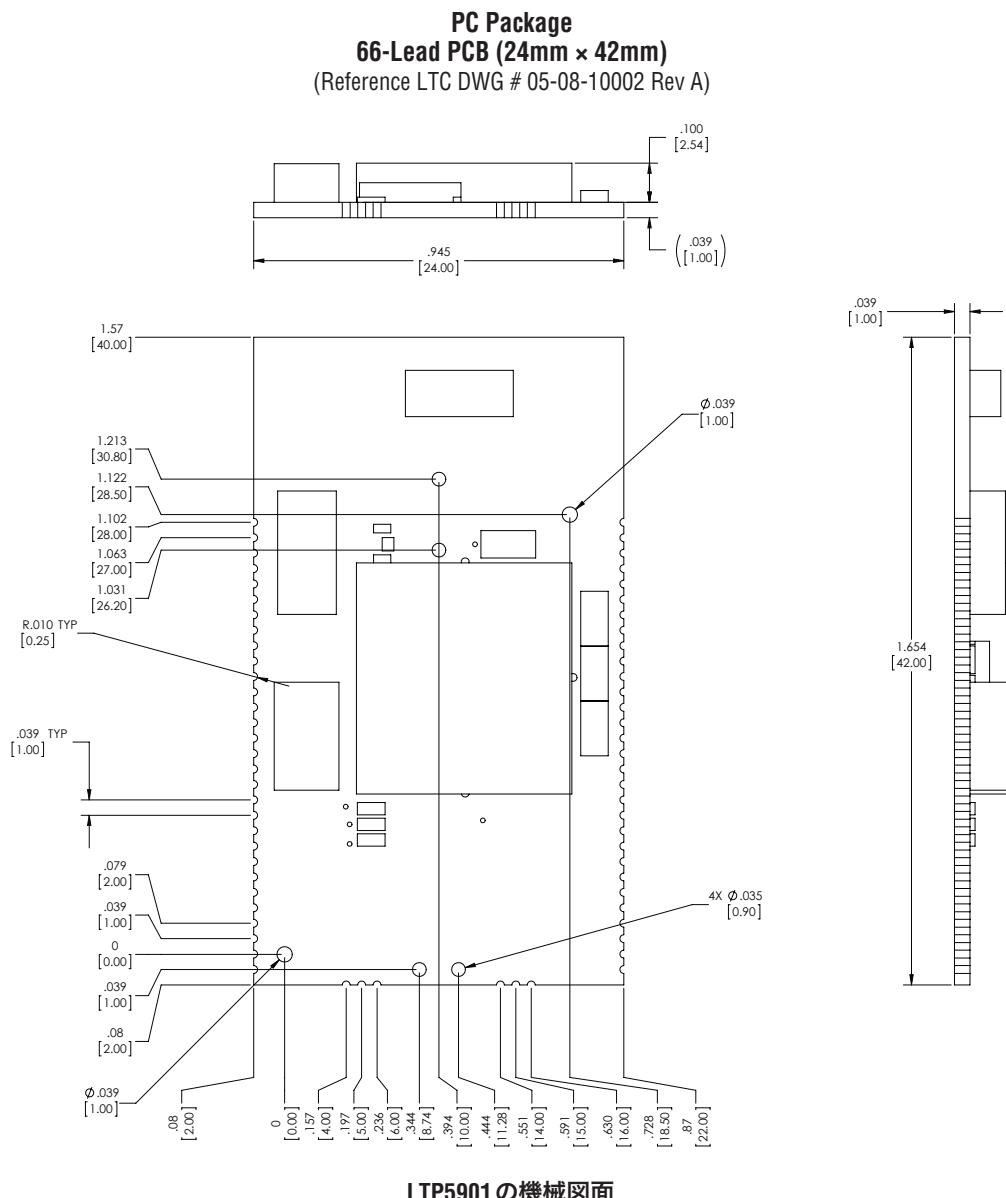

## パッケージ

最新のパッケージ図面については、<http://www.linear-tech.co.jp/designtools/packaging/>を参照してください。

59012ipmf

## パッケージ

最新のパッケージ図面については、<http://www.linear-tech.co.jp/designtools/packaging/> を参照してください。

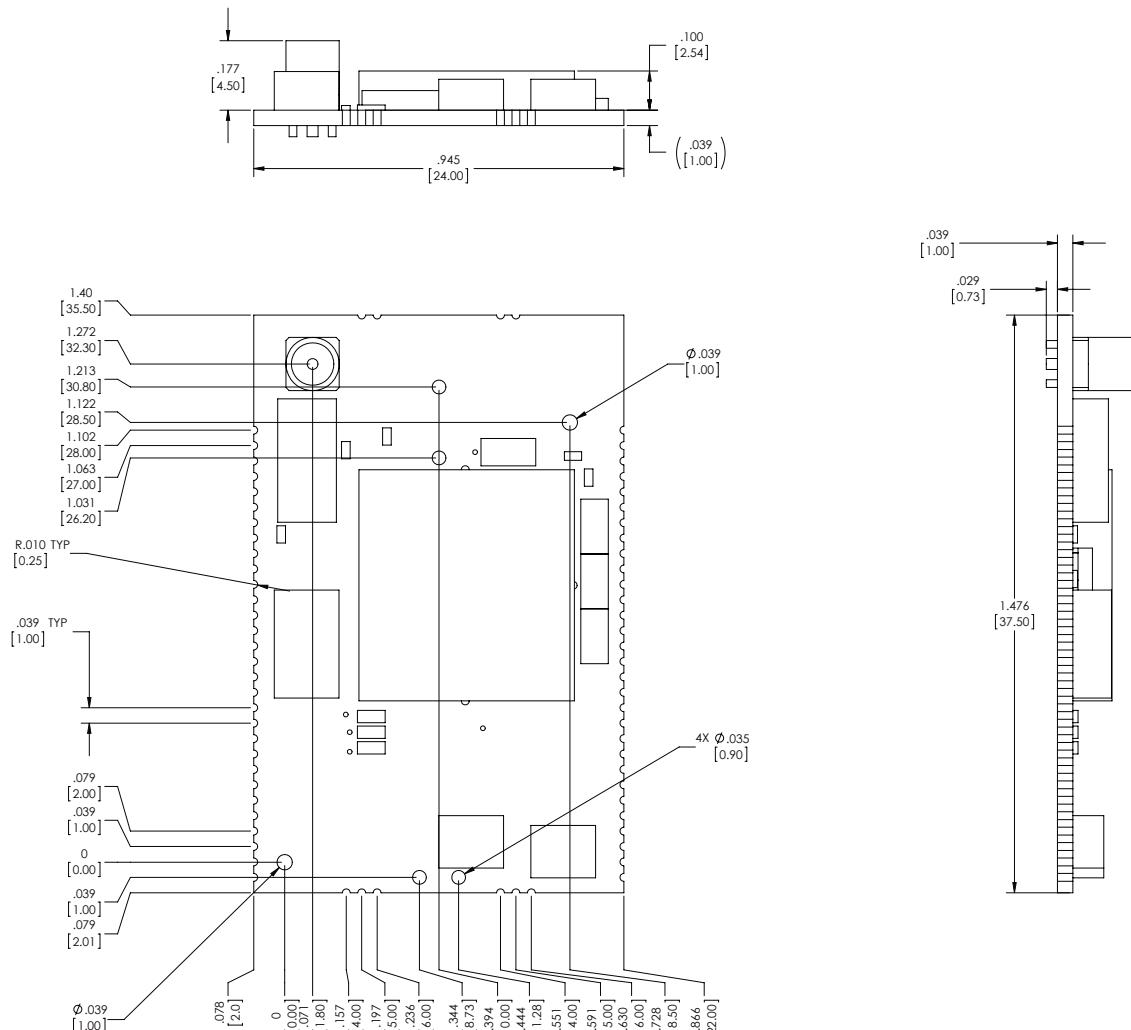

**PC Package**

**66-Lead PCB (24mm × 37.5mm)**

(Reference LTC DWG # 05-08-10003 Rev A)

**LTP5902の機械図面**

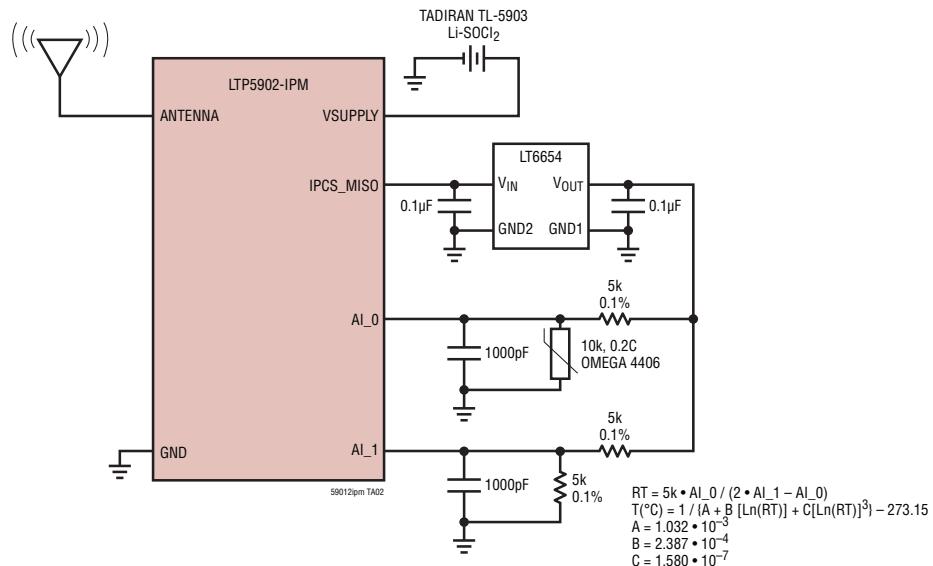

## 標準的応用例

メッシュ・ネットワーク・サーミスタ

## 関連製品

| 製品番号                    | 説明                                                                   | 注釈                                                                                                                                    |

|-------------------------|----------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|

| LTC5800-IPM             | IPワイヤレス・モート                                                          | 超低消費電力モート、72ピン 10mm×10mm QFN                                                                                                          |

| LTP5901-IPRA            | チップ・アンテナを備えたIPワイヤレス・メッシュ32モート・マネージャPCBモジュール                          | 米国、カナダ、欧州、日本、韓国、台湾、インド、オーストラリア、およびニュージーランドでの無線認証モジュール内蔵                                                                               |

| LTP5902-IPRA            | MMCXアンテナ・コネクタを備えたIPワイヤレス・メッシュ32モート・マネージャPCBモジュール                     | 米国、カナダ、欧州、日本、韓国、台湾、インド、オーストラリア、およびニュージーランドでの無線認証モジュール内蔵                                                                               |

| LTP5901-IPRB            | チップ・アンテナを備えたIPワイヤレス・メッシュ100モート・マネージャPCBモジュール                         | 米国、カナダ、欧州、日本、韓国、台湾、インド、オーストラリア、およびニュージーランドでの無線認証モジュール内蔵                                                                               |

| LTP5902-IPRB            | MMCXアンテナ・コネクタを備えたIPワイヤレス・メッシュ100モート・マネージャPCBモジュール                    | 米国、カナダ、欧州、日本、韓国、台湾、インド、オーストラリア、およびニュージーランドでの無線認証モジュール内蔵                                                                               |

| LTP5901-IPRC            | チップ・アンテナ、最大36パケット/秒外部RAMサポートを備えたIPワイヤレス・メッシュ32モート・マネージャPCBモジュール      | 米国、カナダ、欧州、日本、韓国、台湾、インド、オーストラリア、およびニュージーランドでの無線認証モジュール内蔵                                                                               |

| LTP5902-IPRC            | MMCXアンテナ・コネクタ、最大36パケット/秒外部RAMサポートを備えたIPワイヤレス・メッシュ32モート・マネージャPCBモジュール | 米国、カナダ、欧州、日本、韓国、台湾、インド、オーストラリア、およびニュージーランドでの無線認証モジュール内蔵                                                                               |

| LT6654                  | 出力駆動電流の大きい低ノイズ高精度リファレンス                                              | ピーク・トゥ・ピーク・ノイズ: 1.6ppm (0.1Hz ~ 10Hz)、シングルソース電流: ±10mA、最大ドリフト: 5ppm/°C                                                                |

| LTC2379-18              | 18ビット、1.6Msps/1Msps/500ksps/250kspsシリアル、低消費電力ADC                     | 電源電圧: 2.5V、差動入力、SNR: 101.2dB、入力範囲: ±5V、DGC                                                                                            |

| LTC3388-1/<br>LTC3388-3 | 20V高効率ナノパワー降圧レギュレータ                                                  | スリープ時のI <sub>Q</sub> : 860nA、入力: 2.7V ~ 20V、V <sub>OUT</sub> : 1.2V ~ 5V、イネーブル・ピンとスタンバイ・ピン                                            |

| LTC3588-1               | 高効率降圧コンバータ内蔵の圧電発電電源                                                  | V <sub>IN</sub> : 2.7V ~ 20V、V <sub>OUT(MIN)</sub> : 1.8V/2.5V/3.3V/3.6Vに固定、I <sub>Q</sub> : 0.95μA、3mm×3mm DFN-10 および MSOP-10E パッケージ |

| LTC3108-1               | 超低電圧昇圧コンバータおよびパワーマネージャ                                               | V <sub>IN</sub> : 0.02V ~ 1V、V <sub>OUT</sub> : 2.5V/3V/3.7V/4.5Vに固定、I <sub>Q</sub> : 6μA、3mm×4mm DFN-12 および SSOP-16 パッケージ            |

| LTC3459                 | マイクロパワー同期整流式昇圧コンバータ                                                  | V <sub>IN</sub> : 1.5V ~ 5.5V、V <sub>OUT(MAX)</sub> : 10V、I <sub>Q</sub> : 10μA、2mm×2mm DFN、2mm×3mm DFN または SOT-23 パッケージ              |

59012ipmf