## 特長

- デュアル 25A 出力またはシングル 50A 出力

- 入力電圧範囲: 4.5V ~ 15V

- 出力電圧範囲: 0.6V ~ 1.8V

- 入力、負荷、温度の全範囲での全 DC 出力電圧誤差: 最大  $\pm 1.5\%$

- 差動リモート検出アンプ

- 電流モード制御/高速トランジエント応答

- 調整可能なスイッチング周波数

- 周波数同期

- 過電流フォールドバック保護

- 複数の LTM4650 によるマルチフェーズ並列電流分担: 最大 300A

- 内部温度モニタ

- LTM4620(デュアル 13A、シングル 26A) および LTM4630(デュアル 18A、シングル 36A) とピン互換

- 選択可能な Burst Mode® 動作

- ソフトスタート/電圧トラッキング

- 出力過電圧保護

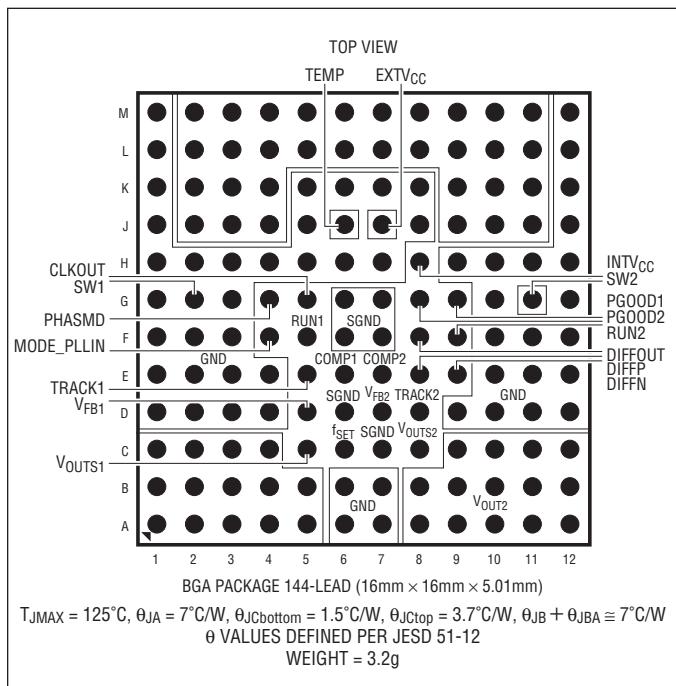

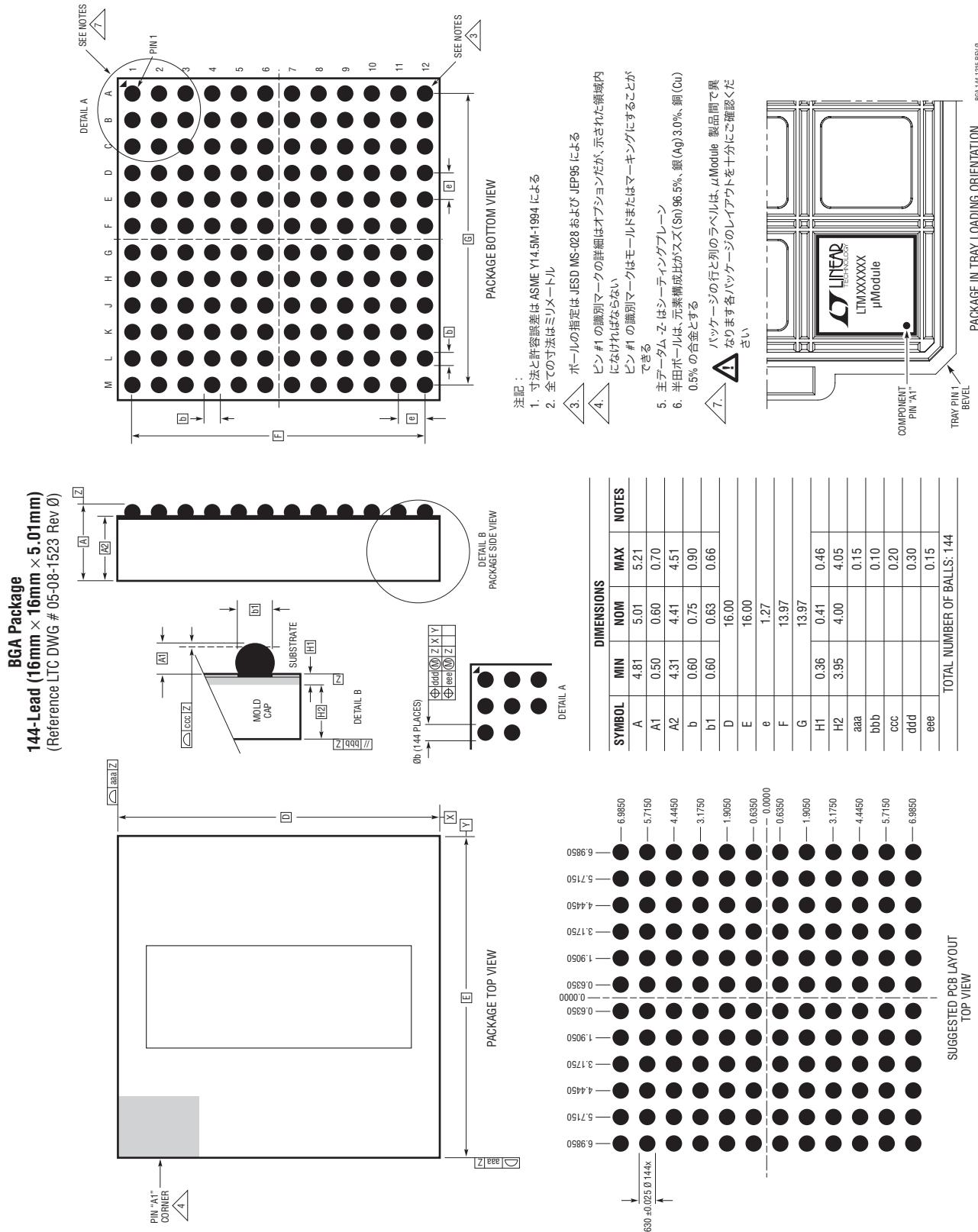

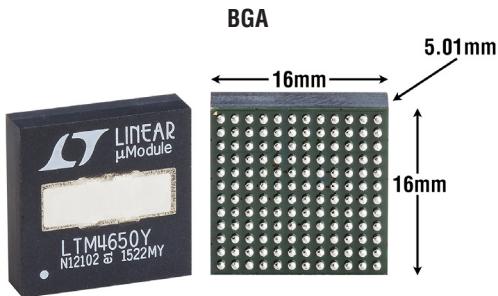

- 16mm × 16mm × 5.01mm BGA パッケージ

## アプリケーション

- プロセッサ、ASIC、および FPGA コアの電源

- 通信機器およびネットワーク機器

- ストレージ・カードおよび ATCA カード

- 産業用機器

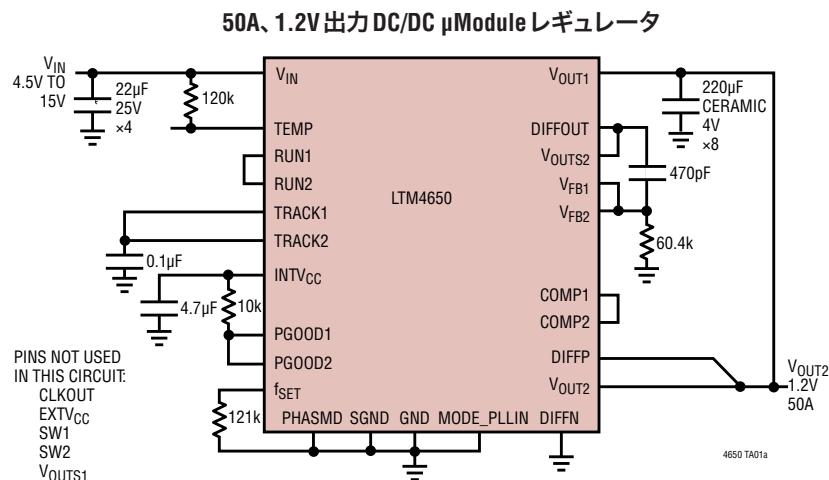

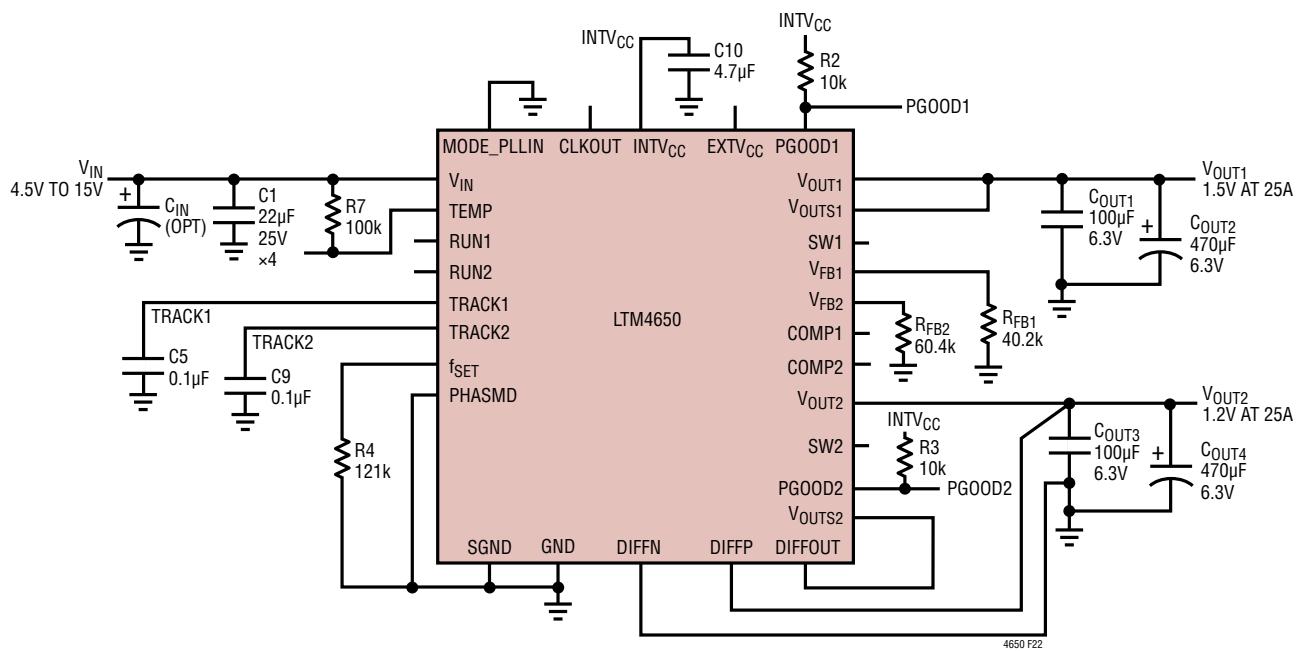

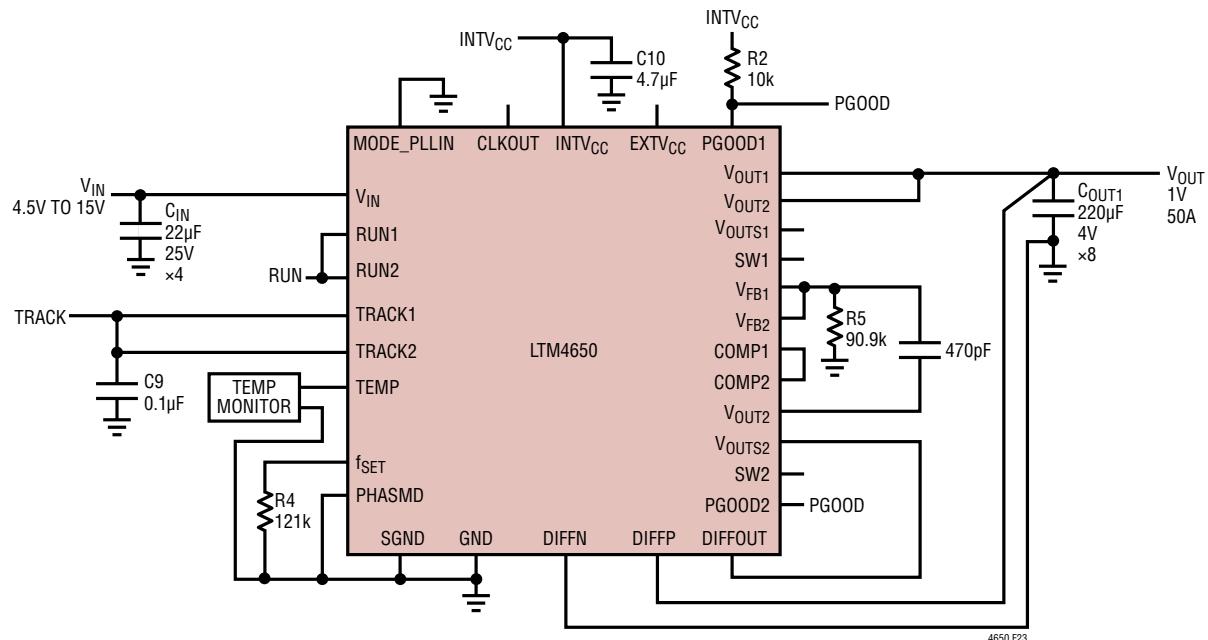

## 標準的応用例

## 概要

LTM®4650 は、デュアル 25A または シングル 50A 出力のスイッチング・モード降圧 DC/DC μModule®(電源モジュール)レギュレータです。スイッチング・コントローラ、パワー FET、インダクタ、および全ての支持部品がパッケージに搭載されています。LTM4650 は、4.5V ~ 15V の入力電圧範囲で動作し、出力電圧の範囲がそれぞれ 0.6V ~ 1.8V の 2 つの出力をサポートしており、出力電圧はそれぞれ 1 本の外付け抵抗で設定されます。高効率設計により、出力ごとに最大 25A の連続電流を供給します。必要な入力コンデンサおよび出力コンデンサはわずか数個です。LTM4650 は、LTM4620(デュアル 13A、シングル 26A) および LTM4630(デュアル 18A、シングル 36A) とピン互換です。

このデバイスは、周波数同期、マルチフェーズ動作、Burst Mode 動作、電源レールのシーケンス制御のための出力電圧トラッキングをサポートしています。また、デバイス温度をモニタするための温度検出ダイオードを内蔵しています。高いスイッチング周波数と電流モード・アーキテクチャにより、安定性を損なうことなく入力および負荷の変動に対するきわめて高速なトランジエント応答が可能です。

フォルト保護機能には、過電圧保護と過電流保護が含まれます。LTM4650 は、16mm × 16mm × 5.01mm の BGA パッケージで供給されます。

LT、LT、LTC、LTM、Linear Technology、Linear のロゴ、μModule、Burst Mode および PolyPhase はリニアテクノロジー社の登録商標です。その他すべての商標の所有権は、それぞれの所有者に帰属します。5481178、5705919、5929620、6100678、6144194、6177787、6304066、6580258 を含む米国特許により保護されています。その他に出席中の特許があります。

# LTM4650

## 絶対最大定格

(Note 1)

|                                                                     |                            |

|---------------------------------------------------------------------|----------------------------|

| $V_{IN}$                                                            | -0.3V ~ 16V                |

| $V_{SW1}, V_{SW2}$                                                  | -1V ~ 16V                  |

| PGOOD1, PGOOD2, RUN1, RUN2, INTV <sub>CC</sub> , EXTV <sub>CC</sub> | -0.3V ~ 6V                 |

| MODE_PLLIN, f <sub>SET</sub> , TRACK1, TRACK2, DIFFOUT, PHASMD      | -0.3V ~ INTV <sub>CC</sub> |

| $V_{OUT1}, V_{OUT2}, V_{OUTS1}, V_{OUTS2}$                          | -0.3V ~ 6V                 |

| DIFFP, DIFFN                                                        | -0.3V ~ INTV <sub>CC</sub> |

| COMP1, COMP2, V <sub>FB1</sub> , V <sub>FB2</sub> (Note 5)          | -0.3V ~ 2.7V               |

| INTV <sub>CC</sub> のピーク出力電流                                         | 100mA                      |

| 内部動作温度範囲 (Note 2)                                                   | -40°C ~ 125°C              |

| 保存温度範囲                                                              | -55°C ~ 125°C              |

| ピーク・パッケージ・ボディ温度                                                     | 245°C                      |

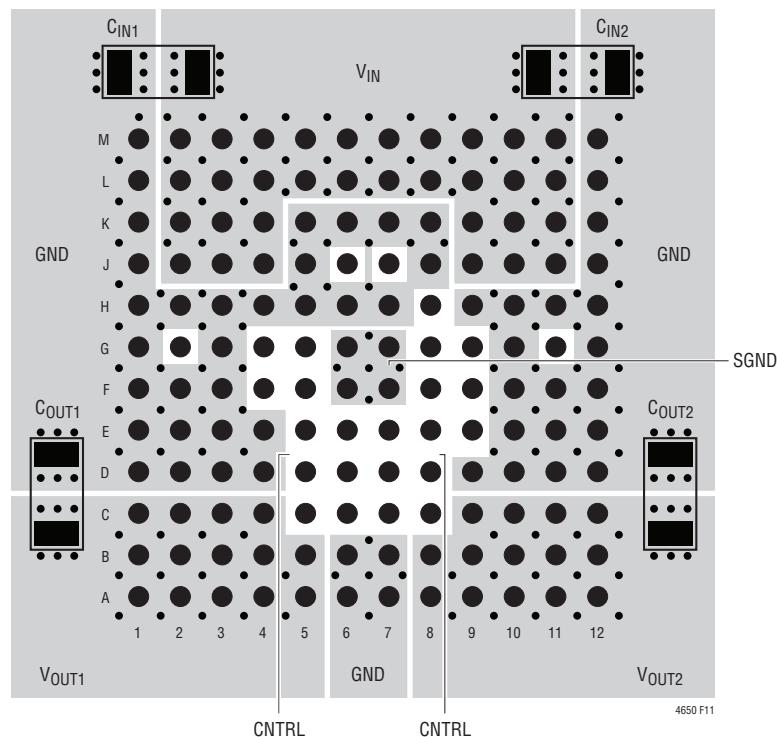

## ピン配置

## 発注情報

(<http://www.linear-tech.co.jp/product/LTM4650#orderinfo>)

| 製品番号          | パッド/ボール仕上げ    | 製品マーキング* |        | パッケージ・タイプ | MSL<br>レーティング | 温度範囲 (Note 2)  |

|---------------|---------------|----------|--------|-----------|---------------|----------------|

|               |               | デバイス     | 仕上げコード |           |               |                |

| LTM4650EY#PBF | SAC305 (RoHS) | LTM4650Y | e1     | BGA       | 3             | -40°C to 125°C |

| LTM4650IY#PBF | SAC305 (RoHS) | LTM4650Y | e1     | BGA       | 3             | -40°C to 125°C |

| LTM4650IY     | SnPb (63/37)  | LTM4650Y | e0     | BGA       | 3             | -40°C to 125°C |

さらに広い動作温度範囲で規定されるデバイスについては、弊社または弊社代理店にお問い合わせください。\* デバイスの温度グレードは出荷時のコンテナのラベルで示しております。

パッドまたはボールの仕上げコードはIPC/JEDEC J-STD-609に準拠しています。

- 端子仕上げの製品マーキング: [www.linear-tech.co.jp/leadfree](http://www.linear-tech.co.jp/leadfree)

- 推奨されるLGA/BGAのPCBアセンブリおよび製造方法: [www.linear-tech.co.jp/umodule/pcbassembly](http://www.linear-tech.co.jp/umodule/pcbassembly)

- LGA/BGAパッケージおよびトレイの図面: [www.linear-tech.co.jp/packaging](http://www.linear-tech.co.jp/packaging)

## 電気的特性

●は規定された全内部動作温度範囲の規格値を意味する。各出力チャネル1つに対する規格値。注記がない限り、 $T_A = 25^\circ\text{C}$  (Note 2)、 $V_{IN} = 12\text{V}$ 、 $V_{RUN1} = V_{RUN2} = 5\text{V}$ 。図22の「標準的応用例」に基づく。

| SYMBOL                             | PARAMETER                                             | CONDITIONS                                                                                                                                                             | MIN     | TYP | MAX   | UNITS |

|------------------------------------|-------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-----|-------|-------|

| $V_{IN}$                           | Input DC Voltage                                      |                                                                                                                                                                        | ● 4.5   | 15  |       | V     |

| $V_{OUT}$                          | Output DC Voltage                                     |                                                                                                                                                                        | ● 0.6   | 1.8 |       | V     |

| $V_{OUT1(DC)}$ ,<br>$V_{OUT2(DC)}$ | Output Voltage, Total Variation with<br>Line and Load | $C_{IN} = 22\mu\text{F} \times 3$ , $C_{OUT} = 100\mu\text{F} \times 2$ Ceramic,<br>470 $\mu\text{F}$ POSCAP<br>$V_{OUT} = 1.5\text{V}$ , $I_{OUT} = 0\text{A}$ to 25A | ● 1.477 | 1.5 | 1.523 | V     |

### 入力の仕様

|                               |                                  |                                                                                                                                                                                                                                                                       |     |      |      |    |

|-------------------------------|----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|------|----|

| $V_{RUN1}$ , $V_{RUN2}$       | RUN Pin On/Off Threshold         | RUN Rising                                                                                                                                                                                                                                                            | 1.1 | 1.25 | 1.40 | V  |

| $V_{RUN1HYS}$ , $V_{RUN2HYS}$ | RUN Pin On Hysteresis            |                                                                                                                                                                                                                                                                       |     | 150  |      | mV |

| $I_{INRUSH(VIN)}$             | Input Inrush Current at Start-Up | $I_{OUT} = 0\text{A}$ , $C_{IN} = 22\mu\text{F} \times 3$ , $C_{SS} = 0.01\mu\text{F}$ ,<br>$C_{OUT} = 100\mu\text{F} \times 3$ , $V_{OUT1} = 1.5\text{V}$ , $V_{OUT2} = 1.5\text{V}$                                                                                 |     | 1    |      | A  |

| $I_Q(VIN)$                    | Input Supply Bias Current        | $V_{IN} = 12\text{V}$ , $V_{OUT} = 1.5\text{V}$ , Burst Mode Operation<br>$V_{IN} = 12\text{V}$ , $V_{OUT} = 1.5\text{V}$ , Pulse-Skipping Mode<br>$V_{IN} = 12\text{V}$ , $V_{OUT} = 1.5\text{V}$ , Switching Continuous<br>Shutdown, RUN = 0, $V_{IN} = 12\text{V}$ |     | 4    |      | mA |

| $I_S(VIN)$                    | Input Supply Current             | $V_{IN} = 4.5\text{V}$ , $V_{OUT} = 1.5\text{V}$ , $I_{OUT} = 25\text{A}$<br>$V_{IN} = 12\text{V}$ , $V_{OUT} = 1.5\text{V}$ , $I_{OUT} = 25\text{A}$                                                                                                                 |     | 10   |      | A  |

|                               |                                  |                                                                                                                                                                                                                                                                       |     | 3.8  |      | A  |

### 出力の仕様

|                                                                      |                                     |                                                                                                                                                                                            |        |      |                   |

|----------------------------------------------------------------------|-------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|------|-------------------|

| $I_{OUT1(DC)}$ , $I_{OUT2(DC)}$                                      | Output Continuous Current Range     | $V_{IN} = 12\text{V}$ , $V_{OUT} = 1.5\text{V}$ (Note 6)                                                                                                                                   | 0      | 25   | A                 |

| $\Delta V_{OUT1(LINE)}/V_{OUT1}$<br>$\Delta V_{OUT2(LINE)}/V_{OUT2}$ | Line Regulation Accuracy            | $V_{OUT} = 1.5\text{V}$ , $V_{IN}$ from 4.5V to 15V<br>$I_{OUT} = 0\text{A}$ for Each Output,                                                                                              | ● 0.01 | 0.1  | %/V               |

| $\Delta V_{OUT1}/V_{OUT1}$<br>$\Delta V_{OUT2}/V_{OUT2}$             | Load Regulation Accuracy            | For Each Output, $V_{OUT} = 1.5\text{V}$ , 0A to 25A<br>$V_{IN} = 12\text{V}$ (Note 6)                                                                                                     | ● 0.5  | 0.75 | %                 |

| $V_{OUT1(AC)}$ , $V_{OUT2(AC)}$                                      | Output Ripple Voltage               | For Each Output, $I_{OUT} = 0\text{A}$ , $C_{OUT} = 100\mu\text{F} \times 3$<br>Ceramic, 470 $\mu\text{F}$ POSCAP, $V_{IN} = 12\text{V}$ ,<br>$V_{OUT} = 1.5\text{V}$ , Frequency = 500kHz |        | 15   | mV <sub>P-P</sub> |

| $f_S$ (Each Channel)                                                 | Output Ripple Voltage Frequency     | $V_{IN} = 12\text{V}$ , $V_{OUT} = 1.5\text{V}$ , $f_{SET} = 1.25\text{V}$ (Note 4)                                                                                                        |        | 500  | kHz               |

| $f_{SYNC}$<br>(Each Channel)                                         | SYNC Capture Range                  |                                                                                                                                                                                            | 400    | 780  | kHz               |

| $\Delta V_{OUTSTART}$<br>(Each Channel)                              | Turn-On Overshoot                   | $C_{OUT} = 100\mu\text{F}$ Ceramic, 470 $\mu\text{F}$ POSCAP, $V_{OUT} = 1.5\text{V}$ , $I_{OUT} = 0\text{A}$ $V_{IN} = 12\text{V}$                                                        |        | 10   | mV                |

| $t_{START}$<br>(Each Channel)                                        | Turn-On Time                        | $C_{OUT} = 100\mu\text{F}$ Ceramic, 470 $\mu\text{F}$ POSCAP,<br>No Load, TRACK/SS with 0.01 $\mu\text{F}$ to GND,<br>$V_{IN} = 12\text{V}$                                                |        | 5    | ms                |

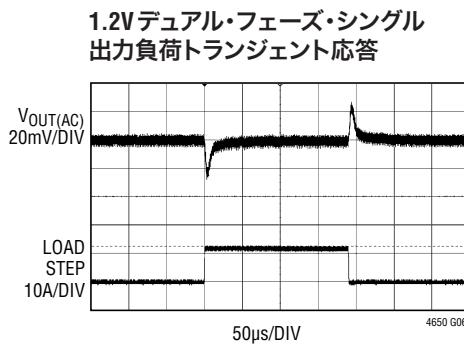

| $\Delta V_{OUT(LS)}$<br>(Each Channel)                               | Peak Deviation for Dynamic Load     | Load:0% to 50% to 0% of Full Load<br>$C_{OUT} = 22\mu\text{F} \times 3$ Ceramic, 470 $\mu\text{F}$ POSCAP<br>$V_{IN} = 12\text{V}$ , $V_{OUT} = 1.5\text{V}$                               |        | 30   | mV                |

| $t_{SETTLE}$<br>(Each Channel)                                       | Settling Time for Dynamic Load Step | Load:0% to 50% to 0% of Full Load,<br>$V_{IN} = 12\text{V}$ , $C_{OUT} = 100\mu\text{F}$ , 470 $\mu\text{F}$ POSCAP                                                                        |        | 20   | $\mu\text{s}$     |

## 電気的特性

●は規定された全内部動作温度範囲の規格値を意味する。各出力チャネル1つに対する規格値。注記がない限り、 $T_A = 25^\circ\text{C}$  (Note 2)、 $V_{IN} = 12\text{V}$ 、 $V_{RUN1} = V_{RUN2} = 5\text{V}$ 。図22の「標準的応用例」に基づく。

| SYMBOL                          | PARAMETER            | CONDITIONS                                      | MIN | TYP | MAX | UNITS |

|---------------------------------|----------------------|-------------------------------------------------|-----|-----|-----|-------|

| $I_{OUT(PK)}$<br>(Each Channel) | Output Current Limit | $V_{IN} = 12\text{V}$ , $V_{OUT} = 1.5\text{V}$ |     | 35  |     | A     |

## 制御セクション

|                                 |                                                                                      |                                                                                                       |   |       |       |       |    |

|---------------------------------|--------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|---|-------|-------|-------|----|

| $V_{FB1}, V_{FB2}$              | Voltage at $V_{FB}$ Pins                                                             | $I_{OUT} = 0\text{A}$ , $V_{OUT} = 1.5\text{V}$                                                       | ● | 0.594 | 0.600 | 0.606 | V  |

| $I_{FB}$                        |                                                                                      | (Note 5)                                                                                              |   |       | -5    | -20   | nA |

| $V_{OVL}$                       | Feedback Overvoltage Lockout                                                         |                                                                                                       | ● | 0.64  | 0.66  | 0.68  | V  |

| TRACK1 (I),<br>TRACK2 (I)       | Track Pin Soft-Start Pull-Up Current                                                 | TRACK1 (I), TRACK2 (I) Start at 0V                                                                    |   | 1     | 1.25  | 1.5   | μA |

| UVLO                            | Undervoltage Lockout (Falling)                                                       |                                                                                                       |   |       | 3.3   |       | V  |

| UVLO Hysteresis                 |                                                                                      |                                                                                                       |   |       | 0.6   |       | V  |

| $t_{ON(MIN)}$                   | Minimum On-Time                                                                      | (Note 5)                                                                                              |   |       | 90    |       | ns |

| $R_{FBHI1}, R_{FBHI2}$          | Resistor Between $V_{OUT1}$ , $V_{OUT2}$ and $V_{FB1}, V_{FB2}$ Pins for Each Output |                                                                                                       |   | 60.05 | 60.4  | 60.75 | kΩ |

| $V_{PGOOD1}, V_{PGOOD2}$<br>Low | PGOOD Voltage Low                                                                    | $I_{PGOOD} = 2\text{mA}$                                                                              |   |       | 0.1   | 0.3   | V  |

| $I_{PGOOD}$                     | PGOOD Leakage Current                                                                | $V_{PGOOD} = 5\text{V}$                                                                               |   |       | ±5    |       | μA |

| $V_{PGOOD}$                     | PGOOD Trip Level                                                                     | $V_{FB}$ with Respect to Set Output Voltage<br>$V_{FB}$ Ramping Negative<br>$V_{FB}$ Ramping Positive |   |       | -10   |       | %  |

|                                 |                                                                                      |                                                                                                       |   |       | 10    |       | %  |

INTV<sub>CC</sub>リニア・レギュレータ

|                                 |                                       |                                                   |  |     |      |     |    |

|---------------------------------|---------------------------------------|---------------------------------------------------|--|-----|------|-----|----|

| $V_{INTVCC}$                    | Internal $V_{CC}$ Voltage             | $6\text{V} < V_{IN} < 15\text{V}$                 |  | 4.8 | 5    | 5.2 | V  |

| $V_{INTVCC}$<br>Load Regulation | INTV <sub>CC</sub> Load Regulation    | $I_{CC} = 0\text{mA}$ to $50\text{mA}$            |  |     | 0.75 | 2   | %  |

| $V_{EXTVCC}$                    | EXTV <sub>CC</sub> Switchover Voltage | EXTV <sub>CC</sub> Ramping Positive               |  | 4.5 | 4.7  |     | V  |

| $V_{EXTVCC(DROP)}$              | EXTV <sub>CC</sub> Dropout            | $I_{CC} = 20\text{mA}$ , $V_{EXTVCC} = 5\text{V}$ |  |     | 50   | 100 | mV |

| $V_{EXTVCC(HYST)}$              | EXTV <sub>CC</sub> Hysteresis         |                                                   |  |     | 220  |     | mV |

## 発振器とフェーズロック・ループ

|                   |                                 |                                                               |  |     |     |     |     |

|-------------------|---------------------------------|---------------------------------------------------------------|--|-----|-----|-----|-----|

| Frequency Nominal | Nominal Frequency               | $f_{SET} = 1.2\text{V}$                                       |  | 450 | 500 | 550 | kHz |

| Frequency Low     | Lowest Frequency                | $f_{SET} = 0.93\text{V}$                                      |  |     | 400 |     | kHz |

| Frequency High    | Highest Frequency               | $f_{SET} > 2.4\text{V}$ , Up to INTV <sub>CC</sub>            |  |     | 780 |     | kHz |

| $f_{SET}$         | Frequency Set Current           |                                                               |  | 9   | 10  | 11  | μA  |

| $R_{MODE\_PLLIN}$ | MODE_PLLIN Input Resistance     |                                                               |  |     | 250 |     | kΩ  |

| CLKOUT            | Phase (Relative to $V_{OUT1}$ ) | PHASMD = GND<br>PHASMD = Float<br>PHASMD = INTV <sub>CC</sub> |  |     | 60  |     | Deg |

|                   |                                 |                                                               |  |     | 90  |     | Deg |

|                   |                                 |                                                               |  |     | 120 |     | Deg |

| CLK High          | Clock High Output Voltage       |                                                               |  | 2   |     |     | V   |

| CLK Low           | Clock Low Output Voltage        |                                                               |  |     | 0.2 |     | V   |

## 電気的特性

●は規定された全内部動作温度範囲の規格値を意味する。各出力チャネル1つに対する規格値。注記がない限り、 $T_A = 25^\circ\text{C}$  (Note 2)、 $V_{IN} = 12\text{V}$ 、 $V_{RUN1} = V_{RUN2} = 5\text{V}$ 。図22の「標準的応用例」に基づく。

| SYMBOL                       | PARAMETER                    | CONDITIONS                                                               | MIN | TYP               | MAX | UNITS      |

|------------------------------|------------------------------|--------------------------------------------------------------------------|-----|-------------------|-----|------------|

| <b>差動アンプ</b>                 |                              |                                                                          |     |                   |     |            |

| $A_V$ Differential Amplifier | Gain                         |                                                                          |     | 1                 |     | V/V        |

| $R_{IN}$                     | Input Resistance             | Measured at DIFFP Input                                                  |     | 80                |     | k $\Omega$ |

| $V_{OS}$                     | Input Offset Voltage         | $V_{DIFFP} = V_{DIFFOUT} = 1.5\text{V}$ , $I_{DIFFOUT} = 100\mu\text{A}$ |     | 3                 |     | mV         |

| PSRR Differential Amplifier  | Power Supply Rejection Ratio | $5\text{V} < V_{IN} < 15\text{V}$                                        |     | 90                |     | dB         |

| $I_{CL}$                     | Maximum Output Current       |                                                                          |     | 3                 |     | mA         |

| $V_{OUT(MAX)}$               | Maximum Output Voltage       | $I_{DIFFOUT} = 300\mu\text{A}$                                           |     | $INTV_{CC} - 1.4$ |     | V          |

| GBW                          | Gain Bandwidth Product       |                                                                          |     | 3                 |     | MHz        |

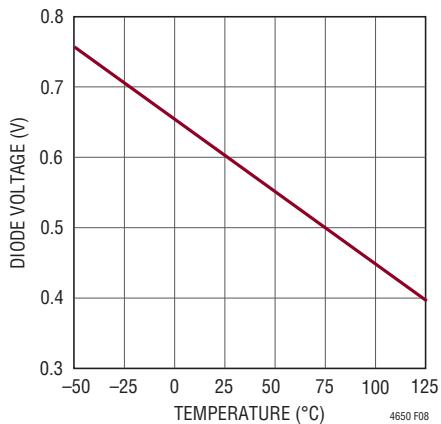

| $V_{TEMP}$                   | Diode Connected PNP          | $I = 100\mu\text{A}$                                                     |     | 0.6               |     | V          |

| TC                           | Temperature Coefficient      |                                                                          | ●   | -2.2              |     | mV/C       |

**Note 1:** 絶対最大定格に記載された値を超えるストレスはデバイスに回復不可能な損傷を与える可能性がある。また、長期にわたって絶対最大定格条件に曝すと、デバイスの信頼性と寿命に悪影響を与えるおそれがある。

**Note 2:** LTM4650は $T_J$ が $T_A$ にほぼ等しいパルス負荷条件でテストされる。LTM4650Eは、 $0^\circ\text{C} \sim 125^\circ\text{C}$ の内部温度で仕様に適合することが保証されている。 $-40^\circ\text{C} \sim 125^\circ\text{C}$ の内部動作温度範囲での仕様は設計、特性評価および統計学的なプロセス・コントロールとの相関で確認されている。LTM4650Iは $-40^\circ\text{C} \sim 125^\circ\text{C}$ の内部動作温度範囲全域で動作することが保証されている。これらの仕様と合致する最大周囲温度は、基板レイアウト、パッケージの定格熱インピーダンスおよび他の環境要因と関連した特定の動作条件によって決まるに注意。

**Note 3:** 2つの出力は別々にテストされ、各出力には同じテスト条件が適用される。

**Note 4:** LTM4650デバイスは400kHz～750kHzで動作するように設計されている。

**Note 5:** これらのパラメータはウェハ選別によってテストされる。

**Note 6:** 異なる $V_{IN}$ 、 $V_{OUT}$ 、および $T_A$ については出力電流のディレーティング曲線を参照。

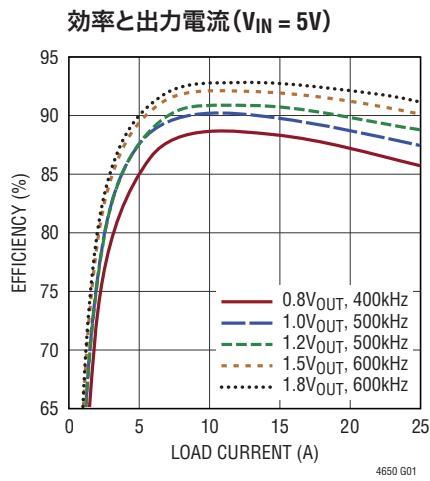

## 標準的性能特性

## 標準的性能特性

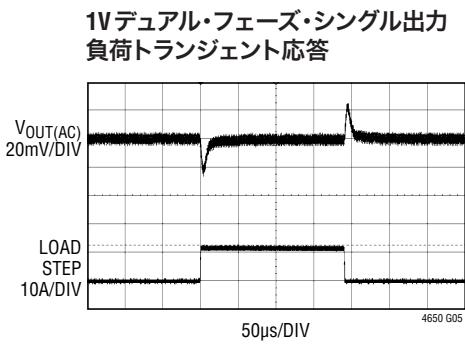

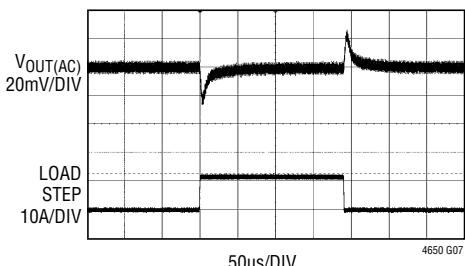

### 1.5V デュアル・フェーズ・シングル 出力負荷トランジエント応答

12V<sub>IN</sub>, 1.5V<sub>OUT</sub>, 600kHz, 12.5A LOAD STEP,

10A/μs STEP-UP AND STEP-DOWN

C<sub>OUT</sub> = 8× 220μF CERAMIC

C<sub>FF</sub> = 470pF

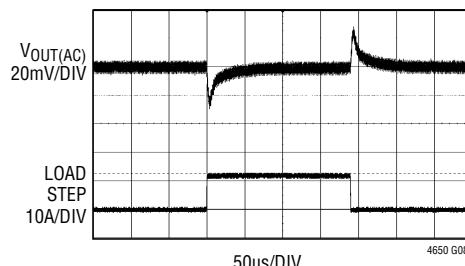

### 1.8V デュアル・フェーズ・シングル 出力負荷トランジエント応答

12V<sub>IN</sub>, 1.8V<sub>OUT</sub>, 600kHz, 12.5A LOAD STEP,

10A/μs STEP-UP AND STEP-DOWN

C<sub>OUT</sub> = 8× 220μF CERAMIC

C<sub>FF</sub> = 470pF

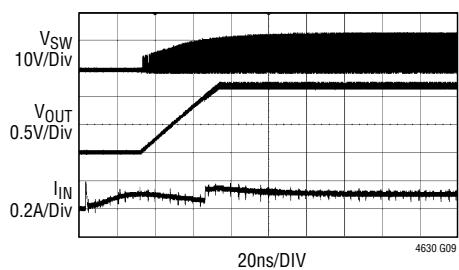

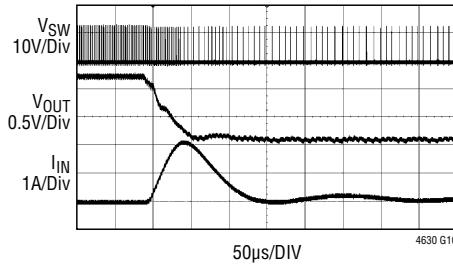

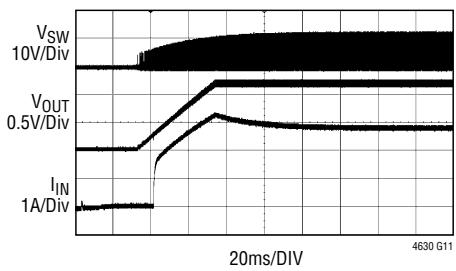

### シングル・フェーズの起動、負荷なし

12V<sub>IN</sub>, 1.2V<sub>OUT</sub>, 500kHz

C<sub>OUT</sub> = 1× 470μF POSCAP + 2× 100μF

CERAMIC, C<sub>SS</sub> = 0.1μF

### シングル・フェーズの起動、25A 負荷

12V<sub>IN</sub>, 1.2V<sub>OUT</sub>, 500kHz

C<sub>OUT</sub> = 1× 470μF POSCAP + 2× 100μF

CERAMIC, C<sub>SS</sub> = 0.1μF

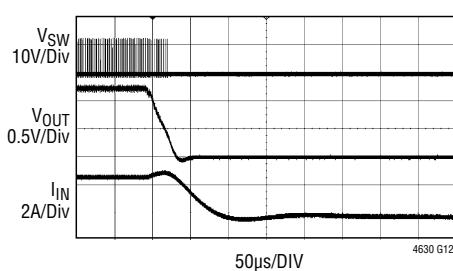

### シングル・フェーズの短絡保護、 負荷なし

12V<sub>IN</sub>, 1.2V<sub>OUT</sub>, 500kHz

C<sub>OUT</sub> = 1× 470μF POSCAP + 2× 100μF

CERAMIC, C<sub>SS</sub> = 0.1μF

### シングル・フェーズの短絡保護、 25A 負荷

12V<sub>IN</sub>, 1.2V<sub>OUT</sub>, 500kHz

C<sub>OUT</sub> = 1× 470μF POSCAP + 2× 100μF

CERAMIC

## ピン機能 (信号ピンの接続をモニタする場合はテスト・ポイントの使用を推奨します)

パッケージの行と列のラベルはμModule 製品間で異なります。各パッケージのレイアウトをよく確認してください。

**V<sub>OUT1</sub> (A1～A5, B1～B5, C1～C4)** : 電源の出力ピン。これらのピンとGNDピンの間に出力負荷を接続します。出力デカップリング・コンデンサはこれらのピンとGNDピンの間に直接配置することを推奨します。表4を参照してください。

**GND (A6～A7, B6～B7, D1～D4, D9～D12, E1～E4, E10～E12, F1～F3, F10～F12, G1, G3, G10, G12, H1～H7, H9～H12, J1, J5, J8, J12, K1, K5～K8, K12, L1, L12, M1, M12)** : 入力帰路と出力帰路の両方の電源グランド・ピン。

**V<sub>OUT2</sub> (A8～A12, B8～B12, C9～C12)** : 電源の出力ピン。これらのピンとGNDピンの間に出力負荷を接続します。出力デカップリング・コンデンサはこれらのピンとGNDピンの間に直接配置することを推奨します。表4を参照してください。

**V<sub>OUTS1</sub>, V<sub>OUTS2</sub> (C5, C8)** : このピンは、各出力の内部トップ帰還抵抗の上端に接続されています。特定の出力に直接接続するか、リモート検出アンプを使用する場合はDIFFOUTに接続します。モジュールを並列で使用する構成では、V<sub>OUTS</sub>ピンのいずれか一方を、リモート検出を使用する場合はDIFFOUTピン、リモート検出を使用しない場合は直接V<sub>OUT</sub>ピンに接続します。これは帰還パスであることから、これらのピンを必ずDIFFOUTまたはV<sub>OUT</sub>のいずれかに接続することがきわめて重要です。開放のままにすることはできません。「アプリケーション情報」を参照してください。

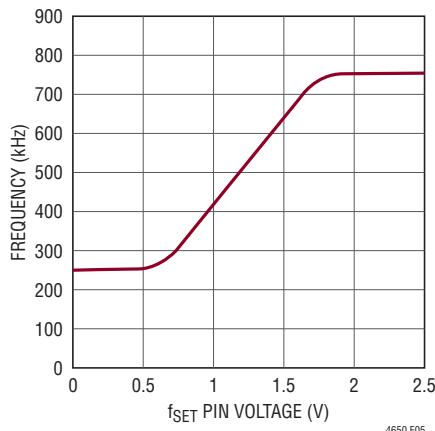

**f<sub>SET</sub> (C6)** : 周波数設定ピン。このピンからは10μAの電流が供給されます。このピンとグランドの間に接続された抵抗によって動作周波数をプログラムする電圧が設定されます。これに代わる方法として、このピンをDC電圧で駆動して動作周波数を設定することもできます。「アプリケーション情報」のセクションを参照してください。

**SGND (C7, D6, G6～G7, F6～F7)** : 信号グランド・ピン。すべてのアナログ回路と低電力回路のリターン・グランド・パス。アプリケーションでは出力コンデンサのGNDに一点接続します。図11のレイアウトのガイドラインを参照してください。

**V<sub>FB1</sub>, V<sub>FB2</sub> (D5, D7)** : 各チャネルのエラーアンプの負入力。このピンは内部で60.4kΩの高精度抵抗を介してV<sub>OUTS1</sub>またはV<sub>OUTS2</sub>に接続されています。V<sub>FB</sub>ピンとGNDピンの間に抵抗を追加して、異なる出力電圧をプログラムすることができます。PolyPhase®動作では、V<sub>FB</sub>ピンを相互接続することによって並列動作が可能になります。詳細については「アプリケーション情報」のセクションを参照してください。

**TRACK1, TRACK2 (E5, D8)** : 出力電圧トラッキングおよびソフトスタートの入力ピン。各チャネルは1.3μAのプルアップ電流源を備えています。一方のチャネルを2つのチャネルのマスタに設定する場合は、このピンとグランドの間のコンデンサによってソフトスタートのランプ・レートが決まります。残りのチャネルはスレーブとして設定でき、スレーブ出力トラッキング・ピンには分圧器を介してマスタの出力を印加します。この分圧器は同時トラッキング用スレーブ出力の帰還分割器と同じです。「アプリケーション情報」のセクションを参照してください。

**COMP1, COMP2 (E6, E7)** : 各チャネルの電流制御しきい値およびエラーアンプの補償点。電流コンパレータのしきい値はこの制御電圧に応じて増加します。並列動作を行うにはCOMPピンを相互に接続します。このデバイスは内部補償されています。

**DIFFP (E8)** : リモート検出アンプの正入力。このピンは、出力電圧のリモート検出ポイントに接続します。「アプリケーション情報」を参照してください。

**DIFFN (E9)** : リモート検出アンプの負入力。このピンは、出力GNDのリモート検出ポイントに接続します。「アプリケーション情報」のセクションを参照してください。

**MODE\_PLLIN (F4)** : 強制連続モード、Burst Mode動作、またはパルス・スキップ・モードの選択ピン、および位相検出器への外部同期入力ピン。両方のチャネルを強制的に強制連続モード動作に設定するには、このピンをSGNDに接続します。パルス・スキップ・モード動作をイネーブルするにはINTV<sub>CC</sub>に接続します。このピンをフロート状態にしておくとBurst Mode動作がイネーブルされます。ピンにクロックを印加すると、両チャネルが強制的に連続動作モードに設定され、印加された外部クロックに同期します。

## ピン機能

(信号ピンの接続をモニタする場合はテスト・ポイントの使用を推奨します)

**RUN1、RUN2 (F5、F9)** : 実行制御ピン。電圧が1.25Vを上回るとモジュールの各チャネルがオンします。RUNピンに1.25Vを下回る電圧を印加すると対応するチャネルがオフします。各RUNピンには1 $\mu$ Aのプルアップ電流が流れ、RUNピンの電圧が1.2Vに達すると、このピンに流れるプルアップ電流は4.5 $\mu$ A増加します。

**DIFFOUT (F8)** : 内部リモート検出アンプの出力。どちらの出力チャネルでリモート検出を使用するかに応じて、VOUTS1またはVOUTS2のいずれかに接続します。並列動作でリモート検出を使用する場合は、VOUTSピンの一方をDIFFOUTピンに接続します。

**SW1、SW2 (G2、G11)** : テスト目的で使われる各チャネルのスイッチング・ノード。RCスナバ・ネットワークを接続して、スイッチ・ノードのリンクを低減または除去することもできます。それ以外の場合はフロート状態のままとします。「アプリケーション情報」のセクションを参照してください。

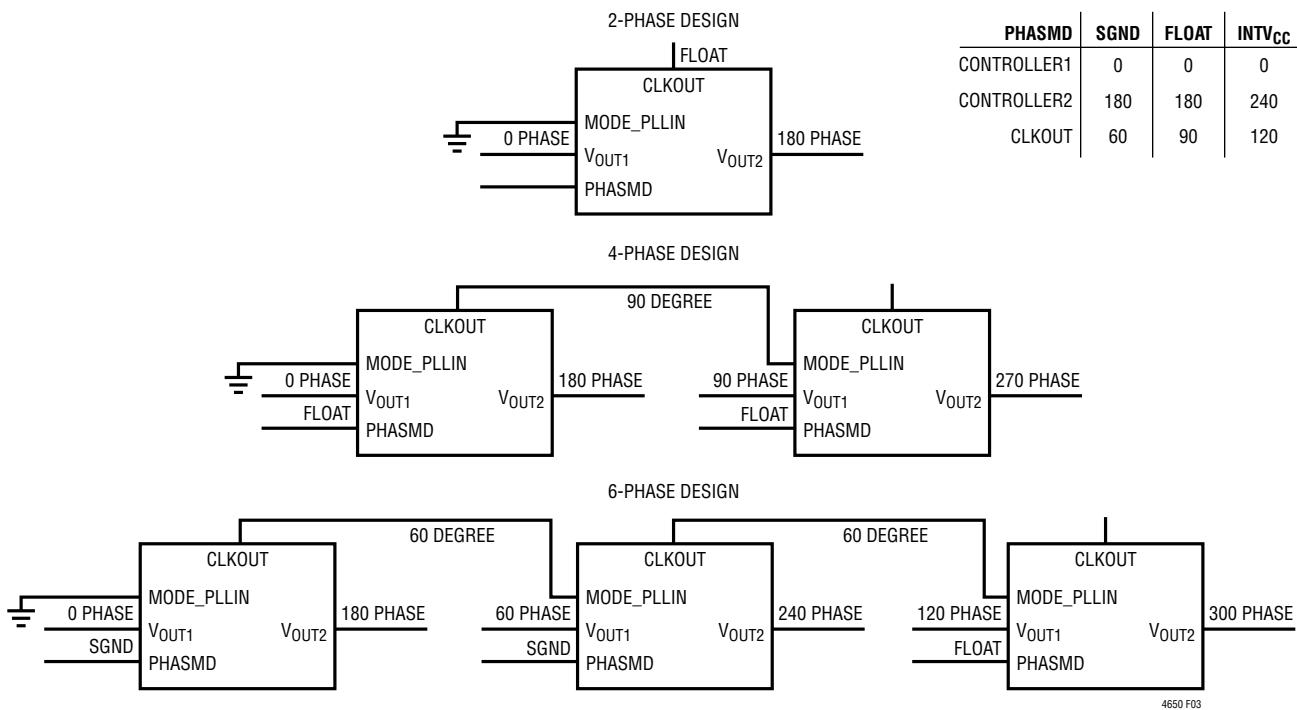

**PHASMD (G4)** : このピンをSGNDまたはINTVCCに接続するか、フロート状態にすることで、CLKOUTの位相をそれぞれ60°、120°、90°に設定できます。

**CLKOUT (G5)** : PHASMDピンによって位相が制御されるクロック出力。このクロックによりデバイス間のマルチフェーズ動作が可能になります。「アプリケーション情報」のセクションを参照してください。

**PGOOD1、PGOOD2 (G9、G8)** : 出力電圧パワーグッド・インジケータ。オープン・ドレインのロジック出力で、出力電圧がレギュレーション・ポイントの±10%以内にないと、グランドに引き下げられます。

**INTVCC (H8)** : 内蔵5Vレギュレータの出力。制御回路と内蔵ゲート・ドライバはこの電圧源から電力を供給されます。このピンは、4.7 $\mu$ F、低ESRのタンタル・コンデンサまたはセラミック・コンデンサを使ってPGNDにデカップリングしてください。RUN1またはRUN2のいずれかをアクティブにすると、INTVCCが有効になります。

**TEMP (J6)** : 温度モニタ。10nFフィルタリング・コンデンサを備えた、このピンとSGNDの間の内部ダイオード接続されたNPNトランジスタ。「アプリケーション情報」のセクションを参照してください。

**EXTVCC (J7)** : EXTVCCが4.7Vを上回ると、INTVCCに接続されたスイッチによって有効になる外部電源入力。この入力は6Vを超えないようにしてください。また、VIN = 5Vで動作させる場合は、このピンをVINに接続します。効率が向上し、その値は(VIN - INTVCC) × (パワーMOSFETの駆動電流)で決まります。必要とされる標準電流は30mAです。VINを印加してからEXTVCCを印加し、EXTVCCを遮断してからVINを遮断する必要があります。

**VIN (M2～M11、L2～L11、J2～J4、J9～J11、K2～K4、K9～K11)** : 電源入力ピン。これらのピンとGNDピンの間に入力電圧を印加します。入力デカップリング・コンデンサはVINピンとGNDピンの間に直接配置することを推奨します。

## 簡略ブロック図

図1.LTM4650の簡略ブロック図

## デカップリングの要件

$T_A = 25^\circ\text{C}$ 。図1の構成を使用。

| SYMBOL               | PARAMETER                                                                                                                                                                                 | CONDITIONS                                         | MIN | TYP | MAX | UNITS         |

|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|-----|-----|-----|---------------|

| $C_{IN1}, C_{IN2}$   | External Input Capacitor Requirement<br>( $V_{IN1} = 4.5\text{V}$ to $15\text{V}$ , $V_{OUT1} = 1.5\text{V}$ )<br>( $V_{IN2} = 4.5\text{V}$ to $15\text{V}$ , $V_{OUT2} = 1.0\text{V}$ )  | $I_{OUT1} = 25\text{A}$<br>$I_{OUT2} = 25\text{A}$ | 44  | 66  |     | $\mu\text{F}$ |

| $C_{OUT1}, C_{OUT2}$ | External Output Capacitor Requirement<br>( $V_{IN1} = 4.5\text{V}$ to $15\text{V}$ , $V_{OUT1} = 1.5\text{V}$ )<br>( $V_{IN2} = 4.5\text{V}$ to $15\text{V}$ , $V_{OUT2} = 1.0\text{V}$ ) | $I_{OUT1} = 25\text{A}$<br>$I_{OUT2} = 25\text{A}$ | 600 | 800 |     | $\mu\text{F}$ |

4650fa

## 動作

### 電源モジュールの概要

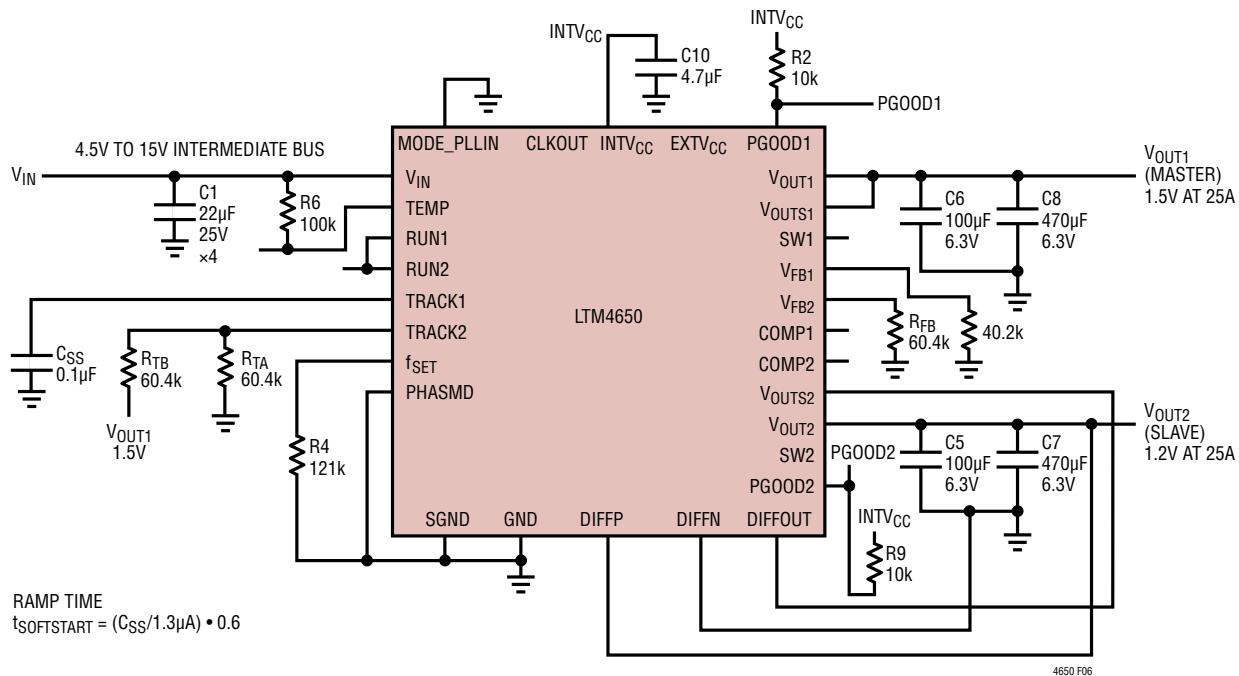

LTM4650はデュアル出力の独立型非絶縁スイッチング・モードDC/DC電源です。数個の入力コンデンサと出力コンデンサ、および設定用の部品を外付けするだけで25Aの出力を2系統供給できます。このモジュールは、入力電圧範囲4.5V～15Vに対して、外付け抵抗によって設定可能な0.6V<sub>DC</sub>～1.8V<sub>DC</sub>の高精度で安定化された出力電圧を供給します。標準的応用例の回路図を図22に示します。

LTM4650は固定周波数電流モード・レギュレータと高速スイッチングが可能な内蔵パワーMOSFETデバイスを集積化しています。出力電圧に応じて、標準スイッチング周波数は400kHz～600kHzの範囲になります。また、400kHz～780kHzの範囲で外部同期可能なので、スイッチング・ノイズに敏感なアプリケーションに対応できます。FSETピンに抵抗を接続することで、自走周波数をプログラムできます。「アプリケーション情報」のセクションを参照してください。

電流モード制御と内部帰還ループ補償により、LTM4650モジュールは、広範囲の出力コンデンサを使って(すべてセラミック出力コンデンサを使用する場合でも)十分に余裕のある安定性と良好な過渡性能を達成します。

電流モード制御により、サイクルごとの高速電流制限および過電流状態でのフォールドバック電流制限が実現されます。内蔵されている過電圧コンパレータと低電圧コンパレータは、出力帰還電圧がレギュレーション・ポイントの上下±10%の範囲を外れると、オープン・ドレインのPGOOD出力を”L”に引き下げます。出力電圧がレギュレーション電圧より10%以上高くなると、ボトムMOSFETがオンして、出力電圧をクランプします。トップMOSFETはオフします。過電圧保護は、帰還電圧を参照します。

RUNピンを1.1Vより下げるとき、両方のMOSFETをオフしてレギュレータを強制的にシャットダウン状態に移行させます。TRACKピンは、起動時の出力電圧のランプと電圧トラッキングをプログラムするのに使われます。また、レギュレータのソフトスタートにも使われます。「アプリケーション情報」のセクションを参照してください。

LTM4650は内部補償され、あらゆる動作条件で安定しています。いくつかの動作条件での入力容量と出力容量のガイドラインを表4に示します。リニアテクノロジーのμModule電源設計ツールにより、トランジエントおよび安定性の解析を行えます。V<sub>FB</sub>ピンは、グランドとの間に1本の外付け抵抗を接続して、出力電圧の設定に使用します。負荷の直近で、出力電圧のいずれか一方、または並列動作の場合ならば出力電圧を、高精度で計測可能な差動リモート検出アンプを搭載しています。

また、MODE\_PLLIN、PHASMD、CLKOUTピンを使って、マルチフェーズ動作を簡単に利用できます。PHASMDピンを異なるレベルにプログラムすることにより、最大12フェーズをカスケード接続し、相互に同時に動作させることができます。「アプリケーション情報」のセクションを参照してください。

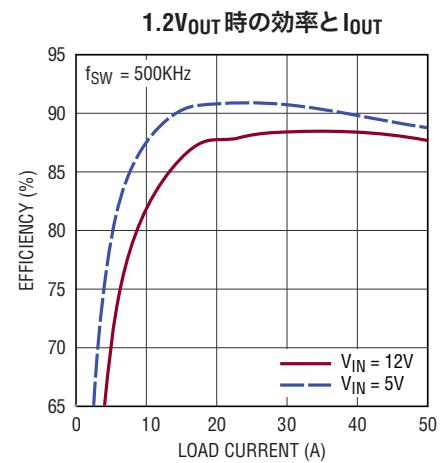

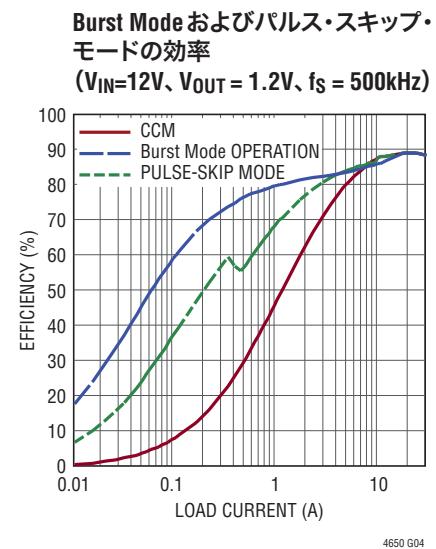

MODE\_PLLINピンを使って選択可能なBurst Mode動作またはパルス・スキップ動作により、負荷が軽い場合も高い効率を実現できます。これらの軽負荷に対応する機能はバッテリ動作に適しています。「標準的性能特性」に軽負荷動作での効率のグラフが掲載されています。詳細については「アプリケーション情報」を参照してください。

モジュールに内蔵された汎用温度検出ダイオードによって、モジュールの温度をモニタできます。詳細については、「アプリケーション情報」のセクションを参照してください。

機能や動作をモニタリングするために、スイッチ・ピンが利用可能です。また、このスイッチ・ピンとグランドの間に抵抗とコンデンサによるスナバ回路を適切に接続することで、遷移エッジにおけるあらゆる高周波リギングを減衰できます。詳細については「アプリケーション情報」のセクションを参照してください。

## アプリケーション情報

LTM4650の代表的なアプリケーション回路を図22に示します。外付け部品の選択は主に最大負荷電流と出力電圧で決まります。個々のアプリケーションに対する外付けコンデンサの具体的な要件については、表4を参照してください。

### $V_{IN}$ から $V_{OUT}$ への降圧比

実現可能な $V_{IN}$ から $V_{OUT}$ への最大降圧比には、与えられた入力電圧に応じた制約があります。LTM4650の各出力は98%のデューティ・サイクルを実現する能力がありますが、 $V_{IN}$ から $V_{OUT}$ の間には負荷電流で決まる最小ドロップアウトが発生し、トップ側スイッチの高デューティ・サイクルに関連した出力電流能力を制限します。 $t_{ON(MIN)} < D/f_{SW}$ であることから、特定の周波数での動作時に規定されたデューティ・サイクルで動作させる場合は、最小オン時間 $t_{ON(MIN)}$ についても考慮する必要があります。ここで、Dはデューティ・サイクル、 $f_{SW}$ はスイッチング周波数です。 $t_{ON(MIN)}$ は電気的パラメータで90nsに規定されています。

### 出力電圧の設定

PWMコントローラには0.6Vの内部リファレンス電圧があります。ブロック図に示したとおり、60.4kΩの内部帰還抵抗が、 $V_{OUTS1}$ と $V_{FB1}$ の間、および $V_{OUTS2}$ と $V_{FB2}$ の間に接続されています。帰還レギュレーションを適切に動作させるには、これらのピンを対応する出力に接続することがきわめて重要です。独立したレギュレータとして使用する場合、または1個以上を並列レギュレータの一部として使用する場合に、 $V_{OUTS1}$ や $V_{OUTS2}$ ピンをフロートのままにすると、過電圧が発生する可能性があります。 $V_{FB1}$ または $V_{FB2}$ のどちらも、帰還抵抗なしの場合は、出力電圧がデフォルト値の0.6Vになります。 $V_{FB}$ ピンとGNDの間に抵抗 $R_{FB}$ を追加すると、出力電圧が次のように設定されます。

$$V_{OUT} = 0.6V \cdot \frac{60.4k + R_{FB}}{R_{FB}}$$

表1. 各種出力電圧に対する $V_{FB}$ 抵抗

| $V_{OUT}$ | 0.6V | 0.8V | 0.9V | 1.0V  | 1.2V  | 1.5V  | 1.8V  |

|-----------|------|------|------|-------|-------|-------|-------|

| $R_{FB}$  | Open | 182k | 121k | 90.9k | 60.4k | 40.2k | 30.2k |

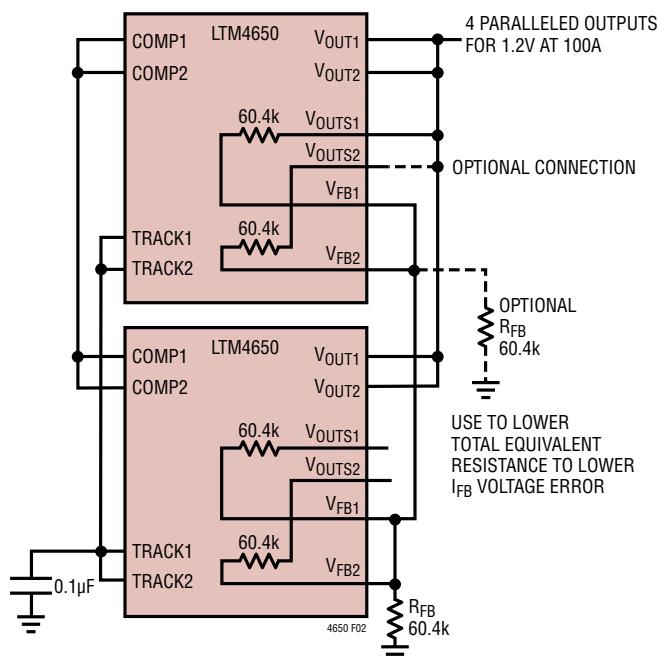

複数チャネルの並列動作では、並列デザインにも同じ帰還設定抵抗を使用できます。それには、図2に示すように $V_{OUTS1}$ と出力を接続することで、内部の60.4k抵抗の1つが出力に接続されます。図2に示すとおり、すべての $V_{FB}$ ピンが共通のプログラミング抵抗に接続されます。

並列動作の場合、 $V_{FB}$ ピンにはチャネルあたり最大20nAの $I_{FB}$ 電流が流れます。この電流による出力電圧の誤差を低減するには、他の $V_{OUTS}$ ピンも $V_{OUT}$ ピンに接続し、 $R_{FB}$ 抵抗も増やすことで、この電流に対する総テブナン等価抵抗を低減します。図2の例では、 $V_{FB}$ ピンの総テブナン等価抵抗は $(60.4k/R_{FB})$ で表され、1.2V出力の場合 $R_{FB}$ は60.4kであることから、その値は30.2kになります。4フェーズを並列接続した場合は帰還電流が増加し、最大で $4 \cdot I_{FB} = 80nA$ となることから、電圧誤差は、 $80nA \cdot 30.2k = 2.4mV$ と計算されます。図2のように $V_{OUTS2}$ も $V_{OUT}$ に接続して、 $V_{FB2}$ とグランドの間に60.4k抵抗をもう1つ接続すれば、電圧誤差は1.2mVに改善します。電圧誤差が許容できる場合は、追加の接続は必要ありません。60.4kの内蔵抵抗の精度は0.5%であり、 $V_{FB}$ 抵抗は、必要な精度に応じてユーザーが選択できます。フェーズ間の電流分担のために、COMPピンはすべて相互に接続します。TRACK/SSピンを相互に接続すれば、ソフトスタート・コンデンサ1個で、レギュレータのソフトスタートを実現できます。ソフトスタートの式には、並列接続されたチャネル数に応じて増加する、ソフトスタート電流のパラメータが必要です。「出力電圧トラッキング」のセクションを参照してください。

図2.4フェーズ並列構成

## アプリケーション情報

### 入力コンデンサ

LTM4650モジュールは低ACインピーダンスのDCソースに接続する必要があります。RMSリップル電流に対応するために、レギュレータの入力にはチャネルごとに2個の22 $\mu$ Fのセラミック・コンデンサが必要です。より大きな入力バルク容量には、47 $\mu$ F～100 $\mu$ Fの表面実装アルミ電解バルク・コンデンサを使うことができます。このバルク入力コンデンサは、長い誘導性のリードやトレースまたはソースの容量不足によって入力のソース・インピーダンスが損なわれる場合にだけ必要です。低インピーダンスの電源プレーンを使用している場合は、このバルク・コンデンサは不要です。

降圧コンバータの場合、スイッチングのデューティ・サイクルは次のように推定することができます。

$$D = \frac{V_{OUT}}{V_{IN}}$$

インダクタの電流リップルを考慮しなければ、入力コンデンサのRMS電流は、各出力に対して次のように概算できます。

$$I_{CIN(RMS)} = \frac{I_{OUT(MAX)}}{\eta\%} \cdot \sqrt{D \cdot (1-D)}$$

上の式で、 $\eta\%$ は電源モジュールの推定効率です。バルク・コンデンサは、スイッチャ定格のアルミ電解コンデンサ、またはポリマー・コンデンサにすることができます。

### 出力コンデンサ

LTM4650は出力電圧リップル・ノイズを小さくし、優れたトランジエント応答が得られるように設計されています。C<sub>OUT</sub>として定義されているバルク出力コンデンサは、出力電圧リップルとトランジエントの要件を満たすために、実効直列抵抗(ESR)が十分に小さいものを選択します。C<sub>OUT</sub>には低ESRのタンタル・コンデンサ、低ESRのポリマー・コンデンサまたはセラミック・コンデンサを使うことができます。各出力の標準的な出力容量の範囲は400 $\mu$ F～600 $\mu$ Fです。出力リップルや動的トランジエント・スパイクを更に低減するために、システム設計者による出力フィルタの追加が必要になる場合があります。異なる出力電圧と、12.5A(25%)負荷ステップの過渡変動での電圧の垂下やオーバーシュートを最小に抑えるための出力コンデンサの一覧を表4に示します。この表では、最適のトランジエ

ント性能を得るために、全等価ESRと全バルク容量が最適化されています。表4の一覧では安定性の判定基準が考慮されており、リニアテクノロジーからLTpowerCAD Design Toolが安定性の解析のために提供されています。マルチフェーズ動作では、位相数に応じて実効出力リップルが低減されます。このノイズ低減と出力リップル電流の相殺については「アプリケーションノート77」で解説していますが、出力容量と安定性やトランジエント応答の関係を注意深く検討する必要があります。リニアテクノロジーの $\mu$ Module Power Design Toolは、実装する位相数をN倍に増やしたときの出力リップルの減少を計算できます。10 $\Omega$ ～50 $\Omega$ の小さな抵抗をV<sub>OUT</sub>とV<sub>OUTS</sub>ピンの間に直列に挿入することで、ボード・プロット・アナライザが制御ループに信号を注入して、レギュレータの安定性を検証できるようにします。同じ抵抗をV<sub>OUT</sub>とDIFPの間に直列に挿入しても、ボード・プロット・アナライザは制御ループに信号を注入してレギュレータの安定性を検証できます。

### Burst Mode動作

LTM4650は、パワーMOSFETが負荷要件に応じて間欠的に動作するBurst Mode動作を、レギュレータごとに実行できるため、静止電流が節減されます。非常に軽い負荷での効率最大化を重視するアプリケーションでは、Burst Mode動作を使用します。MODE\_PLLINピンをフロートさせると、Burst Mode動作がイネーブルされます。この動作の間、COMPピンの電圧が低い値を示しても、インダクタのピーク電流は通常動作における最大ピーク電流値の約1/3に設定されます。インダクタの平均電流が負荷の要求値より大きいと、COMPピンの電圧は下がります。COMPピンの電圧が0.5Vを下回ると、BURSTコンパレータがトリップし、内部のスリープ・ラインが“H”になって両方のパワーMOSFETをオフします。

スリープ・モードでは、内部回路は部分的にオフしており、各出力の静止電流は約450 $\mu$ Aに減少します。このとき、負荷電流は出力コンデンサから供給されます。出力電圧が低下して、COMPが0.5Vを超えると、内部のスリープ・ラインは“L”になり、LTM4650は通常動作を再開します。次の発振器サイクルでトップ・パワーMOSFETがオンし、スイッチング・サイクルを繰り返します。Burst Mode動作は、両レギュレータのいずれに対しても設定できます。

## アプリケーション情報

### パルス・スキップ・モードの動作

低出力リップルおよび中程度の電流での高い効率が望まれるアプリケーションでは、パルス・スキップ・モードを使います。パルス・スキップ動作により、LTM4650は低出力負荷時にサイクルをスキップすることができるので、スイッチング損失が減少して効率が向上します。MODE\_PLLINピンをINTV<sub>CC</sub>に接続すると、パルス・スキップ動作がイネーブルされます。軽い負荷では、内部電流コンパレータが数サイクルにわたって作動したままになり、上側MOSFETを数サイクルにわたって強制的にオフのままにする(つまり、サイクルをスキップする)ことがあります。このモードでは、インダクタ電流は反転しません。実効周波数が高く保たれるため、Burst Mode動作に比べて出力リップルとノイズが低減されます。パルス・スキップ・モードは、両レギュレータのいずれに対しても設定できます。

### 強制連続動作

低電流での効率より周波数固定の動作が重要で、さらに出力リップルを最小限に抑える必要があるアプリケーションでは、強制連続動作を使用する必要があります。MODE\_PLLINピンをGNDに接続すると、強制連続動作をイネーブルできます。このモードでは、インダクタ電流が低出力負荷の間反転可能で、常にCOMP電圧が電流コンパレータのしきい値を制御し、トップMOSFETは発振器のパルスごとに必ずオンします。起動時には、LTM4650の出力電圧が安定化されるまで、強制連続モードがディスエーブルされ、インダクタ電流の反転が防止されます。強制連続モードは、両レギュレータのいずれに対しても設定できます。

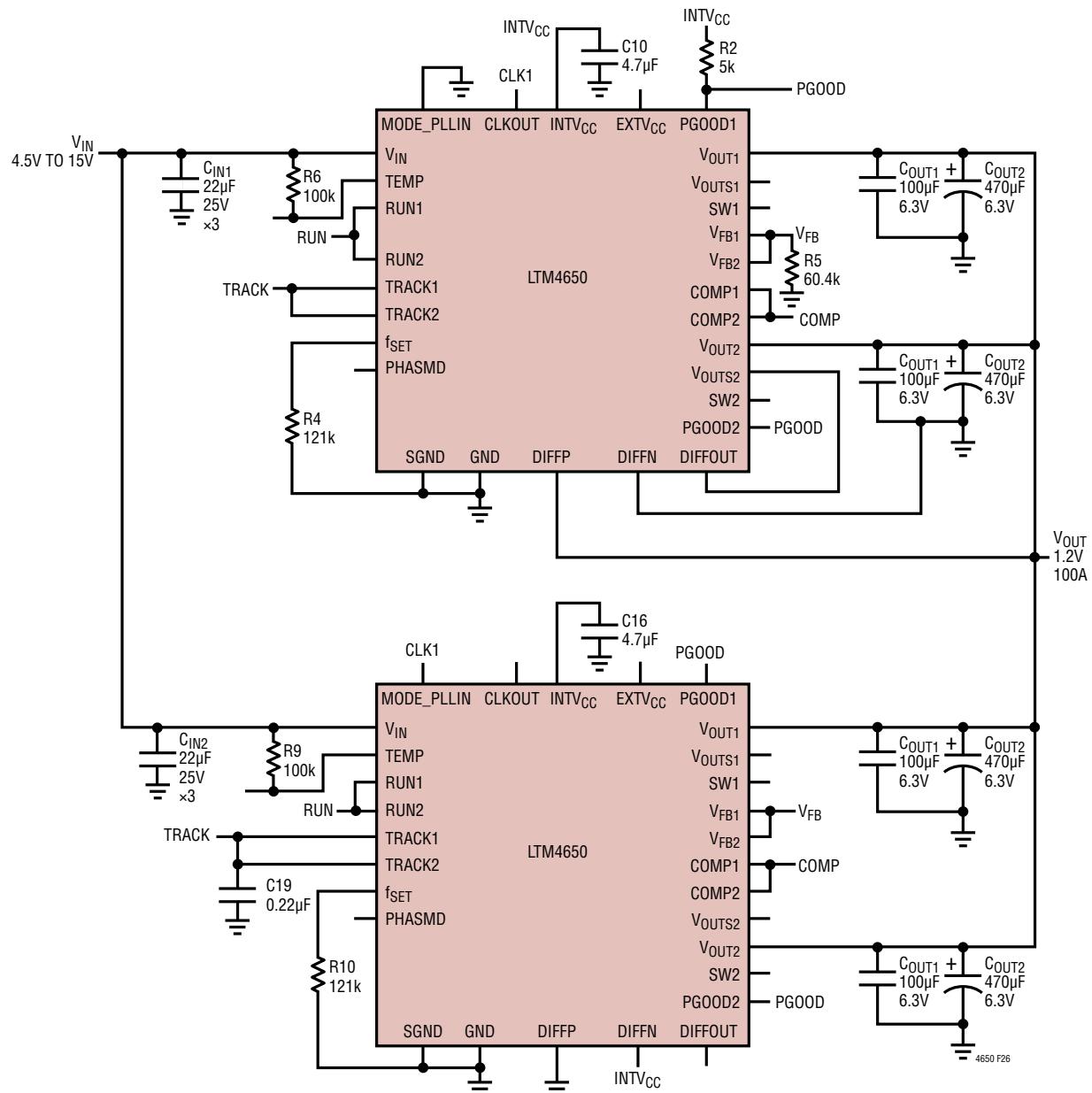

### マルチフェーズ動作

出力負荷が25Aを超える電流を必要とする場合、LTM4650の2つの出力または複数のLTM4650を並列接続した上で、位相をずらして動作させ、入力と出力の電圧リップルを抑えたまま出力電流を増やすことができます。MODE\_PLLINピンによってLTM4650を外部クロック(400kHz～780kHz)に同期させることができ、内部フェーズロック・ループによってLTM4650を入力クロックの位相にロックさせることができます。CLKOUT信号を、次段のMODE\_PLLINピンに接続し、システム全体の周波数と位相の両方を揃えることができます。PHASMDピンを、INTV<sub>CC</sub>またはSGNDに接続するか、フロート状態とすると、それぞれ120°、60°、90°の位相差(MODE\_PLLINとCLKOUT間)を発生できます。LTM4650のチャネル

ごとにPHASMDピンを異なったレベルにプログラムすることにより、合計12フェーズをカスケード接続し、相互に同時に動作させることができます。図3は、クロックの位相制御の設計例として2フェーズ、4フェーズ、6フェーズの構成をPHASMDの表と併せて示したものです。

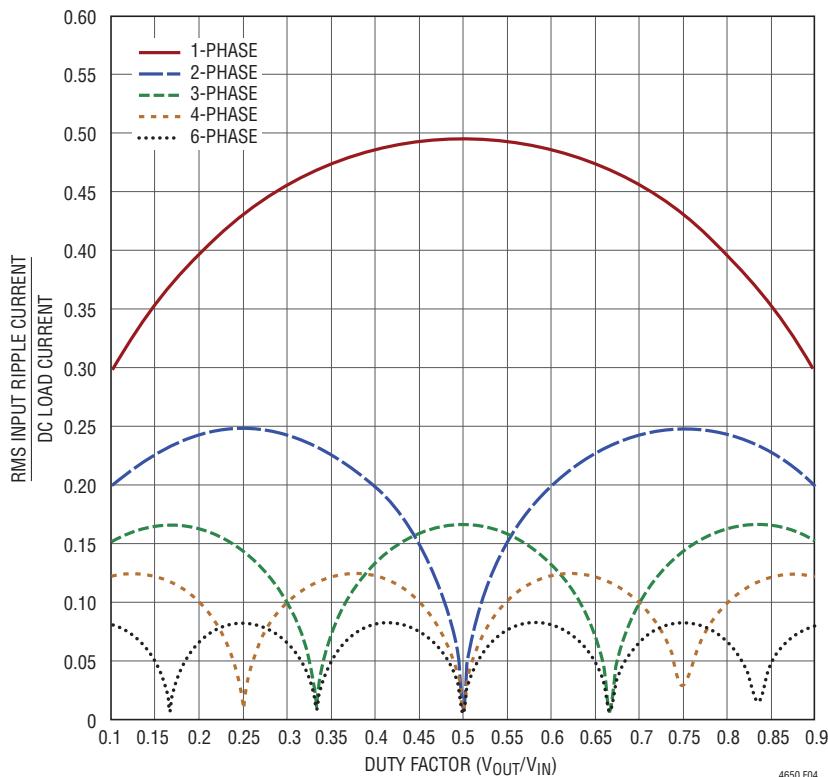

マルチフェーズ電源では、入力と出力のどちらのコンデンサのリップル電流の量も大幅に減少します。RMS入力リップル電流は使用する位相数が増えると低減され、実効リップル周波数は位相数倍されます(入力電圧が、使用される位相数×出力電圧より大きいと仮定)。すべての出力を互いに接続した高電流のシングル出力デザインでは、使用する位相数によって出力リップルの振幅を低減することができます。

LTM4650は本来、電流モードで制御されるデバイスであるため、並列モジュールでは優れた電流分担特性を示し、このため、デザインの発熱バランスがよくなります。図26に、並列動作とピン接続の例を示します。

### 入力RMSリップル電流の相殺

マルチフェーズ動作は「アプリケーションノート77」で詳細に説明されています。入力RMSリップル電流の相殺を数学的に導出し、RMSリップル電流の減少を、インタリープされた位相の数の関数として表したグラフを掲載しています。図4に、そのグラフを再録します。

### 周波数の選択とフェーズロック・ループ (MODE\_PLLINピンとf<sub>SET</sub>ピン)

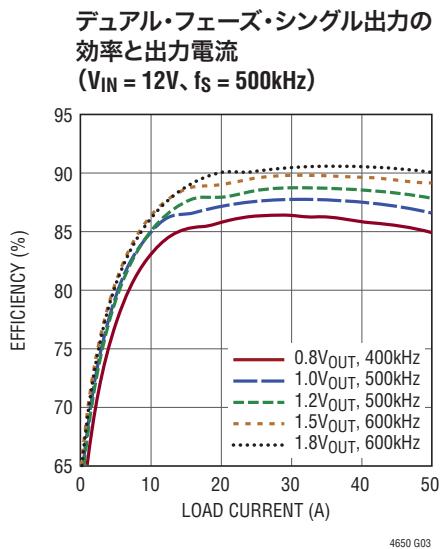

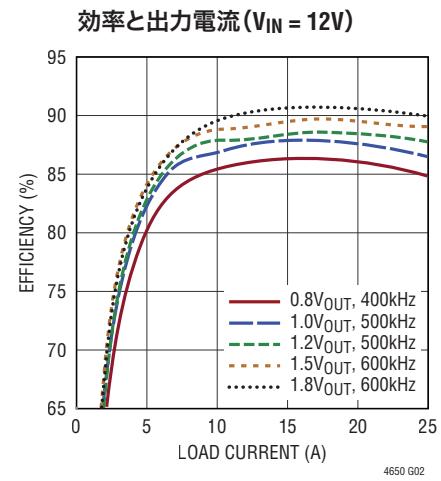

LTM4650デバイスは、電力変換効率を高めるために、広い周波数範囲で動作します。最善の効率とインダクタ電流リップルが得られるようにするため、1.0V未満の出力電圧では400kHz、1.0V～1.5Vの出力電圧では500kHz、1.5Vを上回る出力電圧では600kHzでモジュールを動作させることを推奨します。

LTM4650のスイッチング周波数は、f<sub>SET</sub>ピンとSGND間の外付け抵抗によって設定できます。高精度の10μA電流源から抵抗に供給される電流によって、周波数をプログラムする電圧を設定します。DC電圧を直接印加して設定することもできます。図5にプログラム電圧に対する周波数設定のグラフを示します。周波数範囲400kHz～780kHzについては、MODE\_PLLINピンに0VからINTV<sub>CC</sub>の外部クロックを入力することもできます。クロック入力のHigh側しきい値は1.6V、Low側し

## アプリケーション情報

図3.2 フェーズ、4フェーズ、6フェーズ動作の例(PHASMDの表を併記)

図4.DC負荷電流に対する入力RMS電流の比率のデューティ・サイクル依存性

4650fa

## アプリケーション情報

きい値は1Vです。LTM4650はPLLループ・フィルタの部品を内蔵しています。外部クロックにロックするまでの初期スイッチング周波数を設定するために、周波数設定抵抗は必ず接続してください。両レギュレータは、外部クロックによる駆動中、連続モードで動作します。

PLL位相検出器の出力は、内部フィルタ・ネットワークを充放電する1対の相補型電流源です。外部クロックを印加する場合、f<sub>SET</sub>周波数抵抗は内部スイッチによって切り離され、入力される外部クロックにロックするための周波数調整は電流源によって制御されます。外部クロックが印加されないと、内部スイッチがオンになり、外付けのf<sub>SET</sub>周波数設定抵抗が接続されて自走動作になります。

図5.動作周波数のf<sub>SET</sub>ピン電圧依存性

## 最小オン時間

最小オン時間t<sub>ON</sub>は、LTM4650がいずれかのチャネルのトップMOSFETをオンすることができる最小時間です。これは内部タイミング遅延とトップMOSFETをオンするに必要なゲート電荷の量によって決まります。低デューティ・サイクルのアプリケーションでは、この最小オン時間のリミットに接近する可能性があるので、次の条件が成り立つように注意する必要があります。

$$\frac{V_{OUT}}{V_{IN} \cdot FREQ} > t_{ON(MIN)}$$

デューティ・サイクルが最小オン時間で対応可能な値より低くなると、コントローラはサイクル・スキップを開始します。出力電圧は引き続き安定化されますが、出力リップルと電流が増加します。トップMOSFETのオン時間は、スイッチング周波数を低くすると増加します。経験則から、オン時間は110nsよりも長くすることを推奨します。

## 出力電圧のトラッキング

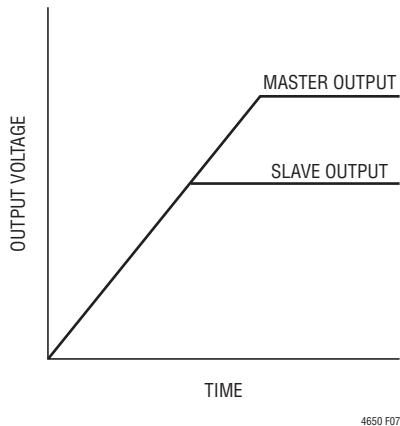

出力電圧のトラッキングはTRACKピンを使って外部よりプログラムできます。出力を別のレギュレータによってトラッキングアップおよびトラッキングダウンすることができます。マスタ・レギュレータの出力は、同時トラッキングを実現するため、スレーブ・レギュレータの帰還抵抗分割器と同じ外部抵抗分割器で分割されます。LTM4650は、各チャネルにトップ帰還抵抗用として60.4kの高精度抵抗を内蔵しています。同時トラッキングの例を図6に示します。式は次のようになります。

$$SLAVE = \left( 1 + \frac{60.4k}{R_{TA}} \right) \cdot V_{TRACK}$$

V<sub>TRACK</sub>はスレーブのTRACK・ピンに印加するTRACK・ランプ電圧です。V<sub>TRACK</sub>の制御範囲は0V～0.6V(内部リファレンスの電圧)です。スレーブの出力を設定するのに使われる抵抗値と同じ値でマスタの出力が分圧されると、スレーブはその最終値に達するまでマスタを同時トラッキングします。マスタはスレーブのレギュレーション点からその最終値まで上昇を続けます。V<sub>TRACK</sub>が0.6Vを超えると、電圧トラッキングはディスエーブルされます。同時トラッキングの場合、図6のR<sub>TA</sub>はR<sub>FB</sub>に等しくなります。同時トラッキングの波形を図7に示します。

マスタ・レギュレータのTRACKピンは、グランドとの間に接続したコンデンサによって制御できます。TRACKピンは、1.3μAの電流源によってリファレンス電圧まで充電され、更に最大INTV<sub>CC</sub>まで電圧が高くなります。0.6Vまでランプアップした後は、TRACKピンに対する制御は解除され、内部電圧リファ

## アプリケーション情報

図6. 出力トラッキング・アプリケーション回路の例

図7. 出力同時トラッキングの波形

レンズが帰還分圧器を介して出力レギュレーションを制御します。トラッキングまたはソフトスタートに含まれる上記のシーケンス実行中は、フォールドバック電流制限はディスエーブルされます。RUNピンが1.2Vを下回ると、TRACKピンはLowに引き下げられます。ソフトスタートの合計時間は次のように計算できます。

$$t_{SOFT-START} = \left( \frac{C_{SS}}{1.3\mu A} \right) \cdot 0.6$$

MODE\_PLLINピンで選択されたモードには関係なく、TRACK = 0.5Vまではレギュレータ・チャネルが常にパルス・スキップ・モードで起動します。TRACK = 0.5V ~ 0.54Vでは強制連続モードで動作し、TRACK > 0.54Vになると選択されたモードに復帰します。LTM4650は、定常状態の動作に移行すると、もう一方のチャネルをトラックするために、V<sub>FB</sub>が0.54Vを下回った時点で、MODE\_PLLINピンの設定に関係なく、強制的に連続モード動作に切り替わります。

レシオメトリック・トラッキングはいくつかの簡単な計算とマスターのTRACKピンに与えられるスルーレートの値によって達成することができます。前述のとおり、TRACKピンの制御範囲は0V ~ 0.6Vです。マスターのTRACKピンのスルーレートはボルト/時間で表したマスターの出力スルーレートにそのまま等しくなります。式は次のようにになります。

$$\frac{MR}{SR} \cdot 60.4k = R_{TB}$$

ここで、MRはボルト/時間で表したマスターの出力スルーレート、SRはスレーブの出力スルーレートです。同時トラッキングが必要な場合には、MRとSRが等しくなるのでR<sub>TB</sub>は60.4kに等しくなります。R<sub>TA</sub>は次式から求められます。

## アプリケーション情報

$$R_{TA} = \frac{0.6V}{\frac{V_{FB}}{60.4k} + \frac{V_{FB}}{R_{FB}} - \frac{V_{TRACK}}{R_{TB}}}$$

ここで、 $V_{FB}$  はレギュレータの帰還電圧リファレンスで、 $V_{TRACK}$  は 0.6V です。 $R_{TB}$  はスルーレートが等しい(つまり同時にトラッキング時の)スレーブ・レギュレータの 60.4k の上側帰還抵抗に等しいので、 $V_{FB} = V_{TRACK}$  のとき、 $R_{TA}$  は  $R_{FB}$  に等しくなります。したがって、図 6 の  $R_{TB} = 60.4k$ 、 $R_{TA} = 60.4k$  になります。

比例トラッキングでは、スレーブ・レギュレータに異なるスルーレートが必要になる可能性があります。SR が MR より低いときの  $R_{TB}$  を求めることができます。スルーレートが十分に速いスレーブ電源を選択して、スレーブの出力電圧がマスターの出力より早く最終値に達するようにしてください。

例えば、 $MR = 1.5V/1ms$ 、および  $SR = 1.2V/1ms$  とした場合、 $R_{TB} = 76.8k$  になります。 $R_{TA}$  について解くと、49.9k が得られます。

各 TRACK ピンは、その特定のチャネルのトラッキングを抵抗分割器によって実装している場合、 $1.3\mu A$  の電流源をオンします。このため、TRACK ピン入力にオフセットが生じます。上式で計算した抵抗値と比が同じで、値がより小さな抵抗を使用してもかまいません。例えば、60.4k が使われている場合、6.04k を使って TRACK ピンのオフセットを無視できる値に下げるることができます。

### パワーグッド

PGOOD ピンはオープン・ドレインのピンで、有効な出力電圧レギュレーションをモニタするのに使うことができます。このピンはレギュレーション・ポイントの上下 10% の範囲をモニタします。モニタ用の抵抗を、最大 6V を超えない特定の電源電圧でプルアップできます。

### 安定性補償

モジュールはあらゆる出力電圧に対して内部で補償済みです。ほとんどのアプリケーションの要件に対して表 4 が与えられています。その他の制御ループの最適化のためには、リニアテクノロジーの μModule 電源設計ツールが提供されています。

### 実行イネーブル

RUN ピンは、最大 1.4V、代表値 1.25V のイネーブルしきい値を持ち、150mV のヒステリシスが付加されています。各チャネルと INTVCC のターンオンを制御します。5V 動作の場合、これらのピンは  $V_{IN}$  にプルアップすることができます。入力が 5V を超える場合は、5V のツエナー・ダイオードと 10k ～ 100k の抵抗を接続してチャネルをイネーブルできます。RUN ピンは、出力電圧のシーケンス制御にも使用できます。並列動作では、RUN ピンを相互に接続して 1 つの信号で制御できます。図 22 の「標準的応用回路」を参照してください。

### INTVCC と EXTVCC

LTM4650 モジュールは、入力電圧から 5V を発生する、低ドロップアウト・レギュレータを内蔵しています。このレギュレータは制御回路とパワー MOSFET のドライバの電源として使われます。最大 70mA を供給でき、通常は ~30mA の消費電流によって最大周波数で動作するデバイスに給電します。この内部 5V 電源は、RUN1 または RUN2 のいずれかによってイネーブルされます。

EXTVCC を使用すると、LTM4650 に外部 5V 電源から電力を供給できるため、内蔵低ドロップアウト 5V レギュレータによる電力損失を低減できます。電力損失の節減量は次式で計算することができます。

$$(V_{IN} - 5V) \cdot 30mA = PLOSS$$

EXTVCC には、アクティブ化するために 4.7V のしきい値があり、最大定格は 6V です。入力が 5V の場合、これを EXTVCC に接続してゲート駆動レベルを 5V に維持することも可能です。EXTVCC は  $V_{IN}$  より後にオンさせ、 $V_{IN}$  より前にオフさせる必要があります。

### 差動リモート検出アンプ

離れた負荷ポイントで低い出力電圧を正確に検出するため、高精度の差動リモート検出アンプを搭載しています。大電流の負荷には特に役立ちます。アンプは、2 つのチャネルのいずれか一方、または並列構成のシングル出力に対して使用できます。DIFFP と DIFFN を出力に、DIFFOUT を  $V_{OUTS1}$  または  $V_{OUTS2}$  のいずれかに適切に接続することが重要です。並列動作の場合は、DIFFP と DIFFN を出力に、DIFFOUT を  $V_{OUTS}$  ピンのいずれか一方に適切に接続します。図 23 の並列構成の回路図と、図 2 を参照してください。

## アプリケーション情報

### SWピン

通常、SWピンはテスト時のモニタリング目的で使用します。また、スイッチング動作する電流パスのLC寄生素子によって発生する、スイッチ・ノード・リンクを減衰させる目的でも使用します。これには通常、スナバ回路と呼ばれる直列RC回路を使用します。抵抗が共振を減衰させるので、コンデンサには、抵抗両端の高周波リンクだけに作用する値を選択します。浮遊インダクタンスまたは容量を測定できる場合、または近似値が既知の場合は、スナバ回路の値を選択するのにある程度解析的な手法を適用できます。通常は、インダクタンスの方が予測が容易です。電源経路のボード・インダクタンスとMOSFET相互接続ボンディング・ワイヤのインダクタンスを組み合わせた値になります。

はじめに、広帯域幅のオシロスコープと高周波のプローブによってSWピンをモニタします。これによって、リンク周波数の値を測定できます。インピーダンスZは次式により計算できます。

$$ZL = 2\pi fL$$

ここで、fはリンク周波数、Lはスイッチ経路の寄生インダクタンスの合計値です。この式のZに等しい抵抗を選べば、リンクは減衰するはずです。スナバのコンデンサの値は、インピーダンスがリンク周波数における抵抗に等しくなるように選択されます。次式で計算されます。ZC = 1/(2πfC)これらの値は、検討を始める初期値として妥当です。最小限の電力損失でリンクを減衰できるように、これらの部品の値は変更する必要があります。

### 温度のモニタリング

ダイオードの絶対温度は、次に示す古典的なダイオードの式によって表される、電流、電圧、温度間の関係を使って測定できます。

$$I_D = I_S \cdot e^{\left( \frac{V_D}{\eta \cdot V_T} \right)}$$

or

$$V_D = \eta \cdot V_T \cdot \ln \frac{I_D}{I_S}$$

ここで、IDはダイオードの電流、VDはダイオードの電圧、ηは理想係数(通常は1.0に近い値)であり、IS(飽和電流)はプロセスに依存するパラメータです。VTは、次のように書き換えることができます。

$$V_T = \frac{k \cdot T}{q}$$

ここでTはダイオードの接合部温度(単位:K)、qは電子電荷、kはボルツマン定数です。VTは室温(298K)で約26mVであり、絶対温度に対して線形に変化します。ダイオードが温度センサに適しているのは、この温度に対する線形性のためです。前述の式のISの項はダイオードの接合を通して流れる電流を、ダイオード端子間の電圧が0Vになる点まで外挿した値です。ISの項はプロセス間や温度によってばらつきますが、その定義から常にIDより小さくなければなりません。すべての定数を1つの項にまとめると、次のようにになります。

$$K_D = \frac{\eta \cdot k}{q}$$

ここでKD = 8.62 · 10<sup>-5</sup>であり、IDが常にISより大きいため、ln(ID/IS)は常に正になることがわかります。これらのことから、次の式が得られます。

$$V_D = T(KELVIN) \cdot K_D \cdot \ln \frac{I_D}{I_S}$$

この式から、VDが温度とともに増加するのがわかります。しかし、電流源によってバイアスされたシリコン・ダイオードの温度係数が約-2mV/°Cになることは広く知られた事実であり(図8)、これは上式と一致しません。実際には、ISの項は温度とともに増加し、ln(ID/IS)の絶対値が減少します。この効果が複合されることで、約-2mV/°Cというダイオードの電圧スロープが得られます。

温度に比例する線形の電圧特性を得るために、自然対数の項のIS変数を消去して、式1からISの依存性を排除します。それには、ダイオードの電圧を、2つの電流I<sub>1</sub>とI<sub>2</sub>で測定して(両者の間にはI<sub>1</sub> = 10 · I<sub>2</sub>の関係があります)、差し引きます。

$$\Delta V_D = T(KELVIN) \cdot K_D \cdot \ln \frac{I_1}{I_S} - T(KELVIN) \cdot K_D \cdot \ln \frac{I_2}{I_S}$$

## アプリケーション情報

図8. ダイオードの電圧  $V_D$  と温度  $T$  (°C)

類似の項をまとめ、自然対数の項を簡単化すると、次式が得られます。

$$\Delta V_D = T(KELV_{IN}) \cdot K_D \cdot \ln(10)$$

定数を次のように定義し直します。

$$K'_D = K_D \cdot \ln(10) = \frac{198 \mu V}{K}$$

式を書き換えると、次のようにになります。

$$\Delta V_D = K'_D \cdot T(KELV_{IN})$$

これを温度について解きます。

$$T(KELVIN) = \frac{\Delta V_D}{K'_D} \text{ (°CELSIUS)} = T(KELVIN) - 273.15$$

ここで、

$$300^{\circ}K = 27^{\circ}C$$

これは、比率が10倍の2つの電流でダイオード両端の電圧を測定して、その差から接合部の絶対温度  $1K$  あたり  $198 \mu V$  の電圧スロープと、 $0K$  での切片として  $0$  が得られたことを意味します。

TEMPピンでダイオード接続したPNPトランジスタを使用して、LTM4650の内部温度をモニタできます。一例としては、図23を参照してください。

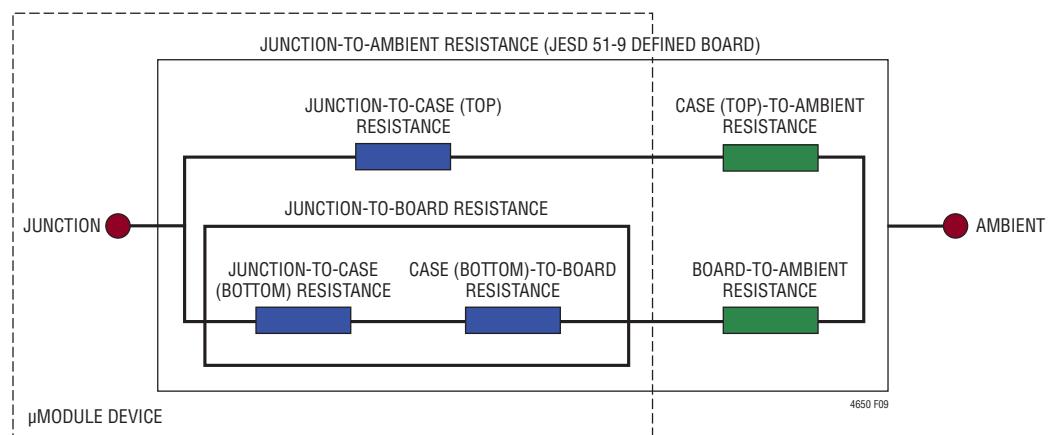

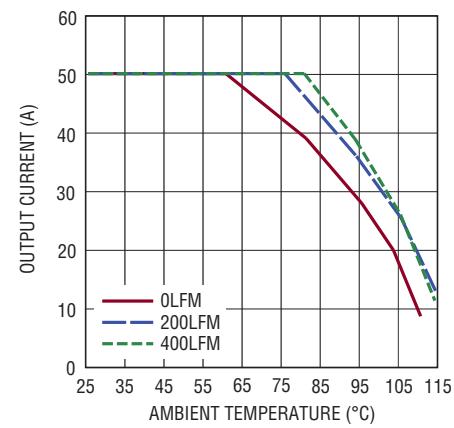

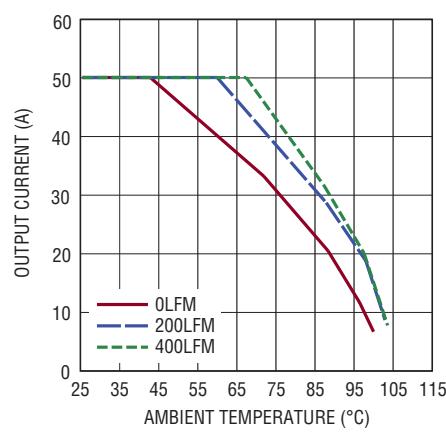

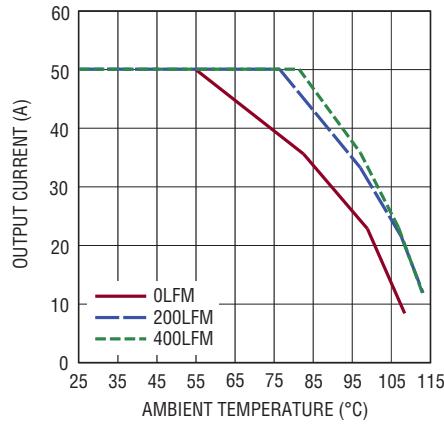

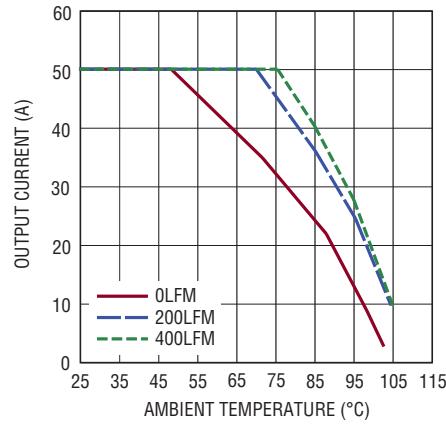

## 熱に関する検討事項と出力電流のディレーティング

データシートの「ピン配置」セクションに記載された熱抵抗は、JESD 51-9に定義されたパラメータと整合しています。これらのパラメータは、有限要素解析(FEA)ソフトウェアのモデリング・ツールでの使用を意図したもので、モーデリング・ツールでは、JESD 51-9 (“Test Boards for Area Array Surface Mount Package Thermal Measurements”)によって定義されたハードウェア・テストボードにμModuleパッケージを実装して行われたハードウェア評価で得られた熱的モデリング、シミュレーション、相関の結果を使用します。これらの熱係数を示す目的は、JESD 51-12 (Guidelines for Reporting and Using Electronic Package Thermal Information)に記載されています。

多くの設計者は、さまざまな電気的および環境的動作条件で動作する実際のアプリケーションにおけるμModuleレギュレータの熱性能を予測するのに、実験室の装置およびデモボードのようなテスト手段の使用を選択して、FEAの作業を補強できます。FEAソフトウェアを使用しない場合、「ピン配置」に記載された熱抵抗は、それだけでは熱性能のガイダンスにはなりません。むしろ、データシートに示されたディレーティング曲線を使った方が、アプリケーションへの適用方法に沿った洞察とガイダンスを得られ、特定のアプリケーションにおける熱性能との相関に適合させることができます。

「ピン配置」には、通常はJESD 51-12に明示的に定義された4つの熱係数が記載されています。以下に、これらの係数の定義の引用または説明を示します。

1.  $\theta_{JA}$  (接合部から周囲までの熱抵抗) は、1立方フィートの密閉された筐体内で測定された、接合部から自然対流する周囲の空気までの熱抵抗です。この環境は、自然対流により空気が移動しますが、「静止空気」と呼ばれることがあります。この値は、JESD 51-9で定義されているテストボードに実装したデバイスを使って決定されます。このテストボードは実際のアプリケーションまたは実現可能な動作条件を反映するものではありません。

2.  $\theta_{JCbottom}$  (接合部から製品のケースの底部までの熱抵抗) は、部品の全電力損失がパッケージの底部を通して流れ出す場合の接合部から基板までの熱抵抗です。標準的なμModuleでは、熱の大半がパッケージの底面から流出しま

## アプリケーション情報

ですが、周囲の環境への熱の流出が必ず発生します。その結果、この熱抵抗値はパッケージの比較には役立ちますが、このテスト条件は一般にユーザーのアプリケーションに合致しません。

3.  $\theta_{JCTOP}$  (接合部から製品のケースの頂部までの熱抵抗) は、部品のほぼ全電力損失がパッケージの頂部を通って流れ出す状態で決定されます。標準的μModuleの電気的接続はパッケージの底部なので、接合部からデバイスの頂部に熱の大半が流れるようにアプリケーションが動作することは稀です。 $\theta_{JCBOTTOM}$ の場合のように、この値はパッケージの比較には役立ちますが、このテスト条件は一般にユーザーのアプリケーションに合致しません。

4.  $\theta_{JB}$  (接合部からプリント回路基板までの熱抵抗) は、熱の大部分がμModuleの底部を通って基板に流れ出すときの接合部から基板までの熱抵抗であり、実際には、 $\theta_{JCBOTTOM}$ と、デバイスの底部から半田接合部を通り、基板の一部までの熱抵抗の和です。基板の温度は、両面の2層基板を使って、パッケージからの規定された距離で測定されます。この基板はJESD 51-9に記述されています。

前述の熱抵抗を図式化したものが図9です。青色で示された部分はμModule レギュレータ内部の熱抵抗、緑色で示された部分はμModule の外部に存在する熱抵抗です。

実際には、JESD51-12または「ピン配置」で定義されている4種類の熱抵抗パラメータの個々のものまたはサブグループは、μModuleの通常の動作条件を再現または表現するものではないことに注意してください。例えば、基板に実装された通常のアプリケーションでは、標準規格が $\theta_{JCTop}$ および $\theta_{JCBottom}$ をそれぞれ定義しているように、デバイスの全電力損失(熱)の100%がパッケージの頂部だけを通って、または底部だけを通って熱的に伝わることは決してありません。実際には、電力損失はパッケージの両面から熱的に放散されます。ヒートシンクと空気流がない場合には、当然、熱流の大部分は基板に流れます。

SIP (System-In-Package) モジュール内部では、電力損失を生じるパワーデバイスや部品が複数存在するので、その結果、部品やダイのさまざまな接合部を基準にした熱抵抗は、パッケージの全電力損失に対して正確に線形ではないことに注意してください。この複雑さを(モデリングの簡単さを犠牲にすることなく、しかも実用的な現実性を無視せずに)調和させるため、制御された環境室でのラボ・テストとともにFEA ソフトウェア・モデリングを使うアプローチが取られ、このデータシートで与えられている熱抵抗値の定義と相関が得られました。(1)はじめに、FEA ソフトウェアを使用し、正確な材料係数に加えて正確な電力損失源の定義を使用することにより、μModule と指定のPCB の機械的形状モデルを高い精度で構築します。

図9.JESD51-12の熱係数の図解

## アプリケーション情報

(2) このモデルによって、JESD51-9に適合するソフトウェア定義のJEDEC環境のシミュレーションを行い、さまざまな界面における電力損失熱流と温度測定値を予測します。その値からJEDEC定義の熱抵抗値を計算できます。(3) モデルとFEAソフトウェアを使用してヒートシンクと空気流がある場合のμModuleの熱性能を評価します。(4) これらの熱抵抗値を計算して分析し、ソフトウェア・モデル内でさまざまな動作条件によるシミュレーションを行った上で、これを再現する徹底した評価実験を実施します。具体的には、制御環境チャンバ内で、シミュレーションと同じ電力損失でデバイスを動作させながら、熱電対を使用して温度を測定します。このプロセスと必要な作業の結果、このデータシートの別のセクションに示されているディレーティング曲線が得られました。これらの実験室での評価を行い、μModuleモデルと相関を得てから $\theta_{JB}$ と $\theta_{BA}$ を合計すると、適切な環境のチャンバ内におけるエアフローおよびヒートシンクなしのμModuleモデルと、きわめてよい相関が得られました。この $\theta_{JB} + \theta_{BA}$ の値は「ピン配置」に示されており、エアフローや頂部に実装したヒートシンクがない状態では、電力損失のほぼ100%が接合部から基板を通って周囲に流れるので、この値は $\theta_{JA}$ の値に正確に等しくなります。熱特性はシステムごとに異なるため、特定のシステムに対してユーザーが熱解析を実施する必要があります。

LTM4650モジュールは、パッケージの上下両面から効率的に放熱できるように設計されています。下面の基板材料はプリント回路基板への熱抵抗がきわめて低くなっています。エアフローへの良好な放熱が可能な外付けのヒートシンクをデバイスの上面に取り付けることができます。

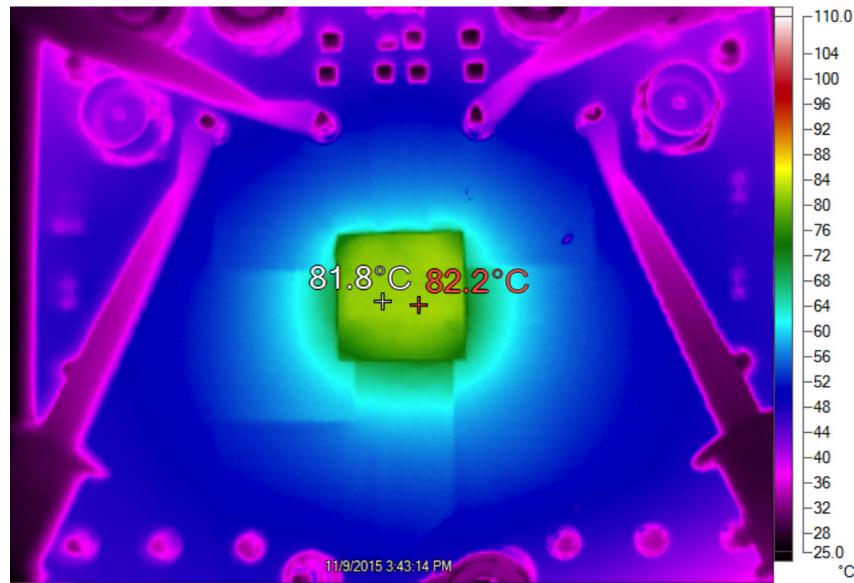

図10に、ヒートシンクおよびエアフロー条件なしでの、12V入力、1.0V/50A出力のLTM4650の温度プロットを示します。

### 安全性に関する検討事項

LTM4650モジュールは $V_{IN}$ と $V_{OUT}$ の間が絶縁されていません。内部にヒューズはありません。必要に応じて、最大入力電流の2倍の定格の低速溶断ヒューズを使って各ユニットを致命的損傷から保護してください。デバイスも過電流保護機能を備えています。内部温度をモニタする温度検出ダイオードを搭載しているため、これを使ってRUNピン制御によるサーマル・シャットダウンが必要であるかどうかを検出できます。

図10. エアフローおよびヒートシンクなし、12V入力、1V/50Aの熱イメージ

(トップ層、ボトム層、全内部層に2オンス銅箔を含む101mm×114mmの4層PCB基板を使用)

## アプリケーション情報

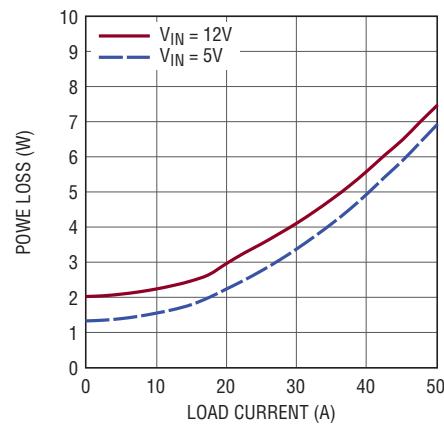

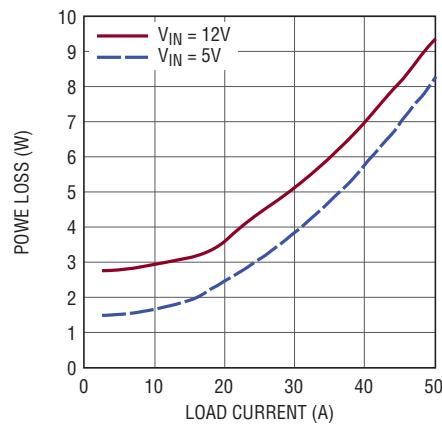

### 電力ディレーティング

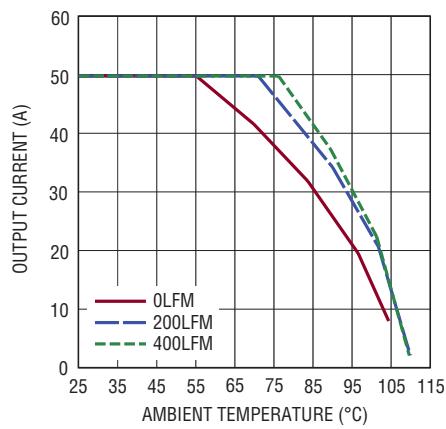

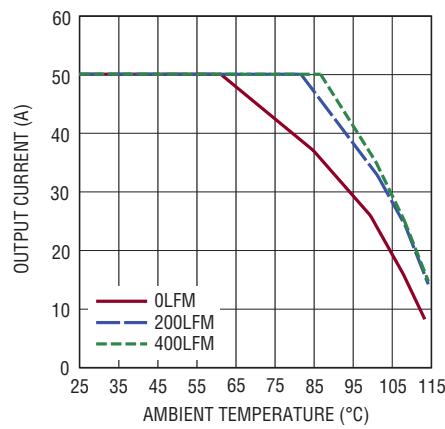

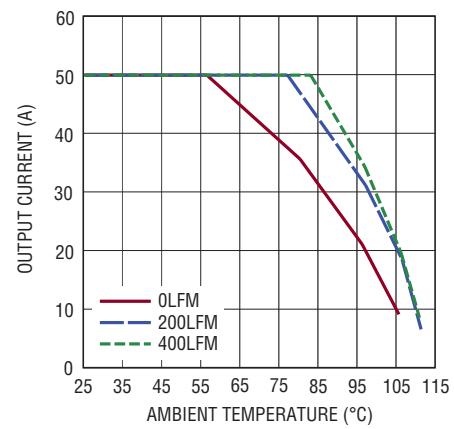

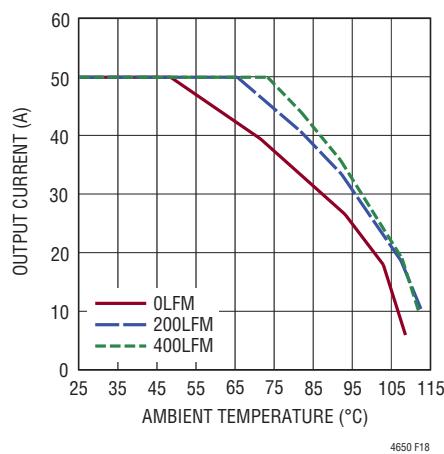

図12と図13の0.9Vと1.5Vの電力損失曲線を図14～図21の負荷電流ディレーティング曲線とともに使って、さまざまなヒートシンクおよびエアフロー条件でのLTM4650のおおよその $\theta_{JA}$ 熱抵抗を計算することができます。電力損失曲線を室温で測定し、その値を120°Cでは倍率1.2で増加させます。

ディレーティング曲線は、CH1とCH2を並列接続したシングル出力動作を、負荷電流50Aから測定します。周囲温度は常温です。出力電圧は0.9Vと1.5Vです。これらの電圧は熱抵抗との相関を取るため、低い方と高い方の出力電圧範囲を含むように選択されています。熱モデルは、制御温度室での数回の温度測定と熱モデリング解析から得られます。

空気流ありと空気流なしの条件で周囲温度を上げながら接合部温度をモニタします。周囲温度の変化による電力損失の増加はディレーティング曲線に加味されています。周囲温度を上げながら、他方、出力電流つまり電力は減らして、接合部温度を最大～120°Cに維持します。周囲温度を上げながら出力電流を減らすと、内部モジュールの損失が減少します。

モニタされた120°Cの接合部温度から周囲動作温度を差し引いた値は、どれだけのモジュール温度の上昇を許容できるかを規定します。図15の例では、200LFMのエアフローとヒートシンクなしで約90°Cのとき負荷電流が約35Aにディレーティングされ、12Vから0.9V/35A出力の電力損失は5.6Wです。5.6Wの損失は、12V入力、0.9V/35A出力での電力損失曲線から得られる約4.7Wの室温での損失、および120°Cの接合部温度での1.20の倍率を使って計算されます。120°Cの接合部温度から90°Cの周囲温度を差し引き、その差の30°Cを5.5Wで割ると5.4°C/Wの熱抵抗 $\theta_{JA}$ が得られます。表2はこれと非常に近い5.5°C/Wの値を規定しています。表2と表3にエアフローとヒートシンクのありとなしの0.9V出力と1.5V出力の等価熱抵抗を示します。

さまざまな条件で得られた表2と表3の熱抵抗に、周囲温度の関数として計算された電力損失を掛けて、周囲温度を超える温度上昇(したがって最大接合部温度)を求めることができます。室温での電力損失は効率曲線から求め、上記の周囲温

度の増加係数を使って調整することができます。プリント回路基板は1.6mm厚の4層構造で、各層に2オンス銅箔を使用しています。PCBの寸法は101mm×114mmです。BGAヒートシンクを表3に示します。

### レイアウトのチェックリスト/例

LTM4650は高度に集積化されているため、PCB基板レイアウトが非常に簡単です。ただし、電気的性能と熱的性能を最適化するにはいくつかのレイアウト上の配慮が依然として必要です。

- $V_{IN}$ 、GND、 $V_{OUT1}$ 、 $V_{OUT2}$ を含む高電流経路にはPCB銅箔面積を広く確保します。PCBの導通損失と熱ストレスを最小限に抑えるのに役立ちます。

- 入力と出力の高周波用セラミック・コンデンサを $V_{IN}$ 、 $PGND$ および $V_{OUT}$ の各ピンに隣接させて配置し、高周波ノイズを最小に抑えます。

- ユニットの下に専用の電源グランド・レイヤを配置します。

- ビアの導通損失を最小に抑え、モジュールの熱ストレスを減らすため、トップ・レイヤと他の電源レイヤの間の相互接続に多数のビアを使います。

- 充填ビアまたはメッキビアでない限り、パッドの上に直接ビアを置かないでください。

- 信号ピンに接続された部品には、別のSGNDグランド銅領域を使います。SGNDとGNDをデバイスの下で接続します。

- 並列モジュールの場合は、 $V_{OUT}$ 、 $V_{FB}$ 、COMPピンを互いに接続します。内部層を使ってこれらのピンを互いに近づけて接続します。TRACKピンはレギュレータのソフトスタート用に共通のコンデンサを接続できます。

- 信号ピンからは、モニタリング用にテスト・ポイントを引き出してください。

推奨レイアウトの良い例を図11に示します。BGAの円形パッドを除いて、LGAおよびBGAのPCBレイアウトは同じです(「パッケージ」のセクションを参照)。

## アプリケーション情報

図11. 推奨されるPCBレイアウト

表2. 0.9V出力

| ディレーティング曲線     | V <sub>IN</sub> (V) | 電力損失曲線    | 空気流 (LFM) | ヒートシンク        | θ <sub>JA</sub> (°C/W) |

|----------------|---------------------|-----------|-----------|---------------|------------------------|

| Figures 14, 15 | 5, 12               | Figure 12 | 0         | None          | 7.5                    |

| Figures 14, 15 | 5, 12               | Figure 12 | 200       | None          | 5.5                    |

| Figures 14, 15 | 5, 12               | Figure 12 | 400       | None          | 5                      |

| Figures 16, 17 | 5, 12               | Figure 12 | 0         | BGA Heat Sink | 7                      |

| Figures 16, 17 | 5, 12               | Figure 12 | 200       | BGA Heat Sink | 4.5                    |

| Figures 16, 17 | 5, 12               | Figure 12 | 400       | BGA Heat Sink | 4                      |

表3. 1.5V出力

| ディレーティング曲線     | V <sub>IN</sub> (V) | 電力損失曲線    | 空気流 (LFM) | ヒートシンク        | θ <sub>JA</sub> (°C/W) |

|----------------|---------------------|-----------|-----------|---------------|------------------------|

| Figures 18, 19 | 5, 12               | Figure 13 | 0         | None          | 7.5                    |

| Figures 18, 19 | 5, 12               | Figure 13 | 200       | None          | 5.5                    |

| Figures 18, 19 | 5, 12               | Figure 13 | 400       | None          | 5                      |

| Figures 19, 20 | 5, 12               | Figure 13 | 0         | BGA Heat Sink | 7                      |

| Figures 19, 20 | 5, 12               | Figure 13 | 200       | BGA Heat Sink | 4.5                    |

| Figures 19, 20 | 5, 12               | Figure 13 | 400       | BGA Heat Sink | 4                      |

| ヒートシンクのメーカー | 製品番号        | Webサイト              |

|-------------|-------------|---------------------|

| Wakefield   | LTN20069-T5 | wakefield-vette.com |

4650fa

## アプリケーション情報

表4. 2相シングル出力(図24を参照)

|         | C <sub>IN</sub> (セラミック) |                    |                      |             | C <sub>OUT</sub> (セラミック) |                      |  |  |

|---------|-------------------------|--------------------|----------------------|-------------|--------------------------|----------------------|--|--|

|         | メーカー                    | 製品番号               | 値                    | メーカー        | 製品番号                     | 値                    |  |  |

| BULK    | Sun Electronics         | 25CE150AX          | 150μF, 25V           | Panasonic   | ETPF470M5H               | 470μF, 2.5V, 5mΩ     |  |  |

| CERAMIC | Murata                  | GRM21BR61E106KA73L | 10μF, 25V, 0805, X5R | Murata      | GRM32ER60J227M           | 220μF, 4V, 1206, X5R |  |  |

|         | Taiyo Yuden             | TMK212BBJ106KG-T   | 10μF, 25V, 0805, X5R | Taiyo Yuden | AMK325ABJ227MM-T         | 220uF, 4V, 1210, X5R |  |  |

|         | Murata                  | GRM31CR61E226KE15L | 22μF, 25V, 1206, X5R |             |                          |                      |  |  |

|         | Taiyo Yuden             | TMK316BBJ226ML-T   | 22μF, 25V, 1206, X5R |             |                          |                      |  |  |

## 25%負荷ステップ(0Aから12.5A)、セラミック出力コンデンサのみのソリューション

| V <sub>IN</sub> | V <sub>OUT</sub> | C <sub>IN</sub> *<br>(パルク) | C <sub>IN</sub><br>(セラミック) | C <sub>OUT</sub><br>(パルク) | C <sub>OUT</sub><br>(セラミック) | C <sub>FF</sub><br>(フィード<br>フォワード・<br>コンデンサ) | PK-PK偏差<br>(V <sub>PK-PK</sub> ) | セッティング時<br>間(t <sub>SETTLE</sub> ) | 負荷ス<br>テップ | 負荷ステッ<br>プのスル<br>ーレート | RFB    | FREQ   |

|-----------------|------------------|----------------------------|----------------------------|---------------------------|-----------------------------|----------------------------------------------|----------------------------------|------------------------------------|------------|-----------------------|--------|--------|

| 12V             | 1.0V             | 150μF                      | 22μF×2                     | None                      | 220μF×8                     | 470pF                                        | 47mV                             | 30μs                               | 12.5A      | 10A/μs                | 90.9kΩ | 500kHz |

| 12V             | 1.2V             | 150μF                      | 22μF×2                     | None                      | 220μF×8                     | 470pF                                        | 49mV                             | 30μs                               | 12.5A      | 10A/μs                | 60.4kΩ | 500kHz |

| 12V             | 1.5V             | 150μF                      | 22μF×2                     | None                      | 220μF×8                     | 470pF                                        | 50mV                             | 30μs                               | 12.5A      | 10A/μs                | 40.2kΩ | 600kHz |

| 12V             | 1.8V             | 150μF                      | 22μF×2                     | None                      | 220μF×8                     | 470pF                                        | 53mV                             | 30μs                               | 12.5A      | 10A/μs                | 30.2kΩ | 600kHz |

## 25%負荷ステップ(0Aから12.5A)、パルクおよびセラミック出力コンデンサのソリューション

| V <sub>IN</sub> | V <sub>OUT</sub> | C <sub>IN</sub> *<br>(パルク) | C <sub>IN</sub><br>(セラミック) | C <sub>OUT</sub><br>(パルク) | C <sub>OUT</sub><br>(セラミック) | C <sub>FF</sub><br>(フィード<br>フォワード・<br>コンデンサ) | PK-PK偏差<br>(V <sub>PK-PK</sub> ) | セッティング時<br>間(t <sub>SETTLE</sub> ) | 負荷ス<br>テップ | 負荷ステッ<br>プのスル<br>ーレート | RFB    | FREQ   |

|-----------------|------------------|----------------------------|----------------------------|---------------------------|-----------------------------|----------------------------------------------|----------------------------------|------------------------------------|------------|-----------------------|--------|--------|

| 12V             | 1.0V             | 150μF                      | 22μF×2                     | 470μF×2                   | 220μF×3                     | None                                         | 58mV                             | 20μs                               | 12.5A      | 10A/μs                | 90.9kΩ | 500kHz |

| 12V             | 1.2V             | 150μF                      | 22μF×2                     | 470μF×2                   | 220μF×3                     | None                                         | 58mV                             | 20μs                               | 12.5A      | 10A/μs                | 60.4kΩ | 500kHz |

| 12V             | 1.5V             | 150μF                      | 22μF×2                     | 470μF×2                   | 220μF×3                     | None                                         | 61mV                             | 30μs                               | 12.5A      | 10A/μs                | 40.2kΩ | 600kHz |

| 12V             | 1.8V             | 150μF                      | 22μF×2                     | 470μF×2                   | 220μF×6                     | None                                         | 64mV                             | 50μs                               | 12.5A      | 10A/μs                | 30.2kΩ | 600kHz |

図12.0.9V出力の電力損失曲線

図13.1.5V出力の電力損失曲線

図14.5V入力、0.9V出力の

ディレーティング曲線、

ヒートシンクなし

## アプリケーション情報

図15. 12V入力、0.9V出力の

ディレーティング曲線、

ヒートシンクなし

図16.5V入力、0.9V出力の

ディレーティング曲線、

BGAヒートシンク

図17.12V入力、0.9V出力の

ディレーティング曲線、

BGAヒートシンク

図18.5V入力、1.5V出力の

ディレーティング曲線、

ヒートシンクなし

図19.12V入力、1.5V出力の

ディレーティング曲線、

ヒートシンクなし

図20.5V入力、1.5V出力の

ディレーティング曲線、

BGAヒートシンク

図21.12V入力、1.5V出力の

ディレーティング曲線、

BGAヒートシンク

4650 F15

4650 F16

4650 F17

4650 F19

4650 F18

4650 F20

4650 F21

4650fa

## アプリケーション情報

図22. 標準的な4.5V<sub>IN</sub>～15V<sub>IN</sub>、1.5Vおよび1.2V/25A出力

## 標準的応用例

\*SEE TABLE 4

4650 F23

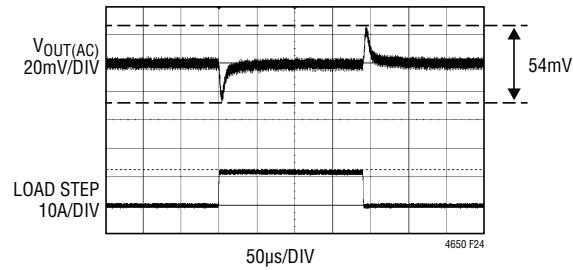

図23. LTM4650による2フェーズ、1V/50Aデザイン

図24. 図23の回路での25% (12.5A) 負荷ステップのトランジエント波形

4650fa

## 標準的応用例

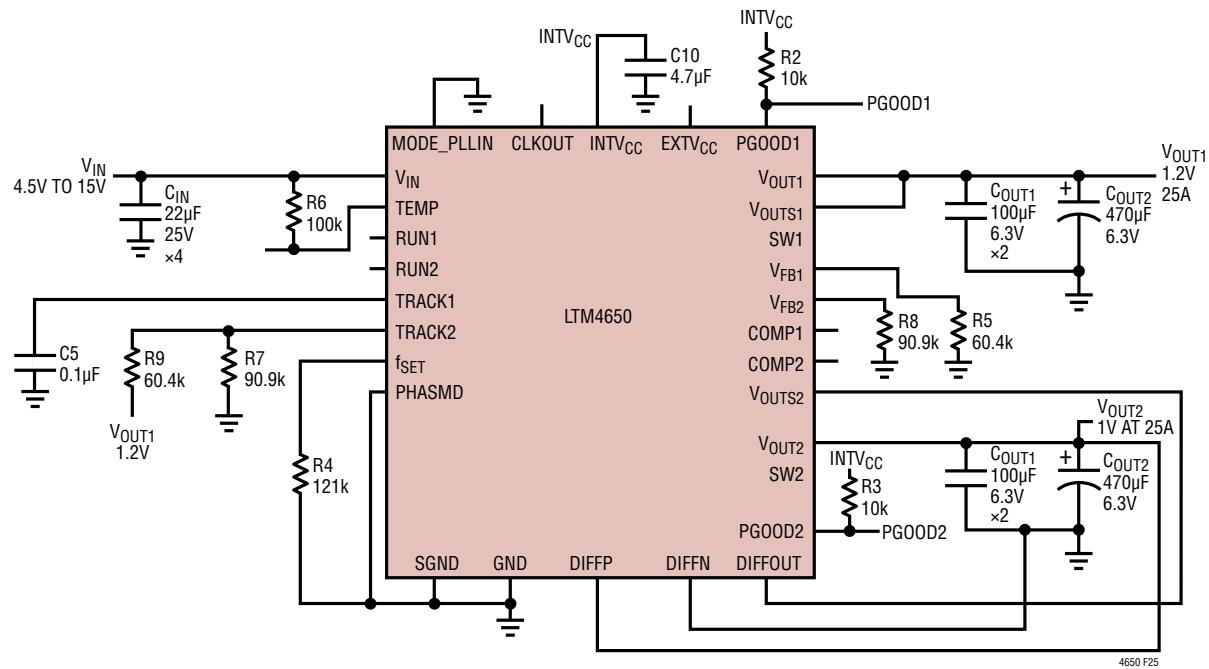

図25. LTM4650による1.2V/1V出力トラッキング

## 標準的応用例

図26.LTM4650による4フェーズ、1.2V/100Aデザイン

## パッケージ

LTM4650 の構成要素の BGA ピン配列

| ピンID | 機能                | ピンID | 機能                | ピンID | 機能                 | ピンID | 機能               | ピンID | 機能     | ピンID | 機能         |

|------|-------------------|------|-------------------|------|--------------------|------|------------------|------|--------|------|------------|

| A1   | V <sub>OUT1</sub> | B1   | V <sub>OUT1</sub> | C1   | V <sub>OUT1</sub>  | D1   | GND              | E1   | GND    | F1   | GND        |

| A2   | V <sub>OUT1</sub> | B2   | V <sub>OUT1</sub> | C2   | V <sub>OUT1</sub>  | D2   | GND              | E2   | GND    | F2   | GND        |

| A3   | V <sub>OUT1</sub> | B3   | V <sub>OUT1</sub> | C3   | V <sub>OUT1</sub>  | D3   | GND              | E3   | GND    | F3   | GND        |

| A4   | V <sub>OUT1</sub> | B4   | V <sub>OUT1</sub> | C4   | V <sub>OUT1</sub>  | D4   | GND              | E4   | GND    | F4   | MODE_PLLIN |

| A5   | V <sub>OUT1</sub> | B5   | V <sub>OUT1</sub> | C5   | V <sub>OUT1S</sub> | D5   | V <sub>FB1</sub> | E5   | TRACK1 | F5   | RUN1       |

| A6   | GND               | B6   | GND               | C6   | f <sub>SET</sub>   | D6   | SGND             | E6   | COMP1  | F6   | SGND       |

| A7   | GND               | B7   | GND               | C7   | SGND               | D7   | V <sub>FB2</sub> | E7   | COMP2  | F7   | SGND       |

| A8   | V <sub>OUT2</sub> | B8   | V <sub>OUT2</sub> | C8   | V <sub>OUT2S</sub> | D8   | TRACK2           | E8   | DIFFP  | F8   | DIFFOUT    |

| A9   | V <sub>OUT2</sub> | B9   | V <sub>OUT2</sub> | C9   | V <sub>OUT2</sub>  | D9   | GND              | E9   | DIFFN  | F9   | RUN2       |

| A10  | V <sub>OUT2</sub> | B10  | V <sub>OUT2</sub> | C10  | V <sub>OUT2</sub>  | D10  | GND              | E10  | GND    | F10  | GND        |

| A11  | V <sub>OUT2</sub> | B11  | V <sub>OUT2</sub> | C11  | V <sub>OUT2</sub>  | D11  | GND              | E11  | GND    | F11  | GND        |

| A12  | V <sub>OUT2</sub> | B12  | V <sub>OUT2</sub> | C12  | V <sub>OUT2</sub>  | D12  | GND              | E12  | GND    | F12  | GND        |

| ピンID | 機能      | ピンID | 機能                 | ピンID | 機能                 | ピンID | 機能              | ピンID | 機能              | ピンID | 機能              |

|------|---------|------|--------------------|------|--------------------|------|-----------------|------|-----------------|------|-----------------|

| G1   | GND     | H1   | GND                | J1   | GND                | K1   | GND             | L1   | GND             | M1   | GND             |

| G2   | SW1     | H2   | GND                | J2   | V <sub>IN</sub>    | K2   | V <sub>IN</sub> | L2   | V <sub>IN</sub> | M2   | V <sub>IN</sub> |

| G3   | GND     | H3   | GND                | J3   | V <sub>IN</sub>    | K3   | V <sub>IN</sub> | L3   | V <sub>IN</sub> | M3   | V <sub>IN</sub> |

| G4   | PHASEMD | H4   | GND                | J4   | V <sub>IN</sub>    | K4   | V <sub>IN</sub> | L4   | V <sub>IN</sub> | M4   | V <sub>IN</sub> |

| G5   | CLKOUT  | H5   | GND                | J5   | GND                | K5   | GND             | L5   | V <sub>IN</sub> | M5   | V <sub>IN</sub> |

| G6   | SGND    | H6   | GND                | J6   | TEMP               | K6   | GND             | L6   | V <sub>IN</sub> | M6   | V <sub>IN</sub> |

| G7   | SGND    | H7   | GND                | J7   | EXTV <sub>CC</sub> | K7   | GND             | L7   | V <sub>IN</sub> | M7   | V <sub>IN</sub> |

| G8   | PGOOD2  | H8   | INTV <sub>CC</sub> | J8   | GND                | K8   | GND             | L8   | V <sub>IN</sub> | M8   | V <sub>IN</sub> |

| G9   | PGOOD1  | H9   | GND                | J9   | V <sub>IN</sub>    | K9   | V <sub>IN</sub> | L9   | V <sub>IN</sub> | M9   | V <sub>IN</sub> |

| G10  | GND     | H10  | GND                | J10  | V <sub>IN</sub>    | K10  | V <sub>IN</sub> | L10  | V <sub>IN</sub> | M10  | V <sub>IN</sub> |

| G11  | SW2     | H11  | GND                | J11  | V <sub>IN</sub>    | K11  | V <sub>IN</sub> | L11  | V <sub>IN</sub> | M11  | V <sub>IN</sub> |

| G12  | GND     | H12  | GND                | J12  | GND                | K12  | GND             | L12  | GND             | M12  | GND             |

## LTM4650

## パッケージ

最新のパッケージ図は、<http://www.linear-tech.co.jp/product/LTM4650#packaging> を参照してください。

660

PACKAGE IN TBAY | LOADING ORIENTATION

4650fa

## 改訂履歴

| REV | 日付    | 概要        | ページ番号 |

|-----|-------|-----------|-------|

| A   | 05/16 | パッケージ図の更新 | 32    |

# LTM4650

## パッケージの写真

## デザイン・リソース

| 主題                   | 説明                                                                                                                       |                                                                                                                             |

|----------------------|--------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|

| µModuleの設計/製造リソース    | デザイン: <ul style="list-style-type: none"><li>選択ガイド</li><li>デモボードおよびGerberファイル</li><li>無料シミュレーション・ツール</li></ul>            | 製造: <ul style="list-style-type: none"><li>クイック・スタート・ガイド</li><li>PCBの設計、組立、および製造ガイドライン</li><li>パッケージおよびボード・レベルの信頼性</li></ul> |

| µModuleレギュレータ製品の検索   | 1. 製品の表をパラメータによって並べ替え、結果をスプレッドシートとしてダウンロードする<br>2. Quick Power Searchパラメトリック・テーブルを使って検索を実行する                             |                                                                                                                             |

| TechClipビデオ          | µModule製品の電気的特性と熱特性のベンチマーク・テストの方法を詳しく説明した短いビデオ                                                                           |                                                                                                                             |

| デジタル・パワーシステム・マネージメント | リニアテクノロジーのデジタル電源管理デバイス・ファミリは、電源の監視、管理、マージン制御およびシーケンス制御などの基本機能を提供する高度に集積されたソリューションであり、ユーザーの構成と�オルト・ログを保存するEEPROMを搭載しています。 |                                                                                                                             |

## 関連製品

| 製品番号      | 説明                                                                    | 注釈                                                                                                                                                                   |

|-----------|-----------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LTM4630   | LTM4650よりも低電流、デュアル18Aまたはシングル36A                                       | LTM4650とピン互換、 $4.5V \leq V_{IN} \leq 15V$ 、 $0.6V \leq V_{OUT} \leq 1.8V$ 、 $15mm \times 15mm \times 4.41mm$ LGAパッケージおよび $15mm \times 15mm \times 5.01mm$ BGAパッケージ   |

| LTM4630A  | LTM4650よりも低電流かつ高出力電圧、最大5.3Vの出力電圧、デュアル18Aまたはシングル26A                    | LTM4650とピン互換、 $4.5V \leq V_{IN} \leq 15V$ 、 $0.6V \leq V_{OUT} \leq 5.3V$ 、 $15mm \times 15mm \times 4.41mm$ LGAパッケージ                                                |

| LTM4630-1 | LTM4650よりも低電流、外部補償付き、 $\pm 0.8\% (-1A)$ または $\pm 1.5\% (-1B)$ の出力電圧制度 | LTM4650とピン互換、 $4.5V \leq V_{IN} \leq 15V$ 、 $0.6V \leq V_{OUT} \leq 1.8V$ 、 $15mm \times 15mm \times 5.01mm$ BGAパッケージ                                                |

| LTM4620   | LTM4650よりも低電流、デュアル13Aまたはシングル26A                                       | LTM4650とピン互換、 $4.5V \leq V_{IN} \leq 16V$ 、 $0.6V \leq V_{OUT} \leq 2.5V$ 、 $15mm \times 15mm \times 4.41mm$ LGAパッケージおよび $15mm \times 15mm \times 5.01mm$ BGAパッケージ   |

| LTM4620A  | LTM4650よりも低電流かつ高出力電圧、最大5.3Vの出力電圧、デュアル13Aまたはシングル26A                    | LTM4650とピン互換、 $4.5V \leq V_{IN} \leq 16V$ 、 $0.6V \leq V_{OUT} \leq 2.5V$ 、 $15mm \times 15mm \times 4.41mm$ LGAパッケージおよび $15mm \times 15mm \times 5.01mm$ BGAパッケージ   |

| LTM4628   | LTM4650よりも低電流かつ高入力電圧および高出力電圧、デュアル8Aまたはシングル16A                         | LTM4650とピン互換、 $4.5V \leq V_{IN} \leq 26.5V$ 、 $0.6V \leq V_{OUT} \leq 5.5V$ 、 $15mm \times 15mm \times 4.32mm$ LGAパッケージおよび $15mm \times 15mm \times 4.92mm$ BGAパッケージ |

| LTM4677   | デュアル18A出力またはシングル36A出力、PSM付き                                           | $4.5V \leq V_{IN} \leq 16V$ 、 $0.5V \leq V_{OUT} \leq 1.8V$ $16mm \times 16mm \times 5.01mm$ BGAパッケージ                                                                |

| LTM4644   | クワッド4A                                                                | $4V \leq V_{IN} \leq 14V$ 、 $0.6V \leq V_{OUT} \leq 5.5V$ $9mm \times 15mm \times 5.01mm$ BGAパッケージ                                                                   |

| LTM4639   | 低入力電圧( $2.375V \leq V_{IN} \leq 7V$ )、20A                             | $0.6V \leq V_{OUT} \leq 5.5V$ $15mm \times 15mm \times 4.92mm$ BGAパッケージ                                                                                              |

4650fa

34

リニアテクノロジー株式会社

〒102-0094 東京都千代田区紀尾井町3-6紀尾井町パークビル8F

TEL 03-5226-7291 • FAX 03-5226-0268 • [www.linear-tech.co.jp](http://www.linear-tech.co.jp)

LT 0516 REV A • PRINTED IN JAPAN

LINEAR

TECHNOLOGY

© LINEAR TECHNOLOGY CORPORATION 2016