# DDR-QDR4メモリ向けの 超薄型トリプル出力降圧 μModule レギュレータ

## 特長

- VDDQ、VTT、VTTR(またはVREF)を含む完全な DDR-QDR4 SRAM 電源ソリューション

- 0.5cm<sup>2</sup>に収まるソリューション・サイズ(両面PCB)

- 広い入力電圧範囲:3.6V～15V

- V<sub>IN</sub>をINTV<sub>CC</sub>に接続した場合と互換の3.3V入力

- 出力電圧範囲:0.6V～2.5V

- シンク電流とソース電流を供給できるデュアル±3A DC 出力電流

- VDDQ/2に等しい±1.5%、±10mA バッファ付きVTTR出力

- 3A VDDQ + 3A VTT または 2相シングル 6A VTT

- 全負荷、入力、および温度での全出力電圧レギュレーション誤差:最大±1.5%

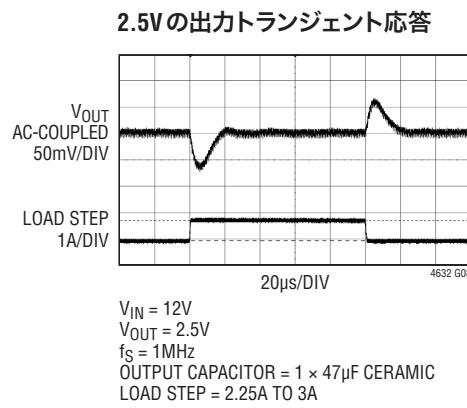

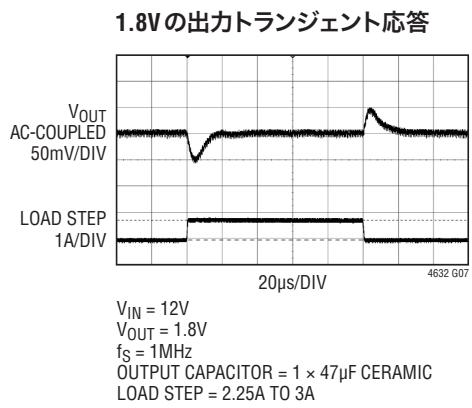

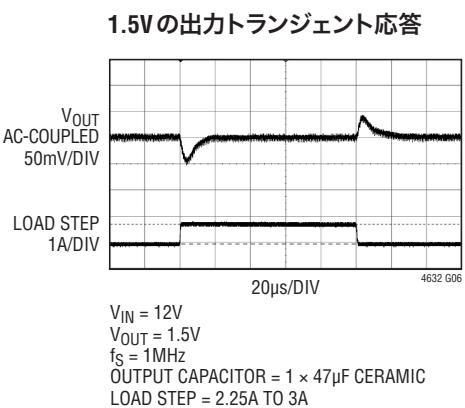

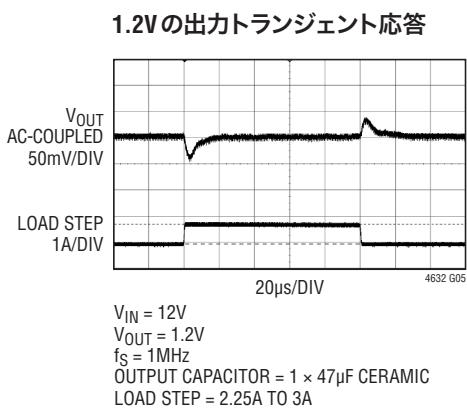

- 電流モード制御、高速トランジメント応答

- 外部の周波数に同期

- 電流分担によりマルチフェーズで並列接続可能

- 選択可能なBurst Mode<sup>®</sup>動作

- 過電圧入力保護と過熱保護

- パワーグッド・インジケータ

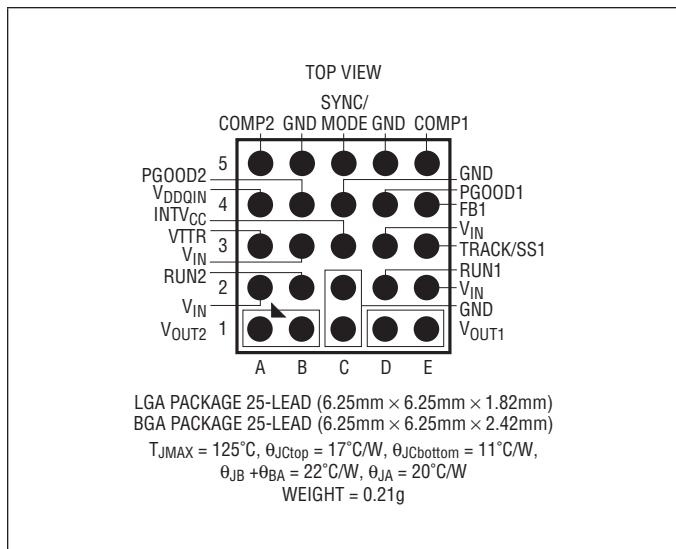

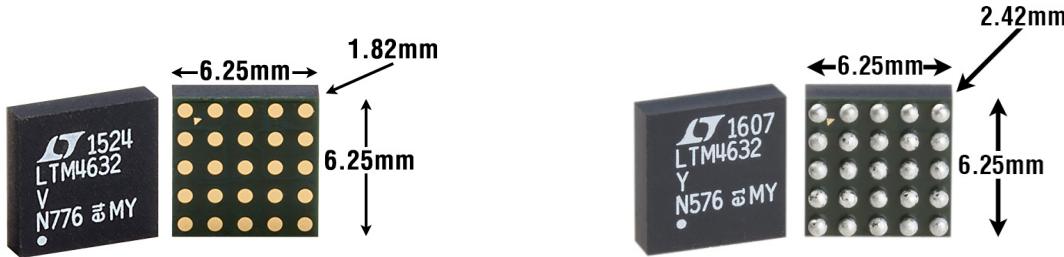

- 6.25mm×6.25mm×1.82mm 超薄型LGAパッケージおよび 6.25mm×6.25mm×2.42mm BGAパッケージ

## アプリケーション

- DDRメモリ電源

- 汎用ポイントオブロード変換

- 通信機器、ネットワーク機器、および産業用機器

## 概要

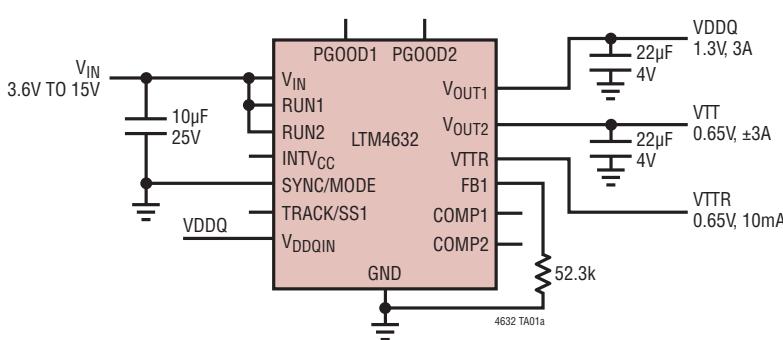

LTM<sup>®</sup>4632は、超薄型のトリプル出力降圧μModule<sup>®</sup>(パワーモジュール)レギュレータで、DDR-QDR4 SRAM向けの完全な電源ソリューションを実現します。LTM4632は、3.6V～15Vの入力電圧範囲で動作し、シンクとソースの両方の電流に対応する2つの±3A出力レールをVDDQとVTTに対してサポートし、この他に10mAの低ノイズ・リファレンスVTTR出力を内蔵しています。VTTとVTTRは、どちらもVDDQ/2に追従し、電圧もVDDQ/2に等しくなります。LTM4632は6.25mm×6.25mm×1.82mm LGAパッケージおよび6.25mm×6.25mm×2.42mm BGAパッケージに収容されており、スイッチング・コントローラ、パワーFET、インダクタ、およびサポート部品を搭載しています。また、このパワーモジュールは2相シングル±6A出力のVTTとして構成することもできます。設計を完了するために必要なのは、入力と出力のセラミック・コンデンサ数個だけです。

LTM4632は、選択可能なBurst Modeモード動作(CH1のみ)と、出力電圧トラッキングによる電源レールのシーケンシングをサポートしています。高いスイッチング周波数と電流モード制御により、安定性を損なうことなく入力および負荷の変動に対するきわめて高速なトランジメント応答が可能です。

フォルト保護機能には、過電圧入力保護、過電流保護、過熱保護が含まれます。

LTM4632は無鉛仕上げで、RoHSに準拠しています。

LT、LT、LTC、LTM、μModule、Burst Mode、Linear TechnologyおよびLinearのロゴはリニアテクノロジー社の登録商標です。その他全ての商標の所有権は、それぞれの所有者に帰属します。

## 標準的応用例

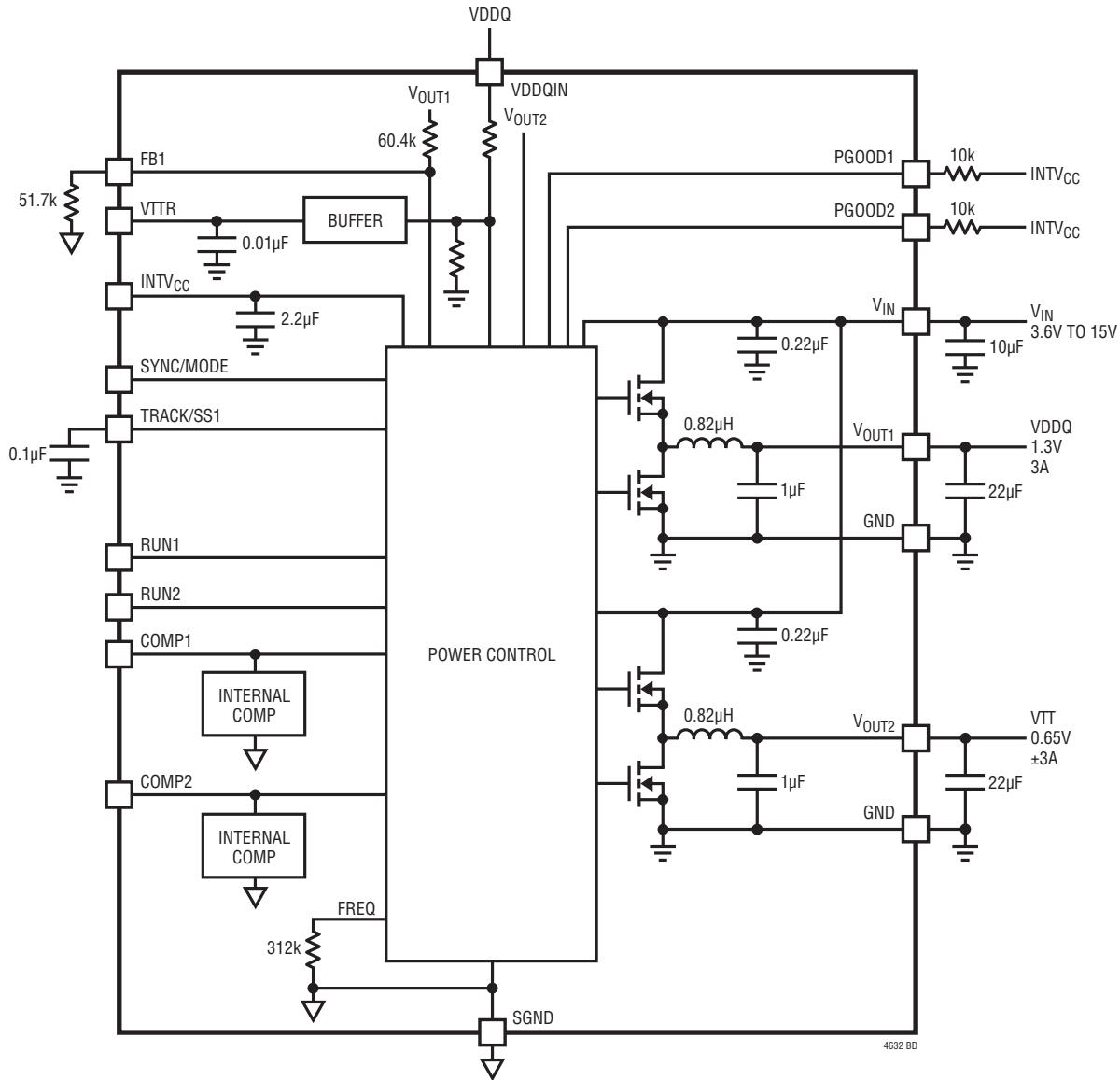

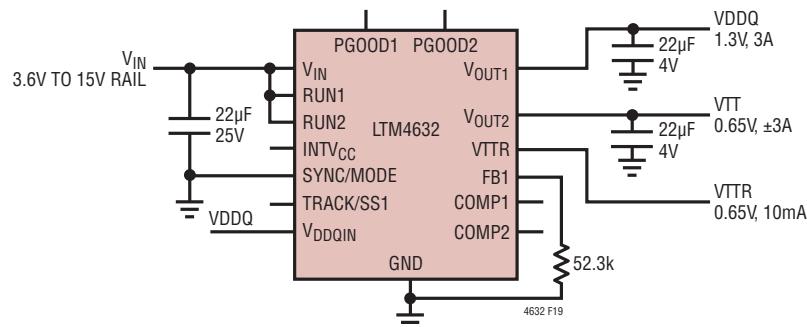

### QDR4メモリ電源μModule レギュレータ

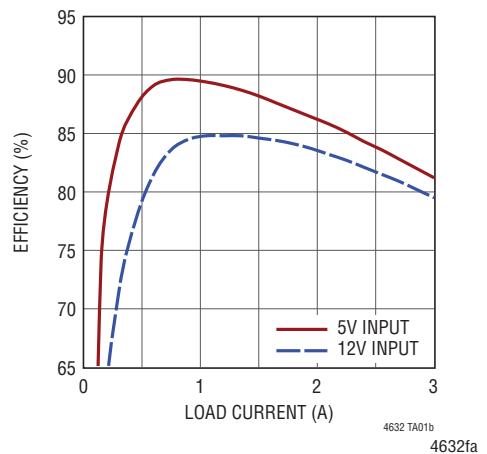

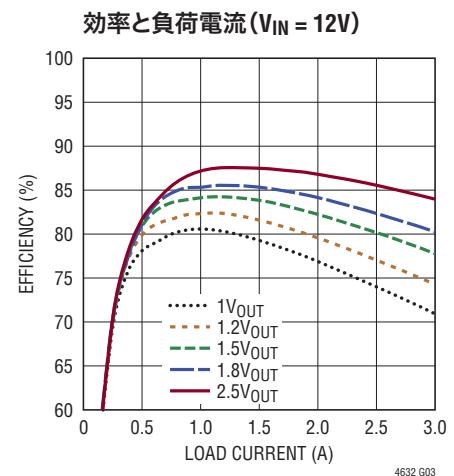

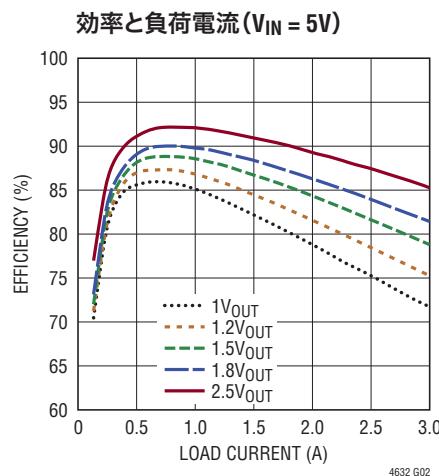

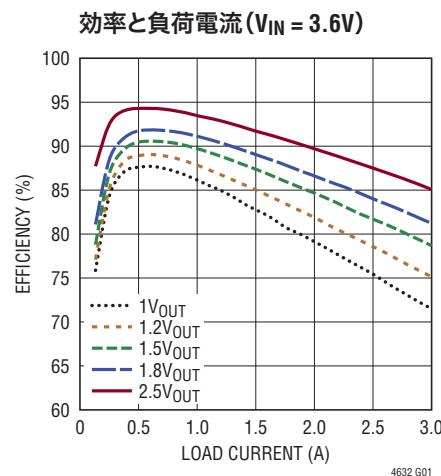

### 出力の効率と負荷電流

# LTM4632

## 絶対最大定格

(Note 1)

|                                                    |                            |

|----------------------------------------------------|----------------------------|

| $V_{IN}$                                           | -0.3V ~ 16V                |

| $V_{OUT}$                                          | -0.3V ~ 6V                 |

| PGOOD1, PGOOD2                                     | -0.3V ~ 16V                |

| RUN1, RUN2                                         | -0.3V ~ $V_{IN}$ + 0.3V    |

| INTV <sub>CC</sub> , TRACK/SS1, $V_{DDQIN}$ , VTTR | -0.3V ~ 3.6V               |

| MODE/SYNC, COMP1, COMP2,                           |                            |

| FB1, FB2                                           | -0.3V ~ INTV <sub>CC</sub> |

| 内部動作温度範囲 (Note 2, 3, 5)                            | -40 ~ 125°C                |

| 保存温度範囲                                             | -55 ~ 125°C                |

| 半田リフローのピーク・ボディ温度                                   | 260°C                      |

## ピン配置

(ピン機能、ピン配置の表を参照)

## 発注情報

<http://www.linear-tech.co.jp/product/LTM4632#orderinfo>

| 製品番号          | パッド/ボール仕上げ    | 製品マーキング* |        | パッケージ・タイプ | MSL 定格 | 温度範囲 (Note 2 参照) |

|---------------|---------------|----------|--------|-----------|--------|------------------|

|               |               | デバイス     | 仕上げコード |           |        |                  |

| LTM4632EV#PBF | Au (RoHS)     | LTM4632V | e4     | LGA       | 3      | -40°C to 125°C   |

| LTM4632IV#PBF | Au (RoHS)     | LTM4632V | e4     | LGA       | 3      | -40°C to 125°C   |

| LTM4632EY#PBF | SAC305 (RoHS) | LTM4632Y | e1     | BGA       | 3      | -40°C to 125°C   |

| LTM4632IY#PBF | SAC305 (RoHS) | LTM4632Y | e1     | BGA       | 3      | -40°C to 125°C   |

| LTM4632IY     | SnPb (63/37)  | LTM4632Y | e0     | BGA       | 3      | -40°C to 125°C   |

- さらに広い動作温度範囲で規定されるデバイスについては、弊社または弊社代理店にお問い合わせください。<sup>\*</sup> デバイスの温度グレードは出荷時のコンテナのラベルで示してあります。パッドまたはボールの仕上げコードはIPC/JEDEC J-STD-609に準拠しています。

- 端子仕上げの製品マーキングの参照先: [www.linear-tech.co.jp/leadfree](http://www.linear-tech.co.jp/leadfree)

- LGA/BGAの推奨のPCBアセンブリ手順および製造手順の参照先: [www.linear-tech.co.jp/u/module/pcbassembly](http://www.linear-tech.co.jp/u/module/pcbassembly)

- LGA/BGAパッケージおよびトレイの図面の参照先: [www.linear-tech.co.jp/packaging](http://www.linear-tech.co.jp/packaging)

## 電気的特性

●は規定された全内部動作温度範囲の規格値を意味する(Note 2)。

注記がない限り、図19の標準的応用例に基づき、 $T_A = 25^\circ\text{C}$  (Note 2)、 $V_{IN} = 12\text{V}$  における各出力チャネルで規定。

| SYMBOL            | PARAMETER             | CONDITIONS                            | MIN | TYP | MAX | UNITS |

|-------------------|-----------------------|---------------------------------------|-----|-----|-----|-------|

| $V_{IN}$          | Input DC Voltage      |                                       | ●   | 3.6 | 15  | V     |

| $V_{IN\_3.3}$     | 3.3V Input DC Voltage | $V_{IN} = \text{INT}V_{CC}$           | ●   | 3.1 | 3.3 | V     |

| $V_{OUT1(RANGE)}$ | Output Voltage Range  | $V_{IN} = 3.6\text{V to } 15\text{V}$ | ●   | 0.6 | 2.5 | V     |

| $V_{OUT2(RANGE)}$ |                       |                                       | ●   | 1.8 | V   | V     |

### 出力の規格(チャネル1)

|                                  |                                                        |                                                                                                                                                                                       |   |      |      |      |               |

|----------------------------------|--------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|------|------|------|---------------|

| $V_{OUT1(DC)}$                   | CH1 Output Voltage, Total Variation with Line and Load | $C_{IN} = 22\mu\text{F}$ , $C_{OUT} = 100\mu\text{F}$ Ceramic<br>$R_{FB1} = 51.7\text{k}$ , MODE = GND, $I_{OUT} = -3\text{A to } 3\text{A}$                                          | ● | 1.28 | 1.30 | 1.32 | V             |

| $I_{OUT1(DC)}$                   | CH1 Output Continuous Current Range                    | $V_{IN} = 12\text{V}$ , $V_{OUT1} = 1.3\text{V}$ (Note 3)                                                                                                                             |   | -3   | 3    | A    |               |

| $I_{Q1(V_{IN})}$                 | CH1 Input Supply Bias Current                          | $V_{IN} = 12\text{V}$ , $V_{OUT1} = 1.3\text{V}$ , MODE = GND<br>$V_{IN} = 12\text{V}$ , $V_{OUT1} = 1.3\text{V}$ , MODE = $\text{INT}V_{CC}$<br>Shutdown, $\text{RUN1} = \text{GND}$ |   | 13   | 400  | 40   | $\mu\text{A}$ |

| $I_{S1(V_{IN})}$                 | CH1 Input Supply Current                               | $V_{IN} = 12\text{V}$ , $V_{OUT1} = 1.3\text{V}$ , $I_{OUT} = 3\text{A}$                                                                                                              |   | 0.4  |      |      | A             |

| $\Delta V_{OUT1(Line)}/V_{OUT1}$ | CH1 Line Regulation Accuracy                           | $V_{OUT1} = 1.3\text{V}$ , $V_{IN} = 3.6\text{V to } 15\text{V}$ , $I_{OUT1} = 0\text{A}$                                                                                             | ● | 0.01 | 0.05 |      | %/V           |

| $\Delta V_{OUT1_Load}/V_{OUT1}$  | CH1 Load Regulation Accuracy                           | $V_{OUT1} = 1.3\text{V}$ , $I_{OUT} = -3\text{A to } 3\text{A}$                                                                                                                       | ● | 0.2  | 1.0  |      | %             |

| $V_{OUT1(AC)}$                   | CH1 Output Ripple Voltage                              | $I_{OUT} = 0\text{A}$ , $C_{OUT} = 47\mu\text{F}$ Ceramic<br>$V_{IN} = 12\text{V}$ , $V_{OUT1} = 1.3\text{V}$                                                                         |   | 30   |      |      | mV            |

| $\Delta V_{OUT1(START)}$         | CH1 Turn-On Overshoot                                  | $I_{OUT} = 0\text{A}$ , $C_{OUT} = 47\mu\text{F}$ Ceramic,<br>TRACK/SS1 = $-0.1\mu\text{F}$ , $V_{IN} = 12\text{V}$ , $V_{OUT1} = 1.3\text{V}$                                        |   | 30   |      |      | mV            |

| $t_{START}$                      | Turn-On Time                                           | $C_{OUT} = 100\mu\text{F}$ Ceramic, TRACK/SS1 = $0.01\mu\text{F}$<br>No Load, $V_{IN} = 12\text{V}$ , $V_{OUT1} = 1.3\text{V}$                                                        |   | 1.2  |      |      | ms            |

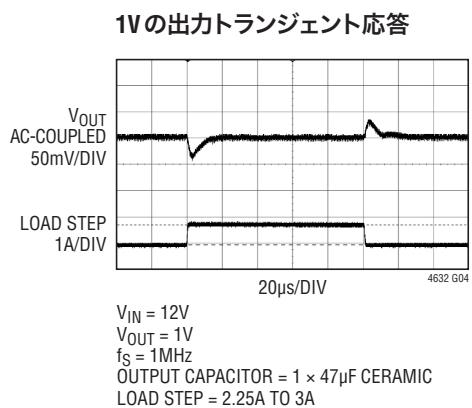

| $\Delta V_{OUT1LS1}$             | CH1 Peak Deviation for Dynamic Load                    | Load:0% to 25% to 0% of Full Load<br>$C_{OUT} = 47\mu\text{F}$ Ceramic, $V_{IN} = 12\text{V}$ , $V_{OUT1} = 1.3\text{V}$                                                              |   | 85   |      |      | mV            |

| $t_{SETTLE1}$                    | CH1 Settling Time for Dynamic Load Step                | Load:0% to 25% to 0% of Full Load<br>$C_{OUT} = 47\mu\text{F}$ Ceramic, $V_{IN} = 12\text{V}$ , $V_{OUT1} = 1.3\text{V}$                                                              |   | 20   |      |      | $\mu\text{s}$ |

| $I_{OUTPK1}$                     | CH1 Output Current Limit                               | $V_{IN} = 12\text{V}$ , $V_{OUT1} = 1.3\text{V}$                                                                                                                                      |   | 4.5  |      |      | A             |

### 出力の規格(チャネル2)

|                                  |                                                        |                                                                                                                                               |   |      |      |     |               |

|----------------------------------|--------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|---|------|------|-----|---------------|

| $V_{OUT2(DC)}$                   | CH2 Output Voltage, Total Variation with Line and Load | $C_{IN} = 22\mu\text{F}$ , $C_{OUT} = 100\mu\text{F}$ Ceramic<br>$V_{DDQIN} = 1.3\text{V}$ , MODE = GND, $I_{OUT} = -3\text{A to } 3\text{A}$ | ● | 637  | 650  | 663 | mV            |

| $I_{OUT2(DC)}$                   | CH2 Output Continuous Current Range                    | $V_{IN} = 12\text{V}$ , $V_{DDQIN} = 1.3\text{V}$ (Note 3)                                                                                    |   | -3   | 3    | A   |               |

| $I_{Q2(V_{IN})}$                 | CH2 Input Supply Bias Current                          | $V_{IN} = 12\text{V}$ , $V_{DDQIN} = 1.3\text{V}$ , MODE = GND<br>Shutdown, $\text{RUN2} = 0$                                                 |   | 7    | 40   |     | $\mu\text{A}$ |

| $I_{S2(V_{IN})}$                 | CH2 Input Supply Current                               | $V_{IN} = 12\text{V}$ , $V_{DDQIN} = 1.3\text{V}$ , $I_{OUT} = 3\text{A}$                                                                     |   | 0.25 |      |     | A             |

| $\Delta V_{OUT2(Line)}/V_{OUT2}$ | CH2 Line Regulation Accuracy                           | $V_{DDQIN} = 1.3\text{V}$ , $V_{IN} = 3.6\text{V to } 15\text{V}$ , $I_{OUT2} = 0\text{A}$                                                    | ● | 0.01 | 0.05 |     | %/V           |

| $\Delta V_{OUT2_Load}/V_{OUT2}$  | CH2 Load Regulation Accuracy                           | $V_{DDQIN} = 1.3\text{V}$ , $I_{OUT} = -3\text{A to } 3\text{A}$                                                                              | ● | 0.2  | 1.0  |     | %             |

| $V_{OUT2(AC)}$                   | CH2 Output Ripple Voltage                              | $I_{OUT} = 0\text{A}$ , $C_{OUT} = 100\mu\text{F}$ Ceramic<br>$V_{IN} = 12\text{V}$ , $V_{DDQIN} = 1.3\text{V}$                               |   | 30   |      |     | mV            |

| $\Delta V_{OUT2LS2}$             | CH2 Peak Deviation for Dynamic Load                    | Load:0% to 25% to 0% of Full Load<br>$C_{OUT} = 47\mu\text{F}$ Ceramic, $V_{IN} = 12\text{V}$ , $V_{OUT1} = 1.3\text{V}$                      |   | 85   |      |     | mV            |

| $t_{SETTLE2}$                    | CH2 Settling Time for Dynamic Load Step                | Load:0% to 25% to 0% of Full Load<br>$C_{OUT} = 47\mu\text{F}$ Ceramic, $V_{IN} = 12\text{V}$ , $V_{OUT1} = 1.3\text{V}$                      |   | 20   |      |     | $\mu\text{s}$ |

| $I_{OUTPK2}$                     | CH2 Output Current Limit                               |                                                                                                                                               |   | 4.5  |      |     | A             |

## 電気的特性

●は規定された全内部動作温度範囲の規格値を意味する(Note 2)。

注記がない限り、図19の標準的応用例に基づき、 $T_A = 25^\circ\text{C}$  (Note 2)、 $V_{IN} = 12\text{V}$  における各出力チャネルで規定。

| SYMBOL                  | PARAMETER                                      | CONDITIONS                                                                                                                 | MIN          | TYP                  | MAX                 | UNITS                |   |

|-------------------------|------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|--------------|----------------------|---------------------|----------------------|---|

| 制御セクション                 |                                                |                                                                                                                            |              |                      |                     |                      |   |

| $V_{FB1}$               | Voltage at $V_{FB1}$ Pin                       | $I_{OUT} = 0\text{A}$ , $V_{OUT1} = 1.5\text{V}$                                                                           | ●            | 0.593                | 0.600               | 0.607                | V |

| $I_{FB1}$               | Current at $V_{FB1}$ Pin                       | (Note 4)                                                                                                                   |              |                      | $\pm 30$            | nA                   |   |

| RFBHI1                  | Resistor Between $V_{OUT1}$ and $V_{FB1}$ Pins |                                                                                                                            | 60.00        | 60.40                | 60.80               | k $\Omega$           |   |

| VTTR                    | VTTR Voltage Reference                         | $V_{DDQIN} = 1.3\text{V}$ ,<br>$IVTTR = \pm 10\text{mA}$ , $CVTTR < 10\text{nF}$                                           | ●            | $0.492x_{V_{DDQIN}}$ | $0.50x_{V_{DDQIN}}$ | $0.508x_{V_{DDQIN}}$ | V |

| $V_{RUN1}$ , $V_{RUN2}$ | RUN Pin On Threshold                           | RUN Threshold Rising<br>RUN Threshold Falling                                                                              | 1.18<br>0.95 | 1.28<br>1.01         | 1.39<br>1.05        | V                    |   |

| $I_{RUN1}$ , $I_{RUN2}$ | RUN Pin Leakage Current                        |                                                                                                                            |              | 0                    | $\pm 1$             | $\mu\text{A}$        |   |

| $I_{TRACK/SS1}$         | TRACK/SS1 Pin Soft-Start Pull-Up Current       | TRACK/SS1 = 0V                                                                                                             |              | 1.2                  |                     | $\mu\text{A}$        |   |

| $t_{ON(MIN)}$           | Minimum On-Time                                | (Note 4)                                                                                                                   |              | 20                   |                     | ns                   |   |

| $t_{OFF(MIN)}$          | Minimum Off-Time                               | (Note 4)                                                                                                                   |              | 45                   |                     | ns                   |   |

| VGGOOD                  | PGOOD Trip Level                               | $V_{FB}$ With Respect to 0.6V<br>$V_{OUT2}$ With Respect to $V_{DDQIN}/2$ (Note 4)<br>Ramping Negative<br>Ramping Positive |              | -8<br>8              | -14<br>14           | %                    |   |

| RPGOOD                  | PGOOD Pull-Down Resistance                     | 1mA Load                                                                                                                   |              | 15                   |                     | $\Omega$             |   |

| $V_{INTVCC}$            | Internal $V_{CC}$ Voltage                      | $V_{IN} = 3.6\text{V}$ to 15V                                                                                              | 3.1          | 3.3                  | 3.5                 | V                    |   |

| $V_{INTVCC}$ Load Reg   | INTVCC Load Regulation                         | $I_{CC} = 0$ to 50mA                                                                                                       |              | 1.3                  |                     | %                    |   |

| $f_{osc}$               | Oscillator Frequency                           |                                                                                                                            |              | 1                    |                     | MHz                  |   |

| SYNC                    | SYNC Threshold Voltage                         |                                                                                                                            |              | 0.95                 |                     | V                    |   |

| $I_{SYNC/MODE}$         | MODE Input Current                             | SYNC/MODE = INTVCC                                                                                                         |              | -1.5                 |                     | $\mu\text{A}$        |   |

**Note 1:** 絶対最大定格に記載された値を超えるストレスはデバイスに永続的損傷を与える可能性がある。また、長期にわたって絶対最大定格条件に曝すと、デバイスの信頼性と寿命に悪影響を与えるおそれがある。

**Note 2:** LTM4632は $T_J$ が $T_A$ にほぼ等しいパルス負荷条件でテストされる。LTM4632Eは、0°C～125°Cの内部動作温度範囲で性能仕様に適合することが保証されている。-40°C～125°Cの内部動作温度範囲での仕様は設計、特性評価および統計学的なプロセス・コントロールとの相関で確認されている。LTM4632Iは-40°C～125°Cの全内部動作温度範囲で仕様に適合することが保証されている。これらの仕様を満たす最大周囲温度は、基板レイアウト、パッケージの定格熱抵抗および他の環境要因と関連した特定の動作条件によって決まるに注意。

**Note 3:** 異なる $V_{IN}$ ,  $V_{OUT}$  および  $T_A$ については出力電流のディレーティング曲線を参照。

**Note 4:** ウェハ・レベルで全数テストされる。

**Note 5:** このデバイスは短時間の過負荷状態の間デバイスを保護するための過熱保護機能を備えている。過熱保護機能が動作しているとき接合部温度は125°Cを超える。規定された最大動作接合部温度を超えた状態で動作が継続すると、デバイスの信頼性を損なう恐れがある。

## 標準的性能特性

## 標準的性能特性

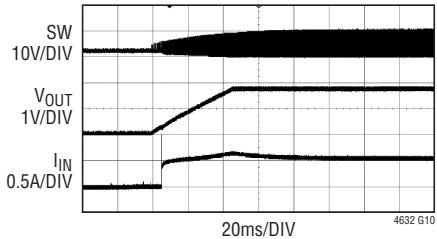

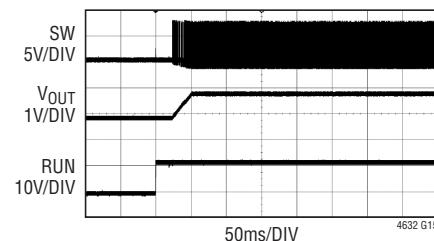

負荷電流3Aでの起動

$V_{IN} = 12V$

$V_{OUT} = 1.8V$

$f_S = 1MHz$

$I_{OUT} = 3A$

INPUT CAPACITOR = 1 × 22 $\mu$ F CERAMIC

OUTPUT CAPACITOR = 1 × 47 $\mu$ F CERAMIC

SOFT-START CAPACITOR = 0.1 $\mu$ F

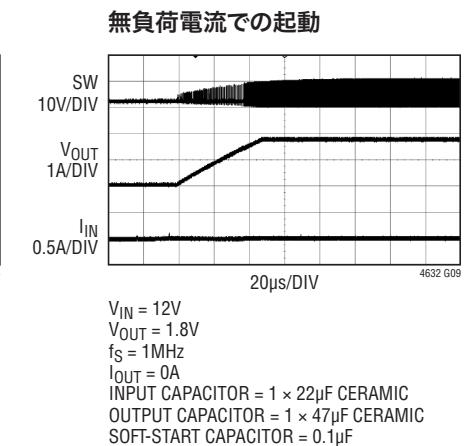

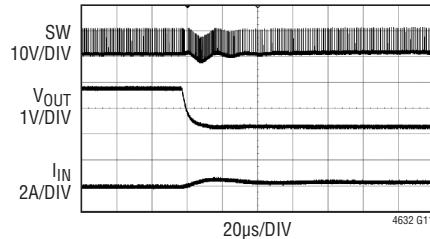

無負荷電流での短絡

$V_{IN} = 12V$

$V_{OUT} = 1.8V$

$f_S = 1MHz$

$I_{OUT} = 0A$

INPUT CAPACITOR = 1 × 22 $\mu$ F CERAMIC

OUTPUT CAPACITOR = 1 × 47 $\mu$ F CERAMIC

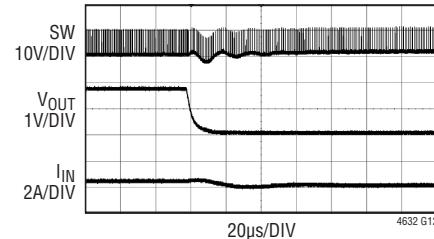

負荷電流3Aでの短絡

$V_{IN} = 12V$

$V_{OUT} = 1.8V$

$f_S = 1MHz$

$I_{OUT} = 3A$

INPUT CAPACITOR = 1 × 22 $\mu$ F CERAMIC

OUTPUT CAPACITOR = 1 × 47 $\mu$ F CERAMIC

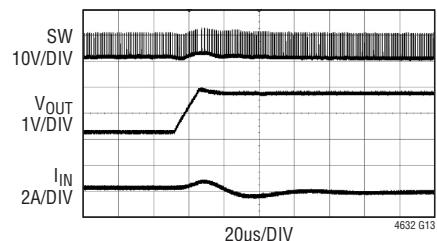

無負荷電流での短絡からの回復

$V_{IN} = 12V$

$V_{OUT} = 1.8V$

$f_S = 1MHz$

$I_{OUT} = 0A$

INPUT CAPACITOR = 1 × 22 $\mu$ F CERAMIC

OUTPUT CAPACITOR = 1 × 47 $\mu$ F CERAMIC

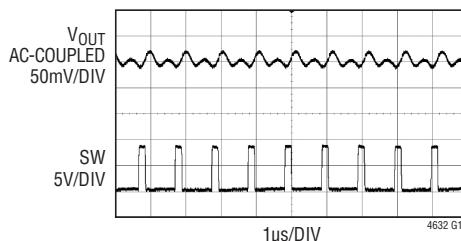

定常状態での出力電圧リップル

$V_{IN} = 12V$

$V_{OUT} = 1.8V$

$f_S = 1MHz$

$I_{OUT} = 0A$

INPUT CAPACITOR = 1 × 22 $\mu$ F CERAMIC

OUTPUT CAPACITOR = 1 × 47 $\mu$ F CERAMIC

プリバイアスされた出力までの起動

$V_{IN} = 12V$

$V_{OUT} = 1.8V$

$f_S = 1MHz$

$I_{OUT} = 0A$

INPUT CAPACITOR = 1 × 22 $\mu$ F CERAMIC

OUTPUT CAPACITOR = 1 × 47 $\mu$ F CERAMIC

## ピン機能

**V<sub>IN</sub> (A2, B3, D3, E2)** : 電源入力ピン。これらのピンとGNDピンの間に入力電圧を印加します。入力デカップリング・コンデンサはV<sub>IN</sub>ピンとGNDピンの間に直接配置することを推奨します。

**V<sub>OUT1</sub> (D1, E1), V<sub>OUT2</sub> (A1, B1)** : 各スイッチング・モード・レギュレータの電源出力ピン。これらのピンとGNDピンの間に出力負荷を接続します。出力デカップリング・コンデンサはこれらのピンとGNDピンの間に直接配置することを推奨します。

**GND (C1 ~ C2, C4, B5, D5)** : 入力帰路と出力帰路の両方の電源グランド・ピン。

**PGOOD1 (D4)** : チャネル1のスイッチング・モード・レギュレータのオープンドレインのロジックを備えた出力パワーグッド。FB1ピンの電圧が0.6Vの内部リファレンスの±8% (標準) 以内に入っていない場合、PGOOD1ピンはグランド電位に低下します。このしきい値には15mVのヒステリシスがあります。

**PGOOD2 (B4)** : チャネル2のスイッチング・モード・レギュレータのオープンドレインのロジックを備えた出力パワーグッド。V<sub>OUT2</sub>ピンの電圧がV<sub>DDQIN</sub>/2の電圧の±8% (標準) 以内に入っていない場合、PGOOD2ピンはグランド電位に低下します。このしきい値には15mVのヒステリシスがあります。

**SYNC/MODE (C5)** : モード選択入力および外部同期入力。すべての出力負荷で連続同期動作を強制するには、このピンをグランドに接続します。このピンをフロート状態にするか、INTV<sub>CC</sub>ピンに接続すると、軽負荷時に効率の高いBurst Mode動作がイネーブルされます。LTM4632のスイッチング周波数を同期させるには、このピンをクロックで駆動します。フェーズロック・ループにより、上側のパワーNMOSのターンオン信号は、クロック信号の立ち上がりエッジと強制的に同期されます。このピンをクロックで駆動すると、強制連続モードが自動的に選択されます。

**INTV<sub>CC</sub> (C3)** : スイッチング・モード・レギュレータ・チャネルの内部3.3Vレギュレータ出力。内部パワー・ドライバおよび制御回路はこの電圧から電力を供給されます。このピンは低ESRの2.2μFセラミック・コンデンサにより、内部でGNDにデカップリングされています。外付けのデカップリング・コンデンサは必要ありません。

**RUN1 (D2), RUN2 (B2)** : スイッチング・モード・レギュレータの各チャネルの動作制御入力。RUNピンを1.28Vより高い電圧に接続すると、デバイスの動作がイネーブルされます。このピンを1Vより低い電圧に接続すると、レギュレータの特定のチャネルがシャットダウンします。このピンはフロート状態にしないでください。

**COMP1 (E5), COMP2 (A5)** : スイッチング・モード・レギュレータの各チャネルの電流制御しきい値およびエラーアンプ補償ポイント。電流コンパレータの作動しきい値は、(通常0.3V ~ 1.8V)この電圧に直線的に比例します。このデバイスは内部補償されています。COMPピンは、2相シングル出力のVTT構成では互いに接続してください。詳細は、「アプリケーション情報」のセクションを参照してください。

**FB1 (E4)** : チャネル1のスイッチング・モード・レギュレータのエラーアンプの負(反転)入力。このピンは内部で60.4kの高精度抵抗を介してV<sub>OUT1</sub>に接続されています。FB1ピンとGNDピンの間に抵抗を追加して、異なる出力電圧を設定することができます。2相シングル出力のVTT構成では、このピンをINTV<sub>CC</sub>に接続してください。詳細は、「アプリケーション情報」のセクションを参照してください。

**TRACK/SS1 (E3)** : チャネル1のスイッチング・モード・レギュレータの出力トラッキングおよびソフトスタート・ピン。このピンを使うと、出力電圧の立ち上がり時間を制御することができます。このピンの電圧が0.6Vより低くなると、エラーアンプへの内部リファレンス入力がバイパスされ、代わりにFBピンがTRACK/SSピンの電圧にサーボ制御されます。0.6Vより高くなるとトラッキング機能が停止し、内部リファレンスによってエラーアンプの制御が再開されます。このピンにはINTV<sub>CC</sub>から1.2μAの内部プルアップ電流が流れるので、このピンにコンデンサを接続すると、ソフトスタート機能を実現できます。

**VTTR (A3)** : リファレンス出力。この出力は、DDRメモリのVREF電圧を供給するために使用します。内蔵のバッファ・アンプは、V<sub>DDQIN</sub>/2と等しい低ノイズのリファレンス電圧を出力します。この出力は10mAの供給能力があります。VTTRには0.01μFの内部コンデンサがあります。RCフィルタを追加することにより、VTTRのリップルを更に低減することができます。チャネル2のエラーアンプは、この電圧をリファレンス電圧として使用します。

**V<sub>DDQIN</sub> (A4)** : チャネル2の外部リファレンス入力。内部抵抗分割器が、この入力に印加される電圧の2分の1と等しくなるようにVTTRピンの電圧を設定します。チャネル2は、VTTRピンの電圧をエラーアンプのリファレンスとして使用します。

## ブロック図

## デカップリングの要件

| SYMBOL           | PARAMETER                                                                                         | CONDITIONS            | MIN | TYP | MAX | UNITS |

|------------------|---------------------------------------------------------------------------------------------------|-----------------------|-----|-----|-----|-------|

| C <sub>IN</sub>  | External Input Capacitor Requirement<br>(V <sub>IN</sub> = 3.6V to 15V, V <sub>OUT</sub> = 1.5V)  | I <sub>OUT</sub> = 3A | 4.7 | 10  |     | μF    |

| C <sub>OUT</sub> | External Output Capacitor Requirement<br>(V <sub>IN</sub> = 3.6V to 15V, V <sub>OUT</sub> = 1.5V) | I <sub>OUT</sub> = 3A | 10  | 22  |     | μF    |

## 動作

LTM4632は、DDR-QDR4 SRAMメモリの電源およびバス終端向けのデュアル出力、独立型、非絶縁スイッチ・モードDC/DC電源です。このデバイスは、入力と出力に数個のセラミック・コンデンサを外付けすることにより、3AのDCシンク電流およびソース電流を供給できる2つの出力レールを実現し、更にV<sub>DDQIN</sub>の電圧の1/2に等しい10mAのバッファ付きVTTR(VREF)リファレンス電圧を発生することができます。

2つ以上のモジュールの出力を並列接続して、シンク電流およびソース電流の供給能力の高い单一のVTT出力を容易に実現できます。電流モード制御ループによって保証されている優れた電流分担機能により、最大8位相を並列接続して同時に動作させることができます。

このモジュールは、3.6V～15Vの入力電圧範囲で、1個の外付け抵抗によって設定可能な0.6V～2.5Vの高精度安定化出力電圧(V<sub>OUT1</sub>)を供給します。INTV<sub>CC</sub>をV<sub>IN</sub>に接続することにより、このモジュールは3.3V入力で動作することができます。

LTM4632は、オン時間固定のデュアル谷電流モード・レギュレータ、パワーMOSFET、インダクタ、その他のディスクリート・サポート部品を内蔵しています。標準的なスイッチング周波数は内部で1MHzに設定されています。スイッチング・ノイズの影響を受けやすいアプリケーションでは、μModuleは設定周波

数から±30%の範囲内のクロックに外部同期可能です。「アプリケーション情報」のセクションを参照してください。

電流モード制御と内部帰還ループ補償により、LTM4632モジュールは、広範囲の出力コンデンサを使用して(全てセラミック出力コンデンサを使用する場合でも)十分に余裕のある安定性と良好なトランジエント性能を達成します。

電流モード制御により、サイクルごとに高速電流制限が行われます。内蔵されている過電圧コンパレータと低電圧コンパレータは、出力帰還電圧がレギュレーション・ポイントから±8%の範囲を外れると、オープン・ドレインのPGOOD出力を“L”に引き下げます。更に、V<sub>IN</sub>が17.5Vより高くなると、2つのパワーMOSFETを両方ともシャットダウンすることによって入力過電圧保護機能を利用し、内部デバイスを保護することができます。

RUNピンの電圧を1Vより低い値まで下げると、コントローラは強制的にシャットダウン状態になり、上下両側のパワーMOSFETおよびほとんどの内部制御回路はオフします。軽負荷電流では、MODEピンの電圧をINTV<sub>CC</sub>に設定することにより、Burst Mode動作をイネーブルして、連続モード(CCM)に比べて高い効率を達成することができます。TRACK/SSピンは電源トラッキングとソフトスタートの設定に使用されます。「アプリケーション情報」のセクションを参照してください。

## アプリケーション情報

LTM4632の代表的なアプリケーション回路を図19に示します。外部部品の選択は主に、入力電圧、出力電圧、および最大負荷電流で決まります。個々のアプリケーションに対する外付けコンデンサの具体的な要件については、表5を参照してください。

### V<sub>IN</sub>からV<sub>OUT</sub>への降圧比

レギュレータには最小オフ時間と最小オン時間の制限があるので、所定の入力電圧で実現可能なV<sub>IN</sub>とV<sub>OUT</sub>との最大降圧比には制約があります。最小オフ時間の制限によって最大デューティ・サイクルが決まり、その値は次のように計算できます。

$$D_{MAX} = 1 - t_{OFF(MIN)} \cdot f_{SW}$$

ここで、t<sub>OFF(MIN)</sub>は最小オフ時間でLTM4632では標準で45nsであり、f<sub>SW</sub>はスイッチング周波数です。反対に、最小オン時間の制限によってコンバータの最小デューティ・サイクルが決まり、その値は次のように計算できます。

$$D_{MIN} = t_{ON(MIN)} \cdot f_{SW}$$

ここで、t<sub>ON(MIN)</sub>は最小オン時間であり、LTM4632では標準で20nsです。最小デューティ・サイクルを超える稀なケースでは、出力電圧はレギュレーション状態に留まりますが、スイッチング周波数は設定値より減少します。さらにサーマル・ディレーティングが適用される可能性があることに注意してください。このデータシートの「熱に関する検討事項と出力電流のディレーティング」のセクションを参照してください。

## アプリケーション情報

### チャネル1の出力電圧のプログラミング(VDDQとして設定)

V<sub>OUT1</sub>のPWMコントローラは0.6Vの内部リファレンス電圧を備えています。「ブロック図」に示すように、V<sub>OUT1</sub>ピンとFB1ピンは60.4kの内部帰還抵抗によって相互に接続されています。FB1ピンとGNDの間に抵抗R<sub>FB</sub>を追加すると、出力電圧は次のように設定されます。

$$R_{FB} = \frac{0.6V}{V_{OUT} - 0.6V} \cdot 60.4k$$

表1. V<sub>FB</sub>の抵抗(1%)とさまざまな出力電圧の表

| V <sub>OUT</sub> (V) | 0.6  | 1.0  | 1.2  | 1.3  | 1.5  | 1.8  | 2.5  |

|----------------------|------|------|------|------|------|------|------|

| R <sub>FB</sub> (k)  | OPEN | 90.9 | 60.4 | 52.3 | 40.2 | 30.1 | 19.1 |

### チャネル2の出力電圧のプログラミング(VTTとして設定)

V<sub>OUT2</sub>のPWMコントローラは、VTTRの電圧をリファレンス電圧として使用します。V<sub>OUT2</sub>はエラー・コンパイラの負極側に直接接続してV<sub>OUT2</sub>を内部で設定し、VTTRの電圧に等しくなるようにしています。また、この電圧はV<sub>DDQIN</sub>の電圧の1/2に等しくなります。

$$V_{OUT2} = VTTR = V_{DDQIN}/2$$

VDDQ電源とVTT終端の両方の出力が必要な完全なDDRメモリ電源アプリケーションでは、FB1ピンとGNDの間に帰還抵抗を追加して、LTM4632のチャネル1をVDDQ出力として構成します。V<sub>OUT1</sub>(VDDQ出力)の電圧をV<sub>DDQIN</sub>ピンに供給してチャネル2をVTT出力として設定し、この電圧をチャネル1(VDDQ出力)の電圧の1/2に等しい値にします。

### 入力デカップリング・コンデンサ

LTM4632モジュールは低ACインピーダンスのDC電源に接続する必要があります。レギュレータの各チャネルには、RMSリップル電流のデカップリングのため、4.7μFの入力セラミック・コンデンサが必要です。バルク入力コンデンサが必要なのは、長い誘導性のリードやトレースまたは電源の容量不足によって入力電源のインピーダンスが損なわれる場合だけです。バルク・コンデンサは、アルミ電解コンデンサでもポリマー・コンデンサでもかまいません。

インダクタの電流リップルを考慮しなければ、入力コンデンサのRMS電流は、各出力に対して次のように概算できます。

$$I_{CIN(RMS)} = \frac{I_{OUT(MAX)}}{\eta\%} \cdot \sqrt{D \cdot (1-D)}$$

ここで、η%はパワー・モジュールの推定効率です。

### 出力デカップリング・コンデンサ

LTM4632は高い周波数と広い帯域幅に合わせて設計が最適化されているので、22μFの低ESR出力セラミック・コンデンサを1つ取り付けるだけで、LTM4632の各出力は低い出力リップル電圧と非常に良好なトランジエント応答を実現できます。出力リップルや動的トランジエント・スパイクを更に低減するため、システム設計者による出力フィルタの追加が必要になる場合があります。0.75A(25%)の負荷ステップ・トランジエント発生時の電圧低下やオーバーシュートを最小限に抑えるための、さまざまな出力電圧と出力コンデンサの一覧を表5に示します。マルチフェーズ動作では、位相数に応じて実効出力リップルが低減されます。このノイズ低減と出力リップル電流の相殺については「アプリケーションノート77」で解説していますが、出力容量は安定性とトランジエント応答によっても変化します。リニアテクノロジーのLTpowerCAD設計ツールをオンラインでダウンロードして、出力リップル、安定性、トランジエント応答を解析し、実装される位相数がN倍に増えるたびに出力リップルがどれだけ低減されるかを計算できます。

### Burst Mode動作

中程度の電流での高い効率の方が出力電圧のリップルより重要なアプリケーションでは、SYNC/MODEピンをINTV<sub>CC</sub>に接続することによってチャネル1でBurst Mode動作を使用し、軽負荷時効率を改善することができます。Burst Mode動作では、電流反転コンパレータ(IREV)が負のインダクタ電流を検出して下側のパワーMOSFETをオフにするので、不連続動作となって効率が高くなります。COMPの電圧がゼロ電流レベルより高くなつて新しいサイクルが開始されるまで、パワーMOSFETは上下両側ともオフのままで、出力コンデンサが負荷電流を供給します。

## アプリケーション情報

### 強制連続電流モード(CCM)動作

低電流での効率より周波数固定の動作が重要で、更に出力リップルを最小限に抑えることが望ましいアプリケーションでは、強制連続動作を使用します。強制連続動作は、SYNC/MODEピンをGNDに接続すればイネーブルできます。このモードでは、インダクタ電流が低出力負荷の間反転可能で、COMPの電圧が電流コンパレータのしきい値を常に制御し、上側のMOSFETは発振器のパルスごとに必ずオンします。起動時には、LTM4632の出力電圧が安定化されるまで、強制連続モードがディスエーブルされ、インダクタ電流の反転が防止されます。

### 動作周波数

LTM4632の動作周波数は、小型パッケージ・サイズと最小出力リップル電圧を達成し、なおかつ高い効率を維持するように最適化されています。デフォルトの動作周波数は内部で1MHzに設定されています。ほとんどのアプリケーションでは、追加の周波数調整は必要ありません。

### 周波数同期

この電源モジュールには電圧制御発振器と位相検出器で構成されるフェーズロック・ループが内蔵されています。これにより、内部の上側MOSFETのターンオンを外部クロックの立ち上がりエッジにロックすることができます。外部クロックの周波数範囲は、設定動作周波数を中心にして±30%以内にする必要があります。パルス検出回路を使用してSYNC/MODEピンのクロックを検出し、フェーズロック・ループをオンします。クロックのパルス幅は100ns以上にする必要があります。クロックの“H”レベルは2Vより高くする必要があります。クロックの“L”レベルは0.3Vより低くする必要があります。外部クロック信号が入力されると、2つのレギュレータは両方とも強制連続モード動作に移行します。レギュレータの起動時、フェーズロック・ループ機能はディスエーブルされます。

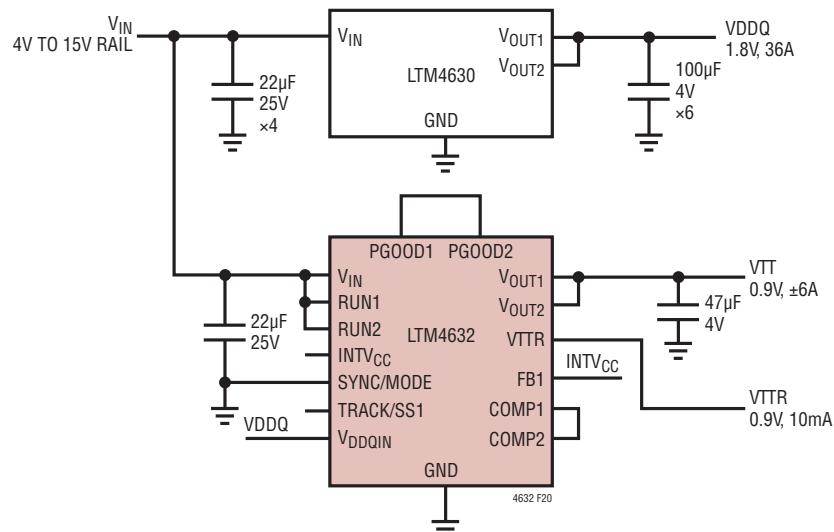

### マルチフェーズ動作 (マルチフェーズのシングル出力VTTとして構成)

VTT終端の出力負荷が3Aを超える電流を必要とする場合は、LTM4632の2つの出力または複数のLTM4632を並列接続した上で、位相をずらして動作させ、ソース電流とシンク電流の供給能力を増強したマルチフェーズのシングル出力VTT終端電源を構築することができます。

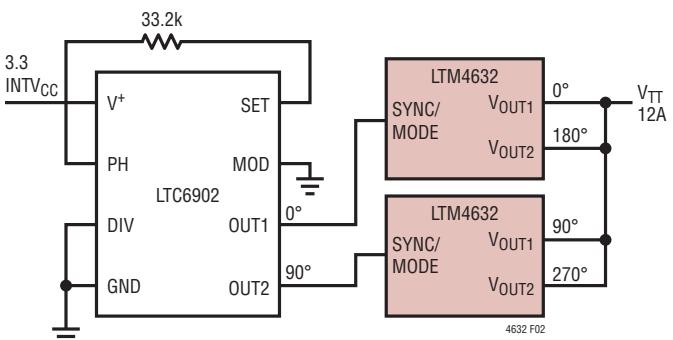

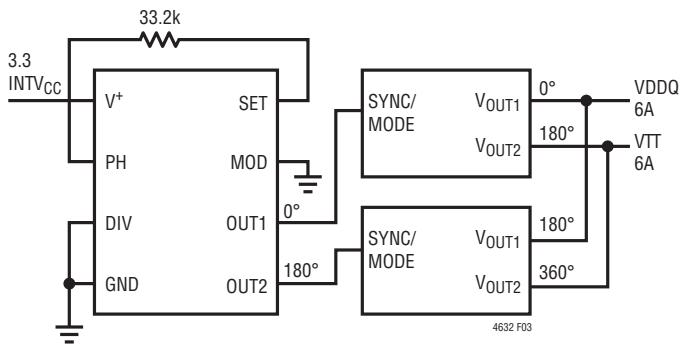

LTM4632の内部にあるスイッチング・モード・レギュレータの2つのチャネルは、位相が180度ずれた状態で動作するよう内部で設定されています。LTM4632のSYNC/MODEをLTC6902のような外部のマルチフェーズ発振器に同期させれば、複数のLTM4632が位相を90度、60度、または45度ずらして動作するには簡単であり、これらはそれぞれ4相、6相、または8相動作に対応します。クロックの位相調整を目的とした4相シングル出力VTT終端電源の設計例を図2に示します。

図2. LTC6902を使用した、4相シングル出力VTT動作に対するクロック位相調整の例

LTM4632のFB1をINTV<sub>CC</sub>ピンに接続して、モジュールを2相シングルVTT出力動作モードにします。これにより、チャネル1のエラーアンプのリファレンス電圧は、内部で0.6VからVTTRの電圧に切り替わり、チャネル2と同じになります。複数のLTM4632を並列接続するアプリケーションでは、LTM4632モジュールごとにこれを繰り返します。

また、並列接続する各チャネルのRUN、TRACK/SS、およびCOMPピンを互いに接続します。並列接続したマルチフェーズ・シングル出力VTT終端電源の動作およびピン接続の例を図20に示します。

LTM4632は、本来は電流モード制御デバイスなので、並列モジュールは非常に優れた電流分担特性を示します。このため、デザインの発熱バランスがよくなります。

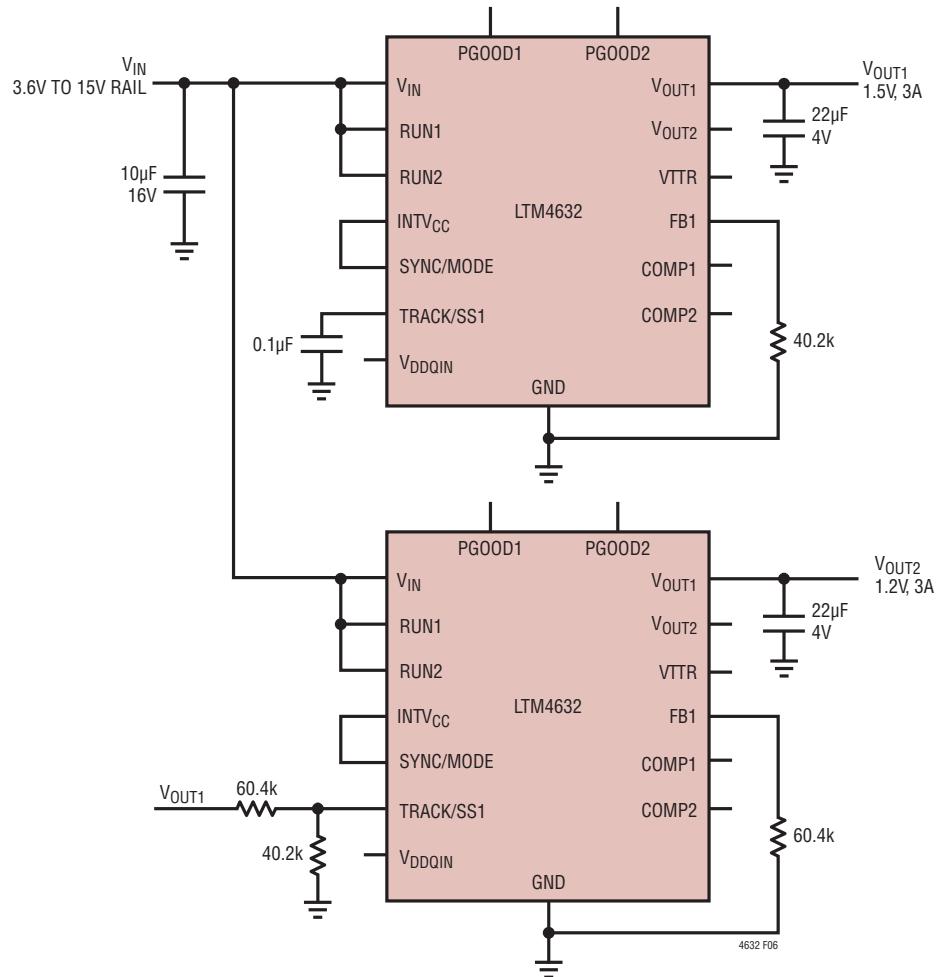

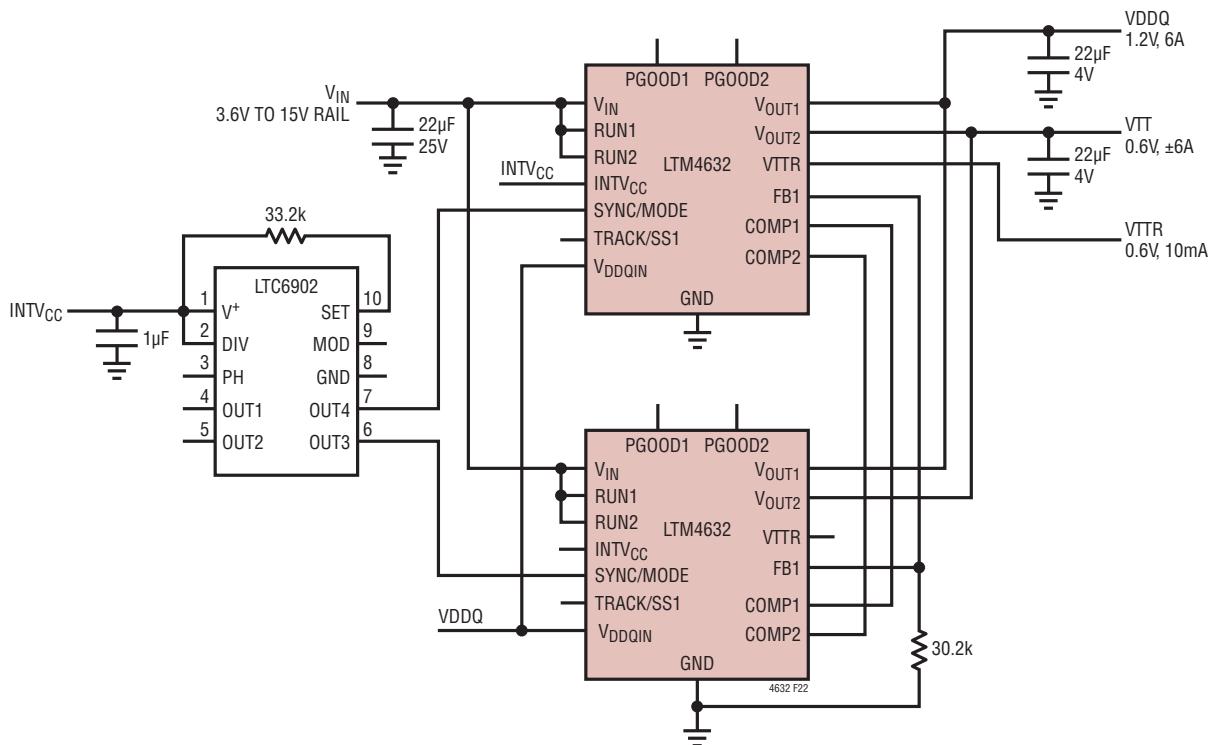

### マルチフェーズ動作(VDDQ+VTTとして構成)

VDDQおよびVTT終端の両方の出力負荷が3Aを超える電流を必要とするアプリケーションでは、異なるLTM4632モジュールの複数のチャネル1出力を並列接続して、マルチフェーズのシングルVDDQ出力を容易に供給すると同時に、異なるLTM4632モジュールの複数のチャネル2出力を並列接続して、マルチフェーズのシングルVTT出力を供給することができます。

## アプリケーション情報

この場合は、LTM4632のSYNC/MODEをLTC6902のような外部のマルチフェーズ発振器に同期させることにより、複数のLTM4632が位相を180度、120度、または90度ずらして動作するよう構成します。これらはそれぞれ2相、3相、または4相動作に対応します。

図3. LTC6902を使用した、2相VDDQ+2相VTT動作に対するクロック位相調整の例

VDDQ出力では、並列接続する各モジュールのRUN1、TRACK/SS1、FB1、およびCOMP1ピンを互いに接続します。VTT出力では、並列接続する各モジュールのRUN2、VDDQIN、FB2、およびCOMP2ピンを互いに接続します。2つのLTM4632を並列接続して6AのVDDQ電源および6AのVTT終端電源を構築した例を図22に示します。

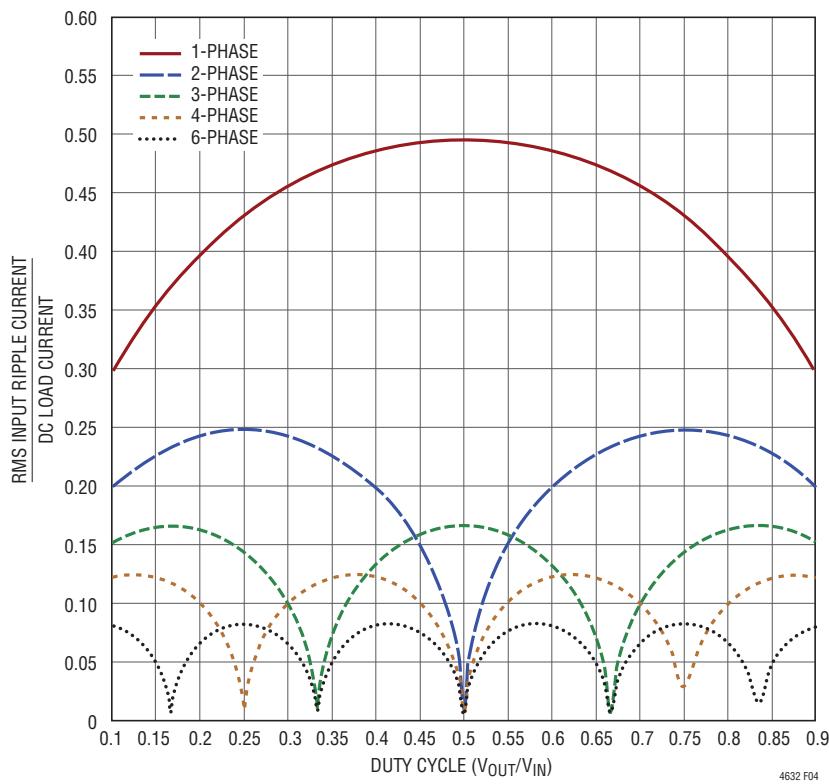

### 入力および出力RMSリップル電流の相殺

マルチフェーズ電源では、入力と出力のどちらのコンデンサのリップル電流の量も大幅に減少します。RMS入力リップル電流は使用する位相数が増えると低減され、実効リップル周波数は位相数倍されます(入力電圧が、使用される位相数×出力電圧より大きいと仮定)。すべての出力を互いに接続した高電流のシングル出力デザインでは、使用する位相数によって出力リップルの振幅を低減することができます。

図4. DC負荷電流に対する入力RMS電流の比率のデューティ・サイクル依存性

## アプリケーション情報

マルチフェーズ動作は「アプリケーションノート77」で詳細に説明されています。入力RMSリップル電流の相殺を数学的に導出し、RMSリップル電流の減少を、インターブされた位相の数の関数として表したグラフを掲載しています。図4に、そのグラフを示します。

### チャネル1の出力電圧トラッキングとソフトスタート

TRACK/SSピンによって、チャネル1のレギュレータをソフトスタートさせることも、別の電源をトラッキングさせることもできます。TRACK/SSピンに接続されたコンデンサにより、チャネル1の出力電圧の上昇率が設定されます。内部の1.2μA電流源が外付けのソフトスタート・コンデンサを充電し、その電圧はINTV<sub>CC</sub>ピンの電圧に近づきます。TRACK/SSピンの電圧が0.6Vより低くなると、出力電圧の制御は0.6Vの内部リファレンス電圧に引き継がれます。ソフトスタートの合計時間は次のように計算できます。

$$t_{SS} = 0.6 \cdot \frac{C_{SS}}{1.2\mu A}$$

ここで、C<sub>SS</sub>はTRACK/SSピンに接続されている容量です。強制連続モードは、ソフトスタートの間ディスエーブルされます。

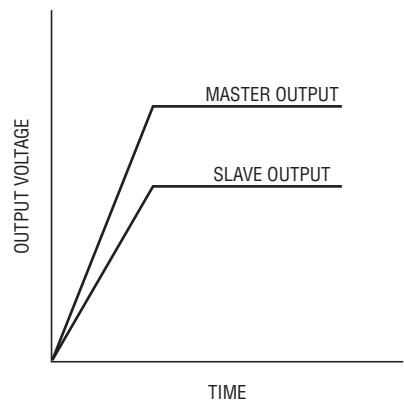

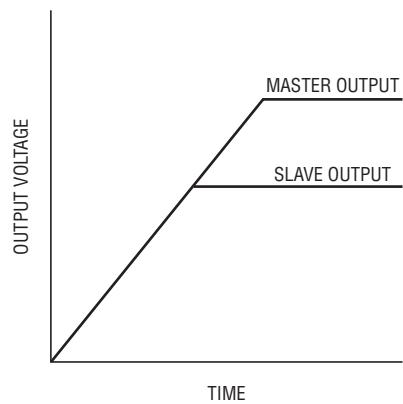

チャネル1の出力電圧のトラッキングは、TRACK/SSピンを使用して外部から設定することもできます。出力を別のレギュレータに追従させて、その電圧を増減させることができます。スレーブ・レギュレータの出力スルーレートがマスタのスルーレートに比例する比例トラッキングの波形および回路図の例を図5および図6に示します。

スレーブ・レギュレータのTRACK/SSピンは抵抗分割器R<sub>TR</sub>(TOP)/R<sub>TR</sub>(BOT)を介してマスタの出力に接続されており、その電圧は、TRACK/SSピンの電圧が0.6Vより低いとき、スレーブの出力電圧を安定化するために使用されるので、スレーブの出力電圧とマスタの出力電圧は起動時に次の式を満たす必要があります。

$$V_{OUT(SL)} \cdot \frac{R_{FB(SL)}}{R_{FB(SL)} + 60.4k} = V_{OUT(MA)} \cdot \frac{R_{TR(TOP)}}{R_{TR(TOP)} + R_{TR(BOT)}}$$

図6に示すように、R<sub>FB</sub>(SL)は帰還抵抗であり、R<sub>TR</sub>(TOP)/R<sub>TR</sub>(BOT)はスレーブ・レギュレータのTRACK/SSピンに接続されている抵抗分割器です。

上記の式に従うと、ボルト/時間を単位とするマスタの出力スルーレート(MR)とスレーブの出力スルーレート(SR)は次式により求められます。

$$\frac{MR}{SR} = \frac{\frac{R_{FB(SL)}}{R_{FB(SL)} + 60.4k}}{\frac{R_{TR(TOP)}}{R_{TR(TOP)} + R_{TR(BOT)}}}$$

例えば、V<sub>OUT(MA)</sub> = 1.5V、MR = 1.5V/1msおよびV<sub>OUT(SL)</sub> = 1.2V、SR = 1.2V/1msとします。前述の式から、R<sub>TR</sub>(TOP) = 60.4kおよびR<sub>TR</sub>(BOT) = 40.2kが比例トラッキングに適した組み合わせであると解くことができます。

図5. 出力比例トラッキングの波形

抵抗分割器を使用して特定のチャネルでのトラッキングを実装している場合、TRACKピンは1.2μAの電流源をオンします。このため、TRACKピン入力にオフセットが生じます。上式で計算した抵抗値と比が同じで、値がより小さな抵抗を使用してもかまいません。例えば、60.4kが使われている場合、6.04kを使ってTRACKピンのオフセットを無視できる値に下げるることができます。

## アプリケーション情報

図6. 出力電圧比例トラッキングの回路例

図7の波形に示すように、同時出力トラッキングは、マスタの出力スルーレート(MR)がスレーブの出力スルーレート(SR)と同じである特殊な比例出力トラッキングとして認識することができます。

式から容易に分かるように、同時トラッキングでは、スレーブ・レギュレータのTRACK/SSピンの抵抗分割器が帰還抵抗分割器と常に同じです。

$$\frac{R_{FB(SL)}}{R_{FB(SL)} + 60.4k} = \frac{R_{TR(TOP)}}{R_{TR(TOP)} + R_{TR(BOT)}}$$

図7. 出力同時トラッキングの波形

## アプリケーション情報

例えば、 $R_{TR(TOP)} = 60.4\text{k}$ および $R_{TR(BOT)} = 60.4\text{k}$ は、 $V_{OUT(MA)} = 1.5\text{V}$ および $V_{OUT(SL)} = 1.2\text{V}$ のアプリケーションの同時トラッキングに適した組み合わせです。

### パワーグッド

PGOODピンはオープン・ドレインのピンで、有効な出力電圧レギュレーションをモニタするのに使うことができます。このピンはレギュレーション点の上下 $\pm 8\%$ の範囲をモニタします。モニタ用の抵抗を特定の電源電圧までプルアップできます。トランジメント時または $V_{OUT}$ の動的変化時にPGOODの不要なグリッチを防ぐため、LTM4632のPGOODの立ち下がりエッジには約40usのブランкиング遅延が含まれています。

### 安定性補償

LTM4632モジュールの内部補償ループは、低ESRのセラミック出力コンデンサのみのアプリケーション向けに設計され、最適化されています。ほとんどのアプリケーションの要件に対して表5が与えられています。制御ループを解析して最適化を進めるために、LTpowerCAD設計ツールをダウンロードして利用できます。

### RUNイネーブル

RUNピンの電圧をグランド電位まで下げるとき、LTM4632は強制的にシャットダウン状態になり、上下両側のパワーMOSFETおよびほとんどの内部制御回路はオフになります。RUNピンの電圧を1.28Vより高くすると、デバイス全体がオンします。

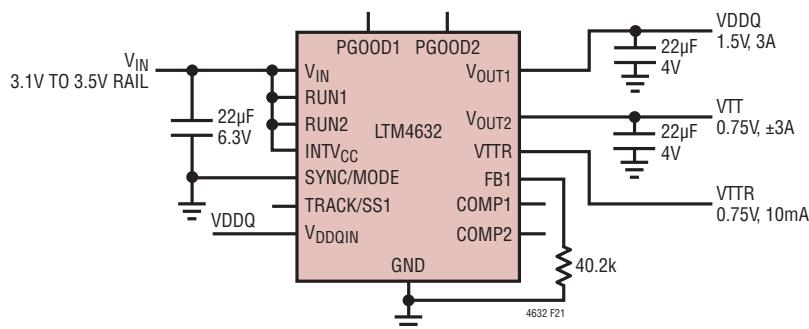

### 低入力電圧アプリケーション

LTM4632は、 $V_{IN}$ ピンをINTVCCピンに接続している場合、3.3V入力で動作することができます。このアプリケーション回路については、図21を参照してください。INTVCCピンの絶対最大定格電圧は3.6Vであることに注意してください。

### プリバイアスされた出力での起動(チャネル1)

出力コンデンサがプリバイアスされた状態で電源を起動する必要がある状況が生じることがあります。この場合、出力のプリバイアスを放電せずに起動することが必要です。LTM4632のチャネル1は、出力コンデンサを放電せずに、プリバイアスした状態で安全に起動できます。

LTM4632は、TRACK/SS1ピンの電圧がチャネル1の0.6Vのリファレンス電圧の80%に達するまで不連続モード(DCM)動作を強制することにより、これを実現します。これにより、プリバイアスされた出力での起動中にBGがオンして出力を放電することを防ぎます。INTVCCの電圧(3.3V)より高い電圧ではLTM4632をプリバイアスしないでください。

### 過熱保護

内蔵されている過熱保護機能は、モジュールの接合部温度をモニタします。接合部温度が約170°Cに達すると、温度が約10°C下がるまで両方のパワースイッチがオフします。

### 入力過電圧保護

内部のパワーMOSFETデバイスをトランジメント電圧スパイクから保護するため、LTM4632では各 $V_{IN}$ ピンを連続してモニタし、過電圧状態の有無を検査します。 $V_{IN}$ が17.5Vを超えると、レギュレータは対応するチャネルの2つのパワーMOSFETを両方ともオフして、動作を一時停止します。 $V_{IN}$ が16.5Vより低くなると、レギュレータは直ちに通常動作を再開します。過電圧状態が解消されると、レギュレータはソフトスタート機能を実行します。

### 熱に関する検討事項と出力電流のディレーティング

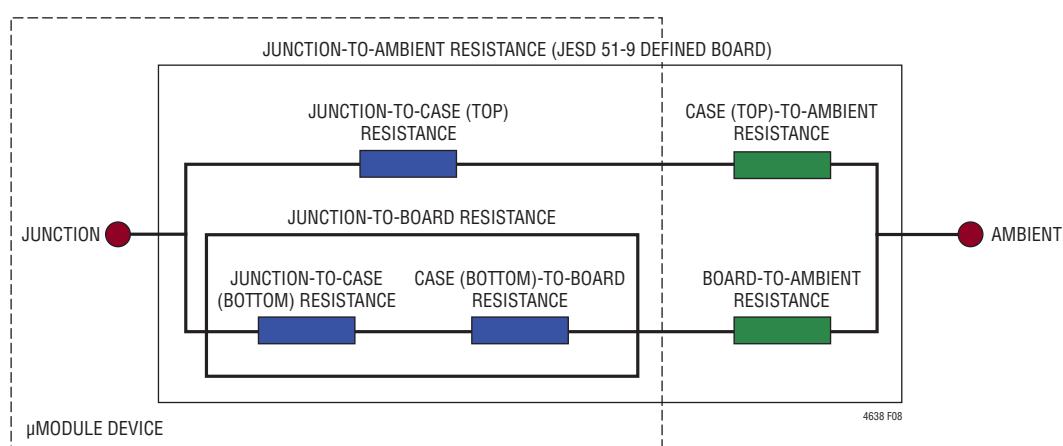

データシートの「ピン配置」セクションに記載された熱抵抗は、JESD 51-9に定義されたパラメータと整合しています。これらのパラメータは、有限要素解析(FEA)ソフトウェアのモデリング・ツールでの使用を意図したものです。モデリング・ツールでは、JESD 51-9 (“Test Boards for Area Array Surface Mount Package Thermal Measurements”)によって定義されたハードウェア・テストボードにμModuleパッケージを実装して行われたハードウェア評価で得られた熱的モデリング、シミュレーション、相関の結果を使用します。これらの熱係数を示す意図は、JESD51-12 (“Guidelines for Reporting and Using Electronic Package Thermal Information”)に示されています。

多くの設計者は、さまざまな電気的および環境的動作条件で動作する実際のアプリケーションにおけるμModuleレギュレータの熱性能を予測するのに、実験室の装置およびデモボードのようなテスト手段の使用を選択して、FEAの作業を補強できます。FEAソフトウェアを使用しない場合、「ピン配置」に記載された熱抵抗は、それだけでは熱性能のガイダンスにはなりません。むしろ、データシートに示されたディレーティング曲線を使った方が、アプリケーションへの適用方法に沿った洞察とガイダンスを得られ、特定のアプリケーションにおける熱性能との相関に適合させることができます。

## アプリケーション情報

「ピン配置」には、通常はJESD 51-12に明示的に定義された4つの熱係数が記載されています。以下に、これらの係数の定義の引用または説明を示します。

1.  $\theta_{JA}$  (接合部から周囲までの熱抵抗)は、1立方フィートの密閉された筐体内で測定された、接合部から自然対流する周囲の空気までの熱抵抗です。この環境は、自然対流により空気が移動しますが、「静止空気」と呼ばれることがあります。この値は、JESD 51-9で定義されているテスト・ボードに実装したデバイスを使って決定されます。このテスト・ボードは実際のアプリケーションまたは実現可能な動作条件を反映するものではありません。

2.  $\theta_{JCbottom}$  (接合部から製品のケースの底面までの熱抵抗)は、部品の全電力損失がパッケージの底面を通過して流れ出す場合の接合部から基板までの熱抵抗です。標準的なμModuleでは、熱の大半がパッケージの底面から流出しますが、周囲の環境への熱の流出が必ず発生します。その結果、この熱抵抗値はパッケージの比較には役立ちますが、このテスト条件は一般にユーザーのアプリケーションには当てはまりません。

3.  $\theta_{JCtop}$  (接合部から製品のケースの上面までの熱抵抗)は、部品のほぼ全電力損失がパッケージの上面を通過して流れ出す状態で決定されます。標準的なμModuleの電気的接続はパッケージの底面なので、熱の大半が接合部からデバイスの上面に流れるようにアプリケーションが動作することは稀です。 $\theta_{JCbottom}$ の場合と同様に、この値はパッケージの比較には役立ちますが、このテスト条件は一般にユーザーのアプリケーションには当てはまりません。

4.  $\theta_{JB}$  (接合部からプリント回路基板までの熱抵抗)は、熱の大部分がμModuleの底面を通過して基板に流れ出すときの接合部から基板までの熱抵抗であり、実際には、 $\theta_{JCbottom}$ と、デバイスの底面から半田接合部を通り、基板の一部までの熱抵抗の和です。基板の温度は、両面の2層基板を使って、パッケージからの規定された距離で測定されます。この基板はJESD 51-9に記述されています。

前述の熱抵抗を図式化したものが図8です。青色の部分はμModule レギュレータ内部の熱抵抗、緑色の部分はμModule パッケージの外部に存在する熱抵抗です。

実際には、JESD51-12または「ピン配置」のセクションで定義されている4種類の熱抵抗パラメータは、個別でもいくつかの組み合わせでも、μModuleの通常の動作条件を再現することも表現することもないので注意してください。例えば、基板に実装された通常のアプリケーションでは、標準規格が $\theta_{JCtop}$ および $\theta_{JCbottom}$ をそれぞれ定義しているように、デバイスの全電力損失(熱)の100%がパッケージの上面だけを通過、または底面だけを通過して熱的に伝わることは決してありません。実際には、電力損失はパッケージの両面から熱的に放散されます。ヒートシンクと空気流がない場合には、当然、熱流の大部分は基板に流れます。

SIP (System-In-Package) モジュール内部では、電力損失を生じるパワーデバイスや部品が複数存在するので、その結果、部品やダイのさまざまな接合部を基準にした熱抵抗は、パッケージの全電力損失に対して正確に線形ではないことに注意してください。この複雑な問題をモデリングの簡潔性を犠牲にすることなく、(しかも実用的な現実性を無視せずに)解決するため、制御環境室でのラボ・テストとともにFEAソフトウェア・モデリングを使用するやり方を採用して、このデータシートに記載されている熱抵抗値を合理的に定義して相関をとります。(1)最初に、FEAソフトウェアを使用し、正しい材料係数に加えて正確な電力損失源の定義を使用することにより、μModuleと指定のPCBの機械的形状モデルを高精度で作成します。(2)このモデルにより、JESD51-12に適合するソフトウェア定義のJEDEC環境のシミュレーションを行い、さまざまな界面での電力損失熱流と温度測定値を予測します。これにより、JEDEC定義の熱抵抗値を計算できます。(3)モデルとFEAソフトウェアを使用してヒートシンクと空気流がある場合のμModuleの熱性能を評価します。(4)これらの熱抵抗値を計算して分析し、ソフトウェア・モデル内でさまざまな動作条件によるシミュレーションを行った上で、徹底した実験室評価を実施してシミュレーションで得た状態を再現します。具体的

## アプリケーション情報

には、制御環境室内で、シミュレーションと同じ電力損失でデバイスを動作させながら、熱電対を使用して温度を測定します。このプロセスと必要な作業の結果、このデータシートの別のセクションに示されているディレーティング曲線が得られました。これらの実験室評価を実施し、μModule モデルとの相関をとつてから  $\theta_{JB}$  と  $\theta_{BA}$  を合計すると、適切な環境のチャンバ内における空気流およびヒートシンクなしの μModule モデルと、きわめてよい相関が得られました。この  $\theta_{JB} + \theta_{BA}$  の値は「ピン配置」セクションに示されていますが、空気流がなく上面にヒートシンクを取り付けていない状態では、電力損失のほぼ 100% が接合部から基板を通って周囲に流れるので、この値は  $\theta_{JA}$  の値に正確に等しくなります。

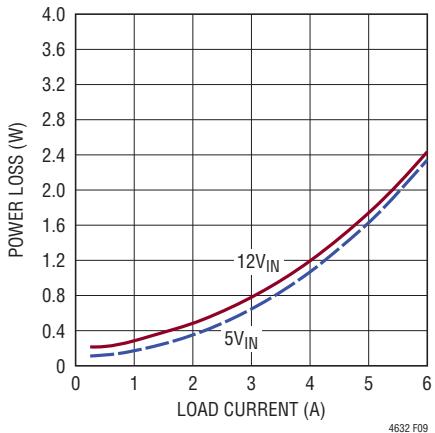

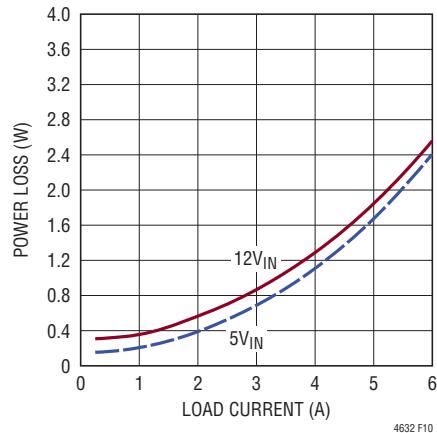

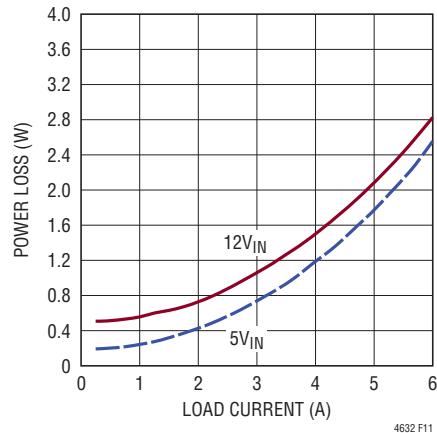

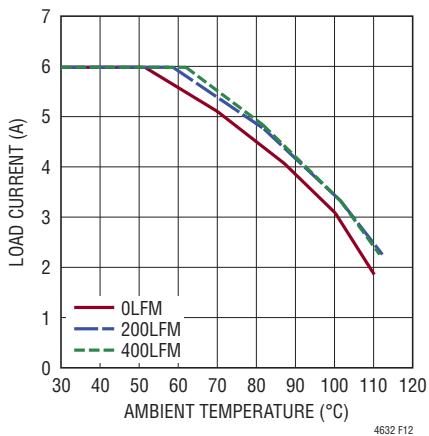

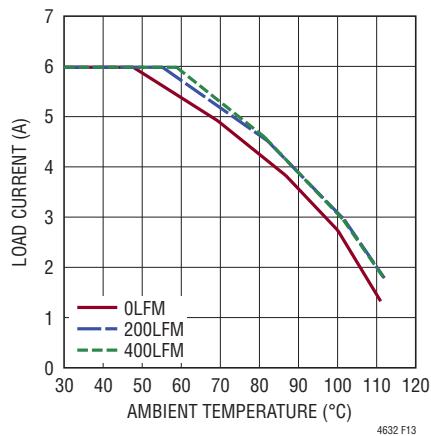

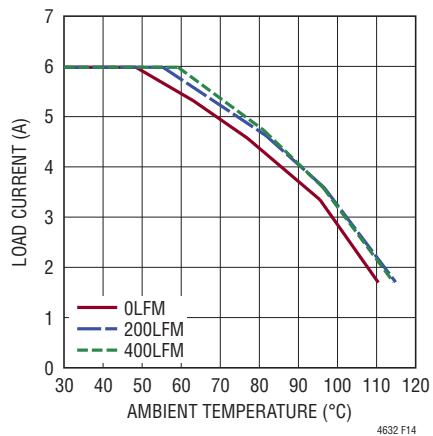

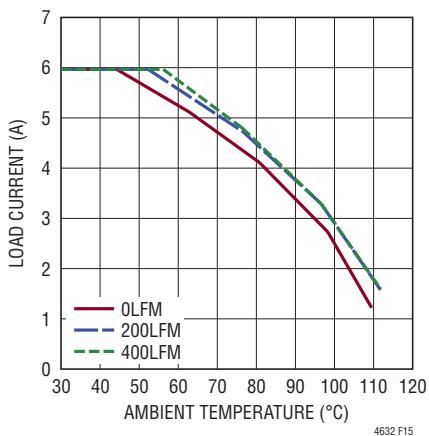

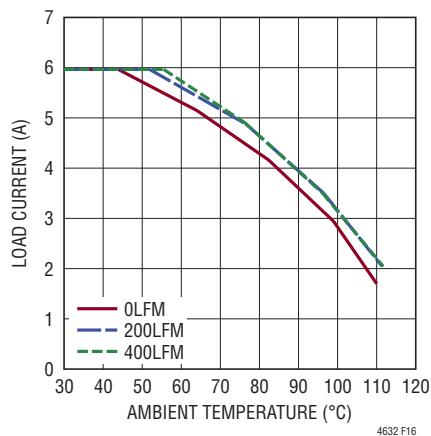

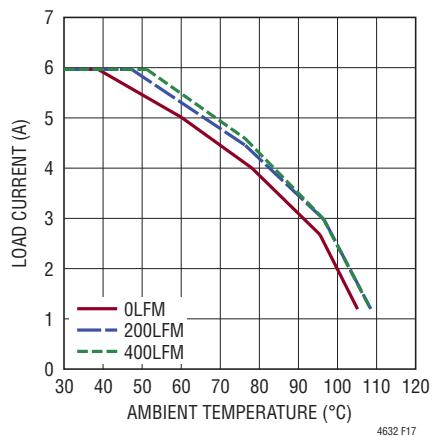

図9～図11に示す 1.0V、1.5V、および 2.5V での電力損失曲線を図12～図17 の負荷電流ディレーティング曲線と組み合わせて使用することにより、ヒートシンクなしでの LTM4632 の概略の  $\theta_{JA}$  熱抵抗をさまざまな空気流条件で計算することができます。電力損失曲線は室温で測定し、120°C の接合部温度を想定した場合は 1.35 の倍率で増加します。ディレーティング曲線は、LTM4632 を 2 相シングル出力構成(図20)にすることにより、6A の出力電流と 40°C の周囲温度を起点としてプロットされます。これらの出力電圧が選ばれたのは、低めおよび高めの出力電圧範囲を対象にして熱抵抗と対応づけるためです。熱モデルは、恒温槽での数回の温度測定と熱モーリング解析から得られます。空気流ありと空気流なしの条件で周囲温度を上げながら接合部温度をモニタします。周囲温

度の変化による電力損失の増加はディレーティング曲線に加味されています。周囲温度の上昇に合わせて出力電流つまり電力が減少するので、接合部温度は最大で 120°C に維持されます。出力電流が減少することにより、周囲温度が上昇するにつれて内部モジュールの損失は減少します。モニタされている接合部温度である 120°C から周囲動作温度を引くと、許容できるモジュールの温度上昇が規定されます。図12 の例では、空気流とヒートシンクなしで約 100°C のとき、負荷電流は約 3A にディレーティングされ、5V 入力から 1V/3A 出力を得る場合の電力損失は約 0.95W です。0.95W の損失は、5V 入力、1V/3A 出力での電力損失曲線から得られる約 0.7W の室温での損失、および 120°C の測定接合部温度での 1.35 の倍率を使って計算されます。120°C の接合部温度から 100°C の周囲温度を引き、その差の 20°C を 0.95W で割ると 20°C/W の熱抵抗  $\theta_{JA}$  が得られます。表2 はこれと非常に近い 19°C ~ 20°C/W の値を規定しています。空気流の有無を条件とした 1.0V、1.5V、および 2.5V 出力の等価熱抵抗を表2～表4 に示します。さまざまな条件で得られた表2～表4 の熱抵抗に、周囲温度の関数として計算された電力損失を掛けて、周囲温度を超える温度上昇(したがって最大接合部温度)を求めるすることができます。室温での電力損失を「標準的性能特性」セクションの効率曲線から求めて、前述の周囲温度の倍率で調整することができます。プリント回路基板は 1.6mm 厚の 4 層構造で、外側 2 層には 2 オンス銅箔、内側 2 層には 1 オンス銅箔を使用しています。PCB の寸法は 95mm × 76mm です。

図 8. JESD51-12 の熱係数の図解

## アプリケーション情報

図9. 1.0V出力での電力損失

図10. 1.5V出力での電力損失

図11. 2.5V出力での電力損失

図12. 5V入力、1.0V出力のディレーティング曲線、ヒートシンクなし

図13. 12V入力、1.0V出力のディレーティング曲線、ヒートシンクなし

図14. 5V入力、1.5V出力のディレーティング曲線、ヒートシンクなし

図15. 12V入力、1.5V出力のディレーティング曲線、ヒートシンクなし

図16. 5V入力、2.5V出力のディレーティング曲線、ヒートシンクなし

図17. 12V入力、2.5V出力のディレーティング曲線、ヒートシンクなし

## アプリケーション情報

表2. 1.0V出力

| ディレーティング曲線 | $V_{IN}$ (V) | 電力損失曲線 | 空気流 (LFM) | ヒートシンク | $\theta_{JA}$ (°C/W) |

|------------|--------------|--------|-----------|--------|----------------------|

| 図12、図13    | 5, 12        | 図9     | 0         | なし     | 19~20                |

| 図12、図13    | 5, 12        | 図9     | 200       | なし     | 18~19                |

| 図12、図13    | 5, 12        | 図9     | 400       | なし     | 17~18                |

表3. 1.5V出力

| ディレーティング曲線 | $V_{IN}$ (V) | 電力損失曲線 | 空気流 (LFM) | ヒートシンク | $\theta_{JA}$ (°C/W) |

|------------|--------------|--------|-----------|--------|----------------------|

| 図14、図15    | 5, 12        | 図10    | 0         | なし     | 19~20                |

| 図14、図15    | 5, 12        | 図10    | 200       | なし     | 18~19                |

| 図14、図15    | 5, 12        | 図10    | 400       | なし     | 17~18                |

表4. 2.5V出力

| ディレーティング曲線 | $V_{IN}$ (V) | 電力損失曲線 | 空気流 (LFM) | ヒートシンク | $\theta_{JA}$ (°C/W) |

|------------|--------------|--------|-----------|--------|----------------------|

| 図16、図17    | 5, 12        | 図11    | 0         | なし     | 19~20                |

| 図16、図17    | 5, 12        | 図11    | 200       | なし     | 18~19                |

| 図16、図17    | 5, 12        | 図11    | 400       | なし     | 17~18                |

## アプリケーション情報

表5. レギュレータのチャネルごとの出力電圧応答と部品の一覧(図19を参照)

25%負荷ステップ時の標準的測定値

| $C_{IN}$<br>(セラミック) | 製品番号               | 値                        | $C_{OUT1}$<br>(セラミック) | 製品番号               | 値                        | $C_{OUT2}$<br>(バルク) | 製品番号     | 値                              |

|---------------------|--------------------|--------------------------|-----------------------|--------------------|--------------------------|---------------------|----------|--------------------------------|

| 村田製作所               | GRM188R61E475KE11# | 4.7 $\mu$ F、25V、0603、X5R | 村田製作所                 | GRM21R60J476ME15#  | 47 $\mu$ F、6.3V、0805、X5R | パナソニック              | 6TPC150M | 150 $\mu$ F、6.3V、3.5×2.8×1.4mm |

| 村田製作所               | GRM188R61E106MA73# | 10 $\mu$ F、25V、0603、X5R  | 村田製作所                 | GRM188R60J226MEA0# | 22 $\mu$ F、6.3V、0603、X5R |                     |          |                                |

| 太陽誘電                | TMK212BJ475KG-T    | 4.7 $\mu$ F、25V、0805、X5R | 太陽誘電                  | JMK212BJ476MG-T    | 47 $\mu$ F、6.3V、0805、X5R |                     |          |                                |

| $V_{OUT}$ (V) | $C_{IN}$<br>(セラミック)<br>( $\mu$ F) | $C_{IN}$<br>(バルク) | $C_{OUT1}$<br>(セラミック)<br>( $\mu$ F) | $C_{OUT2}$<br>(バルク)<br>( $\mu$ F) | $C_{FF}$<br>(pF) | $V_{IN}$<br>(V) | 電圧<br>低下量<br>(mV) | P-P変動量<br>(mV) | 回復時間<br>( $\mu$ s) | 負荷<br>ステップ<br>(A) | 負荷ステップの<br>スルーレート<br>(A/ $\mu$ s) | $R_{FB}$<br>(k $\Omega$ ) |

|---------------|-----------------------------------|-------------------|-------------------------------------|-----------------------------------|------------------|-----------------|-------------------|----------------|--------------------|-------------------|-----------------------------------|---------------------------|

| 1             | 2×10                              | 0                 | 1×47 $\mu$ F                        | 0                                 | 0                | 5, 12           | 0                 | 77             | 15                 | 0.75              | 10                                | 90.9                      |

| 1.2           | 2×10                              | 0                 | 1×47 $\mu$ F                        | 0                                 | 0                | 5, 12           | 0                 | 83             | 15                 | 0.75              | 10                                | 60.4                      |

| 1.5           | 2×10                              | 0                 | 1×47 $\mu$ F                        | 0                                 | 0                | 5, 12           | 0                 | 94             | 18                 | 0.75              | 10                                | 40.2                      |

| 1.8           | 2×10                              | 0                 | 1×47 $\mu$ F                        | 0                                 | 0                | 5, 12           | 0                 | 105            | 20                 | 0.75              | 10                                | 30.1                      |

| 2.5           | 2×10                              | 0                 | 1×47 $\mu$ F                        | 0                                 | 0                | 5, 12           | 0                 | 138            | 20                 | 0.75              | 10                                | 19.1                      |

## アプリケーション情報

### 安全性に関する検討事項

LTM4632モジュールでは、VINとVOUTの間が電気的に絶縁されていません。内部にヒューズはありません。必要に応じて、最大入力電流の2倍の定格の低速溶断ヒューズを使って各ユニットを致命的損傷から保護してください。デバイスはサマル・シャットダウンおよび過電流保護機能を備えています。

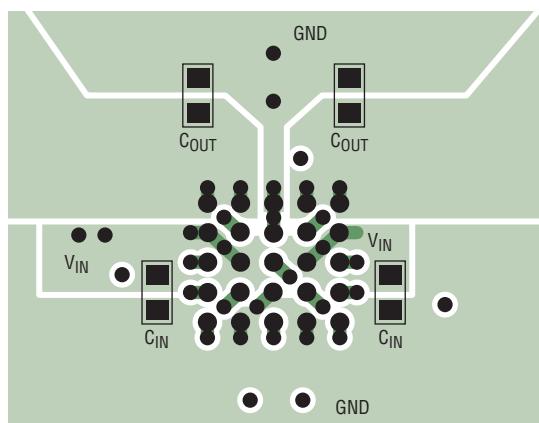

### レイアウトのチェックリスト/例

LTM4632は高度に集積化されているため、PCB基板レイアウトが非常に簡単で容易です。ただし、電気的性能と熱的性能を最適化するにはいくつかのレイアウト上の配慮が依然として必要です。

- VIN、GND、VOUT1、VOUT2を含む高電流経路にはPCB銅箔面積を広く確保します。これはPCBの導通損失と熱ストレスを最小限に抑えるのに役立ちます。

- 入力と出力の高周波用セラミック・コンデンサをVIN、PGNDおよびVOUTの各ピンに隣接させて配置し、高周波ノイズを最小に抑えます。

- デバイスの下に専用の電源グランド層を配置します。

- ビアの導通損失を最小限に抑え、モジュールの熱ストレスを減らすため、トップ層と他の電源層の間の相互接続に多数のビアを使います。

- 充填ビアまたはメッキビアでない限り、パッドの上に直接ビアを置かないでください。

- 信号ピンに接続された部品には、別のSGNDグランド銅領域を使います。SGNDとGNDをデバイスの下で接続します。

- 並列モジュールの場合は、VOUT、VFB、COMPピンを互いに接続します。内部層を使ってこれらのピンを互いに近づけて接続します。TRACKピンはレギュレータのソフトスタート用に共通のコンデンサを接続できます。

- 信号ピンからは、モニタリング用にテスト・ポイントを引き出してください。

推奨レイアウトの良い例を図18に示します。

図18. 推奨のPCBレイアウト

LTM4632

## アプリケーション情報

図19. 3.6V～15V入力、1.5V/3A VDDQ、0.75V/±3A VTTおよび10mA VTTRの設計回路

図 20. 4V～15V 入力、2相シングル出力  $\pm 6A$  VTT 終端設計回路、LTM4630 36A VDDQ 電源と組み合わせ

## アプリケーション情報

図21. 3.3V入力、1.5V/3A VDDQ、0.75V/±3A VTT および10mA VTTR の設計回路

図22. 2つのモジュールを並列接続、3.6V～15V入力、1.2V/6A VDDQ、0.6V/±6A VTT および10mA VTTR の設計回路

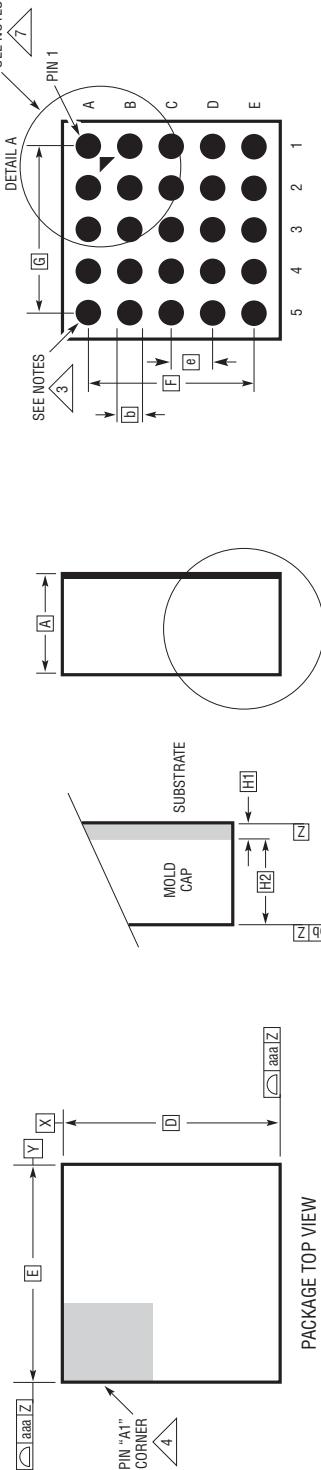

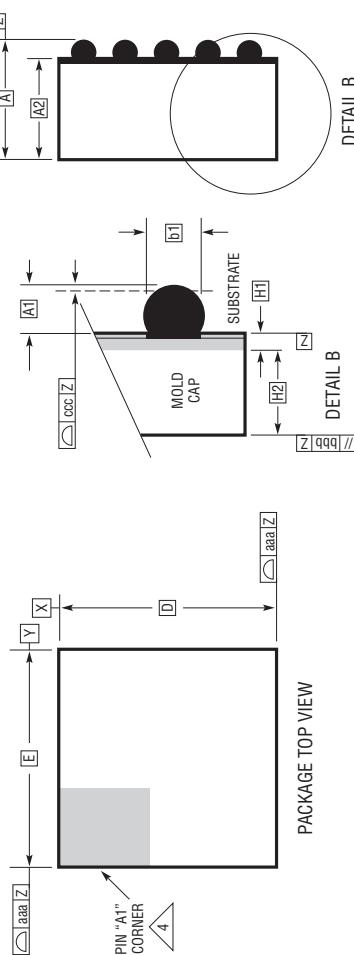

## パッケージ

パッケージの行と列のラベルはμModule製品間で

異なります。各パッケージのレイアウトを

よく確認してください。

LTM4632の構成要素のLGAおよびBGAピン配列

| ピンID | 機能                | ピンID | 機能              | ピンID | 機能                 | ピンID | 機能                 | ピンID | 機能        |

|------|-------------------|------|-----------------|------|--------------------|------|--------------------|------|-----------|

| A1   | V <sub>OUT2</sub> | A2   | V <sub>IN</sub> | A3   | VTTR               | A4   | V <sub>DDQIN</sub> | A5   | COMP2     |

| B1   | V <sub>OUT2</sub> | B2   | RUN2            | B3   | V <sub>IN</sub>    | B4   | PGOOD2             | B5   | GND       |

| C1   | GND               | C2   | GND             | C3   | INTV <sub>CC</sub> | C4   | SGND               | C5   | SYNC/MODE |

| D1   | V <sub>OUT1</sub> | D2   | RUN1            | D3   | V <sub>IN</sub>    | D4   | PGOOD1             | D5   | GND       |

| E1   | V <sub>OUT1</sub> | E2   | V <sub>IN</sub> | E3   | TRACK/SS1          | E4   | FB1                | E5   | COMP1     |

## パッケージ

最新のパッケージ図面については、<http://www.linear-tech.co.jp/product/LTM4632#packaging> を参照してください。

**LGA Package**

**25-Lead (6.25mm × 6.25mm × 1.82mm)**

(Reference LTC DWG # 05-08-1949 Rev 0)

注記:

- 寸法と許容誤差はASME Y14.5M-1994による

- 全ての寸法はミリメートル

- 3 ラントの指定はJESD MO-222、SPP-010による

- 4 パッド#の識別マークの詳細はオブションだが、示された領域内になければならぬ

5. 主データム-Z-はシーティングフレーン

6. パッドの総数: 25

7. パッケージの行と列のラベルは、μModule製品で異なります

各パッケージのレイアウトを十分にご確認ください

| SYMBOL | DIMENSIONS |      |      |  | NOTES |

|--------|------------|------|------|--|-------|

|        | MIN        | NOM  | MAX  |  |       |

| A      | 1.72       | 1.82 | 1.92 |  |       |

| b      | 0.60       | 0.63 | 0.66 |  |       |

| D      | 6.25       |      |      |  |       |

| E      | 6.25       |      |      |  |       |

| e      | 1.27       |      |      |  |       |

| F      | 5.08       |      |      |  |       |

| G      | 5.08       |      |      |  |       |

| H1     | 0.27       | 0.32 | 0.37 |  |       |

| H2     | 1.45       | 1.50 | 1.55 |  |       |

| aaa    |            |      | 0.15 |  |       |

| bbb    |            |      | 0.10 |  |       |

| eee    |            |      | 0.15 |  |       |

SUGGESTED PCB LAYOUT

TOP VIEW

COMPONENT PIN 'A1'

TRAY PIN 1 BEVEL

TOTAL NUMBER OF LGA PADS: 25

LGA25-0613 REV 0

4632fa

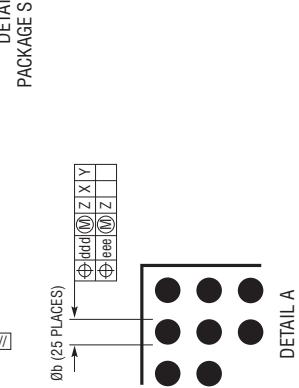

## パッケージ

最新のパッケージ図面については、<http://www.linear-tech.co.jp/product/LTM4632#packaging>を参照してください。

## **BGA Package**

### **225-Lead (6.25mm × 6.25mm × 2.42mm)**

(Reference LTC DWG # 05-08-1502 Rev Q)

| DIMENSIONS |      | NOTES |                         |

|------------|------|-------|-------------------------|

| SYMBOL     | MIN  | NOM   | MAX                     |

| A          | 2.22 | 2.42  | 2.62                    |

| A1         | 0.50 | 0.60  | 0.70                    |

| A2         | 1.72 | 1.82  | 1.92                    |

| b          | 0.60 | 0.75  | 0.90                    |

| b1         | 0.60 | 0.63  | 0.66                    |

| D          | 6.25 |       |                         |

| E          | 6.25 |       |                         |

| e          | 1.27 |       |                         |

| F          | 5.08 |       |                         |

| G          | 5.08 |       |                         |

| H1         | 0.27 | 0.32  | 0.37                    |

| H2         | 1.45 | 1.50  | 1.55                    |

| aaa        |      |       | 0.15                    |

| bbb        |      |       | 0.10                    |

| ccc        |      |       | 0.20                    |

| ddd        |      |       | 0.30                    |

| eee        |      |       | 0.15                    |

|            |      |       | TOTAL NUMBER OF RAIS: 5 |

BGA 25 0515 REV 0

## 改訂履歴

| REV | 日付    | 説明          | ページ番号  |

|-----|-------|-------------|--------|

| A   | 05/16 | BGAパッケージを追加 | 1、2、26 |

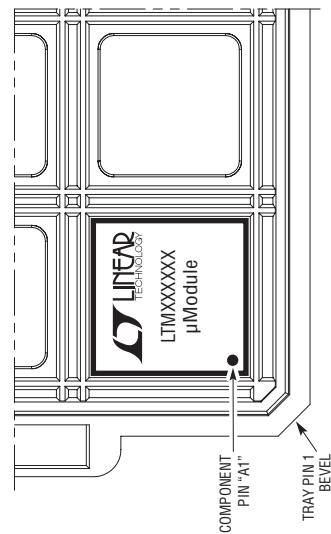

## パッケージの写真

## 設計リソース

| 主題                                    | 説明                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                             |       |                       |  |   |                       |  |   |        |                  |  |   |                  |  |   |                                       |  |  |  |  |  |  |

|---------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|-------|-----------------------|--|---|-----------------------|--|---|--------|------------------|--|---|------------------|--|---|---------------------------------------|--|--|--|--|--|--|

| <a href="#">μModuleの設計/製造リソース</a>     | 設計: <ul style="list-style-type: none"><li>選択ガイド</li><li>デモボードおよびGerberファイル</li><li>無料シミュレーション・ツール</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 製造: <ul style="list-style-type: none"><li>クイック・スタート・ガイド</li><li>PCBの設計、組立、および製造ガイドライン</li><li>パッケージおよびボード・レベルの信頼性</li></ul> |       |                       |  |   |                       |  |   |        |                  |  |   |                  |  |   |                                       |  |  |  |  |  |  |

| <a href="#">μModuleレギュレータ製品の検索</a>    | <ol style="list-style-type: none"> <li>製品の表をパラメータによって並べ替え、結果をスプレッドシートとしてダウンロードする</li> <li><a href="#">Quick Power Search</a>パラメトリック・テーブルを使って検索を実行する</li> </ol> <div style="border: 1px solid #ccc; padding: 10px; margin-top: 10px;"> <p style="margin: 0;">Quick Power Search</p> <table style="width: 100%; border-collapse: collapse;"> <tr> <td style="width: 15%;">Input</td> <td>V<sub>in</sub> (Min)</td> <td style="border: 1px solid #ccc; padding: 2px 10px;"> </td> <td>V</td> <td>V<sub>in</sub> (Max)</td> <td style="border: 1px solid #ccc; padding: 2px 10px;"> </td> <td>V</td> </tr> <tr> <td>Output</td> <td>V<sub>out</sub></td> <td style="border: 1px solid #ccc; padding: 2px 10px;"> </td> <td>V</td> <td>I<sub>out</sub></td> <td style="border: 1px solid #ccc; padding: 2px 10px;"> </td> <td>A</td> </tr> <tr> <td colspan="7" style="text-align: right; padding-top: 5px;"> <input type="button" value="Search"/> </td> </tr> </table> </div> |                                                                                                                             | Input | V <sub>in</sub> (Min) |  | V | V <sub>in</sub> (Max) |  | V | Output | V <sub>out</sub> |  | V | I <sub>out</sub> |  | A | <input type="button" value="Search"/> |  |  |  |  |  |  |

| Input                                 | V <sub>in</sub> (Min)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                             | V     | V <sub>in</sub> (Max) |  | V |                       |  |   |        |                  |  |   |                  |  |   |                                       |  |  |  |  |  |  |

| Output                                | V <sub>out</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                             | V     | I <sub>out</sub>      |  | A |                       |  |   |        |                  |  |   |                  |  |   |                                       |  |  |  |  |  |  |

| <input type="button" value="Search"/> |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                             |       |                       |  |   |                       |  |   |        |                  |  |   |                  |  |   |                                       |  |  |  |  |  |  |

| <a href="#">TechClipビデオ</a>           | <a href="#">μModule</a> 製品の電気的特性と熱特性のベンチマーク・テストの方法を詳しく説明した短いビデオ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                             |       |                       |  |   |                       |  |   |        |                  |  |   |                  |  |   |                                       |  |  |  |  |  |  |

| <a href="#">デジタル・パワーシステム・マネージメント</a>  | リニアテクノロジーのデジタル電源管理デバイス・ファミリは、電源の監視、管理、マージン制御およびシーケンス制御などの基本機能を提供する高度に集積されたソリューションであり、ユーザーの構成とフォルト・ログを保存するEEPROMを搭載しています。                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                             |       |                       |  |   |                       |  |   |        |                  |  |   |                  |  |   |                                       |  |  |  |  |  |  |

## 関連製品

| 製品番号                    | 説明                                           | 注釈                                                                                                                                |

|-------------------------|----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|

| <a href="#">LTM4622</a> | 超薄型、デュアル2.5Aまたはシングル5A降圧μModuleレギュレータ         | 3.6V < V <sub>IN</sub> < 20V、0.6V < V <sub>OUT</sub> < 5.5V、6.25mm×6.25mm×1.82mm LGAパッケージ、6.25mm×6.25mm×2.42 BGAパッケージ             |

| <a href="#">LTM4623</a> | 超薄型、シングル3A降圧μModuleレギュレータ                    | 4V ≤ V <sub>IN</sub> ≤ 20V、0.6V ≤ V <sub>OUT</sub> ≤ 5.5V、6.25mm×6.25mm×1.82mm LGAパッケージ、6.25mm×6.25mm×2.42 BGAパッケージ               |

| <a href="#">LTM4644</a> | クワッド4A降圧μModuleレギュレータ                        | 4V < V <sub>IN</sub> < 14V、0.6V < V <sub>OUT</sub> < 5.5V、9mm×15mm×5.01mm BGAパッケージ                                                |

| <a href="#">LTM4630</a> | 大電力VDDQ電源向けμModuleレギュレータ                     | 4.5V < V <sub>IN</sub> < 15V、0.6V < V <sub>OUT</sub> < 1.8V、シングル36Aまたはデュアル18A、16mm×16mm×5.01mm BGAパッケージ、16mm×16mm×4.41mm LGAパッケージ |

| <a href="#">LTM4650</a> | 大電力FPGA/ASICコア電源向けμModuleレギュレータ              | 4.5V < V <sub>IN</sub> < 15V、0.6V < V <sub>OUT</sub> < 1.8V、シングル50Aまたはデュアル25A、16mm×16mm×5.01mm BGAパッケージ                           |

| <a href="#">LTM4639</a> | 低入力電圧、シングル20A降圧μModuleレギュレータ                 | 2.375V < V <sub>IN</sub> < 7V、0.6V < V <sub>OUT</sub> < 5.5V、15mm×15mm×4.92mm BGAパッケージ                                            |

| <a href="#">LTM4675</a> | PSM機能を備えた大電力、高精度FPGA/ASICコア電源向けμModuleレギュレータ | デジタル・パワーシステム・マネージメント機能を備えたDC/DC μModule、4.5V < V <sub>IN</sub> < 17V、0.5V < V <sub>OUT</sub> < 5.5Vで精度は±0.5%、シングル18Aまたはデュアル9A     |

| <a href="#">LTM4677</a> | PSM機能を備えた大電力、高精度FPGA/ASICコア電源向けμModuleレギュレータ | デジタル・パワーシステム・マネージメント機能を備えたDC/DC μModule、4.5V < V <sub>IN</sub> < 16V、0.5V < V <sub>OUT</sub> < 1.8Vで精度は±0.5%、シングル36Aまたはデュアル18A    |

| <a href="#">LTC3717</a> | DDRメモリ終端用VTTの降圧コントローラ                        | 4V < V <sub>IN</sub> < 36V、I <sub>OUT</sub> = ±20A、インダクタとMOSFETの外付けが必要                                                            |

| <a href="#">LTC6902</a> | マルチフェーズ動作用のマルチフェーズ発振器                        | 2相、3相、または4相、周波数範囲:5kHz～20MHz                                                                                                      |

4632fa