## 特長

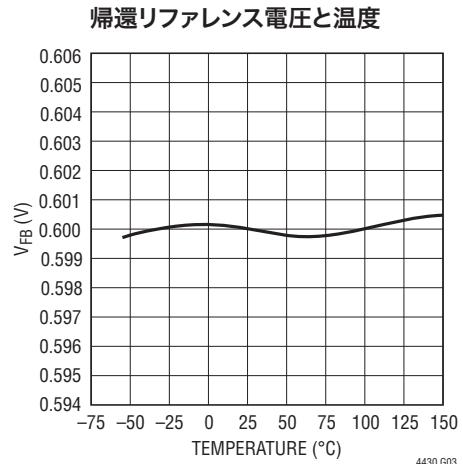

- 600mVリファレンス(全温度範囲で1.25%精度)

- 広い入力電源電圧範囲: 3V~20V

- オーバーシュート制御機能により、起動時または短絡からの回復時に出力オーバーシュートを防止

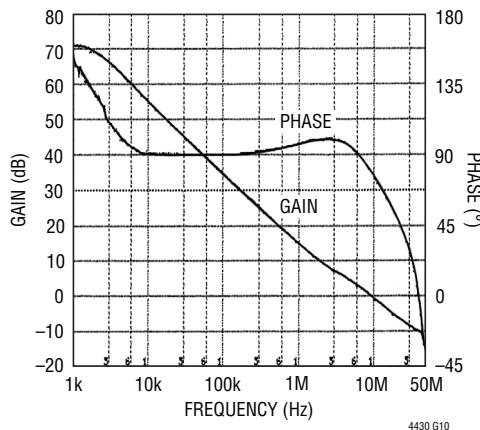

- 広帯域幅のエラーアンプにより、ループ周波数補償が容易

- グランド基準のオプトカプラ・ドライバ

- 電流制限機能を備えた10mAオプトカプラ・ドライバ

- 高さの低い(1mm)ThinSOT™パッケージ

## アプリケーション

- 48V入力絶縁型DC/DCコンバータ

- 絶縁型電気通信用電源システム

- 分散給電降圧コンバータ

- オフライン絶縁型電源

- 産業用制御システム

- 自動車用機器および重機

## 概要

LT<sup>®</sup>4430は、絶縁電源において電気的障壁を横切るオプトカプラを駆動します。このデバイスは高精度で調整されたリファレンス、広帯域幅のエラーアンプ、オプトカプラをドライブするための利得6の反転段、独自のオーバーシュート制御回路を内蔵しています。

LT4430の600mVリファレンスは、全温度範囲で初期精度が $\pm 0.75\%$ 、許容誤差が $\pm 1.25\%$ です。9MHzの広帯域幅エラーアンプにより、周波数補償が容易で、ループの標準クロスオーバー周波数での位相シフトを無視できます。このオプトカプラ・ドライバは10mAの出力電流を供給し、短絡保護されています。独自のオーバーシュート制御機能により、コンデンサを1個接続するだけで、起動時および短絡からの回復時の出力オーバーシュートを防ぎます。

LT4430は高さの低い6ピンTSOT-23パッケージで供給されます。

**LT**、**LT**、**LTC**、**LTM**、**Linear Technology**およびLinearのロゴはリニアテクノロジー社の登録商標です。ThinSOTはリニアテクノロジー社の商標です。その他すべての商標の所有権は、それぞれの所有者に帰属します。

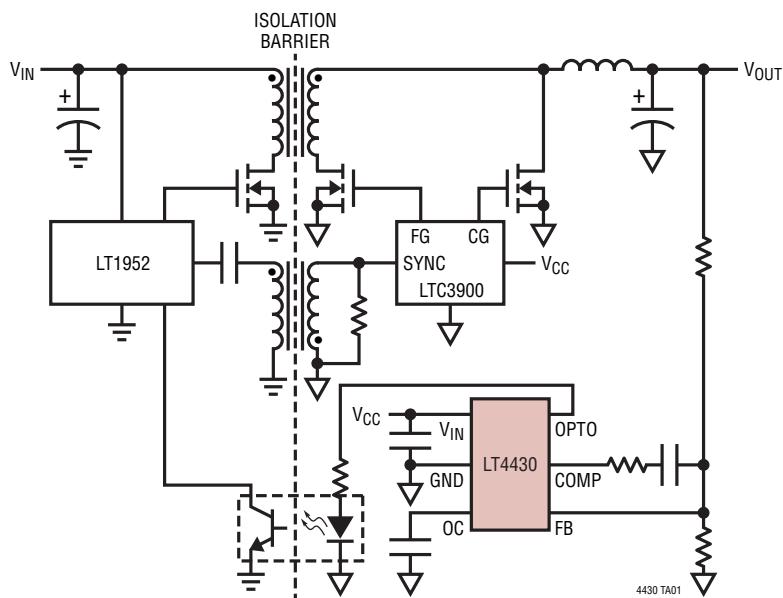

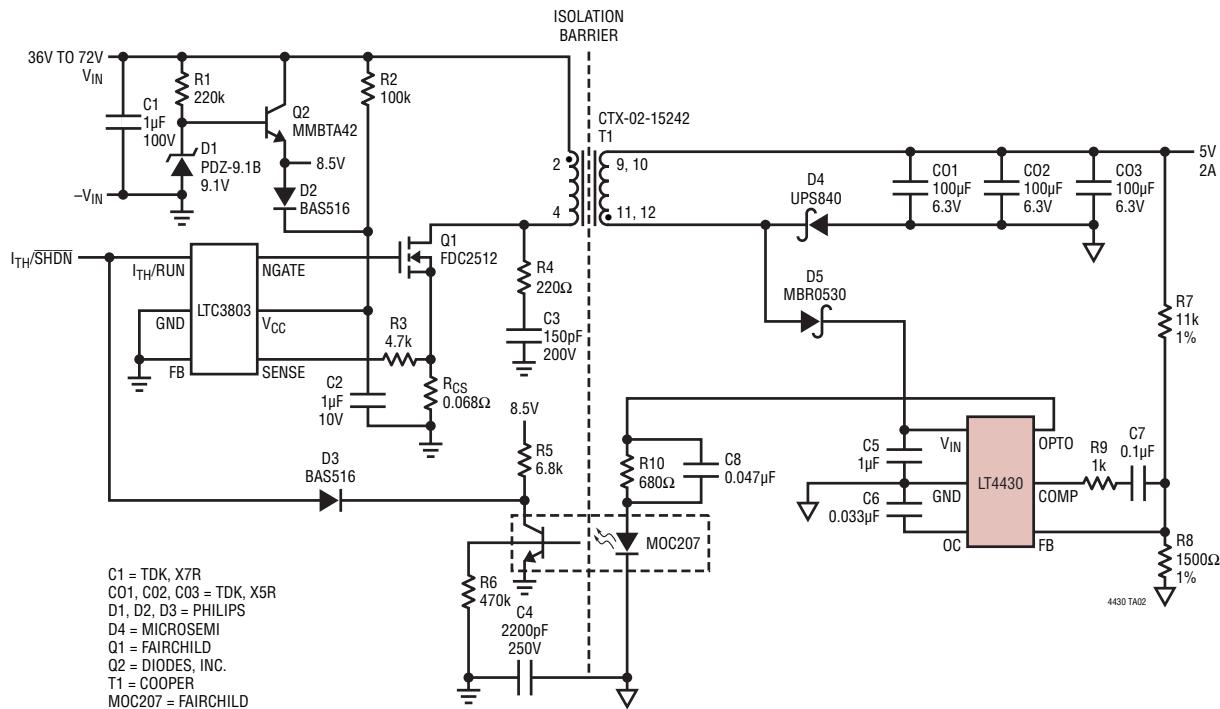

## 標準的応用例

簡単な絶縁型同期整流式フォワード・コンバータ

オーバーシュート制御付き絶縁型

フライバック・テレコム・コンバータの起動

(26ページの図を参照)

## 絶対最大定格

(Note 1)

電源電圧

$V_{IN}$  ..... 20V

FB電圧 ..... -0.3V~6V

OPTO短絡時間 ..... 無期限

動作接合部温度範囲 (Note 2)

E、Iグレード ..... -40°C~125°C

Hグレード ..... -40°C~150°C

MPグレード ..... -55°C~150°C

保存温度範囲 ..... -65°C~150°C

リード温度(半田付け、10秒) ..... 300°C

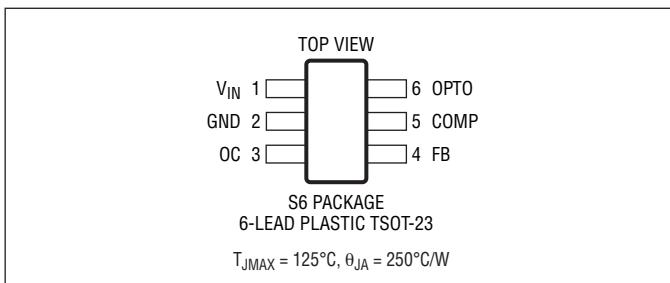

## ピン配置

## 発注情報

| 鉛フリー仕様         | テープアンドリール       | 製品マーキング* | パッケージ                  | 温度範囲           |

|----------------|-----------------|----------|------------------------|----------------|

| LT4430ES6#PBF  | LT4430ES6#TRPB  | LTBFY    | 6-Lead Plastic TSOT-23 | -40°C to 125°C |

| LT4430IS6#PBF  | LT4430IS6#TRPB  | LTBFY    | 6-Lead Plastic TSOT-23 | -40°C to 125°C |

| LT4430HS6#PBF  | LT4430HS6#TRPB  | LTBFY    | 6-Lead Plastic TSOT-23 | -40°C to 150°C |

| LT4430MPS6#PBF | LT4430MPS6#TRPB | LTBFY    | 6-Lead Plastic TSOT-23 | -55°C to 150°C |

| 鉛ベース仕様         | テープアンドリール       | 製品マーキング* | パッケージ                  | 温度範囲           |

| LT4430ES6      | LT4430ES6#TR    | LTBFY    | 6-Lead Plastic TSOT-23 | -40°C to 125°C |

| LT4430IS6      | LT4430IS6#TR    | LTBFY    | 6-Lead Plastic TSOT-23 | -40°C to 125°C |

| LT4430HS6      | LT4430HS6#TR    | LTBFY    | 6-Lead Plastic TSOT-23 | -40°C to 150°C |

| LT4430MPS6     | LT4430MPS6#TR   | LTBFY    | 6-Lead Plastic TSOT-23 | -55°C to 150°C |

さらに広い動作温度範囲で規定されるデバイスについては、弊社または弊社代理店にお問い合わせください。 \*温度グレードは出荷時のコンテナのラベルで識別されます。

鉛フリー仕様の製品マーキングの詳細については、<http://www.linear-tech.co.jp/leadfree/> をご覧ください。テープアンドリールの仕様の詳細については、<http://www.linear-tech.co.jp/tapeandreel/> をご覧ください。

## 電気的特性

●は全動作接合部温度範囲の規格値を意味する。それ以外はT<sub>A</sub> = 25°Cでの値。注記がない限り、V<sub>IN</sub> = 5V、FB = V<sub>FB</sub>、COMP = 1V (Note 3)。

| SYMBOL     | PARAMETER                      | CONDITIONS                                                                                                                                            | MIN                      | TYP               | MAX                | UNITS |

|------------|--------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|-------------------|--------------------|-------|

| $V_{IN}$   | Input Voltage Range            |                                                                                                                                                       | ● 3                      |                   | 20                 | V     |

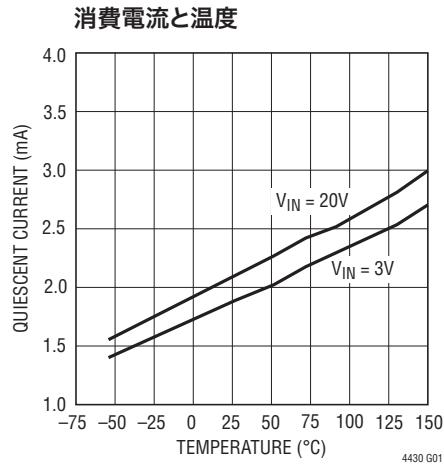

| $I_{IN}$   | Supply Current                 | 3V ≤ $V_{IN}$ ≤ 20V (E-, I-Grades)<br>3V ≤ $V_{IN}$ ≤ 20V (H-, MP-Grades)                                                                             | ● 1.9<br>● 1.9           | 1.9<br>1.9        | 3.9<br>4.3         | mA    |

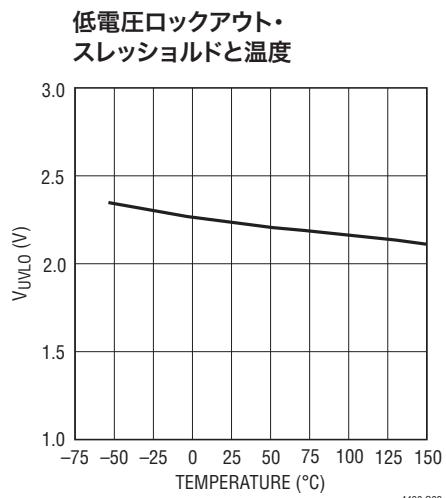

| $V_{UVLO}$ | Undervoltage Lockout Threshold | OC Held Low for $V_{IN} < V_{UVLO}$ (E-, I-Grades)<br>OC Held Low for $V_{IN} < V_{UVLO}$ (H-Grade)<br>OC Held Low for $V_{IN} < V_{UVLO}$ (MP-Grade) | ● 1.95<br>● 1.9<br>● 1.9 | 2.2<br>2.2<br>2.2 | 2.5<br>2.5<br>2.55 | V     |

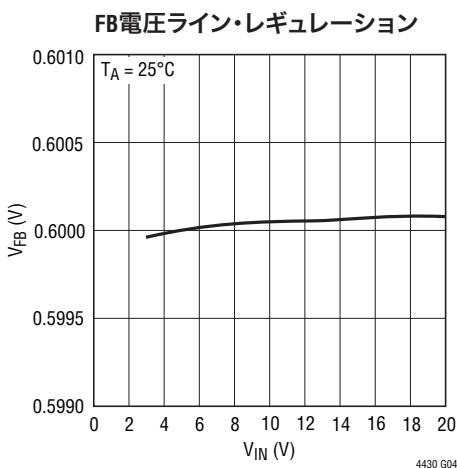

| $V_{FB}$   | Feedback Reference Voltage     | 3V ≤ $V_{IN}$ ≤ 20V                                                                                                                                   | ● 0.5955<br>● 0.5925     | 0.6<br>0.6        | 0.6045<br>0.6075   | V     |

|            | $V_{FB}$ Line Regulation       | 3V ≤ $V_{IN}$ ≤ 20V                                                                                                                                   |                          | 0.02              | 0.1                | %     |

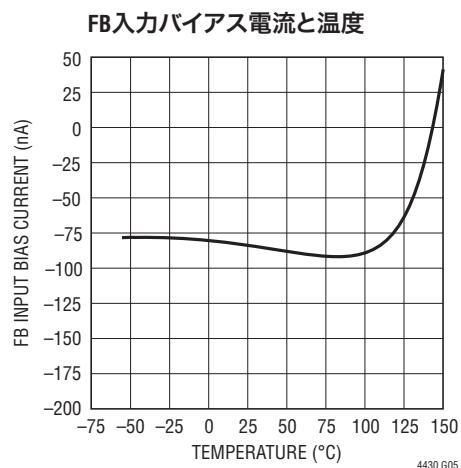

| $I_{FB}$   | FB Input Bias Current          | FB = $V_{FB}$                                                                                                                                         |                          | -150              | -75                | nA    |

## 電気的特性

●は全動作接合部温度範囲の規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。注記がない限り、 $V_{IN} = 5\text{V}$ 、 $FB = V_{FB}$ 、 $COMP = 1\text{V}$  (Note 3)。

| SYMBOL    | PARAMETER                             | CONDITIONS                                                                                                                                                                                                                 | MIN                                                                                                                                                              | TYP                                | MAX                  | UNITS                                           |                                |

|-----------|---------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|----------------------|-------------------------------------------------|--------------------------------|

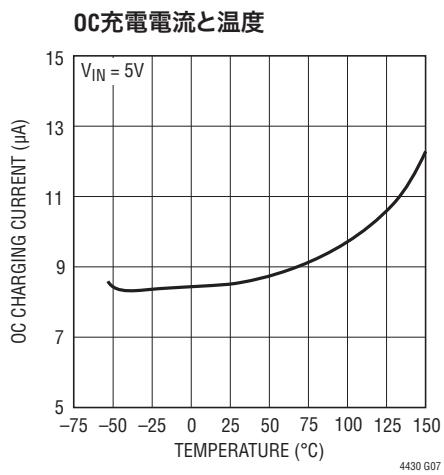

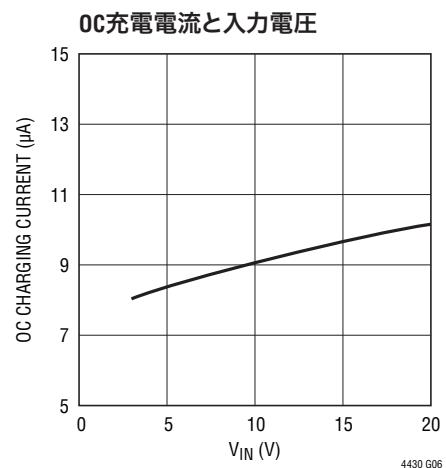

| $I_{OC}$  | Overshoot Control Charging Current    | $V_{OC} = 0\text{V}$ (E-, I-Grades)<br>$V_{OC} = 0\text{V}$ (H-Grade)<br>$V_{OC} = 0\text{V}$ (MP-Grade)                                                                                                                   | -15<br>-17<br>-17                                                                                                                                                | -8.5<br>-8.5<br>-8.5               | -5<br>-5<br>-4       | $\mu\text{A}$<br>$\mu\text{A}$<br>$\mu\text{A}$ |                                |

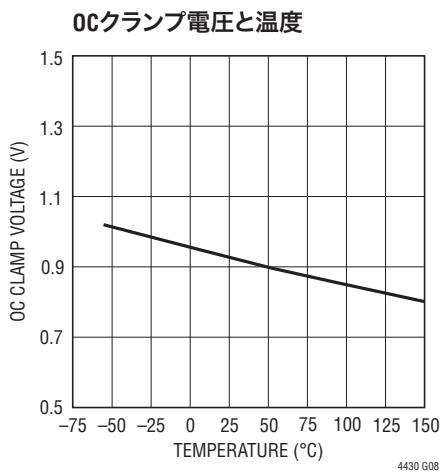

|           | OC Clamp Voltage                      |                                                                                                                                                                                                                            |                                                                                                                                                                  | 0.93                               |                      | V                                               |                                |

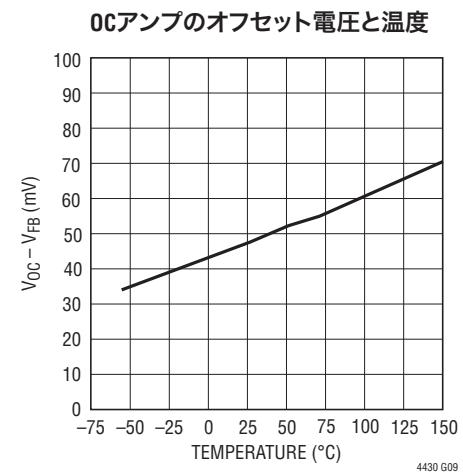

|           | OC Amplifier Offset Voltage           | $FB = 0.3\text{V}$                                                                                                                                                                                                         |                                                                                                                                                                  | 48                                 |                      | mV                                              |                                |

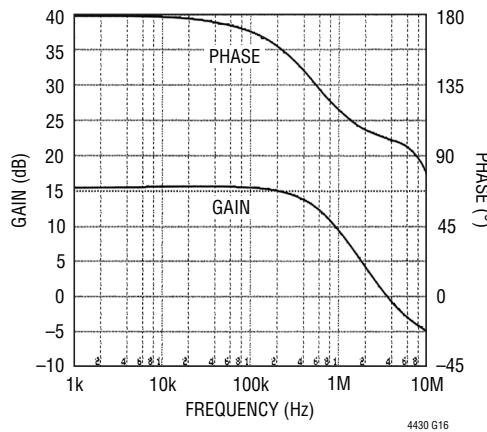

| $A_{VOL}$ | Error Amplifier Open-Loop DC Gain     | $V_{COMP} = 0.8\text{V}$ to $1\text{V}$ (E-, I-Grades)<br>$V_{COMP} = 0.8\text{V}$ to $1\text{V}$ (H-, MP-Grades)                                                                                                          | 60<br>55                                                                                                                                                         | 80<br>80                           |                      | dB<br>dB                                        |                                |

|           | Error Amplifier Unity-Gain Bandwidth  | No Load (Note 4)                                                                                                                                                                                                           |                                                                                                                                                                  | 9                                  |                      | MHz                                             |                                |

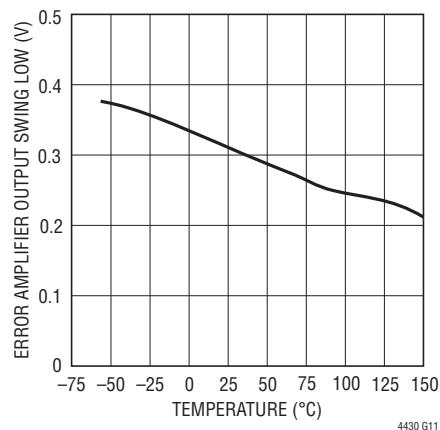

|           | Error Amplifier Output Swing Low      | $FB = 1\text{V}$                                                                                                                                                                                                           | 0.1                                                                                                                                                              | 0.35                               | 0.55                 | V                                               |                                |

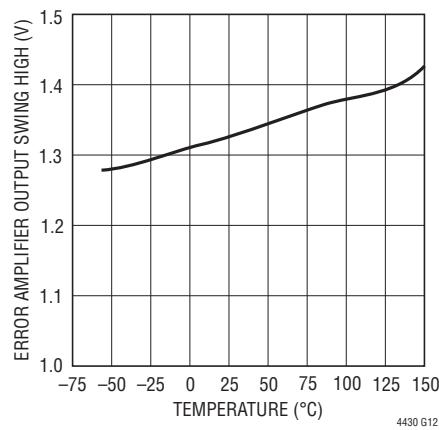

|           | Error Amplifier Output Swing High     | $FB = 0\text{V}$ (E-, I-Grades)<br>$FB = 0\text{V}$ (H-Grade)<br>$FB = 0\text{V}$ (MP-Grade)                                                                                                                               | 1.2<br>1.2<br>1.15                                                                                                                                               | 1.33<br>1.33<br>1.33               | 1.5<br>1.55<br>1.55  | V<br>V<br>V                                     |                                |

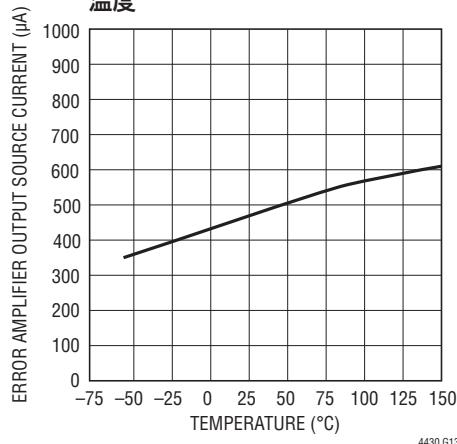

|           | Error Amplifier Output Source Current | $FB = 0\text{V}$ , $COMP = 1\text{V}$ (E-, I-Grades)<br>$FB = 0\text{V}$ , $COMP = 1\text{V}$ (H-Grade)<br>$FB = 0\text{V}$ , $COMP = 1\text{V}$ (MP-Grade)                                                                | -800<br>-825<br>-825                                                                                                                                             | -450<br>-450<br>-450               | -225<br>-225<br>-200 | $\mu\text{A}$<br>$\mu\text{A}$<br>$\mu\text{A}$ |                                |

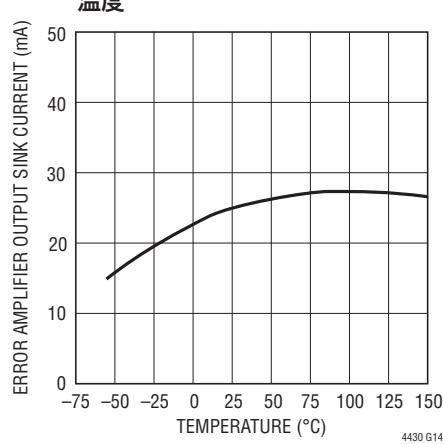

|           | Error Amplifier Output Sink Current   | $FB = 1\text{V}$ , $COMP = 1\text{V}$                                                                                                                                                                                      |                                                                                                                                                                  | 25                                 |                      | mA                                              |                                |

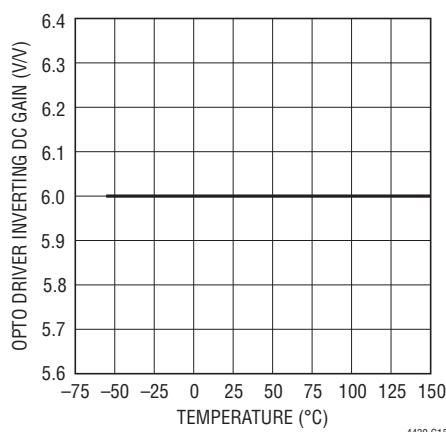

|           | Opto Driver Inverting DC Gain         |                                                                                                                                                                                                                            | -6.4                                                                                                                                                             | -6                                 | -5.6                 | V/V                                             |                                |

|           | Opto Driver -3dB Bandwidth            | No Load (Note 4)                                                                                                                                                                                                           |                                                                                                                                                                  | 600                                |                      | kHz                                             |                                |

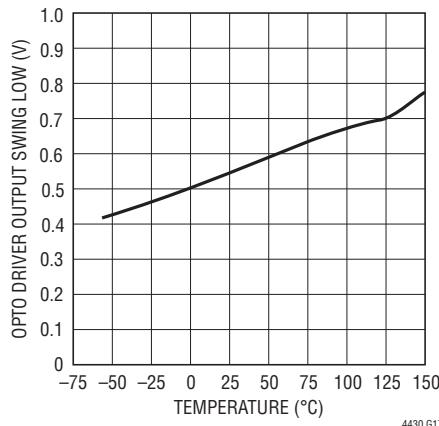

|           | Opto Driver Output Swing Low          | $FB = 0\text{V}$ , $COMP = \text{Open}$ (E-, I-Grades)<br>$FB = 0\text{V}$ , $COMP = \text{Open}$ (H-, MP-Grade)                                                                                                           | 0.5<br>0.5                                                                                                                                                       | 0.85<br>0.9                        |                      | V<br>V                                          |                                |

|           | Opto Driver Output Swing High         | $V_{IN} = 3\text{V}$ , $FB = 1\text{V}$ , $COMP = \text{Open}$ ,<br>$I_{OPTO} = 10\text{mA}$ (E-, I-, H-Grades)<br>$V_{IN} = 3\text{V}$ , $FB = 1\text{V}$ , $COMP = \text{Open}$ ,<br>$I_{OPTO} = 10\text{mA}$ (MP-Grade) | $V_{IN} - 1.25$<br>$V_{IN} - 1.3$                                                                                                                                | $V_{IN} - 1.05$<br>$V_{IN} - 1.05$ |                      | V<br>V                                          |                                |

|           | Opto Driver Output Swing High         | $V_{IN} = 20\text{V}$ , $FB = 1\text{V}$ , $COMP = \text{Open}$ ,<br>$I_{OPTO} = 10\text{mA}$                                                                                                                              | 4.2                                                                                                                                                              | 5.6                                | 7.5                  | V                                               |                                |

|           | $I_{SC}$                              | Opto Driver Output Short-Circuit Current (Sourcing)                                                                                                                                                                        | $FB = 1\text{V}$ , $COMP = \text{Open}$ , $OPTO = 0\text{V}$<br>(E-, I-, H-Grades)<br>$FB = 1\text{V}$ , $COMP = \text{Open}$ , $OPTO = 0\text{V}$<br>(MP-Grade) | 10.5<br>9.5                        | 22<br>22             | 45<br>45                                        | mA<br>mA                       |

|           |                                       | Opto Driver Output Sink Current                                                                                                                                                                                            | $FB = 0\text{V}$ , $OPTO = 1.5\text{V}$ (E-, I-, H-Grades)<br>$FB = 0\text{V}$ , $OPTO = 1.5\text{V}$ (MP-Grade)                                                 | 150<br>135                         | 350<br>350           | 650<br>650                                      | $\mu\text{A}$<br>$\mu\text{A}$ |

**Note 1:**絶対最大定格に記載された値を超えるストレスはデバイスに永続的損傷を与える可能性がある。長期にわたって絶対最大定格条件に曝すと、デバイスの信頼性と寿命に悪影響を与える可能性がある。

**Note 2:**LT4430は、 $T_J$ が $T_A$ にほぼ等しいバ尔斯負荷条件下でテストされている。LT4430Eは $0^\circ\text{C}$ ～ $125^\circ\text{C}$ の接合部温度で性能仕様に適合することが保証されている。 $-40^\circ\text{C}$ ～ $125^\circ\text{C}$ の動作接合部温度範囲での仕様は設計、特性評価および統計学的なプロセス・コントロールとの相関で確認されている。LT4430Hは $-40^\circ\text{C}$ ～ $125^\circ\text{C}$ の動作接合部温度範囲で保証されており、LT4430MPは $-40^\circ\text{C}$ ～ $150^\circ\text{C}$ の動作接合部温度範囲で保証されている。LT4430MP

は $-55^\circ\text{C}$ ～ $150^\circ\text{C}$ の動作接合部温度範囲でテストされて仕様が保証されている。高い接合部温度は動作寿命に悪影響を及ぼす。接合部温度が $125^\circ\text{C}$ を超えると、動作寿命は短くなる。これらの仕様と調和する最大周囲温度は、基板レイアウト、パッケージの定格熱抵抗などの環境要因と関連した特定の動作条件によって決まることに注意。

**Note 3:**デバイス・ピンに入る電流はすべて正である。デバイス・ピンから流れ出る電流はすべて負である。注記がない限り、すべての電圧はGNDを基準にしている。

**Note 4:**このパラメータは相関で保証され、テストされていない。

## 標準的性能特性

## 標準的性能特性

エラーアンプの開ループ利得

および位相と周波数

エラーアンプの出力振幅の“L”

レベルと温度

エラーアンプの出力振幅の“H”

レベルと温度

エラーアンプの出力ソース電流と

温度

エラーアンプの出力シンク電流と

温度

オプト・ドライバの反転DC利得と

温度

オプト・ドライバの反転閉ループ

利得および位相と周波数

## 標準的性能特性

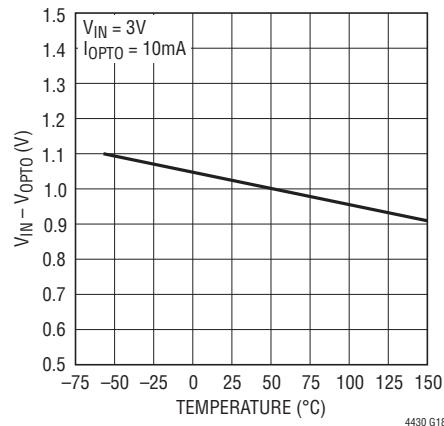

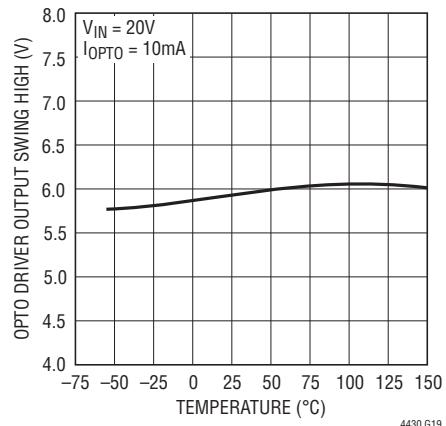

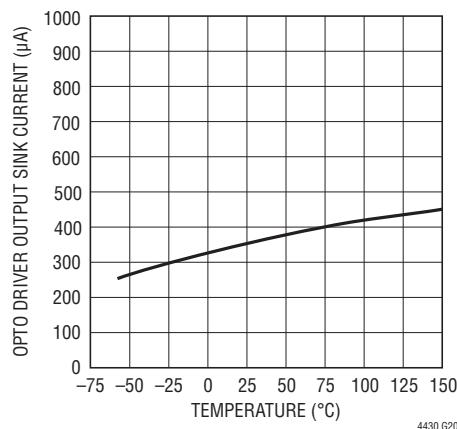

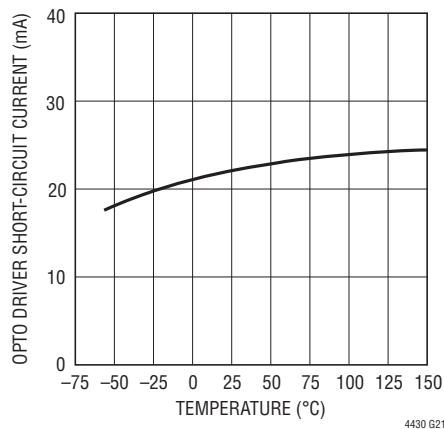

オプト・ドライバの出力振幅の

“L”レベルと温度オプト・ドライバの出力振幅の

“H”レベルと温度オプト・ドライバの出力振幅の

“H”レベルと温度オプト・ドライバの

出力シンク電流と温度オプト・ドライバの出力短絡電流

(ソース)と温度

## ピン機能

**V<sub>IN</sub>(ピン1)**:すべての内部回路に電力を供給する入力電源です。入力電源範囲は最小3Vから最大20Vまで、標準入力消費電流は1.9mAです。V<sub>IN</sub>からGNDに1μFのバイパス・コンデンサを直接接続します。

**GND(ピン2)**:アナログ・グランド・ピン。これは内部0.6Vリファレンスの負のセンス端子でもあります。最高のレギュレーションと性能を得るため、グランドに終端する外付け帰還分割器ネットワークはこのピンに直接接続します。

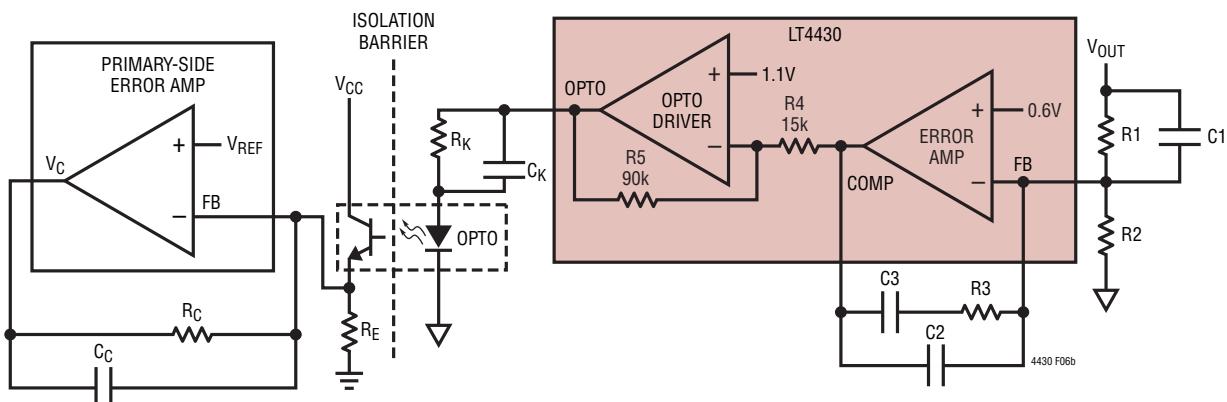

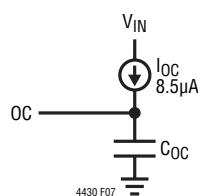

**OC(ピン3)**:オーバーシュート制御ピン。標準8.5μAの電流源とこのピンからGNDに接続されたコンデンサによって、起動時および短絡からの回復時の出力電圧のオーバーシュートを制御します。標準ランプ時間は( $C_{OC} \cdot 0.6V$ )/8.5μAです。V<sub>IN</sub>が(その低電圧ロックアウト・スレッショルドである)V<sub>UVLO</sub>を下回ると、OCピンはアクティブに“L”に保たれます。OCピンはオーバーシュート制御アンプの出力にも接続されます。このアンプはFBピン電圧とエラーアンプの出力をモニタします。短絡フォールト状態によってFBが“L”になると、COMPピンは“H”になります。ロジックによってエラーアンプのCOMPピンの“H”状態が検出され、オーバーシュート制御アンプが起動されます。このアンプは、OCコンデンサをFB電圧に48mVの内部オフセット電圧を加えた値まで放電します。短絡状態が持続すると、アンプはOCの電圧を維持します。短絡状態が解消されると、FBピンは再度OCピンによって制御されます。

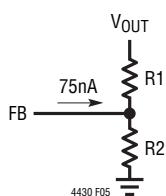

**FB(ピン4)**:これはエラーアンプの反転入力です。非反転入力は内部0.6Vリファレンスに接続されています。このピンから流れ出す入力バイアス電流は標準で75nAです。通常、このピンは抵抗分割器ネットワークに接続して出力電圧を設定します。最高のレギュレーション性能を得るには、外付け抵抗分割器の上側を出力電圧に直接接続します。

**COMP(ピン5)**:これはエラーアンプの出力です。エラーアンプは真の電圧モードのエラーアンプであり、周波数補償はアンプの周辺で行われます。標準的なLT4430の補償手法では、COMPピンからFBピンに、コンデンサと並列接続した直列R-Cネットワークを接続します。COMPは、COMPピンが高クランプ・レベルであるかどうかを検出するオーバーシュート制御アンプ・ロジックにも接続します。このロジックは、COMPが1μs以上クランプ・レベルを保つと、オーバーシュート制御アンプをアクティブにします。

**OPTO(ピン6)**:これはオプトカプラをドライブするアンプの出力です。オプト・ドライバ・アンプは反転利得6の構成を使用し、グランドを基準にオプトカプラをドライブします。GNDを基準にしてオプトカプラをドライブすることによって、低出力電圧に対応でき、従来の「431」トポロジーを用いる2次帰還バスが必要になるのでループ周波数補償が容易になります。オプト・ドライバ・アンプは最大10mAをソースし、標準で350μAをシンクすることができ、短絡保護されています。

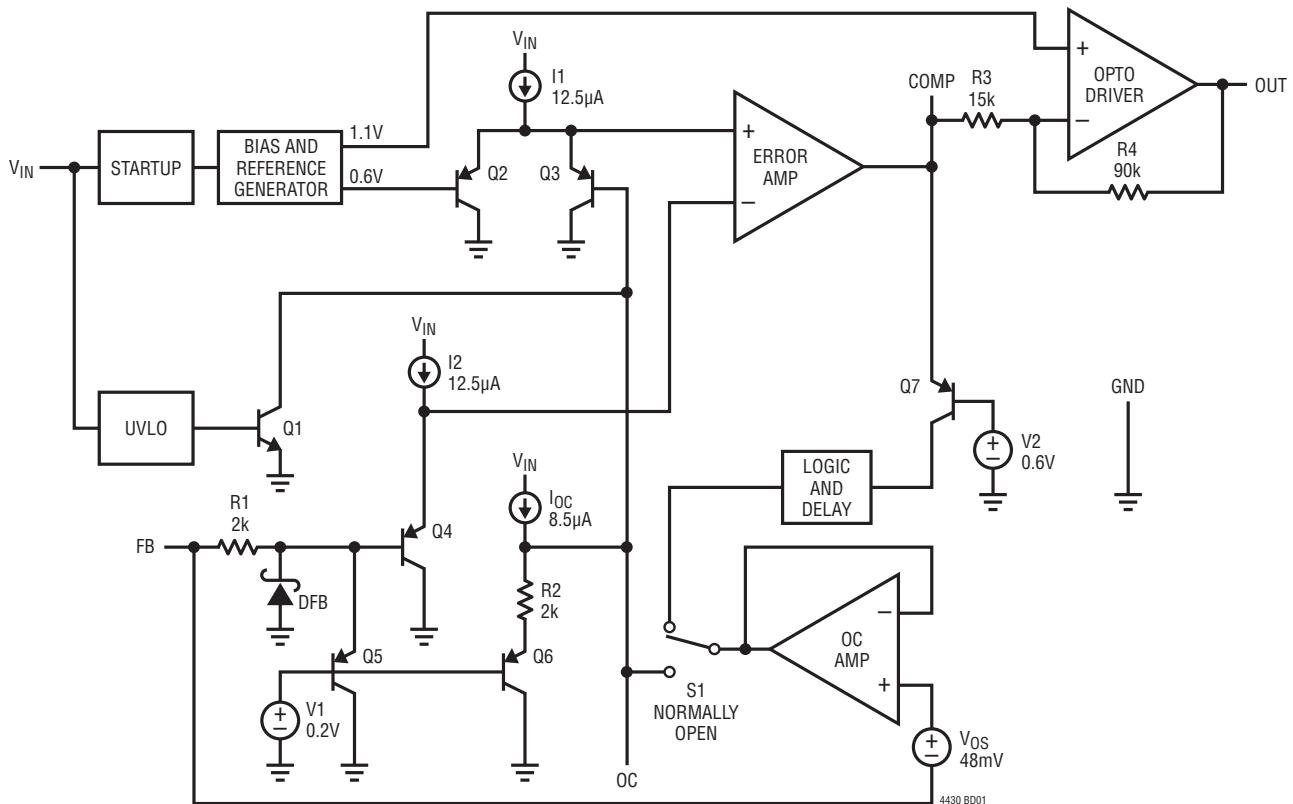

## ブロック図

## アプリケーション情報

### ブロック図の動作

LT4430は、高精度電圧リファレンス、広帯域幅エラーアンプ、反転オプトカプラ・ドライバ、およびオーバーシュート制御アンプで構成されます。ブロック図を参照すると、起動回路によってデバイスのすべての内部電流と電圧バイアスが生成されます。高精度に調整されたバンドギャップによって、オプトカプラ・ドライバの600mVのリファレンス電圧と1.1Vのバイアス電圧が生成されます。室温のリファレンス電圧の精度は±0.75%に規定され、動作温度範囲の許容誤差は±1.25%に規定されています。600mVのリファレンスはエラーアンプの非反転入力に接続されています。

LT4430のエラーアンプは外付けの抵抗分割器によって出力電圧をセンスし、FBピンを600mVに安定化します。FBピンはエラーアンプの反転入力に接続されています。エラーアンプの開ループDC利得は80dBで、ユニティゲインのクロスオーバー周波数は9MHzなので、標準的な帰還ループのクロスオーバー周波数での位相シフトは無視できます。エラーアンプは真の電圧モードのアンプであり、周波数補償回路はアンプの周辺に接続されます。標準的なLT4430の補償手法では、COMPピンからFBピンに、コンデンサと並列接続した直列R-Cネットワークを接続します。

オプトカプラ・ドライバは、COMPピンと反転利得6の非反転端子に印加される1.1Vのバイアス電位の電圧差を増幅します。この信号はGNDを基準にしてオプトカプラをドライブします。GNDを基準にしてオプトカプラをドライブすることによって、低出力電圧に対応でき、従来の「431」トポロジーを用いる2次帰還パスが不要になるのでループ周波数補償が容易になります。オプトカプラと直列に接続された抵抗によって、オプトカプラのDCバイアス電流が設定されます。オプト・ドライバ・アンプは10mAの保証最大電流をソースし、標準で350μAをシンクすることができ、短絡保護されています。オプトカプラ・ドライバ・アンプの標準-3dB帯域幅は600kHzです。オプトカプラの出力がガルバニック絶縁バリアを横切ると、1次側コントローラへの帰還ループを閉じます。

LT4430は独自のオーバーシュート制御機能を備えており、起動時および短絡状態からの回復時に出力電圧をランプさせることによって、オーバーシュートを防止することができます。

OCピンからGNDにコンデンサを接続して8.5μAの内部電流源 $I_{OC}$ で充電することによって、ランプ・レートが設定されます。起動時に、LT4430の $V_{IN}$ が2.2Vの標準的な低電圧ロックアウト・スレッショルドに達するまで、Q1はアクティブにOCコンデンサを低電圧に保ちます。その後、Q1がオフしてOCコンデンサは直線的に充電されます。Q2とQ3は、エラーアンプの非反転端子でOCピン電圧と600mVのリファレンス電圧の論理和をとります。OCピン電圧は、600mVを上回るまではエラーアンプのリファレンス電圧です。帰還ループの制御時には、FBピン電圧はOCピン電圧に従って安定化されます。OCピン電圧が600mVを上回ると、リファレンス電圧がエラーアンプを制御し、FBピンは600mVに安定化されます。OCピン電圧は、R2、Q6、V1によって内部でクランプされるまで上昇します。OCピンの0.93Vの標準クランプ電圧はQ3を確実にオフする電圧です。Q2を流れるI1の全電流は、Q4を流れるI2の電流と一致します。

短絡状態では、出力電圧は安定化レベルをかなり下回る値まで低下します。エラーアンプはCOMPピン電圧を上昇させており、オプトカプラのドライブが低下します。オプトカプラのバイアスが低下すると、1次側コントローラが供給する電力量を増加させて、出力電圧が上昇して安定化された値に戻るようにします。フォールト状態が続く限り、出力電圧は低いままです。エラーアンプのCOMPピン電圧は、Q7とV2によって設定されるクランプ・レベルに達するまで上昇します。Q7に生じるコレクタ電流は、通常はオープンのスイッチS1を閉じる内部ロジックをドライブします。この動作によって、ユニティゲイン・フォロワ構成のオーバーシュート制御アンプが起動します。オーバーシュート制御アンプはFBピン電圧をモニタし、S1を閉じるときに、FBピン電圧に標準48mVの内部オフセット電圧を加えた値までOCピン電圧を下げます。内部オフセット電圧には2つの役割があります。1つ目は、オフセット電圧があることで、オーバーシュート制御アンプが通常の過渡動作状態に干渉するのを防止します。2つ目は、短絡状態が終了すると、帰還ループが直ちに開始して出力電圧が安定化された値まで上昇するように、オフセット電圧は帰還ループをバイアスします。

## アプリケーション情報

フォールト状態が終了すると、出力電圧は上昇します。それに 対して、エラーアンプのCOMPピン電圧は低下します。この動作によってスイッチS1が開き、オーバーシュート制御アンプが停止してOCピンのコンデンサが充電されます。FBピン電圧は、OCピン電圧を超える値まで直ちに上昇します。帰還ループは、FBピンがOCピン電圧に従って安定化されるまでオプトカプラのドライブを向上させます。また、OCピン電圧が600mVを上回ると、リファレンス電圧がエラーアンプを制御し、FBピンは600mVに安定化されます。

### V<sub>IN</sub>バイアス電源の生成

適正に動作させるにはLT4430のバイアスが重要になります。オーバーシュート制御(OC)機能が使用されず、出力電圧が3.3Vを上回る場合、デバイスはV<sub>OUT</sub>からバイアスすることができます。これらの場合、大信号の起動とフォールトからの回復動作を確認しなければなりません。

オーバーシュート制御機能が使用されるか、または出力電圧がLT4430の最小動作電圧(3V)を下回る場合、代わりのバイアス手法を使用する必要があります。LT4430の低電圧ロックアウト(UVLO)回路は、V<sub>IN</sub>によって制御され、V<sub>IN</sub>が2.2Vを下回ると、OCピンのコンデンサがリセットされ低電圧に保たれます。V<sub>IN</sub>が2.2Vを上回ると、この回路はOCピンのコンデンサを開放します。ループ制御をアサートし、出力電圧のオーバーシュートを抑えるため、LT4430の電源電圧は出力電圧よりも早く立ち上がる必要があります。ほとんどの場合、少数のシンプルな部品でこれを実現できます。少数のバイアス部品を追加してオーバーシュートを制御するのが有効です。様々なトポロジーのバイアス回路を検討してみましょう。

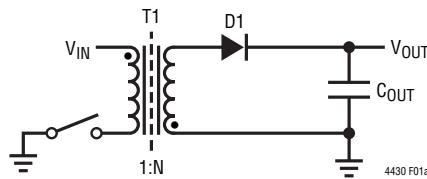

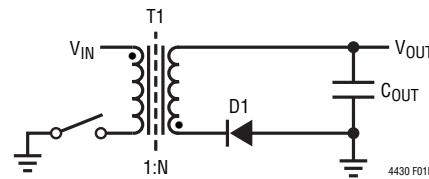

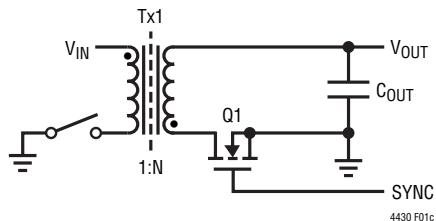

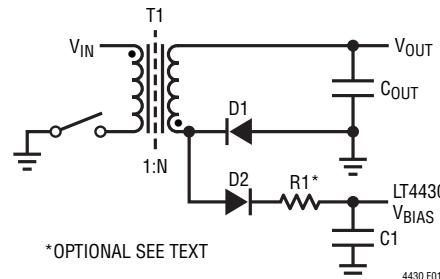

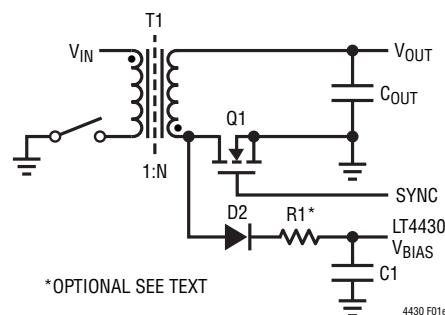

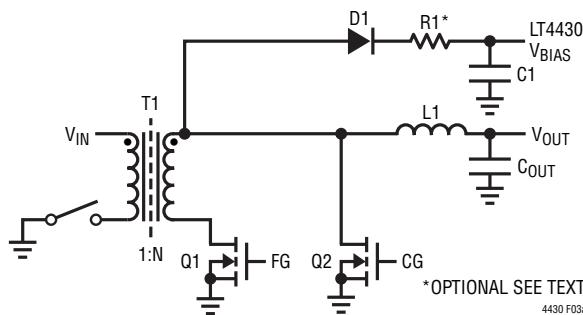

図1a～図1eは、フライバック・コンバータのバイアス電源回路を示します。図1aは標準的なフライバック出力の接続を示します。図1bおよび図1cは等価回路の動作を示しますが、整流器がグランド基準側に対して反転しています。この接続によって、トランジスタの1次側のスイッチがオンしたときの2次側の順方向動作を利用することができます。

図1dおよび図1eはバイアス・ジェネレータ回路を示します。1次側のスイッチがオンになると、2次巻線の両端にV<sub>IN</sub>・Nボルトが生じます。D2は順方向にバイアスしてC1を充電します。この間、2次側電圧はV<sub>OUT</sub>と直列になり、C1は最終的に(V<sub>IN</sub>・N + V<sub>OUT</sub>-V<sub>F</sub>)まで充電されます。V<sub>F</sub>はD2の順方向電圧です。起動時にV<sub>OUT</sub>がゼロの場合、V<sub>IN</sub>・Nボルトが生じてC1が充電されます。C1は通常、C<sub>OUT</sub>よりもはるかに小さな値で、バイアス電源はV<sub>OUT</sub>より先に起動します。図1dと図1eのR1がピーク充電電流を抑えるので、D2の電流定格を小さくできます。またR1は、2次巻線のリーカー・インダクタンスによって誘起される電圧スパイクに対してC1がピーク充電されないようにします。通常、1Ω～10Ωで十分です。C1が低ESRのセラミック・コンデンサであるか、またはトランジスタのリーカー・インダクタンスが大きい場合、通常、R1は必要です。C1が低価格、高ESRの表面実装タンタル・コンデンサの場合には、R1を削除することができます。

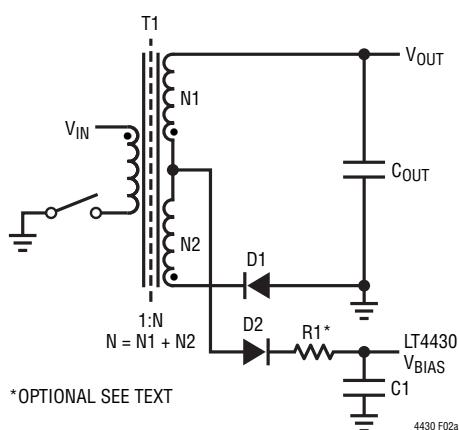

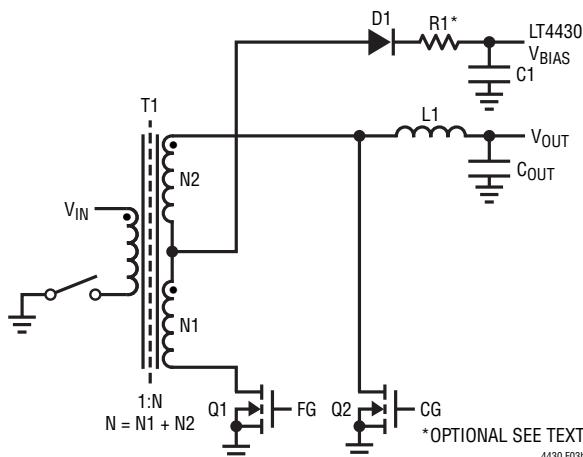

図1dのバイアス電源はV<sub>IN</sub>の変動によって変化します。V<sub>OUT</sub>、トランジスタの巻数比N、V<sub>IN</sub>の範囲によっては、バイアス電源はLT4430のV<sub>IN</sub>の絶対最大定格20Vを超えることがあります。これが生じる場合には、2つの解決策があります。1つは図2aに示すように、2次側のインダクタにタップを設けて低い電圧を生成し、ここから整流します。バイアス電圧は(V<sub>IN</sub>・N1/N+V<sub>OUT</sub>-V<sub>F</sub>)まで低下します。この解決策は、2次側にタップ点に使用できるピンがあることが基本です。

## アプリケーション情報

図1a. 標準的なフライバック・コンバータの接続

図1b. 等価フライバック・コンバータの接続

図1c. 同期整流式フライバック・コンバータの接続

図1d. バイアス・ジェネレータ付きフライバック・コンバータ

図1e. バイアス・ジェネレータ付き同期整流式フライバック

## アプリケーション情報

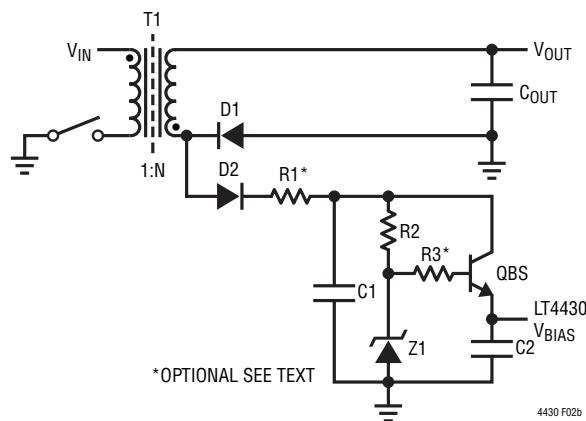

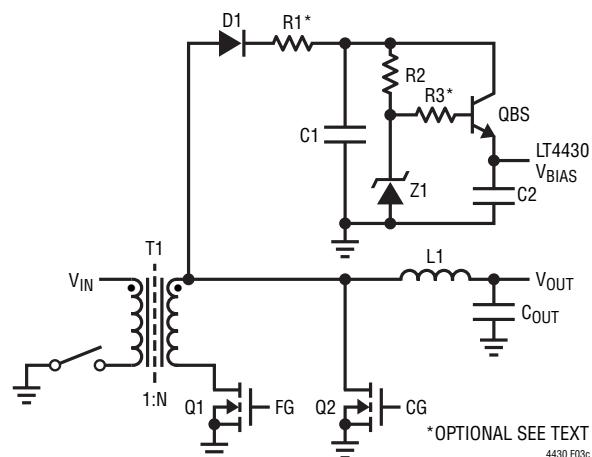

2つ目の解決策は図2bに示すように、プレレギュレータを構成することです。この例では、バイアス電源は( $V_{Z1}-V_{BE}$ )に等しくなります。ツエナー・ダイオードZ1をバイアスしてQBSにベース電流を供給するようにR2を選択します。Q5のベースと直列に(数百オーム程度の)抵抗R3を接続することによって、QBSの選択により生じる可能性がある高周波発振が抑えられます。このプレレギュレータ回路には完全同期整流式コンバータ用にさらに有用性があります。完全同期整流式コンバータは、2次側MOSFETのオン/オフを制御するゲート・ドライバを

必要とします。ゲート・ドライバ回路には、ゲート・ドライバの電源電圧、MOSFETのサイズ、スイッチング周波数に応じて10mA～100mAの範囲の消費電流が必要です。特に、ゲート・ドライバが一般的に5V～12Vの電源電圧を使用するので、プレレギュレータのバイアス電源はLT4430とゲート・ドライバ回路の両方の電力供給に最適です。プレレギュレータ回路は、完全同期整流式フォワード・コンバータ、プッシュプル・コンバータ、フルブリッジ・コンバータで広く使用されています。

図2a. 2次バイアス・タップ付きフライバック・コンバータ

図2b. プレレギュレータ・バイアス付きフライバック・コンバータ

## アプリケーション情報

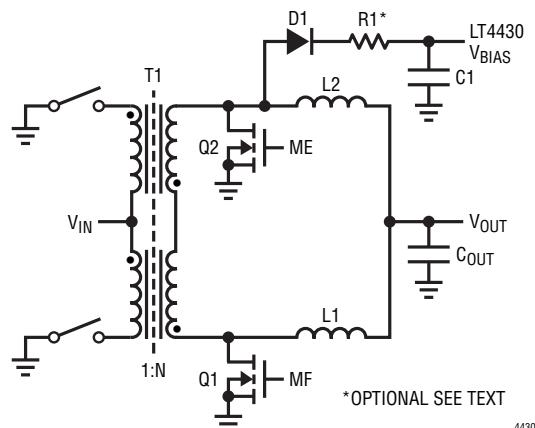

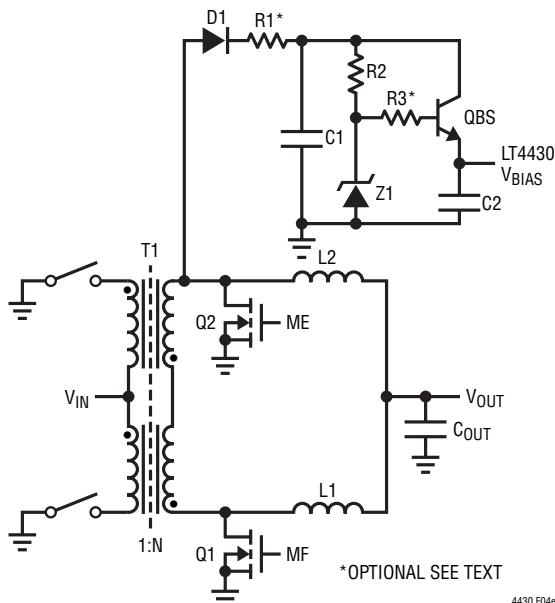

フライバック・コンバータと同様な技法を使用してフォワード・コンバータのバイアス電源を生成します。同期整流式シングル・スイッチ・フォワード・コンバータに共通の、3つのバイアス回路の詳細を図3a～図3cに示します。図1dのフライバック・コンバータでは、バイアス電源は $V_{IN}$ と $V_{OUT}$ に比例します。ただし、

フォワード・コンバータでは、L1があることによって $V_{OUT}$ からバイアス電源がデカップルされます。図3aでは、バイアス電源は $(V_{IN} \cdot N - V_F)$ に等しくなります。図3bでは、バイアス電源は $(V_{IN} \cdot N1/N - V_F)$ に等しくなります。図3cでは、バイアス電源は $(V_{Z1} - V_F)$ に等しくなります。

図3a. バイアス・ジェネレータ付き標準的シングル・スイッチ同期整流式フォワード・コンバータ

図3b. 2次バイアス・ジェネレータ・タップ付きシングル・スイッチ同期整流式フォワード・コンバータ

図3c. プレレギュレータ・バイアス・ジェネレータ付きシングル・スイッチ同期整流式フォワード・コンバータ

## アプリケーション情報

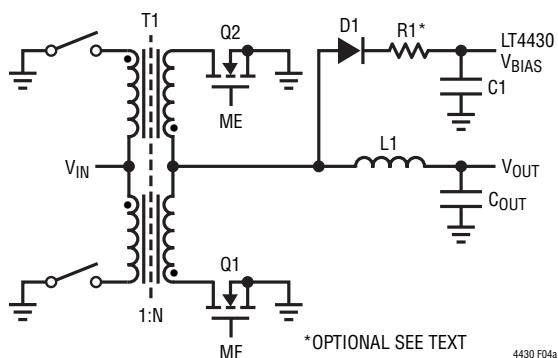

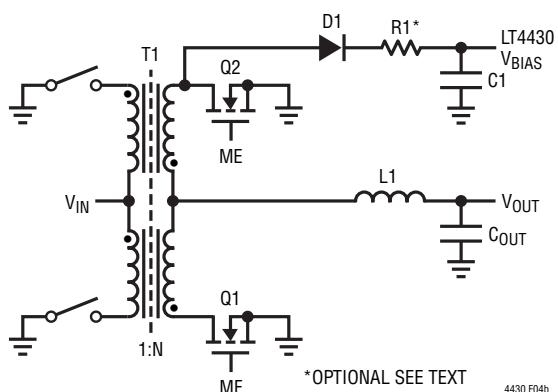

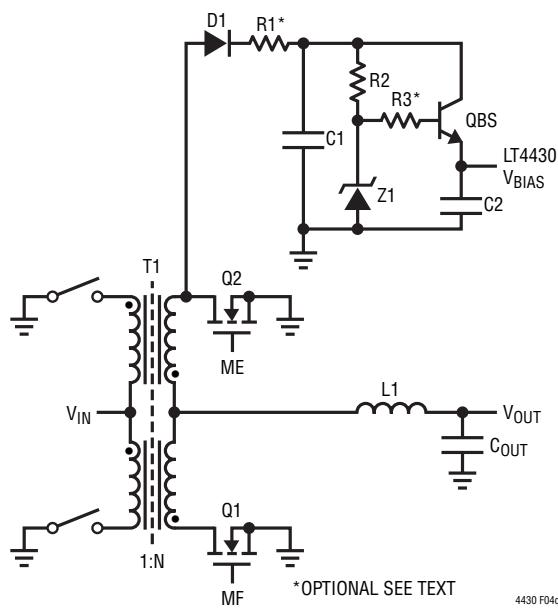

図4a～4dは完全同期整流式プッシュプル・トポロジーのバイアス電源回路を示します。フルブリッジ方式のバイアスは、1次側ドライブにおいて見られる明らかな違いを除けば、プッシュプル回路と同様です。図4aでは、バイアス電源は( $V_{IN} \cdot N - V_F$ )に等しくなります。図4bおよび図4dでは、バイアス電源は( $2 \cdot V_{IN} \cdot N - V_F$ )に等しくなります。図4cおよび図4eでは、バイアス電源は( $V_{Z1} - V_F$ )に等しくなります。

LT4430のアプリケーションでは一般に、簡単で低価格のバイアス方式の1つで十分です。ただし、設計に非常に広い入力電圧範囲などの制約がある場合、別のバイアス回路を採用しなければならないことがあります。その他のバイアス電源の生成手段には、追加のトランジストまたは出力インダクタ巻線、低価格のリニア・レギュレータ、ディスクリートまたはモノリシックのチャージポンプ、昇降圧レギュレータなどがあります。ただし、バイアス電源がこのように複雑になる場合、弊社のアプリケーション・エンジニアにお問い合わせいただければよりシンプルなソリューションを提供いたします。

図4a. バイアス・ジェネレータ付き標準的同期整流式

プッシュプル・コンバータ

図4b. 2倍バイアス・ジェネレータ付き標準的同期整流式

プッシュプル・コンバータ

## アプリケーション情報

図4c. プレレギュレータ・バイアス付き

標準的同期整流式プッシュプル・コンバータ

図4d. バイアス・ジェネレータ付き

標準的同期整流式プッシュプル電流

ダブル・コンバータ

図4e. プレレギュレータ・バイアス付き

標準的同期整流式プッシュプル電流

ダブル・コンバータ

## アプリケーション情報

## 出力電圧の設定

抵抗分割器帰還ネットワークを使用した電源の出力電圧の設定方法を図5に示します。R1の上側をV<sub>OUT</sub>に、R1/R2のタップ点をFBに接続し、R2の下側をLT4430のGNDに直接接続します。FBピンは600mVに安定化され、75nAの標準入力ピン・バイアス電流がピンから流れ出します。

出力電圧は次式で設定されます。

$$V_{OUT} = 0.6V \cdot (1 + R1/R2) - (75nA) \cdot R1$$

図5. 出力電圧の設定

## オプトカプラの帰還および周波数補償

ライン・レギュレーションおよびロード・レギュレーションが良好な絶縁型電源は、一般に次に方法を採用しています。高精度のリファレンス電位で出力電圧の検知と比較を行います。誤差信号を増幅して電源の制御回路にフィードバックし、検知誤差を補正します。制御回路が1次側にある場合、誤差信

号が絶縁バリアを横切るようにします。この信号の結合には、絶縁電位に耐え、さらにループ誤差信号を伝達する素子が必要です。

オプトカプラはDC信号を結合できるので広く使用されています。オプトカプラは通常、絶縁ギャップで分離された入力赤外線発光ダイオード(LED)と出力フォトトランジスタで構成されます。多くのオプトカプラのデータシートでは、入力ダイオード-出力トランジスタ間の利得つまり電流伝達率(CTR)が緩く規定されています。CTRは入力ダイオード電流、温度、時間(エージング)によって大きく変化します。LEDの輝度はエージングによって低下し、動作電流が大きいほど加速されます。CTRの変動はシステム全体のループ利得に直接影響するので、設計時にはすべての変動を考慮する必要があります。効率的な光検出器にするには、出力トランジスタの設計時に、光エネルギーを取り込むためにベース領域を最大限にします。この制約によって、コレクタ-ベース間容量が大きいトランジスタになります。この容量は、出力トランジスタの接続によっては、回路の性能に影響を与えることがあります。

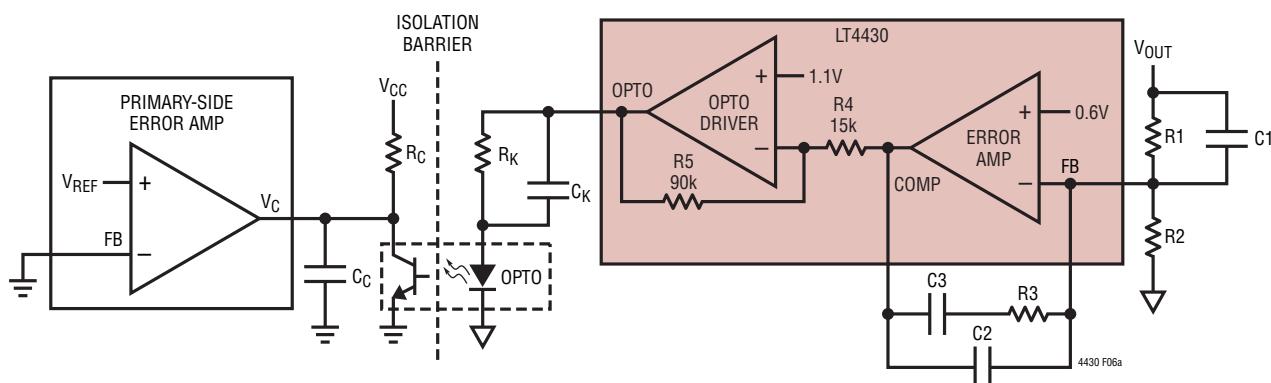

オプトカプラの出力トランジスタの2つの最も一般的なトポロジーは、共通エミッタと共通コレクタの構成です。出力トランジスタのコレクタを1次側コントローラのエラーアンプの出力に接続した、共通エミッタの設計を図6aに示します。

図6a. 共通エミッタ構成のオプトカプラを使用した周波数補償

## アプリケーション情報

この例では、エラーアンプは通常、高出力インピーダンスのトランスクンダクタンス・アンプで、 $R_C$ が $V_C$ ノードのインピーダンスを左右します。この帰還ループの周波数補償は出力トランジスタのコレクタ-ベース間容量に直接影響されます。この容量によって帰還ループにポールが生じるからです。このポールはトランジスタの動作条件によって大きく変化します。多くの場合、このポールによって達成可能なループ帯域幅が制限されます。出力トランジスタをカスケード接続すると、この容量の影響が大きく低減し、達成可能なループ帯域幅が拡大します。ただし、すべての設計にカスケード接続に必要な電圧ヘッドルームがあるわけでもなく、回路をさらに複雑にすることが許容できるわけではありません。出力電圧から1次側エラーアンプの出力までの開ループ伝達関数は以下のようになります。

$$\frac{V_C}{V_{OUT}} = \frac{-A \cdot \left( \frac{R2}{R1 + R2} \right) \cdot (1 + s \cdot R1 \cdot C1) \cdot (1 + s \cdot R3 \cdot C3)}{[s \cdot A \cdot R1 \cdot (C2 + C3)] \cdot \left( 1 + s \cdot R3 \cdot \frac{(C2 \cdot C3)}{(C2 + C3)} \right)} \cdot \\ 6 \cdot \frac{\left( 1 + s \cdot R_K \cdot C_K \right)}{\left( 1 + s \cdot \frac{(R_K \cdot R_D)}{(R_K + R_D)} \cdot C_K \right)} \cdot \frac{CTR \cdot R_C}{(R_K + R_D)} \cdot \\ \frac{1}{\left( 1 + s \cdot r_\pi \cdot \left[ \frac{(CTR \cdot R_C)}{(R_K + R_D)} \cdot C_{CB} + C_{BE} \right] \right)} \cdot \\ \frac{1}{(1 + s \cdot R_C \cdot C_C)}$$

ここで、

$A$  = LT4430の開ループDC利得

$R_D$  = オプトカプラ・ダイオードの小信号等価抵抗

$CTR$  = オプトカプラのAC電流伝達率

$C_{CB}$  = オプトカプラのコレクタ-ベース間非線形形容量

$C_{BE}$  = オプトカプラのベース-エミッタ間非線形容量

$r_\pi$  = オプトカプラのベース-エミッタ間小信号抵抗

図6aとこの伝達関数は設定できるポールとゼロのほとんどを示しており、完全性を考慮して表したもので、実際のアプリケーションでは、すべてのポールとゼロが使用されるとは限らないので、伝達関数はかなりシンプルになります。また、ポールとゼロの様々な組み合わせによって同じ小信号利得/位相特性になることがあります、大信号動作は大幅に異なります。

共通コレクタの構成では出力トランジスタのコレクタ-ベース間容量のミラー効果が取り除かれ、一般に、達成可能なループ帯域幅が拡大します。出力トランジスタのエミッタが1次側コントローラのエラーアンプの反転入力に接続された、共通コレクタの設計を図6bに示します。

図6b. 共通コレクタ構成のオプトカプラを使用した周波数補償

## アプリケーション情報

この例では、エラーアンプは通常、トランスインピーダンス・アンプとして構成される電圧エラーアンプです。オプトカプラのトランジスタのエミッタによって帰還情報がFBピンに直接供給され、FBからGNDに接続された抵抗 $R_E$ によってオプトカプラのDCバイアス条件が設定されます。出力電圧から1次側エラーアンプの出力までの開ループ伝達関数は以下のようになります。

$$\frac{V_C}{V_{OUT}} = \frac{-A \cdot \left( \frac{R_2}{R_1 + R_2} \right) \cdot (1 + s \cdot R_1 \cdot C_1) \cdot (1 + s \cdot R_3 \cdot C_3)}{[s \cdot A \cdot R_1 \cdot (C_2 + C_3)] \cdot \left( 1 + s \cdot R_3 \cdot \frac{(C_2 \cdot C_3)}{(C_2 + C_3)} \right)} \cdot \\ 6 \cdot \frac{(1 + s \cdot R_K \cdot C_K)}{\left( 1 + s \cdot \frac{(R_K \cdot R_D)}{(R_K + R_D)} \cdot C_K \right)} \cdot \frac{CTR \cdot R_C}{(R_K + R_D)} \cdot \\ \frac{1}{(1 + s \cdot r_\pi \cdot C_{BE})} \cdot \frac{1}{(1 + s \cdot R_C \cdot C_C)}$$

図6bとこの伝達関数は設定できるポールとゼロのほとんどを示しており、完全性を考慮して表したものです。実際のアプリケーションでは、すべてのポールとゼロが使用されるとは限らないので、伝達関数はかなりシンプルになります。

両方の構成とも、 $R_D$ 、 $CTR$ 、 $r_\pi$ 、 $C_{CB}$ 、 $C_{BE}$ の項は部品ごとにばらつき、また、バイアス電流によって値が変化します。ほとんどのオプトカプラでは、 $R_D$ は、1mAのDCバイアスで $50\Omega$ 、2mAのDCバイアスで $25\Omega$ です。 $CTR$ は小信号AC電流伝達率です。1つの例として、FairchildのMOC207オプトカプラは、ACの $CTR$ の値は約1ですが、1mAまたは2mAでバイアスされると、DCの $CTR$ はさらに小さくなります。ほとんどのオプトカプラのデータシートでは $C_{CB}$ 、 $C_{BE}$ 、 $r_\pi$ の項は規定されていないので、これらの値は実験値から求める必要があります。

この周波数補償の解説では、出力から1次側の制御ノードへの伝達関数のみを扱っています。帰還ループを完全に補償するには、この伝達関数と（一般に変調器と呼ばれる）電源処理回路の伝達関数を組み合わせる必要があります。絶縁型電源では、変調器の伝達関数は、トポロジー（フライバック、フォワード、ブッシュブル、ブリッジ）、電流モード制御か電圧モード制御か、不連続モードでの動作か連続モードでの動作か、入力/出力電圧、トランスの巻数比、出力負荷電流に依存します。様々な組み合わせに対する伝達関数の詳細はこのデータシートの範囲を超えます。ただし、電源を設計する際には、変調器の伝達関数の特徴を十分に調べて理解し、すべての動作条件に対する帰還ループの周波数補償を適正に行う必要があります。

### オプトカプラ

オプトカプラは様々なパッケージ・スタイルで供給され、性能基準には、絶縁定格、 $CTR$ 、出力トランジスタのブレークダウン電圧、出力トランジスタの電流容量、応答時間などがあります。表1にオプトカプラ・デバイスのいくつかの製造元を示しますが、これが全てではありません。

表1. オプトカプラの製造元

| VENDOR                  | PHONE          | URL                                                              |

|-------------------------|----------------|------------------------------------------------------------------|

| Agilent Technologies    | 800-235-0312   | <a href="http://www.agilent.com">www.agilent.com</a>             |

| Fairchild Semiconductor | 207-775-8100   | <a href="http://www.fairchildsemi.com">www.fairchildsemi.com</a> |

| Isocom                  | 214-495-0755   | <a href="http://www.isocom.com">www.isocom.com</a>               |

| Kodensi Korea Corp.     | 82-63-839-2111 | <a href="http://www.kodensi.co.kr">www.kodensi.co.kr</a>         |

| NEC                     | 81-44-435-1588 | <a href="http://www.ncsd.necel.com">www.ncsd.necel.com</a>       |

| Sharp Microelectronics  | 877-343-2181   | <a href="http://www.sharpsma.com">www.sharpsma.com</a>           |

| Toshiba                 | 949-455-2000   | <a href="http://www.toshiba.com">www.toshiba.com</a>             |

| Vishay                  | 402-563-6866   | <a href="http://www.vishay.com">www.vishay.com</a>               |

## アプリケーション情報

### オーバーシュート制御時間の設定

OCピンからGNDにコンデンサを接続することによってオーバーシュート時間を算出する方法を図7に示します。

オーバーシュート制御時間( $t_{OC}$ )は次式で設定されます。

$$t_{OC} = (C_{OC} \cdot 0.6V) / 8.5\mu A$$

オーバーシュート制御アンプを安定化する必要があるため、OCピンには最小100pFのコンデンサが必要です。これによって、通常、スイッチング・レギュレータの数サイクル程度に相当する、7μsの最小時間が得られます。最小限のコンデンサ値を使用すると、起動特性への影響は生じません。OCコンデンサを大きくすると、オーバーシュート制御時間が増加し、アンプの安定性のみが向上します。外部でOC充電電流を増大させるか、またはOCピンをドライブすることによってオーバーシュート制御時間を変調してはなりません。

図7. オーバーシュート制御時間の設定

### オーバーシュート制御(OC)コンデンサ値の選択

「周波数補償」の項で述べたように安定化のための帰還ループのポールとゼロの位置の設定において、設計での大幅な自由度が得られます。様々なポールとゼロの組み合わせによって同じ利得/位相特性になる可能性がありますが、大信号応答は著しく異なります。小信号応答と大信号応答の両方を最適にする周波数補償の値を選択するのは困難です。多くの場合は妥協値になります。

電源の起動時と短絡からの回復時はワーストケースの大信号の状態です。入力電圧特性および出力負荷特性は電源の動作に大きく影響します。それは電源が出力電圧を安定化させようとするからです。通常動作状態で応答を安定にする周波数補償の値は、起動時および短絡からの回復時には極度な出力電圧オーバーシュートを生じる可能性があります。大きなオーバーシュートは電力が供給されている負荷回路を損傷するか、または破壊することが多いので、望ましい特性ではありません。

LT4430のオーバーシュート制御回路に1個の外付けコンデンサ( $C_{OC}$ )を追加すると、小信号の周波数補償で妥協することなく、起動時と短絡からの回復時の応答を個別に制御できます。最適な $C_{OC}$ 値を選択することが簡単なテスト手順です。以下の説明と1組の写真によってこの手順を説明します。

OCピンのコンデンサの値を選択する前に、電源の残りの設計を完成させます。このプロセスには、選択した $V_{IN}$ バイアス・ジェネレータ・トポロジー(「アプリケーション情報」の項の前の部分を参照してください)の評価、およびすべての通常動作状態での周波数補償の最適化が含まれます。この設計段階の間、 $C_{OC}$ を最小値の100pFに設定します。これによって、オーバーシュート制御回路からの干渉をごくわずかにすることができます。これらの段階が完了したら、起動時および短絡からの回復時の波形をモニタするテストをセットアップします。このテストは出力負荷を軽くして行います。フルスルーレートの動作に続く軽負荷動作は、帰還ループの電力供給が最大から最小に移行するので、ワーストケースになります。

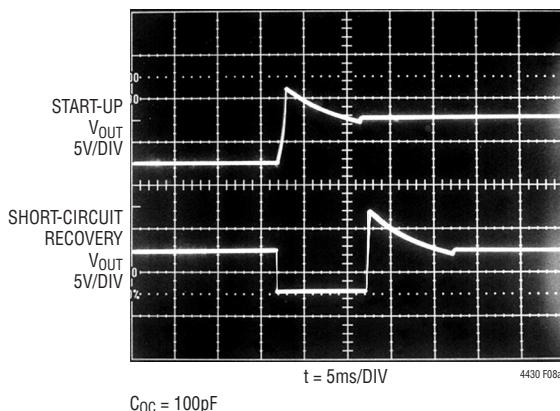

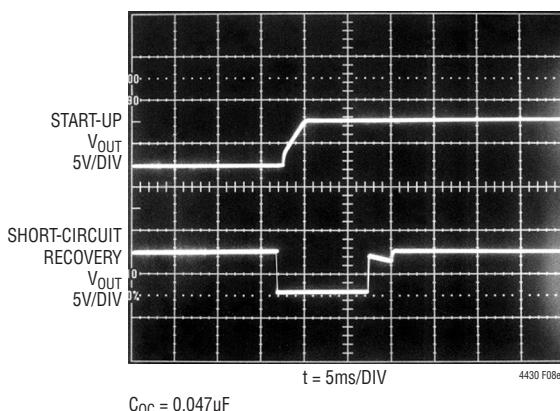

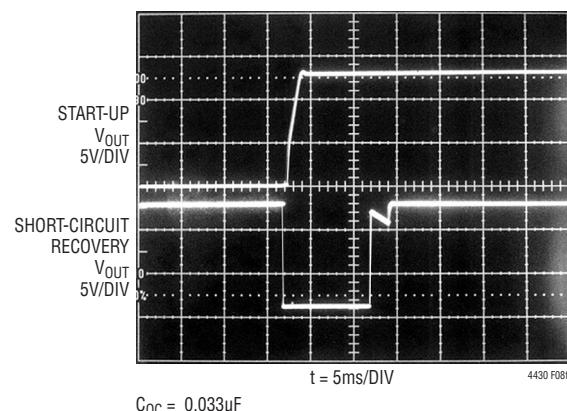

1つの例として、5V、2A絶縁型フライバック・コンバータを示す、最終ページの回路図を参照してください。以下の写真はすべて $V_{IN} = 48V$ 、 $I_{LD} = 20mA$ で撮影されたものです。図8aは、オーバーシュート制御補償なし( $C_{OC} = \text{最小}100pF$ )での、電源の起動時および短絡からの回復時の動作を示します。5V出力は、起動時および短絡からの回復時に、小信号の周波数補償値が控えめなため数ボルトだけオーバーシュートします。

## アプリケーション情報

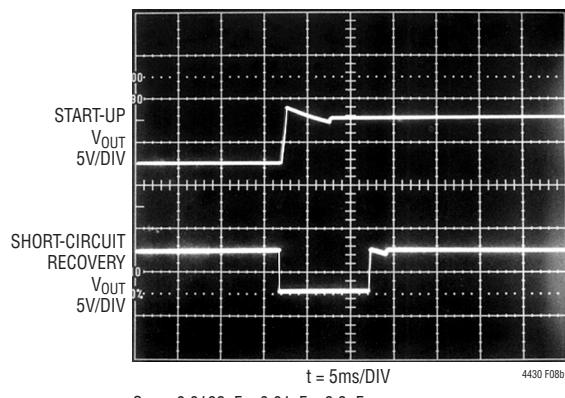

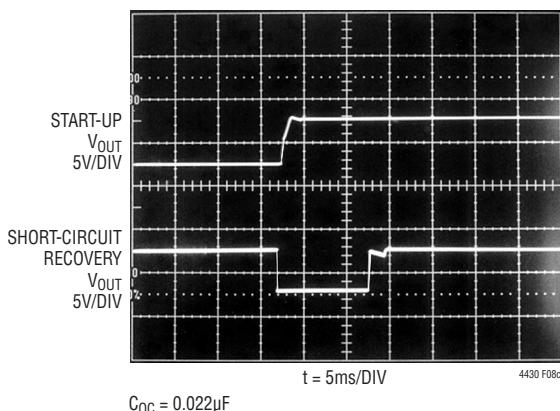

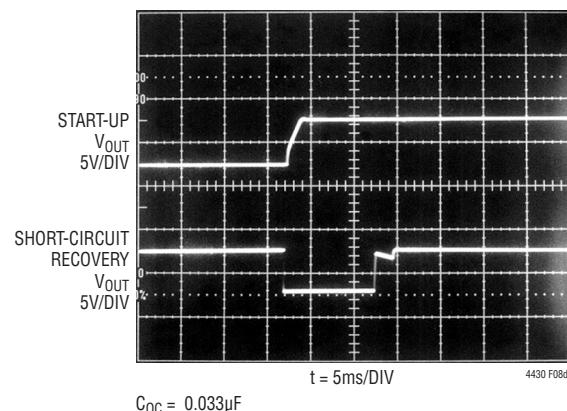

次に、C<sub>OC</sub>の値を大きくします。コンデンサの置き換えボックスを使用するか、または新しい値の各コンデンサを回路に半田付けします。起動時および短絡からの回復時の波形をモニタします。変化があるかを確認します。図8b～図8eは、C<sub>OC</sub>の値を大きくしたときの様子を示します。一般に、C<sub>OC</sub>の値を大きくするとオーバーシュートは減少します。

図8bのC<sub>OC</sub> = 0.0168μFでは、ループ特性に影響が出始めますが、起動時は約1.5Vのオーバーシュートのままでです。短絡からの回復時はかなり抑えられます。図8cのC<sub>OC</sub> = 0.022μFでは、起動時のオーバーシュートが0.5Vに抑えられ、短絡からの回復時は図8bと同様の状態です。図8dのC<sub>OC</sub> = 0.033μFでは、オーバーシュートは100mV以下になり、短絡からの回復時はもう少し抑えられます。図8eのC<sub>OC</sub> = 0.047μFでは、オーバーシュートはゼロになりますが、短絡からの回復時にさらに抑えられ遅延時間が長くなります。この例では、C<sub>OC</sub> = 0.033μFが起動時と短絡からの回復時の両方で最良の値になります。図8fは、波形のスケールを拡大したものです。C<sub>OC</sub>の値を選択したら、V<sub>IN</sub>電源の全範囲と出力負荷を大きくした状態で、起動時および短絡からの回復時の様子を確認します。必要に応じて値を変更します。

様々な設計での起動時および短絡からの回復時の波形は、この例に示す写真とは異なります。これらの波形に影響を与える要因には、選択する絶縁トポロジー、1次側および2次側のバイアス回路、入力/出力条件などがあります。たとえば、多くの絶縁型電源では、メイン・パワー・トランジスタの巻線が1次側制御回路の電源電圧を立ち上げます。短絡時には、1次側制御回路の電源電圧が急落し、リスタート・サイクルが発生します。したがって、短絡からの回復時は起動時と同様です。前述のフ

ライバックの例では、1次側制御回路は常にアクティブです。短絡時でもスイッチングは決して停止しません。LT4430のエラーアンプのCOMPピンは、起動時には低いクラップ・レベルから高い安定値に変化し、短絡からの回復時には高いクラップ・レベルから低い安定点に変化します。この大信号の動作から、起動時の波形と短絡からの回復時の波形に見られる違いが明らかになります。

解説の最後のポイントはC<sub>OC</sub>の値の選択です。設計時には、オーバーシュートを許容できるレベルに制御する値を使用することを推奨しますが、大きすぎてはなりません。電源の「ソフトスタート」機能のようなオーバーシュート制御機能を使用いたします。C<sub>OC</sub>を(オーバーシュートの制御に必要な値を上回る)大きな値にすると、必ずdV/dtの比率が小さくなつて起動時間が長くなります。ただし、C<sub>OC</sub>の値が大きいと、起動時または短絡からの回復時の帰還ループが失速し、出力電圧が「フラットスポット」になるほど時間が長くなることがあります。この棚状の電圧は出力電圧の中間の値で生じることがあり、電力が供給された負荷回路に異常な動作を起こさせます。所期のC<sub>OC</sub>値でこの状況が生じると、ソリューションに回路変更が必要になることがあります。特に、これらの出力電圧がフラットスポットになる間はスイッチングが停止するので、バイアス電源の保持時間は最も重要な問題点です。因みに、このLT4430の回路の目的は出力電圧オーバーシュートを制御して過大にならないようにすること(この機能がないと損傷や破壊を引き起こす)であり、電源のタイミング、シーケンスなどを制御することではありません。システム全体の要件に対して、電源によって生成されるどの波形を受け入れるかの基準の決定は、最終的にはユーザーに委ねられます。

## アプリケーション情報

図8a. 起動時および短絡からの回復時の波形

図8b. 起動時および短絡からの回復時の波形

図8c. 起動時および短絡からの回復時の波形

図8d. 起動時および短絡からの回復時の波形

図8e. 起動時および短絡からの回復時の波形

図8f.  $C_{OC} = 0.033\mu\text{F}$ を選択したときの拡大波形

## 標準的应用例

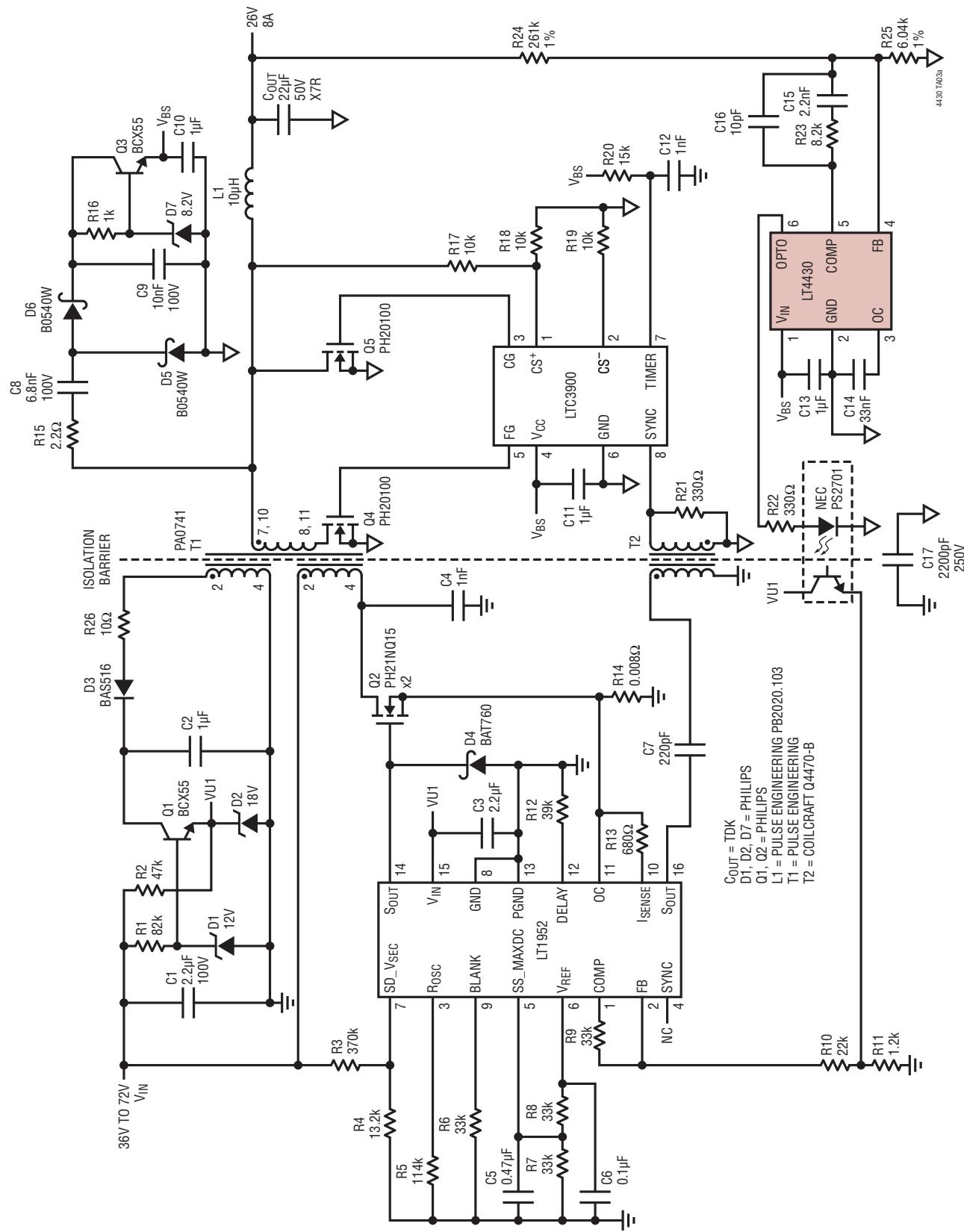

200W、26V、95%の効率のベース・ステーション・コンバータ

4430fc

## 標準的応用例

LTC3723-1の240W、42V～56V入力から12V/20Aの絶縁型1/4ブリッジ(2.3" × 1.45")

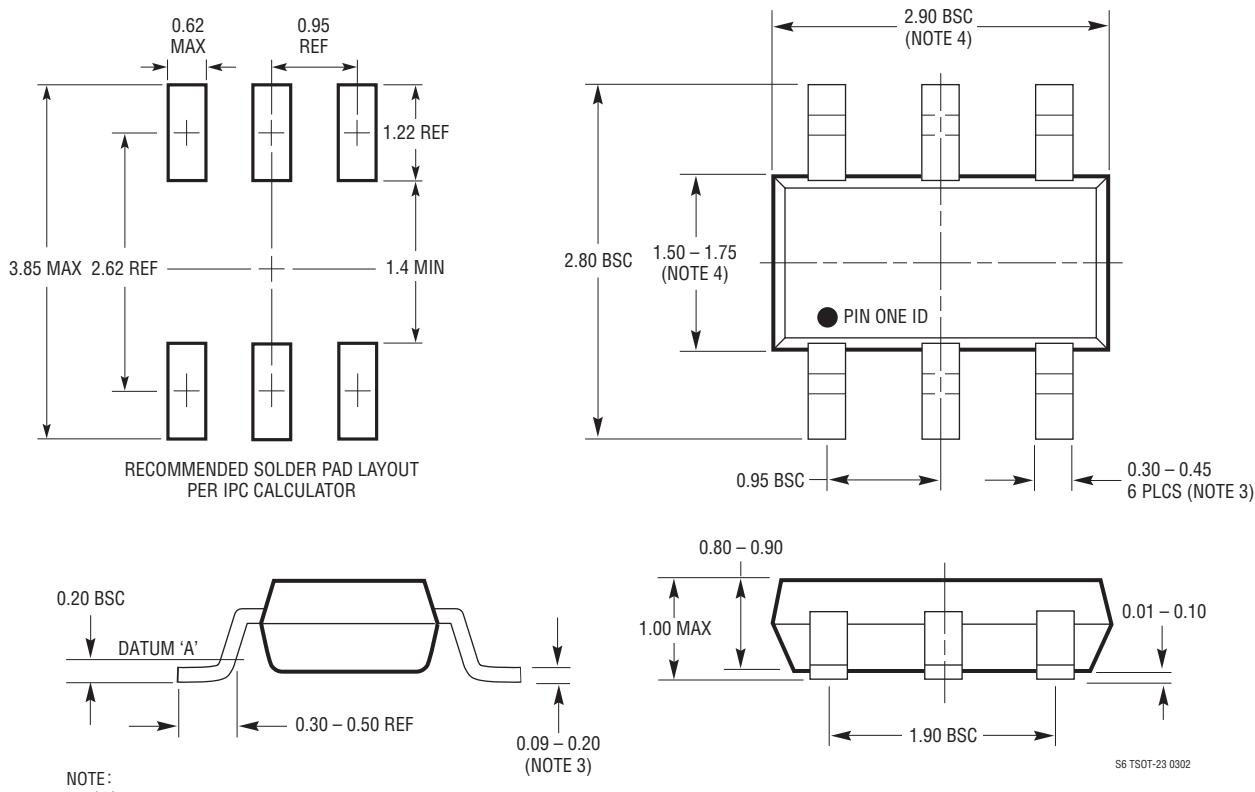

## パッケージ

最新のパッケージ図面は<http://www.linear-tech.co.jp/designtools/packaging>を参照してください。

**S6 Package**

**6-Lead Plastic TSOT-23**

(Reference LTC DWG # 05-08-1636)

NOTE:

- 寸法はミリメートル

- 図は実寸とは異なる

- 寸法にはメッキを含む

- 寸法にはモールドのバリやメタルのバリを含まない

- モールドのバリは0.254mmを超えてはならない

- パッケージのJEDEC参照番号はM0-193

## 改訂履歴 (改訂履歴はRev Bから開始)

| REV | 日付    | 概要                                          | ページ番号   |

|-----|-------|---------------------------------------------|---------|

| B   | 5/11  | HグレードとMPグレード・バージョンを追加、データシート全体に反映           | 1~26    |

| C   | 10/13 | 「ロック図」のQ2をNPNからPNPに修正<br>R24を26.1kから261kに変更 | 8<br>22 |

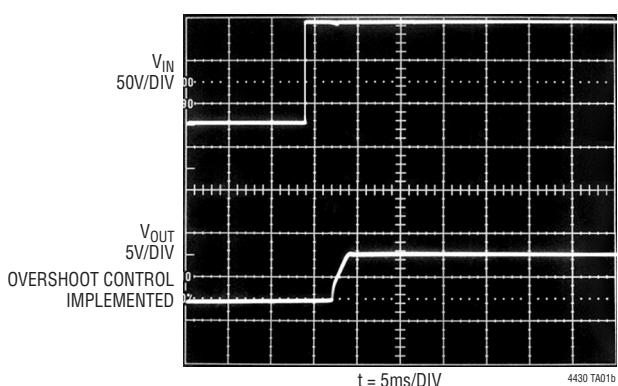

## 標準的応用例

オーバーシュート制御機能が実装されている場合と実装されていない場合の、5V、2A絶縁型フライバック・テレコム・コンバータの起動波形

## 関連製品

| 製品番号                            | 説明                                               | 注釈                                                             |

|---------------------------------|--------------------------------------------------|----------------------------------------------------------------|

| LT1952/LT1952-1                 | 絶縁型同期整流式フォワード・コントローラ                             | 中電力の24Vまたは48V入力アプリケーションに最適                                     |

| LTC3765/LTC3766                 | オプトアイソレータ不要の絶縁型同期整流式<br>フォワード・コントローラ・チップセット      | 中電力の24Vまたは48V入力電圧アプリケーションに最適                                   |

| LTC3723-1/LTC3723-2             | 同期整流式プッシュプルおよびフルブリッジ・コントローラ                      | 高効率、MOSFETドライバを内蔵                                              |

| LTC3721-1/LTC3721-2             | 非同期整流式プッシュプルおよびフルブリッジ・コントローラ                     | 最小限の外付け部品、MOSFETドライバを内蔵                                        |

| LTC3722/LTC3722-2               | 絶縁型同期整流式フルブリッジ・コントローラ                            | 高電力の24Vまたは48V入力アプリケーションに最適                                     |

| LTC3900                         | フォワード・コンバータ用の同期整流器ドライバ                           | プログラム可能なタイムアウト、同期シーケンサ、逆インダクタ電流の検出                             |

| LTC3901                         | プッシュプルおよびフルブリッジ・コンバータ用の<br>同期整流器ドライバ             | プログラム可能なタイムアウト、同期シーケンサ、逆インダクタ電流の検出                             |

| LTC3803/LTC3803-3/<br>LTC3803-5 | 200kHzまたは300kHzの固定周波数で動作する<br>フライバックDC/DCコントローラ  | 外付け部品によってのみ制限されるVINとVOUT、<br>6ピンThinSOTパッケージ                   |

| LTC3805/LTC3805-5               | 固定周波数を70kHz～700kHzの範囲で調節可能な<br>フライバックDC/DCコントローラ | 外付け部品によってのみ制限されるVINとVOUT、<br>MSOP-10Eパッケージと3mm×3mm DFN-10パッケージ |

| LT3748                          | オプトアイソレータ不要の100Vフライバックコントローラ                     | 5V ≤ VIN ≤ 100V、バウンダリ・モード動作、<br>高電圧ピン間の間隔を広げたMSOP-16パッケージ      |

| LT3798                          | アクティブPFC機能を備えたオプトカプラ不要のオフライン<br>絶縁型フライバック・コントローラ | 外付け部品によってのみ制限されるVINとVOUT                                       |