# 18Vデュアル入力マイクロパワー PowerPath プライオリタイザ

## 特長

- 2つの入力から優先順位が高く有効な電源を選択

- 広い動作電圧範囲: 1.8V ~ 18V

- 2Ω、0.5Aのスイッチを2個内蔵

- 少ない動作電流: 3.6µA

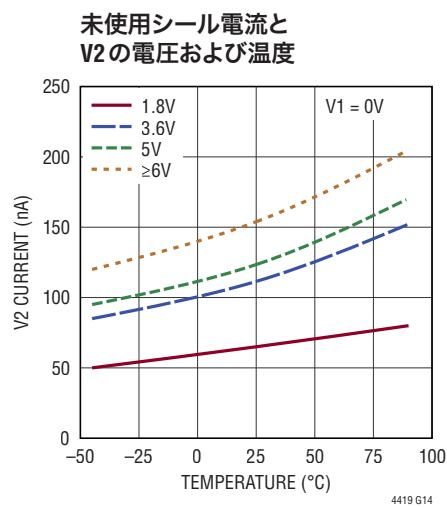

- V1をOUTに接続した場合のV2の電流が320nAと少ない

- 逆電流および相互伝導電流を阻止

- -15Vまでの逆電源電圧保護

- V2未使用シール/出荷モード

- 精度±1.5%の調整可能な切り替えしきい値

- 精度±2.3%の2つの補助電圧コンパレータ

- 過電流保護と過熱保護

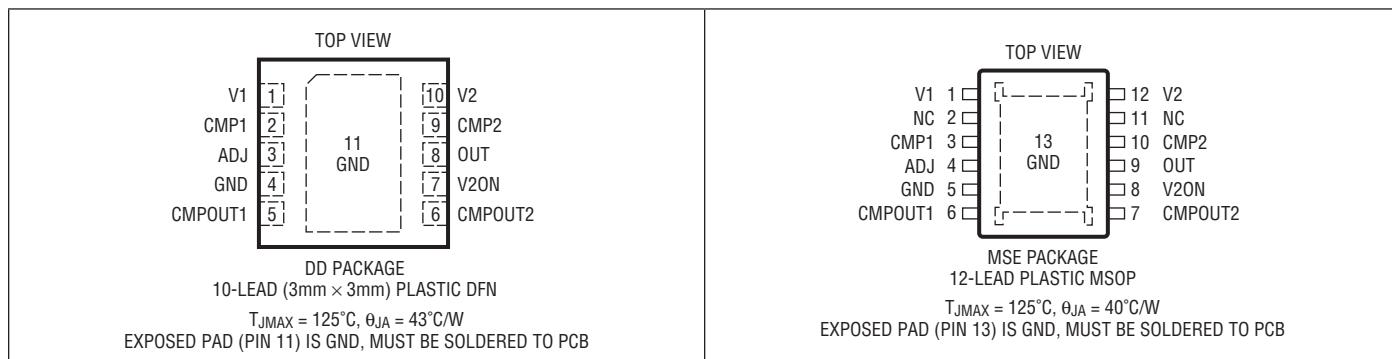

- 熱特性が改善された10ピン3mm×3mm DFNパッケージおよび12ピン露出パッド付きMSOPパッケージ

## アプリケーション

- 低消費電力のバッテリ・バックアップ

- 携帯機器

- POS(販売時点管理)機器

## 概要

LTC<sup>®</sup>4419は低動作電流の2入力モノリシックPowerPath™プライオリタイザで、電源電圧低下や停電などの状態になるとバックアップ電源に切り替えて、肝要な回路を通電状態に維持します。ダイオードOR製品とは異なり、非通電状態の電源の方が動作状態の電源より電圧が高い場合でも、非通電の電源からはほとんど電流が流れません。

内蔵の2Ω電流制限PMOSスイッチにより、1次入力(V1)またはバックアップ入力(V2)から出力までの電源経路を選択することができます。外付けの抵抗分割器を介して設定する調整可能な電圧モニタにより、V1からV2への切り替えしきい値を柔軟に設定することができます。1次入力V1の電圧が低下すると、ADJのモニタにより、OUTはV2に切り替わります。高速の非並行切り替え回路により、逆導通と相互導通を両方とも防止しつつ、出力電圧の低下を最小限に抑えます。

LTC4419は、オープンドレン出力を備え、柔軟な電圧モニタ機能を実現する補助コンパレータを2つ内蔵しています。V2ON出力は、V2がOUTに電力を供給しているかどうかを示します。未使用シール・モードは、保管中や輸送中でのV2バッテリの放電を防止します。

**L**、**LT**、**LTC**、**LTM**、**Linear Technology**およびLinearのロゴはリニアテクノロジー社の登録商標です。PowerPathおよびThinSOTはリニアテクノロジー社の商標です。その他全ての商標の所有権は、それぞれの所有者に帰属します。

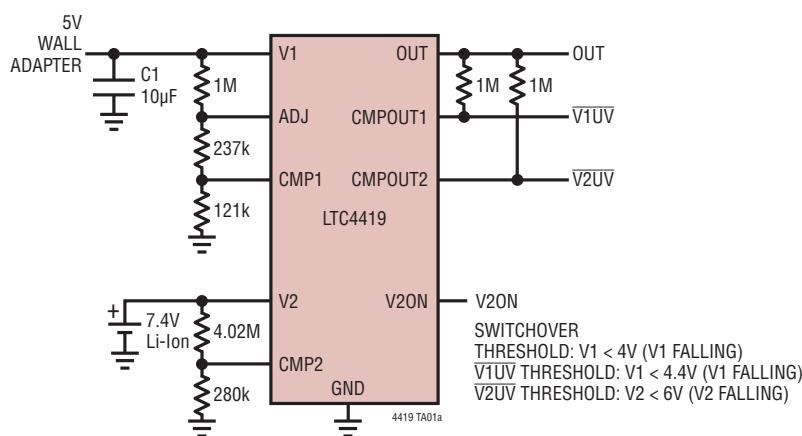

## 標準的応用例

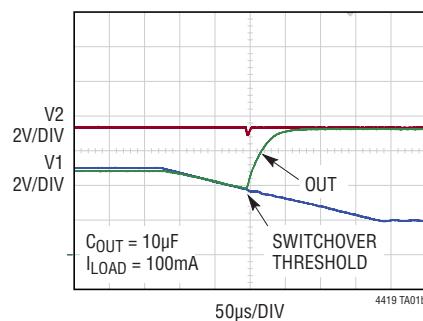

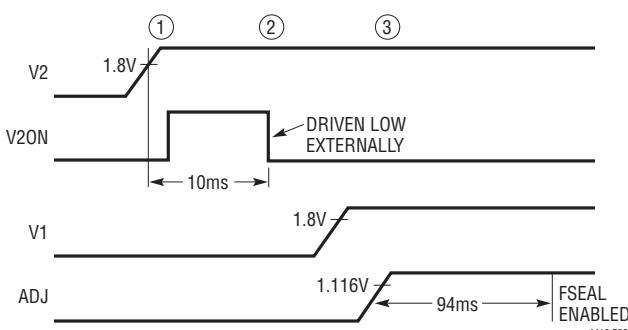

標準的な切り替え波形

## 絶対最大定格 (Note 1, 2)

|                                               |                                |

|-----------------------------------------------|--------------------------------|

| 入力電源電圧                                        | pin current (Note 2)           |

| V1、V2 ..... -15V～24V                          | ADJ、CMP1、CMP2、CMPOUT1、CMPOUT2、 |

| OUT ..... -0.3V～24V                           | V2ON ..... -1mA                |

| OUT - V2 間 ..... -24V～39V                     | 動作周囲温度範囲                       |

| OUT - V1 間 ..... -24V～39V                     | LTC4419C ..... 0°C～70°C        |

| 入力電圧                                          | LTC4419I ..... -40°C～85°C      |

| ADJ、CMP1、CMP2 (Note 3) ..... -0.3V～24V        | 接合部温度 (Note 4, 5) ..... 125°C  |

| 出力電圧                                          | 保存温度範囲 ..... -65°C～150°C       |

| CMPOUT1、CMPOUT2、V2ON (Note 3) ..... -0.3V～24V | リード温度 (半田付け、10秒)               |

|                                               | MSOP パッケージ ..... 300°C         |

## ピン配置

## 発注情報

(<http://www.linear-tech.co.jp/product/LTC4419#orderinfo>)

| 無鉛仕上げ           | テープ・アンド・リール       | 製品マーキング* | パッケージ                            | 温度範囲          |

|-----------------|-------------------|----------|----------------------------------|---------------|

| LTC4419CDD#PBF  | LTC4419CDD#TRPBF  | LGMS     | 10-Lead (3mm×3mm) Plastic DFN    | 0°C to 70°C   |

| LTC4419IDD#PBF  | LTC4419IDD#TRPBF  | LGMS     | 10-Lead (3mm×3mm) Plastic DFN    | -40°C to 85°C |

| LTC4419CMSE#PBF | LTC4419CMSE#TRPBF | 4419     | 12-Lead Plastic Exposed Pad MSOP | 0°C to 70°C   |

| LTC4419IMSE#PBF | LTC4419IMSE#TRPBF | 4419     | 12-Lead Plastic Exposed Pad MSOP | -40°C to 85°C |

更に広い動作温度範囲で規定されるデバイスについては、弊社または弊社代理店にお問い合わせください。<sup>\*</sup> 温度グレードは出荷時のコンテナのラベルで識別されます。

無鉛仕上げの製品マーキングの詳細については、<http://www.linear-tech.co.jp/leadfree/> をご覧ください。

テープアンドリールの仕様の詳細については、<http://www.linear-tech.co.jp/tapeandreel/> をご覧ください。

一部のパッケージは、#TRMPBF接尾部を付けることにより、指定の販売経路を通じて500個入りのリールで供給可能です。

## 電気的特性

●は全動作温度範囲での規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。注記がない限り、 $V1 = 3.6\text{V}$ 、 $V2 = 3.6\text{V}$ 。

| SYMBOL                 | PARAMETER                                                                                                 | CONDITIONS                                                                                                                            | MIN         | TYP               | MAX             | UNITS                                       |               |

|------------------------|-----------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|-------------|-------------------|-----------------|---------------------------------------------|---------------|

| <b>電源電圧および電源電流</b>     |                                                                                                           |                                                                                                                                       |             |                   |                 |                                             |               |

| $V1, V2$               | Operating Voltage Range                                                                                   |                                                                                                                                       | ●           | 1.8               | 18              | V                                           |               |

| $I_{V1}$               | $V1$ Current, $V1$ Powering OUT<br>$V1$ Current, $V2$ Powering OUT                                        | $I_{\text{OUT}} = 0, V1 = 8.4\text{V}, V2 = 3.6\text{V}$<br>$V1 = 8.4\text{V}, V2 = 3.6\text{V}$                                      | ●<br>●      | 3.6<br>500        | 6.3<br>800      | $\mu\text{A}$<br>$\text{nA}$                |               |

| $I_{V2}$               | $V2$ Current, $V2$ Powering OUT<br>$V2$ Current, $V1$ Powering OUT<br>$V2$ Current in Freshness Seal Mode | $I_{\text{OUT}} = 0, V1 = 3.6\text{V}, V2 = 8.4\text{V}$<br>$V1 = 3.6\text{V}, V2 = 8.4\text{V}$<br>$V1 = \text{GND}, V2 = 5\text{V}$ | ●<br>●<br>● | 3.3<br>320<br>120 | 6<br>650<br>220 | $\mu\text{A}$<br>$\text{nA}$<br>$\text{nA}$ |               |

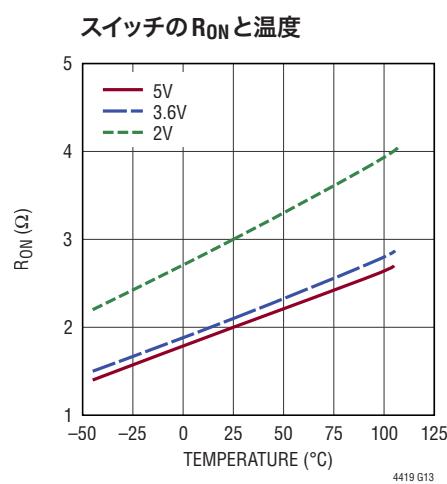

| $R_{ON}$               | Switch Resistance                                                                                         | $V1 = V2 = 5\text{V}, I_{\text{OUT}} = -100\text{mA}$                                                                                 | ●           | 1                 | 2               | $\Omega$                                    |               |

| $t_{\text{VALID}(V1)}$ | Input Qualification Time                                                                                  | $V1$ Rising, ADJ Rising                                                                                                               | ●           | 34                | 64              | ms                                          |               |

| <b>入力コンパレータ</b>        |                                                                                                           |                                                                                                                                       |             |                   |                 |                                             |               |

| $V_{THA}$              | ADJ Threshold                                                                                             | ADJ Falling                                                                                                                           | ●           | 1.032             | 1.047           | 1.062                                       | V             |

| $V_{HYSTA}$            | ADJ Comparator Hysteresis                                                                                 | ADJ Rising                                                                                                                            | ●           | 30                | 50              | 70                                          | mV            |

| $V_{THC}$              | CMP1, CMP2 Threshold                                                                                      | CMP1, CMP2 Falling                                                                                                                    | ●           | 0.378             | 0.387           | 0.396                                       | V             |

| $V_{HYSTC}$            | CMP1, CMP2 Hysteresis                                                                                     | CMP1, CMP2 Rising                                                                                                                     | ●           | 7.5               | 10              | 12.5                                        | mV            |

| $t_{PDA}$              | ADJ Comparator Falling Response Time                                                                      | 10% Overdrive                                                                                                                         | ●           | 4                 | 7.3             | 12                                          | $\mu\text{s}$ |

| $t_{PDC}$              | CMP1, CMP2 Comparator Response Times                                                                      | 20% Overdrive                                                                                                                         | ●           | 30                | 65              | $\mu\text{s}$                               |               |

| <b>電源経路の機能</b>         |                                                                                                           |                                                                                                                                       |             |                   |                 |                                             |               |

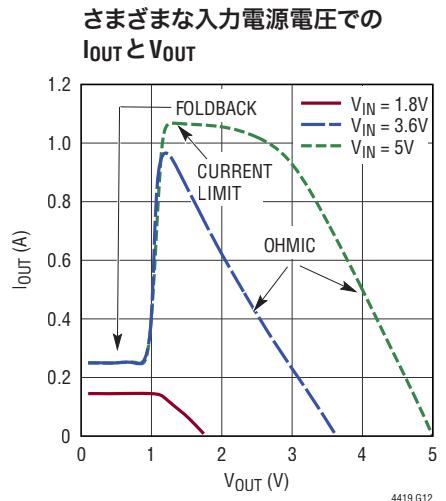

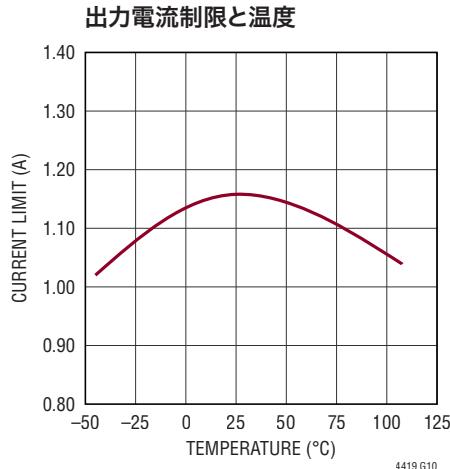

| $I_{\text{LIM}}$       | Output Current Limit                                                                                      | $V1, V2 = 8.4\text{V}$                                                                                                                | ●           | 0.5               | 1.1             | 1.6                                         | A             |

| $V_{\text{REV}}$       | Reverse Comparator Threshold                                                                              | $(V1, V2) - V_{\text{OUT}}$ for Power Path Turn-On                                                                                    | ●           | 25                | 50              | 75                                          | mV            |

| $t_{\text{SWITCH}}$    | Break-Before-Make Switchover Time                                                                         | $V1 = V2 = 5\text{V}, I_{\text{OUT}} < -10\text{mA}$                                                                                  | ●           | 1                 | 2.5             | 5                                           | $\mu\text{s}$ |

| <b>I/O仕様</b>           |                                                                                                           |                                                                                                                                       |             |                   |                 |                                             |               |

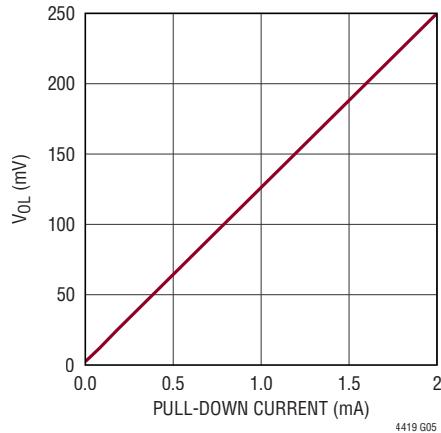

| $V_{OL}$               | Output Voltage Low, CMPOUT1, CMPOUT2 and V2ON                                                             | $I = 100\mu\text{A}$<br>$I = 1\text{mA}$                                                                                              | ●<br>●      | 15<br>120         | 50<br>250       | mV<br>mV                                    |               |

| $V_{OH}$               | V2ON Output High Voltage                                                                                  | $I = -1\mu\text{A}, V2 = 5\text{V}$                                                                                                   | ●           | 1.05              | 1.65            | 2.3                                         | V             |

| $I_{OH}$               | CMPOUT1, CMPOUT2 and V2ON, Output High Leakage                                                            | CMPOUT1, CMPOUT2, V2ON = 18V                                                                                                          | ●           |                   | $\pm 50$        | $\pm 150$                                   | nA            |

| $I_{PU(V2ON)}$         | V2ON Pull-Up Current                                                                                      | $V2 = 5\text{V}, \text{ADJ} = 0\text{V}, V2ON = 0\text{V}$                                                                            | ●           | -2.7              | -5              | -8                                          | $\mu\text{A}$ |

| $I_{\text{LEAK}}$      | ADJ, CMP1, CMP2 Leakage Current                                                                           | ADJ, CMP1, CMP2 = 0V, 1.5V                                                                                                            | ●           |                   | $\pm 1$         | $\pm 5$                                     | nA            |

**Note 1:** 絶対最大定格に記載された値を超えるストレスはデバイスに永続的損傷を与える可能性がある。また、長期にわたって絶対最大定格条件に曝すと、デバイスの信頼性と寿命に悪影響を与えるおそれがある。

**Note 2:** 注記がない限り、ピンに流れ込む電流は全て正で、すべての電圧はGNDを基準にしている。

**Note 3:** これらのピンは、電流を-1mA未満に制限する抵抗を介して、最小-5Vの電圧に接続することができる。

**Note 4:** LTC4419は、短時間の過負荷状態の間デバイスを保護するための過熱保護機能を備えている。過熱保護機能が動作しているとき接合部温度は125°Cを超える。規定された最大動作接合部温度を超えた動作が継続すると、デバイスの信頼性を損なう恐れがある。

**Note 5:** LTC4419は $T_J$ が $T_A$ にほぼ等しいバリス負荷条件でテストされる。接合部温度( $T_J$ (°C))は周囲温度( $T_A$ (°C))および電力損失( $P_D$ (W))から次式に従って計算される。

$$T_J = T_A + (P_D \cdot \theta_{JA})$$

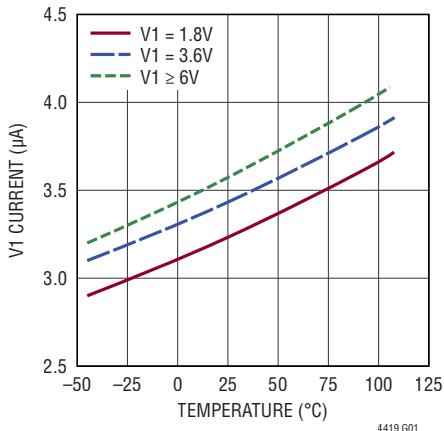

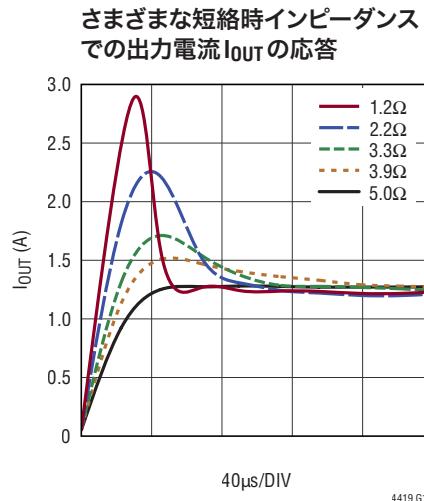

## 標準的性能特性 (指定がない限り、 $T_A = 25^\circ\text{C}$ , $V1 = V2 = 3.6\text{V}$ )。

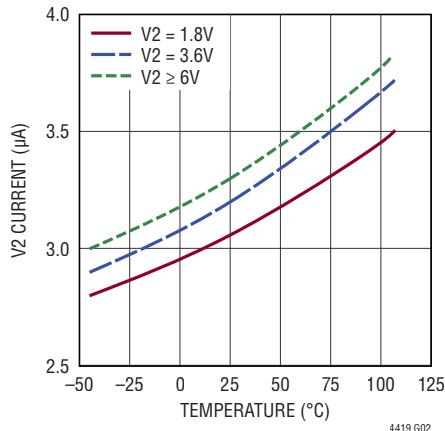

V1の電流、V1がOUTに電力を供給 ( $I_{\text{OUT}} = 0$ )

V2の電流、V2がOUTに電力を供給 ( $I_{\text{OUT}} = 0$ )

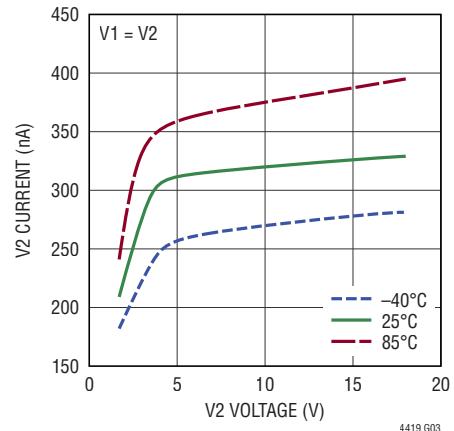

V2の電流、V1がOUTに電力を供給

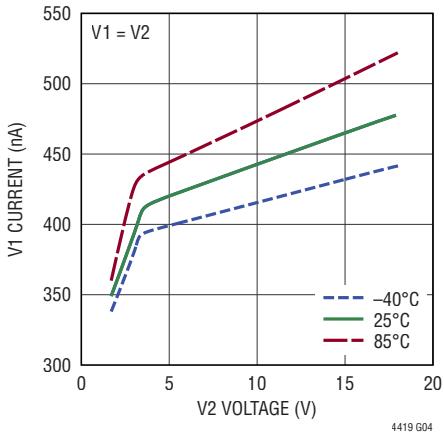

V1の電流、V2がOUTに電力を供給

オープンドレイン(CMPOUT1, CMPOUT2, V2ON)の $V_{OL}$ とプルダウン電流

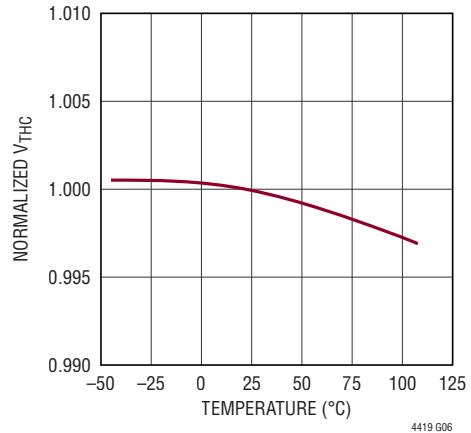

CMP1およびCMP2の正規化立ち下がりしきい値と温度

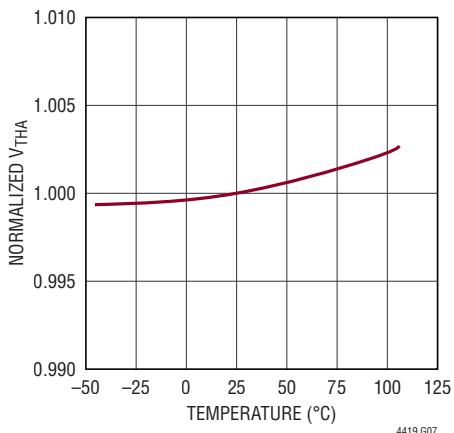

ADJの正規化立ち下がりしきい値と温度

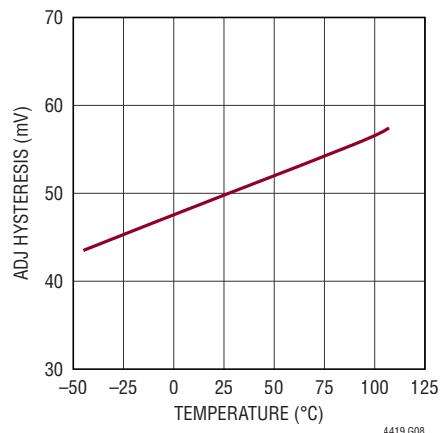

ADJのヒステリシスと温度

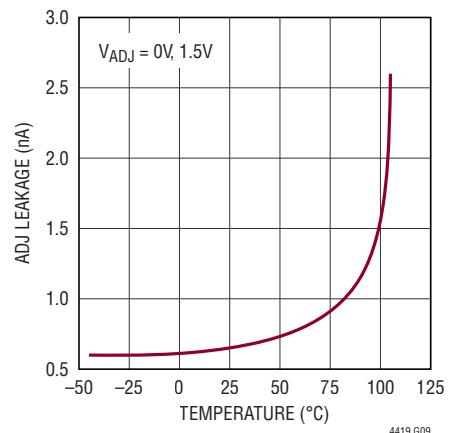

ADJの漏れ電流と温度

## 標準的性能特性 (指定がない限り、 $T_A = 25^\circ\text{C}$ 、 $V1 = V2 = 3.6\text{V}$ )。

## ピン機能

**ADJ:**調整可能なV1切り替えしきい値入力。ADJは切り替えしきい値コンパレータの非反転入力です。V1  $\geq$  1.55VかつADJ  $\geq$  1.097Vの状態が64ms以上続くと、OUTは内部で1次入力V1に切り替わります。V2  $\geq$  1.55Vである場合は、ADJの入力電圧が1.047Vより低いと、OUTは内部でV2に切り替わります。それ以外の場合、OUTは非通電状態のままです。V1からV2への切り替え電圧を設定するため、ADJは抵抗分割器を介してV1に接続します。このピンは開放のままにしないでください。

**CMP1:**補助コンパレータ1のモニタ入力。CMP1は補助コンパレータの非反転入力です。反転入力は内部で0.387Vのリファレンスに接続されています。CMP1を使用しない場合は、GNDに接続してください。

**CMP2:**補助コンパレータ2のモニタ入力。CMP2は第2の補助コンパレータの非反転入力です。反転入力は内部で0.387Vのリファレンスに接続されています。CMP2を使用しない場合は、GNDに接続してください。

**CMPOUT1:**補助コンパレータ1の出力。このオーブンドレインのコンパレータ出力は、CMP1の電圧が0.387Vより低い場合と起動時に“L”になり、それ以外の場合は解放されています。いったん解放状態になると、最大18Vの目的の電源電圧とCMPOUT1の間に抵抗を接続した場合、このピンは“H”になります。使用しない場合は、開放のままにします。

**CMPOUT2:**補助コンパレータ2の出力。このオーブンドレインのコンパレータ出力は、CMP2の電圧が0.387Vより低い場合と起動時に“L”になり、それ以外の場合は解放されています。いったん解放状態になると、最大18Vの目的の電源電圧とCMPOUT2の間に抵抗を接続した場合、このピンは“H”になります。使用しない場合は、開放のままにします。

**露出パッド:**最適な熱性能を得るには、露出パッドを大面積のPCB領域に半田付けします。

**GND:**デバイスのグランド。

**NC:**接続なし。内部で接続されていません。

**OUT:**出力電圧電源。OUTは優先電圧出力で、「アプリケーション情報」セクションの表1に示すように、V1またはV2に接続されているか、または非通電状態です。更に、入力電源への接続を有効にする場合は、OUTの電圧をその入力電源より50mV以上低くする必要があります。1μF以上のコンデンサを使用してバイパスします。バイパス・コンデンサの推奨事項については、「アプリケーション情報」のセクションを参照してください。

**V1:**1次電源。V1  $\geq$  1.55VかつADJ  $\geq$  1.097Vである場合、OUTは内部でV1に切り替わります。未使用シール・モードでは、V1  $\geq$  1.55VかつADJ  $\geq$  1.097Vの状態が32ms続くと、未使用シール・モードが解除されます。1μF以上のコンデンサを使用してバイパスします。使用しない場合はGNDに接続します。

**V2:**バックアップ電源。V2はその電圧が1.55V以上の場合に有効です。V2が有効であることを前提にすると、ADJ  $<$  1.047VまたはV1  $<$  1.55Vである場合、OUTは内部でV2に切り替わります。「アプリケーション情報」のセクションの表1を参照してください。1μF以上のコンデンサを使用してバイパスします。使用しない場合はGNDに接続します。

**V2ON:**V2接続済みステータス。V2ONは、V2からOUTまでの電源経路が通電状態である場合、5μAのプルアップ電流により“H”になる出力です。それ以外の場合は“L”になります。OUTまたはV2とのピンの間に抵抗を接続すると、プルアップ電流は増加します。このピンの使用目的は未使用シール機能をイネーブルすることなので、強制的に“L”にすることや、このピンにプルダウン抵抗を接続することはしないでください。使用しない場合は、開放のままにします。

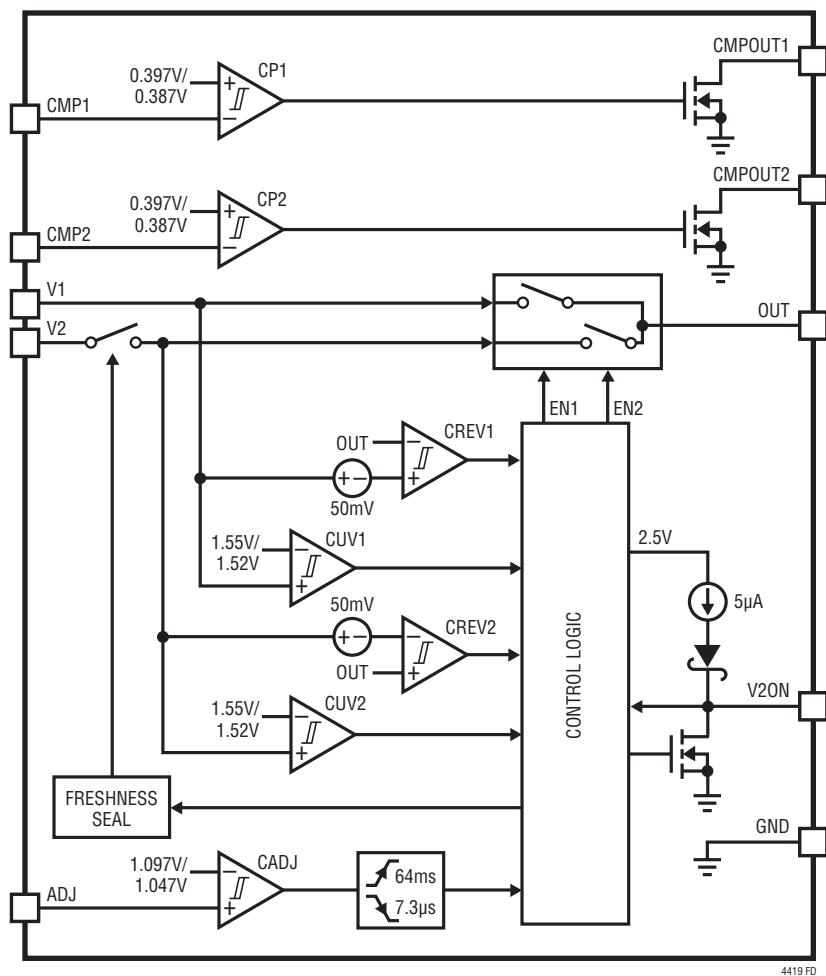

## 機能図

## 動作

「機能図」はLTC4419の主要ブロックを示しています。LTC4419は、1次電源(V1)とバックアップ電源(V2)の間で有効性と優先順位に応じて出力OUTを切り替えるPowerPathプライオリティザで、V1に最高の優先順位を割り当てます。有効な電源がない場合、OUTは非通電状態のままでです。V1、ADJ、GNDの間の抵抗分割器と、コンパレータCUV1およびCADJを使用してV1の電圧をモニタし、有効性を確立します。V1が有効になるのは、 $V1 \geq 1.55V$ かつ $ADJ \geq 1.097V$ の状態が、V1の電圧が1.55Vより高くなつた後に64ms続いた場合です。それ以外の場合、V1は無効です。V2が有効になるのは、コンパレータCUV2がモニタしているV2の電圧が1.55V以上である場合です。それ以外の場合は無効です。切り替えしきい値はV1とV2の相対的な電圧とは関係がないので、V1とV2のどちらがOUTに電力を供給する場合でも、V1をV2よりも低くしても高くしてもかまいません。

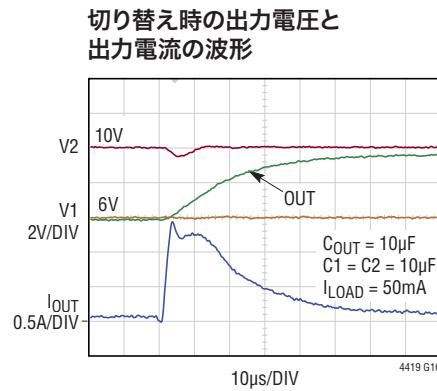

出力への電源接続は、バック・トゥ・バックの内部PチャネルMOSFETを導通させることによって行います。MOSFETによって流れる電流は、OUTの電圧が1Vより高い場合、標準で1.1Aに制限されます。それ以外の場合、この電流は250mAに制限されます。V1からV2に切り替えると、V1からOUTまでの電源経路がまず非導通状態になり、次にコンパレータCREV2がイネーブルされます。CREV2によって検出されるように、OUTの電圧がV2の電圧より50mV低くなると、OUTはV2に接続されます。V2ONは切り替え後に“H”になります。このブ

レーク・ビフォア・メークの方法により、OUTによるV2への逆給電を防止します。V1が再度有効になると、V1に戻る切り替えも同様な方法で行われます。V2の電源経路が非導通状態の場合や、V1またはV2の電圧が初めて印加された最初の電源投入時は、V2ONは“L”になります。

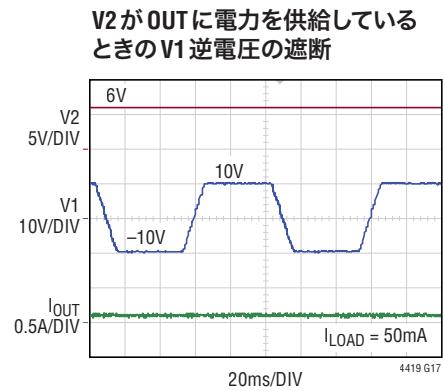

LTC4419は、停止状態のチャネルに逆電圧の状態が発生した場合、最大-15Vの逆電圧を遮断します。また、LTC4419は、対応する入力電源電圧が1.52Vより低くなった場合にもチャネルをディスエーブルします。両方の入力電源電圧が1.55Vより低い場合は、優先入力電源と最も電圧の高い入力電源のいずれかから約3μAと少量の電流が流れます。不使用の電源からは非常に少量の電流(約320nA)が流れます。

LTC4419は、2つの補助コンパレータCP1およびCP2を内蔵しており、そのオープンドレイン出力は、CMP1ピンとCMP2ピンの電圧が0.387Vより低くなつた場合と、最初の電源投入時に“L”になります。これらのコンパレータを使用して電源をモニタし、早期電源障害警告などの有用な情報を示すことができます。

LTC4419をV2未使用シール・モードに移行して、保管中や輸送中のバッテリの放電を防止することができます。V2未使用シール機能を作動させる手順と解除する手順を「アプリケーション情報」のセクションに示します。

## アプリケーション情報

LTC4419は低静止電流の2チャネル・プライオリタイザで、有効な優先入力電源からデバイスの内部回路と出力OUTの両方に電力を供給します。理想ダイオードORとは異なり、LTC4419では、いずれかの電源電圧が1.8Vより高い限り、最も電圧の高い電源から電流が流れるわけではありません。LTC4419の内部静止電流 $I_{CC}$ の電流源となる入力電源と、入力電源が限定された後のOUTの接続先となる電源を表1に示します。

表1. OUTおよびLTC4419の $I_{CC}$ の電源表

| 入力電圧           |                |            | OUTの接続先 | $I_{CC}$ の電流源      |

|----------------|----------------|------------|---------|--------------------|

| V1 > 1.55V     | ADJ > 1.097V   | V2 > 1.55V |         |                    |

| Y <sup>†</sup> | Y <sup>†</sup> | X          | V1      | V1                 |

| X              | N              | Y          | V2      | V2                 |

| Y              | N              | N          | Hi-Z    | V1                 |

| N              | X              | Y          | V2      | V2                 |

| N              | X              | N          | Hi-Z    | V <sub>MAX</sub> * |

注記:X = ドンタケア。

\*V<sub>MAX</sub> = V1とV2のいずれか電圧が高い方。<sup>†</sup>64msの間。

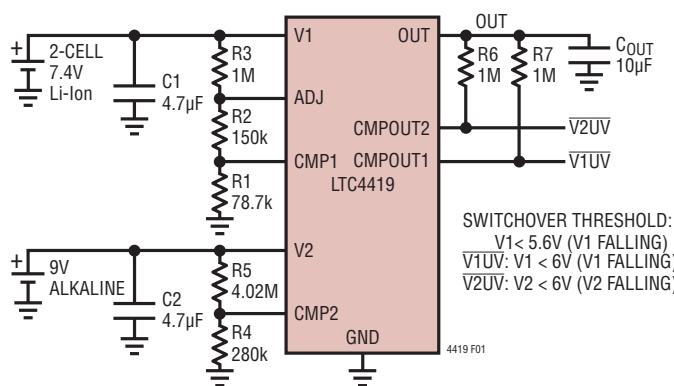

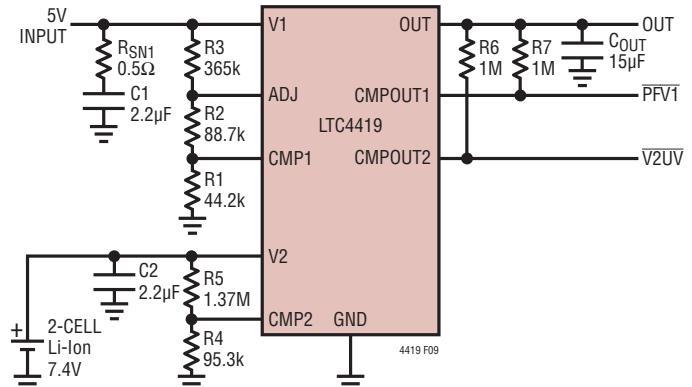

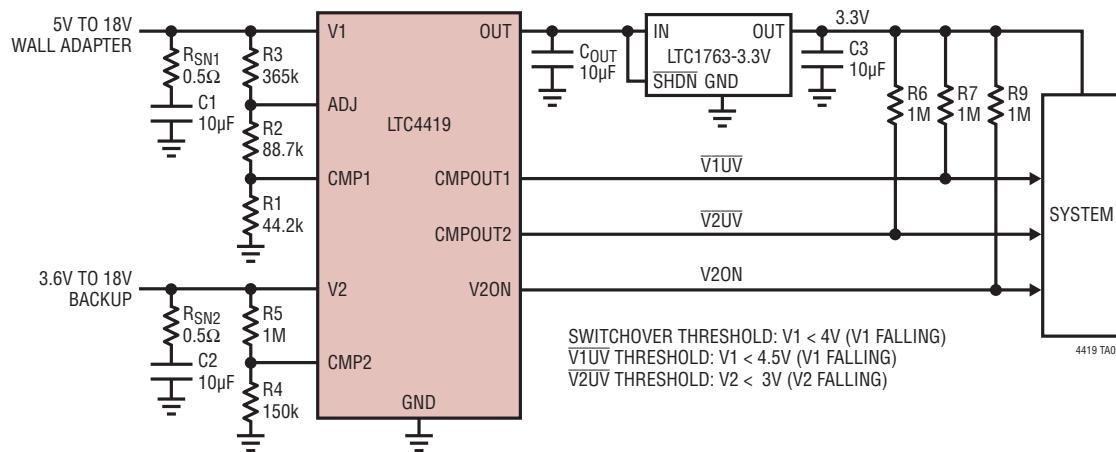

標準的なバッテリ・バックアップのアプリケーションを図1に示します。V1の電源は、安全な放電制限の電圧範囲が5.6V～6Vの2セル・リチウムイオン・バッテリです。V2の電源は、電圧が6Vまで低下すると完全に放電される9Vの長寿命アルカリ電池です。V1の2セル・リチウムイオン・バッテリを保護するため、切り替えしきい値は約5.6Vに設定されています。V2への切り替え後、LTC4419がV1から流すのは少量のスタンバイ電流だけなので、リチウムイオン・バッテリが主に供給するのは抵抗分割器R1～R3の電流だけです。モニタ入力CMP1およびCMP2は、V1およびV2の低電圧警告を出力するよう構成されています。V1とV2の電圧が6Vより低くなると、出力 $\overline{V1UV}$ および $\overline{V2UV}$ は“L”になります。これらの部品の値を

図1. V1の2セル・リチウムイオン・バッテリ・パックが安全な最小電圧より低い電圧まで放電されないよう保護するLTC4419

計算するのに使用する関連の式については、以降のサブセクションで説明します。

### 切り替えしきい値の設定

切り替えしきい値電圧にはいくつかの要因が影響するので、抵抗値を計算する場合には、それらの要因を考慮に入れる必要があります。これらの要因は、抵抗の許容範囲、1.5%のADJコンパレータしきい値誤差、抵抗分割器のインピーダンス、ワーストケースのADJピン漏れ電流などです。また、これらの要因は、モニタ入力CMP1およびCMP2に接続されている抵抗分割器にも当てはまります。図1および「電気的特性」の表を参照すると、V1の標準的な切り替えしきい値は次のとおりです。

$$V_{SW1} = \frac{V_{THA}}{R1+R2} \cdot (R1+R2+R3) \quad (1)$$

V1の標準的な低電圧しきい値は次のとおりです。

$$V_{V1UV} = \frac{V_{THC}}{R1} \cdot (R1+R2+R3) \quad (2)$$

また、V2の標準的な低電圧しきい値は次のとおりです。

$$V_{V2UV} = \frac{V_{THC}}{R4} \cdot (R4+R5) \quad (3)$$

式1～3では、ADJピンとCMPピンの漏れ電流を無視できると仮定しています。ピンの漏れ電流を考慮に入れるには、式1～3を $I_{LEAK} \cdot R_{EQ}$ の項で変更する必要があります、等価抵抗 $R_{EQ}$ はケースバイケースで計算する必要があります。しきい値電圧の最大値と最小値は、部品の値とリファレンス電圧の許容誤差のワーストケースの値を使用して計算する必要があります。例えば、立ち下がり切り替えしきい値電圧の最小値 $V_{SW1}(\text{MIN})$ を計算するには、式1で $V_{THA}(\text{MIN})$ 、 $(R2+R1)(\text{MAX})$ 、および $R3(\text{MIN})$ を使用します。

### 出力コンデンサ $C_{OUT}$ の選択

$C_{OUT}$ は、次のいずれかを制御する目的で選択することができます。それは、切り替え時の出力電圧の低下か、最初の電源投入時または電圧の高い電源への切り替え時の出力立ち上がりスルーレートです。

一般に、出力電圧の低下量 $\Delta V_{OUT}$ は、次式により計算することができます。

$$\Delta V_{OUT} = \frac{t_{NOV} \cdot I_{OUT}}{C_{OUT}} \quad (4)$$

## アプリケーション情報

ここで、 $I_{OUT}$ は、非重複時間つまり「不動作」時間 $t_{NOV}$ の間に $C_{OUT}$ によって供給される電流です。次式に当てはまるように出力コンデンサを選択すると、

$$C_{OUT} \geq \frac{t_{NOV} \cdot I_{OUT}}{\Delta V_{OUT}} \quad (5)$$

出力電圧の低下は $\Delta V_{OUT}$ より少ない値に制限されます。

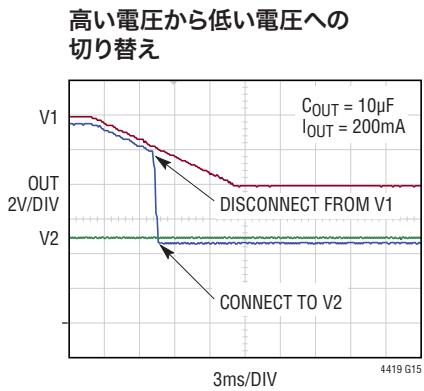

$t_{NOV}$ および $I_{OUT}$ を概算するには、まずV1とV2の両方に電源が存在し、それらの電圧がADJコンパレータの伝播遅延 $t_{PDA}$ と比較して緩やかに変化しているというシナリオについて検討します。このような場合、 $I_{OUT}$ は $I_{LOAD}$ であり、 $t_{NOV}$ は $t_{SWITCH}$ です。 $C_{OUT}$ の容量は、 $I_{OUT} = I_{LOAD}(\text{MAX})$ および $t_{NOV} = t_{SWITCH}(\text{MAX})$ として式5に従って求め、電圧の高い電源に切り替わるときの最大出力電圧低下量を制限することができます。電圧の低い電源に切り替わる場合は、OUTの電圧が切り替え先の電源より $V_{REV}$ だけ電圧が低下して初めて切り替えが始まります。そのような場合には、全出力電圧低下量は $\Delta V_{OUT} + V_{REV}$ になります。

次に、OUTに電力を供給している入力電源が取り外された場合について検討します。OUTは、入力電源ピンに接続されている回路に逆給電します。入力電圧と出力電圧が同じ速度で低下します。図1に関して、OUTをV1に接続しているときにV1のバッテリが取り外されたと仮定します。 $I_{OUT}$ は $I_{LOAD}$ と逆電流 $I_{BACK}$ (この例では $I_{R3}$ )の合計です。OUTとV1は接続されているので、両方ともADJしきい値より電圧が低くなり、次に示す不動作時間の経過後にV2に切り替わります。

$$t_{NOV} = t_{PDA} + t_{SWITCH} \quad (6)$$

ここで、 $t_{PDA}$ はオーバードライブに依存するADJコンパレータの遅延時間です。近似値として、「電気的特性」の表から $t_{PDA}$ を使用して $t_{NOV}$ を概算します。この $t_{NOV}$ と式

$$I_{OUT} = (I_{BACK} + I_{LOAD}) \quad (7)$$

を式5に使用して、 $C_{OUT}$ の容量を次式により求めます。

$$C_{OUT} \geq \frac{(t_{PDA} + t_{SWITCH}) \cdot I_{OUT}}{\Delta V_{OUT}} \quad (8)$$

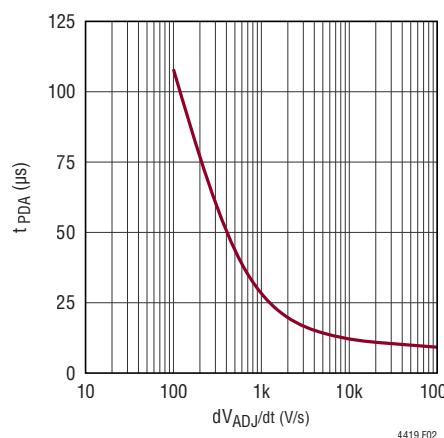

$t_{PDA}$ と $dV_{OUT}/dt$ をより正確に概算するには、図2を参照してください。コンデンサを使用してADJをフィルタ処理すると、その放電時間は抵抗分割器R1～R3を介した場合、 $t_{PDA}$ に増加します。この結果、出力電圧の低下量は、式8で概算した値より増加します。

出力の立ち上がりスルーレート $dV_{OUT}/dt$ を制限するには、次式が成り立つように容量値を設定します。

$$C_{OUT} \geq \frac{I_{LIM}}{\frac{dV_{OUT}}{dt}} \quad (9)$$

これは、LTC4419がOUTの充電電流を $I_{LIM}$ に制限する条件が、OUTの電圧が入力電源電圧に近づいて、その差が $I_{LIM} \cdot R_{ON}$ 以内になるまでだからです。ここで、 $R_{ON}$ はチャネルのスイッチ抵抗です。許容される最大の $C_{OUT}$ を求めるには、「過熱保護と $C_{OUT}$ の最大値」のセクションを参照してください。

図2. スルーレートの関数としてのADJコンパレータの伝播遅延、 $t_{PDA}$ と $dV_{ADJ}/dt$

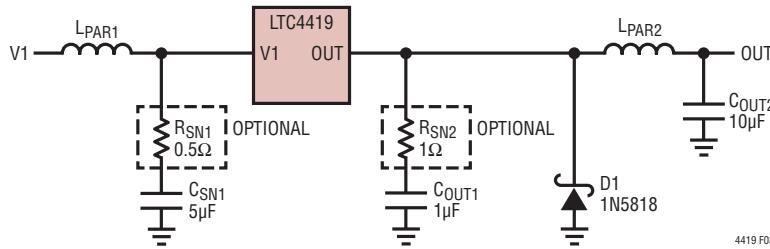

## インダクタ成分の影響

寄生インダクタンスと寄生抵抗は、シナリオによっては入力電圧と出力電圧のオーバーシュートやアンダーシュートを引き起こすので、回路の性能に影響することがあります。電源経路に寄生インダクタンスがあると、LTC4419がオフしたときに、正極に向かうオーバーシュートが入力に発生し、負極に向かうアンダーシュートが出力に発生します。正の入力オーバーシュートが発生するもう1つの原因是、入力電源の活線挿入時に生じるR-L-Cタンク回路のリンクです。入力オーバーシュートが最も顕著なのは、入力タンク回路の全抵抗が低い場合です。過電圧トランジエントがLTC4419の絶対最大定格を超えないよう注意する必要があります。更に、寄生抵抗や寄生インダクタンスは、電源経路の導通時に入力アンダーシュートを引き起こすことがあります。重度の場合は、アンダーシュートによって電源が一時的に無効になり、電源投入サイクルの繰り返し(「モーターーボーティング」)や電源間の不要な切り替えが生じる可能性があります。

## アプリケーション情報

図3. 推奨の誘導性トランジエント抑制回路

これらの問題が発生しないようにするための第1段階は、電源経路内での寄生インダクタンスと寄生抵抗を最小限に抑えることです。プリント回路基板(PCB)上の寄生インダクタンスを最小限に抑えるためのガイドラインを、レイアウトのセクションで説明します。PCBの外側では、電源とグランドの線を撲ってインダクタンスを最小限に抑えます。

第2に、入力にバイパス・コンデンサを使用して、LTC4419の電源経路が非導通のときに入力電圧のオーバーシュートを制限します。ほとんどのアプリケーションでは数μFで十分です。寄生インダクタンスの大きな電源を活線挿入する場合は、R-L-Cタンク回路に公称電源電圧の2倍を超えるリングングが発生する可能性があります。ACアダプタやバッテリには、通常、この大きさのリングングを防止するのに十分な損失(つまり、直列抵抗)があります。ただし、これが問題である場合は、入力コンデンサC<sub>SN1</sub>と抵抗R<sub>SN1</sub>(標準0.5Ω)によるスナバ回路を追加します。この回路網を電源ピンの近くに配置します。

第3に、入力コンデンサを接続できない場合、電源ピンのトランジエントが24Vを超えるアプリケーションでは、TVS(SMAJ16CAなど)を使用します。逆入力保護が必要なアプリケーションでは、双方向のTVSを使用します。TVSは電圧低下やモーター・ボーティングには対応しません。これらを解決する唯一の方法は、入力バイパス処理です。

通常動作時には、LTC4419は電源経路の電流を1.6A未満に制限し、電力経路の非導通時には、OUTにグランド電位より低いリングングが発生しないよう内部回路が動作します。このことは、短絡箇所がLTC4419のOUTピンに近い場合は、出力短絡にも当てはまります。ただし、出力が長い配線を介して短絡している場合は、C<sub>OUT1</sub>の放電により、配線のインダクタンス(図3のL<sub>PAR2</sub>)を流れる電流が発生し、電流値は1.6Aを大幅に超えることがあります。C<sub>OUT1</sub>が完全に放電されると、この電流により、OUTピンには-0.3Vの絶対最大定格より低い電圧のリングングが発生します。この特殊な場合には、出力コンデンサをC<sub>OUT1</sub>とC<sub>OUT2</sub>に分割して、C<sub>OUT1</sub>を小さくします。必要に応じてC<sub>OUT1</sub>に抵抗R<sub>SN2</sub>を接続してスナバ回路を構成し、R-L-Cリングングの振幅を減衰させます。必要な全

出力容量が得られるようにC<sub>OUT2</sub>の容量を設定します。また、OUTピンに-0.3Vより低い電圧のリングングが発生する場合は、LTC4419に近い位置でOUTとグランドの間にダイオードを追加して、負のリングングをクランプします。

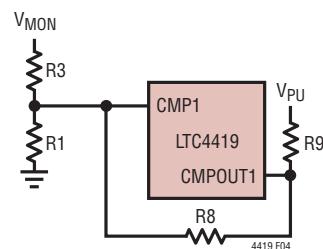

## CMP1およびCMP2のヒステリシスの増加

アプリケーションによっては、組み込みのCMP1ヒステリシスでは不十分な場合があります。このような場合には、図4に示すように、CMP1のヒステリシスを大きくしてもかまいません。R8を接続しているモニタ対象入力V<sub>MON</sub>でのヒステリシスは、R9 << R8であると仮定すると、次式により与えられます。

$$V_{HYST} = V_{HYSTC} \cdot \frac{R3}{R1||R3||R8} + V_{PU} \cdot \frac{R3}{R8} \quad (10)$$

ここで、V<sub>HYSTC</sub>およびV<sub>THC</sub>は「電気的特性」の表に記載されており、標準値はそれぞれ10mVおよび0.387Vです。モニタ対象入力V<sub>MON</sub>の立ち上がりしきい値と立ち下がりしきい値を計算する場合は、電源V<sub>PU</sub>および抵抗R8を考慮してください。

## 電源のインピーダンスとADJコンパレータのヒステリシス

図4. CMP1のヒステリシスの増加

アプリケーションによっては、V1の電源がESRの高いバッテリ・パックから供給されるか、またはかなりの直列抵抗を持つ長いケーブルを介して供給されることがあります。この抵抗を通って流れる負荷電流I<sub>OUT</sub>により、モニタされるV1の電圧は次の値だけ低下します。

$$\Delta V1 = I_{OUT} \cdot R_{ESR} \quad (11)$$

## アプリケーション情報

低下電圧の最大値は次のとおりです。

$$\Delta V = I_{LIM} \cdot R_{ESR} \quad (12)$$

これは、最初に  $C_{OUT}$  を充電するときに低下した電圧です。組み込みの V1 (ADJ) ヒステリシスが不十分な場合は、V1 ピンの電圧が低下すると、V1 と V2 の間の切り替えが繰り返し発生することがあります。

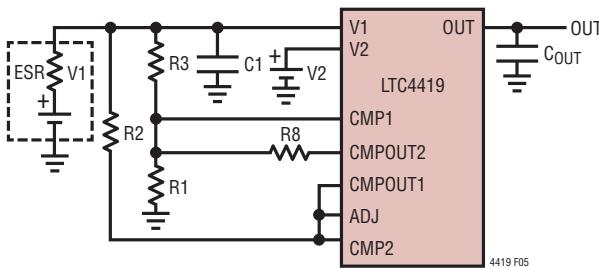

このような場合には、図 5 に示すように、CMP1 を使用して V1 のヒステリシスを設定することができます。V1 の電圧が低下した場合に、CMP1 の電圧が  $V_{THC}$  より低くなると、ADJ および CMP2 は “L” になり、出力 CMPOUT2 はヒステリシス抵抗 R8 を導通させます。V1 から V2 に切り替わると、V1 が供給する電流はゼロになるので、V1 の電圧は上昇します。式 10 で求めた V1 のヒステリシス増大により、V1 に戻る切り替えは阻止されます。

V1 の電圧低下は、 $C_{OUT}$  の初期充電中に大きくなります。図 5 を参照すると、 $C_{OUT}$  の初期充電時に切り替えが繰り返し発生しないようにするには、入力コンデンサ C1 を追加します。理想的には、V1 が切り替えしきい値  $V_{SW1}$  より  $\Delta V$  だけ大きい場合は、次式が成り立つようにして、

$$C_1 \geq \frac{V_{SW1} \cdot C_{OUT} \cdot \left(1 - \frac{\Delta V}{2 \cdot I_{LIM} \cdot R_{ESR}}\right)}{\Delta V} \quad (13)$$

$C_{OUT}$  の初期充電時に切り替えが起こらないようにします。得られた C1 の値が原因で大きな突入電流が流れる場合、C1 の値が物理的に大きすぎる場合、または V1 の電源投入時に大きなスナバ抵抗が必要になる場合（「標準的応用例」のセクションを参照）は、アプリケーションが許容できる最も高い値の C1 を選択します。

また、フィルタ・コンデンサ  $C_{ADJ}$  を ADJ に追加して、最初の出力充電時間を乗り切ることもできます。 $C_{ADJ}$  の容量値は最小限に抑えてください。V1 に給電する入力電源が取り外されるか、入力電源の電圧が急速に低下すると、ADJ の応答速度が低下して、出力電圧が大幅に低下するからです。

図 5. ESR の高いアプリケーションでの電源ヒステリシスの増加

## 入力短絡および電源電圧の低下

入力電源電圧が OUT の電圧より 0.7V 低くなると、LTC4419 は入力短絡または電圧低下状態の間、その動作中の電源経路を一時的に遮断します。1 次入力電源が無効になると、バッカアップ電源に切り替わります。入力電圧が出力電圧の 0.7V 以内に回復すると、電源経路は再通電されます。

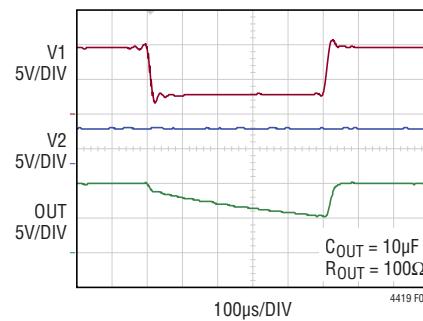

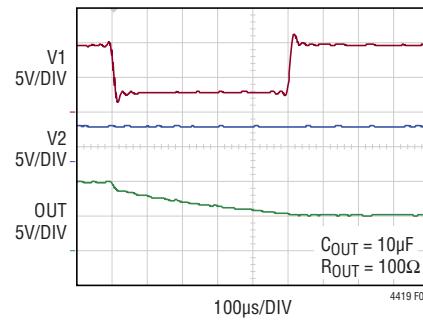

V1 の電圧低下と回復に対する LTC4419 の応答を図 6 に示します。V1 は 1.8V 以上を維持しているので、V2 には切り替わりません。V1 の電圧が低下すると、OUT は V1 から切り離され、負荷抵抗  $R_{OUT}$  により、緩やかに放電されます。V1 の電圧が回復すると、電源経路が再通電され、OUT は V1 に追従します。図 7 では、V1 の電圧が低下すると、V1 の電圧が切り替えしきい値より低くなるのに応じて、OUT は V1 から切り離されます。V1 の電圧が回復したら、64ms の制限時間が経過してから OUT に再接続することが必要です。OUT の電圧は  $R_{OUT}$  によって放電され、OUT の電圧が V2 より 50mV 低くなると、OUT は V2 に接続されます。

図 6. V1 の電圧低下時に V2 への切り替えが行われない場合の電圧波形。切り替えしきい値は 1.8V。

図 7. V1 の電圧低下によって V2 への切り替えが行われた場合の電圧波形。切り替えしきい値は 3V。

## アプリケーション情報

### 逆電圧の遮断

LTC4419は、電源ピンV1およびV2での逆電圧を、GNDを基準にして最大-15Vまで、またOUTを基準にして最大-39Vまで遮断します。V1とV2に接続するトランジエント電圧サブレッサ(TVS)は双方向型にする必要があり、これらのピンに接続するコンデンサは、逆電圧に対応できる定格のものにする必要があります。V2での逆電圧がV1の動作を中断することはなく、逆の場合も同様です。

### 未使用シール

未使用シール・モードは、V1が接続されていないか無効である場合でも、V2をOUTから切り離しておくことにより、V2のバッテリが放電しないようにします。V2からはほとんど電流が流れません。標準でわずか120nAです。次の手順(図8参照)を行うと、LTC4419は未使用シール・モードになります。

1. V1を低電圧に保持したまま、V2の電源を投入して10ms以上待ちます。

2. V2ONの電圧を50mVより低くします。

3. V1とADJの電源を投入して94ms以上待ちます。未使用シール・モードがイネーブルされます。

V2が保管中または輸送中のバックアップ・バッテリである場合は、このモードにします。いったん未使用シール・モードが作動状態になると、V1が切断された場合に、V2はOUTから切斷されたままになります。未使用シール・モードは、V1が次に再有効化されたときに、自動的にディスエーブルされます。

図8. 未使用シール・モードの作動順序

未使用シール・モードが偶発的に作動しないように、V2ONピンの容量は10nF未満に制限します。

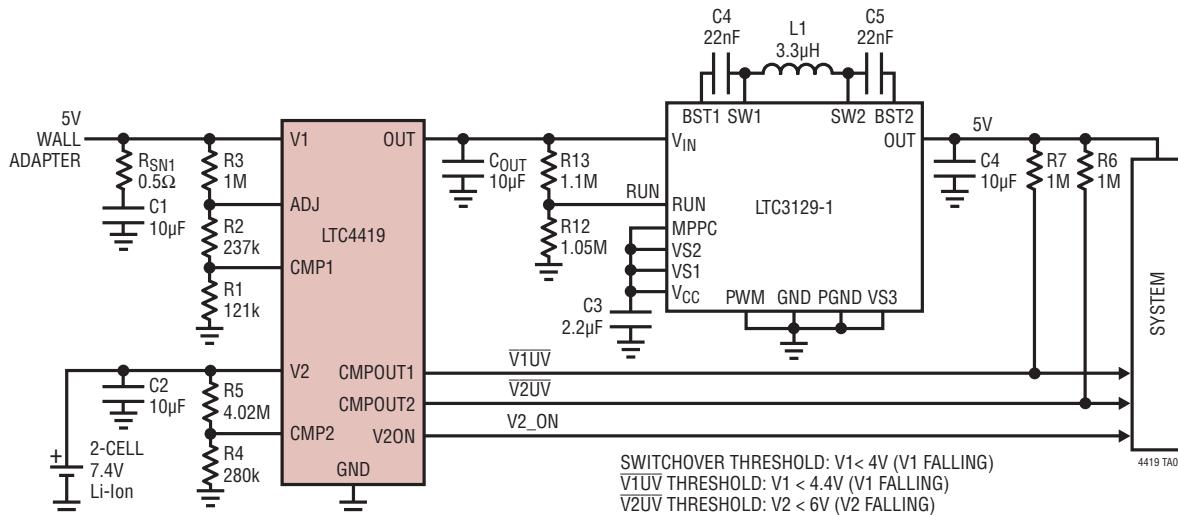

図9. 設計例

### 設計例

図9では、LTC4419は、V1に接続された5Vの電源と、V2に接続された7.4Vの2セル・リチウムイオン・バッテリのいずれかを優先させます。このシステムは、V1が4Vより低くなったらOUTからV2に切り替え、V1が4.5Vより低くなったら早期電源障害警告を出し、バックアップのバッテリ電圧が6Vより低くなったら低バッテリ電圧警告を出す目的で設計されています。予想最大負荷電流は100mAであり、許容最大出力電圧低下量は100mVです。大量の突入電流が流れないようにするため、出力の立ち上がりスルーレートは0.1V/μs未満に制限し、V1とV2の入力容量は10μFに制限します。許容誤差1%の抵抗を使用します。ADJピンとCMPピンの漏れ電流は、設計上の影響が小さいので無視されます。

まず、抵抗分割器を流れる全電流がV1の場合は約10μA、V2の場合は約5μAになるように抵抗を選択します。5V電源では、この結果は次のようにになります。

$$R1+R2+R3 = \frac{5V}{10\mu A} = 500k\Omega \quad (14)$$

目的の切り替えしきい値 $V_{SW1}$ と抵抗分割器の全インピーダンスは既知なので、式1を使用して、まずR3を計算します。R3および式2を使用して、R1およびR2を計算します。式1を書き換えると、次の式が得られます。

$$(R1+R2) = \frac{V_{THA} \cdot (R1+R2+R3)}{V_{SW1}} \quad (15)$$

## アプリケーション情報

式14から  $(R1 + R2 + R3) = 500\text{k}\Omega$  を使用すると、次の式が得られます。

$$(R1+R2)=\frac{1.047V \cdot 500\text{k}\Omega}{4V}=130.9\text{k}\Omega \quad (16)$$

$$R3 \sim (500\text{k}\Omega - 130.9\text{k}\Omega) = 369.1\text{k}\Omega \quad (17)$$

値が最も近い誤差1%の抵抗値を使用すると、 $R3 = 365\text{k}\Omega$  が得られます。

式2を再整理すると、次の式が得られます。

$$R1=\frac{V_{THC} \cdot (R2+R3)}{V_{PFV1}} \quad (18)$$

$$R1=\frac{0.387V}{4.5V} \cdot (500\text{k}\Omega) \quad (19)$$

式16および19を解くと、結果は  $R1 = 43.3\text{k}\Omega$  および  $R2 = 87.6\text{k}\Omega$  となります。値が最も近い誤差1%の抵抗値を使用すると、結果は  $R2 = 88.7\text{k}\Omega$  となります。算出した  $R2$  と  $R3$  の値を使用して式1を再計算し、 $R1$  の  $43.3\text{k}\Omega$  に近い標準的な誤差1%の抵抗値を使用すると、結果は  $R1 = 44.2\text{k}\Omega$  となります。式3と抵抗分割器の全電流を使用し、同様な手順に従って  $R4$  および  $R5$  を計算します。設計式を次に示します。

$$R4+R5=\frac{7.4V}{5\mu A}=1.48\text{M}\Omega \quad (20)$$

抵抗分割器を流れる目的の電流は  $5\mu A$  であるからです。

式3を書き換え、ピンの漏れ電流を無視して、 $R5 >> R4$  であると仮定すると、次のようにになります。

$$R4=\frac{V_{THC} \cdot (R4+R5)}{V_{2UV}} \quad (21)$$

$$R4=\frac{0.387V \cdot 1.48\text{M}\Omega}{6V} \quad (22)$$

式20と22を解くと、 $R4 = 96.2\text{k}\Omega$  および  $R5 = 1.38\text{M}\Omega$  という結果が得られます。値が最も近い誤差1%の抵抗値を選択すると、 $R4 = 95.3\text{k}\Omega$  および  $R5 = 1.37\text{M}\Omega$  となります。

$C_{OUT}$  は、式4で算出する切り替え時のOUTの電圧低下と、式9で算出するOUTの立ち上がりスルーレートの両方に影響します。目的とする出力電圧低下量およびスルーレートの規格値を満たすために必要な  $C_{OUT}$  の最小値を式8および9を使用して計算し、 $C_{OUT}$  の容量が2つの値の大きい方になるようになります。

OUTの電圧低下を  $100\text{mV}$  未満に制限するために必要な  $C_{OUT}$  は、式8で与えられます。

$$C_{OUT} \geq \frac{(t_{PDA} + t_{SWITCH}) \cdot I_{LOAD}}{100\text{mV}} \quad (23)$$

$$C_{OUT} \geq \frac{(7.3\mu s + 2.5\mu s) \cdot 0.1A}{100\text{mV}} = 9.8\mu F \quad (24)$$

OUTのスルーレートを  $0.1\text{V}/\mu s$  未満に制限するために必要な  $C_{OUT}$  は、式9で与えられます。

$$C_{OUT} \geq \frac{I_{LIMIT}}{0.1\text{V}/\mu s} = 11\mu F \quad (25)$$

電圧係数と温度係数を考慮して、 $C_{OUT}$  には最小値が  $11\mu F$  のコンデンサを選択します。この手順を他のコンデンサに対しても同様に行います。PCBレイアウトが適正であることを前提に、C1には  $2.2\mu F$  ( $C_{OUT}$  の約  $1/5$ ) を選択し、誘導性のトランジエントを抑えます。また、C1と  $0.5\Omega$  の抵抗を組み合わせてスナバ回路を形成し、リングングが発生しないようにします。

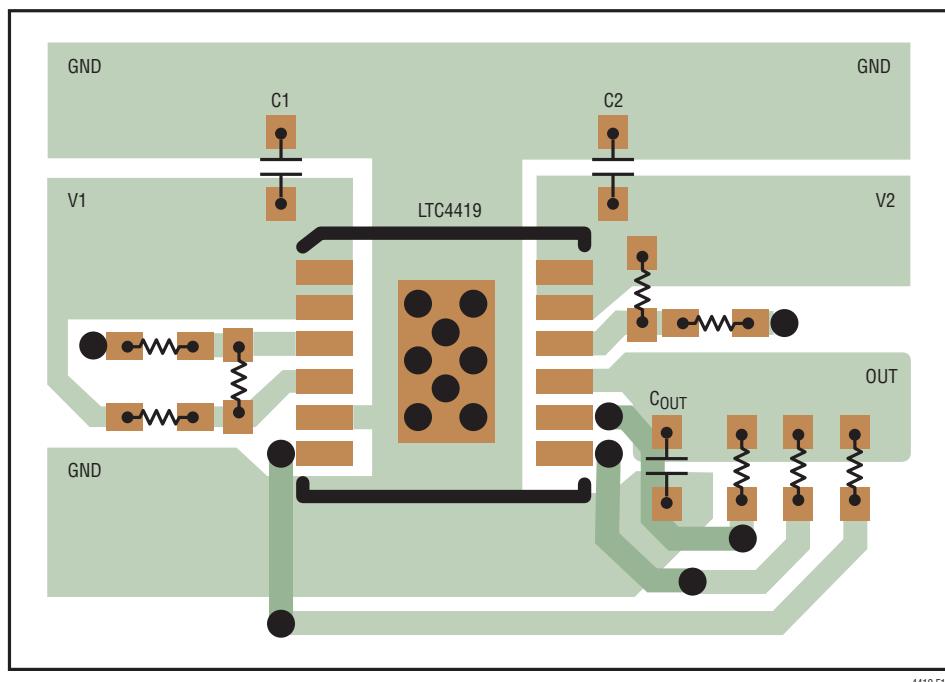

### レイアウトに関する検討事項

電源とグランドのトレースは、できるだけ広くします。バイパス・コンデンサ、スナバ回路の部品、およびTVSデバイスはできるだけピンの近くに配置して、電源経路の抵抗および寄生インダクタンスを低減します。これらの結果、過電圧トランジエントが小さくなり、過電圧保護機能が向上します。抵抗分割器をピンに近づけて配置し、ノイズ耐性を改善します。可能であれば4層基板を使用し、第2層をGND専用にして、露出パッドを大面積のPCB GNDトレースに半田付けし、熱放散を改善します。2層PCBの部分的なレイアウトを図10に示します。

## アプリケーション情報

図10. 12ピンMSEの2層PCB向け推奨レイアウト

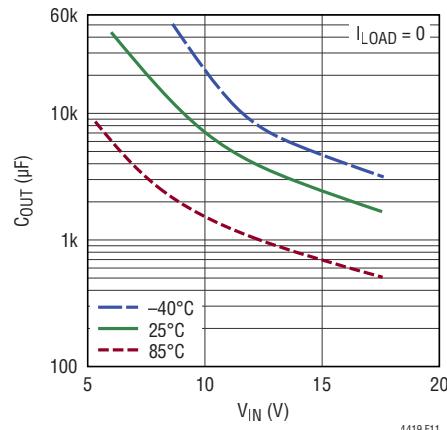

過熱保護とC<sub>OUT</sub>の最大値

入出力間の電圧差によっては、電流制限モードで動作しているときにLTC4419の内部電力損失が大きくなることがあります。この状況になるのは、通常、最初の電源投入時やOUTが電圧の高い電源に切り替わったときに、大容量のC<sub>OUT</sub>を充電する場合です。OUTにDC負荷が接続されると、C<sub>OUT</sub>の充電に使用できる電流が減るので、状況は悪化します。そのような場合には、自己発熱が原因で過熱保護回路が作動して、電源経路が遮断されることがあります。ダイ温度が安全な値まで低下すると、電源経路は再通電されます。電源経路が導通していない時間内に、C<sub>OUT</sub>が負荷電流I<sub>OUT</sub>によって完全に放電される場合、この処理は無期限に繰り返される可能性があります。

過熱保護回路が作動しないようにするC<sub>OUT</sub>の許容最大値は、入力電源電圧、出力電圧、起動時の周囲温度、PCBでの熱放散、DC出力電流など、いくつかの要因によって決まります。可能な場合は、500μF未満のC<sub>OUT</sub>を選択します。それより大容量のC<sub>OUT</sub>が必要な場合は、図11を使用してC<sub>OUT</sub>を選択します。熱放散を改善するには、PCBレイアウトのガイドラインに従ってください。

図11. C<sub>OUT</sub>の許容最大値とさまざまなT<sub>A</sub>での入力電圧

## 標準的応用例

低電圧ロジックとのインターフェースを備えたバッテリのバックアップ回路

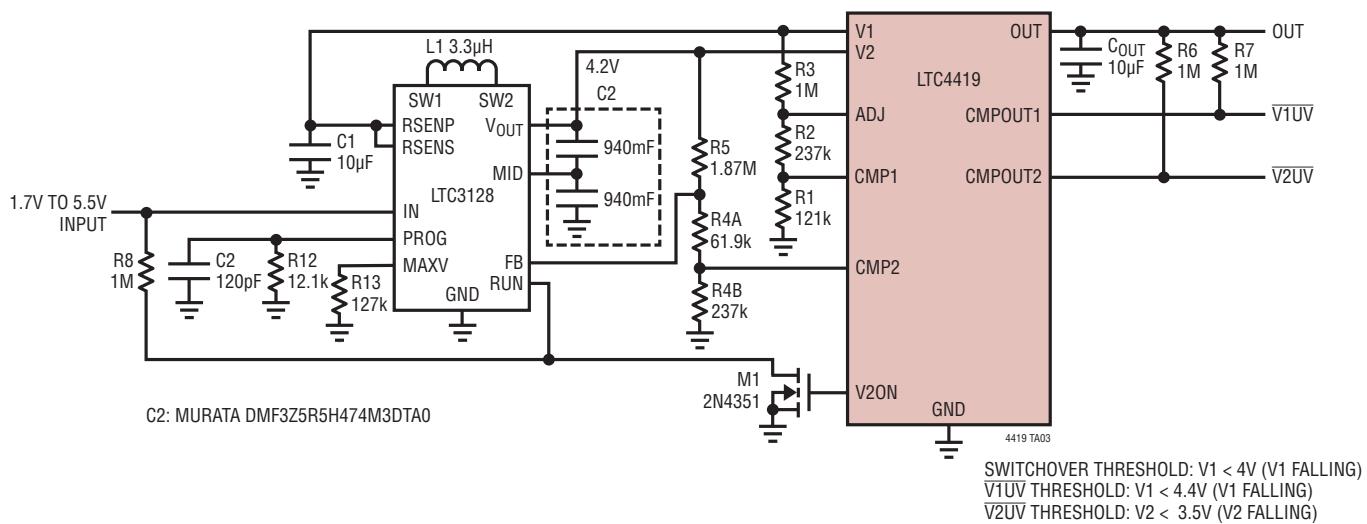

スーパーキャパシタの充電機能を備えたスーパーキャパシタのバックアップ回路

## 標準的応用例

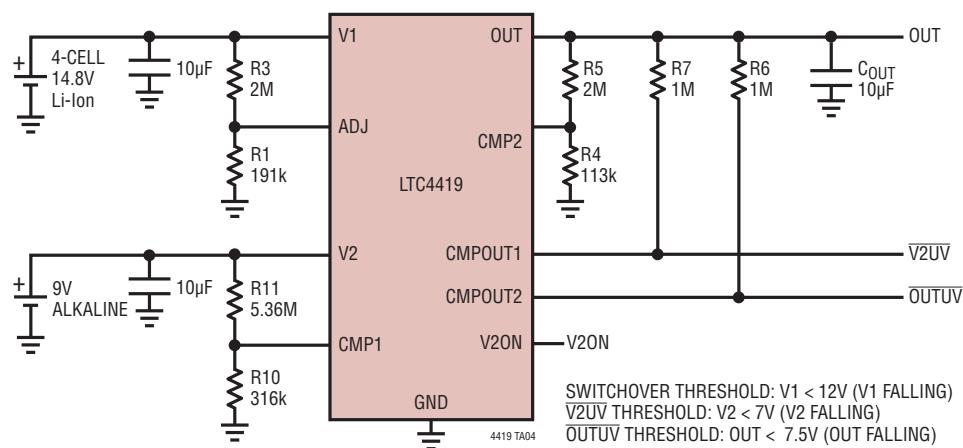

## 1次バッテリ・パック保護回路を備えたトリプル電源モニタ

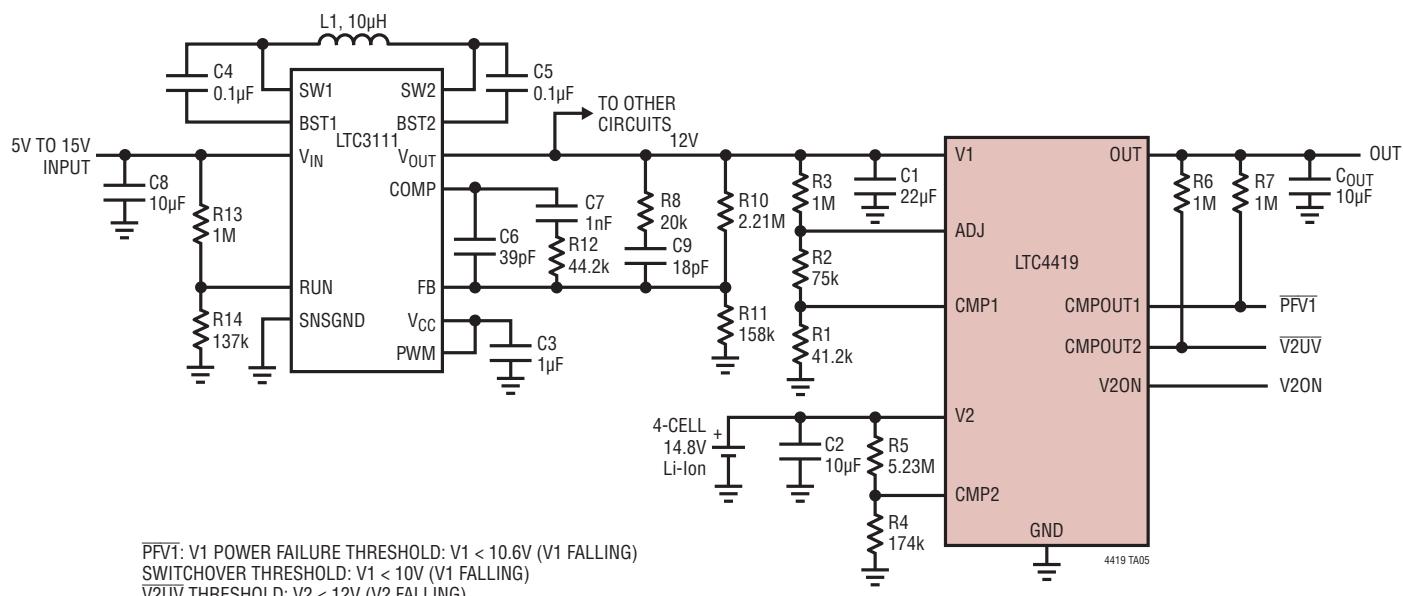

## 低バッテリ電圧表示機能を備えた早期電源障害警告回路

## パッケージ

最新のパッケージ図面については、<http://www.linear-tech.co.jp/product/LTC4419#packaging> を参照してください。

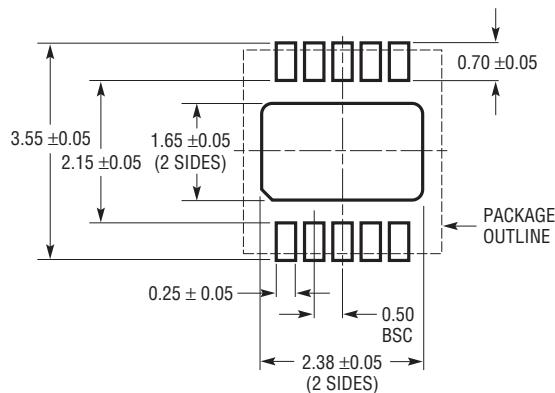

**DD Package**

**10-Lead Plastic DFN (3mm × 3mm)**

(Reference LTC DWG # 05-08-1699 Rev C)

**RECOMMENDED SOLDER PAD PITCH AND DIMENSIONS**

注記：

1. 図は JEDEC のパッケージ外形 M0-229 のバリエーション (WEED-2) になる

予定バリエーションの指定の現状については LTC の Web サイトのデータシートを参照

2. 図は実寸とは異なる

3. 全ての寸法はミリメートル

4. パッケージ底面の露出パッドの寸法にはモールドのバリを含まないモールドのバリは

(もしあれば) 各サイドで 0.15mm を超えないこと

5. 露出パッドは半田メッキとする

6. 灰色の部分はパッケージの上面と底面のピン 1 の位置の参考に過ぎない

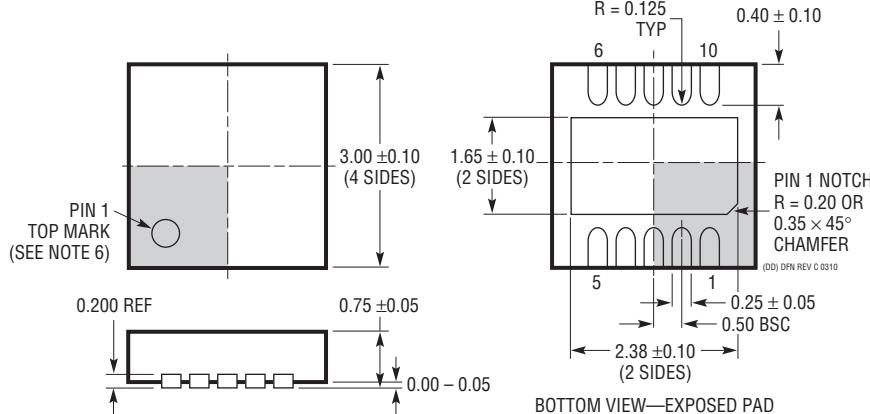

## パッケージ

最新のパッケージ図面については、<http://www.linear-tech.co.jp/product/LTC4419#packaging> を参照してください。

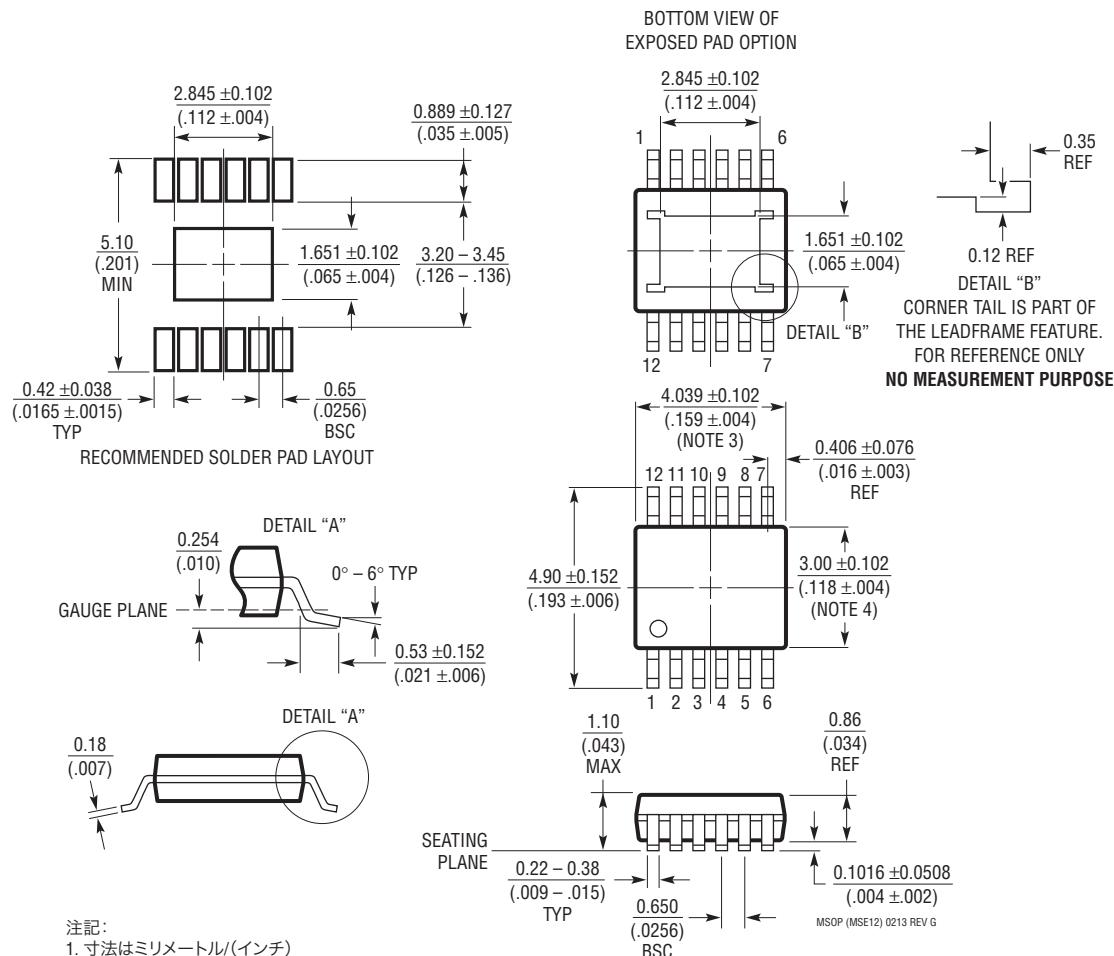

### MSE Package 12-Lead Plastic MSOP, Exposed Die Pad (Reference LTC DWG # 05-08-1666 Rev G)

注記:

- 寸法はミリメートル/(インチ)

- 図は実寸とは異なる

- 寸法にはモールドのバリ、突出部、またはゲートのバリを含まないモールドのバリ、突出部、またはゲートのバリは、各サイドで0.152mm(0.006")を超えないこと

- 寸法には、リード間のバリまたは突出部を含まないリード間のバリまたは突出部は、各サイドで0.152mm(0.006")を超えないこと

- リードの平坦度(整形後のリードの底面)は最大0.102mm(0.004")であること

- 露出パッドの寸法には、モールドのバリを含むE-PAD上のモールドのバリは、各サイドで0.254mm(0.010")を超えないこと

## 標準的応用例

高効率のバックアップ回路

## 関連製品

| 製品番号                    | 説明                                                      | 注釈                                                                                      |

|-------------------------|---------------------------------------------------------|-----------------------------------------------------------------------------------------|

| LT1763                  | 500mA、低ノイズ、マイクロパワー LDO レギュレータ                           | V <sub>IN</sub> : 1.8V ~ 20V、12 ピン DFN、8 ピン SO パッケージ                                    |

| LTC2952                 | 監視機能付きプッシュボタン PowerPath コントローラ                          | V <sub>IN</sub> : 2.7V ~ 28V、オン/オフ・タイマ、ESD 耐圧:<br>±8kV(人体モデル)、TSSOP-20 および QFN-20 パッケージ |

| LTC3103                 | 15V/300mA 同期整流式降圧 DC/DC コンバータ                           | V <sub>IN</sub> : 2.5V ~ 15V、DFN-10 および MSE-10 パッケージ                                    |

| LTC3129/LTC3129-1       | 静止電流が $1.3\mu\text{A}$ の 15V、200mA 同期整流式昇降圧 DC/DC コンバータ | V <sub>IN</sub> : 1.92V ~ 15V、QFN-16 および MSE-16 パッケージ                                   |

| LTC3388-1/<br>LTC3388-3 | 20V/50mA 高効率ナノパワー降圧レギュレータ                               | V <sub>IN</sub> : 2.7V ~ 20V、DFN-10 および MSE-10 パッケージ                                    |

| LTC4411                 | 2.6A 低損失理想ダイオード、ThinSOT™ パッケージ                          | 2.6A の P チャネル内蔵、2.6V ~ 5.5V、I <sub>Q</sub> = 40μA、SOT-23 パッケージ                          |

| LTC4412                 | ThinSOT パッケージの 36V 低損失 PowerPath コントローラ                 | 2.5V ~ 36V、P チャネル、I <sub>Q</sub> = 11μA、SOT-23 パッケージ                                    |

| LTC4415                 | 電流制限を調整可能なデュアル 4A 理想ダイオード                               | デュアル P チャネル内蔵、1.7V ~ 5.5V、MSOP-16 および DFN-16 パッケージ                                      |

| LTC4416                 | 大型 P チャネル FET 向け 36V 低損失デュアル PowerPath コントローラ           | 3.6V ~ 36V、I <sub>Q</sub> : 35μA/電源、MSOP-10 パッケージ                                       |

| LTC4417                 | 3 チャネル優先順位付け PowerPath コントローラ                           | トリプル P チャネル・コントローラ、2.5V ~ 36V、SSOP-24 および QFN-24 パッケージ                                  |

| LTC4355                 | 電源とヒューズ・モニタを備えた正の高電圧理想ダイオード OR                          | デュアル N チャネル、9V ~ 80V、SO-16、MSOP-16 および DFN-14 パッケージ                                     |

| LTC4359                 | 逆入力保護を備えた理想ダイオード・コントローラ                                 | N チャネル、4V ~ 80V、MSOP-8 および DFN-6 パッケージ                                                  |