# SOT-23の負電圧 Hot Swap コントローラ

### 特長

- 電源の入った-48Vのバックプレーンに基板を安全に 挿入/引抜き可能

- フローティング構成により、高電圧動作が可能

- 回路ブレーカ・タイマ付き、プログラム可能なアナログ 電流制限

- 高速応答により、ピーク・フォルト電流を制限

- 改善された堅牢なシャント・レギュレータ

- プログラム可能なタイマ

- プログラム可能な低電圧/過電圧保護

- 高さの低い6ピンSOT-23(ThinSOT™)パッケージ

## アプリケーション

- 活線挿入

- 電子回路ブレーカ

- -48V配電システム

- 負電源制御

- 電話局交換機

- プログラム可能な電流制限回路

- 高可用性サーバ

- ディスク・アレイ

#### 概要

LTC<sup>®</sup>4251B/LTC4251B-1/LTC4251B-2は、電源の入ったバックプレーンに対して基板を安全に挿入および引き抜き可能にする負電圧 Hot Swap™コントローラです。出力電流は電流制限(時限式の回路ブレーカ、アクティブ電流制限、最悪の破滅的なフォルト条件においてピーク電流を制限する高速フィードフォワード経路)によって制御されます。

プログラム可能な低電圧および過電圧検出器により、入力電源が所要の動作範囲を超えると負荷が切り離されます。電源入力はシャント・レギュレータで安定化されるので、電源電圧が非常に高い場合でも安全な動作が可能です。マルチ機能タイマは初期起動に遅延を加え、回路ブレーカの応答時間を制御します。

LTC4251BのUV/OVしきい値は標準的な通信機器の動作範囲である $-43V\sim-75V$ に適合するように設計されています。LTC4251B-1のUV/OVしきい値は、動作範囲 $-36V\sim-72V$ を含むように拡張されています。LTC4251B-2のUVしきい値は-43Vのみです。LTC4251BはLTC4251のシャント・レギュレータをより堅牢なものに改良しています。

△7、LT、LTC、LTM、Linear TechnologyおよびLinearのロゴはリニアテクノロジー社の登録商標です。Hot Swap、およびThinSOTはリニアテクノロジー社の商標です。その他すべての商標の所有権は、それぞれの所有者に帰属します。

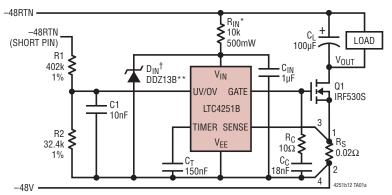

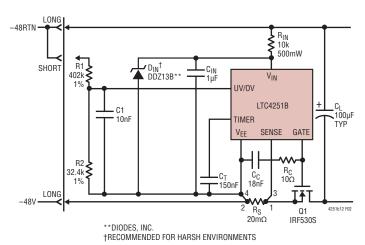

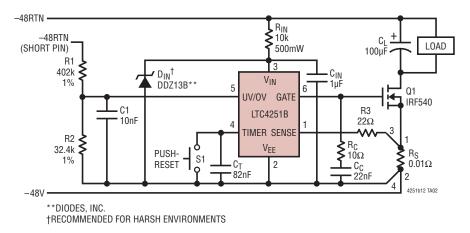

### 標準的応用例

-48V、2.5A のホットスワップ・コントローラ

- \*TWO 0.25W RESISTORS IN SERIES FOR R<sub>IN</sub> ON THE PCB ARE RECOMMENDED.

- \*\*DIODES, INC.

- †RECOMMENDED FOR HARSH ENVIRONMENTS

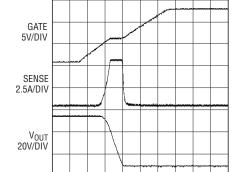

1ms/DIV

起動動作

4251b12 TA01b

# LTC4251B/LTC4251B-1/ LTC4251B-2

# 絶対最大定格

#### (Note 1)すべての電圧は VEE を基準にしている

| V <sub>IN</sub> への流入電流(100μsパルス)  | 100mA                                |

|-----------------------------------|--------------------------------------|

| 最小入力電圧 V <sub>IN</sub>            | 0.3V                                 |

| GATE、UV/OV、TIMERの電圧               | 0.3V~16V                             |

| SENSEの電圧                          | 0.6V~16V                             |

| SENSE ピンから流れ出す電流 (20μs パルス)       | –200mA                               |

| 最大接合部温度                           | 125°C                                |

| 動作温度範囲                            |                                      |

| LTC4251BC/LTC4251BC-1/LTC4251BC-2 | $0^{\circ}$ C $\sim$ $70^{\circ}$ C  |

| LTC4251BI/LTC4251BI-1/LTC4251BI-2 | −40°C ~ 85°C                         |

| 保存温度範囲                            | $-65^{\circ}$ C $\sim 150^{\circ}$ C |

| リード温度(半田付け、10秒)                   | 300°C                                |

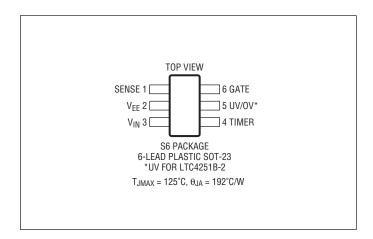

# ピン配置

# 発注情報

#### 無鉛仕上げ

| テープアンドリール(ミニ)        | テープアンドリール           | 製品マーキング* | パッケージ                 | 温度範囲          |

|----------------------|---------------------|----------|-----------------------|---------------|

| LTC4251BCS6#TRMPBF   | LTC4251BCS6#TRPBF   | LTGCT    | 6-Lead Plastic SOT-23 | 0°C to 70°C   |

| LTC4251BIS6#TRMPBF   | LTC4251BIS6#TRPBF   | LTGCT    | 6-Lead Plastic SOT-23 | –40°C to 85°C |

| LTC4251BCS6-1#TRMPBF | LTC4251BCS6-1#TRPBF | LTGDV    | 6-Lead Plastic SOT-23 | 0°C to 70°C   |

| LTC4251BIS6-1#TRMPBF | LTC4251BIS6-1#TRPBF | LTGDV    | 6-Lead Plastic SOT-23 | –40°C to 85°C |

| LTC4251BCS6-2#TRMPBF | LTC4251BCS6-2#TRPBF | LTGDW    | 6-Lead Plastic SOT-23 | 0°C to 70°C   |

| LTC4251BIS6-2#TRMPBF | LTC4251BIS6-2#TRPBF | LTGDW    | 6-Lead Plastic SOT-23 | –40°C to 85°C |

TRM = 500 個。\* 温度グレードは出荷時のコンテナのラベルで識別されます。

より広い動作温度範囲で規定されるデバイスについては、弊社へお問い合わせください。

鉛ベースの仕様の製品の詳細については、弊社へお問い合わせください。

鉛フリー仕様の製品マーキングの詳細については、http://www.linear-tech.co.jp/leadfree/をご覧ください。

テープアンドリールの仕様の詳細については、http://www.linear-tech.co.jp/tapeandreel/をご覧ください。

# 電気的特性 ● は全動作温度範囲での規格値を意味する。それ以外はT<sub>A</sub> = 25℃での値(Note 2、3)。

| SYMBOL            | PARAMETER                                                  | CONDITIONS                                                                                                                                                         |   | MIN  | TYP             | MAX  | UNITS          |

|-------------------|------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|------|-----------------|------|----------------|

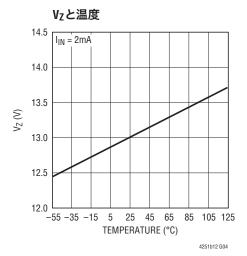

| Vz                | V <sub>IN</sub> to V <sub>EE</sub> Zener Voltage           | I <sub>IN</sub> = 2mA                                                                                                                                              | • | 11.5 | 13              | 14.5 | V              |

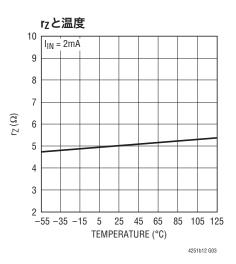

| rz                | V <sub>IN</sub> to V <sub>EE</sub> Zener Dynamic Impedance | I <sub>IN</sub> = 2mA to 30mA                                                                                                                                      |   |      | 5               |      | Ω              |

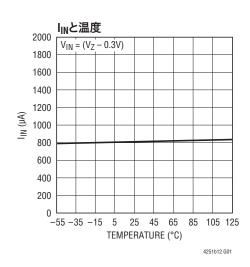

| I <sub>IN</sub>   | V <sub>IN</sub> Supply Current                             | $UV/OV = 4V$ , $V_{IN} = (V_Z - 0.3V)$                                                                                                                             | • |      | 0.8             | 2    | mA             |

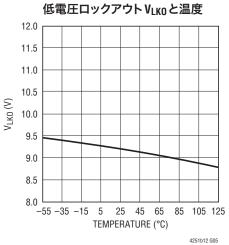

| V <sub>LKO</sub>  | V <sub>IN</sub> Undervoltage Lockout                       | Coming Out of UVLO (Rising V <sub>IN</sub> )                                                                                                                       | • |      | 9.2             | 11.5 | V              |

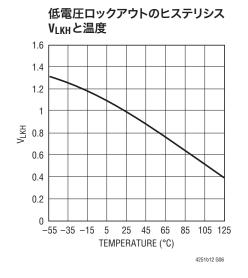

| V <sub>LKH</sub>  | V <sub>IN</sub> Undervoltage Lockout Hysteresis            |                                                                                                                                                                    |   |      | 1               |      | V              |

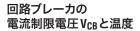

| V <sub>CB</sub>   | Circuit Breaker Current Limit Voltage                      | V <sub>CB</sub> = (V <sub>SENSE</sub> - V <sub>EE</sub> )                                                                                                          | • | 40   | 50              | 60   | mV             |

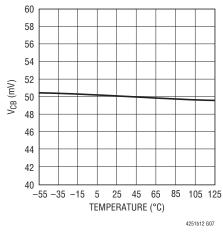

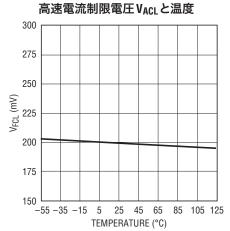

| V <sub>ACL</sub>  | Analog Current Limit Voltage                               | V <sub>ACL</sub> = (V <sub>SENSE</sub> - V <sub>EE</sub> )                                                                                                         | • | 80   | 100             | 120  | mV             |

| V <sub>FCL</sub>  | Fast Current Limit Voltage                                 | V <sub>FCL</sub> = (V <sub>SENSE</sub> – V <sub>EE</sub> )                                                                                                         | • | 150  | 200             | 300  | mV             |

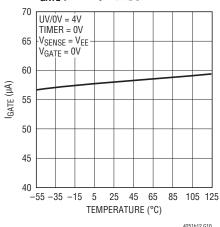

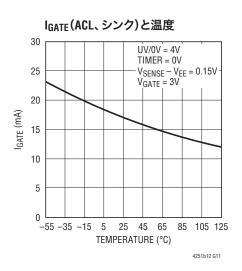

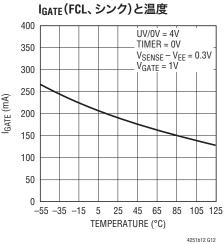

| IGATE             | GATE Pin Output Current                                    | UV/OV = 4V, VSENSE = VEE, VGATE = 0V (Sourcing)<br>UV/OV = 4V, VSENSE - VEE = 0.15V, VGATE = 3V (Sinking)<br>UV/OV = 4V, VSENSE - VEE = 0.3V, VGATE = 1V (Sinking) | • | 40   | 58<br>17<br>190 | 80   | μΑ<br>mA<br>mA |

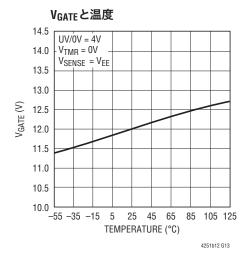

| V <sub>GATE</sub> | External MOSFET Gate Drive                                 | V <sub>GATE</sub> – V <sub>EE</sub> , I <sub>IN</sub> = 2mA                                                                                                        | • | 10   | 12              | Vz   | V              |

# 電気的特性 ● は全動作温度範囲での規格値を意味する。それ以外はTA = 25℃での値。

| SYMBOL             | PARAMETER                    | CONDITIONS                                                                                                                                                                                                                                         |   | MIN            | TYP                     | MAX            | UNITS          |

|--------------------|------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|----------------|-------------------------|----------------|----------------|

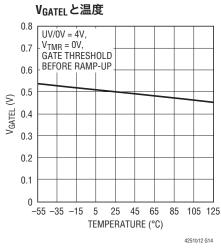

| V <sub>GATEL</sub> | Gate Low Threshold           | (Before Gate Ramp-Up)                                                                                                                                                                                                                              |   |                | 0.5                     |                | V              |

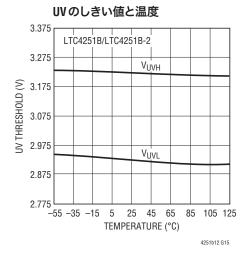

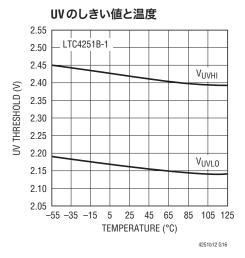

| V <sub>UVHI</sub>  | UV Threshold High            | LTC4251B/LTC4251B-2<br>LTC4251B-1                                                                                                                                                                                                                  | • | 3.075<br>2.300 | 3.225<br>2.420          | 3.375<br>2.540 | V              |

| V <sub>UVLO</sub>  | UV Threshold Low             | LTC4251B/LTC4251B-2<br>LTC4251B-1                                                                                                                                                                                                                  | • | 2.775<br>2.050 | 2.925<br>2.160          | 3.075<br>2.270 | V              |

| Vuvhst             | UV Hysteresis                | LTC4251B/LTC4251B-2<br>LTC4251B-1                                                                                                                                                                                                                  |   |                | 0.30<br>0.26            |                | V              |

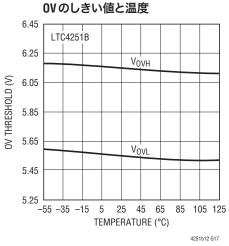

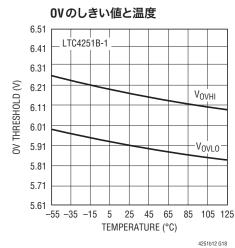

| V <sub>OVHI</sub>  | OV Threshold High            | LTC4251B<br>LTC4251B-1                                                                                                                                                                                                                             | • | 5.85<br>5.86   | 6.15<br>6.17            | 6.45<br>6.48   | V              |

| V <sub>0VL0</sub>  | OV Threshold Low             | LTC4251B<br>LTC4251B-1                                                                                                                                                                                                                             | • | 5.25<br>5.61   | 5.55<br>5.91            | 5.85<br>6.21   | V              |

| Vovhst             | OV Hysteresis                | LTC4251B<br>LTC4251B-1                                                                                                                                                                                                                             |   |                | 0.60<br>0.26            |                | V              |

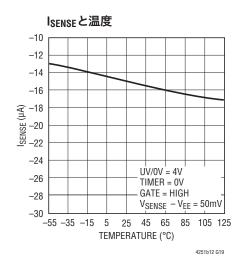

| I <sub>SENSE</sub> | SENSE Input Current          | UV/OV = 4V, V <sub>SENSE</sub> = 50mV                                                                                                                                                                                                              | • | -30            | -15                     |                | μА             |

| I <sub>INP</sub>   | UV/OV Input Current          | UV/0V = 4V                                                                                                                                                                                                                                         | • |                | ±0.1                    | ±1             | μА             |

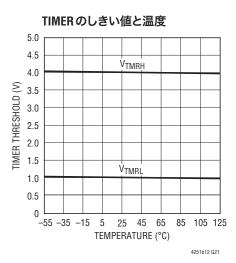

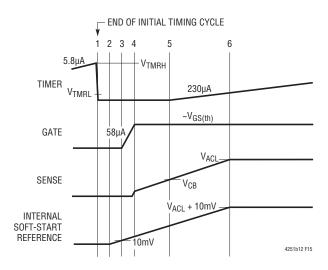

| V <sub>TMRH</sub>  | Timer Voltage High Threshold |                                                                                                                                                                                                                                                    |   |                | 4                       |                | V              |

| V <sub>TMRL</sub>  | Timer Voltage Low Threshold  |                                                                                                                                                                                                                                                    |   |                | 1                       |                | V              |

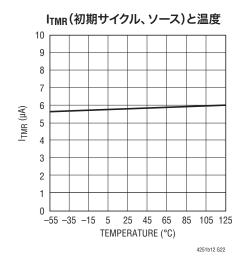

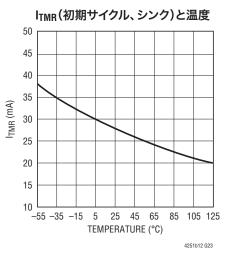

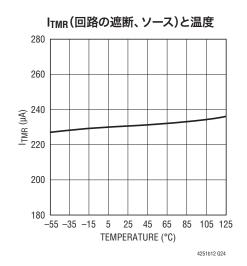

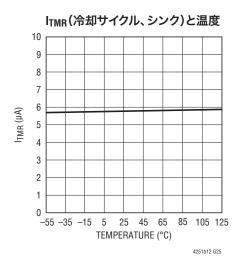

| I <sub>TMR</sub>   | Timer Current                | Timer On (Initial Cycle, Sourcing), V <sub>TMR</sub> = 2V<br>Timer Off (Initial Cycle, Sinking), V <sub>TMR</sub> = 2V<br>Timer On (Circuit Breaker, Sourcing), V <sub>TMR</sub> = 2V<br>Timer Off (Cooling Cycle, Sinking), V <sub>TMR</sub> = 2V |   |                | 5.8<br>28<br>230<br>5.8 |                | μΑ<br>mA<br>μΑ |

| t <sub>PLLUG</sub> | UV Low to GATE Low           |                                                                                                                                                                                                                                                    |   |                | 0.7                     |                | μs             |

| t <sub>PHLOG</sub> | OV High to GATE Low          | LTC4251B/LTC4251B-1                                                                                                                                                                                                                                |   |                | 1                       |                | μs             |

Note 1: 絶対最大定格に記載された値を超えるストレスはデバイスに永続的損傷を与える可能性がある。また、長期にわたって絶対最大定格条件に曝すと、デバイスの信頼性と寿命に悪影響を与える可能性がある。

Note 2: デバイスのピンに流れ込む電流はすべて正。デバイスのピンから流れ出す電流はすべて負。注記がない限り、すべての電圧は $V_{EE}$ を基準にしている。

**Note 3:** UV/OV = 4Vとは、LTC4251B-2の場合、UV = 4Vのことを指す。

# 標準的性能特性 UV/OV = 4Vとは、LTC4251B-2の場合、UV = 4Vのことを指す。

# 標準的性能特性 UV/OV = 4Vとは、LTC4251B-2の場合、UV = 4Vのことを指す。

#### IGATE(ソース)と温度

4251b12f

4251b12 G09

# 標準的性能特性 UV/OV = 4Vとは、LTC4251B-2の場合、UV = 4Vのことを指す。

標準的性能特性 UV/OV = 4Vとは、LTC4251B-2の場合、UV = 4Vのことを指す。

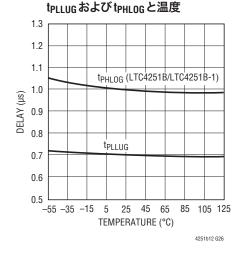

ピン機能 UV/OVは、LTC4251B-2の場合、UVピンのことを指す。LTC4251B-2内部のOVコンパレータはディスエーブルされている。 本文中での過電圧、OV、 $V_{OVHI}$ および $V_{OVLO}$ についての言及内容は、LTC4251B-2には適用されない。

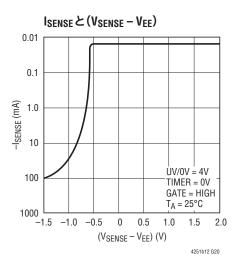

SENSE (ピン1): 回路ブレーカ/電流制限検出ピン。負荷電流は SENSE と  $V_{EE}$  の間に接続された検出抵抗  $R_S$  によってモニタされ、3 段階で制御されます。 SENSE の電圧が  $V_{CB}$  (50mV)を超えると、回路ブレーカのコンパレータが 230 $\mu$ A の TIMER ピン・プルアップ電流を起動します。  $C_T$  が 4 V まで充電されると、LTC4251B/LTC4251B-1/LTC4251B-2 はオフにラッチされます。 SENSE の電圧が  $V_{ACL}$  (100mV)を超えると、アナログ電流制限アンプが GATE の電圧を下げて、MOSFET の電流を  $V_{ACL}/R_S$  に制御します。 破壊的な短絡が発生した場合、SENSE の電圧は 100mV オーバーシュートする可能性があります。 SENSE の電圧が  $V_{FCL}$  (200mV) に達すると、高速電流制限コンパレータが強いプルダウン電流を使って GATEを"L"に引き下げます。 回路ブレーカと電流制限機能を無効にするには、 SENSEを  $V_{FE}$  に接続します。

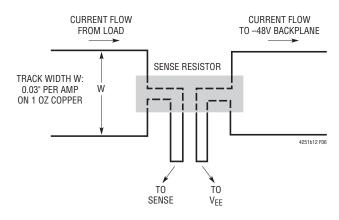

検出抵抗とV<sub>EE</sub>ピンおよびSENSEピンとの接続にはケルビン 検出接続を行うことを強く推奨します。図6を参照してください。

**VEE(ピン2)**: 負電源電圧入力。このピンは電源の負電圧側に接続します。

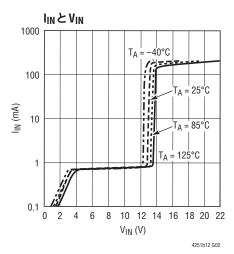

$V_{IN}$  (ピン3): 正電源入力。このピンは、電圧降下抵抗を介して電源の正電圧側に接続します。通常はシャント・レギュレータが $V_{IN}$ を13Vでクランプします。内部の低電圧ロックアウト(UVLO)回路は、 $V_{IN}$ ピンが $V_{LKO}$ (9.2V)より高くなるまでGATEを"L"に保ち、UV/OVを無効にします。UVが"H"でOVが"L"であり、 $V_{IN}$ がUVLOを超えると、TIMER はGATE電圧が上昇し始める前に初期タイミング・サイクルを開始します。 $V_{IN}$ が約8.2Vを下回ると、GATEは直ちに"L"になります。

TIMER (ピン4): タイマ入力。TIMER は、起動時の遅延を発生させる目的や、出力過負荷発生時にシャットダウンを遅延させる目的で使用します。TIMER は、以下の条件が満たされると初期タイミング・サイクルを開始します。条件は、UVが"H"、OVが"L"、 $V_{IN}$ がUVLOより高い、TIMER ピンが"L"、GATEの電圧が $V_{GATEL}$ より低い、および $V_{SENSE}$  –  $V_{EE}$  <  $V_{CB}$ です。その後、 $5.8\mu$ Aのプルアップ電流によって $C_T$ が充電され、遅延時間が発生します。 $C_T$ が充電されて $V_{TMRH}$  (4V)に達すると、タイミング・サイクルは終了し、TIMER はすぐに"L"になってGATEが作動します。

GATEが"H"のときにSENSEの電圧が50mVを超えると、230 $\mu$ Aのプルアップ電流が $C_T$ を充電します。TIMERの電圧が4Vに達する前にSENSEの電圧が50mVより低くなると、5.8 $\mu$ Aのプルダウン電流が $C_T$ を緩やかに放電します。 $C_T$ の電圧が最終的に最大4Vの $V_{TMRH}$ しきい値まで達した場合、TIMERは5.8 $\mu$ Aのプルアップ電流源によって"H"にラッチされ、GATEはすぐに"L"になります。LTC4251B/LTC4251B-1/LTC4251B-2のフォルト・ラッチは、外部デバイスによりTIMERを"L"にするか、UV/OVの電圧を $V_{UVLO}$ より低くすることによって解消されます。

UV/OV (ピン5): 低電圧/過電圧入力。この2つの機能を持つピンは、低電圧ならびに過電圧を検出します。UVコンパレータの"H"側のしきい値は、ヒステリシスVUVHSTを持つVUVHIで設定されます。OVコンパレータの"H"側のしきい値は、ヒステリシスVOVHSTを持つVOVHIで設定されます。UV/OV < VUVLOまたはUV/OV > VOVHIの場合、GATEは"L"になります。UV/OV > VUVHIおよびUV/OV < VOVLOの場合、LTC4251B/LTC4251B-1/LTC4251B-2は起動しようとします。VINの内部UVLOは、UV/OVより常に優先します。UVで"L"になると、内部のフォルト・ラッチがリセットされます。OVで"H"になると、GATEは"L"になりますが、フォルト・ラッチはリセットされません。UV/OVに1nF~10nFのコンデンサを接続すると、過渡電圧とスイッチング・ノイズがUV/OVのしきい値に影響しなくなり、GATEピンでのグリッチの発生を防ぎます。

GATE (ピン6): NチャネルMOSFETのゲート駆動出力。このピンは $58\mu$ Aの電流源によって"H"に引き上げられます。GATEは $V_{\rm IN}$ (UVLO)、UV/OVでの無効な条件、またはフォルト・ラッチによって"L"になります。GATEはアクティブにサーボ制御され、SENSEで測定されるフォルト電流を制御します。GATEに補償コンデンサを接続すると、このループは安定化します。コンパレータはGATEをモニタして、初期タイミング・サイクル、過電圧事象発生後のGATE電圧の上昇、または電流制限障害後の再起動を可能にする前に、GATEが"L"であることを確認します。

# ブロック図

動作 説明を簡単にするため、本文中では以下のことを前提とする。まず、UV/OVはLTC4251B-2のUVピンのことも意味する。 次に、LTC4251B-2ではOVコンパレータがディスエーブルされているので、OV、V<sub>OVHI</sub>、およびV<sub>OVLO</sub>に対するすべての過電圧条件と言及内 容はLTC4251B-2には適用されない。

#### 活線挿入

電源の入っているバックプレーンに回路基板を挿入する場合、電源のバイパス・コンデンサを充電するときに電源バスから大きな過渡電流が流れることがあります。この電流によってコネクタ・ピンが損傷を受け、電源バスにグリッチが生じる結果、システム内の他の基板がリセットされます。LTC4251B/LTC4251B-1/LTC4251B-2は回路基板の電源のオン/オフを制御された状態で行うように設計されているので、グリッチの発生やコネクタの損傷なしに挿入や引き抜きを行なうことができます。

#### 最初の起動

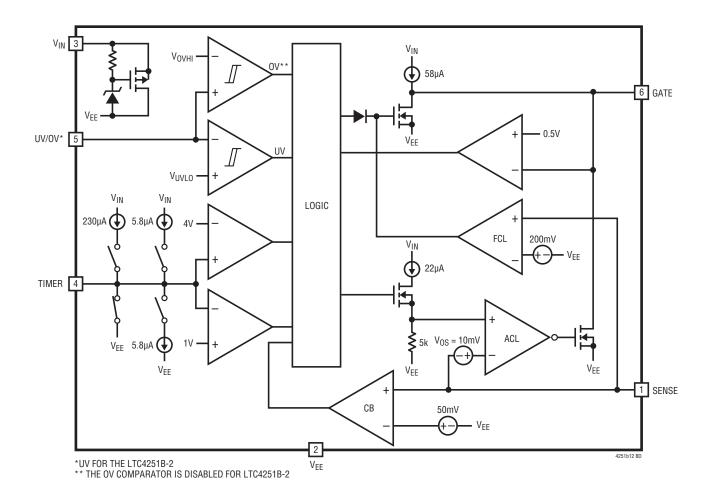

LTC4251B/LTC4251B-1/LTC4251B-2は着脱可能な回路基板上に置かれ、コネクタと負荷または電力変換回路の間の経路を外付けのMOSFETスイッチを使って制御します(図1参照)。突入電流制御と短絡保護の両方ともMOSFETによって行われます。

詳細な回路図を図2に示します。-48Vと-48RTNは最も長いコネクタ・ピンを介して電力が供給されるので、基板が挿入されるとき最初に接続されます。この間、GATEピンがMOSFETをオフに保ちます。UV/OVは、内部の高精度しきい値と外付けの分圧器に基づいて、MOSFETをオンするかどうかを決定します。UV/OVはコネクタが接続されているかどうかもモニタすることにより、2つの役割を果たします。分圧器の上端は、挿入手順中の最後に接続される短いコネクタを介して-48RTNを検出します。

図1. 基本的なLTC4251Bのホットスワップ配置

図2. -48V、2.5Aのホットスワップ・コントローラ

#### インターロック条件

起動シーケンスは5つの初期「インターロック」条件が満たされると開始されます。

- 1. 入力電圧 V<sub>IN</sub>が9.2V(V<sub>LKO</sub>)を超える

- 2. UV/OVの電圧が $V_{UVHI} \sim V_{OVLO}$  (LTC4251B-2の場合は UV >  $V_{UVHI}$ )の範囲内に入る

- 3. (SENSE VFE)の電圧が50mV(VCB)より低い

- 4. タイマ・コンデンサ $(C_T)$ の電圧が $1V(V_{TMRL})$ より低い

- 5. GATEの電圧が0.5V(VGATEL)より低い

最初の2つの条件は常時モニタされ、残りの3つの条件は初期タイミングまたはGATE電圧上昇の前に検査されます。過電圧状態から抜け出すと、TIMERピンの電圧要件は抑制されます。詳細については、「アプリケーション情報」の「タイミング波形」のセクションを参照してください。

TIMER は $5.8\mu$ Aを $C_T$ に供給することによって起動シーケンスを開始します。 $V_{IN}$ またはUV/OVが範囲から外れると、起動サイクルが停止し、TIMER は $C_T$ を1V未満に放電してから、前述の条件が再度満たされるまで待機します。 $C_T$ が4Vまで正常に充電されると、TIMER は"L"になり、GATE は解放されます。GATEからは $58\mu$ A ( $I_{GATE}$ )が流れ出て、MOSFETのゲートとそれに付随した容量を充電します。

### 動作

MOSFETが最初にオンするときは、外付け部品の値、MOSFETの特性、および公称設計電流に応じて、2つの動作モードが可能です。1つ目は、負荷容量への突入電流が小さい値になるように、MOSFETが徐々にオンするモードです。出力は単純に-48Vまで増加するので、MOSFETは完全に導通します。2つ目は、負荷電流が電流制限しきい値である100mV/Rsを超えるモードです。この場合、LTC4251B/LTC4251B-1/LTC4251B-2は、電流(100mV/Rs)を負荷容量に流し込むことにより、出力を上昇させます。どちらの起動モードが使用されるかに関係なく、起動時間がTIMERの遅延時間よりも短くなるようにタイマの遅延時間を設定することが重要です。この条件を満たしていない場合、LTC4251B/LTC4251B-1/LTC4251B-2はTIMERの遅延時間が1回経過した後でシャットダウンすることがあります。

#### 基板の引き抜き

カードケージから基板を引き抜くと、UV/OVの分圧器が最初に切断されます。これにより、MOSFETがオフしてコネクタ内の電流が反転します。その後電源ピンが切り離されるときは、アーク放電が生じません。

#### 電流制御

3つのレベルの保護により、短絡状態と過負荷状態が処理されます。負荷電流はSENSEと抵抗Rsによってモニタされます。SENSEには3つの異なるしきい値があります。それは、時限回路ブレーカ機能用の50mV、アナログ電流制限ループ用の100mV、および破壊的な短絡発生時にピーク電流を制限する高速フィードフォワード・コンパレータ用の200mVです。

出力の過負荷によって $R_S$ 両端の電圧降下が50mVを超えると、TIMERから $C_T$ に $230\mu A$ が流れ込みます。 $C_T$ が最終的に4Vのしきい値まで充電されると、LTC4251B/LTC4251B-1/LTC4251B-2はオフにラッチされます。過負荷状態が解消されてSENSEの測定電圧が50mVより低くなると、 $C_T$ は緩やかに放電します $(5.8\mu A)$ 。このようにして、回路ブレーカ機能は低デューティ・サイクルの過負荷にも応答し、発熱が速く冷却が遅いMOSFETの特性に対処しています。

大きな過負荷はアナログ電流制限ループによって処理されます。 $R_S$  両端の電圧降下が100 mV に達すると、電流制限ループがMOSFET のゲートをサーボ制御して、 $100 \text{mV}/R_S$  という一定の出力電流を維持します。SENSE の電圧が50 mV を超えているため、この時間にTIMER が $C_T$ を充電し、LTC4251B/LTC4251B-1/LTC4251B-2 は最終的にシャットダウンすることに注意してください。

LTC4251B/LTC4251B-1/LTC4251B-2の負荷側の低インピーダンス障害と48V以上の潜在的駆動能力の組み合わせにより、50A/µsを十分超える電流スルーレートが生じることがあります。これらの条件では、オーバーシュートは避けられません。しきい値が200mVの高速SENSEコンパレータがオーバーシュートを検出し、弱い電流制限ループよりもはるかに強力に、したがってはるかに高速にGATEを"L"に引き下げます。その後、100mV/Rsの電流制限ループが引き継ぎ、前述したように電流をサーボ制御します。以前のようにTIMERが動作し、CTが4Vに達すると、LTC4251B/LTC4251B-1/LTC4251B-2はオフにラッチされます。

LTC4251B/LTC4251B-1/LTC4251B-2の回路ブレーカ・ラッチをリセットするには、UV/OVを一時的に"L"にするか、入力電圧  $V_{IN}$ を内部 UVLO しきい値である 8.2V より低くします。

短絡は最も明白な種類の障害ですが、いくつかの動作条件で過電流保護が作動することがあります。バックプレーンや負荷からのスパイク・ノイズ、高電圧電源の追加接続によって生じる入力ステップ、同じ電源バスを共有している隣接回路基板上の障害によって生じる過渡電流、またはホットスワップ非対応製品の挿入により、予想していたより大きな入力電流が生じ、過電流状態が一時的に検出されることがあります。TIMERとCTの動作でこうした事態を排除することにより、LTC4251B/LTC4251B-1/LTC4251B-2は、単純な電流コンパレータを作動させ、場合によってはヒューズを切ることのある、一時的な過負荷や外乱を「乗り切る」ことができます。

#### シャント・レギュレータ

高速応答のシャント・レギュレータにより、 $V_{IN}$ ピンは $13V(V_Z)$ にクランプされます。電力は外付けの電流制限抵抗  $(R_{IN})$ によって-48RTNから供給されます。 $1\mu F$ のデカップリング・コンデンサ  $(C_{IN})$ が電源の過渡電流を除去するので、起動時に短い遅延が生じます。

電流の表面漏れ要件を満たすため、R<sub>IN</sub>は2つ以上の直列抵抗(2つの5.1k抵抗や3つの3.3k抵抗など)に分割することができます。こうすると、1つの部品で可能な間隔より合計の間隔は広くなり、同時に各抵抗の下の隙間の両端間の電位は安定します。LTC4251Bは、-48Vをその基準グランドとして動作する基本的に低電圧のデバイスです。LTC4251Bのピンへのアーク放電からさらに保護するため、LTC4251Bおよび関連するすべての部品の内部領域と周辺領域を、他のプレーン(シャーシ・グランド、戻り線、2次側の電源プレーンやグランド・プレーンなど)がない状態にします。

$V_{IN}$ はパッケージの熱制限の範囲内で30mAを処理できる定格になっており、100 $\mu$ sで100mAのパルスに耐えられることがテストされます。より大きな振幅のスパイクによる損傷から $V_{IN}$ を保護するには、 $V_{IN}$ と $V_{EE}$ の間を13Vのツェナー・ダイオードでクランプします。図2に示すように、 $V_{EE}$ と $V_{EE}$ を基準とするすべての部品を検出抵抗のケルビン端子に星形結線し、 $V_{IN}$ 、 $C_{IN}$ 、 $D_{IN}$ 、および $V_{EE}$ 間のトレースの長さをできるだけ短くします。

#### 内部低電圧ロックアウト(UVLO)

内部回路は $V_{IN}$ が低電圧になっていないかを監視します。正確なしきい値は $V_{LKO}$ とそのヒステリシスである $V_{LKH}$ で定義されます。 $V_{IN}$ が上昇して9.2V ( $V_{LKO}$ )を超えると、チップはイネーブルされます。逆に下降して8.2V ( $V_{LKO}$ - $V_{LKH}$ )より小さくなると、チップはディスエーブルされ、GATEは"L"になります。 $V_{IN}$ のUVLO機能をUV/OVピンの機能と混同しないようにしてください。これらはまったく別の機能です。

#### UV/OVコンパレータ

低電圧および過電圧の状態を検出するための2つのヒステリシス付きコンパレータは、以下のしきい値により、2つの機能を持つUV/OVピンを監視します。

UV は VIIVHIでオン

UVはVUVLOでオフ

OVはV<sub>OVHI</sub>でオフ

OVはV<sub>OVLO</sub>でオン

LTC4251Bでは、UVとOVの作動点の比が、標準的な通信機器の動作範囲である43V~75Vに適合するように設計されています。LTC4251B-2に実装されているのは、43VのUVしきい値のみです。

分圧器 (R1, R2) を使用して電源電圧の大きさを調整します。 R1 = 402k および R2 = 32.4k を使用すると、標準的な動作範囲である 43.2V ~ 74.4V になります。低電圧および過電圧のシャットダウンしきい値は、39.2V および 82.5V になります。しきい値の精度を維持するため、1% 精度の分圧器抵抗を推奨します。同じ抵抗値をLTC4251B-2 に使用することができます。

「標準的応用例」に示すR1-R2分圧器の値では100µAよりもわずかに多い定常電流が設定され、UV/OVでのインピーダンスが30kに定義されます。多くのアプリケーションでは、30kのインピーダンスと300mVのUVヒステリシスの組み合わせにより、LTC4251B/LTC4251B-1/LTC4251B-2はノイズの影響を受けなくなります。ノイズ耐性を高める場合は、UV/OVとVELの間に1nF~10nFのフィルタ・コンデンサを追加します。

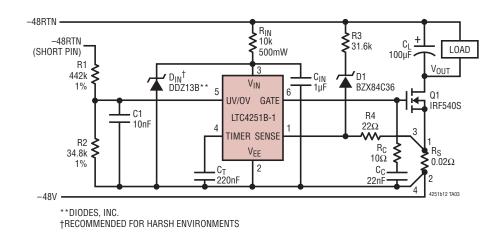

LTC4251B-1では、UVとOVの作動点のしきい値が、標準的な通信機器の動作範囲である $-36V\sim-72V$ を包含するように設計されています。

分圧器 (R1,R2) を使用して電源電圧の大きさを調整します。 R1=442k および R2=34.8k を使用すると、標準的な動作範囲である 33.2V ~ 81V になります。低電圧および過電圧の標準のシャットダウンしきい値は、29.6V および 84.5V になります。 しきい値の精度を維持するため、1% 精度の分圧器抵抗を推奨します。

「標準的応用例」に示すR1-R2分圧器の値では100µAよりもわずかに多い定常電流が設定され、UV/OVでのインピーダンスが32kに定義されます。多くのアプリケーションでは、32kのインピーダンスと260mVのUVヒステリシスの組み合わせにより、LTC4251B-1はノイズの影響を受けなくなります。ノイズ耐性を高める場合は、UV/OVとVEEの間に1nF~10nFのフィルタ・コンデンサを追加します。

#### UV/OVの動作

UVコンパレータへの入力が低いとチップはリセットされ、GATEピンおよびTIMERピンは"L"になります。UVが"L"から"H"へ遷移すると、残る3つのインターロック条件に合致する場合は、初期タイミング・シーケンスが開始されます。

4251b121

OVコンパレータによって過電圧状態が検出されるとGATEも "L"になるので、負荷は遮断されますが、回路ブレーカのラッ チはリセットされません。電源電圧が許容範囲内に戻ると、 TIMER 以外のすべてのインターロック条件が満たされている という前提で、GATEピンは再起動します。

#### **TIMER**

TIMER ピンはいくつかの重要な機能を果たすので、その動作は多少複雑です。LTC4251B/LTC4251B-1/LTC4251B-2のタイミングを得るため、TIMER ピンにはコンデンサ $C_T$ が使用されます。TIMER ピンでは、以下の4つの異なる充放電モードが利用できます。

- 1. 5.8µAの低速充電。初期タイミングの遅延。

- 2. 230µAの高速充電。回路ブレーカの遅延。

- 3.5.8µAの低速放電。回路ブレーカの「冷却」。

- 4. 低インピーダンス・スイッチ。低電圧ロックアウト時および過電圧時に、初期タイミングの遅延後、コンデンサをリセット。

最初の起動では、5.8µAのプルアップが使用されます。この4つのインターロック条件が満たされると、低インピーダンス・スイッチがオフし、5.8µAの電流源がイネーブルされます。次式で与えられる時間が経過すると、CTは4Vまで充電されます。

$$t = \frac{4V \cdot C_T}{5.8\mu A} \tag{1}$$

$C_T$ が4V ( $V_{TMRH}$ )に達すると、低インピーダンス・スイッチがオンして $C_T$ を放電します。GATE出力がイネーブルされ、負荷が導通します。

#### 回路ブレーカのタイマ動作

$R_S$ 両端の電圧が50mVより大きいことをSENSEピンが検出すると、TIMERピンは $230\mu$ Aで $C_T$ を充電します。 $C_T$ が 4Vまで充電されると、GATEピンは"L"になり、LTC4251B/ LTC4251B-1/LTC4251B-2 はオフにラッチされます。UV/OVピンに瞬間的な"L"のパルスが入力されるか、 $V_{IN}$ が一時的にUVLO状態まで低下し、その後元に戻るまで、デバイスはオフにラッチされたままです。回路ブレーカのタイムアウト時間は次式で与えられます。

$$t = \frac{4V \cdot C_T}{230\mu A} \tag{2}$$

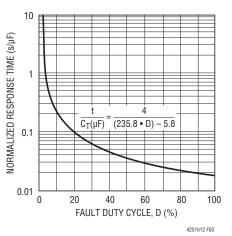

断続的な過負荷によってSENSEでの50mVのしきい値を超えることがありますが、その時間が十分に短ければ、TIMERが4Vに達することはなく、LTC4251B/LTC4251B-1/LTC4251B-2がオフにラッチされることはありません。この状況に対処するため、SENSE電圧が50mVより低い場合は必ず、5.8 $\mu$ Aのプルダウン電流により、TIMERが $C_T$ を緩やかに放電します。したがって、デューティ・サイクルの総計が2.5%以上の断続的な過負荷が存在すると、最終的には回路ブレーカが作動し、LTC4251B/LTC4251B-1/LTC4251B-2をオフにラッチします。1 $\mu$ Fに対して正規化した秒数で回路ブレーカの応答時間を図3に示します。 $C_T$ の充電時間と放電時間が非対称な場合は、MOSFETが発熱しているという適正な尺度になります。

図3. 回路ブレーカの応答時間

#### GATE

GATE は以下のいずれの条件でも $V_{EE}$ まで低下します。それは、UVLO時、初期9イミング・サイクル中、過電圧状態の場合、またはLTC4251B/LTC4251B-1/LTC4251B-2が短絡後にオフにラッチされている場合です。GATEがオンすると、 $58\mu$ Aの電流源がMOSFETのゲートおよび関連したすべての外付け容量を充電します。 $V_{IN}$ はゲート駆動電圧が14.5Vを超えないように制限します。

最初に突然電源を接続したときのゲート/ドレイン間容量  $(C_{GD})$ の貫通により、MOSFETをオンするのに十分なゲート/ソース間電圧が発生することがあります。実際に利用できる電圧が $V_{IN}$ に存在しない場合でも、固有の回路によってGATEが"L"になり、挿入時の電流スパイクが除去されます。このため、 $C_{GD}$ を補償するための大きな外付けゲート/ソース間コンデンサは必要ありません。代わりに、小さな値 (10nF以上)のコンデンサ $C_{C}$ が適しています。 $C_{C}$ にはアナログ電流制限ループの補償機能もあります。

#### **SENSE**

SENSEピンは、回路ブレーカ(CB)コンパレータ、アナログ電流制限(ACL)アンプ、および高速電流制限(FCL)コンパレータによって監視されます。これら3つはそれぞれ $V_{EE}$ を基準にしたSENSEの電位を測定します。SENSEが50mVを超えると、CBコンパレータはTIMERの230 $\mu$ Aプルアップ電流を導通させます。100mVではACLアンプがMOSFETの電流をサーボ制御し、200mVではFCLコンパレータがGATEを急激に"L"に引き下げてMOSFETの電流を制御しようとします。これらの状態のいずれかが、TIMERが $C_T$ を4Vまで充電するのに十分長く持続すると(式(2)を参照)、LTC4251B/LTC4251B-1/LTC4251B-2 はオフにラッチされ、GATEは"L"になります。

SENSEピンが100mVより高い電圧を検出すると、ACLアンプはGATEを下方にサーボ制御してMOSFETの電流を制御しようとします。GATEは通常動作ではMOSFETをオーバードライブするので、ACLアンプはGATEをMOSFETのしきい値まで放電させるのに時間を要します。過負荷が大きくない場合、ACLアンプはMOSFETの電流を制御することができますが、過負荷が極端に大きいと電流にオーバーシュートが生じることがあります。SENSE = 200mVでは、FCLコンパレータが引き継いで、GATEピンをVEEに近い電位まで短時間で放電します。その後、FCLは制御を解放し、ACLアンプが引き継ぎます。この間、TIMERは動作を続けます。FCLの効果は、MOSFETの電流が減少するように制御ループに非線形の応答を付加することです。

システム内での誘導効果により、FCLは通常、電流制限ループを過補正し、GATEにはアンダーシュートが生じます。ループ内にゼロ(ゲートのコンデンサと直列に接続された抵抗R<sub>C</sub>)があると、ACLアンプの回復に役立ちます。

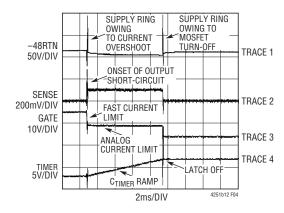

#### 短絡動作

負荷側の低インピーダンスの短絡によって生じる回路動作を図4に示します。GATEピンが機能して $V_{GS}$ が制御状態になるとき(トレース3)、最初、電流はアナログ電流制限レベルである $V_{SENSE} = 100 \text{mV}$ をオーバーシュートします(トレース2)。このオーバーシュートによってバックプレーンに負方向のグリッチが生じ、電流が $100 \text{mV/R}_S$ に減少すると、バックプレーンに正方向のグリッチが生じます。

アナログ電流制限ループがフォルト電流を100mV/ $R_S$ (この場合は5A)に保持している間(トレース2)、TIMERは $C_T$ の充電を開始します(トレース4)。バックプレーンの電圧(トレース1)が負荷によって低下していることに注意してください。 $C_T$ が4Vに達すると、GATEがオフし、負荷電流0に低下してバックプレーンに100Vを超えるリンギングが生じます。正のピーク電圧は、通常はMOSFETのなだれ降伏電圧で制限されます。-48Vと-48RTNの間の入力の両端に過渡電圧サプレッサ(Diodes Inc. 0SMAT70Aなど)を追加すれば、さらに制限を強化できます。

1枚のカードに低インピーダンスの短絡が生じると、同じバックプレーンを共有している他のカードの動作に影響を与えることがあります。図4のトレース1に見られるような初期グリッチやバックプレーンの低下があると、隣接するカードの出力コンデンサから電荷を奪うことがあります。故障したカードがシャットダウンすると、電流が流れ込んでコンデンサをリフレッシュします。LTC4251B、LTC4251B-1、または複数のLTC4251B-2を一貫して使用する場合、これらは突入電流を $100\text{mV/R}_S$ の値まで制限することによって応答します。 $C_T$ の大きさが適切であれば、コンデンサは $C_T$ のタイムアウト時間が経過するはるか前から再充電されます。

図4. 出力短絡時の動作 (すべての波形は VEE を基準にしている)

#### MOSFETの選択

外付けのMOSFETスイッチには、起動時に負荷容量を充電し、TIMERのラッチオフまで短絡状態を処理するための適切な安全動作領域(SOA)が必要です。これらの検討事項はDC電流定格よりも優先します。所定のアプリケーションに対して十分なSOAを備えたMOSFETは必要な電流を常に処理できますが、その逆が正しいとは言えません。メーカのMOSFETデータシートを参照して、安全動作領域と実効過渡サーマル・インピーダンス曲線を確認してください。

MOSFETの選択は3段階の手順です。最初にRSを計算し、その後負荷容量を充電するのに必要な時間を決定します。この時点で、最大短絡電流と最大入力電圧に加えて、MOSFETのSOA曲線と照合する動作点が定まります。

設計を開始するには、必要な負荷電流と負荷容量( $I_L$ および $C_L$ )を最初に指定します。最大負荷電流に対応するために、回路ブレーカの電流作動点(50m $V/R_S$ )を設定します。 $V_{SUPPLY(MIN)}$ ではDC/DCコンバータへの最大入力電流が予想されることに注意してください。 $R_S$ は次式で与えられます。

$$R_{S} = \frac{40\text{mV}}{I_{L(MAX)}} \tag{3}$$

ここで、40mVは保証されている最小の回路ブレーカしきい値を表します。

初期の充電処理中に、LTC4251B/LTC4251B-1/LTC4251B-2 は電流制限状態でMOSFETを動作させ、 $R_S$ の両端に $80mV \sim 120mV$ を強制的に印加することがあります。最小突入電流は次式で与えられます。

$$I_{\text{INRUSH(MIN)}} = \frac{80\text{mV}}{R_{\text{S}}} \tag{4}$$

最大短絡電流の制限値は最大 V<sub>SENSE</sub> を使って計算します。 つまり、次式で与えられます。

$$I_{SHORT-CIRCUIT(MAX)} = \frac{120mV}{R_S}$$

(5)

TIMER コンデンサ $C_T$ は予想される最も遅い充電速度に基づいて選択する必要があります。そうしないと、負荷コンデンサが完全に充電される前にTIMERのタイムアウト時間が経過する可能性があります。 $C_T$ の値は負荷コンデンサを充電するのに要する最大時間に基づいて計算します。この時間は次式で与えられます。

$$t_{CL\ CHARGE} = \frac{C \bullet V}{I} = \frac{C_L \bullet V_{SUPPLY(MAX)}}{I_{INRUSH(MIN)}} \tag{6}$$

I<sub>INRUSH(MIN)</sub>を式(4)で置き換え、(6)と(2)を等しいとすると、 次式が得られます。

$$C_{T} = \frac{C_{L} \cdot V_{SUPPLY (MAX)} \cdot R_{S} \cdot 230\mu A}{(4V \cdot 80mV)}$$

(7)

式(2)に戻り、TIMERの期間を計算し、結果をV<sub>SUPPLY(MAX)</sub> およびI<sub>SHORT-CIRCUIT(MAX)</sub>と組み合わせて使用して、予定しているMOSFETのSOA曲線を確認します。

数値の設計例として、36Vで1Aの入力電流を必要とする 30W負荷について考えます。 $V_{SUPPLY(MAX)} = 72$ Vおよび  $C_L = 100\mu$ Fの場合、式(3)により、 $R_{SENSE} = 40m\Omega$ となります。また、式(7)により、 $C_T = 207$ nFとなります。 $R_{SENSE}$ 、 $C_T$ 、TIMERの電流 $(230\mu A)$ 、およびTIMERのしきい値(4V)の誤差を考慮するため、計算値を1.5倍し、最も近い標準値である  $C_T = 330$ nFが得られます。

短絡が発生すると、式(2)での $C_T$  = 330nFに従って最大 120mV/40m $\Omega$  = 3Aの電流が5.7msの間MOSFETに流れます。MOSFETはこの基準に基づいて選択する必要があります。 IRF530S は 10msの間 100V および 3Aを処理できるので、このアプリケーションで使用しても安全です。

#### 設計フローの要約

設計フローをまとめるため、50W用に設計された、図2に示す アプリケーションについて考えます。

最大負荷電流を計算すると、50W/36V = 1.4A になり、コンバータの効率 83% を考慮すると、 $I_{IN(MAX)} = 1.7A$  になります。

$R_s$ を計算すると、式(3)から $R_s = 20m\Omega$ になります。

$C_T$ を計算すると、式(7)から $C_T = 150$ nFになります(1.5倍の補正係数を含む)。

TIMER 期間を計算すると、式(2)から短絡タイムアウト期間は t = 2.6 ms になります。

最大短絡電流を計算すると、式(5)から最大短絡電流は最大  $120 \text{mV}/20 \text{m}\Omega = 6 \text{A}$  になります。

MOSFETのSOA曲線を調べます。IRF530Sは5msの間72Vで6Aを処理できるので、このアプリケーションで使用しても安全です。

LINEAD

#### 周波数補償

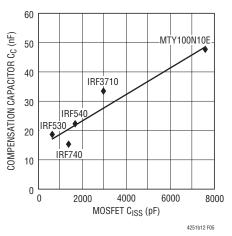

LTC4251B/LTC4251B-1/LTC4251B-2のアナログ電流制限ループ用の標準的な周波数補償回路網は、 $V_{EE}$ に接続されている直列の $R_C$ (10 $\Omega$ )および $C_C$ です。補償コンデンサ $C_C$ とMOSFETの $C_{ISS}$ との関係を図5に示します。MOSFETの $C_{ISS}$ の仕様に基づいて $C_C$ の開始値を選択するために図5の直線を使用します。いくつかの一般的なMOSFETに対する $C_C$ の最適値が示されています。 $C_C$ の最適値と開始値の差は大きくはありません。それでも、基板レベルの短絡テストで補償値を検証する必要があります。

前に図4で示したように、短絡が発生した時点で、直列インダクタンスにより、入力電源電圧に大きなリンギングが生じることがあります。この電圧がMOSFETのなだれ降伏を引き起こすと、MOSFETを通って電流が出力に流れ続けます。アナログ電流制限ループはこの電流を制限できないので、ループにアンダーシュートが生じます。この影響は周波数補償では除去できません。入力電源電圧をクランプしてMOSFETのなだれ降伏を防ぐにはツェナー・ダイオードが必要です。

図5. 推奨の補償コンデンサC<sub>C</sub>と MOSFET C<sub>ISS</sub>

#### 検出抵抗に関する検討事項

回路ブレーカが適正に動作するように、検出抵抗と $V_{EE}$ ピンおよびSENSEピンとの接続にはケルビン検出PCB接続を行うことを強く推奨します。LTC4251B/LTC4251B-1/LTC4251B-2と検出抵抗の間の正しい接続法を図6に示しま

す。配線による誤差を最小限に抑えるため、PCBレイアウトはバランスのとれた対称形にします。さらに、検出抵抗のPCBレイアウトには、検出抵抗の電力損失を最適化するための良好な熱管理手法を組み込みます。

図6. 検出抵抗へのPCB接続の実施

#### タイミング波形

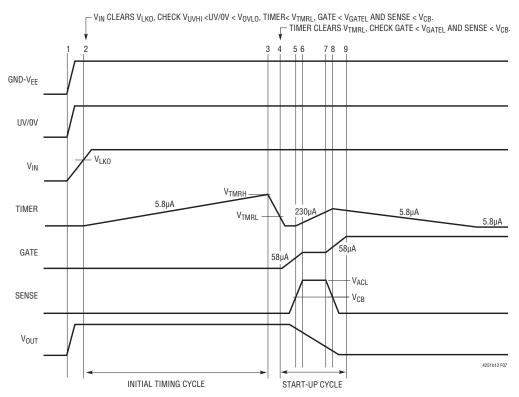

#### システムの電源投入

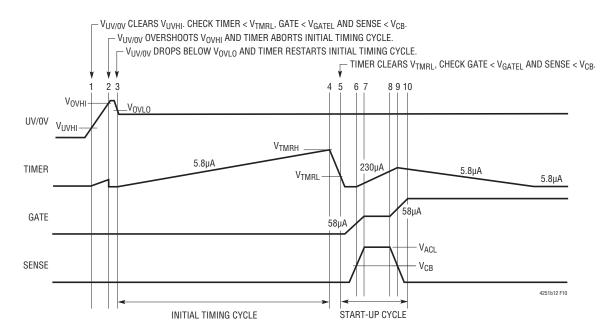

基板が既にバックプレーンに装着されていてシステムの電源 が急に投入された場合の標準的な電源投入シーケンスのタ イミング波形の詳細を図7に示します。時点1で、電源はUV/ OV、および VOUT とともに立ち上がります。 VIN のバイパス・コ ンデンサで設定される遅い速度でVINが続いて立ち上がり ます。時点2で、VINはVLKOを超え、内部ロジックがVIIVHI < UV/OV < V<sub>OVLO</sub>、TIMER < V<sub>TMRL</sub>、GATE < V<sub>GATEL</sub>、お よびSENSE < VCBを検査します。すべての条件が満たされ ると、初期タイミング・サイクルが開始され、TIMERコンデン サは5.8µAのプルアップ電流源によって充電されます。時点3 でTIMERがVTMRHしきい値に達し、初期タイミング・サイク ルが終了します。その後、TIMERコンデンサは短時間で放 電します。時点4でVTMRLしきい値に達するので、起動サイ クルを開始できるようにするには、その前にGATE < VGATEL およびSENSE < VCBの条件が満たされている必要がありま す。GATEは58µAの電流を外付けMOSFETのゲートと補 償回路網に流し込みます。GATE電圧がMOSFETのしきい 値に達すると、電流が負荷コンデンサに流れ込み始めます。 時点5で、SENSE電圧(V<sub>SENSE</sub> – V<sub>EE</sub>)はV<sub>CB</sub>しきい値に達 して、TIMERを作動させます。TIMERコンデンサは230µAの プルアップ電流源によって充電されます。時点6で、アナログ

電流制限ループが作動します。時点6と時点7の間、GATE 電圧は本質的に一定に保持され、検出電圧は $V_{ACL}$ で安定化します。負荷コンデンサが満充電状態に近づくと、その電流は減少し始めます。時点7で負荷電流は減少し、検出電圧は $V_{ACL}$ より低くなります。アナログ電流制限ループがオフし、GATE ピンの電圧がさらに上昇します。時点8で、検出電圧は $V_{CB}$ より低くなり、TIMER は5.8 $\mu$ Aのプルダウン電流源によって放電するようになります。時点9で、GATE は $V_{IN}$ で決定される最大電圧に達します。

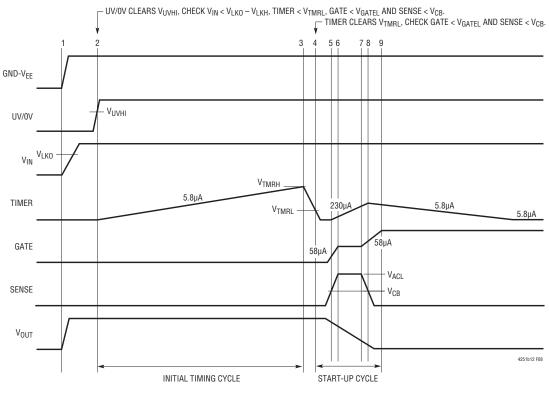

#### UV/OVを短いピンで制御する活線挿入

図8に示すこの例では、長いコネクタ・ピンを介して電力 が供給されるのに対して、UV/OV分圧器は短いピンを介 して接続されます。これにより、電源の接続はLTC4251B/ LTC4251B-1/LTC4251B-2が作動する前に確実に確立され ます。時点1で電源ピンが接続され、VINが立ち上がって VLKOを超えます。時点2でUV/OV分圧器が接続され、そ の電圧がV<sub>UVHI</sub>を超えます。さらに、内部ロジックがV<sub>UVHI</sub> < UV/OV < VOVHI、TIMER < VTMRL、GATE < VGATEL、お よびSENSE < VCBを検査します。すべての条件が満たさ れると、初期タイミング・サイクルが開始され、TIMERコン デンサは5.8µAのプルアップ電流源によって充電されます。 時点3でTIMERがV<sub>TMRH</sub>しきい値に達し、初期タイミング・ サイクルが終了します。その後、TIMERコンデンサは短時間で 放電します。時点4でVTMRLしきい値に達するので、起動サイ クルを開始できるようにするには、その前にGATE < VGATEL および SENSE < VCB の条件が満たされている必要がありま す。GATEは58µAの電流を外付けMOSFETのゲートと補償 回路網に流し込みます。GATE 電圧がMOSFETのしきい値に 達すると、電流が負荷コンデンサに流れ込み始めます。時点5 で、SENSE電圧(V<sub>SENSE</sub> – V<sub>EE</sub>)はV<sub>CB</sub>しきい値に達して、 TIMERを作動させます。TIMERコンデンサは230µAのプル アップ電流源によって充電されます。時点6で、アナログ電流 制限ループが作動します。時点6と時点7の間、GATE電圧は 本質的に一定に保持され、検出電圧はVACLで安定化します。 負荷コンデンサが満充電状態に近づくと、その電流は減少し 始めます。時点7で負荷電流は減少し、検出電圧はVACLより 低くなります。アナログ電流制限ループがオフし、GATEピン の電圧がさらに上昇します。時点8で、検出電圧は $V_{CB}$ より低くなり、TIMERは5.8 $\mu$ Aのプルダウン電流源によって放電するようになります。時点9で、GATEは $V_{IN}$ で決定される最大電圧に達します。

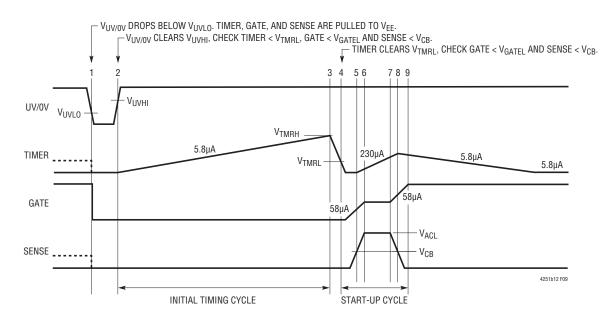

#### 低電圧ロックアウトのタイミング

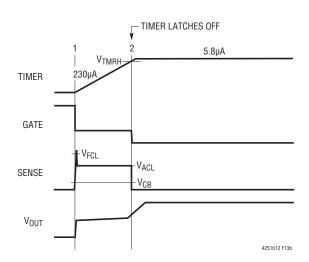

図9では、UV/OVの電圧が $V_{UVLO}$ (時点1)より低くなると、TIMER およびGATEの電圧は"L"になります。それまで電流が流れていた場合、GATEがオフするとSENSEピンの電圧はゼロまで低下します。UV/OVの電圧が回復して $V_{UVHI}$ を超えると(時点2)、初期タイミング・サイクルが開始され、起動サイクルが続きます。

#### 過電圧グリッチを伴う場合の低電圧のタイミング

図10では、UV/OVの電圧がV<sub>UVHI</sub>を超える(時点1)と、初期タイミング・サイクルが始まります。システム・バスの電圧が時点2で示すようにV<sub>OVHI</sub>をオーバーシュートすると、TIMER は放電します。時点3で電源電圧は回復し、V<sub>OVLO</sub>より低くなります。初期タイミング・サイクルが再開され、続いて起動サイクルが始まります。

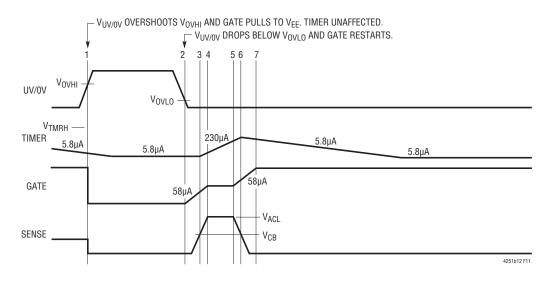

#### 過電圧のタイミング

通常動作時は、図11の時点1に示すように、UV/OVの電圧がVovHIを超えると、TIMERの状態は影響を受けなくなります。それでも、GATEの電圧は低下し、負荷は切り離されます。時点2でUV/OVの電圧は回復し、VovLoしきい値より低くなります。続いてゲートの上昇サイクルが始まります。過電圧グリッチが負荷容量をすべて放電するほど長いと、時点3~6に示すように、完全な起動サイクルが発生することがあります。

#### タイマの動作

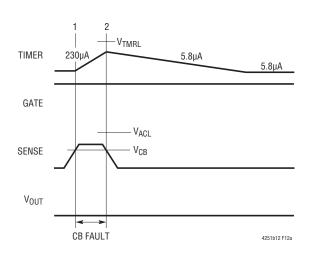

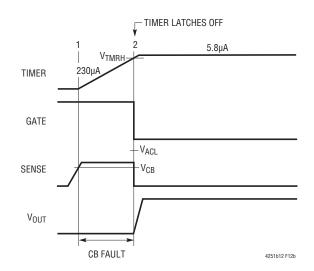

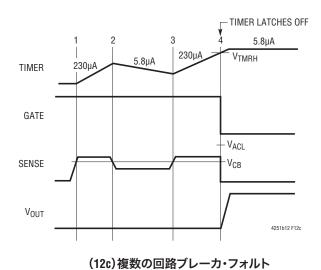

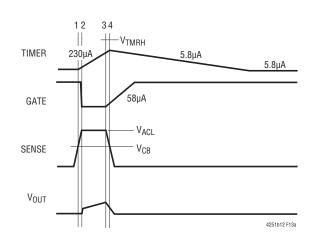

図 12aでは、SENSE ピンが  $V_{CB}$ を超えると、TIMER のコンデンサは  $230\mu$ A で充電されます。SENSE ピンの電圧が  $V_{CB}$  より低くなると、このコンデンサは  $5.8\mu$ A で放電されます。図 12b では、TIMER の電圧が  $V_{TMRH}$  を超えると、TIMER は  $5.8\mu$ A のプルアップ電流によって"H"にラッチされ、GATE の電圧は直ちに低下します。図 12c では、複数の瞬間的な障害により、TIMER コンデンサはラッチされるまで電荷が蓄積されます。

LINEAR

図7. システムの電源電圧上昇のタイミング(すべての波形はVEEを基準にしている)

図 8. 短いピンを使用した場合の電源電圧上昇のタイミング(すべての波形は VEE を基準にしている)

#### アナログ電流制限と高速電流制限

図 13aでは、SENSEの電圧が $V_{ACL}$ を超えると、GATEの電圧はアナログ電流制限アンプのループによって安定化されます。SENSEの電圧が $V_{ACL}$ より低くなると、GATEの電圧を上昇させることができます。図 13bでは、大きな障害が発生すると、SENSEの電圧が $V_{FCL}$ を超え、GATEの電圧が直ちに低下して、アナログ電流アンプが制御を確立するまで低下したままです。TIMERの電圧が $V_{TMRH}$ に達すると、GATEは"L"になり、オフにラッチされます。

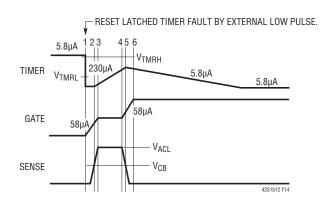

#### フォルト・ラッチのリセット

図 14に示すように、ラッチされたフォルト情報は、UV/OVの電圧を $V_{UVLO}$ より低くするか、または TIMER の電圧を $V_{TMRL}$  より低くすることによってリセットされます。UV/OVを使ってリ

セットする場合は、初期タイミング・サイクルが開始されます。 TIMERを使ってリセットする場合は、初期タイミング・サイクル はスキップされます。

#### 内部ソフトスタート

内部ソフトスタート機能は、最初の起動時にアナログ電流制限アンプの正入力の電圧を上昇させます。上昇期間はおよそ200 $\mu$ sです。この機能は起動時に負荷電流のdl/dtを減少させます。図15に示すように、ソフトスタートはTIMERの電圧が $V_{TMRH}$ から $V_{TMRL}$ に遷移したときか、OV障害の発生後、UV/OVの電圧が $V_{OVLO}$ しきい値より低くなったときに開始されます。ソフトスタートの期間後、負荷電流は $V_{ACL}/R_S$ によって制限されます。

図9. 低電圧ロックアウトのタイミング(すべての波形は VEE を基準にしている)

図10. 過電圧グリッチを伴う場合の低電圧のタイミング(すべての波形は VEE を基準にしている)

図11. 過電圧のタイミング(すべての波形は VEE を基準にしている)

(12a)短時間の回路ブレーカ・フォルト

(12b)回路ブレーカのタイムアウト

図12. タイマの動作(すべての波形は VEE を基準にしている)

(13a)アナログ電流制限でのフォルト

(13a)高速電流制限でのフォルト

図13. 電流制限の動作(すべての波形はVEEを基準にしている)

図14. ラッチされたフォルト情報のリセットのタイミング(すべての波形はVEEを基準にしている)

図15. 内部ソフトスタートのタイミング(すべての波形は VEE を基準にしている)

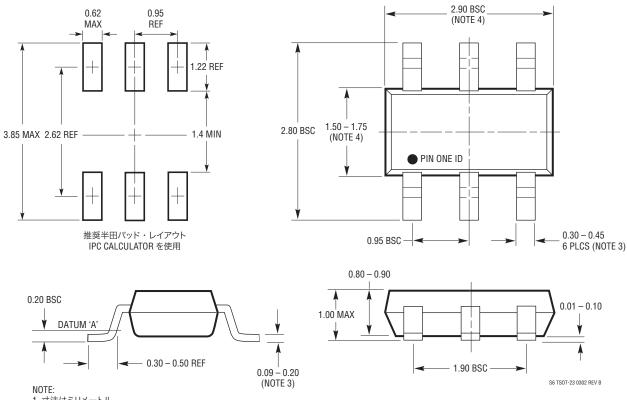

# パッケージ寸法

最新のパッケージ図は、http://www.linear-tech.co.jp/designtools/packaging/を参照してください。

### S6パッケージ 6ピン・プラスチックTSOT-23

(Reference LTC DWG # 05-08-1636)

- 1. 寸法はミリメートル

- 2. 図は実寸とは異なる

- 3. 寸法にはメッキを含む

- 4. 寸法にはモールドのバリやメタルのバリを含まない

- 5. モールドのバリは 0.254mm を超えてはならない 6. JEDEC パッケージ参照番号は M0-193

# 標準的応用例

図16. 逆方向のSENSEピン制限機能およびTIMERピンでの押しボタン・リセット機能を備えた-48V/5Aアプリケーション

図17. 電力が制限された回路ブレーカ・アプリケーション

# 関連製品

| 製品番号                      | 説明                                 | 注釈                                                                    |

|---------------------------|------------------------------------|-----------------------------------------------------------------------|

| LT1640AH/LT1640AL         | 負の高電圧ホットスワップ・コントローラ(SO-8)          | -10V~-80Vの負の高電圧電源                                                     |

| LT1641-1/LT1641-2         | 正の高電圧ホットスワップ・コントローラ(SO-8)          | 9V~80Vを供給、オフにラッチ/自動再試行                                                |

| LTC1642                   | フォルト保護のホットスワップ・コントローラ              | 3V~16.5V、最大33Vの過電圧保護                                                  |

| LTC1921                   | デュアル-48V 電源およびヒューズ・モニタ             | UVしきい値精度:±1V、OVしきい値精度:±1.5V、<br>±200Vの過渡電圧保護、<br>3つの光アイソレータを状態に合わせて駆動 |

| LT4250                    | _48Vのホットスワップ・コントローラ(SO-8)          | アクティブ電流制限、電源は-20V~-80V                                                |

| LTC4252B-1/<br>LTC4252B-2 | 負電圧ホットスワップ・コントローラ(MSOP)            | ドレインによって応答を加速する機能を持つ高速アクティブ電流<br>制限、電源は-15V                           |

| LTC4253B                  | 3出力のシーケンサを備えた<br>負電圧ホットスワップ・コントローラ | ドレインによって応答を加速する機能を持つ高速アクティブ電流<br>制限、電源は-15V                           |