# 超低電圧 ホットスワップ・コントローラ

## 特長

- 通電中のバックプレーンから基板を安全に抜き差し可能

- 0V~6Vの負荷電圧を制御

- 高速応答によるピーク・フォルト電流の制限

- 調整可能なアナログ電流制限

- 突入電流制限機能を備えた調整可能なソフトスタート

- 調整可能な応答時間による過電流保護

- 回路ブレーカの差動しきい値が低い:25mV

- 外付けのゲート・コンデンサ不要

- NチャネルMOSFETのチャージポンプ内蔵

- 出力の起動速度を調整可能

- RESET出力およびFAULT出力

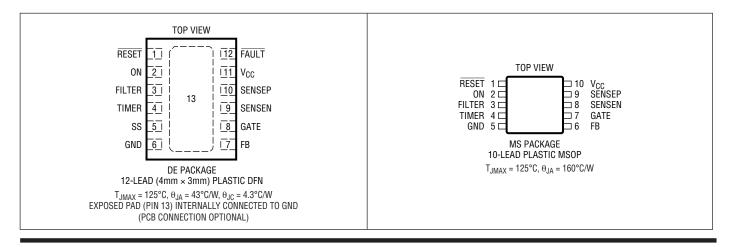

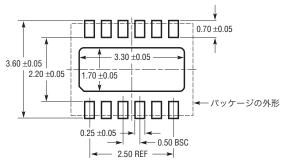

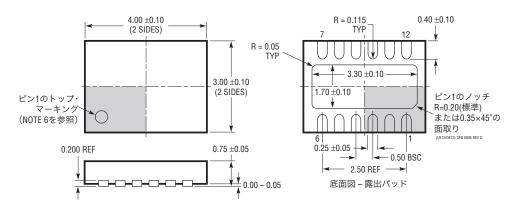

- 10ピンMSOPおよび12ピン(4mm×3mm)DFNパッケージ

## アプリケーション

- 電子回路ブレーカ

- 通電状態での基板の抜き差し

- 産業用ハイサイド・スイッチ/回路ブレーカ

- 光通信

## 概要

LTC<sup>®</sup>4216は、通電中のバックプレーンから基板の安全な抜き差しを可能にする正の低電圧HotSwap™コントローラです。範囲が0V~6Vの負荷電圧を制御し、瞬間的なアナログ電流制限によって厳しいフォルトを分離します。

内蔵のハイサイド・スイッチ・ドライバが外付けNチャネルMOSFETのゲートを制御します。調整可能なソフトスタートにより、起動時の突入電流の変化率が制限されるので、大型の負荷コンデンサを使用できます。アナログ電流制限アンプと、応答時間を調整可能な電子回路ブレーカとを組み合わせることにより、2レベルの過電流保護を実現します。アナログ電流制限ループ補償に外付けのゲート・コンデンサは必要ありません。

FBピンで出力電源電圧をモニタし、 $\overline{RESET}$ 出力ピンに信号を送ります。ONピンにはオン/オフ制御機能があり、 $\overline{FAULT}$ ピンはフォルト状態を通知します。LTC4216は10ピンMSOPパッケージと12ピン(4mm×3mm)DFNパッケージで供給されます。

✓ 、LT、LTC、LTM、Linear TechnologyおよびLinearのロゴはリニアテクノロジー社の登録商標です。HotSwapはリニアテクノロジー社の商標です。

他のすべての商標はそれぞれの所有者に所有権があります。

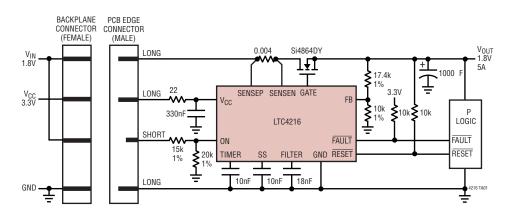

## 標準的応用例

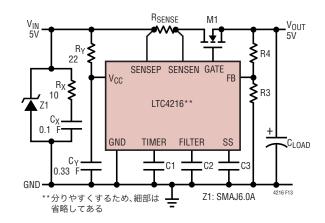

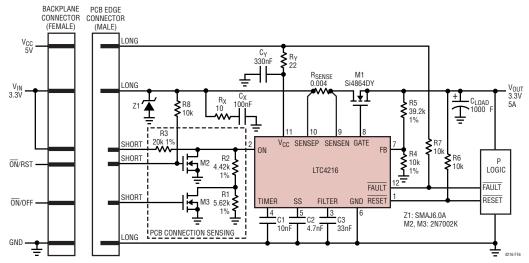

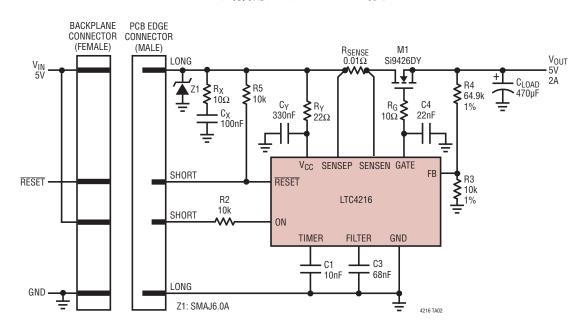

#### シングル·チャネル1.8Vホットスワップ·コントローラ

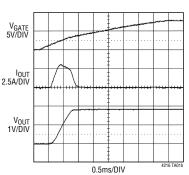

#### ソフトスタートを使った 通常の電源立上げ

4216fa

1

LINEAD

# LTC4216

# 絶対最大定格

| (Note 1)                             |       |

|--------------------------------------|-------|

| バイアス電源電圧(V <sub>CC</sub> )           | ~9V   |

| 入力電圧                                 |       |

| FB、ON、SS、SENSEP、SENSEN0.3V           | ~9V   |

| TIMER, FILTER $-0.3V \sim (V_{CC} +$ | 0.3V) |

| 出力電圧                                 |       |

| RESET, FAULT–0.3V                    | ~9V   |

| GATE0.3V^                            | ~15V  |

|                                      |       |

| 動作温度範囲           |             |

|------------------|-------------|

|                  |             |

| LTC4216C         | 0°C∼70°C    |

| LTC42161         | 40°C∼85°C   |

| 保存温度範囲           |             |

| MS               | −65°C~150°C |

| DE               | −65°C~150°C |

| リード温度 (半田付け、10秒) |             |

| MSパッケージ          | 300°C       |

## ピン配置

# パッケージ/発注情報

| 無鉛仕上げ          | テープアンドリール        | 製品マーキング* | パッケージ                           | 温度範囲          |

|----------------|------------------|----------|---------------------------------|---------------|

| LTC4216CDE#PBF | LTC4216CDE#TRPBF | 4216     | 12-Lead (4mm × 3mm) Plastic DFN | 0°C to 70°C   |

| LTC4216IDE#PBF | LTC4216IDE#TRPBF | 4216     | 12-Lead (4mm × 3mm) Plastic DFN | -40°C to 85°C |

| LTC4216CMS#PBF | LTC4216CMS#TRPBF | LTBKV    | 10-Lead Plastic MSOP            | 0°C to 70°C   |

| LTC4216IMS#PBF | LTC4216IMS#TRPBF | LTBKV    | 10-Lead Plastic MSOP            | -40°C to 85°C |

さらに広い動作温度範囲で規定されるデバイスについては、弊社または弊社代理店にお問い合わせください。\*温度グレードは出荷時のコンテナのラベルで識別されます。

## 電気的特性

●は全動作温度範囲の規格値を意味する。それ以外はTA=25℃での値。注記がない限り、VCC=3.3V。(Note 2)

| SYMBOL                    | PARAMETER                                      | CONDITIONS                    |   | MIN  | TYP  | MAX  | UNITS |

|---------------------------|------------------------------------------------|-------------------------------|---|------|------|------|-------|

| V <sub>CC</sub>           | Bias Supply Range                              |                               | • | 2.3  |      | 6    | V     |

| V <sub>SENSEP</sub>       | V <sub>SENSEP</sub> Supply Range               |                               | • | 0    |      | 6    | V     |

| I <sub>CC</sub>           | Bias Supply Current                            | $V_{ON} = 2V$ , $V_{FB} = 2V$ | • |      | 1.6  | 3    | mA    |

| V <sub>CC(UVL)</sub>      | Bias Supply Undervoltage Lockout               | V <sub>CC</sub> Rising        | • | 1.97 | 2.12 | 2.23 | V     |

| $\Delta V_{CC(UVL,HYST)}$ | Bias Supply Undervoltage<br>Lockout Hysteresis |                               | • | 50   | 120  | 190  | mV    |

無鉛仕上げの製品マーキングの詳細については、http://www.linear-tech.co.jp/leadfree/ をご覧ください。 テープアンドリールの仕様の詳細については、http://www.linear-tech.co.jp/tapeandreel/ をご覧ください。

# 電気的特性

# ●は全動作温度範囲の規格値を意味する。それ以外はTA=25℃での値。注記がない限り、V<sub>CC</sub> = 3.3V。(Note 2)

| SYMBOL                              | PARAMETER                                                                           | CONDITIONS                                                                                                                                                                                                              |   | MIN            | TYP            | MAX               | UNITS          |

|-------------------------------------|-------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|----------------|----------------|-------------------|----------------|

| $\Delta V_{CB(TH)}$                 | Circuit Breaker Trip Voltage Threshold                                              | V <sub>SENSEP</sub> = 0.4V, 3.3V                                                                                                                                                                                        |   | 22.5           | 25             | 27.5              | mV             |

|                                     | (V <sub>SENSEP</sub> – V <sub>SENSEN</sub> )                                        |                                                                                                                                                                                                                         | • | 21.5           | 25             | 28.5              | mV             |

| ΔV <sub>ACL(TH)</sub>               | Analog Current Limit Voltage Threshold (V <sub>SENSEP</sub> – V <sub>SENSEN</sub> ) |                                                                                                                                                                                                                         | • | 32             | 40             | 48                | mV             |

| I <sub>SENSEP(IN)</sub>             | SENSEP Pin Input Current                                                            | V <sub>SENSEP</sub> = V <sub>SENSEN</sub> = V <sub>CC</sub> = 6V<br>V <sub>SENSEP</sub> = V <sub>SENSEN</sub> = 0V, V <sub>CC</sub> = 6V                                                                                | • | 20             | 70<br>-7       | 250<br>-20        | μA<br>μA       |

| I <sub>SENSEN(IN)</sub>             | SENSEN Pin Input Current                                                            | V <sub>SENSEN</sub> = V <sub>SENSEP</sub> = V <sub>CC</sub> = 6V<br>V <sub>SENSEN</sub> = V <sub>SENSEP</sub> = 0V, V <sub>CC</sub> = 6V                                                                                | • | <b>–</b> 5     | 10<br>–10      | 15<br>–15         | μA<br>μA       |

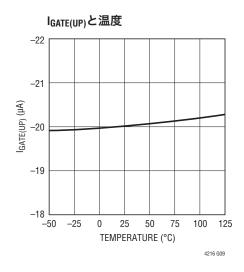

| I <sub>GATE(UP)</sub>               | GATE Pull Up Current                                                                | Gate Drive On, V <sub>GATE</sub> = 0V, V <sub>ON</sub> = 2V                                                                                                                                                             | • | -16            | -20            | -26               | μA             |

| I <sub>GATE(DN)</sub>               | GATE Pull Down Current                                                              | Gate Drive Off, V <sub>GATE</sub> = 5V, V <sub>ON</sub> = 0.6V<br>V <sub>SENSEP</sub> - V <sub>SENSEN</sub> = 55mV, V <sub>GATE</sub> = 5V<br>V <sub>SENSEP</sub> - V <sub>SENSEN</sub> = 100mV, V <sub>GATE</sub> = 5V | • | 100<br>1<br>15 | 600<br>5<br>50 | 1500<br>20<br>100 | μΑ<br>mA<br>mA |

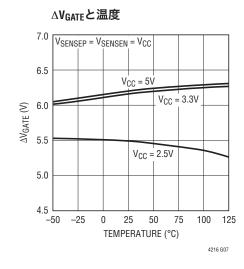

| $\Delta V_{GATE}$                   | External N-Channel Gate Drive (V <sub>GATE</sub> – V <sub>SENSEN</sub> )            | $2.3V \le V_{CC} < 3V$ $3V \le V_{CC} \le 6V$                                                                                                                                                                           | • | 4.0<br>4.5     | 5.0<br>6.2     | 7.9<br>7.9        | V              |

| V <sub>GATE(TH)</sub>               | GATE Pin Threshold Voltage                                                          | V <sub>GATE</sub> Falling                                                                                                                                                                                               | • | 0.15           | 0.2            | 0.3               | V              |

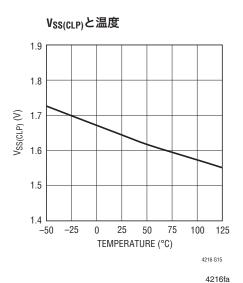

| V <sub>SS(CLP)</sub>                | SS Pin Clamp Voltage                                                                | After End of SS Timing Cycle                                                                                                                                                                                            | • | 1.3            | 1.65           | 2.0               | V              |

| V <sub>SS(TH)</sub>                 | SS Pin Threshold Voltage                                                            | V <sub>SS</sub> Falling                                                                                                                                                                                                 | • | 0.15           | 0.2            | 0.35              | V              |

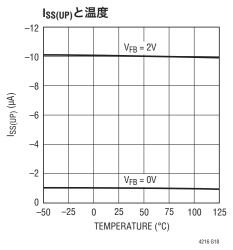

| I <sub>SS(UP)</sub>                 | SS Pull Up Current                                                                  | V <sub>ON</sub> = 2V, V <sub>SS</sub> = 1.2V, V <sub>FB</sub> = 2V<br>V <sub>ON</sub> = 2V, V <sub>FB</sub> = 0V                                                                                                        | • | -7<br>-0.3     | -10<br>-1      | -13<br>-2         | μA<br>μA       |

| I <sub>SS(DN)</sub>                 | SS Pull Down Current                                                                | V <sub>ON</sub> = 0V, V <sub>SS</sub> = 2V                                                                                                                                                                              |   |                | 8              |                   | mA             |

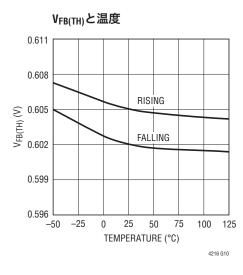

| $V_{FB(TH)}$                        | FB Pin Threshold Voltage                                                            | V <sub>FB</sub> Falling                                                                                                                                                                                                 | • | 0.593          | 0.602          | 0.611             | V              |

| $\Delta V_{FB(LINEREG)}$            | FB Pin Threshold Line Regulation                                                    | $2.3V \le V_{CC} \le 6V$                                                                                                                                                                                                | • |                | 0.2            | 3                 | mV             |

| $\Delta V_{FB(HYST)}$               | FB Pin Hysteresis                                                                   |                                                                                                                                                                                                                         |   |                | 3              |                   | mV             |

| I <sub>FB(IN)</sub>                 | FB Pin Input Current                                                                | V <sub>FB</sub> = 1.2V, V <sub>CC</sub> = 6V                                                                                                                                                                            | • |                | 0              | ±1                | μА             |

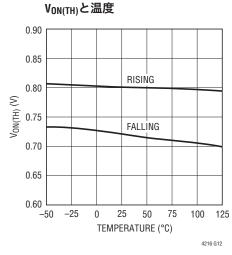

| V <sub>ON(TH)</sub>                 | ON Pin Threshold Voltage                                                            | V <sub>ON</sub> Rising                                                                                                                                                                                                  | • | 0.77           | 0.8            | 0.83              | V              |

| $\Delta V_{ON(HYST)}$               | ON Pin Hysteresis                                                                   |                                                                                                                                                                                                                         | • | 40             | 80             | 130               | mV             |

| V <sub>ON(FC)</sub>                 | ON Pin Fault Clear Threshold Voltage                                                | V <sub>ON</sub> Falling                                                                                                                                                                                                 | • | 0.36           | 0.4            | 0.44              | V              |

| I <sub>ON(IN)</sub>                 | ON Pin Input Current                                                                | V <sub>ON</sub> = 1.2V, V <sub>CC</sub> = 6V                                                                                                                                                                            | • |                | 0              | ±1                | μА             |

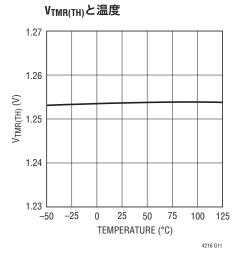

| V <sub>TMR(TH)</sub>                | TIMER Pin Threshold Voltage                                                         | V <sub>TIMER</sub> Rising<br>V <sub>TIMER</sub> Falling                                                                                                                                                                 | • | 1.216<br>0.15  | 1.253<br>0.2   | 1.291<br>0.35     | V              |

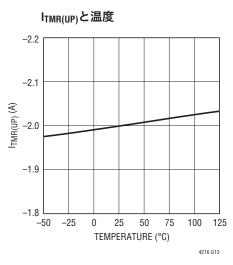

| I <sub>TMR(UP)</sub>                | Timer Pull Up Current                                                               | Timer On, V <sub>ON</sub> = 2V, V <sub>TIMER</sub> = 1V                                                                                                                                                                 | • | -1.5           | -2             | -2.5              | μА             |

| I <sub>TMR(DN)</sub>                | Timer Pull Down Current                                                             | Timer Off, V <sub>ON</sub> = 0V, V <sub>TIMER</sub> = 2V                                                                                                                                                                |   |                | 8              |                   | mA             |

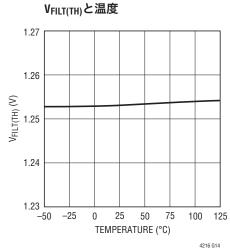

| V <sub>FILT(TH)</sub>               | FILTER Pin Threshold Voltage                                                        | V <sub>FILTER</sub> Rising<br>V <sub>FILTER</sub> Falling                                                                                                                                                               | • | 1.216<br>0.15  | 1.253<br>0.2   | 1.291<br>0.35     | V              |

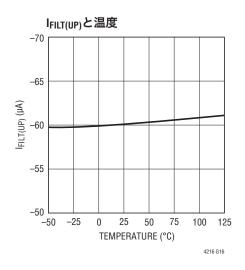

| I <sub>FILT(UP)</sub>               | Filter Pull Up Current                                                              | V <sub>ON</sub> = 2V, V <sub>FILTER</sub> = 1V, In Fault Mode                                                                                                                                                           | • | -45            | -60            | -75               | μА             |

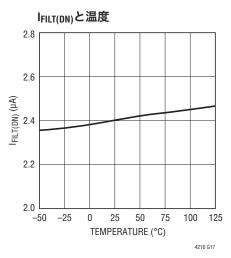

| I <sub>FILT(DN)</sub>               | Filter Pull Down Current                                                            | V <sub>ON</sub> = 2V, V <sub>FILTER</sub> = 1V, No Faults<br>V <sub>ON</sub> = 0V, V <sub>FILTER</sub> = 2V, In Reset Mode                                                                                              | • | 1.5            | 2.4<br>8       | 3.3               | μA<br>mA       |

| V <sub>FAULT</sub> (TH)             | FAULT Pin Threshold Voltage                                                         | V <sub>FAULT</sub> Falling                                                                                                                                                                                              | • | 1.216          | 1.253          | 1.291             | V              |

| $\Delta V_{\overline{FAULT}(HYST)}$ | FAULT Pin Hysteresis                                                                |                                                                                                                                                                                                                         |   |                | 10             |                   | mV             |

| I <sub>FAULT(UP)</sub>              | FAULT Pin Current                                                                   | $V_{ON} = 0V$ , $V_{\overline{FAULT}} = 1.5V$                                                                                                                                                                           | • | -3             | -5             | -7                | μА             |

| $V_{0L}$                            | Output Low Voltage (RESET, FAULT)                                                   | I <sub>RESET</sub> = I <sub>FAULT</sub> = 1.6mA                                                                                                                                                                         | • |                | 0.15           | 0.4               | V              |

| IRESET(LEAK)                        | RESET Pin Input Leakage Current                                                     | V <sub>RESET</sub> = V <sub>CC</sub> = 6V                                                                                                                                                                               |   |                | 0              | ±10               | μA             |

| t <sub>CB(TRIP)</sub>               | Circuit Breaker Trip to Gate Discharging                                            | (V <sub>SENSEP</sub> - V <sub>SENSEN</sub> ) = Step 0V to 150mV<br>(V <sub>SENSEP</sub> - V <sub>SENSEN</sub> ) = Step 0V to 30mV,<br>V <sub>SENSEP</sub> = V <sub>CC</sub> , FILTER = 10nF to GND                      | • | 120            | 1<br>240       | 3<br>360          | μs<br>μs       |

# 電気的特性

●は全動作温度範囲の規格値を意味する。それ以外はTA=25℃での値。注記がない限り、Vcc = 3.3V。(Note 2)

| SYMBOL                   | PARAMETER                                                              | CONDITIONS                                                |   | MIN | TYP | MAX | UNITS |

|--------------------------|------------------------------------------------------------------------|-----------------------------------------------------------|---|-----|-----|-----|-------|

| t <sub>FAULT</sub> (EXT) | FAULT Low to Gate Discharging                                          | V <sub>FAULT</sub> = Step 2V to 0V                        | • |     | 10  | 20  | μs    |

| t <sub>FILTER</sub>      | FILTER High to Gate Discharging                                        | V <sub>FILTER</sub> = Step 0V to 2V                       | • |     | 20  | 40  | μs    |

| t <sub>RST(ONLO)</sub>   | Circuit Breaker Reset Delay Time,<br>ON Low to FAULT High              | V <sub>ON</sub> = Step 2V to 0V                           | • |     | 30  | 60  | μs    |

| t <sub>RST(VCCLO)</sub>  | Circuit Breaker Reset Delay Time,<br>V <sub>CC</sub> Low to FAULT High | V <sub>ON</sub> = 2V, V <sub>CC</sub> = Step 3.3V to 1.8V | • |     | 50  | 100 | μs    |

| t <sub>OFF</sub>         | Turn-Off Time, ON Low to GATE Discharging                              | V <sub>ON</sub> = Step 2V to 0.6V                         |   |     | 15  |     | μѕ    |

Note 1: 絶対最大定格に記載された値を超えるストレスはデバイスに永続的損傷を与える可能性がある。長期にわたって絶対最大定格条件に曝すと、デバイスの信頼性と寿命に悪影響を与える可能性がある。

Note 2: デバイスのピンに流れ込む電流はすべて正。デバイスのピンから流れ出す電流はすべて負。注記がない限り、電圧はすべてGNDを基準。

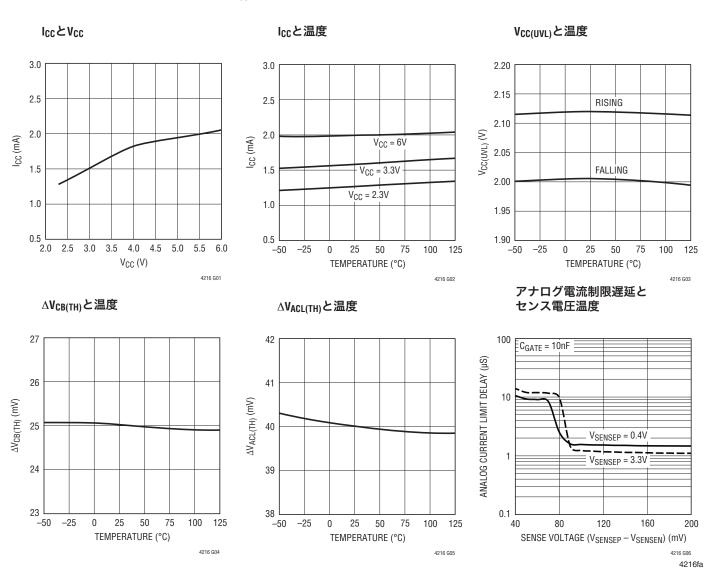

# 標準的性能特性

規格値はT<sub>A</sub> = 25°Cでの値。注記がない限り、V<sub>CC</sub> = 3.3V。

# 標準的性能特性

LINEAR

## 標準的性能特性

## ピン機能 (DE12パッケージ/MSパッケージ)

RESET(ピン1/ピン1):リセットまたはパワーグッド出力。オープン・ドレイン出力で、FBピンの電圧がそのスレッショルド(0.6V)より下に下がると"L"になります。起動サイクル時、RESETピンは、FBピンの電圧がFBスレッショルドを超えた後、2番目のタイミング・サイクルの終了時に高インピーダンスになります。RESETピンには、正電源に接続した外部プルアップが必要です。低電圧ロックアウト状態が発生すると、RESETピンは"L"になり、FBピンの電圧は無視されます。

ON(ピン2/ピン2):オン制御入力。ONピンのスレッショルド(0.8V)より高い立上りエッジにより、起動サイクルが開始され、外部NチャネルMOSFETがオンします。0.72V(80mVのONピンのヒステリシス)より低い立下りエッジにより、MOSFETはオフします。回路ブレーカがトリップした後、このピンが0.4Vより下に引き下げられると、電子回路ブレーカとフォルト・ラッチがリセットされます。

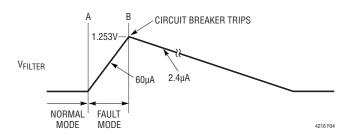

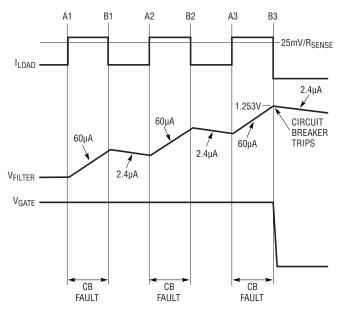

FILTER(ピン3/ピン3):フォルト・フィルタ入力。このピンとグランドのあいだにコンデンサを接続して、フォルト・フィルタの遅延を設定します。このピンは、センス抵抗両端の電圧が25mVを超すと60μAをソースし、25mVを下回ると2.4μAをシンクします。フィルタ・コンパレータの上昇時スレッショルドは、1.253Vです。

**TIMER(ピン4/ピン4)**: タイマ入力。このピンとグランドのあいだにコンデンサを接続して、起動時タイミング・サイ

クルの時間を設定します。また、FBピンの電圧が0.6Vを超した瞬間からのRESETパワーグッド遅延も定めます。このピンはランプアップのあいだ2μAのプルアップ電流をソースします。タイマ・コンパレータの上昇時スレッショルドは、1.253Vです。

SS(ピン5/なし):ソフトスタート制御入力。このピンとグランドのあいだにコンデンサを接続して電源立上げ時のソフトスタートを設定します。このピンはGATEのランプアップを制御し、外部MOSFETがオンするときの突入電流の変化率を制限します。ソフトスタート機能を使わない場合、このピンは未接続のままにします。

GND(ピン6/ピン5):デバイスのグランド。

FB(ピン7/ピン6): リセット出力の出力モニタ。外部 MOSFETのソース端子からの抵抗分割器をこのピンに接続します。このピンの電圧が0.6Vより下に下がると RESETピンが"L"になります。FBコンパレータの下降時 スレッショルドは、0.602Vです。

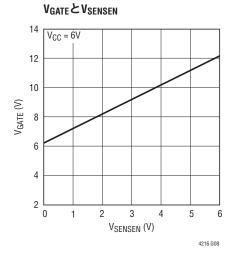

**GATE(ピン8/ピン7)**:外部NチャネルMOSFETのゲート・ドライブ。内部チャージポンプにより、20μAのゲート・プルアップ電流と十分なゲート・オーバードライブが外部NチャネルMOSFETに与えられます。内部シャント・レギュレータによりGATEピンの電圧はSENSEピンの電圧より約6.2V(標準)上に制限されます。

LINEAR

# ピン機能 (DE12パッケージ/MSパッケージ)

SENSEN(ピン9/ピン8):回路ブレーカの負センス入力。このピンは外部NチャネルMOSFETのドレインに配線されたセンス抵抗の端子に接続します。センス抵抗はSENSEPピンとSENSENピンのあいだの電力経路に配置して出力電流を検出します。センス抵抗両端の電圧がフォルト遅延より長く25mVを超すと、電子回路ブレーカがトリップします。

**SENSEP(ピン10/ピン9):**回路ブレーカの正センス入力。このピンは外部出力負荷の正電源入力に配線されたセンス抵抗の端子に接続します。この正電源の範囲は0V~6Vです。

$V_{CC}$ (ピン11/ピン10): バイアス電源入力。2.3V~6Vで動作します。内部の過電圧ロックアウト回路により、 $V_{CC}$ の入

力電源電圧が標準2.12Vを超すまで、デバイスはディス エーブルされます。

FAULT (ピン12/なし):フォルトの入力と出力。入力としては、このピンを"L"(<1.253V)にドライブすると、デバイスはフォルト・モードにラッチオフします。出力としては、このピンは通常の動作状態では内部5µAプルアップによって"H"に引き上げられるか、またはプルアップ抵抗によって外部電源に引き上げられます。回路ブレーカが過電流フォルトによってトリップすると"L"になります。

**露出パッド(ピン13/なし):**露出パッドはオープン状態のままにするか、デバイスのグランドに接続することができます。

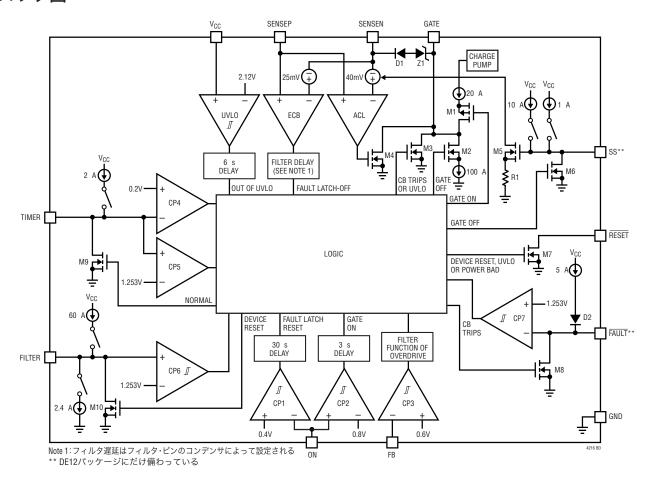

## ブロック図

## 動作

LTC4216は取り外し可能な回路基板とバックプレーンのどちらにでも置かれるホットスワップ・コントローラです。このデバイスは外部NチャネルMOSFETと電流センス抵抗を使って電流をモニタして負荷を保護します(図14~18を参照)。突入電流制限と短絡保護の両方がLTC4216によって与えられます。このデバイスはバイアス電源入力( $V_{CC}$ )を通して給電され、負荷電源( $V_{IN}$ )をモニタするための別のセンスピン(SENSEP)を備えています。負荷電源は0V~6Vの範囲が可能で、最小バイアス電源電圧は2.3Vです。

ONピンが"L"から"H"に引き上げられ、「バイアス電源電圧が低電圧ロックアウトから抜け出し(> 2.12V)、TIMER、SS、FILTERおよびGATEの各ピンの電圧が0.2Vより低い」という条件が満たされたら、TIMERはC1に2μAをソースすることにより、最初のタイミング・サイクルを開始します。C1の電圧がTIMERピンのスレッショルド(1.253V)を超すと、TIMERは"L"になり、SSピンとGATE

ピンの両方を解除します。SSピンのC2がランプアップを開始し、GATEのランプ・レートを制御します。これにより、出力の負荷容量に流れ込む突入電流の変化率が制限されます。FBピンの電圧が0.6Vとそのヒステリシスを超すと、RESETピンは2番目のタイミング・サイクルの後に"H"になります。

外部MOSFETが完全にオンすると、負荷容量への突入電流が小さい場合、出力は負荷電源電圧までランプします。 ただし、突入電流がΔVACL(TH)/RSENSEのアナログ電流リミットを超すと、LTC4216は制限された電流を負荷容量にソースして出力をランプさせます。

LTC4216は、出力の短絡または電流過負荷に対して、スレッショルドが25mVの内部電子回路ブレーカとアナログ電流制限回路を使って保護します。回路ブレーカの応答時間はFILTERピンに接続されたC3によって設定されます。

#### 電源の入った回路への挿入

電源の入っているバックプレーンに回路基板を挿入するとき、電源バイパス・コンデンサを充電するのに電源バスから大きな過渡電流が流れることがあります。この電流により、コネクタ・ピンが損傷を受け、電源バスにグリッチが生じ、システム内の他の基板がリセットされる可能性があります。LTC4216は制御された状態で回路基板の電源をオンまたはオフするように設計されていますので、グリッチを生じたりコネクタに損傷を与えることなしに挿抜が可能です。

#### LTC4216の特長の概要

- 1. 電源の入ったバックプレーンに対しボードを安全に挿抜が可能です。

- 2.0V~6Vの負荷電圧を制御します。

- 3. 外部NチャネルMOSFET用ハイサイド・ゲート・ドライブ。

- 4. 大きな負荷コンデンサへの起動時突入電流の制限機能付きの調節可能なソフトスタート。

- 5. 過電流フォルト状態での回路ブレーカ・タイムアウト機能付きの調節可能なアナログ電流制限(ACL)。ACLループ補償に外付けのゲート・コンデンサは不要です。

- 6. センス抵抗両端の電圧が25mVでトリップする電子回路ブレーカ。応答時間はFILTERピンの外付けコンデンサを使って調節可能です。

- 7. デバイスをオン/オフするONピンを備えています。これは、回路ブレーカがトリップした後デバイスをリセットするのにも使うことができます。

- 8. FBピンを通して出力電源電圧をモニタし、RESETピン 出力に知らせます。

- 9. フォルト状態出力を与えます。

#### ON制御

ONピンはヒステリシスを備えた、スレッショルド・レベルの異なる(0.8Vと0.4V)2つのコンパレータを備えており、それらは2つの目的に役立ちます。

- 1. ONピンの電圧が $6\mu$ sより長く> 0.8Vならばデバイスをオンし、ONピンの電圧が $15\mu$ sより長く< 0.72Vならばデバイスをオフします。

- 2. 回路ブレーカがトリップした後、ONピンの電圧が30µs

より長く<0.4Vならばデバイスをリセットします。

ONピンの電圧を設定する方法がいくつかあります。

- 1. 10kのプルアップ抵抗を使ってONピンを負荷電源 ( $V_{IN}$ )に接続します。

- 2. ONピンをシステム・コントローラからON/OFFロジック信号を使ってドライブします。

- 3. 外部抵抗分割器をONピンに接続します。この分割器を使って、内部VCCの低電圧ロックアウト回路よりも高い値を負荷電源の低電圧ロックアウト電圧に設定することができます。

たとえば、図17に示されているように、 $V_{CC}$ ピンと SENSEPピンの両方が5V負荷電源に接続されている場合、抵抗分割器の値をR1=20k、R2=80.6kのように選択すると、負荷電源の電圧がその最終値の約80%に達したときデバイスがオンします。

#### Vcc低電圧ロックアウト

ヒステリシスをもったコンパレータ(UVLO)がバイアス電源( $V_{CC}$ )の低電圧を監視します。スレッショルドは $V_{CC(UVL)}$  (2.12V)とそのヒステリシス $\Delta V_{CC(UVL)}$  (120mV)で定まります。 $V_{CC}$ が $V_{CC(UVL)}$ を超すと、デバイスがイネーブルされます。 $V_{CC}$ が( $V_{CC(UVL)}$   $\Delta V_{CC(UVL)}$  人なで( $V_{CC}$ ) より下に下がると、デバイスはディスエーブルされ、GATEが引き下げられます。回路ブレーカがトリップした後に続いて、 $V_{CC}$ が200 $\mu$ sより長くこのスレッショルドより下に回帰すると、フォルト・ラッチが解除されます。バイアス電源の10 $\mu$ sより短いどんなグリッチも $V_{CC}$  も $V_{CC}$   $V_{CC}$

#### タイマ

外部コンデンサC1をTIMERピンに使って、LTC4216の2つのタイミング・サイクルを生成します。最初のタイミング・サイクルはONピンが最初にオンするときのデバウンス・サイクルで、GATEピンとSSピンは両方とも"L"に保たれ、どんな短絡フォルトも電子回路ブレーカによって無視されます。2番目のタイミング・サイクルは、FBピンの電圧が0.6Vとそのヒステリシスを超すときRESETピンが"H"になる前のパワーグッド遅延です。

TIMERピンは、2つのタイミング・サイクルのあいだ2 $\mu$ A をC1にソースし、TIMERピンの電圧がそのスレッショルドを超すと、内部Nチャネル・スイッチによって"L"に引き下げられます。

4216fa

C1がTIMERピンのスレッショルド $V_{TMR(TH)}$  (1.253V)まで充電されるタイマ時間は次式で与えられます。

$$t_{TIMER} = \frac{1.253V \cdot C1}{2\mu A} \tag{1}$$

たとえば、C1 = 10nFならば、 $t_{TIMER} = 6.2$ msです。

#### FBのグリッチのフィルタリング

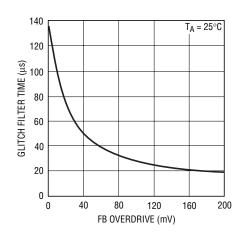

FBピンは抵抗分割器を通して外部MOSFETの出力電圧をモニタするのに使われます。出力の電圧低下スパイクによるFBピンのどんなトランジェントもRESETを"L"に引き下げます。RESETが不要なシステム・リセットを発生するのを防ぐために、FBコンパレータにはこれらのグリッチを乗り切るグリッチ・フィルタが備わっています。フィルタ時間は(150mVを超す)大きなトランジェントの場合20 $\mu$ sで、小さなトランジェントの場合は最大100 $\mu$ sです。グリッチ・フィルタ時間とFBピンの過渡電圧、つまりFBのオーバードライブの関係を図1に示します。

図1. FBコンパレータのグリッチ・フィルタ時間と FBのオーバードライブ

#### 出力電圧モニタ

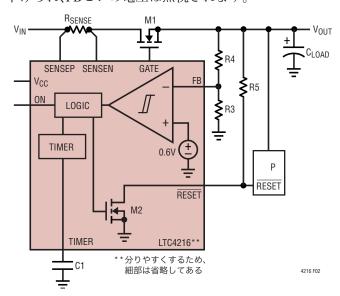

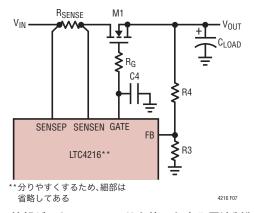

図2に示されているように、出力電圧はFBピンに接続された抵抗分割器(R3とR4)とスレッショルドが0.6VのFBコンパレータを通してモニタされます。

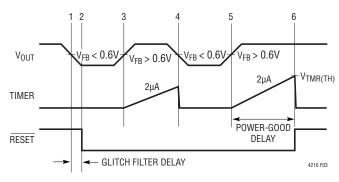

起動サイクル後の出力電圧モニタの通常動作を図3に示します。FBピンの電圧が0.6Vより下に下がる時点1で、FBコンパレータの出力が"H"になります。RESETはグリッチ・フィルタ遅延の後、時点2で内部Nチャネル・スイッチによって"L"に引き下げられます。FBピンの電圧が0.6Vを超すと、FBコンパレータの出力が"L"になり、新しい

タイミング・サイクルが始まります。完全なタイミング・サイクルの後、 $\overline{RESET}$ が時点6で外部プルアップ抵抗R5によって"H"に引き上げられます。式(1)で与えられるタイマ時間により、 $\overline{RESET}$ が"H"になるパワーグッド遅延が設定されます。 $\overline{FB}$ ピンの電圧が時点4でタイミング・サイクルより短い時間0.6Vより上に留まると、 $\overline{RESET}$ 出力は"L"に保たれます。タイミング・サイクル中に電子回路ブレーカによって過電流フォルトが検出されるか、または $\overline{FAULT}$ ピンが外部から"L"にドライブされる場合も、 $\overline{TIMER}$ ピンが"L"に引き下げられ、 $\overline{RESET}$ 出力は"L"に保たれます。

デバイスが低電圧ロックアウト状態に入るか、またはONピンの電圧が0.4Vより下に下がると、RESETは"L"に引き下げられ、FBピンの電圧は無視されます。

図2. 出力電圧モニタのブロック図

図3. 通常動作の出力電圧モニタ波形

#### 電子回路ブレーカ

LTC4216には電子回路ブレーカ機能が備わっており、短絡や電源の過負荷電流状態に対して外部MOSFETを保護します。SENSEPピンとSENSENピンのあいだに接続された外部センス抵抗を使って負荷電流を測定します。センス抵抗両端の電圧がフォルト・フィルタ遅延より長いあいだ回路ブレーカの25mVのトリップ・スレッショルドを超すと、MOSFETのゲートが"L"に引き下げられ、MOSFETはオフします。

フォルト・フィルタの遅延は、式(2)のように、FILTERピンとグランド間に接続されたコンデンサC3によって決まります。FILTERピンは、センス抵抗両端のセンス電圧が25mVを超すと、60μAのプルアップ電流をソースします。それ以外は、2.4μAで引き下げられます。FILTERピンの電圧がVFILT(TH)スレッショルド(1.253V)を超すと、GATEが"L"になる前に20μsの内部遅延があり、FAULTピンが"L"になります。FILTERコンデンサが使われないと、フィルタ・フォルト遅延は既定で20μsになります。FILTERコンデンサ(C3)を使った回路ブレーカの応答時間、つまりフォルト・フィルタの遅延は次式で与えられます。

$$t_{CB(TRIP)} = \frac{1.253V \cdot C3}{60\mu A} + 20\mu s$$

(2)

起動時にアナログ電流制限状態でMOSFET電流が大きな出力負荷容量を充電するとき、フォルト・フィルタの遅延が短かすぎて回路ブレーカがトリップしてしまわないように、FILTERコンデンサ(C3)を選択します。また、この遅延は外部MOSFETの安全動作領域(SOA - safe operating area)を超すほど長くならないようにします。

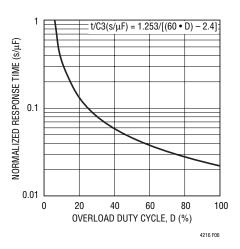

図5のように、間欠的な過負荷が電流制限を超えることがありますが、継続時間が十分短かければ、FILTERピンの電圧は $V_{FILT(TH)}$ スレッショルドに達しないので、デバイスはシャットダウンしません。この状態を処理するため、センス抵抗両端の電圧が25mVより低いときは常にFILTERは $2.4\mu$ Aで放電します。どんな間欠的過負荷も総計デューティ・サイクルが4%を超すと、最終的には回路ブレーカをトリップします。式(3)で与えられているように $1\mu$ Fに正規化した、回路ブレーカの秒単位の応答時間を図6に示します。FILTERの非対称の充電と放電はMOSFETの発熱の目安になります。

$$\frac{t}{C3}(s/\mu F) = \frac{1.253}{(60 \cdot D) - 2.4} \tag{3}$$

回路ブレーカがトリップするとデバイスがラッチオフし、ONピンを少なくとも100μsのあいだ"L"(<0.4V)に引き下げてフォルト・ラッチを解除するまで、FAULTは"L"になります。FILTERピンはONピンの電圧が0.4Vより下に下がると内部Nチャネル・スイッチによって"L"に引き下げられ、コンデンサを急速に放電し、ONピンの電圧が0.8Vを超して新しい起動サイクルを開始すると2.4μAでプルダウンします。FILTERピンの電圧が0.2Vより下に下がるまで、新しいタイミング・サイクルは開始されません。電子回路ブレーカは起動後最初のタイミング・サイクルのあいだディスエーブルされ、短絡フォルトはどれも無視されます。

図4. 連続フォルトのタイミング

図5. 複数回の間欠的過負荷状態

図6. 間欠的過負荷に対する 回路ブレーカ・フィルタの応答

#### アナログ電流制限

電子回路ブレーカに加えて、LTC4216には、GATEピンに外部補償コンデンサを必要としない新しいアナログ電流制限(ACL)アンプが内蔵されています。このアンプの安定性は使用されるMOSFETの大きなゲート入力容量(CISS)によって補償されます。これらのMOSFETの $C_{ISS}$ は通常1nF以上あります。ただし、MOSFETのゲート入力容量(CISS)がループの安定性にとって小さ過ぎる場合、GATEピンとグランドのあいだに外付けコンデンサを接続し、ゲートの総容量を1nF以上に増やします。式(4)で与えられているように、MOSFET電流( $I_{ACL}$ )は、SENSEPピンとSENSENピンのあいだに接続されたセンス抵抗( $I_{SENSE}$ )両端のアナログ電流制限電圧 $I_{ACL}$ (標準 $I_{ACL}$ )に制限されます。

$$I_{ACL} = \frac{\Delta V_{ACL(TH)}}{R_{SENSE}} \tag{4}$$

$\Delta V_{ACL(TH)}$ スレッショルドは $\Delta V_{CB(TH)}$ スレッショルド (標準25mV)より1.6倍高く、2レベルで電流を検出します。ACLアンプがMOSFET電流をセンス抵抗両端で  $\Delta V_{ACL(TH)}$ にサーボ制御すると、MOSFET電流は $\Delta V_{CB(TH)}$ スレッショルドを超すので、FILTER ピンは $60\mu$ Aのプルアップを使ってC3を充電します。この状態が十分長く続き、C3が $V_{FILT(TH)}$ スレッショルド(1.253V)に達すると、GATEが"L"に引き下げられ、FAULTが"L"にラッチします。

センス抵抗両端の電圧が過負荷状態のあいだΔVACL(TH) より大きいと、ACLアンプがGATEを下方にサーボ制御し てMOSFETの電流を制御しようとします。通常動作では GATEピンの電圧がMOSFETをオーバードライブするの で、ACLアンプはゲートを制御するためGATEをMOSFET のスレッショルドまで放電させるのに時間を要します。 過負荷が大きくない場合、ACLアンプはMOSFET電流を 制御することができますが、大きな過負荷が生じると、 MOSFETのゲートは最初大きくオーバードライブされて いるので、MOSFET電流にオーバーシュートが生じるこ とがあります。GATEは急速にグランドに放電され、それ に続いてACLアンプが制御を開始します。GATEが放電す るときのGATEのアンダーシュートからアナログ電流制 限が非常に高速で回復する必要のあるアプリケーション では、図17に示されているように、直列抵抗(Rz)を外部コ ンデンサ(Cz)と一緒にGATEピンに接続します。最適な性 能を得るためには、 $R_Z$ の値を $10\Omega\sim100\Omega$ の範囲にする必 要があります。

#### ソフトスタート

LTC4216にはソフトスタート機能が備わっており、電源立上げ時に突入電流のdi/dtを制御します。低電圧アプリケーションには一般に大きな出力負荷コンデンサが使われているので、通常の突入電流が負荷電源にグリッチを生じるだけ十分大きいことがあります。ソフトスタート機能を使うと、外部MOSFETのゲートを非常に徐々にオンすることができ、電源グリッチを生じさせることなく負荷コンデンサに流れ込む突入電流を制御することができます。

SSピンとグランド間に接続された外部コンデンサ(C2)を使って、GATEはACLアンプによってサーボ制御され、電源立上げのあいだSSのランプアップ・レートを追尾します。SSのランプアップのプロフィールには、10µA電流源のプルアップによる通常のランプ・レートと1µAの電流源のプルアップによる遅いランプ・レートの2つの傾斜があります。SSの両方のランプ・レートは以下のように与えられます。

通常のSSランプ・レート:

$$\frac{dV_{SS(NOM)}}{dt} = \frac{10\mu A}{C2}$$

(5)

低速のSSランプ・レート:

$$\frac{dV_{SS(SLOW)}}{dt} = \frac{1\mu A}{C2}$$

(6)

たとえば、もしC2 = 10nFならば、 $\frac{dV_{SS(NOM)}}{dt} = 1$ V/ms および

$\frac{dV_{SS(SLOW)}}{dt}$  = 0.1V/ms となります。

最初のタイミング・サイクルの後、SSコンデンサは10µA電流源のプルアップによって充電され、GATEはACLアンプによって"L"に保たれます。SSがランプアップし、その入力オフセット電圧を超すとACLアンプはGATEを解除します。この瞬間、SSはプルアップ電流を10µAから1µAに切り替え、ランプ・レートを遅くします。GATEはMOSFETがターンオン・スレッショルド電圧に達するまで20µAのプルアップによって連続して充電されます。外部MOSFETが最初にオンすると、MOSFETの高い利得により、常に電流ステップが生じます。SSの遅いランプ・レートにより、外部MOSFETのゲートは小さな突入電流ステップでオンすることができます。

外部MOSFETがオンすると、負荷電流がセンス抵抗を通って流れ始め、その両端に電圧が発生します。これにより、ACLアンプはGATEをセンス抵抗両端の電圧にサーボ制御することができるので、突入電流の変化率を制御することができます。この瞬間、SSは1 $\mu$ Aの電流源プルアップから10 $\mu$ Aの電流源プルアップに再度切り替え、通常のランプ・レートにします。GATEはACLアンプがサーボ制御するのに従ってランプアップを続け、SSのランプ・レートを追尾します。SSがその最終値に達してSSのランプアップが終了すると、GATEはセンス抵抗両端の  $\Delta V_{ACL(TH)}$ にサーボ制御されます。センス抵抗両端の電圧が負荷電流の低下により $\Delta V_{ACL(TH)}$ より下に下がると、ACLアンプはシャットオフし、GATEは20 $\mu$ Aのプルアップによってさらにランプします。

Vccの低電圧ロックアウト状態、最初のタイミング・サイクルのあいだ、または回路ブレーカ・フォルトがタイムアウトしたときのどの条件でも、SSは"L"に引き下げられます。ソフトスタート機能を使わない場合、SSピンは未接続のままにします。

#### GATEコンデンサを使った突入電流制御

ソフトスタートが電源立上げ時に突入電流のdi/dtを制御する必要のないアプリケーションでは、突入電流を制限

する別の方法として、図7に示されているように、外部コンデンサ(C4)をGATEピンからグランドに接続してGATEピンの電圧のスルーレートを制御します。 $10\Omega$ の外部抵抗 $R_G$ により、MOSFETの高周波自励発振を防ぐことができます。GATEのスルーレートは次式で与えられます。

$$\frac{dV_{GATE}}{dt} = \frac{20\mu A}{C4 + C_{GATE}} \tag{7}$$

ここで、C<sub>GATE</sub>は外部MOSFETのゲート入力容量(C<sub>ISS</sub>)に 関連した寄生GATE容量です。

負荷コンデンサ(C<sub>LOAD</sub>)に流れ込む突入電流は次の値に 制限されます。

$$I_{INRUSH} = C_{LOAD} \bullet \frac{dV_{GATE}}{dt} = \frac{C_{LOAD}}{C4 + C_{GATE}} \bullet 20\mu A \tag{8}$$

たとえば、 $C_{LOAD}$  = 4700 $\mu$ F、C4 = 33nFおよび $C_{GATE}$  = 5nF だと、 $I_{INRUSH}$  = 2.5Aです。

C<sub>LOAD</sub>が非常に大きく、I<sub>INRUSH</sub>がアナログ電流制限を 超すと、GATEがサーボ制御され、突入電流をΔV<sub>ACL(TH)</sub>/ R<sub>SENSE</sub>に制御します。

この手法のひとつの弱点は、GATEピンにコンデンサが追加されることにより、システムのターンオン時間とターンオフ時間が遅くなることです。この手法を使う場合、50nF以下のC4を推奨します。ただし、外部にゲート・コンデンサを付加すると、電源から電力が最初に供給されたとき、MOSFETのドレイン-ゲート間容量を介してGATEピンに結合される電圧スパイクの除去に役立ちます。

図7. 外部ゲート・コンデンサを使った突入電流制御

4216fa

#### 通常のパワーアップとパワーダウン

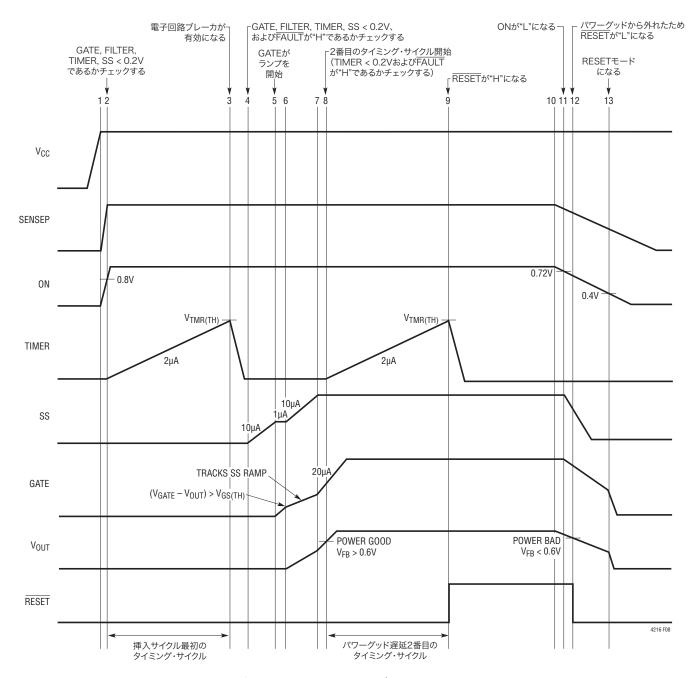

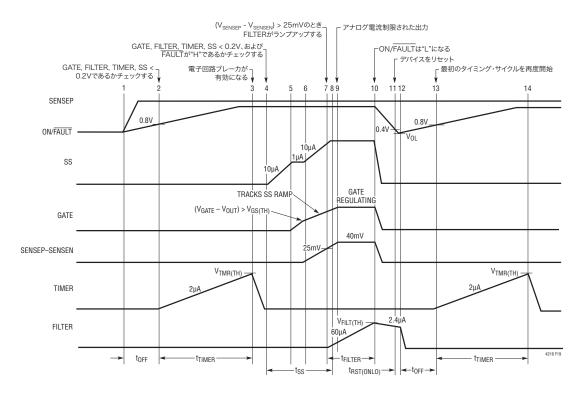

プリント回路基板を電源の入ったバックプレーンに挿入 する場合の通常の電源立上げシーケンスのタイミング図 を図8に示します。

時点1で、バイアス電源(Vcc)がランプアップし、電源電 圧が低電圧ロックアウト・スレッショルド(2.12V)を超す とデバイスをイネーブルします。時点2で、ONピンとと もに、SENSEP電源がランプアップし、ONピンの電圧が 0.8Vを超すと最初のタイミング・サイクルが開始されま す。GATE < 0.2V、FILTER < 0.2V、TIMER < 0.2V、SS < 0.2V という条件がすべて満たされると、TIMERコンデンサを 2μAのプルアップでランプアップさせることができま す。時点3で、TIMERがV<sub>TMR(TH)</sub>スレッショルドに達し、 最初のタイミング・サイクルが終了します。電子回路ブ レーカがイネーブルされ、TIMERコンデンサは急速に放 電します。時点4では、TIMER、GATE、FILTERおよびSSが 0.2Vより下、ΔV<sub>SENSE</sub>が25mVより下、さらにGATEラン プアップ・サイクルが始まる前はFAULTが"H"であるか チェックされます。SSコンデンサが10µAの電流源によっ てランプアップするあいだ、GATEはアナログ電流制限 アンプによって"L"に保たれます。SSがACLアンプの入 力オフセット電圧を横切ると、SSは1µAのプルアップに 切り替わり、ランプ・レートが遅くなります。この時点で、 ACLアンプはGATEを解除し、GATEが20µAのプルアップ でランプアップするのを許します。時点6で、GATEが外 部MOSFETのターンオン・スレッショルドに達すると、 電流が負荷コンデンサに流れ込み始めます。この時点の MOSFETの電流レベルはACLアンプによって制御され、 GATEのランプは遅くなります。SSはプルアップ電流を 1μAから10μAに切り替え、通常のランプ・レートになりま す。時点6と時点7のあいだでは、ACLアンプはGATE電圧 をサーボ制御してSSのランプ・レートを追尾し、負荷電 流のスルーレートを制限します。時点7で、SSはその最終 値に達し、負荷電流がアナログ電流制限されていないと、 GATEは20µAのプルアップでランプアップを続けます。 時点8で、FBピンの電圧が0.6Vを超すと、2番目のタイミ ング・サイクルが開始されます。TIMER < 0.2V、ΔV<sub>SENSE</sub> <25mVおよびFAULTが"H"であるという条件が満たされ ると、TIMERコンデンサはランプアップすることが許さ れます。TIMERが時点9でV<sub>TMR(TH)</sub>スレッショルドに達 するとRESETが"H"になり、システム・コントローラにパ ワーグッド状態であることを知らせます。その後、TIMER は"L"に保たれます。

ONピンの電圧が $(V_{ON(TH)}-\Delta V_{ON(HYST)})$ のスレッショルド(0.72V)より下に下がると、パワーダウン・シーケンスが開始されます。時点11で、GATEはACLアンプと100 $\mu$ A の電流源プルダウンの両方によって放電し、出力電圧を徐々に下げます。FBピンの電圧が時点12で0.6Vより下に下がると、グリッチ・フィルタの遅延の後RESETが"L"になり(「FBのグリッチのフィルタリング」のセクションを参照)、パワーグッド状態ではなくなったことを知らせます。ONピンの電圧が0.4Vより下に下がると、デバイスがリセットし、GATEは強いプルダウン・デバイスによって"L"に引き下げられます。

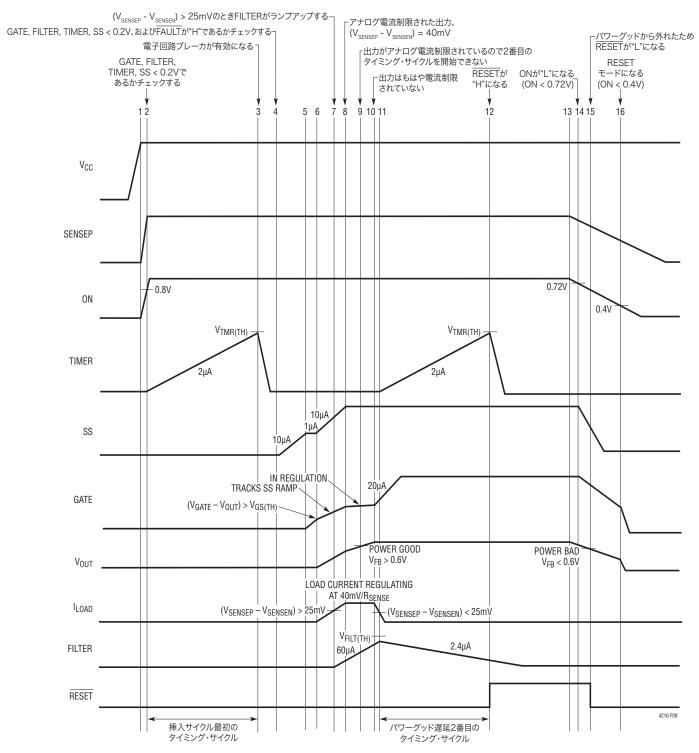

#### アナログ電流制限付きソフトスタート

ソフトスタート時に非常に大きな出力負荷コンデンサが接続されると、GATE電圧がサーボ制御され、突入電流を $\Delta V_{ACL(TH)}/R_{SENSE}$ に制御します。これは図9のタイミング図に示されています。最初のタイミング・サイクルの後、GATEはランプアップを許され、時点5と時点8のあいだでSSのランプ・レートを追尾します。時点7で、GATEピンの電圧が増加するにつれ負荷電流が増加すると、センス抵抗両端の電圧が $\Delta V_{CB(TH)}$  (標準25mV)を超します。FILTERコンデンサは $60\mu A$ の電流源プルアップによって充電を開始します。時点8で、SSのランプ・サイクルの終点でSSはその最終値に達します。これにより、GATEをACLアンプによりセンス抵抗(RSENSE)両端の $\Delta V_{ACL(TH)}$  (標準40mV)に制御することができ、突入電流を次式の値に制限します。

$$I_{LIMIT} = \frac{40mV}{R_{SENSE}} \tag{9}$$

FILTERピンの電圧は、制限された負荷電流で負荷コンデンサが充電されるにつれ、上昇を続けます。時点9で、FBピンの電圧が0.6Vを超しますが、センス抵抗両端の電圧が25mVを超しているので、2番目のタイミング・サイクルを開始することができません。時点10で、負荷コンデンサが完全に充電された状態に近づくにつれて負荷電流が減少し、センス抵抗両端の電圧は40mVより下に低下します。アナログ電流制限ループがシャットオフし、GATEはその最終値までさらにランプします。FILTERコンデンサは、センス抵抗両端の電圧が時点11で25mVより下に下がると、2.4µAのプルダウンにより放電します。時点7と時点11のあいだの時間は、非常に大きな負荷コンデンサの場合にGATEのランプアップのあいだに誤ってタイムアウトが生じるのを避けるため、式(2)で与えられている回路ブレーカの遅延時間より短くなければなりません。

LINEAD TECHNOLOGY

FBピンの電圧が0.6Vを超し、センス抵抗両端の電圧が25mVより下に下がる時点11で2番目のタイミング・サイクルが開始されます。TIMERが $V_{TMR(TH)}$ スレッショルド

に達する2番目のタイミング・サイクルの終点(時点12)で RESETが"H"になります。

図8. 通常のパワーアップ/パワーダウン・シーケンス

図9. 通常のパワーアップ・シーケンス(アナログ電流制限を伴う)

LINEAR TECHNOLOGY

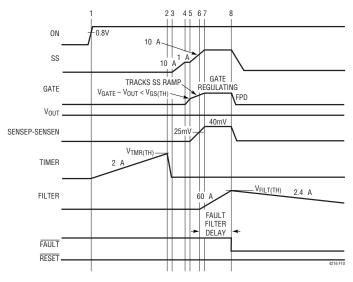

#### 出力短絡状態でのパワーアップ

電源立上げ時に出力が完全に短絡している場合のタイミング図を図10に示します。GATEがランプアップするにつれMOSFET電流は出力の短絡のために増加し、時点6でセンス抵抗両端の電圧が25mVを超します。FILTERは60μAをソースし、外部コンデンサを充電します。時点7で、GATEを制御して出力電流を40mV/R<sub>SENSE</sub>に制限します。時点8でFILTERピンの電圧がそのスレッショルド(1.253V)に達したとき出力が依然アナログ電流制限された状態だと、回路ブレーカがトリップしてGATEが"L"に引き下げられます。デバイスがラッチオフし、FAULTが"L"になり、フォルト状態を知らせます。FILTERコンデンサはデバイスがリセットするまで2.4μAのプルダウンによって放電します。

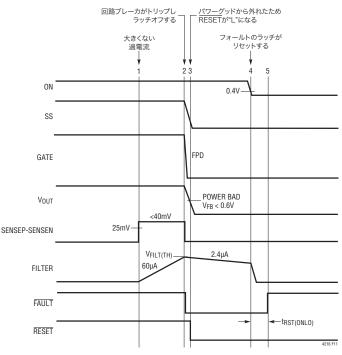

## 電子回路ブレーカのリセット

LTC4216の電子回路ブレーカがフォルト状態でトリップすると、FAULTが"L"になり、RESETピン、SSピンおよびGATEピンがすべてグランドに引き下げられます。これは図11のタイミング図に示されています。LTC4216は外部フォルトが解消されるまでラッチオフしたままです。内部のフォルト・ラッチをクリアしてデバイスを再起動するには時点4でONピンを少なくとも100µsのあいだ"L"(<0.4V)に引き下げます。その後、FAULTは時点5で"H"になります。ONピンを"L"から"H"(>0.8V)にトグルすると新しいスタートアップ・サイクルが開始されます。

図10. 出力が短絡状態で電源を立ち上げると 回路ブレーカがトリップする

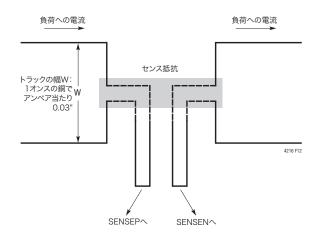

#### センス抵抗に関する検討事項

回路ブレーカの25mVのトリップ・スレッショルドと、SENSEPピンとSENSENピンのあいだに接続されたセンス抵抗の値(R<sub>SENSE</sub>)により、式(10)で与えられているように、トリップ電流のレベルが決まります。フォルト電流レベルがアナログ電流制限を超すと、電流は式(11)で与えられる値に制限されます。過負荷状態が式(2)で与えられるフォルト・フィルタ遅延よりも長く続くと、回路ブレーカがトリップし、デバイスはラッチオフします。

$$I_{TRIP(CB)} = \frac{\Delta V_{CB(TH)}}{R_{SENSE}} = \frac{25mV}{R_{SENSE}}$$

(10)

$$I_{ACL} = \frac{\Delta V_{ACL(TH)}}{R_{SENSE}} = \frac{40mV}{R_{SENSE}} \tag{11}$$

新しい回路デザインでは、これらの抵抗値は最初に正常 状態の最大動作負荷電流と回路ブレーカの最小トリップ・スレッショルドから計算されます。これは次式で与え られます。

$$R_{SENSE} = \frac{\Delta V_{CB(TH,MIN)}}{I_{LOAD(MAX)}} = \frac{21.5mV}{I_{LOAD(MAX)}}$$

(12)

図11. 大きくない過電流で回路ブレーカがトリップし、 続いてデバイスがリセットする

たとえば、 $I_{LOAD(MAX)} = 5A$ ならば、 $R_{SENSE} = 4.3$ m $\Omega$ です。 最も近い標準値は4m $\Omega$ です。

回路ブレーカが正しく動作するように、センス抵抗とLTC4216のSENSEPピンおよびSENSENピンのあいだの接続にはケルビン検出用PCB接続を使うことを強く推奨します。LTC4216とセンス抵抗間の正しい接続法を図12に示します。配線による誤差を小さくするため、PCBレイアウトはバランスのとれた対称形にします。さらに、センス抵抗のPCBレイアウトには、センス抵抗の電力消費を最適化するために正しい熱管理手法を使います。

回路ブレーカがトリップする前に部品が損傷を受けないように、センス抵抗の電力定格はアナログ電流制限のフォルト電流レベルに適合する必要があります。

図12. PCB上のセンス抵抗の接続

## 回路ブレーカのトリップ電流の計算

選択されたR<sub>SENSE</sub>値に対して、回路ブレーカをトリップ する標準負荷電流は次式で与えられます。

$$I_{TRIP(TYP)} = \frac{\Delta V_{CB(TH,TYP)}}{R_{SENSE(TYP)}} = \frac{25mV}{R_{SENSE(TYP)}} \tag{13}$$

回路ブレーカをトリップする最小負荷電流は次式で与えられます。

$$I_{TRIP(MIN)} = \frac{\Delta V_{CB(TH,MIN)}}{R_{SENSE(MAX)}} = \frac{21.5mV}{R_{SENSE(MAX)}}$$

(14)

ここで、

$$R_{SENSE(MAX)} = R_{SENSE(TYP)} \cdot \left(1 + \frac{R_{TOL}}{100}\right)$$

回路ブレーカをトリップする最大負荷電流は次式で与えられます。

$$I_{TRIP(MAX)} = \frac{\Delta V_{CB(TH,MAX)}}{R_{SENSE(MIN)}} = \frac{28.5mV}{R_{SENSE(MIN)}}$$

$$zzv, \qquad (15)$$

$$R_{SENSE(MIN)} = R_{SENSE(TYP)} \cdot \left(1 - \frac{R_{TOL}}{100}\right)$$

たとえば、電流検出に $4m\Omega\pm1\%$ のセンス抵抗 $R_{TOL}$ が使われると、標準トリップ電流 $I_{TRIP(TYP)}=6.25A$ となります。式14と式15から、それぞれ $I_{TRIP(MIN)}=5.3A$ および $I_{TRIP(MAX)}=7.2A$ となります。

正しい動作と、回路ブレーカを不必要にトリップさせないためには、最小トリップ電流(ITRIP(MIN))がMOSFETの出力に接続されている回路の最大動作負荷電流を超えている必要があります。

#### MOSFETの選択

回路ブレーカがトリップする前、外部MOSFETスイッチは短絡状態を扱えるだけの適切な安全動作領域(SOA)を備えている必要があります。これらの考慮点が連続ドレイン電流定格よりも優先します。与えられたアプリケーションに対して適切なSOAをもったMOSFETは必要なドレイン電流を常に扱えますが、その逆は真であるとは限りません。MOSFETの製造元のデータシートを調べて、安全動作領域と実効過渡サーマル・インピーダンス曲線を確認してください。

MOSFETは、ソフトスタート用コンデンサが存在しないと仮定して、3段階のプロセスで選択します。最初にR<sub>SENSE</sub>を選択してから、負荷容量を充電するのに必要な時間を決定します。このタイミング(および最大短絡電流と最大負荷電源電圧)により、MOSFETのSOA曲線に対してチェックされる動作点が定まります。

さらに、次の3つの重要パラメータを検討します。

LINEAD

1. 最大ドレイン-ソース電圧(V<sub>DS(MAX)</sub>)

V<sub>DS(MAX)</sub>の定格はスパイクやリンギングを含む最大負荷 電源電圧を超えている必要があります。

2. ゲート-ソース電圧(V<sub>GS</sub>)のオーバードライブ

VGSの絶対最大定格は、「ロジック・レベル」および「サブロジック・レベル」のMOSFETの場合、標準で±8Vです。

3. ドレイン-ソース抵抗(R<sub>DS(ON)</sub>)

低電圧アプリケーションでは $R_{DS(ON)}$ を小さくし、そのドレイン-ソース電圧 $(V_{DS(ON)})$ を電源電圧の非常に小さなパーセンテージにできるようにします。

設計を開始するには、最大動作負荷電流と負荷容量を最初に規定します。式(12)からR<sub>SENSE</sub>の値を計算します。式(14)で与えられる最小トリップ電流(I<sub>TRIP(MIN)</sub>)は最大動作負荷電流に適応するように設定します。

スタートアップ・サイクルのあいだ、LTC4216はMOSFET をアナログ電流制限状態で動作させ、 $R_{SENSE}$ 両端に32mV  $\sim$ 48mVの $\Delta V_{ACL(TH)}$ を強制することができます。式(16)で与えられる最小突入電流は、最小 $\Delta V_{ACL(TH)}$ と最大 $R_{SENSE}$  値を使って計算されます。

$$I_{INRUSH(MIN)} = \frac{\Delta V_{ACL(TH,MIN)}}{R_{SENSE(MAX)}} = \frac{32mV}{R_{SENSE(MAX)}}$$

(16)

式(17)で与えられる最大短絡電流は、最大 $\Delta V_{ACL(TH)}$ と最小 $R_{SENSE}$ 値を使って計算されます。

$$I_{SHORT-CIRCUIT(MAX)} = \frac{\Delta V_{ACL(TH,MAX)}}{R_{SENSE(MIN)}} = \frac{48mV}{R_{SENSE(MIN)}}$$

(17)

FILTERコンデンサ(C3)は予測される最も遅い充電速度に基づいて選択します。そうしないと、負荷コンデンサが完全に充電される前にFILTERがタイムアウトしてしまう可能性があります。C3の値は負荷コンデンサ(CLOAD)を負荷電源の最大値(VIN(MAX))まで充電するのに必要な最大時間に基づいて計算します。この時間は次式で与えられます。

$$t_{CHARGE(LOAD)} = \frac{C_{LOAD} \cdot V_{IN(MAX)}}{I_{INRUSH(MIN)}}$$

(18)

回路ブレーカの応答時間の式(2)を変形して、FILTERコンデンサ(C3)は次式で与えられます。

$$C3 = \frac{(t_{CHARGE(LOAD)} - 20\mu s) \cdot 60\mu A}{1.253V}$$

(19)

式(2)に戻って、回路ブレーカの応答時間を選択された C3を使って計算し、その値を $V_{IN(MAX)}$ および $I_{SHORT-CIRCUIT(MAX)}$ と一緒に使って、使用予定のMOSFETのSOA 曲線をチェックします。

「標準的応用例」の数値を示した設計例として、 $V_{IN(MAX)}$  = 1.8V+5%、最大動作負荷電流 = 5A、 $C_{LOAD}$  =  $1000\mu$ Fについて検討します。式(12)から $R_{SENSE}$  =  $4.3m\Omega$ となります。 $R_{SENSE}$  =  $4m\Omega(\pm 1\%$ 許容差)を選択します。式(14)と式(16)から、それぞれ $I_{TRIP(MIN)}$  = 5.3A (>  $I_{LOAD(MAX)}$  = 5A)および $I_{INRUSH(MIN)}$  = 7.9Aとなります。式(19)からC3 = 10nFとなります。C3、FILTER電流( $60\mu A$ )およびFILTERスレッショルド(1.253V)の誤差を考慮して、計算値に1.5を掛けると、最も近い標準値としてC3 = 18nFが得られます。

短絡が発生すると、式(2)のC3 = 18nFに支配されて、最大 $I_{SHORTCIRCUIT(MAX)}$  = 12.1Aの電流が400 $\mu$ sのあいだMOSFETを流れます。MOSFETはこの基準に基づいて選択し、SOA曲線に対してチェックする必要があります。

#### Vcc電源のRCネットワーク

LTC4216には電源入力と検出用に2つの別個のピン(V<sub>CC</sub> とSENSEP)が備わっています。

- 1. 内部回路に給電するためのVCCピン。

- 2. 負荷電源から外部センス抵抗とNチャネルMOSFETを 通って出力負荷に流れる電流を(SENSENピンと一緒に) 検出するSENSEPピン。

ほとんどのホットスワップ・デバイスでは、VccとSENSEPは1つの共通ピンで、デバイスの電源と外部MOSFETの電流検出機能を与えます。ただし、出力の短絡によって電源が垂下すると、デバイスを低電圧ロックアウト状態にトリガして、デバイスをディスエーブルし、内部のラッチがリセットする可能性があります。

プラグイン・ボードに置かれた外部MOSFETスイッチの 給電中の電源側にはバイパスコンデンサは許されていま せんので、LTC4216にはバイアス電源入力と負荷電源検 出用に2本の別個のピンが備わっています。

この構成では、図13に示されているRCネットワーク( $R_Y$ と $C_Y$ )を $V_{CC}$ ピンに使って、出力の短絡や隣接するボードの短絡のあいだ電源グリッチを乗り切ることができます。示されているRCネットワークの時定数は $7\mu$ sですが、これは電源がほとんどの電源グリッチを乗り切るのに十分であり、デバイスが不必要に低電圧ロックアウト状態に入ったり、一時的に電源を失うことから保護します。 $V_{CC}$ ピンとSENSEPピンを一緒に接続するとき、 $R_Y$ の値は $V_{CC}$ ピンの電圧がSENSEPより70mV低くなるように選択します。そうしないと、 $V_{CC}$ ピンの電流の一部がSENSEPピンを通って流れます。

デバイスの電源入力と検出機能を分離するこのユニークな方式は、2.3Vの最小バイアス電源電圧で負荷電源をグランドからその電源レールまで動作させるという柔軟性も与えます。正しく動作するには、負荷電源がバイアス電源電圧(最大6V)以下であることが必要です。

## 電源トランジェントに対する保護

電源トランジェントを除去するのにほとんどのアプリケーションで使われる2つの方法があります。

- 1. トランジェントを安全なレベルまでクリップするトランジェント電圧サプレッサ。

- 2. スナバ(直列RC)ネットワーク。

負荷電源電圧が3.3V以上のアプリケーションでは、ホットスワップまたは短絡時のリンギングやオーバーシュートが簡単にLTC4216の絶対最大定格を超すことがあります。リスクを最小に抑えるため、トランジェント電圧サプレッサとスナバ・ネットワークをSENSEPピンに強く推奨します。負荷電源電圧が2.5V以下のアプリケーションでは、電源のリンギングを減らすのに通常はスナバ・ネットワークで十分です。

LTC4216の周りの電源トランジェント保護デバイス(Z1、 $R_X$ および $C_X$ )の接続方法を図13に示します。 $V_{CC}$ ピンの RCネットワーク( $R_Y$ と $C_Y$ )も負荷電源( $V_{IN}$ )のスナバ回路として機能します。PCBレイアウトで、これらのトランジェント保護デバイスは、リード・インダクタンスを小さく抑えるためリードの長さを短くして、LTC4216の負荷電源レールのすぐ近くに実装します。

図13. LTC4216の負荷電源レールに接続した トランジェント保護デバイス

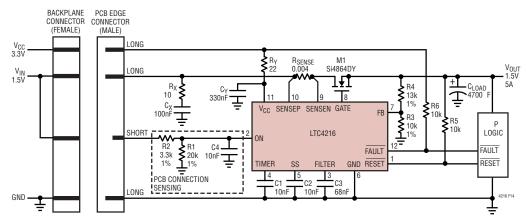

#### スタガピンの接続

LTC4216はコネクタのバックプレーン側またはプリント 回路基板のどちらにも使うことができます。両方の例を 図14と図15に示します。スタガピン付きエッジ・コネクタ を備えたプリント回路基板を推奨します。回路基板の挿抜によりピン接続のシーケンスが制御されるからです。 プリント基板上の電源(VccとSENSEP)とグランドの接続はエッジ・コネクタの長いピン(ブレード)に配線します。エッジ・コネクタを通過する制御信号(ON)と状態信号(RESETとFAULT)は短いピン(ブレード)に配線します。

#### バックプレーンとPCBの接続の検出

LTC4216が起動サイクルを開始する前に、プリント回路 基板がバックプレーンのコネクタに適切に挿入されたか 検知するには、LTC4216のONピンをいくつかの方法で使 うことができます。

一例を図14に示します。この場合、LTC4216はPCBに実装され、R1/R2抵抗分割器がONピンに接続されています。 R2はエッジ・コネクタの短いピンに接続されています。 コネクタ同士が完全にかみ合う前、ONピンはR1によって"L"に保たれ、LTC4216をオフ状態に保ちます。コネクタ同士がかみ合うと、抵抗分割器が負荷電源( $V_{\rm IN}$ )に接続され、ONピンの電圧が0.8Vを超してLTC4216をオンします

LINEAD

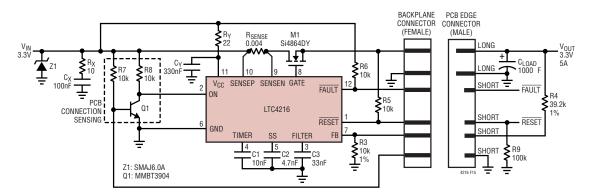

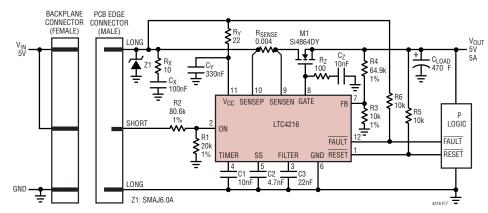

LTC4216がバックプレーンに実装されている例を図15に示します。この場合、NPNトランジスタ(Q1)と2個の抵抗(R7とR8)によりPCB接続検出回路がONピンに形成されます。PCBがバックプレーンのコネクタに挿入されていないと、Q1のベースはR7を介して負荷電源に接続されているので、Q1がオンしてLTC4216のONピンを"L"に引き下げます。Q1のベースはバックプレーンのコネクタ・ピンにも配線されています。PCBがバックプレーンに挿入されると、Q1のベースはPCBの短いピン・コネクションを介して接地されます。これにより、Q1がオフし、LTC4216のONピンはR8を介して負荷電源まで上昇して"H"になることができるので、LTC4216がオンします。

前の2例で、PCB検出回路はシステム・コントローラからの割り込み機能には配線されていません。図16に示されているように、ロジック・レベルのディスクリートNチャネルMOSFET(M2とM3)と2個の抵抗を追加すると、検出回路の割り込み制御が可能です。PCBがバックプレーン

のコネクタにしっかりかみ合うまで、M2のゲートはR8を通して負荷電源まで引き上げられて"H"になっているので、M2はオンに保たれます。 $\overline{ON}/RST$ 信号と $\overline{ON}/OFF$ 信号の両方のロジック・レベルが"L"だと、M2とM3がオフするので、 $\overline{ON}/OFF$ 信号を"H"になることができ、 $\overline{LTC4216}$ がオンします。 $\overline{ON}/OFF$ 信号を"H"にすると、デバイスがオフし、 $\overline{GATE}$ を"L"に引き下げます。 $\overline{ON}/RST$ 信号を"H"にするとデバイスはリセットされます。

#### 5Vホットスワップ・アプリケーション

$V_{CC}$ ピンとSENSEPピンを一緒に5V負荷電源( $V_{IN}$ )に接続したホットスワップ・アプリケーションを図17に示します。抵抗分割器( $R_1/R_2$ )は負荷電源の低電圧スレッショルドを設定して、電源電圧が4Vを超すまではシステムが起動できないようにします。抵抗分割器( $R_3/R_4$ )は $V_{OUT}$ をモニタして、 $V_{OUT}$ が4.5Vを超すと $\overline{RESET}$ を"H"にする信号を出します。

図14. シングル・チャネル1.5Vホットスワップ・コントローラ

図15. バックプレーン側のホットスワップ・コントローラ(スタガ・ピン接続を利用)

図16. ON/OFFコントロール付きPCB接続検出

図17.5Vホットスワップ・アプリケーション

5V電源システムをフォルト状態のリンギングと電圧スパイクから保護するために、トランジェント・サプレッサ(Z1)と、SENSEPピンに接続されたスナバ・ネットワーク( $R_X$ と $C_X$ )を強く推奨します。 $V_{CC}$ ピンに接続されたRCネットワーク( $R_Y$ と $C_Y$ )によりLTC4216のバイアス電源はフォルト状態や隣接する基板の短絡時に電源グリッチを乗り切ることができます。

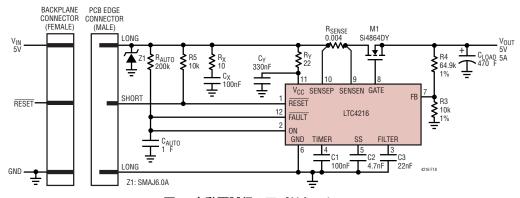

#### フォルト後の再試行

図18に示されているように、FAULTピンとONピンの両方を一緒にRCネットワークに接続することにより、フォルト状態の後に自動的に再試行を行うように、LTC4216を構成することができます。ネットワークは負荷電源(VIN)に接続されたプルアップ抵抗(RAUTO)とグランドに接続された外部コンデンサ(CAUTO)で構成されています。この自動再試行回路は、図19のタイミング図に示されてい

るように、回路ブレーカがトリップした後、LTC4216を 再試行しようとします。自動再試行のシーケンスのあい だTIMER時間によって与えられるクーリング・サイクル に加えて、ONピンの電圧が0.8Vに達するためのRC時定 数により追加のターンオフ時間が与えられるので、外部 MOSFETが過熱から保護されます。自動再試行のデュー ティ・サイクルは次式で与えられます。

ここで、

$t_{TIMER}$  = 式(1)で与えられるTIMER時間; $t_{OFF}$  = コンデンサ( $C_{AUTO}$ )を $\overline{FAULT}$   $V_{OL}$ から $V_{ON(TH)}$ スレッショルド(0.8V)まで充電するのに要する時間です。 $\overline{FAULT}$ ピンには $5\mu$ Aの内部電流源プルアップが備わっているので、 $t_{OFF}$ の式が複雑になります。

これはおよそ次式で与えられます。

$$t_{OFF} \approx \frac{R_{AUTO} \cdot C_{AUTO} \cdot (V_{ON(TH)} - V_{OL})}{(V_{IN} - V_{ON(TH)}) + R_{AUTO} \cdot 5\mu A} \tag{21}$$

$t_{FILTER}$  = 式(2)で与えられる回路ブレーカの応答時間; $t_{SS}$  = ソフトスタート・コンデンサ(C2)を0Vからその最終値 (1.65V)まで $10\mu$ Aの電流源だけで充電するのに要するおよその時間です。

示されている部品の値の場合、外部RC時定数は0.2秒に設定され、 $t_{TIMER} = 62$ ms、 $t_{OFF} = 25$ ms ( $V_{IN} = 5V$ )、 $t_{SS} = 1.6$ ms、 $t_{FILTER} = 480$ µs、自動再試行のデューティ・サイクルは、 $t_{TIMER}$  遅延とRC遅延の両方を増加させることにより、さらに減らすことができます。一例として、 $t_{TIMER}$  できます。一例として、 $t_{TIMER}$  の値を $t_{TIMER}$  の値を $t_{TIMER}$  の値を $t_{TIMER}$  できる $t_{TIMER}$  できる $t_{TIMER}$  の値を $t_{TIMER}$  できます。一例として、 $t_{TIMER}$  できる $t_{TIMER}$  できる

図18. 自動再試行のアプリケーション

図19. 自動再試行のタイミング

## パッケージ

最新のパッケージ図面については、http://www.linear-tech.co.jp/designtools/packaging/をご覧ください。

## DE/UE Package

#### 12-Lead Plastic DFN (4mm × 3mm)

(Reference LTC DWG # 05-08-1695 Rev D)

推奨半田パッドのピッチと寸法 半田付けされない領域には半田マスクを使用する

#### NOTE:

- 1. 図はJEDECのパッケージ外形MO-229のバリエーション (WGED)として提案。

- 2. 図は実寸とは異なる

- 3. すべての寸法はミリメートル

- 4. パッケージ底面の露出パッドの寸法にはモールドのパリ を含まない。モールドのパリは(もしあれば)各サイドで 0.15mmを超えないこと

- 5. 露出パッドは半田メッキとする

- 6. 網掛けの部分はパッケージの上面と底面のピン1の位置 の参考に過ぎない

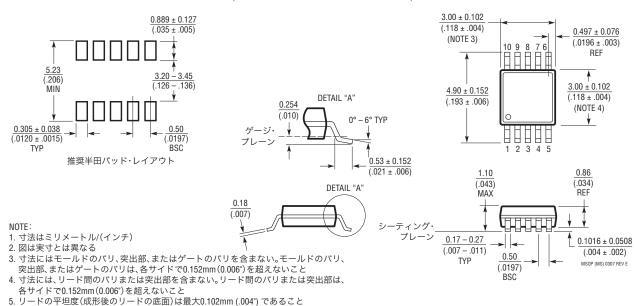

#### MS Package 10-Lead Plastic MSOP

(Reference LTC DWG # 05-08-1661 Rev E)

LINEAR

# 改訂履歴

| REV | 日付   | 概要                                                                      | ページ番号 |

|-----|------|-------------------------------------------------------------------------|-------|

| Α   | 4/13 | 「特長」の10番目の項目を「電源電圧」から「出力」に修正。                                           | 1     |

|     |      | DEの保存温度範囲を150°Cに上げる。「発注情報」を最新のフォーマットで分けて表示。                             | 2     |

|     |      | △V <sub>CB(TH)</sub> の条件を規定。FILTERコンデンサなしのt <sub>CB(TRIP)</sub> を新しく規定。 | 3     |

|     |      | 新規グラフを追加:「アナログ電流制限遅延とセンス電圧」。                                            | 4     |

|     |      | 「V <sub>FAULT(TH)</sub> と温度」のグラフを削除。                                    | 5     |

|     |      | RESETピンの説明文を更新。FILTER、タイマ、FBピンの説明文にしきい値情報を追加。                           | 6     |

|     |      | $R_Z$ の値にガイドラインを記載。                                                     | 12    |

|     |      | 図7にR <sub>G</sub> を追加し、式7の前に説明を追加。                                      | 13    |

# 標準的応用例

#### スルーレート制御用ゲート・コンデンサ付き LTC4216CMS

# 関連製品

| 製品番号                 | 説明                        | 注釈                                  |

|----------------------|---------------------------|-------------------------------------|

| LTC1421              | デュアル・チャネル、ホットスワップ・コントローラ  | 3V ~ 12V で動作、– 12V をサポート、SSOP-24    |

| LTC1422              | シングル・チャネル、ホットスワップ・コントローラ  | 2.7V ~ 12V で動作、SO-8                 |

| LTC1642              | シングル・チャネル、ホットスワップ・コントローラ  | 3V ~ 16.5V で動作、33V までの過電圧保護、SSOP-16 |

| LTC1645              | デュアル・チャネル、ホットスワップ・コントローラ  | 3V~12Vで動作、パワー・シーケンス制御、              |

|                      |                           | SO-8 または SO-14                      |

| LTC1647-1/LTC1647-2/ | デュアル・チャネル、ホットスワップ・コントローラ  | 2.7V ~ 16.5V で動作、SO-8 または SSOP-16   |

| LTC1647-3            |                           |                                     |

| LTC4210-1/LTC4210-2  | シングル・チャネル、ホットスワップ・コントローラ  | 2.7V ~ 16.5V で動作、アクティブ電流制限、SOT23-6  |

| LTC4211              | シングル・チャネル、ホットスワップ・コントローラ  | 2.5V ~ 16.5V で動作、多機能電流制御、MSOP-8 または |

|                      |                           | MSOP-10                             |

| LTC4212              | シングル・チャネル、ホットスワップ・コントローラ  | 2.5V ~ 16.5V で動作、パワーアップ・タイムアウト機能、   |

|                      |                           | MSOP-10                             |

| LTC4214              | 負電圧ホットスワップ・コントローラ         | -6V ~ −16V で動作、MSOP-10              |

| LT4220               | 正電圧と負電圧、デュアル・チャネル、        | ±2.7V ~ ±16.5V で動作、SSOP-16          |

|                      | ホットスワップ・コントローラ            |                                     |

| LTC4221              | デュアル・ホットスワップ・コントローラ/シーケンサ | 1V ~ 13.5V で動作、多機能電流制御、SSOP-16      |

| LTC4230              | トリプル・チャネル、ホットスワップ・コントローラ  | 1.7V ~ 16.5V で動作、多機能電流制御、SSOP-20    |

LT 0413 REV A • PRINTED IN JAPAN

LINEAR

TECHNOLOGY

© LINEAR TECHNOLOGY CORPORATION 2013