## 特長

- 広い入力電圧範囲：

- 動作する範囲は3V～60V

- 電源、シャットダウン、ソフトスタート、UVLO、設定可能な電流制限、および設定可能なパワーグッドが3Aのレギュレータごとに独立

- ダイ温度モニタ

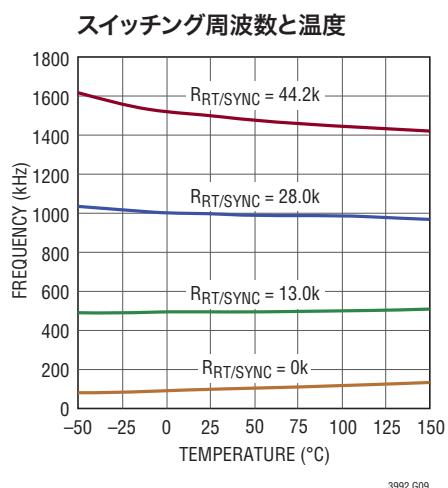

- 同期クロック出力を備えた250kHz～2MHzの調整可能 / 同期可能な固定周波数動作

- 独立した同期スイッチング周波数により、部品サイズを最適化

- 逆位相スイッチング

- 出力を並列接続可能

- 柔軟な出力電圧トラッキング

- 低損失電圧：最大95%のデューティ・サイクル

- 5mm×5mm QFNパッケージ

- FMEA準拠の背面パッド付き38ピンTSSOPパッケージ

## アプリケーション

- 自動車用電源

- 分配型電源の安定化

## 概要

LT<sup>®</sup>3992は、2つの4.6Aスイッチを内蔵したデュアル電流モードPWM降圧DC/DCコンバータです。入力電圧、シャットダウン、帰還、ソフトスタート、UVLO、電流制限、コンパレータのピンがチャネルごとに独立しているので、複雑な電源トラッキング要件や電源シーケンシング要件が簡単なものになります。

効率と部品サイズを最適化するため、2つのコンバータの両方に最大電流制限値を設定可能で、共通の外部クロック入力か、抵抗で設定可能な固定周波数(250kHz～2MHz)の内部発振器に同期します。部品サイズをさらに最適化するため、チャネル1に分周器を備えています。すべての周波数で、チャネル間に180°の位相関係が維持されるので、電圧リップルが少なくなり、部品サイズが小さくなります。また、複数のレギュレータを同期するためのクロック出力が用意されています。

スイッチを複数のクロック・サイクルにわたってオン状態に維持し、昇圧コンデンサの再充電が必要なときにのみオフにすることが可能なので、最小入出力間電圧比が改善されます。SHDNピンを使用して、独立したチャネル動作を設定できます。2つのコンバータを両方ともディスエーブルすると、全静止電流は10µA未溝に減少します。

**L**T、LT、LTC、LTM、Linear Technology、LinearのロゴおよびBurst Modeはリニアテクノロジー社の登録商標です。その他すべての商標の所有権は、それぞれの所有者に帰属します。

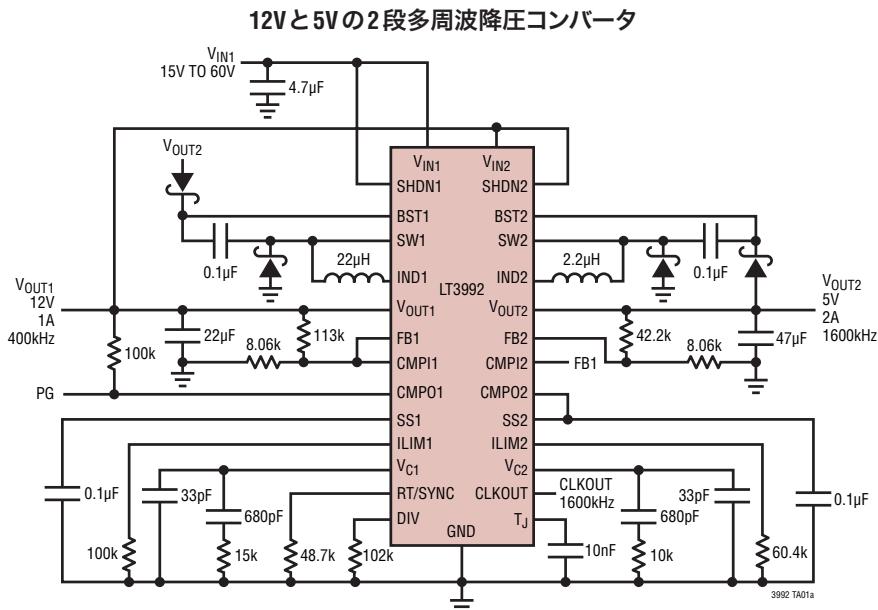

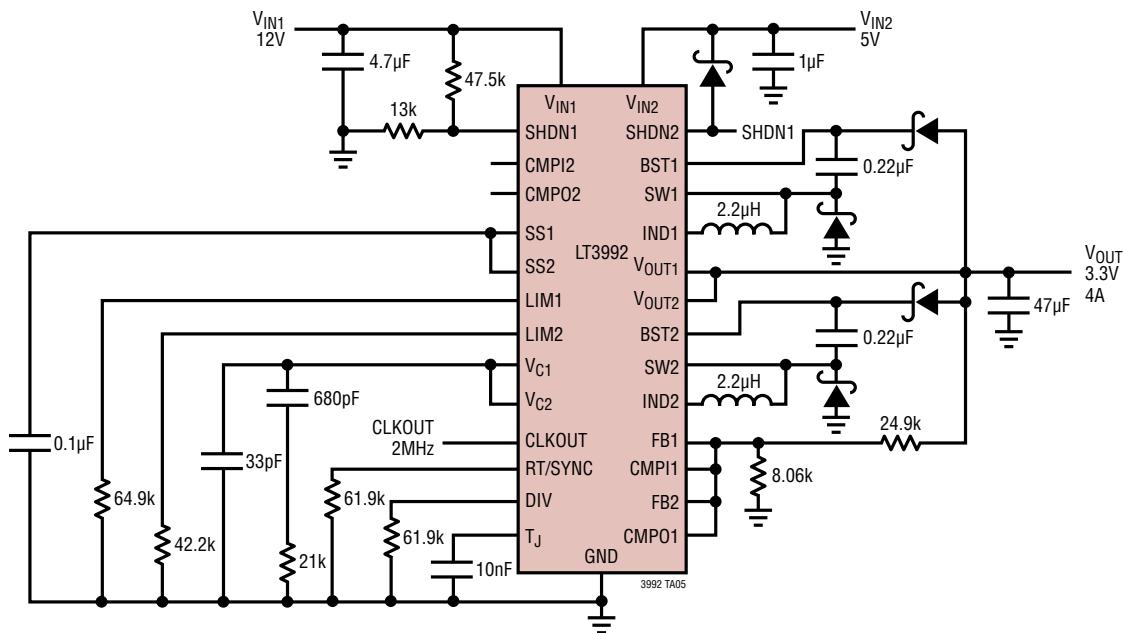

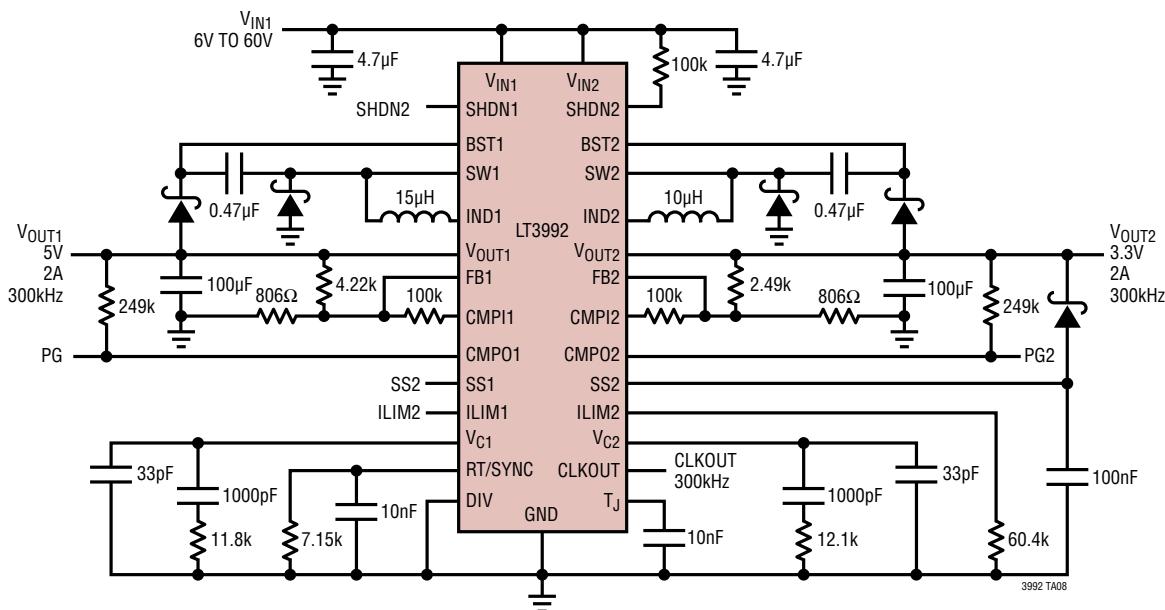

## 標準的応用例

独立した同期スイッチング

周波数により、全周波数

入力範囲が拡大

3992fa

# LT3992

## 絶対最大定格 (Note 1)

|                                     |             |                          |                |

|-------------------------------------|-------------|--------------------------|----------------|

| $V_{IN1/2}$ 、SHDN1/2、CMPO1/2.....   | 60V         | $V_{C1/2}$ 、 $T_J$ ..... | $\pm 100\mu A$ |

| $SW1/2$ .....                       | $V_{IN1/2}$ | 動作接合部温度範囲 (Note 2)       |                |

| $BST1/2$ .....                      | 75V         | LT3992EUH.....           | -40°C ~ 125°C  |

| $BST1/2$ と $SW1/2$ との差 .....        | 25V         | LT3992IUH.....           | -40°C ~ 125°C  |

| $IND1/2$ 、 $V_{OUT1/2}$ .....       | 60V         | LT3992EFE.....           | -40°C ~ 125°C  |

| $FB1/2$ 、 $CMPI1/2$ 、 $SS1/2$ ..... | 5V          | LT3992IFE.....           | -40°C ~ 125°C  |

| $RT/SYNC$ .....                     | 5V          | LT3992HFE.....           | -40°C ~ 150°C  |

| $DIV$ 、 $ILIM1/2$ .....             | 2.5V        | 保存温度範囲.....              | -65°C ~ 150°C  |

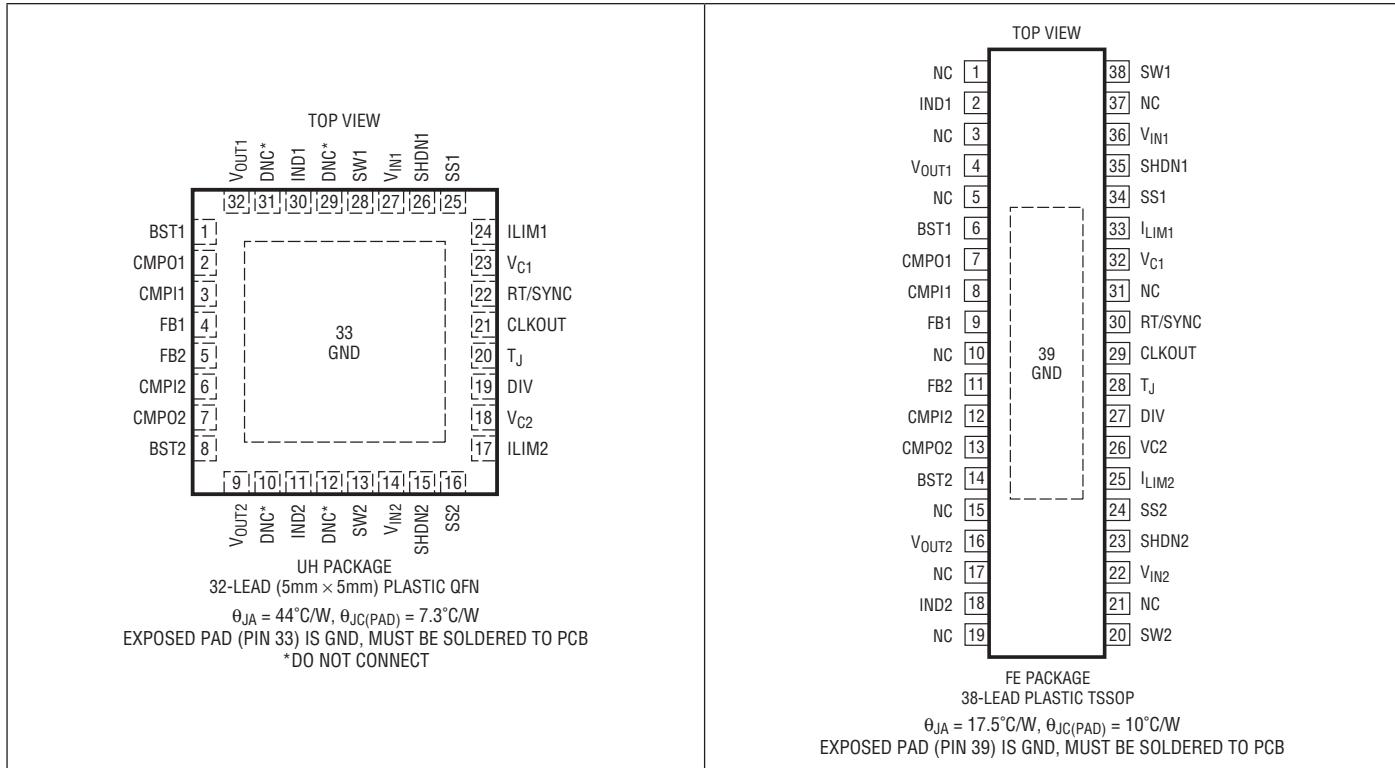

## ピン配置

## 発注情報

| 無鉛仕上げ         | テープアンドリール       | 製品マーキング* | パッケージ                           | 温度範囲          |

|---------------|-----------------|----------|---------------------------------|---------------|

| LT3992EUH#PBF | LT3992EUH#TRPBF | 3992     | 32-Lead (5mm x 5mm) Plastic QFN | -40°C ~ 125°C |

| LT3992IUH#PBF | LT3992IUH#TRPBF | 3992     | 32-Lead (5mm x 5mm) Plastic QFN | -40°C ~ 125°C |

| LT3992EFE#PBF | LT3992EFE#TRPBF | LT3992FE | 38-Lead Plastic TSSOP           | -40°C ~ 125°C |

| LT3992IFE#PBF | LT3992IFE#TRPBF | LT3992FE | 38-Lead Plastic TSSOP           | -40°C ~ 125°C |

| LT3992HFE#PBF | LT3992HFE#TRPBF | LT3992FE | 38-Lead Plastic TSSOP           | -40°C ~ 150°C |

さらに広い動作温度範囲で規定されるデバイスについては、弊社または弊社代理店にお問い合わせください。\* 温度グレードは出荷時のコンテナのラベルで識別されます。

非標準の鉛仕上げの製品の詳細については、弊社または弊社代理店にお問い合わせください。

無鉛仕上げの製品マーキングの詳細については、<http://www.linear-tech.co.jp/leadfree/>をご覧ください。

テープアンドリールの仕様の詳細については、<http://www.linear-tech.co.jp/tapeandreel/>をご覧ください。

**電気的特性** ●は全動作温度範囲での規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。特に規定がない限り、 $V_{VIN1/2} = 15\text{V}$ 。(Note 2)

| PARAMETER                               | CONDITIONS                                                                                                                                                                                                             | MIN    | TYP                 | MAX  | UNITS           |

|-----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|---------------------|------|-----------------|

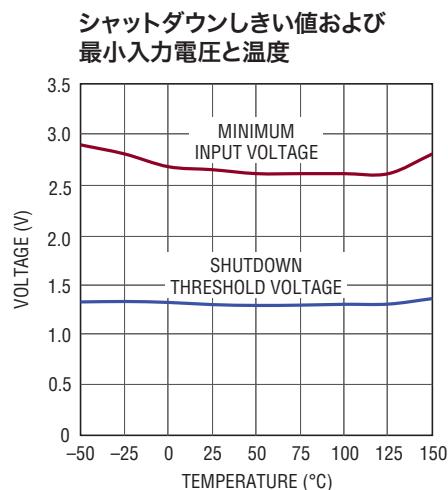

| SHDN Voltage Threshold CH1/2            |                                                                                                                                                                                                                        | ● 1.24 | 1.32                | 1.4  | V               |

| SHDN Input Current CH1/2                | $V_{SHDN} = 1.35\text{V}$                                                                                                                                                                                              | -1     | 0                   | 1    | $\mu\text{A}$   |

| $V_{IN1}$ Undervoltage Lockout (Note 3) |                                                                                                                                                                                                                        | 2.6    | 2.9                 | 3.2  | V               |

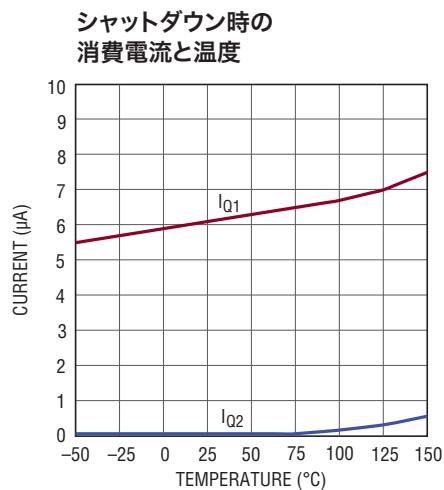

| $V_{IN1}$ Shutdown Current              | $V_{SHDN} = 0\text{V}$                                                                                                                                                                                                 | ● 6    | 13                  |      | $\mu\text{A}$   |

| $V_{IN2}$ Shutdown Current              | $V_{SHDN} = 0\text{V}$                                                                                                                                                                                                 | ● 0.1  | 2                   |      | $\mu\text{A}$   |

| $V_{IN1}$ Quiescent Current             | $V_{FB1/2} = 2\text{V}$                                                                                                                                                                                                | 3      | 4.2                 | 6    | mA              |

| $V_{IN2}$ Quiescent Current             | $V_{FB1/2} = 2\text{V}$                                                                                                                                                                                                | 300    | 530                 | 900  | $\mu\text{A}$   |

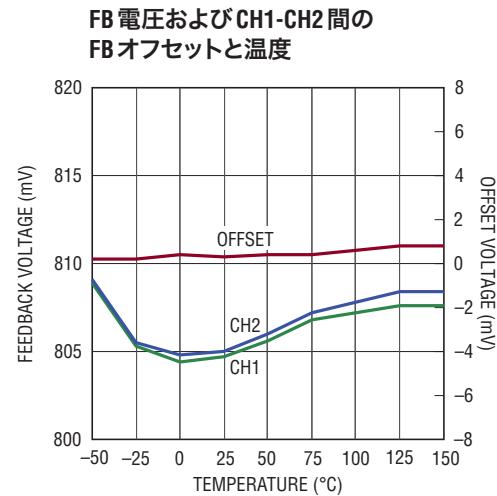

| Feedback Voltage CH1/2                  | $V_{VC1/2} = 1\text{V}$                                                                                                                                                                                                | ● 786  | 806                 | 824  | mV              |

| Feedback Voltage Regulation             | $V_{VIN1/2} = 4\text{V}$ to $60\text{V}$                                                                                                                                                                               | ● 780  | 806                 | 830  | mV              |

| Feedback Voltage Offset CH1 to CH2      | $V_{VC1/2} = 1\text{V}$                                                                                                                                                                                                | ● -13  | 0                   | 13   | mV              |

| Feedback Bias Current CH1/2             | $V_{VC1/2} = 1\text{V}$                                                                                                                                                                                                | ● 0    | 85                  | 300  | nA              |

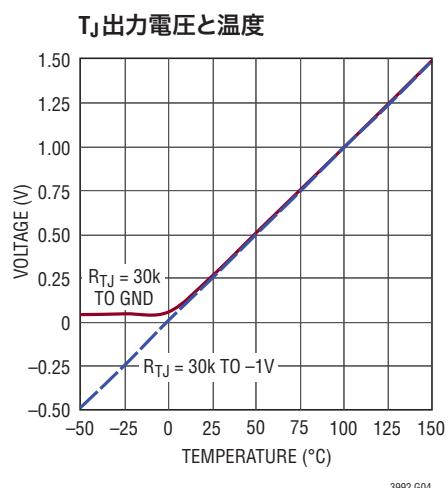

| $T_J$ Output Voltage (Note 4)           | $T_J = 25^\circ\text{C}$ , $I_{TJ} = 25\mu\text{A}$ , Temperature = $25^\circ\text{C}$<br>$I_{TJ} = 25\mu\text{A}$ , Temperature = $125^\circ\text{C}$<br>$I_{TJ} = 25\mu\text{A}$ , Temperature = $-40^\circ\text{C}$ |        | 250<br>1.23<br>-380 |      | mV<br>V<br>mV   |

| $T_J$ Error                             | Temperature = $25^\circ\text{C}$ to $125^\circ\text{C}$                                                                                                                                                                | ● -100 | 0                   | 100  | mV              |

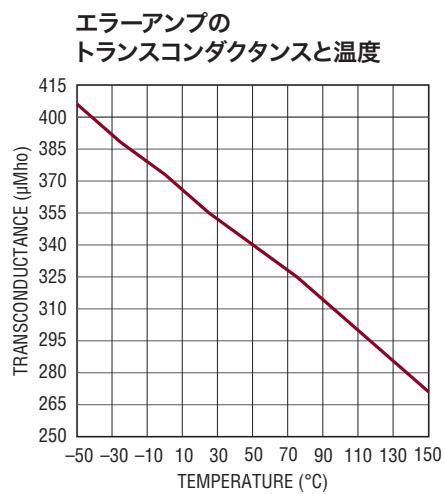

| Error Amp $g_m$ CH1/2                   | $V_{VC1/2} = 1\text{V}$ , $I_{VC1/2} = \pm 10\mu\text{A}$                                                                                                                                                              | 250    | 350                 | 450  | $\mu\text{Mho}$ |

| Error Amp Source Current CH1/2          | $V_{FB1/2} = 0.7\text{V}$ , $V_{VC1/2} = 1\text{V}$                                                                                                                                                                    | 15     | 25                  | 40   | $\mu\text{A}$   |

| Error Amp Sink Current CH1/2            | $V_{FB1/2} = 0.9\text{V}$ , $V_{VC1/2} = 1\text{V}$                                                                                                                                                                    | 15     | 25                  | 40   | $\mu\text{A}$   |

| Error Amp High Clamp CH1/2              | $V_{FB1/2} = 0.7\text{V}$                                                                                                                                                                                              | 1.7    | 1.9                 | 2.1  | V               |

| Error Amp Switching Threshold CH1/2     | $V_{FB1/2} = 0\text{V}$                                                                                                                                                                                                | 0.8    | 1.0                 | 1.2  | V               |

| Soft-Start Source Current CH1/2         | $V_{FB1/2} = 2\text{V}$ , $V_{SS1/2} = 0.07\text{V}$                                                                                                                                                                   | ● 9    | 13.5                | 17   | $\mu\text{A}$   |

| Soft-Start $V_{OH}$ CH1/2               | $V_{FB1/2} = 2.0\text{V}$                                                                                                                                                                                              | 1.9    | 2.15                | 2.4  | V               |

| Soft-Start Sink Current CH1/2           | $V_{FB1/2} = 0.7\text{V}$ , $V_{SS1/2} = 2\text{V}$                                                                                                                                                                    | 0.4    | 0.9                 | 2    | mA              |

| Soft-Start $V_{OL}$ CH1/2               | $V_{FB1/2} = 0\text{V}$                                                                                                                                                                                                | 130    | 170                 | 210  | mV              |

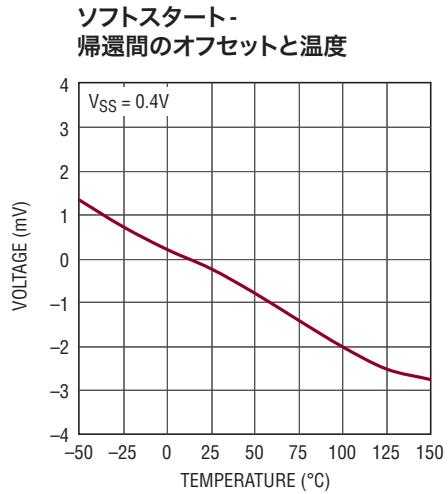

| Soft-Start to Feedback Offset CH1/2     | $V_{VC1/2} = 1\text{V}$ , $V_{SS1/2} = 0.4\text{V}$                                                                                                                                                                    | ● 16   | 0                   | 16   | mV              |

| SS POR Threshold CH1/2                  |                                                                                                                                                                                                                        | 70     | 110                 | 140  | mV              |

| Soft-Start Sink Current CH1/2 POR       | $V_{FB1/2} = 2\text{V}$ , $V_{SS1/2} = 0.14\text{V}$ (Note 5)                                                                                                                                                          | 150    | 450                 | 600  | $\mu\text{A}$   |

| Soft-Start SW Disable CH1/2             | $V_{FB1/2} = 0\text{V}$ (Note 5)                                                                                                                                                                                       | 80     | 115                 | 150  | mV              |

| CMPI Bias Current CH1/2                 | $V_{CMPI1/2} = 0.8\text{V}$                                                                                                                                                                                            | -100   | 0                   | 100  | nA              |

| CMPO Leakage CH1/2                      | $V_{CMPI1/2} = 0.8\text{V}$ , $V_{CMPO1/2} = 60\text{V}$                                                                                                                                                               |        | 70                  | 500  | nA              |

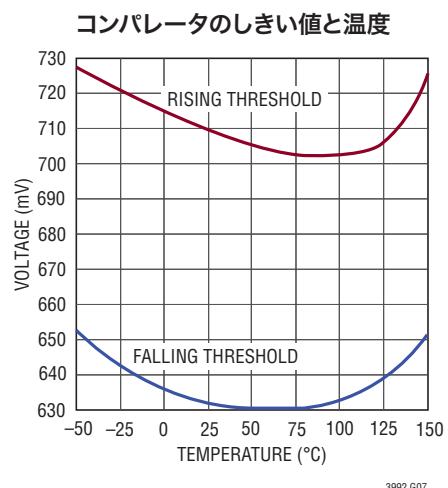

| CMPI Threshold CH1/2                    | $V_{CMPI1/2}$ Rising                                                                                                                                                                                                   | ● 690  | 725                 | 760  | mV              |

| CMPI Threshold CH1/2 of $V_{FB1/2}$     | $V_{CMPI1/2}$ Rising (Note 6)                                                                                                                                                                                          | 86     | 90                  | 94   | %               |

| CMPI Hysteresis CH1/2                   | $V_{CMPI1/2}$                                                                                                                                                                                                          | 50     | 80                  | 105  | mV              |

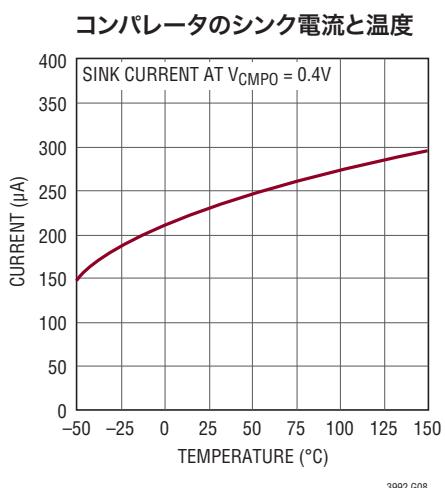

| CMPO Sink Current CH1/2                 | $V_{CMPI1/2} = 0.6\text{V}$ , $V_{CMPO1/2} = 0.2\text{V}$                                                                                                                                                              | 150    | 250                 |      | $\mu\text{A}$   |

| RT/SYNC Reference Current               | $V_{RT/SYNC} = 0.36\text{V}$ E- & I-Grade                                                                                                                                                                              | ● 11.3 | 12                  | 12.7 | $\mu\text{A}$   |

| RT/SYNC Reference Current               | $V_{RT/SYNC} = 0.36\text{V}$ H-Grade                                                                                                                                                                                   | ● 11.2 | 12                  | 13   | $\mu\text{A}$   |

| Minimum Switching Frequency             | $R_{RT/SYNC} = 0\Omega$                                                                                                                                                                                                | 50     | 110                 | 150  | kHz             |

| Switching Frequency                     | $R_{RT/SYNC} = 28\text{k}\Omega$                                                                                                                                                                                       | 900    | 1000                | 1100 | kHz             |

| Maximum Switching Frequency             | $R_{RT/SYNC} = 100\text{k}\Omega$                                                                                                                                                                                      | 2.2    | 2.5                 | 3.0  | MHz             |

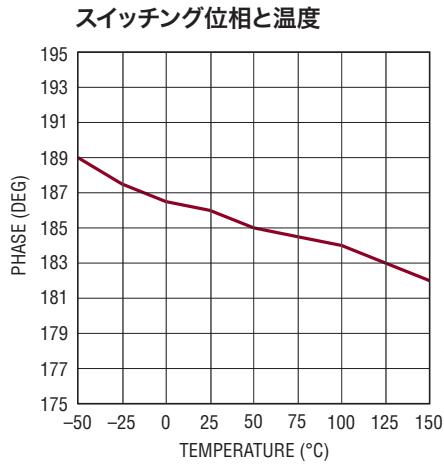

| Switching Phase Angle CH1 $\geq$ CH2    |                                                                                                                                                                                                                        |        | 185                 |      | Deg             |

| DIV Reference Current                   | $V_{DIV} = 1\text{V}$                                                                                                                                                                                                  | ● 10.7 | 12                  | 13.3 | $\mu\text{A}$   |

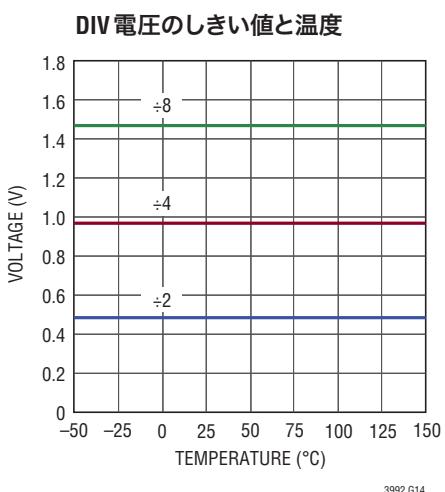

| CH1 DIV 2 Threshold                     | $R_{RT/SYNC} = 0\Omega$                                                                                                                                                                                                | 0.44   | 0.5                 | 0.56 | V               |

3992fa

**電気的特性** ●は全動作温度範囲での規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。特に規定がない限り、 $V_{VIN1/2} = 15\text{V}$ 。(Note 2)

| PARAMETER                                  | CONDITIONS                                                                                                                                                                                                                                                       | MIN  | TYP                      | MAX                      | UNITS                |               |

|--------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--------------------------|--------------------------|----------------------|---------------|

| CH1 DIV 4 Threshold                        | $V_{RT/SYNC} = 0\text{V}$                                                                                                                                                                                                                                        | 0.89 | 1.0                      | 1.06                     | V                    |               |

| CH1 DIV 8 Threshold                        | $V_{RT/SYNC} = 0\text{V}$                                                                                                                                                                                                                                        | 1.39 | 1.5                      | 1.56                     | V                    |               |

| CLKOUT $V_{OL}$                            |                                                                                                                                                                                                                                                                  |      | 0.25                     |                          | V                    |               |

| CLKOUT $V_{OH}$                            |                                                                                                                                                                                                                                                                  |      | 2                        |                          | V                    |               |

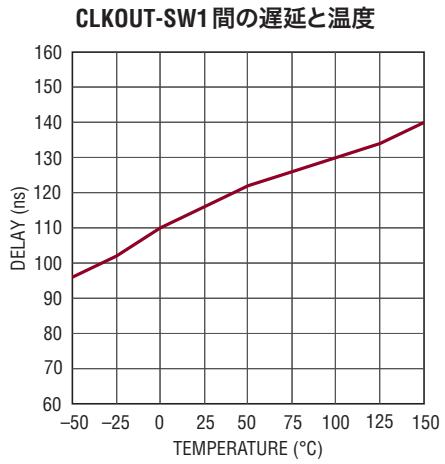

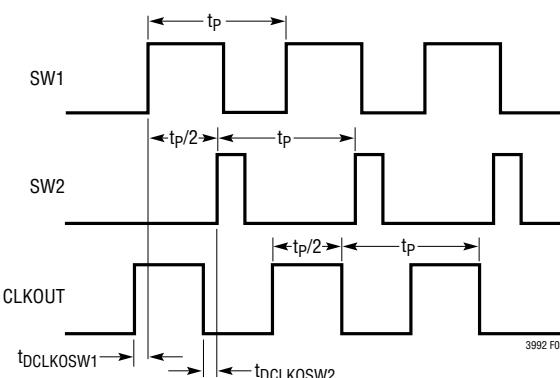

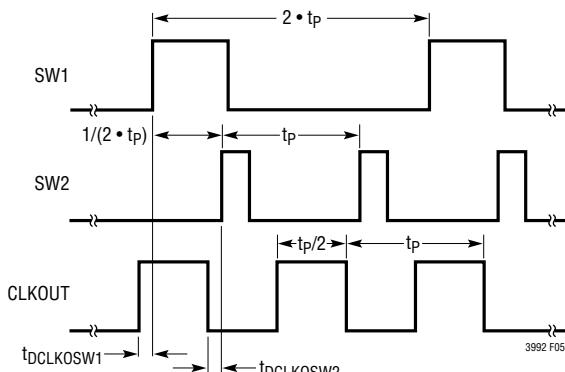

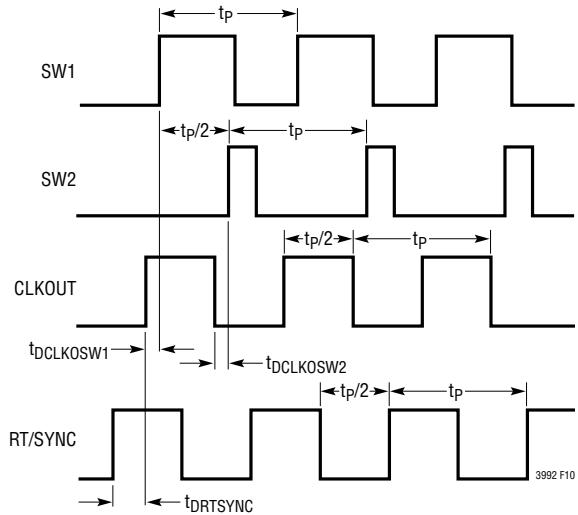

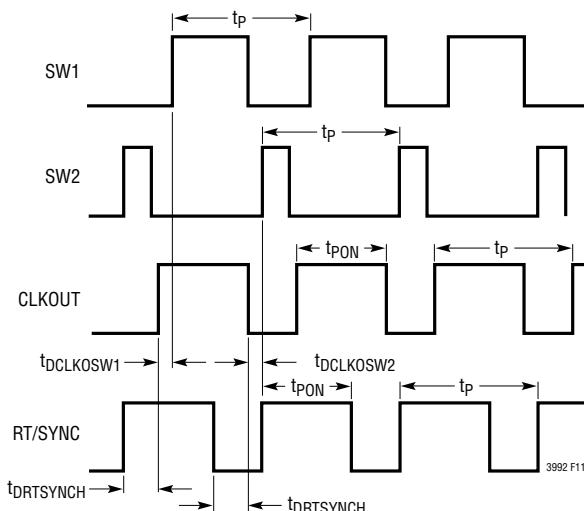

| CLKOUT to SW1ON Delay ( $t_{DCLKOSW1}$ )   | CLKOUT Rising                                                                                                                                                                                                                                                    |      | 60                       |                          | ns                   |               |

| CLKOUT to SW2ON Delay ( $t_{DCLKOSW2}$ )   | CLKOUT Falling                                                                                                                                                                                                                                                   |      | 30                       |                          | ns                   |               |

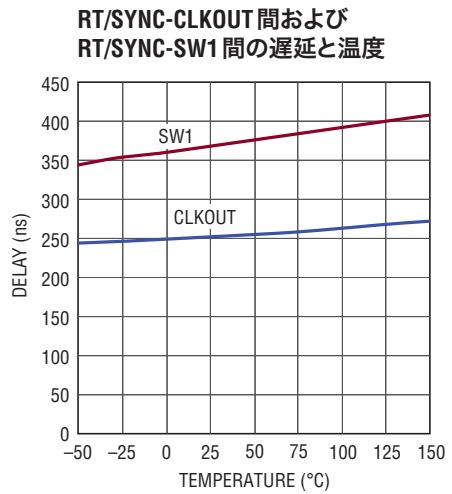

| RT/SYNC to CLKOUT Delay ( $t_{DRTSYNCH}$ ) | $V_{RT/SYNC} = 0\text{V}$ to $2\text{V}$ Rising Edge                                                                                                                                                                                                             |      | 300                      |                          | ns                   |               |

| RT/SYNC to CLKOUT Delay ( $t_{DRTSYNCL}$ ) | $V_{RT/SYNC} = 2\text{V}$ to $0\text{V}$ Falling Edge                                                                                                                                                                                                            |      | 150                      |                          | ns                   |               |

| SYNC Frequency Range                       |                                                                                                                                                                                                                                                                  | 250  | 2000                     |                          | kHz                  |               |

| SYNC Phase Angle CH1 to CH2                | SYNC Frequency = 250kHz                                                                                                                                                                                                                                          |      | 180                      |                          | Deg                  |               |

| Minimum Switch On-Time CH1/2               |                                                                                                                                                                                                                                                                  |      | 160                      |                          | ns                   |               |

| Minimum Switch Off-Time CH1/2              |                                                                                                                                                                                                                                                                  |      | 200                      |                          | ns                   |               |

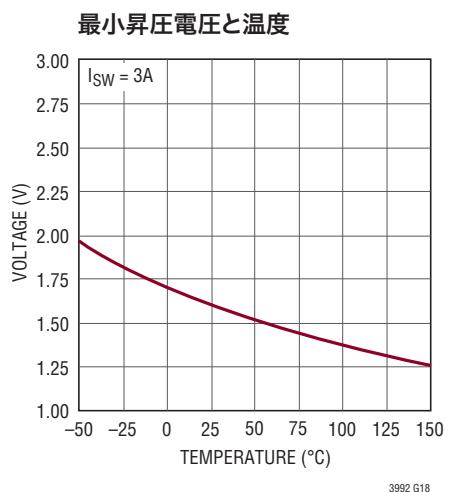

| Minimum Boost for 100% DC CH1/2 (Note 7)   |                                                                                                                                                                                                                                                                  | 1.6  | 2.2                      | 2.6                      | V                    |               |

| IND + $V_{OUT}$ Current CH1/2              | $V_{VOUT1/2} = 0\text{V}$<br>$V_{VOUT1/2} = 5\text{V}$                                                                                                                                                                                                           |      | 1.5<br>0.5               | 5<br>5                   | $\mu\text{A}$        |               |

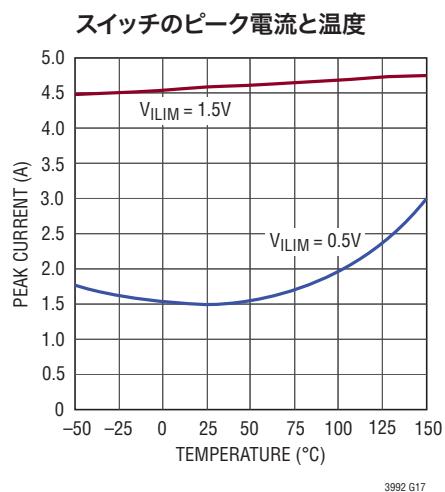

| ILIM1/2 Reference Current                  | $V_{ILIM} = 0\text{V}$                                                                                                                                                                                                                                           | ●    | 10                       | 12                       | 16                   | $\mu\text{A}$ |

| IND to $V_{OUT}$ Maximum Current CH1/2     | $V_{ILIM1/2} = 0.5\text{V}$ , $V_{VOUT} = 1\text{V}$ (Note 8)<br>$V_{ILIM1/2} = 0.5\text{V}$ , $V_{VOUT} = 5\text{V}$ (Note 8)<br>$V_{ILIM1/2} = 1.5\text{V}$ , $V_{VOUT} = 1\text{V}$ (Note 8)<br>$V_{ILIM1/2} = 1.5\text{V}$ , $V_{VOUT} = 5\text{V}$ (Note 8) |      | 0.5<br>0.7<br>3.5<br>3.5 | 1.5<br>1.8<br>4.6<br>4.6 | 3<br>3<br>6.4<br>6.4 | A             |

| Switch Leakage Current CH1/2               | $V_{SW1/2} = 0\text{V}$                                                                                                                                                                                                                                          | ●    |                          | 1                        | 10                   | $\mu\text{A}$ |

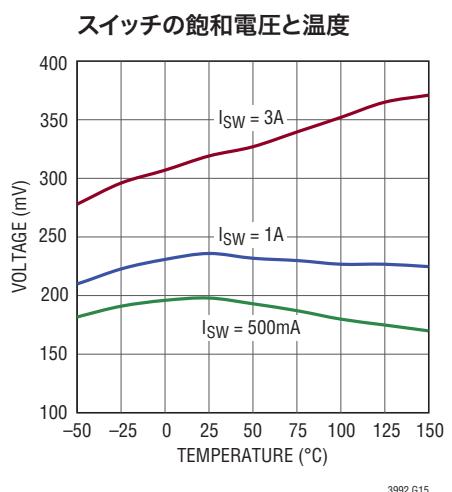

| Switch Saturation Voltage CH1/2            | $I_{SW1/2} = 500\text{mA}$ , $V_{BST1/2} = 18\text{V}$<br>$I_{SW1/2} = 3\text{A}$ , $V_{BST1/2} = 18\text{V}$                                                                                                                                                    |      |                          | 200<br>325               |                      | mV<br>mV      |

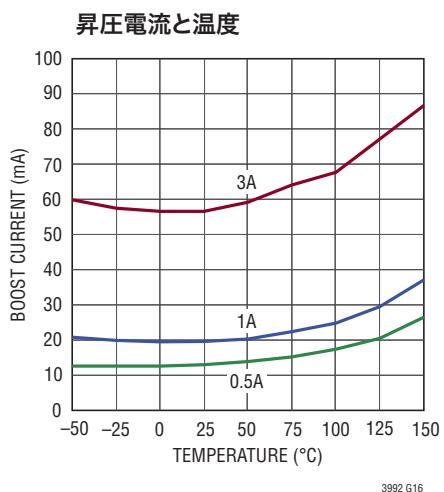

| Boost Current CH1/2                        | $I_{SW1/2} = 500\text{mA}$ , $V_{BST1/2} = 8\text{V}$<br>$I_{SW1/2} = 3\text{A}$ , $V_{BST1/2} = 8\text{V}$                                                                                                                                                      |      | 5<br>35                  | 8<br>55                  | 25<br>85             | mA            |

| Minimum Boost Voltage CH1/2 (Note 9)       | $I_{SW1/2} = 3\text{A}$ , $V_{BST1/2} = 8\text{V}$                                                                                                                                                                                                               |      | 1.0                      | 2.2                      | 3.0                  | V             |

**Note 1:** 絶対最大定格に記載された値を超えるストレスはデバイスに永続的損傷を与える可能性がある。長期にわたって絶対最大定格条件に曝すと、デバイスの信頼性と寿命に悪影響を与える恐れがある。

**Note 2:** LT3992EU/LT3992FFEは、 $0^\circ\text{C} \sim 125^\circ\text{C}$ の接合部温度で性能仕様に適合することが保証されている。 $-40^\circ\text{C} \sim 125^\circ\text{C}$ の動作接合部温度範囲での仕様は設計、特性評価および統計学的なプロセス・コントロールとの相関で確認されている。LT3992IUH/LT3992IFEは $-40^\circ\text{C} \sim 125^\circ\text{C}$ の全動作接合部温度範囲で動作することが保証されている。LT3992HFEは $-40^\circ\text{C} \sim 150^\circ\text{C}$ の全動作接合部温度範囲で動作することが保証されている。接合部温度が高いと動作寿命は短くなる。接合部温度が $125^\circ\text{C}$ を超えると、動作寿命が短くなる。

**Note 3:**  $V_{IN}$ の低電圧ロックアウトは、動作のために $V_{IN}$ ピンが超えなければならない電圧として定義される。しきい値は、内部のバイアス電源が安定化され、スイッチング周波数が一定になることを保証する。安定化出力を維持するための実際の最小入力電圧は、出力電圧と負荷電流によって異なる。「アプリケーション情報」のセクションを参照。

**Note 4:**  $T_J$ 出力電圧は、静止電力を消費しているときのダイの中心の温度を表す。スイッチの電力損失とダイ両端間の温度勾配があるため、 $T_J$ 出力電圧を測定しても、絶対最大接合部温度を超えないことが保証されるわけではない。

**Note 5:** 内部パワー・オン・リセット(POR)のラッチがセットされるのは、SHDN1/2ピンがそのしきい値を正の方向に遷移した場合、サーマル・シャットダウン時、または過電圧ロックアウト時である。ラッチの出力は各SSピンの電流源を作動するが、この電流源は標準で $450\mu\text{A}$ をシンクし、SSコンデンサを放電する。ラッチは両方のSSピンが駆動されてソフトスタートのPORしきい値より低い電圧になるか、SHDNピンがそのしきい値より低い電圧になるとリセットされる。

**Note 6:** しきい値は、チャネルの帰還リファレンス電圧のパーセント値として表される。

**Note 7:** ドロップアウト動作を改善するため、出力スイッチは、昇圧コンデンサ両端の電圧がデューティ・サイクル100%の最小昇圧電圧のしきい値より低くなったときにのみ、最小オフ時間の間オフになる。

**Note 8:** INDから $V_{OUT}$ への最大電流は、 $V_C$ ピンがその“H”クランプ電圧になっているときにスイッチのラッチをリセットする、INDピンから $V_{OUT}$ ピンへ流れる電流の値として定義される。

**Note 9:** これは、内部パワー・スイッチが完全に飽和するのを保証するために必要な昇圧コンデンサ両端の最小電圧である。

## 標準的性能特性

## 標準的性能特性

## 標準的性能特性

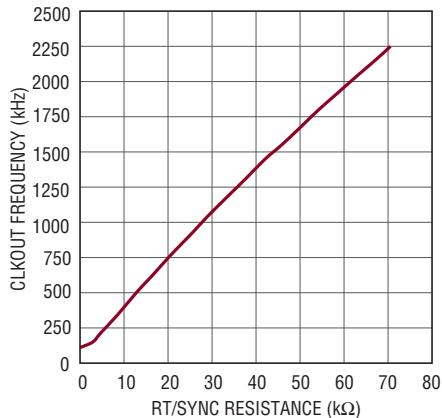

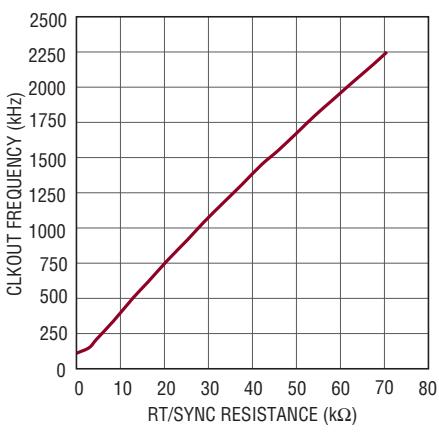

**CLKOUT 周波数と RT/SYNC 抵抗**

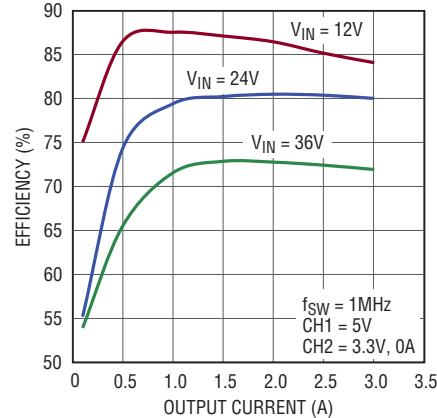

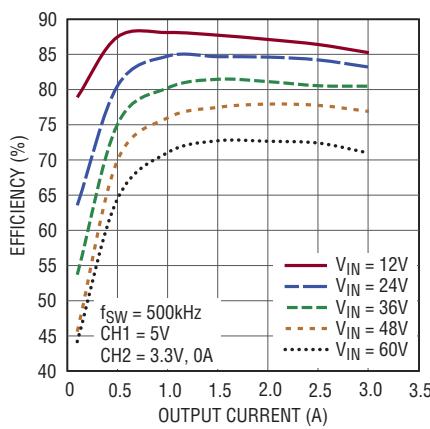

**5V 出力の効率**

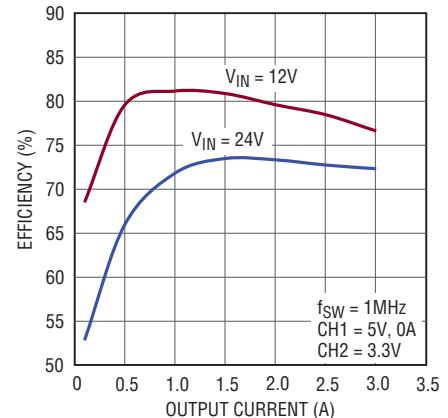

**3.3V 出力の効率**

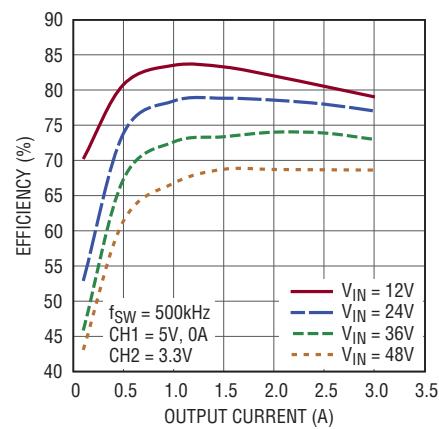

**5V 出力の効率**

**3.3V 出力の効率**

3992 G19

3992 G20

3992 G21

3992 G22

3992 G23

3992fa

## ピン機能

**BST1/2**: BSTピンは、スイッチの電圧降下を小さくするため、 $V_{IN}$ より高いベース駆動電圧をパワーNPNに供給します。BSTピンと $V_{IN}$ ピンの間の電圧が、パワーNPNを完全にオンするために必要な電圧より低い場合、パワー・スイッチはオフになります。BSTコンデンサは再充電されます。

**CMPI1/2**: CMPIピンは、しきい値が725mVでヒステリシスが80mVである、コンパレータへの入力です。CMPIピンをFBピンに接続した場合は、出力がその安定化した値の90%になるとパワーグッド信号が生成されます。

**CMPO1/2**: CMPOピンは、CMPIピンの電圧がそのしきい値より低くなると電流を吸い込むオープン・コレクタ出力です。2.9Vより高い標準的な入力電圧の場合、その出力状態はそのままですが、シャットダウン( $V_{IN1}$ 低電圧ロックアウトまたはサーマル・シャットダウン)時にはその電流シンク能力が低くなります。COMPOピンは開放状態のままにしておくことも、互いに接続して単一のパワーグッド信号を形成することもできます。

**DIV**: DIVピンの電圧は、RT/SYNCピンによって設定されるマスター・クロック周波数とチャネル1の周波数との比を決定します。DIVピンは標準値である12 $\mu$ Aの内部電流源によって駆動されるので、DIVピンとグランドとの間に接続した1つの抵抗でDIV電圧を設定可能であり、またそれによってチャネル1の分周器を設定できます。設定できる比は、1、2、4および8です。詳細については「アプリケーション情報」のセクションを参照してください。

**DNC**: 接続しないでください。

**GND**: 背面パッド・ピンはこのデバイスの唯一のグランド接続箇所です。背面パッドは、広い銅領域に半田付けして、熱抵抗を減らすようにしてください。GNDピンは両方のチャネルに共通であり、小信号グランドとしても機能します。理想的な動作を実現するため、すべての小信号グランド経路は1点でGNDピンに接続して、大電流のグランド帰路が形成されないようにしてください。

**FB1/2**: FBピンはエラーアンプの負入力です。出力は、このピンの電圧が背面のグランド・パッドを基準にして806mVに安定化されるように切り替わります。バイアス電流はFBピンから流れ出します。

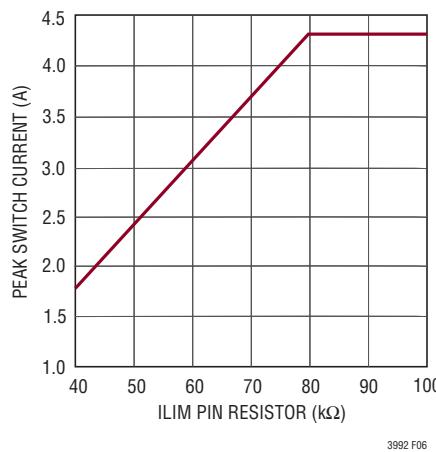

**ILIM1/2**: ILIMピンの電圧は、そのチャネルのピーク・インダクタ電流を決定します。ILIMピンは、標準値である12 $\mu$ Aの内部電流源によって駆動されます。ILIMピンとグランドの間に抵抗を接続すると、ILIM電圧が設定されます。この抵抗値は42.2k~120kにする必要があります。最大電流制限範囲は4.8A~1.8Aで、そのときのILIM電圧はそれぞれ1Vおよび0.5Vです。

**IND1/2**: INDピンは、インダクタへ流れ込む電流を測定する内部センス抵抗の入力です。抵抗に流れる電流が $V_C$ ピンによって規定された電流を超えると、SWラッチがリセット状態に保持され、出力スイッチがディスエーブルされます。バイアス電流はINDピンから流れ出します。

**RT/SYNC**: RT/SYNCピンの電圧は、固定スイッチング周波数を決定します。RT/SYNCピンは標準値である12 $\mu$ Aの内部電流源によって駆動されるので、RT/SYNCピンとグランドとの間に接続した1つの抵抗でRT/SYNC電圧を設定可能であり、またそれによってスイッチング周波数を設定できます。最小スイッチング周波数は $V_{RT/SYNC}$ が0Vのときで標準110kHzであり、最大スイッチング周波数は $V_{RT/SYNC}$ が950mVより高いときで標準2.5MHzです。

RT/SYNCピンを外部クロック信号で駆動すると、スイッチは与えられたクロック信号の周波数に同期します。同期が行われるのは、クロック信号の検出後、クロック信号の立ち上がりエッジです。クロックの各立ち上がりエッジでは、発振器のランプのリセットを開始します。利得制御ループが発振器の充電電流をサーボ制御することにより、発振器の振幅は一定に維持されます。したがって、スロープ補償とチャネル位相の関係は変わりません。クロック信号を取り除くと、発振器は同期検出回路のタイムアウト後に抵抗モードに戻ります。クロックの信号源インピーダンスは、抵抗モード時にRT/SYNCピンから流れ出る電流によって同期周波数とほぼ等しい周波数を生成するように設定してください。詳細については「アプリケーション情報」のセクションを参照してください。

## ピン機能

**SHDN1/2:**シャットダウン・ピンは、各チャネルの動作を制御するために使用します。SHDN1ピンは、チャネル1の制御の他に、両方のチャネルの制御回路も起動するので、チャネル2が動作するためにも必要です。SHDN1の電圧がそのしきい値より低くなると、静止電流は標準値の $6\mu\text{A}$ に減少します。単独チャネルのUVLOをプログラムするには、SHDNピンを入力電圧の分圧器に接続します。詳細については「アプリケーション情報」のセクションを参照してください。シャットダウン機能を使用しない場合は、SHDNピンをVINに接続してください。

**SS1/2:**SSピンから外付けのコンデンサに流れ込む電流は、出力電圧の立ち上がり時間を決定します。SSピンの電圧が $0.806\text{V}$ のリファレンスより低いと、帰還電圧はSSピンの電圧に安定化されます。SSピンがリファレンス電圧を超えると、出力はFBピンの電圧を $0.806\text{V}$ に安定化し、SSピンはそのクランプ電圧まで上昇し続けます。出力が過負荷状態のとき、VCピンはその電圧クランプが作動する最大スイッチ電流レベルを超えて駆動されます。VCクランプが作動すると、SSピンは、最大出力電流が維持できるレギュレーション・ポイントに出力が達するまで放電されます。過負荷状態が解消されると、出力はその電圧からソフトスタート動作を行います。SHDNピン電圧による制御が実行されるか、またはサーマル・シャットダウンが発生した場合は、パワー・オン・リセットのラッチにより、必ず両方のチャネルのコンデンサが完全に放電されてから、いずれか一方が解放されます。2つのSSピンを互いに接続すると、出力は同時にトラッキングするようになります。

**CLKOUT:**CLKOUTピンは、内部発振器に同期した $0\text{V} \sim 2.5\text{V}$ の方形波を生成します。スイッチング周波数を外付け抵抗で設定した場合、得られるクロックのデューティ・サイクルは50%になります。RT/SYNCピンを外部クロック信号源で駆動した場合、得られるCLKOUTデューティ・サイクルは外部信号源を反映した値になります。

**SW1/2:**SWピンは内部パワーNPNのエミッタです。スイッチがオフになると、インダクタはこのピンをグランドより低い電位に大きい $dV/dt$ で駆動します。各SWピンとそれぞれのVINデカップリング・コンデンサのグランドの近くで、外付けのショットキ・キャッチ・ダイオードをグランドに接続して、このピンが過大な負電圧にならないようにする必要があります。

**T<sub>J</sub>:**T<sub>J</sub>ピンは、接合部温度に比例した電圧を出力します。このピンの電圧は $25^\circ\text{C}$ のとき $250\text{mV}$ であり、その勾配は $10\text{mV}/^\circ\text{C}$ です。詳細については「アプリケーション情報」のセクションを参照してください。

**V<sub>C1/2</sub>:**V<sub>C</sub>ピンはエラーアンプの出力であり、ピーク・スイッチ電流コンパレータへの入力です。通常、このピンは周波数補償に使用されますが、電流クランプとして、または制御ループの無効化に使用することもできます。エラーアンプが最大スイッチ電流レベルを超えてV<sub>C</sub>を駆動すると、電圧クランプが作動します。これは、出力が過負荷状態となり、SSピンから電流が流れ出してレギュレーション・ポイントが低下していることを示しています。

**V<sub>IN1</sub>:**V<sub>IN1</sub>ピンは両方のチャネルの内部制御回路に電源を供給し、低電圧ロックアウト・コンパレータによって電圧がモニタされます。V<sub>IN1</sub>ピンは、チャネル1の内蔵パワーNPNスイッチのコレクタにも接続されています。V<sub>IN1</sub>ピンはそのエッジのdI/dtが大きいので、デバイスのピンの近くでグランドにデカップリングする必要があります。

**V<sub>IN2</sub>:**V<sub>IN2</sub>ピンはチャネル2の出力段に電源を供給し、低電圧ロックアウト・コンパレータによって電圧がモニタされます。V<sub>IN2</sub>が動作するためには、V<sub>IN1</sub>の電圧が標準で $2.9\text{V}$ より高くなければなりません。V<sub>IN2</sub>ピンは、チャネル2の内蔵パワーNPNスイッチのコレクタでもあります。V<sub>IN2</sub>ピンはそのエッジのdI/dtが大きいので、デバイスのピンの近くでグランドにデカップリングする必要があります。

**V<sub>OUT1/2</sub>:**V<sub>OUT</sub>ピンは、インダクタへ流れ込む電流を測定する内部センス抵抗の出力です。抵抗に流れる電流がV<sub>C</sub>ピンによって規定された電流を超えると、SWラッチがリセット状態に保持され、出力スイッチがディスエーブルされます。バイアス電流はV<sub>OUT</sub>ピンから流れ出します。

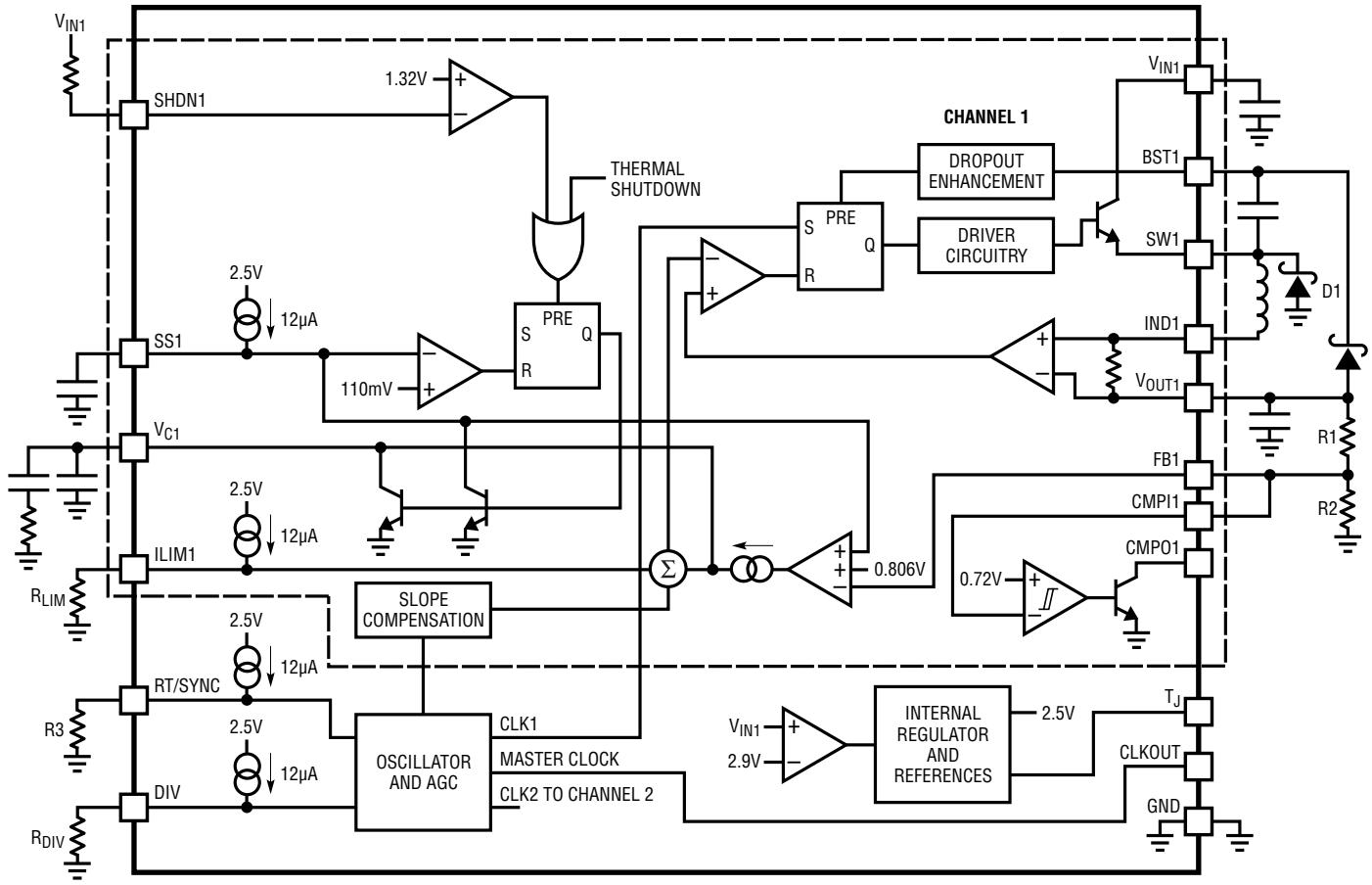

## ブロック図

図1. LT3992のブロック図

LT3992は、デュアル・チャネル、固定周波数、電流モードの降圧コンバータで、4.6Aのスイッチを内蔵しています。各チャネルは独立して制御できますが、共通の内部レギュレータ、発振器、および温度計回路に電源を供給するため、 $V_{IN1}$ は標準で2.9Vの低電圧ロックアウトのしきい値より高くする必要があります。

$SHDN1$ ピンの電圧がそのしきい値である1.32Vより低くなると、LT3992は低静止電流モードになります。このモードでは、LT3992に流れ込む電流は標準で $V_{IN1}$ からは $6\mu A$ 、 $V_{IN2}$ からは $1\mu A$ 未満です。 $SHDN$ ピンが1.32Vより高い電圧に駆動されると、内部のバイアス回路がオンになり、内部安定化電圧、0.806Vの $V_{FB}$ 、 $12\mu A$ のRT/SYNC、DIVおよびILIM電流リファレンス、およびソフトスタート・ラッチを設定するPOR信号が生成されます。

内部のリファレンスがそのレギュレーション・ポイントに達すると、内部発振器は、RT/SYNCピンの電圧によって決まる周波数で、2つのレギュレータのマスター・クロック信号を生成し始めます。

その後、チャネル1のクロックは、DIVピンの電圧に応じて1、2、4、または8分周されます。チャネル2のクロックはマスター・クロック周波数で動作しますが、その位相はチャネル1から $180^\circ$ シフトしています。

一方、同期信号がLT3992のRT/SYNCピンによって検出される場合、マスター・クロック信号は同期パルスの立ち上がりエッジでは入力周波数で生成され、チャネル1は同期信号と同位相になります。周波数分割および位相は、内部で生成したマスター・クロックと同じ状態が維持されます。

さらに、同期中に低調波発振が発生しないよう、内部スロープ補償が自動的に調整されます。いずれのモードの発振器動作でも、CLKOUTピンには、チャネル1に同期したマスター・クロック周波数の方形波が現れます。

2つのレギュレータは、固定周波数の電流モード降圧コンバータです。電流モード・レギュレータは、内部クロックと、パワー・

## ブロック図

スイッチのデューティ・サイクルを制御する2つの帰還ループによって制御されます。通常のエラーアンプの他に、スイッチ電流をサイクルごとにモニタする電流センス・アンプがあります。この技法は、エラーアンプが電圧ではなく、出力に供給される電流を制御することを意味しています。電圧帰還型システムでは、インダクタと出力コンデンサの共振周波数までは位相シフトが小さく、その後急峻に180°のシフトが発生します。電流帰還型システムでは、相當に低い周波数でも90°の位相シフトがありますが、LC共振周波数を大きく超えるまでは、さらに90°シフトすることはありません。これにより、帰還ループの周波数補償がはるかに容易になり、トランジエント応答も大幅に速くなります。

図1のブロック図には、その動作を以下に説明する、一方のスイッチング・レギュレータのみを示します。もう一方のレギュレータも同様に動作しますが、そのクロックは元のレギュレータとは180°位相がずれています。

電源投入時に内部POR信号によってソフトスタート・ラッチがセットされると、正常な起動が確実に行われるよう、両方のSSピンがグランド電位まで放電されます。SSピンの電圧が110mVより低くなると、VCピンは“L”に駆動され、スイッチングがディスエーブルされてソフトスタート・ラッチがリセットされます。ラッチがリセットされると、ソフトスタート・コンデンサは標準値の12µAで充電を開始します。

SSピンの電圧が110mVを超えると、VCピンはエラーアンプによって“H”に駆動されます。VCピンの電圧が1Vを超えると、クロック設定パルスによってドライバのフリップフロップがセットされ、その結果内部のパワーNPNスイッチがオンします。これにより、VINからNPNスイッチ、インダクタ、および内部センス抵抗を流れる電流が増加します。内部センス抵抗両端の電圧降下が、VCピンの電圧によってあらかじめ設定されたレベルを超えると、フリップフロップがリセットされ、内部NPNスイッチはオフします。スイッチがオフすると、外付けのショットキ・ダイオードが導通を開始するまで、インダクタはSWピンの電圧を“L”に駆動して、インダクタを流れる電流を減らします。このサイクルは、各クロック・サイクルが開始されるたびに繰り返されます。ただし、クロック・サイクルの開始時に、内部センス抵抗の電圧があらかじめ設定されていたレベルを超えると、フリップフロップはセットされなくなり、よってインダクタ電流はさらに減少する結果となります。出力電流はVC電圧によって制御されるので、出力のレギュレーションは、

エラーアンプがVCピンの電圧を継続的に調整することによって実現されます。

エラーアンプは、SSピンに現れる電圧または806mVの内部リファレンスのいずれか低い方の電圧とFBの電圧を比較するトランジコンダクタンス・アンプです。ループの補償は、VCピンとグランドとの間に、純然たるコンデンサ1つまたは直列の抵抗/コンデンサを接続することで、容易に実現されます。

レギュレータの出力電流が最大になるのは、エラーアンプによってVCピンがその最大クランプ値に駆動されたときです。最大スイッチ電流の標準値は、ILIMピンとグランドとの間に抵抗を接続することにより、4.6A～1.8Aの範囲で設定することができます。

SSピンは一定の電流源によって駆動されるので、SSピンにコンデンサを1個外付けすれば、出力電圧に制御された直線的なランプを生成することができます。

出力によって要求された電流が、VCピンのクランプによって規定される最大電流を超える場合は、SSピンが放電され、最大電流が出力電圧に対応できるようになるまでレギュレーション・ポイントが下がります。過負荷状態が解消されると、レギュレータは、過負荷時のレギュレーション・ポイントからソフトスタート動作を行います。

シャットダウン制御またはサーマル・シャットダウンではソフトスタート・ラッチがセットされるので、その結果完全なソフトスタート・シーケンスが実行されます。

スイッチ・ドライバはVINまたはBSTの電圧によって動作します。出力NPNを飽和させて高い効率を維持するため、外付けのダイオードおよびコンデンサを使用してVINより高い駆動電圧を生成させます。BSTコンデンサの電圧が十分である場合、スイッチは100%のデューティ・サイクルで動作することができます。昇圧コンデンサが放電して、出力NPNを駆動するには不十分なレベルに近づくと、BSTピンのコンパレータはサイクルのオフ時間を強制的に最小にして、昇圧コンデンサを再充電できるようにします。

エラー状態を検出するため、しきい値が720mVでヒステリシスが80mVであるコンパレータが用意されています。CMPO出力はオープン・コレクタのNPNで、CMPIピンの電圧がしきい値より高いときはこのNPNがオフになります。したがって、抵抗がCMPOピンの電圧を目的の電圧に引き上げることができるようになります。

T<sub>J</sub>ピンに現れる電圧は、LT3992の接合部温度に比例します。T<sub>J</sub>ピンは、ダイ温度が25°Cの場合は250mVであり、温度勾配は10mV/°Cです。

## アプリケーション情報

### 出力電圧の選択

出力電圧は、出力とFBピンの間に接続した抵抗分割器を使用して設定します。次式に従って1%精度の抵抗を選択します。

$$R1 = R2 \cdot \left( \frac{V_{OUT}}{0.806} - 1 \right)$$

バイアス電流による誤差が発生しないように、R2は $10\text{k}\Omega$ 以下にしてください。参照名については、図1のブロック図を参照してください。

### スイッチング周波数の選択

LT3992のスイッチング周波数は図1の抵抗R3によって設定されます。RT/SYNCピンは $12\mu\text{A}$ の電流源によって駆動されます。抵抗R3を設定すると、図2に示すように、マスター発振器の周波数を決定するRT/SYNCピンの電圧が設定されます。R3の抵抗値( $\text{k}\Omega$ )は、次式により、目的のスイッチング周波数(kHz)から計算できます。

$$R3 = 1.86E-6 \cdot f_{SW}^2 + 2.81E-2 \cdot f_{SW} - 1.76$$

(周波数が $150\text{kHz}$ ～ $2000\text{kHz}$ の場合)。マスター発振器と同じ周波数でチャネル1と同位相の $0\text{V}$ ～ $2.5\text{V}$ の方形波が、CLKOUTピンから出力されます。CLKOUT信号を使用すると、複数のスイッチング・レギュレータを同期させることができます。

図2. スイッチング周波数と RT/SYNC 抵抗

最小スイッチオン時間によるデューティ・サイクルの制限を緩和するため、チャネル1のスイッチング周波数はマスター・クロックから1、2、4または8で分周できます。この値は図1の抵抗 $R_{DIV}$ によって決まります。チャネル2のスイッチング周波数はDIVピンの電圧には影響されません。DIVピンは $12\mu\text{A}$ の電流源によって駆動されます。抵抗 $R_{DIV}$ を設定すると、表1に示すように分周比の値を決定するDIVピンの電圧が設定されます。DIVピンの電圧には分周比のしきい値付近の入力ヒステリシスはありません。

表1. チャネル1の分周比と $V_{DIV}$

| DIVの電圧の標準値                            | 分周比 | $R_{DIV}$ ( $\Omega$ ) |

|---------------------------------------|-----|------------------------|

| $V_{DIV} < 0.5\text{V}$               | 1   | 0                      |

| $0.5\text{V} < V_{DIV} < 1.0\text{V}$ | 2   | $61.9\text{k}$         |

| $1.0\text{V} < V_{DIV} < 1.5\text{V}$ | 4   | $102\text{k}$          |

| $1.5\text{V} < V_{DIV}$               | 8   | $150\text{k}$          |

スイッチング周波数は、ソリューション全体のサイズを小さくするために、通常はできるだけ高い値に設定されます。LT3992は高周波領域での損失を改善する手法を採用していますが、スイッチング損失と最小のスイッチオン時間によって効率と最大入力電圧が低下します。

推奨される最大周波数は、次式によって概算できます。

$$\text{Frequency (Hz)} = \frac{V_{OUT} + V_D}{V_{IN} - V_{SW} + V_D} \cdot \frac{1}{t_{ON(MIN)}}$$

ここで、 $V_D$ はキャッチ・ダイオード(図1のD1)の順方向電圧降下、 $V_{SW}$ は内部スイッチの電圧降下、 $t_{ON(MIN)}$ はスイッチの最小オン時間です。

## アプリケーション情報

表2. さまざまな  $R_{RT/SYNC}$  値における3.3V出力時の効率およびサイズの比較

| 周波数(kHz) | $R_{RT/SYNC}$ (kΩ) | 効率<br>$V_{VIN1/2} = 12V(\%)$ | $V_{IN(MAX)}(V)^{\dagger}$ | $L(\mu H)^*$ | $C(\mu F)^*$ | $C+L(面積, mm^2)$ |

|----------|--------------------|------------------------------|----------------------------|--------------|--------------|-----------------|

| 250      | 5.90               | 88                           | 60                         | 15           | 120          | 59.8            |

| 500      | 13.0               | 87                           | 43                         | 8.2          | 60           | 54.6            |

| 1000     | 28.0               | 84                           | 21                         | 3.3          | 30           | 51.9            |

| 1500     | 44.2               | 82                           | 14                         | 2.2          | 22           | 46.9            |

| 2250     | 69.8               | 78                           | 9                          | 1            | 15           | 19.1            |

<sup>†</sup>  $V_{IN(MAX)}$ は、一定の出力電圧リップルを維持する最大入力電圧の標準値として定義される。

\* インダクタとコンデンサの値は安定性と一定のリップル電流を目指して選択された。

以下の例は、表2のデータとともに、单一入力電圧システムでのスイッチ周波数選択の兼ね合いを示しています。

例：

$V_{IN} = 25V$ 、 $V_{OUT} = 3.3V$ 、 $I_{OUT} = 2A$ 、 $t_{ON(MIN)} = 180ns$ 、 $V_D = 0.6V$ 、 $V_{SW} = 0.4V$ 。

$$\text{Max Frequency} = \frac{3.3 + 0.6}{25 - 0.4 + 0.6} \cdot \frac{1}{180\text{ns}} \sim 850\text{kHz}$$

$R_{RT/SYNC}$ : 約 23.2kΩ(図2)

## 入力電圧範囲

スイッチング周波数が決まると、レギュレータの入力電圧範囲を決めることができます。最小入力電圧は、LT3992の最小動作電圧(約2.9V)またはその最大デューティ・サイクルのどちらかによって決まります。デューティ・サイクルとは、クロック・サイクル中に内部スイッチがオンしている時間の割合です。大半の固定周波数レギュレータとは異なり、LT3992は、出力スイッチを完全に飽和させるのに十分な電圧が昇圧コンデンサ(図1のC3)の両端にかかる場合には、各クロック・サイクルの終わりにスイッチをオフすることはありません。スイッチを最

小時間だけ強制的にオフにすることが行われるのは、昇圧コンデンサを再充電する必要がある場合のクロック・サイクルの終わりのみです。この動作には、一定のオフ時間だけクロック周波数を下げるのと同じ効果があり、結果としてデューティ・サイクルが高くなり、最小入力電圧が低下します。得られるデューティ・サイクルは昇圧コンデンサの充電時間に依存し、次式によって概算できます。

$$DC_{MAX} = \frac{1}{1 + \frac{1}{B}}$$

ここで、Bは「電気的特性」の表に示す標準の昇圧電流で3Aを割った値です。

これにより、最小入力電圧は次のようにになります。

$$V_{IN(MIN)} = \frac{V_{OUT} + V_D}{DC_{MAX}} - V_D + V_{SW}$$

ここで、 $V_{SW}$ は内部スイッチの電圧降下です。

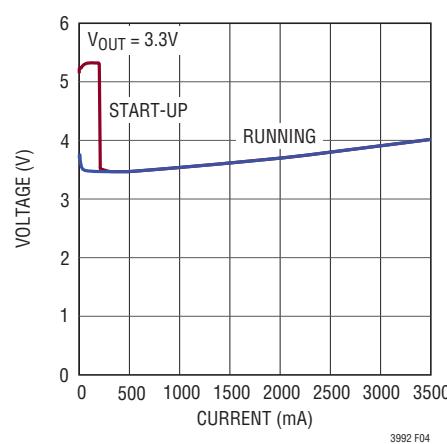

図4には、図15に示す3.3V出力での最小入力電圧と負荷電流の標準的なグラフを示します。

図3. タイミング図( $R_{RT/SYNC} = 28.0\text{k}\Omega$ 、 $t_p = 1\mu\text{s}$ 、 $V_{DIV} = 0V$ )

図4. 最小入力電圧と負荷電流

## アプリケーション情報

最大入力電圧は、VINピンとBSTピンの絶対最大定格、周波数、および最小デューティ・サイクルによって決まります。最小デューティ・サイクルは次式で定義されます。

$$DC_{MIN} = t_{ON(MIN)} \cdot \text{周波数}$$

最大入力電圧は次式で定義されます。

$$V_{IN(MAX)} = \frac{V_{OUT} + V_D}{DC_{MIN}} - V_D + V_{SW}$$

算出された最大電圧よりも入力電圧を高くした場合でも、それがVINピンとBSTピンの最大定格に違反していない限り、LT3992は安定化することに注意してください。ただし、この領域の入力電圧での動作では、パルス・スキップ動作を示します。

例：

$V_{OUT} = 3.3V$ 、 $I_{OUT} = 1A$ 、周波数 = 1MHz、温度 = 25°C、 $V_{SW} = 0.1V$ 、 $B = 50$ (昇圧特性の仕様が基準)、 $V_D = 0.4V$ 、 $t_{ON(MIN)} = 180ns$

$$DC_{MAX} = \frac{1}{1 + \frac{1}{50}} = 98\%$$

$$V_{IN(MIN)} = \frac{3.3 + 0.4}{0.98} - 0.4 + 0.1 = 3.48V$$

$$DC_{MIN} = t_{ON(MIN)} \cdot \text{Frequency} = 0.18$$

$$V_{IN(MAX)} = \frac{3.3 + 0.4}{0.18} - 0.4 + 0.1 = 20.2V$$

図5. タイミング図( $RT/SYNC = 28.0k\Omega$ 、 $tp = 1\mu s$ 、 $V_{DIV} = 0.75V$ )

複数の入力電圧が存在する場合や、チャネル1のVIN/VOUT比がチャネル2と大幅に異なる場合は、DIVピンの抵抗を適切な値に設定することによって、チャネル1の周波数を設定値から2分周、4分周、または8分周することができます。チャネル1の周波数を分周すると、最大入力電圧も同じ割合で増大します。チャネル1の外付け部品は、得られた周波数に従って選択する必要があります。

例：

$V_{OUT} = 3.3V$ 、 $I_{OUT} = 1A$ 、周波数 = 1MHz、温度 = 25°C、 $V_{SW} = 0.1V$ 、 $B = 50$ (昇圧特性の仕様が基準)、 $V_D = 0.4V$ 、 $t_{ON(MIN)} = 180ns$ 、 $R_{DIV} = 102k\Omega$ 。

$$DC_{MIN1} = t_{ON(MIN1)} \cdot \text{Frequency}/4 = 0.045$$

$$V_{IN1(MAX)} = \frac{3.3 + 0.4}{0.045} - 0.4 + 0.1 = 60V$$

## インダクタの選択と最大出力電流

最初に選択するLT3992のインダクタの値としては、次の値が適切です。

$$L = \frac{V_{OUT}}{f}$$

ここで、fは周波数で単位はMHz、Lの単位はμHです。

この値により、全入力電圧範囲にわたって3Aの負荷電流を流すことができます。インダクタのRMS電流定格は使用回路の最大負荷電流より大きい値である必要があります。また、その飽和電流は最大ピーク・スイッチ電流より大きくしてください。これにより、出力電圧リップルが減少します。

1つのチャネルの最大負荷が2.5Aより小さい場合は、インダクタの値を小さくして、より高いリップル電流で動作させることができます。あるいは、ILIMピンによってそのチャネルの最大スイッチ電流を調整することもできます。これにより、物理的に小さなインダクタ、またはDCRが小さいインダクタを使って効率を上げることができます。

インダクタとスイッチのピーク電流は次のとおりです。

$$I_{SW(PK)} = I_{L(PK)} = I_{OUT} + \frac{\Delta I_L}{2}$$

## アプリケーション情報

出力の安定化状態を維持するには、このピーク電流をLT3992のスイッチ電流制限値ILIMより小さくしなければなりません。ILIMは、ILIMピンとグランドとの間に抵抗を接続することにより、チャネルごとに1.8A～4.6Aの範囲内に設定することができます。ILIMピンは12μAの電流源によって駆動されます。抵抗RLIMを設定すると、図6に示すように最大スイッチ電流を決定するILIMピンの電圧が設定されます。RLIMの値は42.2kよりも大きくする必要があります。ILIMピンとグランドとの間にコンデンサを接続するか、出力から抵抗分割器を接続することにより、起動時のピーク電流を制限することができます。コンデンサを使用する場合は、正常動作を確保するため、電源投入前に放電しておく必要があります。

図6を参照すると、ピーク電流制限値が減少するにつれ、スロープ補償によってピーク電流がさらに減少し、デューティサイクルが増加します。

ILIMピンを使用してピーク・スイッチ電流を減らす場合、インダクタ選択の式は次のようにになります。

$$L = \frac{50 \cdot V_{OUT}}{f \cdot R_{ILIM}}$$

ここで、fは周波数で単位はMHz、Lの単位はμH、Rの単位はkΩです。

図6. ピーク・スイッチ電流とILIM抵抗

## 入力コンデンサの選択

LT3992回路の入力は、X7RまたはX5Rタイプで4.7μF以上のセラミック・コンデンサを使用してバイパスしてください。大容量の電解コンデンサまたはタンタル・コンデンサによる補助のバイパスを行う場合には、容量の小さいものや安価なY5Vタイプのものが使用できます。

LT3992の複数の入力電源が、それぞれ異なる入力電圧で動作する場合は、そのチャネルに適したサイズの入力コンデンサを、各チャネルのVINピンのできるだけ近くに配置してください。

入力にセラミック・コンデンサを使用する場合の注意を以下に示します。入力のセラミック・コンデンサは、浮遊インダクタンスと結合して共振タンク回路を形成することがあります。電源を瞬時に投入する(たとえば通電状態の電源に回路を差し込む)と、このタンク回路にリギングが発生して入力電圧が倍になり、LT3992を損傷する可能性があります。解決策としては、入力電圧をクランプするか、損失の大きいコンデンサをセラミック・コンデンサと並列に接続してタンク回路を減衰させます。詳細については、「アプリケーションノート88」を参照してください。

## 出力コンデンサの選択

通常、降圧レギュレータは、スイッチング周波数の1/10である出力クロスオーバー周波数で容易に補償されます。これは、過渡ステップ時に出力コンデンサが出力負荷を供給しなければならない時間がスイッチング周期のおよそ2～3倍であることを意味します。このステップで許容できる出力電圧降下が1%であるとすると、出力コンデンサの初期値として妥当な値は次式で表すことができます。

$$C_{VOUT} = \frac{\text{Max Load Step}}{\text{Frequency} \cdot 0.01 \cdot V_{OUT}}$$

例:

V<sub>OUT</sub> = 3.3V、周波数 = 1MHz、最大負荷ステップ = 2A

$$C_{VOUT} = \frac{2}{1E6 \cdot 0.01 \cdot 3.3V} = 60\mu F$$

計算値は、推奨される初期値に過ぎません。トランジエント応答を改善する必要がある場合は値を大きくし、サイズを優先する場合は容量を減らしてください。出力コンデンサはインダクタ電流をフィルタにかけ、電圧リップルの小さい出力を生成します。また、過渡負荷を満足させてLT3992の制御ループを安定化するために、エネルギーを蓄えます。必要な出力容量の値は、LT3992のスイッチング周波数によって決まります。また、電流モード制御ループは、出力コンデンサの直列抵抗(ESR)を必要としません。こうした理由により、セラミック・コンデンサを自由に使用することで、きわめて小さい出力リップルと小さい回路サイズを実現できます。

## アプリケーション情報

電解コンデンサを使用することもできます。大半のアルミ電解コンデンサはESRが大き過ぎるため、出力リップルを低く抑えることができません。タンタル・コンデンサや、電源での使用を目的とした新しい低ESRの有機電解コンデンサが適しており、メーカーはESRを指定することになります。コンデンサの値は、低リップルの実現に必要なESRに基づいて選択します。コンデンサのESRはコンデンサの体積によって決まるので、同様なリップル性能を示すセラミック・コンデンサよりも、サイズと値の両方が大きくなります。利点の1つは、容量が大きいと、負荷電流が大きく変化した場合に、より良好なトランジエント応答を示す場合があることです。いくつかのコンデンサ・メーカーを表3に示します。

表3

| メーカー   | タイプ                     | シリーズ                           |

|--------|-------------------------|--------------------------------|

| 太陽誘電   | セラミックX5R、X7R            |                                |

| AVX    | セラミックX5R、X7R<br>タンタル    |                                |

| Kemet  | タンタル<br>タンタル有機<br>アルミ有機 | T491、T494、T495<br>T520<br>A700 |

| 三洋     | タンタル/アルミ有機              | POSCAP                         |

| パナソニック | アルミ有機                   | SP CAP                         |

| TDK    | セラミックX5R、X7R            |                                |

### キャッチ・ダイオード

ダイオードD1(図1)は、スイッチがオフの時間だけ電流を流します。順方向電圧降下を制限して効率を向上させるには、ショットキ・ダイオードを使用します。ショットキ・ダイオードは、そのピーク逆電圧がレギュレータの入力電圧と等しくなければならず、通常動作時の平均順方向電流に合わせてサイズを決める必要があります。平均順方向電流は次式で計算できます。

$$I_{D(AVG)} = \frac{I_{OUT}}{V_{IN}} \cdot (V_{IN} - V_{OUT})$$

短絡状態では、ダイオード電流は、ILIMピンによって設定されたLT3992のピーク・スイッチ電流制限によって決まる標準値まで増加します。これは短時間であれば差し支えないのでですが、こうした条件下での連続動作が許容できるかどうかについては、ダイオードのメーカーに問い合わせることをお勧めします。

### BSTピンに関する考察

BSTピンに接続したコンデンサとダイオードは、入力電圧より高い電圧を生成します。ほとんどの場合は、0.47μFのコンデンサと小さいショットキ・ダイオード(BAT41など)で問題なく動作します。80%より高いデューティ・サイクルで最適な性能を確保するには、0.5Aのショットキ・ダイオード(MBR0560など)を使用します。ほとんどあらゆるタイプのフィルム・コンデンサやセラミック・コンデンサが適していますが、スイッチのオフ時間中に完全に再充電できるよう、ESRは1Ω未満としてください。コンデンサの値は、次式によって概算できます。

$$C_{BST} = \frac{I_{OUT(MAX)} \cdot V_{OUT}}{5 \cdot V_{IN} (V_{OUT} - 2) \cdot f}$$

ここで、 $I_{OUT(MAX)}$ は最大負荷電流です。

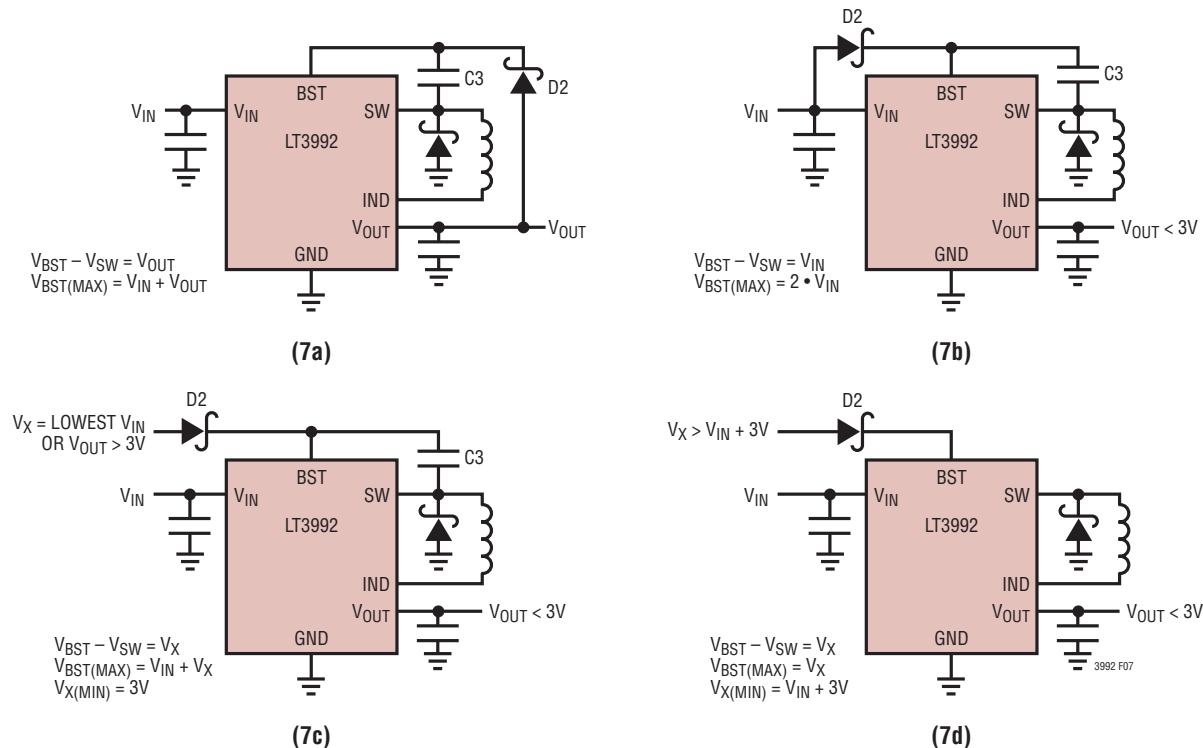

図7に昇圧回路の構成方法を4通り示します。最高の効率を得るには、BSTピンの電圧をSWピンより3V以上高くする必要があります。一般に、3.3V以上の出力を得るには、標準回路(図7a)が最適です。これより低い出力電圧の場合は、昇圧ダイオードを入力に接続することができます(図7b)。電圧の低い方の電圧源からBSTピンの電流が供給されるので、図7aの回路の方が効率が高くなります。3Vより高い利用可能なDC電圧源を供給源とする昇圧電圧源を図7cに示します。最高の効率を実現するには、3Vより高い電圧のうち、最も低い昇圧電圧を選択します。たとえば、3.3Vと1.8Vを発生させる場合で、1.8Vがオンのときは必ず3.3Vもオンになる場合は、1.8Vの昇圧ダイオードを3.3V出力に接続することができます。いずれの場合も、BSTピンでの最大電圧は「絶対最大定格」のセクションで規定されている最大値よりも小さい値にする必要があります。

昇圧回路は、図7dに示すように、入力電圧より3V以上高いDC電圧で直接動作させることもできます。このダイオードは、 $V_{IN}$ が存在する間 $V_X$ が“L”に保持されている場合にLT3992が損傷しないようにする目的で使用されます。この回路では、いくつかの部品を節約できます(両方のBSTピンをD2に接続できます)。ただし、効率が低下する可能性があり、LT3992での電力損失も大きくなる場合があります。また、 $V_X$ が存在しない場合にLT3992は引き続き出力を安定化しようとしていますが、そうすることで効率は非常に低くなり、電力損失も大きくなります。これは、スイッチを飽和させることができず、導通時に電圧が1.5V～2V降下するからです。

## アプリケーション情報

図7. BSTピンに関する考察

先に説明したとおり、LT3992のアプリケーションの最小入力電圧は、最小動作電圧(標準2.9V)および最大デューティ・サイクルによって制限されます。正しく起動するために、最小入力電圧は昇圧回路によっても制限されます。入力電圧が緩やかに上昇するか、出力が既に安定化している状態でSSピンを使用してLT3992をオンする場合は、昇圧コンデンサが満充電されないことがあります。昇圧コンデンサはインダクタに蓄えられたエネルギーによって充電されるので、昇圧回路を適切に動作させるには、回路は一定の最小負荷電流を必要とします。この最小負荷は、入力電圧、出力電圧および昇圧回路の構成に依存します。起動および動作に必要な最小負荷電流を3.3V出力での入力電圧の関数としてプロットしたものを「標準的性能特性」のセクションに示します。多くの場合、放電した出力コンデンサがスイッチャの負荷となるので、スイッチャはこれによって起動できます。プロットは、 $V_{IN}$ が非常に緩やかに上昇するワーストケースの状態を示しています。最低の起動電圧の場合は、ショットキ・ダイオードを使用してください。

## 6Vを超える出力

6Vを超える出力を得るには、インダクタと並列に $1k\Omega$ ～ $2.5k\Omega$ の抵抗を追加してSWノードの不連続リンクを減衰させ、意図しないSW電流が発生しないようにします。「標準的応用例」のセクションの24V出力の回路に、この抵抗の位置を示します。

## 周波数補償

LT3992は電流モード制御を使用して出力を安定化します。これにより、ループ補償が簡素化されます。特に、LT3992は安定性確保のために出力コンデンサのESRを必要とはしていないため、セラミック・コンデンサを自由に使用して出力リップルを下げ、回路サイズを小さくすることができます。周波数補償は、 $V_C$ ピンに接続した部品によって行われます。一般に、グランドへ直列に接続したコンデンサと抵抗によってループ利得が決まります。さらに、小さい値のコンデンサを並列に接続します。このコンデンサはループ補償回路の一部にはなっていませんが、スイッチング周波数でのノイズを除去するために使用します。

## アプリケーション情報

ループ補償は安定性と過渡性能を決定します。補償回路網の設計は少々複雑で、最適値はアプリケーションにより異なり、特に出力コンデンサのタイプに依存します。実用的な手法としては、このデータシートの回路のうち、目的のアプリケーションに似た回路から出発し、補償回路網を調整して性能を最適化します。次に、負荷電流、入力電圧、温度などすべての動作条件にわたって安定性をチェックします。

LT1375のデータシートには、ループ補償のさらに詳細な説明が記載されており、過渡負荷を使用した安定性のテスト方法が説明されています。

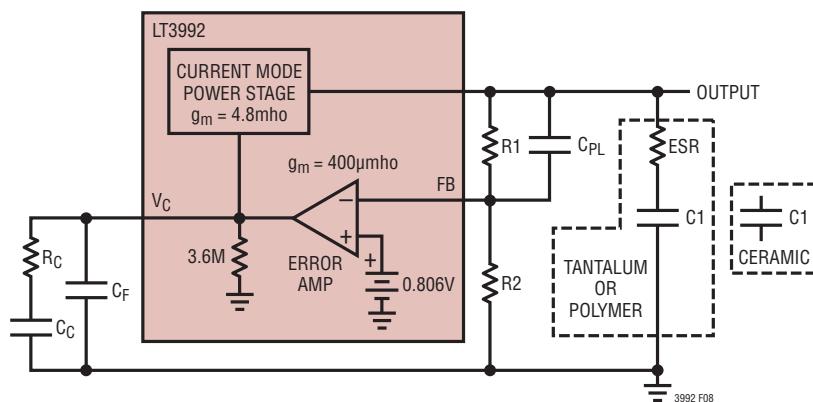

LT3992の制御ループの等価回路を図8に示します。エラーアンプは出力インピーダンスが有限のトランスクンダクタンス・アンプです。変調器、パワー・スイッチおよびインダクタで構成される電源部分は、 $V_C$ ピンの電圧に比例した出力電流を発生するトランスクンダクタンス・アンプとしてモデル化されます。出力コンデンサはこの電流を積分し、 $V_C$ ピンのコンデンサ( $C_C$ )はエラーアンプの出力電流を積分するので、ループに2つのポールが生じることに注意してください。ほとんどの場合ゼロが1つ必要で、これは出力コンデンサのESRか、 $C_C$ に直列な抵抗によって生じます。

この簡単なモデルは、インダクタの値が大き過ぎず、ループのクロスオーバー周波数がスイッチング周波数よりはるかに低い限り正しく機能します。位相リード・コンデンサ(CPL)を帰還分割器と並列に接続すると、トランジメント応答が改善されることがあります。

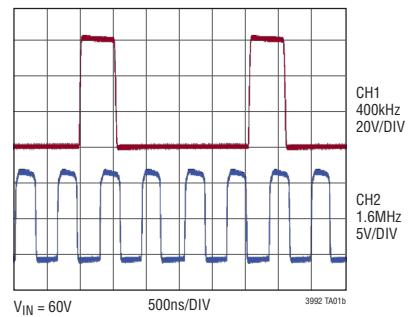

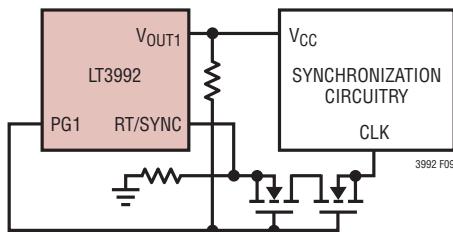

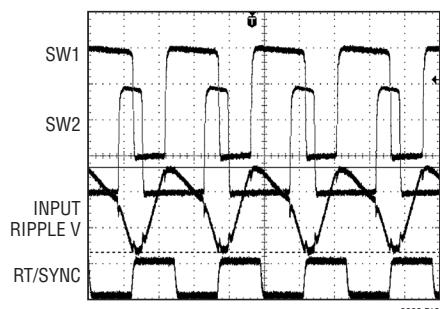

## 同期

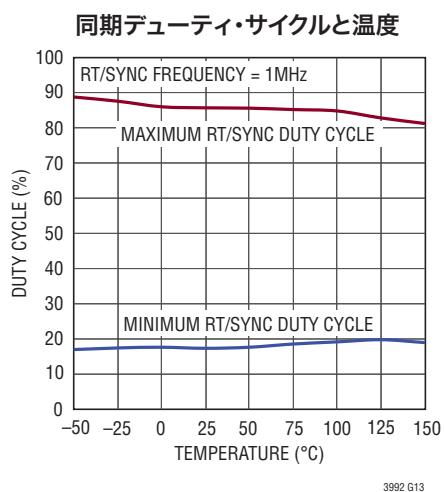

RT/SYNCピンは、レギュレータを外部クロック信号源に同期する目的にも使用できます。RT/SYNC抵抗をクロック信号源で駆動すると、同期検出回路が作動します。同期が検出されると、SW1の立ち上がりエッジはRT/SYNC信号の立ち上がりエッジに同期し、SW2の立ち上がりエッジはRT/SYNC信号の立ち下がりエッジに同期します(図10および11参照)。同期中は、周波数とデューティ・サイクルが同期信号と同じ0V～2.4Vの方形波が、標準で250nsの伝播遅延を伴ってCLKOUTピンを介して出力されます。さらに、内部のAGCループがスロープ補償を調整して低調波発振を防止します。同期信号が停止すると同期検出回路は標準10μsでタイムアウトし、LT3992はその時点でRT/SYNCピンの電圧に基づいて自走周波数に戻ります。

LT3992に入力する同期クロック信号は、200kHz～2MHzの周波数、20%～80%のデューティ・サイクル、0.5Vより低い“L”状態および1.6Vより高い“H”状態が必要です。これらのパラメータから外れた同期信号では、スイッチング動作が不安定になります。RT/SYNCピンが1.6Vより高い電圧に保持されると、スイッチングは必ずディスエーブルされます。

レギュレータの起動時に同期信号が存在しない場合(たとえば、同期回路の電源がレギュレータ出力から供給される場合)は、正常な起動動作になるよう同期回路が動作状態になるまで、RT/SYNCピンを1Vより低い電圧に保つ必要があります。

図8. ループ応答モデル

## アプリケーション情報

同期信号が不定状態( $V_{OL}$ 、 $V_{OH}$ 、高インピーダンス(Hi-Z))で立ち上がる場合は、図9に示すように同期クロックをLT3992に接続します。図に示す回路では、出力電圧が安定化出力の90%より低いと同期信号が分離されます。LT3992は、RT/SYNCピンとグランドとの間に接続されている抵抗によって決まるスイッチング周波数で起動します。

同期信号が低インピーダンス状態( $V_{OL}$ )で立ち上がる場合は、RT/SYNCピンと同期クロックとの間に抵抗を接続します。起動周波数は、RT/SYNCピンから見たグランドへの等価抵抗によって設定されます。

同期信号が高インピーダンス状態(Hi-Z)で立ち上がる場合は、RT/SYNCピンとグランドとの間に抵抗を接続します。起動周波数は、RT/SYNCピンから見たグランドへの等価抵抗によって設定されます。

図9. レギュレータの出力から電力を供給される同期信号

図10. タイミング図

(RT/SYNC = 1MHz、デューティ・サイクル = 50%)

図11. タイミング図

(RT/SYNC = 1MHz、デューティ・サイクル > 50%)

## アプリケーション情報

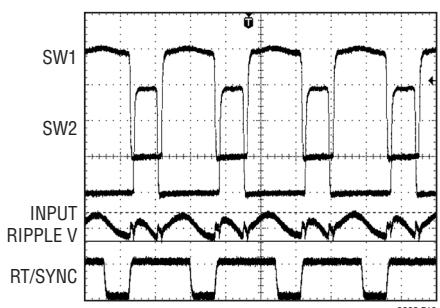

### 入力リップル電圧の低減

同期信号の立ち上がりエッジと立ち下がりエッジにスイッチを同期させると、VIN1とVIN2を同じ電源に接続しているシステムでは、入力リップル電流を低減できる独自の機能が得られます。入力電流リップルが減少すると、必要な入力容量は小さくなります。たとえば、標準的な逆位相のデュアル(14.4V/8.5Vおよび14.4V/3.3V)レギュレータの場合、図12に示す入力リップル電圧は、デューティ・サイクルが71%の同期信号でLT3992を駆動することにより、図13に示すようにピーク値が472mVから160mVに減少します。

図12. 位相180°のデュアル14.4V/8.5V、14.4V/3.3V

図13. 位相256°のデュアル14.4V/8.5V、14.4V/3.3V

### シャットダウンと低電圧/過電圧ロックアウト

通常、低電圧ロックアウト(UVLO)は、入力電源が電流制限されているか、または入力電源の電源抵抗が比較的大きい状況で使用されます。スイッチング・レギュレータは電源から一定の電力を引き出すため、電源電圧が低下するにつれて電源電流が増加します。この現象は電源からは負の抵抗負荷のように見えるため、電源電圧が低い状態では、電源が電流を制限するか、または低電圧にラッチする原因になります。UVLOは、これらの問題が発生する可能性がある電源電圧でレギュレータが動作しないようにします。

内部のコンパレータは、VIN1がその最小値である2.9Vより低くなると、2つのチャネルを強制的にシャットダウンします。この機能を使用すると、バッテリ駆動システムの過剰な放電を防止できます。VIN1の低電圧ロックアウトの他に、SHDN1が1.32Vより低くなると、両方のチャネルがディスエーブルされます。

プログラム可能なUVLOは、入力電圧分圧器といずれかの内部コンパレータを使用することによって実装できます(「標準的応用例」のセクションを参照)。

SHDNピンの電圧を1.32Vより高くすると、その対応するチャネルを動作させることができます。SHDNピンを1.32Vより低い電圧に駆動すると、そのチャネルは低消費電流状態になります。SHDNピンにヒステリシスはありません。

直列抵抗からSHDNピンへの接続を短くし、スイッチング・ノードに対するプレーン間容量や表面容量を最小限に抑えるようにします。

### ソフトスタート

LT3992の出力は、SSピンと内部0.806Vリファレンスのいずれか低い方の電圧に安定化されます。SSピンとグランドとの間に接続されているコンデンサは、内部の12μA電流源によって充電されるので、0Vから安定化出力電圧までの直線的な出力ランプが得られ、その時間は次式で与えられます。

$$t_{RAMP} = \frac{C_{SS} \cdot 0.806V}{12\mu A}$$

電源投入時は、リセット信号によってソフトスタート・ラッチがセットされ、正常な起動が確実に行われるよう両方のSSピンがほぼ0Vまで放電されます。両方のSSピンが完全に放電されるとラッチがリセットされ、内部の12μA電流源がSSピンの充電を開始します。

## アプリケーション情報

SSピンの電圧が110mVより低いと、VCピンは“L”になり、スイッチングはディスエーブルされます。このことから、SSピンをチャネルごとの個別シャットダウンとして使用することができます。

SSピンの電圧が110mVより高くなると、VCピンが解放され、出力はSSピンの電圧に安定化されます。SSピンの電圧が内部の0.806Vリファレンスを超えると、出力はリファレンス電圧に安定化されます。SSピンの電圧は、標準の2.15Vでクランプされるまで上昇し続けます。

VIN1の低電圧ロックアウトが発生した場合には、両方のチャネルにソフトスタート・ラッチがセットされ、完全な起動シーケンスが作動します。一方のチャネルのSHDNピンが1.32Vより低い電圧に駆動された場合、そのチャネルの過電圧ロックアウトがイネーブルされた場合、またはそのチャネルのパワー・スイッチに対応する内部ダイ温度が通常動作時に最大定格を超えた場合は、そのチャネルにソフトスタート・ラッチがセットされます。

さらに、負荷が最大出力スイッチ電流を超えると、出力電圧が低下し始め、それによってVCピンのクランプが作動します。VCピンがクランプされている限りにおいて、SSピンは放電されます。その結果、出力は最大出力電流が対応できる最高の電圧に安定化されます。たとえば、6V出力に1Ωの負荷があると、SSピンは0.46Vに低下し、出力は4.6V(4.6A・1Ω)に安定化されます。過負荷状態が解消されると、出力は、一時電圧レベルから通常のレギュレーション・ポイントまでのソフトスタート動作を行います。

SSピンは標準2.15Vでクランプされ、0.806Vまで放電してからレギュレーションの制御に入る必要があるため、瞬時の過負荷状態は許容され、ソフトスタートによる回復動作は行われません。SSピンが制御を開始するまでの標準時間は次式で求められます。

$$t_{SS(CONTROL)} = \frac{C_{SS} \cdot 1.2V}{0.9mA}$$

### オープン・コレクタのコンパレータ

CMPOピンは内部コンパレータのオープン・コレクタ出力です。このコンパレータは、80mVのヒステリシスでCMPIピンの電圧をリファレンス電圧の90%(0.72V)と比較します。

CMPOピンは、CMPIピンの電圧がしきい値より低いときは標準250µAのシンク能力があり、しきい値を超えると60Vに耐え

ることができます。CMPOピンは、VIN1ピンの電圧が標準で2.9Vを超えている限り作動状態です(シャットダウン時および低電圧ロックアウト・モードではシンク能力が低下します)。

コンパレータを使用して、入力電圧と出力電圧、さらにダイ温度をモニタすることができます。例については、「標準的応用例」の回路集を参照してください。

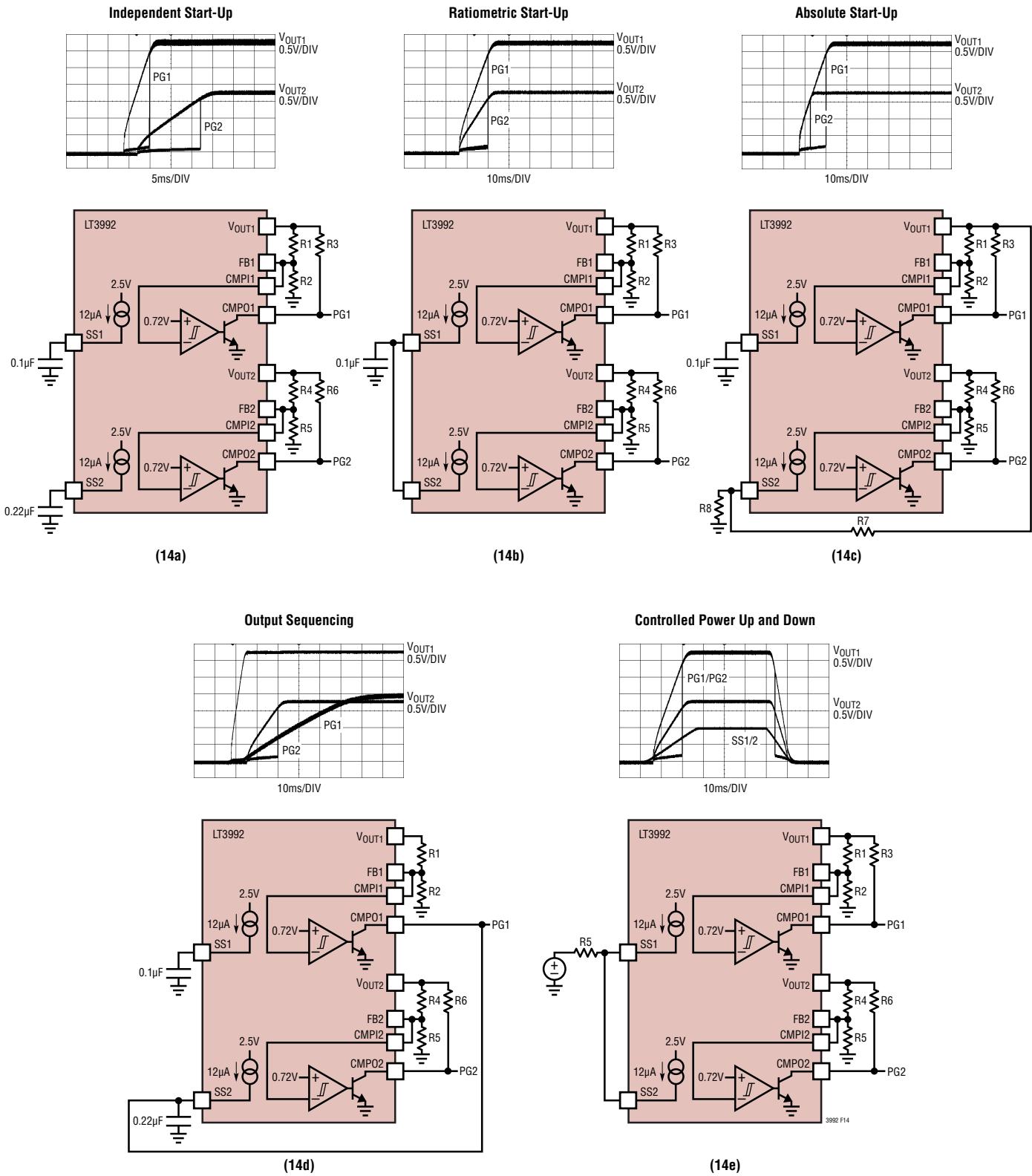

### 出力トラッキング/シーケンス制御

LT3992のSSピンおよびCMPOピンを使用して、チャネル間の複雑な出力トラッキングおよびシーケンス制御を実現できます。3.3Vと1.8Vのアプリケーションでの出力トラッキング/シーケンス制御の構成について、数例を図14に示します。

チャネルごとに独立したソフトスタートを図14aに示します。チャネルごとの出力ランプ時間は、「ソフトスタート」のセクションで説明したように、ソフトスタート・コンデンサによって設定されます。

図14bでは、両方のSSピンを互いに接続することによって比例トラッキングを実現しています。この構成では、SSピンのソース電流が倍(24µA)になるので、出力の立ち上がり時間を計算するときはこれを考慮に入れる必要があります。

VOUT2の電圧を設定したのと同じ比を使って帰還回路網をVOUT1とSS2ピンの間に接続することにより、図14cに示す絶対トラッキングが実現されます。上側の帰還抵抗(R1)の最小値は、VOUT1がその安定化電圧になっているときに、0.9mAのシンク電流でSSピンをグランドまで完全に駆動できるよう設定してください。さらに、SS2の12µAのソース電流により、小さいVOUT2電圧オフセットが現れます。このオフセットは、R2の値をわずかに小さくすることで補正できます。

出力のシーケンス制御を図14dに示します。VOUT1が安定化電圧の10%以内になると、CMPO1がSS2ソフトスタート・ピンを解放するため、VOUT2のソフトスタートが可能になります。この場合、CMPO1はSSピンによって2Vまで引き上げられます。CMPO1のロジックにより高い電圧が必要な場合は、VOUT1にプルアップ抵抗を使用することができます。こうすると、ソフトスタートのランプ時間が短くなり、瞬時の短絡に対する耐性が向上します。

高精度な出力の上昇および下降が必要な場合は、図14eに示すようにSSピンを駆動します。抵抗(R3)の最小値は、電源投入時およびフォールト状態時に0.9mAのシンク電流でSSピンをグランドまで完全に駆動できるように設定してください。

## アプリケーション情報

図14. SSピンの構成

## アプリケーション情報

### アプリケーションの最適化

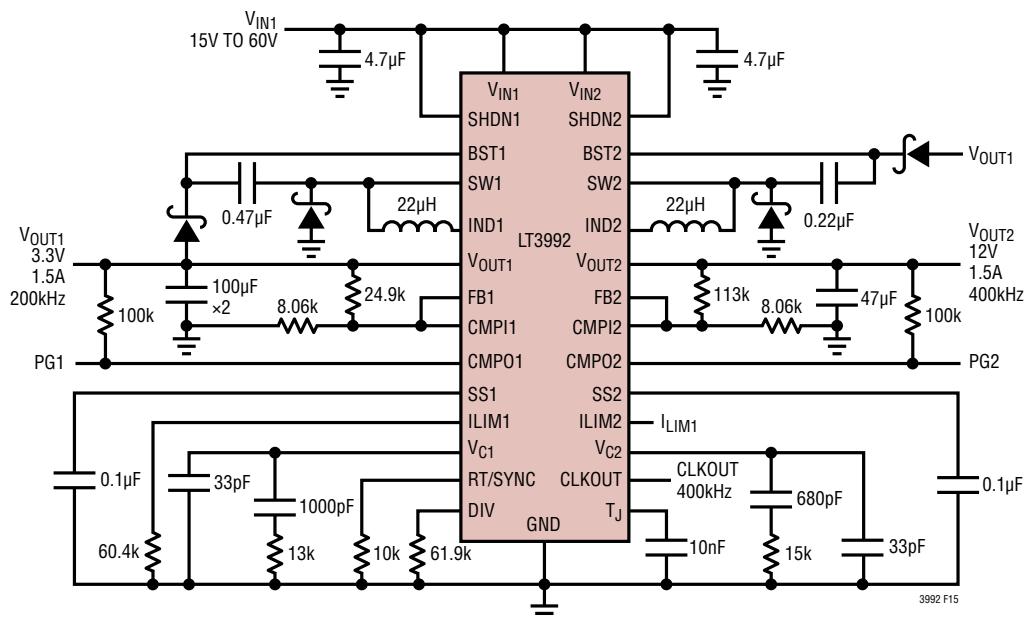

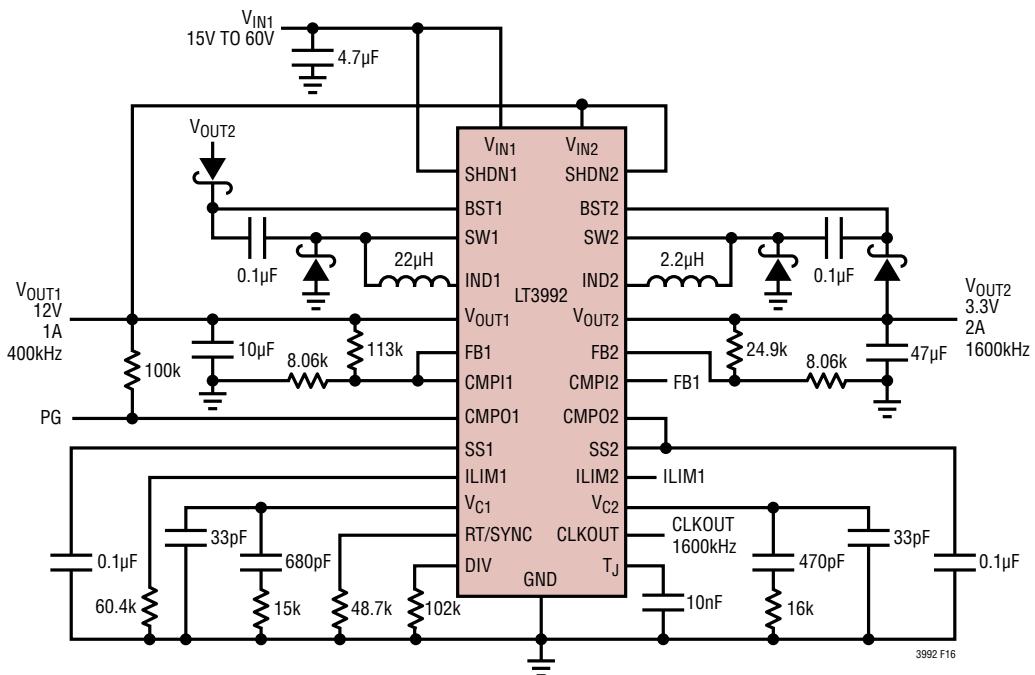

$V_{IN}$ と $V_{OUT}$ の比を大きくすることが必要な複数チャネルのアプリケーションでは、最大周波数とその結果得られるインダクタ・サイズは、比が最大のチャネルによって決まります。LT3992の多周波動作では、チャネルごとに部品サイズを最小限に抑えられると同時に、固定周波数動作を維持できます。この手法を図15の回路に示します。2段降圧手法を多周波動作と組み合わせると、 $V_{IN}$ と $V_{OUT}$ の比が小さい方のチャネルの周波数を高くすることができるので、外付け部品のサイズをさらに小さくすることができます。この手法の欠点は、第1段の出力電力供給能力が第2段から得られる出力電力によって決まることです。図16のデュアル降圧アプリケーションは、入力電圧( $V_{IN1}$ )を最も高い出力電圧に降圧し、その電圧を使用して第2段の入力( $V_{IN2}$ )に電力を供給します。 $V_{OUT1}$ には、その出力の最大負荷に $V_{OUT2}$ の最大負荷を加えた値に対して十分な電流を供給が必要とされます。 $V_{OUT1}$ の電圧は、第2段のチャネルがスイッチングを開始する時点で、「電気的特性」に規定されている $V_{IN2}$ の最小入力電圧(標準2.9V)より高くなればならないことに注意してください。チャネル2を遅延させるには、ソフトスタート・コンデンサを個別にすると、CMP01出力を使ってシーケンス制御を行います。

たとえば、最大入力は60Vであるとします。

$$V_{IN} = 60V, V_{OUT1} = 3.3V(1.5A), V_{OUT2} = 12V(1.5A)$$

$$\text{Frequency (Hz)} = \frac{V_{OUT} + V_D}{V_{IN} - V_{SW} + V_D} \cdot \frac{1}{t_{ON(MIN)}}$$

$$L = \frac{(V_{IN} - V_{OUT}) \cdot V_{OUT}}{V_{IN} \cdot f}$$

1段降圧の場合:

$$\text{Frequency (Hz)} = \frac{3.3 + 0.6}{60V - 0.4 + 0.6} \cdot \frac{1}{180\text{ns}} \approx 350\text{kHz}$$

$$L1 = \frac{(60V - 3.3) \cdot 3.3}{60V \cdot 350\text{kHz}} \geq 9\mu\text{H}$$

$$L2 = \frac{(60V - 12) \cdot 12}{60V \cdot 350\text{kHz}} \geq 27\mu\text{H}$$

2段降圧の場合:

$$\text{Frequency (Hz)} = \frac{12 + 0.6}{60V - 0.4 + 0.6} \cdot \frac{1}{180\text{ns}} \approx 1\text{MHz}$$

$$L1 = \frac{(60V - 12) \cdot 12}{60V \cdot 1\text{MHz}} \geq 10\mu\text{H}$$

$$L2 = \frac{(12 - 3.3) \cdot 3.3}{12 \cdot 1\text{MHz}} \geq 2.4\mu\text{H}$$

2段降圧多周波の場合:

$$R_{DIV} = 61.9\text{k}, \text{FREQ1} = 900\text{kHz}, \text{FREQ2} = 1800\text{kHz}$$

$$L1 = \frac{(60V - 12) \cdot 12}{60V \cdot 900\text{kHz}} \geq 11\mu\text{H}$$

$$L2 = \frac{(12 - 3.3) \cdot 3.3}{12 \cdot 1800\text{kHz}} \geq 1.3\mu\text{H}$$

さらに、 $R_{ILIM2} = 52.3\text{k}$ とすると、チャネル2のピーク電流制限値が2.5Aに減少し、これによってインダクタ・サイズとキャッチ・ダイオードの要件が緩和されます。

## アプリケーション情報

図15. 12Vと3.3Vのデュアル降圧多周波コンバータ

図16. 12Vと3.3Vの2段多周波降圧コンバータ

## アプリケーション情報

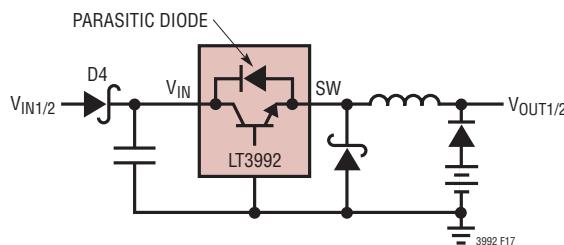

### 短絡入力と逆入力に対する保護

過度に飽和しないようにインダクタを選択すれば、LT3992降圧レギュレータに出力の短絡への耐性を持たせることができます。LT3992に入力が加わっていないときに出力が高く保たれるシステムでは、考慮すべき状況がもう1つあります。これは、バッテリや他の電源がLT3992の出力とダイオードOR結合されているバッテリ充電アプリケーションやバッテリ・バックアップ・システムで生じることがあります。V<sub>IN1/2</sub>ピンをフロート状態にすることができる場合で、SHDNピンが(ロジック信号によって、またはV<sub>IN</sub>に接続されているために)“H”に保持されると、LT3992の内部回路にはそのSWピンを介して静止電流が流れます。この状態で数mAの電流を許容できるシステムであれば、これは問題ありません。SHDNピンを接地すれば、SWピンの電流は実質的にゼロに低下します。ただし、出力を高く保持した状態でV<sub>IN</sub>ピンを接地すると、出力からSWピンおよびV<sub>IN1/2</sub>ピンを通ってLT3992内部の寄生ダイオードに大電流が流れる可能性があります。入力電圧が存在しているときにのみ動作し、短絡入力や逆入力から保護する回路を図17に示します。

図17. ダイオードD4は、出力に接続されたバックアップ用バッテリが短絡入力によって放電するのを防止

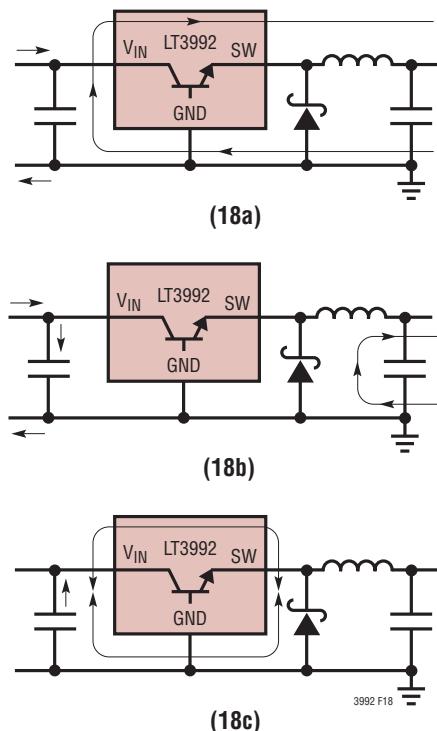

### プリント回路基板のレイアウト

動作を正常にしてEMIを最小にするには、プリント回路基板(PCB)のレイアウト時に注意が必要です。降圧レギュレータ回路内でdi/dtが大きい経路を図18に示します。大きなスイッチング電流がパワー・スイッチ、キャッチ・ダイオード、および入力コンデンサに流れることに注意してください。これらの部品が形成するループは、できるだけ小さくしてください。

これらの部品とインダクタおよび出力コンデンサは回路基板の同じ側に配置し、その層で接続を行うようにしてください。これらの部品の下には切れ目のないローカル・グランド・プレーンを配置し、このグランド・プレーンを1箇所でシステム・グラン

ドに(理想的には出力コンデンサC2のグランド端子に)接続します。すべての小信号アナログ帰路は、パッケージの底面のグランド接続箇所に配線します。さらに、SWとBSTの配線はできるだけ短くするようにしてください。

図18. スイッチがオフのときの電流(18b)からスイッチがオンのときの電流(18a)を減じると、高周波スイッチング電流の経路(18c)が求まる。このループは小さくしておく。SWとBSTの配線の電圧も切り替わるので、この配線はできるだけ短くする。最後に、回路が近くのグランド・プレーンで遮蔽されていることを確認する。

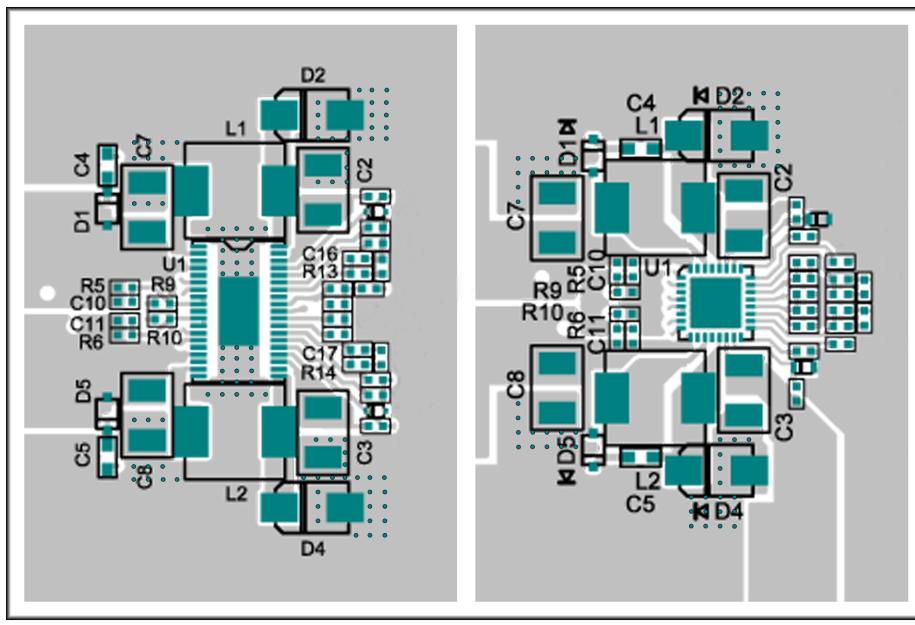

### 熱に関する検討事項

PCBは、LT3992の温度が上がらないよう、放熱機能を備える必要があります。パッケージ底面の露出金属部分をグランド・プレーンに半田付けする必要があります。このグランドは、サーマル・ビアを使用して、下にある他の銅層に接続してください。これらの層は、LT3992が発生する熱を放散します。その他のビアは、キャッチ・ダイオードの近くに配置します。最上層と最下層の銅を増やして、これらの銅と内部プレーンをビアで接続すると、熱抵抗をさらに小さくすることができます。適切な部品の配置と配線を、図19の上面金属と部品の輪郭で示します。

## アプリケーション情報

3992 F19

図19. TSSOPパッケージおよびQFNパッケージでのプリント配線基板トップ層と部品配置

LT3992の高性能4.6Aスイッチにより、コンバータは大量の出力電流を供給することができます。コンバータの動作条件によっては、その結果発生する内部電力損失により、接合部温度がその最大定格を超えて上昇することがあります。動作条件には、入力電圧、出力電圧、スイッチング周波数、出力電流、周囲環境の温度などが含まれます。周囲温度を超える接合部温度上昇分を推定することは、与えられた設計が特定の動作条件で接合部温度の最大定格を超える可能性があるかどうかを判断するのに役立ちます。ただし、温度上昇はPCBの設計や他の熱源との近さによって異なります。コンバータの最終的な設計は、ベンチ上で評価する必要があります。

接合部温度上昇の推定は、どの回路部品が電力を損失するかを突き止めることから始まります。電力損失の推定を簡単にするために、熱源をインダクタ、キャッチ・ダイオード、および

LT3992に限定して考えます。動作条件が求められたら、個々の電力損失は以下の式で計算することができます。

$$\begin{aligned} \text{Power}_{D1,2} &= \left(1 - \frac{V_{OUT}}{V_{IN}}\right) \cdot I_{OUT} \cdot V_{FD} \\ \text{Power}_{IND1,2} &= R_{IND} \cdot I_{OUT}^2 \\ \text{Power}_{CH1,2} &= 0.1 \cdot \frac{V_{OUT}}{V_{IN}} \cdot I_{OUT}^2 + 2 \cdot 10^{-3} \\ &\quad \cdot V_{IN} + \frac{I_{OUT} \cdot V_{OUT} \cdot V_{BOOST}}{40 \cdot V_{IN}} + \\ &\quad V_{IN} \cdot I_{OUT} \cdot f_{SW} \cdot 10^{-6} \cdot \left( \frac{V_{IN}}{2.5} + \frac{I_{OUT}}{0.25} \right) \end{aligned}$$

ここで、

$f_{SW}$  = Switching Frequency in kHz

$R_{IND}$  = Inductor Resistance

$V_{FD}$  = Catch Diode Forward Voltage Drop

$V_{BOOST}$  = Switch Boost Voltage

3992fa

## アプリケーション情報

TSSOPパッケージを使用したLT3992デモ基板の場合、周囲温度を超える接合部温度上昇分の推定値は次式により求められます。

$$\begin{aligned} T_{RISETSSOP} \approx & 10 \cdot (Power_{D1} + Power_{D2}) + \\ & 12.3 \cdot (Power_{IND1} + Power_{IND2}) + 17.5 \cdot \\ & (Power_{CH1} + Power_{CH2}) \end{aligned}$$

LT3992 QFNパッケージ用レイアウトでの周囲温度を超える接合部温度上昇の推定値は、次式のとおりです。

$$\begin{aligned} T_{RISEQFN} \approx & 8.5 \cdot (Power_{D1} + Power_{D2}) + \\ & 13 \cdot (Power_{IND1} + Power_{IND2}) + 23 \cdot \\ & (Power_{CH1} + Power_{CH2}) \end{aligned}$$

たとえば、表5に示す個々の電力損失の寄与分を計算するには、表4に示す標準のアプリケーション回路を使用します。電力損失の推定値と周囲温度を超える接合部温度の上昇分を表6に示します。LT3992のデモ回路基板上では、大きいTSSOPパッケージの方が小型のQFNパッケージよりも良好な熱性能を示していることに注意してください。熱性能に対して有利に働くLT3992のアプリケーションでは、TSSOPパッケージが推奨パッケージ・オプションになります。

表4

| アプリケーション | V <sub>IN1</sub><br>(V) | V <sub>IN2</sub><br>(V) | f <sub>SW<br/>CH1</sub> | f <sub>SW<br/>CH2</sub> | V <sub>OUT1</sub><br>(V) | I <sub>OUT1</sub><br>(A) | V <sub>OUT2</sub><br>(V) | I <sub>OUT2</sub><br>(A) |

|----------|-------------------------|-------------------------|-------------------------|-------------------------|--------------------------|--------------------------|--------------------------|--------------------------|

| 表紙の回路    | 48                      | 12                      | 400                     | 1600                    | 12                       | 1.5                      | 5                        | 2                        |

| 裏表紙の回路   | 48                      | 48                      | 300                     | 300                     | 5                        | 2                        | 3                        | 2                        |

表5

| アプリケーション | PD1<br>(W) | PD2<br>(W) | PL1<br>(W) | PL2<br>(W) | PCH1<br>(W) | PCH2<br>(W) |

|----------|------------|------------|------------|------------|-------------|-------------|

| 表紙の回路    | 0.54       | 0.56       | 0.23       | 0.28       | 0.99        | 0.79        |

| 裏表紙の回路   | 0.88       | 0.92       | 0.28       | 0.2        | 0.95        | 0.91        |

表6

| アプリケーション | P <sub>LOSS</sub> (W) |     | T <sub>RISE</sub> TSSOP (°C) |      | T <sub>RISE</sub> QFN (°C) |      |

|----------|-----------------------|-----|------------------------------|------|----------------------------|------|

|          | 計算値                   | 実測値 | 計算値                          | 実測値  | 計算値                        | 実測値  |

| 表紙の回路    | 3.38                  | 3.2 | 48.3                         | 46.1 | 56.8                       | 53.3 |

| 裏表紙の回路   | 4.14                  | 4.2 | 56.4                         | 53.0 | 64.3                       | 62.9 |

「熱に関する検討事項」のセクションに示す電力損失と温度上昇の式は、接合部温度上昇を推定するための妥当な出発点としての役割を果たします。しかし、LT3992は非常に汎用性の高

いコンバータです。LT3992の入力電圧、出力電圧、出力電流、スイッチング周波数、およびパッケージを個別に選択した結果を組み合わせると、考えられるすべての動作条件に対応できる電力損失の推定手法は存在しなくなります。したがって、コンバータの性能をベンチで評価することが絶対に必要です。

昇圧ダイオード、入力コンデンサ、出力コンデンサ、インダクタのコア損失、配線抵抗など、他の電力部品での電力損失によって銅はさらに発熱するので、デバイスが周囲温度として認識する温度はさらに上昇する可能性があります。LT1767データシートの「熱に関する検討事項」のセクションを参照してください。

### ダイ温度とサーマル・シャットダウン

LT3992のT<sub>J</sub>ピンは、内部の接合部温度に比例した電圧を出力します。T<sub>J</sub>ピンは25°Cでは標準で250mVを出力し、その勾配は10mV/°Cです。外付け回路による補助がない場合でも、最大負荷が100μAであればT<sub>J</sub>ピンの出力は20°C～150°C(200mV～1.5V)の範囲で有効です。

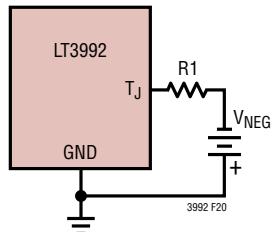

### 全温度範囲の測定

T<sub>J</sub>出力の動作温度範囲を20°Cより低い温度まで広げるには、図20に示すように、T<sub>J</sub>ピンと負電源の間に抵抗を接続します。負のレール電圧とT<sub>J</sub>ピンの抵抗は次式を使用して計算できます。

$$\begin{aligned} V_{NEG} \leq & \frac{2 \cdot TEMP(MIN)^{\circ}C}{100} \\ R1 \leq & \frac{|V_{NEG}|}{33\mu A} \end{aligned}$$

ここで、

TEMP (MIN) °Cは、有効なT<sub>J</sub>ピン出力が必要となる最小温度です。

V<sub>NEG</sub>は、安定化された負の電源電圧です。

例：

$$TEMP(MIN)^{\circ}C = -40^{\circ}C$$

$$V_{NEG} \leq -0.8V$$

$$V_{NEG} = -1, R1 \leq |V_{NEG}| / 33\mu A = 30.2k\Omega$$

## アプリケーション情報

図20. TJピンの動作範囲を広げるための回路

図21. TJピンの動作範囲を広げるために負の電圧レールを生成させる回路

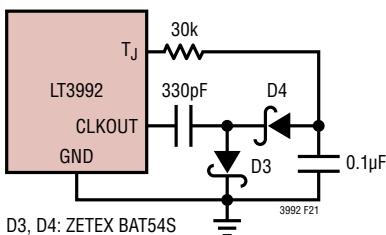

### 負の安定化電圧の生成

図21の単純なチャージポンプ回路では、CLKOUTピンの出力を使用して負電圧を生成することで、外部安定化電源が必要としなくなります。表面実装型コンデンサとデュアル・パッケージのショットキ・ダイオードを使用すると、負の電源電圧を実装するために必要な基板面積が最小限に抑えられます。

安全措置として、LT3992には、付加的なサーマル・シャットダウンのしきい値が163°Cの標準値でチャネルごとに設定されています。このしきい値を超えると、その都度該当チャネルの電源投入シーケンスが開始されます。その後このシーケンスは、熱的な過負荷状態が解消されるまで繰り返されます。

TJピンの電圧は定常状態の温度を示しており、最大接合部温度を超えていないことを保証するために使用するべきではない、という点に注意してください。瞬時の電力の他に温度勾配や時定数の要因が加わると、ダイの一部が最大定格およびサーマル・シャットダウンのしきい値を超してしまう可能性があります。ダイ温度の上昇分は、定常状態(1分超)だけでなく、インパルス条件でも計算するようにしてください。

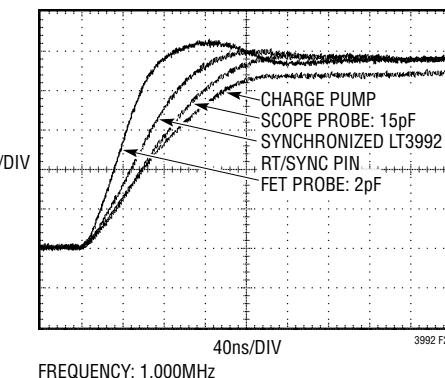

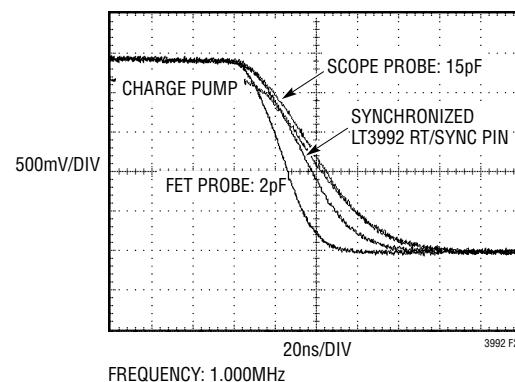

### CLKOUTの容量性負荷

CLKOUTピンから負のレールを生成させる場合の軽微な欠点は、チャージポンプによってCLKOUTピンに容量が追加され、その結果出力同期クロック信号に位相遅れが生じることです。容量性負荷がCLKOUT信号の立ち上がり時間と立

ち下がり時間に及ぼす影響を、図22および図23に示します。10:1で150MHzの標準的なオシロスコープ用プローブでは、CLKOUTノードの容量が大幅に増加するので、正確な測定を行うには低容量のプローブを必要とする、ということに注意してください。CLKOUTで負の電源電圧を生成して他のレギュレータに同期クロックを供給する必要があるアプリケーションでは、チャージポンプ回路より前でCLKOUTをバッファすると有利な場合があります。

### リニアテクノロジー社の他の出版物

「アプリケーションノート」の19、35、および44に、降圧レギュレータと他のスイッチング・レギュレータの詳細な説明と設計情報が記載されています。LT1376のデータシートには、出力リップル、ループ補償、および安定性のテストに関する、さらに広範な説明が記載されています。「デザインノートDN100」には、降圧レギュレータを使用してデュアル(+と-)出力電源を生成する方法が示されています。

図22. CLKOUTの立ち上がり時間

図23. CLKOUTの立ち下がり時間

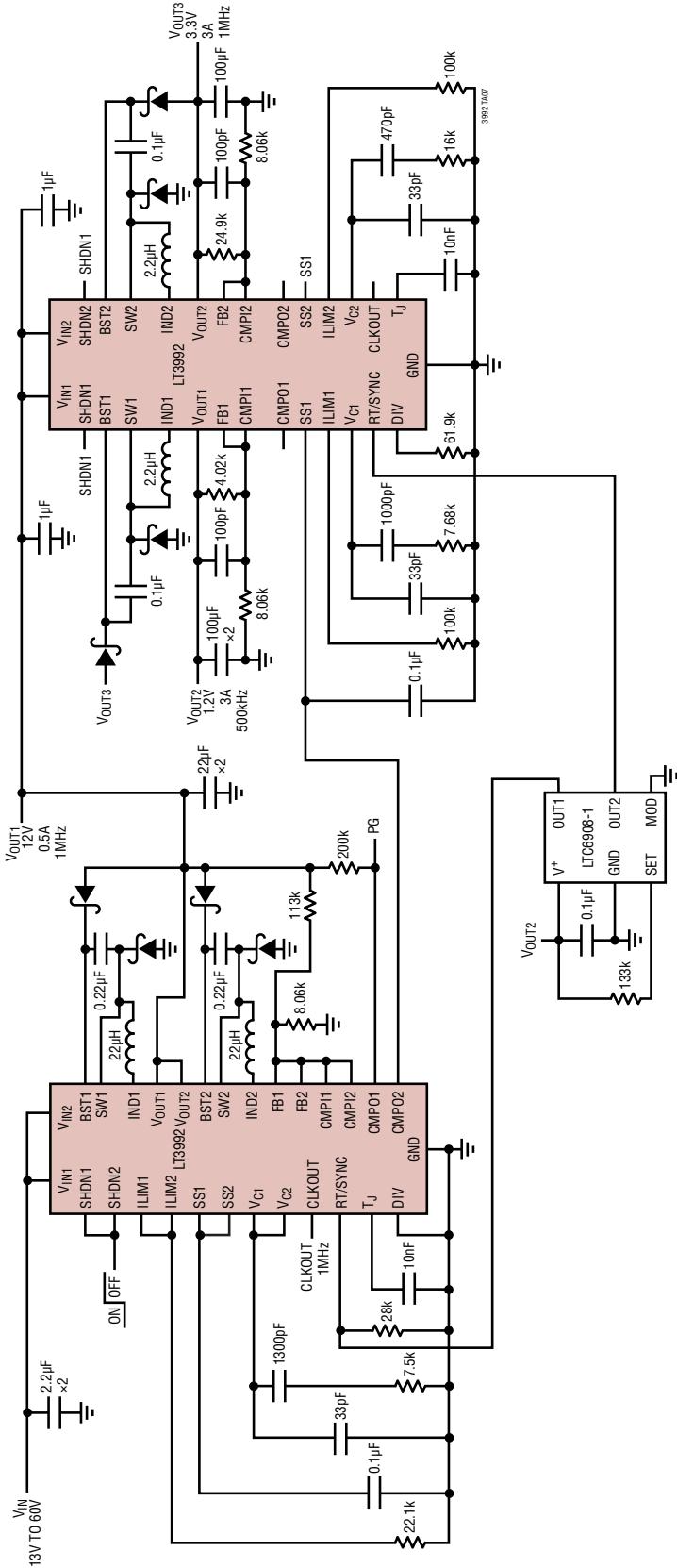

## 標準的應用例

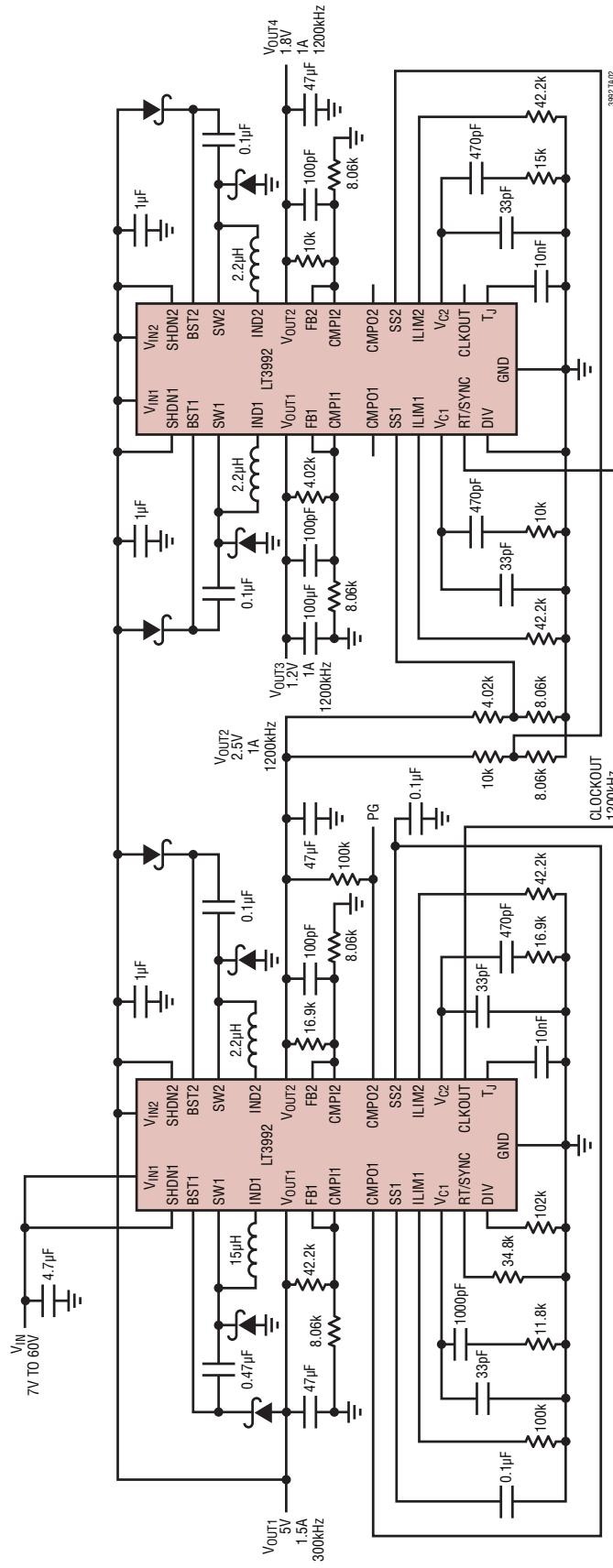

出力シーケンシング、絶対トラッキング、および電流制限機能を備えた5V、2.5V、1.8Vおよび1.2Vのクワッド出力多周波同期2段コンバータ

3992fa

# LT3992

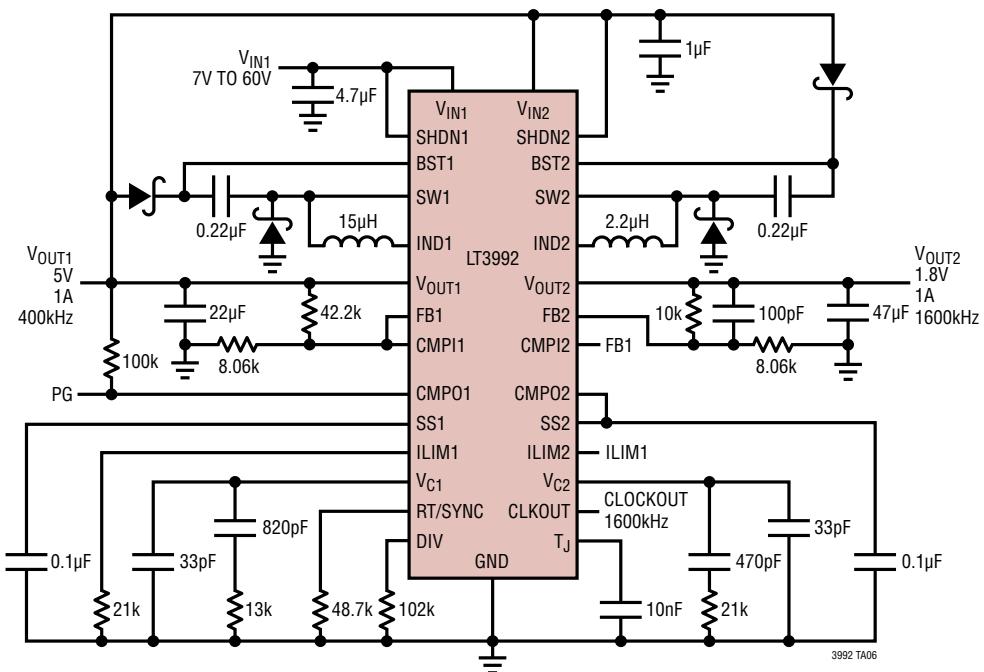

## 標準的応用例

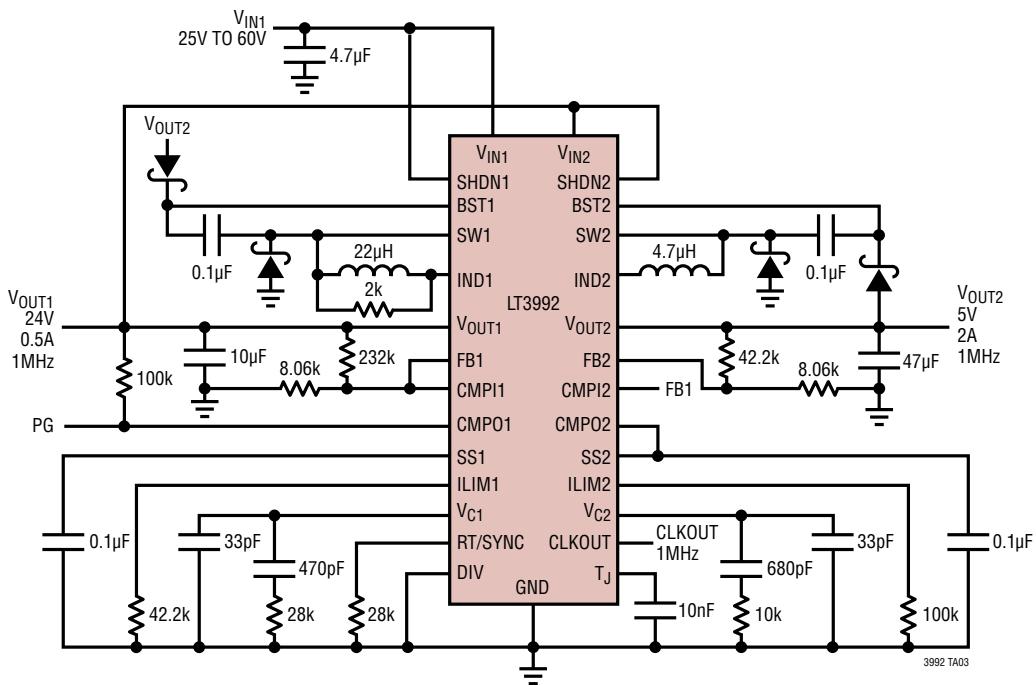

24Vと5Vの2段デュアル降圧コンバータ

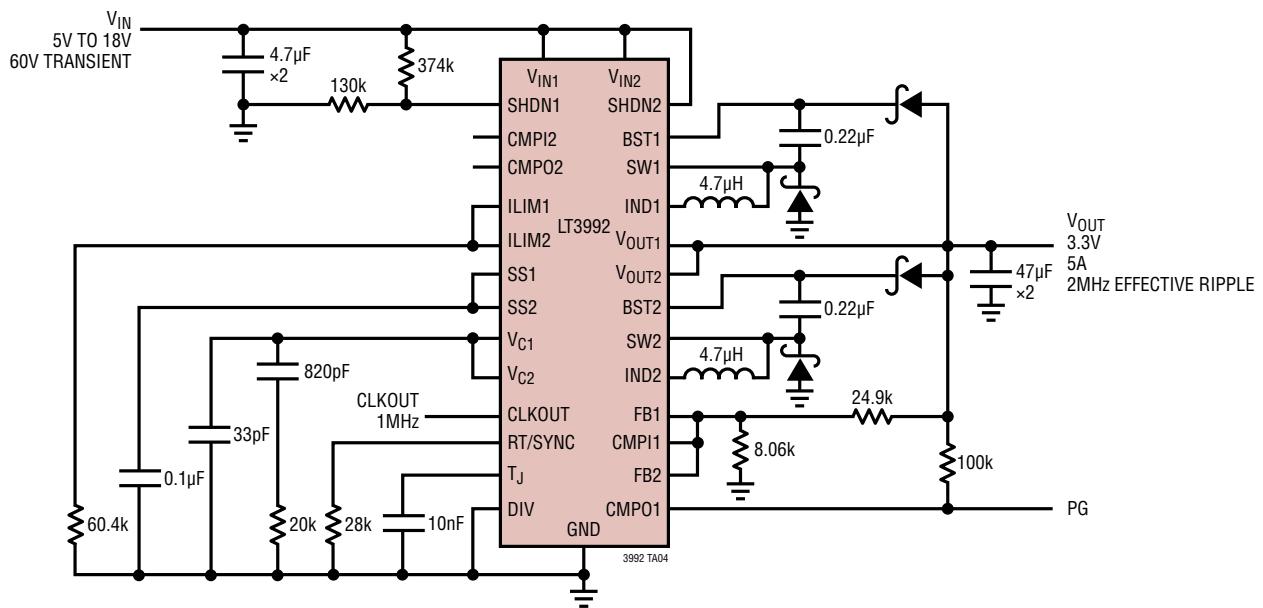

UVLO およびパワーグッド機能を備えた3.3V/5A 単一出力

3992fa

## 標準的応用例

デュアル入力電源、3.3V/4A出力の1段降圧コンバータ

5Vおよび1.8Vのデュアル2段コンバータ

## 標準的応用例

外部同期、出力シーケンス制御、およびトラッキング機能を備えた12V、3.3V、1.2Vトリプル出力

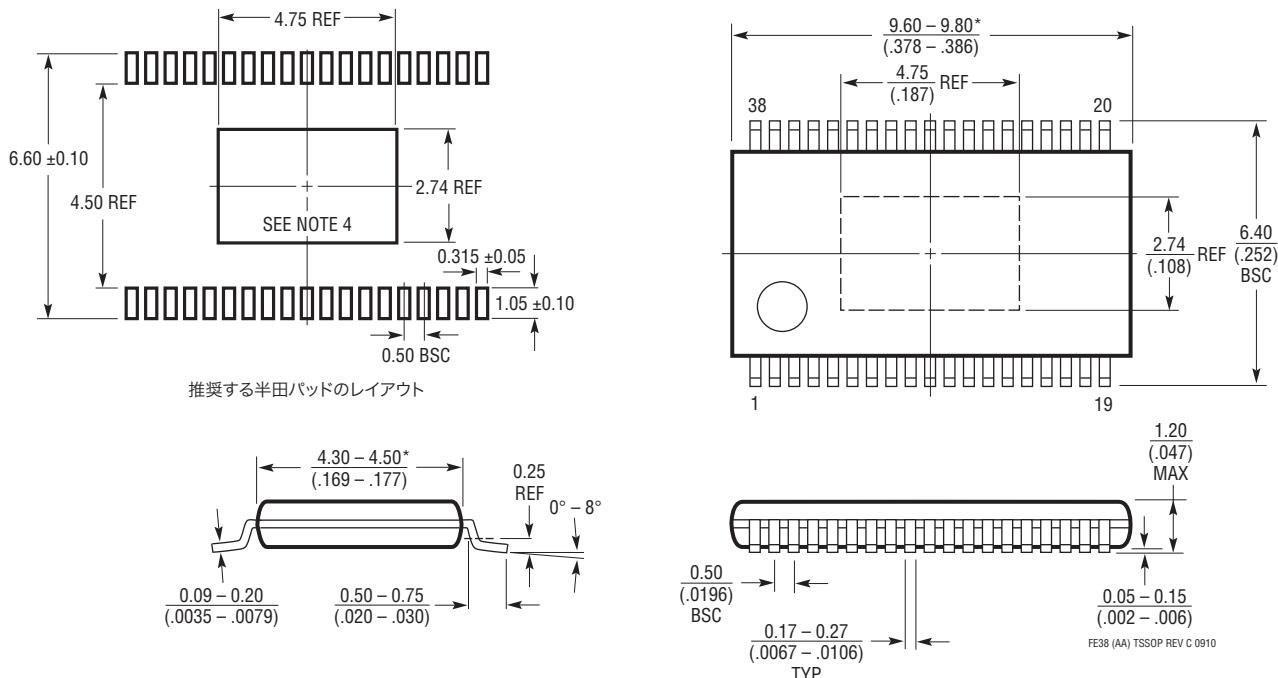

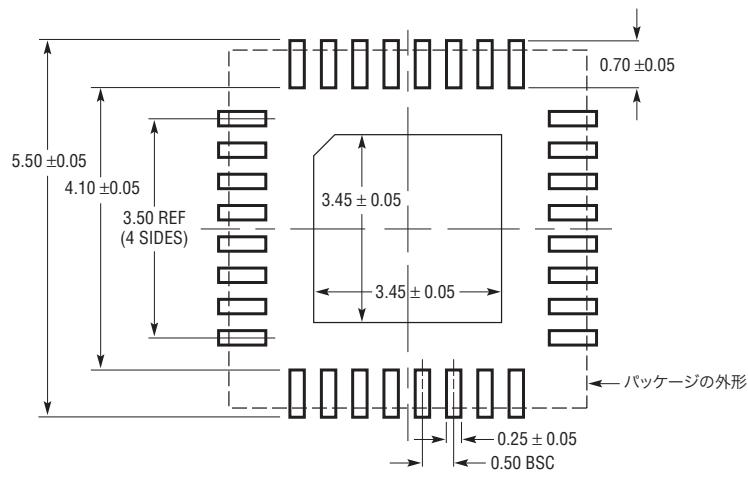

## パッケージ

最新のパッケージ図については、<http://www.linear-tech.co.jp/designtools/packaging> を参照してください。

**FE Package

38-Lead Plastic TSSOP (4.4mm)**

(Reference LTC DWG # 05-08-1772 Rev C)

**Exposed Pad Variation AA**

### NOTE:

- 標準寸法：ミリメートル

- 寸法はミリメートル / (インチ)

- 図は実寸とは異なる

4. 露出パッド接着のための推奨最小 PCB メタルサイズ

\* 寸法にはモールドのバリを含まない。

モールドのバリは各サイドで 0.150mm (0.006") を超えないこと

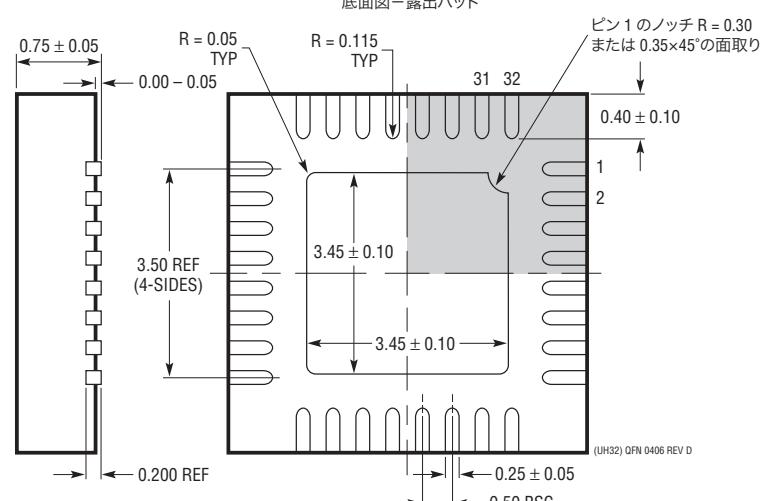

## パッケージ

最新のパッケージ図については、<http://www.linear-tech.co.jp/designtools/packaging> を参照してください。

**UH Package

32-Lead Plastic QFN (5mm × 5mm)**

(Reference LTC DWG # 05-08-1693 Rev D)

推奨する半田パッドのピッチと寸法

半田付けられない領域には半田マスクを使用する

NOTE:

1. 図は JEDEC パッケージ外形 MO-220 のバリエーション WHHD-(X) にすることを提案している(承認予定)。

2. 図は実寸とは異なる

3. 全ての寸法はミリメートル

4. パッケージ底面の露出パッドの寸法にはモールドのバリを含まない。

モールドのバリは(もしあれば)各サイドで 0.20mm を超えないこと

5. 露出パッドは半田メッキとする

6. 網掛けの部分はパッケージの上面と底面のピン 1 の位置の参考に過ぎない

## 改訂履歴

| REV | 日付   | 概要                                                                               | ページ番号                   |

|-----|------|----------------------------------------------------------------------------------|-------------------------|

| A   | 4/13 | Switching Frequencyの標準値を明確化。<br>ブロック図を明確化。<br>最後の段落の図2を図1に修正。<br>アプリケーション情報の明確化。 | 3<br>10<br>12<br>14, 16 |

## 標準的応用例

FMEA フォールト耐性型の 5V/2A および 3.3V/2A デュアル・コンバータ

## 関連製品

| 製品番号               | 説明                                                                                      | 注釈                                                                                                                                         |

|--------------------|-----------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|

| LT3692/<br>LT3692A | 36V、デュアル 3.5A、2.25MHz 高効率降圧 DC/DC コンバータ                                                 | V <sub>IN</sub> = 3V ~ 36V、V <sub>OUT(MIN)</sub> = 0.8V、I <sub>Q</sub> = 4mA、I <sub>SD</sub> < 10µA、5mm×5mm QFN-32、TSSOP-38E               |

| LT3507/<br>LT3507A | 36V、トリプル 2.4、1.4A、1.4A (I <sub>OUT</sub> )、2.5MHz 高効率降圧 DC/DC コンバータ (LDO コントローラ付き)      | V <sub>IN</sub> = 4V ~ 36V、V <sub>OUT(MIN)</sub> = 0.8V、I <sub>Q</sub> = 7mA、I <sub>SD</sub> = 1µA、5mm×7mm QFN-38                          |

| LT3508             | 36V(40Vまでの過渡電圧保護機能あり)、デュアル I <sub>OUT</sub> (1.4A)、3MHz 高効率降圧 DC/DC コンバータ               | V <sub>IN</sub> = 3.7V ~ 37V、V <sub>OUT(MIN)</sub> = 0.8V、I <sub>Q</sub> = 4.6mA、I <sub>SD</sub> = 1µA、4mm×4mm QFN-24、TSSOP-16E            |

| LT3680             | 36V、3A、2.4MHz 高効率マイクロパワー降圧 DC/DC コンバータ                                                  | V <sub>IN</sub> = 3.6V ~ 36V、V <sub>OUT(MIN)</sub> = 0.8V、I <sub>Q</sub> = 75µA、I <sub>SD</sub> < 1µA、3mm×3mm DFN-10、MSOP-10E              |

| LT3693             | 36V、3A、2.4MHz 高効率降圧 DC/DC コンバータ                                                         | V <sub>IN</sub> = 3.6V ~ 36V、V <sub>OUT(MIN)</sub> = 0.8V、I <sub>Q</sub> = 1.3mA、I <sub>SD</sub> < 1µA、3mm×3mm DFN-10、MSOP-10E             |

| LT3480             | 36V(60Vまでの過渡電圧保護機能あり)、2A (I <sub>OUT</sub> )、2.4MHz 高効率降圧 DC/DC コンバータ (Burst Mode®動作可能) | V <sub>IN</sub> = 3.6V ~ 38V(過渡電圧は最大60V)、V <sub>OUT(MIN)</sub> = 0.78V、I <sub>Q</sub> = 70µA、I <sub>SD</sub> < 1µA、3mm×3mm DFN-10、MSOP-10E |

| LT3980             | 58V(80Vまでの過渡電圧保護付き)、2A (I <sub>OUT</sub> )、2.4MHz 高効率降圧 DC/DC コンバータ (Burst Mode動作付き)    | V <sub>IN</sub> = 3.6V ~ 58V(過渡電圧は最大80V)、V <sub>OUT(MIN)</sub> = 0.79V、I <sub>Q</sub> = 75µA、I <sub>SD</sub> < 1µA、3mm×4mm DFN-16、MSOP-16E |

| LT3971             | 38V、1.2A (I <sub>OUT</sub> )、2MHz 高効率降圧 DC/DC コンバータ (静止電流がわずか 2.8µA)                    | V <sub>IN</sub> = 4.2V ~ 38V、V <sub>OUT(MIN)</sub> = 1.2V、I <sub>Q</sub> = 2.8µA、I <sub>SD</sub> < 1µA、3mm×3mm DFN-10、MSOP-10E             |

| LT3991             | 55V、1.2A (I <sub>OUT</sub> )、2MHz 高効率降圧 DC/DC コンバータ (静止電流がわずか 2.8µA)                    | V <sub>IN</sub> = 4.2V ~ 55V、V <sub>OUT(MIN)</sub> = 1.2V、I <sub>Q</sub> = 2.8µA、I <sub>SD</sub> < 1µA、3mm×3mm DFN-10、MSOP-10E             |