# 6A、40Vスイッチを内蔵した 入力電圧範囲の広い 昇圧/SEPIC/反転コンバータ

## 特長

- 広い入力電圧範囲: 1.6V(起動時は2.5V) ~ 40V

- 1本の帰還ピンで正または負の出力電圧をプログラミング

- **PGOOD**による出力電圧の状態通知

- 6A/40Vパワー・スイッチを内蔵

- プログラム可能なソフトスタート

- 1本の外付け抵抗でプログラム可能な動作周波数 (100kHz ~ 1MHz)

- 外部クロックに同期可能

- 低シャットダウン電流: < 1µA

- $V_{IN}$ またはDRIVEを電源とするINTV<sub>CC</sub>レギュレータ

- プログラム可能な入力低電圧ロックアウト (ヒステリシスあり)

- 熱特性が改善されたQFN(5mm×6mm)パッケージおよびTSSOPパッケージ

## アプリケーション

- 自動車

- 通信機器

- 産業用機器

## 概要

LT<sup>®</sup>3959は、1本の帰還ピンで正または負の出力電圧を安定化できる入力電圧範囲の広い電流モードDC/DCコントローラです。昇圧コンバータ、SEPICコンバータ、または反転コンバータとして構成できます。

このデバイスは、 $V_{IN}$ またはDRIVEから供給される内部の安定化電源で駆動する6A/40V定格の低電位側NチャンネルMOSFETを内蔵しています。固定周波数の電流モード・アーキテクチャにより、広い範囲の電源電圧および出力電圧にわたって安定した動作が得られます。LT3959の動作周波数は、外付け抵抗により100kHz ~ 1MHzの範囲で設定可能です。SYNCピンを使用して外部クロックに同期することもできます。

LT3959では、ソフトスタート機能および周波数フォールドバック機能を備えているので、起動時および出力短絡時にインダクタ電流を制限できます。FBXピンのウィンドウ・コンパレータにより、出力電圧の状態が**PGOOD**ピンを介して通知されます。

LT、LT、LTC、LTM、Linear TechnologyおよびLinearのロゴはリニアテクノロジー社の登録商標です。ThinSOTはリニアテクノロジー社の商標です。その他すべての商標の所有権は、それぞれの所有者に帰属します。7825665を含む米国特許によって保護されています。

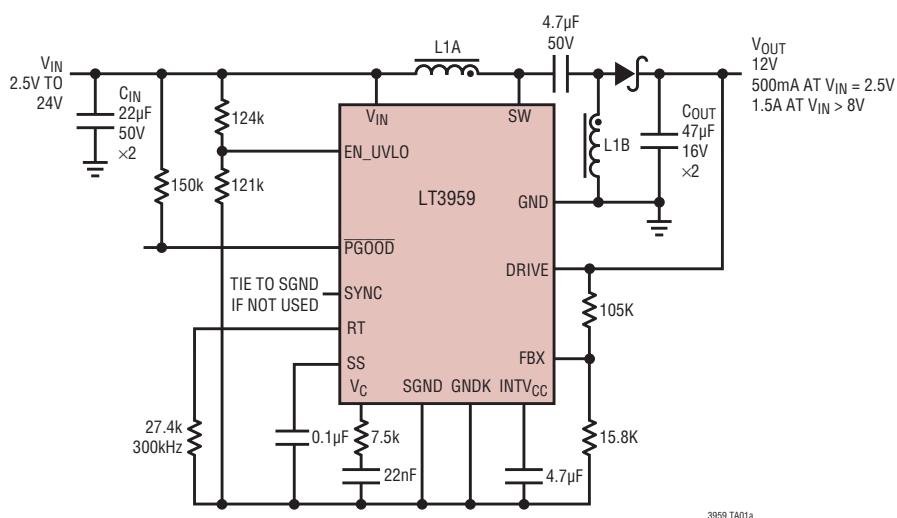

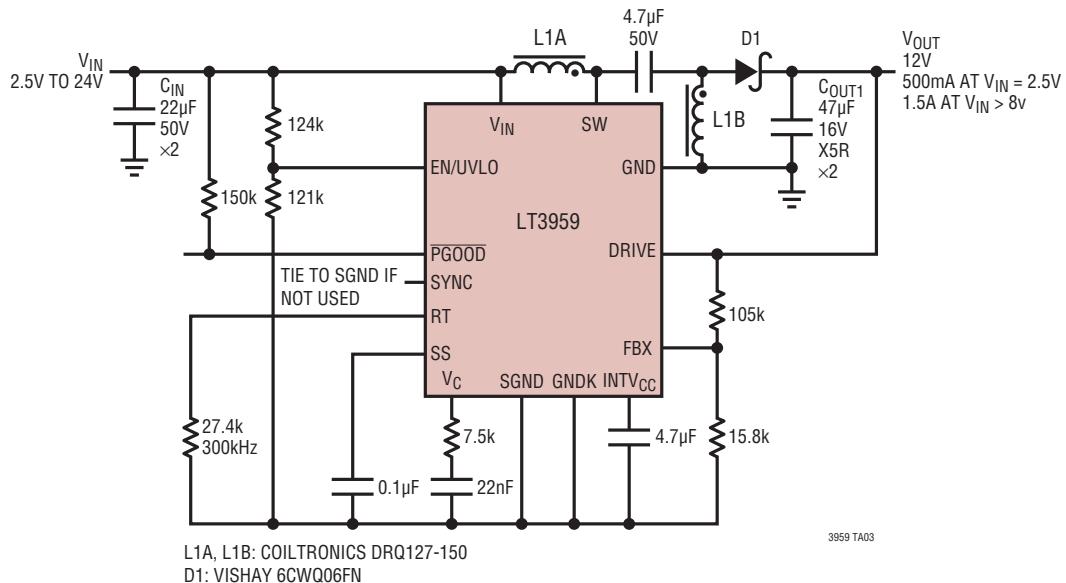

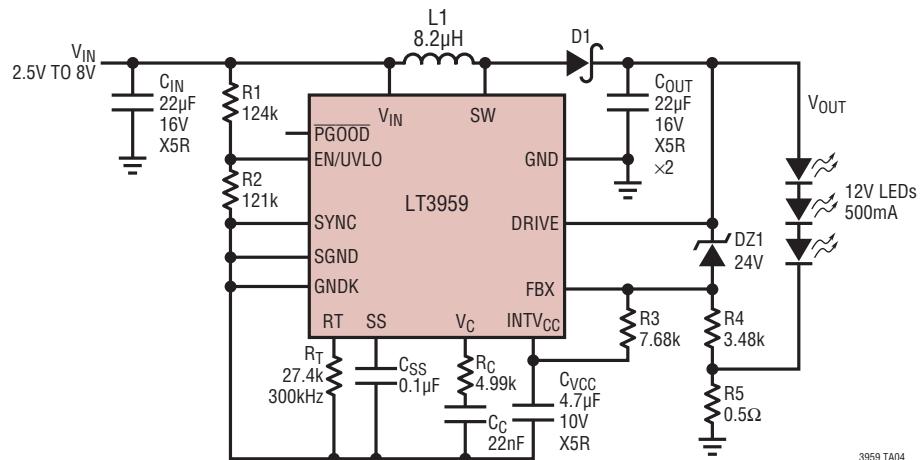

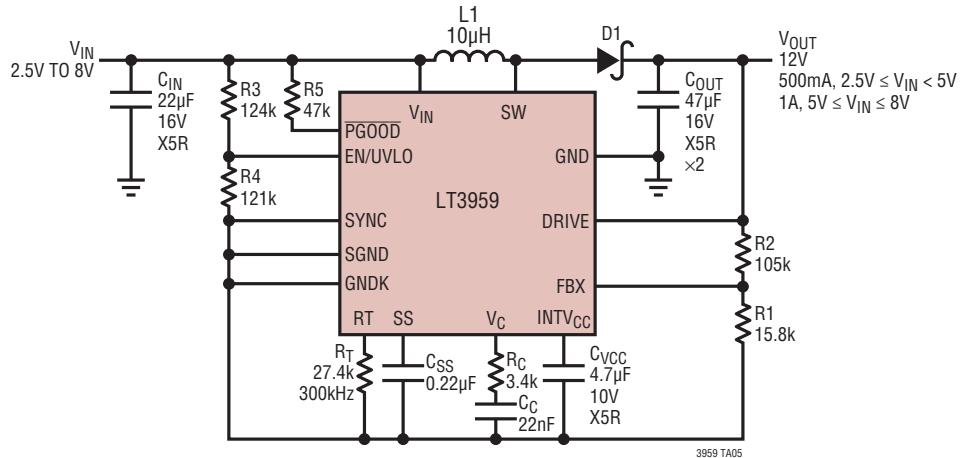

## 標準的応用例

2.5V ~ 24V入力、12V出力のSEPICコンバータ

車載用12Vポストレギュレータに最適

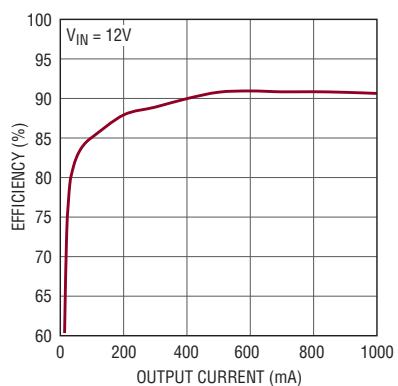

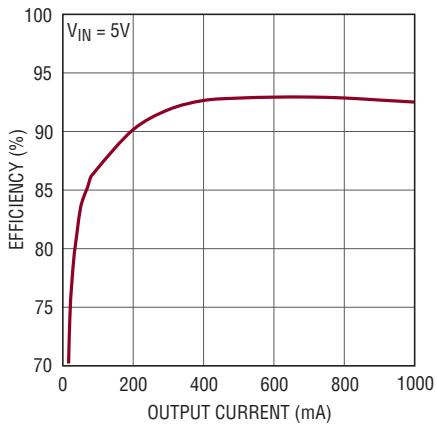

効率と出力電流

3959 TA01b

## 絶対最大定格

(Note 1)

|                    |     |                    |               |

|--------------------|-----|--------------------|---------------|

| $V_{IN}$           | 40V | $V_C$ 、SS          | 3V            |

| EN/UVLO (Note 2)   | 40V | RT                 | 1.5V          |

| DRIVE              | 40V | GND、GNDK から SGND   | $\pm 0.3V$    |

| PGOOD              | 40V | FBX                | -3V ~ 3V      |

| SW                 | 40V | 動作接合部温度範囲 (Note 3) |               |

| INTV <sub>CC</sub> | 8V  | LT3959E/LT3959I    | -40°C ~ 125°C |

| SYNC               | 8V  | 保存温度範囲             | -65°C ~ 125°C |

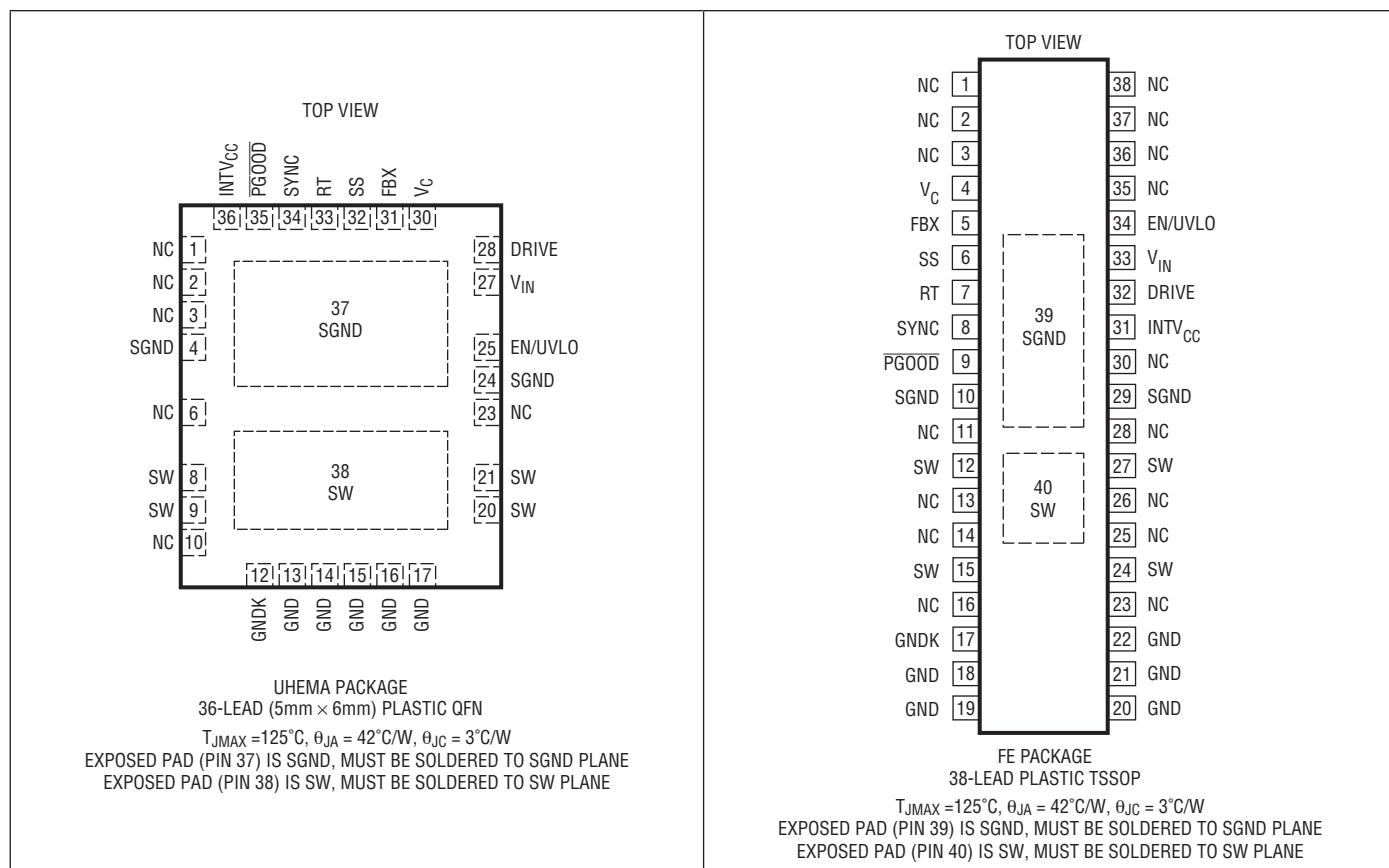

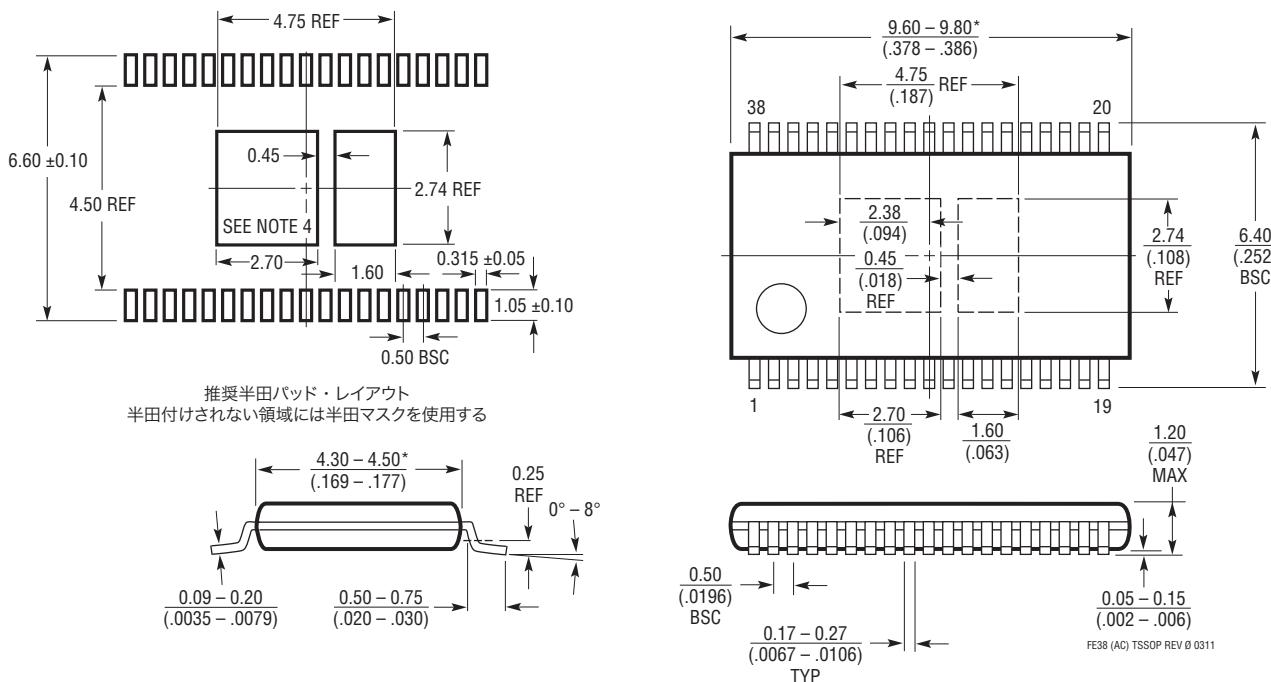

## ピン配置

## 発注情報

| 無鉛仕上げ          | テープアンドリール        | 製品マーキング* | パッケージ                           | 温度範囲           |

|----------------|------------------|----------|---------------------------------|----------------|

| LT3959EUHE#PBF | LT3959EUHE#TRPBF | 3959     | 36-Lead (5mm × 6mm) Plastic QFN | -40°C to 125°C |

| LT3959IUHE#PBF | LT3959IUHE#TRPBF | 3959     | 36-Lead (5mm × 6mm) Plastic QFN | -40°C to 125°C |

| LT3959EFE#PBF  | LT3959EFE#TRPBF  | LT3959FE | 38-Lead Plastic TSSOP           | -40°C to 125°C |

| LT3959IFE#PBF  | LT3959IFE#TRPBF  | LT3959FE | 38-Lead Plastic TSSOP           | -40°C to 125°C |

さらに広い動作温度範囲で規定されるデバイスについては、弊社または弊社代理店にお問い合わせください。\* 温度グレードは出荷時のコンテナのラベルで識別されます。

非標準の鉛仕上げの製品の詳細については、弊社または弊社代理店にお問い合わせください。

無鉛仕上げの製品マーキングの詳細については、<http://www.linear-tech.co.jp/leadfree/> をご覧ください。

テープアンドリールの仕様の詳細については、<http://www.linear-tech.co.jp/tapeandreel/> をご覧ください。

## 電気的特性

●は全動作温度範囲での規格値を意味する。それ以外は  $T_A = 25^\circ\text{C}$  での値。注記がない限り、 $V_{IN} = 12\text{V}$ 、 $\text{EN/UVLO} = 12\text{V}$ 、 $\text{INTV}_{CC} = 4.75\text{V}$ 。

| PARAMETER                               | CONDITIONS                                                        | MIN   | TYP        | MAX    | UNITS         |

|-----------------------------------------|-------------------------------------------------------------------|-------|------------|--------|---------------|

| $V_{IN}$ Operating Voltage              |                                                                   | ● 1.6 |            | 40     | V             |

| $V_{IN}$ Start-Up Voltage               | $R_T = 27.4\text{k}\Omega$ , $\text{FBX} = 0$                     | ● 2.5 |            | 2.65   | V             |

| $V_{IN}$ Shutdown $I_Q$                 | $\text{EN/UVLO} < 0.4\text{V}$<br>$\text{EN/UVLO} = 1.15\text{V}$ |       | 0.1        | 1<br>6 | $\mu\text{A}$ |

| $V_{IN}$ Operating $I_Q$                |                                                                   |       | 350        | 450    | $\mu\text{A}$ |

| DRIVE Shutdown Quiescent Current        | $\text{EN/UVLO} < 0.4\text{V}$<br>$\text{EN/UVLO} = 1.15\text{V}$ |       | 0.1<br>0.1 | 1<br>2 | $\mu\text{A}$ |

| DRIVE Quiescent Current (Not Switching) | $R_T = 27.4\text{k}\Omega$ , $\text{DRIVE} = 6\text{V}$           |       | 2.0        | 2.5    | mA            |

| SW Pin Current Limit                    |                                                                   | ● 6.0 | 7.0        | 8.0    | A             |

| SW Pin On Voltage                       | $I_{SW} = 3\text{A}$                                              |       | 100        |        | mV            |

| SW Pin Leakage Current                  | $\text{SW} = 40\text{V}$                                          |       |            | 5      | $\mu\text{A}$ |

### エラーアンプ

|                                                                                                  |                                                                                                                  |                     |              |                 |               |

|--------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|---------------------|--------------|-----------------|---------------|

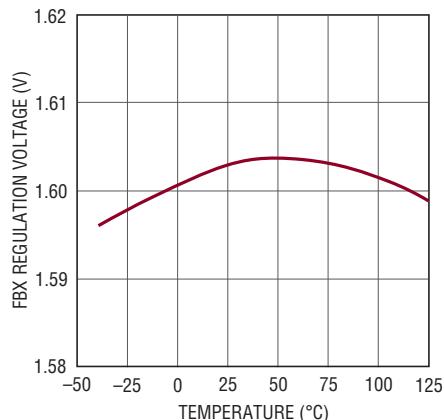

| FBX Regulation Voltage ( $V_{FBX(\text{REG})}$ )                                                 | $\text{FBX} > 0\text{V}$<br>$\text{FBX} < 0\text{V}$                                                             | ● 1.580<br>● -0.815 | 1.6<br>-0.80 | 1.620<br>-0.785 | V             |

| FBX Pin Input Current                                                                            | $\text{FBX} = 1.6\text{V}$<br>$\text{FBX} = -0.8\text{V}$                                                        |                     | -10          | 80<br>10        | nA<br>nA      |

| Transconductance $g_m$ ( $\Delta V_C / \Delta V_{FBX}$ )                                         | $\text{FBX} = V_{FBX(\text{REG})}$                                                                               |                     |              | 240             | $\mu\text{s}$ |

| $V_C$ Output Impedance                                                                           |                                                                                                                  |                     |              | 5               | $M\Omega$     |

| FBX Line Regulation [ $\Delta V_{FBX(\text{REG})} / (\Delta V_{IN} \cdot V_{FBX(\text{REG})})$ ] | $1.6\text{V} < V_{IN} < 40\text{V}$ , $\text{FBX} > 0$<br>$1.6\text{V} < V_{IN} < 40\text{V}$ , $\text{FBX} < 0$ |                     |              | 0.02<br>0.02    | %/V<br>%/V    |

| $V_C$ Source Current                                                                             | $\text{FBX} = 0\text{V}$ , $V_C = 1.3\text{V}$                                                                   |                     |              | -13             | $\mu\text{A}$ |

| $V_C$ Sink Current                                                                               | $\text{FBX} = 1.7\text{V}$ , $V_C = 1.3\text{V}$<br>$\text{FBX} = -0.85\text{V}$ , $V_C = 1.3\text{V}$           |                     |              | 13<br>10        | $\mu\text{A}$ |

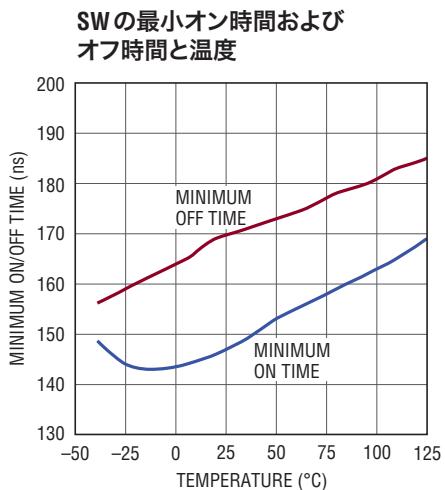

### 発振器

|                     |                                                                                                                                                                         |                      |                    |      |                   |

|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|--------------------|------|-------------------|

| Switching Frequency | $R_T = 27.4\text{k}$ to SGND, $V_{FBX} = 1.6\text{V}$<br>$R_T = 86.6\text{k}$ to SGND, $V_{FBX} = 1.6\text{V}$<br>$R_T = 6.81\text{k}$ to SGND, $V_{FBX} = 1.6\text{V}$ | ● 250<br>100<br>1000 | 300<br>100<br>1000 | 340  | kHz<br>kHz<br>kHz |

| $R_T$ Voltage       | $\text{FBX} = 1.6\text{V}$ , $-0.8\text{V}$                                                                                                                             |                      |                    | 1.13 | V                 |

| SW Minimum Off-Time |                                                                                                                                                                         |                      |                    | 150  | 200               |

| SW Minimum On-Time  |                                                                                                                                                                         |                      |                    | 150  | 200               |

## 電気的特性

●は全動作温度範囲での規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。注記がない限り、 $V_{IN} = 12\text{V}$ 、EN/UVLO = 12V、INTVCC = 4.75V。

| PARAMETER          | CONDITIONS                  |   | MIN | TYP   | MAX | UNITS         |

|--------------------|-----------------------------|---|-----|-------|-----|---------------|

| SYNC Input Low     |                             | ● |     |       | 0.4 | V             |

| SYNC Input High    |                             | ● | 1.5 |       |     | V             |

| SS Pull-Up Current | SS = 0V, Current Out of Pin | ● | -14 | -10.5 | -7  | $\mu\text{A}$ |

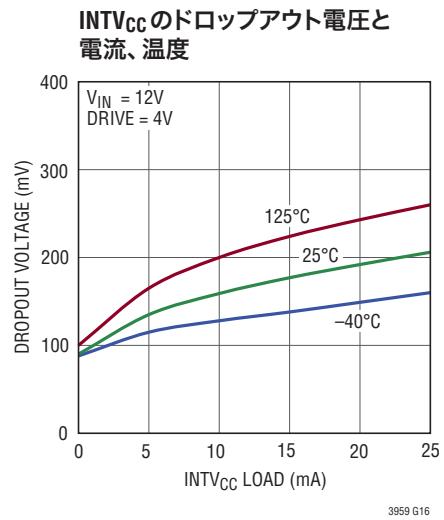

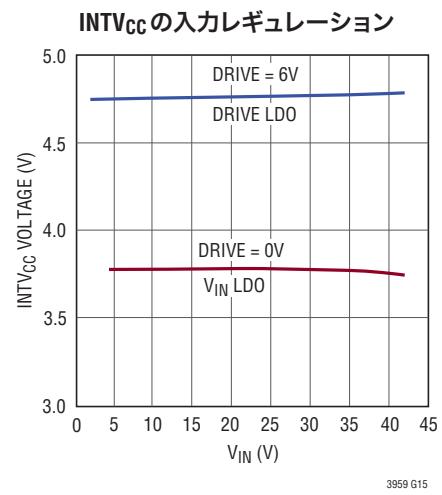

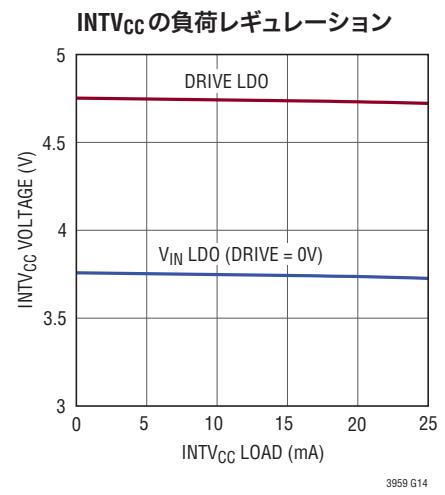

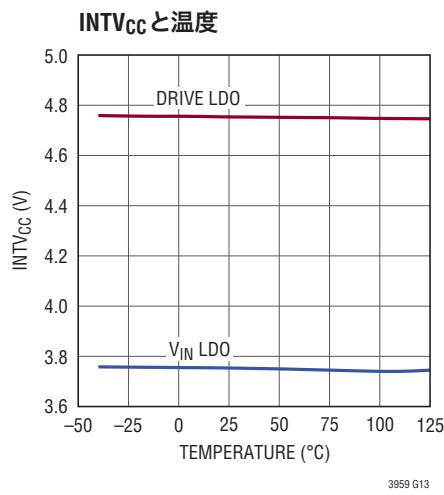

### 低ドロップアウト・レギュレータ(DRIVE LDO および $V_{IN}$ LDO)

|                                                                                       |                                                           |   |      |      |      |               |

|---------------------------------------------------------------------------------------|-----------------------------------------------------------|---|------|------|------|---------------|

| DRIVE LDO Regulation Voltage                                                          | DRIVE = 6V, Not Switching                                 | ● | 4.6  | 4.75 | 4.9  | V             |

| $V_{IN}$ LDO Regulation Voltage                                                       | DRIVE = 0V, Not Switching                                 | ● | 3.6  | 3.75 | 3.9  | V             |

| DRIVE LDO Current Limit                                                               | INTVCC = 4V                                               |   |      | 60   |      | mA            |

| $V_{IN}$ LDO Current Limit                                                            | DRIVE = 0V, INTVCC = 3V                                   |   |      | 60   |      | mA            |

| DRIVE LDO Load Regulation ( $\Delta V_{INTVCC}/V_{INTVCC}$ )                          | $0 < I_{INTVCC} < 20\text{mA}$ , DRIVE = 6V               |   | -1   | -0.6 |      | %             |

| $V_{IN}$ LDO Load Regulation ( $\Delta V_{INTVCC}/V_{INTVCC}$ )                       | DRIVE = 0V, $0 < I_{INTVCC} < 20\text{mA}$                |   | -1   | -0.6 |      | %             |

| DRIVE LDO Line Regulation [ $\Delta V_{INTVCC}/(V_{INTVCC} \cdot \Delta V_{IN})$ ]    | $1.6V < V_{IN} < 40V$ , DRIVE = 6V                        |   |      | 0.03 | 0.07 | %/V           |

| $V_{IN}$ LDO Line Regulation [ $\Delta V_{INTVCC}/(V_{INTVCC} \cdot \Delta V_{IN})$ ] | DRIVE = 0V, $5V < V_{IN} < 40V$                           |   |      | 0.03 | 0.07 | %/V           |

| DRIVE LDO Dropout Voltage ( $V_{DRIVE} - V_{INTVCC}$ )                                | DRIVE = 4V, $I_{INTVCC} = 20\text{mA}$                    | ● |      | 190  | 400  | mV            |

| $V_{IN}$ LDO Dropout Voltage ( $V_{IN} - V_{INTVCC}$ )                                | $V_{IN} = 3V$ , DRIVE = 0V,<br>$I_{INTVCC} = 20\text{mA}$ | ● |      | 190  | 400  | mV            |

| INTVCC Undervoltage Lockout Threshold Falling                                         |                                                           | ● | 1.85 | 2.0  | 2.15 | V             |

| INTVCC Undervoltage Lockout Threshold Rising                                          |                                                           | ● | 2.15 | 2.3  | 2.45 | V             |

| INTVCC Current in Shutdown                                                            | EN/UVLO = 0V                                              |   |      | 25   |      | $\mu\text{A}$ |

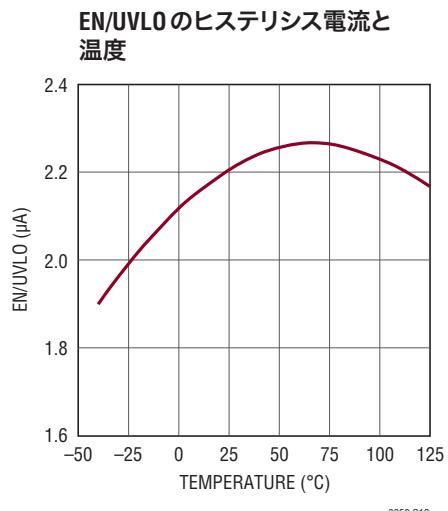

### ロジック

|                                                                     |                                                                                            |   |      |                                                              |      |               |

|---------------------------------------------------------------------|--------------------------------------------------------------------------------------------|---|------|--------------------------------------------------------------|------|---------------|

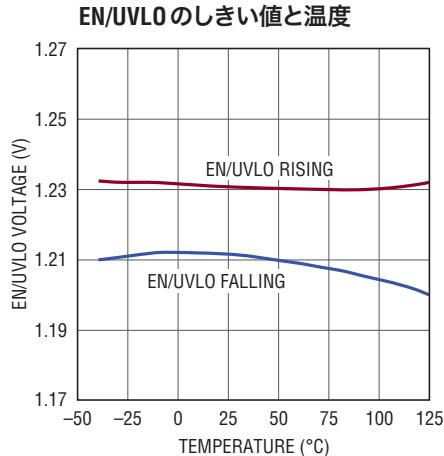

| EN/UVLO Threshold Voltage Falling                                   |                                                                                            | ● | 1.17 | 1.22                                                         | 1.27 | V             |

| EN/UVLO Threshold Voltage Rising Hysteresis                         |                                                                                            |   |      | 20                                                           |      | mV            |

| EN/UVLO Input Low Voltage                                           | $I_{VIN} < 1\mu\text{A}$                                                                   |   |      |                                                              | 0.4  | V             |

| EN/UVLO Pin Bias Current Low                                        | EN/UVLO = 1.15V                                                                            |   | 1.8  | 2.2                                                          | 2.6  | $\mu\text{A}$ |

| EN/UVLO Pin Bias Current High                                       | EN/UVLO = 1.30V                                                                            |   |      | 10                                                           | 100  | nA            |

| FBX Power Good Threshold Voltage                                    | FBX > 0V, $\overline{\text{PGOOD}}$ Falling<br>FBX < 0V, $\overline{\text{PGOOD}}$ Falling |   |      | $V_{FBX(\text{REG})} - 0.08$<br>$V_{FBX(\text{REG})} + 0.04$ |      | V             |

| FBX Overvoltage Threshold                                           | FBX > 0V, $\overline{\text{PGOOD}}$ Rising<br>FBX < 0V, $\overline{\text{PGOOD}}$ Rising   |   |      | $V_{FBX(\text{REG})} + 0.12$<br>$V_{FBX(\text{REG})} - 0.06$ |      | V             |

| $\overline{\text{PGOOD}}$ Output Low ( $V_{OL}$ )                   | $I_{\overline{\text{PGOOD}}} = 250\mu\text{A}$                                             |   |      | 210                                                          | 300  | mV            |

| $\overline{\text{PGOOD}}$ Leakage Current                           | $\overline{\text{PGOOD}} = 40\text{V}$                                                     |   |      |                                                              | 1    | $\mu\text{A}$ |

| INTVCC Minimum Voltage to Enable $\overline{\text{PGOOD}}$ Function |                                                                                            | ● | 2.5  | 2.7                                                          | 2.9  | V             |

| INTVCC Minimum Voltage to Enable SYNC Function                      |                                                                                            | ● | 2.5  | 2.7                                                          | 2.9  | V             |

**Note 1:** 絶対最大定格に記載された値を超えるストレスはデバイスに永続的損傷を与える可能性がある。長期にわたって絶対最大定格条件に曝すと、デバイスの信頼性と寿命に悪影響を与える恐れがある。

**Note 2:** 4Vより下の $V_{IN}$ では、適切な動作のため、EN/UVLO ピンは $V_{IN}$ を超えてはならない。

**Note 3:** LT3959Eは0°C～125°Cの動作接合部温度で性能仕様に適合することが保証されている。 $-40^\circ\text{C} \sim 125^\circ\text{C}$ の動作接合部温度範囲での仕様は設計、特性評価および統計学的なプロセス・コントロールとの相関で確認されている。LT3959Iは $-40^\circ\text{C} \sim 125^\circ\text{C}$ の全動作接合部温度範囲で保証されている。

**Note 4:** LT3959は、 $V_C$ ピンを1.3Vに強制した状態で $V_{FBX}$ をリファレンス電圧(1.6Vおよび-0.8V)にサーボ制御する帰還ループでテストされる。

## 標準的性能特性 注記がない限り $T_A = 25^\circ\text{C}$ 。

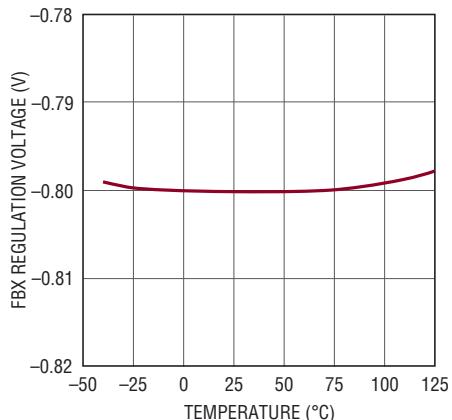

**FBXの正レギュレーション電圧と

温度**

**FBXの負レギュレーション電圧と

温度**

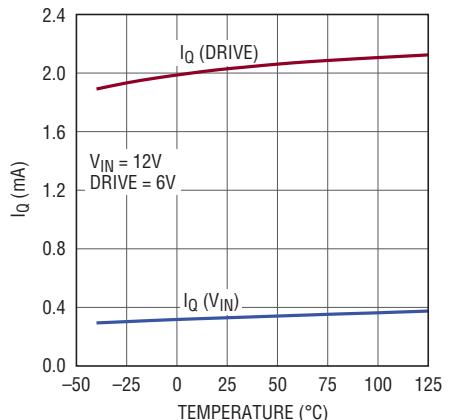

**静止電流と温度**

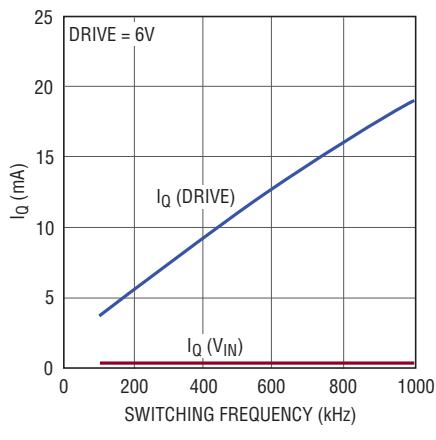

**動作時静止電流と

スイッチング周波数**

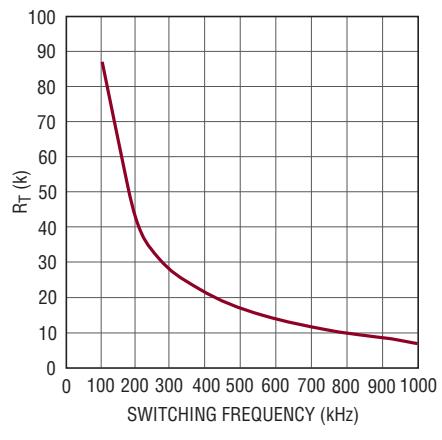

**R\_Tとスイッチング周波数**

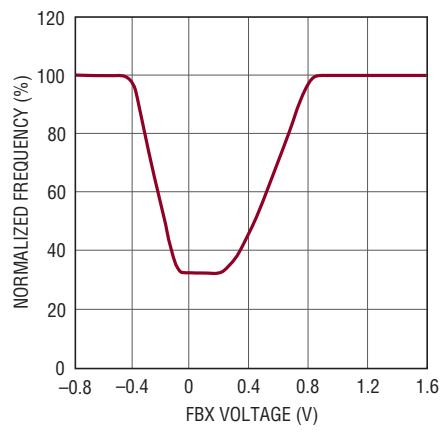

**正規化されたスイッチング周波数

とFBX電圧**

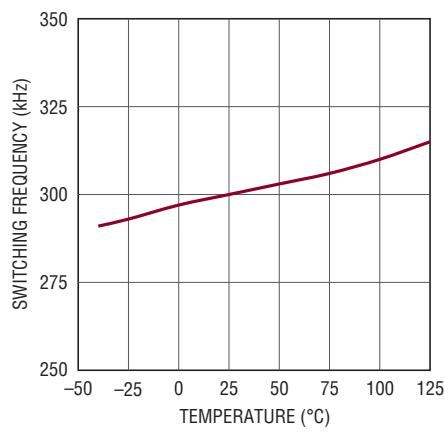

**スイッチング周波数と温度**

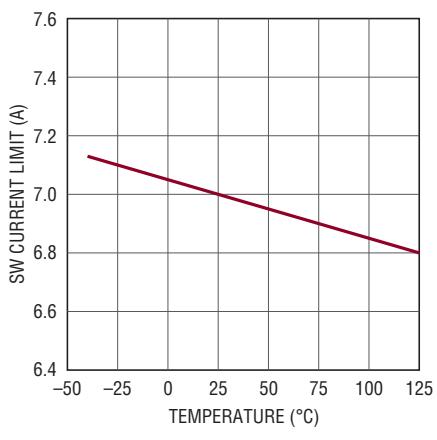

**スイッチ電流制限と温度**

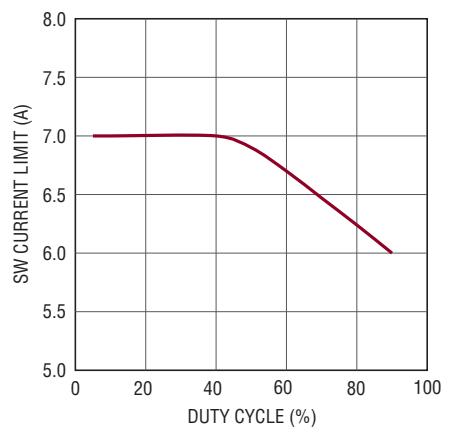

**スイッチ電流制限と

デューティサイクル**

## 標準的性能特性 注記がない限り、 $T_A = 25^\circ\text{C}$ 。

## ピン機能

**DRIVE:** DRIVE LDO電源ピン。このピンは、V<sub>IN</sub>またはDCコンバータの出力のような疑似安定化電圧電源に接続することができます。このピンは、ピンの近くに配置した最小1μFのコンデンサでGNDにバイパスする必要があります。使用しない場合、このピンはV<sub>IN</sub>に接続します。

**EN/UVLO:** シャットダウンおよび低電圧検出ピン。外部設定可能なヒステリシスを備えた1.22V(公称)の高精度下降時しきい値により、電源がスイッチングをイネーブルできる状態になったことを検出します。上昇時のヒステリシスは外部抵抗分割器と正確な内部2.2μA プルダウン電流によって生成されます。低電圧状態になるとソフトスタートがリセットされます。0.4V以下に接続してデバイスをディスエーブルすると、V<sub>IN</sub>の静止電流は1μA未満に減少します。

**FBX:** 正出力または負出力の電圧レギュレーション帰還ピン。このピンを、出力とSGNDの間に接続された抵抗分割器に接続します。FBXは2つのエラーアンプの入力で、これらのエラーアンプの一方は正出力を安定化し、他方は負出力を安定化するように構成されています。選択されたトポロジーに依存して、スイッチングにより、出力は正または負にランプします。適切なアンプが制御を行い、他方のアンプは休止します。さらに、FBXは2つのウインドウ・コンパレータの入力です。これらのコンパレータは、PGOODピンを介して、出力がレギュレーション電圧から5%以内であることを知らせます。また、FBXがSGNDに近い起動時およびフォルト状態の間はスイッチング周波数の変調も行います。

**GND:** スイッチのソース端子およびスイッチ電流コンパレータへのGND入力。

**GNDK:** GNDとSGNDの間のケルビン接続用ピン。このピンを、デバイスに近いSGNDプレーンにケルビン接続します。「基板レイアウト」のセクションを参照してください。

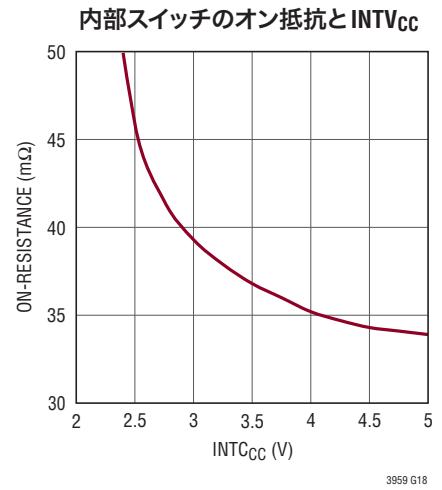

**INTV<sub>CC</sub>:** 内部負荷およびゲート・ドライバ用の安定化された電源。DRIVEから給電される場合は4.75Vに安定化され、V<sub>IN</sub>から給電される場合は3.75Vに安定化されます。INTV<sub>CC</sub>ピンは、ピンの近くに配置した最小4.7μFのコンデンサでSGNDにバイパスする必要があります。

**NC:** 内部接続なし。これらのピンは開放のままにするか、隣接するピンに接続します。

**PGOOD:** 出力レディー状態ピン。PGOODのオープン・コレクタ・プルダウンは、INTV<sub>CC</sub>が2.7Vを上回り、FBXの電圧がレギュレーション電圧から5%(V<sub>FBX</sub> = 1.6Vのとき80mV、V<sub>FBX</sub> = -0.8Vのとき40mV)以内のとき、アサートします。

**RT:** スイッチング周波数調整ピン。SGNDへの抵抗を使って周波数を設定します。RTピンは開放のままにしないでください。

**SGND:** 信号グランド。信号グランド・プレーンに直接半田付けする必要があります。FBXおよびEN/UVLOの外部抵抗分割器、INTV<sub>CC</sub>、SSおよびV<sub>C</sub>のコンデンサ、抵抗R<sub>T</sub>のグランド端子に接続します。

**SS:** ソフトスタート・ピン。このピンは補償ピンの電圧(V<sub>C</sub>)ランプを調整します。ソフトスタート時間は外部コンデンサによって設定されます。このピンには、内部2.5Vレールへの10μA(標準)プルアップ電流源が備わっています。ソフトスタート・ピンは、EN/UVLOの低電圧状態、INTV<sub>CC</sub>の低電圧状態、または内部過熱ロックアウトによってSGNDにリセットされます。

**SW:** 内部パワーNチャネルMOSFETのドレイン。

**SYNC:** 周波数同期ピン。内部発振器を外部クロックに同期させるのに使います。この機能を使う場合、R<sub>T</sub>抵抗を選択して、SYNCパルス周波数より20%遅いスイッチング周波数に設定します。この機能を使用しないときは、SYNCピンをSGNDに接続します。この信号は、FBの周波数フォールドバックの間、またはINTV<sub>CC</sub>が2.7Vを下回ると、無視されます。

**V<sub>IN</sub>:** 内部リードおよびINTV<sub>CC</sub>のV<sub>IN</sub> LDOレギュレータの電源ピン。このピンの近くに配置した最小1μFのコンデンサでGNDにローカルにバイパスする必要があります。

**V<sub>C</sub>:** エラーアンプの補償ピン。外部RCネットワークで電圧ループを安定にするのに使われます。V<sub>C</sub>ピンとSGNDの間に補償部品を配置します。

# LT3959

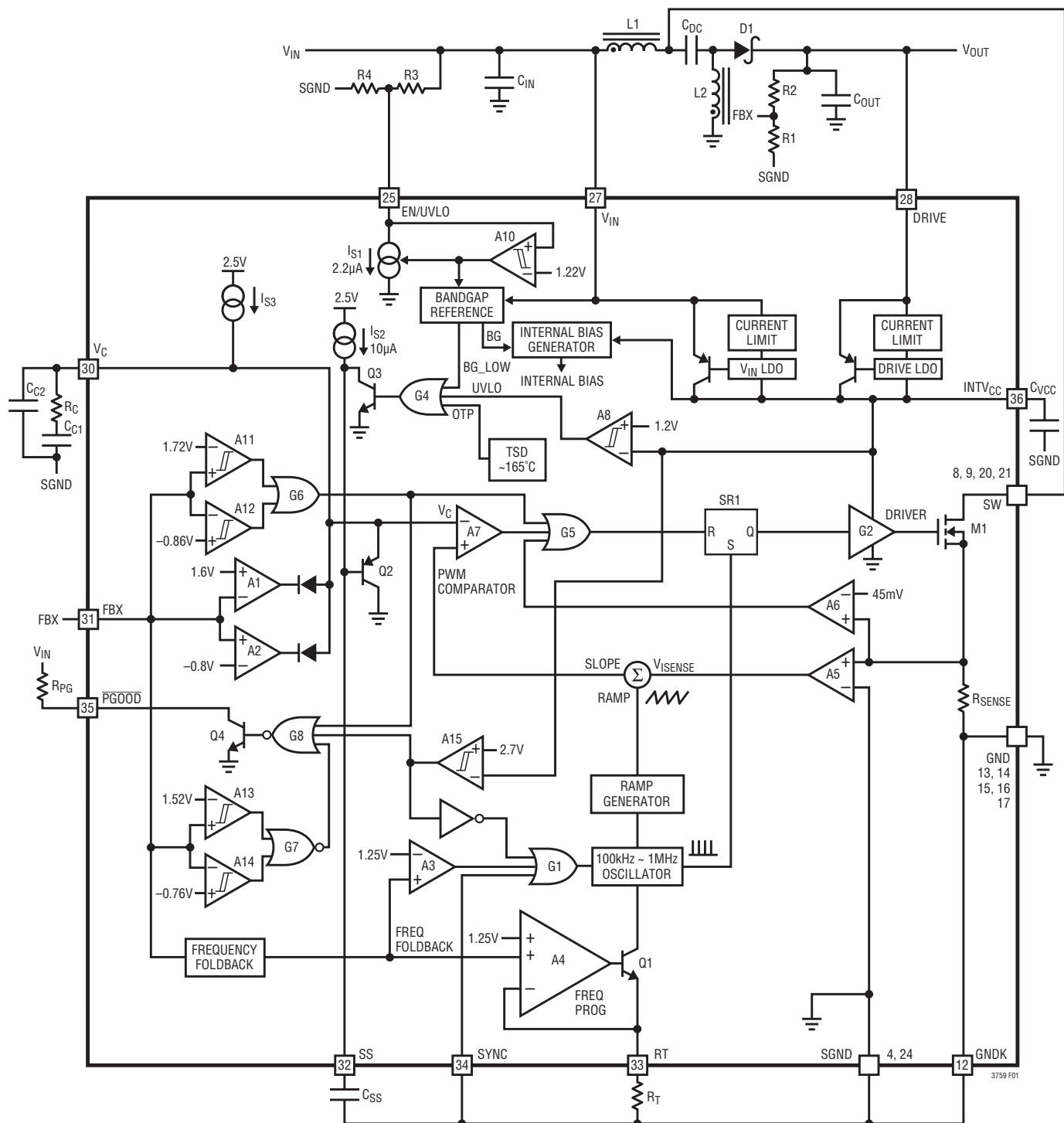

## ブロック図(QFNパッケージ)

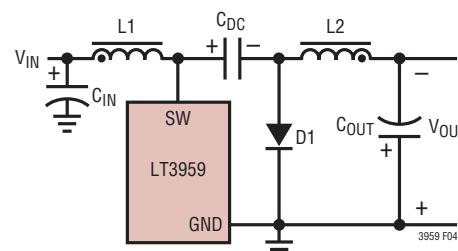

図1.SEPICコンバータとして動作するLT3959のブロック図(QFNパッケージの場合)

## アプリケーション情報

### メイン制御ループ

LT3959は固定周波数の電流モード制御方式を使って、優れた入力レギュレーションと負荷レギュレーションを実現します。図1のブロック図を参照すると動作をよく理解できます。

発振器の各サイクルの開始点でSRラッチ(SR1)がセットされ、ドライバG2によって内部パワーMOSFETスイッチM1をオンします。スイッチ電流が内部電流検出抵抗 $R_{SENSE}$ を通って流れ、スイッチ電流に比例した電圧を発生させます。(A5によって増幅された)この電流検出電圧 $V_{ISENSE}$ が安定化スロープ補償ランプへ加算され、その和(SLOPE)がPWMコンパレータA7の正端子に与えられます。SLOPEがA7の負入力( $V_C$ ピン)のレベルを超えると、SR1がリセットされ、パワースイッチをオフします。A7の負入力のレベルはエラー・アンプA1(またはA2)によって設定され、帰還電圧(FBXピン)とリファレンス電圧(構成設定に依存して1.6Vまたは-0.8V)の差を増幅したものです。このようにして、エラー・アンプは正しいピーク・スイッチ電流レベルを設定し、出力を安定化された状態に保ちます。

LT3959はスイッチ電流制限機能を備えています。電流検出電圧は電流制限コンパレータA6へ入力されます。SENSEの電圧が検出電流制限しきい値 $V_{SENSE(MAX)}$ (標準45mV)よりも高いと、A6は直ちにSR1をリセットしてM1をオフします。

LT3959は1つのFBXピンを使って正または負の出力電圧を生成することができます。昇圧コンバータまたはSEPICコンバータとして構成して正の出力電圧を生成するか、または反転コンバータとして構成して負の出力電圧を生成することができます。図1に示されているように、SEPICコンバータとして構成されている場合、FBXピンは $V_{OUT}$ からSGNDに接続された分圧器(R1とR2)によって、1.6Vの内部バイアス電圧にプルアップされます。コンパレータA2は非アクティブになります。コンパレータA1はFBXから $V_C$ への反転増幅を行います。LT3959が反転構成の場合、FBXピンは $V_{OUT}$ からSGNDに接続された分圧器によって-0.8Vにプルダウンされます。コンパレータA1は非アクティブになります。コンパレータA2はFBXから $V_C$ への非反転増幅を行います。

LT3959は過電圧保護機能を備えており、起動時や短絡状態からの回復時に出力電圧の過度のオーバーシュートからコンバータを保護します。FBXピンの電圧が安定化された正電圧(1.6V)を7.5%超えると、40mVのヒステリシスのある過電圧コンパレータA11がそれを検出し、M1をオフします。同様に、FBXピンの電圧が安定化された負電圧(-0.8V)を7.5%超えると、20mVのヒステリシスのある過電圧コンパレータA12がそれを検出し、M1をオフします。両方のリセット・パルスともG6とG5を通してメインRSラッチ(SR1)に送られます。出力過電圧状態が続いている間、内部のパワーMOSFETスイッチM1はアクティブにオフに保たれます。

### EN/UVLOピンを使ったターンオンとターンオフのしきい値の設定

EN/UVLOピンにより、LT3959をイネーブルするかそれともシャットダウン状態にするかが制御されます。マイクロパワー1.22Vリファレンス、コンパレータA10および制御可能な電流源 $I_{S1}$ により、ユーザーはデバイスがそこでオン/オフする電源電圧を正確にプログラムすることができます。下降時の値は抵抗分割器のR3とR4によって正確に設定されます。EN/UVLOが0.7Vより上で1.22Vのしきい値より下のとき、小さなプルダウン電流源 $I_{S1}$ (標準2.2μA)がアクティブになります。

この電流の目的はユーザーが上昇方向ヒステリシスをプログラマできるようにすることです。コンパレータのブロック図と外部抵抗を図1に示します。標準的な立ち下がりしきい値電圧と立ち上がりしきい値電圧は以下の式によって計算することができます。

$$V_{VIN(FALLING)} = 1.22 \cdot \frac{(R3+R4)}{R4}$$

$$V_{VIN(RISING)} = 2.2\mu A \cdot R3 + V_{IN(FALLING)}$$

EN/UVLOピンがロジック入力としてだけ使われるアプリケーションでは、EN/UVLOピンは常時オン動作のため入力電圧 $V_{IN}$ に直接接続することができます。

## アプリケーション情報

### INTV<sub>CC</sub>低ドロップアウト電圧レギュレータ

LT3959は、異なる電源( $V_{IN}$ とDRIVE)0からそれぞれ給電される2つの低ドロップアウト(LDO)電圧レギュレータ( $V_{IN}$  LDOとDRIVE LDO)を内蔵しています。両方のLDOとも、図1に示されているように、内部INTV<sub>CC</sub>電源を安定化します。INTV<sub>CC</sub>電源は、ゲート・ドライバと内部負荷に給電します。両方のレギュレータとも、逆バイアス状態で、INTV<sub>CC</sub>からLDOの入力に電流が流れないように設計されています。DRIVE LDOはINTV<sub>CC</sub>を4.75Vに安定化し、 $V_{IN}$  LDOはINTV<sub>CC</sub>を3.75Vに安定化します。INTV<sub>CC</sub>電圧が3.75V(標準)より大きいと、 $V_{IN}$  LDOはオフします。4.75V以上だが8Vよりは低い(INTV<sub>CC</sub>の最大電圧定格は8V)電源によってINTV<sub>CC</sub>ピンがドライブされると、両方のLDOをオフすることができます。LDO電源と出力電圧の組み合わせの表を表1に示します。

**表1. LDOの電源と出力電圧の組み合わせ

(LDOのドロップアウト電圧は0.15Vと仮定)**

| 電源電圧                     |                                | LDOの出力              | LDOの状態<br>(Note 7) |

|--------------------------|--------------------------------|---------------------|--------------------|

| $V_{IN}$                 | DRIVE                          | INTV <sub>CC</sub>  |                    |

| $V_{IN} \leq 3.9V$       | $V_{DRIVE} < V_{IN}$           | $V_{IN} - 0.15V$    | #1 is ON           |

|                          | $V_{DRIVE} = V_{IN}$           | $V_{IN} - 0.15V$    | #1 #2 are ON       |

|                          | $V_{IN} < V_{DRIVE} < 4.9V$    | $V_{DRIVE} - 0.15V$ | #2 is ON           |

|                          | $4.9V \leq V_{DRIVE} \leq 40V$ | 4.75V               | #2 is ON           |

| $3.9V < V_{IN} \leq 40V$ | $V_{DRIVE} < 3.9V$             | 3.75V               | #1 is ON           |

|                          | $V_{DRIVE} = 3.9V$             | 3.75V               | #1 #2 are ON       |

|                          | $3.9V < V_{DRIVE} < 4.9V$      | $V_{DRIVE} - 0.15V$ | #2 is ON           |

|                          | $4.9V \leq V_{DRIVE} \leq 40V$ | 4.75V               | #2 is ON           |

Note 7: #1は $V_{IN}$  LDO、#2はDRIVE LDO

DRIVEピンは、スイッチャがイネーブルされて動作しているときだけ利用できる電源から、ゲート・ドライバと内部負荷に柔軟に給電します。使わない場合、DRIVEピンは $V_{IN}$ に接続します。

INTV<sub>CC</sub>ピンは、このピンのすぐ近くに置いた最小4.7μFのセラミック・コンデンサでSGNDにバイパスする必要があります。MOSFETゲート・ドライバが必要とする大きなトランジエント電流を供給するには十分なバイパスが必要です。

### 動作周波数と同期

動作周波数はデバイス内部の電力損失に基づいて選択することができます。ただし、効率と部品サイズの間にはトレードオフがあります。低周波数動作では、ゲート駆動電流および内部MOSFETとダイオードのスイッチング損失が減少して効率が改善されます。ただし、低周波数動作には物理的に大きなインダクタが必要です。スイッチング周波数はループ補償にも関係します。LT3959には固定周波数アーキテクチャが使われており、図1に示されているように、RTピンからSGNDに接続した1個の外付け抵抗を使って100KHz～1MHzの範囲で設定することができます。LT3959が適切に動作するために、外付け抵抗をRTピンからSGNDに接続する必要があります。与えられた動作周波数に対応する $R_T$ 値を選択するための表を表2に示します。

**表2. タイミング抵抗( $R_T$ )の値**

| 発振器周波数(kHz) | $R_T$ (kΩ) |

|-------------|------------|

| 100         | 86.6       |

| 200         | 41.2       |

| 300         | 27.4       |

| 400         | 21.0       |

| 500         | 16.5       |

| 600         | 13.7       |

| 700         | 11.5       |

| 800         | 9.76       |

| 900         | 8.45       |

| 1000        | 6.81       |

LT3959のスイッチング周波数は外部クロック・ソースの立ち上がりエッジに同期させることができます。デジタル・クロック信号をSYNCピンに与えることにより、LT3959はSYNCクロック周波数で動作します。この機能を使う場合、 $R_T$ 抵抗を選択してSYNCパルス周波数より20%遅いスイッチング周波数に設定します。SYNCパルスは最小200nsのパルス幅にします。この機能を使用しないときは、SYNCピンをSGNDに接続します。

## アプリケーション情報

### デューティサイクルに関する検討事項

スイッチング・デューティサイクルはコンバータの動作を定める重要な変数です。したがって、そのリミットを検討する必要があります。最小オン時間は、LT3959が内部パワーMOSFETをオンすることができる最小時間です。この時間は一般に約150ns（標準）です（「電気的特性」の表のMinimum On-Timeを参照）。スイッチング・サイクルごとに、LT3959はパワースイッチを少なくとも150ns（標準）オフに保ちます（「電気的特性」の表のMinimum Off-Timeを参照）。

最小オン時間、最小オフ時間およびスイッチング周波数により、コンバータが生成可能なスイッチング・デューティサイクルの最小値と最大値が定まります。

最小デューティサイクル = 最小オン時間・周波数

最大デューティサイクル = 1 - (最小オフ時間・周波数)

### 出力電圧のプログラミング

出力電圧( $V_{OUT}$ )は、図1に示されているように、抵抗分割器によって設定されます。正の $V_{OUT}$ と負の $V_{OUT}$ は以下の式によって設定されます。

$$V_{OUT(POSITIVE)} = 1.6V \cdot \left(1 + \frac{R2}{R1}\right)$$

$$V_{OUT(NEGATIVE)} = -0.8V \cdot \left(1 + \frac{R2}{R1}\right)$$

抵抗R1とR2は一般に、通常動作時にFBXピンに流れ込む電流によって生じる誤差が1%未満になるように選択します（これは約121kのR1の最大値に相当します）。

### ソフトスタート

LT3959は起動時またはフォルト状態からの回復時にピーク・スイッチ電流と出力電圧( $V_{OUT}$ )のオーバーシュートを制限する機能をいくつか備えています。これらの機能の主な目的は、外付け部品や負荷の損傷を防ぐことです。

スイッチング・レギュレータには、起動時に大きなピーク・スイッチ電流が発生することがあります。 $V_{OUT}$ がその最終値にほど遠く、帰還ループが飽和し、レギュレータは出力コンデンサができるだけ短い時間で充電しようとするので、大きなピーク電流が発生します。大きなサージ電流はインダクタを飽和させるか、またはパワースイッチの機能不良を生じさせることができます。

LT3959はSSピンを使ってこのメカニズムに対応します。図1に示されているように、SSピンはQ2を介して $V_C$ ピンをプルダウンすることにより、内部パワーMOSFETの電流を減らします。このように、SSピンを使って、起動時のピーク電流を制限しながら出力コンデンサをその最終値に向けて徐々に充電することができます。

ソフトスタートは起動によってトリガされますが、 $INTV_{CC}$ の低電圧ロックアウトや過熱ロックアウトによってトリガされることもあります。これらが発生すると、LT3959はスイッチングを直ちに停止します。SSピンはQ3によって放電します。すべてのフォルトが解消されてSSピンが0.2Vより低い電位まで放電すると、 $10\mu A$ の電流源 $I_{S2}$ がSSピンを充電し始め、ソフトスタート動作が開始されます。

ソフトスタート時間は、次式に従ってソフトスタート・コンデンサを選択することにより設定されます。

$$T_{SS} = C_{SS} \cdot \frac{1.25V}{10\mu A}$$

### FBX周波数フォールドバック

起動時または出力の短絡フォルト時に $V_{OUT}$ が非常に低いときは、スイッチのオフ時間中のインダクタ電流の減衰速度が非常に遅いので、スイッチング・レギュレータは、パワースイッチの電流を電流制限範囲内に保つために低いデューティサイクルで動作する必要があります。最小オン時間の制約により、プログラムされたスイッチング周波数ではスイッチャが十分低いデューティサイクルを達成できないことがあります。そのため、スイッチ電流は各スイッチ・サイクルにわたって増加し続け、プログラムされた電流制限を超えます。スイッチのピーク電流がプログラムされた値を超えるのを防ぐため、LT3959は周波数フォールドバック機能を備えており、FBX電圧が低いときスイッチング周波数を下げます（「標準的性能特性」のセクションの「正規化されたスイッチング周波数とFBX電圧」のグラフを参照）。

## アプリケーション情報

いくつかの周波数フォールドバック波形が「標準的応用例」のセクションに示されています。周波数フォールドバック機能は、最小オン時間のため  $I_L$  がプログラムされたリミットを超えるのを防ぎます。

周波数フォールドバックの間、周波数を適切に下げられるように、外部クロックへの同期はディスエーブルされます。

### ループ補償

ループ補償により安定性とトランジエント性能が決まります。LT3959は電流モード制御を使って出力を安定化するので、ループ補償が簡単になります。最適値はコンバータのトポロジー、部品の値および動作条件(入力電圧、負荷電流など)に依存します。LT3959の帰還ループを補償するには、通常、直列RCネットワークを  $V_C$  ピンからSGNDに接続します。標準的な  $V_C$  補償ネットワークを図1に示します。ほとんどのアプリケーションでは、コンデンサは470pF～22nFの範囲、抵抗は5k～50kの範囲にします。多くの場合、内部エラーアンプを介して出力電圧リップルから生じる  $V_C$  電圧リップルを減衰させるために、小さなコンデンサがRC補償ネットワークに並列に接続されます。この並列コンデンサの値は通常10pF～100pFの範囲です。補償ネットワークを設計する実際的な手法としては、このデータシートの回路の中から目的のアプリケーションに似た回路を選んで出発点とし、補償ネットワークを調整して性能を最適化します。次に、負荷電流、入力電圧、温度など全ての動作条件にわたって安定性をチェックします。

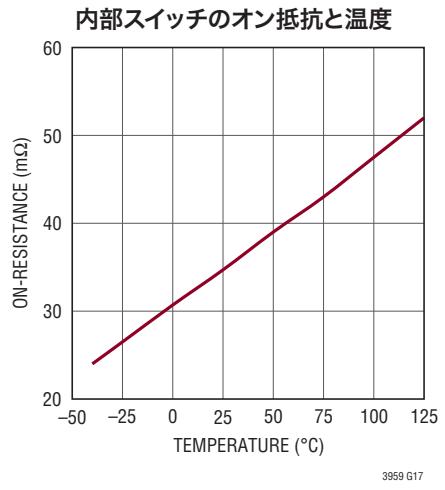

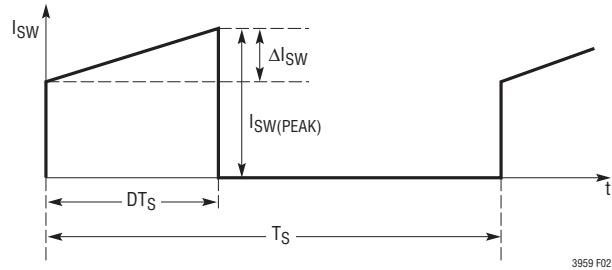

### 内部パワースイッチの電流

制御と保護のため、LT3959はGNDとMOSFETのソースの間にある検出抵抗( $R_{SENSE}$ )を使って内部パワーMOSFETの電流を測定します。内部スイッチ電流( $I_{SW}$ )の標準的な波形を図2に示します。

図2.スイッチング・サイクル中のSW電流

LT3959は内部パワースイッチの電流が制限されているので(最小6A)、定常状態の通常動作時にスイッチのピーク電流  $I_{SW(Peak)}$  が6Aよりも少なく、なおかつ十分なマージン(10%以上を推奨)を取れるようなアプリケーションに使用します。

接合部温度制限値(125°C)を超えていないことを確認するには、定常状態でデバイスの温度を測定することを推奨します。  $T_{J(MAX)}$  が125°Cを超えないように、スイッチング周波数を低くしなければならないことがあります。

LT3959のダイ温度が165°C(標準)の過熱ロックアウトしきい値に達すると、デバイスはいくつかの保護対策を開始します。パワースイッチがオフして、ソフトスタート動作がトリガされます。接合部温度が5°C(公称)下がると、デバイスは再度インペーブルされます。

### アプリケーション回路

LT3959は異なるトポロジーとして構成することができます。部品選択の設計手順はこれらのトポロジーの間でいくらか異なります。最初に検討すべきトポロジーは昇圧コンバータで、続いてSEPICおよび反転コンバータを検討します。

## アプリケーション情報

### 昇圧コンバータ:スイッチのデューティサイクルと周波数

LT3959は、コンバータの出力電圧が入力電圧より高いアプリケーションでは昇圧コンバータとして構成することができます。昇圧コンバータは短絡保護されていないことに注意してください。出力が短絡された状態では、インダクタ電流を制限するのは入力電源の供給能力だけです。短絡保護された昇圧コンバータが必要なアプリケーションについては、SEPICコンバータを扱っている「アプリケーション情報」のセクションを参照してください。

デューティサイクルの関数としての変換比は、

$$\frac{V_{OUT}}{V_{IN}} = \frac{1}{1-D}$$

連続導通モード(CCM)では次のとおりです。

CCMで動作している昇圧コンバータの場合、メイン・スイッチのデューティサイクルは出力電圧( $V_{OUT}$ )および入力電圧( $V_{IN}$ )に基づいて計算することができます。デューティサイクルが最大( $D_{MAX}$ )になるのは、コンバータの入力電圧が最小のときです。

$$D_{MAX} = \frac{V_{OUT} - V_{IN(MIN)}}{V_{OUT}}$$

CCMに代わって選択可能な不連続導通モード(DCM)は、デューティサイクルによって制限されず、所定の周波数で高い変換比が得られます。その代価として、効率が低下し、スイッチング電流が大きく増加します。

### 昇圧コンバータ:最大出力電流能力とインダクタの選択

昇圧トポロジーの場合、最大平均インダクタ電流は次式で与えられます。

$$I_{L(MAX)} = I_{O(MAX)} \cdot \frac{1}{1-D_{MAX}}$$

LT3959は内部パワースイッチの電流が制限されているので、最大出力電流( $I_{O(MAX)}$ )が最大出力電流能力よりも小さく、なおかつ十分なマージン(10%以上を推奨)を取れる昇圧コンバータに使用します。

$$I_{O(MAX)} < \frac{V_{IN(MIN)}}{V_{OUT}} \cdot (6A - 0.5 \cdot \Delta I_{SW})$$

インダクタ・リップル電流  $\Delta I_{SW}$  はインダクタの値の選択とコンバータの最大出力電流能力に直接影響を与えます。小さな値の  $\Delta I_{SW}$  を選択すると出力電流能力は向上しますが、大きなインダクタンスが必要になり、電流ループの利得が減少します(コンバータは電圧モードに近づきます)。大きな  $\Delta I_{SW}$  の値を許容できればトランジエント応答が速くなり、低インダクタンスの使用が可能になりますが、入力電流リップルが大きくなつてコア損失も大きくなり、出力電流能力が低下します。

動作入力電圧範囲が与えられ、動作周波数とインダクタのリップル電流を選んだら、次式を使って昇圧コンバータのインダクタの値を決めることができます。

$$L = \frac{V_{IN(MIN)}}{\Delta I_{SW} \cdot f_{OSC}} \cdot D_{MAX}$$

ピーク・インダクタ電流はスイッチの電流制限値(標準7A)で、RMS インダクタ電流は  $I_{L(MAX)}$  にほぼ等しくなります。飽和電流定格と RMS 電流定格が十分なインダクタを選択する必要があります。

### 昇圧コンバータ:出力ダイオードの選択

効率を最大にするには、順方向の電圧降下が小さく、逆方向のリーク電流の小さな高速スイッチング・ダイオードが最適です。ダイオードが耐えなければならないピーク逆電圧は、レギュレータの出力電圧に、オン時間の間そのアノード-カソード両端に現れる追加リングを加えた電圧に等しくなります。通常動作の平均順方向電流は出力電流に等しくなります。

## アプリケーション情報

ピーク反復逆電圧定格  $V_{RRM}$  が  $V_{OUT}$  より安全マージン分だけ高いものを推奨します(通常は10Vの安全マージンで十分です)。

ダイオードの電力損失は次のとおりです。

$$P_D = I_{D(MAX)} \cdot V_D$$

ここで、 $V_D$  はダイオードの順方向電圧降下で、ダイオードの接合部温度は次のとおりです。

$$T_J = T_A + P_D \cdot R_{\theta JA}$$

この式で使われる  $R_{\theta JA}$  にはデバイスの  $R_{\theta JC}$  およびボードから筐体内の周囲温度までの熱抵抗が通常含まれます。 $T_J$  がダイオードの最大接合部温度定格を超えてはいけません。

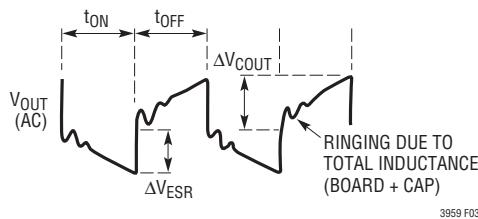

### 昇圧コンバータ: 出力コンデンサの選択

与えられた出力リップル電圧に対する適切な出力コンデンサを選択するとき、ESR(等価直列抵抗)、ESL(等価直列インダクタンス)およびバルク容量が与える影響について考慮する必要があります。標準的昇圧コンバータの場合の、これら3つのパラメータ(ESR、ESL、バルク容量)の出力電圧リップル波形に与える影響を図3に示します。

図3. 昇圧コンバータの出力リップルの波形

部品の選択は、(出力電圧のパーセンテージで表した)最大許容リップル電圧の検討と、このリップルを ESR のステップ  $\Delta V_{ESR}$  と充放電  $\Delta V_{COUT}$  の間でどのように分割すべきかの検討から始めます。単純化するため、最大出力リップルとして2%を選択し、 $\Delta V_{ESR}$  と  $\Delta V_{COUT}$  の間で等分することにします。このパーセンテージ・リップルはアプリケーションの要件に応じて変化しますが、以下の式は簡単に修正することができます。全リップル電圧への影響が1%の場合、出力コンデンサのESRは次式を使って求めることができます。

$$ESR_{COUT} \leq \frac{0.01 \cdot V_{OUT}}{I_{D(Peak)}}$$

バルク容量部品による全リップルへの影響も1%ですが、この場合次のようにになります。

$$C_{OUT} \geq \frac{I_{O(MAX)}}{0.01 \cdot V_{OUT} \cdot f_{osc}}$$

図3に示されているように、昇圧レギュレータの出力コンデンサには大きなRMSリップル電流が流れます。出力コンデンサのRMSリップル電流定格は、次式を使って求めることができます。

$$I_{RMS(COUT)} \geq I_{O(MAX)} \cdot \sqrt{\frac{D_{MAX}}{1-D_{MAX}}}$$

ESRの要件を満たすため、複数のコンデンサを並列に接続することがよくあります。通常、ESRの要件が満たされると、その容量はフィルタリングに関して妥当であり、必要なRMS電流定格を備えています。一般にセラミック・コンデンサを並列に追加して出力コンデンサの寄生インダクタンスの影響を減らします。それによってコンバータの出力の高周波スイッチング・ノイズが減少します。

### 昇圧コンバータ: 入力コンデンサの選択

インダクタが入力に直列に接続されており、入力電流波形が連続的なので、昇圧コンバータの入力コンデンサは出力コンデンサほど条件が厳しくありません。入力電圧源のインピーダンスにより入力コンデンサの容量が決まります。この容量は標準で  $10\mu F \sim 100\mu F$  の範囲です。出力コンデンサの場合ほど条件が厳しくはありませんが、低ESRのコンデンサを推奨します。

昇圧コンバータの入力コンデンサのRMSリップル電流は次のとおりです。

$$I_{RMS(CIN)} = 0.3 \cdot \Delta I_L$$

## アプリケーション情報

### SEPICコンバータのアプリケーション

図1に示されているように、LT3959はSEPIC(シングルエンド・プライマリ・インダクタンス・コンバータ)に構成可能です。このトポロジーにより、必要な出力電圧に比べて、入力を高く、等しく、または低くすることができます。デューティサイクルの関数としての変換比は、

$$\frac{V_{OUT} + V_D}{V_{IN}} = \frac{D}{1-D}$$

連続導通モード(CCM)では次のとおりです。

SEPICコンバータでは、入力と出力の間にDC経路は存在しません。これは、回路がシャットダウン状態のとき入力ソースから出力を切断する必要のあるアプリケーションでは、昇圧コンバータより有利です。

### SEPICコンバータ:スイッチのデューティサイクルと周波数

CCMで動作しているSEPICコンバータの場合、メイン・スイッチのデューティサイクルは、出力電圧( $V_{OUT}$ )、入力電圧( $V_{IN}$ )およびダイオードの順方向電圧( $V_D$ )に基づいて計算することができます。

デューティサイクルが最大( $D_{MAX}$ )になるのは、コンバータの入力電圧が最小のときです。

$$D_{MAX} = \frac{V_{OUT} + V_D}{V_{IN(MIN)} + V_{OUT} + V_D}$$

### SEPICコンバータ:最大出力電流能力とインダクタの選択

図1に示されているように、SEPICコンバータには2個のインダクタL1とL2があります。L1とL2は別個のものでもかまいませんが、スイッチング・サイクルを通してL1とL2には同じ電圧が加わるので同じコアに巻くことができます。

SEPICトポロジーの場合、L1を流れる電流はコンバータの入力電流です。出力電力は理想的には入力電力に等しいという事実に基づいて、L1とL2の最大平均インダクタ電流は以下のようにになります。

$$I_{L1(MAX)} = I_{IN(MAX)} = I_{O(MAX)} \cdot \frac{D_{MAX}}{1-D_{MAX}}$$

$$I_{L2(MAX)} = I_{O(MAX)}$$

LT3959は内部パワースイッチの電流が制限されているので、最大出力電流( $I_{O(MAX)}$ )が最大出力電流能力よりも小さく、なおかつ十分なマージン(10%以上を推奨)を取れるSEPICコンバータに使用します。

$$I_{O(MAX)} < (1-D_{MAX}) \cdot (6A - 0.5 \cdot \Delta I_{SW})$$

インダクタ・リップル電流  $\Delta I_{L1}$  と  $\Delta I_{L2}$  は等しくなります。

$$\Delta I_{L1} = \Delta I_{L2} = 0.5 \cdot \Delta I_{SW}$$

インダクタ・リップル電流  $\Delta I_{SW}$  はインダクタの値の選択とコンバータの最大出力電流能力に直接影響を与えます。小さな値の  $\Delta I_{SW}$  を選択すると、大きなインダクタンスが必要になり、電流ループの利得が減少します(コンバータは電圧モードに近づきます)。大きな  $\Delta I_{SW}$  の値を許容できればインダクタンスを小さくすることができますが、入力電流リップルが大きくなつてコア損失も大きくなり、出力電流能力が低下します。

動作入力電圧範囲が与えられ、動作周波数とインダクタのリップル電流を選んだら、次式を使ってSEPICコンバータのインダクタの値(L1とL2は独立)を求めることができます。

$$L_1 = L_2 = \frac{V_{IN(MIN)}}{0.5 \cdot \Delta I_{SW} \cdot f_{OSC}} \cdot D_{MAX}$$

ほとんどのSEPICアプリケーションでは、等しいインダクタの値は  $1\mu H \sim 100\mu H$  の範囲に収まります。

$L_1 = L_2$  とし、それらを同じコアに巻くと、相互インダクタンスにより前の式のインダクタンスの値は  $2L$  で置き換えられます。

$$L = \frac{V_{IN(MIN)}}{\Delta I_{SW} \cdot f_{OSC}} \cdot D_{MAX}$$

これにより、これらのインダクタには同じリップル電流と蓄積エネルギーが維持されます。ピーク・インダクタ電流は次のようにになります。

$$I_{L1(Peak)} = I_{L1(MAX)} + 0.5 \cdot \Delta I_{L1}$$

$$I_{L2(Peak)} = I_{L2(MAX)} + 0.5 \cdot \Delta I_{L2}$$

最大RMSインダクタ電流は最大平均インダクタ電流にはほぼ等しくなります。

## アプリケーション情報

前の式に基づいて、飽和電流定格とRMS電流定格が十分なインダクタを選択します。

### SEPICコンバータ:出力ダイオードの選択

効率を最大にするには、順方向の電圧降下が小さく、逆方向のリーク電流の小さな高速スイッチング・ダイオードが最適です。通常動作の平均順方向電流は出力電流に等しくなります。

ピーク反復逆電圧定格 $V_{RRM}$ が $V_{OUT} + V_{IN(MAX)}$ より安全マージン分だけ高いものを推奨します(通常は10Vの安全マージンで十分です)。

ダイオードの電力損失は次のとおりです。

$$P_D = I_{O(MAX)} \cdot V_D$$

ここで、 $V_D$ はダイオードの順方向電圧降下で、ダイオードの接合部温度は次のとおりです。

$$T_J = T_A + P_D \cdot R_{\theta JA}$$

この式で使われる $R_{\theta JA}$ には、デバイスの $R_{\theta JC}$ およびボードから筐体内の周囲温度までの熱抵抗が通常含まれます。 $T_J$ がダイオードの最大接合部温度定格を超えてはいけません。

### SEPICコンバータ:出力コンデンサと入力コンデンサの選択

SEPICコンバータの出力コンデンサと入力コンデンサの選択は、昇圧コンバータの場合と同様です。「昇圧コンバータ:出力コンデンサの選択」と「昇圧コンバータ:入力コンデンサの選択」の各セクションを参照してください。

### SEPICコンバータ:DCカップリング・コンデンサの選択

DCカップリング・コンデンサ(図1に示されている $C_{DC}$ )は、DC電圧定格が最大入力電圧より大きいものにします。

$$V_{CDC} > V_{IN(MAX)}$$

$C_{DC}$ の電流は方形に近い波形をしています。スイッチのオフ時間の間 $C_{DC}$ を流れる電流は $I_{IN}$ ですが、オン時間の間は約 $-I_O$ の電流が流れます。カップリング・コンデンサのRMS定格は次式によって決まります。

$$I_{RMS(CDC)} > I_{O(MAX)} \cdot \sqrt{\frac{V_{OUT} + V_D}{V_{IN(MIN)}}}$$

$C_{DC}$ には、ESRとESLの小さなX5RまたはX7Rのセラミック・コンデンサが適しています。

### 反転コンバータのアプリケーション

図4に示されているように、LT3959はデュアル・インダクタ反転トポロジーとして構成可能です。 $V_{OUT}$ と $V_{IN}$ の比は次のとおりです。

$$\frac{V_{OUT} - V_D}{V_{IN}} = -\frac{D}{1-D}$$

連続導通モード(CCM)では次のとおりです。

図4. 簡略化した反転コンバータ

### 反転コンバータ:スイッチのデューティサイクルと周波数

CCMで動作している反転コンバータの場合、メイン・スイッチのデューティサイクルは負の出力電圧( $V_{OUT}$ )および入力電圧( $V_{IN}$ )に基づいて計算することができます。

デューティサイクルが最大( $D_{MAX}$ )になるのは、コンバータの入力電圧が最小のときです。

$$D_{MAX} = \frac{V_{OUT} - V_D}{V_{OUT} - V_D - V_{IN(MIN)}}$$

## アプリケーション情報

### 反転コンバータ:出力ダイオードと入力コンデンサの選択

反転コンバータのインダクタ、出力ダイオードおよび入力コンデンサの選択は、SEPICコンバータの場合と同様です。対応するSEPICコンバータのセクションを参照してください。

### 反転コンバータ:出力コンデンサの選択

反転コンバータの出力リップルを昇圧コンバータやSEPICコンバータと同程度にするには、これらの出力コンデンサよりもかに小さい出力コンデンサで済みます。これは、反転コンバータでは、インダクタL2が出力に直列であり、出力コンデンサを流れるリップル電流が連続であるためです。出力リップル電圧は、出力コンデンサのESRとバルク容量を流れるL2のリップル電流によって生じます。

$$\Delta V_{\text{OUT}(P-P)} = \Delta I_{L2} \cdot \left( ESR_{C\text{OUT}} + \frac{1}{8 \cdot f_{\text{OSC}} \cdot C_{\text{OUT}}} \right)$$

最大出力リップルを定めた後、上の式に従って出力コンデンサを選択することができます。

X5RまたはX7Rの高品質誘電体のセラミック・コンデンサを使うことによって、ESRを最小にすることができます。多くのアプリケーションで、セラミック・コンデンサは出力電圧リップルを制限するのに十分です。

出力コンデンサのRMSリップル電流定格は次の値を超える必要があります。

$$I_{\text{RMS}(C\text{OUT})} > 0.3 \cdot \Delta I_{L2}$$

### 反転コンバータ:DCカップリング・コンデンサの選択

DCカップリング・コンデンサ(図4に示されているC<sub>DC</sub>)は、DC電圧定格が最大入力電圧から出力電圧(負電圧)を差し引いた電圧より大きいものになります。

$$V_{\text{CDC}} > V_{\text{IN(MAX)}} - V_{\text{OUT}}$$

C<sub>DC</sub>の電流は方形に近い波形をしています。スイッチのオフ時間の間C<sub>DC</sub>を流れる電流はI<sub>IN</sub>ですが、オン時間の間は約-I<sub>O</sub>の電流が流れます。カップリング・コンデンサのRMS定格は次式によって決まります。

$$I_{\text{RMS(CDC)}} > I_{O(\text{MAX})} \cdot \sqrt{\frac{D_{\text{MAX}}}{1-D_{\text{MAX}}}}$$

C<sub>DC</sub>には、ESRとESLの小さなX5RまたはX7Rのセラミック・コンデンサが適しています。

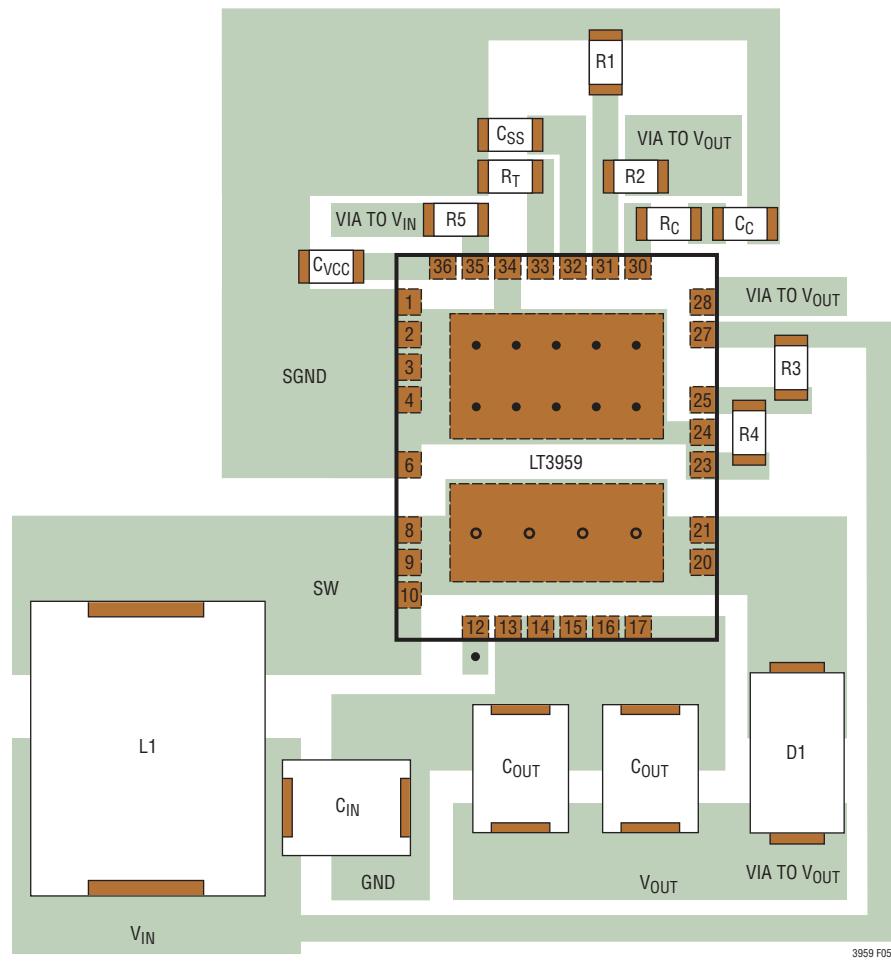

### 基板のレイアウト

LT3959は高電力かつ高速で動作するので、基板のレイアウトと部品の配置には細心の注意が必要です。入力電圧とスイッチング周波数が高く、内部パワースイッチの電流が大きい場合は、LT3959の内部電力損失に十分に注意を払い、接合部温度が125°Cを超えないようする必要があります。周囲温度が高い状態でデバイスを使用する場合、このことは特に重要です。パッケージ底面の露出パッドはデバイスのSGND端子とSW端子であり、それぞれSGNDグランド・プレーンとSWプレーンに半田付けする必要があります。プリント回路基板のビアを多数使って、できるだけ面積の大きな銅プレーンにデバイスの熱を逃がすことを推奨します。

輻射や高周波共振の問題を防ぐには、デバイスに接続する部品、特にdi/dtの高い電力経路を適切にレイアウトすることが不可欠です。以下に示す各種トポロジーの高di/dtループができるだけ狭くして、誘導性リンクを減らします。

- 昇圧構成の高di/dtループには、出力コンデンサ、内部パワーMOSFETおよびショットキ・ダイオードが含まれます。

- SEPIC構成の高di/dtループには、内部パワーMOSFET、出力コンデンサ、ショットキ・ダイオードおよびカップリング・コンデンサが含まれます。

- 反転構成の高di/dtループには、内部パワーMOSFET、ショットキ・ダイオードおよびカップリング・コンデンサが含まれます。

## アプリケーション情報

SW-GND間の電圧をデバイスの端子間で直接測定することによって、内部パワーMOSFETに加わるストレスをチェックします。誘導性リンクが内部パワーMOSFETの最大定格(40V)を超えないようしてください。

小信号部品は高周波数のスイッチング・ノードから離して配置します。最適な負荷レギュレーションと真のリモート検出のために、出力電圧を検出する抵抗分割器の上端は出力コン

デンサの上端に独立に接続し(ケルビン(4線)接続)、どの高  $dV/dt$  トレースからも離しておきます。高インピーダンスのFBX ノードを短くするため、分割器の抵抗はLT3959の近くに配置します。

「標準的応用例」のセクションの2.5V～8V入力、12V出力の昇圧コンバータの推奨レイアウトを図5に示します。

## アプリケーション情報

図5.2.5V～8V入力、12V出力の昇圧コンバータの推奨レイアウト（「標準的応用例」のセクションを参照）(QFNパッケージの場合)

# LT3959

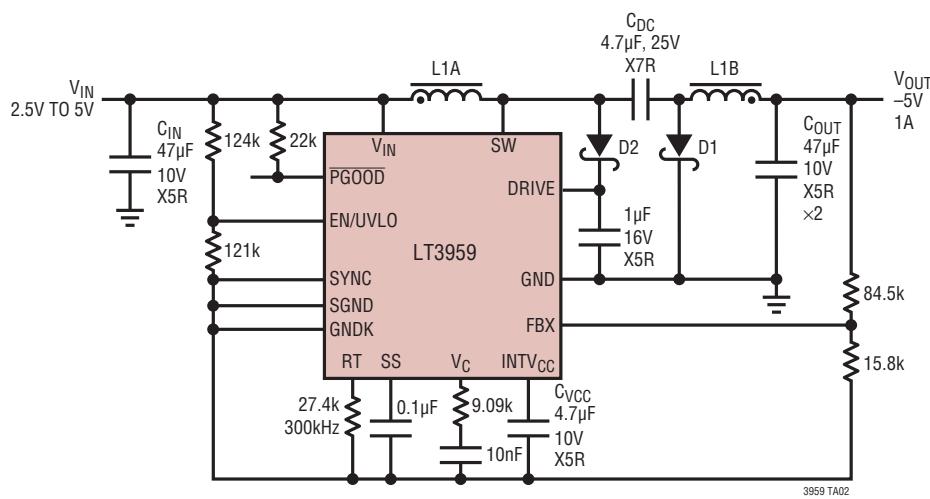

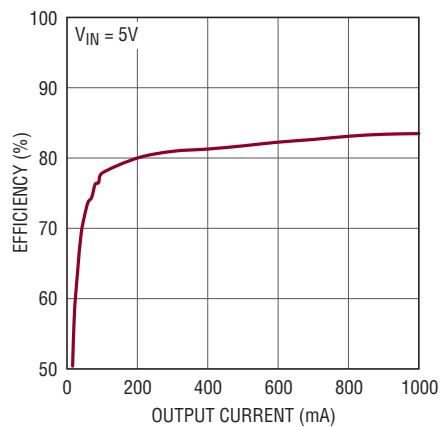

## 標準的応用例

2.5V～5V入力、-5V出力の反転コンバータ

L1A, L1B: COILTRONICS DRQ127-3R3

D1: VISHAY 6CWQ03FN

D2: PHILIPS PMEG2005EJ

効率と出力電流

3759 TA02a

## 標準的応用例

2.5V～24V入力、12V出力のSEPICコンバータ

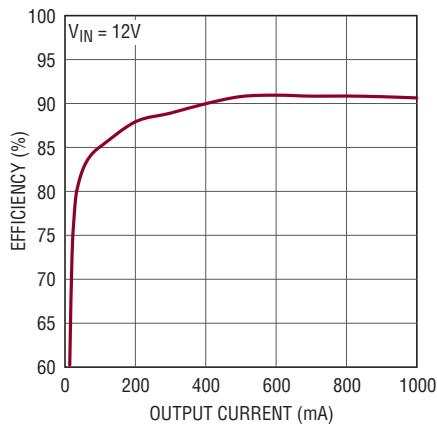

## 効率と出力電流

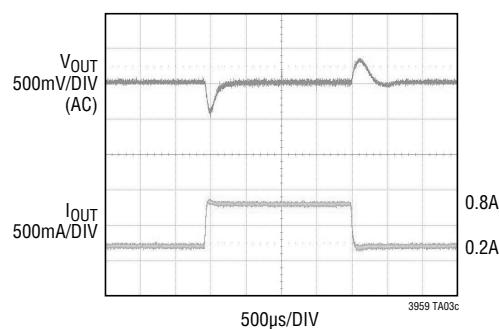

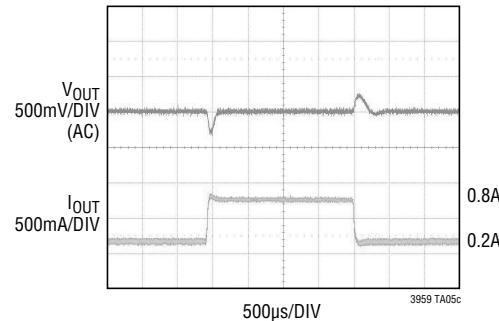

$V_{IN} = 12V$ での負荷ステップ応答

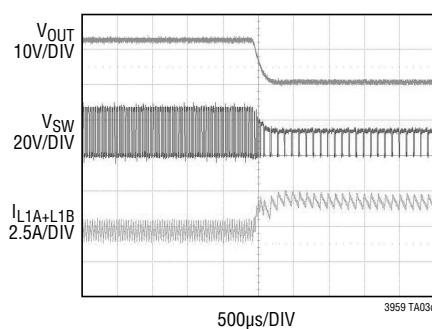

## 出力短絡時の周波数フォールドバック波形

# LT3959

## 標準的応用例

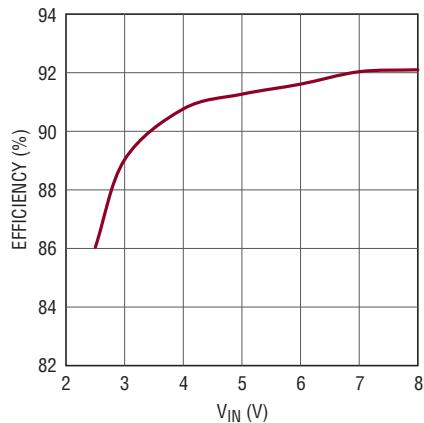

2.5V～8V入力、12VのLEDドライバ

3959 TA04

L1: TOKO 962BS-BR2M

D1: VISHAY SILICONIX 20BQ030

DZ1: CENTRAL SEMICONDUCTOR CMHZ5252B

効率とV<sub>IN</sub>

3959 TA04b

3959fa

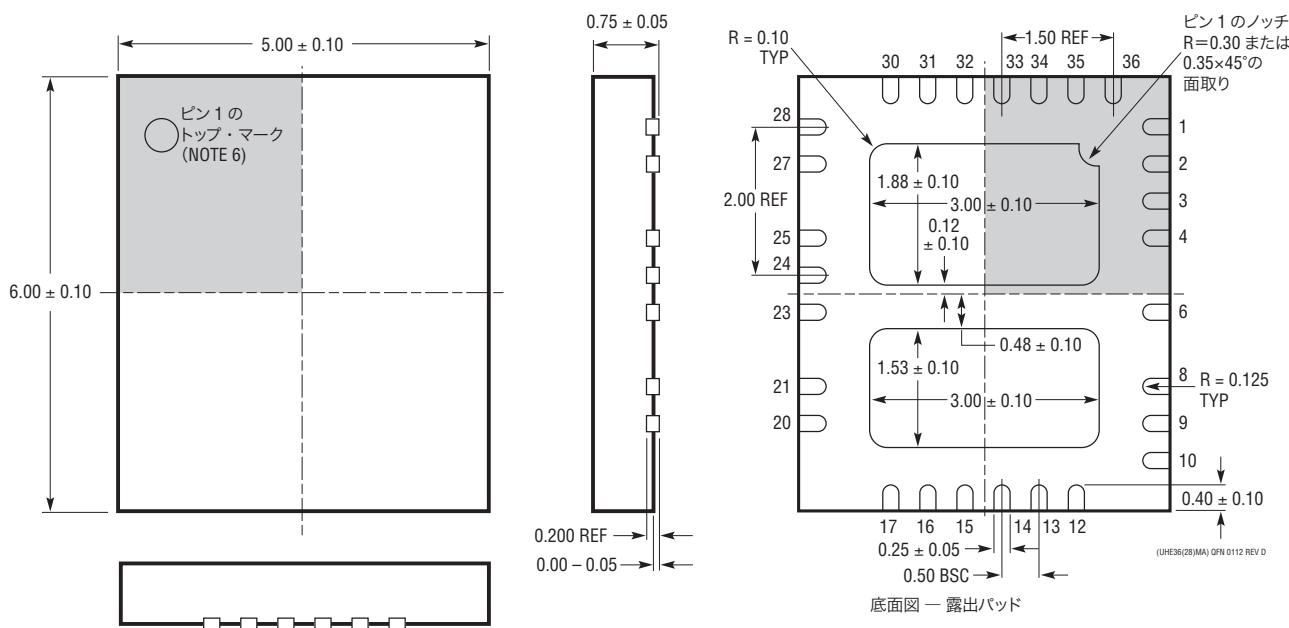

パッケージ

最新のパッケージ図面については、<http://www.linear-tech.co.jp/designtools/packaging/> を参照してください。

**UHE Package

Variation: UHE36(28)MA

36(28)-Lead Plastic QFN (5mm x 6mm)

(Reference LTC DWG # 05-08-1836 Rev D)**

**NOTE :-**

- NOTE :

1. 図は JEDEC パッケージ外形とは異なる

2. 図は実寸とは異なる

3. すべての寸法はミリメートル

4. パッケージ底面の露出パッドの寸法にはモールドのバリを含まない

モールドのバリは(もしあれば)各サイドで 0.20mm を超えないこと

5. 露出パッドは半田めっきとする

6. 網掛けの部分はパッケージの上面と底面のピン 1 の位置の参考に過ぎない

LT3959

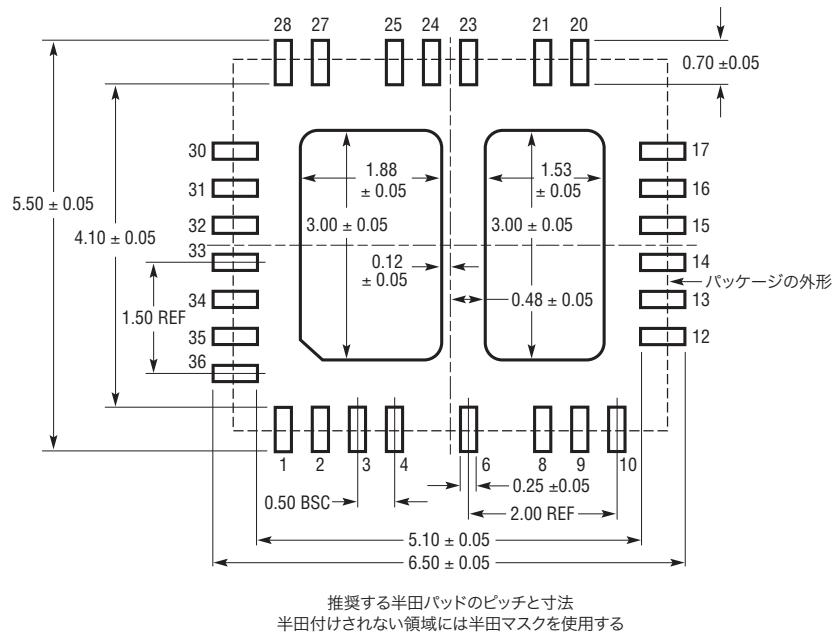

## パッケージ

最新のパッケージ図面については、<http://www.linear-tech.co.jp/designtools/packaging/> を参照してください。

**FE Package

38-Lead Plastic TSSOP (4.4mm)

(Reference LTC DWG # 05-08-1779 Rev Ø)

Split Exposed Pad Variation AC**

**NOTE:**

- NOTE:

1. 標準寸法：ミリメートル

2. 寸法はミリメートル／（インチ）

3. 図は実寸とは異なる

#### 4. 露出パッド接着のための推奨最小 PCB メタルサイズ

\* 寸法にはモールドのバリを含まない

モールドのバリは、各サイドで  $0.150\text{mm}$  ( $0.006"$ ) を超えないこと

## 改訂履歴

| REV | 日付   | 概要                | ページ番号    |

|-----|------|-------------------|----------|

| A   | 6/13 | TSSOP-28パッケージを追加。 | 1、2、7、24 |

# LT3959

## 標準的応用例

### 2.5V～8V入力、12V出力の昇圧コンバータ

L1: COILTRONICS DR125-100

D1: VISHAY SILICONIX 20BQ030

### 効率と出力電流

### V<sub>IN</sub> = 8Vでの負荷ステップ応答

## 関連製品

| 製品番号   | 説明                                           | 注釈                                                                                    |

|--------|----------------------------------------------|---------------------------------------------------------------------------------------|

| LT3957 | 昇圧、フライバック、SEPIC および反転コンバータ、5A/40Vスイッチ付き      | 3V ≤ V <sub>IN</sub> ≤ 40V、100kHz～1MHzの設定可能な動作周波数、5mm×6mm QFNパッケージ                    |

| LT3958 | 昇圧、フライバック、SEPIC および反転コンバータ、3.3A/84Vスイッチ付き    | 5V ≤ V <sub>IN</sub> ≤ 80V、100kHz～1MHzの設定可能な動作周波数、5mm×6mm QFNパッケージ                    |

| LT3759 | 昇圧、フライバック、SEPIC および反転コントローラ                  | 1.6V ≤ V <sub>IN</sub> ≤ 42V、100kHz～1MHzの設定可能な動作周波数、MSOP-12Eパッケージ                     |

| LT3758 | 昇圧、フライバック、SEPIC および反転コントローラ                  | 5.5V ≤ V <sub>IN</sub> ≤ 100V、100kHz～1MHzの設定可能な動作周波数、3mm×3mm DFN-10 および MSOP-10Eパッケージ |

| LT3757 | 昇圧、フライバック、SEPIC および反転コントローラ                  | 2.9V ≤ V <sub>IN</sub> ≤ 40V、設定可能な動作周波数:100kHz～1MHz、3mm×3mm DFN-10 および MSOP-10Eパッケージ  |

| LT3748 | 100V絶縁型フライバック・コントローラ                         | 5V ≤ V <sub>IN</sub> ≤ 100V、オプトカプラ不要のフライバック・コントローラ、高電圧ピン間にスペースを設けたMSOP-16パッケージ        |

| LT3798 | アクティブPFC機能を備えたオプトカプラ不要のオフライン絶縁型フライバック・コントローラ | 外付け部品によってのみV <sub>IN</sub> とV <sub>OUT</sub> を制限                                      |

3959fa