## マルチフェーズ電流モード昇圧 DC/DCコントローラ

## 特長

- 広い入力電圧範囲:動作電圧範囲:5.5V～36V

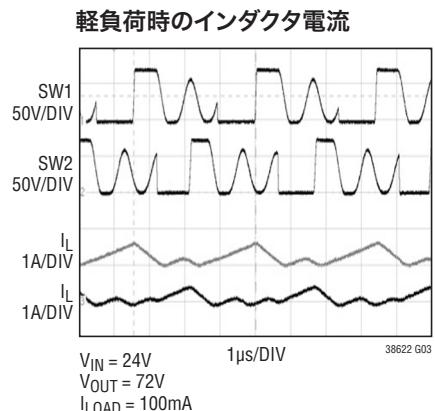

- 2フェーズ動作により入出力容量を低減

- 固定周波数、ピーク電流モード制御

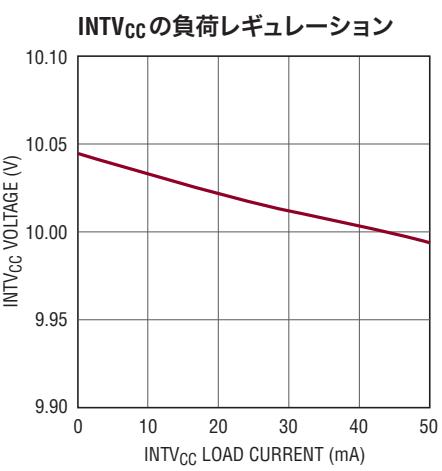

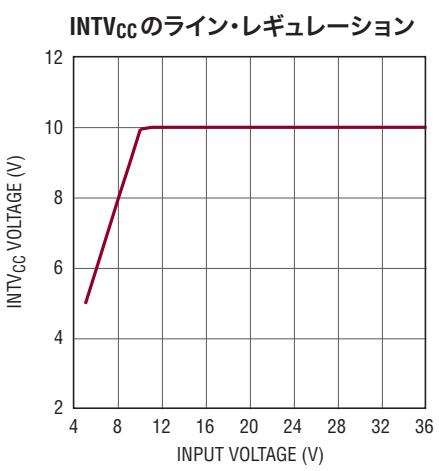

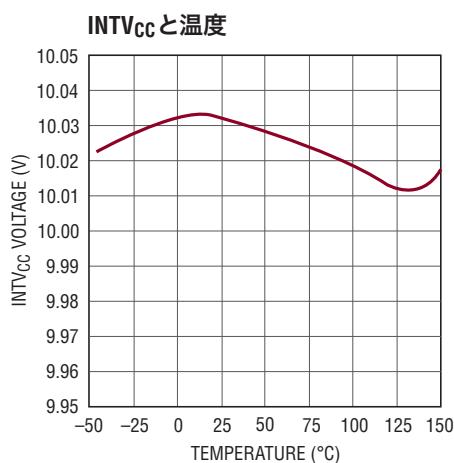

- 内部10V LDOレギュレータ

- UVLOしきい値が低いので、 $V_{GS}$ 定格が6VのMOSFETを使用可能

- 調整可能なスロープ補償利得

- 調整可能な最大デューティサイクル(最大96%)

- 調整可能なリーディングエッジ・ブランкиング

- $\pm 1\%$ 精度の内部電圧リファレンス

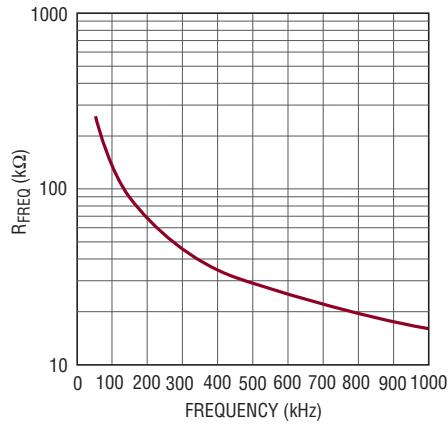

- 1本の外付け抵抗でプログラム可能な動作周波数:75kHz～500kHz

- 位相同期可能な固定周波数(50kHz～650kHz)

- SYNC入力およびCLKOUTにより、2、3、4、6、または12相動作に対応(PHASEMODEでプログラム可能)

- 24ピン細型SSOPパッケージ

- リードピッチが0.65mmの5mm×5mmQFNパッケージ

- 熱特性が改善された24ピンTSSOPパッケージ

## アプリケーション

- ## ■ 自動車用電源、電気通信機器用電源、産業用電源

## 概要

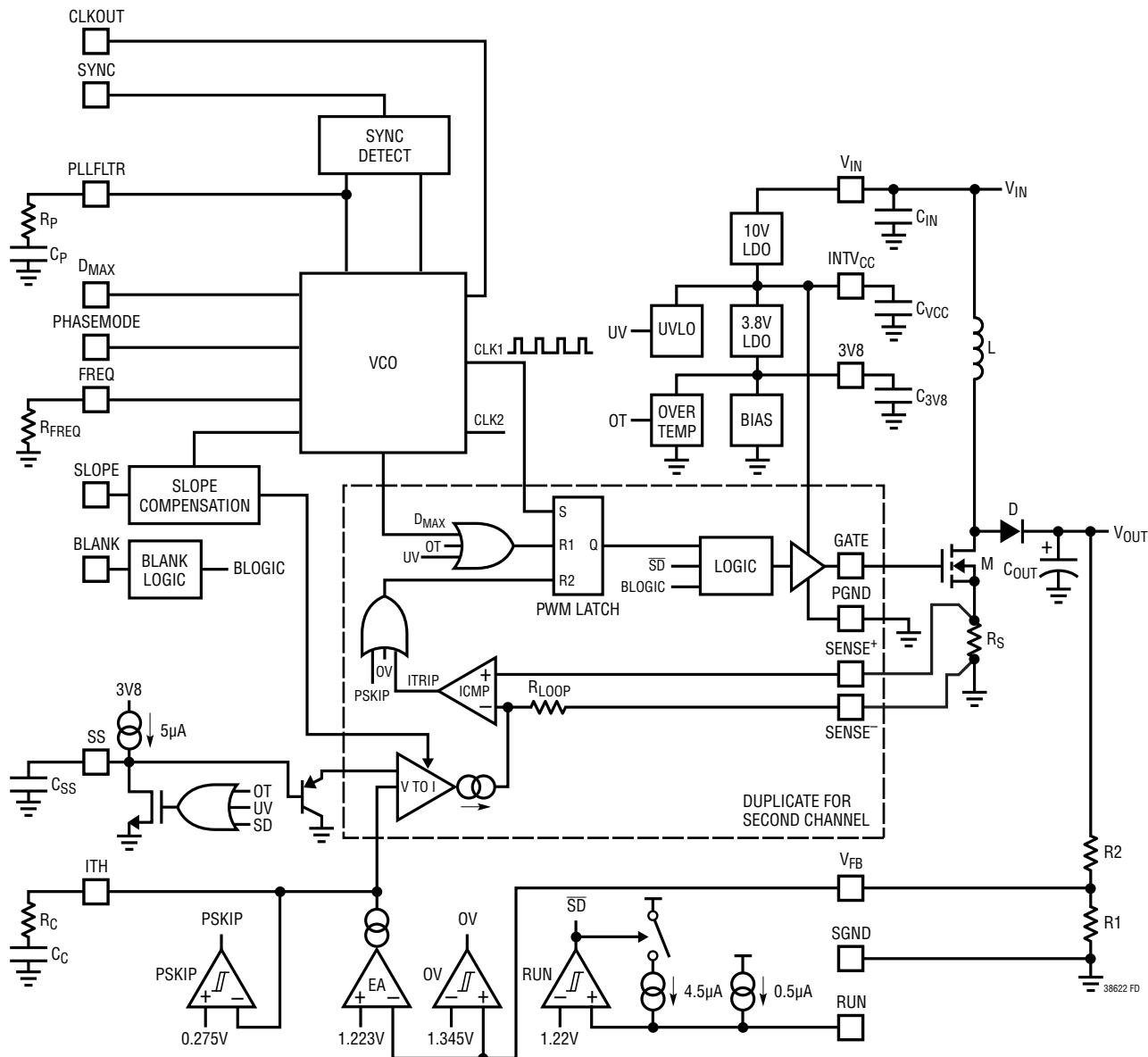

LTC<sup>®</sup>3862-2は、Nチャネル・パワーMOSFETを駆動2相、固定周波数の電流モード昇圧コントローラおよびSEPICコントローラです。2相動作により、システムのフィルタリング容量とインダクタンスの要件が軽減されます。

動作周波数は1本の外付け抵抗により75kHz～500kHzの範囲で設定できますが、内部PLLを使用して外部クロックに同期させることもできます。SYNC入力、CLKOUT出力、およびPHASEMODE制御ピンを使用して、2、3、4、6、12相のマルチフェーズ動作が可能です。

この他の特長は、ゲート・ドライバの低電圧ロックアウト保護機能を備えた内部10V LDO、ヒステリシスをプログラム可能な高精度のRUNピンしきい値、ソフトスタート、プログラム可能なリーディングエッジ・ブランкиングと最大デューティ・サイクルなどです。

| 製品番号      | INTV <sub>CC</sub> | V <sub>IN</sub> オン | V <sub>IN</sub> オフ |

|-----------|--------------------|--------------------|--------------------|

| LTC3862   | 5V                 | 3.3V               | 2.9V               |

| LTC3862-1 | 10V                | 7.5V               | 7.0V               |

| LTC3862-2 | 10V                | 4.4V               | 3.9V               |

LT、LT、LTC、LTM、Linear Technology、Linearのロゴ、およびPolyPhaseはリニアテクノロジー社の登録商標です。No R森SおよびThinSOTはリニアテクノロジー社の商標です。その他すべての商標の所有権は、それぞれの所有者に帰属します。6144194、6498466、6611131を含む米国特許によって保護されています。

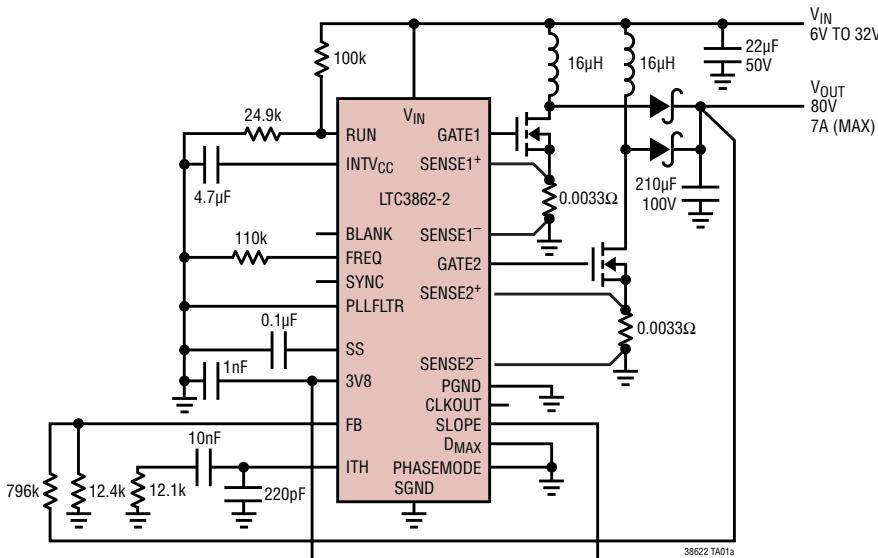

## 標準的應用例

## 絶対最大定格 (Note 1, 2)

|                                                                                            |                        |                       |                        |

|--------------------------------------------------------------------------------------------|------------------------|-----------------------|------------------------|

| 入力電源電圧(V <sub>IN</sub> )                                                                   | -0.3V～40V              | SS、PLLFLTRの電圧         | -0.3V～V <sub>3V8</sub> |

| INTV <sub>CC</sub> の電圧                                                                     | -0.3V～11V              | ITHの電圧                | -0.3V～2.7V             |

| INTV <sub>CC</sub> LDOのRMSの出力電流                                                            | 50mA                   | FBの電圧                 | -0.3V～V <sub>3V8</sub> |

| RUNの電圧                                                                                     | -0.3V～8V               | FREQの電圧               | -0.3V～1.5V             |

| SYNCの電圧                                                                                    | -0.3V～6V               | 動作接合部温度範囲 (Note 3, 4) |                        |

| SLOPE、PHASEMODE、D <sub>MAX</sub>                                                           |                        | LTC3862-2E            | -40°C～85°C             |

| BLANKの電圧                                                                                   | -0.3V～V <sub>3V8</sub> | LTC3862-2I            | -40°C～125°C            |

| SENSE1 <sup>+</sup> 、SENSE1 <sup>-</sup> 、SENSE2 <sup>+</sup> 、<br>SENSE2 <sup>-</sup> の電圧 | -0.3V～V <sub>3V8</sub> | LTC3862-2H            | -40°C～150°C            |

|                                                                                            |                        | 保存温度範囲                | -65°C～150°C            |

|                                                                                            |                        | リフローのピーク・ボディ温度        | 260°C                  |

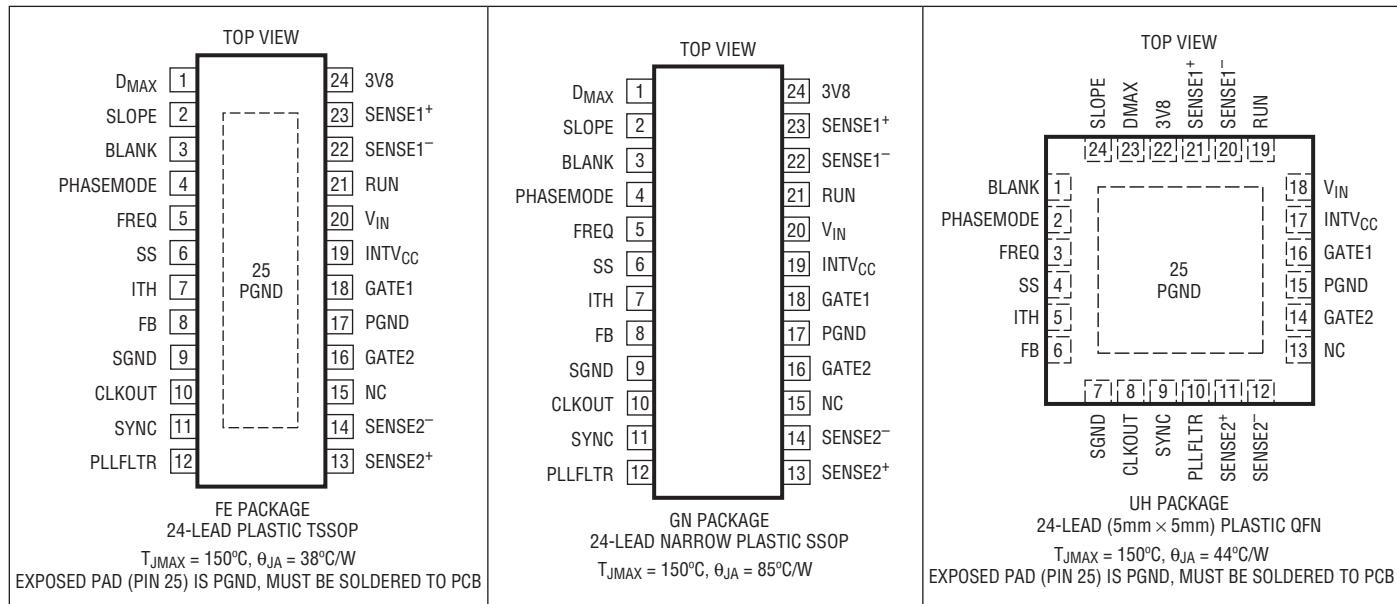

## ピン配置

## 発注情報

| 無鉛仕上げ            | テープアンドリール          | 製品マーキング*    | パッケージ                           | 温度範囲           |

|------------------|--------------------|-------------|---------------------------------|----------------|

| LTC3862EFE-2#PBF | LTC3862EFE-2#TRPBF | LTC3862FE-2 | 24-Lead Plastic TSSOP           | -40°C to 85°C  |

| LTC3862IFE-2#PBF | LTC3862IFE-2#TRPBF | LTC3862FE-2 | 24-Lead Plastic TSSOP           | -40°C to 125°C |

| LTC3862HFE-2#PBF | LTC3862HFE-2#TRPBF | LTC3862FE-2 | 24-Lead Plastic TSSOP           | -40°C to 150°C |

| LTC3862EGN-2#PBF | LTC3862EGN-2#TRPBF | LTC3862GN-2 | 24-Lead Plastic SSOP            | -40°C to 85°C  |

| LTC3862IGN-2#PBF | LTC3862IGN-2#TRPBF | LTC3862GN-2 | 24-Lead Plastic SSOP            | -40°C to 125°C |

| LTC3862HGN-2#PBF | LTC3862HGN-2#TRPBF | LTC3862GN-2 | 24-Lead Plastic SSOP            | -40°C to 150°C |

| LTC3862EUH-2#PBF | LTC3862EUH-2#TRPBF | 38622       | 24-Lead (5mm × 5mm) Plastic QFN | -40°C to 85°C  |

| LTC3862IUH-2#PBF | LTC3862IUH-2#TRPBF | 38622       | 24-Lead (5mm × 5mm) Plastic QFN | -40°C to 125°C |

| LTC3862HUH-2#PBF | LTC3862HUH-2#TRPBF | 38622       | 24-Lead (5mm × 5mm) Plastic QFN | -40°C to 150°C |

さらに広い動作温度範囲で規定されるデバイスについては、弊社または弊社代理店にお問い合わせください。\* 温度グレードは出荷時のコンテナのラベルで識別されます。非標準の鉛仕上げの製品の詳細については、弊社または弊社代理店にお問い合わせください。

無鉛仕上げの製品マーキングの詳細については、<http://www.linear-tech.co.jp/leadfree/> をご覧ください。

テープアンドリールの仕様の詳細については、<http://www.linear-tech.co.jp/tapeandreel/> をご覧ください。

## 電気的特性 (Note 2, 3)

●は規定動作接合部温度範囲の規格値を意味する。それ以外は  $T_A = 25^\circ\text{C}$  の値。注記がない限り、 $V_{IN} = 12\text{V}$ 、 $RUN = 2\text{V}$  および  $SS = \text{開放}$ 。

| SYMBOL                               | PARAMETER                                                        | CONDITIONS                                                                        | MIN    | TYP            | MAX            | UNITS               |

|--------------------------------------|------------------------------------------------------------------|-----------------------------------------------------------------------------------|--------|----------------|----------------|---------------------|

| 入力電源およびINTV <sub>CC</sub> リニア・レギュレータ |                                                                  |                                                                                   |        |                |                |                     |

| $V_{IN}$                             | $V_{IN}$ Supply Voltage Range                                    |                                                                                   | ●      | 5.5            | 36             | V                   |

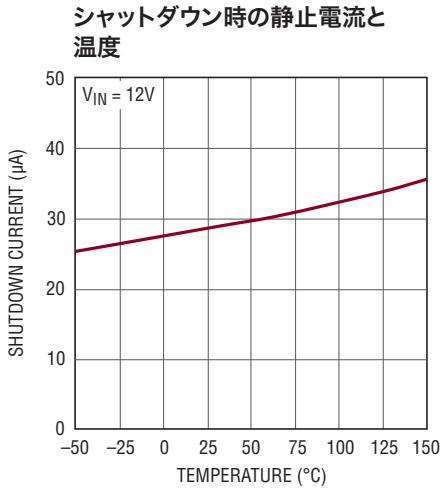

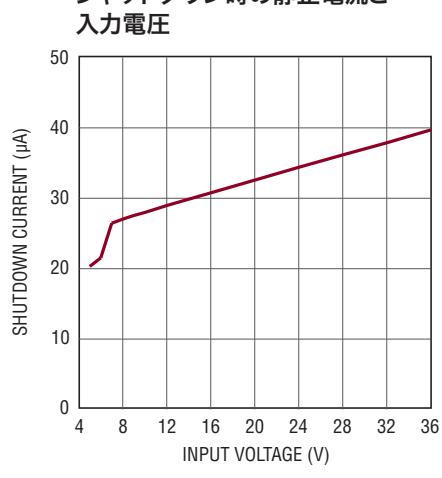

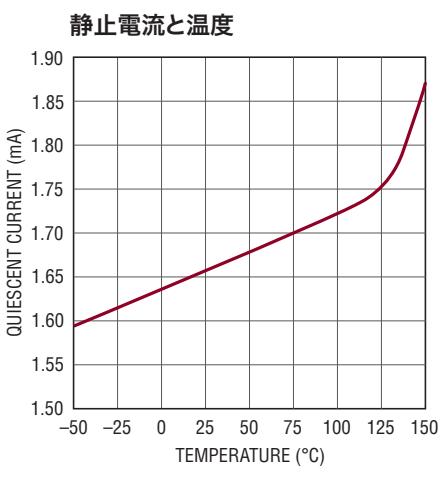

| $I_{VIN}$                            | $V_{IN}$ Supply Current<br>Normal Mode, No Switching<br>Shutdown | (Note 5)<br>$V_{RUN} = 0\text{V}$                                                 | ●<br>● | 1.8<br>30      | 3.0<br>80      | mA<br>$\mu\text{A}$ |

| INTV <sub>CC</sub>                   | LDO Regulator Output Voltage                                     |                                                                                   | 9.5    | 10.0           | 10.5           | V                   |

| $dV_{INTVCC(LINE)}$                  | Line Regulation                                                  | $12\text{V} < V_{IN} < 36\text{V}$                                                |        | 0.002          | 0.02           | %/V                 |

| $dV_{INTVCC(LOAD)}$                  | Load Regulation                                                  | Load = 0mA to 20mA                                                                |        | -2             |                | %                   |

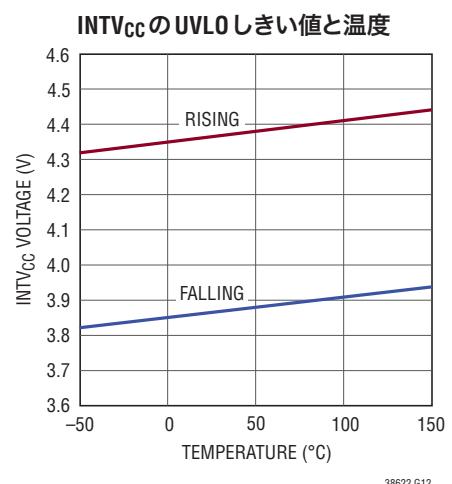

| V <sub>UVLO</sub>                    | INTV <sub>CC</sub> UV <sup>+</sup> Voltage                       | Rising INTV <sub>CC</sub>                                                         |        | 4.4            |                | V                   |

|                                      | INTV <sub>CC</sub> UV <sup>-</sup> Voltage                       | Falling INTV <sub>CC</sub>                                                        |        | 3.9            |                | V                   |

| 3V8                                  | LDO Regulator Output Voltage                                     |                                                                                   |        | 3.8            |                | V                   |

| スイッチャ制御ループ                           |                                                                  |                                                                                   |        |                |                |                     |

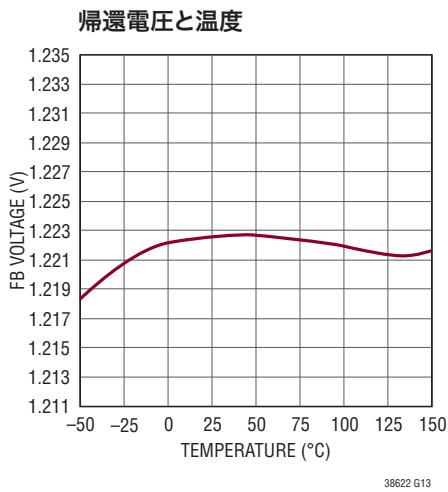

| $V_{FB}$                             | Reference Voltage                                                | $V_{ITH} = 0.8\text{V}$ (Note 6) E-Grade (Note 3)<br>I-Grade and H-Grade (Note 3) | ●<br>● | 1.210<br>1.199 | 1.223<br>1.223 | 1.235<br>1.248      |

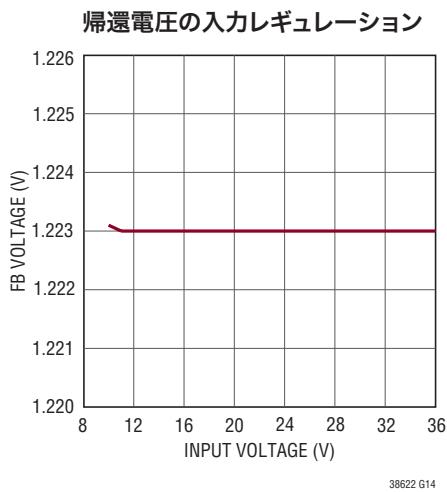

| $dV_{FB}/dV_{IN}$                    | Feedback Voltage $V_{IN}$ Line Regulation                        | $V_{IN} = 5.5\text{V}$ to $36\text{V}$ (Note 6)                                   |        | $\pm 0.002$    | 0.01           | %/V                 |

| $dV_{FB}/dV_{ITH}$                   | Feedback Voltage Load Regulation                                 | $V_{ITH} = 0.5\text{V}$ to $1.2\text{V}$ (Note 6)                                 |        | 0.01           | 0.1            | %                   |

| $g_m$                                | Transconductance Amplifier Gain                                  | $V_{ITH} = 0.8\text{V}$ (Note 6), ITH Pin Load = $\pm 5\mu\text{A}$               |        | 660            |                | $\mu\text{Mho}$     |

| $f_{0dB}$                            | Error Amplifier Unity-Gain Crossover Frequency                   | (Note 7)                                                                          |        | 1.8            |                | MHz                 |

## 電気的特性 (Note 2, 3)

●は規定動作接合部温度範囲の規格値を意味する。それ以外は  $T_A = 25^\circ\text{C}$  の値。注記がない限り、 $V_{IN} = 12\text{V}$ 、 $\text{RUN} = 2\text{V}$  および  $\text{SS} = \text{開放}$ 。

| SYMBOL                    | PARAMETER                                                   | CONDITIONS                                                                            | MIN           | TYP         | MAX      | UNITS         |

|---------------------------|-------------------------------------------------------------|---------------------------------------------------------------------------------------|---------------|-------------|----------|---------------|

| $V_{ITH}$                 | Error Amplifier Maximum Output Voltage (Internally Clamped) | $V_{FB} = 1\text{V}$ , No Load                                                        |               | 2.7         |          | V             |

|                           | Error Amplifier Minimum Output Voltage                      | $V_{FB} = 1.5\text{V}$ , No Load                                                      |               | 50          |          | mV            |

| $I_{ITH}$                 | Error Amplifier Output Source Current                       |                                                                                       |               | -30         |          | $\mu\text{A}$ |

|                           | Error Amplifier Output Sink Current                         |                                                                                       |               | 30          |          | $\mu\text{A}$ |

| $I_{FB}$                  | Error Amplifier Input Bias Currents                         | (Note 6)                                                                              |               | -50         | -200     | nA            |

| $V_{ITH(\text{PSKIP})}$   | Pulse Skip Mode Operation ITH Pin Voltage                   | Rising ITH Voltage (Note 6)<br>Hysteresis                                             |               | 0.275<br>25 |          | V<br>mV       |

| $I_{SENSE(\text{ON})}$    | SENSE Pin Current                                           |                                                                                       |               | 0.01        | 2        | $\mu\text{A}$ |

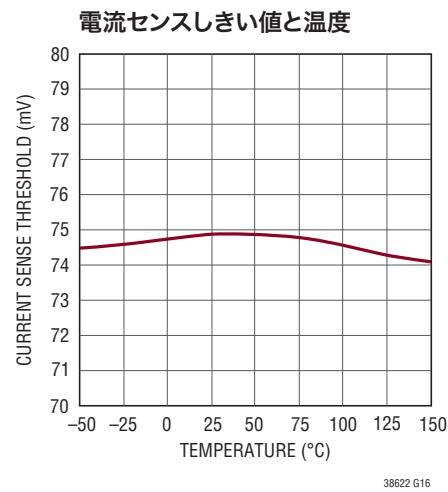

| $V_{SENSE(\text{MAX})}$   | Maximum Current Sense Input Threshold                       | $V_{SLOPE} = \text{Float}$ , Low Duty Cycle<br>(Note 3)                               | ●<br>68<br>65 | 75<br>75    | 82<br>85 | mV<br>mV      |

| $V_{SENSE(\text{MATCH})}$ | CH1 to CH2 Maximum Current Sense Threshold Matching         | $V_{SLOPE} = \text{Float}$ , Low Duty Cycle (Note 3)<br>( $V_{SENSE1} - V_{SENSE2}$ ) | ●             | -7          | 7        | mV            |

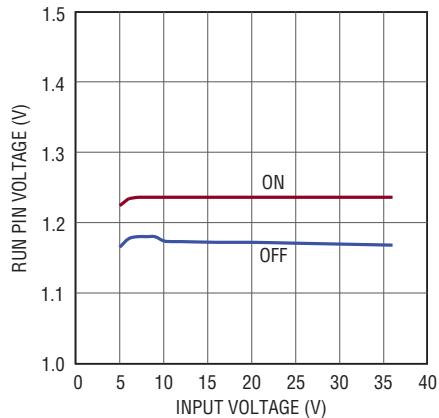

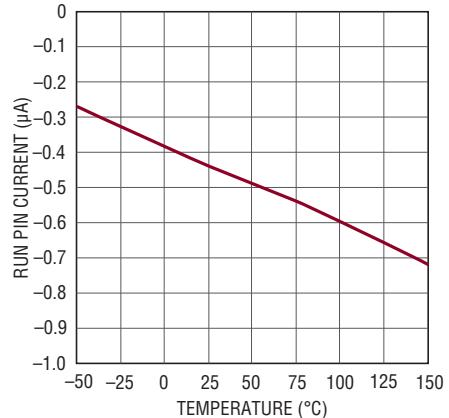

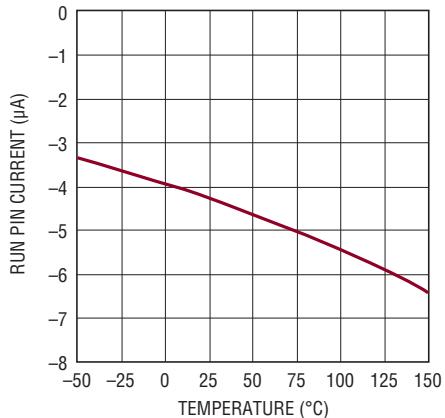

## RUN/ソフトスタート

|              |                                         |                                                  |  |            |  |                                |

|--------------|-----------------------------------------|--------------------------------------------------|--|------------|--|--------------------------------|

| $I_{RUN}$    | RUN Source Current                      | $V_{RUN} = 0\text{V}$<br>$V_{RUN} = 1.5\text{V}$ |  | -0.5<br>-5 |  | $\mu\text{A}$<br>$\mu\text{A}$ |

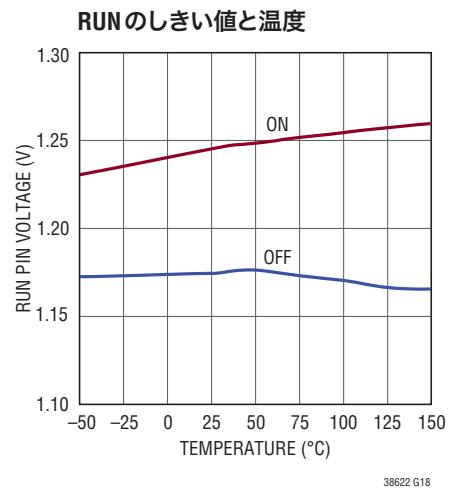

| $V_{RUN}$    | High Level RUN Channel Enable Threshold |                                                  |  | 1.22       |  | V                              |

| $V_{RUNHYS}$ | RUN Threshold Hysteresis                |                                                  |  | 80         |  | mV                             |

| $I_{SS}$     | SS Pull-Up Current                      | $V_{SS} = 0\text{V}$                             |  | -5         |  | $\mu\text{A}$                  |

| $R_{SS}$     | SS Pull-Down Resistance                 | $V_{RUN} = 0\text{V}$                            |  | 10         |  | $\text{k}\Omega$               |

## 発振器

|                     |                                           |                                                                                         |                 |            |                   |                   |

|---------------------|-------------------------------------------|-----------------------------------------------------------------------------------------|-----------------|------------|-------------------|-------------------|

| $f_{OSC}$           | Oscillator Frequency                      | $R_{FREQ} = 45.6\text{k}$<br>$R_{FREQ} = 45.6\text{k}$                                  | ●<br>280<br>260 | 300<br>300 | 320<br>340        | kHz<br>kHz        |

|                     | Oscillator Frequency Range                |                                                                                         | ●               | 75         | 500               | kHz               |

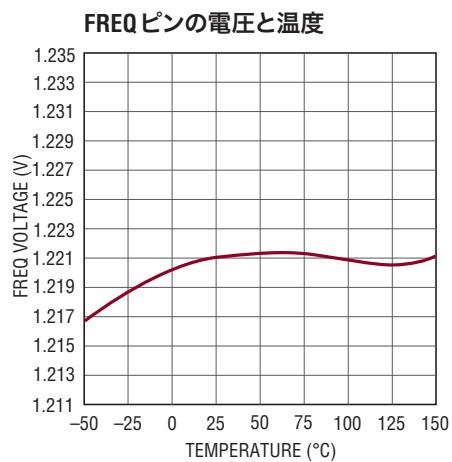

| $V_{FREQ}$          | Nominal FREQ Pin Voltage                  | $R_{FREQ} = 45.6\text{k}$                                                               |                 |            | 1.223             | V                 |

| $f_{SYNC}$          | SYNC Minimum Input Frequency              | $V_{SYNC} = \text{External Clock}$                                                      | ●               |            | 50                | kHz               |

|                     | SYNC Maximum Input Frequency              | $V_{SYNC} = \text{External Clock}$                                                      | ●               | 650        |                   | kHz               |

| $V_{SYNC}$          | SYNC Input Threshold                      | Rising Threshold                                                                        |                 |            | 1.5               | V                 |

| $I_{PLLFLTR}$       | Phase Detector Sourcing Output Current    | $f_{SYNC} > f_{OSC}$                                                                    |                 |            | -15               | $\mu\text{A}$     |

|                     | Phase Detector Sinking Output Current     | $f_{SYNC} < f_{OSC}$                                                                    |                 |            | 15                | $\mu\text{A}$     |

| $\text{CH1-CH2}$    | Channel 1 to Channel 2 Phase Relationship | $V_{PHASEMODE} = 0\text{V}$<br>$V_{PHASEMODE} = \text{Float}$<br>$V_{PHASEMODE} = 3V/8$ |                 |            | 180<br>180<br>120 | Deg<br>Deg<br>Deg |

| $\text{CH1-CLKOUT}$ | Channel 1 to CLKOUT Phase Relationship    | $V_{PHASEMODE} = 0\text{V}$<br>$V_{PHASEMODE} = \text{Float}$<br>$V_{PHASEMODE} = 3V/8$ |                 |            | 90<br>60<br>240   | Deg<br>Deg<br>Deg |

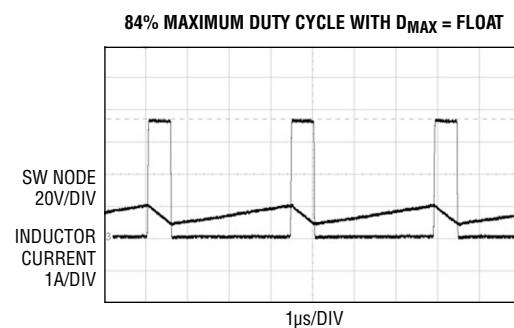

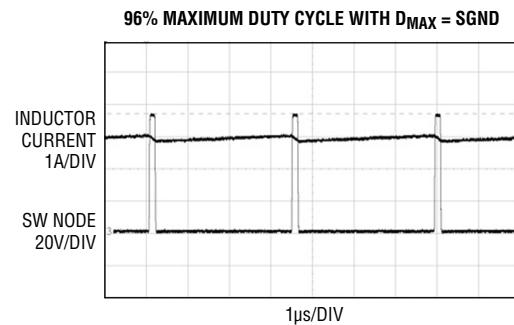

| $D_{MAX}$           | Maximum Duty Cycle                        | $V_{DMAX} = 0\text{V}$ (Note 9)<br>$V_{DMAX} = \text{Float}$<br>$V_{DMAX} = 3V/8$       |                 |            | 96<br>84<br>75    | %<br>%<br>%       |

## 電気的特性 (Note 2, 3)

●は規定動作接合部温度範囲の規格値を意味する。それ以外は  $T_A = 25^\circ\text{C}$  の値。注記がない限り、 $V_{IN} = 12\text{V}$ 、 $\text{RUN} = 2\text{V}$  および  $\text{SS} = \text{開放}$ 。

| SYMBOL         | PARAMETER                                | CONDITIONS                            | MIN | TYP | MAX | UNITS    |

|----------------|------------------------------------------|---------------------------------------|-----|-----|-----|----------|

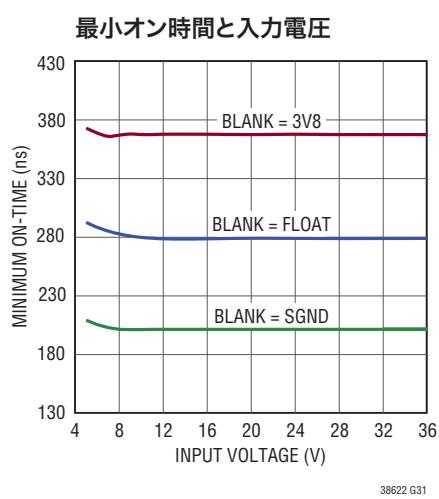

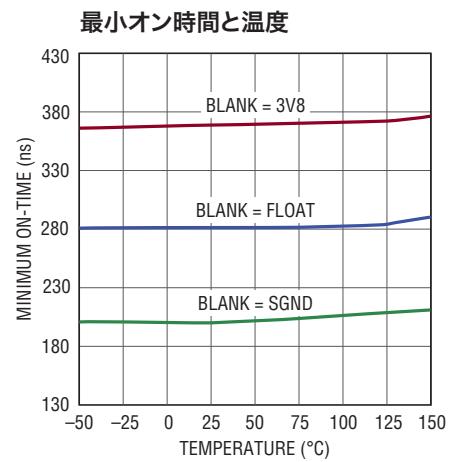

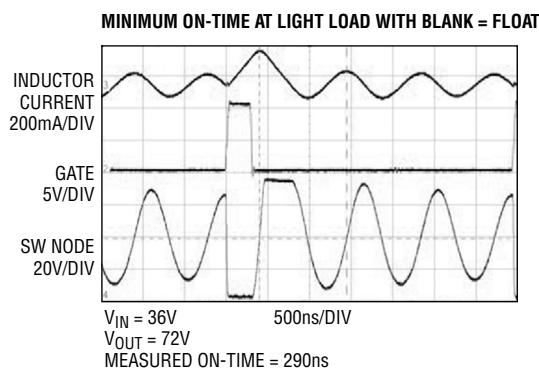

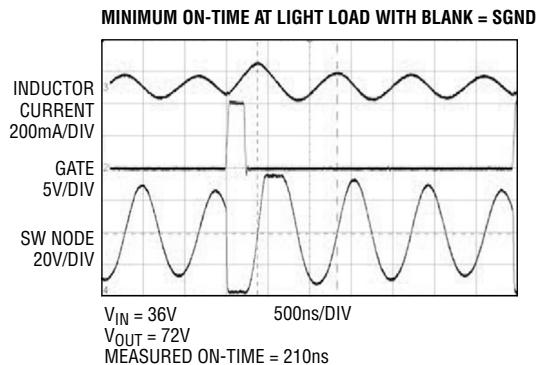

| $t_{ON(MIN)1}$ | Minimum On-Time                          | $V_{BLANK} = 0\text{V}$ (Note 8)      |     | 210 |     | ns       |

| $t_{ON(MIN)2}$ | Minimum On-Time                          | $V_{BLANK} = \text{Float}$ (Note 8)   |     | 290 |     | ns       |

| $t_{ON(MIN)3}$ | Minimum On-Time                          | $V_{BLANK} = 3\text{V}8$ (Note 8)     |     | 375 |     | ns       |

| ゲート・ドライバ       |                                          |                                       |     |     |     |          |

| $R_{DS(ON)}$   | Driver Pull-Up $R_{DS(ON)}$              |                                       |     | 3   |     | $\Omega$ |

|                | Driver Pull-Down $R_{DS(ON)}$            |                                       |     | 0.9 |     | $\Omega$ |

| 過電圧            |                                          |                                       |     |     |     |          |

| $V_{FB(OV)}$   | $V_{FB}$ , Overvoltage Lockout Threshold | $V_{FB(OV)} - V_{FB(NOM)}$ in Percent |     | 8   | 10  | 12       |

|                |                                          |                                       |     |     |     | %        |

**Note 1:** 絶対最大定格に記載された値を超えるストレスはデバイスに永続的損傷を与える可能性がある。長期にわたって絶対最大定格条件に曝すと、デバイスの信頼性と寿命に悪影響を与える恐れがある。

**Note 2:** デバイスのピンに流れ込む電流はすべて正。デバイスのピンから流れ出る電流はすべて負。注記がない限り、すべての電圧はグランドを基準にしている。

**Note 3:** LTC3862E-2は $0^\circ\text{C} \sim 85^\circ\text{C}$ の範囲で性能仕様に適合することが保証されている。 $-40^\circ\text{C} \sim 85^\circ\text{C}$ の動作温度範囲での仕様は設計、特性評価および統計学的なプロセス・コントロールとの相関で確認されている。LTC3862I-2は $-40^\circ\text{C} \sim 125^\circ\text{C}$ の全動作温度範囲で保証されており、LTC3862H-2は $-40^\circ\text{C} \sim 150^\circ\text{C}$ の全動作温度範囲で保証されている。接合部温度が高いと動作寿命は短くなる。接合部温度が $125^\circ\text{C}$ を超えると、動作寿命が短くなる。

**Note 4:** このデバイスには短時間の過負荷状態の間デバイスを保護するための過熱保護機能が備わっている。規定された最大動作接合部温度を超えた状態で動作が継続すると、デバイスの信頼性を損なう恐れがある。

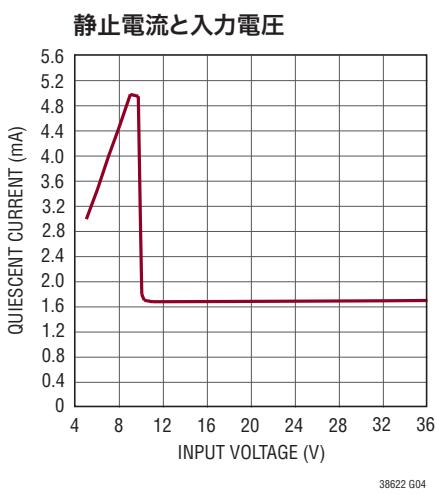

**Note 5:** 通常動作時の電源電流は外部MOSFETのゲートを充電するのに必要な電流によって左右される。この電流は電源電圧と使用される外部MOSFETによって変化する。

**Note 6:** このデバイスは、規定されたエラーアンプ出力電圧になるように  $V_{FB}$  を調節する帰還ループでテストされている。

**Note 7:** 設計によって保証されているが、テストされない。

**Note 8:** 最小オン時間条件は、インダクタのピーク・トゥ・ピーク・リップル電流が30%の場合に規定される(「アプリケーション情報」セクションの「最小オン時間の制限事項」を参照)。

**Note 9:** 最大デューティ・サイクルの制限値は、設定されているスイッチング周波数の12倍の周波数で動作する内部クロックから得られる。詳細については「アプリケーション情報」のセクションを参照してください。

## 標準的性能特性

## 標準的性能特性

## 標準的性能特性

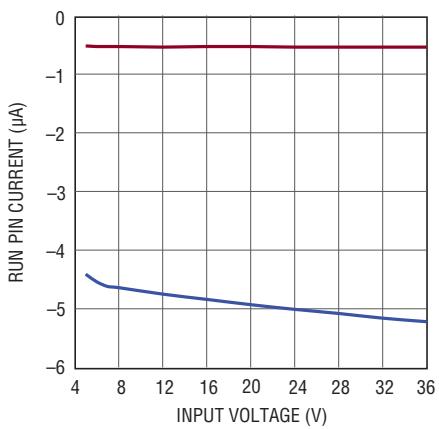

**RUNのしきい値と入力電圧**

**RUN(オフ時)のソース電流と温度**

**RUN(オン時)のソース電流と温度**

**RUNのソース電流と入力電圧**

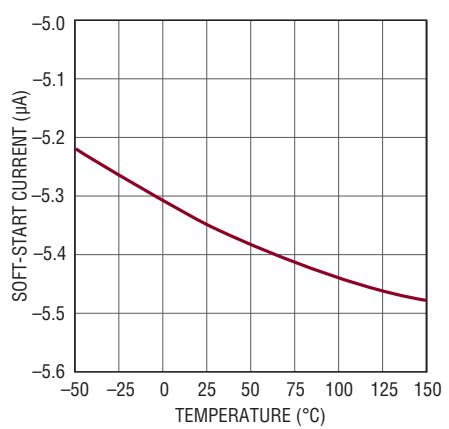

**ソフトスタート電流と温度**

**ソフトスタート電流と

ソフトスタート電圧**

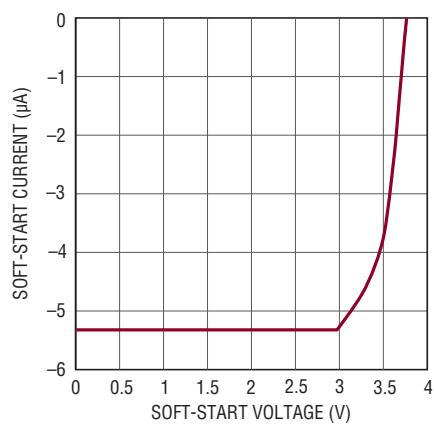

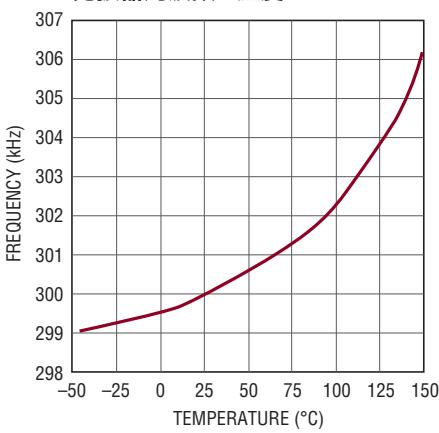

**発振器周波数と温度**

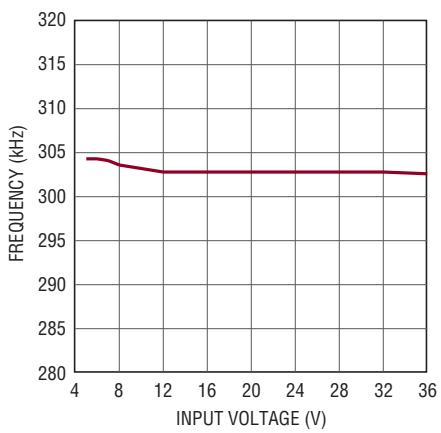

**発振器周波数と入力電圧**

**R<sub>FREQ</sub>と周波数**

## 標準的性能特性

## ピン機能 (SSOP/QFN/TSSOP)

**3V8 (ピン24/ピン22/ピン24)** : INTV<sub>CC</sub>を電源とする内部の3.8V LDOの出力。低電圧のアナログ回路およびデジタル回路の電源ピン。低ESRの1nFセラミック・バイパス・コンデンサを、できるだけデバイスに近づけて、3V8とSGNDの間に接続する必要があります。

**BLANK (ピン3/ピン1/ピン3)** : ブランкиング時間。このピンをフロート状態にすると、最小オン時間は公称の290nsになります。このピンを3V8に接続すると最小オン時間は375nsになります。SGNDに接続すると最小オン時間は210nsになります。

**CLKOUT (ピン10/ピン8/ピン10)** : マルチフェーズ・システムで複数のLTC3862-2をデジーチェーン接続するために使用するデジタル出力。CH1とCH2の間の関係およびCH1とCLKOUTの間の関係は、PHASEMODEピンの電圧によって制御します。

**D<sub>MAX</sub> (ピン1/ピン23/ピン1)** : 最大デューティ・サイクル。最大デューティ・サイクルはこのピンで設定します。このピンをフロート状態にすると、デューティ・サイクルは84%になります。このピンを3V8に接続するとデューティ・サイクルは75%になります。このピンをSGNDに接続するとデューティ・サイクルは96%になります。最大デューティ・サイクルの制限値は、設定されているスイッチング周波数の12倍の周波数で動作する内部クロックから得られます。このため、最大デューティ・サイクルの制限値D<sub>MAX</sub>はきわめて正確です。

**FB (ピン8/ピン6/ピン8)** : エラーアンプの入力。FBピンは、出力電圧を設定するために抵抗分割器の回路網を介してV<sub>OUT</sub>に接続する必要があります。

**FREQ (ピン5/ピン3/ピン5)** : FREQとSGNDの間に抵抗を接続することにより、動作周波数が設定されます。

**GATE1 (ピン18/ピン16/ピン18)** : ゲート駆動出力。LTC3862-2は、PGNDを基準にして高電圧のMOSFETを駆動する10Vのゲート駆動回路を備えています。このゲート・ピンの電圧の絶対最大定格は、最小-0.3V、最大11Vです。

**GATE2 (ピン16/ピン14/ピン16)** : ゲート駆動出力。LTC3862-2は、PGNDを基準にして高電圧のMOSFETを駆動する10Vのゲート駆動回路を備えています。このゲート・ピンの電圧の絶対最大定格は、最小-0.3V、最大11Vです。

**INTV<sub>CC</sub> (ピン19/ピン17/ピン19)** : 内部の10V低損失レギュレータ(LDO)の出力。低ESRの4.7μFセラミック・バイパス・コンデンサ(X5r以上の良質なもの)を、できるだけデバイスに近づけて、INTV<sub>CC</sub>とPGNDの間に接続する必要があります。

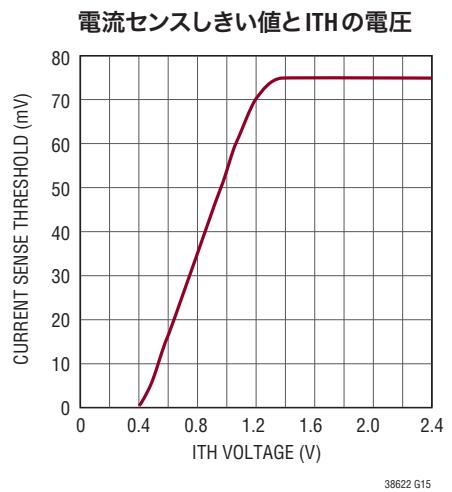

**ITH (ピン7/ピン5/ピン7)** : エラーアンプの出力。電流コンパレータの作動しきい値は、ITHの制御電圧に応じて増加します。ITHピンは、コンバータの制御ループを補償する目的にも使用されます。

**PGND (ピン17/ピン15、露出パッド・ピン25/ピン17、露出パッド・ピン25)** : 電力グランド。このピンはパワーMOSFETのソースに近づけて接続します。PGNDは、V<sub>IN</sub>およびINTV<sub>CC</sub>のバイパス・コンデンサの負端子にも接続する必要があります。PGNDはSGNDピンからは電気的に絶縁されています。QFNパッケージおよびFEパッケージの露出パッドはPGNDに接続されており、電気的な接触と定格の熱性能を確保するためにプリント回路基板のグランドに半田付けする必要があります。

**PHASEMODE (ピン4/ピン2/ピン4)** : CH1とCH2の立ち上がりゲート信号間の位相関係、およびCH1のゲート信号とCLKOUTの間の位相関係は、PHASEMODEピンの電圧によって設定します。このピンをフロート状態にするか、このピンを3V8とSGNDのいずれかに接続すると、CH1、CH2、およびCLKOUTの間の位相関係が変化します。

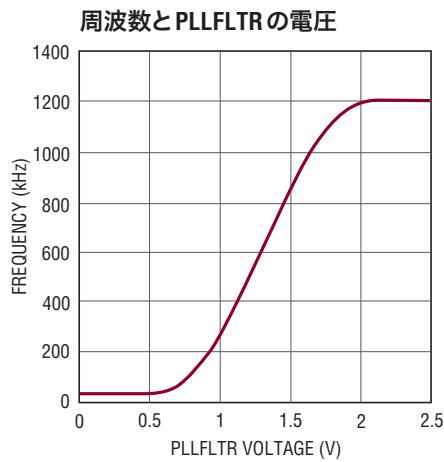

**PLLFLTR (ピン12/ピン10/ピン12)** : PLLのローパス・フィルタ入力。外部クロックに同期するとき、このピンはPLLのローパス・フィルタ入力として機能します。PLLFLTRとSGNDの間に直列の抵抗およびコンデンサを接続すると、PLLの帰還ループが補償されます。

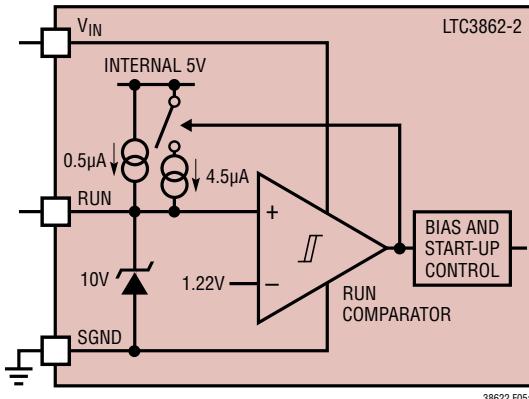

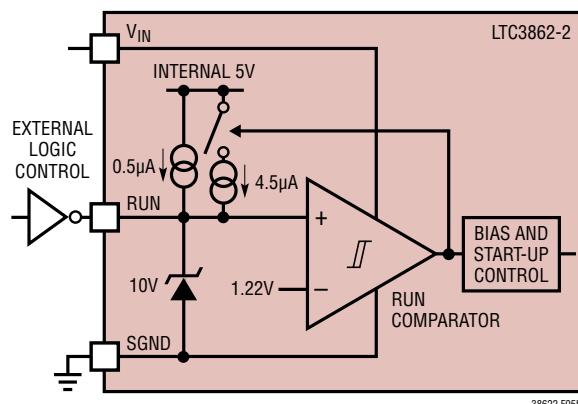

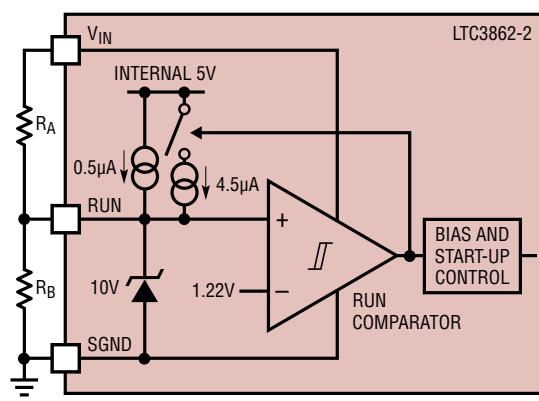

**RUN (ピン21/ピン19/ピン21)** : 実行制御入力。このピンの電圧が1.22Vを超えるとデバイスがオンします。このピンの電圧を1.22Vより低くすると、デバイスはシャットダウンします。このピンには0.5μAのプレアップ電流が流れます。RUNピンの電圧が1.22Vより高くなると、設定可能なヒステリシスを発生させるため、プレアップ電流が4.5μA増加します。

**SENSE1<sup>+</sup> (ピン23/ピン21/ピン23)** : 電流コンパレータの正入力。ピーク電流の作動しきい値を設定するために、ITHピンの電圧によって電流コンパレータのオフセットが設定されます。このピンは通常、パワーMOSFETのソースに接続するセンス抵抗に接続します。

**ピン機能 (SSOP/QFN/TSSOP)**

**SENSE2<sup>+</sup> (ピン13/ピン11/ピン13)** : 電流コンパレータの正入力。ピーク電流の作動しきい値を設定するために、ITHピンの電圧によって電流コンパレータのオフセットが設定されます。このピンは通常、パワーMOSFETのソースに接続するセンス抵抗に接続します。

**SENSE1<sup>-</sup> (ピン22/ピン20/ピン22)** : 電流コンパレータの負入力。このピンは通常、センス抵抗の低電位側に接続します。

**SENSE2<sup>-</sup> (ピン14/ピン12/ピン14)** : 電流コンパレータの負入力。このピンは通常、センス抵抗の低電位側に接続します。

**SGND (ピン9/ピン7/ピン9)** : 信号グランド。すべての帰還接続およびソフトスタート接続は、SGNDに戻してください。負荷レギュレーションを最適にするには、プリント回路基板パターン上の、複数の出力コンデンサの負端子間にSGNDピンをケルビン接続する必要があります。

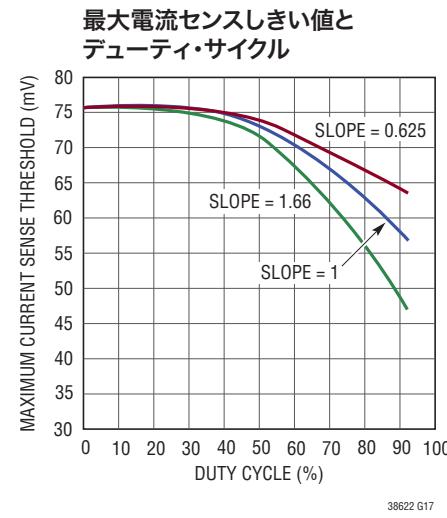

**SLOPE (ピン2/ピン24/ピン2)** : 内蔵のスロープ補償回路の利得はこのピンで設定します。このピンをフロート状態になると、正規化されたスロープ補償利得は1.00になります。このピンを3V8に接続すると、正規化されたスロープ補償は66%増

加し、このピンをSGNDに接続すると、正規化されたスロープ補償は37.5%減少します。詳細については、「アプリケーション情報」のセクションを参照してください。

**SS (ピン6/ピン4/ピン6)** : ソフトスタート入力。ソフトスタート動作を実現するために、このピンとSGNDの間にコンデンサを接続すると、エラーアンプの出力がクランプされます。内蔵の5 $\mu$ A電流源によって、このコンデンサが充電され、コンバータのピーク・スイッチ電流の増加率が設定されます。

**SYNC (ピン11/ピン9/ピン11)** : PLLの同期入力。50kHz～650kHzの外部クロックを入力すると、動作周波数がクロックに同期します。SYNCは50kの内部抵抗によってプルダウンされています。SYNC入力波形の立ち上がりエッジは、閉ループ動作ではGATE1の立ち上がりエッジと同期します。振幅が1.6Vより高いSYNC信号はアクティブ”H”、0.9Vより低い信号はアクティブ”L”とみなされます。

**V<sub>IN</sub> (ピン20/ピン18/ピン20)** : 主電源入力。このピンとSGNDの間に低ESRのセラミック・コンデンサを接続する必要があります。

## 機能図

## 動作

## 制御ループ

LTC3862-2は、2つのチャネルが180度の位相差で動作する、固定周波数、ピーク電流モード昇圧アーキテクチャを採用しています。通常動作時は、各チャネルのクロックがPWMラッチをセットすると、対応する外付けMOSFETがオンし、メイン電流コンパレータICMPがPWMラッチをリセットするとオフします。ICMPが作動してラッチをリセットするピーク・インダクタ電流は、ITHピンの電圧によって制御されます。この電圧はエラーアンプ(EA)の出力です。エラーアンプはV<sub>FB</sub>ピンの出力帰還信号を内部の1.223Vリファレンスと比較し、ITHピンで誤差信号を発生します。負荷電流が増加するとリファレンス電圧に対してV<sub>FB</sub>がわずかに低くなるので、平均インダクタ電流がその後負荷電流に釣り合うまで、エラーアンプはITH電圧を上昇させます。MOSFETがオフすると、インダクタ電流は次のクロック・サイクルが始まるまで、昇圧ダイオードから出力コンデンサおよび負荷に流れます。

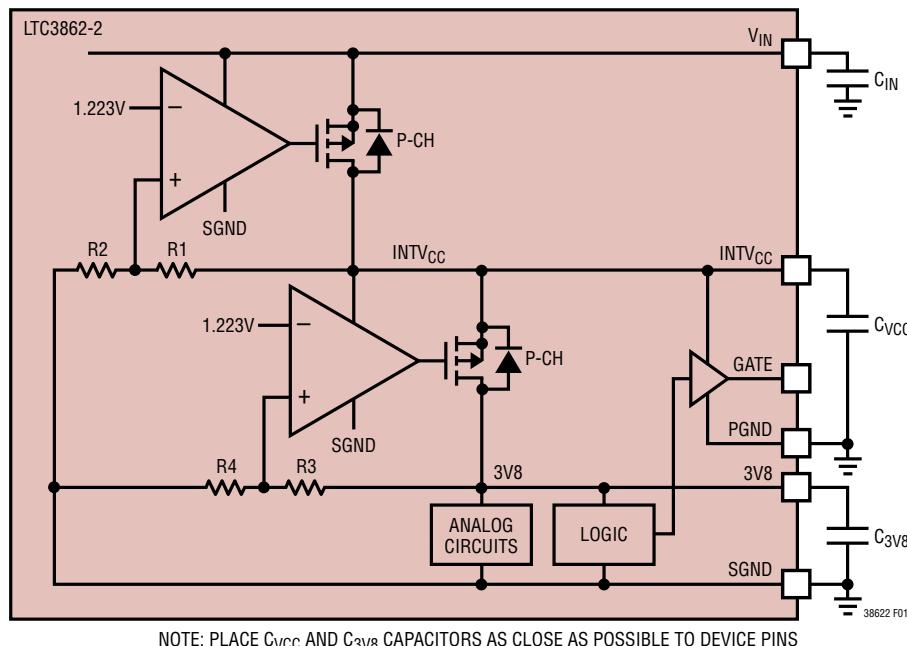

## ゲート・ドライバと制御回路に電力を供給する カスケード接続された LDO

LTC3862-2には、カスケード接続された2つのPMOS出力段を備えた低ドロップアウト電圧レギュレータ(LDO)があります。1つはゲート駆動電源( $INTV_{CC}$ )用であり、もう1つは低

電圧アナログおよびデジタル制御回路(3V8)用です。この電源配置のブロック図を図1に示します。

## ゲート・ドライバ電源のI<sub>DDO</sub>(INTV<sub>cc</sub>)

第1のLDOの10V出力(INTVCC)はVINから給電され、パワーMOSFETのゲート・ドライバに電力を供給します。INTVCCピンは4.7μF以上のセラミック・コンデンサ(X5R以上の良質なもの)でPGNDにバイパスし、セラミック・コンデンサはデバイスのピンのできるだけ近くに配置してください。2個のパワーMOSFETをチャネルごとに並列に接続して出力電力レベルを高くする場合や、Q<sub>G</sub>が50nCより大きい1個のMOSFETを使用する場合は、バイパス容量を10μFに大きくすることを推奨します。

低電圧ロックアウト(UVLO)回路は、INTV<sub>CC</sub>レギュレータの出力を検出して、パワーMOSFETが不十分なゲート駆動電圧によって動作しないよう保護します。LTC3862-2の場合、立ち上がり時のUVLOしきい値は標準で4.4Vであり、ヒステリシスは標準で500mVです。LTC3862-2は、V<sub>GS</sub>が6VのときにR<sub>DS(ON)</sub>の定格を規定している高電圧パワーMOSFETに合わせて最適化されています。ロジック・レベルのパワーMOSFETが必要なアプリケーションの場合は、LTC3862のデータシートを参照してください。

図1. カスケード接続されたLDOによって供給されるゲート駆動回路と制御回路の電力

## 動作

マルチフェーズ・アプリケーションでは、すべてのFBピンをまとめて接続し、すべてのエラーアンプ出力ピン(ITH)をまとめて接続します。**ただし、INTV<sub>CC</sub>ピンはまとめて接続しないでください。** INTV<sub>CC</sub>レギュレータは電流を流し出す能力はありますが、流し込む能力はありません。そのため、複数のINTV<sub>CC</sub>レギュレータ出力をまとめて接続すると、最も高い電圧のレギュレータがすべてのゲート駆動電流および制御電流を供給し、それ以外のレギュレータはオフになります。これにより、出力電圧が最も高いLDOに熱負荷がかかり、最大ダイ温度を超える状況を引き起こす可能性があります。LTC3862-2のマルチフェーズ・アプリケーションでは、各INTV<sub>CC</sub>レギュレータの出力を、各デバイスにできるだけ近づけて、それぞれのPGNDピンに個別にバイパスしてください。

### 低電圧のアナログおよびデジタル電源 LDO (3V8)

図1に示すように、LTC3862-2の内部にある第2のLDOはINTV<sub>CC</sub>から給電され、低電圧のアナログおよびデジタル制御回路への電源として機能します。(PMOS出力デバイスも備える)このLDOの出力電圧は3.8Vです。アナログおよびデジタル制御回路のほとんどは、内部の3V8 LDOから給電されます。3V8ピンは1nFのセラミック・コンデンサ(X5R以上の良質なもの)でSGNDにバイパスし、セラミック・コンデンサはデバイスのピンのできるだけ近くに配置してください。このLDOは外部回路の電源として使うことは意図されていません。

### 熱に関する検討事項とパッケージのオプション

LTC3862-2は3つのパッケージ・オプションで供給されます。5mm×5mmのQFNパッケージ(UH24)の熱抵抗R<sub>TH(JA)</sub>は34°C/W、24ピンTSSOP(FE24)パッケージの熱抵抗は38°C/W、24ピンSSOP(GN24)パッケージの熱抵抗は85°C/Wです。QFNパッケージとTSSOPパッケージのピン間隔は0.65mmであり、GN24オプションのピン間隔は0.025inです。

INTV<sub>CC</sub>レギュレータは全部で最大50mAの電流を供給できます。そのため、デバイスの最大接合部温度を超えないように注意する必要があります。接合部温度は以下の式を使って推算することができます。

$$I_{Q(TOT)} = I_Q + Q_{G(TOT)} \cdot f$$

$$P_{DISS} = V_{IN} \cdot (I_Q + Q_{G(TOT)} \cdot f)$$

$$T_J = T_A + P_{DISS} \cdot R_{TH(JA)}$$

全静止電流(I<sub>Q(TOT)</sub>)は、静止状態での電源電流(I<sub>Q</sub>)とパワーMOSFETのゲート容量を充電するのに必要な電流の合計値です。Q<sub>G(TOT)</sub>の値は、MOSFETのデータシートの「標準的性能特性」セクションに記載されている「V<sub>GS</sub>とQ<sub>G</sub>」のグラフから得られます。電気的仕様に示されている値は、高いV<sub>GS</sub>(15Vなど)で測定されている場合がありますが、目的とする値は10VのINTV<sub>CC</sub>ゲート駆動電圧での値です。

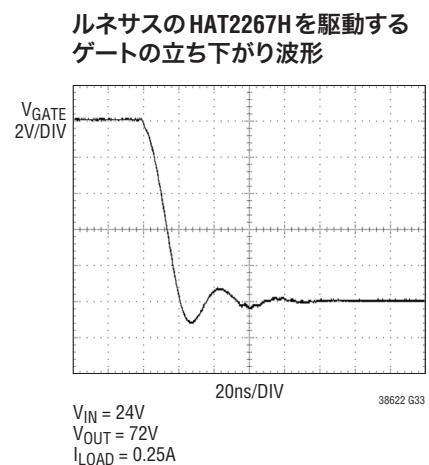

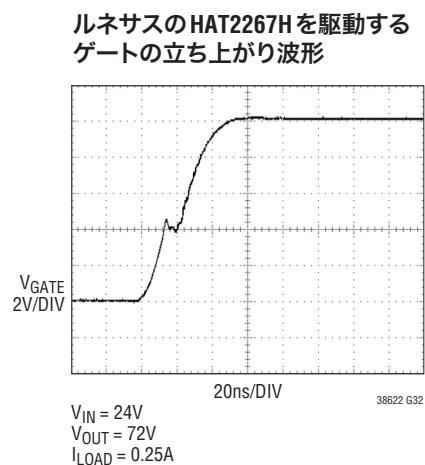

必要な熱解析の例として、入力電圧範囲が5.5V～24Vで出力電圧が72V/1.5Aの2フェーズ昇圧コンバータを考えます。スイッチング周波数は150kHzで、最大周囲温度は70°Cです。このアプリケーションで使用するパワーMOSFETはルネサス・エレクトロニクスのHAT2267Hで、標準のR<sub>Ds(ON)</sub>は13mΩ(V<sub>GS</sub> = 10V時)です。「V<sub>GS</sub>とQ<sub>G</sub>」のグラフから、V<sub>GS</sub> = 10Vでの全ゲート電荷は30nCです(ゲート電荷の温度係数は小さい)。フェーズごとに1個のパワーMOSFETを使用します。QFNパッケージのオプションの場合は、次のようにになります。

$$I_{Q(TOT)} = 3mA + 2 \cdot 30nC \cdot 150kHz = 12mA$$

$$P_{DISS} = 24V \cdot 12mA = 288mW$$

$$T_J = 70^\circ C + 288mW \cdot 34^\circ C/W = 79.8^\circ C$$

この例では、接合部温度の上昇は9.8°Cに過ぎません。これらの式は、ゲート充電電流がデバイスの静止電流に占める割合が通常はどの程度か、パッケージ・オプションの選択と基板の放熱がソリューションの熱性能にどの程度重大な影響を及ぼす可能性があるかを示しています。

## 動作

最大接合部温度を超えないようにするには、最大の  $V_{IN}$  時に連続モード(重負荷)で動作する場合にデバイスに流れ込む入力電源電流を確認しておく必要があります。接合部温度を安全なレベルに保つには、動作周波数とパワー MOSFET のサイズの間のトレードオフが必要です。最後に、赤外線カメラや熱量検出器を使用して最終的なプリント回路基板の熱解析を実施し、計算結果を検証することが重要です。オプションとして、図3に示す外部レギュレータを使用すると、デバイスの全電力損失を低減することができます。

### サーマル シャットダウン保護

(外部または内部に)過温度状態が発生し、ダイ温度が  $170^{\circ}\text{C}$  を超えると、内蔵の温度モニタがゲート・ドライバをシャットダウンし、ソフトスタート・コンデンサをリセットします。高温での誤動作を防ぐため、この温度センサには  $10^{\circ}\text{C}$  のヒステリシスがあります。LTC3862-2に内蔵されている温度センサは、瞬間的な過温度状態時にデバイスを保護することを目的としています。しかし、規定された最大の動作接合部温度を超えた状態で動作が継続すると、デバイスが劣化するおそれがあります。

### 低い電源電圧での動作

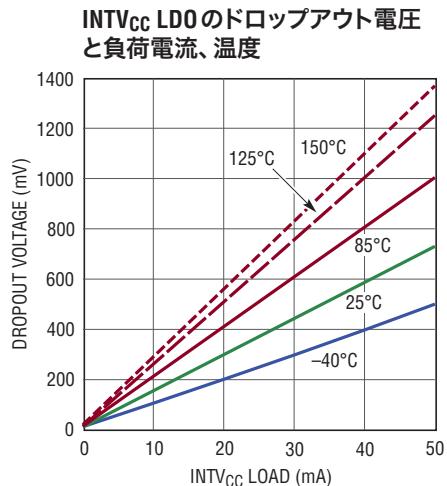

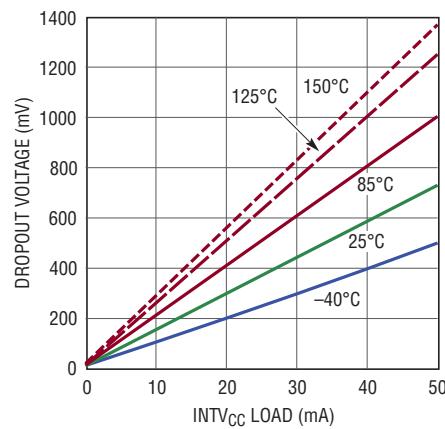

LTC3862-2の最小入力電圧は  $5.5\text{V}$  なので、 $R_{DS(\text{ON})}$  の定格が  $6\text{V}$  で高電圧のパワー MOSFET が必要なアプリケーションに適しています。LTC3862-2のゲート・ドライバは PMOS のプルアップ・デバイスと NMOS のプルダウン・デバイスで構成されているので、パワー MOSFET のスイッチング時には INTVCC の全電圧をゲートに印加することができます。それでもなお、最適なパワー MOSFET を選択するためには、ゲート駆動電源電圧 (INTVCC) の最小値を決定するのに注意が必要です。ゲート駆動電源電圧の最小値に影響する可能性がある重要なパラメータは、最小入力電圧 ( $V_{IN(\text{MIN})}$ )、LDO のドロップアウト電圧、パワー MOSFET の  $Q_G$ 、および動作周波数です。

入力電圧  $V_{IN}$  が十分に低く、INTVCC LDO がドロップアウト状態になる場合、ゲート駆動電源電圧の最小値は次のようになります。

$$V_{INTVCC} = V_{IN(\text{MIN})} - V_{\text{DROPOUT}}$$

LDO のドロップアウト電圧は、デバイスの全ゲート駆動電流と静止電流(標準  $3\text{mA}$ )の関数です。LDO のドロップアウト電圧と出力電流の曲線を図2に示します。LDO ドロップアウト電圧の温度係数は約  $6000\text{ppm}/^{\circ}\text{C}$  です。

LDO を流れる全静止電流 ( $I_{Q(\text{TOT})}$ ) は、コントローラの静止電流 ( $3\text{mA}$ ) と全ゲート充電駆動電流の合計です。

$$I_{Q(\text{TOT})} = I_Q + Q_{G(\text{TOT})} \cdot f$$

計算が完了したら、ゲート駆動波形とゲート・ドライバ電源電圧 (INTVCC - PGND 間) をすべての動作条件(低い  $V_{IN}$ 、公称の  $V_{IN}$ 、および高い  $V_{IN}$ 、さらには軽負荷から最大負荷まで)にわたって測定し、パワー MOSFET の適切な導通状態を確保することが重要です。パワー MOSFET のデータシートを参照して、測定した  $V_{GS}$  に対応する実際の  $R_{DS(\text{ON})}$  を調べ、赤外線カメラや熱量検出器を使用して部品温度を測定することにより、熱計算の結果を検証してください。

図2. INTVCC LDO のドロップアウト電圧と電流

# LTC3862-2

## 動作

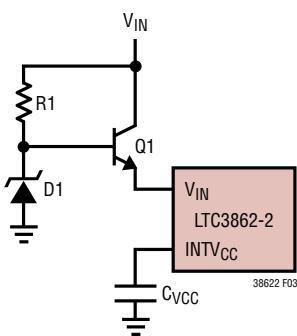

### 高い電源電圧での動作

入力電圧が高いと、LTC3862-2内部のLDOは電力を大量に消費することがあり、それによって最大接合部温度を超える可能性があります。高い動作周波数、複数のパワーMOSFETの使用などの条件によっては、接合部温度が高い水準まで上昇する場合があります。前述した熱計算の式が接合部温度の過剰な上昇を示す場合は、図3に示すように外部のバイアス電源を常に使用して、デバイスの電力損失を低減することができます。

たとえば、12Vのシステム電源を使用できる場合は、それを使ってLTC3862-2に給電する方が24Vの主入力電源を使用するよりも適しています。また、バイアス電源は別個のスイッチング・レギュレータまたはLDOレギュレータを使用して生成することもできます。LDOレギュレータの例を図3に示します。LDOレギュレータの出力電圧は、適切なツエナー・ダイオードを選択することにより、図3のLTC3862-2とQ1との間で電力損失を分けるには十分低い値だが、10Vよりは高い電圧に設定できます。INTVCCピンの電圧の絶対最大定格は11Vです。

図3. 外部バイアス電源を接続したLTC3862-2の使用

### 電源シーケンシング

図1に示すように、LTC3862-2の2個のLDOレギュレータには、PMOS出力トランジスタと並列にボディ・ダイオードがあります。そのため、デバイスのINTVCCピンとV<sub>IN</sub>ピンのバイアスを別

の電源から与えることはできません。INTVCCピンのバイアスを別の電源から個別に与えると、考えられる2つの不具合モードのうちの1つが電源シーケンシング中に発生することがあります。INTVCC電源の方がV<sub>IN</sub>電源より先に立ち上がると、外部のINTVCC電源からLDO PMOSデバイスのボディ・ダイオードを通じて入力コンデンサおよびV<sub>IN</sub>ピンに大電流が流れます。この大電流により、ラッチアップ状態が引き起こされ、デバイスの致命的な故障が発生する可能性があります。

ただし、デバイスへのV<sub>IN</sub>電源がINTVCC電源よりも先に立ち上がると、外部のINTVCC電源はLTC3862-2の内部LDOの負荷として動作し、LDOはその短絡電流でINTVCC出力を充電しようとします。これにより、LTC3862-2の電力損失が過剰になり、熱的過負荷が生じる可能性があります。

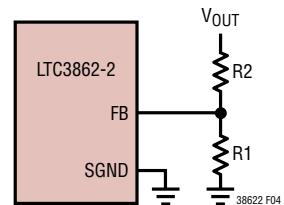

### 出力電圧のプログラミング

出力電圧は次式に従って抵抗分割器によって設定します。

$$V_{OUT} = 1.223V \left( 1 + \frac{R2}{R1} \right)$$

外付けの抵抗分割器は図4に示すように出力に接続します。通常、抵抗R1は、通常動作時にV<sub>FB</sub>ピンから流れる電流によって生じる出力電圧誤差が、抵抗分割器に流れる電流と比較して無視できるように選択します。エラーアンプの入力バイアス電流による出力電圧誤差を0.5%未満にするには、R1の最大値を約30kにします。

図4. 抵抗分割器による出力電圧の設定

## 動作

### RUNピンの動作

LTC3862-2の制御回路をオン/オフするにはRUNピンを使用します。RUNピンの電圧を1.22Vより低くすると強制的にシャットダウン・モードになり、RUNピンを解放すると0.5μAの電流源によってRUNピンの電位が上昇して、「常時オン」のコンバータを設計できます。代わりに、RUNピンの電位を外部から引き上げるか、またはロジックで直接駆動することもできます。このピンの絶対最大定格である8Vを超えないように注意する必要があります。

RUNピンのコンパレータを使用して入力電圧を検出し、低電圧検出回路を設計することもできます。この回路は、入力電流が低入力電圧で非常に高いレベルに達する場合がある昇圧コンバータ・アプリケーションで役立ちます。

$$I_{IN} = \frac{I_{OUT} \cdot V_{OUT}}{V_{IN}}$$

RUNコンパレータの入力しきい値1.22Vは、低電圧検出機能の精度を最大限に高めるため、高精度バンドギャップ・リファレンスから得られます。RUNコンパレータには80mVのヒステリシスが組み込まれています。RUNピンの電圧が1.22Vを超えると、RUNピンに流れ込む電流は0.5μAから5μAの電流に切り替わります。したがって、次式に示すように、ユーザーは外付けの抵抗分割器の抵抗値を使用して、立ち上がりのしきい値とヒステリシスの大きさの両方を設定できます。

$$V_{IN(ON)} = 1.22V \left( 1 + \frac{R_A}{R_B} \right) - 0.5\mu \cdot R_A$$

$$V_{IN(OFF)} = 1.22V \left( 1 + \frac{R_A}{R_B} \right) - 5\mu \cdot R_A$$

考えられるRUNピン制御技法のいくつかを図5に示します。

### 周波数の選択と位相同期ループ

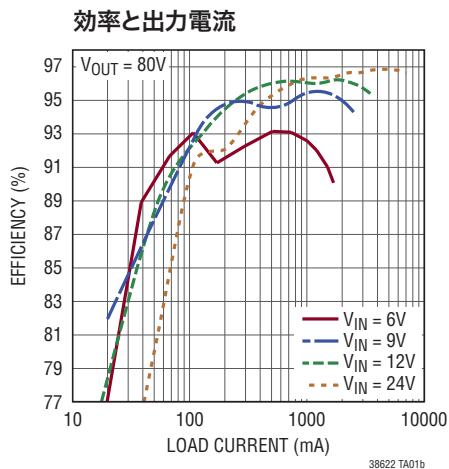

スイッチング周波数の選択は効率と部品サイズの間のトレードオフになります。低周波数動作ではMOSFETのスイッチング損失が減ることで効率が高まりますが、出力リップルを低く抑えるには大きなインダクタや出力コンデンサが必要です。

図5a. 「常時オン」のコンバータに対応したRUNピンの使用

図5b. 外部ロジックを使ったオン/オフ制御

図5c. RUNピンを使った入力電圧のターンオンしきい値とターンオフしきい値の設定

## 動作

LTC3862-2は、FREQピンとグランドとの間に接続した1本の抵抗により、75kHz～500kHzの範囲で設定できる固定周波数アーキテクチャを採用しています。FREQピンの抵抗値と動作周波数との間の関係を図6に示します。

LTC3862-2の動作周波数は次式を使用して近似できます。

$$R_{FREQ} = 5.5096E9(f_{osc})^{-0.9255}$$

LTC3862-2には位相同期ループがあり、SYNCピンに接続された外部クロック信号源に内部発振器を同期させることができます。PLLFLTRピンとSGNDとの間に直列のRC回路網を接続して、PLLの帰還ループを補償します。標準的な補償部品は、0.01μFのコンデンサと10kの抵抗を直列に接続したもので。PLLFLTRピンは位相検出器の出力と電圧制御発振器(VCO)の入力の両方を兼ねています。LTC3862-2の位相検出器は、図7に示すように、PLLFLTRピンの電圧を調整して、GATE1の立ち上がりエッジのタイミングを外部クロック信号の立ち上がりエッジに合わせます。GATE2の立ち上がりエッジは、PHASEMODEピンの電圧に依存します。LTC3862-2のPLLのキャプチャレンジは50kHz～650kHzです。

LTC3862-2の動作周波数は外付け抵抗を使用して設定できるので、同期アプリケーションでは、(外付け抵抗で定まる)自走周波数を同期周波数と同じ値に設定することを推奨します。こうすると、デバイスは外部クロックとほぼ同じ周波数で起動するので、同期信号が入力されると、出力に不連続状態が観測されなくなります。同期信号が失われた場合にも、動作周波数は基本的には一定に維持されます。SYNCピンにはグランドとの間に50kの抵抗が内蔵されています。

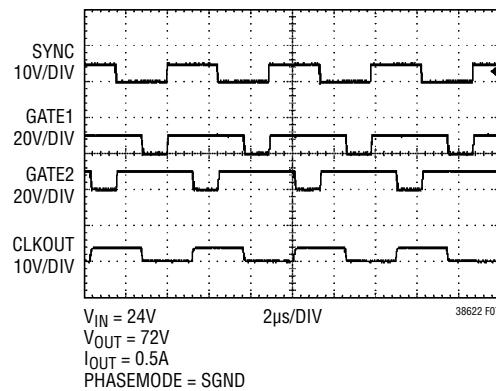

## マルチフェーズ・アプリケーションでのCLKOUTピンとPHASEMODEピンの使用

LTC3862-2には、複数のデバイスを互いにデイジーチェーン接続して、より大電流のマルチフェーズ・アプリケーションに対応するための2つのピン(CLKOUTおよびPHASEMODE)があります。3フェーズまたは4フェーズの設計では、マスタ・コントローラのCLKOUT信号をスレーブ・コントローラのSYNC入力に接続して、单一の大電流出力を得るために追加の電力段を同期させます。PHASEMODEピンは、表1にまとめているように、チャネル1とチャネル2の間の位相関係、ならびにチャネル1とCLKOUTの間の位相関係を調整するのに使用します。位相は、GATE1出力の立ち上がりエッジとして定義され

図6. FREQピンの抵抗値と周波数

図7. PLLを使用したLTC3862-2の外部クロックへの同期

ている0°を基準にして計算されます。6フェーズのアプリケーションでは、マスタ・コントローラのCLKOUTピンは2番目のコントローラのSYNC入力に接続し、2番目のコントローラのCLKOUTピンは3番目のコントローラのSYNCピンに接続します。

表1

| PHASEMODE<br>ピン | CH-1とCH-2の<br>間の位相 | CH-1とCLKOUT<br>の間の位相 | アプリケーション    |

|-----------------|--------------------|----------------------|-------------|

| SGND            | 180°               | 90°                  | 2フェーズ、4フェーズ |

| フロート            | 180°               | 60°                  | 6フェーズ       |

| 3V8             | 120°               | 240°                 | 3フェーズ       |

## 動作

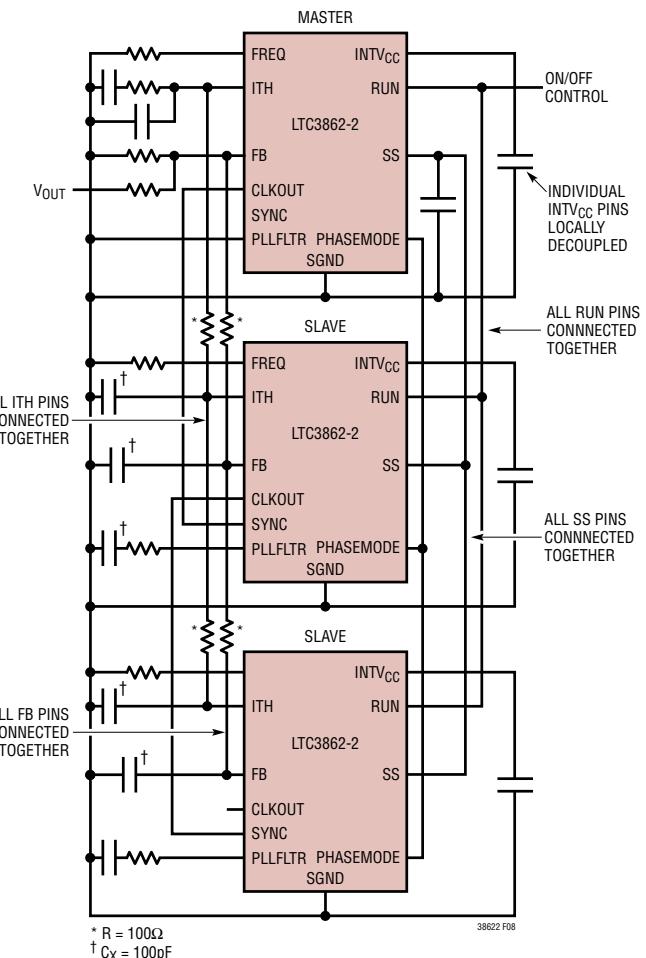

### マルチフェーズ・アプリケーションでのLTC3862-2トランスコンダクタンス( $g_m$ )エラーアンプの使用

LTC3862-2のエラーアンプはトランスコンダクタンス( $g_m$ )アンプです。つまり、DC利得は高いが出力インピーダンスが高いことを意味します(エラーアンプの出力は差動入力電圧に比例した電流です)。この方式のエラーアンプでは、複数のチップに内蔵されているアンプを並列に接続できるので、マルチフェーズ・ソリューションを実装する作業がきわめて容易になります。この場合、図8に示すように、複数のLTC3862-2のFBならびにITHピンを互いに接続できます。複合エラーアンプの $g_m$ は、単純に1個のアンプのトランスコンダクタンスのn倍、つまり $g_m(TOT) = n \cdot 660\mu\text{S}$ になります。ここで、nは並列に接続されているアンプの数を表します。ITHピンから電流コンパレータ入力への伝達関数は、チャネル間およびデバイス間の両方で正確になるように慎重に設計されています。ピーク・インダクタ電流の整合性は、このようにして正確に保たれます。

エラーアンプの出力をバッファに通した後の出力は、電流コンパレータの入力でのしきい値を決定します。ゼロ・ピーク電流を表すITH電圧は0.4Vで、電流制限値を表す電圧は1.2V(デューティ・サイクルが低い場合)です。過負荷状態の間、エラーアンプの出力は、過負荷状態が解消されたときの待ち時間を短くするために、低いデューティ・サイクルで2.6Vにクランプされます。LTC3862-2では特許取得済み回路を使用してスロープ補償信号を回復するので、最大ピーク・インダクタ電流はデューティ・サイクルと強く関係しているわけではありません。

複数のLTC3862-2コントローラを使用するマルチフェーズ・アプリケーションでは、プリント回路基板上のグランド電流によってデバイス間の制御線が乱され、不規則な動作となる可能性があります。こうしたアプリケーションでは、図8に示すように、100Ωの抵抗を介してFBピンを互いに接続し、それぞれのスレーブ側FBピンを100pFのデカップリング・コンデンサを使用して各デバイス付近でグランドに接続する必要があります。

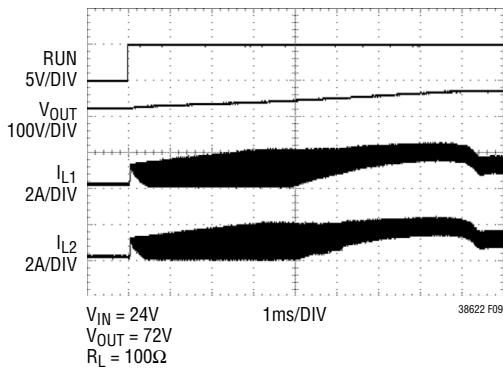

### ソフトスタート

LTC3862-2の起動は、SSピンの電圧によって制御されます。デバイス内部のPNPトランジスタにより、電流コンパレータの検出しきい値はソフトスタート期間中クランプされるので、ピーク・スイッチ電流が制限されます。PNPのベースはSSピンに、エミッタは内部のバッファ付きITHノードに接続されています(ITHピンの電圧はこの期間中はソフトスタート電圧を追跡

図8. マルチフェーズ動作に対応したLTC3862-2のエラーアンプ構成

しないことがあります)。内部の5μA電流源がSSコンデンサを充電し、ソフトスタート・コンデンサの電圧が約0.6Vに達するまでピーク検出しきい値にクランプします。必要なソフトスタート容量は、次式を使用して推算できます。

$$C_{SS} = 5\mu\text{A} \left( \frac{t_{SS}}{0.6\text{V}} \right)$$

SSピンには、内部にオープン・ドレインのNMOSプルダウン・トランジスタがあります。このトランジスタは、RUNピンが“L”になるか、INTVCCピンの電圧がその低電圧ロックアウトしきい値より低くなるか、または過温度状態になるとオンになります。複数のLTC3862-2デバイスを使用するマルチフェーズ・ア

## 動作

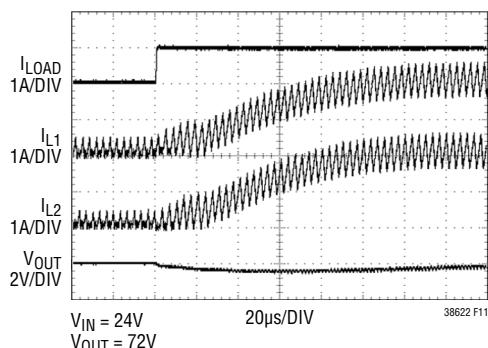

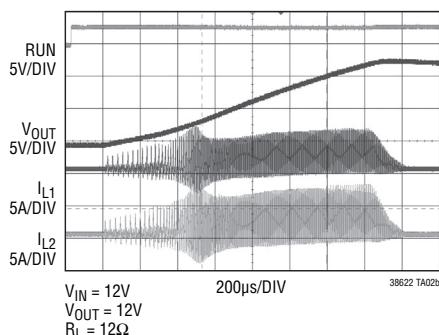

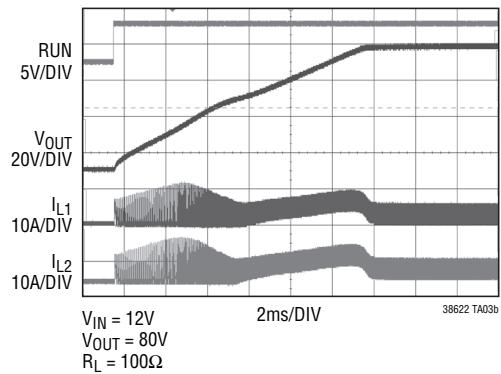

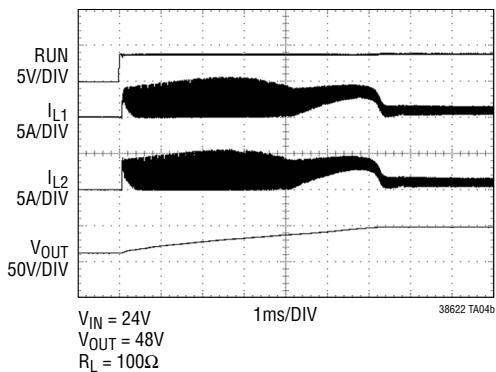

プリケーションでは、すべてのSSピンを互いに接続し、1個の外付けコンデンサを使用してソフトスタート時間を見つめます。この場合、ソフトスタート・コンデンサに流れ込む電流は  $I_{SS} = n \cdot 5\mu A$  となります。ここで、nは互いに接続するSSピンの数です。LTC3862-2の2フェーズ・アプリケーションでの起動波形を図9に示します。

図9. LTC3862-2を使用した昇圧コンバータの標準的な起動波形

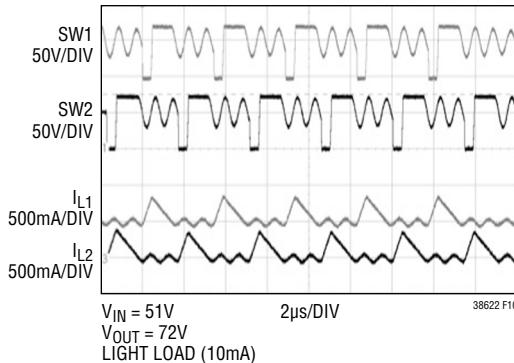

## 軽負荷でのパルス・スキップ動作

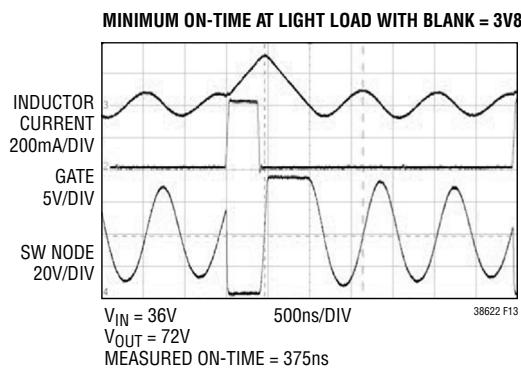

負荷電流が減少するにつれて、コントローラは不連続モード(DCM)に入ります。コントローラの最小オン時間に達するまでは、ピーク・インダクタ電流を低減することができます。負荷電流をさらに減らすと、出力のレギュレーション状態を維持するためにパルス・スキップ動作が発生しますが、これは正常な動作です。このモードでのコントローラの最小オン時間は約210ns(ブランкиング時間をその最小値に設定した場合)で、その大半は立ち上がりエッジのブランкиング時間です。パルス・スキップ動作を開始したときのLTC3862-2のスイッチング波形を図10に示します。

## プログラム可能なスロープ補償

連続導通モード(CCM)で動作している電流モード昇圧レギュレータでは、50%を超えるデューティ・サイクルの場合、低調波発振を避けるためにスロープ補償を追加する必要があります。LTC3862-2の場合、このランプ補償は内部で行われますが、ユーザーが調整可能です。ランプ補償の波形は内部で固定されているので、通常はインダクタの値と動作周波数に応じてある程度の制約が加わります。たとえば、大きさが固定されている内部スロープ補償の場合、インダクタが極端に大

図10. パルス・スキップ動作を開始したときのLTC3862-2の軽負荷でのスイッチング波形

きいとスロープ補償の効果が大きくなりすぎて、コンバータが不安定になる可能性があります。同様に、使用するインダクタが小さすぎると、内部のランプ補償が不十分になり、低調波発振を防止できない場合があります。

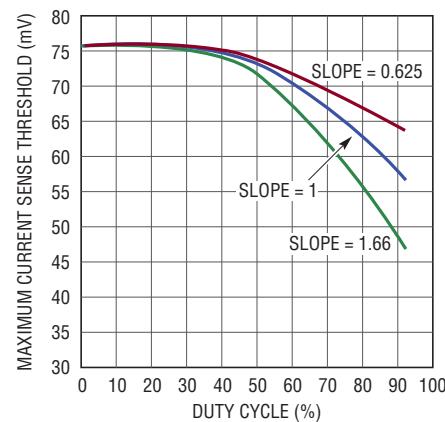

より広い範囲のインダクタンスに対して性能を最適化できるように、LTC3862-2には、ユーザーがスロープ補償の利得を設定できるピンがあります。SLOPEピンをフロート状態にしてある場合、正規化されたスロープ利得は1.00です。SLOPEピンをグランドに接続すると、正規化された利得は0.625に減少し、SLOPEピンを3V8電源に接続すると正規化されたスロープ利得は1.66に増加します。

正規化されたスロープ補償の利得を1.00に設定している場合、設計式では、以前の設計と同様に、インダクタのリップル電流が20%~40%であると仮定しています。ただし、アプリケーション回路によっては、1.00という正規化利得が、選択したインダクタには最適ではないことがあります。インダクタのリップル電流が40%より大きい場合は、SLOPEピンを3V8電源に接続することにより、正規化されたスロープ利得を1.66に増やすことができます(66%の増加)。インダクタのリップル電流が20%より小さい場合は、SLOPEピンをSGNDに接続することにより、正規化されたスロープ利得を0.625に減らすことができます(37.5%の減少)。

スロープ補償の効果を確認するには、出力に負荷ステップを加え、負荷電流の立ち上がりエッジと立ち下がりエッジの間に流れるインダクタ電流の振る舞いをサイクルごとにモニタします。入力電圧を全範囲にわたって変化させ、SWノードの不安定性または低調波発振の兆候がないかサイクルごとに確

## 動作

認してください。スロープ補償が低すぎると、コンバータは過度のジッタや、最悪の場合は低調波発振が生じることがあります。内部の電流センス信号に過度のスロープ補償が加わると、制御ループの位相余裕が低下します。適度に補償されたループのインダクタ電流波形を図11に示します。

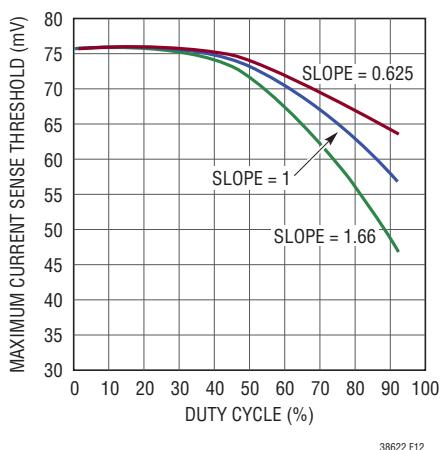

デューティ・サイクルとは強く関係していないSENSE<sup>+</sup>からSENSE<sup>-</sup>間のしきい値を得るため、LTC3862-2は特許取得済みの回路を内蔵しており、適用されるスロープ補償の大半がこの回路によって回復します。ただし、図12に示すように、この検出しきい値は、設定されたスロープ利得の関数です。SENSE<sup>+</sup>とSENSE<sup>-</sup>との電位差に関するデータシートの標準的な規格値である75mVは、正規化されたスロープ利得が1.00で、デューティ・サイクルが低い条件で測定されます。正規化されたスロープ利得が1.00ではないアプリケーションの場合は、図12を参照して、センス抵抗の正しい値を調べてください。

図11. 適切に補償された制御ループのインダクタ電流波形

図12. SENSEピンでのピークしきい値に対するスロープ利得の影響

## 設定可能なブランкиングと最小オン時間

LTC3862-2のBLANKピンを使用すると、ユーザーはSENSEピンでの立ち上がりエッジ・ブランкиングの長さを設定できます。BLANKピンをSGNDに接続すると最小オン時間は210nsになります。BLANKピンをフロート状態にすると最小オン時間は290nsに増加し、BLANKピンを3V8電源に接続すると最小オン時間は375nsになります。電流コンバータの伝播遅延時間(標準25ns)とロジック回路の伝播遅延時間(10ns~15ns)は本質的に短いので、最小オン時間の大部分はこの立ち上がりエッジ・ブランкиング時間で占められます。

立ち上がりエッジ・ブランкиングの目的は、パワーMOSFETが導通するときにSENSEピンのノイズを取り除くことです。パワーMOSFETの導通時には、ゲート駆動電流、SWノードの寄生容量の放電、昇圧ダイオード電荷の回復、およびdi/dtが高い経路での寄生直列インダクタンスのすべてが、電流コンバータの誤作動を引き起こす可能性があるオーバーシュートや高周波ノイズの原因となります。LTC3862-2が適しているアプリケーションの範囲は広いので、内部の立ち上がりエッジ・ブランкиング時間を1つの値に固定したと仮定すると、使用される最も長い時間にすることが必要だったと考えられます。ブランкиング時間を設定できる手段が与えられているので、ユーザーはSENSEピンのフィルタ処理をアプリケーションごとに最適化することができます。昇圧コンバータの最小オン時間に対する設定可能な立ち上がりエッジ・ブランкиング時間の影響を図13に示します。

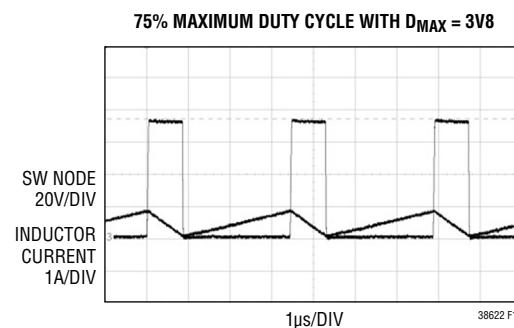

## 設定可能な最大デューティ・サイクル

一定の周波数と低い出力リップル電圧を維持するため、シングルエンドの昇圧コンバータ(またはフライバック・コンバータあるいはSEPICコンバータ)は、いくらかのごく短い時間、サイクルごとにスイッチをオフにする必要があります。このオフ時間により、エネルギーをインダクタから出力コンデンサおよび負荷に移し、過剰なリップル電流およびリップル電圧を防止できます。昇圧コンバータやSEPICコンバータのようなインダクタ・ベースの方式では、特に、入力電圧が低く出力電圧が高いアプリケーションの場合、最大デューティ・サイクルをできるだけ100%に近づけることが望ましいと考えられます。ただし、トランジスト・ベースのソリューションでは、1次スイッチのオフ時間の間に「電圧×時間」のリセットが必要になるので、100%に近い最大デューティ・サイクルにすることは望ましくありません。

## 動作

図13. 最小オン時間に対する立ち上がりエッジ・ブランкиングの影響

これらの異なるアプリケーション要件を満たすため、LTC3862-2には最大デューティ・サイクルを設定する簡単な方法があります。D<sub>MAX</sub>ピンをSGNDに接続すると、最大デューティ・サイクルは96%に制限されます。D<sub>MAX</sub>ピンをフロート状態にするとデューティ・サイクルは84%に制限され、3V8電源に接続すると75%に制限されます。最大デューティ・サイクルを制限したことによる、昇圧コンバータのSWノードの波形に対する影響を図14に示します。

図14. 異なるデューティ・サイクル制限値でのSWノードの波形

LTC3862-2は、2、3、4、6、および12フェーズ動作を行うために、設定されているスイッチング周波数の12倍の周波数で動作する発振器を内蔵しています。ゲート・ドライバの動作周波数を得るため、基本の発振器周波数を分周するのにデジタル・カウンタが使用されます。最大デューティ・サイクルの制限値はこのデジタル・カウンタから得られるので、最大デューティ・サイクルのパーセント値がプロセスの許容誤差や温度によって変動することはありません。

## 動作

### SENSE<sup>+</sup>ピンとSENSE<sup>-</sup>ピン

SENSE<sup>+</sup>ピンおよびSENSE<sup>-</sup>ピンは、各チャネルのCMOS電流コンパレータへの高インピーダンス入力です。公称値として、これらのピンに流れ込むか、これらのピンから流れ出すDC電流はありません。SENSE<sup>+</sup>ピンおよびSENSE<sup>-</sup>ピンとSGNDとの間にはESD保護ダイオードが接続されていますが、高温でもこれらのピンに流れ込む漏れ電流は1 $\mu$ A未満です。

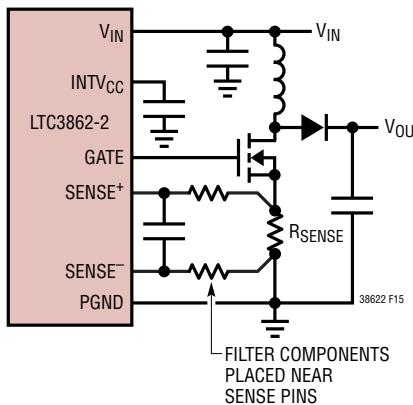

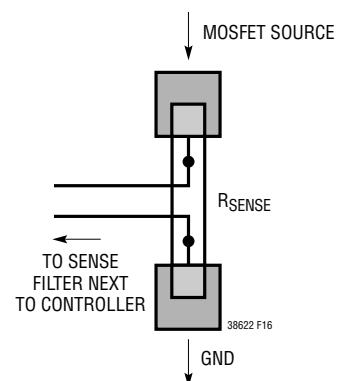

LTC3862-2には立ち上がりエッジのブランкиング回路が内蔵されているので、正常に動作させるために外付けのRCフィルタは不要です。ただし、外付けのフィルタを使用する場合は、図15に示すように、デバイスのSENSE<sup>+</sup>ピンとSENSE<sup>-</sup>ピンの近くにフィルタ部品を配置する必要があります。正と負のセンス・ノード配線は、図16に示すように、互いに平行に配線し、センス抵抗の下でケルビン接続してください。基板上のここ以外の場所で電流を検出すると、電流センス素子に寄生インダクタンスと寄生容量が上乗せされてセンス・ピンでの情報の価値が下がり、設定される電流制限値を予測できなくなることがあります。プリント回路基板のビアを使用してSENSE<sup>-</sup>の配線をグランド・プレーンに接続するのは避けてください。そのように接続すると、予測できない動作が引き起こされるおそれがあります。

センス抵抗は、図16に示すように、短くて幅の広いプリント回路基板配線を使用して、パワーMOSFETのソースとグランド・ノードに接続してください。理想的には、センス抵抗の低電位側の端子は出力コンデンサの負端子のすぐ隣に配置します。

図15. 電流センス・フィルタ部品の適切な配置

この経路は、スイッチ、昇圧ダイオード、出力コンデンサ、およびセンス抵抗で形成される高di/dtループの一部だからです。インダクタを流れる電流は三角波なので、インダクタの配置は重要ではありません。

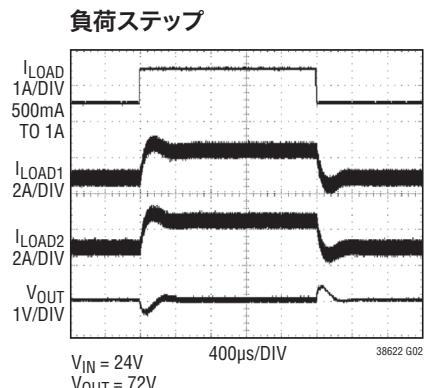

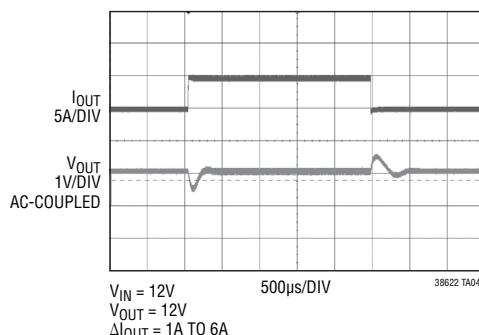

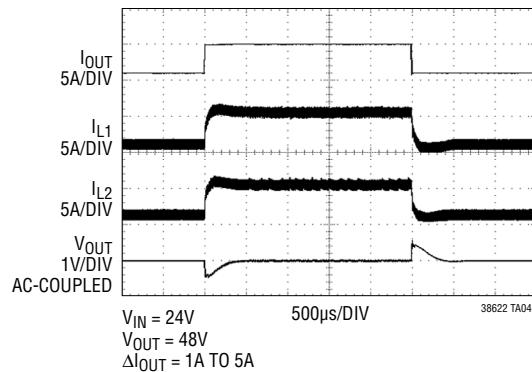

### 負荷トランジエント応答の確認

レギュレータのループ応答は、負荷電流のトランジエント応答を観察すれば確認できます。スイッチング・レギュレータは、DC(抵抗性)負荷電流のステップに応答するのに数サイクルを要します。負荷ステップが発生すると、V<sub>OUT</sub>は $\Delta I_{LOAD}$ (ESR)に等しい大きさだけシフトします。ここで、ESRはC<sub>OUT</sub>の等価直列抵抗です。 $\Delta I_{LOAD}$ によってC<sub>OUT</sub>の充放電も始まります。これにより、帰還誤差信号が発生してレギュレータを電流変化に適応させ、V<sub>OUT</sub>を定常値に回復させます。この回復期間に(安定性に問題があることを示す)過度のオーバーシュートやリングングが発生しないか、V<sub>OUT</sub>をモニタすることができます。

ITHピンが備わっているので制御ループ動作を最適化できるだけでなく、DC結合され、ACフィルタを通した閉ループ応答のテスト・ポイントが得られます。このテスト・ポイントでのDCステップ、立ち上がり時間、およびセトリングは、閉ループ応答を正確に反映します。2次特性が支配的なシステムを想定すれば、位相マージンや減衰係数は、このピンで見られるオーバーシュートのパーセンテージを使用して概算することができます。このピンの立ち上がり時間を調べることにより、帯域幅も概算できます。

図16. SENSE<sup>+</sup>配線およびSENSE<sup>-</sup>配線のケルビン接続を使用したセンス抵抗への接続

## 動作

ITHピンの $R_C$ ・ $C_C$ 直列フィルタにより、中心的なポールゼロ・ループ補償が設定されます。昇圧コンバータとフライバック・コンバータの伝達関数には、右半平面のゼロが含まれています。このゼロは、良好な位相余裕を維持するために、通常はループ交差周波数を大幅に低減することが必要です。 $R_C$ ・ $C_C$ フィルタの値は、通常、プリント回路基板のレイアウトを完了し、特定の出力コンデンサの種類と容量値を決定したら、トランジエンント応答を最適化するために多少(推奨値の0.5倍~2倍)変更することができます。出力コンデンサの実効ESRとバルク容量には、ループ利得と位相に大きく影響するので、出力コンデンサの構成はあらかじめ選択しておく必要があります。立ち上がり時間が $1\mu\text{s} \sim 10\mu\text{s}$ の、全負荷電流の20%~80%の出力電流パルスによって、帰還ループを開くことなく全体的なループの安定性を判断することができる出力電圧波形とITHピンの波形が発生します。パワーMOSFETと負荷抵抗

を出力コンデンサの両端に直接接続し、適当な信号発生器でそのゲートを駆動するのが、高速負荷ステップ状態を発生する実用的な方法です。出力電流のステップ変化によって生じる初期出力電圧ステップは帰還ループの帯域幅に入っていない場合があるため、位相余裕を決定するのにこの信号を使用することはできません。このため、ITHピンの信号を調べる方が確実です。この信号は帰還ループ内にあり、フィルタを通して補償された制御ループ応答です。ループの利得は $R_C$ を大きくすると増加し、ループの帯域幅は $C_C$ を小さくすると広くなります。 $C_C$ を減少させるのと同じ比率で $R_C$ を増加させると、ゼロの周波数は変化しないので、帰還ループの最も重要な周波数範囲で位相シフトが一定に保たれます。出力電圧のセッティング動作は閉ループ・システムの安定性に関係し、電源全体の実際の性能を表します。正常に補償された昇圧コンバータの負荷ステップ応答を図17に示します。

図17. 適切に補償された昇圧コンバータの負荷ステップ応答

## アプリケーション情報

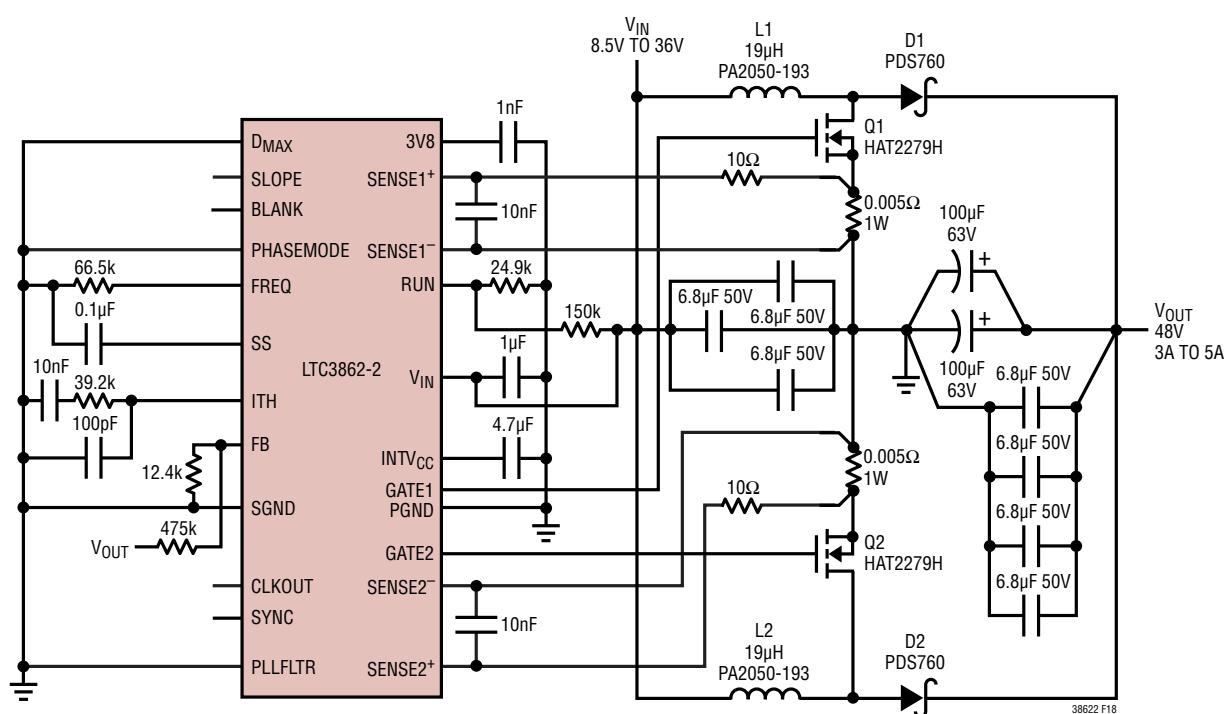

## 標準的な昇圧アプリケーション回路

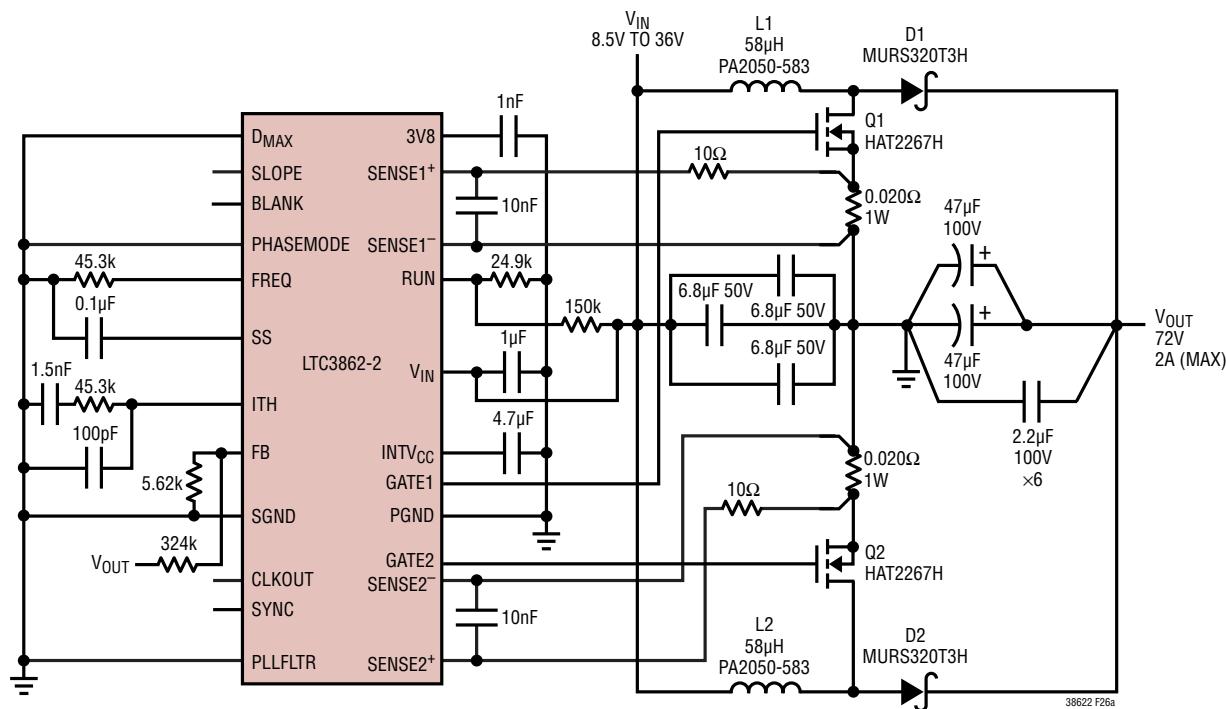

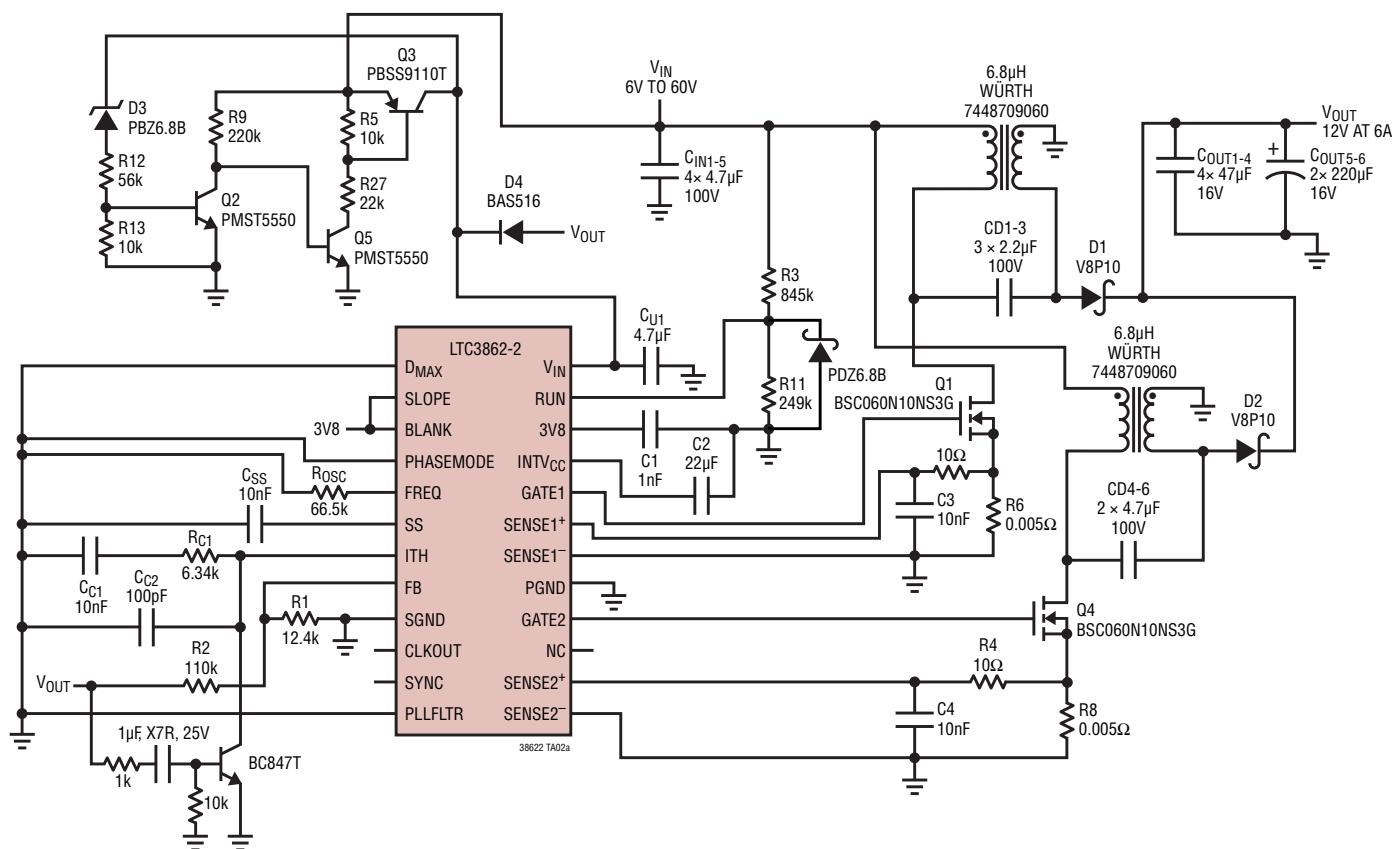

2フェーズ、単一出力の基本的なLTC3862-2アプリケーション回路を図18に示します。外付け部品の選択は、負荷と入力電源の特性に基づいて進めます。

## デューティ・サイクルに関する検討事項

連続導通モード(CCM)で動作している昇圧コンバータでは、主スイッチのデューティ・サイクルが次のようになります。

$$D = \left( \frac{V_0 + V_F - V_{IN}}{V_0 + V_F} \right) = t_{ON} \cdot f$$

ここで、 $V_F$ は昇圧ダイオードの順方向電圧です。CCMで動作する任意のアプリケーションの最小オン時間は次のとおりです。

$$t_{ON(MIN)} = \frac{1}{f} \left( \frac{V_0 + V_F - V_{IN(MAX)}}{V_0 + V_F} \right)$$

与えられた入力電圧範囲および出力電圧では、アプリケーションの最小オン時間が制御ICの最小オン時間にどのくらい近づくかを知ることが重要です。LTC3862-2の最小オン時間は、BLANKピンを使用して210ns～375nsの範囲に設定できます。

### 最小オン時間の制限事項

シングルエンドの昇圧コンバータでは、2つの定常状態条件により、コントローラが最小オン時間で動作することがあります。第1の条件は、入力電圧が出力電圧に近い場合です。 $V_{IN}$ が $V_{OUT}$ に近づくと、インダクタ両端の電圧がスイッチのオフ時間の間にゼロに近づきます。この動作条件では、コンバータが不安定になり、出力に高いリップル電圧の発振が可聴周波数で発生することがあります。入力電圧が出力電圧に近づくか出力電圧を超える場合があるアプリケーションでは、昇圧コンバータではなく、SEPIC方式や昇降圧方式の使用を検討してください。

コントローラが最小オン時間で動作する可能性がある第2の条件は、深い不連続モードの軽負荷時の条件です。コントローラの最小オン時間制限値に達するまでは、負荷電流が減少するにつれて、スイッチのオン時間が短くなります。出力電流がさらに減少すると、パルス・スキップ状態になります。これは、出力レギュレーションを維持するためにサイクルがスキップされるもので、通常は問題のない状態です。

図18. 標準的な2フェーズ、シングル出力の昇圧コンバータ・アプリケーション回路

## アプリケーション情報

### 最大デューティ・サイクルの制限事項

この他に極端な動作が発生するのは、デューティ・サイクルが高く、入力電圧が低く出力電圧が高いときです。この場合は、次式が成立します。

$$D_{MAX} = \left( \frac{V_0 + V_F - V_{IN(MIN)}}{V_0 + V_F} \right)$$

シングルエンドの昇圧コンバータは、入力インダクタから出力コンデンサにエネルギーを移すため、サイクルごとに最小オフ時間が必要です。この最小オフ時間は、言い換えるとコンバータの最大デューティ・サイクルになります。上の式を整理しなおると、与えられた最小入力電圧または最大デューティ・サイクルに対する最大出力電圧を得ることができます。

$$V_{O(MAX)} = \frac{V_{IN}}{1-D_{MAX}} - V_F$$

上の $D_{MAX}$ の式は、アプリケーション回路の最大デューティ・サイクルを求めるための最初の基準として使うことができます。ただし、インダクタ、入力コンデンサ、出力コンデンサ、パワーMOSFET、センス抵抗、およびコントローラ(ゲートの駆動)で発生する損失は、すべてデューティ・サイクルを高くする原因となります。与えられた最小入力電圧での最大出力電圧は、これらの損失の影響によって減少します。

アプリケーション回路の最初の計算が完了したら、回路が正常に動作することを検証するために、回路のプロトタイプを作成し、軽負荷から最大負荷まで、入力電圧範囲全体および全温度範囲にわたって測定することが重要です。

### ピーク入力電流と平均入力電流

LTC3862-2の制御回路は、(パワーMOSFETのソースに接続した抵抗によって)入力電流を測定するので、パワーMOSFETを適切なサイズにするために、出力電流を入力電流に反映させる必要があります。出力電力は理想的には入力電力に等しいという事実に基づいて、最大平均入力電流は次のようにになります。

$$I_{IN(MAX)} = \frac{I_{O(MAX)}}{1-D_{MAX}}$$

各インダクタのピーク電流は次のとおりです。

$$I_{IN(PK)} = \frac{1}{n} \cdot \left( 1 + \frac{\chi}{2} \right) \cdot \frac{I_{O(MAX)}}{1-D_{MAX}}$$

ここで、 $n$ は位相の数を表し、 $\chi$ はインダクタを流れるピーク・トゥ・ピークのリップル電流のパーセンテージを表します。たとえば、30%のリップル電流がインダクタを流れるなどを設計目標にした場合は $\chi = 0.30$ となり、ピーク電流は平均電流より15%大きくなります。

### インダクタの選択

入力電圧範囲、動作周波数、およびリップル電流が与えられている場合、インダクタの値は次式を使用して求めることができます。

$$L = \frac{V_{IN(MIN)}}{\Delta I_L \cdot f} \cdot D_{MAX}$$

ここで、

$$\Delta I_L = \frac{\chi}{n} \cdot \frac{I_{O(MAX)}}{1-D_{MAX}}$$

大きい値の $\Delta I_L$ を選ぶと小さい値のインダクタを使用できますが、出力電圧リップルが高くなり、コア損失が大きくなつて、入力コンデンサおよび出力コンデンサのリップル電流定格が高くなります。妥当な出発点は、インダクタに30%のリップル電流が流れる( $\chi = 0.3$ )ことで、これは次式で表されます。

$$\Delta I_L = \frac{0.3}{n} \cdot \frac{I_{O(MAX)}}{1-D_{MAX}}$$

インダクタの飽和電流定格は、過電流状態のときに流れるワーストケースのピーク・インダクタ電流より大きくなる必要があります。 $I_{O(MAX)}$ が最大定格の負荷電流である場合、通常、電流制限の最大値( $I_{O(CL)}$ )には、 $I_{O(MAX)}$ よりいくらかの係数(たとえば30%)だけ大きい値を選択します。

$$I_{O(CL)} = 1.3 \cdot I_{O(MAX)}$$

これを(電流が測定される)入力に反映させ、リップル電流を考慮に入れるに、インダクタの最小飽和電流定格が次式で得られます。

$$I_{L(SAT)} \geq \frac{1}{n} \cdot \left( 1 + \frac{\chi}{2} \right) \cdot \frac{1.3 \cdot I_{O(MAX)}}{1-D_{MAX}}$$

## アプリケーション情報

インダクタの飽和電流定格は、最小入力電圧(デューティ・サイクルが最高になり、入力電流が最大になる条件)、最大出力電流、および予想最大コア温度で決定する必要があります。市販されているほとんどのインダクタの飽和電流定格は高温で減少します。安全な動作を確認するため、以下の条件でインダクタのコア/巻線の温度特性を評価することを推奨します。その条件とは、1) ワースト・ケースの温度条件、2) 最大許容周囲温度、および 3) 電源を最終的な筐体に取り付けて評価、です。熱特性の評価は、巻線/コア構造に熱電対を密着させるか、巻線自体に熱電対を埋め込むことによって実行できます。

シングルエンドの昇圧コンバータは短絡に対して保護されていないので、出力が短絡している状態では、出力電流は入力電源の供給能力のみによって制限されることに注意してください。短絡保護された昇圧コンバータが必要なアプリケーションでは、SEPIC コンバータ方式またはフォワード・コンバータ方式の使用を検討してください。

### パワー MOSFET の選択

INTV<sub>CC</sub> の電圧によって設定されるピーク・トゥ・ピークのゲート駆動レベルは、LTC3862-2 の場合、通常の動作条件では 10V です。パワー MOSFET の選択基準には、 $R_{DS(ON)}$ 、ゲート電荷  $Q_G$ 、ドレイン-ソース間降伏電圧  $BV_{DSS}$ 、最大連続ドレイン電流  $I_D(\text{MAX})$ 、接合部-周囲雰囲気間熱抵抗  $R_{TH(JA)}$ 、および接合部-ケース間熱抵抗  $R_{TH(JC)}$  があります。

LTC3862-2 のゲート・ドライバは PMOS のプルアップ・デバイスと NMOS のプルダウン・デバイスで構成されているので、パワー MOSFET のスイッチング時には INTV<sub>CC</sub> の全電圧をゲートに印加することができます。それでもなお、パワー MOSFET を完全に導通させるのに最小のゲート駆動電圧で十分であることを確実にするため、注意する必要があります。MOSFET のデータシートを注意深く調べ、INTV<sub>CC</sub> 電圧の公称値である 10V 以下の電圧に対して MOSFET の  $R_{DS(ON)}$  が規定されていることを確認してください。5V 定格のパワー MOSFET が必要なアプリケーションの場合は、LTC3862 のデータシートを参照してください。

アプリケーションでの実際の最大スイッチ電圧と比較して、MOSFET の  $BV_{DSS}$  規格にも十分注意を払ってください。1 本のプローブと広帯域オシロスコープを使用して、MOSFET のスイッチング波形をドレイン端子で直接確認します。ドレイン電圧のリングが MOSFET の  $BV_{DSS}$  に近づかないように注意してください。高周波でのリングが過剰な場合は、通常、 $di/dt$  が高い電流経路の直列インダクタンスが大きすぎる

ことを示しています。この経路には、MOSFET、昇圧ダイオード、出力コンデンサ、センス抵抗、およびこれらの部品を接続するプリント回路基板配線が含まれます。

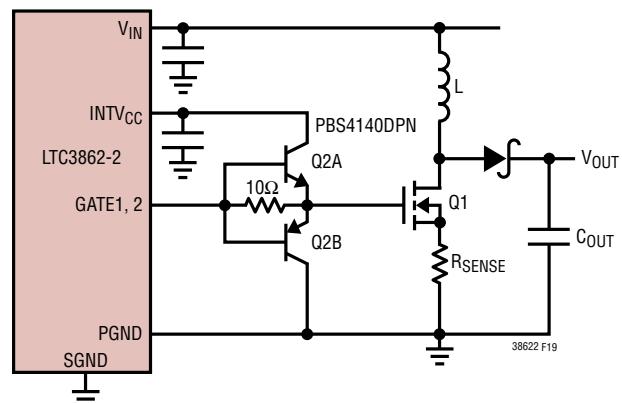

寄生リード・インダクタンスや不適切な PCB レイアウトにより、MOSFET Q1 のターンオン、ターンオフ時にこの MOSFET のゲートでトランジエント電圧スパイクが発生することがあります。このような電圧スパイクは LTC3862-2 の GATE ピンの絶対最大電圧定格を超える可能性があります。GATE ピンの電圧の絶対最大定格は、最小 -0.3V、最大 11V です。このため、図 19 に示すように、MOSFET のゲートの近くに外付けバッファを追加することを推奨します。

図 19. 外付けバッファ回路

最後に、アバランシェ・エネルギー定格(EAS)の有無について MOSFET メーカーのデータシートを調べてください。MOSFET の中にはボディ・ダイオードのアバランシェ定格が定められていないものがあるので、 $V_{DS}$  が MOSFET デバイスの  $BV_{DSS}$  を超えると、それが 1V の数分の 1 であっても致命的な故障が発生します。アバランシェ定格が定められている MOSFET は、オフになる遷移期間中に MOSFET デバイスの  $BV_{DSS}$  に近い高周波のリングがドレイン-ソース間に生じても十分耐えることができます。

### パワー MOSFET のスイッチング損失と導通損失および接合部温度の計算

パワー MOSFET の接合部温度を計算するには、デバイスによって消費される電力を知る必要があります。この消費電力は、デューティ・サイクル、負荷電流、および ( $R_{DS(ON)}$  の正の温度係数による) 接合部温度自体の関数です。そのため、十分正確な値を決めるには何回かの反復計算が通常必要です。

## アプリケーション情報

位相の数が  $n$  のマルチフェーズ昇圧コンバータで MOSFET が消費する電力は次のとおりです。

$$P_{FET} = \left( \frac{I_{0(MAX)}}{n \cdot (1 - D_{MAX})} \right)^2 \cdot R_{DS(ON)} \cdot D_{MAX} \cdot \rho_T + k \cdot V_{OUT}^2 \cdot \frac{I_{0(MAX)}}{n \cdot (1 - D_{MAX})} \cdot C_{RSS} \cdot f$$

上式の第1項はデバイス内での  $I^2R$  損失を表し、第2項はスイッチング損失を表します。定数  $k = 1.7$  はゲート・ドライブ電流に反比例する経験的に得られる係数で、「1/電流」の次元をもっています。

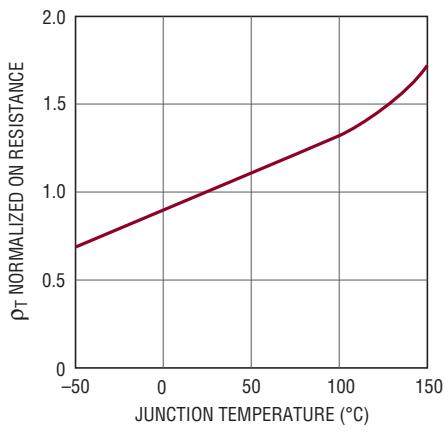

$\rho_T$  の項は MOSFET の  $R_{DS(ON)}$  の温度係数を表しており、標準では  $0.4\%/\text{°C}$  です。標準的なパワー MOSFET の正規化された  $R_{DS(ON)}$  の全温度にわたる変化を図 20 に示します。

パワー MOSFET の消費する既知の電力から、次式を使って接合部温度を求ることができます。

$$T_J = T_A + P_{FET} \cdot R_{TH(JA)}$$

この式で使われている  $R_{TH(JA)}$  にはデバイスの  $R_{TH(JC)}$  およびケースから周囲温度までの熱抵抗  $R_{TH(CA)}$  が通常含まれます。次に  $T_J$  のこの値を反復計算に使用された元の仮定値と比べることができます。

図 20. 正規化されたパワー MOSFET の  $R_{DS(ON)}$  と温度

導通損失を減らすために、 $R_{DS(ON)}$  が非常に小さいパワー MOSFET を選択したくなります。ただし、そうすると、通常はゲート電荷  $Q_G$  が非常に高くなり、スイッチング損失とゲート駆動損失が増加します。スイッチング損失は出力電圧の 2 乗に比例して増加するので、低出力電圧のアプリケーションでは、一般に MOSFET の導通損失が大きくなり、高出力電圧のアプリケーションでは、一般に MOSFET のスイッチング損失が大きくなります。高い出力電圧では、 $R_{DS(ON)}$  が高く  $Q_G$  が低い MOSFET を使用することで、通常は最高の効率が得られます。前述の式は、さまざまな MOSFET の性能を比較するために、2つの成分(導通損失とスイッチング損失)に簡単に分けることができる上に、表計算プログラムに入力することができます。

## 電流制限のプログラミング

LTC3862-2 のピーク検出電圧しきい値は、正規化されたスロープ利得である 1.00 を使用した場合、低デューティ・サイクルで 75mV であり、SENSE<sup>+</sup> と SENSE<sup>-</sup> の間で測定されます。デューティ・サイクルとスロープ利得を変化させた場合の検出電圧のしきい値の変化を図 21 に示します。

図 21. デューティ・サイクルとスロープ利得による最大検出電圧の変化

## アプリケーション情報

電流制限値が最大負荷電流より30%高い値に選択されている昇圧コンバータでは、MOSFETおよびセンス抵抗に流れるピーク電流は次式で表されます。

$$I_{SW(MAX)} = I_{R(SENSE)} = \frac{1}{n} \cdot \left(1 + \frac{\chi}{2}\right) \cdot \frac{1.3 \cdot I_{O(MAX)}}{1 - D_{MAX}}$$

したがって、センス抵抗値は次のようにになります。

$$R_{SENSE} = \frac{V_{SENSE(MAX)} \cdot n \cdot (1 - D_{MAX})}{1.3 \cdot \left(1 + \frac{\chi}{2}\right) \cdot I_{O(MAX)}}$$

ここでも、係数nは使用する位相の数、 $\chi$ はインダクタを流れるリップル電流のパーセンテージを表します。1.3という数字は、電流制限値が最大負荷電流 $I_{O(MAX)}$ を超える係数であることを表しています。たとえば、電流制限値が最大負荷電流を50%超える必要がある場合は、1.3という係数を1.5に置き換える必要があります。

センス抵抗での平均電力損失は、次式で簡単に計算できます。

$$P_{R(SENSE)} = \left( \frac{1.3 \cdot I_{O(MAX)}}{n \cdot (1 - D_{MAX})} \right)^2 \cdot R_{SENSE} \cdot D_{MAX}$$

この式では、センス抵抗に温度係数がないと仮定しています。選択した抵抗の温度係数が大きい場合は、ワーストケースの高い抵抗値をこの式に代入します。

抵抗の温度は次式を使って計算することができます。

$$T_D = T_A + P_{R(SENSE)} \cdot R_{TH(JA)}$$

### 出力ダイオードの選択

効率を最大にするには、順方向の電圧降下が小さく、逆方向の漏れ電流の小さい高速スイッチング・ダイオードが必要です。昇圧コンバータの出力ダイオードはスイッチのオフ時間に電流を流します。ダイオードが耐えなければならないピーク逆電圧はレギュレータの出力電圧に等しくなります。通常動作時の平均順方向電流は出力電流に等しく、ピーク電流はインダクタ電流のピーク値に等しくなります。

$$I_{D(Peak)} = \frac{1}{n} \cdot \left(1 + \frac{\chi}{2}\right) \cdot \frac{I_{O(MAX)}}{1 - D_{MAX}}$$

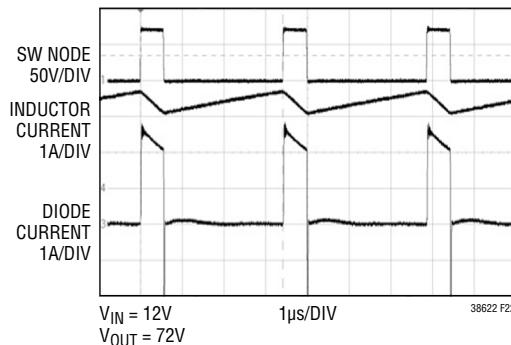

平均ダイオード電流は出力電流と等しくなりますが、デューティ・サイクルが非常に高い( $V_{IN}$ が低く $V_{OUT}$ が高い)アプリケーションでは、図22に示すように、ピーク・ダイオード電流が平均値の数倍になることがあります。この場合には、ダイオード・メーカーのデータシートを調べて、そのピーク電流定格が上の式のピーク電流を超えていることを確認します。さらに、ダイオードでの電力損失を計算するときは、平均出力電流ではなくピーク電流で測定した順方向電圧( $V_F$ )の値を使用してください。ダイオードの直列抵抗では過剰な電力損失が発生しますが、この損失は、前述の式で平均出力電流および順方向電圧が使用された場合には計算に入れられないか

図22. デューティ・サイクルの高いアプリケーションでのダイオード電流波形

## アプリケーション情報

らです。最後に、この追加の電力損失は、ダイオード電流の定格、パッケージ・タイプ、および放熱方法を決めるときに重要なとなります。

ダイオードの電力損失は次のように近似されます。

$$P_D = I_{D(Peak)} \cdot V_{F(Peak)} \cdot (1 - D_{MAX})$$

ダイオードの接合部温度は次のとおりです。

$$T_J = T_A + P_D \cdot R_{TH(JA)}$$

この式で使われる  $R_{TH(JA)}$  にはデバイスの  $R_{TH(JC)}$  および基板から筐体内の周囲温度までの熱抵抗が通常含まれます。適切なダイオードを選択して回路性能を検証したら、サーマル・プローブまたは赤外線カメラを使用して、全動作条件にわたってパワー部品の温度を測定します。

最後に、過度のリングングや電力損失の増加を防ぐため、ダイオードのリード長を短くし、スイッチ・ノードの適切なレイアウトを守ってください(「基板レイアウトのチェックリスト」を参照)。

### 出力コンデンサの選択

昇圧コンバータ・アプリケーションに対して出力コンデンサの正しい組み合わせを選択するときは、ESR(等価直列抵抗)、ESL(等価直列インダクタンス)およびバルク容量が与える影響について考慮する必要があります。出力電圧リップル波形に対するこれら3つのパラメータの影響を、標準的な昇圧コンバータの場合について図23に示します。

部品の選択は、(出力電圧のパーセンテージで表した)最大許容リップル電圧と、このリップルをESRによる電圧ステップと充放電による $\Delta V$ の間でどのように分割すべきかの検討から始めます。説明を簡単にするため、最大出力リップルとして2%を選択し、ESRによる電圧ステップと充放電による $\Delta V$ の間で等分します。このパーセンテージ・リップルはアプリケーションの要件に応じて変化しますが、以下に示す式は簡単に修正できます。

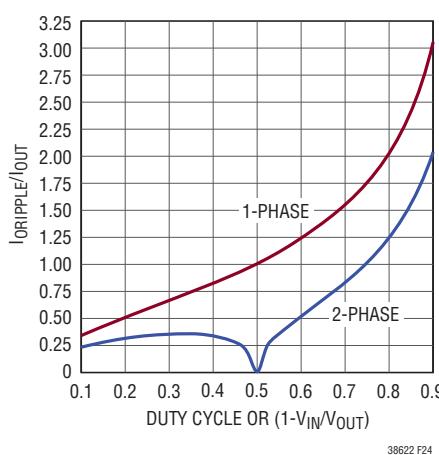

マルチフェーズ動作の主な利点の1つは、昇圧ダイオードによって出力コンデンサに供給されるピーク電流の減少です。その結果、コンデンサのESRの要件が緩和されます。全リップル電圧の1%に寄与する場合、出力コンデンサのESRは次式を使って決めることができます。

$$ESR_{COUT} \leq \frac{0.01 \cdot V_{OUT}}{I_{D(Peak)}}$$

ここで、

$$I_{D(Peak)} = \frac{1}{n} \cdot \left( 1 + \frac{\chi}{2} \right) \cdot \frac{I_{O(MAX)}}{1 - D_{MAX}}$$

係数nは位相の数を表し、係数 $\chi$ はインダクタ・リップル電流のパーセンテージを表します。

図23. 昇圧コンバータのスイッチング波形

## アプリケーション情報

バルク容量の場合、全出力リップルの1%に寄与すると想定していますが、必要な最小の容量は概算で次のとおりです。

$$C_{OUT} \geq \frac{I_{O(MAX)}}{0.01 \cdot n \cdot V_{OUT} \cdot f}$$

多くの設計回路では、ある種類のコンデンサを使用して必要なESRを確保し、別の種類のコンデンサを使用してバルク容量を満たす必要があります。たとえば、低ESRのセラミック・コンデンサを使うとESRによる電圧ステップが減少します。他方、電解コンデンサを使って必要なバルクCを得ることができます。

出力コンデンサの電圧定格は最大出力電圧より高くする必要があります、コンデンサの最大温度を計算に入れた十分なディレーティングを行う必要があります。

出力コンデンサに流れるリップル電流は方形波なので、このコンデンサのリップル電流要件は、デューティ・サイクル、位相の数、および最大出力電流に依存します。出力コンデンサの正規化リップル電流をデューティ・サイクルの関数として図24に示します。出力コンデンサのリップル電流定格を選択するため、最初に出力電圧と入力電圧の範囲に基づいてデューティ・サイクルの範囲を設定します。図24を参照して、最大負荷電流のパーセンテージとして、ワーストケースの大きい正規化リップル電流を選択します。

出力リップル電流は、出力電圧ノードに並列に接続されたいくつかのコンデンサの間で分流されます。セラミック・コンデンサは、(特にX5RおよびX7Rでは)ESRが低いことが一般に知られていますが、これらのコンデンサは電圧係数が比較的高いという弱点があります。したがって、すべてのリップル電流がセラミック・コンデンサを流れると仮定するのは安全ではありません。アルミ電解コンデンサは、バルク容量が高いことから一般に選択されますが、比較的高いESRがあります。その結果、一定量のリップル電流がこのアルミ電解コンデンサに流れます。コンデンサに流れるリップル電流がRMS(実効値)定格を超えると、コンデンサは発熱して実効容量が減り、その信頼性に悪影響が及びます。示されている式を使用して出力コンデンサの構成を決定したら、熱性能が十分であることを検証するために、コンデンサのケース温度を個別に測定してください。

## 入力コンデンサの選択

昇圧コンバータでの入力コンデンサの電圧定格は、最大入力電圧を十分に超えることが必要です。セラミック・コンデンサは過電圧状態を比較的耐えることができますが、アルミ電解コンデンサはそうではありません。入力コンデンサに過度のストレスを与える可能性のある過電圧トランジエントに関して、入力電圧の特性を必ず評価してください。

図24. 昇圧コンバータの出力コンデンサの正規化されたリップル電流(RMS)

## アプリケーション情報

入力コンデンサの値は信号源インピーダンスの関数であり、一般に、信号源インピーダンスが高いほど必要な入力容量も高くなります。必要な入力容量の大きさはデューティ・サイクルによっても大きく影響されます。高いデューティサイクルで動作する高出力電流アプリケーションは、DC電流とリップル電流の両方で、入力電源に大きな負担を負わせることができます。

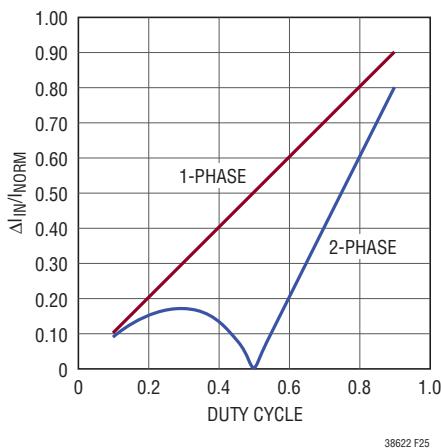

マルチフェーズ昇圧コンバータの入力リップル電流は連続しており、複数のインダクタに分流されているので、(出力リップル電流に比べて)比較的低くなります。それでもなお、入力コンデンサには大きなストレスがかかる可能性があり、特にデューティ・サイクルの高いアプリケーションの場合に当てはまります。正規化された入力リップル電流を図25に示します。

$$I_{INORM} = \frac{V_{IN}}{L \cdot f}$$

図25. 正規化された入力ピーク・トゥ・ピーク・リップル電流

## 設計例

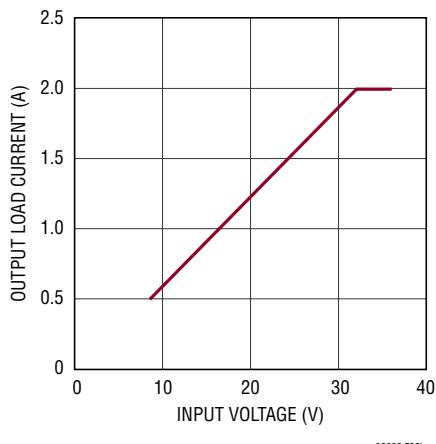

図26aに示すLTC3862-2のアプリケーション回路について検討します。出力電圧は72Vで、入力電圧範囲は8.5V～36Vです。最大出力電流は、入力電圧が24Vのときは1.5Aで、入力電圧が32Vのときは2Aです。入力電圧が32Vより低い場合、電流制限によって最大負荷は直線的に減少し、入力電圧が8.5Vのときは0.5Aになります(図26b参照)。

- (出力で1.5Aを供給可能な)デューティ・サイクルの範囲は次のとおりです。

$$D_{MAX} = \left( \frac{V_0 + V_F - V_{IN}}{V_0 + V_F} \right) = \left( \frac{72V + 0.5V - 24V}{72V + 0.5V} \right) = 66.9\%$$

$$D_{MIN} = \left( \frac{V_0 + V_F - 36V}{V_0 + V_F} \right) = 50.3\%$$

- 動作周波数は300kHzになるよう選択されているので、周期は3.33μsです。図6から、FREQピンとグランドの間に接続されている抵抗は45.3kです。

- 連続導通モード(CCM)で動作するこのアプリケーションの最小オン時間は次のとおりです。

$$t_{ON(MIN)} = \frac{1}{f} \cdot \left( \frac{V_0 + V_F - V_{IN(MAX)}}{V_0 + V_F} \right) = \frac{1}{300\text{kHz}} \cdot \left( \frac{72V + 0.5V - 36V}{72V + 0.5V} \right) = 1.678\mu\text{s}$$

最大DC入力電流は次のとおりです。

$$I_{IN(MAX)} = \frac{I_{O(MAX)}}{1 - D_{MAX}} = \frac{1.5\text{A}}{1 - 0.669} = 4.5\text{A}$$

## アプリケーション情報

図 26a. 8.5V～36V 入力、72V/2A 出力の 2 フェーズ昇圧コンバータ・アプリケーション回路

図 26b. 出力電流と入力電圧

4. 40%のリップル電流が選択されているので、各インダクタのピーク電流は次のようになります。

$$I_{IN(PK)} = \frac{1}{n} \cdot \left(1 - \frac{\chi}{2}\right) \cdot \frac{I_{O(MAX)}}{1 - D_{MAX}} \\ = \frac{1}{2} \cdot \left(1 + \frac{0.4}{2}\right) \cdot \frac{1.5A}{1 - 0.669} = 2.7A$$

5. インダクタのリップル電流は次のとおりです。

$$\Delta I_L = \frac{\chi}{n} \cdot \frac{I_{O(MAX)}}{1 - D_{MAX}} = \frac{0.4}{2} \cdot \frac{1.5A}{1 - 0.669} = 0.9A$$

6. したがって、インダクタの値は次のようにになります。

$$L = \frac{V_{IN(MIN)}}{\Delta I_L \cdot f} \cdot D_{MAX} = \frac{24V}{0.9A \cdot 300kHz} \cdot 0.669 \\ = 59.5\mu H$$

7. 電流制限値が最大負荷電流より 30% 高い場合、次のようにになります。

$$I_{O(CL)} = 1.3 \cdot I_{O(MAX)} = 1.3 \cdot 1.5A = 1.95A$$

したがって、インダクタの飽和電流定格は次の値を超える必要があります。

$$I_{L(SAT)} \geq \frac{1}{n} \cdot \left(1 + \frac{\chi}{2}\right) \cdot \frac{1.3 \cdot I_{O(MAX)}}{1 - D_{MAX}} \\ = \frac{1}{2} \cdot \left(1 + \frac{0.4}{2}\right) \cdot \frac{1.3 \cdot 1.5A}{1 - 0.669} = 3.5A$$

## アプリケーション情報

選択されているインダクタの値は57.8 $\mu$ Hで、製品番号はPA2050-583、メーカーはPulse Engineeringです。このインダクタの飽和電流定格は5Aです。

- このアプリケーションに選択されているパワーMOSFETはルネサス・エレクトロニクスのHAT2267Hです。このMOSFETの標準の $R_{DS(ON)}$ は $V_{GS} = 10V$ で $13m\Omega$ です。 $BV_{DSS}$ の定格は最小80Vであり、最大連続ドレイン電流は25Aです。標準のゲート電荷は $V_{GS} = 10V$ では $30nC$ です。最後に、このMOSFETのアバランシェ・エネルギー絶対最大定格(EAS)は30mJです。致命的な故障に至ることなくアバランシェ崩壊に耐えられる定格を示しています。

- デバイスの全静止電流、デバイスの電力損失、および最大接合部温度は、概算で以下のとおりです。

$$I_{Q(TOT)} = I_Q + 2 \cdot Q_{G(TOT)} \cdot f \\ = 3mA + 2 \cdot 30nC \cdot 300kHz = 21mA$$

$$P_{DISS} = 24V \cdot 21mA = 504mW$$

$$T_J = 70^\circ C + 504mW \cdot 34^\circ C/W = 87.1^\circ C$$

- インダクタのリップル電流は40%になるよう選択されており、最大負荷電流は1.5Aです。電流制限を最大負荷電流より30%高い値に設定してある場合、最大のスイッチ電流とセンス抵抗電流は次のようにになります。

$$I_{SW(MAX)} = I_{R(SENSE)} = \frac{1}{n} \cdot \left(1 + \frac{\chi}{2}\right) \cdot \frac{1.3 \cdot I_{O(MAX)}}{1 - D_{MAX}} \\ = \frac{1}{2} \cdot \left(1 + \frac{0.4}{2}\right) \cdot \frac{1.3 \cdot 1.5A}{1 - 0.669} = 3.5A$$

- LTC3862-2の最大電流センスしきい値は、低デューティ・サイクルで、正規化されたスロープ利得が1.0の場合、75mVです。図21を使うと、デューティ・サイクルが70%で、正規化されたスロープ利得が1のとき、最大検出電圧は68mVなので、センス抵抗は次のように計算されます。

$$R_{SENSE} = \frac{V_{SENSE(MAX)}}{I_{SW(MAX)}} = \frac{68mV}{3.5A} = 19.4m\Omega$$

このアプリケーションでは、20m $\Omega$ 、1Wの表面実装抵抗が位相ごとに使用されています。

- 電流制限時のセンス抵抗での電力損失は次のとおりです。

$$P_{R(SENSE)} = \left( \frac{1.3 \cdot I_{O(MAX)}}{n \cdot (1 - D_{MAX})} \right)^2 \cdot R_{SENSE} \cdot D_{MAX} \\ = \left( \frac{1.3 \cdot 1.5}{2 \cdot (1 - 0.669)} \right)^2 \cdot 0.020 \cdot 0.669 \\ = 0.12W$$

- 昇圧ダイオードを流れる平均電流は出力電流の半分( $1.5A/2 = 0.75A$ )ですが、各ダイオードのピーク電流は次のようになります。

$$I_{D(Peak)} = \frac{1}{n} \cdot \left(1 + \frac{\chi}{2}\right) \cdot \frac{I_{O(MAX)}}{1 - D_{MAX}} \\ = \frac{1}{2} \cdot \left(1 + \frac{0.4}{2}\right) \cdot \frac{1.5A}{1 - 0.669} = 2.7A$$

このアプリケーションに選択されているダイオードはMUR320T3Hで、メーカーはON Semiconductorです。この表面実装ダイオードの最大平均順方向電流は140°Cで3Aであり、最大逆電圧は200Vです。順方向電圧降下の最大値は25°Cで0.875Vであり、150°Cで0.71Vです(直列抵抗の正の温度係数はダイオード順方向電圧の負の温度係数によって補償されます)。

ダイオードの電力損失は概算で次のとおりです。

$$P_D = I_{D(Peak)} \cdot V_{F(Peak)} \cdot (1 - D_{MAX}) \\ = 2.7A \cdot 0.71V \cdot (1 - 0.669) = 0.64W$$

- このアプリケーションでは、2種類の出力コンデンサが並列に接続されています。1つは低ESRのセラミック・コンデンサで、もう1つは大容量のアルミ電解コンデンサです。全リップル電圧の1%に寄与するとした場合、合成出力容量の最大ESRは、次のように概算することができます。

$$ESR_{COUT} \leq \frac{0.01 \cdot V_{OUT}}{I_{D(Peak)}} = \frac{0.01 \cdot 72V}{2.7A} = 0.267\Omega$$

## アプリケーション情報

バルク容量の場合、全出力リップルの1%に寄与すると想定していますが、必要な最小の容量は概算で次のとおりです。

$$C_{\text{OUT}} \geq \frac{I_{\text{O}(\text{MAX})}}{0.01 \cdot n \cdot V_{\text{OUT}} \cdot f} = \frac{1.5\text{A}}{0.01 \cdot 2 \cdot 72\text{V} \cdot 300\text{kHz}} = 3.45\mu\text{F}$$

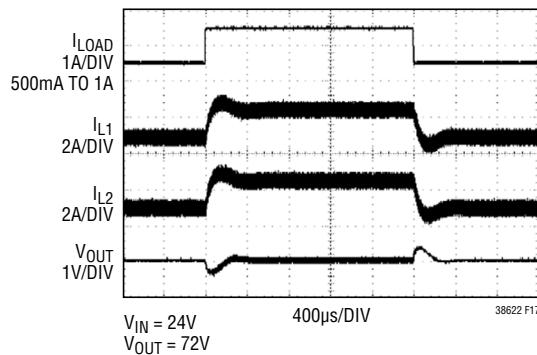

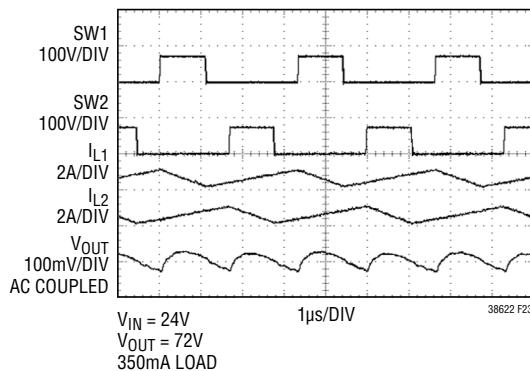

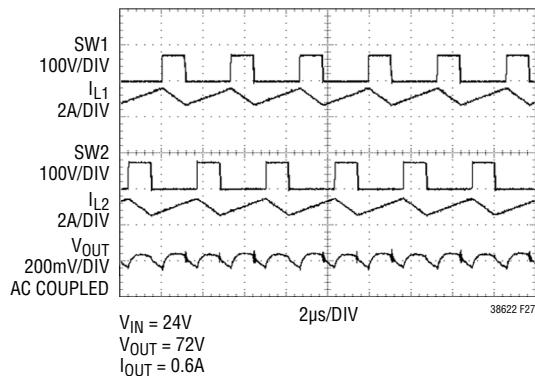

このアプリケーションでは、低ESRと適切なリップル電流定格(図24参照)の両方を実現するために、47μF、100Vのアルミ電解コンデンサ2個を2.2μF、100Vのセラミック・コンデンサ6個と並列に接続しています。このアプリケーション回路のスイッチング波形を図27に示します。

図27. LTC3862-2のスイッチング波形:

72V出力の昇圧コンバータの場合

## プリント回路基板レイアウトのチェックリスト

プリント回路基板をレイアウトするときには、以下のチェックリストを使用してコンバータが正しく動作するようにします。

1. 低電力アプリケーションの場合は、2層プリント回路基板で十分です。しかし、電力レベルが高い場合は、多層プリント回路基板を推奨します。スイッチング・ノイズが動作に影響しないようにするには、回路の下に切れ目のないグランド・プレーンを使用し、部品を適切に配置するのが最も簡単な方法です。

2. MOSFETおよびダイオードから発生する電力を放散しやすくするため、電力部品に最も近い層にグランド・プレーンを設けるようにします。MOSFETおよびダイオードからプリント回路基板への熱拡散を最大にするため、これらの部品にはパワー・プレーンを使用してください。

3. すべての電力部品を狭い領域に配置します。こうすることで、大電流ループのサイズが最小限で済みます。センス抵抗、パワーMOSFET、昇圧ダイオード、および出力コンデンサによって形成されるdi/dtが高いループは、EMIを防ぐため、できるだけ小さくしてください。

4. 入力コンデンサ、出力コンデンサ、および電流センス抵抗の向きを、グランド・プレーンに接続されるパッド間の距離が最小になるように調整します。INTVCC、3V8、およびVINのコンデンサがLTC3862-2にできるだけ近くなるように配置します。

5. INTVCCのデカッピング・コンデンサを、デバイスと同じ層にあるINTVCCピンおよびPGNDピンのできるだけ近くに配置します。低ESRで4.7μF～10μFの(X5R以上の良質な)セラミック・コンデンサを使用する必要があります。

6. グランドに接続するすべてのパッドについて、グランド・プレーンへのローカル・ビアを使用します。電力部品にはビアを複数使います。

7. 小信号部品は、基板上にある高周波数のスイッチング・ノードから離して配置します。LTC3862-2のピン配置は、部品配置が簡単になるように注意深く設計されています。すべての電力部品は、デバイスの片側に配置して、すべての小信号部品から遠ざけることができます。

8. QFNパッケージの底面にある露出領域は、内部でPGNDに接続されていますが、大電流の主な経路としては使用しないでください。

9. MOSFETは基板上でセンス抵抗と同じ層に配置する必要があります。MOSFETのソースは、短くて幅の広いプリント回路基板配線を使用してセンス抵抗に接続してください。

## アプリケーション情報

10. 出力の抵抗分割器はデバイスのできるだけ近くに配置し、下側の抵抗をFBピンとSGNDの間に接続してください。上側の抵抗を出力コンデンサの上側の端子に接続するプリント回路基板配線では、すべての高周波数スイッチング・ノードを避ける必要があります。

11. インダクタはピーク電流モード制御方式では電流源のように動作するので、その基板上での配置は、 $di/dt$ が高い部品と比べると重要ではありません。

12. SENSE<sup>+</sup>とSENSE<sup>-</sup>のプリント回路基板配線は、センス抵抗までの全長で間隔を最小にして互いに平行に配線する必要があります。これらの配線では、レイアウト内のすべての高周波数スイッチング・ノードを避けてください。これらのプリント回路基板配線では、プリント回路基板上の寄生抵抗で生じるIR電圧降下に起因する検出誤差の発生を防ぐため、センス抵抗パッドの内部へのケルビン接続も必要です。

13. センス抵抗とSENSE<sup>+</sup>ピンおよびSENSE<sup>-</sup>ピンの間に外付けのRCフィルタを使用する場合、これらのフィルタ部品はデバイスのSENSE<sup>+</sup>ピンおよびSENSE<sup>-</sup>ピンにできるだけ近づけて配置する必要があります。SENSE<sup>-</sup>の配線は、電流センス抵抗が接地されている箇所でのみグランドに接続するようにしてください。

14. MOSFETのドレイン・ノード(SW1、SW2)は、影響を受けやすい小信号ノード、特に反対側チャネルの電流センス信号から遠ざけてください。SWノードは、そのスルーレートがグランドを基準にして1V/nsを超えることがあるので、LTC3862-2の「出力側に配置することが必要です。

15. パワーMOSFETの端子間でドレイン-ソース間電圧を単独で直接測定することにより、パワーモスFETに加わるストレスを調べます。MOSFETの最大電圧定格を超えることがある誘導性のリンクに注意してください。このリンクに避けることができず、MOSFETの最大定格を超えている場合は、電圧定格がより高いMOSFETを選択するか、スナバ回路の使用を検討します。

16. LTC3862-2を外部クロックに同期させる場合は、ロジック・ゲートのような低インピーダンスの信号源を使用してSYNCピンを駆動し、リードをできるだけ短くします。

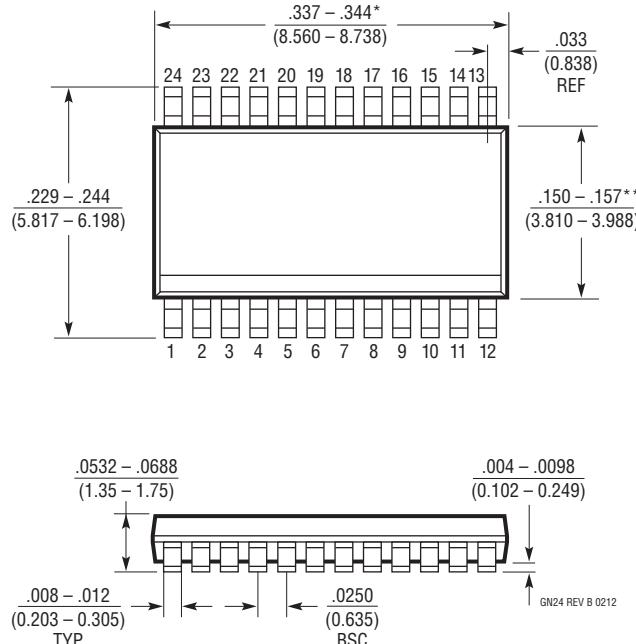

## 標準的応用例

6V～60V入力、12V/6A出力の2フェーズSEPICアプリケーション回路

起動

負荷ステップ

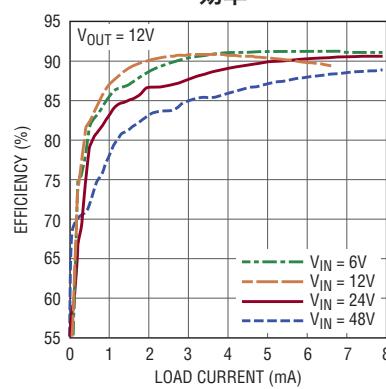

効率

38622fa

# LTC3862-2

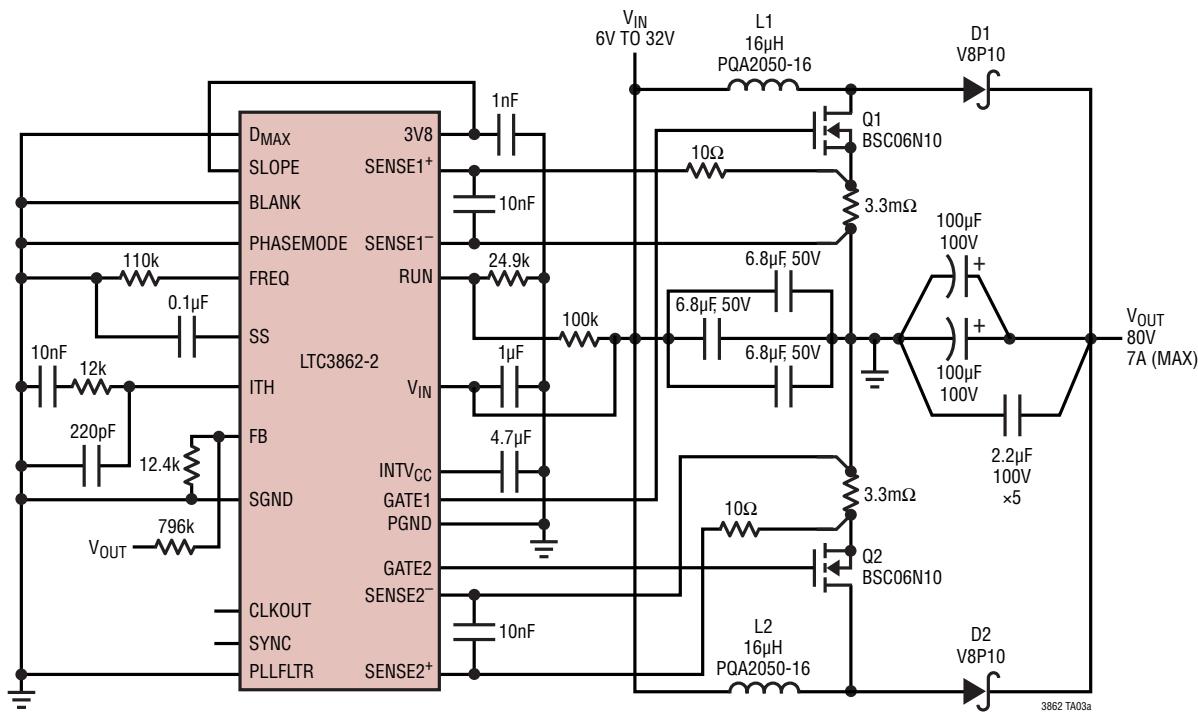

## 標準的応用例

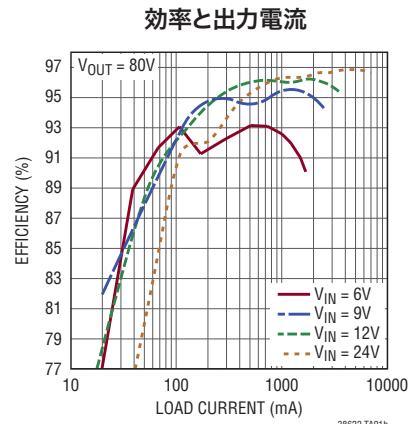

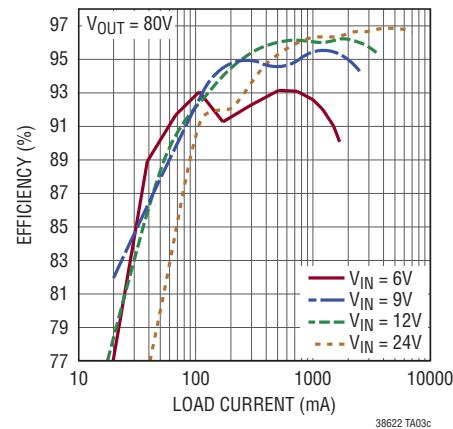

6V～32V入力、80V/7A出力の2フェーズ昇圧コンバータ・アプリケーション回路

起動

効率と出力電流

## 標準的応用例

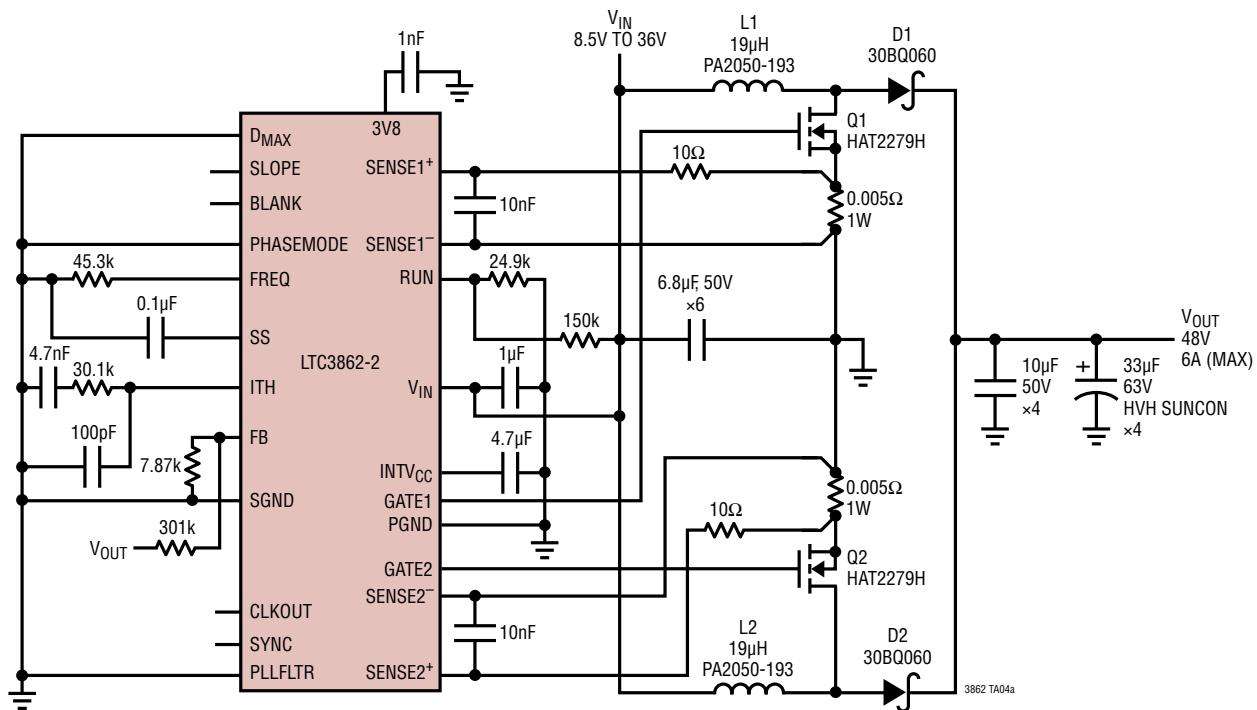

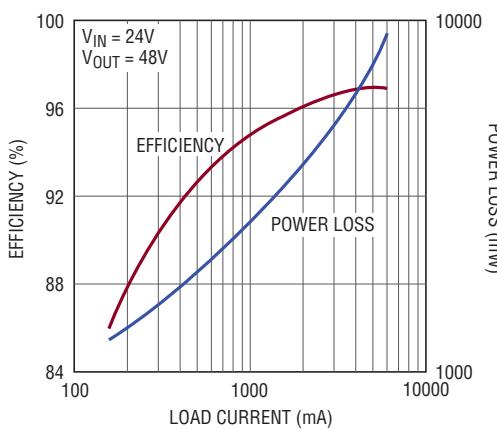

24V入力、48V/6A出力の2フェーズ昇圧コンバータ・アプリケーション回路

起動

負荷ステップ

効率

38622fa

# LTC3862-2

## 標準的應用例

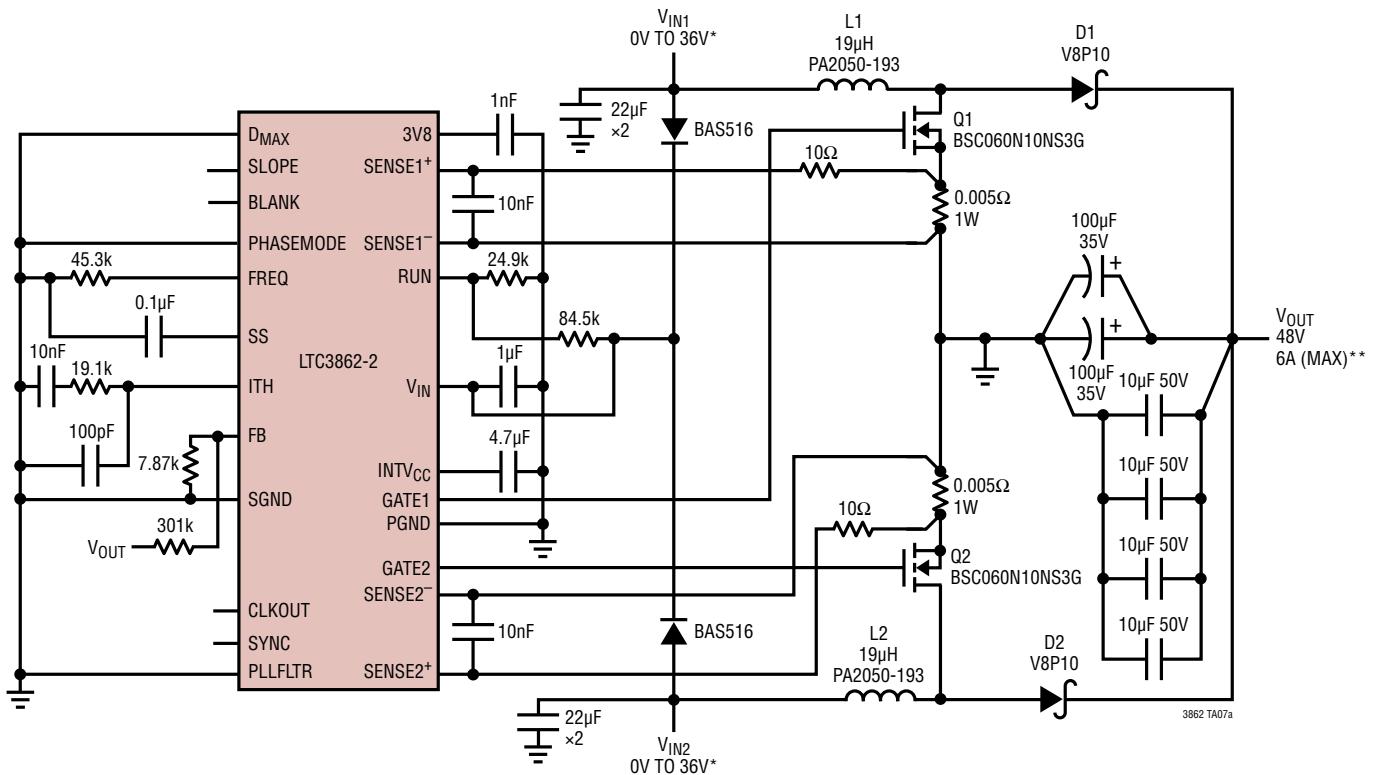

24V デュアル入力、48V/6A 出力の 2 フェーズ昇圧コンバータ・アプリケーション回路

\*AT LEAST ONE INPUT NEEDS TO BE ABOVE 7V

\*\*MAXIMUM 6A OUTPUT CURRENT WHEN BOTH  $V_{IN1}$  AND  $V_{IN2}$  ARE GREATER THAN 7V

## 効率と出力電流

## 標準的応用例

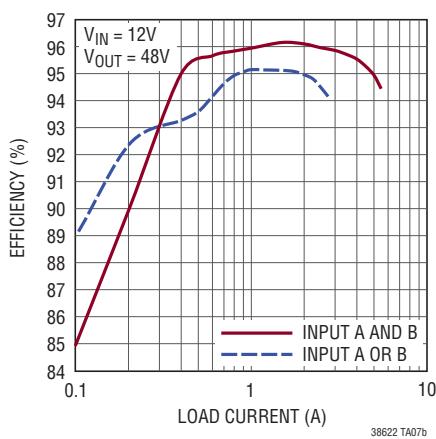

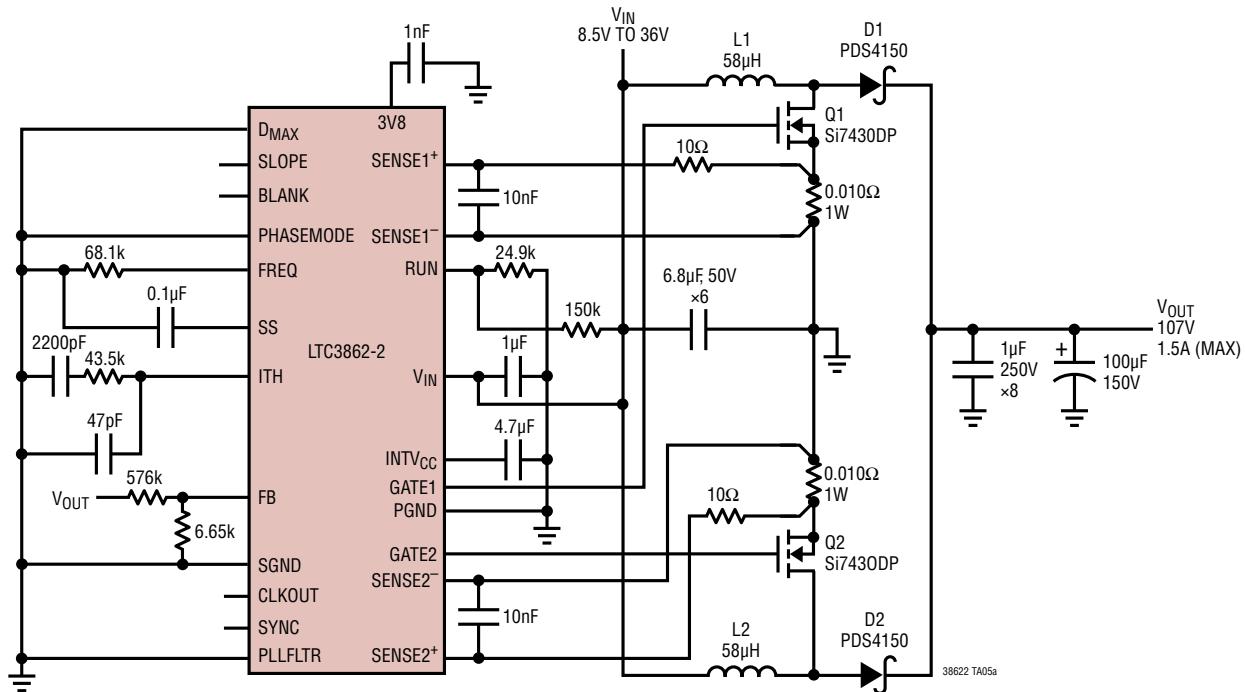

24V 入力、107V/1.5A 出力の2フェーズ昇圧コンバータ・アプリケーション回路

L1, L2: CHAMPS TECHNOLOGIES HRPQA2050-57

PULSE ENGINEERING PA2050-583

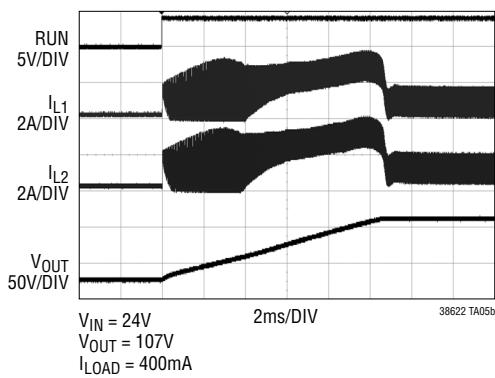

## 起動

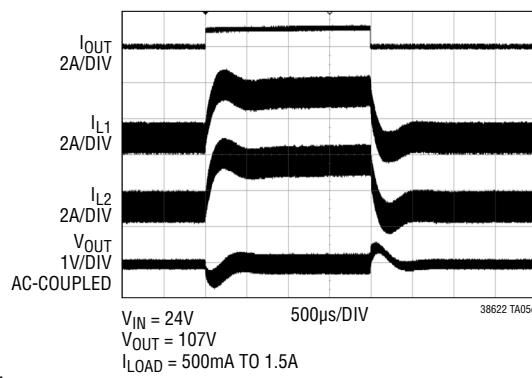

## 負荷ステップ

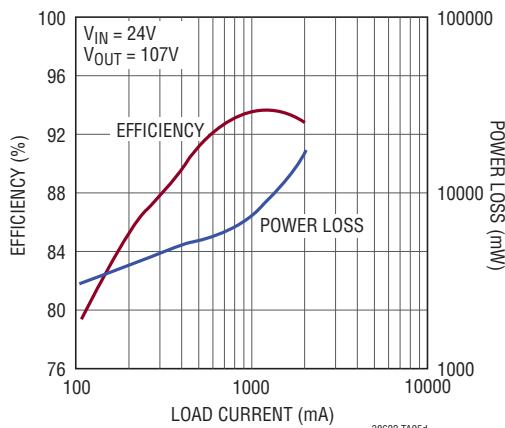

## 効率

38622fa

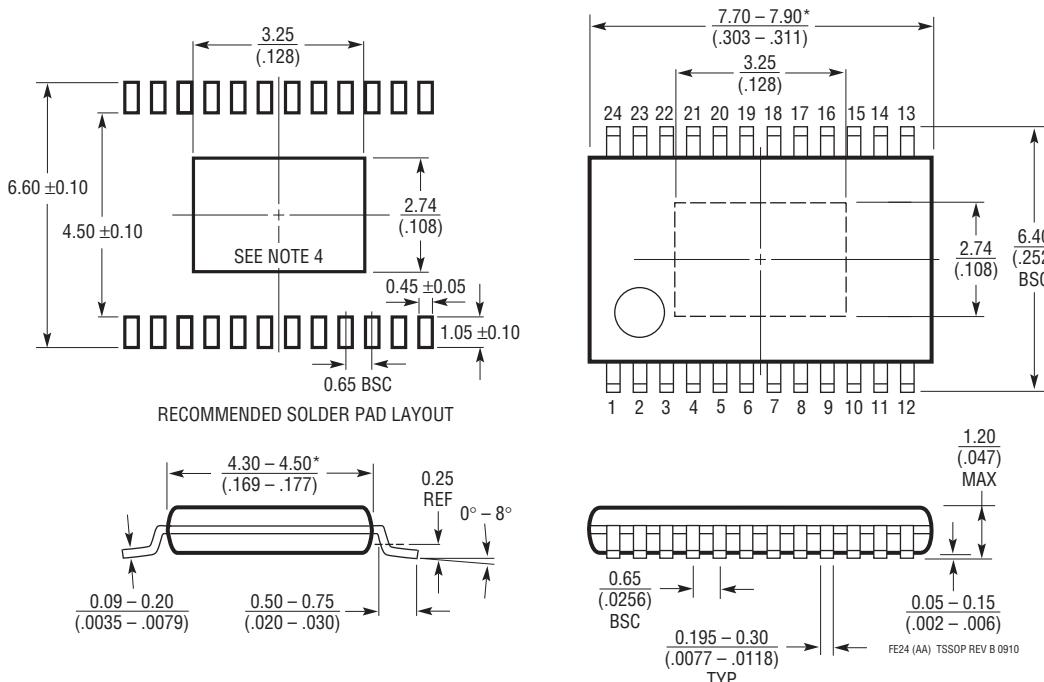

## パッケージ

最新のパッケージ図については、<http://www.linear-tech.co.jp/designtools/packaging/> を参照してください。

**FE Package**

**24-Lead Plastic TSSOP (4.4mm)**

(Reference LTC DWG # 05-08-1771 Rev B)

**Exposed Pad Variation AA**

**NOTE:**

- 標準寸法：ミリメートル

- 寸法は  $\frac{\text{ミリメートル}}{(\text{インチ})}$

- 図は実寸とは異なる

4. 露出パッド接着のための推奨最小 PCB メタルサイズ

\* 寸法にはモールドのバリを含まない。

モールドのバリは各サイドで 0.150mm (0.006") を超えないこと

## パッケージ

最新のパッケージ図については、<http://www.linear-tech.co.jp/designtools/packaging/> を参照してください。

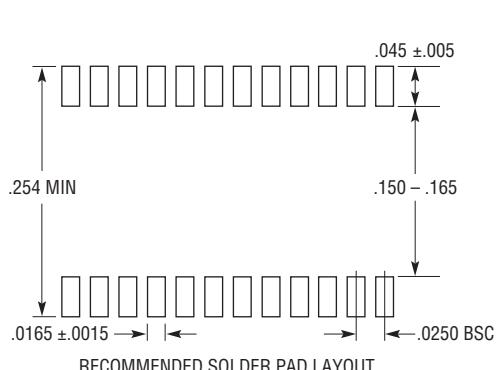

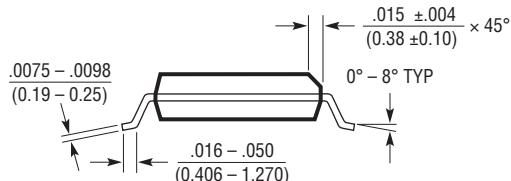

**GN Package**

**24-Lead Plastic SSOP (Narrow .150 Inch)**

(Reference LTC DWG # 05-08-1641 Rev B)

RECOMMENDED SOLDER PAD LAYOUT

NOTE:

1. 標準寸法: インチ

2. 寸法は  $\frac{\text{インチ}}{(\text{ミリメートル})}$

3. 図は実寸とは異なる

4. ピン1は斜めのエッジかへこみのいずれか

\*寸法にはモールドのバリを含まない。

モールドのバリは各サイドで .006" (0.152mm) を超えないこと

\*\*寸法にはリード間のバリを含まない。

リード間のバリは各サイドで .010" (0.254mm) を超えないこと

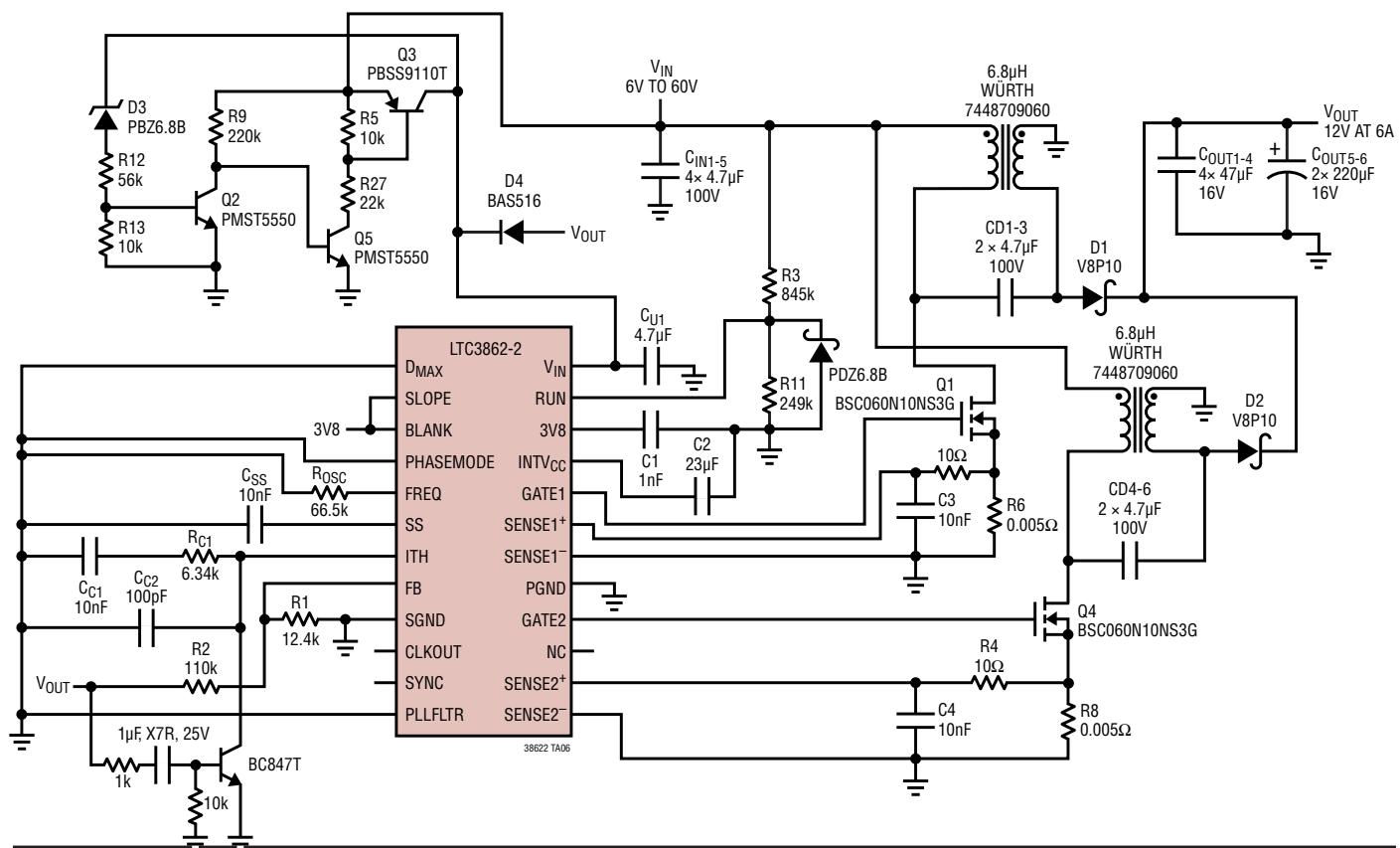

## パッケージ

最新のパッケージ図については、<http://www.linear-tech.co.jp/designtools/packaging/> を参照してください。

**UH Package**

**24-Lead Plastic QFN (5mm x 5mm)**

(Reference LTC DWG # 05-08-1747 Rev A)

### NOTE:

1. 図は JEDEC のパッケージ外形ではない

2. 図は実寸とは異なる

3. 全ての寸法はミリメートル

4. パッケージ底面の露出パッドの寸法にはモールドのバリを含まない。

モールドのバリは(もしあれば)各サイドで 0.20mm を超えないこと

5. 露出パッドは半田メッキとする

6. 網掛けの部分はパッケージの上面と底面のビン1の位置の参考に過ぎない

## 改訂履歴

| REV | 日付    | 概要                             | ページ番号                  |

|-----|-------|--------------------------------|------------------------|

| A   | 12/13 | 比較表を追加。<br>ピン番号を追加。<br>回路図を修正。 | 1<br>10、11<br>39、40、44 |

# LTC3862-2

## 標準的応用例

6V～60V入力、12V/6A出力の2フェーズSEPICアプリケーション回路

## 関連製品

| 製品番号                  | 説明                                    | 注釈                                                                                                                                                 |

|-----------------------|---------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| LTC3787/<br>LTC3787-1 | シングル出力、デュアル・チャネルのマルチフェーズ同期整流式昇圧コントローラ | 4.5V(起動後は2.5Vでも動作) ≤ V <sub>IN</sub> ≤ 38V、V <sub>OUT</sub> :最大60V、固定周波数:50kHz～900kHz、4mm×5mmのQFN-28、SSOP-28                                       |

| LTC3788/<br>LTC3788-1 | デュアル出力、マルチフェーズ同期整流式昇圧コントローラ           | 4.5V(起動後は2.5Vでも動作) ≤ V <sub>IN</sub> ≤ 38V、V <sub>OUT</sub> :最大60V、固定周波数:50kHz～900kHz、5mm×5mmのQFN-32、SSOP-28                                       |

| LTC3786               | 低静止電流の同期整流式昇圧コントローラ                   | 4.5V(起動後は2.5Vでも動作) ≤ V <sub>IN</sub> ≤ 38V、V <sub>OUT</sub> :最大60V、固定周波数:50kHz～900kHz、3mm×3mmのQFN-32、MSOP-16E                                      |

| LT3757A               | 昇圧、フライバック、SEPICおよび反転コントローラ            | 2.9V ≤ V <sub>IN</sub> ≤ 40V、電流モード制御、プログラム可能な動作周波数:100kHz～1MHz、3mm×3mm DFN-10 および MSOP-10E パッケージ                                                   |

| LTC3859AL             | 低静止電流、トリプル出力、降圧/降圧/昇圧同期整流式DC/DCコントローラ | すべての出力がコールドクランク時に安定、4.5V(起動後は2.5Vでも動作) ≤ V <sub>IN</sub> ≤ 38V、V <sub>OUT(BUCKS)</sub> :最大24V、V <sub>OUT(BOOST)</sub> :最大60V、I <sub>Q</sub> = 28µA |

| LTC3789               | 高効率、同期整流式、4スイッチ昇降圧DC/DCコントローラ         | 4V ≤ V <sub>IN</sub> ≤ 38V、0.8V ≤ V <sub>OUT</sub> ≤ 38V、4mm×5mmのQFN-28、SSOP-28                                                                    |