# 差動出力検出付き、 高速で高精度の2フェーズ、 シングル出力降圧DC/DCコントローラ

## 特長

- 広い入力電圧範囲: 4.5V ~ 38V, V<sub>OUT</sub>: 0.6V ~ 5.5V

- 全温度範囲で  $\pm 0.67\%$  の出力電圧精度と差動出力電圧検出により、リモート・グランドで最大  $\pm 500\text{mV}$  のライン損失を許容

- オン時間が制御される谷電流モード制御

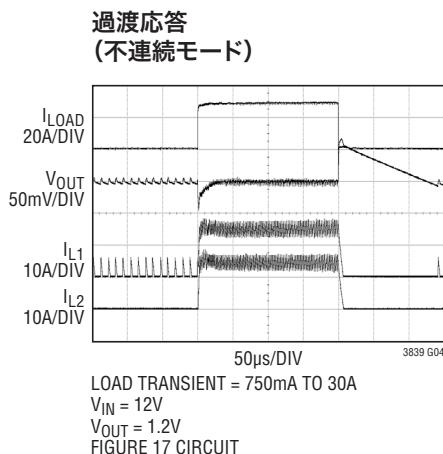

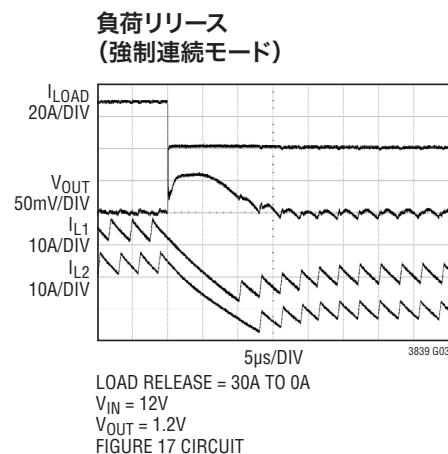

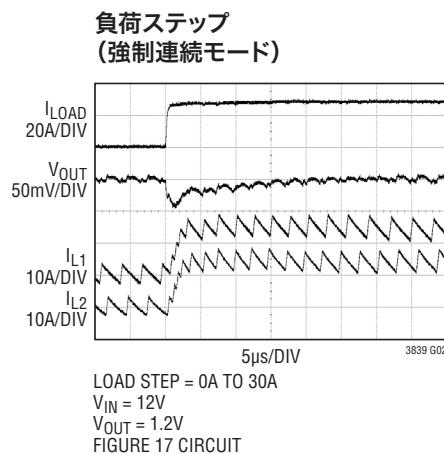

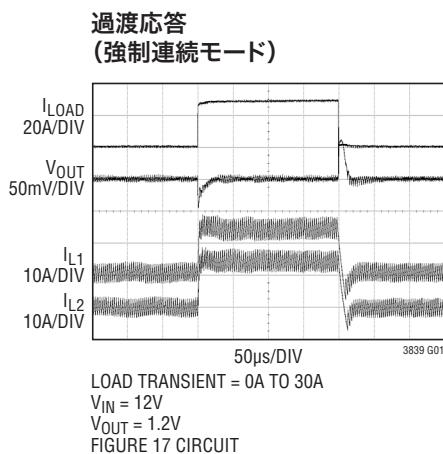

- 高速負荷過渡応答

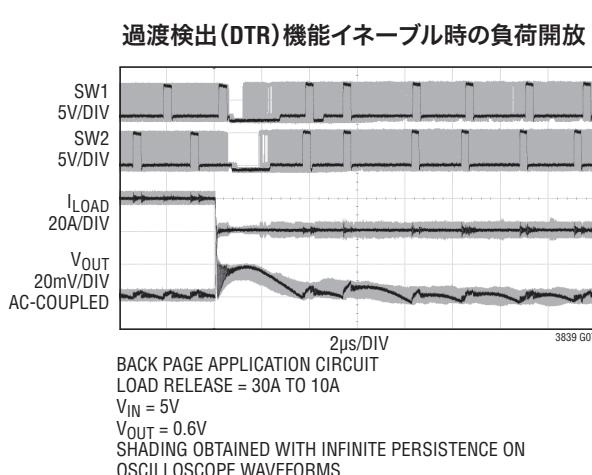

- 軽負荷トランジエント検出(DTR)により、V<sub>OUT</sub>のオーバーシュートを低減

- 200kHz ~ 2MHzの周波数を設定可能、外部クロックに同期可能

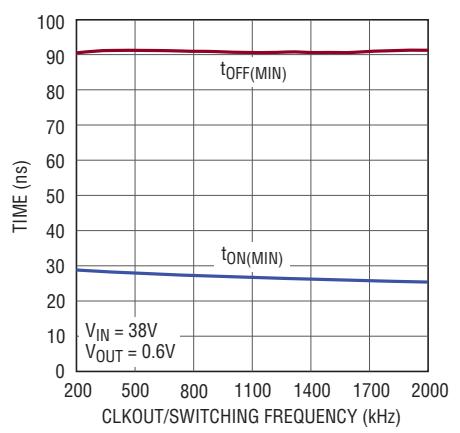

- t<sub>ON</sub>(MIN) = 30ns, t<sub>OFF</sub>(MIN) = 90ns

- 最大 12 フェーズで動作

- R<sub>SENSE</sub> またはインダクタの DCR による電流センス

- 過電圧保護と電流制限フォールドバック

- パワーグッド出力電圧モニタ

- 出力電圧トラッキングと調整可能なソフトスタート

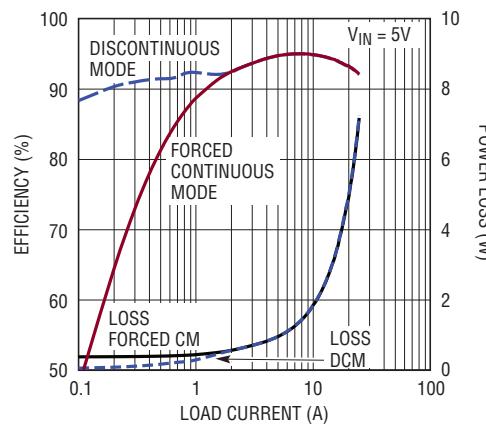

- 熱特性が改善された 32 ピン(5mm × 5mm)QFN パッケージ

## アプリケーション

- 配電システム

- ポイントオブロード・コンバータ

- 計算システム

- データ通信システム

## 概要

LTC<sup>®</sup>3839は、すべてNチャネルのパワーMOSFETをドライブする、2フェーズ、シングル出力、PolyPhase<sup>®</sup>同期整流式降圧スイッチング・レギュレータ・コントローラです。オン時間が制御される谷電流モード制御アーキテクチャにより、V<sub>IN</sub>、V<sub>OUT</sub>、および負荷電流に関係なく、高速過渡応答と定常状態での固定周波数スイッチングが可能です。軽負荷トランジエント検出により、低出力電圧時のオーバーシュートが大幅に低減されます。

差動出力電圧検出と高精度内部リファレンスにより、リモート出力グランドがローカル・グランドから  $\pm 500\text{mV}$  変動した場合でも、 $\pm 0.67\%$  の高精度の出力レギュレーションを実現します。

スイッチング周波数は、外付け抵抗を使って 200kHz ~ 2MHz に設定可能で、外部クロックに同期することもできます。t<sub>ON</sub> 時間と t<sub>OFF</sub> 時間が非常に短いので、それぞれ 0% に近いデューティサイクルと 100% に近いデューティサイクルが可能です。また、電圧トラッキング・ソフトスタートなど、いくつかの安全機能を備えています。

**L**、LT、LTC、LTM、PolyPhase、OPTI-LOOP、Linear Technology および Linear のロゴはリニアテクノロジー社の登録商標です。Hot Swap および Stage Shedding はリニアテクノロジー社の商標です。その他全ての商標の所有権は、それぞれの所有者に帰属します。5481178、5487554、6580258、6304066、6476589、6774611 を含む米国特許により保護されています。

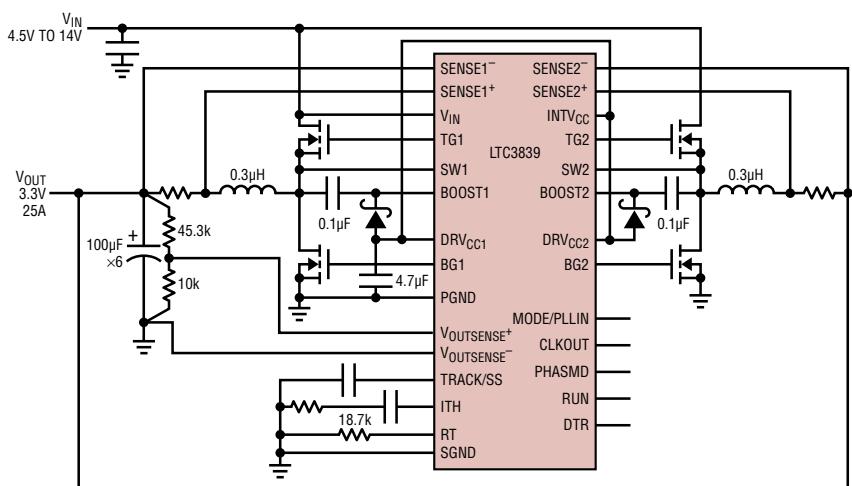

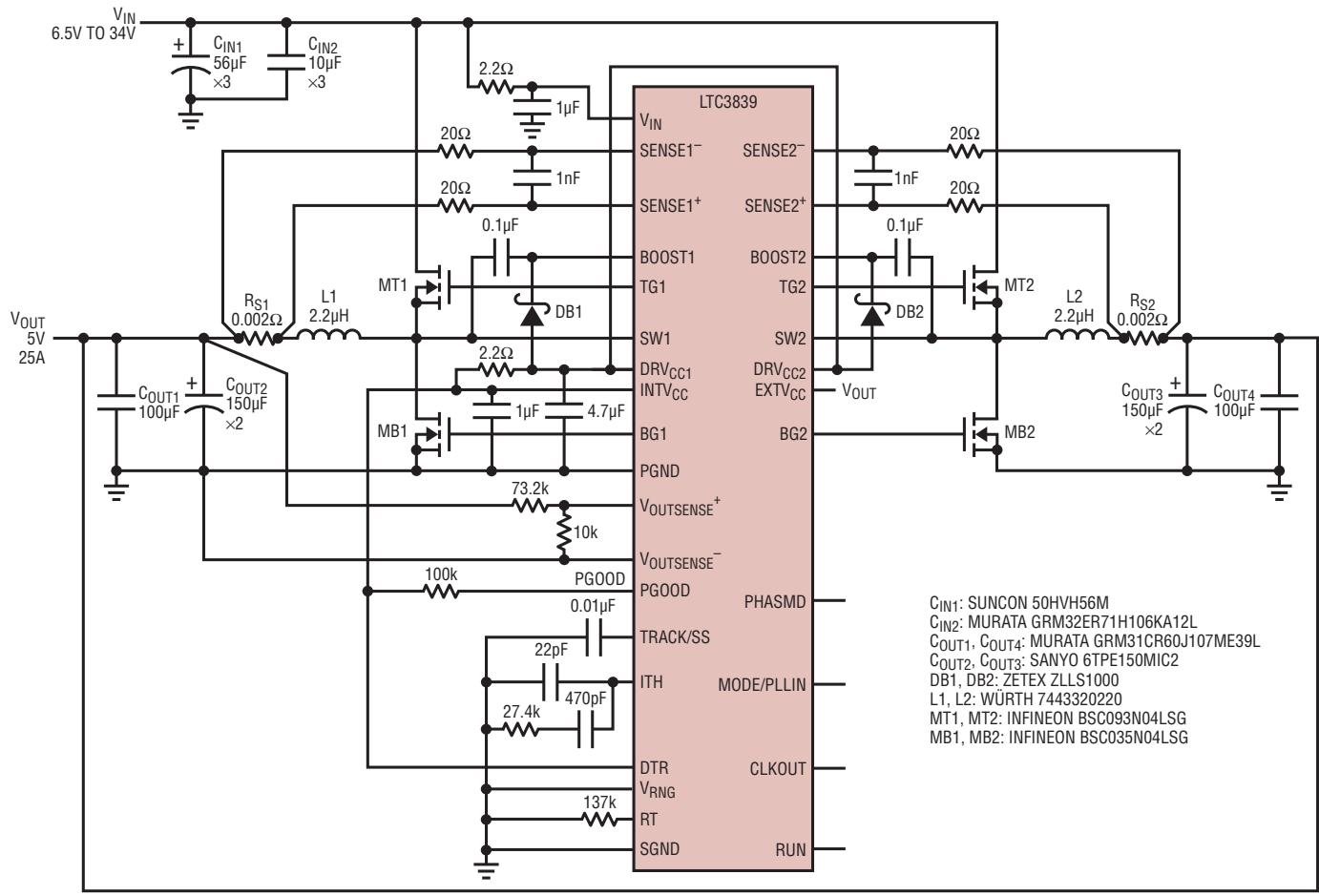

## 標準的応用例

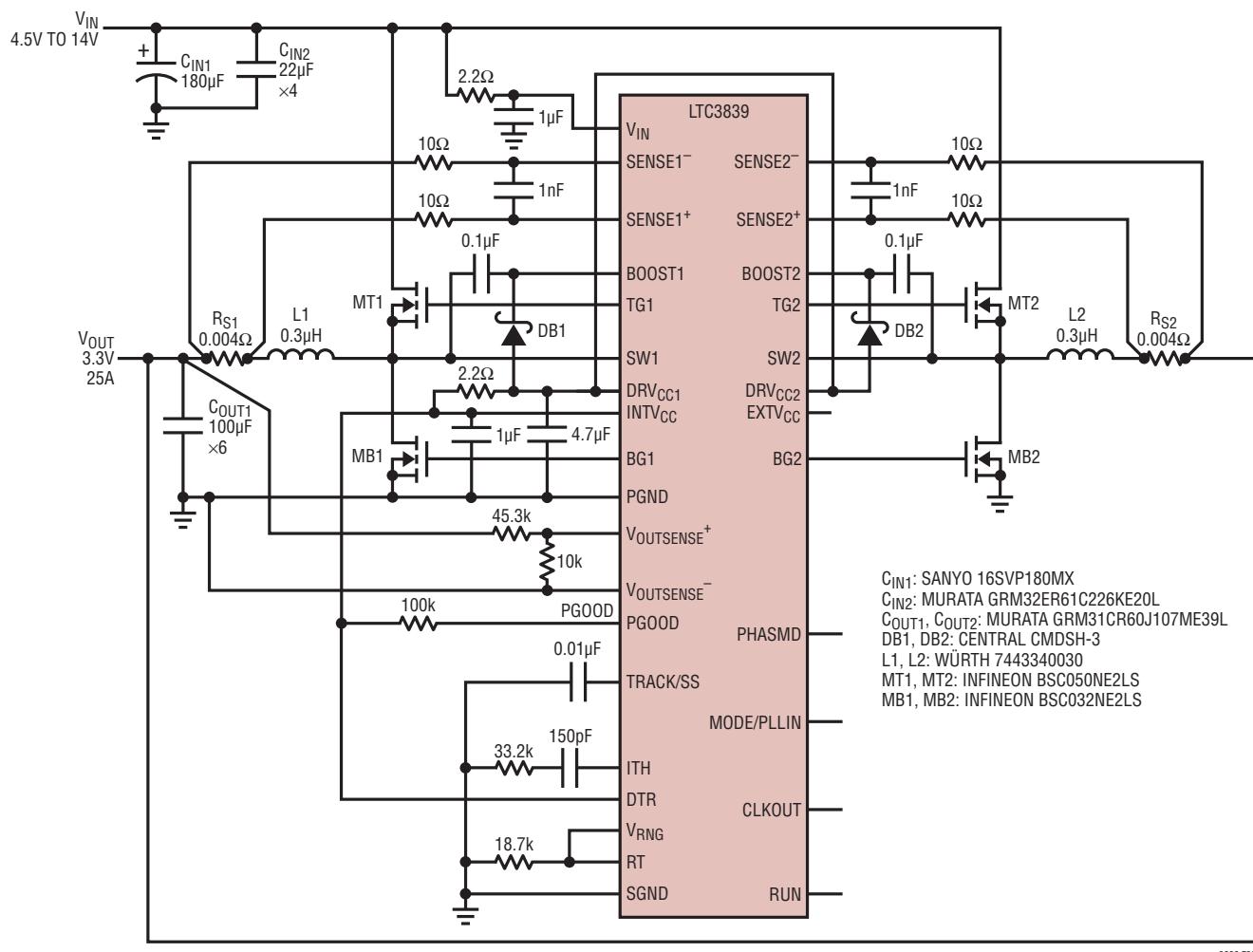

3.3V/25A出力、2MHz降圧コンバータ(設計図全体については図20を参照)

3839 TA01b

## 絶対最大定格 (Note 1)

|                                                                                                                            |                                     |

|----------------------------------------------------------------------------------------------------------------------------|-------------------------------------|

| $V_{IN}$ 電圧                                                                                                                | -0.3V ~ 40V                         |

| BOOST1、BOOST2 電圧                                                                                                           | -0.3V ~ 46V                         |

| SW1、SW2 電圧                                                                                                                 | -5V ~ 40V                           |

| INTV <sub>CC</sub> 、DRV <sub>CC1</sub> 、DRV <sub>CC2</sub> 、EXTV <sub>CC</sub> 、PGOOD、RUN、(BOOST1-SW1)、(BOOST2-SW2)、       |                                     |

| MODE/PLLIN 電圧                                                                                                              | -0.3V ~ 6V                          |

| $V_{OUTSENSE^+}$ 、 $V_{OUTSENSE^-}$ 、SENSE1 <sup>+</sup> 、SENSE2 <sup>+</sup> 、SENSE1 <sup>-</sup> 、SENSE2 <sup>-</sup> 電圧 | -0.6V ~ 6V                          |

| TRACK/SS 電圧                                                                                                                | -0.3V ~ 5V                          |

| DTR、PHASMD、RT、 $V_{RNG}$ 、ITH 電圧                                                                                           | -0.3V ~ (INTV <sub>CC</sub> + 0.3V) |

| 動作接合部温度範囲 (Note 2、3、4)                                                                                                     | -40°C ~ 125°C                       |

| 保存温度範囲                                                                                                                     | -65°C ~ 150°C                       |

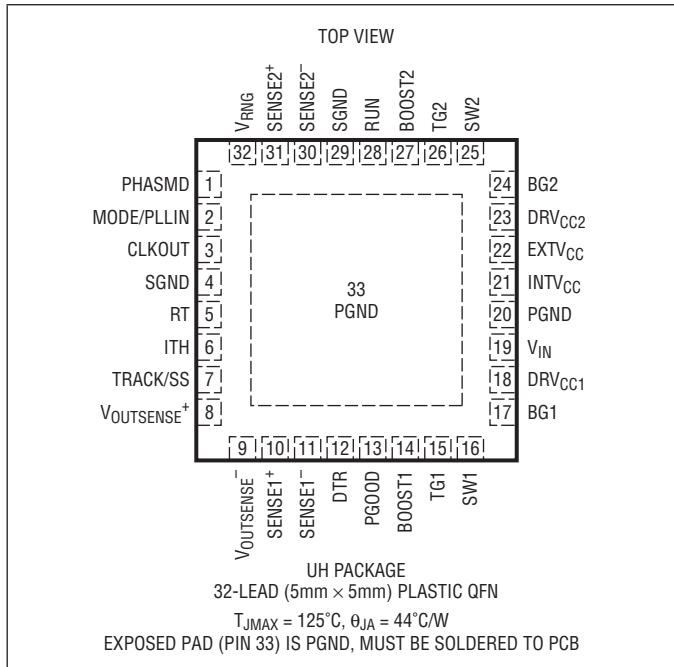

## ピン配置

## 発注情報

| 無鉛仕上げ          | テープアンドリール        | 製品マーキング* | パッケージ                           | 温度範囲           |

|----------------|------------------|----------|---------------------------------|----------------|

| LTC3839EUH#PBF | LTC3839EUH#TRPBF | 3839     | 32-Lead (5mm x 5mm) Plastic QFN | -40°C to 125°C |

| LTC3839IUH#PBF | LTC3839IUH#TRPBF | 3839     | 32-Lead (5mm x 5mm) Plastic QFN | -40°C to 125°C |

さらに広い動作温度範囲で規定されるデバイスについては、弊社または弊社代理店にお問い合わせください。\* 温度グレードは出荷時のコンテナのラベルで識別されます。

非標準の鉛仕上げの製品の詳細については、弊社または弊社代理店にお問い合わせください。

無鉛仕上げの製品マーキングの詳細については、<http://www.linear-tech.co.jp/leadfree/> をご覧ください。

テープアンドリールの仕様の詳細については、<http://www.linear-tech.co.jp/tapeandreel/> をご覧ください。

**電気的特性** ●は規定動作接合部温度範囲の規格値を意味する。それ以外は  $T_A = 25^\circ\text{C}$  での値。注記がない限り、 $V_{IN} = 15\text{V}$  (Note 3)。

| SYMBOL                     | PARAMETER                                                                        | CONDITIONS                                                                                                                                            | MIN                           | TYP               | MAX                      | UNITS               |

|----------------------------|----------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|-------------------|--------------------------|---------------------|

| <b>メイン制御ループ</b>            |                                                                                  |                                                                                                                                                       |                               |                   |                          |                     |

| $V_{IN}$                   | Input Voltage Operating Range                                                    |                                                                                                                                                       | 4.5                           | 38                |                          | V                   |

| $V_{OUT(\text{REG})}$      | Regulated Output Voltage Operating Range                                         | $V_{OUT}$ Regulated Differentially with Respect to $V_{OUTSENSE^-}$                                                                                   | 0.6                           | 5.5               |                          | V                   |

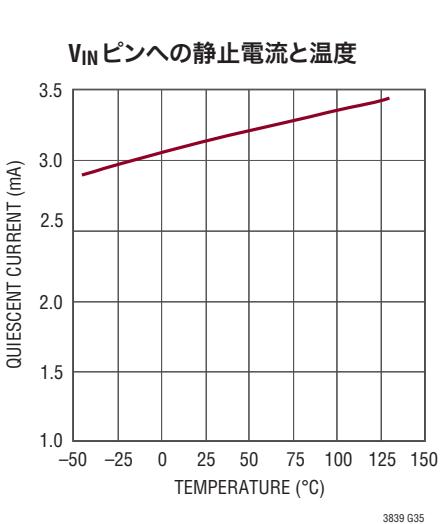

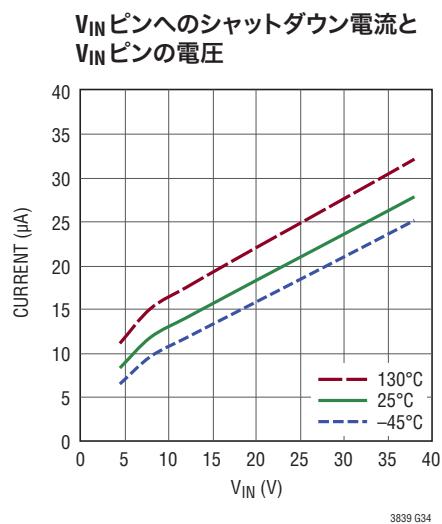

| $I_Q$                      | Input DC Supply Current<br>RUN Enabled<br>Shutdown Supply Current                | MODE/PLLIN = 0V, No Load<br>RUN = 0V                                                                                                                  |                               | 3<br>15           |                          | mA<br>$\mu\text{A}$ |

| $V_{OUTSENSE(\text{REG})}$ | Regulated Differential Feedback Voltage<br>( $V_{OUTSENSE^+} - V_{OUTSENSE^-}$ ) | ITH1 = 1.2V (Note 5)<br>$T_A = 25^\circ\text{C}$<br>$T_A = 0^\circ\text{C}$ to $85^\circ\text{C}$<br>$T_A = -40^\circ\text{C}$ to $125^\circ\text{C}$ | ●<br>0.5985<br>0.596<br>0.594 | 0.6<br>0.6<br>0.6 | 0.6015<br>0.604<br>0.606 | V<br>V<br>V         |

|                            | Regulated Differential Feedback Voltage Over Line, Load and Common Mode          | $V_{IN} = 4.5\text{V}$ to $38\text{V}$ , ITH1 = 0.5V to 1.9V<br>$-0.5\text{V} < V_{OUTSENSE^-} < 0.5\text{V}$ (Notes 5, 7)                            | ●                             | 0.591             | 0.6                      | 0.609               |

**電気的特性** ●は規定動作接合部温度範囲の規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。注記がない限り、 $V_{IN} = 15\text{V}$ (Note 3)。

| SYMBOL            | PARAMETER                            | CONDITIONS                                                                    | MIN | TYP     | MAX      | UNITS         |

|-------------------|--------------------------------------|-------------------------------------------------------------------------------|-----|---------|----------|---------------|

| $I_{VOUTSENSE^+}$ | $V_{OUTSENSE1^+}$ Input Bias Current | $V_{OUTSENSE^+} - V_{OUTSENSE^-} = 0.6\text{V}$                               |     | $\pm 5$ | $\pm 25$ | nA            |

| $I_{VOUTSENSE^-}$ | $V_{OUTSENSE1^-}$ Input Bias Current | $V_{OUTSENSE^+} - V_{OUTSENSE^-} = 0.6\text{V}$                               |     | -25     | -50      | $\mu\text{A}$ |

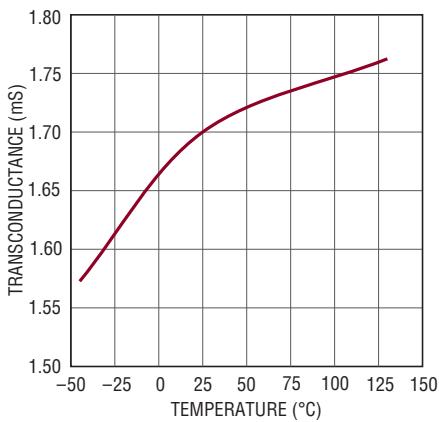

| $g_m(EA)$         | Error Amplifier Transconductance     | $I_{TH} = 1.2\text{V}$ (Note 5)                                               |     | 1.7     |          | $\text{mS}$   |

| $t_{ON(MIN)1,2}$  | Minimum Top Gate On-Time             | $V_{IN} = 38\text{V}$ , $V_{OUT} = 0.6\text{V}$ , $R_T = 20\text{k}$ (Note 6) |     | 30      |          | ns            |

| $t_{OFF(MIN)1,2}$ | Minimum Top Gate Off-Time            | (Note 6)                                                                      |     | 90      |          | ns            |

**電流センス**

|                     |                                                                                                            |                                                                                                                                                                                                                                                        |             |                |                   |                     |                                |

|---------------------|------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|----------------|-------------------|---------------------|--------------------------------|

| $V_{SENSE(MAX)1,2}$ | Maximum Valley Current Sense Threshold ( $(V_{SENSE1,2^+} - V_{SENSE1,2^-})$ )                             | $V_{RNG} = 2\text{V}$ , $V_{FB} = 0.57\text{V}$ , $V_{SENSE^-} = 2.5\text{V}$<br>$V_{RNG} = 0\text{V}$ , $V_{FB} = 0.57\text{V}$ , $V_{SENSE^-} = 2.5\text{V}$<br>$V_{RNG} = \text{INTV}_{CC}$ , $V_{FB} = 0.57\text{V}$ , $V_{SENSE^-} = 2.5\text{V}$ | ●<br>●<br>● | 80<br>21<br>39 | 100<br>30<br>50   | 120<br>40<br>61     | mV<br>mV<br>mV                 |

| $V_{SENSE(MIN)1,2}$ | Minimum Valley Current Sense Threshold ( $(V_{SENSE1,2^+} - V_{SENSE1,2^-})$ )<br>(Forced Continuous Mode) | $V_{RNG} = 2\text{V}$ , $V_{FB} = 0.63\text{V}$ , $V_{SENSE^-} = 2.5\text{V}$<br>$V_{RNG} = 0\text{V}$ , $V_{FB} = 0.63\text{V}$ , $V_{SENSE^-} = 2.5\text{V}$<br>$V_{RNG} = \text{INTV}_{CC}$ , $V_{FB} = 0.63\text{V}$ , $V_{SENSE^-} = 2.5\text{V}$ |             |                | -50<br>-15<br>-25 |                     | mV<br>mV<br>mV                 |

| $I_{SENSE1,2^+}$    | SENSE1,2 <sup>+</sup> Pins Input Bias Current                                                              | $V_{SENSE^+} = 0.6\text{V}$<br>$V_{SENSE^+} = 5\text{V}$                                                                                                                                                                                               |             |                | $\pm 5$<br>1      | $\pm 50$<br>$\pm 2$ | nA<br>$\mu\text{A}$            |

| $I_{SENSE1,2^-}$    | SENSE1,2 <sup>-</sup> Pins Input Bias Current (Internal 500k Resistor to SGND)                             | $V_{SENSE^-} = 0.6\text{V}$<br>$V_{SENSE^-} = 5\text{V}$                                                                                                                                                                                               |             |                | 1.2<br>10         |                     | $\mu\text{A}$<br>$\mu\text{A}$ |

**起動とシャットダウン**

|                    |                                         |                                                         |        |            |            |     |               |

|--------------------|-----------------------------------------|---------------------------------------------------------|--------|------------|------------|-----|---------------|

| $V_{RUN(TH)}$      | RUN Pin On Threshold                    | $V_{RUN}$ Rising                                        | ●      | 1.1        | 1.2        | 1.3 | V             |

| $V_{RUN(HYS)}$     | RUN Pin On Hysteresis                   | $V_{RUN}$ Falling from On Threshold                     |        |            | 100        |     | mV            |

| $I_{RUN(OFF)}$     | RUN Pin Pull-Up Current when Off        | $RUN = SGND$                                            |        |            | 2.5        |     | $\mu\text{A}$ |

| $I_{RUN(HYS)}$     | RUN Pin Pull-Up Current Hysteresis      | $(I_{RUN(ON)} - I_{RUN(OFF)})$                          |        |            | 10         |     | $\mu\text{A}$ |

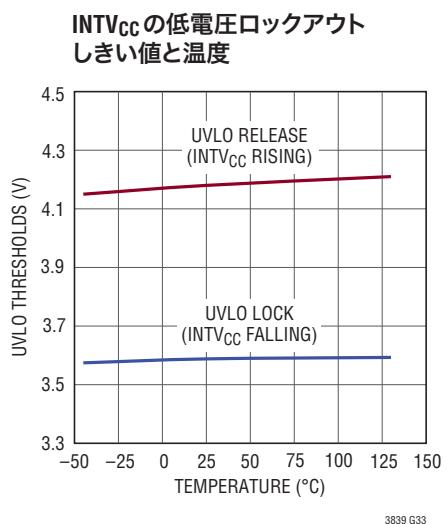

| $V_{UVLO(INTVCC)}$ | INTV <sub>CC</sub> Undervoltage Lockout | INTV <sub>CC</sub> Falling<br>INTV <sub>CC</sub> Rising | ●<br>● | 3.3<br>4.2 | 3.7<br>4.2 | 4.5 | V<br>V        |

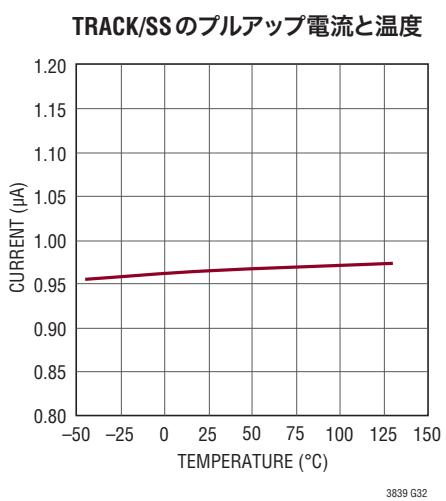

| $I_{TRACK/SS}$     | Soft-Start Pull-Up Current              | $0\text{V} < TRACK/SS < 0.6\text{V}$                    |        |            | 1          |     | $\mu\text{A}$ |

**周波数とクロックへの同期**

|                  |                                                           |                                                                     |  |     |                    |     |                   |

|------------------|-----------------------------------------------------------|---------------------------------------------------------------------|--|-----|--------------------|-----|-------------------|

| $f_{CLKOUT}$     | Clock Output Frequency (Steady-State Switching Frequency) | $R_T = 205\text{k}$<br>$R_T = 80.6\text{k}$<br>$R_T = 18.2\text{k}$ |  | 450 | 200<br>500<br>2000 | 550 | kHz<br>kHz<br>kHz |

| $\phi_{CH2}$     | Channel 2 Phase (Relative to Channel 1)                   | PHASMD = SGND<br>PHASMD = Floating<br>PHASMD = INTV <sub>CC</sub>   |  |     | 180<br>180<br>240  |     | Deg<br>Deg<br>Deg |

| $\phi_{CLKOUT}$  | CLKOUT Phase (Relative to Channel 1)                      | PHASMD = SGND<br>PHASMD = Floating<br>PHASMD = INTV <sub>CC</sub>   |  |     | 60<br>90<br>120    |     | Deg<br>Deg<br>Deg |

| $V_{PLLIN(H)}$   | Clock Input High Level Into MODE/PLLIN                    |                                                                     |  |     | 2                  |     | V                 |

| $V_{PLLIN(L)}$   | Clock Input Low Level Into MODE/PLLIN                     |                                                                     |  |     |                    | 0.5 | V                 |

| $R_{MODE/PLLIN}$ | MODE/PLLIN Input Resistance                               | With Respect to SGND                                                |  |     | 600                |     | $\text{k}\Omega$  |

**ゲート・ドライバ**

|                   |                                           |          |  |     |  |          |

|-------------------|-------------------------------------------|----------|--|-----|--|----------|

| $R_{TG(UP)1,2}$   | TG Driver Pull-Up On Resistance           | TG High  |  | 2.5 |  | $\Omega$ |

| $R_{TG(DOWN)1,2}$ | TG Driver Pull-Down On Resistance         | TG Low   |  | 1.2 |  | $\Omega$ |

| $R_{BG(UP)1,2}$   | BG Driver Pull-Up On Resistance           | BG High  |  | 2.5 |  | $\Omega$ |

| $R_{BG(DOWN)1,2}$ | BG Driver Pull-Down On Resistance         | BG Low   |  | 0.8 |  | $\Omega$ |

| $t_D(TG/BG)1,2$   | Top Gate Off to Bottom Gate On Delay Time | (Note 6) |  | 20  |  | ns       |

| $t_D(BG/TG)1,2$   | Bottom Gate Off to Top Gate On Delay Time | (Note 6) |  | 15  |  | ns       |

## 電気的特性

●は規定動作接合部温度範囲の規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。注記がない限り、 $V_{IN} = 15\text{V}$ (Note 3)。

| SYMBOL                               | PARAMETER                                                                                      | CONDITIONS                                              | MIN | TYP  | MAX  | UNITS         |

|--------------------------------------|------------------------------------------------------------------------------------------------|---------------------------------------------------------|-----|------|------|---------------|

| <b>内部 <math>V_{CC}</math> レギュレータ</b> |                                                                                                |                                                         |     |      |      |               |

| $V_{DRVCC1}$                         | Internally Regulated $DRV_{CC1}$ Voltage                                                       | $6\text{V} < V_{IN} < 38\text{V}$                       | 5.0 | 5.3  | 5.6  | V             |

| $\Delta V_{DRVCC1}$                  | $DRV_{CC1}$ Load Regulation                                                                    | $I_{DRVCC1} = 0\text{mA}$ to $-100\text{mA}$            |     | -1.5 | -3.5 | %             |

| $V_{EXTVCC(TH)}$                     | EXT $V_{CC}$ Switchover Voltage                                                                | EXT $V_{CC}$ Rising                                     | 4.4 | 4.6  | 4.8  | V             |

| $V_{EXTVCC(HYS)}$                    | EXT $V_{CC}$ Switchover Hysteresis                                                             | EXT $V_{CC}$ Falling from Switching Voltage             |     | 200  |      | mV            |

| $\Delta V_{DRVCC2}$                  | EXT $V_{CC}$ to $DRV_{CC2}$ Voltage Drop                                                       | $V_{EXTVCC} = 5\text{V}$ , $I_{DRVCC2} = -100\text{mA}$ |     | 200  |      | mV            |

| <b>PGOOD 出力</b>                      |                                                                                                |                                                         |     |      |      |               |

| $\Delta V_{OUT(OV)}$                 | PGOOD Overvoltage Threshold                                                                    | $V_{OUT}$ Rising, with Respect to Regulated Voltage     | 5   | 7.5  | 10   | %             |

| $\Delta V_{OUT(UV)}$                 | PGOOD Undervoltage Threshold                                                                   | $V_{OUT}$ Falling, with Respect to Regulated Voltage    | -5  | -7.5 | -10  | %             |

| $\Delta V_{OUT(HYS)}$                | PGOOD Threshold Hysteresis                                                                     | $V_{OUT}$ Returning to Reference Voltage                |     | 2    |      | %             |

| $V_{PGOOD(L)}$                       | PGOOD Low Voltage                                                                              | $I_{PGOOD} = 2\text{mA}$                                |     | 0.1  | 0.3  | V             |

| $t_D(PGOOD)$                         | Delay from $V_{FB}$ Fault (OV/UV) to PGOOD Falling<br>Delay from $V_{FB}$ Good to PGOOD Rising |                                                         |     | 50   |      | $\mu\text{s}$ |

|                                      |                                                                                                |                                                         |     | 20   |      | $\mu\text{s}$ |

**Note 1:** 絶対最大定格に記載された値を超えるストレスはデバイスに永続的損傷を与える可能性がある。また、長期にわたって絶対最大定格条件に曝すと、デバイスの信頼性と寿命に悪影響を与える可能性がある。

**Note 2:** 接合部温度( $T_J$ ( $^\circ\text{C}$ ))は周囲温度( $T_A$ ( $^\circ\text{C}$ ))および電力損失( $P_D$ (W))から次式に従って計算される

$$T_J = T_A + (P_D \cdot \theta_{JA})$$

ここで、 $\theta_{JA}$ ( $^\circ\text{C/W}$ )はパッケージの熱インピーダンスである。

**Note 3:** LTC3839は $T_J$ が $T_A$ にほぼ等しいパルス負荷条件でテストされる。LTC3839Eは $0^\circ\text{C} \sim 85^\circ\text{C}$ の動作接合部温度範囲で仕様に適合することが保証されている。 $-40^\circ\text{C} \sim 125^\circ\text{C}$ の動作接合部温度範囲での仕様は、設計、特性評価および統計学的なプロセス・コントロールとの相関で確認されている。LTC3839Iは $-40^\circ\text{C} \sim 125^\circ\text{C}$ の動作接合部温度範囲で仕様に適合することが保証されている。これらの仕様を満たす最大周囲温度は、基板レイアウト、パッケージの定格熱インピーダンスおよび他の環境要因と関連した特定の動作条件によって決まるこに注意。

**Note 4:** このデバイスには短時間の過負荷状態の間デバイスを保護するための過熱保護機能が備わっている。この保護がアクティブなとき、最大定格接合部温度を超えることができる。規定された絶対最大動作接合部温度を超えた動作が継続すると、デバイスの信頼性を損なうか、またはデバイスに永続的損傷を与える恐れがある。

**Note 5:** LTC3839は、規定されたエラーアンプの出力電圧(ITH)を達成するように差動帰還電圧( $V_{OUTSENSE^-} - V_{OUTSENSE^+}$ )を調整する帰還ループでテストされる。

**Note 6:** 遅延時間はトップゲート(TG)とボトムゲート(BG)が最小負荷を駆動する場合で、50%レベルで測定する。

**Note 7:** 全システム誤差の計算を容易にするため、安定化電圧は、ライン、負荷、および同相電圧の変動の影響を含む仕様の組み合わせで定義されている。組み合わされた安定化電圧の仕様は、ライン、負荷、および同相電圧を個別に変化させることによってテストされ、これらは設計によって相互にあまり影響を受けない。ライン、負荷、および同相電圧の変動のどの組み合わせでも、安定化電圧は、製造時に以下の条件でテストされる規定制限値以内にする必要がある。

- ライン: $V_{IN} = 4.5\text{V} \sim 38\text{V}$ ,  $ITH = 1.2\text{V}$ ,  $V_{OUTSENSE^-} = 0\text{V}$

- 負荷: $V_{IN} = 15\text{V}$ ,  $ITH = 0.5\text{V} \sim 1.9\text{V}$ ,  $V_{OUTSENSE^-} = 0\text{V}$

- 同相電圧: $V_{IN} = 15\text{V}$ ,  $ITH = 1.2\text{V}$ ,  $V_{OUTSENSE^-} = \pm 500\text{mV}$

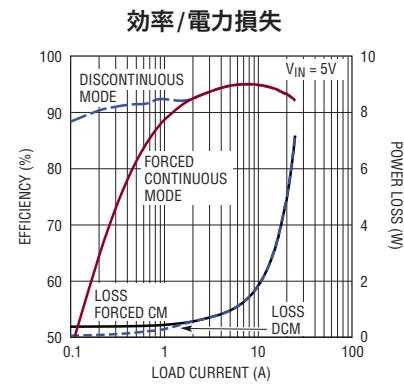

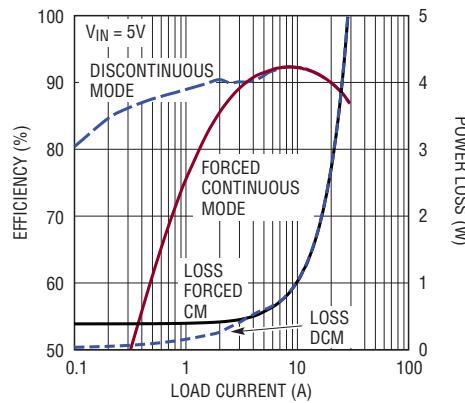

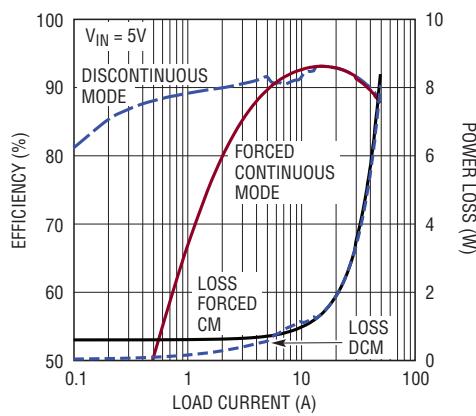

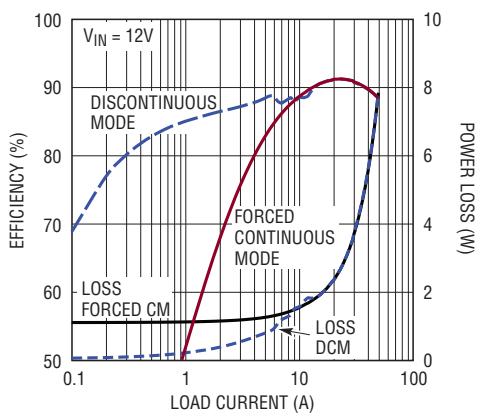

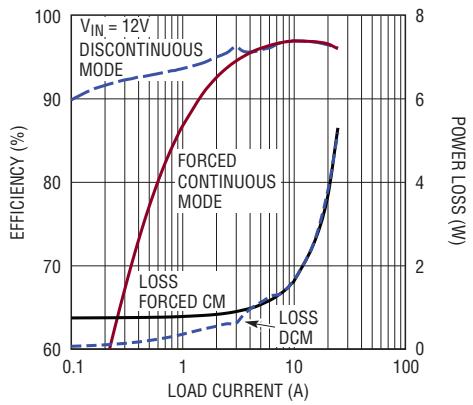

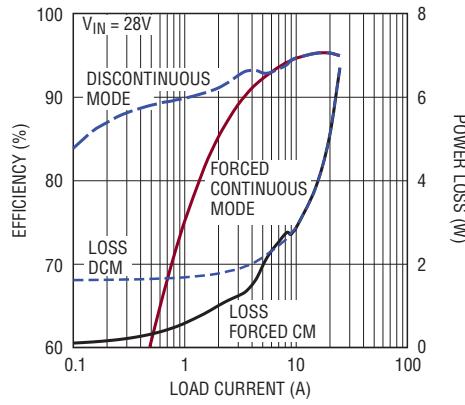

## 標準的性能特性

## 標準的性能特性

FIGURE 13 CIRCUIT

V<sub>IN</sub> = 12V

LOAD = 0A

MODE/PLLIN = 333kHz EXTERNAL CLOCK

FIGURE 13 CIRCUIT

V<sub>IN</sub> = 12V

LOAD = 0A

MODE/PLLIN = 333kHz EXTERNAL CLOCK

FIGURE 13 CIRCUIT

V<sub>IN</sub> = 12V

LOAD = 0A

MODE/PLLIN = 333kHz EXTERNAL CLOCK

## 標準的性能特性

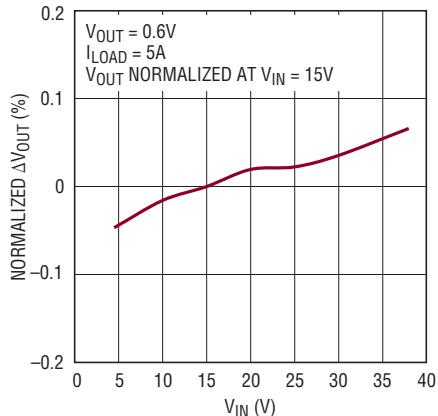

出力レギュレーションと入力電圧

3839 G18

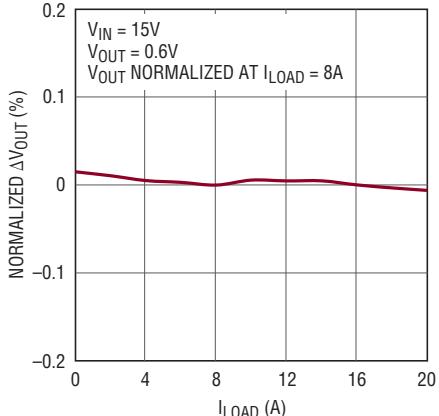

出力レギュレーションと負荷電流

3839 G19

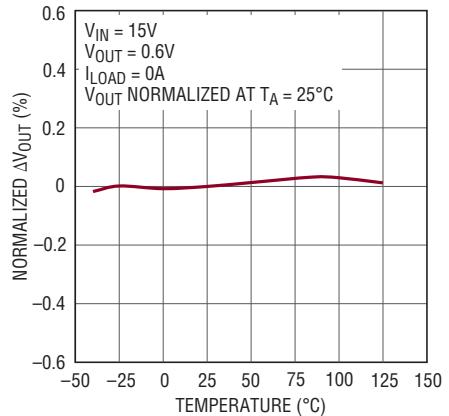

出力レギュレーションと温度

3839 G20

エラーアンプの

トランジスタコンダクタンスと温度

3839 G27

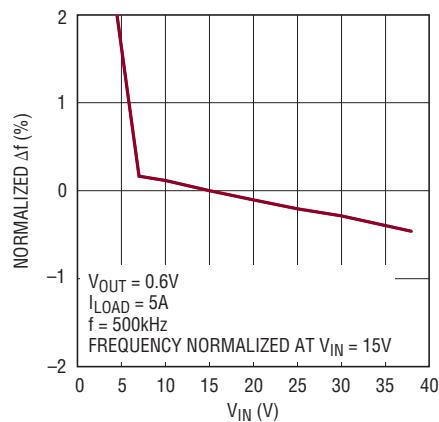

CLKOUT/スイッチング周波数と

入力電圧

3839 G21

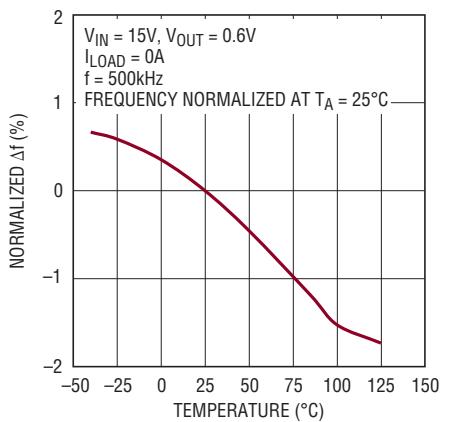

CLKOUT/スイッチング周波数と

温度

3839 G23

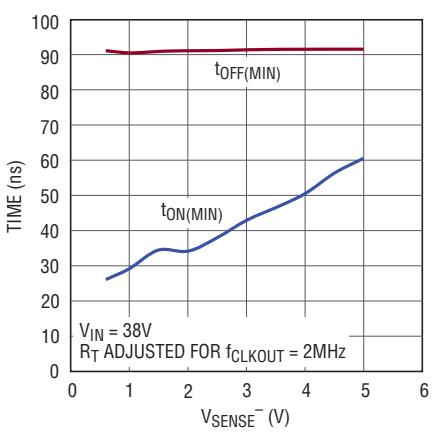

$t_{ON(MIN)}$  および  $t_{OFF(MIN)}$  と

$V_{OUT}$  (SENSE<sup>-</sup>ピンの電圧)

3839 G24

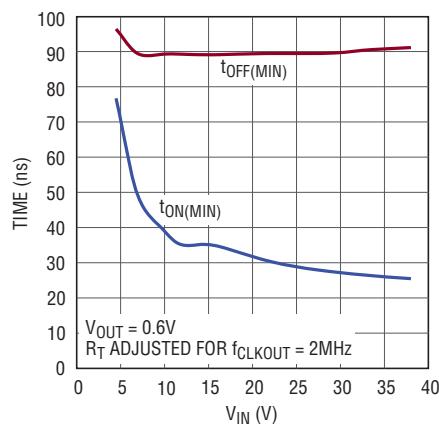

$t_{ON(MIN)}$  および  $t_{OFF(MIN)}$  と

$V_{IN}$  ピンの電圧

3839 G25

$t_{ON(MIN)}$  および  $t_{OFF(MIN)}$  と

スイッチング周波数

3839 G26

## 標準的性能特性

## ピン機能

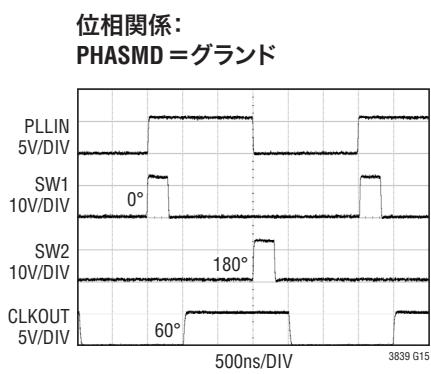

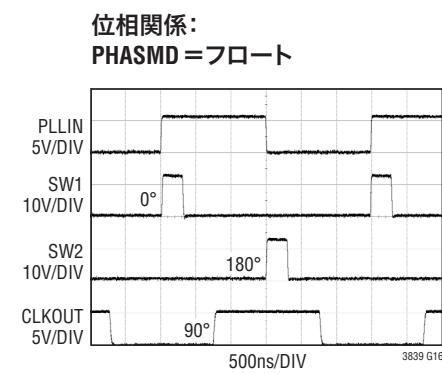

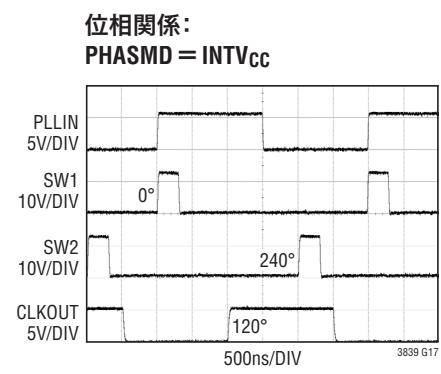

**PHASMD (ピン1)**: フェーズ・セレクタ入力。このピンにより、チャネルとCLKOUT信号の位相関係が決まります。ゼロ位相をTG1の立ち上がりエッジとします。このピンをSGNDに引き下げるとき、TG2が $180^\circ$ に、CLKOUTが $60^\circ$ にロックされます。このピンをINTV<sub>CC</sub>に接続すると、TG2が $240^\circ$ に、CLKOUTが $120^\circ$ にロックされます。このピンをフロート状態にすると、TG2が $180^\circ$ に、CLKOUTが $90^\circ$ にロックされます。

**MODE/PLLIN (ピン2)**: 動作モードの選択または外部クロックの同期入力。このピンをINTV<sub>CC</sub>に接続すると、強制連続モード動作が選択されます。このピンをSGNDに接続すると、不連続モード動作が可能になります。このピンに外部クロックを与えると、両方のチャネルが強制連続モードで動作し、外部クロックに同期します。

**CLKOUT (ピン3)**: 内部クロック発生器のクロック出力。出力レベルはINTV<sub>CC</sub>とSGNDの間を振幅します。MODE/PLLINピンにクロックが入力されると、入力クロックに同期し、PHASMDピンによって位相が設定されます。MODE/PLLINにクロックが入力されないと、周波数はRTピンによって設定されます。別のコントローラに同期させるため、そのコントローラのMODE/PLLINピンに接続することができます。

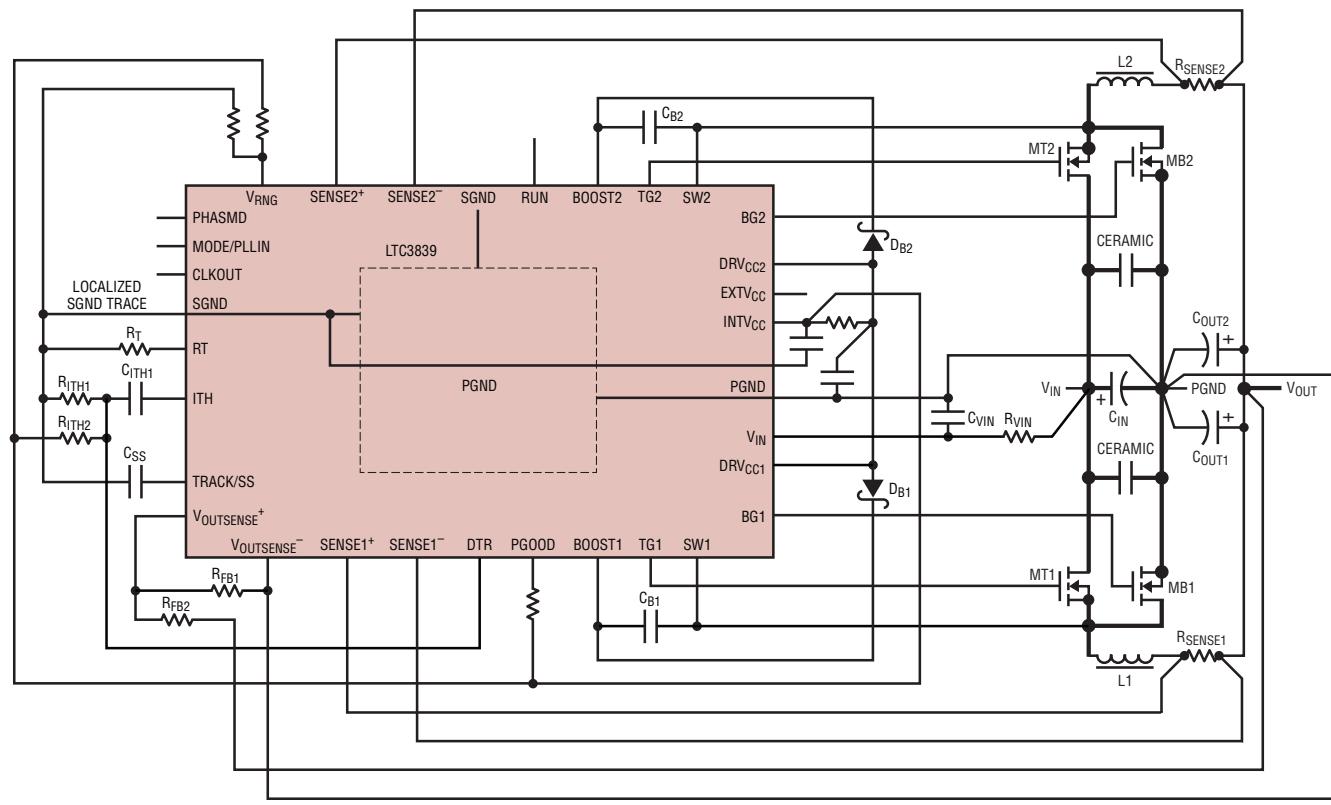

**SGND (ピン4、ピン29)**: 信号グランド。すべての小信号用アナログ部品および補償用部品は、このグランドに接続します。両方のSGNDピンは、1本のPCBトレースを使って露出パッドとPGNDに接続してください。

**RT (ピン5)**: クロック発生器の周波数設定ピン。RTからSGNDに外付け抵抗を接続して、スイッチング周波数を200kHz～2MHzに設定します。周波数に確実にロックするように、MODE/PLLINに与えられる外部クロックはこの設定周波数の±30%以内にします。RTピンがフロート状態の場合、周波数は200kHzよりわずかに低い値に内部設定されます。

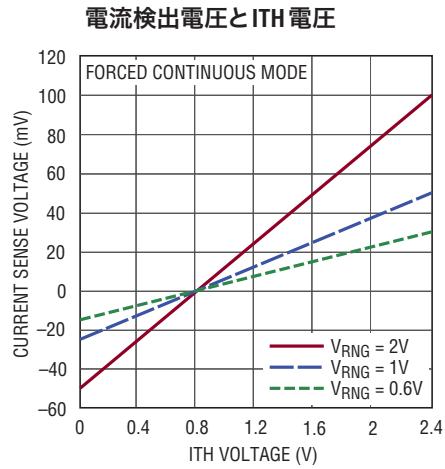

**ITH (ピン6)**: 電流制御しきい値。このピンは、エラーアンプの出力とスイッチング・レギュレータの補償点です。電流コンパレータのしきい値はこの制御電圧に応じて増加します。電圧範囲は0V～2.4Vで、0.8Vがゼロ検出電圧(インダクタ谷電流がゼロ)に相当します。

**TRACK/SS (ピン7)**: 外部トラッキングとソフトスタート入力。LTC3839は帰還電圧(V<sub>OUTSENSE</sub><sup>+</sup>-V<sub>OUTSENSE</sub><sup>-</sup>)を、0.6VとTRACK/SSピンの電圧の低い方に安定化します。温度に依存しない1μAの内部プルアップ電流源がTRACK/SSピンに接続されています。

続されています。このピンとグランドの間に接続したコンデンサにより、最終安定化出力電圧までのランプ時間が設定されます。あるいは、別の電源をこのピンに接続すると、出力が起動時に別の電源をトラッキングすることができます。

**V<sub>OUTSENSE</sub><sup>+</sup>(ピン8)**: 差動出力検出アンプの(+)入力。このピンは、V<sub>OUT</sub>の出力コンデンサの正端子と負端子の間の帰還抵抗分割器に接続します。公称動作時、LTC3839は差動出力電圧V<sub>OUT</sub>を帰還抵抗分割器の比で分圧した0.6Vに安定化しようとします。

**V<sub>OUTSENSE</sub><sup>-</sup>(ピン9)**: 差動出力検出アンプの(-)入力。このピンはV<sub>OUT</sub>の出力負荷コンデンサの負端子に接続します。

**SENSE1<sup>+</sup>、SENSE2<sup>+</sup>(ピン10、ピン31)**: 差動電流センス・コンパレータの(+)入力。ITHピンの電圧、および、SENSE<sup>+</sup>ピンとSENSE<sup>-</sup>ピンの間の制御されたオフセットによって、電流トリップしきい値が設定されます。コンパレータを使ってR<sub>SENSE</sub>による検出またはインダクタのDCRによる検出を行うことができます。R<sub>SENSE</sub>による検出では、SENSE<sup>+</sup>ピンをR<sub>SENSE</sub>の(+)端子にケルビン(4線)接続します。DCRによる検出では、SENSE<sup>+</sup>ピンをインダクタ両端に接続されたDCR検出コンデンサとセンス抵抗の接続点に接続します。

**SENSE1<sup>-</sup>、SENSE2<sup>-</sup>(ピン11、ピン30)**: 差動電流センス・コンパレータの(-)入力。コンパレータを使ってR<sub>SENSE</sub>による検出またはインダクタのDCRによる検出を行うことができます。R<sub>SENSE</sub>による検出では、SENSE<sup>-</sup>ピンをR<sub>SENSE</sub>の(-)端子にケルビン(4線)接続します。DCRによる検出では、SENSE<sup>-</sup>ピンをインダクタのV<sub>OUT</sub>ノード接続点に接続されたDCR検出コンデンサに接続します。これらのピンは、トップMOSFETのオン時間調整用の出力電圧検出ピンとしても機能します。それぞれのSENSE<sup>-</sup>ピンからSGNDに500kの内部抵抗が追加されているので、これらのピンから見たインピーダンスはSENSE<sup>+</sup>ピンから見たインピーダンスとは異なります。

**DTR (ピン12)**: オーバーシュートを低減するための負荷開放過渡検出ピン。負荷電流が急激に減少するときに、このDTRピンの電圧がINTV<sub>CC</sub>の半分を下回ると、ボトム・ゲート(BG)がオフすることにより、インダクタ電流が急速にゼロまで減少するので、V<sub>OUT</sub>のオーバーシュートが低減されます。(詳細については、「アプリケーション情報」のセクションの「負荷開放過渡の検出」を参照してください。)このピンは、5μAの内部電流源によってINTV<sub>CC</sub>にプルアップされています。DTR機能をディスエーブルするには、単にDTRピンをINTV<sub>CC</sub>に接続します。

## ピン機能

**PGOOD (ピン13)**: パワーグッド・インジケータの出力。このオープンドレインのロジック出力は、 $50\mu s$ のパワーバッドマスキング遅延の後、出力電圧がレギュレーション・ポイントを中心とした $\pm 7.5\%$ の範囲から外れると、グランドに引き下げられます。レギュレーション・ポイントに戻る際には、パワーグッドまでに $20\mu s$ の遅延があり、電圧範囲の両側に約2%のヒステリシスがあります。

**BOOST1、BOOST2 (ピン14、ピン27)**: トップ MOSFET ドライバのための昇圧されたフローティング電源。ブートストラップ・コンデンサ  $C_B$  の(+)端子をこのピンに接続します。BOOST ピンは  $V_{IN}$  により、ダイオードの電圧降下分だけ  $DRV_{CC}$  より低い電圧、つまり  $(DRV_{CC}-V_D)$  と  $(V_{IN}+DRV_{CC}-V_D)$  の間で振幅します。

**TG1、TG2 (ピン15、ピン26)**: トップ・ゲート・ドライバの出力。TG ピンは、トップ N チャネル・パワー MOSFET のゲートを SW と BOOST の間の  $V_{DRVCC}$  の電圧振幅でドライブします。

**SW1、SW2 (ピン16、ピン25)**: インダクタへのスイッチ・ノードの接続ピン。電圧振幅は、ダイオードの電圧降下分だけグランドより低い電圧から  $V_{IN}$  までです。ブートストラップ・コンデンサ  $C_B$  の(-)端子をこのノードに接続します。

**BG1、BG2 (ピン17、ピン24)**: ボトム・ゲート・ドライバの出力。BG ピンはボトム N チャネル・パワー MOSFET のゲートを PGND と  $DRV_{CC}$  の間でドライブします。

**DRV<sub>CC1</sub>、DRV<sub>CC2</sub> (ピン18、ピン23)**: ボトム・ゲート・ドライバの電源。 $DRV_{CC1}$  は、 $5.3V$  の内部レギュレータの出力でもあります。 $DRV_{CC2}$  は、 $EXTV_{CC}$  スイッチの出力でもあります。通常、2つの  $DRV_{CC}$  ピンは PCB 上で一緒に短絡し、最小  $4.7\mu F$  のセラミック・コンデンサ  $C_{DRVCC}$  で PGND にデカップリングします。

**$V_{IN}$  (ピン19)**: 入力電源。電源電圧範囲は  $4.5V \sim 38V$  が可能です。ノイズ耐性を改善するため、このピンを RC フィルタで SGND にデカップリングします。このピンの電圧はトップ・ゲートのオン時間の調整にも使用されるので、このピンを RC フィルタを介してメイン入力電源に接続することを推奨します。

**PGND (ピン20、露出パッド・ピン33)**: 電源グランド。このピンは、ボトム N チャネル MOSFET のソース、 $C_{DRVCC}$  の(-)端子、および  $C_{IN}$  の(-)端子へできるだけ近づけて接続します。露出

パッドと PGND ピンは、デバイスの下で 1 本の PCB トレースを使って SGND ピンに接続します。電気的接続と定格熱性能を実現するため、露出パッドは回路基板のグランドに半田付けする必要があります。

**INTV<sub>CC</sub> (ピン21)**: 内部回路の電源入力(ゲート・ドライバを除く)。通常、SGND へのデカップリング RC フィルタ(標準で  $2\Omega$  と  $1\mu F$ )を介して  $DRV_{CC}$  ピンから給電します。

**EXTV<sub>CC</sub> (ピン22)**: 外部電源入力。 $EXTV_{CC}$  が切り替え電圧(標準  $4.6V$ )を超えると、 $INTV_{CC}$  とゲート・ドライバが  $EXTV_{CC}$  から電力を供給されるように、内部スイッチがこのピンを  $DRV_{CC2}$  に接続し、内部レギュレータをシャットダウンします。 $V_{IN}$  ピンもパワーアップする必要がありますが、最小電流が流れます。

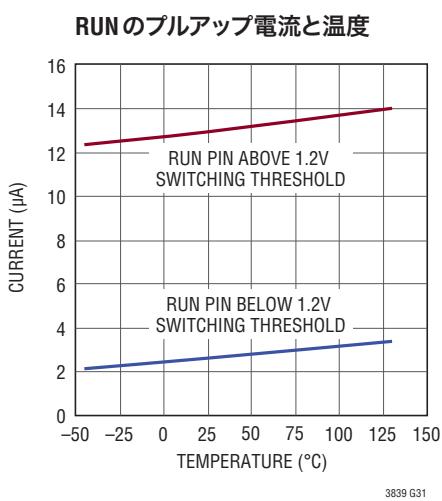

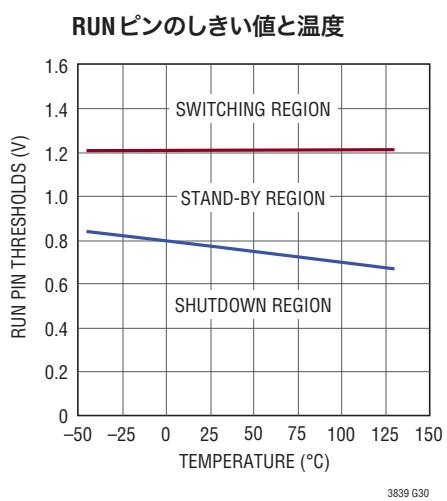

**RUN (ピン28)**: 実行制御入力。このピンには、内部絶対温度比例(PTAT) プルアップ電流源( $25^{\circ}C$  で約  $2.5\mu A$ )が常に接続されています。RUN ピンをしきい値電圧( $25^{\circ}C$  で約  $0.8V$ )よりも下げるとき、 $INTV_{CC}$  と  $DRV_{CC}$  の全てのバイアスがシャットダウンし、LTC3839 がマイクロパワー・シャットダウン・モードになります。RUN ピンをこのしきい値より上げると、内部のバイアス電源と回路がオンします。RUN ピンが  $1.2V$  を上回ると、両方のチャネルの TG ドライバと BG ドライバがオンし、温度に依存しない  $10\mu A$  の追加プルアップ電流源が RUN ピンに内部で接続されます。RUN ピンは、最大  $100\mu A$  をシンクするか、または  $6V$  以下に強制することができます。

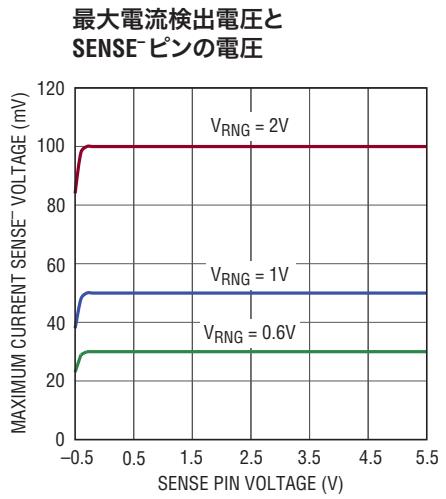

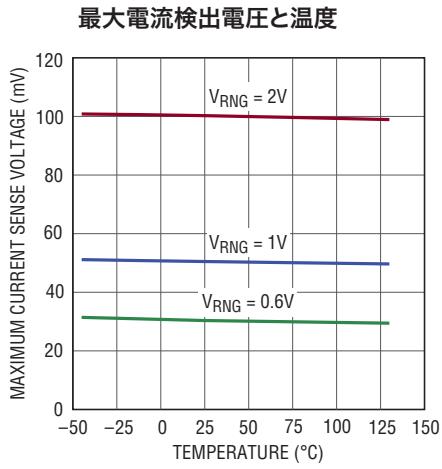

**$V_{RNG}$  (ピン32)**: 電流検出電圧範囲入力。 $0.6V \sim 2V$  の範囲に設定すると、 $V_{RNG}$  に印加された電圧は  $SENSE_1^+$ 、 $2^+$  と  $SENSE_1^-$ 、 $2^-$  の間の最大検出電圧の 20 倍( $20\times$ )、つまり、どちらのチャネルも  $(V_{SENSE}^+-V_{SENSE}^-) = 0.05 \cdot V_{RNG}$  になります。 $V_{RNG}$  を SGND に接続すると、そのチャネルは、 $0.6V$  の  $V_{RNG}$  に相当する  $30mV$  の最大検出電圧で動作し、 $INTV_{CC}$  に接続すると、 $1V$  の  $V_{RNG}$  に相当する  $50mV$  の最大検出電圧で動作します。

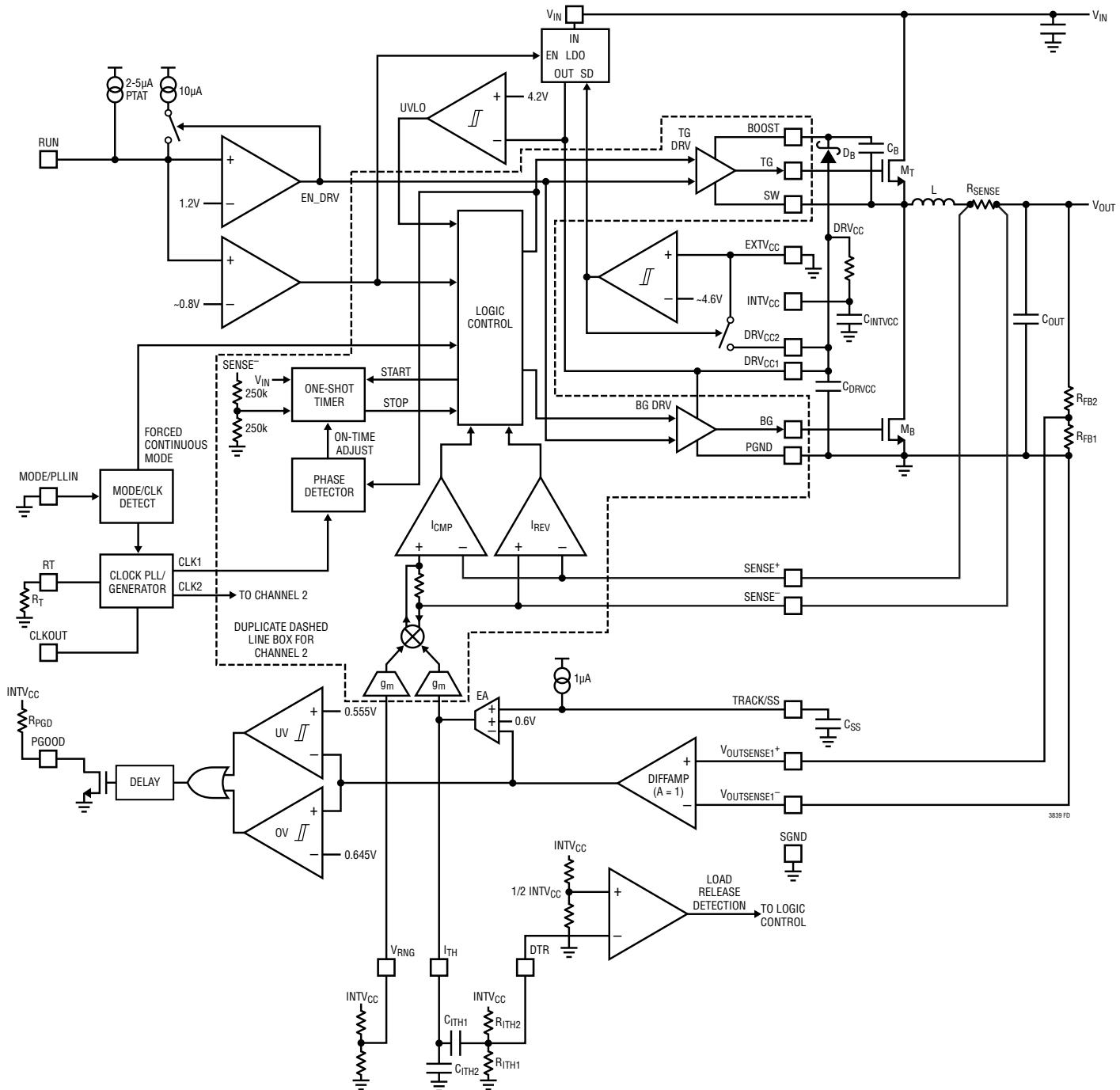

## 機能ブロック図

## 動作（「機能図」を参照）

### メイン制御ループ

LTC3839は、オン時間が制御される、シングル出力の谷電流モード降圧DC/DCコントローラで、2つのチャネルが位相をずらして動作します。各チャネルはメインNチャネルMOSFETと同期NチャネルMOSFETの両方をドライブします。

トップMOSFETは、ワンショット・タイマによって定まる時間オンします。ワンショット・タイマの時間は、固定スイッチング周波数を維持するように制御されます。トップMOSFETがオフすると、短い遅延後にボトムMOSFETがオンします。この遅延、つまりデッドタイムは、トップMOSFETとボトムMOSFETの両方が同時にオンすることによって $V_{IN}$ から電源グランドに直接シートスルー電流が流れるのを防止するためのものです。電流コンパレータ $I_{CMP}$ が、インダクタ電流がITHピンと $V_{RNG}$ ピンの電圧によって設定されたトリップ・レベルを下回ったことを検出すると、次のスイッチング・サイクルが開始されます。ボトムMOSFETが直ちにオフしてトップMOSFETが再度オンすることにより、ワンショット・タイマが再起動し、このサイクルが繰り返されます。シートスルー電流を防ぐため、トップMOSFETがオンする前の短いデッドタイム遅延も備えています。この時点で、インダクタ電流が「谷」に達して再度増加し始めます。

インダクタ電流は、インダクタと直列に接続された値の明確な抵抗を使用するか、またはインダクタの両端に接続されたRCフィルタを介してインダクタのDC抵抗(DCR)の電圧降下を間接的に検出することにより、SENSE<sup>+</sup>とSENSE<sup>-</sup>の間の電圧を検出して測定します。電流コンパレータのトリップ・レベル $I_{CMP}$ は、ITHピンの電圧に比例し、約0.8VのITH電圧に相当するゼロ電流しきい値を備えています。

エラーアンプ(EA)は、帰還信号を0.6Vの内部リファレンス電圧と比較することにより、このITH電圧を調整します。差動アンプ(DIFFAMP)は、差動帰還信号( $V_{OUTSENSE}^+ - V_{OUTSENSE}^-$ )をEAのシングルエンド入力に変換します。出力電圧は、帰還電圧が0.6Vの内部リファレンスと等しくなるよう安定化されます。負荷電流が増加/減少すると、リファレンスに比べて差動帰還電圧が一時的に低下/上昇します。するとEAは、出力電圧が安定化電圧に戻るように、ITH電圧、つまりインダクタの谷電流のセットポイントを、平均インダクタ電流が再度負荷電流と等しくなるまで高く/低くします。

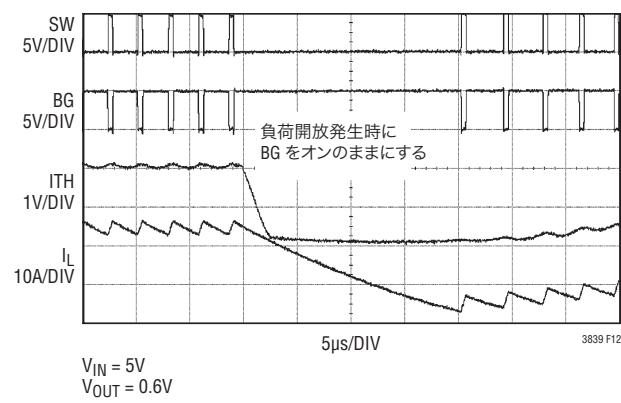

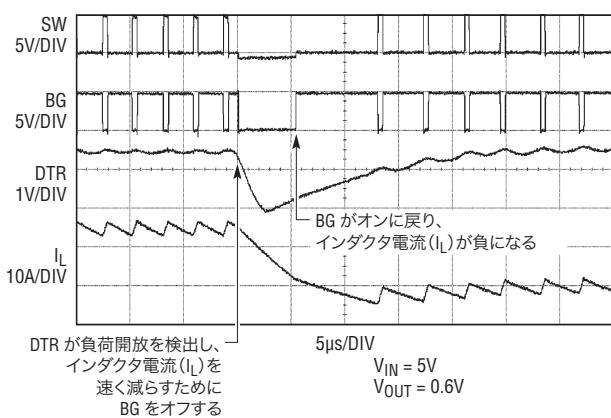

LTC3839は過渡検出(DTR)ピンを備えています。これは、ITH電圧の一次導関数をモニタすることによって「負荷開放」、つまり負荷電流が急に減少する過渡を検出します。検出すると、ボトム・ゲート(BG)がオフし、ボトムMOSFETのボディー・ダイオードにインダクタ電流が流れることにより、SWノードの電圧がボディー・ダイオードの順方向導通電圧分だけPGNDを下回ります。これにより、インダクタ両端に大きな負の電圧差( $V_{SW} - V_{OUT}$ )が生じることによってインダクタ電流が速くゼロまで減少できるので、 $V_{OUT}$ に生じるオーバーシュートが小さくなります。詳細については、「アプリケーション情報」の「負荷開放過渡の検出」を参照してください。

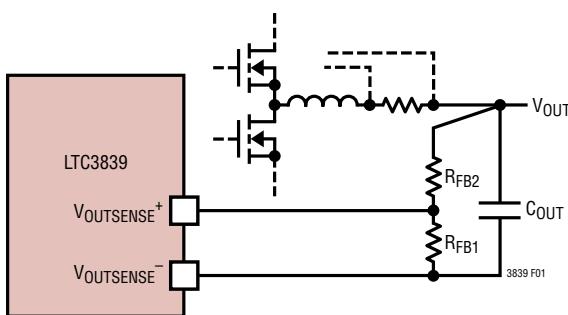

### 差動出力検出

LT3839は、差動出力電圧検出機能を備えています。出力電圧は外部で抵抗分割され、コントローラの帰還電圧が生成されます。内部の差動アンプ(DIFFAMP)が、出力のリモート・グランド・リファレンスに対するこの帰還電圧を検出し、差動帰還電圧を生成します。この手法により、ローカル・グランドとリモート出力グランドの間の全てのグランド・オフセットが除去される結果、より高精度の出力電圧が得られます。これにより、リモート出力グランドが、ローカル・グランド(SGND)に対して最大±500mV変位可能です。

### DRV<sub>CC</sub>/EXTV<sub>CC</sub>/INTV<sub>CC</sub>電源

DRV<sub>CC1</sub>とDRV<sub>CC2</sub>はボトムMOSFETドライバの電源です。通常、2つのDRV<sub>CC</sub>ピンはPCB上で一緒に短絡し、最小4.7μFのセラミック・コンデンサ $C_{DRVCC}$ でPGNDにデカッピングします。トップMOSFETドライバはフローティング・ブーストストラップ・コンデンサ( $C_{B1}, C_{B2}$ )からバイアスされます。このコンデンサは、各サイクル中にトップMOSFETがオフしていてSWピンがスイングダウンしているとき、外付けのショットキ・ダイオードを通して再充電されます。

DRV<sub>CC</sub>には2つの手段で給電することができます。1つは、 $V_{IN}$ から給電され、DRV<sub>CC1</sub>に5.3Vを出力可能な内部の低損失(LDO)リニア電圧レギュレータです。もう1つは、EXTV<sub>CC</sub>ピンをDRV<sub>CC2</sub>に短絡可能な内部のEXTV<sub>CC</sub>スイッチ(オン抵抗が約2Ω)です。

EXTV<sub>CC</sub>ピンがEXTV<sub>CC</sub>の切り替え電圧(標準で4.6Vであり、200mVのヒステリシスをもつ、「電気的特性」の表を参照)を

## 動作（「機能図」を参照）

下回ると、5.3Vの内部LDOがイネーブルされます。EXTV<sub>CC</sub>ピンがこのEXTV<sub>CC</sub>の切り替え電圧より高い外部電圧源に接続されると、LDOがシャットダウンして内部のEXTV<sub>CC</sub>スイッチがEXTV<sub>CC</sub>ピンをDRV<sub>CC2</sub>ピンに短絡します。これにより、DRV<sub>CC</sub>とINTV<sub>CC</sub>が外部電圧源から給電されるので、全体的な効率が向上し、LDO内部の電力損失による内部自己発熱が減少します。降圧コンバータの出力が切り替え電圧の上限の4.8Vより高い電圧に設定されている場合、その出力をこの外部電源とすることができます。V<sub>IN</sub>ピンもパワーアップする必要がありますが、このときに最小電流が流れます。

ゲート・ドライバを除くほとんどの内部制御回路の電力はINTV<sub>CC</sub>ピンから供給されます。INTV<sub>CC</sub>には、結合されたDRV<sub>CC</sub>ピンから（直接、またはスイッチングによるノイズを除去するためにSGNDに接続された外付けRCフィルタを介して）給電できます。

### シャットダウンと起動

RUNピンには、絶対温度比例（PTAT）プルアップ電流源（25°Cで約2.5μA）が内蔵されています。RUNピンを特定のしきい値電圧（25°Cで約0.8V）より下げると、INTV<sub>CC</sub>とDRV<sub>CC</sub>の全てのバイアスがシャットダウンし、LTC3839が、V<sub>IN</sub>ピンのI<sub>Q</sub>が最小のマイクロパワー・シャットダウン・モードになります。LTC3839の（5.3Vの内部LDOレギュレータまたはEXTV<sub>CC</sub>を介した）DRV<sub>CC</sub>と、INTV<sub>CC</sub>から給電される対応するチャネルの内部回路は、RUNピンのいずれかまたは両方が、内部プルアップ電流によるか、またはロジック・ゲート出力などの外部電圧源によって直接ドライブされることにより、0.8Vのしきい値より上にプルアップされると、バイアス・アップされます。

2つのチャネルのどちらも、RUNピンが1.2Vにプルアップされるまでスイッチングを開始しません。RUNピンが1.2Vを上回ると、両方のチャネルのTGドライバとBGドライバがイネーブルされ、TRACK/SSが解放されます。10μAの温度に依存しない追加プルアップ電流源がRUNピンに内部で接続されます。TG、BG、および10μAの追加プルアップ電流源をオフするには、RUNピンを約100mVで1.2V以下にプルダウンする必要があります。これらの組み込まれた電流ヒステリシスと電圧ヒステリシスにより、ジッタによるターンオンやノイズによるターンオフの誤動作を防止します。RUNピンのこれらの機能により、V<sub>IN</sub>からの外付け分圧器を使って入力低電圧ロックアウト（UVLO）を設定できます。

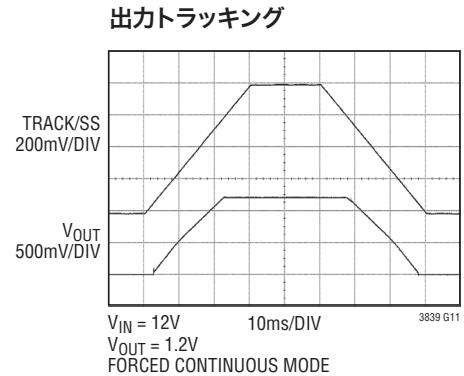

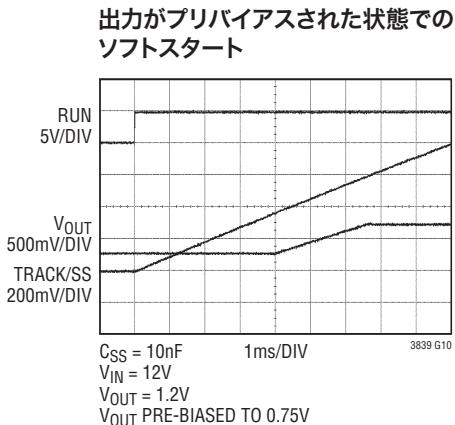

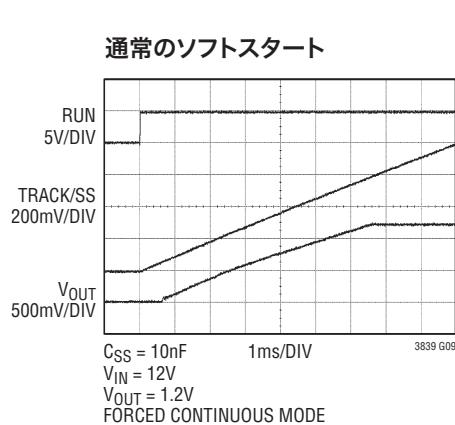

出力電圧（V<sub>OUT</sub>）の立ち上がりはTRACK/SSピンの電圧によって制御されます。TRACK/SSピンの電圧が0.6Vの内部リファレンスより低いと、差動帰還電圧は0.6VのリファレンスではなくTRACK/SS電圧に制御されます。外付けコンデンサをTRACK/SSピンから信号グランドに接続することにより、TRACK/SSピンを使って出力電圧のソフトスタートのランプアップ時間を設定することができます。温度に依存しない1μAの内部プルアップ電流源がこのコンデンサを充電して、TRACK/SSピンに電圧ランプを発生します。TRACK/SS電圧がグランドから0.6Vにリニアに上昇すると、スイッチングが開始され、V<sub>OUT</sub>がその最終値までスムーズにランプアップし、帰還電圧が0.6Vになります。TRACK/SSは、約3.7Vにクランプされるまで、0.6Vを超えて上昇し続けます。

あるいは、TRACK/SSピンを使って、マスタ・スレーブ構成のように外部電源をトラッキングすることもできます。通常、これを行うには、マスタ電源からTRACK/SSピンに抵抗分割器を接続する必要があります（「アプリケーション情報」のセクションを参照）。

RUNピンが1.2Vのしきい値（ヒステリシスあり）より低い電圧に引き下げられるか、あるいはINTV<sub>CC</sub>またはDRV<sub>CC</sub>が低電圧ロックアウト（UVLO）しきい値を下回ると、TRACK/SSが内部で“L”に引き下げられます。

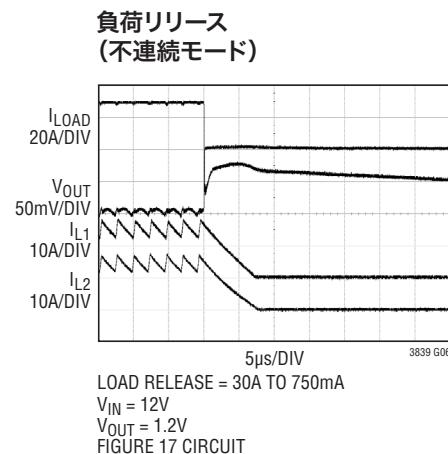

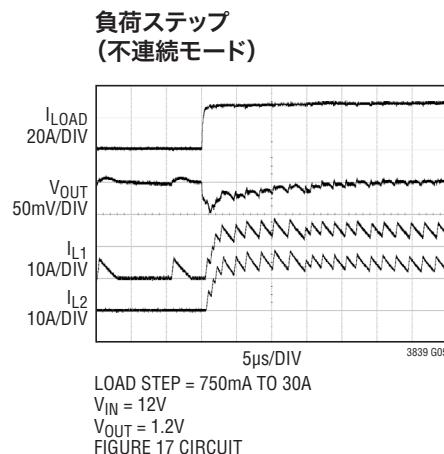

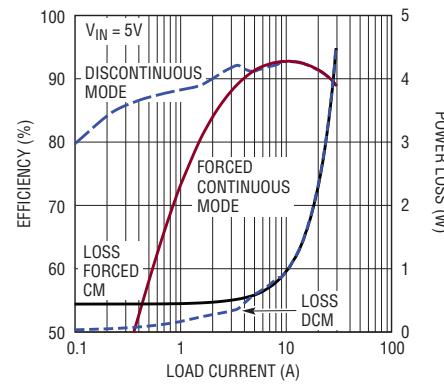

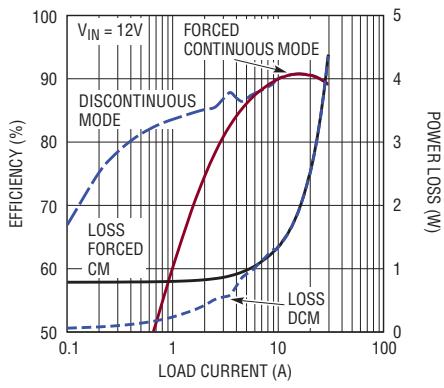

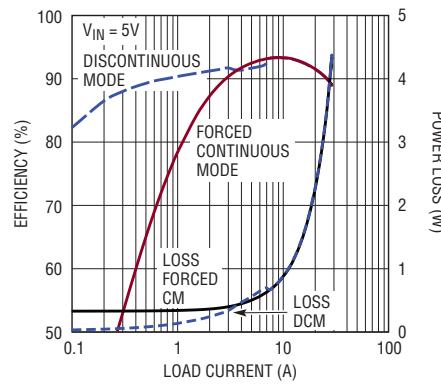

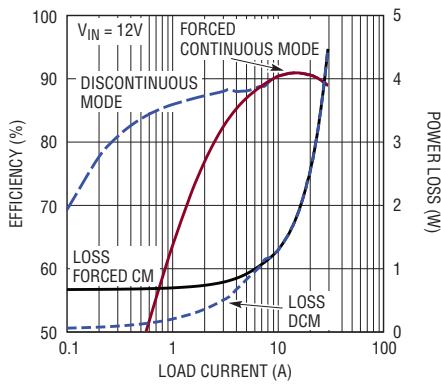

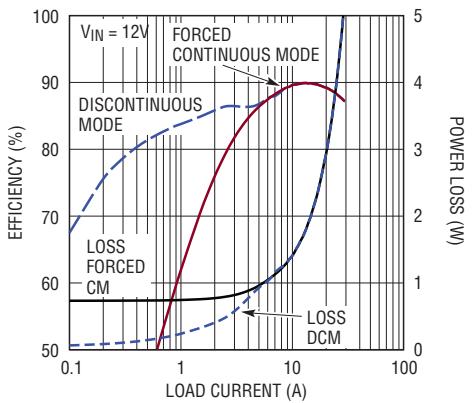

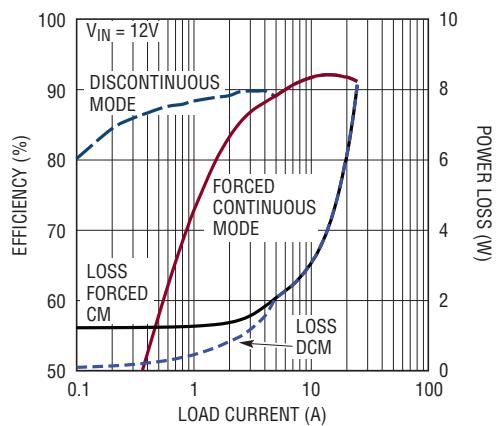

### 軽負荷電流動作

MODE/PLLINピンがINTV<sub>CC</sub>に接続されるか、またはMODE/PLLINに外部クロックが与えられると、LTC3839は連続モードで動作するように強制されます。負荷電流が最大負荷でのピーク・トゥ・ピーク・リップルの半分より小さいときは、インダクタ電流の谷がゼロまで減少するかまたは負になる可能性があります。これによって固定周波数動作が可能になりますが、軽負荷時の効率が低下します。

MODE/PLLINピンを開放のままにするか、または信号グランドに接続すると、チャネルが不連続モード動作に移行します。この場合、インダクタ電流がゼロに近づくと、電流反転コンペレータ（I<sub>REV</sub>）がボトムMOSFET（M<sub>B</sub>）をオフするので、負のインダクタ電流を防止して軽負荷の効率を改善します。このモードでは、両方のスイッチを長期にわたってオフにしておくことができます。出力コンデンサが負荷電流によって放電して出力電圧が低下すると、最終的にEAがITH電圧をゼロ電流レベル（0.8V）より高くして、新しいスイッチング・サイクルを開始します。

## 動作（「機能図」を参照）

### パワーグッドとフォルト保護

PGOODピンは内部のオープンドレインN-チャネルMOSFETに接続されています。このピンは、外付け抵抗または電流源を使って最大6V（たとえば、V<sub>OUT</sub>またはDRV<sub>CC</sub>）まで引き上げることができます。帰還電圧が0.6Vのリファレンス電圧から±7.5%の範囲を外れると、過電圧コンパレータ(OV)または低電圧コンパレータ(UV)がMOSFETをオンしてPGOODピンを“L”に引き下げます。RUNピンが1.2Vのしきい値(ヒステリシスあり)より低いか、または低電圧ロックアウト(UVLO)状態のときも、PGOODピンは“L”に引き下げられます。帰還電圧はV<sub>OUTSENSE</sub><sup>-</sup>に対するV<sub>OUTSENSE</sub><sup>+</sup>によって差動で検出されることに注意してください。

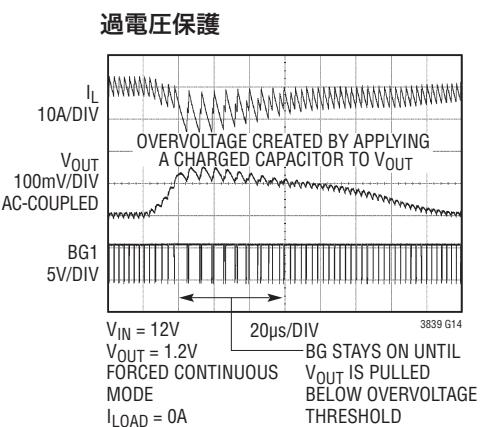

帰還電圧が±7.5%の範囲内に入ると、オープンドレインNMOSがオフし、PGOODピンが外部電源によってプルアップされます。帰還電圧がその範囲内に入った後、PGOODピンは直ちにパワーグッドを示します。ただし、チャネルの帰還電圧がその範囲から外れるときは、PGOODが“L”に引き下げられる前に50μsの内部遅延が生じます。過電圧(OV)状態では、M<sub>T</sub>はオフし、M<sub>B</sub>は遅延なしに直ちにオンして、過電圧状態が解消されるまでオンに保たれます。

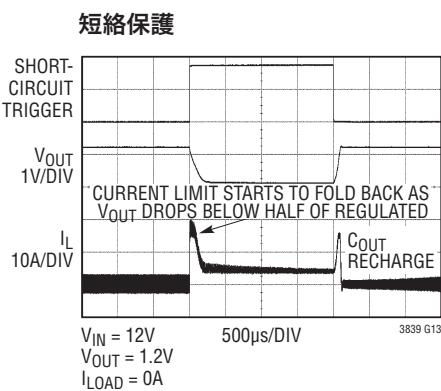

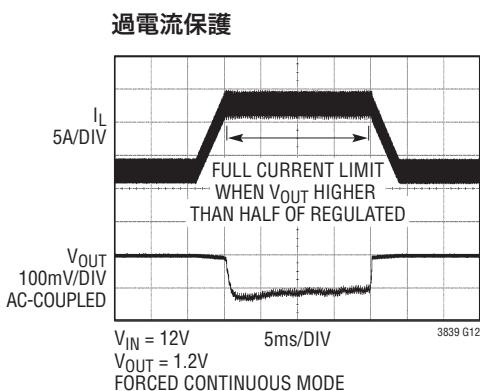

出力がグランドに短絡されるなどで安定化電圧の半分を下回ると、フォールドバック電流制限が行われます。帰還電圧が0Vに近づくと、ITHピンの内部クランプ電圧が2.4Vから約1.3Vに低下することにより、インダクタの谷電流レベルが最大値の約30%に減少します。フォールドバック電流制限は起動時にディスエーブルされます。

### 周波数の選択と外部クロックへの同期

内部発振器(クロック発生器)は、各チャネルをロックアップするために位相がインターリープされた内部クロック信号を供給します。各スイッチング・チャネルのスイッチング周波数と位相は、ワンショット・タイマを使ってトップMOSFETのターンオン時間(オン時間)を調整することにより、個別に制御されます。これは、位相検出器により、トップMOSFETのターンオン信号と内部リファレンス・クロックとの位相関係を検出することによって行われます。また、ワンショット・タイマの時間間隔は、トップMOSFETのターンオンの立ち上がりエッジが常に各チャネルの内部リファレンス・クロック信号に同期するように、サイクルごとに調整されます。

内部発振器の周波数は、RTピンから信号グランド(SGND)に抵抗R<sub>T</sub>を接続することにより、200kHz～2MHzに設定することができます。RTピンは内部で1.2Vに安定化されています。

周波数や干渉に対する要件が厳しいアプリケーションでは、MODE/PLLINピンに接続された外部クロック・ソースを使って、クロックのフェーズロック・ループ(クロックPLL)による内部クロック信号の同期を行うことができます。LTC3839は、外部クロックに同期するときは強制連続モードで動作します。正しく同期させるため、外部クロック周波数は内部発振器周波数の±30%以内にする必要があります。クロックの入力レベルは、“H”では2V以上、“L”では0.5V以下にします。MODE/PLLINピンには600kのプルダウン抵抗が内蔵されています。

## 動作（「機能図」を参照）

### マルチチップ動作

表1に示すように、PHASMDピンにより、2つのチャネルとCLKOUT信号の内部リファレンス・クロック信号間の位相関係が決まります。表に示された位相は、チャネル1の内部リファレンス・クロック信号の立ち上がりエッジとして定義されているゼロ度(0°)を基準にしています。CLKOUT信号を使用することにより、単一の高電流出力または個別の出力に電力を供給しているマルチフェーズ電源ソリューションの追加電力段を同期させることができます。

マルチチップ・ソリューションを使って、最大12フェーズ動作のシステムを構成することができます。チャネルの位相をインターリーブする標準構成を表2に示します。

**表1**

| PHASMD | SGND | フロート | INTV <sub>CC</sub> |

|--------|------|------|--------------------|

| チャネル1  | 0°   | 0°   | 0°                 |

| チャネル2  | 180° | 180° | 240°               |

| CLKOUT | 60°  | 90°  | 120°               |

**表2**

| フェーズ数 | LTC3839の数           | ピンの接続<br>[ピン名称(デバイスの番号)]                                                                                                                                                                                                                               |

|-------|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2     | 1                   | PHASMD(1)=フロートまたはSGND                                                                                                                                                                                                                                  |

| 3     | 2、または<br>1+ LTC3833 | PHASMD(1)=INTV <sub>CC</sub><br>MODE/PLLIN(2)=CLKOUT(1)                                                                                                                                                                                                |

| 4     | 2                   | PHASMD(1)=フロート<br>PHASMD(2)=フロートまたはSGND<br>MODE/PLLIN(2)=CLKOUT(1)                                                                                                                                                                                     |

| 6     | 3                   | PHASMD(1)=SGND<br>PHASMD(2)=SGND<br>MODE/PLLIN(2)=CLKOUT(1)<br>PHASMD(3)=フロートまたはSGND<br>MODE/PLLIN(3)=CLKOUT(2)                                                                                                                                        |

| 12    | 6                   | PHASMD(1)=SGND<br>PHASMD(2)=SGND<br>MODE/PLLIN(2)=CLKOUT(1)<br>PHASMD(3)=フロート<br>MODE/PLLIN(3)=CLKOUT(2)<br>PHASMD(4)=SGND<br>MODE/PLLIN(4)=CLKOUT(3)<br>PHASMD(5)=SGND<br>MODE/PLLIN(5)=CLKOUT(4)<br>PHASMD(6)=フロートまたはSGND<br>MODE/PLLIN(6)=CLKOUT(5) |

LTC3839またはLTC3833デバイスを追加して、3フェーズ以上のシングル出力コンバータを構成できます。

- ITHピンを最初のデバイスのITHピンに接続します。

- RUNピンを最初のデバイスのRUNピンに接続します。

- V<sub>OUTSENSE</sub><sup>+</sup>ピンを最初のデバイスのV<sub>OUTSENSE</sub><sup>+</sup>ピンに接続します。

- V<sub>OUTSENSE</sub><sup>-</sup>ピンを最初のデバイスのV<sub>OUTSENSE</sub><sup>-</sup>ピンに接続します。

- TRACK/SSピンを最初のデバイスのTRACK/SSピンに接続します。

## アプリケーション情報

必要な出力電圧と動作周波数が決定したら、負荷要件に従つて外付け部品の選択を行い、インダクタと電流検出手法（センス抵抗RSENSEによる検出、またはインダクタのDCRによる検出）の選択から始めます。次に、パワーMOSFETを選択します。最後に、入力と出力のコンデンサを選択します。

### 出力電圧の設定

図1に示すように、安定化出力からそのグランド・リファレンスに接続された外付け抵抗分割器を使用して出力電圧を設定します。抵抗分割器のタップが $V_{OUTSENSE}^+$ ピンに接続され、 $V_{OUTSENSE}^-$ ピンによってグランド・リファレンスがリモートセンスされます。差動帰還電圧を0.6Vの内部リファレンスに安定化することにより、次の出力電圧が得られます。

$$V_{OUT} - V_{OUTSENSE}^- = 0.6V \cdot (1 + R_{FB2}/R_{FB1})$$

たとえば、 $V_{OUT}$ が5Vに設定され、SGNDに対する出力のグランド・リファレンスが-0.5Vであると、SGNDに対する出力の絶対値は4.5Vになります。差動出力電圧の最小値は0.6Vの内部リファレンスに制限され、最大値は5.5Vに制限されます。

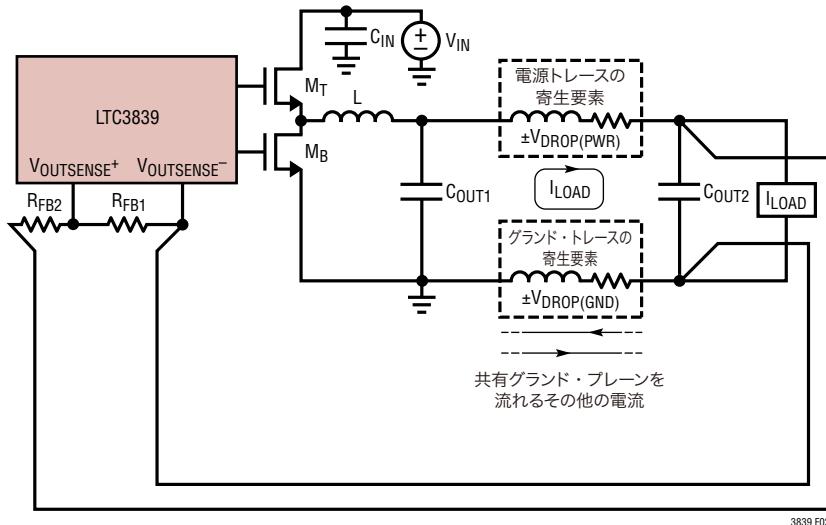

図1. 出力電圧の設定

$V_{OUTSENSE}^+$ ピンは高インピーダンスのピンであり、nA台の漏れ電流以外の入力バイアス電流は流れません。 $V_{OUTSENSE}^-$ ピンからは約30μAの電流が流れ出します。

差動出力検出により、ライン損失が大きな高電力分配システムでも、より高精度の出力レギュレーションが可能になります。寄生要素による電力ラインとグランド・ラインの電位変動を図2に示します。これらの変動は、グランド・プレーンを共有するマルチアプリケーション・システムではさらに大きくなる可能性があります。差動出力検出を行わないと、これらの変動は安定化出力電圧の誤差として直接反映されます。LTC3839の差動出力検出は、出力の電力ラインとグランド・ラインの最大±500mVの変動を補正することができます。

LTC3839の差動出力検出手法は従来の手法とは異なります。従来の手法では差動アンプによって安定化出力とそのグランド・リファレンスが直接検出され、この差動アンプの出力が外付け抵抗分割器によって分圧されてエラーアンプの入力に供給されます。この従来の手法は、差動アンプの同相入力範囲による制約を受け、通常、出力電圧の低い範囲に差動検出が制限されます。

LTC3839では、抵抗分割器で分圧された帰還電圧を差動で検出することによって、シームレスな差動出力検出が可能です。これにより、0.6V～5.5Vの全出力範囲での差動検出が可能になります。差動アンプ(DIFFAMP)は帯域幅が8MHzと十分に大きいので、メイン・ループ補償と過渡動作に影響を与えることはありません。

帰還電圧へのノイズ結合を防ぐため、抵抗分割器は $V_{OUTSENSE}^+$ ピンと $V_{OUTSENSE}^-$ ピンの近くに配置します。リモート出力のトレースとグランド・トレースは、リモート出力への差動ペアとして一緒に配線します。最高の精度を引き出すため、リモート出力とグランドへのこれらのトレースは、望みのレギュレーション・ポイントの出来るだけ近くに接続します。

### スイッチング周波数の設定

動作周波数の選択は、効率と部品サイズのトレードオフになります。動作周波数を低くすると、MOSFETのスイッチング損失が減少して効率が上がりますが、出力リップル電圧を低く抑えるために大きなインダクタンスや容量を必要とします。逆に、動

## アプリケーション情報

図2. 共有グランド・プレーンを使った高電力分配システムでの

ライン損失による電圧変動の補正に使用する差動出力検出

作周波数を高くすると効率が低下しますが、部品サイズは小さくなります。

LTC3839のスイッチング周波数は、RTピンから信号グランドに抵抗を接続することにより、200kHz～2MHzに設定することができます。この抵抗の値は次式に従って選択することができます。

$$R_T [k\Omega] = \frac{41550}{f [kHz]} - 2.2$$

クロックPLLとスイッチング・チャネルを含む全てのコントローラ・システムの同期範囲は、この設定周波数から±30%の範囲になります。したがって、外部クロック同期を行う場合は、外部クロック周波数がこのRTで設定する周波数から±30%の範囲内に入るようにする必要があります。同期マージンを最大にするには、RTで設定する周波数を外部クロックと等しくすることを推奨します。詳細については「位相と周波数の同期」のセクションを参照してください。

#### インダクタ値の計算

動作周波数が高いほど小さな値のインダクタとコンデンサを使用できるという意味で、動作周波数とインダクタの選択には相関関係があります。MOSFETのゲート電荷損失のために、

一般に周波数が高いほど効率が低下します。この基本的なトレードオフに加えて、リップル電流と低電流動作に対するインダクタ値の影響も考慮しなければなりません。

インダクタの値はリップル電流に直接影響を与えます。インダクタ・リップル電流 $\Delta I_L$ は、次式に示すように、インダクタンスまたは周波数が高いほど減少し、 $V_{IN}$ が高いほど増加します。

$$\Delta I_L = \left( \frac{V_{OUT}}{f \cdot L} \right) \left( 1 - \frac{V_{OUT}}{V_{IN}} \right)$$

大きな値の $\Delta I_L$ を許容できれば、低いインダクタンスを使用できますが、出力電圧リップル、出力コンデンサのESR損失、およびコア損失が大きくなります。リップル電流を設定するための妥当な出発点は、 $\Delta I_L = 0.4 \cdot I_{MAX}$ です。 $\Delta I_L$ が最大になるのは、入力電圧が最大のときです。リップル電流が規定された最大値を超えないことを保証するには、次式に従ってインダクタンスを選択します。

$$L = \left( \frac{V_{OUT}}{f \cdot \Delta I_{L(MAX)}} \right) \left( 1 - \frac{V_{OUT}}{V_{IN(MAX)}} \right)$$

## アプリケーション情報

### インダクタのコアの選択

Lの値が分かったら、インダクタの種類を選択する必要があります。基本的に鉄粉とフェライトの2種類があります。鉄粉のインダクタは飽和曲線が滑らかです。つまりフェライトのようにハードに飽和しません。ただし、鉄粉のインダクタはコア損失が大きくなります。フェライトを使った設計ではコア損失が非常に小さく、高いスイッチング周波数に適しているため、設計目標を銅損と飽和を防ぐことに集中することができます。

インダクタ値が同じ場合、コア損失はコア・サイズではなく、選択したインダクタンスに大きく依存します。インダクタンスが大きくなるとコア損失が減少します。インダクタンスを大きくするにはワイヤの巻数を増やす必要があるため、残念ながら銅損失が増加します。

フェライト・コアの材質はハードに飽和します。つまり、設計電流のピーク値を超えるとインダクタンスが急激に低下します。その結果、インダクタのリップル電流が急増し、出力電圧リップルが増加します。コアは絶対に飽和させないでください。

高電流、低電圧アプリケーション用に設計された様々なインダクタが、スミダ電機、パナソニック、Coiltronics、Coilcraft、東光、Vishay、Pulse、Würthなどのメーカーから入手できます。

### 電流センス・ピン

インダクタ電流は、内部電流コンパレータの入力であるSENSE<sup>+</sup>ピンとSENSE<sup>-</sup>ピンの電圧を介して検出されます。SENSEピンの入力電圧範囲は-0.5V～5.5Vです。通常動作時にこれらのピンをフロート状態にしないよう注意してください。SENSE<sup>+</sup>ピンは擬似高インピーダンス入力です。SENSE<sup>+</sup>ピンに対応するチャネルのSENSE<sup>-</sup>ピンが1.1Vより低い電圧からランプアップして1.4Vより低い電圧に保たれるときは、SENSE<sup>+</sup>ピンにバイアス電流は流れません。ただし、対応するSENSE<sup>-</sup>ピンが1.4Vからランプダウンして1.1Vより高い電圧に保たれるときは、SENSE<sup>+</sup>ピンに小さな(約1μA)が流れ込みます。このような電流はSENSE<sup>-</sup>ピンにも流れます。ただし、各SENSE<sup>-</sup>ピンにはSGNDへの500k抵抗が内蔵されています。その結果、電流(V<sub>OUT</sub>/500k)により、SENSE<sup>-</sup>ピンに流れ込む総電流が左右されます。R<sub>SENSE</sub>またはDCRによるインダクタ電流検出を設計する際には、SENSE<sup>+</sup>ピンとSENSE<sup>-</sup>ピンの電流を考慮する必要があります。

### 電流制限の設定

ITHがその2.4Vの最大値にクランプされている場合、電流検出コンパレータのSENSE<sup>+</sup>とSENSE<sup>-</sup>の間の最大トリップ電圧(つまり、「検出電圧」)は、VRNGピンに印加される電圧によって設定され、次式で与えられます。

$$V_{SENSE(MAX)} = 0.05V_{RNG}$$

谷電流モード制御のループでは、インダクタ電流の谷が0.05VRNGを超えないようにします。電流制限時にはITHが2.4Vに近づくことに注意してください。

INTVCCからの外付け抵抗分割器を使って、VRNGピンの電圧を0.6V～2Vに設定できるので、30mV～100mVの最大検出電圧が得られます。このように電圧範囲が広いので、様々なアプリケーションが可能です。VRNGピンをSGNDまたはINTVCCに接続して内部デフォルトを強制することもできます。VRNGをSGNDに接続すると、デバイスのVRNGが0.6Vに等しくなります。VRNGをINTVCCに接続すると、デバイスのVRNGが2Vに等しくなります。

デバイスと外付け部品の許容誤差を考慮するために、十分なマージンを許容する必要があります。「電気的特性」(EC)の表に最大谷電流センスしきい値V<sub>SENSE (MAX)</sub>1,2が示されていますが、これは、LTC3839の2つのチャネルの全動作接合部温度範囲で保証された規格値です。アプリケーションを設計する際には、必ずECの表の最大値を使用し、1つのチャネルの最大可能電流が、ワーストケースのフォルト状態でパワーMOSFETやインダクタなどの外付け部品の定格を超えないようにします。

マルチフェーズのシングル出力アプリケーションが望みの最大負荷電流を供給できるようにするために、アプリケーションの最小出力電流能力をV<sub>SENSE (MAX)</sub>の下限から決定できます。LTC3839では、ワーストケースの許容誤差または統計的許容誤差を使ってこれを行なうことができます。ワーストケースの許容誤差は最も控えめで、ECの表の1つのチャネルのV<sub>SENSE (MAX)</sub>の最小値にフェーズ数(たとえば、2フェーズ・アプリケーションでは2)を掛けることによって計算されます。統計的許容誤差では、両方の電流制限チャネルの分布を考慮に入れて、複数チャネルのV<sub>SENSE (MAX)</sub>の合計の実質的な統計的制限値を予測します。LTC3839の特性から得られる2チャネルの合計[V<sub>SENSE (MAX)</sub>1 + V<sub>SENSE (MAX)</sub>2]の全温度範囲の分布に

## アプリケーション情報

基づき、2フェーズ・アプリケーションの統計的許容デザインに対する(2チャネルの合計の半分として算出された各チャネルの)  $V_{SENSE(MAX)}$  の下限の推奨値は以下のようになります。

- $V_{RNG} = 0.6V$  または SGND で 24mV(標準 30mV)

- $V_{RNG} = 1V$  または INTV<sub>CC</sub> で 42mV(標準 50mV)

- $V_{RNG} = 2V$  で 85mV(標準 100mV)

ワーストケースの制限値も統計的制限値も、LTC3839 の電流制限の絶対最小値が得られるように選択することができます。リニアテクノロジーは、チャネルごとにワーストケースの最小値と最大値を保証していますが、2つのチャネル間の統計的分布または関係は保証していません。

### R<sub>SENSE</sub>によるインダクタ電流検出

LTC3839 は、値が小さい直列電流センス抵抗( $R_{SENSE}$ )またはインダクタのDC抵抗(DCR)を使ってインダクタ電流を検出するように構成設定できます。2つの電流検出手法の間の選択は、主としてコスト、消費電力および精度の間の設計上のトレードオフです。DCRによる検出は高価な電流センス抵抗を省くことができ、特に高電流アプリケーションで電力効率が高いので普及してきています。ただし、電流センス抵抗によってコントローラの最も高精度な電流制限が得られます。

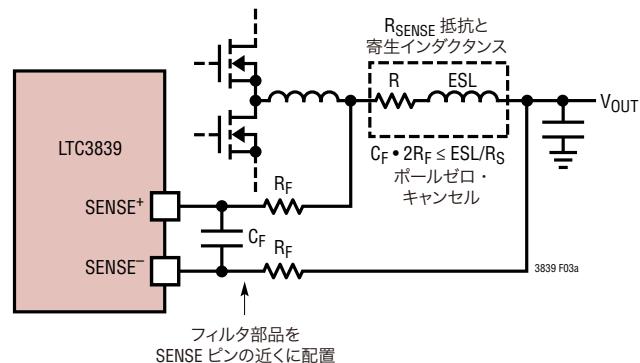

標準的な  $R_{SENSE}$  によるインダクタ電流検出回路を図3aに示します。フィルタ部品( $R_F$ ,  $C_F$ )はデバイスの近くに配置する必要があります。図3bに示すように、正と負の検出トレースは差動ペアとして互いに近づけて配線し、センス抵抗の下でケルビン(4線)接続する必要があります。他の場所で電流を検出すると、寄生インダクタンスが電流センス素子に実質的に追加され、検出端子の情報が劣化して、設定された電流制限を予測不能にすることがあります。

$R_{SENSE}$  は必要な最大出力電流に基づいて選択します。最大電流  $I_{OUT(MAX)}$ 、 $V_{RNG}$  によって設定される最大検出電圧  $V_{SENSE(MAX)}$ 、および最大インダクタ・リップル電流  $\Delta I_L(MAX)$  が与えられると、 $R_{SENSE}$  の値は次式で選択できます。

$$R_{SENSE} = \frac{V_{SENSE(MAX)}}{I_{OUT(MAX)} - \frac{\Delta I_L(MAX)}{2}}$$

図3a.  $R_{SENSE}$  による電流センス

図3b. センス抵抗を使用した検出ラインの配置

逆に、 $R_{SENSE}$  と  $I_{OUT(MAX)}$  が分かれれば、上の式から  $V_{SENSE(MAX)}$  が得られ、従って  $V_{RNG}$  も得られます。最大出力電流を保証するため、様々な動作条件と外付け部品の許容誤差の下での LTC3839 のばらつきを考慮して、十分なマージンを計算に組み込む必要があります。

電流検出ループに PCB ノイズが存在する可能性があるので、 $\Delta V_{SENSE} = \Delta I_L \cdot R_{SENSE}$  の電流検出電圧リップルも設計でチェックして、SN 比を良くする必要があります。一般に、PCB レイアウトに問題がない場合、 $R_{SENSE}$  またはインダクタ DCR のどちらの検出方式のアプリケーションにも、出発点の控えめな値として 10mV の  $\Delta V_{SENSE}$  を推奨します。

現在の高電流密度のソリューションでは、センス抵抗の値は 1mΩ に満たないことがあります。ピーク検出電圧がわずか 20mV になることがあります。さらに、最大 2MHz の動作でインダクタのリップル電流が 50% を超えることも普通になってきています。これらの条件では、センス抵抗の寄生インダクタンス両端の電圧降下がより重要になってきます。PCB の検出トレースに

## アプリケーション情報

結合した容量性および誘導性のノイズの影響を低減するために、デバイスの近くに配置した小さなRCフィルタが従来から使用されてきました。標準的なフィルタは並列の1000pFコンデンサに接続された2本の直列10Ω抵抗で構成され、時定数が20nsになります。

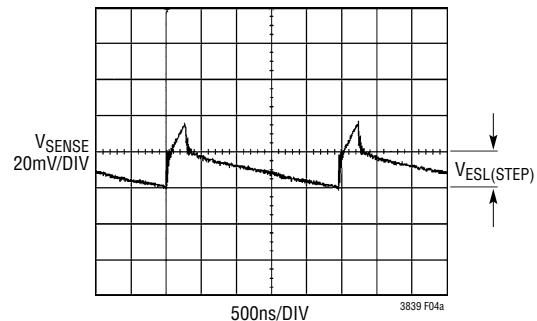

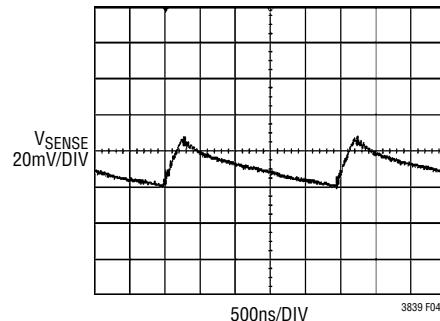

この同じRCフィルタを(小さな修正を加えて)使って、寄生インダクタンスが存在するときの電流検出信号の抵抗成分を抽出することができます。例として、100%負荷で動作している1.2V/15Aのコンバータの2010のフットプリントの2mΩのセンス抵抗の両端の電圧波形を図4aに示します。この波形は純粹に抵抗性の成分と純粹に誘導性の成分を重ね合わせたものです。これは、差動測定を行うために、オシロスコープの2つのプローブと波形計算を使って測定しています。インダクタのリップル電流およびトップ・スイッチのオン時間とオフ時間の追加測定に基づき、次式を使って寄生インダクタンスの値が0.5nHであると計算されました。

$$ESL = \frac{V_{ESL(STEP)}}{\Delta I_L} \cdot \frac{t_{ON} \cdot t_{OFF}}{t_{ON} + t_{OFF}}$$

ここで、 $V_{ESL(STEP)}$ はESLによって生じる電圧ステップ(図4aを参照)、 $t_{ON}$ と $t_{OFF}$ はそれぞれトップMOSFETのオン時間とオフ時間です。寄生インダクタンスをセンス抵抗で割った値( $L/R$ )に近くなるようにRC時定数を選択すると、その結果得られる波形は、図4bに示すように再び抵抗性に見えます。低い $V_{SENSE(MAX)}$ を使用するアプリケーションでは、寄生インダクタンスの情報に関して、センス抵抗メーカーのデータシートをチェックしてください。データが存在しない場合には、センス抵抗の両端で電圧降下を直接測定してESLステップの大きさを求め、上式を使用してESLを決定します。ただし、フィルタをかけすぎないようにしてください。RC時定数をインダクタの時定数以下にして $V_{RSENSE}$ のリップル電圧を十分高く保ちます。

$SENSE1^-$ ピンと $SENSE2^-$ ピンは、出力電圧を検出してトップ・ゲートのオン時間 $t_{ON}$ を調整するためにも使用されていることに注意してください。この目的のため、各 $SENSE^-$ ピンからSGNDに500kの内部抵抗が追加されているので、対応する $SENSE^+$ ピンとのインピーダンス不整合を生じます。 $R_F$ 両端の電圧降下によって検出電圧にオフセットが生じます。たとえば、 $V_{OUT} = V_{SENSE^-} = 5V$ のときに $R_F = 100\Omega$ の場合、検出電圧のオフセットは $V_{SENSE(OFFSET)} = V_{SENSE^-} \cdot R_F / 500k = 1mV$ に

図4a. センス抵抗両端で直接測定した電圧波形

図4b. センス抵抗フィルタの後で測定した電圧波形。 $C_F = 1000pF$ ,  $R_F = 100\Omega$

なります。このように小さいオフセットは電流制限に影響を与えないように思えるかもしれません、電流反転検出( $I_{REV}$ )には大きな影響を与え、不連続モード時に負のインダクタ電流が過大になる可能性があります。また、 $V_{SENSE(MAX)} = 30mV$ のときは、わずか1mVのオフセットによってゼロ電流のITH電圧に $(2.4V - 0.8V) \cdot 1mV / 30mV = 53mV$ の大きなシフトが生じます。ITHフォールドバックによって出力が短絡した後のシフトが大きすぎると、出力電圧が安定化された値に戻れない可能性があります。したがって、大きな値のフィルタ抵抗 $R_F$ を使用している場合は、各 $SENSE^+$ ピンからSGNDに外付け500k抵抗を接続して、対応する $SENSE^-$ ピンの内部500k抵抗と均衡させることを推奨します。

前の説明は、一般に $I_{OUT(MAX)} > 10A$ で値の小さなインダクタが使用されている高密度/高電流のアプリケーションに当てはまります。 $I_{OUT(MAX)} < 10A$ のアプリケーションでは、 $R_F$ を $10\Omega$ 、 $C_F$ を $1000pF$ に設定します。これにより妥当な出発点が与えられます。

## アプリケーション情報

フィルタ部品はデバイスの近くに配置する必要があります。正と負の検出トレースは差動ペアとして配線し、センス抵抗にケルビン(4線)接続する必要があります。

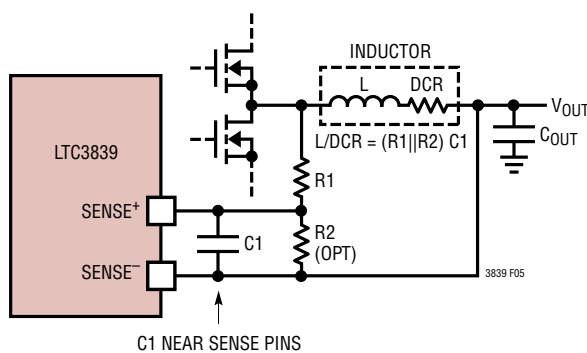

### DCRによるインダクタ電流検出

高負荷電流で高効率を必要とするアプリケーションでは、LTC3839は図5に示すように、インダクタのDCR両端の電圧降下を検出することができます。インダクタのDCRは小さな値のDC巻線抵抗を表し、最近の値の小さい高電流インダクタでは $1\text{m}\Omega$ より小さいことがあります。

このようなインダクタを必要とする高電流のアプリケーションでは、センス抵抗による導通損失はDCRによる検出に比べて効率を数ポイント低下させることができます。

インダクタのDCRは、フィルタ両端にRCフィルタを接続することによって検出します。このフィルタは図5に示すように、通常、1本または2本の抵抗( $R_1$ および $R_2$ )と1個のコンデンサで構成されます。外付けの $(R_1||R_2) \cdot C_1$ の時定数が正確に $L/DCR$ の時定数に等しくなるように選択すると、外付けコンデンサ両端の電圧降下は、インダクタのDCR両端の電圧降下に $R_2/(R_1+R_2)$ を掛けた値に等しくなります。したがって、DCRが目標のセンス抵抗より大きいときは、 $R_2$ を使って検出端子両端の電圧の大きさを変更することができます。電流制限は $V_{RNG}$ ピンを介して設定できるので、 $R_2$ はオプションにすることができます。 $C_1$ は通常、 $0.01\mu\text{F} \sim 0.47\mu\text{F}$ の範囲で選択します。これにより、 $R_1||R_2$ が約 $2\text{k} \sim 4\text{k}$ に強制されるので、SENSEピンの入力バイアス電流によって生じるはずの誤差が減少します。

図5.DCRによる電流センス

抵抗 $R_1$ はスイッチング・ノードの近くに配置して、敏感な小信号ノードへノイズが結合するのを防ぎます。コンデンサ $C_1$ はデバイスのピンの近くに配置します。

DCRによる電流検出の設計の最初のステップはインダクタのDCRを決定することです。通常 $25^\circ\text{C}$ で規定される最大値がメーカーによって与えられていれば、それを使用します。抵抗の温度係数が約 $0.4\%/\text{°C}$ であることを考慮して、この値を増加させます。インダクタ温度 $T_L$ の控えめな値は $100^\circ\text{C}$ です。インダクタのDCRは十分な性能のRLCメータを使って測定することができますが、DCRの許容誤差は常に同じではなく、温度によって変化します。詳細については、メーカーのデータシートを参照してください。

DCRの値から、 $V_{SENSE}(\text{MAX})$ を次のように容易に計算できます。

$$V_{SENSE(\text{MAX})} = DCR_{\text{MAX}(25^\circ\text{C})} \cdot \left[ 1 + 0.4\% (T_L(\text{MAX}) - 25^\circ\text{C}) \right] \cdot \left( I_{\text{OUT}(\text{MAX})} - \frac{\Delta I_L}{2} \right)$$

$V_{SENSE}(\text{MAX})$ が、 $V_{RNG}$ ピンによって設定されるLTC3839の最大検出電圧( $30\text{mV} \sim 100\text{mV}$ )の範囲内である場合、RCフィルタに必要なのは $R_1$ だけです。 $V_{SENSE}(\text{MAX})$ がこの電圧より高い場合は、 $R_2$ を使って、範囲内まで低下するように最大検出電圧をスケールダウンすることができます。

$R_1$ の最大電力損失はデューティ・サイクルと相関関係があり、連続モードの最大入力電圧時に生じます。

$$P_{\text{LOSS}}(R_1) = \frac{(V_{\text{IN}(\text{MAX})} - V_{\text{OUT}}) \cdot V_{\text{OUT}}}{R_1}$$

$R_1$ の電力定格がこの値より大きいことを確認します。軽負荷時に高い効率が必要な場合、DCRによる検出と $R_{\text{SENSE}}$ による検出のどちらを使用するかを決定するときにこの電力損失を検討します。軽負荷での電力損失は、 $R_1$ によって生じる余分のスイッチング損失のため、センス抵抗の場合よりDCRネットワークの方が少し高いことがあります。ただし、DCRによる検出ではセンス抵抗が取り除かれるので、導通損失が減少し、重負荷で効率が改善されます。最大効率はどちらの方法でもほぼ同じです。

## アプリケーション情報

電流検出信号のSN比を良好に保つには、10mVの $\Delta V_{SENSE}$ から始めます。DCRによる検出のアプリケーションでは、実際のリップル電圧は次式で求められます。

$$\Delta V_{SENSE} = \frac{V_{IN} - V_{OUT}}{R1 \cdot C1} \cdot \frac{V_{OUT}}{V_{IN} \cdot f}$$

### パワー MOSFET の選択

LTC3839 コントローラの各チャネルには2つの外付けNチャネルパワー MOSFET を選択する必要があります。トップ(メイン)スイッチ用とボトム(同期)スイッチ用にそれぞれ1個です。ゲート駆動レベルはDRVCC 電圧で設定されます。この電圧は通常5.3Vです。MOSFET のBV<sub>DSS</sub>の仕様にも十分注意を払ってください。ほとんどのロジックレベル MOSFET は30V以下に制限されています。

パワー MOSFET の選択基準には、オン抵抗 R<sub>DS(ON)</sub>、ミラー容量 C<sub>MILLER</sub>、入力電圧、および最大出力電流が含まれます。ミラー容量 C<sub>MILLER</sub> は、MOSFET のメーカーのデータシートに通常記載されているゲート電荷曲線から推定することができます。C<sub>MILLER</sub> は、曲線がほぼ平坦な区間の水平軸に沿ったゲート電荷の増分(または、メーカーのデータシートに規定されている場合にはパラメータ Q<sub>GD</sub>)を、V<sub>DS</sub> の規定されたテスト電圧で割ったものに等しくなります。

$$C_{MILLER} \approx \frac{Q_{GD}}{V_{DS(TEST)}}$$

このデバイスが連続モードで動作しているときの、トップ MOSFET とボトム MOSFET のデューティ・サイクルは、以下の式で与えられます。

$$D_{TOP} = \frac{V_{OUT}}{V_{IN}}$$

$$D_{BOT} = 1 - \frac{V_{OUT}}{V_{IN}}$$

最大出力電流での MOSFET の電力損失は、以下の式で与えられます。

$$P_{TOP} = D_{TOP} \cdot I_{OUT(MAX)}^2 \cdot R_{DS(ON)(MAX)} (1 + \delta) + V_{IN}^2 \cdot \left( \frac{I_{OUT(MAX)}}{2} \right) \cdot C_{MILLER} \left[ \frac{R_{TG(UP)}}{V_{DRVCC} - V_{MILLER}} + \frac{R_{TG(DOWN)}}{V_{MILLER}} \right] \cdot f$$

$$P_{BOT} = D_{BOT} \cdot I_{OUT(MAX)}^2 \cdot R_{DS(ON)(MAX)} \cdot (1 + \delta)$$

ここで、 $\delta$  は R<sub>DS(ON)</sub> の温度依存性、R<sub>TG(UP)</sub> は TG のプルアップ抵抗、R<sub>TG(DOWN)</sub> は TG のプルダウン抵抗です。V<sub>MILLER</sub> はミラー効果の V<sub>GS</sub> 電圧で、MOSFET のデータシートから読み取ります。

I<sup>2</sup>R 損失は両方の MOSFET に共通していますが、トップサイド N チャネルの式には遷移損失の追加項があり、これは入力電圧が高いときに最も高くなります。V<sub>IN</sub> < 20V では、高電流のときの効率は一般に大型 MOSFET を使用すると向上しますが、V<sub>IN</sub> > 20V では遷移損失が急激に増加し、実際には C<sub>MILLER</sub> が小さくて R<sub>DS(ON)</sub> が大きなデバイスを使用する方が効率が高くなるポイントにまで達します。同期 MOSFET の損失は、トップ・スイッチのデューティ・ファクタが低くなる高入力電圧時か、または同期スイッチが周期の 100% 近くオンになる短絡時に最も大きくなります。

MOSFET の (1 +  $\delta$ ) の項は一般に、パワー MOSFET のデータシートの正規化された R<sub>DS(ON)</sub> と温度の曲線で与えられます。低電圧の MOSFET の場合、R<sub>DS(ON)</sub> の変化率を概算するときに 0.5%/度 (°C) を使って  $\delta$  を推定することができます。

$$\delta = 0.005/^\circ\text{C} \cdot (T_J - T_A)$$

ここで、T<sub>J</sub> は MOSFET の推定接合部温度、T<sub>A</sub> は周囲温度です。

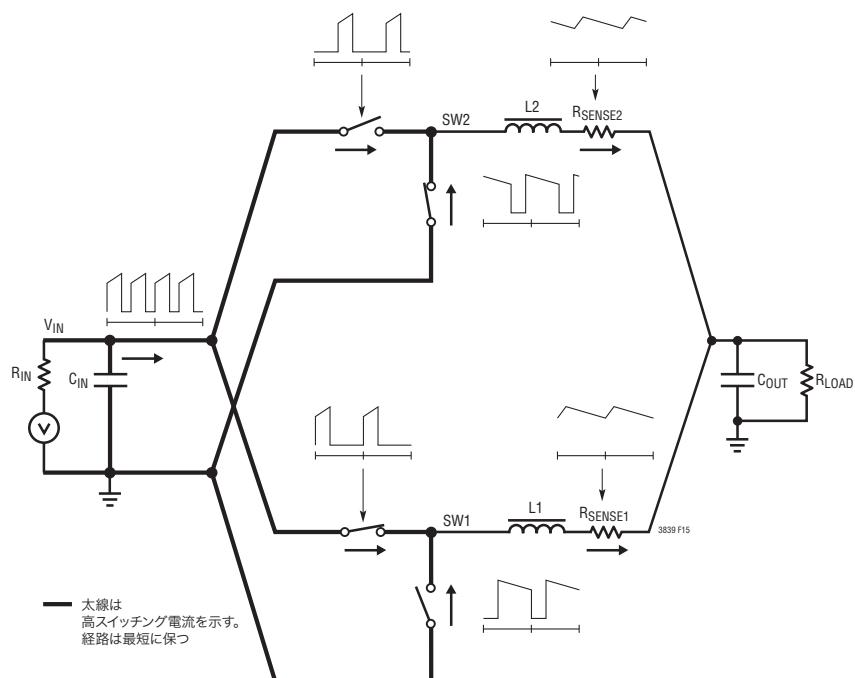

### C<sub>IN</sub> の選択

連続モードでは、トップ N チャネル MOSFET のソース電流は、デューティ・サイクルが V<sub>OUT</sub>/V<sub>IN</sub> の方形波になります。大きな過渡電圧を防止するには、最大 RMS 電流に対応できるサイズの低 ESR 入力コンデンサを使用する必要があります。シングル-フェーズのアプリケーションを想定すると、ワーストケースの RMS 電流になります。コンデンサの最大 RMS 電流は次式で与えられます。

$$I_{RMS} \approx I_{OUT(MAX)} \cdot \frac{V_{OUT}}{V_{IN}} \cdot \sqrt{\frac{V_{IN}}{V_{OUT}} - 1}$$

この式は V<sub>IN</sub> = 2V<sub>OUT</sub> のとき最大値をとり、I<sub>RMS</sub> = I<sub>OUT(MAX)</sub>/2 になります。大きく変化させてもそれほど状況が改善されないため、一般にはこの単純なワーストケース条件が設計に使用されます。多くの場合、コンデンサ・メーカーはリップル電流定格をわずか 2000 時間の寿命時間によって規定しています。このため、コンデンサをさらにディレーティングすること、つまり要求条件よりも高い温度定格のコンデンサを選択することを推奨します。設計でのサイズまたは高さの要件を満たすため、

## アプリケーション情報

数個のコンデンサを並列に接続することもできます。LTC3839は動作周波数が高いので、デバイスとパワースイッチの近くに  $C_{IN}$  と並列に追加のセラミック・コンデンサも接続して、高周波スイッチング・ノイズをバイパスする必要があります。通常、複数のX5RまたはX7Rのセラミック・コンデンサを導電性ポリマーまたはアルミ電解タイプのバルク・コンデンサと並列に接続します。セラミック・コンデンサはESRが小さいので、RMSリップル電流の大部分を吸収します。セラミック・コンデンサのリップル電流定格はメーカーによって十分に規定されてはいませんが、過度のリップル電流によってセラミック・コンデンサが正しく機能しない可能性もあります。疑問点については必ずメーカーにお問い合わせください。

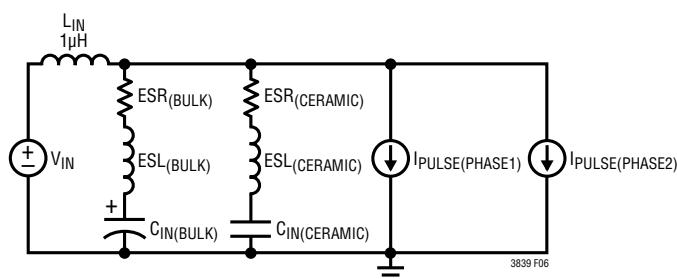

これらのコンデンサそれぞれのリップル電流を計算するための簡略化した回路モデルを図6に示します。入力ソースとコンバータの入力の間の入力インダクタンス( $L_{IN}$ )がコンデンサを流れるリップル電流に影響を与えます。入力インダクタンスを小さくすると、より多くのリップル電流が入力ソースから流れ出するようになります。入力コンデンサを流れるリップル電流が減少します。

図6. 入力コンデンサのリップル電流シミュレーション用の回路モデル

このモデルを使ったシミュレーションでは、一方のフェーズが最大負荷状態で他方のフェーズが無負荷状態の場合の定常状態のときのリップル電流を調べます。これは**一般に**、リップル電流にとってワーストケースになります。それは、一方のフェーズからのリップル電流が他方のフェーズからのリップル電流によってキャンセルされないからです。

この回路モデルを使ったシミュレーションでは、バルク・コンデンサもRMS定格が自己のRMS電流を超える十分なマージンのものを選択する必要があることに注意してください。入力電圧範囲が狭い場合、リップル電流定格が大きくESRが小

さい導電性ポリマーのタイプ(三洋電機のOS-CONなど)を使用することができます。入力電圧範囲が広く、かつ高い電圧定格を必要とする場合、大きな容量と大きな減衰が可能なアルミ電解コンデンサがより適しています。すべてのリップル電流を単独で処理できるほど大きなリップル電流定格をもつアルミ電解コンデンサは、非常に大型になります。ただし、セラミック・コンデンサと並列に接続されているときは、アルミ電解コンデンサはESRが大きいので、アルミ電解コンデンサにはRMSリップル電流のわずか一部しか流れません。しかしながら、アルミ電解コンデンサを流れるリップル電流がその定格値を超えると大きな熱を生じるので、この値を超えないようにすることが極めて重要です。それは、この熱によってコンデンサ内部の電解質が時間とともに乾燥し、その容量が減少してESRが増加するからです。

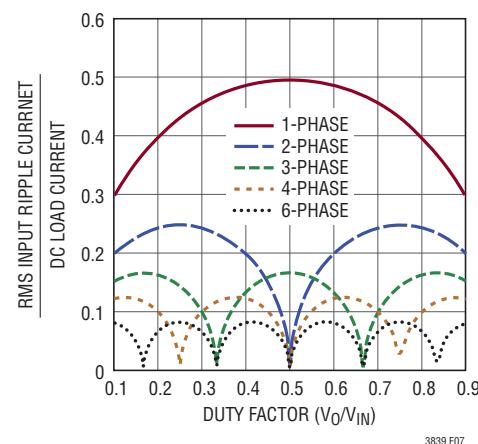

PolyPhase動作の利点は、RMS電流が減少することによって入力コンデンサの電力損失が小さくなることです。さらに、PolyPhaseシステムではピーク電流が減少するので、入力保護ヒューズの抵抗、バッテリ抵抗、およびPC基板のトレース抵抗による各損失も減少します。正確な式の詳細については、「アプリケーションノート77」の大電流アプリケーション用の高効率高密度PolyPhaseコンバータを参照してください。デューティ・サイクルに対するDC出力電流に対して正規化された入力コンデンサのRMSリップル電流を図7に示します。チャネルが同じでそれらの位相が完全にインターリープされていると仮定した場合、このグラフを使ってマルチフェーズ・アプリケーションのコンデンサの最大RMS電流を推定できます。

図7. 正規化されたRMS入力リップル電流

## アプリケーション情報

図7は、多くのフェーズを使用すると、リップル電流がキャンセルされることにより、入力コンデンサを流れるリップル電流が減少することを示しています。ただし、LTC3839は定常状態でだけ正確に位相がインターリープされるので、過渡RMS電流が指定されたフェーズ数に対する曲線より大きくなる可能性があります。したがって、アプリケーションの固有の負荷状況を考慮してコンデンサを選択することを推奨します。入力コンデンサのRMS電流定格は、前述のシングルフェーズのアプリケーションのワースト・ケースに近い値を選択するのが常に最も安全です。この値は、コントローラのチャネルが同時にオンに切り替わるときに生じる損失を想定して計算されます。

ただし、フェーズのオン時間が全ての時間で一致する場合には、通常、入力コンデンサをこのようなワーストケースの条件に対応するサイズにする必要はありません。負荷ステップが生じている間、オン時間の重複は、特にデューティ・サイクルが低いときにはほんの少しの時間しか生じません。スイッチ・ノードが数サイクルの間、重なる過渡が生じても、コンデンサが損傷することはできません。ほとんどのアプリケーションでは、入力コンデンサを100%の定常状態の負荷に対応するサイズにすれば十分です。たとえば、マイクロプロセッサの負荷はオン時間の重複を頻繁に生じる可能性があり、リップル電流が大きくなりますが、負荷電流はI<sub>OUT</sub>(MAX)の100%になるだけです。ワーストケースの負荷電流を使用するには、過渡状態に対して既にマージンが組み込まれているようにします。

V<sub>IN</sub>に接続するトップMOSFETのソースは互いに近づけて配置し、C<sub>IN</sub>を共有するようにします。ソースとC<sub>IN</sub>を離すと、V<sub>IN</sub>に望ましくない電圧共振や電流共振を生じる可能性があります。

小さな(0.1μF～1μF)バイパス・コンデンサをデバイスに近づけて、デバイスのV<sub>IN</sub>ピンとグランド間に設置することを推奨します。C<sub>IN</sub>とV<sub>IN</sub>ピンの間に2.2Ω～10Ωの抵抗を設置することも推奨します。この抵抗により、2つのチャネルのスイッチング・ノイズからさらに絶縁することができます。

### C<sub>OUT</sub>の選択

出力容量C<sub>OUT</sub>は、電圧リップルを最小限に抑えるために、主に等価直列抵抗(ESR)に基づいて選択します。連続モードでの出力電圧リップルΔV<sub>OUT</sub>は次式によって求められます。

$$\Delta V_{OUT} \leq \Delta I_L \left( R_{ESR} + \frac{1}{8 \cdot f \cdot C_{OUT}} \right)$$

ここで、fは動作周波数、ΔI<sub>L</sub>は全フェーズの総インダクタ電流のリップル成分です。ΔI<sub>L</sub>は入力電圧に応じて増加するため、出力リップルは入力電圧が最大のとき最大になります。通常は、C<sub>OUT</sub>のESR要件が満たされれば、一般にRMS電流定格はリップル電流の要件をはるかに上回ります。

LTC3839のマルチフェーズ動作では、出力コンデンサの選択でΔI<sub>L</sub>を決める際に、規定負荷状態でのリップル要件を検討することを推奨します。定常状態では、LTC3839の各位相がインターリープされており、リップルが出力で互いにキャンセルされるので、C<sub>OUT</sub>のリップルは減少します。過渡の間、位相が完全にインターリープされていないと、リップルのキャンセルが機能しない可能性があります。たとえば、負荷電流の大きなステップ変化により、数サイクルの間位相が揃い、総インダクタ電流が短時間でランプアップして、V<sub>OUT</sub>を垂下状態から引き上げる可能性があります。ワーストケースのΔI<sub>L</sub>は、高速過渡の間に揃った各位相のΔI<sub>L</sub>の総和ですが、このように大きなリップルが続くのは、位相が再度インターリープされるまでのほんの短い時間です。

小さな出力容量を選択すると、放電の項のためにリップル電圧が上昇しますが、これはESRが非常に小さいコンデンサを使って補償することができ、リップル電圧を維持することができます。

ESRおよびRMS電流処理の要件を満たすには、並列に配置した複数のコンデンサが必要になることがあります。乾式タンタル、特殊ポリマー、アルミ電解、セラミックの各コンデンサは全て表面実装パッケージで入手できます。特殊ポリマー・コンデンサはESRは非常に小さいのですが、他のタイプに比べて容量密度が低くなっています。タンタル・コンデンサは容量密度は最大ですが、スイッチング電源に使用する場合はサージ・テストを行ったものに限ることが重要です。アルミ電解コンデンサはESRが極めて大きいのですが、リップル電流定格や長期的な信頼性に対して配慮すれば、コスト重視のアプリケーションに使用することができます。

セラミック・コンデンサはESR特性が優れていますが、電圧係数が大きく、可聴圧電効果を示すことがあります。また、トレース・インダクタンスを伴ったセラミック・コンデンサはQが高く、大きなリンクギングを引き起こす場合があります。入力コンデンサとして使用するときは、突入電流によるリンクギングとスイッチングから生じる過電圧でパワースイッチとコントローラを損傷させないように注意が必要です。

## アプリケーション情報

スイッチング周波数が高い場合、出力リップルを小さくしてEMIフィルタリングの効果を上げるために、低ESLで(かつそれに応じて自己共振周波数の高い)値の小さいコンデンサを高ESLで値の大きいコンデンサと並列に配置しなければならないことがあります。これにより、対象となる全周波数スペクトラムで、良好なノイズ・フィルタリングとEMIフィルタリングを実現することができます。セラミック・コンデンサは一般に良好な高周波性能を備えていますが、性能を最適化するために小さいセラミック・コンデンサを大きいコンデンサと並列に接続しなければならないことがあります。

高性能スルーホール・コンデンサを使用することもできますが、そのリード・インダクタンスの影響を低減するためにセラミック・コンデンサを並列に追加することを推奨します。高周波デカップリング・コンデンサを負荷の電力ピンにできるだけ近づけて配置することも忘れないでください。

### トップ MOSFET ドライバの電源( $C_B$ , $D_B$ )

BOOSTピンに接続されている外付けのブートストラップ・コンデンサ $C_B$ は、トップサイドMOSFETのゲート・ドライブ電圧を供給します。このコンデンサは、スイッチ・ノードが“L”的ときにDRVCCからダイオード $D_B$ を通して充電されます。トップMOSFETがオンすると、スイッチ・ノードの電圧が $V_{IN}$ まで上がり、BOOSTピンの電圧は約 $V_{IN} + INTVCC$ まで上がります。昇圧コンデンサは、トップMOSFETが必要とするゲート電荷の約100倍を蓄積する必要があります。ほとんどのアプリケーションでは、 $0.1\mu F \sim 0.47\mu F$ のX5RまたはX7Rの誘電体コンデンサで十分です。DRVCCのコンデンサ $C_{DRVCC}$ が全ての動作条件でトップMOSFETのゲートと昇圧コンデンサに電荷を供給できるように、昇圧コンデンサを $C_{DRVCC}$ の10%より大きくしないことを推奨します。負荷ステップに応答する可変周波数の過渡性能は非常に優れていますが、大きな瞬時ゲート・ドライブを必要とします。ゲート電荷の必要量は、周波数が高くデューティ・ファクタの低いアプリケーションで、負荷ステップが大きいときや起動時に最大になります。

### DRVCC レギュレータとEXTVCC 電源

LTC3839は、 $V_{IN}$ 電源からDRVCCに電力を供給するPMOS低損失(LDO)リニア・レギュレータを備えています。このLDOは、DRVCC1ピンの出力を5.3Vに安定化します。このLDOは100mAの最大電流を供給することができ、最小 $4.7\mu F$ のセラミック・コンデンサでグランドにバイパスする必要があります。

MOSFETゲート・ドライバに必要な大きな過渡電流を供給し、チャネル間の相互干渉を最小限に抑えるため、十分なバイパスが必要です。

高周波数で大きなMOSFETがドライブされる高入力電圧のアプリケーションでは、特にLDOがアクティブでDRVCCに電力を供給している場合に、LTC3839の最大接合部温度定格を超える恐れがあります。この場合にはデバイスの電力損失が最大になり、 $V_{IN}I_{DRVCC}$ にはほぼ等しくなります。「効率に関する検討事項」のセクションで説明されているように、ゲート充電電流は動作周波数に依存します。接合部温度は、「電気的特性」のNote 2に示されている式を使って推定することができます。たとえば、LDOを使用しているときのLTC3839のDRVCC電流は、 $T_A = 70^\circ C$ の場合、38V電源では32mA以下に制限されます。

$$T_J = 70^\circ C + (32\text{mA})(38\text{V})(44^\circ C/\text{W}) = 125^\circ C$$

最大接合部温度を超えないようにするには、最大 $V_{IN}$ での連続導通モード動作時の入力電源電流をチェックする必要があります。

EXTVCCに印加される電圧が切り替え電圧(標準4.6V)を上回ると、 $V_{IN}$ のLDOがオフし、内部スイッチによってEXTVCCがDRVCC2ピンに接続されます。このスイッチは、EXTVCCに印加されている電圧がヒステリシス(約200mV)よりも高く、切り替え電圧よりも低い状態を保っている限り、オン状態のままです。EXTVCCを使用することにより、MOSFETドライバと制御回路への電力は、通常動作時にはLTC3839のスイッチング・レギュレータの出力 $V_{OUT}$ から得ることができ、出力が安定化されていないとき(起動時、短絡時など)にはLDOから得ることができます。EXTVCCを介して規定値以上の電流が必要な場合は、EXTVCCピンとDRVCCピンの間に外付けショットキ・ダイオードを追加できます。EXTVCCピンには6Vより高い電圧は印加しないで、EXTVCCが $V_{IN}$ より低くなるようにしてください。

ドライバと制御回路の電流に起因する $V_{IN}$ 電流は、(デューティ・サイクル)/(スイッチャの効率)に比例するため、スイッチング・コンバータの出力からDRVCCに電力を供給することによって効率と熱特性を大幅に改善できます。

EXTVCCピンを5V電源に接続すると、前の例の接合部温度は $125^\circ C$ から次の値まで下がります。

$$T_J = 70^\circ C + (32\text{mA})(5\text{V})(44^\circ C/\text{W}) = 77^\circ C$$

## アプリケーション情報

ただし、3.3Vなどの低電圧出力の場合、コンバータ出力からDRV<sub>CC</sub>の電力を得るには追加回路が必要です。

以下に、EXTV<sub>CC</sub>に対して可能な4つの接続方法を示します。

1. EXT<sub>VCC</sub>をオープンのままにします(または接地します)。こうすると、5.3Vの内部LDOからINTV<sub>CC</sub>に電力が供給されるため、入力電圧が高いときに効率が最大で10%ほど低下します。

2. スイッチング・コンバータの出力V<sub>out</sub>に直接接続されているEXTV<sub>CC</sub>が、切り替え電圧の上限値(4.8V)よりも高くなるようにします。これによって最大効率が得られます。

3. EXT<sub>VCC</sub>を外部電源に接続します。4.8V以上の外部電源を利用できる場合、MOSFETのゲート・ドライブ要件を満たしていれば、これを使ってEXTV<sub>CC</sub>に電力を供給することができます。

4. EXT<sub>VCC</sub>を出力から得られる昇圧ネットワークに接続します。3.3Vコンバータなどの低電圧コンバータでは、4.8V以上に昇圧した出力から得られる電圧にEXTV<sub>CC</sub>を接続することにより、効率をさらに改善できます。

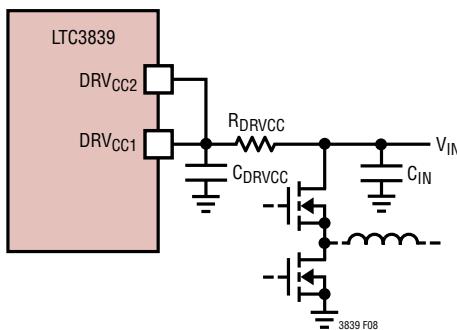

主入力電源が5.3Vを超えることのないアプリケーションでは、図8に示すように、DRV<sub>CC1</sub>ピンとDRV<sub>CC2</sub>ピンを小さな抵抗( $1\Omega \sim 2\Omega$ )を介してV<sub>IN</sub>入力に接続し、ゲート充電電流によって生じる電圧降下を最小限に抑えます。これにより、LDOが無効になり、ドロップアウト電圧によってDRV<sub>CC</sub>が低くなりすぎないようにします。DRV<sub>CC</sub>電圧が外付けMOSFETのR<sub>DSON</sub>テスト電圧(ロジック・レベルのデバイスの場合、標準4.5V)より高いことを確認します。

図8.V<sub>IN</sub> ≤ 5.3Vの設定

### 入力低電圧ロックアウト(UVLO)

LTC3839には、入力低電圧状態の場合にコントローラを保護するのに役立つ2つの機能が備わっています。内部UVLOコンパレータがINTV<sub>CC</sub>電圧とDRV<sub>CC</sub>電圧を常時モニタして、適切な電圧が印加されていることを確認します。コンパレータは内部UVLO信号をイネーブルして、INTV<sub>CC</sub>ピンとDRV<sub>CC1,2</sub>ピンがそれぞれのUVLOしきい値を超えるまで両方のチャネルのスイッチング動作をロックアウトします。INTV<sub>CC</sub>の(UVLOを解除する)上昇時しきい値は標準4.2Vで、(UVLOを再イネーブルする)0.5Vの下降時ヒステリシスを備えています。パワーMOSFETがゲート駆動電圧が十分でないときにオンするのを防ぐため、DRV<sub>CC1,2</sub>のUVLOしきい値はINTV<sub>CC</sub>のしきい値より低い値ですが、パワーMOSFETの標準しきい値電圧より高い値にしてあります。

通常、V<sub>IN</sub>が6Vより高い場合、V<sub>IN</sub>からSGNDに接続された外付け分圧器をRUNピンに使ってV<sub>IN</sub>電源をモニタすることにより、UVLOを設定することができます。分圧器を設計する際には、RUNピンが2つのレベルのしきい値電圧を備えていることに注意してください。1.2Vの高精度ゲート駆動イネーブルしきい値電圧を使って、チャネルのスイッチングをオンするV<sub>IN</sub>電圧を設定することができます。RUNピンに抵抗分割器が使用されている場合、V<sub>IN</sub>が十分に低く、RUNピンが約0.8Vのしきい値より低いと、デバイスはINTV<sub>CC</sub>とDRV<sub>CC</sub>の全てのバイアスをシャットダウンし、マイクロパワー・シャットダウン・モードになります。

RUNピンのバイアス電流はRUNピンの電圧に左右されます。外付け分圧器のUVLO回路を設計する際には、バイアス電流の変化を考慮する必要があります。このピンには、内部絶対温度比例(PTAT)プルアップ電流源(25°Cで約2.5μA)が常に接続されています。RUNピンが1.2Vを上回ると、TGドライバとBGドライバがオンし、温度に依存しない10μAの追加プルアップ電流源がRUNピンに内部で接続されます。RUNピンを1.2Vより80mVのヒステリシス以上引き下げると、TGとBGがオフし、10μAの追加プルアップ電流源が切り離されます。

## アプリケーション情報

RUNピンの電圧が上昇して3V(標準)を超えると、そのバイアス電流が反転を開始してRUNピンに流れ込みます。RUNピンは最大50 $\mu$ Aをシンク可能であり、50 $\mu$ AをシンクしているときにRUNピンが6Vをわずかに超えたとしても、フォルト状態を防ぐため、低インピーダンス電圧源によってRUNピンを6Vより高い電圧に強制することは決してしないでください。

### ソフトスタートとトラッキング

LTC3839はコンデンサを使ってそれ自体でソフトスタートを行うか、または外部電源をトラッキングすることができます。ソフトスタートおよびトラッキング機能は、コントローラの最大出力電流を制限することによってではなく、TRACK/SSピンのランプレートに従って出力ランプ電圧を制御することによって実現されることに注意してください。

LTC3839を自分でソフトスタートを行うように構成設定するときは、コンデンサをTRACK/SSピンに接続します。TRACK/SSは、RUNピンの電圧が1.2Vを超えてUVLOが解除されるまで“L”に保たれ、1.2Vを超えた時点で、1 $\mu$ Aの内部電流がTRACK/SSに接続されたソフトスタート・コンデンサC<sub>SS</sub>を充電します。スムーズなソフトスタートまたはトラッキングを保証するため、この段階の間は電流制限フォールドバックがディスエーブルされます。ソフトスタートまたはトラッキングの範囲は、TRACK/SSピンが0V～0.6Vの電圧範囲に限定されます。合計ソフトスタート時間は次のように計算できます。

$$t_{SS}(\text{SEC}) = 0.6(V) \cdot \frac{C_{SS}(\mu\text{F})}{1(\mu\text{A})}$$

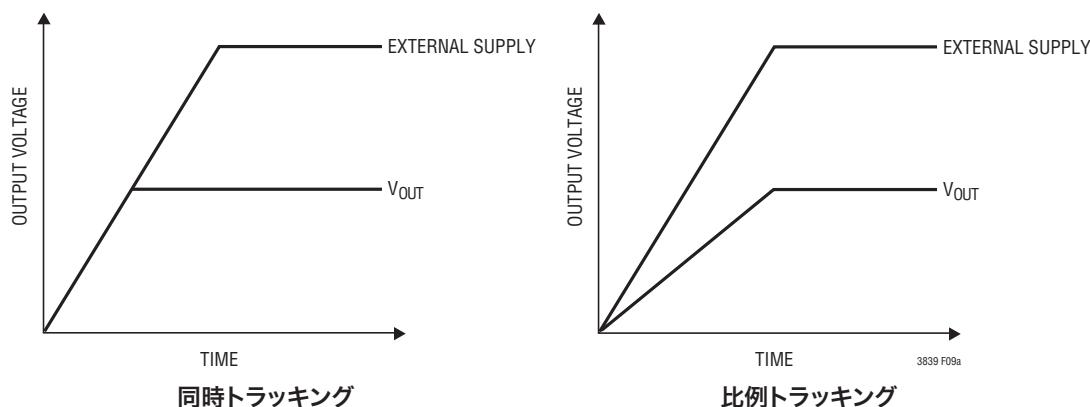

図9a. 出力トラッキングの2つの異なるモード

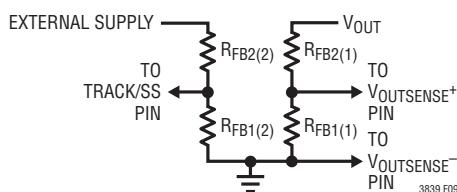

図9b. 外部電源トラッキングの設定

## アプリケーション情報

外部電源をトラッキングするようにLTC3839を構成設定するときは、外部電源からTRACK/SSピンに分圧器を接続して、ランプレートを適切な値に調整することができます。2つの一般的なトラッキングは、同時トラッキングと比例トラッキングです。同時トラッキングの場合は、外部電源からの分圧器の比を差動帰還電圧用の分圧器の比と等しくします。比例トラッキングは、差動帰還とは異なる比を使用することによって実現できます。

ソフトスタート・コンデンサの1 $\mu$ Aの充電電流が流れ続けており、小さなオフセット誤差が生じることに注意してください。この誤差を最小限に抑えるために、トラッキング抵抗分割器には、このオフセット誤差を無視できるほど小さい値を選択します。

比例トラッキングでは、外部電源にダイナミックな変化が生じると、安定化出力も同様に変化します。出力のレギュレーションを良好にするには、比例トラッキング・モードではなく同時トラッキング・モードを使用します。

### 位相と周波数の同期

EMIやスイッチング・ノイズの制御性能の向上が求められるアプリケーションや、特別な同期要件を伴うアプリケーション用に、LTC3839では、トップMOSFETのターンオンをMODE/PLLINピンに与えられる外部クロック信号に同期させることができます。適正な周波数ロックとフェーズロックを保証するため、与えられるクロック信号はRTで設定される周波数から±30%以内である必要があります。クロック信号レベルは通常、V<sub>PLLIN(H)</sub> > 2VおよびV<sub>PLLIN(L)</sub> < 0.5Vを満たしている必要があります。MODE/PLLINピンは、ピンを開放のままにした場合に確実に不連続電流モード動作をするように、600kのプルダウン抵抗を内蔵しています。

LTC3839は、V<sub>IN</sub>とV<sub>OUT</sub>の電圧およびR<sub>T</sub>を使ってトップ・ゲートのオン時間を調整し、広い範囲のV<sub>IN</sub>、V<sub>OUT</sub>、およびR<sub>T</sub>で設定されたスイッチング周波数fに対してフェーズロックと周波数ロックを維持するようにします。

$$t_{ON} \approx \frac{V_{OUT}}{V_{IN} \cdot f}$$

オン時間はスイッチング・レギュレータの出力電圧と相関関係があるので、SENSE-ピンでこの出力を測定して必要なオン時間を設定します。リモートで安定化された出力ポイントは、ライン損失により、ローカル出力ポイントと大幅に異なることがあります。

り、ローカル・グランドに対するローカル出力がt<sub>ON</sub>の計算に必要なV<sub>OUT</sub>であるのが一般的なので、ほとんどのアプリケーションにおいてSENSE-ピンはデバイスのレギュレータのローカル出力ポイントに接続します。

ただし、このV<sub>OUT</sub>で設定されたオン時間が、周波数ロックとフェーズロックを維持するために必要なオン時間と大幅に異なる状況が生じる可能性があります。たとえば、スイッチング・レギュレータの効率が低下すると、必要なオン時間が内部設定されるオン時間より大幅に長くなる可能性があります（「効率に関する検討事項」を参照）。安定化されたV<sub>OUT</sub>が比較的低いと、それに従って、共有グランド・プレーンを流れるその他の電流によるローカル・グランドとリモート・グランドとの間の電位差により、大きな誤差が生じる可能性があります。

必要に応じて、R<sub>T</sub>抵抗の値、V<sub>IN</sub>ピンの電圧、場合によってはSENSEピンの同相電圧を外部で設定し、このような系統的な誤差を補正することができます。システムに部品や動作条件のばらつきを補正するための十分な範囲を持たせるか、または外部クロックに同期させるための目標は、V<sub>IN</sub>、V<sub>OUT</sub>、およびR<sub>T</sub>によって設定されるオン時間を定常状態のオン時間に近い値に設定することです。各SENSE-ピンにはSGNDとの間に500kの内部抵抗がありますが、SENSE+ピンにはないことに注意してください。

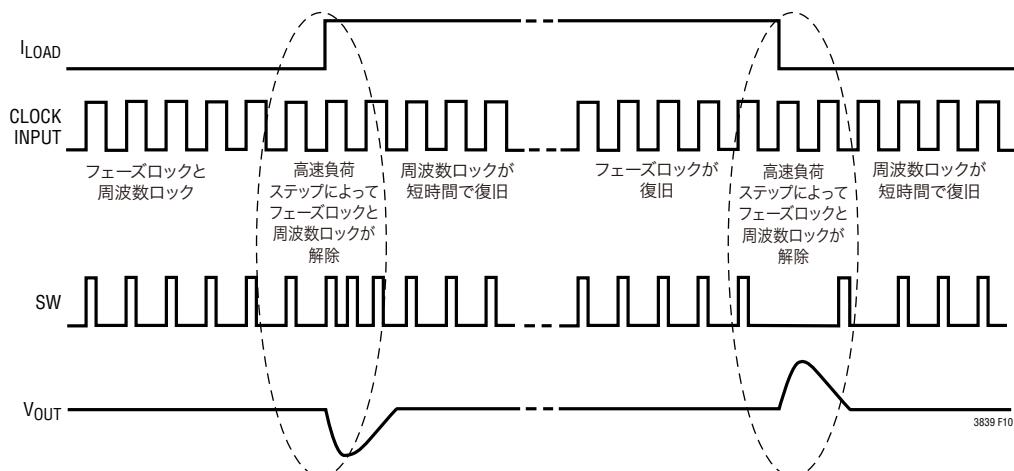

ライン電圧または負荷電流の動的過渡状態（たとえば、負荷ステップや負荷開放）の間、トップ・スイッチはより高速な過渡応答を実現するためにターンオンの頻度を多少増やします。これは、LTC3839のオン時間が制御される谷電流モード・アーキテクチャの利点です。ただし、このプロセスは当然ながら、一時的にフェーズロック、さらには周波数ロックが外れことがあります。変化が比較的遅い場合には、フェーズロックと周波数ロックを維持し続けることができます。スルーレートが速い大きな負荷電流ステップの場合、システムが定常状態に戻るまでフェーズロックは行われません（図10を参照）。フェーズロックが完全に復旧するまでに数百 $\mu$ sかかることがありますが、周波数ロックは通常、フェーズロックが復旧するよりも前に短時間で復旧します。

軽負荷の状態では、位相と周波数の同期はMODE/PLLINピンの設定に依存します。外部クロックが与えられると、同期回路がアクティブになって連続モードに切り替わります。MODE/PLLINをINTV<sub>CC</sub>に接続すると、R<sub>T</sub>で設定される周波数での強制連続モードで動作します。MODE/PLLINピンをSGNDに接続すると、LTC3839は、軽負荷時に不連続モー

## アプリケーション情報

ドで動作し、負荷が大きくなると、 $R_T$ で設定される周波数での連続導通モードに切り替わります。不連続導通モード時のTGのオン時間は意図的にわずかに拡張されており( $V_{IN}$ 、 $V_{OUT}$ 、および $f$ から計算される連続導通モードのオン時間の約1.2倍)、連続導通モードと不連続導通モードの負荷電流の境界にヒステリシスを生じます。

アプリケーションが非常に短い(最小値に近い)オン時間を必要とする場合、システムが全周波数同期範囲を維持することができない可能性があります。最小オン時間に近づけると、無負荷または軽負荷状態でフェーズロックや周波数ロックが外れることもあります。この状況下では、TG/BGのデッドタイムにより、SWのオン時間が実質的にTGのオン時間より長くなります。これについては、以下の「最小オン時間、最小オフ時間、およびドロップアウト動作」で詳しく説明します。

### 最小オン時間、最小オフ時間、およびドロップアウト動作

最小オン時間は、LTC3839のTG(トップ・ゲート)ピンを“H”、つまり「オン」状態に維持できる最小時間です。この時間は、スイッチング・レギュレータの動作条件に依存し、 $V_{IN}$ ピンと $V_{OUT}$ ピンの電圧および外付け抵抗 $R_T$ と相関関係があります。 $V_{OUT}$ ピンを0.6Vの最小値に接続し、 $V_{IN}$ を38Vの最大値に接続すると、30nsの最小オン時間を達成できます。 $V_{OUT}$ の値を大きくしたり、 $V_{IN}$ の値を小さくすると、達成可能な最小オン時間が長くなります。谷モード制御アーキテクチャによってオン時間を短くすることができる所以、LTC3839は高降圧比のアプリケーションに適しています。

SWノードのパルス幅で定義される**有効**オン時間は、外付け部品とスイッチング・レギュレータの負荷条件にも依存するので、このTGのオン時間と異なる場合があります。この違いの要因の1つはパワーMOSFETの特性です。たとえば、トップ・

図10.過渡状態のときのフェーズロック動作と周波数ロック動作

## アプリケーション情報

パワー MOSFET のターンオン遅延がターンオフ遅延よりかなり短いと、有効オン時間が TG のオン時間より長くなり、有効最小オン時間は大きな値に制限されます。

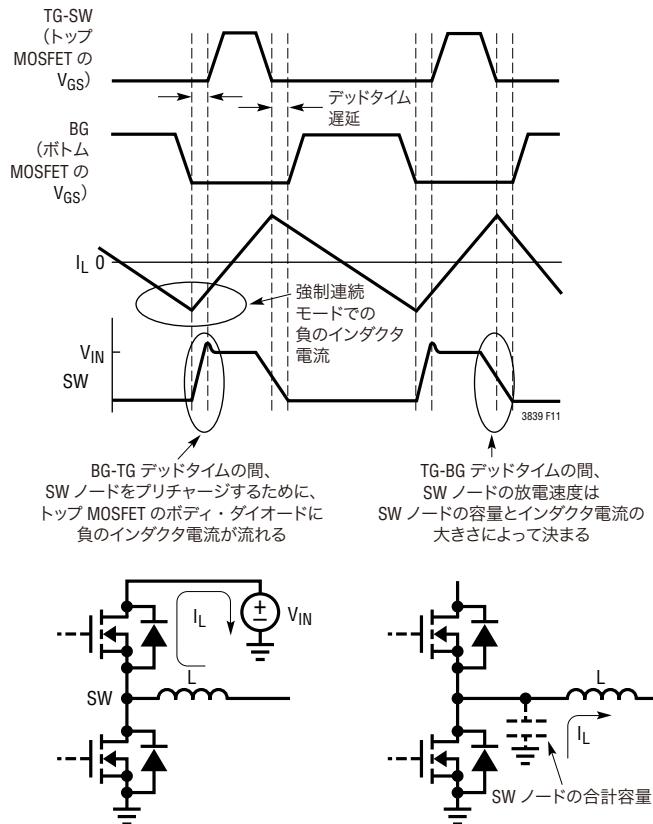

図11に示すように、TGの「オン」状態とBGの「オン」状態の間のデッドタイムにより、強制連続モードでの軽負荷動作では有効オン時間がさらに長くなります。BGのターンオフからTGのターンオンまでのデッドタイムの間、インダクタ電流が逆方向に流れ、TGが実際にオンする前にSWノードが“H”に充電されます。通常、逆電流は小さいので、立ち上がりエッジが長くなります。トップFETがオフしてボトムFETがオンするまでの立ち下がりエッジでは、軽負荷状態でSWノードを“L”に引き下げるのに使用できるピーク・インダクタ電流が小さいので、SWノードは長い時間“H”に留まります。SWノードの立ち上がりエッジと立ち下がりエッジの応答が遅いため、有効オン時間が長くなり、TGのオン時間によって十分には制御されません。最小オン時間に近づくと、軽負荷時にいくらかの位相ジッタが生じることがあります。負荷電流が増加すると、これらのエッジがシャープになり、フェーズロック動作が改善されます。

連続モード動作では、最小オン時間の制限により、最小デューティ・サイクルは次のようにになります。

$$D_{MIN} = f \cdot t_{ON(MIN)}$$

ここで、 $t_{ON(MIN)}$ はスイッチング・レギュレータの有効最小オン時間です。この式が示すように、動作周波数を下げると、最小デューティ・サイクルの制約が緩和されます。LTC3839が提供可能な最小オン時間が、デューティ・サイクルがスイッチング周波数を維持するのに必要なオン時間より長いと、スイッチング周波数はデューティ・サイクルを維持するために下がることになりますが、出力電圧はレギュレーション状態を保ちます。これは、一般に、サイクルをスキップして出力に固定周波数スイッチング・レギュレータで通常見られる大きなリップルを生じさせるより望ましいと言えます。

「標準的性能特性」の $t_{ON(MIN)}$ のグラフは、 $V_{IN}=38V$ (最大)、 $V_{OUT}=0.6V$ (最小)、 $f=2MHz$ (すなわち $RT=18k$ )のすべてあるいはいずれかの条件で、TGとBGの負荷を最小にして測定しています。 $V_{IN}$ 、 $V_{OUT}$ 、 $f$ の設定を変えたアプリケーションでは、 $t_{ON(MIN)}$ の値は一般に長くなります。また、軽負荷での周波数とフェーズロックを保証するために、「電気的特性」のデッドタイム( $t_{D(TG/BG)}+t_{D(TG/BG)}$ )を考慮して十分なマージンを持たせる必要があります。

図11. 強制連続モード動作での軽負荷時のオン時間の延長

必要とするオン時間が比較的短いアプリケーションでは、パワー MOSFET を選択する際に注意を払う必要があります。オン時間が不十分なために MOSFET のゲートが完全にオンすることができない場合、 $R_{DS(ON)}$ が大きくなる結果、大きな熱損失と効率低下が生じる可能性があります。これにより、パワー MOSFET が早期に故障することもあります。

最小オフ時間は、TG ピンを “L” にしてから直ちに “H” に戻すことができる最も短い時間です。この最小オフ時間には、BG(ボトム・ゲート)がオンしてからオフに戻るまでの時間と、TG のオフから BG のオンまで、および BG のオフから TG のオンまでのデッドタイム遅延が含まれます。LTC3839 で実現できる最小オフ時間は 90ns です。

スイッチング・レギュレータの**有効**最小オフ時間、つまり SW ノードが “L” を維持できる最小時間は、この最小オフ時間と

## アプリケーション情報

異なる場合があります。有効最小オフ時間に影響を与える主な要因は、Qg やターンオン/ターンオフ遅延などの、トップ・パワー MOSFET とボトム・パワー MOSFET の電気的特性です。これらの特性は、SW ノードの有効最小オフ時間を長くすることもあれば短くすることもあります。サイズの大きい(高 Qg)パワー MOSFET では、ゲートの充電時間と放電時間が長くなるので、一般に有効最小オフ時間も長くなる傾向があります。これに対し、ターンオン遅延とターンオフ遅延のバランスが悪い場合は、有効オフ時間が短くなることがあります。

最小オフ時間の制限により、最大デューティ・サイクルは次のようにになります。

$$D_{MAX} = 1 - f \cdot t_{OFF(MIN)}$$

ここで、 $t_{OFF(MIN)}$  はスイッチング・レギュレータの有効最小オフ時間です。動作周波数を小さくすると、最大デューティ・サイクルの制約が緩和される場合があります。

たとえば、入力電圧の低下によってデューティ・サイクルがこの最大値に達すると、出力が低下して安定しなくなります。ドロップアウトを避けるための最小入力電圧は次のとおりです。

$$V_{IN(MIN)} = \frac{V_{OUT}}{D_{MAX}}$$

ドロップアウトの開始時には、2つの異なるオフ時間を生じる約 500mV の  $V_{IN}$  の領域があります。1つは最小オフ時間で、もう1つは最小オフ時間より約 40ns ~ 60ns 長いオフ時間です。この2つめのオフ時間は、内部電流コンパレータがトリップする際の追加遅延によるものです。これら2つのオフ時間を平均すると、出力のレギュレーション状態を維持するために必要なデューティ・サイクルになります。SW ノードのジッタが大きくなり、特に外部クロックに同期している場合に顕著になることがあります。出力電圧リップルは比較的小さく保たれます。

### フォールト状態:電流制限と過電圧

電流モード・コントローラの最大インダクタ電流は、本質的に最大検出電圧によって制限されます。LTC3839 では、最大検出電圧は  $V_{RNG}$  ピンの電圧によって制御されます。谷電流モード制御では、最大検出電圧とセンス抵抗によって最大許容インダクタ谷電流が決定されます。対応する出力電流制限は次のようにになります。

$$I_{LIMIT} = \frac{V_{SENSE(MAX)}}{R_{SENSE}} + \frac{1}{2} \cdot \Delta I_L$$

電流制限値は、 $I_{LIMIT(MIN)} > I_{OUT(MAX)}$  を満たすようにチェックする必要があります。電流制限値は、ワーストケースの効率で最大出力電力を発生するのに必要なインダクタ電流より大きくする必要があります。

通常、 $V_{IN}$  と周囲温度が最も高いときにワーストケースの効率になります。想定された MOSFET の接合部温度と、それに基づく(MOSFET スイッチを熱する)  $I_{LIMIT}$  の値の整合性をチェックすることが重要です。

グランドへの短絡が生じたときに電流をさらに制限するため、LTC3839 にはフォールドバック電流制限が備わっています。出力が 50% 以上低下すると、最大検出電圧は帰還電圧が 0V に達するときの最大値の約 30% まで徐々に低下します。

帰還電圧が 0.6V の安定化目標値の 7.5% を超えると、過電圧(OV) 状態と見なされます。このような OV 状態では、トップ MOSFET が直ちにオフし、ボトム MOSFET が、OV 状態が解消されるまで無期限にオンします。つまり、帰還電圧が 7.5% のしきい値より標準 2% のヒステリシス以上低い値に再度低下します。OV の間、電流制限は機能しません。OV が継続し、BG が長時間オンすると、インダクタとボトム MOSFET を流れる電流がそれらの最大定格を超ることにより、それらを犠牲にして負荷を保護する可能性があります。

### OPTI-LOOP 補償

ITH ピンを使って OPTI-LOOP 補償を行えば、幅広い負荷と出力コンデンサに対して過渡応答を最適化することができます。ITH ピンにより、制御ループ動作を最適化できるだけでなく、DC 結合され、AC フィルタを通した閉ループ応答のテスト・ポイントが与えられます。このテスト・ポイントでの DC ステップ、立ち上がり時間、およびセトリングは、閉ループ応答を正確に反映します。2 次特性が支配的なシステムを想定すると、位相マージンや減衰係数はこのピンで見られるオーバーシュートのパーセンテージを使って推定することができます。

ITH ピンの外付け直列  $R_{ITH-CITH1}$  フィルタによって、支配的なポール-ゼロ・ループ補償が設定されます。これらの値は、PCB の最終レイアウトが完了して出力コンデンサの種類と容量値が具体的に決まつたら、過渡応答を最適化するために調

## アプリケーション情報

整することができます。ループの帰還係数の利得と位相は出力コンデンサの種類と値によって決まるので、まず出力コンデンサを選択する必要があります。

ITHピンからSGNDに小さいコンデンサC<sub>ITH2</sub>を追加して、高周波ノイズを減衰させることができます。このC<sub>ITH2</sub>によってループ利得に追加のポールが生じるので、その値が大きすぎると、システムの安定性に影響を与える可能性があります。C<sub>ITH2</sub>は、追加されるポールが十分な余裕を持ってループ帯域幅より高くなるような値を選択します。

レギュレータのループ応答は負荷過渡応答を見てチェックすることもできます。出力電流パルスが最大負荷電流の20%～100%で、その立ち上がり時間が1μs～10μsの場合、帰還ループを閉じたままでループ全体の安定性を判断することができる、V<sub>OUT</sub>とITHの電圧過渡応答波形が生成されます。OPTI-LOOP補償の詳細については「アプリケーションノート76」を参照してください。

スイッチング・レギュレータが負荷電流のステップに応答するには数サイクルを要します。負荷ステップが生じると、V<sub>OUT</sub>はΔI<sub>LOAD</sub>•ESRに等しい大きさだけシフトします。ここで、ESRはC<sub>OUT</sub>の等価直列抵抗です。ΔI<sub>LOAD</sub>はC<sub>OUT</sub>の充電または放電も開始し、レギュレータが使用する帰還誤差信号を生成して、V<sub>OUT</sub>をその定常値に戻します。この回復期間にV<sub>OUT</sub>をモニタして、安定性に問題があることを示すオーバーシュートやリンクギングがないかチェックすることができます。

現実的な負荷ステップを発生する実用的な方法として、抵抗負荷をパワーMOSFETと直列に接続し、さらにこれら2つを出力コンデンサの両端に直接接続して適切な信号発生器でゲートをドライブします。負荷電流のステップ変化によって生じる初期出力電圧ステップは帰還ループの帯域幅内にない場合があるため、位相マージンを決定するのにこの電圧ステップを使用することはできません。出力電圧のセトリング特性は、閉ループ・システムの安定性に大きく関係します。ただし、ITHピンのフィルタされて補償された帰還ループ応答を調べる方が確実です。

ループの利得はR<sub>ITH</sub>を大きくすると増加し、ループの帯域幅はC<sub>ITH1</sub>を小さくすると拡大します。C<sub>ITH1</sub>を減少させるのと同じ比率でR<sub>ITH</sub>を増加させるとゼロ周波数は変化しないので、帰還ループの最もクリティカルな周波数範囲で位相が一定に

保たれます。さらに、図1に示されているように、フィードフォワード・コンデンサC<sub>FF</sub>を追加して高周波数応答を改善することができます。コンデンサC<sub>FF</sub>は、R<sub>FB2</sub>とともに高周波数のゼロを発生させることによって位相リードを与え、位相マージンを改善します。

大容量の電源バイパス・コンデンサを備えた負荷をスイッチを介して接続すると、さらに激しい過渡現象を引き起こすことがあります。負荷の放電しきったバイパス・コンデンサが実質的にコンバータのC<sub>OUT</sub>と並列接続状態になるため、V<sub>OUT</sub>が急速に降下します。C<sub>OUT</sub>を負荷に接続するスイッチが低抵抗であって短時間でドライブされると、どのようなレギュレータでも、この出力電圧の急激なステップ変化を防ぐだけの電流を急速に供給することはできません。解決策は負荷スイッチ・ドライバのターンオン速度を制限することです。Hot Swap™コントローラは特にこの目的のために設計されており、通常、電流制限、短絡保護、ソフトスタートなどの機能を備えています。

### 負荷開放過渡の検出

降圧スイッチング・レギュレータの出力電圧要件が低くなり、V<sub>IN</sub>からV<sub>OUT</sub>への降圧比が大きくなり、負荷過渡が高速になる場合の主な課題は、負荷電流の急激な減少時、つまり「負荷開放」過渡の間のV<sub>OUT</sub>のオーバーシュートを制限することです。

インダクタ電流のスルーレートdI<sub>L</sub>/dt = V<sub>L</sub>/Lは、インダクタ両端の電圧V<sub>L</sub> = V<sub>SW</sub>-V<sub>OUT</sub>に比例します。トップMOSFETがオンすると(V<sub>L</sub> = V<sub>IN</sub>-V<sub>OUT</sub>)、インダクタ電流はランプアップします。ボトムMOSFETがオンすると(V<sub>L</sub> = V<sub>SW</sub>-V<sub>OUT</sub> = -V<sub>OUT</sub>)、インダクタ電流はランプダウンします。V<sub>OUT</sub>が非常に低い場合、ランプダウン時のインダクタ両端の電圧差V<sub>L</sub>が小さいので、インダクタ電流のスルーレートが負荷電流の変化に対応するのに必要な値よりも遅くなります。過度なインダクタ電流で出力コンデンサを充電し、それによってV<sub>OUT</sub>にオーバーシュートが生じます。

負荷開放過渡の間にボトムMOSFETをオフした場合、ボトムMOSFETのボディー・ダイオードをインダクタ電流が流れるので、ボトムMOSFETのボディー・ダイオードの電圧降下を追加して、V<sub>L</sub> = -(V<sub>OUT</sub> + V<sub>BD</sub>)のように式を修正することができます。V<sub>BD</sub>はV<sub>OUT</sub>だけの場合に比べて合計値を大幅に上げるので、出力電圧が低くなるほど有利になります。

## アプリケーション情報

$V_{OUT}$ に負荷開放によるオーバーシュートが生じると、エラー・アンプの出力ITHが短時間で降下します。ITH電圧はインダクタ電流のセットポイントに比例します。負荷過渡は、この負荷電流のセットポイントの短時間の変化によるもの、つまりITH電圧の一次導関数の負のスパイクになります。

LTC3839は、過渡検出(DTR)ピンを使ってITH電圧の一次導関数をモニタし、負荷開放過渡を検出します。「機能図」に示すように、DTRピンはDTRコンパレータの入力であり、DTRコンパレータの内部リファレンス電圧はINTV<sub>CC</sub>の半分です。このピンを過渡検出に使用するには、「機能図」に示すように、ITH補償回路で追加のR<sub>ITH</sub>抵抗をINTV<sub>CC</sub>に接続し、ITH補償部品C<sub>ITH1</sub>、R<sub>ITH1</sub>、およびR<sub>ITH2</sub>の接続点をDTRに接続する必要があります。ここで、DTRピンは、C<sub>ITH1</sub>と(R<sub>ITH1</sub>//R<sub>ITH2</sub>)のハイパス・フィルタを流れるインダクタ電流のセットポイントの一次導関数に比例します。

2本のR<sub>ITH</sub>抵抗は、INTV<sub>CC</sub>からSGNDへの分圧器を構成し、DTRピンの(定常負荷またはITH電圧での)DC電圧をINTV<sub>CC</sub>の半分よりわずかに高い電圧にバイアスします。補償性能は、従来の1本の抵抗のOPTI-LOOP補償に使われているものと同じC<sub>ITH1</sub>を使用し、R<sub>ITH1</sub>//R<sub>ITH2</sub>をR<sub>ITH</sub>と同じ値にすることにより、OPTI-LOOP補償と等価になります。これにより、DTR時間に必要なR-C時定数も得られます。DTRの感度は、DTRとINTV<sub>CC</sub>の半分の間のDCバイアス電圧の差によって調整することができます。この差は、DC負荷電流によるITHリップル電圧がDTRをトリガしない限り、最小200mVに設定可能です。DTRピンから流れる5μAのプルアップ

電流によって抵抗分割器の上側にオフセットが追加されるので、DTRピンのDCバイアス電圧とINTV<sub>CC</sub>の半分の間の全電圧差が以下のようになることに注意してください。

$$V_{DTR(DC)} - 0.5 \cdot V_{INTVCC} = [R_{ITH1}/(R_{ITH1} + R_{ITH2}) - 0.5] \cdot 5.3V + 5\mu A \cdot (R_{ITH1}/R_{ITH2})$$

図12示すように、負荷電流が急に減少すると、 $V_{OUT}$ にオーバーシュートが生じてITHが急激に減少します。DTRピンがコンデンサを介してITHピンに接続されているので、DTRピンの電圧も急激に降下します。負荷過渡が十分に高速でDTR電圧がINTV<sub>CC</sub>の半分を下回ると、負荷開放の発生が検出されます。ボトム・ゲート(BG)がオフするので、ボトムMOSFETのボディー・ダイオードにインダクタ電流が流れます。これにより、SWノードは順方向導通シリコン・ダイオードの電圧降下分PGNDを下回ります。これにより、インダクタ両端に大きな負の電圧差( $V_{SW}-V_{OUT}$ )が生じることによってインダクタ電流を速い速度でゼロまで減少させられるので、 $V_{OUT}$ に生じるオーバーシュートが小さくなります。

DTRコンパレータの出力は、逆インダクタ電流検出( $I_{REV}$ )と過電圧(OV)状態によって無効になります。これは、OV状態でない限り、SENSE<sup>+</sup>がSENSE<sup>-</sup>より高い(つまり、インダクタ電流が正)ときにBGがオフすることを意味します。インダクタ電流がゼロまで減少して反転し始めると、DTRがINTV<sub>CC</sub>の半分を下回ったままで、BGは強制連続モード(たとえば、MODE/PLLINピンがINTV<sub>CC</sub>に接続されているか、または入力クロックが与えられている状態)でオン状態に戻ります。これは、イン

図12. 負荷開放過渡検出(DTR)機能のイネーブル時とディスエーブル時の比較

## アプリケーション情報

ダクタ電流を負にして、V<sub>OUT</sub>のオーバーシュートを短時間でプルダウンするためです。もちろん、MODE/PLLINピンが不連続モードに設定される(つまり、SGNDに接続される)と、インダクタ電流が反転しても、DTR機能がディスエーブルされたとき同様に、BGはオフ状態のままでです。

また、V<sub>OUT</sub>がOVの範囲(標準7.5%)より高くなると、DTR機能が無効になるのでBGはオンします。したがって、V<sub>OUT</sub>のオーバーシュートを低減するDTR機能を有効にするには、OVがトリガされないように、アプリケーションに十分な出力容量を使用する必要があります。これは、オーバーシュートが抑制された望みの負荷ステップを使用し、実験に基づいてテストするのが最善です。

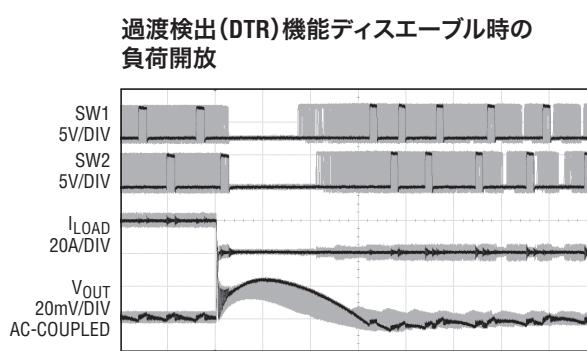

この過渡検出機能は、オーバーシュートのピーク電圧を大幅に下げるだけでなく回復時間を大幅に短縮します(「標準的性能特性」を参照)。

このDTR機能によってボディー・ダイオードの導通によるボトムMOSFETの追加損失が生じることが予想される点に注意してください。頻繁に大きな負荷ステップを生じる負荷では、ボトムMOSFETの温度が高くなる可能性があります。これは、設計に関する重要な検討事項です。デューティ・サイクルが50%で周波数が100kHzの、100%～50%の連続負荷ステップ・パルス列が出力に与えられるときの実験では20°Cの上昇が見られます。

このDTR機能が不要な場合、DTRピンをINTV<sub>CC</sub>に接続するか、または2.5μAの内部電流源がそれ自体をINTV<sub>CC</sub>にプルアップするようにDTRピンを開放のままするだけで、この機能をディスエーブルすることができます。

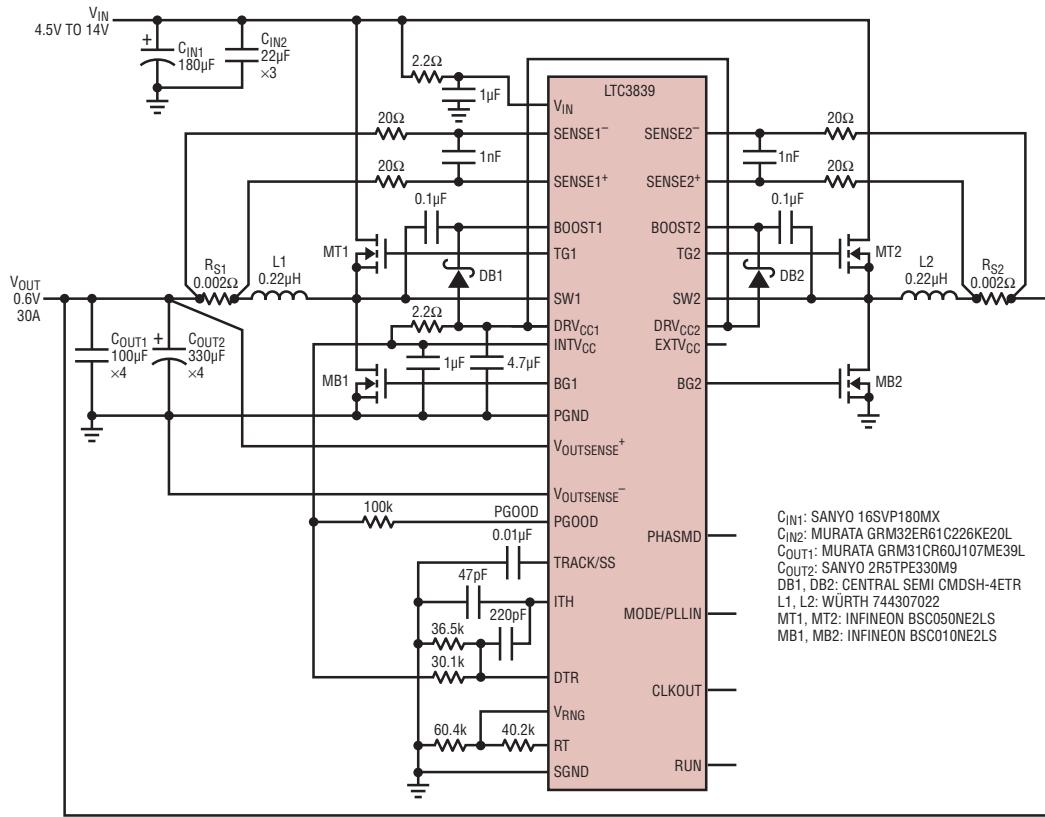

### 効率に関する検討事項

スイッチング・レギュレータのパーセント表示の効率は、出力電力を入力電力で割って100%を掛けたものに等しくなります。多くの場合、何が効率を制限しているのかを特定し、どのような変更を行えば効率を最大限に改善できるのかを判断するには、個々の損失を分析することが有効です。パーセント表示の効率は次式で表すことができます。

$$\% \text{ 効率} = 100\% - (L1\% + L2\% + L3\% + \dots)$$

ここで、L1%、L2%などは入力電力に対するパーセンテージで表した個々の損失です。回路内の電力を消費するすべての要素で電力損失が生じますが、通常、LTC3839の回路の損失の大部分はいくつかの主な損失要因によって生じます。

1. I<sup>2</sup>R損失。この損失は、MOSFETのDC抵抗、インダクタ、電流センス抵抗によって生じ、高出力電流時の電力損失の大部分を占めます。連続モードではインダクタLに平均出力電流が流れますが、この電流はトップMOSFETとボトムMOSFETの間で「こま切れ」にされます。2個のMOSFETのR<sub>D(S)</sub>(ON)がほぼ同じ場合は、1個のMOSFETの抵抗にインダクタのDC抵抗(DCR)と基板トレースの抵抗を加えるだけで、I<sup>2</sup>R損失が得られます。たとえば、それぞれR<sub>D(S)</sub>(ON) = 8mΩ、R<sub>L</sub> = 5mΩ、R<sub>SENSE</sub> = 2mΩとすると、出力電流が1A～10Aで変化する場合の損失の範囲は15mW～1.5Wになります。この結果、損失は、5V出力で0.3%～3%に、または1.5V出力で1%～10%になります。効率は外付け部品と出力電力レベルが同じ場合は、V<sub>OUT</sub>の2乗に反比例して変化します。低出力電圧と高電流の負荷要件の相乗効果が、スイッチング・レギュレータ・システムのこの損失項で重要になります。

2. 遷移損失。この損失のほとんどは、スイッチ・ノードの遷移時に飽和(ミラー)領域でトップMOSFETが費やすわずかな時間によって生じます。この損失は特に、入力電圧、負荷電流、ドライバ能力、MOSFETの容量の各要因に左右され、入力電圧が高くなるか、またはスイッチング周波数が高くなると顕著になる可能性があります。

3. DRV<sub>CC</sub>電流。これはMOSFETドライバ電流とINTV<sub>CC</sub>制御電流の和です。MOSFETドライバ電流は、パワーMOSFETのゲート容量をスイッチングすることによって流れます。MOSFETのゲートが“L”から“H”、そして再び“L”に切り替わるたびに、DRV<sub>CC</sub>からグランドに一定量の電荷dQが移動します。それによって生じるdQ/dtはDRV<sub>CC</sub>から流出する電流であり、通常はコントローラのI<sub>Q</sub>電流よりもはるかに大きくなります。連続モードでは、

$$I_{GATECHG} = f \cdot (Q_{g(TOP)} + Q_{g(BOT)}) \text{ であり、}$$

ここで、Q<sub>g(TOP)</sub>とQ<sub>g(BOT)</sub>はそれぞれトップMOSFETとボトムMOSFETのゲート電荷です。

EXTV<sub>CC</sub>を介してDRV<sub>CC</sub>に電力を供給すると、効率を数パーセント向上させることができます。これはV<sub>IN</sub>の高いアプリケーションで特に顕著です。EXTV<sub>CC</sub>を出力から得られるソースに接続すると、ドライバ回路と制御回路に必要なV<sub>IN</sub>電流は(デューティ・サイクル)/(効率)を比例係数にして減少します。たとえば、20Vから5Vのアプリケーション

## アプリケーション情報

では、DRV<sub>CC</sub>電流が10mAのときは、V<sub>IN</sub>電流は約2.5mAになります。これにより、中間電流損失が10%以上(ドライバがV<sub>IN</sub>から直接電力を供給されている場合)からわずか数パーセントまで減少します。

4. C<sub>IN</sub>損失。入力コンデンサは、レギュレータによって電源からの平均DC電流に流れ込む大きな方形波入力電流を除去します。コンデンサ自体には平均DC電流は流れませんが、方形波のようなAC電流が流れます。したがって、入力コンデンサは、ESRを非常に小さくしてESRのRMS電流損失を最小限に抑える必要があります。また、入力コンデンサには、上流にあるケーブル、ヒューズ、バッテリなどに追加RMS損失が生じないように、入力電流のAC成分を除去するだけの十分な容量が必要です。LTC3839のPolyPhaseアーキテクチャによってESR損失が改善されます。

DC電流の場合でも、「隠れた」銅トレース、ヒューズ、およびバッテリの抵抗により、大きな効率低下を生じる可能性があるので、設計段階ではこれらを考慮することが重要です。C<sub>OUT</sub>のESR損失、ボトムMOSFETのボディー・ダイオードの逆回復損失、インダクタのコア損失などのその他の損失が占めるのは、通常、追加損失の2%以下です。

スイッチング・レギュレータの電力損失は、固定周波数の場合、理想値より高いデューティ・サイクル、つまり長いオン時間として反映されます。この効率を考慮に入れたオン時間は次式で計算できます。

$$t_{ON} \approx t_{ON(IDEAL)} / \text{Efficiency}$$

効率を改善するための調整を行う場合は、入力電流が効率の変化を示す最適な指標になります。変更を加えて入力電流が減少すれば、効率は向上しています。

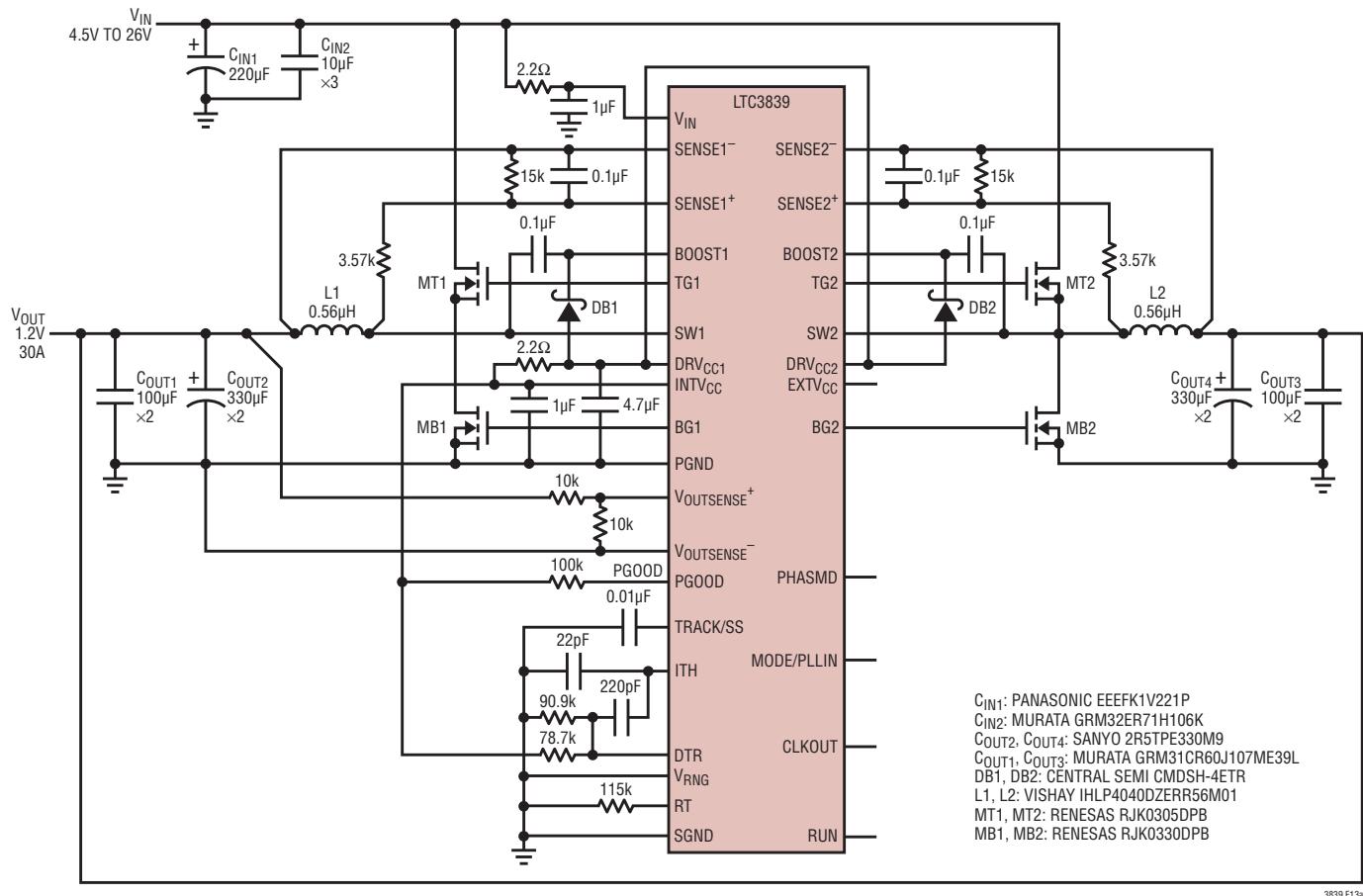

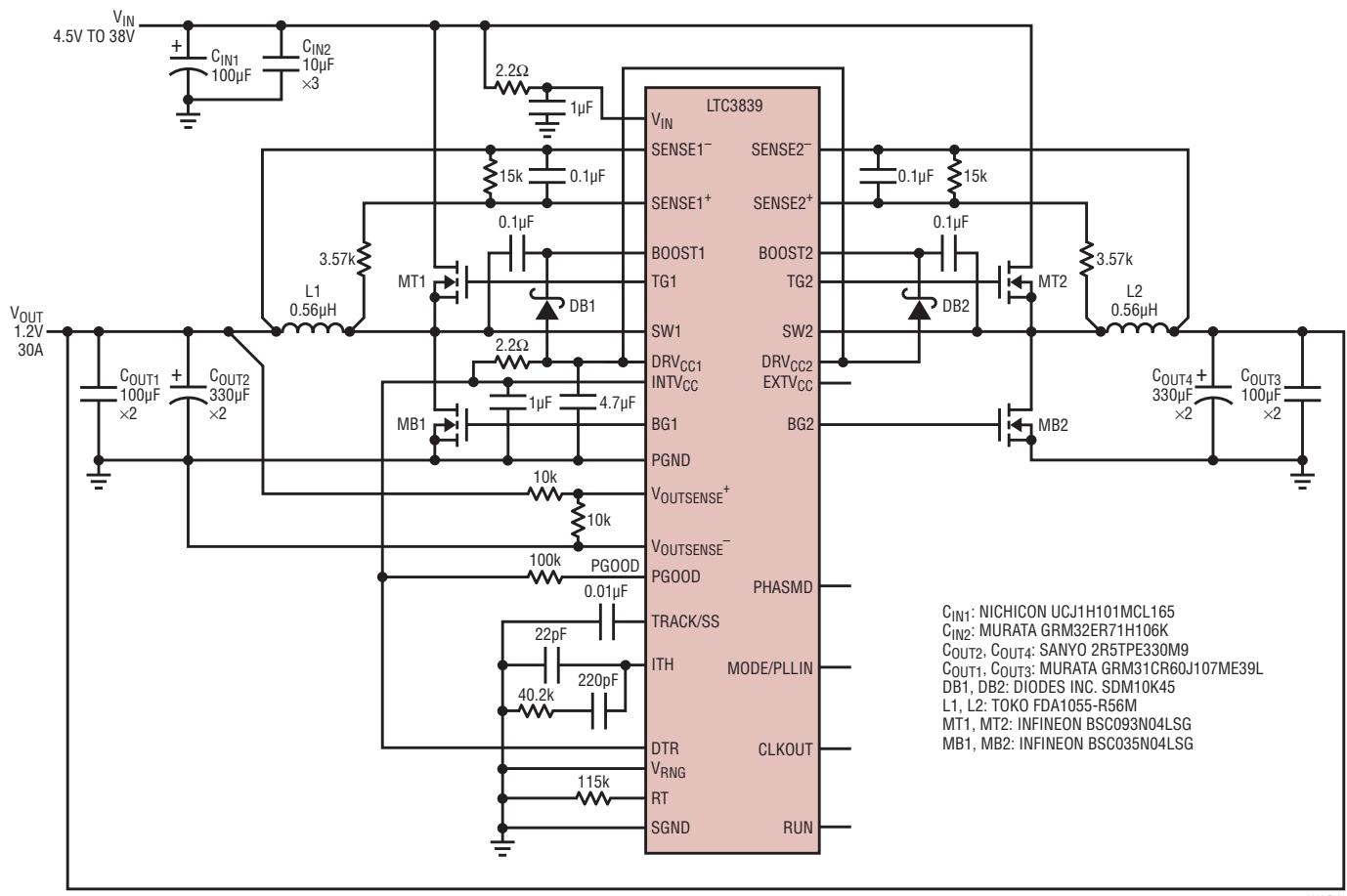

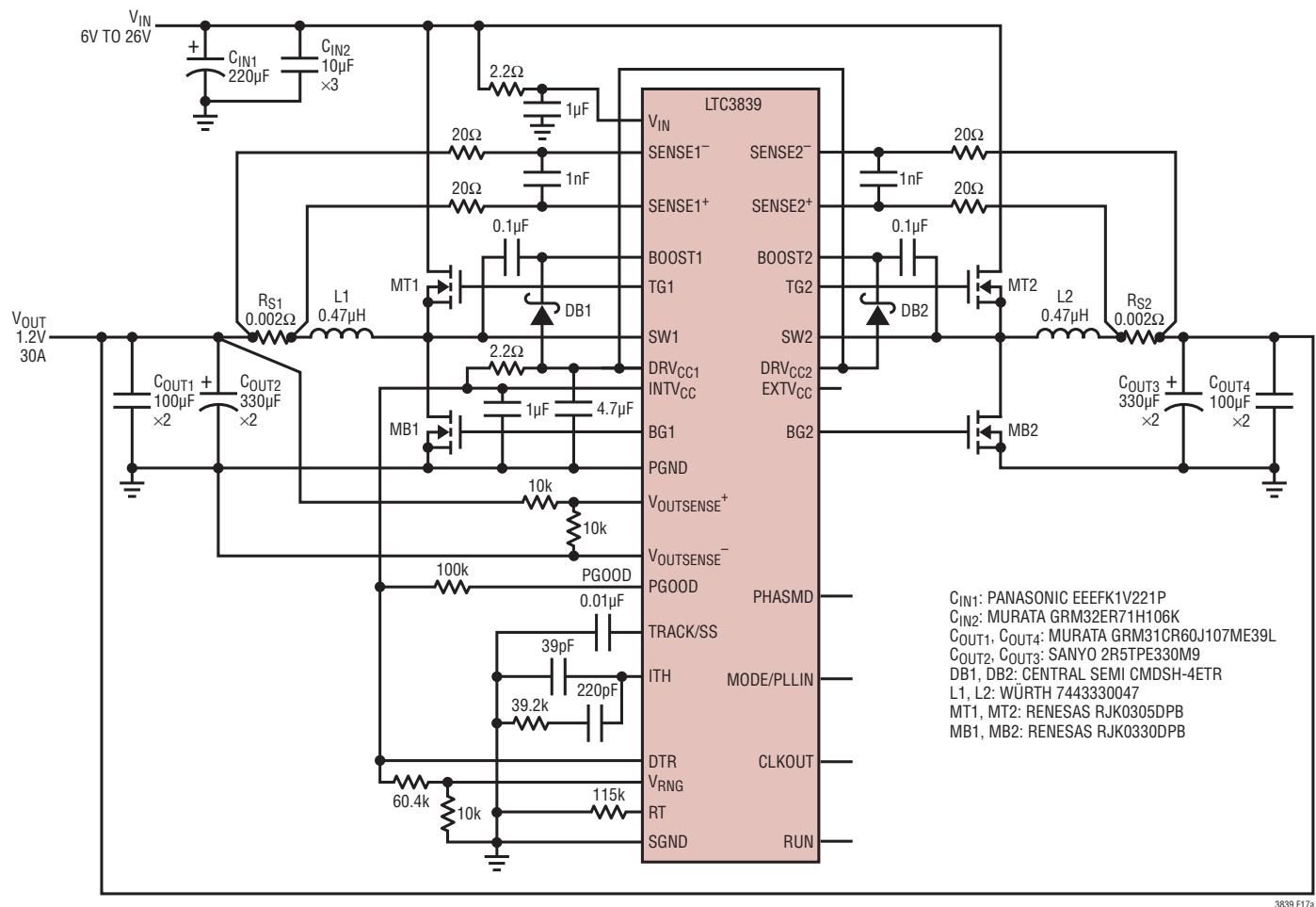

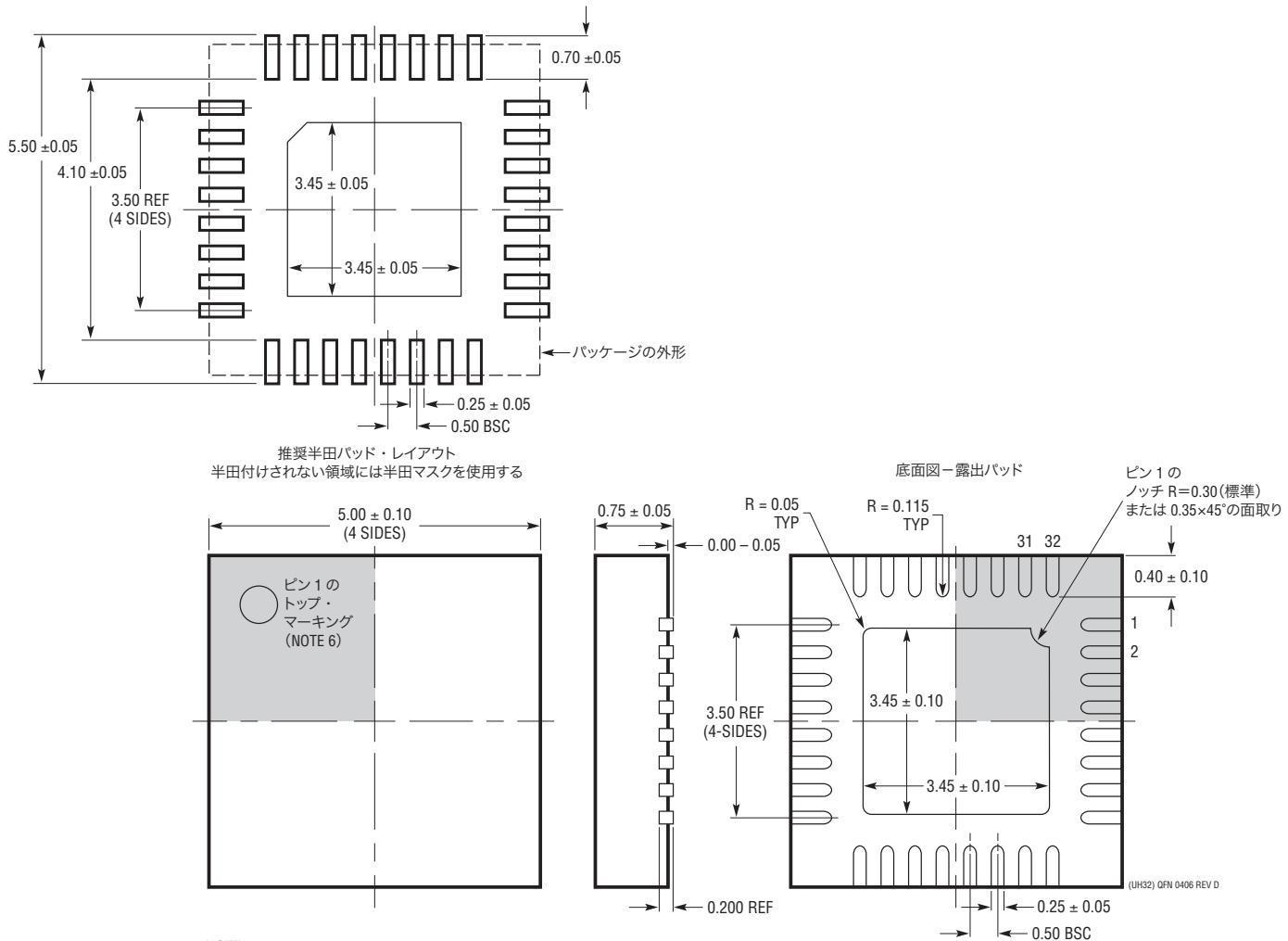

### 設計例

I<sub>OUT</sub>(MAX) = 30Aとf = 350kHzで、V<sub>IN</sub> = 4.5V ~ 26VからV<sub>OUT</sub> = 1.2Vの2フェーズ降圧コンバータを考えます(図13を参照)。

安定化出力電圧は次式で求められます。

$$V_{OUT} = 0.6V \cdot \left( 1 + \frac{R_{FB2}}{R_{FB1}} \right)$$

R<sub>FB1</sub>に10k抵抗を、R<sub>FB2</sub>にも10k抵抗を使用します

周波数は次式で設定されます。

$$R_T [k\Omega] = \frac{41550}{f [kHz]} - 2.2 = \frac{41550}{350} - 2.2 \approx 116.5$$

これに最も近い1%抵抗の標準値である115kを使用します。最小オン時間は最大V<sub>IN</sub>になるように発生します。「標準的性能特性」のt<sub>ON(MIN)</sub>のグラフを参照して、最大V<sub>IN</sub>でのt<sub>ON(MIN)</sub>をLTC3839で実現できる値よりも長くし、デッドタイム(「電気的特性」のt<sub>D(TG/BG)</sub> + t<sub>D(TG/BG)</sub>)によって軽負荷時の有効オン時間が長くなることを考慮して十分なマージンを持たせるようにします。このアプリケーションの最小オン時間は次のようになります。

$$t_{ON(MIN)} = \frac{V_{OUT}}{V_{IN(MAX)} \cdot f} = \frac{1.2V}{24V \cdot 350kHz} = 143ns$$

調整された動作周波数を使って、最大V<sub>IN</sub>でのシングルフェーズ(30A/2 = 15A)のリップル電流が40%となるようにインダクタ値を設定します。

$$L = \left( \frac{1.2V}{350kHz \cdot 40\% \cdot 15A} \right) \left( 1 - \frac{1.2V}{24V} \right) = 0.54\mu H$$

これに最も近い標準値である0.56μHを選択します。

この結果生じる最大リップル電流は次の通りです。

$$\Delta I_L = \left( \frac{1.2V}{350kHz \cdot 0.56\mu H} \right) \left( 1 - \frac{1.2V}{24V} \right) = 5.8A$$

多くの場合、高電力アプリケーションで効率を最大にするには、R<sub>SENSE</sub>による電流センスよりもDCRによる電流センスの方が適しています。DCRフィルタの値を決定するには、まずインダクタのメーカを選択する必要があります。この設計例では、値が0.56μHでDCR<sub>MAX</sub> = 1.8mΩのVishayのIHLP-4040DZ-01モデルを選択します。これから次の値が得られます。

$$V_{SENSE(MAX)} = 1.8m\Omega \cdot [1 + (100^\circ C - 25^\circ C) \cdot 0.4\%/\text{ }^\circ C] \\ \cdot (15A - 5.8A/2) = 28mV$$

最大検出電圧V<sub>SENSE</sub>(MAX)は、追加調整を行なわなくても LTC3839が対応できる範囲内にあります。したがって、DCR

# LTC3839

## アプリケーション情報

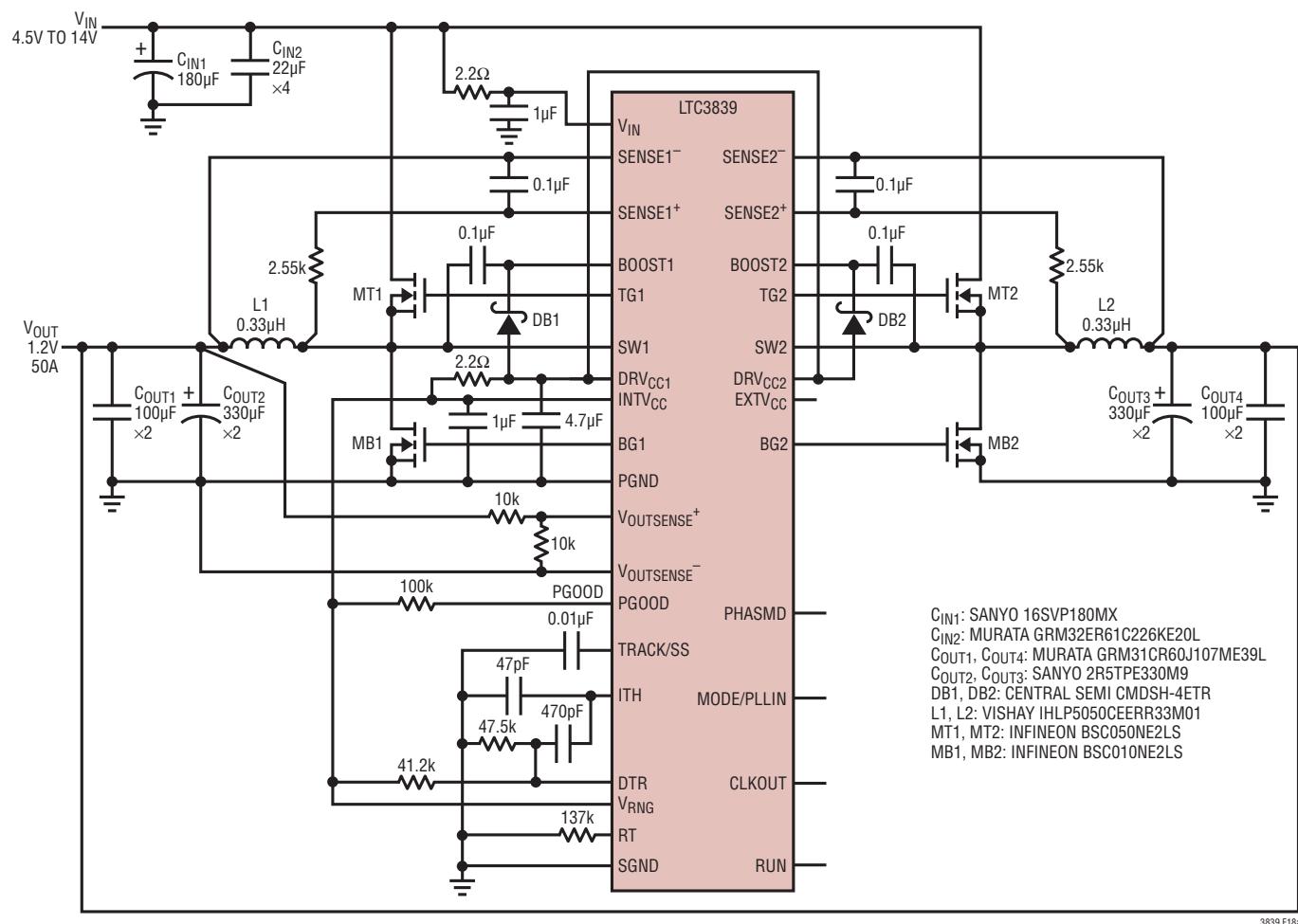

図13. 設計例: DCRによる検出を行い、DTRがイネーブルされた、4.5V～26V入力、1.2V/30A出力、350kHz降圧コンバータ

## アプリケーション情報

フィルタにはインダクタ両端の単純なRCフィルタを使用することができます。Cに $0.1\mu\text{F}$ を選択すると、Rは次のように計算できます。

$$R_{DCR} = \frac{L}{DCR \cdot C_{DCR}} = \frac{0.56\mu\text{H}}{1.8\text{m}\Omega \cdot 0.1\mu\text{F}} = 3.1\text{k}\Omega$$

その結果、 $V_{RNG}$ ピンの電圧は次のようになります。

$$V_{RNG} = \frac{V_{SENSE(MAX)}}{0.05} = 28\text{mV} \cdot 20 = 0.56\text{V}$$

この電圧は、 $\text{INTV}_{CC}$ ピン(5.3V)または $\text{RT}$ ピン(1.2V)から信号グランド(SGND)への抵抗分割器を使って生成することができます。 $V_{IN}$ が下がることによって $\text{INTV}_{CC}$ が低くなるなど、あらゆる条件で最大負荷電流を供給可能にし、デバイス自体の $V_{SENSE}(MAX)$ の変動が規定値以内になるように、 $V_{RNG}$ を高くしてマージンを確保する必要があります。

$V_{RNG}$ を設定するのに推奨される望ましい方法は、單に $V_{RNG}$ ピンをSGNDに接続して0.6Vに等しくなるようにすることですが、最大出力電流を保証するために、「DCRによるインダクタ電流検出」で説明したように、DCRフィルタに抵抗を追加して、デバイス自体の $V_{SENSE}(MAX)$ の規定値の下限を十分なマージンだけ下回る値に $V_{SENSE}(MAX)$ をスケールダウンします。