## 特長

- 電流センス抵抗が不要

- 位相非同調コントローラにより、必要な入力容量を低減

- $V_{OUT2} = 1/2 V_{REF}$

- 対称のソース/シンク出力電流が可能( $V_{OUT2}$ )

- スペクトル拡散動作(イネーブル時)

- 広い入力電圧範囲:2.75V~9.8V

- 固定周波数電流モード動作

- $\pm 1.5\%$ 精度の0.6V電圧リファレンス( $V_{OUT1}$ )

- 低損失動作:100%デューティ・サイクル

- 真のPLLにより、周波数の固定や調整が可能

- ソフトスタート回路を内蔵

- パワーグッド出力電圧モニタ

- 出力過電圧保護

- マイクロパワーのシャットダウン: $I_Q = 9\mu A$

- 高さの低い小型(4mm×4mm)QFNパッケージと細型SSOPパッケージ

## アプリケーション

- DDR、DDR IIおよびQDRメモリ

- SSTL、HSTL終端電源

- サーバ、RAIDシステム

- DC配電システム

## 概要

LTC<sup>®</sup>3776は、DDR/QDRメモリ終端アプリケーション向けの2フェーズ、デュアル出力、同期整流式降圧スイッチング・レギュレータ・コントローラです。第2のコントローラは出力電圧を1/2 $V_{REF}$ に安定化し、対称のソース/シンク出力電流を供給できます。

NO R<sub>SENSE</sub>固定周波数電流モード・アーキテクチャにより、センス抵抗が不要で、効率が向上します。2つのコントローラを位相をずらして動作させることによって、入力コンデンサのESRによる電力損失とノイズを最小に抑えます。

スイッチング周波数を最大750kHzまでプログラム可能なので、小型の表面実装インダクタやコンデンサを使用可能です。また、スイッチング周波数を250kHz~850kHzの範囲で外部同期させたり、スペクトル拡散動作作用にイネーブルすることができるので、ノイズに敏感なアプリケーションに適しています。強制連続動作によってノイズやRF干渉を低減します。 $V_{OUT1}$ 用のソフトスタート機能は内蔵されていますが、外付けコンデンサを使用して拡張できます。

LTC3776は、熱特性が改善された小型の(4mm×4mm)QFNパッケージまたは24ピン細型SSOPパッケージで供給されます。

**L**、**LT**、**LTC**および**LTM**はリニアテクノロジー社の登録商標です。

Burst Modeはリニアテクノロジー社の登録商標です。

No R<sub>SENSE</sub>はリニアテクノロジー社の商標です。

他の全ての商標はそれぞれの所有者に所有権があります。

5481178、5929620、6144194、6580258、6304066、6611131、6498466を含む米国特許により保護されています。

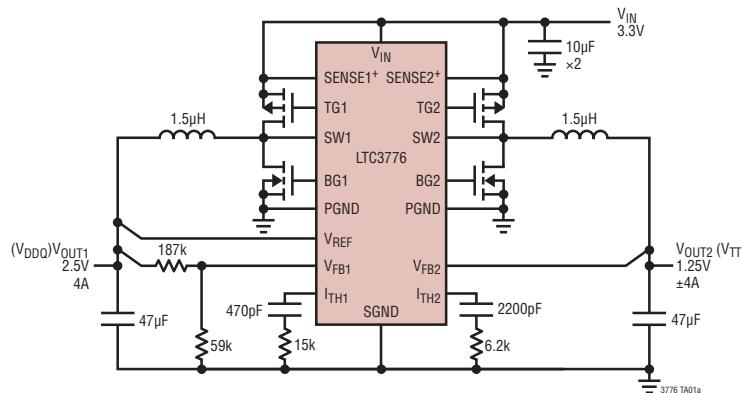

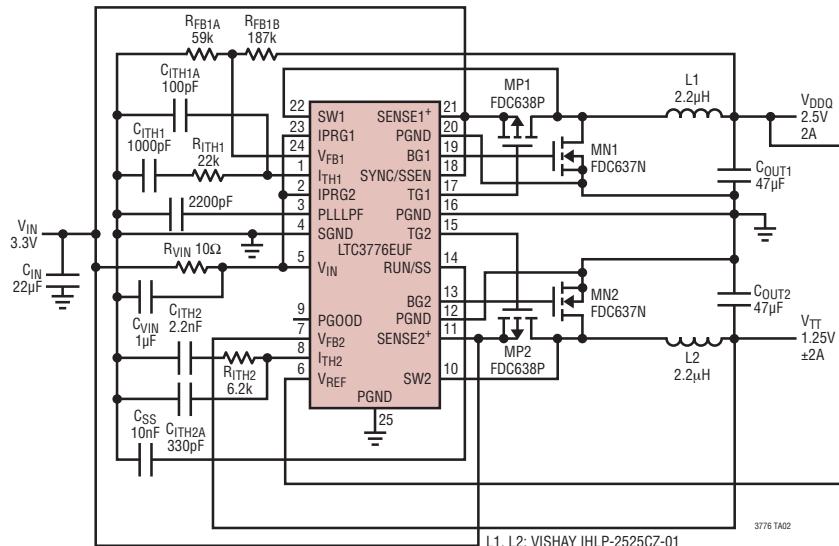

## 標準的応用例

### 高効率、2フェーズ、DDRメモリ( $V_{DDQ}$ と $V_{TT}$ )電源

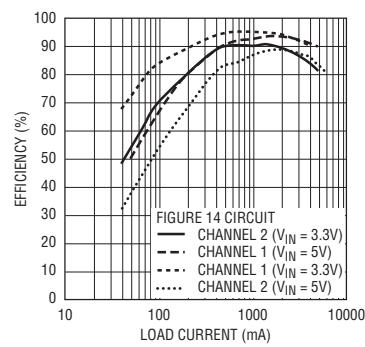

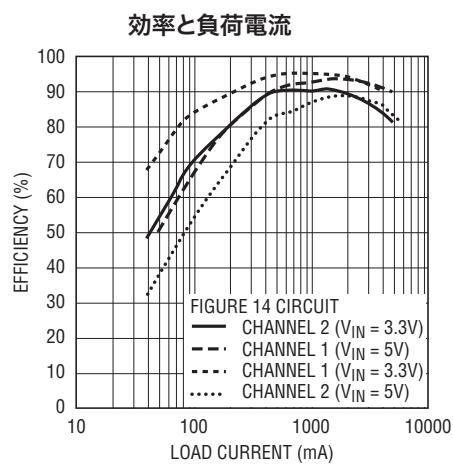

### 効率と負荷電流

3776 TA01b

## 絶対最大定格 (Notes 1)

|                                                                                              |                          |

|----------------------------------------------------------------------------------------------|--------------------------|

| 入力電源電圧 ( $V_{IN}$ )                                                                          | -0.3V~10V                |

| PLLPPF, RUN/SS, SYNC/SSEN, $V_{REF}$ , SENSE1 <sup>+</sup> , SENSE2 <sup>+</sup> , $V_{FB2}$ |                          |

| IPRG1, IPRG2の電圧                                                                              | -0.3V~( $V_{IN}$ +0.3V)  |

| $V_{FB1}$ , $I_{TH1}$ , $I_{TH2}$ の電圧                                                        | -0.3V~2.4V               |

| SW1, SW2の電圧                                                                                  | -2V~ $V_{IN}$ +1V(最大10V) |

| PGOOD                                                                                        | -0.3V~10V                |

|                                    |             |

|------------------------------------|-------------|

| TG1, TG2, BG1, BG2のピーク出力電流 (<10μs) | 1A          |

| 動作温度範囲 (Note 2)                    | -40°C~85°C  |

| 保存温度範囲                             | -65°C~125°C |

| 接合部温度 (Note 3)                     | 125°C       |

| リード温度 (半田付け、10秒)                   |             |

| (LTC3776EGN)                       | 300°C       |

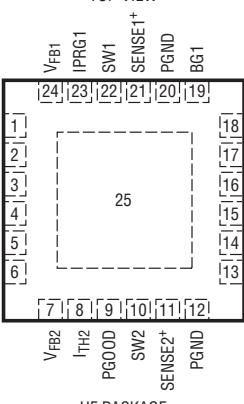

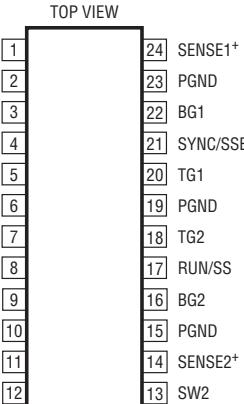

## パッケージ/発注情報

| TOP VIEW                                                                                                                                                                                                                                                               | ORDER PART NUMBER                                                  | TOP VIEW                                                                                                                                                                                          | ORDER PART NUMBER |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| <br>UF PACKAGE<br>24-LEAD (4mm x 4mm) PLASTIC QFN<br>$T_{JMAX} = 125^\circ\text{C}$ , $\theta_{JA} = 37^\circ\text{C/W}$<br>EXPOSED PAD (PIN 25) IS PGND,<br>MUST BE SOLDERED TO PCB | <b>LTC3776EUF</b><br><br><b>UF PART MARKING</b><br><br><b>3776</b> | <br>GN PACKAGE<br>24-LEAD PLASTIC SSOP<br>$T_{JMAX} = 125^\circ\text{C}$ , $\theta_{JA} = 130^\circ\text{C/W}$ | <b>LTC3776EGN</b> |

より広い動作温度範囲で規定されるデバイスについては、弊社へお問い合わせください。

## 電気的特性

- は全動作温度範囲の規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。

- 注記がない限り、 $V_{IN} = 4.2\text{V}$ 。

| PARAMETER                                    | CONDITIONS                                                                                    | MIN    | TYP            | MAX          | UNITS          |

|----------------------------------------------|-----------------------------------------------------------------------------------------------|--------|----------------|--------------|----------------|

| <b>メイン制御ループ</b>                              |                                                                                               |        |                |              |                |

| Input DC Supply Current                      | (Note 4)                                                                                      |        |                |              |                |

| Normal Operation                             | $I_{TH1} = I_{TH2} = 1.3\text{V}$                                                             |        |                | 575          | 850            |

| Shutdown                                     | RUN/SS = 0V                                                                                   |        |                | 9            | 20             |

| UVLO                                         | $V_{IN} < \text{UVLO Threshold} -200\text{mV}$                                                |        |                | 3            | 10             |

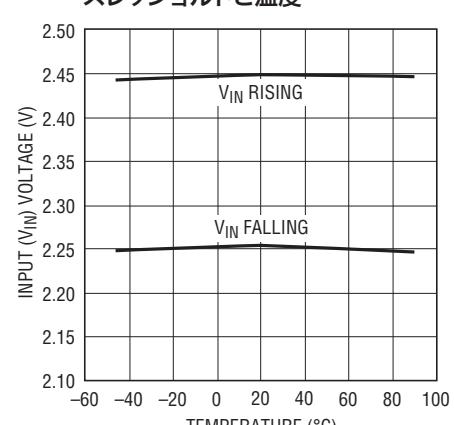

| Undervoltage Lockout Threshold               | $V_{IN}$ Falling<br>$V_{IN}$ Rising                                                           | ●<br>● | 1.95<br>2.15   | 2.25<br>2.45 | 2.55<br>2.75   |

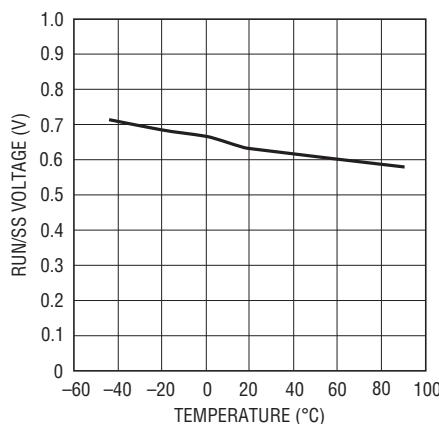

| Shutdown Threshold at RUN/SS                 |                                                                                               |        | 0.45           | 0.65         | 0.85           |

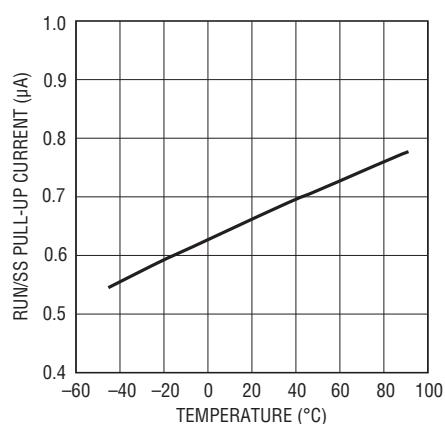

| Start-Up Current Source                      | RUN/SS = 0V                                                                                   |        | 0.4            | 0.7          | 1              |

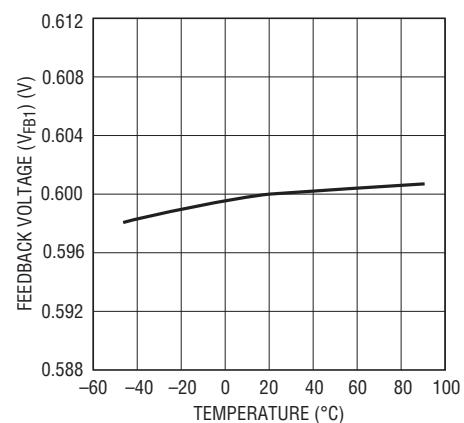

| Regulated Feedback Voltage ( $V_{FB1}$ )     | $0^\circ\text{C}$ to $85^\circ\text{C}$ (Note 5)<br>$-40^\circ\text{C}$ to $85^\circ\text{C}$ | ●<br>● | 0.591<br>0.588 | 0.6<br>0.6   | 0.609<br>0.612 |

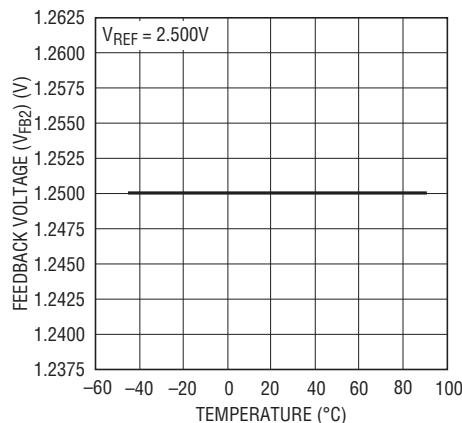

| Regulated Feedback Voltage ( $V_{FB2}$ )     | $V_{REF} = 2.5\text{V}$                                                                       | ●      | 1.232          | 1.250        | 1.268          |

| Output Voltage Line Regulation ( $V_{FB1}$ ) | $2.75\text{V} < V_{IN} < 9.8\text{V}$ (Note 5)                                                |        |                | 0.05         | 0.2            |

| Output Voltage Line Regulation ( $V_{FB2}$ ) |                                                                                               |        |                | 0.02         | 0.1            |

3776fa

## 電気的特性

●は全動作温度範囲の規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。

注記がない限り、 $V_{IN} = 4.2\text{V}$ 。

| PARAMETER                                                                                                       | CONDITIONS                                                      | MIN         | TYP                 | MAX                 | UNITS          |    |

|-----------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|-------------|---------------------|---------------------|----------------|----|

| Output Voltage Load Regulation                                                                                  | $I_{TH} = 0.9\text{V}$ (Note 5)<br>$I_{TH} = 1.7\text{V}$       |             | 0.12<br>-0.12       | 0.5<br>-0.5         | %<br>%         |    |

| $V_{FB1}$ Input Current                                                                                         | (Note 5)                                                        |             | 10                  | 50                  | nA             |    |

| Overvoltage Protect Threshold                                                                                   | Measured at $V_{FB}$ with Respect to Regulated Feedback Voltage | 10          | 13.3                | 16                  | %              |    |

| Overvoltage Protect Hysteresis                                                                                  |                                                                 |             | 3                   |                     | %              |    |

| Top Gate (TG) Drive 1, 2 Rise Time                                                                              | $C_L = 3000\text{pF}$                                           |             | 40                  |                     | ns             |    |

| Top Gate (TG) Drive 1, 2 Fall Time                                                                              | $C_L = 3000\text{pF}$                                           |             | 40                  |                     | ns             |    |

| Bottom Gate (BG) Drive 1, 2 Rise Time                                                                           | $C_L = 3000\text{pF}$                                           |             | 50                  |                     | ns             |    |

| Bottom Gate (BG) Drive 1, 2 Fall Time                                                                           | $C_L = 3000\text{pF}$                                           |             | 40                  |                     | ns             |    |

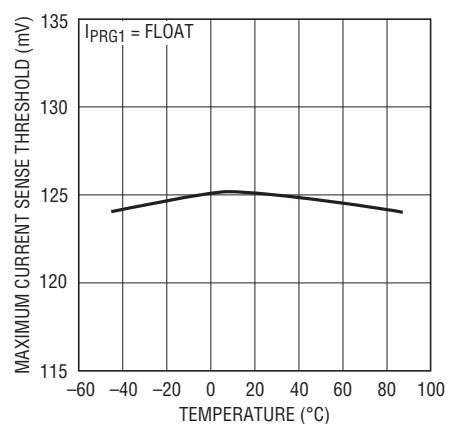

| Maximum Current Sense Voltage (Channel 1)<br>(SENSE1 <sup>+</sup> – SW1)( $\Delta V_{SENSE(MAX)}$ ) (SOURCE)    | IPRG1 = Floating (Note 6)<br>IPRG1 = 0V<br>IPRG1 = $V_{IN}$     | ●<br>●<br>● | 110<br>70<br>185    | 125<br>85<br>204    | mV<br>mV<br>mV |    |

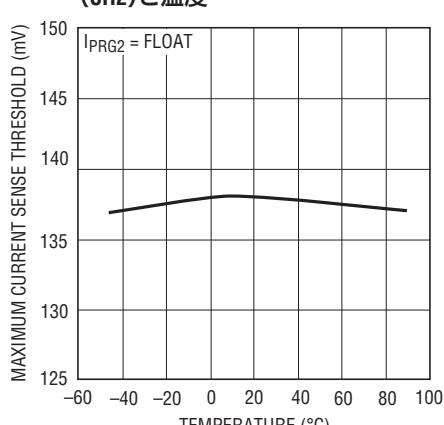

| Maximum Current Sense Voltage (Channel 2)<br>(SENSE2 <sup>+</sup> – SW2)( $\Delta V_{SENSE(MAX)}$ ) (SOURCE)    | IPRG2 = Floating (Note 6)<br>IPRG2 = 0V<br>IPRG2 = $V_{IN}$     | ●<br>●<br>● | 127<br>85<br>215    | 147<br>100<br>245   | mV<br>mV<br>mV |    |

| Minimum Current Sense Voltage (Channel 2 Only)<br>(SENSE2 <sup>+</sup> – SW2)( $\Delta V_{SENSE(MAX)}$ ) (SINK) | IPRG2 = Floating (Note 6)<br>IPRG2 = 0V<br>IPRG2 = $V_{IN}$     | ●<br>●<br>● | -130<br>-90<br>-208 | -112<br>-75<br>-188 | mV<br>mV<br>mV |    |

| Soft-Start Time                                                                                                 | Time for $V_{FB1}$ to Ramp from 0.05V to 0.55V                  |             | 0.667               | 0.833               | 1              | ms |

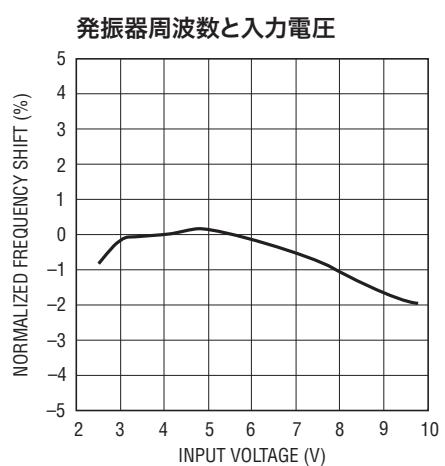

## 発振器とフェーズロック・ループ

|                                                      |                                                                                                     |             |                   |                   |                   |                                |

|------------------------------------------------------|-----------------------------------------------------------------------------------------------------|-------------|-------------------|-------------------|-------------------|--------------------------------|

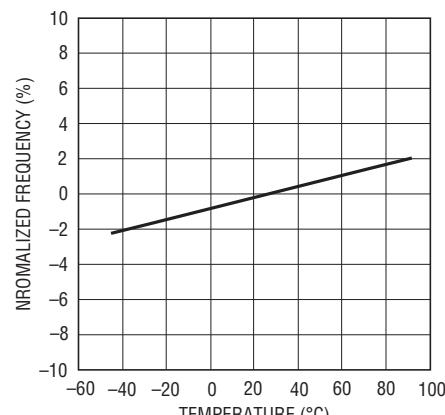

| Oscillator Frequency                                 | Spread Spectrum Disabled (SYNC/SSEN = GND)<br>PLL1PF = Floating<br>PLL1PF = 0V<br>PLL1PF = $V_{IN}$ | ●<br>●<br>● | 460<br>260<br>650 | 550<br>300<br>750 | 610<br>340<br>825 | kHz<br>kHz<br>kHz              |

| Spread Spectrum Frequency Range                      | SYNC/SSEN = $V_{IN}$<br>Minimum Switching Frequency<br>Maximum Switching Frequency                  |             |                   | 450<br>580        |                   | kHz<br>kHz                     |

| Phase-Locked Loop Lock Range                         | SYNC/SSEN Clocked<br>Minimum Synchronizable Frequency<br>Maximum Synchronizable Frequency           | ●<br>●      | 850               | 200<br>1150       | 250               | kHz<br>kHz                     |

| Phase Detector Output Current<br>Sinking<br>Sourcing | $f_{OSC} > f_{SYNC/FCB}$<br>$f_{OSC} < f_{SYNC/FCB}$                                                |             |                   | -4<br>4           |                   | $\mu\text{A}$<br>$\mu\text{A}$ |

## PGOOD出力

|                   |                                                                                                                                                                                                                                                                                         |                       |                                |                       |                  |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|--------------------------------|-----------------------|------------------|

| PGOOD Voltage Low | $I_{PGOOD}$ Sinking 1mA                                                                                                                                                                                                                                                                 |                       | 125                            |                       | mV               |

| PGOOD Trip Level  | $V_{FB}$ with Respect to Set Output Voltage<br>$V_{FB} <$ Regulated Feedback Voltage, Ramping Positive<br>$V_{FB} <$ Regulated Feedback Voltage, Ramping Negative<br>$V_{FB} >$ Regulated Feedback Voltage, Ramping Negative<br>$V_{FB} >$ Regulated Feedback Voltage, Ramping Positive | -13<br>-16<br>7<br>10 | -10.0<br>-13.3<br>10.0<br>13.3 | -7<br>-10<br>13<br>16 | %<br>%<br>%<br>% |

**Note 1:**絶対最大定格に記載された値を超えるストレスはデバイスに永続的損傷を与える可能性がある。長期にわたって絶対最大定格条件に曝すと、デバイスの信頼性と寿命に悪影響を与える可能性がある。

**Note 2:**LTC3776Eは0°C~70°Cの温度範囲で性能仕様に適合することが保証されている。

-40°C~85°Cの動作範囲での仕様は設計、特性評価および統計学的なプロセス・コントロールとの相関で確認されている。

**Note 3:** $T_J$ は周囲温度 $T_A$ および電力損失 $P_D$ から次式に従って計算される。

$$T_J = T_A + (P_D \cdot \theta_J \text{ } ^\circ\text{C/W})$$

**Note 4:**スイッチング周波数で供給されるゲート電荷により動作時消費電流は増える。

**Note 5:**LTC3776は帰還ループを使って $I_{TH}$ を規定電圧にサポートし、そのときの $V_{FB}$ 電圧を測定してテストされる。

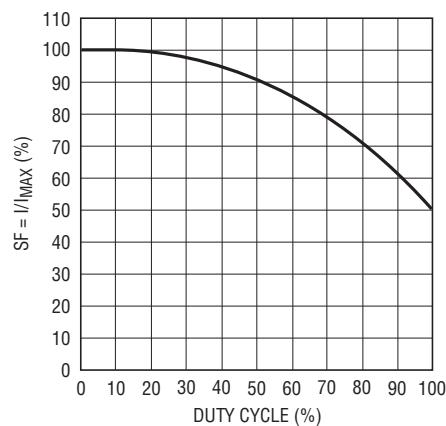

**Note 6:**ピーク電流検出電圧は、デューティ・サイクルに依存して、図2に示されているパーセント値に減少する。

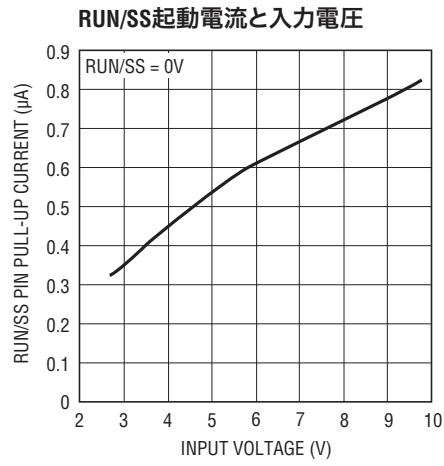

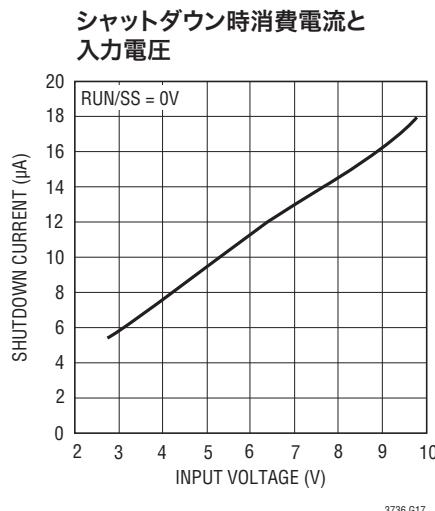

標準的性能特性 注記がない限り、 $T_A = 25^\circ\text{C}$ 。

3776 G01

3776 G06

3776 G07

標準的性能特性 注記がない限り、 $T_A = 25^\circ\text{C}$ 。最大電流検出電圧と $I_{TH2}$ ピンの電圧(CH2)

安定化された帰還電圧(CH2)と温度

安定化された帰還電圧(CH1)と温度

シャットダウン(RUN)

スレッショルドと温度

RUN/SSのプルアップ電流と温度

最大電流検出スレッショルド(CH1)と温度

最大電流検出スレッショルド(CH2)と温度

発振器周波数と温度

低電圧ロックアウト・

スレッショルドと温度

標準的性能特性 注記がない限り、 $T_A = 25^\circ\text{C}$ 。

## ピン機能 (UF/GNパッケージ)

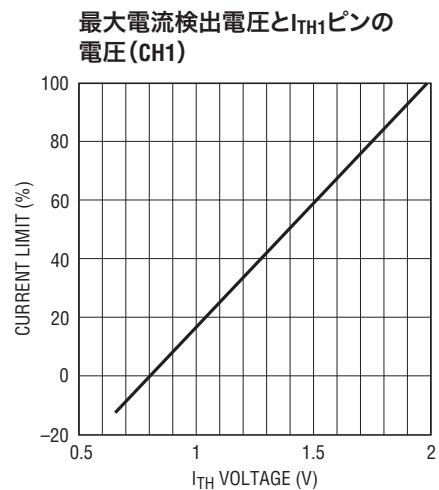

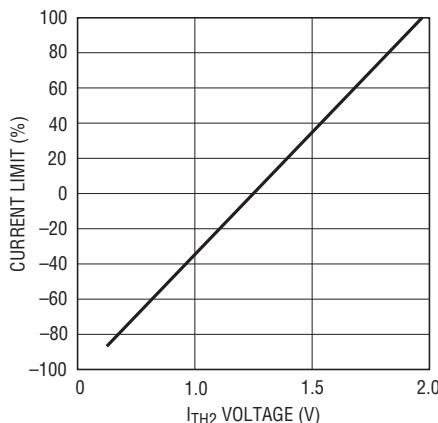

**$I_{TH1}/I_{TH2}$ (ピン1、8/ピン4、11)**：電流スレッショルドおよび誤差アンプの補償点。これらのピンの公称動作範囲は0.7V～2Vです。これらのピンの電圧によりメイン電流コンパレータのスレッショルドが決ります。

**PLL/LPF(ピン3/ピン6)**：周波数設定/PLLのローパス・フィルタ。外部クロックに同期するとき、このピンがフェーズロック・ループのローパス・フィルタ・ポイントとして機能します。通常、このピンとグランド間に直列RCを接続します。

**SYNC/SSEN**がGNDに接続されると、このピンは周波数選択入力として機能します。このピンをGNDに接続すると300kHz動作が選択され、このピンを $V_{IN}$ に接続すると750kHz動作が選択されます。このピンをフロートさせると550kHz動作が選択されます。SYNC/SSENが $V_{IN}$ に接続されて拡散スペクトラム動作がイネーブルされていると、コンデンサ( $1\text{nF}$ ～ $4.7\text{nF}$ )をこのピンからSGNDに接続し、LTC3776の内部発振器の周波数変化をフィルタして平滑化します。

**SGND(ピン4/ピン7)**：小信号グランド。このピンはほとんどの内部回路のグランド接続として機能します。

**$V_{IN}$ (ピン5/ピン8)**：デバイスの信号用電源。このピンはゲート・ドライバを除くデバイス全体に電力を供給します。このピンをローパスRCネットワーク(たとえば、 $R = 10\Omega$ 、 $C = 1\mu\text{F}$ )を使って外部でフィルタして、特に高負荷電流アプリケーションで、ノイズのピックアップを最小に抑えることを推奨します。

**$V_{REF}$ (ピン6/ピン9)**：チャネル2のリファレンス電圧入力。チャネル2の誤差アンプの正入力が、内部抵抗分割器を介してこのピンの電圧の半分を検出します。

**PGOOD(ピン9/ピン12)**：パワーグッド出力電圧モニタのオーブン・ドレインのロジック出力。どちらかの帰還ピン( $V_{FB1}$ 、 $V_{FB2}$ )の電圧が公称設定値の $\pm 13.3\%$ 以内にないとき、このピンはグランドに引き下げられます。

**PGND(ピン12、16、20、25/ピン15、19、23)**：電源グランド。これらのピンはゲート・ドライバと逆電流コンパレータの負入力のグランド接続として機能します。露出パッド(UFパッケージ)はPCBのグランドに半田付けする必要があります。

**RUN/SS(ピン14/ピン17)**：実行制御入力およびオプションの外部ソフトスタート入力。このピンを0.65Vより下に強制すると、デバイス(両方のチャネル)がシャットダウンします。このピンを $V_{IN}$ にドライブするか、またはこのピンを解放すると、デバイス内部のソフトスタートを使ってデバイスをイネーブルします。このピンとグランドの間にコンデンサを接続して、外部ソフトスタートをプログラムすることができます。

**TG1/TG2(ピン17、15/ピン20、18)**：トップ(PMOS)ゲート・ドライバ出力。これらのピンは外部PチャネルMOSFETのゲートをドライブします。これらのピンの出力振幅はPGNDからSENSE<sup>+</sup>までです。

**SYNC/SSEN(ピン18/ピン21)**：同期入力およびスペクトラム拡散変調イネーブル入力。

## ピン機能 (UF/GN/パッケージ)

LTC3776のスイッチング周波数をフェーズロック・ループを使って外部クロックに同期させるには、周波数が250kHz～850kHzのCMOS互換クロックをこのピンに与えます。このピンをGNDに接続して固定周波数動作(PLLFPピンの状態によって定まる300kHz、550kHzまたは750kHz)をイネーブルします。スペクトラム拡散動作をイネーブルするにはこのピンをVINに接続します。スペクトラム拡散モードでは、LTC3776の周波数は450kHz～580kHzでランダムに変化します。

**BG1/BG2(ピン19、13/ピン22、16)**: ボトム(NMOS)ゲート・ドライブ出力。これらのピンは外部NチャネルMOSFETのゲートをドライブします。これらのピンの出力振幅はPGNDからSENSE<sup>+</sup>までです。

**SENSE1<sup>+</sup>/SENSE2<sup>+</sup>(ピン21、11/ピン24、14)**: 差動電流コンパレータの正入力。また、ゲート・ドライバに電力を供給します。通常、外部PチャネルMOSFETのソースに接続します。

**SW1/SW2(ピン22、10/ピン1、13)**: インダクタへのスイッチ・ノードの接続ピン。また、差動ピーク電流コンパレータの負入力および逆電流コンパレータの入力。通常、外部PチャネルMOSFETのドレイン、外部NチャネルMOSFETのドレイン、およびインダクタに接続します。

**IPRG1/IPRG2(ピン23、2/ピン2、5)**: 最大検出電圧スレッショルドを選択するスリーステート・ピン。これらのピンにより、各チャネルのSENSE<sup>+</sup>ピンとSWピン間の最大許容電圧降下(つまり、外部PチャネルMOSFET両端の最大許容電圧降下)が選択されます。VINまたはGNDに接続するか、またはフロートさせて、3つの異なるレベルの1つを選択します。

**V<sub>FB1</sub>/V<sub>FB2</sub>(ピン24、7/ピン3、10)**: 帰還ピン。リモート検出された帰還電圧をコントローラのために受け取ります。

**露出パッド(ピン25/NA)**: 露出パッド(UFパッケージ)はPCBのグランドに半田付けする必要があります。

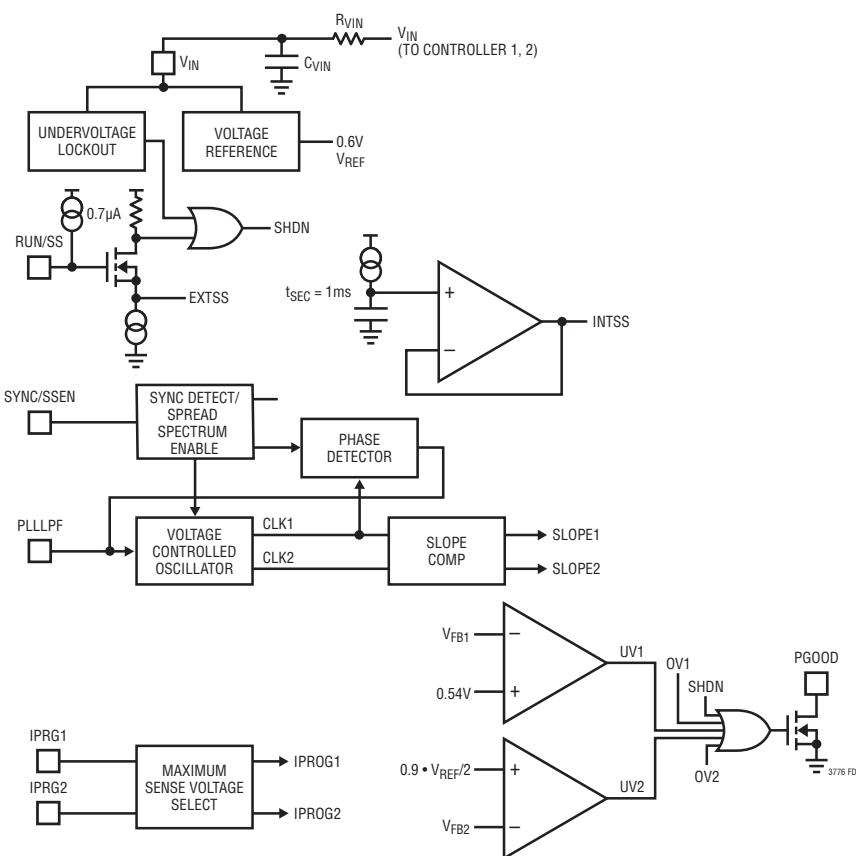

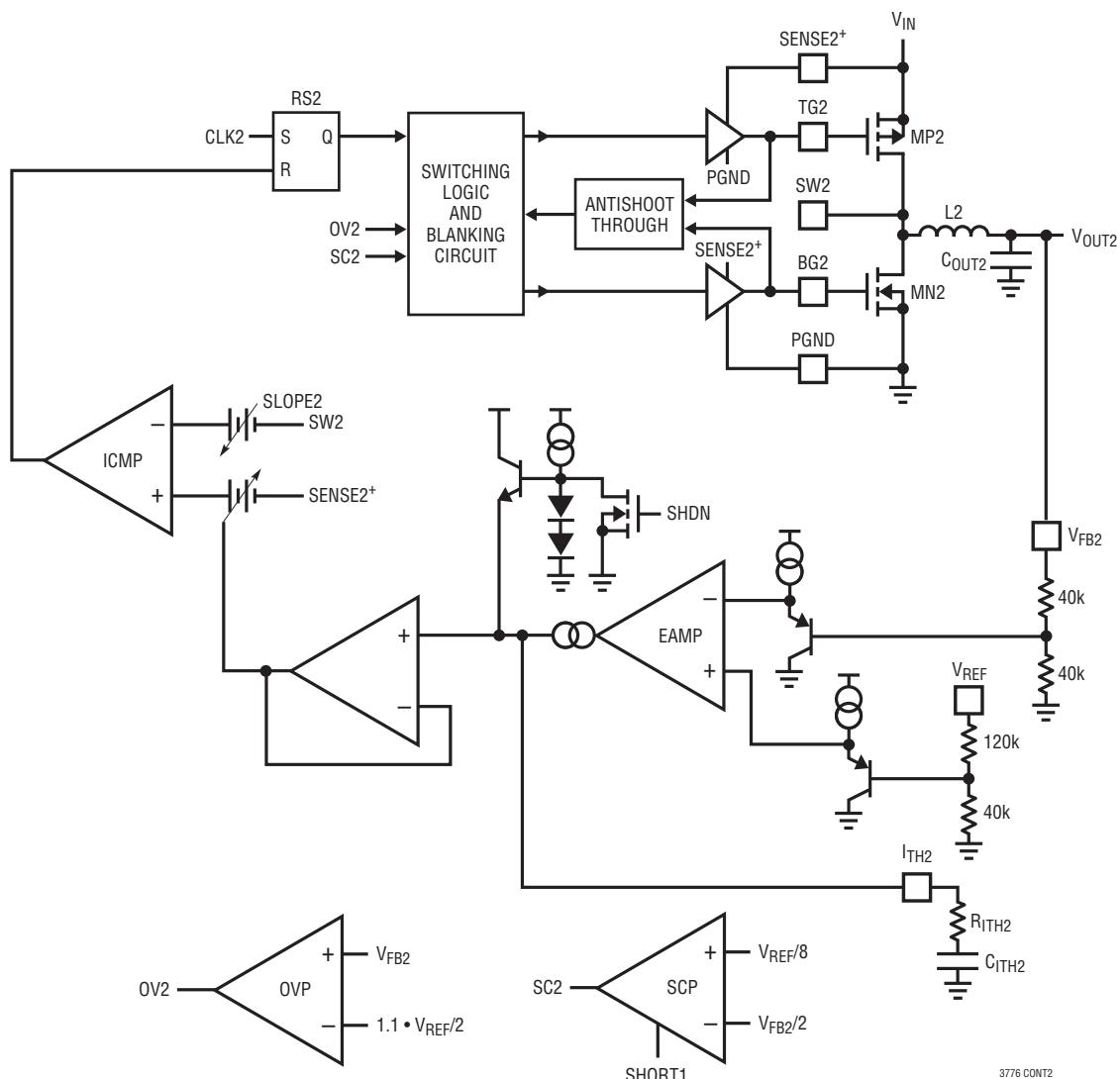

## 機能図 (共通回路)

3776fa

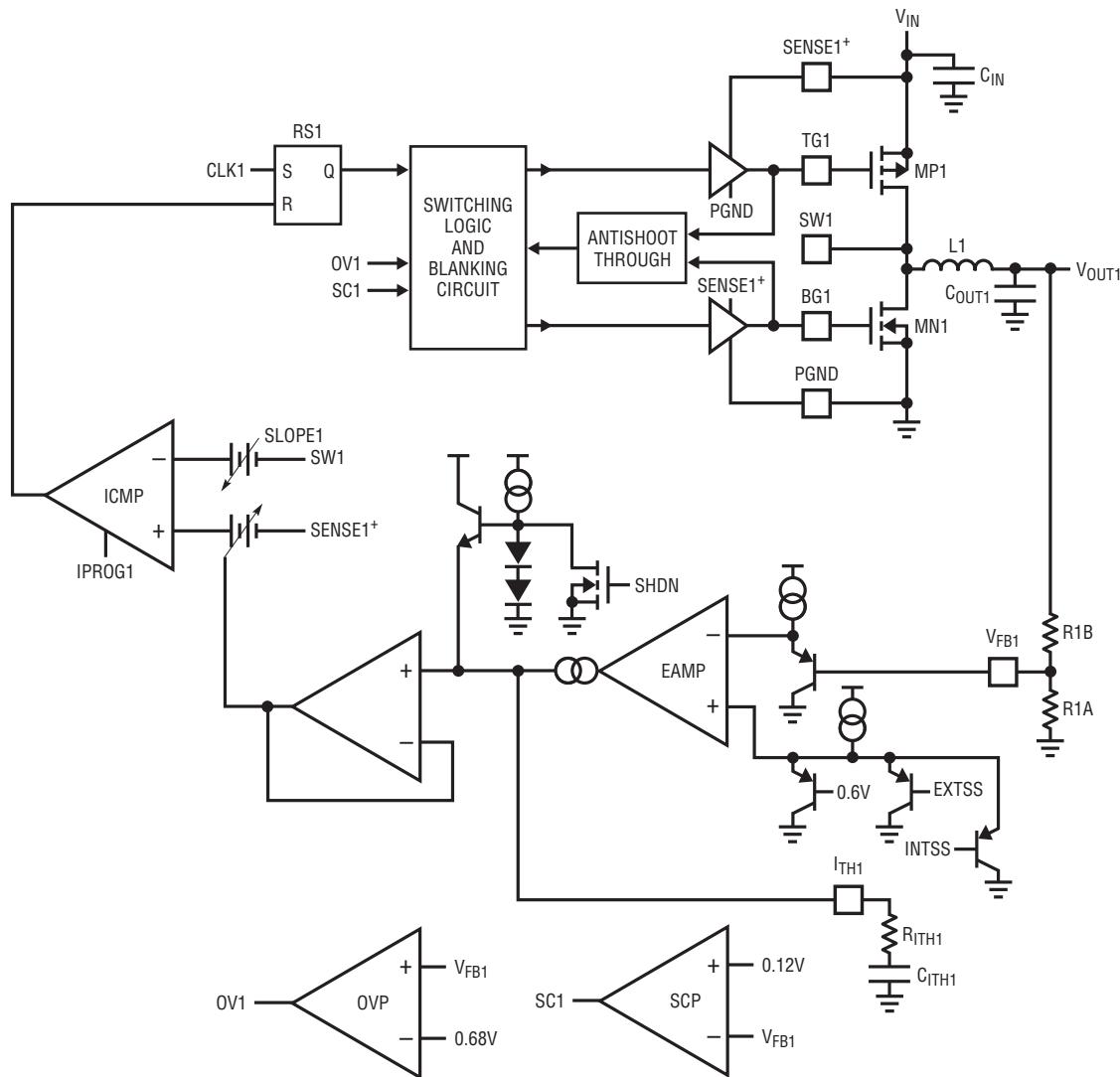

## 機能図 (コントローラ1)

## 機能図 (コントローラ2)

## 動作 (機能図を参照)

## メイン制御ループ

LTC3776は固定周波数の電流モード・アーキテクチャを採用しており、2つのコントローラが180度位相がずれて動作します。通常動作中は、片方のチャネルのクロックがRSラッチをセットすると対応するトップの外部Pチャネル・パワーMOSFETがオンし、電流コンパレータ(I<sub>CMP</sub>)がそのラッチをリセットするとオフします。I<sub>CMP</sub>がRSラッチをリセットするペー

ク・インダクタ電流はI<sub>TH</sub>ピンの電圧によって決まります。このI<sub>TH</sub>ピンは誤差アンプ(EAMP)の出力によってドライブされます。V<sub>FB</sub>ピンは外部抵抗分割器から出力電圧帰還信号を受け取ります。この帰還信号はEAMPによってリファレンス(コントローラ1の場合は内部0.6Vリファレンス、CH2の場合は分圧されたV<sub>REF</sub>ピンのどちらか)と比較されます。

## 動作 (機能図を参照)

負荷電流が増加するとリファレンスに対して $V_{FB}$ がわずかに減少するので、平均インダクタ電流が新たな負荷電流に釣り合うまで $I_{TH}$ 電圧が上昇します。トップPチャネルMOSFETがオフしている間、ボトムNチャネルMOSFETは次のサイクルの始点までオンします。

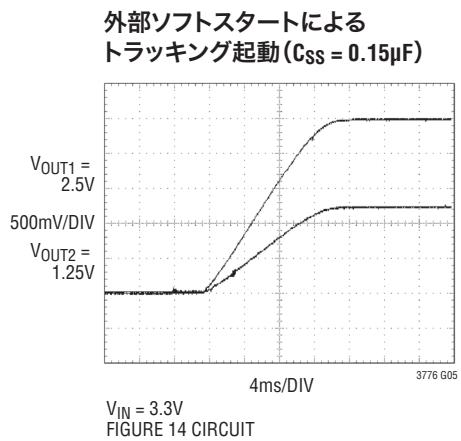

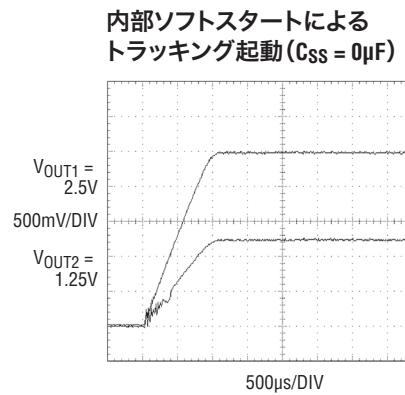

### シャットダウン、ソフトスタート、およびトラッキング起動 (RUN/SSピンとTRACKピン)

RUN/SSピンを“L”に引き下げるときLTC3776はシャットダウンします。シャットダウン時にはコントローラの全機能がディスエーブルされ、デバイスには $9\mu A$ しか流れません。シャットダウン時、TG出力は“H”(オフ)に、BG出力は“L”(オフ)に保たれます。RUN/SSを解放すると、内部の $0.7\mu A$ 電流源がRUN/SSピンを充電することができます。RUN/SSピンが $0.65V$ に達すると、LTC3776の2つのコントローラがイネーブルされます。

$V_{OUT1}$ の起動はLTC3776の内部ソフトスタートによって制御されます。ソフトスタートの間、誤差アンプ(EAMP)は帰還信号 $V_{FB1}$ を( $0.6V$ のリファレンスではなく)内部ソフトスタートのランプ電圧と比較します。このランプ電圧は直線的に $0V$ から $0.6V$ に約1msで上昇します。このため、インダクタ電流の制御を維持したまま、出力電圧は $0V$ からその最終値まで滑らかに上昇することができます。

1msのソフトスタート時間はオプションの外付けソフトスタート・コンデンサ $C_{SS}$ をRUN/SSピンとSGNDピンの間に接続して増加させることができます。RUN/SSピンが(内部の $0.7\mu A$ 電流源によって充電され)約 $0.65V$ から $1.25V$ に直線的に上昇を続けるにつれ、それに比例させてEAMPは $V_{FB1}$ を $0V$ から $0.6V$ まで直線的に制御します。

$V_{OUT2}$ の起動は $V_{REF}$ ピンの電圧によって制御されます。一般には $V_{OUT1}$ を $V_{REF}$ ピンに接続して、 $V_{OUT2}$ の起動が $V_{OUT1}$ の $1/2$ を「追尾」できるようにします。

$V_{OUT1}$ または $V_{OUT2}$ のどちらかが(起動または短絡状態のどちらかで)そのレギュレーション・ポイントの90%(低い方のPGOODスレッショルド)より下だと、チャネル1のインダクタ電流は反転することを許されない(つまり、不連続動作が強制される)ことに注意してください。これは、起動時に最小オン時間状態を防ぐためです。

### 短絡保護

出力がグランドに短絡すると、そのコントローラのスイッチング周波数は通常の動作周波数の $1/5$ に低下します。

$V_{FB2}$ の短絡回路のスレッショルドは $V_{REF}$ ピンの電圧の一部と $0.12V$ の小さい方をベースにしています。また、これにより、 $V_{OUT2}$ はもっと簡単に起動し $V_{OUT1}$ を追尾することができます。 $V_{OUT1}$ が実際に短絡すると( $V_{OUT1} = V_{FB1} = 0V$ )、 $V_{OUT1}$ が $V_{REF}$ ピンに接続されている場合、LTC3776は $V_{OUT2}$ を $0V$ に制御しようと試みることに注意してください。

### 出力過電圧保護

さらなる保護機能として、過電圧コンパレータ(OV)は、過渡オーバーシュートや、出力に過電圧を生じるおそれのある他のより深刻な状態からデバイスを保護します。 $V_{FB}$ ピンの帰還電圧がその分解能ポイントより $13.33\%$ 上に上昇すると、過電圧が解消されるまで外部PチャネルMOSFETがオフし、NチャネルMOSFETがオンします。

### 周波数の選択とフェーズロック・ループ(PLL裴ピンとSYNC/SSENピン)

スイッチング周波数の選択は効率と部品サイズの間のトレードオフになります。低周波数動作はMOSFETのスイッチング損失を減らして効率を上げますが、出力リップル電圧を低く抑えるには大きなインダクタンスや容量を必要とします。

LTC3776のコントローラのスイッチング周波数はPLL裴ピンを使って選択することができます。

SYNC/SSENピンがグランドに接続されていると、PLL裴をフロートさせるか、 $V_{IN}$ またはSGNDに接続して、それぞれ $550\text{kHz}$ 、 $750\text{kHz}$ 、または $300\text{kHz}$ の固定周波数動作を選択することができます。

LTC3776にはフェーズロック・ループ(PLL)が備わっており、SYNC/SSENピンに接続された外部クロック・ソースに内部発振器を同期させることができます。この場合、PLLのループ・フィルタとして機能する直列RCをPLL裴ピンとSGND間に接続します。

## 動作 (機能図を参照)

LTC3776の位相検出器がPLL LPFピンの電圧を調節してコントローラ1の外部PチャネルMOSFETのターンオンを同期信号の立上りエッジに揃えます。こうして、コントローラ2の外部PチャネルMOSFETのターンオンは、外部クロック・ソースの立上りエッジに対して180度位相がずれます。

LTC3776のフェーズロック・ループの標準的キャプチャレンジは約200kHz～1MHzで、全プロセス変動域と全温度範囲で250kHz～850kHzが保証されています。つまり、LTC3776のPLLは250kHz～850kHzの周波数の外部クロック・ソースにロックすることが保証されています。代わりに、SYNC/SSENピン

をV<sub>IN</sub>に接続して、スペクトラム拡散動作をイネーブルすることができます(「スペクトラム拡散動作」のセクションを参照)。

### スペクトラム拡散動作

スイッチング・レギュレータは電磁干渉(EMI)に敏感な環境では特に問題になる可能性があります。スイッチング・レギュレータはサイクル毎の動作をベースにして電力を出力に転送します。ほとんどの場合、動作周波数は固定されているか、または出力負荷に基づいて一定になります。この変換方法では、動作周波数(基本周波数)および動作周波数の倍数(高調波)で大きなノイズ成分が生じます。

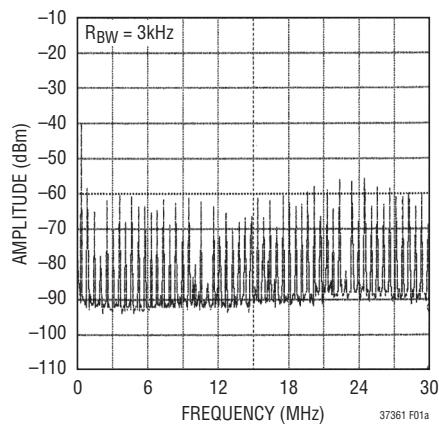

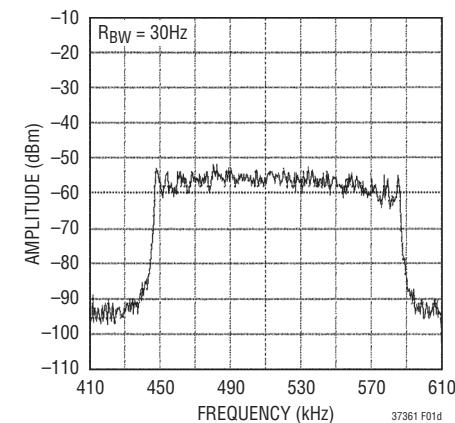

図1a. 基本周波数と高調波周波数を示す、従来型降圧スイッチング・コンバータ(スペクトラム拡散をディスエーブルしたLTC3776)の出力ノイズ・スペクトル

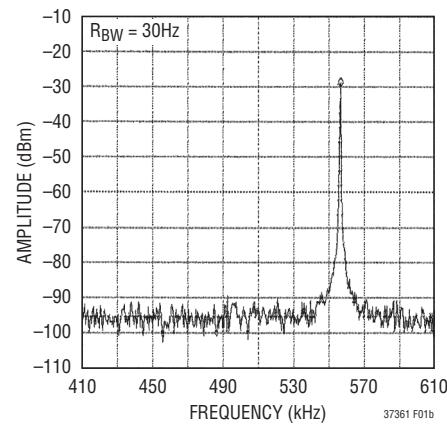

図1b. 従来型降圧スイッチング・コンバータの基本周波数を拡大

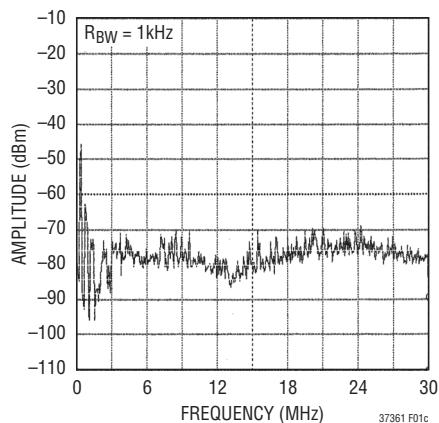

図1c. LTC3776スペクトラム拡散降圧スイッチング・コンバータの出力ノイズ・スペクトル。図1aに比べて基本波と高調波のピーク・スペクトル振幅が減少していることに注意。

図1d. LTC3776スペクトラム拡散スイッチング・コンバータの基本周波数を拡大表示。図1bに比べて、ピーク振幅の20dBを超える減少と周波数スペクトルの拡散(約450kHz～580kHzの範囲)に注意。

## 動作 (機能図を参照)

$V_{IN} = 5V$ 、 $V_{OUT} = 2.5V$ 、および  $I_{OUT} = 2A$  のときの従来の降圧スイッチング・コンバータ(スペクトラム拡散動作をディスエーブルしたLTC3776の1/2)の出力ノイズ・スペクトルを図1aと図1bに示します。

従来の降圧コンバータとは異なり、LTC3776の内部発振器は、SYNC/SSENピンを  $V_{IN}$  に接続することにより、周波数が 450kHz～580kHz の範囲でランダムに変化するクロック・パルスを発生するように選択することができます。このため、周波数範囲にわたってスイッチング・ノイズを拡散してピーク・ノイズを大きく減らす効果があります。 $V_{IN} = 5V$ 、 $V_{OUT} = 2.5V$ 、および  $I_{OUT} = 1A$  のときの、(スペクトラム拡散動作をイネーブルした)LTC3776の出力ノイズ・スペクトルを図1cと図1dに示します。ピーク出力ノイズの大幅な減少に注意してください ( $>20$ dBm)。

### ドロップアウト動作

入力電源電圧 ( $V_{IN}$ ) が出力電圧に向かって低下すると、外部 P チャネル MOSFET がオンしている間の(オン・サイクル)のインダクタ電流の変化率が低下します。この減少は、インダクタ電流が EAMP によって  $I_{TH}$  ピンに設定されているスレッショルドまでランプアップしないと、P チャネル MOSFET が発振器の 1 サイクル以上オン状態に留まることを意味します。入力電源電圧がさらに低下すると、最終的には P チャネル MOSFET が 100% オンし、DC になります。このときの出力電圧は、入力電圧から P チャネル MOSFET とインダクタの電圧降下を差し引いた電圧になります。

### 低電圧ロックアウト

外部 MOSFET が安全な入力電圧レベル以下で動作するのを防ぐため、LTC3776 には低電圧ロックアウトが内蔵されています。入力電源電圧 ( $V_{IN}$ ) が 2.3V より下に下がると、低電圧ブロックを除く全回路および外部の P チャネルと N チャネルの MOSFET がオフします。低電圧ブロックには数  $\mu$ A しか流れません。

### ピーク電流検出電圧の選択とスロープ補償 (IPRG1ピンとIPRG2ピン)

コントローラ1が20%以下のデューティ・サイクルで動作しているとき、外部 P チャネル MOSFET の両端に許容されるピーク電流検出電圧 (SENSE1<sup>+</sup>ピンと SW1 ピンの間) は次式によって決まります。

$$\Delta V_{SENSE(MAX)} = \frac{A1(V_{ITH1} - 0.7V)}{10}$$

ここで、A1 は IPRG1 ピンの状態で決まる定数です。IPRG1 ピンをフロートさせると A1 = 1 が選択されます。IPRG1 を  $V_{IN}$  に接続すると A1 = 5/3 が選択されます。IPRG1 を SGND に接続すると A1 = 2/3 が選択されます。 $V_{ITH1}$  の最大値は標準で約 1.98V なので、外部 P チャネル MOSFET の両端に許容される最大検出電圧は IPRG1 ピンの 3 つの状態に対してそれぞれ 125mV、85mV または 204mV です。

コントローラ2が20%以下のデューティ・サイクルで動作しているとき、外部 P チャネル MOSFET の両端に許容されるピーク電流検出電圧 (SENSE2<sup>+</sup>ピンと SW2 ピンの間) は次式によって決まります。

$$\Delta V_{SENSE(MAX)} = \frac{A2(V_{ITH2} - 1.3V)}{4.6}, V_{ITH2} \geq 1.3V$$

$$\Delta V_{SENSE(MAX)} = \frac{A2(V_{ITH2} - 1.3V)}{5.4}, V_{ITH2} < 1.3V$$

ここで、A2 は IPRG2 ピンの状態で決まる定数です。IPRG2 ピンをフロートさせると A2 = 1 が選択されます。IPRG2 を  $V_{IN}$  に接続すると A2 = 5/3 が選択されます。IPRG2 を SGND に接続すると A2 = 2/3 が選択されます。 $V_{ITH2}$  の最大値は標準で約 1.98V なので、外部 P チャネル MOSFET の両端に許容される最大検出電圧は IPRG2 ピンの 3 つの状態に対してそれぞれ 147mV、100mV または 245mV です。 $V_{ITH2}$  の最小値は標準で約 0.7V なので、最大(最も大きな負の)ピーク検出電圧はそれぞれ -112mV、-75mV または -188mV です。

ただし、コントローラのデューティ・サイクルが 20% を超えるとスロープ補償が開始され、図2の曲線で与えられるスケール・ファクタだけピーク検出電圧が実効的に減少します。

図2. 最大ピーク電流とデューティ・サイクル

## 動作 (機能図を参照)

ピーク・インダクタ電流はピーク検出電圧と外部PチャネルMOSFETのオン抵抗によって決まります。

$$I_{PK} = \frac{\Delta V_{SENSE(MAX)}}{R_{DS(ON)}}$$

### パワーグッド(PGOOD)ピン

ウィンドウ・コンパレータが両方の帰還電圧をモニタして、どちらかまたは両方の帰還電圧がそれらのリファレンス電圧の±10%以内にないと、オープン・ドレインのPGOOD出力ピンが“L”に引き下げられます。LTC3776がシャットダウンまたは低電圧ロックアウト状態のときPGOODは“L”になります。

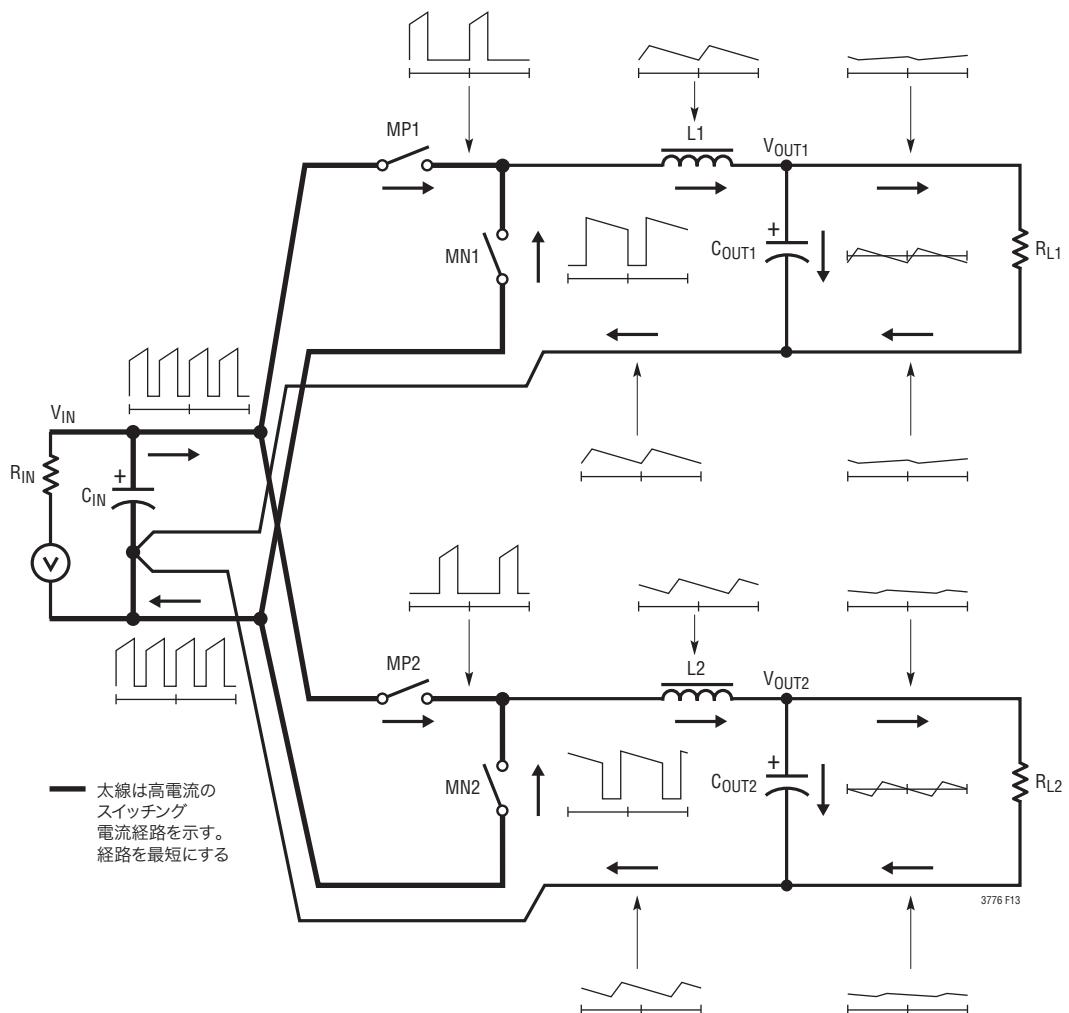

### 2フェーズ動作

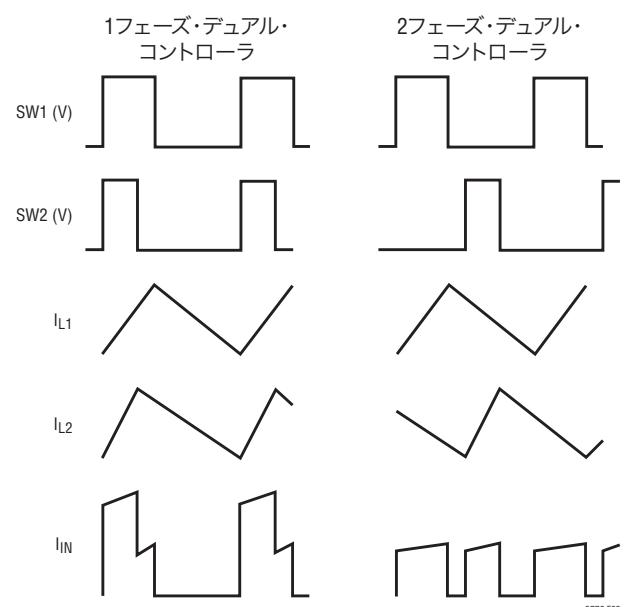

なぜ2フェーズ動作が必要なのでしょうか。最近まで、固定周波数デュアル・スイッチング・レギュレータは、両方のコントローラが同位相で動作していました(つまり1フェーズ動作)。これは、両方のトップサイドMOSFET(Pチャネル)が同時にオンするので、シングル・レギュレータに比べて最大2倍の振幅の電流パルスが入力コンデンサから流れることを意味します。これらの大振幅パルスによって入力コンデンサに流れ込む全RMS電流が増大するので、大きく高価な入力コンデンサが必要になり、入力コンデンサおよび入力電源のEMIと電力損失の両方が増加します。

2フェーズ動作では、LTC3776の2つのコントローラは位相が180度ずれて動作します。これにより、トップサイドMOSFETスイッチからの電流パルスを効果的に交互に差しはさんで、両方が加算されるオーバーラップ時間を大幅に短縮します。その結果、総RMS入力電流が大幅に減少するので小型で安価な入力コンデンサを使用することができ、EMI対策のシールド条件が緩和され、実際の動作効率が向上します。

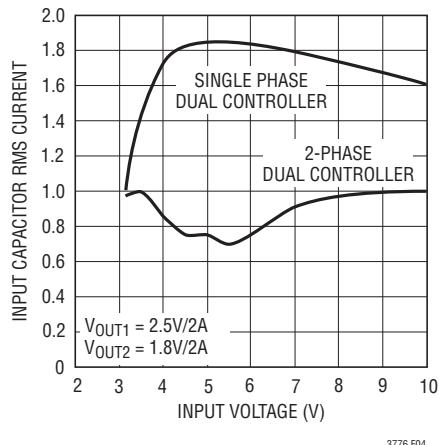

1フェーズ・デュアル・コントローラと2フェーズLTC3776システムの波形の例を図3に概念的に示します。この例では、それぞれ2Aの負荷電流を流している2.5Vと1.8Vの出力は7V(たとえば、2セル・リチウムイオン・バッテリ)の入力電源から得られます。この例では、2フェーズ動作のRMS入力コンデンサ電流は1.79ARMSから0.91ARMSに減少します。これ自体でも大きな減少ですが、電力損失は $I_{RMS}^2$ に比例するので実際の電力浪費は3.86分の1に減少します。

入力リップル電圧の低下は入力電源経路での電力損失の減少も意味します。入力電源経路にはバッテリ、スイッチ、トレスやコネクタの抵抗、および保護回路が含まれます。入力のRMS電流とRMS電圧の減少の直接の結果として伝導EMIと放射EMIも改善されます。RMS電流定格の低い小型で安価な入力コンデンサを使うことができるので、コストを節減し、基板のフットプリントを小さくできます。

図3. 1フェーズ・デュアル・コントローラと2フェーズ

LTC3776の波形例

もちろん、2フェーズ動作で得られる性能の改善は2つのコントローラの相対デューティ・サイクルの関数なので、結局は入力電圧に依存します。2.5Vと1.8Vの出力の1フェーズと2フェーズのデュアル・コントローラのRMS入力電流が広い入力電圧範囲にわたってどのように変化するかを図4に示します。

2フェーズ動作の利点は狭い動作範囲に限定されないで、事実広い領域に及ぶことがすぐに分かります。ほとんどのアプリケーションに適用可能な経験則によれば、2フェーズ動作では入力コンデンサの条件が、最大電流で50%のデューティ・サイクルで1チャネルだけが動作している場合の条件にまで緩和されます。

## アプリケーション情報

図4. RMS入力電流の比較

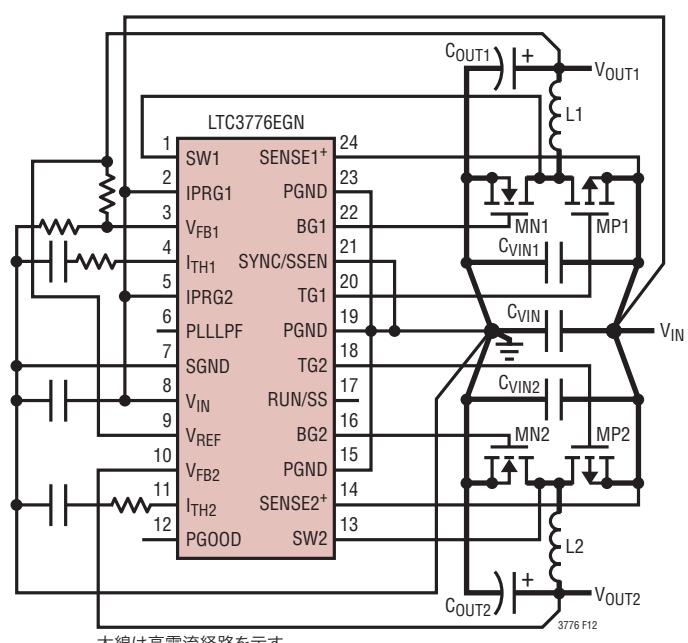

LTC3776の標準的応用回路を図11に示します。LTC3776の各コントローラの外付け部品の選択は負荷条件に基づいて行われ、インダクタ(L)とパワーMOSFET(MPとMN)の選択から始まります。

### パワーMOSFETの選択

LTC3776の2つのコントローラはそれぞれ2個の外付けパワーMOSFETを必要とします。トップ(メイン)スイッチ用のPチャネルMOSFETとボトム(同期)スイッチ用のNチャネルMOSFETです。パワーMOSFETの重要なパラメータは、ブレーキダウン電圧V<sub>BR(DSS)</sub>、スレッショルド電圧V<sub>GS(TH)</sub>、オン抵抗R<sub>DS(ON)</sub>、逆伝達容量C<sub>rss</sub>、ターンオフ遅延時間t<sub>D(OFF)</sub>およびゲート電荷Q<sub>G</sub>です。

ゲート・ドライブ電圧は入力電源電圧です。LTC3776は低い入力電圧でも動作するように設計されているので、これに近い電圧で動作するアプリケーションにはサブロジック・レベルのMOSFET(V<sub>GS</sub>=2.5VでR<sub>DS(ON)</sub>が保証されている)が必要です。これらのMOSFETを使用するときは、LTC3776への入力電源がMOSFETの絶対最大V<sub>GS</sub>定格(標準8V)より低いことを確認してください。

PチャネルMOSFETのオン抵抗は必要な負荷電流に基づいて選択します。最大平均出力電流I<sub>OUT(MAX)</sub>は、ピーク・インダクタ電流からピーク・トゥ・ピーク・リップル電流I<sub>RIPPLE</sub>の半分を差し引いたものに等しくなります。LTC3776の電流コンパレ

タはPチャネルMOSFETのドレイン-ソース電圧V<sub>DS</sub>をモニタします。V<sub>DS</sub>はSENSE<sup>+</sup>ピンとSWピンの間で検出されます。ピーク・インダクタ電流は電流コンパレータのI<sub>TH</sub>ピンの電圧によって設定される電流スレッショルドによって制限されます。I<sub>TH</sub>ピンの電圧は内部でクランプされ、そのため最大電流検出スレッショルドΔV<sub>SENSE(MAX)</sub>が制限されます。

LTC3776が供給できる出力電流は次式で与えられます。

$$I_{OUT(MAX)} = \frac{\Delta V_{SENSE(MAX)}}{R_{DS(ON)}} - \frac{I_{RIPPLE}}{2}$$

妥当な出発点として、リップル電流I<sub>RIPPLE</sub>をI<sub>OUT(MAX)</sub>の40%に設定します。20%未満のデューティ・サイクルの場合、上の式を整理すると次のようになります。

$$R_{DS(ON)(MAX)} = \frac{5}{6} \cdot \frac{\Delta V_{SENSE(MAX)}}{I_{OUT(MAX)}}$$

ただし、デューティ・サイクルが20%を超える動作の場合、必要な量の負荷電流を供給するのに適切なR<sub>DS(ON)</sub>の値を選択するにはスロープ補償を検討する必要があります。

$$R_{DS(ON)(MAX)} = \frac{5}{6} \cdot SF \cdot \frac{\Delta V_{SENSE(MAX)}}{I_{OUT(MAX)}}$$

ここでSFはスケール・ファクタで、その値は図2の曲線から得られます。

これらは、オン抵抗の温度による大きな変化を考慮に入れるため、さらにディレーティングが必要です。次式は25°Cでの必要なR<sub>DS(ON)MAX</sub>(メーカーの仕様)を決定するための良い目安で、LTC3776と外付け部品の値の変動に対するマージンを含みます。

$$R_{DS(ON)(MAX)} = \frac{5}{6} \cdot 0.9 \cdot SF \cdot \frac{\Delta V_{SENSE(MAX)}}{I_{OUT(MAX)} \cdot \rho_T}$$

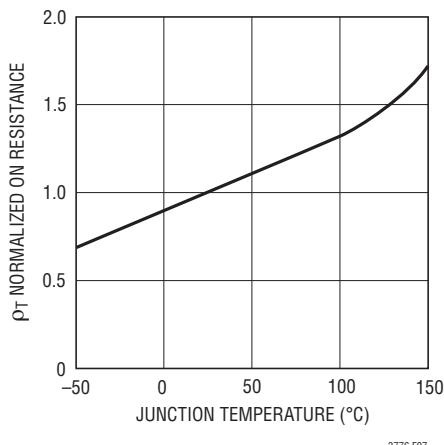

ρ<sub>T</sub>は正規化の項で、温度によるオン抵抗の変化を表し、図5に示されているように標準で約0.4%/°Cです。ほとんどのアプリケーションで、接合部-ケース間温度T<sub>J</sub>Cは約10°Cです。70°Cの最高周囲温度の場合、上の式でρ<sub>80°C</sub>として約1.3を使うのが妥当です。

## アプリケーション情報

図5.  $R_{DS(ON)}$ と温度

トップとボトムのMOSFETで消費される電力はそれぞれのデューティ・サイクルと負荷電流に強く依存します。LTC3776が連続モードで動作しているとき、MOSFETのデューティ・サイクルは次式で表されます。

$$\text{トップPチャネルのデューティ・サイクル} = \frac{V_{OUT}}{V_{IN}}$$

$$\text{ボトムNチャネルのデューティ・サイクル} = \frac{V_{IN} - V_{OUT}}{V_{IN}}$$

最大出力電流でのMOSFETの消費電力は以下のとおりです。

$$P_{TOP} = \frac{V_{OUT}}{V_{IN}} \cdot I_{OUT(MAX)}^2 \cdot \rho_T \cdot R_{DS(ON)} + 2 \cdot V_{IN}^2 \cdot I_{OUT(MAX)} \cdot C_{RSS} \cdot f_{OSC}$$

$$P_{BOT} = \frac{V_{IN} - V_{OUT}}{V_{IN}} \cdot I_{OUT(MAX)}^2 \cdot \rho_T \cdot R_{DS(ON)}$$

両方のMOSFETに $I^2R$ 損失がありますが、 $P_{TOP}$ の式には遷移損失の項が追加されており、これは入力電圧が高いとき最大になります。ボトムMOSFETの損失は、入力電圧が高いとき、またはボトムのデューティ・サイクルがほぼ100%になる短絡時に最も大きくなります。

LTC3776は重なり合わないアンチ・シートスルーのゲート・ドライブ制御方式を使ってPチャネルとNチャネルのMOSFETが同時にオンしないようにしています。正しく動作するには、この制御方式にはDC/DCスイッチング・アプリケーション用のMOSFETを使う必要があります。多くのMOSFETは、特にPチャネルMOSFETは静的なスイッチに使うことが意図されており、オン/オフが速くありません。

PチャネルMOSFETの選択基準の妥当な出発点として、ゲート電荷( $Q_G$ )が(4.5V<sub>GS</sub>で)25nC~30nC以下、ターンオフ遅延時間( $t_{D(OFF)}$ )が約140ns以下のものが一般に必要です。ただし、個々のMOSFETメーカーのテスト方法や仕様の定義が異なり、ゲート・ドライブ電圧( $V_{IN}$ )による $Q_G$ と $t_{D(OFF)}$ の変化が異なるので、PチャネルMOSFETは最終的には実際のLTC3776アプリケーションで正しく動作するか評価すべきです。

PチャネルとNチャネルのMOSFET間のシートスルーは、入力電源電流をモニタすれば簡単に見つけることができます。入力電源電圧が増加するにつれて入力電源電流が急激に増加する場合、おそらくシートスルーが原因です。高い入力電圧(たとえば、 $V_{IN} > 5V$ )でうまく動作しないMOSFETが低い電圧(たとえば、3.3V)で問題なく動作することがあることに注意してください。LTC3776のアプリケーションで問題なく動作することが分っている、いくつかのメーカーから選んだPチャネルMOSFETを表1に示します。

NチャネルMOSFETの選択は一般にもっと簡単です。与えられた $R_{DS(ON)}$ に対して、ゲート電荷およびターンオン遅延時間とターンオフ遅延時間がPチャネルの場合よりはるかに小さいからです。

表1. LTC3776のアプリケーションに適した推奨PチャネルMOSFET

| PART NUMBER  | MANUFACTURER | TYPE              | PACKAGE       |

|--------------|--------------|-------------------|---------------|

| Si7540DP     | Siliconix    | Complementary P/N | PowerPak SO-8 |

| Si9801DY     | Siliconix    | Complementary P/N | SO-8          |

| FDW2520C     | Fairchild    | Complementary P/N | TSSOP-8       |

| FDW2521C     | Fairchild    | Complementary P/N | TSSOP-8       |

| Si3447BDV    | Siliconix    | Single P          | TSOP-6        |

| Si9803DY     | Siliconix    | Single P          | SO-8          |

| FDC602P      | Fairchild    | Single P          | TSOP-6        |

| FDC606P      | Fairchild    | Single P          | TSOP-6        |

| FDC638P      | Fairchild    | Single P          | TSOP-6        |

| FDW2502P     | Fairchild    | Dual P            | TSSOP-8       |

| FDS6875      | Fairchild    | Dual P            | SO-8          |

| HAT1054R     | Hitachi      | Dual P            | SO-8          |

| NTMD6P02R2-D | On Semi      | Dual P            | SO-8          |

## アプリケーション情報

### 動作周波数と同期

動作周波数( $f_{OSC}$ )の選択には、効率と部品サイズの間のトレードオフが必要です。動作周波数が低いと、MOSFETのゲート電荷損失と遷移損失によるMOSFETのスイッチング損失が減少して効率が上がります。ただし、低周波数動作では与えられたリップル電流に対してインダクタンス値を大きくする必要があります。

LTC3776の各コントローラの内部発振器は、PLLLPFピンがフロート状態でSYNC/SSENピンがGNDに接続されているとき、公称550kHzで動作します。PLLLPFをV<sub>IN</sub>に引き上げると750kHz動作が選択され、PLLLPFをGNDに引き下げると300kHz動作が選択されます。

または、LTC3776はSYNC/SSENピンに与えられた250kHz～850kHzの周波数のクロック信号にフェーズロックします（「フェーズロック・ループと周波数同期」を参照）。

スペクトラム拡散動作がイネーブルされていると(SYNC/SSEN = V<sub>IN</sub>)、LTC3776の周波数は450kHz～580kHzの周波数範囲でランダムに変化します。この場合、コンデンサ(1nF～4.7nF)をFREQピンとSGNDの間に接続して周波数の変化を滑らかにします。これにより周波数スペクトルが滑らかになるだけでなく、周波数の突然の変化を防いでスイッチング・レギュレータの安定動作を保ちます。ほとんどのアプリケーションでは2200pFの値が適しています。

### インダクタの値の計算

望みの入力電圧と出力電圧が与えられると、インダクタ値と動作周波数 $f_{OSC}$ によって直ちにインダクタのピーク・トゥ・ピーク・リップル電流が決まります。

$$I_{RIPPLE} = \frac{V_{OUT}}{V_{IN}} \left( \frac{V_{IN} - V_{OUT}}{f_{OSC} \cdot L} \right)$$

リップル電流が小さいと、インダクタのコア損失、出力コンデンサのESR損失、さらに出力電圧リップルが減少します。したがって、周波数が低くリップル電流が小さいと高効率動作が実現されます。ただし、これを達成するには大きなインダクタが必要です。

妥当な出発点として、I<sub>OUT(MAX)</sub>の約40%のリップル電流を選択します。最大入力電圧で最大リップル電流が発生することに注意してください。リップル電流が規定された最大値を超えないようにするには、次式に従ってインダクタを選択します。

$$L \geq \frac{V_{IN} - V_{OUT}}{f_{OSC} \cdot I_{RIPPLE}} \cdot \frac{V_{OUT}}{V_{IN}}$$

### インダクタのコアの選択

インダクタンスの値が決まつたら、次にインダクタの種類を選択します。一定のインダクタの値に対して実際のコア損失はコア・サイズには依存せず、選択したインダクタンスに大きく依存します。インダクタンスが増加するとコア損失が低下します。インダクタンスを大きくするにはワイヤの巻数を増やす必要があるため残念ながら銅損失が増加します。

フェライトを使用した設計ではコア損失がきわめて低く、高いスイッチング周波数に適しているため、設計目標を銅損失と飽和を防ぐことに集中することができます。フェライト・コアの材質は「ハードに」飽和します。つまり、最大設計ピーク電流を超えるとインダクタンスが突然低落します。その結果、インダクタのリップル電流が突然増加し、そのため出力電圧リップルが増加します。コアを飽和させないでください。

コアの材質と形状が異なると、インダクタのサイズ/電流の関係および価格/電流の関係が変化します。フェライトやパーマロイを素材とするトロイド・コアやシールドされた壺型コアは小型で、エネルギー放射は大きくありませんが、類似の特性を有する鉄粉コアのインダクタより一般に高価です。使用的インダクタの種類の選択は価格とサイズの条件や放射フィールド/EMIの条件に主に依存します。新しいデザインの表面実装型インダクタをCoiltronics、Coilcraft、Tokoおよびスミダ電機から入手できます。

### ショットキー・ダイオードの選択(オプション)

図16のショットキー・ダイオードD1とD2は、パワーMOSFETの導通期間の間隙に生じるデッドタイムに電流を流します。これによってボトムNチャネルMOSFETのボディー・ダイオードがオンしてデッドタイム中に電荷が蓄積するのを防ぎます。このような電荷蓄積は効率を1%ほど低下させる可能性があります。

Kool MuはMagnetics, Inc.の登録商標です。

## アプリケーション情報

1Aのショットキー・ダイオードは比較的小さい平均電流を流すので、一般にLTC3776のほとんどのアプリケーションにとって十分なサイズです。これより大きなダイオードは接合容量が大きいため遷移損失が増加します。効率の低下を許容できる場合、このダイオードは省くことができます。

### $C_{IN}$ と $C_{OUT}$ の選択

$C_{IN}$ の選択は、2フェーズ・アーキテクチャと、入力回路(バッテリ/ヒューズ/コンデンサ)を流れるワーストケースRMS電流へのこのアーキテクチャの影響によって単純化されます。コンデンサのワーストケースRMS電流はコントローラが1つだけ動作しているときに流れることを示すことができます。最大RMSコンデンサ電流の条件を求めるには、下の式で $V_{OUT}$ と $I_{OUT}$ の積が最大になる方のコントローラを使用する必要があります。他方のコントローラから引き出される出力電流を増やすと、入力RMSリップル電流が実際にはその最大値から減少します。位相をずらす方式では、1フェーズの電源ソリューションと比較すると、入力コンデンサのRMSリップル電流が一般に30%~70%ほど減少します。

連続モードでは、PチャネルMOSFETのソース電流はデューティ・サイクルが $(V_{OUT})/(V_{IN})$ の方形波になります。大きな過渡電圧を防止するには、1つのチャネルの最大RMS電流に対応できる容量の低ESRコンデンサを使用します。コンデンサの最大RMS電流は次式で与えられます。

$$\text{要求される} I_{RMS} \approx \frac{I_{MAX}}{V_{IN}} \left[ (V_{OUT})(V_{IN} - V_{OUT}) \right]^{1/2}$$

この式は $V_{IN} = 2V_{OUT}$ で最大値をとります。ここで、 $I_{RMS} = I_{OUT}/2$ です。大きく変化させてもそれほど状況が改善されないため、一般にはこの単純な最悪条件が設計に使用されます。多くの場合、コンデンサ・メーカーはリップル電流定格をわずか2000時間の寿命時間によって規定しています。このため、コンデンサをさらにディレーティングする、つまり要求条件よりも高い温度定格のコンデンサを選択するようにしてください。サイズまたは高さの設計条件に適合させるため、複数のコンデンサを並列に接続することができます。LTC3776の動作周波数が高いため、 $C_{IN}$ にセラミック・コンデンサを使用することもできます。疑問点については必ずメーカーに問い合わせてください。

LTC3776の2フェーズ動作の利点は、電力の高い方のコントローラに対する上式を使用し、次に両方のコントローラが同時にオンするとき生じるであろう損失を計算することによって評価することができます。両方のコントローラが動作しているときは、入力コンデンサのESRを流れる電流パルスの重なり合った部分の減少により、合計RMS電力損失が減少します。この理由により、ワーストケースのコントローラについて上で計算した入力コンデンサの条件はデュアル・コントローラの設計に対して適切です。さらに、2フェーズ・システムではピーク電流が減少するため、入力保護ヒューズの抵抗、バッテリ抵抗、およびPCボードのトレース抵抗による各損失も減少します。マルチフェーズ・デザインの全体的利点は、電源/バッテリのソース・インピーダンスを効率テストに含めるとき初めて完全に把握されます。PチャネルMOSFETのソースは互いに1cm以内に配置し、共通 $C_{IN}$ を共有させます。ソースと $C_{IN}$ を分離すると、 $V_{IN}$ に望ましくない電圧共振や電流共振を生じる可能性があります。

小さな(0.1 $\mu$ F~1 $\mu$ F)バイパス・コンデンサをLTC3776に近づけて、デバイスの $V_{IN}$ ピンとグランドの間に配置することも推奨します。 $C_{IN}$ (C1)と $V_{IN}$ ピンの間に10 $\Omega$ 抵抗を置くと2つのチャネルはさらに分離されます。

$C_{OUT}$ は等価直列抵抗(ESR)に基づいて選択します。一般に、ESRの要件が満たされると、その容量はフィルタ機能にとって十分です。出力リップル( $\Delta V_{OUT}$ )は次式で近似できます。

$$\Delta V_{OUT} \approx I_{RIPPLE} \left( ESR + \frac{1}{8fC_{OUT}} \right)$$

ここで、 $f$ は動作周波数、 $C_{OUT}$ は出力容量、 $I_{RIPPLE}$ はインダクタのリップル電流です。 $I_{RIPPLE}$ は入力電圧に応じて増加するため、出力リップルは入力電圧が最大のときに最も高くなります。

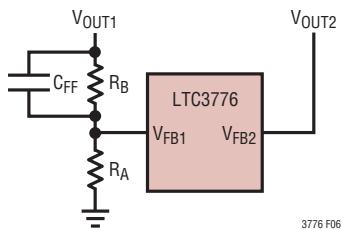

### 出力電圧の設定

LTC3776のチャネル1の出力電圧は、図6に示されているように、出力両端に注意深く配置した外部帰還抵抗分割器によって設定されます。安定化された出力電圧は次式によって決まります。

$$V_{OUT1} = 0.6V \cdot \left( 1 + \frac{R_B}{R_A} \right)$$

## アプリケーション情報

チャネル2の出力電圧は、V<sub>FB2</sub>ピンをV<sub>OUT2</sub>に接続することにより、1/2 V<sub>REF</sub>に設定されます。周波数応答を改善するには、フィードフォワード・コンデンサ(C<sub>FF</sub>)を使うことができます。V<sub>FB</sub>ラインはインダクタやSWラインなどのノイズ源から離して配線するように十分注意してください。

図6. 出力電圧の設定

### 実行/ソフトスタート機能

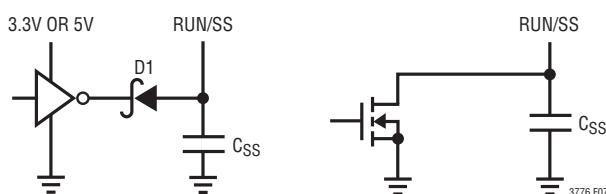

RUN/SSピンには2つの役目があり、オプションの外部ソフトスタート機能とLTC3776をシャットダウンする機能を備えています。

RUN/SSピンを0.65Vより下に引き下げるとき、LTC3776は低消費電流(I<sub>Q</sub> = 9μA)のシャットダウン・モードになります。RUN/SSがグランドまで完全に引き下げられているとき、LTC3776がシャットダウンから抜け出すまでに次式で与えられる遅延時間が経過します。

$$t_{\text{DELAY}} = 0.65V \cdot \frac{C_{\text{SS}}}{0.7\mu\text{A}} = 0.93\text{s}/\mu\text{F} \cdot C_{\text{SS}}$$

このピンは図7に示されているように直接ロジックでドライブ可能です。図7のダイオードD1によってスタート遅延時間は短くなりますが、C<sub>SS</sub>をゆっくり上昇させてソフト・スタート機能を実現することができます。外部ソフトスタートが不要ならば、このダイオード(およびコンデンサ)を除くことができます。

図7. RUN/SSピンのインターフェース

ソフトスタートの間、誤差アンプへの正リファレンスを0Vから0.6VにゆっくりランプアップさせることによりV<sub>OUT1</sub>の起動が制御されるので、V<sub>OUT1</sub>は0Vからその最終値まで滑らかに上昇します。既定の内部ソフトスタート時間は1msです。これはRUN/SSピンとSGNDの間にコンデンサを接続して増加させることができます。この場合、ソフトスタート時間はおよそ次のようになります。

$$t_{\text{SS1}} = C_{\text{SS}} \cdot \frac{600\text{mV}}{0.7\mu\text{A}}$$

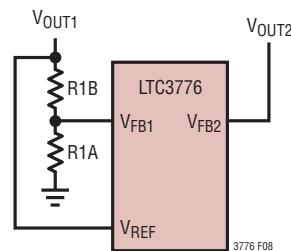

### V<sub>REF</sub>ピン

V<sub>OUT2</sub>の安定化はV<sub>REF</sub>ピンの電圧によって制御されます。このピンは通常DDRメモリ終端アプリケーションで使われる所以、図8に示されているように、V<sub>OUT2</sub>は1/2 V<sub>OUT1</sub>をトラッキングします。

図8. V<sub>REF</sub>ピンの使い方(V<sub>OUT2</sub>は1/2 V<sub>REF</sub> = 1/2 V<sub>OUT1</sub>に安定化される)

### フェーズロック・ループと周波数同期

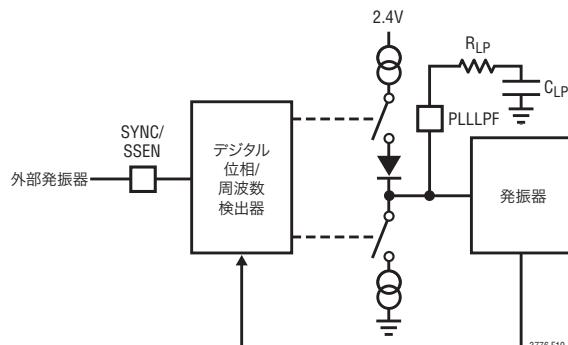

LTC3776には電圧制御発振器(VCO)と位相検出器で構成されるフェーズロック・ループ(PLL)が内蔵されています。これにより、コントローラ1の外部PチャネルMOSFETのターンオンを、SYNC/SSENピンに与える外部クロック信号の立上りエッジにロックさせることができます。したがって、コントローラ2の外部PチャネルMOSFETのターンオンは、外部クロックに対して180度位相がずれます。位相検出器はエッジに反応するデジタル・タイプで、外部発振器と内部発振器の位相のずれをゼロ度にします。このタイプの位相検出器は、外部クロックの高調波に誤ってロックすることはありません。

位相検出器の出力は、PLLLPFピンに接続された外部フィルタ・ネットワークを充放電する1対の相補型電流源です。

## アプリケーション情報

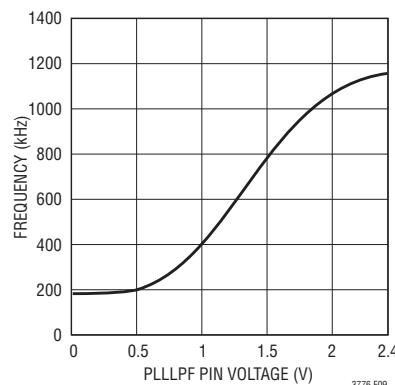

SYNC/SSENにクロック信号が与えられているときのPLLLPFピンの電圧と動作周波数の関係が図9に示されており、「電気的特性」の表で規定されています。LTC3776は周波数がLTC3776の内部VCOの範囲(公称200kHz～1MHz)の外部クロックにだけ同期することができることに注意してください。これは全温度範囲とプロセスの全変動域で250kHz～850kHzの範囲が保証されています。簡略化したブロック図を図10に示します。

図9. 外部クロックに同期しているときの発振器周波数とPLLLPFピンの電圧の関係

図10. フェーズロック・ループのブロック図

外部クロックの周波数が内部発振器の周波数( $f_{OSC}$ )より高いと、電流が位相検出器の出力から連続的にソースされ、PLLLPFピンを引き上げます。外部クロックの周波数が $f_{OSC}$ より低いと、電流は連続的にシンクされ、PLLLPFピンを引き下げます。外部周波数と内部周波数が等しいが位相が異なると、位相差に対応した時間だけ電流源がオンします。PLLLPFピンの電圧は、内部発信器と外部発振器の位相と周波数が

等しくなるまで調整されます。安定した動作点では、位相検出器の出力は高インピーダンスになり、フィルタ・コンデンサ $C_{LP}$ がその電圧を保持します。

ループ・フィルタの部品( $C_{LP}$ と $R_{LP}$ )により、位相検出器からの電流パルスが平滑化され、安定した入力が電圧制御発振器に与えられます。フィルタ部品の $C_{LP}$ と $R_{LP}$ により、ループがロックする速度が決定されます。一般に、 $R_{LP} = 10k$ で、 $C_{LP}$ は2200pF～0.01μFです。

外部クロック入力の(SYNC/SSENピン)“H”のスレッショルドは標準で1.6V、“L”のスレッショルドは1.2Vです。

PLLLPFを使用できる異なった状態を表2に示します。

表2

| PLLLPFピン         | SYNC/SSENピン | 周波数                            |

|------------------|-------------|--------------------------------|

| 0V               | GND         | 300kHz                         |

| フロート             | GND         | 550kHz                         |

| $V_{IN}$         | GND         | 750kHz                         |

| RCループ・フィルタ       | クロック信号      | 外部クロックにフェーズロック                 |

| $V_{IN}$ へのコンデンサ | $V_{IN}$    | スペクトラム拡散動作<br>450kHz to 550kHz |

### 低電源電圧動作

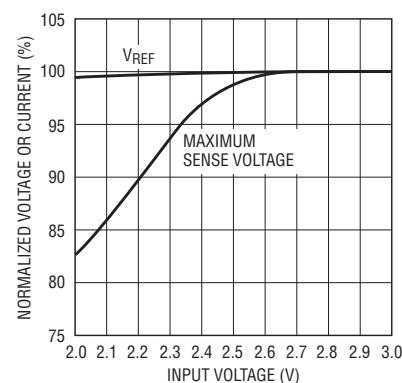

LTC3776は2.4Vより下まで動作可能ですが、 $V_{IN}$ が3Vより低くなると、最大許容出力電流が低下します。電源が2.4Vまで低下したときの変化量を図11に示します。 $V_{REF}$ に対する影響も示されています。

図11.  $V_{REF}$ のライン・レギュレーションと低入力電源の最大検出電圧

## アプリケーション情報

### 最小オン時間に関する検討事項

最小オン時間 $t_{ON(MIN)}$ は、LTC3776がトップPチャネルMOSFETをオンしてから再度オフすることができる最小時間です。これは内部タイミング遅延とトップMOSFETをオンするのに必要なゲート電荷の量によって決まります。デューティ・サイクルが低く周波数が高いアプリケーションではこの最小オン時間の限界値に接近する可能性があるので、次の条件を満たすように注意が必要です。

$$t_{ON(MIN)} < \frac{V_{OUT}}{f_{OSC} \cdot V_{IN}}$$

デューティ・サイクルが最小オン時間で対応可能な値より低くなると、LTC3776は過電圧保護によって安定化します。LTC3776の最小オン時間は標準で約200nsです。ただし、ピーク検出電圧( $I_{L(PEAK)} \cdot R_{DS(ON)}$ )が減少するにつれ、最小オン時間が約250nsまで徐々に増加します。

### 効率に関する検討事項

スイッチング・レギュレータの効率は「出力電力÷入力電力×100%」で表されます。個々の損失を解析して、効率を制限する要素がどれであり、また何が変化すれば最も効率が改善されるかを判断できる場合がよくあります。効率は次式で表すことができます。

$$\text{効率} = 100\% - (L_1 + L_2 + L_3 + \dots)$$

ここで、 $L_1, L_2$ などは入力電力に対するパーセンテージで表した個々の損失です。

回路内の電力を消費する全ての要素で損失が生じますが、LTC3776の回路の損失の大部分は4つの主な損失要因によって生じます。1) LTC3776のDCバイアス電流、2) MOSFETのゲート電荷による電流、3)  $I^2R$ 損失、および4) 遷移損失です。

1)  $V_{IN}$ (ピン)電流は「電気的特性」に記載されているDC消費電流であり、MOSFETドライバ電流は含まれません。 $V_{IN}$ 電流によって小さな損失が発生し、この損失は $V_{IN}$ に従って増加します。

2) パワーMOSFETのゲート容量をスイッチングすると、MOSFETのゲート電荷による電流が流れます。MOSFETのゲートが“L”から“H”、そして再び“L”に切り替わるたびに、SENSE+からグランドに微小電荷 $dQ$ が移動します。その結果生じる $dQ/dt$ はSENSE+から流出する電流であり、一般にDC消費電流よりはるかに大きくなります。連続モードで

は、 $I_{GATECHG} = f \cdot Q_P$ となります。

3)  $I^2R$ 損失はMOSFETとインダクタの各DC抵抗から計算されます。連続モードでは平均出力電流がLを流れますが、トップPチャネルMOSFETとボトムNチャネルMOSFETの間で「こま切れ」にされます。各MOSFETの $R_{DS(ON)}$ にデューティ・サイクルを掛け、Lの抵抗値と加算して $I^2R$ 損失を求めることができます。

4) 遷移損失はトップの外部PチャネルMOSFETで生じ、動作周波数と入力電圧が高いほど大きくなります。遷移損失は次式から推算できます。

$$\text{遷移損失} = 2 (V_{IN})^2 I_{O(MAX)} C_{RSS}(f)$$

$C_{IN}$ や $C_{OUT}$ のESR消費損失やインダクタのコア損失など他の損失は一般に全付加損失の2%以下に過ぎません。

### 過渡応答のチェック

レギュレータのループ応答は負荷過渡応答を見てチェックすることができます。スイッチング・レギュレータは負荷電流ステップに対して応答するのに数サイクルを要します。負荷ステップが生じると、 $V_{OUT}$ は直ちに( $\Delta I_{LOAD}$ )(ESR)に等しい量だけシフトします。ここで、ESRは $C_{OUT}$ の等価直列抵抗です。また、 $\Delta I_{LOAD}$ は $C_{OUT}$ を充電または放電し始め、それにより帰還誤差信号が生じます。次に、レギュレータ・ループが $V_{OUT}$ を定常状態の値に戻します。この回復時間の間、オーバーシュートやリンギングがないか $V_{OUT}$ をモニタすることができます。OPTI-LOOP補償により、広範な出力容量とESR値に対して過渡応答の最適化を図ることができます。

$I_{TH}$ の直列 $R_C$ - $C_C$ フィルタ(「機能図」を参照)により、支配的なポール-ゼロ・ループ補償が設定されます。このデータシートの表紙の「標準的応用例」に示されている $I_{TH}$ ピンの外付け部品はほとんどのアプリケーションにおいて妥当な出発点となります。これらの値は、プリント基板のレイアウトを完了し、特定の出力コンデンサの種類と容量値を決定したら、過渡応答を最適化するために多少は(推奨値の0.2倍~5倍)変更することができます。出力コンデンサのさまざまな種類と値によってループの帰還係数(利得と位相)が決まるので、まず出力コンデンサを決定する必要があります。

## アプリケーション情報

立上り時間が1μs～10μsの、全負荷電流の20%から100%の出力電流パルスによって出力電圧波形とI<sub>TH</sub>ピンの波形を発生させ、それによって全体的なループの安定性を判断することができます。ループの利得はR<sub>C</sub>を大きくすると増加し、ループの帯域幅はC<sub>C</sub>を小さくすると拡大します。出力電圧のセトリングの様子は閉ループ・システムの安定性に関係し、電源全体の実際の性能を表します。制御ループ理論の要点を含む補償部品の最適化の詳細については、「アプリケーションノート76」を参照してください。

次に、大容量の(>1μF)電源バイパス・コンデンサが接続されている負荷のスイッチが入れられると、さらに大きな過渡が発生します。放電しきったバイパス・コンデンサが実質的にC<sub>OUT</sub>と並列接続状態になるため、V<sub>OUT</sub>が急速に降下します。負荷スイッチの抵抗が低く、しかもそのスイッチが高速でドライブされると、どんなレギュレータでもこの問題を防止するのに十分な電流を供給することはできません。唯一の解決策は、スイッチ・ドライブの立上り時間を制御して、負荷の立上り時間を約(25)(C<sub>LOAD</sub>)に制限することです。したがって、10μFのコンデンサでは250μsの立上り時間が必要で、充電電流は約200mAに制限されます。

### PCボードのレイアウトのチェックリスト

PCボードをレイアウトするときは、以下のチェックリストを使用してLTC3776が正しく動作するようにします。これらの項目は図12のレイアウト図に示してあります。2フェーズ・デュアル・レギュレータの各電流経路の電流波形を図13に示します。

1) 各チャネルの電源ループ(入力コンデンサ、MOSFET、インダクタ、出力コンデンサ)はできるだけ小さくし、他のチャネルの電源ループからできるだけ分離します。理想的には、PチャネルとNチャネルのFETのドレインは互いに近づけて接続し、入力コンデンサはFETに近接させてFETのソース両端に(PチャネルのソースからNチャネルのソースに)接続します。値の小さな2個の入力コンデンサ(たとえば、各チャネルに1個づつ、2個の10μF)を個別に使う方が、両チャネルが共通接続で共有する値の大きな(たとえば、22μF)1個のコンデンサを使うよりも良いでしょう。

2) 信号グランドと電源グランドは分離します。信号グランドは、帰還抵抗分割器、I<sub>TH</sub>補償ネットワークおよびSGNDピンで構成されます。電源グランドは入力コンデンサと出力コンデ

ンサの(-)端子およびNチャネルMOSFETのソースで構成されます。各チャネルには(上の(1)で説明した)それぞれの電源ループのための独自のグランドを持たせます。2つのチャネルの電源グランドは共通ポイントで相互に接続します。大きなスイッチング電流が流れるグランド経路を互いに離しておくことは非常に重要です。

LTC3776デバイスのPGNDピンを互いに短絡し、(スイッチング電流から離して)共通電源グランド接続に接続します。

3) 帰還抵抗はV<sub>FB</sub>ピンに近づけて配置します。トップ帰還抵抗(R<sub>B</sub>)を出力コンデンサに接続するトレースはケルビン・トレースにします。I<sub>TH</sub>補償部品もLTC3776のすぐ近くに配置します。

4) 電流検出トレース(SENSE<sup>+</sup>とSW)はPチャネルMOSFETのソースとドレインに直接ケルビン接続します。

5) スイッチ・ノード(SW1、SW2)とゲート・ドライバ・ノード(TG1、TG2、BG1、BG2)を小信号部品、特に反対側のチャネルの帰還抵抗、I<sub>TH</sub>補償部品および電流検出ピン(SENSE<sup>+</sup>とSW)から離してください。

図12. LTC3776のレイアウト図

図13. ブランチ電流の波形

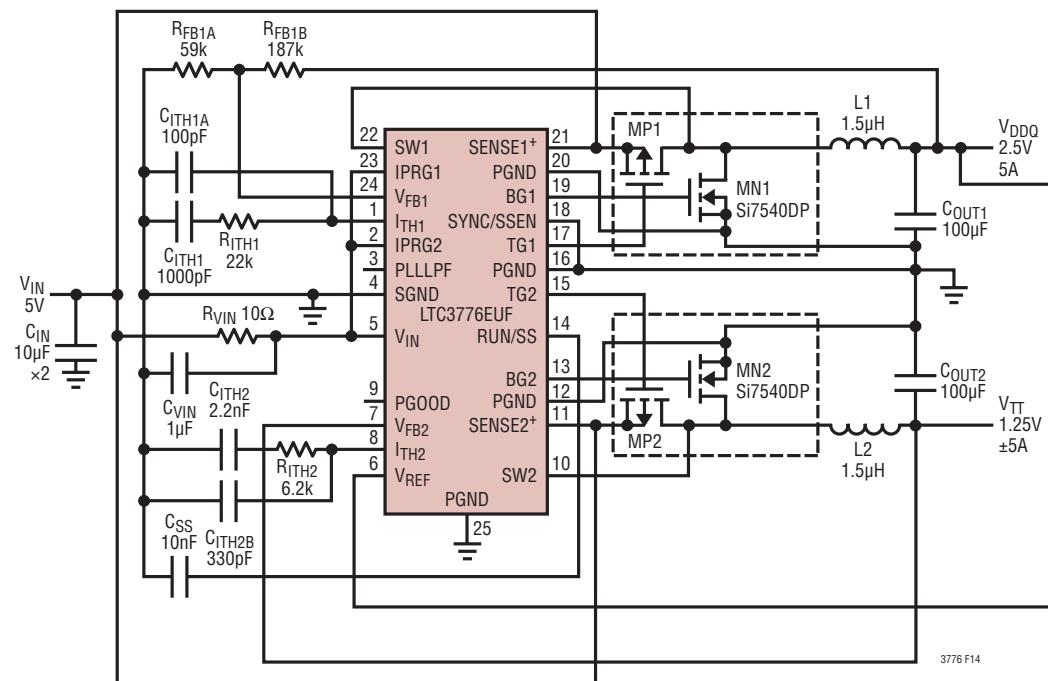

## 標準的応用例

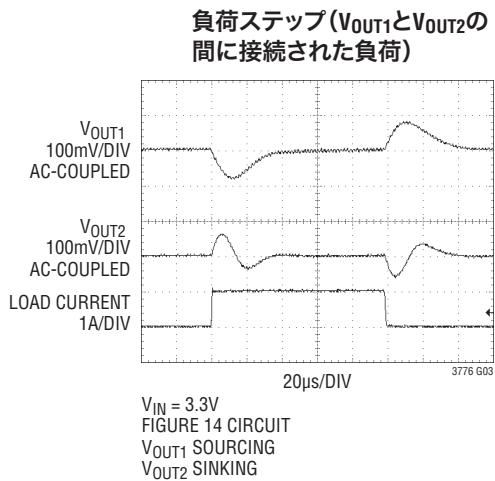

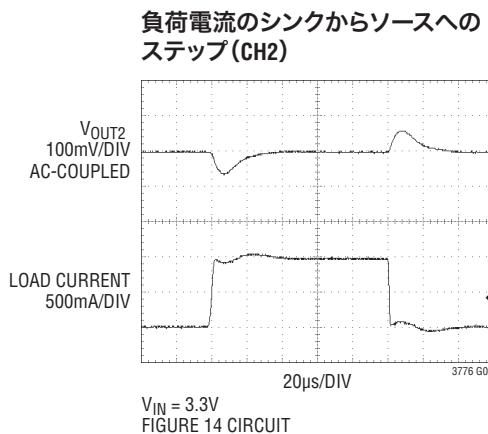

図14. 2フェーズ、550kHz、DDRメモリ電源

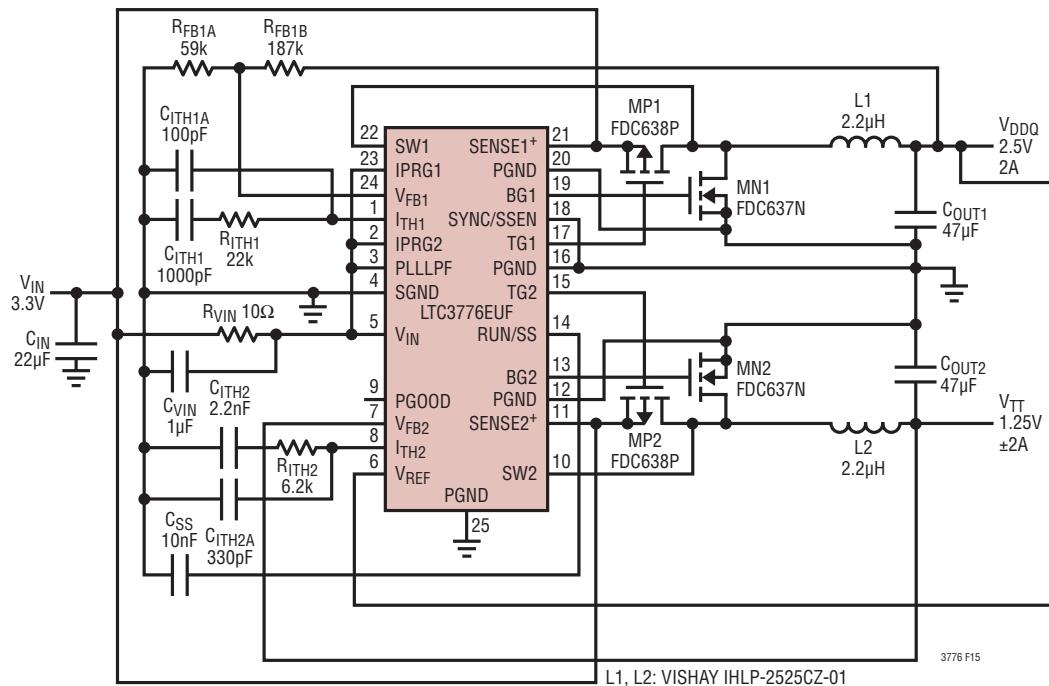

## 標準的応用例

図15. 出力にセラミック・コンデンサを使った、2フェーズ、750kHz、DDRメモリ電源

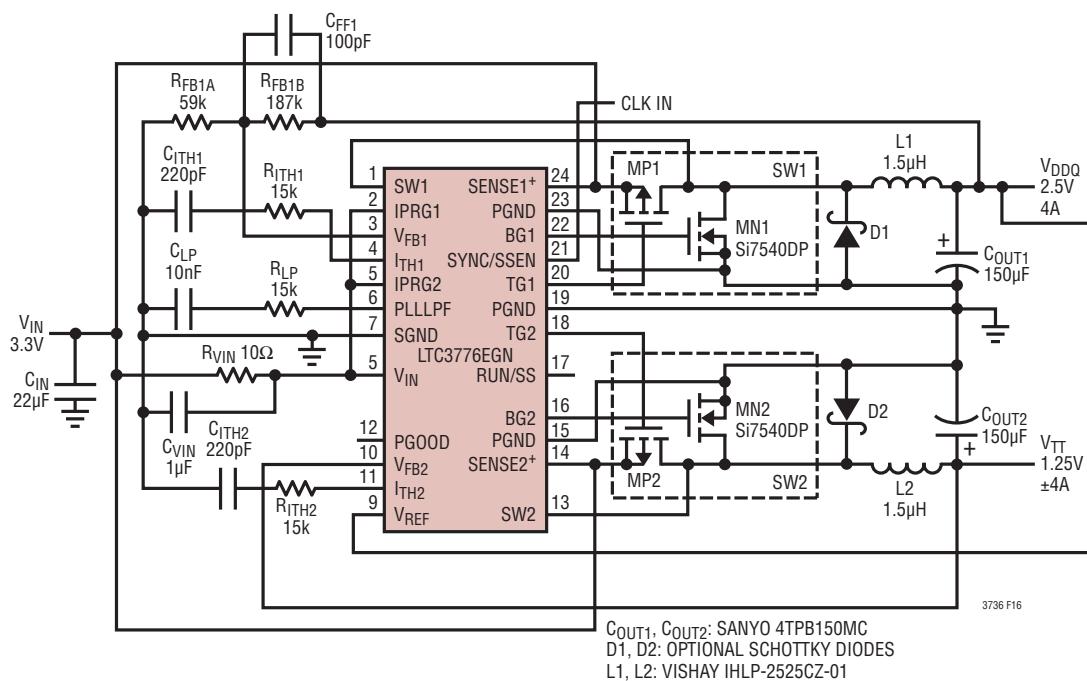

## 標準的応用例

図16. 同期可能な2フェーズDDRメモリ電源

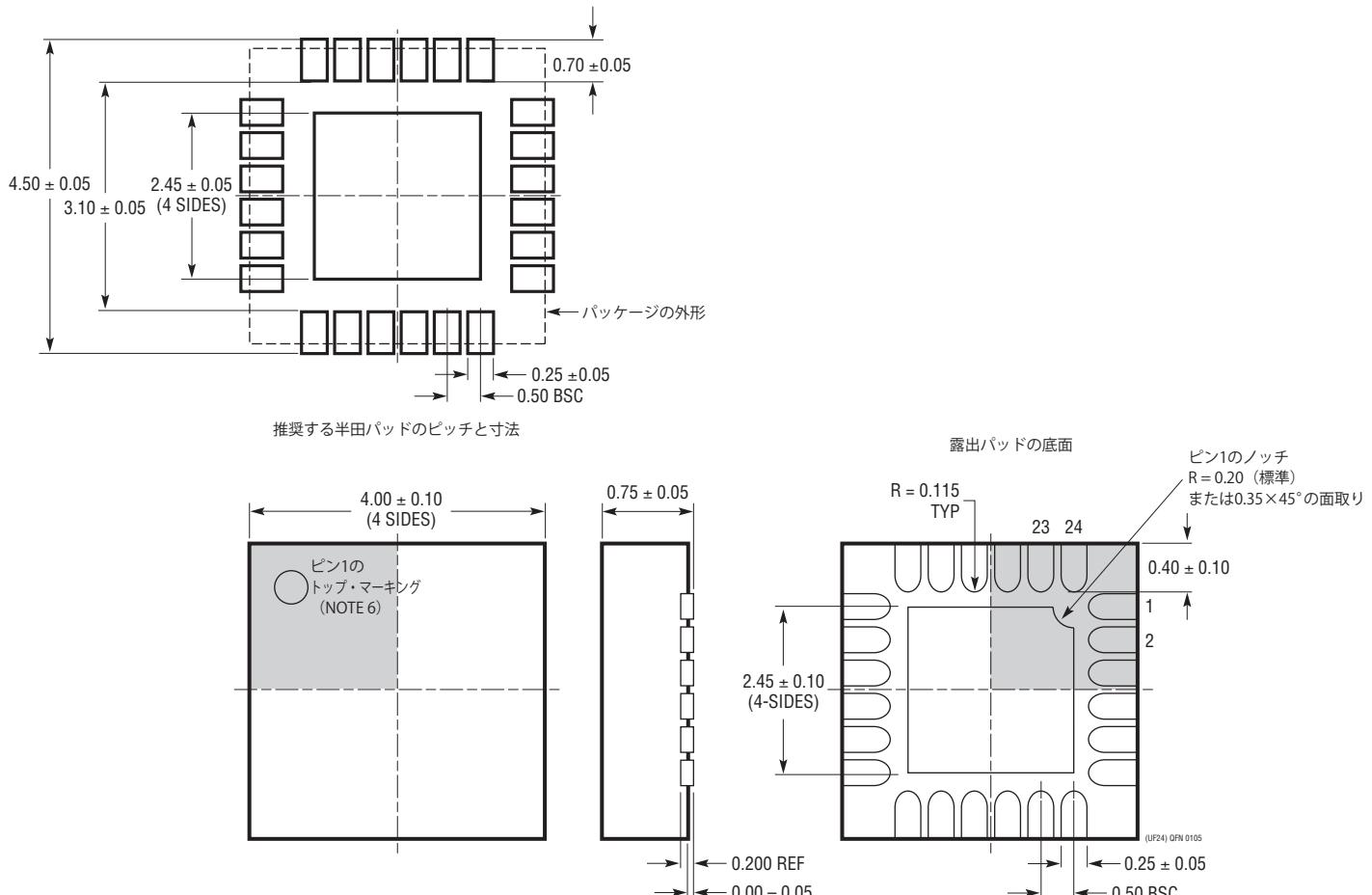

## パッケージ

UFパッケージ

24ピン・プラスチックQFN (4mm×4mm)

(Reference LTC DWG # 05-08-1697)

注記:

1. 図はJEDECパッケージ外形MO-220のバリエーション (WGDD-X) にするよう提案されている (承認待ち)

2. 図は実寸とは異なる

3. 全ての寸法はミリメートル

4. パッケージ底面の露出パッドの寸法にはモールドのバリを含まない。

モールドのバリは (もしあれば) 各サイドで0.15mmを超えないこと

5. 露出パッドは半田メッキとする

6. 網掛けの部分はパッケージのトップとボトムのピン1の位置の参考に過ぎない

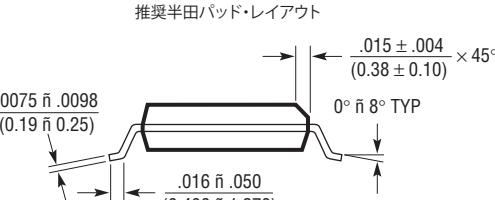

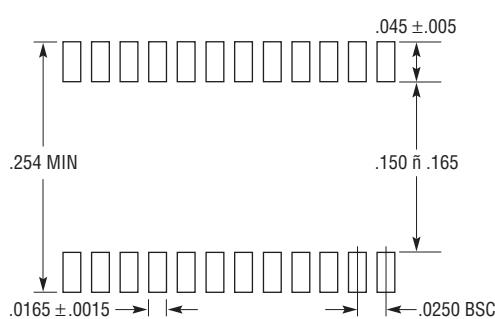

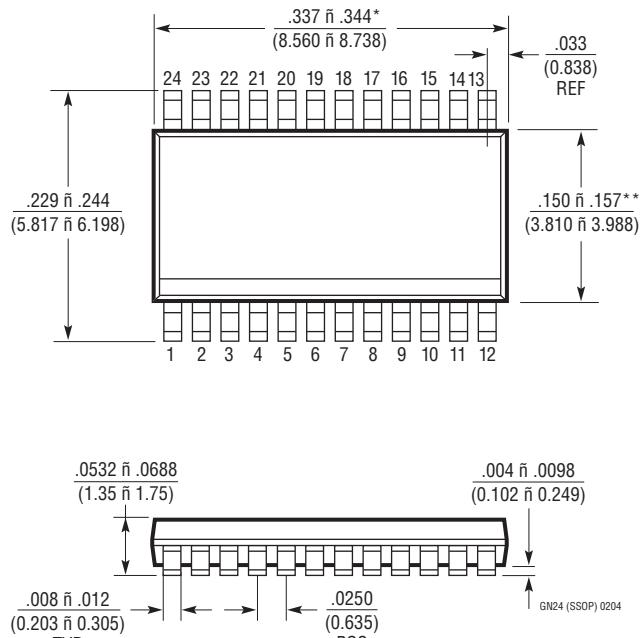

## パッケージ

**GNパッケージ**

**24ピン・プラスチックSSOP(細型0.150インチ)**

(Reference LTC DWG # 05-08-1641)

注記:

- 標準寸法: インチ

- 寸法は  $\frac{\text{インチ}}{\text{ミリメートル}}$

3. 図は実寸とは異なる

\* 寸法にはモールドのバリを含まない。モールドのバリは各サイドで0.006" (0.152mm) を超えないこと

\*\* 寸法にはリード間のバリを含まない。リード間のバリは各サイドで0.010" (0.254mm) を超えないこと

## 標準的応用例

出力にセラミック・コンデンサを使った、2フェーズ、スペクトラム拡散DDRメモリ電源

## 関連製品

| 製品番号             | 説明                                                          | 注釈                                                                                                                        |

|------------------|-------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|

| LTC1735          | 高効率同期整流式降圧コントローラ                                            | Burst Mode動作、16 ピン細型SSOP、フォールト保護、<br>3.5V ≤ V <sub>IN</sub> ≤ 36V                                                         |

| LTC1772          | 固定周波数電流モード降圧DC/DCコントローラ                                     | 2.5V ≤ V <sub>IN</sub> ≤ 9.8V、I <sub>OUT</sub> :最大4A、SOT-23パッケージ、<br>550kHz DC/DCコントローラ                                   |

| LTC1778          | No R <sub>SENSE</sub> ™同期整流式降圧コントローラ                        | センス抵抗なしの電流モード動作、高速過渡応答、<br>4V ≤ V <sub>IN</sub> ≤ 36V                                                                     |

| LTC2923          | 電源トラッキング・コントローラ                                             | 3電源まで制御、10ピンMSOP                                                                                                          |

| LTC3411          | 1.25A (I <sub>OUT</sub> )、4MHz同期整流式降圧DC/DCコンバータ             | 95%の効率、V <sub>IN</sub> :2.5V～5.5V、V <sub>OUT</sub> = 0.8V、I <sub>Q</sub> = 60μA、<br>I <sub>SD</sub> = <1μA、MSパッケージ        |

| LTC3412          | 2.5A (I <sub>OUT</sub> )、4MHz同期整流式降圧DC/DCコンバータ              | 95%の効率、V <sub>IN</sub> :2.5V～5.5V、V <sub>OUT</sub> = 0.8V、I <sub>Q</sub> = 60μA、<br>I <sub>SD</sub> = <1μA、TSSOP-16Eパッケージ |

| LTC3413          | 3Aモリシック DDRメモリ終端レギュレータ                                      | 出力電流:±3A、2.25V ≤ V <sub>IN</sub> ≤ 5.5V                                                                                   |

| LTC3701          | 2フェーズ、低入力電圧デュアル降圧DC/DC コントローラ                               | 2.5V ≤ V <sub>IN</sub> ≤ 9.8V、550kHz、PGOOD、PLL、16ピンSSOP                                                                   |

| LTC3708          | 高速2フェーズNO R <sub>SENSE</sub> 降圧コントローラ、<br>出力トラッキング付き        | 固定オン時間デュアル・コントローラ、V <sub>IN</sub> :最大36V、非常に低い<br>デューティ・サイクル動作、5mm×5mm QFNパッケージ                                           |

| LTC3717          | ハイパワーDDRメモリ終端レギュレータ                                         | 4V ≤ V <sub>IN</sub> ≤ 36V、V <sub>OUT</sub> はV <sub>IN</sub> またはV <sub>REF</sub> をトラッキングする、<br>I <sub>OUT</sub> :1A～20A   |

| LTC3728/LTC3728L | デュアル、550kHz、2フェーズ同期整流式<br>降圧スイッチング・レギュレータ                   | 固定周波数、V <sub>IN</sub> :最大36V、5Vと3.3VのLDO、5mm×5mm<br>QFNまたは28ピンSSOP                                                        |

| LTC3736          | デュアル、2フェーズNo R <sub>SENSE</sub><br>同期整流式コントローラ、出力トラッキング付き   | V <sub>IN</sub> :2.75V～9.8V、I <sub>OUT</sub> :最大5A、4mm×4mm<br>QFNパッケージ                                                    |

| LTC3736-1        | デュアル、2フェーズ、No R <sub>SENSE</sub> 同期整流式コントローラ、<br>スペクトラム拡散付き | V <sub>IN</sub> :2.75～9.8V、スペクトラム拡散動作、<br>出力電圧トラッキング、4mm×4mm QFNパッケージ                                                     |

| LTC3737          | デュアル、2フェーズNo R <sub>SENSE</sub> コントローラ、出力<br>トラッキング付き       | V <sub>IN</sub> :2.75V～9.8V、I <sub>OUT</sub> :最大5A、4mm×4mm<br>QFNパッケージ                                                    |

| LTC3831          | ハイパワーDDRメモリ終端レギュレータ                                         | V <sub>OUT</sub> が1/2 V <sub>IN</sub> またはV <sub>REF</sub> をトラッキング、3V ≤ V <sub>IN</sub> ≤ 8V、<br>I <sub>OUT</sub> :1A～20A  |

No R<sub>SENSE</sub>はリニアテクノロジー社の商標です。

3776fa