## 特長

- Direct Flux Limit™により、飽和しないことを保証

- 高速および高精度の平均電流制限

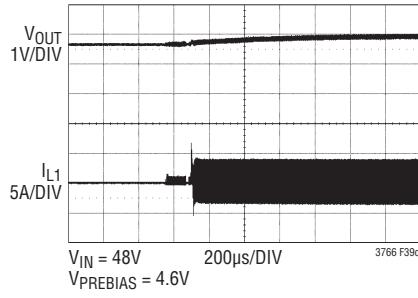

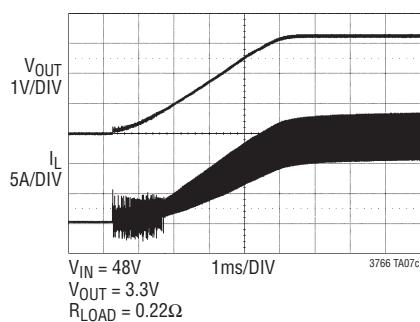

- 出力がプリバイアスされていてもクリーンな起動が可能

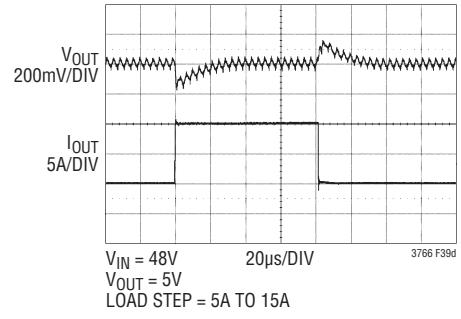

- 2次側制御により、高速過渡応答が可能

- シンプルなセルフスタート・アーキテクチャ

- 同期 MOSFET の逆電流制限

- PolyPhase®動作により、高電力設計を簡素化

- 真のリモートセンス差動アンプ

- リモートセンスの逆電圧保護

- 高電圧リニア・レギュレータ・コントローラ

- 内部 LDO が  $V_{OUT}$  からゲートドライブに電力を供給

- 過温度/過電圧保護

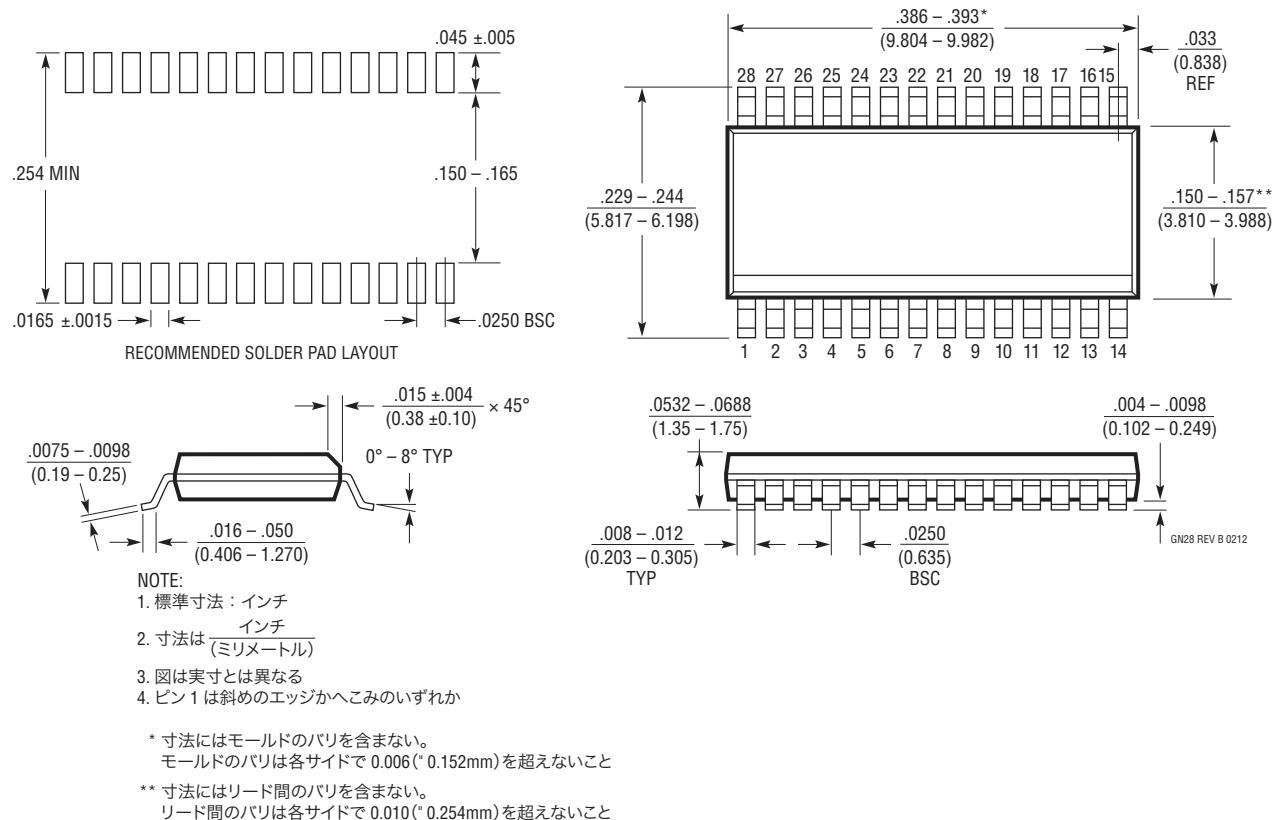

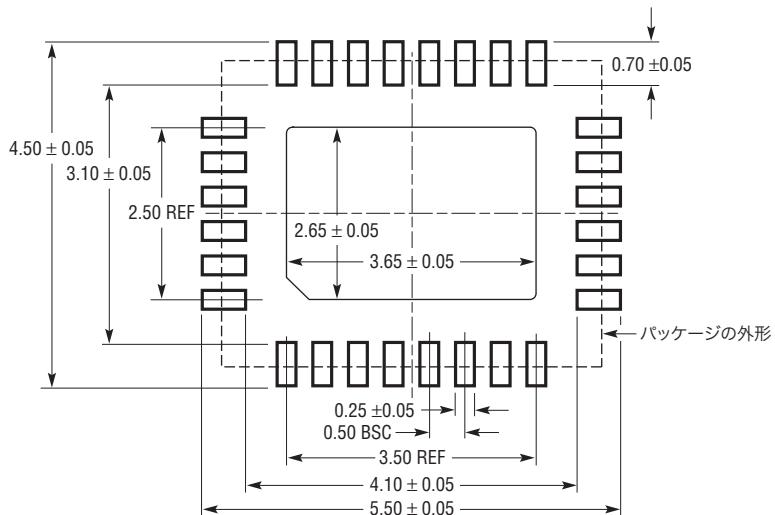

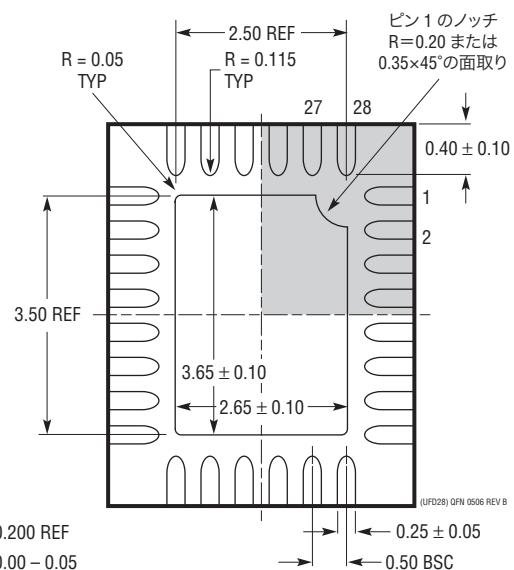

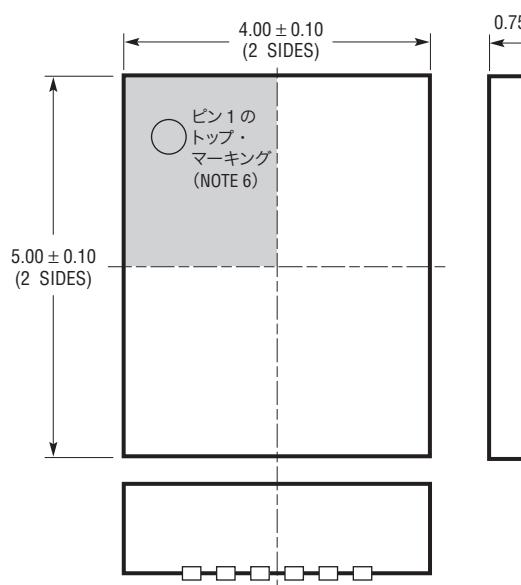

- 高さの低い 4mm×5mm QFN パッケージと

細型 28 ピン SSOP パッケージ

## アプリケーション

- 絶縁型 48V テレコム・システム

- 絶縁型バッテリ・チャージャ

- 車載システムと軍用システム

- 産業用機器、アビオニクス機器および重機

LT, LTC, LTM, PolyPhase, Linear Technology, およびLinearのロゴはリニアテクノロジー社の登録商標です。Direct Flux Limitはリニアテクノロジー社の商標です。他の全ての商標はそれぞれの所有者に所有権があります。7200014 および 6144194 を含む米国特許によって保護されています。その他特許出願中。

## 概要

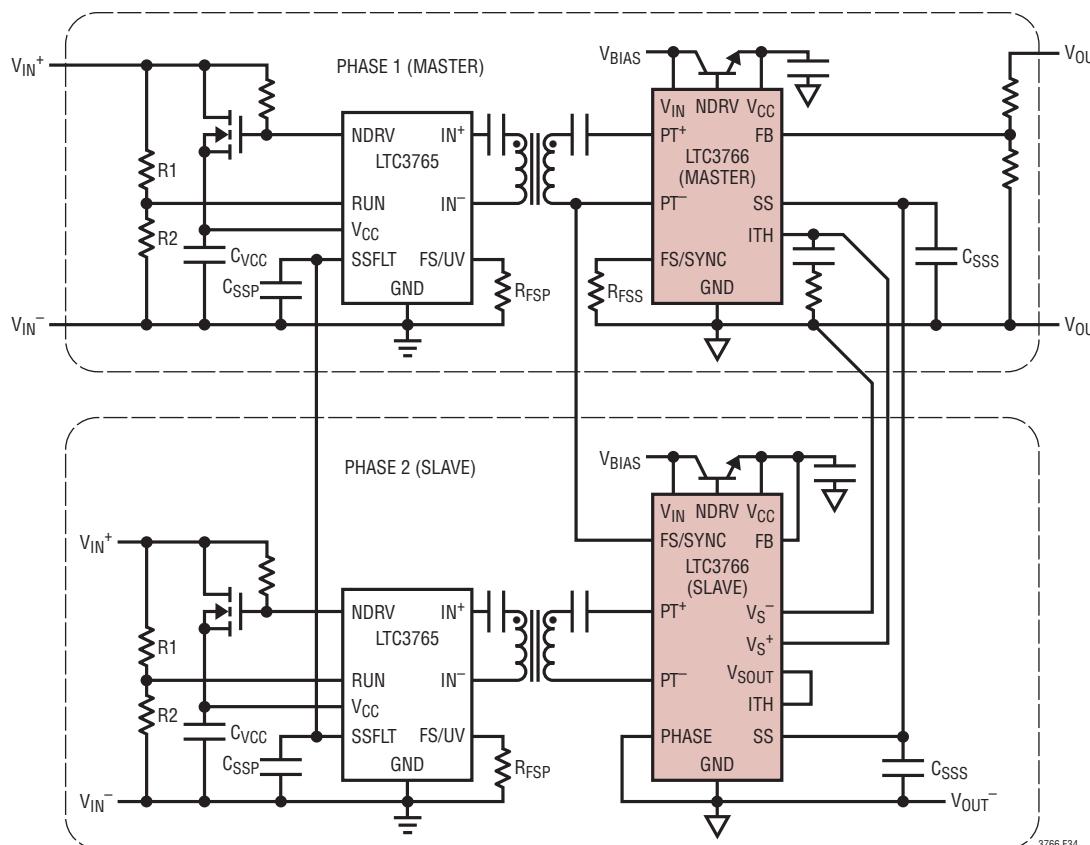

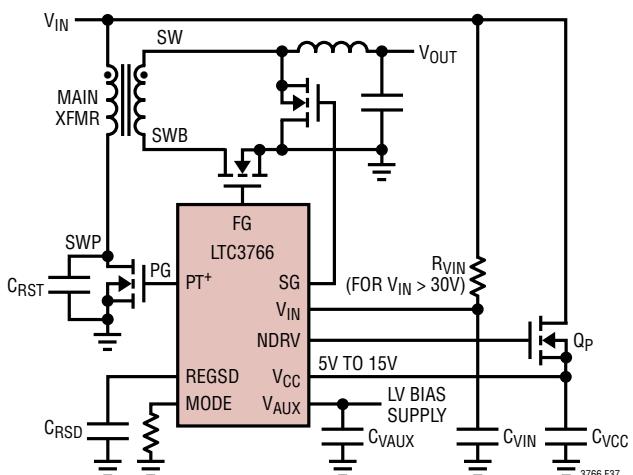

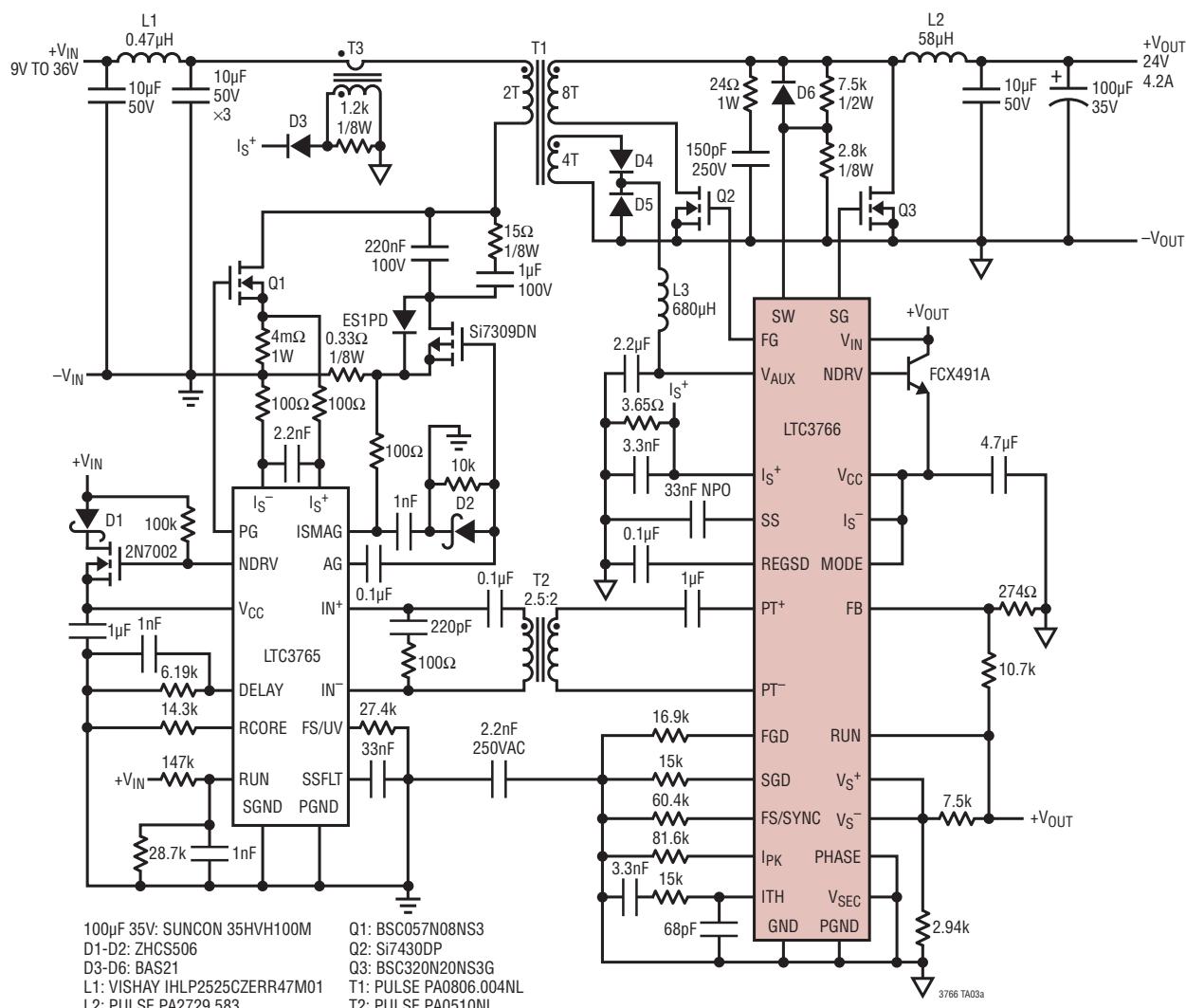

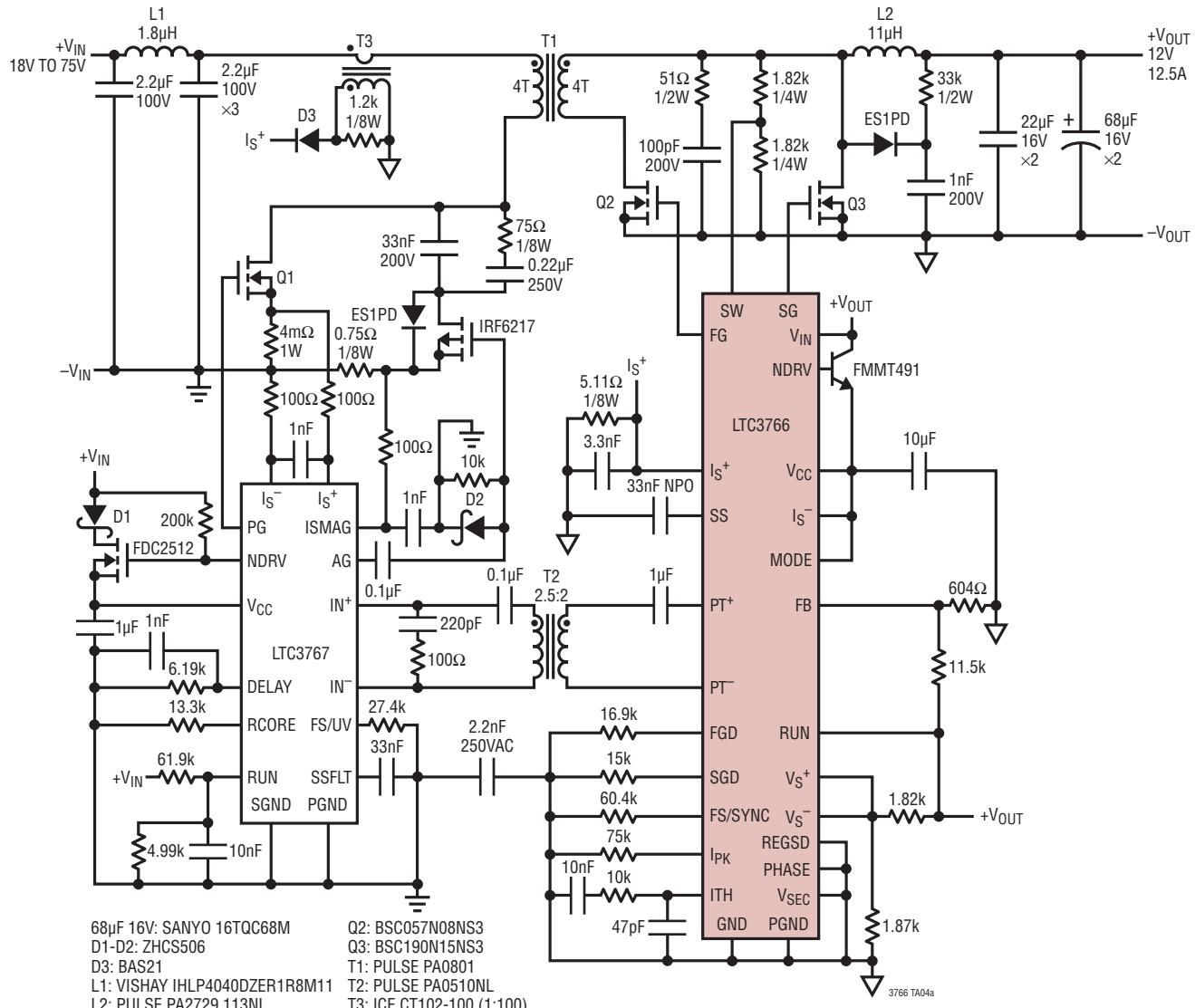

LTC®3766 は、同期整流式フォワード・コンバータ向けの PolyPhase が可能な 2 次側コントローラです。このデバイスは LTC3765 アクティブ・クランプ・フォワード・コントローラおよびゲート・ドライバと共に使用することで、マルチフェーズ動作の電力と 2 次側制御の速度を組み合わせた絶縁電源を構成します。

LTC3766 は、アクティブ・クランプ・フォワード・コンバータの設計を簡素化するために設計されました。このデバイスは LTC3765 と共に使用することにより、2 次側制御アプリケーションで通常使用される個別のバイアス・レギュレータが不要となる堅牢なセルフスタート・コンバータを構成します。また、高精度の電流制限機能を備え、負荷がプリバイアスされていてもクリーンな起動が可能なので、高電力バッテリ・チャージャ・アプリケーションに最適です。

LTC3766 は広範なリモートセンス機能と出力保護機能を備えており、同時に Direct Flux Limit によって、過渡応答を遅らせることなくトランジストの飽和を防ぎます。また、リニア・レギュレータ・コントローラとバイパス LDO を内蔵しているので、2 次側バイアス電圧を容易に生成できます。

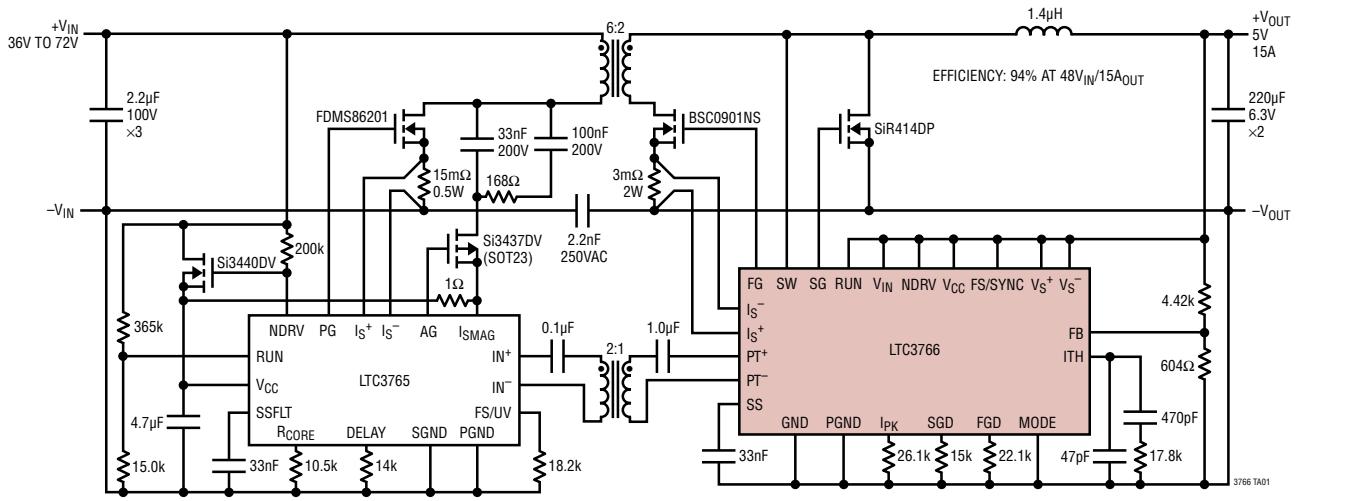

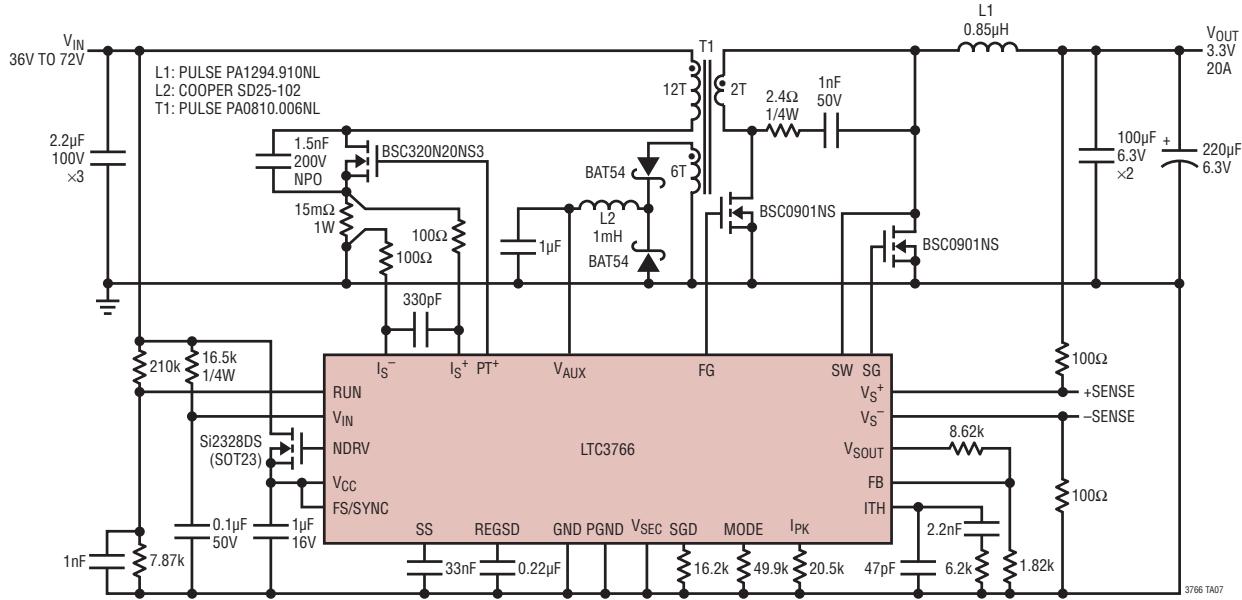

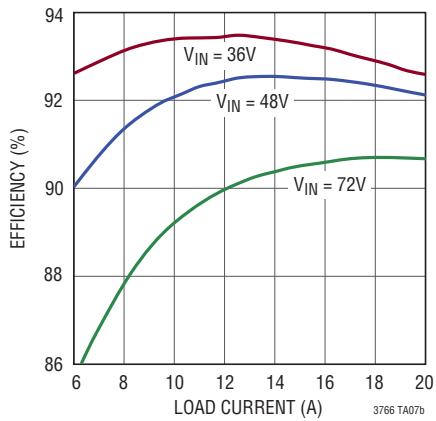

## 標準的応用例

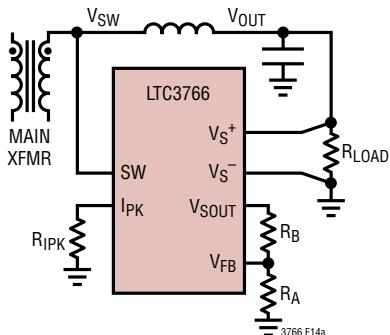

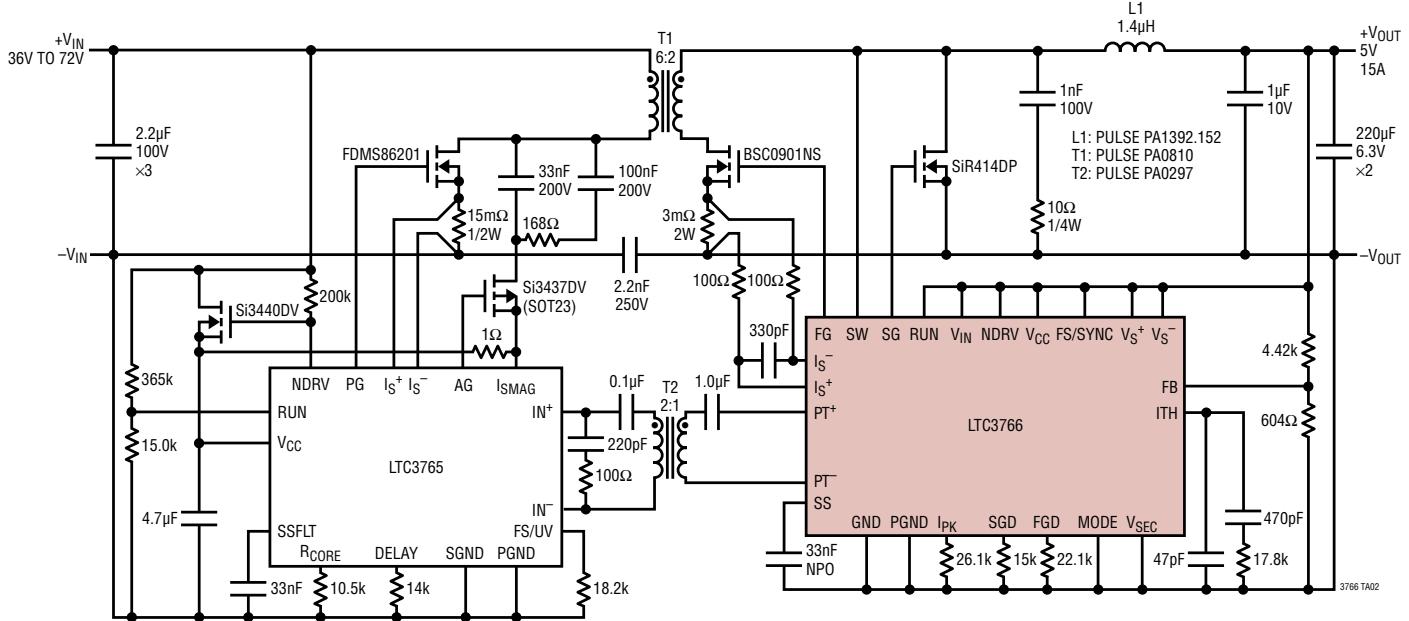

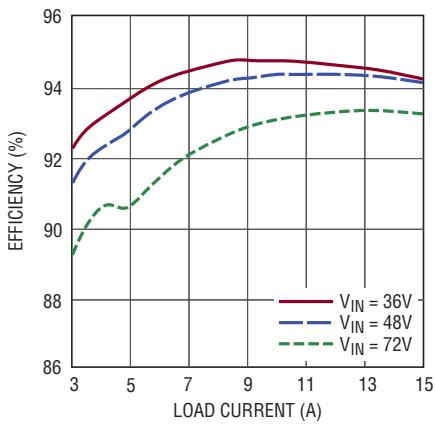

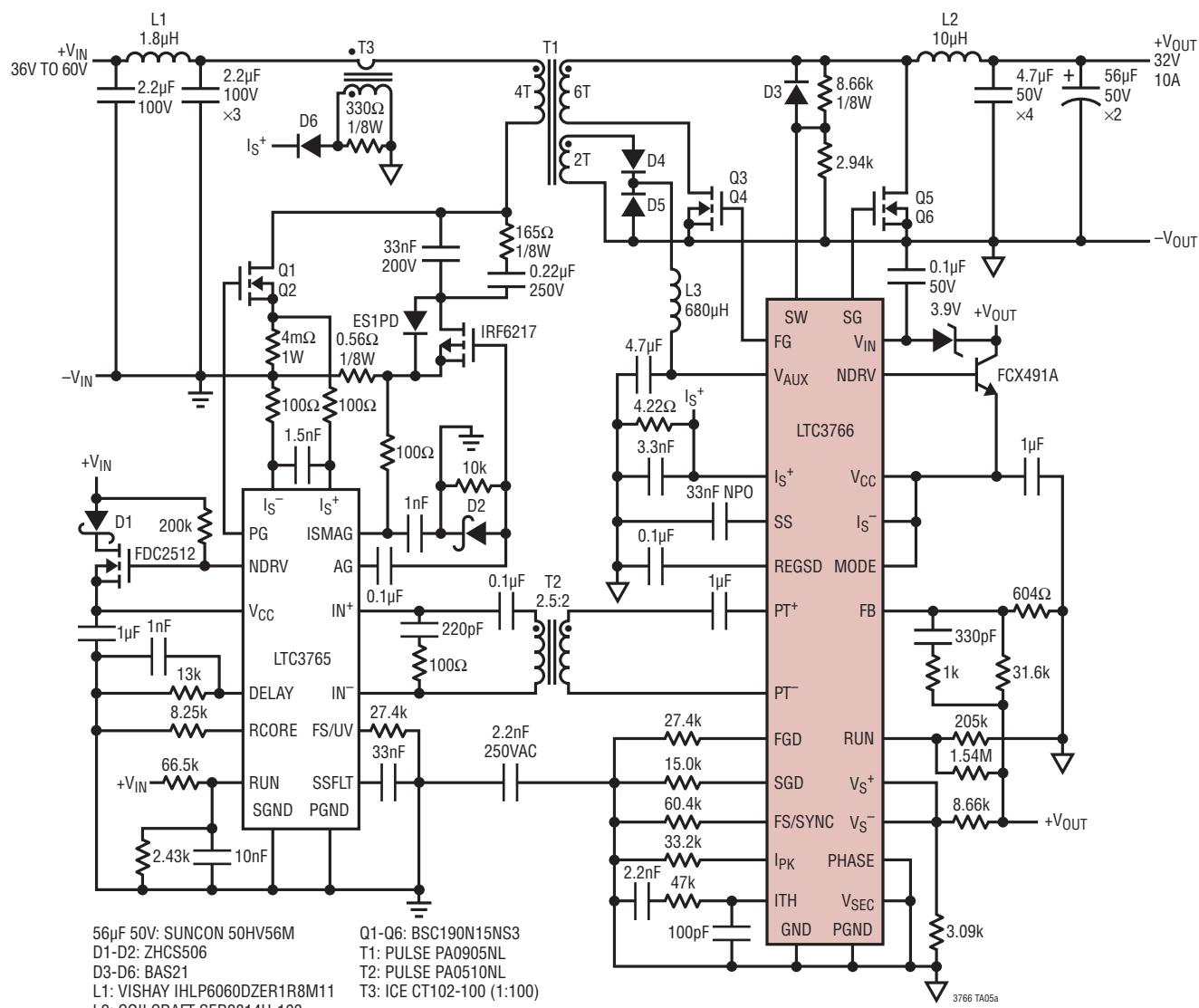

### 36V～72V から 5V/15A のアクティブ・クランプ絶縁型フォワード・コンバータ

## 絶対最大定格 (Note 1)

|                                                                                                       |           |

|-------------------------------------------------------------------------------------------------------|-----------|

| V <sub>CC</sub> 電圧                                                                                    | -0.3V～12V |

| V <sub>IN</sub> 電圧                                                                                    | -0.3V～33V |

| RUNの電圧                                                                                                | -0.3V～33V |

| SW                                                                                                    |           |

| 低インピーダンス・ソース                                                                                          | -5V～40V   |

| 供給される電流 ... 2mA DC または 0.2A (<1μs)、ピンへ流れ込む*                                                           |           |

| V <sub>AUX</sub> 、V <sub>S<sup>+</sup></sub> 、V <sub>S<sup>-</sup></sub> 、V <sub>SOUT</sub> 、NDRV の電圧 | -0.3V～16V |

| ITH、I <sub>S<sup>+</sup></sub> 、REGSD の電圧                                                             | -0.3V～6V  |

| PHASE の電圧                                                                                             | -0.3V～6V  |

| I <sub>S<sup>-</sup></sub> 、SGD、FGD の電圧                                                               | -0.3V～12V |

| FS/SYNC、FB、MODE の電圧                                                                                   | -0.3V～12V |

V<sub>SEC</sub>電圧 ..... -0.3V～3V

I<sub>PK</sub>、SS の電圧 ..... -0.3V～4V

動作接合部温度範囲 (Note 2、3)

LTC3766E、LTC3766I ..... -40°C～125°C

LTC3766H ..... -40°C～150°C

LTC3766MP ..... -55°C～150°C

保存温度範囲 ..... -65°C～150°C

リード温度(半田付け、10秒)

GNパッケージ ..... 300°C

\*LTC3766は50Vのクランプを内蔵しており、SWピンの電圧を制限します。

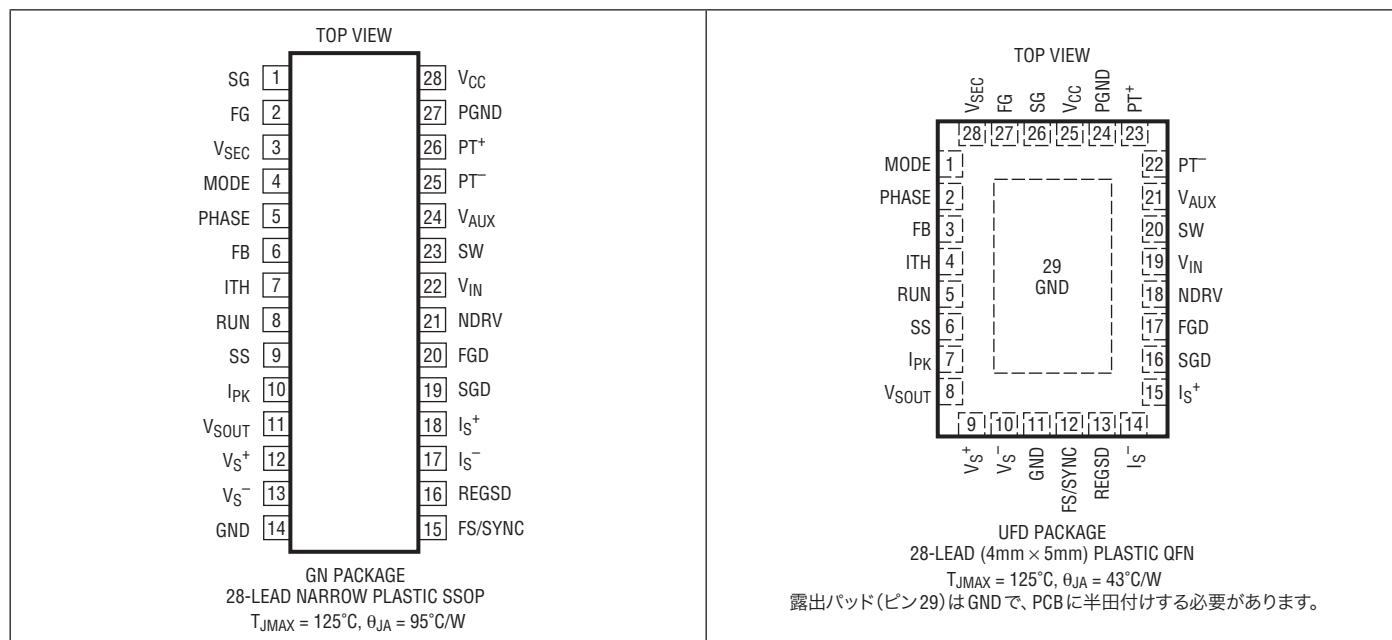

## ピン配置

## 発注情報

| 鉛フリー仕様           | テープアンドリール          | 製品マーキング*  | パッケージ                           | 温度範囲           |

|------------------|--------------------|-----------|---------------------------------|----------------|

| LTC3766EGN#PBF   | LTC3766EGN#TRPBF   | LTC3766GN | 28-Lead Narrow Plastic SSOP     | -40°C to 125°C |

| LTC3766IGN#PBF   | LTC3766IGN#TRPBF   | LTC3766GN | 28-Lead Narrow Plastic SSOP     | -40°C to 125°C |

| LTC3766HGN#PBF   | LTC3766HGN#TRPBF   | LTC3766GN | 28-Lead Narrow Plastic SSOP     | -40°C to 150°C |

| LTC3766MPGN#PBF  | LTC3766MPGN#TRPBF  | LTC3766GN | 28-Lead Narrow Plastic SSOP     | -55°C to 150°C |

| LTC3766EUFD#PBF  | LTC3766EUFD#TRPBF  | 3766      | 28-Lead (4mm × 5mm) Plastic QFN | -40°C to 125°C |

| LTC3766IUFD#PBF  | LTC3766IUFD#TRPBF  | 3766      | 28-Lead (4mm × 5mm) Plastic QFN | -40°C to 125°C |

| LTC3766HUFD#PBF  | LTC3766HUFD#TRPBF  | 3766      | 28-Lead (4mm × 5mm) Plastic QFN | -40°C to 150°C |

| LTC3766MPUFD#PBF | LTC3766MPUFD#TRPBF | 3766      | 28-Lead (4mm × 5mm) Plastic QFN | -55°C to 150°C |

さらに広い動作温度範囲で規定されるデバイスについては、弊社または弊社代理店にお問い合わせください。\* 温度グレードは出荷時のコンテナのラベルで識別されます。

非標準の鉛ベース仕様の製品の詳細については、弊社または弊社代理店にお問い合わせください。

鉛フリー仕様の製品マーキングの詳細については、<http://www.linear-tech.co.jp/leadfree/> をご覧ください。

テープアンドリールの仕様の詳細については、<http://www.linear-tech.co.jp/tapeandreel/> をご覧ください。

**電気的特性** ●は規定動作接合部温度範囲の規格値を意味する。それ以外は  $T_A = 25^\circ\text{C}$  での値 (Note 2)。注記がない限り、 $V_{IN} = 15\text{V}$ 、 $GND = PGND = 0\text{V}$ 。

| SYMBOL                   | PARAMETER                            | CONDITIONS                                                                                                              | MIN        | TYP         | MAX         | UNITS    |    |

|--------------------------|--------------------------------------|-------------------------------------------------------------------------------------------------------------------------|------------|-------------|-------------|----------|----|

| <b>メイン制御ループ</b>          |                                      |                                                                                                                         |            |             |             |          |    |

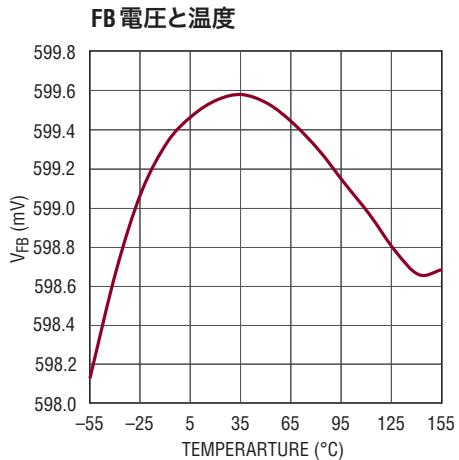

| $V_{FB}$                 | Regulated Feedback Voltage           | (Note 4) ITH = 1.2V                                                                                                     | ●          | 0.592       | 0.600       | 0.608    | V  |

| $I_{FB}$                 | Feedback Input Current               | (Note 4)                                                                                                                |            | 2           | 50          | nA       |    |

| $\Delta V_{FB(LINREG)}$  | Feedback Voltage Line Regulation     | $V_{IN} = 5\text{V}$ to $32\text{V}$ , ITH = 1.2V                                                                       |            | 0.001       |             | %/V      |    |

| $\Delta V_{FB(LOADREG)}$ | Feedback Voltage Load Regulation     | Measured in Servo Loop, ITH = 0.5V to 2V                                                                                | ●          | -0.01       | -0.1        | %        |    |

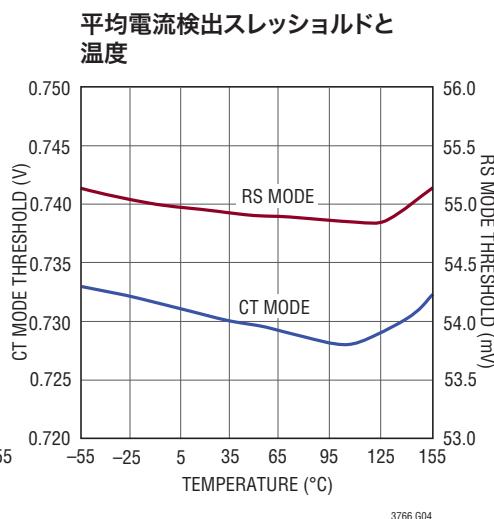

| $V_{ISAVG}$              | Average Current Sense Threshold      | Resistor Sense (RS) Mode<br>Current Transformer (CT) Mode                                                               | 47<br>0.66 | 55<br>0.73  | 63<br>0.80  | mV<br>V  |    |

| $V_{ISADJ}$              | Current Sense Ripple Compensation    | RS Mode<br>CT Mode<br>$V_{SW} = 10\text{V}$ , $V_S^+ = 5\text{V}$ , FS/SYNC = $V_{CC}$ , $R_{IPK} = 23.7\text{k}\Omega$ |            | 10<br>140   |             | mV<br>mV |    |

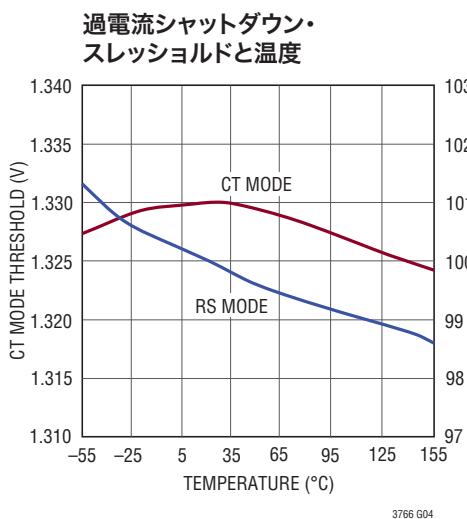

| $V_{ISOC}$               | Overcurrent Shutdown Threshold       | RS Mode: $V_S^- = 0\text{V}$<br>CT Mode: $V_S^- = V_{CC}$                                                               | 86<br>1.22 | 100<br>1.33 | 113<br>1.44 | mV<br>V  |    |

| $I_{SIN}$                | $I_S^+$ and $I_S^-$ Input Current    |                                                                                                                         |            | 280         | 500         | nA       |    |

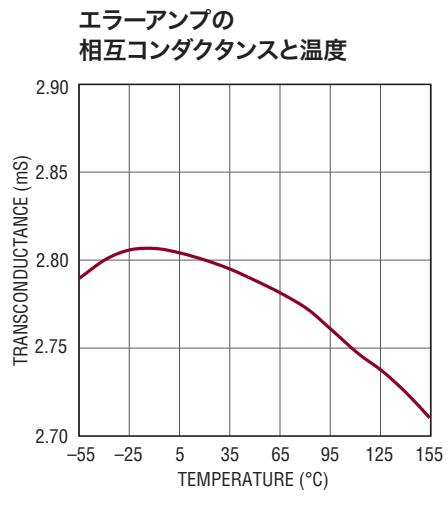

| $g_m$                    | Error Amplifier $g_m$                |                                                                                                                         |            | 2.2         | 2.7         | 3.2      | mS |

| $R_{EA}$                 | Error Amplifier Output Resistance    | (Note 7)                                                                                                                |            | 5           |             | MΩ       |    |

| $I_{SOFT(C)}$            | Soft-Start Charge Current            | $V_{SS} = 2\text{V}$                                                                                                    |            | 4           | 5           | 6        | μA |

| $I_{SOFT(D)}$            | Soft-Start Discharge Current         | $V_{SS} = 2\text{V}$                                                                                                    |            | 3           |             | μA       |    |

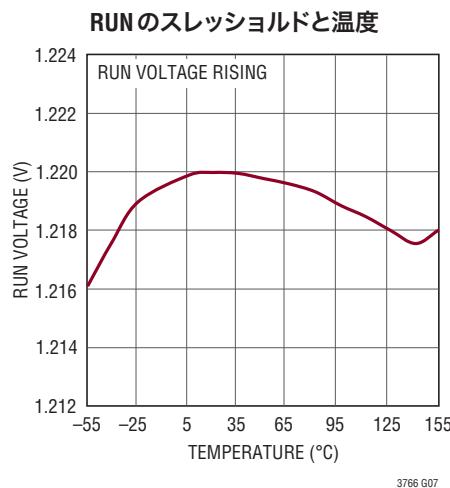

| $V_{RUNR}$               | RUN Pin On Threshold                 | $V_{RUN}$ Rising                                                                                                        | ●          | 1.18        | 1.22        | 1.26     | V  |

| $V_{RUNF}$               | RUN Pin Off Threshold                | $V_{RUN}$ Falling                                                                                                       | ●          | 1.13        | 1.17        | 1.21     | V  |

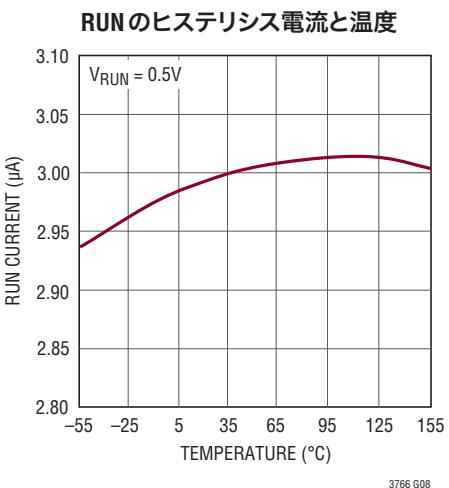

| $I_{RUN}$                | RUN Pin Hysteresis Current           | $V_{RUN} = 0.5\text{V}$                                                                                                 |            | 2.2         | 3.0         | 3.6      | μA |

| $t_{ON(MIN)}$            | Minimum Controllable On Time         |                                                                                                                         |            | 200         |             | ns       |    |

| $D_{MAX}$                | Maximum Duty Cycle                   | $FGD = SGD = GND$                                                                                                       |            | 77          | 79          | 81       | %  |

| $\Delta V_{SEC(TH)}$     | Volt-Second Limit Threshold Accuracy | $2\text{V} \leq V_{SW} < 5\text{V}$<br>$5\text{V} \leq V_{SW} \leq 40\text{V}$                                          | -6<br>-4   |             | 6<br>4      | %        |    |

| $R_{VSDN}$               | Volt-Second Discharge Resistance     |                                                                                                                         |            | 75          |             | Ω        |    |

| $V_{SWCL}$               | SW Clamp Voltage                     | $I_{SW} = 1\text{mA}$                                                                                                   |            | 43          | 51          | 60       | V  |

| $\Delta V_{FB(OV)}$      | Output Overvoltage Threshold         | $V_{FB}$ Rising                                                                                                         |            | 15          | 17          | 19       | %  |

**電気的特性** ●は規定動作接合部温度範囲の規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値(Note 2)。注記がない限り、 $V_{IN} = 15\text{V}$ 、 $GND = PGND = 0\text{V}$ 。

| SYMBOL                        | PARAMETER                                                     | CONDITIONS                                                                 | MIN          | TYP          | MAX          | UNITS                          |        |

|-------------------------------|---------------------------------------------------------------|----------------------------------------------------------------------------|--------------|--------------|--------------|--------------------------------|--------|

| <b>ドライバおよび制御回路</b>            |                                                               |                                                                            |              |              |              |                                |        |

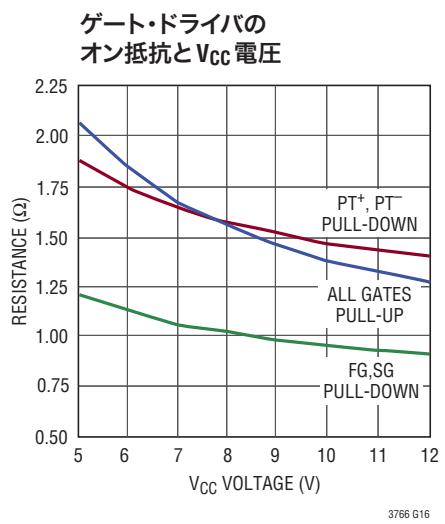

| $FG, SG\ R_{UP}$              | FG, SG Driver Pull-Up On-Resistance                           |                                                                            |              | 1.5          |              | $\Omega$                       |        |

| $FG, SG\ R_{DOWN}$            | FG, SG Driver Pull-Down On-Resistance                         |                                                                            |              | 1.0          |              | $\Omega$                       |        |

| $PT^+, PT^- R_{UP}$           | PT <sup>+</sup> , PT <sup>-</sup> Driver Pull-Up Resistance   |                                                                            |              | 1.5          |              | $\Omega$                       |        |

| $PT^+, PT^- R_{DOWN}$         | PT <sup>+</sup> , PT <sup>-</sup> Driver Pull-Down Resistance |                                                                            |              | 1.5          |              | $\Omega$                       |        |

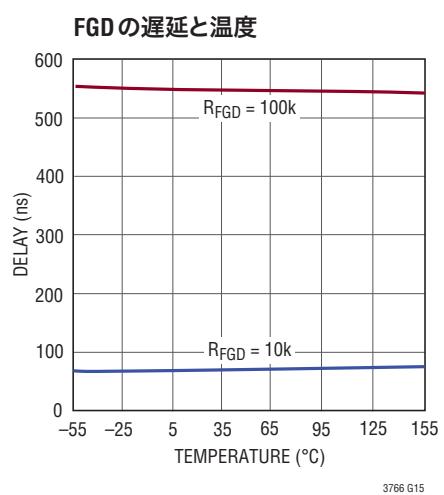

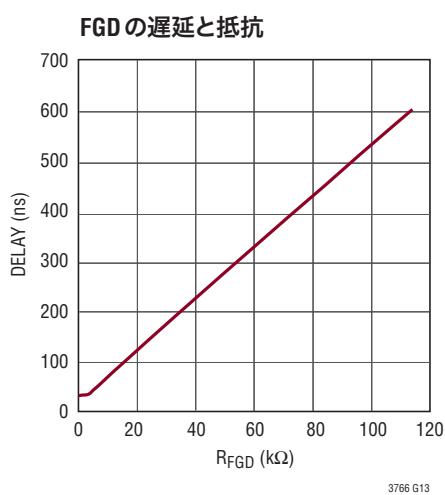

| $t_{FGD}$                     | FGD Delay                                                     | $R_{FGD} = 10\text{k}\Omega$<br>$R_{FGD} = 100\text{k}\Omega$              | 50<br>436    | 65<br>545    | 80<br>654    | ns<br>ns                       |        |

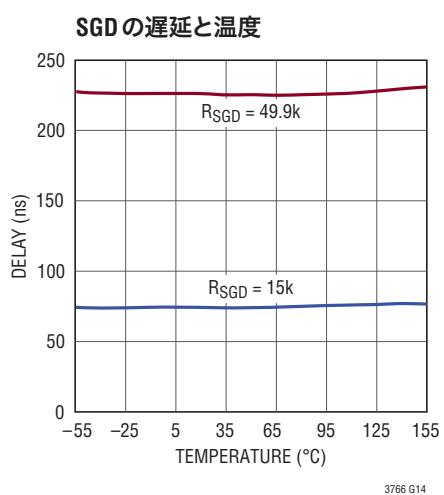

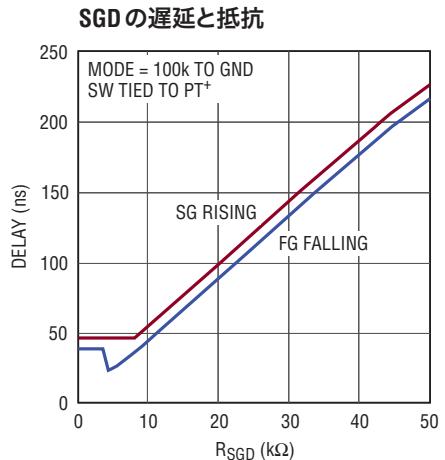

| $t_{SGD}$                     | SGD Delay                                                     | $R_{SGD} = 15\text{k}\Omega$<br>$R_{SGD} = 50\text{k}\Omega$               | 60<br>195    | 75<br>230    | 90<br>265    | ns<br>ns                       |        |

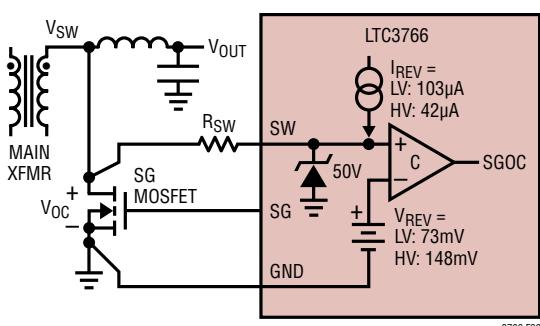

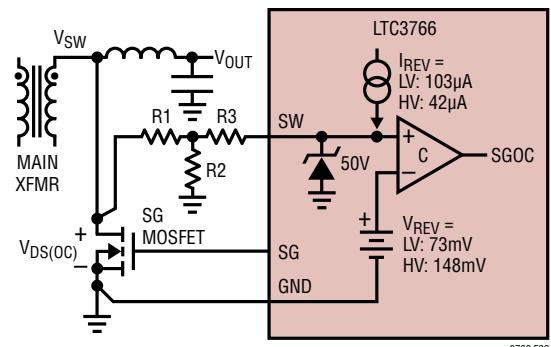

| $V_{SW(\text{REV})}$          | SG Reverse Overcurrent SW Threshold                           | LV MODE<br>HV MODE                                                         | 66<br>140    | 73<br>148    | 79<br>156    | mV<br>mV                       |        |

| $I_{SW(\text{REV})}$          | SG Reverse Overcurrent Adjust Current                         | LV MODE<br>HV MODE                                                         | -86<br>-34.5 | -103<br>-42  | -120<br>-49  | $\mu\text{A}$<br>$\mu\text{A}$ |        |

| <b><math>V_{CC}</math>電源</b>  |                                                               |                                                                            |              |              |              |                                |        |

| $V_{CCOP}$                    | $V_{CC}$ Operating Voltage Range                              |                                                                            | 5            | 10           |              | V                              |        |

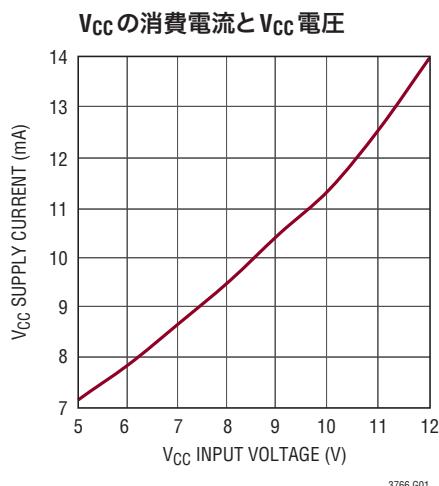

| $I_{CC}$                      | Supply Current<br>Normal Mode<br>Shutdown                     | $V_{FS/SYNC} = V_{CC} = 7\text{V}$ (Note 5)<br>$V_{RUN} = GND$             |              | 5<br>210     |              | mA<br>$\mu\text{A}$            |        |

| $V_{UVLOR}$                   | UV Lockout Rising                                             | $V_{CC}$ Rising, LV MODE<br>$V_{CC}$ Rising, HV MODE                       | ●<br>●       | 4.6<br>7.7   | 4.7<br>7.9   | 4.8<br>8.1                     | V<br>V |

| $V_{UVLOF}$                   | UV Lockout Falling                                            | $V_{CC}$ Falling, LV MODE<br>$V_{CC}$ Falling, HV MODE                     | ●<br>●       | 3.8<br>6.7   | 3.9<br>6.9   | 4.0<br>7.1                     | V<br>V |

| $V_{REGSD}$                   | REGSD Threshold Voltage                                       | $V_{REGSD}$ Rising                                                         |              | 1.21         |              | V                              |        |

| $I_{REGSD(C)}$                | REGSD Charge Current                                          | $V_{REGSD} = 0.7\text{V}$                                                  |              | 13           |              | $\mu\text{A}$                  |        |

| $I_{REGSD(D)}$                | REGSD Discharge Current                                       | $V_{REGSD} = 0.7\text{V}$                                                  |              | 3            |              | $\mu\text{A}$                  |        |

| <b><math>V_{AUX}</math>電源</b> |                                                               |                                                                            |              |              |              |                                |        |

| $V_{AUXOP}$                   | $V_{AUX}$ Operating Voltage Range                             |                                                                            | 5            | 15           |              | V                              |        |

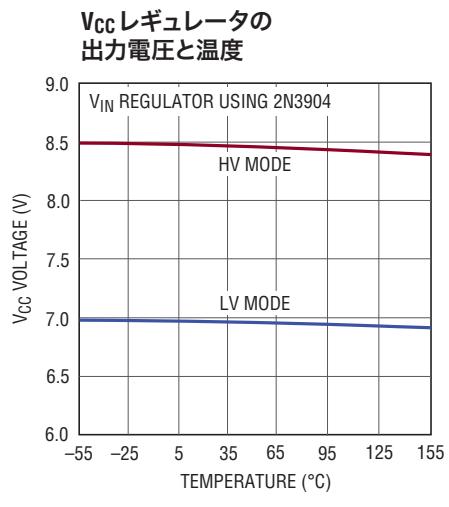

| $V_{CCVAUX}$                  | Regulated $V_{CC}$ Output Voltage                             | $V_{AUX} = 15\text{V}$ , LV MODE<br>$V_{AUX} = 15\text{V}$ , HV MODE       | 6.7<br>8.1   | 7.0<br>8.5   | 7.3<br>8.9   | V<br>V                         |        |

| $V_{AUXLR}$                   | $V_{CC}$ Load Regulation                                      | $I_{CC} = 0\text{mA}$ to $120\text{mA}$ , $V_{AUX} = 8\text{V}$ , LV MODE  |              | 0.8          | 2            | %                              |        |

| $V_{AUXSWP}$                  | $V_{AUX}$ Switchover Voltage Rising                           | $V_{AUX}$ Ramping Positive, LV MODE<br>$V_{AUX}$ Ramping Positive, HV MODE | 4.50<br>7.65 | 4.70<br>8.00 | 4.88<br>8.35 | V<br>V                         |        |

| $V_{AUXSWN}$                  | $V_{AUX}$ Switchover Voltage Falling                          | $V_{AUX}$ Ramping Negative, LV MODE<br>$V_{AUX}$ Ramping Negative, HV MODE | 4.30<br>7.35 | 4.50<br>7.70 | 4.70<br>8.05 | V<br>V                         |        |

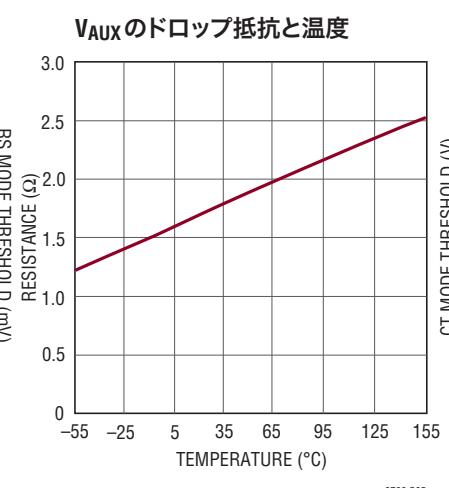

| $R_{AUX}$                     | $V_{AUX}$ Dropout Resistance                                  | $I_{CC} = 120\text{mA}$ , $V_{AUX} = 4.9\text{V}$                          |              | 1.7          | 2.5          | $\Omega$                       |        |

| $R_{PSL}$                     | $V_{AUX}$ Pre-Switchover Load                                 | $V_{AUX} = 4\text{V}$                                                      |              | 920          |              | $\Omega$                       |        |

| <b><math>V_{IN}</math>電源</b>  |                                                               |                                                                            |              |              |              |                                |        |

| $V_{INOP}$                    | $V_{IN}$ Operating Voltage Range                              |                                                                            | 5            | 32           |              | V                              |        |

| $V_{INCL}$                    | $V_{IN}$ Clamp Voltage                                        | $I_{VIN} = 2\text{mA}$ , $V_{RUN} = GND$                                   | 28           | 30           | 32           | V                              |        |

| $I_{CLMAX}$                   | $V_{IN}$ Clamp Current Limit                                  | $V_{IN} = 33\text{V}$ , $V_{RUN} = GND$                                    | 3.8          | 5.5          | 7.2          | mA                             |        |

| $V_{CCVIN}$                   | Regulated $V_{CC}$ Output Voltage                             | LV MODE (Note 6)<br>HV MODE (Note 6)                                       | 6.7<br>8.1   | 7.2<br>8.5   | 7.3<br>8.9   | V<br>V                         |        |

| $I_{IN}$                      | Supply Current<br>Operating<br>Shutdown                       | $V_{FS/SYNC} = V_{CC}$<br>$V_{RUN} = GND$                                  |              | 900<br>450   | 1200         | $\mu\text{A}$<br>$\mu\text{A}$ |        |

| $V_{INUVLO}$                  | $V_{IN}$ Undervoltage Lockout                                 | $V_{IN}$ Rising                                                            | 2.6          | 3.2          | 3.8          | V                              |        |

**電気的特性** ●は規定動作接合部温度範囲の規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値(Note 2)。注記がない限り、 $V_{IN} = 15\text{V}$ 、 $GND = PGND = 0\text{V}$ 。

| SYMBOL                       | PARAMETER                           | CONDITIONS                                                       | MIN      | TYP | MAX  | UNITS            |

|------------------------------|-------------------------------------|------------------------------------------------------------------|----------|-----|------|------------------|

| <b>発振器とフェーズロック・ループ</b>       |                                     |                                                                  |          |     |      |                  |

| $I_{FS/SYNC}$                | FS/SYNC Pin Sourcing Current        |                                                                  |          | 20  |      | $\mu\text{A}$    |

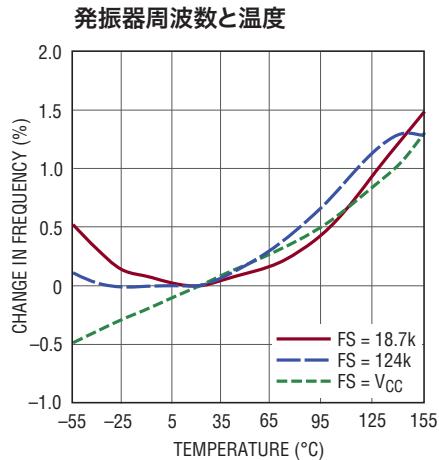

| $f_{HIGH}$                   | Oscillator High Frequency Set Point | $V_{FS/SYNC} = V_{CC}$                                           | 234      | 275 | 316  | $\text{kHz}$     |

| $\Delta f$ ( $R_{FS/SYNC}$ ) | Oscillator Resistor Set Accuracy    | $18.75\text{k}\Omega < R_{FS/SYNC} < 125\text{k}\Omega$          | ●<br>-12 | 12  |      | %                |

| $f_{PLL(RANGE)}$             | PLL Sync Frequency Range            |                                                                  | 100      |     | 500  | $\text{kHz}$     |

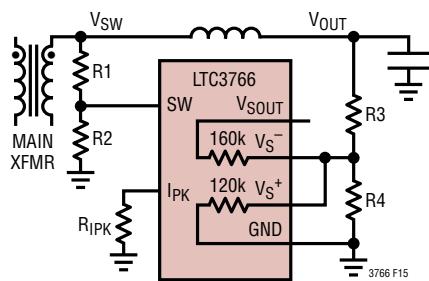

| <b>差動アンプ</b>                 |                                     |                                                                  |          |     |      |                  |

| $A_{DA}$                     | Gain                                | $1.5\text{V} \leq V_{SOUT} \leq 15\text{V}, V_{IN} = 20\text{V}$ | 0.99     | 1   | 1.01 | $\text{V/V}$     |

| $CMRR_{DA}$                  | Common Mode Rejection Ratio         | $V_{IN} = 20\text{V}$                                            |          | 75  |      | $\text{dB}$      |

| $R_{INP}$                    | $V_S^+$ Input Resistance            | $V_{IN} = 20\text{V}$                                            |          | 120 |      | $\text{k}\Omega$ |

| $R_{INM}$                    | $V_S^-$ Input Resistance            | $V_{IN} = 20\text{V}$                                            |          | 160 |      | $\text{k}\Omega$ |

| $I_{OH}$                     | Output Sourcing Current             | $V_{IN} = 20\text{V}, V_S^+ = 5\text{V}, V_{SOUT} = 2.5\text{V}$ | ●<br>0.8 | 3.0 |      | $\text{mA}$      |

| $V_{IN}-V_{OHST}$            | Output High Fault Threshold         | $V_S^+ \text{ Rising}$                                           |          | 1.2 | 1.5  | $\text{V}$       |

**Note 1:** 絶対最大定格に記載された値を超えるストレスはデバイスに永続的損傷を与える可能性がある。長期にわたって絶対最大定格条件に曝すと、デバイスの信頼性と寿命に悪影響を与える可能性がある。

**Note 2:** LTC3766Eは $0^\circ\text{C} \sim 85^\circ\text{C}$ の温度範囲で仕様に適合することが保証されている。 $-40^\circ\text{C} \sim 125^\circ\text{C}$ の動作接合部温度範囲での仕様は設計、特性評価および統計学的なプロセス・コントロールとの相関で確認されている。LTC3766Iは $-40^\circ\text{C} \sim 125^\circ\text{C}$ の動作接合部温度範囲で保証されており、LTC3766Hは $-40^\circ\text{C} \sim 150^\circ\text{C}$ の動作接合部温度範囲で保証されており、LTC3766MPは $-55^\circ\text{C} \sim 150^\circ\text{C}$ の動作接合部温度範囲でテストされ、保証されている。接合部温度が高いと動作寿命が短くなる。125°Cを超える接合部温度では動作寿命はディレーティングされる。これらの仕様が満たされる最大周囲温度は、基板レイアウト、パッケージの定格熱抵抗、および他の環境要因と関連した特定の動作条件によって決まるに注意。

**Note 3:**  $T_J$ は周囲温度( $T_A$ )および電力損失( $P_D$ )から次式に従って計算される。

$$T_J = T_A + (P_D \cdot \theta_{JA} \text{ } ^\circ\text{C/W})$$

ここで、 $\theta_{JA}$ はSSOPの場合 $95^\circ\text{C/W}$ 、QFNパッケージの場合 $43^\circ\text{C/W}$ である。

**Note 4:** LTC3766は、規定 $I_{TH}$ 電圧( $V_{ITH} = 1.2\text{V}$ )を得るように、 $V_{FB}$ を内部 $0.6\text{V}$ リファレンス電圧に近い電圧にサポート制御する帰還ループでテストされる。

**Note 5:** 動作電源電流はテストモードで測定される。動作時消費電流はスイッチング周波数で供給される内部ゲート電荷により増加する。「標準的性能特性」を参照。

**Note 6:**  $V_{IN}$ レギュレータは、安定化された $V_{CC}$ 出力電圧を発生するのに外部バス・デバイスを採用している。LTC3766は、外部バス・デバイスとして2N3904 NPNを使ってテストされている。

**Note 7:** 設計により保証されている。

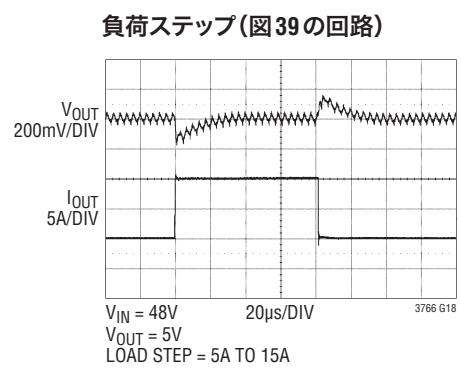

## 標準的性能特性

## 標準的性能特性

## ピン機能 (SSOP/QFN)

**SG (ピン1/ピン26)**: 同期MOSFETのゲート・ドライブ。

**FG (ピン2/ピン27)**: フォワードMOSFETのゲート・ドライブ。

**V<sub>SEC</sub> (ピン3/ピン28)**: ボルト秒の制限。抵抗をSWからV<sub>SEC</sub>に接続し、コンデンサをV<sub>SEC</sub>からGNDに接続して、メイン・パワートランスに与えられる最大ボルト秒積を設定します。PWMのオン時間は、V<sub>SEC</sub>電圧が内部で生成されるスレッショルドを超えると終了します。使用しない場合、GNDに接続します。

**MODE (ピン4/ピン1)**: LTC3765を使った通常の絶縁型アプリケーションでは、GNDまたはV<sub>CC</sub>に接続して、(同期MOSFETとフォワードMOSFETのゲートをドライブする必要に応じて)動作電圧をそれぞれ低電圧モードまたは高電圧モードに設定します。非絶縁型アプリケーションでは、100kまたは50kの抵抗を介してグランドに接続し、(それぞれ低電圧動作または高電圧動作の)スタンダアロン・モードを有効にします。このモードでは、PT<sup>+</sup>ピンを1次側MOSFETのゲートに直接接続することができます。リファレンス・クロック信号がPT<sup>-</sup>ピンに生成されます。スタンダアロン・モードでは、FGDピンは無視され、関連した遅延は適応設定されます。

**PHASE (ピン5/ピン2)**: フェーズ・セレクタへの制御入力。このピンは、FS/SYNCピンの同期信号を基準にした内部コントローラのCLKのフェーズを決めます。

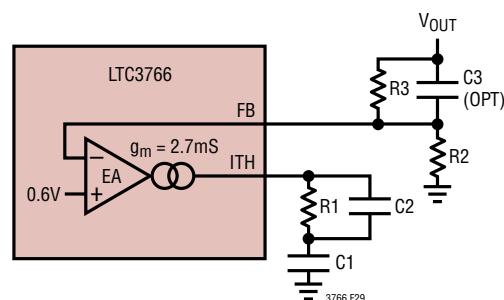

**FB (ピン6/ピン3)**: メイン・ループのエラーアンプの反転入力。PolyPhaseアプリケーションのスレーブ・モードをイネーブルするにはV<sub>CC</sub>に接続します。

**ITH (ピン7/ピン4)**: メイン・ループのエラーアンプの出力。ITHピンとGNDの間に補償部品を配置します。

**RUN (ピン8/ピン5)**: 実行制御入力。このピンを1.22Vより下に保持すると、ICをシャットダウンし、ソフトスタート・ピンとREGSDピンを0Vにリセットします。

**SS (ピン9/ピン6)**: ソフトスタート入力。このピンとグランドの間に接続したコンデンサにより、出力電圧のランプ時間が設定されます。

**I<sub>PK</sub> (ピン10/ピン7)**: ピーク電流制限とインダクタのリップルのキャンセル。このピンは、インダクタの電流リップルの大きさに基づいてピーク電流制限を調整するのに使われ、それによって電流制限時に一定の平均出力電流を供給します。メイン出力インダクタに比例する抵抗をGNDに接続します。ピーク電流制限を固定する場合、このピンをフロート状態のままにします。このピンの寄生容量を最小に抑えます。

**V<sub>SOUT</sub>、V<sub>S</sub><sup>+</sup>、V<sub>S</sub><sup>-</sup> (ピン11、12、13/ピン8、9、10)**: V<sub>SOUT</sub>は、高精度ユニティゲイン差動アンプの出力です。V<sub>S</sub><sup>+</sup>とV<sub>S</sub><sup>-</sup>をメインDC/DCコンバータの出力に接続して、真のリモート差動検出を行います。V<sub>S</sub><sup>+</sup>は、インダクタのリップル・キャンセルのための出力電圧の直接検出にも使用されます。詳細については「アプリケーション情報」のセクションを参照してください。

**GND (ピン14/ピン11、露出パッドのピン29)**: 信号グランドおよびSGの逆過電流の4端子検出。同期MOSFETのソースのところでパワーグランドに接続します。定格熱性能を得るには露出パッドをPCBのグランドに半田付けする必要があります。

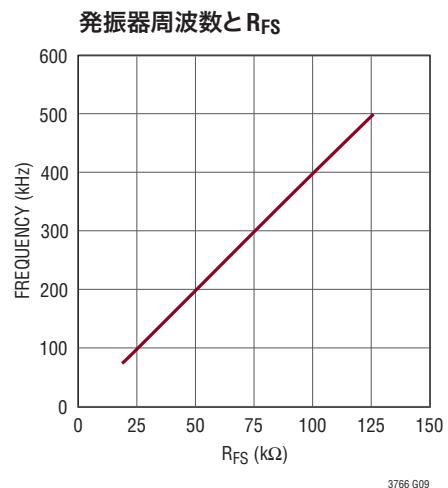

**FS/SYNC (ピン15/ピン12)**: 周波数設定とSYNCの組み合わせピン。275kHzで動作させるにはV<sub>CC</sub>に接続します。このピンからグランドに抵抗を接続して、75kHz～500kHzの周波数を設定します。同期させるには、このピンをクロック信号でドライブして、100kHz～500kHzのPLLによる同期を行います。20μAの電流をソースします。

**REGSD (ピン16/ピン13)**: レギュレータ・シャットダウン・タイマ。コンデンサをグランドに接続して、高電圧リニア・レギュレータ・コントローラが動作する時間を制限します。REGSD電圧が1.21Vを超えると、リニア・レギュレータはシャットダウンします。このピンは、リニア・レギュレータがアクティブなとき13μAの電流をソースします。

**I<sub>S</sub><sup>-</sup> (ピン17/ピン14)**: 電流検出回路への負入力。下側の電流検出抵抗の負端に接続します。電流検出トランスを使用する場合、I<sub>S</sub><sup>+</sup>を、高い最大トリップ・レベルで、シングルエンドで検出するには、このピンをV<sub>CC</sub>に接続します。

**I<sub>S</sub><sup>+</sup> (ピン18/ピン15)**: 電流検出回路への正入力。下側電流検出抵抗の正端または電流検出トランスの出力に接続します。

**SGD (ピン19/ピン16)**: 同期ゲートの立ち上がりエッジの遅延。GNDへの抵抗が、1次側ゲートのターンオフ(PT<sup>+</sup>の立ち下がり)からSGの立ち上がり(およびFGの立ち下がり)までの遅延を設定します。この遅延を使って、1次側MOSFETのターンオフとSGのターンオンの間のデッドタイムを最適化します。この遅延を、SWピンの電圧の立ち下がりエッジに基づいて、適応設定するには、SGDをGNDに接続します。「アプリケーション情報」のセクションの「ゲート・ドライバの遅延の設定」を参照してください。

## ピン機能 (SSOP/QFN)

**FGD(ピン20/ピン17)**: フォワード・ゲートの立ち上がりエッジの遅延。GNDに接続した抵抗が、PT<sup>+</sup>の立ち上がりからFGの立ち上がり(およびSGの立ち下がり)までの遅延を設定します。この遅延を使って、SGのターンオフと1次側MOSFETのターンオンの間のデッドタイムを最適化します。スタンダードアロン・モードでは(MODEに100kまたは50kの抵抗)、このデッドタイムは適応設定され、FGDピンは接地することができます。「アプリケーション情報」のセクションの「ゲート・ドライバの遅延の設定」を参照してください。

**NDRV(ピン21/ピン18)**: 高電圧リニア・レギュレータ・コントローラの外部パス・デバイスのドライブ出力。外部Nタイプ・デバイスのベース(NPN)またはゲート(MOSFET)に接続します。内部LDO(V<sub>AUX</sub>ピン)しか使用しない場合、V<sub>CC</sub>ピンに接続します。

**V<sub>IN</sub>(ピン22/ピン19)**: リニア・レギュレータ・コントローラを使用するとき、電圧の高い方のバイアス電源に接続します。V<sub>IN</sub>ピンは、内部スタンバイ回路とモニタ回路、リニア・レギュレータ・コントローラ、および差動アンプにバイアスを供給します。内部LDOしか使用しない場合、V<sub>AUX</sub>ピンに接続します。

**SW(ピン23/ピン20)**: 同期MOSFETのドレインに(4端子)接続します。この入力は、適応型シートスルー防止およびリーディングエッジ・ブランкиング、高レベルSWノード電圧のモニタ、およびSGの逆電流保護に使われます。SWが“H”的とき、このピンの電圧は内部で測定され、インダクタ・リップル・キャンセル回路およびボルト秒制限回路で使われます。SWが“L”でSGが“H”的とき、このピンは小電流をソースし、SGの逆過電流保護に使われます。SWピンと同期MOSFETのドレインの間に抵抗を接続して、SGの逆過電流スレッショルドを調整することができます。SWピンは内部で50Vにクランプされています。

**V<sub>AUX</sub>(ピン24/ピン21)**: 補助電源入力。これは、V<sub>CC</sub>に接続されている内部LDOへの電源入力です。このLDOは、V<sub>AUX</sub>が4.7V(または、高電圧モードでは8V)より大きいと、V<sub>IN</sub>から給電されるメイン・リニア・レギュレータをバイパスして、V<sub>CC</sub>に電力を供給します。「アプリケーション情報」セクションの「V<sub>AUX</sub>の接続」を参照してください。V<sub>AUX</sub>ピンは16Vを超えないようにしてください。

**PT<sup>-</sup>、PT<sup>+</sup>(ピン25、26/ピン22、23)**: パルストラ ns・ドライバの出力。ほとんどのアプリケーションでは、これらを直列DCブロッキング・コンデンサを介してパルストラ nsに接続します。PWM情報はDC電力と多重化され、パルストラ nsを介して1次側に送られます。PWM信号は次に、LTC3765のアクティブ・クラップ・フォワード・コントローラとゲート・ドライバによってデコードされます。スタンダードアロン・モードでは(MODEに100kまたは50kの抵抗)、PT<sup>+</sup>ピンには標準的PWM信号があり、1次側MOSFETのゲートに直接接続することができます。他方、リファレンス・クロック信号はPT<sup>-</sup>ピンに生成されます。

**PGND(ピン27/ピン24)**: ゲート・ドライバのグランド・ピン。同期MOSFETのソースのところでパワーグランドに接続します。

**V<sub>CC</sub>(ピン28/ピン25)**: 全てのドライバおよび制御回路のメインV<sub>CC</sub>入力。

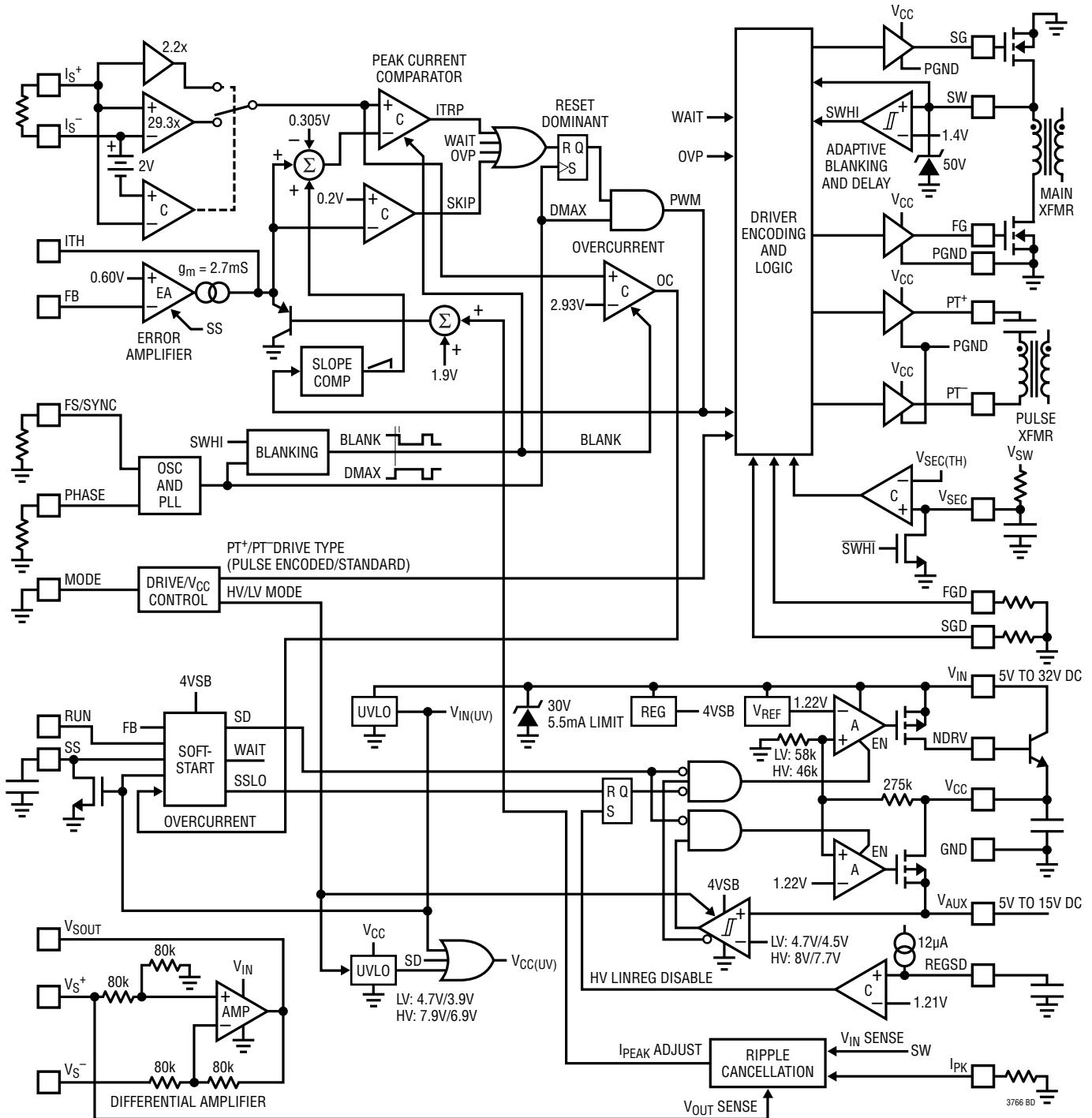

## ブロック図

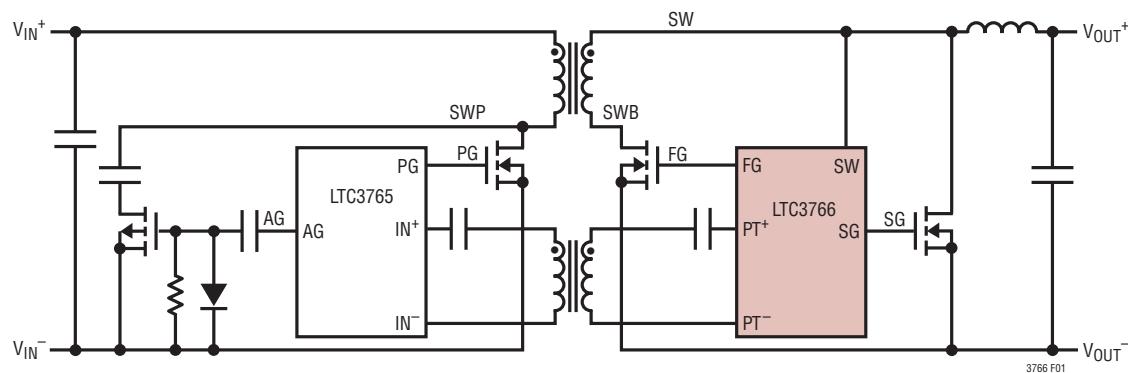

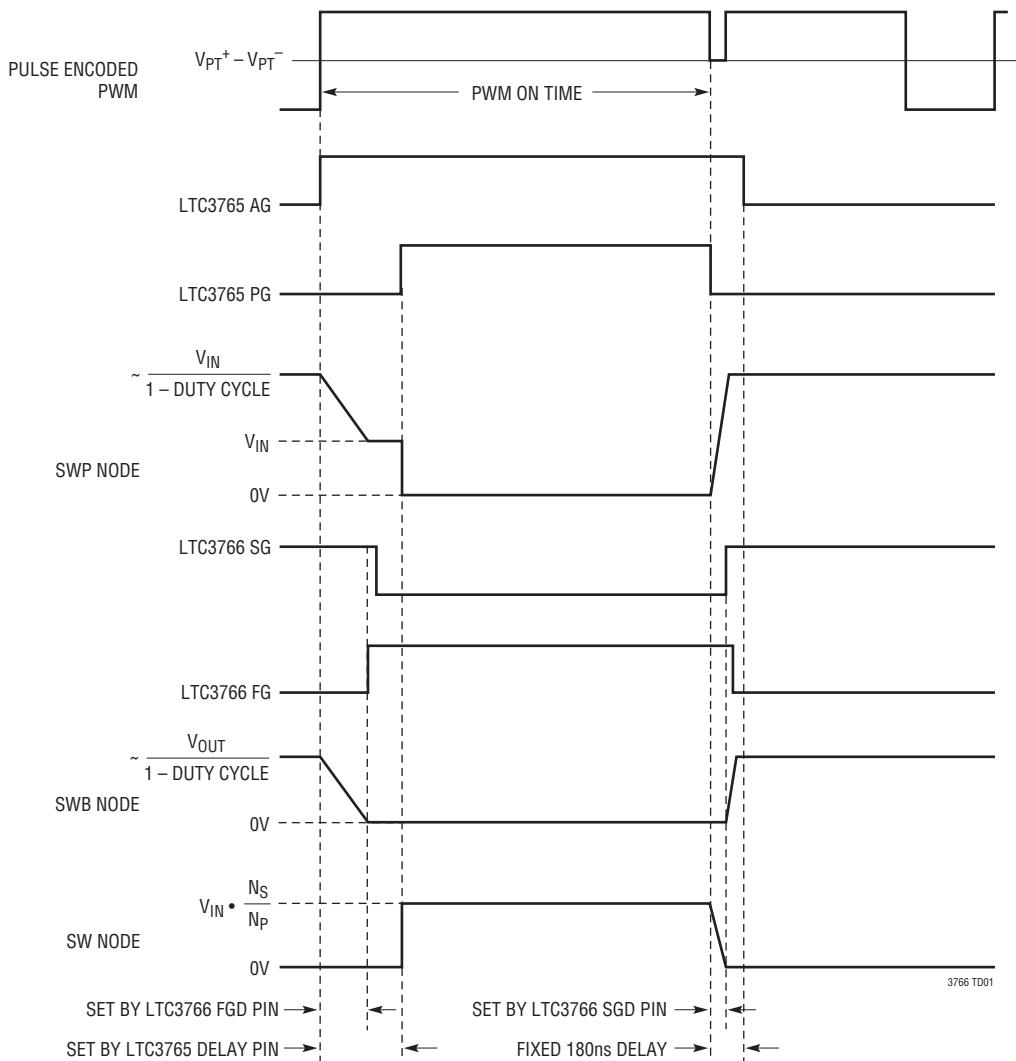

## タイミング図

図1. タイミング図の参考回路図

## 動作

LTC3766は、フォワード・コンバータに使用するように設計された2次側PWMコントローラで、アクティブ・クランプ・リセットと同期整流機能を備えています。LTC3765アクティブ・クランプ・フォワード・コントローラおよびゲート・ドライバと組み合わせて使用すると、最少の外部部品で、高効率で堅牢な絶縁型電源を構成します。LTC3766は、2次側制御アーキテクチャを利用することにより、負荷を直接モニタしながら並外れた過渡応答を実現して、出力電圧と出力電流の両方を精密に制御することができます。このアーキテクチャは優れた性能を実現し、非常にシンプルで、高電力バッテリ・チャージャのアプリケーションに特に適しています。

### 自己起動

ほとんどのアプリケーションで、LTC3766はLTC3765と組み合わせて使い、2次側制御の、自己起動するフォワード・コンバータを構成します。2次側には最初は利用できるバイアス電圧がないので、LTC3765は1次側が開ループ状態で起動する必要があります。1次側に最初に電力が与えられると、LTC3765は自己の内部発振器を使って、開ループのソフトスタートを開始します。1次側メインMOSFETをスイッチングすることにより、電力が2次側に供給されます。スイッチングのデューティサイクルは、SSFLTピンの電圧の上昇速度によって制御されつつ、0%から70%に徐々に増加します。2次側では、ピーク充電回路や適切な他の方法を使って、バイアス電圧をメイン・トランジスタから直接発生することができます。LTC3766は、その起動要件を満たす適切な電圧が与えられていると、図2に示すように、パルストラnsを通してデューティサイクルの情報を伝えます。LTC3765はこの信号を検出すると、ゲート・ドライバの制御をLTC3766に引き渡し、LTC3766が出力電圧のソフトスタートを引き継ぎます。この1次側から2次側への制御の引き渡しは、一般に、出力電圧がその最終レベルの半分以下のとき行われます。LTC3765は次にリニア・レギュレータをオフし、この信号から(内蔵整流器を通して)1次側MOSFETのバイアス電力を引き出します。

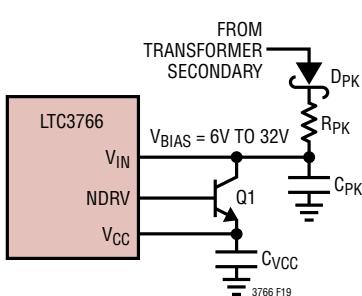

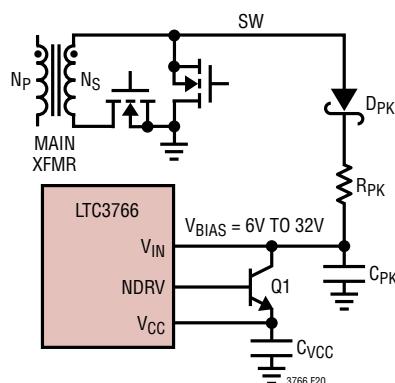

### リニア・レギュレータ

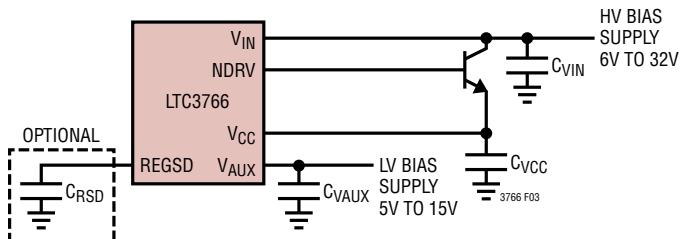

2次側で発生させたバイアス電圧は、一般に、フォワードMOSFETおよび同期MOSFETの動作に望ましいレベルより高くなります。したがって、LTC3766は、内部PMOSを備えた15V V<sub>AUX</sub>バイパス・レギュレータとともに高電圧リニア・レギュレータ・コントローラを搭載しており、どちらもV<sub>CC</sub>ピンの電圧

を安定化するのに使うことができます。リニア・レギュレータ・コントローラは、NDRVピンを外部のNタイプ・パス・デバイスのベースまたはゲートに接続して使用します。LTC3766のV<sub>IN</sub>ピンは、内部のスタンバイ回路やモニタ回路とともにリニア・レギュレータ・コントローラにバイアスを供給します。V<sub>AUX</sub>ピンで適切な電圧が検出されると、V<sub>AUX</sub>バイパス・レギュレータがアクティブになります。高電圧リニア・レギュレータ・コントローラがシャットダウンして電力損失を減らします。代わりに、V<sub>AUX</sub>レギュレータだけが必要なら、NDRVピンをV<sub>CC</sub>に接続し、V<sub>IN</sub>をV<sub>AUX</sub>に接続することができます。2つのリニア・レギュレータをこのように柔軟に組み合わせることにより、広範なアプリケーションのV<sub>CC</sub>バイアス電圧を手軽に効率よく発生することができます。

MODEピンを使って、両方のリニア・レギュレータの出力電圧を、(フォワードMOSFETと同期MOSFETのゲートをドライブするのに必要なレベルに基づいて)7Vまたは8.5Vに設定することができます。低電圧ロックアウト(UVLO)の設定ポイントとV<sub>AUX</sub>の切り替えレベルが、V<sub>CC</sub>の安定化レベルに伴って調整されることに注意してください。これにより、適切なゲート・ドライブ電圧が与えられているときだけMOSFETはスイッチングします。

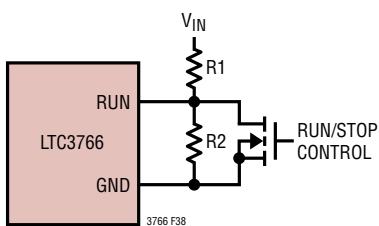

### 実行制御とソフトスタート

LTC3766のメイン・オン/オフ制御はRUNピンで行われます。このピンは、内部ヒステリシスと外部で調整可能なヒステリシスの両方を備えた精密スレッショルドを備えています。このピンを使って、2次側バイアス電圧またはメイン出力電圧をモニタして、1次側から2次側へのハンドオフ(制御の引き渡し)が生じるポイントを制御することができます。代わりに、制御信号で直接それをドライブすることができます。LTC3766をスタンダードアロンで使用する非絶縁型アプリケーションでは、主電源の入力電圧をモニタすることにより、このピンを低電圧ロックアウトとして使うことができます。詳細については、「アプリケーション情報」のセクションの「非絶縁型アプリケーション」を参照してください。

LTC3766は、RUNピンが“H”になり、適切な電圧がV<sub>IN</sub>ピンとV<sub>CC</sub>ピンの両方に与えられており、SWピンのスイッチングが検出されると、ソフトスタートのシーケンスを開始します。LTC3765が制御を引き渡す用意ができていることを確認するため、LTC3766はソフトスタート・シーケンスを開始する前に、SWピンのスイッチングを検出する必要があることに注意

## 動作

してください。ソフトスタートのシーケンスは、最初にFBピンの電圧を測定し、ソフトスタート・コンデンサの電圧を出力電圧( $V_{OUT}$ )に対応するレベルまで予め素早く設定して開始されます。これは、1次側から2次側に制御が移るとき出力電圧が滑らかにランプするように、また、不必要的起動時の遅延を避けるために行われます。ソフトスタート・コンデンサが適切なレベルに予め設定されたら、LTC3766はパルストラ nsを介して短いパルス・シーケンスを送り、LTC3766とLTC3765の間の通信をロックします。このポイントで、LTC3766は1次側のMOSFETの制御を引き受け、 $5\mu A$ の定電流でソフトスタート・コンデンサの充電を開始し、メイン出力電圧のソフトスタートを継続します。エラーアンプのリファレンスの実効レベルを制限するのにソフトスタート電圧が使われることに注意してください。この手法により、2次側のソフトスタート期間に出力電圧の閉ループ制御が維持されます。

### ゲート・ドライブ・エンコーディング

LTC3766コントローラは絶縁バリアの2次側に通常置かれるので、1次側ゲート・ドライバとの通信は小さなパルストラ nsを介して行う必要があります。ゲート・ドライブ(PWM)情報を伝える一般的な方式では、短いパルスを利用し、パワーMOSFETがオンすべきかオフすべきかを「覚えておく」レシバ・ラッチを使います。ただし、このシステムは誤った状態に落ち込みやすく、有効なゼロ・デューティサイクル信号と信号の欠落を見分けることが困難です。これらの弱点を補うため、LTC3766は独自のゲート・ドライブ・エンコーディング方式を使い、遅れることなく、高い信頼性で、絶縁バリアを越えて常時通信を維持します。

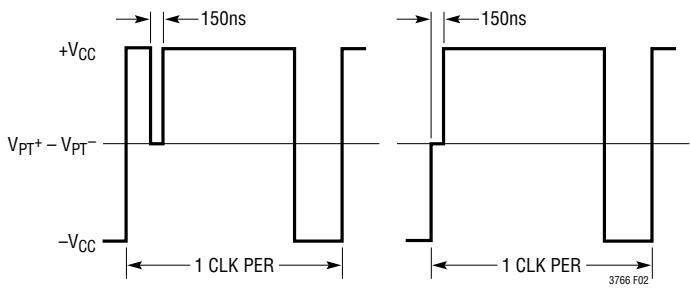

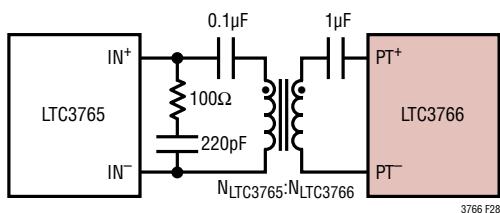

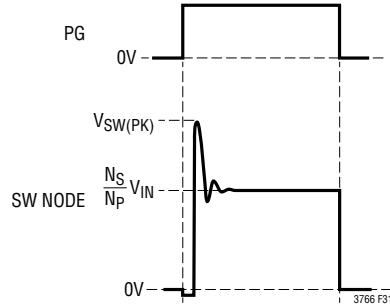

LTC3766はエンコードしたPWM情報を $PT^+$ 出力と $PT^-$ 出力に生成します。これらの出力はDCブロッキング・コンデンサを介して小さなパルストラ nsに接続されます。これらの出力は79%の一定のデューティサイクルの相補形式でドライブされます。これによりボルト秒のバランスが安定するので、パルストラ nsによって伝達される信号の振幅が一定になります。図2に示すように、 $(V_{PT^+} - V_{PT^-})$ が正である期間の開始点が1次側メインMOSFETのターンオンにほぼ一致します。同様に、 $(V_{PT^+} - V_{PT^-})$ が負である期間の開始点が、最大デューティサイクル(1次側メインMOSFETの強制ターンオフ)に一致します。正の期間の適切な時点に、パルストラ nsの両端にゼロボルト差を短時間与えることにより、「オン」時間の終点(PWMが“L”になる)が知られます。ゼロのデューティサイクルの信号を送る必要がある場

合、正の期間の開始点でゼロの電圧差を与えます。このようにして、0%から最大79%までの任意のデューティサイクルを、遅延なしに、パルストラ nsを越えて送ることができます。このエンコーディング方式の動作を図2に示します。

図2. ゲート・ドライブのエンコード方式

(MODE = GNDまたはMODE =  $V_{CC}$ )

1次側では、LTC3765がDC復元コンデンサを介してパルストラ nsから信号を受け取ります。2つのデバイスの間の通信がロックされた後、LTC3765はクロックとデューティサイクル情報を信号から抽出し、それを使ってゲート・ドライバの出力を制御します。微小なパルスを除き、この方式は常にパルストラ nsの両端に差電圧を与えることに注意してください。したがって、LTC3765はほとんど瞬時に信号の欠損を検出してパワーMOSFETをオフすることができます。

### フォワード・コンバータとメイン・ループの動作

LTC3766とLTC3765の間の通信がロックされると、LTC3766は1次側MOSFETのスイッチングを制御することができます。通常動作の間、2次側のフォワードMOSFETのいくらか後に、(LTC3765のPGに接続された)1次側メインMOSFETがオンします。これにより、入力電圧がトランジスタの両端に加わり、2次側のSWノードが上昇します。SWノードの電圧は出力電圧より高いので、インダクタ電流が上方にランプします。インダクタ電流がITHピンの電圧によって定まるピーク値までランプアップすると、電流検出コンパレータがトリップし、1次側MOSFETをオフします。短い遅延の後、フォワードMOSFETがオフし、同期MOSFETが再度オンするので、インダクタ電流が下方にランプダウンします。LTC3766の内部クロックの次の立ち上がりエッジで、同期MOSFETがオフし、フォワードMOSFETと1次側のメインMOSFETが再度オンして、サイク

## 動作

ルが繰り返されます。LTC3766のエラーアンプがメイン出力電圧を検出し、ITH電圧を調整して、出力電圧を望みのレギュレーション・レベルに保つに必要なピーク・インダクタ電流を得ます。

アプリケーションによっては、メイン出力電圧と負荷の間にかなりの抵抗性電圧降下が生じることがあります。これを解決するため、LTC3766は高精度差動アンプを搭載しており、それを使って15Vまでの負荷電圧をリモートで検出することができます。

### 電流検出、スロープ補償、およびブランкиング

LTC3766は、電流検出抵抗または絶縁された電流トランスのいずれを使った電流検出もサポートします。電流検出抵抗を使う場合、 $I_{S^+}$ ピンと $I_{S^-}$ ピンは差動で動作し、最大ピーク電流スレッショルドは約75mVです。電流検出抵抗は通常フォワードMOSFETのソースに接続し、電力損失を最少に抑えます。電流トランスを使って1次側スイッチ電流を検出する場合、 $I_{S^-}$ 入力を $V_{CC}$ に接続し、 $I_{S^+}$ ピンを電流トランスの出力に接続します。これにより、内部電流検出アンプの利得が減少するので、最大ピーク電流スレッショルドは約1Vに増加します。

固定周波数ピーク電流制御を使うどんなPWMコントローラでもそうであるように、電流ループを安定させ、ノイズマージンを改善するには、スロープ補償が必要です。LTC3766は固定スロープ補償を内蔵しています。スロープの大きさは、広範なアプリケーションに適するように選択されています。スロープ補償の使用は通常、電流制限の精度に悪い影響を与えますが、LTC3766は独自の回路を使って、電流制限性能に対するスロープ補償の影響をなくしています。

LTC3766の電流ループはスイッチ電流を検出するので、MOSFETのターンオン電流スパイクによる電流コンパレータの誤作動を防止するため、リーディングエッジのブランкиングが必要です。LTC3766は、(同期MOSFETのドレインに接続した)SWピンの電圧を使って、約180nsの適応型リーディングエッジ・ブランкиングを行います。電流コンパレータのブランкиングは、SWの電圧が1.4Vを超えた後初めて開始されます。この適応型ブランкиングが不可欠なのは、PT<sup>+</sup>が立ち上がるときから、SWノードが立ち上がり、出力インダクタ内で電流がランプアップを開始するまでの遅延が潜在的に長いためです。また、このブランкиングは外部フィルタの必要性を最小にします。

### ゲート・ドライバの遅延の調整

全てのフォワード・コンバータの場合と同様、バランスのとれた電圧時間積を維持して飽和を防ぐため、メイン・トランスのコアを適切にリセットする必要があります。この作業は、アクティブ・クランプ・ゲート・ドライバを備えたLTC3765によって1次側で行われます。アクティブ・クランプMOSFETはコンデンサと一緒に動作して、メイン・トランスの最適リセット電圧を発生します。この最適リセット電圧は1次側のメインMOSFETの電圧ストレスを最小に抑え、磁束密度の変化を減らすことにより、パワートランスのコアの利用率を最大にします。

一般に、アクティブ・クランプMOSFETは、1次側メインMOSFETに対して相補的にスイッチングします。アクティブ・クランプMOSFETはPMOSなので、アクティブ・クランプ・ゲート・ドライバ(AG)と1次側メイン・ゲート・ドライバ(PG)の電圧は「同位相」になり、オーバーラップ時間はプログラミング可能で、LTC3765のDELAYピンによって設定されます。

アクティブ・クランプPMOSのターンオフと1次側スイッチNMOSのターンオンの間の遅延時間は効率の最適化にとって非常に重要です。アクティブ・クランプがオンのとき、1次側NMOSのドレイン(つまり1次側スイッチ・ノード(SWP))は、メイン・トランスによって約 $V_{IN}/(1-D)$ の電圧にドライブされます。アクティブ・クランプがオフするとき、トランスの磁化インダクタンスの電流により、この電圧は直線的に $V_{IN}$ までランプダウンします。SWPの電圧が最小のとき、1次側スイッチをオンすることにより、電力損失が最小になります。LTC3765のDELAYピンからグランドに接続した抵抗により、PGのターンオンの固定遅延時間が設定されます。

1次側スイッチのターンオフとアクティブ・クランプのターンオンの間の遅延時間は、それほど重要ではありません。1次側スイッチがオフすると、トランスを介して反射したインダクタのピーク電流によって、メイン・トランスの漏れインダクタンスがバイアスされます。この電流がアクティブ・クランプPMOS両端の電圧を短時間に0Vにドライブします。この遷移後にPMOSをオンすると、スイッチングによる電力損失が小さくなります。LTC3765のアクティブ・クランプのターンオン遅延は内部で180nsに固定されており、通常はアクティブ・クランプPMOSはゼロ電圧でスイッチングします。

## 動作

2次側では、フォワード・ゲート(FG)と同期ゲート(SG)のMOSFETのターンオン遅延は、それぞれFGDピンとSGDピンによって調整されます。これらの遅延は、1次側MOSFETのシートスルーを防ぎながら、(負荷電流がMOSFETのボディ・ダイオードを通って流れているときの)デッドタイムを最小にするように、GNDへの抵抗を使って設定します。PGゲートとSGゲート、またはAGゲートとFGゲートのどちらでも同時に“H”になると、シートスルー状態になります。SGのMOSFETのターンオン遅延には最小リミットがあり、SWノードの立ち下がりエッジによって定まることに注意してください。SGピンは、SWが0.5Vを下回るまで“H”なりません。詳細については、「アプリケーション情報」のセクションの「遅延抵抗の選択」を参照してください。スタンダアロン・モードでは(MODEに100kまたは50kの抵抗)、シートスルーを防ぐように、PGとSGの間のデッドタイムを適応設定します。

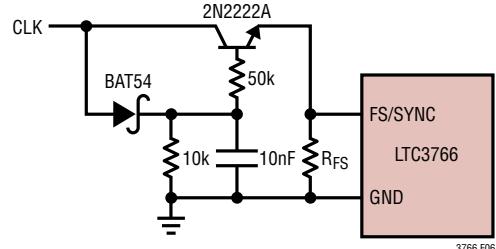

## 周波数設定と同期

LTC3766は1つのピンを使って動作周波数を設定するか、または内蔵フェーズロック・ループ(PLL)を使って内部発振器を基準クロックに同期させます。FS/SYNCピンは20µAの電流をソースします。このピンをV<sub>CC</sub>に接続して固定275kHz動作にするか、または1個の抵抗をGNDに接続して、スイッチング周波数をf<sub>SW</sub>=4R<sub>F</sub>に設定することができます。クロック信号(>2V)がFSピンで検出されると、LTC3766は内部のPLLを使って、この信号の立ち下がりエッジに自動的に同期します。

## 電流制限とインダクタのリップルのキャンセル

LTC3766はピーク電流制御を利用して、負荷電流需要が電流制限の設定ポイントを超えて増加すると、ピーク・インダクタ電流が制限されます。ピーク電流制限は、ITH電圧の最大レベルの内部クランプによって定まります。ただし、平均電流は、インダクタ・リップル電流の半分に等しい量だけピーク電流を下回ります。電流制限の間、このリップル電流は、V<sub>IN</sub>、V<sub>OUT</sub>、およびスイッチング周波数の変化に伴って大きく変化します。インダクタ・リップルがキャンセルされないと、この

リップル電流の変化により、(ピーク電流が一定値に保持されたとしても)平均出力電流の大きな変化も生じます。

平均電流を電流制限の間ほぼ一定に保つため、LTC3766は、ピーク電流制限(つまり、ITHクランプ・レベル)をインダクタ・リップル電流の大きさに比例させて調整することにより、リップル電流の影響をキャンセルします。これは、サイクルごとに、インダクタ電流のランプを真似た内部ランプを発生し、この内部ランプの振幅をITHクランプ電圧に追加することによって達成されます。オン時間の間、インダクタ電流のスロープは次式で与えられます。

$$\frac{dI_L}{dt} = \frac{V_{SW} - V_S^+}{L}$$

LTC3766は(V<sub>SW</sub>-V<sub>S</sub><sup>+</sup>)/15の電圧をI<sub>PK</sub>ピンに発生します。これはSWが“H”的ときのオン時間の間の出力インダクタ両端の電圧の1/15です。出力インダクタに比例する抵抗R<sub>IPK</sub>を選択すると(R<sub>IPK</sub>=KL)、R<sub>IPK</sub>を流れる電流はインダクタ電流の勾配に比例します。

$$I_{RIPK} = \frac{V_{SW} - V_S^+}{15R_{IPK}} = \frac{V_{SW} - V_S^+}{15KL}$$

SWが“H”的間、LTC3766は、R<sub>IPK</sub>の電流を使って内蔵コンデンサC<sub>RIP</sub>を充電することにより、内部ランプを発生します。この内部ランプ電圧の勾配は次式で与えられます。

$$\frac{dV_{RAMP}}{dt} = \frac{I_{RIPK}}{C_{RIP}} = \frac{V_{SW} - V_S^+}{15KLC_{RIP}}$$

この内部ランプの振幅がITHのクランプ・レベルに動的に追加されます。したがって、R<sub>IPK</sub>の適切な値を選択することにより、電流制限時の平均電流はリップル電流の変化に基本的に依存しなくなります。

固定周波数動作を維持する全てのDC/DCコンバータの場合と同様、サイクルごとの電流制限は、制御可能な最小オン時間よりオン時間が大きなデューティサイクルでだけ効果があり

## 動作

ます。たとえば、短絡状態では、LTC3766は別の過電流コンパレータを使って電流を制限します。この過電流コンパレータがトリップすると、LTC3766はフォールトを発生し、続いてソフトスタートをリトライします。このヒップ・モード過電流保護は、短絡状態で電力損失を最小に抑えるのに非常に効果があります。

### Direct Flux Limit(直接磁束制限)

アクティブ・クランプ・フォワード・コンバータでは、負荷の過渡変動の間または出力が予めバイアスされた状態で起動するときにコアの飽和を防ぐため、トランスの磁束密度を精密に制限することが不可欠です。アクティブ・クランプの手法は、定常動作の間適切なリセット電圧を与えますが、負荷ステップに応答して生じるデューティサイクルの急激な増加により、トランスの磁束の増加ないし「walk」が生じることがあり、飽和するおそれがあります。これが生じるのは、アクティブ・クランプ・コンデンサのリセット電圧が、急速に変化するデューティサイクルに追いつけないからです。この影響は、低い入力電圧で顕著に現れます。なぜなら、低い入力電圧では、出力インダクタの電流をランプアップするのに使える電圧が低いため、電圧ループがデューティサイクルの増加を要求するからです。

従来は、コンバータの最大デューティサイクルを制限することにより、または、ループを遅くしてデューティサイクルが変化する速度を制限することにより、トランスのコアの飽和を防いでいました。低入力では、最大デューティサイクルの制限によりデューティサイクルの最大値がクランプされるので、負荷ステップに対してコンバータの飽和を防ぎます。ただし、高い入力電圧では最大デューティサイクルのクランプは効果的ではなく、トランスは簡単に飽和してしまいます。アクティブ・クランプ・コンデンサがデューティサイクルの変化に十分追従できるように、デューティサイクルの変化の速度を制限することも、多くの状況で飽和を防ぐのに役立ちますが、過渡応答が非常に悪くなります。これらの従来の手法はどれも、全ての状況でトランスが飽和するのを防ぐことを保証はしません。たとえば、出力が予めバイアスされた状態で起動するとき、デューティサイクルは急速に0%から75%に変化するので、これらの従来の手法を使うと簡単に飽和状態になります。さらに、これらの従来の手法はどれも、デューティサイクルの急な減少によって生じことがある負方向の変化で飽和を防ぐことができません。

LTC3765とLTC3766は、トランスのコア内の磁束の増加をモニタして直接制限する新しい独自システムを実装しています。アクティブ・クランプPMOSがオンしているリセット・サイクルの間、PMOSのソースに直列に接続されたセンス抵抗によって磁化電流を直接測定し、制限します。これにより、負方向の飽和を防ぎます。PMOSがオフし、メインNMOSスイッチがオンすると、LTC3765のRUNピンで検出される入力電圧と、(LTC3765のRCOREピンからグランドに接続された抵抗によって特定のコアに対してカスタム化された)トランスのコアのパラメータに基づいて、LTC3765は磁化電流を内部で精確に近似します。この精確な内部近似により、磁化電流がオン時間の間制限されます。前の方法とは異なり、直接磁束制限は、磁束の増加を直接測定し、モニタして、出力が予めバイアスされた状態で起動するときでも、トランスがどちらの方向でも飽和しないことを保証します。この手法は、非常に高いデューティサイクルを一時的に許し、絶対的に必要なときだけデューティサイクルを制限するので、可能な限り最良の過渡応答も与えます。さらに、この手法は、(多くのアクティブ・クランプ・フォワード・コンバータの設計で潜在的に重大な弱点である)過電流によるアクティブ・クランプPMOSへの損傷を防ぎます。

### その他の保護機能

LTC3766は広範な保護機能を搭載しており、異常状態が持続するときDC/DCコンバータを保護します。一般に、保護機能はフォールトまたは制限によって分類されます。フォールトが検出されると、全てのスイッチングが停止し、LTC3766はソフトスタートのリトライを開始します。この種のフォールトには、過電流、過温度、差動アンプの誤配線、および通信のロックのフォールトが含まれます。

電流制限時にピーク電流がその正常値の約133%を超えると、過電流フォールトが生じます。インダクタ・リップル・キャンセルが使用されるとき、電流制限時のピーク電流がインダクタの電流リップルに伴って変化することに注意してください。過温度フォールトは165°Cに設定されており、20°Cのヒステリシスがあります。これは、外部デバイスの不具合や他の異常状態が生じたとき、DC/DCコンバータの温度を制限するのに役立ちます。差動アンプの配線フォールトは、差動アンプの入力が逆になるか、または、必要なVSOUT電圧をサポートするのに十分な電圧がVINピンに与えられていないと生じます。これは、

## 動作

出力の過電圧状態を防ぐのに重要です。最後に、LTC3766がLTC3765と常に通信状態にあることが不可欠なので、通信のロックが失われた場合もフォールトが発生します。SWノードの電圧をモニタし、それが、1次側に送られてくるPWM信号に応答して上昇と下降の両方を行っていることを確認することによって、通信のロック状態を検出します。SWノードの電圧が適切なし方で上昇および下降を行っていないと、ロック・フォールトが発生します。

フォールトを発生する4つの保護機能の他に、フォールトを発生せずにクランプまたは制限を行う4つの保護機能もあります。まず、LTC3766は高精度ボルト・秒クランプを備えています。この機能は、LTC3766を(直接磁束制限機能を内蔵している)LTC3765と一緒に使うときは不要です。ただし、LTC3766をスタンドアロンで使う場合、抵抗をSWノードからV<sub>SEC</sub>ピンに接続し、コンデンサをV<sub>SEC</sub>からGNDに接続することにより、ボルト秒制限機能を使うことができます。SWノードが“L”的とき、コンデンサは内蔵NMOSによって放電します。SWノードが“H”的とき、V<sub>SEC</sub>のコンデンサが充電されます。コンデンサの電圧が内部で発生させたスレッショルドを超えると、1次側メイン・スイッチがオフするので、メイン・トランジistorに与えられる電圧時間積が制限されます。RC充電回路の指數関数的性質を補償するため、LTC3766はボルト秒コンパレータのスレッショルドを次式にしたがって調整します。

$$V_{\text{SEC}(\text{TH})} = 0.6 - \frac{0.16}{V_{\text{SW(HI)}}}$$

ここで、V<sub>SW(HI)</sub>は1次側スイッチのオン時間の間のSWピンの電圧です。これにより、2V～40VのSWノードの電圧に対して、ボルト秒のリミットが基本的に一定に保たれます。

2番目に、メイン出力電圧がその安定化の目標値を17%以上超えると、LTC3766は過電圧状態を検出します。これが起きると、LTC3766は直ちに1次側メインMOSFETをオフし、同期MOSFETをオンします。これは、出力電圧をプルダウンする効果があり、負荷を潜在的損傷から保護します。過電圧保護はラッチされず、出力電圧がその安定化レベルの15%以下になると通常動作に戻ります。

3番目に、LTC3766は調整可能な同期MOSFETの逆過電流保護を備えています。これは、同期MOSFETがオンのとき(SGピンが“H”)、SW電圧をモニタすることにより達成されます。SWの電圧が予め定められたスレッショルドを超えると、同期MOSFETがオフし、損傷を与える可能性のある電流レベルからそれを保護します。逆過電流検出のこのSWスレッショルドは、(SGピンが“H”的とき電流をソースする)SWピンに直列に抵抗を接続することにより下げることができます。SGの逆過電流スレッショルドとSWピンのソース電流は、MODEピンの状態に基づいて調整されることに注意してください。これは、高電圧MOSFETまたは低電圧MOSFETの使用に対応するために行われます。これらのMOSFETのオン抵抗は通常大きく異なります。過電圧状態では、SGの逆過電流は過電圧保護をオーバーライドし、SGを“L”に強制して、過電圧状態が持続する間SGの逆MOSFET電流を基本的に高いレベルに安定化します。ただし、SGの逆過電流はLTC3766が通信をロックした後で初めてアクティブになります。

最後に、REGSDピンを使って、高電圧リニア・レギュレータ・コントローラがアクティブになる時間の長さを制限することができます。これは、LTC3766が非絶縁型フォワード・コンバータにスタンドアロンで使用されるとき特に役立ちます。このアプリケーションでは、リニア・レギュレータ・コントローラのパス・デバイスがかなりの電力を消費することがあります。リニア・レギュレータ・コントローラがアクティブなとき、REGSDピンは13μAの電流をソースします。REGSDからGNDに接続したコンデンサが1.21Vより高い電圧に充電されると、リニア・レギュレータ・コントローラはディスエーブルされます。

## ゲート・ドライバのモード制御

LTC3765と一緒に使用する他に、LTC3766は、非絶縁型フォワード・コンバータのアプリケーションで、スタンドアロンで使用することもできます。この場合、MODEピンを使って、100k抵抗(V<sub>CC</sub>=7Vの動作の場合)または50k抵抗(V<sub>CC</sub>=8.5Vの動作の場合)を介してMODEをGNDに接続することにより、ゲート・ドライブのエンコーディングをディスエーブルすることができます。これにより、正常なPWM信号がPT+に現れ、リファレンス・クロックがPT-に現れます。

## アプリケーション情報

### 2次側バイアスと起動

ほとんどのアプリケーションでは、LTC3766はそのバイアス電圧を2次側で発生させた電源から受け取ります。2次側バイアスを発生する方法は、出力電圧およびDC/DCコンバータの入力電圧の変化に依存します。ただし、全てのアプリケーションで、2次側バイアスは常に、出力が安定化レベルに達する前に立ち上がる必要があります。これは、最初の起動は開ループ状態で1次側から行われるので、出力の過電圧状態を防ぐために不可欠です。詳細については、「2次側バイアスの発生」を参照してください。

LTC3766は、RUNピンが“H”になり、適切な電圧がVINピンとVCCピンの両方に与えられ、SWピンのスイッチングが検出されるまでは、ソフトスタートのシーケンスを開始せず、スイッチングを開始しないことに注意してください。LTC3766はSWピンのスイッチングをモニタして、LTC3765がアクティブであり、制御の引き渡しの用意ができていることを確認します。スイッチングを検出するには、SWノードの波形に50kHz～700kHzの少なくとも8個の連続したパルスが必要です。SWノードの波形には1.4Vより高いピークと、0.5Vより低い谷も必要です。LTC3766は、スタンドアロン・モードでは、SWピンでスイッチング波形が検出されるのを待つことなく、ソフトスタート・シーケンスを開始します。

### リニア・レギュレータの動作

LTC3766は2つのレギュレータを備えており、それらを使って、利用可能なバイアス電圧を、MOSFETをドライブするのに適したレベルに安定化します。バイアス電源の電圧が15Vより高い場合、高電圧リニア・レギュレータ・コントローラを使うことができます。この場合、Nタイプの外部バス・デバイスを利用します。0.22μF以上のコンデンサをVINに、1μF以上のコンデンサをVCCに接続します。VINピンに接続したバイアス電源の出力インピーダンスが比較的高い場合、VINに大きなコンデンサを使用して、VCCのコンデンサの充電中にVINピンの電圧が下がるのを防ぐ必要があるかもしれません。リニア・レギュレータの起動時のVCCの充電速度は、LTC3766によって約0.5V/μsに設定されるので、 $(0.5 \cdot 10^6) C_{VCC}$ の充電電流が発生します。この充電電流がNタイプのバス・デバイスのSOAを超えないように、特に高いVIN電圧で動作するとき注意します。VCCの安定化レベルは、MODEピンを使って、7Vまたは

8.5Vのどちらか望む方に設定することができます。詳細については、「VCCとドライブ・モードの選択」のセクションを参照してください。

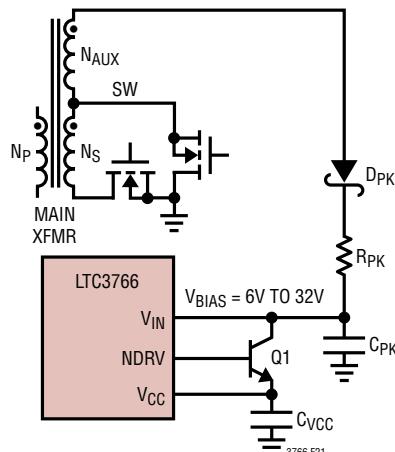

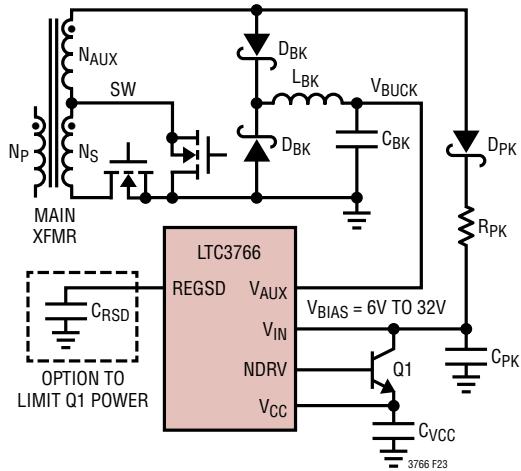

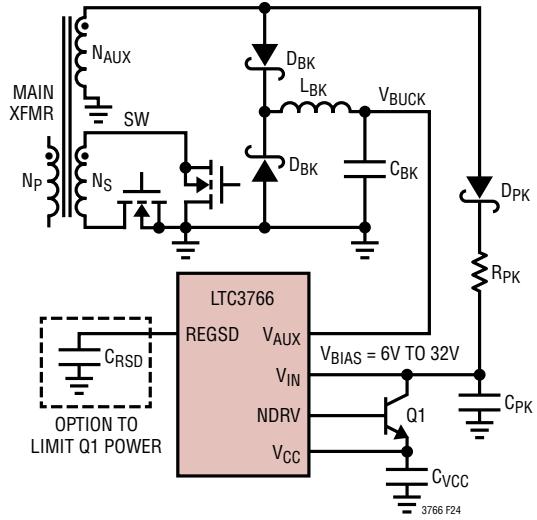

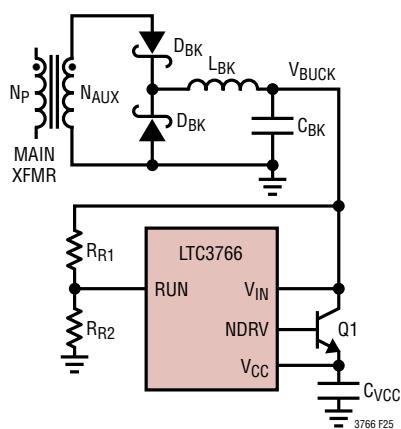

LTC3766は15VのバイパスLDOも内蔵しています。VAUXピンの電圧がVAUX切り替えスレッショルドを超えると、高電圧リニア・レギュレータはディスエーブルされ、内部PMOSバスLDOがVAUXを使ってVCCに電力を供給します。これにより、最初の起動には高電圧リニア・レギュレータを使い、通常動作では高効率のバイパスLDOを使うことができます。両方のリニア・レギュレータを使うこのような構成方法を図3に示します。

VAUXピンの電圧が切り替えスレッショルドより低いと、VAUXピンには約920Ωの抵抗性負荷が内部で与えられます。この内部負荷は、バイパス・レギュレータが起動する前に、VAUX電源が十分安定するように使用され、VAUXレギュレータがイネーブルされた後取り去られます。

場合によっては、外部バス・デバイスの温度上昇を制限するため、高電圧リニア・レギュレータを起動時に短時間だけ使用するのが望ましいでしょう。これを実現するには、REGSDピンからグランドに次のようなコンデンサを接続します。

$$C_{RSD} = \frac{t_{HVREG} (13\mu A)}{1.21V}$$

ここで、 $t_{HVREG}$ は高電圧レギュレータが動作する時間です。高電圧レギュレータが動作しているとき、13μAの電流がREGSDピンからソースされ、それがシャットダウンすると(たとえば、バイパス・レギュレータがアクティブ)、3μAの電流がREGSDピンにシンクされます。REGSD電圧が1.21Vを超えると、高電圧レギュレータはディスエーブルされます。通常の起動時間より長い $t_{HVREG}$ 時間を選択してください。起動後、VAUXピンの電圧が低下すると、高電圧リニア・レギュレータが限られた時間だけ再度アクティブになります。

図3. リニア・レギュレータの標準的接続方法

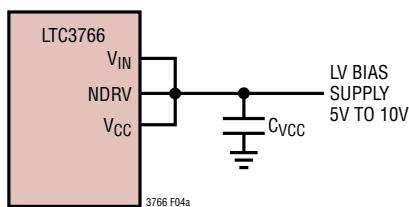

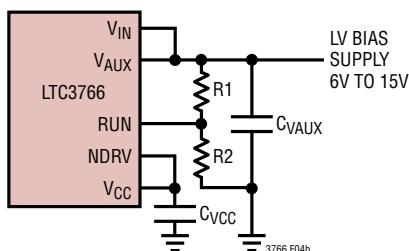

## アプリケーション情報

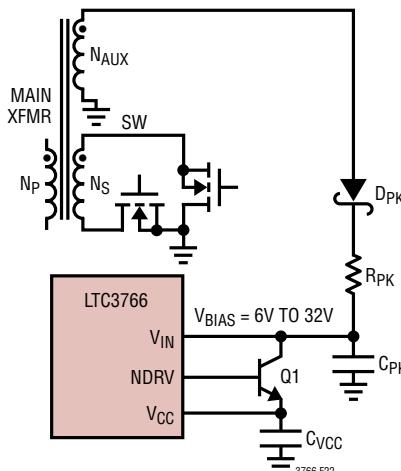

5V～10Vのバイアス電源と一緒に使う場合、図4aに示すとおり、V<sub>CC</sub>ピンをバイアス電源に直接接続することができます。内部回路を適切に動作させるには、V<sub>IN</sub>ピンとNDRVピンもバイアス電源に接続する必要があることに注意してください。6V～15Vのバイアス電源を利用できるとき、図4bに示すように、VAUXバイパス・リニア・レギュレータをスタンドアロンで使うことができます。この場合、NDRVピンをV<sub>CC</sub>ピンに接続することにより、適切な起動を確実に行うことができます。ただし、NDRVに外部バス・デバイスがないので、実効UVLOレベルは、V<sub>CC</sub>のUVLOスレッショルドの代わりに、VAUXの切り替えスレッショルドによって支配されます。VAUXのスレッショルドに頼るのではなく、起動レベルとシャットダウン・レベルは通常、図4bに示すように、RUNピンを使ってバイアス電源電圧をモニタすることにより設定されます。詳細については、「RUNピンの動作」のセクションを参照してください。

利用できるバイアス電源が30Vを超えるアプリケーションでは、LTC3766はV<sub>IN</sub>ピンに電流制限された30Vクランプも備えています。このクランプは最大3.5mAをシンクすることができるので、V<sub>IN</sub>ピンをシャント・レギュレータとして使うことができます。これは、LTC3766がスタンドアロンで使われる非絶縁型アプリケーションで特に有用です。詳細については、「非絶縁型アプリケーション」のセクションを参照してください。

図4a. リニア・レギュレータを使用しない

図4b. スタンドアロンでVAUXレギュレータを使用

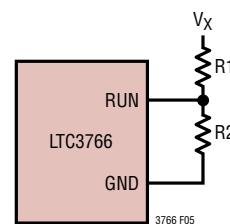

### RUNピンの動作

RUNの電圧がその1.22Vのスレッショルドを超えると、通常動作がイネーブルされます。図5に示すように、外部の抵抗分割器と一緒にRUNピンを使って、検出されたV<sub>X</sub>の電圧に基づいてLTC3766の動作をイネーブルすることができます。自己起動するアプリケーションでは、V<sub>X</sub>は通常コンバータの出力電圧(V<sub>OUT</sub>)またはバイアス電圧のいずれかです。非絶縁型アプリケーションでは、V<sub>X</sub>は通常コンバータの入力電圧(V<sub>IN</sub>)です。非絶縁型アプリケーションでのRUNピンの使い方の詳細については、「非絶縁型アプリケーション」を参照してください。

図5. RUNピンを使った起動の検出

RUNピンがそのスレッショルドより低いとき3μAの電流がRUNピンに流れ込み、R1の選択値と組み合わされて、ヒステリシスを内部の4%より大きくします。このように使用するとき、R1とR2の値は、必要な上昇時および下降時のV<sub>X</sub>のスレッショルドに基づき、以下の式に従って計算することができます。

$$R1 = \frac{V_{X(RISING)} - 1.043 \cdot V_{X(FALLING)}}{3\mu A}$$

$$R2 = \frac{1.17 \cdot R1}{V_{X(FALLING)} - 1.17}$$

LTC3765が開ループでソフトスタートを行う自己起動アプリケーションでは、電圧V<sub>X</sub>をコンバータのV<sub>OUT</sub>に接続して(V<sub>X</sub>=V<sub>OUT</sub>)、出力電圧が与えられたレベルを超えるまで、LTC3766の起動を禁じることができます。これにより、ソフトスタートの制御を1次側から2次側に引き渡す正確な出力電圧が設定されます。この引き渡し出力電圧は、LTC3766が最初に制御を受け取るときパルス・スキップ動作を防ぐのに十分なだけ高く設定します。ピーク充電回路を使ってバイアス電圧を発生するアプリケーションで過度のパルス・スキップが発生す

## アプリケーション情報

ると、バイアス電源が下がり、適切な起動を妨げます。この可能性をなくすには、RUNピンを使って、出力電圧が少なくとも次の値になるまでLTC3766の起動を禁じます。

$$V_{\text{OUT(ON)}} > 300 \text{ns} \frac{N_S f_{\text{SW}} V_{\text{IN(MAX)}}}{N_P}$$

自己起動アプリケーションでは、LTC3765を使って、1次側だけでRUN/STOPの直接制御を行うことに注意してください。LTC3765がディスエーブルされると、1次側がスイッチングを停止したことをLTC3766が検出して、自動的にシャットダウンします。出力の過電圧の可能性をなくすため、LTC3765をマニュアルでディスエーブルしてから、LTC3766をマニュアルでディスエーブルしてください。

RUNピンの機能が不要であれば、このピンをV<sub>IN</sub>ピンに直接接続することができます。

### スイッチング周波数の設定と同期

LTC3766のスイッチング周波数はFS/SYNCピンを使って設定します。このピンは20μAの電流をソースし、このピンからグランドへ接続した抵抗がスイッチング周波数を次式に等しい値に設定します。

$$f_{\text{SW}} = 4R_{\text{FS}}$$

代わりに、FS/SYNCピンをV<sub>CC</sub>に接続して、スイッチング周波数を275kHzの固定値に設定することができます。一般に、スイッチング周波数が高いほど、インダクタとトランジスタのサイズが小さくなります。その代わり効率が低下します。LTC3766は75kHz～500kHzで動作可能ですが、フォワード・コンバータの効率とサイズの間の最良のバランスは、150kHz～350kHzで動作するとき得られます。

クロック信号(>2V)がFSピンで検出されると、LTC3766はこの信号の立ち下がりエッジに自動的に同期します。FS/SYNCピンの動作を表1にまとめておきます。

表1

| FS/SYNCピン              | スイッチング周波数                                             |

|------------------------|-------------------------------------------------------|

| V <sub>CC</sub>        | 275kHz                                                |

| R <sub>FS</sub> to GND | f <sub>SW</sub> = 4R <sub>FS</sub>                    |

| Reference Clock        | f <sub>SW</sub> = f <sub>REF</sub> (100kHz to 500kHz) |

PolyPhaseアプリケーションでは、マスターのPT-ピンを各スレーブのFS/SYNCピンに接続することにより、同期させることができます。各スレーブの相対的位相遅れはPHASEピンを使って設定します。表2に示されている、予め設定された5つの値の中の1つをどちらでも選択することができます。PT-の立ち下がりエッジはPWMサイクルの始まりに対応するので、位相遅れはFS/SYNCピンに入ってくるリファレンス・クロックの立ち下がりエッジを基準にしていることに注意してください。

表2

| PHASEピン                 | 位相遅れ | アプリケーション            |

|-------------------------|------|---------------------|

| GND                     | 180° | 2-Phase and 4-Phase |

| 25k to GND              | 240° | 3-Phase             |

| 50k to GND              | 120° | 3-Phase             |

| 100k to GND             | 90°  | 4-Phase             |

| 100k to V <sub>CC</sub> | 270° | 4-Phase             |

アプリケーションによっては、特定の周波数でスイッチングを開始し、その後、クロック・リファレンス信号に同期するのが望ましいことがあります。これは図6に示されている回路を使って実現することができます。

図6. 自走後に同期

LTC3766が一旦同期したら、LTC3766もシャットダウンするのでのない限り、外部同期クロックを取り去らないでください。同期した後外部クロックを取り去ると、一定期間低い周波数の動作になります。そのため外部部品に非常に大きな電流が流れることができます。

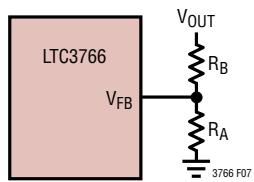

### 出力電圧の設定

LTC3766の出力電圧は、図7に示されているように、出力に接続した外付け帰還抵抗分割器によって設定されます。安定化出力電圧は次式から求まります。

$$V_{\text{OUT}} = 0.6V \cdot \left( 1 + \frac{R_B}{R_A} \right)$$

## アプリケーション情報

これらの分圧器抵抗をFBピンのすぐ近くに置いて、敏感なFB信号のトレース長を短くし、ノイズピックアップを最小に抑えるよう注意します。出力電圧の分圧器に低抵抗(<2k)を使つても、FBピンのノイズを最小にします。リモート・センスアンプを使う場合、分圧器はVsoutピンとGNDの間に接続します。詳細については、「リモートセンス」のセクションを参照してください。

図7. 出力電圧の設定

### メイン・トランスの選択

フォワード・コンバータのトランスの役割りは、1次側と2次側の間を絶縁しながら、電圧を上げたり、下げたりすることです。理想的には、このトランスは(その磁化インダクタンスが無限で)エネルギーを全く保存しません。この目標はフライバック・コンバータに使用されるトランスの目標と大きく異なることに注意してください。フライバック・コンバータに使用されるトランスは実際は結合されたインダクタであり、その目的は、1次側のオン時間の間にエネルギーを保存し、オフ時間の間にそれを2次側に供給することです。対照的に、フォワード・コンバータでは1次側のオン時間の間に電力が送られ、トランスのコアに意図せず保存された少量のエネルギーを回収するのにオフ時間が使われます。

ほとんど全てのアプリケーションで、市販のトランスを選択することができます。平面巻きの手法を使ったトランスは広く供給されており、漏れインダクタンスと部品の高さを最小に抑えるのに最適です。市販のトランスの適切なファミリーを選択するとき考慮すべき2つの基本事項があります。1)絶縁要件と、2)電力レベルの要件です。アプリケーション回路に特定の絶縁要件がある場合、絶縁レベルがその要件を満たすトランス・ファミリーを選択します。絶縁電圧定格の他に、アプリケーションが特定の機関で認証されたトランスを必要とするか、または特定の種類の絶縁(たとえば、基礎絶縁や機能絶縁)を必要とすることがあります。電力レベルに関しては、必要な出

力電力レベルを超える定格電力レベルのトランス・ファミリーを選択します。多くの電子装置は開発中に電力要件が増える傾向があるので、「成長」の余地を残すように注意します。

トランス・ファミリーを選択したら、次のステップはそのファミリーの中から最適のトランスを選択することです。これは主に、適正な1次巻数と2次巻数(N<sub>P</sub>とN<sub>S</sub>)を選択することからなります。N<sub>S</sub>の値は次式から計算できます。

$$N_S = \frac{10^8 V_{OUT}}{f_{SW} A_C B_M}$$

ここで、A<sub>C</sub>はcm<sup>2</sup>で表した(通常トランスのデータシートに記載されている)コアの断面積、B<sub>M</sub>は望みの最大AC磁束密度です。「標準的応用例」のセクションで使用されているPulseのPA08XXシリーズのパワートランスの場合、A<sub>C</sub>=0.59cm<sup>2</sup>です。PulseのPA09XXシリーズのパワートランスの場合、A<sub>C</sub>=0.81cm<sup>2</sup>です。最も高い周波数向けのトランスにはフェライトのコア材が使用されます。したがって、スイッチング周波数が150kHz～350kHzである限り、最大AC磁束密度が2000ガウスのものを出発点として選択するのが良いでしょう。B<sub>M</sub>のこの値は、過渡変動の間に余裕を与え、過度のコア損失を防ぎます。スイッチング周波数とともにB<sub>M</sub>の選択により、特定のトランスのコア損失の大きさが定まるに注意してください。トランスのデータシートを調べて、発生するコア損失と温度上昇を評価してください。場合によっては、B<sub>M</sub>とそれに関連した温度上昇を下げるため、N<sub>S</sub>をいくらか増やす必要があるかもしれません。全ての場合に、トランスのコアの飽和磁束密度より十分下に留まることを確認してください。

N<sub>S</sub>の値を選択したら、トランスの必要な巻数比を次式から計算することができます。

$$\frac{N_P}{N_S} = \frac{D_{MAX} V_{IN(MIN)}}{V_{OUT}}$$

ここで、V<sub>IN(MIN)</sub>は最小入力電圧、D<sub>MAX</sub>は最大デューティサイクルです。LTC3766の最大デューティサイクルは79%ですが(D<sub>MAX</sub>=0.79)、通常は上式でD<sub>MAX</sub>のもっと低い値を選択して、最小入力電圧で動作するとき負荷の過渡変動に適応するためのデューティサイクルの余裕を確保します。ほとんどのアプリケーションで、0.65～0.70のD<sub>MAX</sub>の値が適切です。

## アプリケーション情報

特定のトランスを選択したら、トランスの巻線の銅損失を計算します。これらの損失は、最大デューティサイクルかつ最大負荷で動作するとき最高になります。ただし、50%のデューティサイクルの公称動作ポイントでの銅損失を評価する方が良く、そこでの損失はおよそ次のようになります。

$$P_{CU} = \frac{(I_{MAX})^2}{2} \left( R_{SEC} + \left( \frac{N_S}{N_P} \right)^2 R_{PRI} \right)$$

ここで、 $R_{PRI}$ と $R_{SEC}$ はそれぞれ1次巻線と2次巻線の抵抗、 $I_{MAX}$ は最大出力電流です。トランスの最適設計では、銅損失とコア損失がうまく均衡しています。それらが大きく異なる場合、2次巻数を調整し(必要な巻数比を再度計算し)、このような均衡を実現します。

### インダクタの値の計算

出力インダクタの選択は基本的に降圧コンバータの場合と同じです。与えられた入力電圧と出力電圧に対して、インダクタの値と動作周波数によってリップル電流が決まります。リップル電流 $\Delta I_L$ は $V_{IN}$ が高いほど増加し、インダクタンスが高いほど減少します。

$$\Delta I_L = \frac{V_{OUT}}{f_{SWL}} \left( 1 - \frac{V_{OUT}}{V_{IN}} \cdot \frac{N_P}{N_S} \right)$$

大きな値の $\Delta I_L$ を許容すれば、低いインダクタンスを使用できますが、出力電圧リップルが高くなりコア損失が大きくなります。リップル電流を設定するための妥当な出発点は、公称 $V_{IN}$ で $\Delta I_L = 0.3 (I_{MAX})$ です。入力電圧が最大のときに $\Delta I_L$ が最大になります。

### インダクタのコアの選択

$L$ の値が求まつたら、次にインダクタの種類を選択します。高効率コンバータは低価格の鉄粉コアに見られるコア損失は一般に許容できないので、もっと高価なフェライト・コアを使わざるをえません。インダクタ値が同じ場合、実際のコア損失は基本的にコア・サイズではなく、選択したインダクタンスによって

大きく異なります。インダクタンスが大きいほどコア損失が減少します。インダクタンスを大きくするにはワイヤの巻数を増やす必要があるため、残念ながら銅損失が増加します。

フェライトを使ったタイプはコア損失が極めて低く、高いスイッチング周波数には最適なので、設計目標を銅損失と飽和を防ぐことに集中することができます。フェライト・コアの材質は「ハードに」飽和します。つまり、最大設計ピーク電流を超えるとインダクタンスが突然低落します。その結果、インダクタのリップル電流が突然増加し、そのため出力電圧リップルが増加します。コアを飽和させないでください。

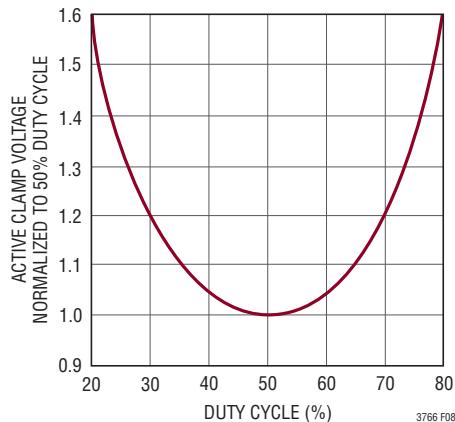

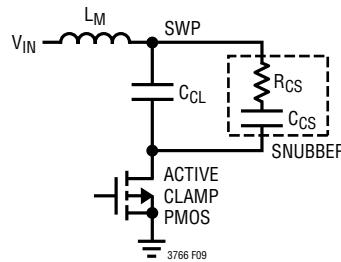

### アクティブ・クランプ・コンデンサ

アクティブ・クランプ・コンデンサ( $C_{CL}$ )は、トランスの多サイクルにわたる平均リセット電圧を保持します。クランプ・コンデンサの電圧は、トランスのコアのリセット電流によって発生し、他のパラメータには関係なく、本質的に最適リセット電圧に調整されます。最大負荷でのコンデンサ両端の電圧はおよそ次のように与えられます。

$$V_{CL} = \frac{V_{IN}}{V_{IN} - 1.15 \left( V_{OUT} \cdot \frac{N_P}{N_S} \right)}$$

$N_P/N_S$ はメイン・トランスの巻数比です。1.15の係数は標準的な損失と遅延を考慮したものです。LTC3765のPGとAGが“L”的とき、クランプ・コンデンサの下側が接地され、リセット電圧( $V_{CL}$ )をSWPノードに与えます。PGとAGが“H”的とき、コンデンサの上側が接地され、コンデンサの下側は $-V_{CL}$ になります。したがって、コンデンサに現れる電圧は、PGのMOSFETとAGのMOSFETのドレインに現れる電圧でもあります。

図8に示すように、 $V_{CL}$ 電圧は、コンバータが50%で動作しているとき最小になります。したがって、 $V_{IN}$ の特定の範囲では、最小 $V_{IN}$ と最大 $V_{IN}$ のどちらの入力電圧でコンバータが50%のデューティサイクルから最も離れて動作するかに依存して、最小 $V_{IN}$ または最大 $V_{IN}$ のどちらかで最大クランプ電圧( $V_{CL(MAX)}$ )になります。最大 $V_{CL}$ 電圧は、この式に $V_{IN}$ の最大値または

## アプリケーション情報

図8. V<sub>CL</sub>電圧とデューティサイクル

最小値を代入し、どちらか大きい方を選択することにより、決定することができます。オーバーシュートの余地を与えるため、この最大V<sub>CL</sub>値より50%以上大きな電圧定格のコンデンサを選択します。一般に、良質の(X7R)セラミック・コンデンサはC<sub>CL</sub>に最適です。また、コンデンサの電圧係数を必ず計算に入れてください。多くのセラミック・コンデンサは、その値の最大50%を定格電圧で失います。

クランプ・コンデンサの値は、コンデンサのリップル電圧を最小にして、MOSFETから見た電圧ストレスを減らすのに十分なだけ大きくなります。ただし、大きなクランプ・コンデンサは結局、負荷過渡時にトランスの飽和を防ぐための過渡応答が遅くなります。Direct Flux Limitは飽和を防ぐのに必要なだけPWMのオン時間を自動的に制限しますが、大きなクランプ・コンデンサは負荷過渡に応答して充電または放電を行うにもっと長い時間を必要とします。したがって、クランプ・コンデンサの値は、過渡応答とMOSFETの電圧ストレスの間を妥協させた値を表します。クランプ・コンデンサの妥当な値は次式を使って計算することができます。

$$C_{CL} = \frac{1}{2L_M} \cdot \left( \frac{4}{2\pi f_{SW}} \right)^2$$

メイン・トランスの磁化インダクタンスL<sub>M</sub>とクランプ・コンデンサC<sub>CL</sub>の間に共振が生じるため、C<sub>CL</sub>に対する設計上の他の制約が生じます。この共振のQが高すぎると、負荷過渡時に1

次側MOSFETに対する電圧ストレスが増加します。また、L<sub>M</sub>とC<sub>CL</sub>の間の共振のQが高いと、電圧ループの補償が複雑になり、特定の条件では発振する可能性があります。この共振に関連した問題を回避するには、図9に示すように、常にクランプ・コンデンサに並列にRCスナバを使用します。このRCスナバの値は次式を使って計算することができます。

$$R_{CS} = \frac{1}{1 - \left( \frac{V_0}{V_{IN(MIN)}} \cdot \frac{N_p}{N_s} \right)} \sqrt{\frac{L_M}{C_{CL}}}$$

および

$$C_{CS} = 6C_{CL}$$

アクティブ・クランプ・コンデンサとRCスナバの標準的な接続方法を図9に示します。C<sub>CS</sub>とC<sub>CL</sub>の両方の電圧係数の影響を計算に入れて、C<sub>CS</sub>とC<sub>CL</sub>の間の上述の関係が維持されるように注意してください。

図9. アクティブ・クランプ・コンデンサとスナバ

### Direct Flux Limit(直接磁束制限)

アクティブ・クランプ・フォワード・コンバータでは、負荷の過渡変動の間または出力が予めバイアスされた状態で起動するときにコアの飽和を防ぐため、トランスの磁束密度を精密に制限することが不可欠です。LTC3765とLTC3766は、トランスのコア内の磁束の増加をモニタして直接制限する新しい独自システムを実装しています。前の方法とは異なり、直接磁束制限は、磁束の増加を直接測定し、モニタして、出力が予めバイアスされた状態で起動するときでも、トランスがどちらの方向でも飽和しないことを保証します。この手法は、非常に高い

## アプリケーション情報

デューティサイクルを一時的に許し、絶対的に必要なときだけデューティサイクルを制限するので、可能な限り最良の過渡応答も与えます。さらに、この手法は、(多くのアクティブ・クランプ・フォワード・コンバータの設計で潜在的に重大な弱点である)過電流によるアクティブ・クランプPMOSへの損傷を防ぎます。

直接磁束制限機能は1次側のLTC3765に実装されているので、2次側で調整すべきことは何もありません。この機能の使用の詳細に関しては、LTC3765のデータシートを参照してください。磁束の増加を制限するため、LTC3765がPGのMOSFETのオン時間を時期尚早に終了すると、LTC3766はSWノードで時期尚早の立ち下がりを検出することに注意して下さい。それに応答して、LTC3766は自動的にFGのオン時間を終了し、トランスのコアがリセットできるようにします。LTC3765が何らかの理由でシャットダウンしたときも、SWノードが時期尚早に立ち下がります。したがって、LTC3766がSWノードの連続した19の時期尚早な立ち下がりエッジをSWピンで検出すると、LTC3766はロック・フォールトを発生してシャットダウンします。

### 1次側パワーMOSFETの選択

1次側では、Nチャネル・メイン・スイッチとPチャネル・アクティブ・クランプ・スイッチの両方のピーク・トゥ・ピーク・ドライブ・レベルは、LTC3765のV<sub>CC</sub>ピンの電圧によって決まります。この電圧は通常パルストランスによって与えられ、一般に8.5V～12Vに設定されます。1次側にロジック・レベルのMOSFETを使用できるアプリケーションであっても、適切な動作のため、LTC3765のV<sub>CC</sub>電圧はこの範囲でなければならないことに注意してください。

NチャネルMOSFETの選択では、オン抵抗と寄生容量に関連した損失をバランスさせながら、ブレークダウン電圧(BV<sub>DSS</sub>)と最大ドレン電流の要件を注意深く検討します。アクティブ・クランプ・トポロジーでは、このMOSFETから見た最大ドレン電圧はおおよそ次のようになります。

$$V_{DS(PG)} = 1.2 \cdot V_{CL(MAX)}$$

ここで、V<sub>CL</sub>(MAX)は、「アクティブ・クランプ・コンデンサの選択」のセクションで与えられている最大アクティブ・クランプ電圧です。クランプ・コンデンサのリンクギングとリップルのマージ

ンを与えるため、1.2の係数が追加されています。効率を最大にするため、このMOSFETにはできるだけ低い電圧定格のものを選択することが重要です。アクティブ・クランプ・コンデンサのRCスナバ(図10を参照)は、動作損失を増やすことなく、1次側MOSFETに対するピーク電圧ストレスを減らすことに注意してください。また、最大負荷でのメイン・トランスの漏れインダクタンスは、アクティブ・クランプ・コンデンサに大きなリップルを生じ、1次側MOSFETから見たピーク電圧ストレスを押し上げることがあります。このリップルは、大きなアクティブ・クランプ・コンデンサと、それに比例して大きなRCスナバ・コンデンサを使用することにより、減らすことができます。詳細については、「アクティブ・クランプ・コンデンサ」のセクションを参照してください。

NチャネルMOSFETの必要なBV<sub>DSS</sub>が分かつたら、スイッチング・アプリケーションに最適化された(低Q<sub>G</sub>の)、入手できるものの中でオン抵抗(R<sub>DSON</sub>)が最小のMOSFETを選択します。MOSFETは、ほとんどのアプリケーションで、最大定格電流よりかなり小さなドレン電流で使用されるので、この定格は通常は検討されません。最大出力電流でのNチャネルMOSFETと関連した全損失は、次式を使って推定することができます。

$$\begin{aligned} P_{PG} &= \left(\frac{N_P}{N_S}\right) \frac{V_{OUT}(I_{MAX})^2}{V_{IN}} (1+\delta) R_{DSON} \\ &+ \left(\frac{N_S}{N_P}\right) \frac{V_{CL} I_{MAX} R_{DR} Q_{GD} f_{SW}}{2V_{MILLER}} + Q_{GTOT} V_{CC} f_{SW} \end{aligned}$$

ここで、 $\delta$ はオン抵抗の温度依存性、V<sub>CL</sub>はアクティブ・クランプ電圧です(「アクティブ・クランプ・コンデンサ」のセクションを参照)。R<sub>DR</sub>(LTC3765では約1.7Ω)は、MOSFETのミラー効果によるプラトー電圧(V<sub>MILLER</sub>)でのゲート・ドライブの出力抵抗です。Q<sub>DG</sub>、Q<sub>GTOT</sub>、およびV<sub>MILLER</sub>の各値は、MOSFETのデータシートで普通与えられている「V<sub>GS</sub>とQ<sub>G</sub>」曲線から得ることができます。Q<sub>GD</sub>は、V<sub>GS</sub>電圧がほぼ一定でミラー電圧(V<sub>MILLER</sub>)に等しくなる領域でのゲート電荷(Q<sub>G</sub>)の変化量です。全ゲート電荷(Q<sub>GTOT</sub>)は、V<sub>GS</sub>=V<sub>CC</sub>のときのゲート電荷です。上式の3つの部分は、それぞれ導通損失、遷移損失、およびゲート・ドライブ損失を表します。遷移損失とゲート・ドライブ損失の和と、導通損失の間のバランスがと

## アプリケーション情報

れたMOSFETを選択することにより、最高効率が得られます。上の $P_{PG}$ の式は仮定を含む近似であることに注意してください。まず、メイン・トランスの漏れインダクタンスのため、ターンオン遷移損失は比較的小さいと仮定しています。また、1次側スイッチのターンオフでこの漏れインダクタンスに貯えられたエネルギーは、アクティブ・クランプ・コンデンサによって完全に回収されると仮定しています。これらの仮定はほとんどのアプリケーションで有効であり、上式は良い近似を与えます。

アクティブ・クランプのPチャネルMOSFETの $BV_{DSS}$ の要件は、NチャネルMOSFETの要件と同じです。PチャネルMOSFETは磁化電流を扱うだけなので、通常ははるかに小さくなります(一般にSOTパッケージ)。異常な過渡変動に適応するため、パルス・ドレイン電流定格が2A以上のPチャネルMOSFETを使います。また、NチャネルMOSFETがオフするとき、漏れインダクタンスにより、反射された負荷電流がPチャネルMOSFETのボディ・ダイオードに短時間流れることに注意してください。したがって、ボディ・ダイオードの定格が次の順方向パルス電流を扱える必要があります。

$$I_{D(MAX)} = \left(\frac{N_S}{N_P}\right) I_{MAX}$$

場合によっては、PチャネルMOSFETのボディ・ダイオードに並列に別のダイオードを追加する方が実際的です。

1次側PチャネルMOSFETは、LTC3765のAGピンのドライブ電圧を下方にシフトさせる、簡単なレベルシフト回路によってドライブすることができます。代わりに、PチャネルMOSFETのソースをLTC3765の $V_{CC}$ ピンに戻すならば、レベルシフト回路を省くことができます。詳細については、LTC3765のデータシートを参照してください。

LTC3766をスタンドアロンで使う非絶縁型アプリケーションでは、アクティブ・クランプ・リセットの代わりに、共振リセットの手法を使う必要があります。その結果、1次側MOSFETの選択では、特殊な検討事項があります。詳細については、「非絶縁型アプリケーション」のセクションを参照してください。

### 2次側パワーMOSFETの選択

2次側では、NチャネルMOSFETのピーク・トゥ・ピーク・ドライブ・レベルは、LTC3766の $V_{CC}$ ピンによって決まります。LTC3766の片方または両方のリニア・レギュレータを使用すると仮定すると、 $V_{CC}$ の安定化電圧はMOSFETのゲートのドライブに必要な7Vまたは8.5Vのどちらかに設定することができます。

2次側MOSFETを選択する際の最初のステップとして、必要なブレークダウン電圧を決めます。同期MOSFETから見た最大電圧はおおよそ次のようにになります。

$$V_{DS(SG)} = 1.2 \cdot \left(\frac{N_S}{N_P}\right) V_{IN(MAX)}$$

ここで、リンギングとオーバーシュートに対応するため、1.2の係数が追加されています。これは、スナバがメイン・トランスの2次側に使われていると仮定しています(「RCスナバ」のセクションを参照)。スナバを使用しない場合、リンギングとピーク・オーバーシュートがかなり高くなります。フォワードMOSFETから見た最大電圧はおおよそ次のようにになります。

$$V_{DS(FG)} = \frac{1.2 \cdot V_{OUT}}{1 - \frac{V_{OUT}}{V_{IN(MIN)}} \left(\frac{N_P}{N_S}\right)}$$

ここで、リンギングとオーバーシュートに対応するため、1.2の係数が再度追加されています。

フォワードMOSFETと同期MOSFETの $BV_{DSS}$ の要件を決めたら、次のステップはオン抵抗の選択です。2次側の両方のMOSFETはゼロ電圧でスイッチされるので、 $R_{DS(ON)}$ が小さく、同期整流器として使用するように最適化されていて、できればボディ・ダイオードの逆回復が高速のMOSFETを選択します。ほとんどのアプリケーションで、公称入力電圧は約50%のデューティサイクルに相当するので、フォワードMOSFETと同期MOSFETは、 $R_{DS(ON)}$ が同じになるように選択されます。フォワードMOSFETに関連する電力損失は次式で近似することができます。

$$P_{FG} = \left(\frac{N_P}{N_S}\right) \frac{V_{OUT} (I_{MAX})^2}{V_{IN}} (1 + \delta) R_{DS(ON)} + Q_{GTOT} V_{BIAS} f_{SW}$$

ここで、 $\delta$ はオン抵抗の温度依存性、 $V_{BIAS}$ は(もし使用されているれば)LTC3766のリニア・レギュレータへの入力です。 $Q_{GTOT}$ の値は、MOSFETのデータシートで与えられている「 $V_{GS}$ と $Q_G$ 」曲線から得ることができます。 $Q_{GTOT}$ は $V_{GS} = V_{CC}$ のときの $Q_G$ の値です。ここで、 $V_{CC}$ はLTC3766の $V_{CC}$ ピ

## アプリケーション情報

の電圧です。同期 MOSFET の場合、電力損失はおおよそ次のようにになります。

$$P_{SG} = \left(1 - \frac{N_P}{N_S} \frac{V_{OUT}}{V_{IN}}\right) (I_{MAX})^2 (1 + \delta) R_{DS(ON)} \\ + Q_{GTOT} V_{BIAS} f_{SW}$$

同期 MOSFET とフォワード MOSFET の電力損失は、一般に導通損失によって支配されます。上の電力損失の両方の式で、(MOSFET のボディ・ダイオードが導通しているときの) デッドタイムは最小化されていると仮定しています。デッドタイムの最小化の詳細については、「ゲート・ドライブ遅延の設定」のセクションを参照してください。

### V<sub>CC</sub>とドライブ・モードの選択

2次側 MOSFET が必要とする様々な動作ゲート電圧に適合するため、MODE ピンを使って、LV モードまたは HV モードの動作のどちらかに LTC3766 を設定することができます。LV モードでは、両方のリニア・レギュレータのための V<sub>CC</sub> の安定化レベルは 7V に設定され、V<sub>CC</sub> の UVLO と V<sub>AUX</sub> の切り替えの上昇時スレッショルドは 4.7V に調整されます。HV モードでは、V<sub>CC</sub> の安定化レベルは 8.5V に設定され、V<sub>CC</sub> の UVLO と V<sub>AUX</sub> の切り替えの上昇時スレッショルドはそれぞれ 7.9V と 8V に調整されます。4V ~ 5V の動作に定格が定められている MOSFET には LV モードを使い、7V ~ 10V の動作に定格が定められている MOSFET には HV モードを使います。UVLO 電圧および切り替え電圧とともに、V<sub>CC</sub> の安定化レベルは、両方のタイプの MOSFET が安全に効率よく動作するように最適化されています。一般に、V<sub>DS</sub> 定格が高い MOSFET は、動作ゲート電圧定格も高くなります。その結果、出力電圧が約 12V 以上のアプリケーションは一般に、7V ~ 10V のゲート動作向けに定格が定められた MOSFET を使います。

V<sub>CC</sub> の安定化レベル、UVLO と V<sub>AUX</sub> 切り替えレベルの変更の他に、HV モードまたは LV モードの選択により、SG の逆過電流の振る舞いも変わります。LV モードでは、SW ピンの逆過電流のスレッショルドは 73mV、調整電流は 103μA です。HV モードでは、これらのレベルは 148mV と 42μA に変更され、低電圧 MOSFET のオン抵抗より高い高電圧 MOSFET のオン抵抗に適応します。詳細については、「SG の逆過電流の設定」を参照してください。

LTC3765 と一緒に LTC3766 を使うアプリケーションでは、PT<sup>+</sup> ピンと PT<sup>-</sup> ピンの信号には、振幅が V<sub>CC</sub> 電圧に等しいエンコードされた PWM 情報が含まれています。このエンコードされたゲート・ドライブ信号は LTC3765 によって受け取られ、1 次側 MOSFET をドライブする PWM とクロック情報にデコードされます。ただし、LTC3766 は、非絶縁型フォワード・コンバータ・アプリケーションでは、スタンドアロンでも使えます。このようなアプリケーションでは、MODE ピンを使って、PT<sup>+</sup> ピンと PT<sup>-</sup> ピンの PWM エンコーディングをディスエーブルすることができます。その結果、LTC3766 は通常の PWM ゲート・ドライブ信号を PT<sup>+</sup> ピンに発生し、リファレンス・クロックを PT<sup>-</sup> ピンに発生します。また、スタンドアロン・モードでは、FGD ピンは無視され、SG の立ち下がりと PT<sup>+</sup> の立ち上がりの間のデッドタイムは適応設定されます。

MODE ピンには可能な 4 つの状態があります。MODE を GND または V<sub>CC</sub> に接続すると、それぞれ LV モードまたは HV モード動作のどちらかで、エンコードされたゲート・ドライブ信号を与えます。100k または 50k の抵抗を介して MODE を GND に接続すると、それぞれ LV モードまたは HV モード動作のどちらかで、標準的 PWM ゲート・ドライブ信号を与えます。動作電圧とゲート・ドライブ・エンコーディング・モードを設定する MODE ピンの使用法が表 3 にまとめてあり、低電圧と高電圧のゲート・ドライブの動作モードの効果が表 4 にまとめあります。

表 3

| MODE ピン         | ドライブ・レベル | PT <sup>+</sup> /PT <sup>-</sup> モード | 目的のアプリケーション                                  |

|-----------------|----------|--------------------------------------|----------------------------------------------|

| GND             | LV       | エンコードされた PWM                         | LTC3765 を使った V <sub>OUT</sub> の低い絶縁型アプリケーション |

| V <sub>CC</sub> | HV       | エンコードされた PWM                         | LTC3765 を使った V <sub>OUT</sub> の高い絶縁型アプリケーション |

| 100k を GND へ    | LV       | 標準的 PWM                              | V <sub>OUT</sub> の低い非絶縁型アプリケーション、スタンドアロン     |

| 50k を GND へ     | HV       | 標準的 PWM                              | V <sub>OUT</sub> の高い非絶縁型アプリケーション、スタンドアロン     |

表 4

| ドライブ・レベル | V <sub>CC</sub> | V <sub>CC</sub> の UVLO スレッショルド (上昇時 / 下降時) | V <sub>AUX</sub> 切り替えスレッショルド (上昇時 / 下降時) | SG の過電流         |                 |

|----------|-----------------|--------------------------------------------|------------------------------------------|-----------------|-----------------|

|          |                 |                                            |                                          | V <sub>TH</sub> | I <sub>SW</sub> |

| LV       | 7.0V            | 4.7V/3.9V                                  | 4.7V/4.5V                                | 73mV            | 103μA           |

| HV       | 8.5V            | 7.9V/6.9V                                  | 8.0V/7.7V                                | 148mV           | 42μA            |

## アプリケーション情報

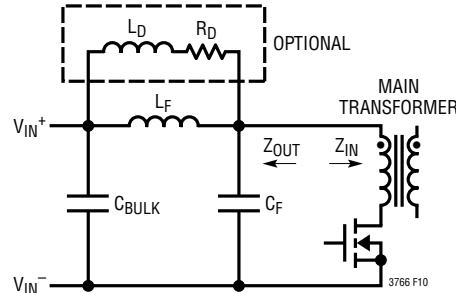

### 入力コンデンサ/フィルタの選択

低インピーダンスのソースを使ったアプリケーションや入力電圧が比較的低いアプリケーションでは、簡単な容量性入力フィルタが一般に適しています。このコンデンサのESRは非常に小さくなければならず、ワーストケースの次のようなRMS入力電流を扱える定格でなければなりません。

$$I_{C(RMS)} = \left( \frac{N_S}{N_P} \right) \frac{I_{OUT(MAX)}}{2}$$

多くの場合、コンデンサ・メーカーはリップル電流定格をわずか2000時間の寿命時間によって規定しています。このため、コンデンサをさらにディレーティングする、つまり要求条件よりも高い温度定格のコンデンサを選択するようにしてください。サイズまたは高さの設計条件に適合させるため、複数のコンデンサを並列に接続することができます。LTC3766の動作周波数は高いので、 $C_{IN}$ にセラミック・コンデンサを使用することもできます。疑問点については必ずメーカーに問い合わせください。

ただし、入力電圧が高いアプリケーションでは、必要なRMS電流を扱うように定格が定められたバルク容量を使うと非常にコスト高になることがあります。また、入力フィルタとして簡単なコンデンサを使うと、電源が大きなシステムに組み込まれたとき、AC入力電流がどこを流れるか正確に知るのが難しくなります。これらの問題を避けるため、図10に示されているようにLCフィルタを電源入力に使うことができます。これは、大きなAC電流を、RMS電流定格が知られている、比較的小さくて安価なコンデンサに封じ込めます。LCフィルタを次のように選択します。

$$\frac{1}{2\pi\sqrt{L_F C_F}} < \frac{f_{SW}}{5}$$

RMS入力電流のAC成分を、約5分の1に減衰させます。これにより、バルク入力コンデンサのRMS電流要件が大幅に緩和されます。フィルタ・インダクタの飽和電流は少なくとも次のようにします。

$$I_{SAT(LF)} \geq 1.3 \cdot \frac{V_{OUT} I_{OUT(MAX)}}{V_{IN(MIN)}}$$

出力のリップル電圧を妥当なレベルに抑えるため、次式を満たす $L_F$ と $C_F$ の値を選択します。

$$\sqrt{\frac{L_F}{C_F}} < 2.9 \cdot \left[ \left( \frac{N_S}{N_P} \right) \frac{V_{RIPPLE}}{I_{OUT(MAX)}} + \frac{R_{ESR}}{2} \right]$$

ここで、 $V_{RIPPLE}$ は入力フィルタの出力の望みのリップル電圧、 $R_{ESR}$ はコンデンサ $C_F$ のESRです。 $V_{RIPPLE}$ の妥当な目標値は公称 $V_{IN}$ の3%です。

LC入力フィルタを使用するとき、そのLCフィルタの出力インピーダンスの大きさは、DC/DCコンバータの電力段を見込む入力インピーダンスより決して大きくてはいけません。これはループが不安定になるのを防ぐのに必要です。ほとんどのアプリケーションでは、この条件は自然に満たされます。なぜなら、バルク入力容量( $C_{BULK}$ )のESRはLC入力フィルタのQを下げるのに十分なだけ高く、それによってその出力インピーダンスのピーキングを安全なレベルに下げるからです。大きな値の $C_F$ を使ってもQが下がりますが、 $V_{IN}$ の高いアプリケーションでは高価につくことがあります。状況によっては、図10に示すように、直列減衰ネットワークを追加する必要があります。

図10. オプションの減衰ネットワーク付き入力フィルタ

臨界減衰を与えるため、次式に従って $L_D$ と $R_D$ を選択します。

$$L_D = \frac{L_F}{5} \text{ and } R_D = 0.8 \sqrt{\frac{L_F}{C_F}}$$

## アプリケーション情報

減衰インダクタ  $L_D$  は DC 入力電流を流しません。ただし、大きな過渡変動の間適切に減衰させるため、飽和電流が少なくとも次のようなインダクタを選択します。

$$I_{SAT(LD)} \geq 0.6 \left( \frac{V_{OUT} I_{OUT(MAX)}}{V_{IN(MIN)}} \right)$$

### 出力コンデンサの選択

$C_{OUT}$  は、等価直列抵抗 (ESR) と、それによって生じる出力電圧リップルに基づいて選択します。一般に、ESR の要件が満たされると、その容量はフィルタ機能にとって十分です。出力リップル ( $\Delta V_{OUT}$ ) は次式で近似できます。

$$\Delta V_{OUT} \approx \Delta I_L \left( ESR + \frac{1}{8f_{SW} C_{OUT}} \right)$$

ここで、 $f_{SW}$  は動作周波数、 $C_{OUT}$  は出力容量、 $\Delta I_L$  はインダクタのリップル電流です。 $\Delta I_L$  は入力電圧に応じて増加するので、出力リップルは入力電圧が最大のとき最大になります。

### 電流検出と平均電流制限

LTC3766 は、電流検出抵抗または絶縁された電流トランスのいずれを使った電流検出もサポートします。電流トランスは一般にもっと効率が良く、絶縁型アプリケーションでは 1 次側で電流を検出する利点があります。これは、負荷過渡時にメイン・トランスが飽和しないように、追加の防護手段を与えるので重要です。さらに、電流トランスは、センス抵抗よりはるかに大きな電流検出信号を発生することができるので、はるかに優れた信号対雑音比になります。これにより、ノイズのピックアップに対するボードレイアウト時の懸念が緩和され、ジッタも減少します。また、LTC3766 の電流制限の精度が、電流検出モードの場合より、電流トランス・モードではかなり良くなります。

電流トランスに比べて、電流検出抵抗は安価で、使うのがいくらか簡単です。アクティブ・クランプ・フォワード・コンバータの 2 次側で電流を検出する場合、トランスの飽和と 1 次側の MOSFET への損傷を防ぐため、直接磁束制限が必要です。これは、電流ループは磁化電流を検知せず、飽和に対する自己の保護手段を持たないからです。ただし、非絶縁型アプリケー-

ションでは、電流検出抵抗が 1 次側スイッチに直列に接続されるので、電流ループは磁化電流をモニタすることに注意してください。

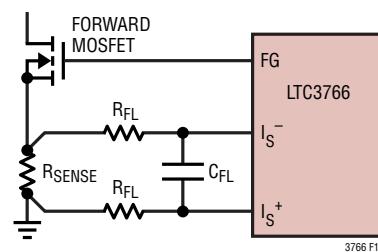

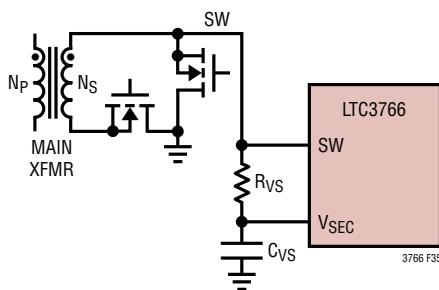

電流検出抵抗を使う場合、 $I_{S+}$  ピンと  $I_{S-}$  ピンは差動で動作し、最大ピーク電流スレッショルドは約 75mV です。電流検出抵抗は、図 11 に示されているように、通常フォワード MOSFET のソースに接続します。PCB レイアウトおよび  $I_{S+}$  ピンと  $I_{S-}$  ピンに向かうトレースのシールドに依存して、図 11 に示されているように、小さなフィルタ機能を追加することが必要になることがあります。一般に、 $R_{FL} = 100\Omega$  および  $C_{FL} = 200\text{pF}$  から  $1\text{nF}$  が、電流ループの応答に大きな影響を与えることなく、ノイズのピックアップを適切にフィルタします。

図 11. 電流検出抵抗の使い方

このフィルタは、センス抵抗の ESL (寄生インダクタンス) の影響を補正するのにも役立ちます。これは  $2\text{m}\Omega$  未満の  $R_{SENSE}$  の値では重要なことがあります。次のように RC フィルタを選択すると、ESL の影響がキャンセルされます。

$$R_{FL} C_{FL} = \frac{ESL}{R_{SENSE}}$$

LTC3766 は平均電流制限アーキテクチャを実装しているので、必要な平均電流制限に基づいて  $R_{SENSE}$  の値を選択します。

$$R_{SENSE} = \frac{55\text{mV}}{I_{LIM(AVG)}}$$

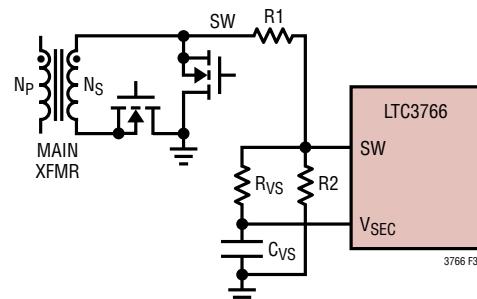

代わりに、電流トランスを使って 1 次側スイッチ電流を検出するのであれば、 $I_{S-}$  ピンを  $V_{CC}$  に接続し、 $I_{S+}$  ピンを電流トランスの出力に接続します。これにより、内部電流検出アンプの利

## アプリケーション情報

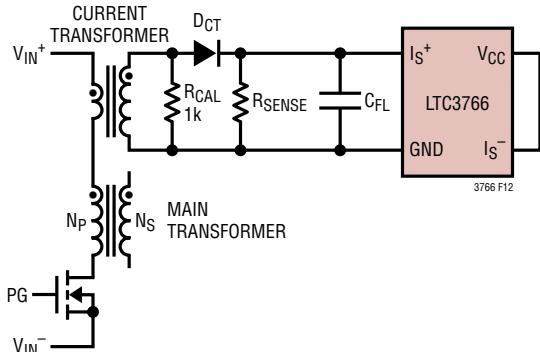

得が減少するので、最大ピーカ電流に相当する電圧は約1Vに増加します。電流トランスの接続方法を図12に示します。

図12. 電流検出トランスの使い方

一般に、電流トランスは、メイン・トランスへの電源フィードに直列に接続します。これにより、同相ノイズが減少し、一般にPCBレイアウトが簡単になります。小さなフィルタ・コンデンサ(1nF~3.3nF)、つまり75ns未満の時定数RSENSE・CFLを使って、高周波数ノイズを除去します。トランスのコアの適切なりセットを可能にするにはダイオードDCTが必要です。

電流トランスを使用するときは、次式を使ってRSENSEの値を設定します。

$$R_{SENSE} = \frac{0.73V}{K_{CT}I_{LIM(AVG)}} \cdot \frac{N_p}{N_s}$$

ここで、Np/Nsはメイン・トランスの巻数比、K<sub>CT</sub>はトランスの電流利得、I<sub>LIM (AVG)</sub>は必要な平均電流制限です。ほとんどのアプリケーションで、電流トランスの適切な巻数比は1:100です(K<sub>CT</sub> = 0.01)。

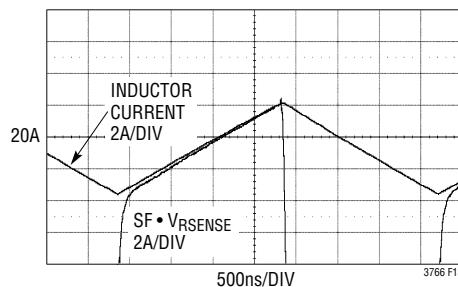

メイン・トランスと電流検出トランスの磁化電流の影響(R<sub>SENSE</sub>)の電圧が予想されるよりいくらか(2%~8%)高くなります)を補償するため、抵抗RCALが追加されています。一般に、RCALは1.5k~5kの範囲です。可能な最高の精度を得るには、RCALの値を調整して、注意深くRSENSEの電圧を測定し、それを出力インダクタ電流と比較することにより、最大負荷および公称入力電圧での電流検出を較正します。十分較正された電流検出トラン

スの例を図13に示します。RSENSEの電圧は次の係数でスケール調整されています。

$$SF = \frac{N_p}{R_{SENSE} K_{CT} N_s}$$

磁化電流により、スケール調整されたRSENSE電圧の勾配は、インダクタ電流の勾配に正確には一致しません。スケール調整されたRSENSEの電圧とインダクタ電流がピークで一致するようにRCALを選びます。

図13. 適切に較正した電流トランス

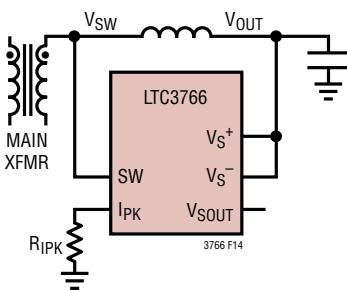

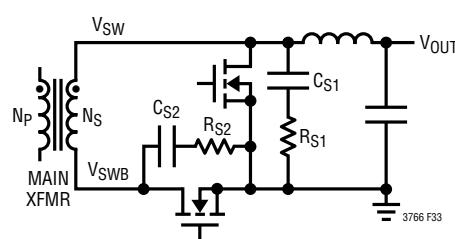

電流制限中に一定の平均電流を維持するため、LTC3766はピーク電流制限の値を自動的に調整して、インダクタ・リップル電流の影響をキャンセルします。これは、インダクタ電流リップルを真似た内部ランプを発生することにより達成されます。ランプの振幅はIPKピンの抵抗によって決まり、出力インダクタに比例するように設定する必要があります。LTC3766は(V<sub>sw</sub> - V<sub>s+</sub>)/15の電圧をIPKピンに発生します。これはSWが“H”的ときのオン時間の間の出力インダクタ両端の電圧の1/15です。したがって、LTC3766がインダクタの電圧を適正に検出できるためには、図14または図15に示すように、SWピンとV<sub>s+</sub>ピンを接続することが不可欠です。差動アンプが不要であれば、図14bに示されているように、V<sub>s-</sub>とV<sub>s+</sub>と一緒にV<sub>out</sub>に接続します。

SWノードのプラトー電圧が40Vを上回るような、V<sub>out</sub>が高いアプリケーションでは、図15に示されているように、抵抗分器をSWピンとV<sub>s+</sub>ピンの両方に追加する必要があります。この分圧器はSWピンの電圧を制限し、同時に、SGの逆過電流トリップ・スレッショルドに影響を与えます。SWピンの抵抗分器の選択の詳細については、「SGの逆過電流の設定」を参照してください。

## アプリケーション情報

図14a. 平均電流制限の設定(R<sub>IPK</sub>)

図14b. 差動アンプなしの場合のR<sub>IPK</sub>の設定

図15. V<sub>OUT</sub>の高いアプリケーションのR<sub>IPK</sub>の設定

SWピンとV<sub>S+</sub>ピンの抵抗分割器の比は、トリップ・キャンセル機能が適切に動作するには、同じでなければならないことに注意してください。これには、次式が成り立つことが必要です。

$$K_R = \frac{R_2}{R_1 + R_2} = \frac{69k \cdot R_4}{69k \cdot R_4 + R_3(69k + R_4)}$$

ここで、69kはV<sub>S+</sub>ピンとV<sub>S-</sub>ピンの内部抵抗を計算に入れてあります。

抵抗検出モードでは、次式を使って選択された抵抗をI<sub>PK</sub>ピンに接続します。

$$R_{IPK} = \frac{K_R L_{IPK}}{(17.6nF) R_{SENSE}}$$

ここで、L<sub>IPK</sub>はI=I<sub>LIM</sub>(AVG)のときの出力インダクタのインダクタンスです。SWノードに分圧器が不要なV<sub>OUT</sub>の低いアプリケーションでは、K<sub>R</sub>=1です。電流トランジスト・モードでは、次式を使います。

$$R_{IPK} = \frac{K_R L_{IPK}}{(1.32nF) K_{CT} R_{SENSE}} \cdot \frac{N_P}{N_S}$$

LTC3766が電流制限状態にあって出力電圧が非常に低いとき、出力電流の制御はコンバータの最小オン時間によって制限されます。この最小オン時間に達した後、電流制限状態で出力電圧がさらに低下すると、インダクタ電流が上昇を続け、過電流制限に達します。これにより、LTC3766がシャットダウンし、再起動を試みるので、ヒップ・モードの動作が生じます。

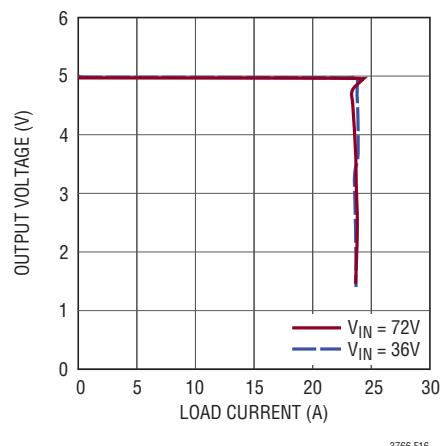

標準的な平均電流制限の性能を図16に示します。負荷に供給される平均電流は、出力電圧が低レベル(コンバータがヒップ・モードに入るポイント)まで減少していくとき、実質的に一定に保持されることに注意してください。特定のアプリケーションによっては、2次側のバイアス電圧の喪失(UVLO)により、または過電流フォールトにより、ヒップ・モードに入ります。

図16. 標準的な電流制限性能

## アプリケーション情報

### 平均電流制限の精度の推定

平均電流制限は、(寄生要素のパラメータを含む)アプリケーションの多数の回路パラメータとLTC3766の仕様に依存します。したがって、平均電流制限の精度を正確に計算するのは困難です。ただし、3つの主要な誤差源を注意深く検討することにより、この精度を推定することができます。

1. 電流検出抵抗と電流検出トランスの精度 抵抗による検出では、電流検出抵抗の精度は通常1%です。ただし、2mΩ未満の検出抵抗では、寄生インダクタンスにより、検出される電流に大きな誤差が生じることがあります。この誤差は、図11に示すようなRCフィルタを追加することにより、除去することができます。

電流トランスを使用するとき、電流トランスの2次側の検出抵抗およびトランスの巻数比( $K_{CT}$ と $N_p/N_s$ の両方)の精度は一般に1%より良い精度です。ただし、電流検出トランスがどこに置かれるかに依存して、メイン・トランスと電流検出トランスの両方の磁化電流により、1%～4%の誤差が追加されることがあります。一般に、この誤差は比較的一定のオフセットの形をとり、特定の設計の公称入力電圧と最大負荷電流に対して調整して取り除くことができます。磁化電流の影響のばらつきによる許容誤差は一般に2%未満なので、電流トランスによる検出全体の精度は約3%です。

2. 平均電流検出スレッショルド $V_{IS(AVG)}$ の精度。LTC3766の電流検出スレッショルドの精度は「電気的特性」の表に与えられており、選択された電流検出モードに依存します。電流トランス・モードは10%の精度を与え、抵抗検出モードの15%より精確です。

3. インダクタ・リップル電流補償の精度 インダクタ・リップル補償の精度は、 $V_{ITH}$ の内部調整および出力インダクタ自体の許容誤差の両方に依存します。ほとんどのアプリケーション回路では、リップル補償の精度は、電流トランス・モードでは25%より良く、抵抗検出モードでは35%より良くなります。インダクタ電流リップルは一般に平均電流制限の30%から60%であり、このピーク・トゥ・ピーク・リップルの半分だけが

補償されます。その結果、リップル補償の精度の平均電流制限に対する影響は次の係数だけ減少します。

$$F_R = \frac{R}{R+2}$$

ここで、Rは平均電流制限に対するピーク・トゥ・ピーク・インダクタ・リップル電流の比です。たとえば、30%～60%のリップルの場合、 $F_R$ の値は0.13～0.23で変化します。

上の各要素を考慮して、平均電流制限のワーストケースの許容誤差は次のように推定することができます。

$$\Delta I_{AVG} = 3\% + 10\% + 0.23 (25\%) = 18.5\%$$

これは電流トランス・モードの場合です。

$$\Delta I_{AVG} = 1\% + 15\% + 0.23 (35\%) = 24\%$$

これは抵抗検出モードの場合です。3つの誤差源は統計的に独立しているので、電流トランス・モードと抵抗検出モードの電流制限許容誤差は、RSS法を使って、それぞれ約12%および17%と計算することができます。

### ゲート・ドライブ遅延の設定

フォワード・スイッチのゲート・ドライバ(FG)と同期スイッチのゲート・ドライバ(SG)は、FGの立ち上がりエッジのマイク・ビフォア・ブレーク・タイミング、およびSGの立ち上がりエッジの同時タイミングで動作します。1次側MOSFETのスイッチングを基準にしたこれらの遷移の遅延は、効率の最適化にとって非常に重要であり、SGDピンとFGDピンを使って独立に設定することができます。

SGの立ち上がり遅延を調整して、スイッチ・ノード(SW)のボディ・ダイオードの導通を最小にします。最大負荷では、ボディ・ダイオードでの電力損失が大きく、SGの立ち上がり遅延が効率に大きな影響を与えることがあります。PGの立ち下がりとSGの立ち上がりの間のデッドタイムを(シートスルーを防ぎつつ)最小にすることにより、この電力損失も最小にします。同様に、(FGの立ち上がり遅延によって設定される) SGの立ち下がりとPGの立ち上がりの間のデッドタイムも最小にします。

## アプリケーション情報

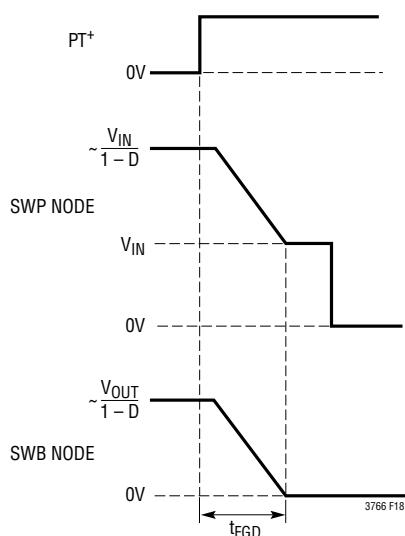

FGの立ち上がり遅延は、SGの立ち下がりとPGの立ち上がりの間のデッドタイムを最小にするために設定するだけでなく、(フォワード・スイッチ(SWB)がオンするときそのドレインが0Vに近くなるようにして)スイッチング損失を最小にするためにも調整します。LTC3765のアクティブ・クランプ・スイッチがオフすると、1次側スイッチ(SWP)のドレイン電圧が $V_{IN}/(1-D)$ から $V_{IN}$ に直線的に下がります(ここで、Dはデューティサイクルです)。トランスの2次側では、SWBが $V_{OUT}/(1-D)$ から0Vにランプします。スイッチング電力損失は、FGとPGのMOSFETがそれらの最小ドレン-ソース電圧でスイッチするとき、最小になります。FGとPGの立ち上がり遅延を調整して、スイッチがオンするとき確実にSWBノードとSWPノードが最小になるようにします。

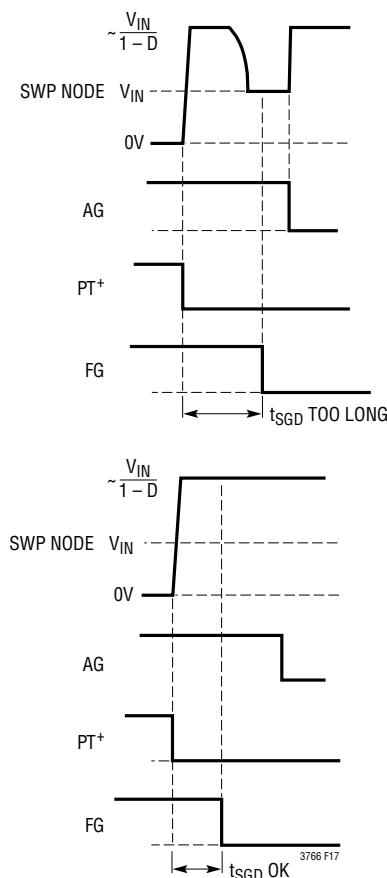

遅延を設定するとき、以下の関係に配慮します(「タイミング図」と図1を参照)。

1. フォワード・ゲート(FG)は常に、同期ゲート(SG)を基準にして、マイク・ビフォア・ブレークのタイミングでオンします。これにより、負のインダクタ電流が同期スイッチのドレンに過度の電圧を発生することはありません。

2. 同期ゲート(SG)とLTC3765の1次側ゲート(PG)が同時に“H”的とき、または、フォワード・ゲート(FG)が“H”で、LTC3765のアクティブ・ゲート(AG)が“L”的とき、シートスルーが生じます。メイン・トランスの漏れインダクタンスは、数十ナノ秒のシートスルーによる大きな電力損失を防ぎます。ただし、PGゲートとSGゲートまたはFGゲートとAGゲートが長い時間同時にオンすると、シートスルーが電力損失や過度の熱を生じ、短期間でデバイスを取り替えることになります。

3. AGまたはPGの1次側のターンオフは、FGスイッチとSGスイッチの前に起きるようにし、1次側のターンオンはFGスイッチとSGスイッチの後に起きるようにします。たとえば、特定のサイクルで、AGがまず“H”になり(PMOSをオフし)、次にFGが“H”になり、次にSGが“L”になり、次にPGが“H”になります。PGをオフするエッジでは、PGがまず“L”になり、次にFGが“L”になり、SGが“H”になり、次にAGが“L”になります(PMOSをオンします)。

### 遅延抵抗の選択 PG のターンオフ遷移

一般に、PGのターンオフ遅延の設定は、PGのターンオン遅延に比べて比較的簡単で、それほど重要ではありません。PWMのオン時間の終点で、LTC3766がPT<sup>+</sup>ピンの立ち下がりエッジをアサートし、それにより、LTC3765が直ちにPGのMOSFETをオフします。180nsの固定遅延の後、LTC3765がAGのMOSFETをオンします。したがって、この遷移でなすべき唯一の遅延調整は、LTC3766のSGDピンを使って2次側で行います。このピンは、PT<sup>+</sup>の立ち下がりからFGの立ち下がり/SGの立ち上がりまでの遅延を設定するのに使われ、これはPGのターンオフ後、AGのターンオン前に起きる必要があります。

SGDの遅延を設定する際、PGとSGの間のデッドタイムを減らすことを最初に考慮します。このデッドタイムの間、同期MOSFETのボディ・ダイオードが負荷電流を流します。PGのターンオフ後、2次側のSWノードが、SGのMOSFETのボディ・ダイオードによってクランプされるまで、急速に降下します。その目的は、SWノードが0Vを横切るとき、SGのMOSFETをオンすることです。LTC3766は、これを達成するのを容易にするため、SWノードを直接検出し、SWが0.5Vを下回るまでSGのターンオンを禁止します。つまり、SGDの遅延をPT<sup>+</sup>の立ち下がりからSWが0Vを下回るまでの遅延時間以下の値に設定することにより、PGとSGの間のデッドタイムを最小にすることができます。一般に、この遅延時間は50ns～100nsの範囲です。SGDからグランドに接続して特定の遅延t<sub>SGD</sub>を与える抵抗は、次式を使って計算することができます。

$$R_{SGD} = (t_{SGD} - 12\text{ns}) \cdot \frac{1\text{k}\Omega}{4.3\text{ns}}$$

SGDからグランドに接続した10k抵抗は、FGの立ち下がり/SGの立ち上がりの遅延を約50nsに設定します。これは一般に妥当な出発点です。**FGのMOSFETとAGのMOSFETの間の損傷を与える交差導通を防ぐため、SGDの遅延は、AGのMOSFETの180nsの固定ターンオン遅延より長く設定しないでください。** SGDの遅延を選択するときは、常に小さい値から始めます。こうしても、適応型の制限によってSGの時期尚早のターンオンは禁じられているので、安全です。

## アプリケーション情報

SGDの遅延を設定する際の別の重要な検討事項は、FGの過度のターンオフ遅延によるSWPの急落の防止です。PGのターンオフ後、トランスのリークにより、SWPノードは短時間で“H”にドライブされ、約 $V_{IN}/(1-D)$ のレベルに達します。理想的には、このノードは、FGがオフし、SGがオンし、次いでAGがオンする間、この電圧に留まるようにします。ただし、FGがオフするまでの遅延が長すぎると、SWPの電圧は短時間 $V_{IN}$ に向かって下降し、AGのターンオンによって“H”に強制されるまで再度上昇することはありません。SWPノードのこの低落は図17に示されており、負荷が軽いほど顕著です。

これは、SWPノードがサイクルごとに充放電するので効率をかなり下げる可能性がありますが、SGDの遅延をさらに短くすることにより簡単に防ぐことができます。LTC3766は $SW < 0.5V$ となるまでSGのターンオンを禁じますが、これはFGのターンオフまでの遅延については当てはまりません。 $PT^+$ の立ち下がりからFGのターンオフまでの遅延はSGのターンオンの適応型の制限を超えて短くすることができるので、FGとSG

のエッジは、それらの間の小さなデッドタイムによって分離することができます。これは、回路の寄生要素に基づいて、FGのターンオフを別個に最適化可能にするのに重要です。ほとんどのアプリケーションでは、SWPの低落がないように、またFGのターンオフとSGのターンオンの間に小さなデッドタイムがあるようにSGDの遅延が設定されるとき、最大負荷での効率がピークになります。

効率がそれほど重要ではないアプリケーションでは、SGDをGNDに接続することにより、この遅延を適応させつつ設定することができます。この場合、FGの立ち下がりとSGの立ち上がりは両方とも、 $SW < 0.5V$ となるまで禁じられます。固定遅延モードでは、常に8k以上の抵抗をSGDピンに使って、適応型遅延モードが起動するのを防ぎます。

### 遅延抵抗の選択 PG のターンオン遷移

PGのターンオン遷移に関連した遅延は、LTC3765のDELAYピンとLTC3766のFGDピンによって設定されます。LTC3766はPWMのオン時間の始点で $PT^+$ を“H”にアサートし、次に、FGDピンの抵抗で設定された遅延の後、FGをオンし、SGをオフします。1次側では、 $PT^+$ の立ち上がりに応答して、LTC3765が直ちにAGのMOSFETをオフし、次に、LTC3765のDELAYピンの抵抗で決まる遅延の後、PGのMOSFETをオンします。2次側のFGD遅延の抵抗は、1次側の遅延と注意深く関連させて選択する必要があります。したがって、LTC3765とLTC3766の両方の部品の選択手順の概要を次に説明します。

まず、PGのターンオン遅延を設定する目的は、最小のドレン電圧でPGとFGのMOSFETをオンすることにより、スイッチング損失を最小にすることです。AGのMOSFETがオフした後、PGとFGのドレン電圧(SWPとSWB)は、それぞれ約 $V_{IN}$ と0Vまで自然にランプダウンします。これらの電圧は低下するのに、メイン・トランスの磁化インダクタンスやMOSFETのドレンの寄生容量に依存して、100ns～500nsまたはそれより長くかかります。遅延設定を正しく選択すると、MOSFETのスイッチングによる電力損失に大きく影響を与えることができます。

特定の設計で最も効果的な手順は、結果として生じるSWPとSWBの波形に基づいて、PGとFGの遅延を設定することです。これらの波形を評価するため、最初は長い遅延を選択します。ただし、損傷を与えるおそれのあるPG/SGの交差導通を防ぐ

図17. 長い遅延によるSWPの急落の防止

## アプリケーション情報

ため、FGの遅延をPGの遅延より小さくする必要があります。最初は、415nsの遅延のため75kの抵抗をFGDからグランドに使い、622nsの遅延のため60kの抵抗をDELAYからグランドに使います。SWPとSWBの波形は図18のように見えます。

SWBとSWPのランプレートは、1次近似ではデューティサイクルに依存しませんが、ランプの開始点はデューティサイクルの関数です。したがって、 $V_{IN}$ が最小のときの高いデューティサイクルで遅延時間が最長になります。入力電圧の全範囲でスイッチング損失を最小にするには、 $V_{IN}$ が最小動作電圧のときの波形に基づいて遅延を選択します。

FGDピンからグランドへ接続する抵抗の値を最初に選択します。これは、 $PT^+$ の立ち上がりからSWBが約0Vにランプダウンするまでの時間に等しい遅延を与えるように選択します。FGDの抵抗の値は次式から求めることができます。

$$R_{FGD} = \left( t_{FGD} - 18\text{ns} \right) \cdot \frac{1\text{k}\Omega}{5.1\text{ns}}$$

SWPとSWBの電圧がそれらの最小値に自然に低下する前にFGがオンすると、それらはFGのMOSFETのターンオンによって直ちにそれらの最小値にプルダウンされることに注意してください。このため、SWBが0Vにランプした後FGがオンす

図18. SWPとSWBの波形

るよう見えますが、実際には時期尚早です。FGを時期尚早にオンすると、スイッチング損失の増加により効率がわずかに下がりますが、SWPとSWBの立ち下がり時間が600nsの最大FGD遅延を超える場合は、低い入力電圧でFGが時期尚早にオンしても問題はありません。一般に、高い $V_{IN}$ では遅延は適切であり、完全なランプダウンを可能にします。

稀な例として、LTC3765とLTC3766は、最小 $V_{IN}$ 電圧で動作しているとき、遅延フェーズアウト・モードになります。これは、遅延を測定すると、どちらかまたは両方のデバイスのプログラマされた遅延より短くなるのですぐ判ります。この機能により、LTC3765とLTC3766は、プログラムされた遅延を短縮しなければ最大デューティサイクルが制限されるであろうとき、プログラムされた遅延を短縮することにより、最大79%までのデューティサイクルで動作することができます。このモードになることが前もって明らかであれば、遅延フェーズアウトがもはやアクティブではなくなるまで $V_{IN}$ を上げてから、FGDの遅延を上述のように設定します。

FGDの遅延を設定して低電圧のスイッチングを最適化したら、次にPGの遅延を選択してSGのターンオフとPGのターンオンの間のデッドタイムを最小にします。1次側のゲートの遅延は、設定された遅延の許容誤差と立ち上がり/立ち下がり時間を考慮して決めることができます。LTC3766のFGの遅延の設定とLTC3765のPGの遅延の設定は両方とも、抵抗値の範囲で15%以内です。この精度を前提すると、LTC3765の遅延時間の妥当な選択として、PGの遅延時間を $1.22 \cdot t_{FGD}$ に設定します。

SGの立ち下がり時間とPGの立ち上がり時間を無視できないことに注意してください。たとえば、入力容量が大きいMOSFETをSGがドライブしており、入力容量が小さいMOSFETをPGがドライブしていると、SGは低速で降下し、PGは高速で上昇します。これにより、シートスルーの可能性が高くなります。さらに、FGがオンするまでSGはオフしないので(メイク・ビフォア・ブレーク)、FGの立ち上がり時間も関係します。最後の検討事項は、パルストラ nsによる $PT^+$ の立ち上がりの遅延のLTC3765に対する影響です。これら全ての検討事項は、次式により、遅延抵抗の選択で計算に入れることができます。この式で、 $t_D(PT)$ はLTC3765の $PT^+$ の立ち上がりから $IN^+$ の立ち上がりまでの遅延時間、 $t_R(FG)$ は2VまでのFGの立ち上がり時間、 $t_F(SG)$ は1VまでのSGの立ち下がり時

## アプリケーション情報

間、 $t_R(PG)$ は1VまでのPGの立ち上がり時間です。次に、遅延時間をこのように選択することができます。

$$t_{PGD} = 1.22 \cdot t_{FGD} + t_{R(FG)} + t_{F(SG)} - t_{R(PG)} - t_{D(PT)}$$

次式を使って、LTC3765のDELAYピンからグランドに接続する抵抗を選択して、この遅延を与えることができます。

$$R_{DELAY} = \frac{(t_{PGD} - 45\text{ns})}{9.5\text{ns}} \cdot \frac{1\text{k}\Omega}{}$$

実際には、LTC3765のPGのターンオン遅延は、PGとSGの波形をモニタすることによって最適化します。控えめな手法として、PGの遅延を設定して、これらの遅延の許容誤差(標準で合計遅延の22%)に対応したデッドタイムを、SGの立ち下がりとPGの立ち上がりの間に与えます。もっと積極的な手法では、トランジスタの漏れインダクタンスにより、PGのターンオンの効果(つまり、SWノードの立ち上がり)が最大負荷では75ns～150nsまたはそれ以上遅れる事実を計算に入れます。また、トランジスタの漏れインダクタンスは、トランジスタ電流の立ち上がり時間を見くることにより、少量のシートスルーレベルの影響を和らげます。最大負荷での効率は、PGのターンオンをSGのターンオフに近づけて設定することによって高くすることができます。さらに、PGのターンオンでのデッドタイムを短くすると、スイッチ・ノードのオーバーシュートとリギングを減らすことができ、それによって、必要なRCスナバのサイズを小さくし、関連した電力損失を減らすことができます。

PGのターンオン時のデッドタイムを短くすると最大負荷での性能を改善できますが、無負荷時のワーストケースのシートスルーレベルが安全限界内に十分取るように注意する必要があります。

## 最大デューティサイクルと遅延のフェーズアウト

PGのターンオン遅延時間はターンオンのスイッチング損失を減らすのに重要ですが、この遅延時間の間は入力電源から出力負荷へ電力が送られません。ほとんどのフォワード・コンバータ・システムでは、利用できる最大デューティサイクルはこの遅延により人為的に制限され、最適遅延時間と利用できる最大デューティサイクルの間にトレードオフを強制します。LTC3765とLTC3766はユニークな遅延フェーズアウト機能を実装しており、要求されるデューティサイクルが79%の最大値に近づくにつれ、PGとFGのターンオン遅延が徐々に減ります。この機能により、公称入力電圧では最適遅延で、低い入力電圧では最大デューティサイクルに近づくようにフォワード・コンバータを設計することができるので、電力トランジスタを効率的に利用できます。

## 2次側バイアスの生成

絶縁型アプリケーションでLTC3766のバイアスを生成する最も良い方法を決めるとき、検討すべき5つの事項があります。

- 必要な動作電流。これには、1次側と2次側の両方のMOSFETのゲート・ドライブ電流、およびLTC3765とLTC3766の両方の動作消費電流が含まれます。

- MOSFETのゲートに必要な動作電圧。ロジック・レベルMOSFETまたは標準スレッショルドMOSFETのどちらが使用されているかに従って、V<sub>CC</sub>動作電圧レベルと低電圧ロックアウト(UVLO)レベルを、MODEピンを使って設定することができます。バイアス電源は、LTC3766のV<sub>CC</sub>ピンをそのUVLOレベルより上に保ち、全体の電源がピーク効率で動作し続けるように適切な電圧を供給する必要があります。

- 低出力電圧での電流制限動作。通常の動作V<sub>OUT</sub>を基準にした電流制限時に必要な最小V<sub>OUT</sub>は、バイアス電源の設計に大きな影響を与えます。バイアス電源はV<sub>OUT</sub>電圧のこの範囲にわたって適切な電圧を供給する必要があります。

- 入力電圧の変動。最小入力電圧では、バイアス電源は適切な動作のために依然として十分な電圧を供給する必要があります。最大電圧では、バイアス電源は最大定格を超えてはならず、そうでないと過度の電力を消費します。

- 1次側から2次側への制御の素早い引き渡しの潜在的必要性。PolyPhaseアプリケーションでは、最大負荷電流が输出に現れる前に電流分担と適切なフェージングを確立できるように、起動時に制御を2次側に素早く引き渡すことが重要です。対照的に、アプリケーションによっては、出力が安定化の値に達する直前まで、制御を2次側に引き渡す必要がないことがあります。ただし、全てのアプリケーションで、2次側バイアスは常に、出力が安定化レベルに達する前に立ち上がり、制御が引き渡される必要があります。

2次側バイアス電源によって供給される必要がある電流は、次式を使って推定することができます。

$$I_{VCC} \approx (Q_{GPR}f_{SW} + 3\text{mA})N_{PT} + Q_{GSEC}f_{SW} + 18\text{mA}$$

## アプリケーション情報

ここで、QGPRIは全ての1次側MOSFETの合計ゲート電荷、QGSECは全ての2次側MOSFETの合計ゲート電荷、N<sub>PT</sub>はパルストラ nsの巻数比です。1次側電流は、パルストラ nsの巻数比によってスケールが定められることに注意してください。上式の18mAの定数には、ゲート・ドライブの標準的スイッチング電流およびパルストラ nsに関連した損失が含まれます。

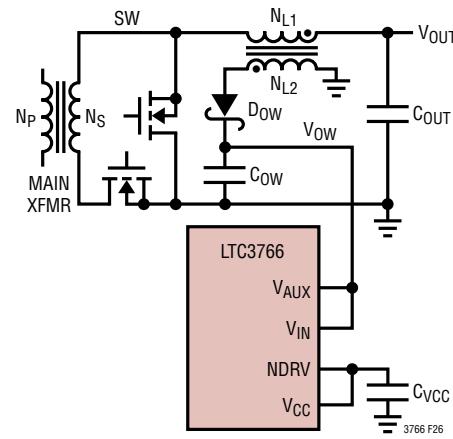

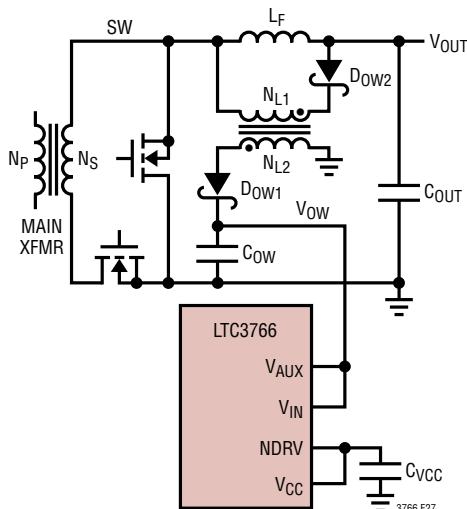

### 2次側バイアスへのV<sub>OUT</sub>の直接利用