## 特長

- 入力電源電圧範囲: 6V ~ 55V

- 32の独立したLED出力: 最大 30mA/13V

- 6ビット・ドット補正電流調整

- 12ビット・グレースケール PWM 調光

- 最小 LED オン時間: 0.5μs

- LED バス電圧の適応制御により高効率を達成

- カスケード接続可能な 30MHz シリアル・データ・インターフェース

- 診断および保護機能: 個々のオープン/短絡 LED および過温度フォールト

## アプリケーション

- 大画面ディスプレイの LED バックライト

- モノカラー、マルチカラー、フルカラーの LED ディスプレイ

- LED の広告塔や看板

LT、LT、LTC、LTM、Linear Technology および Linear のロゴはリニアテクノロジー社の登録商標です。他の全ての商標はそれぞれの所有者に所有権があります。

## 概要

LT<sup>®</sup>3746 は 32 チャネル LED ドライバと 55V 降圧コントローラを一体化しています。LED ドライバはチャネルごとに最大 30mA/13V の直列 LED を点灯させ、降圧コントローラは並列 LED ストリングに適応してバス電圧を生成します。各チャネルごとに 6 ビット・ドット補正電流調整機能と 12 ビット・グレースケール PWM 調光機能を備えています。ドット補正とグレースケール調光はいずれも TTL/CMOS ロジックのシリアル・データ・インターフェースを介してアクセス可能です。

LT3746 はオープン/短絡 LED と過温度フォールトに対する診断および保護を行います。フォールト状態は、シリアル・データ・インターフェースを介して通知されます。完全にバッファされ、スキーのバランスがとれた、カスケード接続可能な 30MHz のシリアル・データ・インターフェースを備えた LT3746 は、大画面 LCD のダイナミック・バックライトや、モノカラー、マルチカラーおよびフルカラー LED ディスプレイに最適です。

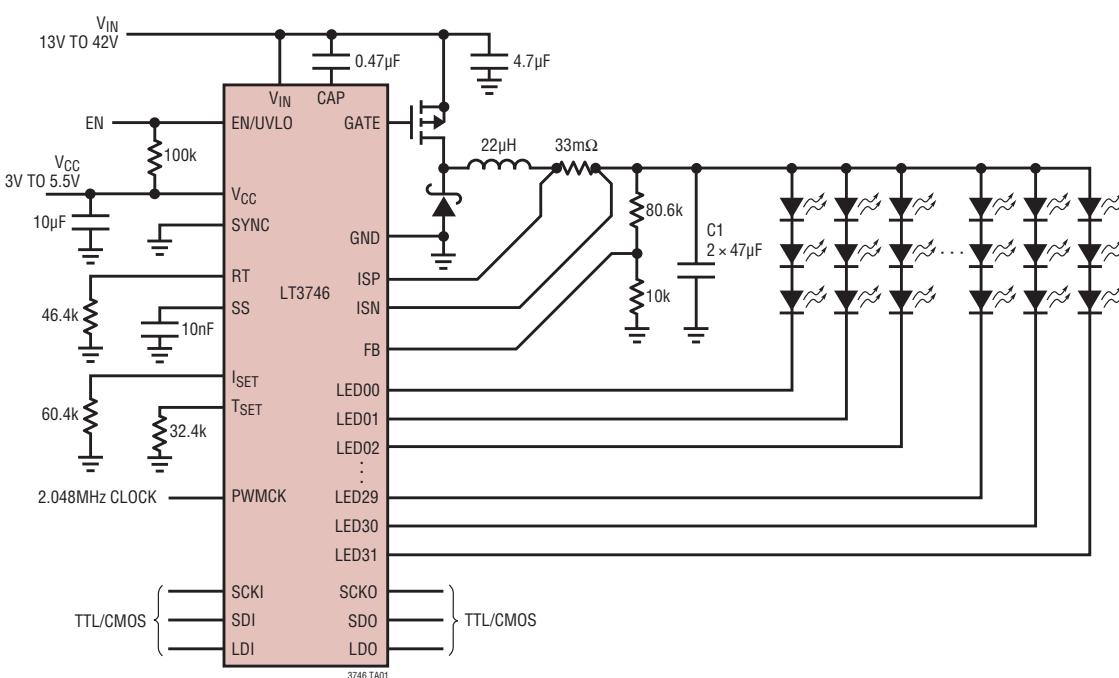

## 標準的応用例

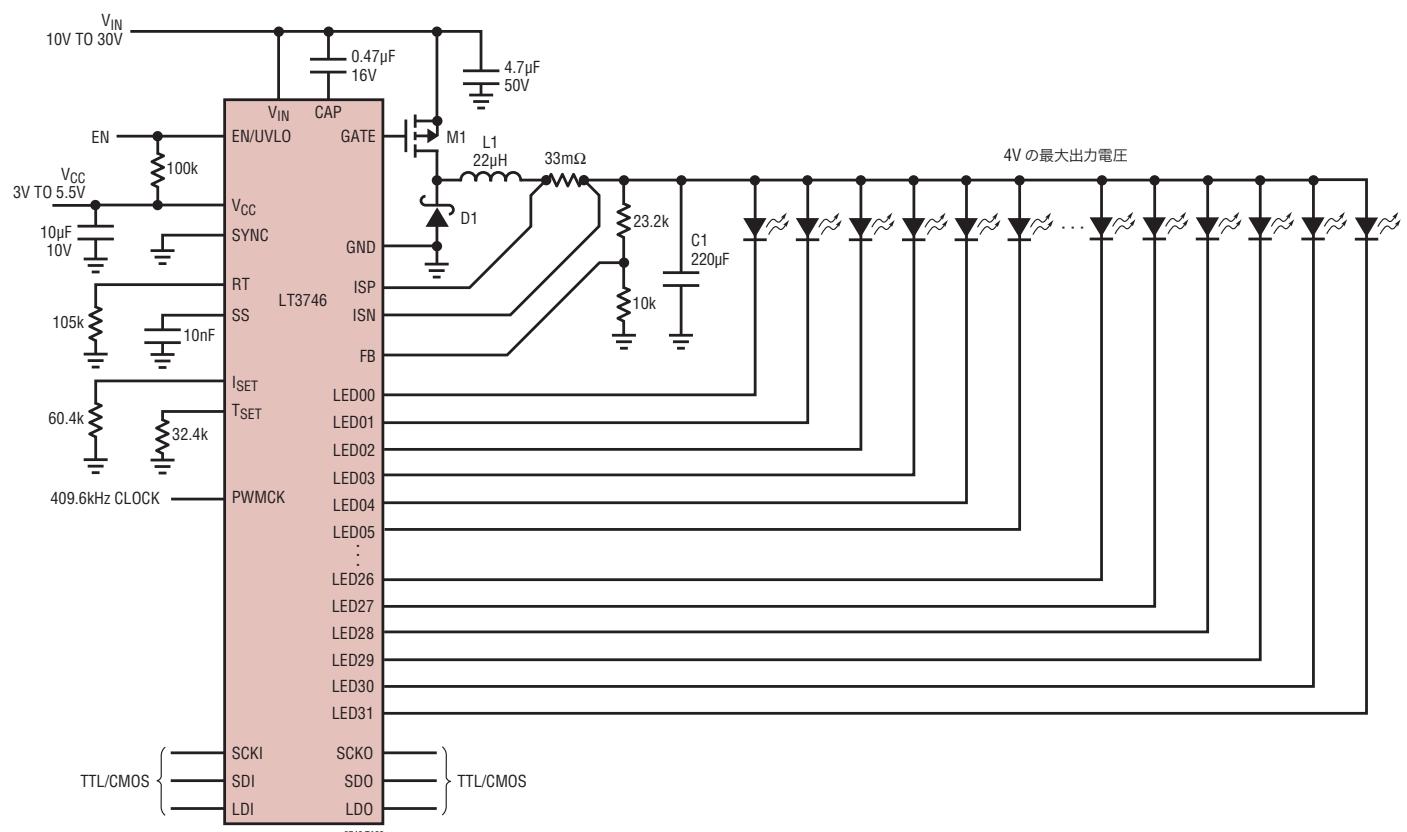

32 チャネル LED ドライバ、1MHz 降圧、チャネル当たり 3 LED 10mA ~ 30mA、500Hz で 12 ビット調光

3746fa

## 絶対最大定格

(Note 1)

|                                                                   |                           |

|-------------------------------------------------------------------|---------------------------|

| $V_{IN}$ .....                                                    | 57V                       |

| CAP .....                                                         | $V_{IN} - 8V \sim V_{IN}$ |

| GATE .....                                                        | $CAP \sim V_{IN}$         |

| LED00 ~ LED31, SP, ISN .....                                      | 13V                       |

| ISP .....                                                         | $ISN - 1V \sim ISN + 1V$  |

| FB, RT, TSET, ISET .....                                          | 2V                        |

| $V_{CC}$ .....                                                    | -0.3V ~ 6V                |

| SCKI, SCKO, SDI, SDO, LDI, LDO, PWMCK, SYNC,<br>SS, EN/UVLO ..... | -0.3V ~ $V_{CC}$          |

| 動作接合部温度範囲                                                         |                           |

| (Note 2, 3) .....                                                 | -40°C ~ 125°C             |

| 保存温度範囲 .....                                                      | -65°C ~ 125°C             |

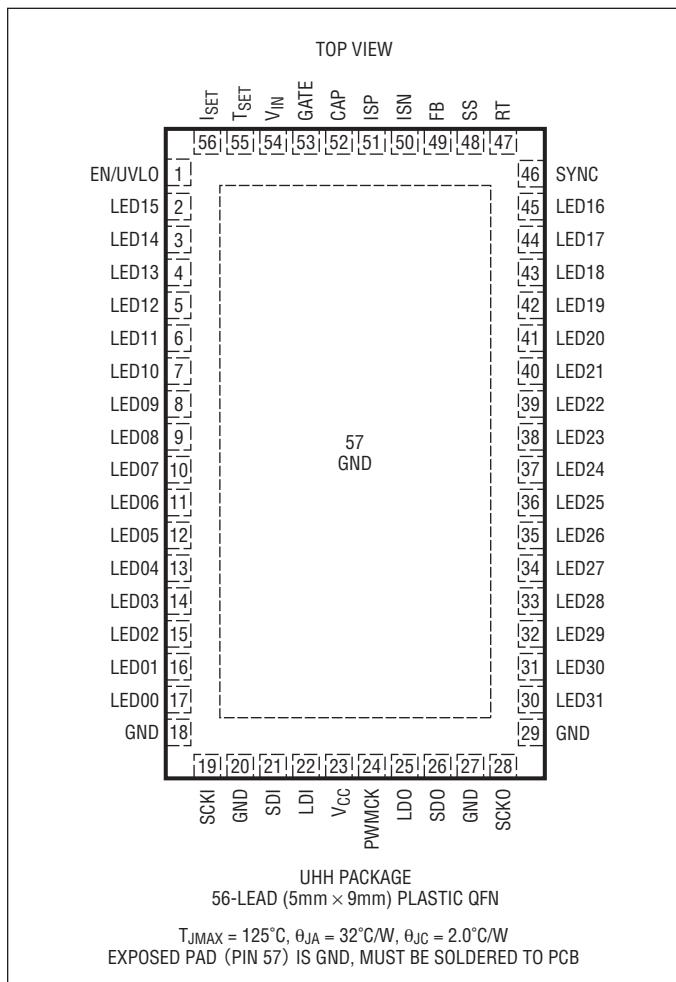

## ピン配置

## 発注情報

| 無鉛仕上げ          | テープアンドリール        | 製品マーキング* | パッケージ                           | 温度範囲           |

|----------------|------------------|----------|---------------------------------|----------------|

| LT3746EUHH#PBF | LT3746EUHH#TRPBF | 3746     | 56-Lead (5mm × 9mm) Plastic QFN | -40°C to 125°C |

| LT3746IUHH#PBF | LT3746IUHH#TRPBF | 3746     | 56-Lead (5mm × 9mm) Plastic QFN | -40°C to 125°C |

さらに広い動作温度範囲で規定されるデバイスについては、弊社または弊社代理店にお問い合わせください。\* 温度グレードは出荷時のコンテナのラベルで識別されます。非標準の鉛仕上げの製品の詳細については、弊社または弊社代理店にお問い合わせください。

無船仕上げのコーカンゲの詳細については、<http://www.linen-tack.co.jp/bedfro/>をご覧ください。

無鉛仕上げのマーキングの詳細については、<http://www.linear-tech.co.jp/leadfree/> をご覧ください。

テープアンドリールの仕様の詳細については、<http://www.linear-tech.co.jp/tapeandreel/> をご覧ください。

## 電気的特性

●は全動作温度範囲の規格値を意味する。それ以外は  $T_A = 25^\circ\text{C}$  での値。注記がない限り、 $V_{IN} = 24\text{V}$ 、 $V_{CC} = 3.3\text{V}$ 、 $V_{EN/UVLO} = 1.5\text{V}$ 、 $V_{FB} = 1.5\text{V}$ 、 $V_{ISP} = V_{ISN} = 0\text{V}$ 、 $R_T = 105\text{k}$ 、 $R_{ISET} = 60.4\text{k}$ 、 $C_{CAP} = 0.47\mu\text{F}$  ( $V_{IN}$  に接続)。

| SYMBOL           | PARAMETER                                              | CONDITIONS                                                                                                                                 | MIN                  | TYP                    | MAX                | UNITS                           |                   |

|------------------|--------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|----------------------|------------------------|--------------------|---------------------------------|-------------------|

| 電源               |                                                        |                                                                                                                                            |                      |                        |                    |                                 |                   |

| $V_{IN}$         | $V_{IN}$ Operating Voltage                             |                                                                                                                                            | ● 6                  | 55                     | 55                 | V                               |                   |

| $I_{VIN}$        | $V_{IN}$ Supply Current                                | $V_{EN/UVLO} = 0\text{V}$<br>No Switching                                                                                                  |                      | 0.2<br>0.4             | 2<br>0.55          | $\mu\text{A}$<br>mA             |                   |

| $V_{CC}$         | $V_{CC}$ Operating Voltage                             |                                                                                                                                            | ● 3                  | 5.5                    | 5.5                | V                               |                   |

| $I_{VCC}$        | $V_{CC}$ Supply Current (Note 4)                       | $V_{EN/UVLO} = 0\text{V}$<br>LED Channel Off, 30MHz Data Off<br>LED Channel On, 30MHz Data Off<br>LED Channel On, 30MHz Data On            |                      | 0.1<br>3.3<br>10<br>19 | 1<br>4.0           | $\mu\text{A}$<br>mA<br>mA<br>mA |                   |

| 低電圧ロックアウト(UVLO)  |                                                        |                                                                                                                                            |                      |                        |                    |                                 |                   |

|                  | $V_{CC}$ UVLO Threshold                                | $V_{CC}$ Rising<br>$V_{CC}$ Falling                                                                                                        | 2.82<br>2.61         | 2.89<br>2.68           | 2.96<br>2.75       | V                               |                   |

|                  | EN/UVLO Shutdown Threshold<br>UVLO Threshold           | $I_{VCC} < 20\mu\text{A}$<br>$V_{EN/UVLO}$ Rising<br>$V_{EN/UVLO}$ Falling                                                                 | 0.35<br>1.28<br>1.19 | 1.31<br>1.22           | 1.34<br>1.25       | V<br>V<br>V                     |                   |

| $I_{EN/UVLO}$    | EN/UVLO Bias Current                                   | $V_{EN/UVLO} = V_{CC}$                                                                                                                     |                      | 0.1                    | 1                  | $\mu\text{A}$                   |                   |

|                  | $(V_{IN} - V_{CAP})$ UVLO Threshold                    | $(V_{IN} - V_{CAP})$ Rising<br>$(V_{IN} - V_{CAP})$ Falling                                                                                | 4.6<br>4.1           | 4.9<br>4.4             | 5.2<br>4.7         | V<br>V                          |                   |

| ソフトスタート(SS)      |                                                        |                                                                                                                                            |                      |                        |                    |                                 |                   |

| $I_{SS}$         | Soft Start Charge Current                              | $V_{SS} = 1\text{V}$                                                                                                                       |                      | -16                    | -12                | -8                              | $\mu\text{A}$     |

|                  | Soft Start Discharge Current                           | $V_{SS} = V_{CC}$ , $V_{EN/UVLO} = 1\text{V}$                                                                                              |                      | 330                    |                    |                                 | $\mu\text{A}$     |

| $V_{SS(TH)}$     | Soft Start Reset Threshold                             |                                                                                                                                            |                      | 0.35                   |                    |                                 | V                 |

| 発振器              |                                                        |                                                                                                                                            |                      |                        |                    |                                 |                   |

| $V_{RT}$         | RT Pin Voltage                                         |                                                                                                                                            |                      | 1.186                  | 1.205              | 1.224                           | V                 |

| $I_{RT}$         | RT ピンの電流リミット                                           | $V_{RT} = 0\text{V}$                                                                                                                       |                      | -80                    |                    |                                 | $\mu\text{A}$     |

| $f_{OSC}$        | Oscillator Frequency                                   | $R_T = 280\text{k}$ , $V_{IN} = 12\text{V}$<br>$R_T = 105\text{k}$ , $V_{IN} = 12\text{V}$<br>$R_T = 46.4\text{k}$ , $V_{IN} = 12\text{V}$ |                      | 185<br>470<br>950      | 205<br>510<br>1050 | 225<br>550<br>1150              | kHz<br>kHz<br>kHz |

| $f_{SYNC}$       | Sync Frequency Range (Note 5)                          | $R_T = 348\text{k}$ , $V_{IN} = 12\text{V}$                                                                                                |                      | 200                    | 1000               |                                 | kHz               |

|                  | SYNC LOGIC<br>High Level Voltage<br>Low Level Voltage  | $V_{IN} = 12\text{V}$ , $V_{CC} = 3\text{V}$ to $5.5\text{V}$                                                                              |                      | 2.4<br>0               | $V_{CC}$<br>0.6    |                                 | V<br>V            |

| エラーアンプおよびループの動特性 |                                                        |                                                                                                                                            |                      |                        |                    |                                 |                   |

| $V_{FB}$         | FB Regulation Voltage                                  | $V_{ISP} = V_{ISN} = 5\text{V}$                                                                                                            | ●                    | 1.186                  | 1.210              | 1.234                           | V                 |

| $I_{FB}$         | FB Input Bias Current                                  | $V_{ISP} = V_{ISN} = 5\text{V}$ , $V_{FB}$ Regulated                                                                                       |                      | -120                   |                    |                                 | nA                |

|                  | LED Regulation Voltage                                 | $V_{ISP} = V_{ISN} = 5\text{V}$ , $V_{FB} = 1\text{V}$                                                                                     |                      | 0.44                   | 0.54               | 0.64                            | V                 |

| $T_{OFF(MIN)}$   | Minimum GATE Off Time                                  | $V_{IN} = 12\text{V}$ , $V_{ISP} = V_{ISN} = 5\text{V}$ , $V_{FB} = 1\text{V}$                                                             |                      | 120                    |                    |                                 | ns                |

| $T_{ON(MIN)}$    | Minimum GATE On Time                                   | $V_{IN} = 12\text{V}$ , $(V_{ISP} - V_{ISN}) = 60\text{mV}$ , $V_{ISN} = 5\text{V}$ , $V_{FB} = 1\text{V}$                                 |                      | 200                    |                    |                                 | ns                |

| 電流検出アンプ          |                                                        |                                                                                                                                            |                      |                        |                    |                                 |                   |

|                  | ISP/ISN Pin Common Mode                                | $V_{ISP} = V_{ISN}$                                                                                                                        | ●                    | 0                      | 13                 | 13                              | V                 |

|                  | $V_{IN}$ to ISN Dropout Voltage ( $V_{IN} - V_{ISN}$ ) | $V_{IN} = 12\text{V}$ , $V_{ISP} = V_{ISN}$ , $V_{FB} = 1\text{V}$                                                                         | ●                    | 1.7                    | 2                  | 2                               | V                 |

|                  | Current Limit Sense Threshold ( $V_{ISP} - V_{ISN}$ )  | $V_{FB} = 1\text{V}$                                                                                                                       |                      | 34                     | 46.5               | 59                              | mV                |

| $I_{ISP}$        | ISP Input Bias Current                                 |                                                                                                                                            |                      | -23                    |                    |                                 | $\mu\text{A}$     |

| $I_{ISN}$        | ISN Input Bias Current                                 |                                                                                                                                            |                      | -48                    |                    |                                 | $\mu\text{A}$     |

**電気的特性** ●は全動作温度範囲の規格値を意味する。それ以外は  $T_A = 25^\circ\text{C}$  での値。注記がない限り、 $V_{IN} = 24\text{V}$ 、 $V_{CC} = 3.3\text{V}$ 、 $V_{EN/UVLO} = 1.5\text{V}$ 、 $V_{FB} = 1.5\text{V}$ 、 $V_{ISP} = V_{ISN} = 0\text{V}$ 、 $R_T = 105\text{k}\Omega$ 、 $R_{ISET} = 60.4\text{k}\Omega$ 、 $C_{CAP} = 0.47\mu\text{F}$  ( $V_{IN}$  に接続)。

| SYMBOL                   | PARAMETER                                                                | CONDITIONS                                                                                                                                         | MIN  | TYP             | MAX                | UNITS            |                |

|--------------------------|--------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|------|-----------------|--------------------|------------------|----------------|

| <b>ゲート・ドライバ</b>          |                                                                          |                                                                                                                                                    |      |                 |                    |                  |                |

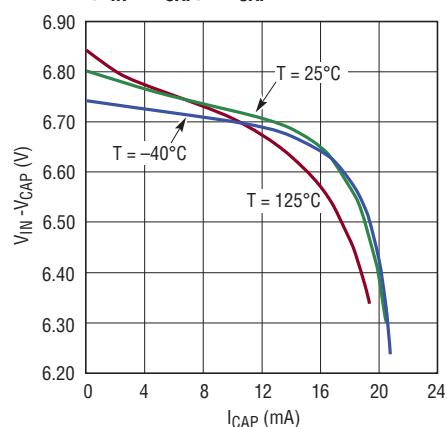

| $V_{BIAS}$               | CAP Bias Voltage ( $V_{IN} - V_{CAP}$ )                                  | $7\text{V} < V_{IN} < 55\text{V}$                                                                                                                  | 6.54 | 6.77            | 7.00               | V                |                |

| $I_{CAP}$                | CAP Bias Current Limit                                                   | $(V_{IN} - V_{CAP}) = V_{BIAS} - 0.5\text{V}$                                                                                                      |      | 22              |                    | mA               |                |

|                          | GATE High Level ( $V_{IN} - V_{GATE}$ )                                  | $I_{GATE} = -100\text{mA}$                                                                                                                         |      | 0.4             |                    | V                |                |

|                          | GATE Low Level ( $V_{GATE} - V_{CAP}$ )                                  | $I_{GATE} = 100\text{mA}$                                                                                                                          |      | 0.3             |                    | V                |                |

|                          | GATE Rise Time                                                           | $C_{GATE} = 3.3\text{nF}$ to $V_{IN}$ , $V_{IN} = 12\text{V}$                                                                                      |      | 30              |                    | ns               |                |

|                          | GATE Fall Time                                                           | $C_{GATE} = 3.3\text{nF}$ to $V_{IN}$ , $V_{IN} = 12\text{V}$                                                                                      |      | 30              |                    | ns               |                |

| <b>LED ドライバ</b>          |                                                                          |                                                                                                                                                    |      |                 |                    |                  |                |

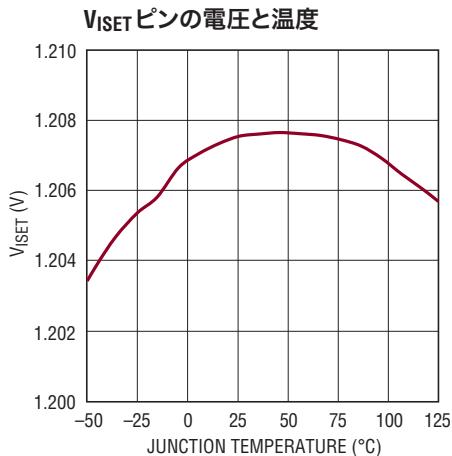

| $V_{ISET}$               | Trimmed $I_{SET}$ Pin Voltage                                            |                                                                                                                                                    | ●    | 1.181           | 1.205              | 1.229            | V              |

|                          | LED $_{xx}$ Operating Voltage                                            | $V_{ISP} = V_{ISN} = V_{LED_{xx}}$                                                                                                                 | ●    | 0               | 13                 |                  | V              |

|                          | LED $_{xx}$ Leakage Current                                              | LED Channel Off, $V_{ISP} = V_{ISN} = 5\text{V}$ ,<br>$V_{LED_{xx}} = 3\text{V}$                                                                   |      |                 | 0.2                |                  | $\mu\text{A}$  |

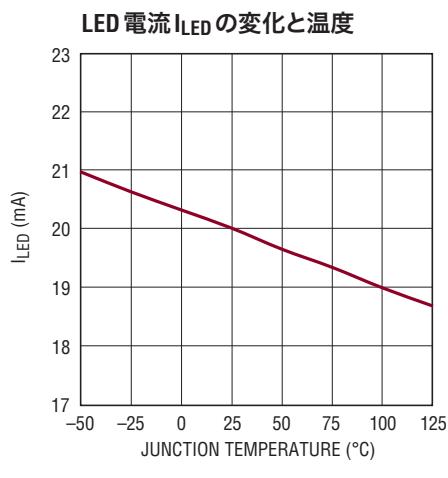

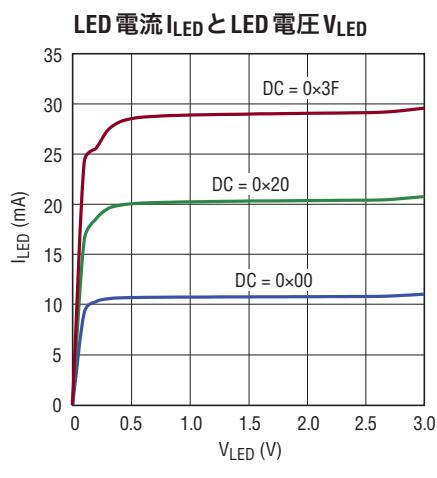

| $I_{LED}$                | LED Constant Sink Current                                                | $V_{ISP} = V_{ISN} = 5\text{V}$ , $V_{LED_{xx}} = 0.5\text{V}$<br>$\text{REG}_{DC} = 0x00$<br>$\text{REG}_{DC} = 0x20$<br>$\text{REG}_{DC} = 0x3F$ |      | 7<br>15.5<br>23 | 11.5<br>21.5<br>30 | 16<br>27.5<br>37 | mA<br>mA<br>mA |

| $\Delta I_{LEDC}$        | Current Mismatch Between Channels                                        | $V_{ISP} = V_{ISN} = 5\text{V}$ , $V_{LED_{xx}} = 0.5\text{V}$ ,<br>$\text{REG}_{DC} = 0x20$ (Note 6)                                              |      |                 | 8                  | 20               | %              |

| $\Delta I_{LEDD}$        | Current Mismatch Between Devices                                         | $V_{ISP} = V_{ISN} = 5\text{V}$ , $V_{LED_{xx}} = 0.5\text{V}$ ,<br>$\text{REG}_{DC} = 0x20$ (Note 7)                                              |      | -15             | 5                  | 20               | %              |

| $\Delta I_{LINE}$        | LED Current Line Regulation                                              | $V_{ISP} = V_{ISN} = 5\text{V}$ , $V_{LED_{xx}} = 0.5\text{V}$ ,<br>$\text{REG}_{DC} = 0x20$ , $V_{CC} = 3\text{V}$ to $5.5\text{V}$ (Note 8)      |      | -0.2            | 0.2                | 1                | %/V            |

| $\Delta I_{LOAD}$        | LED Current Load Regulation                                              | $V_{ISP} = V_{ISN} = 5\text{V}$ , $\text{REG}_{DC} = 0x20$ ,<br>$V_{LED_{xx}} = 0.5\text{V}$ to $2.5\text{V}$ (Note 9)                             |      | -1              | 1                  | 3                | %/V            |

| $V_{OPEN}$               | Open LED Threshold                                                       | $V_{ISP} = V_{ISN} = 5\text{V}$ , $V_{LED_{xx}}$ Falling                                                                                           |      |                 | 0.1                |                  | V              |

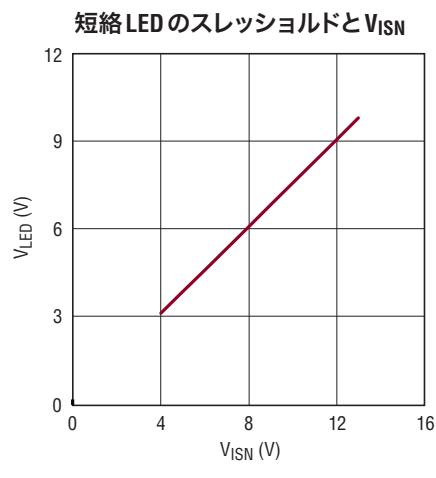

| $V_{SHT}$                | Short LED Threshold                                                      | $V_{ISP} = V_{ISN} = 5\text{V}$ , $V_{LED_{xx}}$ Rising                                                                                            |      | 3.65            | 3.9                | 4.15             | V              |

| $T_{LEDON}$              | Minimum LED On Time                                                      | $V_{ISP} = V_{ISN} = 5\text{V}$ , $\text{REG}_{GS} = 0x001$                                                                                        |      |                 | 0.5                |                  | $\mu\text{s}$  |

|                          | PWMCK LOGIC<br>High Level Voltage<br>Low Level Voltage                   | $V_{CC} = 3\text{V}$ to $5.5\text{V}$                                                                                                              |      | 2.4<br>0        | $V_{CC}$<br>0.6    |                  | V<br>V         |

| <b>熱保護</b>               |                                                                          |                                                                                                                                                    |      |                 |                    |                  |                |

| $I_{TSET}$               | TSET Output Current                                                      | $V_{TSET} = 1\text{V}$                                                                                                                             | ●    | 19.0            | 19.8               | 20.6             | $\mu\text{A}$  |

|                          | TSET Over Temperature Threshold                                          | $T_A = 25^\circ\text{C}$                                                                                                                           |      |                 | 510                |                  | mV             |

| <b>シリアル・データ・インターフェース</b> |                                                                          |                                                                                                                                                    |      |                 |                    |                  |                |

| $V_{SIH}$<br>$V_{SIL}$   | Single-Ended Input (Note 10)<br>High Level Voltage<br>Low Level Voltage  | $V_{CC} = 3\text{V}$ to $5.5\text{V}$                                                                                                              |      | 2.4<br>0        | $V_{CC}$<br>0.6    |                  | V<br>V         |

| $I_{SI}$                 | Single-Ended Input Current                                               | $V_{CC} = 3\text{V}$ to $5.5\text{V}$ , $SI = V_{CC}$ or GND                                                                                       |      | -0.2            | 0.2                |                  | $\mu\text{A}$  |

| $V_{SOH}$<br>$V_{SOL}$   | Single-Ended Output (Note 10)<br>High Level Voltage<br>Low Level Voltage | $V_{CC} = 3\text{V}$ to $5.5\text{V}$<br>$I_{SO} = -1\text{mA}$<br>$I_{SO} = 1\text{mA}$                                                           |      | $V_{CC} - 0.1$  |                    | 0.1              | V<br>V<br>V    |

## タイミング特性

●は全動作温度範囲の規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。注記がない限り、 $V_{IN} = 24\text{V}$ 、 $V_{CC} = 3\text{V} \sim 5.5\text{V}$ 、 $V_{EN/UVLO} = 1.5\text{V}$ 、 $V_{FB} = 1.5\text{V}$ 、 $V_{ISP} = V_{ISN} = 5\text{V}$ 、 $V_{LEDXX} = 0.5\text{V}$ 、 $R_T = 105\text{k}$ 、 $R_{ISET} = 60.4\text{k}$ 、 $C_{CAP} = 0.47\mu\text{F} \sim V_{IN}$ 、 $C_{SCKO} = C_{SDO} = C_{LDO} = 27\text{pF}$  (GNDに接続)。

| SYMBOL                 | PARAMETER                             | CONDITIONS                                                        | MIN | TYP | MAX | UNITS |    |

|------------------------|---------------------------------------|-------------------------------------------------------------------|-----|-----|-----|-------|----|

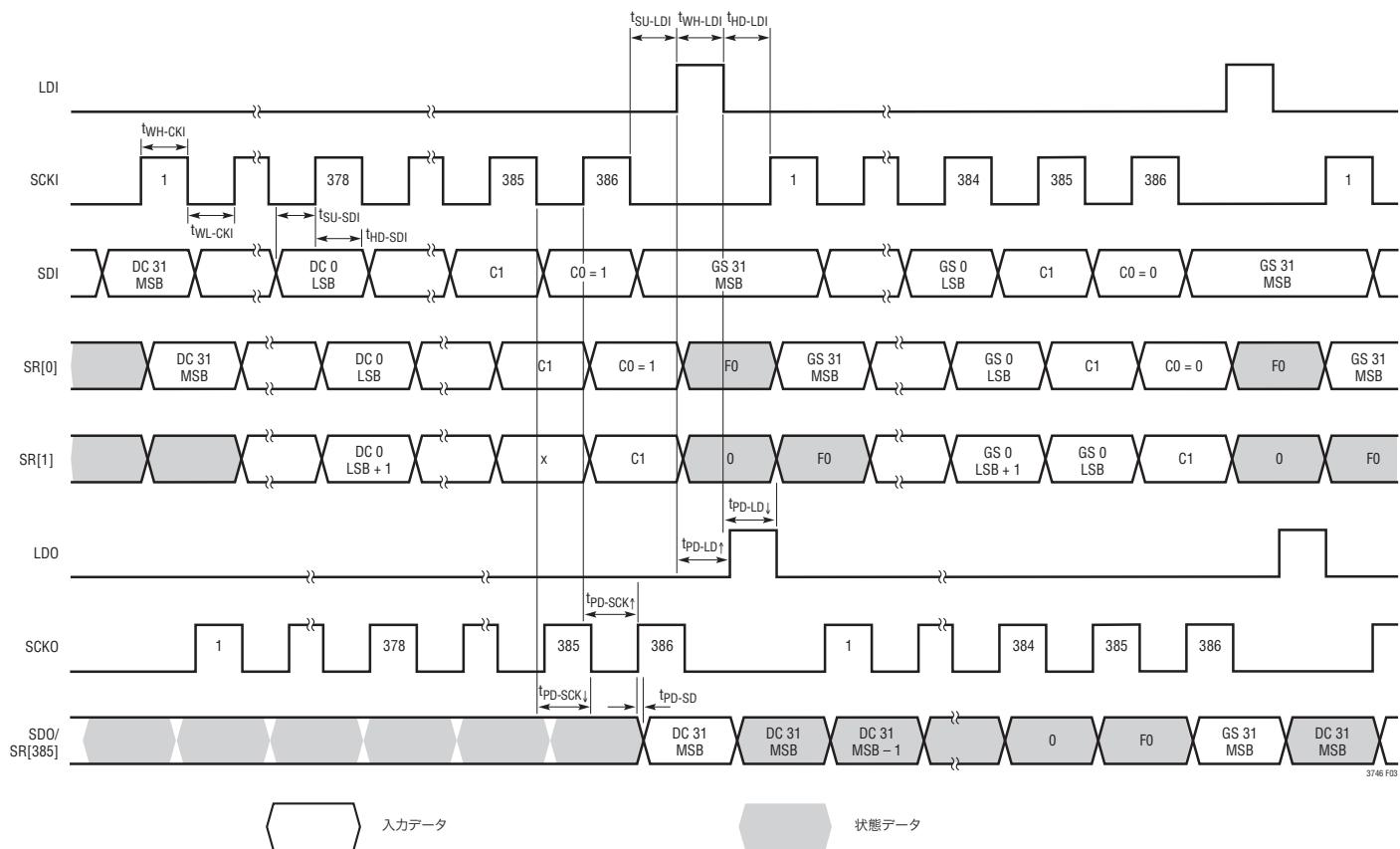

| $f_{SCKI}$             | Data Shift Clock Frequency            |                                                                   |     | 30  |     | MHz   |    |

| $f_{PWMCK}$            | PWMCK Clock Frequency                 |                                                                   |     | 25  |     | MHz   |    |

| $t_{WH-CKI}$           | SCKI Pulse Duration                   | $SCKI = H$ (Figure 3)<br>$SCKI = L$ (Figure 3)                    | ●   | 16  |     | ns    |    |

| $t_{WL-CKI}$           |                                       |                                                                   | ●   | 16  |     | ns    |    |

| $t_{WH-PWM}$           | PWMCK Pulse Duration                  | $PWMCK = H$ (Figure 4)<br>$PWMCK = L$ (Figure 4)                  | ●   | 20  |     | ns    |    |

| $t_{WL-PWM}$           |                                       |                                                                   | ●   | 20  |     | ns    |    |

| $t_{WH-LDI}$           | LDI Pulse Duration                    | $LDI = H$ (Figure 3)                                              | ●   | 20  |     | ns    |    |

| $t_{SU-SDI}$           | SDI-SCKI Setup Time                   | $SDI - SCKI \uparrow$ (Figure 3)                                  | ●   | 2   |     | ns    |    |

| $t_{HD-SDI}$           | SCKI-SDI Hold Time                    | $SCKI \uparrow - SDI$ (Figure 3)                                  | ●   | 2   |     | ns    |    |

| $t_{SU-LDI}$           | SCKI-LDI Setup Time                   | $SCKI \downarrow - LDI \uparrow$ (Figure 3)                       | ●   | 5   |     | ns    |    |

| $t_{HD-LDI}$           | LDI-SCKI Hold Time                    | $LDI \downarrow - SCKI \uparrow$ (Figure 3)                       | ●   | 15  |     | ns    |    |

| $t_{PD-SCK\uparrow}$   | SCKI-SCKO Propagation Delay (Rising)  | $SCKI \uparrow - SCKO \uparrow$ (Figure 3)                        | ●   | 27  | 44  | ns    |    |

| $t_{PD-SCK\downarrow}$ | SCKI-SCKO Propagation Delay (Falling) | $SCKI \downarrow - SCKO \downarrow$ (Figure 3)                    | ●   | 30  | 50  | ns    |    |

| $\Delta t_{PD-SCK}$    | SCK Duty Cycle Change                 | $\Delta t_{PD-SCK} = t_{PD-SCK \uparrow} - t_{PD-SCK \downarrow}$ |     | -3  |     | ns    |    |

| $t_{PD-SD}$            | SCKO-SDO Propagation Delay            | $SCKO \uparrow - SDO$ (Figure 3)                                  | ●   | 2.2 | 4.5 | 7     | ns |

| $t_{PD-LD\uparrow}$    | LDI-LDO Propagation Delay (Rising)    | $LDI \uparrow - LDO \uparrow$ (Figure 3)                          | ●   | 27  | 44  | ns    |    |

| $t_{PD-LD\downarrow}$  | LDI-LDO Propagation Delay (Falling)   | $LDI \downarrow - LDO \downarrow$ (Figure 3)                      | ●   | 30  | 50  | ns    |    |

| $\Delta t_{PD-LD}$     | LD Duty Cycle Change                  | $\Delta t_{PD-LD} = t_{PD-LD \uparrow} - t_{PD-LD \downarrow}$    |     | -3  |     | ns    |    |

| $t_{PD-PWM}$           | PWMCK-LED Propagation Delay           | $PWMCK \uparrow - I_{LED}$ (Figure 4)                             |     | 80  |     | ns    |    |

| $t_{R-SO}$             | SCKO/SDO/LDO Rise Time                | $C_{LOAD} = 27\text{pF}$ , 10% to 90%                             |     | 3   |     | ns    |    |

| $t_{F-SO}$             | SCKO/SDO/LDO Fall Time                | $C_{LOAD} = 27\text{pF}$ , 90% to 10%                             |     | 3   |     | ns    |    |

表1. テストパラメータの式

|                                                                                                                                                                  |     |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| $\frac{ I_{OUT(MAX)(0-31)} - I_{OUT(MIN)(0-31)} }{2 \cdot I_{OUTavg(0-31)}} \cdot 100$                                                                           | (1) |

| $\Delta I_{LEDD}(\%) = \frac{ I_{OUT(AVG)(0-31)} - I_{OUT(CAL)} }{I_{OUT(CAL)}} \cdot 100$                                                                       | (2) |

| $I_{OUT(CAL)} = 1000 \cdot \left( \frac{1.205\text{V}}{R_{ISET}} \right)$                                                                                        | (3) |

| $\Delta I_{LINE}(\% / V) = \frac{ I_{OUTn} _{VCC=5.5\text{V}} -  I_{OUTn} _{VCC=3.0\text{V}}}{ I_{OUTn} _{VCC=3.0\text{V}}} \cdot \frac{100}{2.5\text{V}}$       | (4) |

| $\Delta I_{LOAD}(\% / V) = \frac{ I_{OUTn} _{VOUTn=2.5\text{V}} -  I_{OUTn} _{VOUTn=0.5\text{V}}}{ I_{OUTn} _{VOUTn=0.5\text{V}}} \cdot \frac{100}{2.0\text{V}}$ | (5) |

## 電気的特性

**Note 1:** 絶対最大定格に記載された値を超えるストレスはデバイスに永続的損傷を与える可能性がある。長期にわたって絶対最大定格条件に曝すと、デバイスの信頼性と寿命に悪影響を与える可能性がある。

**Note 2:** LT3746Eは、0°C～125°Cの接合部温度で性能仕様に適合することが保証されている。-40°C～125°Cの動作接合部温度範囲での仕様は設計、特性評価および統計的なプロセス、コントロールとの相関で確認されている。LT3746Iは-40°C～125°Cの動作接合部温度範囲で動作することが保証されている。

**Note 3:** このデバイスには短時間の過負荷状態の間デバイスを保護するためのサーマル・シャットダウン保護機能が備わっている。サーマル・シャットダウン保護機能がアクティブなとき接合部温度は125°Cを超える。規定された最高動作接合部温度を超えた動作が継続するとき、デバイスの信頼性を損なうおそれがある。

**Note 4:** LEDチャネルがオンしているときのV<sub>CC</sub>の消費電流は、LED電流の設定値とLEDxxピンの電圧に大きく依存する。そのテスト条件は、R<sub>SET</sub> = 60.4k、REG<sub>DC</sub> = 0x3F、REG<sub>GS</sub> = 0xFFFF、V<sub>ISP</sub> = V<sub>ISN</sub> = 5V、V<sub>LEDxx</sub> = 0.5V。シリアル・データ・インターフェースがオンしているときのV<sub>CC</sub>

消費電流は、V<sub>CC</sub>電源電圧、シリアル・データ・インターフェースのクロック周波数、SCK0/SD0/LD0の負荷容量、およびPWMCKクロック周波数に大きく依存する。そのテスト条件は、V<sub>CC</sub> = 3.3V、f<sub>SCKI</sub> = 30MHz、C<sub>SCK0</sub> = C<sub>SD0</sub> = C<sub>LD0</sub> = 27pF、f<sub>PWMCK</sub> = 409.6kHz。

**Note 5:** SYNC周波数はRTでプログラムされる発振器周波数より高くする必要があり、約20%高くすることを推奨する。推奨値より高いどんなSYNC周波数も、スロープ補償が不十分なため、コンバータに低調波発振を生じる可能性がある。「アプリケーション情報」のセクションを参照。

**Note 6:** チャネル間の電流の不整合は表1の式1のように計算される。

**Note 7:** デバイス間の電流の不整合は表1の式2および式3のように計算される。

**Note 8:** LED電流のライン・レギュレーションは表1の式4のように計算される。

**Note 9:** LED電流のロード・レギュレーションは表1の式5のように計算される。

**Note 10:** シングルエンド入力SIの仕様は、SCKI、SDIおよびLDIの各ピンに適用される。シングルエンド出力SOの仕様は、SCK0、SD0およびLD0の各ピンに適用される。

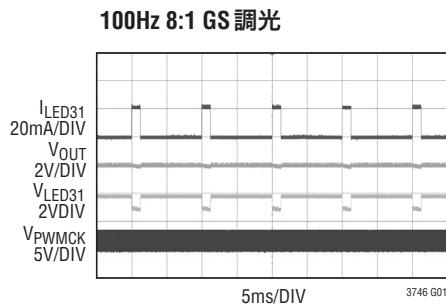

標準的性能特性 注記がない限り  $T_A = 25^\circ\text{C}$ 。

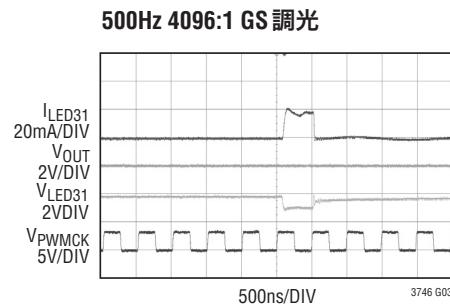

CIRCUIT OF FIGURE 7:

$DC_{31} = 0x20$ ,

$GS_{31} = 0x200$

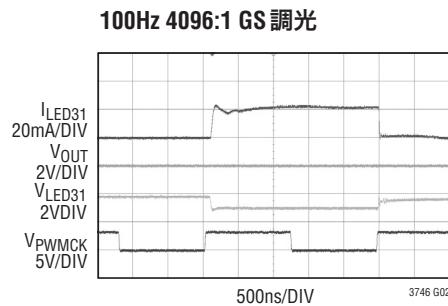

CIRCUIT OF FIGURE 7:

$DC_{31} = 0x20$ ,

$GS_{31} = 0x001$

CIRCUIT OF FIGURE 7:

$DC_{31} = 0x20$ ,

$GS_{31} = 0x001$

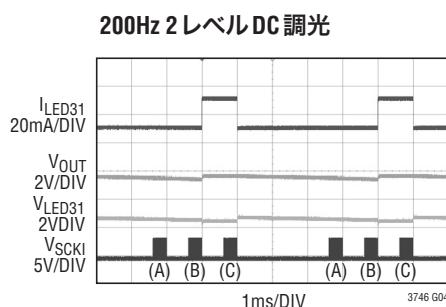

CIRCUIT OF FIGURE 7:

(A)  $EN = 1$ ,  $GS_{31} = 0xFF$ ;

(B)  $EN = 1$ ,  $DC_{31} = 0x3F$ ;

(C)  $EN = 1$ ,  $DC_{31} = 0x00$

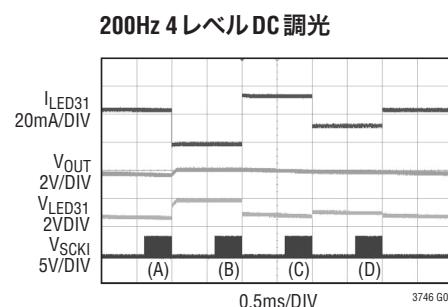

CIRCUIT OF FIGURE 7:

(A)  $EN = 0$ ,  $GS_{31} = 0xFFFF$ ,

(B)  $EN = 1$ ,  $DC_{31} = 0x3F$ ,

(C)  $EN = 1$ ,  $DC_{31} = 0x00$

(D)  $EN = 1$ ,  $DC_{31} = 0x20$

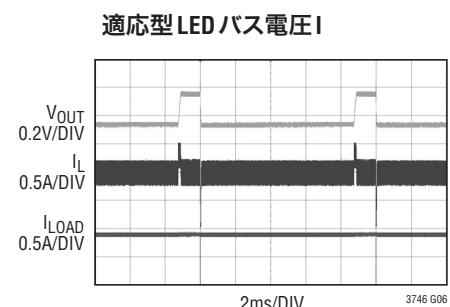

CIRCUIT OF FIGURE 7:

$DC_{00-31} = 0x3F$ ,

$GS_{00-31} = 0xFFFF$

CIRCUIT OF FIGURE 7:

$DC_{00-31} = 0x20$ ,

$GS_{00-31} = 0x800$

CIRCUIT OF FIGURE 7:

$DC_{00-31} = 0x3F$ ,  $GS_{00-03} = 0x1FF$ ,  $GS_{04-07} = 0x3FF$ ,

$GS_{08-11} = 0x5FF$ ,  $GS_{12-15} = 0x7FF$ ,  $GS_{16-19} = 0x9FF$ ,

$GS_{20-23} = 0xBFF$ ,  $GS_{24-27} = 0xDFF$ ,  $GS_{28-31} = 0xFFFF$

CIRCUIT OF FIGURE 7:

$DC_{00-07} = 0x3F$ ,  $GS_{00-07} = 0x3FF$ ,  $DC_{08-15} = 0x2F$ ,

$GS_{08-15} = 0x7FF$ ,  $DC_{16-23} = 0x1F$ ,  $DC_{16-23} = 0xBFF$ ,

$DC_{24-31} = 0x0F$ ,  $GS_{24-31} = 0xFFFF$

## 標準的性能特性

注記がない限り  $T_A = 25^\circ\text{C}$ 。

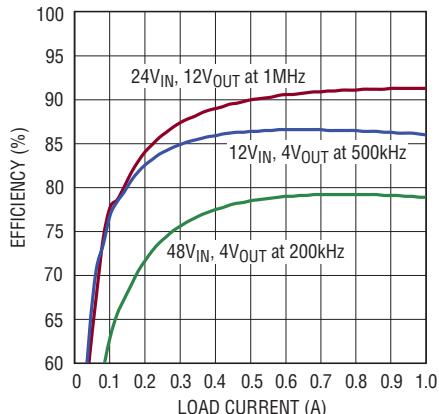

### 降圧の効率

3746 G10

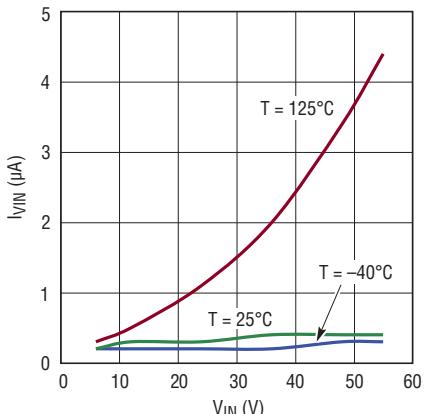

### シャットダウン時の $I_{VIN}$ と $V_{IN}$

3746 G11

### 静止 $I_{VIN}$ と $V_{IN}$

3746 G12

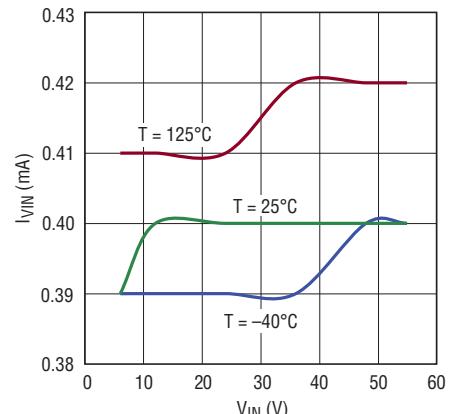

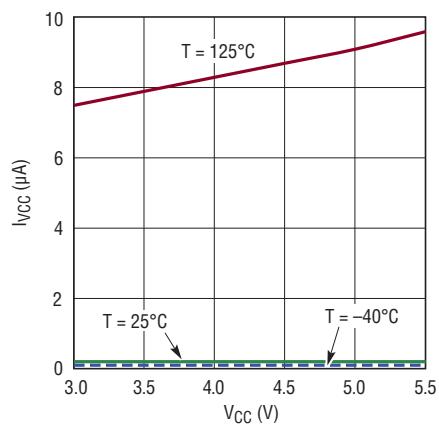

### $I_{VCC}$ と $V_{CC}$ - シャットダウン・モード

3746 G13

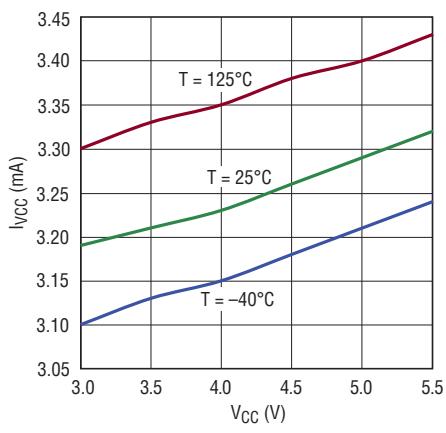

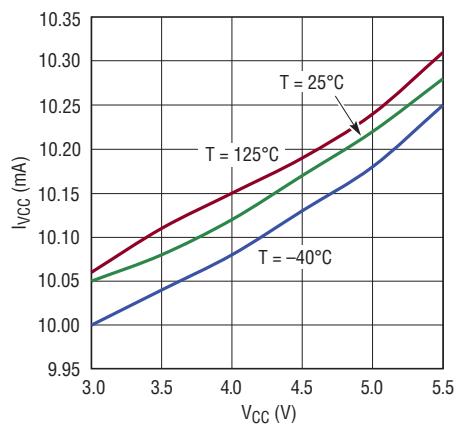

### $I_{VCC}$ と $V_{CC}$ - チャネルはオフ、データはオフ

3746 G14

### $I_{VCC}$ と $V_{CC}$ - チャネルはオン、データはオフ

3746 G15

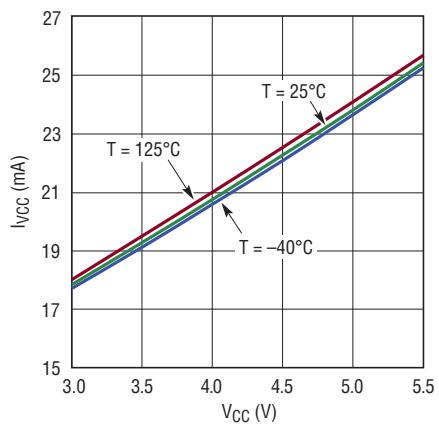

### $I_{VCC}$ と $V_{CC}$ - チャネルはオン、データはオン

3746 G16

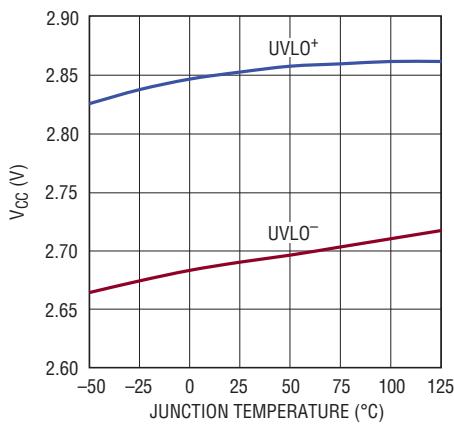

### $V_{CC}$ の UVLO スレッショルドと温度

3746 G17

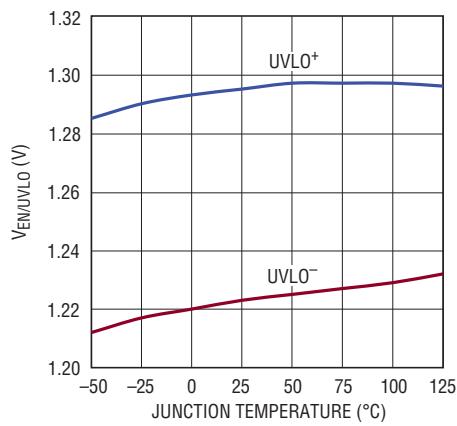

### EN/UVLO の UVLO スレッショルドと温度

3746 G18

標準的性能特性 注記がない限り  $T_A = 25^\circ\text{C}$ 。

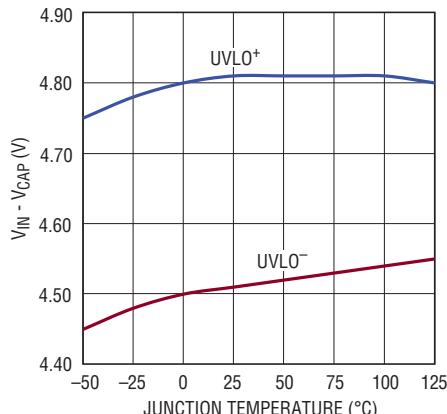

$(V_{IN} - V_{CAP})$  UVLOスレッショルドと

温度

3746 G19

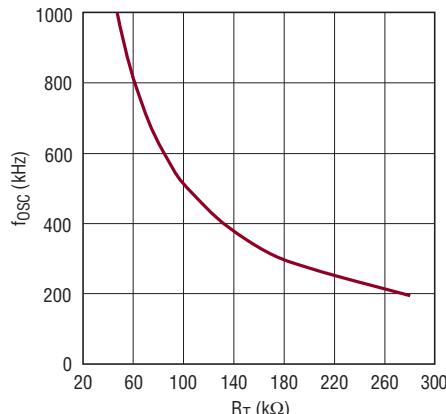

発振器周波数  $f_{osc}$  と  $R_T$

3746 G20

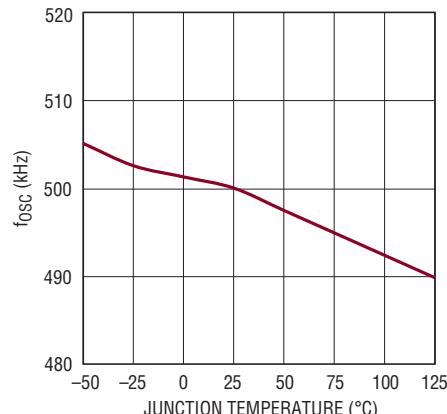

発振器周波数  $f_{osc}$  と温度

3746 G21

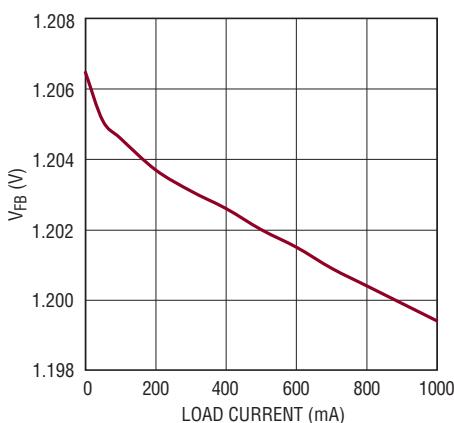

FBの安定化電圧と負荷電流

3746 G22

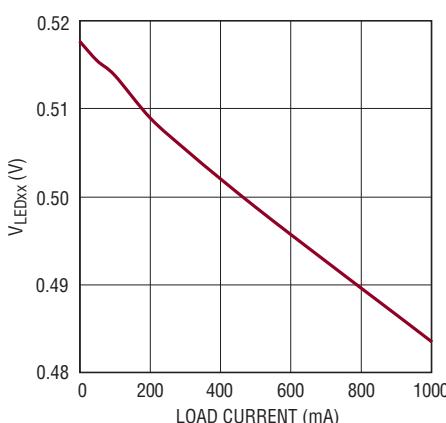

LEDの安定化電圧と負荷電流

3746 G23

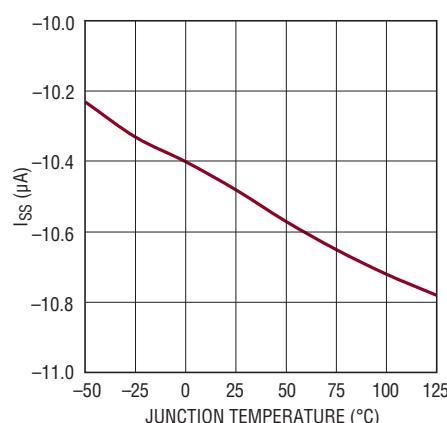

ソフトスタート充電電流  $I_{SS}$  と温度

3746 G24

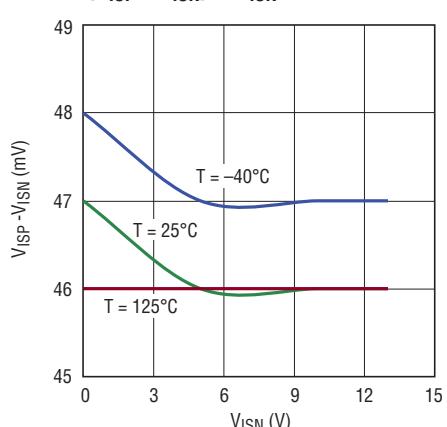

電流検出スレッショルド

( $V_{ISP} - V_{ISN}$ ) と  $V_{ISN}$

3746 G25

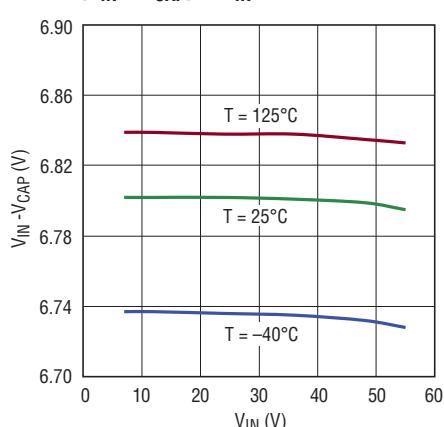

CAPのバイアス電圧

( $V_{IN} - V_{CAP}$ ) と  $V_{IN}$

3746 G26

CAPのバイアス電圧

( $V_{IN} - V_{CAP}$ ) と  $I_{CAP}$

3746 G27

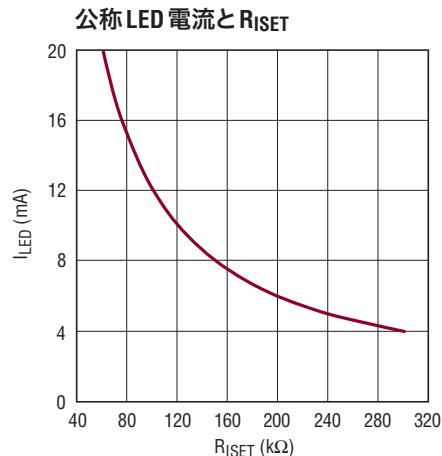

標準的性能特性 注記がない限り  $T_A = 25^\circ\text{C}$ 。

## ピン機能

**EN/UVLO (ピン1)** : イネーブルおよび低電圧ロックアウト(UVLO)ピン。このピンはデジタル入力信号を受け入れて、デバイスをイネーブルまたはディスエーブルすることができます。デバイスをシャットダウンするには0.35V以下に接続し、通常動作を行うには1.34V以上に接続します。このピンは、抵抗分割器を介してV<sub>IN</sub>に接続して、電源入力のUVLOスレッショルドをプログラムすることもできます。イネーブル機能とUVLO機能の両方とも使用しない場合、このピンをV<sub>CC</sub>ピンに接続します。

**LED00～LED31(ピン2～17、30～45)** : LEDドライバの出力ピン。LEDストリングのカソードをこれらのピンに接続します。

**GND(ピン18、20、27、29)** : グランド・ピン。

**SCKI(ピン19)** : シリアル・インターフェースのTTL/CMOSロジックのクロック入力ピン。

**SDI (ピン21)** : シリアル・インターフェースのTTL/CMOSロジックのデータ入力ピン。

**LDI(ピン22)** : シリアル・インターフェースのTTL/CMOSロジックのラッチ入力ピン。このピンの非同期入力信号により、シフトレジスタ内のシリアル・データが適切なレジスタにラッチされ、状態情報を次に来るクロック・パルスによってシフトアウトする準備ができます。詳細については、「動作」のセクションを参照してください。

**V<sub>CC</sub>(ピン23)** : ロジックおよび制御回路の電源ピン。このピンはシリアル・データ・インターフェースおよび内部制御回路に給電します。グランドに接続したコンデンサでローカルにバイパスする必要があります。

**PWMCK (ピン24)** : グレースケールPWM調光のTTL/CMOSロジックのクロック・ピン。個々のPWM調光信号は、このクロック・パルスを、ゼロからその12ビット・グレースケールPWMレジスタ内のビットまでカウントすることにより、生成されます。

**LDO (ピン25)** : シリアル・インターフェースのTTL/CMOSロジックのラッチ出力ピン。

**SDO (ピン26)** : シリアル・インターフェースのTTL/CMOSロジックのデータ出力ピン。

**SCKO(ピン28)** : シリアル・インターフェースのTTL/CMOSロジックのクロック出力ピン。

**SYNC(ピン46)** : スイッチング周波数同期ピン。内部発振器の周波数を、SYNKピンに与えられた外部クロックに同期させます。SYNKピンはTTL/CMOSロジックに適合しています。使用しない場合、グランドまたはV<sub>CC</sub>に接続します。

**RT (ピン47)** : タイミング抵抗ピン。スイッチング周波数を200kHz～1MHzにプログラムします。一般的なスイッチング周波数に対する推奨R<sub>T</sub>値については、表2を参照してください。

**SS(ピン48)** : ソフトスタート・ピン。コンデンサをここに接続すると、ソフトスタートのタイミングがプログラムされ、起動時のインダクタ突入電流を制限します。V<sub>CC</sub>、EN/UVLOおよび(V<sub>IN</sub> - V<sub>CAP</sub>)の全ての電圧がそれぞれのUVLOスレッショルドより高くなるまでは、ソフトスタート・サイクルは開始されません。

**FB(ピン49)** : 帰還ピン。このピンは、起動時およびプリチャージ・フェーズの間、内部バンドギャップ・リファレンスの1.205Vに安定化されます。降圧コンバータの出力から抵抗分割器に接続して最大LEDバス電圧を設定します。詳細については、「アプリケーション情報」のセクションを参照してください。

**ISN(ピン50)** : 負のインダクタ電流検出ピン。このピンは、外部インダクタ電流検出抵抗の1つの端子、および並列LEDチャネルに給電する降圧コンバータの出力に接続されます。

**ISP(ピン51)** : 正のインダクタ電流検出ピン。このピンはインダクタおよび外部インダクタ電流検出抵抗の他の端子に接続されます。

**CAP(ピン52)** : V<sub>IN</sub>を基準にしたレギュレータ電源のコンデンサ・ピン。このピンは、ゲート・ドライバ回路をバイアスするのに使われる、V<sub>IN</sub>を基準にした内部の6.8Vリニア・レギュレータの負端子を保持します。V<sub>IN</sub>に接続したコンデンサでローカルにバイパスする必要があります。

**GATE(ピン53)** : ゲート・ドライバ・ピン。このピンは、ピーク電流が標準1Aの外部Pチャネル・パワーMOSFETをドライブします。このピンは、短くて幅の広いPCBトレースでパワーMOSFETのゲートに接続し、トレースのインダクタンスを最小に抑えます。

**V<sub>IN</sub>(ピン54)** : パワー入力電源ピン。グランドに接続したコンデンサでローカルにバイパスする必要があります。

**T<sub>SET</sub> (ピン55)** : 温度スレッショルド設定ピン。グランドに接続した抵抗で過温度スレッショルドをプログラムします。詳細については、「アプリケーション情報」のセクションを参照してください。

**I<sub>SET</sub> (ピン56)** : 公称LED電流の設定ピン。グランドに接続した抵抗で全チャネルの公称LED電流をプログラムします。詳細については、「アプリケーション情報」のセクションを参照してください。

**露出パッド(ピン57)** : グランド・ピン。ダイ温度を下げ、デバイスの電力能力を上げるため、連続銅グランド・プレーンに半田付けする必要があります。

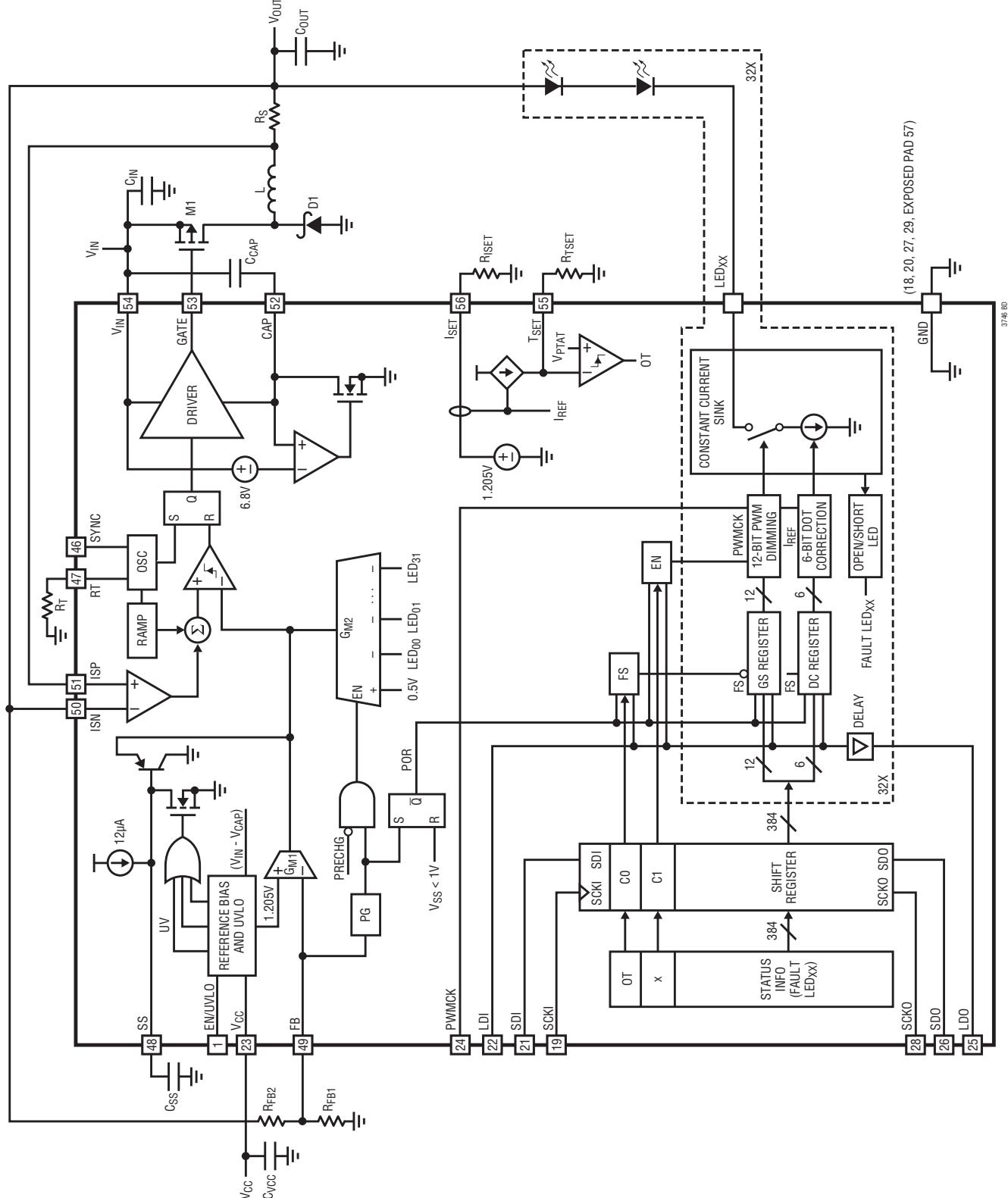

## ブロック図

## 動作

LT3746は1個の固定周波数電流モード非同期整流式降圧コントローラを内蔵しており、32の線形電流シンクを備えています。降圧コントローラは適応型出力LEDバス電圧を発生して並列LEDストリングに供給し、32の線形電流シンクが個々のLEDストリングのレギュレーションと変調を行います。その動作は、ブロック図を参照するとよく理解できます。

### スタートアップ

EN/UVLOピンが0.35Vより下のとき、LT3746はシャットダウン・モードになり、電流はほとんどゼロになります。EN/UVLOピンが0.35Vを超えると、デバイスは内部バイアス電流を流し始め、様々なリファレンスを発生し、コンデンサCCAPを6.8Vのレギュレーション電圧に向けて充電し始めます。この $V_{IN}$ を基準にした電圧レギュレータ( $V_{IN} - V_{CAP}$ )は、通常動作では外部PチャネルMOSFETを駆動する内部ゲート・ドライバ回路に給電します。EN/UVLO、V<sub>CC</sub>、および( $V_{IN} - V_{CAP}$ )UVLOのフラグのどれか1つが“H”である限り、LT3746は低電圧ロックアウト(UVLO)モードに留まります。それらのUVLOスレッショルドは、それぞれ標準1.31V、2.89V、および4.9Vです。全てのUVLOフラグがクリアされた後、降圧コントローラはスイッチングを開始し、ソフトスタートSSピンがリリースされて12 $\mu$ Aの電流源で充電され、それによってインダクタ電流と出力LEDバス電圧がスムーズにランプアップします。

### パワーオン・リセット(POR)

スタートアップの間、内部パワーオン・リセット(POR)の“H”信号が、シリアル・データ・インターフェースへの入力信号をブロックし、386ビットのシフトレジスタを除く全ての内部レジスタをリセットします。1ビットのフレーム・セレクト(FS)レジスタ、1ビットのLEDチャネル・イネーブル(EN)レジスタ、個々の12ビット・グレースケール(GS)レジスタ、および個々の6ビット・ドット補正(DC)レジスタが全てゼロにリセットされます。こうして、全てのLEDチャネルが最初オフし、既定のグレースケール(0x000)およびドット補正(0x00)に設定されます。デバイスがソフトスタートを完了し(つまり、SSピンの電圧が1Vより高くなり)、出力LEDバス電圧がシパワーグッド状態だと(つまり、FBによってプログラムされたレギュレーション・レベルの5%以内)、POR信号が“L”になり、入力信号がシリアル・データ・インターフェースに受け入れられます。ソフトスタートをトリガするなどのフォールトも、PORの“H”信号を発生し、内部レジスタを再度リセットします。

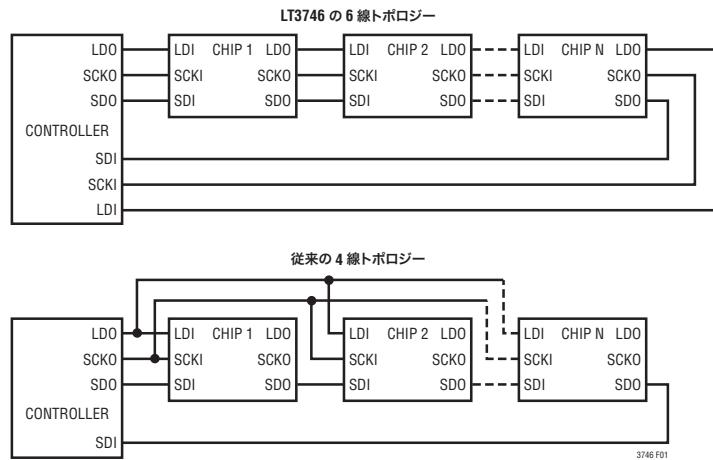

### シリアル・データ・インターフェース

LT3746は、バッファ付きの、スキーのバランスのとれた、カスケード接続可能な30MHzシリアル・データ・インターフェースを備えています。このインターフェースは、新しい6線(LDI、SCKI、SDI、LDO、SCKO、およびSDO)トポロジーを使用しており、マイクロコントローラ、デジタル信号プロセッサ(DSP)、またはフィールド・プログラマブル・ゲートアレイ(FPGA)に接続することができます。

図1に示されている従来の4線トポロジーでは、LDIとSCKIの信号はグローバルな配線を必要としますが、SDI信号はチップ間のローカルな配線だけを必要とします。カスケード接続されたチップの個数とシステムPCBボードに依存して、信号のスキーを最小にするため、対応するドライブ能力を備えた外部クロック・ツリー・タイプのバッファが、LDI信号とSCKI信号の両方に必要です。SCKI信号に対するバッファの挿入によって生じる伝播遅延により、SCKI信号とSDI信号の間にクロック・スキーが生じるので、一般にカスタマの側でそれをバランスさせる必要があります。SDI信号とSDO信号の両方が、送信および受信に同じSCKI信号を必要とするので、SDI信号とSDO信号の間の伝播遅延により、カスケード内のデバイスの個数およびシリアル・データ・インターフェースのクロック周波数が制限されます。

新しい6線トポロジーでは、LDI信号とSCKI信号のためのグローバル配線およびバッファの挿入が不要になります。代わりに、SDO信号とともにLDO信号とSCKO信号を与えて、次のデバイスをドライブします。LDI、SCKIおよびSDIの各信号の間のデバイス内部のスキーは内部でバランスされます。LDO、SCKOおよびSDOの各信号の間のデバイス外部のスキーは、デバイス間でこれらの信号を並列に配線することによって容易にバランスさせることができます。SDI信号はSCKI信号とともに送信され、SDO信号はSCKO信号によって受信されます。プロセスのばらつき、電源電圧および動作温度によって、SCKI信号とSCKO信号の間でデューティ・サイクルがわずかに変化することがあります。このデューティ・サイクルの変化は、SCKI/SCKOの正負のエッジの伝播遅延の差に起因し、SCKIの速度に依存して、カスケード可能なデバイスの最大数に影響を与えます。まとめると、6線トポロジーはカスケード可能なデバイスの個数を増やし、シリアル・データ・インターフェースのクロック周波数を上げ、グローバル信号の挿入を不要にし、PCBのレイアウトを簡単にします。カスケード接続されるデバイスの個数が少ない低速アプリケーションでは、LDO出力とSCKO出力を無視して、6線トポロジーを4線トポロジーに簡素化することができます。

## 動作

図1.LT3746の6線トポロジーと従来の4線トポロジー

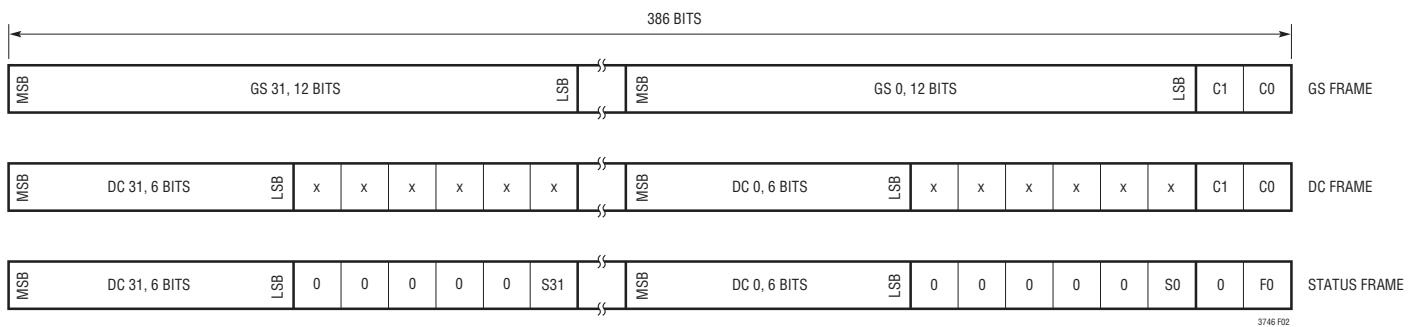

コマンド・レジスタ：

C1: ENABLE LED CHANNELS - ENABLE = 1, DISABLE = 0

C0: FRAME SELECT - GS FRAME = 0, DC FRAME = 1

状態レジスタ：

S0-S31: LED 0-31 FAULT - FAULT = 1, OK = 0

F0: OT - OVER TEMPERATURE = 1, OK = 0

図2. シリアル・データ・フレーム・フォーマット

## 動作

図3. シリアル・データの入力および出力のタイミング図

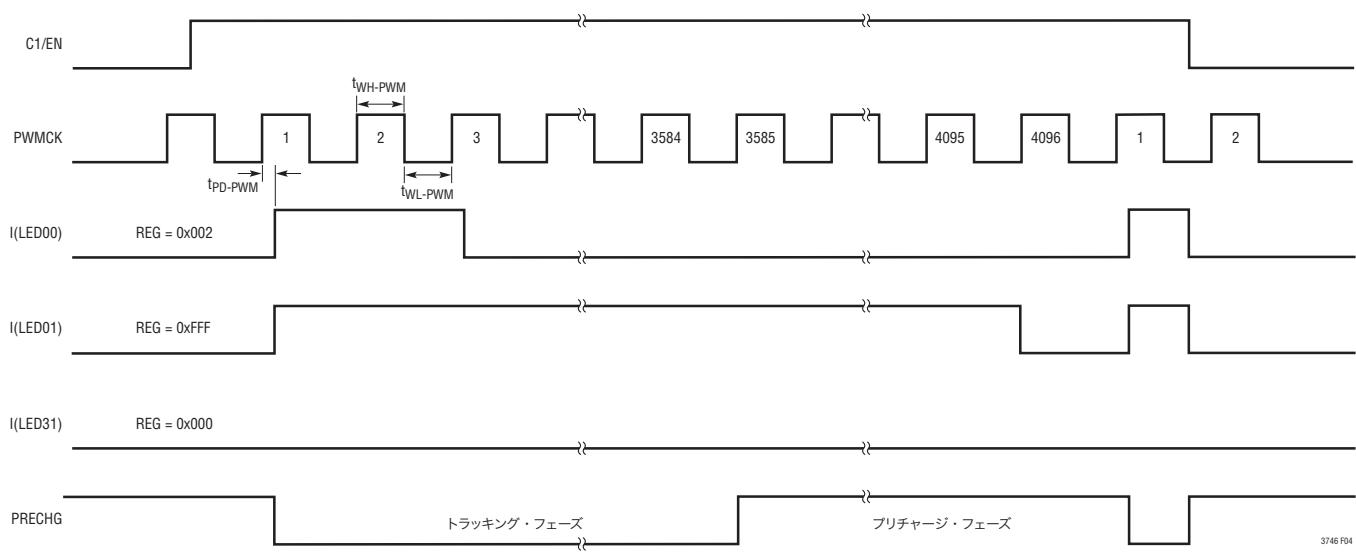

図4. グレースケールPWM調光とプリチャージ信号のタイミング図

## 動作

2つのシリアル・データ入力SDIフレーム(GSフレームとDCフレーム)および1つのシリアル・データ出力SDOフレーム(状態フレーム)を図2に示します。全てのフレームの長さは386ビットで同じであり、MSBが最初に送信され、LSBが最後に送信されます。SDIフレームはSCKI信号とともに送信され、SDOフレームはSCKO信号によって受信されます。C0ビット(フレーム選択)は、SDIフレームがGSフレーム( $C0 = 0$ )とDCフレーム( $C0 = 1$ )のどちらであるかを決定し、C1ビット(EN)は、全てのLEDチャネルをイネーブル( $C1 = 1$ )またはディスエーブル( $C1 = 0$ )します。状態フレームは、TSETピンの抵抗でプログラム可能な過温度フラグ、個々のオープン/短絡LEDフォールト・フラグ、さらに個々の6ビットDC設定を読み出します。

デバイスの内部には、1個の386ビット・シフトレジスタSR[0:385]、1個のフレーム選択(FS)レジスタ、1個の1ビット・イネーブルLEDチャネル(EN)レジスタ、32個の12ビット・グレースケール(GS)レジスタ、32個の6ビット・ドット補正(DC)レジスタ、1個の1ビット過温度(OT)フラグ・レジスタ、および32個の1ビットLEDフォールト・フラグ・レジスタがあります。386ビット・シフトレジスタの入力、つまり最初のビットSR[0]の入力はSDI信号に接続されています。386ビット・シフトレジスタの出力、つまり最後のビットSR[385]の出力はSDO信号に接続されています。SCKI信号は立ち上がりエッジでSDIフレーム(GSまたはDCフレーム)を386ビット・シフトレジスタにシフトし、SCKO信号は立ち上がりエッジでSDOフレーム(状態フレーム)を386ビット・シフトレジスタからシフトします。LDIの“H”信号が、386ビット・シフトレジスタから、対応するFS、EN、GSまたはDCの各レジスタにSDIフレーム(GSまたはDCフレーム)をラッチし、OTおよびLEDフォールト・フラグ・レジスタから386ビット・シフトレジスタにSDOフレーム(状態フレーム)を同時にロードします。LDO信号はLDI信号をバッ

ファしたもので、一定の遅延を加えて、SCKI信号とSCKO信号の間の遅延に一致させます。したがって、同時書き込み読み出し能力を備えたデイジーチェーン型のループ通信が実装されています。

シリアル入力信号とシリアル出力信号の間のタイミング関係の詳細を図3に示します。1つのDCフレームとそれに続くもう1つのGSフレームが、LDI、SCKIおよびSDI信号によって送信されます。同時に、LDO、SCKOおよびSDO信号によって、2個の状態フレームが受信されます。SCKI信号の立ち上がりエッジにより、386ビットのデータ・フレームがSDIピンから386ビットのシフトレジスタSR[0:385]にシフトされます。386クロック・サイクルの後、386ビットの全データが所定の場所に収まり、LDI信号を待ちます。非同期LDIの“H”信号により、1ビットFSレジスタ、1ビットENレジスタ、および個々の12ビットGSレジスタ(FS = 0のとき)または各チャネルの6ビットDCレジスタ(FS = 1のとき)がラッチされます。同時に、過温度フラグおよび個々のオープン/短絡LEDフォールト・フラグを含む状態情報のフレームが386ビット・シフトレジスタに並列にロードされ、入ってくるクロック・サイクルによってシフトアウトされます。

## 定電流シンク

各LEDチャネルにはローカル定電流シンクが備わっており、LEDバスの電圧 $V_{OUT}$ には関係なく、それぞれのLED電流を安定化します。LEDピンの推奨電圧範囲は0.5V～2.5Vです。「標準的性能特性」の「 $I_{LED}$ と $V_{LED}$ 」の曲線で示されているように、LEDピンの電圧 $V_{LED}$ が0.5V～2.5Vに収まるとき、LED電流 $I_{LED}$ の負荷レギュレーションが最良になります。もっと低いLEDバス電圧 $V_{OUT}$ では、全温度範囲、電流範囲、および製造時のばらつきに対して、LEDチャネルの全ては安定

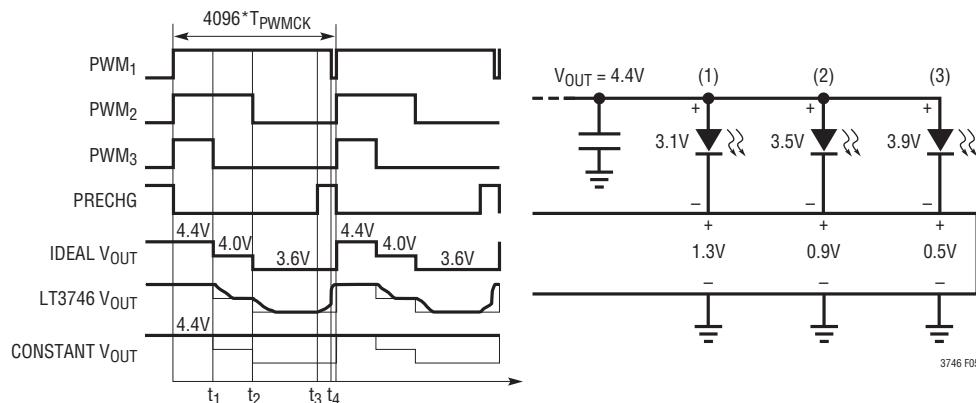

図5. 適応型トラッキングおよびLEDバスのプリチャージの方法

## 動作

化しないことがあります。他方、もっと高いLEDバス電圧  $V_{OUT}$  では、電流シンク両端にもっと高いLEDピン電圧が強制され、それによって、デバイス内部の電力損失が増えます。LEDバス電圧および電力損失の計算の詳細に関しては、「アプリケーション情報」のセクションを参照してください。

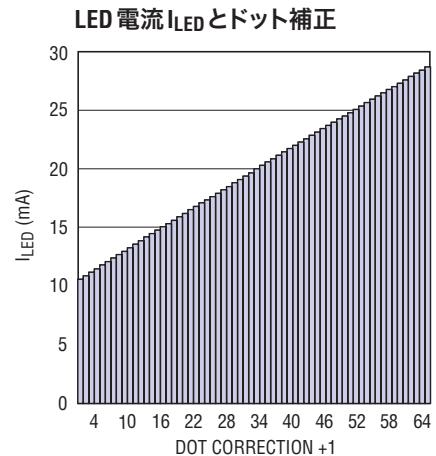

### ドット補正およびグレースケールD/A変換

$I_{SET}$  ピンの抵抗により、全てのチャネルの公称LED電流 (4mA～20mA) がプログラムされます。個々のLEDチャネルは、それぞれの6ビット・ドット補正レジスタによって、異なった電流設定に調整することができます。調整可能なLED電流の範囲は、リニアな63ステップで、公称LED電流の0.5倍～1.5倍です。「アプリケーション情報」のセクションの公称LED電流の設定とドット補正に関する詳細説明を参照してください。

ドット補正電流の調整に加えて、個々のLEDチャネルをそれぞれのグレースケールPWM調光信号によって変調することができます。さらに良い性能を達成するため、全てのグレースケールPWM調光信号は同じ周波数に同期し、立ち上がりエッジ同士の間に位相のシフトがありません。各定電流シンクは、そのグレースケールPWM調光信号が“H”または“L”になると、イネーブルまたはディスエーブルされます。この周期的なグレースケールPWM調光信号は、それぞれの12ビット・グレースケール・レジスタによって発生し、デューティ・サイクルが $0/4096 \sim 4095/4096$ 、周期が $4096 \text{ PWMCK サイクル}$ に等しくなります。

グレースケールPWM調光信号の発生は図4を参照するとよく理解できます。EN = 1に設定後、PWMCK信号の最初の立ち上がりエッジが、内部12ビット・グレースケール・カウンタをゼロから1に上げ、全LEDチャネルをゼロではないグレースケール値でオンします。後に続くPWMCK信号の各立ち上がりエッジにより、グレースケール・カウンタが1だけ増加します。どのLEDチャネルも、その12ビット・グレースケール・レジスタの値がグレースケール・カウンタの値に等しくなるとオフします。全てのグレースケールPWM調光信号に100%デューティ・サイクルを発生するには、個々の12ビット・グレースケール・レジスタ内の値までカウントする前に、PWMCK信号を休止させることができます。EN = 0に設定すると、グレースケール・カウンタがゼロにリセットされ、直ちに全てのLEDチャネルがオフします。

### デュアル・ループのアナログOR制御

スイッチング周波数は、RTピンに接続した抵抗によって200kHz～1MHzにプログラムすることができます、SYNCピンを使って外部クロックに同期させることもできます。各スイッチング・サイクルは、ゲート・ドライバが外部PチャネルMOSFET (M1)をオンするとスタートし、インダクタ電流はISPピンとISNピンの間のセンス抵抗( $R_S$ )によってサンプルされます。この電流が増幅され、勾配補償ランプ信号に加えられ、その和がPWMコンパレータの正端子に供給されます。この電圧がPWMコンパレータの負入力のレベルを超えると、ゲート・ドライバがM1をオフします。PWMコンパレータの負端子のレベルは、2個のエラーアンプGM1とGM2のいずれかによって設定されます。このデュアル・ループ・アナログOR制御では、FBループのGM1がFBピンの電圧を1.205Vに安定化し、LEDループのGM2が最小アクティブLEDピン電圧(LED00～LED31)を0.5Vに安定化します。起動時、GM2はディスエーブルされ、出力LEDバスの電圧は帰還抵抗によってプログラムされたLEDバス電圧に向かって安定化されます。FBによってプログラムされたこの電圧が最大LEDバス電圧を定めるので、温度、電流および製造時のばらつきの全範囲にわたってワーストケースのLEDストリングに十分供給できるだけ、高くプログラムします。

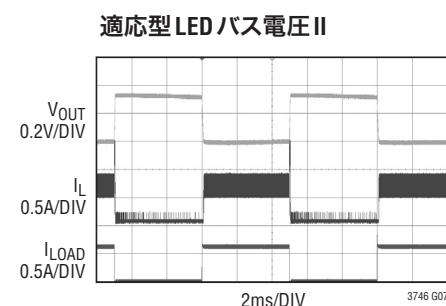

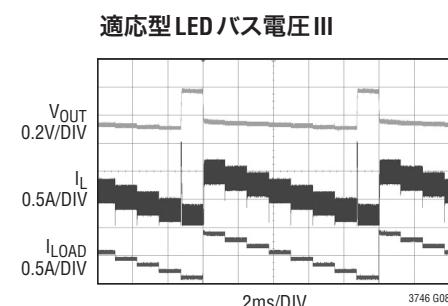

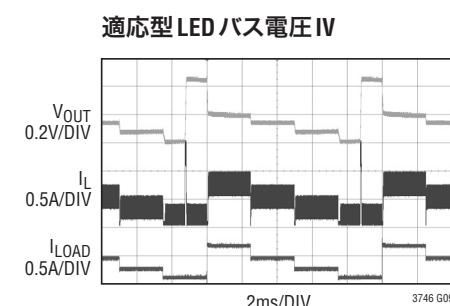

### 適応型トラッキング・プラス・プリチャージ

高いシステム効率と高速過渡応答は、個々に変調されるマルチ・チャネルLEDドライバ・デバイスに期待される2つの仕様です。LT3746は特許申請中の適応型トラッキング・プラス・プリチャージ手法を使ってそれら両方を同時に達成します。

32個の内部グレースケールPWM調光信号の他に、デバイスは別のプリチャージ信号PRECHGも発生します。図4に示されているように、PRECHG信号はグレースケールPWM調光サイクルを2つのフェーズに分割します。PRECHG = 0のときのトラッキング・フェーズと、PRECHG = 1のときのプリチャージ・フェーズです。各グレースケールPWM調光サイクル(4096 PWMCKサイクル)の間、PRECHG信号は最初の3584サイクル(PWM調光周期の7/8)の間“L”に留まり、残りの512クロック・サイクル(PWM調光周期の1/8)の間“H”になります。3585番目のPWMCKクロックの前に、LEDチャネルの全てがアクティブではなくなるとき(つまりフォールト状態またはオフ状態)、PRECHG信号が直ちに“H”になります。

## 動作

適応型トラッキング・プラス・プリチャージ手法について分かりやすく説明するため、3チャネルLEDアレイの簡略化したアプリケーション・システムを図5に示します。各チャネルは、順方向電圧降下がそれぞれ3.1V、3.5Vおよび3.9Vの1個のLEDで構成されています。3個の内部グレースケールPWM調光信号(PWM1、PWM2およびPWM3)が使われており、各LEDチャネルを変調します。

各グレースケールPWM調光サイクルの開始点で、3つのLEDチャネルの全てがオンし、PRECHG = 0でトラッキング・フェーズが開始されます。アンプG<sub>M2</sub>がイネーブルされ、アンプG<sub>M1</sub>から制御を引き継ぎ、最小アクトィブLEDピン電圧を0.5Vに安定化します。V<sub>LED3</sub>が0.5Vに等しいとき、出力LEDバス電圧は4.4Vにトラッキングします。続いて、ある時点t<sub>1</sub>で3番目のチャネルがオフし、最小LEDピン電圧がV<sub>LED2</sub>(0.9V)に移行します。次に、アンプG<sub>M2</sub>により出力LED電圧は4Vまでトラッキングし、最小LEDピン電圧を再度0.5Vに保ちます。同様に、次の時点t<sub>2</sub>では、出力LEDバス電圧は3.6Vまでトラッ

キングします。このようにして、適応型トラッキング手法は、電流シンクによる不要な電力損失を除去し、固定4.4V出力電圧に比べて、優れたシステム効率を実現します。

その後、時点t<sub>3</sub>でPRECHG信号が“H”になり、アンプG<sub>M2</sub>がディスエーブルされ、制御がアンプG<sub>M1</sub>に戻されます。アンプG<sub>M1</sub>は、出力LEDバス電圧を、FBによってプログラムされた最大値4.4Vに向かって安定化し、次のグレースケールPWM調光サイクルの最小LEDオン時間の短縮を保証します。プリチャージ・フェーズがないと、3つのLEDチャネルの全てが再度オンする次のグレースケールPWM調光サイクルの前、出力LEDバス電圧は3.6Vに留まります。その時点で、3.6VのLEDバス電圧は、全てのLEDチャネルを安定化状態に保つには低すぎ、出力コンデンサを3.6Vから4.4Vに充電するスイッチング降圧コンバータの低速過渡応答に適応するため、最小LEDオン時間が大きく増加します。この適応型トラッキング・プラス・プリチャージLEDバス電圧の手法は、LT3746の電力損失を下げ、同時にLEDの最小オン時間を短く保ちます。

## アプリケーション情報

グローバルには、LT3746は高い入力電圧を1つの低いLEDバス電圧( $V_{OUT}$ )に変換し、適応型トラッキング・プラス・リチャージ手法によって、32の並列LEDストリングに給電します。ローカルには、デバイスは、TTL/CMOSロジックのシリアル・データ・インターフェースによって送られてきた個別のドット補正およびグレースケールPWM調光設定に、各ストリングの電流を安定化し、変調します。この「アプリケーション情報」のセクションは、外部部品(「ブロック図」を参照)の選択、および標準的アプリケーションでよく見られる落とし穴の回避のためのガイドラインとして役立ちます。

### 最大 $V_{OUT}$ のプログラミング

適応型トラッキング・プラス・リチャージ手法は、起動およびリチャージ・フェーズの間は $V_{OUT}$ をその最大値に安定化し、トラッキング・フェーズの間は、適応させつつ電圧を下げて最小アクティブLEDピン電圧を約0.5Vに保ちます。したがって、最大 $V_{OUT}$ は十分高くプログラムして、全てのLEDピン電圧を0.5Vより高く保ち、温度、電流および製造時のばらつきの全範囲にわたり、LED電流をレギュレーション状態に維持します。出発点として、最大LEDバス電圧( $V_{OUT(MAX)}$ )を次のように計算することができます。

$$V_{OUT(MAX)} = 0.5V + n \cdot V_{F(MAX)}$$

ここで、nはストリング当たりのLEDの個数、 $V_{F(MAX)}$ は最高動作電流および最低動作電流でのLEDの最大定格順方向電圧です。

$V_{OUT(MAX)}$ は出力とFBピンの間の抵抗分割器を使ってプログラムします。抵抗値は次のように計算します。

$$R_{FB2} = R_{FB1} \left( \frac{V_{OUT(MAX)}}{1.205V} - 1 \right)$$

帰還抵抗の許容誤差により出力電圧にさらに誤差が加わるので、1%抵抗を使用します。FBピンの出力バイアス電流は標準120nAなので、非常に高い値の帰還抵抗を使うとバイアス電流誤差を生じることがあります。 $R_{FB1}$ の標準的な値は10kです。

### $V_{IN}$ 入力電源範囲:

LT3746の入力電源の範囲は6V～55Vで、広い範囲の産業用電源をカバーしています。最小入力電圧 $V_{IN(MIN)}$ に対する

別の制約は、 $V_{IN}$ ピンとISNピンの間の2Vの最小損失電圧であり、したがって、 $V_{IN(MIN)}$ は次のように計算します。

$$V_{IN(MIN)} = V_{OUT(MAX)} + 2V$$

### スイッチング周波数の選択

スイッチング周波数の選択には効率と部品サイズの間のトレードオフが必要です。低周波数動作ではMOSFETのスイッチング損失とゲート充電損失が減少して効率が改善されます。ただし、低周波数動作には大きなインダクタとコンデンサの値が必要です。

スイッチング周波数に対する別の制約は、最小スイッチ・オンおよびスイッチ・オフ時間によって生じる入力と出力の電圧範囲によります。与えられたアプリケーションの最高スイッチング周波数 $f_{SW(MAX)}$ は次のように計算することができます。

$$f_{SW(MAX)} = \text{MIN} \left( \frac{D_{MIN}}{t_{ON(MIN)}}, \frac{1-D_{MAX}}{t_{OFF(MIN)}} \right)$$

ここで、最小デューティ・サイクル $D_{MIN}$ と最大デューティ・サイクル $D_{MAX}$ は次式によって決まります。

$$D_{MIN} = \frac{V_{OUT(MIN)} + V_D}{V_{IN(MAX)} + V_D} \text{ and } D_{MAX} = \frac{V_{OUT(MAX)} + V_D}{V_{IN(MIN)} + V_D}$$

$t_{ON(MIN)}$ は最小スイッチ・オン時間(約200ns)、 $t_{OFF(MIN)}$ は最小スイッチ・オフ時間(約120ns)、 $V_{OUT(MIN)}$ は最小適応出力電圧、 $V_{IN(MAX)}$ は最大入力電圧、 $V_D$ はキャッチ・ダイオードの順方向電圧(約0.5V)です。 $f_{SW(MAX)}$ の計算は次のように簡単になります。

$$f_{SW(MAX)} = \text{MIN} \left( 5 \cdot \frac{V_{OUT(MIN)} + V_D}{V_{IN(MAX)} + V_D}, 8.33 \cdot \frac{V_{IN(MIN)} - V_{OUT(MAX)}}{V_{IN(MIN)} + V_D} \right) \text{MHz}$$

明らかに、低周波数動作は $V_{OUT}$ 対 $V_{IN}$ の非常に高い比と非常に低い比の両方に適応します。

これらの共通の検討事項の他に、スイッチング周波数の選択に際しては、特定のアプリケーションも重要な役割を果たします。ノイズに敏感なシステムでは、スイッチング・ノイズが敏感

## アプリケーション情報

な周波数帯の内側にこないようスイッチング周波数を選択します。

### スイッチング周波数の設定と同期

LT3746には固定スイッチング周波数が使われており、RTピンからグランドに接続した抵抗を使って200KHz～1MHzにプログラムすることができます。よく使われるスイッチング周波数に対応するRTの値を表2に示します。

表2. スイッチング周波数f<sub>SW</sub>とR<sub>T</sub>の値

| f <sub>SW</sub> (kHz) | R <sub>T</sub> * (kΩ) |

|-----------------------|-----------------------|

| 200                   | 280                   |

| 300                   | 182                   |

| 400                   | 133                   |

| 500                   | 105                   |

| 600                   | 84.5                  |

| 700                   | 71.5                  |

| 800                   | 60.4                  |

| 900                   | 53.6                  |

| 1000                  | 46.4                  |

\* 推奨1%標準値

LT3746の発振器は、SYNCピンを使って外部周波数に同期させることができます。TTL/CMOSロジックと互換性のある方形波の振幅は、0.6Vより下の谷と2.4Vより上の山が必要です。同期周波数の範囲も200KHz～1MHzであり、R<sub>T</sub>抵抗を選択して内部スイッチング周波数を同期周波数の約20%下に設定します。200kHzの同期周波数の場合、R<sub>T</sub> = 348kを推奨します。同期周波数がR<sub>T</sub>でプログラムした内部周波数よりも高いとき、内部スロープ補償がかなり減少し、そのため、50%を超えるデューティ・サイクルで低調波発振がトリガされることがあるので注意が必要です。

### インダクタ電流検出抵抗R<sub>S</sub>と電流制限

電流検出抵抗(R<sub>S</sub>)はISPピンとISNピンの間のインダクタ電流をモニタします。これらのピンは内部電流検出アンプへの入力です。電流検出アンプの同相入力電圧の範囲は、0Vから(V<sub>IN</sub> - 2V)または13Vの絶対最大値のどちらか低い方までです。電流検出アンプは電流モード制御を形成する電流情報

を提供するだけでなく、46.5mVのスレッショルドを与えます。R<sub>S</sub>抵抗両端の46.5mVのスレッショルドは正確な電流制限を課して、PチャネルMOSFET M1とキャッチダイオードD1の両方を保護し、また、インダクタ電流の飽和を防ぎます。正確な電流制限には正確な4端子法による検出が必要です。R<sub>S</sub>抵抗の値は次のように求めることができます。

$$I_{OUT(MAX)} = I_{L(MAX)} - \frac{\Delta I_L}{2}$$

ここで、最大インダクタ電流I<sub>L(MAX)</sub>は次式で設定されます。

$$I_{L(MAX)} = \frac{46.5mV}{R_S}$$

I<sub>OUT(MAX)</sub>は最大出力負荷電流、ΔI<sub>L</sub>はインダクタのピーク・トゥ・ピーク・リップル電流です。リップル電流の適当なマージンと外部部品の許容誤差を見込んで、R<sub>S</sub>は次のように推算することができます。

$$R_S = \frac{35mV}{I_{OUT(MAX)}}$$

### インダクタの選択

インダクタ選択の重要なパラメータは、インダクタンス値、DCまたはRMS電流、飽和電流およびDCR抵抗です。与えられた入力電圧と出力電圧に対して、インダクタの値と動作周波数によってピーク・トゥ・ピーク・リップル電流ΔI<sub>L</sub>が決まります。ΔI<sub>L</sub>値は通常、最大出力負荷電流(I<sub>OUT(MAX)</sub>)の20%～50%の範囲です。ΔI<sub>L</sub>の値が低いほど、大きく高価なインダクタが必要です。ΔI<sub>L</sub>の値が高いほど、ピーク電流とインダクタのコア損失が増加します。30%～40%のインダクタ電流リップルは、インダクタの性能とインダクタのサイズおよびコストの間の良い妥協点を与えます。ただし、デューティ・サイクルの高いアプリケーションでは、約20%のΔI<sub>L</sub>の値を使って、不十分なスロープ補償による低調波発振を防ぎます。

## アプリケーション情報

最大  $V_{IN}$  で最大インダクタ・リップル電流が発生します。リップル電流が規定された最大値を超えないようにするには、次式に従ってインダクタンスを選択します。

$$L \geq \frac{V_{OUT} + V_D}{V_{IN(MAX)} + V_D} \cdot \frac{V_{IN(MAX)} - V_{OUT}}{f_{SW} \cdot \Delta I_L}$$

インダクタのDCまたはRMS電流定格は最大出力負荷電流  $I_{OUT(MAX)}$  より大きくなければならず、その飽和電流は最大インダクタ電流  $I_L(MAX)$  より大きくなればなりません。高い効率を達成するには、DCR抵抗値が  $0.1\Omega$  より小さく、コア材が高周波アプリケーション向きのものにします。

### パワー MOSFET の選択

外部PチャネルMOSFET M1の重要なパラメータには、ドレイン-ソース間ブレーカダウン電圧( $V_{(BR)DSS}$ )、最大連続ドレン電流( $I_D(MAX)$ )、最大ゲート-ソース電圧( $V_{GS(MAX)}$ )、総ゲート電荷( $Q_G$ )、ドレイン-ソースのオン抵抗( $R_{DS(ON)}$ )、逆伝達容量( $C_{RSS}$ )が含まれます。MOSFETの  $V_{(BR)DSS}$  の規定値は、MOSFETのソースからドレンの最大電圧(これは  $V_{IN(MAX)}$  に  $V_D$  を加えたもの)を超えるようにします。 $I_D(MAX)$  はピーク・インダクタ電流( $I_L(MAX)$ )を超えるようにします。ゲート・ドライバ回路は、 $V_{IN}$  を基準にする 6.8V の内部レギュレータによって給電されるので、 $V_{GS(MAX)}$  の定格は少なくとも 10V にします。

MOSFETのゲートがオフしてオンする各スイッチング・サイクルに、 $V_{IN}$  ピンから GATE ピンへ、さらに GATE ピンから CAP ピンへと、ゲート電荷  $Q_G$  のたまりが移動します。その結果生じる  $dQ/dt$  は電流であり、内部レギュレータから  $C_{CAP}$  コンデンサに供給する必要があります。内部レギュレータの最大 20mA 電流能力は、それが供給できる最大  $Q_G(MAX)$  を制限します。

$$Q_{G(MAX)} = \frac{20mA}{f_{SW}}$$

したがって、MOSFETのデータシート上の  $V_{GS} = 6.8V$  での  $Q_G$  は、 $Q_G(MAX)$  より小さくなるようにします。

最大の効率を得るには、 $R_{DS(ON)}$  と  $C_{RSS}$  の両方を最小にします。 $R_{DS(ON)}$  が低いほど導通損失が小さくなり、 $C_{RSS}$  が低いほど遷移損失が減少します。あいにく、 $R_{DS(ON)}$  と  $C_{RSS}$  が逆方向の関係にあることです。したがって、導通損失と遷移損失を均衡させるのは、MOSFETの選択の良い基準になります。 $V_{IN}$  電圧の高い( $\geq 24V$ )アプリケーションでは、低い  $R_{DS(ON)}$  より低い  $C_{RSS}$  の方が重要です。

### キャッチ・ダイオードの選択

キャッチ・ダイオード D1 はスイッチのオフタイムに負荷電流を流します。キャッチダイオードの重要なパラメータには、ピーク反復逆電圧( $V_{RRM}$ )、順方向電圧( $V_F$ )、および最大平均順方向電流( $I_{F(AV)}$ )が含まれます。ダイオードの  $V_{RRM}$  の規定値は、その両端の最大逆電圧、つまり  $V_{IN(MAX)}$  を超えるようにします。 $V_F$  の低い高速ショットキー・ダイオードを使って電力損失を下げ、効率を上げます。

連続導通モードでは、キャッチダイオードによって流れる平均電流は次のように計算します。

$$I_{D(AVG)} = I_{OUT} \cdot (1 - D)$$

ダイオードにとっての最悪条件は、最大  $V_{IN}$  および最大  $I_{OUT}$  で  $V_{OUT}$  がグランドに短絡されたときです。この場合、ダイオードは、ほとんどの時間、最大負荷電流を安全に流す必要があります。効率を改善し、短絡動作での適切なマージンを与えるため、少なくとも最大出力電流の定格のショットキー・ダイオードを推奨します。

### $C_{IN}$ 、 $C_{VCC}$ および $C_{CAP}$ コンデンサの選択

入力電流は立ち上がり時間と立ち下がり時間が高速のパルスなので、降圧コンバータにはローカル入力バイパス・コンデンサ  $C_{IN}$  が必要です。入力コンデンサの選択基準は、電圧定格、バルク容量および RMS 電流能力に基づいています。コンデンサの電圧定格は  $V_{IN(MAX)}$  より大きくなればなりません。バルク容量により入力電源のリップル電圧が決まり、コンデンサの過熱を防ぐには RMS 電流能力を使います。

## アプリケーション情報

バルク容量は最大入力リップル電圧( $\Delta V_{IN}$ )に基づいて計算します。

$$C_{IN} = \frac{D_{MAX} \cdot I_{OUT(MAX)}}{\Delta V_{IN} \cdot f_{SW}}$$

$\Delta V_{IN}$ は一般にユーザーに受け入れられるレベルで選択されます。出発点として100mVが良いでしょう。セラミック・コンデンサの場合、X5RとX7RのタイプはY5VやZ5Uなど他のタイプに比べて広い電圧範囲と温度範囲で容量を維持するので、X5RまたはX7Rのタイプだけを使います。アルミ電解コンデンサは単位面積当たりの容量が高いので、高電圧のバルク容量に適しています。

コンデンサのRMS電流は次のとおりです。

$$I_{CIN(RMS)} = I_{OUT} \cdot \sqrt{\frac{V_{OUT} \cdot (V_{IN} - V_{OUT})}{V_{IN}^2}}$$

もし適用可能であれば最悪条件( $V_{IN} = 2 \cdot V_{OUT}$ )で計算します。メーカーによって規定されたコンデンサのRMS電流定格は、計算された $I_{CIN(RMS)}$ を超えるようにします。セラミック・コンデンサのESRは低いので、セラミック・コンデンサは高電圧、高RMS電流の処理に適しています。アルミ電解コンデンサのメーカーの規定するリップル電流定格は2000時間の寿命時間に基づいていることに注意してください。このため、コンデンサをさらにディレーティングする、つまり要件よりも高い温度定格のコンデンサを選択することを推奨します。

高電圧コンデンサの値がもっと大きい場合、経済的アプローチとしてアルミ電解コンデンサとセラミック・コンデンサを組み合わせます。サイズまたは高さの設計条件を満たすため、複数のコンデンサを並列に接続することもできます。コンデンサはMOSFETスイッチおよびキャッチダイオードに近接させて配置し、短く幅の広いPCBトレースを使って寄生インダクタンスを最小に抑えます。

上の一般的説明は、 $V_{CC}$ ピンのコンデンサ $C_{VCC}$ および $V_{IN}$ ピンと $CAP$ ピンの間のコンデンサ $C_{CAP}$ にも適用されます。一般に、 $C_{VCC}$ には10V定格の10 $\mu$ Fセラミック・コンデンサ、 $C_{CAP}$ には16V定格の0.47 $\mu$ Fセラミック・コンデンサで十分です。

### $C_{OUT}$ コンデンサの選択

出力コンデンサには2つの基本的な機能があります。インダクタとともに、出力コンデンサはLT3746が生成する方形波をフィルタ処理して、制御された電圧リップルを含むDC出力を生成します。また、負荷過渡変動に十分応え、デュアル・ループ動作を安定させるためにエネルギーを貯蔵します。このように、 $C_{OUT}$ の選択基準は、電圧定格、等価直列抵抗ESR、およびバルク容量をベースにしています。いつものとおり、電圧定格が $V_{OUT(MAX)}$ より大きな $C_{OUT}$ を選択します。

LT3746は出力を支配的ポールとして利用してデュアル・ループ動作を安定化するので、 $C_{OUT}$ の値によってユニティゲイン周波数 $f_{UGF}$ が決まり、この周波数はスイッチング周波数の約1/10に設定します。起動およびプリチャージ・フェーズの間FBループを安定化するため、またトラッキング・フェーズの間LEDループを安定化するため、低ESRコンデンサ(数10m $\Omega$ )を使い、その最小 $C_{OUT}$ を次のように計算します。

$$C_{OUT} = \text{MAX} \left( \frac{0.25}{R_S \cdot f_{UGF}}, \frac{1.5}{V_{OUT(MAX)} \cdot R_S \cdot f_{UGF}} \right)$$

適応型トラッキング・プラス・プリチャージ手法は、 $V_{OUT}$ をグレースケールPWM調光周波数に伴って変化させ、システム効率を改善します。 $C_{OUT}$ としてセラミック・コンデンサを選択すると、セラミック素材の圧電効果により、不可避的に可聴ノイズを発生します。可聴ノイズに敏感なアプリケーションでは、低ESRタンタル・コンデンサまたはアルミ・コンデンサが適しています。コンデンサを選択するときは、データシートを注意深く調べて、動作条件(加えられる電圧や温度)での実際の容量を確認してください。物理的に大きなコンデンサまたは電圧定格が高いコンデンサが必要なことがあります。

### 低電圧ロックアウト(UVLO)とシャットダウン

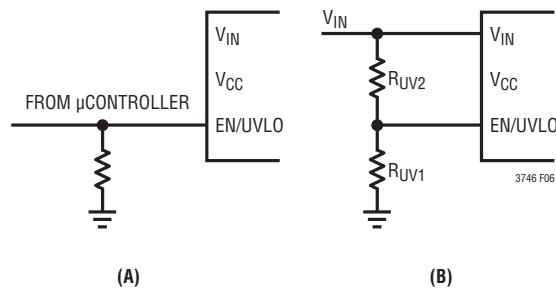

LT3746には、EN/UVLOピン、 $V_{CC}$ ピンおよび $CAP$ ピンに、ヒステリシスをもった3つのUVLOスレッショルドがあります。このデバイスは、EN/UVLO、 $V_{CC}$ 、および( $V_{IN} - V_{CAP}$ )の全ての電圧が、それぞれの標準スレッショルド(1.31V、2.89Vおよび4.9V)を超えるまで、スイッチングを行わずにUVLOモードに留まります。図6に示されているように、EN/UVLOピンは2つの異なる方法で制御することができます。EN/UVLOピンはデジタル入力信号を受け入れて、デバイスをイネーブルまたはディスエーブルすることができます。デバイスをシャットダウンするには0.35V以下に接続し、通常動作を行うには1.34V以上に接続します。このピンは、 $V_{IN}$ とグランドの間の抵抗分割

## アプリケーション情報

器に接続して、電源入力  $V_{IN}$  のUVLOスレッショルドをプログラムすることもできます。  $R_{UV1}$  を選択した後、  $R_{UV2}$  を次式で計算することができます。

$$R_{UV2} = R_{UV1} \cdot \left( \frac{V_{IN(ON)}}{1.31V} - 1 \right)$$

ここで、 $V_{IN(ON)}$  は、そこを超えるとデバイスが通常動作に入る電源入力電圧です。EN/UVLOピンの電圧がその6Vの絶対最大定格を超えないことを確認することが重要です。

$$V_{IN(MAX)} \cdot \frac{R_{UV1}}{R_{UV1} + R_{UV2}} < 6V$$

### ソフトスタート

ソフトスタートの間、SSピンの電圧はインダクタ電流と出力電圧を滑らかにランプアップさせます。SSピンの実効電圧範囲は0V～1Vです。したがって、標準ソフトスタート時間は次のようにになります。

$$t_{SS} = \frac{C_{SS} \cdot 1V}{12\mu A}$$

ここで、CSSはSSピンに接続されているコンデンサ、12 $\mu$ Aはソフトスタート充電電流です。UVLOまたはサーマル・シャットダウンが生じると、SSピンは放電し、UVLOイベントが解消し、SSピンがそのリセットスレッショルド(0.35V)に達するまで、デバイスはスイッチングを停止します。それから、デバイスは新しいソフトスタート・サイクルを開始します。

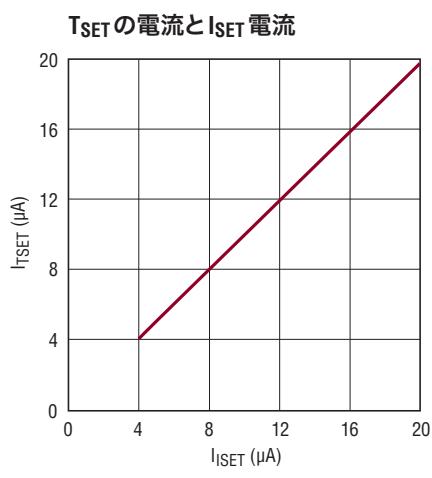

### 公称LED電流の設定

公称LED電流は、全ての個別ドット補正レジスタが0x20に設定されているとき、32チャネルにわたる平均LED電流として定義されています。公称LED電流は、ISETピンとグランドの間の1個の抵抗( $R_{ISET}$ )によって、プログラムします。ISETピンの電圧( $V_{ISET}$ )は、1.205Vに精確にトリムされ、 $R_{ISET}$ に反比例する電流を発生します。公称LED電流( $I_{LED(NOM)}$ )は次式から計算することができます。

$$I_{LED(NOM)} = \frac{V_{ISET}}{R_{ISET}} \cdot 1000$$

図6. EN/UVLOピンの制御方法

$I_{LED(NOM)}$  は4mA～20mAに設定する必要があります。様々な公称LED電流の標準的 $R_{ISET}$ 抵抗の値を、表3に示します。

表3. 公称LED電流  $I_{LED(NOM)}$  と  $R_{ISET}$  の値

| $I_{LED(NOM)}$ (mA) | $R_{ISET}^*$ (k $\Omega$ ) |

|---------------------|----------------------------|

| 4                   | 301                        |

| 10                  | 121                        |

| 15                  | 80.6                       |

| 20                  | 60.4                       |

\* 推奨1%標準値

### ドット補正の設定

LT3746は各チャネルのLED電流を独立に調整することができます。ドット補正とも呼ばれる、この電流の微調整は、LEDチャネル間の輝度の偏差を較正するのに主に使われます。6ビット(64ステップ)ドット補正の設定により、各LED電流は、次式に従って、公称LED電流の0.5倍～1.5倍に調整されます。

$$I_{LEDn} = I_{LED(NOM)} \cdot \left( \frac{DC_n + 32}{64} \right)$$

ここで、 $I_{LEDn}$  はn番目のLED電流、 $DC_n$  はn番目のプログラムされたドット補正の設定です( $DC_n = 0 \sim 63$ )。公称LED電流に対する微小電流ステップにより優れた分解能が得られます。

$$\frac{\Delta I_{LED}}{I_{LED(NOM)}} = \frac{1}{64} \approx 1.56\%$$

これにより、較正として使われると、相対的LED電流整合の精度が上がりります。

## アプリケーション情報

### グレースケールの設定

LED電流を調整すると、その照度の強さ、つまり輝度が変化しますが、色度の基準がシフトすることにより、LEDチャネル間の色整合も影響を受けます。輝度調整の最良の方法は、パルス幅変調(PWM)によりLEDのオン/オフ時間を制御することです。

LT3746は各チャネルの輝度を独立に調整することができます。12ビット・グレースケールPWM調光により、0%～99.98%の4096のリニアな輝度ステップが生じます。チャネルnの輝度レベルGS<sub>n</sub>%は次のように計算することができます。

$$GS_n\% = \frac{GS_n}{4096} \cdot 100\%$$

ここで、GS<sub>n</sub>はn番目のプログラムされたグレースケール設定(GS<sub>n</sub> = 0～4095)です。

### オープン/短絡LEDフォールト

LT3746には、個々のLEDフォールトの診断回路が備わっており、各チャネルのオープンと短絡の両方のLEDフォールトを検出します。オープンLEDフォールトは、LEDストリングがオープンしている、つまり回路から切断されていることとして定義されており、短絡LEDフォールトは、LEDがそれ自体の両端で短絡していることとして定義されています。最初の500nsのブランкиングを伴うオン状態の間、LEDピンの電圧が0.1V(標準)より低いと、オープンLEDフラグがセットされます。LEDピンの電圧がLEDバス電圧V<sub>OUT</sub>の75%より高いと、いつでも短絡LEDフラグがセットされます。1つのLEDチャネルがそれ自体の両端で短絡すると、そのチャネルはオフし、不要な電力損失を防ぎます。この機能は、LEDピンを出力に直接接続することにより、LEDチャネルをディスエーブルするのにも使うことができます。オープンLEDと短絡LEDの両方のフラグが結合されて、状態フレーム内のLEDフォールト・ビット(S0～S31)を1にセットします。

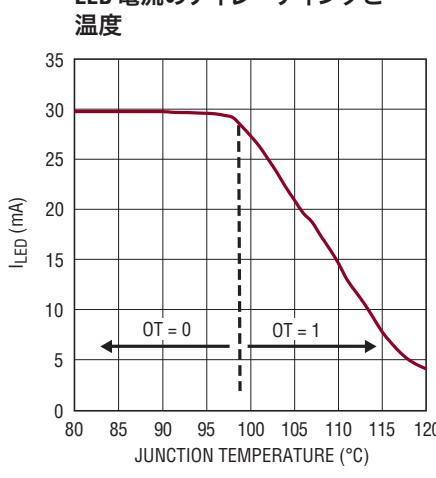

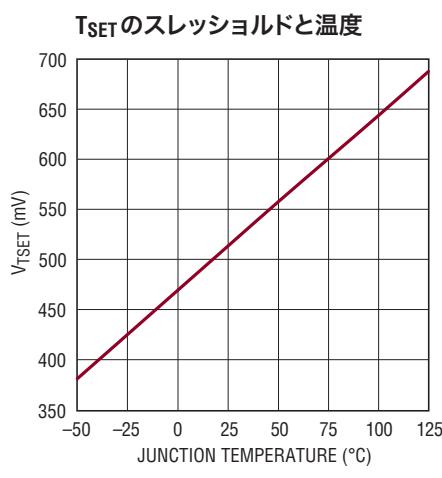

### 熱保護

LT3746には2つの過温度スレッショルドがあります。1つは固定内部サーマル・シャットダウンであり、他の1つはT<sub>SET</sub>ピンとグランドの間の抵抗(R<sub>TSET</sub>)によってプログラムされます。接合部温度が165°Cを超えると、デバイスはサーマル・シャットダウン・モードになり、シリアル・データ・インターフェースをシャットダウンし、LEDチャネルをオフし、スイッチングを停止します。接合部温度が155°Cを下回った後、デバイスは新しいソフトスタートを開始します。

R<sub>TSET</sub>をT<sub>SET</sub>ピンに接続すると、R<sub>ISET</sub>を通って流れる電流に等しい電流がR<sub>TSET</sub>を流れ、T<sub>SET</sub>ピンに電圧V<sub>TSET</sub>を発生します。この電圧は次のように計算されます。

$$V_{TSET} = 1.205V \cdot \frac{R_{TSET}}{R_{ISET}}$$

次に、V<sub>TSET</sub>が内部の絶対温度に比例する電圧V<sub>PTAT</sub>と比較されます。

$$V_{PTAT} = 1.72mV \cdot (T_J + 273.15)$$

ここで、T<sub>J</sub>は°Cを単位とするLT3746の接合部温度です。V<sub>PTAT</sub>がV<sub>TSET</sub>より高いと、過温度フラグOT = 1がセットされます。R<sub>TSET</sub>によってプログラムされた温度を超えると、デバイスは公称LED電流I<sub>LED</sub>(NOM)を徐々にディレーティングして、その通常動作を中断することなく、総電力損失を制限します。

### デバイスのカスケード接続とシリアル・データ・インターフェースのクロックの決定

大きなLCDバックライトまたはLEDディスプレイ・システムでは、複数個のLT3746を容易にカスケード接続して、全てのLEDストリングをドライブすることができます。LT3746は6線トポロジーに適応し、容易なPCBレイアウトを使って、内部クロック・スキューレーションをバランスさせ、外部トレースの容量を整合させます。

大きなディスプレイ・システムの最小シリアル・データ・インターフェース周波数f<sub>SCKI</sub>は、次のように計算することができます。

$$f_{SCKI} = N_{LT3746} \cdot 386 \cdot f_{REFRESH}$$

ここで、N<sub>LT3746</sub>はLT3746の個数、f<sub>REFRESH</sub>はシステム全体のリフレッシュ・レートです。

### 電力損失の計算

デバイス内部の総電力損失は次のように計算することができます。

$$P_{TOTAL} = V_{IN} \cdot (I_{VIN} + f_{SW} \cdot Q_G) + V_{CC} \cdot I_{VCC} + \sum_{n=0}^{31} GS_n \% \cdot I_{LEDn} \cdot V_{LEDn}$$

## アプリケーション情報

ここで、 $I_{VIN}$  は電源入力  $V_{IN}$  の消費電流、 $I_{VCC}$  は  $V_{CC}$  の消費電流、 $V_{LEDn}$  はチャンネル  $n$  の LED ピンの電圧です。

総電力損失  $P_{TOTAL}$  から、接合部温度  $T_J$  を次のように計算することができます。

$T_J$  を最大動作接合部温度  $125^{\circ}\text{C}$  より下に保ちます。

$$T_J = T_A + P_{TOTAL} \cdot \theta_{JA}$$

## 標準的応用例

M1: VISHAY Si9407BDY

D1: DIODES DFLS160

L1: WÜRTH ELECTRONIK 7447779122

C1: SANYO 6TPE220M1

図7. 32 チャネルLEDドライバ、500kHz降圧、チャネル当たり1 LED 10mA～30mA、100Hzで12ビット調光

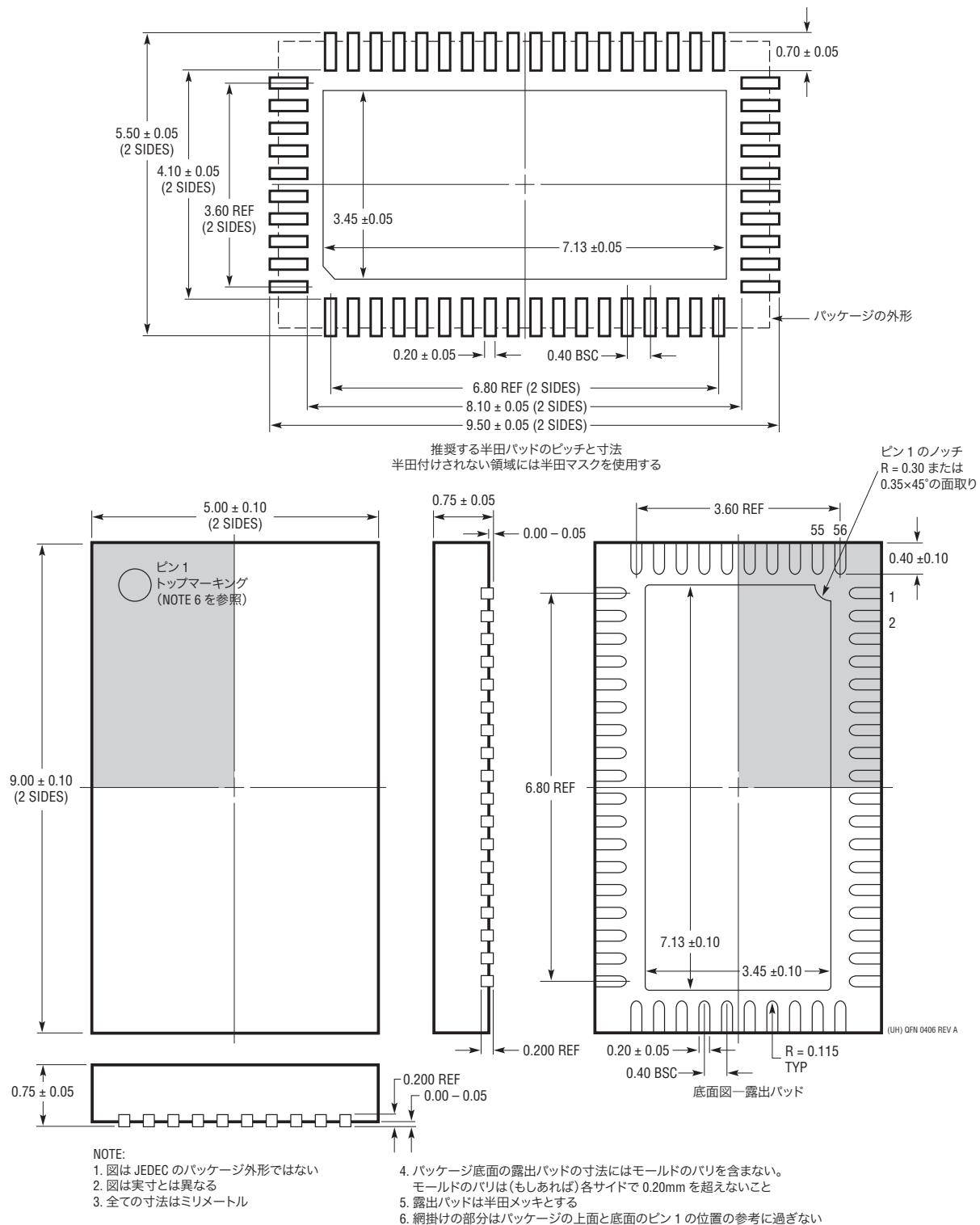

## パッケージ

最新のパッケージ図面については、<http://www.linear-tech.co.jp/designtools/packaging>をご覧ください。

**UHH Package**

**56-Lead Plastic QFN (5mm x 9mm)**

(Reference LTC DWG # 05-08-1727 Rev A)

## 改訂履歴

| Rev | 日付   | 概要                                                                                                                                            | ページ番号             |

|-----|------|-----------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| A   | 4/13 | $f_{OSC}$ と $I_{VCC}$ の仕様を明確化。<br>$I_{LED}$ 、 $\Delta I_{LEDC}$ 、 $\Delta I_{LINE}$ 、 $\Delta I_{LOAD}$ の仕様を明確化。<br>表1の式を明確化。<br>FBピンの説明を明確化。 | 3<br>4<br>5<br>11 |

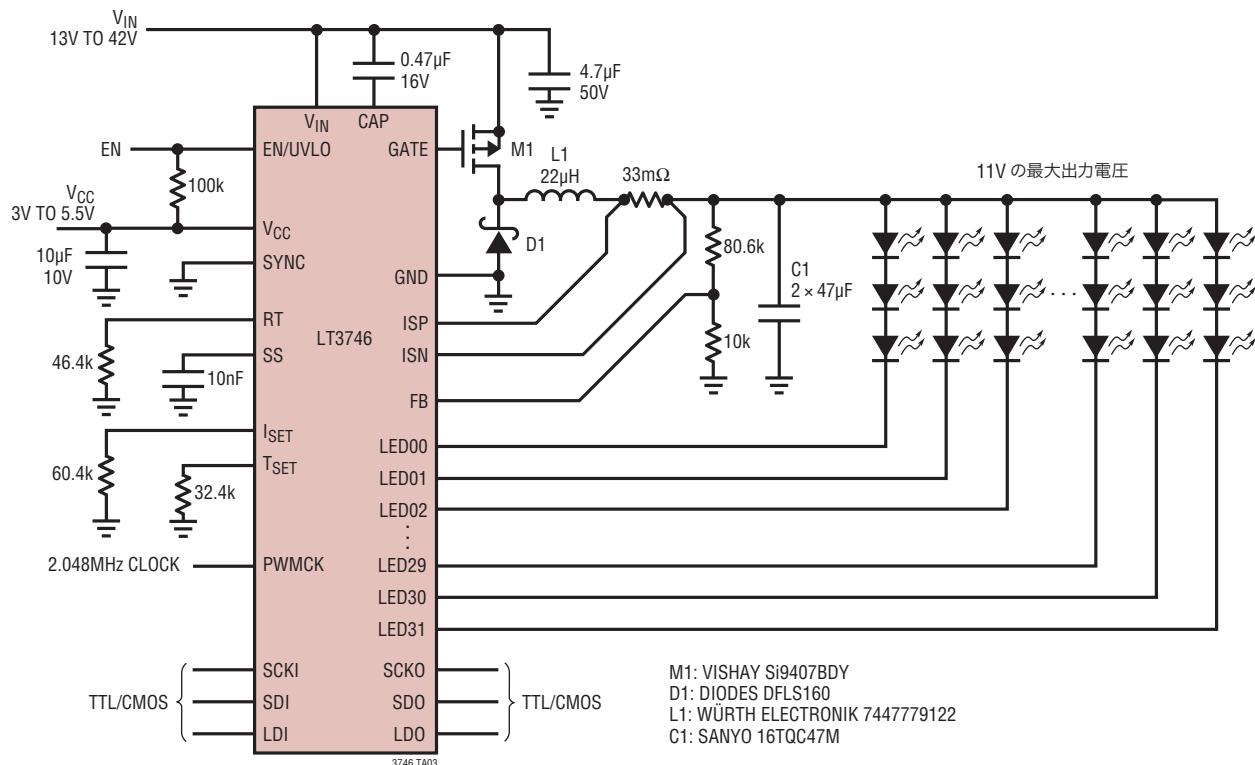

## 標準的応用例

図8. 32チャネルLEDドライバ、1MHz降圧、チャネル当たり3LED 10mA～30mA、500Hzで12ビット調光

## 関連製品

| 製品番号                | 説明                                                              | 注釈                                                                                                                                    |

|---------------------|-----------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|

| LT3476              | クワッド出力1.5A、2MHz高電流LEDドライバ、1,000:1の調光付き                          | V <sub>IN</sub> :2.8V～16V、V <sub>OUT</sub> (MAX) = 36V、True Color PWM調光 = 1000:1、I <sub>SD</sub> < 10µA、5mm×7mm QFN-10パッケージ           |

| LT3486              | デュアル1.3A、2MHz、高電流LEDドライバ                                        | V <sub>IN</sub> :2.5V～24V、V <sub>OUT</sub> (MAX) = 36V、True Color PWM調光 = 1000:1、I <sub>SD</sub> < 1µA、5mm×3mm DFNおよびTSSOP-16Eパッケージ   |

| LT3496              | トリプル出力750mA、2.1MHz高電流LEDドライバ、3,000:1の調光付き                       | V <sub>IN</sub> :3V～30V、V <sub>OUT</sub> (MAX) = 60V、True Color PWM調光 = 3000:1、I <sub>SD</sub> < 1µA、4mm×5mm QFN-28パッケージ              |

| LT3595              | 45V、2.5MHz、16チャネルのフル機能LEDドライバ                                   | V <sub>IN</sub> :4.5V～45V、V <sub>OUT</sub> (MAX) = 45V、True Color PWM調光 = 5000:1、I <sub>SD</sub> < 1µA、5mm×9mm QFN-56パッケージ            |

| LT3598              | 44V、1.5A、2.5MHz昇圧6チャネル30mA LEDドライバ                              | V <sub>IN</sub> :3V～40V、V <sub>OUT</sub> (MAX) = 44V、True Color PWM調光 = 1000:1、I <sub>SD</sub> < 1µA、4mm×4mm QFN-24パッケージ              |

| LT3599              | 44V、2A、2.5MHz昇圧4チャネル120mA LEDドライバ                               | V <sub>IN</sub> :3V～40V、V <sub>OUT</sub> (MAX) = 44V、True Color PWM調光 = 1000:1、I <sub>SD</sub> < 1µA、4mm×4mm QFN-24パッケージ              |

| LT3754              | 60V、1MHz昇圧16チャネル50mA LEDドライバ、True Color 3000:1 PWM調光および2.8%電流整合 | V <sub>IN</sub> :4.5V～40V、V <sub>OUT</sub> (MAX) = 60V、True Color PWM調光 = 3000:1、I <sub>SD</sub> < 1µA、5mm×5mm QFN-32パッケージ            |

| LT3755/<br>LT3755-1 | ハイサイド40V、1MHz LEDコントローラ、3,000:1のTrue Color PWM調光付き              | V <sub>IN</sub> :4.5V～40V、V <sub>OUT</sub> (MAX) = 60V、True Color PWM調光 = 3000:1、I <sub>SD</sub> < 1µA、3mm×3mm QFN-16およびMSOP-16Eパッケージ |

| LT3756/<br>LT3756-1 | ハイサイド100V、1MHz LEDコントローラ、3,000:1のTrue Color PWM調光付き             | V <sub>IN</sub> :6V～100V、V <sub>OUT</sub> (MAX) = 100V、True Color PWM調光 = 3000:1、I <sub>SD</sub> < 1µA、3mm×3mm QFN-16およびMSOP-16Eパッケージ |

| LT3760              | 60V、1MHz昇圧8チャネル100mA LEDドライバ、3000:1のTrue Color PWM調光および2.8%電流整合 | V <sub>IN</sub> :4.5V～40V、V <sub>OUT</sub> (MAX) = 60V、True Color PWM調光 = 3000:1、I <sub>SD</sub> < 1µA、TSSOP-28Eパッケージ                 |