## 特長

- 広い入力電圧範囲: 4V~30V

- 広い出力電圧範囲: 0.8V~ $V_{IN}$

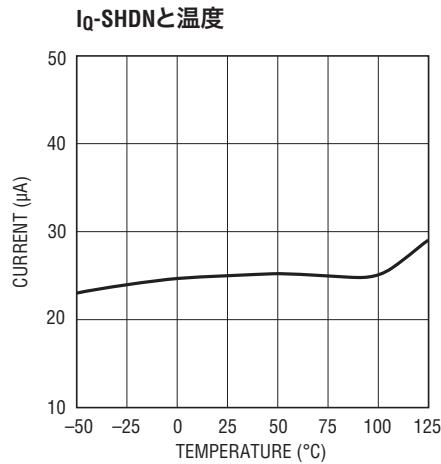

- シャットダウン時の低消費電流: 20μA

- 位相をずらしたコントローラにより、必要な入力容量と電源によるノイズを低減

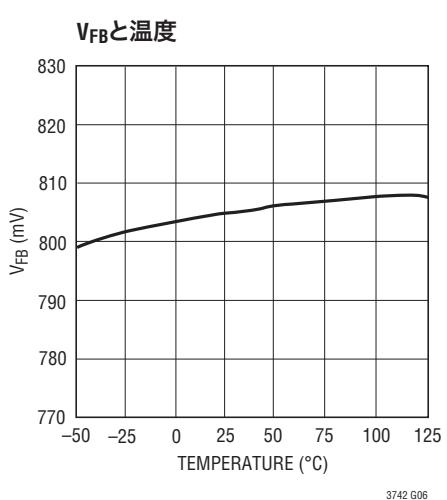

- ±1.5%精度の0.8V電圧リファレンス

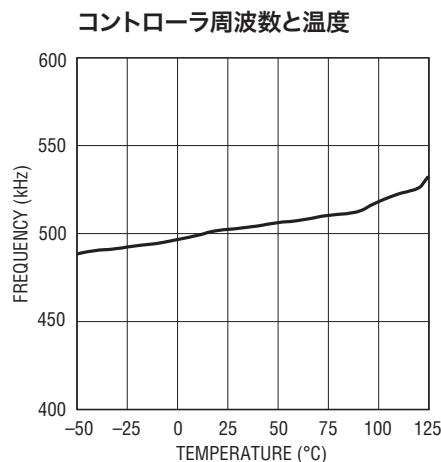

- 500kHz電流モード固定周波数動作

- 内部の昇圧コンバータによりNチャネルMOSFETゲート・ドライブ用のバイアス・レールを供給

- 各出力ごとのパワーグッド電圧モニタ

- プログラム可能なソフトスタート

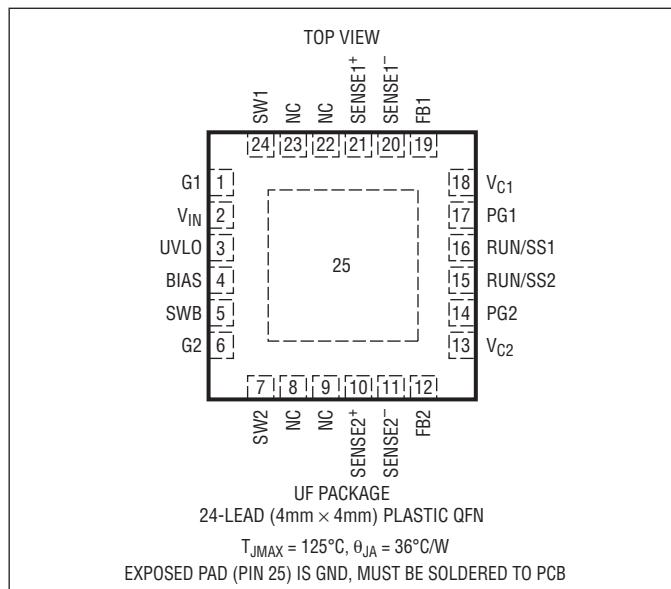

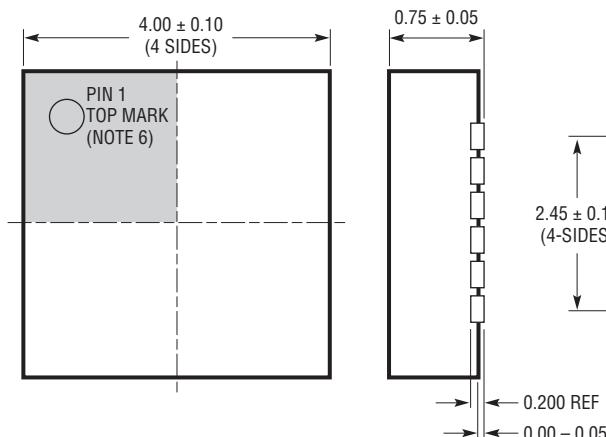

- 24ピン4mm×4mm×0.75mmパッケージ

## アプリケーション

- 衛星およびケーブルTVセットトップ・ボックス

- 分配電源の安定化

- 車載システム

- スーパーコンデンサ・チャージャ

## 概要

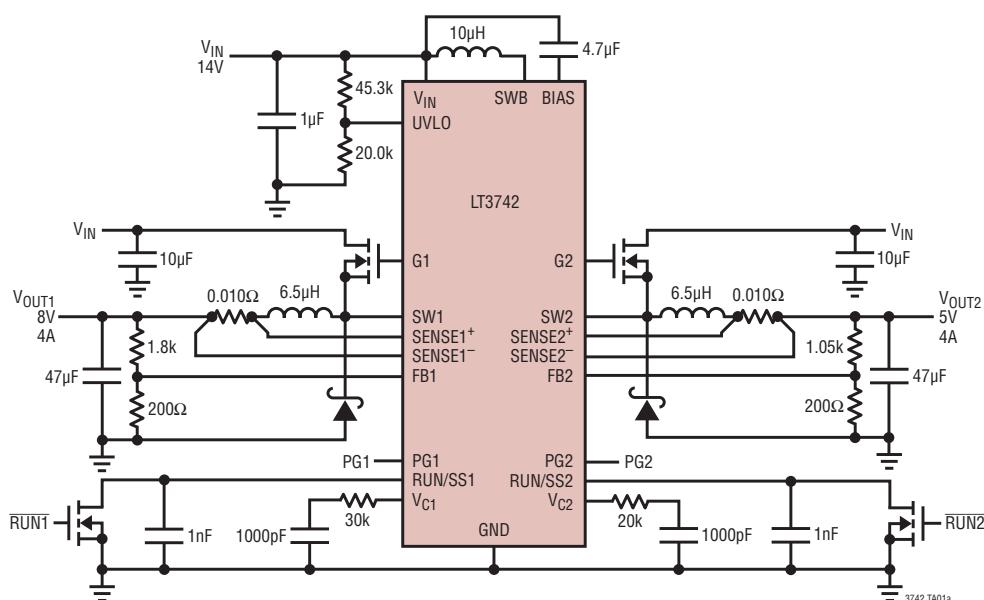

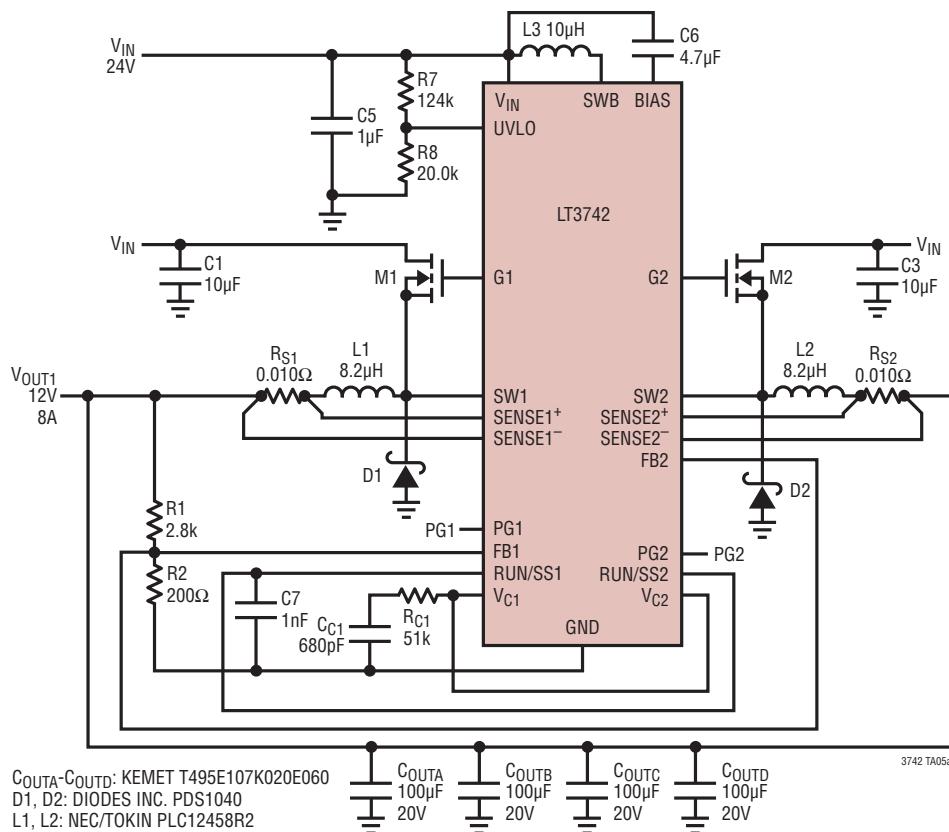

LT<sup>®</sup>3742はハイサイドNチャネル・パワーMOSFETをドライブするデュアル降圧DC/DCスイッチング・レギュレータ・コントローラです。500kHzの固定周波数電流モード・アーキテクチャにより、シンプルなループ補償部品を使用した高速過渡応答とサイクルごとの電流制限を実現します。2つのコントローラの出力段は位相を180°ずらして動作することによって入力リップル電流を低減するので、入力電源のノイズを最小限に抑え、入力容量を低減することができます。

内部の昇圧レギュレータがNチャネルMOSFETのゲートドライブを供給するための $V_{IN}+7V$ のバイアス・レールを生成するので、低損失の100%デューティサイクル動作が可能です。LT3742は、両方のコントローラが単独で動作することが必要なアプリケーションでも、両方のコントローラを使用して1つの高電流出力を供給するアプリケーションでも使用可能です。

LT3742は熱特性が改善された4mm×4mm QFNパッケージで供給されます。

**LT**、**LT**、**LTC**、**LTM**、Linear Technology、Linearのロゴ、PolyPhaseおよびBurst Modeはリニアテクノロジー社の登録商標です。No RSENSEはリニアテクノロジー社の商標です。その他すべての商標の所有権は、それぞれの所有者に帰属します。

## 標準的応用例

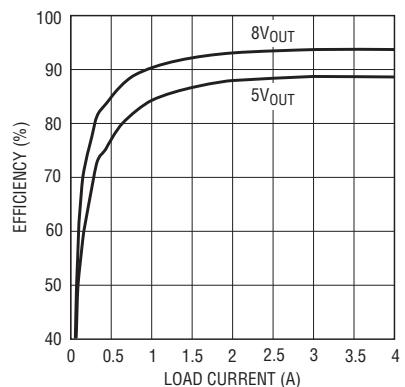

8Vと5Vのデュアル降圧コンバータ

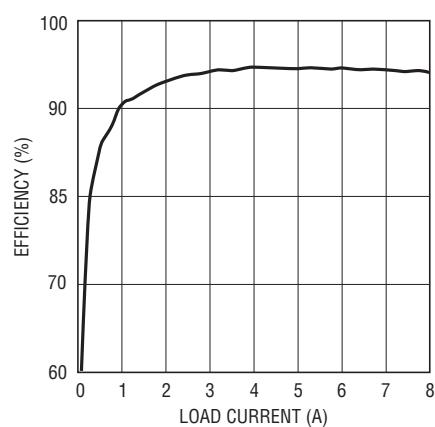

効率と負荷電流

3742 TA01b

3742fa

## 絶対最大定格

(Note 1)

|                                              |             |

|----------------------------------------------|-------------|

| V <sub>IN</sub> 電圧                           | 30V         |

| UVLO電圧                                       | 30V         |

| PG1、PG2の電圧                                   | 30V         |

| SWB、BIASの電圧                                  | 40V         |

| SENSE1 <sup>+</sup> 、SENSE2 <sup>+</sup> の電圧 | 30V         |

| SENSE1 <sup>-</sup> 、SENSE2 <sup>-</sup> の電圧 | 30V         |

| RUN/SS1、RUN/SS2の電圧                           | 6V          |

| FB1、FB2の電圧                                   | 6V          |

| V <sub>C1</sub> 、V <sub>C2</sub> の電圧         | 6V          |

| 接合部温度                                        | 125°C       |

| 動作接合部温度範囲 (Note 2)                           | -40°C~125°C |

| 保存温度範囲                                       | -65°C~125°C |

## ピン配置

## 発注情報

| 鉛フリー仕様        | テープアンドリール       | 製品マーキング | パッケージ                           | 温度範囲                    |

|---------------|-----------------|---------|---------------------------------|-------------------------|

| LT3742EUF#PBF | LT3742EUF#TRPBF | 3742    | 24-Lead (4mm × 4mm) Plastic QFN | -40°C to 125°C (Note 2) |

さらに広い動作温度範囲で規定されるデバイスについては、弊社または弊社代理店にお問い合わせください。

非標準の鉛ベース仕様の製品についても、弊社または弊社代理店にお問い合わせください。

鉛フリー仕様の製品マーキングの詳細については、<http://www.linear-tech.co.jp/leadfree/> をご覧ください。テープアンドリールの仕様の詳細については、<http://www.linear-tech.co.jp/tapeandreel/> をご覧ください。

## 電気的特性

●は全動作温度範囲の規格値を意味する。それ以外は $T_A = 25^{\circ}\text{C}$ での値。注記がない限り、 $V_{IN} = 5\text{V}$ 。

| PARAMETER                       | CONDITIONS                                                  | MIN | TYP   | MAX   | UNITS |    |

|---------------------------------|-------------------------------------------------------------|-----|-------|-------|-------|----|

| Minimum Operating Input Voltage | $V_{UVLO} = 1.5\text{V}$                                    | ●   | 3.5   | 4.0   | V     |    |

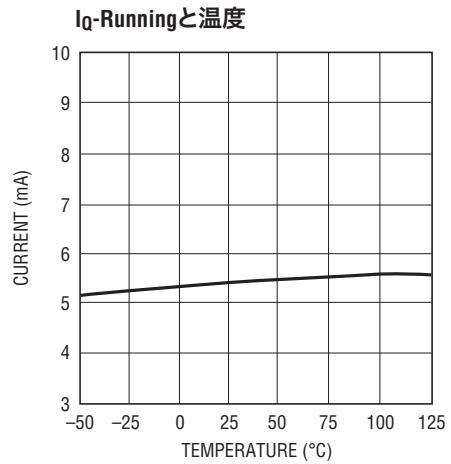

| Quiescent Current               | $V_{RUN/SS1} = V_{RUN/SS2} = V_{FB1} = V_{FB2} = 1\text{V}$ |     | 5.0   | 7.0   | mA    |    |

| Shutdown Current                | $V_{RUN/SS1} = V_{RUN/SS2} = 0\text{V}$                     |     | 20    | 35    | μA    |    |

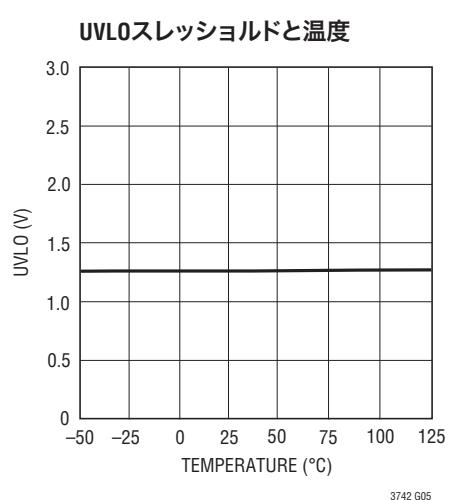

| UVLO Pin Threshold              | UVLO Pin Voltage Rising                                     | ●   | 1.20  | 1.25  | 1.28  | V  |

| UVLO Pin Hysteresis Current     | $V_{UVLO} = 1\text{V}$ , Current Flows Into Pin             |     | 1.8   | 3     | 4     | μA |

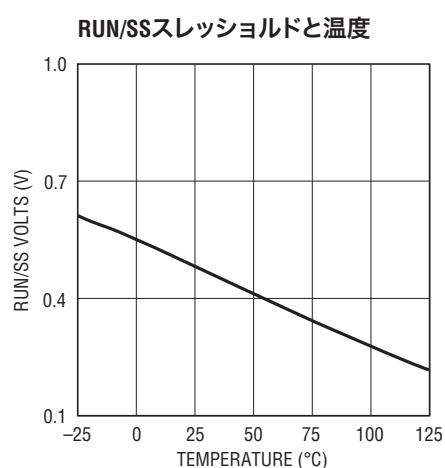

| RUN/SS Pin Threshold            |                                                             |     | 0.2   | 0.5   |       | V  |

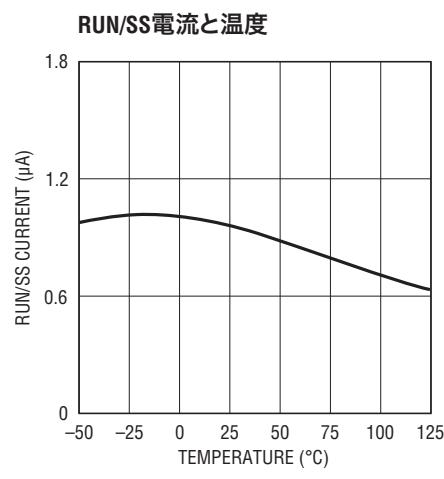

| RUN/SS Pin Charge Current       | $V_{RUN/SS} = 0\text{V}$                                    |     | 0.5   | 1     | 1.5   | μA |

| FB Pin Voltage                  |                                                             | ●   | 0.788 | 0.800 | 0.812 | V  |

| FB Pin Voltage Line Regulation  | $V_{IN} = 5\text{V}$ to $30\text{V}$                        |     | 0.01  |       | %/V   |    |

## 電気的特性

●は全動作温度範囲の規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。注記がない限り、 $V_{IN} = 5\text{V}$ 。

| PARAMETER                                   | CONDITIONS                                                         | MIN            | TYP          | MAX            | UNITS                        |    |

|---------------------------------------------|--------------------------------------------------------------------|----------------|--------------|----------------|------------------------------|----|

| FB Pin Bias Current                         | $V_{FB} = 0.8\text{V}, V_C = 0.4\text{V}$                          |                | 50           | 200            | nA                           |    |

| FB Pin Voltage Matching                     |                                                                    | -4             | 0            | 4              | mV                           |    |

| Error Amplifier Transconductance            |                                                                    |                | 250          |                | $\mu\text{mho}$              |    |

| Error Amplifier Voltage Gain                |                                                                    |                | 500          |                | V/V                          |    |

| $V_C$ Pin Source Current                    | $V_{FB} = 0.6\text{V}$                                             |                | 15           |                | $\mu\text{A}$                |    |

| $V_C$ Pin Sink Current                      | $V_{FB} = 1\text{V}$                                               |                | 15           |                | $\mu\text{A}$                |    |

| Controller Switching Frequency              |                                                                    | 440            | 500          | 560            | kHz                          |    |

| Switching Phase                             |                                                                    |                | 180          |                | Deg                          |    |

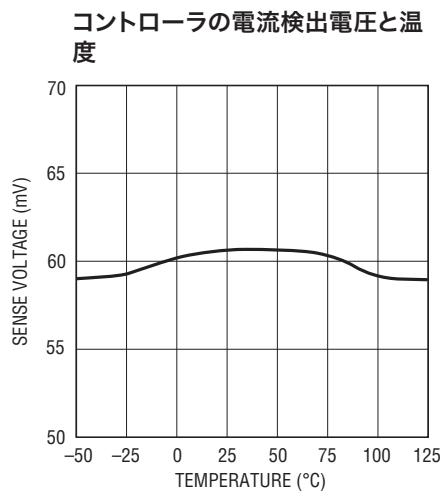

| Maximum Current Sense Voltage               | $V_{SENSE^-} = 3.3\text{V}$                                        | ●              | 50           | 60             | 70                           | mV |

| Current Sense Matching                      | Between Controllers                                                |                | $\pm 5$      |                | %                            |    |

| Current SENSE Pins Total Current            | $SENSE^-, SENSE^+ = 0\text{V}$<br>$SENSE^-, SENSE^+ = 3.3\text{V}$ |                | -1.0<br>40   |                | $\text{mA}$<br>$\mu\text{A}$ |    |

| Gate Rise Time                              | $C_{LOAD} = 3300\text{pF}$                                         |                | 40           |                | ns                           |    |

| Gate Fall Time                              | $C_{LOAD} = 3300\text{pF}$                                         |                | 60           |                | ns                           |    |

| Gate On Voltage ( $V_G - V_{SW}$ )          | $V_{BIAS} = 12\text{V}$                                            | 6.0            | 6.7          | 7.0            | V                            |    |

| Gate Off Voltage ( $V_G - V_{SW}$ )         | $V_{BIAS} = 12\text{V}$                                            |                | 0.4          | 0.75           | V                            |    |

| PG Pin Voltage Low                          | $I_{PG} = 100\mu\text{A}$                                          |                | 0.20         | 0.5            | V                            |    |

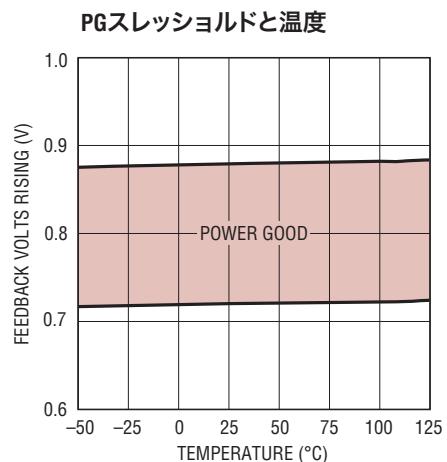

| Lower PG Trip Level (Relative to $V_{FB}$ ) | $V_{FB}$ Increasing                                                | -7             | -10          | -13            | %                            |    |

| Lower PG Trip Level (Relative to $V_{FB}$ ) | $V_{FB}$ Decreasing                                                | -10            | -13          | -16            | %                            |    |

| Upper PG Trip Level (Relative to $V_{FB}$ ) | $V_{FB}$ Increasing                                                | 7              | 10           | 13             | %                            |    |

| Upper PG Trip Level (Relative to $V_{FB}$ ) | $V_{FB}$ Decreasing                                                | 4              | 7            | 10             | %                            |    |

| PG Pin Leakage Current                      | $V_{PG} = 2\text{V}$                                               |                | 0.1          |                | $\mu\text{A}$                |    |

| PG Pin Sink Current                         | $V_{PG} = 0.5\text{V}$                                             | 200            | 500          |                | $\mu\text{A}$                |    |

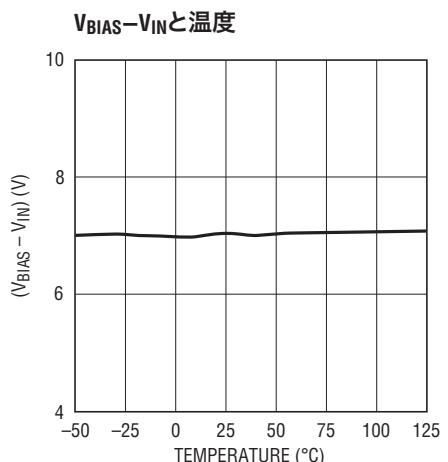

| Bias Pin Voltage                            |                                                                    | $V_{IN} + 6.6$ | $V_{IN} + 7$ | $V_{IN} + 7.7$ | V                            |    |

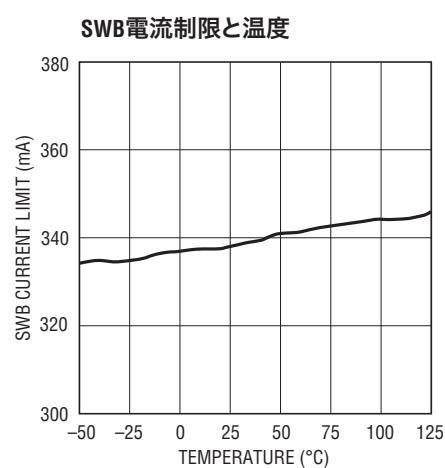

| SWB Pin Current Limit                       |                                                                    | 250            | 340          | 500            | mA                           |    |

| SWB Pin Leakage Current                     | $V_{SWB} = 12\text{V}$                                             |                | 0.01         | 1              | $\mu\text{A}$                |    |

| Bias Supply Switching Frequency             |                                                                    | 0.88           | 1.0          | 1.12           | MHz                          |    |

Note 1: 絶対最大定格に記載された値を超えるストレスはデバイスに永続的損傷を与える可能性がある。長期にわたって絶対最大定格条件に曝すと、デバイスの信頼性と寿命に悪影響を与える可能性がある。

Note 2: LT3742Eは $0^\circ\text{C} \sim 125^\circ\text{C}$ の動作接合部温度範囲で性能仕様に適合することが保証されている。 $-40^\circ\text{C} \sim 125^\circ\text{C}$ の動作接合部温度範囲での仕様は、設計、特性評価および統計学的なプロセス・コントロールとの相関で確認されている。

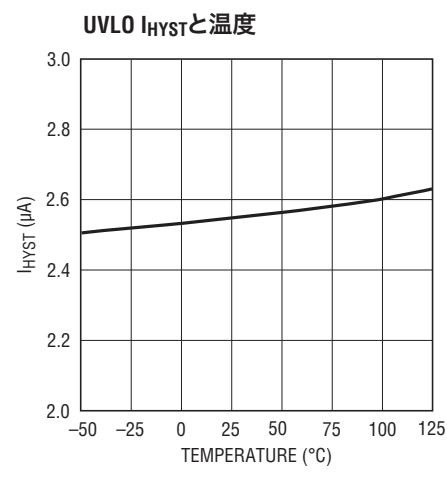

## 標準的性能特性

## 標準的性能特性

## ピン機能

**G1、G2(ピン1、6)**: ゲート・ドライブ。これらのピンは外部NチャネルMOSFETの高電流ゲート・ドライブを与えます。これらのピンはフローティング・ドライバの出力で、それらの電圧はBIASピンとSWピンの間を振幅します。

**V<sub>IN</sub>(ピン2)**: 入力電圧。このピンはLT3742の内部回路に電流を供給します。このピンはコンデンサでローカルにバイパスする必要があります。

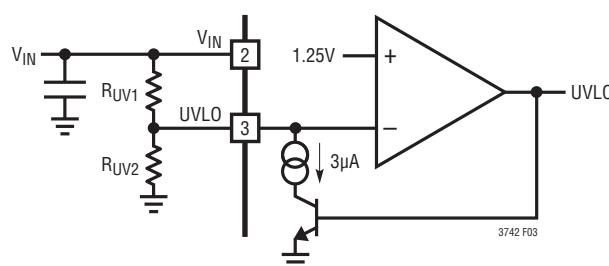

**UVLO(ピン3)**: 低電圧ロックアウト。このピンをオープン状態のままにしないでください。使用しない場合はV<sub>IN</sub>に接続してください。V<sub>IN</sub>に接続された抵抗分割器をこのピンに接続して、LT3742が動作する最小入力電圧をプログラムします。このピンが1.25Vを下回ると、コントローラがディスエーブルされます(RUN/SSピンは各スイッチング・レギュレータをオンするのに依然として使われます)。このピンが1.25Vより下に下がると、3μAの電流シンクがこのピンに電流を流してUVLOのプログラム可能なヒステリシスを与えます。

**BIAS(ピン4)**: ゲート・ドライブのバイアス。このピンは、外部NチャネルMOSFETをドライブするための、入力電圧より高いバイアス電圧を与えます。このピンの電圧はV<sub>IN</sub>+7Vに安定化されます。

**SWB(ピン5)**: バイアス・レギュレータ・スイッチ。これは、外部NチャネルMOSFETのゲートをドライブするバイアス電圧を発生するのに使われる内部NPNスイッチのコレクタです。

**RUN/SS1、RUN/SS2(ピン16、15)**: 実行/ソフトスタート・ピン。これらのピンは各コントローラをシャットダウンするのに使われます。これらは、外部コンデンサを追加するとソフトスタート機能も提供します。どのレギュレータをシャットダウンするにも、オープン・ドレインまたはオープン・コレクタのデバイスを使ってRUN/SSピンをグランドに引き下げます。どちらの機能も利用しない場合、これらのピンは未接続のままになります。

**PG1、PG2(ピン17、14)**: パワーグッド。これらのピンは内部コンパレータのオープン・コレクタ出力です。PGはFBピンが最終安定化電圧の90%以内に入るまで“L”に保たれます。PGピンは、出力の安定化状態の表示だけでなく、スイッチング・レギュレータのシーケンスの制御に使うことができます。PG出力はV<sub>IN</sub>が4Vを超えており、どちらかのRUN/SSピンが“H”的とき有効です。パワーグッド・コンパレータはシャットダウン時にはディスエーブルされます。使用しない場合、これらのピンは未接続のままになります。

**V<sub>C1</sub>、V<sub>C2</sub>(ピン18、13)**: 内部誤差アンプの制御電圧と補償ピン。これらのピンからグランドに直列にRCを接続して各スイッチング・レギュレータのループを補償します。

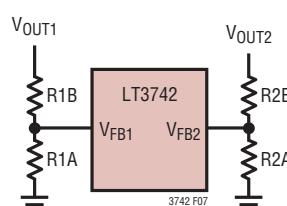

**FB1、FB2(ピン19、12)**: 帰還ピン。LT3742はこれらのピンを800mVに安定化します。帰還抵抗をこのピンに接続して各スイッチング・レギュレータの出力電圧を設定します。

**SENSE1<sup>-</sup>、SENSE2<sup>-</sup>(ピン20、11)**: 負電流検出入力。(SENSE<sup>+</sup>ピンとともに)これらのピンは各スイッチング・レギュレータのインダクタ電流を検出するのに使います。

**SENSE1<sup>+</sup>、SENSE2<sup>+</sup>(ピン21、10)**: 正電流検出入力。(SENSE<sup>-</sup>ピンとともに)これらのピンは各スイッチング・レギュレータのインダクタ電流を検出するのに使います。

**SW1、SW2(ピン24、7)**: スイッチ・ノード。これらのピンは外部NチャネルMOSFETのソースおよび外部のインダクタとダイオードに接続します。

**露出パッド(ピン25)**: グランド。パッケージの露出パッドにより、グランドへの電気的接触とプリント回路基板への十分な熱的接触の両方が与えられます。最適動作を保証するため、露出パッドを回路基板に半田付けする必要があります。

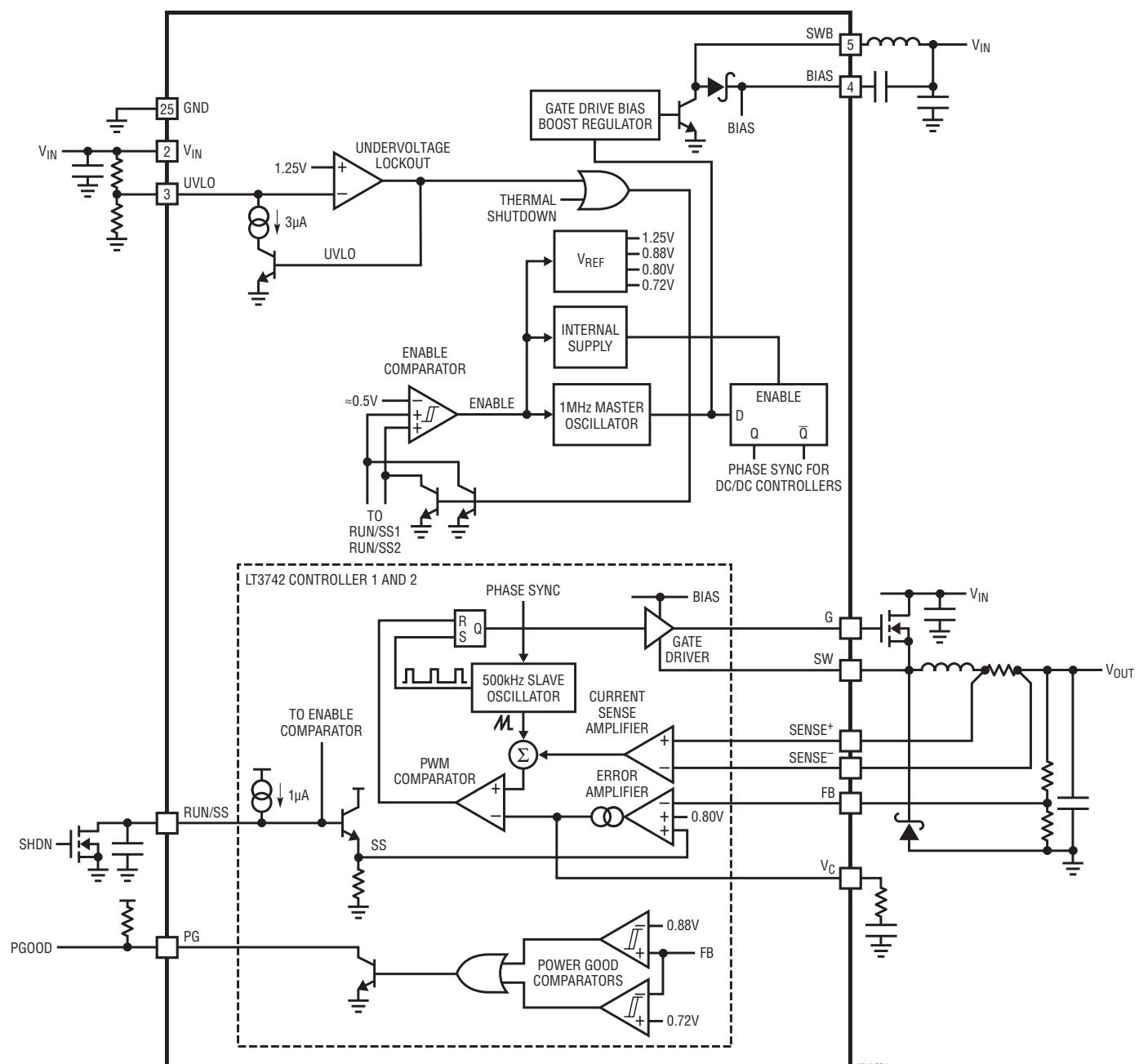

## ブロック図

## 動作

LT3742はデュアル、固定周波数、電流モードDC/DC降圧コントローラです。各デバイスに内蔵された2個のコントローラは、保護回路、内部バイアス電源、電圧リファレンス、マスタ発振器およびゲート・ドライブ用昇圧レギュレータを含む共通回路を共有しています。ブロック図には共有された共通回路と両方のDC/DCコントローラの独立した回路が示されています。

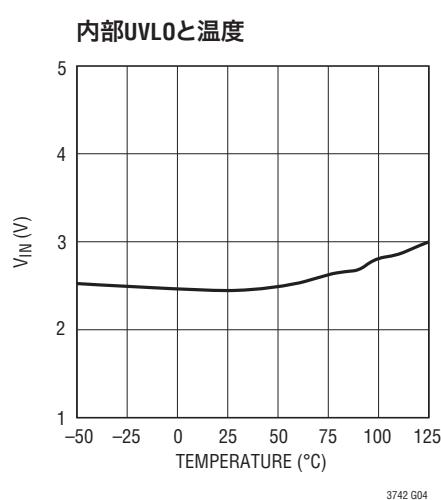

LT3742に含まれている重要な保護機能は低電圧ロックアウトとサーマル・シャットダウンです。これらの状態のどちらかが存在すると、ゲート・ドライブ・バイアス・レギュレータと両方のDC/DCコントローラがディスエーブルされ、両方のRUN/SSピンが0.5Vに放電して新しいソフトスタート・サイクルに備えます。低電圧ロックアウト(UVLO)は2個の外部抵抗を使ってプログラムします。UVLOピンが1.25Vより下に下がると、 $3\mu\text{A}$ の電流シンクが作動してUVLO機能のプログラム可能なヒステリシスを与えます。 $V_{IN}$ が2.5Vを下回ると、精度が劣る別の内部低電圧ロックアウトがLT3742をディスエーブルします。

全ての内部フォールト状態がクリアされると、ゲート・ドライブ用昇圧レギュレータがイネーブルされます。このレギュレータは内部NPNパワー・スイッチとショットキー・ダイオードの両方を使って、入力電圧より7V高い電圧をBIASピンに発生します。BIAS電圧がその最終安定化電圧の約90%に達するまで、両方のDC/DCコントローラはディスエーブルされます。これにより、ドライバがオンするのを許される前に、外部MOSFETを完全にエンハンスされた状態にするのに十分なゲート・ドライブが存在することが保証されます。

マスタ発振器は1MHzで動作し、この周波数でゲート・ドライブ用昇圧レギュレータにクロックを与えます。マスタ発振器は、DC/DCコントローラのために、180°位相がずれた2つの500kHzクロックも発生します。

FBピンが800mVの内部リファレンス電圧の±10%以内になると、パワーグッド・コンパレータがPGピンを“L”に引き下げます。PGはFBピンが安定化しているときオフしているNPNのオープン・コレクタ出力なので、外部抵抗によりPGピンを“H”に引き上げることができます。デバイスがイネーブルされていて(RUN/SSが“H”)、 $V_{IN}$ が4V以上のときだけ、このパワーグッドの表示は有効です。

LT3742は、各コントローラのRUN/SSピンが0.5Vを超えるとき、各コントローラが自己のソフトスタート・ランプを発生するとき、各コントローラを独立にイネーブルします。起動時、誤差アンプはFBピンを(800mVリファレンスの代わりに)ソフトスタート・ランプと比較しますので、出力電圧が抵抗でプログラムされた安定化ポイントに達するまで、出力電圧をゆっくり上昇させます。出力電圧に達するまで、インダクタ電流が厳密に制御されます。LT3742は両方のDC/DCコントローラが個別に動作する必要のあるアプリケーションに最適です。

500kHz発振器からのパルスにより、RSフリップ・フロップがセットされ、外部NチャネルMOSFETをオンします。スイッチと外部インダクタを流れる電流が増加し始めます。この電流が制御電圧( $V_C$ )で定まるレベルに達すると、PWMコンパレータがフリップ・フロップをリセットしてMOSFETをオフします。すると、インダクタの電流は外部ショットキー・ダイオードを通って流れ、減少し始めます。スレーブ発振器からの次のセット・パルスにより、このサイクルが再度開始されます。このようにして、 $V_C$ ピンの電圧により、インダクタを通して出力に流れる電流が制御されます。内部誤差アンプは $V_C$ ピンの電圧を連続的に調整して出力電圧を安定化します。サイクルごとのピーク・インダクタ電流の直接制御は電流検出アンプによって管理されます。インダクタ電流が常時モニタされるので、デバイスは本質的に優れた出力短絡保護を与えます。

## アプリケーション情報

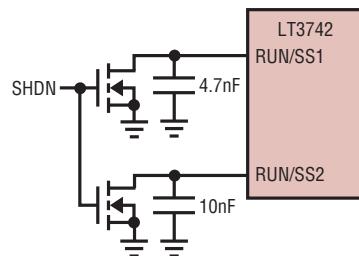

### ソフトスタートとシャットダウン

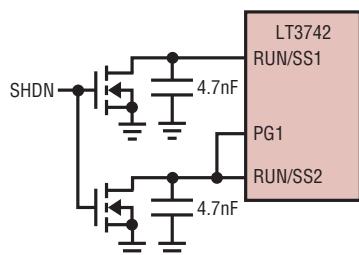

RUN/SS(実行/ソフトスタート)ピンは各コントローラを独立にイネーブルするのに使われ、また、起動時にピーク電流を下げて出力電圧のオーバーシュートを防ぐためのユーザーがプログラマ可能なソフトスタート機能を与えるのに使われます。どちらのコントローラをディスエーブルするにも、オープン・ドラインまたはオープン・コレクタのデバイスを使って該当するRUN/SSピンをグランドに引き下げます。両方のRUN/SSピンをグランドに引き下げるときLT3742はシャットダウン・モードになります。消費電流は $20\mu A$ に減少します。内部 $1\mu A$ 電流源が各RUN/SSピンを引き上げ、どちらかのピンが $0.5V$ に達すると、内部バイアス電源、ゲート・ドライブ用昇圧レギュレータ、電圧リファレンスおよびマスター発振器とともに、該当するコントローラがイネーブルされます。両方の出力が常に一緒にイネーブルされる場合、両方のRUN/SSピンと一緒に接続して1個のソフトスタート・コンデンサを使うことができます。

### ソフトスタートの利点

コンデンサがRUN/SSピンからグランドに接続されているとき、内部 $1\mu A$ プルアップ電流源によりこのピンの電圧がランプアップします。起動時、誤差アンプはFBピンを(800mVリファレン

スの代わりに)このランプと比較しますので、インダクタ電流の制御を維持しながら、出力電圧をその最終値までゆっくり滑らかに上昇させます。インダクタ電流と出力電圧の波形を常にチェックして、プログラムされたソフトスタート時間が十分長いことを保証します。 $V_{IN}$ が(UVLOピンを使ってプログラムされた)低電圧ロックアウトをトリガするのに十分なだけ低下するか、またはLT3742のダイ温度がサーマル・シャットダウンを超えると、新たにソフトスタート・サイクルが開始されます。ソフトスタート・コンデンサの標準的値は $1nF$ です。

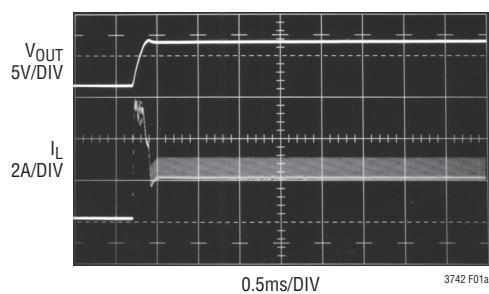

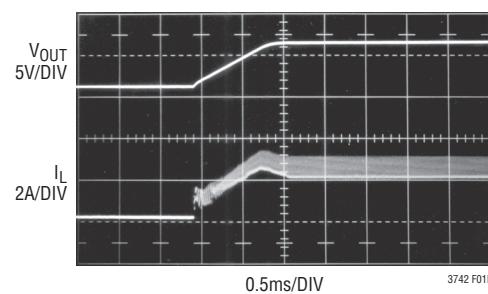

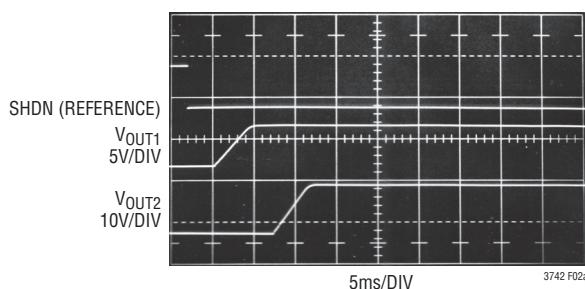

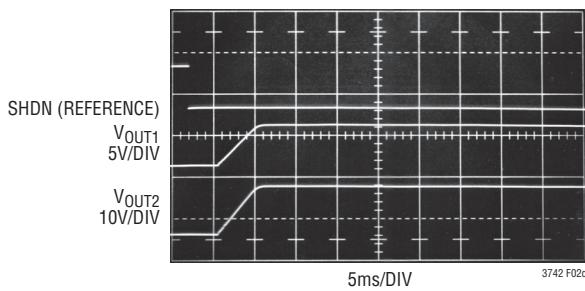

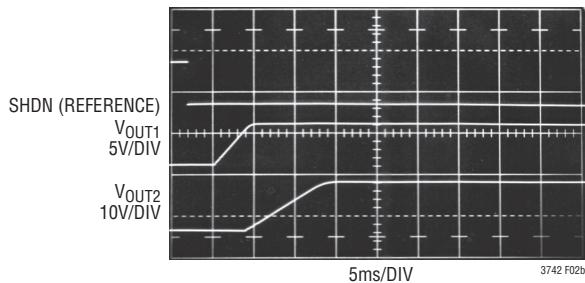

ソフトスタートは外部のパワーMOSFETとキャッチ・ダイオードに与えるストレスを最小に抑えるので、LT3742の全てのアプリケーションにソフトスタートを強く推奨します。ソフトスタートなしでは、これら両方の部品は起動サイクルごとに最大電流リミットに曝されます。表紙ページの回路のソフトスタートの起動波形とソフトスタートなしの起動波形を図1aと図1bに示します。ソフトスタートを使わない場合の、大きなインダクタ電流スパイクと出力電圧のオーバーシュートに注目してください。システムによってはこれを許容できるかもしれません、1個のコンデンサを追加すると各DC/DCコントローラの起動時の振舞いが劇的に改善されます。

図1a. ソフトスタートなしの起動波形

図1b. 1nFソフトスタート・コンデンサを使った起動波形

## アプリケーション情報

### パワーグッド・インジケータ

PGピンは内部ウインドウ・コンパレータのオープン・コレクタ出力であり、FBピンが $\pm 800\text{mV}$ の内部リファレンス電圧の $\pm 10\%$ 以内にないと“L”に引き下げられます。PGピンは $200\mu\text{A}$ 以下の電流を流すプルアップ抵抗を使って $30\text{V}$ 以下の電源に接続します。このピンは、FBピンの電圧に関係なく、LT3742がシャットダウン・モードになるとオブンになります。LT3742がイネーブルされていて(RUN/SSが“H”)、 $V_{IN}$ が $4\text{V}$ 以上のときだけ、パワーグッドの表示は有効です。

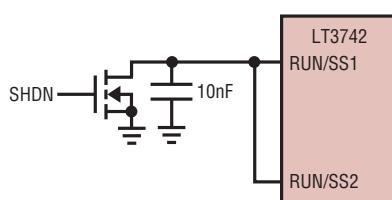

図2a. コントローラ1が安定化されるまでコントローラ2が遅延する電源シーケンシング

図2b. コントローラ1に対するコントローラ2の遅延が固定されている電源シーケンシング

図2c. レシオメトリック・トラッキングで両方のコントローラが一緒に起動

## アプリケーション情報

大きくなります。この方法に関して注意すべき1つの特性は、コントローラ1の出力がパワーグッド・コンパレータをトリップするほど安定化状態から外れると、コントローラ2がディスエーブルされることです。

図2bで、RUN/SS2のコンデンサの方がわずかに大きいと、コントローラ1に比べてコントローラ2のターンオンが遅れます。この方法の起動波形は図6aに示されている波形に非常によく似ていますが、この場合はコントローラ1が安定化状態から外れてもコントローラ1はディスエーブルされません。

図2cでは、両方のRUN/SSピンが1個のコンデンサを共有しており、同時に起動します。同じソフトスタート信号を共有しているので、この方法では2つの出力のレシオメトリック・トラッキングが実現されます。

### 低電圧ロックアウト(UVLO)

外部抵抗分割器を使って、LT3742が動作する最小入力電圧を精確に設定することができます。基本となるUVLO動作を図3に示します。UVLOピンが1.25Vより下に下がると、低電圧ロックアウトの発生が通知され、3μA電流源がオンしてヒステリシスを与えます。

UVLOが発生している間、両方のコントローラとゲート・ドライブ用昇圧レギュレータがディスエーブルされます。LT3742の場合、全てのRUN/SSピンが放電し、新たなソフトスタート・サイクルの準備が整います。イネーブルされている各コントローラでは、入力電圧が上側のUVLOトリップ電圧を超えて上昇するまで、該当するRUN/SSピンが500mVに保たれます。コントローラの片方または両方がRUN/SSピンによってイネーブルされているときだけUVLO機能は作動します。デバイスを直接起

動するためにUVLOピンを使うことはできません。使わない場合、UVLOピンは未接続のままにしないで $V_{IN}$ に接続します。 $V_{IN}$ が2.5Vを下回ると、精度が劣る別の内部低電圧ロックアウトがLT3742をディスエーブルします。

望みの最小動作電圧( $V_{IN(MIN)}$ )と望みの大きさのヒステリシス( $V_{HYST}$ )を与えるようにUVLO抵抗の値を選択します。LT3742は入力電圧が( $V_{IN(MIN)} + V_{HYST}$ )を超えるとオンし、一旦オンした後は、 $V_{IN}$ が $V_{IN(MIN)}$ より下に下がるとオフします。 $R_{UV1}$ の値を最初に選択してから $R_{UV2}$ の値を選択します。

$$R_{UV1} = \frac{V_{HYST}}{3\mu A}$$

$$R_{UV2} = R_{UV1} \cdot \frac{1.25V}{V_{IN(MIN)} - 1.25V}$$

### 入力電圧範囲

最小入力電圧はLT3742の4Vの最小動作電圧(UVLO)または与えられたアプリケーションの出力電圧のどちらかによって決まります。LT3742は100%のデューティ・サイクルで動作可能なので、入力電圧が出力電圧の1つの近くまで、または等しい値まで低下すると、コントローラは低ドロップアウト動作(100%デューティ・サイクル)になります。デューティ・サイクルは各スイッチ・サイクルでNチャネルMOSFETがオンしている時間の割合であり、次のように入力電圧と出力電圧によって決まります。

$$DC = \left( \frac{V_{OUT} + V_D}{V_{IN} - V_{DS} + V_D} \right)$$

ここで $V_D$ はキャッチ・ダイオードの順方向電圧降下(約0.4V)、 $V_{DS}$ はMOSFETの標準的電圧降下(約0.1V)です。

図3. 低電圧ロックアウト

## アプリケーション情報

最大入力電圧はV<sub>IN</sub>ピンとBIASピンの絶対最大定格(それぞれ30Vと40V)および最小デューティ・サイクル(DC<sub>MIN</sub>=15%)によって決まります。

$$V_{IN(MAX)} = \left( \frac{V_{OUT} + V_D}{DC_{MIN}} \right) + V_{SW} - V_D$$

上式はデバイスがパルス・スキップなしに安定化するのを可能にする最大入力電圧を計算しますが、最大入力電圧は主に出力電圧が3.3Vより低いアプリケーションで問題になります。たとえば、2.5Vの出力では、最大入力電圧は次のようになります。

$$V_{IN(MAX)} = \left( \frac{2.5V + 0.4V}{0.15} \right) + 0.1V - 0.4V = 19V$$

19Vより高い入力電圧が使われる場合、2.5Vの出力はそれでも正しく安定化しますが、そうするためにデバイスはパルス・スキップする必要があります。パルス・スキップはLT3742に損傷を与えるはしませんが、インダクタ電流波形が不規則になり、ピーク電流が高くなります。これは特定の出力電圧にだけ適応される動作入力電圧に対する制限であることに注意してください。回路自体は絶対最大定格までの入力に耐えます。

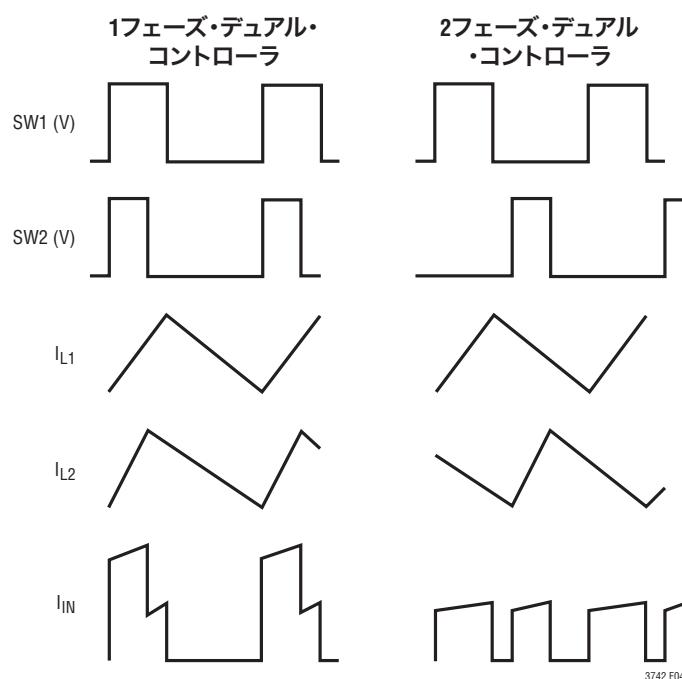

## 2フェーズ動作の利点

従来、デュアル・コントローラは単一位相で動作します。つまり、両方のパワーMOSFETが同時にオンするので、単一レギュレータの電流パルスの振幅の2倍の振幅の電流パルスが入力コンデンサから流れます。これらの振幅の大きなパルスによって入力コンデンサに流れ込むRMS電流が増大するので、大きく高価な入力コンデンサを使う必要があり、EMIが増加し、入力コンデンサと入力電源の電力損失が増加します。

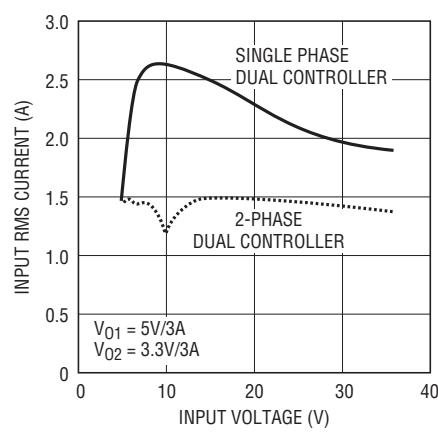

LT3742の2個のコントローラは180°位相がずれて動作することが設計によって保証されています。これにより、各パワーMOSFETの電流が決してオーバーラップしないことが保証されますので、常に入力コンデンサに要求されるピーク電流とRMS電流がかなり低くなります。このため、小さく安価なコンデンサを使用することが可能になり、EMI性能と実際の動作効率が改善されます。

1フェーズ・デュアル・コントローラと2フェーズLT3742システムの波形の例を図4に示します。この場合、それぞれ2Aの負荷電流を流す、5Vと3.3Vの出力が12V電源から得られます。この例では、2フェーズ動作のRMS入力コンデンサ電流は約

図4. 1フェーズ・デュアル・コントローラと2フェーズLT3742の波形例

## アプリケーション情報

1.8ARMSから約0.8ARMSに減少します。これ自体でも大きな減少ですが、電力損失は $I_{RMS}$ の二乗に比例するので、入力コンデンサによって実際に浪費される電力は約4分の1に減少することに注意してください。標準的アプリケーションのRMSリップル電流の減少を図5に示します。

入力リップル電流の減少は、入力電力経路で失われる電力も減少することを意味します。入力のRMS電流とRMS電圧の減少の直接の結果として伝導EMIと放射EMIも改善されます。RMS電流定格の低い小型で安価な入力コンデンサを使うことができるので、コストと基板のフットプリントを大幅に節約できます。

もちろん、2フェーズ動作で得られる性能の改善は2つのコントローラの相対デューティ・サイクルの関数なので、結局は入力電圧( $DC \approx V_{OUT}/V_{IN}$ )に依存します。

2フェーズ動作の利点は狭い動作範囲に限定されないで、事実広い領域に及ぶことがすぐに分かります。ほとんどのアプリケーションに適用可能な経験則によれば、2フェーズ動作では入力コンデンサの条件が、最大電流で50%のデューティ・サイクルで1チャネルだけが動作している場合の条件にまで緩和されます。

### インダクタの値の選択

インダクタの値はインダクタ・リップル電流( $I_{RIPPLE}$ )と最大出力電流( $I_{OUT(MAX)}$ )に直接影響を与えます。リップル電流が小さいと、インダクタのコア損失、出力コンデンサのESR損失、さらに出力電圧リップルが減少します。ただし、値が大きすぎると、物理的に大きなインダクタになります。妥当なトレードオフとして、最大出力電流の約30%のインダクタ・リップル電流を選択します。これは、インダクタのサイズ、最大出力電流およびリップル電流の大きさの間に妥当なトレードオフを与えます。最大リップル電流は最も高い入力電圧で生じますので、 $V_{IN}$ 範囲が広いアプリケーションでは、インダクタの値を計算するとき $V_{IN(TYP)}$ と $V_{IN(MAX)}$ の両方を考慮に入れるよう注意してください。

$$L \geq \frac{V_{IN} - V_{OUT}}{0.3 \cdot I_{OUT(MAX)}} \cdot \frac{V_{OUT}}{V_{IN}} \cdot \frac{1}{500\text{kHz}}$$

この式はインダクタの値を選択するときの妥当な出発点を与えます。ほとんどのシステムは10%～50%の範囲のリップル電流を容易に許容しますので、計算値からのわずかな偏りはほとんどのアプリケーションで問題ありません。

図5. RMS入力電流の比較

## アプリケーション情報

上で計算した値に近い標準値のインダクタを選択し、リップルの大きさを再チェックします。

$$I_{\text{RIPPLE}} = \frac{V_{\text{IN}} - V_{\text{OUT}}}{L} \cdot \frac{V_{\text{OUT}}}{V_{\text{IN}}} \cdot \frac{1}{500\text{kHz}}$$

インダクタのDC抵抗(DCR)は $I^2R_{\text{DCR}}$ の電力損失を生じるので、システム全体の効率に大きな影響を与えることがあります。インダクタを選択するときは、インダクタンスの値、DCRおよび電流定格を検討します。推奨インダクタ・メーカーを数社表1に示します。各社とも、多様な値、電流定格、およびパッケージ寸法の多数のデバイスを提供しています。

表1. 推奨インダクタ・メーカー

| VENDOR    | WEBSITE                                                                |

|-----------|------------------------------------------------------------------------|

| Sumida    | <a href="http://www.sumida.com">www.sumida.com</a>                     |

| Toko      | <a href="http://www.toko.com">www.toko.com</a>                         |

| Würth     | <a href="http://www.we-online.com">www.we-online.com</a>               |

| NEC-Tokin | <a href="http://www.nec-tokinamerica.com">www.nec-tokinamerica.com</a> |

| TDK       | <a href="http://www.tdk.com">www.tdk.com</a>                           |

### 最大出力電流( $R_{\text{SENSE}}$ の値の選択)

最大出力電流は電流センス抵抗 $R_{\text{SENSE}}$ の値(これによってインダクタのピーク電流が設定されます)とインダクタの値(これによってインダクタのリップル電流が設定されます)によって大体決まります。LT3742の電流コンパレータは50mVの保証最小スレッショルドを備えており、これはデューティ・サイクルにともなって変化することはありません。最大出力電流は次のように計算されます。

$$I_{\text{OUT(MAX)}} = \frac{50\text{mV}}{R_{\text{SENSE}}} - \frac{I_{\text{RIPPLE}}}{2}$$

上式を整理して $R_{\text{SENSE}}$ を次のように求めます。

$$R_{\text{SENSE}} = \frac{50\text{mV}}{I_{\text{OUT(MAX)}} + \left(\frac{I_{\text{RIPPLE}}}{2}\right)}$$

### インダクタ、キャッチ・ダイオードおよびMOSFETの電流定格

インダクタと $R_{\text{SENSE}}$ の値を選択したら、インダクタ、キャッチ・ダイオードおよびMOSFETの電流定格を決めることができます。LT3742の電流コンパレータは70mVの保証最大スレッショルドを備えており、電流検出コンパレータの応答時間によって生じる少量の電流オーバーシュートがあります。部品は次の電流を扱えるように定格が定められています。

$$I_{\text{RATED}} \geq \frac{70\text{mV}}{R_{\text{SENSE}}} + \left(\frac{V_{\text{IN}}}{L} \cdot 100\text{ns}\right)$$

### ショットキー・キャッチ・ダイオードの選択

出力の短絡時、ダイオードはほとんどの時間電流を流しますので、電流定格が十分なデバイスを選択することが重要です。さらに、ダイオードの逆電圧定格は最大入力電圧より大きくなればなりません。多くの表面実装型ショットキー・ダイオードが非常に小さなパッケージで供給されています。それらは一般に温度によるディレーティングが必要なので、それらのデータシートを注意深く読んでください。基本的に、過熱状態では、それらを最大定格電流で効果的に使用することが妨げられます。いくつかの推奨ダイオードを表2に示します。

表2. 推奨ショットキー・ダイオード

| VENDOR                                                                 | DEVICE                                 |

|------------------------------------------------------------------------|----------------------------------------|

| Diodes, Inc.<br><a href="http://www.diodes.com">www.diodes.com</a>     | PDS540 (5A, 40V)<br>SBM1040 (10A, 40V) |

| Microsemi<br><a href="http://www.microsemi.com">www.microsemi.com</a>  | UPS340 (3A, 40V)<br>UPS840 (8A, 40V)   |

| On Semiconductor<br><a href="http://www.onsemi.com">www.onsemi.com</a> | MBRD320 (3A, 20V)<br>MBRD340 (3A, 40V) |

### パワーMOSFETの選択

Nチャネル・パワーMOSFETを選択するとき検討すべき重要ないくつかのパラメータがあります。それらは、ドレン電流(最大 $I_D$ )、ブレークダウン電圧(最大 $V_{DS}$ と $V_{GS}$ )、スレッショルド電圧( $V_{GS(\text{TH})}$ )、オン抵抗( $R_{DS(\text{ON})}$ )、逆伝達容量( $C_{RSS}$ )、および全ゲート電荷( $Q_G$ )です。選択作業を容易にするいくつかの簡単なガイドラインがあります。

## アプリケーション情報

最大ドレイン電流が、前のページで計算した最大定格電流( $I_{RATED}$ )より大きくなればなりません。 $I_D$ の仕様は温度に大きく依存するので(周囲温度が高いほど $I_D$ が低くなる)、これを示すため、ほとんどのデータシートには「 $I_D$ と温度」のグラフまたは表が与えられていることに注意してください。

$V_{DS}$ ブレークダウン電圧が最大入力電圧より大きく、 $V_{GS}$ ブレークダウン電圧が8V以上であることを確認してください。各MOSFETのピーク・トゥ・ピーク・ゲート・ドライブは約7Vなので、選択したデバイスが7Vの $V_{GS}$ で完全にエンハンスされることも確認してください。このため、 $V_{GS}$ 定格が20VのMOSFETの中にはスレッショルド電圧が高すぎるものがあるので、それらの使用が除外されることがあります。大雑把に言うと、最大スレッショルド電圧は $V_{GS(TH)}(\text{MAX}) \leq 3\text{V}$ にします。4.5V MOSFETも使えます。

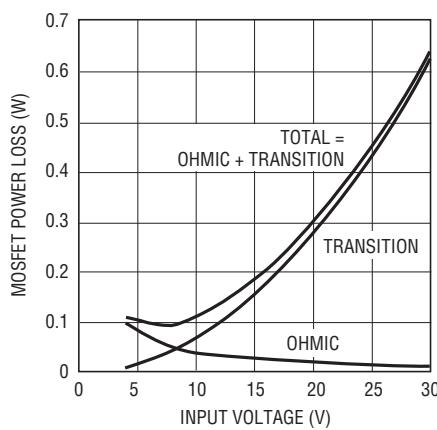

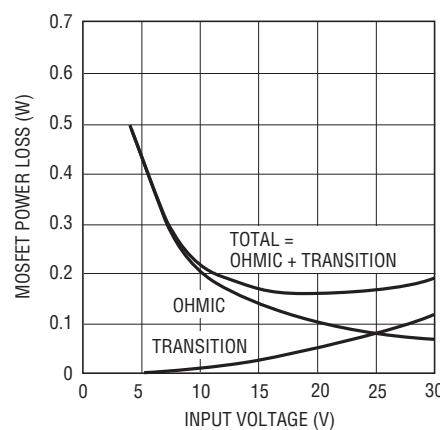

NチャネルMOSFETの電力損失は2つの主な要因、つまりオン抵抗( $R_{DS(ON)}$ )と逆伝達容量( $C_{RSS}$ )から生じます。オン抵抗はオーミック損失( $I^2 R_{DS(ON)}$ )を生じ、一般に約16Vより下の入力電圧で支配的です。逆伝達容量は遷移損失を生じ、約15Vより上の入力電圧で支配的です。もっと高い入力電圧では、遷移損失が急速に増加し、 $C_{RSS}$ が低くて $R_{DS(ON)}$ が大きいデバイスを使う方が実際には効率が上がるポイントにまで達します。MOSFETの電力損失は以下の式で近似することができます。

$$P_{LOSS} = (\text{オーミック損失}) + (\text{遷移損失})$$

$$P_{LOSS} \approx \left( \frac{V_{OUT} + V_D}{V_{IN} + V_D} \cdot I_{OUT}^2 R_{DS(ON)} \cdot \rho_T \right) \\ \left( 2 \cdot V_{IN}^2 \cdot I_{OUT} \cdot C_{RSS} \cdot f \right)$$

ここで、 $f$ はスイッチング周波数(500kHz)、 $\rho_T$ は温度によるオン抵抗の変化を考慮した正規化項です。70°Cの最大周囲温度では、妥当な選択として $\rho_T \approx 1.3$ を使います。

$R_{DS(ON)}$ と $C_{RSS}$ のトレードオフは実際のMOSFETの値を使った例によって容易に見て取ることができます。3.3V、3A(10W)の出力を発生するため、2つの標準的Nチャネル・パワーMOSFETを検討します。両方とも $V_{DS} = 30\text{V}$ で定格が定められており、両方とも同じSO-8パッケージで供給されますが、オン抵抗と逆伝達容量に約5倍の差があります。

M1:  $I_D = 11.5\text{A}$ ,  $V_{GS} = 12\text{V}$ ,  $R_{DS(ON)} = 10\text{m}\Omega$ ,  $C_{RSS} = 230\text{pF}$

M2:  $I_D = 6.5\text{A}$ ,  $V_{GS} = 20\text{V}$ ,  $R_{DS(ON)} = 50\text{m}\Omega$ ,  $C_{RSS} = 45\text{pF}$

両方のデバイスの電力損失が広い入力電圧範囲( $4\text{V} \leq V_{IN} \leq 30\text{V}$ )にわたって計算され、(10Wの総電力のパーセンテージとして)図6に示されています。 $R_{DS(ON)}$ の低いデバイスの電力損失は、 $C_{RSS}$ の低いデバイスに比べて、低い入力電圧では1/5ほどですが、高い入力電圧では3倍大きいことに注意してください。

図6a. M1の電力損失の例(10mΩ、230pF)

図6b. M2の電力損失の例(50mΩ、45pF)

## アプリケーション情報

総ゲート電荷( $Q_G$ )は $C_{RSS}$ に緊密に関係しています。低ゲート電荷は小さな値の $C_{RSS}$ に対応します。多くのメーカーはMOSFETを「低ゲート電荷」デバイス(これは低 $C_{RSS}$ デバイスであることを意味します)として宣伝しますが、それらは遷移損失を下げるよう特に設計されており、入力電圧の高いアプリケーションに最適です。

### 入力コンデンサの選択

ほとんどのアプリケーションでは、 $10\mu F \sim 22\mu F$ の範囲のコンデンサで十分です。最適ノイズ耐性を得るために、小さな $1\mu F$ バイパス・コンデンサをLT3742の近くで、 $V_{IN}$ ピンとグランド・ピンの間に接続することも推奨します。降圧レギュレータには入力電源から高速の立上りと立下りを伴うパルス電流が流れます。その結果LT3742に生じる電圧リップルを減らし、非常に高い周波数のこのスイッチング電流を狭いローカル・ループに閉じ込めてEMIを抑えるために入力コンデンサが必要です。これを効果的に実現するには、入力コンデンサはスイッチング周波数でのインピーダンスが小さく、リップル電流定格が十分でなければなりません。2つのコントローラは同じ周波数で動作しますが、位相とデューティ・サイクルは異なっているので、入力コンデンサのRMS電流の計算は簡単ではありません。ただし、ほとんどの電力( $V_{OUT} \cdot I_{OUT}$ )を供給しているチャネルのRMS入力電流を控えめな値として使えます。

$$I_{RMS(CIN)} = \frac{I_{OUT}}{V_{IN}} \cdot \sqrt{V_{OUT} \cdot (V_{IN} - V_{OUT})}$$

$I_{RMS(CIN)}$ は $V_{IN} = 2V_{OUT}$ (DC = 50%)のとき最大になります。2番目の低電力チャネルに入力電流が流れるとき、位相のずれた電流が高電力チャネルに流れる電流を相殺するので、入力コンデンサのRMS電流は実際には減少します。したがって、RMSリップル電流定格が $I_{OUT,MAX}/2$ の入力コンデンサを選択すれば十分です。

セラミック・コンデンサはサイズが小さく、インピーダンスが低いので(低等価直列抵抗ESR)この用途に適しています。ESRが小さいと入力電圧リップルが非常に低くなり、コンデンサは大量のRMS電流を扱うことができます。セラミック・コンデンサは比較的堅牢であり、定格電圧で使うことができます。X5RとX7Rのタイプは他のセラミックに比べて広い電圧範囲と温度範囲で容量を維持するので、X5RまたはX7Rのタイプだけを使用します。

値の大きなセラミック・コンデンサの代替は、値の小さな( $1\mu F$ )セラミックと値の大きな( $10\mu F \sim 22\mu F$ )電解コンデンサまたはタンタル・コンデンサの併用です。入力ソースが印加されるとき入力コンデンサには大きなサージ電流が流れる可能性が高いので、タンタル・コンデンサは常にサージ定格が規定されている必要があります。メーカーがコンデンサの定格電圧より低い電圧での使用を推奨していることもあります。 $1\mu F$ のセラミック・コンデンサをNチャネル・パワーMOSFETのできるだけ近くに必ず配置します。

### 出力コンデンサの選択

出力容量の妥当な出発点としての値は、出力電流1Aごとに $10\mu F$ の $C_{OUT}$ を与えることです。低い出力電圧(3.3V以下)の場合や、できるだけ良い過渡性能を必要とするアプリケーションの場合、この比を出力電流1Aごとに $20\mu F \sim 30\mu F$ の $C_{OUT}$ にします。X5RとX7Rのセラミック・コンデンサは出力容量に最適です。アルミ電解コンデンサを使うこともできますが、出力電圧リップルを小さくするには一般にESRが大きすぎます。タンタル・コンデンサおよび新しい低ESR有機電解コンデンサも選択でき、メーカーでESRを規定しています。コンデンサの大きさでESRが決まるので、同様の出力リップル電圧性能を与えるセラミック・コンデンサに比べて、サイズと値の両方が大きくなります。

## アプリケーション情報

出力コンデンサはインダクタのリップル電流をフィルタして低リップルの出力を発生します。また、過渡負荷に十分供給してLT3742の制御ループを安定させるためにエネルギーを貯蔵します。以下の式を使って出力リップルを推算することができます。

$$V_{\text{RIPPLE}} = \Delta I_L \left( \frac{1}{8 \cdot f_{\text{SW}} \cdot C_{\text{OUT}}} + \text{ESR} \right)$$

ここで、 $\Delta I_L$ はインダクタ・リップル電流、 $f_{\text{SW}}$ はスイッチング周波数(500kHz)です。セラミック・コンデンサのESRは非常に小さいので、上式で省くことができます。出力電圧リップルは入力電圧が最大のとき最大になります( $\Delta I_L$ は入力電圧に応じて増加します)。低ESRコンデンサのメーカーを数社表3に示します。

表3. 低ESR表面実装コンデンサ

| VENDOR                                                                          | TYPE                                 | SERIES                           |

|---------------------------------------------------------------------------------|--------------------------------------|----------------------------------|

| Taiyo Yuden<br><a href="http://www.t-yuden.com">www.t-yuden.com</a>             | Ceramic X5R, X7R                     |                                  |

| Murata<br><a href="http://www.murata.com">www.murata.com</a>                    | Ceramic X5R, X7R                     |                                  |

| Kemet<br><a href="http://www.kemet.com">www.kemet.com</a>                       | Tantalum<br>Ta Organic<br>Al Organic | T491, T494, T495<br>T520<br>A700 |

| Sanyo<br><a href="http://www.sanyo.com">www.sanyo.com</a>                       | Ta or Al Organic                     | POSCAP                           |

| Panasonic<br><a href="http://www.panasonic.com">www.panasonic.com</a>           | Al Organic                           | SP CAP                           |

| TDK<br><a href="http://www.tdk.com">www.tdk.com</a>                             | Ceramic X5R, X7R                     |                                  |

| Nippon Chemicon<br><a href="http://www.chemi-con.co.jp">www.chemi-con.co.jp</a> | Ceramic X5R, X7R                     |                                  |

## 出力電圧の設定

バイポーラ・コントローラの出力には、スイッチ・ピンからソースされる電流が出力コンデンサを望みの出力電圧より上まで充電するのを防ぐために最小負荷が必要です。この電流(約5mA)は帰還経路の中で処理するか、またはユーザーがアプリケーションで最小負荷を強制することを選択することができます。

各コントローラの出力電圧は出力とFBピンの間に接続した抵抗分割器を使ってプログラムします。最高の出力電圧精度を得るため、常に1%(またはさらに良い)抵抗を使います。 $R_A$ の値は8k以下にし、 $R_1$ は次式に従って選択します。

$$R_B = R_A \cdot \left( \frac{V_{\text{OUT}}}{0.8V} - 1 \right)$$

## 出力短絡保護

LT3742はインダクタ電流を常時モニタするので、両方のデバイスとも本質的に優れた出力短絡保護を与えます。NチャネルMOSFETは、インダクタ電流が電流検出コンパレータのスレッショルドより下でない限り、オンすることができます。これにより、インダクタ電流が「暴走」しないことが保証され、インダクタ電流が電流検出スレッショルドより下に下がるまで、コントローラはサイクルをスキップします。

## ループ補償

$V_C$ ピンからグランドに直列に接続された外部の抵抗とコンデンサが各コントローラのループ補償を与えます。場合によっては、値の小さな2番目のコンデンサを並列に接続して、 $V_C$ ピンからのスイッチング周波数ノイズをフィルタします。ループ補償により各コントローラの安定性と過渡性能が決まります。

実際的な手法としては、 $R_C = 10k$ および $C_C = 330\text{pF}$ の値から出発し、補償ネットワークを調整して性能を最適化します。これらの値を調整する際、一度に1つの値だけ( $R_C$ または $C_C$ )変えてから、過渡応答がどのように影響を受けたかを観察します。ループの安定性をチェックする最も簡単な方法として、負荷電流ステップを与えて、出力の過渡応答を観察します。次に、負荷電流、入力電圧、温度など全ての動作条件にわたって安定性をチェックし、堅牢なデザインを保証します。

図7. FBピンによる出力電圧の設定

## アプリケーション情報

### バイアス電源に関する検討事項

LT3742は内部昇圧レギュレータを使って、外部MOSFETをエンハンス状態にするバイアス・レールを与えます。このバイアス・レールは $V_{IN}+7V$ に安定化され、どちらのコントローラもスイッチングを開始することを許される前に、安定化状態になる必要があります。これは高速スイッチング・レギュレータなので、外部部品の配置に関しては、標準的な手順に従う必要があります。SWBノードはEMIの影響を減らすため小さくし、バイアス・デカップリング・コンデンサ(CBIAS)はBIASピンと $V_{IN}$ の近くに配置します。わずかな余剰電力をこの電源から利用することができ、厳密なエンジニアリング評価の後、タップを接続することができます。

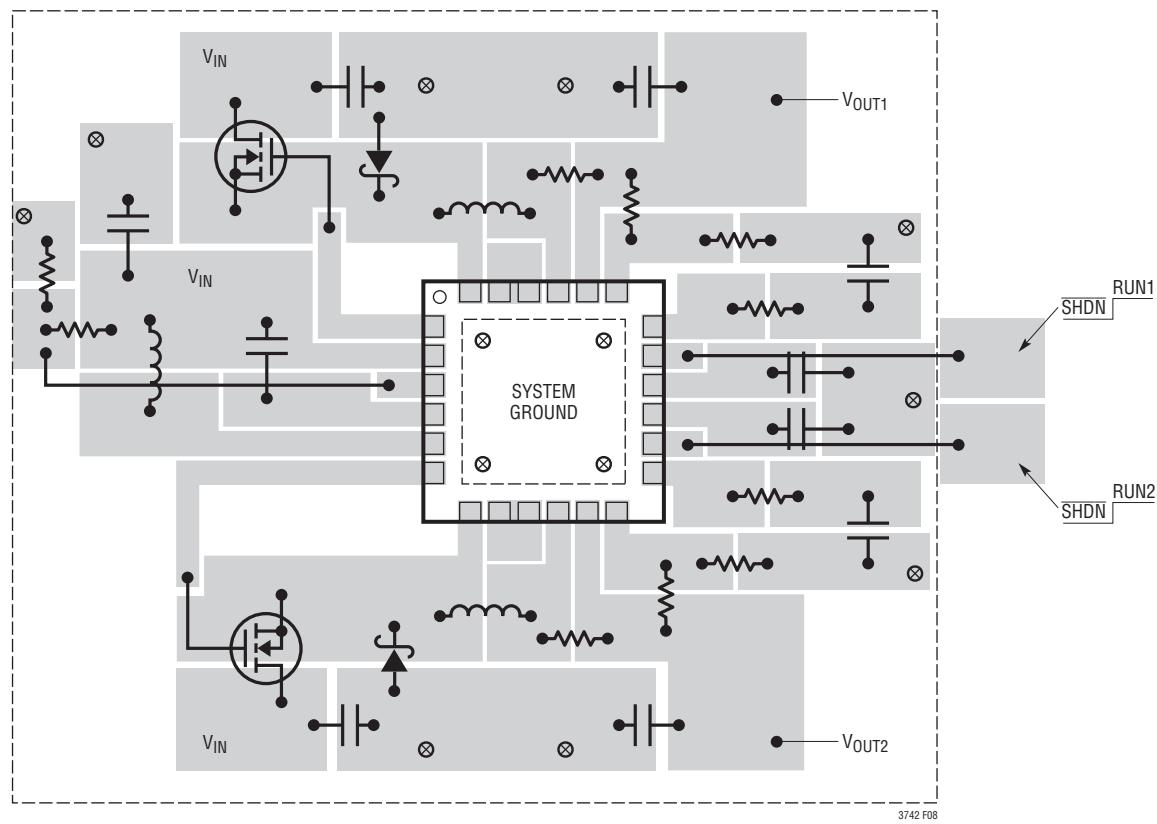

### PCボードのレイアウトに関する検討事項

全てのスイッチング・レギュレータの場合と同様、PCB基板のレイアウトと部品配置には細心の注意が必要です。

- 電力部品は短く幅の広い配線トレースを使って一緒に近づけて配置します。電力部品は、トップMOSFET、キャッチ・ダイオードおよびコンデンサ $C_{IN}$ と $C_{OUT}$ によって構成されます。これを解決する1つの方法は、最初にそれらを基板上に配置することです。

- 昇圧コンバータを形成する電力部品にも同様の注意を払います。それらを短く幅の広いトレースを使って一緒に近づけて配置します。

- スイッチング・レギュレータの下には常にグランド・プレーンを使ってプレーン間の結合を最小に抑えます。

- $C_{IN}$ 、MOSFETおよびキャッチ・ダイオードのループの寄生インダクタンスを最小に抑えます。このループには大きなスイッチング電流が流れます。

- MOSFETの冷却力を改善し、EMIを低く抑えるためにスイッチ・ノード(SW)にはコンパクト・プレーンを使います。

- 十分な電圧フィルタリングを維持し、電力損失を低く抑えるため、 $V_{IN}$ と $V_{OUT}$ にはプレーンを使います。未使用の領域は銅で埋めてDCノード( $V_{IN}$ 、 $V_{OUT}$ 、GND)のどれかに接続することができます。

- CBはBIASピンと入力コンデンサの近くに配置します。

- $dv/dt$ の高いノード(SW1、G1、G2、 $C_{IN1}$ 、 $C_{IN2}$ 、SWB)は、敏感な小信号ノードから離します。

信頼性の高いレイアウトを助けるため、デモ用ボードのガーバーファイルが提供されています。レイアウトが不適切だとデータシートの性能仕様を達成するのが困難になります。

## アプリケーション情報

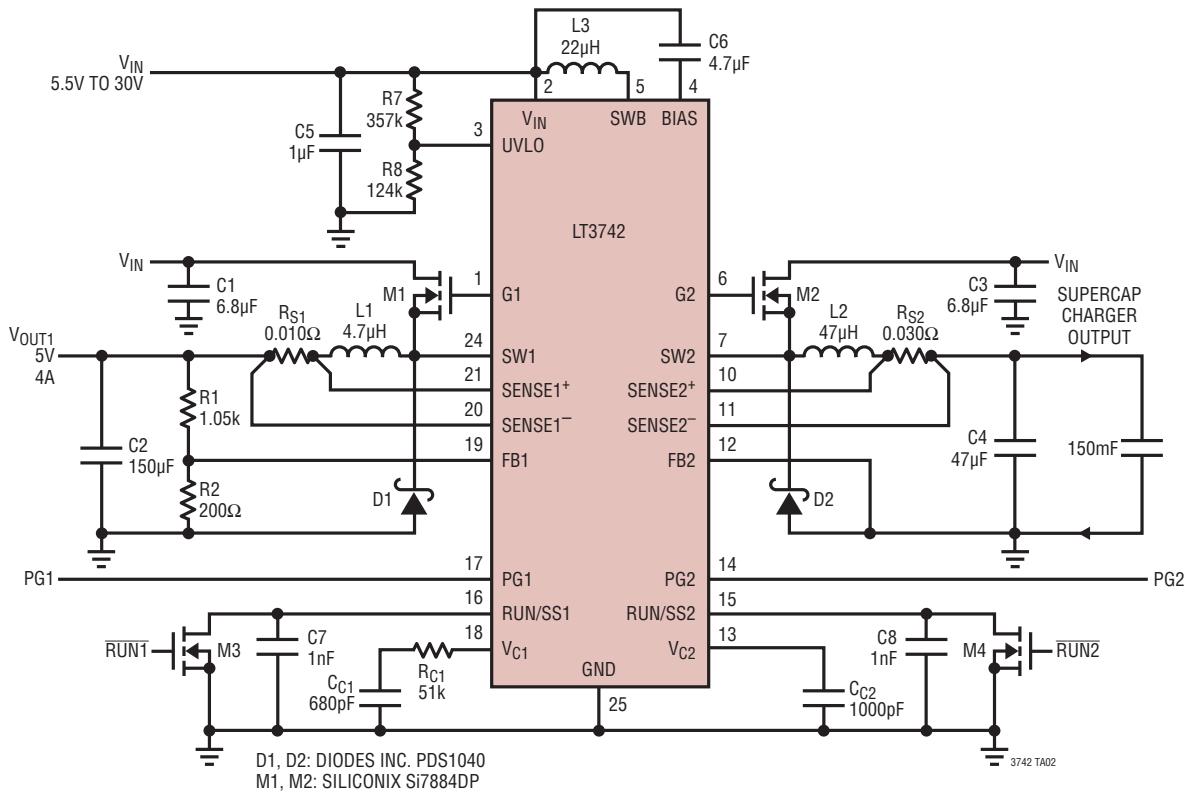

## 標準的応用例

スーパー・コンデンサ・チャージャとDC/DC降圧コンバータ

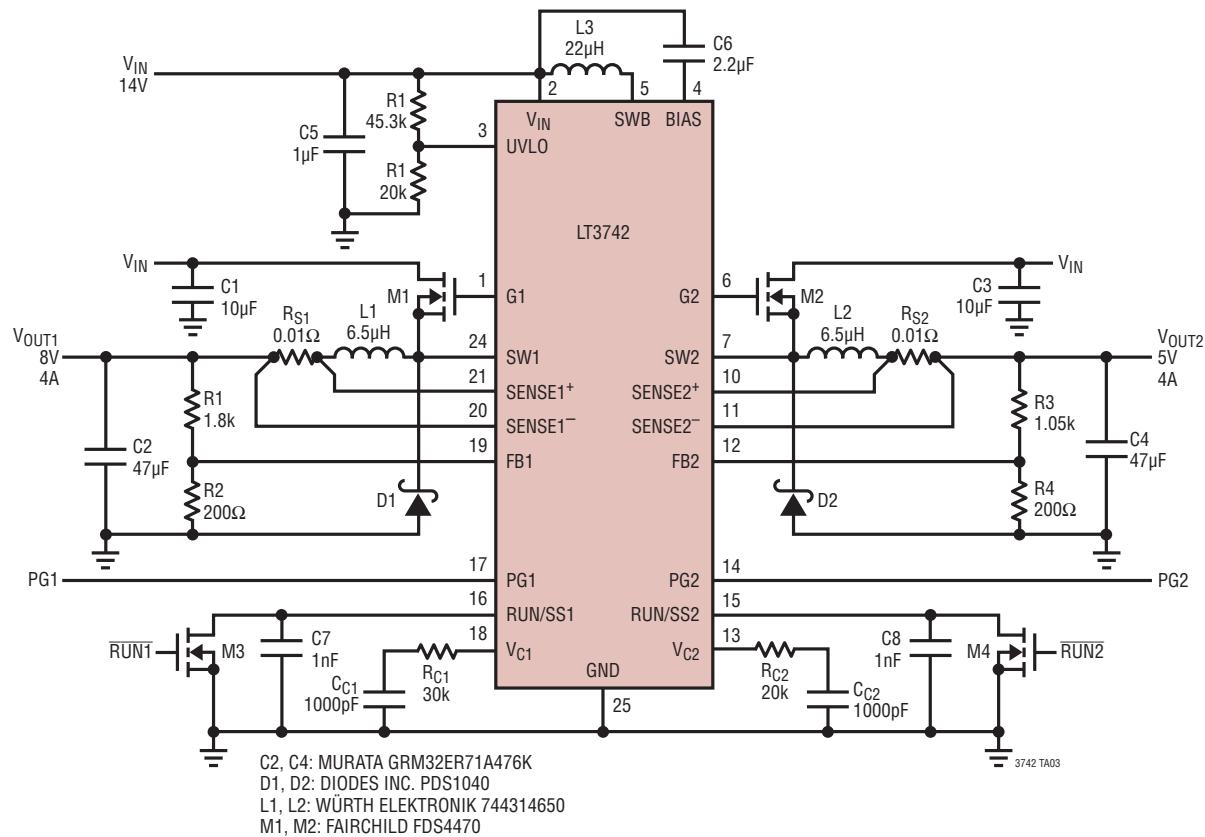

## 標準的应用例

#### 8Vと5Vのデュアル降圧コンバータ

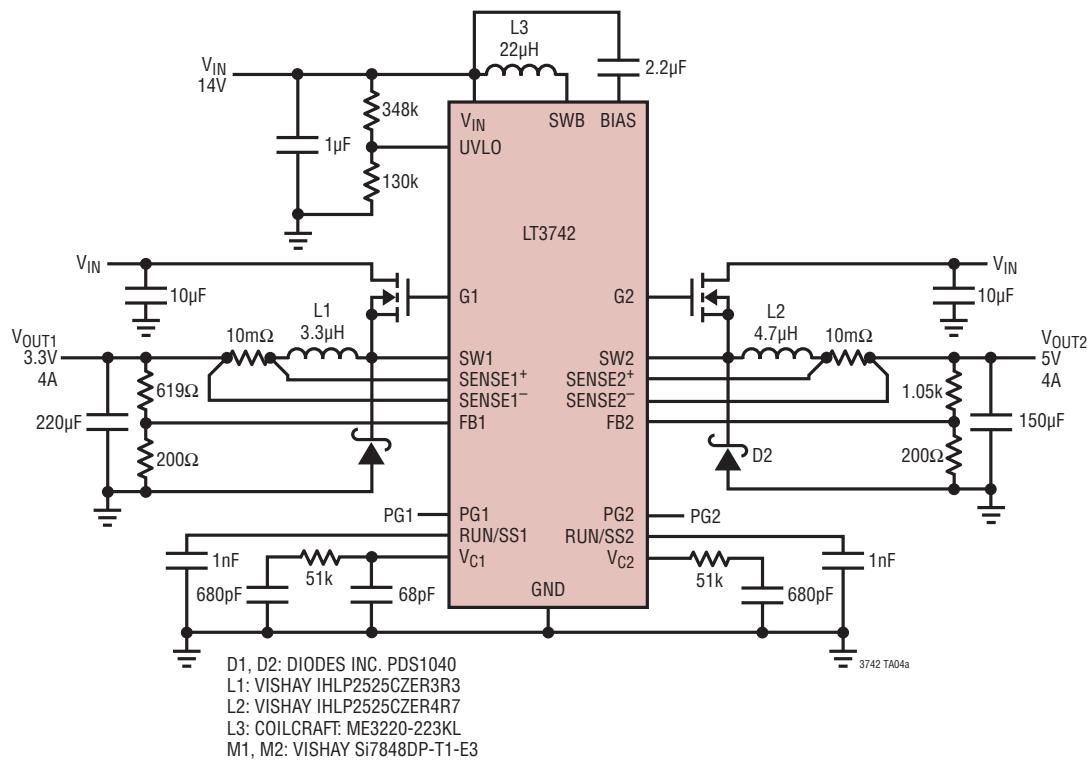

## 標準的応用例

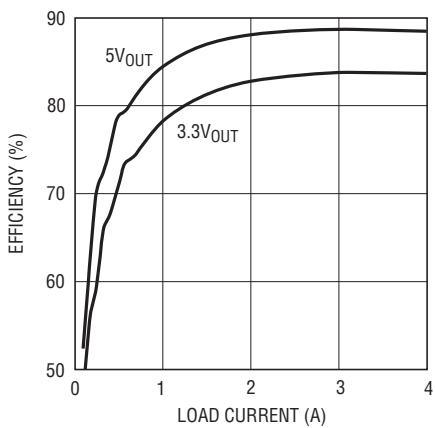

5Vと3.3Vのデュアル降圧コンバータ

効率と負荷電流

3742 TA04b

3742fa

## 標準的応用例

高電流、低リップル12V降圧コンバータ

12V<sub>OUT</sub>の効率と負荷電流

3742 TA05b

3742fa

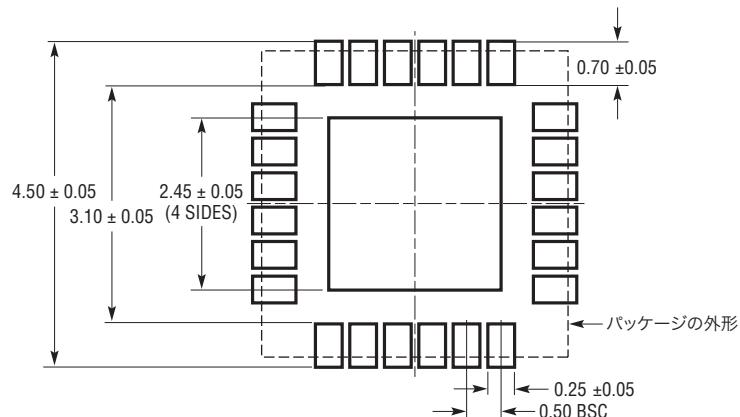

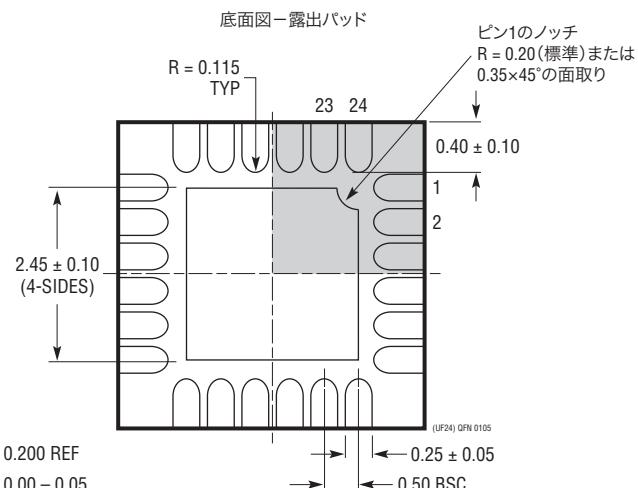

## パッケージ

**UFパッケージ

24ピン・プラスチックQFN(4mm×4mm)**

(Reference LTC DWG # 05-08-1697)

推奨する半田パッドのピッチと寸法

NOTE:

1. 図はJEDECパッケージ外形MO-220のバリエーション(WGDD-X)にするよう提案されている(承認待ち)

2. 図は実寸とは異なる

3. すべての寸法はミリメートル

4. パッケージ底面の露出パッドの寸法にはモールドのバリを含まない

モールドのバリは(もしあれば)各サイドで0.15mmを超えないこと

5. 露出パッドは半田メッキとする

6. 網掛けの部分はパッケージの上面と底面のPin1の位置の参考に過ぎない

底面図—露出パッド

## 改訂履歴 (改訂履歴はRev Aから開始)

| REV | 日付   | 概要                                                                                                                      | ページ番号                 |

|-----|------|-------------------------------------------------------------------------------------------------------------------------|-----------------------|

| A   | 5/11 | 「電気的特性」セクションの条件を更新<br>「標準的性能特性」セクションのグラフG04のタイトルを更新<br>「ピン機能」セクションのPG1、PG2ピンの説明を更新<br>「ロック図」「動作」「アプリケーション情報」セクションの数値を更新 | 2,3<br>4<br>6<br>7~12 |

## 関連製品

| 製品番号              | 説明                                   | 注釈                                                                                                         |

|-------------------|--------------------------------------|------------------------------------------------------------------------------------------------------------|

| LTC1625/LTC1775   | No RSENSE™電流モード同期整流式降圧コントローラ         | 効率:97%、センス抵抗が不要、16ピンSSOP                                                                                   |

| LTC1735           | 高効率同期整流式降圧スイッチング・レギュレータ              | 出力フォールト保護、16ピンSSOP                                                                                         |

| LTC1778           | No RSENSE、広い動作範囲の同期整流式降圧コントローラ       | 効率:最大97%、 $4V \leq V_{IN} \leq 36V$ 、 $0.8V \leq V_{OUT} \leq (0.9)(V_{IN})$ 、 $I_{OUT}$ :最大20A            |

| LT3430/LT3431     | モノリシック3A、200kHz/500kHz降圧レギュレータ       | $5.5V \leq V_{IN} \leq 60V$ 、 $0.1\Omega$ 飽和スイッチ、16ピンSSOPパッケージ                                             |

| LTC3703/LTC3703-5 | 100V同期整流式スイッチング・レギュレータ・コントローラ        | No RSENSE、電圧モード・コントロール、GN16パッケージ                                                                           |

| LT3724            | 高電圧電流モード・スイッチング・レギュレータ・コントローラ        | $V_{IN}$ :最大60V、 $I_{OUT} \leq 5A$ 、16ピンTSSOPパッケージ、内蔵バイアス・レギュレータ、Burst Mode®動作、 $I_Q < 100\mu A$ 、200kHz動作 |

| LT3800            | 高電圧同期整流式コントローラ                       | $V_{IN}$ :最大60V、 $I_{OUT} \leq 20A$ 、電流モード、内蔵バイアス・レギュレータ、Burst Mode動作、 $I_Q < 100\mu A$ 、16ピンTSSOPパッケージ    |

| LT3844            | 動作周波数をプログラム可能な高電圧電流モード・コントローラ        | $V_{IN}$ :最大60V、 $I_{OUT} \leq 5A$ 、内蔵バイアス・レギュレータ、Burst Mode動作、同期機能、 $I_Q = 120\mu A$ 、16ピンTSSOPパッケージ      |

| LTC3727A-1        | デュアル2フェーズ同期整流式コントローラ                 | 非常に低いドロップアウト動作、 $V_{OUT} \leq 14V$                                                                         |

| LTC3728           | 2フェーズ550kHz、デュアル同期整流式降圧コントローラ        | QFNおよびSSOPパッケージ、小型のLおよびCに適した高周波数                                                                           |

| LTC3729           | 20A～200AのPolyPhase®同期整流式コントローラ       | 2フェーズから12フェーズに拡張可能、全て表面実装型部品を使用可能、ヒートシンク不要                                                                 |

| LTC3731           | 3フェーズ、600kHz同期整流式降圧コントローラ            | $0.6V \leq V_{OUT} \leq 6V$ 、 $4.5V \leq V_{IN} \leq 32V$ 、 $I_{OUT} \leq 60A$ 、内蔵MOSFETドライバ               |

| LTC3773           | トリプル出力DC/DC同期整流式コントローラ               | 3フェーズ降圧DC/DCコントローラ、 $3.3V \leq V_{IN} \leq 36V$ 、固定周波数160kHz～700kHz                                        |

| LTC3826/LTC3826-1 | 30μAの $I_Q$ 、デュアル、2フェーズ同期整流式降圧コントローラ | 2フェーズ動作；1チャネル無負荷 $I_Q:30\mu A$ (合計50μA)、 $4V \leq V_{IN} \leq 36V$ 、 $0.8V \leq V_{OUT} \leq 10V$          |

| LTC3827/LTC3827-1 | 低 $I_Q$ 、デュアル同期整流式コントローラ             | 2フェーズ動作、無負荷 $I_Q:115\mu A$ (合計)、 $4V \leq V_{IN} \leq 36V$ 、1チャネルがオンした無負荷 $I_Q:80\mu A$                    |

| LTC3834/LTC3834-1 | 低 $I_Q$ の同期整流式降圧コントローラ               | 無負荷 $I_Q:30\mu A$ 、 $4V \leq V_{IN} \leq 36V$ 、 $0.8V \leq V_{OUT} \leq 10V$                               |

| LTC3835/LTC3835-1 | 低 $I_Q$ の同期整流式降圧コントローラ               | 無負荷 $I_Q:80\mu A$ 、 $4V \leq V_{IN} \leq 36V$ 、 $0.8V \leq V_{OUT} \leq 10V$                               |

| LTC3850           | デュアルの2フェーズ同期整流式降圧DC/DCコントローラ         | 2フェーズ動作、 $4V \leq V_{IN} \leq 24V$ 、効率:95%、No RSENSEオプション、 $I_{OUT}$ :最大20A、4mm×4mm QFN                    |

| LT3845            | 高電圧同期整流式降圧シングル出力コントローラ               | 非常に低い静止電流(120μA)、 $V_{IN}$ :最大60V、100kHz～500kHzの固定周波数、最高600kHzまで同期可能                                       |