## 特長

- 広い入力電圧範囲:

- 3V～36Vで動作

- OVLOにより60Vまでの過渡電圧から回路を保護

- 各3.5Aレギュレータごとに電源、シャットダウン、ソフトスタート、プログラム可能な電流制限、プログラム可能なパワーグッドを搭載

- ダイ温度モニタ

- 同期クロック出力を備え、調整可能/同期可能な固定周波数動作: 250kHz～2.25MHz

- 独立した同期スイッチング周波数により、部品サイズを最適化

- 逆位相スイッチング

- 出力を並列接続可能

- 柔軟な出力電圧トラッキング

- 強化された短絡保護機能

- 低損失電圧: 最大95%のデューティサイクル

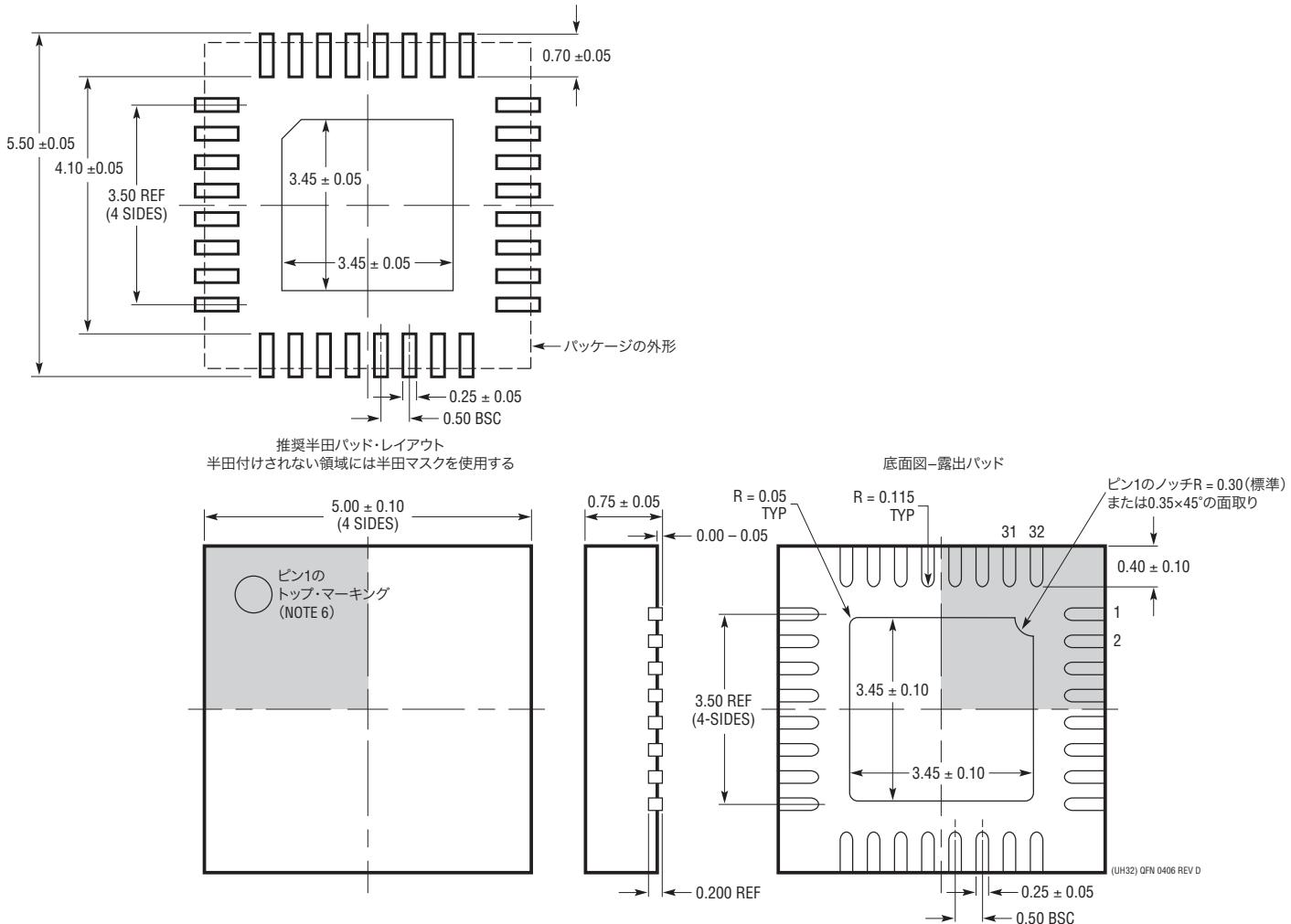

- 5mm×5mm QFN パッケージ

## アプリケーション

- 車載用電源

- 分配型電源の安定化

## 概要

LT<sup>®</sup>3692は2個の3.8Aスイッチを内蔵するデュアル電流モードPWM降圧DC/DCコンバータです。入力電圧、シャットダウン、帰還、ソフトスタート、電流制限、コンパレータのためのピンが各チャネルにそれぞれ備わっているので、電源の複雑なトラッキングやシーケンス制御が簡単です。

効率と部品のサイズを最適化するため、どちらのコンバータも最大電流制限を設定可能で、共通の外部クロック入力または抵抗で設定可能な250kHz～2.25MHzの固定周波数の内部発振器のいずれかに同期します。LT3692はチャネル1に分周器を搭載しているので、部品サイズをさらに最適化します。すべての周波数でチャネル間に180°の位相差が保たれるので、電圧リップルと部品のサイズを低減します。また、クロック出力を使用して、複数のレギュレータを同期させることができます。

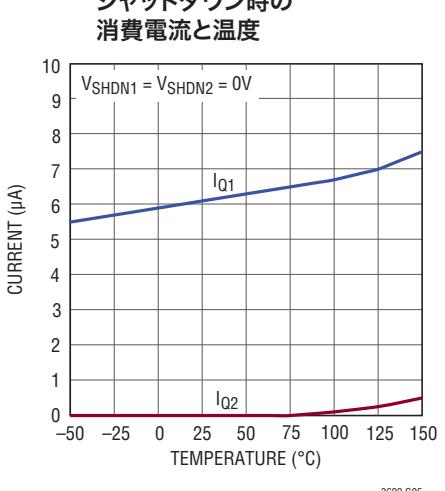

スイッチが複数のクロック・サイクルにわたってオンにとどまるなどを許し、昇圧コンデンサの再充電が必要なときにのみオフするので、最小入出力電圧比が改善されています。また、SHDNピンを使用して、独立したチャネル動作を設定可能です。両方のコンバータをディスエーブルすると、総消費電流が10µA未満に減少します。

LT、LT、LTC、LTM、Burst Mode、Linear TechnologyおよびLinearのロゴはリニアテクノロジー社の登録商標です。その他すべての商標の所有権は、それぞれの所有者に帰属します。

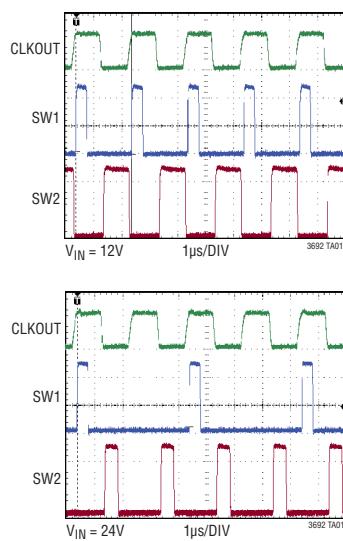

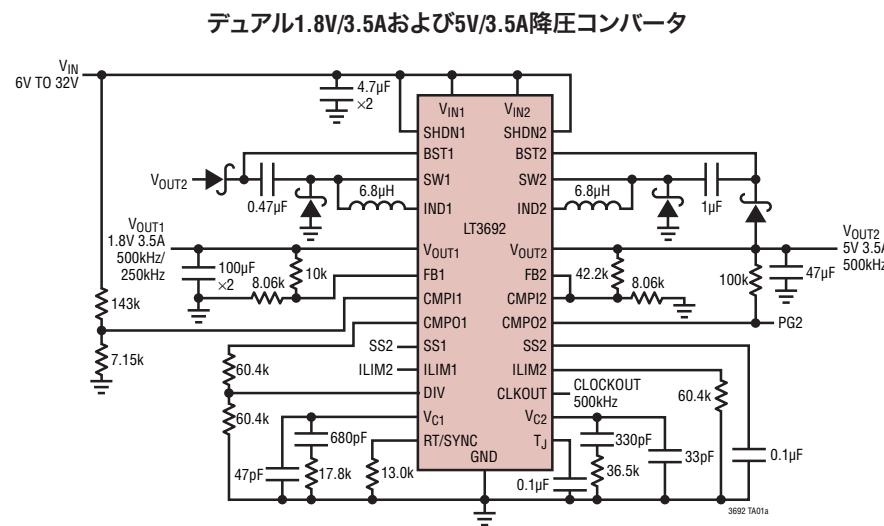

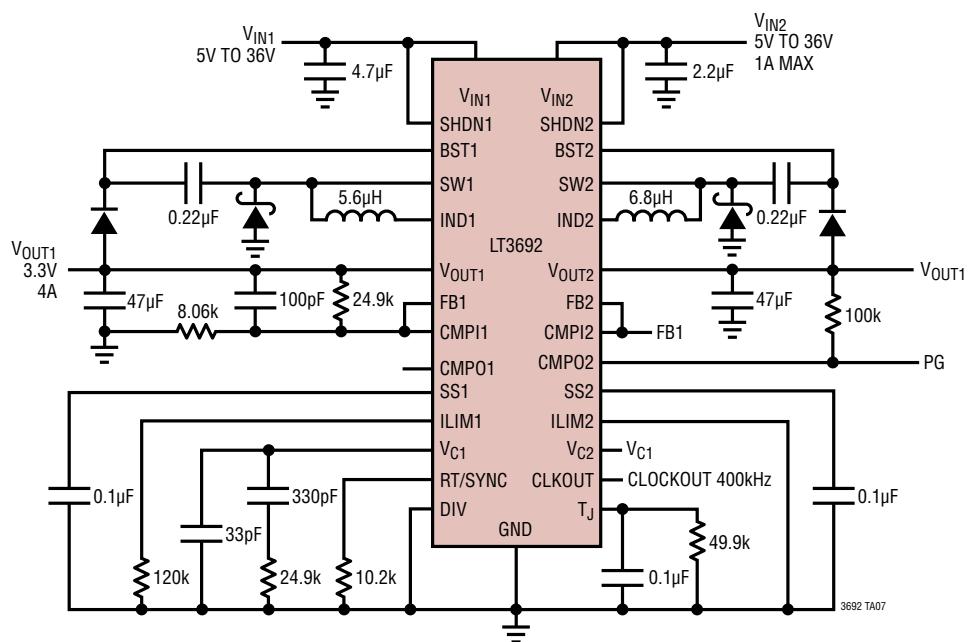

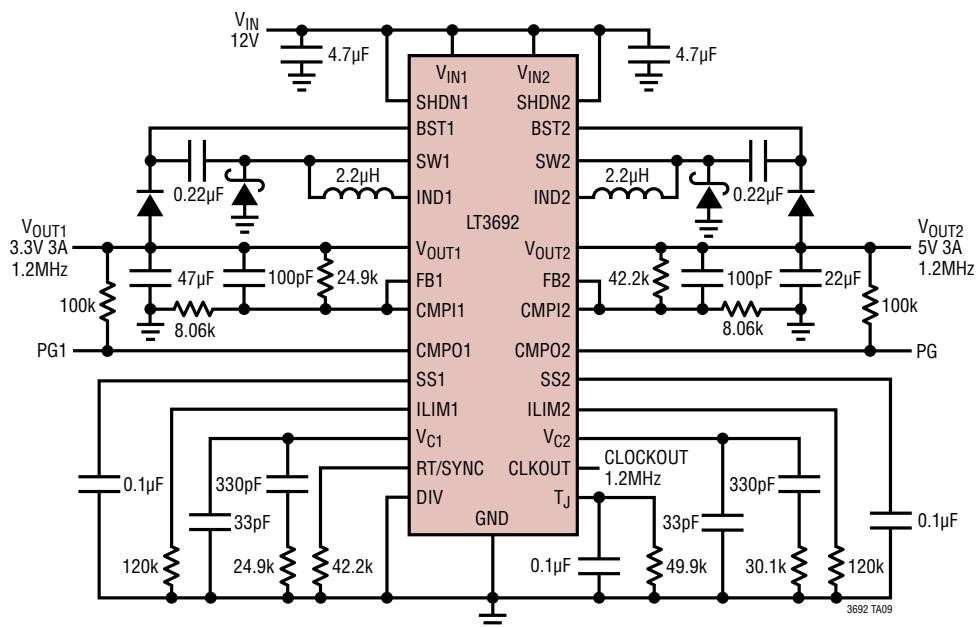

## 標準的応用例

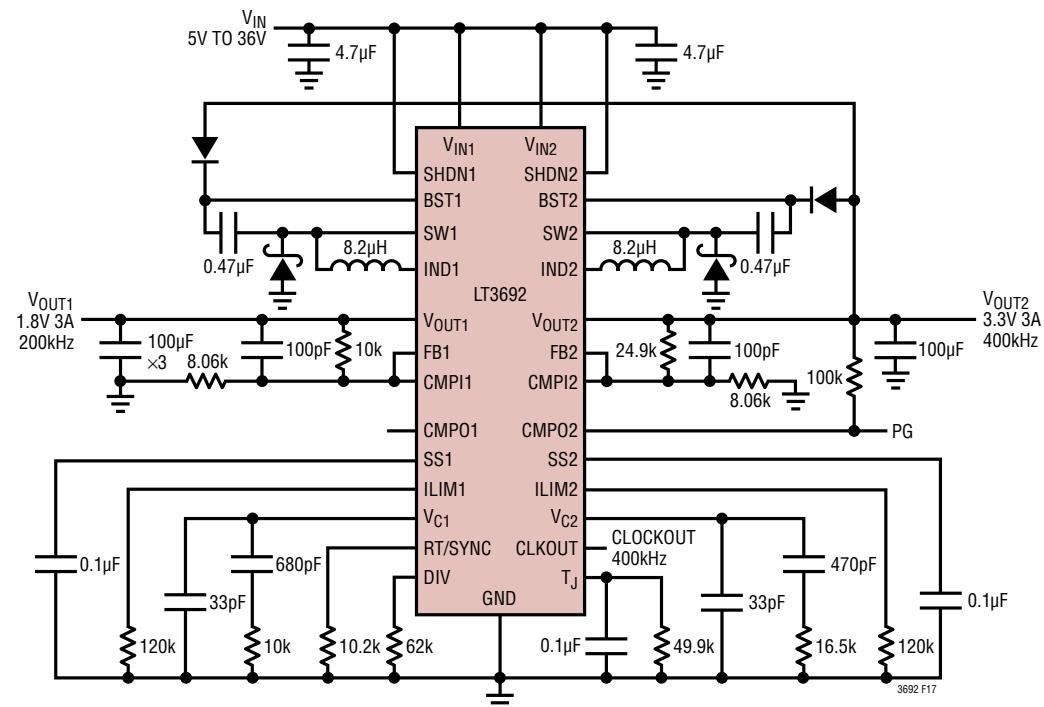

### 独立した同期スイッチング周波数により全周波数入力範囲を拡張

3692fa

## 絶対最大定格

(Note 1)

|                              |                |

|------------------------------|----------------|

| $V_{IN1/2}$ 、SHDN1/2、CMP01/2 | 40V/-0.3V      |

| $V_{IN1/2}$ の過渡電圧 (Note 2)   | 60V/-0.3V      |

| $SW1/2$                      | $V_{IN1/2}$    |

| $BST1/2$                     | 60V/-0.3V      |

| ( $BST1/2$ - $SW1/2$ ) 電圧    | 25V            |

| $IND1/2$ 、 $V_{OUT1/2}$      | 40V/-0.3V、7A   |

| $FB1/2$ 、 $CMP1/2$ 、 $SS1/2$ | 5V             |

| RT/SYNC                      | 5V             |

| DIV、ILIM1/2                  | 2.5V           |

| $V_{C1/2}$ 、 $T_J$           | $\pm 100\mu A$ |

| 動作接合部温度範囲 (Note 3)           |                |

| LT3692EUH                    | -40°C~125°C    |

| LT3692IUH                    | -40°C~125°C    |

| 保存温度範囲                       | -65°C~150°C    |

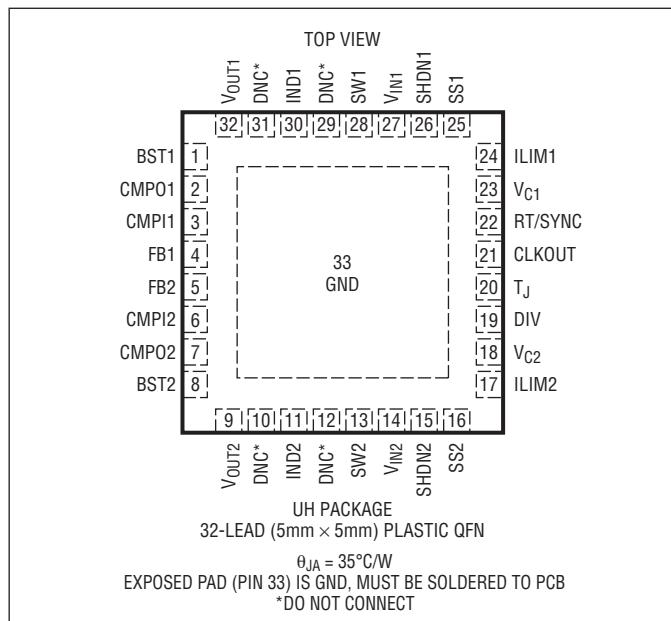

## ピン配置

## 発注情報

| 鉛フリー仕様        | テープアンドリール       | 製品マーキング* | パッケージ                           | 温度範囲           |

|---------------|-----------------|----------|---------------------------------|----------------|

| LT3692EUH#PBF | LT3692EUH#TRPBF | 3692     | 32-Lead (5mm x 5mm) Plastic QFN | -40°C to 125°C |

| LT3692IUH#PBF | LT3692IUH#TRPBF | 3692     | 32-Lead (5mm x 5mm) Plastic QFN | -40°C to 125°C |

さらに広い動作温度範囲で規定されるデバイスについては、弊社または弊社代理店にお問い合わせください。 \*温度グレードは出荷時のコンテナのラベルで識別されます。

非標準の鉛ベース仕様の製品の詳細については、弊社または弊社代理店にお問い合わせください。

鉛フリー仕様の製品マーキングの詳細については、<http://www.linear-tech.co.jp/leadfree/> をご覧ください。

テープアンドリールの仕様の詳細については、<http://www.linear-tech.co.jp/tapeandreel/> をご覧ください。

## 電気的特性

●は全動作温度範囲での規格値を意味する。それ以外は $T_A = 25^\circ C$ での値。注記がない限り、 $V_{VIN1/2} = 15V$ 。(Note 3)

| PARAMETER                                    | CONDITIONS                                                | MIN    | TYP  | MAX  | UNITS   |

|----------------------------------------------|-----------------------------------------------------------|--------|------|------|---------|

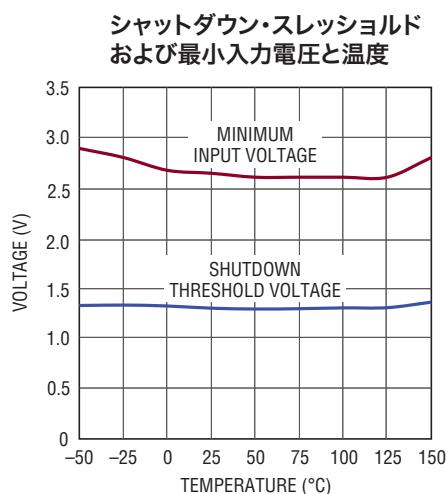

| SHDN Voltage Threshold Ch 1/2 (Note 4)       |                                                           | ● 1.24 | 1.32 | 1.4  | V       |

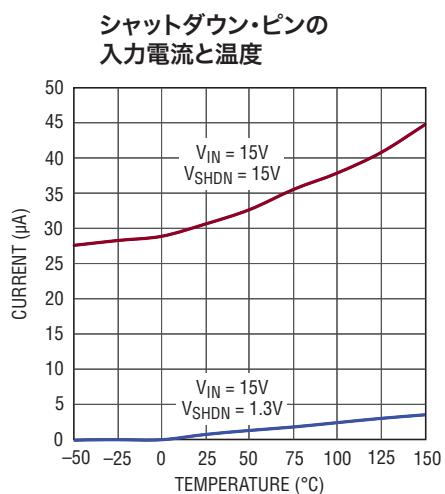

| SHDN Input Current Ch 1/2                    | $V_{SHDN} = 1.3V$                                         |        | 1.5  | 5    | $\mu A$ |

| $V_{IN1}$ Undervoltage Lockout (Note 5)      | $V_{FB1/2} = 0V$ , $V_{VOUT1/2} = 0V$ , $V_{IND1/2} = 0V$ | 2.5    | 2.8  | 3.1  | V       |

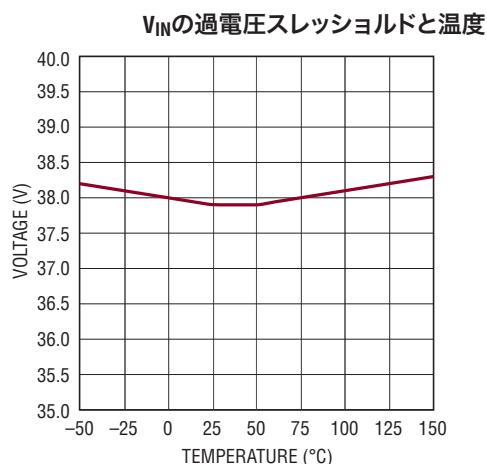

| $V_{IN}$ Overvoltage Lockout Ch 1/2 (Note 6) |                                                           | 36     | 38   | 41   | V       |

| $V_{IN1}$ Shutdown Current                   | $V_{SHDN} = 0V$                                           | ● 6    | 10   | 10   | $\mu A$ |

| $V_{IN2}$ Shutdown Current                   | $V_{SHDN} = 0V$                                           | ● 0    | 2    | 2    | $\mu A$ |

| $V_{IN1}$ Quiescent Current                  | $V_{FB1/2} = 0.9V$                                        | 3      | 4    | 5    | mA      |

| $V_{IN2}$ Quiescent Current                  | $V_{FB1/2} = 0.9V$                                        | 400    | 630  | 1000 | $\mu A$ |

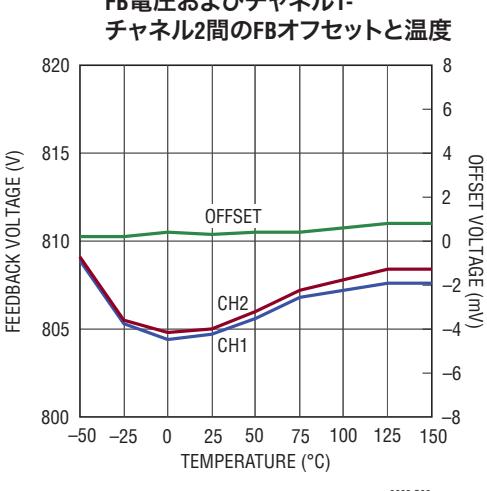

| Feedback Voltage Ch 1/2                      | $V_{VC1/2} = 1V$                                          | ● 790  | 806  | 822  | mV      |

## 電気的特性

●は全動作温度範囲での規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。注記がない限り、 $V_{VIN1/2} = 15\text{V}$ 。(Note 3)

| PARAMETER                                | CONDITIONS                                                                                                                                                                                                             | MIN    | TYP                 | MAX  | UNITS         |                 |

|------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|---------------------|------|---------------|-----------------|

| Feedback Voltage Regulation              | $V_{VIN1/2} = 3$ to $40\text{V}$ , $V_{VC1/2} = 0.6$ to $1.6\text{V}$                                                                                                                                                  | ● 780  | 806                 | 830  | mV            |                 |

| Feedback Voltage Offset Ch 1 to Ch 2     | $V_{VC1/2} = 1\text{V}$                                                                                                                                                                                                | ● -12  | 0                   | 12   | mV            |                 |

| Feedback Bias Current Ch 1/2             | $V_{FB1/2} = 0.8\text{V}$ , $V_{VC1/2} = 1\text{V}$                                                                                                                                                                    | ● 0    | 85                  | 200  | nA            |                 |

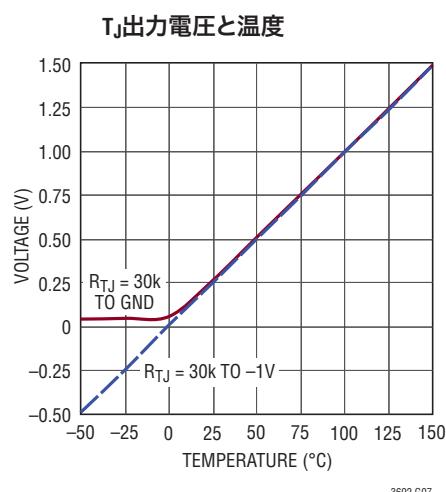

| $T_J$ Output Voltage (Note 7)            | $T_J = 25^\circ\text{C}$ , $I_{TJ} = 25\mu\text{A}$ , Temperature = $25^\circ\text{C}$<br>$I_{TJ} = 25\mu\text{A}$ , Temperature = $125^\circ\text{C}$<br>$I_{TJ} = 25\mu\text{A}$ , Temperature = $-40^\circ\text{C}$ |        | 250<br>1.23<br>-380 |      | mV<br>V<br>mV |                 |

| $T_J$ Error                              |                                                                                                                                                                                                                        | ● -60  | 0                   | 60   | mV            |                 |

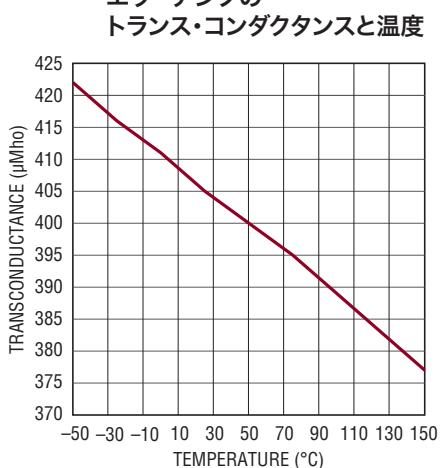

| Error Amp $g_m$ Ch 1/2                   | $V_{VC1/2} = 1\text{V}$ , $I_{VC1/2} = \pm 5\mu\text{A}$                                                                                                                                                               |        | 350                 | 400  | 450           | $\mu\text{Mho}$ |

| Error Amp Source Current Ch 1/2          | $V_{FB1/2} = 0.6\text{V}$ , $V_{VC1/2} = 1\text{V}$                                                                                                                                                                    |        | 19                  | 25   | 31            | $\mu\text{A}$   |

| Error Amp Sink Current Ch 1/2            | $V_{FB1/2} = 1\text{V}$ , $V_{VC1/2} = 1\text{V}$                                                                                                                                                                      |        | 22                  | 28   | 34            | $\mu\text{A}$   |

| Error Amp High Clamp Ch 1/2              | $V_{FB1/2} = 0.6\text{V}$                                                                                                                                                                                              |        | 1.7                 | 1.9  | 2.1           | V               |

| Error Amp Switching Threshold Ch 1/2     | $V_{FB1/2} = 0.6\text{V}$                                                                                                                                                                                              |        | 0.75                | 0.9  | 1.05          | V               |

| Soft-Start Source Current Ch 1/2         | $V_{FB1/2} = 0.9\text{V}$ , $V_{SS1/2} = 0.05\text{V}$                                                                                                                                                                 | ● 9.5  | 12                  | 14.5 | $\mu\text{A}$ |                 |

| Soft-Start $V_{OH}$ Ch 1/2               | $V_{FB1/2} = 0.9\text{V}$                                                                                                                                                                                              |        | 1.9                 | 2.15 | 2.4           | V               |

| Soft-Start Sink Current Ch 1/2           | $V_{FB1/2} = 0.4\text{V}$ , $V_{SS1/2} = 2\text{V}$                                                                                                                                                                    |        | 0.9                 | 1.4  | 2             | mA              |

| Soft-Start $V_{OL}$ Ch 1/2               | $V_{FB1/2} = 0\text{V}$                                                                                                                                                                                                |        | 120                 | 160  | 200           | mV              |

| Soft-Start to Feedback Offset Ch 1/2     | $V_{VC1/2} = 1\text{V}$ , $V_{SS1/2} = 0.4\text{V}$                                                                                                                                                                    | ● -12  | 0                   | 12   | mV            |                 |

| Soft-Start Sink Current Ch 1/2 POR       | $V_{FB1/2} = 0\text{V}$ , $V_{SS1/2} = 0.12\text{V}$ (Note 8)                                                                                                                                                          |        | 150                 | 400  | 600           | $\mu\text{A}$   |

| Soft-Start POR Threshold Ch 1/2          | $V_{FB1/2} = 0\text{V}$ (Note 8)                                                                                                                                                                                       |        | 70                  | 90   | 120           | mV              |

| Soft-Start SW Disable Ch 1/2             | $V_{FB1/2} = 0\text{V}$ (Note 8)                                                                                                                                                                                       |        | 95                  | 115  | 150           | mV              |

| CMPI Bias Current Ch 1/2                 | $V_{CMP1/2} = 0.8\text{V}$                                                                                                                                                                                             |        | -100                | 0    | 100           | nA              |

| CMPO Leakage Ch 1/2                      | $V_{CMP1/2} = 0.8\text{V}$ , $V_{CMPO1/2} = 25\text{V}$                                                                                                                                                                |        |                     | 70   | 200           | nA              |

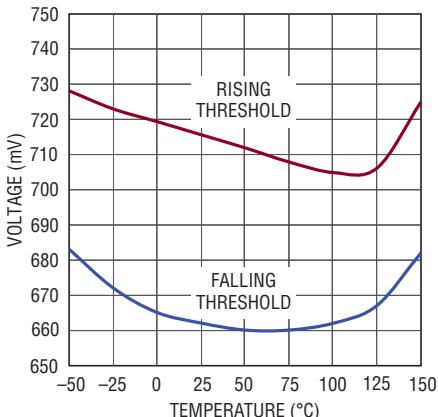

| CMPI Threshold Ch 1/2                    | $V_{CMP1/2}$ Rising                                                                                                                                                                                                    | ● 700  | 720                 | 740  | mV            |                 |

| CMPI Threshold Ch 1/2 of $V_{FB1/2}$     | $V_{CMP1/2}$ Rising (Note 9)                                                                                                                                                                                           |        | 86                  | 90   | 94            | %               |

| CMPI Hysteresis Ch 1/2                   | $V_{CMP1/2}$                                                                                                                                                                                                           |        | 35                  | 60   | 85            | mV              |

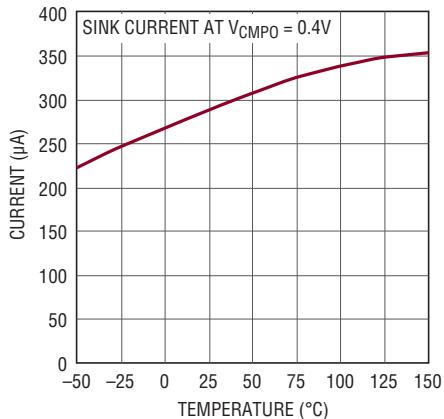

| CMPO Sink Current Ch 1/2                 | $V_{CMP1/2} = 0.6\text{V}$ , $V_{CMPO1/2} = 0.2\text{V}$                                                                                                                                                               |        | 200                 | 300  | 400           | $\mu\text{A}$   |

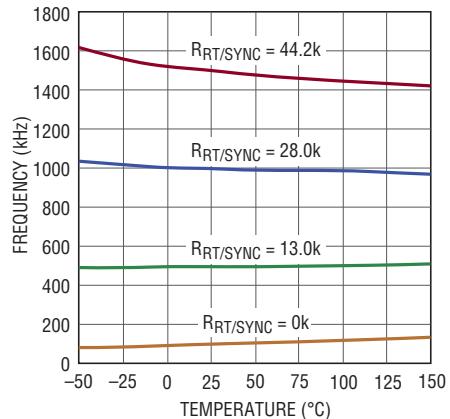

| RT/SYNC Reference Current                | $V_{FB1/2} = 0.9\text{V}$ , $V_{RT/SYNC} = 0.5\text{V}$                                                                                                                                                                | ● 11.3 | 12                  | 12.7 | $\mu\text{A}$ |                 |

| Minimum Switching Frequency              | $R_{RT/SYNC} = 0\Omega$                                                                                                                                                                                                |        | 50                  | 110  | 150           | kHz             |

| Switching Frequency                      | $R_{RT/SYNC} = 28\text{k}$                                                                                                                                                                                             |        | 925                 | 1    | 1075          | MHz             |

| Maximum Switching Frequency              | $R_{RT/SYNC} = 100\text{k}$                                                                                                                                                                                            |        | 2.25                | 2.5  | 2.75          | MHz             |

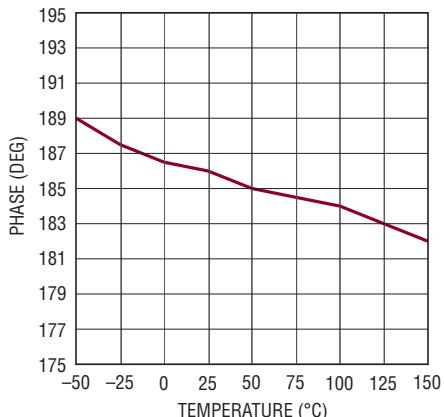

| Switching Phase Angle Ch 1 $\geq$ Ch 2   |                                                                                                                                                                                                                        |        |                     | 185  |               | Deg             |

| DIV Reference Current                    | $V_{FB1/2} = 0.9\text{V}$ , $V_{DIV} = 0.5\text{V}$                                                                                                                                                                    | ● 10.5 | 12                  | 13.5 | $\mu\text{A}$ |                 |

| CH1 DIV 2 Threshold                      | $R_{RT/SYNC} = 0\text{V}$                                                                                                                                                                                              |        | 0.51                | 0.58 | 0.61          | V               |

| CH1 DIV 4 Threshold                      | $R_{RT/SYNC} = 0\text{V}$                                                                                                                                                                                              |        | 0.9                 | 1.05 | 1.1           | V               |

| CH1 DIV 8 Threshold                      | $R_{RT/SYNC} = 0\text{V}$                                                                                                                                                                                              |        | 1.45                | 1.55 |               | V               |

| CLKOUT $V_{OL}$                          | $I_{CLKOUT} = -100\mu\text{A}$                                                                                                                                                                                         |        |                     | 0.25 |               | V               |

| CLKOUT $V_{OH}$                          | $I_{CLKOUT} = 100\mu\text{A}$                                                                                                                                                                                          |        |                     | 2    |               | V               |

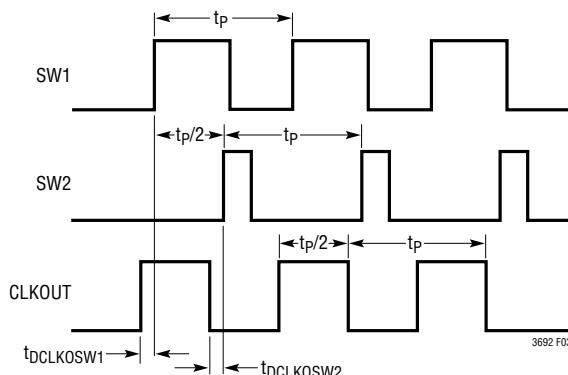

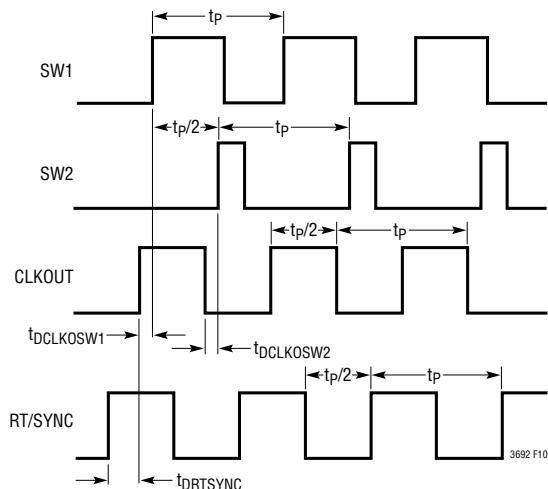

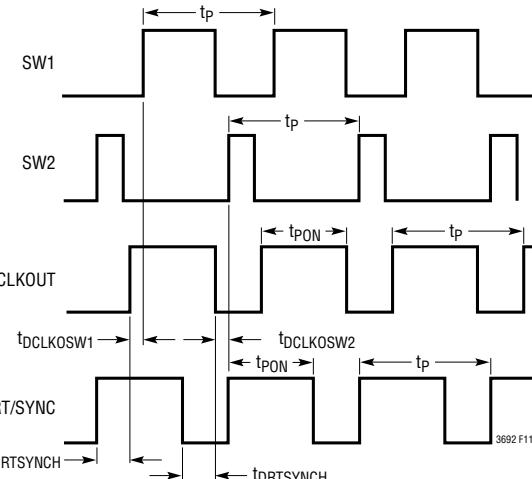

| CLKOUT to SW1ON Delay ( $t_{DCLKOSW1}$ ) | CLKOUT Rising                                                                                                                                                                                                          |        |                     | 60   |               | ns              |

| CLKOUT to SW2ON Delay ( $t_{DCLKOSW2}$ ) | CLKOUT Falling                                                                                                                                                                                                         |        |                     | 30   |               | ns              |

## 電気的特性

●は全動作温度範囲での規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。注記がない限り、 $V_{VIN1/2} = 15\text{V}$ 。(Note 3)

| PARAMETER                                  | CONDITIONS                                                                                                                                                                                                                                                                                                                                                                                           | MIN | TYP                               | MAX                                  | UNITS                                   |                            |   |

|--------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----------------------------------|--------------------------------------|-----------------------------------------|----------------------------|---|

| RT/SYNC to CLKOUT Delay ( $t_{DRTSYNCH}$ ) | $V_{RT/SYNC} = 0\text{V}$ to $2\text{V}$ Rising Edge                                                                                                                                                                                                                                                                                                                                                 |     | 300                               |                                      | ns                                      |                            |   |

| RT/SYNC to CLKOUT Delay ( $t_{DRTSYNCL}$ ) | $V_{RT/SYNC} = 2\text{V}$ to $0\text{V}$ Falling Edge                                                                                                                                                                                                                                                                                                                                                |     | 150                               |                                      | ns                                      |                            |   |

| SYNC Frequency Range                       |                                                                                                                                                                                                                                                                                                                                                                                                      | 250 |                                   | 2000                                 | kHz                                     |                            |   |

| SYNC Phase Angle Ch 1 to Ch 2              | SYNC Frequency = 250kHz                                                                                                                                                                                                                                                                                                                                                                              |     | 180                               |                                      | Deg                                     |                            |   |

| Minimum Switch On-Time Ch 1/2              |                                                                                                                                                                                                                                                                                                                                                                                                      |     | 180                               |                                      | ns                                      |                            |   |

| Minimum Switch Off-Time Ch 1/2             |                                                                                                                                                                                                                                                                                                                                                                                                      |     | 200                               |                                      | ns                                      |                            |   |

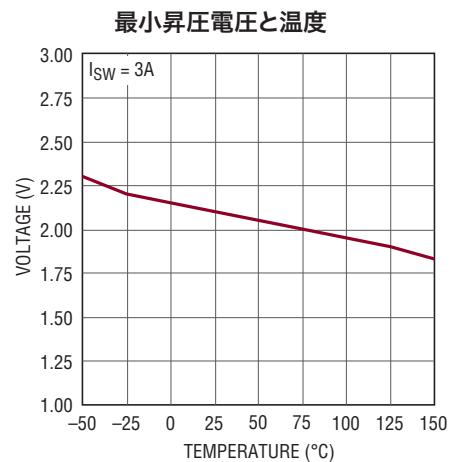

| Minimum Boost for 100% DC Ch 1/2 (Note 10) |                                                                                                                                                                                                                                                                                                                                                                                                      | 1.4 | 1.8                               | 2.2                                  | V                                       |                            |   |

| IND + $V_{OUT}$ Current Ch 1/2             | $V_{VOUT1/2} = 0\text{V}$<br>$V_{VOUT1/2} = 5\text{V}$                                                                                                                                                                                                                                                                                                                                               |     | 1.5<br>0.5                        | 5<br>5                               | $\mu\text{A}$                           |                            |   |

| ILIM1/2 Reference Current                  | $V_{FB1/2} = 0.9\text{V}$ , $V_{ILIM} = 0.4\text{V}$                                                                                                                                                                                                                                                                                                                                                 | ●   | 10                                | 12                                   | 14                                      | $\mu\text{A}$              |   |

| IND to $V_{OUT}$ Maximum Current Ch 1/2    | $V_{ILIM1/2} = 0\text{V}$ , $V_{VOUT} = 1\text{V}$ (Note 11)<br>$V_{ILIM1/2} = 0\text{V}$ , $V_{VOUT} = 5\text{V}$ (Note 11)<br>$V_{ILIM1/2} = 0.5\text{V}$ , $V_{VOUT} = 1\text{V}$ (Note 11)<br>$V_{ILIM1/2} = 0.5\text{V}$ , $V_{VOUT} = 5\text{V}$ (Note 11)<br>$V_{ILIM1/2} = 1.5\text{V}$ , $V_{VOUT} = 1\text{V}$ (Note 11)<br>$V_{ILIM1/2} = 1.5\text{V}$ , $V_{VOUT} = 5\text{V}$ (Note 11) |     | 1<br>1.25<br>1.6<br>1.8<br>●<br>● | 1.8<br>2<br>2.6<br>3.6<br>4.8<br>4.8 | 2.6<br>2.75<br>3.6<br>3.8<br>5.8<br>5.8 | A<br>A<br>A<br>A<br>A<br>A |   |

| Switch Leakage Current Ch 1/2              | $V_{SW1/2} = 0\text{V}$                                                                                                                                                                                                                                                                                                                                                                              | ●   |                                   | 1                                    | 5.0                                     | $\mu\text{A}$              |   |

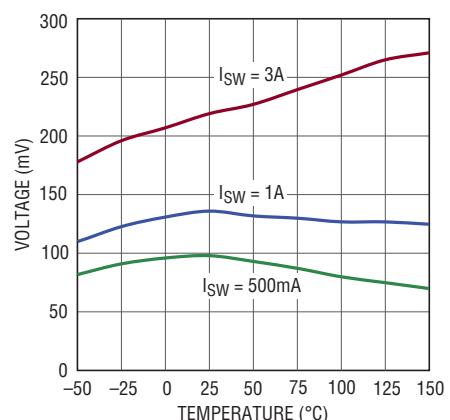

| Switch Saturation Voltage Ch 1/2           | $I_{SW1/2} = 500\text{mA}$ , $V_{BST1/2} = 18\text{V}$<br>$I_{SW1/2} = 3\text{A}$ , $V_{BST1/2} = 18\text{V}$                                                                                                                                                                                                                                                                                        |     |                                   | 100<br>300                           |                                         | mV<br>mV                   |   |

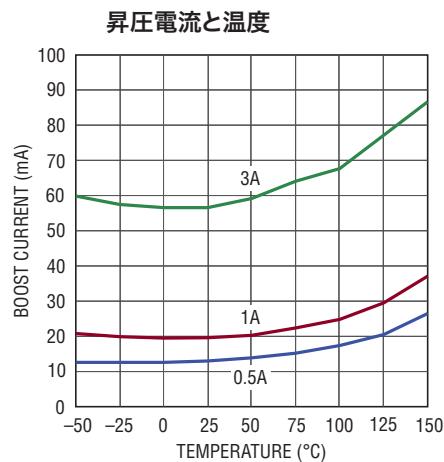

| Boost Current Ch 1/2                       | $I_{SW1/2} = 500\text{mA}$ , $V_{BST1/2} = 18\text{V}$<br>$I_{SW1/2} = 3\text{A}$ , $V_{BST1/2} = 18\text{V}$                                                                                                                                                                                                                                                                                        |     | 9<br>40                           | 13<br>55                             | 17<br>70                                | mA<br>mA                   |   |

| Minimum Boost Voltage Ch1/2 (Note 12)      | $I_{SW1/2} = 3\text{A}$ , $V_{BST1/2} = 18\text{V}$                                                                                                                                                                                                                                                                                                                                                  |     |                                   | 1.75                                 | 2.0                                     | 2.5                        | V |

**Note 1:**絶対最大定格に記載された値を超えるストレスはデバイスに永続的損傷を与える可能性がある。長期にわたって絶対最大定格条件に曝すと、デバイスの信頼性と寿命に悪影響を与える可能性がある。

**Note 2:** $V_{IN1/2}$ ピンおよびSHDN1/2ピンの絶対最大電圧は、繰り返さない1秒間の過渡の場合は60V、連続動作では40Vである。

**Note 3:**LT3692EUHは $0^\circ\text{C}$ ～ $125^\circ\text{C}$ の接合部温度範囲で性能仕様に適合することが保証されている。 $-40^\circ\text{C}$ ～ $125^\circ\text{C}$ の動作温度範囲での仕様は、設計、特性評価および統計学的なプロセス・コントロールとの相関で確認されている。LT3692IUHは、 $-40^\circ\text{C}$ ～ $125^\circ\text{C}$ の動作接合部温度範囲で保証されている。

**Note 4:**SHDNピンは $V_{IN}$ に接続するか、直列電流制限抵抗を接続したロジックレベル・ソースによってドライブすることができる。

**Note 5:** $V_{IN}$ の低電圧ロックアウトは、動作時に $V_{IN}$ ピンが超えなければならない電圧として定義される。このスレッショルドは、内部バイアス・ラインのレギュレーションと一定のスイッチング周波数を保証する。安定化出力を維持するための実際の最小入力電圧は、出力電圧と負荷電流により異なる。「アプリケーション情報」を参照。

**Note 6:** $V_{IN}$ の過電圧ロックアウトは、その値を超えるとコンバータの動作が停止する電圧として定義される。「アプリケーション情報」を参照。

**Note 7:** $T_J$ の出力電圧は、静止電力消費時のダイ中央部の温度を表わす。スイッチの電力損失とダイの温度勾配のため、 $T_J$ の出力電圧を測定しても絶対最大接合部温度を超えないことが保証されるわけではない。

**Note 8:**内部パワーオン・リセット(POR)のラッチは、スレッショルドを横切るSHDN1/2ピンの正方向遷移、サーマル・シャットダウン、または過電圧ロックアウトによりセットされる。このラッチの出力は各SSピンの電流源をアクティブにし、標準400 $\mu\text{A}$ の電流をシンクしてSSコンデンサを放電させる。両方のSSピンがソフトスタートPORスレッショルドを下回るか、SHDNピンがそのスレッショルドを下回ると、ラッチはリセットされる。

**Note 9:**スレッショルドは、そのチャネルの帰還リファレンス電圧のパーセンテージとして表わされる。

**Note 10:**ドロップアウト動作を改善するため、昇圧コンデンサ両端の電圧が100%デューティサイクル・スレッショルドの最小昇圧値を下回ったときに限り、出力スイッチが最小オフ時間の間オフされる。

**Note 11:**INDから $V_{OUT}$ への最大電流は、 $V_C$ ピンが高クランプ状態にある時、スイッチのラッチをリセットする、INDピンから $V_{OUT}$ ピンへ流れる電流の値として定義される。

**Note 12:**これは、内部パワースイッチを飽和させるのに必要な、昇圧コンデンサ両端の最小電圧である。

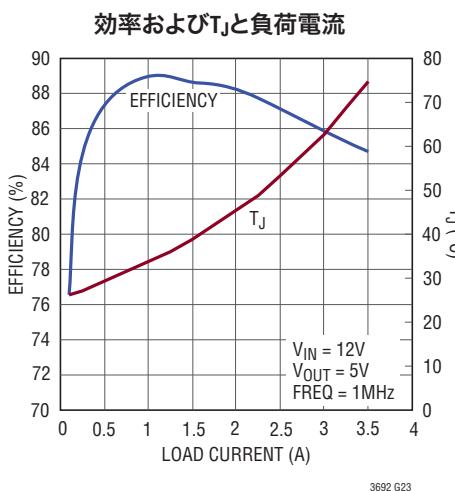

## 標準的性能特性

## 標準的性能特性

## コンパレータのスレッショルドと温度

3692 G10

## コンパレータのシンク電流と温度

3692 G11

## スイッチング周波数と温度

3692 G12

## スイッチング位相と温度

3692 G13

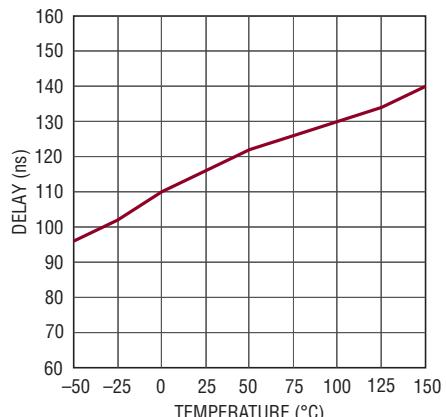

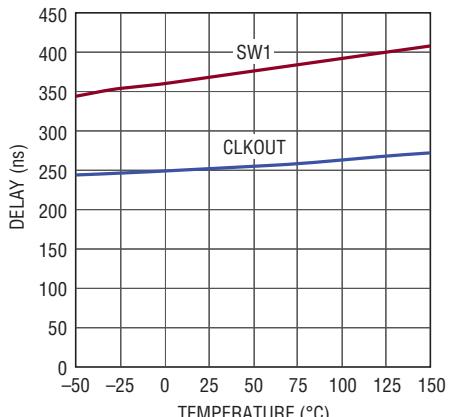

## CLKOUTとSW1間の遅延と温度

3692 G14

RT/SYNCからCLKOUT

およびSW1の遅延と温度

3695 G15

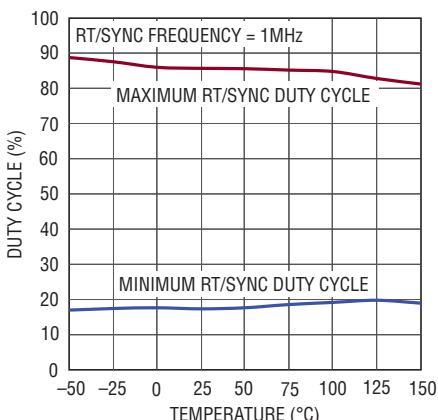

## 同期デューティサイクルと温度

3692 G16

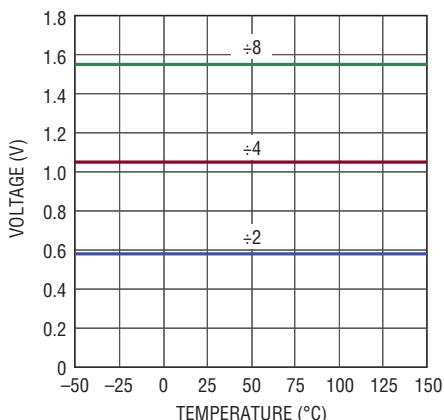

## DIV電圧スレッショルドと温度

3695 G17

## スイッチの飽和電圧と温度

3692 G18

3692fa

## 標準的性能特性

## ピン機能

**BST1/2:** BSTピンは、スイッチの電圧降下を小さくするために、 $V_{IN}$ よりも高い電圧でパワーNPNのベースをドライブします。BSTピンと $V_{IN}$ ピンの間の電圧がパワーNPNを完全にオンするためには必要な電圧よりも低い場合は、BSTコンデンサを再充電するためにパワースイッチがオフされます。

**CMPI1/2:** CMPIピンはコンパレータへの入力で、スレッショルドは720mV、ヒステリシスは60mVです。CMPIピンをFBピンに接続すると、出力がその安定化電圧の90%以内の時はパワーグッド信号が生成されます。

**CMPO1/2:** CMPOピンはオープンコレクタ出力で、CMPIピンがそのスレッショルドを下回ると電流をシンクします。2.8V以上の標準入力電圧における出力状態は仕様値を維持しますが、シャットダウン時、 $V_{IN1}$ の低電圧ロックアウト時、またはサーマル・シャットダウン時は電流シンク能力が低下します。COMPOピンはオープン状態のままにするか、1つのパワーグッド信号を形成するために互いに接続します。

**DIV:** DIVピンの電圧は、RT/SYNCピンによって設定されるマスター・クロック周波数に対するチャネル1の周波数の比率を決定します。DIVピンは標準12 $\mu$ Aの内部電流源によってドライブされるので、DIVピンからグランドに接続した1つの抵抗でDIV電圧を設定でき、その電圧でチャネル1の分周器を設定することができます。分周比は1、2、4、および8に設定可能です。詳細については「アプリケーション情報」のセクションを参照してください。

**DNC:** 接続しないでください。

**GND:** 露出パッド・ピンがこのデバイスの唯一のグランド接続です。露出パッドは、熱抵抗を減らすために広い銅エリアに半田付けする必要があります。GNDピンは両方のチャネルに共通で、小信号グランドとして使用することもできます。理想的な動作を実現するには、大電流のグランド・リターンが形成されるのを避けながら、すべての小信号グランド経路を1点でGNDピンに接続する必要があります。

**FB1/2:** FBピンはエラーアンプへの負入力です。出力スイッチは、このピンを露出グランド・パッドに対して806mVに安定化します。バイアス電流はFBピンから流出します。

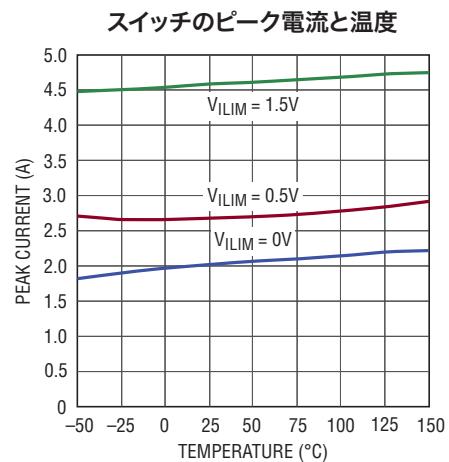

**ILIM1/2:** ILIMピンの電圧は、そのチャネルのピーク・インダクタ電流を決定します。ILIMピンは、標準値12 $\mu$ Aの内部電流源によってドライブされます。ILIMピンからグランドへの抵抗がILIM電圧を設定します。最大電流制限範囲は4.8Aから2Aまでで、その際のILIM電圧はそれぞれ1.5Vと0Vです。

**IND1/2:** INDピンは、インダクタへ流入する電流を測定する内部センス抵抗への入力です。抵抗の電流が $V_C$ ピンによって規定される電流を超えるとSWラッチがリセット位置に維持され、出力スイッチがディスエーブルされます。バイアス電流はINDピンから流出します。

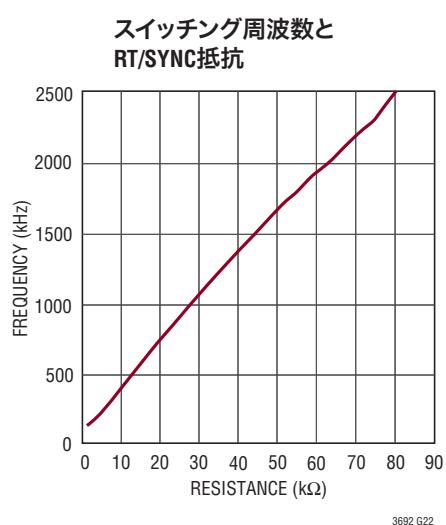

**RT/SYNC:** RT/SYNCピンの電圧は、固定スイッチング周波数を決定します。RT/SYNCピンは標準12 $\mu$ Aの内部電流源によってドライブされるので、RT/SYNCピンからグランドに接続した1つの抵抗を使ってRT/SYNC電圧を設定でき、その電圧でスイッチング周波数を設定することができます。最小スイッチング周波数は $V_{RT/SYNC}$ が0Vの時に標準110kHz、 $V_{RT/SYNC}$ が950mVより高い時は標準2.5MHzです。

RT/SYNCピンを外部クロック信号でドライブすると、スイッチは与えられた周波数に同期します。同期は、クロック信号検出後にクロック信号の立ち上がりエッジで行なわれます。クロックのそれぞれの立ち上がりエッジで発振器のランプがリセットされ、利得制御ループが発振器の充電電流をサーボ制御して発振器の振幅を一定に維持します。したがって、スロープ補償とチャネル位相の関係は変わりません。クロック信号が取り除かれた場合は、同期検出回路のタイムアウト後に発振器が抵抗モードに戻ります。クロック・ソースのインピーダンスは、抵抗モードでRT/SYNCピンから流出する電流が同期周波数とほぼ同じ周波数を発生させるように設定する必要があります。詳細については「アプリケーション情報」のセクションを参照してください。

## ピン機能

**SHDN1/2:**シャットダウン・ピンは各チャネルの動作を制御するために使用します。チャネル1の制御に加え、SHDN1ピンは両方のチャネルの制御回路をアクティブにする機能も備えているので、チャネル2を動作させるために必要です。SHDN1の電圧がそのしきい値より低くなると、両方のチャネルでスイッチングが停止します。SHDN1の電圧をさらに0.6Vまで下げると、消費電流は6 $\mu$ A(標準)に減少します。シャットダウン機能を使用しない場合は、SHDNピンをV<sub>IN</sub>に接続することができます。SHDNピンをロジック信号によってドライブする場合は直列抵抗が必要です。「アプリケーション情報」を参照してください。

**SS1/2:**SSピンから外付けコンデンサに流れる電流が、出力電圧の立ち上がり時間とを決定します。SSピンの電圧が0.8Vのリファレンス電圧より低い場合、帰還電圧はSS電圧に安定化されます。SSピン電圧がリファレンス電圧よりも高い場合は、出力がFBピン電圧を0.8Vに安定化して、SSピンはそのクランプ電圧まで上昇を続けます。出力過負荷時はV<sub>C</sub>ピンが最大スイッチ電流レベルよりも高い値にドライブされ、その電圧クランプがアクティブになります。V<sub>C</sub>のクランプがアクティブになると、SSピンは、出力が最大出力電流を維持できるだけのレギュレーション・ポイントに達するまで放電されます。過負荷状態が解消されると、出力はその電圧からソフトスタートを開始します。SHDNまたはサーマル・シャットダウンの場合は、パワーオン・リセット・ラッチによって、どちらかのコンデンサが解放される前に両方のチャネルのコンデンサが完全に放電されます。両方のSSピンを互いに接続すると、出力は同時にトラッキングを行ないます。

**CLKOUT:**CLKOUTピンは、内部発振器に同期した0V～2.5Vの矩形波を生成します。スイッチング周波数が外付け抵抗によって設定された場合、クロックのデューティサイクルは50%になります。RT/SYNCピンが外部クロック・ソースによってドライブされた場合、CLKOUTのデューティサイクルにはその外部ソースの状態が反映されます。

**SW1/2:**SWピンは内部パワーNPNのエミッタです。スイッチ・オフ時は、このピンはインダクタによって高dV/dtでグランド以下にドライブされます。このピンが過大な負電圧になるのを避けるために、SWピンとそれぞれのV<sub>IN</sub>デカップリング・コンデンサのグランドの近くで、グランドとの間に外付けのショットキー・キヤッチャ・ダイオードを接続する必要があります。

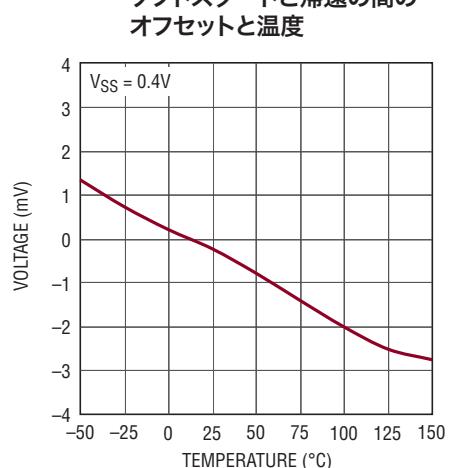

**T<sub>J</sub>:**T<sub>J</sub>ピンは、接合部温度に比例する電圧を出力します。このピンは25°Cで250mVを出力し、出力の勾配は10mV/°Cです。詳細については「アプリケーション情報」のセクションを参照してください。

**V<sub>C1/2</sub>:**V<sub>C</sub>ピンはエラーアンプの出力であり、ピーク・スイッチ電流コンパレータへの入力です。通常、このピンは周波数補償に使われますが、電流クランプや制御ループのオーバーライドに使用することもできます。エラーアンプがV<sub>C</sub>を最大スイッチ電流レベルよりも高い値にドライブすると、電圧クランプがアクティブになります。これは、出力が過負荷となってSSピンから電流が流れ、レギュレーション・ポイントが下がることを示しています。

**V<sub>IN1</sub>:**V<sub>IN1</sub>ピンは両方のチャネルの内部制御回路に電力を供給し、過電圧/低電圧ロックアウト・コンパレータによってモニタされます。V<sub>IN1</sub>ピンは、チャネル1の内蔵パワーNPNスイッチのコレクタにも接続されます。V<sub>IN1</sub>ピンのエッジは高dI/dtなので、デバイスのピン近くでグランドにデカップリングする必要があります。

**V<sub>IN2</sub>:**V<sub>IN2</sub>ピンはチャネル2の出力段に電力を供給し、過電圧/低電圧ロックアウト・コンパレータによってモニタされます。V<sub>IN2</sub>を動作させるには、V<sub>IN1</sub>電圧が2.8Vより高くななければなりません。V<sub>IN2</sub>ピンは、チャネル2の内蔵パワーNPNスイッチのコレクタでもあります。V<sub>IN2</sub>ピンのエッジは高dI/dtなので、デバイスのピン近くでグランドにデカップリングする必要があります。

**V<sub>OUT1/2</sub>:**V<sub>OUT</sub>ピンは、インダクタを流れる電流を測定する内部センス抵抗の出力です。抵抗の電流がV<sub>C</sub>ピンによって規定される電流を超えるとSWラッチがリセット状態に保持され、出力スイッチがディスエーブルされます。バイアス電流はV<sub>OUT</sub>ピンから流れ出します。

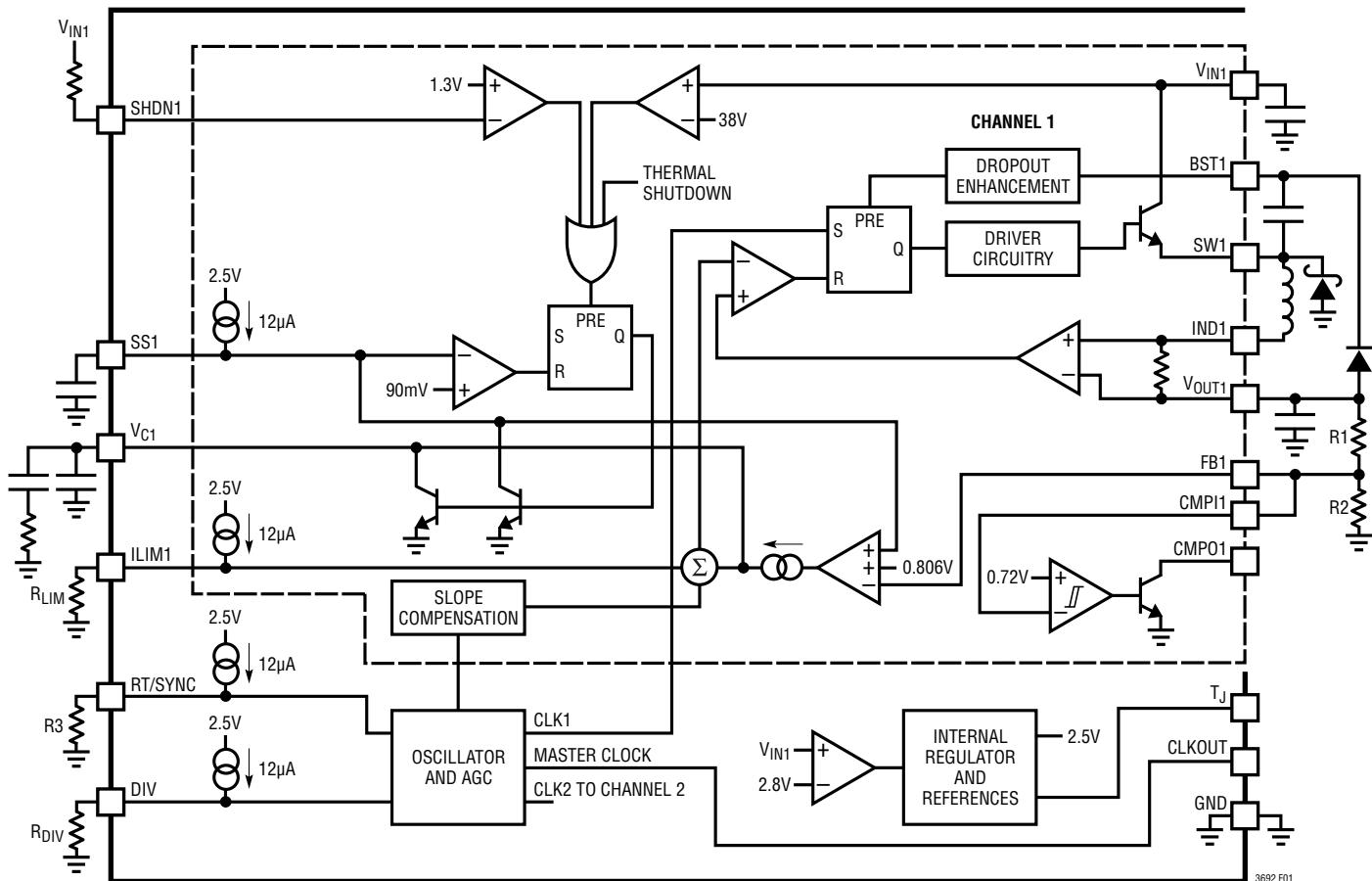

## ブロック図

図1. LT3692ブロック図

## アプリケーション情報

LT3692は、デュアル・チャネル、固定周波数、電流モードの降圧コンバータで、3.5Aスイッチを内蔵しています。それぞれのチャネルは独立して制御することができますが、共通の内蔵レギュレータ、発振器、および温度計回路に電力を供給するには、VIN1の電圧が2.8Vの低電圧ロックアウト・スレッショルドより高くななければなりません。

SHDN1ピンの電圧がそのスレッショルドである1.3Vを下回ると、両方のチャネルのスイッチングがディスエーブルされます。SHDN1をさらに0.6V(標準)より低い電圧に下げる、LT3692は低消費電流モードになります。通常、このモードでLT3692が消費する電流はVIN1から6µA、VIN2からは1µA未満です。SHDNピン電圧が1.3Vを超えると内部バイアス回路がオンして、内部安定化電圧、0.806VFB、12µA RT/SYNC、DIVおよびILIM電流リファレンス、およびソフトスタート・ラッチを設定するPOR信号を生成します。

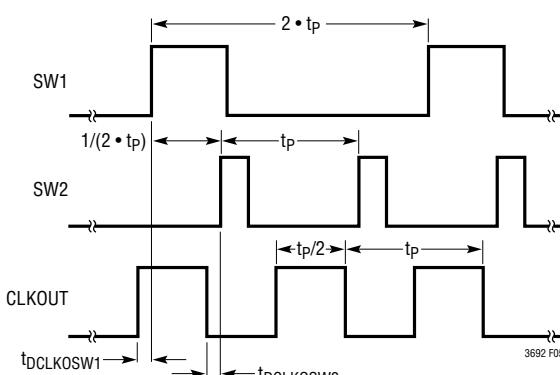

内部リファレンスがそのレギュレーション・ポイントに達すると、内部発振器が、RT/SYNCピンの電圧によって決定される周波数で2つのレギュレータ用にマスタークロック信号の生成を開始します。チャネル1のクロックは、DIVピンの電圧に応じて1、2、4、または8で分周されます。チャネル2のクロックはマスタークロック周波数で動作しますが、チャネル1とは180°の位相シフトが生じます。

このほか、同期信号がLT3692のRT/SYNCピンによって検出された場合、マスタークロックは同期パルスの立ち上がりエッジで入力周波数で生成され、チャネル1は同期信号と同位相になります。分周と位相は、内部生成したマスタークロックと同じに維持されます。

## アプリケーション情報

さらに、同期時の低調波発振を防ぐために、内部スロープ補償が自動的に調整されます。どちらのモードの発振器動作でも、CLKOUTピンからはチャネル1に同期したマスタークロック周波数の矩形波が outputされます。

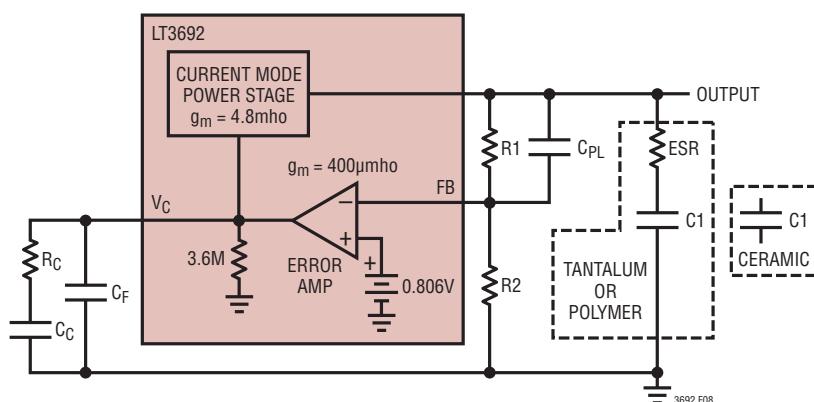

2つのレギュレータは、固定周波数の電流モード降圧コンバータです。電流モード・レギュレータは、内部クロックと、パワースイッチのデューティサイクルを制御する2つの帰還ループによって制御されます。通常のエラーアンプに加えて、サイクルごとにスイッチ電流をモニタする電流検出アンプがあります。この方法は、エラーアンプが outputへの(電圧ではなく)電流の供給を支配することを意味します。電圧供給型システムではインダクタと出力コンデンサの共振周波数までは位相シフトが小さく、そこから突然180°の位相シフトが生じます。電流供給型システムではごく低い周波数で90°の位相シフトがありますが、LC共振周波数より十分高い周波数に達するまでさらに90°の位相シフトが生じることはありません。このため、帰還ループの周波数補償がはるかに容易で、過渡応答もはるかに速くなります。

図1のブロック図には1個のスイッチング・レギュレータしか示されていません。その動作について以下で説明します。もう1つのレギュレータも同じように動作しますが、そのクロックの位相が他方のレギュレータと180°ずれている点だけが異なります。

パワーアップ時に内部POR信号がソフトスタート・ラッチを設定する時は、正常な起動動作を保証するために、両方のSSピンがグランドまで放電されます。SSピンの電圧が90mVを下回るとVCピンが”L”にドライブされてスイッチングがディスエーブルされ、ソフトスタート・ラッチがリセットされます。ラッチがリセットされると、ソフトスタート・コンデンサが12μAの標準値で充電を開始します。

SSピンの電圧が115mVを超えると、VCピンがエラーアンプによって”H”にドライブされます。VCピンの電圧が0.8Vを超えるとクロック・セット・パルスがドライバ・フリップフロップをセットし、このフリップフロップが内部パワーNPNスイッチをオンします。これにより、VINからNPNスイッチ、インダクタ、および内部センス抵抗を経由して流れる電流が増加します。内部センス抵抗両端での電圧降下がVCピンの電圧であらかじめ設定されたレベルを超えると、フリップフロップがリセットされて内部NPNスイッチがオフします。スイッチがオフすると、外付けのショットキー・ダイオードが導通を開始するまでインダクタが

SWピンの電圧を”L”にドライブし、インダクタの電流を減らします。このサイクルはクロック・サイクルの開始ごとに繰り返されます。しかし、クロック・サイクル開始時に内部センス抵抗の電圧が既定レベルを超えるとフリップフロップがセットされず、インダクタ電流がさらに減少する結果となります。出力電流はVC電圧によって制御されるので、出力のレギュレーションは、エラーアンプが継続的にVCピン電圧を調整することによって実現されます。

エラーアンプはトランスコンダクタンス・アンプで、FBの電圧をSSピンの最小電圧または内部806mVリファレンスと比較します。ループの補償は、単純なコンデンサまたは直列抵抗/コンデンサをVCピンからグランドに接続することによって容易に実現されます。

レギュレータの最大出力電流は、VCピンがエラーアンプによってその最大クランプ電圧にドライブされた時に発生します。最大スイッチ電流の値は、ILIMピンからグランドに抵抗を接続することによって、4.8A～2Aの範囲でプログラムすることができます。

SSピンは定電流源によってドライブされるので、ソフトスタート・ピンにコンデンサを1個接続すれば、出力電圧のランプアップを制御された直線的なものとすることができます。

出力に求められる電流がVCピンのクランプによって規定される最大電流を超える場合は、SSピンが放電し、最大電流が出力電圧に対応可能になるまでレギュレーション・ポイントが下がります。過負荷状態が解消されれば、レギュレータは過負荷レギュレーション・ポイントからソフトスタートを開始します。

シャットダウン制御、VINの過電圧、またはサーマル・シャットダウンはソフトスタート・ラッチをセットするので、ソフトスタート・シーケンスが始めから実行されます。

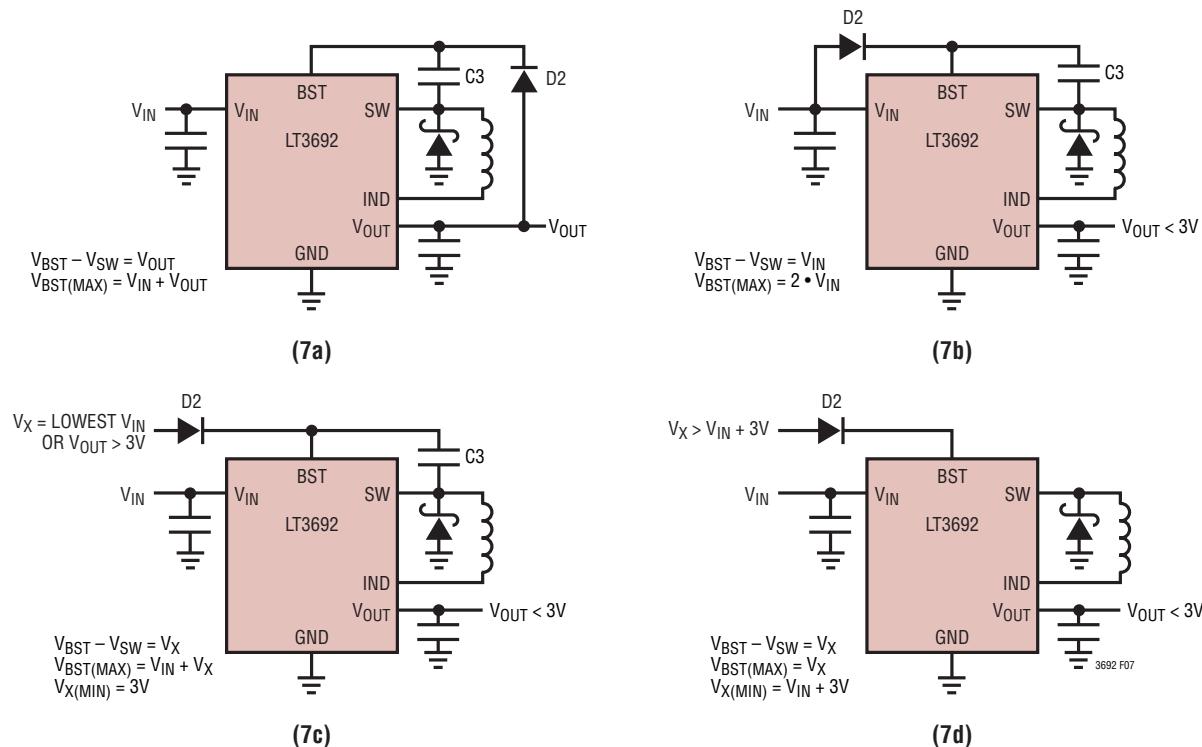

スイッチ・ドライバはVIN電圧またはBST電圧で動作します。外付けのダイオードとコンデンサを使用することにより、VINよりも高いドライブ電圧を生成し、出力NPNを飽和させて高効率を維持します。BSTコンデンサの電圧が十分であれば、スイッチは100%デューティサイクルまで動作させることができます。出力NPNをドライブするには不十分なレベルまで昇圧コンデンサが放電してしまった場合は、BSTピンのコンパレータがサイクル・オフ時間を強制的に最小値にして、昇圧コンデンサを再充電できるようにします。

## アプリケーション情報

エラー状態を検出するために、720mVのスレッショルドと60mVのヒステリシスを持つコンパレータが備わっています。CMPO出力はオープンコレクタNPNで、CMPIピンがスレッショルドを上回っている場合はこのNPNがオフして、抵抗がCMPOピンを必要な電圧まで引き上げられるようにします。

$T_J$ ピンの電圧はLT3692の接合部温度に比例します。ダイ温度が25°Cの時の $T_J$ ピン電圧は250mVで、その出力勾配は10mV/°Cです。

### 出力電圧の選択

出力電圧は、出力とFBピンの間の抵抗分割器によって設定されます。次の式に従って1%抵抗を選択してください。

$$R1 = R2 \cdot \left( \frac{V_{OUT}}{0.806} - 1 \right)$$

バイアス電流の誤差を避けるために、R2は10k以下にする必要があります。式中の参照記号についてはブロック図を参照してください。

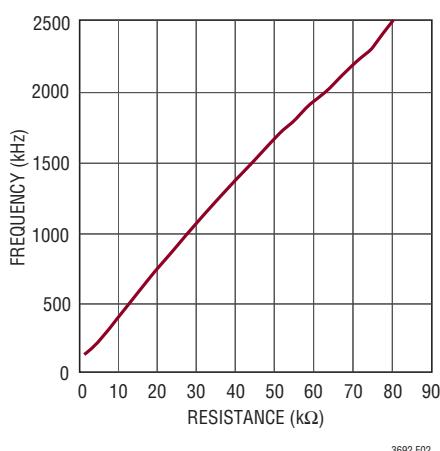

図2. スイッチング周波数とRT/SYNC抵抗

### スイッチング周波数の選択

LT3692のスイッチング周波数は、図1の抵抗R3によって設定されます。RT/SYNCピンは、12μAの電流源によってドライブされます。抵抗R3を設定するとRT/SYNCピンの電圧が設定され、それによって図2に示すようにマスター発振器の周波数が決まります。CLKOUTピンからは、マスター発振器と同じ周波数でチャネル1と同位相の0V～2.5V矩形波が outputされます。

このCLKOUT信号は、複数のスイッチング・レギュレータを同期させるために使用することができます。

最小スイッチング時間によるデューティサイクル上の制限を緩和するために、チャネル1のスイッチング周波数は、マスタークロックから1、2、4、または8の比率で分周することができ、この分周比は図1の抵抗 $R_{DIV}$ によって決定されます。チャネル2のスイッチング周波数はDIVピンには影響されません。DIVピンは、12μAの電流源によってドライブされます。抵抗 $R_{DIV}$ を設定するとDIVピンの電圧が設定され、さらにそれによって表1に示すように分周比が決まります。比率のスレッショルド付近ではDIVピンの入力ヒステリシスはありません。

表1. チャネル1の分周比と $V_{DIV}$

| DIV電圧                   | 分周比 | $R_{DIV}$ |

|-------------------------|-----|-----------|

| $V_{DIV} < 0.5V$        | 1   | 0         |

| $0.5V < V_{DIV} < 1.0V$ | 2   | 62k       |

| $1.0V < V_{DIV} < 1.5V$ | 4   | 100k      |

| $1.5V < V_{DIV}$        | 8   | 150k      |

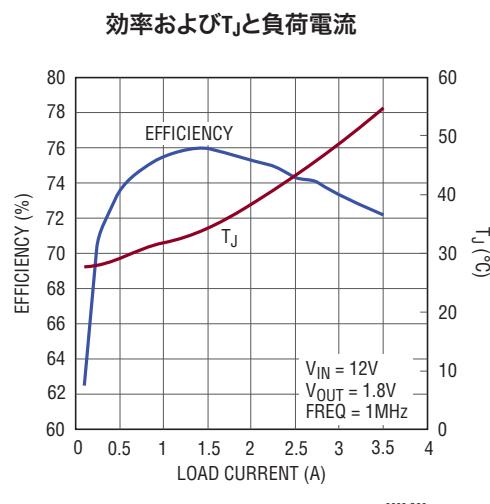

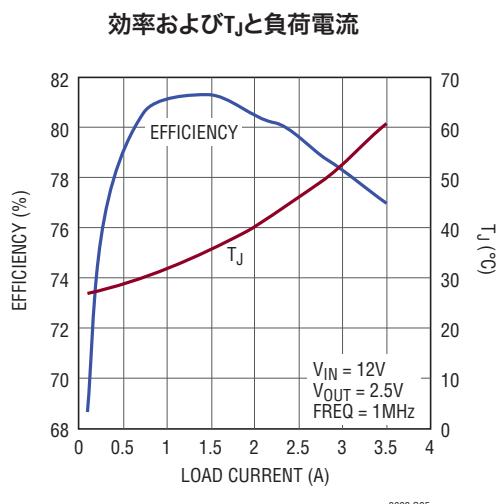

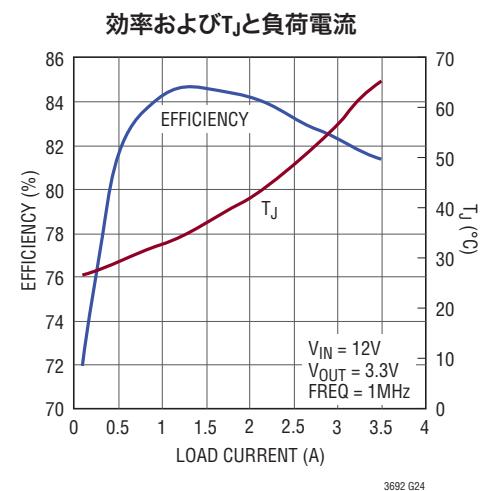

ソリューション全体のサイズを小さくするために、スイッチング周波数は、通常、できるだけ高い値に設定されます。LT3692は高周波域での損失を改善するための手法を採用していますが、スイッチング損失と最小スイッチング時間のために効率と最大入力電圧が低下します。

最大推奨周波数は次の式で概算することができます。

$$\text{周波数 (Hz)} = \frac{V_{OUT} + V_D}{V_{IN} - V_{SW} + V_D} \cdot \frac{1}{t_{ON(MIN)}}$$

ここで $V_D$ はキャッチ・ダイオード(図2のD1)の順方向電圧降下、 $V_{SW}$ は内部スイッチの電圧降下、 $t_{ON(MIN)}$ はスイッチの最小オン時間です。

以下の例と表2のデータには、シングル入力電圧システムの周波数選択におけるトレードオフが示されています。

## アプリケーション情報

表2. 各種RT/SYNC値における効率とサイズの比較、3.3V出力

| 周波数     | RT/SYNC | 効率<br>V <sub>VIN1/2</sub> = 12V | V <sub>IN(MAX)</sub> <sup>†</sup> | L*     | C*    | C+L(面積)             |

|---------|---------|---------------------------------|-----------------------------------|--------|-------|---------------------|

| 250kHz  | 5.90kΩ  | 77.8%                           | 38V                               | 12μH   | 120μF | 59.8mm <sup>2</sup> |

| 500kHz  | 13.0kΩ  | 81.2%                           | 31V                               | 6.8μH  | 60μF  | 54.6mm <sup>2</sup> |

| 1000kHz | 28.0kΩ  | 80.5%                           | 16V                               | 3.3μH  | 30μF  | 51.9mm <sup>2</sup> |

| 1500kHz | 44.2kΩ  | 79.3%                           | 10V                               | 1.5μH  | 22μF  | 46.9mm <sup>2</sup> |

| 2250kHz | 71.5kΩ  | 76.7%                           | 6.5V                              | 0.82μH | 15μF  | 19.1mm <sup>2</sup> |

<sup>†</sup>V<sub>IN(MAX)</sub>は、一定の出力電圧リップルを維持できる最大入力電圧として定義される。

\*インダクタとコンデンサは、安定性と一定のリップル電流が得られるように選択。

例：

V<sub>IN</sub> = 25V, V<sub>OUT</sub> = 3.3V, I<sub>OUT</sub> = 2.5A, t<sub>ON(MIN)</sub> = 250ns, V<sub>D</sub> = 0.6V, V<sub>SW</sub> = 0.4V:

$$\text{最大周波数} = \frac{3.3 + 0.6}{25 - 0.4 + 0.6} \cdot \frac{1}{250e-9} \sim 600\text{kHz}$$

RT/SYNC~15.8kΩ(図2)

### 入力電圧範囲

スイッチング周波数が決まれば、レギュレータの入力電圧範囲を決定することができます。最小入力電圧は、LT3692の最小動作電圧(約2.8V)、またはその最大デューティサイクルのどちらかによって決まります。デューティサイクルは、1クロック・サイクル中に内部スイッチがオンになる時間の比率です。他の多くの固定周波数レギュレータと異なり、昇圧コンデンサ(図1のC3)の両端に出力スイッチを完全に飽和させられるだけの十分な電圧がかかっている場合、LT3692は各クロック・サイクルの終了時にスイッチをオフしません。スイッチを最小時間だけ強制的にオフするのは、クロック・サイクル終了時に昇圧コンデンサを再充電する必要がある場合に限られます。この動作は、固定されたオフ時間の間クロック周波数を下げるのと同

図3. タイミング図(RT/SYNC = 28.0k, tp = 1μs, V<sub>DIV</sub> = 0V)

じ効果があり、結果としてデューティサイクルが上がって最小入力電圧が低下します。最終的なデューティサイクルは昇圧コンデンサの充電時間に依存し、次式を使って概算することができます。

$$DC_{MAX} = \frac{1}{1 + \frac{1}{B}}$$

ここでBは、3Aを「電気的特性」の表に示す標準昇圧電流で除した値です。

これにより、次式に従って最小入力電圧が得られます。

$$V_{IN(MIN)} = \frac{V_{OUT} + V_D}{DC_{MAX}} - V_D + V_{SW}$$

ここでV<sub>SW</sub>は内部スイッチの電圧降下です。

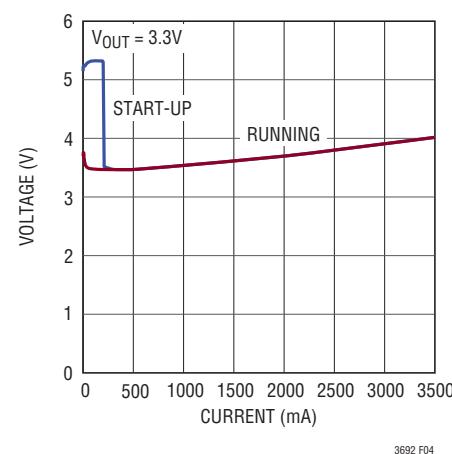

図19に示す3.3Vアプリケーションと1.8Vアプリケーションの最小入力電圧と負荷電流の標準的なグラフを図4に示します。

図4. 最小入力電圧と負荷電流

3692fa

## アプリケーション情報

最大入力電圧は、VINピンとBSTピンの絶対最大定格、および周波数と最小デューティサイクルによって決定されます。最小デューティサイクルは次式で得られます。

$$DC_{MIN} = t_{ON(MIN)} \cdot \text{周波数}$$

最大入力電圧は次式で得られます。

$$V_{IN(MAX)} = \frac{V_{OUT} + V_D}{DC_{MIN}} - V_D + V_{SW}$$

入力電圧を算出された最大入力電圧より高くしても、VINピンとBSTピンの最大定格に違反しない限りLT3692はレギュレーションを行います。しかし、この入力電圧範囲における動作ではパルス・スキップ動作を示します。

例：

$V_{OUT} = 3.3V$ 、 $I_{OUT} = 1A$ 、周波数 = 1MHz、温度 = 25°C、 $V_{SW} = 0.1V$ 、 $B = 50$  (昇圧特性の仕様より)、 $V_D = 0.4V$ 、 $t_{ON(MIN)} = 225ns$ ：

$$DC_{MAX} = \frac{1}{1 + \frac{1}{50}} = 98\%$$

$$V_{IN(MIN)} = \frac{3.3 + 0.4}{0.98} - 0.4 + 0.1 = 3.48V$$

$$DC_{MIN} = t_{ON(MIN)} \cdot \text{周波数} = 0.225$$

$$V_{IN(MAX)} = \frac{3.3 + 0.4}{0.225} - 0.4 + 0.1 = 16.1V$$

図5. タイミング図

(RT/SYNC = 28.0k,  $t_p = 1\mu s$ ,  $V_{DIV} = 0.75V$ )

複数の入力電圧が存在する場合や、チャネル1のVIN/VOUTの比率がチャネル2と著しく異なる場合は、DIVピンの抵抗を適切な値に設定することによって、チャネル1の周波数を設定値から2、4、または8の比率で分周することができます。チャネル1の周波数を分周すると、最大入力電圧も同じ比率で増大します。チャネル1の外付け部品は、最終的な周波数に合わせて選択しなければなりません。

例：

$V_{OUT} = 3.3V$ 、 $I_{OUT} = 1A$ 、周波数 = 1MHz、温度 = 25°C、 $V_{SW} = 0.1V$ 、 $B = 50$  (昇圧特性の仕様より)、 $V_D = 0.4V$ 、 $t_{ON(MIN)} = 225ns$ 、 $V_{DIV} = 0.75V$ ：

$$DC_{MIN1} = t_{ON(MIN1)} \cdot \text{周波数}/2 = 0.1125$$

$$V_{IN1(MAX)} = \frac{3.3 + 0.4}{0.1125} - 0.4 + 0.1 = 32.6V$$

## インダクタの選択と最大出力電流

LT3692のインダクタの初期値としては以下の値が妥当です。

$$L = \frac{V_{OUT}}{f}$$

ここでfは周波数で単位はMHz、Lの単位は $\mu H$ です。

この値での最大負荷電流は約3.5Aとなり、これは入力電圧には関係しません。インダクタのRMS電流定格は最大負荷電流より大きくなればならず、その飽和電流は最大ピーク・スイッチ電流より大きくする必要があります。また、これにより出力電圧リップルは減少します。

1つのチャネルの最大負荷が2.5A未満の場合はインダクタの値を減らし、より高いリップル電流で動作させることができます。あるいは、ILIMピンによってそのチャネルの最大スイッチ電流を調整することができます。これによって物理的に小さいインダクタや低DCRのインダクタを使用することが可能になり、結果として効率が向上します。

インダクタとスイッチのピーク電流は次式で求められます。

$$I_{SW(PK)} = I_{L(PK)} = I_{OUT} + \frac{\Delta I_L}{2}$$

安定した出力を維持するには、このピーク電流がLT3692のスイッチ電流制限ILIMよりも小さくなければなりません。ILIM

## アプリケーション情報

は、ILIMピンからグランドに抵抗を接続することによって、チャネルごとに2A～4.8Aの間で設定することができます。ILIMピンは12μAの電流源によってドライブされます。抵抗 $R_{LIM}$ を設定するとILIMピンの電圧が設定され、さらにそれによって図6に示すように最大スイッチ電流が決まります。起動時のピーク電流は、ILIMピンからグランドに接続したコンデンサ、または出力に接続した抵抗分割器を使用して制限することができます。コンデンサを使用する場合は、デバイスが正常に動作するようにパワーアップ前にコンデンサを放電しなければなりません（「標準的応用例」の3.3Vおよび1.8V、2段降圧マルチ周波数コンバータを参照）。

図6では、ピーク電流制限が小さくなるとスロープ補償によってピーク電流がさらに減少し、デューティサイクルが増加します。

ILIMピンを使用してピーク・スイッチ電流を減らすときは、インダクタ選択の式は次のようにになります。

$$L = \frac{50 \cdot V_{OUT}}{f \cdot R_{ILIM}}$$

ここで、fは周波数で単位はMHz、Lの単位はμH、RはkΩです。

図6. ピーク・スイッチ電流とILIM抵抗

### 入力コンデンサの選択

LT3692回路の入力は、4.7μF以上のX7RまたはX5Rタイプのセラミック・コンデンサでバイパスしてください。サイズの大きな電解コンデンサやタンタル・コンデンサによって追加的なバイパスを行なう場合は、これより値の小さいコンデンサや、より安価なY5Vタイプのコンデンサを使用することもできます。

LT3692の入力電源が異なる入力電圧で動作しているときは、そのチャネルに合わせたサイズの入力コンデンサを、それぞれの $V_{IN}$ ピンのできるだけ近くに配置する必要があります。

入力にセラミック・コンデンサを使用する場合の注意を以下に示します。セラミック入力コンデンサは、浮遊インダクタンスと結合して共振タンク回路を形成する可能性があります。電源が瞬時に投入されると（たとえば通電状態の電源にいきなり回路を差し込む場合）、このタンク回路がリングギングを生じて入力電圧が倍になります。LT3692を損傷することがあります。解決策としては、入力電圧をクランプするか、セラミック・コンデンサに並列にESRの大きなコンデンサを追加してタンク回路を減衰させます。詳細については「アプリケーションノート88」を参照してください。

### 出力コンデンサの選択

通常、降圧レギュレータは、スイッチング周波数の1/10の出力クロスオーバー周波数によって容易に補償することができます。これは、過渡ステップで出力コンデンサが出力負荷電流を供給しなければならない時間が、スイッチング周期のおよそ2～3倍であることを意味します。このステップで許容できる出力電圧の低下を1%とすると、出力コンデンサの初期値としては次の値が妥当です。

$$C_{VOUT} = \frac{\text{Max Load Step}}{\text{Frequency} \cdot 0.01 \cdot V_{OUT}}$$

例：

$V_{OUT} = 3.3V$ 、周波数 = 1MHz、最大負荷ステップ = 2A。

$$C_{VOUT} = \frac{2}{1E6 \cdot 0.01 \cdot 3.3V} = 60\mu F$$

算出した値は推奨初期値に過ぎません。過渡応答を改善する必要がある場合は値を大きくしてください。あるいは、サイズが優先される場合は容量を小さくします。出力コンデンサはインダクタ電流をフィルタして、電圧リップルの小さい出力を生成します。また、負荷電流の変動に対応してLT3692の制御ループを安定させるためにエネルギーを蓄積します。LT3692のスイッチング周波数により、必要な出力コンデンサの値が決まります。また、電流モードの制御ループは、出力コンデンサの直列抵抗(ESR)を必要としません。これらの理由から、セラミック・コンデンサを使用して出力リップルを極めて低い値に抑え、回路サイズを小さくすることも可能です。

## アプリケーション情報

また、電解コンデンサを使用することもできます。ほとんどのアルミ電解コンデンサは、出力リップルを低く抑えるにはESRが大き過ぎます。タンタル・コンデンサや電源用の新しい低ESR有機電解コンデンサが適しており、ESRの仕様はメーカーによって規定されています。低リップルを実現するために必要なESRに基づいて、コンデンサの値を選択します。コンデンサの大きさによってESRが決まるので、同様のリップル性能を持つセラミック・コンデンサに比べて、サイズも容量も大きくなります。利点の1つは、大きいコンデンサを使用すると、負荷電流が大きく変化した場合の過渡応答が改善されることです。表3にいくつかのコンデンサのメーカーを示します。

表3

| メーカー        | タイプ                                  | シリーズ                             |

|-------------|--------------------------------------|----------------------------------|

| Taiyo Yuden | Ceramic X5R, X7R                     |                                  |

| AVX         | Ceramic X5R, X7R<br>Tantalum         |                                  |

| Kemet       | Tantalum<br>TA Organic<br>AL Organic | T491, T494, T495<br>T520<br>A700 |

| Sanyo       | TA/AL Organic                        | POSCAP                           |

| Panasonic   | AL Organic                           | SP CAP                           |

| TDK         | Ceramic X5R, X7R                     |                                  |

### キャッチ・ダイオード

ダイオードD1は、スイッチ・オフ時間のみ導通します。順方向電圧降下を制限して効率を向上させるために、ショットキー・ダイオードを使用してください。ショットキー・ダイオードは、ピーク逆電圧がレギュレータの入力電圧に等しくなければならず、通常動作時の平均順方向電流に合わせてサイズを選ぶ必要があります。平均順方向電流は次式で計算できます。

$$I_{D(AVG)} = \frac{I_{OUT}}{V_{IN}} \cdot (V_{IN} - V_{OUT})$$

短絡状態では、ILIMピンによって設定されるLT3692のピーク・スイッチ電流制限で決まる標準値までダイオード電流が増加します。これは短時間であれば問題ありませんが、このような状態での連続動作を許容できるかどうかダイオードのメーカーに確認することをお勧めします。

### BSTピンに関する検討事項

BSTピンに接続するコンデンサとダイオードは、入力電圧より高い電圧を発生させます。ほとんどの場合は、0.47μFのコンデンサと小さいショットキー・ダイオード(CMDSH-4Eなど)で問題なく動作します。80%を超えるデューティサイクルで最適性能が得られるようにするには、0.5Aのショットキー・ダイオード(PMEG4005など)を使用してください。ほとんどあらゆるタイプのフィルム・コンデンサやセラミック・コンデンサを使用できますが、スイッチのオフ時間中に完全に再充電できるように、ESRは1Ω未満とする必要があります。コンデンサの値は次式で概算できます。

$$C_{BST} = \frac{I_{OUT(MAX)} \cdot V_{OUT}}{5 \cdot V_{IN} (V_{OUT} - 2) \cdot f}$$

ここで $I_{OUT(MAX)}$ は最大負荷電流です。

図7に昇圧回路の構成方法を4通り示します。最大限の効率を実現するには、BSTピンの電圧がSWピンより3V以上高くなればなりません。一般に、3.3V以上の出力を得るには標準回路(図7a)が最も適しています。出力電圧がこれより低い場合は、昇圧ダイオードを入力に接続することができます(図7b)。図7aではより低い電圧源からBSTピンの電流が供給されるので、こちらの回路の方がより効率的です。3Vより高い利用可能なDCソースを使用した昇圧電圧源を図7cに示します。最も高い効率は、3Vを超える範囲で最も低い昇圧電圧を選ぶことによって得られます。たとえば3.3Vと1.8Vを発生させる場合、1.8Vがオンしている時は常に3.3Vがオンしているとすると、1.8Vの昇圧ダイオードを3.3V出力に接続することができます。また、いかなる場合においても、BSTピンの最大電圧が「絶対最大定格」のセクションで規定されている最大値より低くなるようにする必要があります。

昇圧回路は、図7dに示すように、入力電圧より3V以上高いDC電圧で直接動作させることもできます。 $V_{IN}$ が与えられている状態で $V_x$ が”L”に保持された場合にLT3692が損傷を受けるのを防ぐために、ダイオードを使用します。この回路ではいくつかの部品を省くことができます(BSTピンは両方ともD2に接続できる)、効率が低下してLT3692の損失も大きくなります。また、 $V_x$ が与えられていない場合でもLT3692は出力を安定化しようとしますが、安定化時の効率は非常に低く、損失も大きくなります。これは、スイッチを飽和させることができず、導通時に電圧が1.5V～2V低下するからです。

## アプリケーション情報

図7. BSTピンに関する検討事項

LT3692のアプリケーションの最小入力電圧は、上に述べたように最小動作電圧(<3V)と最大デューティサイクルによって制限されます。正常な起動を行なう場合、最小入力電圧は昇圧回路によっても制限されます。入力電圧がゆっくりとランプアップする場合や、すでに出力がレギュレーション状態でSSピンによりLT3692をオンする場合は、昇圧コンデンサを完全に充電することができません。昇圧コンデンサはインダクタに蓄積されたエネルギーで充電されるので、昇圧回路を正常に動作させるために、回路にはいくらかの最小負荷電流が必要です。この最小負荷電流は、入力電圧と出力電圧、および昇圧回路の構成に依存します。起動および動作に必要な最小負荷電流を、3.3V出力の場合の入力電圧の変化に応じてプロットしたものが、「標準的性能特性」のセクションに示されています。多くの場合、放電した出力コンデンサがスイッチャの負荷となるので、スイッチャは起動できます。これらのプロットは、V<sub>IN</sub>が非常にゆっくりとランプアップするワーストケースの状況を示しています。起動電圧を最小にするには、ショットキー・ダイオードを使用してください。

## 6Vを超える出力

6Vを超える出力を得るには、インダクタと並列に1k~2.5kの抵抗を追加してSWノードの不連続リンクを緩和し、予期せぬSW電流が流れるのを防ぎます。「標準的応用例」のセクションの12V出力回路にはこの抵抗の位置が示されています。

## 周波数補償

LT3692は電流モード制御を使用して出力を安定化します。これによってループ補償が容易になります。特に、LT3692は安定動作のために出力コンデンサのESRを必要としないので、セラミック・コンデンサを使用して出力リップルを下げ、回路サイズを小さくすることができます。周波数補償は、V<sub>C</sub>ピンに接続した部品によって行なわれます。一般的には、グランドに直列に接続したコンデンサと抵抗がループ利得を決定します。さらに、低容量のコンデンサを並列に接続します。このコンデンサはループ補償の一部ではなく、スイッチング周波数のノイズを除去するために使用します。

## アプリケーション情報

ループ補償は安定性と過渡性能を決定します。補償ネットワークの設計は多少複雑で、最良の値はアプリケーションと出力コンデンサのタイプによって異なり、特に出力コンデンサが大きく影響します。実際的な手法としては、このデータシートの回路の中から目的のアプリケーションに似た回路を選んで出発点とし、補償ネットワークを調整して性能を最適化します。次に、負荷電流、入力電圧、温度などを含め、全ての動作条件にわたって安定性をチェックします。

LT1375のデータシートにはループ補償に関する詳しい説明と、過渡負荷を使用して安定性をテストするための方法が記載されています。

LT3692制御ループの等価回路を図8に示します。エラーアンプは、出力インピーダンスが有限のトランスクンダクタンス・アンプです。変調器、パワースイッチ、およびインダクタで構成される電源部分は、 $V_C$ ピンの電圧に比例した出力電流を発生するトランスクンダクタンス・アンプとしてモデル化されます。出力コンデンサはこの電流を積分し、 $V_C$ ピンのコンデンサ( $C_C$ )はエラーアンプの出力電流を積分するので、ループには2つのポールが生じます。ほとんどの場合はゼロが1つ必要で、これは出力コンデンサのESR、または $C_C$ に直列に接続した抵抗によって生じます。

このシンプルなモデルは、インダクタ値が大き過ぎず、ループのクロスオーバー周波数がスイッチング周波数よりも十分に低ければうまく動作します。帰還抵抗分割器に並列に位相リード・コンデンサ( $C_{PL}$ )を接続すると、過渡応答が改善されることがあります。

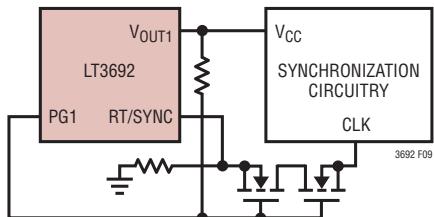

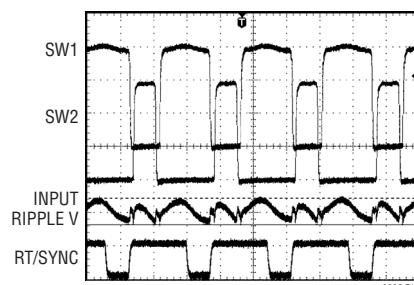

## 同期

RT/SYNCピンは、レギュレータを外部クロック・ソースに同期させるために使用することもできます。クロック・ソースによってRT/SYNC抵抗をドライブすると、同期検出回路がトリガされます。同期が検出されると、SW1の立ち上がりエッジがRT/SYNC信号の立ち上がりエッジに同期し、SW2の立ち上がりエッジはRT/SYNC信号の立ち下がりエッジに同期します(図10と図11を参照)。同期中は、同期信号と同じ周波数とデューティサイクルを持つ0V～2.4Vの矩形波が、250nsの標準伝播遅延でCLKOUTピンから出力されます。さらに、低調波発振を防ぐために内部AGCループがスロープ補償を調整します。同期信号が停止すると同期検出回路が標準10μsでタイムアウトし、その時点でLT3692は、RT/SYNCピンの電圧に基づく自走周波数に戻ります。

LT3692に入力する同期クロック信号は、周波数が200kHz～2MHz、デューティサイクルが20%～80%で、"L"状態が0.5Vより低く"H"状態が1.6Vより高くなればなりません。これらのパラメータ範囲外の同期信号は、異常なスイッチング動作を招きます。RT/SYNCピンを常時1.6Vより高い電圧に維持すると、スイッチングはディスエーブルされます。

レギュレータの起動時に同期信号が存在しない場合は(たとえば同期回路がレギュレータの出力から電力を供給されている場合)、正常な起動動作を行なわせるために、同期回路がアクティブになるまでRT/SYNCピンを1V未満に維持しなければなりません。

図8. ループ応答のモデル

## アプリケーション情報

同期信号が不定状態(V<sub>OL</sub>、V<sub>OH</sub>、Hi-Z)でパワーアップされる場合は、図9に示す要領でLT3692に同期クロックを接続します。図に示す回路は、出力電圧が安定化出力の90%未満の場合、同期信号を遮断します。LT3692は、RT/SYNCピンからグランドへの抵抗で決まるスイッチング周波数で起動します。

低インピーダンス状態(V<sub>OL</sub>)で同期信号がパワーアップする場合は、RT/SYNCピンと同期クロックの間に抵抗を接続します。RT/SYNCピンからグランドへの等価抵抗が、スタートアップ周波数を設定します。

高インピーダンス状態(Hi-Z)で同期信号がパワーアップする場合は、RT/SYNCピンからグランドへ抵抗を接続します。RT/SYNCピンからグランドへの等価抵抗が、起動周波数を設定します。

図9. レギュレータの出力から電力を供給される同期信号

図10. タイミング図 (RT/SYNC = 1MHz、デューティサイクル = 50%)

図11. タイミング図 (RT/SYNC = 1MHz、デューティサイクル > 50%)

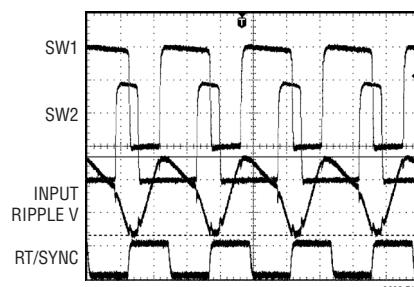

### 入力リップル電圧の低減

同期信号の立ち上がりエッジと立ち下がりエッジにスイッチを同期させると、V<sub>IN1</sub>とV<sub>IN2</sub>を同じ電源に接続したシステムでは、入力リップル電流を低減する独自な機能を得ることができます。入力電流リップルが減少すれば、必要な入力容量を小さくすることができます。たとえば、図12に示す標準的な逆位相デュアル14.4V/8.5Vおよび14.4V/3.3Vレギュレータの入力リップル電圧のピーク値は、71%デューティサイクルの同期信号によってLT3692をドライブすることにより、図13に示すように472mVから160mVに低下します。

図12. 180°位相のデュアル14.4V/8.5V、14.4V/3.3V

図13. 256°位相のデュアル14.4V/8.5V、14.4V/3.3V

## アプリケーション情報

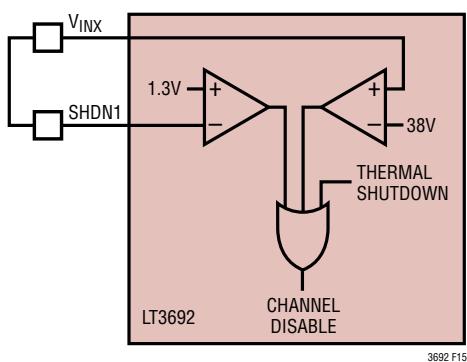

### シャットダウンと低電圧/過電圧ロックアウト

通常、低電圧ロックアウト(UVLO)は入力電源が電流制限されているか、比較的大きいソース抵抗を持つような状況で使われます。スイッチング・レギュレータはソースから一定の電力供給を受けるので、ソース電圧が低下するにつれてソース電流が増加します。この現象はソースからは負の抵抗負荷のように見えるため、ソース電圧が低い状態では、ソースが電流を制限したり、低電圧にラッチすることができます。UVLOは、この問題が発生するおそれのあるソース電圧でレギュレータが動作しないようにします。

通常、過電圧ロックアウト(OVLO)は、有害と思われる入力過渡電圧が発生した時にスイッチング・レギュレータをシャットダウンするために使われます。

図14に示すように、SHDNピンをV<sub>IN</sub>ピンに接続すると、過電圧ロックアウトのスレッショルドは38Vの標準最大値に設定されます。

さらに、2.8Vの最小V<sub>IN1</sub>を下回ると、内部コンパレータが両方のチャネルを強制的にシャットダウンします。この機能は、バッテリ駆動システムの過度の放電を避けるために使用できます。V<sub>IN1</sub>の低電圧ロックアウトに加えて、SHDN1が1.3Vを下回ると両方のチャネルがディスエーブルされます。

入力分圧器と内部コンパレータの1つを使用すれば、プログラム可能なUVLOを実装することができます(「標準的応用例」のセクションを参照)。

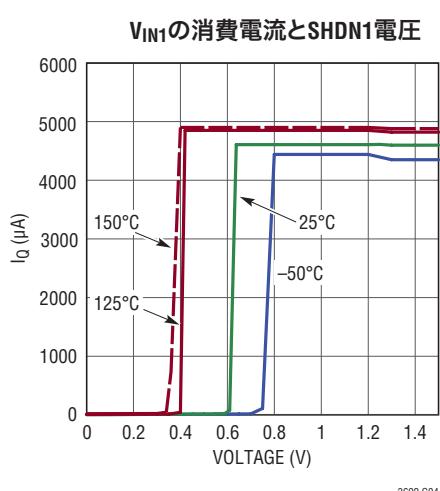

SHDNピンの電圧を1.3Vより高くすれば、対応するチャネルを動作させることができます。SHDNピン電圧を1.3Vより低くすると、そのチャネルがディスエーブルされます。SHDN1の電圧を0.6Vより低くすると、LT3692は低消費電流モードになります。「標準的性能特性」セクションに消費電流とSHDN1電圧の

図14. SHDNをV<sub>IN</sub>に接続してデフォルトのOVLOとUNVLOを選択

関係を示すグラフが記載されています。SHDNピンにヒステリシスはありません。SHDNピンをV<sub>IN</sub>に接続しない場合は、内部クランプがSHDNピンを2.5Vに安定化します。

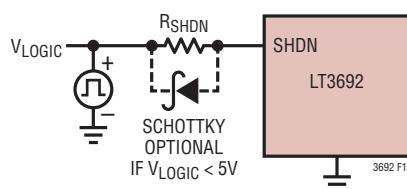

2.5Vよりも高いロジック信号によってSHDNピンをドライブする場合は、SHDNピンへの電流が10 $\mu$ Aを超えないよう制限するために、直列抵抗が必要です。

図15の例の場合、標準的なロジックレベル信号に対しては249kの抵抗で十分です。ロジック信号が5V以上の場合は、R<sub>SHDN</sub> = (V<sub>LOGIC</sub> - 2.5V) / 10 $\mu$ Aに等しい電流制限抵抗を選択します。図15に示すように、小さいショットキー・ダイオード(BAT54など)を電流制限抵抗と並列に接続してください。

直列抵抗からSHDNピンへの接続は短くし、スイッチング・ノードへのプレーン間容量や表面容量を最小限に抑えるようにします。

図15. SHDNピンの外部制御

### ソフトスタート

LT3692の出力は、SSピンまたは内部0.806Vリファレンスのどちらか低い方の電圧に安定化されます。SSピンからグランドへのコンデンサは内部12 $\mu$ A電流源によって充電されるので、0Vから安定化出力電圧まで線形の出力ランプが得られ、その時間は次式で与えられます。

$$t_{RAMP} = \frac{C_{SS} \cdot 0.806V}{12\mu A}$$

パワーアップ時は、リセット信号によってソフトスタート・ラッチがセットされ、正常な起動を保証するために両方のSSピンをほぼ0Vまで放電します。両方のSSピンが完全に放電されるとラッチがリセットされ、内部の12 $\mu$ A電流源がSSピンの充電を開始します。

SSピンの電圧が115mVより低い場合はV<sub>C</sub>ピンが”L”になり、それによってスイッチングがディスエーブルされます。これにより、SSピンを各チャネル個別のシャットダウンとして使用することができます。

3692fa

## アプリケーション情報

SSピンの電圧が90mVを超えるとVCピンが解放され、出力はSS電圧に安定化されます。SSピンの電圧が内部0.806Vリファレンスを超えると、出力はこのリファレンスに安定化されます。SSピン電圧は、2Vでクランプされるまで上昇を続けます。

V<sub>IN1</sub>の低電圧ロックアウトが生じた場合は、両方のチャネルのソフトスタート・ラッチがセットされて、起動シーケンスが始めからトリガれます。1つのチャネルのSHDNピンが1.3V未満にドライブされた場合、その過電圧ロックアウトがイネーブルされた場合、あるいはそのパワースイッチの内部ダイ温度が通常動作中に最大定格値を超えた場合は、そのチャネルのソフトスタート・ラッチがセットされます。

さらに、負荷が最大出力スイッチ電流を超えると出力が低下し始め、VCピンのクランプがアクティブになります。VCピンがクランプされている間はSSピンが放電されます。結果として、出力は、最大出力電流が対応できる最大電圧に安定化されます。たとえば6V出力に1Ωの負荷がかけられると、SSピンは0.48Vに低下して出力が4.8V(4.8A・1Ω)に安定化されます。過電圧状態が解消されると、出力は一時的な電圧レベルから通常のレギュレーション・ポイントまでソフトスタートを開始します。

SSピンは2Vでクランプされ、レギュレーションの制御を行なう前に0.806Vまで放電しなければならないので、一時的な過負荷状態は許容されます。ソフトスタートによる回復は行なわれません。SSピンが制御を開始するまでの標準時間は次式で得られます。

$$t_{SS(CONTROL)} = \frac{C_{SS} \cdot 1.2V}{1.4mA}$$

### オープンコレクタ・コンパレータ

CMPOピンは内部コンパレータのオープンコレクタ出力です。コンパレータは、60mVのヒステリシスでCMPIピン電圧をリファレンス電圧の90%(0.72V)と比較します。

CMPOピンは、CMPIピンがスレッショルドより低い時は標準で300μAのシンク能力を持ち、スレッショルドを超えた場合は38Vに耐えることができます。CMPOピンは、V<sub>IN1</sub>ピン電圧が2.8Vよりも高い間アクティブです(シャットダウン時と低電圧ロックアウト時はシンク能力が低下します)。

コンパレータは、入力電圧と出力電圧、およびダイ温度のモニタに使用することができます。例について「標準的応用例」のセクションに示す一連の回路を参照してください。

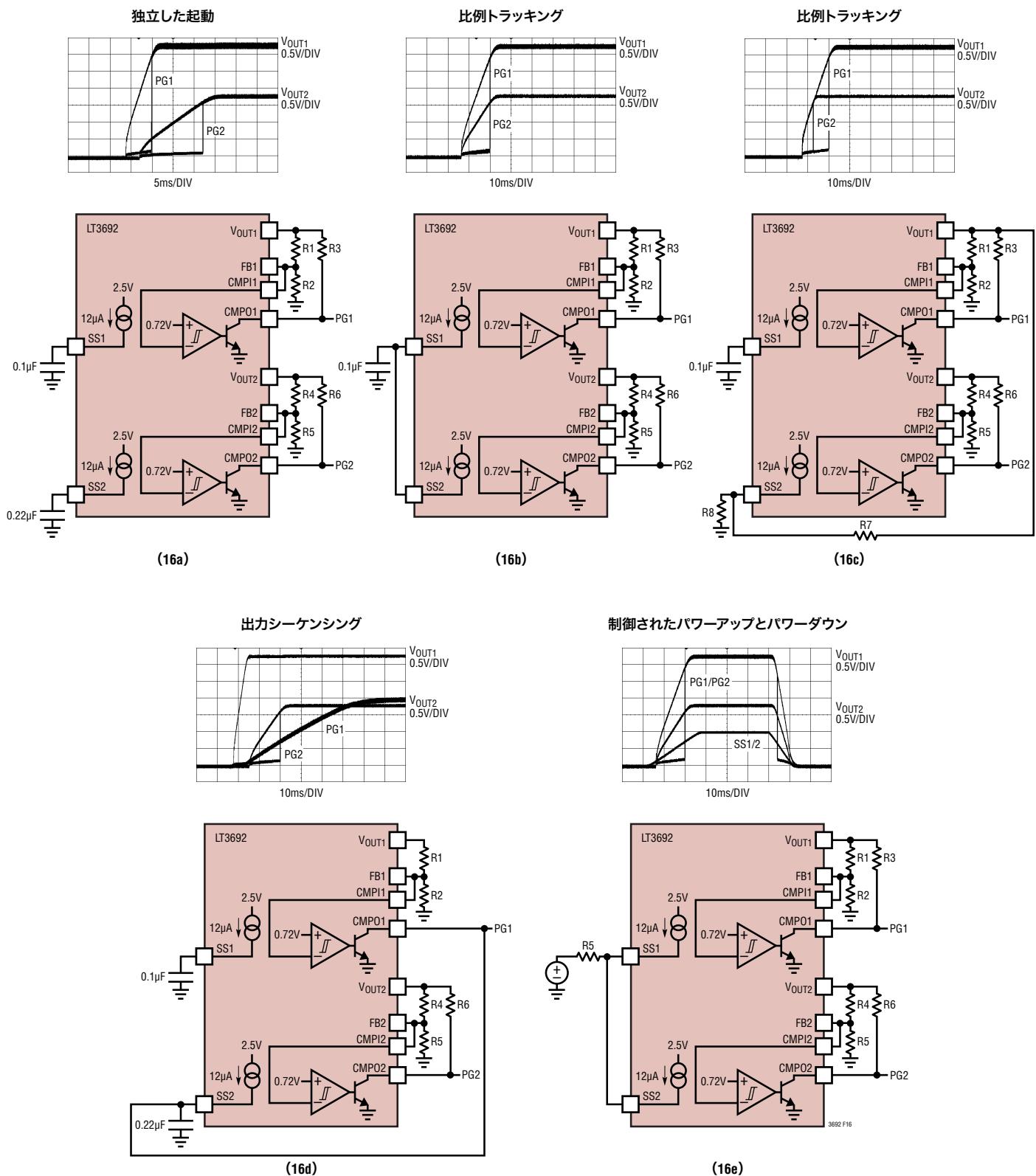

### 出力トラッキング/シーケンシング

LT3692のSSピンとCMPOピンを使用すれば、チャネル間の複雑なトラッキングとシーケンシングを行なうことができます。3.3Vおよび1.8Vアプリケーションにおける出力トラッキング/シーケンシング用の構成を図16にいくつか示します。

各チャネル用の個別ソフトスタートを図16aに示します。各チャネルの出力ランプ時間は、「ソフトスタート」のセクションに示したようにソフトスタート・コンデンサによって設定されます。

図16bでは、両方のSSピンを互いに接続することによって比例トラッキングを行なっています。この構成ではSSピンのソース電流が2倍(24μA)になるので、出力の立ち上がり時間を計算するにはこの点を考慮する必要があります。

V<sub>OUT1</sub>からの帰還ネットワークを、V<sub>OUT2</sub>電圧の設定と同じ比率でSS2ピンに接続することによって、図16cに示す絶対トラッキングが実現されます。トップ帰還抵抗(R1)の最小値は、V<sub>OUT1</sub>が安定化電圧にある時に1.4mAのシンク電流でSSピンをグランドまで完全にドライブできるように設定する必要があります。さらに、SS2の12μAのソース電流によって、V<sub>OUT2</sub>電圧にはわずかなオフセットが生じます。このオフセットは、R2の値を少し小さくすることによって補正できます。

出力シーケンシングの例を図16dに示します。V<sub>OUT1</sub>がその安定化電圧の10%以内になると、CMPO1がSS2ソフトスタート・ピンを解放してV<sub>OUT2</sub>のソフトスタートを可能にします。この場合、CMPO1はSSピンによって2Vにプルアップされます。CMPO1のロジック用により高い電圧が必要な場合は、V<sub>OUT1</sub>へのプルアップ抵抗を使用することができます。こうすると、ソフトスタート時のランプ時間が短くなり、一時的な短絡に対する耐性が向上します。

精密なランプアップとランプダウンが必要なら、図16eに示すようにSSピンをドライブします。抵抗(R3)の最小値は、パワーアップ時とフォールト時に、1.4mAのシンク電流でSSピンをグランドまで完全にドライブできるように設定する必要があります。

## アプリケーション情報

図16. SSピンの構成

## アプリケーション情報

### アプリケーションの最適化

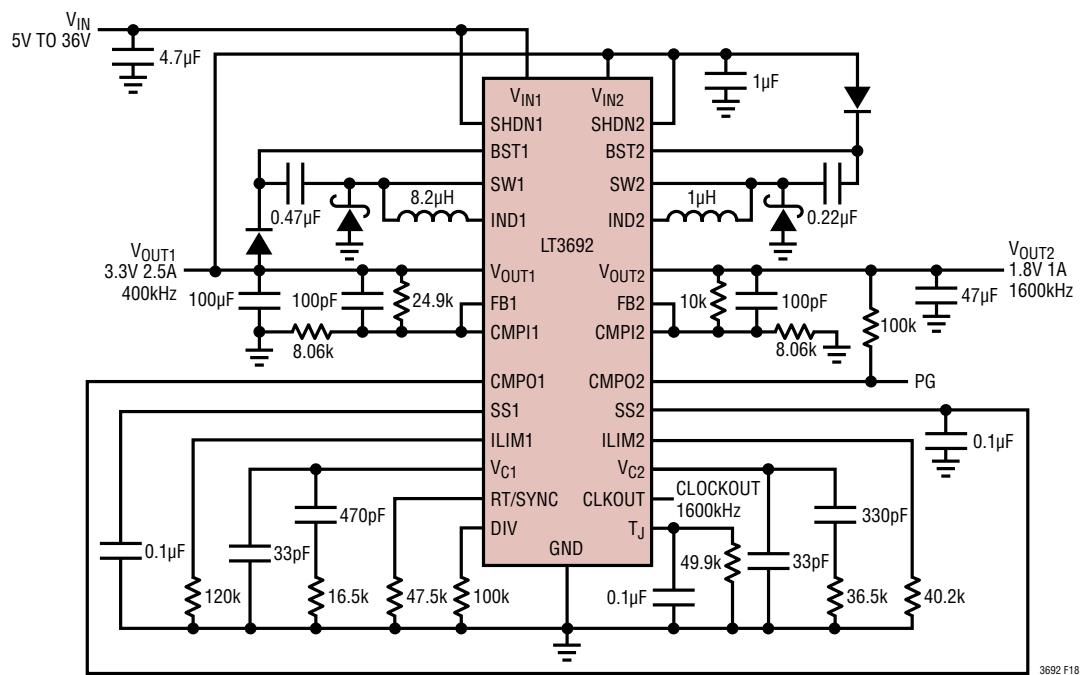

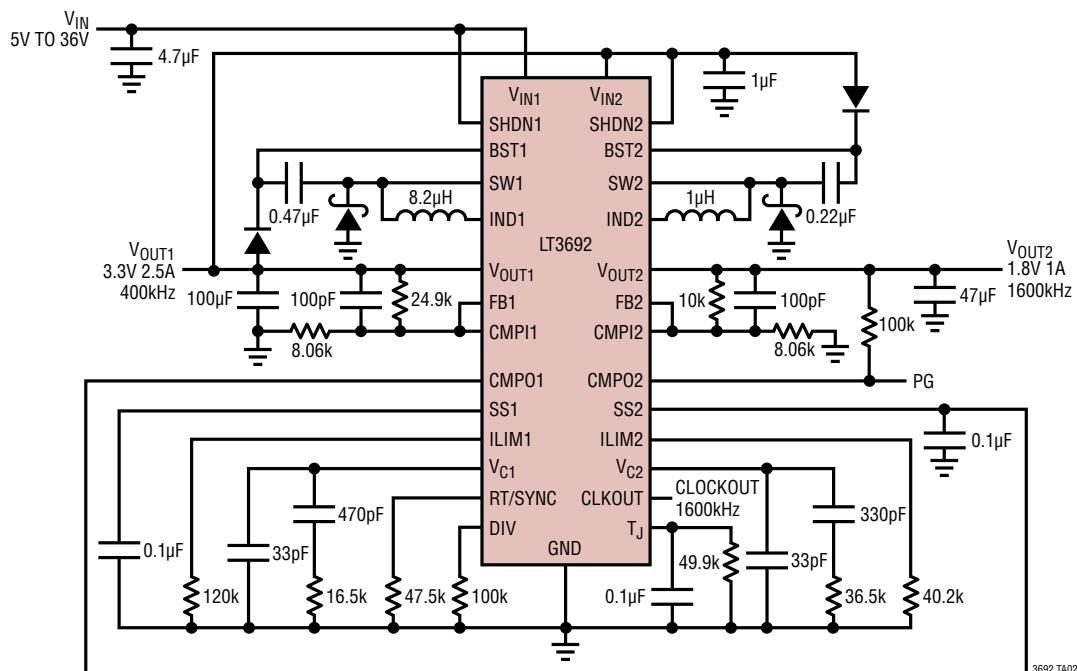

$V_{IN}$ と $V_{OUT}$ の比率を大きくする必要のあるマルチチャネル・アプリケーションでは、最大周波数とそれに基づくインダクタ・サイズは、比率の最も大きいチャネルによって決まります。LT3692はマルチ周波数動作により、固定周波数動作を維持しながら、各チャネルの部品サイズを最小限に抑えることができます。この手法を図17の回路に示します。マルチ周波数動作に2段降圧手法を組み合わせれば、 $V_{IN}$ と $V_{OUT}$ の比率の小さいチャネルの周波数を上げることができます。外付け部品のサイズをさらに小型化します。この手法の欠点は、第1段の出力電力能力が、第2段から供給される出力電力によって決まることがあります。図18のデュアル降圧アプリケーションは、入力電圧( $V_{IN1}$ )を最も高い出力電圧に降圧し、さらにその電圧を使用して2番目の入力( $V_{IN2}$ )に電力を供給します。 $V_{OUT1}$ は、その出力と $V_{OUT2}$ の最大負荷の両方に対応できるだけの十分な電流を供給できなければなりません。 $V_{OUT1}$ 電圧は、2番目のチャネルがスイッチを開始する時点で、「電気的特性」に示す $V_{IN2}$ の最小入力電圧(2.8V)より高くななければなりません。チャネル2の遅延は、独立したソフトスタート・コンデンサを使用するか、CMP01出力によるシーケンシングを行なうことで実現できます。

たとえば、最大入力が36Vだとします。

$$V_{IN} = 36V, V_{OUT1} = 3.3V(1.5A), V_{OUT2} = 1.8V(1.5A)$$

$$\text{周波数(Hz)} = \frac{V_{OUT} + V_D}{V_{IN} - V_{SW} + V_D} \cdot \frac{1}{t_{ON(MIN)}}$$

$$L = \frac{(V_{IN} - V_{OUT}) \cdot V_{OUT}}{V_{IN} \cdot f}$$

### 1段降圧

$$\text{Frequency (Hz)} = \frac{1.8 + 0.6}{36V - 0.4 + 0.6} \cdot \frac{1}{225\text{ns}} \approx 250\text{kHz}$$

$$L_1 = \frac{(36V - 3.3) \cdot 3.3}{36V \cdot 250\text{kHz}} \geq 12\mu\text{H}$$

$$L_2 = \frac{(36V - 1.8) \cdot 1.8}{36V \cdot 250\text{kHz}} \geq 6.8\mu\text{H}$$

### 2段降圧

$$\text{Frequency (Hz)} = \frac{3.3 + 0.6}{36V - 0.4 + 0.6} \cdot \frac{1}{225\text{ns}} \approx 400\text{kHz}$$

$$L_1 = \frac{(36V - 3.3) \cdot 3.3}{36V \cdot 400\text{kHz}} \geq 7.5\mu\text{H}$$

$$L_2 = \frac{(3.3 - 1.8) \cdot 1.8}{3.3 \cdot 400\text{kHz}} \geq 2\mu\text{H}$$

### 2段降圧マルチ周波数

$$R_{DIV} = 100k, \text{FREQ1} = 400\text{kHz}, \text{FREQ2} = 1600\text{kHz}.$$

$$L_1 = \frac{(36V - 3.3) \cdot 3.3}{36V \cdot 400\text{kHz}} \geq 7.5\mu\text{H}$$

$$L_2 = \frac{(3.3 - 1.8) \cdot 1.8}{3.3 \cdot 2\text{MHz}} \geq 500\text{nH}$$

さらに、 $R_{ILIM2} = 40.2k$ とするとチャネルのピーク電流制限が2.5Aに減少し、これによってインダクタのサイズとキャッチ・ダイオードに関する要件が緩和されます。

## アプリケーション情報

図17. 3.3Vおよび1.8Vのデュアル降圧マルチ周波数コンバータ

図18. 3.3Vおよび1.8Vのデュアル2段降圧マルチ周波数コンバータ

## アプリケーション情報

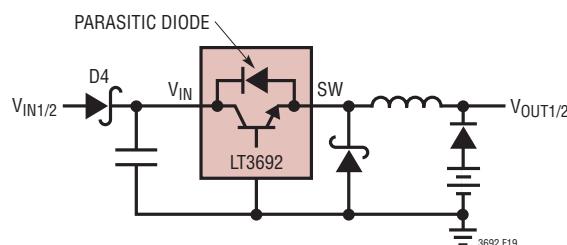

### 短絡入力と逆入力に対する保護

過度に飽和しないようにインダクタを選択すれば、LT3692降圧レギュレータは出力の短絡に耐えることができます。LT3692に入力が与えられていないときに出力が”H”に保持されるシステムでは、考慮すべき状況がもう1つあります。このような状況は、バッテリ充電アプリケーション、またはバッテリや他の電源がLT3692の出力とダイオードOR結合されているバッテリ・バックアップ・システムで生じことがあります。 $V_{IN1/2}$ ピンをフロート状態にすることにより、SHDNピンが(ロジック信号によって、あるいは $V_{IN}$ に接続されていることによって)”H”に保持されている場合は、LT3692の内部回路にはSWピンを通して静止電流が流れます。この状態で数mAの電流を許容できるシステムであれば、これは特に問題とはなりません。SHDNピンを接地すればSWピンの電流は実質的にゼロに低下します。ただし、出力を”H”に保持した状態で $V_{IN}$ を接地すると、出力からSWピンおよび $V_{IN1/2}$ ピンを通ってLT3692内部の寄生ダイオードに大きな電流が流れる可能性があります。入力電圧が与えられているときだけ動作し、短絡入力や逆入力に対する保護機能を備えた回路を図19に示します。

図19. 入力が短絡したとき出力に接続された

バックアップ・バッテリが放電するのを防ぐダイオードD4

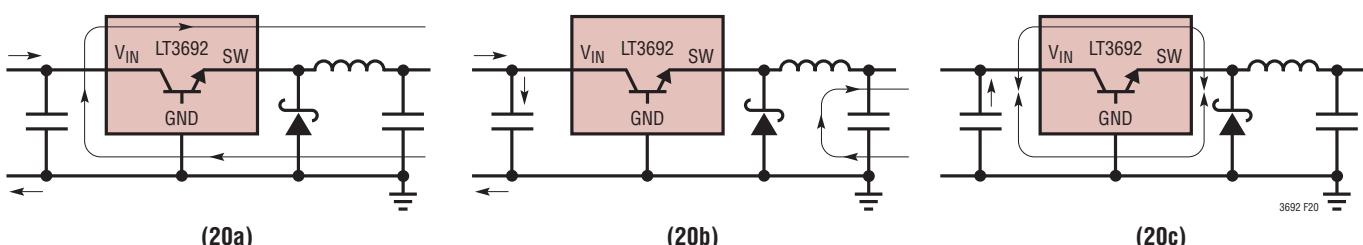

### PCBレイアウト

デバイスを正しく動作させてEMIを最小限に抑えるには、プリント回路基板(PCB)のレイアウトに注意を払う必要があります。降圧レギュレータ回路の高di/dt経路を図20に示します。パワースイッチ、キャッチ・ダイオード、および入力コンデンサに流れるスイッチ電流が大きい点に注意してください。これらの部品によって形成されるループはできるだけ小さくする必要があります。

これらの部品はインダクタや出力コンデンサとともに回路基板の同じ側に配置して、接続もその層で行なう必要があります。これらの部品の下には切れ目のないローカル・グランド・プレーンを配置し、このグランド・プレーンはシステム・グランドに1点接続します。接続箇所は、出力コンデンサC2のグランド端子が理想的です。さらに、SWとBSTのトレースは出来るだけ短くします。

### 熱に関する検討事項

LT3692の温度上昇を防ぐには、PCBにヒートシンクを備える必要があります。また、パッケージ底面の金属露出部分はグランド・プレーンに半田付けしなければなりません。このグランドはサーマル・ビアを使って下にある別の銅層に接続します。これらの層はLT3692が発生する熱を分散させます。ビアを追加する場合はキャッチ・ダイオードの近くに配置してください。最上層と最下層の銅を増やしてこれらの銅と内部プレーンをビアで接続すると、熱抵抗をさらに下げることができます。これらの対策を施すことにより、ダイ(または接合部)から周囲への熱抵抗を $\theta_{JA} = 35^{\circ}\text{C}/\text{W}$ まで減らすことができます。

図20. スイッチ・オフ時の電流(20b)からスイッチオン時の電流(20a)を差し引くと、高周波スイッチング電流の経路(20c)がわかる。

このループは小さくすること。SWトレースとBSTトレースの電圧もスイッチングされるので、これらのトレースはできるだけ短くする。

最後に、ローカル・グランド・プレーンを使って回路を必ずシールドする。

## アプリケーション情報

キャッチ・ダイオード、昇圧ダイオード、インダクタなどの他の電力部品で消費される電力が銅をさらに熱して、ICから見た周囲温度をさらに上昇させることができます。LT1767の「熱に関する検討事項」のセクションを参照してください。

### ダイ温度とサーマル・シャットダウン

LT3692のT<sub>J</sub>ピンは、内部接合部温度に比例する電圧を出力します。T<sub>J</sub>ピンは25°Cで250mVを出力し、出力勾配は10mV/°Cです。T<sub>J</sub>ピンの出力は20°C～150°C(200mV～1.5V)の範囲で有効であり、外部回路の助けは必要ありません。最大負荷は100μAです。

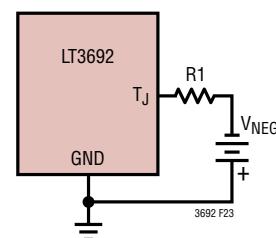

### 全温度範囲の測定

20°C未満におけるT<sub>J</sub>出力の動作温度範囲を拡大するには、図21に示すようにT<sub>J</sub>ピンから負電源へ抵抗を接続します。負のレール電圧とT<sub>J</sub>ピン抵抗は、次の式を使って計算できます。

$$V_{NEG} \leq \frac{2 \cdot TEMP(MIN)^\circ C}{100}$$

$$R1 \leq \frac{|V_{NEG}|}{33\mu A}$$

ここで、

TEMP(MIN)°Cは、T<sub>J</sub>ピンで有効な出力が求められる最小温度です。

V<sub>NEG</sub> = 安定化負電圧電源。

例：

$$TEMP(MIN)^\circ C = -40^\circ C$$

$$V_{NEG} \leq -0.8V$$

$$V_{NEG} = -1, R1 \leq |V_{NEG}|/33\mu A = 30.2k\Omega$$

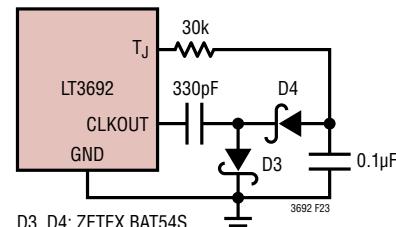

### 負の安定化電圧の生成

図22に示すシンプルなチャージポンプ回路はCLKOUTピンの出力を使用して負電圧を生成するので外部安定化電源が不要です。表面実装コンデンサとデュアル・パッケージのショットキー・ダイオードを使用して、負電源の実装に必要な基板面積を最小限に抑えます。

図21. T<sub>J</sub>ピンの動作範囲拡大のための回路

図22. T<sub>J</sub>ピンの動作範囲拡大のための負電圧レール生成回路

## アプリケーション情報

LT3692の各チャネルには、安全策として標準値163°Cの追加的なサーマル・シャットダウン・スレッショルドが設定されています。このスレッショルドを超えると、その都度該当チャネルのパワーオン・シーケンスが開始されます。このシーケンスは熱過負荷状態が解消されるまで繰り返されます。

$T_J$ ピンの電圧は定常温度を示すものであり、最大接合部温度を超えないようにするために使用すべきではないという点に注意してください。ダイの部分的な温度は、熱勾配や時定数に加え、瞬間的電力によっても最大定格値やサーマル・シャットダウン・スレッショルドを超える可能性があります。ダイ温度上昇の計算は、定常状態(>1分)での値に加えてインパルスを使った値についても行なってください。

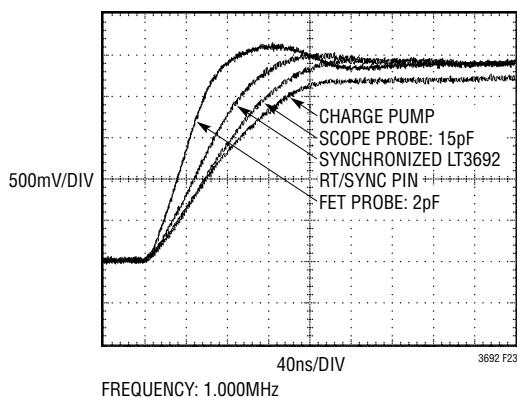

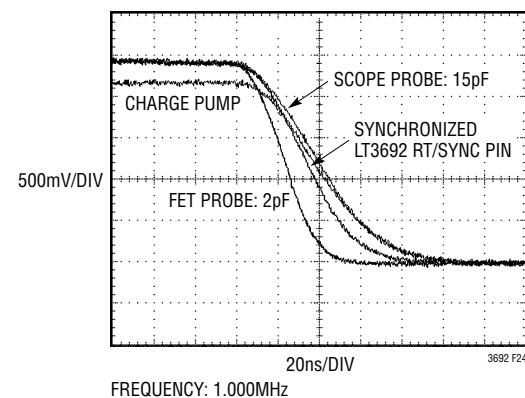

### CLKOUTの容量性負荷

CLKOUTピンから負のレールを生成する際の小さな欠点の1つは、チャージポンプによってCLKOUTピンに余分な容量が生じることで、これによって出力同期クロック信号に位相遅れ

が生じます。容量性負荷がCLKOUT信号の立ち上がり時間と立ち下がり時間に与える影響を図23と図24に示します。10:1、150MHzの標準的なオシロスコープ用プローブはCLKOUTノードの容量を大幅に増加させるので、正確な計測を行なうには低容量のプローブが必要です。CLKOUTによって負電源電圧を生成し、他のレギュレータに同期クロックを提供する必要のあるアプリケーションでは、チャージポンプ回路の前でCLKOUTをバッファすると有効な場合があります。

### リニアテクノロジーの他の出版物

アプリケーションノートAN19、AN35、AN44には、降圧レギュレータおよびその他のスイッチング・レギュレータに関するより詳細な説明と設計情報が記載されています。LT1376のデータシートでは、出力リップル、ループ補償、および安定性テストに関して、より広範な検討が加えられています。また、デザインノートDN100には、降圧レギュレータを使用してデュアル(+と-)出力電源を作成する方法が示されています。

図23. CLKOUTの立ち上がり時間

図24. CLKOUTの立ち下がり時間

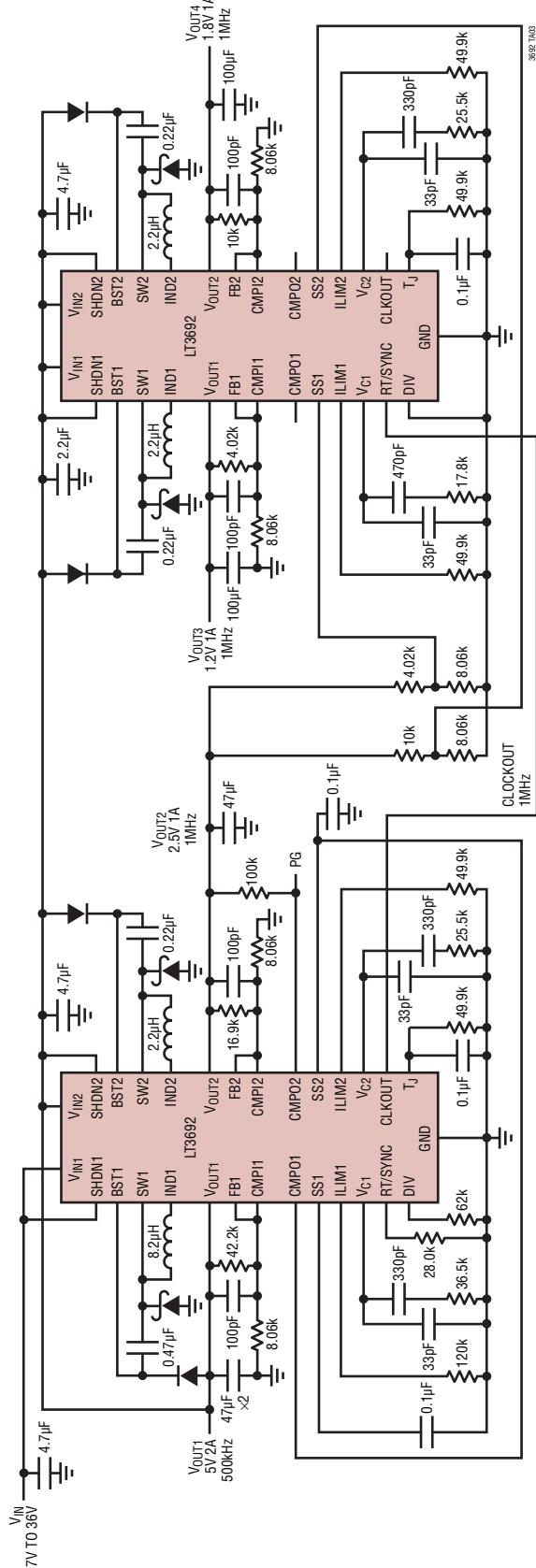

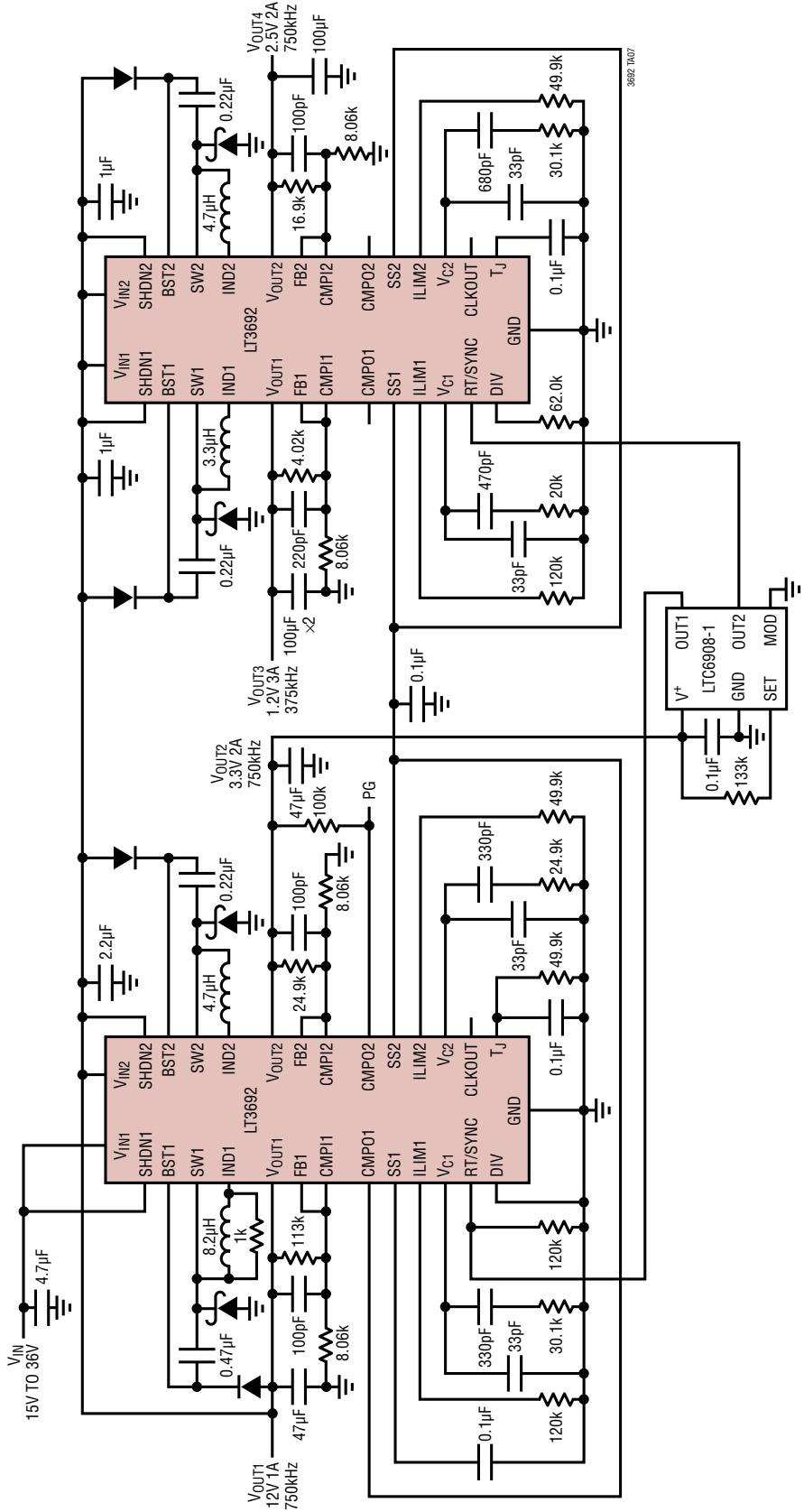

## 標準的応用例

出力シーケンシング、絶対トラッキング、および電流制限機能を備えた、

5V、2.5V、1.8V、1.2Vのクワッド出力の、同期をとったマルチ周波数2段コンバータ

3692fa

## 標準的応用例

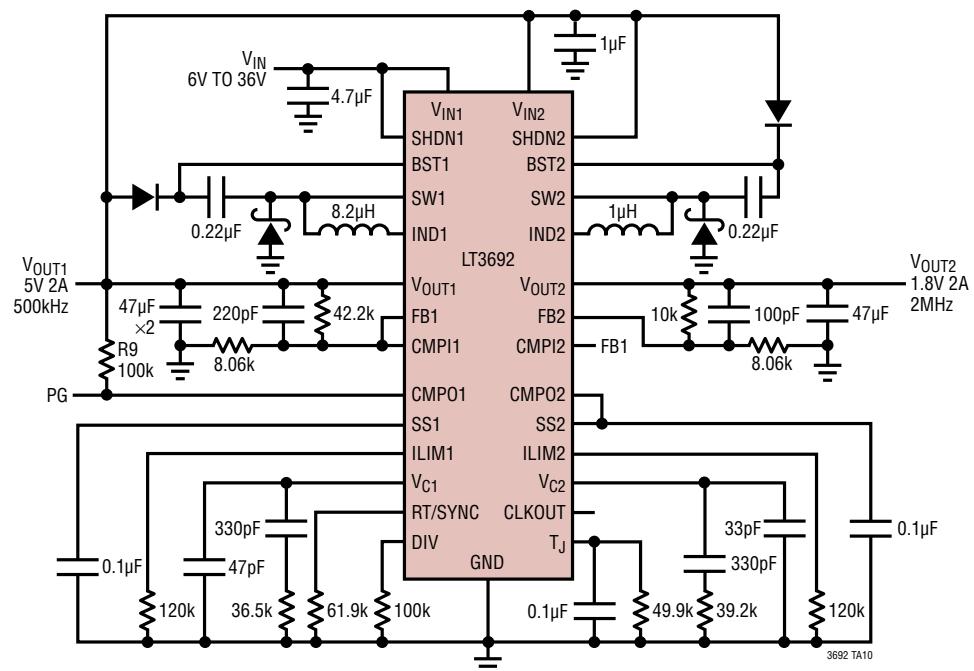

## 3.3Vおよび1.8Vのデュアル2段降圧マルチ周波数コンバータ

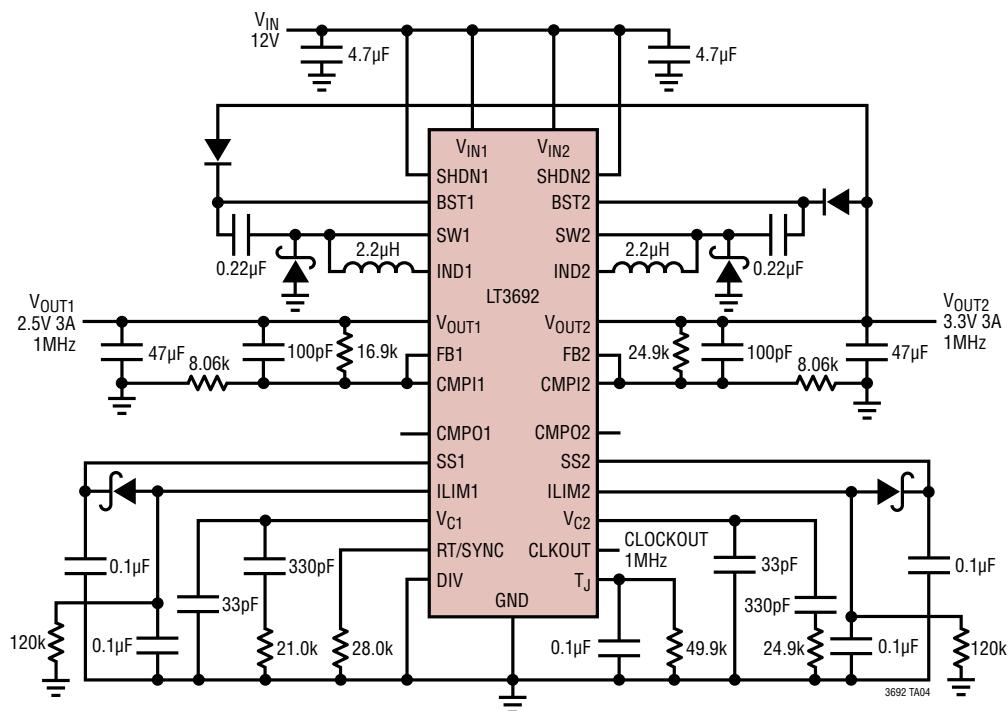

## 起動時電流制限機能を備えた12V/3.3Vおよび12V/2.5Vコンバータ

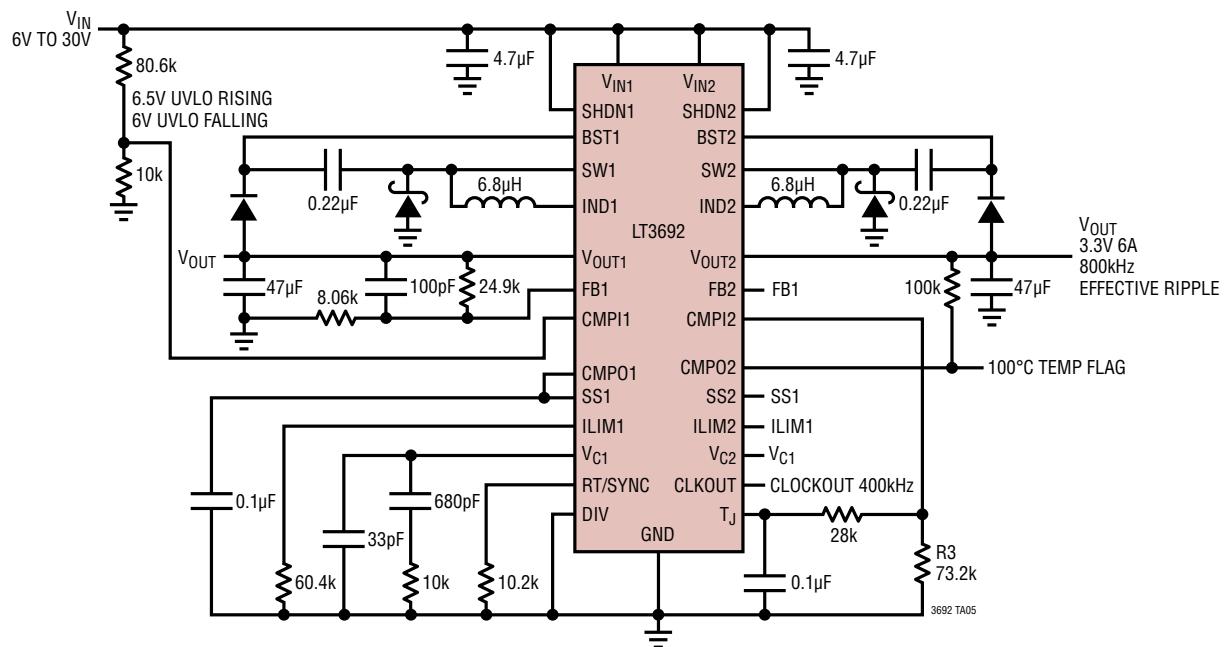

## 標準的応用例

UVLOおよび100°C温度警告機能を備えた3.3V/6Aシングル出力

デュアル電源入力、シングル3.3V/4A出力の降圧コンバータ

## 標準的応用例

## 5Vおよび1.8Vのデュアル2段コンバータ

3692fa

## 標準的応用例

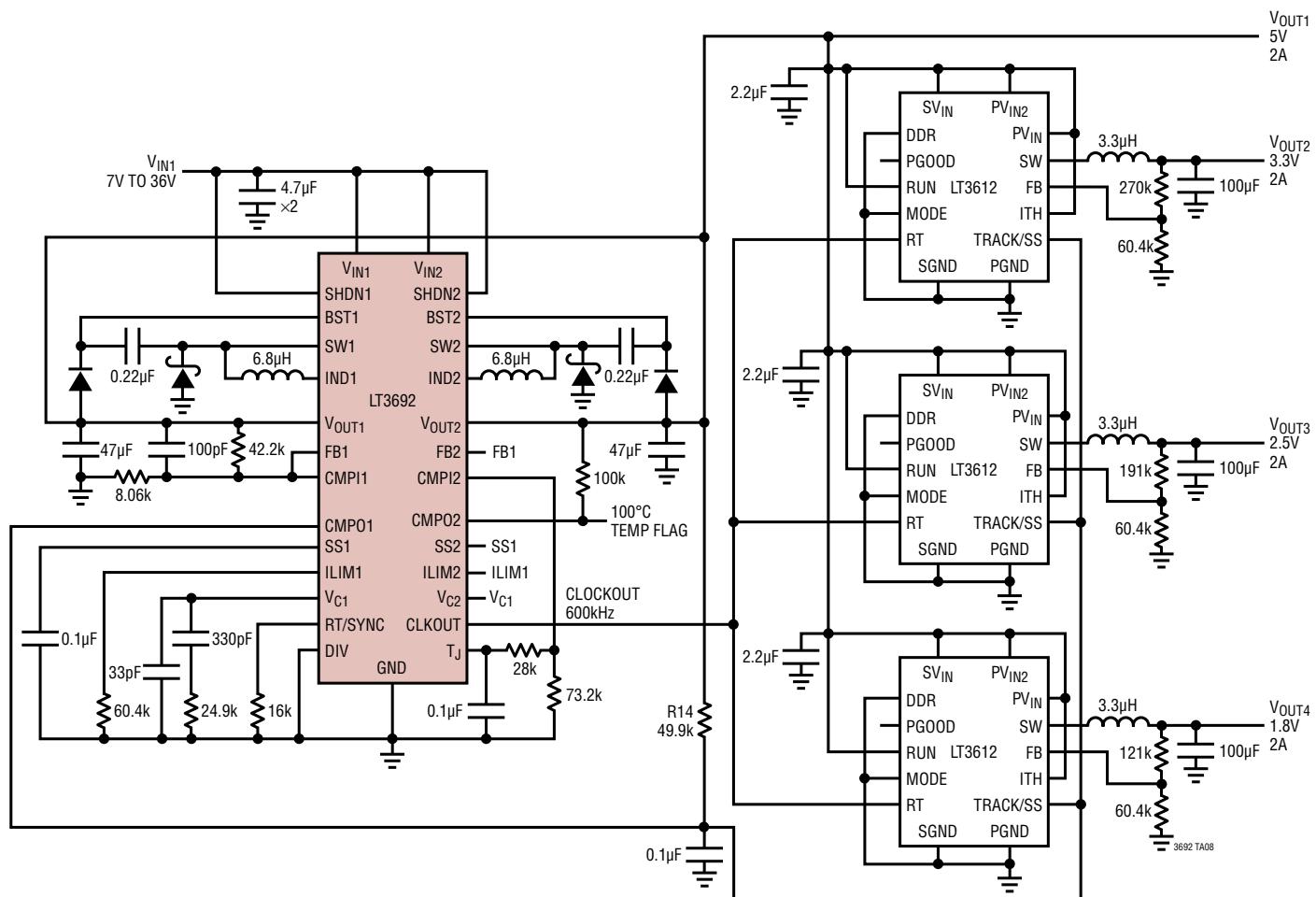

外部同期、出力シーケンシング、およびトラッキング機能を備えた、12V、3.3V、2.5V、1.2Vクワッド出力のアプリケーション

3692fa

## 標準的応用例

5V、3.3V、2.5V、1.8V同期クワッド出力

3692fa

## パッケージ

最新のパッケージ図面については、<http://www.linear-tech.co.jp/designtools/packaging/>をご覧ください。

UH/パッケージ

32ピン・プラスチックQFN (5mm×5mm)

(Reference LTC DWG # 05-08-1693 Rev D)

## 改訂履歴

| REV | 日付   | 概要                                                                                                                       | ページ番号              |

|-----|------|--------------------------------------------------------------------------------------------------------------------------|--------------------|

| A   | 3/13 | 「シャットダウン時の消費電流と温度」のグラフを明確化。<br>SHDN1/2のピン機能の記述を明確化。<br>一般記述におけるアプリケーション情報でSHDNピン動作を明確化。<br>[アプリケーション情報]でSHDNピン動作の記述を明確化。 | 5<br>9<br>10<br>20 |

## 標準的応用例

1.2MHz、12V入力、3.3V/3Aおよび5V/3A出力

## 関連製品

| 製品番号   | 説明                                                                              | 注釈                                                                                                                                     |

|--------|---------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|

| LT3507 | LDOコントローラ付き36V、トリプル2.4A、1.5A、1.5A ( $I_{OUT}$ )、2.5MHz高効率降圧DC/DCコンバータ           | $V_{IN}$ :4V~36V、 $V_{OUT}$ (MIN) = 0.8V、 $I_Q$ = 7mA、 $I_{SD}$ = 1 $\mu$ A、5mm×7mm QFN38パッケージ                                         |

| LT3508 | 40Vまでの過渡保護付き36V、デュアル1.4A ( $I_{OUT}$ )、2.5MHz高効率降圧DC/DCコンバータ                    | $V_{IN}$ :3.7V~36V、 $V_{OUT}$ (MIN) = 0.8V、 $I_Q$ = 4.6mA、 $I_{SD}$ = 1 $\mu$ A、4mm×4mm QFN24およびTSSOP16Eパッケージ                          |

| LT3680 | 36V、3.5A、2.4MHz高効率マイクロパワー降圧DC/DCコンバータ                                           | $V_{IN}$ :3.6V~36V、 $V_{OUT}$ (MIN) = 0.8V、 $I_Q$ = 75 $\mu$ A、 $I_{SD}$ < 1 $\mu$ A、3mm×3mm DFN10およびMSOP10Eパッケージ                      |

| LT3693 | 36V、3.5A、2.4MHz高効率降圧DC/DCコンバータ                                                  | $V_{IN}$ :3.6V~36V、 $V_{OUT}$ (MIN) = 0.8V、 $I_Q$ = 1.3mA、 $I_{SD}$ < 1 $\mu$ A、3mm×3mm DFN10およびMSOP10Eパッケージ                           |

| LT3480 | 最大60Vの過渡電圧に対する保護機能付き、Burst Mode®動作を行う36V、2A ( $I_{OUT}$ )、2.4MHz高効率降圧DC/DCコンバータ | $V_{IN}$ :3.6V~36V、60Vまでの過渡電圧からデバイスを保護、 $V_{OUT}$ (MIN) = 0.79V、 $I_Q$ = 70 $\mu$ A、 $I_{SD}$ < 1 $\mu$ A、3mm×3mm DFN10およびMSOP10Eパッケージ |

| LT3980 | 最大80Vの過渡電圧に対する保護機能付き、Burst Mode動作を行う58V、2A ( $I_{OUT}$ )、2.4MHz高効率降圧DC/DCコンバータ  | $V_{IN}$ :3.6V~58V、80Vまでの過渡電圧からデバイスを保護、 $V_{OUT}$ (MIN) = 0.79V、 $I_Q$ = 85 $\mu$ A、 $I_{SD}$ < 1 $\mu$ A、3mm×4mm DFN16およびMSOP16Eパッケージ |

| LT3971 | 消費電流がわずか2.8 $\mu$ Aの38V、1.2A ( $I_{OUT}$ )、2MHz高効率降圧DC/DCコンバータ                  | $V_{IN}$ :4.3V~38V、 $V_{OUT}$ (MIN) = 1.2V、 $I_Q$ = 2.8 $\mu$ A、 $I_{SD}$ < 1 $\mu$ A、3mm×3mm DFN10およびMSOP10Eパッケージ                     |

| LT3991 | 消費電流がわずか2.8 $\mu$ Aの55V、1.2A ( $I_{OUT}$ )、2MHz高効率降圧DC/DCコンバータ                  | $V_{IN}$ : 4.3V~55V、 $V_{OUT}$ (MIN) = 1.2V、 $I_Q$ = 2.8 $\mu$ A、 $I_{SD}$ < 1 $\mu$ A、3mm×3mm DFN10およびMSOP10Eパッケージ                    |