## 特長

- 双方向同期整流式昇圧キャパシタシステム・バックアップ用のチャージャ/降圧レギュレータ

- 広い入力電圧範囲:3V~17V

- 高エネルギー・バックアップ用の最大40Vのキャパシタ蓄電電圧

- 最大2AのCAP充電電流

- Nチャネル・パワーMOSFET内蔵(上側150mΩ、下側75mΩ)

- 出力/CAP切断用のNチャネル・パワーMOSFET内蔵(50mΩ)

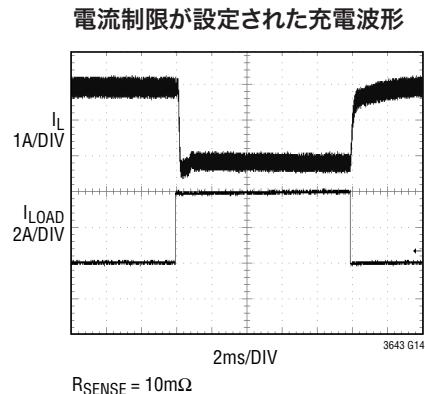

- 充電時の入力電流制限

- 高速なスイッチング周波数:1MHz

- システム電圧レギュレーションのリファレンス精度: $\pm 1\%$

- 充電状態および入力電源障害のインジケータ出力

- 高さの低い24ピン3mm×5mm QFNパッケージ

## アプリケーション

- バックアップ・キャパシタ・システム

- 電源障害バックアップ・システム

- 半導体ドライブ

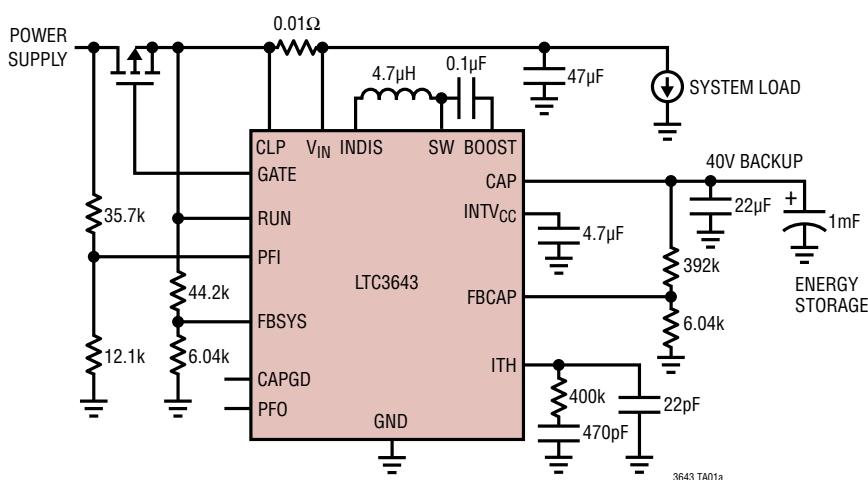

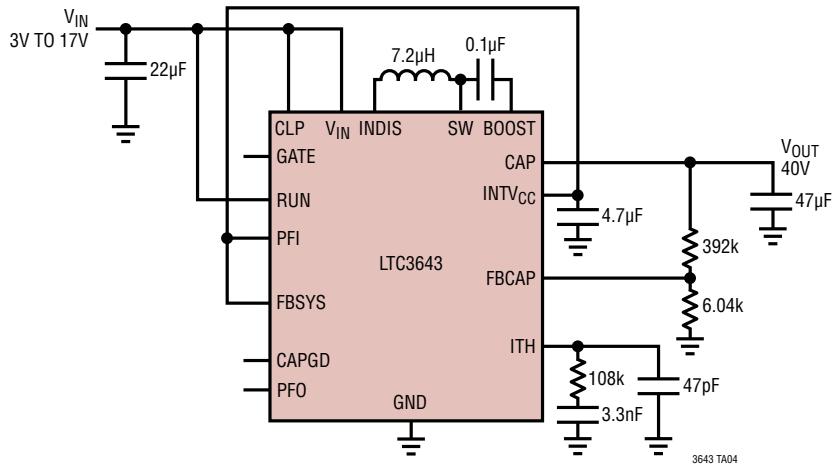

## 標準的応用例

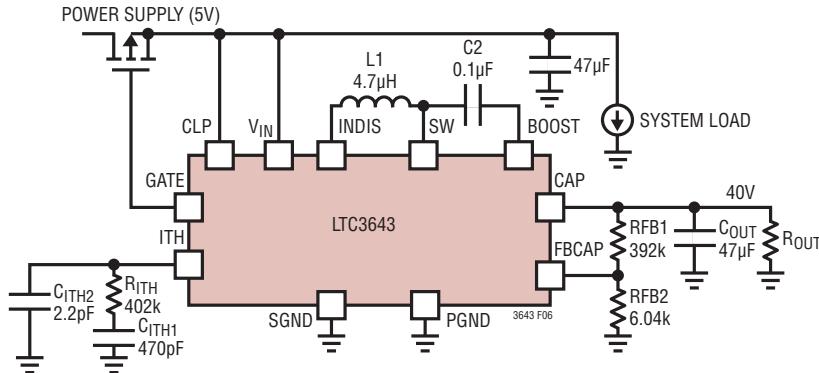

システム電源を5Vに安定化する40Vバックアップ・システム

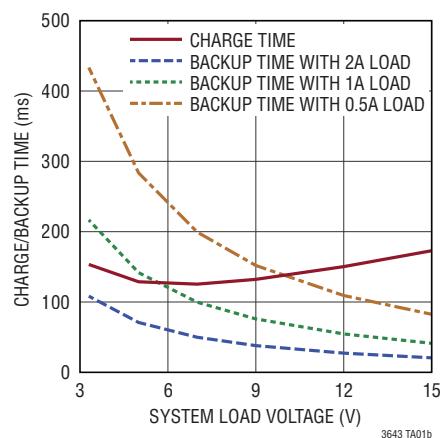

蓄電キャパシタ1mFあたりのおおよその

充電/バックアップ時間(40Vバックアップ)

## 絶対最大定格

(Note 1)

|                      |                             |

|----------------------|-----------------------------|

| $V_{IN}$             | -0.3V ~ 17V                 |

| RUN                  | -0.3V ~ $V_{IN} + 0.3V$     |

| CLP                  | -0.3V ~ 17V                 |

| CAP                  | -0.3V ~ 42V                 |

| BOOST-SW             | -0.3V ~ 4V                  |

| INTVCC, FBSYS, FBCAP | -0.3V ~ 4V                  |

| PFI                  | -0.3V ~ 4V                  |

| $I_{LIM}$            | -0.3V ~ $V_{INTVCC} + 0.3V$ |

| PFO, CAPGD           | -0.3V ~ 6V                  |

動作接合部温度範囲

(Note 2) ..... -40°C ~ 125°C

保存温度範囲 ..... -65°C ~ 150°C

リード温度(半田付け、10秒) ..... 260°C

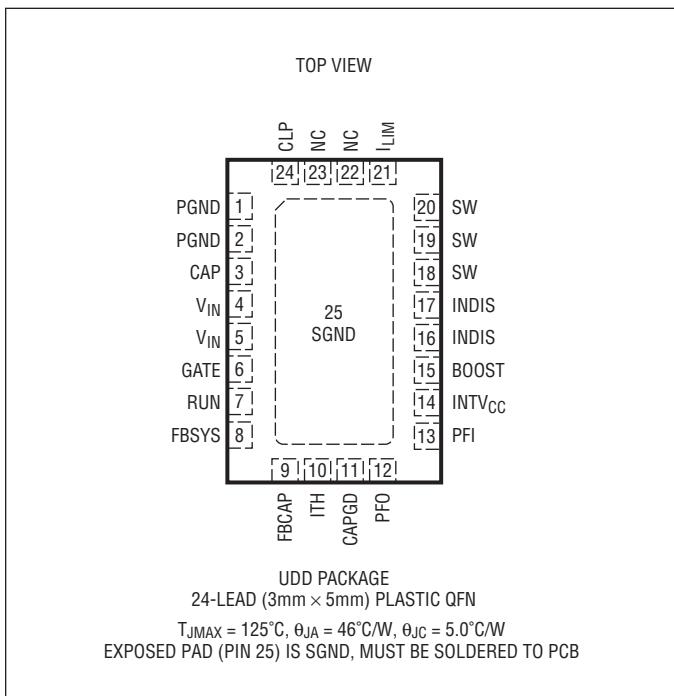

## ピン配置

## 発注情報

| 無鉛仕上げ           | テープアンドリール        | 製品マーキング* | パッケージ                         | 温度範囲           |

|-----------------|------------------|----------|-------------------------------|----------------|

| LTC3643EUDD#PBF | LTC3643EUDD#TRPB | LGSX     | 24-Lead (3mm×5mm) Plastic QFN | -40°C to 125°C |

| LTC3643IUDD#PBF | LTC3643IUDD#TRPB | LGSX     | 24-Lead (3mm×5mm) Plastic QFN | -40°C to 125°C |

さらに広い動作温度範囲で規定されるデバイスについては、弊社または弊社代理店にお問い合わせください。\* 温度グレードは出荷時のコンテナのラベルで識別されます。

無鉛仕上げの製品マーキングの詳細については、<http://www.linear-tech.co.jp/leadfree/>をご覧ください。

テープ・アンド・リールの仕様の詳細については、<http://www.linear-tech.co.jp/tapeandreel/>をご覧ください。

#TRMPBFの接尾辞の付いた一部のパッケージは、指定販売チャネルを通じて500個単位のリールで提供されます。

## 電気的特性

●は規定の動作接合部温度範囲の規格値を意味する。それ以外は $T_J = 25^\circ\text{C}$ での値。注記がない限り、 $V_{IN} = 5\text{V}$ 、 $V_{RUN} = 2\text{V}$ 。(Note 2)

| SYMBOL       | PARAMETER                                                                  | CONDITIONS                                                                       | MIN              | TYP              | MAX            | UNITS |

|--------------|----------------------------------------------------------------------------|----------------------------------------------------------------------------------|------------------|------------------|----------------|-------|

| $V_{IN}$     | Operating Voltage                                                          | $V_{IN}$<br>CAP                                                                  | 3.0              | 17               | 40             | V     |

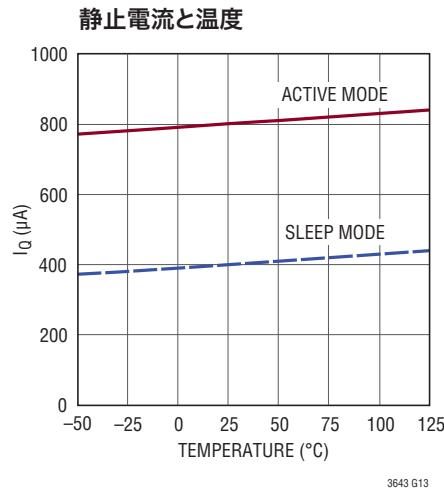

| $I_{Q-IN}$   | Input Quiescent Current                                                    | Active Mode<br>Burst Mode®<br>Shutdown Mode; RUN = 0V                            | 800<br>400<br>10 | 800<br>800<br>20 | μA<br>μA<br>μA |       |

| $R_{DS(ON)}$ | Switch A On Resistance<br>Switch B On Resistance<br>Switch C On Resistance | $V_{CAP} \geq V_{IN}$<br>$V_{INTVCC} = 3.3\text{V}$<br>$V_{BOOST} = 8.3\text{V}$ | 50<br>75<br>150  |                  |                | mΩ    |

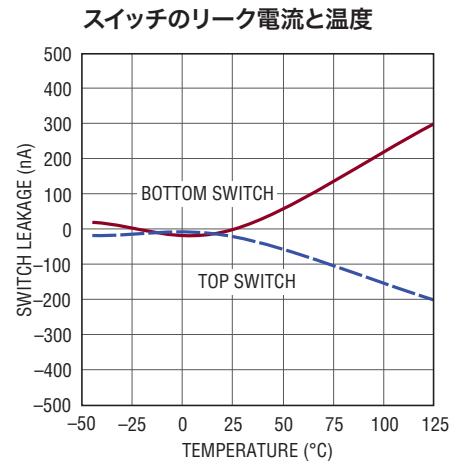

| $I_{SW}$     | Top Switch Leakage<br>Bottom Switch Leakage                                | $V_{CAP} = 40\text{V}$ , $V_{SW} = 0$<br>$V_{CAP} = V_{SW} = 40\text{V}$         | 0.1<br>0.1       | 1<br>1           | 1              | μA    |

### 昇圧チャージャのレギュレーション

|                      |                                                           |               |   |            |          |            |          |

|----------------------|-----------------------------------------------------------|---------------|---|------------|----------|------------|----------|

| $V_{CAP}$            | Cap Voltage                                               |               |   | 40         |          | V          |          |

| $V_{FBCAP}$          | Regulated Output Feedback Voltage                         |               | ● | 0.594      | 0.6      | 0.606      | V        |

| $I_{FBCAP}$          | FBCAP Input Current                                       |               |   |            | ±10      | nA         |          |

| $g_m(EA)$            | Error Amplifier Transconductance                          | ITH = 1.2V    |   | 210        | 270      | 330        | μS       |

| $I_{LIM-BOOST}$      | Peak Inductor Current Limit<br>(Bottom Switch Peak Limit) |               | ● | 3.0<br>2.8 | 3.2      | 3.4        | A        |

| $t_{OFF(MIN)-BOOST}$ | Minimum Off-Time                                          |               |   |            | 70       |            | ns       |

| $f_{SW}$             | Switching Frequency                                       |               |   |            | 1        |            | MHz      |

|                      | Input Current Limit Amplifier Regulated Voltage           | $V_{CLP-VIN}$ | ● | 48.5<br>46 | 50<br>50 | 51.5<br>54 | mV<br>mV |

### 降圧レギュレータの電圧レギュレーション

|                    |                                                               |                                                                             |             |                   |                   |                   |             |

|--------------------|---------------------------------------------------------------|-----------------------------------------------------------------------------|-------------|-------------------|-------------------|-------------------|-------------|

| $V_{FBSYS}$        | Regulated System Feedback Voltage                             |                                                                             | ●           | 0.594             | 0.6               | 0.606             | V           |

| $I_{FBSYS}$        | FBSYS Input Current                                           |                                                                             |             |                   | ±10               | nA                |             |

| $I_{LIM-BUCK}$     | Valley Inductor Current Limit<br>(Bottom Switch Valley Limit) | $I_{LIM} = \text{FLOAT}$<br>$I_{LIM} = 0\text{V}$<br>$I_{LIM} = V_{INTVCC}$ | ●<br>●<br>● | 2.0<br>2.9<br>3.8 | 2.6<br>3.7<br>4.7 | 3.2<br>4.5<br>5.6 | A<br>A<br>A |

| $t_{ON(MIN)-BUCK}$ | Minimum On-Time                                               |                                                                             |             |                   | 30                |                   | ns          |

### INTV<sub>CC</sub> レギュレータ

|  |                                      |                           |  |     |      |     |   |

|--|--------------------------------------|---------------------------|--|-----|------|-----|---|

|  | INTV <sub>CC</sub> Regulated Voltage |                           |  | 3.0 | 3.2  | 3.4 | V |

|  | INTV <sub>CC</sub> UVLO              | INTV <sub>CC</sub> Rising |  | 2.6 | 2.75 | 2.9 | V |

### I/O ピン

|           |                                   |                                                |        |              |            |              |         |

|-----------|-----------------------------------|------------------------------------------------|--------|--------------|------------|--------------|---------|

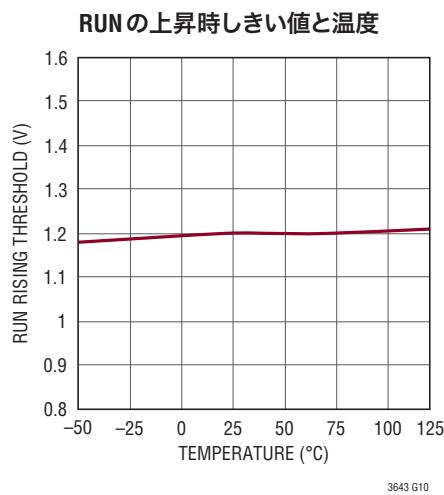

| $V_{RUN}$ | RUN High Rising<br>RUN Hysteresis |                                                | ●      | 1.12<br>100  | 1.2        | 1.28         | V<br>mV |

|           | RUN Input Current                 | $V_{RUN} = 12\text{V}$ , $V_{IN} = 12\text{V}$ |        |              | 0          | ±10          | nA      |

| $V_{PFI}$ | PFI Input Threshold               | Falling<br>Rising (100mV hysteresis)           | ●<br>● | 0.95<br>1.05 | 1.0<br>1.1 | 1.05<br>1.15 | V<br>V  |

## 電気的特性

●は規定の動作接合部温度範囲の規格値を意味する。それ以外は  $T_J = 25^\circ\text{C}$  での値。注記がない限り、 $V_{IN} = 5\text{V}$ 、 $V_{RUN} = 2\text{V}$ 。(Note 2)

| SYMBOL | PARAMETER              | CONDITIONS                                  | MIN | TYP       | MAX        | UNITS                          |               |

|--------|------------------------|---------------------------------------------|-----|-----------|------------|--------------------------------|---------------|

|        | PFI Delay Time         | Falling<br>Rising                           |     | 3<br>20   | 6<br>40    | $\mu\text{s}$<br>$\mu\text{s}$ |               |

|        | GATE Turn-on Time      | To CLP-GATE > 2.5V, $C_{GATE} = 1\text{nF}$ |     | 70        | 100        | $\mu\text{s}$                  |               |

|        | GATE Turn-off Time     | To CLP-GATE < 1V, $C_{GATE} = 1\text{nF}$   |     | 3         | 6          | $\mu\text{s}$                  |               |

|        | GATE Pull-Down Current |                                             | ●   | 45        | 70         | 95                             | $\mu\text{A}$ |

|        | CAPGD Threshold        | FBCAP Rising<br>Hysteresis                  |     | 550<br>15 | 570<br>590 | $\text{mV}$<br>$\text{mV}$     |               |

|        | CAPGD Resistance       |                                             |     | 170       | 250        | $\Omega$                       |               |

|        | /PFO Resistance        |                                             |     | 170       | 250        | $\Omega$                       |               |

Note 1: 絶対最大定格に記載された値を超えるストレスはデバイスに永続的損傷を与える可能性がある。また、長期にわたって絶対最大定格条件に曝すと、デバイスの信頼性と寿命に悪影響を与えるおそれがある。

Note 2:LTC3643は、 $T_J$ が  $T_A$  にほぼ等しいパルス負荷条件でテストされる。LTC3643Eは、0°C～85°Cの温度範囲で規定された性能に適合することが保証されている。 $-40^\circ\text{C} \sim 125^\circ\text{C}$  の動作接合部温度範囲での仕様は設計、特性評価および統計学的なプロセス・コントロールとの相関で確認されている。LTC3643Iは、 $-40^\circ\text{C} \sim 125^\circ\text{C}$  の全動作接合部温度範囲で保証されている。これらの仕様と合致する最大周囲温度は、基板レイアウト、パッケージの定格熱インピーダンスおよび他の環境要因と関連した特定の動作条件によって決まるに注意。

$T_J$ は周囲温度( $T_A$ )および電力損失( $P_D$ )から次式に従って計算される。 $T_J = T_A + (P_D \cdot \theta_{JA})$

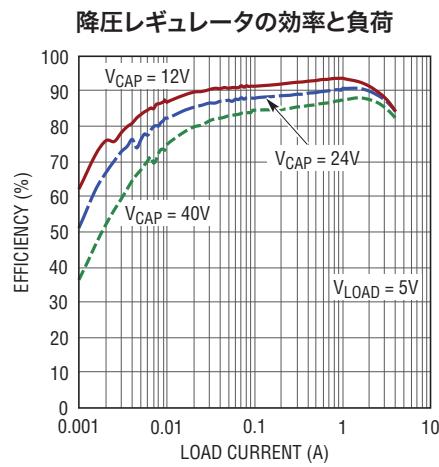

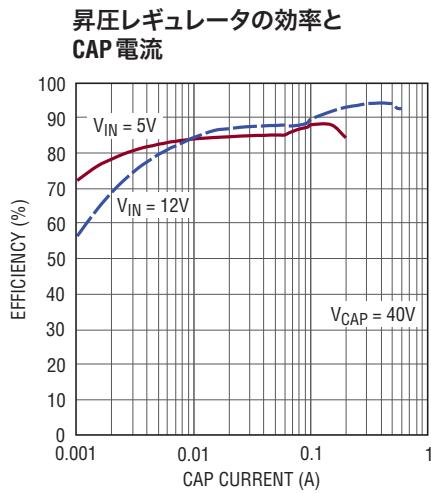

## 標準的性能特性

注記がない限り  $T_A = 25^\circ\text{C}$ 。

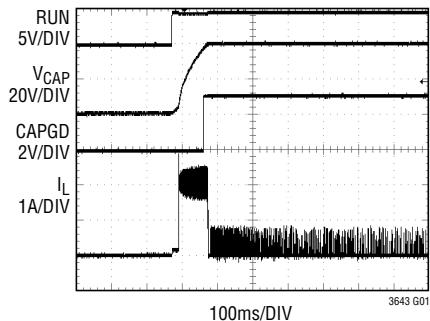

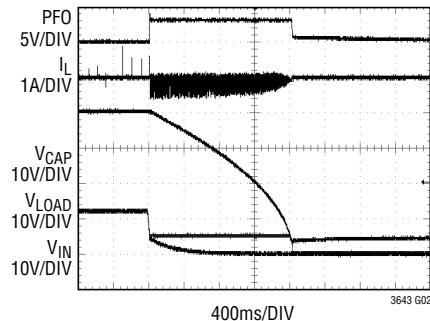

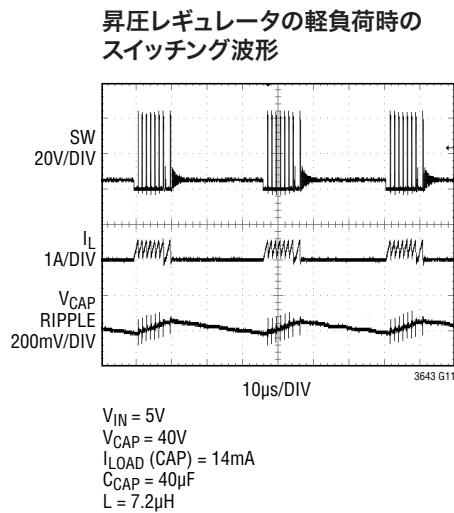

昇圧充電波形

$V_{IN} = 5\text{V}$

$V_{CAP} = 40\text{V}$

NO LOAD

START-UP FROM RUN

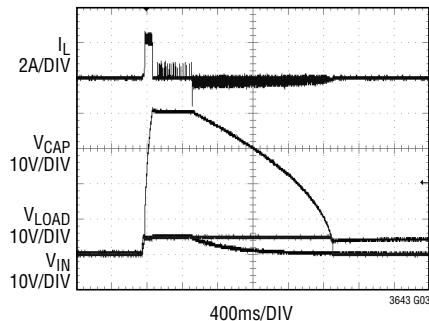

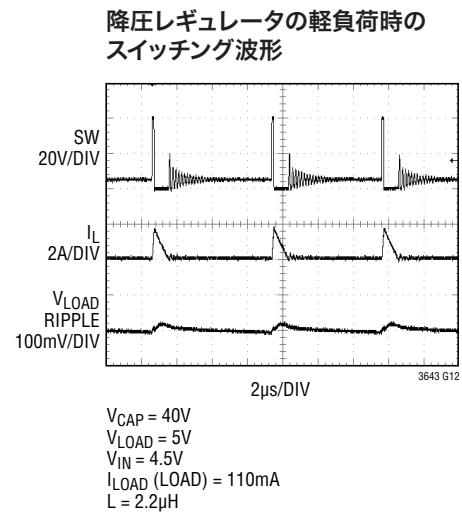

降圧放電波形

$V_{IN} = 12\text{V}$

$V_{CAP} = 40\text{V}$

$V_{LOAD} = 5\text{V}$

$I_{LOAD} = 100\text{mA}$

昇圧から降圧への切り替え時の波形

$V_{IN} = 5\text{V}$

$V_{CAP} = 40\text{V}$

$V_{LOAD} = 5\text{V}$ , (SYSTEM LOAD)

$I_{LOAD} = 100\text{mA}$

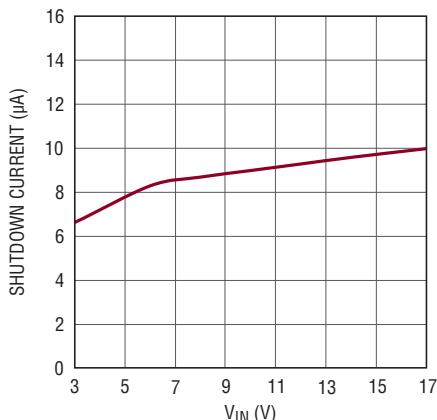

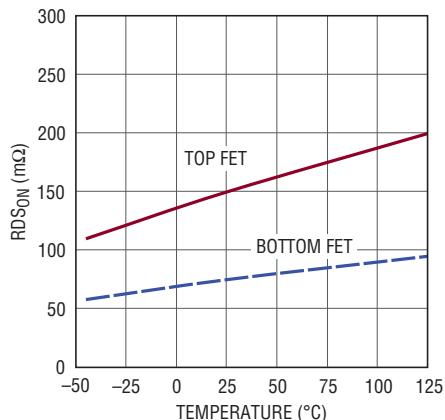

シャットダウン電流と  $V_{IN}$  $R_{DS(ON)}$  と 温度

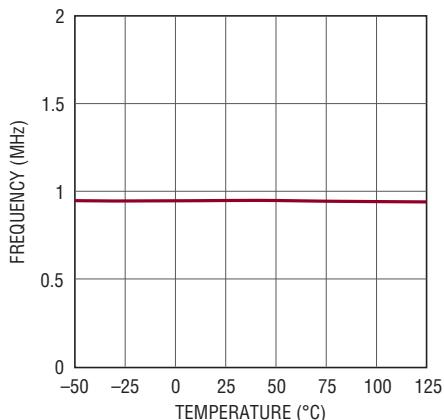

周波数と 温度

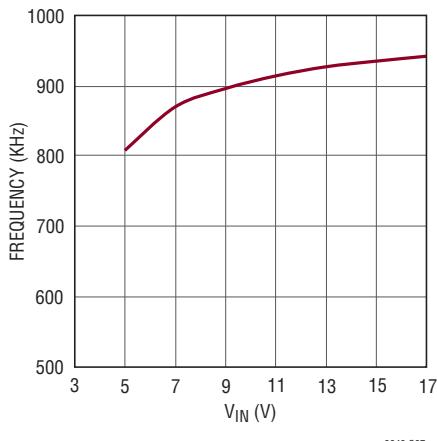

周波数と  $V_{IN}$

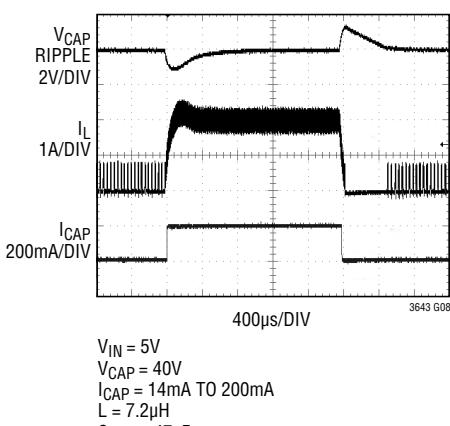

昇圧レギュレータのトランジエント応答

$V_{IN} = 5\text{V}$

$V_{CAP} = 40\text{V}$

$I_{CAP} = 14\text{mA TO } 200\text{mA}$

$L = 7.2\mu\text{H}$

$C_{OUT} = 47\mu\text{F}$

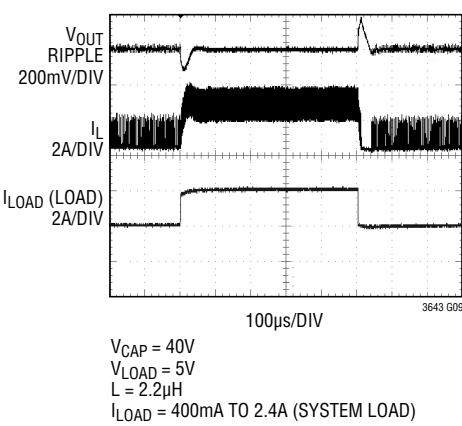

降圧レギュレータのトランジエント応答

$V_{CAP} = 40\text{V}$

$V_{LOAD} = 5\text{V}$

$L = 2.2\mu\text{H}$

$I_{LOAD} = 400\text{mA TO } 2.4\text{A}$ , (SYSTEM LOAD)

# LTC3643

## 標準的性能特性

注記がない限り、 $T_A = 25^\circ\text{C}$ 。

## ピン機能

**PGND(ピン1～2)**: パワー・スイッチのグランド・ピン。

**CAP(ピン3)**: 蓄電キャパシタの接続。このピンは、降圧レギュレータのメイン・スイッチ(昇圧レギュレータの同期スイッチ)への電源入力であり、バックアップ蓄電キャパシタに直接接続します。

**V<sub>IN</sub>(ピン4～5)**: 昇圧チャージャの入力電源および降圧レギュレータの安定化出力電圧。この入力は、INTV<sub>CC</sub> LDO および電流レギュレーション・アンプの入力にも電力を供給します。

**GATE(ピン6)**: PowerPathスイッチのゲート・ドライバ。このピンは、主電源をシステム負荷に接続する外付けPMOSスイッチのゲートを駆動します。この出力の電圧振幅範囲はV<sub>IN</sub>とGNDの間です。

**RUN(ピン7)**: ロジック制御RUN入力。このピンはフロート状態のままにしないでください。高精度のV<sub>IN</sub>低電圧しきい値を実現するために、抵抗分割器をV<sub>IN</sub>とGNDの間に配置します。

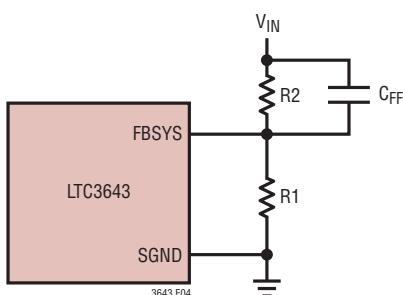

**FBSYS(ピン8)**: 降圧レギュレータ制御ループへの帰還入力。抵抗分割器のタップをこのピンに接続します。V<sub>IN</sub>電圧は、V<sub>IN</sub>=0.6V (1+R2/R1)となるよう調整できます(図4を参照)。

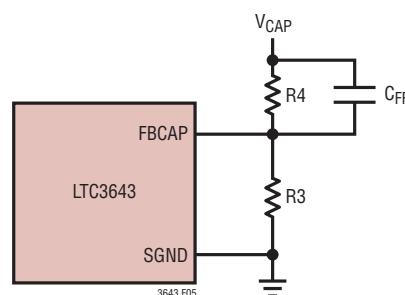

**FBCAP(ピン9)**: CAP電圧レギュレーション・ループのエラーアンプへの帰還入力。抵抗分割器のタップをこのピンに接続します。CAP電圧は、V<sub>CAP</sub>=0.6V (1+R4/R3)となるよう調整できます(図5を参照)。

**ITH(ピン10)**: エラーアンプの出力および昇圧レギュレータのスイッチング・レギュレータ補償ポイント。電流コンパレータのトリップしきい値は、この電圧に線形に比例します。降圧レギュレータの補償は、デバイスによって内部で設定されます。

**CAPGD(ピン11)**: キャパシタのパワーグッド・オープンドレイン状態出力。この出力の電圧は、LTC3643が蓄電キャパシタを充電している間、引き下げられます。このピンは、出力CAP電圧が設定された充電電圧の95%に達すると、高インピーダンスになります。

**PFO(ピン12)**: パワーフェイル・オープンドレイン状態出力。このピンの電圧は、主電源電圧がPFIピンで設定されたしきい値よりも高い場合、引き下げられます。

**PFI(ピン13)**: 電源障害入力。このピンは、コンバータが昇圧チャージャ・モードから降圧レギュレータ・モードに切り替わるしきい値を設定します。電源電圧が設定したしきい値未満に低下したときに降圧レギュレータ・モードに切り替えるには、このピンを主電源からの抵抗分割器に接続します。

**INTV<sub>CC</sub>(ピン14)**: 低ドロップアウト・レギュレータ。1μF以上の低ESRキャパシタを使用してグランドにバイパスします。

**BOOST(ピン15)**: 昇圧レール。0.1μFのキャパシタをこのピンとSWノードの間に接続して、同期整流式昇圧スイッチのゲート・ドライバに電力を供給します。

**INDIS(ピン16～17)**: 入力切断ピン。出力切断機能を実現する内部パワー・スイッチが、V<sub>IN</sub>ピンとINDISピンの間に配置されています。

**SW(ピン18～20)**: 電力レギュレータへのスイッチ・ノード接続ピン。

**I<sub>LIM</sub>(ピン21)**: 降圧モードのピーク電流設定ピン。3.2Aのピーク電流制限の場合、このピンをフロート状態のままにし、2.4Aのピーク電流制限の場合、このピンを接地し、4Aのピーク電流制限の場合、このピンをINTV<sub>CC</sub>に接続します。

**CLP(ピン24)**: 電流レギュレーション・アンプへの入力。このピンは、電流レギュレーション・アンプの反転入力であり、CLPがV<sub>IN</sub>から50mVを超えて上した場合に充電電流を減少させます。

**SGND(露出パッド・ピン25)**: レギュレータの信号グランドピン。一点でPGNDに接続します。定格熱性能を得るために、PCBのグランド・プレーンに接続します。

# LTC3643

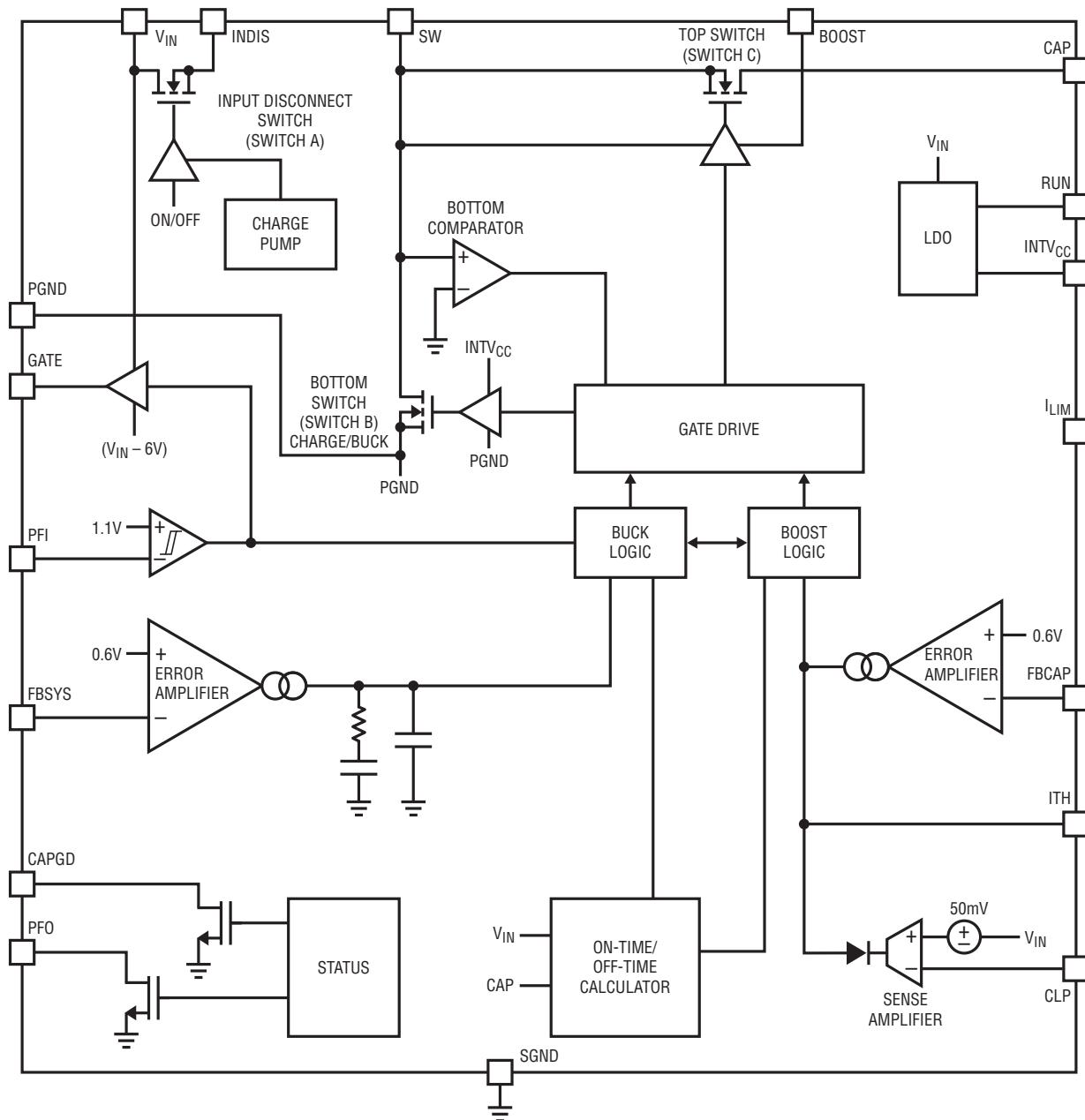

## ブロック図

## 動作

LTC3643は、PFI電圧の状態に応じて、 $V_{IN}$ からCAP(蓄電キャパシタ)またはCAPから $V_{IN}$ に電力を供給できる双方向レギュレータです。

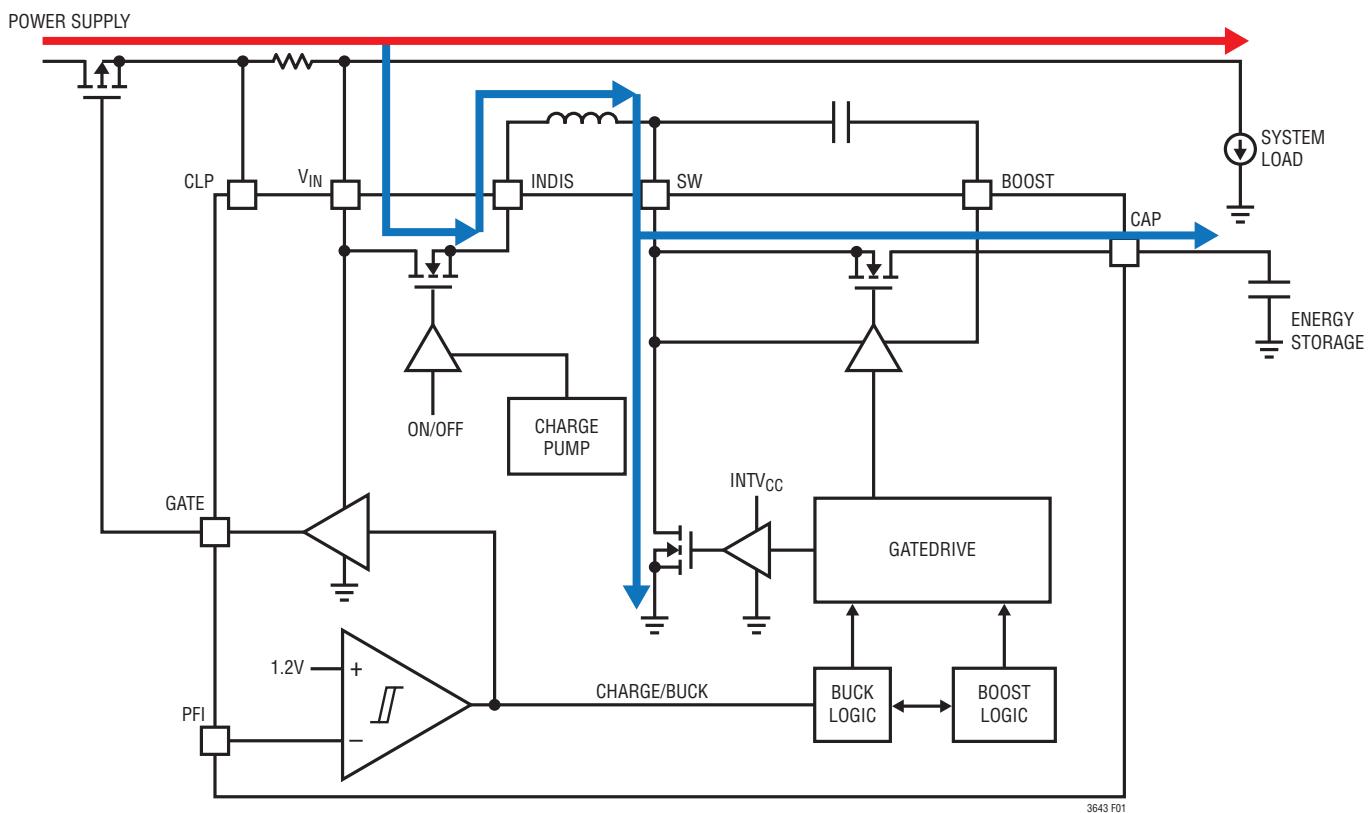

PFI電圧が“H”的場合、電源が正常であり、電力が $V_{IN}$ からCAPに供給されていることを示しています(図1を参照)。このモードでは、LTC3643は、入力が切断されたピーク電流モードの固定オフ時間昇圧レギュレータとして動作します。このモードでは、電力を電源からシステム負荷に直接供給することができ、CAPの蓄電素子の充電に使用できます。

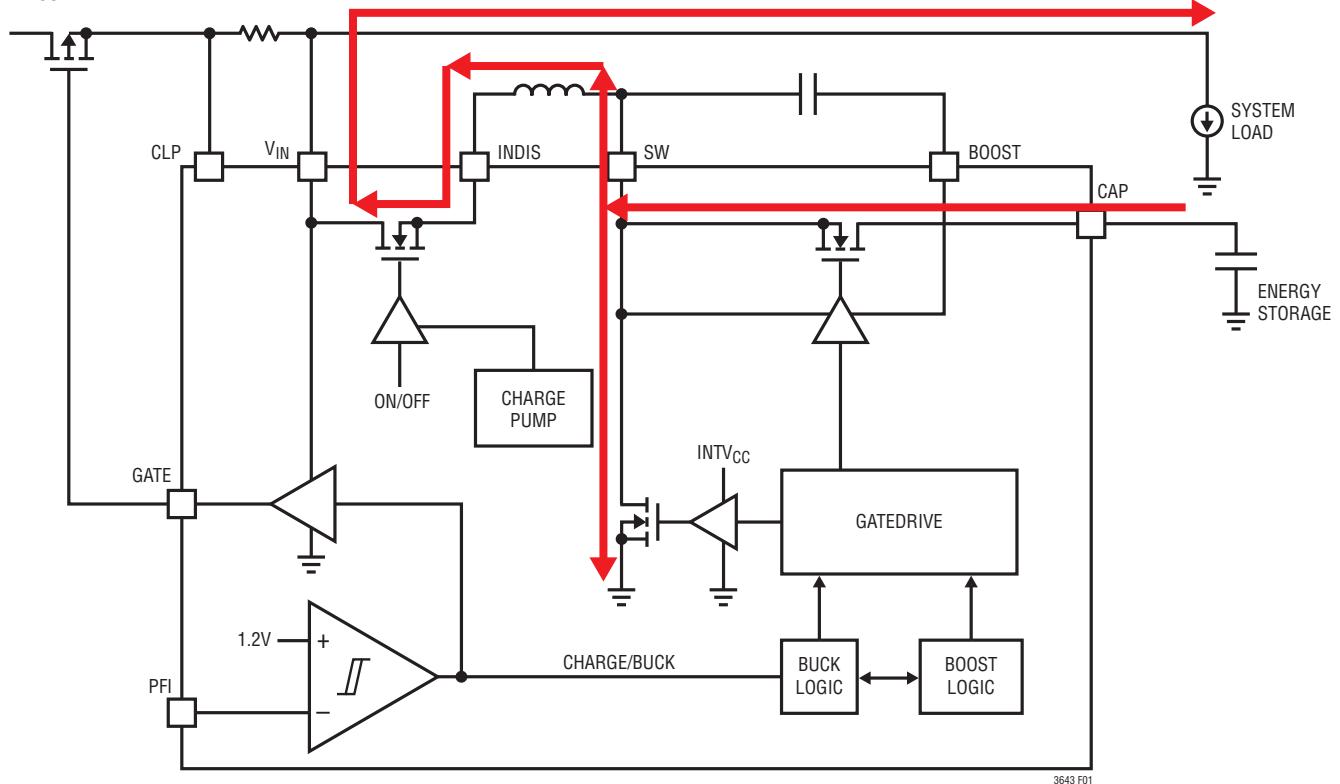

PFI電圧が“L”的場合、電源の電圧が必要なしきい値を下回っており、電力供給が反転し、デバイスが谷電流モードの固定オン時間降圧レギュレータとして動作して、CAPから $V_{IN}$ に可能な限り長時間電力を供給していることを示しています。電力経路を図2に示します。

$V_{IN}$ で電力を維持できる期間は、システム負荷の大きさ、蓄電CAPのサイズ、およびCAPノードが充電された電圧によって決まります。

LTC3643は、オン時間/オフ時間のみによって設定される擬似固定周波数で動作します。このオン時間/オフ時間は、 $V_{IN}$ とCAPの電圧に基づいて内部で計算され、1MHzになるように設定されます。軽出力負荷状態では、LTC3643はBurst Modeで動作し、パルスをスキップして、システムの電力損失を最小限に抑えます。出力負荷電流が増加すると、LTC3643は連続PWMスイッチング動作にシームレスに移行し、出力電力を供給します。LTC3643は、入力が切断されたスタンドアロン昇圧レギュレータとして動作するように構成できますが、システム電源が除去された場合に $V_{IN}$ に電力を戻し、「Dying Gasp」状態でシステム・レギュレーションを維持するために、高電圧蓄電キャパシタを充電する必要のあるアプリケーションを主なターゲットにしています。

図1. 電力経路ブロック - 電源から供給される電力

## 動作

POWER SUPPLY

図2. 電力経路ブロック - 蓄電素子から供給される電力

### 昇圧モードの制御ループ

PFI電圧が1.1Vを超えると、入力電源が正常であると見なされ、電力がV<sub>IN</sub>からCAPに供給されます。十分な負荷がCAPに存在する場合、またはCAP電圧がまだ最終的な設定値に達していない場合、昇圧レギュレータが連続的にスイッチングして必要な電力を供給します。このような状況では、下側スイッチがオンになるため、インダクタの電流が上昇します。電流がI<sub>TH</sub>電圧で設定された特定のレベルに達すると、下側スイッチがオフになり、上側(同期)スイッチがオンになります。上側スイッチは、固定期間(オフ時間)の間オンを維持した後に遮断され、このサイクルを反復することができます。

オフ時間は、定常状態でレギュレータが約1MHzの周波数で動作するように計算されます。したがって、オフ時間は次の式の値になります。

$$t_{OFF-BOOST} = 1\mu s \cdot \frac{V_{IN}}{V_{CAP}}$$

昇圧モード制御ループは、外部ITHピンを通じて補償されます。このループを補償する方法については、「アプリケーション情報」セクションで詳細に説明します。

### 昇圧モードの低電流動作

CAP電圧が設定された電圧に達すると、負荷が最小になり、LTC3643は連続モード動作からBurst Mode動作に自動的に移行します。このモードでは、I<sub>TH</sub>電圧は、CAP電圧に応じてスリープしきい値よりも高い電圧または低い電圧に遷移します。CAP電圧がレギュレーション・ポイントよりもわずかに低い電圧に減少すると、レギュレータがスリープ状態から復帰し、インダクタ電流が800mAのバースト電流クランプに達するまで、下側スイッチがオンになります。この電流値に達すると、固定期間(t<sub>OFF-BOOST</sub>)の間、下側スイッチがオフになり、上側スイッチがオフになります。このスイッチング・サイクルは、CAPが十分に補充されてI<sub>TH</sub>の電圧がスリープしきい値を下回るまで繰り返されます。この電圧がスリープしきい値を下回ると、両方のスイッチがオフになり、静止電流が400μAに減少します。

3643fa

## 動作

### 昇圧モードの起動

LTC3643は、RUN電圧が1.2Vを超えて上昇し、 $V_{IN}$ が3Vよりも高くなると、動作を開始します。上側スイッチのボディ・ダイオードを介して $V_{IN}$ からCAPに導通するのを防ぐために、入力切断スイッチが $V_{IN}$ とINDISの間に配置されています。この切斷スイッチのボディ・ダイオードと上側スイッチのボディ・ダイオードは、極性が反対です。そのため、CAPの電圧が $V_{IN}$ よりも低い場合に、電流の導通を防ぐことができます。切斷スイッチのゲートは、レギュレータが動作を開始するまで接地されたままになります。

レギュレータが動作を開始すると、内部チャージポンプが切斷スイッチのゲートを緩やかに充電し、このゲートの電圧を100mAの電流のみがスイッチに流れるように安定化します。そのため、この100mAの電流は、INDISとSWの間のインダクタ、および上側スイッチのボディ・ダイオードに流れ、CAPノードのキャパシタを充電します。100mAの制限は、切斷スイッチと上側スイッチからの電力損失を制限し、これらのスイッチを過熱から保護するための手段として設定されます。この期間の間、INDISとSWの電圧はCAPの電圧を1ダイオード電圧降下分超える電圧にクランプされます。

INDIS電圧が $V_{IN}$ に近づき、内部切斷スイッチが完全に導通したことが検出されると、内部信号が発行されて、CAP電圧を設定された値まで充電するために、必要に応じて上側スイッチと下側スイッチが動作できます。

### 昇圧出力の過電流/短絡発生時の動作

切斷スイッチを通る電流は、過電流状態を解消するために常にモニタされています。スイッチが完全に導通して、切斷スイッチを流れる電流が4.8Aを超えた場合、信号が制御回路に送信され、この電流レベルが低下するまで上側スイッチのオンを無期限に維持します。

出力短絡状態の間、CAP電圧が $V_{IN}$ 電圧未満に低下した場合、単純に上側スイッチをオンのままにしてインダクタ電流を放電しても、効果がありません。そのような状況では、切斷スイッチを流れる電流が8Aを超えた場合、切斷スイッチのゲートの電圧が直ちに引き下げられ、切斷スイッチが実質的に遮断されます。同時に、上側スイッチ下側スイッチが両方とも遮断されます。その後、インダクタの電流が、上側スイッチのボディ・ダイオードを介して導通し、0Aに低下します。その状態から、起動の場合と全く同様に、内部チャージポンプが切斷スイッチのゲートを再び緩やかに充電し、スイッチを流れる電流を100mAに安定化します。

### 降圧モードの制御ループ

PFI電圧が1.15V未満に低下すると、CAPから $V_{IN}$ に電力が供給されます。 $V_{IN}$ のシステム負荷が十分に高い場合、レギュレータが連続的にスイッチングします。標準的なサイクルでは、固定期間(オン時間)の間、上側スイッチがオンになります。この期間が経過すると、上側スイッチがオフになり、下側スイッチがオンになります。インダクタ電流は、内部で補償される $I_{TH}$ 電圧で設定されたしきい値で谷電流レベルに達するまで放電されます。この電流レベルに達すると、再び下側スイッチがオフになり、上側スイッチがオンになって、このサイクルが繰り返されます。

定常状態において、レギュレータが約1MHzの周波数で動作するように、オン時間が再計算されます。したがって、オン時間は次の式の値になります。

$$t_{ON-BUCK} = 1\mu s \cdot \frac{V_{IN}}{V_{CAP}}$$

降圧モード制御ループは、内部RCネットワークによって補償され、外部 $I_{TH}$ ピンは内部スイッチを介して接地されます。

### 降圧モードの低電流動作

$V_{IN}$ が設定されたレギュレーション電圧に達し、最小負荷が存在する場合、レギュレータは自動的にBurst Mode動作に移行します。このモードでは、 $I_{TH}$ 電圧は、 $V_{IN}$ 電圧に応じてスリープしきい値よりも高い電圧または低い電圧に遷移します。 $V_{IN}$ 電圧がレギュレーション・ポイントをわずかに下回って減少すると、レギュレータがスリープ状態から復帰し、固定期間( $t_{ON-BUCK}$ )の間、上側スイッチがオンになります。その後、インダクタ電流が0Aに達するまで、上側スイッチがオフになり、下側スイッチがオンになります。このスイッチング・サイクルは、 $V_{IN}$ の電圧が十分に補充されて $I_{TH}$ の電圧がスリープしきい値を下回ると、両方のスイッチがオフになり、静止電流が400 $\mu A$ に減少します。

## 動作

### 降圧モードの充電動作の終了

CAPのエネルギー貯蔵器は、 $V_{IN}$ をレギュレーション・ポイントで維持するために、できるだけ長い間エネルギーを供給し続けます。ただし、 $V_{IN}$ のシステム負荷が存在し続けた場合、ある時点でCAP電圧が十分低くなり、最小オフ時間制限のために $V_{IN}$ のレギュレーション電圧を維持できなくなります。最小オフ時間制限は、全てのサイクルで下側スイッチがオンになる必要があるため、存在しています。この状態に達すると、 $V_{IN}$ 電圧がCAP電圧の約93%に安定化します。スイッチング・レギュレータは、RUN電圧が1.1Vを下回るか、 $V_{IN}$ 電圧がレギュレータの動作に必要な電圧(標準で2.8V)を下回るまで、この動作を継続します。どちらかの状態に達すると、上側スイッチと下側スイッチが両方ともオフになり、切断スイッチのゲートが“L”に引き下げられます。

### 昇圧/降圧切り替え動作

LTC3643の動作は、PFI電圧に応じて、昇圧モードと降圧モードの間で切り替わります。PFI電圧が1.2Vを超えると、入力電源の電力が正常であり、昇圧段階に入ったと見なされます。PFI電圧が1.15Vを下回ると、入力電源がシステム負荷に電力を供給するには不十分になり、降圧段階に入ったと見なされます。PFOピンは、入力電源障害が発生しているかどうかを示すインジケータ・ピンです。このピンから既知のレール(6V未満)にプルアップ抵抗を接続します。このピンが“H”的場合、入力電源が不十分であることを示しています。

昇圧モードから降圧モードへの移行は、降圧レギュレータが作動する前に $V_{IN}$ の電圧が放電し過ぎるのを防ぐために、比較的に高速(約2μs)ですが、降圧モードから昇圧モードへの移行は、やや低速(約20μs)です。この時間遅延は、PFIしきい値電圧の50mVのヒステリシスと組み合わせて、PFIピンでの瞬間的なグリッチを除去し、モードの不要な遷移を防ぎます。

### 外付けPMOSスイッチのゲート制御

多くの場合、 $V_{IN}$ 電圧がPFIしきい値未満に低下して降圧モードが作動する際に、消耗した電源に逆導通電流が流れのを防ぐために、遮断素子を備える必要があります。これは、電源とCLPの間にショットキ・ダイオードを配置することによって実現できますが、高負荷時に電源が存在する場合、このダイオードによって大きな電力損失が発生します。

この電力損失を軽減するには、ショットキ・ダイオードの代わりに、低いRDS<sub>ON</sub>を持つ外付けパワーPMOSデバイスを使用し、そのゲートをLTC3643のGATEピンに接続します。アプリケーションが昇圧モードから降圧モードに移行する際に、GATE電圧が瞬間に $V_{IN}$ に引き上げられるため、外付けPMOSが遮断されます。再び電源が使用可能になると、GATE電圧が70μAの電流源によって緩やかに引き下げられます。この電圧は、内部でクランプされ、 $V_{IN}$ よりも6V低い電圧まで低下します。

### 昇圧モードの電流制限

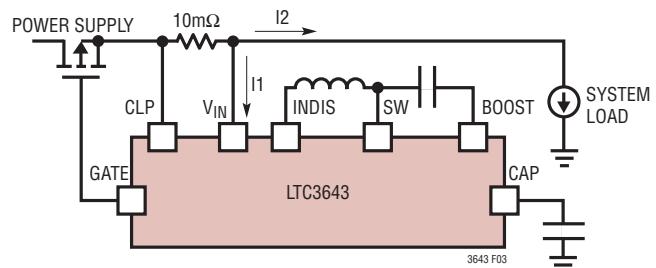

電源の電流が制限されている場合、LTC3643は、昇圧レギュレータの入力電流を制限し、昇圧レギュレータとシステム負荷の積算電流が設定された値を超えないようにすることができます。この電流制限は、CLPピンと $V_{IN}$ ピンの間の検出抵抗で設定します。

図3のアプリケーション例では、10mΩの抵抗がCLPと $V_{IN}$ の間に配置されています。これらのピンの間の電圧は、50mVを超えないように設計されています。そのため、昇圧レギュレータ(I1)とシステム負荷(I2)には、5Aの積算電流が流れることができます。アプリケーションのI2が4Aの場合、最大1Aの電流が昇圧レギュレータを流れることができます。I2が最小の場合、I1は昇圧レギュレータの最大電流によって制限されます。さらに、I2が5Aの制限を超えた場合、レギュレータの $I_{TH}$ 電圧は“L”に引き下げられ、デバイスはスリープ・モードに移行します。

図3. CLPで設定できる昇圧レギュレータのPowerPath

## 動作

### INTV<sub>CC</sub>レギュレータ

LTC3643は、V<sub>IN</sub>から給電される低ドロップアウト・レギュレータを内蔵しており、INTV<sub>CC</sub>の電圧は3.3Vに安定化されます。そのため、このLDOの電力損失は、 $(V_{IN} - 3.3V) \cdot I_{INTVCC}$ に等しくなります。標準的アプリケーションでは、レギュレーターが連続モードで動作している場合、デバイスがINTV<sub>CC</sub>から流す電流は約10mAです。

### V<sub>IN</sub>の低電圧の設定

LTC3643は、レギュレータを起動するための高精度のRUNしきい値を備えています。そのため、V<sub>IN</sub>とGNDの間に抵抗分割器を配置し、その中間ノードをRUNに帰還させて、高精度のV<sub>IN</sub>低電圧しきい値を設定できます。入力電圧が上昇すると、RUNの電圧がV<sub>RUN</sub>上昇時しきい値(1.2V)を超えて、レギュレータがオンになります。同様に、入力電圧がV<sub>RUN</sub>下降時しきい値(1.1V)未満に低下すると、レギュレータがオフになります。

図4. 降圧モードでのV<sub>IN</sub>電圧の設定

### 出力電圧の設定

降圧コンバータの出力V<sub>IN</sub>および昇圧チャージャの出力V<sub>CAP</sub>は、次の式に従って外付け抵抗分割器で設定します。

$$V_{IN} = 0.6V \left( 1 + \frac{R2}{R1} \right)$$

$$V_{CAP} = 0.6V \left( 1 + \frac{R4}{R3} \right)$$

周波数応答を改善するには、フィードフォワード・キャパシタC<sub>FF</sub>を使うこともできます。FBSYSまたはFBCAPのラインは、インダクタやSWトレースなどのノイズ源から離して配線するよう、十分注意してください。

図5. 昇圧モードでのV<sub>CAP</sub>電圧の設定

## アプリケーション情報

### 入力キャパシタ( $C_{IN}$ )の選択

LTC3643を昇圧方向でしか使用しない場合、入力フィルタ・キャパシタは、入力電源から流れるピーク電流を削減し、入力スイッチング・ノイズを減らすためにのみ必要になります。少なくとも $4.7\mu F$ の容量を持つ低ESRのバイパス・キャパシタを、できるだけ $V_{IN}$ ピンの近くに取り付けてください。

ただし、降圧モードが作動するアプリケーションでは、さらに多くのバイパス容量が必要になります。 $C_{IN}$ の選択は、電圧リップルと負荷ステップによるトランジエントを最小に抑えるのに必要な等価直列抵抗(ESR)、および制御ループの安定性を確保するのに必要なバルク容量の大きさによって決まります。ループの安定性は、負荷トランジエント応答を観察することによってチェックすることができます。入力リップル  $\Delta V_{IN}$  は次式で決定されます。

$$\Delta V_{IN} < \Delta I_L \left( \frac{1}{8 \cdot f \cdot C_{IN}} + ESR \right)$$

$\Delta I_L$ は入力電圧に応じて増加するので、出力リップルは入力電圧が最大のとき最大になります。ESRおよびRMS電流処理の要件を満たすには、複数のキャパシタを並列に配置することが必要な場合があります。乾式タンタル、特殊ポリマー、アルミ電解およびセラミックの各キャパシタはすべて表面実装パッケージで入手できます。特殊ポリマー・キャパシタはESRが非常に低いのですが、他のタイプに比べて容量密度が低くなります。タンタル・キャパシタは容量密度が最高ですが、スイッチング電源に使用するにはサージ・テストが実施されているタイプのみを使うことが重要です。アルミ電解キャパシタはESRがかなり大きいのですが、リップル電流定格および長期信頼性に対して配慮すれば、コスト重視のアプリケーションに使用することができます。セラミック・キャパシタは実装面積が小さく、低ESRの優れた特性をもっています。

### $V_{IN}$ およびCAPでのセラミック・キャパシタの使用

現在では、値の大きい低価格セラミック・キャパシタが小型ケース・サイズで入手できるようになっています。これらはリップル電流と電圧定格が大きく、ESRが小さいので、スイッチング・レギュレータのアプリケーションに最適です。ただし、入力と出力にこれらのキャパシタを使うときは注意が必要です。入力にセラミック・キャパシタを使用し、コードの長いACアダプタで電力を供給すると、出力の負荷ステップによって $V_{CAP}$ 入力にリングングが誘起されることがあります。最善の場合でも、このリングングが出力に結合して、ループの不安定性と誤認されることがあります。最悪の場合、長いコードを通して電流が急に突入すると、 $V_{CAP}$ に電圧スパイクが生じてデバイスを損傷するのに十分な大きさになる恐れがあります。

入力と出力にセラミック・キャパシタを選択する場合は、X5RやX7Rの誘電体を使ったものを選択します。これらの誘電体は、ある特定の値とサイズについてすべてのセラミックの中で温度特性と電圧特性が最も優れています。

セラミック・キャパシタのESRは非常に小さいため、代わりに入力キャパシタと出力キャパシタが電荷保存の要件を満たす必要があります。降圧モードと昇圧モードのどちらの場合でも、負荷ステップ発生時には、帰還ループがスイッチ電流を十分増加させて負荷を支えるまで、 $V_{IN}$ およびCAPの各キャパシタが即座に電流を供給して負荷を支える必要があります。

降圧モードで負荷ステップに応答するには標準で約5サイクルが必要ですが、最初のサイクルだけ $V_{IN}$ 電圧が直線的に低下します。 $V_{IN}$ 電圧の低下量 $V_{DROOP}$ は、通常最初のサイクルの直線的な低下の約3倍です。したがって、おおよそ以下の $V_{IN}$ キャパシタの値から開始するのが良いでしょう。

$$C_{IN} = 3 \frac{\Delta I_{IN}}{f_0 \cdot V_{DROOP}}$$

昇圧モードの応答は、通常、降圧モードの応答よりも非常に遅く、アプリケーションのデューティ・サイクルに依存します。通常、昇圧モードのループ応答は、降圧モードのループ応答よりも3倍以上遅くなります。そのため、容量の大きいセラミック・キャパシタがCAPで必要になる場合があります。ただし、ほとんどのアプリケーションでは、LTC3643を使用してバルク・キャパシタを充電します。その場合、単に方形波電流を除去するために、 $22\mu F$ のセラミック・キャパシタをバルク・キャパシタと並列に配置すれば十分です。

## アプリケーション情報

### インダクタの選択

望みの入力電圧と出力電圧が与えられると、インダクタ値と動作周波数(1MHz)によってリップル電流が決まります。

$$\Delta I_L = \frac{V_{IN}}{10^6 \cdot L} \left( 1 - \frac{V_{IN}}{V_{CAP(MAX)}} \right)$$

リップル電流が低下すると、インダクタのコア損失が削減され、 $V_{IN}$ の電圧リップルが減少します。ただし、リップル電流が極端に低いと、インダクタ電流検出で問題が発生します。効率が最高の動作は、低周波数でリップル電流が適度に小さいときに行われます。ただし、これを達成するには大きなインダクタが必要です。部品のサイズ、効率および動作周波数の間には交換条件があります。

妥当な出発点として、 $I_{OUT}(MAX)$ の約50%のリップル電流を選択します。リップル電流が規定のインダクタ飽和電流定格を超えないことを保証するには、次式に従ってインダクタンスを選択します。

$$L = \frac{V_{IN}}{10^6 \cdot \Delta I_{L(MAX)}} \left( 1 - \frac{V_{IN}}{V_{CAP(MAX)}} \right)$$

$L$ の値が分かつたら、インダクタの種類を選択する必要があります。コア損失は、選択する材質、周波数、およびインダクタンスに極めて依存します。インダクタンスを大きくするとリップルが減少します。インダクタンスを大きくするには、ワイヤの巻数を増やす必要があるため、銅損失は残念ながら増加します。

フェライト材はコア損失がきわめて低いため高いスイッチング周波数に適しており、設計目標を銅損失と飽和防止に集中することができます。フェライト・コアの材質は急激に飽和します。

つまり、設計ピーク電流を超えると、インダクタンスは突然低下します。その結果、インダクタのリップル電流が急激に増加し、そのため出力電圧リップルも増加します。コアを飽和させないでください。

コアの材質と形状が異なると、インダクタのサイズ/電流の関係および価格/電流の関係が変化します。フェライトやパーマロイを素材とするトロイド・コアやシールドされたポット型コアは小型で、エネルギー放射は大きくありませんが、同等の特性を有する鉄粉コアのインダクタより通常は高価です。使用するインダクタの種類をどう選択するかは、主に価格とサイズの要件や放射フィールド/EMIの要件に依存します。新しいデザインの表面実装型インダクタは、東光、Vishay、NECトーキン、Cooper、TDK、およびWürth Electronikから入手できます。詳細については表1を参照してください。

### 昇圧モードのトランジエント応答

昇圧モードのLTC3643は、外部ITHピンのRCネットワークを使用して補償されるピーク電流モード制御を使用します。図6に示されているITHピンの外付け部品ネットワークはほとんどのアプリケーションにおいて妥当な出発点となります。RCフィルタにより、支配的なポール-ゼロのループ補償が設定されます。PCレイアウトが完了し、出力キャパシタの種類と容量値が具体的に決定したら、これらの値はトランジエント応答を最適化するために変更できます。さまざまなタイプと値によってループ帰還係数と位相が決まるので、まず出力キャパシタを選択する必要があります。立ち上がり時間が $1\mu s$ ～ $10\mu s$ の、最大負荷電流の20%～100%の出力電流パルスによって発生する出力電圧波形とITHピンの波形により、帰還ループを開くことなく全体的なループの安定性を判断することができます。

表1. インダクタの選択表

| メーカー         | 製品名             | L<br>( $\mu H$ ) | I<br>(A)  | L<br>(mm) | W<br>(mm) | H<br>(mm) |

|--------------|-----------------|------------------|-----------|-----------|-----------|-----------|

| Ceilcraft    | XAL5030(50)-XXX | 0.16-22          | 31-3.6    | 5.28      | 5.48      | 3.1-5.1   |

| Ceilcraft    | XAL6030(60)-XXX | 0.18-22          | 39-5.6    | 6.36      | 6.56      | 3.1-6.1   |

| SUMIDA       | CDEP105NP-XXX   | 0.15-8.8         | 55-4      | 10        | 10        | 5.6       |

| SUMIDA       | CEP125NP-XXX    | 0.8-10           | 35-5      | 12.9      | 12.9      | 5.6       |

| Wurth Elekt. | 744393580XX     | 1-10             | 17-5.8    | 8.3       | 8.8       | 7.8       |

| Wurth Elekt. | 7440280000XX    | 0.056-6.8        | 6-0.55    | 2.8       | 2.8       | 1.1       |

| Ceiltronics  | DR73-XXX-R      | 0.33-1000        | 14.4-0.25 | 6.0       | 7.6       | 3.55      |

## アプリケーション情報

図6. 5Vから40Vへの昇圧アプリケーション

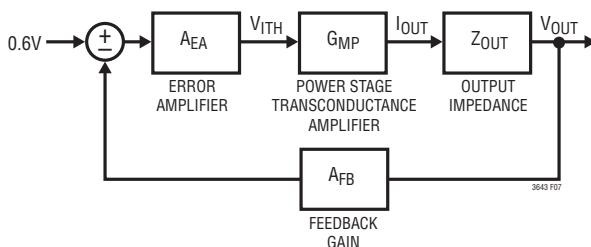

図7に、図6のアプリケーションの簡略ブロック図を示します。このブロック図を使用して、特定の補償部品を備えるアプリケーションの安定性を分析することができます。

図7. 昇圧レギュレータのブロック図

$A_{EA}$ は、内部エラーアンプの電圧利得を表します。 $A_{EA}$ は、FB入力誤差の差分を $I_{TH}$ 出力電圧に変換します。エラーアンプの $g_m$ ( $g_m(EA)$ )は、レギュレータに対して固定され、 $210\mu mho$ (標準)になります。 $I_{TH}$ の補償ネットワークにより、エラーアンプのゼロを超える周波数( $Z_1$ )では、利得はおおよそ $A_{EA}(\text{FLATBAND})$ になります。

$$Z_1 = \frac{1}{2\pi \cdot R_{ITH} \cdot C_{ITH1}} = 0.85\text{kHz}$$

$$A_{EA(\text{FLATBAND})} = g_m(EA) \cdot R_{ITH1} = 82.8\text{V/V}$$

$C_{ITH2}$ は、単に高周波信号を除去するために使用され、そのサイズが $C_{ITH1}$ よりも非常に小さい限り、レギュレータのループの安定性に影響を与えません。

$G_{MP}$ は、 $V_{ITH}$ から $I_{OUT}$ への相互コンダクタンス利得です。レギュレータのアキテクチャにより、 $V_{ITH}$ から $I_L$ (インダクタ電流)への利得は、内部で $3\text{mmho}$ に固定されています。さらに、 $I_L$ から $I_{OUT}$ へのDC利得は、次のAMPに等しくなります。

$$A_{MP} = \frac{\eta \cdot V_{IN}}{V_{CAP}} \text{A/A}$$

ここで、 $\eta$ はレギュレータの効率です。90%の効率および5V入力/40V出力のアプリケーションを仮定すると、次のようになります。

$$A_{MP} = 0.1125 \text{ A/A}$$

$G_{MP}$ のAC成分は、主に昇圧レギュレータのRHPゼロ( $Z_2$ )に起因します。

$$Z_2 = \frac{V_{IN}^2}{2\pi \cdot P_{OUT(\text{MAX})} \cdot L_1} \text{Hz}$$

$P_{OUT(\text{MAX})} = V_{IN} \cdot I_{L(\text{MAX})} \cdot \eta$ であるため、次の値が得られます。

$$Z_2 = \frac{V_{IN}}{2\pi \cdot \eta \cdot I_{L(\text{MAX})} \cdot L_1} = 94\text{kHz}$$

全ループは、クロスオーバー周波数が $Z_2$ の周波数よりも10倍以上遅くなるように補償する必要があります。

## アプリケーション情報

$Z_{OUT}$ はアプリケーションの出力インピーダンスです。 $Z_{OUT}$ は、 $R_{OUT}$ のDC利得および次の $P_1$ でポールを持っています。

$$P_1 = \frac{1}{2\pi \cdot R_{OUT} \cdot C_{OUT}} \text{Hz}$$

その結果、負荷ポールは、次の周波数でユニティゲインのインピーダンスを持ちます。

$$\frac{1}{2\pi \cdot C_{OUT}} = 6.8 \text{kHz}$$

ループの最後の成分は $A_{FB}$ です。 $A_{FB}$ は、 $V_{OUT}$ から $V_{FB}$ への利得であり、このアプリケーションでは、単純に $0.015V/V$ です。

ループ全体のクロスオーバー周波数をおおまかに推定するために、周波数 $Z_1$ で分析を行うことができます。この周波数では、次のようにになります。

$$A_{EA} \approx A_{EA(\text{FLATBAND})} = 82.8V/V$$

$$G_{MP} \approx 3 \cdot A_{MP} = 0.33\Omega$$

$$Z_{OUT} \approx \frac{P_1}{Z_1} = 8\Omega$$

$$A_{FB} = 0.015V/V$$

したがって、 $Z_1$ での全ループ利得は、全ての成分の積( $3.27V/V$ )に等しくなります。また、この周波数では、エラーアンプのゼロ周波数に既に達しているため、システムはシングル・ポール・システムのようになり、その結果、クロスオーバー周波数はおおよそ次の値になります。

$$3.27 \cdot Z_1 = 2.8 \text{kHz}$$

大きい蓄電キャパシタが $C_{OUT}$ と並列に配置されるアプリケーションの場合、ブロック図の $Z_{OUT}$ 成分を再モデル化する必要があります。ただし、多くの場合、大きいキャパシタのESRとその容量のゼロ周波数は、ループのクロスオーバー周波数よりもはるかに低くなるため、ループの安定性の分析では無視できます。

## 降圧モードのトランジエント応答

降圧モードのトランジエント応答は、負荷応答を見て確認できます。スイッチング・レギュレータは負荷電流のステップに応答するのに数サイクルを要します。負荷ステップが生じると、 $V_{IN}$ は $\Delta I_{LOAD} \cdot ESR$ に等しい大きさだけ即座にシフトします。ここで、ESRは $C_{IN}$ の等価直列抵抗です。また、 $\Delta I_{LOAD}$ によって $C_{IN}$ が充電または放電し始めるので、レギュレータが $V_{IN}$ をその定常値に戻すのに使用する帰還誤差信号が生じます。この回復期間に $V_{IN}$ をモニタして、安定性に問題があることを示すオーバーシュートやリンギングがないかチェックすることができます。LTC3643の降圧モードの補償は、デバイスの内部で実装されています。

初期出力電圧ステップが帰還ループの帯域幅内にない場合があるため、位相余裕を決定するのに、標準的2次オーバーシュート/DC比を使用することはできません。

出力電圧のセトリング動作は閉ループ・システムの安定性に関係し、電源全体の実際の性能を表します。制御ループ理論の要点を含む補償部品の最適化の詳細については、「アプリケーションノート76」を参照してください。

アプリケーションによっては、(1μFを超える)大容量の入力キャパシタが接続されている負荷でスイッチングが行われるとさらに大きなトランジエントが発生することがあります。放電した入力キャパシタが実質的に $C_{IN}$ と並列接続された状態になるため、 $V_{IN}$ の急激な低下を引き起こします。負荷に接続しているスイッチの抵抗が低く、急速に駆動された場合、この問題を防止するのに十分な電流を供給できるレギュレータはありません。解決策は負荷スイッチのドライバがオンになる速度を制限することです。Hot Swap™コントローラはこの目的専用に設計され、通常は電流制限機能、短絡保護、ソフトスタート機能が組み込まれています。

## 効率に関する検討事項

スイッチング・レギュレータのパーセント表示の効率は、出力電力を入力電力で割って100%を掛けたものに等しくなります。個々の損失を解析して、効率を制限する要素が何であり、また何が変化すれば最も効率が改善されるかを判断することができます。多くの場合有益です。パーセント表示での効率は、次式で表すことができます。

$$\% \text{効率} = 100\% - (L_1 + L_2 + L_3 + \dots)$$

## アプリケーション情報

ここで、L1、L2などは入力電力に対するパーセント値で表した個々の損失です。回路内の電力を消費する全ての素子で損失が生じますが、LTC3643の回路での損失の大部分は、通常、主に次の3つの要因によって生じます。これらは、1)I<sup>2</sup>R損失、2)スイッチングとバイアスでの損失、および3)その他の損失です。

1. I<sup>2</sup>R損失は、内部スイッチのDC抵抗( $R_{SW}$ )および外部インダクタの抵抗( $R_L$ )から計算できます。連続モードでは、平均入力電流がインダクタLおよびフロントエンドの切断スイッチを流れますが、内部の上側および下側パワーMOSFETの間で「ショッピング」されます。したがって、SWピンを見たときの直列抵抗は、次式のように、上側MOSFETおよび下側MOSFETの両方の $R_{DS(ON)}$ とデューティサイクル(DC)の関数になります。

$$R_{SW} = (R_{DS(ON)TOP})(1-DC) + (R_{DS(ON)BOT})(DC) + R_{DS(ON)BLKFET}$$

上側MOSFETと下側MOSFETの $R_{DS(ON)}$ は、両方とも「標準的性能特性」の曲線から求めることができます。したがって、I<sup>2</sup>R損失は次式で求められます。

$$I^2R \text{ losses} = I_L^2(R_{SW} + R_L)$$

2. スイッチング電流は、MOSFETドライバ電流と制御電流の合計です。パワーMOSFETドライバ電流はパワーMOSFETのゲート容量をスイッチングすることによって流れます。パワーMOSFETのゲートが“L”から“H”、さらに再び“L”に切り替わるたびに、ある量の電荷dQがV<sub>IN</sub>からグランドに移動します。結果として得られるdQ/dtはV<sub>IN</sub>から流出する電流であり、通常はDC制御バイアス電流よりも大きくなります。連続モードでは、I<sub>GATECHG</sub> = f (Q<sub>T</sub> + Q<sub>B</sub>)です。ここで、Q<sub>T</sub>およびQ<sub>B</sub>は内蔵の上側および下側パワーMOSFETのゲート電荷であり、fはスイッチング周波数です。したがって、電力損失は次のようにになります。

$$\text{スイッチング損失} = I_{GATECHG} \cdot V_{IN}$$

3. 遷移損失、銅線の抵抗、内部負荷抵抗など、その他の「隠れた」損失が電源システム全体のさらなる効率低下の原因になる可能性があります。これらの「システム」レベルの損失をシステムの設計段階で盛り込むことが非常に重要です。遷移損失は、スイッチ・ノードの遷移中に上側パワーMOSFETが短時間飽和領域に留まることから生じます。LTC3643の内部パワー・デバイスは十分速く切り替わるので、これらの損失は他の要因に比べると大きくはありません。デッドタイム中のダイオードの導通損失やインダクタのコア損失などその他の損失は、一般に全追加損失の2%に満たない値です。

### 熱的条件

大半のアプリケーションでは、LTC3643は効率が高く、その底面が露出したQFNパッケージの熱抵抗は低いので、熱はありません。ただし、高い周囲温度、高いV<sub>IN</sub>、最大出力負荷電流でLTC3643が動作するアプリケーションでは、発熱によってデバイスの最大接合部温度を超える可能性があります。接合部温度が約160°Cに達すると、温度が約15°C下がるまで両方のパワースイッチがオフします。

LTC3643が最大接合部温度を超えるのを防ぐには、若干の熱解析が必要です。熱解析の目的は、電力損失によりデバイスが最大接合部温度を超えるかどうかを判断することです。温度上昇は次式で与えられます。

$$t_{RISE} = P_D \cdot \theta_{JA}$$

一例として、V<sub>IN</sub> = 5V、I<sub>L</sub> = 2A、V<sub>CAP</sub> = 40VのアプリケーションにLTC3643を使用する場合を検討します。パワーMOSFETの等価抵抗 $R_{SW}$ は次のようにになります。

$$\begin{aligned} R_{SW} &= R_{DS(ON)TOP} \cdot \frac{V_{IN}}{V_{CAP}} + R_{DS(ON)BOT} \cdot \left(1 - \frac{V_{IN}}{V_{CAP}}\right) \\ &\quad + R_{DS(ON)BLKFET} \\ &= 150m\Omega \cdot \frac{5V}{40V} + 75m\Omega \cdot \left(1 - \frac{5V}{40V}\right) + 50m\Omega \\ &= 134m\Omega \end{aligned}$$

通常、INTVCCから流れる電流は10mAです。

したがって、デバイスによる全電力損失は次のとおりです。

$$\begin{aligned} P_D &= I_{OUT}^2 \cdot R_{SW} + V_{IN} \cdot I_{INTVCC} \\ &= 4A^2 \cdot 134m\Omega + 5V \cdot 10mA \\ &= 587.5mW \end{aligned}$$

## アプリケーション情報

QFNパッケージの接合部から周囲の熱抵抗 $\theta_{JA}$ は約46°C/Wです。したがって、25°Cの周囲温度で動作しているレギュレータの接合部温度は、およそ次のとおりです。

$$T_J = 0.587W \cdot 46^\circ\text{C}/\text{W} + 25^\circ\text{C} = 52^\circ\text{C}$$

上の接合部温度は25°Cでの $R_{DS(ON)}$ から得られたことに留意すると、 $R_{DS(ON)}$ は温度に依存して増加するので、より大きな $R_{DS(ON)}$ に基づいて接合部温度を再計算することもできます。52°Cで $R_{SW}$ が10%大きくなると仮定して再計算すると、新しい接合部温度は54.4°Cになります。より高い周囲温度またはスイッチング周波数あるいはその両方がアプリケーションで要求される場合は、ヒートシンクまたは空気流を使用してデバイスの温度上昇を減らすよう注意が必要です。

### 基板レイアウトに関する検討事項

プリント回路基板をレイアウトするときには、以下のチェックリストを使用して LTC3643 が正しく動作するようにします。レイアウトでは、以下の項目をチェックしてください。

1. キャパシタ $C_{CAP}$ はCAP端子とGND端子にできるだけ近づけて接続されていますか。

2.  $C_{IN}$ とLは近づけて接続されていますか。 $C_{IN}$ の(-)電極はGNDと $C_{CAP}$ の(-)電極に電流を戻します。

3. パッケージの裏面にある露出パッド(ピン25)は、GNDプレーンに半田付けしてください。このGNDプレーンをサーマルビアを介して他の層に接続すると、LTC3643から熱を放散するのに役立ちます。

4. 影響を受けやすい部品はSWピンから遠ざけてください。補償部品の $C_{ITH}$ と $R_{ITH}$ 、全ての抵抗分割器、および $INTV_{CC}$ のバイパス・キャパシタは、SWのトレースおよびインダクタから離して配線します。

5. グランド・プレーンが必要です。

6. 全ての層の未使用領域は銅で覆ってください。これにより、電力部品の温度上昇が小さくなります。これらの銅領域はGNDに接続してください。

### ホールドアップ時間の計算

電圧が目的のバックアップ電圧未満に低下する前に蓄電キャパシタから供給されるエネルギーの量は、次式の値になります。

$$E_{CAP} = \frac{1}{2} C_{CAP} (V_{CAP}^2 - V_{IN}^2)$$

バックアップを実行するために必要なエネルギーの量は、次式の値になります。

$$E_{LOAD} = I_{SYS} \cdot V_{IN} \cdot t_{HT}$$

ここで、 $t_{HT}$ は必要なバックアップ時間です。

効率を $\eta$ (この値はアプリケーションによって異なります)と仮定すると、合計バックアップ時間は次式の値になります。

$$t_{HT} = \frac{E_{CAP} \cdot \eta}{I_{SYS} \cdot V_{IN}} = \frac{C_{CAP} (V_{CAP}^2 - V_{IN}^2) \cdot \eta}{2 \cdot I_{SYS} \cdot V_{IN}}$$

ここで、 $I_{SYS}$ はバックアップ時のシステム負荷です。

### 設計例

設計例として、以下の仕様のアプリケーションに LTC3643 を使用する場合を考えます。

$$V_{IN} = 4V \sim 8V$$

$$V_{CAP} = 40V$$

$$I_{CAP}(\text{入力}) = 2A$$

内部で設定されるスイッチング周波数が1MHzであることを前提にして、最大 $V_{IN}$ での約40%のリップル電流(2Aの出力電流の平均に基づく800mA)に対するインダクタ値は、次の値になります。

$$L = \left( \frac{8V}{1MHz \cdot 0.8A} \right) \left( 1 - \frac{8V}{40V} \right) = 8\mu\text{H}$$

のことから判断して、8.2μHのインダクタで十分です。

昇圧モードと降圧モードのそれぞれの出力電圧リップル要件を満たすために必要な条件に基づいて、 $C_{CAP}$ および $C_{IN}$ を選択します。ほとんどのアプリケーションでは、両方のノードの22μFまたは47μFのキャパシタで十分です。

## アプリケーション情報

### システム・バックアップ電源アプリケーションのC<sub>CAP</sub>のサイズ選択

このセクションでは、電力が失われたときに入力電源を維持できる十分なエネルギーを保証するために、CAPのキャパシタ(C<sub>CAP</sub>)のサイズを決定する方法について説明します。以下の場合の設計例について考えます。

$$V_{IN} = 5V$$

$$V_{CAP} = 40V$$

$$\text{ホールドアップ時間}(t_{HT}) = 10\text{msec}$$

$$\text{システム電流負荷}(I_{SYS}) = 2A$$

ホールドアップ時間の間に必要な合計エネルギーは、次の値になります。

$$E_{DISS} = V_{IN} \cdot I_{SYS} \cdot t_{HT} = 100\text{mW}\cdot\text{sec}$$

供給される合計エネルギーは、次の式の値になります。

$$E_{AVAL} = \frac{C_{CAP}}{2} \left( V_{CAP}^2 - V_{IN}^2 \right) = 787.5 \cdot C_{CAP} (\text{W}\cdot\text{sec})$$

レギュレータには損失があるので、次の式を満たすように効率を考慮する必要があります。

$$E_{AVAL} \cdot \text{eff} > E_{DISS}$$

$$C_{CAP} = \frac{E_{DISS}}{\text{eff} \cdot E_{AVAL}}$$

90%の効率を仮定し、システムが必要とする 100mW·sec の合計エネルギーでは、C<sub>CAP</sub>は141μF以上である必要があります。

慎重に見積もり、キャパシタのある程度の電圧係数および許容誤差を考慮するために、必要な値よりも 30% 以上大きいキャパシタを推奨します。この特定の例では、4 個の 47μF キャパシタ(合計 188μF)を推奨します。

### CAPのキャパシタ(C<sub>CAP</sub>)の選択

CAPのキャパシタは、ピーク・インダクタ電流の大きさとリップル電圧仕様に基づいて選択します。出力電圧リップルには、キャパシタのESR(等価直列抵抗)と、サイクルごとにキャパシタに保存される電荷の両方が関係します。

電荷によるリップルは、ほぼ次の式で与えられる値になります。

$$V_{RIPPLE(CHARGE)} \equiv \frac{I_p \cdot V_{IN}}{C_{CAP} \cdot V_{CAP} \cdot f}$$

ここで、I<sub>P</sub>はピーク・インダクタ電流です。

通常、ほとんどの電力コンバータにおいて、リップルに最も大きく影響する要素はC<sub>CAP</sub>のESRです。キャパシタのESRによるリップルは次の式で与えられます。

$$V_{RIPPLE(ESR)} = I_{LOAD} \cdot R_{ESR} \cdot \frac{V_{OUT}}{V_{IN}}$$

ここで、R<sub>ESR</sub>はキャパシタのESRと同じです。

大きい蓄電キャパシタを使用するアプリケーションでは、ESRが低いため、さらに小さいセラミック・バイパス・キャパシタをレギュレータに近づけて使用することも必要になります。通常、ほとんどのアプリケーションでは22μFのセラミック・キャパシタで十分です。

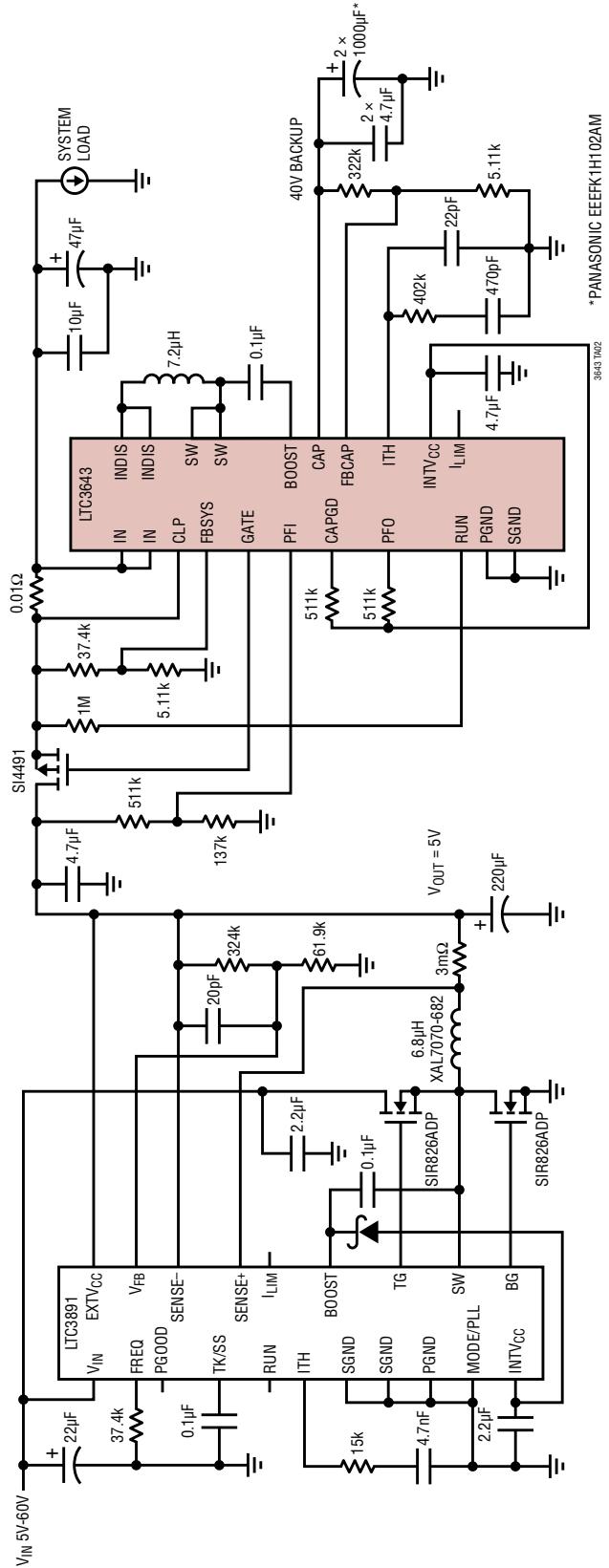

## 標準的応用例

$V_{IN}$ が5V～60Vの5Vバックアップ・システム

3643fa/2

\*PANASONIC EEEFK1H102AM

3643fa

LTC3643

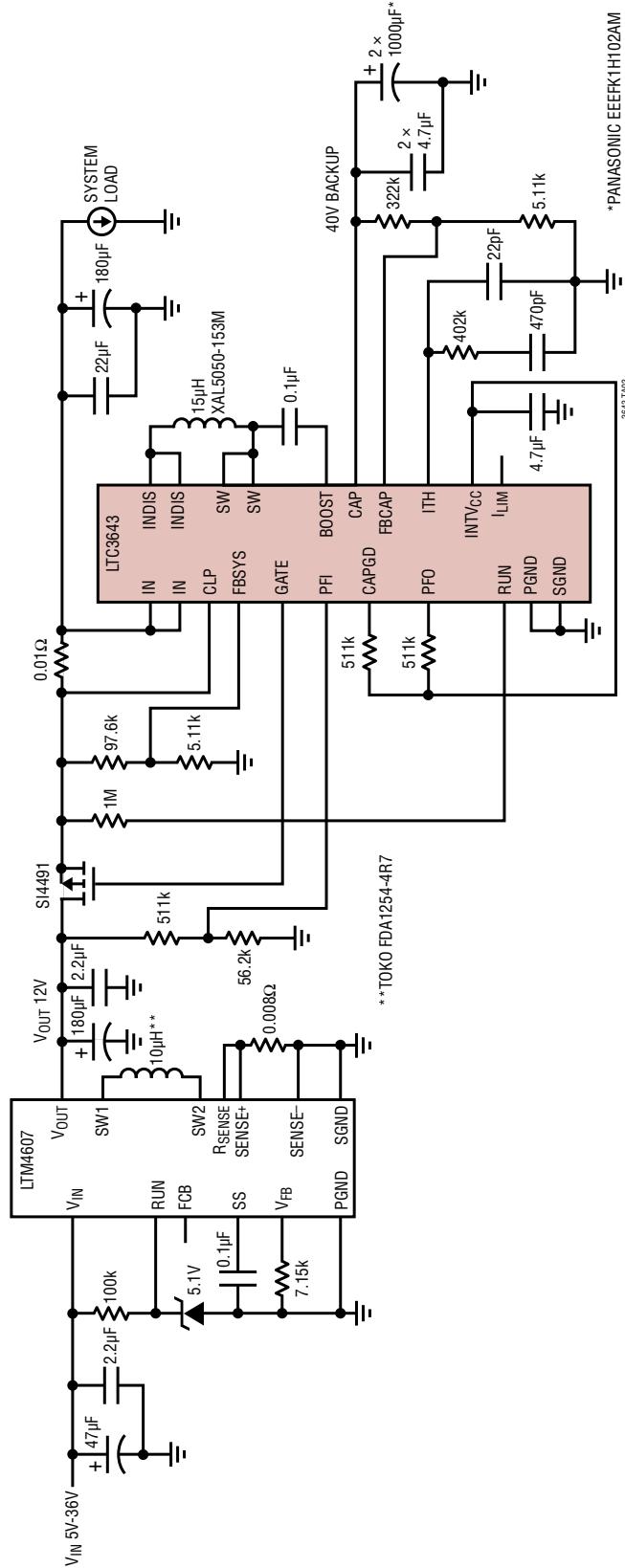

## 標準的應用例

車載アプリケーション用の12Vバッテクアップ・システム

3643fa

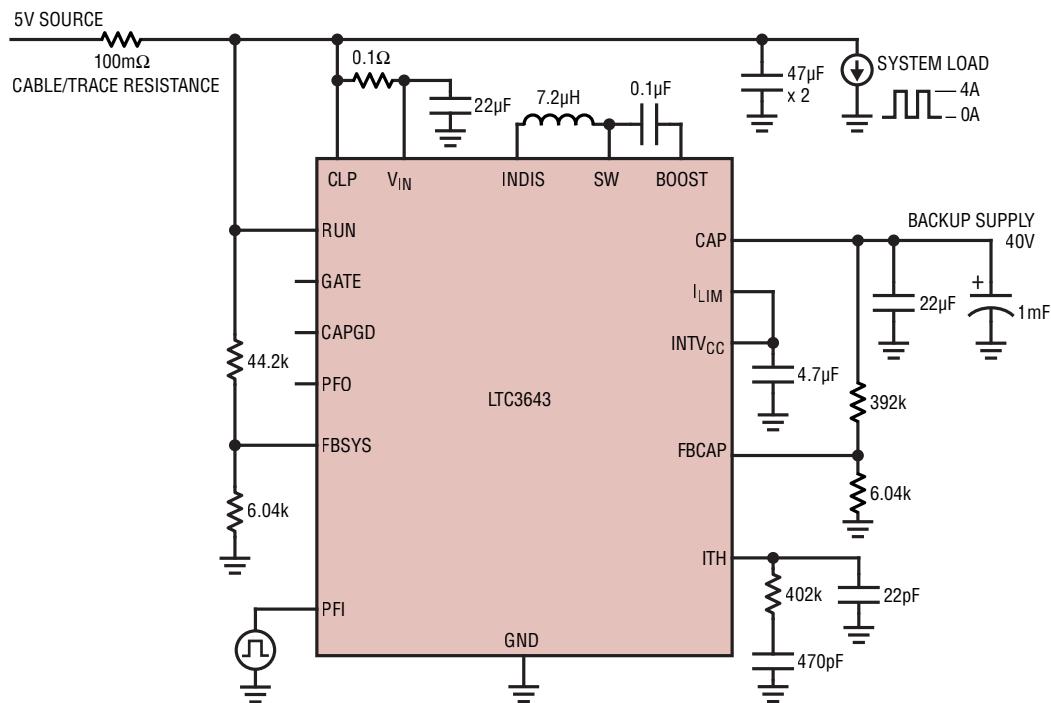

## 標準的応用例

一時的な電源昇圧器

NOTE: DRIVE PFI PIN HIGH WHEN HIGH LOAD IS PRESENT TO MAINTAIN DESIRED VOLTAGE AT THE SYSTEM LOAD

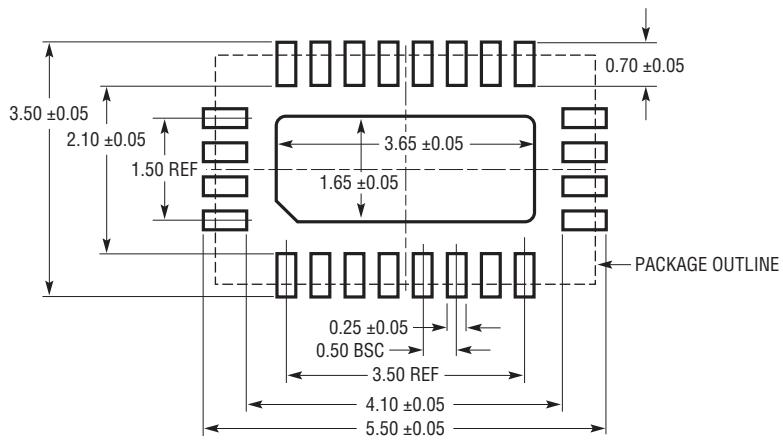

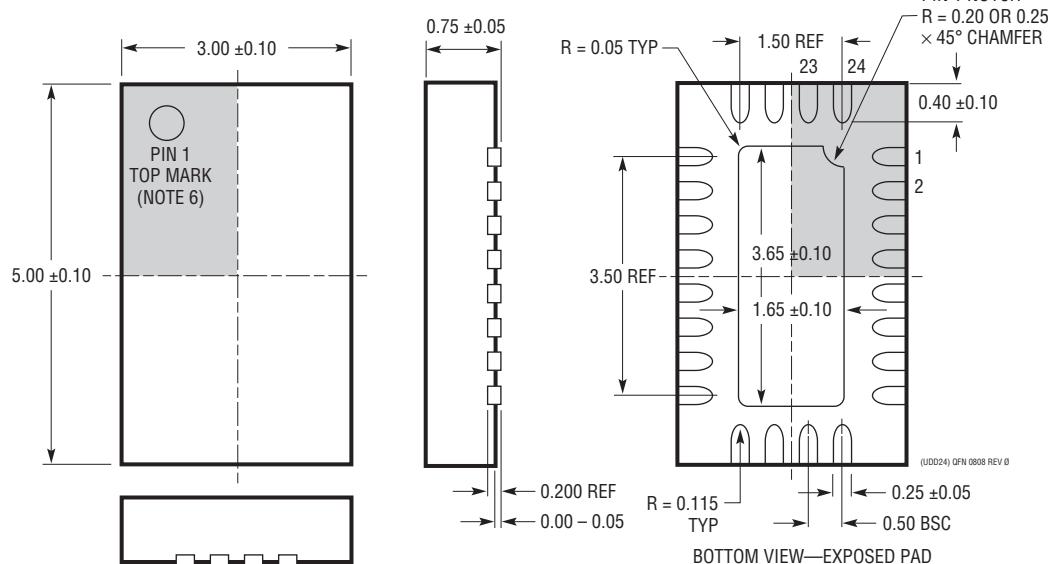

## パッケージの寸法

最新のパッケージ図については、<http://www.linear-tech.co.jp/product/LTC3643#packaging> を参照してください。

**UDD Package

24-Lead Plastic QFN (3mm × 5mm)**

(Reference LTC DWG # 05-08-1833 Rev Ø)

RECOMMENDED SOLDER PAD PITCH AND DIMENSIONS

APPLY SOLDER MASK TO AREAS THAT ARE NOT SOLDERED

注記:

1. 図はJEDECのパッケージ外形ではない

2. 図は実寸とは異なる

3. 全ての寸法はミリメートル

4. パッケージ底面の露出パッドの寸法にはモールドのバリを含まない

モールドのバリは(もしあれば)各サイドで0.15mmを超えないこと

5. 露出パッドは半田メッキとする

6. 灰色の部分はパッケージの上面と底面のピン1の位置の参考に過ぎない

## 改訂履歴

| REV | 日付    | 説明              | ページ番号 |

|-----|-------|-----------------|-------|

| A   | 12/15 | 「標準的応用例」のグラフを変更 | 1     |

# LTC3643

## 標準的応用例

入力切断機能を備えた40V同期整流式昇圧レギュレータ

## 関連製品

| 製品番号    | 説明                                            | 注釈                                                                                                                                                                          |

|---------|-----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LTC3110 | 2A 双方向昇降圧DC/DCレギュレータおよびチャージャ/バランサ             | V <sub>CAP</sub> の電圧範囲:0.1V～5.5V、V <sub>SYS</sub> の範囲:1.71V～5.25V、充電モードからバックアップ・モードへの自動切り替え 24ピンTSSOPおよび4mm×4mm QFNパッケージ                                                    |

| LTC3128 | 入力電流制限精度の高い3Aモノリック昇降圧スーパー・キャパシタ・チャージャ/バランサ    | 3Aまでプログラム可能な高精度(±2%)平均入力電流制限、アクティブな充電バランス調整、1個または2個のキャパシタを充電、V <sub>IN</sub> の範囲:1.73V～5.5V、V <sub>OUT</sub> の範囲:1.8V～5.5V、20ピン4mm×5mm QFNパッケージおよび24ピンTSSOPパッケージ            |

| LTC3226 | バックアップPowerPathコントローラ付き2セル・スーパー・キャパシタ・チャージャ   | 1x2xマルチモード・チャージポンプ・スーパー・キャパシタ・チャージャ、自動セル・バランシング、PowerPath、2A LDO バックアップ電源、メイン/バックアップの自動切り替え、2.5V～5.5V、16ピン3mm×3mm QFNパッケージ                                                  |

| LTC3350 | 大電流スーパー・キャパシタ・バックアップ・コントローラ/システム・モニタ          | 1～4個の直列スーパー・キャパシタの高効率の充電バックアップ時の昇圧モード、システム状態のモニタ。38ピン5mm×7mm QFNパッケージ                                                                                                       |

| LTC3355 | SCAPチャージャとバックアップ・レギュレータを内蔵した20V/1A降圧DC/DCシステム | V <sub>IN</sub> :3V～20V、V <sub>OUT</sub> :2.7V～5V、1Aメイン降圧レギュレータ、1個のスーパー・キャパシタから給電される5A昇圧バックアップ・レギュレータ、過電圧保護。20ピン4mm×4mm QFNパッケージ                                            |

| LTC3625 | 自動セル・バランシング付き、1A高効率2セル・スーパー・キャパシタ・チャージャ       | 直列に接続された2個のスーパー・キャパシタを高効率で昇圧/降圧充電。自動セル・バランシング。プログラム可能な充電電流:最大500mA(1個のインダクタ)、1A(2個のインダクタ)。12ピン3mm×4mm DFNパッケージ                                                              |

| LTC4425 | 電流制限付き理想ダイオードとV/Iモニタを備えたリニア・スーパー・キャパシタ・チャージャ  | 2セル直列スーパー・キャパシタ・スタック用定電流/定電圧リニア・チャージャ。V <sub>IN</sub> :リチウムイオン/ポリマー・バッテリ、USBポート、または2.7V～5.5Vの電流制限電源。2A充電電流、自動セル・バランシング、2μA未満のシャットダウン電流。12ピン3mm×3mm DFNパッケージまたは12ピンMSOPパッケージ |

| LTC4040 | 2.5Aバッテリ・バックアップ・パワーマネージャ                      | V <sub>IN</sub> :3.5V～55V、単一セルのリチウムイオンLiFePO <sub>4</sub> 電池から電源をバックアップする高電流昇圧DC/DCレギュレータを内蔵、24ピン4mm×5mm QFNパッケージ                                                           |