# DDRメモリ電源用の15V、 デュアル3Aモノリシック 降圧レギュレータ

## 特長

- 入力電圧範囲:3.6V ~ 15V

- 1チャネル当たりの出力電流:±3A

- 効率:最大 95%

- チャネル間の位相偏移を選択可能:90°/180°

- 調整可能なスイッチング周波数:500kHz ~ 4MHz

- $VTTR = V_{DDQ}/2 = V_{TT}$  リファレンス

- 0.75Vでの $VTTR$ の精度: $\pm 1.6\%$

- 最適な出力電圧範囲:0.6V ~ 3V

- $\pm 10\text{mA}$ のバッファ出力が $V_{REF}$ リファレンス電圧を供給

- 電流モード動作により、優れた入力および

負荷トランジエント応答を実現

- 外部クロックに同期

- 短絡保護

- 入力過電圧保護および過熱保護

- パワーグッド状態出力

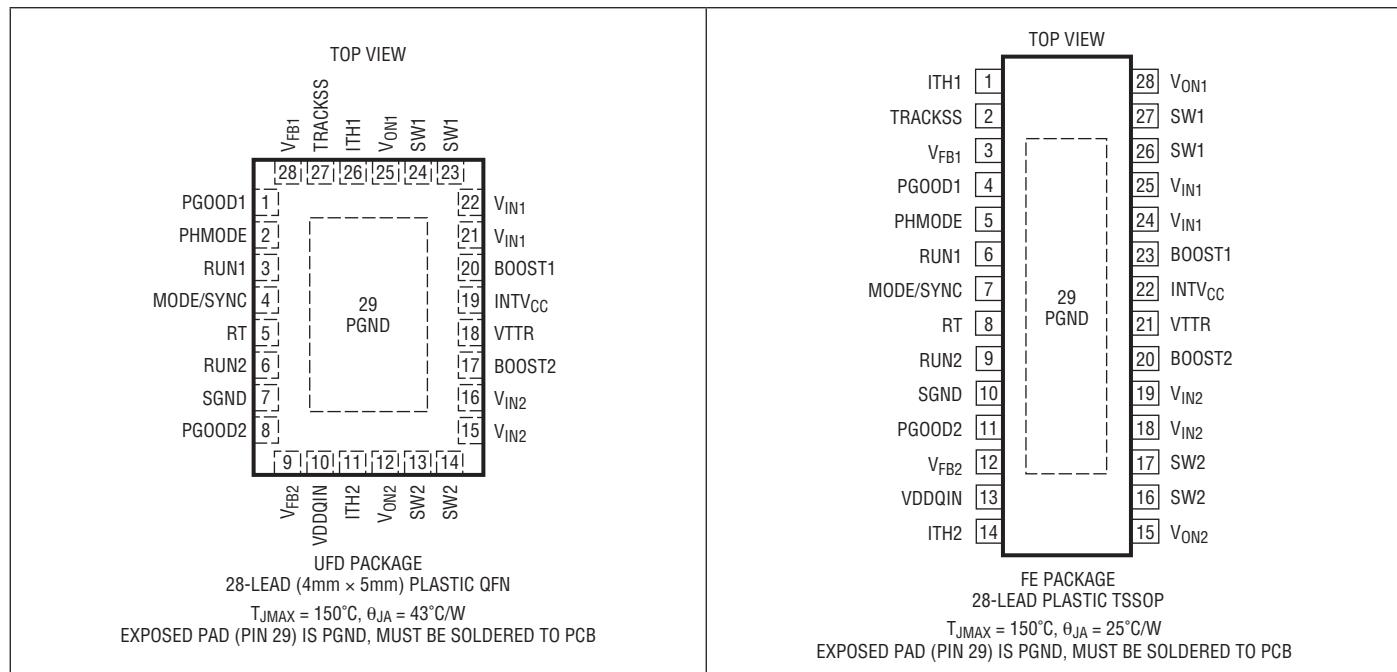

- (4mm×5mm) QFN-28および熱特性が改善された

28ピンTSSOPパッケージ

## アプリケーション

- DDRメモリ電源

LT、LT、LTC、LTM、Linear Technology、リニアのロゴ、Burst ModeおよびPolyPhaseはリニアテクノロジー社の登録商標です。Hot Swapはリニアテクノロジー社の商標です。その他すべての商標の所有権は、それぞれの所有者に帰属します。5481178、5847554、6580258、6476589、6774611を含む米国特許により保護されています。

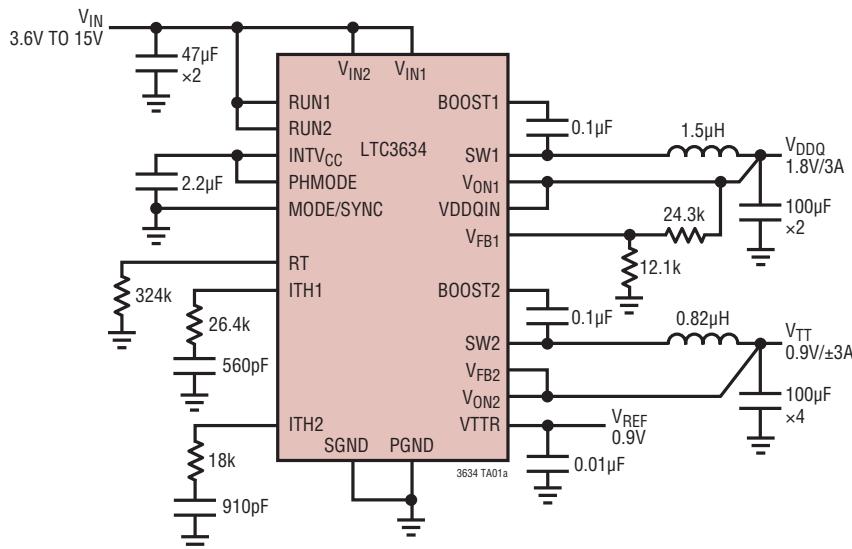

## 概要

LTC<sup>®</sup>3634は、デュアル・チャネルの高効率モノリシック同期整流式降圧レギュレータで、DDR1、DDR2、およびDDR3 SDRAMコントローラの電源レールとバス終端レールに電力を供給します。3.6V ~ 15Vの入力電圧範囲で動作するので、5Vまたは12V入力からのポイントオブロード電源アプリケーションや、さまざまなバッテリ駆動システムに適しています。

$V_{TT}$ 安定化出力電圧は $V_{DDQIN} \cdot 0.5$ に等しくなります。10mAの負荷を駆動できる内蔵バッファは低ノイズのリファレンス出力( $VTTR$ )を備えており、この値も $V_{DDQIN} \cdot 0.5$ に等しくなります。

1本の外付け抵抗により、500kHz ~ 4MHzの範囲で動作周波数の設定と同期が可能です。2つのチャネルは位相を180°ずらして動作できるので、入力容量と出力容量の要件が緩和されます。独自のオン時間制御アーキテクチャは、12V電源からDDRアプリケーションに高スイッチング周波数で電力を供給するのに最適なので、小型の外付け部品を使用することができます。

LTC3634は、28ピン4mm×5mm QFNパッケージおよび28ピン露出パッド付きTSSOPパッケージで供給されます。

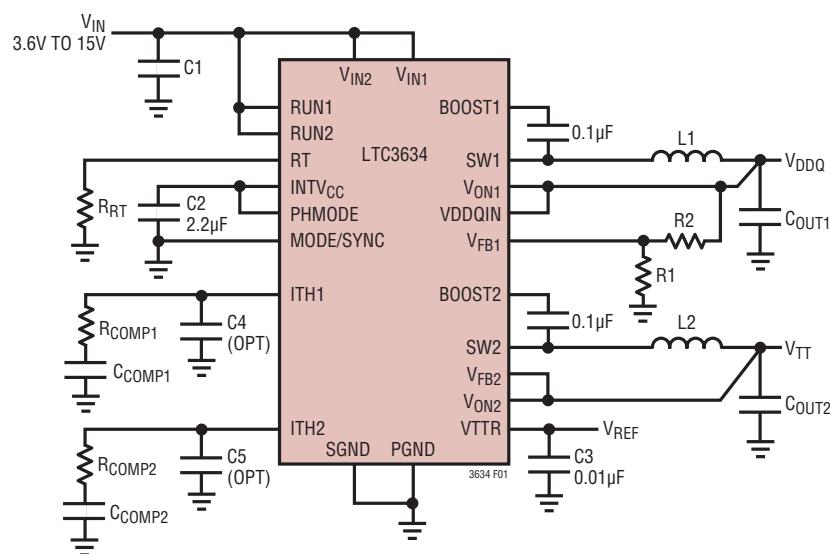

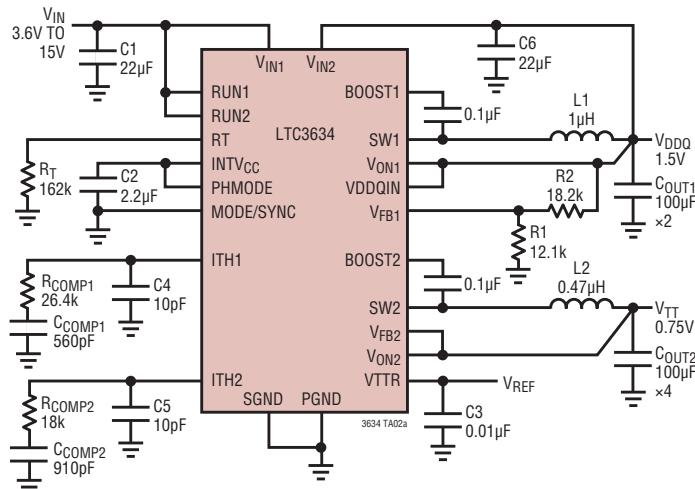

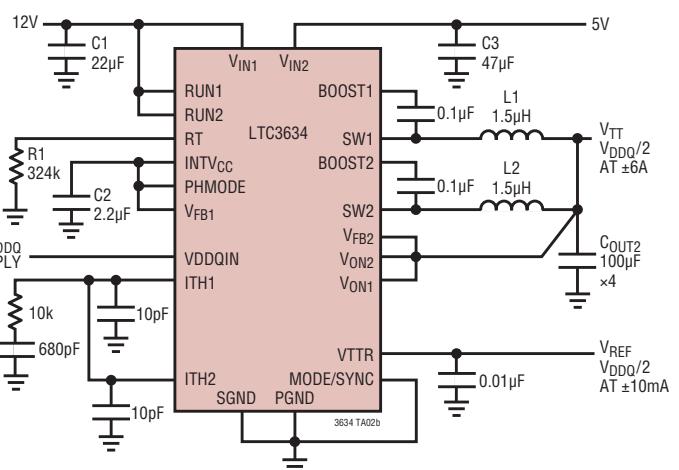

## 標準的応用例

## 絶対最大定格 (Note 1)

|                                            |                                   |

|--------------------------------------------|-----------------------------------|

| $V_{IN1}, V_{IN2}$                         | -0.3V ~ 16V                       |

| $V_{IN1}, V_{IN2}$ 過渡電圧 (Note 2)           | 18V                               |

| PGOOD1, PGOOD2, $V_{ON1}, V_{ON2}$         | -0.3V ~ 16V                       |

| VTTR, INTV <sub>CC</sub> , TRACKSS, VDDQIN | -0.3V ~ 3.6V                      |

| ITH1, ITH2, RT, MODE/SYNC                  | -0.3V ~ INTV <sub>CC</sub> + 0.3V |

| $V_{FB1}, V_{FB2}$ , PHMODE                | -0.3V ~ INTV <sub>CC</sub> + 0.3V |

| BOOST1-SW1, BOOST2-SW2                     | -0.3V ~ 3.6V                      |

| BOOST1, BOOST2                             | -0.3V ~ 19.6V                     |

| RUN1, RUN2                                 | -0.3V ~ $V_{IN} + 0.3V$           |

|                              |               |

|------------------------------|---------------|

| SWソース電流およびシンク電流(DC) (Note 3) | 3A            |

| 動作接合部温度範囲 (Note 4, 5, 8)     |               |

| LTC3634E, LTC3634I           | -40°C ~ 125°C |

| LTC3634H                     | -40°C ~ 150°C |

| LTC3634MP                    | -55°C ~ 150°C |

| 保存温度範囲                       | -65°C ~ 150°C |

| リード温度(半田付け、10秒、TSSOPパッケージ)   | 260°C         |

## ピン配置

## 発注情報

| 無鉛仕上げ           | テープアンドリール         | 製品マーキング*  | パッケージ                           | 温度範囲           |

|-----------------|-------------------|-----------|---------------------------------|----------------|

| LTC3634EUF#PBF  | LTC3634EUF#TRPBF  | 3634      | 28-Lead (5mm × 4mm) Plastic QFN | -40°C to 125°C |

| LTC3634IUF#PBF  | LTC3634IUF#TRPBF  | 3634      | 28-Lead (5mm × 4mm) Plastic QFN | -40°C to 125°C |

| LTC3634HUF#PBF  | LTC3634HUF#TRPBF  | 3634      | 28-Lead (5mm × 4mm) Plastic QFN | -40°C to 150°C |

| LTC3634MPUF#PBF | LTC3634MPUF#TRPBF | 3634      | 28-Lead (5mm × 4mm) Plastic QFN | -55°C to 150°C |

| LTC3634EFE#PBF  | LTC3634EFE#TRPBF  | LTC3634FE | 28-Lead Plastic TSSOP           | -40°C to 125°C |

| LTC3634IFE#PBF  | LTC3634IFE#TRPBF  | LTC3634FE | 28-Lead Plastic TSSOP           | -40°C to 125°C |

| LTC3634HFE#PBF  | LTC3634HFE#TRPBF  | LTC3634FE | 28-Lead Plastic TSSOP           | -40°C to 150°C |

| LTC3634MPFE#PBF | LTC3634MPFE#TRPBF | LTC3634FE | 28-Lead Plastic TSSOP           | -55°C to 150°C |

さらに広い動作温度範囲で規定されるデバイスについては、弊社または弊社代理店にお問い合わせください。 \* 温度グレードは出荷時のコンテナのラベルで識別されます。

非標準の鉛仕上げの製品の詳細については、弊社または弊社代理店にお問い合わせください。

無鉛仕上げの製品マーキングの詳細については、<http://www.linear-tech.co.jp/leadfree/> をご覧ください。

テープアンドリールの仕様の詳細については、<http://www.linear-tech.co.jp/taapeandreel/> をご覧ください。

## 電気的特性

●は規定接合部温度範囲での規格値を意味する。それ以外は  $T_A = 25^\circ\text{C}$  での値 (Note 4)。注記がない限り、 $V_{IN} = 12\text{V}$ 、 $\text{INTV}_{CC} = 3.3\text{V}$ 。

| SYMBOL         | PARAMETER                                       | CONDITIONS                                                                              | MIN    | TYP                    | MAX                   | UNITS                  |

|----------------|-------------------------------------------------|-----------------------------------------------------------------------------------------|--------|------------------------|-----------------------|------------------------|

| $V_{IN}$       | $V_{IN1}$ , Operating Supply Range              | $V_{IN1} > 3.6\text{V}$                                                                 | ●<br>● | 3.6<br>1.4             | 15<br>15              | V<br>V                 |

|                | $V_{IN2}$ , Operating Supply Range              |                                                                                         |        |                        |                       |                        |

| $I_Q$          | Output Voltage Range                            | $V_{ON} = V_{OUT}$ (Note 6)                                                             |        | 0.6                    | 3                     | V                      |

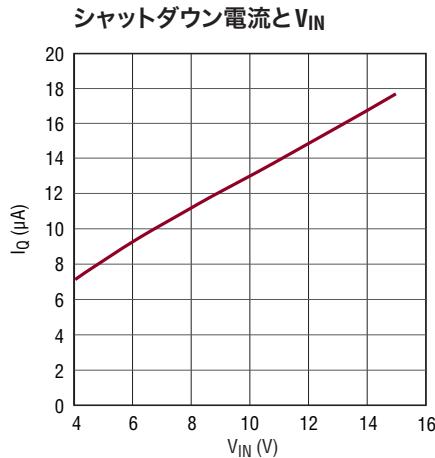

| $I_Q$          | Input DC Supply Current ( $V_{IN1} + V_{IN2}$ ) | RUN1 = RUN2 = $V_{IN}$<br>RUN1 = RUN2 = 0V                                              |        | 1.3<br>15              | mA<br>$\mu\text{A}$   | mA<br>$\mu\text{A}$    |

|                | Active (Note 7)                                 |                                                                                         |        |                        |                       |                        |

|                | Shutdown                                        |                                                                                         |        |                        |                       |                        |

| $V_{FBREG1}$   | Feedback Reference Voltage                      | 3.6V < $V_{IN}$ < 15V, 0.5V < ITH < 1.8V<br>0°C < $T_A$ < 85°C<br>-55°C < $T_A$ < 150°C | ●<br>● | 0.594<br>0.592         | 0.6<br>0.6            | 0.606<br>0.606         |

|                |                                                 |                                                                                         |        |                        |                       |                        |

| $V_{FBREG2}$   | Feedback Reference Voltage                      | 3.6V < $V_{IN}$ < 15V, 0.5V < ITH < 1.8V                                                | ●      | VTTR - 6               | VTTR                  | VTTR + 6               |

| $VTTR$         | VTTR Voltage Reference                          | 1.5V < $V_{DDQIN}$ < 2.6V<br>$I_{LOAD} = \pm 10\text{mA}$ , $C_{LOAD} < 10\text{nF}$    | ●      | 0.492 •<br>$V_{DDQIN}$ | 0.50 •<br>$V_{DDQIN}$ | 0.508 •<br>$V_{DDQIN}$ |

| $I_{FB}$       | Feedback Pin Input Current                      |                                                                                         |        |                        | ±30                   | nA                     |

| $g_m(EA)$      | Error Amplifier Transconductance                | ITH = 1.2V                                                                              |        |                        | 1.0                   | mS                     |

| $t_{ON(MIN)}$  | Minimum On-Time                                 | $V_{ON} = 0.5\text{V}$ , $V_{IN} = 4\text{V}$                                           |        |                        | 20                    | ns                     |

| $t_{OFF(MIN)}$ | Minimum Off-Time                                | $V_{IN} = 6\text{V}$                                                                    |        |                        | 40                    | ns                     |

| $f_{osc}$      | Oscillator Frequency                            | $V_{RT} = \text{INTV}_{CC}$<br>$R_T = 162\text{k}$<br>$R_T = 80.6\text{k}$              |        | 1.4<br>1.7<br>3.4      | 2<br>2<br>4           | 2.6<br>2.3<br>4.6      |

|                |                                                 |                                                                                         |        |                        |                       |                        |

|                |                                                 |                                                                                         |        |                        |                       |                        |

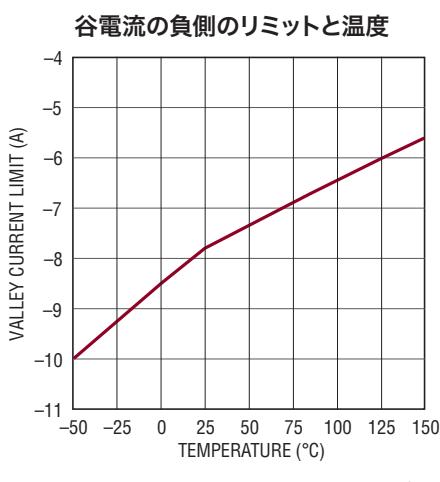

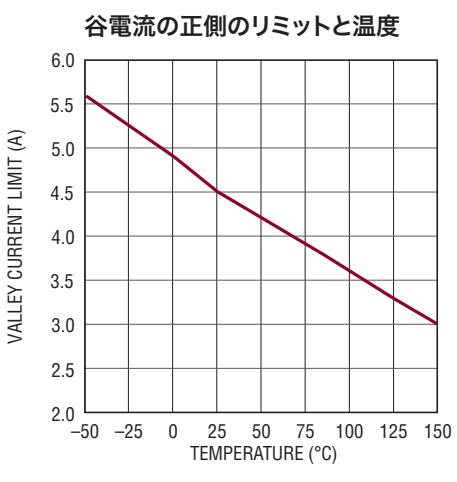

| $I_{LIM1}$     | Channel 1 Valley Switch Current Limit           |                                                                                         |        | 3.3<br>8               | 4.4<br>5.5            | A<br>A                 |

|                | Positive Limit                                  |                                                                                         |        |                        |                       |                        |

|                | Negative Limit                                  |                                                                                         |        |                        |                       |                        |

| $I_{LIM2}$     | Channel 2 Valley Switch Current Limit           |                                                                                         |        | 3.3<br>8               | 4.4<br>5.5            | A<br>A                 |

|                | Positive Limit                                  |                                                                                         |        |                        |                       |                        |

|                | Negative Limit                                  |                                                                                         |        |                        |                       |                        |

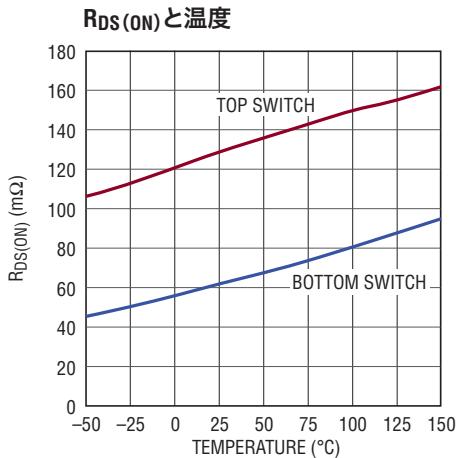

| $R_{DS(ON)}$   | Channel 1                                       | Top Switch On-Resistance<br>Bottom Switch On-Resistance                                 |        | 130<br>65              | mΩ<br>mΩ              | mΩ<br>mΩ               |

|                | Channel 2                                       |                                                                                         |        |                        |                       |                        |

|                |                                                 | Top Switch On-Resistance<br>Bottom Switch On-Resistance                                 |        | 130<br>65              | mΩ<br>mΩ              | mΩ<br>mΩ               |

|                |                                                 |                                                                                         |        |                        |                       |                        |

## 電気的特性

●は規定動作温度範囲での規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値(Note 4)。注記がない限り、 $V_{IN} = 12\text{V}$ 、 $\text{INTV}_{CC} = 3.3\text{V}$ 。

| SYMBOL        | PARAMETER                                     | CONDITIONS                                             | MIN          | TYP          | MAX          | UNITS                          |

|---------------|-----------------------------------------------|--------------------------------------------------------|--------------|--------------|--------------|--------------------------------|

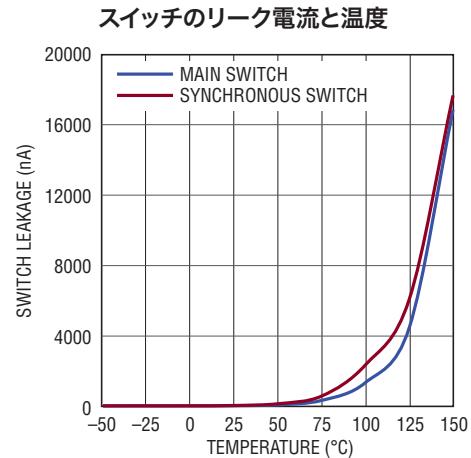

|               | Switch Leakage Current                        | $V_{IN} = 15\text{V}$ , $V_{RUN} = 0\text{V}$          |              | 0.01         | $\pm 1$      | $\mu\text{A}$                  |

|               | $V_{IN}$ Overvoltage Lockout Threshold        | $V_{IN}$ Rising<br>$V_{IN}$ Falling                    | 16.8<br>15.8 | 17.5<br>16.5 | 18<br>17     | V                              |

|               | INTV <sub>CC</sub> Voltage                    | $3.6\text{V} < V_{IN} < 15\text{V}$ , 0mA Load         | 3.1          | 3.3          | 3.5          | V                              |

|               | INTV <sub>CC</sub> Load Regulation            | 0mA to 50mA Load, $V_{IN} = 4\text{V}$ to $15\text{V}$ |              | 0.7          |              | %                              |

|               | RUN Threshold Rising<br>RUN Threshold Falling |                                                        | ●<br>●       | 1.18<br>0.98 | 1.22<br>1.01 | V<br>V                         |

|               | RUN Leakage Current                           |                                                        |              | 0            | $\pm 1$      | $\mu\text{A}$                  |

|               | PGOOD Good-to-Bad Threshold                   | $V_{FB}$ Rising<br>$V_{FB}$ Falling                    |              | 8<br>-8      | 10<br>-10    | %<br>%                         |

|               | PGOOD Hysteresis                              | $V_{FB}$ from Bad-to-Good                              |              | 15           |              | mV                             |

| $R_{PGOOD}$   | PGOOD Pull-Down Resistance                    | 10mA Load                                              |              | 15           |              | $\Omega$                       |

|               | Power Good Filter Time                        |                                                        | 20           | 40           |              | $\mu\text{s}$                  |

| $t_{SS1}$     | Channel 1 Internal Soft-Start Ramp Rate       |                                                        | 0.7          | 1.2          |              | V/ms                           |

| $t_{SS2}$     | Channel 2 Internal Soft-Start Ramp Rate       |                                                        | 1.5          | 2.2          |              | V/ms                           |

|               | $V_{FB1}$ During Tracking                     | TRACKSS = 0.3V                                         | 0.28         | 0.3          | 0.315        | V                              |

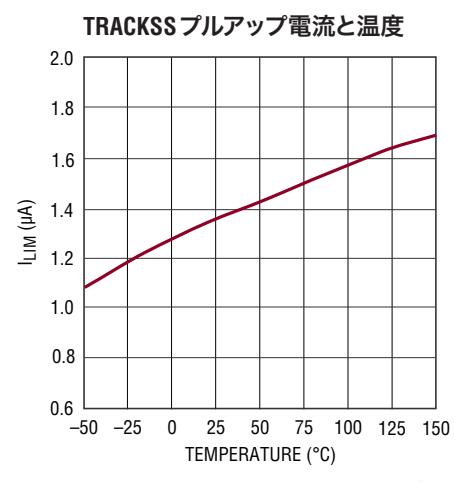

| $I_{TRACKSS}$ | TRACKSS Pull-Up Current                       |                                                        |              | 1.4          |              | $\mu\text{A}$                  |

|               | Phase Shift Between Channel 1 and Channel 2   | PHMODE = 0V<br>PHMODE = INTV <sub>CC</sub>             |              | 90<br>180    |              | deg<br>deg                     |

|               | PHMODE Threshold Voltage                      | $V_{IH}$<br>$V_{IL}$                                   |              | 1            | 0.3          | V<br>V                         |

|               | MODE/SYNC Threshold Voltage                   | $V_{IH}$<br>$V_{IL}$                                   |              | 1            | 0.4          | V<br>V                         |

|               | SYNC Threshold Voltage                        | $V_{IH}$                                               |              | 0.95         |              | V                              |

|               | MODE/SYNC Input Current                       | MODE = 0V<br>MODE = INTV <sub>CC</sub>                 |              | 1.5<br>-1.5  |              | $\mu\text{A}$<br>$\mu\text{A}$ |

**Note 1:** 絶対最大定格に記載された値を超えるストレスはデバイスに永続的損傷を与える可能性がある。長期にわたって絶対最大定格条件に曝すと、デバイスの信頼性と寿命に悪影響を与える可能性がある。

**Note 2:** 過渡的なイベントの持続時間はデバイスの全寿命の1%未満にする必要がある。

**Note 3:** 長期電流密度制限によって保証されている。

**Note 4:** LTC3634は $T_J$ が $T_A$ にほぼ等しくなるバルス負荷条件でテストされる。LTC3634Eは、 $0^\circ\text{C}$ ～ $85^\circ\text{C}$ の接合部温度で規定の性能に適合することが保証されている。 $-40^\circ\text{C}$ ～ $125^\circ\text{C}$ の動作接合部温度範囲での仕様は設計、特性評価および統計学的なプロセス・コントロールとの相関で確認されている。LTC3634Iは $-40^\circ\text{C}$ ～ $125^\circ\text{C}$ の動作接合部温度範囲で仕様に適合することが保証されている。LTC3634Hは $-40^\circ\text{C}$ ～ $150^\circ\text{C}$ の動作接合部温度範囲で性能仕様に適合することが保証されている。LTC3634MPは $-55^\circ\text{C}$ ～ $150^\circ\text{C}$ の動作接合部温度範囲でテストされ、性能仕様に適合することが保証されている。高い接合部温度は動作寿命に悪影響を及ぼす。接合部温度が $125^\circ\text{C}$ を超えると、動作寿命は短くなる。これらの仕様を満たす最大周囲温度は、基板レイアウト、パッケージの定格熱インピーダンスおよび他の環境要因と関連した特定の動作条件によって決まる。

**Note 5:** 接合部温度( $T_J$ 、単位:  $^\circ\text{C}$ )は、周囲温度( $T_A$ 、単位:  $^\circ\text{C}$ )、パッケージの熱インピーダンス( $\theta_{JA}$ 、単位:  $^\circ\text{C}/\text{W}$ )、および電力損失( $P_D$ 、単位: W)を基に次式に従って計算される。 $T_J = T_A + P_D \cdot \theta_{JA}$

**Note 6:** 3Vを超える出力電圧設定は、オン時間制御動作には最適ではない。3Vを超える出力電圧を設定する設計の場合は、最適化された範囲外でのデバイスの動作について「アプリケーション情報」のセクションを参照すること。

**Note 7:** スイッチング周波数で供給される内部ゲート電荷により動的消費電流は大きくなる。

**Note 8:** このデバイスには短時間の過負荷状態の間、デバイスを保護するための過温度保護機能が備わっている。過温度保護機能がアクティブなとき接合部温度は $150^\circ\text{C}$ を超える。規定された最大動作接合部温度を超えた動作が継続すると、デバイスの信頼性を損なう恐れがある。

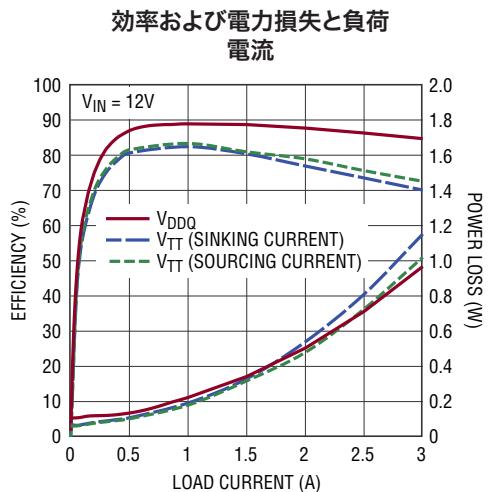

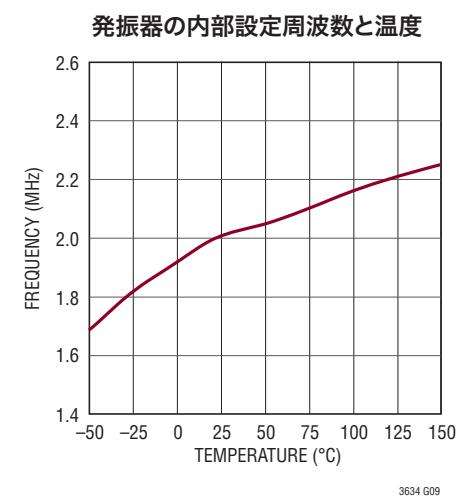

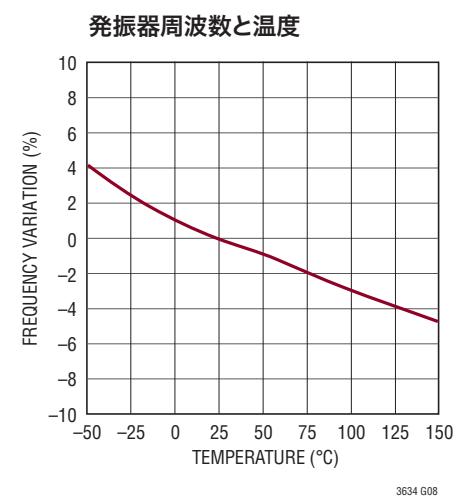

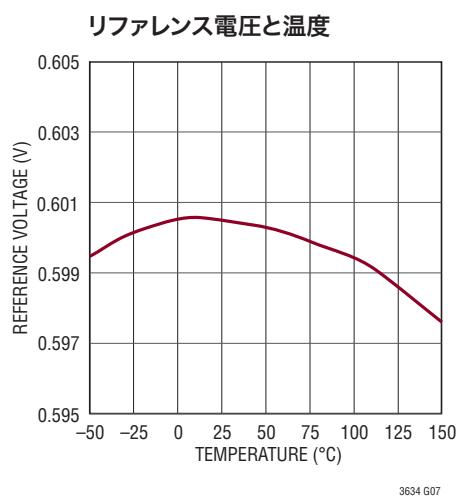

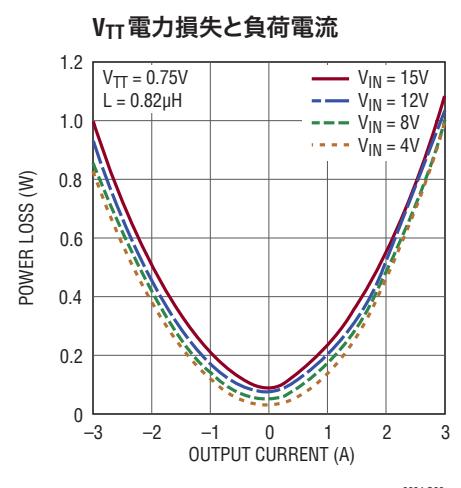

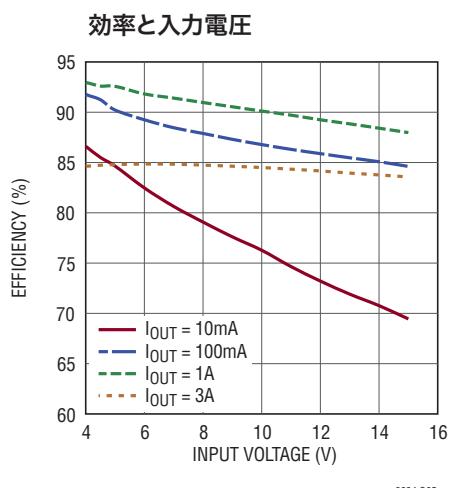

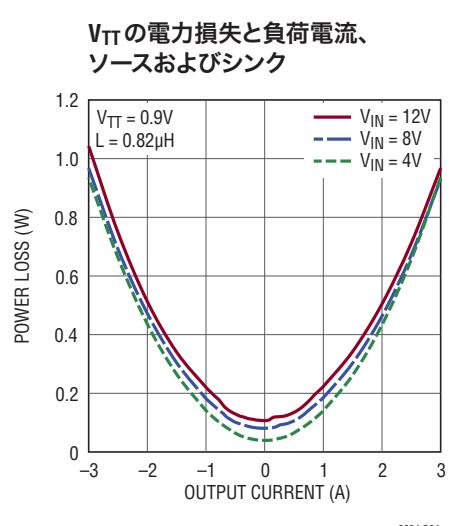

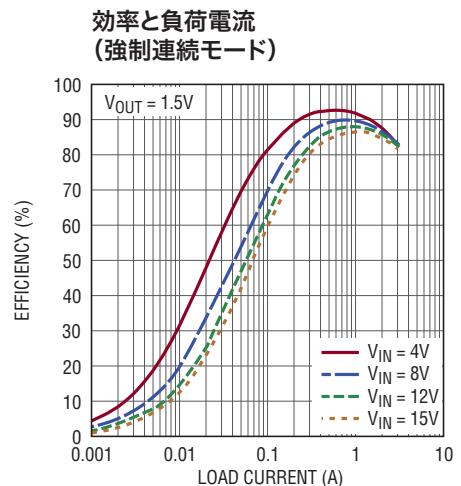

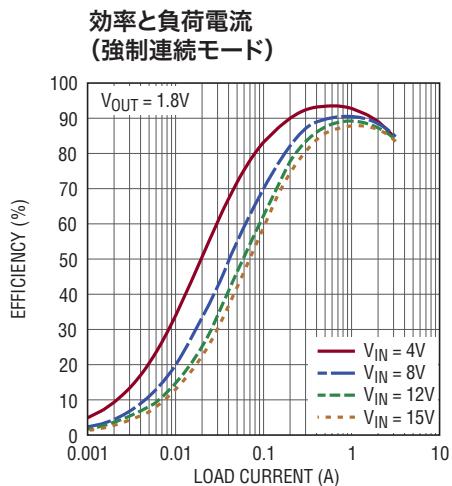

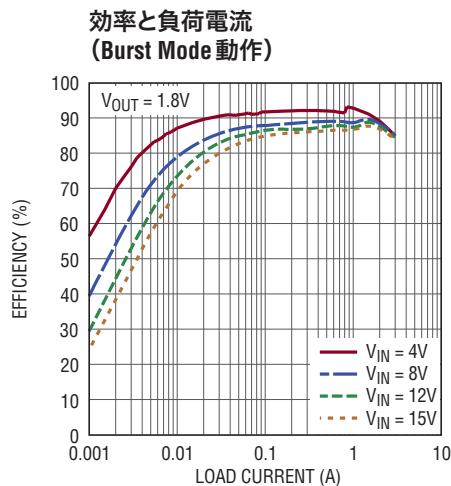

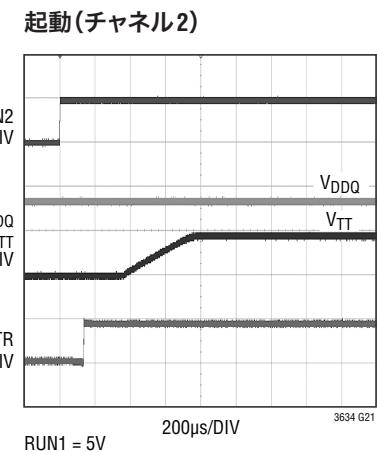

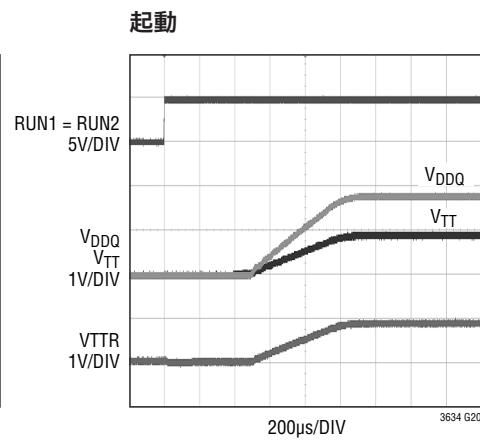

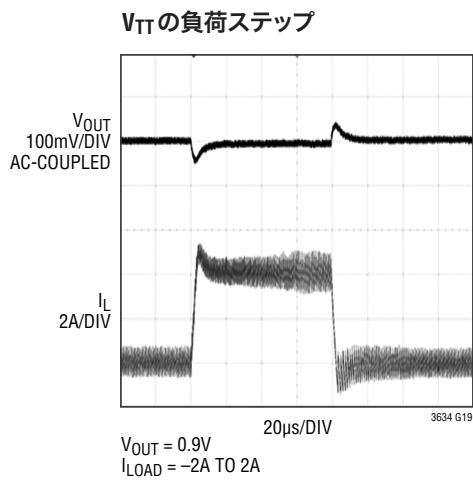

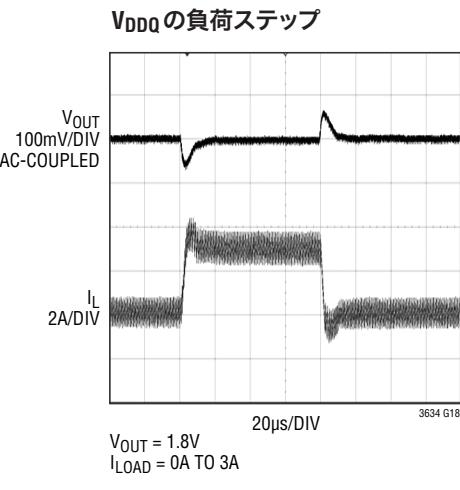

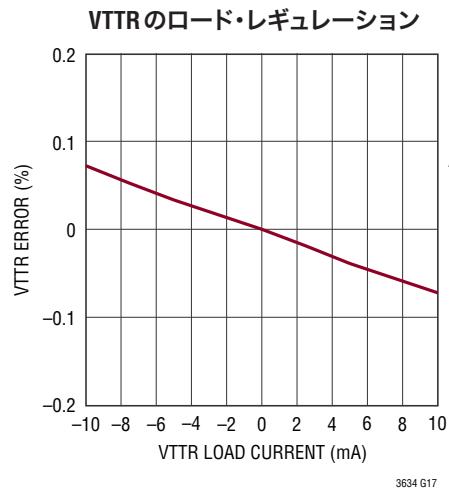

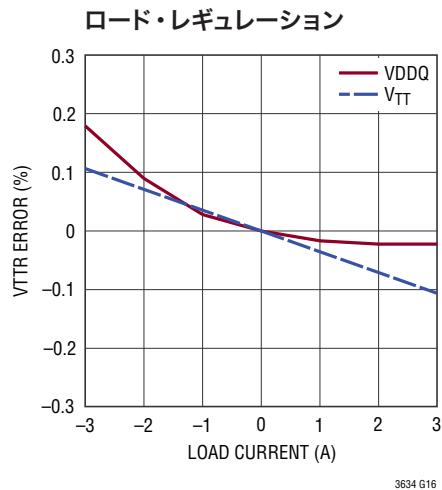

**標準的性能特性** 注記がない限り、 $T_A = 25^\circ\text{C}$ 、 $V_{IN} = 12\text{V}$ 、 $f_{SW} = 1\text{MHz}$ 、 $L = 1.5\mu\text{H}$ 。

標準的性能特性 注記がない限り、 $T_A = 25^\circ\text{C}$ 、 $V_{IN} = 12\text{V}$ 、 $f_{SW} = 1\text{MHz}$ 、 $L = 1.5\mu\text{H}$ 。

標準的性能特性 注記がない限り、 $T_A = 25^\circ\text{C}$ 、 $V_{IN} = 12\text{V}$ 、 $f_{SW} = 1\text{MHz}$ 、 $L = 1.5\mu\text{H}$ 。

## ピン機能 (QFN/TSSOP)

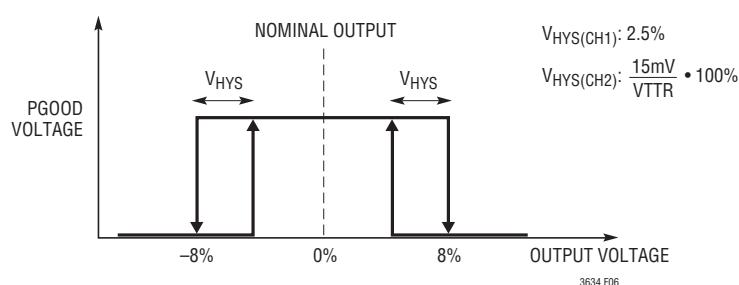

**PGOOD1(ピン1/ピン4)** : チャネル1のオープンドレイン・パワーグッド出力ピン。V<sub>FB1</sub>ピンの電圧が内部の0.6Vリファレンスの±8% (標準) 以内に入っていないと、PGOOD1はグランドに引き下げられます。このスレッショルドには15mVのヒステリシスがあります。

**PHMODE(ピン2/ピン5)** : 位相選択入力。2つのチャネルを両方とも90°位相をシフトしてスイッチングさせるには、このピンをグランドに接続します。2つのチャネルを両方とも180°位相をシフトしてスイッチングさせるには、このピンをINTV<sub>CC</sub>に接続します。このピンはフロート状態にしないでください。

**RUN1(ピン3/ピン6)** : チャネル1のレギュレータ・イネーブル・ピン。RUN1を1.22Vより高い電圧に接続することにより、チャネル1の動作をイネーブルします。1Vより低い電圧に接続すると、チャネル1はシャットダウンします。このピンはフロート状態にしないでください。

**MODE/SYNC(ピン4/ピン7)** : チャネル1のモード選択入力および外部同期入力。チャネル1の同期動作を強制的に続行するには、このピンをグランドに接続します。このピンをフロート状態にするか、INTV<sub>CC</sub>に接続すると、軽負荷時に高効率のBurst Mode<sup>®</sup>動作がイネーブルされます。チャネル2の動作は、このピンの状態とは関係なく強制的に続行されます。LTC3634スイッチング周波数を同期するには、このピンをクロックでドライブします。内部のフェーズロック・ループにより、下側のパワーNMOSのターンオン信号は、CLKIN信号の立ち上がりエッジと強制的に同期されます。このピンをクロックでドライブすると、強制連続モードが自動的に選択されます。

**RT(ピン5/ピン8)** : 発振器周波数の設定ピン。周波数を500kHz～4MHzに設定するには、外付け抵抗(80kΩ～640kΩ)をこのピンからSGNDに接続します。RTをINTV<sub>CC</sub>に接続すると、スイッチング周波数は既定の2MHzになります。「アプリケーション情報」のセクションを参照してください。

**RUN2(ピン6/ピン9)** : チャネル2のレギュレータ・イネーブル・ピン。RUN2を1.22Vより高い電圧に接続することにより、チャネル2の動作をイネーブルします。1Vより低い電圧に接続すると、チャネル2はシャットダウンします。このピンはフロート状態にしないでください。

**SGND(ピン7/ピン10)** : 信号グランド・ピン。このピンはリファレンス・グランドへの低ノイズ接続が必要です。帰還抵抗ネットワーク、外部補償ネットワーク、およびR<sub>T</sub>抵抗をこのグランドに接続します。

**PGOOD2(ピン8/ピン11)** : チャネル2のオープンドレイン・パワーグッド出力ピン。V<sub>FB2</sub>ピンの電圧がVDDQIN・0.5の8% (標準) 以内に入っていないと、PGOOD2はグランドに引き下げられます。このスレッショルドには15mVのヒステリシスがあります。

**V<sub>FB2</sub>(ピン9/ピン12)** : チャネル2出力の帰還電圧ピン。帰還電圧をVTTRと比較する誤差アンプへの入力。V<sub>OUT2</sub>をVTTRと同じ値に設定するには、このピンを出力に直接接続します。

**VDDQIN(ピン10/ピン13)** : チャネル2の外部リファレンス入力。内部抵抗分割器が、この入力に印加される電圧の2分の1と等しくなるようにVTTRピンの電圧を設定します。チャネル2は、VTTRピンの電圧をその誤差アンプのリファレンスとして使用します。

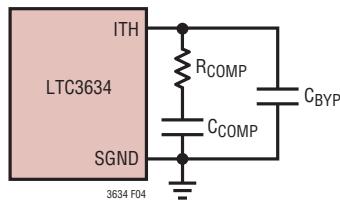

**ITH2(ピン11/ピン14)** : チャネル2の誤差アンプの出力およびスイッチング・レギュレータの補償ピン。レギュレータのループの周波数応答を補償するには、このピンを適切な外付け部品に接続します。部品選択の指針については、「アプリケーション情報」のセクションを参照してください。

**V<sub>ON2</sub>(ピン12/ピン15)** : チャネル2のオン時間電圧入力。このピンは、オン時間コンパレータのトリップ電圧を設定します。このピンを出力電圧に接続すると、V<sub>OUT2</sub> < 3Vのとき、オン時間はV<sub>OUT2</sub>に比例します。V<sub>OUT2</sub> > 3Vのとき、スイッチング周波数は設定周波数より高くなる場合があります(「アプリケーション情報」のセクションを参照)。このピンのインピーダンスは公称150kΩです。

**SW2(ピン13、14/ピン16、17)** : 外付けインダクタへのチャネル2スイッチ・ノードの接続箇所。SWの電圧振幅は、グランドよりダイオードの電圧だけ低い電圧からV<sub>IN2</sub>よりダイオードの電圧だけ高い電圧までです。

**V<sub>IN2</sub>(ピン15、16/ピン18、19)** : チャネル2の電源入力。チャネル2の内蔵パワーMOSFETへの入力電圧。この入力は、V<sub>IN1</sub>とは異なる電源電圧からの動作が可能です。

**BOOST2(ピン17/ピン20)** : チャネル2の昇圧されたフロート・ドライバ電源。ブートストラップ・コンデンサの(+)端子をこのピンに接続し、(-)端子をSWピンに接続します。このピンの通常の動作電圧振幅の範囲は、INTV<sub>CC</sub>よりダイオードの電圧降下分だけ低い電圧からV<sub>IN2</sub> + INTV<sub>CC</sub>までです。

## ピン機能 (QFN/TSSOP)

**VTTR (ピン18/ピン21)** : リファレンスの出力。この出力は、DDRメモリのV<sub>REF</sub>電圧を供給するために使用します。内蔵のバッファ・アンプは、VDDQIN/2と等しい低ノイズのリファレンス電圧を出力します。この出力は10mAの供給能力があります。バッファ出力は0.01μFまでの容量性負荷をドライブできます。チャネル2の誤差アンプは、この電圧をそのリファレンス電圧として使用します。

**INTV<sub>CC</sub> (ピン19/ピン22)** : 内蔵の3.3Vレギュレータ出力。内部ゲート・ドライバおよび制御回路はこの電圧から電力を供給されます。このピンは、最小1μFの低ESRセラミック・コンデンサで電源グランドから分離してください。RUN1とRUN2の入力によってチャネル1とチャネル2の両方がディスエーブルされると、内部レギュレータはディスエーブルされます。

**BOOST1 (ピン20/ピン23)** : チャネル1の昇圧されたフロート・ドライバ電源。ブーストトラップ・コンデンサの(+)端子をこのピンに接続し、(-)端子をSWピンに接続します。このピンの通常の動作電圧振幅の範囲は、INTV<sub>CC</sub>よりダイオードの電圧降下分だけ低い電圧からV<sub>IN1</sub> + INTV<sub>CC</sub>までです。

**V<sub>IN1</sub> (ピン21、22/ピン24、25)** : チャネル1の電源入力。チャネル1の内蔵パワーMOSFETへの入力電圧。INTV<sub>CC</sub>の内蔵LDOはこのピンから電力を供給されます。

**SW1 (ピン23、24/ピン26、27)** : 外付けインダクタへのチャネル1スイッチ・ノードの接続箇所。SWの電圧振幅は、グランドよりダイオードの電圧降下分だけ低い電圧からV<sub>IN1</sub>よりダイオードの電圧だけ高い電圧までです。

**V<sub>ON1</sub> (ピン25/ピン28)** : チャネル1のオン時間電圧入力。このピンは、オン時間コンパレータのトリップ電圧を設定します。このピンを安定化出力電圧に接続すると、V<sub>OUT1</sub> < 3Vのとき、オン時間はV<sub>OUT1</sub>に比例します。V<sub>OUT1</sub> > 3Vのとき、スイッチング周波数は設定周波数より高くなる場合があります(「アプリケーション情報」のセクションを参照)。このピンのインピーダンスは公称150kΩです。

**ITH1 (ピン26/ピン1)** : チャネル1の誤差アンプの出力およびスイッチング・レギュレータの補償ピン。レギュレータのループの周波数応答を補償するには、このピンを適切な外付け部品に接続します。部品選択の指針については、「アプリケーション情報」のセクションを参照してください。

**TRACKSS (ピン27/ピン2)** : チャネル1の出力トラッキングおよびソフトスタート入力ピン。このピンの電圧を強制的に0.6Vより低くすると、誤差アンプへの内部リファレンス入力がバイパスされます。LTC3634はFBピンをTRACK電圧へサーボ制御します。0.6Vより上ではトラッキング機能は停止し、内部リファレンスが誤差アンプの制御を再開します。INTV<sub>CC</sub>から流れる1.4μAの内部プルアップ電流を使うと、このピンとSGNDとの間にコンデンサを接続することにより、ソフトスタート機能を実現できます。

**V<sub>FB1</sub> (ピン28/ピン3)** : チャネル1出力の帰還電圧ピン。帰還電圧を内部の0.6Vリファレンス電圧と比較する誤差アンプへの入力。目的の出力電圧を設定するには、このピンを抵抗分割器ネットワークに接続します。このピンをINTV<sub>CC</sub>に接続すると、LTC3634は2相の単一出力動作に設定されます。詳細については、「アプリケーション情報」のセクションを参照してください。

**PGND (露出パッド・ピン29/露出パッド・ピン29)** : 電源グランド・ピン。入力バイパス・コンデンサC<sub>IN</sub>の(-)端子と出力コンデンサC<sub>OUT</sub>の(-)端子を低インピーダンス接続でこのピンに接続します。電源グランドへの低インピーダンスの電気的接続とPCBへの十分な熱接触の両方を実現するため、このピンはPCBに半田付けする必要があります。

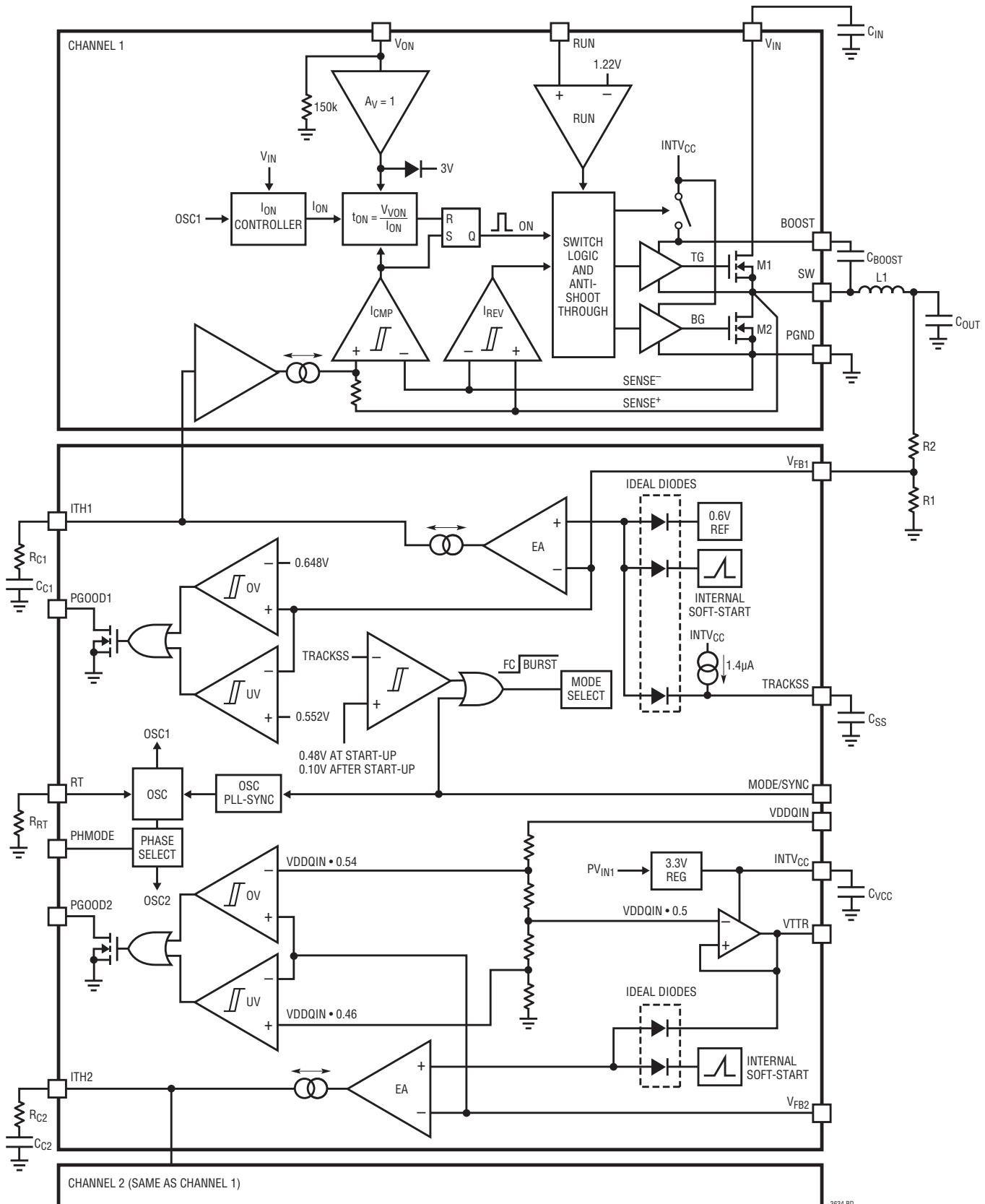

## 機能ブロック図

3634 BD

## 動作

LTC3634は、デュアル・チャネルの電流モード・モノリシック降圧レギュレータで、DDRメモリ電源やバス終端向けに高効率の電力変換を提供する目的で設計されています。その独自のオン時間制御アーキテクチャにより、きわめて低い降圧比が得られると同時に、高速で一定のスイッチング周波数を維持できます。各チャネルはRUNピンの電圧を公称で1.22Vより高くするとイネーブルされます。

### メイン制御ループ

通常動作では、内蔵の上側MOSFETはワンショット・タイマ（「機能ブロック図」のON信号）によって決まる一定時間でオンします。上側のパワーMOSFETがオフすると、下側のパワーMOSFETがオンし、これは電流コンパレータICMPがトリップするまで続きます。電流コンパレータがトリップするとワンショット・タイマが再起動し、次のサイクルを開始します。インダクタ電流は、下側のパワーMOSFETの電圧降下を検出することで測定します。ITHピンの電圧により、インダクタの谷電流に対応したコンパレータ・スレッショルドが設定されます。誤差アンプEAは、（出力電圧から得られる）帰還信号V<sub>FB</sub>と内部の0.6Vリファレンス電圧（チャネル1）またはVTTR電圧（チャネル2）と比較することにより、このITH電圧を調整します。負荷電流が増加すると、リファレンス電圧に対して帰還電圧が降下します。そのため、ITH電圧は平均インダクタ電流が負荷電流に釣り合うまで上昇します。

スイッチング周波数は、内部発振器の電流を設定するR<sub>T</sub>抵抗の値によって決まります。内部フェーズロック・ループは、内部発振器信号のエッジがSWノード信号のエッジにフェーズロックし、一定のスイッチング周波数が強制されるようにワンショット・タイマ（ON信号）をサーボ制御します。この独特なオン時間制御アーキテクチャでは、外部クロック信号源をMODE/SYNCピンに加えると、スイッチング周波数をその外部クロック信号源に同期させることもできます。チャネル1は、クロック信号を印加すると、既定で強制連続動作になります（チャネル2は常に強制連続動作です）。

### VTTR出力バッファ

VTTRピンは、VDDQINの2分の1に等しい電圧を出力します。このピンには、10mAのソース/シンク電流供給能力と、0.01μFまでの容量性負荷をドライブする能力があります。チャネル2の誤差アンプは、この電圧をそのリファレンス電圧として使用します。

### 高効率Burst Mode動作

軽負荷電流では、インダクタ電流は0に低下し、負になることがあります。（チャネル1でのみ使用可能な）Burst Mode動作では、電流反転コンパレータ（I<sub>REV</sub>）が負のインダクタ電流を検出して、下側のパワーMOSFETをオフにします。この結果、不連続動作となって効率が高くなります。2つのパワーMOSFETは、ITH電圧が上昇して電流が0になるレベルより高くなり、別のサイクルを開始するまで両方ともオフのままとなります。この時間中は出力コンデンサが負荷電流を供給し、デバイスは低電流のスリープ・モードに入ります。Burst Mode動作はMODE/SYNCピンをグランドに接続するとディスエーブルされます。こうすると、出力負荷電流に関係なく強制的に連続同期動作になります。

### パワーグッド状態出力

レギュレータの出力がレギュレーション・ポイントの±8%の範囲から外れると、PGOODオープンドレイン出力は“L”に引き下げられます。このスレッショルドには、V<sub>FB</sub>ピンを基準にして15mVのヒステリシスがあります。過渡電圧の発生時や動的なV<sub>OUT</sub>の変動時にPGOODの誤動作を防止するため、LTC3634のPGOOD立ち下がりエッジには、約40μsのフィルタ時間が含まれています。V<sub>TT</sub>出力（チャネル2）の場合は、VTTRがレギュレーション・ポイントです。PGOOD2ピンは、VTTR出力電圧が300mV未満のとき必ず“L”になります。

### V<sub>IN</sub>過電圧保護

内蔵のパワーMOSFETデバイスを長い過渡電圧イベントから保護するため、LTC3634は過電圧状態の有無について各V<sub>IN</sub>ピンを絶えず監視します。V<sub>IN</sub>が17.5Vを超えると、レギュレータは対応するチャネルの2つのパワーMOSFETを両方ともオフして、動作を一時停止します。V<sub>IN</sub>が16.5Vを下回ると、レギュレータは直ちに通常動作を再開します。レギュレータは、過電圧状態から抜け出るときはソフトスタート機能を実行しません。

### 位相のシフトした動作

PHMODEピンを“H”に接続すると、SW2の立ち下がりエッジはSW1の立ち下がりエッジと180°位相がシフトした状態に設定されます。2つのチャネルを位相がシフトした状態で動作させることには、大きな利点があります。2つのチャネルが同位相で動作している場合、上側のMOSFETは同時にオンするの

## 動作

で、大電流パルスが入力コンデンサと電源から同時に流れ出します。LTC3634の2つのチャネルを位相がシフトした状態で動作させると、大電流パルスは交互に流れ、パルスが重なり合う時間が実質的に短くなります。したがって全RMS入力電流が減少し、それによって $V_{IN}$ バイパス・コンデンサの容量要件が緩和され、電源ラインでの電圧ノイズが減少します。この構成の不利な点が生じる可能性があるのは、一方のチャネルを50%のデューティ・サイクルで動作している場合です。この

状況では、SWノードの遷移が一方のチャネルからもう一方のチャネルに場合によっては結合する可能性があり、その結果、一方または両方のチャネルに周波数のジッタが生じます。この影響は優れた設計の基板レイアウトを使うことで軽減できます。あるいは、PHMODEを“L”に接続すると位相差は90°に変化するため、これによってSW1とSW2が同じ特定時点に遷移するのを防止できる場合があります。

## アプリケーション情報

LTC3634の一般的な応用回路を図1に示します。外付け部品の選択の主な条件は、負荷要件とスイッチング周波数です。部品選択は、通常、目的の出力電圧を設定する帰還抵抗の選択から始まります。次に、インダクタLと抵抗 $R_T$ を選択します。インダクタを選択したら、入力コンデンサ( $C_{IN}$ )および出力コンデンサ( $C_{OUT}$ )を選択できます。最後に、ループ補償部品を選択して、降圧レギュレータを安定化することができます。その後、ループ補償、TRACKSS、 $V_{IN}$ 、UVLO、PGOODなどの機能について、残りのオプションの外付け部品を選択できます。

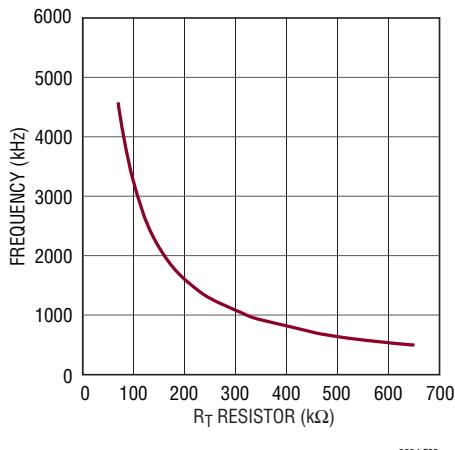

### スイッチング周波数の設定

スイッチング周波数の選択には、効率と部品サイズ間のトレードオフが必要です。動作周波数を高くすると、小さい値のインダクタとコンデンサを使うことができます。低い周波数で動作させると内部ゲート電荷による損失が減るので効率が改善されますが、出力リップル電圧を低く抑えるには、通常はインダクタンスと容量の値を大きくする必要があります。 $RT$ ピンから $SGND$ に抵抗を接続すると、スイッチング周波数( $f$ )は次式に従って500kHz～4MHzに設定されます。

$$R_{RT} = \frac{3.2E^{11}}{f}$$

ここで、 $R_{RT}$ の単位はΩ、 $f$ の単位はHzです。

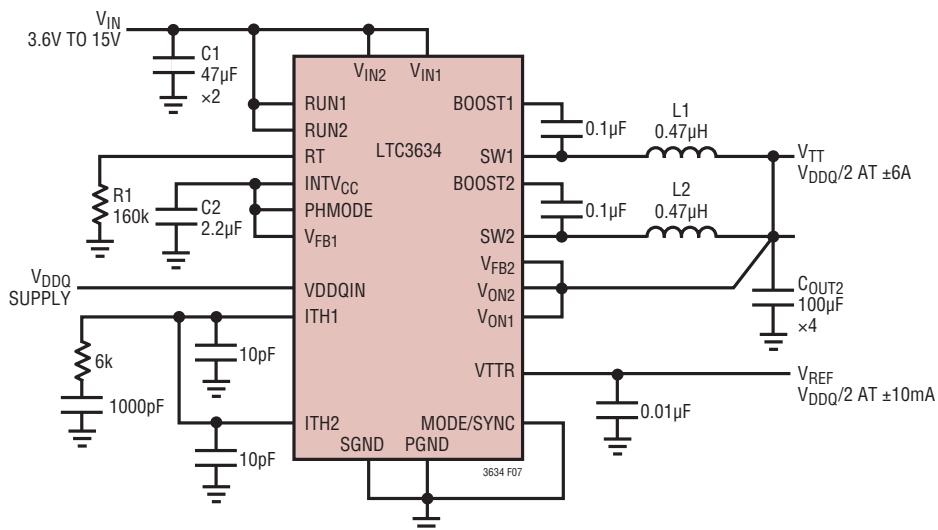

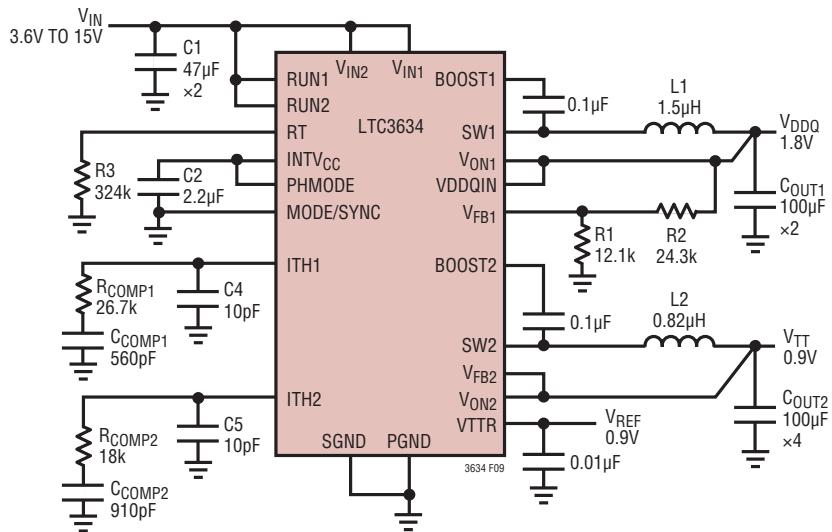

図1. DDRメモリ電源の標準的な応用回路

## アプリケーション情報

図2. スイッチング周波数とRT

RTをINTV<sub>CC</sub>に接続すると、スイッチング周波数は内部抵抗によって約2MHzの既定値に設定されます。この内部抵抗は、プロセスのばらつきと温度の変動に対して外付け抵抗よりも影響を受けやすい（「標準的性能特性」のセクションを参照）ので、スイッチング周波数があまり重要ではないアプリケーションに使用するのが最適です。

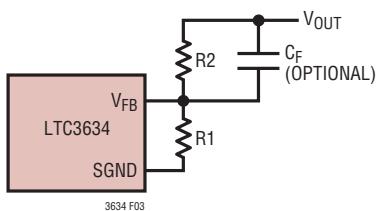

### 出力電圧の設定

各レギュレータの出力電圧は、外付けの抵抗分割器で次式に従って設定されます。

$$V_{\text{OUT}} = V_{\text{FBREG}} \left( 1 + \frac{R_2}{R_1} \right)$$

ここでV<sub>FBREG</sub>は「電気的特性」の表に規定されているリファレンス電圧です。リファレンス電圧はチャネル1の場合は600mVです。チャネル2の場合、リファレンス電圧はVTTRピンの電圧に等しくなります。目的の出力電圧は、図3に示すように抵抗R1およびR2を選択して設定します。

図3. 出力電圧の設定

VTTRピンの公称バッファ出力電圧は、VDDQIN電圧の半分に等しい値です。このため、V<sub>OUT2</sub>をDDRメモリのV<sub>TT</sub>バス終端電源として設定するには、V<sub>OUT2</sub>をV<sub>FB2</sub>と短絡し、VDDQINをV<sub>OUT1</sub>（V<sub>DDQ</sub>の電源）に直接接続します。

R1とR2に大きい値を選択すると、負荷が0のときの効率が向上する結果が得られますが、V<sub>FB</sub>ノードでの浮遊容量により、好ましくないノイズ結合や位相マージンの低下を招く恐れがあります。V<sub>FB</sub>トレースは、SWトレースなどのノイズ発生源から離して配線するよう注意が必要です。

LTC3634のオン時間制御アーキテクチャは0.6V～3Vの出力電圧範囲で最適化されており、これはDDRメモリへの給電に適しています。LTC3634は、より高い出力電圧を安定化することができますが、オン時間制御は保証されません。出力電圧が3Vより大きくなると、降圧レギュレータは出力を安定化するためにスイッチング周波数を増加するよう強制されます。さらに、外部クロックによる同期は可能ではなくなり、チャネル2はチャネル1を基準にした90°/180°位相動作を維持できません。つまり、LTC3634はオン時間制御レギュレータではなくオノン時間一定のレギュレータのように動作します。したがって、3Vより大きい出力電圧を使用するのは、スイッチング周波数とチャネル間位相ロックが重要ではないアプリケーションに限定してください。

### インダクタの選択

入力電圧と出力電圧が与えられている場合は、インダクタの値と動作周波数によってインダクタのリップル電流が決まります。より具体的には、インダクタのリップル電流は、インダクタ値が高くなるか動作周波数が高くなると次式に従って減少します。

$$\Delta I_L = \left( \frac{V_{\text{OUT}}}{f \cdot L} \right) \left( 1 - \frac{V_{\text{OUT}}}{V_{\text{IN}}} \right)$$

ここで、 $\Delta I_L$  = インダクタのリップル電流、 $f$  = 動作周波数、 $L$  = インダクタ値です。この式から、部品サイズ、効率、および動作周波数間のトレードオフを確認できます。大きい値の $\Delta I_L$ を許容すると、小さい値のインダクタを使用できますが、インダクタのコア損失が大きくなり、出力コンデンサのESR損失が大きくなつて、出力電圧リップルが大きくなる結果となります。一般に、動作周波数が低くリップル電流が小さいと、効率が最高の動作が得られます。

## アプリケーション情報

妥当な出発点としては、600mA p-p ~ 1.2A p-p の範囲内のリップル電流を選択します。V<sub>IN</sub>が最大のときに最大リップル電流が生じることに注意してください。出力電圧リップルを最小限に抑えるため、1.8Aを超えることは推奨しません。リップル電流が規定の最大値を超えないことを保証するには、次式に従ってインダクタンスを選択します。

$$L = \left( \frac{V_{OUT}}{f \cdot \Delta I_{L(MAX)}} \right) \left( 1 - \frac{V_{OUT}}{V_{IN(MAX)}} \right)$$

Lの値が分かったら、インダクタの種類を選択する必要があります。インダクタ値が固定の場合、実際のコア損失はコア・サイズに無関係ですが、選択したインダクタンスに大きく依存します。インダクタンスが大きいほどコア損失が減少します。残念ながら、インダクタンスを大きくするにはワイヤの巻数を増やす必要があるため DCR と銅損失の増加を招きます。

フェライトを使用した設計が示すコア損失はきわめて小さく、高いスイッチング周波数に適しているため、銅損失と飽和を防ぐことに設計目標を集中することができます。フェライト・コアの材質は「ハードに」飽和します。つまり、設計ピーク電流を超えるとインダクタンスが突然低下します。この結果、インダクタのリップル電流が突然増加するため、コアが飽和しないよう確認することが重要です。

コアの材質と形状が異なると、インダクタのサイズ/電流の関係および価格/電流の関係が変化します。フェライトやパーマロイを素材とするトロイド・コアやシールドされたボット型コアは小型で、エネルギー放射は大きくありませんが、類似の特性を有する鉄粉コアのインダクタより一般に高価です。使用的なインダクタの種類の選択は、価格とサイズの条件や放射フィールド/EMIの条件に主に依存します。入手可能な表面実装型インダクタのサンプルを表1に示します。

表1. インダクタの選択表

| INDUCTANCE<br>( $\mu$ H)                    | DCR<br>(m $\Omega$ ) | MAX<br>CURRENT (A) | DIMENSIONS<br>(mm) | HEIGHT<br>(mm) |

|---------------------------------------------|----------------------|--------------------|--------------------|----------------|

| <b>Würth Electronik WE-HC 744310 Series</b> |                      |                    |                    |                |

| 0.24                                        | 2.1                  | 18.0               | 7 × 7              | 3.3            |

| 0.55                                        | 3.8                  | 14.0               |                    |                |

| 0.95                                        | 6.4                  | 11.0               |                    |                |

| 1.15                                        | 9.0                  | 8.5                |                    |                |

| 2.00                                        | 14.0                 | 6.5                |                    |                |

| <b>Vishay IHLP-2020BZ-01 Series</b>         |                      |                    |                    |                |

| 0.22                                        | 5.2                  | 15                 | 5.2 × 5.5          | 2              |

| 0.33                                        | 8.2                  | 12                 |                    |                |

| 0.47                                        | 8.8                  | 11.5               |                    |                |

| 0.68                                        | 12.4                 | 10                 |                    |                |

| 1                                           | 20                   | 7                  |                    |                |

| <b>Toko FDV0620 Series</b>                  |                      |                    |                    |                |

| 0.20                                        | 4.5                  | 12.4               | 7 × 7.7            | 2.0            |

| 0.47                                        | 8.3                  | 9.0                |                    |                |

| 1.0                                         | 18.3                 | 5.7                |                    |                |

| <b>Coilcraft D01813H Series</b>             |                      |                    |                    |                |

| 0.33                                        | 4                    | 10                 | 6 × 8.9            | 5.0            |

| 0.56                                        | 10                   | 7.7                |                    |                |

| 1.2                                         | 17                   | 5.3                |                    |                |

| <b>TDK RLF7030 Series</b>                   |                      |                    |                    |                |

| 1.0                                         | 8.8                  | 6.4                | 6.9 × 7.3          | 3.2            |

| 1.5                                         | 9.6                  | 6.1                |                    |                |

### C<sub>IN</sub>とC<sub>OUT</sub>の選択

入力容量C<sub>IN</sub>は、上側パワーMOSFETのドレインで台形波電流をフィルタするのに必要です。大きな過渡電圧が発生しないようにするには、最大RMS電流に合わせたサイズの低ESR入力コンデンサを推奨します。1つのレギュレータの最大RMS電流は、次式により求められます。

$$I_{RMS} = I_{OUT(MAX)} \frac{\sqrt{V_{OUT}(V_{IN} - V_{OUT})}}{V_{IN}}$$

2つのレギュレータがアクティブである場合、入力電流波形は大幅に異なります。さらに、入力RMS電流は各出力の負荷電流だけでなく、V<sub>TT</sub>が電流をシンクしているかソースしているかによっても変化します。

## アプリケーション情報

SW1とSW2が180°位相がシフトした状態で動作する場合、V<sub>TT</sub>電源が電流をシンクしていて、V<sub>DDQ</sub>が同じ量の電流をソースしていると、最悪の入力RMS電流が生じます。DDRアプリケーションではV<sub>OUT2</sub>がV<sub>OUT1</sub>の2分の1であることが分かっているので、この場合の入力RMS電流は次式により求められます。

$$I_{RMS} = I_{OUT(MAX)} \sqrt{D1 \left(1.5 - \frac{D1}{4}\right)} \text{ for } D1 < 0.5$$

$$I_{RMS} = I_{OUT(MAX)} \sqrt{1 - \frac{3}{4}D1} \text{ for } D1 > 0.5$$

ここで、D1はチャネル1(V<sub>DDQ</sub>電源)のデューティ・サイクルです。これらの式は、IRMSが最大になるのはデューティ・サイクルが50% (V<sub>IN</sub> = 2•V<sub>OUT1</sub>)のときであることを示しています。デューティ・サイクルがこれとは違っても状況が大幅に緩和されるわけではないため、この単純な最悪条件を設計に使用できます。コンデンサ・メーカーの規定するリップル電流定格は多くの場合わずか2000時間の寿命試験に基づいているので、コンデンサをさらにディレーティングする、つまり要求より高い温度定格のコンデンサを選択することを推奨します。

設計のサイズまたは高さの要件を満たすため、数個のコンデンサを並列に接続することもできます。入力電圧が低いアプリケーションでは、出力負荷の変化時に過渡変動の影響を最小限に抑えるのに十分なバルク入力容量が必要です。LTC3634の設計には過電圧保護回路が組み込まれていますが、入力過渡電圧がデバイスへの過電圧の危険を生じないよう、常に注意する必要があります。

C<sub>OUT</sub>の選択は、電圧リップルと負荷ステップ過渡電圧を最小に抑えるのに必要な等価直列抵抗(ESR)、および制御ループの安定性を確保するのに必要なバルク容量の大きさによって決まります。ループの安定性は、負荷過渡応答を観察することによってチェックすることができます。出力リップル $\Delta V_{OUT}$ は次式で近似されます。

$$\Delta V_{OUT} < \Delta I_L \left( ESR + \frac{1}{8 \cdot f \cdot C_{OUT}} \right)$$

低ESRのセラミック・コンデンサを使用する場合は、電荷蓄積要件を満足するように出力コンデンサの値を選択する方が実用的です。負荷ステップ発生時には、帰還ループがスイッチ電流を十分増加させて負荷を支えるまで、出力コンデンサが即座に電流を供給して負荷を支える必要があります。帰還ループが応答するのに要する時間は補償と出力コンデンサのサイズに依存します。負荷ステップに応答するには標準で3~4サイクルを要しますが、最初のサイクルだけ出力が直線的に低下します。出力垂下電圧V<sub>DROOP</sub>は、ループのクロスオーバー周波数が最大になっているとすると、通常は最初のサイクルの直線的降下の約3倍です。したがって、およそ以下の出力コンデンサのサイズから開始するのが良いでしょう。

$$C_{OUT} \approx \frac{3 \cdot \Delta I_{OUT}}{f \cdot V_{DROOP}}$$

この式からは良好な近似結果が得られますが、デューティ・サイクルと負荷ステップの要件によっては、より大きな容量が必要なことがあります。実際のV<sub>DROOP</sub>については、出力に負荷ステップを加えて検証することが必要です。

### セラミックの入力コンデンサおよび出力コンデンサの使用

値の大きい低価格のセラミック・コンデンサを小さなケース・サイズで入手できます。これらはリップル電流定格と電圧定格が大きく、ESRが小さいので、スイッチング・レギュレータのアプリケーションに最適です。ただし、セラミック・コンデンサの種類によっては、その自己共振特性や高いQ特性が原因で、入力に使用する場合には注意する必要があります。セラミック・コンデンサを入力に使い、ACアダプタで長いコードを通して電源を供給すると、出力の負荷ステップによってV<sub>IN</sub>入力にリンクングが誘起されることがあります。最善の場合でも、このリンクングが出力に結合して、ループの不安定性と誤認されることがあります。最悪の場合、長いコードを通して電流が急に突入すると、V<sub>IN</sub>に電圧スパイクが生じてデバイスを損傷するのに十分な大きさになる恐れがあります。詳細な説明については、「アプリケーションノート88」を参照してください。

入力と出力にセラミック・コンデンサを選択する場合は、X5RやX7Rの誘電体を使ったものを選択します。これらの誘電体は、ある特定の値とサイズについてすべてのセラミックの中で温度特性と電圧特性が最も優れています。

## アプリケーション情報

### 補償部品の選択

ループ補償は複雑な主題であり、電流モードのスイッチング・レギュレータでループ帯域幅を最大にすることについての詳細な説明については、「アプリケーションノート76」を参照することを推奨します。このセクションでは、LTC3634レギュレータの適切な補償部品を選択する簡単な方法を説明します。

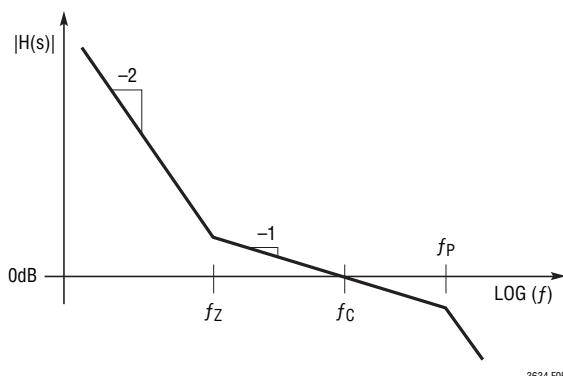

ITHピンに接続する推奨の部品を図4に示し、それらの部品を使用した降圧レギュレータ・ループの概略のボーデ・プロットを図5に示します。系の主要なポール(出力コンデンサのポールと誤差アンプ出力のポール)は、クロスオーバー周波数より低い周波数に位置すると仮定します。

図4. 補償およびフィルタ用の部品

図5. レギュレータ・ループのボーデ図

最初のステップとして、クロスオーバー周波数 $f_C$ を選択することです。クロスオーバー周波数を高くすると、ループ過渡応答は高速になります。ただし、スイッチング電力段からの高次ループ特性の影響を避けるため、 $f_C$ がスイッチング周波数( $f_{sw}$ )の10分の1を超えないことを推奨します。

$f_C$ を選択したら、このクロスオーバー周波数を設定する  $R_{COMP}$ の値を次式によって計算できます。

$$R_{COMP} = \left( \frac{2\pi \cdot f_C \cdot C_{OUT}}{g_m(EA) \cdot g_m(MOD)} \right) \left( \frac{V_{OUT}}{V_{FBREG}} \right)$$

ここで、 $g_m(EA)$ は誤差アンプの相互コンダクタンス(「電気的特性」のセクションを参照)であり、 $g_m(MOD)$ はモジュレータの相互コンダクタンス(ITH電圧から電流コンバレータ・スレッショルドまでの伝達関数)です。LTC3634の場合、この相互コンダクタンスは公称で $7\Omega^{-1}$ です。

$R_{COMP}$ を決定したら、 $C_{COMP}$ を選択してゼロ周波数( $f_Z$ )を次式で設定できます。

$$f_Z = \frac{1}{2\pi \cdot C_{COMP} \cdot R_{COMP}}$$

90°の位相マージンを確保するには、 $f_C$ の10分の1より低い  $f_Z$ を選択します。

ITHノードはノイズ結合の影響を受けやすいので、小容量のバイパス・コンデンサ( $C_{BYP}$ )を使用して基板ノイズを除去することができます。ただし、このコンデンサは次式で求められる  $f_P$ でのポールの一因となり、クロスオーバー周波数で多少の位相損失を生じることがあります。

$$f_P = \frac{1}{2\pi \cdot C_{BYP} \cdot R_{COMP}}$$

最適な結果を得るには、位相マージンがあまり大きな影響を受けないように  $f_P$ を十分高い周波数に設定します。

必要な場合は、(図3に示したように)コンデンサ $C_F$ を使って一定の位相リードを追加できます。

## アプリケーション情報

### 過渡応答のチェック

レギュレータのループ応答は負荷ステップに対するシステムの応答を観察すればチェックできます。ITHピンでは制御ループ動作を最適化できるだけでなく、DC結合され、ACフィルタを通した閉ループ応答のテスト・ポイントも得られます。このテスト・ポイントでのDCステップ、立ち上がり時間、およびセトリング動作は、閉ループ応答を反映します。2次特性が支配的なシステムを想定すれば、位相マージンや減衰係数はこのピンで見られるオーバーシュートのパーセンテージを使って推定することができます。

前のセクションで説明したように補償点の値を選択後、設計をテストして安定性を検証します。PCBのレイアウトを完了し、特定の出力コンデンサの種類と容量値を決定したら、過渡応答を最適化するために部品の値を多少変更することができます。出力コンデンサのさまざまな種類と値によってループの利得と位相が決まるので、出力コンデンサを選択する必要があります。立ち上がり時間が $1\mu\text{s}$ 程度までの、全負荷電流の20%～100%の出力電流パルスによって、帰還ループを開くことなく全体的なループの安定性を判断することができる出力電圧波形とITHピンの波形が発生します。

スイッチング・レギュレータは負荷電流のステップに応答するのに数サイクルを要します。負荷ステップが発生すると、 $V_{\text{OUT}}$ は $\Delta I_{\text{LOAD}} \cdot ESR$ に等しい大きさだけ即座にシフトします。ここで、 $ESR$ は $C_{\text{OUT}}$ の等価直列抵抗です。 $\Delta I_{\text{LOAD}}$ は $C_{\text{OUT}}$ の充電または放電も開始し、レギュレータが使用する帰還誤差信号を生成して、 $V_{\text{OUT}}$ をその定常値に戻します。この回復期間に $V_{\text{OUT}}$ をモニタして、安定性に問題があることを示すオーバーシュートやリンギングがないかチェックすることができます。

負荷ステップに対する $V_{\text{OUT}}$ の応答を観察するときには、初期出力電圧ステップが帰還ループの帯域幅内にない場合があるため、標準の2次オーバーシュート/DC比を使用して位相マージンを決定することはできません。出力電圧のセトリング動作は閉ループ・システムの安定性に関係し、電源全体の実際の性能を表します。制御ループ理論の要点を含む補償部品の最適化の詳細については、「アプリケーションノート76」を参照してください。

アプリケーションによっては、大容量(>10 $\mu\text{F}$ )の入力コンデンサを備えた負荷をスイッチを介して接続すると大きな過渡電圧が発生することがあります。放電した入力コンデンサが実質的に $C_{\text{OUT}}$ と並列接続された状態になるため、 $V_{\text{OUT}}$ の急激な低下を引き起こします。負荷に接続しているスイッチの抵抗が低く、急速にドライブされた場合、この問題を防止するのに十分な電流を供給できるレギュレータはありません。解決策は負荷スイッチのドライバのターンオン速度を制限することです。Hot Swap™コントローラはこの目的専用に設計され、通常は電流制限機能、短絡保護、ソフトスタート機能が組み込まれています。

### INTV<sub>CC</sub>レギュレータのバイパス・コンデンサ

内部の低損失(LDO)レギュレータは、内部バイアス回路に電力を供給する3.3V電源を生成し、内部MOSFETスイッチのゲートをドライブします。INTV<sub>CC</sub>ピンはこのレギュレータの出力に接続されており、最小1 $\mu\text{F}$ のセラミック・バイパス容量をグランドとの間に接続する必要があります。LTC3634によって要求される過渡電流を供給するため、このコンデンサのINTV<sub>CC</sub>ピンおよびPGNDピンへの電気的接続が低インピーダンスになるようにします。この電源は追加のDC負荷電流を必要に応じて供給することのみを目的にしており、大きな過渡電圧やAC動作を安定化する目的はありません。その状況ではLTC3634の動作に影響を及ぼす可能性があるためです。

### 昇圧コンデンサ

LTC3634は、印加されている入力電圧 $V_{\text{IN}}$ より高い電圧レベルを生成するために、ブートストラップ回路を採用しています。特に昇圧コンデンサ $C_{\text{BOOST}}$ は、下側のパワーMOSFETがオンするたびに、INTV<sub>CC</sub>とほぼ等しい電圧まで充電されます。このコンデンサの電荷は、必要な過渡電流を残りのスイッチング・サイクルの間に供給するために使用されます。上側のMOSFETがオンすると、BOOSTピンの電圧は $V_{\text{IN}} + 3.3\text{V}$ にほぼ等しくなります。大半のアプリケーションでは、0.1 $\mu\text{F}$ のセラミック・コンデンサをBOOSTピンとSWピンの間に近づけて接続することにより、十分な性能が得られます。

## アプリケーション情報

### 最小オフ時間/オン時間に関する検討事項

最小オフ時間は、LTC3634が下側のパワーMOSFETをオンし、電流コンパレータをトリップさせて、パワーMOSFETをオフに戻すことができるまでの最小時間です。この時間は標準40nsです。制御されたオン時間制御アーキテクチャでは、最小オフ時間の制限により、次の最大デューティ・サイクルが課せられます。

$$DC_{MAX} = 1 - f \cdot (t_{OFF(MIN)} + 2 \cdot t_{DEAD})$$

ここで、 $f$ はスイッチング周波数、 $t_{DEAD}$ はスイッチの非オーバーラップ時間、つまりデッドタイム（標準10ms）、 $t_{OFF(MIN)}$ は最小オフ時間です。たとえば、入力電圧が低下したために最大デューティ・サイクルを超えると、出力は安定化状態から外れてしまいます。このドロップアウト状態を回避するための最小入力電圧は次のとおりです。

$$V_{IN(MIN)} = \frac{V_{OUT}}{1 - f \cdot (t_{OFF(MIN)} + 2 \cdot t_{DEAD})}$$

逆に、最小オン時間は、上側のパワーMOSFETがそのオン状態を存続できる最小時間です。この時間は標準20nsです。連続モード動作では、最小オン時間の制限により、次の最小デューティ・サイクルが課せられます。

$$DC_{MIN} = (f \cdot t_{ON(MIN)})$$

ここで、 $t_{ON(MIN)}$ は最小オン時間です。式が示すように、動作周波数を下げるとき最小デューティ・サイクルの制約が緩和されます。

レギュレータの出力が電流をシンクしている場合、コンバータの実効最小オン時間は、各SWノードの遷移中にパワーMOSFETの非オーバーラップ時間（つまり「デッドタイム」）によって増加します。この「デッドタイム」は公称15nsであるため、電流をシンクしているとき、最小オン時間は実質的に15ns + 15ns + 20ns = 50nsとなります。

最小オン時間の制約を超えると、出力の安定状態を維持するため、コンバータは自動的にそのスイッチング周波数を減らします。コンバータがそのスイッチング周波数を減らすと、位相情報は失われ、2つのチャネルは非同期でスイッチングするようになります。

さらに、スイッチング周波数が低くなるため、レギュレータは控えめに補償することが必要な場合があります。

### MODE/SYNC動作

MODE/SYNCピンは、モード選択と動作周波数同期の両方が可能な多目的ピンです。このピンをフロート状態にするかINTV<sub>CC</sub>に接続すると、チャネル1でのBurst Mode動作がイネーブルされます。これにより、軽負荷電流での効率が向上しますが、その代償として出力電圧リップルが若干高くなります。MODE/SYNCピンをグランドに接続すると、強制連続モード動作が選択され、発生する固定出力リップルは最小になりますが、軽負荷時の効率が代償となります。

LTC3634はMODE/SYNCピンで外部クロック信号の存在を検出し、入力クロックの位相および周波数に内部発振器を同期させます。外部クロックの存在が検出されると、2つのレギュレータは両方とも強制連続モード動作に移行します。R<sub>T</sub>抵抗は、外部クロックに同期させる場合、必ずしも必要なわけではありませんが、外部クロック信号が突然取り去られたり再度印加されたときに、スイッチング・レギュレータのバイアス状態を常に正しく保持するため、公称の外部クロック周波数に対応するR<sub>T</sub>抵抗を使うことを推奨します。

### チャネル1の出力電圧トラッキングとソフトスタート

LTC3634では、ユーザーがTRACKSSピンによってチャネル1の出力電圧ランプ・レートを制御できます。0V～0.6Vでは、誤差アンプに入力される0.6Vの内部リファレンスがTRACKSS電圧によって無効になり、帰還電圧はTRACKSSピンの電圧に安定化されます。TRACKSSが0.6Vを超えると、トラッキングはディスエーブルされ、帰還電圧は内部リファレンス電圧に安定化されます。

TRACKSSピンの電圧は外部電源でドライブできます。あるいは、ユーザーは内部の1.4μA プルアップ電流源を活用し、TRACKSSピンとグランドとの間に外付けコンデンサ(C<sub>SS</sub>)を接続することにより、ソフトスタート機能を実装することもできます。出力の立ち上がり時間とTRACKSSの容量との関係は次式により求められます。

$$t_{SS} = 430000\Omega \cdot C_{SS}$$

## アプリケーション情報

既定の内部ソフトスタート・ランプでは、400 $\mu$ sという最小ソフトスタート時間中にTRACKSSピン入力を無効にすることにより、このソフトスタート時間が強制されます。この理由から、約1000pFより小さい容量値は、ソフトスタート動作に大きく影響することはありません。

### 起動動作

起動すると、2つのチャネルは既定では両方ともすぐに不連続動作になります。チャネル1はその出力が上昇して最終値( $V_{FB} > 480$ mV)の80%を超えるまで不連続Burst Mode動作のままです。出力がこの電圧を超えると、レギュレータの動作モードは、前述したようにMODE/SYNCピンで選択したモードに切り替わります。通常動作時は、(たとえば、追跡時に降下する場合など)出力がその最終値の10%を下回るまで降下すると、レギュレータはBurst Mode動作に自動的に切り替わり、インダクタの飽和を防いでTRACKSSピンの精度を改善します。

チャネル2( $V_{TT}$ 終端電源)は、その出力が上昇して300mVを超えるまで不連続動作のままです。300mVになると、チャネル2は強制連続動作に自動的に切り替わります。これにより、レギュレータの出力が、インダクタを連続モードで放電するのに

十分な電圧に到達し、インダクタでのエネルギーの過剰な蓄積を確実に防止します。

### 出力パワーグッド

LTC3634のPGOOD出力は、15 $\Omega$ (標準)のオープンドレイン・プルダウン・デバイスによってドライブされます。出力電圧がターゲットのレギュレーション・ポイントの8% (標準)のレギュレーション範囲から外れると、15 $\Omega$ の出力抵抗を持つオープンドレイン出力がグランドに引き下げられ、PGOODピン電圧が降下します。このプルダウン・デバイスは出力がこの範囲内に再度入り、少量のヒステリシスを上回るまでオフしません。この動作を図6で示します。

40 $\mu$ s (標準)のフィルタ時間は、 $V_{OUT}$ の過渡イベント中にPGOOD出力が誤って変化するのを防止する役割を果たします。このため、出力電圧はPGOODピンがグランドに引き下げられるまで40 $\mu$ sの間8%のレギュレーション範囲から外れる必要があります。逆に、出力電圧はPGOODピンが“H”に引き上げられるまで40 $\mu$ sの間ターゲットのレギュレーション範囲内に入っている必要があります。

図6. PGGOODピンの動作

## アプリケーション情報

### 2相の単一V<sub>TT</sub>出力構成

LTC3634の2つのレギュレータを組み合わせると、最大6Aのソース電流およびシンク電流を供給できる単一の2相V<sub>TT</sub>終端電源を簡単に作成できます。この回路を図7に示します。

この回路では、V<sub>FB1</sub>をINTV<sub>CC</sub>に接続して、LTC3634を2相動作にします。2相動作に構成すると、チャネル1の相互コンダクタンス誤差アンプへの入力は、チャネル2の入力(V<sub>FB2</sub>およびVTTR)と同じになるよう切り替えられるため、チャネル1をチャネル2の誤差アンプと並列にすることができます。ITH1ピンとITH2ピンは外部で互いに接続して、等しい電流を2チャネル間で分担させます。

ITHノードで必要なのは1つの補償回路網のみですが、基板レイアウトによってはITHピンごとにフィルタ・コンデンサを個別に接続すると役立つ場合があります。この並列構成では、実効g<sub>m</sub>(EA)および実効g<sub>m</sub>(MOD)は單一チャネルの場合の2倍であることに注意することが重要です。

この2相構成の1つの利点は、単相の6Aコンバータ・ソリューションと比較して、入力電流リップルと出力電流リップルが両方とも大幅に低減されることです。これは各レギュレータからの電流波形がインターリープされるためです。PolyPhase®コンバータに関する詳細な説明と分析については、「アプリケーションノート77」を参照してください。

V<sub>IN1</sub>とV<sub>IN2</sub>には、別個の電源電圧から電力を供給してもかまいません(図12参照)。このことは、2つの異なる電源間で電力を共有する必要がある場合に便利です。V<sub>TT</sub>出力が電流をシンクする場合、その電流はコンバータを通して逆流し、V<sub>IN</sub>ピンから流れ出ることに注意することが重要です。入力電源がこの状態に確実に対応できるよう注意する必要があります。

### 効率に関する検討事項

スイッチング・レギュレータのパーセント表示の効率は、出力電力を入力電力で割って100%を掛けたものに等しくなります。個々の損失を解析して、効率を制限する要素がどれであり、また何が変化すれば最も効率が改善されるかを判断できる場合がよくあります。パーセント表示の効率は次式で表すことができます。

$$\% \text{効率} = 100\% - (L1 + L2 + L3 + \dots)$$

ここで、L1、L2などは入力電力に対するパーセンテージで表した個々の損失です。回路内の電力を消費するすべての素子で損失が生じますが、LTC3634の回路での損失の大部分は、通常、主に次の3つの要因によって生じます。それは、1)導通損失、2)スイッチング損失と静止電力損失、3)遷移損失とその他の損失です。

図7. 2相、±6A単一V<sub>TT</sub>出力の応用回路

## アプリケーション情報

- 導通損失は内部スイッチのDC抵抗 $R_{SW}$ と外付けのインダクタのDC抵抗 $R_L$ を基に計算されます。連続モードでは、平均出力電流はインダクタ $L$ を流れますが、内蔵の上側パワーMOSFETと下側パワーMOSFETとの間で分かれます。したがって、SWピンを見たときの直列抵抗は、次式のように、上側MOSFETおよび下側MOSFETの両方の $R_{DS(ON)}$ とデューティサイクル(DC)の関数になります。

$$R_{SW} = (R_{DS(ON)TOP})(DC) + (R_{DS(ON)BOT})(1 - DC)$$

上側MOSFETと下側MOSFETの $R_{DS(ON)}$ は、両方とも「標準的性能特性」の曲線から求めることができます。したがって導通損失を計算するには次式を使用します。

$$\text{導通損失} = I_{OUT}^2 (R_{SW} + R_L)$$

- 内蔵のLDOは $INTV_{CC}$ レールに電力を供給します。ここでの全電力損失は、スイッチング損失と、制御回路の静止電流損失の合計です。

パワーMOSFETのゲートが“L”から“H”、さらに再び“L”に切り替わるたびに、 $V_{IN}$ からグランドに一定量の電荷 $dQ$ が移動します。結果として得られる $dQ/dt$ は $INTV_{CC}$ から流出する電流であり、通常はDC制御バイアス電流よりもはるかに大きくなります。連続モードでは、 $I_{GATECHG} = f \cdot (Q_T + Q_B)$ です。ここで、 $Q_T$ および $Q_B$ は内蔵の上側パワーMOSFETおよび下側パワーMOSFETのゲート電荷、 $f$ はスイッチング周波数です。概算を目的とした場合、LTC3634レギュレータの各チャネルで $(Q_T + Q_B)$ は約2.3nCです。

LDO負荷による全電力損失を計算するには、次式に示すように、ゲート電荷電流と消費電流を単純に加え、それに $V_{IN}$ を掛けます。

$$P_{LDO} = (I_{GATECHG} + I_Q) \cdot V_{IN}$$

- 遷移損失、銅トレース抵抗、内部負荷電流など、その他の隠れた損失は、電源システム全体でさらなる効率低下の原因となる可能性があります。遷移損失は、スイッチ・ノードの遷移中に上側パワーMOSFETが短時間飽和領域に留まることから生じます。LTC3634の内蔵パワー・デバイスは十分速く切り替わるので、これらの損失は他の要因に比べると大きくはありません。デッドタイムのダイオードの導通損失やインダクタのコア損失など、その他の損失が占める割合は、一般に全追加損失の2%未満です。

## 熱に関する検討事項

LTC3634では、露出したパッケージ裏面の金属板(PGND)をプリント回路基板に十分半田付けして、良好な熱接触を得ることが必要です。こうすると、QFNおよびTSSOPパッケージは非常に優れた熱特性を示します。この熱特性はデバイスが通常動作時に過剰に自己発熱しないようにするために必要です。

LTC3634は効率が高く、その底面露出型QFNパッケージの熱抵抗は小さいので、大半のアプリケーションでは大量に発熱することはありません。ただし、高い周囲温度、高い $V_{IN}$ 、高いスイッチング周波数、最大出力電流負荷でLTC3634が動作するアプリケーションでは、発熱によってデバイスの最大接合部温度を超える可能性があります。接合部温度が約170°Cに達すると、この温度が160°Cに戻るまで2つのパワー・スイッチは両方ともオフします。

LTC3634が最大接合部温度の125°Cを超えないようにするには、何らかの熱解析を行う必要があります。熱解析の目的は、電力損失によりデバイスが接合部温度を超えるかどうかを判断することです。温度上昇は次式で与えられます。

$$T_{RISE} = P_D \cdot \theta_{JA}$$

一例として、DDR2 SDRAMに電源を供給するために、最大周囲温度が70°C、 $V_{IN} = 12V$ 、周波数=1MHz、 $V_{DDQ} = 1.8V$ 、 $V_{TT} = 0.9V$ 、 $I_{LOAD} = 2A$ (両チャネル)というアプリケーションでLTC3634を使用する場合を考えます。

「標準的性能特性」のセクションの $R_{DS(ON)}$ のグラフから、周囲温度70°Cでは上側スイッチのオン抵抗は公称140mΩであり、下側スイッチのオン抵抗は公称75mΩであることが分かります。 $V_{DDQ}$ 電源の場合、パワーMOSFETの等価抵抗 $R_{SW1}$ は次式のようになります。

$$R_{DS(ON)TOP} \cdot \frac{1.8V}{12V} + R_{DS(ON)BOT} \cdot \frac{10.2V}{12V} = 84.8m\Omega$$

$V_{TT}$ 電源(0.9V)に対して同じ計算を行うと、 $R_{SW2} = 79.9m\Omega$ という結果が得られます。

## アプリケーション情報

ゲート・ドライブに関する前のセクションの説明から、レギュレータごとのゲート充電電流の合計は  $1\text{MHz} \cdot 2.3\text{nC} = 2.3\text{mA}$  であり、2チャネル合計の  $I_Q$  は  $1.3\text{mA}$  であると推定されます（「電気的特性」のセクションを参照）。したがって、2つのレギュレータによる全電力損失は次のとおりです。

$$P_D = \left[ (I_{OUT1})^2 \cdot R_{SW1} \right] + \left[ (I_{OUT2})^2 \cdot R_{SW2} \right]$$

$$+ V_{IN} \cdot (I_{GATECHG} + I_Q)$$

$$P_D = (2\text{A})^2 \cdot 0.0848\Omega + (2\text{A})^2 \cdot 0.0799\Omega$$

$$+ 12\text{V} \cdot [(2.3\text{mA} \cdot 2) + 1.3\text{mA}] = 0.730\text{W}$$

4mm×5mmのQFNパッケージの接合部から周囲の熱抵抗  $\theta_{JA}$  は  $43^\circ\text{C}/\text{W}$  前後です。したがって、 $70^\circ\text{C}$  の周囲温度で動作しているレギュレータの接合部温度は、およそ次のとおりです。

$$T_J = 0.730\text{W} \cdot 43^\circ\text{C}/\text{W} + 70^\circ\text{C} = 101^\circ\text{C}$$

これは最大接合部温度である  $125^\circ\text{C}$  より低い温度です。周囲温度がさらに高い場合は、接合部から周囲の熱抵抗を下げるため、ヒートシンクや冷却ファンを検討します。あるいは、消費電力の大きいアプリケーションでは露出パッドのTSSOPパッケージを選択した方が良い場合があります。TSSOPパッケージの方がQFNパッケージより熱特性が優れているからです。

前述の接合部温度は  $70^\circ\text{C}$  での  $R_{DS(ON)}$  から得られたことに留意すると、 $R_{DS(ON)}$  は温度とともに増加するので、より高い値に基づいて接合部温度を再計算します。 $R_{SW}$  は  $101^\circ\text{C}$  で 12% 増加すると仮定して計算をやり直すと、新たに  $105^\circ\text{C}$  という接合部温度が得られます。

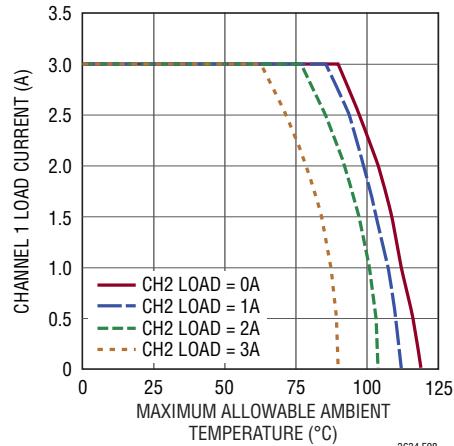

図8はDC1708デモ用ボード(QFNパッケージ)をベースにした温度ディレーティング曲線です。この曲線は、最大接合部温度である  $125^\circ\text{C}$  を超えることがないように、与えられたDC負荷電流での許容最大周囲温度を推定するための目安として使用できます。

## 接合部温度の測定

接合部周囲間熱抵抗は、デバイスが実装されているプリント回路基板上の放熱用銅領域の面積と量、さらにデバイスに対するエアフローの量に応じて変化します。この熱抵抗を正しく評価するため、接合部温度を測定する必要があります。接合部温度を直接測定する賢明な方法は、いずれかのPGOODピンにある内部接合ダイオードを使用し、周囲温度の変化に基づいてそのダイオード電圧の変化を測定する方法です。

図8. DC1708デモ用回路の温度ディレーティング曲線

まず、外付けの受動部品をPGOODピンからすべて取り外し、次にPGOODピンから  $100\mu\text{A}$  を引き出してその内部接合ダイオードを導通させ、PGOODピンに負電圧のバイアスをかけます。出力電流負荷なしで、 $25^\circ\text{C}$ 、 $75^\circ\text{C}$  および  $125^\circ\text{C}$  の周囲温度でPGOODの電圧を測定し、PGOODの電圧と周囲温度との関係の勾配を確定します。この勾配を確定したら、接合部温度の上昇を、パッケージ内の電力損失と対応する出力負荷電流の関数として測定することができます。この方法でこの測定を行うと、PGOODピンでの絶対最大電圧定格に違反しますが、印加される電力はきわめて小さいため、デバイスを損傷するほどの危険性はありません。

## 基板レイアウトの検討事項

プリント回路基板をレイアウトするときは、以下のチェックリストを使用してLTC3634が正しく動作するようにします。レイアウトでは、以下の項目をチェックしてください。

1. 入力コンデンサはできるだけ  $V_{IN}$  ピンと PGND ピンの近くに接続しましたか。このコンデンサは内蔵のパワー MOSFET とそれらのドライバに AC 電流を供給します。

2. 損失を最小限に抑えるため、出力コンデンサ  $C_{OUT}$  とインダクタ  $L$  は近くに接続します。 $C_{OUT}$  の(−)電極は PGND と  $C_{IN}$  の(−)電極の両方に近づけて接続します。

3. 抵抗分割器(たとえば、図1のR1およびR2)は、 $C_{OUT}$  の(+)電極と SGND の近くに終端しているグランド・ラインとの間に接続する必要があります。帰還信号  $V_{FB}$  は SW ラインのようなノイズの多い部品やトレースから離して配線し、帰還

## アプリケーション情報

- 信号のトレースはできるだけ短くします。さらに、 $R_T$ 抵抗とループ補償部品はSGNDに終端します。

- 影響を受けやすい部品はSWピンから遠ざけます。 $R_T$ 抵抗、補償部品、帰還抵抗、およびINTVCCバイパス・コンデンサは、SWのトレースおよびインダクタLからすべて離して配線します。

- グランド・プレーンがあることが望まれますが、設けられない場合は、信号グランドと電源グランドを分離して、両方を低ノイズの共通基準点に接続します。PGNDピンへの接続は、基準点からのトレースの抵抗が最小になるように行います。

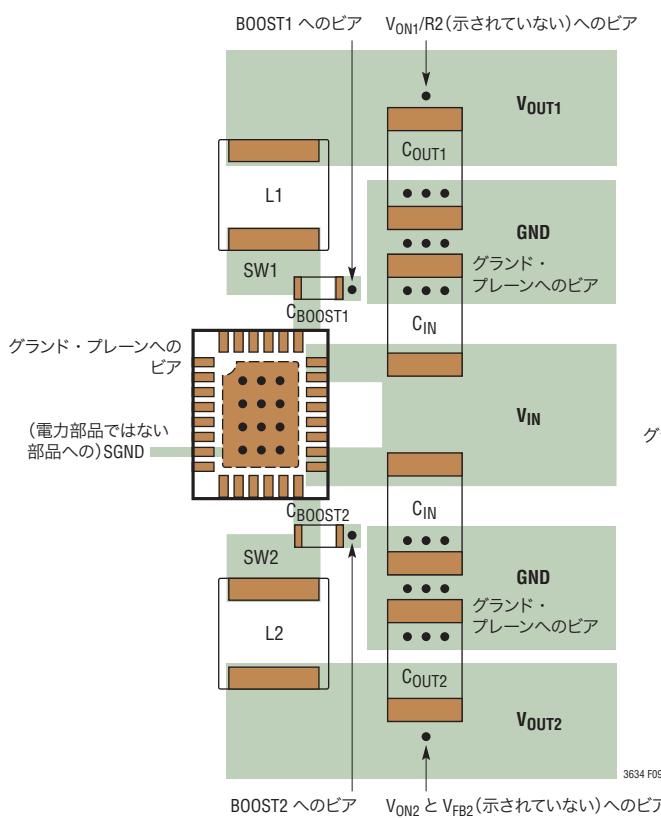

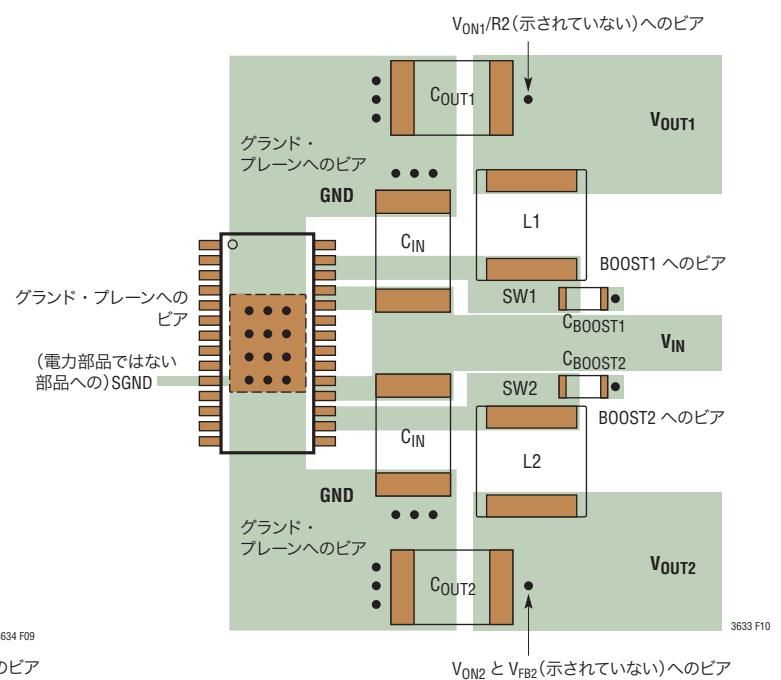

- 電力部品の温度上昇を低減するため、すべての層の未使用領域は銅で覆います。これらの銅領域は、パッケージの金属が露出した裏面(PGND)に接続します。基板レイアウトの例については、図10および11を参照してください。

### 設計例

設計例として、(図1に示すように)LTC3634を使用して、 $V_{IN(MAX)} = 13.2V$ 、 $I_{OUT(MAX)} = \pm 2A$ 、 $f = 1MHz$ 、 $V_{DROOP(VDDQ)} < 60mV$ 、 $V_{DROOP(VTT)} < 30mV$ という仕様でDDR2 SDRAMに電源を供給することを検討します。以下の説明では、前のセクションの式を使います。

まず、1MHzのスイッチング周波数に合わせて正しい $R_T$ 抵抗値を選択する必要があります。前述の説明に基づいて、 $R_T$ は次のように計算されます。

$$R_T = \left( \frac{3.2E^{11}}{f} \right) = 320k\Omega$$

この値に最も近い標準値は324k $\Omega$ です。

次に、チャネル1( $V_{DDQ}$ )をDDR2 SDRAM用に1.8Vに設定するようにR1とR2の値を選択します。R1を選択して12.1k $\Omega$ にすると、R2は次のように計算されます。

$$R2 = 12.1k \cdot \left( \frac{1.8V}{0.6V} - 1 \right) = 24.2k$$

この値に最も近い標準値は24.3k $\Omega$ です。 $V_{DDQIN}$ を $V_{OUT1}$ に接続すると、 $V_{OUT2}$ は $V_{OUT1}$ の半分の値に設定されます。

次に、 $V_{DDQ}$ 出力と $V_{TT}$ 出力の両方のインダクタ値を選択します。以下の式で示すように、 $V_{IN}$ が最大のときに電流リップルが1Aになるようにインダクタを選択します。

$$L1 = \left( \frac{1.8V}{1MHz \cdot 1A} \right) \left( 1 - \frac{1.8V}{13.2V} \right) = 1.55\mu H$$

$$L2 = \left( \frac{0.9V}{1MHz \cdot 1A} \right) \left( 1 - \frac{0.9V}{13.2V} \right) = 0.838\mu H$$

標準値である1.5 $\mu H$ と0.82 $\mu H$ を使用します。

$C_{OUT}$ にはセラミック・コンデンサを使用し、電荷蓄積要件に基づいて選択します。以下の式のように、最悪の場合の4A負荷ステップ(-2A～2A)を想定します。

$$C_{OUT1} \approx \frac{3 \cdot 4A}{1MHz \cdot 60mV} = 200\mu F$$

$$C_{OUT2} \approx \frac{3 \cdot 4A}{1MHz \cdot 30mV} = 400\mu F$$

最後に補償部品を選択します。クロスオーバー周波数 $f_C = 50kHz$ を選択すると、以下のようになります。

$$R_{COMP1} = \left( \frac{2\pi \cdot 50kHz \cdot 200\mu F}{1m\Omega^{-1} \cdot 7\Omega^{-1}} \right) \left( \frac{1.8V}{0.6V} \right) = 27k\Omega$$

$$R_{COMP2} = \left( \frac{2\pi \cdot 50kHz \cdot 400\mu F}{1m\Omega^{-1} \cdot 7\Omega^{-1}} \right) \left( \frac{0.9V}{0.9V} \right) = 18k\Omega$$

ゼロ周波数を10kHzにすると、 $C_{COMP1} = 589pF$ 、 $C_{COMP2} = 884pF$ となります。これらの値に最も近い補償部品の標準値は、それぞれ26.7k、18k、560pF、910pFです。

最終的な回路を図9に示します。

## アプリケーション情報

図9. 設計回路例

図10. QFNパッケージのパワー部品レイアウトの例

図11. TSSOPパッケージのパワー部品のレイアウトの例

3634fa

## パッケージ

最新のパッケージ図面については、<http://www.linear-tech.co.jp/designtools/packaging/>をご覧ください。

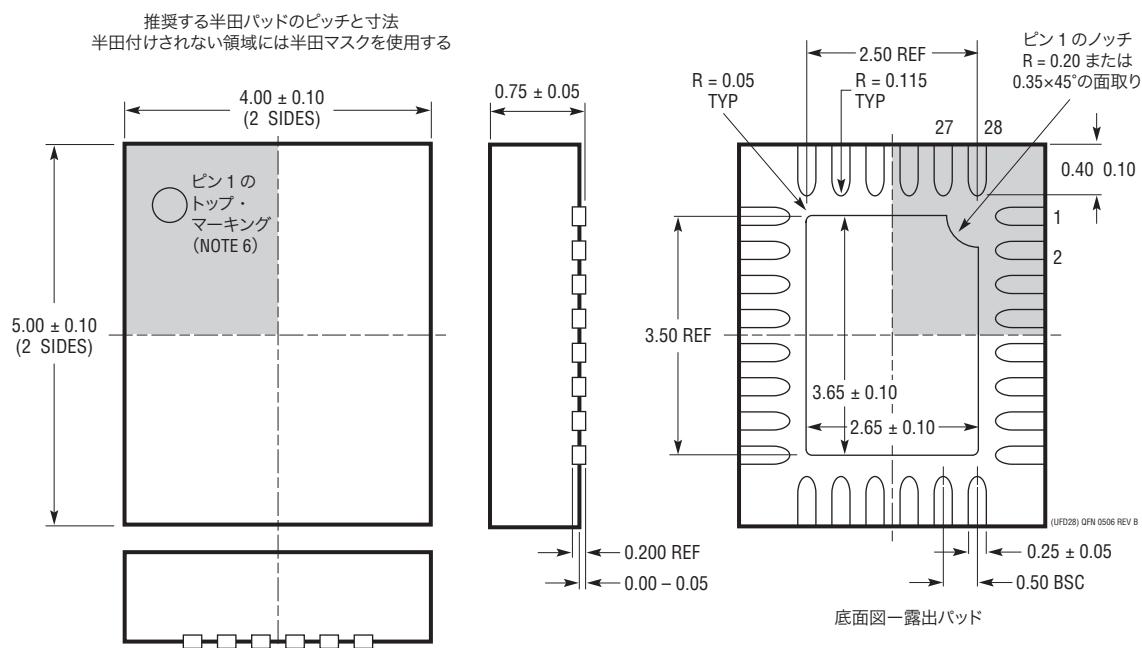

**UFD Package

28-Lead Plastic QFN (4mm x 5mm)

(LTC DWG # 05-08-1712 Rev B)**

底面図—露出パッド

## NOTE:

1. 図は JEDEC パッケージ外形 MO-220 のバリエーション (WXXX-X) にするよう提案されている

2. 図は実寸とは異なる

3. 全ての寸法はミリメートル

4. パッケージ底面の露出パッドの寸法にはモールドのバリを含まない。

5. 露出パッドは半田メッキとする

6. 網掛けの部分はパッケージの上面と底面のピン 1 の位置の参考に過ぎない

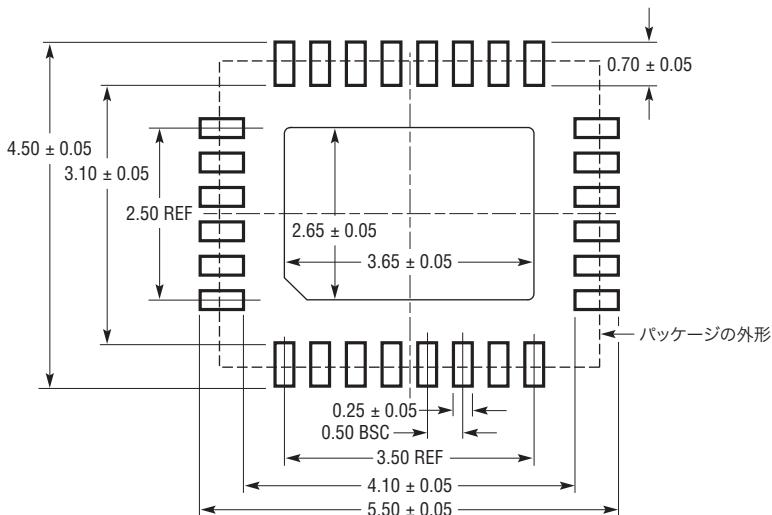

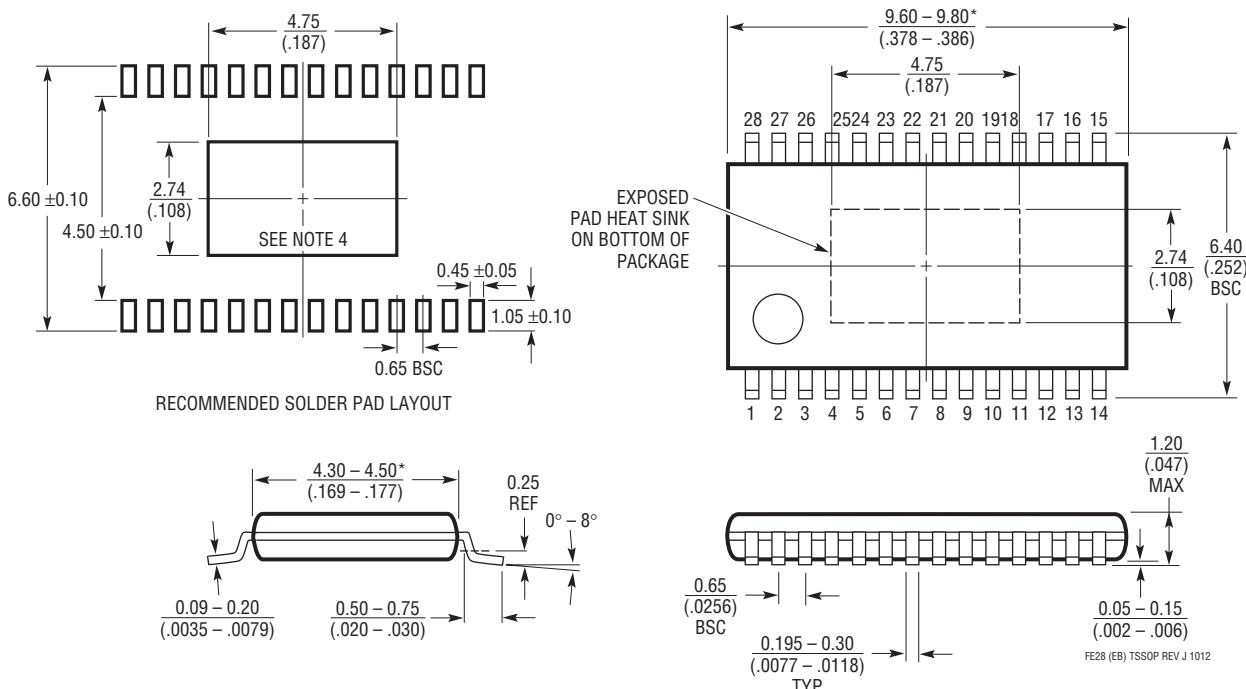

## パッケージ

最新のパッケージ図面については、<http://www.linear-tech.co.jp/designtools/packaging/>をご覧ください。

**FE Package**

**28-Lead Plastic TSSOP (4.4mm)**

(LTC DWG # 05-08-1663 Rev J)

**Exposed Pad Variation EB**

**NOTE:**

- 標準寸法：ミリメートル

- 寸法は ミリメートル

(インチ)

- 図は実寸とは異なる

- 露出パッド接着のための推奨最小 PCB メタルサイズ

- \* 寸法にはモールドのバリを含まない

モールドのバリは各サイドで 0.150mm (0.006") を超えないこと

## 改訂履歴

| REV | 日付   | 概要                                                                                                                                                                                | ページ番号                                    |

|-----|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|

| A   | 9/13 | 絶対最大定格を明確化、発注情報にHグレードとMPグレードを追加。<br>パラメータを明確化。<br>グラフを明確化。<br>RUN1、RUN2ピン機能、INTV <sub>CC</sub> を明確化。<br>最小オン時間の記述を明確化。<br>熱に関する検討事項の最大接合部温度を明確化。<br>関連製品を明確化、LTC3786とLTC3633Aを追加。 | 2<br>3、4<br>5、6<br>7、8<br>18<br>21<br>28 |

## 標準的應用例

図12a.  $V_{TT}$ の電源を  $V_{DDQ}$  から供給

図12b. 2つの入力電源を使用した2相V<sub>TT</sub>終端

## 関連製品

| 製品番号     | 説明                                                               | 注釈                                                                                                                                                 |

|----------|------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| LTC3633  | 15V、デュアル3A( $I_{OUT}$ )、4MHz同期整流式降圧DC/DCコンバータ                    | 効率:95%、 $V_{IN(MIN)} = 3.6V$ 、 $V_{IN(MAX)} = 15V$ 、 $V_{OUT(MIN)} = 0.6V$ 、 $I_Q = 500\mu A$ 、 $I_{SD} < 15\mu A$ 、4mm×5mm QFN-28、TSSOP-28Eパッケージ  |

| LTC3605  | 15V、5A( $I_{OUT}$ )、4MHz同期整流式降圧DC/DCコンバータ                        | 効率:95%、 $V_{IN(MIN)} = 4V$ 、 $V_{IN(MAX)} = 15V$ 、 $V_{OUT(MIN)} = 0.6V$ 、 $I_Q = 2mA$ 、 $I_{SD} < 15\mu A$ 、4mm×4mm QFN-24パッケージ                   |

| LTC3604  | 15V、2.5A( $I_{OUT}$ )、4MHz同期整流式降圧DC/DCコンバータ                      | 効率:95%、 $V_{IN(MIN)} = 3.6V$ 、 $V_{IN(MAX)} = 15V$ 、 $V_{OUT(MIN)} = 0.6V$ 、 $I_Q = 300\mu A$ 、 $I_{SD} < 15\mu A$ 、4mm×4mm QFN-20、MSOP-16Eパッケージ   |

| LTC3603  | 15V、2.5A( $I_{OUT}$ )、3MHz同期整流式降圧DC/DCコンバータ                      | 効率:95%、 $V_{IN(MIN)} = 4.5V$ 、 $V_{IN(MAX)} = 15V$ 、 $V_{OUT(MIN)} = 0.6V$ 、 $I_Q = 75\mu A$ 、 $I_{SD} < 1\mu A$ 、4mm×4mm QFN-20、MSOP-16Eパッケージ     |

| LTC3601  | 15V、1.5A( $I_{OUT}$ )、4MHz同期整流式降圧DC/DCコンバータ                      | 効率:95%、 $V_{IN(MIN)} = 4V$ 、 $V_{IN(MAX)} = 15V$ 、 $V_{OUT(MIN)} = 0.6V$ 、 $I_Q = 300\mu A$ 、 $I_{SD} < 15\mu A$ 、4mm×4mm QFN-20、MSOP-16Eパッケージ     |

| LTC3413  | 5.5V、3A( $I_{OUT}$ シンク/ソース)、2MHzモノリシック同期整流式レギュレータ(DDR/QDRメモリ終端用) | 効率:90%、 $V_{IN(MIN)} = 2.25V$ 、 $V_{IN(MAX)} = 5.5V$ 、 $V_{OUT(MIN)} = V_{REF}/2$ 、 $I_Q = 280\mu A$ 、 $I_{SD} < 1\mu A$ 、TSSOP16Eパッケージ            |

| LTC3612  | 5.5V、3A、4MHz同期整流式降圧DC/DCコンバータ                                    | 効率:95%、 $V_{IN(MIN)} = 2.25V$ 、 $V_{IN(MAX)} = 5.5V$ 、 $V_{OUT(MIN)} = 0.6V$ 、 $I_Q = 75\mu A$ 、 $I_{SD} < 1\mu A$ 、3mm×4mm QFN-20、TSSOP-20Eパッケージ  |

| LTC3614  | 5.5V、4A、4MHz同期整流式降圧DC/DCコンバータ                                    | 効率:95%、 $V_{IN(MIN)} = 2.25V$ 、 $V_{IN(MAX)} = 5.5V$ 、 $V_{OUT(MIN)} = 0.6V$ 、 $I_Q = 75\mu A$ 、 $I_{SD} < 1\mu A$ 、3mm×5mm QFN-24パッケージ            |

| LTC3616  | 5.5V、6A、4MHz同期整流式降圧DC/DCコンバータ                                    | 効率:95%、 $V_{IN(MIN)} = 2.25V$ 、 $V_{IN(MAX)} = 5.5V$ 、 $V_{OUT(MIN)} = 0.6V$ 、 $I_Q = 75\mu A$ 、 $I_{SD} < 1\mu A$ 、3mm×5mm QFN-24パッケージ            |

| LTC3615  | 5.5V、デュアル3A、4MHz同期整流式降圧DC/DCコンバータ                                | 効率:95%、 $V_{IN(MIN)} = 2.25V$ 、 $V_{IN(MAX)} = 5.5V$ 、 $V_{OUT(MIN)} = 0.6V$ 、 $I_Q = 130\mu A$ 、 $I_{SD} < 1\mu A$ 、4mm×4mm QFN-24、TSSOP-24Eパッケージ |

| LTC3876  | $V_{TT}$ リファレンス付き、DDR電源用、38VデュアルDC/DCコントローラ                      | 効率: 95%、 $V_{IN(MIN)} = 4.5V$ 、 $V_{IN(MAX)} = 38V$ 、 $V_{PPQ} = 1V \sim 2.5V$ 、 $V_{TT} = 1/2 V_{PPQ}$ 、5mm×7mm QFN-38、TSSOP-38パッケージ              |

| LTC3633A | 20V、デュアル3A( $I_{OUT}$ )、4MHz同期整流式降圧DC/DCコンバータ                    | 効率: 95%、 $V_{IN(MIN)} = 3.6V$ 、 $V_{IN(MAX)} = 20V$ 、 $I_Q = 500\mu A$ 、 $I_{SD} < 15\mu A$ 、4mm×5mm QFN-28、TSSOP-28Eパッケージ                         |