## 特長

- 出力電圧を上回る/下回る、または出力電圧と等しい入力電圧での出力安定化

- 入力および出力電圧範囲: 1.8V ~ 5.5V

- 1Aの連続出力電流:  $V_{IN} \geq 3V$ ,  $V_{OUT} = 3.3V$

- 出力電圧精度:  $\pm 1\%$

- 低ノイズ昇降圧アーキテクチャ

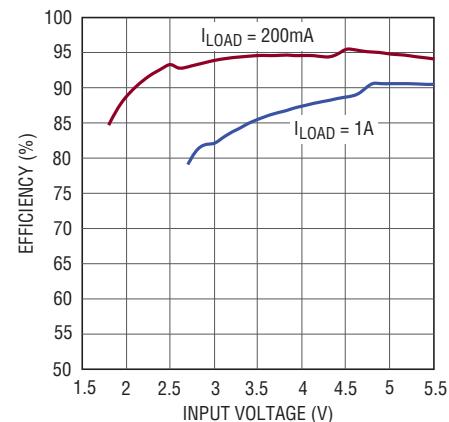

- 効率: 最大 95%

- プログラム可能な周波数: 300kHz ~ 2MHz

- 同期可能な発振器

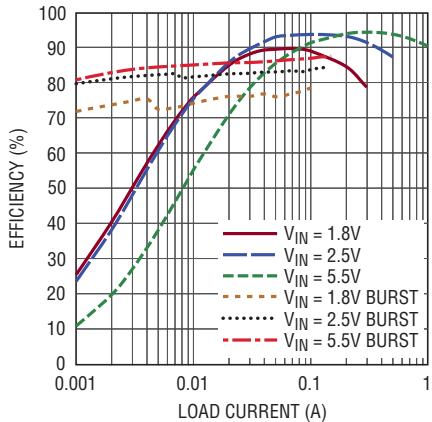

- Burst Mode®動作:  $I_Q = 32\mu A$

- 1msの内部ソフトスタート

- シャットダウン時の出力切斷

- シャットダウン電流: 1 $\mu A$

- 短絡保護

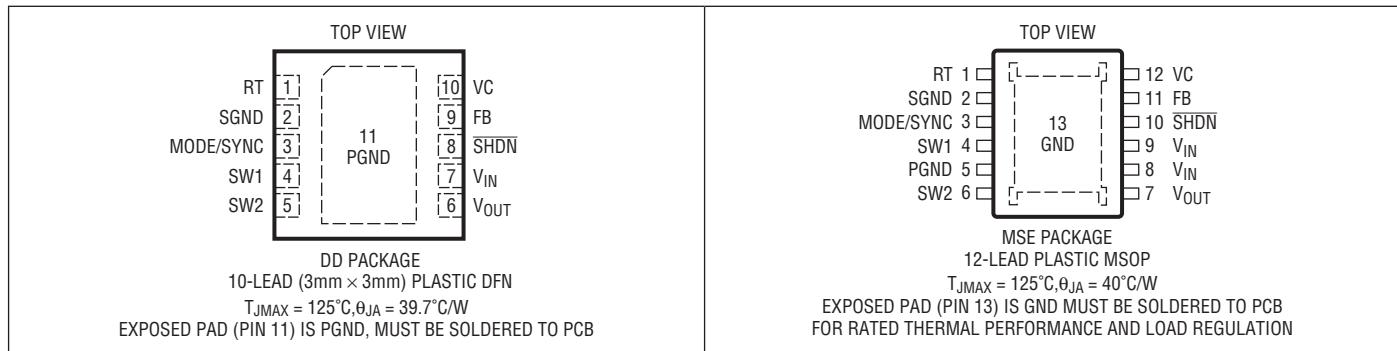

- 熱特性が改善された小型12ピンMSOPパッケージと10ピン(3mm×3mm)DFNパッケージ

## アプリケーション

- ワイヤレス在庫端末

- ハンドヘルド医療計測器

- ワイヤレス・ロケーター、マイクロフォン

- スーパーキャバシタのバックアップ電源

## 概要

LTC®3536は、入力電圧範囲が広い、固定周波数の同期整流式昇降圧DC/DCコンバータです。出力電圧を上回るまたは下回る入力電圧でも、また出力電圧と等しい入力電圧でも動作し、安定化された出力を供給します。このデバイスは低ノイズで動作するトポロジーを採用しているので、RFや高精度測定などのアプリケーションに最適です。

LTC3536は最大1Aの連続出力電流を生成可能で、2個のNチャネルMOSFETスイッチと2個のPチャネルMOSFETスイッチを内蔵しています。外付け抵抗を使って最大2MHzまでのスイッチング周波数を設定可能で、発振器を外部クロックに同期させることができます。Burst Mode動作時の消費電流はわずか32 $\mu A$ なので、携帯アプリケーションのバッテリ寿命を最大限に延ばすことができます。Burst Mode動作はユーザーが制御可能で、軽負荷での効率を高めます。

この他に、1 $\mu A$ のシャットダウン電流、内部ソフトスタート、過熱保護、電流制限などを特長としています。LTC3536は熱特性が改善された12ピンMSOPパッケージと10ピン(3mm×3mm)DFNパッケージで供給されます。

、LT、LTC、LTM、Burst Mode、LTSpice、Linear TechnologyおよびLinearのロゴはリニアテクノロジー社の登録商標です。PowerPathおよびNo RSENSEはリニアテクノロジー社の商標です。その他すべての商標の所有権は、それぞれの所有者に帰属します。

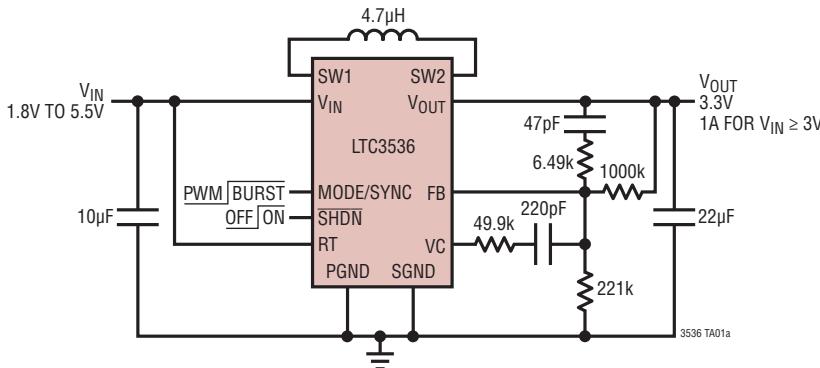

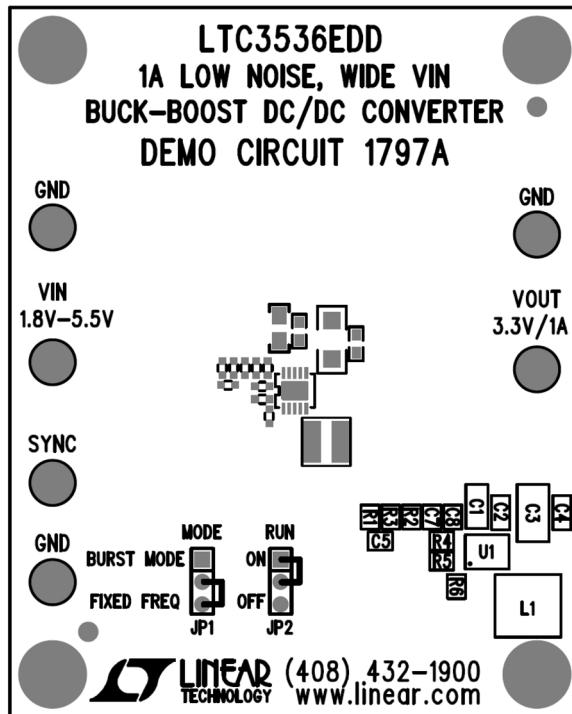

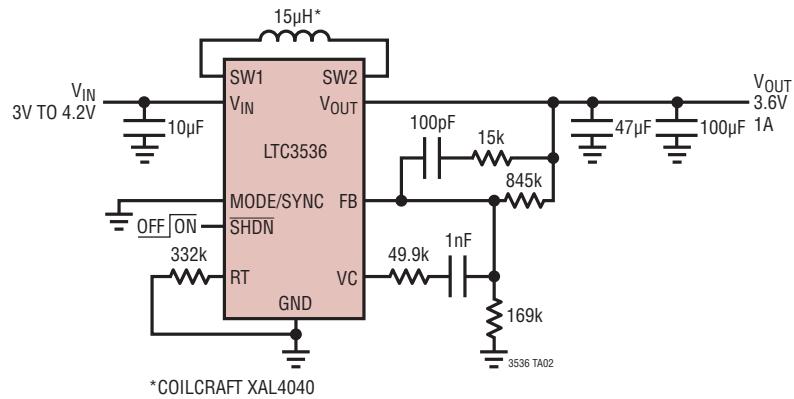

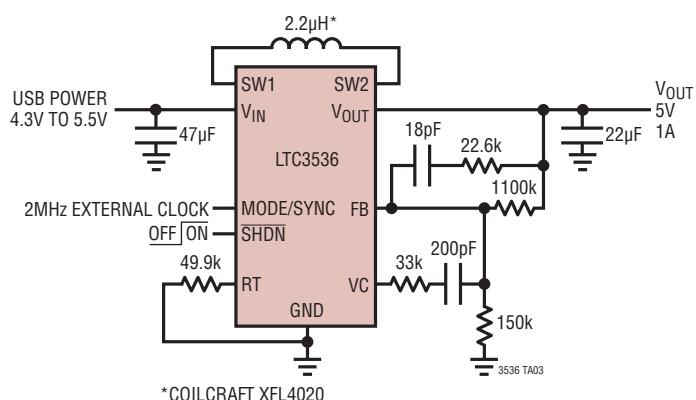

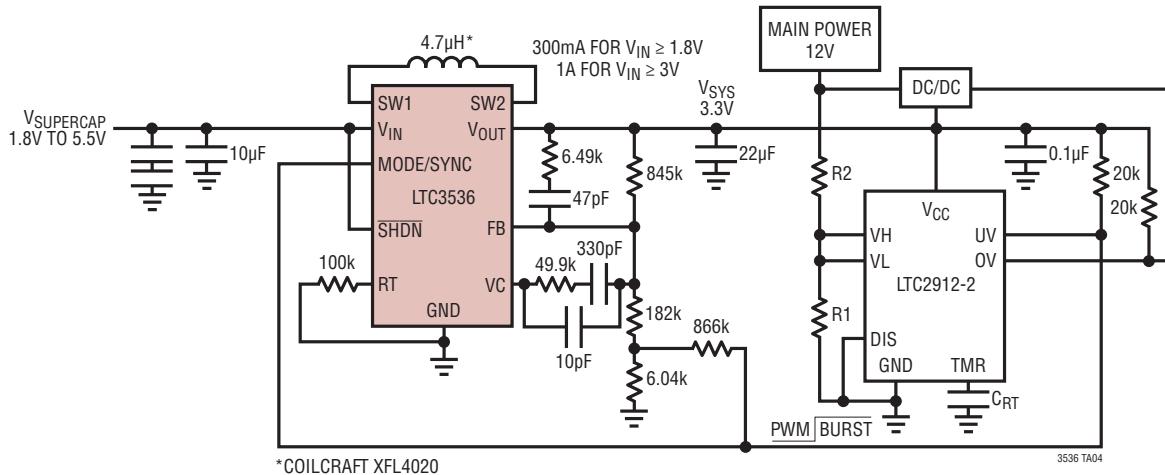

## 標準的応用例

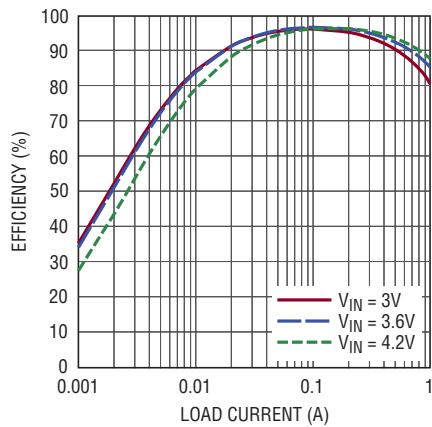

効率と入力電圧

3536 TA01b

## 絶対最大定格 (Note1)

|                                                     |            |                           |

|-----------------------------------------------------|------------|---------------------------|

| $V_{IN}$ 、 $V_{OUT}$ 、( $SV_{IN}$ 、 $PV_{IN}$ ) の電圧 | -0.3V ~ 6V | 動作接合部温度範囲                 |

| SW1、SW2 の電圧                                         |            | (Note 2, 3) -40°C ~ 125°C |

| DC                                                  | -0.3V ~ 6V | 保存温度範囲 -65°C ~ 150°C      |

| パルス(<100ns)                                         | -1.0V ~ 7V | リード温度(半田付け、10秒)           |

| $VC$ 、 $RT$ 、 $FB$ 、 $SHDN$ の電圧                     | -0.3V ~ 6V | MSE 300°C                 |

| MODE/SYNC の電圧                                       | -0.3V ~ 6V |                           |

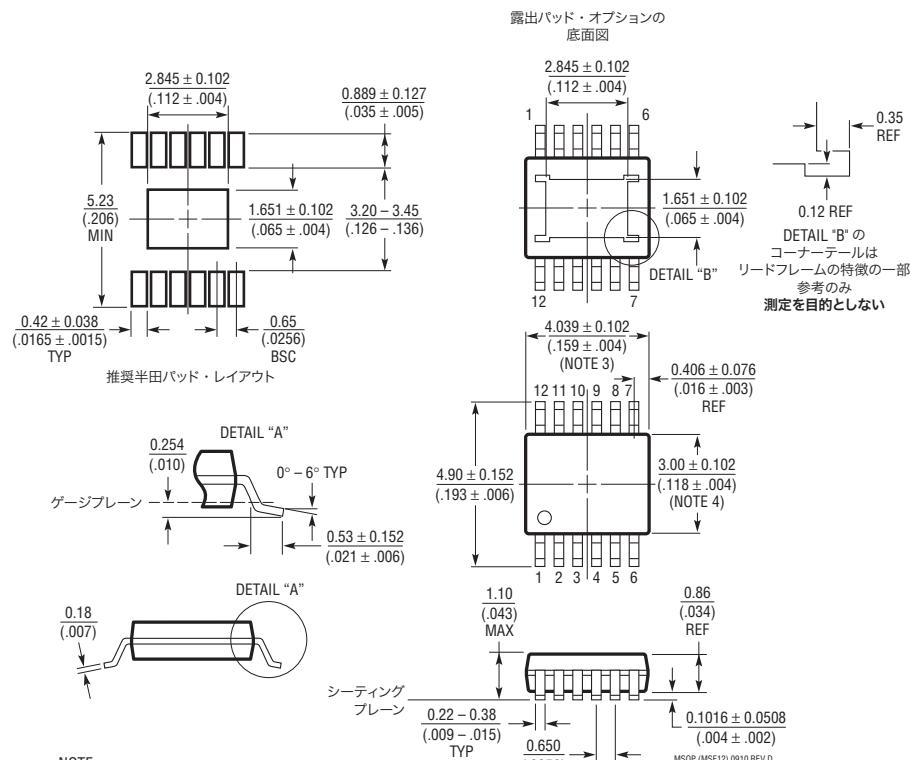

## ピン配置

## 発注情報

| 鉛フリー仕様          | テープアンドリール         | 製品マーキング* | パッケージ                           | 温度範囲           |

|-----------------|-------------------|----------|---------------------------------|----------------|

| LTC3536EDD#PBF  | LTC3536EDD#TRPBF  | LFZD     | 10-Lead (3mm x 3mm) Plastic DFN | -40°C to 125°C |

| LTC3536IDD#PBF  | LTC3536IDD#TRPBF  | LFZD     | 10-Lead (3mm x 3mm) Plastic DFN | -40°C to 125°C |

| LTC3536EMSE#PBF | LTC3536EMSE#TRPBF | 3536     | 12-Lead Plastic MSOP            | -40°C to 125°C |

| LTC3536IMSE#PBF | LTC3536IMSE#TRPBF | 3536     | 12-Lead Plastic MSOP            | -40°C to 125°C |

さらに広い動作温度範囲で規定されるデバイスについては、弊社または弊社代理店にお問い合わせください。<sup>\*</sup> 温度グレードは出荷時のコンテナのラベルで識別されます。

非標準の鉛ベース仕様の製品の詳細については、弊社または弊社代理店にお問い合わせください。

鉛フリー仕様の製品マーキングの詳細については、<http://www.linear-tech.co.jp/leadfree/> をご覧ください。

テープアンドリールの仕様の詳細については、<http://www.linear-tech.co.jp/tapeandreel/> をご覧ください。

**電気的特性** ●は全動作接合部温度範囲の規格値を意味する。それ以外は  $T_A = 25^\circ\text{C}$  での値 (Note 2)。注記がない限り、 $V_{IN} = 3.3\text{V}$ 、 $V_{OUT} = 3.3\text{V}$ 、 $R_T = 100\text{k}\Omega$ 。

| PARAMETER                                 | CONDITIONS                                                                                           | MIN    | TYP            | MAX         | UNITS |

|-------------------------------------------|------------------------------------------------------------------------------------------------------|--------|----------------|-------------|-------|

| Input Operating Range                     |                                                                                                      | ●      | 1.8            | 5.5         | V     |

| Output Voltage Adjust Range               |                                                                                                      | ●      | 1.8            | 5.5         | V     |

| Undervoltage Lockout Threshold            | $V_{IN}$ Ramping Down<br>$V_{IN}$ Ramping Up                                                         | ●<br>● | 1.6<br>1.75    | 1.67<br>1.8 | V     |

| Feedback Voltage                          | $0^\circ\text{C} < T_J < 85^\circ\text{C}$ (Note 5)<br>$-40^\circ\text{C} < T_J < 125^\circ\text{C}$ | ●      | 0.594<br>0.591 | 0.6<br>0.6  | V     |

| Feedback Pin Input Current (FB)           | $V_{FB} = 0.6\text{V}$ in Servo Loop, $V_{MODE/SYNC} = 0\text{V}$                                    |        |                | 50          | nA    |

| Quiescent Current, Burst Mode Operation   | $V_{FB} = 0.7\text{V}$ , $V_{MODE/SYNC} = V_{IN}$                                                    |        |                | 32          | 42    |

| Quiescent Current, Shutdown ( $I_{VIN}$ ) | $V_{SHDN} = 0\text{V}$                                                                               |        |                | 0.1         | 1     |

3536fa

**電気的特性** ●は全動作接合部温度範囲の規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値(Note 2)。注記がない限り、 $V_{IN} = 3.3\text{V}$ 、 $V_{OUT} = 3.3\text{V}$ 、 $R_T = 100\text{k}\Omega$ 。

| PARAMETER                               | CONDITIONS                                                                                  | MIN    | TYP  | MAX  | UNITS         |     |

|-----------------------------------------|---------------------------------------------------------------------------------------------|--------|------|------|---------------|-----|

| Quiescent Current, Active ( $I_{VIN}$ ) | $V_{FB} = 0.7\text{V}$ , $V_{MODE/SYNC} = 0\text{V}$                                        |        |      | 800  | $\mu\text{A}$ |     |

| Input Current Limit                     | $V_{MODE/SYNC} = 0\text{V}$ (Note 4)                                                        | ●      | 2    | 2.5  | A             |     |

| Peak Current Limit                      | $V_{MODE/SYNC} = 0\text{V}$ (Note 4)                                                        |        |      | 3.4  | 4             | A   |

| Burst Mode Peak Current Limit           | $V_{MODE/SYNC} = V_{IN}$ (Note 4)                                                           |        | 0.4  | 0.6  | A             |     |

| Reverse Current Limit                   | (Note 4)                                                                                    | ●      | 0.3  | 0.55 | A             |     |

| NMOS Switch Leakage                     | Switch B, C: $SW1 = SW2 = 5.5\text{V}$ , $V_{IN} = 5.5\text{V}$ , $V_{OUT} = 5.5\text{V}$   |        | 0.1  | 1    | $\mu\text{A}$ |     |

| PMOS Switch Leakage                     | Switch A, D: $SW1 = SW2 = 0\text{V}$ , $V_{IN} = 5.5\text{V}$ , $V_{OUT} = 5.5\text{V}$     |        | 0.1  | 1    | $\mu\text{A}$ |     |

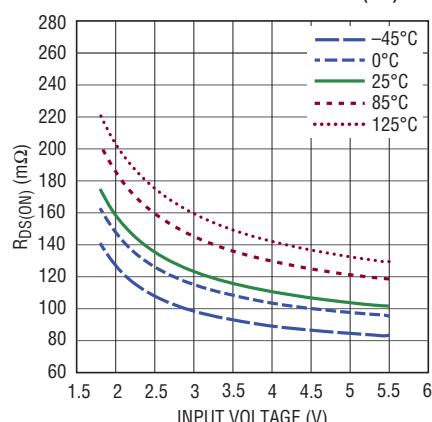

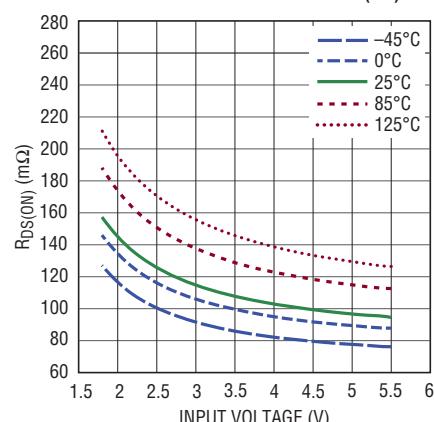

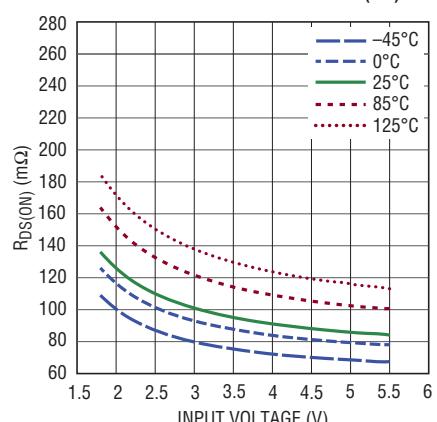

| NMOS Switch On-Resistance               | Switch B (From $SW1$ to GND) (Note 6)<br>Switch C (From $SW2$ to GND) (Note 6)              |        | 0.11 |      | $\Omega$      |     |

| PMOS Switch On-Resistance               | Switch A (From $V_{IN}$ to $SW1$ ) (Note 6)<br>Switch D (From $V_{OUT}$ to $SW2$ ) (Note 6) |        | 0.12 |      | $\Omega$      |     |

| Frequency Accuracy                      | $R_T = 100\text{k}$                                                                         | ●      | 0.8  | 1    | 1.2           | MHz |

| Frequency Accuracy Default              | $R_T = V_{IN}$                                                                              | ●      | 0.96 | 1.2  | 1.44          | MHz |

| Internal Soft-Start Time                | $V_{FB}$ from $0.06\text{V}$ to $0.54\text{V}$                                              |        | 0.6  | 0.9  | 1.2           | ms  |

| Maximum Duty Cycle                      | Percentage of Period $SW2$ is Low in Boost Mode                                             | ●      | 88   | 91   | %             |     |

| Minimum Duty Cycle                      | Percentage of Period $SW1$ is High in Buck Mode                                             | ●      |      | 0    | %             |     |

| Error Amplifier AVOL                    |                                                                                             |        | 90   |      | dB            |     |

| Error Amplifier Sink Current            | $FB = 1.3\text{V}$ , $VC = 1\text{V}$                                                       |        | 250  | 300  | $\mu\text{A}$ |     |

| Error Amplifier Source Current          | $FB = 0.3\text{V}$ , $VC = 0\text{V}$                                                       |        | 400  | 480  | $\mu\text{A}$ |     |

| MODE/SYNC Input Logic Threshold         | Disable Burst Mode Operation                                                                |        | 0.3  | 1    | V             |     |

| MODE/SYNC External Synchronization      | SYNC Level High<br>SYNC Level Low                                                           | ●<br>● | 1.2  | 0.4  | V             |     |

| MODE/SYNC Synchronization Frequency     |                                                                                             | ●      | 0.3  | 2    | MHz           |     |

| MODE/SYNC Input Current                 | $V_{MODE/SYNC} = 5.5\text{V} = V_{IN}$                                                      |        |      | 1    | $\mu\text{A}$ |     |

| SHDN Input Logic Threshold              |                                                                                             | ●      | 0.3  | 1    | V             |     |

| SHDN Input Current                      | $V_{SHDN} = 5.5\text{V} = V_{IN}$                                                           |        |      | 1    | $\mu\text{A}$ |     |

**Note 1:** 絶対最大定格に記載された値を超えるストレスはデバイスに永続的損傷を与える可能性がある。長期にわたって絶対最大定格条件に曝すと、デバイスの信頼性と寿命に悪影響を与える可能性がある。

**Note 2:** LTC3536 は  $T_J$  が  $T_A$  にほぼ等しいパルス負荷条件でテストされる。LTC3536E は  $0^\circ\text{C} \sim 125^\circ\text{C}$  の接合部温度範囲で性能仕様に適合することが保証されている。 $-40^\circ\text{C} \sim 125^\circ\text{C}$  の動作接合部温度範囲での仕様は、設計、特性評価および統計学的なプロセス・コントロールとの相関で確認されている。LTC3536I は  $-40^\circ\text{C} \sim 125^\circ\text{C}$  の全動作接合部温度範囲で動作することが保証されている。これらの仕様に調和する最大周囲温度は、基板レイアウト、パッケージの定格熱インピーダンスおよび他の環境要因と関連した特定の動作条件によって決まるごとに注意。接合部温度 ( $T_J$  ( $^\circ\text{C}$ )) は周囲温度 ( $T_A$  ( $^\circ\text{C}$ )) および電力損失 ( $P_D$  (W)) から次式に従って計算される。

$$T_J = T_A + (P_D \cdot \theta_{JA}) \text{。ここで} \\ \theta_{JA} \text{(単位: } ^\circ\text{C/W}) \text{はパッケージの熱インピーダンス。}$$

**Note 3:** このデバイスには、短時間の過負荷状態の間デバイスを保護するための過温度保護機能が備わっている。この保護がアクティブなとき、最大定格接合部温度を超えることができる。規定された絶対最大動作接合部温度を超えた動作が継続すると、デバイスの信頼性を損なうか、またはデバイスに永続的損傷を与える恐れがある。

**Note 4:** 電流の測定は、LTC3536 がスイッチング動作を行っていないときに行われる。動作時に測定された電流制限値は、コンパレータの伝搬遅延のためにいくらか大き目の値となる。

**Note 5:** 設計、特性評価および統計的プロセス制御との相関によって保証されている。

**Note 6:** 相関と設計によって保証されている。

## 標準的性能特性 注記がない限り、 $T_A = 25^\circ\text{C}$ 、 $V_{IN} = V_{OUT} = 3.3\text{ V}$ 。

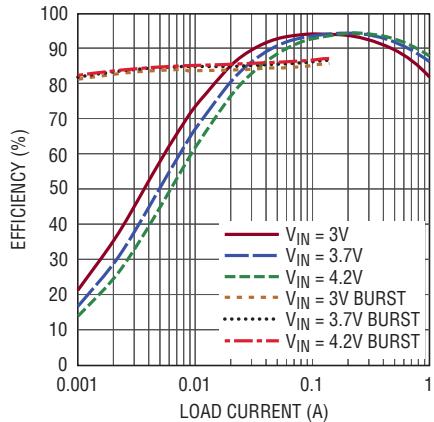

効率(3.3V)と負荷電流

3536 G01

リチウムイオン・バッテリ(3V、3.7V、4.2V)から3.3V出力の効率

3536 G02

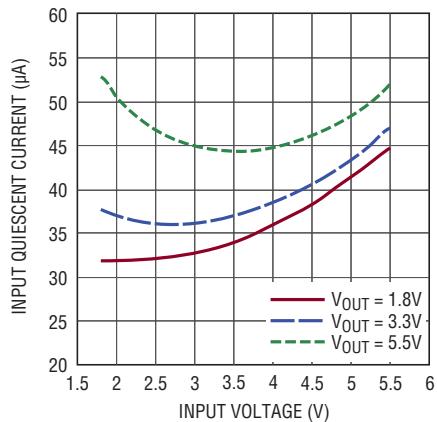

Burst Mode動作(MODE =  $V_{IN}$ )の無負荷消費電流

3536 G03

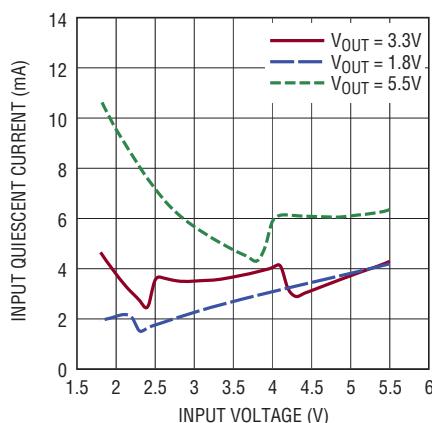

PWMモード動作の無負荷消費電流

3536 G04

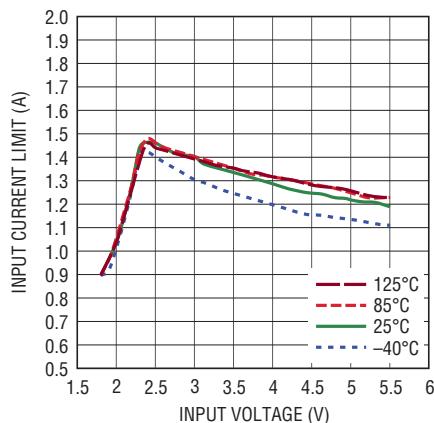

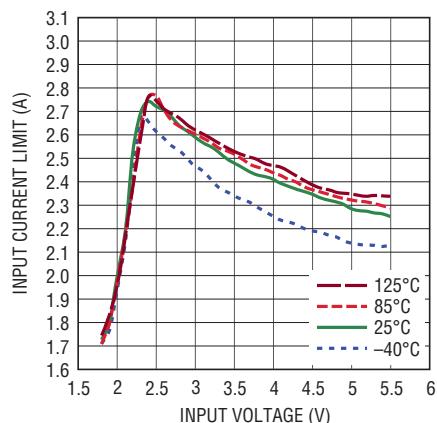

入力電流制限と電源電圧( $V_{OUT} = \text{GND}$ )

3536 G05

入力電流制限と電源電圧( $V_{OUT} = 3.3\text{ V}$ )

3536 G06

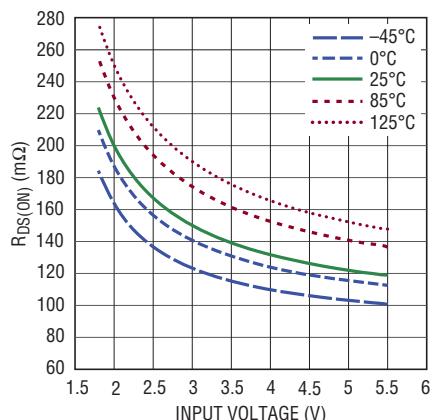

Pチャネル・スイッチAの $R_{DS(ON)}$

3536 G07

Nチャネル・スイッチBの $R_{DS(ON)}$

3536 G08

Nチャネル・スイッチCの $R_{DS(ON)}$

3536 G09

標準的性能特性 注記がない限り、 $T_A = 25^\circ\text{C}$ 、 $V_{IN} = V_{OUT} = 3.3\text{ V}$ 。

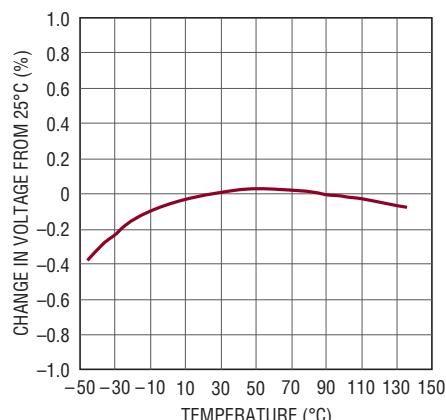

Pチャネル・スイッチDの $R_{DS(ON)}$

帰還電圧

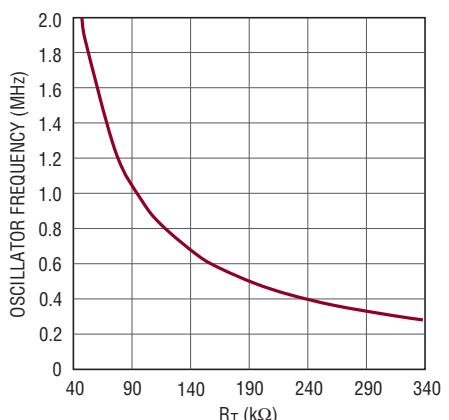

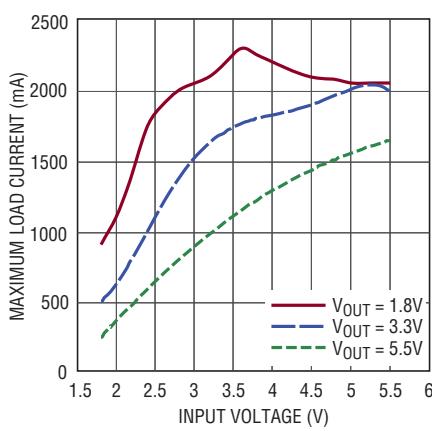

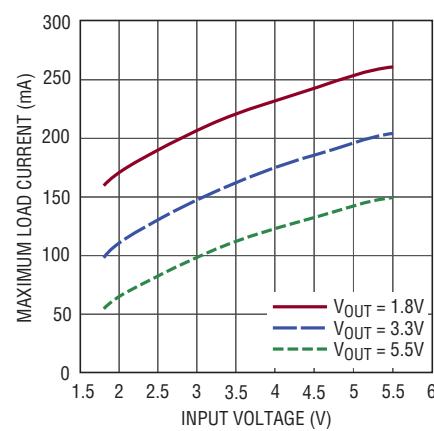

発振器の周波数と $R_T$ PWMモードの最大負荷電流と入力電圧 (1MHzのスイッチング周波数、 $4.7\mu\text{H}$ のインダクタ値)

Burst Mode動作の最大負荷電流と入力電圧

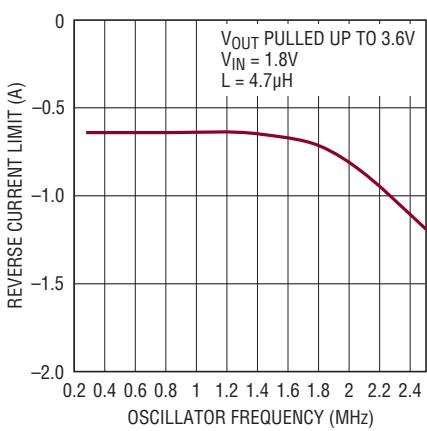

負インダクタ電流と発振器の周波数

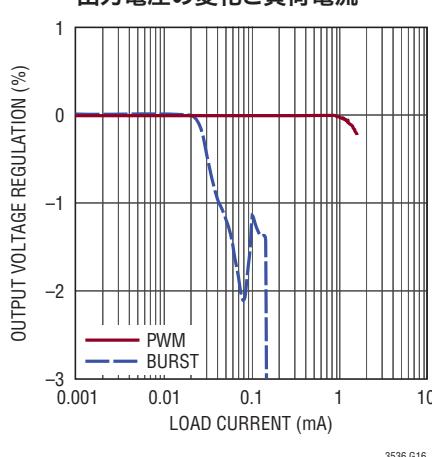

3.3V出力および3.3V入力での出力電圧の変化と負荷電流

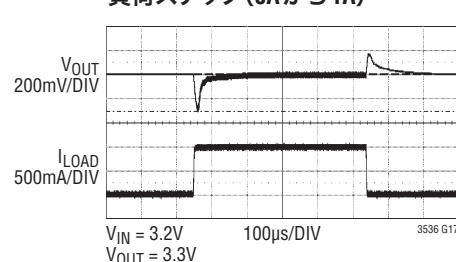

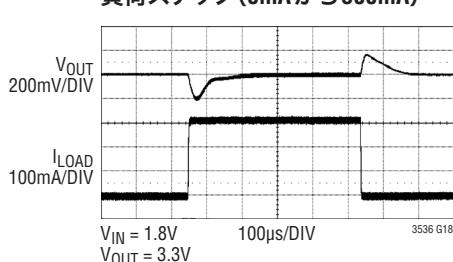

負荷ステップ(0Aから1A)

負荷ステップ(0mAから300mA)

## 標準的性能特性 注記がない限り、 $T_A = 25^\circ\text{C}$ 、 $V_{IN} = V_{OUT} = 3.3\text{ V}$ 。

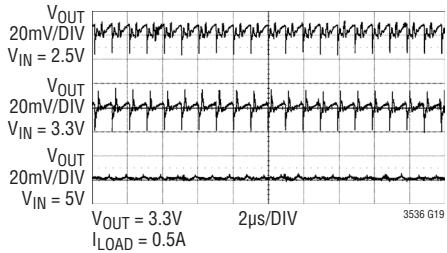

### PWM モードの 出力電圧リップル

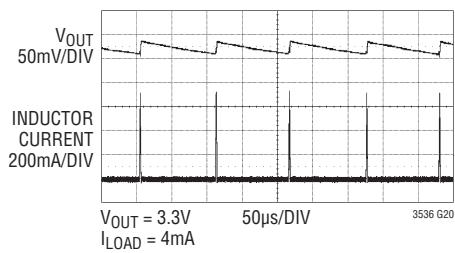

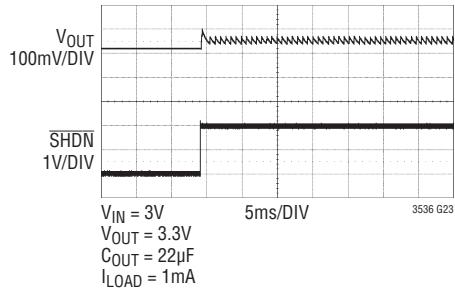

### Burst Mode 動作の 出力電圧リップル

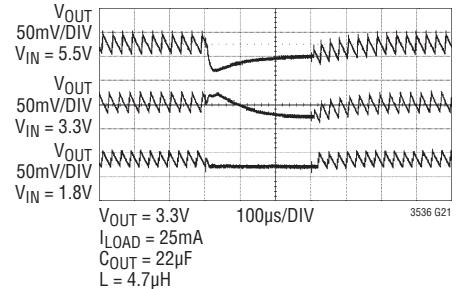

### Burst Mode 動作から PWM モードへの移行

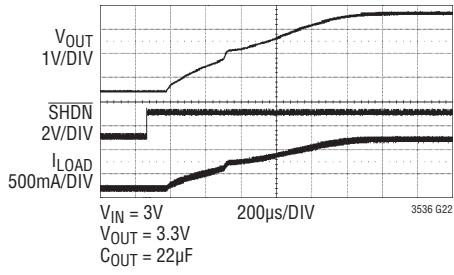

### ソフトスタート

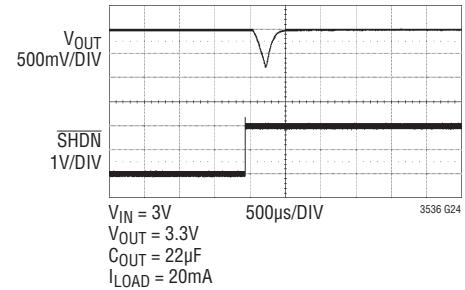

### 出力をプリチャージした Burst Mode 動作の起動

### 出力をプリチャージした PWM モード動作の起動

## ピン機能 (DFN/MSOP)

**RT(ピン1/ピン1)** : 発振器周波数の設定入力。RTからGNDに抵抗を接続して内部発振器の周波数を設定します。周波数は次式で与えられます。

$$f_{OSC} (\text{MHz}) = 100/R_T (\text{k}\Omega)$$

ここで、 $R_T$ の単位はk $\Omega$ 、 $f_{OSC}$ の範囲は0.3MHz～2MHzです。RTピンを $V_{IN}$ に接続すると、内部発振器のデフォルト周波数1.2MHzをイネーブルします。

**SGND(ピン2/ピン2)** : LTC3536のグランド接続。グランド・プレーンを強く推奨します。グランドで終端される敏感なアナログ部品は4端子接続でGNDピンに接続し、高電流経路から離します。

**MODE/SYNC(ピン3/ピン3)** : パルス幅変調/Burst Modeの選択および同期入力。MODEをロジック0状態にドライブすると、固定周波数、低ノイズPWM動作が設定されます。MODEをロジック1状態にドライブすると、Burst Mode動作が設定され、軽負荷時に効率が最大になります。Burst Mode動作では、出力電流能力がPWM動作で得られるよりも大幅に低下します。詳細についてはこのデータシートの「アプリケーション情報」のセクションを参照してください。MODE/SYNCにクロック・パルスが与えられると、周波数同期が行われます。外部クロック・パルスは、1.2V以上の振幅と10%～90%のデューティ・サイクルが必要です。LTC3536の発振器の自走周波数は、同期クロック周波数より低くも高くも設定できます。

**SW1(ピン4/ピン4)** : スイッチ・ピン。内部パワー・スイッチAおよびBに接続されています。昇降圧インダクタの片側をSW1に接続します。インダクタからSW1までのPCBトレースを短く幅を広くし、過渡電圧とノイズを最小限に抑えます。

**SW2(ピン5/ピン6)** : スイッチ・ピン。内部パワー・スイッチCおよびDに接続されています。昇降圧インダクタの片側をSW2に接続します。インダクタからSW2までのPCBトレースを短く幅を広くし、過渡電圧とノイズを最小限に抑えます。

**$V_{OUT}$ (ピン6/ピン7)** : 出力電圧。このピンはレギュレータの電力出力です。このピンとグランド・プレーンの間に低ESRコンデンサを接続します。コンデンサはできるだけこのピンの近くに配置し、グランドへのリターン・パスを短くします。

**$V_{IN}$ (ピン7/ピン8、9)** : コンバータの電源入力。このピンとグランドの間には10 $\mu$ F以上の低ESRバイパス・コンデンサを接続します。コンデンサはできるだけこのピンの近くに配置し、グランドへのリターン・パスを短くします。

**$\overline{SHDN}$  (ピン8/ピン10)** : イネーブル入力。 $\overline{SHDN}$ をロジック1にすると、昇降圧レギュレータが起動します。 $\overline{SHDN}$ をロジック0にすると、昇降圧レギュレータが停止します。

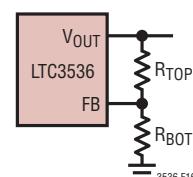

**FB (ピン9/ピン11)** : 出力電圧を設定する帰還分割器入力。レギュレータの出力電圧はFBに接続された分圧器によって設定されます。昇降圧出力は次式によって与えられます。

$$V_{OUT} = 0.6V \cdot (1 + R_{TOP}/R_{BOT}) (V)$$

ここで、 $R_{BOT}$ はFBとグランドの間に接続された抵抗、 $R_{TOP}$ はFBと $V_{OUT}$ の間に接続された抵抗です。昇降圧出力電圧は1.8V～5.5Vの範囲で調節できます。

**VC (ピン10/ピン12)** : エラーアンプの出力。VCとFBの間に周波数補償部品を接続し、コンバータの動作を安定させます。設計の詳細については、このデータシートの「アプリケーション情報」のセクションを参照してください。

**PGND(露出パッド・ピン11/ピン5、露出パッド・ピン13)** : 電源グランド。露出パッドはPCBに半田付けし、できるだけ短く最小のインピーダンスの接続を介して電気的にグランドに接続する必要があります。

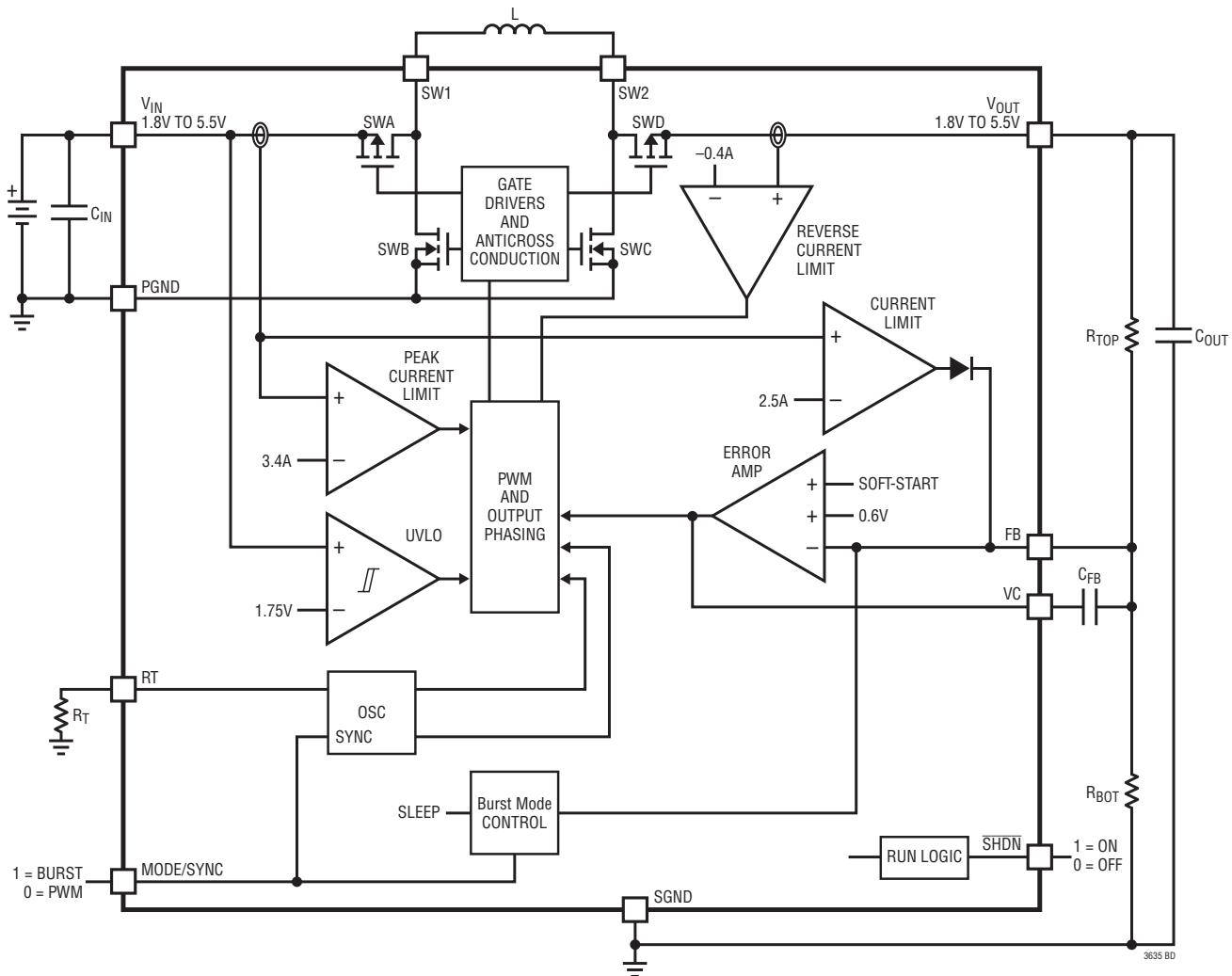

## ブロック図

## 動作

### はじめに

LTC3536は、最小1.8Vから最大5.5Vの入力および出力電圧で動作可能なモノリシック昇降圧コンバータです。独自のスイッチ制御アルゴリズムにより、昇降圧コンバータは、出力電圧を上回るまたは下回る入力電圧でも、また出力電圧と等しい入力電圧でも出力電圧の安定化を維持します。これらの動作モード間の移行はシームレスで、過渡や低調波スイッチングが生じません。

LTC3536は300kHz～2MHzの幅広いスイッチング周波数範囲で動作するように構成できるので、アプリケーションでの基板面積と効率に対する最適化が可能です。LTC3536は、スイッチング周波数が1本の外付け抵抗で容易に設定可能な、固定周波数の発振器を内蔵しています。ノイズに敏感なアプリケーションでは、MODE/SYNCピンを介してコンバータを外部クロックに同期させることもできます。RTが $V_{IN}$ に接続されている場合、動作周波数はデフォルトで1.2MHzになり、外付け抵抗は不要です。

LTC3536は、バッテリ駆動装置など消費電流が重視されるアプリケーションに対して、シャットダウン時とスタンバイ時の入力電流を低減するように最適化されています。Burst Mode動作では、無負荷でのスタンバイ電流はわずか32 $\mu$ Aで、シャットダウン時には、全消費電流は1 $\mu$ A以下に減少します。

### PWMモードの動作

MODE/SYNCピンを“L”に強制するか、または外部クロックでドライブすると、LTC3536は、電圧モード制御ループを使った固定周波数のパルス幅変調(PWM)モードで動作します。このモードの動作では、コンバータから供給することができる出力電流が最大になり、出力電圧リップルが減少し、固定周波数のスイッチング・スペクトルが低ノイズになります。独自のスイッチング・アルゴリズムにより、全ての動作領域にわたって動作モード間をシームレスに移行し、平均インダクタ電流、インダクタ電流リップル、およびループの伝達関数の不連続性を除去します。これらの利点により、従来の4スイッチ昇降圧コンバータに比べて効率が向上し、ループの安定性が改善され、出力電圧リップルが小さくなります。

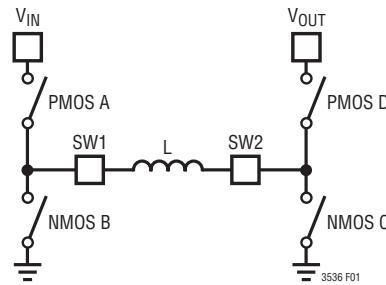

2個のPチャネルMOSFETスイッチ、2個のNチャネルMOSFETスイッチ、およびこれらの関連ゲート・ドライバで構成されるLTC3536の電力段のトポロジーを図1に示します。エラーアンプの出力に応答して、内部のパルス幅変調器がスイッチの適正なデューティ・サイクルを生成し、出力電圧のレギュレーションを維持します。

図1. 電力段の回路図

入力電圧が出力電圧よりかなり大きいと、昇降圧コンバータは降圧モードで動作します。スイッチDは継続的にオンし、スイッチCはオフのまま留まります。スイッチAおよびBはパルス幅変調され、必要なデューティ・サイクルを発生して出力の安定化電圧をサポートします。入力電圧が低下すると、スイッチAはスイッチング・サイクルの大部分でオンを維持します。デューティ・サイクルが約90%に達すると、スイッチ・ペアACがスイッチング周期のわずかな部分でオンし始めます。入力電圧がさらに低下すると、ACスイッチ・ペアはもっと長い時間オン状態に留まり、BDフェーズの継続時間が比例して減少します。この時点で、スイッチAは継続的にオン状態に留まり、スイッチ・ペアCDは望みの出力電圧を得るためにパルス幅変調されます。この時点では、コンバータは昇圧モードでだけ動作しています。

### 発振器とフェーズロック・ループ

LTC3536は、RTとグランドの間の1本の外付け抵抗で設定可能なスイッチング周波数の内部発振器で動作します。RTを $V_{IN}$ に接続すると、標準1.2MHzのデフォルト内部動作周波数に設定されます。RTピンが外部で $V_{IN}$ より高いレベルにドライブされるときは、電流制限抵抗を使用します。RTピンが6Vの場合、1Mの抵抗で電流が6 $\mu$ Aに制限されます。電流制限抵

## 動作

抗に加えて、RTピンからVINにショットキー・ダイオードを接続することもできます。ノイズに敏感なアプリケーションでは、内部フェーズロック・ループにより、LTC3536をMODE/SYNCピンに与えられる外部クロック信号に同期させることができます。発振器の自走周波数は、同期クロック周波数より低くも高くも設定できます。

内部発振器で動作するときも外部クロック信号に同期するときも、LTC3536は、300kHz～2MHzのスイッチング周波数で動作することができるので、外付け部品のサイズを最小限に抑えて電力変換効率を最適化します。

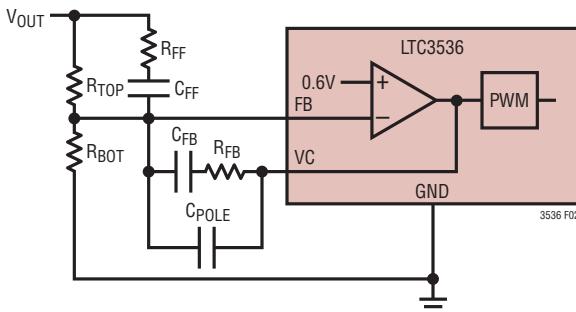

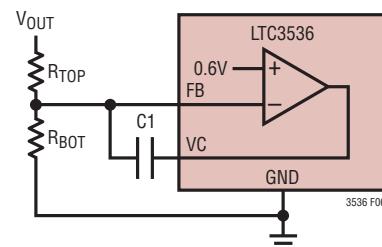

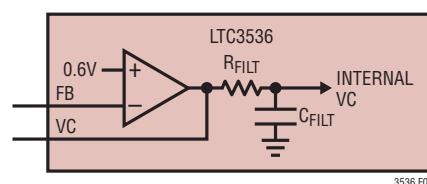

## エラーアンプ

LTC3536は、出力電圧レギュレーションを維持する制御ループの周波数補償を行う高利得オペアンプを内蔵しています。この制御ループを安定させるため、応用回路に外部補償ネットワークを実装する必要があります。ほとんどのアプリケーションには図2に示すようなタイプIIIの補償ネットワークを推奨します。その理由は、コンバータの過渡応答を最適化する柔軟性を与えると同時に、出力電圧のDC誤差を最小限に抑えるからです。LTC3536のアプリケーションでの補償ネットワークの設計の詳細については、このデータシートの「アプリケーション情報」のセクションを参照してください。

図2. エラーアンプと補償ネットワーク

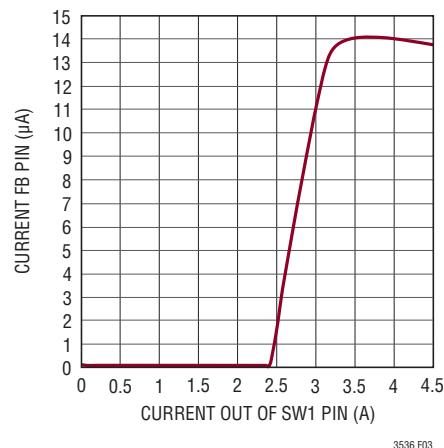

## 入力電流制限とピーク電流制限

LTC3536は、ピーク・インダクタ電流を制限して、出力短絡状態や過負荷状態のときにスイッチ電流を確実にデバイスの能力以内に抑えるように設計された、2つの電流制限回路を備えています。入力電流制限では、インダクタ電流が入力電流

制限スレッショルド(標準2.5A)を超える分に比例して電流を帰還ピンに注入します。この帰還ループは利得が大きいので、この注入された電流は、インダクタを流れる平均電流がほぼ電流制限スレッショルドに減少するまでエラーアンプの出力が減少するよう強制します。この電流制限機能が最も有効に働くには、FBからグランドへのテブナン抵抗(RBOT//RTOP)が100kΩを超えるようにします。

図3. 入力電流制限のFB電流

この入力電流制限回路はエラーアンプをアクティブ状態に保つので、電流制限フォールト状態が解消するとスムーズに回復しオーバーシュートを最小限に抑えます。ハードな出力短絡では、入力電流制限が応答してインダクタ電流を減らす前に、インダクタ電流が電流制限スレッショルドを超えてかなり増加する可能性があります。この理由で、2つ目の電流制限(ピーク電流制限)回路があり、スイッチAを流れる電流が約3.4Aの制限スレッショルドを超えるとパワースイッチAをオフします。これにより、瞬時のハードな出力短絡が生じた場合に追加の保護が行われ、1つ目の電流制限が応答するための時間が与えられます。入力電圧が2.4Vより低い場合、入力電流制限スレッショルドとピーク電流制限スレッショルドは徐々に減少します。最小入力電圧(1.8V)では、これらはそれぞれ標準で1.7Aと2.3Aになります。最大出力電流能力を得るためのインダクタ値については、「標準的性能特性」と「インダクタの選択」のセクションを参照してください。

## 動作

### 逆電流制限

PWMモードの動作では、LTC3536は、レギュレーションを維持するのに必要な場合に出力電流が流れるのをアクティブに防ぐことができます。出力がレギュレーションを超えた状態に保たれると、これによって大きな逆電流が生じる可能性があります。この状況は、LTC3536の出力が、パワーアップやパワーダウンのシーケンスの間に生じることがあるように、別の電源によって一時的に保持されるときに発生する可能性があります。このような状態でのデバイスの損傷を防ぐため、LTC3536は、負荷からパワースイッチDに流入する電流をモニタする逆電流コンパレータを備えています。この電流が0.55A(標準)を超えると、逆インダクタ電流が安全でないレベルに達するのを防ぐため、スイッチング・サイクルの残りの時間スイッチDをオフします。

無負荷電流のアプリケーションでは、インダクタ電流リップルは最小逆電流制限の2倍( $0.3A \cdot 2 = 0.6A$ )の最大インダクタ電流リップル)より小さくなければなりません。インダクタ電流リップルの計算方法については、「インダクタの選択」のセクションを参照してください。

### 出力電流能力

LTC3536から供給可能な最大出力電流は多くの要素に依存しますが、最も影響が大きいのは入力電圧と出力電圧です。 $V_{OUT} = 3.3V$ および $V_{IN} \geq 3V$ の場合、LTC3536は1Aの負荷を継続的にサポートすることができます。 $V_{OUT} = 3.3V$ および $V_{IN} = 1.8V$ の場合、LTC3536は300mAの負荷を継続的にサポートすることができます。

一般に、出力電流能力は入力電圧が出力電圧にほぼ等しいときに最大になります。昇圧電圧比が大きいときは、スイッチDのデューティ・サイクルが減少することによって所定の負荷をサポートするのに必要なインダクタ電流が増加するので、出力電流能力は低下します。さらに、昇圧電圧比が大きいときは、達成可能な最大インダクタ電流を低減するインダクタ電流リップルが大きくなるので、一般に出力電流能力は低下します。

出力電流能力はインダクタの特性によって影響されることもあります。インダクタのDC抵抗が大きいと、特に昇圧モード動作で出力電流能力は低下します。さらに、インダクタの値を大きくすると、一般にインダクタ電流リップルを小さくすることによって出力電流能力を最大化します。詳細については、「標準的性能特性」と「インダクタの選択」のセクションを参照してください。

### Burst Mode動作

MODE/SYNCが“H”に保持されると、昇降圧コンバータは可変周波数スイッチング・アルゴリズムを使用してBurst Mode動作を行います。このアルゴリズムは、無負荷の入力消費電流を最小限に抑え、軽負荷時にスイッチングの量を、その負荷をサポートするのに必要な最小レベルに抑えることによって効率を改善します。Burst Mode動作の出力電流能力はPWMモードよりはるかに低く、軽いスタンバイ負荷のサポートを意図したものです。Burst Modeの最大負荷電流と入力電圧および出力電圧の関係を示す曲線については、このデータシートの「標準的性能特性」のセクションを参照してください。Burst Mode動作のコンバータの負荷がBurst Modeの最大電流能力を超えると、出力が不安定になります。

スイッチAおよびCがオンしてインダクタに流れる電流がリニアに増加すると、各Burst Modeサイクルが開始されます。インダクタ電流がBurst Modeのピーク電流制限(標準で0.6A)に達すると、スイッチBおよびDがオンし、インダクタに蓄積されたエネルギーが出力コンデンサと負荷に放電されます。インダクタ電流がゼロに達すると、全てのスイッチがオフしてサイクルが終了します。このようにして生成された電流パルスは、必要に応じて繰り返し生成されて出力電圧のレギュレーションを維持します。Burst Mode動作では、バースト・コンパレータとしてエラーアンプを使用します。MODEピンが外部で $V_{IN}$ より高いレベルにドライブされるときは、電流制限抵抗を使用します。MODEピンが6Vの場合、1Mの抵抗で電流が $6\mu A$ に制限されます。電流制限抵抗に加えて、MODEピンから $V_{IN}$ にショットキー・ダイオードを接続することもできます。

### ソフトスタート

パワーアップ時の入力過渡電流を最小限に抑えるため、LTC3536は公称持続時間が0.9msのソフトスタート回路を内蔵しています。ソフトスタートは、ソフトスタートの期間中にエラーアンプのリファレンス電圧がリニアに上昇することによって行われます。そのため、ソフトスタートの継続時間が出力コンデンサのサイズや出力安定化電圧に影響されることはありません。閉ループ特性をもったソフトスタートの場合、コンバータはソフトスタートの合間に生じる負荷過渡に応答することができます。ソフトスタート時間はサーマル・シャットダウンと $V_{IN}$ のUVLOイベントによってリセットされ、動作モードは常にPWMになります。

## 動作

起動時の出力電圧が既に目標値の90%（標準）以上にプリチャージされている場合、内部ソフトスタートがスキップされ、LTC3536はMODEピンで設定されている動作モードに直ちに移行します。

MODEピンが“H”に接続されてBurst Mode動作が選択されると、出力電圧は目標電圧値までスムーズに安定化されます。代わりに、MODEピンが“L”に接続されてPWMモードが選択されると、エラーアンプがVCピンを充電する必要があり、出力電圧はメイン補償コンデンサの値に比例する短時間の間、低い電圧値に引き下げられる可能性があります。

## 低電圧ロックアウト

適切な動作をさせるため、LTC3536は低電圧ロックアウト（UVLO）回路を内蔵しています。V<sub>IN</sub>が個々のUVLOスレッショルド（標準1.67V）を下回ると、コンバータがディスエーブルされます。入力電圧がこのレベルを下回ると、入力電圧が1.75V（公称）を上回るまでスイッチングがディスエーブルされます。

## 出力切断

LTC3536は、両方のPチャネルMOSFET整流器を開放状態にすることによって真の出力切断ができるように設計されています。これにより、シャットダウンの間V<sub>OUT</sub>をゼロボルトにすることができ、入力ソースから電流が流れません。

---

## アプリケーション情報

LTC3536の基本的な応用回路がこのデータシートの表紙の「標準的応用例」に示されています。外付け部品を選択する際は、アプリケーションごとにそのICに必要な性能に基づいて、PCBの面積、コスト、出力電圧および入力電圧、許容リップル電圧、効率および熱などのトレードオフに配慮して適切な部品を選択してください。ここでは、外付け部品の選択と応用回路の設計に役立ついくつかの基本的ガイドラインと検討事項について説明します。

## 熱に関する検討事項

LTC3536のパワースイッチは、内部電流制限スレッショルドまでの電流で継続的に動作するように設計されています。ただし、高電流レベルで動作しているときは、デバイス内部でかなりの熱が発生する可能性があります。そのため、効率を最適化してLTC3536が最大定格出力電流を供給できるようにするため、デバイスの温度環境に注意深い検討を行う必要があります。特に、DDパッケージとMSOPパッケージのどちらの露出パッドもPC基板に半田付けし、PC基板はデバイスのパッケージからの放熱が最大になるように設計します。

ダイ温度が約165°Cを超えると、デバイスは過温度シャットダウン状態になって全てのスイッチングが停止します。ダイが約10°Cだけ冷えるまで、デバイスはディスエーブルされたままになります。ソフトスタート回路は過温度シャットダウン時に再初期化され、フォールト状態が解除されるとスムーズに回復します。

SHDNピンが外部でV<sub>IN</sub>より高いレベルにドライブされるときは、電流制限抵抗を使用します。SHDNピンが6Vの場合、1Mの抵抗で電流が6μAに制限されます。電流制限抵抗に加えて、SHDNピンからV<sub>IN</sub>にショットキー・ダイオードを接続することもできます。

## インダクタの選択

LTC3536の応用回路に使用されるインダクタの選択により、供給可能な最大出力電流、インダクタ電流リップルの大きさ、および電力変換効率が決まります。インダクタのDC直列抵抗は小さくなければなりません。つまり、出力電流能力と効率は妥協することになります。インダクタンス値を大きくするとインダクタ電流リップルが減るので、一般に出力電流能力が上がります。DC抵抗が一定の場合、インダクタンスの値を大きくす

## アプリケーション情報

ると、ピーク電流が減少して平均出力電流に近づくことにより効率が上がるのに、高RMS電流による抵抗損失が最小限に抑えられます。ただし、所定のインダクタ・ファミリー内の大きなインダクタは一般に直列抵抗が大きいので、この効率向上が抑制されます。

LTC3536のアプリケーションで使用されるインダクタは、飽和電流定格がワーストケースの平均インダクタ電流にリップル電流の半分を加えた電流を超えている必要があります。各動作モードのピーク・トゥ・ピーク・インダクタ電流リップルは以下の式から計算することができます。ここで、fはMHzを単位とするスイッチング周波数、LはμHを単位とするインダクタンスです。

$$\Delta I_{L(P-P)(BUCK)} = \frac{V_{OUT}}{f \cdot L} \left( \frac{V_{IN} - V_{OUT}}{V_{IN}} \right)$$

$$\Delta I_{L(P-P)(BOOST)} = \frac{V_{IN}}{f \cdot L} \left( \frac{V_{OUT} - V_{IN}}{V_{OUT}} \right)$$

電力変換効率に対する影響に加え、インダクタのDC抵抗は特に低入力電圧での昇降圧コンバータの最大出力能力にも影響を与えることがあります。降圧モードでは、昇降圧コンバータの出力電流はインダクタ電流が電流制限スレッショルドに達することによってだけ制限されます。ただし、昇圧モードでは、特に大きな昇圧比では、出力電流能力は電力段の合計抵抗損失によても制限されます。これらにはスイッチ抵抗、インダクタ抵抗およびPCBのトレース抵抗が含まれます。DC抵抗が大きいインダクタを使用すると、出力電流能力が、このデータシートの「標準的性能特性」のセクションに示されている値から低下することがあります。ガイドラインとして、ほとんどのアプリケーションでは、インダクタのDC抵抗を120mΩの標準パワースイッチ抵抗より大幅に小さくします。

最小インダクタ値は、ワーストケースの平均入力電流にリップル電流の半分を加えた値が入力電流制限スレッショルドに達しないようにする必要があります。1MHzのスイッチング周波数では、推奨する標準インダクタ値は4.7μHです。これより高いスイッチング周波数と低いスイッチング周波数では、同じ電

流リップルになるようにインダクタ値を変更します(2MHzでは2.2μH、300kHzでは15μH)。

インダクタのコア材と種類により、所定の電流定格でのインダクタのサイズと価格が異なります。シールドされた構造は、他の回路との干渉の可能性を最小限に抑えるので一般に適しています。インダクタの種類の選択は、特定のアプリケーションの価格、サイズ、およびEMIに対する要件に依存します。LTC3536の多くのアプリケーションに十分適したインダクタのサンプルを表1に示します。

表1. 推奨インダクタ

| メーカー                                                                                         | 部品/種類                                                                                                           |

|----------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|

| Coilcraft<br>847-639-6400<br><a href="http://www.coilcraft.com">www.coilcraft.com</a>        | LPO2506<br>LPS4012, LPS4018<br>MSS6122<br>MSS4020<br>MOS6020<br>DS1605, D01608<br>XPL4020<br>XAL4040<br>XFL4020 |

| Coiltronics<br><a href="http://www.cooperet.com">www.cooperet.com</a>                        | SD52, SD53<br>SD3114, SD311B                                                                                    |

| Murata<br>714-852-2001<br><a href="http://www.sumida.com">www.sumida.com</a>                 | LQH55D                                                                                                          |

| Sumida<br>847-956-0666<br><a href="http://www.sumida.com">www.sumida.com</a>                 | CDH40D11                                                                                                        |

| Taiyo Yuden<br><a href="http://www.t-yuden.com">www.t-yuden.com</a>                          | NP04S8<br>NR3015<br>NR4018                                                                                      |

| TDK<br>847-803-6100<br><a href="http://www.component.tdk.com">www.component.tdk.com</a>      | VLP, LTF<br>VLF, VLCF                                                                                           |

| Würth Elektronik<br>201-785-8800<br><a href="http://www.we-online.com">www.we-online.com</a> | WE-TPC Type S, M, MH                                                                                            |

### 出力コンデンサの選択

出力電圧リップルを最小限に抑えるため、昇降圧コンバータの出力には低ESRの出力コンデンサを使用します。積層セラミック・コンデンサはESRが小さく、実装面積の小さいものが入手できるので最適です。十分大きな値のコンデンサを選択して出力電圧リップルを許容レベルに下げます。

## アプリケーション情報

コンデンサのESRとESLを無視すると、ピーク・トゥ・ピーク出力電圧リップルは以下の式で計算することができます。ここで、 $f$ はMHzを単位とする周波数、 $C_{OUT}$ は $\mu$ Fを単位とする容量、 $I_{LOAD}$ はアンペアを単位とする出力電流です。

$$\Delta V_{(P-P)(BUCK)} = \frac{V_{OUT}}{8 \cdot f^2 \cdot L \cdot C_{OUT}} \left( \frac{V_{IN} - V_{OUT}}{V_{IN}} \right)$$

$$\Delta V_{(P-P)(BOOST)} = \frac{I_{LOAD}}{f \cdot C_{OUT}} \left( \frac{V_{OUT} - V_{IN}}{V_{OUT}} \right)$$

出力電流は昇圧モードでは不連続だと仮定すると、このモードのリップルは一般に降圧モードのリップルよりはるかに大きくなります。

出力容量の両端に生じる出力電圧リップルに加えて、出力コンデンサの内部抵抗の両端にも出力電圧リップルが生じます。ESRによって生じる出力電圧リップルは出力コンデンサの直列抵抗に比例します。

### 入力コンデンサの選択

$P_{VIN}$ ピンは全インダクタ電流を流し、デバイスの内部制御回路に電力を供給します。入力電圧リップルを最小限に抑えてデバイスに適切な動作をさせるため、少なくとも $10\mu$ Fの値の低ESRバイパス・コンデンサをこのピンにできるだけ近づけて配置します。このコンデンサを $P_{VIN}$ に接続するトレースとグランド・プレーンはできるだけ短くします。 $S_{VIN}$ ピンは内部回路に電力を供給します。全てのアプリケーションで、 $S_{VIN}$ と $P_{VIN}$ をPC基板上で相互接続する必要があります。

### 推奨する入力と出力のコンデンサ

LTC3536の入力と出力のフィルタに使用するコンデンサは、低ESRであり、スイッチング・コンバータが発生する大きなAC電流に対応した定格である必要があります。これはデバイスの適切な動作を維持し、出力電圧リップルを減らすのに重要です。

コンデンサの種類の選択は、主にコスト、サイズ、リーコ電流のトレードオフによって決まります。スイッチング・コンバータのアプリケーションには、小型、低ESR、および低リーコ電流であることから、多くの場合セラミック・コンデンサが使用されま

す。ただし、電力アプリケーション用に設計されたセラミック・コンデンサの多くは、DCバイアス電圧が上昇するにつれ、容量が定格値から大きく減少します。たとえば、小型表面実装セラミック・コンデンサがその定格電圧近くで動作するとき、その定格容量の50%以上を失うことは珍しくありません。そのため、場合によっては最大動作電圧で意図する容量を実現させるため、大きな値の容量や必要以上に電圧定格の高いコンデンサを使用する必要があります。応用回路で意図する容量を実現させるため、コンデンサ・メーカーの容量対DCバイアス電圧の曲線を必ず参照してください。

表2に示すコンデンサは、LTC3536の応用回路に十分適した小型表面実装セラミック・コンデンサの例です。温度に対する容量低下を最小限に抑えるため、示されている全てのコンデンサはX5RまたはX7Rの誘電体のものです。

表2. 代表的バイパス・コンデンサおよび出力コンデンサ

| 製品番号         | 値( $\mu$ F) | 電圧(V) | サイズ(mm)<br>LxWxH(実装面積) |

|--------------|-------------|-------|------------------------|

| AVX          |             |       |                        |

| 12066D106K   | 10          | 6.3   | 3.2×1.6×0.5 (1206)     |

| 12066D226K   | 22          | 6.3   | 3.2×1.6×0.5 (1206)     |

| 12066D476K   | 47          | 6.3   | 3.2×1.6×0.5 (1206)     |

| Kemet        |             |       |                        |

| C0603C106K9P | 10          | 6.3   | 1.6×0.8×0.8 (0603)     |

| C0805C226K9P | 22          | 6.3   | 2.0×1.25×1.25 (0805)   |

| C0805C476K9P | 47          | 6.3   | 2.0×1.25×1.25 (0805)   |

| Murata       |             |       |                        |

| GRM21        | 10          | 10    | 2.0×1.25×1.25 (0805)   |

| GRM21        | 22          | 6.3   | 2.0×1.25×1.25 (0805)   |

| TDK          |             |       |                        |

| C2102X5R0J   | 22          | 6.3   | 2.0×1.25×0.85 (0805)   |

| C2102X5R0J   | 47          | 6.3   | 2.0×1.25×1.25 (0805)   |

| Taiyo Yuden  |             |       |                        |

| JMK212BJ     | 22          | 6.3   | 2.0×1.25×0.85 (0805)   |

| JMK212BJ     | 47          | 6.3   | 2.0×1.25×0.85 (0805)   |

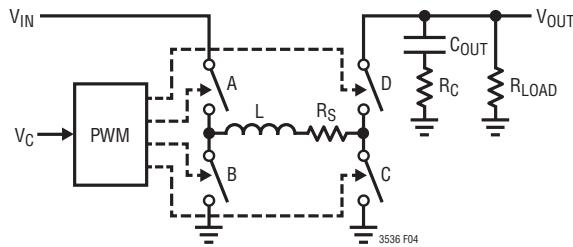

### 小信号モデル

LTC3536は電圧モード制御ループを使って出力電圧のレギュレーションを維持します。外部補償されたエラーアンプは $VC$ ピンをドライブして、パワースイッチの適切なデューティ・サイクルを発生します。外部補償ネットワークを使用することにより、広い範囲の出力電圧、スイッチング周波数、およびLTC3536

## アプリケーション情報

図4. 小信号モデル

がサポートする外付け部品の値に対する閉ループ特性を柔軟に最適化できます。

$V_{IN}$ は入力電源電圧、 $V_{OUT}$ は設定された出力電圧、 $L$ は外付け昇降圧インダクタ、 $C_{OUT}$ は出力コンデンサ、 $R_S$ は電力経路の直列抵抗(パワースイッチの平均抵抗の2倍とインダクタのDC抵抗の和として概算可能)、 $R_C$ は出力コンデンサのESRです。

### 降圧モード

昇降圧コンバータの小信号伝達関数は降圧モードと昇圧モードの動作で異なるので、両方の動作領域で確実に安定するように注意する必要があります。高い入力電圧から低い出力電圧に降圧するときコンバータは降圧モードで動作し、エラーアンプの出力 $V_C$ からコンバータの出力電圧への小信号伝達関数は次式で与えられます。

$$\left. \frac{V_{OUT}(s)}{V_C} \right|_{Buck Mode} = 2.64 \cdot V_{IN} \cdot \frac{1 + sR_C C_{OUT}}{1 + \frac{s}{\omega_0 Q} + \left( \frac{s}{\omega_0} \right)^2}$$

この伝達関数には、出力コンデンサのESRによって生じる1個のゼロと1対の共振ポールがあります。ほとんどのアプリケーションでは、出力電圧リップルを許容レベルに下げるため、ESRが非常に小さい出力コンデンサが使用されます。コンデンサのESRのこのように小さい値は非常に高い周波数のゼロを生じるので、このゼロは帰還ループの補償に大きな影響を与えるには一般に周波数が高すぎます。

降圧モードの伝達関数の分母は電力段の $L C_{OUT}$ フィルタによって生じる1対の共振ポールを示しています。電力段の共振周波数 $f_0$ は次式で与えられます。ここで、 $L$ はヘンリーを単位とするインダクタの値です。

$$\omega_0 = \frac{1}{\sqrt{L C_{OUT}}}, f_0 = \frac{1}{2\pi\sqrt{L C_{OUT}}}$$

クオリティ・ファクタ $Q$ は電圧ループの補償に大きく影響します。高い $Q$ は共振周波数の近くで位相の急激な減少を生じるからです。クオリティ・ファクタは電力段の減衰量に対して反比例の関係にあり、電力段の平均直列抵抗 $R_S$ によって大きく影響されます。 $R_S$ の値が小さいと $Q$ が増加して共振周波数の近くで位相が急激に遅延するので、位相ブーストを強めるか、または適切な位相マージンを維持するために帯域幅を狭める必要があります。

$$Q = \frac{\sqrt{L C_{OUT}}}{C_{OUT} (R_C + R_S) + \frac{L}{R_{LOAD}}}$$

### 昇圧モード

低い入力電圧から高い出力電圧に昇圧するとき昇降圧コンバータは昇圧モードで動作し、制御電圧 $V_C$ から出力電圧への小信号伝達関数は次式で与えられます。

$$\left. \frac{V_{OUT}(s)}{V_C} \right|_{Boost Mode} = 2.64 \cdot G \cdot \frac{(1 + sR_C C_{OUT}) \left( 1 - \frac{s}{\omega_Z} \right)}{1 + \frac{s}{\omega_0 Q} + \left( \frac{s}{\omega_0} \right)^2}$$

昇圧モード動作では、降圧モードと同様、1対の共振ポールと出力コンデンサのESRによって生じる1個のゼロによって伝達関数の特性が決まります。ただし、これらに加えて右半平面のゼロがあり、高い周波数では利得が増加し、位相が遅延します。その結果、十分な位相マージンを維持するため、昇圧

## アプリケーション情報

モード動作のクロスオーバー周波数は一般に降圧モードの場合より低く設定する必要があります。

$$G = V_{IN} \cdot \frac{R_{LOAD}}{R_S} \cdot \frac{1 - \frac{R_S}{R_{LOAD}} \cdot \left( \frac{V_{OUT}}{V_{IN}} \right)^2}{1 + \frac{R_{LOAD}}{R_S} \cdot \left( \frac{V_{IN}}{V_{OUT}} \right)^2}$$

$$\omega_0 = \sqrt{\frac{R_S + R_{LOAD} \left( \frac{V_{IN}}{V_{OUT}} \right)^2}{LC_{OUT} (R_{LOAD} + R_C)}}$$

昇圧モード動作では、右半平面のゼロの周波数  $f_Z$  は次式で与えられます。右半平面のゼロの周波数は高負荷および大きなインダクタでは減少します。

$$\omega_Z = \frac{\left( \frac{V_{IN}}{V_{OUT}} \right)^2 R_{LOAD} - R_S}{L}, f_Z = \frac{\left( \frac{V_{IN}}{V_{OUT}} \right)^2 R_{LOAD} - R_S}{2\pi L}$$

最後に、昇圧モード動作の電力段のクオリティ・ファクタの大きさは次式で与えられます。

$$Q = \frac{\sqrt{LC_{OUT} (R_{LOAD} + R_C)} \sqrt{R_S + R_{LOAD} \left( \frac{V_{IN}}{V_{OUT}} \right)^2}}{L + C_{OUT} R_{LOAD} R_C \left( \frac{V_{IN}}{V_{OUT}} \right)^2 + R_S C_{OUT} (R_{LOAD} + R_C)}$$

## 昇降圧モード

このモードでは、コンバータは昇降圧モードで動作し、制御電圧  $V_C$  から出力電圧への小信号伝達関数は次式で与えられます。

$$\frac{V_{OUT}(s)}{V_C} \Big|_{\text{Buck-Boost Mode}} = \frac{17.62 \cdot G \cdot \frac{(1+sR_C C_{OUT}) \left( 1 - \frac{s}{\omega_Z} \right)}{1 + \frac{s}{\omega_0 Q} + \left( \frac{s}{\omega_0} \right)^2}}{1 + \frac{s}{\omega_0 Q} + \left( \frac{s}{\omega_0} \right)^2}$$

昇降圧モード動作でも、降圧モードおよび右半平面のゼロと同様、1対の共振ポールと出力コンデンサのESRによって生じる1個のゼロによって伝達関数の特性が決まります。

$$G = \frac{0.15 \cdot V_{OUT} (R_{LOAD} \cdot \epsilon^2 \cdot 1.85 - R_S \cdot (1.85 - \epsilon))}{\epsilon \cdot (1.85 - \epsilon) \cdot (R_S + R_{LOAD} \cdot \epsilon^2)}$$

ここで、変数  $\epsilon$  は次式で定義されます。

$$\epsilon = \frac{V_{IN} \cdot 1.85}{V_{OUT} + V_{IN}}$$

$$\omega_0 = \sqrt{\frac{R_S + R_{LOAD} \cdot \epsilon^2}{LC_{OUT} (R_{LOAD} + R_C)}}$$

昇降圧モード動作では、右半平面のゼロの周波数  $f_Z$  は次式で与えられます。右半平面のゼロの周波数は高負荷および大きなインダクタでは減少します。

$$\omega_Z = \frac{1.85 \cdot \epsilon^2 R_{LOAD} - R_S \cdot (1.85 - \epsilon)}{L \cdot (1.85 - \epsilon)}$$

## アプリケーション情報

最後に、昇降圧モード動作の電力段のクオリティ・ファクタの大きさは次式で与えられます。

$$Q = \frac{\sqrt{LC_{OUT}(R_{LOAD} + R_C)} \sqrt{R_S + R_{LOAD} \cdot \epsilon^2}}{L + C_{OUT}R_{LOAD}R_C \cdot \epsilon^2 + R_S C_{OUT}(R_{LOAD} + R_C)}$$

### 電圧ループの補償

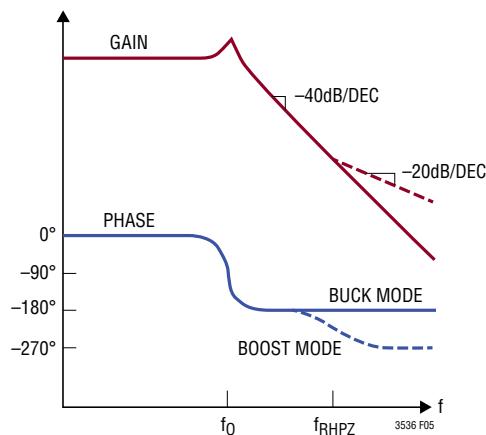

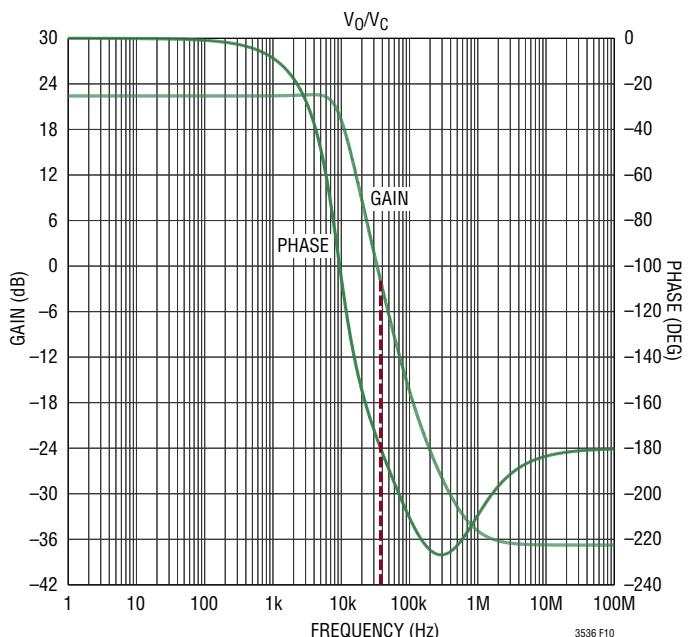

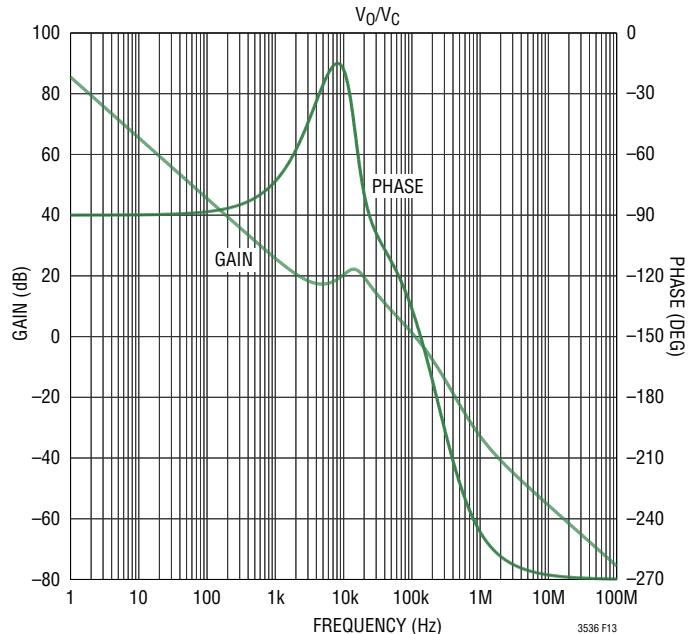

エラーアンプの出力 VC から出力電圧への伝達関数が、図5のボード線図に示すように、1組の共振ポールと出力コンデンサのESRによって生じる可能性のあるゼロによって特性が決まることを、LTC3536の小信号モデルは明らかにしています。昇圧モード動作では、右半平面に追加のゼロがあり、高い周波数では位相遅延を生じて利得が増加します。一般に、ループのクロスオーバー周波数が十分低くて右半平面のゼロによる位相の遅延が最小限に抑えられるように、補償ネットワークは設計されます。降圧モードの低周波数利得は一定ですが、昇圧モードでは  $V_{IN}$  と  $V_{OUT}$  の両方に伴って変化します。

図5. 昇降圧コンバータのボード線図

充電など最適化された出力電圧の過渡応答を必要としないアプリケーションでは、図6に示すようなシンプルなタイプIの補償ネットワークを使って電圧ループを安定化することができます。十分な位相マージンを確保するため、制御ループのクロスオーバー周波数が共振周波数より十分低くなるようにエラーアンプの利得を十分小さくする必要があります。

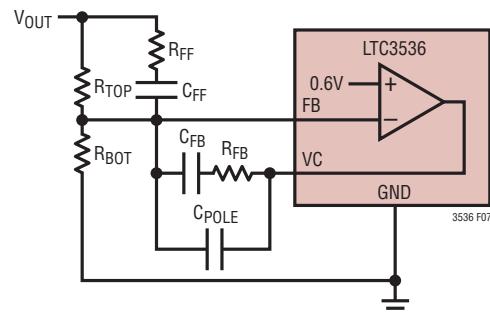

ほとんどのアプリケーションでは、タイプIで補償されたループが狭帯域なので、十分な過渡応答性能が得られません。広い帯域幅の帰還ループを実現し、過渡応答を最適化し、出力コンデンサのサイズを最小限に抑えるには、図7に示すようなタイプIIIの補償ネットワークが必要です。

図6. タイプIの補償を備えたエラーアンプ

図7. タイプIIIの補償を備えたエラーアンプ

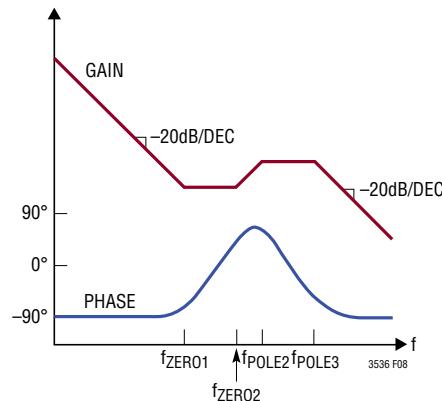

タイプIIIの補償ネットワークのボード線図を図8に示します。タイプIIIの補償ネットワークは原点近くのポールを与え、DCで非常に高いループ利得を生じ、安定化電圧の定常状態の誤差を最小限に抑えます。f<sub>ZERO1</sub>とf<sub>ZERO2</sub>に位置する2個のゼロは十分な位相ブーストを与えるので、ループのクロスオーバー周波数を電力段の共振周波数  $f_0$  より上に設定することができます。タイプIIIの補償ネットワークは2番目と3番目のポールも生じます。周波数  $f_{POLE2}$  に位置する2番目のポールはエラーアンプの利得をゼロ勾配に減少させて、ループのクロスオーバーが高すぎる周波数に拡張するのを防ぎます。周波数  $f_{POLE3}$  に位置する3番目のポールは高周波数スイッチング・ノイズを減衰させます。

## アプリケーション情報

図8. タイプ III の補償のボード線図

補償されたタイプ III のエラーアンプの、抵抗分割器の入力からエラーアンプの出力 VC への伝達関数は次のとおりです。

$$\frac{V_{C(S)}}{V_{OUT(S)}} = G_{EA} \frac{\left(1 + \frac{s}{2\pi f_{ZERO1}}\right) \left(1 + \frac{s}{2\pi f_{ZERO2}}\right)}{s \left(1 + \frac{s}{2\pi f_{POLE1}}\right) \left(1 + \frac{s}{2\pi f_{POLE2}}\right)}$$

エラーアンプの利得は次式で与えられます。 $C_{FB}$  は一般に  $C_{POLE}$  よりはるかに値が大きいので、ほとんどの場合、簡単な近似値で十分高精度です。

$$G_{EA} = \frac{1}{R_{TOP} (C_{FB} + C_{POLE})} \approx \frac{1}{R_{TOP} C_{FB}}$$

タイプ III の補償ネットワークのポールとゼロの周波数は以下の式を使って計算することができます。ここで、全ての周波数の単位は Hz、抵抗の単位はオーム、容量の単位はファラッドです。

$$f_{ZERO1} = \frac{1}{2\pi R_{FB} C_{FB}}$$

$$f_{ZERO2} = \frac{1}{2\pi (R_{TOP} + R_{FF}) C_{FF}} \approx \frac{1}{2\pi R_{TOP} C_{FF}}$$

$$f_{POLE2} = \frac{C_{FB} + C_{POLE}}{2\pi C_{FB} C_{POLE} R_{FB}} \approx \frac{1}{2\pi C_{POLE} R_{FB}}$$

$$f_{POLE3} = \frac{1}{2\pi C_{FF} R_{FF}}$$

ほとんどのアプリケーションでは、ループのクロスオーバー周波数が電力段の共振周波数を上回っても、昇圧モードの右半平面のゼロを十分下回るように補償ネットワークが設計され、追加の位相遅延を最小限に抑えます。クロスオーバー周波数が決定されると、位相マージンを最大にするため、補償ネットワークによって与えられる位相ブーストはそのポイントを中心にします。ゼロと高次のポールの周波数が大きく離れていると、大きなピーク位相ブーストが与えられます。エラーアンプの利得も増加して、ループのクロスオーバー周波数を押し上げることがあります。

電力段の Q はどれだけ急速に電力段の 180° の位相遅延が生じるかを決定するので、この Q は補償ネットワークの設計に大きく影響する可能性があります。直列抵抗  $R_S$  の値が非常に小さいと Q が高くなり、急峻な位相遅延が生じます。このような場合、共振周波数より上で電力段の位相は急速に -180° に遅延し、総位相マージンは補償ネットワークによって与える必要があります。

ただし、電力段の損失が大きいと (大きな  $R_S$ )、Q ファクタは下がり、位相遅延は徐々に起きます。その結果、電力段の位相はクロスオーバー周波数で -180° にそれほど近づかず、補償ネットワークに要求される位相ブーストは小さくなります。

LTC3536 のエラーアンプは、スイッチング・ノイズを除去してそれが制御ループに干渉するのを防ぐため、固定最大帯域幅になるように設計されています。周波数領域の観点からは、図9に示すように、これは追加の 1 ポールと見ることができます。このポールの公称周波数は 400kHz です。約 40kHz より低い標準

図9. 内部ループ・フィルタ

## アプリケーション情報

的ループのクロスオーバー周波数の場合、この追加ポールに起因する位相は一般にごくわずかです(40kHzでは約-5.7°)。ただし、クロスオーバー周波数の高いループでは、この追加の位相遅延を考慮に入れて補償ネットワークを設計します。

### ループ補償の例

このセクションでは、LTC3536の標準的な応用回路の補償ネットワークの設計を例を使って説明します。この例では、1.8V～5.5Vの範囲の入力電力源から300mAの負荷に電力を供給する能力のある3.3V安定化出力電圧を発生します。効率を最適化するため、1MHzのスイッチング周波数を選択しました。このアプリケーションでは、最大インダクタ電流リップルは最大入力電圧で発生します。ワーストケースのインダクタ電流リップルを制限するため、4.7μHのインダクタの値が選択されました。値が22μFの低ESR出力コンデンサが指定され、(ワーストケースの昇圧比と最大負荷電流で生じる)約10mVのワーストケースの出力電圧リップルを生じます。まとめると、このLTC3536の応用例の電力段の主な仕様は以下のとおりです。

$f = 1\text{MHz}$

$V_{IN} = 1.8\text{V} \sim 5.5\text{V}$

$V_{OUT} = 3.3\text{V}$  (300mA)

$C_{OUT} = 22\mu\text{F}$ 、

$R_C = 10\text{m}\Omega$

$L = 4.7\mu\text{H}$ 、

$R_L = 60\text{m}\Omega$

電力段のパラメータが規定されたので、補償ネットワークを設計することができます。妥当な方法として、このワーストケースの箇所で補償ネットワークを設計し、他の動作条件全体で十分な位相マージンが存在することを検証します。この応用例( $V_{IN} = 1.8\text{V}$ 、最大300mAの負荷電流)では、右半平面のゼロは100kHzに位置し、これが制御ループの帯域幅を決定する支配的要素になります。

補償ネットワークの設計の最初のステップとして、補償されるループの目標クロスオーバー周波数を決定します。この例では、パラメータのばらつきや動作条件の変動に対して適切な性能が得られるように、60°の位相マージンで設計します。その結果、目標クロスオーバー周波数 $f_C$ はそこで昇降圧コンバータの位相が-180°に達するポイントになります。この周波

数を解析して求めることは、電力段の共振のQファクタに大きく影響されるため、一般に困難です。そのため、図10に示すように、昇降圧コンバータのボード線図から求めるのが最善です。このボード線図は前に規定した電力段のパラメータを使ったLTC3536昇降圧コンバータのものであり、LTSpice®ソフトウェアを使って小信号モデルの式から作成しました。

この場合、位相は37.8kHzで-180°に達するので、 $f_C = 37.8\text{kHz}$ が補償ループの目標クロスオーバー周波数になります。図9のボード線図から、目標クロスオーバー周波数での電力段の利得は-2dBです。

設計プロセスのこのポイントで、補償ネットワークに対して設定された3つの制約があります。その利得は $f_C = 37.8\text{kHz}$ で+2dB、ピーク位相ブーストは60°、位相ブーストの中心は $f_C = 37.8\text{kHz}$ でなければなりません。

解析手法を使って、望みの位相ブースト、中心周波数、および利得を備えた補償ネットワークを設計することができます。この手順は、タイプIIIの補償ネットワークの自由度が大きいため、一般に煩雑になる可能性があります。ただし、両方の補償のゼロが同じ周波数 $f_Z$ で生じ、両方の高次ポール( $f_{POLE2}$ と

図10. コンバータのボード線図、 $V_{IN} = 1.8\text{V}$ 、 $I_{LOAD} = 300\text{mA}$

## アプリケーション情報

$f_{POLE3}$ が共通の周波数  $f_P$  で生じると仮定することにより、設計プロセスを簡素化することができます。

これは補償ネットワークを決定するための妥当な出発点です。ただし、ループ全体のボード線図を全動作条件および部品の値のばらつきに対してチェックし、全ての場合に十分な位相マージンと利得マージンが存在することを確認します。

妥当な選択として、ポールの周波数  $f_P$  がゼロの周波数  $f_Z$  の約 50 倍になるように選択します。これにより、前に仮定したように、約  $\Phi_{MAX} = 60^\circ$  のピーク位相ブーストが与えられます。次に、ピーク位相が目標クロスオーバー周波数で生じるように位相ブーストの中心を定める必要があります。最大位相ブーストの周波数  $f_C$  は次式のように、ポールとゼロの周波数の相乗平均です。

$$f_C = \sqrt{f_P \cdot f_Z} = \sqrt{50 \cdot f_Z^2} = 7 \cdot f_Z$$

したがって、ポールとゼロ周波数の間に 50 倍の開きがある場合に位相ブーストの中心を定めるには、以下の式で与えられているように、ゼロをクロスオーバー周波数の  $1/7$  に位置させ、ポールをクロスオーバー周波数の 7 倍に位置させます。

$$f_Z = \frac{1}{7} \cdot f_C = \frac{1}{7} \cdot (37.8 \text{kHz}) = 5.4 \text{kHz}$$

$$f_P = 7 \cdot f_C = 7 \cdot (37.8 \text{kHz}) = 264.6 \text{kHz}$$

ポールとゼロのこの配置により、クロスオーバー周波数  $f_C$  を中心とした  $60^\circ$  のピーク位相ブーストが生じます。次に、望みの目標クロスオーバー周波数を実現するため、最大位相ブースト・ポイントでの補償ネットワークの利得  $G_{CENTER}$  を  $+2 \text{dB}$  に設定する必要があります。最大位相利得のポイントでの補償されたエラーアンプの利得は次式で与えられます。

$$G_{CENTER} = 10 \log \left[ \frac{2\pi f_P}{(2\pi f_Z)^3 (R_{TOP} C_{FB})^2} \right]$$

ポール周波数とゼロ周波数の間の 50 倍の開きを仮定すると、上式は次式に簡素化されます。

$$G_{CENTER} = 20 \log \left[ \frac{50}{(2\pi f_C) (R_{TOP} C_{FB})} \right]$$

補償部品の値を定める最初のステップとして、抵抗分割器を流れる消費電流を許容できる程度に低くする  $R_{TOP}$  の値を選択します。妥当な選択値は  $R_{TOP} = 845 \text{k}\Omega$  です。次に、 $C_{FB}$  の値を求めることができます。

$$G_{CENTER} = 2 \text{dB}$$

$$C_{FB} \frac{50}{2\pi \cdot (37.8 \text{kHz}) \cdot 845 \text{k}\Omega \cdot 10^{\frac{20}{20}}} = 198 \text{pF} \approx 180 \text{pF}$$

前のセクションに与えられているポールとゼロの周波数の式を使って、補償ポールを  $264.6 \text{kHz}$  に、ゼロを  $5.4 \text{kHz}$  に設定することができます。最初のゼロの周波数  $f_{ZERO1}$  を  $5.4 \text{kHz}$  に設定すると、 $R_{FB}$  は次の値になります。

$$R_{FB} = \frac{1}{2\pi \cdot (180 \text{pF}) \cdot 5.4 \text{kHz}} = 163 \text{k}\Omega \approx 162 \text{k}\Omega$$

これにより、自由なパラメータ  $C_{POLE}$  が次のように、周波数  $f_{POLE1}$  を  $264.6 \text{kHz}$  の共通ポール周波数に設定します。

$$C_{POLE} = \frac{1}{2\pi \cdot (162 \text{k}\Omega) \cdot 264.6 \text{kHz}} = 3.71 \text{pF} \approx 3.9 \text{pF}$$

次に、 $C_{FF}$  を選択して、2 番目のゼロ  $f_{ZERO2}$  を  $5.4 \text{kHz}$  の共通ゼロ周波数に設定することができます。

$$C_{FF} = \frac{1}{2\pi \cdot (845 \text{k}\Omega) \cdot 5.4 \text{kHz}} = 34.9 \text{pF} \approx 33 \text{pF}$$

最後に、抵抗値  $R_{FF}$  を選択して 2 番目のポールを  $264.6 \text{kHz}$  に配置することができます。

$$R_{FF} = \frac{1}{2\pi \cdot (33 \text{pF}) \cdot 264.6 \text{kHz}} = 18.2 \text{k}\Omega$$

## アプリケーション情報

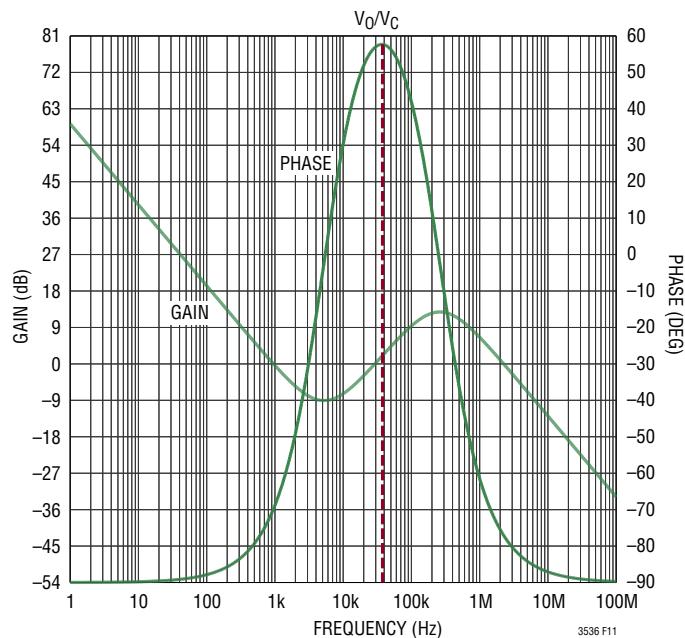

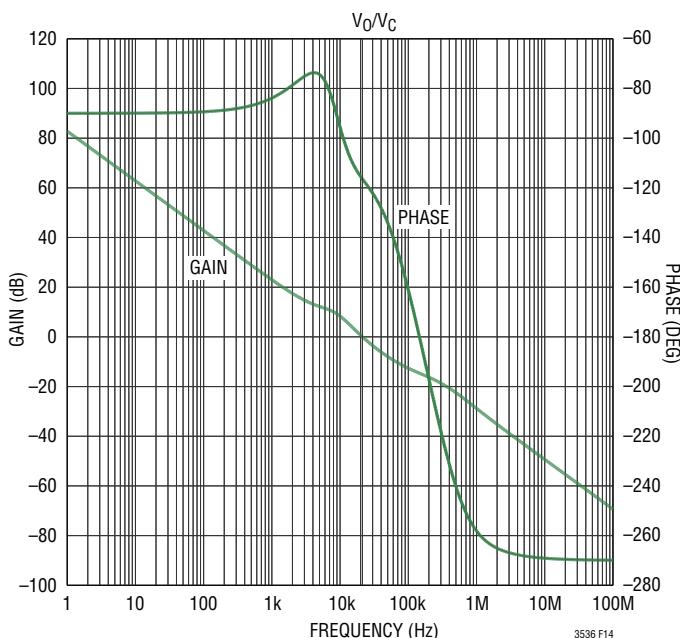

設計された補償部品の値を使ったエラーアンプのボード線図を図11に示します。ボード線図から、ピーク位相が37.8kHzに生じ、そのポイントの位相ブーストが約60°であることが確認できます。さらに、ピーク位相周波数での利得は2dBで、設計目標に近い値です。

図11. 補償されたエラーアンプのボード線図

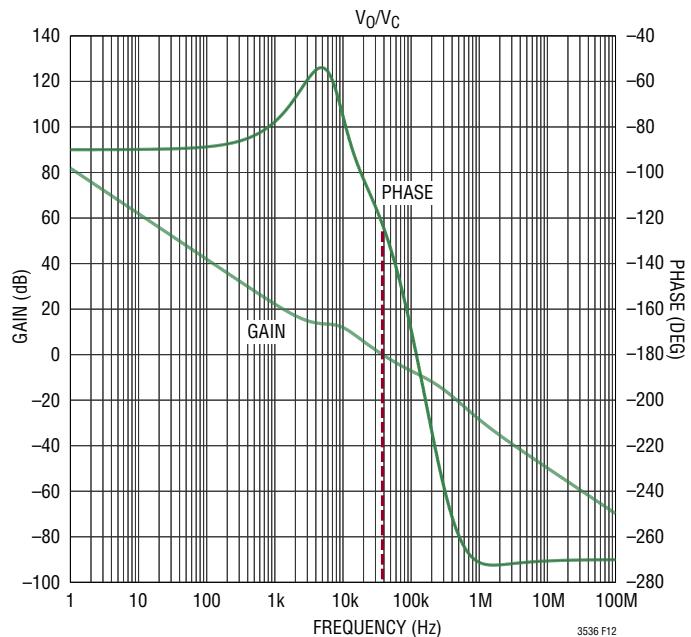

設計プロセスの最後のステップとして、設計された補償ネットワークを使ってループ全体のボード線図を計算し、その位相マージンとクロスオーバー周波数を確認します。この例のループ全体のボード線図を図12に示します。ループのクロスオーバー周波数は37.8kHzで設計目標に一致し、位相マージンは約60°です。

ループ全体のボード線図を全動作条件および部品の値のばらつきに対してチェックし、全ての場合に十分な位相マージンと利得マージンが存在することを確認します。時間領域のシミュレーションによって、また実際の回路でコンバータの過渡応答を評価して、ループの安定性も確認します。

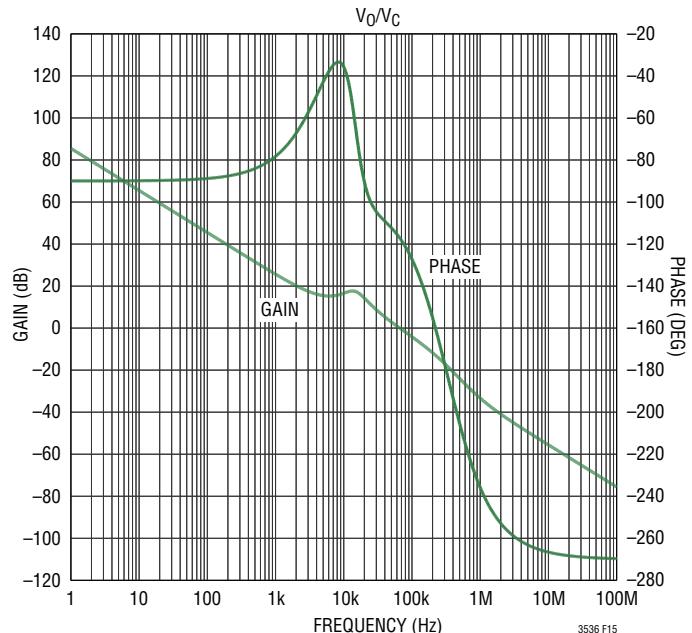

この例では $V_{IN}$ が1.8Vから5.5Vまで変化します。昇降圧動作( $0.85 \cdot V_{OUT} < V_{IN} < V_{OUT}/0.85$ の場合)では、ループ全体のボード線図は $V_{IN} = V_{OUT} = 3.3V$ で40°の位相マージンを示します。実際、このモードの動作ではDC利得が増加し、多くの場合、これが補償する最も困難な領域になります。

図12. 昇圧動作モードのループ全体のボード線図

図13. 昇降圧動作モードのループ全体のボード線図

## アプリケーション情報

昇降圧モードの動作でも安定性を向上させるため、次のように2個の補償ゼロを異なる周波数に移すことができます。

$$f_{ZERO2} = \frac{1}{2\pi R_{TOP} C_{FF}} = 5.4\text{kHz}$$

$$f_{ZERO1} = \frac{1}{2\pi R_{FB} C_{FB}} = 2 \cdot f_{ZERO2} = 10.8\text{kHz}$$

新たな $R_{FB}$ 値は次のようにになります。

$$R_{FB} = \frac{1}{2\pi \cdot (180\text{pF}) \cdot 10.8\text{kHz}} = 81.9\text{k}\Omega \approx 80.6\text{k}\Omega$$

結果として、 $f_{POLE2}$ は高い周波数に移ります。

$$f_{POLE2} = \frac{1}{2\pi C_{POLE} R_{FB}} = 532\text{kHz}$$

図14と図15から分かるように、このとき安定性は昇降圧領域( $V_{IN} = 3\text{V}$ )では向上し、昇圧領域( $V_{IN} = 1.8\text{V}$ )では良好に保たれます。

降圧モードには右半平面のゼロは存在せず、一般に安定になります。

図14. 昇圧動作モードのループ全体のボード線図

図15. 昇降圧動作モードのループ全体のボード線図

## 出力電圧の設定

出力電圧は、抵抗 $R_{TOP}$ および $R_{BOT}$ で構成される外付け抵抗分割器によって設定されます。抵抗分割器の値は次式に従って出力の安定化電圧を決めます。

$$V_{OUT} = 0.6 \left( 1 + \frac{R_{TOP}}{R_{BOT}} \right) V$$

出力電圧の設定に加えて、 $R_{TOP}$ の値は補償ネットワークの動作を制御する手段になります。この抵抗の値を変更するときは、これによって補償ネットワークが影響されることを理解する注意が必要です。「入力電流制限とピーク電流制限」のセクションで説明するように、「電流制限機能が最も有効に働くには、FBからグランドへのテブナン抵抗( $R_{TOP}/R_{BOT}$ )が100kを超えるようにします」。

図16.FBの抵抗ネットワーク

## アプリケーション情報

### スイッチング周波数の選択

スイッチング周波数を高くすると、小さなインダクタとともに小さな入力と出力のフィルタ・コンデンサを使用することができる。ソリューション・サイズが小さくなつて部品の高さが低くなります。ただし、スイッチング周波数を高くすることは、一般にスイッチング損失が増すことによって変換効率を低下させることになります。さらに、このデータシートの「標準的性能特性」の最大デューティサイクルとスイッチング周波数の曲線に示されているように、スイッチング周波数が高いと最大電圧昇圧比はわずかに減少します。

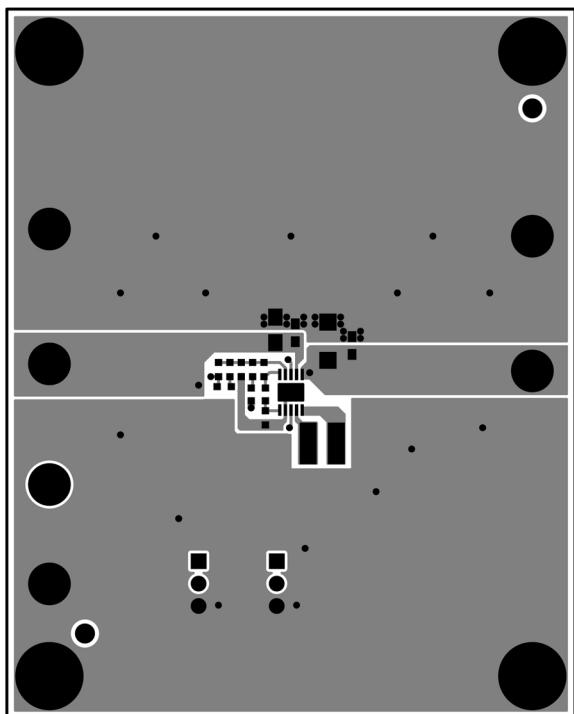

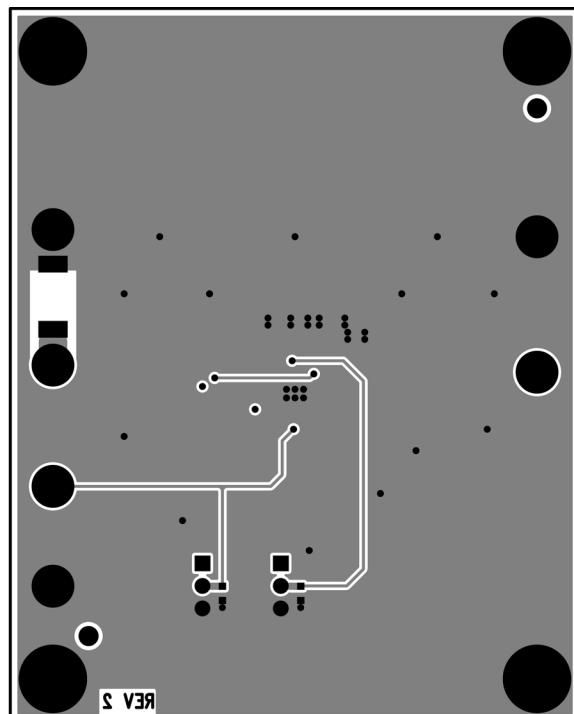

### PCBのレイアウトに関する検討項目

LTC3536の昇降圧コンバータは大きな電流を高い周波数でスイッチングします。ノイズのない安定した効率の良い応用回路にするには、PC基板レイアウトに特別の注意が必要です。主なガイドラインを以下にまとめます。

- 循環する全ての高電流経路の寄生インダクタンスと寄生抵抗を最小限に抑えます。これは配線をできるだけ短く、幅を広くすることによって実現できます。コンデンサのグランドはできるだけ短い配線を通し、ビアを使ってグランド・プレーンに接続します。PV<sub>IN</sub>とV<sub>OUT</sub>のバイパス・コンデンサはできるだけデバイスの近くに配置し、グランドへの経路をできるだけ短くします。

- DDパッケージのLTC3536では、露出パッドが電源グランドに電気的に接続されています。多数のビアでバックパッドを直接グランド・プレーンに接続します。さらに、バックパッドに接続されるメタルを最大にすると熱環境が改善され、どちらのパッケージのデバイスの電力処理能力も改善されます。

- 接続箇所に高電流が流れる部品は全てグランド・プレーン上に配置し、ループの断面積を最小限に抑えます。これにより、EMIが最小になります。

- 高電流が流れる全ての部品への接続をできるだけ幅広くして直列抵抗を減らします。これにより、効率が改善され、昇降圧コンバータの出力電流能力が最大化されます。

- グランド・プレーンの大きな循環電流がLTC3536の動作を妨害しないように、全ての小信号グランドは専用の4端子配線を経由してGNDに直接戻します。これには、RTピンの抵抗のグランド接続と帰還ネットワークのグランド接続が含まれます。

- 高インピーダンスでノイズに敏感な入力FBおよびRTに接続する配線は、ノイズの混入を減らすためにできるだけ短くします。例は、デバイスを外部クロックに同期させた場合のMODEからの配線です。

図17a.4層PCBの例のファブリケーション・レイヤ

図17b.PCBの例のトップ層

図17c.PCBの例のボトム層

## 標準的応用例

300kHz高効率リチウムイオン・バッテリから3.6V/1A、

パルスによるマニュアル・モード制御

効率(3.6V、300kHz)と負荷電流

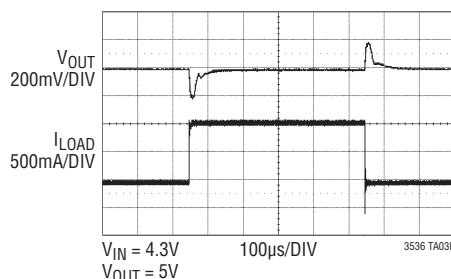

## USBから5Vのコンバータ

## 負荷ステップ

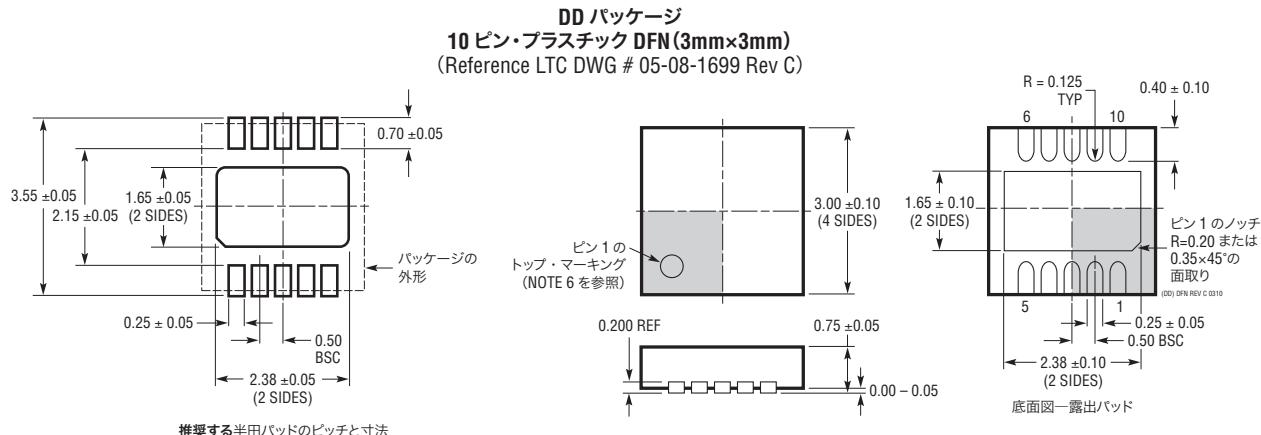

## パッケージ

最新のパッケージ図面については、<http://www.linear-tech.co.jp/designtools/packaging/>をご覧ください。

(DD DFN REV C110)

底面図—露出パッド

**MSE パッケージ**

**12 ピン・プラスチック MSOP、露出ダイ・パッド**

(Reference LTC DWG # 05-08-1666 Rev D)

MSOP (MSE12) 0910 REV D

## 改訂履歴

| REV | 日付    | 概要                                                                                                                                                                                                                                                                                               | ページ番号                       |

|-----|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|

| A   | 11/11 | 「特長」に新項目「シャットダウン時の出力切断」を追加。<br>「絶対最大定格」セクションで(Note1、2)を(Note 1)に(Note2、3)を(Note 2)に変更。<br>電気的特性表のError Amplifier Sink CurrentとError Amplifier Source Currentに条件を追加。<br>「ピン機能」のPGNDピンの記述に露出パッド・ピン13を追加、最後の文を削除。<br>ピーク電流制限コンパレータの負入力を3.4Vに、UVLOコンパレータの負入力を1.75Vに変更。<br>「動作」セクションに新セクション「出力切断」を追加。 | 1<br>2<br>3<br>7<br>8<br>12 |

## 標準的応用例

### バックアップ電源

## 関連製品

| 製品番号    | 説明                                                                      | 注釈                                                                                                                               |

|---------|-------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|

| LTC3440 | 600mA (I <sub>OUT</sub> )、2MHz 同期整流式昇降圧DC/DCコンバータ                       | 95%の効率、V <sub>IN</sub> :2.5V ~ 5.5V、V <sub>OUT(MIN)</sub> = 2.5V、I <sub>Q</sub> = 25μA、I <sub>SD</sub> ≤ 1μA、10ピンMSOPおよびDFNパッケージ |

| LTC3442 | 1.2A (I <sub>OUT</sub> )、2MHz 同期整流式昇降圧DC/DCコンバータ、プログラム可能なBurst Mode動作付き | V <sub>IN</sub> :2.4V ~ 5.5V、V <sub>OUT</sub> :2.4 ~ 5.25V、I <sub>Q</sub> = 35μA、I <sub>SD</sub> ≤ 1μA、DFNパッケージ                  |

| LTC3444 | 400mA (I <sub>OUT</sub> )、2MHz 同期整流式昇降圧DC/DCコンバータ                       | V <sub>IN</sub> :2.75V ~ 5.5V、V <sub>OUT</sub> :0.5 ~ 5V、I <sub>Q</sub> = 35μA、I <sub>SD</sub> ≤ 1μA、DFNパッケージ                    |

| LTC3101 | 入力電圧範囲の広い複数出力DC/DCコンバータとPowerPath™コントローラ                                | V <sub>IN</sub> :1.8V ~ 5.5V、V <sub>OUT</sub> :1.5V ~ 5.25V、I <sub>Q</sub> = 38μA、I <sub>SD</sub> ≤ 15μA、QFNパッケージ                |

| LTC3113 | 3A (I <sub>OUT</sub> )、2MHz 同期整流式昇降圧DC/DCコンバータ                          | V <sub>IN</sub> :1.8V ~ 5.5V、V <sub>OUT</sub> :1.8V ~ 5.25V、I <sub>Q</sub> = 30μA、I <sub>SD</sub> < 1μA、DFNおよびTSSOPパッケージ         |

| LTC3533 | 2A (I <sub>OUT</sub> )、2MHz 同期整流式昇降圧DC/DCコンバータ                          | V <sub>IN</sub> :1.8V ~ 5.5V、V <sub>OUT</sub> :1.8V ~ 5.25V、I <sub>Q</sub> = 40μA、I <sub>SD</sub> < 1QA、DFNパッケージ                 |

| LTC3534 | 7V、500mA (I <sub>OUT</sub> )、1MHz 同期整流式昇降圧DC/DCコンバータ                    | 94%の効率、V <sub>IN</sub> :2.4V ~ 7V、V <sub>OUT</sub> :1.8V ~ 7V、I <sub>Q</sub> = 25μA、I <sub>SD</sub> < 1μA、DFNおよびGNパッケージ          |

| LTC3530 | 600mA (I <sub>OUT</sub> )、2MHz 同期整流式昇降圧DC/DCコンバータ                       | V <sub>IN</sub> :1.8V ~ 5.5V、V <sub>OUT</sub> :1.8V ~ 5.25V、I <sub>Q</sub> = 12μA、I <sub>SD</sub> < 2μA、QFNパッケージ                 |

| LTC3112 | 2.5A (I <sub>OUT</sub> )、15V 同期整流式昇降圧DC/DCコンバータ                         | V <sub>IN</sub> :2.7V ~ 15V、V <sub>OUT</sub> :2.5V ~ 14V、I <sub>Q</sub> = 40μA、I <sub>SD</sub> < 1μA、DFNおよびTSSOPパッケージ            |

| LTC3127 | 1A (I <sub>OUT</sub> )、1.2MHz 同期整流式昇降圧DC/DCコンバータ、プログラム可能な入力電流制限付き       | 96%の効率、V <sub>IN</sub> :1.8V ~ 5.5V、V <sub>OUT</sub> :1.8V ~ 5.25V、I <sub>Q</sub> = 30μA、I <sub>SD</sub> < 4μA、DFNおよびMSOPパッケージ   |

| LTC3780 | 高効率、同期整流式4スイッチ昇降圧コントローラ                                                 | 98%の効率、V <sub>IN</sub> :4V ~ 36V、V <sub>OUT</sub> :0.8V < V <sub>OUT</sub> < 30V、I <sub>SD</sub> = 55μA、SSOPおよびQFNパッケージ          |

| LTC3785 | 10V、高効率、同期整流式、No RSENSE™、昇降圧コントローラ                                      | 96%の効率、V <sub>IN</sub> およびV <sub>OUT</sub> :2.7V ~ 10V、I <sub>SD</sub> = 15μA、I <sub>Q</sub> = 86μA、QFNパッケージ                     |

| LTC3789 | 高効率、同期整流式4スイッチ昇降圧コントローラ                                                 | 98%の効率、V <sub>IN</sub> :4V ~ 38V、V <sub>OUT</sub> :0.8V < V <sub>OUT</sub> < 38V、I <sub>SD</sub> = 40μA、SSOPおよびQFNパッケージ          |