# モノリシック、高電圧、 絶縁型フライバック・コンバータ

## 特長

- 入力電圧範囲: 4.5V ~ 100V

- 240mA、150Vのパワー・スイッチを内蔵

- バウンダリ・モード動作

- トランスの3次巻線やオプトアイソレータを必要としないレギュレーション

- 1次側巻線帰還によるロード・レギュレーションを改善

- 出力電圧を2本の外付け抵抗で設定

- 内部バイアス電源とパワー・スイッチ・ドライバ用のBIASピン

- 外付け起動抵抗が不要

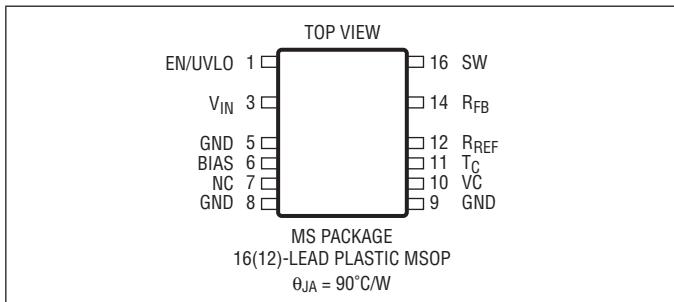

- 16ピンMSOPパッケージ

## アプリケーション

- テレコム用絶縁型電源

- 絶縁型補助電源/ハウスキーピング用電源

- 産業用、車載および医療用絶縁型電源

## 概要

LT®3511は絶縁型フライバック・トポロジー向けに特に設計された、高電圧モノリシック・スイッチング・レギュレータです。出力電圧を1次側フライバック波形から直接検出するので、レギュレーションを行うのに3次巻線やオプトアイソレータは不要です。このデバイスは240mA、150Vのパワー・スイッチ、高電圧回路、および制御回路を、4本のピンを取り去った高電圧16ピンMSOPパッケージに搭載しています。

LT3511は4.5V~100Vの入力電圧で動作し、最大2.5Wの絶縁された出力電力を供給します。出力電圧は、2本の外付け抵抗とトランスの巻数比で容易に設定されます。いくつかのアプリケーションで既製トランスを使用できます。高い集積度とバウンダリ・モード動作の使用により、従来難題だった絶縁電力供給に対する、高精度に安定化されたシンプルでクリーンなソリューションを提供します。

**LT**、**LTC**、**LTM**、**Burst Mode**、**Linear Technology**およびLinearのロゴはリニアテクノロジー社の登録商標です。No RSENSEはリニアテクノロジー社の商標です。その他すべての商標の所有権は、それぞれの所有者に帰属します。5438499、7471522を含む米国特許によって保護されています。

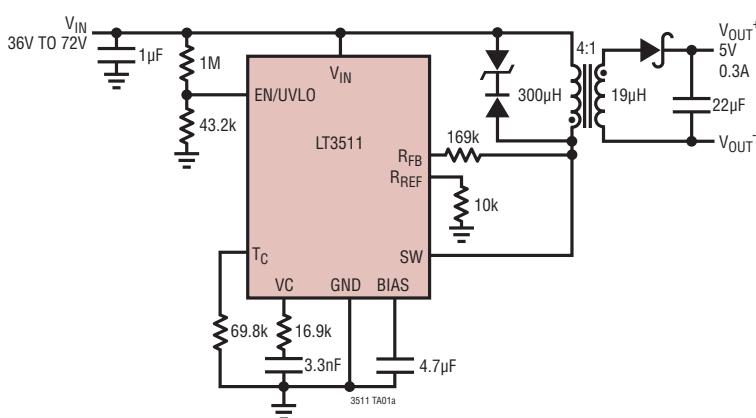

## 標準的応用例

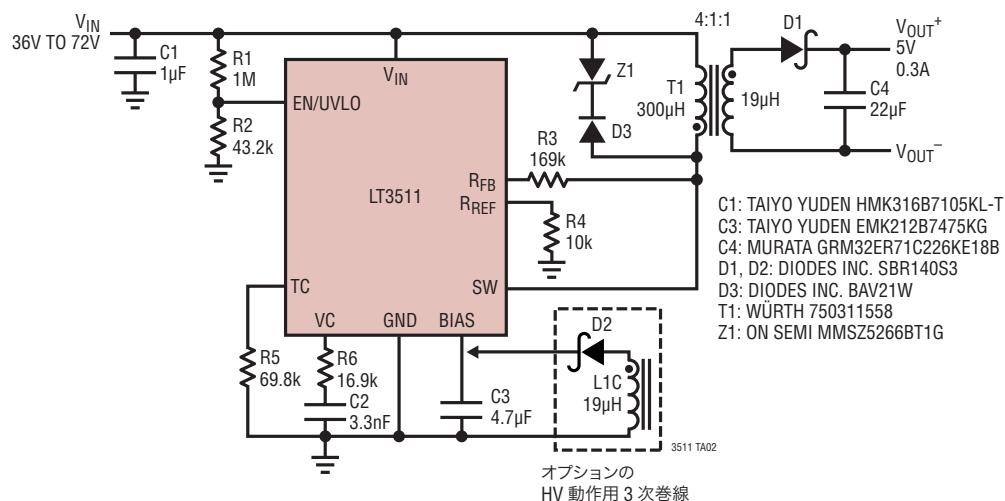

### 48Vから5Vの絶縁型フライバック・コンバータ

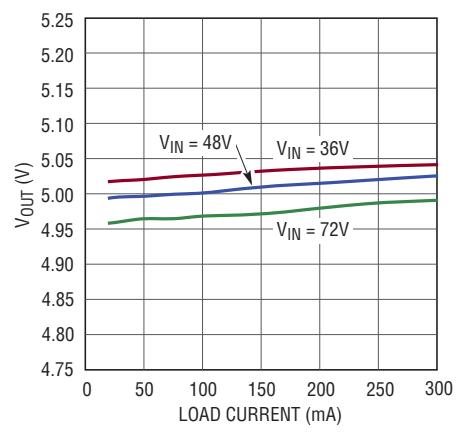

### 出力負荷およびライン・レギュレーション

3511 TA01b

## 絶対最大定格

(Note 1)

|                                            |                             |

|--------------------------------------------|-----------------------------|

| SW (Note 4) .....                          | 150V                        |

| V <sub>IN</sub> 、EN/UVLO、RFB .....         | 100V                        |

| V <sub>IN</sub> ~ R <sub>FB</sub> 間 .....  | ±6V                         |

| BIAS .....                                 | 20V と V <sub>IN</sub> の小さい方 |

| R <sub>REF</sub> 、T <sub>C</sub> 、VC ..... | 6V                          |

| 動作接合部温度範囲 (Note 2)                         |                             |

LT3511E, LT3511I ..... -40°C ~ 125°C

LT3511H ..... -40°C ~ 150°C

LT3511MP ..... -55°C ~ 150°C

保存温度範囲 ..... -65°C ~ 150°C

## ピン配置

## 発注情報

| 無鉛仕上げ          | テープアンドリール        | 製品マーキング* | パッケージ                | 温度範囲           |

|----------------|------------------|----------|----------------------|----------------|

| LT3511EMS#PBF  | LT3511EMS#TRPBF  | 3511     | 16-Lead Plastic MSOP | -40°C to 125°C |

| LT3511IMS#PBF  | LT3511IMS#TRPBF  | 3511     | 16-Lead Plastic MSOP | -40°C to 125°C |

| LT3511HMS#PBF  | LT3511HMS#TRPBF  | 3511     | 16-Lead Plastic MSOP | -40°C to 150°C |

| LT3511MPMS#PBF | LT3511MPMS#TRPBF | 3511     | 16-Lead Plastic MSOP | -55°C to 150°C |

さらに広い動作温度範囲で規定されるデバイスについては、弊社または弊社代理店にお問い合わせください。\* 温度グレードは出荷時のコンテナのラベルで識別されます。

非標準の鉛仕上げの製品の詳細については、弊社または弊社代理店にお問い合わせください。

無鉛仕上げの製品マーキングの詳細については、<http://www.linear-tech.co.jp/designtools/leadfree/> をご覧ください。

テープアンドリールの仕様の詳細については、<http://www.linear-tech.co.jp/tapeandreel/> をご覧ください。

電気的特性 ●は全動作温度範囲での規格値を意味する。それ以外は T<sub>A</sub> = 25°C での値。注記がない限り、V<sub>IN</sub> = 24V。

| PARAMETER                                | CONDITIONS                                                 | MIN               | TYP      | MAX           | UNITS    |

|------------------------------------------|------------------------------------------------------------|-------------------|----------|---------------|----------|

| Input Voltage Range                      | V <sub>IN</sub> = BIAS                                     | ●<br>6<br>4.5     |          | 100<br>15     | V        |

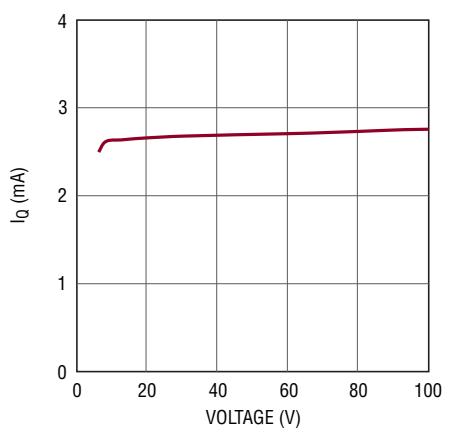

| Quiescent Current                        | Not Switching<br>V <sub>EN/UVLO</sub> = 0.2V               |                   | 2.7<br>0 | 3.5           | mA<br>μA |

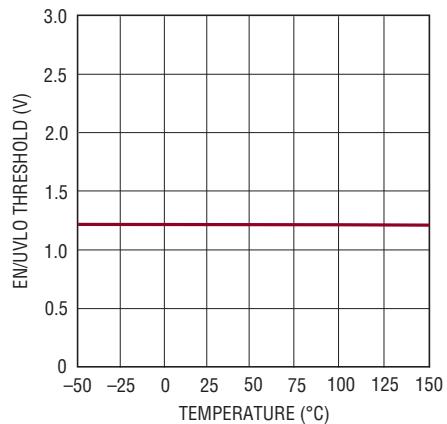

| EN/UVLO Pin Threshold                    | EN/UVLO Pin Voltage Rising                                 | ●<br>1.15         | 1.21     | 1.27          | V        |

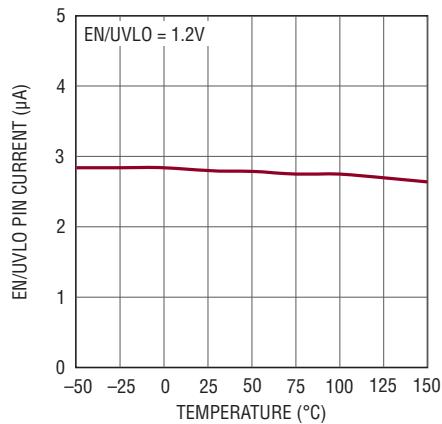

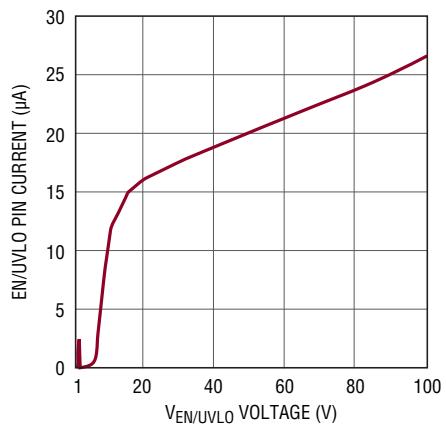

| EN/UVLO Pin Current                      | V <sub>EN/UVLO</sub> = 1.1V<br>V <sub>EN/UVLO</sub> = 1.4V |                   | 2.0<br>0 | 2.6<br>3.3    | μA<br>μA |

| Maximum Switching Frequency              |                                                            |                   |          | 650           | kHz      |

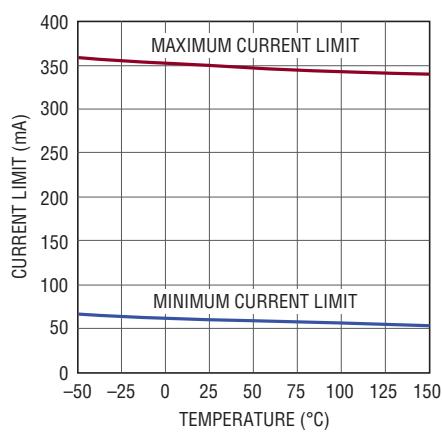

| Maximum Current Limit                    |                                                            |                   | 240      | 330           | 430      |

| Minimum Current Limit                    |                                                            |                   | 35       | 60            | 90       |

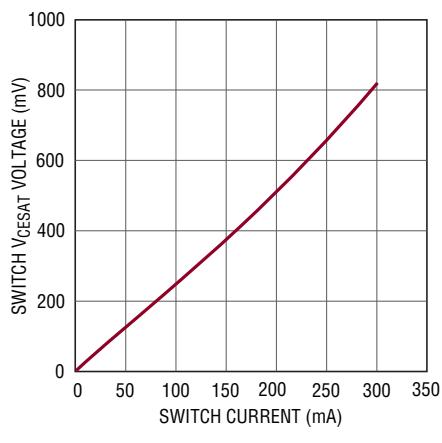

| Switch V <sub>CESAT</sub>                | I <sub>SW</sub> = 100mA                                    |                   |          | 0.3           | V        |

| R <sub>REF</sub> Voltage                 |                                                            | ●<br>1.18<br>1.17 | 1.20     | 1.215<br>1.23 | V        |

| R <sub>REF</sub> Voltage Line Regulation | 6V < V <sub>IN</sub> < 100V                                |                   |          | 0.01          | %/V      |

| R <sub>REF</sub> Pin Bias Current        | (Note 3)                                                   | ●<br>80           |          | 400           | nA       |

| Error Amplifier Voltage Gain             |                                                            |                   |          | 150           | V/V      |

| Error Amplifier Transconductance         | ΔI = 2μA                                                   |                   |          | 140           | μmhos    |

## 電気的特性

●は全動作温度範囲での規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。注記がない限り、 $V_{IN} = 24\text{V}$ 。

| PARAMETER                    | CONDITIONS                    | MIN | TYP | MAX | UNITS         |

|------------------------------|-------------------------------|-----|-----|-----|---------------|

| Minimum Switching Frequency  |                               |     | 40  |     | kHz           |

| $T_C$ Current into $R_{REF}$ | $R_{TC} = 53.6\text{k}\Omega$ |     | 9.5 |     | $\mu\text{A}$ |

| BIAS Pin Voltage             | Internally Regulated          | 3   | 3.1 | 3.2 | V             |

**Note 1:** 絶対最大定格に記載された値を超えるストレスはデバイスに永続的損傷を与える可能性がある。また、長期にわたって絶対最大定格条件に曝すと、デバイスの信頼性と寿命に悪影響を与える可能性がある。

**Note 2:** LT3511Eは、 $0^\circ\text{C} \sim 125^\circ\text{C}$ の接合部温度で性能仕様に適合することが保証されている。 $-40^\circ\text{C} \sim 125^\circ\text{C}$ の動作接合部温度範囲での仕様は、設計、特性評価および統計学的なプロセス・コントロールとの関連で確認されている。LT3511Hは $-40^\circ\text{C} \sim 125^\circ\text{C}$ の動作接合部温度範囲で性能仕様に適合することが保証されている。LT3511Hは $-40^\circ\text{C} \sim 150^\circ\text{C}$ の動作接合部温

度範囲で性能仕様に適合することが保証されている。LT3511MPは $-55^\circ\text{C} \sim 150^\circ\text{C}$ の全動作接合部温度範囲で保証されている。高い接合部温度は動作寿命に悪影響を及ぼす。接合部温度が $125^\circ\text{C}$ を超えると、動作寿命が短くなる。

**Note 3:** 電流は $R_{REF}$ ピンから流れ出す。

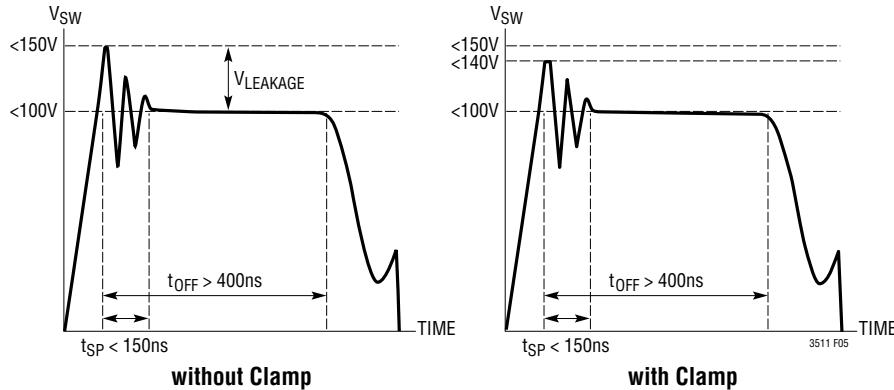

**Note 4:** SWピンの過渡電圧定格は最大 $150\text{V}$ である。図5に示すように、SWピンの動作波形はフライバック波形のペデスタルを $100\text{V}$ 以下に保つ必要がある。

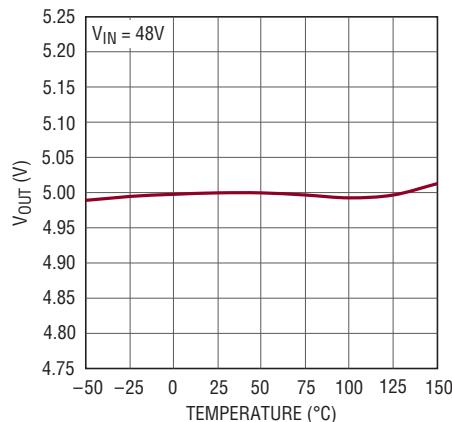

## 標準的性能特性

注記がない限り、 $T_A = 25^\circ\text{C}$ 。

出力電圧

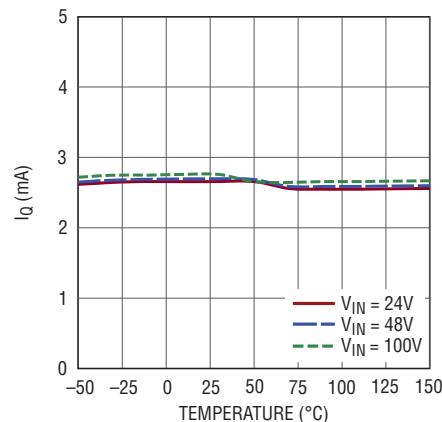

消費電流

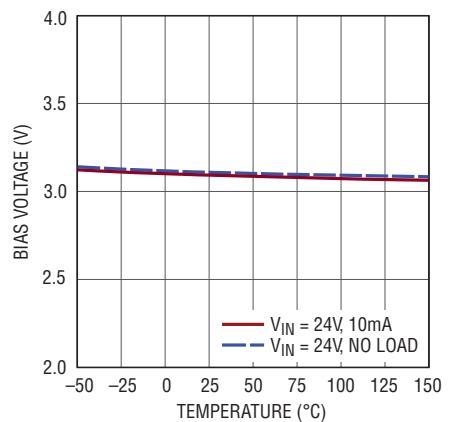

BIASピンの電圧

スイッチの $V_{CESAT}$

スイッチの電流制限値

消費電流と $V_{IN}$

## 標準的性能特性 注記がない限り、 $T_A = 25^\circ\text{C}$ 。

### EN/UVLOピンの(ヒステリシス)

電流と温度

3511 G07

### EN/UVLOピンの電流と $V_{EN/UVLO}$

3511 G08

### EN/UVLOスレッショルドと温度

3511 G09

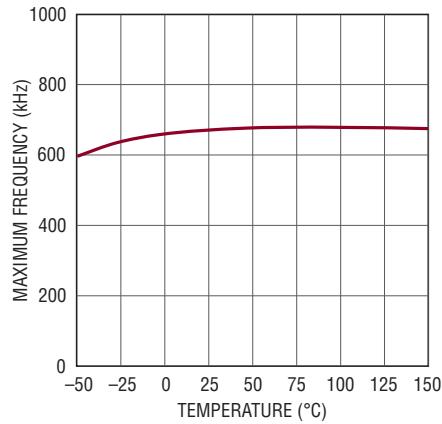

### 最大周波数と温度

3511 G10

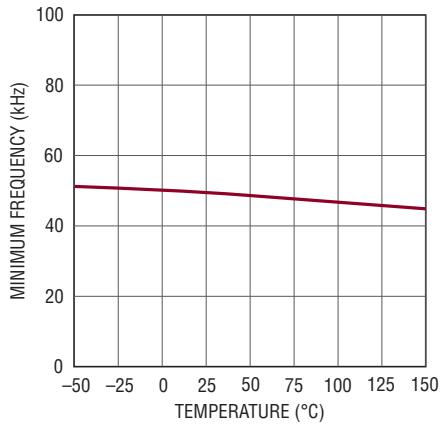

### 最小周波数と温度

3511 G11

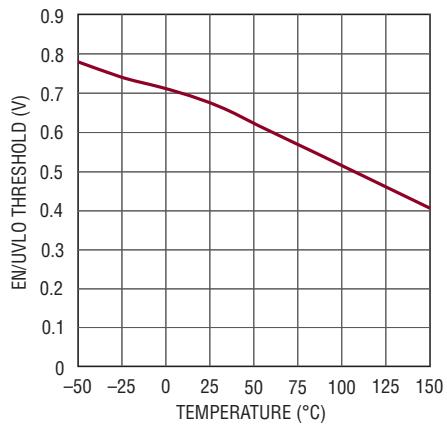

### EN/UVLOシャットダウン・スレッショルドと温度

3511 G14

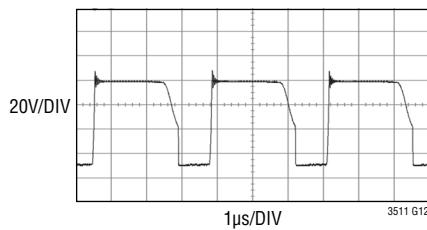

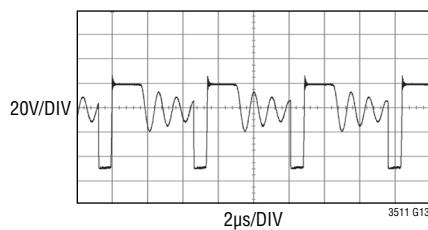

### バウンダリ・モードの波形

3511 G12

### 軽負荷時不連続モードの波形

3511 G13

## ピン機能

**EN/UVLO (ピン1) :** イネーブル/低電圧ロックアウト。EN/UVLOピンはLT3511を起動するのに使用します。このピンを0Vに引き下げるとき、LT3511はシャットダウンします。このピンは1.21Vの高精度スレッショルドを備えており、電源からグランドに接続した抵抗分割器を使って、低電圧ロックアウト(UVLO)スレッショルドを設定するのに使用することができます。2.6 $\mu$ Aのピン電流ヒステリシスにより、低電圧ロックアウト(UVLO)ヒステリシスを設定することができます。EN/UVLOはV<sub>IN</sub>に直接接続することができます。このピンをオープン状態のままにすると、デバイスは起動しません。

**V<sub>IN</sub> (ピン3) :** 入力電源ピン。このピンは内部起動回路に電流を供給し、DCMコンパレータおよび帰還回路の基準電圧として機能します。このピンのすぐ近くにコンデンサを接続してバypassする必要があります。

**GND (ピン5、8、9) :** グランド・ピン。3つのピンはすべてローカル・グランド・プレーンに直接接続します。

**BIAS (ピン6) :** バイアス電圧。このピンはLT3511のスイッチ・ドライバおよび内部回路に電流を供給します。3次巻線を使用しておらずV<sub>IN</sub>が20Vより低い場合は、このピンをV<sub>IN</sub>に接続することもできます。BIASとV<sub>IN</sub>が互いに接続されている場合、デバイスは最小で4.5Vまで動作可能です。3次巻線が使用されている場合には、適正に動作させるためにBIAS電圧を入力電圧より低く、3.3Vより高くします。BIASは、ピンの近くに配置した4.7 $\mu$ Fのコンデンサでバypassする必要があります。

**VC (ピン10) :** 内部エラーアンプの補償ピン。このピンからグランドに直列のRCを接続してスイッチング・レギュレータを補償します。このピンからグランドに100pFのコンデンサを追加すると、ノイズの除去に役立ちます。

**T<sub>C</sub> (ピン11) :** 出力電圧の温度補償。グランドとの間に抵抗を接続し、絶対温度に比例した電流を発生してR<sub>REF</sub>ノードにソースします。

$$I_{TC} = 0.55V/R_{TC}$$

**R<sub>REF</sub> (ピン12) :** グランドを基準とした外付けリファレンス抵抗の入力ピン。このピンの抵抗は10k $\Omega$ にします。非絶縁型アプリケーションでは、V<sub>OUT</sub>からこのピンに従来の抵抗分割器を接続することができます。

**R<sub>FB</sub> (ピン14) :** 外付け帰還抵抗の入力ピン。このピンはトランジスタの1次側(V<sub>SW</sub>)に接続します。R<sub>REF</sub>抵抗に対するこの抵抗の比に内部バンドギャップ・リファレンスを掛けた値によって出力電圧が決定します(これに1以外のトランジスタの巻数比の影響が加わります)。非絶縁型アプリケーションの場合は、このピンを1M $\Omega$ の抵抗でGNDに接続します。

**SW (ピン16) :** スイッチ・ピン。内部パワー・スイッチのコレクタ。EMIと電圧スパイクを最小限に抑えるため、このピンのトレイス面積を最小限に抑えます。

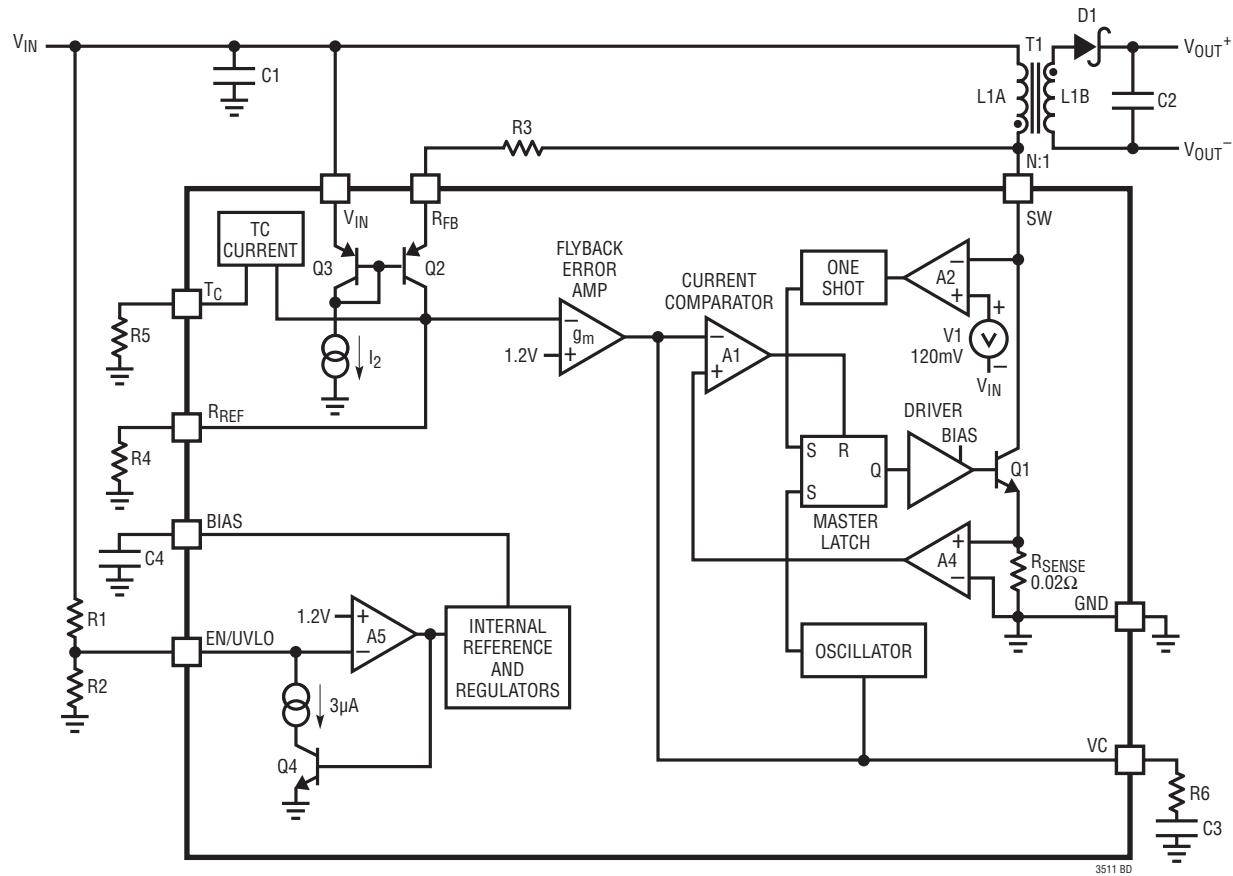

## ブロック図

## 動作

LT3511は、特に絶縁型フライバック・トポロジー用に設計された、電流モードのスイッチング・レギュレータICです。絶縁型トポロジーの主な課題は、出力電圧に関する情報を、トランスの絶縁された2次側から1次側へどのように伝達するかです。従来は、オプトアイソレータや追加のトランス巻線によってトランスを越えて、この情報を伝達していました。オプトアイソレータ回路は出力電力を浪費し、追加の部品によって電源のコストと物理的サイズが増大します。また、オプトアイソレータは、制限されたダイナミック応答、非直線性、ユニットごとのばらつき、経年変化などのため問題を生じることがあります。追加のトランス巻線を採用した回路にも短所があります。追加の巻線を使用すると、トランスの物理的サイズとコストが増大し、多くの場合ダイナミック応答の質が劣ります。

LT3511では、1次側のフライバック・パルスにより、絶縁された出力電圧についての情報が与えられます。この方法では、レギュレーションにオプトアイソレータも追加のトランス巻線も不要です。2本の抵抗によって出力電圧が設定されます。このデバイスはバウンダリ・モードで動作するので、2次側電流がほとんどゼロのときのスイッチ・ピンからの出力電圧を計算します。

システムの全体像を「ブロック図」に示します。ブロックの多くは従来のスイッチング・レギュレータにあるものと同様で、内部バイアス・レギュレータ、発振器、ロジック、電流アンプ、電流コンパレータ、ドライバ、出力スイッチなどです。目新しい部分は、特殊なフライバック・エラーアンプと温度補償回路です。さらに、ロジック・システムにはバウンダリ・モード動作のための追加ロジックが含まれています。

LT3511は、連続導通モードと不連続導通モードの境界でデバイスが動作するバウンダリ・モード制御機能を備えています。VCピンは通常の電流モード動作と全く同様に電流レベル

を制御しますが、デバイスは発振器の周期の開始点でスイッチをオンせずに、2次側の巻線電流がゼロになるときにスイッチをオンします。

### バウンダリ・モード動作

バウンダリ・モードは、可変周波数、電流モードのスイッチング方式で動作します。スイッチがオンし、VCピンによって制御される電流制限値に達するまでインダクタ電流が増加します。スイッチがオフすると、SWピンの電圧は、出力電圧をトランスの2次対1次の巻数比で割った電圧に入力電圧を加えた電圧まで上昇します。ダイオードを流れる2次側電流がゼロまで減少すると、SWピンの電圧がVINを下回ります。不連続導通モード(DCM)コンパレータがこの事象を検出し、スイッチを再度オンします。

バウンダリ・モードではサイクルごとに2次側の電流をゼロに戻すので、寄生抵抗の電圧降下によるロード・レギュレーションの誤差は生じません。また、バウンダリ・モードでは連続導通モードに比べて小型のトランスを使用することができ、低調波発振が生じません。

LT3511は、出力電流が小さいときにスイッチのターンオンを遅らせるので、不連続モードで動作します。従来のフライバック・コンバータとは異なり、出力電圧の情報を更新するためにスイッチがオンする必要があります。VCピンの電圧が0.6Vより低いと、電流コンパレータのレベルはその最小値まで減少し、内部発振器の周波数が低下します。内部発振器の周波数の低下に伴い、デバイスはDCM(不連続導通モード)での動作を開始します。フライバック・エラーアンプの最小スイッチ・オフ時間を見込んだ上で、出力電流を低減することができます。VCが0Vのときの内部発振器の標準的な最小周波数は40kHzです。

## アプリケーション情報

### 擬似DC理論

「ブロック図」の  $R_{REF}$  ( $R_4$ ) と  $R_{FB}$  ( $R_3$ ) は、出力電圧の設定に使用される外付け抵抗です。LT3511は、帰還情報をフライバック・パルスから得る特殊なエラーアンプを採用していることを除き、従来の電流モード・スイッチャと同様の動作をします。

動作は次のとおりです。出力スイッチ  $Q_1$  がオフすると、そのコレクタ電圧が上昇して  $V_{IN}$  レールを上回ります。このフライバック・パルスの振幅(つまり、コレクタ電圧と  $V_{IN}$  の差)は次式で与えられます。

$$V_{FLBK} = (V_{OUT} + V_F + I_{SEC} \cdot ESR) \cdot NPS$$

$V_F$  = D1 の順方向電圧

$I_{SEC}$  = トランジスタの2次側電流

$ESR$  = 2次側回路の全インピーダンス

$NPS$  = トランジスタの1次対2次の実効巻数比

$R_{FB}$  と  $Q_2$  はフライバック電圧を電流に変換します。この電流の大半は抵抗  $R_{REF}$  を通って流れ、グランド基準の電圧を生じます。この結果得られる電圧がフライバック・エラーアンプへの入力になります。フライバック・エラーアンプは、2次側の巻線電流がゼロのとき電圧の情報をサンプリングします。バンドギャップ電圧(1.20V)がフライバック・エラーアンプのリファレンスとして機能します。

ループ全体の利得が比較的大きいので、 $R_{REF}$  の電圧はバンドギャップ・リファレンス電圧  $V_{BG}$  にほぼ等しくなります。したがって、 $V_{FLBK}$  と  $V_{BG}$  の関係はほぼ次のようにになります。

$$\left( \frac{V_{FLBK}}{R_{FB}} \right) = \frac{V_{BG}}{R_{REF}} \text{ or } V_{FLBK} = V_{BG} \left( \frac{R_{FB}}{R_{REF}} \right)$$

$V_{BG}$  = 内部バンドギャップ・リファレンス

上式と前に得られた  $V_{FLBK}$  の結果を組み合わせると、次式が得られます。

$$V_{OUT} = V_{BG} \left( \frac{R_{FB}}{R_{REF}} \left( \frac{1}{NPS} \right) - V_F - I_{SEC} (ESR) \right)$$

この式は  $V_{OUT}$  を内部リファレンス、設定抵抗、トランジスタの巻数比、およびダイオードの順方向電圧降下の項で表しています。さらに、これにはゼロではない2次側の出力インピーダンス

( $ESR$ ) の影響が含まれています。バウンダリ制御モードでは、このインピーダンスの項の影響が最小になります。

### 温度補償

$V_{OUT}$  の式の最初の項には温度依存性はありませんが、ダイオードの順方向電圧降下には大きな負の温度係数があります。これを補償するために、正の温度係数の電流源が  $R_{REF}$  ピンに接続されています。 $T_C$  ピンからグランドに接続された抵抗によって補償電流が設定されます。

温度係数のキャンセル方法を次式に示します。

$$\frac{\delta V_F}{\delta T} = -\frac{R_{FB}}{R_{TC}} \cdot \frac{1}{NPS} \cdot \frac{\delta V_{TC}}{\delta T} \text{ or,}$$

$$R_{TC} = \frac{-R_{FB}}{NPS} \cdot \frac{1}{\delta V_F / \delta T} \cdot \frac{\delta V_{TC}}{\delta T} \approx \frac{R_{FB}}{NPS}$$

$(\delta V_F / \delta T)$  = ダイオードの順方向電圧の温度係数

$$(\delta V_{TC} / \delta T) = 2mV$$

$$V_{TC} = 0.55V$$

この結果得られた  $R_{TC}$  の値を実験によって検証し、必要に応じて調整して全温度範囲にわたって最適なレギュレーションを達成します。

温度補償電流の追加により、出力電圧の式は以下のように修正されます。

$$V_{OUT} = V_{BG} \left( \frac{R_{FB}}{R_{REF}} \left( \frac{1}{NPS} \right) - V_F - \left( \frac{V_{TC}}{R_{TC}} \right) \cdot \frac{R_{FB}}{NPS} - I_{SEC} (ESR) \right)$$

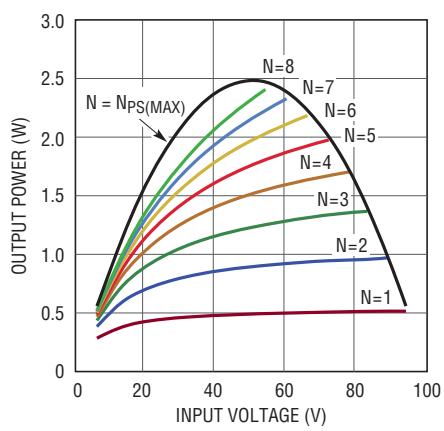

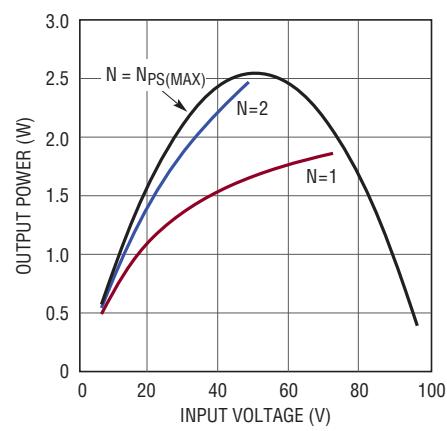

### 出力電力

フライバック・コンバータは、降圧コンバータや昇圧コンバータに比べて、入力電流と出力電流の間に複雑な関係があります。昇圧コンバータは入力電圧に関係なく最大入力電流が比較的一定であり、降圧コンバータは入力電圧に関係なく最大出力電流が比較的一定です。これは2つの電流の動作が連続していく切り替わらないからです。フライバック・コンバータは入力電流と出力電流の両方が不連続なので、非絶縁型昇降圧コンバータに似たものになります。デューティ・サイクルが入力

## アプリケーション情報

電流と出力電流に影響を与えるので、出力電力を予測するのには困難です。さらに、出力電流を増加させるため、スイッチ電圧が高くなることを代償に巻数比を変えることができます。

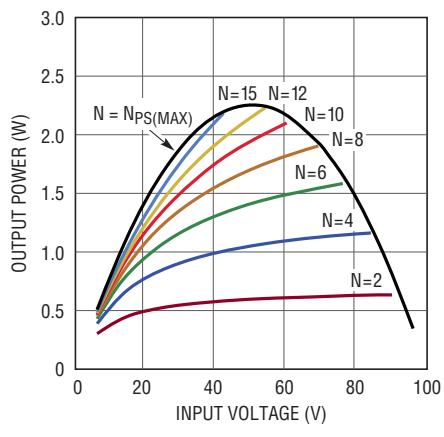

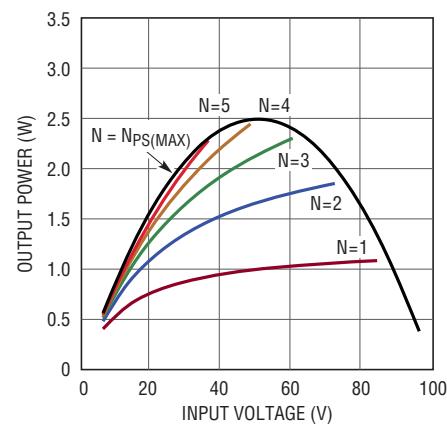

図1～図4のグラフは、3.3V、5V、12V、および24Vの出力電圧に対して可能な標準的最大出力電力を示しています。この最大出力電力曲線は、オフ時間の間のスイッチの電圧が100Vの場合の計算によって得られた出力電力です。漏れ電圧スパイクに対して50Vのマージンが見込まれています。与えられた入力でこの電力レベルを実現するには、スイッチに100Vを印加する巻数比の値を計算する必要があります。半端な値の比になることがあります。以下の曲線は、一般的な巻数比の値と、与えられた入力電圧での出力電力の大きさの例です。

設計の一例は、最小入力電圧が36V、最大入力電圧が72Vの5V出力のコンバータです。4:1の巻数比がこの設計例に適合し、出力は72Vで1.6Wに近い値となります。36Vでは1Wまで減少します。

以下の式により出力電力が計算されます。

$$\text{電力} = \eta \cdot V_{IN} \cdot D \cdot I_{PEAK} \cdot 0.5$$

効率 =  $\eta$  = 約 85%

$$\text{Duty Cycle} = D = \frac{(V_{OUT} + V_F) \cdot N_{PS}}{(V_{OUT} + V_F) \cdot N_{PS} + V_{IN}}$$

ピーク・スイッチ電流 =  $I_{PEAK} = 0.26A$

図1. 3.3V出力での出力電力

図3. 12V出力での出力電力

図2. 5V出力での出力電力

図4. 24V出力での出力電力

## アプリケーション情報

## トランスの設計に関する検討事項

LT3511をうまく使用できるかはトランスの適切な仕様と設計に依存します。高周波数用絶縁型電源トランスの設計に関する従来のガイドラインに加えて、以下の情報を注意深く検討してください。

リニアテクノロジーは、LT3511と共に使用するために事前に設計されたフライバック・トランスを製造するため、主要な磁気部品メーカー数社と協力してきました。これらのトランスの詳細を表1に示します。

表1. 事前に設計されたトランス

| トランスの<br>製品番号 | L <sub>PRI</sub> ( $\mu$ H) | 漏れインダクタンス<br>( $\mu$ H) | N <sub>P</sub> :N <sub>S</sub> :N <sub>B</sub> | 絶縁電圧(V) | 飽和電流(mA) | メーカー             | ターゲット・<br>アプリケーション                                                                                                       |

|---------------|-----------------------------|-------------------------|------------------------------------------------|---------|----------|------------------|--------------------------------------------------------------------------------------------------------------------------|

| 750311558     | 300                         | 1.5                     | 4:1:1                                          | 1500    | 500      | Würth Elektronik | 48V to 5V, 0.3A<br>24V to 5V, 0.2A<br>12V to 5V, 0.13A<br>48V to 3.3V, 0.33A<br>24V to 3.3V, 0.28A<br>12V to 3.3V, 0.18A |

| 750311019     | 400                         | 5                       | 6:1:2                                          | 1500    | 750      | Würth Elektronik | 24V to 5V, 0.26A<br>12V to 5V, 0.17A<br>48V to 3.3V, 0.43A<br>24V to 3.3V, 0.35A<br>12V to 3.3V, 0.2A                    |

| 750311659     | 300                         | 2                       | 1:1:0.2                                        | 1500    | 560      | Würth Elektronik | 48V to 24V, 0.07A                                                                                                        |

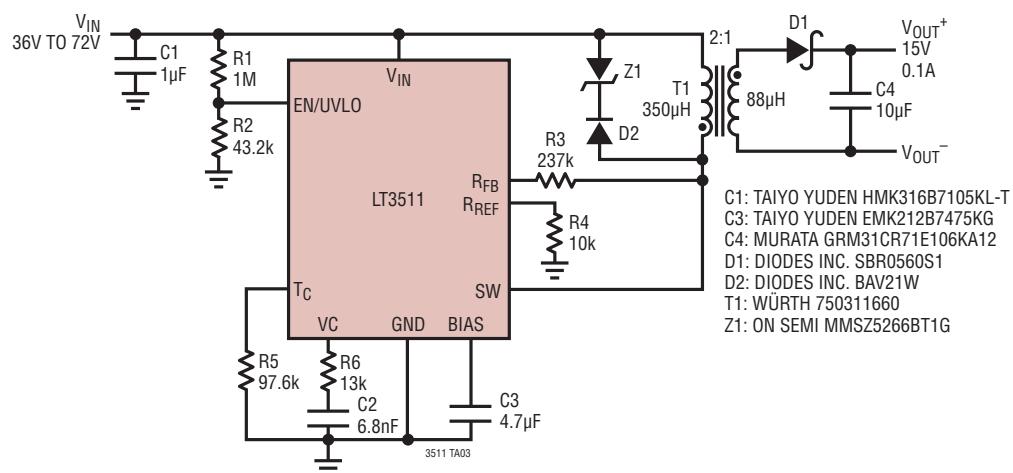

| 750311660     | 350                         | 3                       | 2:1:0.33                                       | 1500    | 520      | Würth Elektronik | 48V to 15V, 0.1A<br>48V to 12V, 0.12A<br>24V to 15V, 0.09A<br>12V to 15V, 0.045A                                         |

| 750311838     | 350                         | 3                       | 2:1:1                                          | 1500    | 520      | Würth Elektronik | 48V to $\pm$ 15V, 0.05A<br>48V to $\pm$ 12V, 0.06A<br>24V to $\pm$ 15V, 0.045A                                           |

| 750311963     | 200                         | 0.4                     | 1:5:5                                          | 1500    | 650      | Würth Elektronik | 12V to $\pm$ 70V, 0.004A<br>12V to $\pm$ 100V, 0.003A<br>12V to $\pm$ 150V, 0.002A                                       |

| 750311966     | 120                         | 0.45                    | 1:5:0.5                                        | 1500    | 900      | Würth Elektronik | 12V to +120V and<br>-12V, 0.002A                                                                                         |

| 10396-T024    | 300                         | 2.0                     | 4:1:1                                          | 1500    | 500      | Sumida           | 48V to 5V, 0.3A<br>24V to 5V, 0.2A<br>12V to 5V, 0.13A<br>48V to 3.3V, 0.33A<br>24V to 3.3V, 0.28A<br>12V to 3.3V, 0.18A |

| 10396-T026    | 300                         | 2.5                     | 6:1:2                                          | 1500    | 500      | Sumida           | 24V to 5V, 0.26A<br>12V to 5V, 0.17A<br>48V to 3.3V, 0.43A<br>24V to 3.3V, 0.35A<br>12V to 3.3V, 0.2A                    |

| 01355-T057    | 250                         | 2.0                     | 1:1:0.2                                        | 1500    | 500      | Sumida           | 48V to 24V, 0.07A                                                                                                        |

| 10396-T022    | 300                         | 2.0                     | 2:1:0.33                                       | 1500    | 500      | Sumida           | 48V to 15V, 0.1A<br>48V to 12V, 0.12A<br>24V to 15V, 0.09A<br>12V to 15V, 0.045A                                         |

| 10396-T028    | 300                         | 2.5                     | 2:1:1                                          | 1500    | 500      | Sumida           | 48V to $\pm$ 15V, 0.05A<br>48V to $\pm$ 12V, 0.06A<br>24V to $\pm$ 15V, 0.045A                                           |

## アプリケーション情報

### 巻数比

出力電圧を設定するのに  $R_{FB}/R_{REF}$  の抵抗比を使用すると、所定のアプリケーションに適合するようにトランスの巻数比を比較的自由に選択できることに注目してください。対照的に、小さな整数の単純な比(1:1, 2:1, 3:2など)を使うと、全巻数と相互インダクタンスをより自由に設定できます。

一般に、トランスの巻数は利用可能な出力電力が最大になるように選択します。低い出力電圧(3.3Vや5V)では、1次巻数を2次巻数の複数倍にして、N:1の巻数比を使用し、トランスの電流利得(および出力電力)を最大にすることができます。ただし、SWピンには、最大入力電源電圧と、出力電圧に巻数比を乗じた電圧の和に等しい電圧が現れることに注意してください。さらに、漏れインダクタンスは、この反映された電圧の上に電圧スパイク( $V_{LEAKAGE}$ )を生じます。この全体の大きさは、内部パワー・スイッチの破損を防ぐため、SWピンの絶対最大定格より低く保つ必要があります。これらの条件を総合することによって、所定のアプリケーションの巻数比(N)の上限が決まります。次式を満たすように十分小さな巻数比を選択します。

$$N < \frac{150V - V_{IN(MAX)} - V_{LEAKAGE}}{V_{OUT} + V_F}$$

N:1の値が大きい場合は、追加の電流を供給するために物理的サイズが大きなトランスを選択します。さらに、出力電圧を測定するのに十分な長さのオフ時間になるように、十分大きなインダクタンスを選択します。

出力電力レベルが低い場合は、トランスのサイズを絶対的に最小にするために、1:1または1:Nのトランスを選択します。1:Nのトランスを使うと励磁インダクタンス(およびサイズ)は最小になりますが、利用可能な出力電力も制限されます。1:Nの巻数比を大きくすると、内部パワー・スイッチのブレークダウン電圧を超えることなく非常に高い出力電圧が可能になります。

絶縁型帰還方式では巻数比が重要な要素の1つです。トランスのメーカーが±1%以内の巻数比の精度を保証していることを確認してください。

### 飽和電流

トランスの巻線の電流は定格飽和電流を超えてはなりません。コアが飽和すると、注入されたエネルギーは2次側に伝達されずにコア内で消費されます。飽和電流の情報はトランスのメーカーから得られます。LT3511と共に使用するために設計されたトランスの飽和電流を表1に示します。

### 1次側インダクタンスの要件

LT3511は、スイッチ・ピンに反映された出力電圧から出力電圧の情報を得ます。2次巻線に電流が流れると、1次側の出力電圧に反映されます。サンプリング回路は、反映された出力電圧をセトリングさせてサンプリングするのに最小400nsを必要とします。適切なサンプリングを行うためには、2次巻線に最小400nsの間電流を流す必要があります。以下の式から1次側励磁インダクタンスの最小値が与えられます。

$$L_{PRI} \geq \frac{t_{OFF(MIN)} \cdot N_{PS} \cdot (V_{OUT} + V_F)}{I_{PEAK(MIN)}}$$

$$t_{OFF(MIN)} = 400\text{ns}$$

$$I_{PEAK(MIN)} = 55\text{mA}$$

サンプリング時間に関する1次側インダクタンス要件の他に、LT3511には、スイッチのオン時間を100nsより短くするという内部回路の制約があります。その時間内にインダクタ電流が所期の電流リミットを超えると、電流制御ループがその制御能力を失って出力が発振する可能性があります。1次側励磁インダクタンスを選択するときは、最大入力電圧に基づいて以下の式にも従う必要があります。

$$L_{PRI} \geq \frac{t_{ON(MIN)} \cdot V_{IN(MAX)}}{I_{PEAK(MIN)}}$$

$$t_{ON(MIN)} = 100\text{ns}$$

$$I_{PEAK(MIN)} = 55\text{mA}$$

## アプリケーション情報

図5. SWピンのフライバック波形の最大電圧

## 漏れインダクタンスとクランプ回路

トランスの漏れインダクタンスが(1次側または2次側のいずれかに)あると、出力スイッチがオフした後に電圧スパイクが1次側に発生します。このスパイクは負荷電流が大きくなるほど顕著になり、より大きな蓄積エネルギーを消費しなければなりません。アプリケーションを設計する際には、漏れ電圧スパイクの影響に対して十分なマージンを確保します。ほとんどの場合は、1次側に反映された出力電圧と $V_{IN}$ の和は100V以下に保たれます。これにより、ライン条件および負荷条件にわたり、漏れスパイクについて少なくとも50Vのマージンが得られます。巻数が不十分なトランスや過度の漏れインダクタンスに対しては、さらに大きな電圧マージンが必要です。この点について図5に示します。トランスの漏れインダクタンスは最小限に抑えてください。

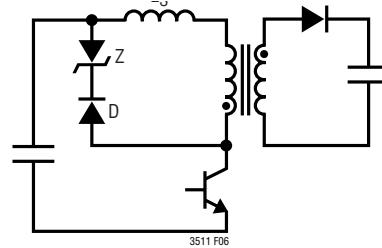

ほとんどのアプリケーションには、クランプ回路を推奨します。内部パワー・スイッチの保護が可能な回路には、RCD(抵抗-コンデンサ-ダイオード)クランプとDZ(ダイオード-ツェナー)クランプの2種類があります。クランプ回路は、漏れインダクタンスに蓄積されたエネルギーを消費します。LT3511の推奨クランプはDZクランプです。DZクランプは設計しやすく、クランプ電圧が高く、電力レベルが低いので、好ましいソリューションです。さらに、DZクランプは明確に定まった一定のクランプ電圧を保証します。スイッチ波形に対するクランプの効果を図5に、DZクランプの接続回路を図6に示します。

図6. DZクランプ

ダイオードとツェナー・ダイオードの両方を選択するときは十分な注意を払う必要があります。通常はショットキー・ダイオードが最適ですが、漏れインダクタンスによるスパイクを制限するのに十分速くオンする場合に使用できるPNダイオードもあります。逆電圧定格が最大スイッチ電圧より高いダイオードを選択します。ツェナー・ダイオードのブレークダウン電圧は、電力損失とスイッチ電圧の保護のバランスがとれるように選択します。最善の妥協案は、最も高いブレークダウン電圧を選択することです。適切に選択するには次式を使用します。

$$V_{ZENER(MAX)} \leq 150V - V_{IN(MAX)}$$

最大入力電圧が72Vのアプリケーションでは、 $V_{ZENER(MAX)}$ が(78Vの最大値より低い)72Vである、68Vの $V_{ZENER}$ を選択します。

クランプの電力損失によってツェナー・ダイオードの電力定格が決まります。クランプの電力損失は、最大負荷と最小入力

## アプリケーション情報

電圧のときに最大になります。スイッチ電流は、漏れインダクタンスに蓄積されたエネルギーを加えて、この時点での最大になります。最大の  $V_{ZENER}$  を選択した場合、0.5Wのツエナーがほとんどのアプリケーションの要件を満たします。 $V_{ZENER}$  に小さい値を選択すると、次式に示すように、過度の電力損失を生じます。

$$\text{DZ Power Loss} = \frac{1}{2} \cdot L_I \cdot I_{PK(VIN(MIN))}^2 \cdot f_{SW} \cdot \\ \left( 1 + \frac{N_{PS} \cdot (V_{OUT} + V_F)}{V_{ZENER} - N_{PS} \cdot (V_{OUT} + V_F)} \right)$$

$L_I$  = 漏れインダクタンス

$$I_{PK(VIN(MIN))} = \frac{V_{OUT} \cdot I_{OUT} \cdot 2}{\eta \cdot V_{IN(MIN)} \cdot D_{VIN(MIN)}}$$

$$f_{SW} = \frac{1}{t_{ON} + t_{OFF}} = \frac{1}{\frac{L_{PRI} \cdot I_{PK(VIN(MIN))}}{V_{IN(MIN)}} + \frac{L_{PRI} \cdot I_{PK(VIN(MIN))}}{N_{PS} \cdot (V_{OUT} + V_F)}}$$

推奨するダイオードおよびツエナー・ダイオードのいくつかを、表2および表3に示します。

表2. 推奨するツエナー・ダイオード

| 部品           | $V_{ZENER}$<br>(V) | 電力<br>(W) | ケース     | メーカー                  |

|--------------|--------------------|-----------|---------|-----------------------|

| MMSZ5266BT1G | 68                 | 0.5       | SOD-123 | On Semi               |

| MMSZ5270BT1G | 91                 | 0.5       | SOD-123 |                       |

| CMHZ5266B    | 68                 | 0.5       | SOD-123 | Central Semiconductor |

| CMHZ5267B    | 75                 | 0.5       | SOD-123 |                       |

| BZX84J-68    | 68                 | 0.5       | SOD323F | NXP                   |

| BZX100A      | 100                | 0.5       | SOD323F |                       |

表3. 推奨するダイオード

| 部品     | I(A)  | $V_{REVERSE}$<br>(V) | ケース     | メーカー        |

|--------|-------|----------------------|---------|-------------|

| BAV21W | 0.625 | 200                  | SOD-123 | Diodes Inc. |

| BAV20W | 0.625 | 150                  | SOD-123 |             |

### 漏れインダクタンスのブランкиング

パワー・スイッチがオフすると、フライバック・パルスが発生します。ただし、トランスの1次側の電圧波形が出力電圧に近くなるまでには、ある有限の時間が経過します。SWノードの立ち

上がり時間とトランスの漏れインダクタンスによって遅延が生じます。漏れインダクタンスで、トランスの1次側に非常に高速の電圧スパイクも生じます。漏れスパイクの振幅は、パワー・スイッチの電流が最大のときに最も大きくなります。スイッチのターンオフとサンプリングの開始の間に内部固定遅延を設けて、前述の現象に対する耐性をもたせます。LT3511では、内部ブランкиングが150nsに設定されています。場合によっては、漏れインダクタンスによるスパイクが内部ブランкиングより長く続くことがあります、出力のレギュレーションに大きく影響することはありません。

### 2次側漏れインダクタンス

1次側漏れインダクタンスに加えて、2次側漏れインダクタンスがアプリケーションの設計に重要な影響を与えます。2次側漏れインダクタンスは、トランスの2次側に誘導性分割器を形成します。誘導性分割器は1次側換算のフライバック・パルスの大きさを実効的に減らします。フライバック・パルスが小さくなると、安定化出力電圧が高くなります。2次側漏れインダクタンスの誘導性分割器の影響は負荷に依存しません。2次側漏れインダクタンスが(製造時のばらつきも含めて)一定の割合の相互インダクタンスである限りでは、RFB/RREF比を調整してこの影響に対応することができます。

### 巻線抵抗の影響

1次側と2次側のどちらの抵抗成分も全体の効率( $P_{OUT}/P_{IN}$ )を低下させます。LT3511のバウンダリ・モード動作により、十分な出力電圧レギュレーションが巻線抵抗に関係なく維持されます。

### バイファイラ巻き

バイファイラ巻きや同様の巻線手法は、漏れインダクタンスの問題を最小限に抑えるのに有効です。ただし、これは1次側-2次側間の静電容量も増やして1次側-2次側間のブレーカダウン電圧を制限するので、バイファイラ巻きが常に実用的であるとは限らないことに注意してください。リニアテクノロジーのアプリケーション・グループがトランスの選択や設計をお手伝いします。

## アプリケーション情報

### アプリケーション設計に関する検討事項

#### 反復設計手順

LT3511は、絶縁された出力電圧を安定化するのに独自のサンプリング手法を使用しています。この絶縁手法を使用するには、帰還抵抗と温度補償抵抗を選択するシンプルな反復手順が必要です。帰還抵抗と温度補償抵抗の値は、選択されたアプリケーション、トランスおよび出力ダイオードに大きく依存します。

反復手順を通して抵抗値が定まるごとに、この値が、選択されたトランスと出力ダイオードとともに一定の出力電圧を生成します。トランスの巻数比が $\pm 1\%$ 以内であることが保証されなければならぬ点に注意してください。このデータシートに記載されたトランスのメーカーでは、この規格に従ったトランスの製造が可能です。

#### R<sub>FB</sub>とR<sub>REF</sub>の抵抗値の選択

以下のセクションにR<sub>FB</sub>およびR<sub>REF</sub>の値を設定する式を示します。この式は目安にすぎません。「設計手順」で概説する手順に従い、反復設計手順を使ってR<sub>FB</sub>、R<sub>REF</sub>およびR<sub>TC</sub>の正確な値を設定します。

「動作」のセクションで導き出した、「温度補償」のセクションのV<sub>OUT</sub>の式を整理すると、以下のようなR<sub>FB</sub>の式が得られます。

$$R_{FB} = \frac{R_{REF} \cdot N_{PS} [(V_{OUT} + V_F) + V_{TC}]}{V_{BG}}$$

ここで、

V<sub>OUT</sub> = 出力電圧

V<sub>F</sub> = スイッチング・ダイオードの順方向電圧

N<sub>PS</sub> = 1次対2次の実効巻数比

V<sub>TC</sub> = 0.55V

この式は以下を仮定しています。

$$R_{TC} = \frac{R_{FB}}{N_{PS}}$$

式ではダイオードとV<sub>TC</sub>の温度係数が等しいと仮定していますが、1次近似としてはこれで十分です。

厳密にいえば、上式はR<sub>FB</sub>を絶対値としてではなくR<sub>REF</sub>の比として定義しています。したがって、次の問題は、R<sub>REF</sub>として適切な値は何か、ということになります。「R<sub>REF</sub>は約10kΩにする」が答えです。LT3511はこのR<sub>REF</sub>の値を使って調整され、仕様が規定されています。R<sub>REF</sub>のインピーダンスが10kΩから大きく変化すると、余計な誤差が生じます。ただし、R<sub>REF</sub>のばらつきは数パーセントであれば許容できます。したがって、公称のR<sub>FB</sub>/R<sub>REF</sub>比を実現するのに、標準の1%抵抗値を選択すれば問題ありません。

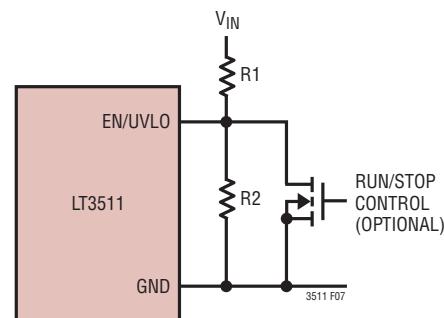

#### 低電圧ロックアウト(UVLO)

V<sub>IN</sub>ピンからEN/UVLOピンに抵抗分割器を接続することによって低電圧ロックアウト(UVLO)が実現されます。この構成を図7に示します。EN/UVLOピンのスレッショルドは1.21Vに設定されています。

また、EN/UVLOピンの電圧が1.21Vより低いと、このピンに2.6μAが流れます。この電流はR1の値に基づいてユーザーが設定可能なヒステリシスを与えます。実効的なUVLOスレッショルドは以下のようになります。

$$V_{IN(UVLO,RISING)} = \frac{1.2V \cdot (R1+R2)}{R2} + 2.6\mu A \cdot R1$$

$$V_{IN(UVLO,FALLING)} = \frac{1.2V \cdot (R1+R2)}{R2}$$

図7では、UVLO機能を使って外部シャットダウン制御を行う回路も示しています。NMOSをオンするとEN/UVLOピンが接地され、LT3511は消費電流が1μA未満のシャットダウン状態になります。

図7. 低電圧ロックアウト(UVLO)

## アプリケーション情報

### 最小負荷の要件

LT3511はフライバック・パルスを使って出力電圧の情報を回収します。スイッチがオフして2次巻線に電流が流れると、フライバック・パルスが発生します。出力電圧を安定化させるため、LT3511はフライバック・パルスをサンプリングする必要があります。LT3511は、軽負荷状態のときも最小量のエネルギーを供給して出力電圧の正確な情報を確保します。最小量のエネルギーを供給するには、個々のアプリケーションに応じて10mA～15mAの最小負荷が必要になります。各アプリケーションの最小負荷要件を検証してください。事前に負荷をかけることが認められない場合は、ツエナー・ブレーカダウン電圧が出力電圧より20%高いツエナー・ダイオードを最小負荷として使用できます。出力電圧が5Vの場合には、カソードを出力に接続した6Vのツエナー・ダイオードを使用します。

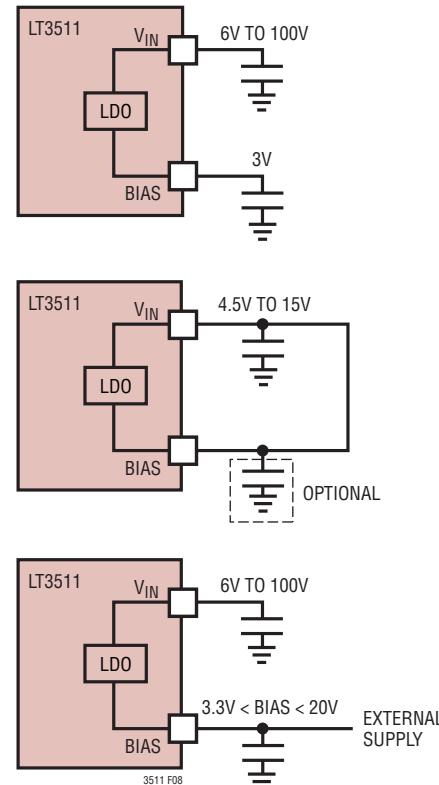

### BIASピンに関する検討事項

BIASピンはLT3511の内部回路に電力を供給します。BIASピンを安定化させるための、3つの異なる構成があります。1つの構成では、VIN電源から内部LDOを介してBIASピンを内部でドライブします。2つ目の構成では、VIN電源をBIASピンに直接接続し、内部LDOを迂回することにより、VIN電源がBIASピンを直接ドライブします。この構成では、デバイスは最小4.5V、最大15Vで動作することができます。3つ目の構成では、外部電源または3次巻線がBIASピンをドライブします。入力電源より低い電源が存在するときは、このオプションを使用します。内部LDOをディスエーブルするには、3.3Vより高い電源でBIASピンをドライブします。電源電圧を低くすると、内部回路の電源効率が向上します。

### 3次巻線によるBIASピンのオーバードライブ

LT3511はオプトカプラや3次巻線を必要とせずに優れた出力電圧の安定化を実現しますが、入力電圧が高い(>20V)アプリケーションの中には、新たな巻線(多くの場合3次巻線と呼ばれる)を追加することでシステム全体の効率を向上できるものがあります。3次巻線は、出力電圧が3.3V～12Vになるように設計します。VINが48Vの標準的なアプリケーションでは、BIASピンをオーバードライブすると、効率が4%～5%向上します。

図8. BIASピンの構成

### ループ補償

LT3511では、抵抗とコンデンサのネットワークをVCピンに外付けすることで補償をします。標準的な補償値は $R_C = 20k\Omega$ および $C_C = 2.2nF$ の近辺です(他の可能な値については「標準的応用例」のセクションの各種回路を参照)。安定性と許容可能な過渡応答を実現するには、 $R_C$ と $C_C$ の両方を適切に選択することが重要です。たとえば、 $R_C$ が大きすぎると、高周波ノイズとジッタの影響を受けやすくなります。これに対して、 $R_C$ が小さすぎると、過渡性能が低下します。 $C_C$ の値に関しては、これと逆になります。 $C_C$ が大きすぎると過渡応答が悪化し、 $C_C$ が小さすぎると不安定になります。 $R_C$ および $C_C$ の具体的な値は、アプリケーションとトランジスタの選択によって異なります。基板レベルの評価と過渡応答性能をもって、個々の選択を検証してください。

## アプリケーション情報

### 設計手順/設計例

LT3511のアプリケーションを設計するための目安として、以下の設計手順を使用します。独自のサンプリング・アーキテクチャは適切な抵抗値を選択するための反復手順を必要とする、ということに注意してください。

この設計例では、100mAの負荷電流と36V～72Vの入力範囲で15V出力を設計します。

$$V_{IN(MIN)} = 36V, V_{IN(NOM)} = 48V, V_{IN(MAX)} = 72V, \\ V_{OUT} = 15V \text{ および } I_{OUT} = 100mA$$

### ステップ1:トランジスタの巻数比を選択します。

$$N_{PS} < \frac{V_{SW(MAX)} - V_{IN(MAX)} - V_{LEAKAGE}}{V_{OUT} + V_F}$$

$V_{SW(MAX)}$  = 内部スイッチの最大定格 = 150V

$V_{LEAKAGE}$  = トランジスタの漏れスパイクのマージン = 40V

$V_F$  = 出力ダイオードの順方向電圧 = 約0.5Vと仮定

例:

$$N_{PS} < \frac{150V - 72V - 40V}{15V + 0.5V}$$

$$N_{PS} < 2.45$$

$$N_{PS} = 2$$

「出力電力」のセクションで説明したように、出力電力を決定するときは巻数比の選択が重要です。この時点で、効率を向上させるため、トランジスタに3次巻線を追加してLT3511のBIASピンをドライブすることができます。効率を最大にするには、3次巻線の電圧が3.3V～6Vに安定化するように設定する巻数比を選択します。

BIAS巻線を5Vでドライブするための、3次巻線の巻数比を選択します。(オプション)

例:

$$\frac{N_{THIRD}}{N_S} = \frac{V_{THIRD}}{V_{OUT}} = \frac{5V}{15V} = 0.33$$

トランジスタの巻数比は、次のように選択します。

$$N_{PRIMARY}:N_{SECONDARY}:N_{THIRD} = 2:1:0.33$$

### ステップ2:最小 $V_{IN}$ での最大出力電力を計算します。

$$P_{OUT(VIN(MIN))} = \eta \cdot V_{IN(MIN)} \cdot I_{IN} = \eta \cdot V_{IN(MIN)} \cdot D \cdot I_{PEAK} \cdot 0.5$$

$$D = \frac{(V_{OUT} + V_F) \cdot N_{PS}}{(V_{OUT} + V_F) \cdot N_{PS} + V_{IN(MIN)}}$$

$\eta$  = 効率 = 約75%

$$I_{PEAK} = ピーク・スイッチ電流 = 0.26A$$

例:

$$D = 0.46$$

$$P_{OUT(VIN(MIN))} = 1.62$$

$$I_{OUT(VIN(MIN))} = P_{OUT(VIN(MIN))}/V_{OUT} = 0.11A$$

選択した巻数比は100mAの出力電流要件を満たします。出力電流が小さすぎると、最小入力電圧が高めに調整される可能性があります。スイッチ電圧要件と、漏れインダクタンスによる電圧スパイクのマージンが与えられると、この例の巻数比の値が最大に設定されます。

### ステップ3:1次側インダクタンス、スイッチング周波数、および飽和電流を決定します。

最小オフ時間および最小オン時間の要件を満たすため、トランジスタの1次側インダクタンスは最小値より大きい値に設定する必要があります。

$$L_{PRI} \geq \frac{t_{OFF(MIN)} \cdot N_{PS} \cdot (V_{OUT} + V_F)}{I_{PEAK(MIN)}}$$

$$t_{OFF(MIN)} = 400ns$$

$$I_{PEAK(MIN)} = 55mA$$

$$L_{PRI} \geq \frac{t_{ON(MIN)} \cdot V_{IN(MAX)}}{I_{PEAK(MIN)}}$$

$$t_{ON(MIN)} = 100ns$$

$$I_{PEAK(MIN)} = 55mA$$

## アプリケーション情報

例:

$$L_{PRI} \geq \frac{400\text{ns} \cdot 2 \cdot (15+0.5)}{0.055}$$

$$L_{PRI} \geq 225\mu\text{H}$$

$$L_{PRI} \geq \frac{100\text{ns} \cdot 72}{0.055}$$

$$L_{PRI} \geq 131\mu\text{H}$$

さらに、1次側インダクタンスはスイッチング周波数も決定します。

$$f_{SW} = \frac{1}{t_{ON} + t_{OFF}} = \frac{1}{\frac{L_{PRI} \cdot I_{PEAK}}{V_{IN}} + \frac{L_{PRI} \cdot I_{PEAK}}{N_{PS} \cdot (V_{OUT} + V_F)}}$$

$$I_{PEAK} = \frac{V_{OUT} \cdot I_{OUT} \cdot 2}{\eta \cdot V_{IN} \cdot D}$$

例:

公称の  $V_{IN}$  である 48V でのスイッチング周波数を計算してみます。

$$D = \frac{(15+0.5) \cdot 2}{(15+0.5) \cdot 2 + 48} = 0.39$$

$$I_{PEAK} = \frac{15V \cdot 0.1A \cdot 2}{0.75 \cdot 48V \cdot 0.39} = 0.21A$$

$L_{PRI} = 350\mu\text{H}$  を選択することにします。ほとんどのトランジスタでは、1次側インダクタンスの許容差が  $\pm 20\%$  に規定されていることに注意してください。

$$f_{SW} = 256\text{kHz}$$

最後に、トランジスタの定格は、ライン条件および負荷条件に対して適切な飽和電流レベルに定められている必要があります。与えられた例では、スイッチ電流のワーストケースの条件は、最小  $V_{IN}$  でありかつ最大負荷であるときです。

$$I_{PEAK} = \frac{V_{OUT} \cdot I_{OUT} \cdot 2}{\eta \cdot V_{IN} \cdot D}$$

$$I_{PEAK} = \frac{15V \cdot 0.1A \cdot 2}{0.75 \cdot 36V \cdot 0.46} = 0.24A$$

飽和電流が定常状態の動作条件、起動条件および過渡条件を満たしていることを確認します。これらの条件を満たすには、定常状態の計算値より 50% 以上大きな飽和電流を選択します。この例では、400mA ~ 500mA の範囲の飽和電流を選択しています。

事前に設計されたフライバック・トランジスタのリストを表 1 に示します。このアプリケーションでは、Würth の 750311660 トランジスタを使用します。

### ステップ 4: 適切な出力ダイオードを選択します。

出力ダイオードの主な 2 つの選択基準は、順方向電流定格と逆電圧定格です。最大負荷要件は、出力ダイオードの平均電流要件としての、良好な 1 次推定値になります。さらに良好な推定値は、RMS 電流です。

$$I_{RMS} = I_{PEAK(V_{IN(MIN)})} \cdot N_{PS} \cdot \sqrt{\frac{1 - D_{V_{IN(MIN)}}}{3}}$$

例:

$$I_{RMS} = 0.24 \cdot 2 \cdot \sqrt{\frac{1 - 0.46}{3}} = 0.2A$$

次に、最大  $V_{IN}$  を使用して、逆電圧要件を計算します。

$$V_{REVERSE} = V_{OUT} + \frac{V_{IN(MAX)}}{N_{PS}}$$

例:

$$V_{REVERSE} = 15V + \frac{72V}{2} = 51V$$

Diodes 社の 60V/0.5A ダイオード (SBR0560S1) を使用します。

### ステップ 5: 出力コンデンサを選択します。

出力コンデンサは出力電圧リップルが最小になるように選択し、大容量のコンデンサの場合は、サイズとコストの妥協点を見つけます。公称  $V_{IN}$  では以下の式を使用します。

$$C = \frac{I_{OUT} \cdot D}{\Delta V_{OUT} \cdot f_{SW}}$$

## アプリケーション情報

例：

リップル・レベルが50mV以下になるように設計します。

$$C = \frac{0.1A \cdot 0.39}{0.05V \cdot 256\text{kHz}} = 3.1\mu\text{F}$$

10μF/25Vの出力コンデンサを選択します。セラミック・コンデンサは印加電圧によって容量が減少することに注意してください。容量は、最大電圧定格のときに想定容量の40%まで減少する可能性があります。

### ステップ6：クランプ回路を設計します。

クランプ回路は、漏れインダクタンスによるスパイクからスイッチを保護します。クランプ回路には、DZクランプが適しています。ツエナーとダイオードを選択する必要があります。

ツエナーの最大値は、最大 $V_{IN}$ に従って、次のように設定します。

$$V_{ZENER(MAX)} \leq 150V - V_{IN(MAX)}$$

例：

$$V_{ZENER(MAX)} \leq 150V - 72V$$

$$V_{ZENER(MAX)} \leq 78V$$

また、前に説明したように、クランプ回路の電力損失はクランプ電圧に反比例します。クランプ電圧が高くなると、電力損失は小さくなります。

最大電圧が72Vの68Vツエナーが最適な保護を行い、電力損失を最小限に抑えます。0.5Wのツエナーは、LT3511に関するほとんどのクランプ・アプリケーションの要件を満たします。電力損失は、「漏れインダクタンスとクランプ回路」のセクションに示す式を使用して計算できます。

選択するツエナーは、On Semiconductorの68V/0.5Wツエナー(MMSZ5266BT1G)です。

高速であり、逆ブレークダウン電圧が十分なダイオードを選択します。

$$V_{REVERSE} > V_{SW(MAX)}$$

$$V_{SW(MAX)} = V_{IN(MAX)} + V_{ZENER(MAX)}$$

例：

$$V_{REVERSE} > 140V$$

ダイオードは、0.24Aと算出されたスイッチのピーク・スイッチ電流を処理する必要があります。Diodes社の200V/0.6Aダイオード(BAV21W)を選択します。

### ステップ7：補償を行います。

補償は、設計手順の最後の方で最適化ていきます。VCノードからグランドに、抵抗とコンデンサを接続します。20kΩの抵抗と2.2nFのコンデンサを使用します。

### ステップ8：R<sub>FB</sub>抵抗とR<sub>TC</sub>抵抗を選択します。

次の式を使用して、R<sub>FB</sub>とR<sub>TC</sub>の出発点の値を選択します。R<sub>REF</sub>を10kΩに設定します。

$$R_{FB} = \frac{(V_{OUT} + V_f + 0.55V) \cdot N_{PS} \cdot R_{REF}}{1.2V}$$

$$R_{REF} = 10k$$

$$R_{TC} = \frac{R_{FB}}{N_{PS}}$$

例：

$$R_{FB} = \frac{(15 + 0.5 + 0.55V) \cdot 2 \cdot 10k}{1.2V} = 267k$$

$$R_{TC} = \frac{267k}{2} = 133k$$

### ステップ9：出力電圧に基づいてR<sub>FB</sub>を調整します。

実際に部品を接続したアプリケーションに電源を投入して、安定化された出力電圧を測定します。測定された出力電圧に基づいてR<sub>FB</sub>を再調整します。

$$R_{FB(NEW)} = \frac{V_{OUT}}{V_{OUT(MEAS)}} \cdot R_{FB(OLD)}$$

例：

$$R_{FB(NEW)} = \frac{15V}{16.8V} \cdot 267k = 237k$$

### ステップ10：R<sub>TC</sub>を取り去って、全温度範囲で出力電圧を測定します。

恒温槽のような温度が制御された環境で出力電圧を測定し、出力の温度係数を求めます。一定の負荷電流および入力電圧での出力電圧を、全動作温度範囲にわたって測定します。この手順により、全温度範囲でライン・レギュレーションとロード・レギュレーションが最適化されます。

## アプリケーション情報

$V_{OUT}$ の温度係数を計算します。

$$\frac{\Delta V_{OUT}}{\Delta Temp} = \frac{V_{OUT(HOT)} - V_{OUT(COLD)}}{T_{HOT}(^{\circ}\text{C}) - T_{COLD}(^{\circ}\text{C})}$$

例:

100mA および  $V_{IN} = 48\text{V}$  の条件で測定された  $V_{OUT}$

$$\frac{\Delta V_{OUT}}{\Delta Temp} = \frac{15.70\text{V} - 15.37\text{V}}{125^{\circ}\text{C} - (-50^{\circ}\text{C})} = 1.9\text{mV/}^{\circ}\text{C}$$

### ステップ11: $R_{TC}$ の新しい値を計算します。

$$R_{TC(NEW)} = \frac{R_{FB}}{N_{PS}} \cdot \frac{1.85\text{mV/}^{\circ}\text{C}}{\frac{\Delta V_{OUT}}{\Delta Temp}}$$

例:

$$R_{TC(NEW)} = \frac{237\text{k}}{2} \cdot \frac{1.85}{1.9} = 118\text{k}$$

ステップ12:  $R_{TC}$  に新しい値を設定して  $V_{OUT}$  を測定し、 $R_{TC}$  の変更に応じて  $R_{FB}$  を再調整します。

$$R_{FB(NEW)} = \frac{V_{OUT}}{V_{OUT(MEAS)}} \cdot R_{FB(OLD)}$$

例:

$$R_{FB(NEW)} = \frac{15\text{V}}{15\text{V}} \cdot 237\text{k} = 237\text{k}$$

ステップ13:  $R_{FB}$  および  $R_{TC}$  の新しい値を全温度範囲で検証します。

$R_{TC}$  を接続し、全温度範囲で出力電圧を測定します。

### ステップ14: 補償を最適化します。

$R_{FB}$  および  $R_{TC}$  の値が定まったので、補償を最適化します。補償は、出力の負荷ステップの過渡応答に対して最適化してください。全負荷範囲で過渡応答をチェックします。

例:

アプリケーションの最適な補償は次のようにになります。

$$R_C = 22.1\text{k}, C_C = 4.7\text{nF}$$

### ステップ15: 最小負荷を確保します。

最大入力電圧での最小負荷要件をチェックします。最小負荷が生じるのは、出力で消費されるよりも大きなエネルギーをコンバータが供給するのに伴って出力電圧が上昇し始める時点です。

例:

入力電圧が  $72\text{V}$  のときの最小負荷は、

7mA です。

### ステップ16: EN/UVLO 抵抗の値を求めます。

必要なヒステリシスの大きさを決定します。

$$\text{電圧ヒステリシス} = 2.6\mu\text{A} \cdot R_1$$

例:

2V のヒステリシスを選択します。

$$R_1 = \frac{2\text{V}}{2.6\mu\text{A}} = 768\text{k}$$

UVLO のスレッショルドを決定します。

$$V_{IN(UVLO,FALLING)} = \frac{1.2\text{V} \cdot (R_1 + R_2)}{R_2}$$

$$R_2 = \frac{1.2\text{V} \cdot R_1}{V_{IN(UVLO,FALLING)} - 1.2\text{V}}$$

UVLO の下降時スレッショルドを  $30\text{V}$  に設定します。

$$R_2 = \frac{1.2\text{V} \cdot 768\text{k}}{30\text{V} - 1.2\text{V}} = 32.4\text{k}$$

$$V_{IN(UVLO,FALLING)} = \frac{1.2\text{V} \cdot (R_1 + R_2)}{R_2}$$

$$= \frac{1.2\text{V} \cdot (768\text{k} + 32.4\text{k})}{32.4\text{k}} = 30\text{V}$$

$$V_{IN(UVLO,RISING)} = V_{IN(UVLO,FALLING)} + 2.6\mu\text{A} \cdot R_1 = 30\text{V} + 2.6\mu\text{A} \cdot 768\text{k} = 32\text{V}$$

# LT3511

## 標準的応用例

48Vから5Vの絶縁型フライバック・コンバータ

48Vから15Vの絶縁型フライバック・コンバータ

## 標準的応用例

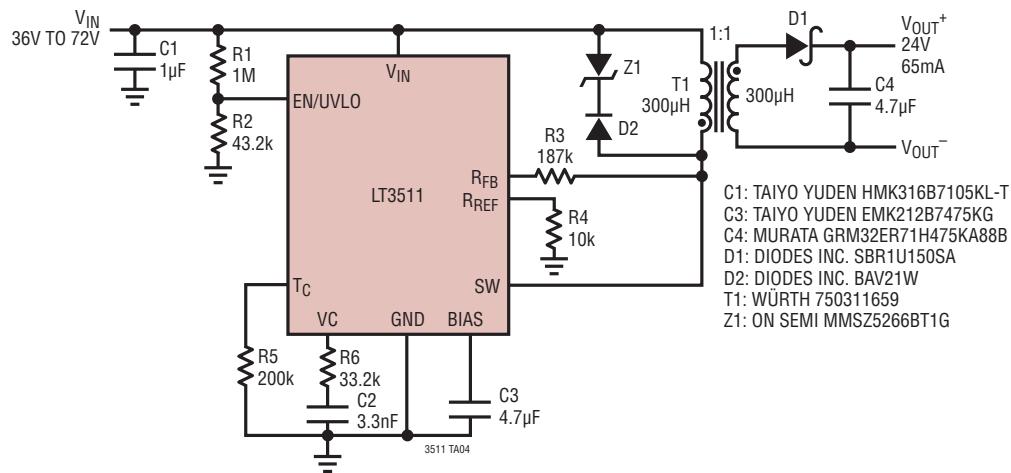

## 48Vから24Vの絶縁型フライバック・コンバータ

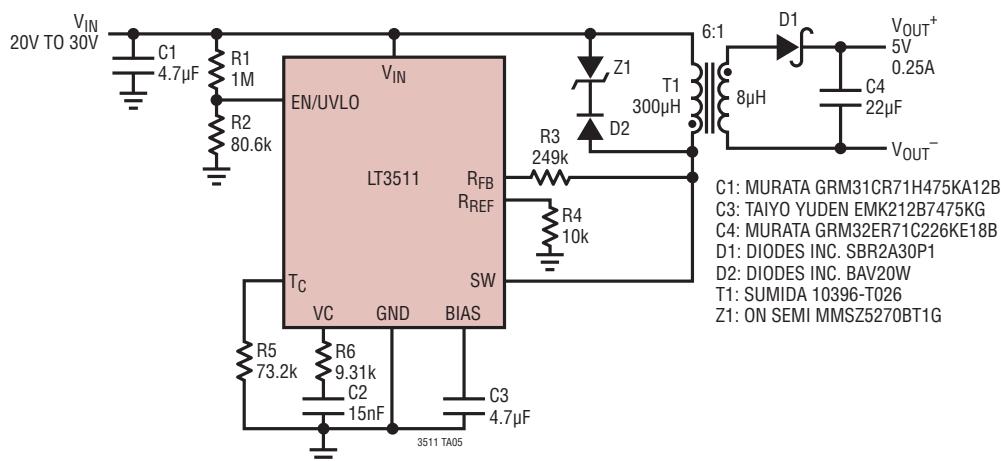

## 24Vから5Vの絶縁型フライバック・コンバータ

# LT3511

## 標準的応用例

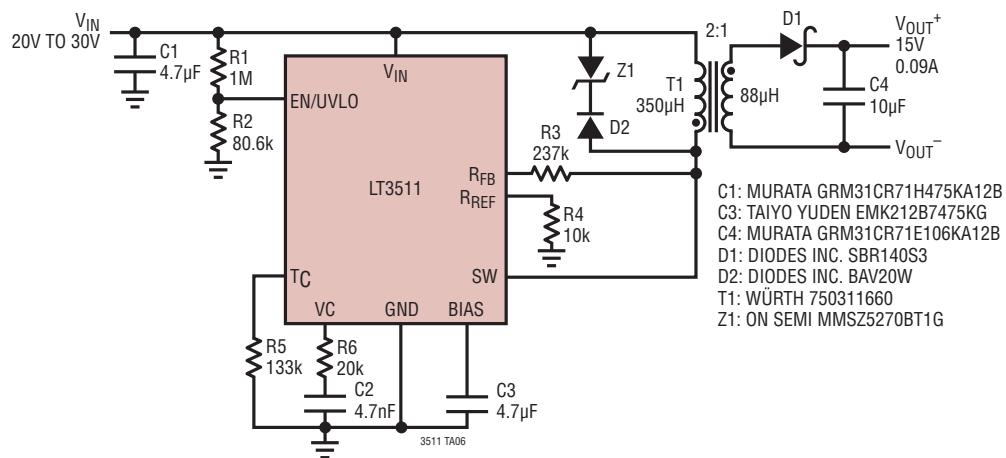

24Vから15Vの絶縁型フライバック・コンバータ

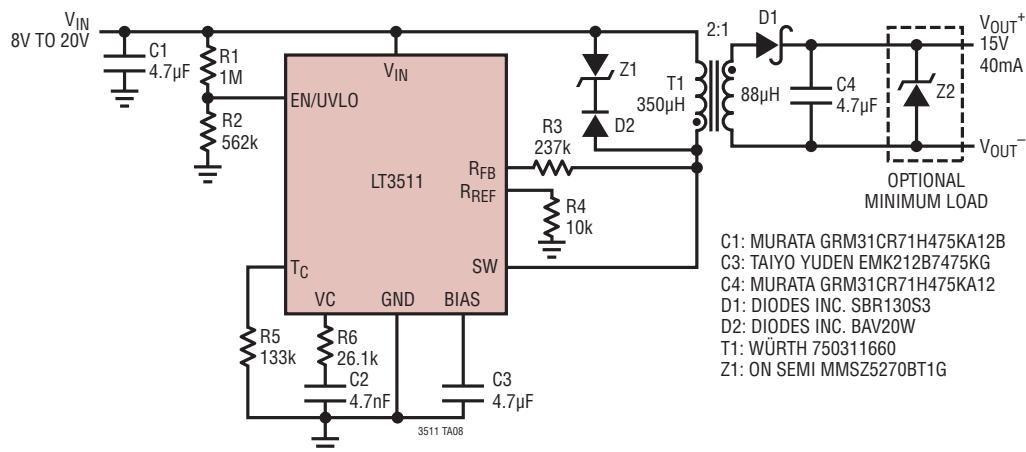

12Vから15Vの絶縁型フライバック・コンバータ

## 標準的応用例

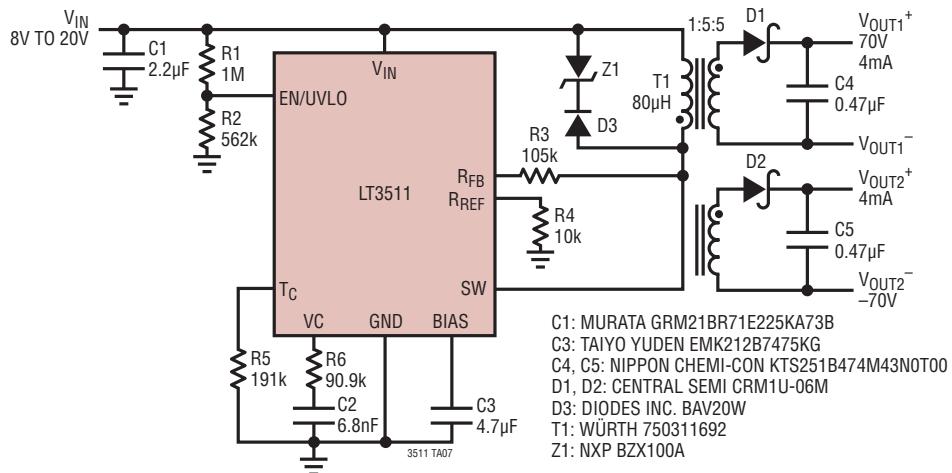

## 12Vから±70Vの絶縁型フライバック・コンバータ

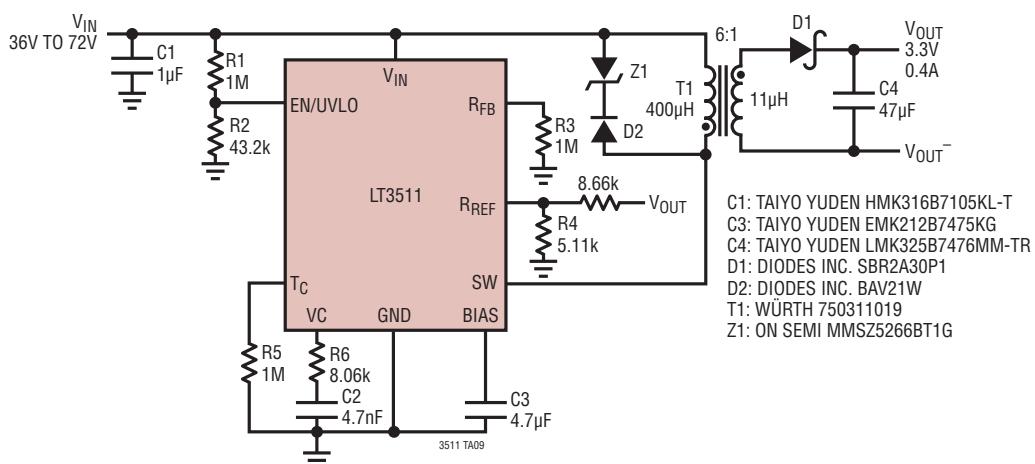

## 48Vから3.3Vの非絶縁型フライバック・コンバータ

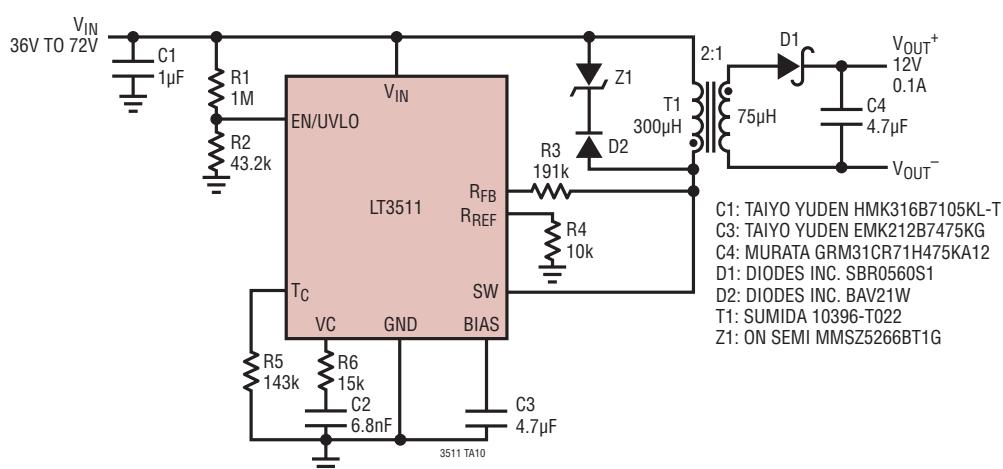

## 48Vから12Vの絶縁型フライバック・コンバータ

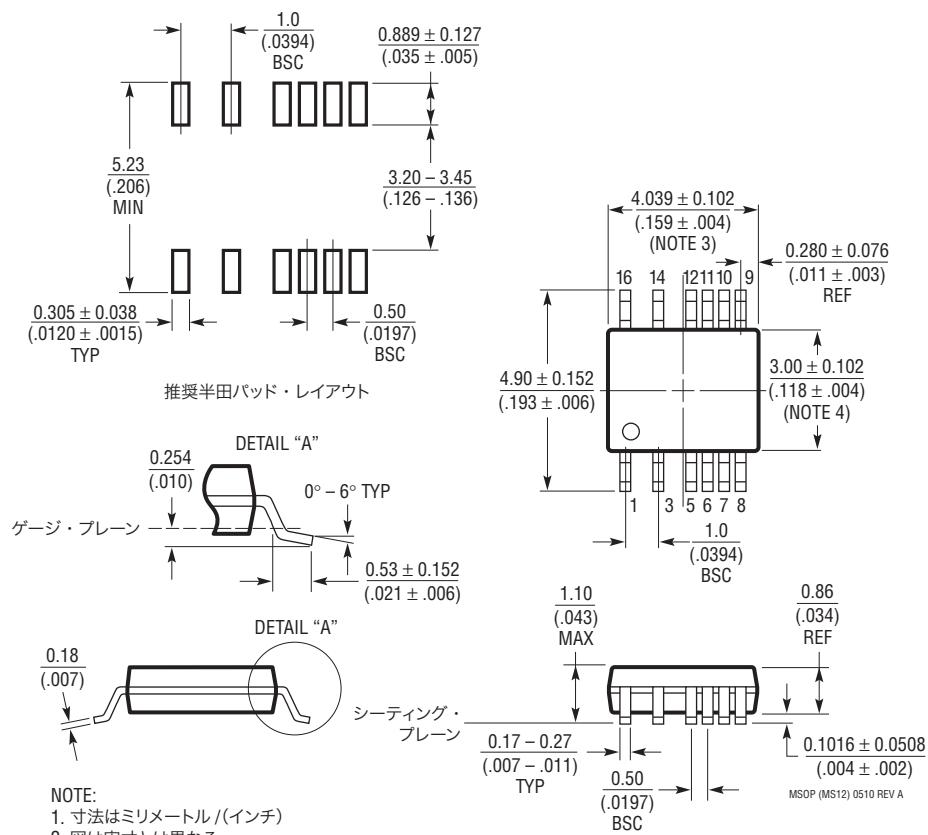

## パッケージ寸法

最新のパッケージ図面については、<http://www.linear-tech.co.jp/designtools/packaging/>をご覧ください。

**MSパッケージ

バリエーション: MS16(12)

16ピン・プラスチック MSOP(4本のピンを除去)

(Reference LTC DWG # 05-08-1847 Rev A)**

## 改訂履歴

| REV | 日付    | 概要                                                                                                                                                                                                                                                                                          | ページ番号                                      |

|-----|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|

| A   | 4/11  | MPグレードを追加。<br>「ピン機能」のセクションで $R_{FB}$ ピンの説明を改訂。<br>「アプリケーション情報」のセクションで効率の式と表1を更新。<br>「標準的応用例」の図を改訂。                                                                                                                                                                                          | 2, 3<br>5<br>9, 10<br>20, 21               |

| B   | 6/11  | 「巻数比」のセクションから文章を削除し、「アプリケーション情報」の「1次側インダクタンスの要件」に文章を追加。<br>「アプリケーション情報」の「漏れインダクタンスとクランプ回路」のセクションで文章を微細なレベルで編集し、表3を改訂<br>「アプリケーション情報」の「設計手順/設計例」のセクションでステップ3を置き換え<br>「アプリケーション情報」の「設計手順/設計例」のセクションのステップ6で式を改訂し、文章を微細なレベルで編集<br>すべての「標準的応用例」で「D2: Diodes」の製品番号を更新<br>「関連製品」のセクションに LT3512 を追加 | 11<br>12-13<br>16<br>18<br>20-23, 26<br>26 |

| C   | 12/11 | 絶対最大定格とHグレードの温度範囲を改訂<br>標準的応用例の図 TA07 と TA08 の抵抗値を修正                                                                                                                                                                                                                                        | 2<br>23                                    |

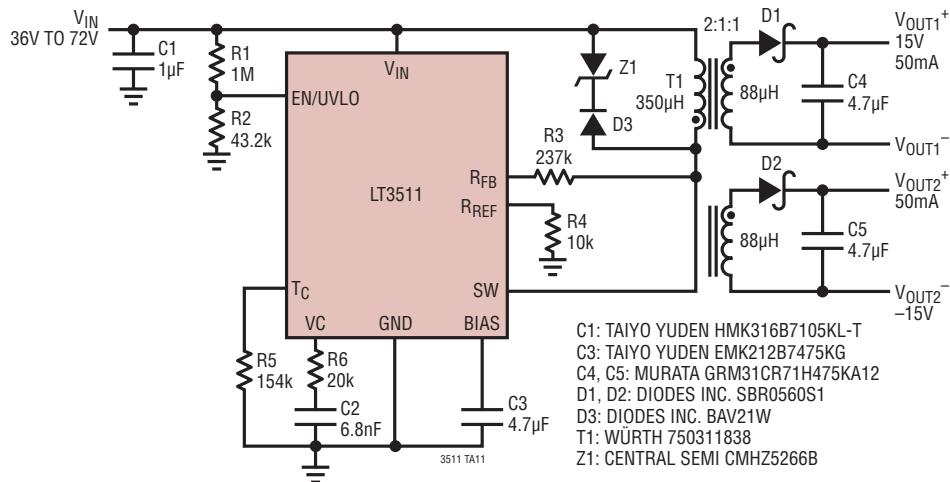

## 標準的応用例

## 48Vから±15Vの絶縁型フライバック・コンバータ

## 関連製品

| 製品番号                            | 説明                                        | 注釈                                                                                                   |

|---------------------------------|-------------------------------------------|------------------------------------------------------------------------------------------------------|

| LT3512                          | モノリシック、高電圧、絶縁型フライバック・コンバータ、オプトカプラー不要      | 4.5V ≤ V <sub>IN</sub> ≤ 100V、420mA/150Vのパワー・スイッチを内蔵、高電圧ピン間にスペースを設けたMSOP-16(12)パッケージ                 |

| LT3958                          | 高入力電圧の昇圧、フライバック、SEPICおよび反転コンバータ           | 5V ≤ V <sub>IN</sub> ≤ 80V、3.3A/84Vパワー・スイッチを内蔵、高電圧ピン間にスペースを設けた5mm×6mm QFN-36パッケージ                    |

| LT3748                          | 100V絶縁型フライバック・コントローラ                      | 5V ≤ V <sub>IN</sub> ≤ 100V、オプトアイソレータや3次巻線が不要、ゲート・ドライバ内蔵、高電圧ピン間にスペースを設けたMSOP-16パッケージ                 |

| LT3957                          | 昇圧、フライバック、SEPICおよび反転コンバータ                 | 3V ≤ V <sub>IN</sub> ≤ 40V、5A/40Vパワー・スイッチを内蔵、高電圧ピン間にスペースを設けた5mm×6mm QFN-36パッケージ                      |

| LT3956                          | 定電流/定電圧の昇圧、降圧、昇降圧、SEPICまたはフライバック・コンバータ    | 4.5V ≤ V <sub>IN</sub> ≤ 80V、3.3A/84Vパワー・スイッチを内蔵、True Color PWM調光、高電圧ピン間にスペースを設けた5mm×6mm QFN-36パッケージ |

| LT3575                          | 60V/2.5Aスイッチを内蔵した絶縁型フライバック・スイッチング・レギュレータ  | 3V ≤ V <sub>IN</sub> ≤ 40V、オプトアイソレータや3次巻線が不要、出力電力:最大14W、TSSOP-16Eパッケージ                               |

| LT3573                          | 60V/1.25Aスイッチを内蔵した絶縁型フライバック・スイッチング・レギュレータ | 3V ≤ V <sub>IN</sub> ≤ 40V、オプトアイソレータや3次巻線が不要、出力電力:最大7W、MSOP-16Eパッケージ                                 |

| LT3574                          | 60V/0.65Aスイッチを内蔵した絶縁型フライバック・スイッチング・レギュレータ | 3V ≤ V <sub>IN</sub> ≤ 40V、オプトアイソレータや3次巻線が不要、出力電力:最大3W、MSOP-16パッケージ                                  |

| LT3757                          | 昇圧、フライバック、SEPICおよび反転コントローラ                | 2.9V ≤ V <sub>IN</sub> ≤ 40V、設定可能な動作周波数:100kHz～1MHz、3mm×3mm DFN-10およびMSOP-10Eパッケージ                   |

| LT3758                          | 昇圧、フライバック、SEPICおよび反転コントローラ                | 5.5V ≤ V <sub>IN</sub> ≤ 100V、設定可能な動作周波数:100kHz～1MHz、3mm×3mm DFN-10およびMSOP-10Eパッケージ                  |

| LTC1871/LTC1871-1/<br>LTC1871-7 | No RSENSE™、低消費電流のフライバック、昇圧およびSEPICコントローラ  | 2.5V ≤ V <sub>IN</sub> ≤ 36V、Burst Mode®動作                                                           |