**LOGY** モニタ機能とケーブル電圧低下

補償機能を備えた40V、2.1A

低ドロップアウト可変リニア・レギュレータ

特長

- 広い入力電圧範囲:1.4V～40V

- 1本の抵抗で出力電圧を設定:0.4V～32V

- 出力電流:2.1A

- 入力、負荷、温度の全範囲での許容誤差: $\pm 2\%$

- 出力電流モニタ: $I_{MON} = I_{OUT}/1000$

- 熱制限をプログラム可能な温度モニタ

- プログラム可能なケーブル電圧降下補償

- 複数デバイスの並列接続により出力電流値を向上

- ドロップアウト電圧:330mV

- 1個のコンデンサで出力をソフトスタートさせ、ノイズを低減

- 低出力ノイズ:40 $\mu$ V<sub>RMS</sub>(10Hz～100kHz)

- プログラム可能な高精度の外部電流制限

- しきい値をプログラム可能なパワーグッド・フラグ

- セラミック出力コンデンサ:最小10 $\mu$ F

- シャットダウン時の静止電流:<1 $\mu$ A

- バッテリ逆接続保護、逆電流保護および逆出力保護

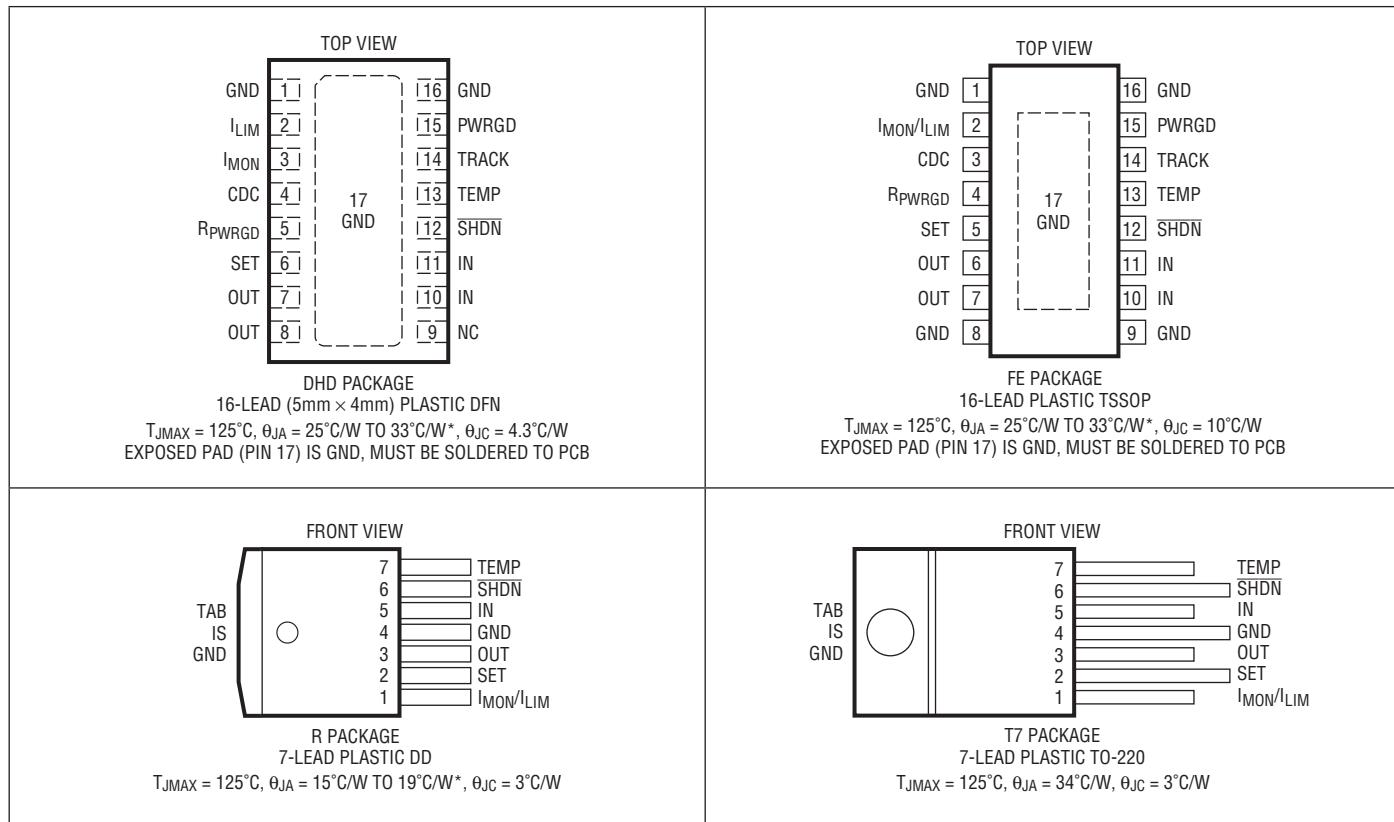

- 5mm×4mmの16ピンDFN、16ピンTSSOP、7ピンDD-PAK、および7ピンT0-220パッケージで供給可能

## アプリケーション

- プログラム可能なリニア・レギュレータ

- スイッチング電源のポスト・レギュレータ

- USB 電源

- 高信頼性電源

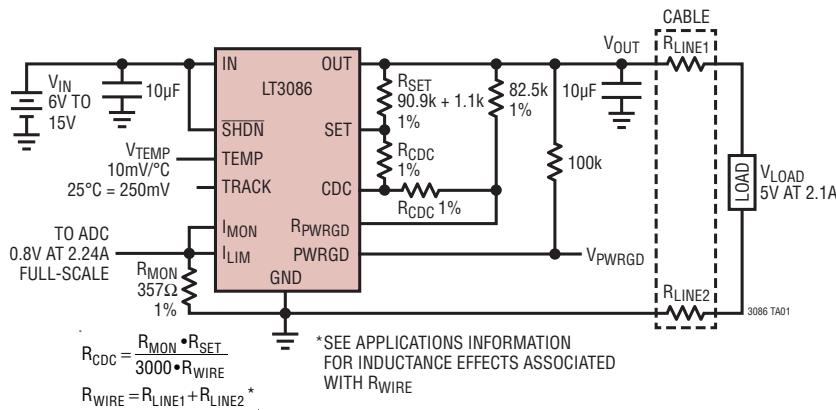

## 標準的應用例

ケーブルの電圧降下を補償した5V、2.1AのUSB電源

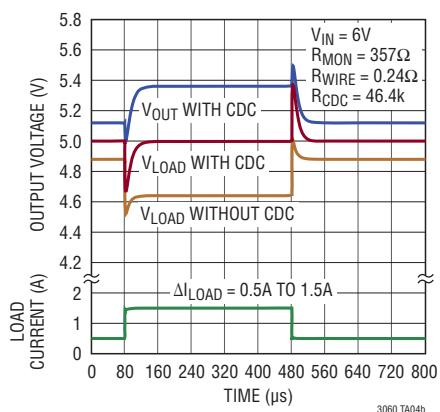

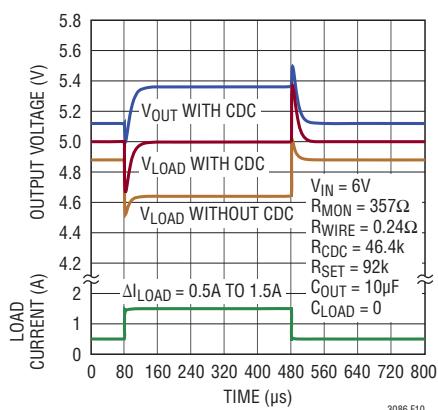

### ケーブルの電圧降下を補償(CDC) したトランジエント応答

## 絶対最大定格 (Note 1)

|                               |                       |                            |               |

|-------------------------------|-----------------------|----------------------------|---------------|

| IN ピンの電圧                      | ±45V                  | PWRGD ピンの電圧                | -0.3V、36V     |

| OUT ピンの電圧                     | ±36V                  | R_PWRGD ピンの電圧              | -0.3V、36V     |

| 入出力間の電圧差 (Note 2)             | ±45V                  | 出力短絡時間                     | 無期限           |

| SET ピンの電圧                     | -0.3V、36V             | 動作接合部温度 (Note 3, 5, 12)    |               |

| SHDN ピンの電圧                    | ±45V                  | E グレード、I グレード              | -40°C ~ 125°C |

| CDC ピンの電流 (内部でクランプ、ピンに流れ込む電流) | <8mA                  | MP グレード                    | -55°C ~ 125°C |

| I_MON ピンの電圧                   | -0.3V、7V              | 保存温度範囲                     | -65°C ~ 150°C |

| I_LIM ピンの電圧                   | -0.3V、2V              | リード温度 (半田付け、10秒)           |               |

| TRACK ピンの電圧                   | -0.3V、内部で 1.25V にクランプ | (TSSOP, DD-PAK, TO-220 のみ) | 300°C         |

| TEMP ピンの電圧                    | -0V、5V                |                            |               |

## ピン配置

\*「アプリケーション情報」のセクションを参照。

## 発注情報

| 無鉛仕上げ          | テープアンドリール        | 製品マーキング* | パッケージ                           | 温度範囲           |

|----------------|------------------|----------|---------------------------------|----------------|

| LT3086EDHD#PBF | LT3086EDHD#TRPBF | 3086     | 16-Lead (5mm × 4mm) Plastic DFN | -40°C to 125°C |

| LT3086IDHD#PBF | LT3086IDHD#TRPBF | 3086     | 16-Lead (5mm × 4mm) Plastic DFN | -40°C to 125°C |

| LT3086EFE#PBF  | LT3086EFE#TRPBF  | 3086FE   | 16-Lead Plastic TSSOP           | -40°C to 125°C |

| LT3086IFE#PBF  | LT3086IFE#TRPBF  | 3086FE   | 16-Lead Plastic TSSOP           | -40°C to 125°C |

| LT3086MPFE#PBF | LT3086MPFE#TRPBF | 3086FE   | 16-Lead Plastic TSSOP           | -55°C to 125°C |

| LT3086ER#PBF   | LT3086ER#TRPBF   | LT3086R  | 7-Lead Plastic DD-Pak           | -40°C to 125°C |

| LT3086IR#PBF   | LT3086IR#TRPBF   | LT3086R  | 7-Lead Plastic DD-Pak           | -40°C to 125°C |

| LT3086MPR#PBF  | LT3086MPR#TRPBF  | LT3086R  | 7-Lead Plastic DD-Pak           | -55°C to 125°C |

| LT3086ET7#PBF  | N/A              | LT3086T7 | 7-Lead Plastic TO-220           | -40°C to 125°C |

| LT3086IT7#PBF  | N/A              | LT3086T7 | 7-Lead Plastic TO-220           | -40°C to 125°C |

| LT3086MPT7#PBF | N/A              | LT3086T7 | 7-Lead Plastic TO-220           | -55°C to 125°C |

さらに広い動作温度範囲で規定されるデバイスについては、弊社または弊社代理店にお問い合わせください。\* 温度グレードは出荷時のコンテナのラベルで識別されます。

非標準の鉛仕上げ製品の詳細については、弊社または弊社代理店にお問い合わせください。

無鉛仕上げの製品マーキングの詳細については、<http://www.linear-tech.co.jp/leadfree/>をご覧ください。

テープ・アンド・リールの仕様の詳細については、<http://www.linear-tech.co.jp/tapeandree/>をご覧ください。

## 電気的特性

● は全動作温度範囲での規格値を意味する。それ以外は  $T_A = 25^\circ\text{C}$  の値。

| PARAMETER                                                                           | CONDITIONS                                                                                                                                                             |                            | MIN        | TYP                                   | MAX                                                 | UNITS         |

|-------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|------------|---------------------------------------|-----------------------------------------------------|---------------|

| Minimum Input Voltage (Note 4)                                                      | $I_{LOAD} = 2.1\text{A}, \Delta V_{OUT} = -1\%$                                                                                                                        | ●                          |            | 1.4                                   | 1.55                                                | V             |

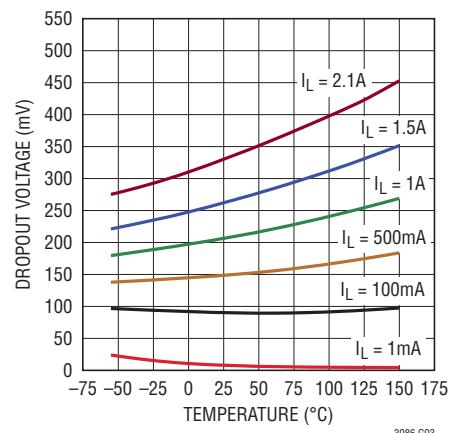

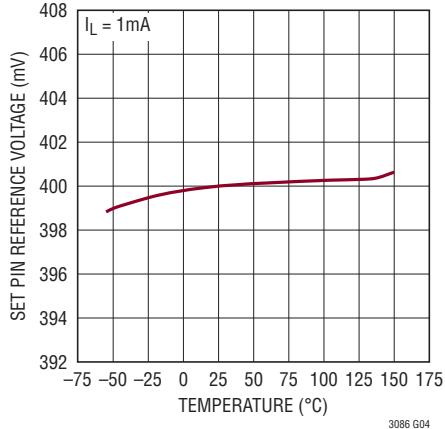

| Reference Voltage<br>(Notes 3, 5)                                                   | $V_{IN} = 1.55\text{V}, I_{LOAD} = 1\text{mA}$<br>$1.55\text{V} < V_{IN} < 40\text{V}, 1\text{mA} < I_{LOAD} < 2.1\text{A}$                                            | ●                          | 396<br>392 | 400<br>400                            | 404<br>408                                          | mV            |

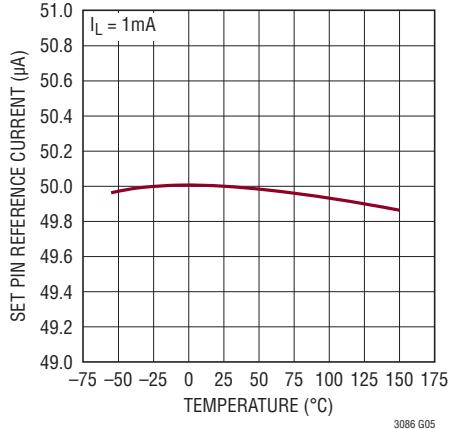

| Reference Current                                                                   | $V_{IN} = 1.55\text{V}, I_{LOAD} = 1\text{mA}$<br>$1.55\text{V} < V_{IN} < 40\text{V}, 1\text{mA} < I_{LOAD} < 2.1\text{A}$                                            | ●                          | 49.5<br>49 | 50<br>50                              | 50.5<br>51                                          | $\mu\text{A}$ |

| Line Regulation                                                                     | $V_{IN} = 1.55\text{V} \text{ to } 40\text{V}, I_{LOAD} = 1\text{mA}$                                                                                                  | ●<br>●                     |            | 0.1<br>-0.12                          | 0.8<br>-0.03                                        | $\text{mV}$   |

| Load Regulation<br>(Notes 6, 7)                                                     | $I_{LOAD} = 1\text{mA} \text{ to } 2.1\text{A}, V_{IN} = V_{OUT} + 0.55\text{V}$                                                                                       | ●<br>●                     |            | 0.25<br>0.02                          | 1<br>0.08                                           | $\text{mV}$   |

| Minimum Load Current (Note 16)                                                      |                                                                                                                                                                        | ●                          |            |                                       | 1                                                   | $\text{mA}$   |

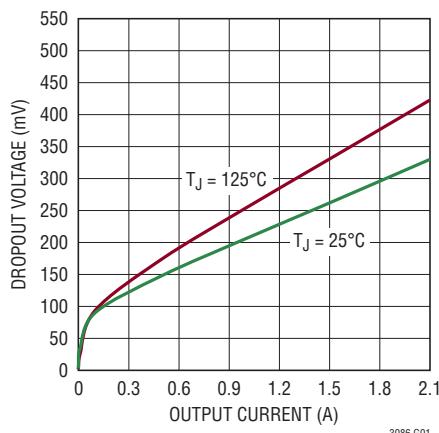

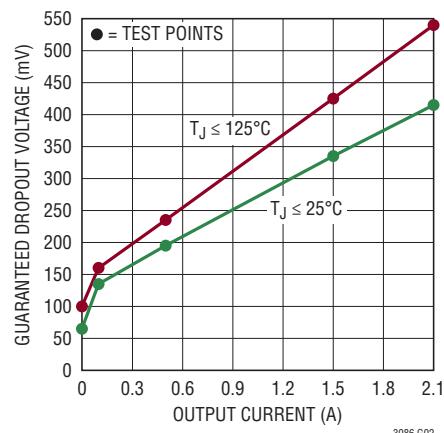

| Dropout Voltage<br>$V_{IN} = V_{OUT(\text{NOMINAL})}$ , (Notes 7, 8)                | $I_{LOAD} = 1\text{mA}$<br>$I_{LOAD} = 100\text{mA}$<br>$I_{LOAD} = 500\text{mA}$<br>$I_{LOAD} = 1.5\text{A}$<br>$I_{LOAD} = 2.1\text{A}$                              | ●<br>●<br>●<br>●<br>●      |            | 10<br>100<br>100<br>150<br>260<br>330 | 65<br>100<br>135<br>160<br>195<br>425<br>415<br>540 | $\text{mV}$   |

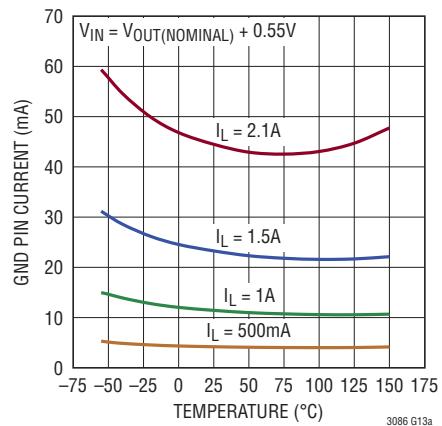

| GND Pin Current<br>$V_{IN} = V_{OUT(\text{NOMINAL})} + 0.55\text{V}$ , (Notes 7, 9) | $I_{LOAD} = 0\mu\text{A}$<br>$I_{LOAD} = 1\text{mA}$<br>$I_{LOAD} = 100\text{mA}$<br>$I_{LOAD} = 500\text{mA}$<br>$I_{LOAD} = 1.5\text{A}$<br>$I_{LOAD} = 2.1\text{A}$ | ●<br>●<br>●<br>●<br>●<br>● |            | 1.2<br>1.3<br>1.8<br>4.5<br>23<br>44  | 2.4<br>2.6<br>3.6<br>9<br>46<br>88                  | $\text{mA}$   |

3086fa

## 電気的特性

●は全動作温度範囲での規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。

| PARAMETER                                                                        | CONDITIONS                                                                                                                                                                                                                                             | MIN                   | TYP                              | MAX                               | UNITS                             |                                                  |

|----------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|----------------------------------|-----------------------------------|-----------------------------------|--------------------------------------------------|

| Quiescent Current in Shutdown                                                    | $V_{IN} = 40V, V_{SHDN} = 0V$                                                                                                                                                                                                                          |                       | 0.1                              | 1                                 | $\mu\text{A}$                     |                                                  |

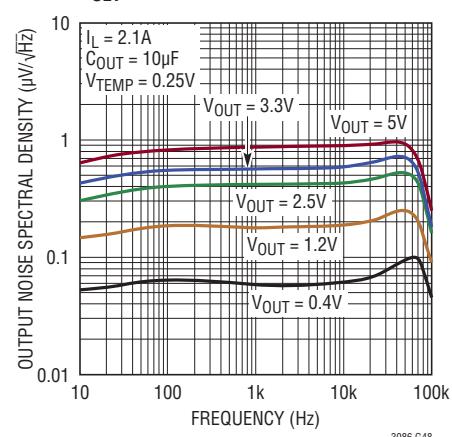

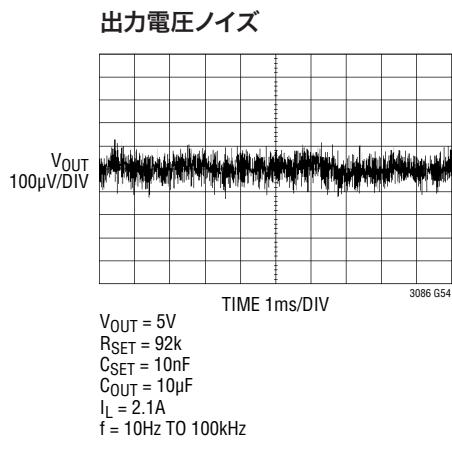

| Output Voltage Noise                                                             | $C_{SET} = 0.01\mu\text{F}, C_{OUT} = 10\mu\text{F}, I_{LOAD} = 2.1\text{A}$<br>$V_{OUT} = 5V, \text{BW} = 10\text{Hz to } 100\text{kHz}$                                                                                                              |                       | 40                               |                                   | $\mu\text{VRMS}$                  |                                                  |

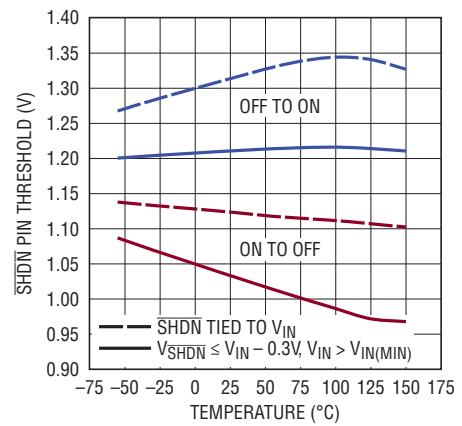

| Shutdown Threshold                                                               | $V_{OUT} = \text{Off to On}$<br>$V_{OUT} = \text{On to Off}$                                                                                                                                                                                           | ●<br>●                | 1.12<br>0.85                     | 1.22<br>1.03                      | V<br>V                            |                                                  |

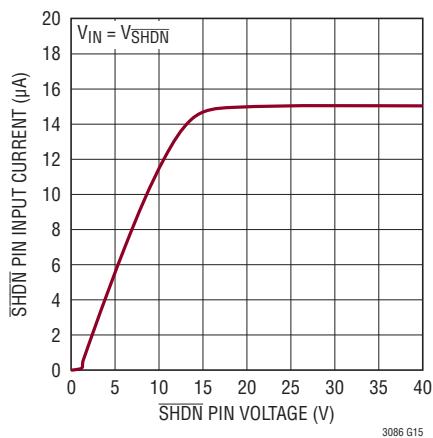

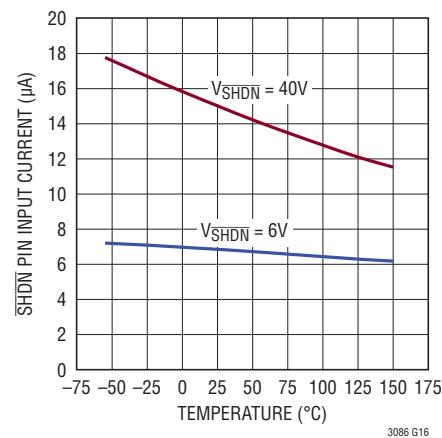

| SHDN Pin Current (Note 10)<br>$1.55V < V_{IN} < 40V$                             | $V_{SHDN} = 0V$<br>$V_{SHDN} = 40V$                                                                                                                                                                                                                    | ●<br>●                |                                  | 1<br>15<br>35                     | $\mu\text{A}$<br>$\mu\text{A}$    |                                                  |

| TEMP Voltage (Note 13)                                                           | $T_J = 25^\circ\text{C}$<br>$T_J = 125^\circ\text{C}$                                                                                                                                                                                                  |                       |                                  | 0.25<br>1.25                      | V<br>V                            |                                                  |

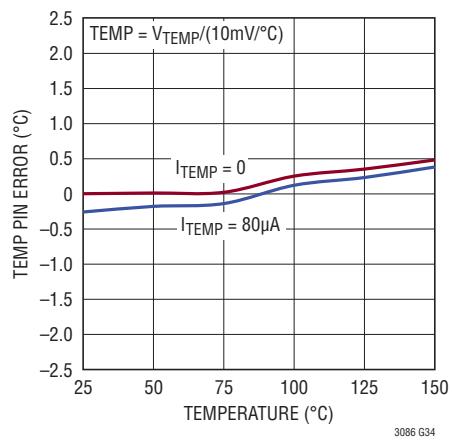

| TEMP Error (Note 13)                                                             | $0^\circ\text{C} < T_J < 125^\circ\text{C}, I_{TEMP} = 0$<br>$0^\circ\text{C} < T_J < 125^\circ\text{C}, I_{TEMP} = 0\mu\text{A} \text{ to } 80\mu\text{A}$                                                                                            |                       | -0.09<br>-0.1                    | 0.09                              | V<br>V                            |                                                  |

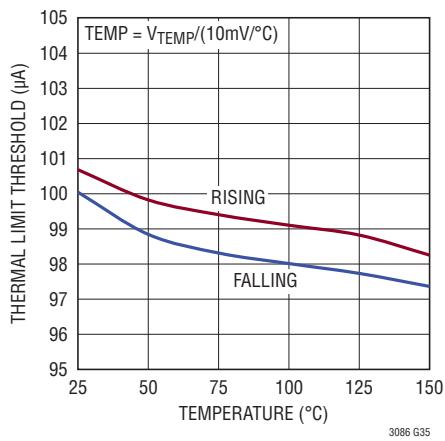

| $I_{TEMP}$ Thermal Limit Current Threshold                                       | $25^\circ\text{C} < T_J < 125^\circ\text{C}$                                                                                                                                                                                                           |                       | 95                               | 100                               | 105                               | $\mu\text{A}$                                    |

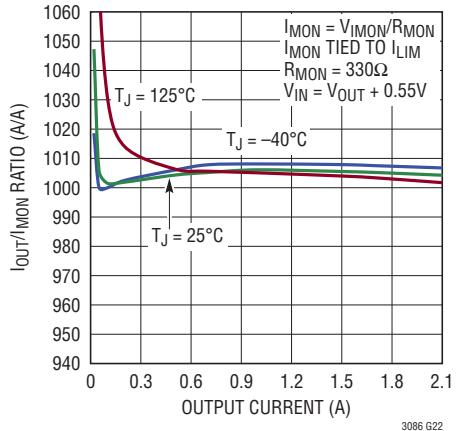

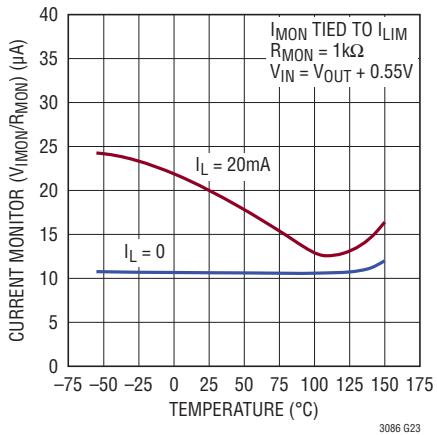

| $I_{MON}$ Output Current<br>$V_{IN} = V_{OUT(\text{NOMINAL})} + 0.55V$ (Note 15) | $I_{LOAD} = 20\text{mA}, R_{MON} = 1\text{k}\Omega$<br>$I_{LOAD} = 500\text{mA}, R_{MON} = 330\Omega$<br>$I_{LOAD} = 1\text{A}, R_{MON} = 330\Omega$<br>$I_{LOAD} = 1.5\text{A}, R_{MON} = 330\Omega$<br>$I_{LOAD} = 2.1\text{A}, R_{MON} = 330\Omega$ | ●<br>●<br>●<br>●<br>● | 5<br>440<br>0.95<br>1.43<br>2.02 | 20<br>500<br>1.00<br>1.50<br>2.10 | 75<br>560<br>1.05<br>1.57<br>2.18 | $\mu\text{A}$<br>$\mu\text{A}$<br>mA<br>mA<br>mA |

| Output Current Sharing Error (Note 14)                                           | $R_{MON} = 330\Omega, I_{OUT(\text{MASTER})} = 2.1\text{A}$                                                                                                                                                                                            |                       | -10                              | 0                                 | 10                                | %                                                |

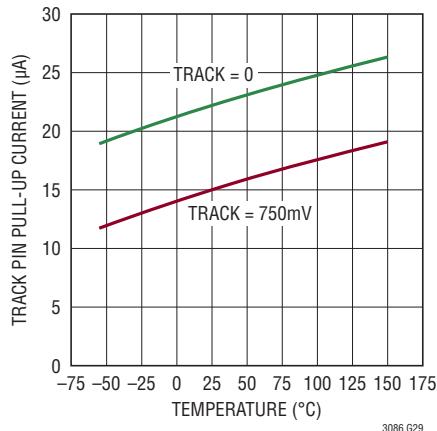

| TRACK Pin Pull-Up Current                                                        | $V_{TRACK} = 750\text{mV}$                                                                                                                                                                                                                             | ●                     | 7                                | 15                                | 25                                | $\mu\text{A}$                                    |

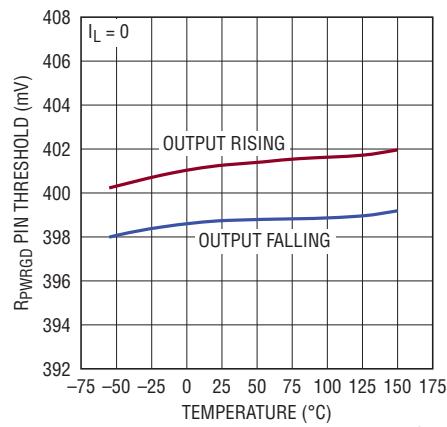

| RPWRGD Reference Voltage                                                         | $1.55V < V_{IN} < 40V$                                                                                                                                                                                                                                 | ●                     | 390                              | 400                               | 410                               | mV                                               |

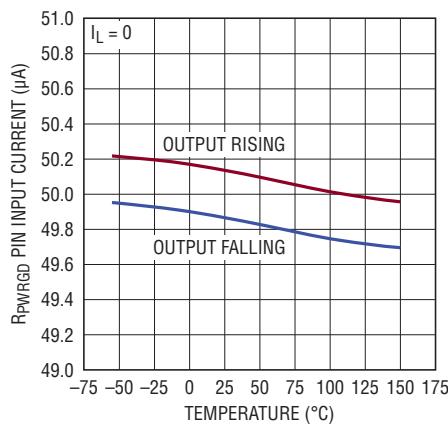

| RPWRGD Reference Current                                                         | $1.55V < V_{IN} < 40V$                                                                                                                                                                                                                                 | ●                     | 48.75                            | 50                                | 51.25                             | $\mu\text{A}$                                    |

| RPWRGD Reference Voltage Hysteresis                                              | $1.55V < V_{IN} < 40V$                                                                                                                                                                                                                                 |                       |                                  | 2.4                               |                                   | mV                                               |

| RPWRGD Reference Current Hysteresis                                              | $1.55V < V_{IN} < 40V$                                                                                                                                                                                                                                 |                       |                                  | 300                               |                                   | nA                                               |

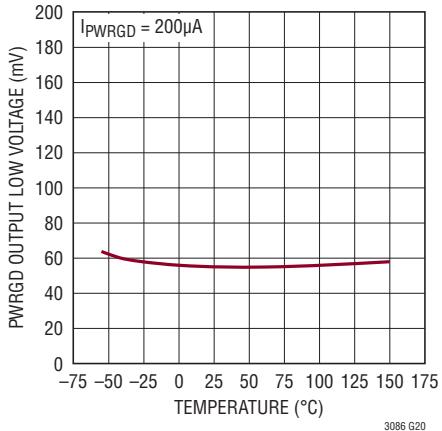

| PWRGD $V_{OL}$                                                                   | $I_{PWRGD} = 200\mu\text{A}$ (Fault Condition)                                                                                                                                                                                                         | ●                     |                                  | 55                                | 200                               | mV                                               |

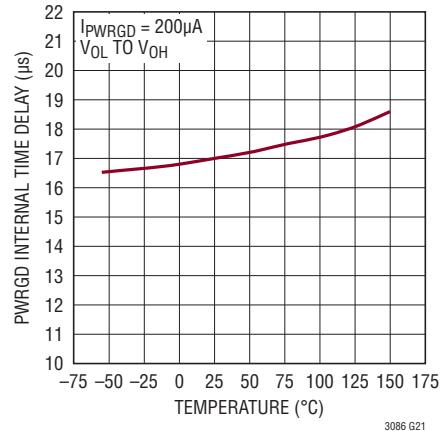

| PWRGD Internal Time Delay                                                        | $V_{OL} \text{ TO } V_{OH}$ (Rising Edge)                                                                                                                                                                                                              | ●                     | 8                                | 17                                | 25                                | $\mu\text{s}$                                    |

| PWRGD Pin Leakage Current                                                        | $V_{PWGRD} = 32V, V_{RPWGRD} = 500\text{mV}$                                                                                                                                                                                                           | ●                     |                                  |                                   | 1                                 | $\mu\text{A}$                                    |

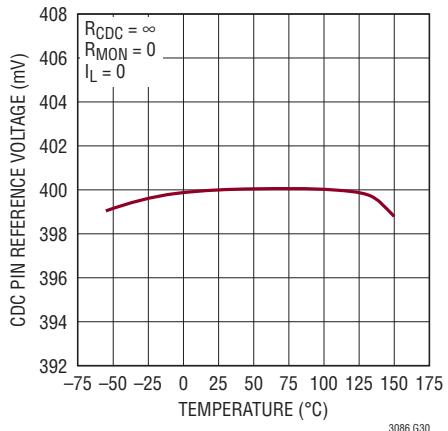

| CDC Reference Voltage                                                            | $1.55V < V_{IN} < 40V, I_{MON} = 0V$                                                                                                                                                                                                                   | ●                     | 390                              | 400                               | 410                               | mV                                               |

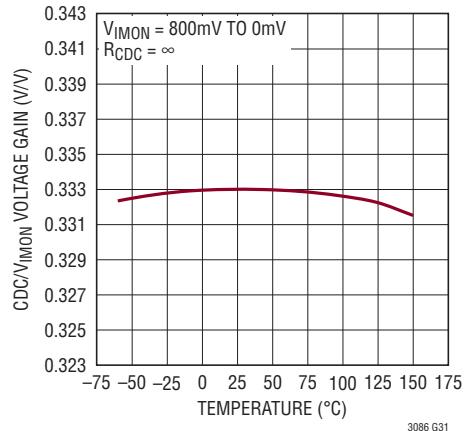

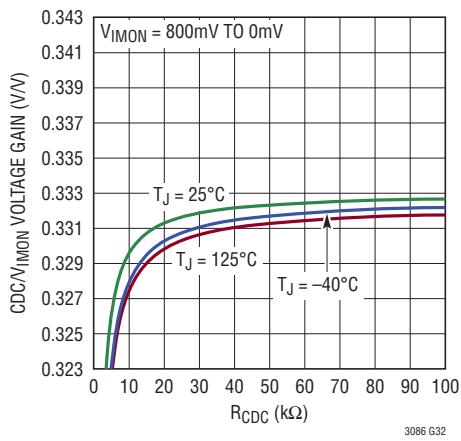

| CDC/ $V_{IMON}$ Voltage Gain                                                     | $1.55V < V_{IN} < 40V, 0 < I_{CDC} < 20\mu\text{A}, V_{IMON} = 800\text{mV to } 0$                                                                                                                                                                     | ●                     | 0.320                            | 0.333                             | 0.343                             | V/V                                              |

| Ripple Rejection                                                                 | $V_{IN} = 1.9V$ (AVG), $V_{RIPPLE} = 0.5V_{P-P}, V_{OUT} = 1V$<br>$f_{RIPPLE} = 120\text{Hz}, I_{LOAD} = 2.1\text{A}$                                                                                                                                  |                       | 65                               | 80                                |                                   | dB                                               |

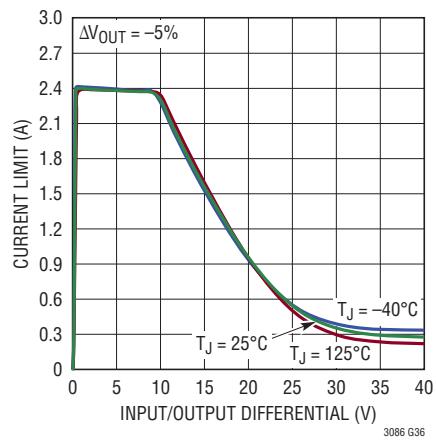

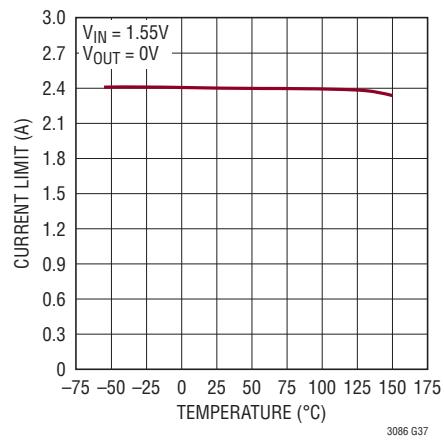

| Internal Current Limit                                                           | $V_{IN} = 1.55V$<br>$V_{IN} = V_{OUT(\text{NOMINAL})} + 0.55V$ (Notes 7, 12), $\Delta V_{OUT} = -5\%$                                                                                                                                                  | ●<br>●                | 2.2<br>2.2                       | 2.4                               | 2.9                               | A<br>A                                           |

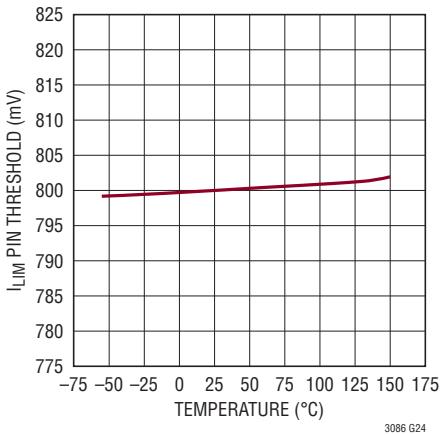

| $I_{LIM}$ Threshold Voltage                                                      | $1.55V < V_{IN} < 40V$                                                                                                                                                                                                                                 | ●                     | 775                              | 800                               | 825                               | mV                                               |

| Input Reverse-Leakage Current                                                    | $V_{IN} = -40V, V_{OUT} = 0$                                                                                                                                                                                                                           | ●                     |                                  |                                   | 2                                 | mA                                               |

| Reverse-Output Current (Note 11)                                                 | $V_{OUT} = 32V, V_{IN} = 0, V_{SHDN} = 0$                                                                                                                                                                                                              |                       |                                  | 1                                 | 10                                | $\mu\text{A}$                                    |

**Note 1:** 絶対最大定格に記載された値を超えるストレスはデバイスに永続的損傷を与える可能性がある。長期にわたって絶対最大定格条件に曝すと、デバイスの信頼性と寿命に悪影響を与える恐れがある。

**Note 2:** 入力-出力間の電圧差の絶対最大定格は、INピンの定格電圧とOUTピンの定格電圧のすべての組み合わせで達成可能なわけではない。INピンが $45V$ のとき、OUTピンを $0V$ より下げる事はできない。INピンとOUTピンの全電圧差が $\pm 45V$ を超えてはならない。

**Note 3:** LT3086は $T_J$ が $T_A$ にほぼ等しくなるようなパルス負荷条件でテストされ、仕様が規定されている。LT3086Eは $T_A = 25^\circ\text{C}$ で全数テストされ、 $0^\circ\text{C} \sim 125^\circ\text{C}$ での性能が保証されている。 $-40^\circ\text{C} \sim 125^\circ\text{C}$ での性能は設計、特性評価および統計学的なプロセス・コントロールとの相関で保証されている。LT3086Iは $-40^\circ\text{C} \sim 125^\circ\text{C}$ の全動作接合部温度範囲で動作することが保証されている。LT3086MPは $-55^\circ\text{C} \sim 125^\circ\text{C}$ の動作接合部温度範囲で全数テストされている。

**Note 4:** LT3086は、SETピンをOUTピンに接続し、 $V_{OUT} = 0.4V$ に設定した条件でテストされ、仕様が規定されている。

**Note 5:** 最大接合部温度は動作条件を制限する。安定化出力電圧の仕様は、入力電圧と出力電流のすべての可能な組み合わせに対して適用されるわけではない。入出力間の電圧差が大きい条件下動作する場合は、出力電流範囲を制限する。最大出力電流で動作する場合は、入出力間の電圧差を制限する。電流制限フオールドバック機能は、入力-出力間の電圧差に応じて最大出力電流を制限する。「標準的性能特性」セクションの「電流制限と $V_{IN} - V_{OUT}$ 」を参照。

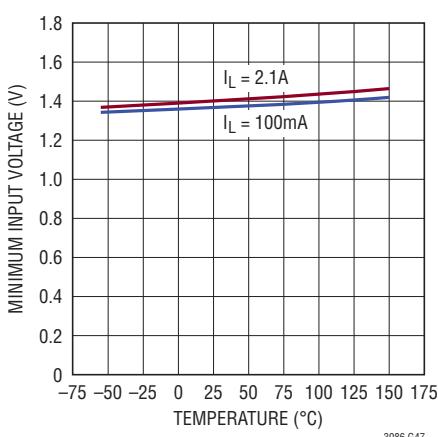

**Note 6:** 負荷レギュレーションはパッケージの位置でケルビン検出される。

**Note 7:** 最小入力電圧の要件を満足するため、LT3086は、OUTピンとSETピンの間に $32\text{k}$ の抵抗を接続して出力電圧が $2V$ になる条件でテストされ仕様が規定されている。

## 電気的特性

**Note 8 :** ドロップアウト電圧とは、規定の出力電流でレギュレーションを維持するのに必要な最小入出力間電圧差のことである。ドロップアウト状態では、出力電圧は( $V_{IN} - V_{DROPOUT}$ )等しくなる。低出力電圧で一定の負荷条件では、最小入力電圧の要件によってドロップアウト電圧が制限される。「標準的性能特性」セクションの「最小入力電圧」のグラフを参照。

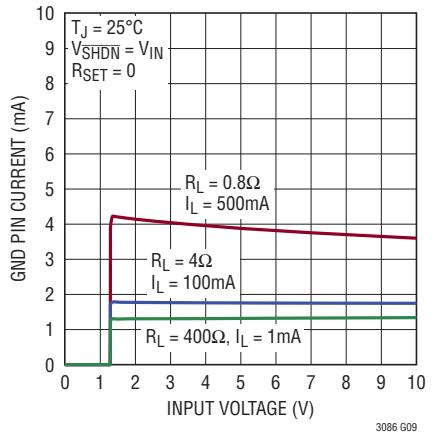

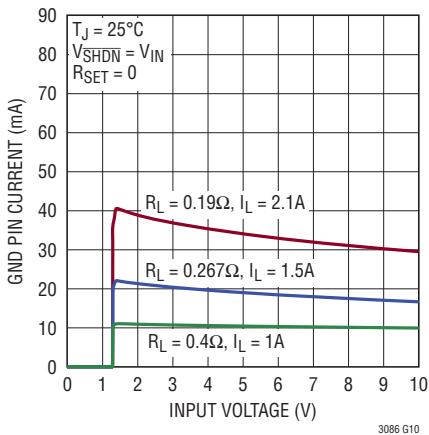

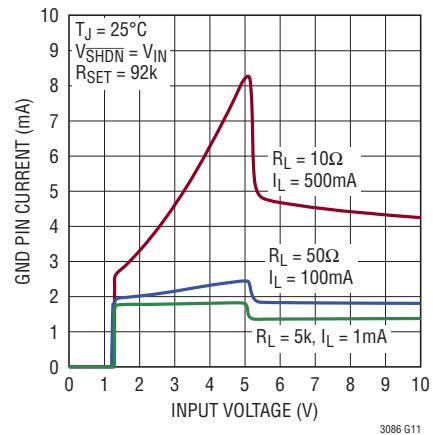

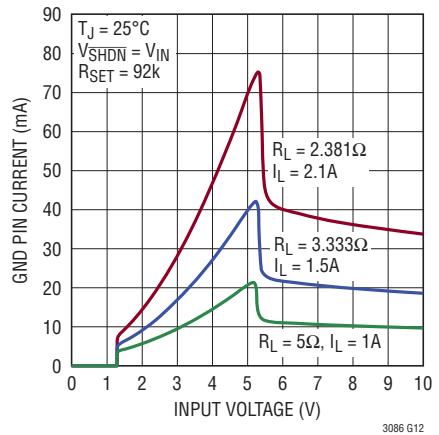

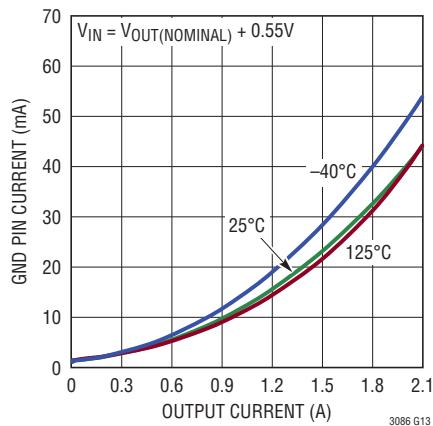

**Note 9 :** GNDピンの電流は $V_{IN} = V_{OUT(NOMINAL)} + 0.55V$ でPWRGDピンをフロート状態にしてテストされる。ドロップアウト時には、GNDピンの電流は増加する。「標準的性能特性」セクションの「GNDピンの電流」のグラフを参照してください。

**Note 10 :** SHDNピンの電流はSHDNピンに流れ込む。

**Note 11 :** 逆出力電流は、INピンを接地し、OUTピンに一定の電圧を強制的に加えた状態でテストされる。この電流はOUTピンに流れ込み、GNDピンから流れ出す。

**Note 12 :** このデバイスは瞬間的な過負荷状態の間デバイスを保護する過熱保護回路を内蔵している。TEMPピンに負荷をかけることによって熱制限の温度を125°Cより低い温度に外部から設定しない限り、過熱保護回路が作動しているときは接合部温度が125°Cを超える。規定された最大接合部温度を超えた状態で動作が継続すると、デバイスの信頼性を損なう恐れがある。

**Note 13 :** TEMPピンの出力電圧はパワー・トランジスタのすぐ近くの平均的ダイ温度を表すが、パワー・トランジスタの中心の温度は大電力状態時には大幅に高くなる可能性がある。デバイスの電力損失とダイ両端間の温度勾配があるため、TEMPピンの出力電圧を測定しても、絶対最大接合部温度を超えないことが保証されるわけではない。

**Note 14 :** Output Current Sharing Error(出力電流分担誤差)とは、2つのLT3086レギュレータを並列接続した場合、マスタを基準としたスレーブの出力電流の差のこと。デバイスは、理想マスタが2.1Aを出力しているとき、 $V_{TRACK} = 0.693V$ 、 $R_{MON} = 330\Omega$ および $V_{SET} = 0.4V$ の条件でスレーブとしてテストされる。規格の制限値は、スレーブの出力トラッキング誤差(2.1Aからの誤差)とマスタが関与する可能性があるワーストケースの誤差( $V_{SET}$ の0.4Vからの最大偏差と $I_{MON}$ の2.1mAからの最大偏差)を見込んでいる。

**Note 15 :** LT3086は、 $I_{MON}$ ピンと $I_{LIM}$ ピンを互いに接続した状態でテストされ、仕様が規定されている。

**Note 16 :** LT3086は、適切なレギュレーションと安定性を保証するため、最小負荷電流を必要とする。

## 標準的性能特性 注記がない限り、 $T_A = 25^\circ C$ 。

標準ドロップアウト電圧

保証されたドロップアウト電圧

ドロップアウト電圧

## 標準的性能特性 注記がない限り、 $T_A = 25^\circ\text{C}$ 。

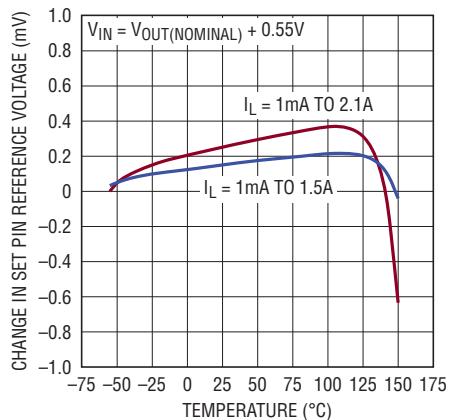

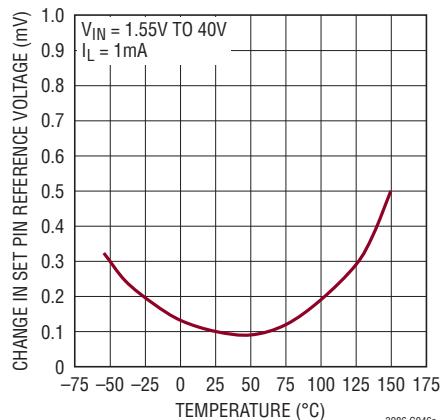

**SETピンのリファレンス電圧**

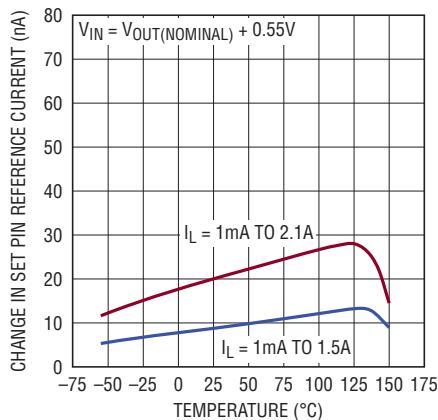

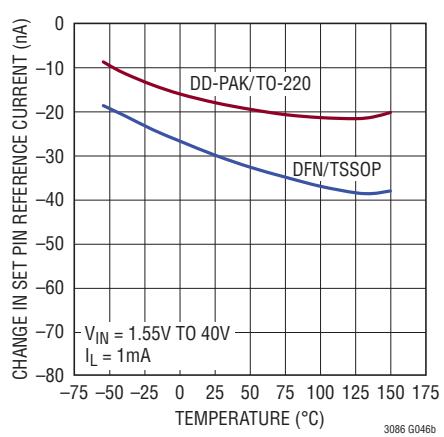

**SETピンのリファレンス電流**

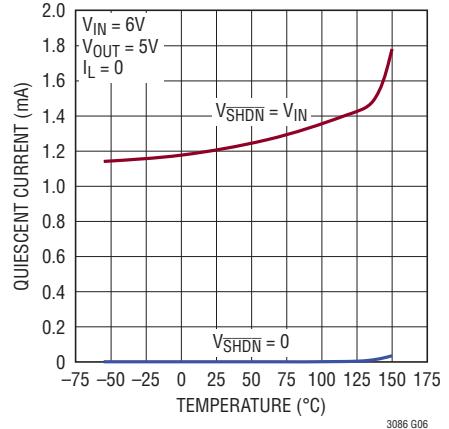

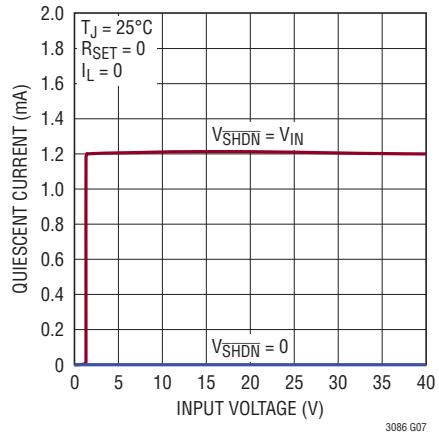

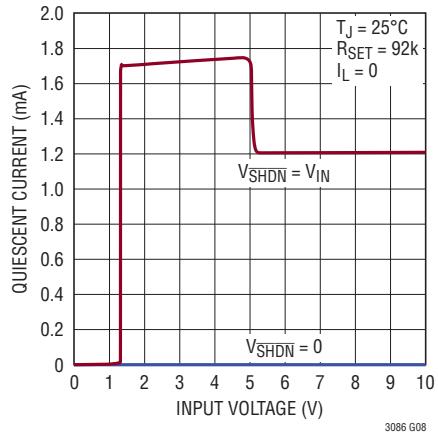

**静止電流**

**静止電流、 $V_{OUT} = 0.4\text{V}$**

**静止電流、 $V_{OUT} = 5\text{V}$**

**GNDピンの電流、 $V_{OUT} = 0.4\text{V}$ (軽負荷)**

**GNDピンの電流、 $V_{OUT} = 0.4\text{V}$ (重負荷)**

**GNDピンの電流、 $V_{OUT} = 5\text{V}$ (軽負荷)**

**GNDピンの電流、 $V_{OUT} = 5\text{V}$ (重負荷)**

## 標準的性能特性

注記がない限り、 $T_A = 25^\circ\text{C}$ 。

GNDピンの電流と $I_{LOAD}$

GNDピンの電流と温度

SHDNピンのしきい値

SHDNピンの入力電流

SHDNピンの入力電流

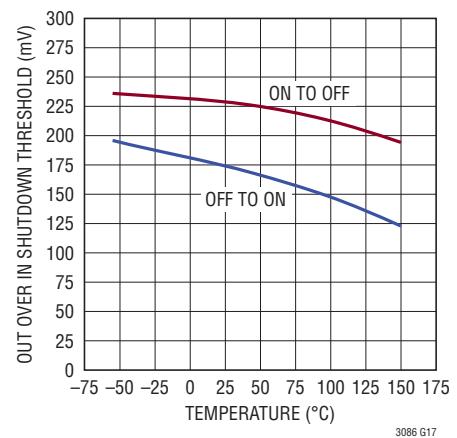

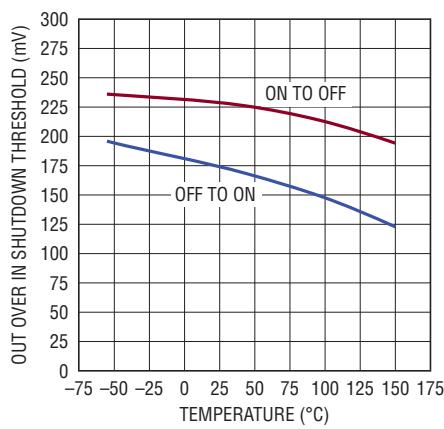

OUTピンとINピンの電圧差によるシャットダウンしきい値

RPWRGDピンの電圧しきい値

RPWRGDピンの入力電流

## 標準的性能特性 注記がない限り、 $T_A = 25^\circ\text{C}$ 。

PWRGD ピンの出力“L”電圧

PWRGD の内部遅延時間

$I_{\text{OUT}}/I_{\text{MON}}$  の比

軽負荷時の電流モニタ

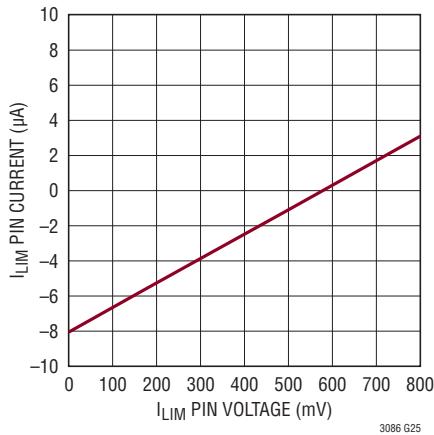

$I_{\text{LIM}}$  ピンのしきい値電圧

$I_{\text{LIM}}$  ピンの入力電流

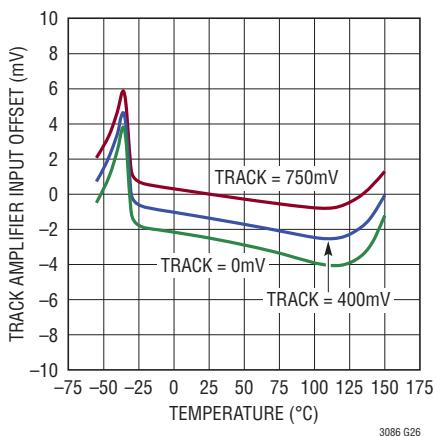

TRACK アンプの入力オフセット

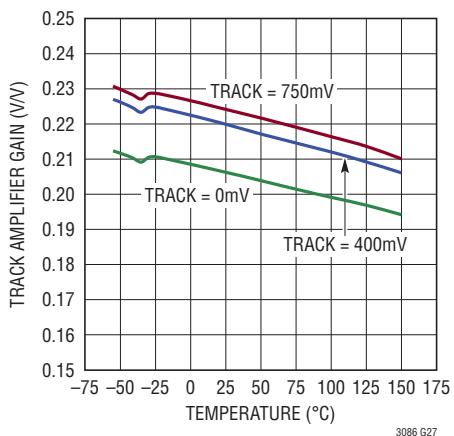

TRACK アンプの利得

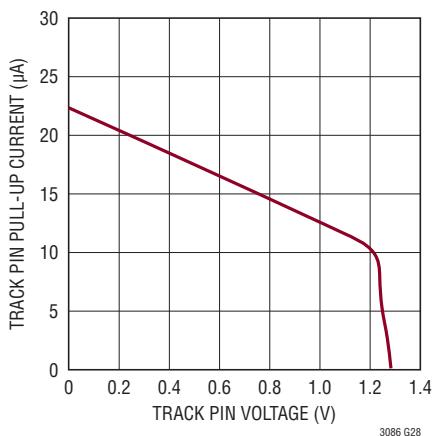

TRACK ピンのプルアップ電流

## 標準的性能特性

注記がない限り、 $T_A = 25^\circ\text{C}$ 。

TRACKピンのプルアップ電流

CDCピンのリファレンス電圧

CDCアンプの利得

CDCアンプの利得

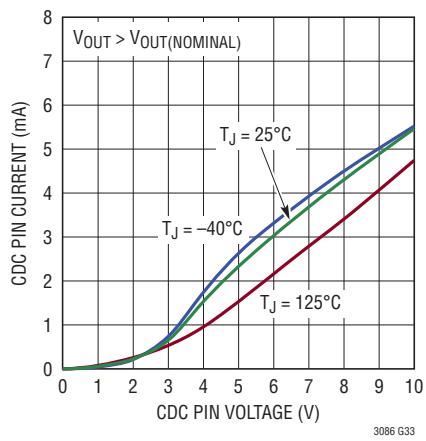

CDCピンの内部クランプ・フォルト電流

TEMPピンの誤差

$I_{TEMP}$ の熱制限しきい値内部電流制限と $V_{IN} - V_{OUT}$

内部電流制限と温度

## 標準的性能特性 注記がない限り、 $T_A = 25^\circ\text{C}$ 。

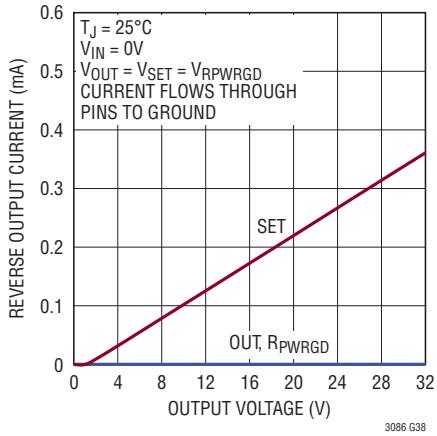

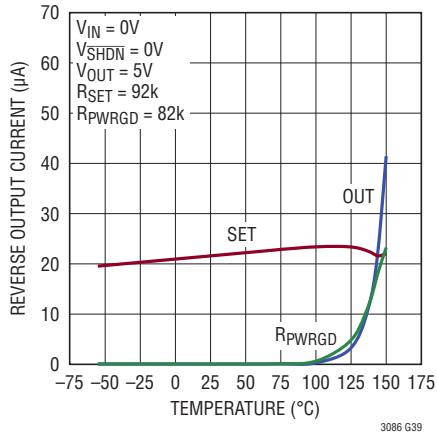

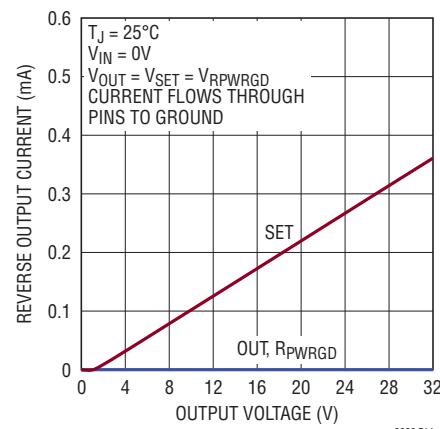

### 逆出力電流

### 逆出力電流

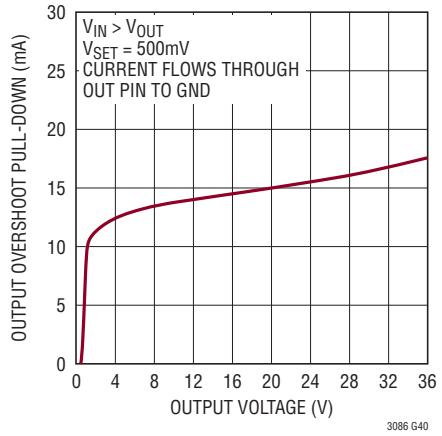

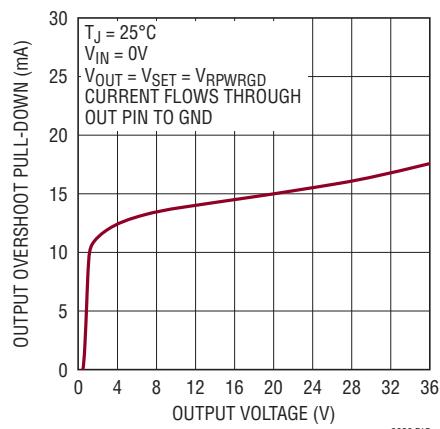

### オーバーシュートの プルダウン電流

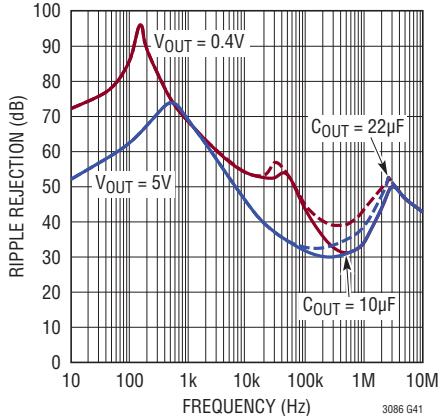

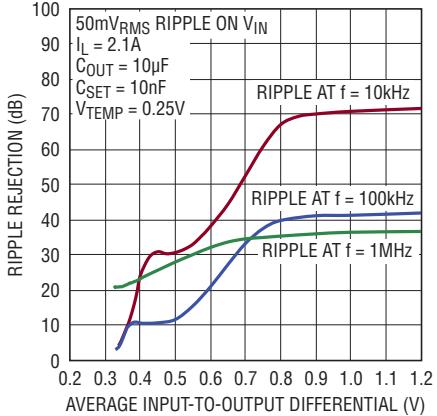

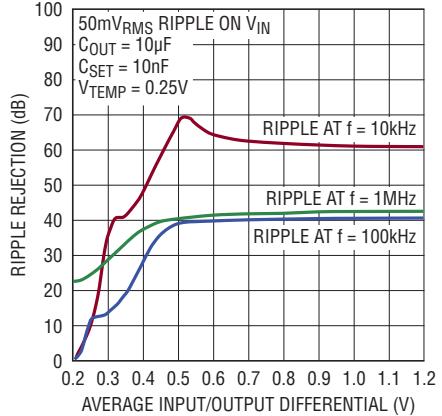

### 入力リップル除去比

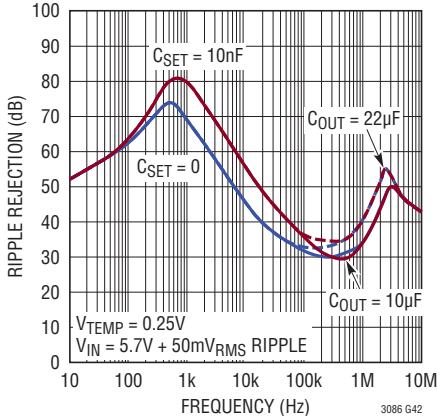

### 5V、2.1Aでの入力リップル除去比

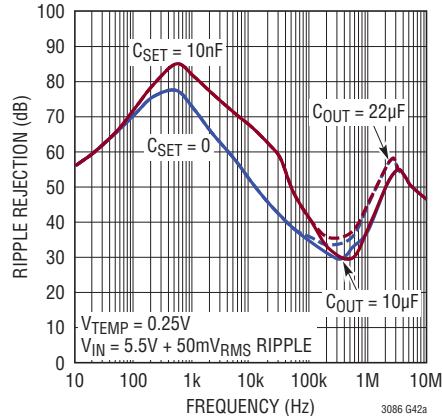

### 5V、1Aでの入力リップル除去比

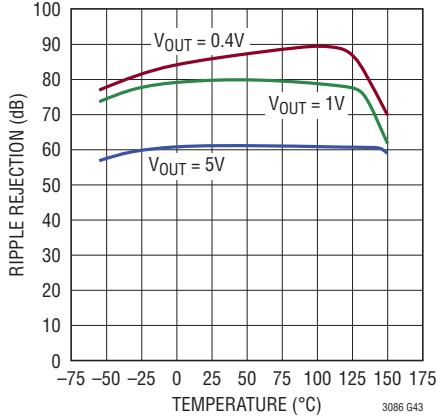

### リップル除去比と温度

### 5V、2.1Aでのリップル除去比と $V_{IN} - V_{OUT}$

### 5V、1Aでのリップル除去比と $V_{IN} - V_{OUT}$

## 標準的性能特性 注記がない限り、 $T_A = 25^\circ\text{C}$ 。

### リファレンス電圧の負荷レギュレーション

### リファレンス電流の負荷レギュレーション

### リファレンス電圧のラインレギュレーション

### リファレンス電流のラインレギュレーション

### 最小入力電圧

### 出力ノイズのスペクトラム密度、 $C_{SET} = 0$

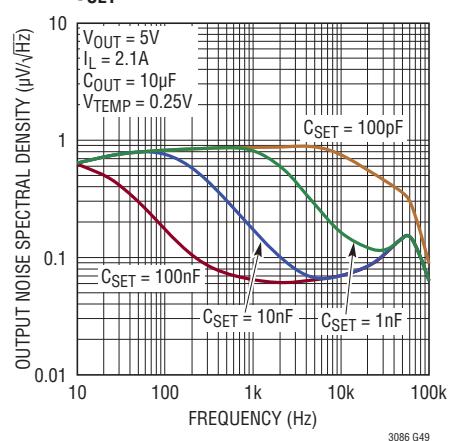

### 出力ノイズのスペクトラム密度と $C_{SET}$

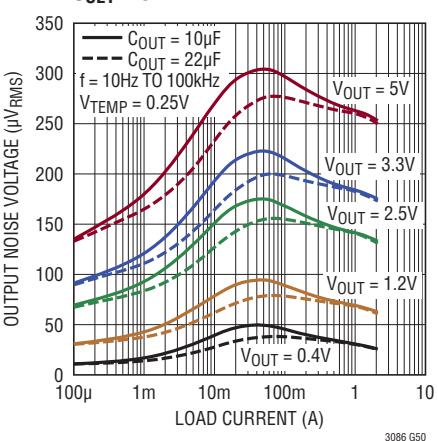

### RMS 出力ノイズと負荷電流、 $C_{SET} = 0$

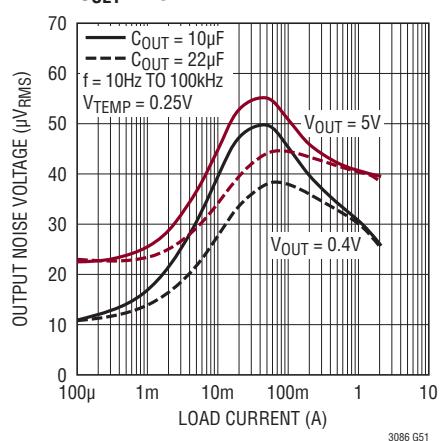

### RMS 出力ノイズと負荷電流、 $C_{SET} = 10\text{nF}$

## 標準的性能特性 注記がない限り、 $T_A = 25^\circ\text{C}$ 。

## ピン機能 (DFN/TSSOP/DD-PAK/TO-220)

**GND(ピン1、16、露出パッド・ピン17/ピン1、8、9、16、露出パッド・ピン17/ピン4/ピン4)**: グランド。DFNパッケージやTSSOPパッケージの露出パッドと同様に、DD-PAKやTO-220パッケージのタブもGNDとの電気的接続点です。適正な電気的性能と熱性能を確保するため、露出パッドまたはタブは、該当するパッケージの残りのGNDピンおよびPCBのグランドと直接接続してください。GNDピンの電流は無負荷時は標準1.2mAで、最大負荷時は約44mAまで増加します。

**I<sub>LIM</sub>(ピン2/ピン2/ピン1/ピン1)**: 電流制限の外部プログラミング。このピンをI<sub>MON</sub>に接続し、このピンとGNDの間に抵抗を接続すると、電流制限値を外部設定できます。I<sub>LIM</sub>ピンの電圧が0.8Vに等しくなると電流制限回路が作動します。電流制限値は  $1000 \cdot (0.8V/R_{MON})$  に等しくなります。内部のクランプ回路により、I<sub>LIM</sub>ピンの電圧は標準で1Vに制限されます。外部電流制限値を1A未満に設定する場合は、1k-10nFの直列回路網とR<sub>MON</sub>抵抗を並列に接続して安定性を確保します。V<sub>IN</sub> - V<sub>OUT</sub>の電圧差が過大な場合は、内部の電流制限フォールドバックによって外部設定の電流制限が無効になります。外部電流制限のプログラミングを使用しない場合は、このピンを接地してください。

**I<sub>MON</sub>(ピン3/ピン2/ピン1/ピン1)**: 出力電流モニタ。このピンからは出力負荷電流の1/1000に等しい電流が流れ出します。I<sub>MON</sub>とGNDの間に抵抗を接続すると、負荷電流依存電圧を設定して、A/Dコンバータでモニタすることができます。I<sub>MON</sub>をI<sub>LIM</sub>に接続すると、電流制限値を外部で設定できます。

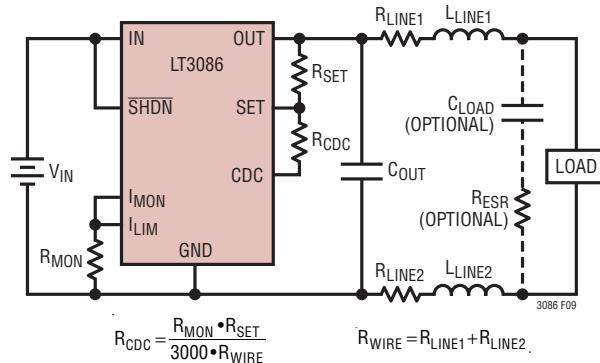

**CDC(ピン4/ピン3/NA/NA)**: ケーブル電圧降下補償。CDCピンとSETピンの間に1本の抵抗(R<sub>CDC</sub>)を接続すると、負荷との抵抗性接続に起因する出力電圧誤差を打ち消すプログラム可能なケーブル電圧降下補償を実現できます。I<sub>MON</sub>とGNDの間の抵抗(R<sub>MON</sub>)は、ケーブル電圧降下補償を有効にするために必要です。まず、必要な電流制限値に基づいてR<sub>MON</sub>を選択します。

$$R_{MON} = 0.8V \cdot 1000/I_{LIM}$$

次の式により、R<sub>CDC</sub>の値を計算します。

$$R_{CDC} = (R_{MON} \cdot R_{SET}) / (3000 \cdot R_{WIRE})$$

ここでR<sub>WIRE</sub>は、負荷との間を往復するケーブルまたはワイヤ(銅線)の全抵抗です。実用的なアプリケーションの観点から、リニアテクノロジーでは、良好なレギュレーションを必要とするアプリケーションに備えて、ケーブル電圧降下補償をV<sub>OUT</sub>の20%までに制限することを推奨します。銅線抵抗は

50°Cの温度変化に対して約19%変化するので、制限要因はワイヤ温度の変動です。出力レギュレーション要件が緩い場合(2次レギュレータの使用時など)は、ケーブル電圧降下補償を最大50%まで使用できます。

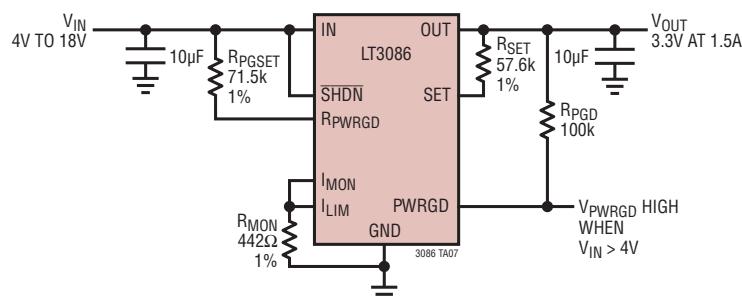

**R<sub>PWRGD</sub>(ピン5/ピン4/NA/NA)**: パワーグッドしきい値電圧のプログラミング。このピンはパワーグッド・コンパレータの入力です。OUTとR<sub>PWRGD</sub>の間に抵抗を接続すると、調整可能なパワーグッドしきい値電圧を設定できます。しきい値電圧はR<sub>PWRGD</sub>ピンで0.4Vであり、R<sub>PWRGD</sub>とGNDの間には50μAの電流源が接続されています。R<sub>PWRGD</sub>での電圧が0.4Vより低くなると、PWRGDフラグがアサートされ、“L”になります。R<sub>PWRGD</sub>での電圧が0.4Vより高くなると、PWRGDフラグはデアサートされ、高インピーダンスになります。ほとんどのアプリケーションでは、PWRGDはプルアップ抵抗により“H”になります。次の式により、R<sub>PWRGD</sub>の値を計算します。

$$R_{PWRGD} = (X \cdot V_{OUT(NOMINAL)} - 0.4V) / 50\mu A$$

ここで、Xは通常85%～95%の範囲に入ります。

17μsのデグリッチ・フィルタにより、PWRGDの立ち上がりエッジでの瞬時リセットによるPWRGDフラグの誤作動を防止します。R<sub>PWRGD</sub>ピンでのヒステリシスは、0.4Vのしきい値と50μAの電流源の場合、標準で0.6%です。

**SET(ピン6/ピン5/ピン2/ピン2)**: 出力電圧のプログラミング。このピンはエラーアンプの反転端子です。このピンの電圧は0.4Vに安定化され、50μAの電流源がSETとGNDの間に接続されています。OUTとSETの間に1本の抵抗を接続すると、出力電圧を設定できます。必要な抵抗の値は次式から計算します。

$$R_{SET} = (V_{OUT} - 0.4V) / 50\mu A$$

R<sub>SET</sub>と並列にコンデンサを接続すると、出力電圧のソフトスタート機能、トランジエント応答の向上、出力電圧ノイズの減少を実現できます。

LT3086のエラーアンプ回路は、レギュレータが常に単位利得で動作するように構成されています。

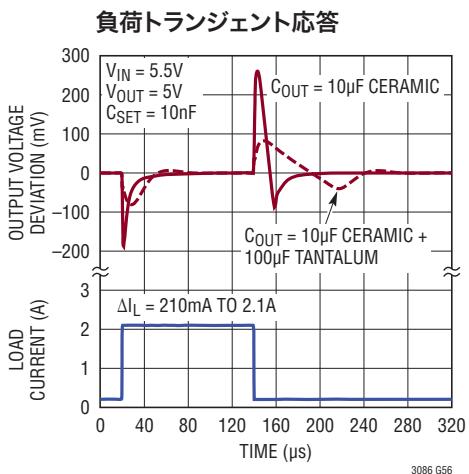

**OUT(ピン7、8/ピン6、7/ピン3/ピン3)**: 出力。これらのピンは負荷に電力を供給します。DHDパッケージとFEパッケージでは、適正な動作を確保するため、すべてのOUTピンを互いに接続してください。安定させるには、ESRが100mΩ未満で最小10μFのセラミック出力コンデンサを使用して発振を防ぐ必要があります。出力負荷トランジエントが大きい場合は、電

## ピン機能

(DFN/TSSOP/DD-PAK/TO-220)

圧トランジエントのピーク値を制限するために大きな値の出力容量が必要です。許容出力電圧範囲は0.4V～32Vです。LT3086は、適正なレギュレーションと安定性を確保するために1mAの最小負荷電流が必要です。

**IN(ピン10、11/ピン10、11/ピン5/ピン5)**: 入力。これらのピンはデバイスに電力を供給します。DHDパッケージとFEパッケージでは、適正な動作を確保するため、すべてのINピンを互いに接続してください。LT3086が主な入力フィルタ・コンデンサから数インチ以上離れている場合は、INピンの近くにバイパス・コンデンサが必要です。一般に、バッテリの出力インピーダンスは周波数とともに上昇するので、バッテリ駆動回路にはバイパス・コンデンサを追加することを推奨します。通常は10μFの最小入力コンデンサで充分です。INピンは、45Vの逆電圧に耐えます。デバイスは電流の流れを制限するので、OUTピンに負電圧は現れません。デバイスは、逆向きに差し込まれたバッテリからデバイスと負荷の両方を保護します。

**SHDN(ピン12/ピン12/ピン6/ピン6)**: シャットダウン/UVLO。SHDNピンを標準で1Vより低くすると、LT3086は低消費電力状態になります。出力はオフになります。シャットダウン時の静止電流は標準で1μA未満です。SHDNピンのオンしきい値は標準で1.22Vです。このピンはシャットダウン機能または低電圧ロックアウト機能として使用できます。このピンを低電圧ロックアウト機能として使用する場合は、INとGNDの間に抵抗分割器を接続し、中間タップをSHDNに接続します。このピンをシャットダウン機能として使用する場合は、ロジック回路またはオープン・コレクタとプルアップ抵抗の組み合わせを使用してこのピンを駆動します。この抵抗は、オープン・コレクタ/オープン・ドレイン・ロジックのプルアップ電流(通常は数マイクロアンペア)とSHDNピン電流(標準で6V時に10μA未満)を供給します。使用しない場合、SHDNピンはINに接続してください。

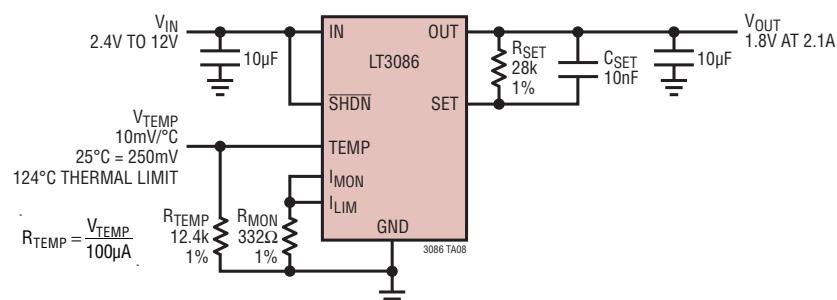

**TEMP(ピン13/ピン13/ピン7/ピン7)**: ダイの接合部温度。このピンは、LT3086のダイ接合部温度の平均値を示す電圧を出力します。25°Cでは、このピンは標準で250mVを出力します。TEMPピンの電圧の傾斜は10mV/°Cに等しいので、125°Cではこのピンは標準で1.25Vを出力します。TEMPピンは0°C未満の温度は読み取りません。TEMPピンは高精度の温度センサ用ではありませんが、PCBに実装されたパッケージの熱抵抗のデバッグ、モニタ、計算に役立ちます。TEMPピンには、

標準の内部サーマル・シャットダウン温度である165°Cより低い熱制限温度を設定する機能も組み込まれています。TEMPとGNDの間に抵抗を接続すると、作動点が100μAの熱制限が設定されます。抵抗の値は次式から計算します。

$$R_{TEMP} = \frac{\left(T_{SHDN} - \frac{10mV}{^{\circ}C}\right)}{100\mu A}$$

ここで、T<sub>SHDN</sub>は所望のダイ熱制限温度です。

レギュレータ出力のオンとオフを繰り返すサーマル・シャットダウンには、数度のヒステリシスがあります。TEMPピンの容量は100pF未満に制限します。TEMPピンの出力デバイスでの飽和を防止するため、V<sub>IN</sub>がV<sub>TEMP</sub>より必ず250mV高くなるようにしてください。

**TRACK(ピン14/ピン14/NA/NA)**: 並列接続用のトラック・ピン。TRACKピンにより、複数のLT3086をマスタ/スレーブ構成に並列接続して、出力電流の大きいアプリケーションに対応させることができます。この構成により、PCB上で熱を放散させることもできます。この回路技法では安定抵抗が不要なので、負荷レギュレーションは低下しません。スレーブ・デバイスのTRACKピンをマスタ・デバイスのI<sub>MON</sub>/I<sub>LIM</sub>ピンに接続すると、この機能がイネーブルされます。TRACK機能を使用しない場合、TRACKピンはデフォルトで“H”状態にクランプされます。スレーブ・デバイスのTRACKピンの電圧を1.2Vより低くすると、SETピンでの50μA内部リファレンス電流が遮断され、マスタ・デバイスの50μAリファレンス電流だけが流れます。マスタ/スレーブ構成では、すべてのSETピンを互いに接続する必要があります。

**PWRGD(ピン15/ピン15/NA/NA)**: パワーグッド・フラグ。PWRGDピンは、パワーグッド・コンパレータの出力に接続されたオープン・コレクタ・ロジック・ピンです。RPWRGDピンの電圧が400mVより低くなると、PWRGDピンは“L”にアサートされます。200μAのシンク電流に対して、“L”的最大出力レベルである200mVが全温度範囲で規定されています。RPWRGDピンの電圧が400mVより高くなると、PWRGDピンはデアサートされ、高インピーダンスになります。PWRGDピンは、入力電圧に関係なく、内部回路を損傷させずに36Vまで引き上げることができます。

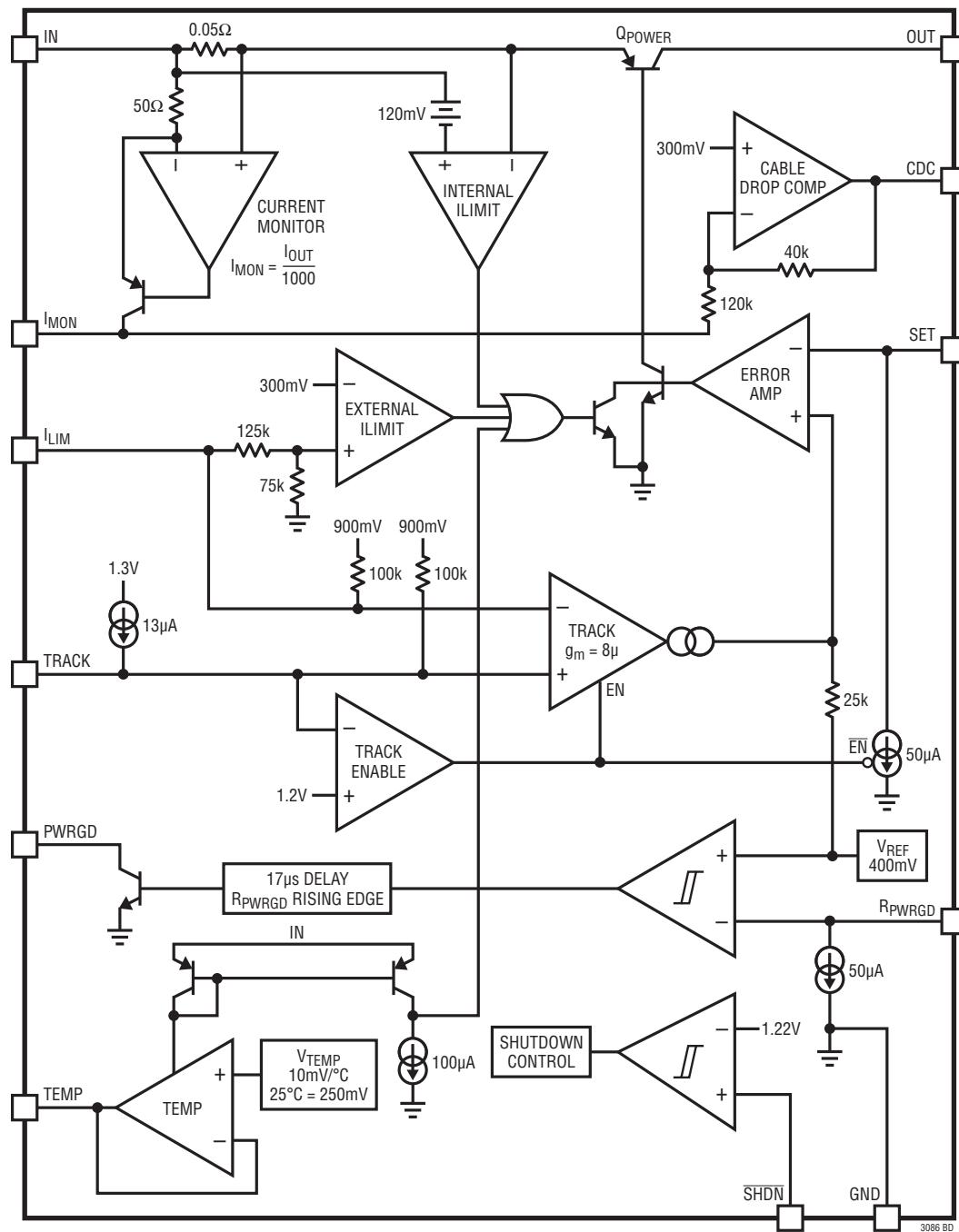

## ブロック図

## アプリケーション情報

LT3086は、多機能、低ドロップアウト、低ノイズのリニア・レギュレータで、シャットダウン回路と調整可能なパワーグッド回路を内蔵しています。このデバイスは330mVの標準的ドロップアウト電圧で2.1Aを供給し、1.4V～40Vの広い入力電源電圧範囲で動作します。

動作時の静止電流は1.2mAで、シャットダウン時には1μA未満に減少します。LT3086レギュレータは、低ESRの10μFセラミック出力コンデンサで安定性とトランジエント応答を最適化します。1本の抵抗により出力電圧を0.4V～32Vの範囲内に設定します。同様に、パワーグッドしきい値も1本の抵抗で設定します。このレギュレータは、標準で0.1%の入力レギュレーションと0.1%の負荷レギュレーションを実現します。

LT3086は、使い勝手の良いプログラム可能な診断機能を備えています。標準で出力電流の1/1000である出力電流モニタにより、標準2.4Aの内部制限値より低い電流制限値を設定できます。標準10mV/°C (250mV = 25°C)の温度モニタにより、標準165°Cの内部熱制限値より低い熱制限値を設定できます。

負荷での電圧誤差がLT3086と負荷の間の接続点での抵抗に起因するアプリケーションでは、プログラム可能なケーブル電圧降下補償により、1本の抵抗で誤差が打ち消されます。複数のLT3086レギュレータを並列接続することにより、負荷電流の増加に対応することや、安定抵抗を外付けする必要なしに熱拡散を行うことが可能になります。

出力が(0.8V以上の安定化出力電圧を)オーバーシュートする負荷トランジエント時に、内部プルダウン電流により、OUTピンからグランドへ約15mAが流れます。出力電圧がレギュレーション電圧以下のとき、プルダウン電流はディスエーブルされます。レギュレータと出力オーバーシュートのプルダウン電流は、出力電圧が入力電圧より標準で225mV高くなるとオフになります。「OUTピンとINピンの電圧差によるシャットダウンしきい値」のグラフを「標準的性能特性」セクションに示します。

内部保護回路には、バッテリ逆接続保護回路、逆出力保護回路、逆電流保護回路、フォールドバック特性の電流制限回路、サーマル・シャットダウン回路があります。

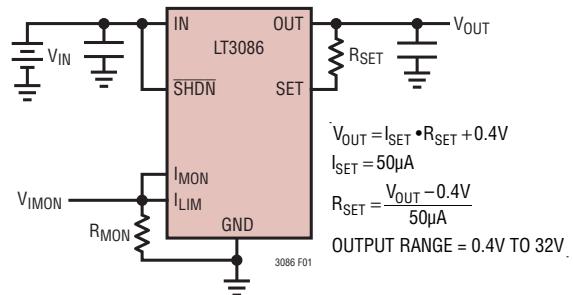

### 出力電圧の設定

LT3086の出力電圧範囲は0.4V～32Vです。出力電圧は、図1に示すように、OUTピンとSETピンの間に1本の抵抗( $R_{SET}$ )を接続することによって設定します。SETピンにはグランドに流れる50μAの電流源が内蔵されており、これによって $R_{SET}$ の両端に電圧降下が発生します。デバイスは出力をサーボ制

御し、SETピンの電圧を(グランドを基準にして)0.4Vに維持します。図1の式を使って出力電圧を計算します。「SETピンのリファレンス電圧」と「SETピンのリファレンス電流」のグラフを「標準的性能特性」のセクションに示します。

図1. 出力電圧の設定

表1. 出力電圧と $R_{SET}$ の値

| $V_{OUT}$ (V) | R <sub>SET</sub> (Ω) |        |              | 1%精度抵抗1本の場合の $V_{OUT}$ の誤差 |

|---------------|----------------------|--------|--------------|----------------------------|

|               | 理想値                  | 1%精度1本 | 1%精度2本       |                            |

| 1             | 12k                  | 12.1k  | 11.8k + 200  | 0.5%                       |

| 1.2           | 16k                  | 16.2k  | 15.8k + 200  | 0.8%                       |

| 1.5           | 22k                  | 22.1k  | 21.5k + 511  | 0.3%                       |

| 1.8           | 28k                  | 28k    | N/A          | 0%                         |

| 2             | 32k                  | 32.4   | 31.6k + 383  | 1.0%                       |

| 2.5           | 42k                  | 42.2k  | 41.2k + 825  | 0.4%                       |

| 3.3           | 58k                  | 57.6k  | 57.6k + 383  | -0.6%                      |

| 5             | 92k                  | 90.9k  | 90.9k + 1.1k | -1.1%                      |

| 12            | 232k                 | 232k   | N/A          | 0%                         |

いくつかの一般的な出力電圧について、最も近い1%精度の抵抗値とともに、理想の抵抗値を使用しないために生じる出力誤差を表1に示します。標準の1%精度抵抗間の間隔が2%なので、これらの誤差は最大でも1%です。出力の許容範囲を狭くすることが必要な場合は、より高精度の抵抗の使用を検討してください。別の方針として、値の小さい1%精度の抵抗を直列に接続して $R_{SET}$ を微調整することもできます。表1のデュアル1%の列を参照してください。

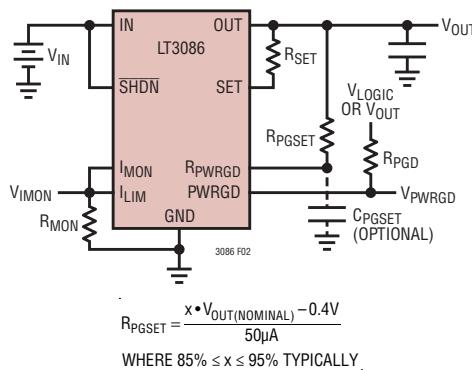

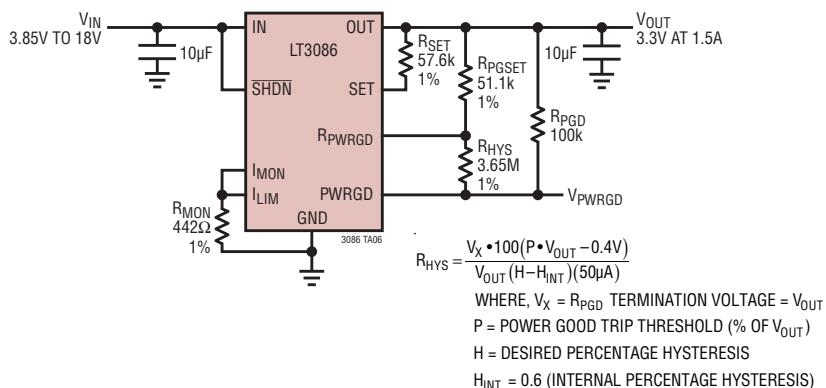

### パワーグッドのプログラミング

調整可能なパワーグッドしきい値は、出力電圧を $R_{SET}$ で設定する方法と同様に、1本の抵抗 $R_{PGSET}$ で設定します。SETピンの場合と同様に、 $R_{PWRGD}$ ピンでは、0.4Vのリファレンス電圧と50μAの高精度プルダウン電流との組み合わせによってパワーグッドしきい値が決まります。 $R_{PWRGD}$ の電圧が0.4Vよ

## アプリケーション情報

り高くなると、パワーグッド信号は“H”になります。0.4Vの電圧しきい値と50 $\mu$ Aの電流源の両方について、標準0.6%のヒステリシスが組み込まれています。RPWRGDピンとPWRGDピンの間に抵抗を接続すると、パワーグッド・ヒステリシスを大きくすることができます。例については、アプリケーション回路を参照してください。

図2. パワーグッドのプログラミング

PWRGDピンは、パワーグッドのオープン・コレクタ・ロジック出力です。標準17 $\mu$ sの内部遅延は、(レギュレータの出力電圧がパワーグッドしきい値を超えたとき)立ち上がりエッジにのみ生じ、起動時のノイズやチャタリングを除去します。パワーグッド機能が不要な場合は、RPWRGDピンとPWRGDピンをフロート状態のままにしておきます。

パワーグッドしきい値は、標準では安定化出力電圧の85%～95%に設定されます。レギュレータ・パラメータのばらつきと抵抗のばらつきにより、パワーグッドしきい値を出力電圧の95%より高く設定するのは現実的ではありません。それは、負荷トランジエントが生じると、出力電圧は一瞬低下した後に回復するからです。出力容量を増やして出力電圧のオーバーシュートを低減する場合や、パワーグッドしきい値をより低い値に設定できない場合は、RPWRGDとグランドの間にコンデンサCPGSETを接続すると出力信号のフィルタリングと遅延が可能になります。こうすると、パワーグッドしきい値に達する前に、構成可能なデグリッチ期間を設けることができます。たとえば、パワーグッドしきい値をV<sub>OUT(NOMINAL)</sub>の90%に設定した、10 $\mu$ Fの出力容量を使用する公称1V出力のアプリケーションについて検討します。1.5Aの出力負荷ステップがあると、一時的にV<sub>OUT</sub>のアンダーシュートが発生して90%のしきい値を下回る時間が4 $\mu$ sより長くなり、PWRGDピンのレベルが“L”になります。容量が270pFより大きなCPGSETを使用すれば、パワーグッド・コ

ンパレータのグリッチが除去され、4 $\mu$ sより短時間のアンダーシュートではPWRGDピンが“L”なりません。

ケーブル電圧降下補償を使用し、パワーグッド信号を必要とするアプリケーションでは、LT3086の出力電圧ではなく、負荷での電圧に基づいてRPGSETの値を計算します。パワーグッドしきい値が、負荷電流の関数としてのLT3086の出力電圧のケーブル電圧降下補償の調整に左右されないようにするために、CDCとRPWRGDの間にRCDC(CDC-SET間の抵抗)と同じ値の抵抗を接続します。この技法では、RPGSET抵抗を長いトレース/ワイヤを介して負荷電圧に接続しないようにしておき、RPWRGDピンへの潜在的な浮遊信号結合を取り除いています。例については、表紙の「標準的応用例」の回路を参照してください。

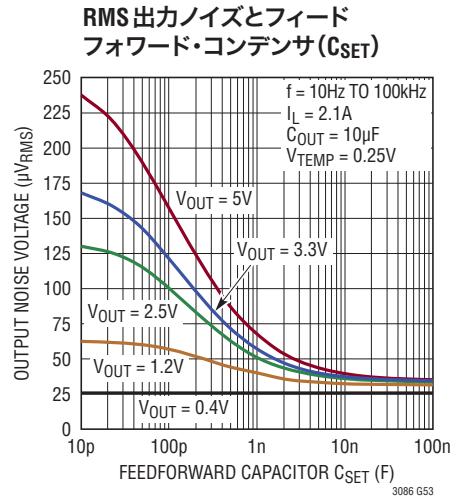

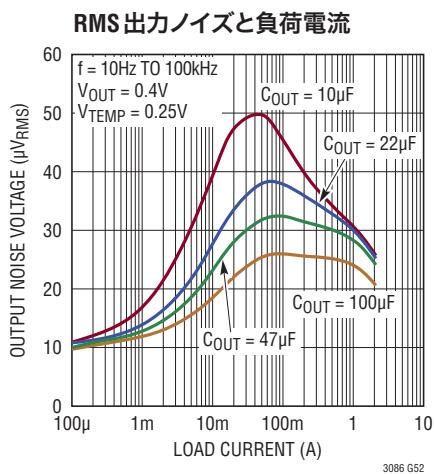

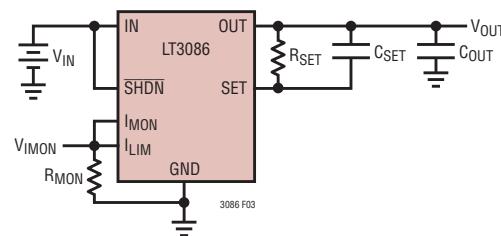

## 出力電圧ノイズとトランジエント応答

LT3086レギュレータは、最大負荷で動作しているときに10Hz～100kHzの帯域幅での出力電圧ノイズが低い特性を備えています。単位利得出力電圧が2.1Aで0.4Vの場合、出力電圧ノイズは、この周波数帯域幅で約65nV/ $\sqrt{Hz}$ です。

出力電圧が高い場合に出力電圧ノイズを低減するには、図3に示すように、OUTピンとSETピンの間にフィードフォワード・コンデンサCSETを取り付けます。高品質で低漏れ電流のコンデンサを推奨します。このコンデンサは電圧設定抵抗RSETをバイパスしているので、低周波ノイズのポールが形成されます。CSETに10nFを使用すると、出力電圧を5Vに設定した場合、出力電圧ノイズは2.1Aのとき280 $\mu$ V<sub>RMS</sub>から40 $\mu$ V<sub>RMS</sub>に減少します。

回路レイアウトとテストに関して注意を払わないと、大きな値の出力電圧ノイズが測定されることがあります。近くのアクティブな信号トレースからのクロストークにより、LT3086の出力に不要なノイズが誘起されます。電源のリップル除去も考慮する必要があります。LT3086レギュレータの電源リップル除去能力は無限ではないので、入力ノイズの一部は出力に達します。

図3. トランジエント応答改善のためのフィードフォワード・コンデンサ

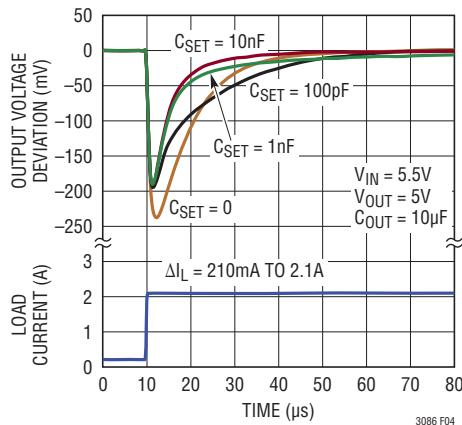

## アプリケーション情報

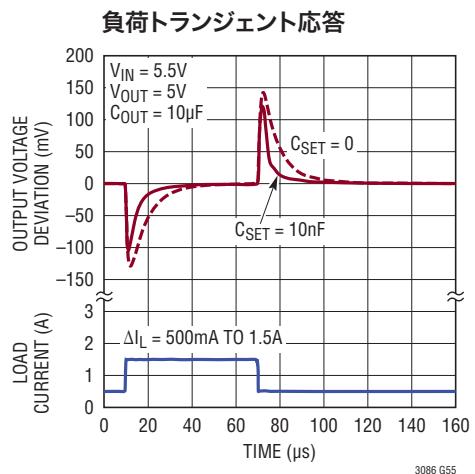

フィードフォワード・コンデンサ  $C_{SET}$  を使用すると、0.4Vより高い出力電圧でトランジエント応答が改善されるという利点があります。フィードフォワード・コンデンサを使用しない場合は、出力電圧が0.4Vより高い値に設定されているので、セッティング時間が長くなり、出力電圧のトランジエントが大きくなります。図4と、「標準的性能特性」セクションの「トランジエント応答」のグラフを参照してください。

図4. トランジエント応答とフィードフォワード・コンデンサ

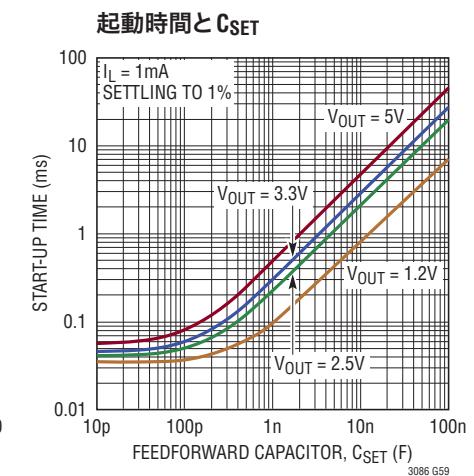

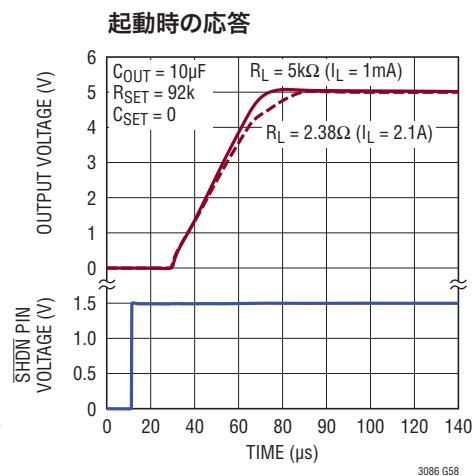

起動時間はフィードフォワード・コンデンサ  $C_{SET}$  の使用によって影響されます。起動時間は、フィードフォワード・コンデンサのサイズと出力電圧に直接比例します。1%以内へのセッティング時間はおよそ次のとおりです。

$$t_{SETTLE} = \frac{4.2 \cdot V_{OUT} \cdot C_{SET}}{50\mu A}$$

「標準的性能特性」セクションの「起動時間と  $C_{SET}$ 」のグラフを参照してください。LT3086をケーブル電圧降下補償用に構成する場合、リニアテクノロジーはフィードフォワード・コンデンサの使用を推奨しません。 $C_{SET}$  によってCDC補正信号がフィルタリングされ、負荷電流変動に対するトランジエント応答性能が低下するからです。

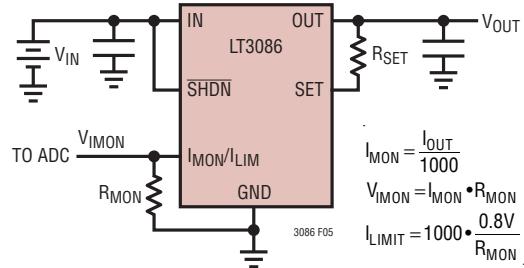

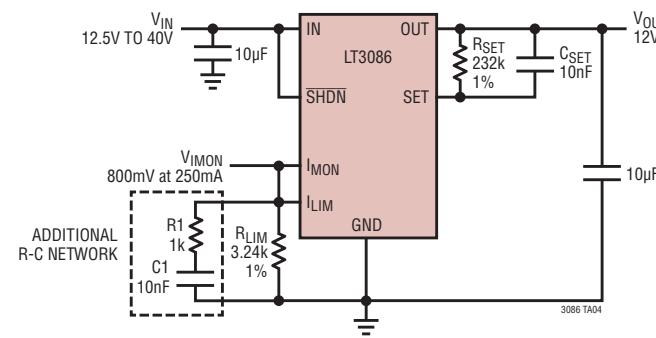

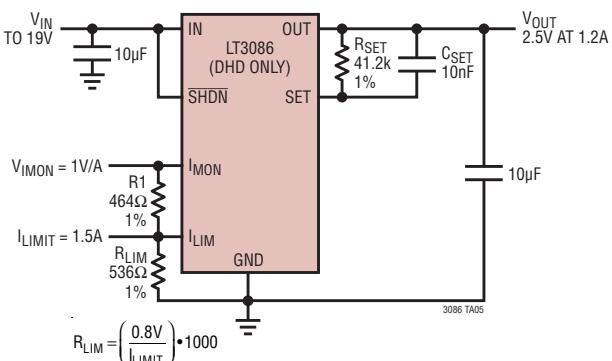

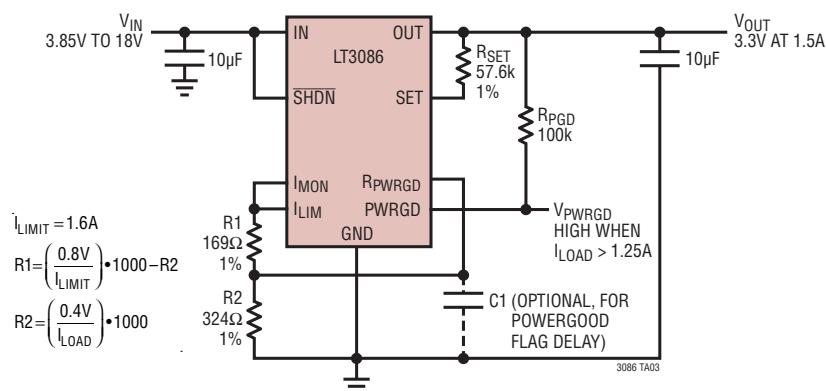

## 出力電流モニタと外部電流制限

$I_{MON}$  ピンからの電流は、標準ではレギュレータの出力電流の1/1000に相当します。出力電流モニタは、ドロップアウト状態時でも全入力電圧範囲にわたって精度を維持します。図5に示すように、 $I_{MON}$  とグランドの間に抵抗  $R_{MON}$  を接続することにより、A/Dコンバータと組み合わせて使用する場合の電圧換算係数を設定できます。たとえば、 $R_{MON}$  として  $442\Omega$  を使用すると、 $I_{OUT} = 1.5A$  のとき、 $V_{IMON}$  は0.663Vに設定されます。

図5. 出力電流モニタと外部電流制限

$I_{LIM}$  ピンの電圧が標準0.8Vのしきい値を超えると、外部電流制限が作動します。 $I_{MON}$  ピンと  $I_{LIM}$  ピンを互いに接続すると、目的の電流制限値を出力電流に基づいて設定できます。内部電流制限(標準2.4A)は常に動作状態なので、 $I_{LIM}$  を接地している場合でも出力電流を制限します。さらに、 $V_{IN} - V_{OUT}$  の電圧差が過大になると、内部の電流制限フォールドバックによって外部電流制限は無効になります。

出力電流モニタが表すのは負荷電流だけではなく、出力コンデンサに流れ込む電流も含まれることに注意してください。起動時や大きな負荷トランジエント時に、出力電流モニタは、負荷電流のほかに、出力コンデンサを充電するために必要な電流を示します。外部電流制限が中途半端に作動しないように、外部電流制限値は最大負荷電流より大きく設定して、電流制限のない状態で出力コンデンサを回復できるようにします。

外部電流制限値を1A未満に設定する場合は、 $I_{LIM}$  とグランドの間に  $1k$ - $10nF$  のRC回路網を直列に接続して、電流制限ループの安定性を確保します。また、 $I_{LIM}$  とグランドの間にRC回路網を追加すると電流モニタ信号が遅延するので、限られた時間だけ出力電流を外部電流制限値より多く流すことが可能ですが、起動時や大きな負荷トランジエント時に外部電流制限が作動してしまい、出力電圧の回復が遅れてしまうような出力容量が大きなアプリケーションでは、この方法が役立ちます。外部電流制限の安定性を保証するには、 $I_{LIM}$  とGND間のRC回路網のコンデンサの値を  $10nF$  以上に、抵抗値を  $0.01 \cdot C^{-0.6} \sim 1k$  の範囲内にします。Cはファラッド単位でのコンデンサの値です。リニアテクノロジーでは、ケーブル電圧降下補償機能と並列化機能を使用する場合、 $1k$ - $10nF$  の組み合わせ以外のRC回路網は推奨しません。

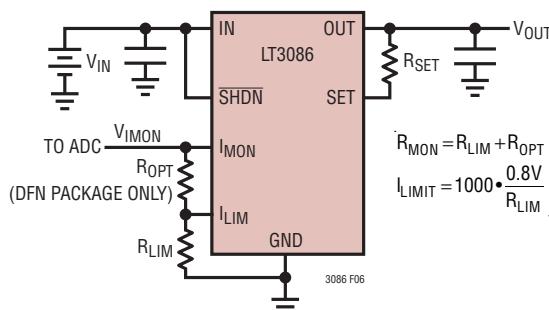

## アプリケーション情報

出力電流モニタと外部電流制限を正しく設定するには、必要な電流制限値とフルスケールのモニタ出力電圧を決定します。IMONをILIMに接続すると、電圧は0.8Vに制限されます。外部電流制限値は標準では最大負荷電流より10%～20%高い値に設定されているので、大きなトランジエントの発生やILIMしきい値のばらつきに対応できます。たとえば、最大負荷電流が1.5AでIMONピンとILIMピンを互いに接続している場合、442ΩのRMONスケーリング抵抗により、外部電流制限値は1.8Aになります。

より高い出力電流モニタ電圧が必要な場合、図6に示すように、DFNパッケージはIMONピンとILIMピンを1本の抵抗で分離する機能を備えています。IMON出力デバイスでの飽和を防止するため、VIMONがVINより0.6V以上低くなるようにRMONを選択してください。外部電流が必要ない場合は、ILIMピンを接地してください。

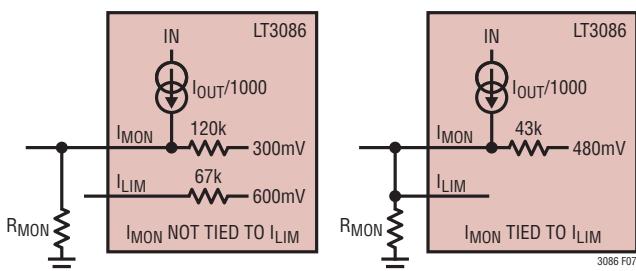

出力電流が非常に少ない場合の出力電流モニタ精度は、電流モニタ・アンプのオフセットと寄生電流経路によって制限されます。寄生電流経路の等価回路を図7に示します。IMONピンとILIMピンを互いに接続した場合、出力負荷電流をゼロにすると、RMONに流れる電流は標準で11μAになります。この結果、0mA～11mAの範囲の負荷電流は通常は測定できません。「標準的性能特性」セクションの「軽負荷時の電流モニタ」のグラフを参照してください。

図6. 独立したIMONおよびILIM(DFNパッケージのみ)

図7. IMONおよびILIMの等価回路

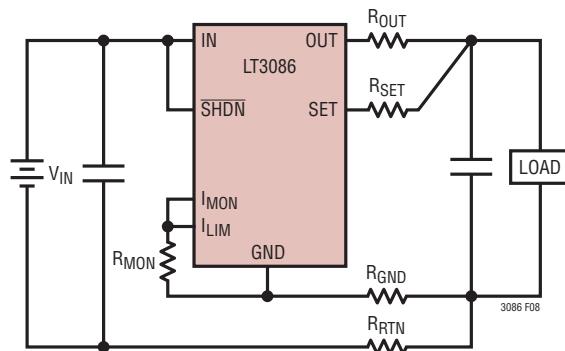

## 負荷レギュレーションとケーブル電圧降下補償

LT3086の出力負荷レギュレーションは、標準で0.1%です。R<sub>SET</sub>帰還抵抗をレギュレータのOUTピンに接続すると、最適なレギュレーションが得られます。大電流アプリケーションでは、レギュレータと負荷の間のPCBトレースまたはワイヤの抵抗に起因する小さな電圧降下が生じます。図8に示すように、R<sub>SET</sub>を負荷の出力側に直接接続すれば、これらの電圧降下を取り除くことができます。ROUTの両端とR<sub>RTN</sub>の両端で生じる電圧降下が、レギュレータのドロップアウト電圧に加わることに注意してください。RGND両端の電圧降下も最小限に抑えて、GNDピンの電流に起因する出力電圧誤差を低減する必要があります。「標準的性能特性」セクションの「GNDピンの電流」のグラフを参照してください。

LT3086は、既知の固定抵抗を持つ2本のワイヤだけを使用して、十分に安定化した電圧を離れた負荷に供給できるケーブル電圧降下補償(CDC)機能を備えています。図9に示すように、SETピンとCDCピンの間に抵抗(R<sub>CDC</sub>)を接続することにより、ユーザーが補償を設定します。

図8. ケルビンセンス接続

図9. ケーブル電圧降下補償

3086fa

## アプリケーション情報

負荷電流がゼロのとき、CDCピンの電圧は通常はSETピンと同じ電圧に安定化されます。この電圧はIMONピンの電圧変化の1/3に等しい速度で減少します。たとえば、VIMONが0Vから0.6Vまで増加すると、VCDCは0.2V減少します。その結果、RCDCを流れる電流は、RSET両端の電圧を大きくする負荷電流に比例するので、実質的に出力電圧が高くなります。OUTピンの電圧が高くなつて、負荷に接続されているケーブルでの電圧降下が打ち消されるように、RCDCは以下の式を使用して選択します。

$$R_{CDC} = \frac{R_{MON} \cdot R_{SET}}{3000 \cdot R_{WIRE}}$$

ここでRWIREは、電源のケーブル配線およびLT3086を負荷に接続する戻りケーブル配線の全抵抗です。

ケーブルの電圧降下を補償したトランジエント応答を図10に示します。補償していると、負荷での出力電圧はほぼ一定で推移します。出力電圧の過渡的な電圧低下は補償がない場合の電圧低下とほぼ同じですが、出力電圧は補償後の正しい電圧に戻ります。

図10. ケーブルの電圧降下を補償したトランジエント応答

長いケーブルを使用する場合は、補助の電源バイパス・コンデンサCLOADを負荷に直接追加して、大きな負荷トランジエント状態に対処する必要があります。COUTも引き続きOUTピンに直接接続して、LT3086の安定動作を確保し、出力コンデンサのESRおよびESLを最小限に抑える必要があります。長いケーブルにはインダクタンスがあり、このワイヤ・インダクタンスLWIREとCLOADの間に共振が生じます。減衰させるには、直

列抵抗RESRをCLOADに追加します。RESRの値はおよそ次のとおりです。

$$R_{ESR} = \sqrt{2 \cdot \frac{L_{WIRE}}{C_{LOAD}}}$$

ケーブル電圧降下補償を使用して補償できる電圧降下量には限界があります。ケーブル電圧降下補償を使用すると、負荷レギュレーションが電流モニタ電圧出力とケーブル配線抵抗のばらつきの影響を受けます。リニアテクノロジーでは、良好なレギュレーションを必要とするアプリケーションに備えて、ケーブル電圧降下補償をVOUTの20%までに制限することを推奨します。銅線抵抗は50°Cの温度変化に対して約19%変化するので、制限要因はワイヤ温度の変動です。出力レギュレーション要件が緩い場合(2次レギュレータの使用時など)は、ケーブル電圧降下補償を最大50%まで使用できます。

電流モニタ出力からのノイズは、出力で観測されるノイズに影響します。ILIMとグランドの間にRC回路網を追加して電流モニタ出力をフィルタリングすると、このノイズ源を低減するのに効果があります(特に軽負荷時)。詳細については、「出力電流モニタ」と「外部電流制限」のセクションを参照してください。

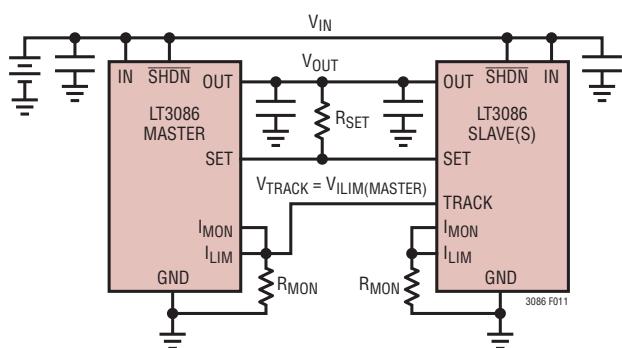

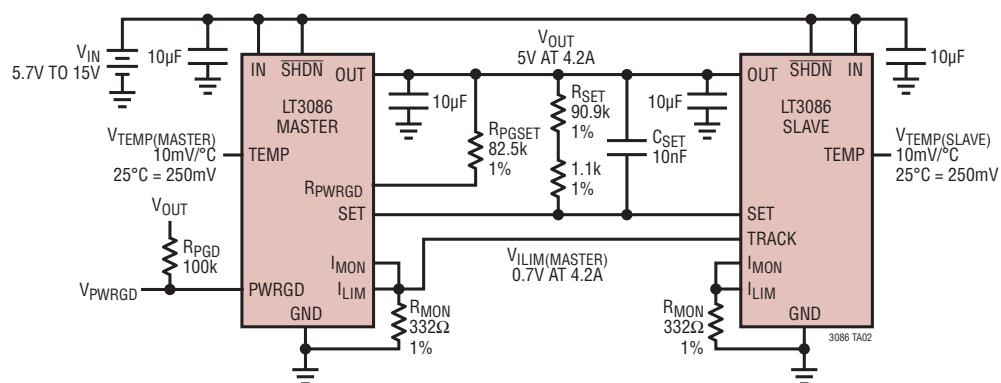

## 複数のレギュレータの並列接続

LT3086は、特に複数のレギュレータを容易に並列接続する目的で設計されています。並列接続により、アプリケーションの全出力電流を増加し、レギュレータが放散した熱をPCB上の広い領域に拡散させることができます。並列方式はマスター/スレーブの原則に基づいており、図11に示すように、1つのLT3086がマスターとして指定され、その他のレギュレータは全負荷電流を能動的に分担するスレーブとして動作します。スレーブの内部電流トラッキング・アンプは、マスターからの電流

図11. 並列化のためのマスター/スレーブ構成

## アプリケーション情報

モニタ出力とスレーブのI<sub>LIM</sub>ピンに現れる電流モニタ出力を比較し、スレーブの出力電流をサーボ制御してマスタの出力電流と一致するようにします。

マスタのLT3086の接続構成は、そのI<sub>LIM</sub>ピンに現れる出力電流モニタ電圧を共通の電流トラッキング信号として使用する単一のレギュレータとまったく同一です。スレーブ・デバイスはこの信号をスレーブ自体のTRACKピンに接続して、出力電流がマスタと等しくなるようにします。

TRACKピンには、0.75Vのとき標準で15μAの内部プルアップ電流が流れます。TRACKピンを使用しない場合、TRACKピンはプルアップされて1.25Vにクランプされるので、電流トラッキング・アンプはディスエーブルされます。TRACKピンをマスタの電流トラッキング信号に接続すると、TRACKピンの電圧が1.2Vのしきい値より低くなるので、電流トラッキング・アンプがイネーブルされ、スレーブの50μAリファレンス電流(I<sub>SET</sub>)がディスエーブルされます。リファレンス電流がディスエーブルされると、マスタが出力電圧を制御する唯一のデバイスになることが確実になります。マスタの電流トラッキング信号の最大値を0.8Vに設定して、外部電流制限が中途半端に作動しないようにしてください。スレーブの電流トラッキング・アンプがディスエーブルされないようにするには、スレーブのTRACKピンをマスタのI<sub>LIM</sub>ピンに接続する必要があります。マスタのI<sub>LIM</sub>ピンは1Vのクランプ回路を内蔵しており、これはスレーブの電流トラッキング・アンプのイネーブルしきい値である1.2Vより低い値です。

複数のスレーブを使用する場合は、使用するマスタのR<sub>MON</sub>抵抗をより小さくして、スレーブのすべてのTRACKピンからのプルアップ電流を補償する必要があります。たとえば、2.1Aを供給しているマスタのI<sub>LIM</sub>ピンの電圧は、332ΩのR<sub>MON</sub>抵抗を使用した場合、標準で0.697Vです。「標準的性能特性」の「TRACKピンのプルアップ電流」のグラフを参照すると、TRACKピンの電圧が0.697Vの場合、各スレーブから標準で15μAがマスタの2.1mA I<sub>MON</sub>出力に追加されます。5つのスレーブを接続するアプリケーションでは、R<sub>MON</sub>の値を次の値まで減らしてください。

$$R_{MON} = \frac{0.697V}{[2.1mA + (5 \cdot 15\mu A)]} = 325\Omega$$

最も近い1%精度の抵抗値は324Ωです。

すべてのスレーブ・レギュレータのSETピンはマスタのSETピンに接続する必要があります。TRACKアンプは、マスタとス

レーブの電流モニタ電圧の差の関数としてスレーブの内部リファレンス電圧をわずかに調整することによって動作します。これにはスレーブの出力電流に強い影響があり、スレーブの出力電流はマスタと整合するよう強制されます。

内部リファレンス電圧および電流モニタ出力のマスタとスレーブの間での不一致、スレーブのTRACKアンプのオフセット、およびTRACKピンのプルアップ電流は、すべて出力電流の分担誤差の原因になります。オフセットが負の場合、スレーブが流す電流はマスタより少くなります。非常に軽い負荷では、負のオフセットによってスレーブの出力オーバーシュート・プルダウン回路がイネーブルされ、マスタから強制的に電流を供給させて出力電圧をレギュレーション状態に維持します。その結果、マスタ/スレーブ構成で非常に軽い負荷では静止電流が増えることがあります。

一部のアプリケーションでは、複数のレギュレータ間に一定の間隔をあけて熱分布を最適化できます。こうすると、各レギュレータを近くの接地系統に接続して、グランド・ループが負荷電流によって形成されないように、低抵抗トレースを使用するのが重要になります。各レギュレータのグランド電流は1.5A時に最大30mA、2.1A時に最大50mAになります。グランド・ピンの電圧の差を10mV未満に制限すれば、トラッキング誤差を最小限に抑えられます。マスタとスレーブの間のグランド・トレース抵抗は負荷が1.5Aのとき10mV/30mA = 0.33Ω未満に、負荷が2.1Aのとき10mV/50mA = 0.2Ω未満にする必要があります。

## 出力容量

LT3086レギュレータは広範囲の出力コンデンサで安定します。出力コンデンサのESRは、特に小容量のコンデンサの場合、安定性に影響を与えます。発振を防止するため、ESRが0.1Ω以下の最小10μFの出力コンデンサを使用してください。出力の負荷トランジェント応答は出力容量の関数です。出力容量の値を大きくすると、負荷電流の大きな変化に対してピーク変動が減り、トランジェント応答が改善されます。負荷電流トランジェントが大きなアプリケーションでは、多くの場合、バルクのタンタル・コンデンサと低ESRのセラミック・コンデンサを並列接続することによって、最適に減衰された応答が得られます。たとえば、ESRが0.1Ωの47μFタンタル・コンデンサとESRが0.01Ω未満の10μFセラミック・コンデンサを並列接続すると、大きなトランジェント負荷に対して出力変動が約2:1に減少し、ループの位相余裕が増加します。

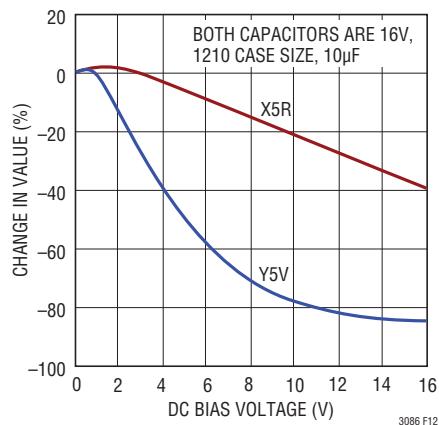

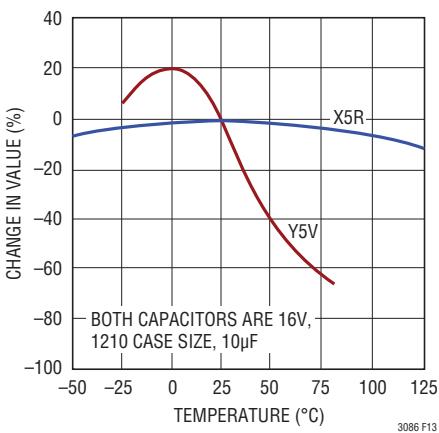

## アプリケーション情報

セラミック・コンデンサを使用する際には、特に検討が必要です。セラミック・コンデンサは様々な誘電体を使用して製造されており、それぞれ温度や印加される電圧によって動作が異なります。最も広く使われている誘電体は、Z5U、Y5V、X5RおよびX7RのEIA温度特性コードによって規定されています。Z5UとY5Vの誘電体は小型のパッケージで高C-V積を低コストで実現していますが、図12と図13に示すように、電圧係数と温度係数が大きくなります。5Vのレギュレータに使用した場合、16V 10 $\mu$ FのY5Vコンデンサは、印加されたDCバイアス電圧と動作温度範囲でわずか1 $\mu$ F～2 $\mu$ Fの小さな実効値になる可能性があります。X5RとX7Rの誘電体を使用するとさらに安定した特性が得られるので、これらは出力コンデンサとして使用するのにより適しています。

X7Rタイプはより広い温度範囲にわたって動作し、温度安定性が優れていますが、X5Rタイプは安価で大きな値のものが入手

可能です。X5RやX7Rのコンデンサを使用する場合でも注意する必要があります。X5RとX7Rのコードは動作温度範囲と全温度範囲での最大容量変化を規定しているだけです。X5RやX7Rのコンデンサの場合は、DCバイアスによる容量変化が小さいものの、コンデンサの値が適切なレベルより小さくなるのに十分なほど大きい可能性があります。コンデンサのDCバイアス特性は部品のケースのサイズが大きいほど向上する傾向がありますが、動作電圧での必要な容量を検証する必要があります。

電圧係数と温度係数だけが問題の原因ではありません。セラミック・コンデンサの中には圧電応答を示すものがあります。圧電素子は、圧電加速度計やマイクロホンの動作原理と同様、機械的応力によって端子間に電圧を生じます。セラミック・コンデンサでは、システムの振動や熱過渡によって応力が生じます。その結果発生した電圧によってかなりの大きさのノイズが生じることがあります。

### 入力容量

入力とグランドのリード線が短いアプリケーションでは、低ESRのセラミック入力バイパス・コンデンサを使用できます。ただし、長いワイヤを使用して電源をLT3086に接続するアプリケーションは、電圧スパイク、信頼性上の懸念、アプリケーション固有の基板発振が発生しやすい傾向があります。

多くのバッテリ駆動アプリケーションで見られる入力ワイヤのインダクタンスを低ESRのセラミック・コンデンサと組み合わせると、Qの高いLC共振タンク回路が形成されます。場合によっては、この共振周波数が出力電流に依存するLDOの帯域幅とぶつかり、正常な動作に干渉することがあります。この場合、簡単な回路修正が必要になります。この挙動はLT3086の不安定さを示すものではなく、アプリケーションに共通の問題です。

ワイヤの自己インダクタンス(つまり、ワイヤ単独のインダクタンス)はその長さに正比例します。ワイヤの直径はワイヤの自己インダクタンスの主要因ではありません。例えば、単独の2-AWGワイヤ(直径 = 0.26インチ)の自己インダクタンスは、30-AWGワイヤ(直径 = 0.01インチ)の自己インダクタンスの約1/2です。1フィートの30-AWGワイヤの自己インダクタンスは約465nHです。ワイヤの自己インダクタンスを減らすには2つの方法があります。1つの方法は、LT3086に流れ込む電流を2つの並列な導体に分割することです。この場合、ワイヤが互いに遠く離れているほど自己インダクタンスが減少し、数インチ離すと最大50%減少します。ワイヤの分割は2個の等し

図12. セラミック・コンデンサのDCバイアス特性

図13. セラミック・コンデンサの温度特性

## アプリケーション情報

いインダクタを並列に接続することに相当しますが、それらを近接させると、ワイヤの相互インダクタンスが自己インダクタンスに加わります。全体のインダクタンスを減らす2番目の(最も効果的な)方法は、電流の往路と復路の両方の導体(入力のワイヤとGNDのワイヤ)を非常に近づけて配置することです。往路と復路の電流の導体に、0.02インチ離した2本の30-AWGワイヤを使用すると、1本の独立したワイヤを使用した場合に比べて全体の自己インダクタンスは約1/5に減少します。

近くに装着したバッテリでLT3086に電力を供給する場合は、 $10\mu F$ の入力コンデンサで十分に安定性を確保できます。ただし、遠く離れた電源からLT3086に電力を供給する場合は、より大きな値の入力コンデンサを使用してください。おおまかな目安としては、( $10\mu F$ の最小値とは別に)ワイヤの長さ8インチにつき $1\mu F$ を使用してください。アプリケーション回路を安定化するために必要な入力容量の最小値も、電源の出力インピーダンスのばらつきによって変動します。LT3086の出力容量を増やすことも効果的です。ただし、このためには追加のLT3086入力バイパス・コンデンサと比較して1桁大きい容量が必要です。また、電源とLT3086の入力の間に直列抵抗を接続することもアプリケーションの安定化に役立ちます。わずか $0.1\Omega \sim 0.5\Omega$ の小さな抵抗で十分です。このインピーダンスによってLCタンク回路の共振が減衰しますが、代償としてドロップアウト電圧が発生します。より優れた代替手段は、入力に高ESRの入力容量(タンタル・コンデンサや電解コンデンサ)を追加するか、低ESRのセラミック・コンデンサと直列に抵抗を追加する方法です。

### 過負荷状態からの回復

多くのICパワー・レギュレータと同様に、LT3086は安全動作領域保護機能を備えています。安全動作領域保護機能により、入出力間の電圧差が増加するにつれて電流制限値が減少し、パワー・トランジスタは、入出力間電圧のすべての値について安全動作領域内に保たれます。LT3086は、規定された最大動作電圧である45Vまで、入出力間電圧のすべての値で一定の出力電流を供給します。 $V_{IN} - V_{OUT}$ の電圧差が過大な場合は、電流制限フォールドバックによって外部の電流制限が無効になります(使用している場合)。

最初に電源が印加されるとき、入力電圧が上昇して出力が入力に追随するので、レギュレータは非常に重い負荷で起動することができます。起動時には入力電圧が上昇中なので、入出力間の電圧差が小さく、レギュレータは大量の出力電流を供給できます。入力電圧が高いと、出力の短絡状態を解除しても出力電圧が回復しないという問題が発生する可能性があります。LT1083/LT1084/LT1085ファミリやLT1764Aなどのレギュレータもこの現象を示すので、LT3086に固有の問題ではありません。この問題は、出力負荷が重い場合に、入力電圧が高く、出力電圧が低いと発生します。こうした状況になりやすいのは、短絡状態が解消された直後か、入力電圧が既に投入されていてその後にシャットダウン・ピンが“H”になった場合です。負荷線は出力電流曲線と2点で交わるので、レギュレータには安定した出力動作点が2つあります。このように2つの交点があるので、出力を回復するには、入力電源を一旦0Vにしてから再度立ち上げる必要があります。

### 熱に関する検討事項

LT3086の電力処理能力は、最大定格接合部温度である $125^\circ C$ で制限されます。デバイスによる電力損失は次の3つの要素で構成されます。

- 出力電流と入出力間電圧差の積:

$$I_{OUT} \cdot (V_{IN} - V_{OUT})$$

- GNDピン電流と入力電圧の積:

$$I_{GND} \cdot V_{IN}$$

- 電流モニタ電流と入力/電流モニタ間電圧差の積:

$$I_{MON} \cdot (V_{IN} - V_{IMON})$$

GNDピンの電流は、「標準的性能特性」セクションの「GNDピンの電流」のグラフを使用して求めます。電力損失は前述した3つの要素の和に等しくなります。

LT3086レギュレータは、過負荷状態時にデバイスを保護する熱制限回路を内蔵しています。通常状態を継続する場合、 $125^\circ C$ の最大接合部温度を超えてはなりません。LT3086の近くに取り付けられている他の熱源を含め、接合部から周囲までのすべての熱抵抗源について注意深く検討します。

## アプリケーション情報

LT3086のDFNパッケージとTSSOPパッケージの下側には、リードフレームからダイ・アタッチメントまでの露出した金属部分( $10.5\text{mm}^2$ )があります。これらのパッケージでは、ダイの接合部からプリント回路基板の金属部分に熱を直接伝達できます。デュアル・インラインのピン配置により、PCBの上面(部品側)にあるパッケージの端を超えて金属部分を伸ばすことができます。この金属部分はPCBのGNDに接続します。LT3086にINピンとOUTピンが複数あることも、熱をPCBに拡散するのに役立ちます。

表面実装デバイスの場合は、PC基板とその銅トレースの熱分散能力を利用して放熱を実現します。パワー・デバイスが発生する熱を分散するのに、銅ボード硬化材とメッキ・スルーホールを利用することもできます。

一定のボード・サイズ上でのいくつかの上面銅箔領域の熱抵抗を表2と表3に示します。すべての測定は、静止空气中で、1オンスの切れ目のない内部プレーンと2オンスの外部トレース・プレーンを有し、合計基板厚が1.6mmの4層FR-4ボードで行いました。4つの層にはサーマル・ビアが存在せず、電気的に絶縁されていました。低い熱抵抗を実現するには、細部にわたる注意と慎重なPCBレイアウトが必要です。熱抵抗と高熱伝導性テストボードの詳細については、JEDEC規格JESD51、特にJESD51-12およびJESD51-7を参照してください。サーマル・ビアの使用、銅重量の増加、および空気流により、得られる熱抵抗は改善されます。

表2. DHDおよびFEパッケージの熱抵抗測定結果

| 銅箔面積 |                         | 基板面積<br>( $\text{mm}^2$ ) | 熱抵抗<br>(接合部・周囲間) |

|------|-------------------------|---------------------------|------------------|

| 上面*  | 裏面<br>( $\text{mm}^2$ ) |                           |                  |

| 2500 | 2500                    | 2500                      | 25°C/W           |

| 1000 | 2500                    | 2500                      | 26°C/W           |

| 225  | 2500                    | 2500                      | 28°C/W           |

| 100  | 2500                    | 2500                      | 33°C/W           |

\* デバイスは上面に実装。

表3. Rパッケージの熱抵抗測定結果

| 銅箔面積 |                         | 基板面積<br>( $\text{mm}^2$ ) | 熱抵抗<br>(接合部・周囲間) |

|------|-------------------------|---------------------------|------------------|

| 上面*  | 裏面<br>( $\text{mm}^2$ ) |                           |                  |

| 2500 | 2500                    | 2500                      | 15°C/W           |

| 1000 | 2500                    | 2500                      | 16°C/W           |

| 225  | 2500                    | 2500                      | 19°C/W           |

\* デバイスは上面に実装。

### T7パッケージの熱抵抗測定結果

熱抵抗(接合部-ケース間)= $3^\circ\text{C}/\text{W}$ 。

LT3086は、出力電流と温度のモニタ・ピンを観測することによって熱性能を確認する機能を備えています。放熱、外匣器、および空気の動きの影響を、特殊な計測器を使用せずに瞬時に分析できます。

### 接合部温度の計算

例: 出力電圧が5V、入力電圧範囲が6V±5%、最大出力電流範囲が1A ( $R_{MON}$ として $698\Omega$ を使用)、最大周囲温度が $75^\circ\text{C}$ の場合、最大接合部温度は何°Cになるでしょうか。

デバイスの電力損失は次のようにになります。

$$I_{OUT(MAX)} \cdot (V_{IN(MAX)} - V_{OUT}) + I_{GND} \cdot V_{IN(MAX)} + I_{MON(MAX)} \cdot (V_{IN(MAX)} - V_{IMON(MAX)})$$

ここで、

$$I_{OUT(MAX)} = 1\text{A}$$

$$V_{IN(MAX)} = 6.3\text{V}$$

$$(I_{OUT} = 1\text{A}, V_{IN} = 6.3\text{V}) \text{ での } I_{GND} = 11\text{mA}$$

$$(I_{OUT} = 1\text{A}, R_{MON} = 698\Omega) \text{ での } V_{IMON} = 0.698\text{V}$$

したがって、次のようにになります。

$$P = 1\text{A} \cdot (6.3\text{V} - 5\text{V}) + 11\text{mA} \cdot 6.3\text{V} + 1\text{mA} \cdot (6.3\text{V} - 0.698\text{V}) = 1.38\text{W}$$

DFNパッケージを使用する場合、熱抵抗は上面の銅箔面積に応じて $25^\circ\text{C}/\text{W} \sim 33^\circ\text{C}/\text{W}$ の範囲になります。したがって、周囲温度を超える接合部温度の上昇分はおよそ次のようになります。

$$1.38\text{W} \cdot 30^\circ\text{C}/\text{W} = 41.4^\circ\text{C}$$

最大接合部温度は、最大周囲温度と、周囲温度を超える接合部の最大温度上昇分との和になります。これは次のとおりです。

$$T_{JMAX} = 75^\circ\text{C} + 41.4^\circ\text{C} = 116.4^\circ\text{C}$$

## アプリケーション情報

### 保護機能

LT3086レギュレータはいくつかの保護機能を内蔵しているので、バッテリ駆動回路で使用するのに最適です。電流制限や熱制限など、モノリシック・レギュレータに関連した通常の保護機能を備えているほか、このデバイスは逆入力電圧、逆出力電圧、出力から入力への逆電圧に対しても保護されています。

電流制限による保護と熱過負荷保護は、デバイスの出力の電流過負荷状態に対してデバイスを保護します。標準のサーマル・シャットダウン温度は165°Cで、約7°Cのヒステリシスが組み込まれています。通常動作では、最大定格接合部温度の125°Cを超えないようにしてください。

LT3086のINピンは45Vの逆電圧に耐えます。デバイスに流れる電流は2mA未満(標準では1μA未満)に制限され、OUTに負電圧は出力されません。このデバイスは、逆向きに差し込まれたバッテリからデバイス自体と負荷を保護します。

LT3086は出力がグランドより低い電圧になつても損傷を受けることはありません。入力が開放状態のままか、または接地されている場合、出力はグランドより36V下げるることができます。出力からパス・トランジスタを介して電流が流出することはありません。ただし、電流は帰還抵抗を流れます(しかし、帰還抵抗によって制限されます)。帰還抵抗は、出力電圧を設定するR<sub>SET</sub>と、パワーグッドしきい値を設定するR<sub>PWRGD</sub>です。SETピンとR<sub>PWRGD</sub>ピンの内部クランプ回路から外部回路に電流が流れることにより、OUTピンの電圧はグランドより低くなります。電源によって入力に電力が供給される場合、デバイスは内部クランプの作動時にパワー・デバイスをオフにしてデバイス自体を保護します。ショットキ・ダイオードを使用してSETピンとR<sub>PWRGD</sub>ピンがそれらの内部クランプを作動しないようにした場合、出力からは電流制限能力に等しい電流が流れ出るので、LT3086は熱制限によってデバイス自体を保護します。この場合、SHDNピンをグランドに接続するとデバイスがオフし、出力からのソース電流が停止します。逆電流は図14に示すグラフに従います。

SETピンとR<sub>PWRGD</sub>ピンの電圧をグランドより最大36V高くしても、LT3086は損傷しません。入力を開放のままにするか接地すると、SETピンはダイオードと直列に接続された大きな抵抗(標準で80k)のように動作します。

2次電源が出力電圧を上昇させ、R<sub>SET</sub>で設定された安定化電圧より高くなる回路では、出力電圧が入力電圧より低い限り、出力オーバーシュート回路によって出力ピンからグランドに電流が流れます。出力オーバーシュート電流は図15に示

すグラフに従います。出力電圧を入力電圧より標準で225mV高くすると、LT3086は図16に示すようにシャットダウンし、15mAのオーバーシュート・プルダウン電流源はオフします。

図14. 逆出力電流

図15. 出力オーバーシュートのプルダウン電流

図16. OUTピンとINピンの電圧差によるシャットダウンしきい値

# LT3086

## 標準的応用例

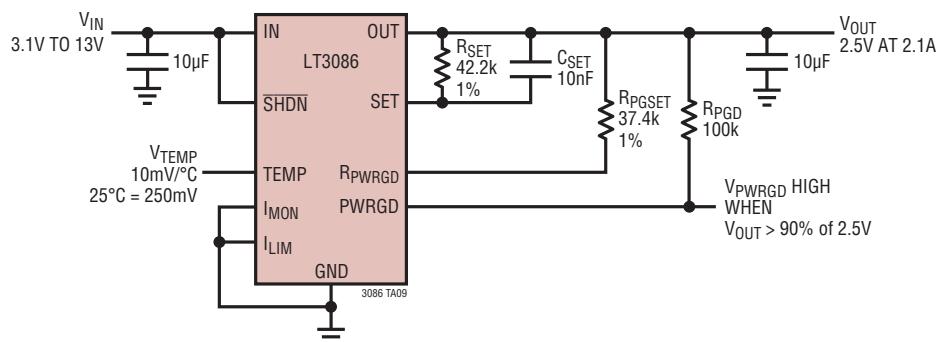

パワーグッド機能を備えた2.5V低ノイズ・レギュレータ

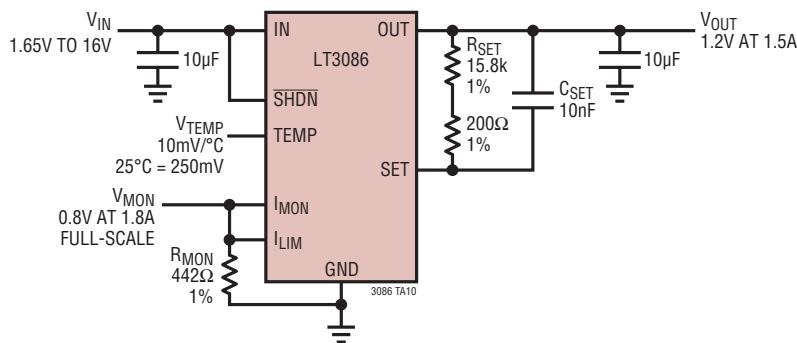

1.8A外部電流制限機能を備えた1.2V、1.5A低ノイズ・レギュレータ

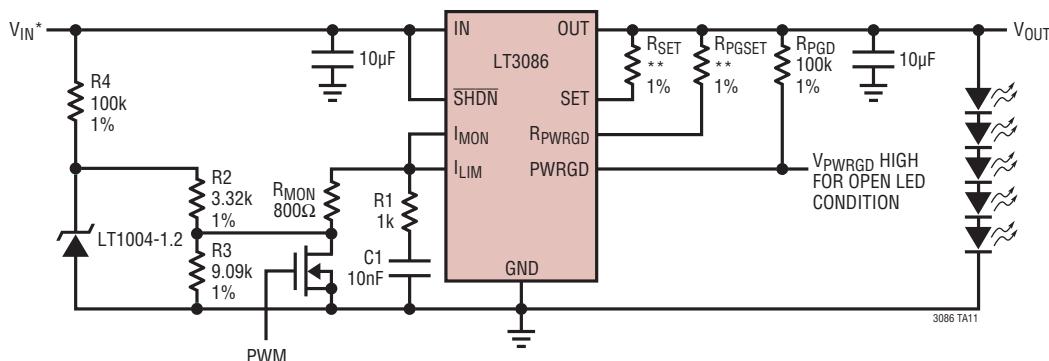

PWM調光機能とLED開放検出機能を備えた5段白色LEDドライバ

NOTE: ADJUST  $R_{MON}$  TO SET MAXIMUM LED CURRENT (SET TO 800Ω FOR 1A)

DRIVE PWM LOW TO TURN OFF LED STRING (PULSE TO DIM)

\*INPUT VOLTAGE REQUIRED IS DEPENDENT ON THE LED STRING VOLTAGE

\*\*CHOOSE  $R_{SET}$  AND  $R_{PGSET}$  BASED ON LED STRING

## 標準的応用例

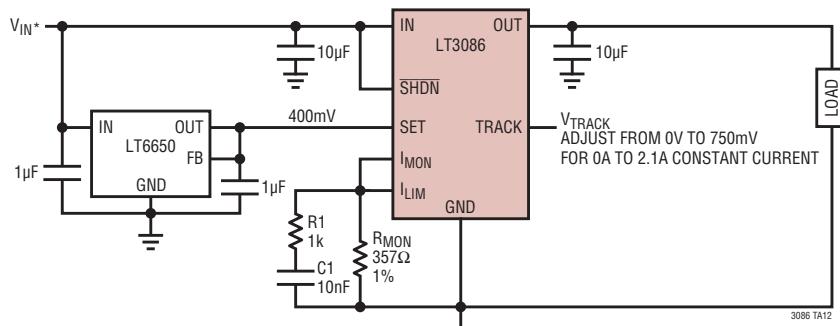

可変電圧制御電流源

\*RESTRICT INPUT VOLTAGE RANGE TO LIMIT POWER DISSIPATION

AND PREVENT FOLDBACK CURRENT LIMIT FROM INTERFERING

WITH PROPER OPERATION

$I_{LIM} \leq 1A$ 達成のための外部電流制限の安定性確保

## 電流モニタ出力電圧の増加

## パワーグッド・ヒステリシスの増加(例:2%)

# LT3086

## 標準的応用例

### パワーグッドを使用した負荷電流モニタ

### パワーグッドを使用した入力低電圧検出器

### 熱制限温度のプログラミング

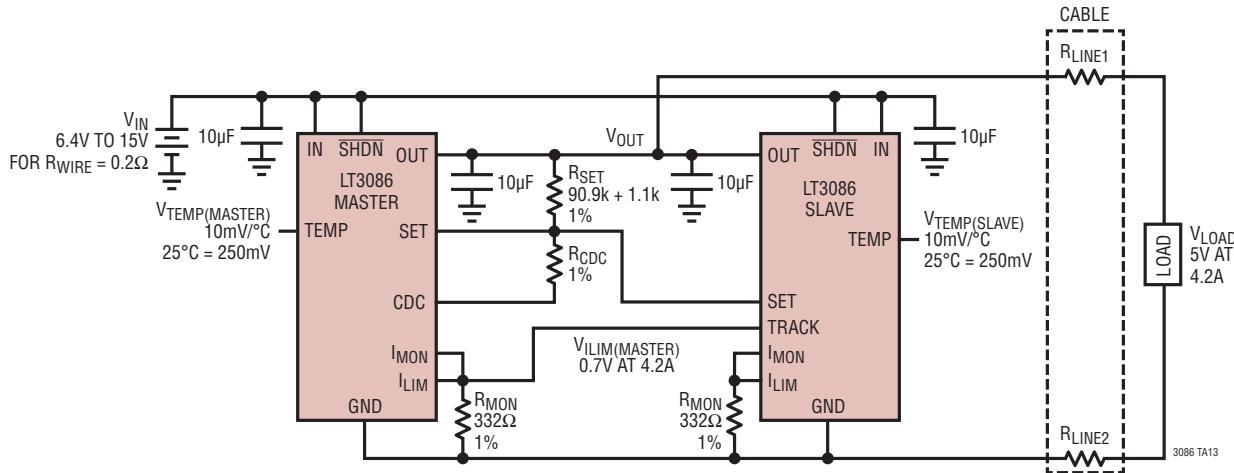

### 5V、4.2A達成のための2つのレギュレータの並列接続

3086fa

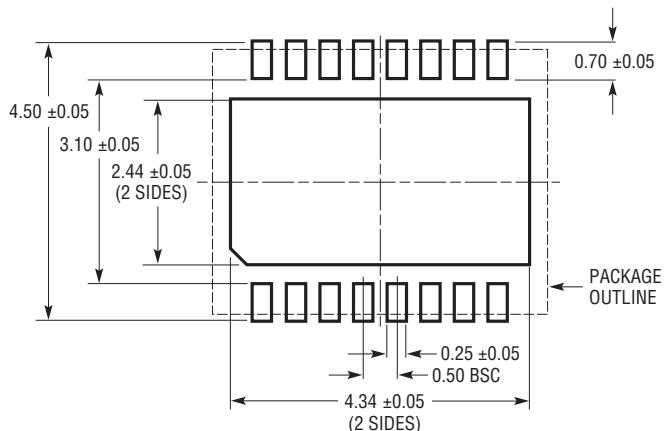

## パッケージ

最新のパッケージ図面については、<http://www.linear-tech.co.jp/designtools/packaging/> を参照してください。

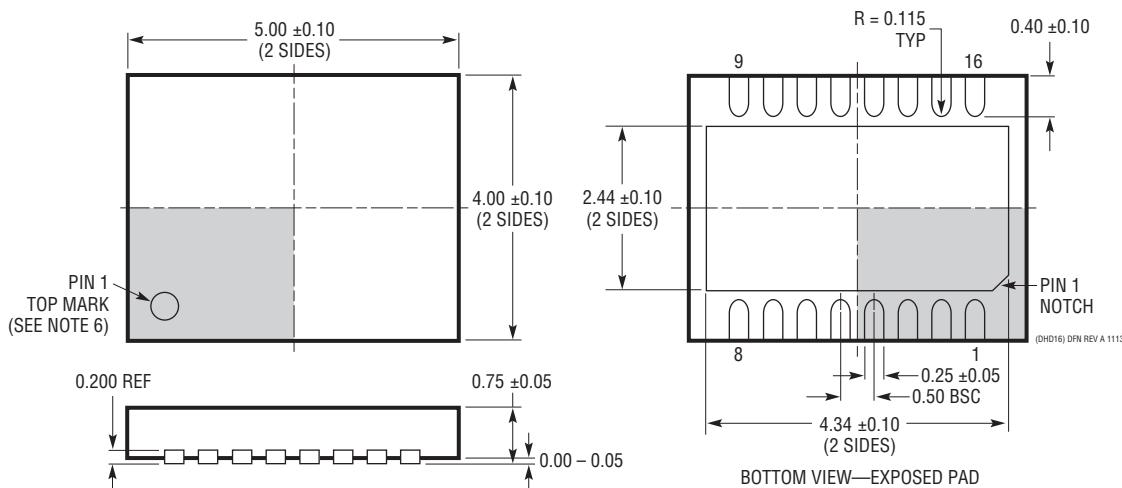

**DHD Package

16-Lead Plastic DFN (5mm × 4mm)**

(Reference LTC DWG # 05-08-1707 Rev A)

RECOMMENDED SOLDER PAD PITCH AND DIMENSIONS

注記：

1. 図は JEDEC パッケージ・アウトライン MO-229 のバージョンの

バリエーション(WJGD-2)として提案。

2. 図は実寸とは異なる

3. 全ての寸法はミリメートル

4. パッケージ底面の露出パッドの寸法にはモールドのバリを含まない。

モールドのバリは(もしあれば)各サイドで 0.15mm を超えないこと

5. 露出パッドは半田メッキとする

6. 線掛けの部分はパッケージの上面と底面のピン 1 の位置の参考に過ぎない

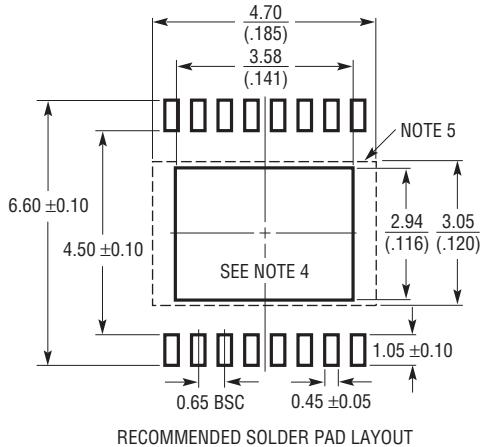

## パッケージ

最新のパッケージ図面については、<http://www.linear-tech.co.jp/designtools/packaging/> を参照してください。

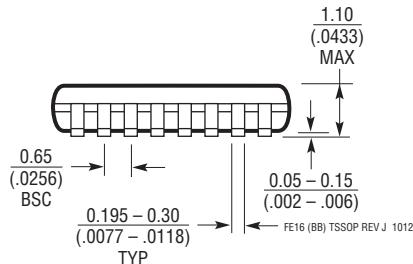

**FE Package

16-Lead Plastic TSSOP (4.4mm)

(Reference LTC DWG # 05-08-1663 Rev J)**

**Exposed Pad Variation BB**

### 注記:

- 標準寸法:ミリメートル

- 寸法は ミリメートル

(インチ)

- 図は実寸とは異なる

- 露出パッド接着のための推奨最小PCB

メタルサイズ

- 露出パッド底面のこの部分には金属の突出部があってもよい。

PCB レイアウト上この部分には配線やビアを配置しないこと

- \*寸法にはモールドのバリを含まない。

モールドのバリは各サイドで0.150mm(0.006")を超えないこと

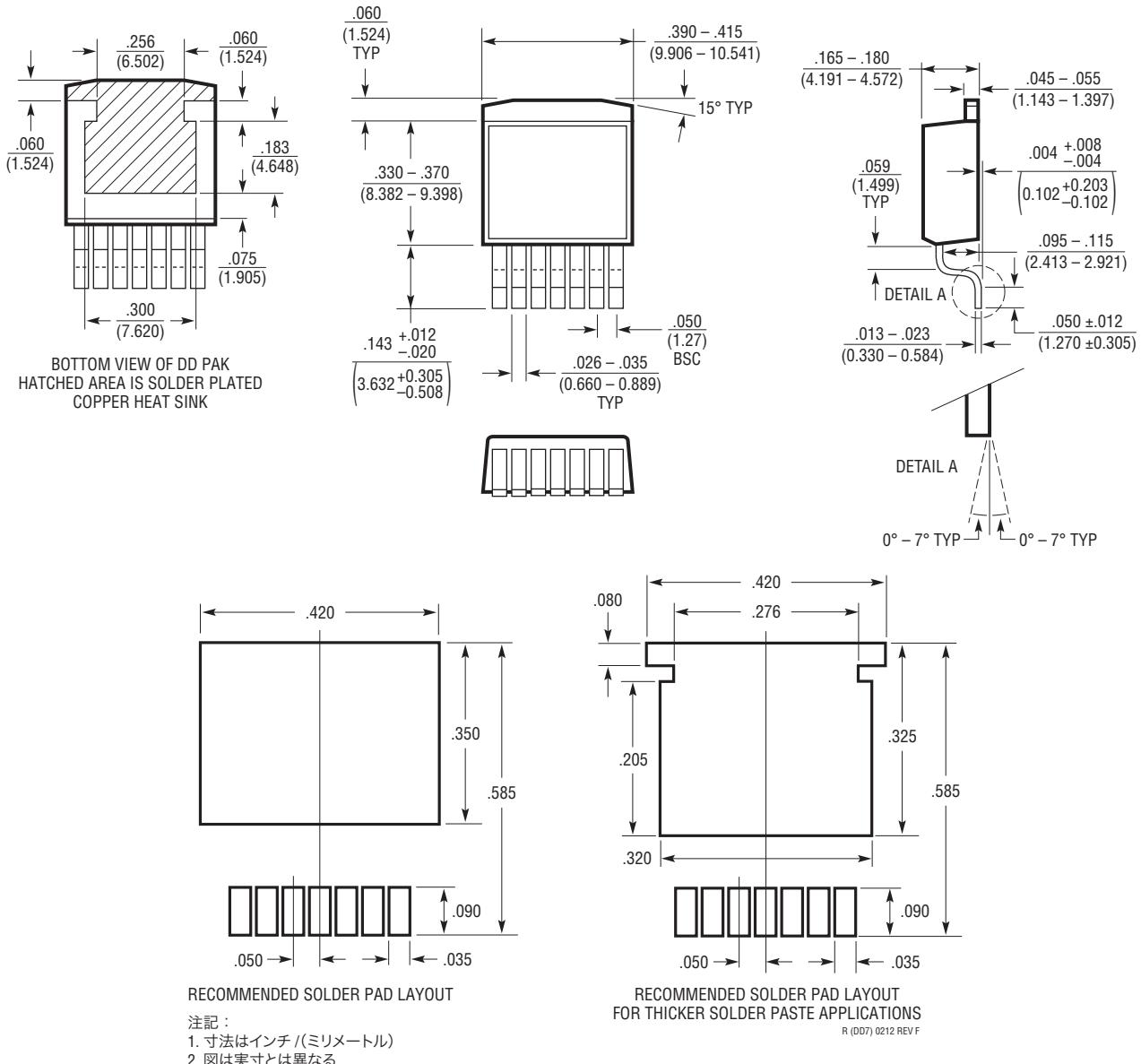

## パッケージ

最新のパッケージ図面については、<http://www.linear-tech.co.jp/designtools/packaging/> を参照してください。

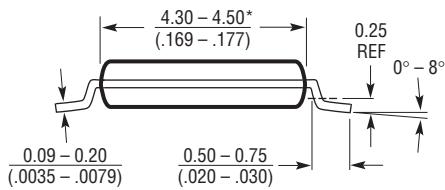

**R Package

7-Lead Plastic DD Pak**

(Reference LTC DWG # 05-08-1462 Rev F)

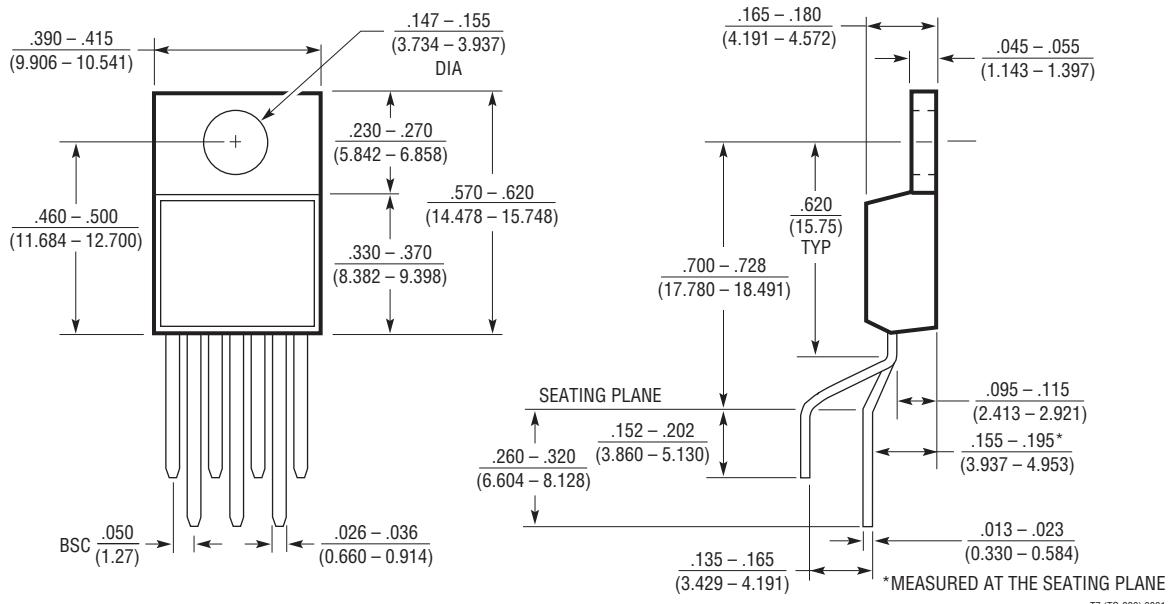

## パッケージ

最新のパッケージ図面については、<http://www.linear-tech.co.jp/designtools/packaging/> を参照してください。

**T7 Package

7-Lead Plastic TO-220 (Standard)**

(Reference LTC DWG # 05-08-1422)

T7 (TO-220) 0801

## 改訂履歴

| REV | 日付   | 概要                                                                                                                                                                                                                 | ページ番号                            |

|-----|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| A   | 6/14 | TSSOP、DD-Pak、TO-220パッケージに対して、MPグレード追加。<br>電気的特性表に、Minimum Load Currentの欄と、Note 16を追加。<br>2つのGNDピン電流のグラフ、2つの1AでのPSRRのグラフ、2つのラインレギュレーショングラフを追加と修正。<br>出力電圧ノイズのグラフを修正。<br>DHD、FE、Rパッケージに対する熱抵抗を更新。<br>DHDパッケージの記述を更新。 | 2~4<br>3、5<br>7~12<br>2、24<br>29 |

## 標準的応用例

5V、4.2A達成のための2つのレギュレータの並列接続、ケーブル電圧降下補償(CDC)機能付き

$$R_{CDC} = \frac{R_{MON} \cdot R_{SET}}{(X+1) \cdot 3000 \cdot R_{WIRE}}$$

$$R_{WIRE} = R_{LINE1} + R_{LINE2}$$

WHERE X=NUMBER OF SLAVES

## 関連製品

| 製品番号                | 説明                                                                          | 注釈                                                                                                                                                                                                                                 |

|---------------------|-----------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LT1764/<br>LT1764A  | 3A、高速トランジエント応答、低ノイズLDO                                                      | ドロップアウト電圧:340mV、低ノイズ:40µVRMS、V <sub>IN</sub> :2.7V~20V、TO-220およびDDパッケージ、LT1764Aもセラミック・コンデンサで安定                                                                                                                                     |

| LT1963/<br>LT1963A  | 1.5A、低ノイズ、高速トランジエント応答LDO                                                    | ドロップアウト電圧:340mV、低ノイズ:40µVRMS、V <sub>IN</sub> :2.5V~20V、LT1963Aはセラミック・コンデンサで安定、TO-220、DD-PAK、SOT-223およびSO-8パッケージ                                                                                                                    |

| LT1965              | 1.1A、低ノイズ、低ドロップアウト・リニア・レギュレータ                                               | ドロップアウト電圧:310mV、低ノイズ:40µVRMS、V <sub>IN</sub> :1.8V~20V、V <sub>OUT</sub> :1.2V~19.5V、セラミック・コンデンサで安定、TO-220、DD-PAK、MSOPおよび3mm×3mm DFNパッケージ                                                                                           |

| LT3022              | 1A、低電圧 VLDO リニア・レギュレータ                                                      | ドロップアウト電圧:145mV、V <sub>IN</sub> :0.9V~10V、V <sub>OUT</sub> :0.2V~9.5V、低ESRのセラミック出力コンデンサで安定、16ピンDFN(5mm×3mm)および16ピンMSOPパッケージ                                                                                                        |

| LT3070              | V <sub>OUT</sub> をプログラム可能なドロップアウト電圧 85mV のデジタル・マージニング機能付き低ノイズ 5A リニア・レギュレータ | ドロップアウト電圧:85mV、デジタル・プログラム可能なV <sub>OUT</sub> :0.8V~1.8V、デジタル出力マージニング:±1%、±3%または±5%、低出力ノイズ:25µVRMS、直接並列接続可能、低ESRセラミック出力コンデンサで安定(最小15µF)、28ピン4mm×5mm QFNパッケージ                                                                        |

| LT3071              | V <sub>OUT</sub> をプログラム可能なドロップアウト電圧 85mV のアナログ・マージニング機能付き低ノイズ 5A リニア・レギュレータ | ドロップアウト電圧:85mV、デジタル・プログラム可能なV <sub>OUT</sub> :0.8V~1.8V、アナログ・マージニング:±10%、低出力ノイズ:25µVRMS、直接並列接続可能、I <sub>MON</sub> 出力電流モニタ、低ESRセラミック出力コンデンサで安定(最小15µF)、28ピン4mm×5mm QFNパッケージ                                                         |

| LT3080/<br>LT3080-1 | 並列接続可能な1.1A、低ノイズ、低ドロップアウト・リニア・レギュレータ                                        | ドロップアウト電圧:300mV(2電源動作)、低ノイズ:40µVRMS、V <sub>IN</sub> :1.2V~36V、V <sub>OUT</sub> :0V~35.7V、電流ベースのリファレンス、1本の抵抗でV <sub>OUT</sub> を設定、直接並列接続可能(オペアンプ不要)、セラミック・コンデンサで安定、TO-220、DD-PAK、SOT-223、MSOPおよび3mm×3mm DFN-8パッケージ、LT3080-1は安定抵抗を内蔵 |

| LT3081              | モニタ機能を備えた单一抵抗型の堅牢な1.5Aリニア・レギュレータ                                            | 広い安全動作領域、V <sub>IN</sub> :1.2V~36V、V <sub>OUT</sub> :0V~34.5V、電流ベースのリファレンス、プログラム可能な電流制限、出力電流モニタおよび温度モニタ                                                                                                                            |

| LT3083              | 並列接続可能な3A、低ノイズ、低ドロップアウト・リニア・レギュレータ                                          | ドロップアウト電圧:310mV(2電源動作)、低ノイズ:40µVRMS、V <sub>IN</sub> :1.2V~23V、V <sub>OUT</sub> :0V~22.6V、電流ベースのリファレンス、1本の抵抗でV <sub>OUT</sub> を設定、直接並列接続可能(オペアンプ不要)、セラミック・コンデンサで安定、TO-220、DD-PAK、TSSOP、4mm×4mm DFN-12パッケージ                          |

| LT3085              | 並列接続可能な500mA、低ノイズ、低ドロップアウト・リニア・レギュレータ                                       | ドロップアウト電圧:275mV(2電源動作)、低ノイズ:40µVRMS、V <sub>IN</sub> :1.2V~36V、V <sub>OUT</sub> :0V~35.7V、電流ベースのリファレンス、1本の抵抗でV <sub>OUT</sub> を設定、直接並列接続可能(オペアンプ不要)、セラミック・コンデンサで安定、MS8Eおよび2mm×3mm DFN-6パッケージ                                        |