# 広範囲のI<sup>2</sup>C電力、電荷、およびエネルギー・モニタ

## 特長

- レール・トゥ・レールの入力電圧範囲:0V～100V

- 広い入力電源電圧範囲:2.7V～100V

- 100Vを超える電源用のシャント・レギュレータ

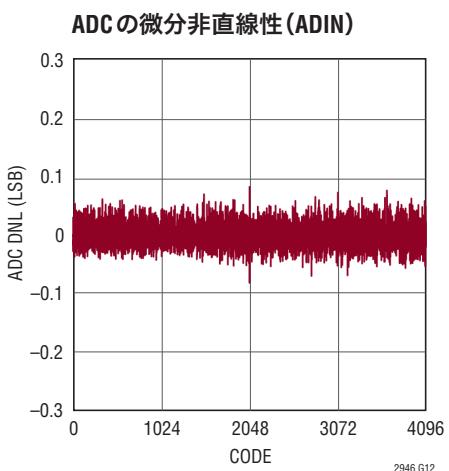

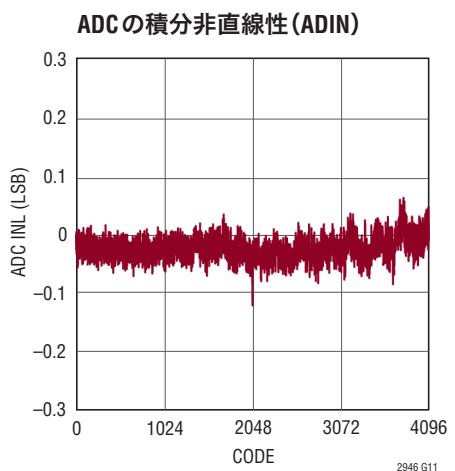

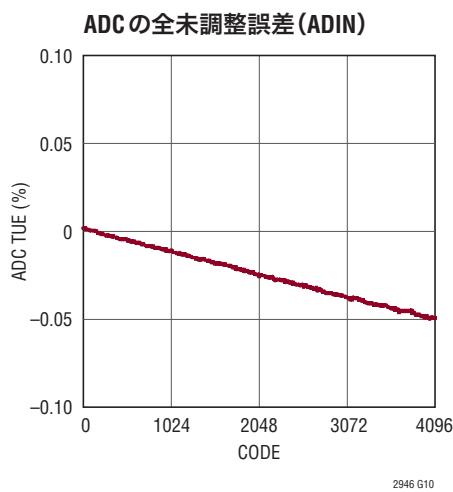

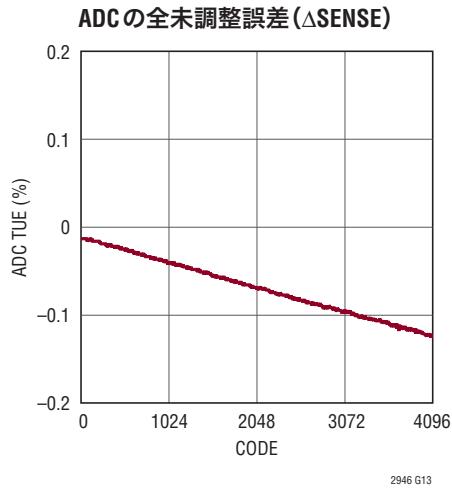

- 全未調整誤差が±0.4%未満の△Σ型A/Dコンバータ

- 電流と電圧の分解能:12ビット

- ±1%精度の電力およびエネルギー測定

- ±0.6%精度の電流および電荷測定

- 追加のA/Dコンバータ入力により外部電圧をモニタ

- 内部(±5%)タイム・ベースまたは外部タイム・ベース

- 連続スキヤン・モードとスナップショット・モード

- 最小値と最大値を記憶

- 制限値を超えた場合は警告

- SDAピンの分割により光絶縁が容易

- I<sub>Q</sub>が40μA未満のシャットダウン・モード

- 4mm×3mm DFNパッケージおよび

16ピンMSOPパッケージで供給可能

## アプリケーション

- 通信機器のインフラ

- 産業用機器

- 汎用エネルギー測定

## 概要

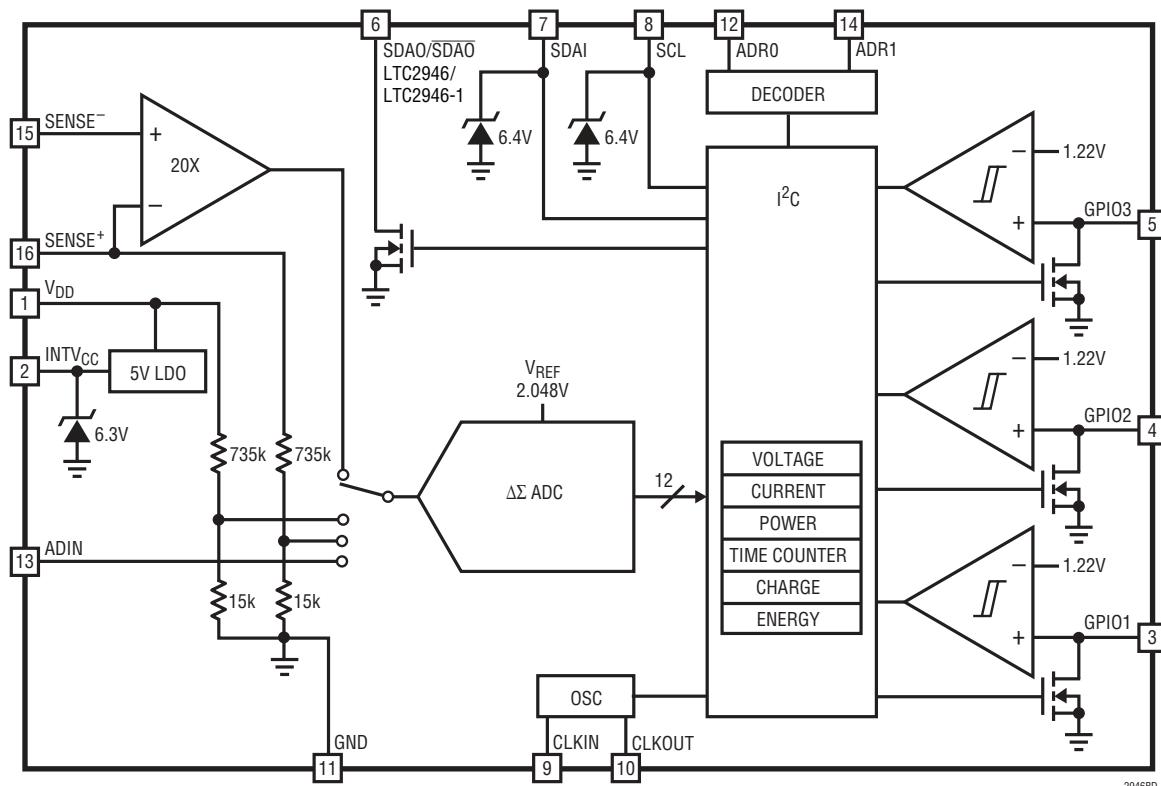

LTC<sup>®</sup>2946は、電流、電圧、電力、電荷、およびエネルギーを測定するレール・トゥ・レールのシステム・モニタです。2.7V～100Vの動作電圧範囲を特長としており、100Vを超える電源向けにシャント・レギュレータを内蔵しています。0V～100Vでの電流測定同相範囲は入力電源に依存しません。12ビットA/Dコンバータにより、負荷電流、入力電圧、および補助外部電圧を測定します。負荷電流と内部で計算される電力は、外部クロック、水晶発振器、または内部発振器タイム・ベースの間積分され、電荷とエネルギーが求められます。高精度のタイム・ベースを使用することにより、LTC2946は、電荷の場合は±0.6%より高い測定精度、電力とエネルギーの場合は±1%より高い測定精度を実現できます。最小値および最大値が記憶され、プログラム可能なしきい値を持つオーバーレンジ警報機能により、ソフトウェアによるポーリングの必要性が最小限に抑えられます。データは標準のI<sup>2</sup>Cインターフェースを介して通知されます。

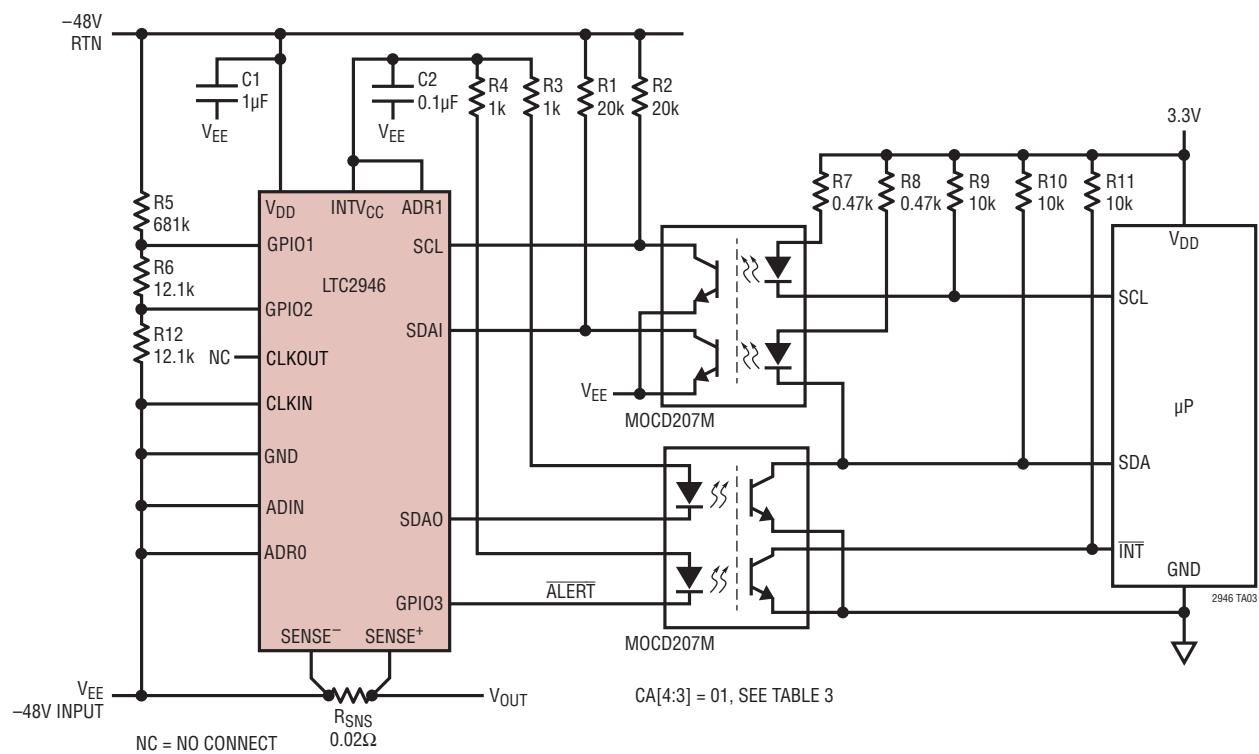

LTC2946のI<sup>2</sup>Cインターフェースは、データ入力ピンとデータ出力ピンが別個になっているので、標準または光絶縁型のI<sup>2</sup>C接続で使用できます。LTC2946-1は反転型のデータ出力を内蔵しているので、反転型の光アイソレータ構成で使用できます。

、LT、LTC、LTM、Linear TechnologyおよびLinearのロゴはリニアテクノロジー社の登録商標です。Hot Swapはリニアテクノロジー社の商標です。その他すべての商標の所有権は、それぞれの所有者に帰属します。

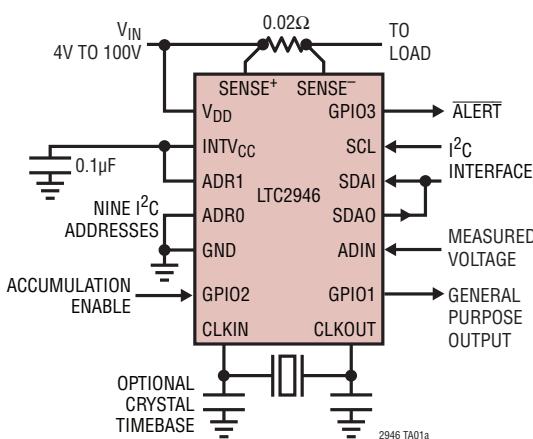

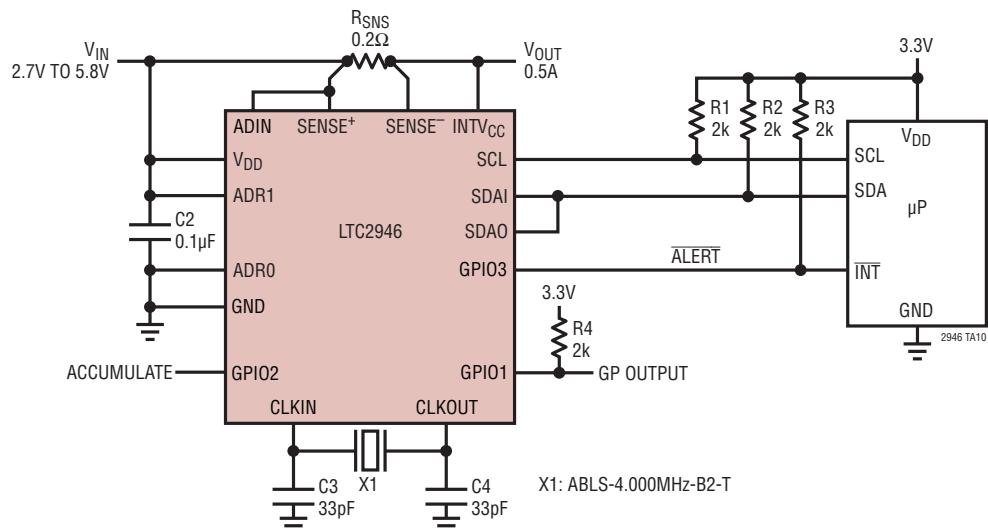

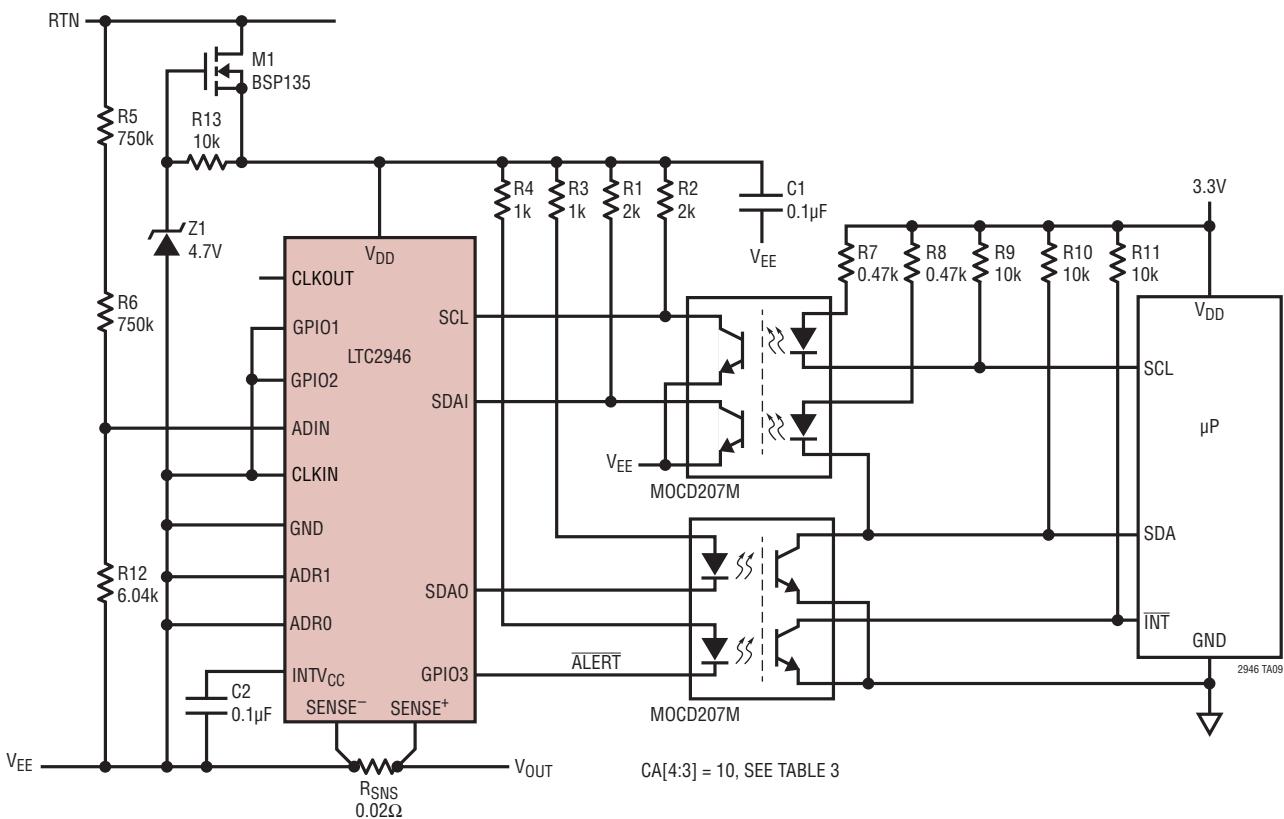

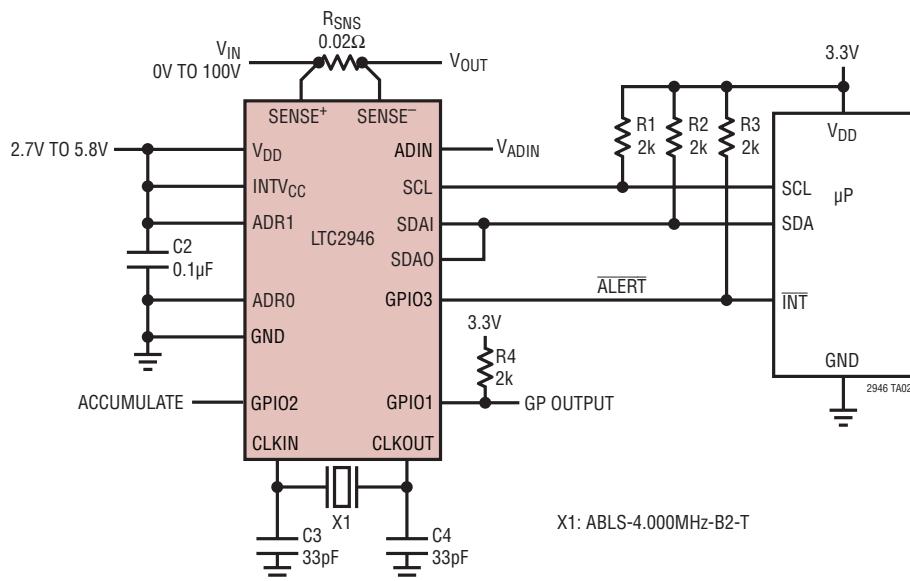

## 標準的応用例

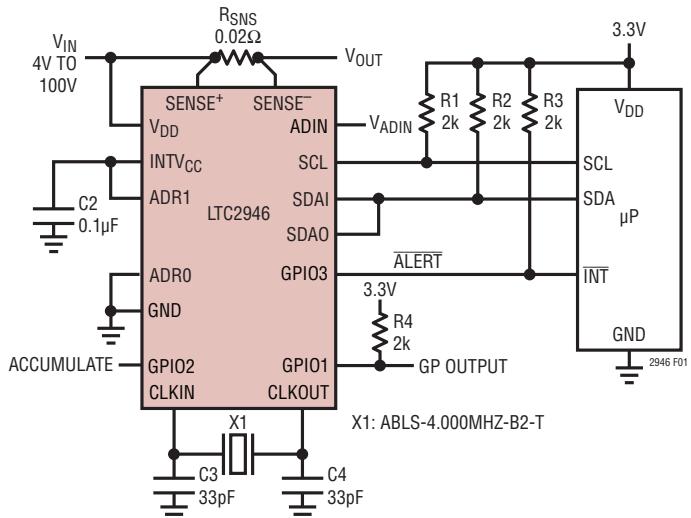

A/DコンバータおよびI<sup>2</sup>C内蔵の広範囲電力、電荷、およびエネルギー・モニタ

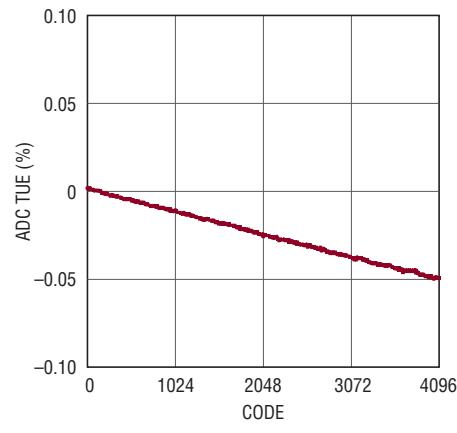

A/Dコンバータの全未調整誤差(ADIN)

## 絶対最大定格 (Note 1、2)

|                           |                                                         |

|---------------------------|---------------------------------------------------------|

| V <sub>DD</sub> 電圧        | -0.3V～100V                                              |

| SENSE <sup>+</sup> 電圧     | -1V～100V                                                |

| SENSE <sup>-</sup> 電圧     | -1V または SENSE <sup>+</sup> - 1V～SENSE <sup>+</sup> + 1V |

| INTV <sub>CC</sub> 電圧     |                                                         |

| (Note 3)                  | -0.3V～5.8V または V <sub>DD</sub> + 0.3V の低い方              |

| ADR1、ADRO、ADIN、SDAO、SDAO、 |                                                         |

| GPIO1～GPIO3 電圧            | -0.3V～7V                                                |

| CLKOUT 電圧                 | -0.3V～INTV <sub>CC</sub> + 0.3V                         |

| CLKIN 電圧                  | -0.3V～5.5V                                              |

| INTV <sub>CC</sub> クランプ電流 | 35mA                                                    |

|                      |             |

|----------------------|-------------|

| SCL、SDAI 電圧 (Note 4) | -0.3V～5.9V  |

| SCL、SDAI クランプ電流      | 5mA         |

| 動作温度範囲               |             |

| LTC2946C             | 0°C～70°C    |

| LTC2946I             | -40°C～85°C  |

| LTC2946H             | -40°C～125°C |

| LTC2946MP            | -55°C～125°C |

| 保存温度範囲               | -65°C～150°C |

| リード温度(半田付け、10秒)      |             |

| MSパッケージのみ            | 300°C       |

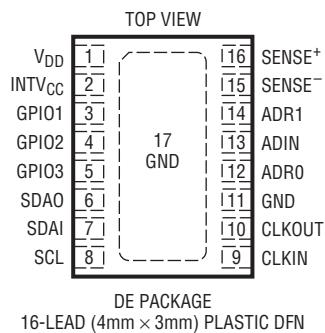

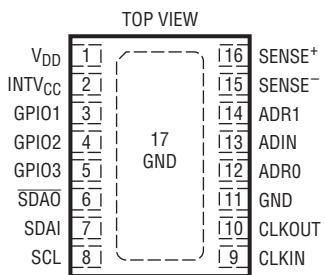

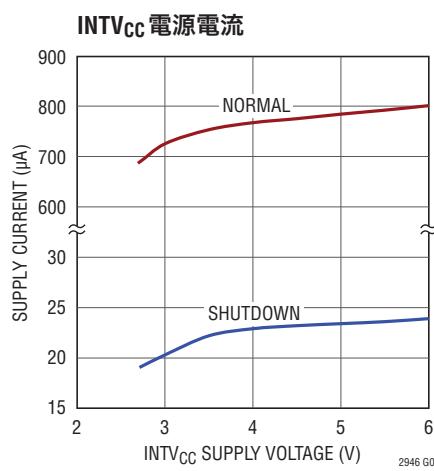

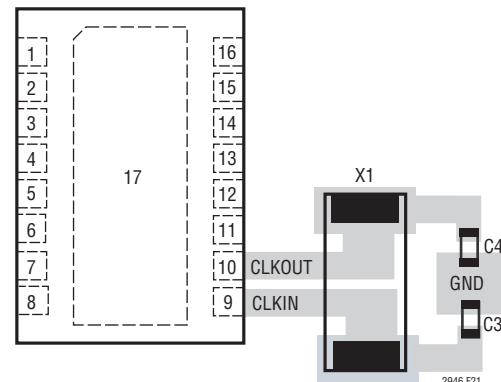

## ピン配置

LTC2946

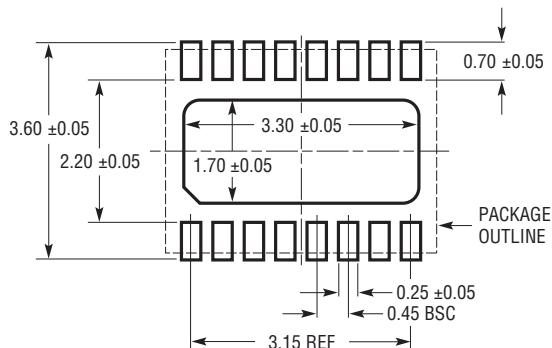

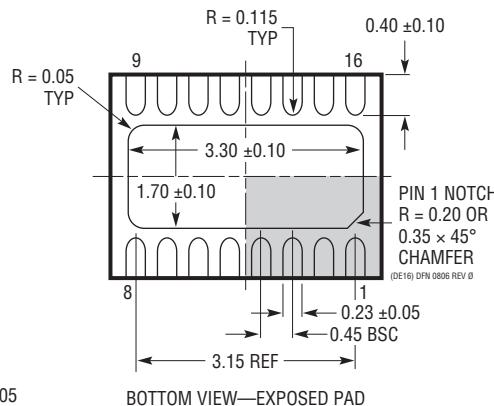

DE PACKAGE

16-LEAD (4mm × 3mm) PLASTIC DFN

T<sub>JMAX</sub> = 125°C, J<sub>A</sub> = 43°C/W, E PAD GND SOLDERED DOWN

EXPOSED PAD (PIN 17) IS GND, PCB GND CONNECTION IS OPTIONAL

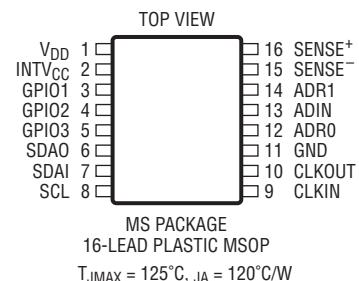

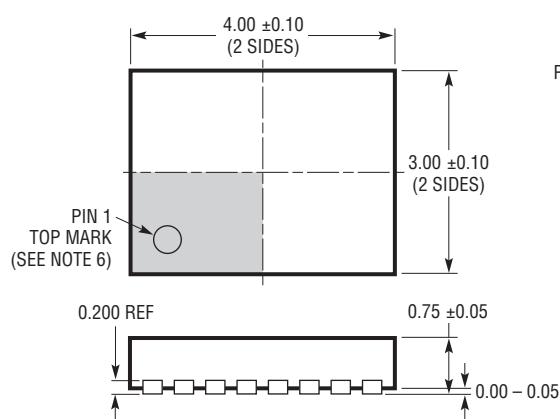

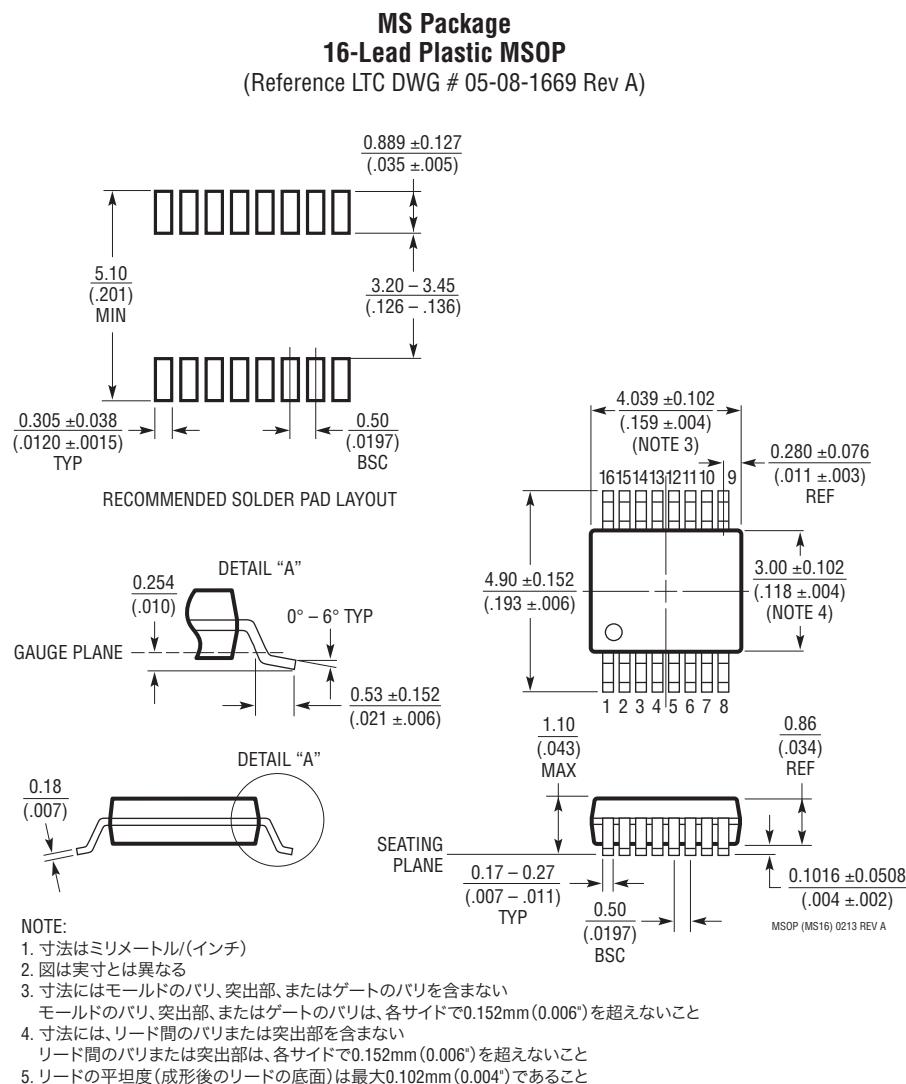

MS PACKAGE

16-LEAD PLASTIC MSOP

T<sub>JMAX</sub> = 125°C, J<sub>A</sub> = 120°C/W

LTC2946-1

DE PACKAGE

16-LEAD (4mm × 3mm) PLASTIC DFN

T<sub>JMAX</sub> = 125°C, J<sub>A</sub> = 43°C/W, E PAD GND SOLDERED DOWN

EXPOSED PAD (PIN 17) IS GND, PCB GND CONNECTION IS OPTIONAL

MS PACKAGE

16-LEAD PLASTIC MSOP

T<sub>JMAX</sub> = 125°C, J<sub>A</sub> = 120°C/W

## 発注情報

| 無鉛仕上げ             | テープ・アンド・リール         | 製品マーキング | パッケージ                         | 温度範囲           |

|-------------------|---------------------|---------|-------------------------------|----------------|

| LTC2946CDE#PBF    | LTC2946CDE#TRPBF    | 2946    | 16-Lead (4mm×3mm) Plastic DFN | 0°C to 70°C    |

| LTC2946IDE#PBF    | LTC2946IDE#TRPBF    | 2946    | 16-Lead (4mm×3mm) Plastic DFN | -40°C to 85°C  |

| LTC2946HDE#PBF    | LTC2946HDE#TRPBF    | 2946    | 16-Lead (4mm×3mm) Plastic DFN | -40°C to 125°C |

| LTC2946CDE-1#PBF  | LTC2946CDE-1#TRPBF  | 29461   | 16-Lead (4mm×3mm) Plastic DFN | 0°C to 70°C    |

| LTC2946IDE-1#PBF  | LTC2946IDE-1#TRPBF  | 29461   | 16-Lead (4mm×3mm) Plastic DFN | -40°C to 85°C  |

| LTC2946HDE-1#PBF  | LTC2946HDE-1#TRPBF  | 29461   | 16-Lead (4mm×3mm) Plastic DFN | -40°C to 125°C |

| LTC2946CMS#PBF    | LTC2946CMS#TRPBF    | 2946    | 16-Lead Plastic MSOP          | 0°C to 70°C    |

| LTC2946IMS#PBF    | LTC2946IMS#TRPBF    | 2946    | 16-Lead Plastic MSOP          | -40°C to 85°C  |

| LTC2946HMS#PBF    | LTC2946HMS#TRPBF    | 2946    | 16-Lead Plastic MSOP          | -40°C to 125°C |

| LTC2946MPMS#PBF   | LTC2946MPMS#TRPBF   | 2946    | 16-Lead Plastic MSOP          | -55°C to 125°C |

| LTC2946CMS-1#PBF  | LTC2946CMS-1#TRPBF  | 29461   | 16-Lead Plastic MSOP          | 0°C to 70°C    |

| LTC2946IMS-1#PBF  | LTC2946IMS-1#TRPBF  | 29461   | 16-Lead Plastic MSOP          | -40°C to 85°C  |

| LTC2946HMS-1#PBF  | LTC2946HMS-1#TRPBF  | 29461   | 16-Lead Plastic MSOP          | -40°C to 125°C |

| LTC2946MPMS-1#PBF | LTC2946MPMS-1#TRPBF | 29461   | 16-Lead Plastic MSOP          | -55°C to 125°C |

さらに広い動作温度範囲で規定されるデバイスについては、弊社または弊社代理店にお問い合わせください。

非標準の鉛仕上げの製品の詳細については、弊社または弊社代理店にお問い合わせください。

無鉛仕上げの製品マーキングの詳細については、<http://www.linear-tech.co.jp/leadfree/> をご覧ください。

テープアンドリールの仕様の詳細については、<http://www.linear-tech.co.jp/tapeandreel/> をご覧ください。

## 電気的特性

●は全動作温度範囲の規格値を意味する。それ以外は  $T_A = 25^\circ\text{C}$  での値。注記がない限り、 $V_{DD} = 4V \sim 100V$ 。(Note 2)

| SYMBOL               | PARAMETER                                           | CONDITIONS                                                            | MIN    | TYP       | MAX       | UNITS                          |

|----------------------|-----------------------------------------------------|-----------------------------------------------------------------------|--------|-----------|-----------|--------------------------------|

| <b>電源</b>            |                                                     |                                                                       |        |           |           |                                |

| $V_{DD}$             | $V_{DD}$ Input Supply Voltage                       |                                                                       | ●      | 4         | 100       | V                              |

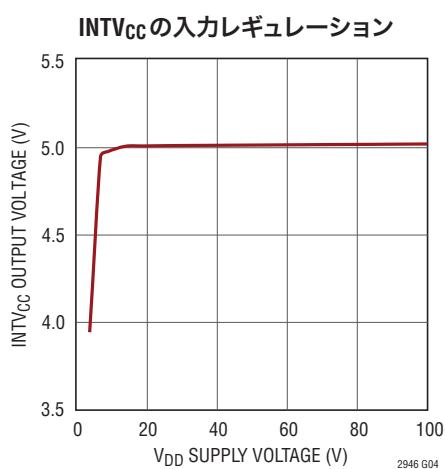

| $V_{CC}$             | INTV <sub>CC</sub> Input Supply Voltage             |                                                                       | ●      | 2.7       | 5.8       | V                              |

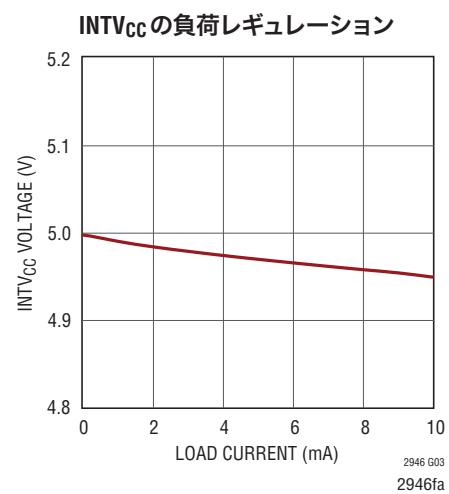

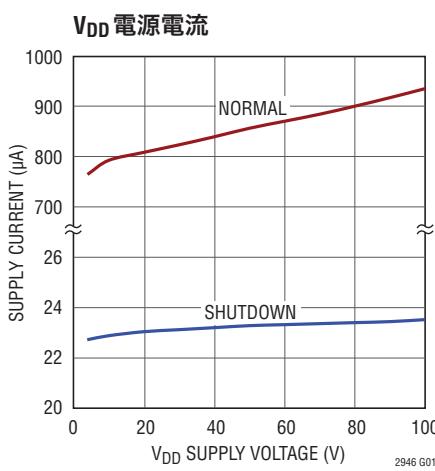

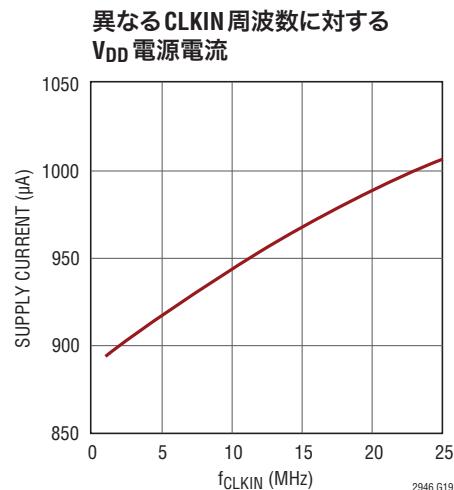

| $I_{DD}$             | $V_{DD}$ Supply Current                             | $V_{DD} = 48V$ , INTV <sub>CC</sub> Open Shutdown                     | ●<br>● | 0.9<br>15 | 1.3<br>40 | mA<br>$\mu\text{A}$            |

| $I_{CC}$             | INTV <sub>CC</sub> Supply Current                   | INTV <sub>CC</sub> = $V_{DD} = 5V$ Shutdown                           | ●<br>● | 0.7<br>15 | 1.0<br>40 | mA<br>$\mu\text{A}$            |

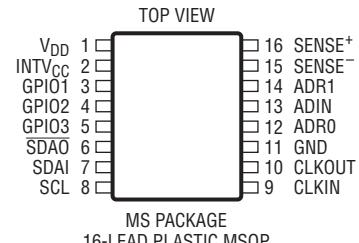

| $V_{CC(LDO)}$        | INTV <sub>CC</sub> Linear Regulator Voltage         | $8V < V_{DD} < 100V$ , $I_{LOAD} = 0mA$                               | ●      | 4.4       | 5         | 5.4                            |

| $\Delta V_{CC(LDO)}$ | INTV <sub>CC</sub> Linear Regulator Load Regulation | $8V < V_{DD} < 100V$ , $I_{LOAD} = 0mA$ to $10mA$                     | ●      | 100       | 200       | mV                             |

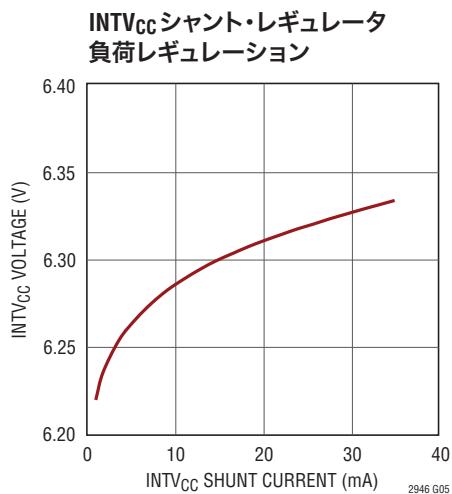

| $V_{CCZ}$            | Shunt Regulator Voltage at INTV <sub>CC</sub>       | $V_{DD} = 48V$ , $I_{CC} = 1mA$                                       | ●      | 5.8       | 6.3       | 6.7                            |

| $\Delta V_{CCZ}$     | Shunt Regulator Load Regulation                     | $V_{DD} = 48V$ , $I_{CC} = 1mA$ to $35mA$                             | ●      |           | 250       | mV                             |

| $V_{CC(UVL)}$        | INTV <sub>CC</sub> Supply Undervoltage Lockout      | INTV <sub>CC</sub> Rising, $V_{DD} = \text{INTV}_{CC}$                | ●      | 2.3       | 2.6       | 2.69                           |

| $V_{DD(UVL)}$        | $V_{DD}$ Supply Undervoltage Lockout                | $V_{DD}$ Rising, INTV <sub>CC</sub> Open                              | ●      | 2.4       | 2.8       | 3                              |

| $V_{DDI2C(RST)}$     | $V_{DD}$ I <sup>2</sup> C Logic Reset               | $V_{DD}$ Falling, INTV <sub>CC</sub> Open                             | ●      | 1.7       | 2.1       | V                              |

| $V_{CCI2C(RST)}$     | INTV <sub>CC</sub> I <sup>2</sup> C Logic Reset     | INTV <sub>CC</sub> Falling, $V_{DD} = \text{INTV}_{CC}$               | ●      | 1.7       | 2.1       | V                              |

| <b>SENSE 入力</b>      |                                                     |                                                                       |        |           |           |                                |

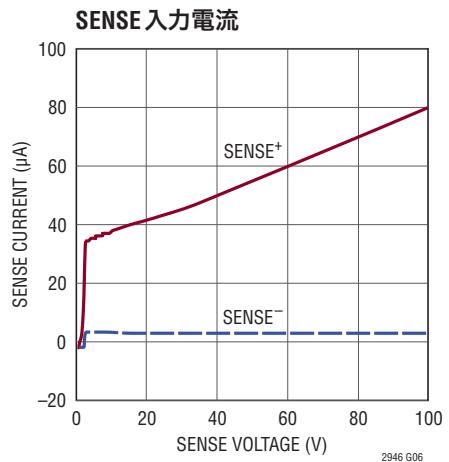

| $I_{SENSE+(HI)}$     | 48V SENSE <sup>+</sup> Input Current                | SENSE <sup>+</sup> , SENSE <sup>-</sup> , $V_{DD} = 48V$ Shutdown     | ●<br>● | 100<br>1  | 150<br>1  | $\mu\text{A}$<br>$\mu\text{A}$ |

| $I_{SENSE-(HI)}$     | 48V SENSE <sup>-</sup> Input Current                | SENSE <sup>+</sup> , SENSE <sup>-</sup> , $V_{DD} = 48V$ Shutdown     | ●<br>● |           | 20<br>1   | $\mu\text{A}$<br>$\mu\text{A}$ |

| $I_{SENSE+(LO)}$     | 0V SENSE <sup>+</sup> Source Current                | SENSE <sup>+</sup> , SENSE <sup>-</sup> = 0V, $V_{DD} = 48V$ Shutdown | ●<br>● |           | -10<br>-1 | $\mu\text{A}$<br>$\mu\text{A}$ |

2946fa

## 電気的特性

●は全動作温度範囲の規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。注記がない限り、 $V_{DD} = 4V \sim 100V$ 。(Note 2)

| SYMBOL                   | PARAMETER                            | CONDITIONS                                                               | MIN    | TYP | MAX      | UNITS                          |

|--------------------------|--------------------------------------|--------------------------------------------------------------------------|--------|-----|----------|--------------------------------|

| $I_{SENSE^-(\text{LO})}$ | 0V SENSE <sup>-</sup> Source Current | SENSE <sup>+</sup> , SENSE <sup>-</sup> = 0V, $V_{DD} = 48V$<br>Shutdown | ●<br>● |     | -5<br>-1 | $\mu\text{A}$<br>$\mu\text{A}$ |

ADC(SENSE<sup>+</sup>, SENSE<sup>-</sup> = 0V, 100V) (Note 5)

|                   |                                 |                                                                                                                                                                                                                       |                            |                                                 |                                                                            |                                                        |                              |

|-------------------|---------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|-------------------------------------------------|----------------------------------------------------------------------------|--------------------------------------------------------|------------------------------|

| RES               | Resolution (No missing codes)   | (Note 7)                                                                                                                                                                                                              | ●                          | 12                                              |                                                                            | Bits                                                   |                              |

| TUE               | Total Unadjusted Error (Note 6) | $\Delta\text{SENSE}$ (C-, I-Grade)<br>$\Delta\text{SENSE}$ (H-, MP-Grade)<br>SENSE <sup>+</sup> , $V_{DD}$ (C-, I-Grade)<br>SENSE <sup>+</sup> , $V_{DD}$ (H-, MP-Grade)<br>ADIN (C-, I-Grade)<br>ADIN (H-, MP-Grade) | ●<br>●<br>●<br>●<br>●<br>● |                                                 | $\pm 0.6$<br>$\pm 0.7$<br>$\pm 0.4$<br>$\pm 0.5$<br>$\pm 0.3$<br>$\pm 0.4$ | %<br>%<br>%<br>%<br>%<br>%                             |                              |

| $V_{FS}$          | Full-Scale Voltage              | $\Delta\text{SENSE}$ (C-, I-Grade)<br>$\Delta\text{SENSE}$ (H-, MP-Grade)<br>SENSE <sup>+</sup> , $V_{DD}$ (C-, I-Grade)<br>SENSE <sup>+</sup> , $V_{DD}$ (H-, MP-Grade)<br>ADIN (C-, I-Grade)<br>ADIN (H-, MP-Grade) | ●<br>●<br>●<br>●<br>●<br>● | 101.8<br>101.7<br>102<br>101.9<br>2.042<br>2.04 | 102.4<br>102.4<br>102.4<br>102.4<br>2.048<br>2.048                         | 103<br>103.1<br>102.8<br>102.9<br>2.054<br>2.056       | mV<br>mV<br>V<br>V<br>V<br>V |

| LSB               | LSB Step Size                   | $\Delta\text{SENSE}$<br>SENSE <sup>+</sup> , $V_{DD}$<br>ADIN                                                                                                                                                         |                            |                                                 | 25<br>25<br>0.5                                                            | $\mu\text{V}$<br>mV<br>mV                              |                              |

| $V_{OS}$          | Offset Error                    | $\Delta\text{SENSE}$ (C-, I-Grade)<br>$\Delta\text{SENSE}$ (H-, MP-Grade)<br>SENSE <sup>+</sup> , $V_{DD}$<br>ADIN                                                                                                    | ●<br>●<br>●<br>●           |                                                 | $\pm 2.1$<br>$\pm 3.1$<br>$\pm 1.5$<br>$\pm 1.1$                           | LSB<br>LSB<br>LSB<br>LSB                               |                              |

| INL               | Integral Nonlinearity           | $\Delta\text{SENSE}$<br>SENSE <sup>+</sup> , $V_{DD}$<br>ADIN                                                                                                                                                         | ●<br>●<br>●                |                                                 | $\pm 2.5$<br>$\pm 2$<br>$\pm 2$                                            | LSB<br>LSB<br>LSB                                      |                              |

| $\Sigma_\tau$     | Transition Noise (Note 7)       | $\Delta\text{SENSE}$<br>SENSE <sup>+</sup> , $V_{DD}$<br>ADIN                                                                                                                                                         |                            |                                                 | 1.2<br>0.3<br>10                                                           | $\mu\text{VRMS}$<br>$\text{mVRMS}$<br>$\mu\text{VRMS}$ |                              |

| $t_{CONV}$        | Conversion Time (Snapshot Mode) | $\Delta\text{SENSE}$<br>SENSE <sup>+</sup> , $V_{DD}$ , ADIN                                                                                                                                                          | ●<br>●                     | 62.4<br>31.2                                    | 65.6<br>32.8                                                               | 68.8<br>34.4                                           | ms<br>ms                     |

| R <sub>ADIN</sub> | ADIN Input Resistance           | $V_{DD} = 48V$ , ADIN = 3V                                                                                                                                                                                            | ●                          | 3                                               | 10                                                                         | MΩ                                                     |                              |

## CLKIN, CLKOUT, GPIO

|                         |                            |                                      |   |      |         |      |               |

|-------------------------|----------------------------|--------------------------------------|---|------|---------|------|---------------|

| $V_{CLKIN(\text{TH})}$  | CLKIN Input Threshold      |                                      | ● | 0.7  | 1       | 1.3  | V             |

| $f_{CLKIN(\text{MAX})}$ | Maximum CLKIN Frequency    |                                      | ● | 25   |         |      | MHz           |

| $I_{CLKIN(\text{IN})}$  | CLKIN Input Current        | $V_{CLKIN} = 5V$                     | ● |      | 5       | 10   | $\mu\text{A}$ |

| $I_{CLKOUT}$            | CLKOUT Output Current      | $V_{CLKIN} = 0V$ , $V_{CLKOUT} = 0V$ | ● | -70  | -100    | -130 | $\mu\text{A}$ |

| $V_{GPIO(\text{TH})}$   | GPIO Input Threshold       | $V_{GPIO}$ Rising                    | ● | 1.06 | 1.22    | 1.32 | V             |

| $V_{GPIO(\text{HYST})}$ | GPIO Input Hysteresis      |                                      |   |      | 36      |      | mV            |

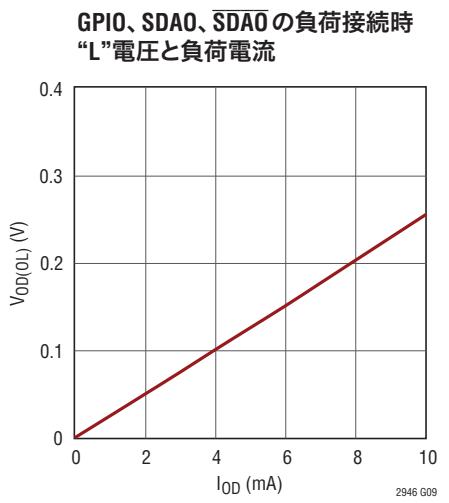

| $V_{GPIO(\text{OL})}$   | GPIO Output Low Voltage    | $I_{GPIO} = 8\text{mA}$              | ● |      | 0.15    | 0.4  | V             |

| $I_{GPIO(\text{IN})}$   | GPIO Input Leakage Current | $V_{GPIO} = 5V$                      | ● | 0    | $\pm 1$ |      | $\mu\text{A}$ |

I<sup>2</sup>Cインターフェース( $V_{DD} = 48V$ )

|                          |                                                          |                                                     |   |     |         |          |               |

|--------------------------|----------------------------------------------------------|-----------------------------------------------------|---|-----|---------|----------|---------------|

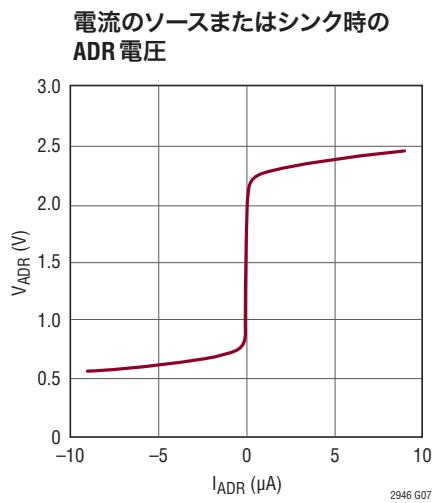

| $V_{ADR(H)}$             | ADR0, ADR1 Input High Threshold                          |                                                     | ● | 1.9 | 2.4     | 2.7      | V             |

| $V_{ADR(L)}$             | ADR0, ADR1 Input Low Threshold                           |                                                     | ● | 0.3 | 0.6     | 0.9      | V             |

| $I_{ADR(\text{IN})}$     | ADR0, ADR1 Input Current                                 | ADR0, ADR1 = 0V, 3V                                 | ● |     |         | $\pm 13$ | $\mu\text{A}$ |

| $I_{ADR(\text{IN,Z})}$   | Allowable Leakage When Open                              |                                                     | ● |     |         | $\pm 7$  | $\mu\text{A}$ |

| $V_{OD(\text{OL})}$      | SDAO, $\overline{\text{SDAO}}$ , Output Low Voltage      | $I_{SDAO}, I_{\overline{\text{SDAO}}} = 8\text{mA}$ | ● |     | 0.15    | 0.4      | V             |

| $I_{SDA,SCL(\text{IN})}$ | SDAI, SDAO, $\overline{\text{SDAO}}$ , SCL Input Current | SDAI, SDAO, $\overline{\text{SDAO}}$ , SCL = 5V     | ● | 0   | $\pm 1$ |          | $\mu\text{A}$ |

2946fa

## 電気的特性

●は全動作温度範囲の規格値を意味する。それ以外は  $T_A = 25^\circ\text{C}$  での値。注記がない限り、 $V_{DD} = 4V \sim 100V$ 。(Note 2)

| SYMBOL            | PARAMETER                 | CONDITIONS                       | MIN | TYP | MAX | UNITS |   |

|-------------------|---------------------------|----------------------------------|-----|-----|-----|-------|---|

| $V_{SDA,SCL(TH)}$ | SDAI, SCL Input Threshold |                                  | ●   | 1.5 | 1.8 | 2.1   | V |

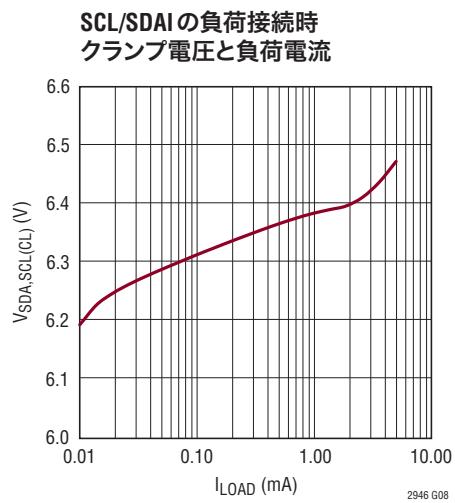

| $V_{SDA,SCL(CL)}$ | SDAI, SCL Clamp Voltage   | $I_{SDAI}, I_{SCL} = 3\text{mA}$ | ●   | 5.9 | 6.4 | 6.9   | V |

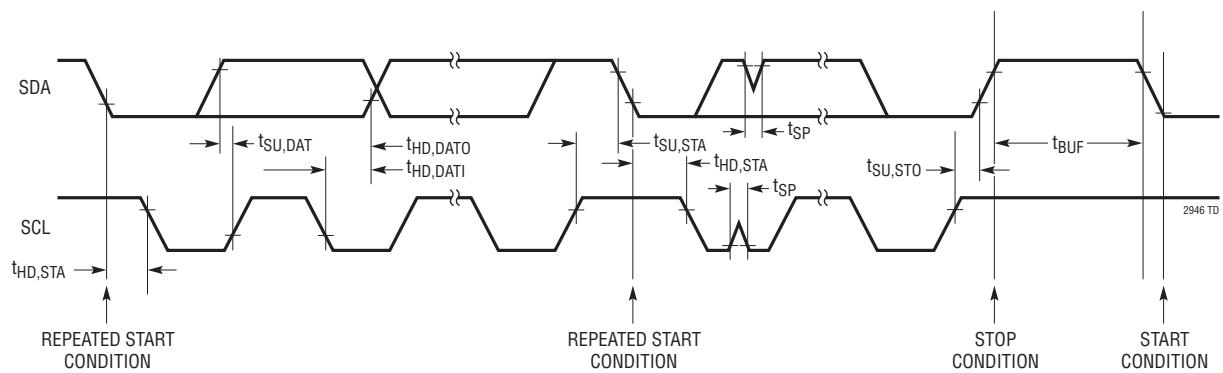

### I<sup>2</sup>Cインターフェースのタイミング

|                                  |                                                    |                      |   |      |     |     |    |

|----------------------------------|----------------------------------------------------|----------------------|---|------|-----|-----|----|

| $f_{SCL(\text{MAX})}$            | Maximum SCL Clock Frequency                        |                      | ● | 400  |     | kHz |    |

| $t_{\text{LOW}}$                 | Minimum SCL LOW Period                             |                      | ● | 0.65 | 1.3 | μs  |    |

| $t_{\text{HIGH}}$                | Minimum SCL HIGH Period                            |                      | ● | 50   | 600 | ns  |    |

| $t_{\text{BUF}(\text{MIN})}$     | Minimum Bus Free Time Between STOP/START Condition |                      | ● | 0.12 | 1.3 | μs  |    |

| $t_{\text{HD,STA}(\text{MIN})}$  | Minimum Hold Time After (Repeated) START Condition |                      | ● | 140  | 600 | ns  |    |

| $t_{\text{SU,STA}(\text{MIN})}$  | Minimum Repeated START Condition Setup Time        |                      | ● | 30   | 600 | ns  |    |

| $t_{\text{SU,STOP}(\text{MIN})}$ | Minimum STOP Condition Setup Time                  |                      | ● | 30   | 600 | ns  |    |

| $t_{\text{HD,DATI}(\text{MIN})}$ | Minimum Data Hold Time Input                       |                      | ● | -100 | 0   | ns  |    |

| $t_{\text{HD,DATO}(\text{MIN})}$ | Minimum Data Hold Time Output                      |                      | ● | 300  | 600 | 900 | ns |

| $t_{\text{SU,DAT}(\text{MIN})}$  | Minimum Data Setup Time                            |                      | ● | 30   | 100 | ns  |    |

| $t_{\text{SP}(\text{MAX})}$      | Maximum Suppressed Spike Pulse Width               |                      | ● | 50   | 110 | 250 | ns |

| $t_{\text{RST}}$                 | Stuck Bus Reset Time                               | SCL or SDAI Held Low | ● | 25   | 33  | ms  |    |

| $C_X$                            | SCL, SDAI Input Capacitance (Note 7)               |                      |   | 5    | 10  | pF  |    |

Note 1: 絶対最大定格に記載された値を超えるストレスはデバイスに永続的損傷を与える可能性がある。長期にわたって絶対最大定格条件に曝すと、デバイスの信頼性と寿命に悪影響を与える恐れがある。

Note 2: ピンに流れ込む電流は全て正とする。注記がない限り、全ての電圧はグランドを基準にしている。

Note 3: 内部シャント・レギュレータがINTV<sub>CC</sub>ピンを最小5.8Vに制限する。このピンを5.8Vより高い電圧にドライブするとデバイスを損傷するおそれがある。このピンは、電流を35mA未満に制限する抵抗を介して、より高い電圧に安全に接続することができる。

Note 4: 内蔵クランプがSCLおよびSDAIピンを最小5.9Vに制限する。これらのピンをクランプより高い電圧にドライブするとデバイスを損傷するおそれがある。このピンは、電流を5mA未満に制限する抵抗を介して、より高い電圧に安全に接続することができる。

Note 5: ASENSEの定義は  $V_{\text{SENSE}^+} - V_{\text{SENSE}^-}$  である。

Note 6: TUE = (ACTUAL CODE - IDEAL CODE) / 4096 • 100% である。ここでIDEAL CODEは0Vのコード0とV<sub>FS</sub>の理論コード4096を通る直線から求められるコード。

Note 7: 設計によって保証されており、テストは行われない。

## 標準的性能特性

## 標準的性能特性

## 標準的性能特性

## ピン機能

**ADIN:** A/Dコンバータの入力。内蔵のA/Dコンバータは、GNDまたはINTV<sub>CC</sub>を基準として0V～2.048Vの電圧を測定します。使用しない場合はグランドに接続します。詳細は、「アプリケーション情報」のセクションの表3を参照してください。

**ADR1, ADR0:** I<sup>2</sup>Cデバイス・アドレス入力。これらのピンをINTV<sub>CC</sub>またはGNDに接続するか、開放のままにすることで、可能な9つのアドレスのうち1つに設定されます。詳細は、「アプリケーション情報」のセクションの表1を参照してください。

**CLKIN:** クロック入力。内部の±5%クロックを使用する場合、グランドに接続します。精度を良くするには、外付けの水晶発振器を接続するか、外部クロックでドライブします。

**CLKOUT:** クロック出力。外付けの水晶発振器回路に接続します。使用しない場合は、開放のままにします。

**露出パッド:** 露出パッドは開放のままで、デバイスのグランドに接続してもかまいません。最適の熱性能を得るには、大面积のPCB領域に接続します。

**GND:** デバイスのグランド。

**GPIO1:** 汎用入出力(オープン・ドレイン)。汎用の出力または入力に構成できます。使用しない場合はグランドに接続します。詳細は、「アプリケーション情報」のセクションの表9を参照してください。

**GPIO2:** 汎用入出力(オープン・ドレイン)。汎用の出力、入力、またはゲート内部アキュムレータへのアキュムレーション・イネーブル(ACC)として構成できます。使用しない場合はグランドに接続します。詳細は、「アプリケーション情報」のセクションの表9を参照してください。

**GPIO3:** 汎用入出力(オープン・ドレイン)。汎用の出力、入力、またはALERTとして構成できます。ALERTとして構成した場合、�トが発生するとグランドにプルダウンされ、ホスト・コントローラに警告を発します。�ト・アラートは、表5および表8に示すとおり ALERTレジスタの対応するビットをセットすることでイネーブルされます。使用しない場合はグランドに接続します。詳細は、「アプリケーション情報」のセクションの表9を参照してください。

**INTV<sub>CC</sub>:** 内部低電圧電源入力/出力。このピンは内部回路への給電に使用します。低電圧電源の直接入力、V<sub>DD</sub>に接続されたより高い電源電圧からのリニア・レギュレータ、またはシャント・レギュレータのいずれかに構成できます。2.7V～5.8Vの電源が使用可能ならば、直接このピンに接続してください。INTV<sub>CC</sub>を外部電源から給電する場合、V<sub>DD</sub>ピンをINTV<sub>CC</sub>に短絡させます。V<sub>DD</sub>が4V～100Vの電源に接続されている場合、INTV<sub>CC</sub>は外部回路に最大10mAを供給できる内部直列レギュレータの5V出力になります。更に高い電源電圧、またはフロート・トポロジーが必要な場合は、INTV<sub>CC</sub>を6.3Vシャント・レギュレータとして使用できます。シャント・レギュレータ電流を35mA未満に制限する抵抗または電流源を介して、電源をINTV<sub>CC</sub>に接続します。このピンの電圧が2.5Vを下回ると、低電圧ロックアウト回路がADCをディスエーブルします。このピンとグランドの間に0.1μF以上のバイパス・コンデンサを接続してください。外部負荷が存在する場合は、ループ安定性のため、0.22μF以上のバイパス・コンデンサを使用してください。

**SCL:** I<sup>2</sup>Cバス・クロック入力。SDAIピンのデータは、SCLの立ち上がりエッジでシフト・インまたはシフト・アウトされます。このピンは、マスター・コントローラのオープン・コレクタ出力によって駆動されます。SCLとV<sub>DD</sub>またはINTV<sub>CC</sub>の間には、外付けのプルアップ抵抗または電流源が必要です。SCLの電圧は内部で6.4V(標準)にクランプされます。

## ピン機能

**SDAI**: I<sup>2</sup>Cバス・データ入力。アドレス、コマンド、データのビットをシフト・インするために使用します。このピンは、マスタ・コントローラのオープン・コレクタ出力によって駆動されます。SDAIとVDDまたはINTV<sub>CC</sub>の間には、外付けのプルアップ抵抗または電流源が必要です。SDAIの電圧は内部で6.4V(標準)にクランプされます。SDAOに接続すると、通常のI<sup>2</sup>C動作になります。

**SDAO**: LTC2946のみ。I<sup>2</sup>Cバス・データ出力。データをマスタ・コントローラに送り返すため、または書き込み動作のアクノレッジを返すために使用されるオープンドレイン出力。外付けのプルアップ抵抗または電流源が必要です。SDAIに接続すると、通常のI<sup>2</sup>C動作になります。

**SDAO**: LTC2946-1のみ。I<sup>2</sup>Cバス・データの反転出力。データをマスタ・コントローラに送り返すため、または書き込み動作のアクノレッジを返すために使用されるオープンドレイン出力。光絶縁使用時の利便性のためにデータが反転されています。外付けのプルアップ抵抗または電流源が必要です。LTC2946-1は、追加の部品なしには非絶縁型I<sup>2</sup>Cアプリケーションで使用できません。

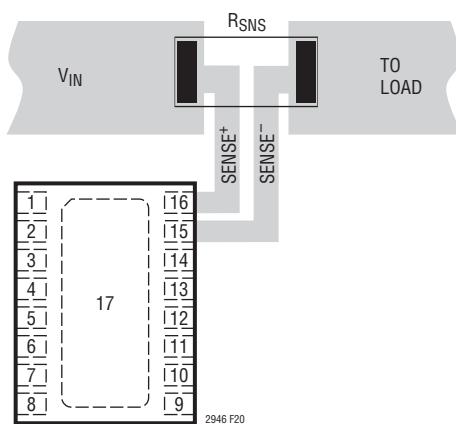

**SENSE<sup>+</sup>**: 電源電圧および電流の検出入力。内部電流検出アンプの電源および電流検出入力として使用します。このピンの電圧は、フルスケール入力範囲102.4Vの内蔵ADCによってモニタされます。推奨されるケルビン接続については図20を参照してください。

**SENSE<sup>-</sup>**: 電流センス入力。SENSE<sup>+</sup>とSENSE<sup>-</sup>の間に外付けの検出抵抗を接続します。SENSE<sup>+</sup>とSENSE<sup>-</sup>の間の差動電圧が、フルスケール検出電圧102.4mVの内蔵ADCによってモニタされます。

**V<sub>DD</sub>**: 高電圧電源入力。このピンは、入力電圧範囲が4V~100Vの内部直列レギュレータの給電に使用され、V<sub>DD</sub>が8Vを上回るとINTV<sub>CC</sub>に5Vを発生します。INTV<sub>CC</sub>ピンに外部負荷を接続する場合は、このピンとグランドの間に0.1μF以上のバイパス・コンデンサを接続してください。内蔵12ビットADCは、フルスケール入力範囲102.4VでV<sub>DD</sub>の電圧をモニタするように構成できます。

# LTC2946

## ブロック図

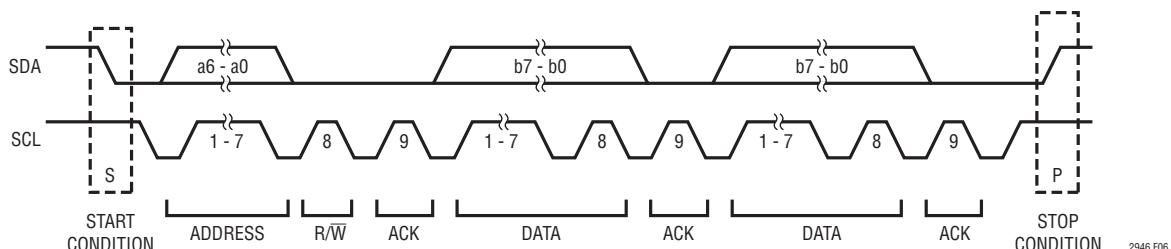

## タイミング図

## 動作

LTC2946は、0V～100Vのあらゆる電源レールの電流、電圧、電力を精確にモニタします。内部リニア・レギュレータによって、4V～100Vのレールから直接動作させるか、2.7V～5.8Vの外部電源電圧によって動作させることができます。通常動作時の静止電流は1.3mA未満です。I<sup>2</sup>Cインターフェースを介してシャットダウン・モードをイネーブルすると、静止電流が40μA未満に減少します。

内蔵12ビットA/Dコンバータ(以下ADC)は連続動作させるか、スナップショット・モードにより必要に応じて動作させることができます。7種類の連続スキャン・モードがあり、I<sup>2</sup>Cを介して選択できます。これらのモードでは、ADCは、SENSE<sup>+</sup>とSENSE<sup>-</sup>間の差動電圧(フルスケール：102.4mV)、SENSE<sup>+</sup>またはV<sub>DD</sub>ピンの電圧(フルスケール：102.4V)、ADINピンに印加される電圧(フルスケール：2.048V)を内部的に設定されたデューティ・サイクルで繰り返し測定するよう構成されます。詳細については、「アプリケーション情報」のセクションを参照してください。変換結果は内蔵レジスタに格納されます。

スナップショット・モードでは、選択された1つの電圧または電流を1回だけ測定します。STATUS2レジスタのステータス・ビットはADC変換の進行状況をモニタし、変換が完了すると変換結果は対応するデータ・レジスタに保存されます。

GPIO1～GPIO3ピンは汎用入力または汎用オープンドレイン出力です。GPIO2は、アキュムレータのイネーブル入力としても構成できます。同様に、GPIO3はALERT出力としても構成できます。

内蔵ロジックは各ADC測定の最小値と最大値を保存し、保存された電流と電圧のデータをデジタル乗算することで電力を計算します。更にオプションで、ADCの測定値がプログラムされたウィンドウから逸脱すると、GPIO3ピンを“L”にプルダウンすることでアラートをトリガします。LTC2946には、測定した電流と電力を経時的に積算し、電荷値とエネルギー値を求めるアキュムレータが内蔵されています。アキュムレータの積算の速度は、内部でトリミングされた±5%クロック、外付けの水晶で生成される高精度クロック、または外部クロックのいずれかに基づきます。アキュムレータには値をプリセット可能で、オプションで、オーバーフロー時にアラートを生成できます。

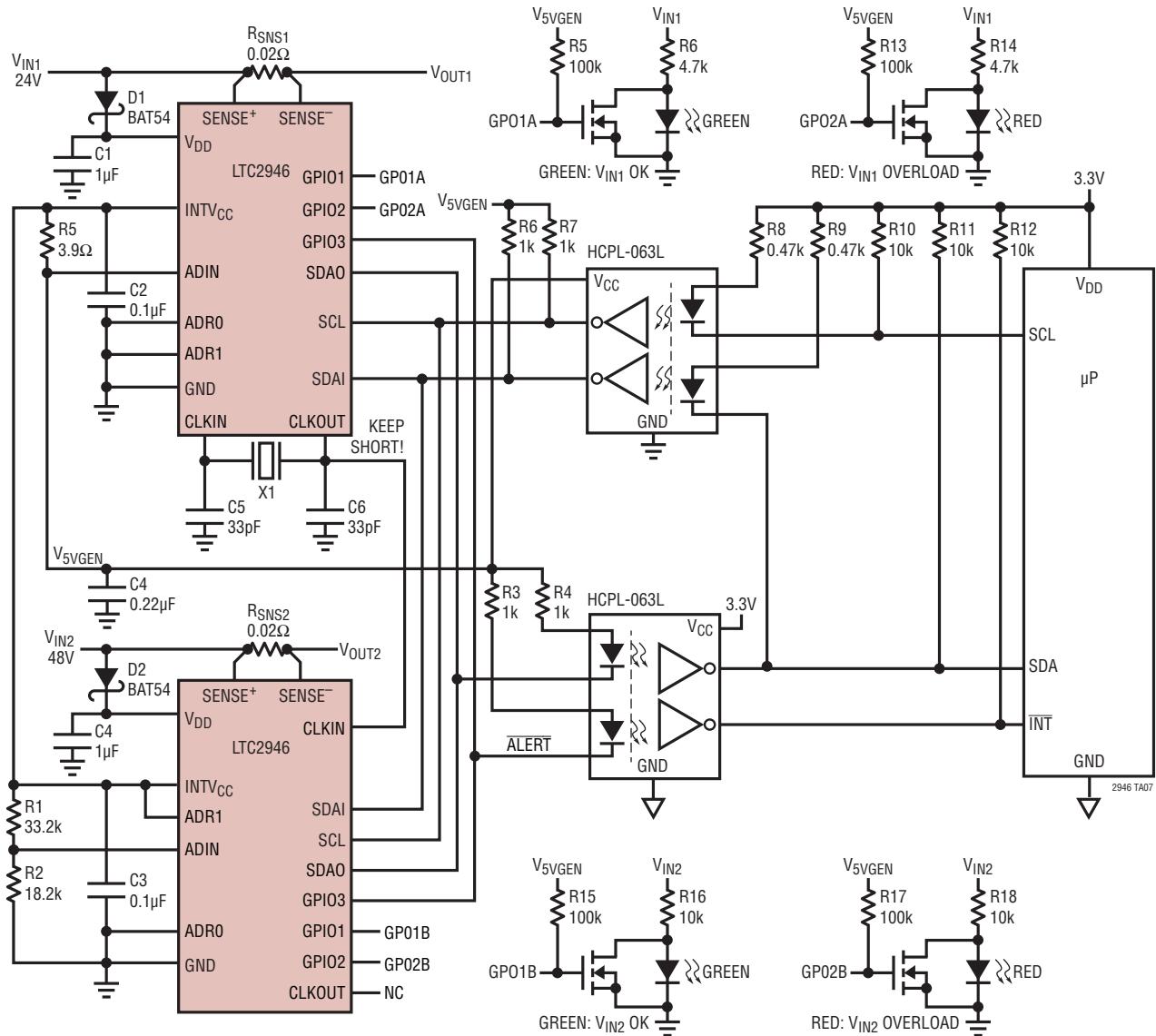

LTC2946は、内蔵データ・レジスタへのアクセスや、アラートしきい値、構成、および制御レジスタのプログラムに使用するI<sup>2</sup>Cインターフェースを備えています。2つのトライステート・ピンADR1とADR0をデコードすることで9通りのデバイス・アドレスを使用できます(表1参照)。SDAピンは、光絶縁を容易にするために、SDAI(入力)とSDAO(出力、LTC2946)またはSDAO(出力、LTC2946-1)に分割されています。SDAIとSDAOを相互接続すると、通常の非絶縁型I<sup>2</sup>C動作になります。

## アプリケーション情報

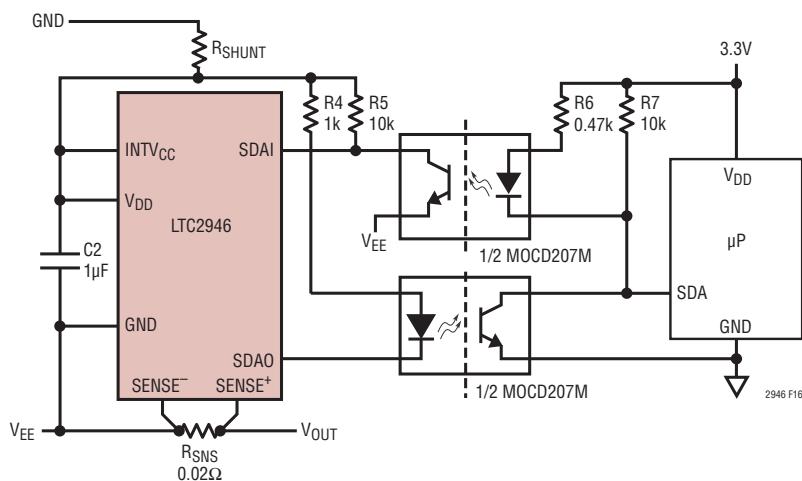

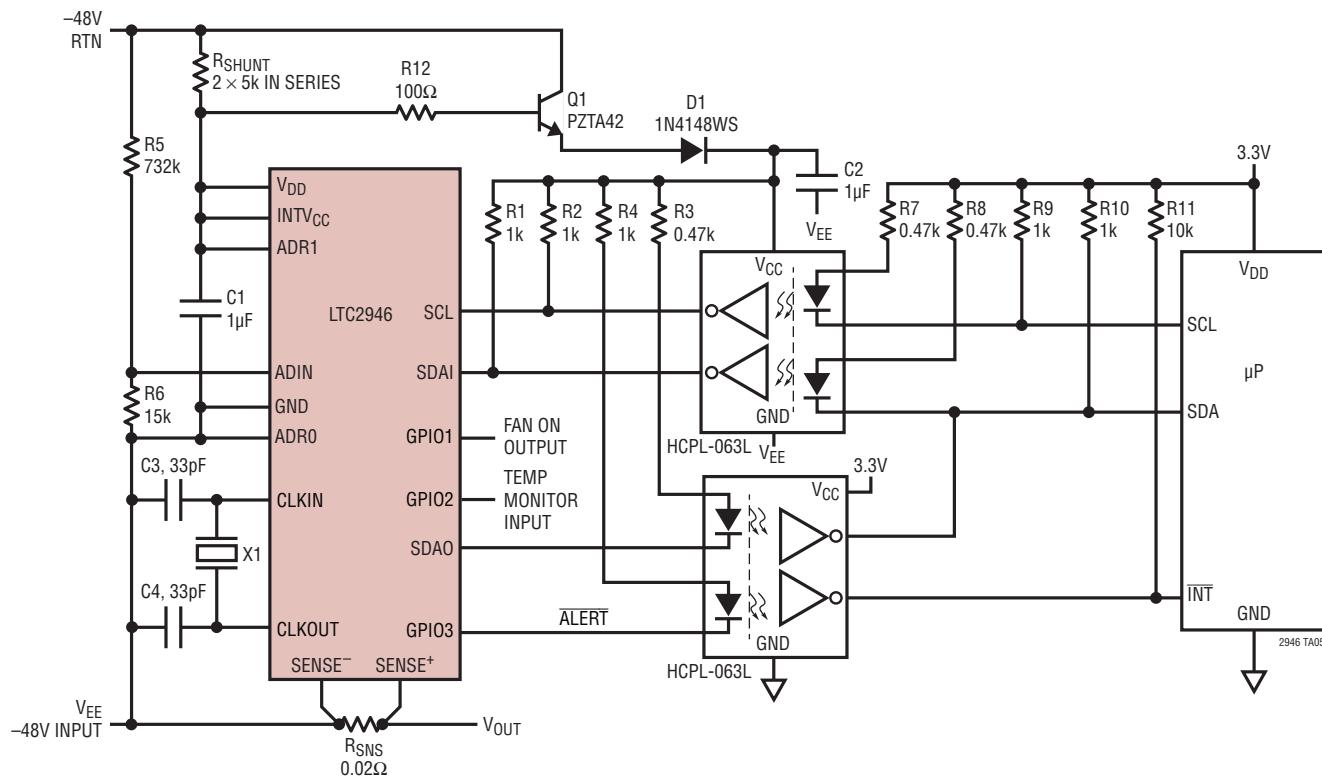

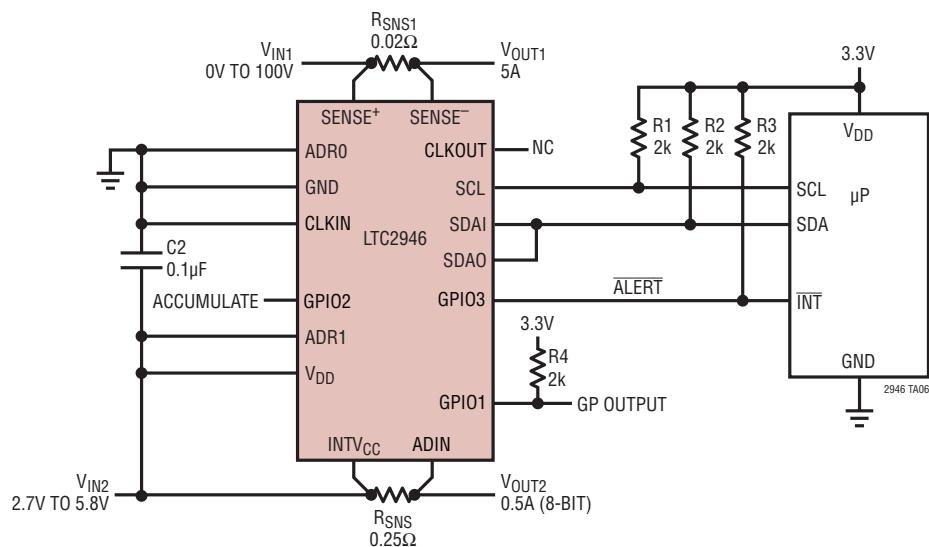

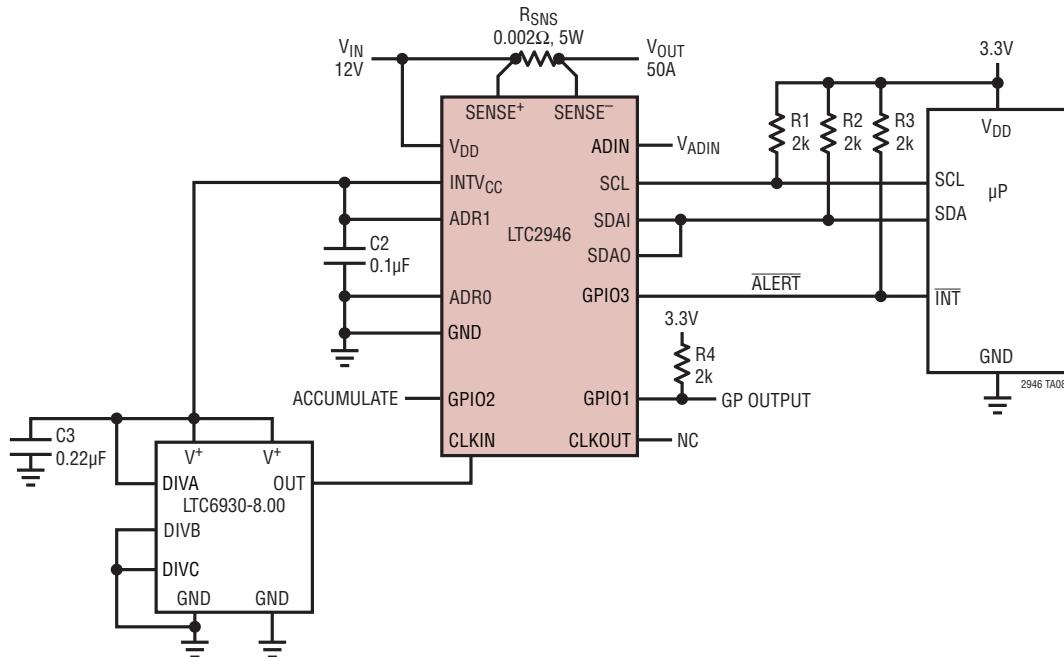

LTC2946は、エネルギーおよび電荷アキュムレータを内蔵し、ハイサイドおよびローサイドの電力をモニタする、小型ながら完結した解決策を提供します。0V～100Vの入力同相範囲と、2.7V～100Vの幅広い入力電源動作電圧範囲を実現したこのデバイスは、自動車、産業用、通信機器インフラストラクチャなどの多岐にわたるパワー・マネージメント・アプリケーションに最適です。図1に示す基本的なアプリケーション回路は、0.02Ωの抵抗によるハイサイド電流(フルスケール5.12A)、入力電圧(フルスケール102.4V)、外部電圧(フルスケール2.048V)を、いずれも12ビットの内部ADCによってモニタします。

図1. LTC2946によるハイサイド電力、エネルギー、および電荷モニタ

## アプリケーション情報

### データ・コンバータ、乗算器、アキュムレータ

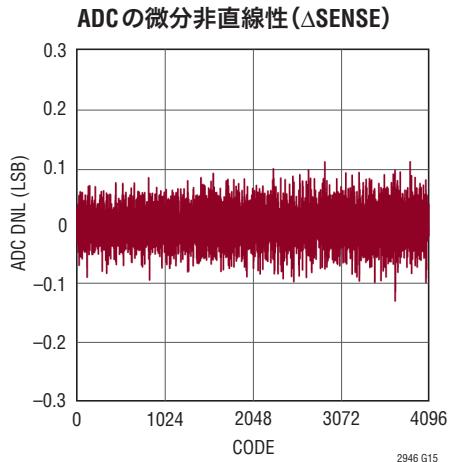

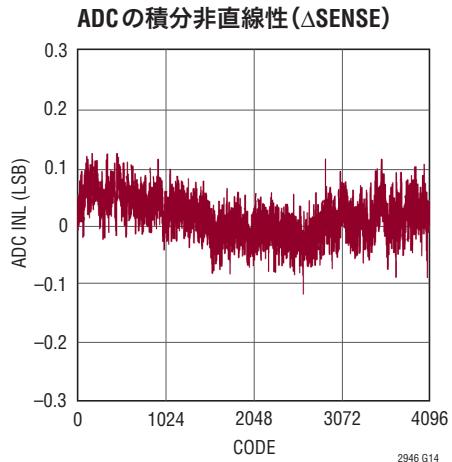

LTC2946は、原理的に変換時間ウインドウの全域で入力ノイズとノイズが平均化される、12ビットの $\Delta\Sigma$ ADCを搭載しています。SENSE<sup>+</sup>とSENSE<sup>-</sup>の間の差動電圧( $\Delta$ SENSE)は、25 $\mu$ V/LSBの分解能(フルスケール 102.4mV)でモニタされるため、非常に小さな値のシャント抵抗両端の電圧でも負荷電流を精度よく測定できます。V<sub>DD</sub>またはSENSE<sup>+</sup>の電源電圧は、25mV/LSBの分解能(フルスケール 102.4V)で直接測定されます。コミットされていないADINピンの電圧も0.5mV/LSB分解能(フルスケール 2.048V)で測定できるため、任意の外部電圧をモニタできます。

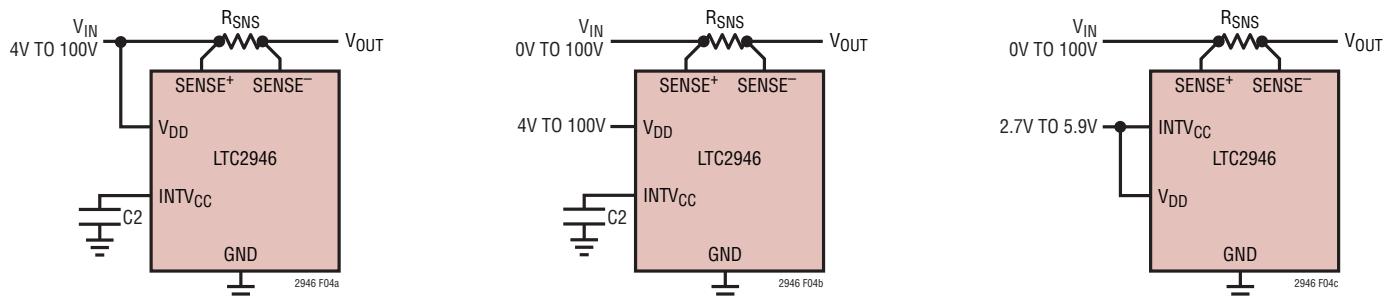

電源電圧データは、外部アプリケーション回路に応じてV<sub>DD</sub>、SENSE<sup>+</sup>、またはADINから派生します。図4(4a～4c)および図5bに示すように、デフォルトでは、通常電源電圧に接続されているSENSE<sup>+</sup>が選択されます。図5dに示すような負の電源電圧システムでは、V<sub>DD</sub>を使用して、デバイス・グラウンドを基準としたGNDの電源電圧を測定します。図5aおよび図5cのように正/負の電源電圧が100Vを超える場合、外付け抵抗を使用してADINの電圧を分割して電源電圧を測定することができます。CTRLAレジスタのCA[4:3]は、電源電圧データをV<sub>DD</sub>、SENSE<sup>+</sup>、ADINから選択します。詳細は表3に記載されています。12ビットの負荷電流データと12ビットの電源電圧データをデジタル乗算することにより、24ビットの電力値が生成されます。電力の下位1ビットは、電圧の下位1ビットに $\Delta$ SENSE(電流)の下位1ビットを乗じた値です。結果は、3つの隣接するPOWERレジスタに格納されます(表2)。

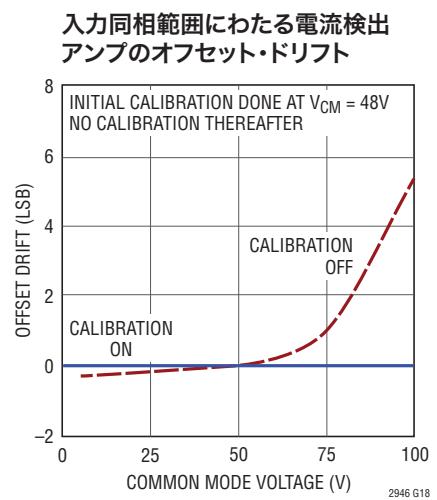

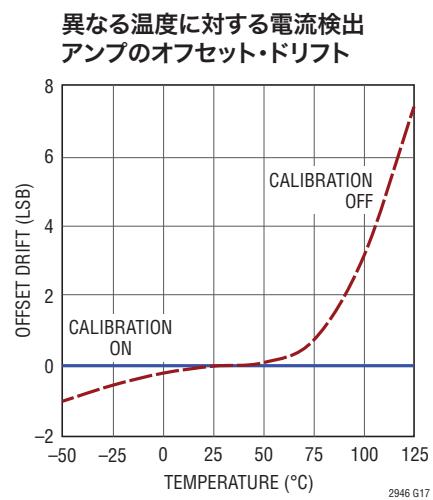

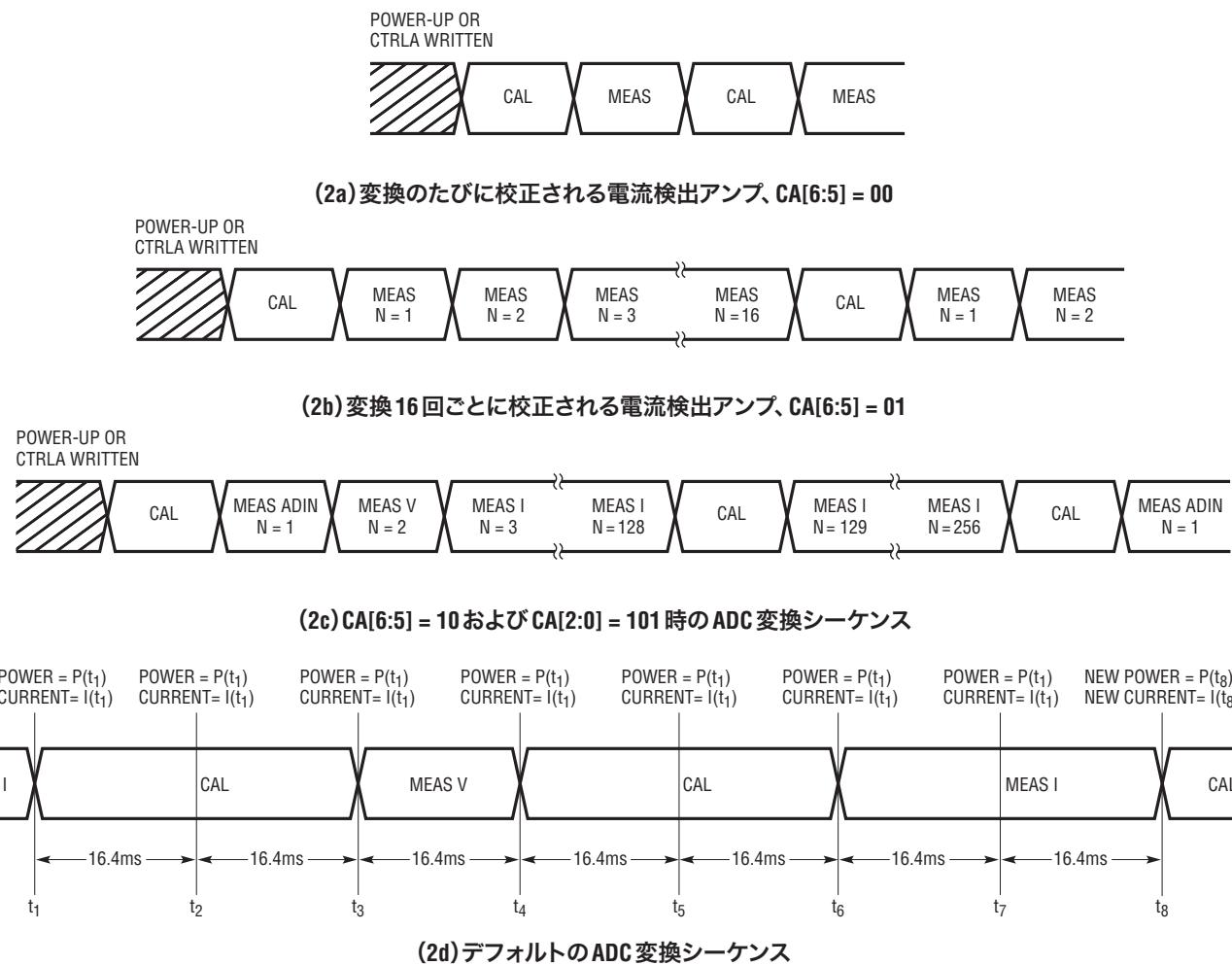

変換中、データ・コンバータの入力は多重化され、 $\Delta$ SENSE、電流検出アンプのオフセット、V<sub>DD</sub>またはV<sub>SENSE+</sub>、およびV<sub>ADIN</sub>の4つの電圧を測定します。そのデューティー・サイクルは、CTRLAレジスタ(表3)のCA[6:5]およびCA[2:0]の構成によって、幅広く設定できます。図2(2a～2c)にいくつかの構成を示し、さまざまなタイミング・シーケンスを説明していきます。図2aでは、起動後もしくはCTRLAレジスタへのI<sup>2</sup>C書き込み処理後、ADCは電流検出アンプのオフセットの1回目の測定を実行し(校正)、変換のたびに再校正します。この変換は、V<sub>ADIN</sub>、電源電圧(V<sub>DD</sub>またはV<sub>SENSE+</sub>)、または負荷電流( $\Delta$ SENSE)のいずれかです。図2bでは、ADCは変換16回ごとに定期的に校正を実行します。図2cでは、ADCは定期的に電流検出アンプを校正し、かつ、その間の変換で他の電圧がシーケンスされます。

これらの構成のどれを選択するかについては、次の2つの要素を考慮する必要があります。

1. ADCが電流をサンプリングしていないときにウインドウと同期する負荷電流高調波が存在するかどうか。これらの高調波を持つ負荷電流信号の測定精度は、 $\Delta$ SENSEに高いデューティー・サイクルを選択することで向上できます。測定漏れをなくすため、CA[2:0]を110にセットすることで、ADCが電流を連続的に測定するよう構成できます。

2. 電流測定のデューティー・サイクルを高くすると、電流検出アンプのオフセットおよび電源電圧値の更新頻度が低くなります。そのため、時間と温度に対するそれらのドリフト量によって、最善の構成が決まります。また、CTRLAレジスタへのI<sup>2</sup>C書き込み処理を1回行うと、電流検出アンプのオフセットおよび電源電圧の新規測定が命令されるため、必要に応じた更新が可能です。その結果は、オフセットの校正と乗算器の電圧値を得るのに使用されます。たとえば、CA[6:5]をコード11にセットし、CA[2:0]を110にセットした場合、I<sup>2</sup>Cの書き込み処理後に2回ADC変換を行った後に、新しいオフセット値および電圧値が生成されます。その後は、ADCは電流を連続的に測定します。

図2dのタイミング図は、デフォルト構成において、変換後に電力データとアキュムレータ・データが生成されるシーケンスを示しています。t<sub>1</sub>において、ADCは電流( $\Delta$ SENSE)信号の変換を終えた直後です。t<sub>1</sub>の新しい電流データが電荷アキュムレータに追加される一方で、タイム・カウンタが1カウント分インクリメントされます。I<sub>(t1)</sub>に前の電圧(V<sub>IN</sub>)データを乗算することで新しい電力値が生成され、その電力値がエネルギー・アキュムレータに追加されます。t<sub>1</sub>からt<sub>3</sub>までは、電流検出アンプのシステムチェック・オフセットが測定され保存されます。その後、ADCはV<sub>IN</sub>の変換を行います。t<sub>4</sub>でもう一度校正を行った後、ADCは $\Delta$ SENSEを変換します。電荷アキュムレータとエネルギー・アキュムレータは、t<sub>2</sub>、t<sub>3</sub>、t<sub>4</sub>、t<sub>5</sub>、t<sub>6</sub>、t<sub>7</sub>でインクリメントされ、時間t<sub>1</sub>で生成された電流データおよび電力データを持ちます。タイム・カウンタは、発生した積算の回数をカウントします。t<sub>8</sub>で新しい電流および電力データが入手でき、各値が電荷アキュムレータとエネルギー・アキュムレータに追加されます。その他のCA構成では、電荷アキュムレータとエネルギー・アキュムレータは同様に動作します。つまり、校正中のとき、および電流測定中以外のとき、直近の電流値が積算および電力の計算に使用されます。

## アプリケーション情報

各測定電圧に対応する12ビットのデジタル・ワードは、合計6つのADCデータ・レジスタ( $\Delta$ SENSE MSB/LSB、 $V_{IN}$  MSB/LSB、ADIN MSB/LSB)の隣接する2つに保存されます。上位8ビットは第1のレジスタ(MSB)、下位4ビットが第2のレジスタ(LSB)に格納されます(表2参照)。LSBレジスタの最下位4ビットは0に設定されます。これらのデータレジスタは、対応するADC変換の完了後、ただちに更新されます。

4バイトのタイム・カウンタは、電流測定値および電力測定値が電荷アキュムレータ、エネルギー・アキュムレータにそれぞれ追加される間、経過した時間をカウントします。1カウントあたり16.395msの場合、最長2.23年カウントします(表15を参照)。タイマ内の時間でエネルギー/電荷を割ると、タイマ内の

時間全体での平均電力/電流が求められます。電荷アキュムレータは最上位32ビットがアクセス可能な36ビット・レジスタであるため、1つの電荷ビットは、電流の $16(2^4)$ カウント分のタイマー1刻みに相当します。同様に、エネルギー・アキュムレータは最上位32ビットがアクセス可能な48ビット・レジスタであるため、1つのエネルギー・ビットは、電力の $65536(2^{16})$ カウント分のタイマー1刻みに相当します。フルスケールの電流および電力では、電荷アキュムレータおよびエネルギー・アキュムレータは3.2日分のデータを保存できます。これは、定格電流および電力レベルでは数か月に相当します。

アキュムレータには2バイト以上のデータが含まれるため、データの整合性を保つには、アキュムレータにはシングル・

図2

## アプリケーション情報

ページ読み出し処理が必要です。すべてのアキュムレータは書き込み可能であり、指定した値を事前ロード可能です。そして、指定した量のエネルギーまたは電荷が輸送されたら、もしくは事前に設定した時間が経過したら、オーバーフロー・アラートを生成するようLTC2946を構成できます。

また、選択した電圧( $\Delta\text{SENSE}$ 、 $\text{VDD}$ または $\text{VSENSE}^+$ 、 $\text{VADIN}$ のいずれか)を1つだけ測定するスナップショット・モードも備えています。スナップショット測定を実行するには、CTRLAレジスタにバイト書き込みコマンドを使用して、CA[4:3]に目的とするADCチャネルの2ビット・コードを書き込み、CA[2:0]にコード111を書き込みます。バイト書き込みコマンドが完了すると、ADCは選択された電圧の変換を開始し、変換が進行中であることを示すビジー・ビット(STATUS2レジスタのS2[3]、表10を参照)がセットされます。変換が完了すると、ADCは停止し、ビジー・ビットがリセットされてデータが用意できたことを知らせます。ALERT2レジスタのビットAL2[7]をセットすると、スナップショット変換の最後にアラートを生成することができます(表8)。スナップショット測定を再度実行するには、CTRLAレジスタに再書き込みします。スナップショット・モードでは、POWERレジスタ、タイム・カウンタ、電荷アキュムレータ、およびエネルギー・アキュムレータはリフレッシュされません。

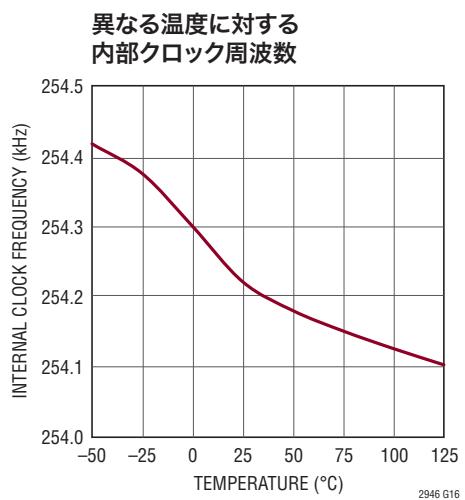

### 水晶発振器/外部クロック

電力/電流を積算することによって高精度にエネルギー/電荷を測定するには、積算期間が正確であることが要求されます。LTC2946の内蔵クロックは、 $\pm 5\%$ 以内にトリミングされます。内蔵クロックでタイミング管理を行うには、CLKINをGNDに接続し、CLKOUTを開放のままにします。精度をさらに高めるため、水晶発振器または共振器をCLKINおよびCLKOUTピンに接続することができます(図1参照)。別の方法として、CLKOUTは未接続にして、1MHz～25MHzの外部クロックをCLKINに印加することもできます。CLKINのクロック周波数は、CLK\_DIVレジスタ(表13参照)の値を4倍した数値で除算され、データ・コンバータの $\Delta\Sigma$ モジュレータ用に250kHzの目標周波数における内部クロックを生成します。外部クロックまたは水晶を使用した場合、ADCのサンプリング周波数はCLK\_DIVレジスタ(レジスタ43h)を構成することで調整できます。サンプリング・クロックを100kHz～400kHzの間、かつ $f_{IN}$ より少なくとも20kHz上または下になるよう制限します。

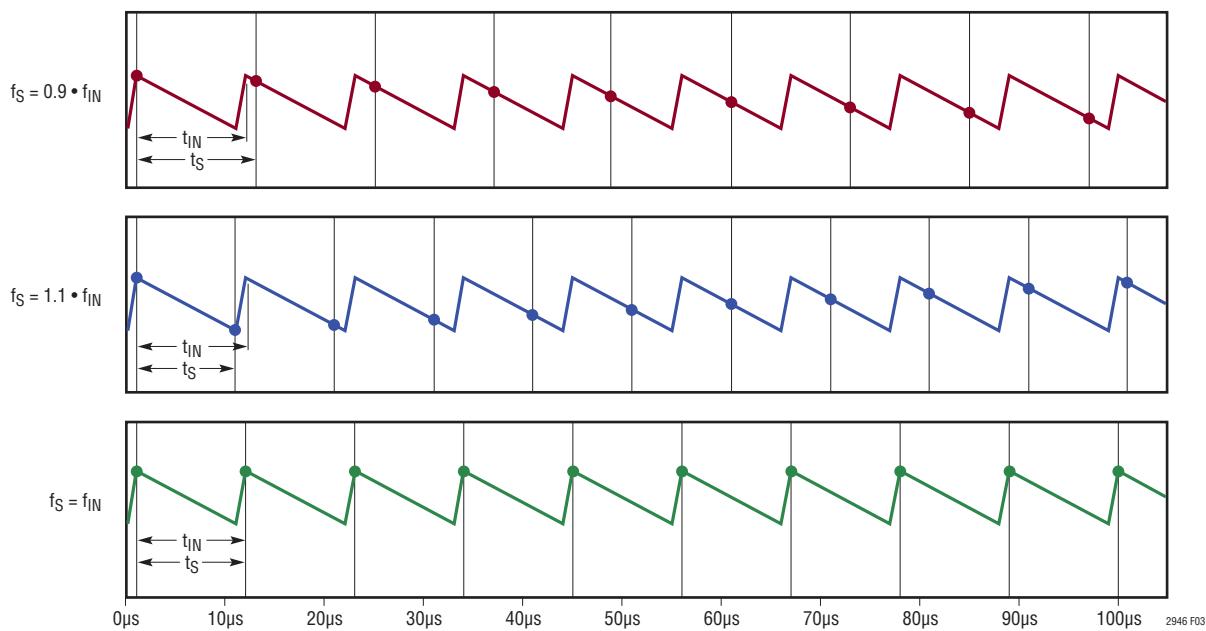

$\Delta\Sigma$ ADCでは、その原理上入力信号が平均化されるため、ほとんどのアプリケーションにおいてアンチエイリアシング・フィルタが必要です。しかし、モジュレータのサンプリング周波数( $f_S$ )の整数倍で発生するノイズ・リップル( $f_{IN}$ )の問題は残り

図3.エイリアシングの影響を示す波形

## アプリケーション情報

ます。図3は、入力周波数の関数としてのサンプリング周波数が誤差の量に与える影響を示しています。 $f_S = f_{IN}$ のとき、ワーストケースにおいて、入力信号は完全にピーク(またはトラフ)でサンプリングでき、平均出力値  $V_{PEAK}$  (または  $V_{TROUGH}$ ) が得られます。入力の実際の平均値は、 $\frac{1}{2} \cdot (V_{PEAK} - V_{TROUGH})$  です。サンプリング周波数を少し調整すると、波形全体を代表する複数のサンプルが変換期間全体にわたって平均化されるため、誤差が除去されます。このことを示しているのが、 $f_S = 0.9f_{IN}$  と  $f_S = 1.1f_{IN}$  の各波形です。ピークとトラフに挟まれた複数のインスタンスで入力がサンプリングされているのが分かります。十分な数のサンプルの平均を取ることで、正確な結果が得られます。

### LTC2946の柔軟な電源

LTC2946は、広範囲の電源からデバイス電源を派生させる、外部からの設定が可能です。LTC2946は、INTVCCピンに接続された低電圧の内部回路に、高いV<sub>DD</sub>電圧からの給電を可能とするリニア・レギュレータを内蔵しています。リニア・レギュレータは4V～100VのV<sub>DD</sub>電圧で動作し、100Vより高い電圧ではシャント・レギュレータを使用できます。リニア・レギュレータは、V<sub>DD</sub>が8Vより高い場合、INTVCCピンに10mAの電流を供給できる5V出力を発生します。レギュレータは接合部温度が150°Cを上回るとディスエーブルされ、出力

は偶發的な短絡に対して保護されています。最適なトランジエント性能を得るには、V<sub>DD</sub>とINTVCCの両ピンに0.1μF以上のバイパス・コンデンサを接続することを推奨します。高いV<sub>DD</sub>電圧による動作は、著しい電力損失につながることに注意し、最大動作接合部温度が125°C未満に保たれるように気をつけてください。熱抵抗を改善するには、DFNパッケージを使用して、露出パッドをPCBの大きな銅領域に半田付けします。

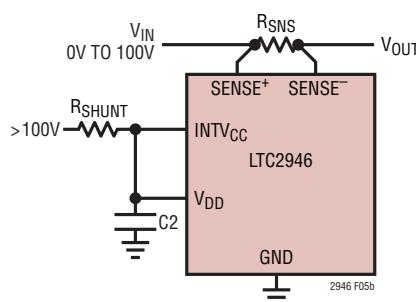

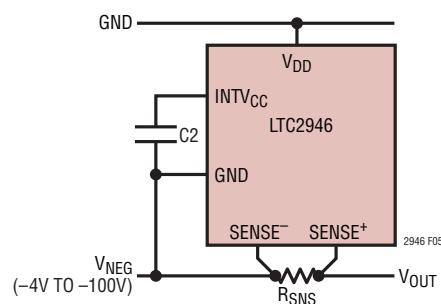

図4aに4V～100Vの入力電源のモニタにLTC2946を使用した例を示します。V<sub>DD</sub>を直接入力電源に接続できるため、2次電源は必要ありません。LTC2946を0V～100Vの入力電源モニタ用に使用する場合は、図4bに示すように、V<sub>DD</sub>ピンに接続された広範囲の2次電源からデバイス電源を派生させることができます。SENSE<sup>+</sup>/SENSE<sup>-</sup>ピンにはデバイス電源電圧とは独立したバイアスが可能です。これらに代わる方法として、低電圧の電源が存在する場合は、図4cに示すようにINTVCCピンに接続することで、オンチップの電力損失を最小化することもできます。INTVCCを2次電源から給電する場合は、V<sub>DD</sub>ピンをINTVCCに接続します。

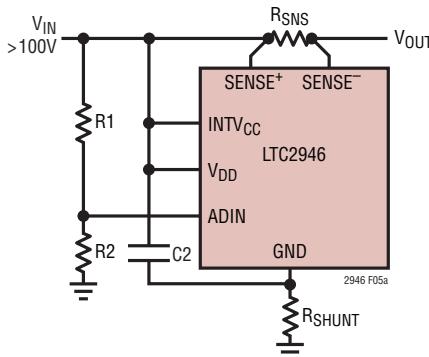

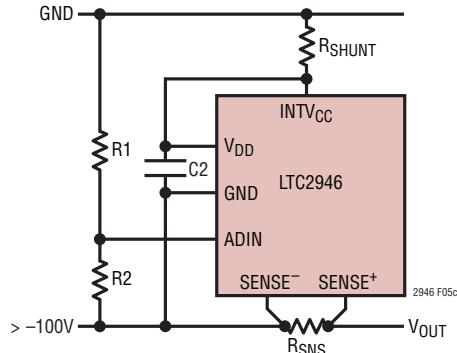

100Vを超える電源電圧に対しては、ハイサイドとローサイドのいずれの構成にもINTVCCシャント・レギュレータを使用でき、外付けのシャント抵抗R<sub>SHUNT</sub>を介したLTC2946への電力供給が可能になります。図5aに、ハイサイド・シャント・レギュ

(4a) モニタ中の電源から

デバイス電源を派生するLTC2946

(4b) 広範囲の2次電源から

デバイス電源を派生するLTC2946

(4c) 低電圧の2次電源から

デバイス電源を派生するLTC2946

図4

## アプリケーション情報

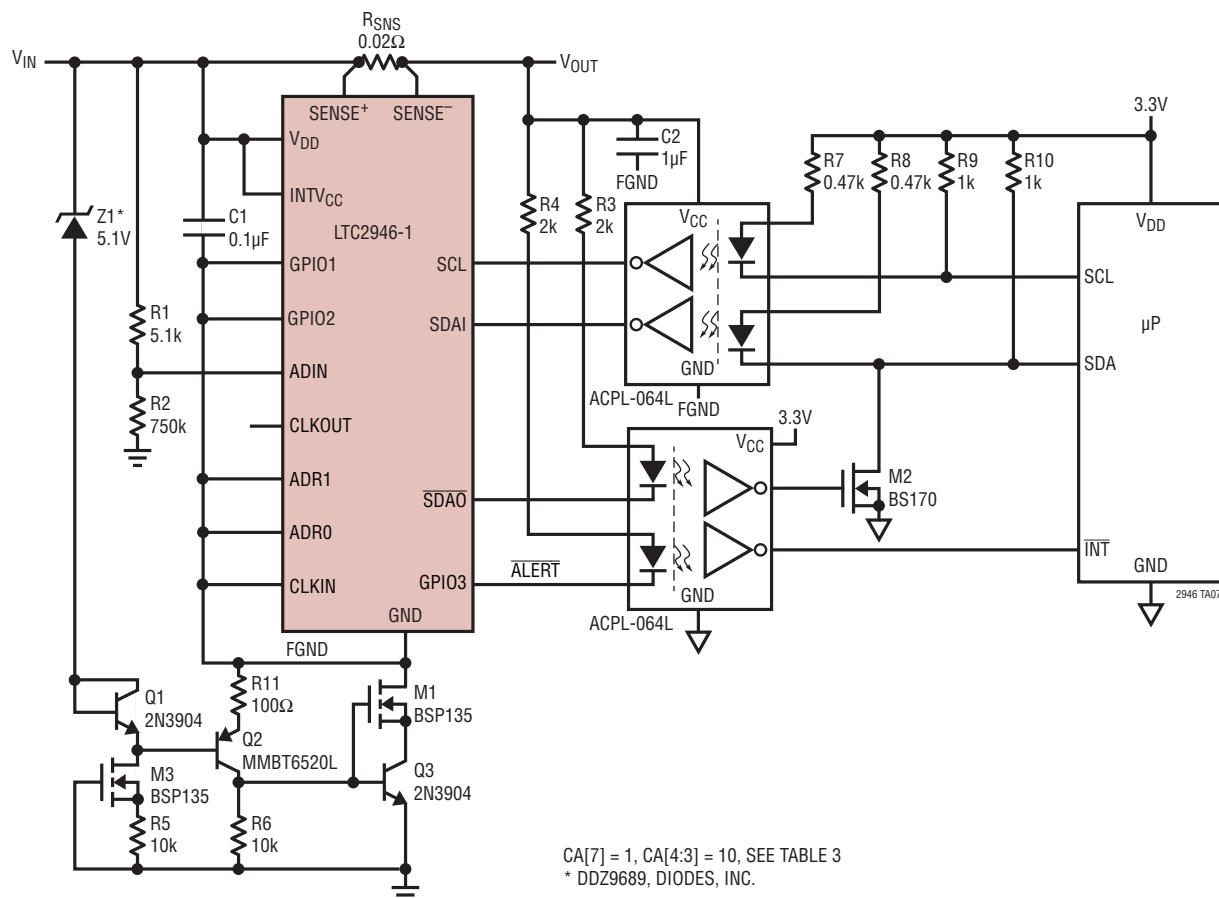

レータ構成を用い、100Vを超える入力モニタ範囲でハイサイドの電力をモニタする回路を示します。デバイスのグランドは RSHUNT によってグランドから分離され、入力電源よりも 6.3V 低い電圧にクランプされます。グランド・レベルが異なることから、このデバイスからの I<sup>2</sup>C 信号は他のグランド基準の部品との通信を行う場合、レベルをシフトする必要があることに注意してください。バス電圧は、ADIN に接続された抵抗器列によって測定されます。ADC が GND ではなく INTV<sub>CC</sub> を基準に ADIN を測定するよう、CTRLA レジスタの CA[7] を設定します。すると、ADIN の測定範囲は、INTV<sub>CC</sub> ~ INTV<sub>CC</sub> - 2.048V になります。

図 5b は、100V を超える 2 次電源から電源を派生するハイサイドのレール・トゥ・レール電力モニタです。INTV<sub>CC</sub> の電圧は、デバイスに給電するために、ローサイド・シャント・レギュレータ構成によってグランドよりも 6.3V 高い電圧にクランプされて

います。ローサイド電力モニタでは、図 5c に示すとおり、デバイスのグランドと電流検出入力が、入力電源の負側端子に接続されます。ローサイド・シャント・レギュレータ構成を使用すれば、100V を超える入力電源でも INTV<sub>CC</sub> にクランプすることで動作が可能になります。R<sub>SHUNT</sub> の値は、次式に従って決定します。

$$\frac{V_{S(MAX)} - V_{CCZ(MIN)}}{I_{CC(ABSMAX)}} \leq R_{SHUNT} \leq \frac{V_{S(MIN)} - V_{CCZ(MAX)}}{I_{CC(MAX)} + I_{LOAD(MAX)}} \quad (1)$$

$$\frac{V_{S(MAX)} - 5.8V}{35mA} \leq R_{SHUNT} \leq \frac{V_{S(MIN)} - 6.7V}{1mA + I_{LOAD(MAX)}}$$

ここで V<sub>S(MAX)</sub> と V<sub>S(MIN)</sub> は、電源の動作上限電圧および下限電圧です。I<sub>LOAD(MAX)</sub> は、シャント・レギュレータに接続された、外部電流負荷の最大値です。更に、シャント抵抗はワーストケースの電力を安全に消費できる定格のものを選ぶ必要

(5a) ハイサイド・シャント・レギュレータから

デバイス電源を派生する LTC2946

(5b) ハイサイド電流検出トポロジにおいて

ローサイド・シャント・レギュレータからデバイス電源を

派生する LTC2946

(5c) ローサイド電流検出トポロジにおいて

ローサイド・シャント・レギュレータからデバイス電源を

派生する LTC2946

(5d) ローサイド電流検出トポロジにおいて

モニタ中の電源からデバイス電源を派生する LTC2946

図 5

## アプリケーション情報

があります。例として、電源が $-36V \sim -72V$ で動作し、最大4mAの外部負荷に給電するためにシャント・レギュレータを使用するような $-48V$ 電気通信システムを考えます。RSHUNTは、前式により $1.9k \sim 5.9k$ の範囲である必要があり、電力損失を低減するには、より大きな値の抵抗の方が有利です。 $5.36k$ のRSHUNTで消費されるワーストケースの電力は $0.8W$ と計算されます。したがって、この例では、定格 $0.5W$ の $1.8k$ 抵抗を3個直列に接続すれば十分でしょう。

電源入力が $100V$ 未満の場合シャント抵抗は不要で、図5dに示すように、 $V_{DD}$ を電源のGNDに接続できます。

### 電源低電圧ロックアウト

電源投入時に、内部I<sup>2</sup>CロジックとADCは、 $V_{DD}$ またはINTV<sub>CC</sub>のいずれかが低電圧ロックアウトしきい値を超えた時点でイネーブルされます。電源遮断時に、ADCは、 $V_{DD}$ とINTV<sub>CC</sub>がそれぞれの低電圧ロックアウトしきい値を下回るとディスエーブルされます。また、 $V_{DD}$ とINTV<sub>CC</sub>がそれぞれのI<sup>2</sup>Cリセットしきい値を下回ると、内部I<sup>2</sup>Cロジックがリセットされます。

### シャットダウン・モード

LTC2946は、低静止電流のシャットダウン・モードを備えています。このモードは、CTRLBレジスタのビットCB[6]によって制御されます(表4)。CB[6]をセットすると、デバイスがシャットダウン・モードに移行し、ADC、内部リファレンス、内蔵リニア・レギュレータの電源を遮断します。ただし内部I<sup>2</sup>Cバスはアクティブ状態を保ち、ADR1とADR0ピンはディスエーブルされるものの、デバイスは最後にプログラムされたI<sup>2</sup>Cバス・アドレスを保持します。内蔵レジスタは、いずれもその内容を保持し、I<sup>2</sup>Cインターフェースを介してアクセスできます。ADC変換を再度イネーブルするには、CTRLBレジスタのビットCB[6]をリセットします。アナログ回路の電源が立ち上がり、全てのレジスタの内容は保持されます。

シャットダウン・モードでは電力を節減するために内蔵リニア・レギュレータはディスエーブルされます。光カプラまたはプルアップなどの外付けのI<sup>2</sup>Cバス関連回路への給電に内蔵リニア・レギュレータを使用している場合は、シャットダウンされたときにI<sup>2</sup>C通信が失われます。シャットダウン・モードを終了するには、LTC2946の電源サイクルによるリセットが必要になります。低I<sub>Q</sub>モードが必要ない場合は、ソフトウェア開発時にCTRLBレジスタのビットCB[6]がマスクされていることを確認

してください。このようなアプリケーションでLTC2946のパワーダウンが必要な場合は、外付けのレギュレータを使用することを推奨します。このシナリオの保護機能を強化するため、システム構成中にCTRLBレジスタのビットCB[4]をセットすることで、I<sup>2</sup>Cラインが33msより長い間“L”になったとき(I<sup>2</sup>Cに給電しているLTC2946内蔵リニア・レギュレータを誤ってシャットダウンしたときに起こることがある現象)、LTC2946が自動的にシャットダウン・モードを終了するように設定できます。ALERT2レジスタにビットAL2[3]をセットすることで、このイベントをユーザにアラートするよう選択できます。(表8)シャットダウン・モードでは、内部レギュレータがディスエーブルされ静止電流が $40\mu A$ 未満に低下します。

### GPIOピンの構成

LTC2946には3本のGPIOピンがあります。GPIOピンは、GPIO\_CFGレジスタ(表9)で構成して、汎用入出力ピンとして使用できます。汎用入力としては、GPIO1～GPIO3はアクティブ“H”またはアクティブ“L”的いずれにも設定できます。さらに、GPIO2は、ビットCB[3:2] = [10]に書き込むことで、タイム・カウンタ、電荷アキュムレータ、エネルギー・アキュムレータの積算を有効にするアキュムレーション・イネーブル入力としても使用できます。GPIO1～GPIO3ピンは、各ピンの電圧をモニタするしきい値 $1.22V$ のコンパレータを備えており、比較結果はSTATUS2レジスタ(表10)のビットS2[6:4]から読み出し可能です。ALERT2レジスタにおいて、ビットAL2[6]がセットされてGPIO1が入力としてアクティブなとき、またはAL2[5]がセットされてGPIO2が入力としてアクティブなとき、アラートが生成されることがあります。

GPIO1～3は、汎用出力として“L”にプルダウンできます。それ以外の場合、高インピーダンスです。GPIO3はデフォルトでは、アラート・イベントが存在するときに“L”にプルダウンするALERT出力です。GPIO3(ALERT)をアラート・イベントがないときに“L”にプルダウンするには、GPIO3\_CTRLレジスタ(表12)のGC[7]をセットします。このビットをクリアすると、GPIO3(ALERT)が解放されます。GPIO3がALERT出力として構成されていない場合、GC[7]はGPIO3に影響を与えません。同様に、GPIO3が汎用出力として構成されていないとき、GC[6]はGPIO3に影響を与えません。GC[7]は、GPIO3の構成にかかわらず、アラート・イベントが発生するたびにセットされます。GPIO3をALERTに構成する前に、GC[7]をリセットしてください。

## アプリケーション情報

### I<sup>2</sup>Cのリセット

CTRLB レジスタのビット CB[1:0]に[01]を書き込むことで、ホストがアキュムレータ・データの最後のバイト(3Fh)を読み出した後、アキュムレータが自己リセットするようプログラムできます(表4)。この機能により、LTC2946 の積算データをポーリングした後、リセット・コマンドを発行する必要がなくなります。リセット後、アキュムレータは積算を継続します。このような読み取りコマンドなしでアキュムレータをリセットするには、ビット CB[1:0] に [10] を書き込みます。CB[1:0] = [10] の場合、アキュムレータはリセットのままになります。CB[1:0] = [11] のときすべてのレジスタがリセットされ、これらのビットは[00]に自動リセットされます。

CTRLA レジスタがリセットされたとしても、ADC シーケンス構成は I<sup>2</sup>C リセット中も保持されます。リセット後にシーケンス構成を変更するには、CTRLA レジスタに再書き込みします。

### 最小値と最大値の記憶

LTC2946 は、電力の計算値を含む毎回の測定値を、対応する各パラメータの MIN および MAX レジスタ(表2)に格納された値と比較します。新しい変換値が、格納済みの最小値または最大値を超えていた場合、MIN または MAX レジスタを新しい値で更新します。MIN および MAX レジスタは、連続スキャン・モードとスナップショット・モードのいずれにおいても、対応する ADC 変換の最後にリフレッシュされます。MIN/MAX レジスタの格納値を超える値を、ADC レジスタに I<sup>2</sup>C バスを介して書き込んだ場合にも、両レジスタはリフレッシュされます。新しいピーク保持サイクルを開始するには、MIN レジスタにオール「1」、MAX レジスタにオール「0」を I<sup>2</sup>C バスを介して書き込みます。これらのレジスタは、次の対応する ADC 変換の完了時に更新されます。

LTC2946 は、電力の計算値も含め、測定されるパラメータに対する MIN および MAX しきい値レジスタ(表2)も備えています。

す。電源投入時、最大しきい値はオール「1」、最小しきい値はオール「0」に設定され、両方とも実質的にディスエーブルされます。しきい値は、I<sup>2</sup>C バスを介して、必要な任意の値に再プログラムできます。

### FAULT・ALERTとFAULTのリセット

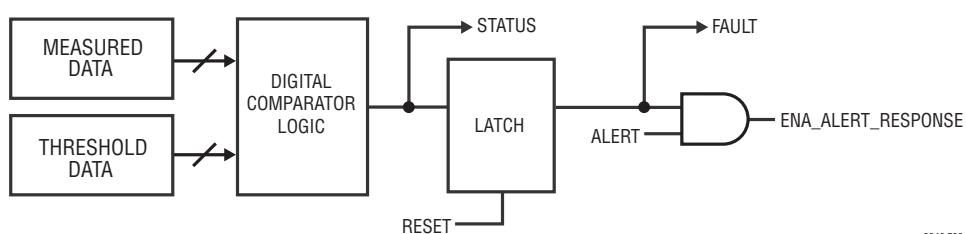

測定値が最小しきい値を下回るか、最大しきい値を上回ると、LTC2946 は STATUS1(表6) レジスタ内の対応するフラグをセットし、FAULT1(表7) レジスタにラッチします(図6参照)。GPIO のステート変更など、スタックバス状態の起動、アキュムレータのオーバーフローなどの他のイベントでは、現在のステータスが STATUS2(表10) レジスタに保存され、FAULT は FAULT2(表11) レジスタにラッチされます。GPIO3 ピンは、ALERT1(表5) および ALERT2(表8) レジスタの適切なビットがセットされて ALERT 出力として構成されている場合は、「L」にプルダウンされます。アラート動作の詳細は、「アラート応答プロトコル」のセクションに記載されています。

アクティブなFAULT表示は、FAULT レジスタの対応するビットに0を書き込むか、CTRLB レジスタのCB[5]ビットをセットすることでリセットできます。ビット CB[5] をセットした場合、FAULT1 または FAULT2 レジスタを読み出すと、対応するレジスタがリセットされます。V<sub>DD</sub> と INTV<sub>CC</sub> が、それぞれ対応する I<sup>2</sup>C ロジック・リセットしきい値を下回った場合にも FAULT レジスタの全ビットがクリアされます。STATUS1 および STATUS2 レジスタに表示される未解消のFAULTは、クリアしてもすぐに再表示されることに注意してください。

アキュムレータ(時間、電荷、およびエネルギー)がオーバーフローした場合、STATUS2 レジスタの対応するビットがセットされ、その後もセットされたままになります。STATUS2 レジスタはオーバーフロー・FAULT を表示しつづけるため、FAULT2 レジスタのアキュムレータ・オーバーフロー・ビットは I<sup>2</sup>C を介してクリアしても、また表示されます。

2946 F06

図6. LTC2946 のFAULT・ALERT生成ブロック

## アプリケーション情報

アキュムレータ・オーバーフロー・フォルトをクリアするには、次の手順を推奨します。

1. アキュムレータを読み出します。

2. その値を外部メモリに保存します。

3. ビットCB[1:0]に[10]を書き込み、アキュムレータにリセットを発行します。その後、ビットCB[1:0]に[00]を書き込んで、リセットをディスエーブルします。

4. 保存した値をアキュムレータに書き戻します。

現在の値から積算を続行する必要がない場合は、手順2および4を省略できます。

## I<sup>2</sup>Cインターフェース

LTC2946は、内蔵レジスタにアクセスするための、I<sup>2</sup>C/SMBus互換のインターフェースを備えています。図6に、I<sup>2</sup>Cバスを用いた一般的なデータ伝送フォーマットを示します。

LTC2946は読み出し/書き込みスレーブ・デバイスとして、SMBusのバイト読み出し、バイト書き込み、ワード読み出し、ワード書き込みプロトコルをサポートします。更に、2バイトより大きいデータを読み書きできる、拡張読み出し/書き込みコマンドにも対応しています。ワード読み出し/書き込みまたは拡張読み出し/書き込みコマンドを使用する場合、バス・マスターは初期レジスタ・アドレスを発行し、内部レジスタ・アドレス・

図7. I<sup>2</sup>Cによる一般的なデータ伝送

| S           | ADDRESS | W   | A     | COMMAND | A     | DATA | A | P |

|-------------|---------|-----|-------|---------|-------|------|---|---|

| 1 1 0 a3:a0 | 0 0     | X X | b5:b0 | 0       | b7:b0 | 0    |   |   |

□ FROM MASTER TO SLAVE    A: ACKNOWLEDGE (LOW)    W: WRITE BIT (LOW)

□ FROM SLAVE TO MASTER    A: NOT ACKNOWLEDGE (HIGH)    S: START CONDITION

R: READ BIT (HIGH)              P: STOP CONDITION

図8.LTC2946のシリアル・バス SDAバイト書き込みプロトコル

| S           | ADDRESS | W   | A     | COMMAND | A     | DATA | A     | DATA | A     | P |

|-------------|---------|-----|-------|---------|-------|------|-------|------|-------|---|

| 1 1 0 a3:a0 | 0 0     | X X | b5:b0 | 0       | b7:b0 | 0    | b7:b0 | 0    | b7:b0 | 0 |

2946 F09

図9.LTC2946のシリアル・バス SDAワード書き込みプロトコル

| S           | ADDRESS | W   | A     | COMMAND | A     | DATA | A     | DATA | A   | ...   | DATA | A | P |

|-------------|---------|-----|-------|---------|-------|------|-------|------|-----|-------|------|---|---|

| 1 1 0 a3:a0 | 0 0     | X X | b5:b0 | 0       | b7:b0 | 0    | b7:b0 | 0    | ... | b7:b0 | 0    |   |   |

2946 F10

図10.LTC2946のシリアル・バス SDAページ書き込みプロトコル

| S           | ADDRESS | W   | A     | COMMAND | A           | S   | ADDRESS | R | A     | DATA | A | DATA | A | P |

|-------------|---------|-----|-------|---------|-------------|-----|---------|---|-------|------|---|------|---|---|

| 1 1 0 a3:a0 | 0 0     | X X | b5:b0 | 0       | 1 1 0 a3:a0 | 1 0 | b7:b0   | 0 | b7:b0 | 1    |   |      |   |   |

2946 F11

図11.LTC2946のシリアル・バス SDAバイト読み出しプロトコル

| S           | ADDRESS | W   | A     | COMMAND | A           | S   | ADDRESS | R | A     | DATA | A | DATA | A | P |

|-------------|---------|-----|-------|---------|-------------|-----|---------|---|-------|------|---|------|---|---|

| 1 1 0 a3:a0 | 0 0     | X X | b5:b0 | 0       | 1 1 0 a3:a0 | 1 0 | b7:b0   | 0 | b7:b0 | 1    |   |      |   |   |

2946 F12

図12.LTC2946のシリアル・バス SDAワード読み出しプロトコル

| S           | ADDRESS | W   | A     | COMMAND | A           | S   | ADDRESS | R | A     | DATA | A     | DATA | ... | DATA  | A | P |

|-------------|---------|-----|-------|---------|-------------|-----|---------|---|-------|------|-------|------|-----|-------|---|---|

| 1 1 0 a3:a0 | 0 0     | X X | b5:b0 | 0       | 1 1 0 a3:a0 | 1 0 | b7:b0   | 0 | b7:b0 | 0    | b7:b0 | 0    | ... | b7:b0 | 1 |   |

2946 F13

図13. LTC2946のシリアル・バス SDAページ読み出しプロトコル

2946fa

## アプリケーション情報

ポインタは1バイトのデータが読み書きされるごとに自動的に1だけインクリメントします。レジスタ・アドレスが43hに達すると、00hにロール・オーバーし、インクリメントを継続します。STOP条件はレジスタ・アドレス・ポインタを00hにリセットします。上記のコマンドのデータ・フォーマットを図7～図13に示します。E7およびE8(MFR\_SPECIAL\_ID)レジスタでは、バイト読み出しコマンドのみ使用できることに注意してください(表2)。

### I<sup>2</sup>Cデバイスのアドレス指定

表1に示すように、トライステート・ピンのADR0とADR1を使って、9つの異なるI<sup>2</sup>Cバス・アドレスを構成できます。

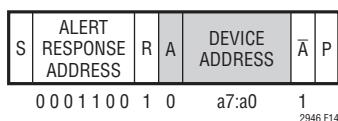

ADR0とADR1をINTVCCまたはGNDに接続するかフロートのままにして(NC)、アドレスの下位4ビットを構成します。低電力シャットダウン・モード中、アドレスの選択状態は、スタンバイ電源で動作するメモリにラッチされます。アドレス・ビットのa6,a5,a4は110bに固定されており、最下位ビットはR/Wビットです。LTC2946は一括書き込みの共通アドレス1100\_110bにも応答します。このため、バス・マスターは複数のLTC2946に、それぞれの個別アドレス設定にかかわらず、同時に書き込むことができます。GPIO3(ALERT)ピンがアサートされている場合、LTC2946はARAアドレス0001\_100bにも応答します。詳細については、「アラート応答プロトコル」のセクションを参照してください。アラートが発生していない場合は、ARAアドレスに応答しません。

### START条件とSTOP条件

I<sup>2</sup>Cバスがアイドルの場合、SCLとSDAはともに“H”状態になります。バス・マスターは、SCLを“H”に保持したままSDAを“H”から“L”に遷移させるSTART条件によって送信の開始を通知します。マスターはスレーブとの通信を終了すると、SCLを“H”に保持したままSDAを“L”から“H”に遷移させるSTOP条件を発行します。この動作によりバスは解放され、次の送信を開始できます。

### スタックバス・リセット

LTC2946のI<sup>2</sup>Cインターフェースは、SCL信号が伝送中に割り込まれてバス・ラインが永久に“L”に保持されることを防ぐ、スタックバス・リセット・タイマを備えています。このタイマは、SCLまたはSDAIのいずれかが“L”になると動作を開始し、SCLとSDAIの両方が“H”にプルアップされるとリセットされます。SCLまたはSDAIのいずれかが33msよりも長く“L”に保持されると、スタックバス・タイマの期限が満了し、内部I<sup>2</sup>CインターフェースとSDAOピンのプルダウン・ロジックがリセットされてバスを解放します。通常の通信は、次のSTARTコマンドから再開されます。

### アクノリッジ

アクノリッジ信号はマスターとスレーブの間のハンドシェークに使用され、データの最終バイトが受信されたことを知らせます。マスターはアクノリッジ・クロック・パルスの間、必ずSDAラインを解放します。LTC2946は、9番目のクロック・サイクルでSDAラインを“L”にプルダウンすることで、データ受信に対してアクノリッジ(肯定応答)します。スレーブがSDAを“H”的ままでアクノリッジを返さないと、マスターがSTOP条件を生成して送信を中止する可能性があります。マスターがスレーブからデータを受信しているときは、マスターが9番目のクロック・パルスでSDAラインをプルダウンして、データ・バイトの受信をスレーブに知らせるアクノリッジを発行する必要があります。最終バイトを受信した後、マスターはSDAラインを“H”的ままで(アクノリッジを返さずに)STOP条件を発行して通信を終了します。

### 書き込みプロトコル

マスターは、START条件とそれに続く7ビットのスレーブ・アドレスおよび0に設定されたR/Wビットによって、書き込み動作を開始します。アドレス指定されたLTC2946がアドレス・バイトに対してアクノリッジを返すと、マスターは書き込み先の内部レジスタを示すコマンド・バイトを送信します。LTC2946はこれに対してもアクノリッジを返し、次いでコマンド・バイトの下位6ビットを内部レジスタ・アドレス・ポインタにラッチします。次に、マスターはデータ・バイトを送り、LTC2946は再度アクノリッジを返してから、レジスタ・アドレス・ポインタが指す内部レジスタにデータを書き込みます。マスターがワード書き込みまたは拡張書き込みコマンドによって、その後も引き続きデータ・バイトを送信する場合、新たなデータ・バイトがLTC2946によってアクノリッジされ、レジスタ・アドレス・ポインタが自動的に1だけインクリメントした上で、上記と同様にデータが書き込まれます。マスターがSTOP条件を送信すると、書き込み動作が終了し、レジスタ・アドレス・ポインタは00hにリセットされます。

### 読み出しプロトコル

マスターは、START条件とそれに続く7ビットのスレーブ・アドレスおよび0にセットされたR/Wビットによって読み出し動作を開始します。アドレス指定されたLTC2946がアドレス・バイトに対してアクノリッジを返すと、マスターは読み出し対象の内部

## アプリケーション情報

レジスタを示すコマンド・バイトを送信します。LTC2946はこれに対してもアクノリッジを返し、次いでコマンド・バイトの下位6ビットを内部レジスタ・アドレス・ポインタにラッチします。次に、マスタは反復START条件に続き、R/Wビットだけ今回は1にセットされ、残りは先ほどと同じ7ビットのアドレスを送ります。LTC2946はアクノリッジを返し、要求されたレジスタの内容を送信します。マスタがSTOP条件を送信すると伝送は終了します。ワード読み出しコマンドの場合のように、マスタが送信されたデータ・バイトに対してアクノリッジを返すと、LTC2946は次のレジスタの内容を送ります。マスタがアクノリッジを返しつづける限り、LTC2946はレジスタ・アドレス・ポインタのインクリメントを継続し、データ・バイトを送信しつづけます。マスタがSTOP条件を送信すると、読み出し動作が終了し、レジスタ・アドレス・ポインタは00hにリセットされます。

### アラート応答プロトコル

ALERT1またはALERT2レジスタ内の適切なビットがセットされており、GPIO3がALERT出力として構成されている場合、FAULT1およびFAULT2レジスタ内のフォルト・ビットのいずれかがセットされた時点でバス・アラートが生成されます。この機能によって、バス・マスタはどのフォルトによってアラートを生成するかを選択できます。電源投入時、両方のALERTレジスタがクリアされ(アラートは全てディスエーブル)、GPIO3(ALERT)ピンは“H”になります。アラートがイネーブルされていれば、対応するフォルトの発生時にGPIO3(ALERT)ピンが“L”にプルダウンされます。バス・マスタはSMBusのアラート応答プロトコルに従い、アラート応答アドレス0001\_100bをブロードキャストすることで応答します。LTC2946は、これに対して自らのアドレスを返信し、GPIO3(ALERT)ピンを解放します(図14)。GPIO3(ALERT)ラインは、CB[7]がセットされ、LTC2946が任意のメッセージの宛先になっている場合(表4参照)にも解放されます。FLTレジスタが別のフォルトの発生を示すまで、または元のフォルトがクリアされてから再度発生するまで、GPIO3(ALERT)信号が再び“L”にプルダウンされることはありません。これは、フォルトが反復または継続して発生しても、対応するFLTレジスタ・ビットがクリアされるまでは、アラートが生成されないことを意味するので注意が必要です。

図14. LTC2946のシリアル・バス SDAアラート応答プロトコル

ARAがブロードキャストされ、同一バスに接続されている複数のLTC2946がアラートを生成している場合、バス・マスタはGPIO3(ALERT)ラインが解放されるまでアラート応答プロトコルを繰り返します。標準のI<sup>2</sup>Cアービトレーションにより、優先度が最高のデバイス(アドレス値が最小)が最初に返信し、優先度が最低のデバイス(アドレス値が最大)が最後に返信します。

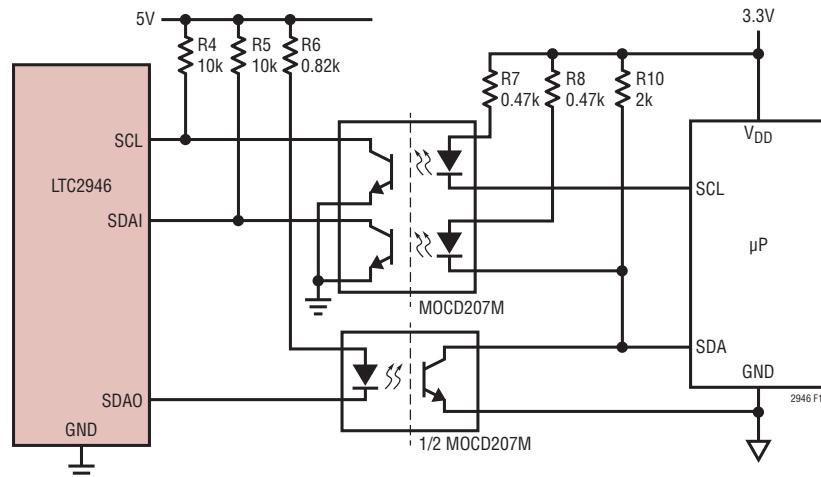

### I<sup>2</sup>Cバスの光絶縁

標準のI<sup>2</sup>Cデバイスの光絶縁は、SDAピンが双方向であることから複雑になります。LTC2946/LTC2946-1は、標準のI<sup>2</sup>C SDAラインをSDAI(入力)とSDAO(出力、LTC2946)またはSDAO(反転出力、LTC2946-1)に分割することで、この問題をできるだけ軽減しています。SCLは入力専用ピンであるため、絶縁に特別な回路を必要としません。通常の非絶縁I<sup>2</sup>CアプリケーションではLTC2946を使用し、SDAIとSDAOピンを互いに接続して標準的なI<sup>2</sup>CのSDAピンとします。

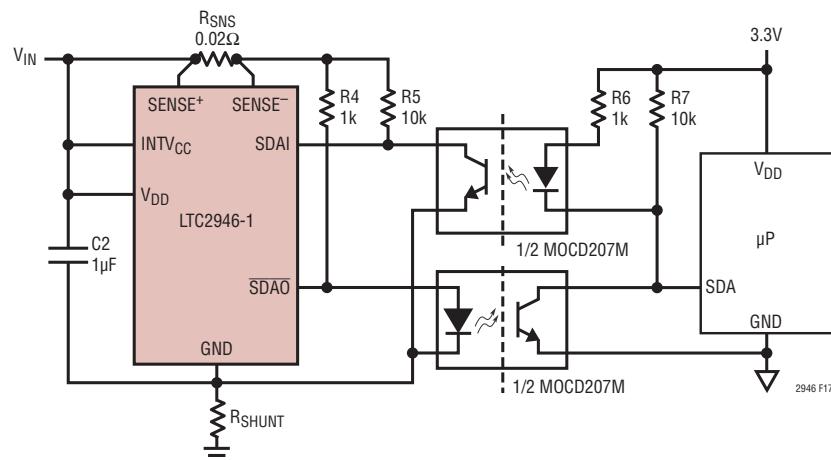

標準のオープン・ドレイン光アイソレータを使用する低速の絶縁インターフェースでは、図15のようにLTC2946のSDAIとSDAOピンを分割して使用できます。SDAIには受信用光アイソレータの出力を接続します。同時にINTV<sub>CC</sub>またはローカルな5V電源へのプルアップ抵抗を接続します。SDAOには送信用光アイソレータのカソードを接続します。アノードには電流制限抵抗を直列に接続します。絶縁サイドでは入力と出力を互いに接続し、LTC2946がI<sup>2</sup>Cのアービトレーションに参加できるようにする必要があります。I<sup>2</sup>Cバスの最大スピードは、通常このアプリケーションで使用される光カプラのスピードによって制限されることに注意してください。

図16と図17に示すとおり、シャント・レギュレータは最大34mAの電流を供給して光アイソレータとプルアップ抵抗を駆動できます。SDAI/SCLのプルアップ抵抗が同一の場合の最大負荷は次式で表されます。

$$I_{LOAD(MAX)} = V_{CCZ(MAX)} \cdot \left( \frac{2}{R5} + \frac{1}{R4} \right) \quad (2)$$

$$I_{LOAD(MAX)} = 6.7V \cdot \left( \frac{2}{R5} + \frac{1}{R4} \right)$$

# LTC2946

## アプリケーション情報

図15.LTC2946とマイクロコントローラ間の10kHz I<sup>2</sup>C インタフェースの光絶縁

図16. ローサイド・シャント・レギュレータから給電される低速10kHz光アイソレータ(図を見やすくするためにSCLは省略した)

図17. ハイサイド・シャント・レギュレータから給電される低速10kHz光アイソレータ(図を見やすくするためにSCLは省略した)

2946fa

## アプリケーション情報

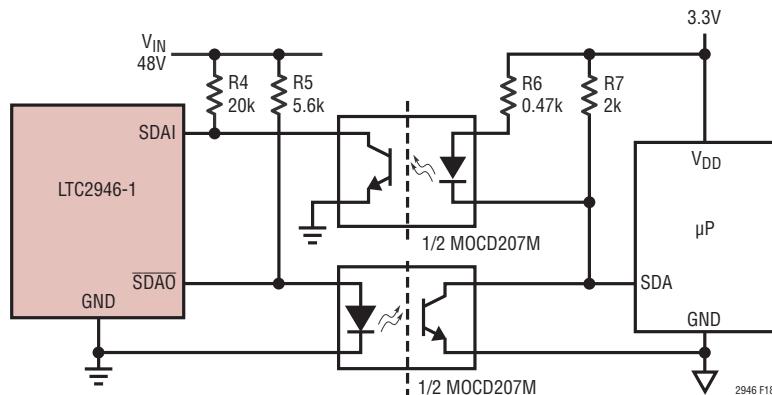

この値と式1からR<sub>SHUNT</sub>を計算できます。ここで述べたシャント・レギュレータ・アプリケーションには、LTC2946とLTC2946-1の両方を適用できることに注意してください。図18は低速の光カプラとLTC2946-1を用いた代替接続です。この回路では、内部クランプされているSDAIピンに電流制限プルアップを適用し、SDAOピンは送信用光アイソレータの入力ダイオードによってクランプしています。これによって、低電圧の補助電源がない場合でもバイアスのためのINTV<sub>CC</sub>が不要になります。クランプを適切に動作させるには、次式を満足する必要があります。

$$\frac{V_{S(MAX)} - V_{SDA,SCL(MIN)}}{I_{SDA,SCL(MAX)}} \leq R4 \leq \frac{V_{S(MAX)} - V_{SDA,SCL(MAX)}}{I_{SDA,SCL(MIN)}} \quad (3)$$

$$\frac{V_{S(MAX)} - 5.9V}{5mA} \leq R4 \leq \frac{V_{S(MAX)} - 6.9V}{0.5mA}$$

例えば、36V～72Vで動作する電源では、R4の値として13k～58kが必要になります。このアプリケーションではSDAO信号の極性が正しく設定されるように、LTC2946-1を使用する必要があります。

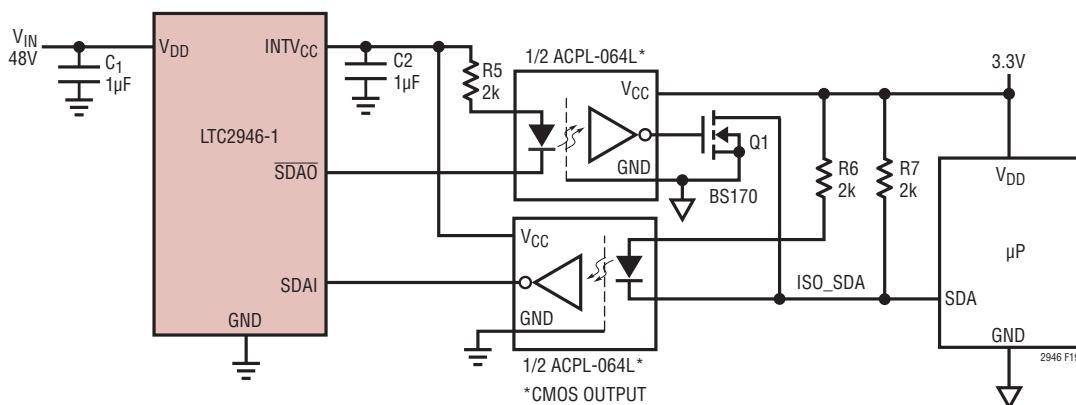

LTC2946-1は、図19に示すように、プッシュプル出力と反転ロジックを用いることで高速の光カプラにも適用できます。受信用光アイソレータはINTV<sub>CC</sub>から電力の供給を受けます。データ出力はSDAIピンに直接接続し、プルアップは不要です。INTV<sub>CC</sub>ピンから流れる電流が、このピンの最大供給能力である10mAを超えないことを確認してください。SDAOピンは、送信用光カプラのカソードに接続され、電流制限抵抗をINTV<sub>CC</sub>に接続します。送信用光カプラの出力には、ディスクリートなNチャネルMOSFETを接続して、I<sup>2</sup>Cバスに必要なオープン・ドレンのプルダウンを可能にする必要があります。最後に、低速の場合と同様に、受信用光アイソレータの入力を出力に戻します。

図18. LTC2946-1とマイクロコントローラ間の1.5kHz I<sup>2</sup>Cインターフェースの光絶縁(図を見やすくするためにSCLは省略した)

図19. 低電力、高速の光カプラによるI<sup>2</sup>Cインターフェースの光絶縁(図を見やすくするためにSCLは省略した)

## アプリケーション情報

### レイアウトに関する検討事項

検出抵抗  $R_{SNS}$  と LTC2946 の間は、正確に電流を検出できるようにケルビン接続することを推奨します(図 20)。トレースが適切な温度を保つようにするための 1 オンスの銅箔の最小推奨トレース幅はアンプ 1 個当たり 0.02 インチです。より望ましい幅はアンプ 1 個当たり 0.03 インチ以上です。1 オンスの銅には約  $530\mu\Omega/\text{平方}$  のシート抵抗があることに注意してください。センサ抵抗の電力損失が著しく大きい超高電流アプリケーションでは、ビアを多くし、金属領域を広くするなどの優れた熱管理テクニックを PCB レイアウトに採用する必要があります。

水晶発振器のクロック振幅は、CLKOUT ピンの浮遊容量や、CLKIN ピンと CLKOUT ピン間のカップリングなどの寄生素子に敏感です。LTC2946 から水晶発振器ネットワークへの CLKIN および CLKOUT トレースは実用上できる限り短くし、負荷コンデンサを水晶の隣に配置することを推奨します(図 21 参照)。浮遊容量を最小限に抑えるため、水晶ネットワークの近くに大きなグランド・プレーンおよびデジタル信号を配置しないでください。

### 設計例

$20m\Omega$  センス抵抗を使用するものとして、電流、電力、電荷、およびエネルギー・レジスタに対する最下位ビットあたりの重みを計算します。

|       |                                                                                                                     |

|-------|---------------------------------------------------------------------------------------------------------------------|

| 電流    | $= 25\mu\text{V}/\text{ LSB}/R_{SNS}$                                                                               |

|       | $= 1.25\text{mA}/\text{ LSB}$                                                                                       |

| 電圧    | $= 25\text{mV}/\text{ LSB}$<br>(SENSE <sup>+</sup> /V <sub>DD</sub> は電圧を検出)                                         |

| 電源    | $= 1.25\text{mA}/\text{ LSB} \bullet 25\text{mV}/\text{ LSB}$<br>$= 31.25\mu\text{W}/\text{ LSB}$                   |

| 時間    | $= 16.39543\text{ms}/\text{ LSB}$<br>(デフォルト構成目標周波数 250kHz)                                                          |

| 電荷    | $= 1.25\text{mA}/\text{ LSB} \bullet 16 \bullet 16.384\text{ms}/\text{ LSB}$<br>$= 327.9086\mu\text{C}/\text{ LSB}$ |

| エネルギー | $= 31.25\mu\text{W} \bullet 65536 \bullet 16.39543\text{ms}$<br>$= 33.578\text{mJ}/\text{ LSB}$                     |

図20. ケルビン接続の推奨レイアウト

図21. 水晶発振器の推奨レイアウト

## アプリケーション情報

表1.LTC2946のデバイス・アドレス指定

| 説明             | デバイス・アドレス(16進) | デバイス・アドレス(2進) |    |    |    |    |    |    |    |     | LTC2946のアドレス・ピン |      |

|----------------|----------------|---------------|----|----|----|----|----|----|----|-----|-----------------|------|

|                |                | h             | a6 | a5 | a4 | a3 | a2 | a1 | a0 | R/W | ADR1            | ADR0 |

| Mass Write     | CC             | 1             | 1  | 0  | 0  | 1  | 1  | 0  | 0  | 0   | X               | X    |

| Alert Response | 19             | 0             | 0  | 0  | 1  | 1  | 0  | 0  | 1  | 1   | X               | X    |

| 0              | CE             | 1             | 1  | 0  | 0  | 1  | 1  | 1  | 1  | X   | H               | L    |

| 1              | D0             | 1             | 1  | 0  | 1  | 0  | 0  | 0  | 0  | X   | NC              | H    |

| 2              | D2             | 1             | 1  | 0  | 1  | 0  | 0  | 1  | 1  | X   | H               | H    |

| 3              | D4             | 1             | 1  | 0  | 1  | 0  | 1  | 0  | 0  | X   | NC              | NC   |

| 4              | D6             | 1             | 1  | 0  | 1  | 0  | 1  | 1  | 1  | X   | NC              | L    |

| 5              | D8             | 1             | 1  | 0  | 1  | 1  | 0  | 0  | 0  | X   | L               | H    |

| 6              | DA             | 1             | 1  | 0  | 1  | 1  | 0  | 1  | 1  | X   | H               | NC   |

| 7              | DC             | 1             | 1  | 0  | 1  | 1  | 1  | 1  | 0  | X   | L               | NC   |

| 8              | DE             | 1             | 1  | 0  | 1  | 1  | 1  | 1  | 1  | X   | L               | L    |

表2. LTC2946のレジスタのアドレスと内容

| レジスタ・アドレス | レジスタ名                    | 読み出し/書き込み | 内容                                             | デフォルト |

|-----------|--------------------------|-----------|------------------------------------------------|-------|

| 00h       | CTRLA                    | R/W       | Operation Control Register A                   | 18h   |

| 01h       | CTRLB                    | R/W       | Operation Control Register B                   | 00h   |

| 02h       | ALERT1                   | R/W       | Selects Which Primary Faults Generate Alerts   | 00h   |

| 03h       | STATUS1                  | R         | Primary Status Information                     | 00h   |

| 04h       | FAULT1                   | R/W       | Primary Fault Log                              | 00h   |

| 05h       | POWER MSB2               | R/W       | Power MSB2 Data                                | XXh   |

| 06h       | POWER MSB1               | R/W       | Power MSB1 Data                                | XXh   |

| 07h       | POWER LSB                | R/W       | Power LSB Data                                 | XXh   |

| 08h       | MAX POWER MSB2           | R/W       | Maximum Power MSB2 Data                        | 00h   |

| 09h       | MAX POWER MSB1           | R/W       | Maximum Power MSB1 Data                        | 00h   |

| 0Ah       | MAX POWER LSB            | R/W       | Maximum Power LSB Data                         | 00h   |

| 0Bh       | MIN POWER MSB2           | R/W       | Minimum Power MSB2 Data                        | FFh   |

| 0Ch       | MIN POWER MSB1           | R/W       | Minimum Power MSB1 Data                        | FFh   |

| 0Dh       | MIN POWER LSB            | R/W       | Minimum Power LSB Data                         | FFh   |

| 0Eh       | MAX POWER THRESHOLD MSB2 | R/W       | Maximum POWER Threshold MSB2 to Generate Alert | FFh   |

| 0Fh       | MAX POWER THRESHOLD MSB1 | R/W       | Maximum POWER Threshold MSB1 to Generate Alert | FFh   |

| 10h       | MAX POWER THRESHOLD LSB  | R/W       | Maximum POWER Threshold LSB to Generate Alert  | FFh   |

| 11h       | MIN POWER THRESHOLD MSB2 | R/W       | Minimum POWER Threshold MSB2 to Generate Alert | 00h   |

| 12h       | MIN POWER THRESHOLD MSB1 | R/W       | Minimum POWER Threshold MSB1 to Generate Alert | 00h   |

| 13h       | MIN POWER THRESHOLD LSB  | R/W       | Minimum POWER Threshold LSB to Generate Alert  | 00h   |

| 14h       | ΔSENSE MSB               | R/W       | ΔSENSE MSB Data                                | XXh   |

| 15h       | ΔSENSE LSB               | R/W       | ΔSENSE LSB Data                                | X0h   |

| 16h       | MAX ΔSENSE MSB           | R/W       | Maximum ΔSENSE MSB Data                        | 00h   |

| 17h       | MAX ΔSENSE LSB           | R/W       | Maximum ΔSENSE LSB Data                        | 00h   |

| 18h       | MIN ΔSENSE MSB           | R/W       | Minimum ΔSENSE MSB Data                        | FFh   |

| 19h       | MIN ΔSENSE LSB           | R/W       | Minimum ΔSENSE LSB Data                        | F0h   |

| 1Ah       | MAX ΔSENSE THRESHOLD MSB | R/W       | Maximum ΔSENSE Threshold MSB to Generate Alert | FFh   |

2946fa

## アプリケーション情報

|     |                                   |     |                                                         |     |

|-----|-----------------------------------|-----|---------------------------------------------------------|-----|

| 1Bh | MAX ΔSENSE THRESHOLD LSB          | R/W | Maximum ΔSENSE Threshold LSB to Generate Alert          | F0h |

| 1Ch | MIN ΔSENSE THRESHOLD MSB          | R/W | Minimum ΔSENSE Threshold MSB to Generate Alert          | 00h |

| 1Dh | MIN ΔSENSE THRESHOLD LSB          | R/W | Minimum ΔSENSE Threshold LSB to Generate Alert          | 00h |

| 1Eh | V <sub>IN</sub> MSB               | R/W | ADC V <sub>IN</sub> MSB Data                            | XXh |

| 1Fh | V <sub>IN</sub> LSB               | R/W | ADC V <sub>IN</sub> LSB Data                            | X0h |

| 20h | MAX V <sub>IN</sub> MSB           | R/W | Maximum V <sub>IN</sub> MSB Data                        | 00h |

| 21h | MAX V <sub>IN</sub> LSB           | R/W | Maximum V <sub>IN</sub> LSB Data                        | 00h |

| 22h | MIN V <sub>IN</sub> MSB           | R/W | Minimum V <sub>IN</sub> MSB Data                        | FFh |

| 23h | MIN V <sub>IN</sub> LSB           | R/W | Minimum V <sub>IN</sub> LSB Data                        | F0h |

| 24h | MAX V <sub>IN</sub> THRESHOLD MSB | R/W | Maximum V <sub>IN</sub> Threshold MSB to Generate Alert | FFh |

| 25h | MAX V <sub>IN</sub> THRESHOLD LSB | R/W | Maximum V <sub>IN</sub> Threshold LSB to Generate Alert | F0h |

| 26h | MIN V <sub>IN</sub> THRESHOLD MSB | R/W | Minimum V <sub>IN</sub> Threshold MSB to Generate Alert | 00h |

| 27h | MIN V <sub>IN</sub> THRESHOLD LSB | R/W | Minimum V <sub>IN</sub> Threshold LSB to Generate Alert | 00h |

| 28h | ADIN MSB                          | R/W | ADIN MSB Data                                           | XXh |

| 29h | ADIN LSB                          | R/W | ADIN LSB Data                                           | X0h |

| 2Ah | MAX ADIN MSB                      | R/W | Maximum ADIN MSB Data                                   | 00h |

| 2Bh | MAX ADIN LSB                      | R/W | Maximum ADIN LSB Data                                   | 00h |

| 2Ch | MIN ADIN MSB                      | R/W | Minimum ADIN MSB Data                                   | FFh |

| 2Dh | MIN ADIN LSB                      | R/W | Minimum ADIN LSB Data                                   | F0h |

| 2Eh | MAX ADIN THRESHOLD MSB            | R/W | Maximum ADIN Threshold MSB to Generate Alert            | FFh |

| 2Fh | MAX ADIN THRESHOLD LSB            | R/W | Maximum ADIN Threshold LSB to Generate Alert            | F0h |

| 30h | MIN ADIN THRESHOLD MSB            | R/W | Minimum ADIN Threshold MSB to Generate Alert            | 00h |

| 31h | MIN ADIN THRESHOLD LSB            | R/W | Minimum ADIN Threshold LSB to Generate Alert            | 00h |

| 32h | ALERT2                            | R/W | Selects Which Secondary Faults Generate Alerts          | 00h |

| 33h | GPIO_CFG                          | R/W | GPIO Configuration                                      | 00h |

| 34h | TIME COUNTER MSB3                 | R/W | Time Counter MSB Data3                                  | XXh |

| 35h | TIME COUNTER MSB2                 | R/W | Time Counter MSB Data2                                  | XXh |

| 36h | TIME COUNTER MSB1                 | R/W | Time Counter MSB Data1                                  | XXh |

| 37h | TIME COUNTER LSB                  | R/W | Time Counter LSB Data                                   | XXh |

| 38h | CHARGE MSB3                       | R/W | Charge MSB Data3                                        | XXh |

| 39h | CHARGE MSB2                       | R/W | Charge MSB Data2                                        | XXh |

| 3Ah | CHARGE MSB1                       | R/W | Charge MSB Data1                                        | XXh |

| 3Bh | CHARGE LSB                        | R/W | Charge LSB Data                                         | XXh |

| 3Ch | ENERGY MSB3                       | R/W | Energy MSB Data3                                        | XXh |

| 3Dh | ENERGY MSB2                       | R/W | Energy MSB Data2                                        | XXh |

| 3Eh | ENERGY MSB1                       | R/W | Energy MSB Data1                                        | XXh |

| 3Fh | ENERGY LSB                        | R/W | Energy LSB Data                                         | XXh |

| 40h | STATUS2                           | R   | Secondary Status Information                            | 00h |

| 41h | FAULT2                            | R/W | Secondary Fault Log                                     | 00h |

| 42h | GPIO3_CTRL                        | R/W | GPIO3 Control Command                                   | 00h |

| 43h | CLK_DIV                           | R/W | Clock Divider Command                                   | 04h |

| E7h | MFR_SPECIAL_ID MSB                | R   | Manufacturer Special ID MSB Data                        | 60h |

| E8h | MFR_SPECIAL_ID LSB                | R   | Manufacturer Special ID LSB Data                        | 01h |

## アプリケーション情報

表3. CTRLAレジスタ(00h):読み出し/書き込み

| ビット     | レジスタ名                            | 動作                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | デフォルト |

|---------|----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| CA[7]   | ADIN Configuration               | [1] = ADIN Measured with Respect to INTV <sub>CC</sub><br>[0] = ADIN Measured with Respect to GND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 0     |

| CA[6:5] | Offset Calibration Configuration | Offset Calibration<br>[11] = 1st Power-Up or Use Last Calibrated Result<br>[10] = Once Every 128 Conversions<br>[01] = Once Every 16 Conversions<br>[00] = Every Conversion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 00    |

| CA[4:3] | Voltage Selection                | [11] = SENSE*<br>[10] = ADIN<br>[01] = V <sub>DD</sub><br>[00] = ΔSENSE**                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 11    |

| CA[2:0] | Channel Configuration            | [111] = Snapshot Mode (Channel Defined by CA[4:3]).No Power, Energy or Charge Data Generated<br>[110] = Voltage Measurement Once Followed by Current Measurement Indefinitely*<br>[101] = ADIN, Voltage, Current Measurement at 1/256, 1/256 and 254/256 Duty Cycle, Respectively*<br>[100] = ADIN, Voltage, Current Measurement at 1/32, 1/32 and 30/32 Duty Cycle, Respectively*<br>[011] = Alternate ADIN, Voltage and Current Measurement*<br>[010] = Voltage, Current Measurement at 1/128 and 127/128 Duty Cycle, Respectively*<br>[001] = Voltage, Current Measurement at 1/16 and 15/16 Duty Cycle, Respectively*<br>[000] = Alternate Voltage, Current Measurement* | 000   |

\* ポーリング・モードにおいて CA[4:3] で定義される電圧。

\*\* ΔSENSE(00)を選択して、スナップ・ショット・モード(111)以外のチャネル構成を選択した場合、電圧データは常にモード変更前のV<sub>IN</sub>レジスタ内の値になる。

ポーリング・モードを使用する際は、ΔSENSEを選択しないことを推奨する。

表4. CTRLBレジスタ(01h):読み出し/書き込み

| ビット     | レジスタ名                          | 動作                                                                                                                                                              | デフォルト |

|---------|--------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| CB[7]   | ALERT Clear Enable             | Clear ALERT if Device is Addressed by the Master<br>[1] = Enable<br>[0] = Disable                                                                               | 0     |

| CB[6]   | Shutdown                       | [1] = Shutdown<br>[0] = Power-Up                                                                                                                                | 0     |

| CB[5]   | Cleared on Read Control        | FAULT Registers Cleared on Read<br>[1] = Cleared on Read<br>[0] = Registers Not Affected by Reading                                                             | 0     |

| CB[4]   | Stuck Bus Timeout Auto Wake-Up | Allows Part to Exit Shutdown Mode When Stuck-Bus Timer Is Reached<br>[1] = Enable<br>[0] = Disable                                                              | 0     |

| CB[3:2] | Enable Accumulation            | [11] = Reserved<br>[10] = Follows ACC State (GPIO2, See Table 9)<br>ACC High, Accumulate<br>ACC Low, No Accumulate<br>[01] = No Accumulate<br>[00] = Accumulate | 00    |

| CB[1:0] | Auto-Reset Mode/Reset          | [11] = Reset All Registers<br>[10] = Reset Accumulator (Time Counter, Charge and Energy) Registers<br>[01] = Enable Auto-Reset<br>[00] = Disable Auto-Reset     | 00    |

## アプリケーション情報

表5.ALERT1レジスタ(02h):読み出し/書き込み

| ビット    | レジスタ名                         | 動作                                                                                                                  | デフォルト |

|--------|-------------------------------|---------------------------------------------------------------------------------------------------------------------|-------|

| AL1[7] | Maximum POWER Alert           | Enables Alert When POWER > Maximum POWER Threshold<br>[1] = Enable Alert<br>[0] = Disable Alert                     | 0     |

| AL1[6] | Minimum POWER Alert           | Enables Alert When POWER < Minimum POWER Threshold<br>[1] = Enable Alert<br>[0] = Disable Alert                     | 0     |

| AL1[5] | Maximum ISENSE Alert          | Enables Alert When ISENSE > Maximum ISENSE Threshold<br>[1] = Enable Alert<br>[0] = Disable Alert                   | 0     |

| AL1[4] | Minimum ISENSE Alert          | Enables Alert When ISENSE < Minimum ISENSE Threshold<br>[1] = Enable Alert<br>[0] = Disable Alert                   | 0     |

| AL1[3] | Maximum V <sub>IN</sub> Alert | Enables Alert When V <sub>IN</sub> > Maximum V <sub>IN</sub> Threshold<br>[1] = Enable Alert<br>[0] = Disable Alert | 0     |

| AL1[2] | Minimum V <sub>IN</sub> Alert | Enables Alert When V <sub>IN</sub> < Minimum V <sub>IN</sub> Threshold<br>[1] = Enable Alert<br>[0] = Disable Alert | 0     |

| AL1[1] | Maximum ADIN Alert            | Enables Alert When ADIN > Maximum ADIN Threshold<br>[1] = Enable Alert<br>[0] = Disable Alert                       | 0     |

| AL1[0] | Minimum ADIN Alert            | Enables Alert When ADIN < Minimum ADIN Threshold<br>[1] = Enable Alert<br>[0] = Disable Alert                       | 0     |

表6.STATUS1レジスタ(03h):読み出し

| ビット   | レジスタ名                      | 動作                                                                                                                              | デフォルト |

|-------|----------------------------|---------------------------------------------------------------------------------------------------------------------------------|-------|

| S1[7] | POWER Overvalue            | POWER > Maximum POWER Threshold<br>[1] = POWER Overvalue<br>[0] = POWER Not Overvalue                                           | 0     |

| S1[6] | POWER Undervalue           | POWER < Minimum POWER Threshold<br>[1] = POWER Undervalue<br>[0] = POWER Not Undervalue                                         | 0     |

| S1[5] | ISENSE Overvalue           | ISENSE > Maximum ISENSE Threshold<br>[1] = ISENSE Overvalue<br>[0] = ISENSE Not Overvalue                                       | 0     |

| S1[4] | ISENSE Undervalue          | ISENSE < Minimum ISENSE Threshold<br>[1] = ISENSE Undervalue<br>[0] = ISENSE Not Undervalue                                     | 0     |

| S1[3] | V <sub>IN</sub> Overvalue  | V <sub>IN</sub> > Maximum V <sub>IN</sub> Threshold<br>[1] = V <sub>IN</sub> Overvalue<br>[0] = V <sub>IN</sub> Not Overvalue   | 0     |

| S1[2] | V <sub>IN</sub> Undervalue | V <sub>IN</sub> < Minimum V <sub>IN</sub> Threshold<br>[1] = V <sub>IN</sub> Undervalue<br>[0] = V <sub>IN</sub> Not Undervalue | 0     |

| S1[1] | ADIN Overvalue             | ADIN > Maximum ADIN Threshold<br>[1] = ADIN Overvalue<br>[0] = ADIN Not Overvalue                                               | 0     |

| S1[0] | ADIN Undervalue            | ADIN < Minimum ADIN Threshold<br>[1] = ADIN Undervalue<br>[0] = ADIN Not Undervalue                                             | 0     |

2946fa

## アプリケーション情報

表7. FAULT1レジスタ(04h) : 読み出し/書き込み

| ビット   | レジスタ名                               | 動作                                                                                                                                                                       | デフォルト |

|-------|-------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| F1[7] | POWER Overvalue Fault               | POWER > Maximum POWER Threshold<br>[1] = POWER Overvalue Fault Occurred<br>[0] = No POWER Overvalue Fault Occurred                                                       | 0     |

| F1[6] | POWER Undervalue Fault              | POWER < Minimum POWER Threshold<br>[1] = POWER Undervalue Fault Occurred<br>[0] = No POWER Undervalue Fault Occurred                                                     | 0     |

| F1[5] | I <sub>SENSE</sub> Overvalue Fault  | I <sub>SENSE</sub> > Maximum I <sub>SENSE</sub> Threshold<br>[1] = I <sub>SENSE</sub> Overvalue Fault Occurred<br>[0] = No I <sub>SENSE</sub> Overvalue Fault Occurred   | 0     |

| F1[4] | I <sub>SENSE</sub> Undervalue Fault | I <sub>SENSE</sub> < Minimum I <sub>SENSE</sub> Threshold<br>[1] = I <sub>SENSE</sub> Undervalue Fault Occurred<br>[0] = No I <sub>SENSE</sub> Undervalue Fault Occurred | 0     |

| F1[3] | V <sub>IN</sub> Overvalue Fault     | V <sub>IN</sub> > Maximum V <sub>IN</sub> Threshold<br>[1] = V <sub>IN</sub> Overvalue Fault Occurred<br>[0] = No V <sub>IN</sub> Overvalue Fault Occurred               | 0     |

| F1[2] | V <sub>IN</sub> Undervalue Fault    | V <sub>IN</sub> < Minimum V <sub>IN</sub> Threshold<br>[1] = V <sub>IN</sub> Undervalue Fault Occurred<br>[0] = No V <sub>IN</sub> Undervalue Fault Occurred             | 0     |

| F1[1] | ADIN Overvalue Fault                | ADIN > Maximum ADIN Threshold<br>[1] = ADIN Overvalue Fault Occurred<br>[0] = No ADIN Overvalue Fault Occurred                                                           | 0     |

| F1[0] | ADIN Undervalue Fault               | ADIN < Minimum ADIN Threshold<br>[1] = ADIN Undervalue Fault Occurred<br>[0] = No ADIN Undervalue Fault Occurred                                                         | 0     |

表8.ALERT2レジスタ(32h) : 読み出し/書き込み

| ビット    | レジスタ名                           | 動作                                                                                                                                                                                    | デフォルト |

|--------|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| AL2[7] | ADC Conversion Done Alert       | Alert When ADC Finishes a Conversion<br>[1] = Enable<br>[0] = Disable                                                                                                                 | 0     |

| AL2[6] | GPIO1 Input Alert               | Alert if<br>GPIO1 Is Low When GP[7:6] = [01] (GPIO1 Input Active Low), or<br>GPIO1 Is High When GP[7:6] = [00] (GPIO1 Input Active High)<br>[1] = Enable Alert<br>[0] = Disable Alert | 0     |

| AL2[5] | GPIO2 Input Alert               | Alert if<br>GPIO2 Is Low When GP[5:4] = [01] (GPIO2 Input Active Low), or<br>GPIO2 Is High When GP[5:4] = [00] (GPIO2 Input Active High)<br>[1] = Enable Alert<br>[0] = Disable Alert | 0     |

| AL2[4] | Reserved                        |                                                                                                                                                                                       | 0     |

| AL2[3] | Stuck-Bus Timeout Wake-Up Alert | Alert if Part Exits Shutdown Mode After Stuck-Bus Timer Expires with CB[4] = 1<br>[1] = Enable Alert<br>[0] = Disable Alert                                                           | 0     |

| AL2[2] | Energy Overflow Alert           | Alert if Energy Register Overflow<br>[1] = Enable Alert<br>[0] = Disable Alert                                                                                                        | 0     |

## アプリケーション情報

|        |                             |                                                                                      |   |

|--------|-----------------------------|--------------------------------------------------------------------------------------|---|

| AL2[1] | Charge Overflow Alert       | Alert if Charge Register Overflow<br>[1] = Enable Alert<br>[0] = Disable Alert       | 0 |

| AL2[0] | Time Counter Overflow Alert | Alert if Time Counter Register Overflow<br>[1] = Enable Alert<br>[0] = Disable Alert | 0 |

表9.GPIO\_CFG レジスタ(33h)：読み出し/書き込み

| ビット     | レジスタ名           | 動作                                                                                                                                                                         | デフォルト |

|---------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| GP[7:6] | GPIO1 Configure | [11] = General Purpose Input, Active High<br>[10] = General Purpose Input, Active Low<br>[01] = General Purpose Output, Hi-Z<br>[00] = General Purpose Output, Pulls Low   | 00    |

| GP[5:4] | GPIO2 Configure | [11] = General Purpose Input, Active High<br>[10] = General Purpose Input, Active Low<br>[01] = General Purpose Output, GPIO = GP[1]<br>[00] = Accumulate Input            | 00    |

| GP[3:2] | GPIO3 Configure | [11] = General Purpose Input, Active High<br>[10] = General Purpose Input, Active Low<br>[01] = General Purpose Output, See Register 42h (Table 12)<br>[00] = ALERT Output | 00    |

| GP[1]   | GPIO2 Output    | [1] = Pulls Low<br>[0] = Hi-Z                                                                                                                                              | 0     |

| GP[0]   | Reserved        |                                                                                                                                                                            | 0     |

## アプリケーション情報

表10. STATUS2 レジスタ(40h) : 読み出し

| ビット   | 名称                             | 動作                                                                                                                 |       |                           |                                     | デフォルト |