## 特長

- 柔軟な電源トラッキング

- 上昇下降両方のトラッキング

- 電源シーケンシング

- 電源の安定性に影響なし

- シリーズFETなしで2つの電源を制御

- 1個のシリーズFETを使用して第3の電源を制御

- ランプ・レートを調整可能

- 電子回路ブレーカ

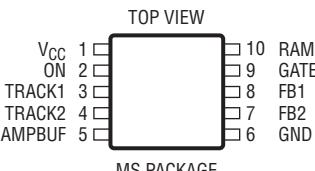

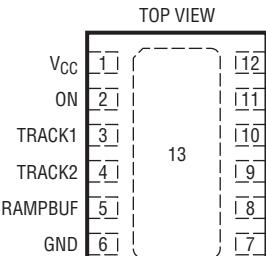

- 10ピンMSおよび12ピン(4mm×3mm)DFNパッケージ

## アプリケーション

- $V_{CORE}$ および $V_{I/O}$ 電源のトラッキング

- マイクロプロセッサ、DSPおよびFPGA用電源

- サーバー

- 通信システム

**LTC**、**LTC**、**LT**はリニアテクノロジー社の登録商標です。その他すべての商標の所有権は、それぞれの所有者に帰属します。特許申請中。

## 概要

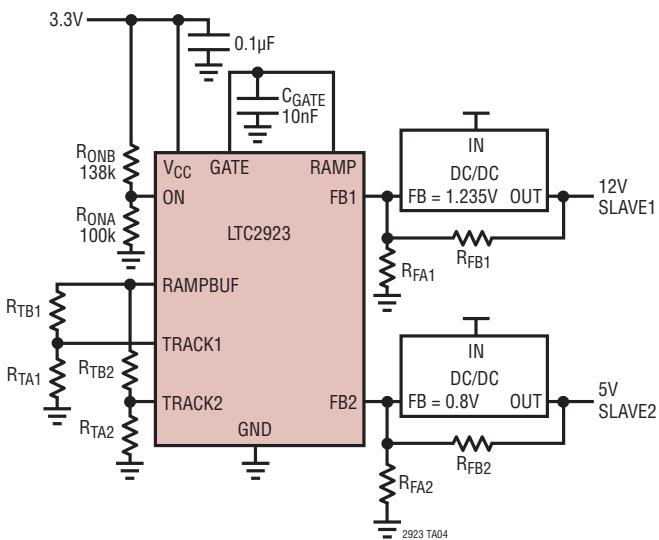

LTC®2923は電源のトラッキングとシーケンシングの要件を簡単に満たします。数個の抵抗を選択することにより、複数の電源が電圧オフセットや遅延をともない、または異なったランプ・レートでランプアップ/ランプダウンするように設定することができます。

2つの独立したスイッチング・レギュレータの帰還ノードに電流を流し込むことにより、LTC2923はこれらの電源の出力がパス素子の損失なしにトラッキングをおこなうようにします。電流はオープンループ方式で制御されるので、LTC2923が過渡応答や電源の安定性に影響を与えることはありません。さらに、起動が完了するとハイ・インピーダンスになるので、DC/DC回路から事実上切り離されます。

第3の電源が必要なシステムで使用する場合、1つの電源を1個のFETで制御できます。このオプションのシリーズFETは、帰還抵抗への直接アクセスを許容しない電源(パワー・モジュールなど)やその出力を強制的に接地できない電源(3端子リニア・レギュレータなど)も制御することができます。FETが使用される場合、電子回路ブレーカによって短絡状態から保護します。

## 標準的応用例

# LTC2923

## 絶対最大定格 (Note 1)

|                    |                         |                 |             |

|--------------------|-------------------------|-----------------|-------------|

| 電源電圧 ( $V_{CC}$ )  | -0.3V~10V               | 平均電流            |             |

| 入力電圧               |                         | TRACK1、TRACK2   | 5mA         |

| ON                 | -0.3V~10V               | FB1、FB2         | 5mA         |

| TRACK1、TRACK2      | -0.3V~( $V_{CC}+0.3V$ ) | RAMPBUF         | 5mA         |

| RAMP               | -0.3V~( $V_{CC}+1V$ )   |                 |             |

| 出力電圧               |                         | 動作温度範囲          |             |

| FB1、FB2、SDO、STATUS | -0.3V~10V               | LTC2923C        | 0°C~70°C    |

| RAMPBUF            | -0.3V~( $V_{CC}+0.3V$ ) | LTC2923I        | -40°C~85°C  |

| GATE (Note 2)      | -0.3V~11.5V             | 保存温度範囲          | -65°C~150°C |

|                    |                         | リード温度(半田付け、10秒) |             |

|                    |                         | MSパッケージ         | 300°C       |

## パッケージ/発注情報

| TOP VIEW<br><br><br>MS PACKAGE<br>10-LEAD PLASTIC MSOP<br>$T_{JMAX} = 125^\circ\text{C}, \theta_{JA} = 120^\circ\text{C/W}$ | ORDER PART NUMBER | TOP VIEW<br><br><br>DE12 PACKAGE<br>12-LEAD (4mm x 3mm) PLASTIC DFN<br>$T_{JMAX} = 125^\circ\text{C}, \theta_{JA} = 43^\circ\text{C/W}$<br>EXPOSED PAD (PIN 13) INTERNALLY CONNECTED TO GND (PCB CONNECTION OPTIONAL) | ORDER PART NUMBER |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

|                                                                                                                                                                                                               | LTC2923CMS        |                                                                                                                                                                                                                                                                                                          | LTC2923CDE        |

|                                                                                                                                                                                                               | LTC2923IMS        |                                                                                                                                                                                                                                                                                                          | LTC2923IDE        |

|                                                                                                                                                                                                               | MS PART MARKING   |                                                                                                                                                                                                                                                                                                          | DE PART MARKING   |

| LTAED<br>LTAEE                                                                                                                                                                                                |                   |                                                                                                                                                                                                                                                                                                          | 2923              |

さらに広い動作温度範囲で規定されるデバイスについては、弊社または弊社代理店にお問い合わせください。

## 電気的特性

●は全動作温度範囲での規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。注記がない限り、 $2.9V < V_{CC} < 5.5V$  (Note 3)

| SYMBOL                   | PARAMETER                                             | CONDITIONS                                              | MIN | TYP   | MAX   | UNITS |

|--------------------------|-------------------------------------------------------|---------------------------------------------------------|-----|-------|-------|-------|

| $V_{CC}$                 | Input Supply Range                                    |                                                         | ●   | 2.9   | 5.5   | V     |

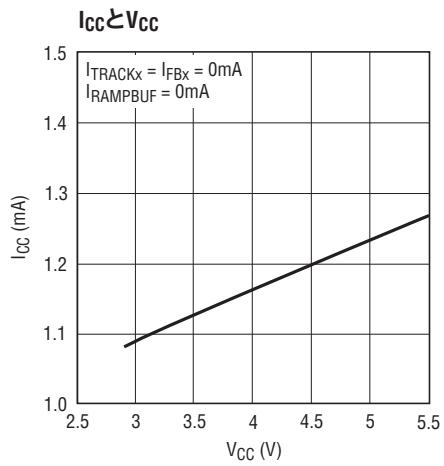

| $I_{CC}$                 | Input Supply Current                                  | $I_{FBX} = 0, I_{TRACKX} = 0$                           | ●   | 1.3   | 3     | mA    |

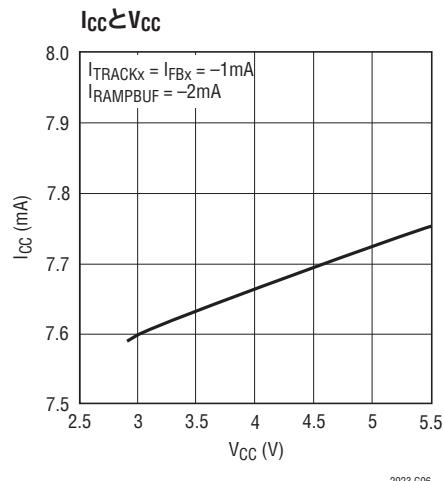

|                          |                                                       | $I_{FBX} = -1mA, I_{TRACKX} = -1mA, I_{RAMPBUF} = -2mA$ | ●   | 5     | 7     | 10    |

| $V_{CC(UVL)}$            | Input Supply Undervoltage Lockout                     | $V_{CC}$ Rising                                         | ●   | 2.2   | 2.5   | 2.7   |

| $\Delta V_{CC(UVLHYST)}$ | Input Supply Undervoltage Lockout Hysteresis          |                                                         |     | 25    |       | mV    |

| $\Delta V_{GATE}$        | External N-Channel Gate Drive ( $V_{GATE} - V_{CC}$ ) | $I_{GATE} = -1\mu\text{A}$                              | ●   | 5     | 5.5   | 6     |

| $I_{GATE}$               | GATE Pin Current                                      | Gate On, $V_{GATE} = 0V$ , No Faults                    | ●   | -7    | -10   | -13   |

|                          |                                                       | Gate Off, $V_{GATE} = 5V$ , No Faults                   | ●   | 7     | 10    | 13    |

|                          |                                                       | Gate Off, $V_{GATE} = 5V$ , Short-Circuit Fault         | ●   | 5     | 20    | 50    |

| $V_{ON(TH)}$             | ON Pin Threshold Voltage                              | $V_{ON}$ Rising                                         | ●   | 1.212 | 1.230 | 1.248 |

| $\Delta V_{ON(HYST)}$    | ON Pin Hysteresis                                     |                                                         | ●   | 30    | 75    | 150   |

## 電気的特性

●は全動作温度範囲での規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。注記がない限り、 $2.9\text{V} < V_{CC} < 5.5\text{V}$ (Note 3)。

| SYMBOL              | PARAMETER                                                                                           | CONDITIONS                                                  | MIN                | TYP        | MAX            | UNITS         |

|---------------------|-----------------------------------------------------------------------------------------------------|-------------------------------------------------------------|--------------------|------------|----------------|---------------|

| $V_{ON(FC)}$        | ON Pin Fault Clear Threshold Voltage                                                                |                                                             | ● 0.3              | 0.4        | 0.5            | V             |

| $I_{ON}$            | ON Pin Input Current                                                                                | $V_{ON} = 1.2\text{V}, V_{CC} = 5.5\text{V}$                | ● 0                | 0          | $\pm 100$      | nA            |

| $\Delta V_{DS(TH)}$ | FET Drain-Source Overcurrent Voltage Threshold ( $V_{CC} - V_{RAMP}$ )                              |                                                             | ● 160              | 200        | 240            | mV            |

| $I_{RAMP}$          | RAMP Pin Input Current                                                                              | $0\text{V} < RAMP < V_{CC}, V_{CC} = 5.5\text{V}$           | ● 0                | 0          | $\pm 1$        | $\mu\text{A}$ |

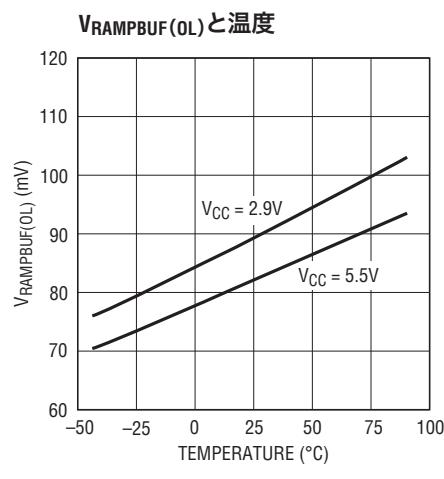

| $V_{RAMPBUF(OL)}$   | RAMPBUF Low Voltage                                                                                 | $I_{RAMPBUF} = 2\text{mA}$                                  | ● 90               | 150        |                | mV            |

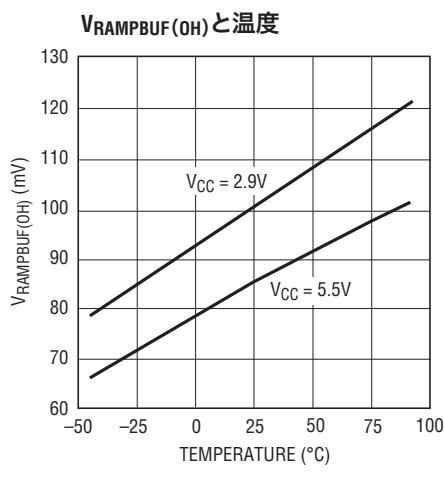

| $V_{RAMPBUF(OH)}$   | RAMPBUF High Voltage ( $V_{CC} - V_{RAMPBUF}$ )                                                     | $I_{RAMPBUF} = -2\text{mA}$                                 | ● 100              | 200        |                | mV            |

| $V_{OS}$            | Ramp Buffer Offset ( $V_{RAMPBUF} - V_{RAMP}$ )                                                     | $V_{RAMPBUF} = V_{CC}/2, I_{RAMPBUF} = 0\text{A}$           | -30                | 0          | 30             | mV            |

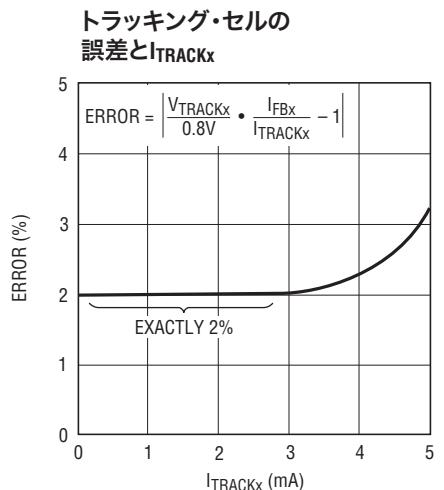

| $I_{ERROR(\%)}$     | $I_{FBx}$ to $I_{TRACKx}$ Current Mismatch<br>$I_{ERROR(\%)} = ( I_{FBx} - I_{TRACKx} )/I_{TRACKx}$ | $I_{TRACKx} = -10\mu\text{A}$<br>$I_{TRACKx} = -1\text{mA}$ | ● 0                | 0          | $\pm 5$        | %             |

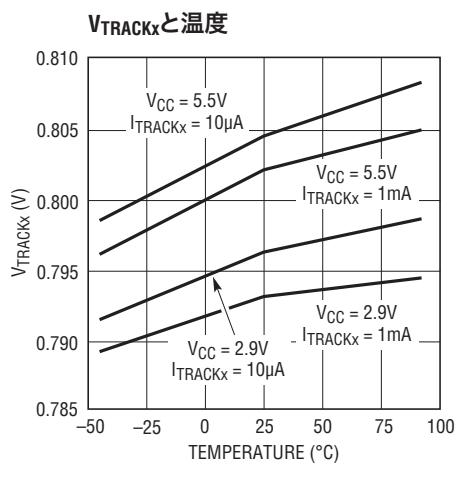

| ●<br>$V_{TRACKx}$   | TRACK Pin Voltage                                                                                   | $I_{TRACKx} = -10\mu\text{A}$<br>$I_{TRACKx} = -1\text{mA}$ | ● 0.776<br>● 0.776 | 0.8<br>0.8 | 0.824<br>0.824 | V<br>V        |

| $I_{FB(LEAK)}$      | $I_{FB}$ Leakage Current                                                                            | $V_{FB} = 1.5\text{V}, V_{CC} = 5.5\text{V}$                | ● $\pm 1$          | $\pm 100$  |                | nA            |

| $V_{FB(CLAMP)}$     | $V_{FB}$ Clamp Voltage                                                                              | $1\mu\text{A} < I_{FB} < 1\text{mA}$                        | ● 1.5              | 1.7        | 2              | V             |

| $V_{SDO(OL)}$       | SDO Output Low Voltage                                                                              | $I_{SDO} = 3\text{mA}$                                      | ● 0.2              | 0.4        |                | V             |

| $V_{STATUS(OL)}$    | STATUS Output Low Voltage                                                                           | $I_{STATUS} = 3\text{mA}$                                   | ● 0.2              | 0.4        |                | V             |

| $t_{PSC}$           | Short-Circuit Propagation Delay $V_{DS}$ High to GATE Low                                           | $V_{DS} = V_{CC}, V_{CC} = 2.9\text{V}$                     |                    | 10         | 20             | $\mu\text{s}$ |

Note 1: 絶対最大定格はそれを超えるとデバイスの寿命に影響を及ぼす値。

Note 3: デバイスのピンに流れ込む電流はすべて正。デバイスのピンから流れ出す電流はすべて負。注記がない限り、すべての電圧はグランドを基準にしている。

Note 2: GATEピンは内部で11.5Vの最小値に制限されている。このピンをクランプを超す電圧にドライブするとデバイスを損傷するおそれがある。

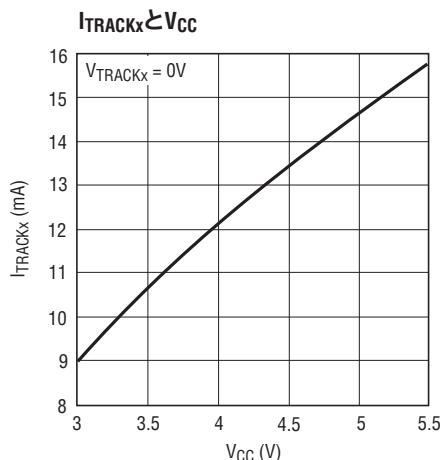

## 標準的性能特性

注記がない限り、規格値は $T_A = 25^\circ\text{C}$ での値。

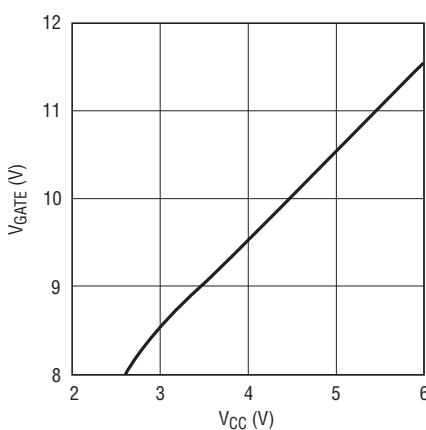

$V_{GATE}$ と $V_{CC}$

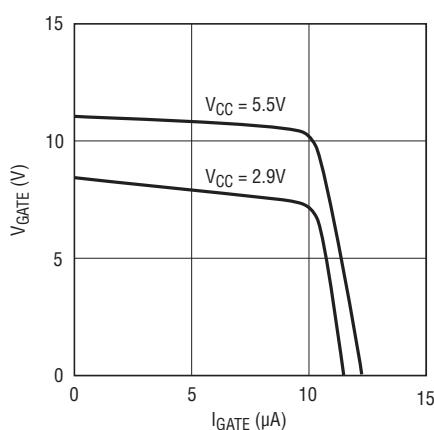

$V_{GATE}$ と $I_{GATE}$

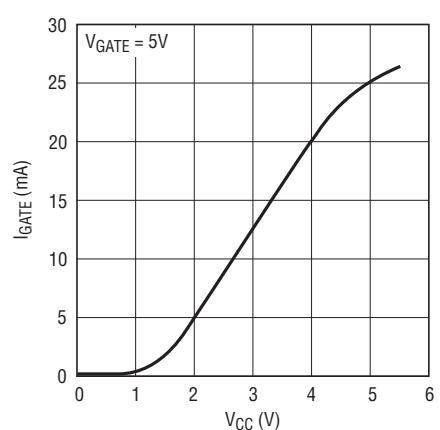

$I_{GATE}$ と $V_{CC}$ の高速プルダウン

2923 G03

## 標準的性能特性

注記がない限り、規格値は $T_A = 25^\circ\text{C}$ での値。

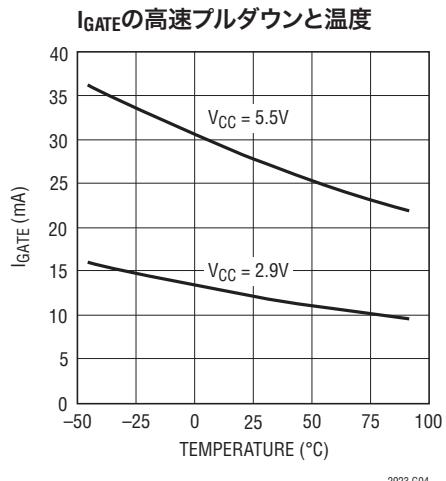

2923 G04

2923 G05

2923 G06

2923 G07

2923 G08

2923 G09

2923 G11

2923 G10

2923 G12

## ピン機能 MS/DEパッケージ

**V<sub>CC</sub>(ピン1)**: 正電源入力ピン。動作電源入力範囲は2.9V～5.5Vです。低電圧ロックアウト回路は電源が2.5Vより低いとデバイスをリセットします。V<sub>CC</sub>は0.1μFのコンデンサを使ってGNDにバイパスします。

**ON(ピン2)**: オン制御入力。ONピンのスレッショルドは1.23Vで、75mVのヒステリシスがあります。アクティブ“H”になるとGATEピンから10μAが流れ出し、電源をランプアップします。アクティブ“L”になるとGATEピンから10μAが流れ込み、電源をランプダウンします。ONピンを0.4Vより下に引き下げると、LTC2923の電子回路ブレーカーをリセットします。V<sub>CC</sub>に接続された抵抗分割器がONピンをドライブする場合、V<sub>CC</sub>に電力が完全に供給されると、電源が自動的に起動します。

**TRACK1, TRACK2(ピン3, 4)**: トラッキング制御入力ピン。RAMPBUFおよびTRACKx間の抵抗分割器により、スレーブ電源のトラッキング・プロファイルが決定されます(「アプリケーション情報」を参照)。TRACKxは0.8Vまでプルアップし、TRACKxで供給される電流はFBxにミラーリングされます。TRACKxピンはV<sub>CC</sub> = 2.9Vのとき少なくとも1mAを供給する能力があります。TRACKxピンは短絡状態では30mAまで供給できるので、TRACKxをGNDに長時間接続しないようにします。各TRACKxピンの容量は25pF未満に制限します。未使用の場合、TRACKピンはフロートさせます。

**RAMPBUF(ピン5)**: ランプ・バッファ出力。RAMPピンの信号をバッファして、低インピーダンスの出力として供給します。このバッファされた出力はTRACKxピンに接続された抵抗分割器をドライブします。RAMPBUFピンの容量は100pF未満に制限します。

**GND(ピン6, 13)**: 回路のグランド。

**FB1, FB2(ピン8, 7)**: 帰還制御出力。FBxはスレーブ電源の帰還ノードをプルアップします。トラッキングはTRACKxからFBxに電流をミラーリングすることにより実現されます。適当な抵抗分割器をRAMPBUFとTRACKxに接続すると、FBx電流はOUTxがRAMPをトラッキングするように強制します。スレーブ電源への損傷を防ぐため、FBxピンはスレーブの帰還ノードを1.7Vより上には強制しません。さらに、LTC2923に電力が供給されていないときでも、このピンはこのノードから能動的には電流をシンクしません。未使用の場合、FBピンはフロートさせます。

**GATE(ピン9/ピン11)**: 外部NチャネルFETのゲート・ドライブ。ONピンが“H”的とき、内部10μA電流源が外部NチャネルMOSFETのゲートを充電します。GATEからGNDに接続されたコンデンサによりランプ・レートが設定されます。内部チャージポンプにより、GATEがV<sub>CC</sub>より5V上までプルアップしてロジック・レベルのNチャネルFETが完全に導通するように保証します。ONピンが“L”に引き下げられると、GATEピンは10μAの電流源によってGNDに引き下げられます。短絡状態では、LTC2923の電子回路ブレーカーは直ちに20mAでGATEを“L”に引き下げます。未使用の場合、GATEはGNDに接続します。FETの高周波数発振を防ぐために、このコンデンサとFETのゲート間に10Ωの抵抗を追加することを推奨します。

**RAMP(ピン10/ピン12)**: ランプ・バッファ入力。RAMPピンが外部NチャネルFETのソースに接続されていると、スレーブ電源はFETのソースがランプアップ/ランプダウンするにつれ、それをトラッキングします。GATEが完全に導通し(GATE > RAMP +4.9V)、(V<sub>CC</sub>-RAMP > 200mV)が出力の短絡を示すと、電子回路ブレーカーがトリップして、GATEは20mAで急速に“L”に引き下げられます。ONが0.4Vより下まで引き下げられ、次に1.23Vより上に引き上げられるまで、GATEは再度ランプアップすることはありません。代わりに、外部FETを使わない場合、RAMPピンを直接GATEピンに接続することができます。この構成法では、ONピンによって制御される10μAの電流源によってGATEピンのコンデンサが充放電するにつれて、電源はこのコンデンサをトラッキングします。(GATEピンでドライブする場合を除き)RAMPをV<sub>CC</sub>より上にドライブしてはなりません。

**SDO(ピン9, DEパッケージのみ)**: スレーブ電源のシャットダウン出力。 $\overline{\text{SDO}}$ は、ONピンの電圧が1.23Vより上になるまでスレーブ電源のシャットダウン(RUN/SS)ピンを“L”に保持するオープンドレイン出力です。スレーブ電源がLTC2923の最小動作電圧2.9Vより低い入力電源で動作可能なときは、 $\overline{\text{SDO}}$ ピンを使ってスレーブ電源をオフに保つことができます。RAMPが100mVより下になり、ONが1.23Vより下になると、 $\overline{\text{SDO}}$ は再び“L”になります。

**STATUS(ピン10, DEパッケージのみ)**: パワーグッド状態インジケータ。STATUSピンは、GATEがフルに充電されるまで“L”になっているオープンドレイン出力です。GATEがフルに充電された時点では、すべての電源は最終動作電圧に達しています。

# LTC2923

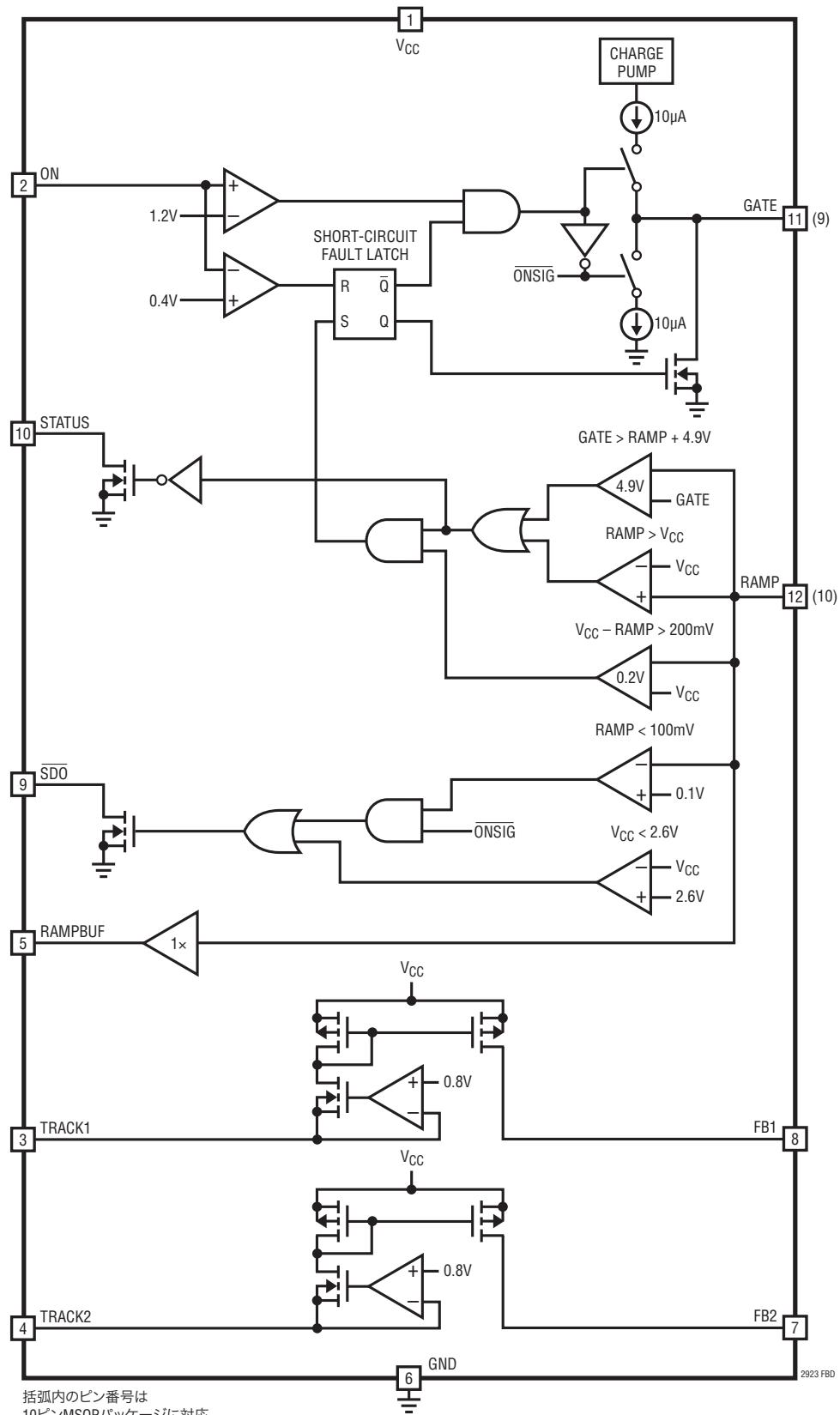

## 機能ブロック図

## アプリケーション情報

### 電源のトラッキングとシーケンシング

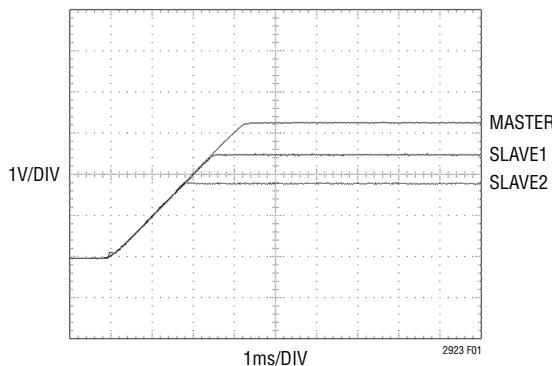

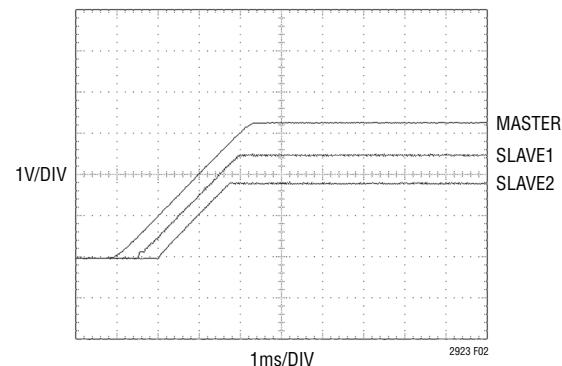

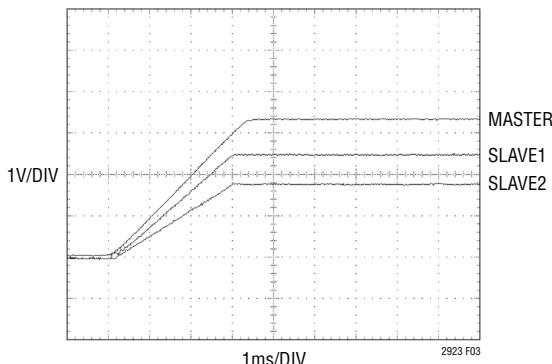

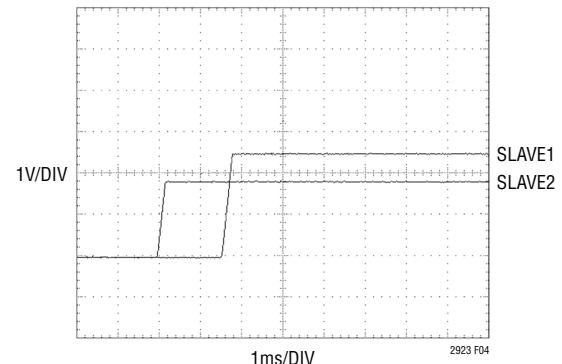

LTC2923は種々の電源立上げプロファイルを処理し、FPGA、PLD、DSP、マイクロプロセッサなどのデジタル・ロジック回路の要件を満たします。これらの要件は図1～図4に示されている4つの一般的なカテゴリーのどれかに当てはまります。

アプリケーションによっては、2つの電源の電位差がどんな場合でも規定された電圧を超えないことが要求されます。この要件は定常動作時だけでなくパワーアップ/パワーダウン時にも適用され、多くの場合、デュアル電源のASICの破壊的なラップアップを防ぎます。一般に、これは2つの電源を同時にランプアップ/ランプダウンすることによって達成されます(図1)。他のアプリケーションでは、それらの電源のあいだのオフセット電圧を固定してランプアップ/ランプダウンさせるか(図2)、あるいは比例的にランプアップ/ランプダウンさせる(図3)ことが望まれます。

特定のアプリケーションでは、片方の電源が起動した後、他方が起動することが必要です。たとえば、システム・クロックはロジック・ブロックより先に起動する必要があるかもしれません。この場合、電源は図4のように順序づけられ、1.8V電源が完全に起動してから、2.5V電源がランプアップします。

### 動作

LTC2923は図1～図4に示されている電源のトラッキングとシーケンシングのすべてのプロファイルを簡単に実現します。1個のLTC2923が最大3個の電源を制御し、そのうち2個の「スレーブ」電源は1個の「マスタ」信号をトラッキングします。2個の抵抗を使うだけで、スレーブ電源はマスタ信号の関数としてランプアップするように構成されます。このマスタ信号を3番目の電源にすることもでき、外部FETを通してランプアップします。そのランプ・レートは1個のコンデンサで設定するか、またはGATEピンとRAMPピンを外付けのコンデンサに接続して信号を発生することもできます。

図1. 同時トラッキング

図2. オフセット・トラッキング

図3. 比例トラッキング

図4. 電源シーケンシング

## アプリケーション情報

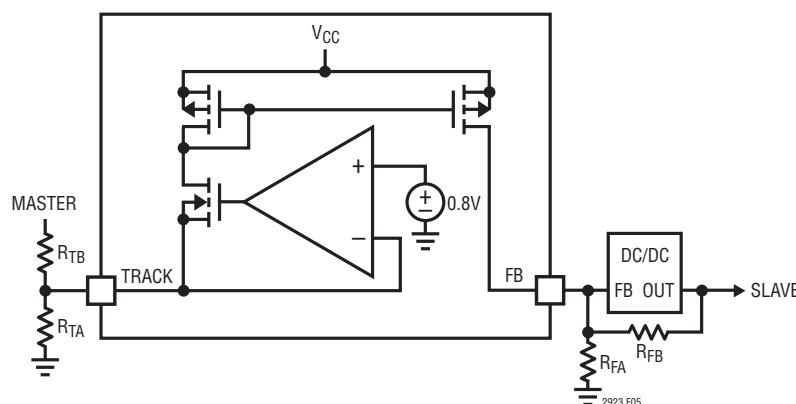

### トラッキング・セル

LTC2923の動作は図5に示されているトラッキング・セルをベースにしています。これには固有技術の広範囲電流ミラーが使用されています。図5に示されているトラッキング・セルはTRACKピンを0.8Vにサーボ制御します。TRACKピンの供給する電流はFBピンにミラーリングされ、スレーブ電源の出力電圧を確定します。スレーブの出力電圧はマスタ信号によって変化するので、 $R_{TA}$ と $R_{TB}$ によって設定される項にしたがって、スレーブ電源をマスタ信号の関数として制御することができます。 $R_{TA}$ と $R_{TB}$ の適当な値を選択することにより、図1～図4のどのプロファイルでも発生させることができます。

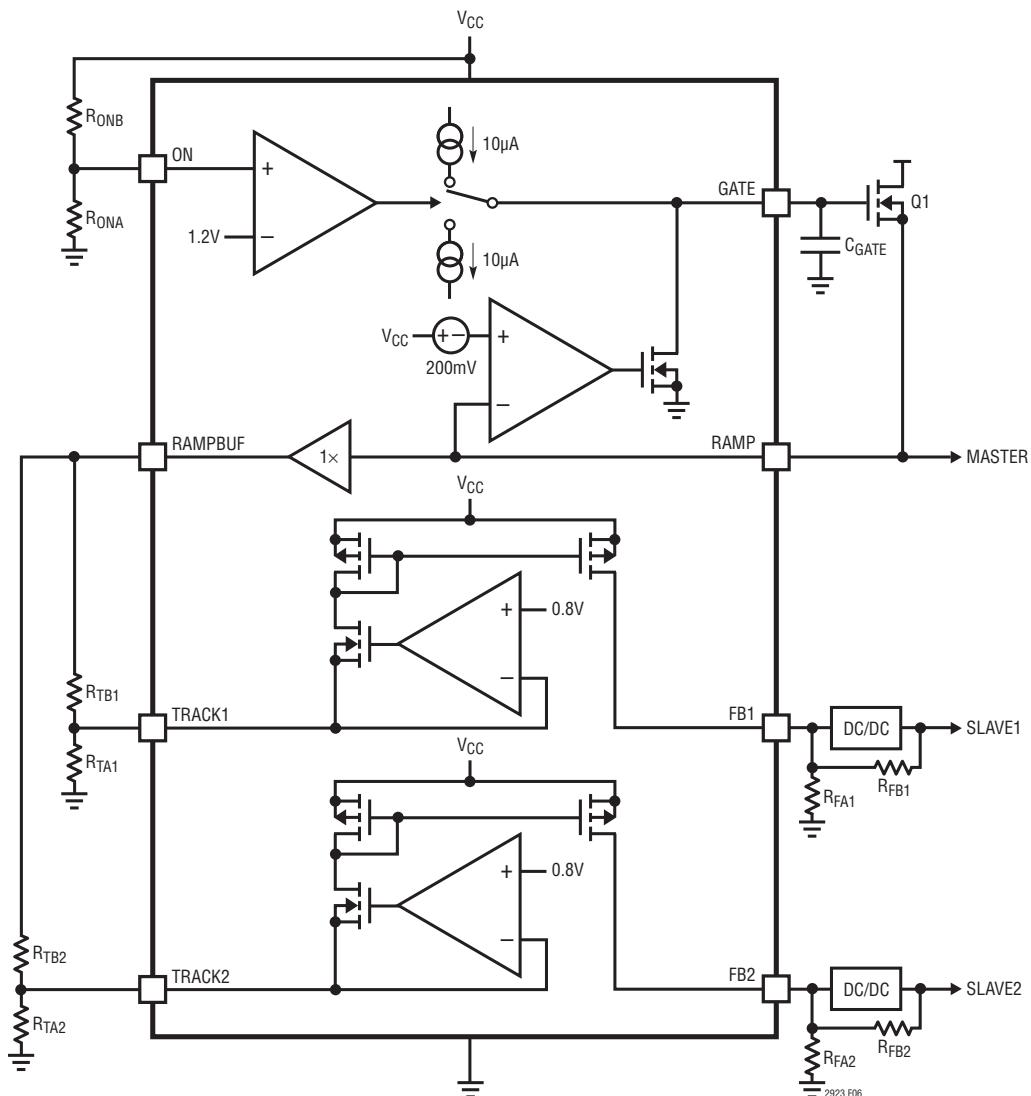

### ランプアップ/ランプダウン動作の制御

LTC2923の動作は図6の簡略機能図を参照すると簡単に理解できます。ONピンが“L”的とき、GATEピンはグランドまで引き下げられるので、マスタ信号は“L”に留まります。 $R_{TB1}$ と $R_{TB2}$ を流れる電流はマスタ信号が“L”的とき最大なので、FB1およびFB2からの電流も最大になります。これらの電流はスレーブの出力をそれらの最小電圧にドライブします。

ONピンが1.23Vを超えて上昇すると、マスタ信号が上昇し、スレーブ電源はマスタ信号をトラッキングします。ランプ・レートは、内部チャージポンプの10 $\mu$ A電流源によってドライブされる外付けコンデンサによって設定されます。外部FETが使用されない場合、ランプ・レートは、外付けコンデンサの片方の端子にRAMPピンとGATEピンと一緒に結合することにより設定されます（「比例トラッキングの例」を参照）。

適当に設計されたシステムでは、マスタ信号が最大電圧に達すると、TRACKxピンからの電流はゼロになります。この場合、FBxピンからの電流はないので、LTC2923はスレーブ電源の出力電圧の精度、過渡応答、安定性に影響を与えません。

ONピンが $V_{ON(TH)} - \Delta V_{ON(HYST)}$ （標準で1.225V）より下になると、GATEピンは10 $\mu$ Aで引き下げられ、マスタ信号とスレーブ電源は前に上昇したときと同じ速度で下降します。

ONピンはデジタルI/Oピンで制御することができますが、このピンを使って入力電源をモニタすることもできます。入力電源からONピンに抵抗分割器を接続すると、電源はモニタされる電源が予め設定された電圧に達した後だけランプアップします。

### オプションの外部FET

同時トラッキングの例（図10と図11）では、オプションの外部NチャネルFETを使って、マスタ信号になる1個の電源をランプアップする方法が示されています。FETが使われる場合、そのゲートはGATEピンにより充電され、ソースはRAMPピンに接続されます。通常動作では、GATEピンは10 $\mu$ Aをソースまたはシンクして、GATEピンに接続されている外付けコンデンサによって設定される速度でFETのゲートをランプアップまたはランプダウンします。高周波数発振を防ぐために、FETのゲートと外付けコンデンサの間に10 $\Omega$ を追加することを推奨します。

図5. 簡略化したトラッキング・セル

## アプリケーション情報

図6. 簡略化した機能図

LTC2923は電子回路ブレーカ機能を備えており、オプションのシリーズFETを短絡から保護します。FETが完全に導通すると( $GATE > RAMP + 4.9V$ )、電子回路ブレーカがイネーブルされます。次に、 $V_{CC}$ からRAMPまで測定したときのFETの両端の電圧( $V_{DS}$ )が約10μs以上200mVを超すと、FETのゲートは20mAで引き下げられ、FETはオフします。スレーブ電源はRAMPピンをトラッキングするので、短絡フォールトが生じるとトラッキング回路によってスレーブ電源は“L”に引き下げられます。短絡フォールト後、ONピンを0.4Vより下に引き下げてフォールトが解消されるまでFETはラッチオフされます。

ランプ・バッファ

RAMPピンの電圧をバッファした電圧がRAMPBUFピンにより与えられ、TRACKxピンの抵抗分割器をドライブします。外部FETが存在しない場合、GATEピンは10 $\mu$ Aしか供給しませんが、このピンは抵抗をドライブするため2mAまで供給します。RAMPBUFピンは外部FETを使ったシステムでも役立つことが実証されます。上の簡略化された機能図のトラッキング・セルはTRACKxピンを0.8Vにドライブするので、 $R_{TBx}$ がFETのソースに直接接続されると、FETがオフのときTRACKxピンは潜在的にFETのソースを0.8Vに向かって引き上げる可能性があります。RAMPBUFはこの経路を遮断します。

## アプリケーション情報

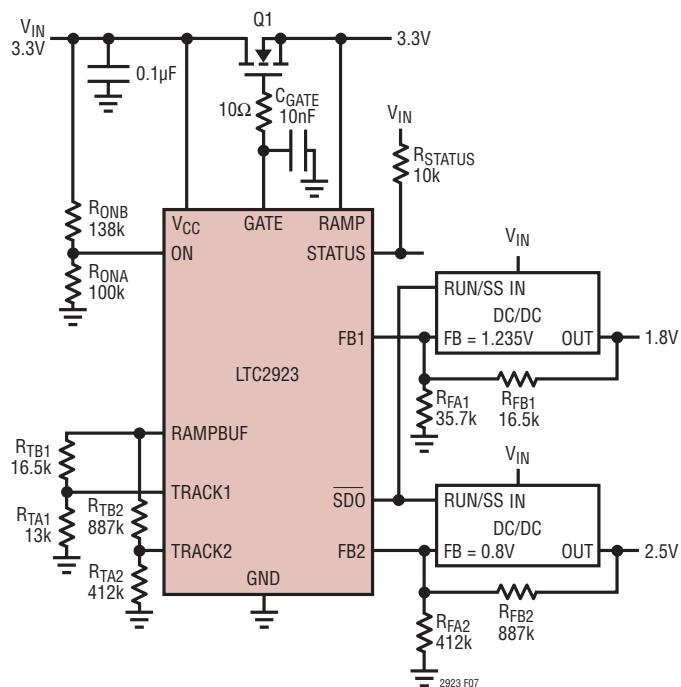

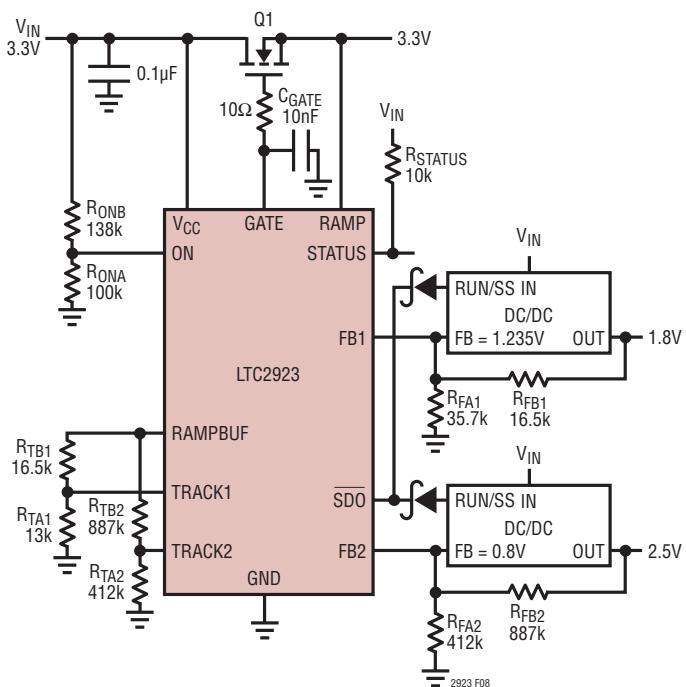

### シャットダウン出力

アプリケーションによっては、12ピンのLTC2923CDEまたはLTC2923IDEを使ってスレーブ電源のシャットダウン・ピンまたはRUN/SSピンを制御しなければならない場合があります。V<sub>CC</sub>が2.9Vより低いと、FB1ピンとFB2ピンから流れ出す電流の定格1mAをLTC2923が供給できない可能性があります。スレーブ電源が低い入力電圧で動作可能な場合は、オープンドレインのSDO出力を使ってスレーブ電源のSHDNピンまたはRUN/SSピンをドライブしてください(図7を参照)。これにより、ONピンの電圧が1.23Vを超えると、V<sub>CC</sub>が2.6Vの低電圧ロックアウト状態より上になり、短絡フォールトがラッチされていない状態になるまで、スレーブ電源の出力は“L”に保持されます。ONピンの電圧が1.23Vより低くなりRAMPピンの電圧が約100mVを下回ると、スレーブ電源は再び“L”になります。2つの

図7

電源のRUN/SSピンまたはSHDNピンを個別に制御する必要があるときは、それぞれのピンとSDO出力の間にショットキー・ダイオードを接続します(図8を参照)。

### ステータス出力

STATUSピンは、電源のランプアップが終了したことを示します。このピンはオープンドレイン出力で、GATEがフルに充電されるまで“L”になります。GATEピンは外付けFETのゲート、またはFETが使用されないときはRAMPピンを直接ドライブするので、GATEピンがフルに充電されると、電源はランプアップを完了しています。短絡フォールトが発生するか、ONピンが“L”になったことにより、GATEピンが“L”になると、STATUSピンは再び“L”になります。

図8

## アプリケーション情報

### 3ステップの設計手順

以下の3ステップの手順により、図1～図4に示されているトラッキングまたはシーケンシングのプロファイルのどれでも設計を完了することができます。基本的な3電源のアプリケーション回路を図9に示します。

#### 1. マスタ信号のランプ・レートを設定します。

マスタ電源 $S_M$ の所望のランプ・レート(V/s)に基づいて、 $C_{GATE}$ (GATEピンのコンデンサ)の値を求めます。

$$C_{GATE} = \frac{I_{GATE}}{S_M} \text{ ここで、} I_{GATE} \approx 10\mu A \quad (1)$$

外部FETのゲート容量が $C_{GATE}$ に近ければ、外部コンデンサの値を減らしてFETのゲート容量を補償します。

外部FETを使わない場合、GATEピンとRAMPピンを結合します。

#### 2. 遅延なしと仮定して、スレーブ電源の所望のランプ・レートを与える一対の抵抗の値を求めます。

スレーブ電源 $S_S$ のランプ・レートを選択します。スレーブ電源がマスタ電源と一緒に、または一定の電圧オフセットでランプアップする場合、ランプ・レートはマスタ電源のランプ・レートに等しくなります。マスタ電源が最終電源電圧に達する前にスレーブ電源がランピングを終了するように、スレーブ電源のランプ・レートは十分速くしてください。そうしないと、マスタ電源により、スレーブ電源は所期の安定化電圧値より低く抑えられます。以下の式を使って所望のランプ・レートのための抵抗値を決定します。ここで、 $R_{FB}$ と $R_{FA}$ はスレーブ電源の帰還抵抗で、 $V_{FB}$ はスレーブ電源の帰還基準電圧です。

$$R_{TB} = R_{FB} \cdot \frac{S_M}{S_S} \quad (2)$$

$$R_{TA'} = \frac{V_{TRACK}}{\frac{V_{FB}}{R_{FB}} + \frac{V_{FB}}{R_{FA}} - \frac{V_{TRACK}}{R_{TB}}} \quad (3)$$

ここで、 $V_{TRACK}$ は約0.8Vです。

マスタのランプ・レートに対するスレーブのランプ・レートの比( $S_S/S_M$ )が大きいと、 $R_{TA'}$ が負の値になる可能性があります。ステップ3で十分大きな遅延が使われると $R_{TA}$ は正になりますが、それ以外は $S_S/S_M$ を小さくする必要があります。

#### 3. $R_{TA}$ を選択して所望の遅延を得ます。

同時トラッキングや比例トラッキングの場合のように遅延が不要であれば、単純に $R_{TA} = R_{TA'}$ にします。オフセット・トラッキングや電源シーケンシングの場合のように遅延が望ましい場合、 $R_{TA''}$ を計算して $R_{TA}$ の値を決定します。ここで、 $t_D$ は所望の遅延(単位:秒)です。

$$R_{TA''} = \frac{V_{TRACK} \cdot R_{TB}}{t_D \cdot S_M} \quad (4)$$

$$R_{TA} = R_{TA'} \parallel R_{TA''} \quad (5)$$

$R_{TA'}$ と $R_{TA''}$ の並列組み合わせ

ステップ2で注記したように、遅延が小さく、マスタのランプ・レートに対するスレーブのランプ・レートの比が大きいと(通常、シーケンシングの場合にだけ見られます)、 $R_{TA}$ の解が負の値になる可能性があります。このような場合、遅延を大きくするか、またはマスタのランプ・レートに対するスレーブのランプ・レートの比を小さくする必要があります。

図9. 3電源のアプリケーション

## アプリケーション情報

### 同時トラッキングの例

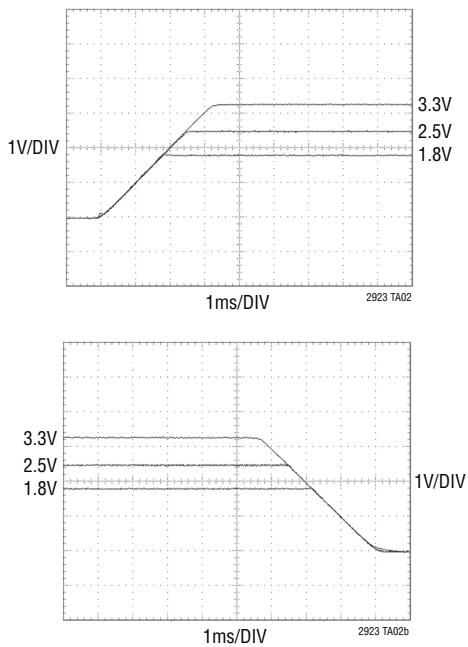

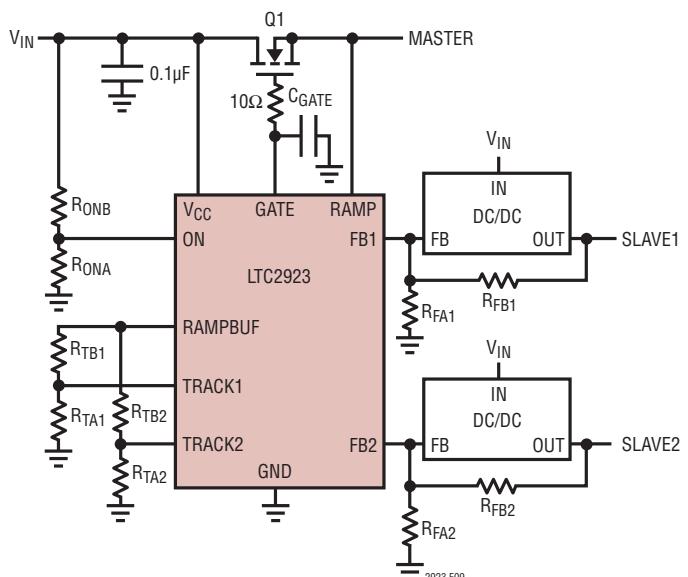

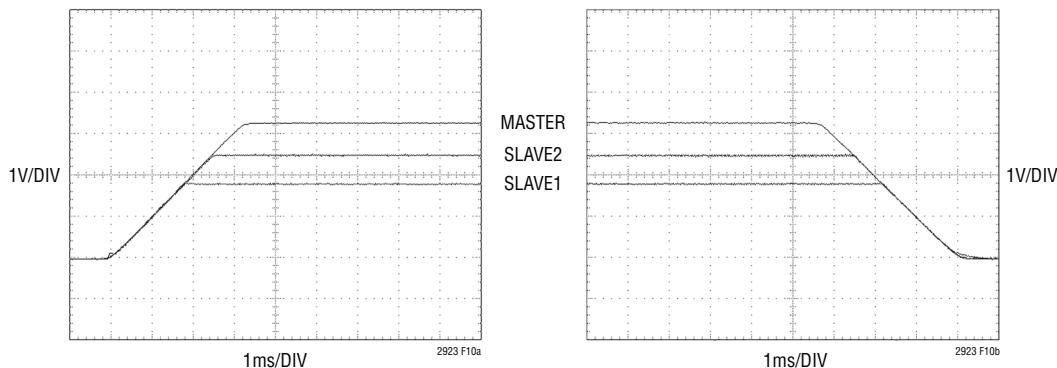

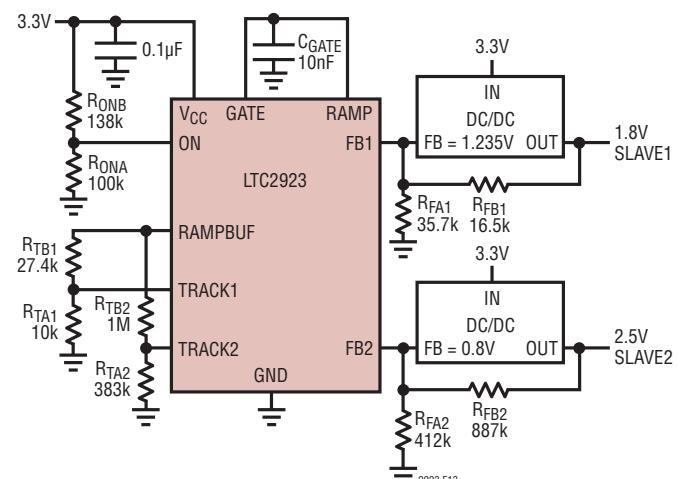

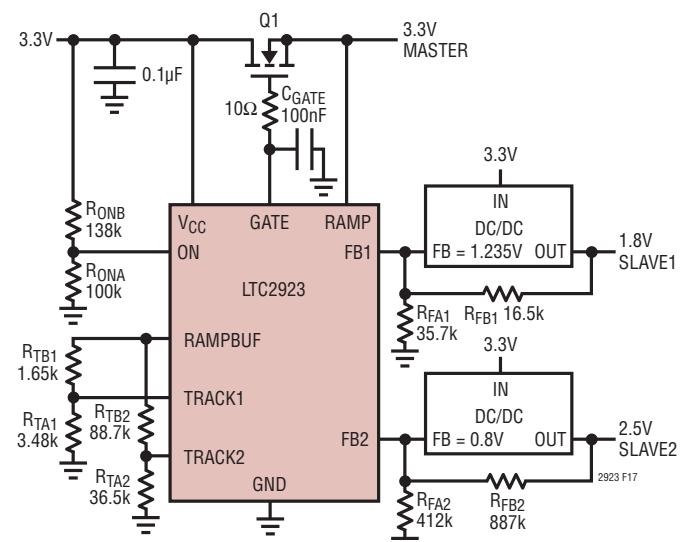

図10. 同時トラッキング(図11から)

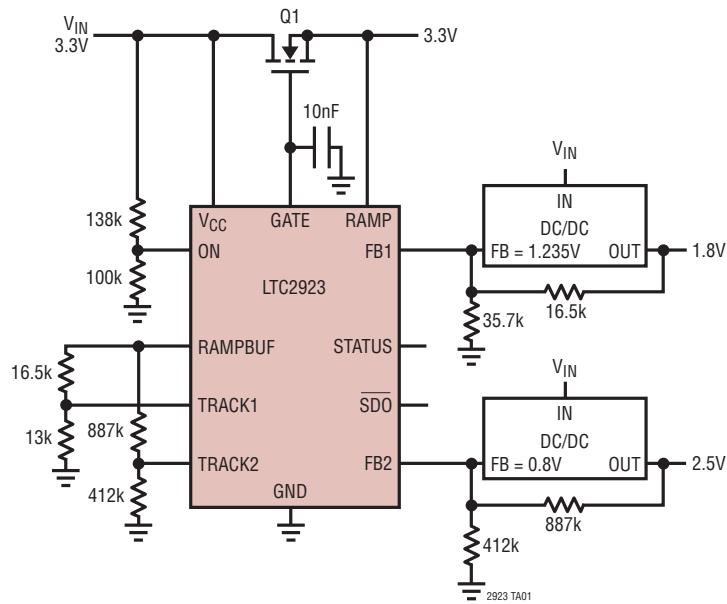

標準的な3電源アプリケーションを図11に示します。マスタ信号は3.3Vのモジュールです。スレーブ1電源は1.8Vのスイッチング電源で、スレーブ2電源は2.5Vのスイッチング電源です。両方のスレーブ電源は、外部FETで制御される3.3Vの電源を同時にトラッキングします。これらの電源のランプ・レートは1000V/sです。以前詳説した3ステップの設計手順を使って部品の値を決定することができます。手順はスレーブ2電源の場合も同じなので、スレーブ1電源についてだけここでは考察します。

#### 1. マスタ信号のランプ・レートを設定します。

式1から：

$$C_{GATE} = \frac{10\mu A}{1000V/s} = 10nF$$

#### 2. 遅延なしと仮定して、スレーブ電源の所望の動作を与える一対の抵抗を求めます。

式2から：

$$R_{TB} = 16.5k\Omega \cdot \frac{1000V/s}{1000V/s} = 16.5k\Omega$$

式3から：

$$R_{TA}' = \frac{0.8V}{\frac{1.235V}{16.5k\Omega} + \frac{1.235V}{35.7k\Omega} - \frac{0.8V}{16.5k\Omega}} \approx 13k\Omega$$

#### 3. $R_{TA}$ を選択して所望の遅延を得ます。

遅延は不要なので、 $R_{TA} = R_{TA}'$

図11. 同時トラッキングの例

この例では、ONピンが1.23Vより下に保たれているあいだ、すべての電源は“L”に留まります。ONピンが1.23Vを超して上昇すると、10μAによりC<sub>GATE</sub>とFETのゲートが1000V/sで引き上げられます。FETのゲートが上昇すると、ソースが追従して出力を1000V/sの速度で3.3Vに引き上げます。この出力はマスタ信号として機能し、RAMPピンからRAMPBUFピンへとバッファされます。この出力とRAMPBUFピンが上昇すると、TRACKピンからの電流が減少します。その結果、スレーブ電源の出力の電圧が上昇し、スレーブ電源はマスタ電源をトラッキングします。ONピンが再度1.23Vより下に引き下げられると、10μAによってC<sub>GATE</sub>とFETのゲートが1000V/sの速度で引き下げられます。出力の負荷が十分でも、すべての出力は同時に1000V/sの速度で追従して下がります。

## アプリケーション情報

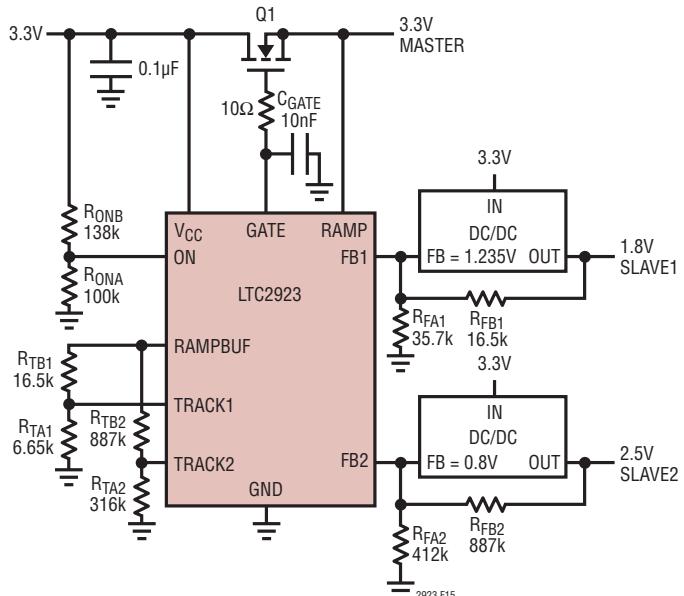

### 比例トラッキングの例

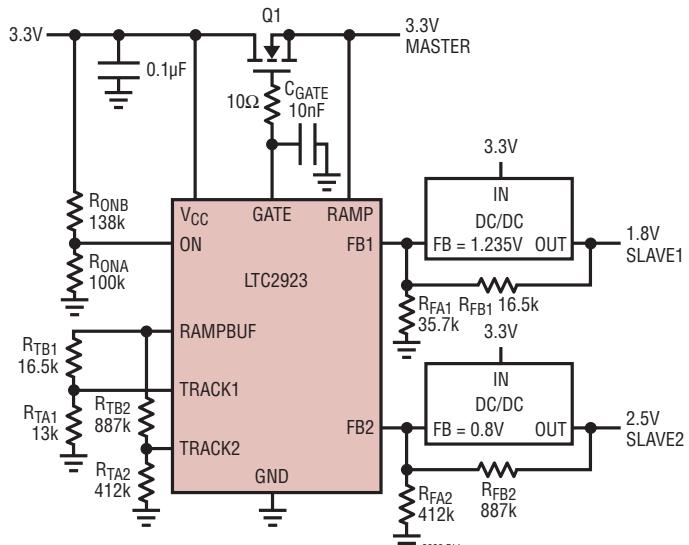

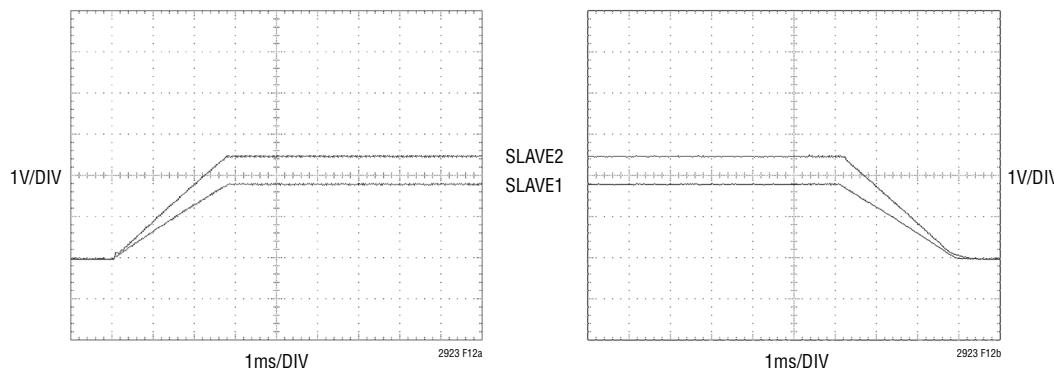

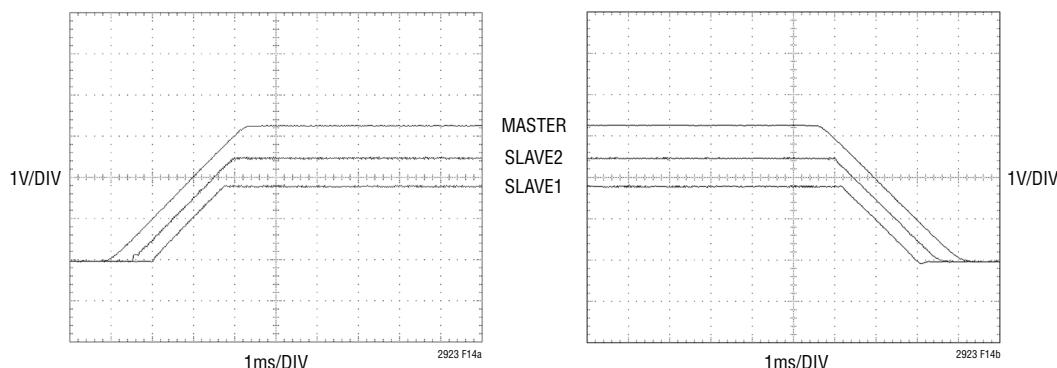

図12. 比例トラッキング(図13から)

この例では、同時トラッキングの例が、外部FETなしに2個の電源を使って、図12に示されている比例トラッキングのプロファイルに変わります。マスタ信号のランプ・レートは不变で(ステップ1)、比例トラッキング(ステップ3)に遅延はないので、3ステップ設計手順のステップ2の結果だけ考察する必要があります。この例では、1.8Vのスレーブ1電源は600V/sでランプアップし、2.5Vのスレーブ2電源は850V/sでランプアップします。選択されたランプ・レートを使うと、RAMPBUFがV<sub>CC</sub>に達する前に電源が完全にランプアップできることを常に検証してください。1.8V電源が500V/sでランプアップするとすれば、1.65Vにしか達しないでしょう。なぜなら、スレーブ電源が1.8Vに達する前にRAMPBUF信号がV<sub>CC</sub> = 3.3Vの最終値に達するからです。

### 2. 遅延なしと仮定して、スレーブ電源の所望の動作を与える一対の抵抗の値を求めます。

式2から：

$$R_{TB} = 16.5k\Omega \cdot \frac{1000V/s}{600V/s} \approx 27.4k\Omega$$

式3から：

$$R_{TA'} = \frac{0.8V}{\frac{1.235V}{16.5k\Omega} + \frac{1.235V}{35.7k\Omega} - \frac{0.8V}{27.5k\Omega}} = 10k\Omega$$

ステップ3は不要です。なぜなら遅延がなく、R<sub>TA</sub> = R<sub>TA'</sub>だからです。

図13. 比例トラッキングの例

## アプリケーション情報

### オフセット・トラッキングの例

図14. オフセット・トラッキング(図15から)

同時トラッキングの回路例を図14に示されているオフセット・トラッキングに作り変えるのは比較的簡単です。この場合、1.8Vのスレーブ1電源はマスタより1V下でランプアップします。ランプ・レートは同じなので(1000V/s)、3ステップ設計手順のステップ1とステップ2は変更する必要がありません。ステップ3だけ検討する必要があります。選択した電圧オフセットにより、スレーブ電源が完全にランプアップできることを必ず検証してください。この例では、電圧オフセットが2Vだとすれば、スレーブ電源は3.3V-2V = 1.3Vまでしかランプアップしないでしょう。

### 3. R<sub>TA</sub>を選択して所望の遅延を得ます。

まず、ランプ・レートを使って所望の電圧オフセットV<sub>OS</sub>を遅延t<sub>D</sub>に変換します。

$$t_D = \frac{V_{OS}}{S_S} = \frac{1V}{1000V/s} = 1ms \quad (6)$$

式4から:

$$R_{TA}'' = \frac{0.8V \cdot 16.5k\Omega}{1ms \cdot 1000V/s} = 13.2k\Omega$$

式5から:

$$R_{TA} = 13.1k\Omega \parallel 13.2k\Omega \approx 6.65k\Omega$$

図15. オフセット・トラッキングの例

## アプリケーション情報

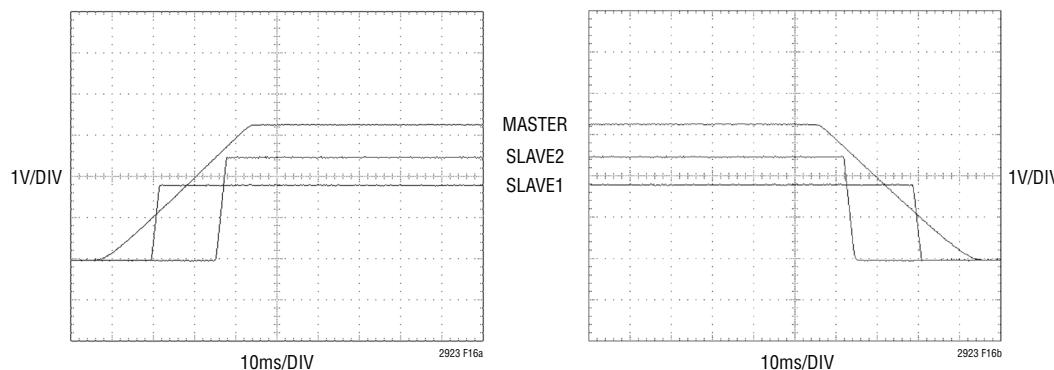

### 電源シーケンシングの例

図16. 電源シーケンシング(図17から)

図16で、スレーブ1電源とスレーブ2電源はトラッキングせず、シーケンスが設定されます。3.3Vの電源は外部FETを使って100V/sでランプアップし、マスタ信号として機能します。1.8Vのスレーブ1電源は、マスタ信号がランプアップを開始した10ms後に、1000V/sでランプアップを開始します。2.5Vのスレーブ2電源は、マスタ信号がランプアップを開始した25ms後に、1000V/sでランプアップを開始します。ランプ・レートと遅延のすべての組み合わせが可能なわけではないことに注意してください。遅延が小さく、マスタのランプ・レートに対するスレーブのランプ・レートの比が大きいと、負の抵抗が必要になることがあります。このような場合、遅延を大きくするか、またはマスタのランプ・レートに対するスレーブのランプ・レートの比を小さくする必要があります。この例では、スレーブ1電源について解くと次のようになります。

#### 1. マスタ信号のランプ・レートを設定します。

式1から：

$$C_{GATE} = \frac{10\mu A}{100V/s} = 100nF$$

#### 2. 遅延なしと仮定して、スレーブ電源の所望の動作を与える一対の抵抗の値について求めます。

式2から：

$$R_{TB} = 16.5k\Omega \cdot \frac{100V/s}{1000V/s} = 1.65k\Omega$$

式3から：

$$R_{TA}' = \frac{0.8V}{\frac{1.235V}{16.5k\Omega} + \frac{1.235V}{35.7k\Omega} - \frac{0.8V}{1.65k\Omega}} = -2.13k\Omega$$

#### 3. $R_{TA}$ を選択して所望の遅延を得ます。

式4から：

$$R_{TA}'' = \frac{0.8V \cdot 1.65k\Omega}{10ms \cdot 100V/s} = 1.32k\Omega$$

式5から：

$$R_{TA} = -2.13k\Omega || 1.32k\Omega = 3.48k\Omega$$

図17. 電源シーケンシングの例

## アプリケーション情報

### 最終チェック

以下の一連の式は実現不可能なソリューションを識別するのに役立ちます。

ステップ2で述べたように、スレーブ電源は、マスタ信号が最終電圧に達する前にランプアップを終了する必要があります。これは次の式によって検証することができます。

$$V_{\text{TRACK}} \left(1 + \frac{R_{\text{TB}}}{R_{\text{TA}}} \right) < V_{\text{CC}}, \text{ここで, } V_{\text{TRACK}} = 0.8\text{V}$$

「電気的特性」の表が保証するよりも大きな電流をLTC2923が供給することを必要とする抵抗値を選択する可能性があります。この状態を避けるには、 $I_{\text{TRACKx}}$ が1mAを超えず、 $I_{\text{RAMPBUF}}$ が±2mAを超えないことをチェックします。

$I_{\text{TRACKx}} < 1\text{mA}$  (TRACKxピンの最大保証電流)であることを確認するには、次のことを検証します。

$$\frac{V_{\text{TRACK}}}{R_{\text{TA}} \parallel R_{\text{TB}}} < 1\text{mA}$$

最後に、RAMPBUFが0VのときRAMPBUFが2mA以上シングルするよう強制されず、またRAMPBUFが $V_{\text{CC}}$ のとき2mA以上ソースするよう強制されないことを確認します。

$$\frac{V_{\text{TRACK}}}{R_{\text{TB}1}} + \frac{V_{\text{TRACK}}}{R_{\text{TB}2}} < 2\text{mA} \text{ および}$$

$$\frac{V_{\text{CC}}}{R_{\text{TA}1} + R_{\text{TB}1}} + \frac{V_{\text{CC}}}{R_{\text{TA}2} + R_{\text{TB}2}} < 2\text{mA}$$

### 昇圧レギュレータとリニア・レギュレータに関する注意事項

LTC2923のトラッキング・セルは、あらゆる種類の電源の出力を制御できるわけではないことに注意してください。この制御できない種類の電源の1つ(帰還ノードを介した出力制御ができない)を制御する必要がある場合、直列にFETを使って1つの電源の出力を制御することができます。たとえば、一般に、昇圧レギュレータは入力電源と出力電源の間にインダクタとダイオードを備えているので、出力電圧が入力電圧より下がるとDC電流経路を与えます。そのため、LTC2923のトラッキング・セルは実質的に電源の出力を入力より下にはドライブしません。

リニア・レギュレータの使用を検討するときは特に注意が必要です。3端子リニア・レギュレータのリファレンス電圧は、グランドではなく出力電源を基準としています。この場合、レギュレータの帰還ノードに電流を流し込むと、その出力電圧は下降せず上昇します。低損失レギュレータ(LDO)など、リファレンス電圧がグランドを基準にしているリニア・レギュレータでも問題となることがあります。一般に、リニア・レギュレータは出力がリファレンス電圧より下にならないようにする回路を搭載しています。データシートではこれが明確でないことがあるので、LTC2923のトラッキング・セルを使ってリニア・レギュレータを制御するときは、必ず実験室で試験することを推奨します。

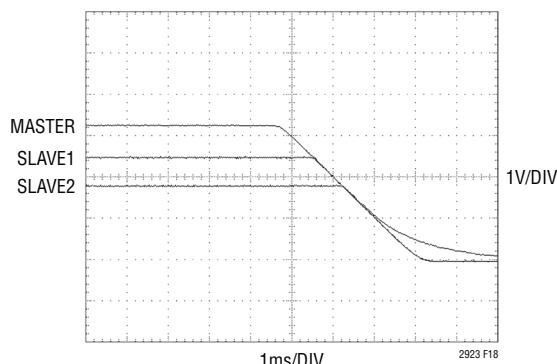

### 負荷の必要条件

電源が急速にランプダウンするとき、負荷または電源自体がランプ・レートをサポートするのに十分な電流をシンクする能力が必要です。たとえば、電源に大きな出力コンデンサと弱い抵抗性負荷が接続されていると、電流をシンクしない電源の場合、負荷と出力コンデンサのRC時定数によってランプダウンの速度が制限されます。グランドの近くでは1.8V電源と3.3V電源に追従しない2.5V電源の場合を図18に示します。

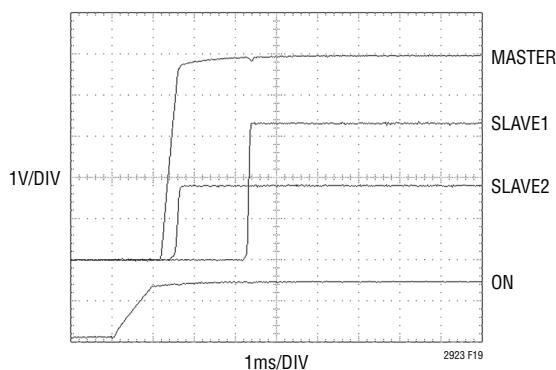

### スタートアップ遅延

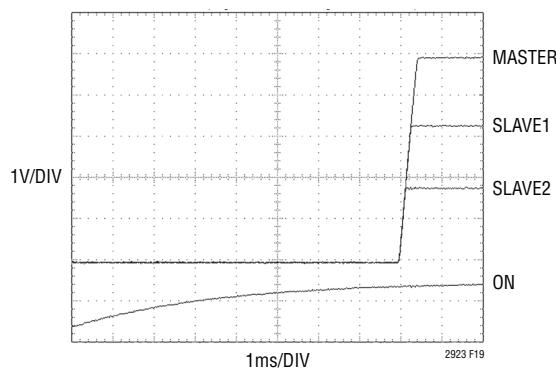

多くの場合、電源はその入力に電源が接続されたとき直ちは起動しません。入力電源が接続されるやいなやLTC2923がこれらの電源をランプアップさせようと試みると、出力の起動が遅れて、トラッキング回路が無効になることがあります(図19)。多くの場合、この遅延はソフトスタート・コンデンサによって意図的に設定されます。これは、スレーブ電源のソフトスタート・コンデンサを小さくするか、あるいはONピンの抵抗分割器にコンデンサを接続してランプアップを遅らせることによって、修正することができます。図20を参照してください。

## アプリケーション情報

図18. 弱い抵抗性負荷

図19. 電源の起動を遅らせた場合

図20. ONピンを遅らせた場合

## レイアウトの検討事項

0.1 $\mu$ Fのバイパス・コンデンサをLTC2923の電源ピンのできるだけ近くに配置します。10 $\Omega$ の抵抗をFETの近くに配置し、FETのゲートと外付けコンデンサ( $C_{GATE}$ )の間に接続することを推奨します。こうすると、FETとPCBの寄生素子とのやり取りで生じる可能性のある厄介な高周波数発振がほぼ確実になくなります。

スレーブ電源の出力ノイズを最小に抑えるため、LTC2923のFBxピンとスレーブ電源の帰還ノードを接続するトレースをできるだけ短くします。さらに、これらのトレースは高速の過渡とともに信号に隣接して配線しないでください。状況によっては、スレーブ電源の帰還ノードの近くに、LTC2923のFBxピンに直列に抵抗を追加するとよいかもしれません。

この抵抗は次の値を超してはいけません。

$$R_{SERIES} = \frac{1.5V - V_{FB}}{I_{MAX}} = \left( \frac{1.5V}{V_{FB}} - 1 \right) (R_{FA} \parallel R_{FB})$$

スレーブ電源の帰還ノードにコンデンサ(多くの場合、補償部品)が既に接続されているれば、この抵抗は最も効果的です。スレーブ電源の帰還ノードの容量を大きくするとノイズ耐性がさらに改善されますが、電源の安定性と過渡応答に影響を与えることがあります。

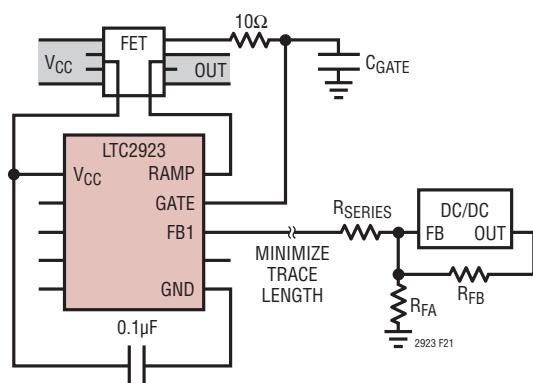

図21. レイアウトの検討事項

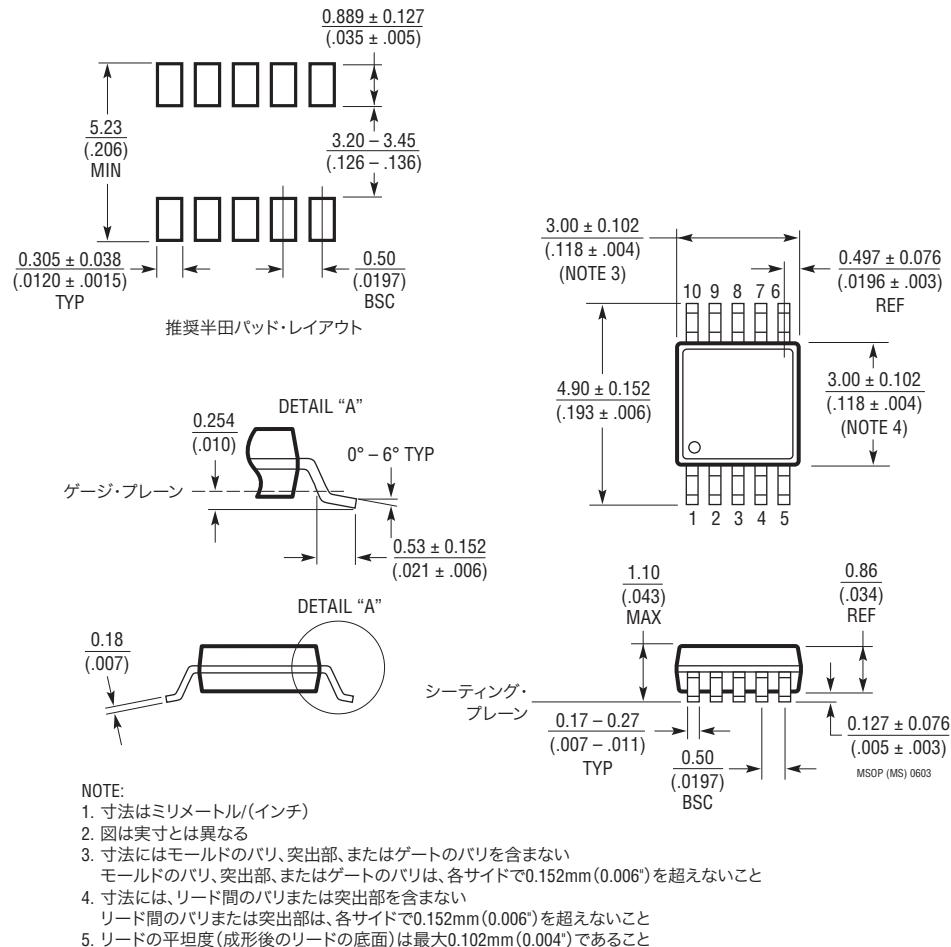

## パッケージ

**MS/パッケージ

10ピン・プラスチックMSOP**

(Reference LTC DWG # 05-08-1661)

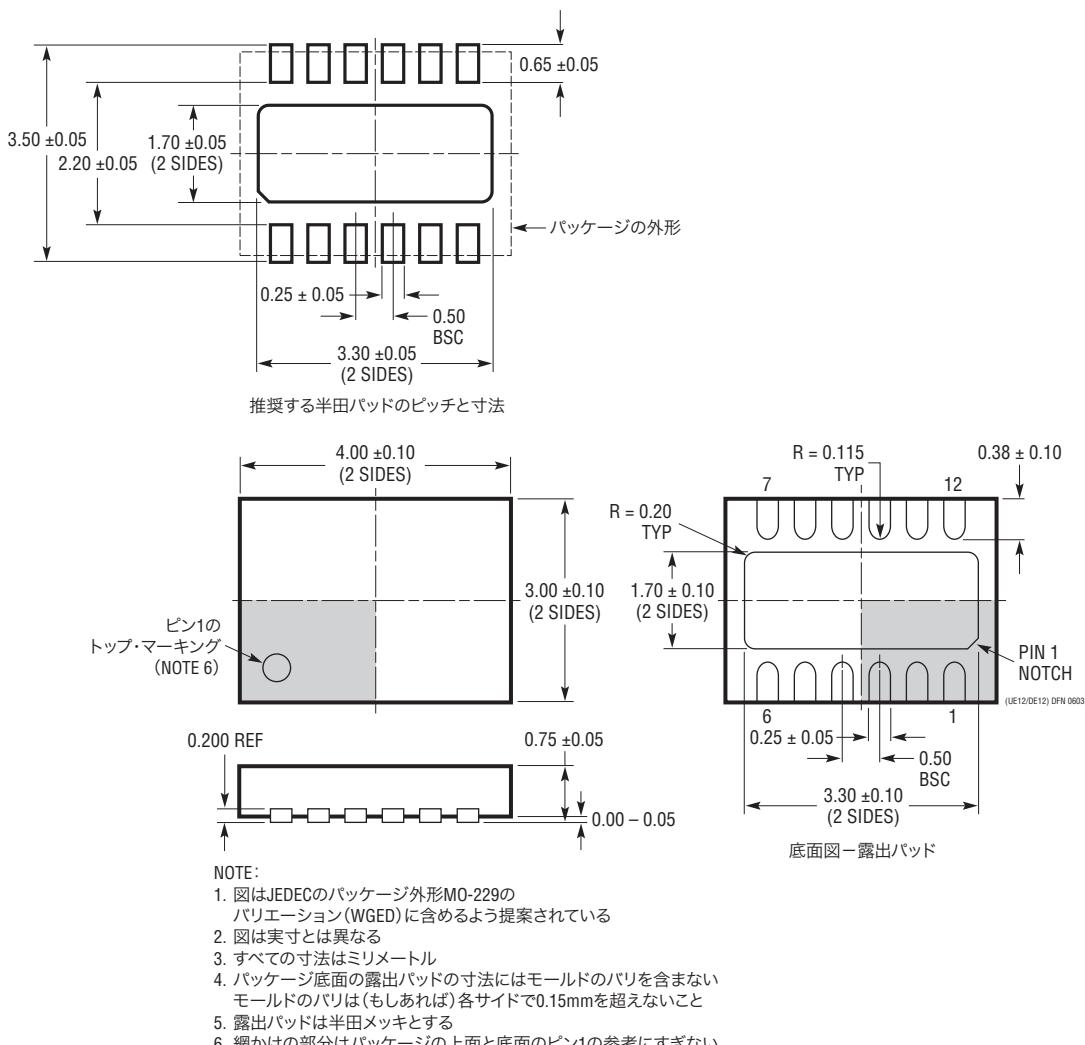

## パッケージ

DEパッケージ

12ピン・プラスチックDFN(4mm×3mm)

(Reference LTC DWG # 05-08-1695)

# LTC2923

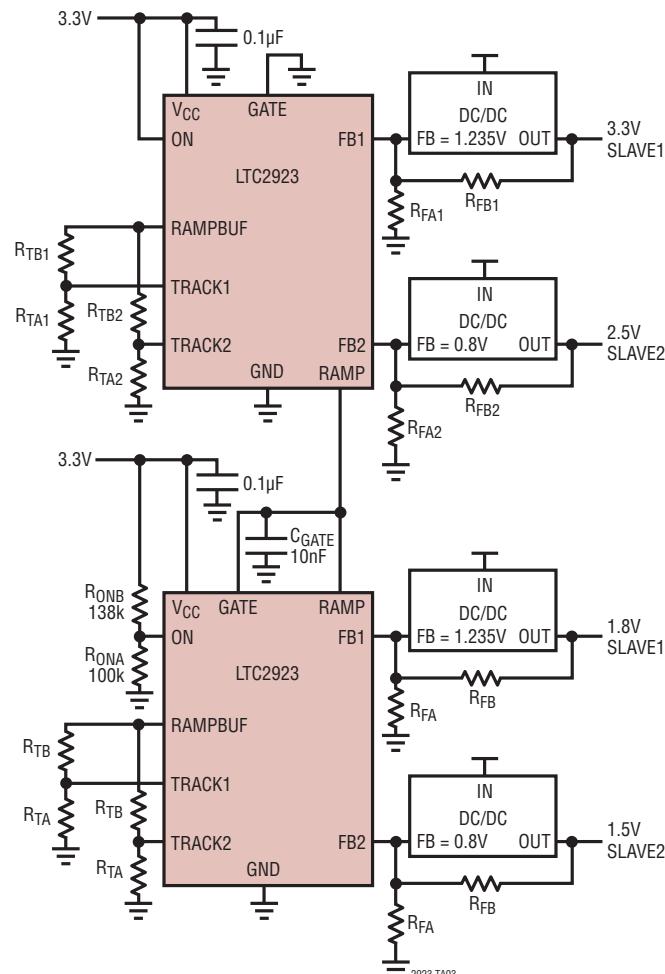

## 標準的応用例

デイジーチェイン接続を使ったアプリケーション

高電圧電源のアプリケーション

## 関連製品

| 製品番号            | 説明                            | 注釈                                                    |

|-----------------|-------------------------------|-------------------------------------------------------|

| LTC1645         | デュアルHot Swap™コントローラ           | 1.2V～12Vで動作し、動作シーケンシングが可能                             |

| LTC2920         | 電源マージニング・コントローラ               | シングルまたはデュアルのバージョン、対称/非対称の高電圧および低電圧マージニング              |

| LTC2921/LTC2922 | 入力モニタ付き電源トラッカ                 | 3個(LTC2921)または5個(LTC2922)のリモート・センス・スイッチ内蔵             |

| LTC2925         | 複数電源トラッキング・コントローラ             | 最大4個の電源、ステータス・ピンとフォールト・ピン、スレーブ電源のシャットダウン、リモートセンス・スイッチ |

| LT®4220         | デュアル電源Hot Swapコントローラ          | ±2.7V～±16.5V、電源トラッキング・モード                             |

| LTC4230         | マルチ機能電流制御付きトリプルHot Swapコントローラ | 1.7V～16.5V、アクティブ突入電流制限、高速コンパレータ                       |

| LTC4253         | -48V Hot Swapコントローラおよび電源シーケンサ | -15Vからのフローティング電源、アクティブ電流制限、3個のDC/DCコンバータをイネーブル        |

Hot Swapはリニアテクノロジー社の商標です。

2923fa