パラレルI/O付き

12/14/16ビット

電流出力SoftSpan DAC

## 特長

- 6つのプログラム可能な出力範囲:

ユニポーラ:0V~5V, 0V~10V

バイポーラ: $\pm 5V$ ,  $\pm 10V$ ,  $\pm 2.5V$ ,  $-2.5V$ ~ $+7.5V$

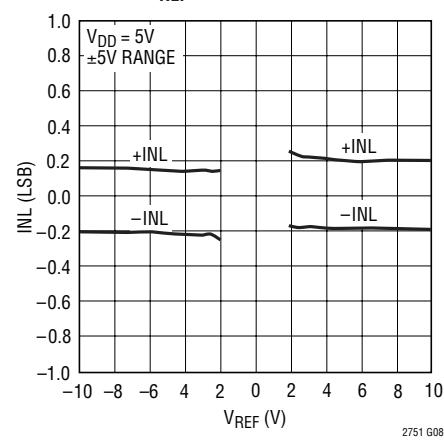

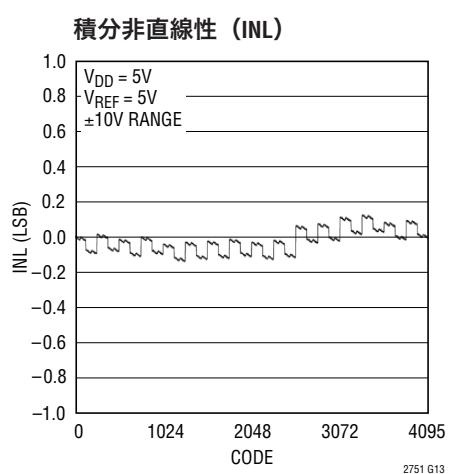

- 16ビットINL誤差:全温度範囲で $\pm 1$  LSB(最大)

- 低消費電流: $1\mu A$ (最大)

- 全温度範囲で単調性を保証

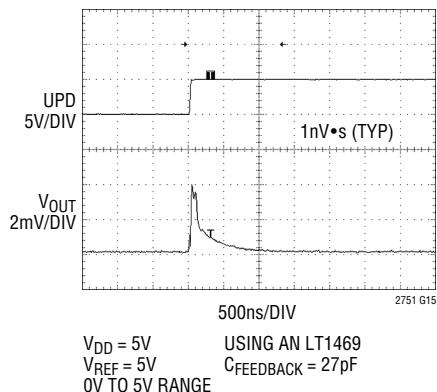

- 低いグリッチ・インパルス: $1nV \cdot s$

- 2.7V~5.5Vの単一電源動作

- $\pm 1$  LSBへのセッティング時間: $2\mu s$

- リファレンス入力: $\pm 15V$

- すべてのレジスタを読み出しできるパラレル・インターフェース

- 非同期CLRピンにより、すべての出力範囲でDAC出力を0Vにクリア

- 0Vへのパワーオン・リセット

- 38ピン5mm×7mm QFNパッケージ

## アプリケーション

- 高分解能のオフセットおよび利得調整

- プロセス制御および産業用オートメーション

- 自動テスト装置

- データ収集システム

## 概要

LTC<sup>®</sup>2751は、12、14および16ビット乗算型パラレル入力、電流出力DACファミリです。これらのDACは、2.7V~5.5Vの単一電源で動作し、全温度範囲で単調性が保証されています。LTC2751A-16は調整なしで全温度範囲で16ビット性能( $\pm 1$  LSBのINLとDNL)を実現します。これらのSoftSpan<sup>TM</sup> DACは6つの出力範囲(2つのユニポーラ範囲と4つのバイポーラ範囲)をパラレル・インターフェースを介してプログラムするか、あるいは、1つの範囲で動作するようにピン・ストラップすることが可能です。

これらのデバイスはあらゆる内部レジスタの読み出しを可能にする双方向入出力パラレル・インターフェースを使用しています。電源が最初に印加されるとき、パワーオン・リセット回路によってDAC出力が0Vにクリアされます。また、CLRピンをロジック“L”にすると、いずれの出力範囲でもDACが0Vに非同期クリアされます。

これらのデバイスはコマーシャル温度範囲とインダストリアル温度範囲で規定されています。

**L**、**LT**、**LTC**、**LTM**、**Linear Technology**およびLinear Technologyのロゴはリニアテクノロジー社の登録商標です。SoftSpanはリニアテクノロジー社の商標です。その他すべての商標の所有権は、それぞれの所有者に帰属します。

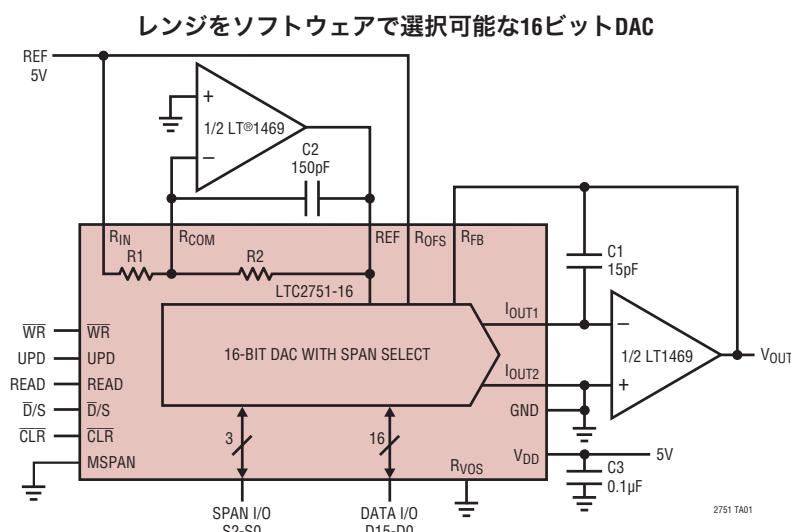

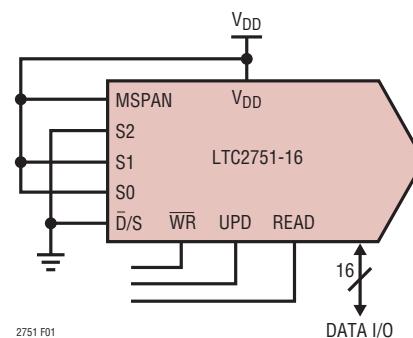

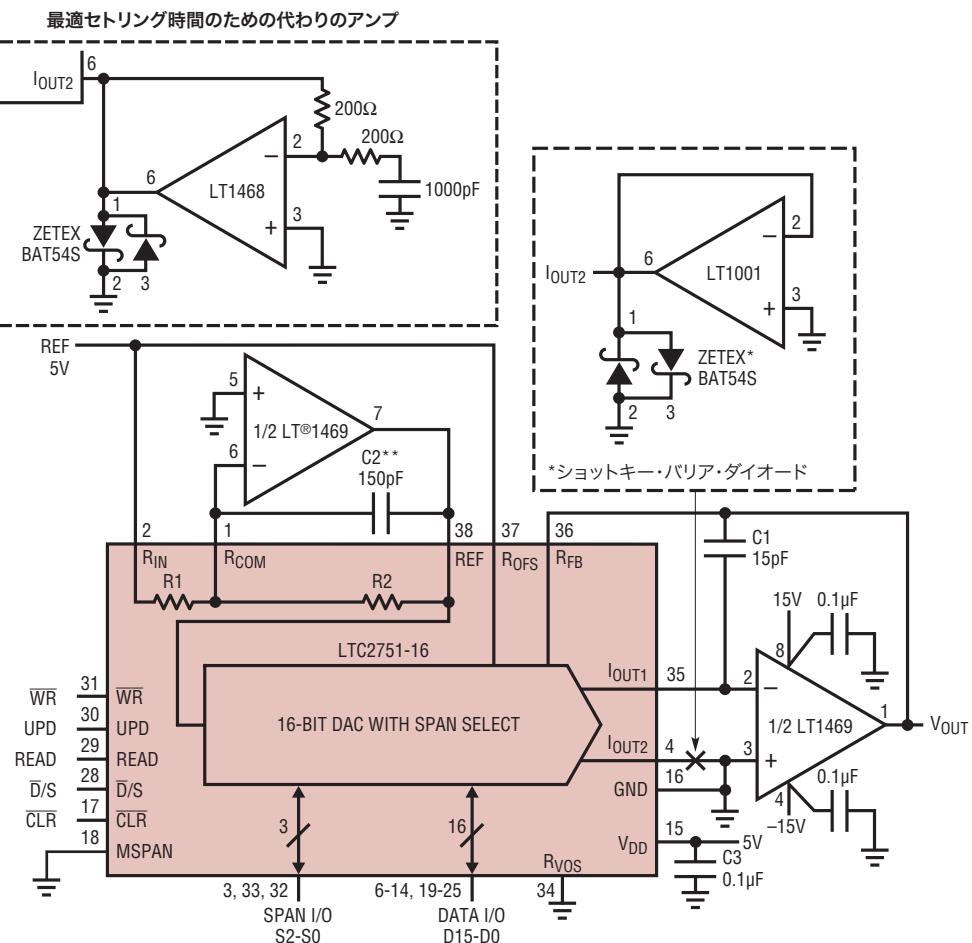

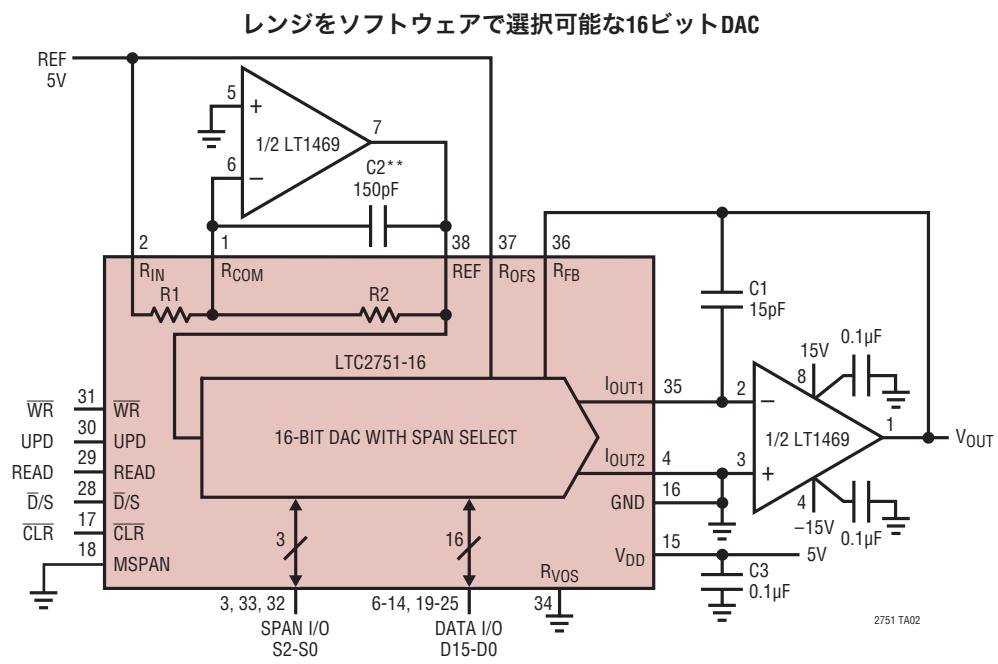

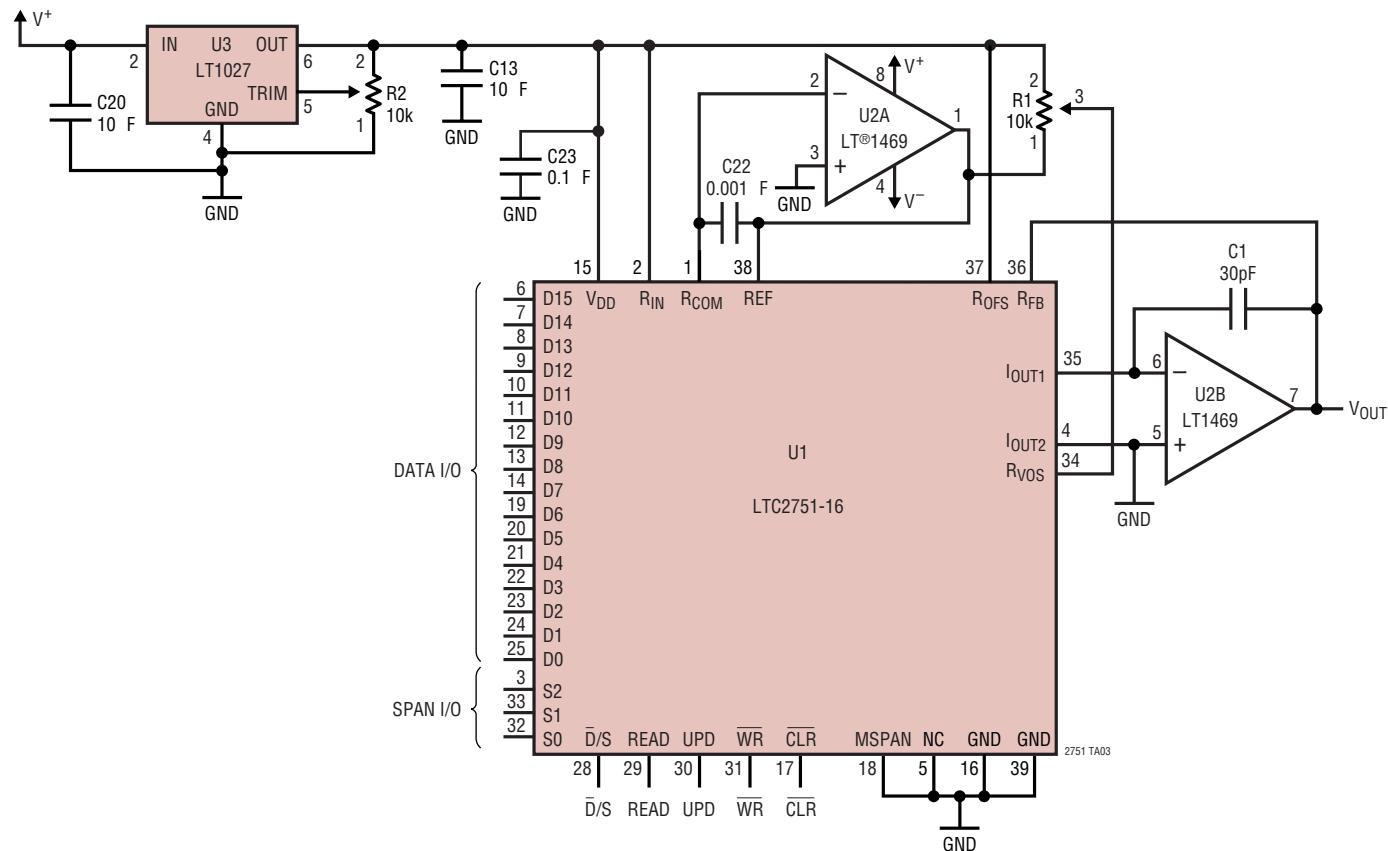

## 標準的応用例

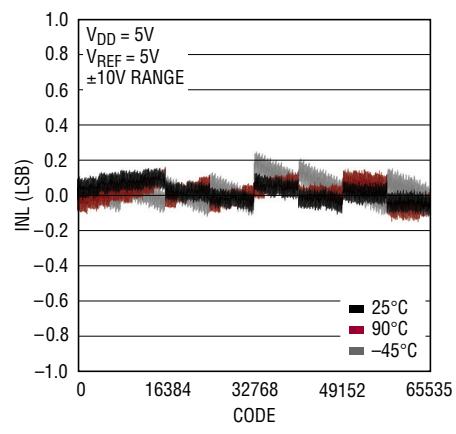

LTC2751-16の積分非直線性

2751 TA01b

LTC2751

## 絶対最大定格 (Note 1,2)

|                                                                                                 |                                      |                           |

|-------------------------------------------------------------------------------------------------|--------------------------------------|---------------------------|

| I <sub>OUT1</sub> 、I <sub>OUT2</sub> 、R <sub>COM</sub> からGND                                    | ±0.3V                                | 動作温度範囲                    |

| R <sub>FB</sub> 、R <sub>OFS</sub> 、R <sub>IN</sub> 、REF、R <sub>VOS</sub> からGND                  | ±15V                                 | LTC2751C ..... 0°C~70°C   |

| V <sub>DD</sub> からGND                                                                           | -0.3V~7V                             | LTC2751I ..... -40°C~85°C |

| S2、S1、S0、D15~D0、MSPAN、READ、 $\overline{D}$ /S、 $\overline{WR}$ 、<br>UPD、 $\overline{CLR}$ からGND | -0.3V~(V <sub>DD</sub> +0.3V) (最大7V) | 最大接合部温度 ..... 125°C       |

|                                                                                                 |                                      | 保存温度範囲 ..... -65°C~150°C  |

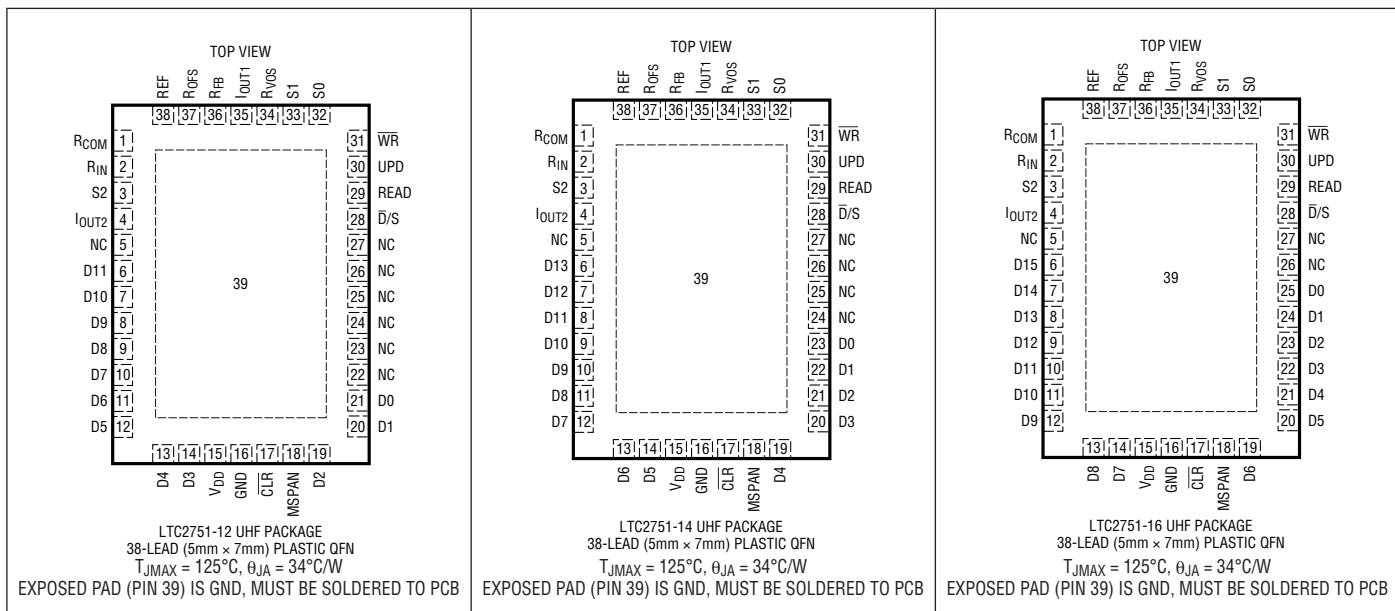

## ピン配置

## 発注情報

| 無鉛仕上げ               | テープアンドリール             | 製品マーキング* | パッケージ                           | 温度範囲          |

|---------------------|-----------------------|----------|---------------------------------|---------------|

| LTC2751CUHF-12#PBF  | LTC2751CUHF-12#TRPBF  | 275112   | 38-Lead (5mm × 7mm) Plastic QFN | 0°C to 70°C   |

| LTC2751IUHF-12#PBF  | LTC2751IUHF-12#TRPBF  | 275112   | 38-Lead (5mm × 7mm) Plastic QFN | -40°C to 85°C |

| LTC2751CUHF-14#PBF  | LTC2751CUHF-14#TRPBF  | 275114   | 38-Lead (5mm × 7mm) Plastic QFN | 0°C to 70°C   |

| LTC2751IUHF-14#PBF  | LTC2751IUHF-14#TRPBF  | 275114   | 38-Lead (5mm × 7mm) Plastic QFN | -40°C to 85°C |

| LTC2751BCUHF-16#PBF | LTC2751BCUHF-16#TRPBF | 275116   | 38-Lead (5mm × 7mm) Plastic QFN | 0°C to 70°C   |

| LTC2751BIUHF-16#PBF | LTC2751BIUHF-16#TRPBF | 275116   | 38-Lead (5mm × 7mm) Plastic QFN | -40°C to 85°C |

| LTC2751ACUHF-16#PBF | LTC2751ACUHF-16#TRPBF | 275116   | 38-Lead (5mm × 7mm) Plastic QFN | 0°C to 70°C   |

| LTC2751AIUHF-16#PBF | LTC2751AIUHF-16#TRPBF | 275116   | 38-Lead (5mm × 7mm) Plastic QFN | -40°C to 85°C |

さらに広い動作温度範囲で規定されるデバイスについては、弊社または弊社代理店にお問い合わせください。\*温度グレードは出荷時のコンテナのラベルで識別されます。非標準の鉛仕上げの製品の詳細については、弊社または弊社代理店にお問い合わせください。

無鉛仕上げの製品マーキングの詳細については、<http://www.linear-tech.co.jp/leadfree> をご覧ください。テープアンドドリルの仕様の詳細については、<http://www.linear-tech.co.jp/tapeanddrill> をご覧ください。

## 電気的特性

注記がない限り、 $V_{DD} = 5V$ 、 $V_{REF} = 5V$ 。●は全動作温度範囲の規格値を意味する。それ以外は $T_A = 25^\circ C$ での値。

| SYMBOL            | PARAMETER                            | CONDITIONS                                         | LTC2751-12                                          |        |       | LTC2751-14 |       |      | LTC2751B-16 |       |       | LTC2751A-16 |       |        | UNITS |

|-------------------|--------------------------------------|----------------------------------------------------|-----------------------------------------------------|--------|-------|------------|-------|------|-------------|-------|-------|-------------|-------|--------|-------|

|                   |                                      |                                                    | MIN                                                 | TYP    | MAX   | MIN        | TYP   | MAX  | MIN         | TYP   | MAX   | MIN         | TYP   | MAX    |       |

| <b>スタチック性能</b>    |                                      |                                                    |                                                     |        |       |            |       |      |             |       |       |             |       |        |       |

|                   | Resolution                           |                                                    | ●                                                   | 12     |       | 14         |       | 16   |             | 16    |       | 16          |       | Bits   |       |

|                   | Monotonicity                         |                                                    | ●                                                   | 12     |       | 14         |       | 16   |             | 16    |       | 16          |       | Bits   |       |

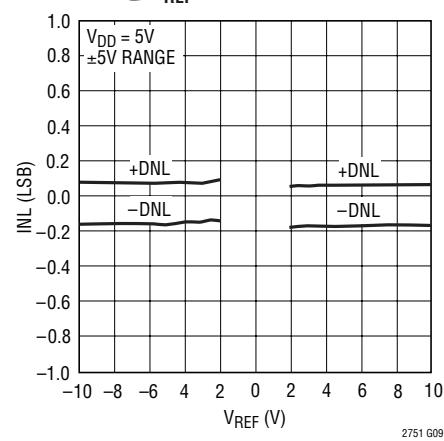

| DNL               | Differential Nonlinearity            |                                                    | ●                                                   |        | ±1    |            | ±1    |      | ±1          |       | ±0.2  | ±1          |       | LSB    |       |

| INL               | Integral Nonlinearity                |                                                    | ●                                                   |        | ±1    |            | ±1    |      | ±2          |       | ±0.4  | ±1          |       | LSB    |       |

| GE                | Gain Error                           | All Output Ranges                                  | ●                                                   | ±0.5   | ±2    | ±1.5       | ±5    |      | ±20         |       | ±4    | ±14         |       | LSB    |       |

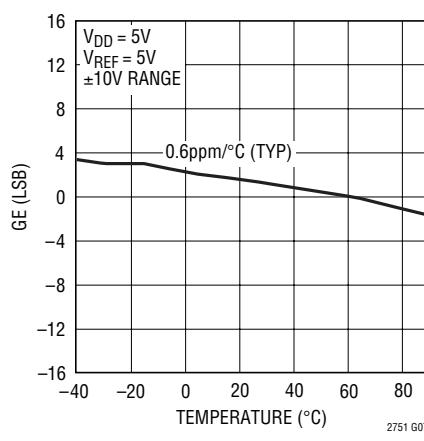

| GE <sub>TC</sub>  | Gain Error Temperature Coefficient   | ΔGain/ΔTemp                                        |                                                     | ±0.6   |       | ±0.6       |       | ±0.6 |             | ±0.6  |       | ±0.6        |       | ppm/°C |       |

| BZE               | Bipolar Zero Error                   | All Bipolar Ranges                                 | ●                                                   | ±0.2   | ±1    | ±0.6       | ±3    |      | ±12         |       | ±2    | ±8          |       | LSB    |       |

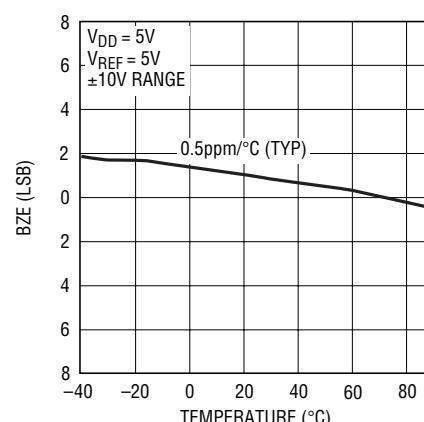

| BZS <sub>TC</sub> | Bipolar Zero Temperature Coefficient |                                                    |                                                     | ±0.5   |       | ±0.5       |       | ±0.5 |             | ±0.5  |       | ±0.5        |       | ppm/°C |       |

| PSR               | Power Supply Rejection               | $V_{DD} = 5V, \pm 10\%$<br>$V_{DD} = 3V, \pm 10\%$ | ●                                                   | ±0.025 |       | ±0.1       |       | ±0.4 |             | ±0.03 | ±0.2  |             | LSB/V |        |       |

| ●                 | I <sub>LKG</sub>                     | I <sub>OUT1</sub> Leakage Current                  | $T_A = 25^\circ C$<br>$T_{MIN} \text{ to } T_{MAX}$ | ●      | ±0.05 | ±2         | ±0.05 | ±2   | ±0.05       | ±2    | ±0.05 | ±2          |       | nA     |       |

| ●                 | C <sub>OUT1</sub>                    | Output Capacitance                                 | Full-Scale Zero Scale                               |        | 75    | 45         | 75    | 45   | 75          | 45    | 75    | 45          |       | pF     |       |

注記がない限り、 $V_{DD} = 5V$ 、 $V_{REF} = 5V$ 。●は全動作温度範囲の規格値を意味する。それ以外は $T_A = 25^\circ C$ での値。

| SYMBOL             | PARAMETER                        | CONDITIONS                                             | MIN | TYP  | MAX  | UNITS  |

|--------------------|----------------------------------|--------------------------------------------------------|-----|------|------|--------|

| <b>抵抗 (Note 3)</b> |                                  |                                                        |     |      |      |        |

| R1/R2              | Reference Inverting Resistors    | (Note 4)                                               | ●   | 16   | 20   | kΩ     |

| R <sub>REF</sub>   | DAC Input Resistance             |                                                        | ●   | 8    | 10   | kΩ     |

| R <sub>FB</sub>    | Feedback Resistor                | (Note 3)                                               | ●   | 8    | 10   | kΩ     |

| R <sub>OFFS</sub>  | Bipolar Offset Resistor          | (Note 3)                                               | ●   | 16   | 20   | kΩ     |

| R <sub>VOS</sub>   | Offset Adjust Resistor           |                                                        | ●   | 800  | 1000 | kΩ     |

| <b>ダイナミック性能</b>    |                                  |                                                        |     |      |      |        |

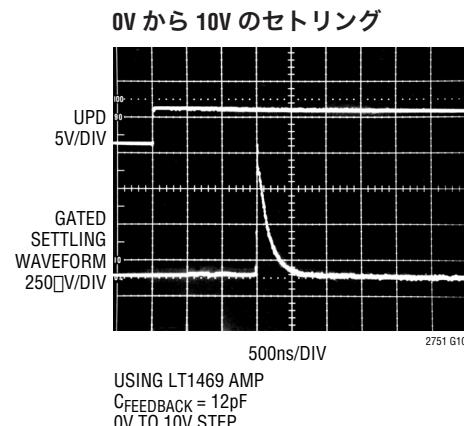

|                    | Output Settling Time             | 0V to 10V Range, 10V Step. To ±0.0015% FS (Note 5)     |     | 2    |      | μs     |

|                    | Glitch Impulse                   | (Note 6)                                               |     | 1    |      | nV•s   |

|                    | Digital-to-Analog Glitch Impulse | (Note 7)                                               |     | 1    |      | nV•s   |

|                    | Multiplying Feedthrough Error    | 0V to 10V Range, $V_{REF} = \pm 10V$ , 10kHz Sine Wave |     | 0.5  |      | mV     |

| THD                | Total Harmonic Distortion        | (Note 8) Multiplying                                   |     | -110 |      | dB     |

|                    | Output Noise Voltage Density     | (Note 9) at I <sub>OUT1</sub>                          |     | 13   |      | nV/√Hz |

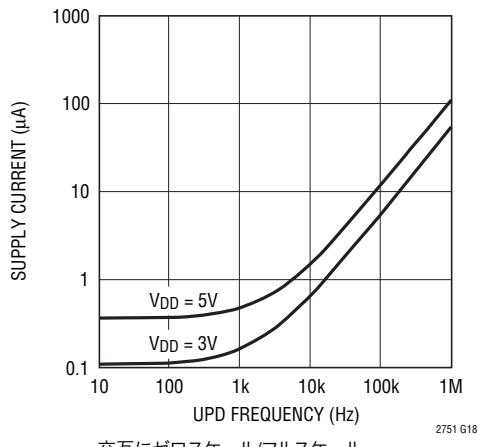

| <b>電源</b>          |                                  |                                                        |     |      |      |        |

| V <sub>DD</sub>    | Supply Voltage                   |                                                        | ●   | 2.7  | 5.5  | V      |

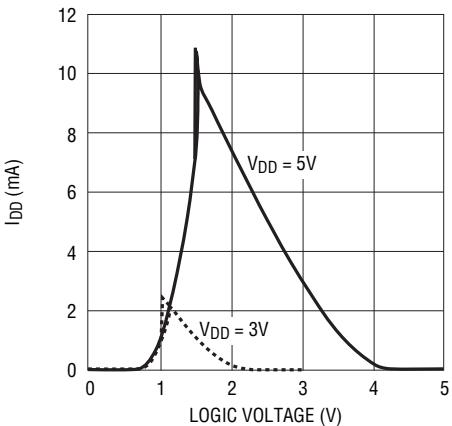

| I <sub>DD</sub>    | Supply Current, $V_{DD}$         | Digital Inputs = 0V or $V_{DD}$                        | ●   | 0.5  | 1    | μA     |

## 電気的特性

注記がない限り、 $V_{DD} = 5V$ 、 $V_{REF} = 5V$ 。●は全動作温度範囲の規格値を意味する。それ以外は $T_A = 25^\circ C$ での値。

| SYMBOL        | PARAMETER                  | CONDITIONS                                                | MIN    | TYP            | MAX        | UNITS   |

|---------------|----------------------------|-----------------------------------------------------------|--------|----------------|------------|---------|

| <b>デジタル入力</b> |                            |                                                           |        |                |            |         |

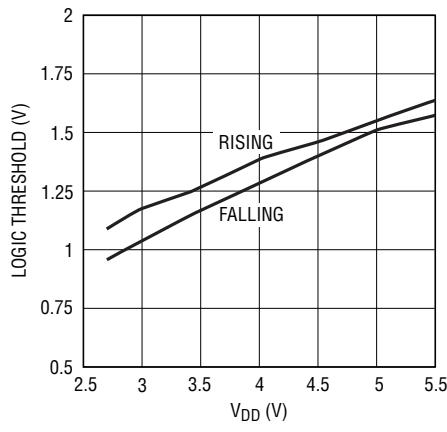

| $V_{IH}$      | Digital Input High Voltage | $3.3V \leq V_{DD} \leq 5.5V$<br>$2.7V \leq V_{DD} < 3.3V$ | ●<br>● | 2.4<br>2       |            | V       |

| $V_{IL}$      | Digital Input Low Voltage  | $4.5V < V_{DD} \leq 5.5V$<br>$2.7V \leq V_{DD} \leq 4.5V$ | ●<br>● |                | 0.8<br>0.6 | V       |

| $I_{IN}$      | Digital Input Current      | $V_{IN} = GND$ to $V_{DD}$                                | ●      |                | $\pm 1$    | $\mu A$ |

| $C_{IN}$      | Digital Input Capacitance  | $V_{IN} = 0V$ (Note 10)                                   | ●      |                | 6          | pF      |

| <b>デジタル出力</b> |                            |                                                           |        |                |            |         |

| $V_{OH}$      | $I_{OH} = 200\mu A$        |                                                           | ●      | $V_{DD} - 0.4$ |            | V       |

| $V_{OL}$      | $I_{OL} = 200\mu A$        |                                                           | ●      |                | 0.4        | V       |

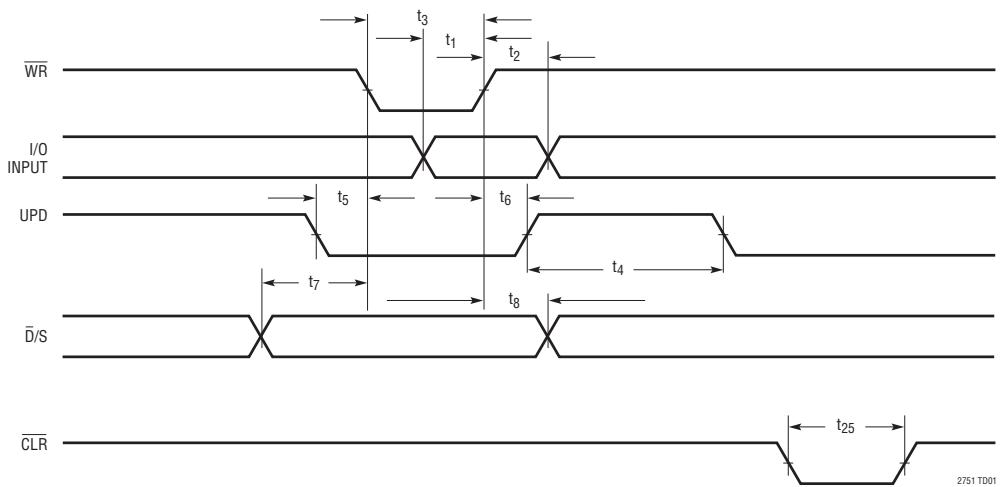

## タイミング特性

注記がない限り、 $V_{DD} = 5V$ 、 $V_{REF} = 5V$ 。●は全動作温度範囲の規格値を意味する。それ以外は $T_A = 25^\circ C$ での値。

| SYMBOL                    | PARAMETER                                                          | CONDITIONS            | MIN | TYP | MAX | UNITS |

|---------------------------|--------------------------------------------------------------------|-----------------------|-----|-----|-----|-------|

| $V_{DD} = 4.5V \sim 5.5V$ |                                                                    |                       |     |     |     |       |

| <b>書き込みと更新のタイミング</b>      |                                                                    |                       |     |     |     |       |

|                           |                                                                    |                       |     |     |     |       |

| $t_1$                     | I/O Valid to $\overline{WR}$ Rising Edge Set-Up                    |                       | ●   | 9   |     | ns    |

| $t_2$                     | I/O Valid to $\overline{WR}$ Rising Edge Hold                      |                       | ●   | 9   |     | ns    |

| $t_3$                     | $\overline{WR}$ Pulse Width                                        |                       | ●   | 20  |     | ns    |

| $t_4$                     | UPD Pulse Width                                                    |                       | ●   | 20  |     | ns    |

| $t_5$                     | UPD Falling Edge to $\overline{WR}$ Falling Edge                   | No Data Shoot-Through | ●   | 0   |     | ns    |

| $t_6$                     | $\overline{WR}$ Rising Edge to UPD Rising Edge                     | (Note 10)             | ●   | 0   |     | ns    |

| $t_7$                     | $\overline{D/S}$ Valid to $\overline{WR}$ Falling Edge Set-Up Time |                       | ●   | 9   |     | ns    |

| $t_8$                     | $\overline{WR}$ Rising Edge to $\overline{D/S}$ Valid Hold Time    |                       | ●   | 9   |     | ns    |

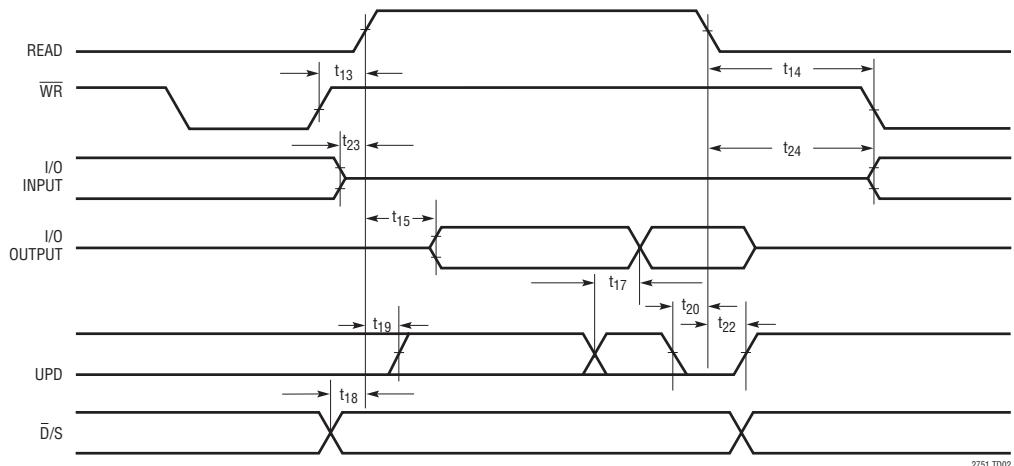

| <b>読み出しのタイミング</b>         |                                                                    |                       |     |     |     |       |

| $t_{13}$                  | $\overline{WR}$ Rising Edge to READ Rising Edge                    |                       | ●   | 9   |     | ns    |

| $t_{14}$                  | READ Falling Edge to $\overline{WR}$ Falling Edge                  | (Note 10)             | ●   | 20  |     | ns    |

| $t_{15}$                  | READ Rising Edge to I/O Propagation Delay                          | $C_L = 10pF$          | ●   |     | 30  | ns    |

| $t_{17}$                  | UPD Valid to I/O Propagation Delay                                 | $C_L = 10pF$          | ●   |     | 30  | ns    |

| $t_{18}$                  | $\overline{D/S}$ Valid to READ Rising Edge                         | (Note 10)             | ●   | 9   |     | ns    |

| $t_{19}$                  | READ Rising Edge to UPD Rising Edge                                | No Update             | ●   | 9   |     | ns    |

| $t_{20}$                  | UPD Falling Edge to READ Falling Edge                              | No Update             | ●   | 9   |     | ns    |

| $t_{22}$                  | READ Falling Edge to UPD Rising Edge                               | (Note 10)             | ●   | 9   |     | ns    |

| $t_{23}$                  | I/O Bus Hi-Z to READ Rising Edge                                   | (Note 10)             | ●   | 0   |     | ns    |

| $t_{24}$                  | READ Falling Edge to I/O Bus Active                                | (Note 10)             | ●   | 20  |     | ns    |

| <b>CLRのタイミング</b>          |                                                                    |                       |     |     |     |       |

| $t_{25}$                  | CLR Pulse Width Low                                                |                       | ●   | 20  |     | ns    |

## タイミング特性

注記がない限り、 $V_{DD} = 5V$ 、 $V_{REF} = 5V$ 。●は全動作温度範囲の規格値を意味する。それ以外は $T_A = 25^\circ C$ での値。

| SYMBOL | PARAMETER | CONDITIONS | MIN | TYP | MAX | UNITS |

|--------|-----------|------------|-----|-----|-----|-------|

|--------|-----------|------------|-----|-----|-----|-------|

$V_{DD} = 2.7V \sim 3.3V$

### 書き込みと更新のタイミング

|       |                                                                    |                       |   |    |  |    |

|-------|--------------------------------------------------------------------|-----------------------|---|----|--|----|

| $t_1$ | I/O Valid to $\overline{WR}$ Rising Edge Set-Up                    |                       | ● | 18 |  | ns |

| $t_2$ | I/O Valid to $\overline{WR}$ Rising Edge Hold                      |                       | ● | 18 |  | ns |

| $t_3$ | $\overline{WR}$ Pulse Width                                        |                       | ● | 30 |  | ns |

| $t_4$ | UPD Pulse Width                                                    |                       | ● | 30 |  | ns |

| $t_5$ | UPD Falling Edge to $\overline{WR}$ Falling Edge                   | No Data Shoot-Through | ● | 0  |  | ns |

| $t_6$ | $\overline{WR}$ Rising Edge to UPD Rising Edge                     | (Note 10)             | ● | 0  |  | ns |

| $t_7$ | $\overline{D/S}$ Valid to $\overline{WR}$ Falling Edge Set-Up Time |                       | ● | 18 |  | ns |

| $t_8$ | $\overline{WR}$ Rising Edge to $\overline{D/S}$ Valid Hold Time    |                       | ● | 18 |  | ns |

### 読み出しのタイミング

|          |                                                   |              |   |    |  |    |

|----------|---------------------------------------------------|--------------|---|----|--|----|

| $t_{13}$ | $\overline{WR}$ Rising Edge to Read Rising Edge   |              | ● | 18 |  | ns |

| $t_{14}$ | Read Falling Edge to $\overline{WR}$ Falling Edge | (Note 10)    | ● | 40 |  | ns |

| $t_{15}$ | Read Rising Edge to I/O Propagation Delay         | $C_L = 10pF$ | ● | 40 |  | ns |

| $t_{17}$ | UPD Valid to I/O Propagation Delay                | $C_L = 10pF$ | ● | 40 |  | ns |

| $t_{18}$ | $\overline{D/S}$ Valid to Read Rising Edge        | (Note 10)    | ● | 18 |  | ns |

| $t_{19}$ | Read Rising Edge to UPD Rising Edge               | No Update    | ● | 9  |  | ns |

| $t_{20}$ | UPD Falling Edge to Read Falling Edge             | No Update    | ● | 9  |  | ns |

| $t_{22}$ | READ Falling Edge to UPD Rising Edge              | (Note 10)    | ● | 18 |  | ns |

| $t_{23}$ | I/O Bus Hi-Z to Read Rising Edge                  | (Note 10)    | ● | 0  |  | ns |

| $t_{24}$ | Read Falling Edge to I/O Bus Active               | (Note 10)    | ● | 40 |  | ns |

### CLRのタイミング

|          |                     |  |   |    |  |    |

|----------|---------------------|--|---|----|--|----|

| $t_{25}$ | CLR Pulse Width Low |  | ● | 30 |  | ns |

|----------|---------------------|--|---|----|--|----|

**Note 1:** 絶対最大定格に記載された値を超えるストレスはデバイスに永続的損傷を与える可能性がある。長期にわたって絶対最大定格条件に曝すと、デバイスの信頼性と寿命に悪影響を与える可能性がある。

**Note 2:** 規定された最高動作接合部温度を超えた動作が継続すると、デバイスの信頼性を損なうおそれがある。

**Note 3:** 独自のSoftSpanスイッチング・アーキテクチャなので、I<sub>OUT1</sub>ピンとI<sub>OUT2</sub>ピンがグランドに保持されていると、指定された各ピンを見込む測定された抵抗値は全ての出力レンジで一定である。

**Note 4:** R1はR<sub>IN</sub>～R<sub>COM</sub>で測定される。R2はREF～R<sub>COM</sub>で測定される。

**Note 5:**  $C_{FEEDBACK} = 15pF$ でLT1469を使う。1.7 $\mu s$ の±0.0015%セトリング時間は個別に時定数を最適化して達成することができる。アプリケーションノート74「Component and

Measurement Advances Ensure 16-Bit DAC Settling Time (16ビットDACのセトリング時間と保証する部品と測定技術の進歩)」を参照。

**Note 6:** メジャー・キャリーの遷移で測定される(0V～5Vレンジ)。出力アンプ:LT1469;  $C_{FB} = 27pF$ 。

**Note 7:** フルスケールの遷移; REF = 0V。

**Note 8:** REF = 1kHzで6V<sub>RMS</sub>、0V～5Vレンジ。DACのコード = FS。出力アンプ = LT1469。

**Note 9:**  $V_n = \sqrt{4kTBR}$ から計算。ここで、 $k = 1.38E-23$  J/K(ボルツマン定数)； $R$  = 抵抗 (Ω)、 $T$  = 温度 (K)、 $B$  = 帯域幅 (Hz)。

**Note 10:** 設計により保証。製造時にはテストされない。

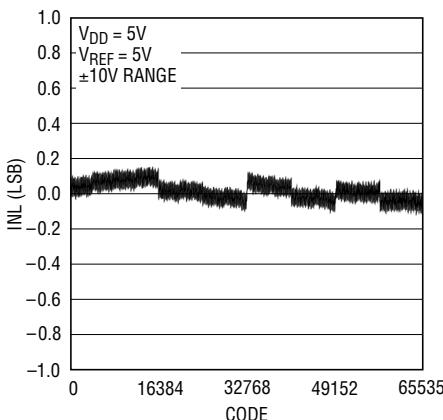

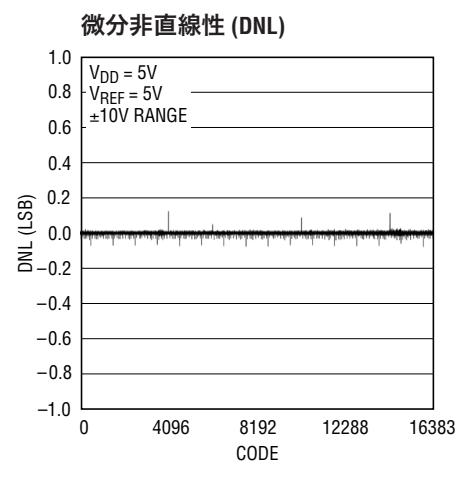

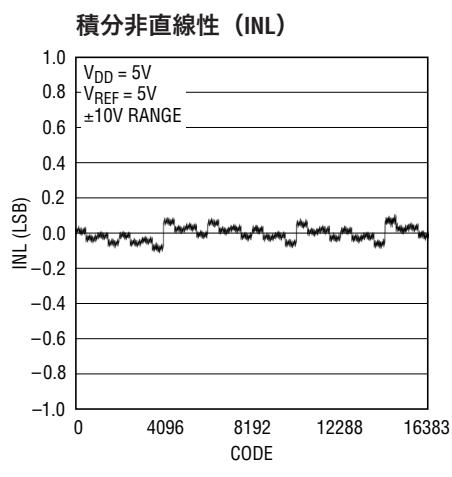

標準的性能特性 注記がない限り、 $T_A = 25^\circ\text{C}$ 。

LTC2751-16

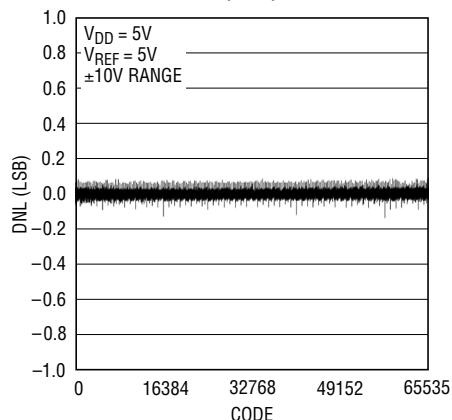

### 積分非直線性 (INL)

### 微分非直線性 (DNL)

2751 G01

2751 G02

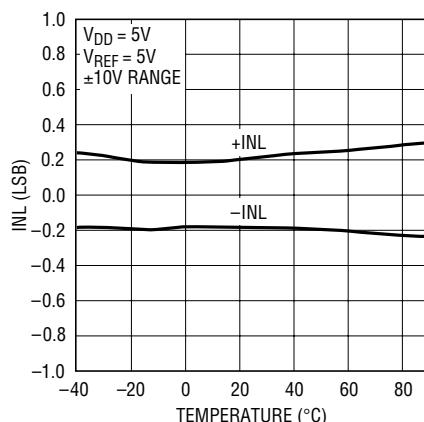

### INL と 温度

2751 G04

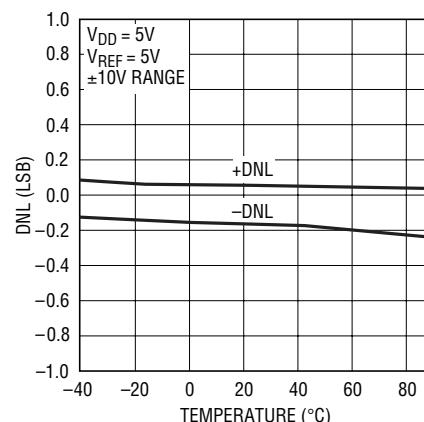

### DNL と 温度

2751 G05

### バイポーラのゼロと 温度

2751 G06

### 利得誤差と 温度

2751 G07

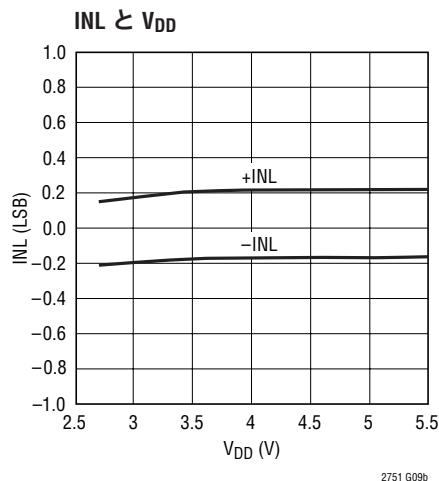

### INL と $V_{REF}$

2751 G08

### DNL と $V_{REF}$

2751 G09

2751fa

標準的性能特性 注記がない限り、 $T_A = 25^\circ\text{C}$ 。

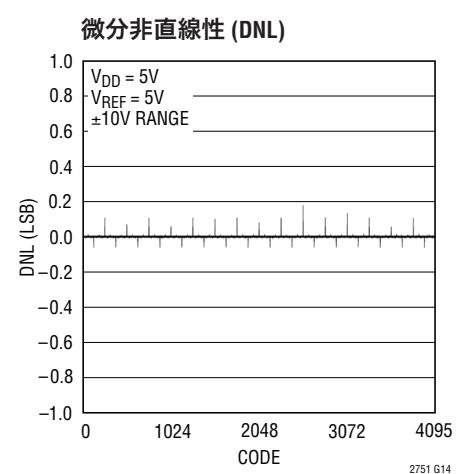

LTC2751-16

LTC2751-14

LTC2751-12

# LTC2751

標準的性能特性 注記がない限り、 $T_A = 25^\circ\text{C}$ 。

LTC2751-12, LTC2751-14, LTC2751-16

## ミッドスケール・グリッチ

$V_{DD} = 5\text{V}$     $V_{REF} = 5\text{V}$     $C_{FEEDBACK} = 27\text{pF}$

OV TO 5V RANGE   USING AN LT1469

## 電源電流とロジック入力電圧

全てのデジタル・ピンは共通接続

(GNDに接続されたREADは除く)

## ロジックのスレッショルド電圧 と電源電圧

## 電源電流と更新周波数

交互にゼロスケール/フルスケール

(LTC2751-16)

## ピン機能

**R<sub>IN</sub>(ピン1):**R<sub>IN</sub>とREFのセンタータップ・ポイント。通常は外部リファレンス反転アンプの負入力に接続されます。

**R<sub>IN</sub>(ピン2):**外部リファレンス反転アンプの入力抵抗。通常は外部リファレンス電圧V<sub>REF</sub>とR<sub>OFS</sub>(ピン37)に接続されます。標準5Vで、±15Vまで受け入れます。

**S2(ピン3):**スパンI/Oビット2。ピンS0、S1およびS2は、DACの出力レンジをプログラムし、読み出すのに使われます。

**I<sub>OUT2</sub>(ピン4):**DACの電流出力のコンプリメント。I<sub>OUT2</sub>はGNDに接続します。

**NC(ピン5):**接続なし。GNDに接続する必要があり、I<sub>OUT2</sub>に必要なシールドを与えます。

**D3～D11(ピン6～ピン14):**LTC2751-12のみ。DACの入力/出力データ・ビット。これらのI/OピンはDACのコードを設定し、読み出します。D11がMSBです。

**D5～D13(ピン6～ピン14):**LTC2751-14のみ。DACの入力/出力データ・ビット。これらのI/OピンはDACのコードを設定し、読み出します。D13がMSBです。

**D7～D15(ピン6～ピン14):**LTC2751-16のみ。DACの入力/出力データ・ビット。これらのI/OピンはDACのコードを設定し、読み出します。D15がMSBです。

**V<sub>DD</sub>(ピン15):**正電源入力(2.7V ≤ V<sub>DD</sub> ≤ 5.5V)。GNDへの0.1μFのバイパス・コンデンサが必要です。

**GND(ピン16):**グランド。グランドに接続します。

**CLR(ピン17):**非同期クリア。CLRをロジック“L”に引き下げるとき、データ・レジスタが現在の出力レンジのゼロボルトのコードにリセットされます(V<sub>OUT</sub> = 0V)。

**MSPAN(ピン18):**手動スパン制御ピン。MSPANは、单一の固定出力レンジで動作するようにLTC2751を構成するのに使います。シングル・スパン動作に構成されると、出力レンジはハードウェアによるピンストラッピングによって設定されます。スパン入力とDACレジスタは透過的で、書き込みや更新のコマンドに応答しません。

デバイスをシングル・スパンで使用するように構成するには、MSPANを直接V<sub>DD</sub>に接続します。代わりに、MSPANをGNDに接続すると(SoftSpan構成)、書き込み、更新および読み出しの動作を使って出力レンジを設定および検証することができます。「動作」のセクションの「手動によるスパンの構成設定」を参照してください。

MSPANはGND(SoftSpan構成)またはV<sub>DD</sub>(シングル・スパン構成)のどちらかに直接接続する必要があります。

**D0～D2(ピン19～ピン21):**LTC2751-12のみ。DACの入力/出力データ・ビット。これらのI/OピンはDACのコードを設定し、読み出します。D0がLSBです。

**D0～D4(ピン19～ピン23):**LTC2751-14のみ。DACの入力/出力データ・ビット。これらのI/OピンはDACのコードを設定し、読み出します。D0がLSBです。

**D0～D6(ピン19～ピン25):**LTC2751-16のみ。DACの入力/出力データ・ビット。これらのI/OピンはDACのコードを設定し、読み出します。D0がLSBです。

**NC(ピン22～ピン27):**LTC2751-12のみ。接続なし。

**NC(ピン24～ピン27):**LTC2751-14のみ。接続なし。

**NC(ピン26, 27):**LTC2751-16のみ。接続なし。

**D/S(ピン28):**データ/スパンの選択。このピンは、データI/OピンまたはスパンI/Oピン(それぞれD0～D15またはS0～S2)を、それらの対応する専用レジスタとともに、書き込みまたは読み出し動作のために選択してアクティブにするのに使われます。全ての更新でデータ・レジスタとスパン・レジスタの両方が影響を受けるので、更新動作ではD/Sは無視されます。シングル・スパン動作では、D/SをGNDに接続します。

**READ(ピン29):**読み出しピン。READが“H”にアサートされると、データI/Oピン(D0～D15)またはスパンI/Oピン(S0～S2)から選択されたレジスタの内容が出力されます(表1を参照)。シングル・スパン動作では、スパンI/Oピンの読み出しはディスエーブルされます。

**UPD(ピン30):**更新およびバッファ選択ピン。READが“L”に保たれ、UPDが“H”にアサートされると、入力レジスタの内容(データとスパンの両方)がそれらの対応するDACレジスタにコピーされます。DACの出力が更新され、DACレジスタの新しい値が反映されます。

READが“H”に保たれているとき、更新機能はディスエーブルされ、UPDピンはバッファ・セレクタとして機能します(ロジック“L”で入力レジスタを選択し、“H”でDACレジスタを選択します)。「動作」のセクションの「読み出し」を参照してください。

**WR(ピン31):**アクティブ“L”の書き込みピン。書き込み動作はデータI/OピンまたはスパンI/Oピン(それぞれD0～D15またはS0～S2)のデータを入力レジスタにコピーします。READが“H”的とき、書き込み機能はディスエーブルされます。

**S0(ピン32):**スパンI/Oビット0。ピンS0、S1およびS2は、DACの出力レンジをプログラムし、読み出すのに使われます。

## ピン機能

**S1(ピン33)**:スパンI/Oビット1。ピンS0、S1およびS2は、DACの出力レンジをプログラムし、読み出すのに使われます。

**R<sub>VOS</sub>(ピン34)**:DACのオフセット調整。公称入力レンジは±5Vです。使わない場合、R<sub>VOS</sub>はI<sub>OUT2</sub>に短絡します。

**I<sub>OUT1</sub>(ピン35)**:DACの電流出力:通常はI/Vコンバータ・アンプの負入力に接続されます。

**R<sub>FB</sub>(ピン36)**:DACの帰還抵抗:通常はI/Vコンバータ・アンプの出力に接続されます。I<sub>OUT1</sub>からのDACの出力電流は帰還抵抗を通ってR<sub>FB</sub>ピンに流れます。

**R<sub>0FS</sub>(ピン37)**:バイポーラ・オフセット・ネットワーク。このピンはバイポーラ・スパンの出力電圧レンジを変換します。±15Vまで受け入れ、通常はR<sub>IN</sub>(ピン2)の正リファレンス電圧に接続されます。

**REF(ピン38)**:リファレンス反転アンプの帰還抵抗、およびDACのリファレンス入力。通常はリファレンス反転アンプの出力に接続されます。標準で-5V。±15Vまで受け入れます。

**露出パッド(ピン39)**:グランド。露出パッドはPCBに半田付けする必要があります。

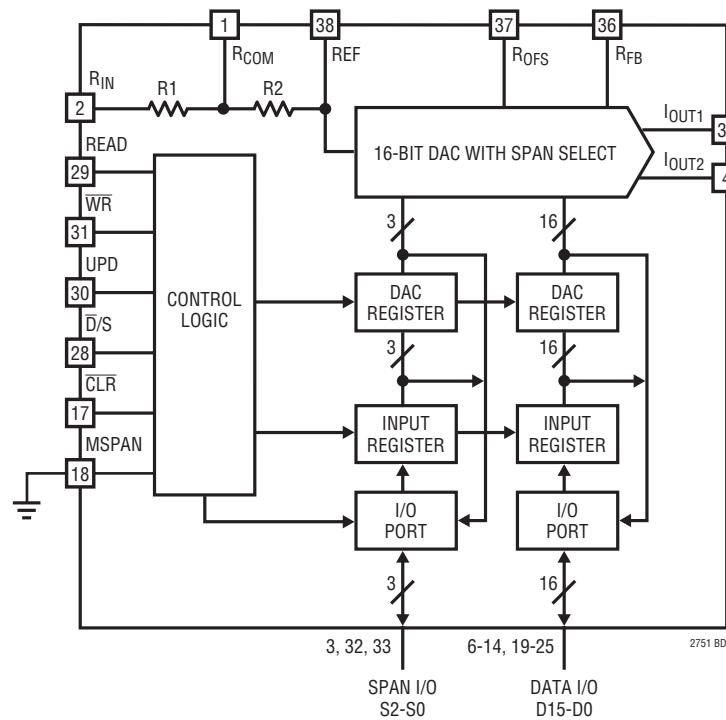

## ブロック図

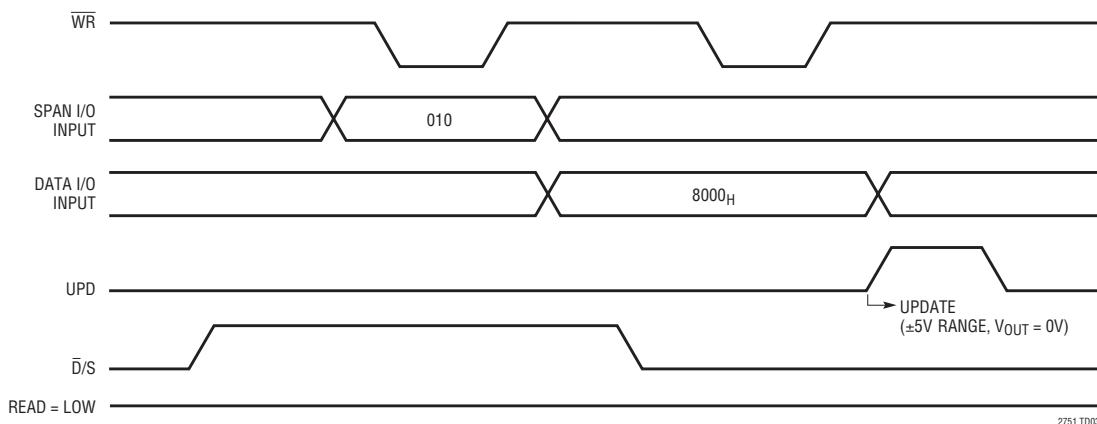

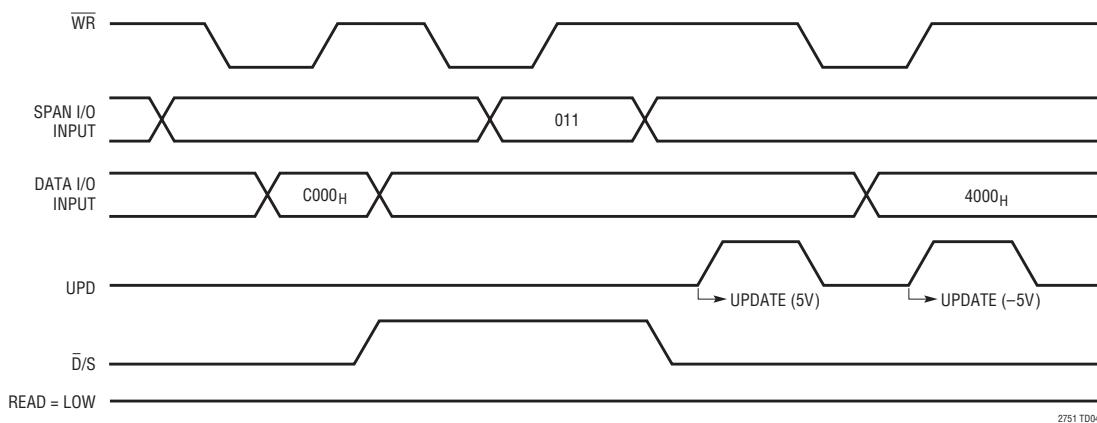

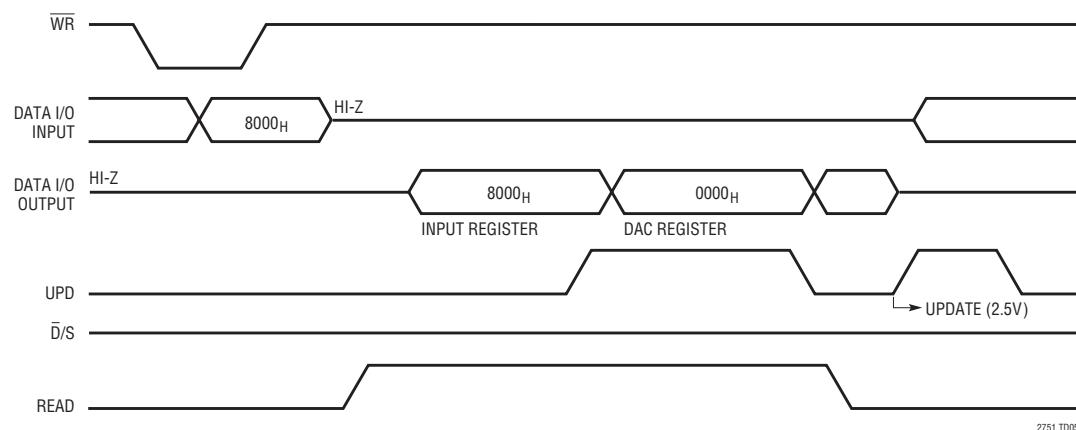

## タイミング図

書き込み、更新およびクリアのタイミング

読み出しのタイミング

## 動作

### 出力レンジ

LTC2751は電流出力、パラレル入力の高精度乗算型DACで、出力レンジはソフトウェアでプログラム可能です。SoftSpanにより、2つのユニポーラ出力レンジ(0V~5Vおよび0V~10V)、および4つのバイポーラ・レンジ( $\pm 2.5V$ 、 $\pm 5V$ 、 $\pm 10V$ および $-2.5V$ ~ $7.5V$ )が与えられます。これらのレンジは外部高精度5Vリファレンスを使う場合に得られます。2Vのリファレンス電圧を使う場合、SoftSpanのレンジは次のようにになります。0V~2V、0V~4V、 $\pm 1V$ 、 $\pm 2V$ 、 $\pm 4V$ および $-1V$ ~ $3V$ 。2Vおよび5V以外のリファレンスの場合、出力レンジはリニアにスケーリングされます。

### デジタル・セクション

LTC2751製品ファミリーは4個の内部インターフェース・レジスタを備えています(ブロック図を参照)。これらのうちの2個(1個の入力レジスタと1個のDACレジスタ)はデータI/Oポート専用で、2個はスパンI/Oポート専用です。このように、各ポートは二重にバッファされています。二重にバッファされているので、スパンとコードを同時に更新可能で、出力レンジの変更の際に滑らかに電圧を遷移させることができます。複数のDACの同時更新も可能です。

## 動作

### 書き込みと更新の動作

データ入力レジスタは、 $\bar{D}/S$ ピンを“L”に保ってから $\bar{WR}$ ピンに“L”的パルスを与えることにより、16ビットのマイクロプロセッサ・バスから直接ロードされます。2番目のレジスタ(DACレジスタ)はUPDピンに“H”的パルスを与えることによってロードされ、入力レジスタに保持されているデータがDACレジスタにコピーされます。更新には常にデータとスパンの両方が含まれることに注意してください。ただし、入力レジスタの値が書き込みによって変更されていない限り、DACレジスタの値は変化しません。

スパン入力レジスタへのロードは、 $\bar{D}/S$ ピンを“H”に保ってから $\bar{WR}$ ピンを“L”にすることにより、似た方法で実現されます。スパン・レジスタとデータレジスタの構造は、パラレル・ビットの個数以外は同じです(スパン・レジスタは3ビットですが、データ・レジスタは12、14または16ビットです)。

フロースルー・モードで両方のレジスタを透過的にするには、 $\bar{WR}$ を“L”に接続し、UPDを“H”に接続します。ただし、これによってデグリッチャ動作が無効になり、出力グリッヂ・インパルスが増加することがあります。デグリッチャはUPDピンの立上りエッジでアクティブになります。

このインターフェースは、入力レジスタとDACレジスタをマスター/スレーブ構成またはエッジ・トリガ構成で使用することも可能になります。このモードの動作は、 $\bar{WR}$ とUPDが一緒に結線され、单一のクロック信号によってドライブされるとき起きます。データ・ビットはクロックの立下りエッジで入力レジスタにロードされてから、立上りエッジでDACレジスタにロードされます。

書き込みと読み出し動作がデータとスパンで分離されているので、スパン・ピンのS2～S0がデータのLSB(D2～D0)とバス・ラインを共有できるようにすることにより、16ビット幅の1本のデータ・バス上でデータとスパンの両方を制御することができます。どの書き込みや読み出し動作もスパンとデータの両方を含むことはないので、衝突が生じることはありません。

非同期クリア・ピンは、どの出力レンジでもLTC2751を0V(ゼロ・スケール、1/2スケールまたは1/4スケールのコード)にリセットします。 $\bar{CLR}$ は入力レジスタとDACデータ・レジスタの両方をリセットしますが、スパン・レジスタは影響を受けず、そのまま保たれます。

これらのデバイスはパワーオン・リセットも備えています。SoftSpanに構成設定されると、デバイスは0V～5Vの出

力レンジのゼロ・スケールに初期化されます。シングル・スパン動作に構成設定されると、デバイスは選択された出力レンジのゼロ・ボルト・コードに初期化されます。

LTC2751の諸機能を図1に示します。

表1. 書込み、更新および読み出し機能

| READ | $\bar{D}/S$ | WR | UPD | スパンI/O       | データI/O       |

|------|-------------|----|-----|--------------|--------------|

| 0    | 0           | 0  | 0   | -            | 入力レジスタに書き込む  |

| 0    | 0           | 0  | 1   | -            | 書き込み/更新(透過的) |

| 0    | 0           | 1  | 0   | -            | -            |

| 0    | 0           | 1  | 1   | DACレジスタを更新   | DACレジスタを更新   |

| 0    | 1           | 0  | 0   | 入力レジスタに書き込む  | -            |

| 0    | 1           | 0  | 1   | 書き込み/更新(透過的) | -            |

| 0    | 1           | 1  | 0   | -            | -            |

| 0    | 1           | 1  | 1   | DACレジスタを更新   | DACレジスタを更新   |

| 1    | 0           | X  | 0   | -            | 入力レジスタを読み出す  |

| 1    | 0           | X  | 1   | -            | DACレジスタを読み出す |

| 1    | 1           | X  | 0   | 入力レジスタを読み出す  | -            |

| 1    | 1           | X  | 1   | DACレジスタを読み出す | -            |

X=ドントケア

### 手動によるスパンの構成設定

アプリケーションによっては複数の出力レンジは不要です。LTC2751をシングル・スパン動作に構成するには、MSPANピンを直接 $V_{DD}$ に接続し、 $\bar{D}/S$ ピンをGNDに接続します。次に、いつものようにスパンI/Oピン(S0、S1およびS2)によって望みの出力レンジを指定しますが、ピンをGNDまたは $V_{DD}$ に直接接続することによってプログラムします(図1と表2を参照)。この構成では、デバイスは起動時に選択された出力レンジに初期化され、 $V_{OUT} = 0V$ になります。

手動スパン動作に構成されていると、スパン・ピンの読み出しへはディスエーブルされます。

図1. LTC2751のシングル・スパン動作の構成設定(±10Vレンジ)

## 動作

表2. スパンのコード

| S2 | S1 | S0 | スパン             |

|----|----|----|-----------------|

| 0  | 0  | 0  | ユニポーラ0V~5V      |

| 0  | 0  | 1  | ユニポーラ0V~10V     |

| 0  | 1  | 0  | バイポーラ-5V~5V     |

| 0  | 1  | 1  | バイポーラ-10V~10V   |

| 1  | 0  | 0  | バイポーラ-2.5V~2.5V |

| 1  | 0  | 1  | バイポーラ-2.5V~7.5V |

示されていないコードは予備であり、使用してはならない。

### 読み出し

4つのインターフェース・レジスタのどのレジスタの内容も、 $\bar{D/S}$ ピンおよびUPDピンと組み合わせてREADピンを使うことにより、読み出すことができます。

読み出し動作はREADをロジック“H”に引き上げることにより開始されます。I/OピンはREADが“L”的ときは高インピーダンスのデジタル入力ですが、読み出しの間は選択的に低インピーダンスのロジック出力に切り替わります。

I/Oピンはデータとスパンの2つのポートで構成されています。データI/OポートはD0~D11、D0~D13またはD0~D15のピン(それぞれ、LTC2751-12、LTC2751-14またはLTC2751-16)で構成されています。スパンI/Oポートは全てのデバイスでS0、S1およびS2のピンで構成されています。

それぞれのI/Oポートが1個の専用入力レジスタと1個の専用DACレジスタを備えています。レジスタの構成をブロック図に示します。

どちらのI/Oポート(データまたはスパン)を構成設定してそのレジスタの内容を読み出すか選択するのに $\bar{D/S}$ ピンが使われます。選択されないI/Oポートのピンは高インピーダンス入力のまま保たれます。

I/Oポートが選択された後、その入力レジスタまたはDACレジスタが、読み出しのためにUPDピンによって選択されます。UPDは2つの機能を持ったピンであることに注意し

てください。READが“H”的とき更新機能はディスエーブルされ、代わりに、UPDピンは読み出しのために入力レジスタまたはDACレジスタを選択します。LTC2751の読み出し機能を表1に示します。

最も一般的な読み出し動作は、入力レジスタに書き込んだ後、その新しいデータでDACレジスタを更新する前に入力レジスタの内容をチェックすることです。これを行うには、UPDを“L”に保ったままREADを“H”に引き上げます。選択されたポートの入力レジスタの内容はデータまたはスパンのI/Oピンによって出力されます。

DACレジスタの内容を読み出すには、READを“H”に引き上げてから、UPDを“H”に引き上げます。選択されたデータまたはスパンのDACレジスタの内容はデータまたはスパンのI/Oピンによって出力されます。注記: 読出し動作の後、更新を望まないのであれば、READを“L”に引き下げる前にUPDを“L”に戻す必要があります。そうしないと、UPDピンはその主要機能に戻り、DACを更新します。

### システムのオフセットの調整

多くのシステムがシステム全体のオフセットの補償を必要とします。R<sub>VOS</sub>オフセット調節ピンはこの目的のために備わっています。ノイズ耐性と調節のし易さのために、制御電圧はDACの出力に減衰されます。

$$V_{OS} = -0.01 \cdot V(R_{VOS}) [0V \sim 5V, \pm 2.5V \text{のスパン}]$$

$$V_{OS} = -0.02 \cdot V(R_{VOS}) [0V \sim 10V, \pm 5V, -2.5V \sim 7.5V \text{のスパン}]$$

$$V_{OS} = -0.04 \cdot V(R_{VOS}) [\pm 10V \text{のスパン}]$$

このピンの公称入力レンジは $\pm 5V$ です。必要ならば、 $\pm 15V$ までの他のリファレンス電圧を使用することができます。R<sub>VOS</sub>ピンの入力インピーダンスは $1M\Omega$ です。LTC2751のセトリング性能を維持するには、このピンを $10k\Omega$ 以下のテブナン等価インピーダンスでドライブします。使わない場合、R<sub>VOS</sub>はI<sub>OUT2</sub>に短絡します。

## 動作 - 例

1.  $\pm 5V$ のレンジをロードし、出力は0Vにします。スパンとコードは一緒に更新されるので、出力が0Vで開始されると出力はそこに留まることに注意してください。

2. 出力は5Vで $\pm 10V$ のレンジをロードし、-5Vに変更します。

3. 更新前に入力レジスタとDACレジスタの内容をチェックするために読み出しを使って、0V～5Vレンジのミッドスケール・コード( $V_{OUT} = 2.5V$ )を書き込み、更新します。

## アプリケーション情報

### オペアンプの選択

16ビットLTC2751-16は精度が非常に高いので、このデバイスの有している並外れた性能を十分引き出すには、慎重に検討してオペアンプを選択する必要があります。さくわい、オペアンプのオフセットに対するINLとDNLの感度は、前の世代の乗算型DACに比べて大幅に減少しています。

ユニポーラまたはバイポーラの出力レンジでプログラムされたときの、LTC2751の精度に対するオペアンプのパラメータの影響を評価するための式を表3と表4に示します。

表3. 表4の式を調整する各出力レンジの変数

| OUTPUT RANGE  | A1  | A2 | A3   | A4  | A5  |

|---------------|-----|----|------|-----|-----|

| 5V            | 1.1 | 2  | 1    |     | 1   |

| 10V           | 2.2 | 3  | 0.5  |     | 1.5 |

| ±5V           | 2   | 2  | 1    | 1   | 1.5 |

| ±10V          | 4   | 4  | 0.83 | 1   | 2.5 |

| ±2.5V         | 1   | 1  | 1.4  | 1   | 1   |

| -2.5V to 7.5V | 1.9 | 3  | 0.7  | 0.5 | 1.5 |

表4. 全ての出力レンジでDACの精度に対するオペアンプの影響を求める使いやすい式(ページ1の回路)。添字の1は出力アンプを指し、添字の2はリファレンス反転アンプを指します。

| OP AMP           | INL (LSB)                                                   | DNL (LSB)                                                    | ユニポーラのオフセット (LSB)                                                   | バイポーラのゼロ誤差 (LSB)                                                                 | ユニポーラの利得誤差 (LSB)                                            | バイポーラの利得誤差 (LSB)                                            |

|------------------|-------------------------------------------------------------|--------------------------------------------------------------|---------------------------------------------------------------------|----------------------------------------------------------------------------------|-------------------------------------------------------------|-------------------------------------------------------------|

| $V_{OS1}$ (mV)   | $V_{OS1} \cdot 3.2 \cdot \left(\frac{5V}{V_{REF}}\right)$   | $V_{OS1} \cdot 0.82 \cdot \left(\frac{5V}{V_{REF}}\right)$   | $A3 \cdot V_{OS1} \cdot 13.2 \cdot \left(\frac{5V}{V_{REF}}\right)$ | $A3 \cdot V_{OS1} \cdot 19.8 \cdot \left(\frac{5V}{V_{REF}}\right)$              | $V_{OS1} \cdot 13.2 \cdot \left(\frac{5V}{V_{REF}}\right)$  | $V_{OS1} \cdot 13.2 \cdot \left(\frac{5V}{V_{REF}}\right)$  |

| $I_{B1}$ (nA)    | $I_{B1} \cdot 0.0003 \cdot \left(\frac{5V}{V_{REF}}\right)$ | $I_{B1} \cdot 0.00008 \cdot \left(\frac{5V}{V_{REF}}\right)$ | $I_{B1} \cdot 0.13 \cdot \left(\frac{5V}{V_{REF}}\right)$           | $I_{B1} \cdot 0.13 \cdot \left(\frac{5V}{V_{REF}}\right)$                        | $I_{B1} \cdot 0.0018 \cdot \left(\frac{5V}{V_{REF}}\right)$ | $I_{B1} \cdot 0.0018 \cdot \left(\frac{5V}{V_{REF}}\right)$ |

| $A_{VOL1}$ (V/V) | $A1 \cdot \left(\frac{16.5k}{A_{VOL1}}\right)$              | $A2 \cdot \left(\frac{1.5k}{A_{VOL1}}\right)$                | 0                                                                   | 0                                                                                | $A5 \cdot \left(\frac{131k}{A_{VOL1}}\right)$               | $A5 \cdot \left(\frac{131k}{A_{VOL1}}\right)$               |

| $V_{OS2}$ (mV)   | 0                                                           | 0                                                            | 0                                                                   | $A4 \cdot \left(V_{OS2} \cdot 13.1 \cdot \left(\frac{5V}{V_{REF}}\right)\right)$ | $V_{OS2} \cdot 26.2 \cdot \left(\frac{5V}{V_{REF}}\right)$  | $V_{OS2} \cdot 26.2 \cdot \left(\frac{5V}{V_{REF}}\right)$  |

| $I_{B2}$ (mV)    | 0                                                           | 0                                                            | 0                                                                   | $A4 \cdot \left(I_{B2} \cdot 0.13 \cdot \left(\frac{5V}{V_{REF}}\right)\right)$  | $I_{B2} \cdot 0.26 \cdot \left(\frac{5V}{V_{REF}}\right)$   | $I_{B2} \cdot 0.26 \cdot \left(\frac{5V}{V_{REF}}\right)$   |

| $A_{VOL2}$ (V/V) | 0                                                           | 0                                                            | 0                                                                   | $A4 \cdot \left(\frac{66k}{A_{VOL2}}\right)$                                     | $\left(\frac{131k}{A_{VOL2}}\right)$                        | $\left(\frac{131k}{A_{VOL2}}\right)$                        |

表5. LTC2751と共に使用することを推奨するLTC高精度アンプの一部とその仕様のリスト

| AMPLIFIER     | AMPLIFIER SPECIFICATIONS |          |                |                               |                               |                      |                            |                                     |                      |

|---------------|--------------------------|----------|----------------|-------------------------------|-------------------------------|----------------------|----------------------------|-------------------------------------|----------------------|

|               | $V_{OS}$ $\mu$ V         | $I_B$ nA | $A_{VOL}$ V/mV | VOLTAGE NOISE nV/ $\sqrt{Hz}$ | CURRENT NOISE pA/ $\sqrt{Hz}$ | SLEW RATE V/ $\mu$ s | GAIN BANDWIDTH PRODUCT MHz | $t_{SETTLING}$ with LTC2751 $\mu$ s | POWER DISSIPATION mW |

| LT1001        | 25                       | 2        | 800            | 10                            | 0.12                          | 0.25                 | 0.8                        | 120                                 | 46                   |

| LT1097        | 50                       | 0.35     | 1000           | 14                            | 0.008                         | 0.2                  | 0.7                        | 120                                 | 11                   |

| LT1112 (Dual) | 60                       | 0.25     | 1500           | 14                            | 0.008                         | 0.16                 | 0.75                       | 115                                 | 10.5/Op Amp          |

| LT1124 (Dual) | 70                       | 20       | 4000           | 2.7                           | 0.3                           | 4.5                  | 12.5                       | 19                                  | 69/Op Amp            |

| LT1468        | 75                       | 10       | 5000           | 5                             | 0.6                           | 22                   | 90                         | 2                                   | 117                  |

| LT1469 (Dual) | 125                      | 10       | 2000           | 5                             | 0.6                           | 22                   | 90                         | 2                                   | 123/Op Amp           |

## アプリケーション情報

オペアンプのオフセットは大部分が出力オフセットと利得誤差に寄与し、INLとDNLに対する影響は微小です。LTC2751-16の場合、250 $\mu$ Vのオペアンプのオフセットは、5Vのリファレンスで約0.8LSBのINLの劣化と0.2LSBのDNLの劣化を引き起こします。5Vのユニポーラ・モードにプログラムされたLTC2751では、同じ250 $\mu$ Vのオペアンプのオフセットが、3.3LSBのゼロスケール誤差と3.3LSBの利得誤差を生じます。

表3と表4の簡単な式では直接扱ってはいませんが、ユニポーラとバイポーラのアプリケーションに対する温度の影響も同様に簡単に扱うことができます。まず、オペアンプのデータシートを調べて、全温度範囲にわたるワーストケースの $V_{OS}$ と $I_B$ を見つけます。次に、これらの数値を表4の $V_{OS}$ と $I_B$ の式に代入して温度による影響を計算します。

高速セトリング時間が重要なアプリケーションの場合、アプリケーションノート74「部品と測定方法の進歩による16ビットDACのセトリング時間の保証」で16ビットDACのセトリング時間とオペアンプの選択について詳細に説明されています。

### 高精度電圧リファレンスの検討

LTC2751と一緒に使うオペアンプの選択がシステムの性能にとって決定的に重要であるのと同様、高精度電圧リファレンスの選択にも相応の手間をかける必要があります。LTC2751の出力電圧は電圧リファレンスの影響を直接受けますので、電圧リファレンスの誤差は全てDACの出力電圧誤差として現れます。

16ビットのアプリケーション用の高精度電圧リファレンスの選択時に検討すべき主な誤差源が3つあります。つまり、初期出力電圧許容差、出力電圧の温度係数および出力電圧ノイズです。

リファレンスの初期出力電圧許容差が修正されないと、フルスケールの誤差項を生じます。LT1236のような出力電圧の初期許容差が低い( $\pm 0.05\%$ )リファレンスを選択すると、リファレンスによって生じる利得誤差を小さくできます。ただし、システムのゼロ誤差とフルスケール誤差を修正する較正シーケンスを必ず実行することを推奨します。

リファレンスの出力電圧の温度係数は、フルスケール誤差だけでなく、回路のINLとDNLの性能にも影響します。

出力電圧の温度係数が大きなりファレンスを選択すると、DACの出力電圧とその伝達特性が周囲条件に大きく依存するようになります。リファレンスの温度係数による誤差を小さく抑えるには、出力電圧の温度係数が低い高精度リファレンスを選択するか、回路の周囲温度を厳密に制御して温度勾配を小さくします。

高精度DACのアプリケーションが16ビット以上の性能に移行するにつれ、リファレンスの出力電圧ノイズがシステムのノイズの支配的部分を占める可能性があります。その結果、システムのダイナミックレンジとSN比を低下させる可能性があります。要求されるシステムの分解能に対して、できるだけ出力ノイズ電圧が低い電圧リファレンスを選択するように注意が必要です。LT1236のような高精度電圧リファレンスは0.1Hz～10Hzの領域で低い出力ノイズを発生しますが、5Vまたは10Vのフルスケールのシステムの16ビットLSBレベルより十分小さいレベルです。ただし、回路の帯域幅が増加すると、リファレンスの出力にフィルタをかけて出力ノイズを抑える必要があるかもしれません。

表6. LTC2751と共に使用することを推奨するLTCの高精度リファレンスの一部とその仕様のリスト

| REFERENCE                | INITIAL TOLERANCE | TEMPERATURE DRIFT   | 0.1Hz to 10Hz NOISE       |

|--------------------------|-------------------|---------------------|---------------------------|

| LT1019A-5,<br>LT1019A-10 | $\pm 0.05\%$      | 5ppm/ $^{\circ}$ C  | 12 $\mu$ V <sub>P-P</sub> |

| LT1236A-5,<br>LT1236A-10 | $\pm 0.05\%$      | 5ppm/ $^{\circ}$ C  | 3 $\mu$ V <sub>P-P</sub>  |

| LT1460A-5,<br>LT1460A-10 | $\pm 0.075\%$     | 10ppm/ $^{\circ}$ C | 20 $\mu$ V <sub>P-P</sub> |

| LT1790A-2.5              | $\pm 0.05\%$      | 10ppm/ $^{\circ}$ C | 12 $\mu$ V <sub>P-P</sub> |

### 接地

どんな高分解能のコンバータの場合でもそうですが、クリーンな接地が重要です。低インピーダンスのアナログ・グランド・プレーンとスター・グランドのテクニックを使う必要があります。I<sub>OUT2</sub>はできるだけ低い抵抗でスター・グランドに接続する必要があります。I<sub>OUT2</sub>の近くにスター・グランドを配置できないときは、低抵抗のトレースを使ってこのピンをスター・グランドに配線します。これにより、コードに依存してグランドに流れる電流によって生じる、このピンからグランドへの電圧降下が抑えられます。この回路基板トレースの抵抗が1 $\Omega$ を超えるときは、強制/検出の増幅構成を使ってこのピンをドライブする必要があります(図2参照)。これによりLTC2751-16のすぐれた精度(1LSBのINLとDNL)が維持されます。

## 標準的応用例

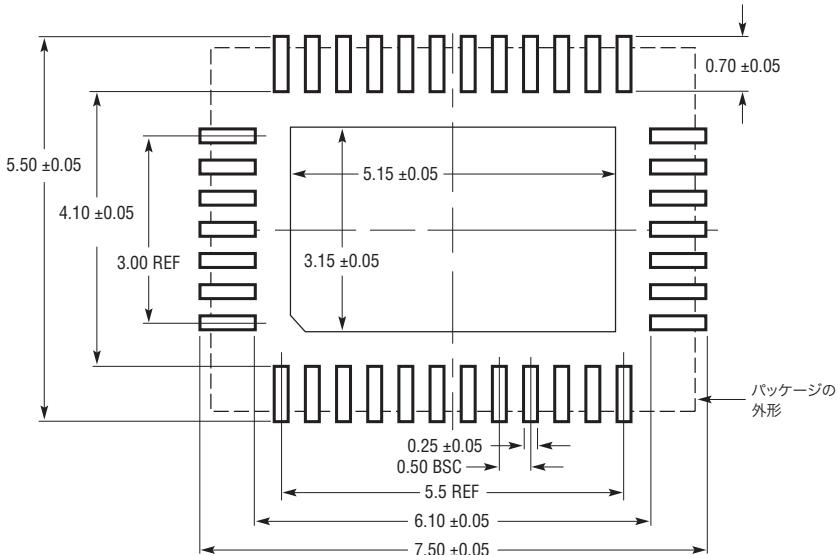

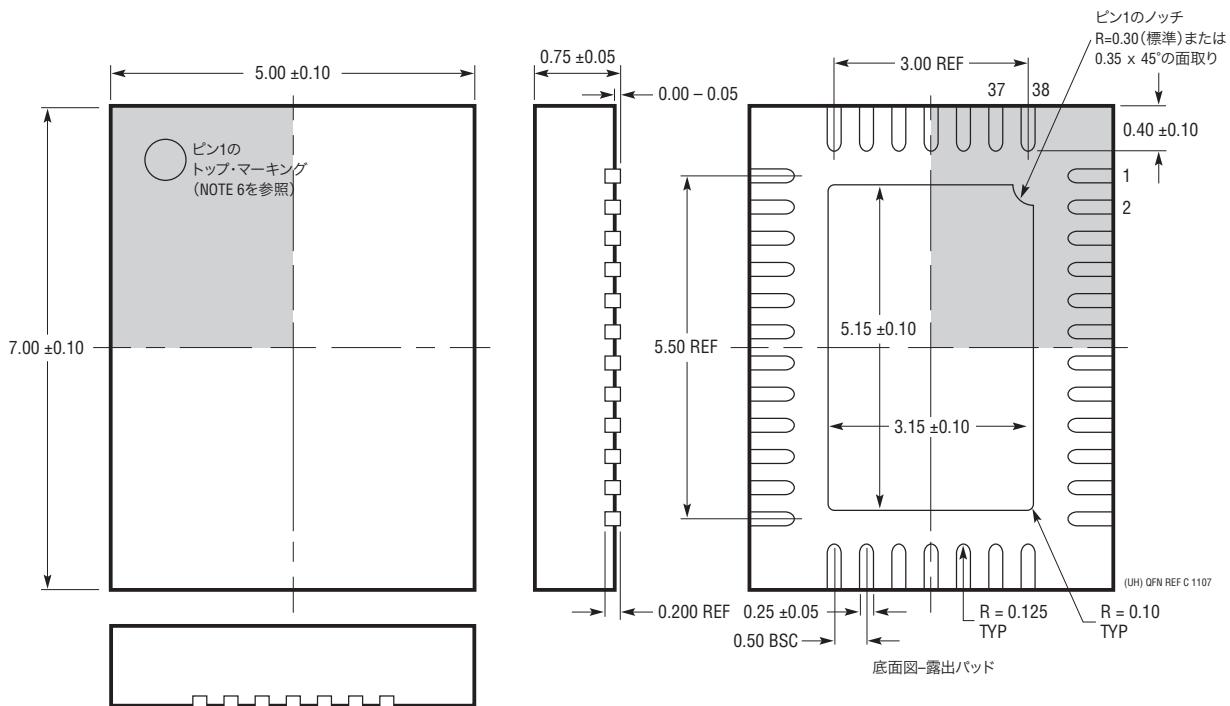

## パッケージ

最新のパッケージ図については、<http://www.linear-tech.co.jp/designtools/packaging/>をご覧ください。

**UHFパッケージ

38ピン・プラスチックQFN (5mm×7mm)

(Reference LTC DWG # 05-08-1701 Rev C)**

推奨半田パッド・レイアウト

半田付けされない領域には半田マスクを使用する

**NOTE:**

- NOTE:

1. 図面はJEDECのパッケージ外形MO-220の

バリエーション(WHKD)に適合

2. 図は実寸とは異なる

3. すべての寸法はミリメートル

4. パッケージ底面の露出パッドの寸法にはモールドのバリを含まない。

モールドのバリは(もしあれば)各サイドで0.20mmを超えないこと

5. 露出パッドは半田メッキとする

6. 網掛けの部分はパッケージの上面と底面のピン1の位置の参考に過ぎない

## 改訂履歴

| REV | 日付    | 概要           | ページ番号 |

|-----|-------|--------------|-------|

| A   | 11/12 | 標準的応用例の図を修正。 | 1、18  |

2751fa

リニアテクノロジー・コーポレーションがここで提供する情報は正確かつ信頼できるものと考えておりますが、その使用に関する責務は一切負いません。また、ここに記載された回路結線と既存特許とのいかなる関連についても一切関知いたしません。なお、日本語の資料はあくまでも参考資料です。訂正、変更、改版に追従していない場合があります。最終的な確認は必ず最新の英語版データシートでお願いいたします。

21

# LTC2751

## アプリケーション情報

標準的応用例。オフセットと利得の調整回路。LT1027からV<sub>DD</sub>に給電して静かな電源を保証

## 関連製品

| 製品番号                     | 説明                                              | 注釈                                                          |

|--------------------------|-------------------------------------------------|-------------------------------------------------------------|

| LT1027                   | 精密リファレンス                                        | 最大ドリフト:2ppm/°C                                              |

| LT1236A-5                | 精密リファレンス                                        | 最大許容誤差:0.05%、0.1Hz~10Hzノイズ:1ppm                             |

| LT1468                   | 16ビット精度のオペアンプ                                   | GBW:90MHz、スルーレート:22V/μs                                     |

| LT1469                   | デュアル、16ビット精度のオペアンプ                              | GBW:90MHz、スルーレート:22V/μs                                     |

| LTC1588/LTC1589/ LTC1592 | シリアル、12/14/16ビット、I <sub>OUT</sub> シングルDAC       | ソフトウェアで選択可能な(SoftSpan)レンジ、INL/DNL:±1LSB、16ピンSSOPパッケージ       |

| LTC1591/LTC1597          | パラレル14/16ビットI <sub>OUT</sub> シングルDAC            | 内蔵4象限抵抗                                                     |

| LTC1821                  | パラレル16ビットV <sub>OUT</sub> シングルDAC               | INL/DNL:±1LSB、0V~10V、0V~-10V、±10V出力レンジ                      |

| LTC2601/LTC2611/ LTC2621 | シリアル、12/14/16ビット、V <sub>OUT</sub> シングルDAC       | シングルDAC、SPI互換、単一電源、0V~5V出力、3mm×3mm DFN-10パッケージ              |

| LTC2606/LTC2616/ LTC2626 | シリアル、12/14/16ビット、V <sub>OUT</sub> シングルDAC       | シングルDAC、I <sup>2</sup> C互換、単一電源、0V~5V出力、3mm×3mm DFN-10パッケージ |

| LTC2641/LTC2642          | シリアル、12/14/16ビット、バッファなしV <sub>OUT</sub> シングルDAC | INL:±2LSB、DNL:±1LSB、セトリング:1μs、小型MSOP-10、3mm×3mm DFN-10パッケージ |

| LTC2704                  | シリアル、12/14/16ビット、V <sub>OUT</sub> クワッドDAC       | ソフトウェアで選択可能な(SoftSpan)レンジ、内蔵アンプ                             |

2751fa