最大10ppm/°Cのリファレンスを内蔵したオクタル16ビット/12ビット・レール・トゥ・レールDAC

## 特長

- 最大10ppm/°Cの高精度リファレンス

- 最大INL誤差:±4LSB(16ビット)

- 全温度範囲で単調性を保証

- 内部リファレンスまたは外部リファレンスを選択可能

- 電源範囲:2.7V～5.5V(LTC2656-L)

- リファレンス・バッファを内蔵

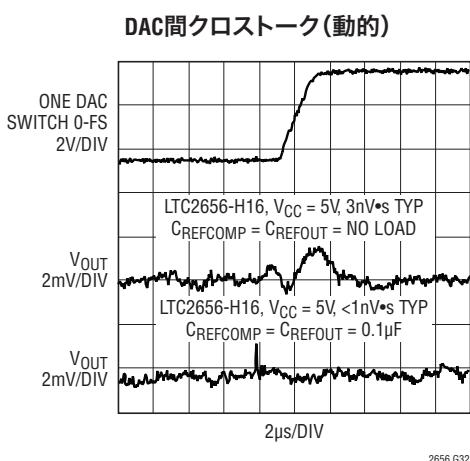

- 非常に小さいDAC間クロストーク(<1nV・s)

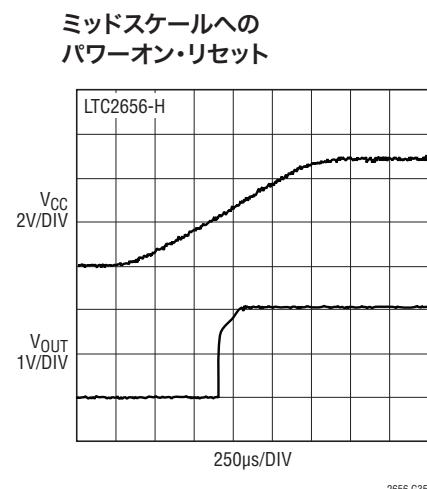

- ゼロスケールまたはミッドスケールへのパワーオン・リセット

- 非同期LDAC更新ピン

- 小型20ピン4mm×5mm QFNパッケージと熱特性が改善された20ピンTSSOPパッケージ

## アプリケーション

- モバイル通信

- プロセス制御および産業用オートメーション

- 計測

- 自動テスト装置

- 車載機器

## 概要

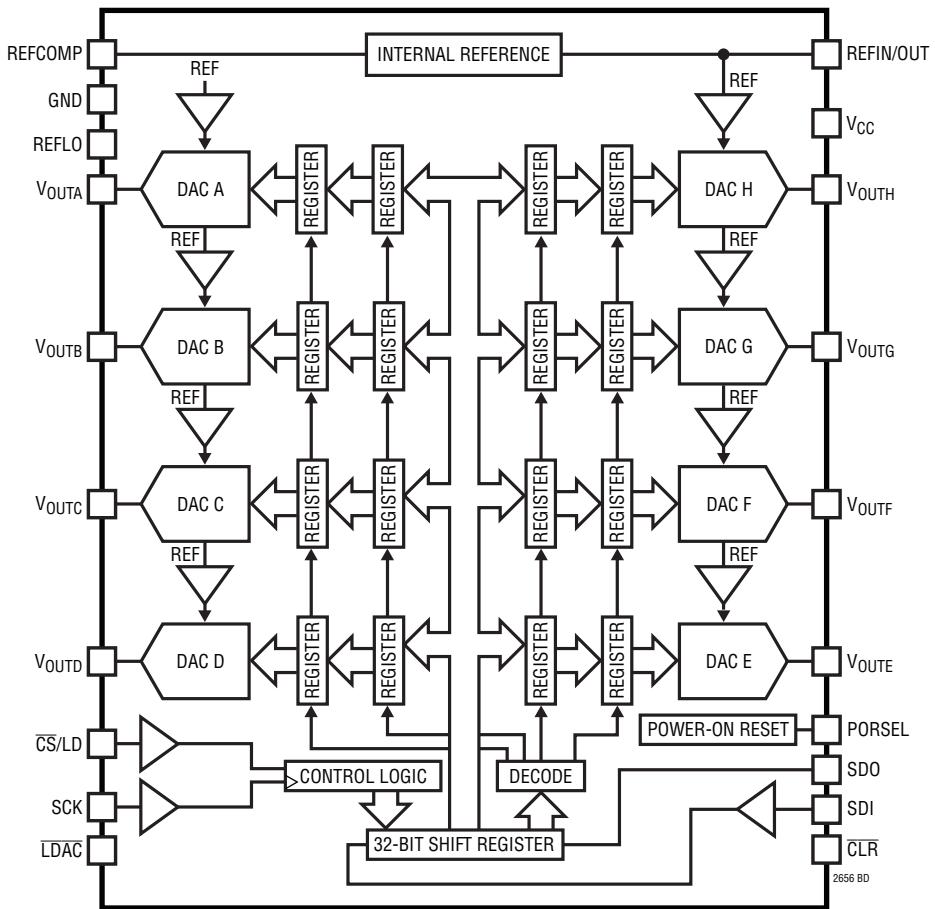

LTC<sup>®</sup>2656は、高精度リファレンスを内蔵したオクタル16ビット/12ビット・レール・トゥ・レールDACファミリです。これらのDACは高性能レール・トゥ・レール出力バッファを内蔵し、単調性が保証されています。LTC2656-Lは10ppm/°Cの内部リファレンスを使用して2.5Vのフルスケール出力電圧を生成し、2.7V～5.5Vの単一電源で動作します。LTC2656-Hは内部リファレンスを使用して4.096Vのフルスケール出力電圧を生成し、4.5V～5.5Vの単一電源で動作します。各DACは外部リファレンスを使用して動作することも可能で、DACのフルスケール出力は外部リファレンス電圧の2倍に設定されます。

これらのDACは、最大50MHzのクロックレートで動作するSPI/MICROWIRE<sup>™</sup>互換4線シリアル・インターフェースで通信します。LTC2656は、PORSELピンで制御されるパワーオン・リセット回路を内蔵しています。PORSELがGNDに接続されていると、DACはゼロスケールにリセットされ、PORSELがV<sub>CC</sub>に接続されていると、ミッドスケールにリセットされます。

**LT**、**LT**、**LTC**、**LTM**、**Linear Technology**およびLinearのロゴはリニアテクノロジー社の登録商標です。他のすべての商標はそれぞれの所有者に所有権があります。5396245、6891433を含む米国特許によって保護されています。

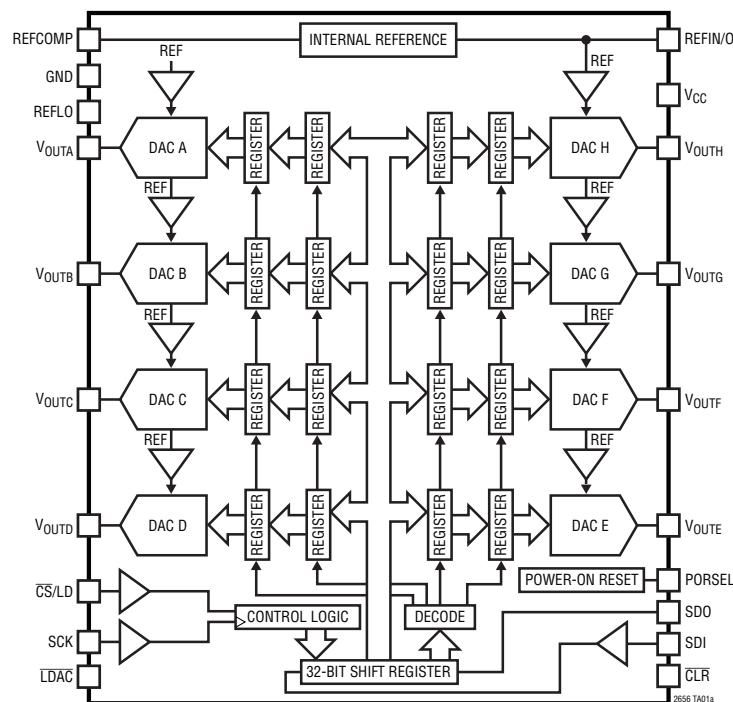

## ブロック図

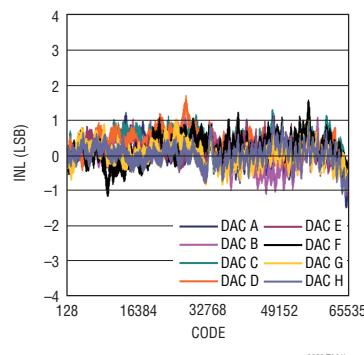

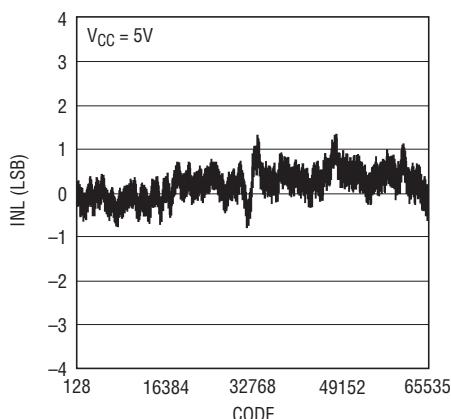

INLとコード

2656fa

## 絶対最大定格 (Note 1,2)

|                                                               |                               |                 |             |

|---------------------------------------------------------------|-------------------------------|-----------------|-------------|

| 電源電圧 ( $V_{CC}$ )                                             | -0.3V~6V                      | 最大接合部温度         | 150°C       |

| $\overline{CS}/LD$ 、 $SCK$ 、 $SDI$ 、 $LDAC$ 、 $CLR$ 、 $REFLO$ | -0.3V~6V                      | 保存温度範囲          | -65°C~150°C |

| $V_{OUTA}$ ~ $V_{OUTH}$                                       | -0.3V~最小 ( $V_{CC}+0.3V$ 、6V) | リード温度(半田付け、10秒) |             |

| $REFIN/OUT$ 、 $REFCOMP$                                       | -0.3V~最小 ( $V_{CC}+0.3V$ 、6V) | FEパッケージ         | 300°C       |

| $PORSEL$ 、 $SDO$                                              | -0.3V~最小 ( $V_{CC}+0.3V$ 、6V) |                 |             |

| 動作温度範囲                                                        |                               |                 |             |

| LTC2656C                                                      | 0°C~70°C                      |                 |             |

| LTC2656I                                                      | -40°C~85°C                    |                 |             |

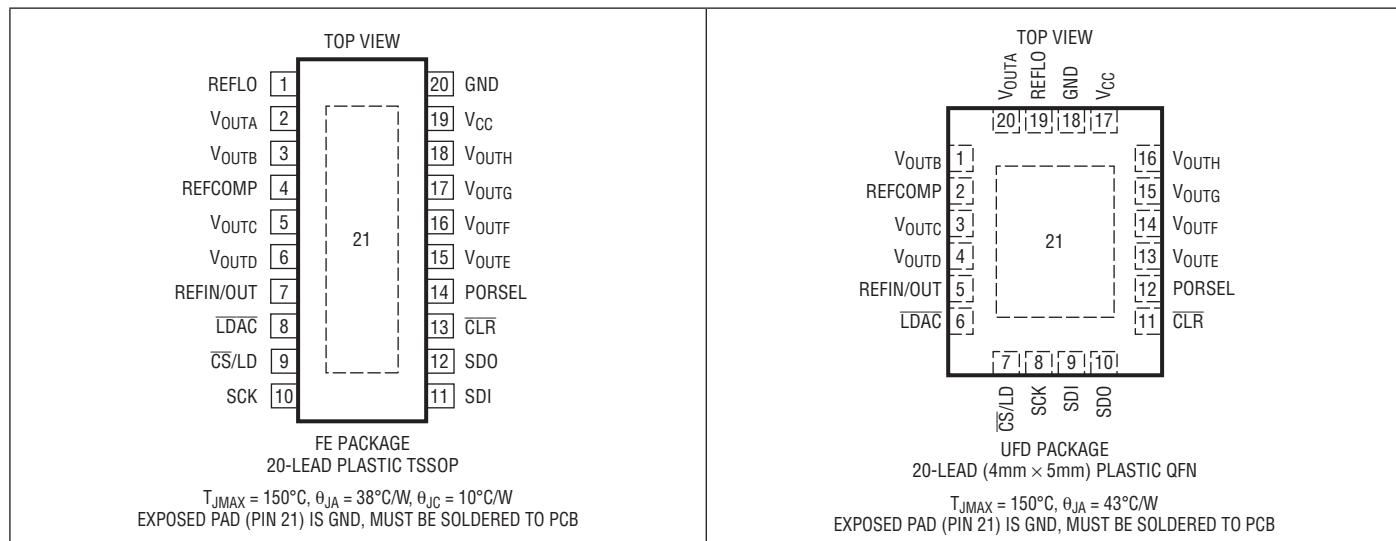

## ピン配置

## 製品選択ガイド

非標準の鉛ベース仕様の製品の詳細については、弊社または弊社代理店にお問い合わせください。

鉛フリー仕様の製品マーキングの詳細については、<http://www.linear-tech.co.jp/leadfree/> をご覧ください。

テープアンドリールの仕様の詳細については、<http://www.linear-tech.co.jp/tapeandreel/> をご覧ください

# LTC2656

## 発注情報

| 鉛フリー仕様               | テープアンドリール              | 製品マーキング*       | パッケージ                            | 温度範囲          | 最大INL |

|----------------------|------------------------|----------------|----------------------------------|---------------|-------|

| LTC2656BCFE-L16#PBF  | LTC2656BCFE-L16#TRPBF  | LTC2656FE-L16  | 20-Lead Thermally Enhanced TSSOP | 0°C to 70°C   | ±4    |

| LTC2656BIFE-L16#PBF  | LTC2656BIFE-L16#TRPBF  | LTC2656FE-L16  | 20-Lead Thermally Enhanced TSSOP | -40°C to 85°C | ±4    |

| LTC2656BCUFD-L16#PBF | LTC2656BCUFD-L16#TRPBF | 56L16          | 20-Lead (4mm × 5mm) Plastic QFN  | 0°C to 70°C   | ±4    |

| LTC2656BIUFD-L16#PBF | LTC2656BIUFD-L16#TRPBF | 56L16          | 20-Lead (4mm × 5mm) Plastic QFN  | -40°C to 85°C | ±4    |

| LTC2656BCFE-H16#PBF  | LTC2656BCFE-H16#TRPBF  | LTC2656FE-H16  | 20-Lead Thermally Enhanced TSSOP | 0°C to 70°C   | ±4    |

| LTC2656BIFE-H16#PBF  | LTC2656BIFE-H16#TRPBF  | LTC2656FE-H16  | 20-Lead Thermally Enhanced TSSOP | -40°C to 85°C | ±4    |

| LTC2656BCUFD-H16#PBF | LTC2656BCUFD-H16#TRPBF | 56H16          | 20-Lead (4mm × 5mm) Plastic QFN  | 0°C to 70°C   | ±4    |

| LTC2656BIUFD-H16#PBF | LTC2656BIUFD-H16#TRPBF | 56H16          | 20-Lead (4mm × 5mm) Plastic QFN  | -40°C to 85°C | ±4    |

| LTC2656CCFE-L16#PBF  | LTC2656CCFE-L16#TRPBF  | LTC2656CFE-L16 | 20-Lead Thermally Enhanced TSSOP | 0°C to 70°C   | ±12   |

| LTC2656CIFE-L16#PBF  | LTC2656CIFE-L16#TRPBF  | LTC2656CFE-L16 | 20-Lead Thermally Enhanced TSSOP | -40°C to 85°C | ±12   |

| LTC2656CCUFD-L16#PBF | LTC2656CCUFD-L16#TRPBF | 6CL16          | 20-Lead (4mm × 5mm) Plastic QFN  | 0°C to 70°C   | ±12   |

| LTC2656CIUFD-L16#PBF | LTC2656CIUFD-L16#TRPBF | 6CL16          | 20-Lead (4mm × 5mm) Plastic QFN  | -40°C to 85°C | ±12   |

| LTC2656CFE-L12#PBF   | LTC2656CFE-L12#TRPBF   | LTC2656FE-L12  | 20-Lead Thermally Enhanced TSSOP | 0°C to 70°C   | ±1    |

| LTC2656IFE-L12#PBF   | LTC2656IFE-L12#TRPBF   | LTC2656FE-L12  | 20-Lead Thermally Enhanced TSSOP | -40°C to 85°C | ±1    |

| LTC2656CUFD-L12#PBF  | LTC2656CUFD-L12#TRPBF  | 56L12          | 20-Lead (4mm × 5mm) Plastic QFN  | 0°C to 70°C   | ±1    |

| LTC2656IUFD-L12#PBF  | LTC2656IUFD-L12#TRPBF  | 56L12          | 20-Lead (4mm × 5mm) Plastic QFN  | -40°C to 85°C | ±1    |

| LTC2656CFE-H12#PBF   | LTC2656CFE-H12#TRPBF   | LTC2656FE-H12  | 20-Lead Thermally Enhanced TSSOP | 0°C to 70°C   | ±1    |

| LTC2656IFE-H12#PBF   | LTC2656IFE-H12#TRPBF   | LTC2656FE-H12  | 20-Lead Thermally Enhanced TSSOP | -40°C to 85°C | ±1    |

| LTC2656CUFD-H12#PBF  | LTC2656CUFD-H12#TRPBF  | 56H12          | 20-Lead (4mm × 5mm) Plastic QFN  | 0°C to 70°C   | ±1    |

| LTC2656IUFD-H12#PBF  | LTC2656IUFD-H12#TRPBF  | 56H12          | 20-Lead (4mm × 5mm) Plastic QFN  | -40°C to 85°C | ±1    |

さらに広い動作温度範囲で規定されるデバイスについては、弊社または弊社代理店にお問い合わせください。 \*温度グレードは出荷時のコンテナのラベルで識別されます。

非標準の鉛ベース仕様の製品の詳細については、弊社または弊社代理店にお問い合わせください。

鉛フリー仕様の製品マーキングの詳細については、<http://www.linear-tech.co.jp/leadfree/> をご覧ください。

テープアンドリールの仕様の詳細については、<http://www.linear-tech.co.jp/tapeandreel/> をご覧ください。

## 電気的特性

●は全動作温度範囲の規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。注記がない限り、 $V_{CC} = 2.7\text{V} \sim 5.5\text{V}$ 、 $V_{OUT}$ は無負荷。

LTC2656B-L16/LTC2656C-L16/LTC2656-L12(内部リファレンス = 1.25V)

| SYMBOL      | PARAMETER                        | CONDITIONS                                                                                                    | LTC2656-L12 |       |           | LTC2656B-L16/<br>LTC2656C-L16 |      |     | UNITS  |

|-------------|----------------------------------|---------------------------------------------------------------------------------------------------------------|-------------|-------|-----------|-------------------------------|------|-----|--------|

|             |                                  |                                                                                                               | MIN         | TYP   | MAX       | MIN                           | TYP  | MAX |        |

| <b>DC性能</b> |                                  |                                                                                                               |             |       |           |                               |      |     |        |

|             | Resolution                       |                                                                                                               | ●           | 12    |           | 16                            |      |     | Bits   |

|             | Monotonicity                     | (Note 3)                                                                                                      | ●           | 12    |           | 16                            |      |     | Bits   |

| DNL         | Differential Nonlinearity        | (Note 3)                                                                                                      | ●           |       | ±0.1 ±0.5 |                               | ±0.3 | ±1  | LSB    |

| INL         | Integral Nonlinearity (Note 3)   | LTC2656B-L16: $V_{CC} = 5.5\text{V}$ , $V_{REF} = 2.5\text{V}$                                                | ●           |       | ±0.5 ±1   |                               | ±2   | ±4  | LSB    |

|             |                                  | LTC2656C-L16: $V_{CC} = 5.5\text{V}$ , $V_{REF} = 2.5\text{V}$                                                | ●           |       |           |                               | ±6   | ±12 | LSB    |

|             | Load Regulation                  | $V_{CC} = 5\text{V} \pm 10\%$ , Internal Reference, Mid-Scale, $-15\text{mA} \leq I_{OUT} \leq 15\text{mA}$   | ●           | 0.04  | 0.125     | 0.6                           | 2    |     | LSB/mA |

|             |                                  | $V_{CC} = 3\text{V} \pm 10\%$ , Internal Reference, Mid-Scale, $-7.5\text{mA} \leq I_{OUT} \leq 7.5\text{mA}$ | ●           | 0.06  | 0.25      | 1                             | 4    |     | LSB/mA |

| ZSE         | Zero-Scale Error                 |                                                                                                               | ●           | 1     | 3         | 1                             | 3    |     | mV     |

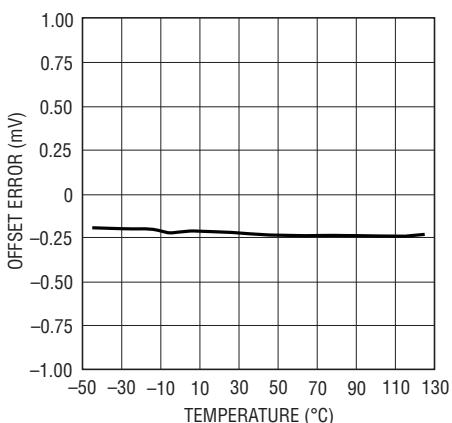

| $V_{OS}$    | Offset Error                     | $V_{REF} = 1.25\text{V}$ (Note 4)                                                                             | ●           | ±1    | ±2        | ±1                            | ±2   |     | mV     |

|             | $V_{OS}$ Temperature Coefficient |                                                                                                               |             |       | 2         |                               | 2    |     | µV/°C  |

| GE          | Gain Error                       |                                                                                                               | ●           | ±0.02 | ±0.1      | ±0.02                         | ±0.1 |     | %FSR   |

|             |                                  |                                                                                                               |             |       | 1         |                               | 1    |     | ppm/°C |

| SYMBOL           | PARAMETER                             | CONDITIONS                                                                                                                                      | MIN | TYP                               | MAX  | UNITS             |

|------------------|---------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----------------------------------|------|-------------------|

| $V_{OUT}$        | DAC Output Span                       | Internal Reference<br>External Reference = $V_{EXTREF}$                                                                                         |     | 0 to 2.5<br>0 to 2 • $V_{EXTREF}$ |      | V<br>V            |

| PSR              | Power Supply Rejection                | $V_{CC} \pm 10\%$                                                                                                                               |     | -80                               |      | dB                |

| R <sub>OUT</sub> | DC Output Impedance                   | $V_{CC} = 5\text{V} \pm 10\%$ , Internal Reference, Mid-Scale, $-15\text{mA} \leq I_{OUT} \leq 15\text{mA}$                                     | ●   | 0.04                              | 0.15 | Ω                 |

|                  |                                       | $V_{CC} = 3\text{V} \pm 10\%$ , Internal Reference, Mid-Scale, $-7.5\text{mA} \leq I_{OUT} \leq 7.5\text{mA}$                                   | ●   | 0.04                              | 0.15 | Ω                 |

| I <sub>SC</sub>  | DC Crosstalk (Note 5)                 | Due to Full-Scale Output Change<br>Due to Load Current Change<br>Due to Powering Down (per Channel)                                             |     | ±1.5<br>±2<br>±1                  |      | µV<br>µV/mA<br>µV |

|                  |                                       |                                                                                                                                                 |     |                                   |      |                   |

| I <sub>SC</sub>  | Short-Circuit Output Current (Note 6) | $V_{CC} = 5.5\text{V}$ , $V_{EXTREF} = 2.75\text{V}$<br>Code: Zero-Scale, Forcing Output to $V_{CC}$<br>Code: Full-Scale, Forcing Output to GND | ●   | 20                                | 65   | mA                |

|                  |                                       |                                                                                                                                                 | ●   | 20                                | 65   | mA                |

|                  |                                       | $V_{CC} = 2.7\text{V}$ , $V_{EXTREF} = 1.35\text{V}$<br>Code: Zero-Scale, Forcing Output to $V_{CC}$<br>Code: Full-Scale, Forcing Output to GND | ●   | 10                                | 40   | mA                |

|                  |                                       |                                                                                                                                                 | ●   | 10                                | 40   | mA                |

## リファレンス

|                                        |                                                                                                |   |       |          |       |                  |

|----------------------------------------|------------------------------------------------------------------------------------------------|---|-------|----------|-------|------------------|

| Reference Output Voltage               |                                                                                                |   | 1.248 | 1.25     | 1.252 | V                |

| Reference Temperature Coefficient      | C-Grade (Note 7)<br>I-Grade (Note 7)                                                           |   |       | ±2<br>±2 | ±10   | ppm/°C<br>ppm/°C |

| Reference Line Regulation              | $V_{CC} \pm 10\%$                                                                              |   |       | -80      |       | dB               |

| Reference Short-Circuit Current        | $V_{CC} = 5.5\text{V}$ , Forcing Output to GND                                                 | ● | 3     | 5        |       | mA               |

| REFCOMP Pin Short-Circuit Current      | $V_{CC} = 5.5\text{V}$ , Forcing Output to GND                                                 | ● | 60    | 200      |       | µA               |

| Reference Load Regulation              | $V_{CC} = 3\text{V} \pm 10\%$ or $5\text{V} \pm 10\%$ , $I_{OUT} = 100\mu\text{A}$<br>Sourcing |   |       | 40       |       | mV/mA            |

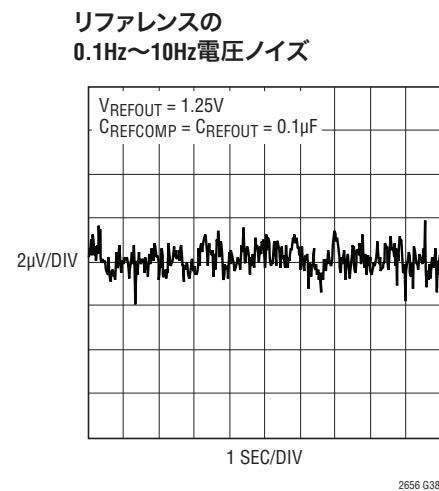

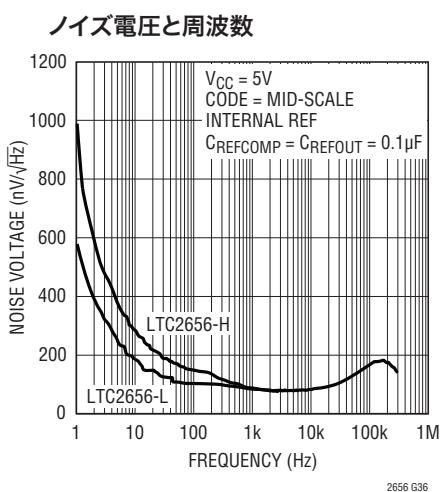

| Reference Output Voltage Noise Density | $C_{REFCOMP} = C_{REFIN/OUT} = 0.1\mu\text{F}$ at $f = 1\text{kHz}$                            |   |       | 30       |       | nV/√Hz           |

## 電気的特性

●は全動作温度範囲の規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。注記がない限り、 $V_{CC} = 2.7\text{V} \sim 5.5\text{V}$ 、 $V_{OUT}$ は無負荷。

LTC2656B-L16/LTC2656C-L16/LTC2656-L12(内部リファレンス = 1.25V)

| SYMBOL | PARAMETER                            | CONDITIONS                        | MIN     | TYP | MAX        | UNITS         |

|--------|--------------------------------------|-----------------------------------|---------|-----|------------|---------------|

|        | Reference Input Range                | External Reference Mode (Note 13) | ● 0.5   |     | $V_{CC}/2$ | V             |

|        | Reference Input Current              |                                   | ● 0.001 | 1   |            | $\mu\text{A}$ |

|        | Reference Input Capacitance (Note 9) |                                   | ● 40    |     |            | $\text{pF}$   |

### 電源

|            |                                          |                                               |       |      |               |

|------------|------------------------------------------|-----------------------------------------------|-------|------|---------------|

| $V_{CC}$   | Positive Supply Voltage                  | For Specified Performance                     | ● 2.7 | 5.5  | V             |

| $I_{CC}$   | Supply Current (Note 8)                  | $V_{CC} = 5\text{V}$ , Internal Reference On  | ● 3.1 | 4.25 | $\text{mA}$   |

|            |                                          | $V_{CC} = 5\text{V}$ , Internal Reference Off | ● 2.7 | 3.7  | $\text{mA}$   |

|            |                                          | $V_{CC} = 3\text{V}$ , Internal Reference On  | ● 3.0 | 3.8  | $\text{mA}$   |

|            |                                          | $V_{CC} = 3\text{V}$ , Internal Reference Off | ● 2.6 | 3.2  | $\text{mA}$   |

| $I_{SHDN}$ | Supply Current in Shutdown Mode (Note 8) | $V_{CC} = 5\text{V}$                          | ● 3   |      | $\mu\text{A}$ |

### デジタルI/O

|          |                                    |                                                                                                  |                  |     |               |

|----------|------------------------------------|--------------------------------------------------------------------------------------------------|------------------|-----|---------------|

| $V_{IH}$ | Digital Input High Voltage         | $V_{CC} = 3.6\text{V} \text{ to } 5.5\text{V}$<br>$V_{CC} = 2.7\text{V} \text{ to } 3.6\text{V}$ | ● 2.4            |     | V             |

| $V_{IL}$ | Digital Input Low Voltage          | $V_{CC} = 4.5\text{V} \text{ to } 5.5\text{V}$                                                   | ●                | 0.8 | V             |

|          |                                    | $V_{CC} = 2.7\text{V} \text{ to } 4.5\text{V}$                                                   | ●                | 0.6 | V             |

| $V_{OH}$ | Digital Output High Voltage        | Load Current = $-100\mu\text{A}$                                                                 | ● $V_{CC} - 0.4$ |     | V             |

| $V_{OL}$ | Digital Output Low Voltage         | Load Current = $100\mu\text{A}$                                                                  | ● 0.4            |     | V             |

| $I_{LK}$ | Digital Input Leakage              | $V_{IN} = \text{GND}$ to $V_{CC}$                                                                | ● $\pm 1$        |     | $\mu\text{A}$ |

| $C_{IN}$ | Digital Input Capacitance (Note 9) |                                                                                                  | ● 8              |     | $\text{pF}$   |

### AC性能

|       |                                |                                                                                                 |  |            |                                                              |

|-------|--------------------------------|-------------------------------------------------------------------------------------------------|--|------------|--------------------------------------------------------------|

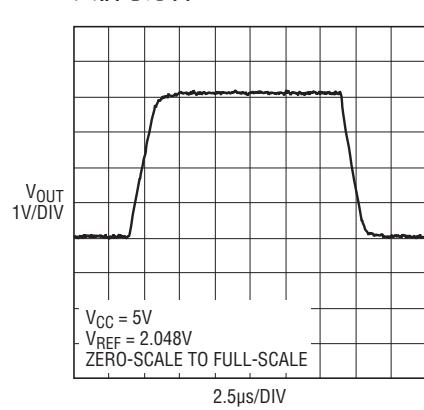

| $t_S$ | Settling Time (Note 10)        | $\pm 0.024\%$ ( $\pm 1\text{LSB}$ at 12 Bits)<br>$\pm 0.0015\%$ ( $\pm 1\text{LSB}$ at 16 Bits) |  | 4.2<br>8.9 | $\mu\text{s}$                                                |

|       | Settling Time for 1LSB Step    | $\pm 0.024\%$ ( $\pm 1\text{LSB}$ at 12 Bits)<br>$\pm 0.0015\%$ ( $\pm 1\text{LSB}$ at 16 Bits) |  | 2.2<br>4.9 | $\mu\text{s}$                                                |

|       | Voltage Output Slew Rate       |                                                                                                 |  | 1.8        | $\text{V}/\mu\text{s}$                                       |

|       | Capacitive Load Driving        |                                                                                                 |  | 1000       | $\text{pF}$                                                  |

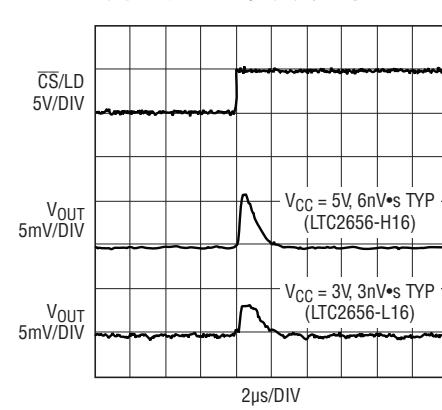

|       | Glitch Impulse (Note 11)       | At Mid-Scale Transition, $V_{CC} = 3\text{V}$                                                   |  | 3          | $\text{nV}\cdot\text{s}$                                     |

|       | DAC-to-DAC Crosstalk (Note 12) | Due to Full-Scale Output Change,<br>$C_{REFCOMP} = C_{REFOUT} = \text{No Load}$                 |  | 2          | $\text{nV}\cdot\text{s}$                                     |

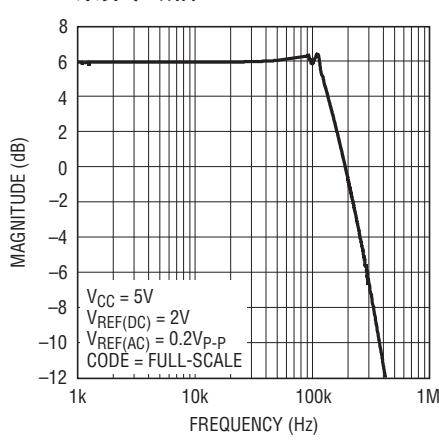

|       | Multiplying Bandwidth          |                                                                                                 |  | 150        | kHz                                                          |

| $e_n$ | Output Voltage Noise Density   | At $f = 1\text{kHz}$<br>At $f = 10\text{kHz}$                                                   |  | 85<br>80   | $\text{nV}/\sqrt{\text{Hz}}$<br>$\text{nV}/\sqrt{\text{Hz}}$ |

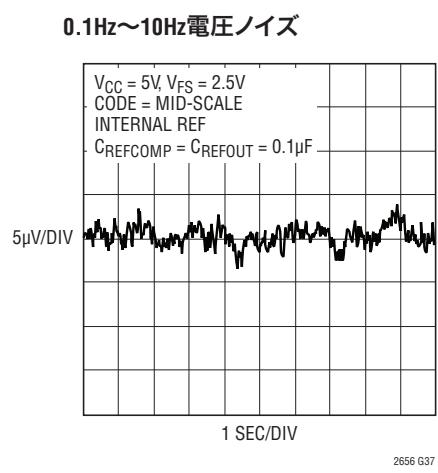

|       | Output Voltage Noise           | 0.1Hz to 10Hz, Internal Reference<br>0.1Hz to 200kHz, Internal Reference                        |  | 8<br>600   | $\mu\text{V}_{\text{P-P}}$<br>$\mu\text{V}_{\text{P-P}}$     |

## 電気的特性

●は全動作温度範囲の規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。注記がない限り、 $V_{CC} = 4.5\text{V} \sim 5.5\text{V}$ 、 $V_{OUT}$ は無負荷。

LTC2656B-H16/LTC2656-H12(内部リファレンス = 2.048V)

| SYMBOL      | PARAMETER                        | CONDITIONS                                                                                                  | LTC2656-H12 |       |           | LTC2656B-H16 |         |     | UNITS  |

|-------------|----------------------------------|-------------------------------------------------------------------------------------------------------------|-------------|-------|-----------|--------------|---------|-----|--------|

|             |                                  |                                                                                                             | MIN         | TYP   | MAX       | MIN          | TYP     | MAX |        |

| <b>DC性能</b> |                                  |                                                                                                             |             |       |           |              |         |     |        |

|             | Resolution                       |                                                                                                             | ●           | 12    |           | 16           |         |     | Bits   |

|             | Monotonicity                     | (Note 3)                                                                                                    | ●           | 12    |           | 16           |         |     | Bits   |

| DNL         | Differential Nonlinearity        | (Note 3)                                                                                                    | ●           |       | ±0.1 ±0.5 |              | ±0.3 ±1 |     | LSB    |

| INL         | Integral Nonlinearity (Note 3)   | $V_{CC} = 5.5\text{V}$ , $V_{REF} = 2.5\text{V}$                                                            | ●           |       | ±0.5 ±1   |              | ±2 ±4   |     | LSB    |

|             | Load Regulation                  | $V_{CC} = 5\text{V} \pm 10\%$ , Internal Reference, Mid-Scale, $-15\text{mA} \leq I_{OUT} \leq 15\text{mA}$ | ●           | 0.04  | 0.125     | 0.6          | 2       |     | LSB/mA |

| ZSE         | Zero-Scale Error                 |                                                                                                             | ●           | 1     | 3         | 1            | 3       |     | mV     |

| $V_{OS}$    | Offset Error                     | $V_{REF} = 2.048\text{V}$ (Note 4)                                                                          | ●           | ±1    | ±2        | ±1           | ±2      |     | mV     |

|             | $V_{OS}$ Temperature Coefficient |                                                                                                             |             |       | 2         |              | 2       |     | µV/°C  |

| GE          | Gain Error                       |                                                                                                             | ●           | ±0.02 | ±0.1      | ±0.02        | ±0.1    |     | %FSR   |

|             | Gain Temperature Coefficient     |                                                                                                             |             |       | 1         |              | 1       |     | ppm/°C |

| SYMBOL    | PARAMETER                                | CONDITIONS                                                                                                                                      | MIN    | TYP                                     | MAX      | UNITS |

|-----------|------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|--------|-----------------------------------------|----------|-------|

|           |                                          |                                                                                                                                                 |        |                                         |          |       |

| $V_{OUT}$ | DAC Output Span                          | Internal Reference<br>External Reference = $V_{EXTREF}$                                                                                         |        | 0 to 4.096<br>0 to $2 \cdot V_{EXTREF}$ |          | V     |

| PSR       | Power Supply Rejection                   | $V_{CC} \pm 10\%$                                                                                                                               |        | -80                                     |          | dB    |

| $R_{OUT}$ | DC Output Impedance                      | $V_{CC} = 5\text{V} \pm 10\%$ , Internal Reference, Mid-Scale, $-15\text{mA} \leq I_{OUT} \leq 15\text{mA}$                                     | ●      | 0.04                                    | 0.15     | Ω     |

|           | DC Crosstalk (Note 5)                    | Due to Full-Scale Output Change<br>Due to Load Current Change<br>Due to Powering Down (per Channel)                                             |        | ±1.5<br>±2<br>±1                        |          | µV    |

|           |                                          |                                                                                                                                                 |        |                                         |          | µV/mA |

|           |                                          |                                                                                                                                                 |        |                                         |          | µV    |

| $I_{SC}$  | Short-Circuit Output Current<br>(Note 6) | $V_{CC} = 5.5\text{V}$ , $V_{EXTREF} = 2.75\text{V}$<br>Code: Zero-Scale, Forcing Output to $V_{CC}$<br>Code: Full-Scale, Forcing Output to GND | ●<br>● | 20<br>20                                | 65<br>65 | mA    |

## リファレンス

|  |                                         |                                                                     |       |          |            |                  |

|--|-----------------------------------------|---------------------------------------------------------------------|-------|----------|------------|------------------|

|  | Reference Output Voltage                |                                                                     | 2.044 | 2.048    | 2.052      | V                |

|  | Reference Temperature Coefficient       | C-Grade (Note 7)<br>I-Grade (Note 7)                                |       | ±2<br>±2 | ±10        | ppm/°C<br>ppm/°C |

|  | Reference Line Regulation               | $V_{CC} \pm 10\%$                                                   |       | -80      |            | dB               |

|  | Reference Short-Circuit Current         | $V_{CC} = 5.5\text{V}$ , Forcing Output to GND                      | ●     | 3        | 5          | mA               |

|  | REFCOMP Pin Short-Circuit Current       | $V_{CC} = 5.5\text{V}$ , Forcing Output to GND                      | ●     | 60       | 200        | µA               |

|  | Reference Load Regulation               | $V_{CC} = 5\text{V} \pm 10\%$ , $I_{OUT} = 100\mu\text{A}$ Sourcing |       | 40       |            | mV/mA            |

|  | Reference Output Voltage Noise Density  | $C_{REFCOMP} = C_{REFIN/OUT} = 0.1\mu\text{F}$ at $f = 1\text{kHz}$ |       | 35       |            | nV/√Hz           |

|  | Reference Input Range                   | External Reference Mode (Note 13)                                   | ●     | 0.5      | $V_{CC}/2$ | V                |

|  | Reference Input Current                 |                                                                     | ●     | 0.001    | 1          | µA               |

|  | Reference Input Capacitance<br>(Note 9) |                                                                     | ●     | 40       |            | pF               |

## 電気的特性

●は全動作温度範囲の規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。注記がない限り、 $V_{CC} = 4.5\text{V} \sim 5.5\text{V}$ 、 $V_{OUT}$ は無負荷。

LTC2656B-H16/LTC2656-H12(内部リファレンス = 2.048V)

| SYMBOL         | PARAMETER                                | CONDITIONS                                                                                      | MIN    | TYP            | MAX         | UNITS                        |

|----------------|------------------------------------------|-------------------------------------------------------------------------------------------------|--------|----------------|-------------|------------------------------|

| <b>電源</b>      |                                          |                                                                                                 |        |                |             |                              |

| $V_{CC}$       | Positive Supply Voltage                  | For Specified Performance                                                                       | ●      | 4.5            | 5.5         | V                            |

| $I_{CC}$       | Supply Current (Note 8)                  | $V_{CC} = 5\text{V}$ , Internal Reference On<br>$V_{CC} = 5\text{V}$ , Internal Reference Off   | ●<br>● | 3.3<br>3.0     | 4.25<br>3.7 | mA                           |

| $I_{SHDN}$     | Supply Current in Shutdown Mode (Note 8) | $V_{CC} = 5\text{V}$                                                                            | ●      |                | 3           | $\mu\text{A}$                |

| <b>デジタルI/O</b> |                                          |                                                                                                 |        |                |             |                              |

| $V_{IH}$       | Digital Input High Voltage               | $V_{CC} = 4.5\text{V} \text{ to } 5.5\text{V}$                                                  | ●      | 2.4            |             | V                            |

| $V_{IL}$       | Digital Input Low Voltage                | $V_{CC} = 4.5\text{V} \text{ to } 5.5\text{V}$                                                  | ●      |                | 0.8         | V                            |

| $V_{OH}$       | Digital Output High Voltage              | Load Current = $-100\mu\text{A}$                                                                | ●      | $V_{CC} - 0.4$ |             | V                            |

| $V_{OL}$       | Digital Output Low Voltage               | Load Current = $100\mu\text{A}$                                                                 | ●      |                | 0.4         | V                            |

| $I_{LK}$       | Digital Input Leakage                    | $V_{IN} = \text{GND}$ to $V_{CC}$                                                               | ●      |                | $\pm 1$     | $\mu\text{A}$                |

| $C_{IN}$       | Digital Input Capacitance (Note 9)       |                                                                                                 | ●      |                | 8           | $\text{pF}$                  |

| <b>AC性能</b>    |                                          |                                                                                                 |        |                |             |                              |

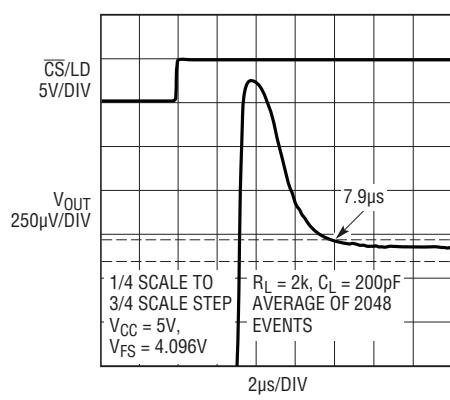

| $t_S$          | Settling Time (Note 10)                  | $\pm 0.024\%$ ( $\pm 1\text{LSB}$ at 12 Bits)<br>$\pm 0.0015\%$ ( $\pm 1\text{LSB}$ at 16 Bits) |        | 4.6<br>7.9     |             | $\mu\text{s}$                |

|                | Settling Time for 1LSB Step              | $\pm 0.024\%$ ( $\pm 1\text{LSB}$ at 12 Bits)<br>$\pm 0.0015\%$ ( $\pm 1\text{LSB}$ at 16 Bits) |        | 2.0<br>3.8     |             | $\mu\text{s}$                |

|                | Voltage Output Slew Rate                 |                                                                                                 |        | 1.8            |             | $\text{V}/\mu\text{s}$       |

|                | Capacitive Load Driving                  |                                                                                                 |        | 1000           |             | $\text{pF}$                  |

|                | Glitch Impulse (Note 11)                 | At Mid-Scale Transition, $V_{CC} = 5\text{V}$                                                   |        | 6              |             | $\text{nV}\cdot\text{s}$     |

|                | DAC-to-DAC Crosstalk (Note 12)           | Due to Full-Scale Output Change,<br>$C_{REFCOMP} = C_{REFOUT} = \text{No Load}$                 |        | 3              |             | $\text{nV}\cdot\text{s}$     |

|                | Multiplying Bandwidth                    |                                                                                                 |        | 150            |             | $\text{kHz}$                 |

| $\epsilon_n$   | Output Voltage Noise Density             | At $f = 1\text{kHz}$<br>At $f = 10\text{kHz}$                                                   |        | 85<br>80       |             | $\text{nV}/\sqrt{\text{Hz}}$ |

|                | Output Voltage Noise                     | 0.1Hz to 10Hz, Internal Reference<br>0.1Hz to 200kHz, Internal Reference                        |        | 12<br>650      |             | $\mu\text{V}_{\text{P-P}}$   |

## 電気的特性

●は全動作温度範囲の規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。

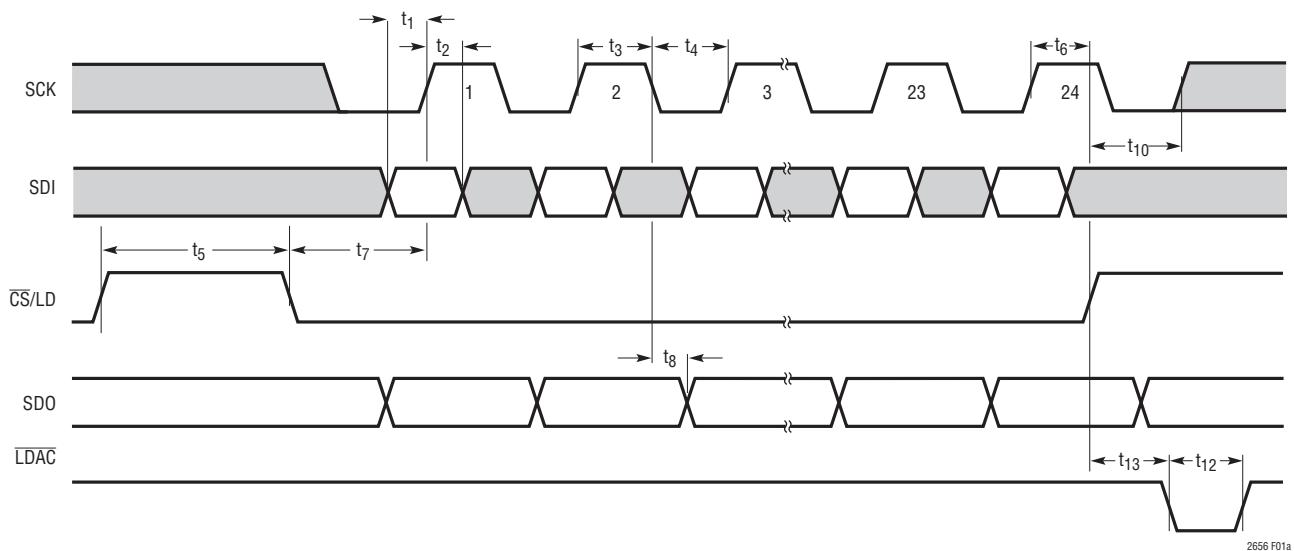

LTC2656B-L16/LTC2656C-L16/LTC2656-L12/LTC2656B-H16/LTC2656-H12(図1を参照)。

| SYMBOL                                                    | PARAMETER                                                 | CONDITIONS                                                                                                                   | MIN    | TYP      | MAX | UNITS    |

|-----------------------------------------------------------|-----------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|--------|----------|-----|----------|

| <b><math>V_{CC} = 2.7\text{V} \sim 5.5\text{V}</math></b> |                                                           |                                                                                                                              |        |          |     |          |

| $t_1$                                                     | SDI Valid to SCK Setup                                    |                                                                                                                              | ●      | 4        |     | ns       |

| $t_2$                                                     | SDI Valid to SCK Hold                                     |                                                                                                                              | ●      | 4        |     | ns       |

| $t_3$                                                     | SCK High Time                                             |                                                                                                                              | ●      | 9        |     | ns       |

| $t_4$                                                     | SCK Low Time                                              |                                                                                                                              | ●      | 9        |     | ns       |

| $t_5$                                                     | $\bar{CS}/LD$ Pulse Width                                 |                                                                                                                              | ●      | 10       |     | ns       |

| $t_6$                                                     | LSB SCK High to $\bar{CS}/LD$ High                        |                                                                                                                              | ●      | 7        |     | ns       |

| $t_7$                                                     | $\bar{CS}/LD$ Low to SCK High                             |                                                                                                                              | ●      | 7        |     | ns       |

| $t_8$                                                     | SDO Propagation Delay from SCK Falling Edge               | $C_{LOAD} = 10\text{pF}$<br>$V_{CC} = 4.5\text{V} \text{ to } 5.5\text{V}$<br>$V_{CC} = 2.7\text{V} \text{ to } 4.5\text{V}$ | ●<br>● | 20<br>45 |     | ns<br>ns |

| $t_9$                                                     | $\bar{CLR}$ Pulse Width                                   |                                                                                                                              | ●      | 20       |     | ns       |

| $t_{10}$                                                  | $\bar{CS}/LD$ High to SCK Positive Edge                   |                                                                                                                              | ●      | 7        |     | ns       |

| $t_{12}$                                                  | $\bar{LDAC}$ Pulse Width                                  |                                                                                                                              | ●      | 15       |     | ns       |

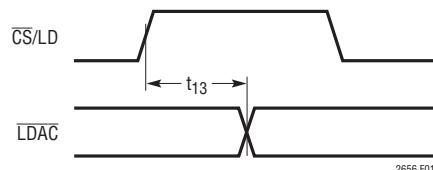

| $t_{13}$                                                  | $\bar{CS}/LD$ High to $\bar{LDAC}$ High or Low Transition |                                                                                                                              | ●      | 200      |     | ns       |

|                                                           | SCK Frequency                                             | 50% Duty Cycle                                                                                                               | ●      |          | 50  | MHz      |

**Note 1:**絶対最大定格に記載された値を超えるストレスはデバイスに永続的損傷を与える可能性がある。長期にわたって絶対最大定格条件に曝すと、デバイスの信頼性と寿命に悪影響を与える可能性がある。

**Note 2:**すべての電圧はGNDを基準にしている。

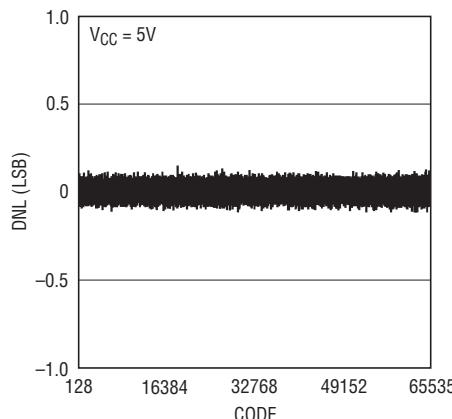

**Note 3:**直線性と単調性はコード $kL$ からコード $2^N - 1$ まで定義されている。ここで、 $N$ は分解能、 $kL$ は出力制限が生じない下端のコード。 $V_{REF} = 2.5\text{V}$ および $N = 16$ では、 $kL = 128$ で、直線性はコード128からコード65535で定義される。 $V_{REF} = 2.5\text{V}$ および $N = 12$ では、 $kL = 8$ で、直線性はコード8からコード4,095で定義される。

**Note 4:**コード128(LTC2656-16)またはコード8(LTC2656-12)での測定から推測されている。

**Note 5:**DCクロストークは、 $V_{CC} = 5\text{V}$ で、内部リファレンスを使ってミッドスケールのDACで測定される。

**Note 6:**このデバイスには短時間の過負荷状態の間デバイスを保護するための電流制限が備わっている。電流制限時に接合部温度が最大定格を超えることがある。規定された最大動作接合部温度を超えた動作が継続すると、デバイスの信頼性を損なうおそれがある。

**Note 7:**温度係数は出力電圧の最大変化を規定温度範囲で割って計算される。

**Note 8:** $0\text{V}$ または $V_{CC}$ でのデジタル入力。

**Note 9:**設計によって保証されているが、製造時にはテストされない。

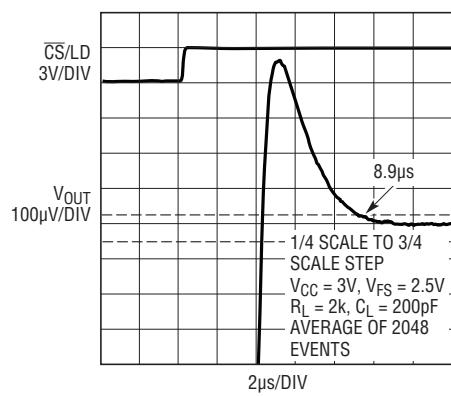

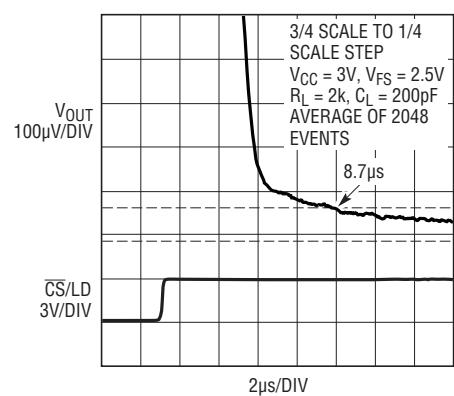

**Note 10:**内部リファレンス・モード。DACは1/4スケールから3/4スケールへ、さらに3/4スケールから1/4スケールへステップさせる。負荷はGNDに並列に接続した $2\text{k}\Omega$ と $200\text{pF}$ 。

**Note 11:** $V_{CC} = 5\text{V}$ 、内部リファレンス・モード。DACはハーフスケールと(ハーフスケール-1LSB)の間を $\pm 1\text{LSB}$ でステップさせる。負荷はGNDに並列に接続した $2\text{k}$ と $200\text{pF}$ 。

**Note 12:**DAC間のクロストークは、あるDACの出力のフルスケールの変化によって別のDACの出力に現れるグリッチである。それは、 $V_{CC} = 5\text{V}$ で、内部リファレンスを使い、ミッドスケールのDACで測定される。

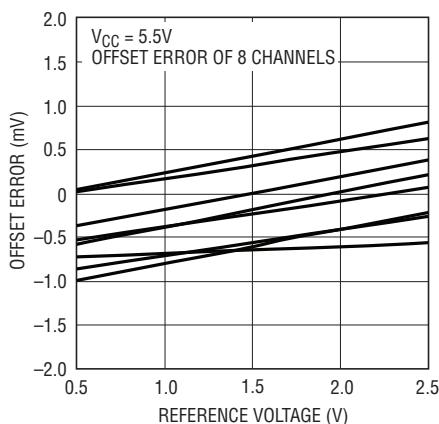

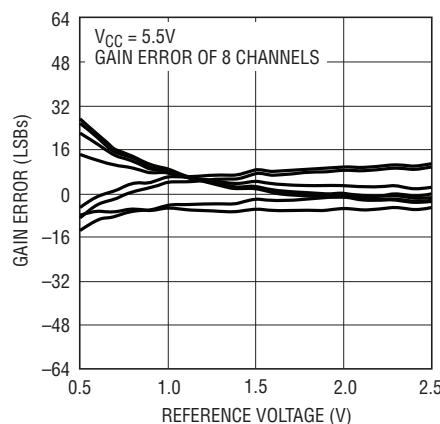

**Note 13:**利得誤差の仕様は、1Vよりも小さいリファレンス入力電圧ではグレードが下げられることがある。「標準的性能特性」のセクションの「利得誤差とリファレンス入力」の曲線を参照。

# LTC2656

標準的性能特性 注記がない限り $T_A = 25^\circ\text{C}$ 。

LTC2656-L16

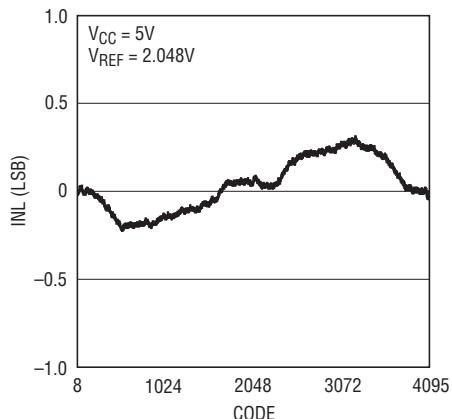

## 積分非直線性(INL)

2656 G01

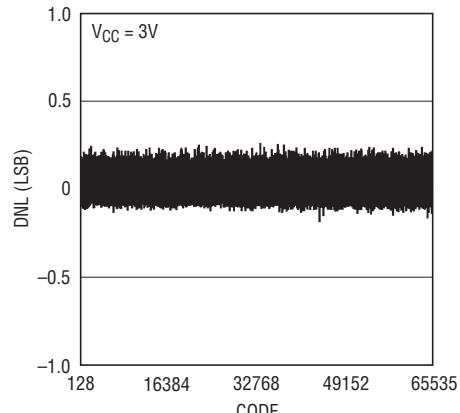

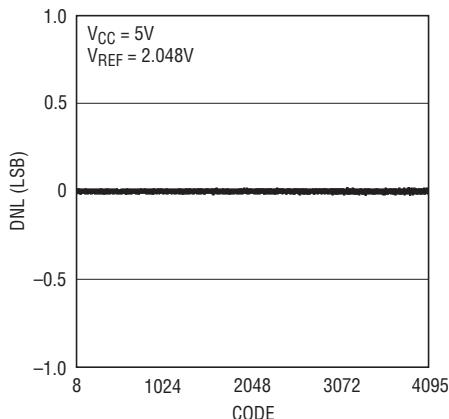

## 微分非直線性(DNL)

2656 G02

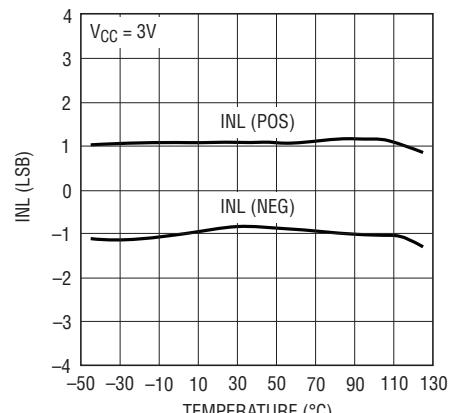

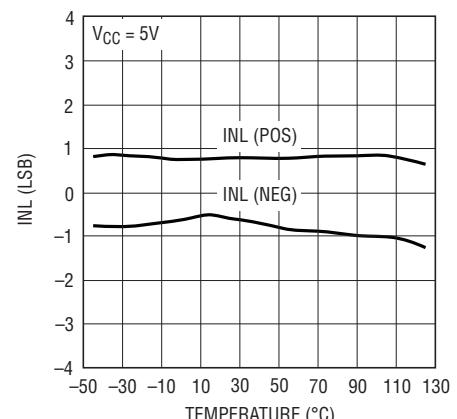

## INLと温度

2656 G03

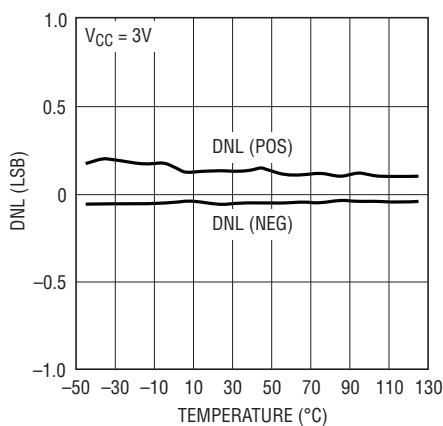

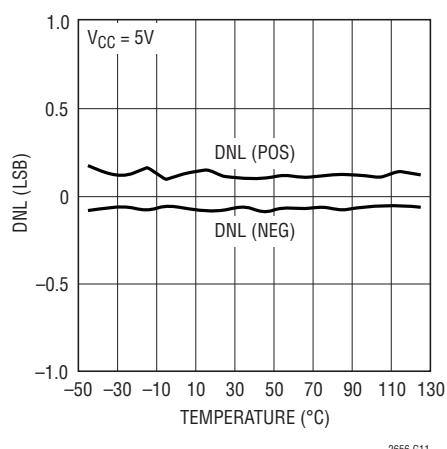

## DNLと温度

2656 G04

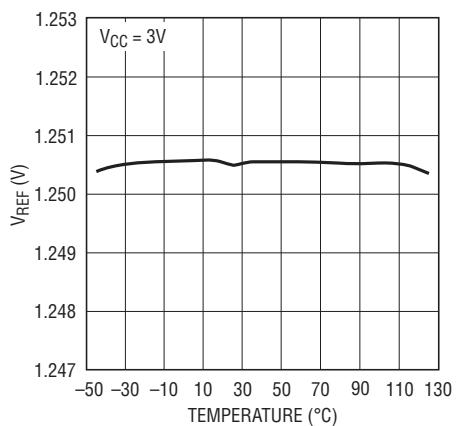

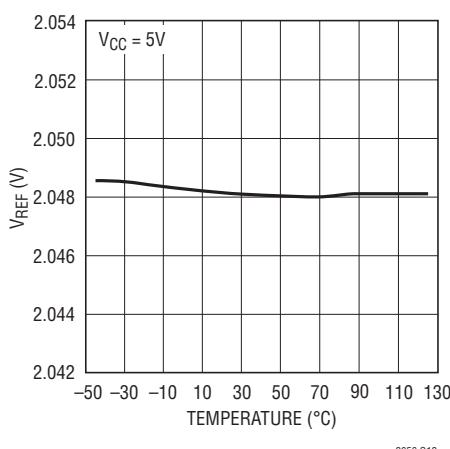

## REFOUT電圧と温度

2656 G05

## ±1LSBへのセトリング(立ち上がり)

2656 G06

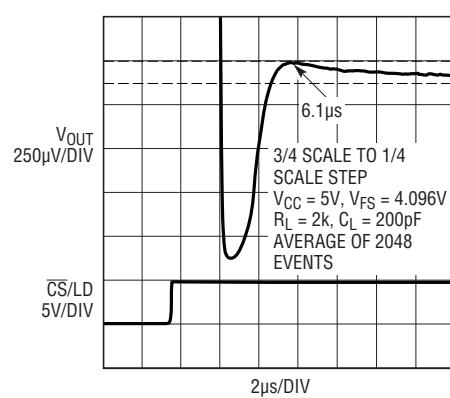

## ±1LSBへのセトリング(立ち下がり)

2656 G07

2656fa

標準的性能特性 注記がない限り  $T_A = 25^\circ\text{C}$ 。

LTC2656-H16

## 積分非直線性 (INL)

## 微分非直線性 (DNL)

## INLと温度

## DNLと温度

## REFOUT電圧と温度

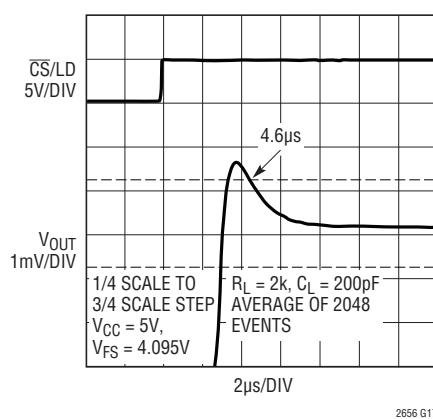

## ±1LSBへのセトリング(立ち上がり)

## ±1LSBへのセトリング(立ち下がり)

# LTC2656

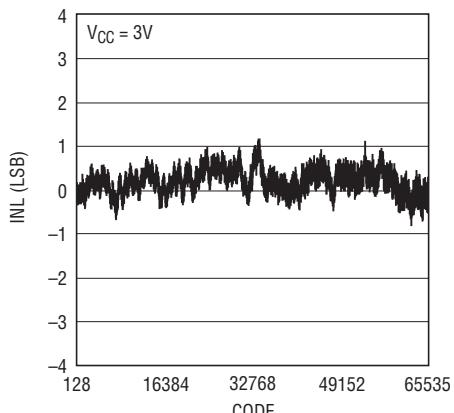

標準的性能特性 注記がない限り $T_A = 25^\circ\text{C}$ 。

LTC2656-12

## 積分非直線性 (INL)

2656 G15

## 微分非直線性 (DNL)

2656 G16

## ±1LSBへのセッティング (12ビット、立ち上がり)

2656 G17

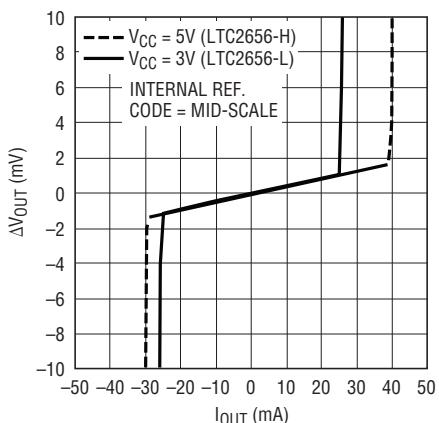

## 負荷レギュレーション

2656 G18

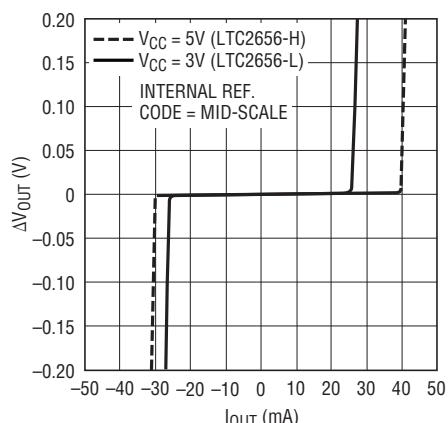

## 電流制限

2656 G19

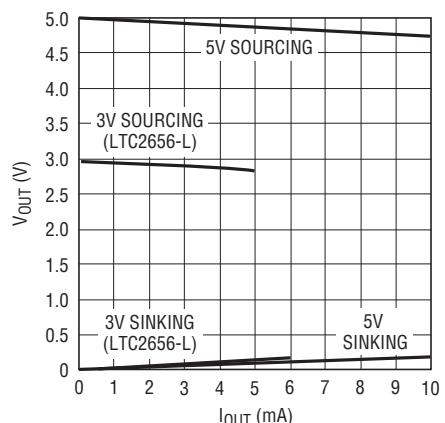

## レールの空き高と出力電流

2656 G20

## オフセット誤差と温度

3656 G21

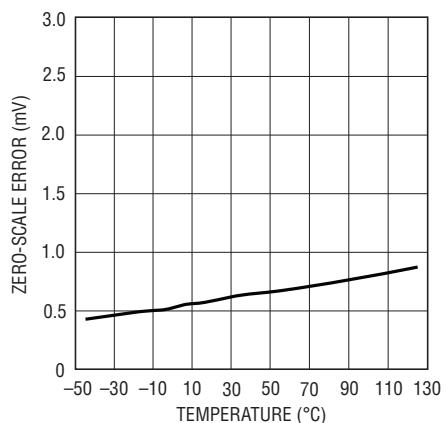

## ゼロスケール誤差と温度

2656 G22

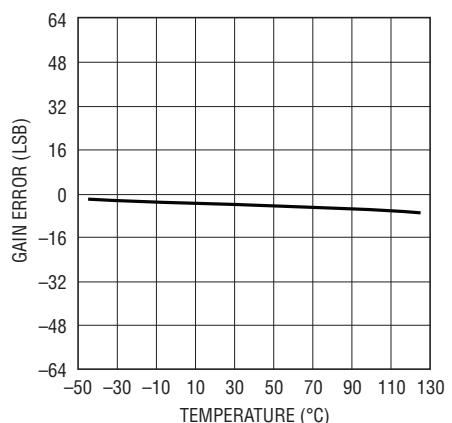

## 利得誤差と温度

2656 G23

2656fa

標準的性能特性 注記がない限り $T_A = 25^\circ\text{C}$ 。

LTC2656-16

## オフセット誤差とリファレンス入力

## 利得誤差とリファレンス入力

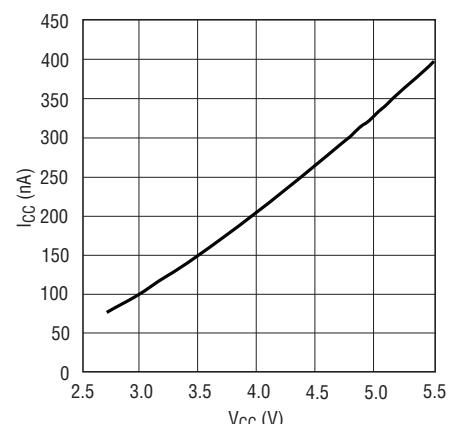

$I_{CC}$ (シャットダウン時)と $V_{CC}$

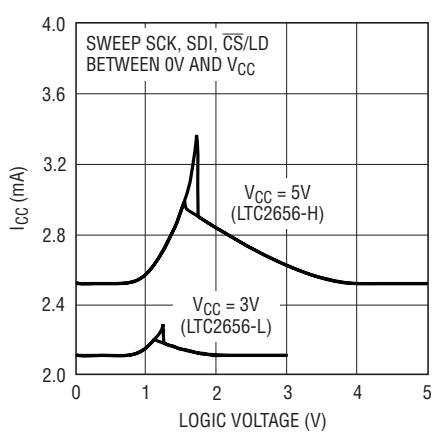

## 電源電流とロジック電圧

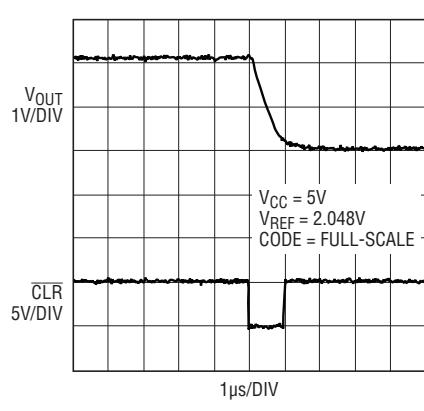

## ハードウェアCLRからミッドスケールまで

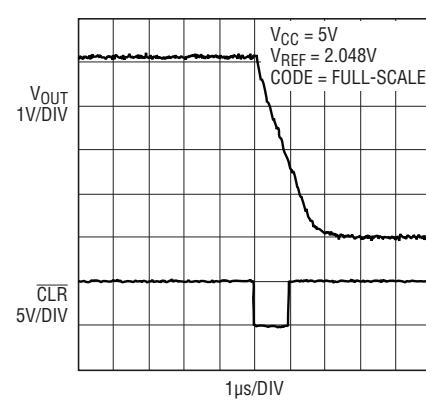

## ハードウェアCLRからゼロスケールまで

## 乗算帯域幅

## 大信号応答

## ミッドスケール・グリッチ・インパルス

# LTC2656

標準的性能特性 注記がない限り  $T_A = 25^\circ\text{C}$ 。

LTC2656

2656fa

## ピン機能 (TSSOP/QFN)

**REFLO(ピン1/ピン19)**: リファレンス・ロー・ピン。このピンの電圧がすべてのDACのゼロスケールを設定します。REFLOはGNDに接続します。

**V<sub>OUTA</sub>～V<sub>OUTH</sub>(ピン2、3、5、6、15、16、17、18/ピン20、1、3、4、13、14、15、16)**: DACのアナログ電圧出力。出力範囲は0VからREFIN/OUTピンの電圧の2倍までです。

**REFCOMP(ピン4/ピン2)**: 内部リファレンス補償ピン。ノイズを低減しリファレンスを安定させるため、0.1 $\mu$ FのコンデンサをこのピンからGNDに接続します。起動時に外部リファレンスを使用できるようにするには、REFCOMPをGNDに接続します。

**REFIN/OUT(ピン7/ピン5)**: このピンは内部リファレンス・モードでは内部リファレンスの出力として機能し、外部リファレンス・モードではリファレンス入力として機能します。出力として機能するとき、このピンの公称電圧はLオプションでは1.25V、Hオプションでは2.048Vです。ノイズを低減しリファレンスを安定させるため、コンデンサをこのピンからGNDに接続します。このコンデンサの値はCREFCOMP以下でなければなりません。ここで、CREFCOMPはREFCOMPピンに接続される容量です。外部リファレンス・モードでは、許容できるリファレンス入力電圧範囲は0.5V～V<sub>CC</sub>/2です。

**LDAC(ピン8/ピン6)**: 非同期DAC更新ピン。 $\overline{CS/LD}$ が“H”的場合、 $\overline{LDAC}$ の立ち下がりエッジにより、DACレジスタが入力レジスタの内容で直ちに更新されます(ソフトウェアの更新と同様)。 $\overline{CS/LD}$ が“L”的ときに $\overline{LDAC}$ が“L”になると、 $\overline{CS/LD}$ が“H”に戻った後にDACレジスタが更新されます。 $\overline{LDAC}$ ピンが“L”になると、DAC出力がパワーアップされます。 $\overline{LDAC}$ が“L”的ときに $\overline{CS/LD}$ が“H”になった場合は、ソフトウェアのすべてのパワーダウン・コマンドが無視されます。

**$\overline{CS/LD}$ (ピン9/ピン7)**: シリアル・インターフェースのチップ・セレクト/ロード入力。 $\overline{CS/LD}$ が“L”的とき、SCKがイネーブルされ、SDIのデータをレジスタにシフトします。 $\overline{CS/LD}$ が“H”になると、SCKはディスエーブルされ、指定されたコマンド(表1を参照)が実行されます。

**SCK(ピン10/ピン8)**: シリアル・インターフェースのクロック入力。CMOSおよびTTL互換です。

**SDI(ピン11/ピン9)**: シリアル・インターフェースのデータ入力。データはSDIに与えられ、SCK(ピン10)の立ち上がりエッジでデバイスに転送されます。LTC2656は24ビットまたは32ビットの長さの入力ワードを受け入れます。

**SDO(ピン12/ピン10)**: シリアル・インターフェースのデータ出力。このピンはデイジーチェーン動作に使用されます。シフト・レジスタのシリアル出力はSDOピンから出力されます。SDIピンを介してデバイスに転送されたデータは、SCKの32の立ち上がりエッジだけ遅れてから、次の立ち下がりエッジで出力されます。このピンは連続的にドライブされており、 $\overline{CS/LD}$ がアクティブ“H”になっても高インピーダンスになりません。

**$\overline{CLR}$ (ピン13/ピン11)**: 非同期クリア入力。PORSELピンがGNDに接続されている場合、このレベルトリガ入力がロジック“L”になると、すべてのレジスタがクリアされ、DAC電圧出力が0Vまで低下します。PORSELピンがV<sub>CC</sub>に接続されている場合、 $\overline{CLR}$ がロジック“L”になると、すべてのレジスタがミッドスケール・コードに設定され、DAC電圧出力がミッドスケールになります。

**PORSEL(ピン14/ピン12)**: パワーオン・リセット選択ピン。このピンがGNDに接続されていると、DACは起動時にゼロスケールにリセットされます。V<sub>CC</sub>に接続されていると、DACは起動時にミッドスケールにリセットされます。

**V<sub>CC</sub>(ピン19/ピン17)**: 電源電圧入力。Lオプションでは2.7V  $\leq$  V<sub>CC</sub>  $\leq$  5.5V、Hオプションでは4.5V  $\leq$  V<sub>CC</sub>  $\leq$  5.5Vです。

**GND(ピン20/ピン18)**: グラウンド。

**露出パッド(ピン21/ピン21)**: グラウンド。PCBのグラウンドに半田付けする必要があります。

## タイミング図

図1a

図1b

## 動作

LTC2656はオクタル電圧出力DACファミリで、20ピン4mm×5mm QFNおよび熱的に強化された20ピンTSSOPパッケージに収められています。各DACは外部リファレンス・モードでレール・トゥ・レールで動作するか、または内蔵リファレンスで設定されるフルスケール電圧で動作することができます。精度(16ビットまたは12ビット)とフルスケール電圧(2.5Vまたは4.096V)の4種類の組合せを利用することができます。LTC2656は4線式SPI/MICROWIRE互換のインターフェースを使って制御します。

### パワー・オン・リセット

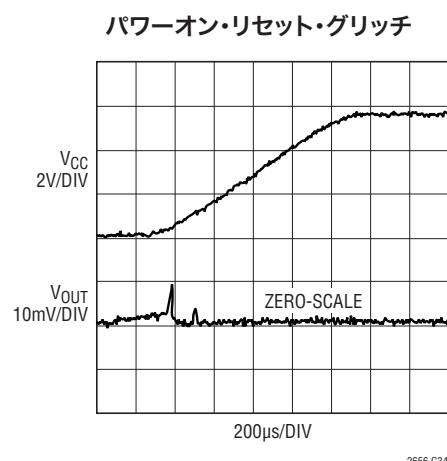

LTC2656-L/LTC2656-Hは、最初の電源投入時にPORSELピンがGNDに接続されると、出力をゼロスケールにクリアしてシステムの初期状態を一定に保ち、反復可能になります。アプリケーションによっては、DACの起動時に下流回路がアクティブ状態であり、この間DACからのゼロでない出力の影響を受けることがあります。LTC2656にはパワー・オン・グリッチを減少させる回路が備わっています。電源が1ms以上かかると5Vまでランプする場合、通常、電源投入時にアナログ出力がゼロスケールよりも10mV以上上昇することはありません。グリッチ振幅は一般に電源のランプ時間が増加するにつれて低下します。「標準的性能特性」の「パワー・オン・リセット・グリッチ」を参照してください。

代わりに、PORSELピンがV<sub>CC</sub>に接続されると、LTC2656-L/LTC2656-Hは最初の電源投入時に出力をミッドスケールに設定します。

### 電源のシーケンシングと起動

LTC2656ファミリ・デバイスの場合、起動時に内部リファレンスが既定でパワー・アップします。外部リファレンスを使う場合、REFCOMPピンをGNDにハードワイヤ接続する必要があります。パワー・アップ時にREFCOMPをGNDにハードワイヤ接続させるとREFIN/OUTピンが高インピーダンスになり、起動時に外部リファレンスを使用できるようになります。ただし、この構成設定では、内部リファレンスはREFIN/OUTピンから切断されてもオンしたままで、消費電流が流れます。パワー・アップ後に外部リファレンスを使用するには、「外部リファレンスを選択する」コマンド(0111b)を使って内部リファレンスをオフにします(表1参照)。

外部リファレンスを使用する場合、REFIN/OUTの電圧は $-0.3V \leq \text{REFIN/OUT} \leq V_{CC} + 0.3V$ の範囲内に保ちます(「絶対最大定格」を参照)。V<sub>CC</sub>の電圧が遷移している電源のター

ンオン・シーケンスとターンオフ・シーケンスの間、これらのリミットが守られるように特に注意が必要です。

### 伝達関数

デジタルからアナログへの伝達関数は次のとおりです。

$$V_{\text{OUT(IDEAL)}} = \left( \frac{k}{2^N} \right) \cdot 2 \cdot (V_{\text{REF}} - V_{\text{REFLO}}) + V_{\text{REFLO}}$$

ここで、kはDACの2進数の入力コードに相当する10進数、NはDACの分解能、V<sub>REF</sub>はREFIN/OUTピンの電圧です。REFLOをGNDに接続する必要があるので、DACの出力範囲は0V～ $2 \cdot V_{\text{REF}}$ です。内部リファレンス・モードでは、V<sub>REF</sub>は通常LTC2656-Lの場合1.25V、LTC2656-Hの場合2.048Vです。

表1. コマンドおよびアドレスのコード

| コマンド*    |    |    |    |                                |

|----------|----|----|----|--------------------------------|

| C3       | C2 | C1 | C0 |                                |

| 0        | 0  | 0  | 0  | 入力レジスタnに書き込む                   |

| 0        | 0  | 0  | 1  | DACレジスタnを更新(パワー・アップ)する         |

| 0        | 0  | 1  | 0  | 入力レジスタnに書き込み、すべてを更新(パワー・アップ)する |

| 0        | 0  | 1  | 1  | nに書き込み、更新(パワー・アップ)する           |

| 0        | 1  | 0  | 0  | nをパワーダウン                       |

| 0        | 1  | 0  | 1  | デバイス(すべてのDACとリファレンス)をパワーダウン    |

| 0        | 1  | 1  | 0  | 内部リファレンスを選択する(リファレンスをパワー・アップ)  |

| 0        | 1  | 1  | 1  | 外部リファレンスを選択する(リファレンスをパワー・ダウン)  |

| 1        | 1  | 1  | 1  | 非動作                            |

| アドレス(n)* |    |    |    |                                |

| A3       | A2 | A1 | A0 |                                |

| 0        | 0  | 0  | 0  | DAC A                          |

| 0        | 0  | 0  | 1  | DAC B                          |

| 0        | 0  | 1  | 0  | DAC C                          |

| 0        | 0  | 1  | 1  | DAC D                          |

| 0        | 1  | 0  | 0  | DAC E                          |

| 0        | 1  | 0  | 1  | DAC F                          |

| 0        | 1  | 1  | 0  | DAC G                          |

| 0        | 1  | 1  | 1  | DAC H                          |

| 1        | 1  | 1  | 1  | すべてのDAC                        |

\*示されていないコマンドとアドレス・コードは予備のため使用不可。

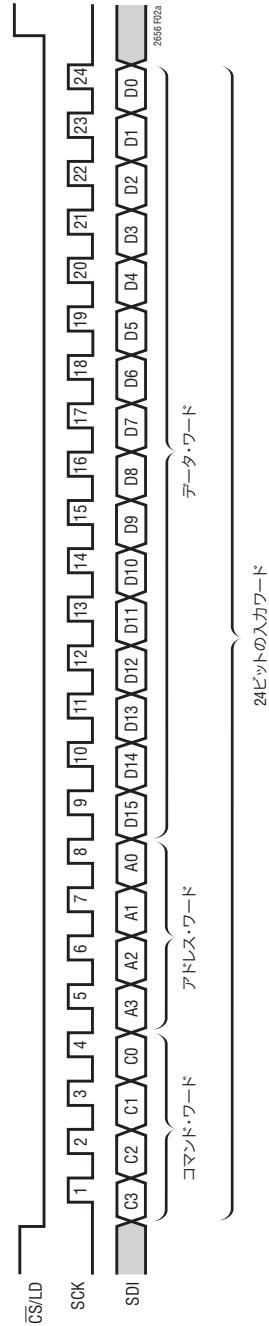

### シリアル・インターフェース

CS/LDはレベルトリガ入力です。この入力を“L”にするとチップ・セレクト信号として機能し、SDIとSCKのバッファをパワー・オンし、入力シフト・レジスタをイネーブルします。データ(SDI入力)は後続の24のSCKの立ち上がりエッジで転送されます。

## 動作

最初に4ビットのコマンド(C3～C0)、次に4ビットのDACアドレス(A3～A0)、そして最後に16ビットのデータ・ワードがロードされます。LTC2656-16の場合、データ・ワードはMSBからLSBへと並んだ16ビットの入力コードで構成されます。LTC2656-12の場合、データ・ワードはMSBからLSBへと並んだ12ビットの入力コードと、それに続く4つのドントケア・ビットで構成されます。データは $\overline{\text{CS}}/\text{LD}$ 信号が“L”的ときだけLTC2656に転送することができます。 $\overline{\text{CS}}/\text{LD}$ の立ち上がりエッジでデータの転送が終了し、24ビットの入力ワードで指定されたアクションがデバイスによって実行されます。すべてのシーケンスを図2aに示します。

コマンド(C3～C0)とアドレス(A3～A0)の割り当てを表1に示します。表の中の最初の4つのコマンドは書き込みと更新の操作です。書き込み操作により、16ビットのデータ・ワードが32ビットのシフト・レジスタから選択されたDAC(n)の入力レジスタにロードされます。更新操作により、データ・ワードが入力レジスタからDACレジスタにコピーされます。DACレジスタにコピーされると、データ・ワードはアクティブな16ビットまたは12ビットの入力コードになり、DAC出力でアナログ電圧に変換されます。また、選択されたDACがパワーダウン・モードになつていれば、更新操作によってパワーアップされます。データ・パスとレジスタを「ブロック図」に示します。

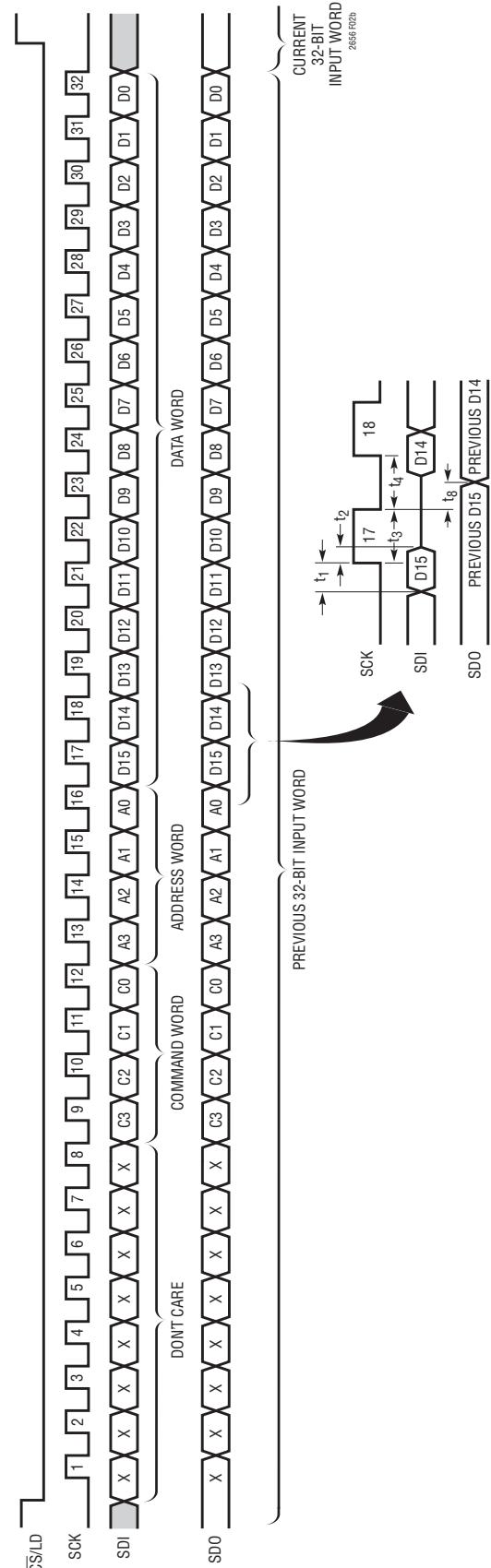

最小入力ワードは24ビットですが、オプションで32ビットに拡張することができます。32ビットのワード幅を使用するには、8つのドントケア・ビットを最初にデバイスに転送し、続いて上述のように24ビットのワードを転送します。32ビットのシーケンスを図2bに示します。32ビット・ワードはデイジーチェーン動作に必要で、最小ワード幅16ビット(2バイト)のマイクロプロセッサに対応させるためにも有効です。16ビットのデータ・ワードは、書き込み操作を含まないすべてのコマンドで無視されます。

### デイジーチェーン動作

シフト・レジスタのシリアル出力はSDOピンから出力されます。SDI入力からデバイスに転送されたデータは、SCKの32の立ち上がりエッジだけ遅れてから、次のSCKの立ち下がりエッジで出力されます。SDOピンは常にドライブされ、 $\overline{\text{CS}}/\text{LD}$ がアクティブ“H”になつても高インピーダンスになりません。

SDO出力を使うと、单一の3線シリアル・ポート(つまり、SCK、SDIおよび $\overline{\text{CS}}/\text{LD}$ )から複数のシリアル・デバイスを簡単に制御することができます。このような「デイジーチェーン」の直列接続は、連鎖の上流に位置する各デバイスのSDOを次に位置するデバイスのSDIに接続することによって構成されます。これ

らのデバイスのシフト・レジスタはこのように直列に連結され、実質的に、連鎖全体にわたる单一入力のシフト・レジスタを形成します。このため、これらのデバイスは、それらへの入力ワードを連結するだけで、個別にアドレスを指定して制御することができます(最初の命令は連鎖の最後のデバイスのアドレスを指定します。以下同様)。 $\text{SCK}$ 信号と $\overline{\text{CS}}/\text{LD}$ 信号は直列に接続されたすべてのデバイスに共通です。

使用時には、最初に $\overline{\text{CS}}/\text{LD}$ を“L”にします。次に、最初のデバイスのSDIをデータ入力に使って、連結された入力データを連鎖に転送します。データの転送が完了すると、 $\overline{\text{CS}}/\text{LD}$ を“H”にして、すべてのデバイスの命令シーケンスを同時に完了します。連鎖内の1つのデバイス以外のデバイスに対しては「非動作」コマンド(1111b)を使うことにより、その1つのデバイスだけを制御することができます。

### パワーダウン・モード

電力が制限されているアプリケーションでは、8本のDAC出力のすべては必要ないときはパワーダウン・モードを使って消費電流を減らすことができます。パワーダウン時、バッファ・アンプ、バイアス回路および内蔵リファレンス回路はディスエーブルされ、実質的に電流は流れません。DAC出力は高インピーダンス状態になり、出力ピンは個別の80k抵抗によって受動的にグランドに引き下げられます。入力レジスタとDACレジスタの内容はパワーダウンの影響を受けません。

コマンド0100bを適切なDACアドレス(n)と組み合わせて使うことにより、いずれのDACチャネルも、またはどのような組み合わせの複数のDACチャネルもパワーダウン・モードにすることができます。コマンド0111bを使って外部リファレンスを選択すると、内蔵リファレンスは自動的にパワーダウンします。さらに、「デバイスをパワーダウン」コマンド(0101b)を使って、すべてのDACチャネルと内蔵リファレンスを一緒にパワーダウン・モードにすることができます。すべてのパワーダウン・コマンドで16ビットのデータ・ワードは無視されます。

ソフトウェアで、表1に示すようなDACの更新を含むコマンドのいずれかを実行することによって、または非同期 $\overline{\text{LDAC}}$ ピンを“L”にすることによって、通常動作が再開されます。選択されたDACは、その電圧出力が更新されるとパワーアップします。パワーダウン状態のDACのパワーアップおよび更新時には、通常のセトリングに遅延が生じます。更新コマンドの実行前にパワーダウン状態のDACが7個以下の場合、パワーアップ遅延は12 $\mu\text{s}$ です。一方、8個のすべてのDACおよび内部リファ

## 動作

図2a. LTC2656-16のSDIデータ・ワード:12ビットの入力コード+4つのドットケア・ビット

LTC2656-12のSDIデータ・ワード

図2b. LTC2656-16の32ビットのロード・シーケンス

LTC2656-12のSDI/SD0データ・ワード:12ビットの入力コード+4つのドットケア・ビット

## 動作

レンスがパワーダウンされると、個々のDACのアンプや内蔵リファレンスに加えて、主バイアス発生回路ブロックが自動的にシャットダウンされます。この場合、パワーアップ遅延は14 $\mu$ sです。内蔵リファレンスのパワーアップはそれをパワーダウンしたコマンドに依存します。「外部リファレンスを選択する」コマンド(0111b)を使ってリファレンスをパワーダウンした場合、「内部リファレンスを選択する」コマンド(0110b)を使わない限り再度パワーアップすることができません。ただし、「デバイスをパワーダウン」コマンド(0101b)を使ってリファレンスをパワーダウンした場合、「内部リファレンスを選択する」コマンド(0110b)のほか、DACをパワーアップするとのコマンドでも内部リファレンスがパワーアップします。

### LDACによるDACの非同期更新

表1に示す更新コマンドに加えて、LDACピンによってすべてのDACレジスタを入力レジスタの内容で非同期に更新することができます。

CS/LDが“H”的場合、LDACピンを“L”にすると、すべてのDACレジスタが入力レジスタの内容で更新されます。

CS/LDが“L”的場合、CS/LDの立ち上がりエッジの前にLDACピンに立ち下がりパルスが印加されると、すべてのDAC出力がパワーアップしますが、出力の更新は行われません。CS/LDの立ち上がりエッジ後もLDACが“L”的ままならば、LDACの状態が検知され、直前に転送された24ビット・ワードで指定されたコマンドが実行されて、DAC出力が更新されます。

DAC出力は、CS/LDの状態にかかわらず、LDACを“L”にするとパワーアップされます。内蔵リファレンスが「デバイスをパワーダウン」コマンド(0101b)を使ってパワーダウンされている場合は、内蔵リファレンスもパワーアップされます。内蔵リファレンスが「外部リファレンスを選択する」コマンド(0111b)を使ってパワーダウンされている場合は、LDACを“L”にしても内蔵リファレンスはパワーアップされません。

CS/LDが“H”になったときにLDACが“L”的場合は、入力ワードでソフトウェアのどのパワーダウン・コマンド(「nをパワーダウン」、「デバイスをパワーダウン」、「外部リファレンスを選択する」)が指定されていても、実行されません。

### リファレンス・モード

精確な外部リファレンスを利用できないアプリケーションのため、LTC2656はユーザーが選択できる内蔵リファレンスを備え

ています。LTC2656-Lは2.5VのDACフルスケール出力を提供する1.25Vリファレンスを備えています。LTC2656-Hは4.096VのDACフルスケール出力を提供する2.048Vリファレンスを備えています。両方のリファレンスとも2ppm/ $^{\circ}$ Cの標準温度ドリフトを示します。内部リファレンス・モードはコマンド0110bを使って選択することができ、起動時のデフォルトです。内部リファレンスが外部回路をドライブする必要がある場合は、バッファが必要です。リファレンスの安定性とノイズ低減のため、0.1 $\mu$ FのコンデンサをREFCOMPとGNDの間に接続することを推奨します。この構成設定では、安定性の問題を生じることなく、内部リファレンスは最大0.1 $\mu$ Fの容量性負荷をドライブすることができます。安定動作を確実にするため、REFIN/OUTピンの容量性負荷がREFCOMPピンの容量性負荷を超えないようにします。

コマンド0111bを使って、DACを外部リファレンス・モードで動作させることもできます。このモードでは、REFIN/OUTピンはDACのリファレンス電圧を設定する入力として機能します。この入力は高インピーダンスであり、外部リファレンス・ソースに負荷をかけません。このピンの許容電圧範囲は0.5V  $\leq$  REFIN/OUT  $\leq$  V<sub>CC</sub>/2です。その結果生じるフルスケール出力電圧は2  $\cdot$  V<sub>REFIN/OUT</sub>です。起動時の外部リファレンスの使用については、「電源シーケンシングと起動」のセクションを参照してください。

### 内蔵リファレンス・バッファ

LTC2656の8個のDACはそれぞれ個別に高性能リファレンス・バッファを内蔵しています。これらのバッファは入力インピーダンスが非常に高く、リファレンス電圧源に負荷をかけません。また、DACのスイッチングによって生じるグリッチからリファレンス電圧を遮蔽し、DAC間の動的クロストークを最小限に抑えます。通常、DAC間のクロストークは3nV  $\cdot$  s未満です。0.1 $\mu$ FのコンデンサをREFCOMPとGNDの間、またREFIN/OUTとGNDの間にも接続することにより、この数値を1nV  $\cdot$  s未満に低減することができます。「標準的性能特性」のセクションの「DAC間クロストーク(動的)」の曲線を参照してください。

### 電圧出力

LTC2656に内蔵されている8個のレール・トゥ・レール出力アンプは、それぞれ5Vで最大15mA(3Vで最大7.5mA)をソースまたはシンクするときの負荷レギュレーションが保証されています。

負荷レギュレーションは、広い範囲の負荷条件にわたって定格電圧精度を維持する、アンプの能力の指標です。負荷電流

## 動作

を強制的に1mA変化させたときの出力電圧の変化の測定値はLSB/mAで表されます。

DC出力インピーダンスは負荷レギュレーションと等価で、LSB/mAから $\Omega$ に単位を変えて計算するだけで求めることができます。アンプのDC出力インピーダンスは、レールから十分離れた負荷をドライブしているとき $0.040\Omega$ です。

どちらかのレールから負荷電流が流れているとき、そのレールを基準にした出力電圧の空き高は出力デバイスの標準的チャネル抵抗 $30\Omega$ によって制限されます。たとえば、1mAをシンクしているとき、最小出力電圧 =  $30\Omega \cdot 1\text{mA} = 30\text{mV}$ になります。「標準性能特性」のセクションの「レールの空き高と出力電流」のグラフを参照してください。

アンプは最大 $1000\text{pF}$ の容量性負荷を安定的にドライブします。

## 基板のレイアウト

これらのデバイスのすぐれた負荷レギュレーションとDCクロストークの性能は、「信号」グランドと「電源」グランドを分離することによりある程度実現されます。

PCボードには、回路のアナログ部分用とデジタル部分用に別々の領域が必要です。こうすれば、敏感なアナログ信号からデジタル信号を遠ざけることができ、分離されたデジタル・グランド・プレーンとアナログ・グランド・プレーンを使いやすくなり、容量性および抵抗性の相互作用を最小限に抑えられます。デジタル・グランド・プレーンとアナログ・グランド・プレー

ンは1点接続し、デバイスのグランド・ピンにできるだけ近づけてシステムのスター・グランドを形成します。理想的には、アナログ・グランド・プレーンはボードの部品側に配置し、デバイスをノイズからシールドするためにデバイスの下にくるようにします。アナログ・グランドは(必要なピン・パッドやビア以外は)遮るもののない連続したプレーンにして、信号用トレースは別のレイヤに配置します。

GNDピンはデバイス内の電源電流のリターンパスとして機能し、アナログ・グランドに接続します。REFLOピンはシステムのスター・グランドに接続します。REFLOピンからシステムのスター・グランドまでの抵抗をできるだけ小さくします。

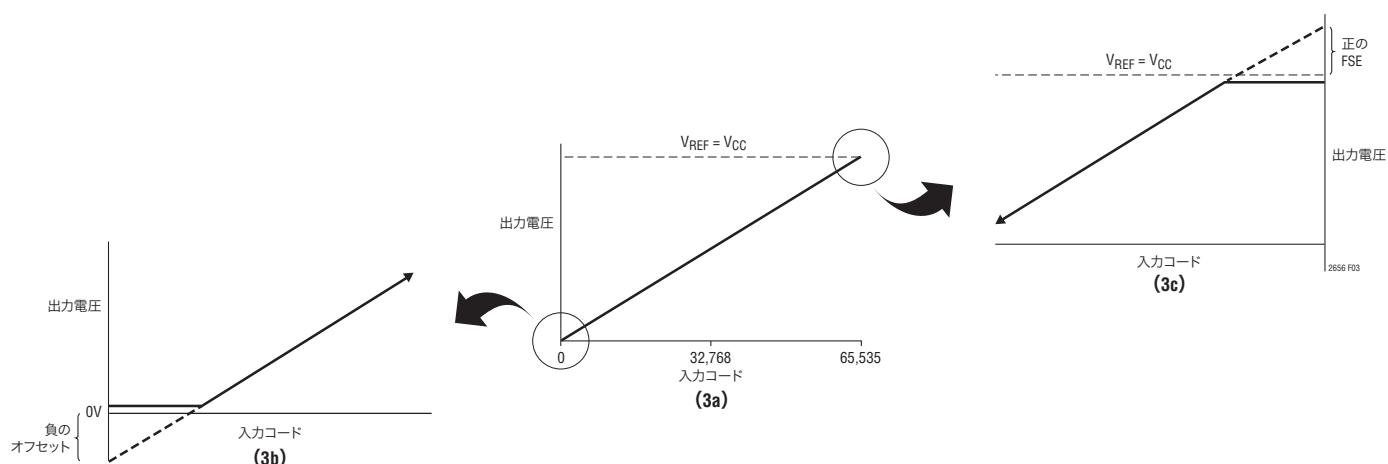

## レール・トゥ・レール出力に関する検討事項

どのようなレール・トゥ・レール電圧出力デバイスでも、出力は電源電圧範囲内に制限されています。

デバイスのアナログ出力はグランドを下回ることができないので、図3bに示されているように、この出力が最低コードを制限することができます。同様に、REFIN/OUTピンが $V_{CC}/2$ のとき、外部リファレンス・モードではフルスケールの近くで制限が生じことがあります。 $V_{REFIN/OUT} = V_{CC}/2$ で、DACのフルスケール誤差(FSE)が正のとき、最高コードの出力が、図3cに示されているように、 $V_{CC}$ に制限されます。 $V_{REFIN/OUT} \leq (V_{CC} - FSE)/2$ であると、フルスケールの制限は生じません。

オフセットと直線性は、DACの伝達関数の出力制限が生じない領域について定義され、テストされます。

図3. DAC伝達曲線に対するレール・トゥ・レール動作の影響。(3a)全体の伝達関数 (3b)ゼロスケール近くのコードに対する負のオフセットの影響(3c)フルスケール近くのコードに対する正のフルスケール誤差の影響

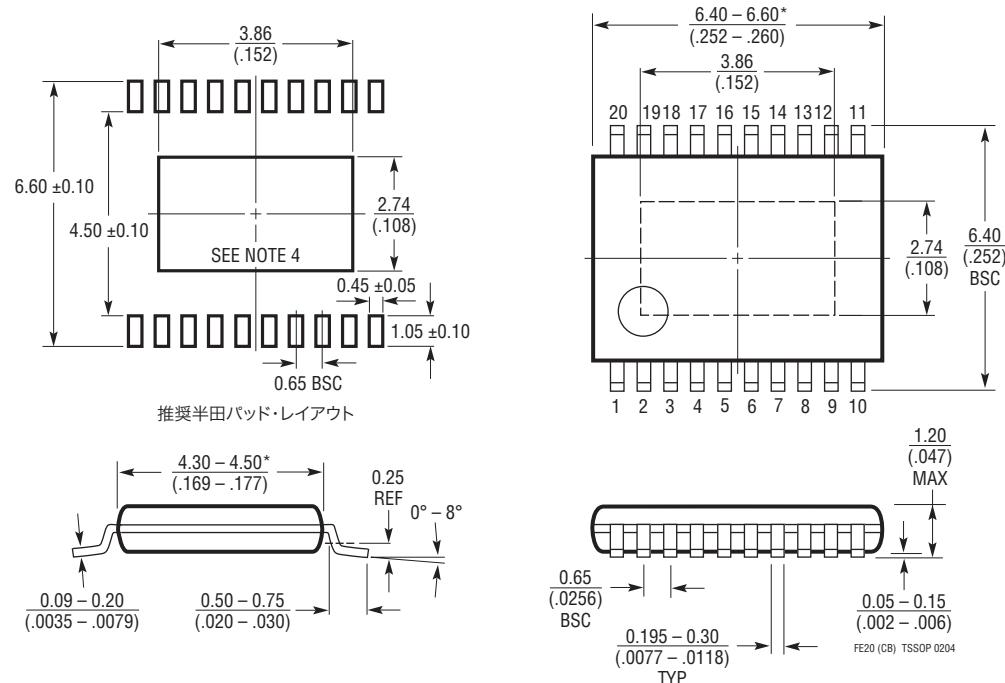

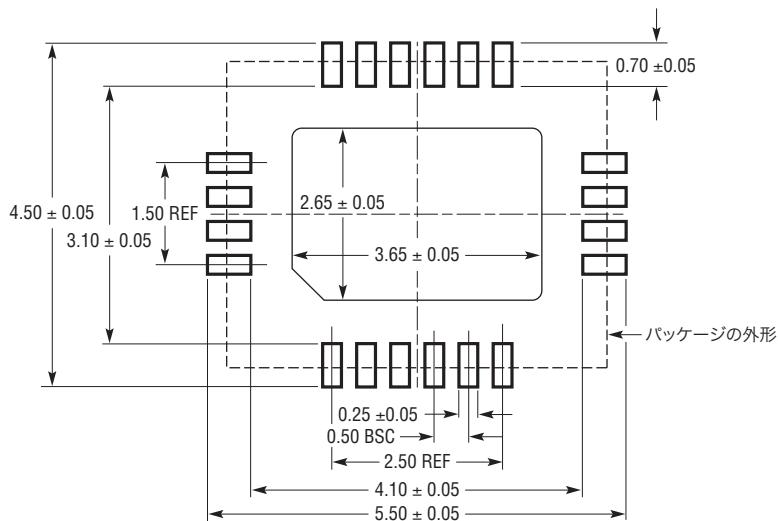

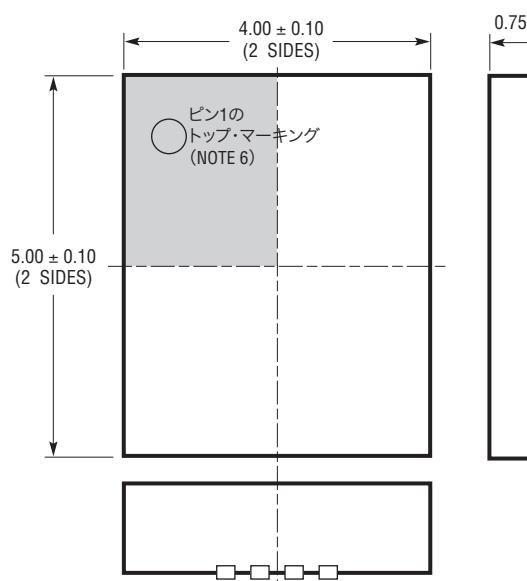

## パッケージ

FEパッケージ

20ピン・プラスチックTSSOP(4.4mm)

(Reference LTC DWG # 05-08-1663)

露出パッドのバリエーションCB

## NOTE:

1. 標準寸法:ミリメートル

2. 寸法は  $\frac{\text{ミリメートル}}{(\text{インチ})}$

3. 図は実寸とは異なる

4. 露出パッド接着のための推奨最小PCBメタルサイズ

\*寸法にはモールドのバリを含まない

モールドのバリは各サイドで0.150mm(0.006")を超えないこと

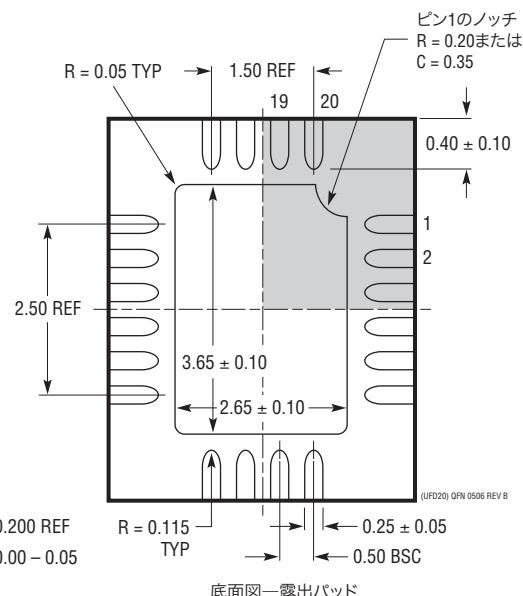

## パッケージ

UFDパッケージ

20ピン・プラスチックQFN (4mmx5mm)

(Reference LTC DWG # 05-08-1711 Rev B)

推薦する半田パッドのピッチと寸法

半田付けされない領域には半田マスクを使用する

底面図—露出パッド

NOTE:

1. 図はJEDECパッケージ外形MO-220のバリエーション(WXXX-X)にするよう提案されている

2. 図は実寸とは異なる

3. すべての寸法はミリメートル

4. パッケージ底面の露出パッドの寸法にはモールドのバリを含まない

モールドのバリは(もしあれば)各サイドで0.15mmを超えないこと

5. 露出パッドは半田メッキとする

6. 線掛けの部分はパッケージの上面と底面のピン1の位置の参考に過ぎない

## 改訂履歴 (Rev Aよりスタート)

| REV | 日付    | 概要                                      | 概要         |

|-----|-------|-----------------------------------------|------------|

| A   | 11/10 | Cグレードをデータシートに追加<br>Hグレードのため「電気的特性」の表を更新 | 3~6.9<br>7 |

# LTC2656

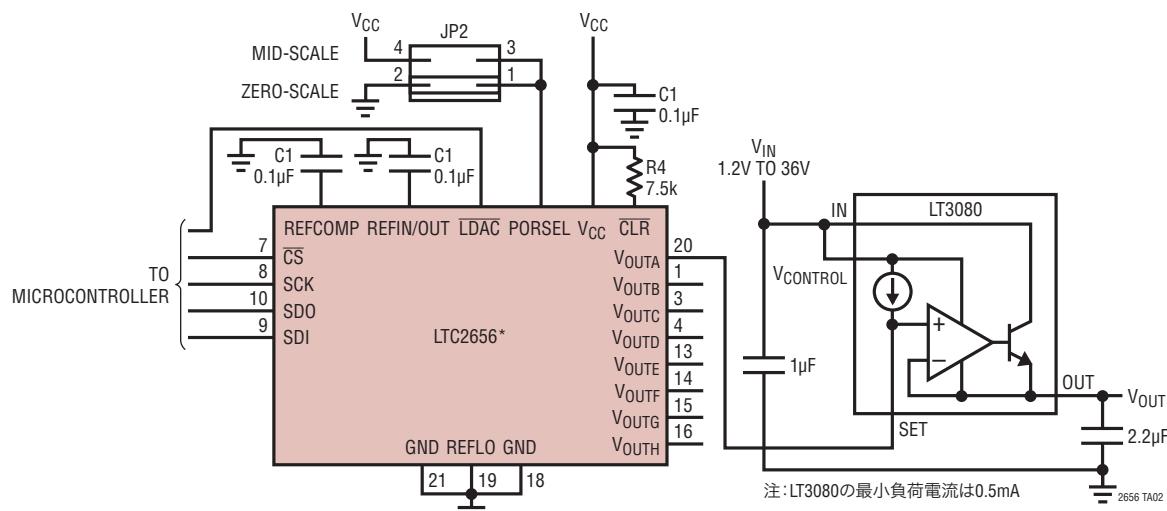

## 標準的応用例

### 出力電圧がデジタル制御される1.1A電源

## 関連製品

| 製品番号                    | 説明                                                            | 注釈                                                                       |

|-------------------------|---------------------------------------------------------------|--------------------------------------------------------------------------|

| LTC1660/LTC1665         | 16ピン細型SSOPのオクタル10/8ビットV <sub>OUT</sub> DAC                    | V <sub>CC</sub> = 2.7V~5.5V、マイクロパワー、レール・トゥ・レール出力                         |

| LTC1664                 | 16ピン細型SSOPのクワッド10ビットV <sub>OUT</sub> DAC                      | V <sub>CC</sub> = 2.7V~5.5V、マイクロパワー、レール・トゥ・レール出力                         |

| LTC1821                 | シングル16ビットV <sub>OUT</sub> DAC、±1LSBのINL、DNL                   | パラレル・インターフェース、10Vのステップに対して2μsで高精度16ビット・セトリング                             |

| LTC2600/LTC2610/LTC2620 | 16ピン細型SSOPのオクタル16/14/12ビットV <sub>OUT</sub> DAC                | 250μA/DAC、2.5V~5.5V電源範囲、レール・トゥ・レール出力、SPIシリアル・インターフェース                    |

| LTC2601/LTC2611/LTC2621 | 10ピンDFNのシングル16/14/12ビットV <sub>OUT</sub> DAC                   | 300μA/DAC、2.5V~5.5V電源範囲、レール・トゥ・レール出力、SPIシリアル・インターフェース                    |

| LTC2602/LTC2612/LTC2622 | 8ピンMSOPのデュアル16/14/12ビットV <sub>OUT</sub> DAC                   | 300μA/DAC、2.5V~5.5V電源範囲、レール・トゥ・レール出力、SPIシリアル・インターフェース                    |

| LTC2604/LTC2614/LTC2624 | 16ピンSSOPのクワッド16/14/12ビットV <sub>OUT</sub> DAC                  | 250μA/DAC、2.5V~5.5V電源範囲、レール・トゥ・レール出力、SPIシリアル・インターフェース                    |

| LTC2605/LTC2615/LTC2625 | I <sup>2</sup> Cインターフェース付きオクタル16/14/12ビットV <sub>OUT</sub> DAC | 250μA/DAC、2.7V~5.5V電源範囲、レール・トゥ・レール出力                                     |

| LTC2606/LTC2616/LTC2626 | I <sup>2</sup> Cインターフェース付きシングル16/14/12ビットV <sub>OUT</sub> DAC | 270μA/DAC、2.7V~5.5V電源範囲、レール・トゥ・レール出力                                     |

| LTC2609/LTC2619/LTC2629 | I <sup>2</sup> Cインターフェース付きクワッド16/14/12ビットV <sub>OUT</sub> DAC | 250μA/DAC、2.7V~5.5V電源範囲、レール・トゥ・レール出力、各DACに個別V <sub>REF</sub> ピン付き        |

| LTC2636                 | オクタル12/10/8ビットV <sub>OUT</sub> DAC、10ppm/°Cリファレンス付き           | 125μA/DAC、2.7V~5.5V電源範囲、1.25Vまたは2.048Vの内部リファレンス、レール・トゥ・レール出力、SPIインターフェース |

| LTC2641/LTC2642         | シングル16/14/12ビットV <sub>OUT</sub> DAC、±1LSBのINLとDNL             | INLおよびDNLが±1LSB(最大)、3mm×3mm DFNおよびMSOPパッケージ、120μAの消費電流、SPIインターフェース       |

| LTC2704                 | クワッド16/14/12ビットV <sub>OUT</sub> DAC、±2LSBのINL、±1LSBのDNL       | ソフトウェアでプログラム可能な出力範囲:最大±10V、SPIインターフェース                                   |

| LTC2755                 | クワッド16/14/12ビットI <sub>OUT</sub> DAC、±1LSBのINL、±1LSBのDNL       | ソフトウェアでプログラム可能な出力範囲:最大±10V、パラレル・インターフェース                                 |

2656fa