## 特長

### ■ 最小のピン互換オクタルDAC:

LTC2605:16 ビット

LTC2615:14 ビット

LTC2625:12 ビット

### ■ 全温度範囲で単調性を保証

### ■ 400kHz I<sup>2</sup>Cインターフェイス

### ■ 広い電源範囲:2.7V ~ 5.5V

### ■ 低消費電力動作:250µA/DAC(3V電源時)

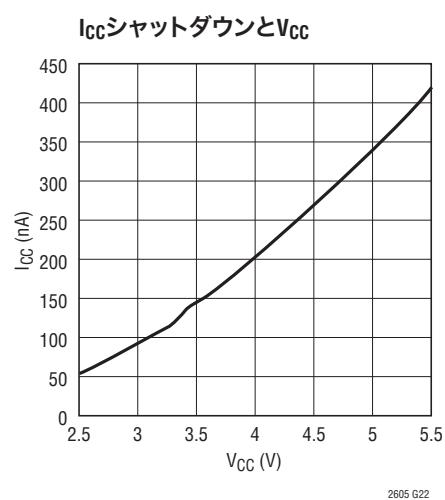

### ■ 1µA(最大)の個別チャネル・パワーダウン

### ■ 非常に小さいDAC 間のクロストーク:10µV以下

### ■ 高いレール・トゥ・レール出力ドライブ:±15mA(最小)

### ■ ダブルバッファ・デジタル入力

### ■ 27 のアドレスを選択可能

### ■ LTC2605/LTC2615/LTC2625:ゼロスケールにパワーオン・リセット

### ■ LTC2605-1/LTC2615-1/LTC2625-1:ミッドスケールにパワーオン・リセット

### ■ 小型16ピン細型SSOPパッケージ

## アプリケーション

### ■ モバイル通信

### ■ プロセス制御、産業用オートメーション

### ■ 計測

### ■ 自動試験装置

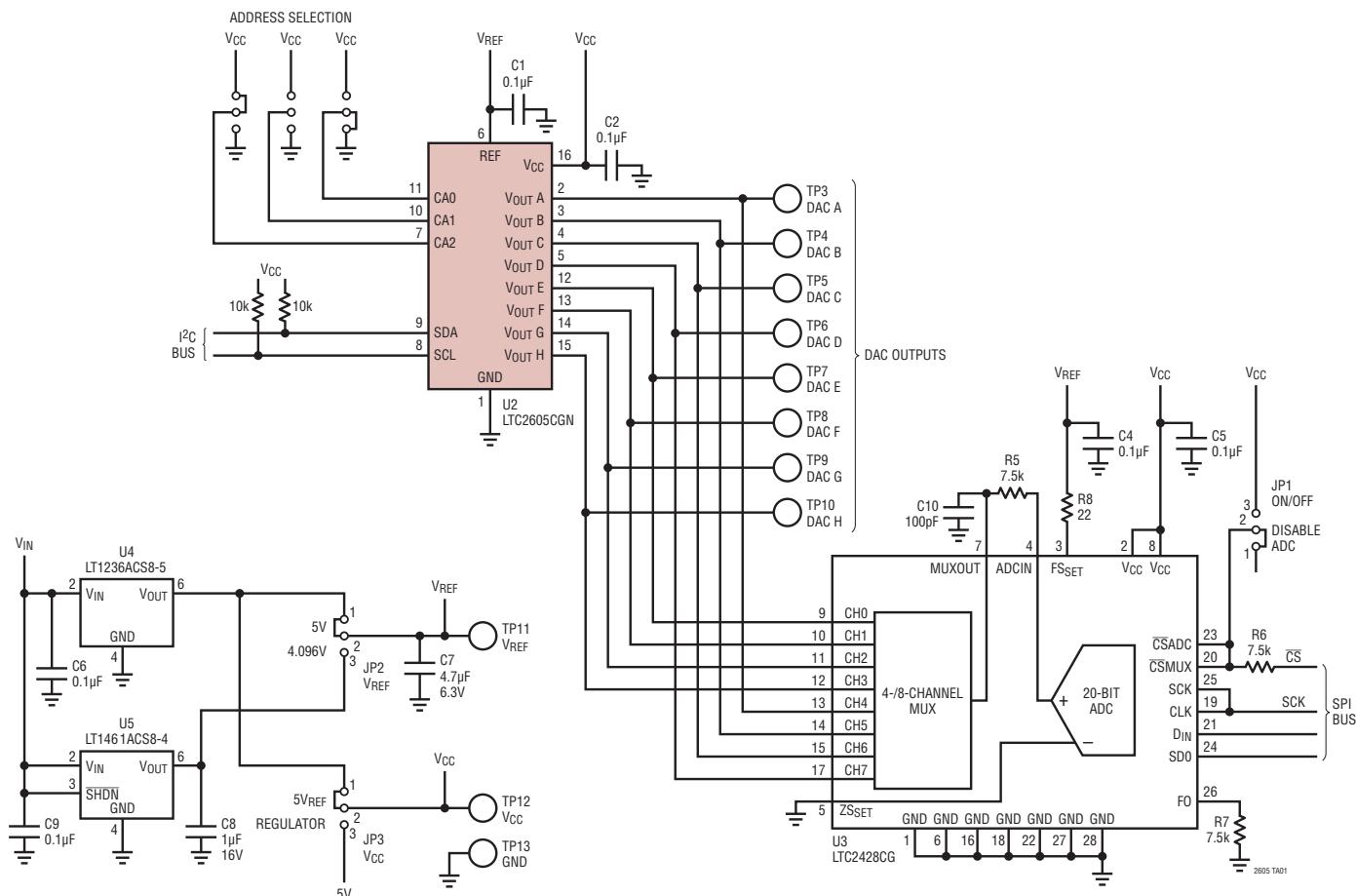

## 標準的応用例

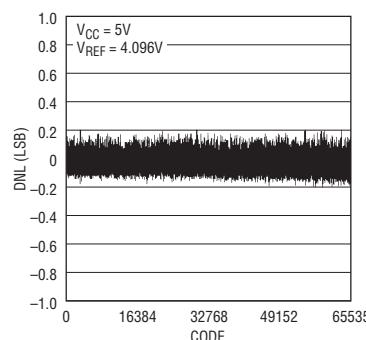

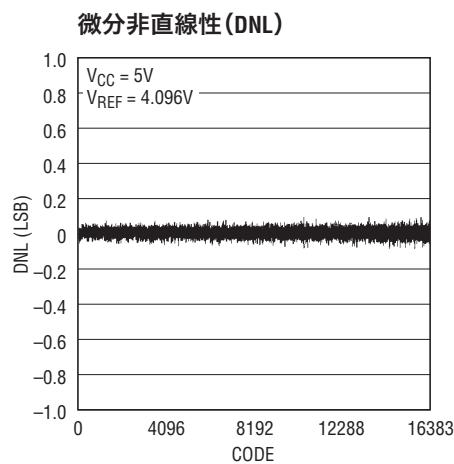

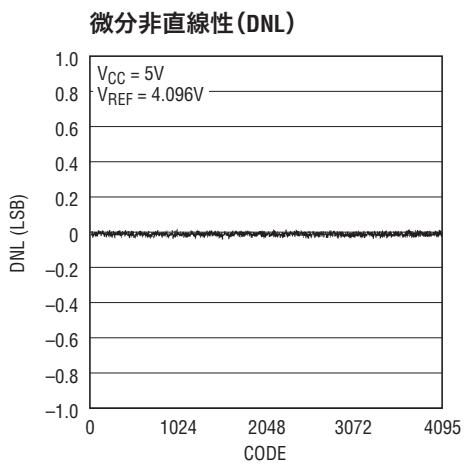

微分非直線性(LTC2605)

# LTC2605/LTC2615/LTC2625

## 絶対最大定格

(Note 1)

|                                        |             |

|----------------------------------------|-------------|

| すべてのピンからGND .....                      | -0.3V~6V    |

| すべてのピンからV <sub>CC</sub> .....          | -6V~0.3V    |

| 最大接合部温度.....                           | 125°C       |

| 動作温度範囲                                 |             |

| LTC2605C/LTC2615C/LTC2625C.....        | 0°C~70°C    |

| LTC2605C-1/LTC2615C-1/LTC2625C-1.....  | 0°C~70°C    |

| LTC2605I/LTC2615I/LTC2625I .....       | -40°C~85°C  |

| LTC2605I-1/LTC2615I-1/LTC2625I-1 ..... | -40°C~85°C  |

| 保存温度範囲.....                            | -65°C~150°C |

| リード温度(半田付け、10秒).....                   | 300°C       |

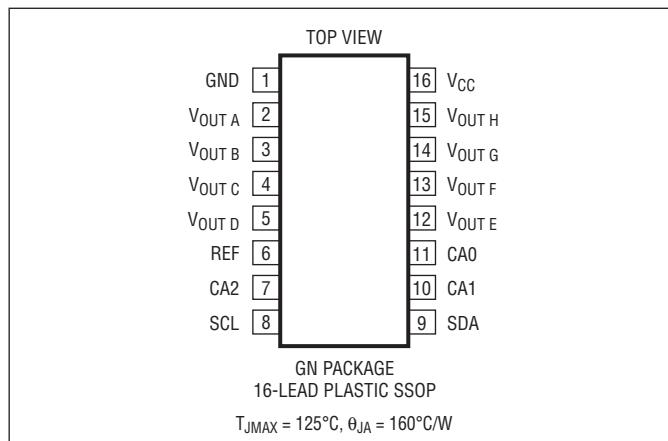

## ピン配置

## 発注情報

| 鉛フリー仕様           | テープアンドリール          | 製品マーキング | パッケージ                | 温度範囲          |

|------------------|--------------------|---------|----------------------|---------------|

| LTC2605CGN#PBF   | LTC2605CGN#TRPBF   | 2605    | 16-Lead Plastic SSOP | 0°C to 70°C   |

| LTC2605CGN-1#PBF | LTC2605CGN-1#TRPBF | 26051   | 16-Lead Plastic SSOP | 0°C to 70°C   |

| LTC2605IGN#PBF   | LTC2605IGN#TRPBF   | 2605I   | 16-Lead Plastic SSOP | -40°C to 85°C |

| LTC2605IGN-1#PBF | LTC2605IGN-1#TRPBF | 2605I1  | 16-Lead Plastic SSOP | -40°C to 85°C |

| LTC2615CGN#PBF   | LTC2615CGN#TRPBF   | 2615    | 16-Lead Plastic SSOP | 0°C to 70°C   |

| LTC2615CGN-1#PBF | LTC2615CGN-1#TRPBF | 26151   | 16-Lead Plastic SSOP | 0°C to 70°C   |

| LTC2615IGN#PBF   | LTC2615IGN#TRPBF   | 2615I   | 16-Lead Plastic SSOP | -40°C to 85°C |

| LTC2615IGN-1#PBF | LTC2615IGN-1#TRPBF | 2615I1  | 16-Lead Plastic SSOP | -40°C to 85°C |

| LTC2625CGN#PBF   | LTC2625CGN#TRPBF   | 2625    | 16-Lead Plastic SSOP | 0°C to 70°C   |

| LTC2625CGN-1#PBF | LTC2625CGN-1#TRPBF | 26251   | 16-Lead Plastic SSOP | 0°C to 70°C   |

| LTC2625IGN#PBF   | LTC2625IGN#TRPBF   | 2625I   | 16-Lead Plastic SSOP | -40°C to 85°C |

| LTC2625IGN-1#PBF | LTC2625IGN-1#TRPBF | 2625I1  | 16-Lead Plastic SSOP | -40°C to 85°C |

さらに広い動作温度範囲で規定されるデバイスについては、弊社または弊社代理店にお問い合わせください。

非標準の鉛ベース仕様の製品の詳細については、弊社または弊社代理店にお問い合わせください。

鉛フリー仕様の製品マーキングの詳細については、<http://www.linear-tech.co.jp/leadfree/> をご覧ください。

テープアンドリールの仕様の詳細については、<http://www.linear-tech.co.jp/tapeandreel/> をご覧ください。

# LTC2605/LTC2615/LTC2625

## 電気的特性

●は全動作温度範囲の規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。

注記がない限り、REF = 4.096V( $V_{CC} = 5\text{V}$ )、REF = 2.048V( $V_{CC} = 2.7\text{V}$ )、 $V_{OUT}$ 無負荷。

| SYMBOL                | PARAMETER                        | CONDITIONS                                                                                                                                            | LTC2625/LTC2625-1 |      |       | LTC2615/LTC2615-1 |      |     | LTC2605/LTC2605-1 |      |     | UNITS  |

|-----------------------|----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|------|-------|-------------------|------|-----|-------------------|------|-----|--------|

|                       |                                  |                                                                                                                                                       | MIN               | TYP  | MAX   | MIN               | TYP  | MAX | MIN               | TYP  | MAX |        |

| <b>DC Performance</b> |                                  |                                                                                                                                                       |                   |      |       |                   |      |     |                   |      |     |        |

|                       | Resolution                       |                                                                                                                                                       | ●                 | 12   |       | 14                |      | 16  |                   |      |     | Bits   |

|                       | Monotonicity                     | (Note 2)                                                                                                                                              | ●                 | 12   |       | 14                |      | 16  |                   |      |     | Bits   |

| DNL                   | Differential Nonlinearity        | (Note 2)                                                                                                                                              | ●                 |      | ±0.5  |                   | ±1   |     | ±1                |      |     | LSB    |

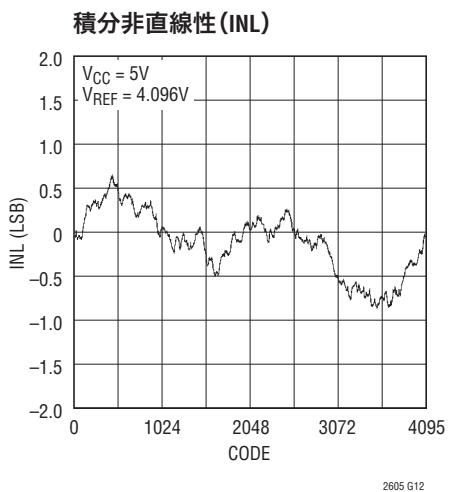

| INL                   | Integral Nonlinearity            | (Note 2)                                                                                                                                              | ●                 | ±1   | ±4    | ±4                | ±16  |     | ±18               | ±64  |     | LSB    |

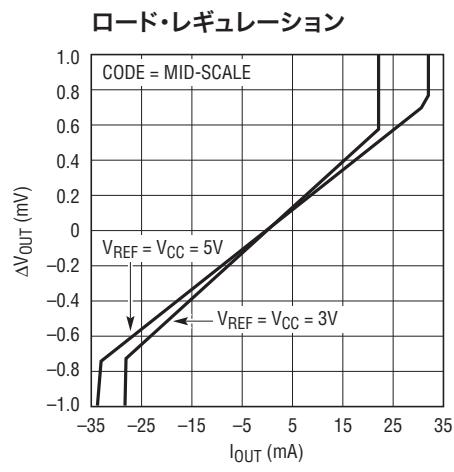

|                       | Load Regulation                  | $V_{REF} = V_{CC} = 5\text{V}$ , Mid-Scale<br>$I_{OUT} = 0\text{mA}$ to $15\text{mA}$ Sourcing<br>$I_{OUT} = 0\text{mA}$ to $15\text{mA}$ Sinking     | ●                 | 0.02 | 0.125 | 0.07              | 0.5  |     | 0.3               | 2    |     | LSB/mA |

|                       |                                  |                                                                                                                                                       | ●                 | 0.03 | 0.125 | 0.10              | 0.5  |     | 0.4               | 2    |     | LSB/mA |

|                       |                                  | $V_{REF} = V_{CC} = 2.7\text{V}$ , Mid-Scale<br>$I_{OUT} = 0\text{mA}$ to $7.5\text{mA}$ Sourcing<br>$I_{OUT} = 0\text{mA}$ to $7.5\text{mA}$ Sinking | ●                 | 0.04 | 0.25  | 0.15              | 1    |     | 0.6               | 4    |     | LSB/mA |

|                       |                                  |                                                                                                                                                       | ●                 | 0.07 | 0.25  | 0.20              | 1    |     | 0.8               | 4    |     | LSB/mA |

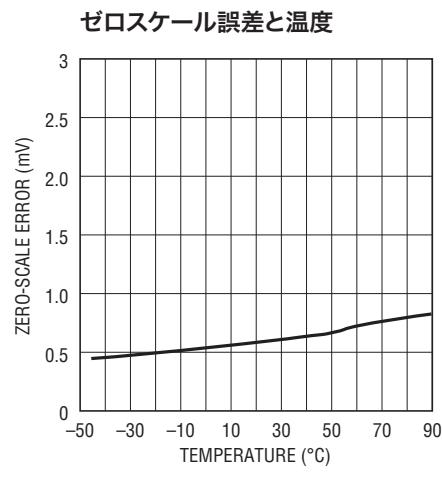

| ZSE                   | Zero-Scale Error                 | Code = 0                                                                                                                                              | ●                 | 1.7  | 9     | 1.7               | 9    |     | 1.7               | 9    |     | mV     |

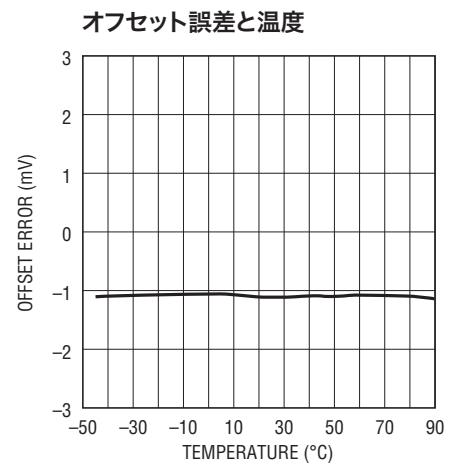

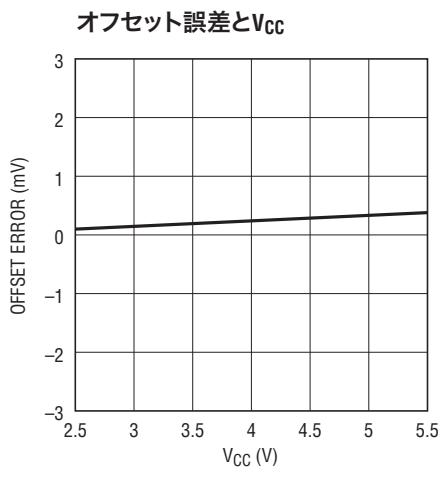

| $V_{OS}$              | Offset Error                     | (Note 4)                                                                                                                                              | ●                 | ±1   | ±9    | ±1                | ±9   |     | ±1                | ±9   |     | mV     |

|                       | $V_{OS}$ Temperature Coefficient |                                                                                                                                                       |                   |      | ±5    |                   | ±5   |     | ±5                |      |     | µV/°C  |

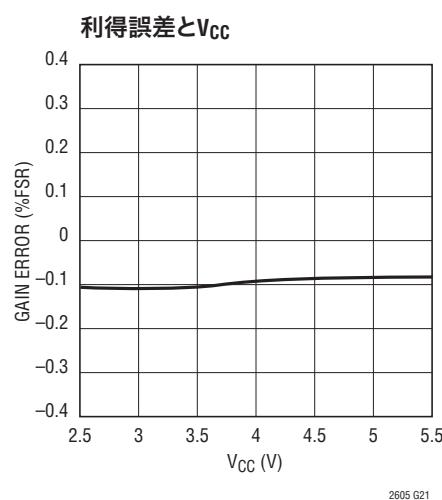

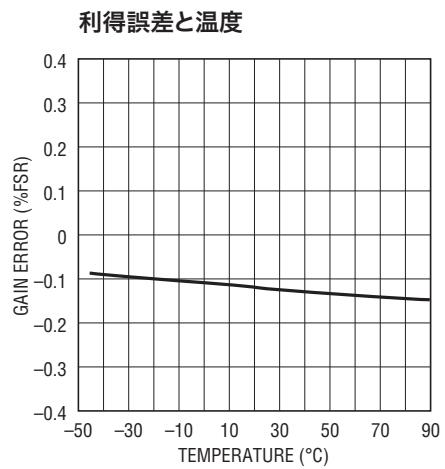

| GE                    | Gain Error                       |                                                                                                                                                       | ●                 | ±0.1 | ±0.7  | ±0.1              | ±0.7 |     | ±0.1              | ±0.7 |     | %FSR   |

|                       | Gain Temperature Coefficient     |                                                                                                                                                       |                   |      | ±8    |                   | ±8   |     | ±8                |      |     | ppm/°C |

●は全動作温度範囲の規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。

注記がない限り、REF = 4.096V( $V_{CC} = 5\text{V}$ )、REF = 2.048V( $V_{CC} = 2.7\text{V}$ )、 $V_{OUT}$ 無負荷。(Note 9)

| SYMBOL    | PARAMETER                    | CONDITIONS                                                                                                                                                                               |   |     |    | MIN  | TYP  | MAX | UNITS |

|-----------|------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-----|----|------|------|-----|-------|

|           |                              |                                                                                                                                                                                          |   |     |    |      |      |     |       |

| PSR       | Power Supply Rejection       | $V_{CC} \pm 10\%$                                                                                                                                                                        |   |     |    | -80  |      |     | dB    |

| $R_{OUT}$ | DC Output Impedance          | $V_{REF} = V_{CC} = 5\text{V}$ , Mid-Scale; $-15\text{mA} \leq I_{OUT} \leq 15\text{mA}$<br>$V_{REF} = V_{CC} = 2.7\text{V}$ , Mid-Scale; $-7.5\text{mA} \leq I_{OUT} \leq 7.5\text{mA}$ | ● |     |    | 0.02 | 0.15 |     | Ω     |

|           |                              |                                                                                                                                                                                          | ● |     |    | 0.03 | 0.15 |     | Ω     |

| $I_{SC}$  | DC Crosstalk (Note 10)       | Due to Full-Scale Output Change (Note 11)<br>Due to Load Current Change<br>Due to Powering Down (per Channel)                                                                            |   |     |    | ±10  |      |     | µV    |

|           |                              |                                                                                                                                                                                          |   |     |    | ±3.5 |      |     | µV/mA |

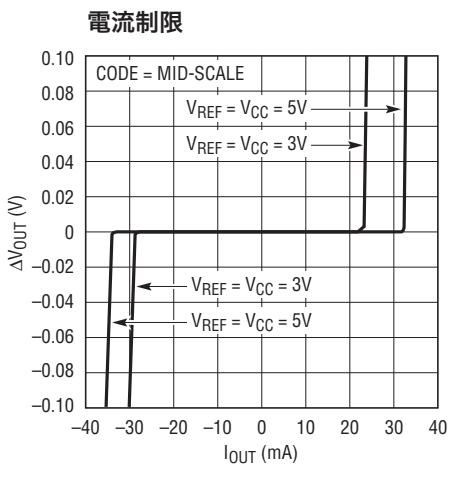

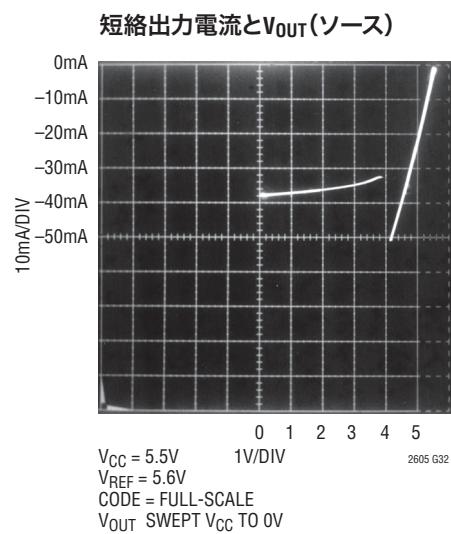

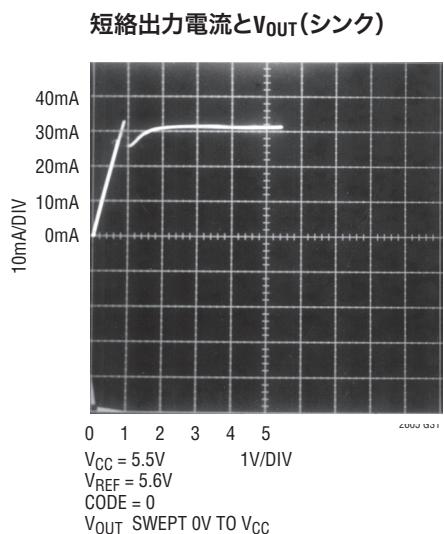

|           | Short-Circuit Output Current | $V_{CC} = 5.5\text{V}$ , $V_{REF} = 5.5\text{V}$<br>Code: Zero-Scale; Forcing Output to $V_{CC}$<br>Code: Full-Scale; Forcing Output to GND                                              | ● | 15  | 34 | 60   |      |     | mA    |

|           |                              |                                                                                                                                                                                          | ● | 15  | 34 | 60   |      |     | mA    |

|           |                              | $V_{CC} = 2.7\text{V}$ , $V_{REF} = 2.7\text{V}$<br>Code: Zero-Scale; Forcing Output to $V_{CC}$<br>Code: Full-Scale; Forcing Output to GND                                              | ● | 7.5 | 20 | 50   |      |     | mA    |

|           |                              |                                                                                                                                                                                          | ● | 7.5 | 27 | 50   |      |     | mA    |

## Reference Input

|           |                                    |                  |   |    |       |          |  |  |    |

|-----------|------------------------------------|------------------|---|----|-------|----------|--|--|----|

|           | Input Voltage Range                |                  | ● | 0  |       | $V_{CC}$ |  |  | V  |

|           | Resistance                         | Normal Mode      | ● | 11 | 16    | 20       |  |  | kΩ |

|           | Capacitance                        |                  |   |    |       | 90       |  |  | pF |

| $I_{REF}$ | Reference Current, Power-Down Mode | DAC Powered Down | ● |    | 0.001 | 1        |  |  | µA |

## Power Supply

|          |                         |                                                                                                                                                                      |   |     |      |     |  |  |    |

|----------|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-----|------|-----|--|--|----|

| $V_{CC}$ | Positive Supply Voltage | For Specified Performance                                                                                                                                            | ● | 2.7 |      | 5.5 |  |  | V  |

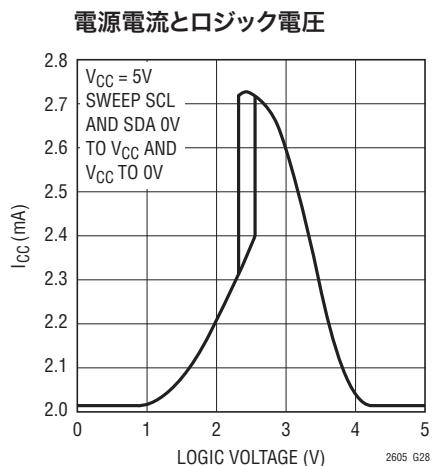

| $I_{CC}$ | Supply Current          | $V_{CC} = 5\text{V}$ (Note 3)<br>$V_{CC} = 3\text{V}$ (Note 3)<br>DAC Powered Down (Note 3), $V_{CC} = 5\text{V}$<br>DAC Powered Down (Note 3), $V_{CC} = 3\text{V}$ | ● |     | 2.50 | 4.0 |  |  | mA |

# LTC2605/LTC2615/LTC2625

## 電気的特性

●は全動作温度範囲の規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。

注記がない限り、REF = 4.096V( $V_{CC} = 5\text{V}$ )、REF = 2.048V( $V_{CC} = 2.7\text{V}$ )、 $V_{OUT}$ 無負荷。(Note 9)

| SYMBOL                      | PARAMETER                                                                   | CONDITIONS                                                                                                | MIN | TYP            | MAX           | UNITS |

|-----------------------------|-----------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|-----|----------------|---------------|-------|

| <b>Digital I/O (Note 9)</b> |                                                                             |                                                                                                           |     |                |               |       |

| $V_{IL}$                    | Low Level Input Voltage (SDA and SCL)                                       |                                                                                                           | ●   |                | 0.3 $V_{CC}$  | V     |

| $V_{IH}$                    | High Level Input Voltage (SDA and SCL)                                      |                                                                                                           | ●   | 0.7 $V_{CC}$   |               | V     |

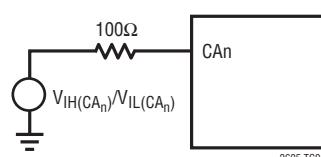

| $V_{IL(CA)}$                | Low Level Input Voltage (CA0 to CA2)                                        | See Test Circuit 1                                                                                        | ●   |                | 0.15 $V_{CC}$ | V     |

| $V_{IH(CA)}$                | High Level Input Voltage (CA0 to CA2)                                       | See Test Circuit 1                                                                                        | ●   | 0.85 $V_{CC}$  |               | V     |

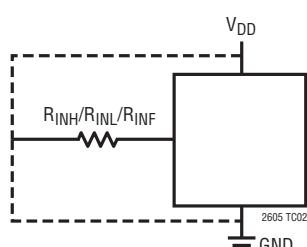

| $R_{INH}$                   | Resistance from CAn ( $n = 0, 1, 2$ ) to $V_{CC}$ to Set CAn = $V_{CC}$     | See Test Circuit 2                                                                                        | ●   |                | 10            | kΩ    |

| $R_{INL}$                   | Resistance from CAn ( $n = 0, 1, 2$ ) to GND to Set CAn = GND               | See Test Circuit 2                                                                                        | ●   |                | 10            | kΩ    |

| $R_{INF}$                   | Resistance from CAn ( $n = 0, 1, 2$ ) to $V_{CC}$ or GND to Set CAn = FLOAT | See Test Circuit 2                                                                                        | ●   | 2              |               | MΩ    |

| $V_{OL}$                    | Low Level Output Voltage                                                    | Sink Current = 3mA                                                                                        | ●   | 0              | 0.4           | V     |

| $t_{OF}$                    | Output Fall Time                                                            | $V_0 = V_{IH(\text{MIN})}$ to $V_0 = V_{IL(\text{MAX})}$ , $C_B = 10\text{pF}$ to $400\text{pF}$ (Note 7) | ●   | 20 + 0.1 $C_B$ | 250           | ns    |

| $t_{SP}$                    | Pulse Width of Spikes Surpassed by Input Filter                             |                                                                                                           | ●   | 0              | 50            | ns    |

| $I_{IN}$                    | Input Leakage                                                               | $0.1V_{CC} \leq V_{IN} \leq 0.9V_{CC}$                                                                    | ●   |                | 1             | μA    |

| $C_{IN}$                    | I/O Pin Capacitance                                                         | (Note 12)                                                                                                 | ●   |                | 10            | pF    |

| $C_B$                       | Capacitance Load for Each Bus Line                                          |                                                                                                           | ●   |                | 400           | pF    |

| $C_{CAn}$                   | External Capacitive Load on Address Pins CA0, CA1 and CA2                   |                                                                                                           | ●   |                | 10            | pF    |

●は全動作温度範囲の規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。

注記がない限り、REF = 4.096V( $V_{CC} = 5\text{V}$ )、REF = 2.048V( $V_{CC} = 2.7\text{V}$ )、 $V_{OUT}$ 無負荷。(Note 9)

| SYMBOL                | PARAMETER                            | CONDITIONS                                                                                                                                       | LTC2625/LTC2625-1 |      |     | LTC2615/LTC2615-1 |      |     | LTC2605/LTC2605-1 |      |     | UNITS             |

|-----------------------|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|------|-----|-------------------|------|-----|-------------------|------|-----|-------------------|

|                       |                                      |                                                                                                                                                  | MIN               | TYP  | MAX | MIN               | TYP  | MAX | MIN               | TYP  | MAX |                   |

| <b>AC Performance</b> |                                      |                                                                                                                                                  |                   |      |     |                   |      |     |                   |      |     |                   |

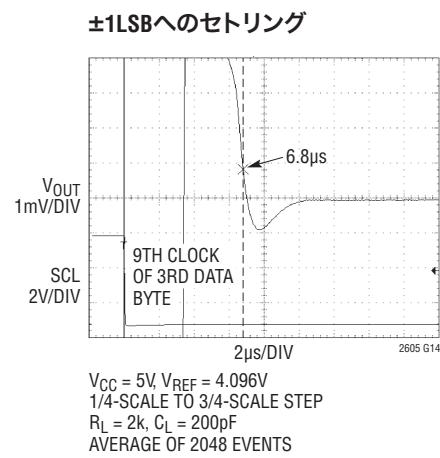

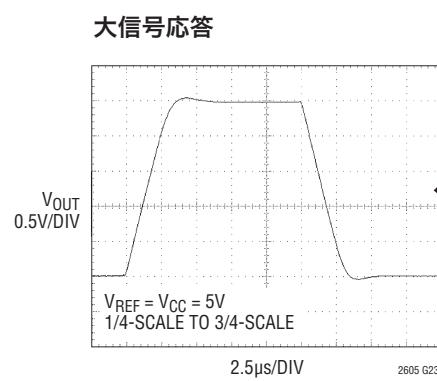

| $t_S$                 | Settling Time (Note 5)               | $\pm 0.024\%$ ( $\pm 1\text{LSB}$ at 12 Bits)<br>$\pm 0.006\%$ ( $\pm 1\text{LSB}$ at 14 Bits)<br>$\pm 0.0015\%$ ( $\pm 1\text{LSB}$ at 16 Bits) | 7                 | 7    | 9   | 7                 | 9    | 10  | 7                 | 9    | 10  | μs                |

|                       | Settling Time for 1LSB Step (Note 6) | $\pm 0.024\%$ ( $\pm 1\text{LSB}$ at 12 Bits)<br>$\pm 0.006\%$ ( $\pm 1\text{LSB}$ at 14 Bits)<br>$\pm 0.0015\%$ ( $\pm 1\text{LSB}$ at 16 Bits) | 2.7               | 2.7  | 4.8 | 2.7               | 4.8  | 5.2 | 2.7               | 4.8  | 5.2 | μs                |

|                       | Voltage Output Slew Rate             |                                                                                                                                                  | 0.80              | 0.80 |     | 0.80              | 0.80 |     | 0.80              | 0.80 |     | V/μs              |

|                       | Capacitive Load Driving              |                                                                                                                                                  | 1000              | 1000 |     | 1000              | 1000 |     | 1000              | 1000 |     | pF                |

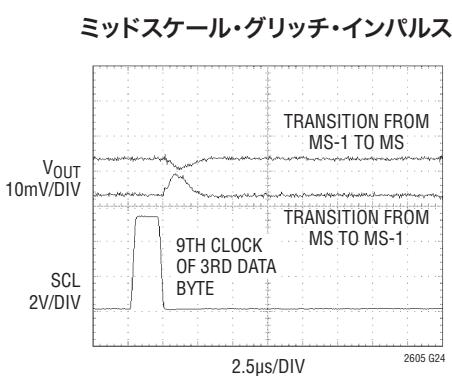

|                       | Glitch Impulse                       | At Mid-Scale Transition                                                                                                                          | 12                | 12   |     | 12                | 12   |     | 12                | 12   |     | nV•s              |

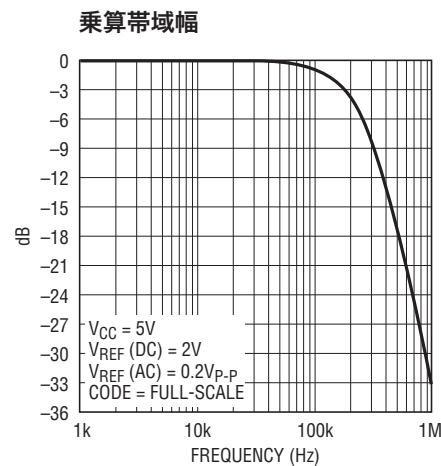

|                       | Multiplying Bandwidth                |                                                                                                                                                  | 180               | 180  |     | 180               | 180  |     | 180               | 180  |     | kHz               |

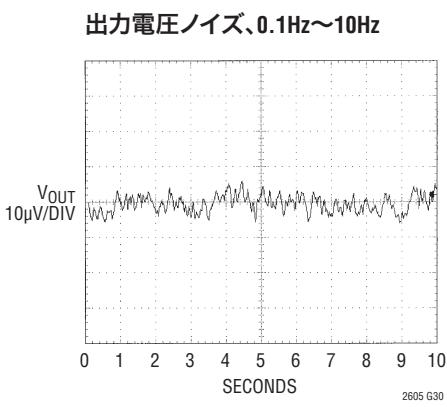

| $e_n$                 | Output Voltage Noise Density         | At $f = 1\text{kHz}$<br>At $f = 10\text{kHz}$                                                                                                    | 120               | 120  |     | 100               | 100  |     | 120               | 120  |     | nV/√Hz            |

|                       | Output Voltage Noise                 | 0.1Hz to 10Hz                                                                                                                                    | 15                | 15   |     | 15                | 15   |     | 15                | 15   |     | μV <sub>P-P</sub> |

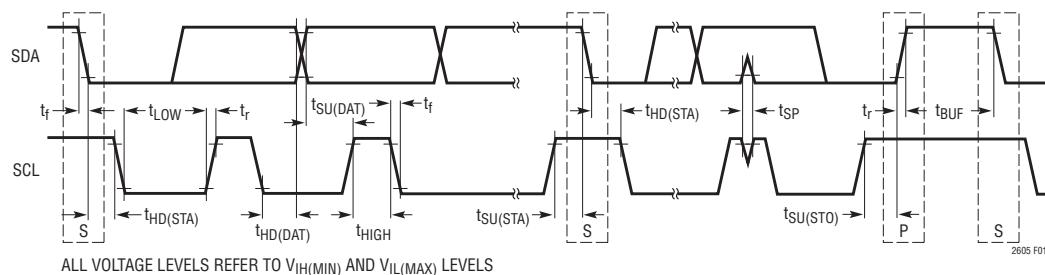

## 電気的特性

●は全動作温度範囲の規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。(図1を参照) (Note 8, 9)

| SYMBOL                                                               | PARAMETER                                        | CONDITIONS | MIN | TYP        | MAX | UNITS |

|----------------------------------------------------------------------|--------------------------------------------------|------------|-----|------------|-----|-------|

| <b><math>V_{CC} = 2.7\text{V}</math> to <math>5.5\text{V}</math></b> |                                                  |            |     |            |     |       |

| $f_{SCL}$                                                            | SCL Clock Frequency                              |            | ●   | 0          | 400 | kHz   |

| $t_{HD(STA)}$                                                        | Hold Time (Repeated) Start Condition             |            | ●   | 0.6        |     | μs    |

| $t_{LOW}$                                                            | Low Period of the SCL Clock Pin                  |            | ●   | 1.3        |     | μs    |

| $t_{HIGH}$                                                           | High Period of the SCL Clock Pin                 |            | ●   | 0.6        |     | μs    |

| $t_{SU(STA)}$                                                        | Set-Up Time for a Repeated Start Program         |            | ●   | 0.6        |     | μs    |

| $t_{HD(DAT)}$                                                        | Data Hold Time                                   |            | ●   | 0          | 0.9 | μs    |

| $t_{SU(DAT)}$                                                        | Data Set-Up Time                                 |            | ●   | 100        |     | ns    |

| $t_r$                                                                | Rise Time of Both SDA and SCL Signals            | (Note 7)   | ●   | 20 + 0.1CB | 300 | ns    |

| $t_f$                                                                | Fall Time of Both SDA and SCL Signals            | (Note 7)   | ●   | 20 + 0.1CB | 300 | ns    |

| $t_{SU(STO)}$                                                        | Set-Up Time for Stop Condition                   |            | ●   | 0.6        |     | μs    |

| $t_{BUF}$                                                            | Bus Free Time Between a Stop and Start Condition |            | ●   | 1.3        |     | μs    |

**Note 1:**絶対最大定格に記載された値を超えるストレスはデバイスに永続的損傷を与える可能性がある。長期にわたって絶対最大定格条件に曝すと、デバイスの信頼性と寿命に悪影響を与える可能性がある。

**Note 2:**直線性と単調性はコード $k_L$ からコード $2^N - 1$ まで定義されている。ここで、 $N$ は分解能で、 $k_L$ は $k_L = 0.016(2^N/V_{REF})$ で求められ、最も近い整数コードに丸められている。 $V_{REF} = 4.096\text{V}$ で $N = 16$ の場合、 $k_L = 256$ となり、直線性はコード256からコード65,535まで定義される。

**Note 3:**0Vまたは $V_{CC}$ 、CA0、CA1およびCA2 フローティング時は、SDA、SCL。

**Note 4:**コード256(LTC2605/LTC2605-1)、コード64(LTC2615/LTC2615-1)またはコード16(LTC2625/LTC2625-1)およびフルスケールでの測定から推定される。

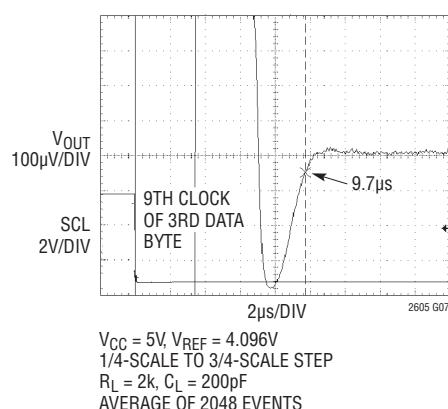

**Note 5:** $V_{CC} = 5\text{V}$ 、 $V_{REF} = 4.096\text{V}$ 。DACは1/4スケールから3/4スケールへ、さらに3/4スケールから1/4スケールへステップさせる。負荷はGNDに200pFと並列に接続した $2\text{k}\Omega$ 。

**Note 6:** $V_{CC} = 5\text{V}$ 、 $V_{REF} = 4.096\text{V}$ 。DACは、ハーフスケールと(ハーフスケール-1)の間を±1LSBでステップさせる。負荷はGNDに200pFと並列に接続した $2\text{k}\Omega$ 。

**Note 7:** $C_B = 1$ パスラインの容量(pF)。

**Note 8:**いずれの値も $V_{IH}$ (最小)と $V_{IL}$ (最大)レベルを指す。

**Note 9:**これらの仕様は、LTC2605/LTC2605-1、LTC2615/LTC2615-1およびLTC2625/LTC2625-1に適用される。

**Note 10:**DCクロストークは、注記がない限り、 $V_{CC} = 5\text{V}$ および $V_{REF} = 4096\text{V}$ で、ミッドスケールで測定されたDACを使用して測定される。

**Note 11:** $R_L = 2\text{k}\Omega$ をGNDまたは $V_{CC}$ に接続。

**Note 12:**設計上、保証されているが、製造時のテストは行われていない。

## 電気的特性

テスト回路1

テスト回路2

# LTC2605/LTC2615/LTC2625

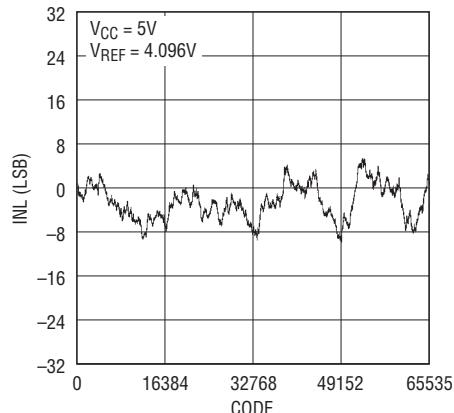

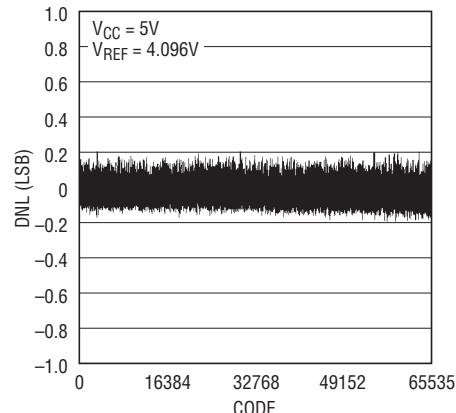

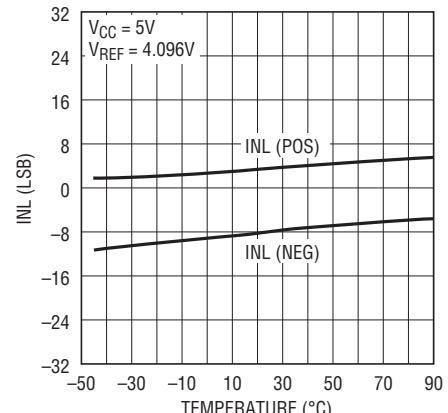

## 標準的性能特性

LTC2605

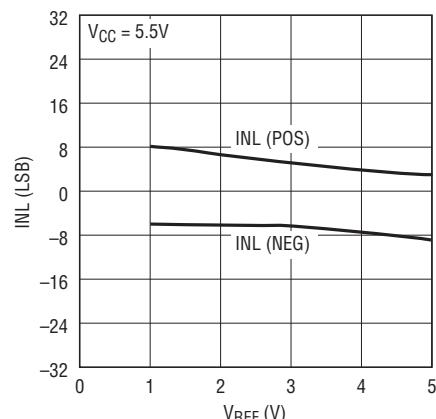

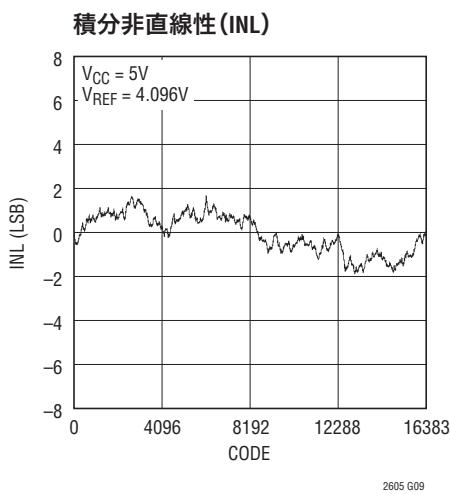

### 積分非直線性(INL)

2605 G01

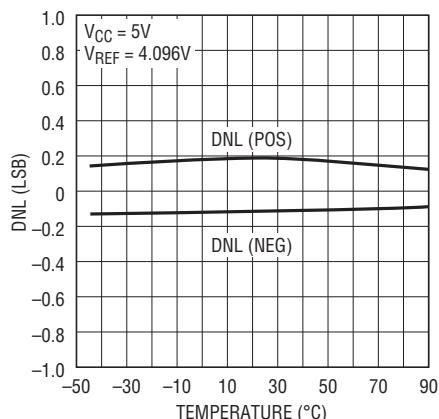

### 微分非直線性(DNL)

2605 G02

### INLと温度

2605 G03

### DNLと温度

2605 G04

### INLと $V_{REF}$

2605 G05

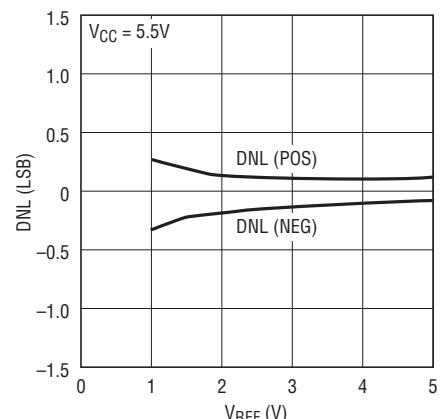

### DNLと $V_{REF}$

2605 G06

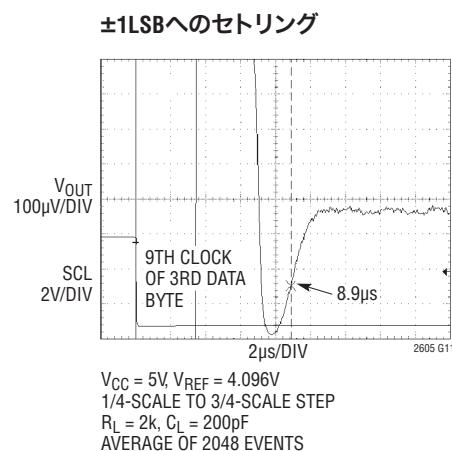

### $\pm 1$ LSBへのセッティング

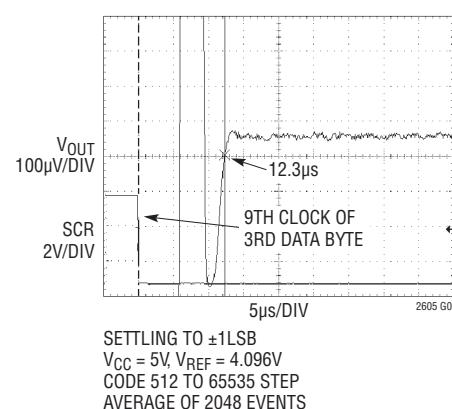

### フルスケール・ステップのセッティング

2605fa

## 標準的性能特性

LTC2615

LTC2625

LTC2605/LTC2615/LTC2625

# LTC2605/LTC2615/LTC2625

## 標準的性能特性

LTC2605/LTC2615/LTC2625

2605fa

## 標準的性能特性

LTC2605/LTC2615/LTC2625

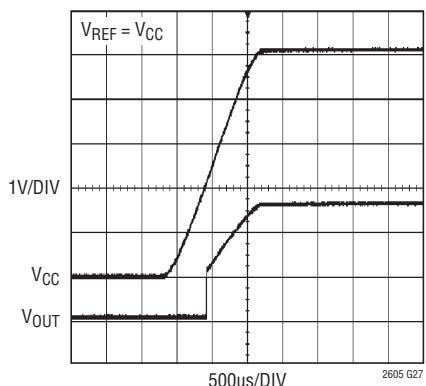

ミッドスケールに

パワーオン・リセット

# LTC2605/LTC2615/LTC2625

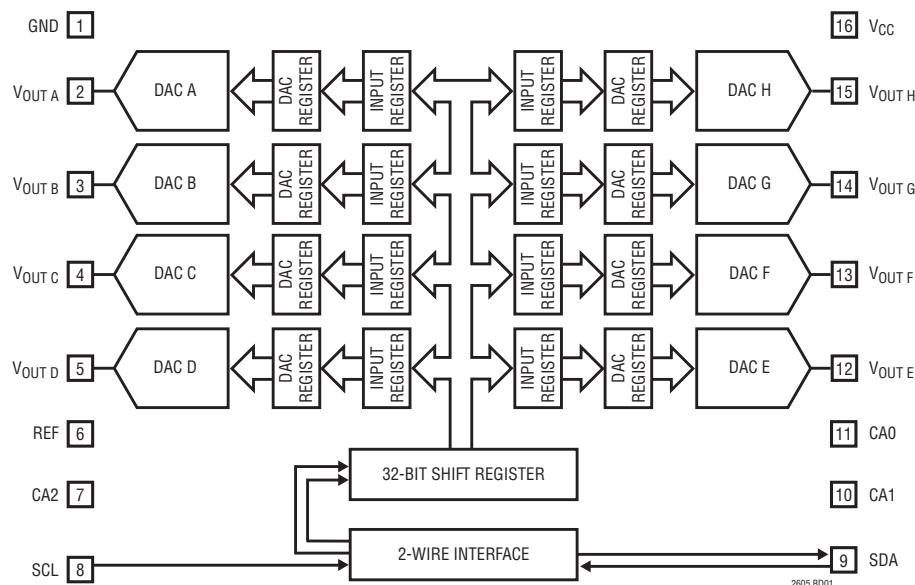

## ピン機能

**GND(ピン1)**: アナログ・グランド。

**V<sub>OUT A</sub>~V<sub>OUT H</sub>(ピン2~5と12~15)**: DACアナログ電圧出力。出力範囲は、0V~V<sub>REF</sub>です。

**REF(ピン6)**: リファレンス電圧入力。0V ≤ V<sub>REF</sub> ≤ V<sub>CC</sub>

**CA2(ピン7)**: チップ・アドレス・ビット2。このピンをV<sub>CC</sub>、GNDに接続するか、フローティングのままにして、I<sup>2</sup>Cスレーブ・アドレスを選択します(表2)。

**SCL(ピン8)**: シリアル・クロック入力ピン。クロックの立ち上がりエッジでデータがSDAピンにシフトされます。このハイ・インピーダンス・ピンには、プルアップ抵抗またはV<sub>CC</sub>への電流ソースが必要です。

**SDA(ピン9)**: シリアル・データ双方向ピン。データは、SDAピンにシフトされ、SDAピンでその受信を確認します。データがシフトされてきたときは、このピンはハイ・インピーダンス状態です。データ受信時は、オープン・ドレインNチャネル出力です。このピンには、プルアップ抵抗またはV<sub>CC</sub>への電流ソースが必要です。

**CA1(ピン10)**: チップ・アドレス・ビット1。このピンをV<sub>CC</sub>、GNDに接続するか、フローティングのままにして、I<sup>2</sup>Cスレーブ・アドレスを選択します(表2)。

**CA0(ピン11)**: チップ・アドレス・ビット0。このピンをV<sub>CC</sub>、GNDに接続するか、フローティングのままにして、I<sup>2</sup>Cスレーブ・アドレスを選択します(表2)。

**V<sub>CC</sub>(ピン16)**: 電源電圧入力。2.7V ≤ V<sub>CC</sub> ≤ 5.5V。

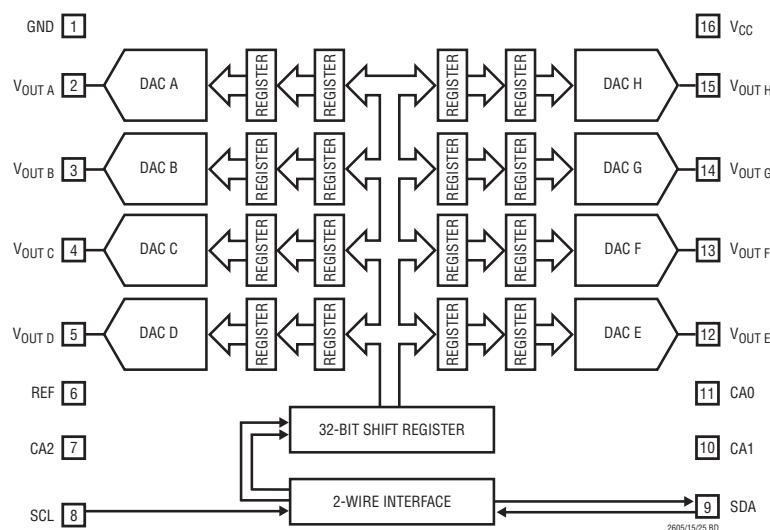

## ブロック図

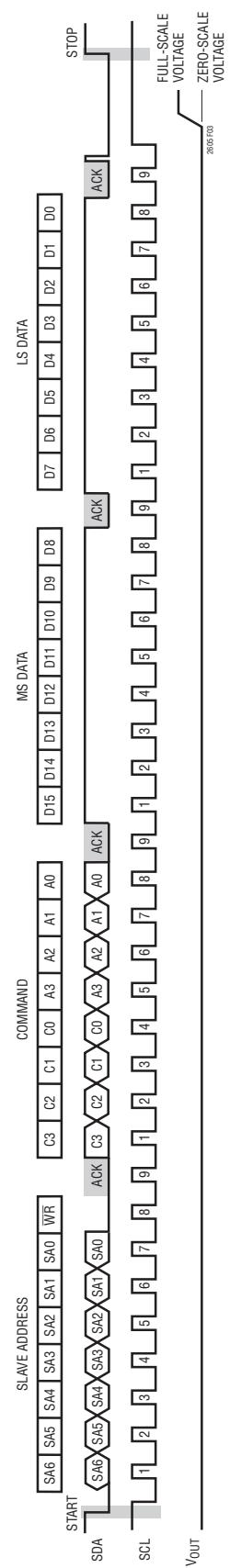

## タイミング図

図1

2605fa

## 動作

### パワーオン・リセット

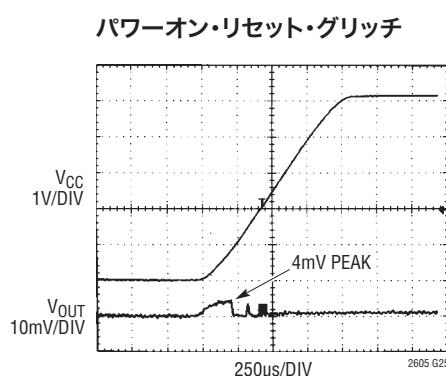

LTC2605/LTC2615/LTC2625は、最初の電源投入時にゼロ・スケールへの出力をクリアすることによって、システムの初期状態を一定に保ち、反復可能にします。LTC2605-1/LTC2615-1/LTC2625-1は、最初の電源投入時に電圧出力をミッドスケールに設定します。

アプリケーションによっては、DACの起動時に下流の回路がアクティブ状態であり、この間DACからの非ゼロの出力の影響を受けやすくなることがあります。LTC2605/LTC2615/LTC2625には、パワーオン・グリッチを低減させる回路が装備されています。電源投入時に電圧が1msあるいはそれ以上の時間で5Vまで急峻に立ち上がる場合、アナログ出力は通常、ゼロ・スケールより10mV以上上昇することはありません。一般的に電源の立ち上がり時間が長くなるほど、グリッチ振幅は減少します。「標準的性能特性」の項目の「パワーオン・リセット・グリッチ」を参照してください。

### 電源シーケンス制御

REF(ピン6)の電圧は、 $-0.3V \leq V_{REF} \leq V_{CC} + 0.3V$ の範囲に保つ必要があります(「絶対最大定格」を参照)。V<sub>CC</sub>(ピン16)の電圧が遷移しているときには、電源のターンオン・シーケンスとターンオフ・シーケンス間にこれらのリミットを遵守するように注意することが特に重要です。

### 伝達関数

デジタルからアナログへの伝達関数は次のとおりです。

$$V_{OUT(IDEAL)} = \left( \frac{k}{2^N} \right) V_{REF}$$

表1.

| COMMAND* |    |    |    |                                 |

|----------|----|----|----|---------------------------------|

| C3       | C2 | C1 | C0 |                                 |

| 0        | 0  | 0  | 0  | 入力レジスタnに書き込む                    |

| 0        | 0  | 0  | 1  | DACレジスタnを更新(パワーアップ)する           |

| 0        | 0  | 1  | 0  | 入力レジスタnに書き込み、すべてのnを更新(パワーアップ)する |

| 0        | 0  | 1  | 1  | nに書き込み、更新(パワーアップ)する             |

| 0        | 1  | 0  | 0  | nをパワーダウンする                      |

| 1        | 1  | 1  | 1  | 動作なし                            |

\*表示されないアドレス・コードとコマンド・コードは予備のため、使用不可。

ここで、kはDACの2進数の入力コードに相当する10進数、Nは分解能、V<sub>REF</sub>はREFの電圧です(ピン6)。

### シリアル・デジタル・インターフェイス

LTC2605/LTC2615/LTC2625は標準の2線デジタル・インターフェイスを使用してホストとやりとりします。タイミング図(図1)にバス上の信号のタイミング関係を示します。SDAとSCLの2つのバス・ラインは、バスが使用されていないときは、“H”である必要があります。これらのラインには、外部プルアップ抵抗または電流源が必要です。これらのプルアップ抵抗の値は、電源によって異なり、I<sup>2</sup>Cの仕様から得ることができます。高速モードで動作するI<sup>2</sup>Cバスでは、バス容量が200pFを超えると、アクティブ・プルアップが必要になります。内部ESD保護ダイオードを介したI<sup>2</sup>Cバス・ラインのロードを避けるため、I<sup>2</sup>Cバスがアクティブの時にはLTC2605/LTC2615/LTC2625からV<sub>CC</sub>電源を取り外してはなりません。

LTC2605/LTC2615/LTC2625は受信専用(スレーブ)デバイスです。マスタがLTC2605/LTC2615/LTC2625に書き込むことができます。LTC2605/LTC2615/LTC2625は、マスタからの読み込みに対して応答することはできません。

### START(S)条件とSTOP(P)条件

バスが使用されていないときは、SCLとSDAのいずれもが“H”である必要があります。バス・マスタは、START条件を送信することでやりとりの開始をスレーブに伝えます。SCLが“H”的に、SDAが“H”から“L”に遷移することによって、START条件が生成されます。

| ADDRESS (n)* |    |    |    |          |

|--------------|----|----|----|----------|

| A3           | A2 | A1 | A0 |          |

| 0            | 0  | 0  | 0  | DAC A    |

| 0            | 0  | 0  | 1  | DAC B    |

| 0            | 0  | 1  | 0  | DAC C    |

| 0            | 0  | 1  | 1  | DAC D    |

| 0            | 1  | 0  | 0  | DAC E    |

| 0            | 1  | 0  | 1  | DAC F    |

| 0            | 1  | 1  | 0  | DAC G    |

| 0            | 1  | 1  | 1  | DAC H    |

| 1            | 1  | 1  | 1  | All DACs |

# LTC2605/LTC2615/LTC2625

## 動作

マスタがスレーブとのやりとりを終了すると、STOP条件を送出します。SCLが“H”的ときに、SDAが“L”から“H”に遷移することによって、STOP条件が生成されます。その後は、バスは自由に他のI<sup>2</sup>Cデバイスとやりとりを行うことができます。

## 肯定応答

肯定応答信号を使用して、マスタとスレーブ間のハンドシェークを行います。スレーブによって生成された肯定応答(アクティブ・ロー:負論理)信号で最新情報のバイトが受信されたことをマスタが知ることができます。肯定応答関連のクロック・パルスはマスタによって生成されます。マスタは、肯定応答クロック・パルス時にSDAライン(“H”)を送ります。肯定応答のクロック・パルス時にスレーブ・レシーバがSDAをプルダウンする必要があります。それによってこのクロック・パルスの“H”期間の間は安定した“L”状態になります。LTC2605/LTC2615/LTC2625はこのようにしてマスタからの書き込みに応答します。LTC2605/LTC2615/LTC2625は、読み込みには応答しません(クロック・パルス受信時は、SDAは“H”的ままでです)。

## チップ・アドレス

CA0、CA1およびCA2の状態で部品のスレーブ・アドレスが決まります。CA0、CA1およびCA2のピンは、それぞれV<sub>CC</sub>、GNDまたはFLOATのいずれか1つの状態に設定されます。それがその部品の27個の選択可能なアドレスになります。CA0、CA1およびCA2の状態に応じたアドレスとグローバル・アドレスを表2に示します。

デバイスは、アドレス・ピンによって選択されたアドレスだけではなく、グローバル・アドレスにも応答します。このアドレスによってLTC2605、LTC2615およびLTC2625の全デバイスへの共通書き込みが可能になります。これは、I<sup>2</sup>Cバス上での3バイトでの一度の書き込み動作で行われます。グローバル・アドレスは、7ビットのハードワイヤード・アドレスでCA0、CA1およびCA2では選択されません。アドレス・ピン(CA0、CA1およびCA2)に許容される最大容量負荷は、10pFです。

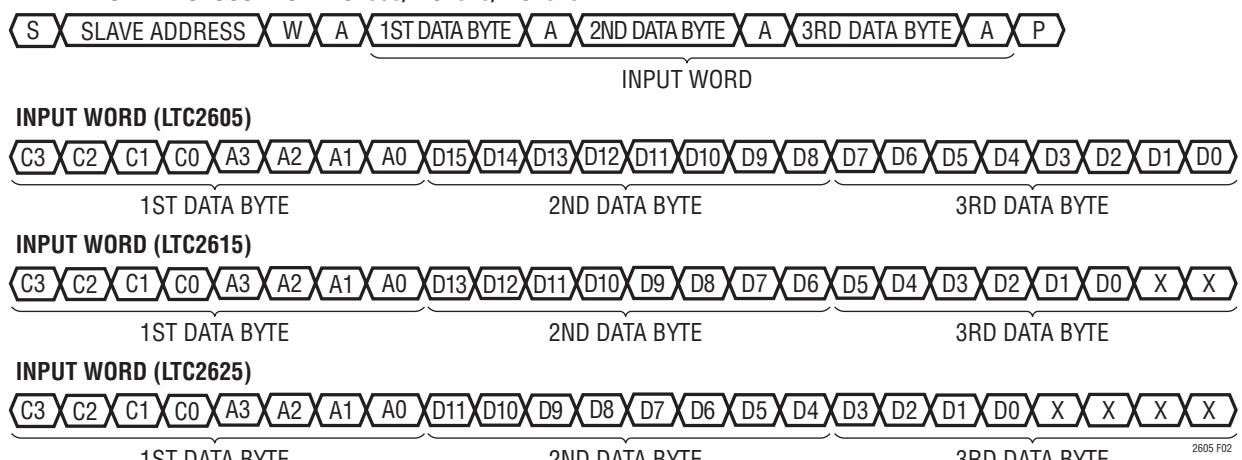

## 書き込みワード・プロトコル

マスタは、START条件と書き込みビット(W)=0に続く7ビット・スレーブ・アドレスによってLTC2605/LTC2615/LTC2625とのやりとりを開始します。7ビット・スレーブ・アドレスがデバイスのアドレス(CA0、CA1およびCA2によって設定)またはグローバル・アドレスと一致すると、9つめのクロックでSDAピン

表2. スレーブ・アドレス・マップ

| CA2             | CA1             | CA0             | SA6 | SA5 | SA4 | SA3 | SA2 | SA1 | SA0 |

|-----------------|-----------------|-----------------|-----|-----|-----|-----|-----|-----|-----|

| GND             | GND             | GND             | 0   | 0   | 1   | 0   | 0   | 0   | 0   |

| GND             | GND             | FLOAT           | 0   | 0   | 1   | 0   | 0   | 0   | 1   |

| GND             | GND             | V <sub>CC</sub> | 0   | 0   | 1   | 0   | 0   | 1   | 0   |

| GND             | FLOAT           | GND             | 0   | 0   | 1   | 0   | 0   | 1   | 1   |

| GND             | FLOAT           | FLOAT           | 0   | 1   | 0   | 0   | 0   | 0   | 0   |

| GND             | FLOAT           | V <sub>CC</sub> | 0   | 1   | 0   | 0   | 0   | 0   | 1   |

| GND             | V <sub>CC</sub> | GND             | 0   | 1   | 0   | 0   | 0   | 1   | 0   |

| GND             | V <sub>CC</sub> | FLOAT           | 0   | 1   | 0   | 0   | 0   | 1   | 1   |

| GND             | V <sub>CC</sub> | V <sub>CC</sub> | 0   | 1   | 1   | 0   | 0   | 0   | 0   |

| FLOAT           | GND             | GND             | 0   | 1   | 1   | 0   | 0   | 0   | 1   |

| FLOAT           | GND             | FLOAT           | 0   | 1   | 1   | 0   | 0   | 1   | 0   |

| FLOAT           | GND             | V <sub>CC</sub> | 0   | 1   | 1   | 0   | 0   | 1   | 1   |

| FLOAT           | FLOAT           | GND             | 1   | 0   | 0   | 0   | 0   | 0   | 0   |

| FLOAT           | FLOAT           | FLOAT           | 1   | 0   | 0   | 0   | 0   | 0   | 1   |

| FLOAT           | FLOAT           | V <sub>CC</sub> | 1   | 0   | 0   | 0   | 0   | 1   | 0   |

| FLOAT           | V <sub>CC</sub> | GND             | 1   | 0   | 0   | 0   | 0   | 1   | 1   |

| FLOAT           | V <sub>CC</sub> | FLOAT           | 1   | 0   | 1   | 0   | 0   | 0   | 0   |

| FLOAT           | V <sub>CC</sub> | V <sub>CC</sub> | 1   | 0   | 1   | 0   | 0   | 0   | 1   |

| V <sub>CC</sub> | GND             | GND             | 1   | 0   | 1   | 0   | 0   | 1   | 0   |

| V <sub>CC</sub> | GND             | FLOAT           | 1   | 0   | 1   | 0   | 0   | 1   | 1   |

| V <sub>CC</sub> | GND             | V <sub>CC</sub> | 1   | 1   | 0   | 0   | 0   | 0   | 0   |

| V <sub>CC</sub> | FLOAT           | GND             | 1   | 1   | 0   | 0   | 0   | 0   | 1   |

| V <sub>CC</sub> | FLOAT           | FLOAT           | 1   | 1   | 0   | 0   | 0   | 1   | 0   |

| V <sub>CC</sub> | FLOAT           | V <sub>CC</sub> | 1   | 1   | 0   | 0   | 0   | 1   | 1   |

| V <sub>CC</sub> | V <sub>CC</sub> | GND             | 1   | 1   | 1   | 0   | 0   | 0   | 0   |

| V <sub>CC</sub> | V <sub>CC</sub> | FLOAT           | 1   | 1   | 1   | 0   | 0   | 0   | 1   |

| V <sub>CC</sub> | V <sub>CC</sub> | V <sub>CC</sub> | 1   | 1   | 1   | 0   | 0   | 1   | 0   |

| GLOBAL ADDRESS  |                 |                 |     |     |     |     |     |     |     |

| 1               |                 |                 |     |     |     |     |     |     |     |

を“L”にプルして、LTC2605/LTC2615/LTC2625による肯定応答が行われます。そこでマスタは、3バイト・データを送出します。LTC2605/LTC2615/LTC2625は、各データ・バイト伝送の9つめのクロックでSDAラインを“L”にプルすることでデータの各バイトを肯定応答します。データの3バイトをすべて受信すると、LTC2605/LTC2615/LTC2625は、24ビット・ワードで指定されたコマンドを実行します。

有効な7ビット・スレーブ・アドレス後に3バイトを超えるデータ・バイトが送信されると、LTC2605/LTC2615/LTC2625はそれらの余分なデータ・バイトを肯定応答しません(SDAは、9つめのクロックで“H”)。

## 動作

### WRITE WORD PROTOCOL FOR LTC2605/LTC2615/LTC2625

図2

3つのデータ・バイトの書式を図2に示します。入力ワードの最初の1バイトは、4ビットのコマンドと4ビットのDACアドレスで構成されています。その次の2バイトは、16ビット・データ・ワードです。16ビット・データ・ワードは、MSBからLSBに至る16、14、12ビットの入力コードで構成され、それに0、2、4ビットのドントケア・ビットが続きます(それぞれLTC2605、LTC2615、LTC2625に該当)。代表的なI<sup>2</sup>C書き込み動作を図3に示します。

コマンド(C3～C0)とアドレス(A3～A0)の割り当てを表1に示します。表1の最初の4つのコマンドが書き込みおよび更新動作のものです。書き込み動作によって32ビット・シフト・レジスタから16ビット・データ・ワードを選択されたDACの入力レジスタnにロードします。更新動作で入力レジスタのデータ・ワードをDACレジスタにコピーします。いったんDACレジスタからコピーされると、データ・ワードはアクティブな16、14、あるいは12ビット入力コードとなり、DAC出力でアナログ電圧に変換されます。DACがパワーダウン・モードのときは、更新動作によつても選択されたDACが起動されます。データ・バスとレジスタをブロック図に示します。

### パワーダウン・モード

電力に制約のあるアプリケーションでは、8つの出力のすべてを必要としないのであれば、パワーダウン・モードを使用して消費電流を軽減します。パワーダウン時には、バッファ・アンプとリファレンス入力がオフになるので、実質的に電流は流れま

せん。DAC出力は、ハイ・インピーダンス状態になり、出力ピンは個々の90k抵抗によって受動的にグランドに引き下げられます。8つのDACがすべてパワーダウンすると、バイアス生成回路もオフになります。入力レジスタとDACレジスタはパワーダウンの間に影響を受けることはありません。

どのチャネルでも、あるいはチャネルを組み合わせても適切なDACアドレス(n)を組み合わせたコマンド0100<sub>b</sub>を使用してパワーダウン・モードにすることができます。16ビットのデータ・ワードは無視されます。各DACがパワーダウンすると、消費電流とリファレンス電流が約1/8減少します。8つのDACがすべてパワーダウンすると、REF(ピン6)の実効抵抗が上昇し、ハイインピーダンス入力(通常、1GΩ以上)となります。

通常動作は、表1に示すように、DAC更新を含むどのコマンドを実行しても再開できます。選択されたDACはその電圧出力が更新されるとパワーアップされます。

DACパワーアップ時に、通常のセトリング動作前に初期遅延が生じます。更新コマンドの前にパワーダウン状態にあるDACが8個未満の場合、パワーアップ遅延は、5μsです。それに対して、8個のDACすべてがパワーダウン状態では、バイアス生成回路もオフとなっているため、再起動する必要があります。この場合、パワーアップ遅延時間は、12μs(V<sub>CC</sub> = 5Vの場合)、または30μs(V<sub>CC</sub> = 3Vの場合)です。

# LTC2605/LTC2615/LTC2625

## 動作

図3. 標準的なLTC2605 入力波形 - フルスケールのプログラミングDAC出力

2605fa

## 動作

### 電圧出力

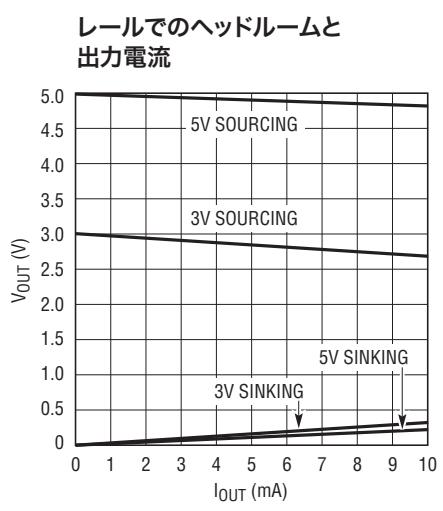

これらのデバイスに内蔵されている8個のレール・トゥ・レール・アンプは、それぞれ5Vで最大15mA(3Vで7.5mA)をソースまたはシンクするとき、ロード・レギュレーションが保証されています。

ロード・レギュレーションは、広い範囲の負荷条件にわたって定格電圧精度を維持するアンプ性能の指標です。負荷電流を強制的に1mA変化させたときの出力電圧の変化の測定値は、LSB/mAで表されます。

DC出力インピーダンスは、ロード・レギュレーションに相当し、 LSB/mAからオームに単位を変えて計算するだけで求めることができます。レールから十分離れた負荷をドライブしているときのアンプのDC出力インピーダンスは、0.020Ωです。

どちらか一方のレールから負荷電流が流れている場合、そのレールを基準にした出力電圧のヘッドルームは出力デバイスの標準30Ωのチャネル抵抗によって制限されます。たとえば、1mAをシンクしていると、最小出力電圧 =  $30\Omega \cdot 1\text{mA} = 30\text{mV}$ になります。「標準的性能特性」の項目の「レールでのヘッドルームと出力電流」のグラフを参照してください。

このアンプは、最大1000pFの容量性負荷を安定してドライブします。

### 基板のレイアウト

これらのデバイスの優れたロード・レギュレーションおよびDCクロストークの性能は、「信号」グランドと「電源」グランドを内部的に分離し、共有内部抵抗を0.005Ωに軽減することによってある程度実現します。

GNDピンには、リファレンス電圧と出力電圧の基準となるノードとして、そしてデバイスの電源電流のリターン・パスとしての両方の機能があります。したがって、定格性能を確実に得るために、グランド方式と基板のレイアウトに十分な注意を払う必要があります。

PCボードには、回路上でアナログ部分とデジタル部分とで別々の領域を用意する必要があります。こうすることで周囲の影響を受けやすいアナログ信号からデジタル信号を離しておくことができ、分離されたデジタル・グランド・プレーンとアナログ・グランド・プレーンを扱いやすくなり、容量性および抵抗性の相互干渉を最小限に抑えることができます。

デジタル・グランド・プレーンとアナログ・グランド・プレーンを一点接続し、デバイスのグランド・ピンにできるだけ近づけてシステムのスター・グランドを形成します。理想的には、アナログ・グランド・プレーンはボードの部品側に配置し、デバイスをノイズからシールドするためにデバイスの下を通すようにします。アナログ・グランドは、必要なピン・パッドやビアを除き、連続した切れ目のないプレーンにし、信号トレースは別の層に配置します。

デバイスのGNDピンは、アナログ・グランドに接続します。GNDピンからシステムのスター・グランドまでの抵抗はできるだけ小さくします。この抵抗は、デバイスの実効DC出力インピーダンス(通常、0.020Ω)に直接蓄積され、DCクロストークを劣化させます。同じタイプのデバイスに比べ、LTC2605/LTC2615/LTC2625はこれらの影響を受けにくくなっているばかりか、過度な内部抵抗で達成可能な性能が制約を受けることなくレイアウトをベースにしてパフォーマンスの改善を実現していることに注意してください。

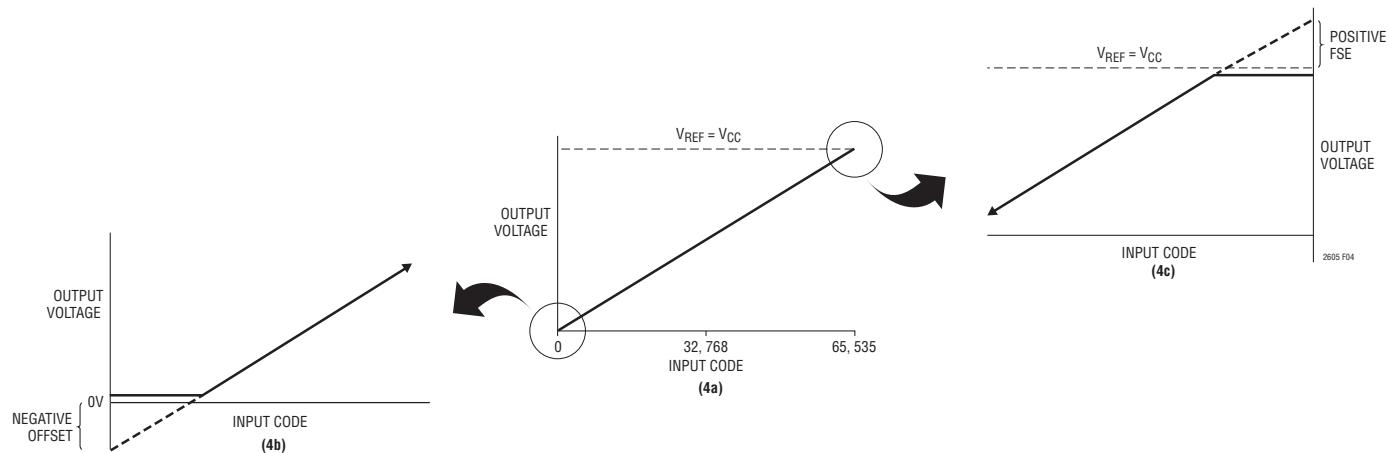

### レール・トゥ・レール出力に関する検討事項

レール・トゥ・レールの電圧出力デバイスはどれも、出力は電源電圧範囲内に制限されています。

デバイスのアナログ出力はグランドを下回ることができないので、図4bに示すように最下位コードで制約を受けます。同様に、REFピンがV<sub>CC</sub>に接続されていると、フルスケール近くでも制約が発生します。V<sub>REF</sub> = V<sub>CC</sub>で、DACのフルスケール誤差(FSE)が正の場合、図4cに示すように最上位コードの出力がV<sub>CC</sub>で制約を受けます。V<sub>REF</sub>がV<sub>CC</sub>-FSEより小さい場合は、フルスケールの制約は生じません。

オフセットと直線性は、出力の制約が生じないDACの伝達関数の領域にわたって定義され、テストされます。

# LTC2605/LTC2615/LTC2625

## 動作

図 4. DAC の伝達曲線に対するレール・トゥ・レール動作の影響(a) 全体の伝達関数、(b) ゼロスケール近くのコードに対する負のオフセットの影響、(c) フルスケール近くのコードに対する正のフルスケール誤差の影響

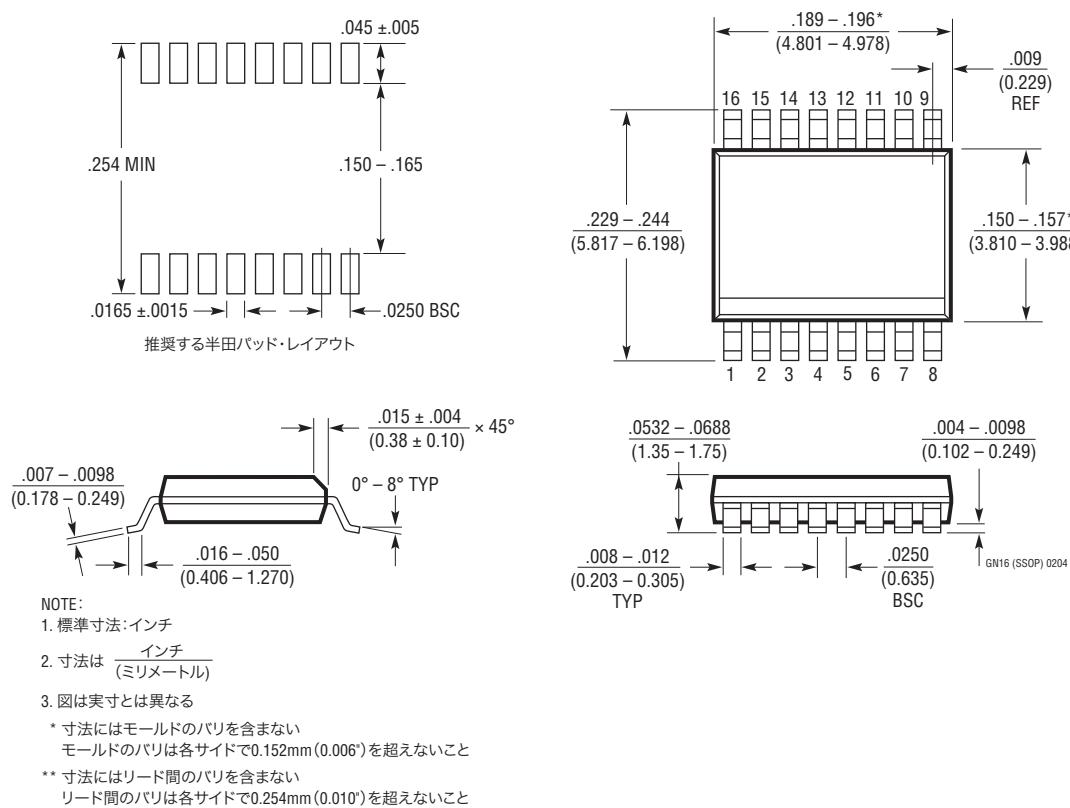

## パッケージ

GN/パッケージ

16ピン・プラスチックSSOP(細型0.150インチ)

(Reference LTC DWG # 05-08-1641)

## 改訂履歴

| REV | 日付    | 修正内容                    | 頁番号 |

|-----|-------|-------------------------|-----|

| A   | 11/09 | シリアル・デジタル・インターフェースに文章追加 | 11  |

2605fa

リニアテクノロジー・コーポレーションがここで提供する情報は正確かつ信頼できるものと考えておりますが、その使用に関する責務は一切負いません。また、ここに記載された回路結線と既存特許とのいかなる関連についても一切関知いたしません。なお、日本語の資料はあくまでも参考資料です。訂正、変更、改版に追従していない場合があります。最終的な確認は必ず最新の英語版データシートでお願いいたします。

# LTC2605/LTC2615/LTC2625

## 標準的応用例

デモ回路 - LTC2428 20 ビットADCによる主要性能パラメータの測定

## 関連製品

| 製品番号                        | 説明                                                                         | 注釈                                                                                                                                              |

|-----------------------------|----------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| LTC1458/LTC1458L            | クワッド12ビット・レール・トゥ・レール出力DAC、追加機能付き                                           | LTC1458: V <sub>CC</sub> = 4.5V ~ 5.5V, V <sub>OUT</sub> = 0V ~ 4.096V<br>LTC1458L: V <sub>CC</sub> = 2.7V ~ 5.5V, V <sub>OUT</sub> = 0V ~ 2.5V |

| LTC1654                     | デュアル14ビット・レール・トゥ・レールV <sub>OUT</sub> DAC                                   | プログラマブル・スピード/パワー、3.5μs/750μA、8μs/450μA                                                                                                          |

| LTC1655/LTC1655L            | シングル16ビットV <sub>OUT</sub> DAC、シリアル・インターフェイス、SO-8                           | V <sub>CC</sub> = 5V(3V)、低消費電力、グリッチ低減                                                                                                           |

| LTC1657/LTC1657L            | パラレル 5V/3V 16 ビットV <sub>OUT</sub> DAC                                      | 低消費電力、グリッチ低減、レール・トゥ・レールV <sub>OUT</sub>                                                                                                         |

| LTC1660/LTC1665             | 16 ピン細型SSOPのオクタル10/8 ビットV <sub>OUT</sub> DAC                               | V <sub>CC</sub> = 2.7V ~ 5.5V、マイクロパワー、レール・トゥ・レール出力                                                                                              |

| LTC1821                     | パラレル16 ビット電圧出力DAC                                                          | 10Vステップに対して2μsの高精度16ビット・セトリング                                                                                                                   |

| LTC2600/LTC2610/<br>LTC2620 | 16ピンSSOPのオクタル16/14/12ビットV <sub>OUT</sub> DAC                               | 250μA/DAC、2.5V~5.5Vの電源電圧範囲、<br>レール・トゥ・レール出力、SPIインターフェイス                                                                                         |

| LTC2601/LTC2611/<br>LTC2621 | 10 ピンDFNのシングル16/14/12 ビットV <sub>OUT</sub> DAC                              | 300μA/DAC、2.5V~5.5Vの電源電圧範囲、<br>レール・トゥ・レール出力、SPIインターフェイス                                                                                         |

| LTC2602/LTC2612/<br>LTC2622 | 8 ピンMSOPのデュアル16/14/12 ビットV <sub>OUT</sub> DAC                              | 300μA/DAC、2.5V~5.5Vの電源電圧範囲、<br>レール・トゥ・レール出力、SPIインターフェイス                                                                                         |

| LTC2604/LTC2614/<br>LTC2624 | 16ピンSSOPのクワッド16/14/12 ビットV <sub>OUT</sub> DAC                              | 250μA/DAC、2.5V~5.5Vの電源電圧範囲、<br>レール・トゥ・レール出力、SPIインターフェイス                                                                                         |

| LTC2606/LTC2616/<br>LTC2626 | 10ピンDFNのシングル16/14/12ビットV <sub>OUT</sub> DAC、<br>I <sup>2</sup> Cインターフェイス付き | 270μA/DAC、2.7V~5.5Vの電源電圧範囲、<br>レール・トゥ・レール出力、I <sup>2</sup> Cインターフェイス                                                                            |

2605fa