## 特長

### ■ 最小のピン互換デュアルDAC

LTC2602:16ビット

LTC2612:14ビット

LTC2622:12ビット

### ■ 全温度範囲で16ビット単調性を保証

■ 広い電源電圧範囲:2.5V~5.5V

■ 低消費電力動作:300 $\mu$ A/DAC(3V電源時)

■ 1 $\mu$ A(最大)への個別チャネル・パワーダウン

■ 非常に小さいDAC間クロストーク:30 $\mu$ V未満

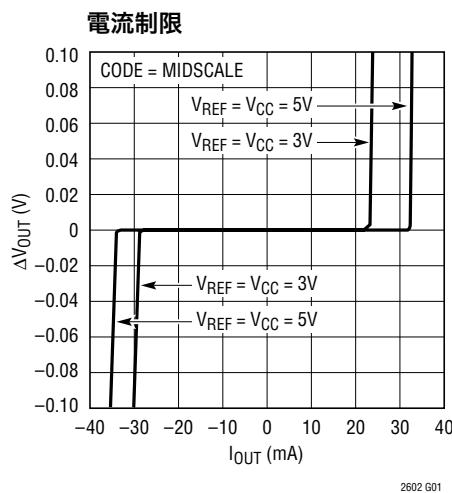

■ 高いレール・トゥ・レール出力ドライブ: $\pm$ 15mA

■ ダブルバッファ・データ・ラッチ

■ 10ビット・バージョンのLTC1661とピン互換

■ 小型8ピンMSOPパッケージ

## アプリケーション

■ モバイル通信

■ プロセス制御、産業用オートメーション

■ 計測

■ 自動試験装置

## 概要

LTC<sup>®</sup>2602/LTC2612/LTC2622はデュアルの16、14、12ビット、2.5V~5.5V動作、レール・トゥ・レール電圧出力DACで、8ピンMSOPパッケージで供給されます。高性能出力バッファを内蔵しており、単調性が保証されています。

これらのデバイスは、単一電源、複数の電圧出力で出力ドライブ、クロストーク、ロード・レギュレーションなど優れた性能を誇ります。

これらのデバイスは最大50MHzのクロック・レートで動作可能なシンプルなSPI/MICROWIRE<sup>TM</sup>互換3線シリアル・インターフェースを使用します。

LTC2602/LTC2612/LTC2622はパワーオン・リセット回路を内蔵しています。起動時の出力電圧はゼロスケールから10mV以内で、起動後はゼロスケールにとどまり、それを有効な書き込み、更新が発生するまで維持します。

、LTC、LTはリニアテクノロジー社の登録商標です。

他のすべての商標はそれぞれの所有者に所有権があります。

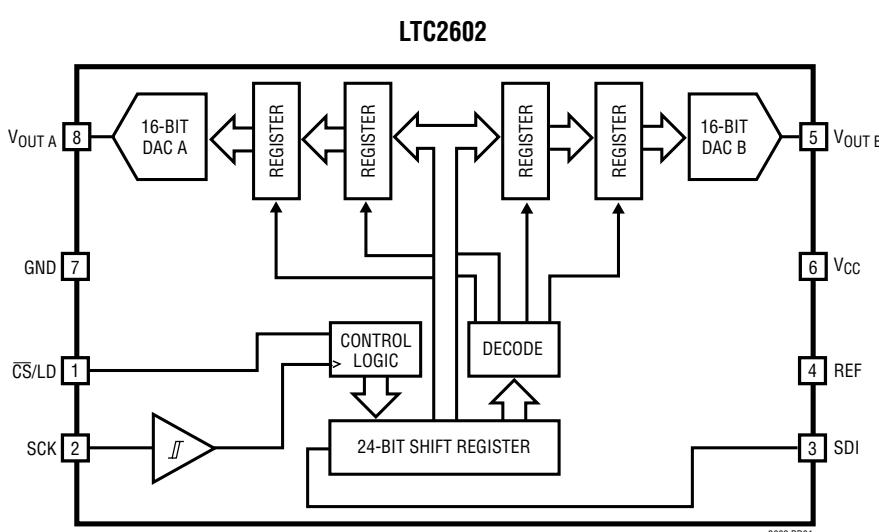

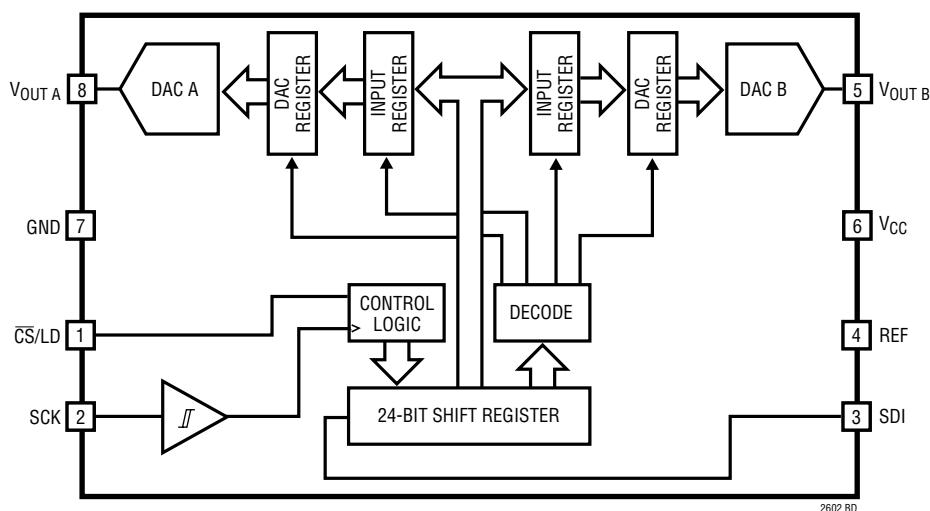

## ブロック図

2602fa

# LTC2602/LTC2612/LTC2622

## 絶対最大定格

(Note 1)

|                            |             |

|----------------------------|-------------|

| 任意のピンからGND                 | -0.3V~6V    |

| 任意のピンから $V_{CC}$           | -6V~0.3V    |

| 最大接合部温度                    | 125°C       |

| 動作温度範囲                     |             |

| LTC2602C/LTC2612C/LTC2622C | 0°C~70°C    |

| LTC2602I/LTC2612I/LTC2622I | -40°C~85°C  |

| 保存温度範囲                     | -65°C~150°C |

| リード温度(半田付け、10秒)            | 300°C       |

## パッケージ/発注情報

|                                                                                                                                                                                                                                        |                                                                                        |                                                    |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|----------------------------------------------------|

| <p>TOP VIEW</p> <p>MS8 PACKAGE<br/>8-LEAD PLASTIC MSOP</p> <p><math>T_{JMAX} = 125^{\circ}\text{C}</math>, <math>\theta_{JA} = 300^{\circ}\text{C/W}</math></p>                                                                        | ORDER PART NUMBER                                                                      | MS8 PART MARKING                                   |

|                                                                                                                                                                                                                                        | LTC2602CMS8<br>LTC2602IMS8<br>LTC2612CMS8<br>LTC2612IMS8<br>LTC2622CMS8<br>LTC2622IMS8 | LTACX<br>LTACY<br>LTACZ<br>LTADA<br>LTADB<br>LTADC |

| <p><b>Order Options</b> Tape and Reel: Add #TR<br/>Lead Free: Add #PBF Lead Free Tape and Reel: Add #TRPBF<br/>Lead Free Part Marking: <a href="http://www.linear-tech.co.jp/leadfree/">http://www.linear-tech.co.jp/leadfree/</a></p> |                                                                                        |                                                    |

より広い動作温度範囲で規定されるデバイスについては、弊社へお問い合わせください。

## 電気的特性

●は全動作温度範囲の規格値を意味する。それ以外は $T_A = 25^{\circ}\text{C}$ での値。注記がない限り、 $V_{CC} = 2.5\text{V} \sim 5.5\text{V}$ 、 $V_{REF} \leq V_{CC}$ 、 $V_{OUT}$ は無負荷。

| SYMBOL                | PARAMETER                    | CONDITIONS                                                                                                                                           | LTC2622 |       |       | LTC2612 |      |     | LTC2602 |      |     | UNITS  |

|-----------------------|------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-------|-------|---------|------|-----|---------|------|-----|--------|

|                       |                              |                                                                                                                                                      | MIN     | TYP   | MAX   | MIN     | TYP  | MAX | MIN     | TYP  | MAX |        |

| <b>DC Performance</b> |                              |                                                                                                                                                      |         |       |       |         |      |     |         |      |     |        |

|                       | Resolution                   |                                                                                                                                                      | ●       | 12    |       | 14      |      | 16  |         |      |     | Bits   |

|                       | Monotonicity                 | $V_{CC} = 5\text{V}$ , $V_{REF} = 4.096\text{V}$ (Note 2)                                                                                            | ●       | 12    |       | 14      |      | 16  |         |      |     | Bits   |

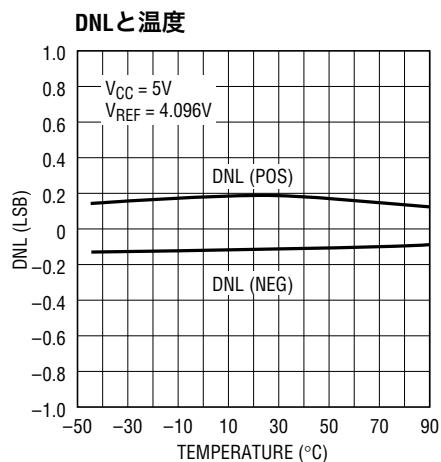

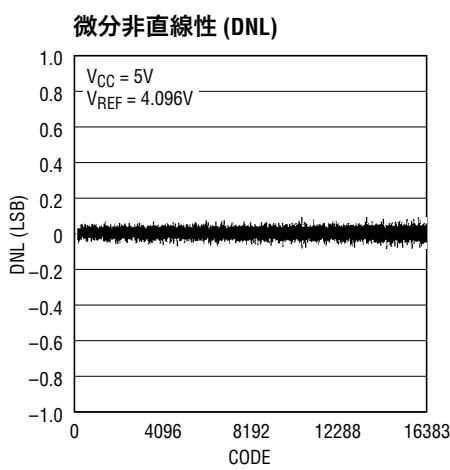

| DNL                   | Differential Nonlinearity    | $V_{CC} = 5\text{V}$ , $V_{REF} = 4.096\text{V}$ (Note 2)                                                                                            | ●       |       | ±0.5  |         | ±1   |     | ±1      |      |     | LSB    |

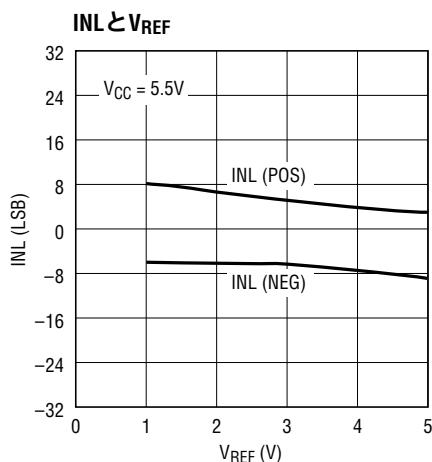

| INL                   | Integral Nonlinearity        | $V_{CC} = 5\text{V}$ , $V_{REF} = 4.096\text{V}$ (Note 2)                                                                                            | ●       | ±0.75 | ±4    | ±3      | ±16  |     | ±12     | ±64  |     | LSB    |

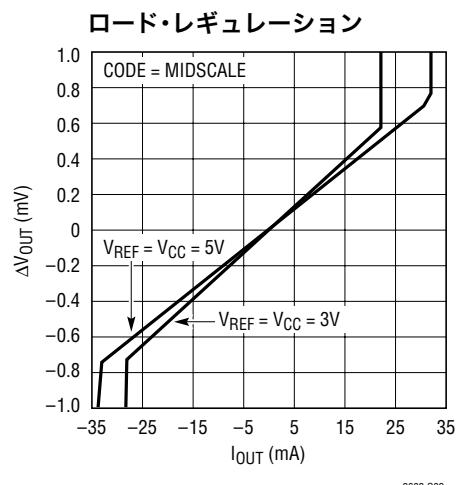

|                       | Load Regulation              | $V_{REF} = V_{CC} = 5\text{V}$ , Midscale<br>$I_{OUT} = 0\text{mA}$ to $15\text{mA}$ Sourcing<br>$I_{OUT} = 0\text{mA}$ to $15\text{mA}$ Sinking     | ●       | 0.025 | 0.125 | 0.1     | 0.5  |     | 0.4     | 2    |     | LSB/mA |

|                       |                              |                                                                                                                                                      | ●       | 0.05  | 0.125 | 0.2     | 0.5  |     | 0.65    | 2    |     | LSB/mA |

|                       |                              | $V_{REF} = V_{CC} = 2.5\text{V}$ , Midscale<br>$I_{OUT} = 0\text{mA}$ to $7.5\text{mA}$ Sourcing<br>$I_{OUT} = 0\text{mA}$ to $7.5\text{mA}$ Sinking | ●       | 0.05  | 0.25  | 0.2     | 1    |     | 0.9     | 4    |     | LSB/mA |

|                       |                              |                                                                                                                                                      | ●       | 0.1   | 0.25  | 0.4     | 1    |     | 1.3     | 4    |     | LSB/mA |

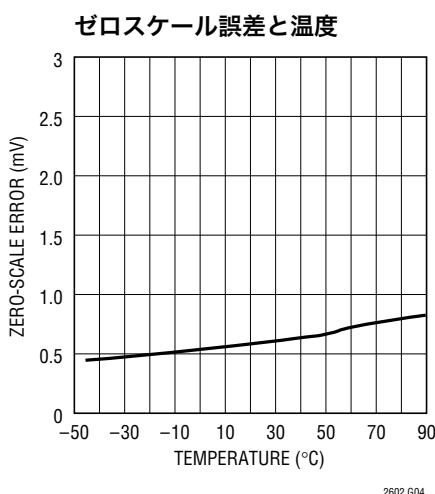

| ZSE                   | Zero-Scale Error             | $V_{CC} = 5\text{V}$ , $V_{REF} = 4.096\text{V}$ Code = 0                                                                                            | ●       | 1     | 9     | 1       | 9    |     | 1       | 9    |     | mV     |

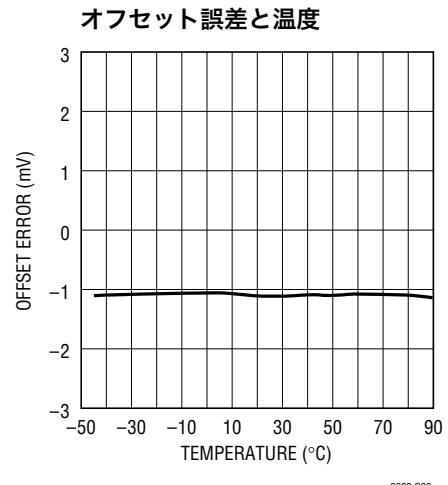

| Vos                   | Offset Error                 | $V_{CC} = 5\text{V}$ , $V_{REF} = 4.096\text{V}$ (Note 7)                                                                                            | ●       | ±1    | ±9    | ±1      | ±9   |     | ±1      | ±9   |     | mV     |

|                       | Vos Temperature Coefficient  |                                                                                                                                                      |         |       | ±5    |         | ±5   |     | ±5      |      |     | µV/°C  |

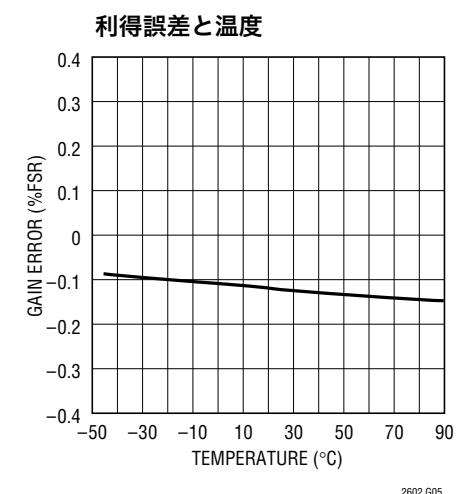

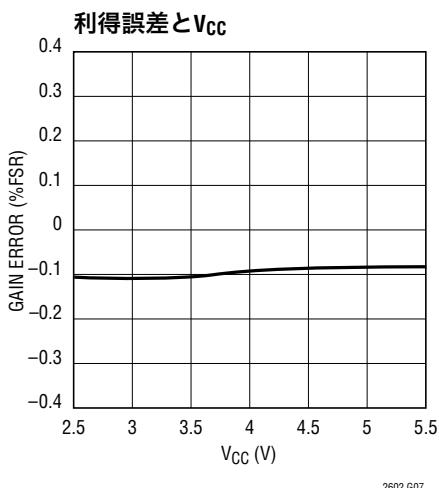

| GE                    | Gain Error                   | $V_{CC} = 5\text{V}$ , $V_{REF} = 4.096\text{V}$                                                                                                     | ●       | ±0.1  | ±0.7  | ±0.1    | ±0.7 |     | ±0.1    | ±0.7 |     | %FSR   |

|                       | Gain Temperature Coefficient |                                                                                                                                                      |         |       | ±3    |         | ±3   |     | ±3      |      |     | ppm/°C |

## 電気的特性

●は全動作温度範囲の規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。注記がない限り、 $V_{CC} = 2.5\text{V} \sim 5.5\text{V}$ 、 $V_{REF} \leq V_{CC}$ 、 $V_{OUT}$ は無負荷。

| SYMBOL    | PARAMETER                    | CONDITIONS                                                                                                                                                                             | LTC2602/LTC2612/LTC2622 |              |                                 | UNITS                                                     |

|-----------|------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|--------------|---------------------------------|-----------------------------------------------------------|

|           |                              |                                                                                                                                                                                        | MIN                     | TYP          | MAX                             |                                                           |

| PSRR      | Power Supply Rejection Ratio | $V_{CC} = 5\text{V} \pm 10\%$                                                                                                                                                          |                         |              | -80                             | dB                                                        |

| $R_{OUT}$ | DC Output Impedance          | $V_{REF} = V_{CC} = 5\text{V}$ , Midscale; $-15\text{mA} \leq I_{OUT} \leq 15\text{mA}$<br>$V_{REF} = V_{CC} = 2.5\text{V}$ , Midscale; $-7.5\text{mA} \leq I_{OUT} \leq 7.5\text{mA}$ | ●<br>●                  | 0.05<br>0.05 | 0.15<br>0.15                    | $\Omega$<br>$\Omega$                                      |

|           | DC Crosstalk (Note 4)        | Due to Full Scale Output Change (Note 5)<br>Due to Load Current Change<br>Due to Powering Down (per Channel)                                                                           |                         |              | $\pm 30$<br>$\pm 16$<br>$\pm 4$ | $\mu\text{V}$<br>$\mu\text{V}/\text{mA}$<br>$\mu\text{V}$ |

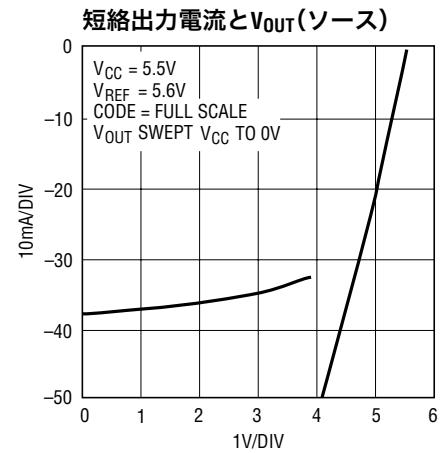

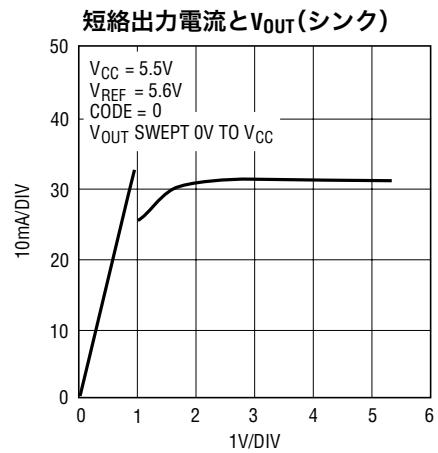

| $I_{SC}$  | Short-Circuit Output Current | $V_{CC} = 5.5\text{V}$ , $V_{REF} = 5.5\text{V}$<br>Code: Zero Scale; Forcing Output to $V_{CC}$<br>Code: Full Scale; Forcing Output to GND                                            | ●<br>●                  | 15<br>15     | 34<br>38                        | 60<br>60                                                  |

|           |                              | $V_{CC} = 2.5\text{V}$ , $V_{REF} = 2.5\text{V}$<br>Code: Zero Scale; Forcing Output to $V_{CC}$<br>Code: Full Scale; Forcing Output to GND                                            | ●<br>●                  | 7.5<br>7.5   | 20<br>28                        | 50<br>50                                                  |

|           |                              |                                                                                                                                                                                        |                         |              |                                 | mA<br>mA                                                  |

|           |                              |                                                                                                                                                                                        |                         |              |                                 | mA<br>mA                                                  |

### Reference Input

|           |                                    |                       |   |    |          |                  |

|-----------|------------------------------------|-----------------------|---|----|----------|------------------|

|           | Input Voltage Range                |                       | ● | 0  | $V_{CC}$ | V                |

|           | Resistance                         | Normal Mode           | ● | 44 | 64       | $\text{k}\Omega$ |

|           | Capacitance                        |                       |   |    | 23       | pF               |

| $I_{REF}$ | Reference Current, Power Down Mode | All DACs Powered Down | ● |    | 0.001    | $\mu\text{A}$    |

### Power Supply

|          |                         |                                                                                                                                                                              |                  |                            |                    |                                                              |

|----------|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|----------------------------|--------------------|--------------------------------------------------------------|

| $V_{CC}$ | Positive Supply Voltage | For Specified Performance                                                                                                                                                    | ●                | 2.5                        | 5.5                | V                                                            |

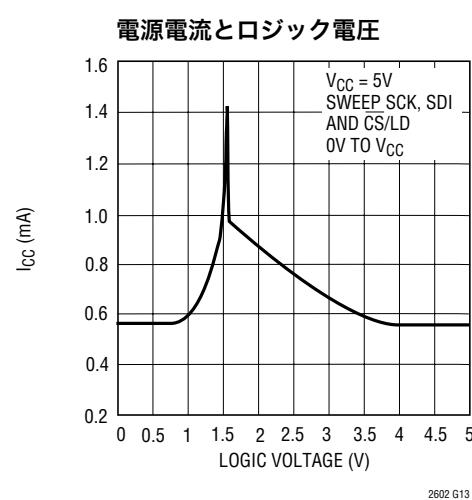

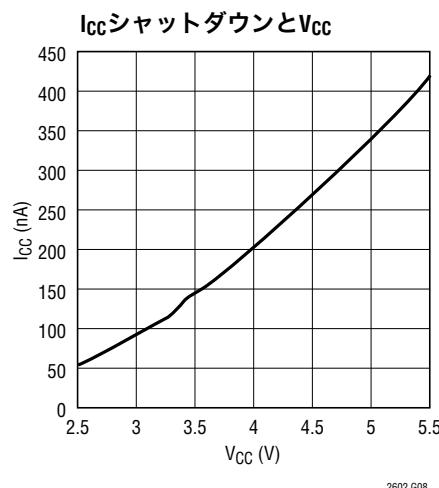

| $I_{CC}$ | Supply Current          | $V_{CC} = 5\text{V}$ (Note 3)<br>$V_{CC} = 3\text{V}$ (Note 3)<br>All DACs Powered Down (Note 3) $V_{CC} = 5\text{V}$<br>All DACs Powered Down (Note 3) $V_{CC} = 3\text{V}$ | ●<br>●<br>●<br>● | 0.7<br>0.6<br>0.35<br>0.10 | 1.3<br>1<br>1<br>1 | $\text{mA}$<br>$\text{mA}$<br>$\mu\text{A}$<br>$\mu\text{A}$ |

### Digital I/O

|          |                            |                                                                                                                               |             |            |                   |               |

|----------|----------------------------|-------------------------------------------------------------------------------------------------------------------------------|-------------|------------|-------------------|---------------|

| $V_{IH}$ | Digital Input High Voltage | $V_{CC} = 2.5\text{V}$ to $5.5\text{V}$<br>$V_{CC} = 2.5\text{V}$ to $3.6\text{V}$                                            | ●<br>●      | 2.4<br>2.0 |                   | V<br>V        |

| $V_{IL}$ | Digital Input Low Voltage  | $V_{CC} = 4.5\text{V}$ to $5.5\text{V}$<br>$V_{CC} = 2.7\text{V}$ to $5.5\text{V}$<br>$V_{CC} = 2.5\text{V}$ to $5.5\text{V}$ | ●<br>●<br>● |            | 0.8<br>0.6<br>0.5 | V<br>V<br>V   |

| $I_{LK}$ | Digital Input Leakage      | $V_{IN} = \text{GND}$ to $V_{CC}$                                                                                             | ●           |            | $\pm 1$           | $\mu\text{A}$ |

| $C_{IN}$ | Digital Input Capacitance  | (Note 6)                                                                                                                      | ●           |            | 8                 | pF            |

| SYMBOL                | PARAMETER                            | CONDITIONS                                                                                                                                       | LTC2622 |     |      | LTC2612 |     |      | LTC2602 |     |                              | UNITS |

|-----------------------|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|---------|-----|------|---------|-----|------|---------|-----|------------------------------|-------|

|                       |                                      |                                                                                                                                                  | MIN     | TYP | MAX  | MIN     | TYP | MAX  | MIN     | TYP | MAX                          |       |

| <b>AC Performance</b> |                                      |                                                                                                                                                  |         |     |      |         |     |      |         |     |                              |       |

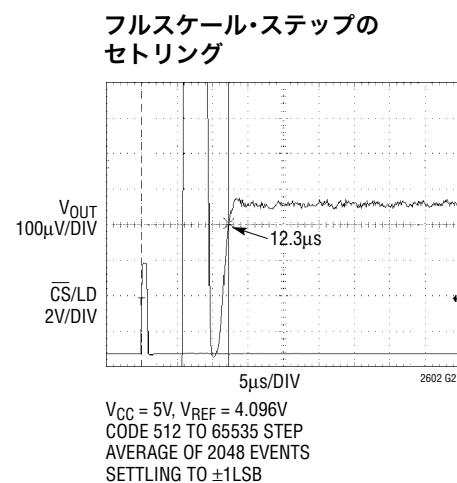

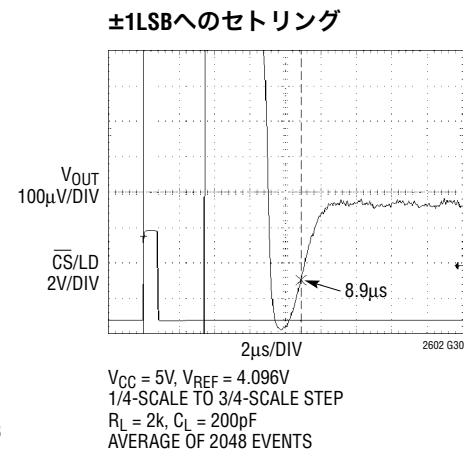

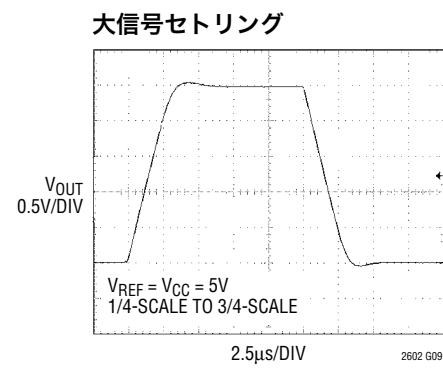

| $t_s$                 | Settling Time (Note 8)               | $\pm 0.024\%$ ( $\pm 1\text{LSB}$ at 12 Bits)<br>$\pm 0.006\%$ ( $\pm 1\text{LSB}$ at 14 Bits)<br>$\pm 0.0015\%$ ( $\pm 1\text{LSB}$ at 16 Bits) | 7       |     | 7    | 7       |     | 7    | 7       |     | $\mu\text{s}$                |       |

|                       |                                      |                                                                                                                                                  |         |     |      | 9       |     | 9    | 9       |     | $\mu\text{s}$                |       |

|                       |                                      |                                                                                                                                                  |         |     |      | 10      |     | 10   | 10      |     | $\mu\text{s}$                |       |

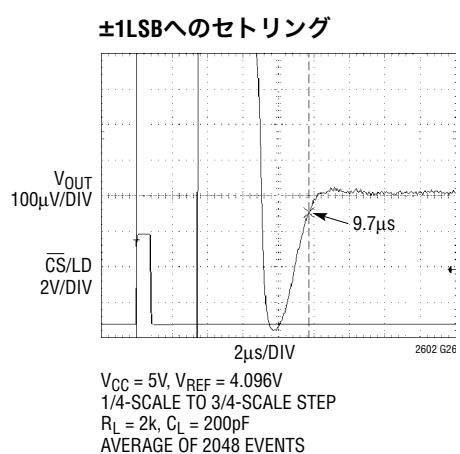

|                       | Settling Time for 1LSB Step (Note 9) | $\pm 0.024\%$ ( $\pm 1\text{LSB}$ at 12 Bits)<br>$\pm 0.006\%$ ( $\pm 1\text{LSB}$ at 14 Bits)<br>$\pm 0.0015\%$ ( $\pm 1\text{LSB}$ at 16 Bits) | 2.7     |     | 2.7  | 2.7     |     | 2.7  | 2.7     |     | $\mu\text{s}$                |       |

|                       |                                      |                                                                                                                                                  |         |     |      | 4.8     |     | 4.8  | 4.8     |     | $\mu\text{s}$                |       |

|                       |                                      |                                                                                                                                                  |         |     |      | 5.2     |     | 5.2  | 5.2     |     | $\mu\text{s}$                |       |

|                       | Voltage Output Slew Rate             |                                                                                                                                                  | 0.80    |     | 0.80 | 0.80    |     | 0.80 | 0.80    |     | $\text{V}/\mu\text{s}$       |       |

|                       | Capacitive Load Driving              |                                                                                                                                                  | 1000    |     | 1000 | 1000    |     | 1000 | 1000    |     | pF                           |       |

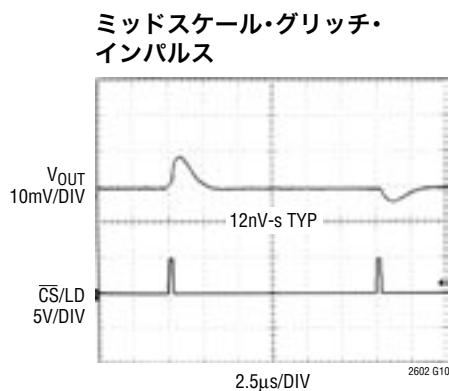

|                       | Glitch Impulse                       | At Midscale Transition                                                                                                                           | 12      |     | 12   | 12      |     | 12   | 12      |     | $\text{nV} \cdot \text{s}$   |       |

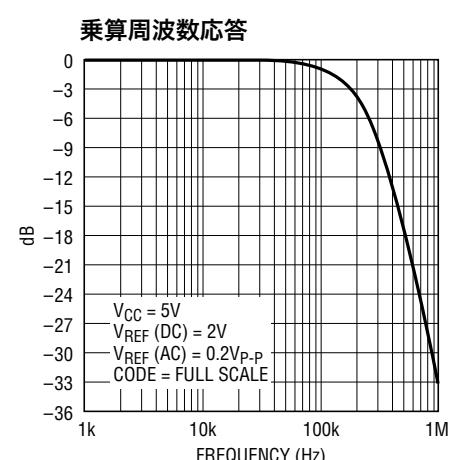

|                       | Multiplying Bandwidth                |                                                                                                                                                  | 180     |     | 180  | 180     |     | 180  | 180     |     | kHz                          |       |

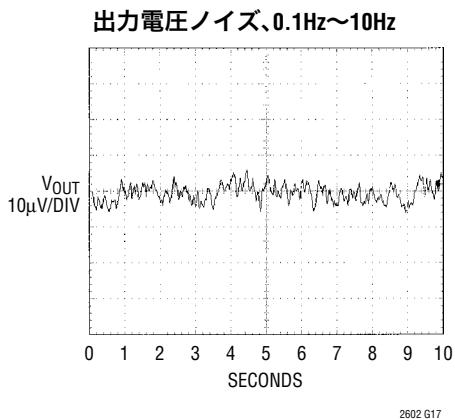

| $e_n$                 | Output Voltage Noise Density         | At $f = 1\text{kHz}$<br>At $f = 10\text{kHz}$                                                                                                    | 120     |     | 120  | 120     |     | 120  | 120     |     | $\text{nV}/\sqrt{\text{Hz}}$ |       |

|                       | Output Voltage Noise                 | 0.1Hz to 10Hz                                                                                                                                    | 15      |     | 15   | 15      |     | 15   | 15      |     | $\mu\text{V}_{\text{P-P}}$   |       |

# LTC2602/LTC2612/LTC2622

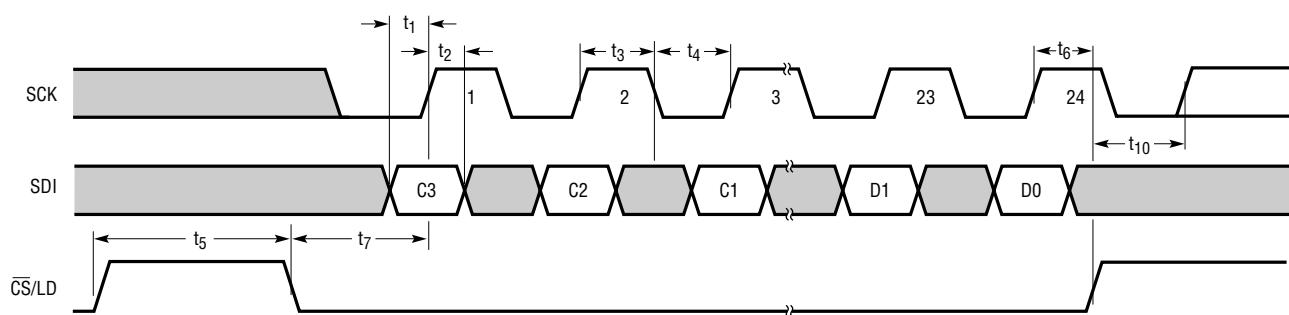

## タイミング特性

●は全動作温度範囲の規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。(図1を参照)(Note 6)

| SYMBOL                                                   | PARAMETER                               | CONDITIONS     | MIN | TYP | MAX | UNITS |

|----------------------------------------------------------|-----------------------------------------|----------------|-----|-----|-----|-------|

| <b><math>V_{CC} = 2.5\text{V to } 5.5\text{V}</math></b> |                                         |                |     |     |     |       |

| $t_1$                                                    | SDI Valid to SCK Setup                  |                | ●   | 4   |     | ns    |

| $t_2$                                                    | SDI Valid to SCK Hold                   |                | ●   | 4   |     | ns    |

| $t_3$                                                    | SCK High Time                           |                | ●   | 9   |     | ns    |

| $t_4$                                                    | SCK Low Time                            |                | ●   | 9   |     | ns    |

| $t_5$                                                    | $\bar{CS}/LD$ Pulse Width               |                | ●   | 10  |     | ns    |

| $t_6$                                                    | LSB SCK High to $\bar{CS}/LD$ High      |                | ●   | 7   |     | ns    |

| $t_7$                                                    | $\bar{CS}/LD$ Low to SCK High           |                | ●   | 7   |     | ns    |

| $t_{10}$                                                 | $\bar{CS}/LD$ High to SCK Positive Edge |                | ●   | 7   |     | ns    |

|                                                          | SCK Frequency                           | 50% Duty Cycle | ●   |     | 50  | MHz   |

**Note 1:** 絶対最大定格はそれを超えるとデバイスの寿命に影響を及ぼす値。

**Note 2:** 直線性と単調性はコード $k_L$ からコード $2^N - 1$ まで定義されている。ここで、 $N$ は分解能で、 $k_L = 0.016(2^N/V_{REF})$ で与えられ、最も近い整数のコードに丸められている。 $V_{REF} = 4.096\text{V}$ で $N = 16$ の場合、 $k_L = 256$ となり、直線性はコード256からコード65,535まで定義される。

**Note 3:** 0Vまたは $V_{CC}$ でのデジタル入力。

**Note 4:** DCクロストークは、注記がない限り、 $V_{CC} = 5\text{V}$ および $V_{REF} = 4.096\text{V}$ で、ミッドスケールで測定されたDACを使って測定される。

**Note 5:** テストしていないDACの出力にはGNDまたは $V_{CC}$ への $R_L = 2\text{k}\Omega$ 。

**Note 6:** 設計によって保証されているが、製造時にはテストされない。

**Note 7:** コード256 (LTC2602)、コード64 (LTC2612)またはコード16 (LTC2622)、およびフルスケールでの測定から推測されている。

**Note 8:**  $V_{CC} = 5\text{V}$ 、 $V_{REF} = 4.096\text{V}$ 。DACは1/4スケールから3/4スケールへ、さらに3/4スケールから1/4スケールへステップさせる。負荷はGNDに並列に接続した $2\text{k}$ と $200\text{pF}$ 。

**Note 9:**  $V_{CC} = 5\text{V}$ 、 $V_{REF} = 4.096\text{V}$ 。DACはハーフスケールと(ハーフスケール - 1)の間を $\pm 1\text{LSB}$ でステップさせられる。負荷はGNDに並列に接続した $2\text{k}$ と $200\text{pF}$ 。

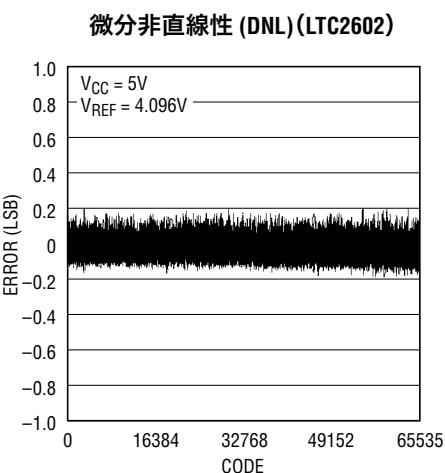

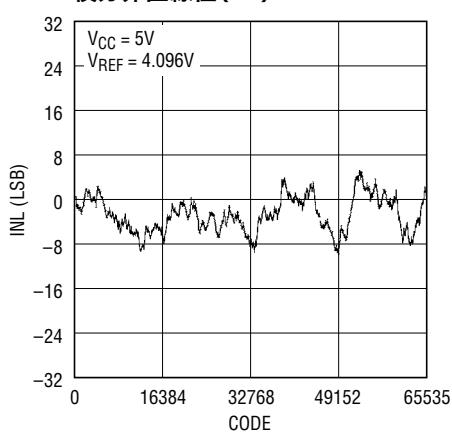

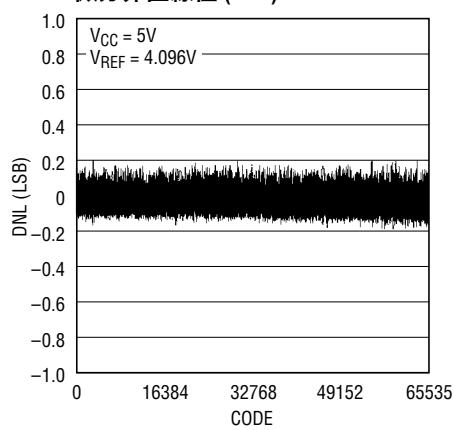

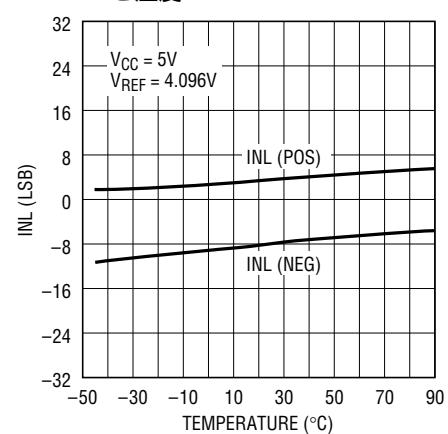

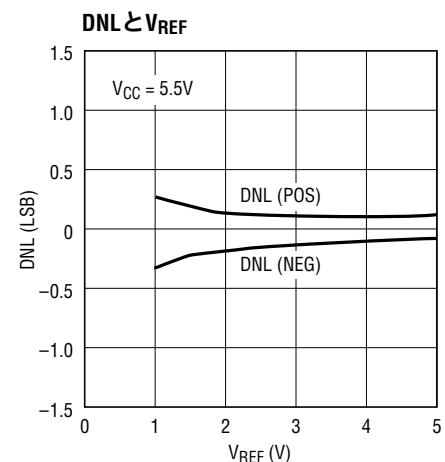

## 標準的性能特性

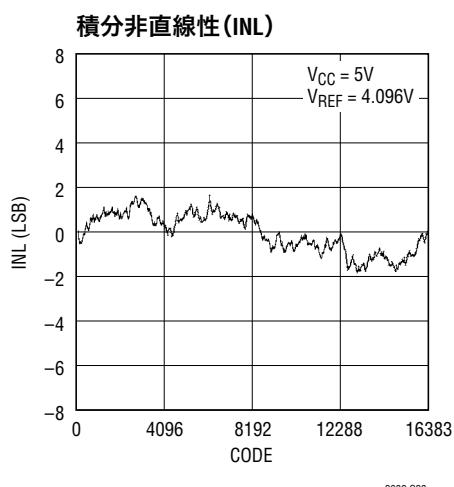

### (LTC2602)

#### 積分非直線性 (INL)

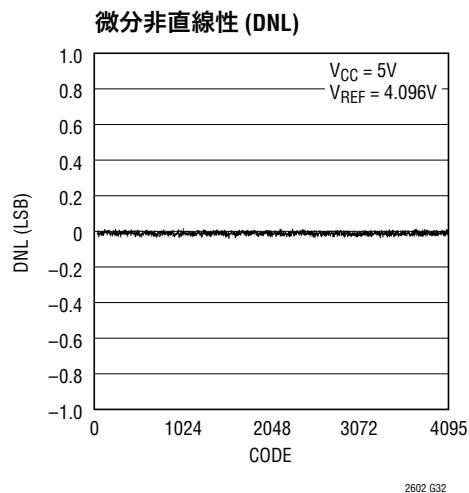

#### 微分非直線性 (DNL)

#### INLと温度

## 標準的性能特性

(LTC2602)

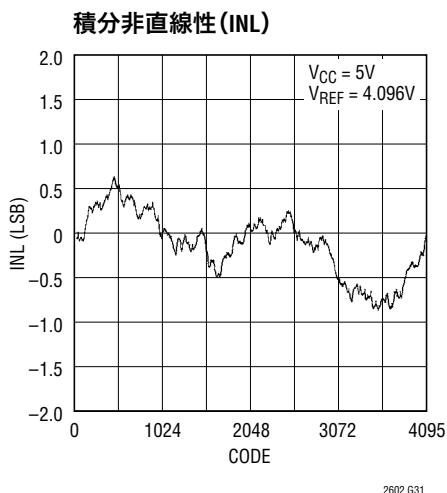

(LTC2612)

2602fa

# LTC2602/LTC2612/LTC2622

## 標準的性能特性

(LTC2622)

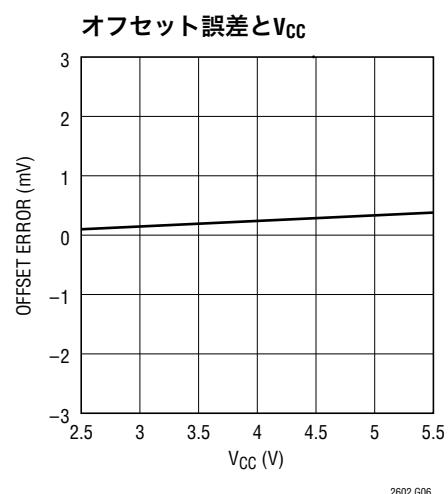

(LTC2602/LTC2612/LTC2622)

## 標準的性能特性

(LTC2602/LTC2612/LTC2622)

# LTC2602/LTC2612/LTC2622

## 標準的性能特性

(LTC2602/LTC2612/LTC2622)

2602fa

## ピン機能

**CS/LD(ピン1):**シリアル・インターフェースのチップ・セレクト/ロード入力。 $\overline{\text{CS}}/\text{LD}$ が“L”的とき、SCKがイネーブルされ、SDIのデータをレジスタにシフトします。 $\overline{\text{CS}}/\text{LD}$ が“H”に引き上げられると、SCKはディスエーブルされ、指定されたコマンド(表1を参照)が実行されます。

**SCK(ピン2):**シリアル・インターフェースのクロック入力。

CMOS と TTL に対して互換。

**SDI(ピン3):**シリアル・インターフェースのデータ入力。データはSDIに与えられ、SCKの立上りエッジでデバイス

に転送されます。LTC2602/LTC2612/LTC2622は24ビットまたは32ビットの入力ワード長を受け入れます。

**REF(ピン4):**リファレンス電圧入力。0V  $\leq$  V<sub>REF</sub>  $\leq$  V<sub>CC</sub>。

**V<sub>OUT\_B</sub>およびV<sub>OUT\_A</sub> (ピン5とピン8):**DACのアナログ電圧出力。出力範囲は0~V<sub>REF</sub>です。

**V<sub>CC</sub>(ピン6):**電源電圧入力、2.5V ≤ V<sub>CC</sub> ≤ 5.5V。

## GND(ピンク)・アカログ・グランド

## ブロック図

## タイミング図

1

# LTC2602/LTC2612/LTC2622

## 動作

### パワーオン・リセット

LTC2602/LTC2612/LTC2622は電源が最初に入れられたとき出力をゼロスケールにクリアして、システムの初期状態を一定に保ち、反復可能にします。

アプリケーションによっては、DACの起動時に下流の回路がアクティブ状態であり、この間DACからのゼロではない出力に対して敏感な場合があります。LTC2602/LTC2612/LTC2622はパワーオン・グリッチを減らす回路を備えています。さらに、電源のランプレートを小さくすることにより、グリッチの振幅を小さくすることができます。たとえば、電源が1msで5Vまでランプする場合、パワーオン時にアナログ出力がグランドより10mV(標準)以上上昇することはありません。「標準的性能特性」のセクションの「パワーオン・リセット・グリッチ」を参照してください。

### 電源シーケンシング

REF(ピン4)の電圧は $-0.3V \leq V_{REF} \leq V_{CC} + 0.3V$ の範囲に保ちます(「絶対最大定格」を参照)。電源のターンオン・シーケンスとターンオフ・シーケンスの間(このとき $V_{CC}$ (ピン6)の電圧は遷移しています)、これらのリミットが守られるように特に注意が必要です。

### 伝達関数

デジタルからアナログへの伝達関数は次のとおりです。

$$V_{OUT(IDEAL)} = \left( \frac{k}{2^N} \right) V_{REF}$$

ここで、kはDACの2進数の入力コードに相当する10進数、Nは分解能、 $V_{REF}$ はREF(ピン4)の電圧です。

表1.

| コマンド*    |    |    |                                     |

|----------|----|----|-------------------------------------|

| C3       | C2 | C1 | C0                                  |

| 0 0 0 0  |    |    | 入力レジスタ n に書き込む                      |

| 0 0 0 1  |    |    | DAC のレジスタ n を更新(パワーアップ)する           |

| 0 0 1 0  |    |    | 入力レジスタ n に書き込み、すべての n を更新(パワーアップ)する |

| 0 0 1 1  |    |    | n に書き込み、更新(パワーアップ)する                |

| 0 1 0 0  |    |    | n をパワーダウン                           |

| 1 1 1 1  |    |    | 動作なし                                |

| アドレス(n)* |    |    |                                     |

| A3       | A2 | A1 | A0                                  |

| 0 0 0 0  |    |    | DAC A                               |

| 0 0 0 1  |    |    | DAC B                               |

| 1 1 1 1  |    |    | 全ての DAC                             |

\*示されていないコマンドとアドレス・コードは予備であり、使用してはならない。

### シリアル・インターフェース

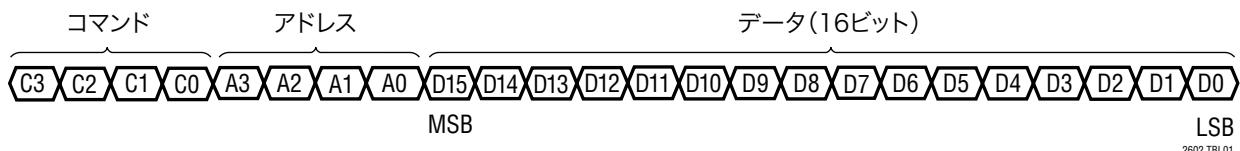

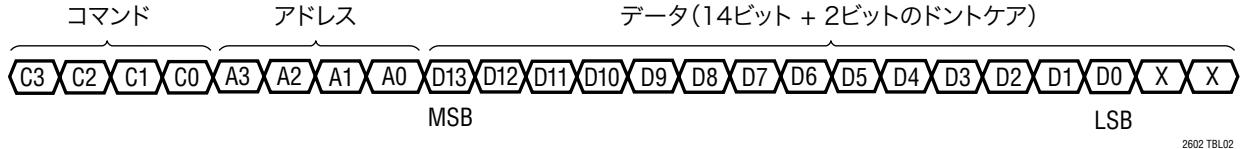

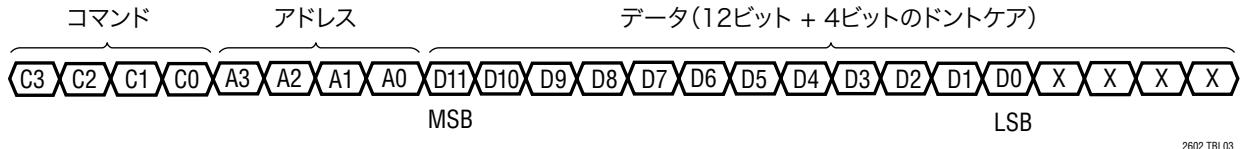

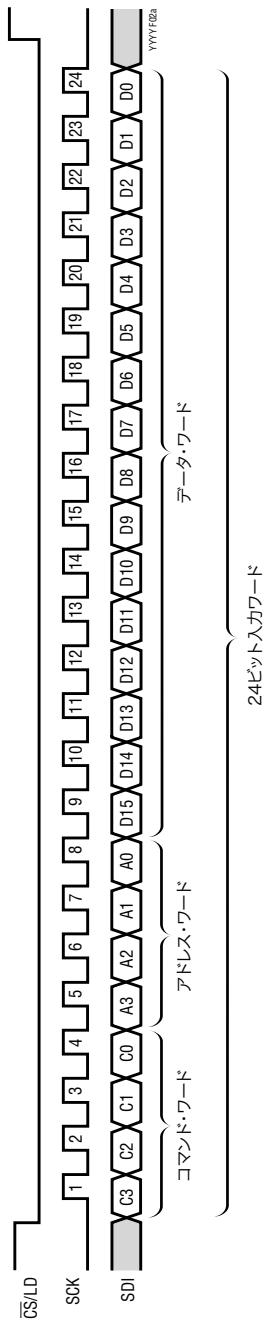

CS/LD入力はレベル・トリガれます。この入力が“L”に引き下げられるとチップ・セレクト信号として機能し、SDIとSCKのバッファが作動状態になり、入力のシフト・レジスタをイネーブルします。データ(SDI入力)は次に続く24のSCKの立上りエッジで転送されます。最初に4ビットのコマンド(C3~C0)、次に4ビットのDACアドレス(A3~A0)、そして最後に16ビットのデータ・ワードがロードされます。データ・ワードは、MSBからLSBに向かって並んだ16、14、または12ビットの入力コードと、それに続く0、2、または4ビットのドントケア(対象外)ビットで構成されます(それぞれ、LTC2602、LTC2612およびLTC2622)。データはCS/LDが“L”的きだけデバイスに取り込むことができます。完全なシーケンスを図2aに示します。

コマンド(C3~C0)とアドレス(A3~A0)の割当てを表1に示します。表の中の最初の4つのコマンドは書き込みと更新の操作です。書き込み操作は、32ビットのシフト・レジスタから16ビットのデータ・ワードを、選択されたDAC(n)の入力レジスタにロードします。更新操作はデータ・ワードを入力レジスタからDACレジスタにコピーします。DACレジスタにコピーされると、データ・ワードはアクティブな16、14、または12ビットの入力コードになり、DAC出力でアナログ電圧に変換されます。また、パワーダウン・モードであれば、更新操作により、選択されたDACがパワーアップされます。データ・パスとレジスタをブロック図に示します。

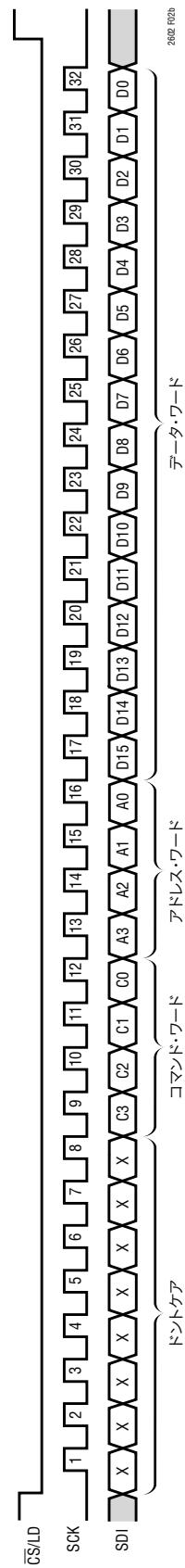

最小入力ワードは24ビットですが、16ビット(2バイト)の最小ワード幅のマイクロプロセッサに適合させるために32ビットに拡張することもできます。32ビットのワード幅を利用するには、ドントケア(対象外)の8ビットが最初にデバイスに転送され、続いて上で説明した24ビットのワードが転送されます。32ビットのシーケンスを図2bに示します。

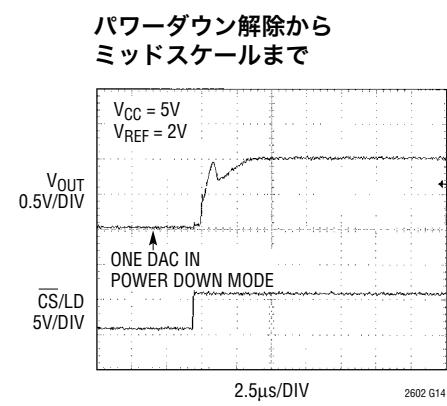

### パワーダウン・モード

電力が制限されているアプリケーションでは、2本の出力の全ては必要ないときはパワーダウン・モードを使って電源電流を減らすことができます。パワーダウン時、バッファ・アンプ、バイアス回路およびリファレンス入力はディスエーブルされ、実質的に電流は流れません。

## 動作

### 入力ワード (LTC2602)

### 入力ワード (LTC2612)

### 入力ワード (LTC2622)

DAC出力は高インピーダンス状態になり、出力ピンは個別の90kΩ抵抗によって受動的にグランドに引き下げられます。入力レジスタとDACレジスタの内容はパワーダウンの間乱されません。

どちらかのチャネルまたは両方のチャネルを、適切なDACアドレス( $n$ )と組み合わせたコマンド $0100_b$ を使ってパワーダウン・モードにすることができます。16ビットのデータ・ワードは無視されます。電源電流とリファレンスの電流は、パワーダウンされるDACごとに約50%だけ減少します。REF(ピン4)の実効抵抗はそれに従って増加し、両方のDACがパワーダウンすると高インピーダンス入力(一般に1GΩ以上)になります。

表1に示されているように、DACの更新を含むどのコマンドを実行しても、通常の動作を再開することができます。選択されたDACはその電圧出力が更新されるとパワーアップされます。パワーダウン状態のDACがパワーアップされ、更新されると、通常のセトリングが遅延させられます。2つのDACのうち片方が更新コマンドの前にパワーダウン状態であれば、パワーアップ遅延は5μsです。他方、両方のDACがパワーダウンされると、個々のDACのアンプやリファレンス入力に加えて、主バイアス発生回路ブロックが自動的にシャットダウンされます。この場合、パワーアップ遅延時間は12μs( $V_{CC} = 5V$ の場合)または30μs( $V_{CC} = 3V$ の場合)です。

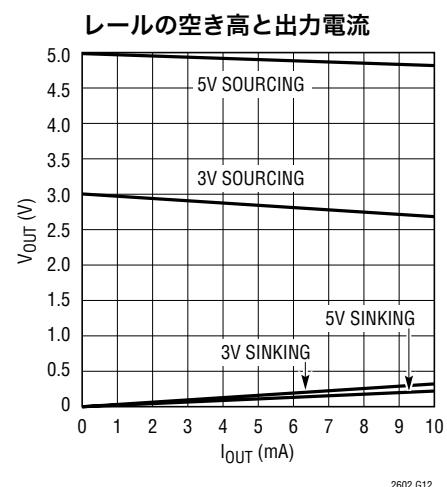

### 電圧出力

これらのデバイスに内蔵されている2個のレール・トゥ・レール・アンプは、それぞれ5Vで最大15mA(3Vで最大7.5mA)をソースまたはシンクするときロード・レギュレーションが保証されます。

ロード・レギュレーションは、広い範囲の負荷条件にわたって定格電圧精度を維持する、アンプの能力の指標です。負荷電流を強制的に1mA変化させたときの出力電圧の変化の測定値はLSB/mAで表現されます。

DC出力インピーダンスはロード・レギュレーションと等価で、単にLSB/mAからオームに単位を変えて計算するだけで求めることができます。アンプのDC出力インピーダンスはレールから十分離れた負荷をドライブしているとき0.050Ωです。

どちらかのレールから負荷電流が流れているとき、そのレールを基準にした出力電圧の空き高は出力デバイスの標準チャネル抵抗25Ωによって制限されます。たとえば、1mAをシンクしているとき、最小出力電圧 =  $25\Omega \cdot 1mA = 25mV$ になります。「標準性能特性」のセクションの「レールの空き高と出力電流」のグラフを参照してください。

アンプは最大1000pFの容量性負荷を安定してドライブします。

## 動作

### 基板のレイアウト

これらのデバイスの優れたロード・レギュレーションとDCクロストークの性能は、「信号」グランドと「電源」グランドを内部で分離し、共有内部抵抗を減らすことにより実現されています。

リファレンス電圧と出力電圧が基準とするノードとして、さらにデバイスの電源電流のリターン・パスとしてGNDピンは機能します。このため、定格性能を実現するには、接地方式とボードのレイアウトに十分配慮する必要があります。

PCボードには、回路のアナログ部分とデジタル部分のために別の領域が必要です。こうすれば、敏感なアナログ信号からデジタル信号を離しておくことができ、分離されたデジタル・グランド・プレーンとアナログ・グランド・プレーンを使いやすくなり、容量性および抵抗性の相互反応を最小に抑えられます。

デジタル・グランド・プレーンとアナログ・グランド・プレーンは1点接続し、デバイスのグランド・ピンにできるだけ近づけてシステムのスター・グランドを形成します。理想的には、アナログ・グランド・プレーンはボードの部品側に配置し、デバイスをノイズからシールドするためデバイスの下にくるようにします。アナログ・グランドは(必要なピン・パッドやビア以外は)遮るものがない連続したプレーンにして、信号用トレースは別のレイヤに配置します。

デバイスのGNDピンはアナログ・グランドに接続します。GNDピンからシステムのスター・グランドまでの抵抗はできるだけ小さくします。この抵抗はデバイスの実効DC出力インピーダンス(標準で $0.050\Omega$ )に直接追加され、DCクロストークを悪化させます。LTC2602/LTC2612/LTC2622は、同種の他のデバイスに比べて、これらの影響を受けやすくはないことに注意してください。それどころか、これらのデバイスは、達成可能な性能が大きすぎる内部抵抗によって制限されるというよりは、レイアウトに基づく際立った性能向上を可能にします。

### レール・トゥ・レール出力に関する検討事項

どんなレール・トゥ・レールの電圧出力のデバイスでも、出力は電源電圧範囲内に制限されます。

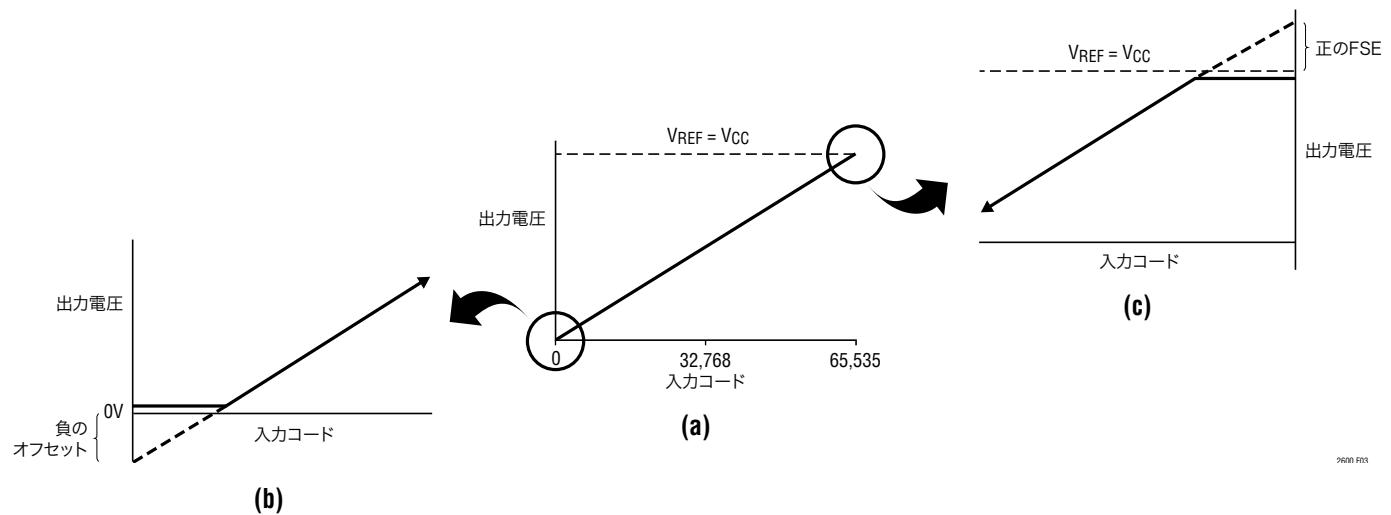

デバイスのアナログ出力はグランドより下にはなれないで、図3bに示されているように、これらの出力は最低コードを制限することができます。同様に、REFピンがV<sub>CC</sub>に接続されているとき、フルスケールの近くで出力が制限されることがあります。V<sub>REF</sub> = V<sub>CC</sub>で、DACのフルスケール誤差(FSE)が正のとき、最高コードの出力が、図3cに示されているように、V<sub>CC</sub>に制限されます。V<sub>REF</sub>がV<sub>CC</sub> - FSEより小さいと、フルスケールの制限は生じません。

オフセットと直線性は、DACの伝達関数の(出力の制限が生じない)領域にわたって定義され、テストされます。

## 動作

図2a. LTC2602の24ビットのロード・シーケンス(最小入力ワード)

LTC2612 SDIのデータ・ワード 14ビット入力コード+ドントケアの2ビット

LTC2622 SDIのデータ・ワード 12ビット入力コード+ドントケアの4ビット

コマンド・ワード アドレス・ワード データ・ワード

図2b. LTC2602の32ビットのロード・シーケンス

LTC2612 SDIのデータ・ワード 14ビット入力コード+ドントケアの2ビット

LTC2622 SDIのデータ・ワード 12ビット入力コード+ドントケアの4ビット

コマンド・ワード アドレス・ワード ドントケア データ・ワード

## 動作

図3. DAC伝達曲線に対するレール・トゥ・レール動作の影響 (a)全体の伝達関数 (b)ゼロスケール近くのコードに対する負のオフセットの影響 (c)フルスケール近くのコードに対する正のフルスケール誤差の影響

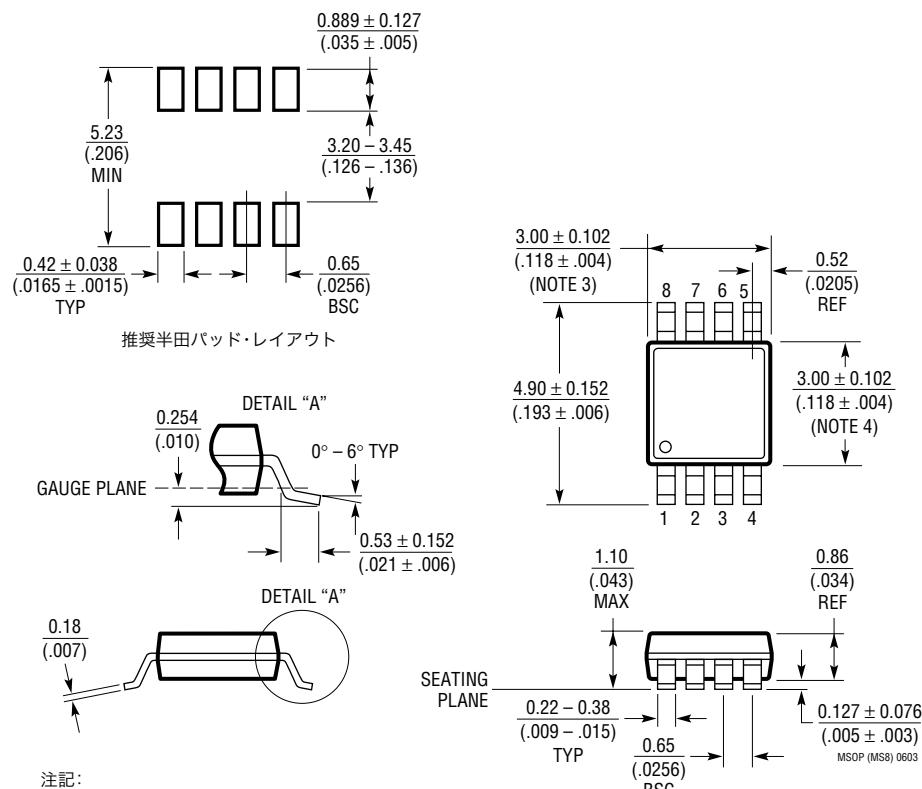

## パッケージ寸法

**MS8パッケージ

8ピン・プラスチックMSOP

(Reference LTC DWG # 05-08-1660)**

- 注記: (.0256)

1. 寸法はミリメートル/(インチ) BSC

2. 図は実寸とは異なる

3. 寸法にはモールドのバリ、突出部、またはゲートのバリを含まない。

モールドのバリ、突出部、またはゲートのバリは、各サイドで 0.152mm(0.006") を超えないこと

4. 寸法には、リード間のバリまたは突出部を含まない。

リード間のバリまたは突出部は各サイドで 0.152mm(0.006") を超えないこと

5. リードの平面度(整形後のリードの底面)は最大 0.102mm (.004") であること

# LTC2602/LTC2612/LTC2622

## 関連製品

| 製品番号                        | 説明                                                    | 注釈                                                                                                                                  |

|-----------------------------|-------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|

| LTC1458/LTC1458L            | 追加機能付きレール・トゥ・レール出力の<br>クワッド12ビットDAC                   | LTC1458:V <sub>CC</sub> = 4.5V~5.5V、V <sub>OUT</sub> = 0V~4.096V<br>LTC1458L:V <sub>CC</sub> = 2.7V~5.5V、V <sub>OUT</sub> = 0V~2.5V |

| LTC1654                     | レール・トゥ・レールV <sub>OUT</sub> のデュアル14ビットDAC              | プログラム可能な速度/電力、3.5μs/750μA, 8μs/450μA                                                                                                |

| LTC1655/LTC1655L            | シリアル・インターフェース付きシングル16ビットV <sub>OUT</sub><br>DAC(SO-8) | V <sub>CC</sub> = 5V(3V)、低消費電力、グリッヂ低減                                                                                               |

| LTC1657/LTC1657L            | 5V/3Vのパラレル16ビットV <sub>OUT</sub> DAC                   | 低消費電力、グリッヂ低減、レール・トゥ・レールV <sub>OUT</sub>                                                                                             |

| LTC1660/LTC1665             | 16ピン細型SSOP入りオクタル10/8ビットV <sub>OUT</sub> DAC           | V <sub>CC</sub> = 2.7V~5.5V、マイクロパワー、<br>レール・トゥ・レール出力                                                                                |

| LTC1661                     | 8ピンMSOPパッケージのデュアル10ビットV <sub>OUT</sub> DAC            | V <sub>CC</sub> = 2.7V~5.5V、60μA/DAC、レール・トゥ・レール出力                                                                                   |

| LTC1821                     | パラレル16ビット電圧出力DAC                                      | 10Vのステップに対して2μsで高精度16ビット・<br>セトリング                                                                                                  |

| LTC2600/LTC2610/<br>LTC2620 | 16ピンSSOP、オクタル16/14/12ビット・<br>レール・トゥ・レールDAC            | 250μA/DAC、2.5V~5.5V電源範囲、<br>レール・トゥ・レール出力                                                                                            |

2602fa