## 特長

- Easy Drive技術により、差動入力電流がゼロのレール・トゥ・レール入力が可能

- 最大限の精度で高インピーダンス・センサを直接デジタル化

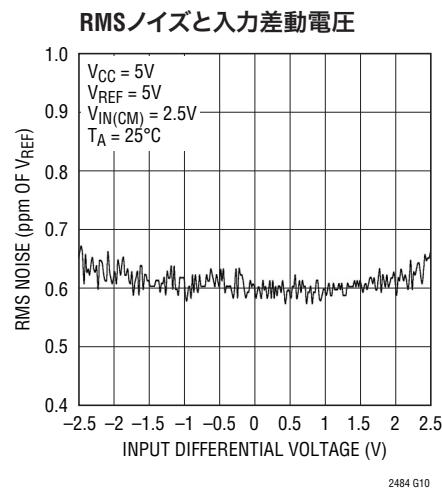

- RMSノイズ: 600nV

- GND～V<sub>CC</sub>の入力/リファレンス同相範囲

- 50Hz、60Hzまたは50Hz/60Hz同時の除去モードをプログラム可能

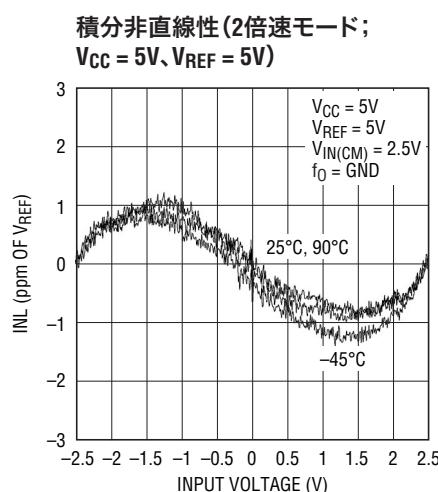

- INLが $\pm 2$ ppm、ミッキング・コードなし

- オフセットが1ppm、全未調整誤差が $\pm 15$ ppm

- 選択可能な2倍速モード

(内部発振器を使用した場合15Hz)

- 待ち時間なし: デジタル・フィルタは1サイクルでセトリング

- 2.7V～5.5V单一電源動作

- 内部発振器

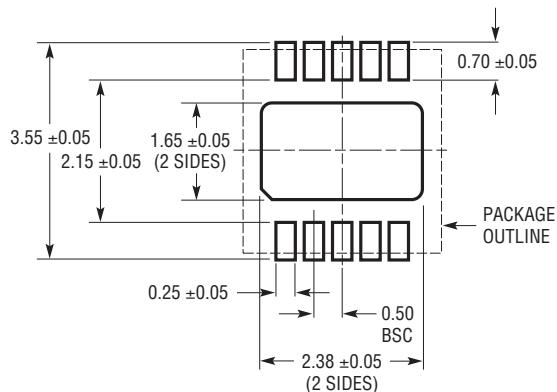

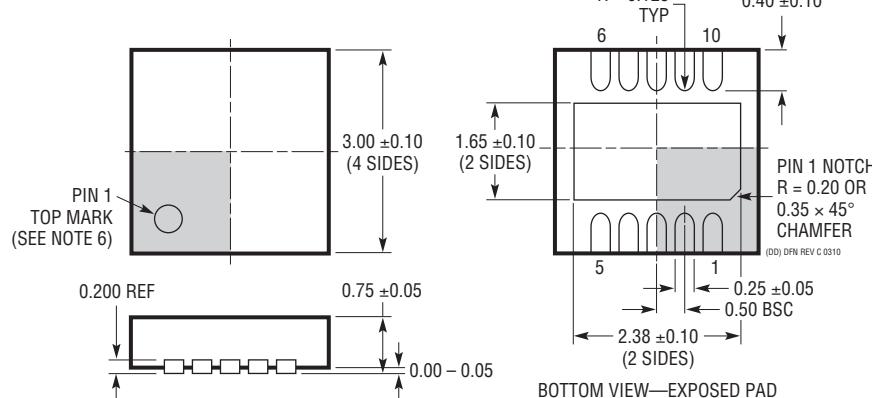

- 小型(3mm×3mm)10ピンDFNパッケージ

## アプリケーション

- ダイレクト・センサ・デジタイザ

- 秤

- 直接温度測定

- ストレイン・ゲージ・トランスジューサ

- 計測

- 産業用プロセス制御

- DVMおよびメータ

## 概要

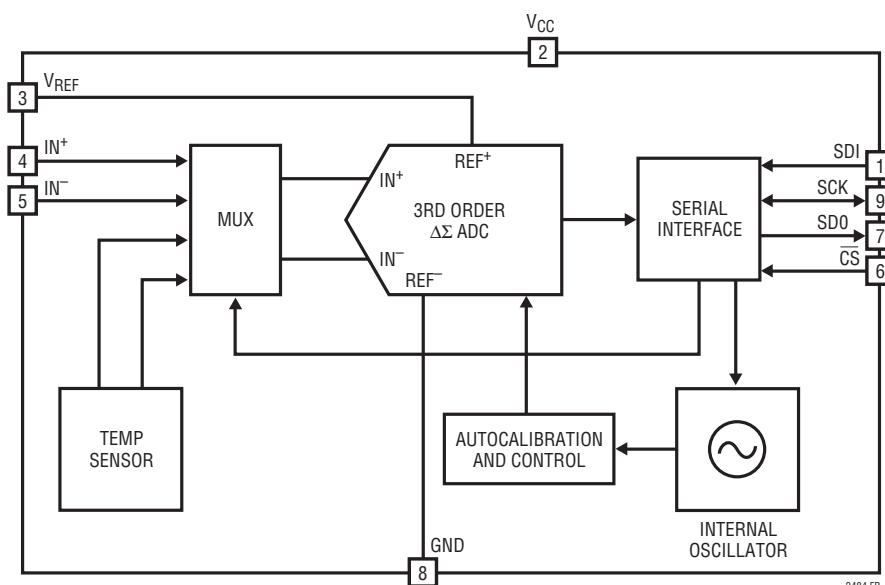

LTC<sup>®</sup>2484は、24ビットNo Latencyデルタシグマ・アナログ-デジタル・コンバータと特許取得のEasy Drive<sup>™</sup>技術を組み合わせたデバイスです。特許取得のサンプリング回路は、差動入力電流の自動キャンセルにより、ダイナミック入力電流誤差や内部バッファの欠点を排除します。このため、優れたDC精度を維持しながら、大きな外部ソース・インピーダンスを許容可能で、レール・トゥ・レールの入力範囲の入力信号を直接デジタル化できます。

LTC2484は温度センサと発振器を内蔵しています。LTC2484は、外部信号または内部温度センサを測定し、入力周波数を除去するように構成可能です。50Hz、60Hz、または50Hz/60Hz同時の入力周波数除去比を選択可能で、2倍速モードに設定することもできます。

LTC2484はリファレンス電圧と関係なく、広い同相入力電圧範囲(0V～V<sub>CC</sub>)が可能です。リファレンスは100mVという低電圧が可能、もしくは、V<sub>CC</sub>に直接接続可能です。LTC2484は調整された発振器を内蔵しているので、外付けの水晶発振子や発振器が不要です。連続した自動的なオフセットおよびフルスケール較正により、絶対精度と低ドリフトが自動的に維持されます。

**LT**、**LT**、**LTC**、**LTM**、**Linear Technology**および**Linear**のロゴはリニアテクノロジー社の登録商標です。**No Latency**  $\Delta\Delta$ と**Easy Drive**はリニアテクノロジー社の商標です。その他すべての商標の所有権は、それぞれの所有者に帰属します。特許出願中。

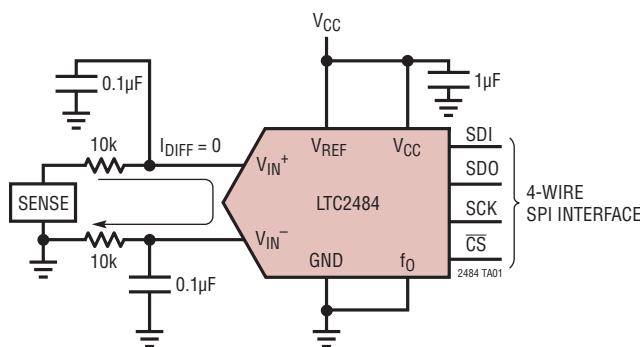

## 標準的応用例

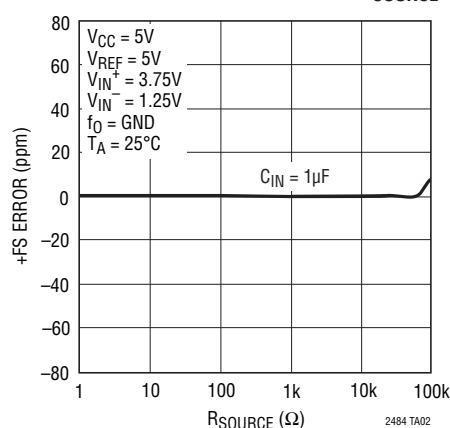

+FS誤差とIN<sup>+</sup>およびIN<sup>-</sup>のR<sub>SOURCE</sub>

## 絶対最大定格

(Note 1)

電源電圧( $V_{CC}$ )からGND .....  $-0.3V \sim 6V$

アナログ入力電圧からGND .....  $-0.3V \sim (V_{CC} + 0.3V)$

リファレンス入力電圧からGND .....  $-0.3V \sim (V_{CC} + 0.3V)$

デジタル入力電圧からGND .....  $-0.3V \sim (V_{CC} + 0.3V)$

デジタル出力電圧からGND .....  $-0.3V \sim (V_{CC} + 0.3V)$

動作温度範囲

LTC2484C .....  $0^{\circ}C \sim 70^{\circ}C$

LTC2484I .....  $-40^{\circ}C \sim 85^{\circ}C$

保存温度範囲 .....  $-65^{\circ}C \sim 125^{\circ}C$

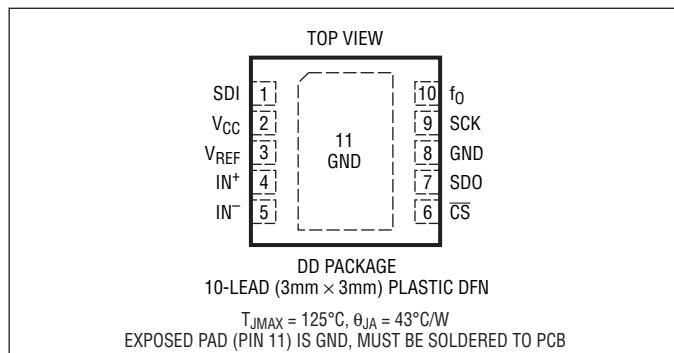

## ピン配置

## 発注情報

| 鉛フリー仕様         | テープアンドリール        | 製品マーキング* | パッケージ                           | 温度範囲                            |

|----------------|------------------|----------|---------------------------------|---------------------------------|

| LTC2484CDD#PBF | LTC2484CDD#TRPBF | LBSS     | 10-Lead (3mm x 3mm) Plastic DFN | $0^{\circ}C$ to $70^{\circ}C$   |

| LTC2484IDD#PBF | LTC2484IDD#TRPBF | LBSS     | 10-Lead (3mm x 3mm) Plastic DFN | $-40^{\circ}C$ to $85^{\circ}C$ |

さらに広い動作温度範囲で規定されるデバイスについては、弊社または弊社代理店にお問い合わせください。 \*温度グレードは出荷時のコンテナのラベルで識別されます。

鉛フリー仕様の製品マーキングの詳細については、<http://www.linear-tech.co.jp/leadfree/> をご覧ください。

テープアンドリールの仕様の詳細については、<http://www.linear-tech.co.jp/tapeandreel/> をご覧ください。

## 電気的特性(通常の速度)

●は全動作温度範囲の規格値を意味する。それ以外は $T_A = 25^{\circ}C$ での値。(Note 3, 4)

| PARAMETER                       | CONDITIONS                                                                                                                                                                                                          | MIN | TYP    | MAX | UNITS                                                    |

|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--------|-----|----------------------------------------------------------|

| Resolution (No Missing Codes)   | $0.1 \leq V_{REF} \leq V_{CC}$ , $-FS \leq V_{IN} \leq +FS$ (Note 5)                                                                                                                                                | ●   | 24     |     | Bits                                                     |

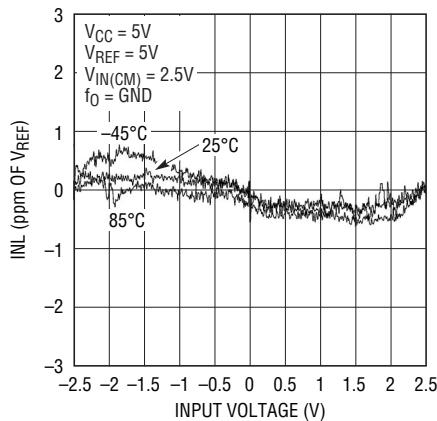

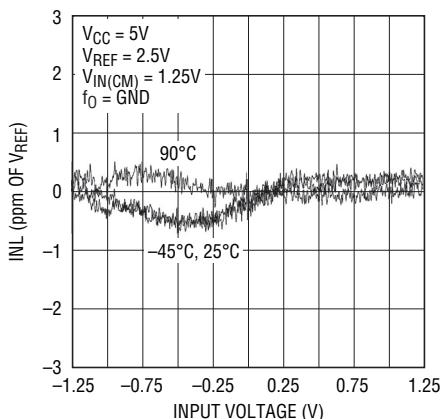

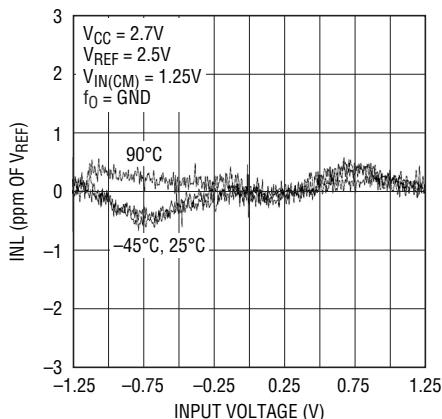

| Integral Nonlinearity           | $5V \leq V_{CC} \leq 5.5V$ , $V_{REF} = 5V$ , $V_{IN(CM)} = 2.5V$ (Note 6)<br>$2.7V \leq V_{CC} \leq 5.5V$ , $V_{REF} = 2.5V$ , $V_{IN(CM)} = 1.25V$ (Note 6)                                                       | ●   | 2<br>1 | 10  | ppm of $V_{REF}$<br>ppm of $V_{REF}$                     |

| Offset Error                    | $2.5V \leq V_{REF} \leq V_{CC}$ , $GND \leq IN^+ = IN^- \leq V_{CC}$ (Note 14)                                                                                                                                      | ●   | 0.5    | 2.5 | $\mu V$                                                  |

| Offset Error Drift              | $2.5V \leq V_{REF} \leq V_{CC}$ , $GND \leq IN^+ = IN^- \leq V_{CC}$                                                                                                                                                |     | 10     |     | $nV/\text{ }^{\circ}C$                                   |

| Positive Full-Scale Error       | $2.5V \leq V_{REF} \leq V_{CC}$ , $IN^+ = 0.75V_{REF}$ , $IN^- = 0.25V_{REF}$                                                                                                                                       | ●   |        | 25  | ppm of $V_{REF}$                                         |

| Positive Full-Scale Error Drift | $2.5V \leq V_{REF} \leq V_{CC}$ , $IN^+ = 0.75V_{REF}$ , $IN^- = 0.25V_{REF}$                                                                                                                                       |     |        | 0.1 | ppm of $V_{REF}/\text{ }^{\circ}C$                       |

| Negative Full-Scale Error       | $2.5V \leq V_{REF} \leq V_{CC}$ , $IN^+ = 0.75V_{REF}$ , $IN^- = 0.25V_{REF}$                                                                                                                                       | ●   |        | 25  | ppm of $V_{REF}$                                         |

| Negative Full-Scale Error Drift | $2.5V \leq V_{REF} \leq V_{CC}$ , $IN^+ = 0.75V_{REF}$ , $IN^- = 0.25V_{REF}$                                                                                                                                       |     |        | 0.1 | ppm of $V_{REF}/\text{ }^{\circ}C$                       |

| Total Unadjusted Error          | $5V \leq V_{CC} \leq 5.5V$ , $V_{REF} = 2.5V$ , $V_{IN(CM)} = 1.25V$<br>$5V \leq V_{CC} \leq 5.5V$ , $V_{REF} = 5V$ , $V_{IN(CM)} = 2.5V$<br>$2.7V \leq V_{CC} \leq 5.5V$ , $V_{REF} = 2.5V$ , $V_{IN(CM)} = 1.25V$ |     |        | 15  | ppm of $V_{REF}$<br>ppm of $V_{REF}$<br>ppm of $V_{REF}$ |

| Output Noise                    | $5V \leq V_{CC} \leq 5.5V$ , $V_{REF} = 5V$ , $GND \leq IN^- = IN^+ \leq V_{CC}$ (Note 13)                                                                                                                          |     |        | 0.6 | $\mu V_{RMS}$                                            |

| Internal PTAT Signal            | $T_A = 27^{\circ}C$                                                                                                                                                                                                 |     | 390    | 450 | mV                                                       |

## 電気的特性(2倍速)

●は全動作温度範囲の規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。(Note 3, 4)

| PARAMETER                       | CONDITIONS                                                                                                                                                                                                                                                      | MIN | TYP    | MAX | UNITS                                              |

|---------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--------|-----|----------------------------------------------------|

| Resolution (No Missing Codes)   | $0.1 \leq V_{\text{REF}} \leq V_{\text{CC}}$ , $-\text{FS} \leq V_{\text{IN}} \leq +\text{FS}$ (Note 5)                                                                                                                                                         | ●   | 24     |     | Bits                                               |

| Integral Nonlinearity           | $5\text{V} \leq V_{\text{CC}} \leq 5.5\text{V}$ , $V_{\text{REF}} = 5\text{V}$ , $V_{\text{IN(CM)}} = 2.5\text{V}$ (Note 6)<br>$2.7\text{V} \leq V_{\text{CC}} \leq 5.5\text{V}$ , $V_{\text{REF}} = 2.5\text{V}$ , $V_{\text{IN(CM)}} = 1.25\text{V}$ (Note 6) | ●   | 2<br>1 | 10  | ppm of $V_{\text{REF}}$<br>ppm of $V_{\text{REF}}$ |

| Offset Error                    | $2.5\text{V} \leq V_{\text{REF}} \leq V_{\text{CC}}$ , $\text{GND} \leq \text{IN}^+ = \text{IN}^- \leq V_{\text{CC}}$ (Note 14)                                                                                                                                 | ●   | 0.5    | 2   | mV                                                 |

| Offset Error Drift              | $2.5\text{V} \leq V_{\text{REF}} \leq V_{\text{CC}}$ , $\text{GND} \leq \text{IN}^+ = \text{IN}^- \leq V_{\text{CC}}$                                                                                                                                           |     | 100    |     | nV/ $^\circ\text{C}$                               |

| Positive Full-Scale Error       | $2.5\text{V} \leq V_{\text{REF}} \leq V_{\text{CC}}$ , $\text{IN}^+ = 0.75V_{\text{REF}}$ , $\text{IN}^- = 0.25V_{\text{REF}}$                                                                                                                                  | ●   |        | 25  | ppm of $V_{\text{REF}}$                            |

| Positive Full-Scale Error Drift | $2.5\text{V} \leq V_{\text{REF}} \leq V_{\text{CC}}$ , $\text{IN}^+ = 0.75V_{\text{REF}}$ , $\text{IN}^- = 0.25V_{\text{REF}}$                                                                                                                                  |     | 0.1    |     | ppm of $V_{\text{REF}}/^\circ\text{C}$             |

| Negative Full-Scale Error       | $2.5\text{V} \leq V_{\text{REF}} \leq V_{\text{CC}}$ , $\text{IN}^+ = 0.75V_{\text{REF}}$ , $\text{IN}^- = 0.25V_{\text{REF}}$                                                                                                                                  | ●   |        | 25  | ppm of $V_{\text{REF}}$                            |

| Negative Full-Scale Error Drift | $2.5\text{V} \leq V_{\text{REF}} \leq V_{\text{CC}}$ , $\text{IN}^+ = 0.75V_{\text{REF}}$ , $\text{IN}^- = 0.25V_{\text{REF}}$                                                                                                                                  |     | 0.1    |     | ppm of $V_{\text{REF}}/^\circ\text{C}$             |

| Output Noise                    | $5\text{V} \leq V_{\text{CC}} \leq 5.5\text{V}$ , $V_{\text{REF}} = 5\text{V}$ , $\text{GND} \leq \text{IN}^- = \text{IN}^+ \leq V_{\text{CC}}$ (Note 13)                                                                                                       |     | 0.84   |     | $\mu\text{VRMS}$                                   |

## コンバータ特性

●は全動作温度範囲の規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。(Note 3, 4)

| PARAMETER                                       | CONDITIONS                                                                                                                         | MIN | TYP | MAX | UNITS |

|-------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|-------|

| Input Common Mode Rejection DC                  | $2.5\text{V} \leq V_{\text{REF}} \leq V_{\text{CC}}$ , $\text{GND} \leq \text{IN}^- = \text{IN}^+ \leq V_{\text{CC}}$ (Note 5)     | ●   | 140 |     | dB    |

| Input Common Mode Rejection 50Hz $\pm 2\%$      | $2.5\text{V} \leq V_{\text{REF}} \leq V_{\text{CC}}$ , $\text{GND} \leq \text{IN}^- = \text{IN}^+ \leq V_{\text{CC}}$ (Note 5)     | ●   | 140 |     | dB    |

| Input Common Mode Rejection 60Hz $\pm 2\%$      | $2.5\text{V} \leq V_{\text{REF}} \leq V_{\text{CC}}$ , $\text{GND} \leq \text{IN}^- = \text{IN}^+ \leq V_{\text{CC}}$ (Note 5)     | ●   | 140 |     | dB    |

| Input Normal Mode Rejection 50Hz $\pm 2\%$      | $2.5\text{V} \leq V_{\text{REF}} \leq V_{\text{CC}}$ , $\text{GND} \leq \text{IN}^- = \text{IN}^+ \leq V_{\text{CC}}$ (Notes 5, 7) | ●   | 110 | 120 | dB    |

| Input Normal Mode Rejection 60Hz $\pm 2\%$      | $2.5\text{V} \leq V_{\text{REF}} \leq V_{\text{CC}}$ , $\text{GND} \leq \text{IN}^- = \text{IN}^+ \leq V_{\text{CC}}$ (Notes 5, 8) | ●   | 110 | 120 | dB    |

| Input Normal Mode Rejection 50Hz/60Hz $\pm 2\%$ | $2.5\text{V} \leq V_{\text{REF}} \leq V_{\text{CC}}$ , $\text{GND} \leq \text{IN}^- = \text{IN}^+ \leq V_{\text{CC}}$ (Notes 5, 9) | ●   | 87  |     | dB    |

| Reference Common Mode Rejection DC              | $2.5\text{V} \leq V_{\text{REF}} \leq V_{\text{CC}}$ , $\text{GND} \leq \text{IN}^- = \text{IN}^+ \leq V_{\text{CC}}$ (Note 5)     | ●   | 120 | 140 | dB    |

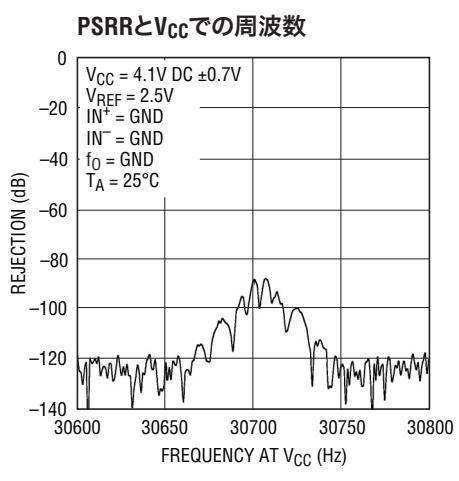

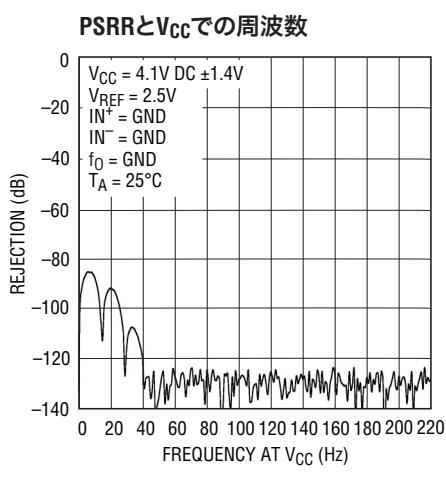

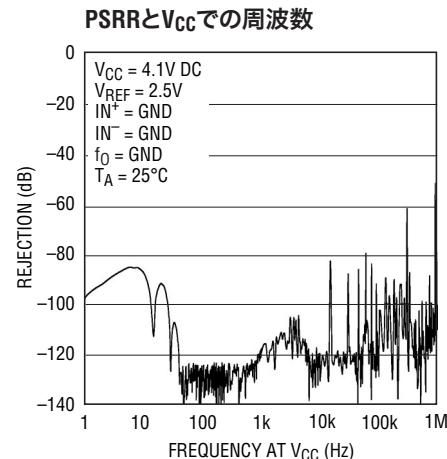

| Power Supply Rejection DC                       | $V_{\text{REF}} = 2.5\text{V}$ , $\text{IN}^- = \text{IN}^+ = \text{GND}$                                                          |     | 120 |     | dB    |

| Power Supply Rejection, 50Hz $\pm 2\%$          | $V_{\text{REF}} = 2.5\text{V}$ , $\text{IN}^- = \text{IN}^+ = \text{GND}$ (Note 7)                                                 |     | 120 |     | dB    |

| Power Supply Rejection, 60Hz $\pm 2\%$          | $V_{\text{REF}} = 2.5\text{V}$ , $\text{IN}^- = \text{IN}^+ = \text{GND}$ (Note 8)                                                 |     | 120 |     | dB    |

## アナログ入力とリファレンス

●は全動作温度範囲の規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。(Note 3)

| SYMBOL           | PARAMETER                                                            | CONDITIONS | MIN        | TYP                  | MAX                           | UNITS |

|------------------|----------------------------------------------------------------------|------------|------------|----------------------|-------------------------------|-------|

| $\text{IN}^+$    | Absolute/Common Mode $\text{IN}^+$ Voltage                           |            | GND - 0.3V |                      | $V_{\text{CC}} + 0.3\text{V}$ | V     |

| $\text{IN}^-$    | Absolute/Common Mode $\text{IN}^-$ Voltage                           |            | GND - 0.3V |                      | $V_{\text{CC}} + 0.3\text{V}$ | V     |

| FS               | Full-Scale of the Differential Input ( $\text{IN}^+ - \text{IN}^-$ ) |            | ●          | 0.5 $V_{\text{REF}}$ |                               | V     |

| LSB              | Least Significant Bit of the Output Code                             |            | ●          | $\text{FS}/2^{24}$   |                               |       |

| $V_{\text{IN}}$  | Input Differential Voltage Range ( $\text{IN}^+ - \text{IN}^-$ )     |            | ●          | -FS                  | +FS                           | V     |

| $V_{\text{REF}}$ | Reference Voltage Range                                              |            | ●          | 0.1                  | $V_{\text{CC}}$               | V     |

## アナログ入力とリファレンス

●は全動作温度範囲の規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。(Note 3)

| SYMBOL                                | PARAMETER                             | CONDITIONS                                   | MIN | TYP  | MAX | UNITS |    |

|---------------------------------------|---------------------------------------|----------------------------------------------|-----|------|-----|-------|----|

| $C_S(\text{IN}^+)$                    | $\text{IN}^+$ Sampling Capacitance    |                                              |     | 11   |     | pF    |    |

| $C_S(\text{IN}^-)$                    | $\text{IN}^-$ Sampling Capacitance    |                                              |     | 11   |     | pF    |    |

| $C_S(V_{\text{REF}})$                 | $V_{\text{REF}}$ Sampling Capacitance |                                              |     | 11   |     | pF    |    |

| $I_{\text{DC\_LEAK}}(\text{IN}^+)$    | $\text{IN}^+$ DC Leakage Current      | Sleep Mode, $\text{IN}^+ = \text{GND}$       | ●   | -10  | 1   | 10    | nA |

| $I_{\text{DC\_LEAK}}(\text{IN}^-)$    | $\text{IN}^-$ DC Leakage Current      | Sleep Mode, $\text{IN}^- = \text{GND}$       | ●   | -10  | 1   | 10    | nA |

| $I_{\text{DC\_LEAK}}(V_{\text{REF}})$ | $V_{\text{REF}}$ DC Leakage Current   | Sleep Mode, $V_{\text{REF}} = V_{\text{CC}}$ | ●   | -100 | 1   | 100   | nA |

## デジタル入力とデジタル出力

●は全動作温度範囲の規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。(Note 3)

| SYMBOL          | PARAMETER                                                            | CONDITIONS                                                  | MIN | TYP                   | MAX | UNITS         |

|-----------------|----------------------------------------------------------------------|-------------------------------------------------------------|-----|-----------------------|-----|---------------|

| $V_{\text{IH}}$ | High Level Input Voltage<br>$\overline{\text{CS}}, f_0, \text{SDI}$  | $2.7\text{V} \leq V_{\text{CC}} \leq 5.5\text{V}$ (Note 16) | ●   | $V_{\text{CC}} - 0.5$ |     | V             |

| $V_{\text{IL}}$ | Low Level Input Voltage<br>$\overline{\text{CS}}, f_0, \text{SDI}$   | $2.7\text{V} \leq V_{\text{CC}} \leq 5.5\text{V}$           | ●   |                       | 0.5 | V             |

| $V_{\text{IH}}$ | High Level Input Voltage<br>SCK                                      | $2.7\text{V} \leq V_{\text{CC}} \leq 5.5\text{V}$ (Note 10) | ●   | $V_{\text{CC}} - 0.5$ |     | V             |

| $V_{\text{IL}}$ | Low Level Input Voltage<br>SCK                                       | $2.7\text{V} \leq V_{\text{CC}} \leq 5.5\text{V}$ (Note 10) | ●   |                       | 0.5 | V             |

| $I_{\text{IN}}$ | Digital Input Current<br>$\overline{\text{CS}}, f_0, \text{SDI}$     | $0\text{V} \leq V_{\text{IN}} \leq V_{\text{CC}}$           | ●   | -10                   | 10  | $\mu\text{A}$ |

| $I_{\text{IN}}$ | Digital Input Current<br>SCK                                         | $0\text{V} \leq V_{\text{IN}} \leq V_{\text{CC}}$ (Note 10) | ●   | -10                   | 10  | $\mu\text{A}$ |

| $C_{\text{IN}}$ | Digital Input Capacitance<br>$\overline{\text{CS}}, f_0, \text{SDI}$ |                                                             |     | 10                    |     | pF            |

| $C_{\text{IN}}$ | Digital Input Capacitance<br>SCK                                     |                                                             |     | 10                    |     | pF            |

| $V_{\text{OH}}$ | High Level Output Voltage<br>SDO                                     | $I_0 = -800\mu\text{A}$                                     | ●   | $V_{\text{CC}} - 0.5$ |     | V             |

| $V_{\text{OL}}$ | Low Level Output Voltage<br>SDO                                      | $I_0 = 1.6\text{mA}$                                        | ●   |                       | 0.4 | V             |

| $V_{\text{OH}}$ | High Level Output Voltage<br>SCK                                     | $I_0 = -800\mu\text{A}$                                     | ●   | $V_{\text{CC}} - 0.5$ |     | V             |

| $V_{\text{OL}}$ | Low Level Output Voltage<br>SCK                                      | $I_0 = 1.6\text{mA}$                                        | ●   |                       | 0.4 | V             |

| $I_{\text{OZ}}$ | Hi-Z Output Leakage<br>SDO                                           |                                                             | ●   | -10                   | 10  | $\mu\text{A}$ |

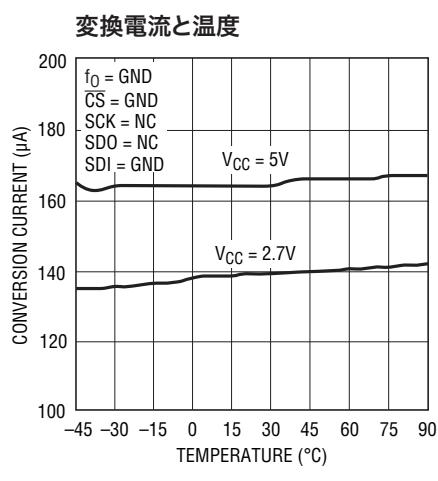

## 電源要件

●は全動作温度範囲の規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。(Note 3)

| SYMBOL          | PARAMETER      | CONDITIONS                                        | MIN | TYP | MAX | UNITS         |

|-----------------|----------------|---------------------------------------------------|-----|-----|-----|---------------|

| $V_{\text{CC}}$ | Supply Voltage |                                                   | ●   | 2.7 | 5.5 | V             |

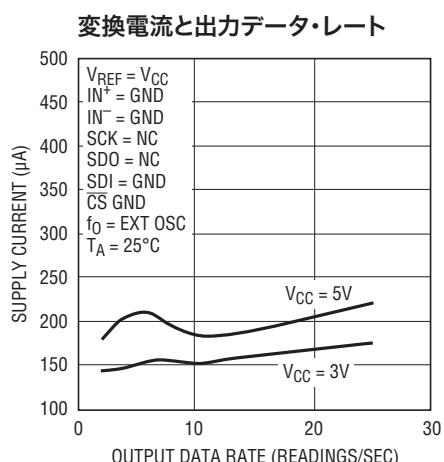

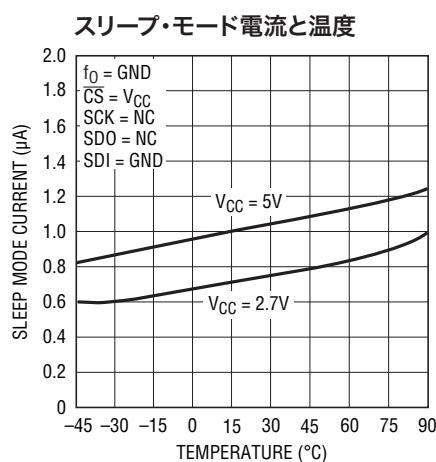

| $I_{\text{CC}}$ | Supply Current | Conversion Mode (Note 12)<br>Sleep Mode (Note 12) | ●   | 160 | 250 | $\mu\text{A}$ |

|                 |                |                                                   | ●   | 1   | 2   | $\mu\text{A}$ |

## タイミング特性

●は全動作温度範囲の規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。(Note 3)

| SYMBOL                  | PARAMETER                                             | CONDITIONS                                                                   | MIN              | TYP                                                          | MAX                              | UNITS                |

|-------------------------|-------------------------------------------------------|------------------------------------------------------------------------------|------------------|--------------------------------------------------------------|----------------------------------|----------------------|

| $f_{\text{EOSC}}$       | External Oscillator Frequency Range                   | (Note 15)                                                                    | ●                | 10                                                           | 1000                             | kHz                  |

| $t_{\text{HEO}}$        | External Oscillator High Period                       |                                                                              | ●                | 0.125                                                        | 100                              | μs                   |

| $t_{\text{LEO}}$        | External Oscillator Low Period                        |                                                                              | ●                | 0.125                                                        | 100                              | μs                   |

| $t_{\text{CONV\_1}}$    | Conversion Time for 1x Speed Mode                     | 50Hz Mode<br>60Hz Mode<br>Simultaneous 50Hz/60Hz Mode<br>External Oscillator | ●<br>●<br>●<br>● | 157.2<br>131.0<br>144.1<br>41036/ $f_{\text{EOSC}}$ (in kHz) | 160.3<br>133.6<br>146.9<br>163.5 | ms<br>ms<br>ms<br>ms |

| $t_{\text{CONV\_2}}$    | Conversion Time for 2x Speed Mode                     | 50Hz Mode<br>60Hz Mode<br>Simultaneous 50Hz/60Hz Mode<br>External Oscillator | ●<br>●<br>●<br>● | 78.7<br>65.6<br>72.2<br>20556/ $f_{\text{EOSC}}$ (in kHz)    | 80.3<br>66.9<br>73.6<br>81.9     | ms<br>ms<br>ms<br>ms |

| $f_{\text{SCK}}$        | Internal SCK Frequency                                | Internal Oscillator (Note 10)<br>External Oscillator (Notes 10, 11)          |                  |                                                              | 38.4<br>$f_{\text{EOSC}}/8$      | kHz<br>kHz           |

| $D_{\text{SCK}}$        | Internal SCK Duty Cycle                               | (Note 10)                                                                    | ●                | 45                                                           | 55                               | %                    |

| $f_{\text{ESCK}}$       | External SCK Frequency Range                          | (Note 10)                                                                    | ●                |                                                              | 4000                             | kHz                  |

| $t_{\text{LESCK}}$      | External SCK Low Period                               | (Note 10)                                                                    | ●                | 125                                                          |                                  | ns                   |

| $t_{\text{HESCK}}$      | External SCK High Period                              | (Note 10)                                                                    | ●                | 125                                                          |                                  | ns                   |

| $t_{\text{DOUT\_ISCK}}$ | Internal SCK 32-Bit Data Output Time                  | Internal Oscillator (Notes 10, 12)<br>External Oscillator (Notes 10, 11)     | ●<br>●           | 0.81<br>256/ $f_{\text{EOSC}}$ (in kHz)                      | 0.83<br>0.85                     | ms<br>ms             |

| $t_{\text{DOUT\_ESCK}}$ | External SCK 32-Bit Data Output Time                  | (Note 10)                                                                    | ●                |                                                              | 32/ $f_{\text{ESCK}}$ (in kHz)   | ms                   |

| $t_1$                   | $\overline{\text{CS}} \downarrow$ to SDO Low          |                                                                              | ●                | 0                                                            | 200                              | ns                   |

| $t_2$                   | $\overline{\text{CS}} \uparrow$ to SDO Hi-Z           |                                                                              | ●                | 0                                                            | 200                              | ns                   |

| $t_3$                   | $\overline{\text{CS}} \downarrow$ to SCK $\downarrow$ | (Note 10)                                                                    | ●                | 0                                                            | 200                              | ns                   |

| $t_4$                   | $\overline{\text{CS}} \downarrow$ to SCK $\uparrow$   | (Note 10)                                                                    | ●                | 50                                                           |                                  | ns                   |

| $t_{\text{KQMAX}}$      | SCK $\downarrow$ to SDO Valid                         |                                                                              | ●                |                                                              | 200                              | ns                   |

| $t_{\text{KQMIN}}$      | SDO Hold After SCK $\downarrow$                       | (Note 5)                                                                     | ●                | 15                                                           |                                  | ns                   |

| $t_5$                   | SCK Set-Up Before $\overline{\text{CS}} \downarrow$   |                                                                              | ●                | 50                                                           |                                  | ns                   |

| $t_6$                   | SCK Hold After $\overline{\text{CS}} \downarrow$      |                                                                              | ●                |                                                              | 50                               | ns                   |

| $t_7$                   | SDI Setup Before SCK $\uparrow$                       | (Note 5)                                                                     | ●                | 100                                                          |                                  | ns                   |

| $t_8$                   | SDI Hold After SCK $\uparrow$                         | (Note 5)                                                                     | ●                | 100                                                          |                                  | ns                   |

**Note 1:**絶対最大定格に記載された値を超えるストレスはデバイスに永続的損傷を与える可能性がある。長期にわたって絶対最大定格条件に曝すと、デバイスの信頼性と寿命に悪影響を与える可能性がある。

**Note 2:**すべての電圧値はGNDを基準にしている。

**Note 3:**注記がない限り、 $V_{\text{CC}} = 2.7\text{V} \sim 5.5\text{V}$ 。

$$V_{\text{REFCM}} = V_{\text{REF}}/2, F_{\text{S}} = 0.5V_{\text{REF}} \\ V_{\text{IN}} = \text{IN}^+ - \text{IN}^-, V_{\text{IN(CM)}} = (\text{IN}^+ + \text{IN}^-)/2$$

**Note 4:**注記がない限り、内部変換クロックまたは $f_{\text{EOSC}} = 307.2\text{kHz}$ の外部変換クロック・ソースを使う。

**Note 5:**設計によって保証されているが、テストされない。

**Note 6:**積分非直線性は、実際の伝達曲線のエンドポイントを通る直線からのコードの偏差として定義されている。偏差は量子化幅の中心から測定される。

**Note 7:**50Hzモード(内部発振器)または $f_{\text{EOSC}} = 256\text{kHz} \pm 2\%$ (外部発振器)

**Note 8:**60Hzモード(内部発振器)または $f_{\text{EOSC}} = 307.2\text{kHz} \pm 2\%$ (外部発振器)

**Note 9:**同時50Hz/60Hzモード(内部発振器)または $f_{\text{EOSC}} = 280\text{kHz} \pm 2\%$ (外部発振器)

**Note 10:**SCKは外部SCKモードまたは内部SCKモードで構成設定することができる。外部SCKモードでは、SCKピンはデジタル入力として使われ、ドライビング・クロックは $f_{\text{ESCK}}$ である。内部SCKモードでは、SCKピンはデジタル出力として使われ、データ出力時の出力クロック信号は $f_{\text{SCK}}$ である。

**Note 11:**外部発振器は $f_0$ ピンに接続されている。外部発振器の周波数( $f_{\text{EOSC}}$ )はkHzで表されている。

**Note 12:**コンバータは内部発振器を使用する。

**Note 13:**出力ノイズには内部較正動作によって生じる分が含まれる。

**Note 14:**設計およびテストの相関により保証されている。

**Note 15:**性能とデータ・レートのグラフについては、「アプリケーション情報」のセクションを参照。

**Note 16:** $V_{\text{CC}} < 3\text{V}$ の場合、 $f_0$ ピンの $V_{\text{IH}}$ は2.5V。

## 標準的性能特性

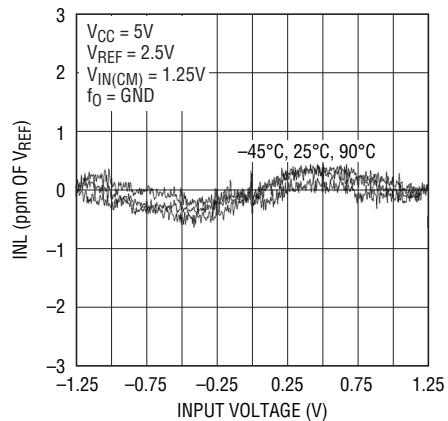

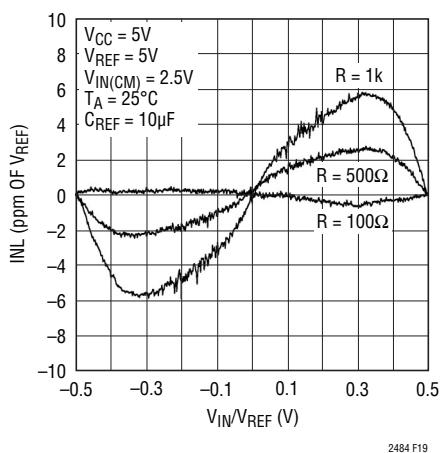

### 積分非直線性

( $V_{CC} = 5V$ 、 $V_{REF} = 5V$ )

### 積分非直線性

( $V_{CC} = 5V$ 、 $V_{REF} = 2.5V$ )

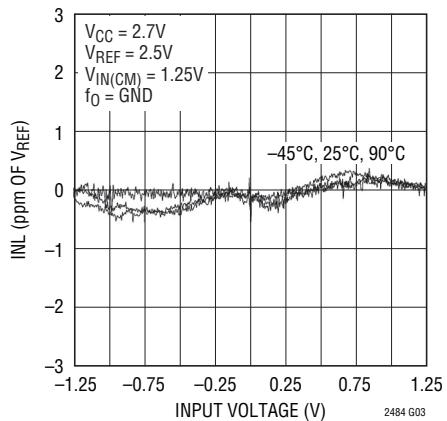

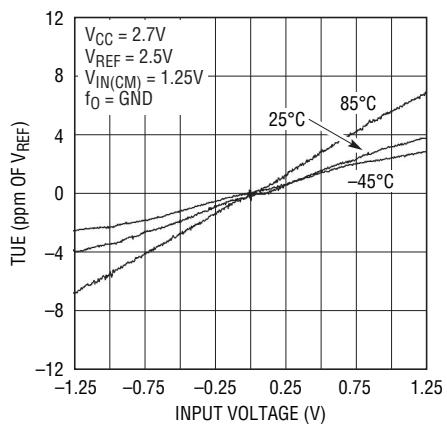

### 積分非直線性

( $V_{CC} = 2.7V$ 、 $V_{REF} = 2.5V$ )

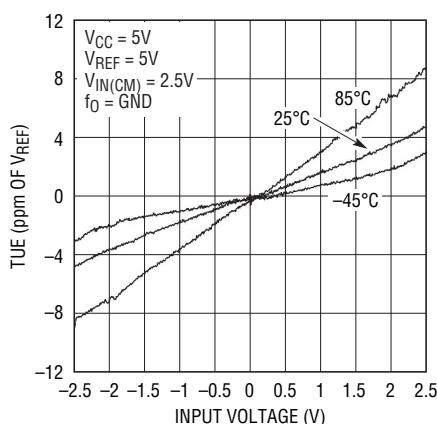

### 全未調整誤差

( $V_{CC} = 5V$ 、 $V_{REF} = 5V$ )

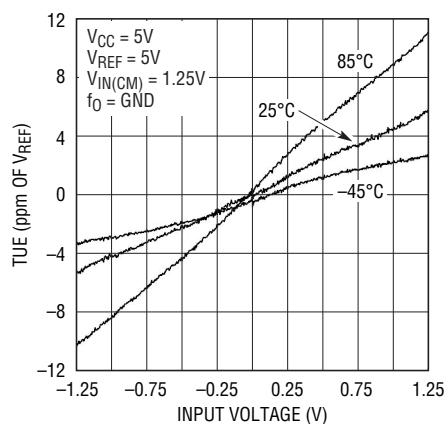

### 全未調整誤差

( $V_{CC} = 5V$ 、 $V_{REF} = 2.5V$ )

### 全未調整誤差

( $V_{CC} = 2.7V$ 、 $V_{REF} = 2.5V$ )

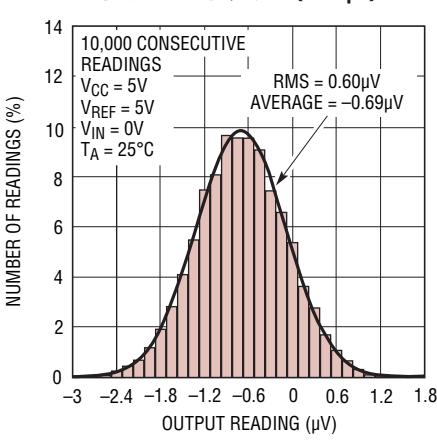

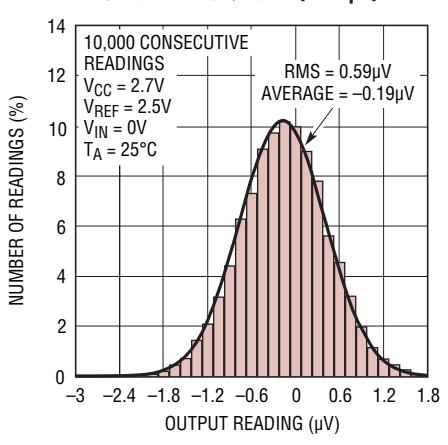

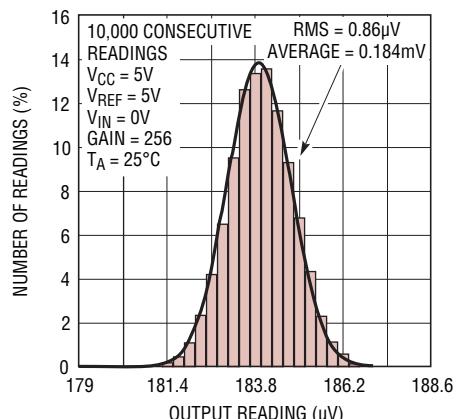

### ノイズのヒストグラム (6.8sps)

### ノイズのヒストグラム (7.5sps)

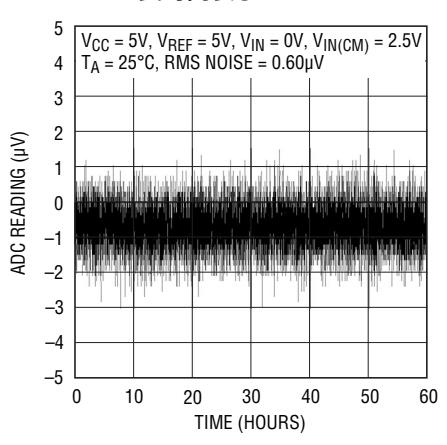

### ADCの長時間表示

## 標準的性能特性

## 標準的性能特性

## 標準的性能特性

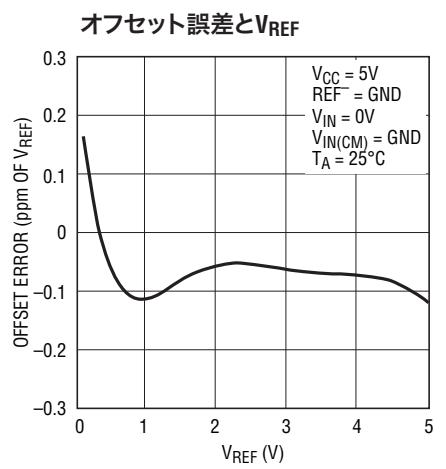

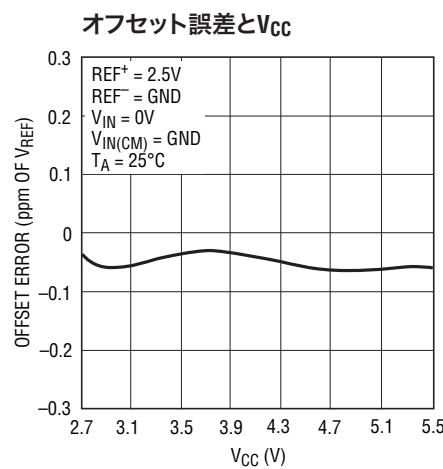

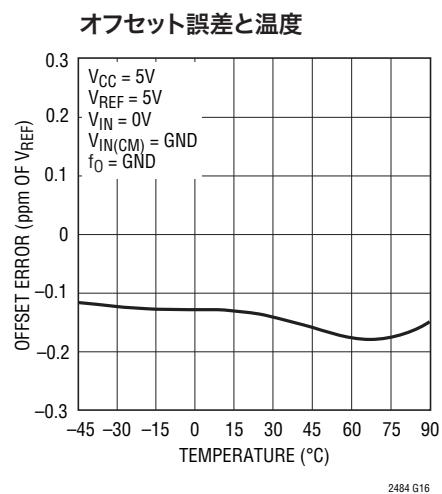

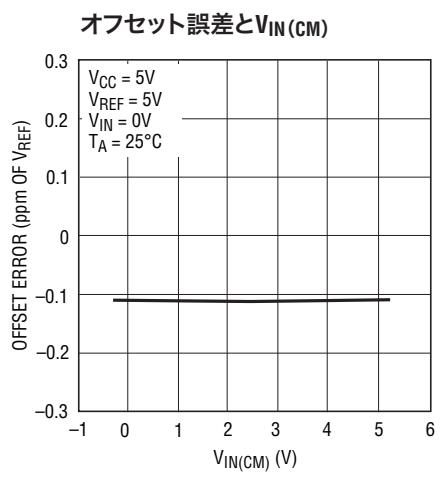

積分非直線性(2倍速モード;

$V_{CC} = 5V$ ,  $V_{REF} = 2.5V$ )積分非直線性(2倍速モード;

$V_{CC} = 2.7V$ ,  $V_{REF} = 2.5V$ )ノイズのヒストグラム

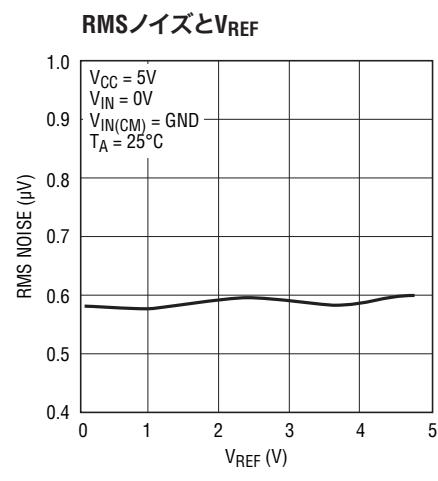

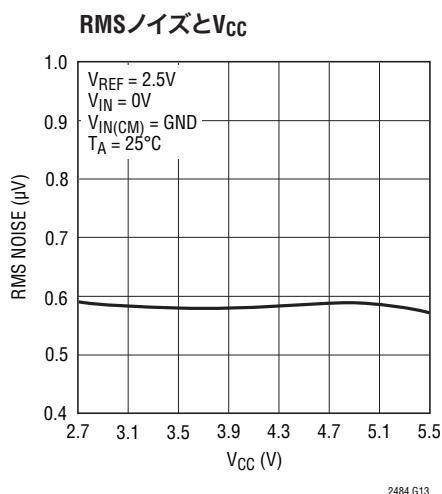

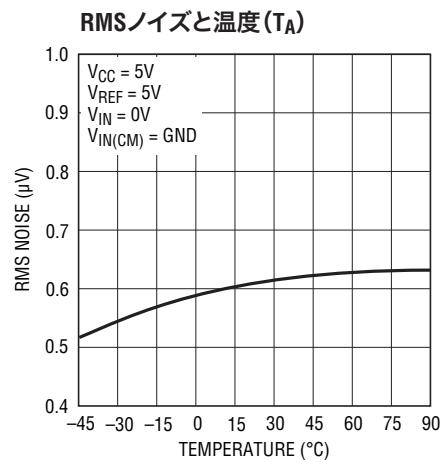

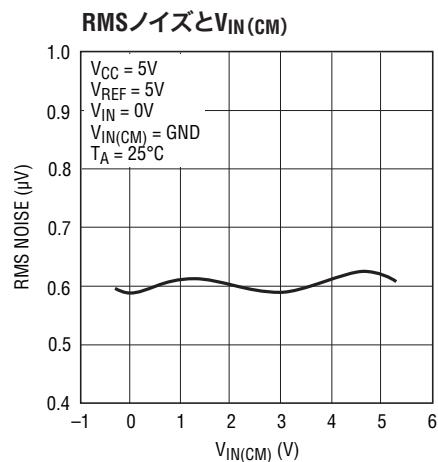

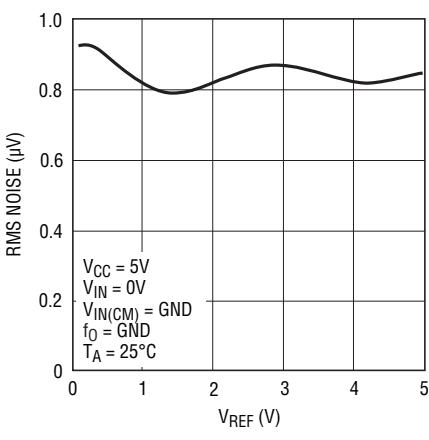

(2倍速モード)RMSノイズと $V_{REF}$

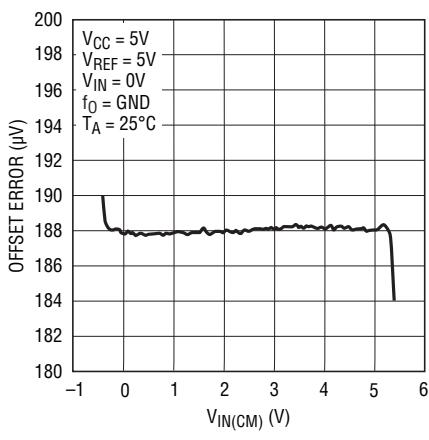

(2倍速モード)オフセット誤差と $V_{IN(CM)}$

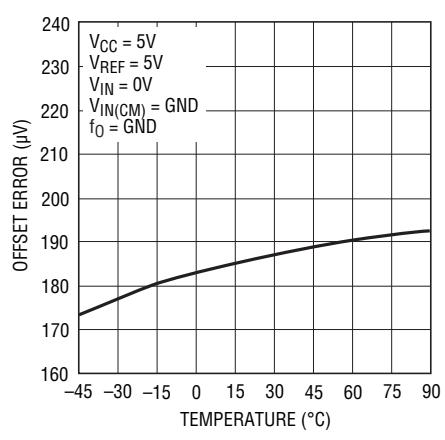

(2倍速モード)オフセット誤差と温度

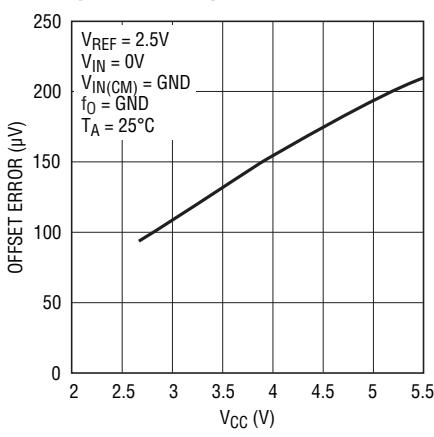

(2倍速モード)オフセット誤差と $V_{CC}$

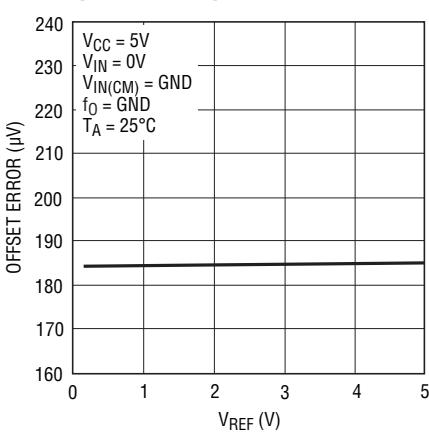

(2倍速モード)オフセット誤差と $V_{REF}$

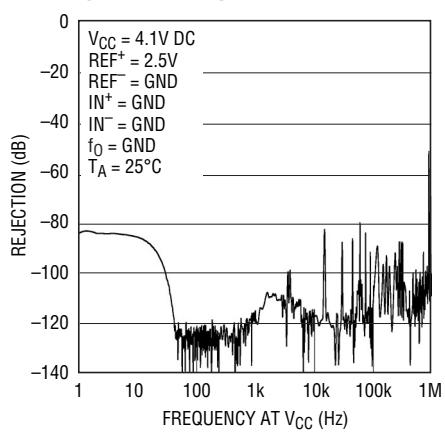

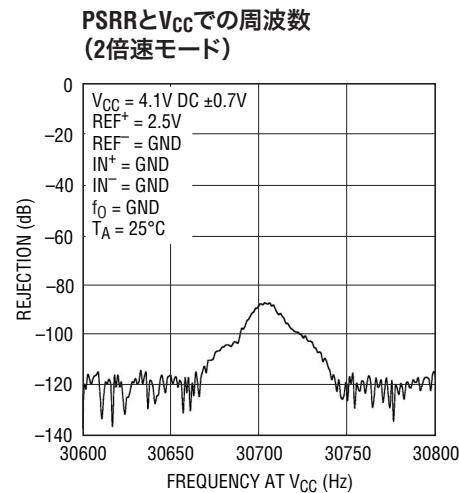

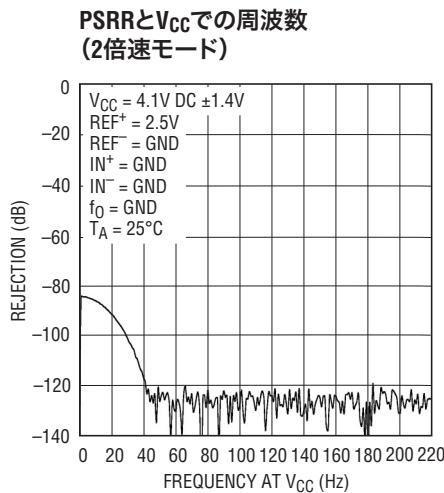

(2倍速モード)PSRRと $V_{CC}$ での周波数

(2倍速モード)

## 標準的性能特性

## ピン機能

**SDI(ピン1):**シリアル・データ入力。このピンは、ライン周波数除去、入力、温度センサおよび2倍速モードを選択するのに使います。データはシリアル・クロック(SCK)の立上りエッジでシフトされてSDIピンに入力されます。

**V<sub>CC</sub>(ピン2):**正電源電圧。1μFのタンタル・コンデンサと0.1μFのセラミック・コンデンサを並列に使って、デバイスのできるだけ近くでGND(ピン8)にバイパスします。

**V<sub>REF</sub>(ピン3):**正のリファレンス入力。このピンの電圧は0.1VとV<sub>CC</sub>のあいだの任意の値にすることができます。負のリファレンス入力はGND(ピン8)です。

**IN<sup>+</sup>(ピン4)、IN<sup>-</sup>(ピン5):**差動アナログ入力。これらのピンの電圧はGND-0.3VとV<sub>CC</sub>+0.3Vのあいだの任意の値をとることができます。これらのリミット内では、コンバータのバイポーラ入力範囲(V<sub>IN</sub> = IN<sup>+</sup>-IN<sup>-</sup>)は-0.5 • V<sub>REF</sub>~0.5 • V<sub>REF</sub>となります。この入力範囲の外側では、コンバータは固有のオーバーレンジとアンダーレンジの出力コードを発生します。

**CS(ピン6):**アクティブ“L”的チップ・セレクト。このピンを“L”にすると、デジタル入力/出力がイネーブルされ、ADCが覚醒します。各変換の後、ADCは自動的にスリープ・モードに入り、CSが“H”に留まる限りこの省電力状態に保たれます。「データ出力」の転送中にCSが“L”から“H”に遷移すると、データ転送が中止され、新たに変換が開始されます。

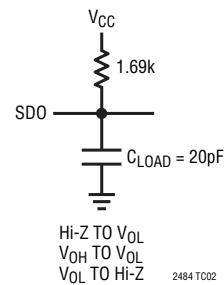

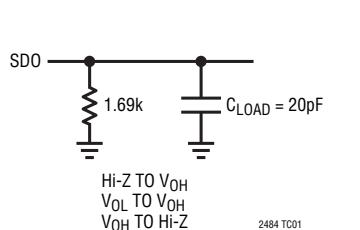

**SDO(ピン7):**スリーステートのデジタル出力。「データ出力」の期間中、このピンはシリアル・データ出力として使われます。チップ・セレクトCSが“H”的とき(CS = V<sub>CC</sub>)、SDOピンは高インピーダンス状態になります。変換とスリープのあいだ、このピンは変換状態出力として使われます。変換状態はCSを“L”に引き下げるとき観察することができます。

**GND(ピン8):**グランド。アナログ・グランド、デジタル・グランドおよびリファレンス・グランドの共通ピン。最小のインピーダンスで直接グランド・プレーンに接続します。

## ピン機能

**SCK(ピン9):** 双方向デジタル・クロック・ピン。内部シリアル・クロック動作モードでは、SCKはデータの入力/出力期間中は内部シリアル・インターフェース・クロックのデジタル出力として使われます。外部シリアル・クロック動作モードでは、SCKはデータ出力期間中は外部シリアル・インターフェース・クロックのデジタル入力として使われます。内部シリアル・クロック動作モードでは、弱い内部プルアップが自動的に動作状態になります。シリアル・クロック動作モードは電源立上げ時または $\overline{CS}$ の最新の立下りエッジのあいだSCKピンに与えられるロジック・レベルによって決まります。

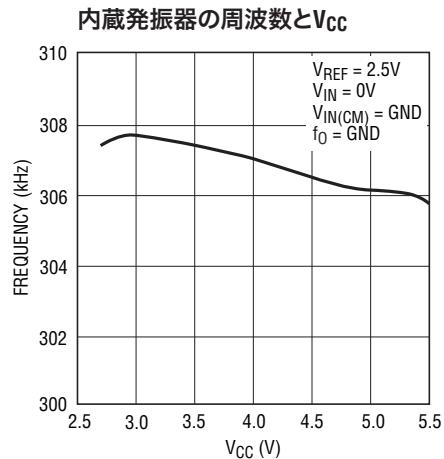

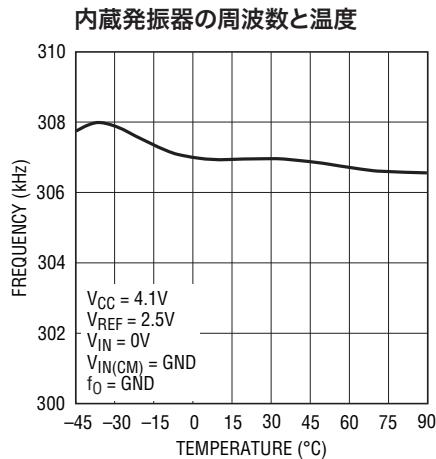

**$f_0$ (ピン10):** 周波数制御ピン。変換クロックを制御するデジタル入力。 $f_0$ がGNDに接続されていると、コンバータは307.2kHzで動作している内部発振器を使います。出力レートまたはデジタル・フィルタの除去ヌルを変更するため、 $f_0$ ピンを外部クロックでドライブして変換クロックを無効にすることもできます。

**露出パッド(ピン11):** このピンはグランドで、PCBのグランド・プレーンに半田付けします。プロトタイプの作成では、このピンをフロートさせたままでもかまいません。

## 機能ブロック図

## テスト回路

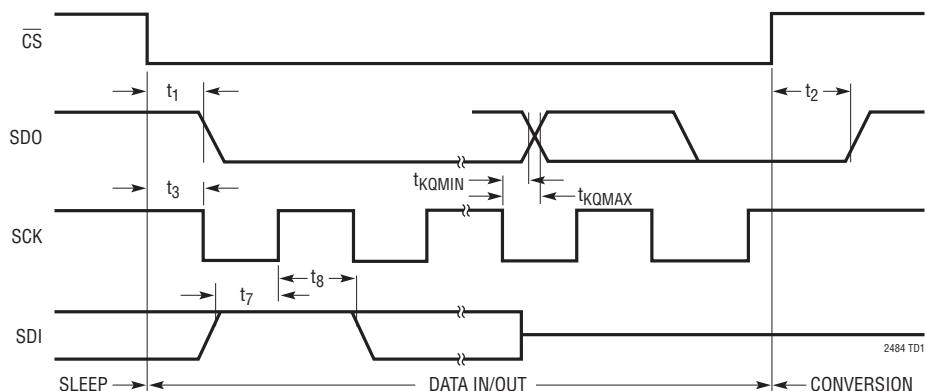

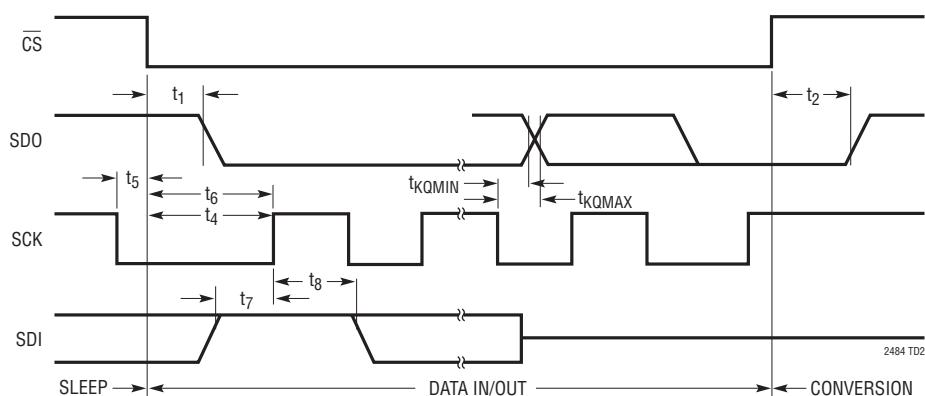

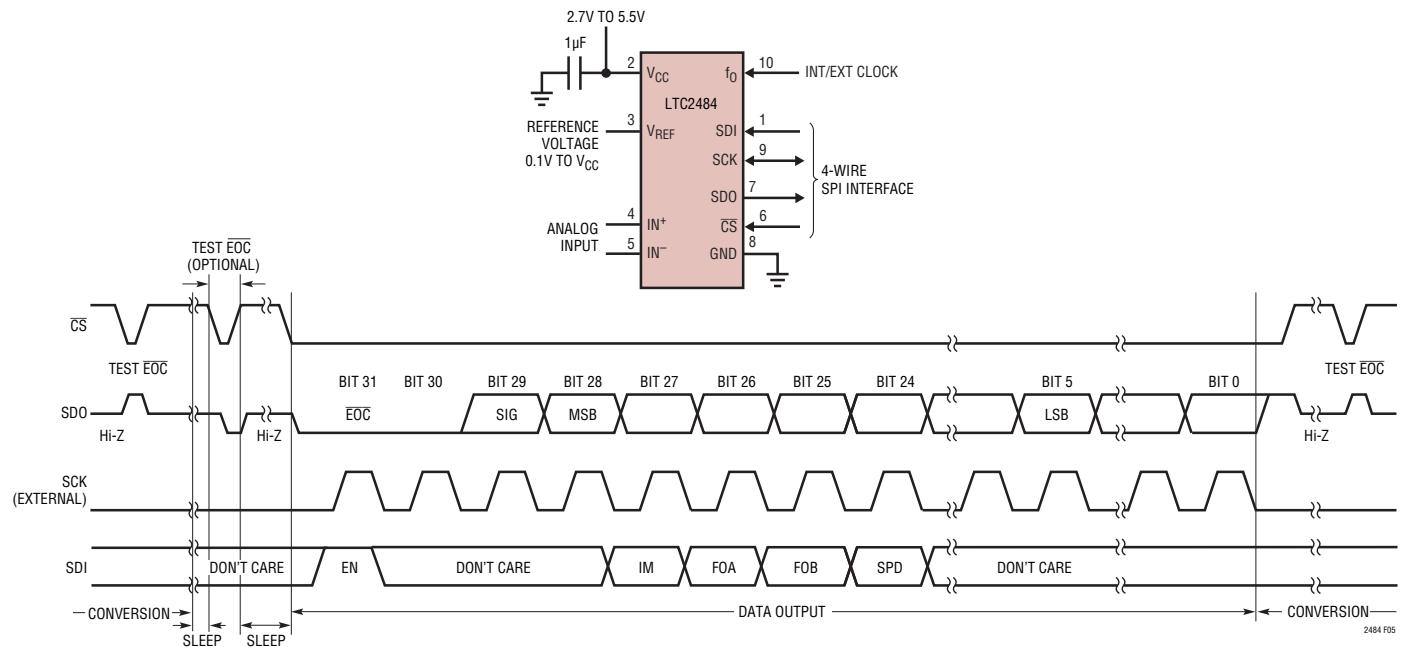

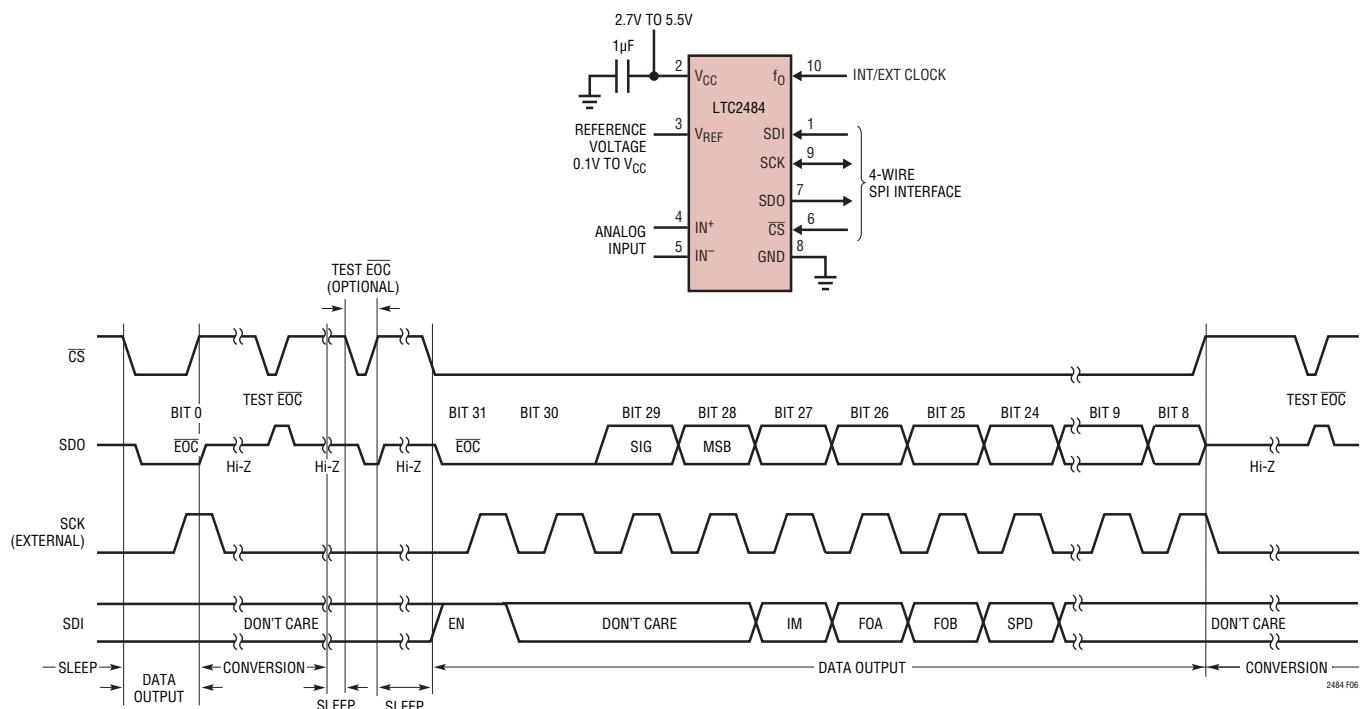

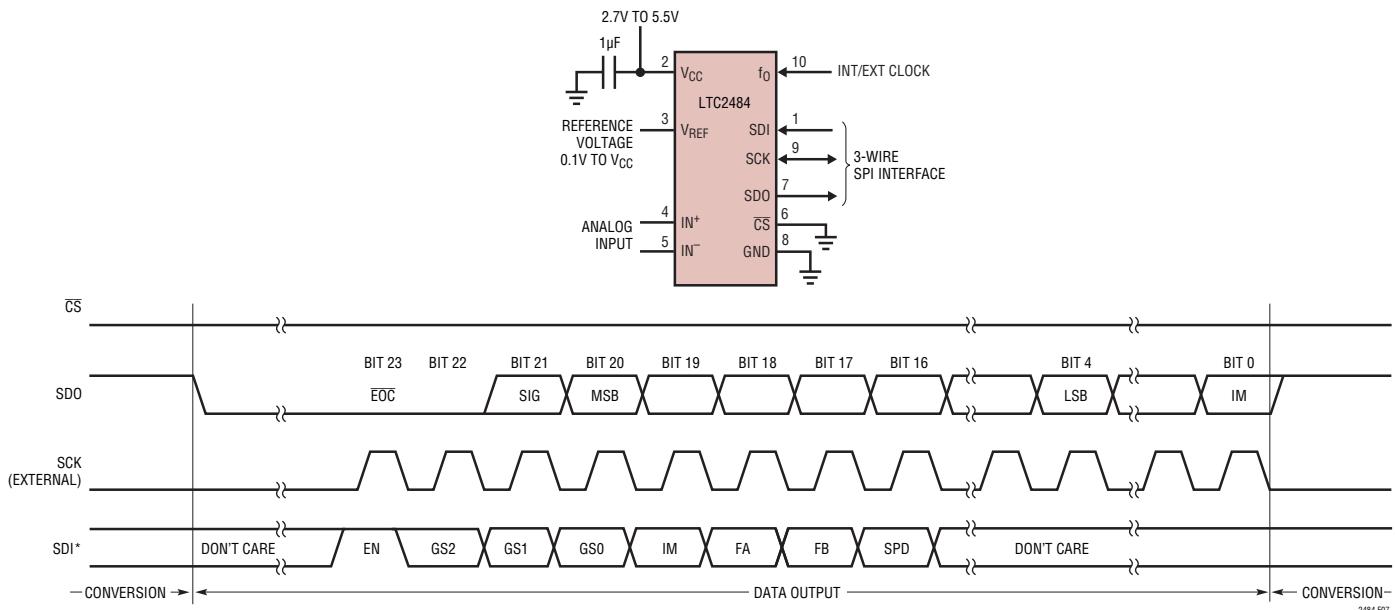

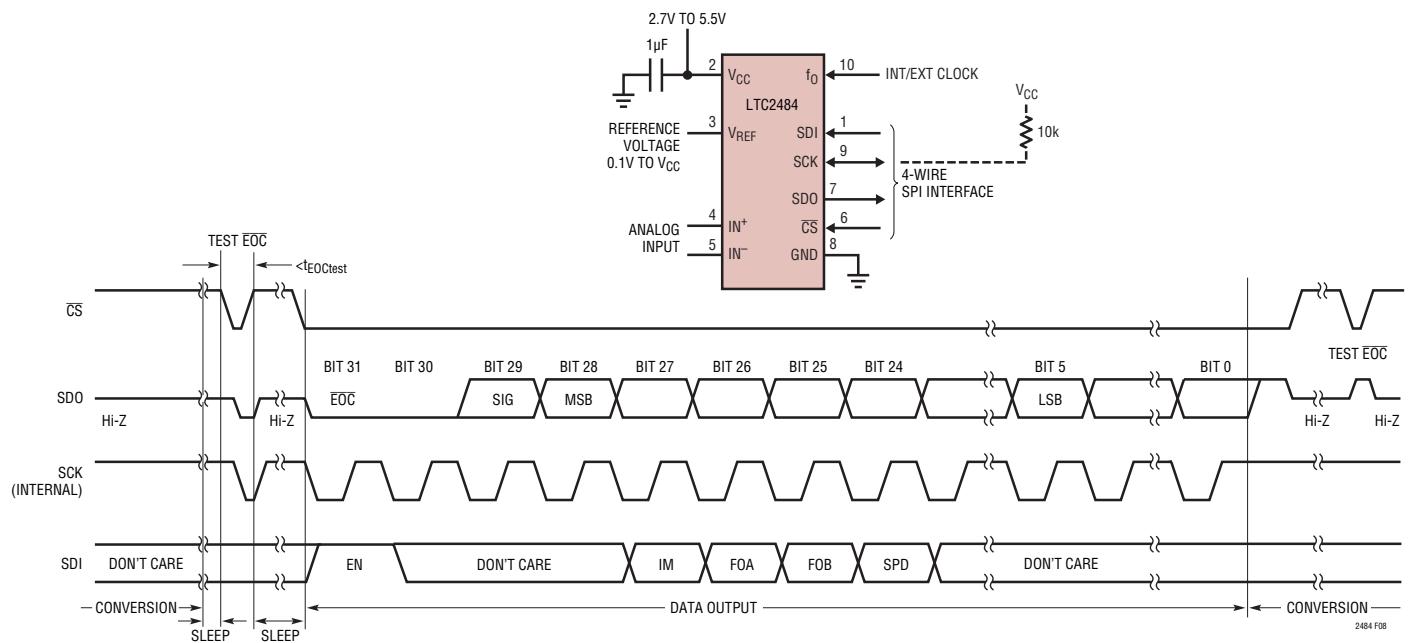

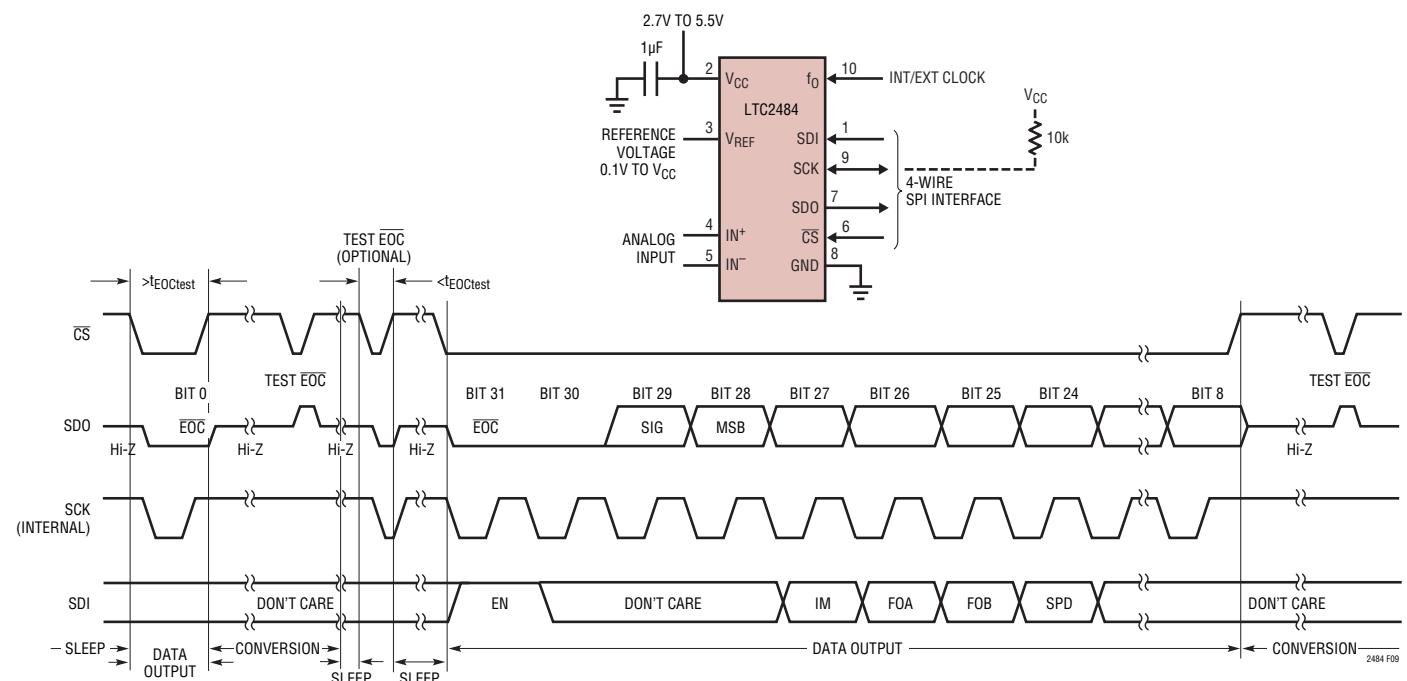

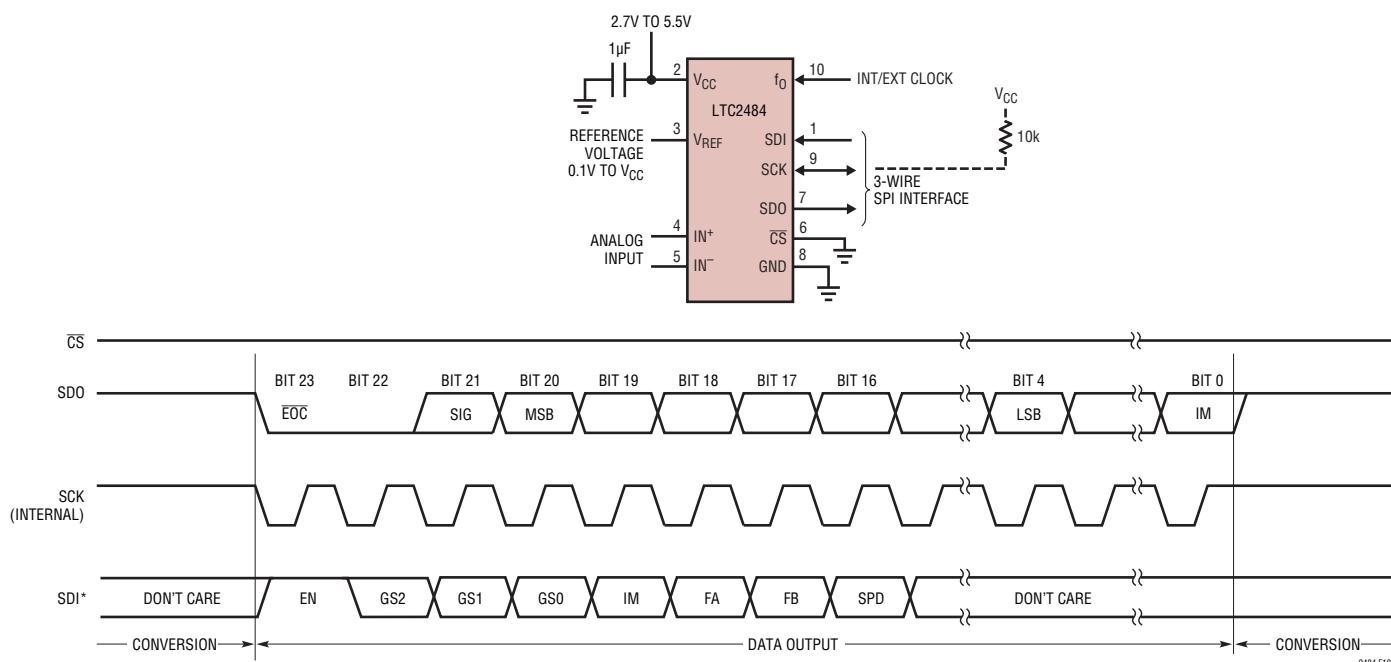

## タイミング図

内部SCKを使った場合のタイミング図

外部SCKを使った場合のタイミング図

## アプリケーション情報

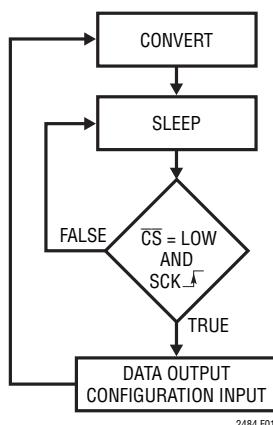

### コンバータの動作

#### コンバータの動作サイクル

LTC2484は低電力デルタシグマADコンバータで、使いやすい4線式シリアル・インターフェースと自動差動入力電流キャンセル機能を備えています。その動作は3つの状態で構成されています。コンバータの動作サイクルは変換ステートから始まり、省電力のスリープ・ステートがそれに続き、データ出力ステートで終了します(図1を参照)。4線式のインターフェースはシリアル・データ出力(SDO)、シリアル・クロック(SCK)、チップ・セレクト( $\overline{CS}$ )およびシリアル・データ入力(SDI)で構成されています。

図1. LTC2484の状態遷移図

LTC2484は最初に変換をおこないます。変換が完了すると、デバイスはスリープ・ステートに入ります。このスリープ・ステートのあいだ、電力消費は2桁減少します。 $\overline{CS}$ が“H”に保たれている限り、デバイスはスリープ・ステートに留まります。コンバータがスリープ・ステートのあいだ、変換結果は無期限にスタチック・シフトレジスタ内に保存されます。

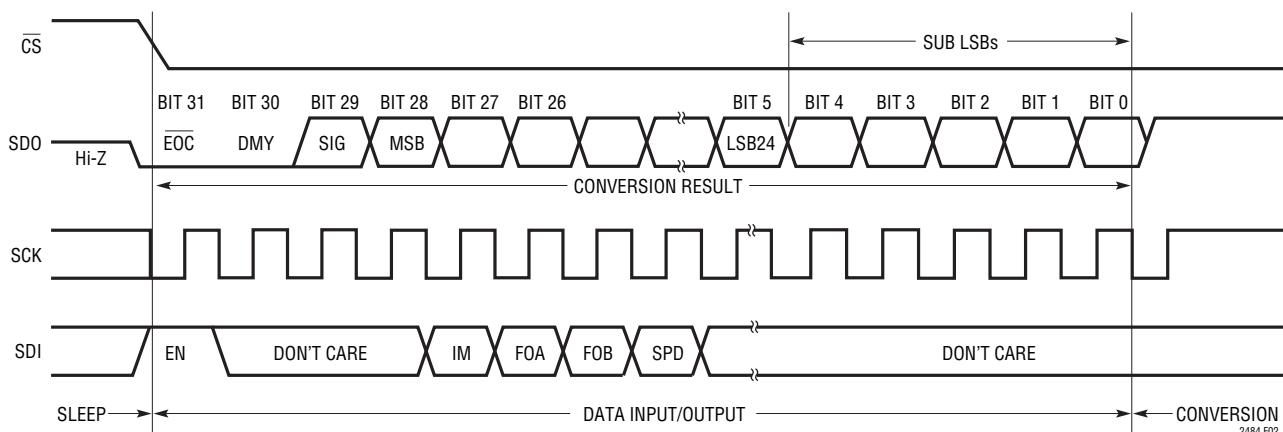

$\overline{CS}$ が“L”に引き下げられると、デバイスは省電力モードから出て、データ出力ステートに入ります。SCKの最初の立上りエッジの前に $\overline{CS}$ が“H”に引き上げられると、デバイスは省電力のスリープ・モードに戻り、変換結果は内部のスタチック・シフトレジスタ内に依然として保たれます。SCKの最初の立上りエッジの後 $\overline{CS}$ が“L”的ままだと、デバイスは変換結果を出力し始めます。この時点では $\overline{CS}$ を“H”にすると、データの入出力状態が終了し、新しい変換が開始されます。変換結果はシリアル・クロック(SCK)の立下りエッジによってシフトされ、シリアル・データ出力ピン(SDO)を通じてデバイスから出力されます(図2を参照)。LTC2484はシリアル・データ入力ピン(SDI)を備えています。データはSCKの立上りエッジでデバイスにラッチされます(図2を参照)。このピンに与えられるビット・ストリームを使って、内蔵温度センサ、ライン周波数除去、出力データ・レートなど、LTC2484の多様な機能を選択することができます。代わりに、このピンをグランドに接続すると、デバイスは既定の状態で変換を実行します。既定の状態では(SDIを接地)、デバイスは単に50Hzと60Hzのライン周波数を同時に除去して、ユーザーの与える入力を変換します。

図2. 入力/出力データのタイミング

## アプリケーション情報

CSピンとSCKピンのタイミング制御によって、LTC2484はいくつかの動作モード(内部または外部のSCKと自走変換の各モード)を柔軟に提供します。これらの多様なモードはプログラミング用構成レジスタを必要としません。さらに、上記の周期動作を乱すことがありません。これらの動作モードについては「シリアル・インターフェースのタイミング・モード」のセクションで詳しく説明します。

### Easy Drive入力電流キャンセル

LTC2484は高精度デルタシグマADCを自動差動入力電流キャンセル・フロントエンドと組み合わせています。独自のフロントエンド受動サンプリング・ネットワークが透過的に差動入力電流を除去します。これにより、外部RCネットワークと高インピーダンス・センサを、外部アンプなしに、直接LTC2484にインターフェースさせることができます。残りの同相入力電流は、差動入力のインピーダンスをバランスさせるか、または同相入力を同相リファレンスに等しく設定して除去します(「自動差動入力電流キャンセル」のセクションを参照)。このユニークなアーキテクチャには内蔵バッファが不要なので、入力信号はグランドからV<sub>CC</sub>まで完全に振幅することができます。さらに、このキャンセル機能はオフセットとフルスケールの透過的な自動較正と干渉しないので、外部RCネットワークが付加されても、絶対精度(フルスケール+オフセット+直線性)が維持されます。

### LTC2484の特殊機能へのアクセス

LTC2484では、高分解能、低ノイズのΔΣADコンバータが、内蔵されている選択可能な温度センサ、プログラム可能なデジタル・フィルタおよび出力レート・コントロールと組み合わされています。これらの特殊機能はデータ入力/出力サイクルのあいだに1個の8ビット・シリアル入力ワードによって選択されます(図2を参照)。

LTC2484はほとんどの測定で一般に使用される既定のモードで立ち上がります。デバイスはシリアル・データ入力(SDI)が“L”である限り、このモードに留まります。この既定モードでは、測定入力は外部、デジタル・フィルタは50Hzと60Hzのライン周波数ノイズを同時に除去、速度のモードは1倍速です(オフセットは自動連続較正)。

簡単なシリアル・インターフェースにより、LTC2484に備わっている任意の、またはすべての特殊機能にアクセスすることができます。動作モードを変更するため、イネーブル・ビット(EN)とそれに続く最大7ビットのデータがシフトされてデバイスに入力されます(表1を参照)。LTC2480とのピン互換性を保つため、最初の3ビットは「ドントケア」で、“H”と“L”的どちらでもかまいません。4番目のビット(IM)は内部の温度センサを変換入力として選択するのに使われ、5番目と6番目のビット(FA、FB)は結合されて、ライン周波数の除去モードを決定します。7番目のビット(SPD)は、オフセットの自動較正をディスエーブルすることにより、出力レートを2倍にするのに使います。

### 温度センサ(IM)

LTC2484は温度センサを内蔵しています。温度センサはシリアル入力データ・ストリーム内でIM = 1に設定すると選択されます。コンバータは温度センサに対して直接変換をおこないます。このモードで動作しているあいだ、デバイスは温度からビットへのコンバータとして振舞います。デジタル表示値はデバイスの絶対温度に比例します。この機能により、コンバータは温度センサを直線化するか、または外部温度センサから温度の影響を連続的に除去することができます。この機能を活用したいいくつかのアプリケーションについて、アプリケーションのセクションで詳細に説明します。このモードで動作しているあいだ、制御ビットSPDには無関係に、速度は通常速度に設定されます。

表1. 特殊モードの選択

| EN | IM | FoA | FoB | SPD | Comments                                                    |

|----|----|-----|-----|-----|-------------------------------------------------------------|

| 0  | X  | X   | X   | X   | Keep Previous Mode                                          |

| 1  | 0  | 0   | 0   | 0   | External Input, 50Hz and 60Hz Rejection, Autocalibration    |

| 1  | 0  | 0   | 1   | 0   | External Input, 50Hz Rejection, Autocalibration             |

| 1  | 0  | 1   | 0   | 0   | External Input, 60Hz Rejection, Autocalibration             |

| 1  | 0  | 0   | 0   | 1   | External Input, 50Hz and 60Hz Rejection, 2x Speed           |

| 1  | 0  | 0   | 1   | 1   | External Input, 50Hz Rejection, 2x Speed                    |

| 1  | 0  | 1   | 0   | 1   | External Input, 60Hz Rejection, 2x Speed                    |

| 1  | 1  | 0   | 0   | X   | Temperature Input, 50Hz and 60Hz Rejection, Autocalibration |

| 1  | 1  | 0   | 1   | X   | Temperature Input, 50Hz Rejection, Autocalibration          |

| 1  | 1  | 1   | 0   | X   | Temperature Input, 60Hz Rejection, Autocalibration          |

| 1  | X  | 1   | 1   | X   | Reserved, Do Not Use                                        |

2484 TBL1

2484ff

## アプリケーション情報

### 除去モード(FA、FB)

LTC2484には高精度の発振器が内蔵されており、外付け部品は不要です。LTC2484は4次のデジタル・ローパス・フィルタと結合されてライン周波数ノイズを除去します。既定モードでは、LTC2484は少なくとも87dBだけ50Hzと60Hzを同時に除去します。50Hzまたは60Hzを選択的に110dB以上除去するようにLTC2484を構成することもできます。

### 速度モード(SPD)

LTC2484は連続的にオフセットを較正します。変換サイクルごとに、2回の変換が自動的におこなわれ(既定)、それらの結果が結合されます。この結果にはオフセットとドリフトが含まれません。オフセットが重要ではないアプリケーションでは、自動較正機能をディスエーブルして、出力レートを2倍にすることができます。

直線性、フルスケール精度、フルスケール・ドリフトは2倍速と1倍速の両方のモードで同一です。1倍速と2倍速の両方で、待ち時間はありません。このため、入力ステップまたはマルチプレクサ・チャネルの切替えは1変換サイクルでセトリングすることができますので、システムのオーバーヘッドが緩和され、実効変換レートが増加します。

### 出力データのフォーマット

LTC2484のシリアル出力のデータ・ストリームは32ビット長です。最初の3ビットは状態情報を表し、符号と変換状態を示します。次の24ビットは変換結果で、MSBが最初にきます。残りの5ビットは24ビット・レベルより下のサブLSBです。3番目と4番目のビットは一緒になってアンダーレンジ状態(差動入力電圧が-FSより下)またはオーバーレンジ状態(差動入力電圧が+FSより上)を示すのにも使われます。

32ビットすべてを出力する前に $\overline{CS}$ を“H”に引き上げてデータの出力転送を中止し、新しい変換を開始することができます。

ビット31(最初の出力ビット)は変換終了( $\overline{EOC}$ )のインジケータです。このビットは、変換ステートおよびスリープ・ステートのあいだ、 $\overline{CS}$ ピンが“L”的ときSDOピンから読み出せます。このビットは変換中は“H”で、変換が完了すると“L”になります。

ビット30(2番目の出力ビット)はダミービット(DMY)で、常に“L”です。

ビット29(3番目の出力ビット)は変換結果の符号のインジケータ(SIG)です。 $V_{IN}$ が $>0$ ならば、このビットは“H”になります。 $V_{IN}$ が $<0$ ならば、このビットは“L”になります。

ビット28(4番目の出力ビット)は結果の最上位ビット(MSB)です。このビットはビット29と組み合わされてアンダーレンジまたはオーバーレンジも表示します。ビット29とビット28が両方とも“H”的場合、差動入力電圧が+FSを超えています。ビット29とビット28が両方とも“L”的場合、差動入力電圧が-FSより低くなっています。

これらのビットの機能は表2にまとめてあります。

表2. LTC2484の状態ビット

| INPUT RANGE                           | BIT 31<br>EOC | BIT 30<br>DMY | BIT 29<br>SIG | BIT 28<br>MSB |

|---------------------------------------|---------------|---------------|---------------|---------------|

| $V_{IN} \geq 0.5 \cdot V_{REF}$       | 0             | 0             | 1             | 1             |

| $0V \leq V_{IN} < 0.5 \cdot V_{REF}$  | 0             | 0             | 1/0           | 0             |

| $-0.5 \cdot V_{REF} \leq V_{IN} < 0V$ | 0             | 0             | 0             | 1             |

| $V_{IN} < -0.5 \cdot V_{REF}$         | 0             | 0             | 0             | 0             |

ビット28からビット5までは24ビットの変換結果で、MSBが先にきます。

ビット4からビット0までは24ビット・レベルより下のサブLSBです。ビット4からビット0までは平均計算に含めるか、または分解能を損なうことなしに破棄することができます。

データはシリアル・クロック(SCK)の制御のもとにSDOピンからシフトされて出力されます(図2を参照)。 $\overline{CS}$ が“H”的ときは常にSDOは高インピーダンスとなり、内部のデータ出力用シフトレジスタは外部で発生したSCKクロック・パルスをすべて無視します。

変換結果をデバイスからシフトして出力するには、最初に $\overline{CS}$ を“L”にドライブする必要があります。 $\overline{CS}$ が“L”に引き下げられると、デバイスのSDOピンに $\overline{EOC}$ が現われます。 $\overline{EOC}$ は変換完了時にリアルタイムで“H”から“L”に変化します。この信号は外部のマイクロコントローラへの割り込み信号として使うこと

## アプリケーション情報

ができます。ビット31( $\overline{\text{EOC}}$ )はSCKの最初の立上りエッジで捕捉することができます。ビット30はSCKの最初の立下りエッジでシフトされてデバイスから出力されます。最後のデータ・ビット(ビット0)は31番目のSCKの立下りエッジでシフトされて出力され、32番目のSCKパルスの立上りエッジでラッチすることができます。32番目のSCKパルスの立下りエッジで、SDOは“H”になり、新しい変換サイクルの開始を示します。このビットは次の変換サイクルの $\overline{\text{EOC}}$ (ビット31)として機能します。出力データのフォーマットが表3にまとめてあります。

$\text{IN}^+$ ピンと $\text{IN}^-$ ピンの電圧が $-0.3\text{V} \sim (\text{V}_{\text{CC}} + 0.3\text{V})$ の絶対最大動作範囲に留まる限り、 $-\text{FS} = -0.5 \cdot \text{V}_{\text{REF}}$ から $+\text{FS} = 0.5 \cdot \text{V}_{\text{REF}}$ までの任意の差動入力電圧 $\text{V}_{\text{IN}}$ に対して変換結果が生成されます。 $+\text{FS}$ を超える差動入力電圧の場合、変換結果は $+\text{FS} + 1\text{LSB}$ に相当する値にクランプされます。 $-\text{FS}$ より低い差動入力電圧の場合、変換結果は $-\text{FS} - 1\text{LSB}$ に相当する値にクランプされます。

## 変換クロック

従来型のコンバータに較べてデルタシグマ・コンバータが与える主な利点は(一般にSINCフィルタまたは櫛形フィルタとして実装される)内蔵デジタル・フィルタです。高分解能で低周波数のアプリケーションの場合、このフィルタは一般に50Hzまたは60Hzのライン周波数およびそれらの高調波を除去するように設計されます。フィルタの除去性能はコンバータのシステム・クロックの精度に直接関係します。LTC2484には高精度の発振器が内蔵されています。したがって、水晶や発振器など外部で周波数を設定する部品は不要です。

周波数除去の選択( $f_0$ )

LTC2484の内部発振器は、50Hz $\pm 2\%$ または60Hz $\pm 2\%$ のライン周波数と(255次までの)すべての高調波の通常モードの除去率が110dBを超える、48Hz $\sim$ 62.4Hzの通常モードの除去率が87dBを超えます。除去モードは内部構成レジスタに書き込むことによって選択され、PORの既定のモードは同時50Hz/60Hz除去です。

50Hzまたは60Hzと異なる基本除去周波数が要求される場合、またはコンバータを外部ソースに同期させる必要がある場合、外部の変換クロックを使ってLTC2484を動作させることができます。コンバータは $f_0$ ピンに外部クロック信号が与えられていることを自動的に検知し、内部発振器をオフします。外部信号が検出されるには、その周波数 $f_{\text{EOSC}}$ は少なくとも10kHzあることが必要です。外部クロック信号のデューティ・サイクルは、“H”と“L”的期間( $t_{\text{HEO}}$ と $t_{\text{LEO}}$ )の最小と最大の規定値が守られる限り重要ではありません。

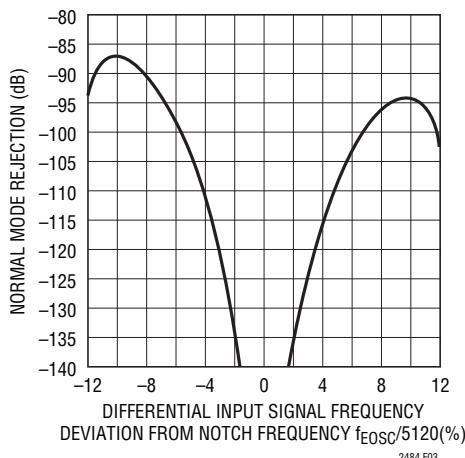

周波数が $f_{\text{EOSC}}$ の外部変換クロックを使って動作しているとき、 $f_{\text{EOSC}}/5120 \pm 4\%$ の周波数範囲およびその高調波に対し、LTC2484は110dBを超す通常モードの除去率を与えます。 $f_{\text{EOSC}}/5120$ からの入力周波数の偏差の関数としての通常モードの除去率を図3に示します。

$f_0$ ピンに外部クロックが与えられていないとき、コンバータは内部発振器を自動的に起動して、「内部変換クロック」モードに入ります。コンバータが外部のシリアル・クロックを使っているとき、スリープ・ステートまたはデータ出力ステートのあいだに変換クロック・ソースが変更された場合、LTC2484の動作は

表3. LTC2484の出力データのフォーマット

| DIFFERENTIAL INPUT VOLTAGE<br>$\text{V}_{\text{IN}}^*$ | BIT 31<br>$\overline{\text{EOC}}$ | BIT 30<br>DMY | BIT 29<br>SIG | BIT 28<br>MSB | BIT 27 | BIT 26 | BIT 25 | ... | BIT 0 |

|--------------------------------------------------------|-----------------------------------|---------------|---------------|---------------|--------|--------|--------|-----|-------|

| $\text{V}_{\text{IN}}^* \geq \text{FS}^{**}$           | 0                                 | 0             | 1             | 1             | 0      | 0      | 0      | ... | 0     |

| $\text{FS}^{**} - 1\text{LSB}$                         | 0                                 | 0             | 1             | 0             | 1      | 1      | 1      | ... | 1     |

| $0.5 \cdot \text{FS}^{**}$                             | 0                                 | 0             | 1             | 0             | 1      | 0      | 0      | ... | 0     |

| $0.5 \cdot \text{FS}^{**} - 1\text{LSB}$               | 0                                 | 0             | 1             | 0             | 0      | 1      | 1      | ... | 1     |

| 0                                                      | 0                                 | 0             | 1/0***        | 0             | 0      | 0      | 0      | ... | 0     |

| $-1\text{LSB}$                                         | 0                                 | 0             | 0             | 1             | 1      | 1      | 1      | ... | 1     |

| $-0.5 \cdot \text{FS}^{**}$                            | 0                                 | 0             | 0             | 1             | 1      | 0      | 0      | ... | 0     |

| $-0.5 \cdot \text{FS}^{**} - 1\text{LSB}$              | 0                                 | 0             | 0             | 1             | 0      | 1      | 1      | ... | 1     |

| $-\text{FS}^{**}$                                      | 0                                 | 0             | 0             | 1             | 0      | 0      | 0      | ... | 0     |

| $\text{V}_{\text{IN}}^* < -\text{FS}^{**}$             | 0                                 | 0             | 0             | 0             | 1      | 1      | 1      | ... | ****  |

\* 差動入力電圧 $\text{V}_{\text{IN}} = \text{IN}^+ - \text{IN}^-$ 。

\*\* フルスケール電圧 $\text{FS} = 0.5 \cdot \text{V}_{\text{REF}}$ 。

\*\*\* デバイスが2倍速モードで動作している時、符号ビットは出力コードが0の間に状態を変えます。

\*\*\*\* 2倍速モードで動作している時、アンダーレンジ出力コードは0xFFFFFxxxです。

## アプリケーション情報

図3. 内部発振器使用時のLTC2484の通常モードの除去率

乱されません。変換ステートのあいだに変更されると、進行中の変換結果は仕様から外れることがあります。それに続く変換は影響を受けません。データ出力ステートのあいだに変更が起き、コンバータが内部SCKモードだと、シリアル・クロックのデューティ・サイクルが影響を受けることがあります。シリアル・データ・ストリームは有効なままでです。

$f_0$ の関数としての各ステートの持続時間と実現可能な出力データ・レートを表4にまとめています。

## 使いやすさ

LTC2484のデータ出力には、待ち時間、フィルタのセッティング・遅延、または変換サイクルに関連した冗長データがありません。変換と出力データのあいだには1対1対応の関係があります。したがって、複数のアナログ電圧の多重化は簡単です。

LTC2484は変換サイクルごとにオフセットとフルスケールの較正をおこないます。この較正はユーザーからは見えず、上記のサイクル動作には影響を与えません。連続較正の利点は、時間経過、電源電圧の変化、および温度ドリフトに対してオフセットとフルスケールの測定値がきわめて安定していることです。

## 電源立上げシーケンス

LTC2484は電源電圧V<sub>CC</sub>が約2Vより下に下がると自動的に内部リセット状態になります。この機能により、変換結果とシリアル・インターフェース・モードの選択の完全性が保証されます。

V<sub>CC</sub>電圧がこの臨界スレッショルドを超えると、コンバータは約4msの長さの内部パワーオン・リセット(POR)信号を発生

表4. LTC2484のステートの持続時間

| ステート  | 動作モード                          |                                                             | 持続時間                                                                                                                                                   |

|-------|--------------------------------|-------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| 変換    | 内部発振器                          | 60Hzの除去                                                     | 133ms、出力データ・レート $\leq$ 7.5の読み取り/s(1倍速モード)<br>67ms、出力データ・レート $\leq$ 15の読み取り/s(2倍速モード)                                                                   |

|       |                                | 50Hzの除去                                                     | 160ms、出力データ・レート $\leq$ 6.2の読み取り/s(1倍速モード)<br>80ms、出力データ・レート $\leq$ 12.5の読み取り/s(2倍速モード)                                                                 |

|       |                                | 50Hz/60Hzの除去                                                | 147ms、出力データ・レート $\leq$ 6.8の読み取り/s(1倍速モード)<br>73.6ms、出力データ・レート $\leq$ 13.6の読み取り/s(2倍速モード)                                                               |

|       | 外部発振器                          | $f_0$ = 周波数が $f_{EOSC}$ kHzの外部発振器<br>( $f_{EOSC}/5120$ の除去) | 41036/ $f_{EOSC}$ s、出力データ・レート $\leq$ $f_{EOSC}/41036$ の読み取り/s<br>(1倍速モード)<br>20556/ $f_{EOSC}$ s、出力データ・レート $\leq$ $f_{EOSC}/20556$ の読み取り/s<br>(2倍速モード) |

| スリープ  |                                |                                                             | $\overline{CS}$ = "H"である限り、変換完了後                                                                                                                       |

| データ出力 | 内部シリアル・クロック                    | $f_0$ = LOW/HIGH<br>(内部発振器)                                 | $\overline{CS}$ = "L"である限り、ただし0.83msは超えない<br>(32 SCKサイクル)                                                                                              |

|       |                                | $f_0$ = 周波数が $f_{EOSC}$ kHzの外部発振器                           | $\overline{CS}$ = "L"である限り、ただし256/ $f_{EOSC}$ msは超えない<br>(32 SCKサイクル)                                                                                  |

|       | 周波数が $f_{SCK}$ kHzの外部シリアル・クロック |                                                             | $\overline{CS}$ = "L"である限り、ただし32/ $f_{SCK}$ msは超えない<br>(32 SCKサイクル)                                                                                    |

2484ff

## アプリケーション情報

します。POR信号により、すべての内部レジスタがクリアされます。POR信号に続き、LTC2484は通常の変換サイクルを開始し、図1に示されている状態が継続します。PORに続く最初の変換結果の精度は、PORの時間間隔が経過する前に電源電圧が動作範囲(2.7V~5.5V)内に回復していれば、デバイスの仕様を満たします。

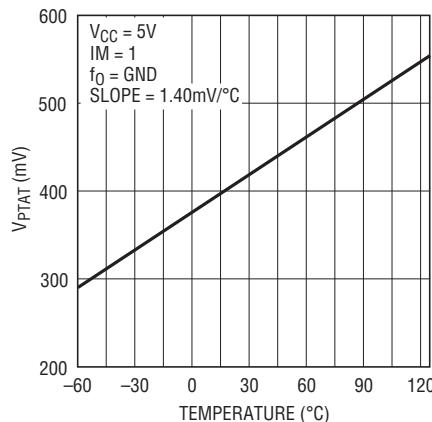

### 内蔵温度センサ

LTC2484には内部PTAT(絶対温度に比例した)信号が備わっています。温度センサとして利用することができます。内部PTATの標準値は27°Cで420mVであり、図4に示されているように、 $420/(27+273) = 1.40\text{mV/}^{\circ}\text{C}$ (傾き)の温度係数で絶対温度に比例します。内部PTAT信号は内部でデバイスのグランドを基準にしたシングルエンド・モードで使用されます。内部PTAT信号の測定でも、自動オフセット較正を使う1倍速モードが自動的に選択されます。

内部温度センサを使うとき、出力コードが $R_{SDO} = V_{PTAT}/V_{REF}$ に正規化されると、温度は以下の式を使って計算されます。

$$T_K = \frac{R_{SDO} \cdot V_{REF}}{\text{SLOPE}} \text{ in Kelvin}$$

and

$$T_C = \frac{R_{SDO} \cdot V_{REF}}{\text{SLOPE}} - 273 \text{ in } ^{\circ}\text{C}$$

ここで、SLOPEは通常1.4mV/°Cです。

PTAT信号は初期値にバラツキがあり、SLOPEに誤差があることがあるので、温度測定の精度を上げるには、SLOPEの値を調節するために一度較正が必要です。既知のある温度 $T_0$ (°C)で、PTAT信号( $R_{0SDO}$ )のコンバータ出力を測定し、SLOPEを次のように計算します。

$$\text{SLOPE} = \frac{R_{0SDO} \cdot V_{REF}}{T_0 + 273}$$

この較正されたSLOPEを使って温度を計算することができます。

較正と温度測定のあいだ同じ $V_{REF}$ ソースが使われると、下の計算に示されているように、温度を測定するのに実際の $V_{REF}$ の値は不要です。

$$\begin{aligned} T_C &= \frac{R_{SDO} \cdot V_{REF}}{\text{SLOPE}} - 273 \\ &= \frac{R_{SDO}}{R_{0SDO}} \cdot (T_0 + 273) - 273 \end{aligned}$$

図4. 内部PTAT信号と温度

### リファレンス電圧範囲

LTC2484の外部リファレンスの電圧範囲は0.1V~ $V_{CC}$ です。コンバータの出力ノイズはフロントエンド回路の熱ノイズによって決まるので、ナノボルトで表したその値はリファレンス電圧に対してほぼ一定です。リファレンス電圧が減少すると、かなり高い出力データ・レートで外部変換クロック(外部 $f_O$ 信号)を使って動作させると、コンバータの性能が改善されます(「出力データ・レート」のセクションを参照)。内部温度センサを使うには、 $V_{REF}$ は $\geq 1.1\text{V}$ でなければなりません。

コンバータへの負リファレンス入力は内部でGNDに接続されています。GND(ピン8)はできるだけ短いトレースを使ってグランド・プレーンに接続し、電圧降下を最小に抑えます。LTC2484の平均動作電流は160 $\mu\text{A}$ なので、0.1 $\Omega$ の寄生抵抗では、16 $\mu\text{V}$ の電圧降下により $V_{REF} = 5\text{V}$ に対して3.2ppmの利得誤差が生じます。

## アプリケーション情報

### 入力電圧範囲

アナログ入力は真に差動で、 $IN^+$ と $IN^-$ の入力ピンの絶対同相範囲はGND-0.3V～V<sub>CC</sub>+0.3Vです。これらのリミットの外側では、ESD保護用デバイスがオンし始め、入力の漏れ電流による誤差が急速に増加します。これらのリミット内では、LTC2484はバイポーラ差動入力信号 $V_{IN} = IN^+ - IN^-$ を- $FS$ ～+ $FS$ で変換します(ここで、 $FS = 0.5 \cdot V_{REF}$ です)。この範囲の外側では、コンバータは固有の出力コードを使ってオーバーレンジまたはアンダーレンジの状態を表示します。差動入力電流のキャンセルは内蔵バッファに依存しないので、DC性能とともに電流のキャンセルもレール・トゥ・レールで維持されます。

$IN^+$ ピンと $IN^-$ ピンに与えられる入力信号は、グランドより300mV下およびV<sub>CC</sub>より300mV上まで達することができます。どんなフォールト電流も制限するため、デバイスの性能に影響を与えることなく、最大5kの抵抗を $IN^+$ ピンと $IN^-$ ピンに直列に追加することができます。コンバータの精度に対する直列抵抗の影響は、「入力電流/リファレンス電流」のセクションに示されている曲線から評価することができます。さらに、直列抵抗は入力漏れ電流により、温度に依存したオフセット誤差を生じます。V<sub>REF</sub> = 5Vのとき、1nAの入力漏れ電流により、5kの抵抗には1ppmのオフセット誤差が生じます。この誤差の温度依存性は非常に大きくなります。

### シリアル・インターフェースのタイミング・モード

LTC2484の4線のインターフェースはSPIおよびMICROWIREと互換性があります。このインターフェースにより、いくつかの柔軟な動作モードが実現できます。これらには内部/外部シリアル・クロック、3線または4線のI/O、シングル・サイクル変換または連続変換が含まれます。以下のセクションではこれらのシリアル・インターフェースのそれぞれのタイミング・モードを詳細に説明します。これらすべての場合に、コンバータは内部発振器( $f_O = "L"$ または $f_O = "H"$ )または $f_O$ ピンに接続された外部発振器

を使うことができます。表5にまとめられていますので参照してください。

### 外部シリアル・クロック、シングル・サイクル動作 (SPI/MICROWIRE互換)

このタイミング・モードでは、外部シリアル・クロックを使って変換結果をシフトして出力し、 $\overline{CS}$ 信号を使って変換サイクルの状態をモニタして制御します(図5を参照)。

シリアル・クロック・モードは $\overline{CS}$ の立下りエッジで選択されます。外部シリアル・クロック・モードを選択するには、 $\overline{CS}$ の各立下りエッジのあいだシリアル・クロック・ピン(SCK)を“L”にする必要があります。

シリアル・データ出力ピン(SDO)は、 $\overline{CS}$ が“H”的あいだはHi-Zになります。変換サイクル中はいつでも、コンバータの状態をモニタするために $\overline{CS}$ を“L”に引き下げることができます。 $\overline{CS}$ が“L”に引き下げられているあいだ、 $\overline{EOC}$ がSDOピンに出力されます。変換中は $\overline{EOC} = 1$ となり、デバイスがスリープ状態だと $\overline{EOC} = 0$ となります。 $\overline{CS}$ には関係なく、変換が完了するとデバイスは自動的に省電力のスリープ・ステートに入ります。

デバイスがスリープ・ステートのとき、変換結果は内部のスタッカ・シフトレジスタに保存されます。 $\overline{CS}$ が“L”的あいだにSCKの最初の立上りエッジが現れるまでデバイスはスリープ・ステートに留まります。次に入力データが(最初の立上りエッジを含む)SCKの立上りエッジでシフトされてSDIピンを通して入力され、出力データがSCKの各立下りエッジでシフトされてSDOピンから出力されます。このため、外部回路はSCKの立上りエッジを使って出力をラッチすることができます。 $\overline{EOC}$ はSCKの最初の立上りエッジを使ってラッチすることができ、変換結果の最後のビットはSCKの32番目の立上りエッジを使ってラッチすることができます。SCKの32番目の立下りエッジで、デバイスは新しい変換を開始します。SDOが“H”( $\overline{EOC} = 1$ )になり、変換中であることを示します。

表5. LTC2484のインターフェースのタイミング・モード

| CONFIGURATION                                   | SCK SOURCE | CONVERSION CYCLE CONTROL   | DATA OUTPUT CONTROL        | CONNECTION and WAVEFORMS |

|-------------------------------------------------|------------|----------------------------|----------------------------|--------------------------|

| External SCK, Single Cycle Conversion           | External   | $\overline{CS}$ and SCK    | $\overline{CS}$ and SCK    | Figures 5, 6             |

| External SCK, 3-Wire I/O                        | External   | SCK                        | SCK                        | Figure 7                 |

| Internal SCK, Single Cycle Conversion           | Internal   | $\overline{CS} \downarrow$ | $\overline{CS} \downarrow$ | Figures 8, 9             |

| Internal SCK, 3-Wire I/O, Continuous Conversion | Internal   | Continuous                 | Internal                   | Figure 10                |

# LTC2484

## アプリケーション情報

図5. 外部シリアル・クロック、シングル・サイクル動作

図6. 外部シリアル・クロック、短縮されたデータ出力長

2484ff

## アプリケーション情報

データ・サイクルの完了時に $\overline{CS}$ を“L”のままにしておくことができます。 $\overline{EOC}$ は変換終了時の割り込み信号としてモニタすることができます。代わりに、 $\overline{CS}$ を“H”にドライブしてSDOをHi-Zに設定することができます。上述のように、変換状態をモニタするために、 $\overline{CS}$ をいつでも“L”に引き下げることができます。

通常、 $\overline{CS}$ はデータ出力ステートのあいだ“L”に保たれます。ただし、SCKの最初の立上りエッジと32番目の立下りエッジのあいだに、いつでも $\overline{CS}$ を“H”に引き上げてデータ出力ステートを中止することができます(図6を参照)。 $\overline{CS}$ の立上りエッジで、デバイスはデータ出力ステートを中止し、直ちに新しい変換を開始します。 $\overline{CS}$ が“H”に引き上げられるまでにデバイスがSDIの最後の入力ビットSPDをロードし終わらないと、SDIの情報は破棄され、前の構成が維持されます。これは出力データの32ビットすべては必要としないシステムでは有用で、無効の変換サイクルを中止するか、変換の開始点を同期させます。

### 外部シリアル・クロック、3線式I/O

このタイミング・モードでは3線式シリアルI/Oインターフェースを利用します。変換結果は外部で作られたシリアル・クロック(SCK)信号によってシフトされてデバイスから出力されます(図7参照)。 $\overline{CS}$ は永続的にグランドに接続することができ、

ユーザー・インターフェースや絶縁バリヤを超えた転送が簡素化されます。

外部シリアル・クロック・モードは起動時リセット(POR)サイクルの終わりに選択されます。PORサイクルは $V_{CC}$ が約2Vを超してから標準で4ms後に終了します。この時点でSCKに与えられたレベルによってSCKが内部であるか外部であるかが決まります。外部シリアル・クロックのタイミング・モードに入るには、PORの終了前にSCKを“L”にドライブする必要があります。

$\overline{CS}$ が“L”に固定されているので、変換ステートおよびスリープ・ステートのあいだ、変換終了( $\overline{EOC}$ )をSDOピンで連続してモニタすることができます。 $\overline{EOC}$ は外部コントローラへの割り込み信号として使うことができ、変換結果が用意できていることを示します。変換中は $\overline{EOC} = 1$ となり、変換が終了すると $\overline{EOC} = 0$ となります。 $\overline{EOC}$ の立下りエッジで、変換結果が内部のスタチック・シフトレジスタにロードされます。次に入力データが(最初の立上りエッジを含む)SCKの立上りエッジでシフトされてSDIピンを通して入力され、出力データがSCKの各立下りエッジでシフトされてSDOピンから出力されます。 $\overline{EOC}$ はSCKの最初の立上りエッジでラッチすることができます。SCKの32番目の立下りエッジで、SDOは“H”になり( $\overline{EOC} = 1$ )、新しい変換サイクルが開始されたことを示します。

図7. 外部シリアル・クロック、 $\overline{CS} = 0$ の動作

## アプリケーション情報

### 内部シリアル・クロック、シングル・サイクル動作

このタイミング・モードでは、内部シリアル・クロックを使って変換結果をシフトして出力し、 $\overline{CS}$ 信号を使って変換サイクルの状態をモニタして制御します(図8を参照)。

内部シリアル・クロック・タイミング・モードを選択するには、 $\overline{CS}$ の立下りエッジより前にシリアル・クロック・ピン(SCK)をフロート(Hi-Z)にするか、または“H”に引き上げる必要があります。SCKが $\overline{CS}$ の立下りエッジで“L”にドライブされると、デバイスは内部シリアル・クロック・モードに入りません。内部の弱いプルアップ抵抗が $\overline{CS}$ の立下りエッジのあいだSCKピンに対して働くので、SCKが外部からドライブされないと内部シリアル・クロック・タイミング・モードが自動的に選択されます。

シリアル・データ出力ピン(SDO)は、 $\overline{CS}$ が“H”的あいだはHi-Zになります。変換サイクル中はいつでも、コンバータの状態をモニタするために $\overline{CS}$ を“L”に引き下げることができます。 $\overline{CS}$ が“L”に引き下げられると、SCKが“L”になり、 $\overline{EOC}$ がSDOピンに出力されます。変換中は $\overline{EOC} = 1$ となり、デバイスがスリープ状態だと $\overline{EOC} = 0$ となります。

$\overline{EOC}$ をテストするとき、変換が完了していると( $\overline{EOC} = 0$ )、デバイスは $\overline{EOC}$ テストのあいだ省電力モードから抜け出します。デバイスが省電力スリープ・ステートに戻れるようにするには、SCKの最初の立上りエッジより前に $\overline{CS}$ を“H”に引き上げる必要があります。内部SCKタイミング・モードでは、SCKは“H”になり、デバイスは( $\overline{EOC} = 0$ ならば) $\overline{CS}$ の立下りエッジ後、 $t_{EOCtest}$ の時点でデータを出力し始め、( $\overline{EOC}$ の立下りエッジで $\overline{CS}$ が“L”ならば) $\overline{EOC}$ が“L”になった後、 $t_{EOCtest}$ の時点でデータを出力し始めます。デバイスが内部発振器を使用している場合、 $t_{EOCtest}$ の値は12 $\mu$ sです。周波数が $f_{EOSC}$ の外部発振器で $f_0$ がドライブされると、 $t_{EOCtest}$ は3.6/ $f_{EOSC}$ (秒)となります。 $t_{EOCtest}$ の前に $\overline{CS}$ が“H”に引き上げられると、デバイスはスリープ・モードに戻り、変換結果は内部のスタチック・シフトレジスタ内に保たれます。

$\overline{CS}$ が $t_{EOCtest}$ より長く“L”に留まると、SCKの最初の立上りエッジが生じ、変換結果がシリアルにシフトされSDOピンから出力されます。データI/Oサイクルは32番目の立上りエッジの後終了します。入力データが(最初の立上りエッジを含む)SCKの立上りエッジでシフトされてSDIピンを通して入力され、出力データがSCKの各立下りエッジでシフトされてSDOピンから出力されます。内部で作られたシリアル・クロックはSCKピンに出力されます。この信号を使って変換結果を外部回路にシフトすることができます。 $\overline{EOC}$ はSCKの最初の立上りエッジを使ってラッチすることができます。変換結果の最後のビットはSCKの32番目の立

上りエッジを使ってラッチすることができます。32番目の立上りエッジの後、SDOは“H”になり( $\overline{EOC} = 1$ )、SCKは“H”的ままつまり、新しい変換サイクルが始まります。

$\overline{CS}$ はデータの出力ステートのあいだ“L”に保たれます。ただし、SCKの最初の立上りエッジと32番目の立上りエッジのあいだに、いつでも $\overline{CS}$ を“H”に引き上げてデータ出力ステートを中止することができます(図9を参照)。 $\overline{CS}$ の立上りエッジで、デバイスはデータ出力ステートを中止し、直ちに新しい変換を開始します。 $\overline{CS}$ が“H”に引き上げられるまでにデバイスがSDIの最後の入力ビット(SPD)をロードし終わらないと、SDIの情報は破棄され、前の構成がそのまま維持されます。これは32ビット出力データのすべては必要としないシステムでは有用で、無効の変換サイクルを中止したり、変換の開始点を同期させます。コンバータがSCKを“L”にドライブしている状態で $\overline{CS}$ が“H”に引き上げられると、SCKをロジック“H”的状態に戻すのに内部プルアップが使えなくなります。このため、デバイスは $\overline{CS}$ の次の立下りエッジで内部シリアル・クロック・モードから抜け出します。これは、外付けの10kプルアップ抵抗をSCKピンに追加するか、SCKが“L”的とき決して $\overline{CS}$ を“H”に引き上げないようにして、避けることができます。

SCKが“L”的ときはいつもLTC2484のSCKピンの内部プルアップはディスエーブルされます。通常、デバイスが内部SCKタイミング・モードだと、SCKは外部からドライブされません。ただし、特定のアプリケーションでは、SCKに外部ドライバが必要なことがあります。このドライバが“L”信号を出力した後Hi-Zになると、LTC2484の内部プルアップはディスエーブルされたままになります。したがって、SCKは“L”的になります。 $\overline{CS}$ の次の立下りエッジで、デバイスは外部SCKタイミング・モードに切り替わります。10kプルアップ抵抗をSCKに外付けすると、このピンは外部ドライバがHi-Zになると“H”的になります。 $\overline{CS}$ の次の立下りエッジで、デバイスは内部SCKタイミング・モードのまま留まります。

変換状態をテストするために $\overline{CS}$ を“H-L-H”とトグルするとき、スリープ・ステートで同様の状況が起きことがあります。デバイスがスリープ・ステート( $\overline{EOC} = 0$ )ならば、SCKは“L”的になります。 $\overline{CS}$ が( $t_{EOCtest}$ として上で定義された時間内に)“H”になると、内部プルアップがアクティブになります。SCKピンに大きな容量性負荷があると、内部プルアップでは $\overline{CS}$ が再度“L”になる前にSCKを“H”レベルに戻すのに十分ではないことがあります。これは、 $\overline{CS}$ が $\overline{EOC} = 0$ を検出した後“L”に留まる通常の場合は問題ではありません。この状況は10kプルアップ抵抗をSCKピンに外付けすることにより簡単に克服されます。

## アプリケーション情報

図8. 内部シリアル・クロック、シングル・サイクル動作

図9. 内部シリアル・クロック、短縮されたデータ出力長

## アプリケーション情報

### 内部シリアル・クロック、3線式I/O、連続変換

このタイミング・モードでは3線式インターフェースを使います。変換結果は内部で作られたシリアル・クロック(SCK)信号によってシフトされてデバイスから出力されます(図10参照)。 $\overline{CS}$ は永続的にグランドに接続することができ、ユーザー・インターフェースや絶縁バリヤを超えた転送が簡素化されます。

内部シリアル・クロック・モードは起動時リセット(POR)サイクルの終わりに選択されます。PORサイクルは $V_{CC}$ が2Vを超してから約1ms後に終了します。内部の弱いプルアップはPORサイクルのあいだアクティブなので、SCKが外部で“L”にドライブされないと、内部シリアル・クロック・タイミング・モードが自動的に選択されます(内部プルアップがピンを“H”に引き上げられないほどSCKに負荷がかかっていると、外部SCKモードが選択されます)。

変換中、SCKとシリアル・データ出力ピン(SDO)は“H”になります( $\overline{EOC} = 1$ )。変換が完了すると、SCKとSDOは“L”になります( $\overline{EOC} = 0$ )、変換が終了してデバイスが省電力のスリープ・ステートに入ったことを示します。デバイスは最小時間(内部SCKの周期の1/2)のあいだスリープ・ステートに留まってから、直ちにデータを出力し始めます。データの入力/出力サイクルはSCKの最初の立上りエッジで始まり、32番目の立上りエッジの後に終了します。次に入力データが(最初の立上りエッジを含む)SCKの立上りエッジでシフトされてSDIピンを通して入力され、出力データがSCKの各立下りエッジでシフトされてSDOピンから出力されます。内部で作られたシリアル・クロックはSCKピンに出力されます。この信号を使って変換結果を外部回路にシフトすることができます。 $\overline{EOC}$ はSCKの最初の立上りエッジを使ってラッチすることができます。変換結果の最後のビットはSCKの32番目の立上りエッジを使ってラッチすることができます。32番目の立上りエッジの後、SDOは“H”になります( $\overline{EOC} = 1$ )、新しい変換が進行中であることを示します。変換中、SCKは“H”的ままでです。

図10. 内部シリアル・クロック、 $\overline{CS} = 0$  連続動作

## アプリケーション情報

### コンバータの精度の維持

デバイスのデカッピング、PCBのレイアウト、アンチエイリアシング回路、ライン周波数の乱れなどの影響を変換結果ができるだけ受けないようにLTC2484は設計されています。にもかかわらず、このデバイスの24ビット精度の性能を維持するには、いくつかの簡単な注意が必要です。

### デジタル信号レベル

LTC2484のデジタル・インターフェースは使うのが簡単です。そのデジタル入力(SDI、 $f_O$ 、 $\overline{CS}$ 、および外部SCKモード動作のSCK)は標準CMOSロジック・レベルを受け入れ、内部ヒステリシス・レシーバは100 $\mu$ sまでの遅いエッジ遷移時間を許容できます。ただし、このコンバータの並はずれた精度と低電源電流の利点を生かすにはいくらかの配慮が必要です。

デジタル出力信号(SDOと内部SCKモード動作のSCK)は変換ステートのあいだ一般にアクティブではないので、それほど心配いりません。

デジタル入力信号は0.5V～(V<sub>CC</sub>−0.5V)の範囲ですが、CMOS入力レシーバには電源から追加の電流が流れます。デジタル入力信号(SDI、 $f_O$ 、 $\overline{CS}$ 、および外部SCKモード動作のSCK)のどれかがこの範囲内のとき、問題の信号が有効なロジック・レベルであっても、電源電流が増加する可能性があることに注意してください。マイクロパワー動作では、すべてのデジタル入力信号をフルCMOSレベル[V<sub>IL</sub> < 0.4VおよびV<sub>OH</sub> > (V<sub>CC</sub>−0.4V)]にドライブすることを推奨します。

変換周期のあいだ、ピンに接続されている高速デジタル信号のアンダーシュートやオーバーシュートがAD変換過程を大きく乱すことがあります。アンダーシュートとオーバーシュートは、外部制御信号の遷移時間がドライバからLTC2484までの伝播遅延の2倍より短いとき、コンバータのピンのところのインピーダンスの不整合によって生じます。参考までに、普通のFR-4基板の場合、信号の伝播速度は内部トレースで約183ps/インチ、表面トレースで170ps/インチです。したがって、1nsの最小遷移時間で制御信号を発生しているドライバは、2.5インチより短いトレースでコンバータに接続する必要があります。こ

の問題は、共通制御ラインが使用され、多数の反射が起きる可能性があるとき特に困難になります。解決策はすべての伝送ラインをそれらの特性インピーダンスに近い値で注意深く終端することです。

LTC2484のピンの近くで並列終端するとこの問題が解決されますが、ドライバの電力消費が増加します。ドライバの出力ピンの近くに27 $\Omega$ ～56 $\Omega$ の直列抵抗を接続しても、追加の電力消費なしにこの問題が解決されます。実際の抵抗値はトレースのインピーダンスと接続トポロジーに依存します。

代わりの解決策は制御信号のエッジレートを下げることです。エッジを非常に遅くすると、遷移時間のあいだのコンバータの電源電流が増加することに注意が必要です。差動入力アーキテクチャでは、グランド電流に対するコンバータの敏感さが減少します。

LTC2484を外部変換クロックで使用するとき、 $f_O$ 信号の接続には特に注意が必要です。このクロックは変換時間のあいだアクティブで、内部デジタル・フィルタが与える通常モードの除去率はこの周波数ではありません。コンバータのリファレンス端子のこの周波数の通常モード信号はDC利得とINL誤差を生じることがあります。コンバータの入力端子のこの周波数の通常モード信号はDCオフセット誤差を生じることがあります。このような乱れは、 $f_O$ 信号のトレースとコンバータの入力やリファレンスの接続トレースのあいだの非対称の容量性結合によって生じことがあります。直接的解決法は $f_O$ 信号のトレースと入力/リファレンス信号のあいだの間隔をできるだけ大きく保つことです。 $f_O$ 信号がコンバータの近くで並列に終端されていると、 $f_O$ 接続トレース、終端、およびグランド・リターン経路によって形成されるループにかなりのAC電流が流れます。したがって、コンバータの入力やリファレンスに乱された信号の誘導性結合を生じことがあります。このような状況では、ユーザーは差動入力とリファレンス接続のループ面積だけでなく、 $f_O$ 信号のループ面積も最小に抑える必要があります。 $f_O$ がドライブされない場合でも、他の近傍の信号による同様のEMIの危険がありますが、これは良いレイアウト手法に従うことにより最小に抑えられます。

## アプリケーション情報

### 入力とリファレンスのドライブ

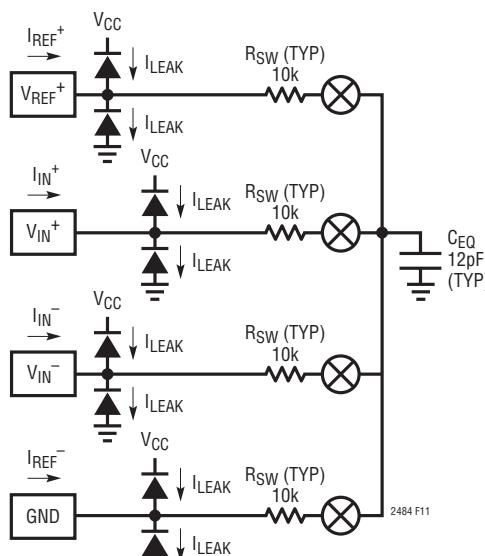

LTC2484コンバータの入力ピンとリファレンス・ピンはサンプリング・コンデンサのネットワークに直接接続されています。差動入力電圧と差動リファレンス電圧の関係に依存して、これらのコンデンサはこれらの4つのピンのあいだで切り替わり、その過程で少量の電荷を転送します。簡略化された等価回路を図11に示します。

簡単な近似法として、アナログ入力ピン( $IN^+$ 、 $IN^-$ 、 $V_{REF}^+$ またはGND)をドライブしているソース・インピーダンス $R_S$ は( $R_{SW}$ および $C_{EQ}$ (図11を参照)と一緒に)時定数 $\tau = (R_S + R_{SW}) \cdot C_{EQ}$ の1次パッシブ・ネットワークを形成していると考えることができます。コンバータは、サンプリング周期が入力回路の時定数 $\tau$ より少なくとも14倍大きいと、1ppmより良い精度で入力信号をサンプリングすることができます。4つのアナログ入力ピンのサンプリング過程は半分独立しているので、各時定数はそれだけで考慮すべきで、最悪の状況では誤差が加算されることがあります。

内部発振器を使っているとき、LTC2484のフロントエンド・スイッチトキャパシタ・ネットワークは8.1μsのサンプリング周期に対応する123kHzのクロックで駆動されます。したがって、セト

ング誤差を1ppm未満にするには、 $\tau \leq 8.1\mu s / 14 = 580\text{ns}$ となるようにドライブ・ソースのインピーダンスを選択します。周波数が $f_{EOSC}$ の外部発振器を使うと、サンプリング周期は $2.5/f_{EOSC}$ で、1ppm未満のセトリング誤差の場合、 $\tau \leq 0.178/f_{EOSC}$ です。

### 自動差動入力電流キャンセル

センサの出力インピーダンスが低い(外部バイパス・コンデンサなしで最大10kΩ、または0.001μFのバイパス付きで最大500Ω)アプリケーションでは、入力は完全にセトリングします。この場合、誤差は持ち込まれないので、センサを直接デジタル化することができます。

多くのアプリケーションでは、センサの出力インピーダンスは外部バイパス・コンデンサと結合して1ppmの精度に必要な580nsをはるかに超えるRC時定数を生じます。たとえば、0.1μFのバイパス・コンデンサをドライブする10kΩのブリッジでは、必要な最大値より1桁大きな時定数になります。従来から、セトリングの問題はバッファを使って解決されてきました。これらのバッファは、ノイズの増加、DC性能(オフセット/ドリフト)の低下、入力/出力振幅の制限(グランドまたはV<sub>CC</sub>に近い信号をデジタル変換できない)、システムのコストと電力の増加を引き起こしました。LTC2484は独自のスイッチング・アルゴリズ

SWITCHING FREQUENCY

$f_{SW} = 123\text{kHz}$  INTERNAL OSCILLATOR

$f_{SW} = 0.4 \cdot f_{EOSC}$  EXTERNAL OSCILLATOR

$$I_{(IN^+)}_{AVG} = I_{(IN^-)}_{AVG} = \frac{V_{IN(CM)} - V_{REF(CM)}}{0.5 \cdot R_{EQ}}$$

$$I_{(REF^+)}_{AVG} = \frac{1.5 \cdot V_{REF} - V_{IN(CM)} + V_{REFCM}}{0.5 \cdot R_{EQ}} - \frac{V_{IN}^2}{V_{REF} \cdot R_{EQ}} - \frac{0.5 \cdot V_{REF} \cdot D_T}{R_{EQ}} \cong \frac{1.5V_{REF} + (V_{REF(CM)} - V_{IN(CM)})}{0.5 \cdot R_{EQ}} - \frac{V_{IN}^2}{V_{REF} \cdot R_{EQ}}$$

where:

$$V_{REFCM} = \left( \frac{V_{REF}^+}{2} \right)$$

$$V_{IN} = IN^+ - IN^-$$

$$V_{INCM} = \left( \frac{IN^+ + IN^-}{2} \right)$$

$R_{EQ} = 2.71\text{M}\Omega$  INTERNAL OSCILLATOR 60Hz MODE

$R_{EQ} = 2.98\text{M}\Omega$  INTERNAL OSCILLATOR 50Hz AND 60Hz MODE

$R_{EQ} = (0.833 \cdot 10^{12}) / f_{EOSC}$  EXTERNAL OSCILLATOR

$D_T$  IS THE DENSITY OF A DIGITAL TRANSITION AT THE MODULATOR OUTPUT

WHERE  $REF^-$  IS INTERNALLY TIED TO GND

図11. LTC2484の等価アナログ入力回路

## アプリケーション情報

ムを使って、外部のセトリング誤差とは無関係に、平均差動入力電流をゼロに強制します。これにより、バッファを必要とせずに、高インピーダンスのセンサを精確に直接デジタル化できます。整合していない漏れ電流によって生じる追加誤差も考慮に入れる必要があります。

このスイッチング・アルゴリズムは、正入力( $I_{IN^+}$ )の平均入力電流を負入力( $I_{IN^-}$ )の平均入力電流に等しくなるように強制します。変換サイクル全体にわたって、平均差動入力電流( $I_{IN^+} - I_{IN^-}$ )はゼロになります。差動入力電流はゼロですが、同相入力電流( $I_{IN^+} + I_{IN^-}$ )/2は同相入力電圧( $V_{INCM}$ )と同相リファレンス電圧( $V_{REFCM}$ )の差に比例します。

バランス・ブリッジ型のアプリケーションのように、入力同相電圧がリファレンス同相電圧に等しいアプリケーションでは、差動と同相の両方の入力電流がゼロになります。コンバータの精度はセトリング誤差による影響を受けません。 $IN^+$ と $IN^-$ のソース・インピーダンスの不整合も精度に影響を与えません。

入力同相電圧が一定だがリファレンス同相電圧とは異なるアプリケーションでは、差動入力電流はゼロに保たれますが、同相入力電流は $V_{INCM}$ と $V_{REFCM}$ の差に比例します。リファレンス同相電圧が2.5Vで、入力同相電圧が1.5Vの場合、(同時に50Hz/60Hz除去モードでは)同相入力電流は約0.74μAです。この同相入力電流は、 $IN^+$ と $IN^-$ に接続された外部ソースのインピーダンスが整合していれば、精度に影響を与えません。これらのソース・インピーダンスが整合していないと、固定オフセット誤差が生じますが、直線性やフルスケールの読み取りには影響を与えません。1kのソース抵抗の1%の不整合により、オフセット電圧が15ppm(74μV)シフトします。

同相入力電圧が入力信号レベルの関数として変化するアプリケーション(シングルエンド入力、RTD、半ブリッジ、電流センサなど)では、同相入力電流は入力電圧に比例して変化します。バランスのとれた入力インピーダンスの場合、同相入力電流の影響はLTC2484の大きなCMRRによって除去され、精度

はほとんど低下しません。ソース・インピーダンスが整合していないと、同相入力電圧と同相リファレンス電圧の差に比例した利得誤差が生じます。1kのソース抵抗の1%の不整合により、(リファレンスと入力の同相電圧の差が1Vの場合)15ppmのレベルのワーストケース利得誤差が生じます。整合していないソース・インピーダンスと、リファレンス/入力の同相電圧の差の影響が表6にまとめています。

表6. LTC2484の推奨入力構成

|                                   | バランスのとれた入力抵抗                                                      | バランスのとれない入力抵抗                                                                           |

|-----------------------------------|-------------------------------------------------------------------|-----------------------------------------------------------------------------------------|

| 一定の<br>$V_{IN(CM)} - V_{REF(CM)}$ | $IN^+$ と $IN^-$ の両方で<br>$C_{IN} > 1nF$ 。大きなソース抵抗を取ることができ、誤差は無視できる | $IN^+$ と $IN^-$ の両方で<br>$C_{IN} > 1nF$ 。大きなソース抵抗を取ることができる。バランスのとれない抵抗によりオフセットが生じるが、較正可能 |

| $V_{IN(CM)} - V_{REF(CM)}$ が変化    | $IN^+$ と $IN^-$ の両方で<br>$C_{IN} > 1nF$ 。大きなソース抵抗を取ることができ、誤差は無視できる | $IN^+$ と $IN^-$ のコンデンサを最小にして大きなソース・インピーダンスを避ける(<5kを推奨)                                  |

ダイナミック入力電流の大きさは非常に安定した内部サンプリング・コンデンサのサイズとコンバータのサンプリング・クロックの精度に依存します。全温度範囲と電源範囲で、内部クロックの精度は標準で0.5%より良くなります。この仕様は外部クロックでも簡単に実現できます。比較的安定した(50ppm/°C)抵抗が $IN^+$ と $IN^-$ から見た外部ソース・インピーダンスに使われると、ダイナミック電流の予想ドリフトとオフセットは無視できるほど小さくなります(全温度範囲と電圧範囲でそれぞれの値の約1%)。要求の非常に厳しいアプリケーションであっても、一度較正しておけば十分でしょう。

入力サンプリング電荷に加えて、入力ESD保護ダイオードには温度に依存した漏れ電流が流れます。公称1nA(最大 $\pm 10nA$ )のこの電流により小さなオフセットのシフトが生じます。1kのソース抵抗により、標準1μV、最大10μVのオフセット電圧が生じます。

## アプリケーション情報

### リファレンス電流

同様に、LTC2484は差動リファレンス・ピン( $V_{REF}^+$ とGND)をサンプリングして、少量の電荷を外部のドライブ回路とやり取りしますので、ダイナミックなリファレンス電流が生じます。この電流はコンバータのオフセットは変化させませんが、利得とINL性能を下げることがあります。この電流の影響は明確に区別される2つの状況で分析することができます。

外部リファレンス・コンデンサの値が比較的小ないと( $C_{REF} < 1nF$ )、サンプリング・コンデンサの電圧はほとんど完全にセトリングし、ソース・インピーダンスの値が比較的大きくても、小さな誤差が生じるだけです。 $C_{REF}$ のこのような値では、リファレンスのフィルタの大きな利点は得られず、コンバータのオフセットと利得性能を悪くするので、ユーザーはこのような値は避けた方が良いでしょう。

特定の構成ではリファレンス・フィルタとして、もっと大きな値( $C_{REF} > 1nF$ )のリファレンス・コンデンサが必要でしょう。このようなコンデンサはリファレンス・サンプリング電荷を平均

化するので、外部ソース抵抗は擬似的に一定のリファレンス差動インピーダンスを見ることになります。

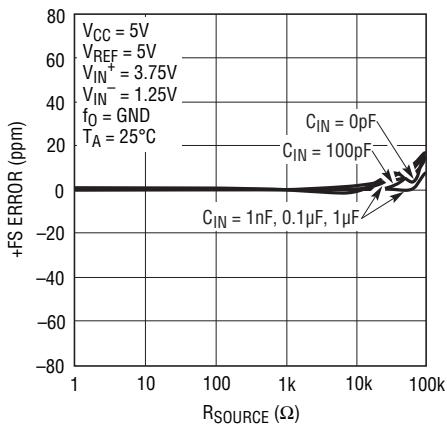

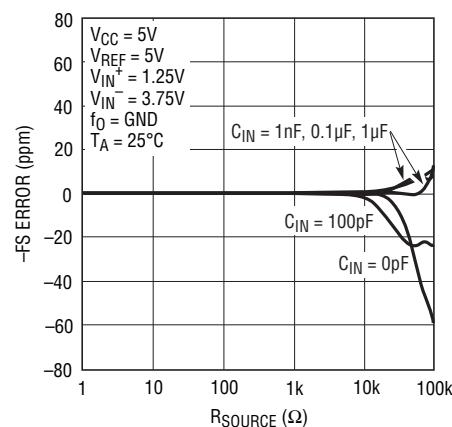

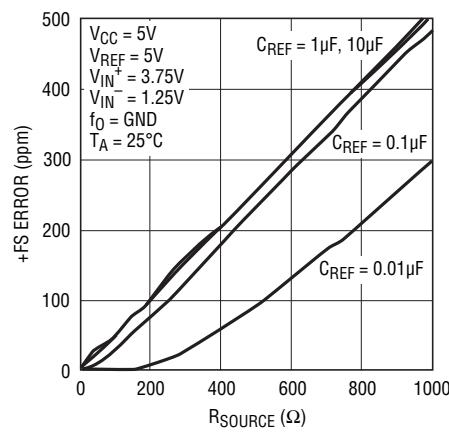

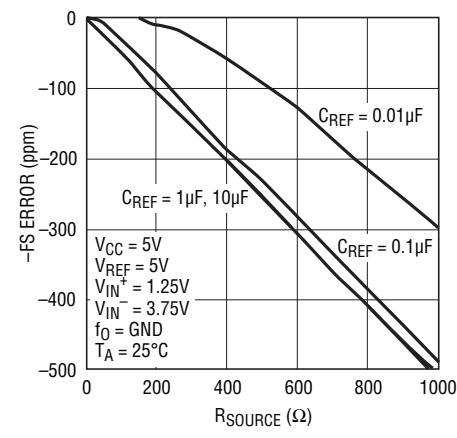

以下の説明では、入力とリファレンスの同相電圧は等しいと仮定します。60Hzモードで内部発振器を使うと、標準的差動リファレンス抵抗は $1M\Omega$ なので $V_{REF}$ ピンをドライブしているソース抵抗 $1\Omega$ ごとに $0.51ppm$ のフルスケール( $V_{REF}/2$ )利得誤差が生じます。50Hz/60Hzモードでは、関連する差動抵抗は $1.1M\Omega$ なので、フルスケール誤差は $V_{REF}$ ピンをドライブしているソース抵抗 $1\Omega$ ごとに $0.46ppm$ になります。50Hzモードでは、関連する差動抵抗は $1.2M\Omega$ なので、フルスケール誤差は $V_{REF}$ ピンをドライブしているソース抵抗 $1\Omega$ ごとに $0.42ppm$ になります。周波数が $f_{EOSC}$ の外部発振器によって $f_0$ がドライブされるとき(外部変換クロック動作)、標準的差動リファレンス抵抗は $0.30 \cdot 10^{12}/f_{EOSC}\Omega$ であり、 $V_{REF}$ ピンをドライブしているソース抵抗 $1\Omega$ ごとに $1.67 \cdot 10^{-6} \cdot f_{EOSC}ppm$ の利得誤差を生じます。 $V_{REF}$ ピンから見たソース抵抗とそのピンに接続された外部容量の様々な組合せに対する標準的+FSと-FSの誤差を図15～図18に示します。

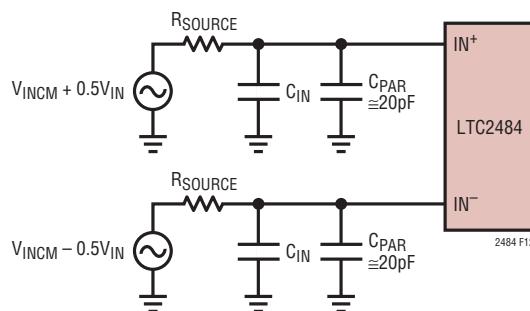

図12. IN<sup>+</sup>とIN<sup>-</sup>のRCネットワーク

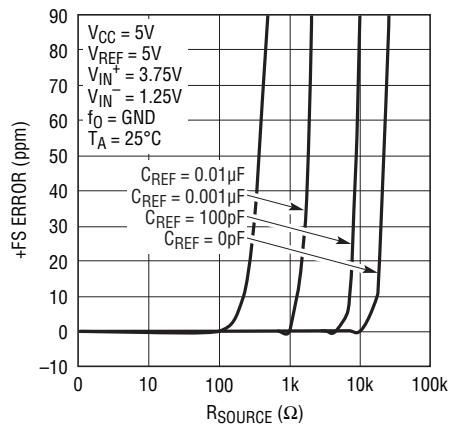

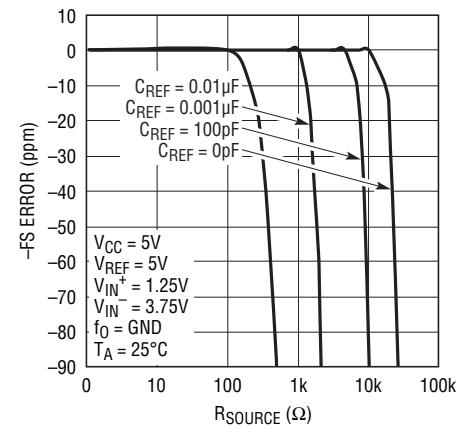

図13. +FS誤差とIN<sup>+</sup>またはIN<sup>-</sup>のR<sub>SOURCE</sub>

図14. -FS誤差とIN<sup>+</sup>またはIN<sup>-</sup>のR<sub>SOURCE</sub>

## アプリケーション情報

この利得誤差に加えて、コンバータのINL性能がリファレンスのソース・インピーダンスによって低下します。INLは、図11に示されているリファレンス・ピンの電流の式の、入力に依存する  $-V_{IN}^2/(V_{REF} \cdot R_{EQ}) - (0.5 \cdot V_{REF} \cdot D_T)/R_{EQ}$  の項によって生じます。内部発振器と60Hzモードを使うと、リファレンス・ソース抵抗の100Ωごとに約0.67ppmのINL誤差が追加されます。内部発振器と50Hz/60Hzモードを使うと、リファレンス・ソース抵抗の100Ωごとに約0.61ppmのINL誤差が追加されます。内

部発振器と50Hzモードを使うと、リファレンス・ソース抵抗の100Ωごとに約0.56ppmのINL誤差が追加されます。周波数が  $f_{EOSC}$  の外部発振器によって  $f_0$  がドライブされるとき、 $V_{REF}$  ピンをドライブしているソース抵抗の100Ωごとに約  $2.18 \cdot 10^{-6} \cdot f_{EOSC}$  ppm のINL誤差が追加されます。大きな  $C_{REF}$  値が使われるとき  $V_{REF}$  ピンをドライブしているソース抵抗によって生じる標準的INL誤差を図19に示します。 $V_{REF}$  ピンをドライブしているソース・インピーダンスを最小にすることを推奨します。

図15. +FS誤差と $V_{REF}$ の $R_{SOURCE}$ (小さな $C_{REF}$ )

図16. -FS誤差と $V_{REF}$ の $R_{SOURCE}$ (小さな $C_{REF}$ )

図17. +FS誤差と $V_{REF}$ の $R_{SOURCE}$ (大きな $C_{REF}$ )

図18. -FS誤差と $V_{REF}$ の $R_{SOURCE}$ (大きな $C_{REF}$ )

## アプリケーション情報

リファレンス同相電圧と入力同相電圧が異なるアプリケーションでは、余分の誤差が生じます。リファレンスと入力の同相電圧の差( $V_{REFCM} - V_{INCM}$ )の各1Vと5Vリファレンスに対して、リファレンス・ソース抵抗の1Ωごとに( $V_{REFCM} - V_{INCM}$ )/ $(V_{REF} \cdot R_{EQ})$ の余分のフルスケール利得誤差が生じ、この誤差は内部発振器と60Hzモードを使うとき0.074ppmになります。内部発振器と50Hz/60Hzモードを使うとき、余分のフルスケール利得誤差は0.067ppmです。内部発振器と50Hzモードを使うとき、余分の利得誤差は0.061ppmです。外部クロックを使うと、対応する余分の利得誤差は $0.24 \cdot 10^{-6} \cdot f_{EOSC}$ ppmです。

図19. INLと差動入力電圧およびリファレンスのソース抵抗( $C_{REF} > 1\mu F$ )

ダイナミック・リファレンス電流の大きさは非常に安定した内部サンプリング・コンデンサのサイズとコンバータのサンプリング・クロックの精度に依存します。全温度範囲と電源範囲で、内部クロックの精度は標準で0.5%より良くなります。この仕様は外部クロックでも簡単に実現できます。比較的安定した( $50\text{ppm}/^{\circ}\text{C}$ )抵抗が $V_{REF}^+$ とGNDから見た外部ソース・インピーダンスに使われると、ダイナミック電流の利得誤差の予想ドリフトは無視できるほど小さくなります(全温度範囲と電圧範囲でその値の約1%)。要求の非常に厳しいアプリケーションであっても、一度較正しておけば十分でしょう。

入力サンプリング電荷に加えて、リファレンス・ピンのESD保護ダイオードには温度に依存した漏れ電流が流れます。公称1nA(最大 $\pm 10\text{nA}$ )のこの漏れ電流により小さな利得誤差が生じます。100Ωのソース抵抗により、標準0.05μV、最大0.5μVのフルスケール誤差が生じます。

## 出力データ・レート

内部発振器を使っているとき、LTC2484は60Hzのノッチ周波数で1秒間に最大7.5のサンプル(sps)をとり、50Hzのノッチ周波数では6.25sps、さらに50Hz/60Hz除去モードでは6.8spsとなります。実際の出力データ・レートはスリープとデータ出力のフェーズの長さに依存しますが、これらはユーザーによって制御され、ほとんど無視できるほど短くすることができます。外部変換クロックを使って動作させると( $f_0$ を外部発振器に接続)、LTC2484の出力データ・レートを望むように増加させることができます。変換フェーズの持続時間は $41036/f_{EOSC}$ です。 $f_{EOSC} = 307.2\text{kHz}$ ならば、コンバータは、まるで内部発振器が使われ、ノッチが60Hzに設定されているかのように動作します。

$f_{EOSC}$ を公称307.2kHzを超えて増加させると、最大出力データ・レートが比例して増加します。ただし、出力レートの増加は2つの潜在的影響を伴いますので、それらについて注意深く検討する必要があります。

第一に、 $f_{EOSC}$ が変化すると、内部のノッチの位置が比例して変化し、コンバータの電源ライン周波数の差動モード除去が減少します。多くのアプリケーションで、その結果生じる性能低下は、LTC2484の並外れた同相除去に依存することにより、また入力回路の同相モードから差動モードへの変換ソースを注意深く除去することにより、大きく減らすことができます。ユーザーはシングルエンド入力フィルタを避け、 $IN^+$ ピンと $IN^-$ ピンをドライブする回路内で非常に高度な整合性と対称性を維持すべきです。

## アプリケーション情報

第二に、クロック周波数の増加により、入力ピンとリファレンス・ピンを通って転送されるサンプリング電荷の量が比例して増加します。大きな外部入力コンデンサやリファレンス・コンデンサ( $C_{IN}$ 、 $C_{REF}$ )が使われる場合、 $f_{EOSC}$ の任意の値でのコンバータの性能に対するソース抵抗の影響の評価のための式が前のセクションに与えられています。小さな外部入力コンデンサやリファレンス・コンデンサ( $C_{IN}$ 、 $C_{REF}$ )が使われる場合、LTC2484の標準的性能に対する外部ソース抵抗の影響を図13、14、15および16から推測することができます。これらの図で、横軸は $307200/f_{EOSC}$ で目盛られています。

2484 F20

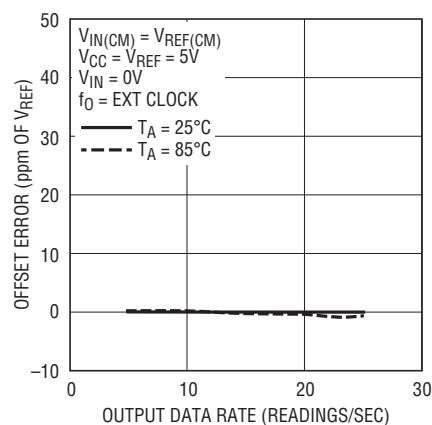

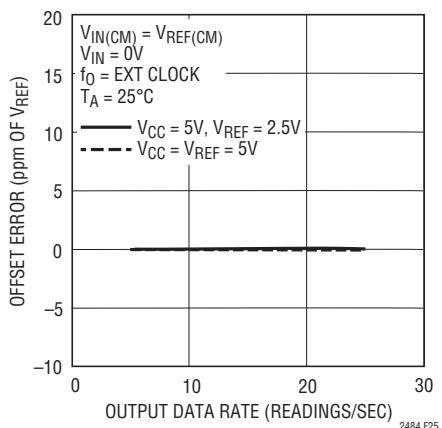

図20. オフセット誤差と出力データ・レートおよび温度

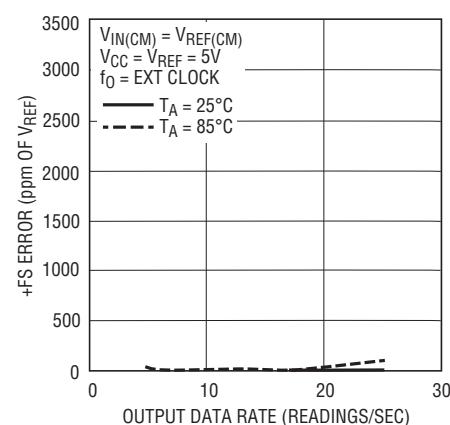

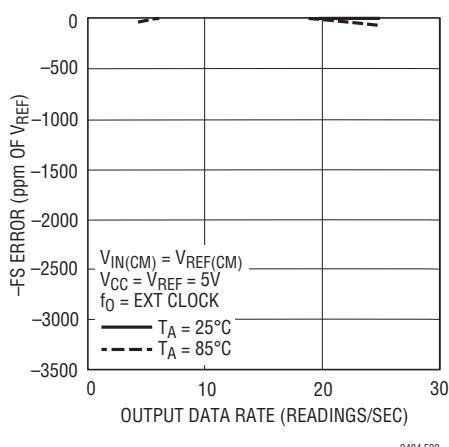

1秒あたり最大25までの読み取りの出力データ・レートの標準的な測定性能曲線を図20～図27に示します。1秒あたり20の読み取りを超す出力データ・レートで、このコンバータで可能な最高レベルの精度を得るには、ユーザーは使用する電源電圧を最大にし、最高周囲動作温度を制限するとよいでしょう。状況によっては、差動リファレンス電圧を下げた方が良いことがあります。

2484 F21

図21. +FS誤差と出力データ・レートおよび温度

2484 F22

図22. -FS誤差と出力データ・レートおよび温度

2484 F23

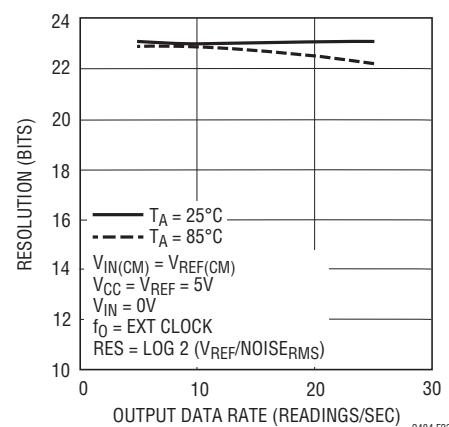

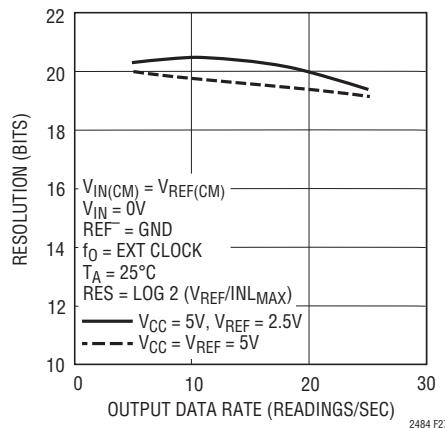

図23. 分解能( $Noiser_{RMS} \leq 1\text{ LSB}$ )と出力データ・レートおよび温度

## アプリケーション情報

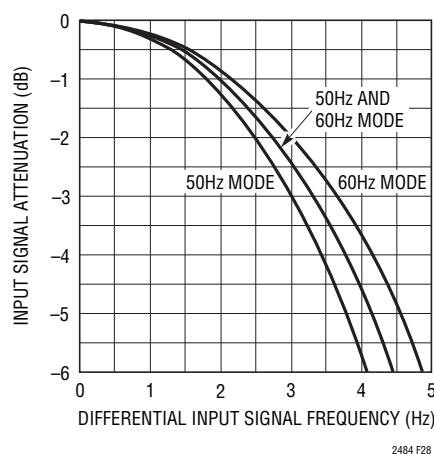

### 入力帯域幅

内部SINC<sup>4</sup>デジタル・フィルタとアナログおよびデジタルの自動較正回路を結合した効果により、LTC2484の入力帯域幅が決まります。ノッチを60Hzに設定して内部発振器を使うと、3dB入力帯域幅は3.63Hzになります。ノッチを50Hzに設定して内部発振器を使うと、3dB入力帯域幅は3.02Hzになります。周波数が $f_{EOSC}$ の外部変換クロック発生器を $f_O$ ピンに接続すると、3dB入力帯域幅は $11.8 \cdot 10^{-6} \cdot f_{EOSC}$ になります。

複雑なフィルタリングと較正アルゴリズムが利用されているため、コンバータの入力帯域幅はポールが3dB周波数に位置する1次フィルタではありません。内部発振器が使われる場合のLTC2484の入力帯域幅の形を図28に示します。周波数が $f_{EOSC}$ の外部発振器が使われる場合のLTC2484の入力帯域幅の形は、図28の60Hzモードの曲線から得ることができます。この図の横軸は $f_{EOSC}/307200$ で目盛られています。

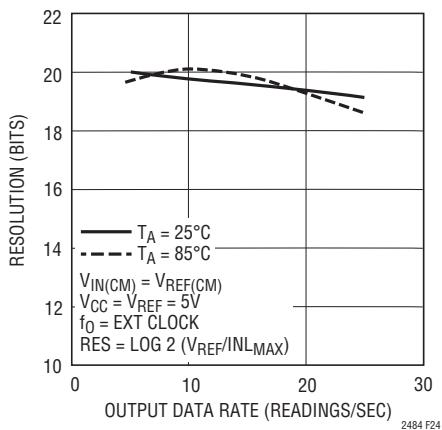

図24. 分解能( $INL_{MAX} \leq 1\text{LSB}$ )と出力データ・レートおよび温度

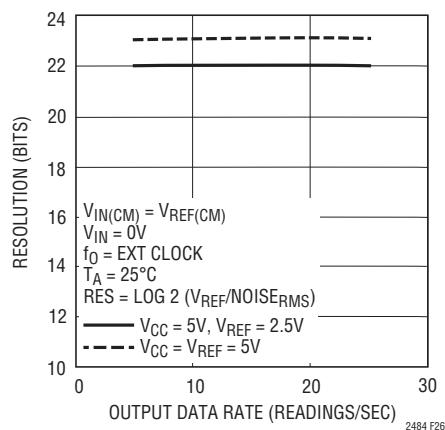

図26. 分解能( $NOISE_{RMS} \leq 1\text{LSB}$ )と出力データ・レートおよびリファレンス電圧

図25. オフセット誤差と出力データ・レートおよびリファレンス電圧

図27. 分解能( $INL_{MAX} \leq 1\text{LSB}$ )と出力データ・レートおよびリファレンス電圧

## アプリケーション情報

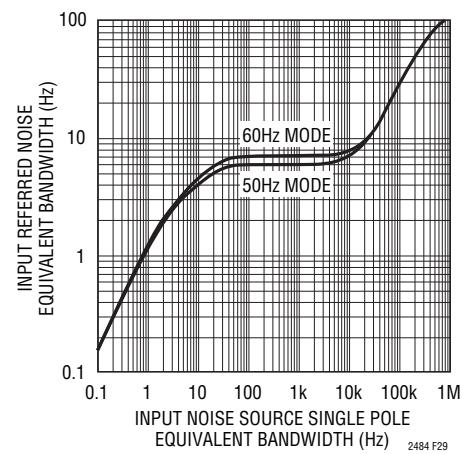

変換ノイズ( $V_{REF} = 5V$ で標準600nVRMS)は、ノイズの無いコンバータに接続されたホワイトノイズ源でモデル化することができます。帯域幅が無限のノイズ源のノイズスペクトル密度は  $47nV/\sqrt{Hz}$ 、0.5MHzの单一ポールのノイズ源では  $64nV/\sqrt{Hz}$  です。これらの数字から、外部増幅回路の設計には特に注意する必要があることは明らかです。このような回路は、出力を基準にしたノイズを減らすための非常に低い帯域幅(わずか数Hz)と、入力のスイッチトキャパシタ・ネットワークをドライブするのに必要な比較的高い帯域幅(少なくとも500kHz)の両方の必要条件に直面します。可能な解決法は、高利得で低帯域幅のアンプ段の後ろに高帯域幅のユニティゲインのバッファを置くことです。

外部のアンプがLTC2484をドライブする場合、ADCの入力を基準にしたシステム・ノイズの計算は、図29を使うと簡単になります。LTC2484の入力ピンをドライブしているアンプのノイズは帯域を制限されたホワイトノイズ源としてモデル化することができます。その帯域幅はコーナー周波数が  $f_i$  の単一ポール・ローパス・フィルタの帯域幅によって近似することができます。

アンプのノイズスペクトル密度は  $n_i$  です。図29から、x軸の値の選択に  $f_i$  を使って、入力をドライブしているアンプのノイズに相当する帯域幅  $freq_i$  をy軸上に見つけることができます。この帯域幅には、ADCの内部較正とフィルタリングの帯域制限効果が含まれています。これらの効果を含む、コンバータの入力を基準にしたドライビング・アンプのノイズは、 $N = n_i \cdot \sqrt{freq_i}$  として計算することができます。このように、LTC2484の入力を基準にした全システム・ノイズは、ADCの入力を基準にする3つのノイズ源(LTC2484の内部ノイズ、 $IN^+$ をドライブするアンプのノイズ、 $IN^-$ をドライブするアンプのノイズ)を二乗の和の平方根として合計して求めることができます。

周波数が  $f_{EOSC}$  の外部発振器で  $f_0$  ピンをドライブする場合、x軸が  $f_{EOSC}/307200$  で目盛られていれば、ノイズの計算に図29をそのまま使うことができます。 $f_{EOSC}/307200$  の比の値が大きくなると、図29の曲線の精度が低下し始めますが、同時に、LTC2484のノイズフロアが上がる所以、ドライブするアンプのノイズの寄与分が重要ではなくなくなります。

図28. 内部発振器を使ったときの入力信号の帯域幅

図29. 入力を基準にしたノイズに等価な、入力に接続されたホワイトノイズ源の帯域幅

## アプリケーション情報

### 通常モード除去とアンチエイリアシング

従来のADCに比べたデルタシグマADCの利点の1つは、チップに内蔵されたデジタル・フィルタです。大きなオーバーサンプリング比と組み合わせると、LTC2484のアンチエイリアシング・フィルタの必要条件は大幅に緩和されます。さらに、LTC2484の入力電流キャンセル機能により、デバイスのDC性能を下げることなく、外部ローパス・フィルタを利用できます。

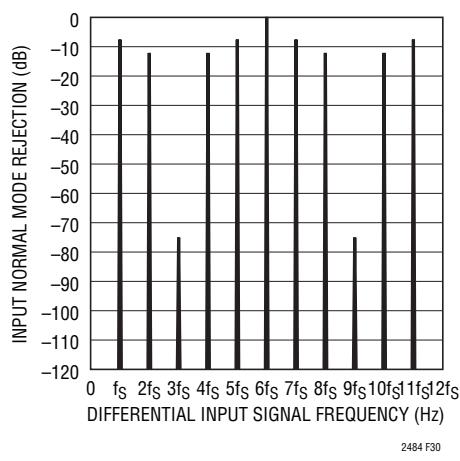

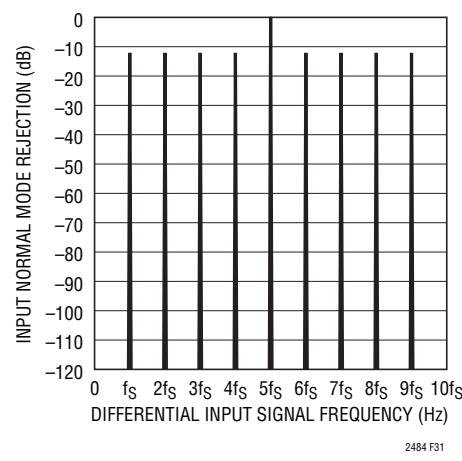

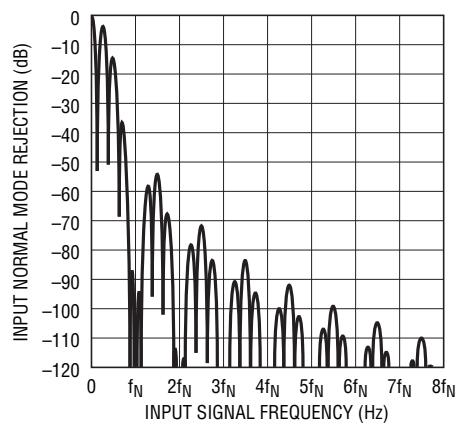

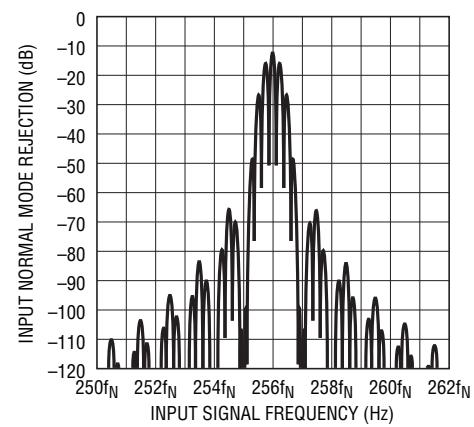

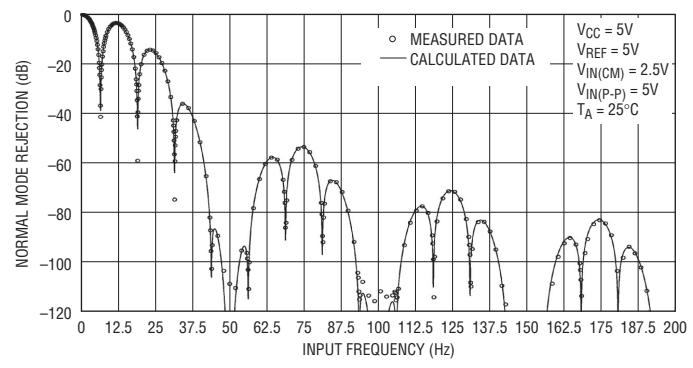

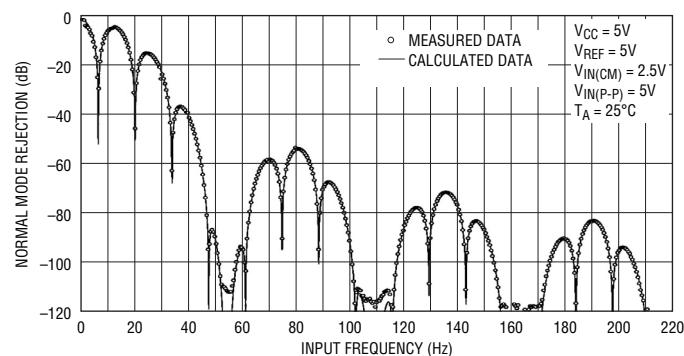

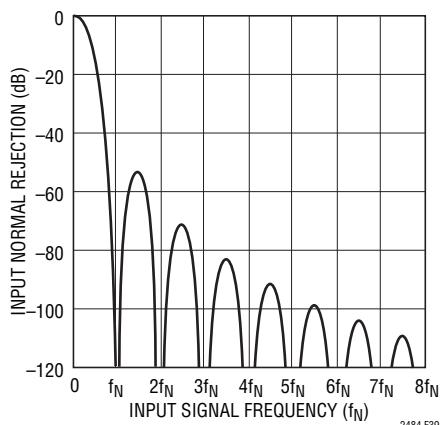

SINC<sup>4</sup>デジタル・フィルタにより、DCと変調器のサンプリング周波数( $f_S$ )の整数倍を除くすべての周波数で通常モードの除去が120dBを超えます。LTC2484の自動較正回路は、アナログとデジタルの両方の領域での追加の通常モード信号フィルタリングにより、アンチエイリアシングの必要条件をさらに簡単にします。動作モードには無関係に、 $f_S = 256 \cdot f_N = 2048 \cdot f_{OUT(MAX)}$ です。ただし、 $f_N$ はノッチ周波数、 $f_{OUT(MAX)}$ は最大出力データ・レートです。ノッチが50Hzに設定された内部発振器モードでは $f_S = 12800\text{Hz}$ 、50Hz/60Hzの除去では $f_S = 13960\text{Hz}$ 、60Hzのノッチ設定では $f_S = 15360\text{Hz}$ です。外部発振器モードでは $f_S = f_{EOSC}/20$ です。通常モードの除去率を図30と図31に示します。

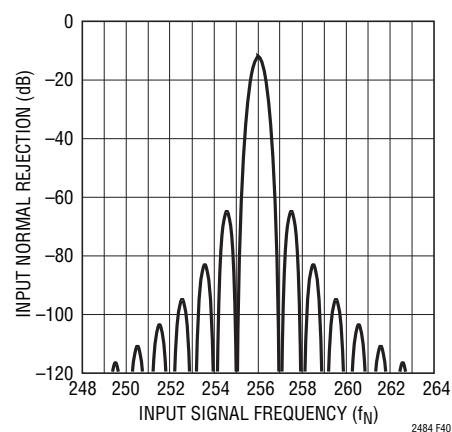

1倍速モードでは、 $f_S$ の整数倍で生じる低除去率の領域の帯域幅は非常に狭くなります。通常モードの除去率曲線の拡大した細部を図32(DCの近くでの除去)と図33( $f_S = 256f_N$ での除去)に示します。ただし、 $f_N$ はノッチ周波数を表します。これらの曲線は外部発振器モードで得られましたが、それらは $f_N$ の値を適切に選択することによりすべての動作モードで使えます。

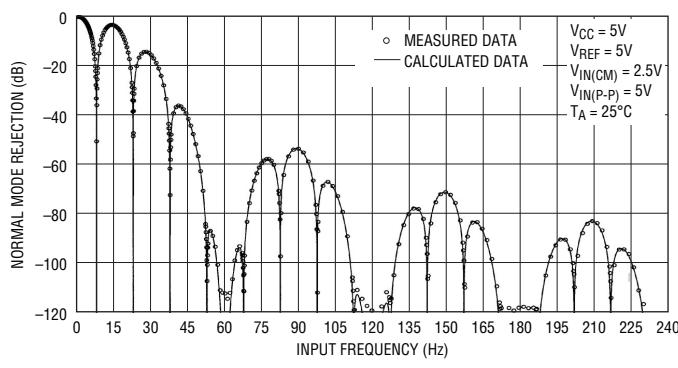

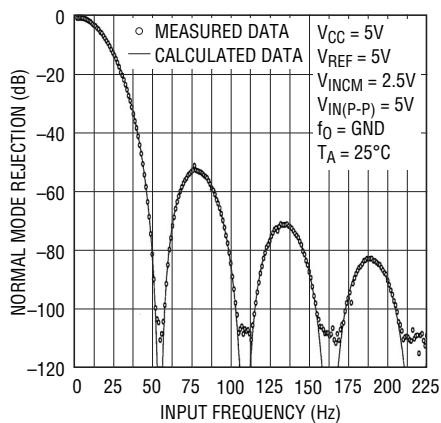

図34、図35および図36に示されているように、ユーザーは内部発振器を使ってこのレベルの性能の実現を期待することができます。内部発振器を使い、60Hzのノッチ設定で動作しているLTC2484の通常モードの除去率の標準的測定値を、計算された理論曲線に重ね合わせて図34に示します。同様に、50Hz除去モードと50Hz/60Hz除去モードでの、LTC2484の測定された通常モード除去率を図35と図36に示します。

これらの並外れた通常モードの仕様のおかげで、LTC2484の前段のアンチエイリアシングのフィルタリングは(もし必要だとしても)最小のもので十分です。LTC2484の前に受動RC部品を置く場合、入力のダイナミック電流について検討します(「入力電流」のセクションを参照)。この場合、LTC2484の差動入力電流キャンセル機能により、DC性能を大きく下げることなく、外部RCネットワークを使うことができます。

図30. 入力通常モードの除去率、

内部発振器と50Hzノッチ・モード

図31. 入力通常モードの除去率、

内部発振器と外部発振器の60Hzノッチ・モード

## アプリケーション情報

2484 F32

図32. DCでの入力通常モードの除去率

2484 F33

図33.  $f_S = 256f_N$ での入力通常モードの除去率

2484 F34

図34. 入力通常モードの除去率と入力周波数、

100%フルスケールの入力の搅乱(60Hzのノッチ)

2484 F35

図35. 入力通常モードの除去率と入力周波数、

100%フルスケールの入力の搅乱(50Hzのノッチ)

2484 F36

図36. 入力通常モードの除去率と入力周波数、

100%フルスケールの入力の搅乱(50Hz/60Hzモード)

## アプリケーション情報

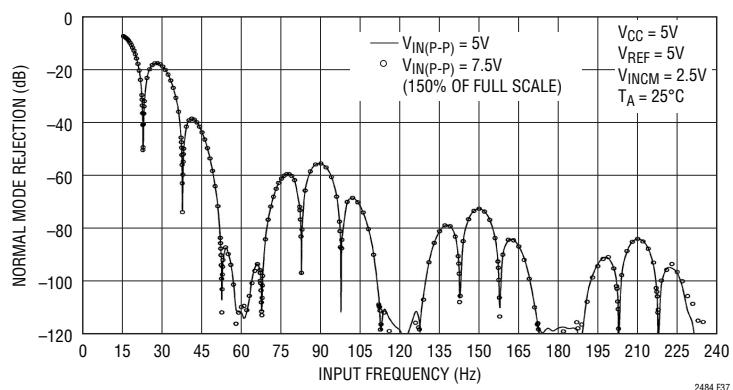

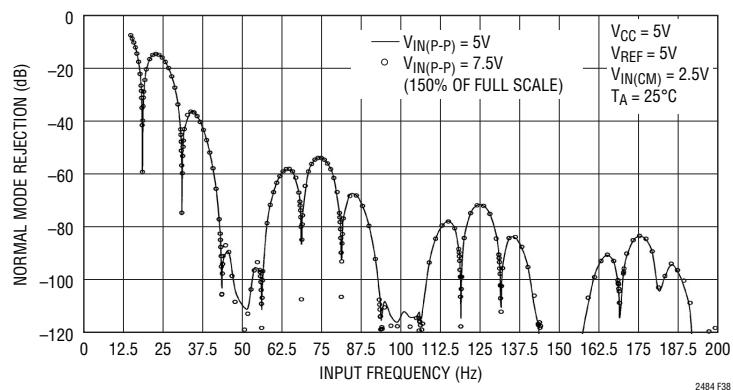

従来の高次デルタシグマ変調器は非常に良い直線性と分解能を与えますが、大きな入力信号レベルでは潜在的に不安定です。LTC2484の3次変調器に使われている独自アーキテクチャはこの問題を解決し、フルスケールの最大150%の入力信号レベルで予測可能な安定動作を保証します。多くの産業用アプリケーションでは、ボルト・レベルの乱れに重ねられたマイクロボルト・レベルの信号を測定しなければならないことが珍しくありませんが、LTC2484は並外れてこのような課題に適しています。乱れが差動のとき、関係のある仕様は大きな入力信号レベルに対する通常モードの除去率です。リファレンス電圧  $V_{REF} = 5V$  のとき、LTC2484のフルスケール差動入力範囲は

5Vピーク・トゥ・ピークです。5Vピーク・トゥ・ピーク(フルスケール)入力信号を使って得られた従来の通常モードの除去率の結果に重ね合わせた、7.5Vピーク・トゥ・ピーク(フルスケールの150%)入力信号を使った、LTC2484の通常モードの除去率の測定結果を図37と図38に示します。図37では、LTC2484はノッチを60Hz( $f_O = "L"$ )に設定して内部発振器を使い、図38では、ノッチを50Hzに設定して内部発振器を使っています。LTC2484の除去性能はこの極端な状況でも低下せずに保たれていることが明らかです。大きな入力信号レベルで動作しているとき、ユーザーはこのような信号がデバイスの絶対最大定格を超さないよう注意する必要があります。

図37. 測定された入力通常モードの除去率と入力周波数、

150%フルスケールの入力の搅乱(60Hzのノッチ)

図38. 測定された入力通常モードの除去率と入力周波数、

150%フルスケールの入力の搅乱(50Hzのノッチ)

## アプリケーション情報

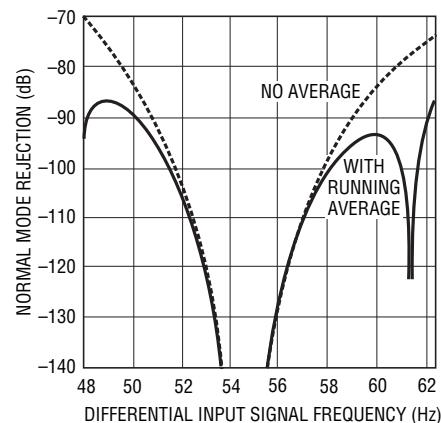

LTC2484の2倍速モードを使うと、デバイスは出力データ・レートを2倍にするためデジタル・オフセット較正動作はおこないません。図30と図31に示されているように、すぐれた通常モードの除去率は維持されます。ただし、DCと $f_S = 256f_N$ の近くでは拡大した細部が異なります(図39および図40を参照)。2倍速モードのとき、帯域幅は50Hz除去モードでは11.4Hz、60Hz除去モードでは13.6Hz、50Hz/60Hz除去モードでは12.4Hzです。内部発振器を使い2倍速モードで動作しているLTC2484の通常モード除去率の標準的測定値を図41に示します。

LTC2484が2倍速モードに構成設定されているとき、移動平均をとることにより、SINC<sup>1</sup>ノッチはSINC<sup>4</sup>デジタル・フィルタと組み合わされ、1倍速の通常モード除去率と同一の通常モード除去率を与えます。以下のアルゴリズムを使った平均化処理によって出力レートが保たれます。

図39. 2倍速モードでの入力通常モードの除去率

結果1 = 平均 (サンプル0、サンプル1)

結果2 = 平均 (サンプル1、サンプル2)

.....

結果n = 平均 (サンプルn-1、サンプルn)

移動平均の主な利点は、図42に示されているように、2倍の実効出力レートで50Hz/60Hzの同時除去を実現することです。処理前の出力データは48Hz～62.4Hzで70dBより良い除去率を与えます。これは50Hz±2%と60Hz±2%の両方をカバーします。移動平均を使うと、除去率は50Hz±2%と60Hz±2%の両方で87dBより良くなります。

図40. 2倍速モードでの入力通常モードの除去率

図41. 入力通常モードの除去率と入力周波数、

2倍速モードと50Hz/60Hzモード

図42. 2倍速モードでの入力通常モードの除去率

## アプリケーション情報

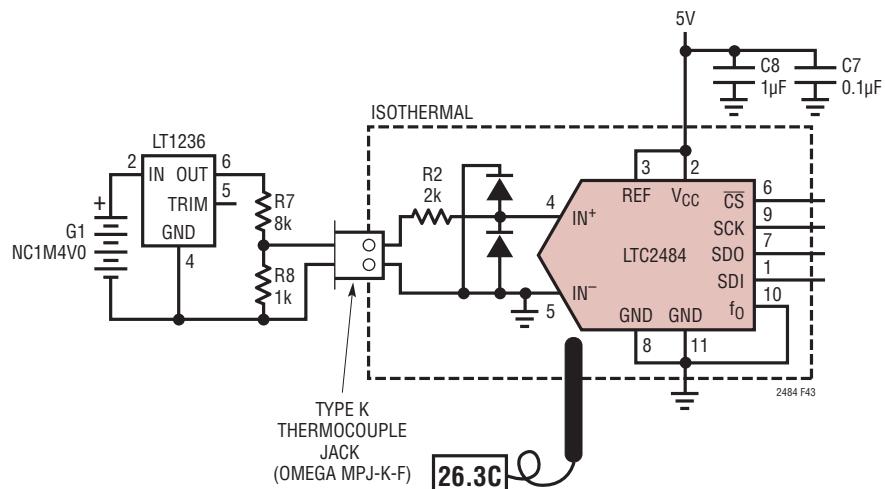

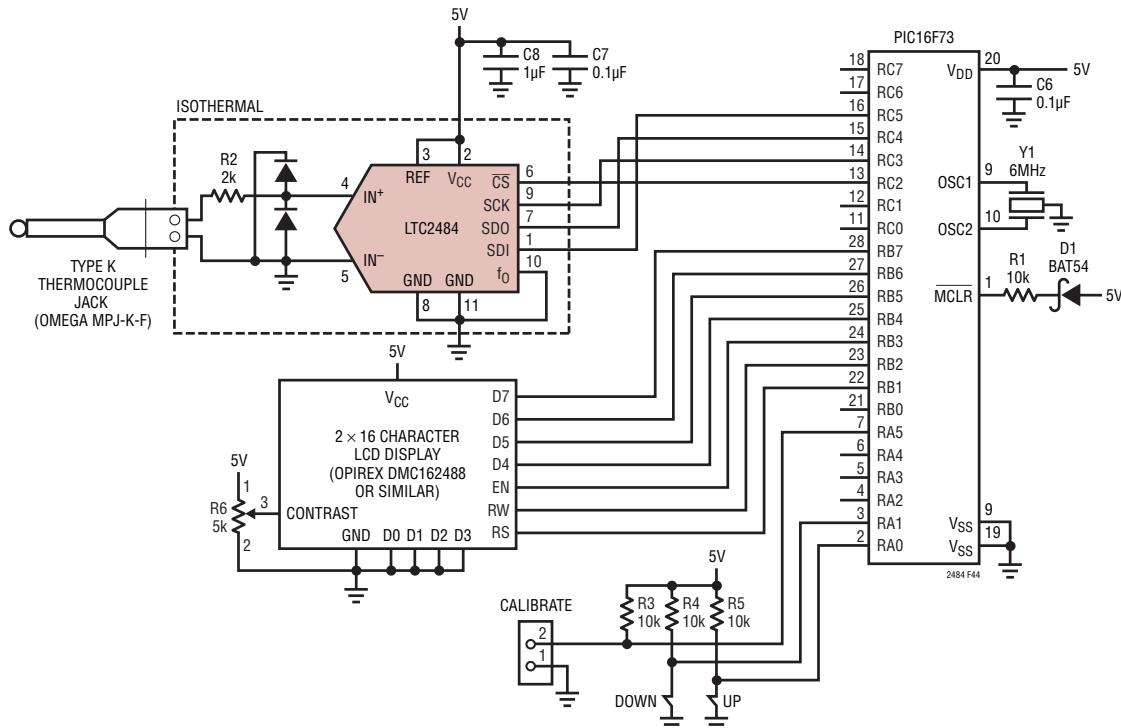

### 冷接点補償付きの完全な熱電対測定システム

LTC2484は熱電対や他の低電圧出力のセンサを直接デジタル変換するのに最適です。入力には標準500nV(最大2.5 $\mu$ V)のオフセット誤差、10nV/ $^{\circ}$ Cのオフセット・ドリフトおよび600nVRMSのノイズ・レベルがあります。

図44(このデータシートの最後のページ)は完全なK型熱電対計です。信号調整回路は簡単なサージ保護回路だけです。どんな熱電対計でも、冷接点温度センサは熱電対の素材間の接点およびプリント回路基板の銅トレースと同じ温度でなければなりません。小型のLTC2484はOmega MPJ-K-F熱電対のソケットの下にきちんと押し込むことができ、確実に熱結合されます。

LTC2484の1.4mV/ $^{\circ}$ CのPTAT回路により冷接点の温度が測定されます。熱電対の電圧と冷接点の温度が知られると、直線近似、参照表、適当な多項式曲線など、多くの熱電対温度

の計算法が使えます。図43に示されているように、LT<sup>®</sup>1236リファレンスから得られる精確な500mVをADC入力に与え、精確な温度計を使ってローカル温度を測定することにより較正がおこなわれます。較正モードで、上下ボタンを使ってローカル温度の読み取り値が精確な温度計に合致するまで調整します。電圧と温度の両方の較正を簡単に自動化することができます。

このアプリケーションの完全なマイクロコントローラ用コードがLTC2484製品のウェブページで入手できます。

<http://www.linear.com>

これは多くの異なる計器のテンプレートとして利用することができ、組込型温度センサの較正係数の生成方法を示しています。多数のコメントによりプログラムの動作が詳細に説明されています。read\_LTC2484()関数はLTC2484の動作を制御します。参考までに以下に掲載します。

図43. 較正方法

## アプリケーション情報

```

/** read_LTC2484() ****

This is the function that actually does all the work of talking to the LTC2484.

The spi_read() function performs an 8 bit bidirectional transfer on the SPI bus.

Data changes state on falling clock edges and is valid on rising edges, as

determined by the setup_spi() line in the initialize() function.

```

A good starting point when porting to other processors is to write your own spi\_write function. Note that each processor has its own way of configuring the SPI port, and different compilers may or may not have built-in functions for the SPI port. Also, since the state of the LTC2484's SDO line indicates when a conversion is complete you need to be able to read the state of this line through the processor's serial data input. Most processors will let you read this pin as if it were a general purpose I/O line, but there may be some that don't.

When in doubt, you can always write a "bit bang" function for troubleshooting purposes.

The "fourbytes" structure allows byte access to the 32 bit return value:

```

struct fourbytes // Define structure of four consecutive bytes

{

// To allow byte access to a 32 bit int or float.

int8 te0; // te0

int8 te1; // te1 The make32() function in this compiler will

int8 te2; // te2 also work, but a union of 4 bytes and a 32 bit int

int8 te3; // te3 is probably more portable.

};

Also note that the lower 4 bits are the configuration word from the previous conversion. The 4 LSBs are cleared so that they don't affect any subsequent mathematical operations. While you can do a right shift by 4, there is no point if you are going to convert to floating point numbers - just adjust your scaling constants appropriately.

****

signed int32 read_LTC2484(char config)

{

union

{

signed int32 bits32; // adc_code.bits32    all 32 bits

struct fourbytes by; // adc_code.by.te0    byte 0

struct fourbytes by; // adc_code.by.te1    byte 1

struct fourbytes by; // adc_code.by.te2    byte 2

struct fourbytes by; // adc_code.by.te3    byte 3

} adc_code;

output_low(CS); // Enable LTC2484 SPI interface

while(!input(PIN_C4)) {} // Wait for end of conversion. The longest

// you will ever wait is one whole conversion period

// Now is the time to switch any multiplexers because the conversion is finished

// and you have the whole data output time for things to settle.

adc_code.by.te3 = 0; // Set upper byte to zero.

adc_code.by.te2 = spi_read(config); // Read first byte, send config byte

adc_code.by.te1 = spi_read(0); // Read 2nd byte, send speed bit

adc_code.by.te0 = spi_read(0); // Read 3rd byte. '0' argument is necessary

// to act as SPI master!! (compiler

// and processor specific.)

output_high(CS); // Disable LTC2484 SPI interface

// Clear configuration bits and subtract offset. This results in

// a 2's complement 32 bit integer with the LTC2484's MSB in the 2^20 position

adc_code.by.te0 = adc_code.by.te0 & 0xF0;

adc_code.bits32 = adc_code.bits32 - 0x00200000;

return adc_code.bits32;

} // End of read_LTC2484()

```

## パッケージ