# Easy Drive入力電流キャンセル機能 およびI<sup>2</sup>Cインターフェース付き 16ビット・デルタシグマADC

## 特長

- Easy Drive™技法により、差動入力電流がゼロのレール・トゥ・レール入力が可能

- 最大限の精度で高インピーダンス・センサを直接デジタル化

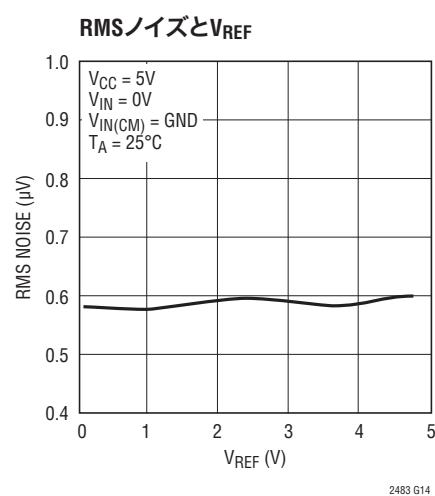

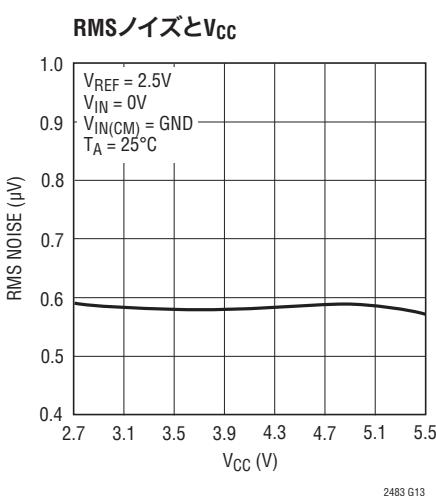

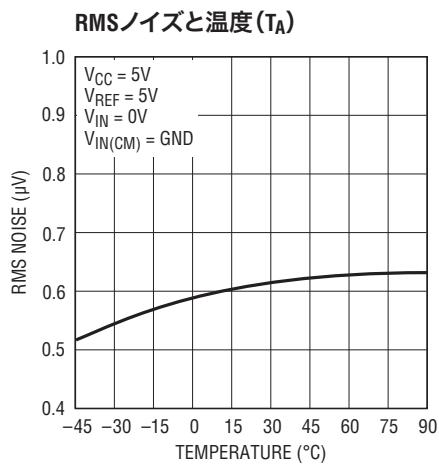

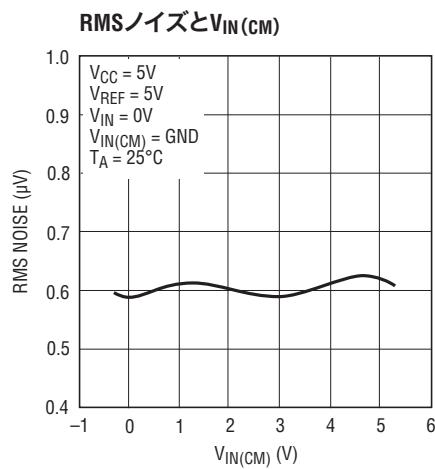

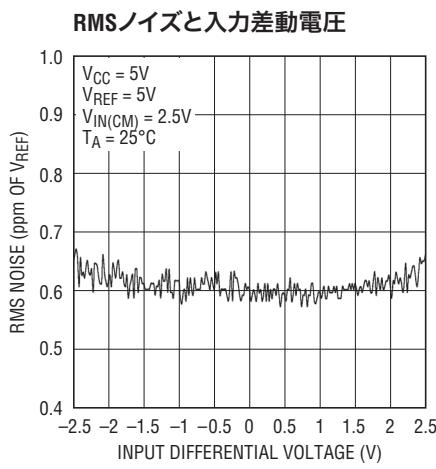

- ノイズ:  $V_{REF}$ と無関係に  $600nV_{RMS}$

- GND～ $V_{CC}$ の入力/リファレンス同相範囲

- 2線I<sup>2</sup>Cインターフェース

- 50Hz/60Hz同時除去モード

- NLが $\pm 2ppm$  ( $0.25LSB$ )、ミッシングコードなし

- オフセットが $\pm 1ppm$ 、フルスケール誤差が $\pm 15ppm$

- 待ち時間なし: デジタル・フィルタは1サイクルでセトリング

- 2.7V～5.5Vの単一電源動作

- 内部発振器

- 6つのアドレスを使用可能

- 小型(3mm×3mm)10ピンDFNパッケージ

## アプリケーション

- ダイレクト・センサ・デジタイザ

- 秤

- 直接温度測定

- ストレイン・ゲージ・トランスジューサ

- 計測

- 産業用プロセス制御

- DVMおよびメータ

## 概要

LTC<sup>®</sup>2483は、16ビットおよび符号ビットのNo Latency ΔΣ™アナログー・デジタル・コンバータを、特許取得のEasy Drive技法およびI<sup>2</sup>Cデジタル・インターフェースと組み合わせたデバイスです。特許取得のサンプリング回路は、差動入力電流の自動キャンセルにより、ダイナミック入力電流誤差や内部バッファの弱点を除去しています。このため、優れたDC精度を維持しながら、大きい外部ソース・インピーダンスを許容し、レール・トゥ・レールの入力範囲の入力信号を直接デジタル化できます。

LTC2483はリファレンス電圧と関係なく、広い同相入力電圧範囲(0V～ $V_{CC}$ )が可能です。リファレンスは100mVまで低くすることも、 $V_{CC}$ に直接接続することもできます。ノイズ・レベルは $V_{REF}$ と関係なく  $600nV_{RMS}$  です。このため、低電圧信号を16ビット精度で直接デジタル化できます。LTC2483は調整された発振器を内蔵しているので、外付けの水晶発振子や発振器が不要となり、50Hzおよび60Hzのライン周波数ノイズの除去比が $\pm 87dB$ となります。連続した透過的なオフセットとフルスケール較正により、絶対精度と低ドリフトが自動的に維持されます。

**LT**、LT、LTC、LTM、Linear TechnologyおよびLinearのロゴはリニアテクノロジー社の登録商標であり、No Latency ΔΣおよびEasy Driveはリニアテクノロジー社の商標です。他のすべての商標はそれぞれの所有者に所有権があります。特許申請中。

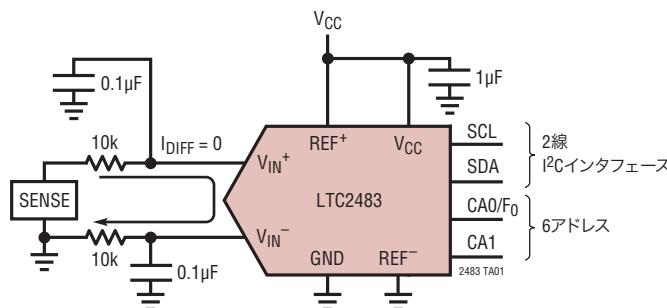

## 標準的応用例

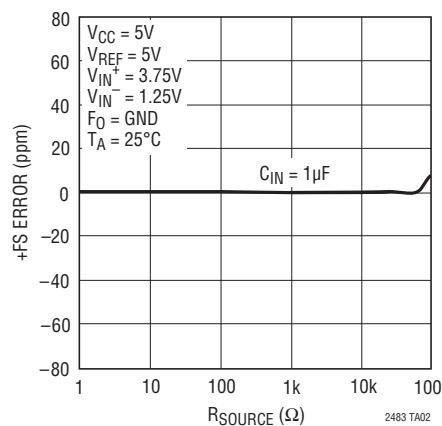

+FS誤差とIN<sup>+</sup>およびIN<sup>-</sup>のR<sub>SOURCE</sub>

## 絶対最大定格

(Note 1,2)

電源電圧( $V_{CC}$ )からGND .....  $-0.3V \sim 6V$

アナログ入力電圧からGND .....  $-0.3V \sim (V_{CC} + 0.3V)$

リファレンス入力電圧からGND .....  $-0.3V \sim (V_{CC} + 0.3V)$

デジタル入力電圧からGND .....  $-0.3V \sim (V_{CC} + 0.3V)$

デジタル出力電圧からGND .....  $-0.3V \sim (V_{CC} + 0.3V)$

動作温度範囲

LTC2483C .....  $0^{\circ}C \sim 70^{\circ}C$

LTC2483 .....  $-40^{\circ}C \sim 85^{\circ}C$

保存温度範囲 .....  $-65^{\circ}C \sim 125^{\circ}C$

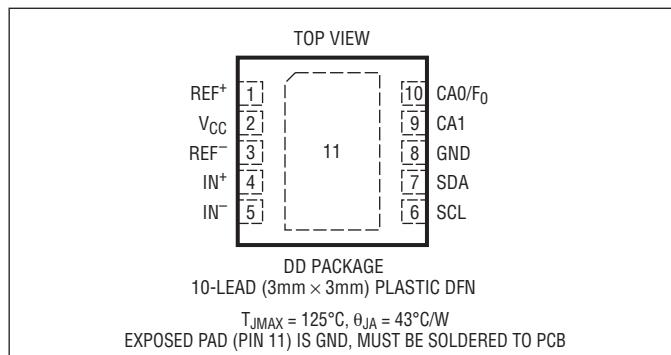

## ピン配置

## 発注情報

| 鉛フリー仕様         | テープアンドリール        | 製品マーキング* | パッケージ                           | 温度範囲                            |

|----------------|------------------|----------|---------------------------------|---------------------------------|

| LTC2483CDD#PBF | LTC2483CDD#TRPBF | LBSR     | 10-Lead (3mm × 3mm) Plastic DFN | $0^{\circ}C$ to $70^{\circ}C$   |

| LTC2483IDD#PBF | LTC2483IDD#TRPBF | LBSR     | 10-Lead (3mm × 3mm) Plastic DFN | $-40^{\circ}C$ to $85^{\circ}C$ |

| 鉛ベース仕様         | テープアンドリール        | 製品マーキング* | パッケージ                           | 温度範囲                            |

| LTC2483CDD     | LTC2483CDD#TR    | LBSR     | 10-Lead (3mm × 3mm) Plastic DFN | $0^{\circ}C$ to $70^{\circ}C$   |

| LTC2483IDD     | LTC2483IDD#TR    | LBSR     | 10-Lead (3mm × 3mm) Plastic DFN | $-40^{\circ}C$ to $85^{\circ}C$ |

さらに広い動作温度範囲で規定されるデバイスについては、弊社または弊社代理店にお問い合わせください。 \*温度グレードは出荷時のコンテナのラベルで識別されます。

鉛フリー仕様の製品マーキングの詳細については、<http://www.linear-tech.co.jp/leadfree/> をご覧ください。

テープアンドリールの仕様の詳細については、<http://www.linear-tech.co.jp/tapeandreel/> をご覧ください。

## 電気的特性

●は全動作温度範囲での規格値を意味する。それ以外は $T_A = 25^{\circ}C$ での値。(Note 3,4)

| PARAMETER                       | CONDITIONS                                                                                                                                                                                                                                     | MIN      | TYP            | MAX | UNITS                                                    |

|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|----------------|-----|----------------------------------------------------------|

| Resolution (No Missing Codes)   | $0.1 \leq V_{REF} \leq V_{CC}$ , $-FS \leq V_{IN} \leq +FS$ (Note 5)                                                                                                                                                                           | ● 16     |                |     | Bits                                                     |

| Integral Nonlinearity           | $5V \leq V_{CC} \leq 5.5V$ , $V_{REF} = 5V$ , $V_{IN(CM)} = 2.5V$ (Note 6)<br>$2.7V \leq V_{CC} \leq 5.5V$ , $V_{REF} = 2.5V$ , $V_{IN(CM)} = 1.25V$ (Note 6)                                                                                  | ● 2<br>1 | 10             | 10  | ppm of $V_{REF}$<br>ppm of $V_{REF}$                     |

| Offset Error                    | $2.5V \leq V_{REF} \leq V_{CC}$ , $GND \leq IN^+ = IN^- \leq V_{CC}$ (Note 13)                                                                                                                                                                 | ● 0.5    | 2.5            |     | $\mu V$                                                  |

| Offset Error Drift              | $2.5V \leq V_{REF} \leq V_{CC}$ , $GND \leq IN^+ = IN^- \leq V_{CC}$                                                                                                                                                                           |          | 10             |     | $nV/\text{ }^{\circ}C$                                   |

| Positive Full-Scale Error       | $2.5V \leq V_{REF} \leq V_{CC}$ , $IN^+ = 0.75V_{REF}$ , $IN^- = 0.25V_{REF}$                                                                                                                                                                  | ● 25     |                |     | ppm of $V_{REF}$                                         |

| Positive Full-Scale Error Drift | $2.5V \leq V_{REF} \leq V_{CC}$ , $IN^+ = 0.75V_{REF}$ , $IN^- = 0.25V_{REF}$                                                                                                                                                                  |          | 0.1            |     | ppm of $V_{REF}/\text{ }^{\circ}C$                       |

| Negative Full-Scale Error       | $2.5V \leq V_{REF} \leq V_{CC}$ , $IN^- = 0.75V_{REF}$ , $IN^+ = 0.25V_{REF}$                                                                                                                                                                  | ● 25     |                |     | ppm of $V_{REF}$                                         |

| Negative Full-Scale Error Drift | $2.5V \leq V_{REF} \leq V_{CC}$ , $IN^- = 0.75V_{REF}$ , $IN^+ = 0.25V_{REF}$                                                                                                                                                                  |          | 0.1            |     | ppm of $V_{REF}/\text{ }^{\circ}C$                       |

| Total Unadjusted Error          | $5V \leq V_{CC} \leq 5.5V$ , $V_{REF} = 2.5V$ , $V_{IN(CM)} = 1.25V$ (Note 6)<br>$5V \leq V_{CC} \leq 5.5V$ , $V_{REF} = 5V$ , $V_{IN(CM)} = 2.5V$ (Note 6)<br>$2.7V \leq V_{CC} \leq 5.5V$ , $V_{REF} = 2.5V$ , $V_{IN(CM)} = 1.25V$ (Note 6) |          | 15<br>15<br>15 |     | ppm of $V_{REF}$<br>ppm of $V_{REF}$<br>ppm of $V_{REF}$ |

| Output Noise                    | $5V \leq V_{CC} \leq 5.5V$ , $V_{REF} = 5V$ , $GND \leq IN^- = IN^+ \leq V_{CC}$ (Note 12)                                                                                                                                                     |          | 0.6            |     | $\mu V_{RMS}$                                            |

## コンバータの特性

●は全動作温度範囲での規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。(Note 3, 4)

| PARAMETER                                       | CONDITIONS                                                                                             | MIN | TYP | MAX | UNITS |

|-------------------------------------------------|--------------------------------------------------------------------------------------------------------|-----|-----|-----|-------|

| Input Common Mode Rejection DC                  | $2.5V \leq V_{\text{REF}} \leq V_{\text{CC}}$ , GND $\leq IN^- = IN^+ \leq V_{\text{CC}}$ (Note 5)     | ●   | 140 |     | dB    |

| Input Common Mode Rejection 50Hz $\pm 2\%$      | $2.5V \leq V_{\text{REF}} \leq V_{\text{CC}}$ , GND $\leq IN^- = IN^+ \leq V_{\text{CC}}$ (Note 5)     | ●   | 140 |     | dB    |

| Input Common Mode Rejection 60Hz $\pm 2\%$      | $2.5V \leq V_{\text{REF}} \leq V_{\text{CC}}$ , GND $\leq IN^- = IN^+ \leq V_{\text{CC}}$ (Note 5)     | ●   | 140 |     | dB    |

| Input Normal Mode Rejection 50Hz $\pm 2\%$      | $2.5V \leq V_{\text{REF}} \leq V_{\text{CC}}$ , GND $\leq IN^- = IN^+ \leq V_{\text{CC}}$ (Notes 5, 7) | ●   | 110 | 120 | dB    |

| Input Normal Mode Rejection 60Hz $\pm 2\%$      | $2.5V \leq V_{\text{REF}} \leq V_{\text{CC}}$ , GND $\leq IN^- = IN^+ \leq V_{\text{CC}}$ (Notes 5, 8) | ●   | 110 | 120 | dB    |

| Input Normal Mode Rejection 50Hz/60Hz $\pm 2\%$ | $2.5V \leq V_{\text{REF}} \leq V_{\text{CC}}$ , GND $\leq IN^- = IN^+ \leq V_{\text{CC}}$ (Notes 5, 9) | ●   | 87  |     | dB    |

| Reference Common Mode Rejection DC              | $2.5V \leq V_{\text{REF}} \leq V_{\text{CC}}$ , GND $\leq IN^- = IN^+ \leq V_{\text{CC}}$ (Note 5)     | ●   | 120 | 140 | dB    |

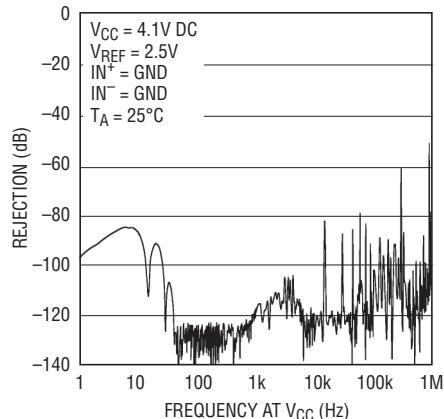

| Power Supply Rejection DC                       | $V_{\text{REF}} = 2.5V$ , $IN^- = IN^+ = \text{GND}$                                                   |     |     | 120 | dB    |

| Power Supply Rejection, 50Hz $\pm 2\%$          | $V_{\text{REF}} = 2.5V$ , $IN^- = IN^+ = \text{GND}$ (Notes 7, 9)                                      |     |     | 120 | dB    |

| Power Supply Rejection, 60Hz $\pm 2\%$          | $V_{\text{REF}} = 2.5V$ , $IN^- = IN^+ = \text{GND}$ (Notes 8, 9)                                      |     |     | 120 | dB    |

## アナログ入力とリファレンス

●は全動作温度範囲での規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。(Note 3)

| SYMBOL                                 | PARAMETER                                              | CONDITIONS                                   | MIN        | TYP                 | MAX                    | UNITS |    |

|----------------------------------------|--------------------------------------------------------|----------------------------------------------|------------|---------------------|------------------------|-------|----|

| $IN^+$                                 | Absolute/Common Mode $IN^+$ Voltage                    |                                              | GND – 0.3V |                     | $V_{\text{CC}} + 0.3V$ | V     |    |

| $IN^-$                                 | Absolute/Common Mode $IN^-$ Voltage                    |                                              | GND – 0.3V |                     | $V_{\text{CC}} + 0.3V$ | V     |    |

| FS                                     | Full-Scale of the Differential Input ( $IN^+ - IN^-$ ) |                                              | ●          | 0.5V <sub>REF</sub> |                        | V     |    |

| LSB                                    | Least Significant Bit of the Output Code               |                                              | ●          | $FS/2^{16}$         |                        |       |    |

| $V_{\text{IN}}$                        | Input Differential Voltage Range ( $IN^+ - IN^-$ )     |                                              | ●          | –FS                 | +FS                    | V     |    |

| $V_{\text{REF}}$                       | Reference Voltage Range ( $REF^+ - REF^-$ )            |                                              | ●          | 0.1                 | $V_{\text{CC}}$        | V     |    |

| $C_S (IN^+)$                           | $IN^+$ Sampling Capacitance                            |                                              |            |                     | 11                     | pF    |    |

| $C_S (IN^-)$                           | $IN^-$ Sampling Capacitance                            |                                              |            |                     | 11                     | pF    |    |

| $C_S (V_{\text{REF}})$                 | $V_{\text{REF}}$ Sampling Capacitance                  |                                              |            |                     | 11                     | pF    |    |

| $I_{\text{DC\_LEAK}} (IN^+)$           | $IN^+$ DC Leakage Current                              | Sleep Mode, $IN^+ = \text{GND}$              | ●          | –10                 | 1                      | 10    | nA |

| $I_{\text{DC\_LEAK}} (IN^-)$           | $IN^-$ DC Leakage Current                              | Sleep Mode, $IN^- = \text{GND}$              | ●          | –10                 | 1                      | 10    | nA |

| $I_{\text{DC\_LEAK}} (V_{\text{REF}})$ | $REF^+, REF^-$ DC Leakage Current                      | Sleep Mode, $V_{\text{REF}} = V_{\text{CC}}$ | ●          | –100                | 1                      | 100   | nA |

# LTC2483

## I<sup>2</sup>Cのデジタル入力とデジタル出力

●は全動作温度範囲での規格値を意味する。それ以外はT<sub>A</sub> = 25°Cでの値。(Note 3)

| SYMBOL                      | PARAMETER                                                                                           | CONDITIONS                                             | MIN                    | TYP | MAX | UNITS |

|-----------------------------|-----------------------------------------------------------------------------------------------------|--------------------------------------------------------|------------------------|-----|-----|-------|

| V <sub>IH</sub>             | High Level Input Voltage                                                                            |                                                        | 0.7V <sub>CC</sub>     |     |     | V     |

| V <sub>IL</sub>             | Low Level Input Voltage                                                                             |                                                        | 0.3V <sub>CC</sub>     |     |     | V     |

| V <sub>IL(CA1)</sub>        | Low Level Input Voltage for Address Pin                                                             |                                                        | 0.05V <sub>CC</sub>    |     |     | V     |

| V <sub>IH(CA0/F0,CA1)</sub> | High Level Input Voltage for Address Pins                                                           |                                                        | 0.95V <sub>CC</sub>    |     |     | V     |

| R <sub>INH</sub>            | Resistance from CA0/F <sub>0</sub> ,CA1 to V <sub>CC</sub> to Set Chip Address Bit to 1             |                                                        | 10                     |     |     | kΩ    |

| R <sub>INL</sub>            | Resistance from CA1 to GND to Set Chip Address Bit to 0                                             |                                                        | 10                     |     |     | kΩ    |

| R <sub>INF</sub>            | Resistance from CA0/F <sub>0</sub> , CA1 to V <sub>CC</sub> or GND to Set Chip Address Bit to Float |                                                        | 2                      |     |     | MΩ    |

| I <sub>I</sub>              | Digital Input Current                                                                               |                                                        | -10                    |     | 10  | μA    |

| V <sub>HYS</sub>            | Hysteresis of Schmitt Trigger Inputs                                                                | (Note 5)                                               | 0.05V <sub>CC</sub>    |     |     | V     |

| V <sub>OL</sub>             | Low Level Output Voltage SDA                                                                        | I = 3mA                                                | 0.4                    |     |     | V     |

| t <sub>OF</sub>             | Output Fall Time from V <sub>IHMIN</sub> to V <sub>ILMAX</sub>                                      | Bus Load C <sub>B</sub> 10pF to 400pF (Note 14)        | 20 + 0.1C <sub>B</sub> |     | 250 | ns    |

| t <sub>SP</sub>             | Input Spike Suppression                                                                             |                                                        | 50                     |     |     | ns    |

| I <sub>IN</sub>             | Input Leakage                                                                                       | 0.1V <sub>CC</sub> ≤ V <sub>IN</sub> ≤ V <sub>CC</sub> | 1                      |     |     | μA    |

| C <sub>I</sub>              | Capacitance for Each I/O Pin                                                                        |                                                        | 10                     |     |     | pF    |

| C <sub>B</sub>              | Capacitance Load for Each Bus Line                                                                  |                                                        | 400                    |     |     | pF    |

| C <sub>CAx</sub>            | External Capacitive Load on Chip Address Pins (CA0/F <sub>0</sub> ,CA1) for Valid Float             |                                                        | 10                     |     |     | pF    |

| V <sub>IH(EXT,OSC)</sub>    | High Level CA0/F <sub>0</sub> External Oscillator                                                   | 2.7V ≤ V <sub>CC</sub> < 5.5V                          | V <sub>CC</sub> - 0.5V |     |     | V     |

| V <sub>IL(EXT,OSC)</sub>    | Low Level CA0/F <sub>0</sub> External Oscillator                                                    | 2.7V ≤ V <sub>CC</sub> < 5.5V                          | 0.5                    |     |     | V     |

## 電源要件

●は全動作温度範囲での規格値を意味する。それ以外はT<sub>A</sub> = 25°Cでの値。(Note 3)

| SYMBOL          | PARAMETER      | CONDITIONS                                        | MIN      | TYP      | MAX | UNITS |

|-----------------|----------------|---------------------------------------------------|----------|----------|-----|-------|

| V <sub>CC</sub> | Supply Voltage |                                                   | 2.7      |          | 5.5 | V     |

| I <sub>CC</sub> | Supply Current | Conversion Mode (Note 11)<br>Sleep Mode (Note 11) | 160<br>1 | 250<br>2 |     | μA    |

## タイミング特性

●は全動作温度範囲での規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。(Note 3)

| SYMBOL               | PARAMETER                           | CONDITIONS                                              | MIN    | TYP                               | MAX            | UNITS    |

|----------------------|-------------------------------------|---------------------------------------------------------|--------|-----------------------------------|----------------|----------|

| $f_{\text{EOSC}}$    | External Oscillator Frequency Range |                                                         | ●      | 10                                | 4000           | kHz      |

| $t_{\text{HEO}}$     | External Oscillator High Period     |                                                         | ●      | 0.125                             | 100            | μs       |

| $t_{\text{LEO}}$     | External Oscillator Low Period      |                                                         | ●      | 0.125                             | 100            | μs       |

| $t_{\text{CONV\_1}}$ | Conversion Time                     | Simultaneous 50Hz/60Hz<br>External Oscillator (Note 10) | ●<br>● | 144.1<br>41036/ $f_{\text{EOSC}}$ | 146.9<br>149.9 | ms<br>ms |

## I<sup>2</sup>Cタイミング特性

●は全動作温度範囲での規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。(Note 3、15)

| SYMBOL               | PARAMETER                                  | CONDITIONS | MIN | TYP           | MAX | UNITS |

|----------------------|--------------------------------------------|------------|-----|---------------|-----|-------|

| $f_{\text{SCL}}$     | SCL Clock Frequency                        |            | ●   | 0             | 400 | kHz   |

| $t_{\text{HD(SDA)}}$ | Hold Time (Repeated) START Condition       |            | ●   | 0.6           |     | μs    |

| $t_{\text{LOW}}$     | LOW Period of the SCL Clock Pin            |            | ●   | 1.3           |     | μs    |

| $t_{\text{HIGH}}$    | HIGH Period of the SCL Clock Pin           |            | ●   | 0.6           |     | μs    |

| $t_{\text{SU(STA)}}$ | Set-Up Time for a Repeated START Condition |            | ●   | 0.6           |     | μs    |

| $t_{\text{HD(DAT)}}$ | Data Hold Time                             |            | ●   | 0             | 0.9 | μs    |

| $t_{\text{SU(DAT)}}$ | Data Set-Up Time                           |            | ●   | 100           |     | ns    |

| $t_r$                | Rise Time for Both SDA and SCL Signals     | (Note 14)  | ●   | $20 + 0.1C_B$ | 300 | ns    |

| $t_f$                | Fall Time for Both SDA and SCL Signals     | (Note 14)  | ●   | $20 + 0.1C_B$ | 300 | ns    |

| $t_{\text{SU(STO)}}$ | Set-Up Time for STOP Condition             |            | ●   | 0.6           |     | μs    |

Note 1: 絶対最大定格に記載された値を超えるストレスはデバイスに永続的損傷を与える可能性がある。長期にわたって絶対最大定格条件に曝すと、デバイスの信頼性と寿命に悪影響を与える可能性がある。

Note 2: すべての電圧値はGNDを基準にしている。

Note 3: 注記がない限り、 $V_{\text{CC}} = 2.7\text{V} \sim 5.5\text{V}$ 。

$$V_{\text{REF}} = \text{REF}^+ - \text{REF}^-, V_{\text{REFCM}} = (\text{REF}^+ + \text{REF}^-)/2, F_S = 0.5V_{\text{REF}}; \\ V_{\text{IN}} = \text{IN}^+ - \text{IN}^-, V_{\text{INCM}} = (\text{IN}^+ + \text{IN}^-)/2.$$

Note 4: 注記がない限り、内部変換クロックまたは $f_{\text{EOSC}} = 307.2\text{kHz}$ の外部変換クロック・ソースを使う。

Note 5: 設計によって保証されているが、テストされない。

Note 6: 構成非直線性は、実際の伝達曲線のエンドポイントを通る直線からのコードの偏差として定義されている。偏差は量子化幅の中心から測定される。

Note 7: 50Hz:  $f_{\text{EOSC}} = 256\text{kHz} \pm 2\%$  (外部発振器)

Note 8: 60Hz:  $f_{\text{EOSC}} = 307.2\text{kHz} \pm 2\%$  (外部発振器)

Note 9: 50Hz/60Hz同時モード (内部発振器) または  $f_{\text{EOSC}} = 280\text{kHz} \pm 2\%$  (外部発振器)

Note 10: 外部発振器はCA0/F0ピンに接続される。外部発振器の周波数 ( $f_{\text{EOSC}}$ ) はkHzで表されている。

Note 11: コンバータは内部発振器を使用する。

Note 12: 出力ノイズには内部較正動作によって生じる分が含まれる。

Note 13: 設計およびテストの相関により保証されている。

Note 14:  $C_B = 1$ 本のバスラインの容量 (pF)。

Note 15: すべての値は $V_{\text{IH(MIN)}}$ と $V_{\text{IL(MAX)}}$ のレベルを基準にしている。

## 標準的性能特性

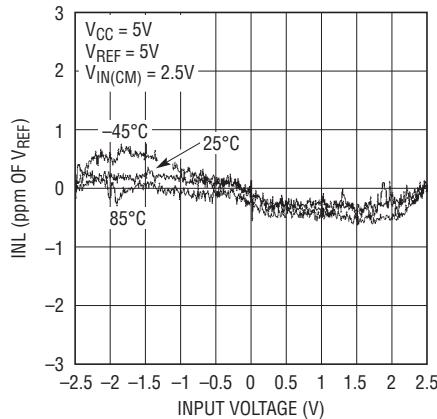

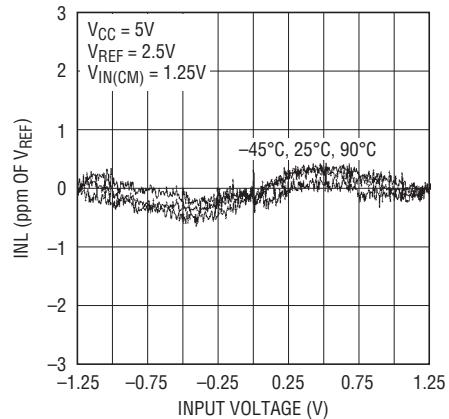

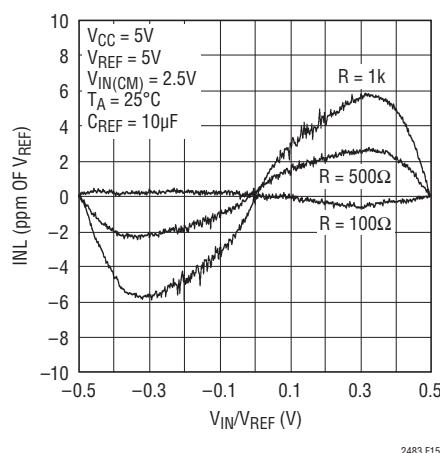

### 積分非直線性

( $V_{CC} = 5V$ ,  $V_{REF} = 5V$ )

2483 G01

### 積分非直線性

( $V_{CC} = 5V$ ,  $V_{REF} = 2.5V$ )

2483 G02

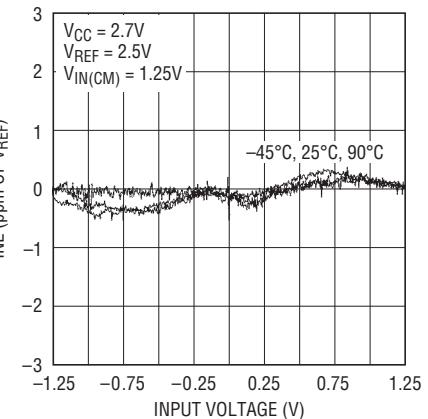

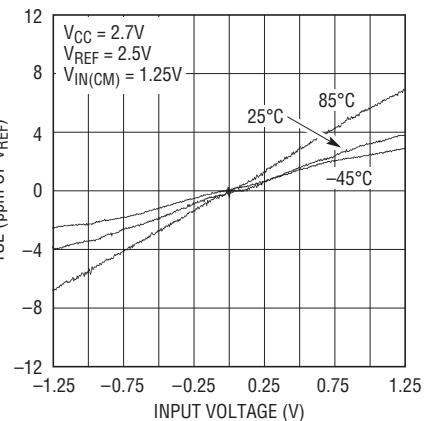

### 積分非直線性

( $V_{CC} = 2.7V$ ,  $V_{REF} = 2.5V$ )

2483 G03

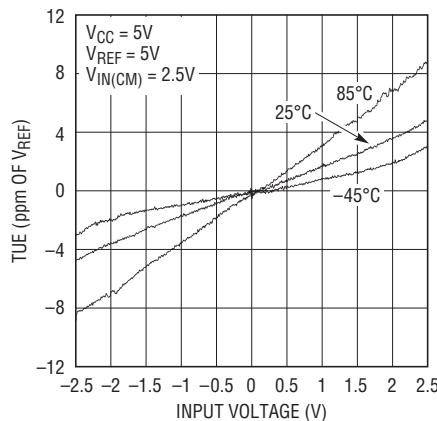

### 全未調整誤差

( $V_{CC} = 5V$ ,  $V_{REF} = 5V$ )

2483 G04

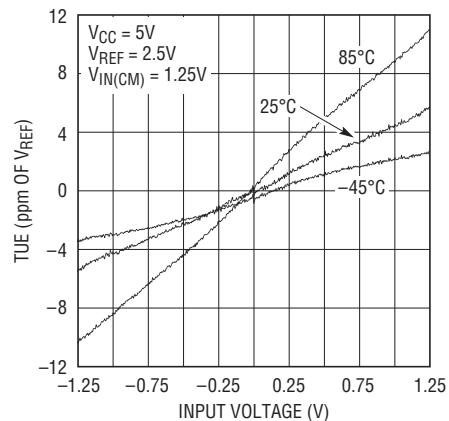

### 全未調整誤差

( $V_{CC} = 5V$ ,  $V_{REF} = 2.5V$ )

2483 G05

### 全未調整誤差

( $V_{CC} = 2.7V$ ,  $V_{REF} = 2.5V$ )

2483 G06

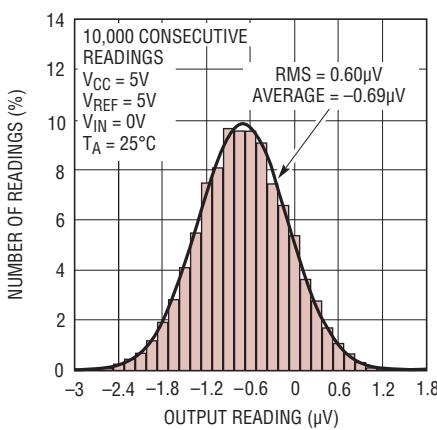

### ノイズのヒストグラム(6.8sps)

2483 G07

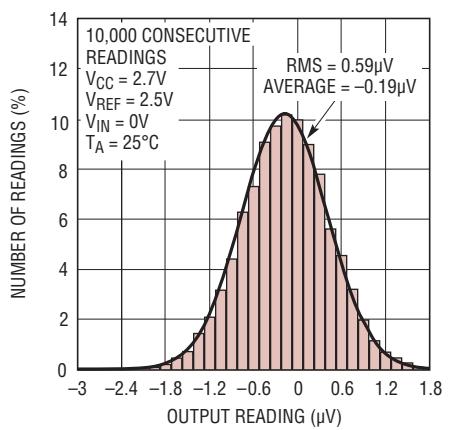

### ノイズのヒストグラム(7.5sps)

2483 G08

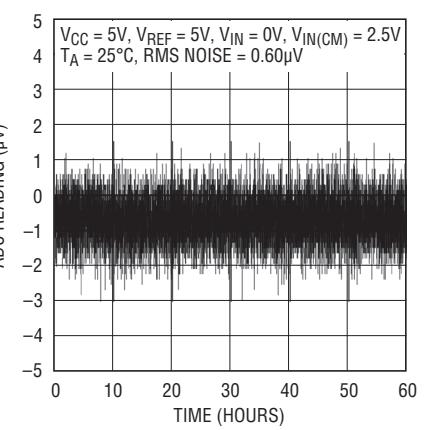

### ADCの長時間読み取り値

2483 G09

2483fc

## 標準的性能特性

## 標準的性能特性

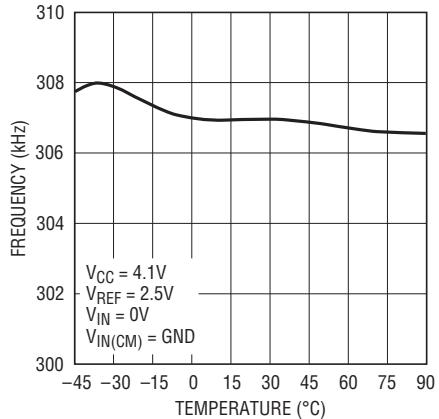

内部発振器の周波数と温度

2483 G21

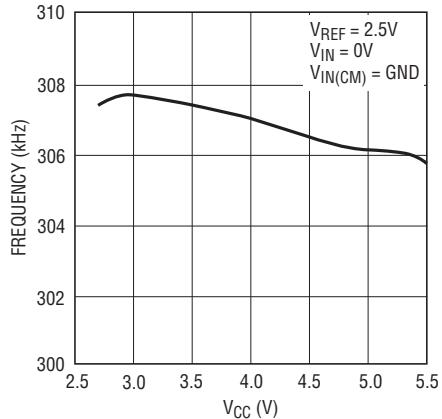

内部発振器の周波数と $V_{CC}$

2483 G22

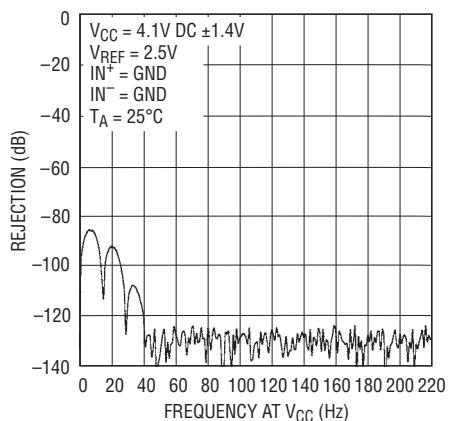

PSRRと $V_{CC}$ での周波数

2483 G23

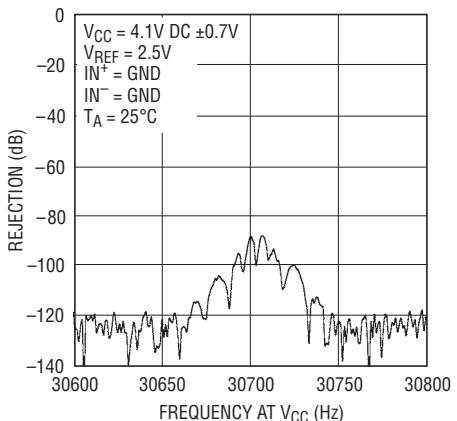

PSRRと $V_{CC}$ での周波数

2483 G24

PSRRと $V_{CC}$ での周波数

2483 G25

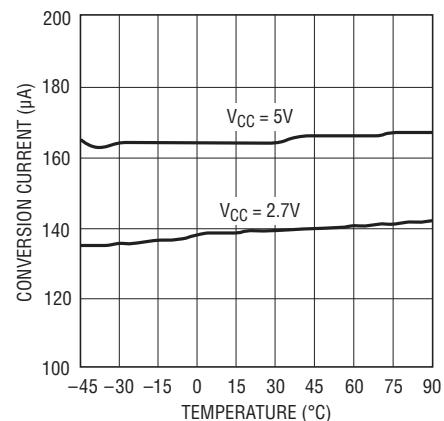

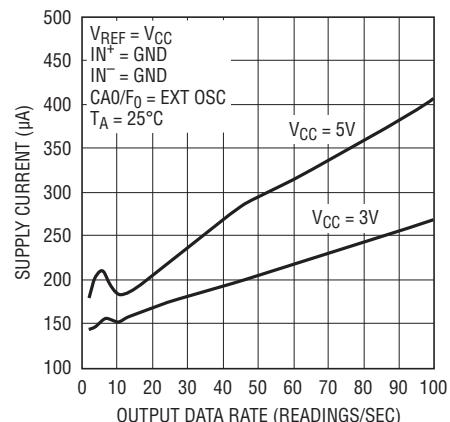

変換電流と温度

2483 G26

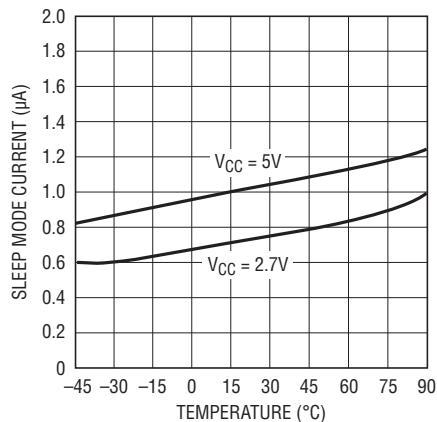

スリープ・モード電流と温度

2483 G27

変換電流と出力データ・レート

2483 G28

2483fc

## ピン機能

**REF<sup>+</sup>(ピン1)、REF<sup>-</sup>(ピン3)**: 差動リファレンス入力。これらのピンの電圧は、リファレンスの正入力REF<sup>+</sup>がリファレンスの負入力REF<sup>-</sup>よりも少なくとも0.1Vだけ高い限り、GND～V<sub>CC</sub>の範囲の任意の電圧にすることができます。

**V<sub>CC</sub>(ピン2)**: 正電源電圧。1μFのタンタル・コンデンサと0.1μFのセラミック・コンデンサを並列に接続して、デバイスのできるだけ近くでGND(ピン8)にバイパスします。

**IN<sup>+</sup>(ピン4)、IN<sup>-</sup>(ピン5)**: 差動アナログ入力。これらのピンの電圧はGND-0.3V～V<sub>CC</sub>+0.3Vの範囲の任意の値にすることができます。これらのリミット内では、コンバータのバイポーラ入力範囲( $V_{IN} = IN^+ - IN^-$ )は $-0.5 \cdot V_{REF} \sim 0.5 \cdot V_{REF}$ となります。この入力範囲の外側では、コンバータは固有のオーバーレンジとアンダーレンジの出力コードを発生します。

**SCL(ピン6)**: I<sup>2</sup>Cインターフェースのシリアル・クロック・ピン。LTC2483はスレーブとして機能することができるだけで、SCLピンは外部シリアル・クロックだけを受け入れます。データはSCLクロックの立ち下がりエッジでSDAピンからシフトアウトされます。

**SDA(ピン7)**: I<sup>2</sup>Cインターフェースのシリアル・データ出力ライン。トランスマッタ・モード(読み出し)では変換結果がSDAピンを介して出力されます。このピンはオープン・ドレインのNチャネル・ドライバなので、V<sub>CC</sub>への外部プルアップ抵抗または電流源が必要です。

**GND(ピン8)**: グランド。このピンを1つのグランド・プレーンに低インピーダンスで接続します。

**CA1(ピン9)**: チップ・アドレス制御ピン。CA1ピンはデバイスのI<sup>2</sup>Cアドレスのためのスリーステート("L"、"H"、またはフロート)のアドレス制御ビットとして設定されます。

**CA0/F<sub>0</sub>(ピン10)**: チップ・アドレス制御ピン/外部クロック入力ピン。CA0/F<sub>0</sub>ピンで遷移が検出されない場合、このピンはデバイスのI<sup>2</sup>Cアドレスの2ステート("H"またはフロート)のアドレス制御ビットになります。少なくとも10kHzの周波数f<sub>EOSC</sub>の外部クロック信号によってこのピンがドライブされると、コンバータはこの信号をそのシステム・クロックとして使い、デジタル・フィルタの基本除去ヌル周波数はf<sub>EOSC</sub>/5120に位置し、チップ・アドレスCA0を内部で"H"に設定します。

# LTC2483

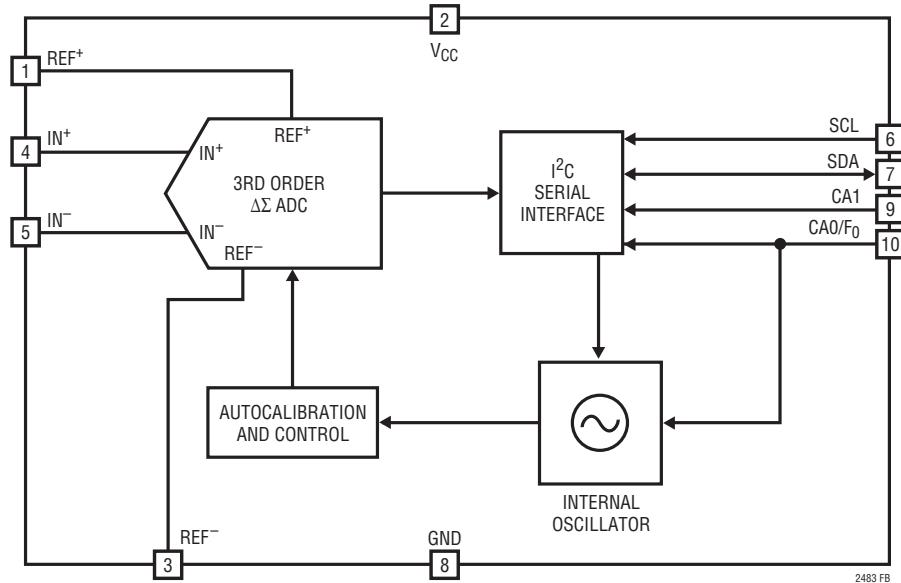

## 機能ブロック図

## アプリケーション情報

### コンバータの動作

#### コンバータの動作サイクル

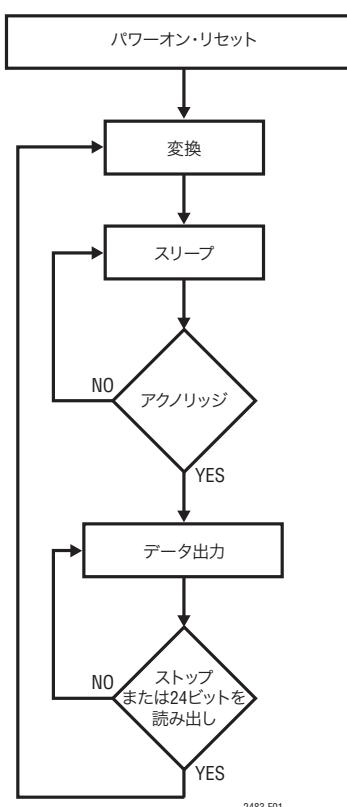

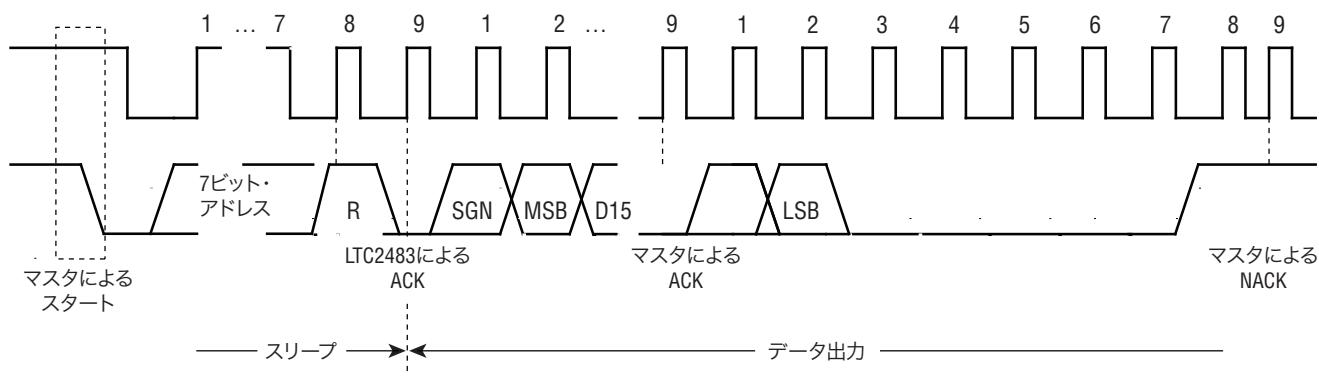

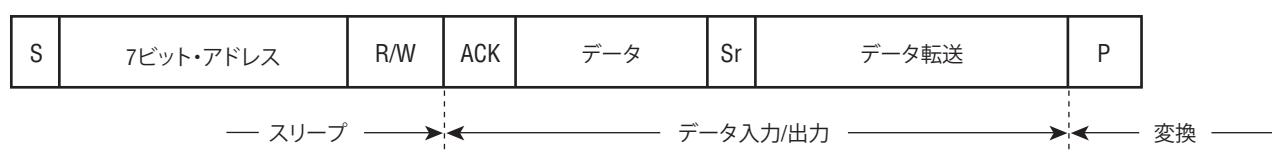

LTC2483は低消費電力の $\Delta\Sigma$ アナログ-デジタル・コンバータで、I<sup>2</sup>Cインターフェースを備えています。パワーオン・リセット後の動作は3つの状態で構成されています。コンバータの動作サイクルは変換から始まり、省電力のスリープ状態がそれに続き、データの出力で終了します(図1を参照)。

図1. LTC2483の状態遷移図

LTC2483は最初に変換を行います。変換が完了すると、デバイスはスリープ状態に入ります。このスリープ状態の間、電力消費は2桁減少します。読み出し動作のために呼び出されない限り、デバイスはスリープ状態に留まります。コンバータがスリープ状態の間、変換結果は無期限にスタティック・シフト・レジ斯特内に保存されます。

変換中、LTC2483は外部からのリクエストに対してアクノリッジを返しません。変換が終了すると、読み出しリクエストを受け入れる用意ができます。LTC2483は読み出し動作のために呼び出されると、シリアル・クロック(SCL)の制御下で変換結果の出力を開始します。変換結果に待ち時間はありません。データ出力は24ビット長で、変換結果の16ビットと符号を含んでいます。この結果はSCLの制御下でSDAピンからシフトアウトされます。データはSCLの立ち下がりエッジで更新されるので、ユーザーはSCLの立ち上がりエッジで確実にデータをラッチすることができます。データ読み出し動作(全24ビットの読み出し)が完了すると新たに変換が開始されます。

#### I<sup>2</sup>Cインターフェース

LTC2483はI<sup>2</sup>Cインターフェースを介して通信を行います。I<sup>2</sup>Cインターフェースは2線式オープンドレイン・インターフェースで、複数のデバイスと複数のマスターを单一バスでサポートします。接続されているデバイスはバスラインを“L”にするだけで、“H”にドライブすることはできません。バスラインは電流源またはプルアップ抵抗を介して外部で正電源電圧に接続することができます。バスが解放されると、両方のラインが“H”になります。I<sup>2</sup>Cバスのデータは標準モードでは最大100kビット/秒、高速モードでは400kビット/秒で転送することができます。内部のESD保護デバイスを介してI<sup>2</sup>Cバスラインに負荷がかかるのを避けるため、I<sup>2</sup>CバスがアクティブのときはV<sub>CC</sub>電源をデバイスから取り去らないでください。

I<sup>2</sup>Cバス上の各デバイスはデバイスに保存されている固有アドレスで識別され、デバイスの機能に応じて、トランスマッタまたはレシーバのどちらかとして動作することができます。トランスマッタとレシーバに加えて、デバイスはデータ転送時にマスターまたはスレーブとみなすこともできます。マスターはバス上でデータ転送を開始するデバイスで、転送を可能にするクロック信号を生成します。同時に、呼び出されたどのデバイスもスレーブとみなされます。

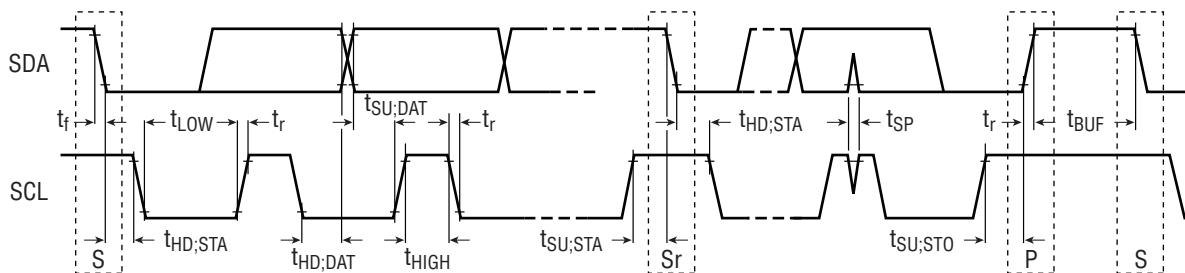

LTC2483はスレーブとしてのみ呼び出すことができます。呼び出されると、最後の変換結果を転送することができます。したがって、シリアル・クロック・ラインSCLは入力のみで、データ・ラインSDAは双方向(データ出力/アドレス入力)です。デバイスは標準モードと最大400ビット/秒のデータ転送速度の高速モードをサポートします。I<sup>2</sup>Cバスの高速/標準モード・デバイスのタイミングの定義を図2に示します。

## アプリケーション情報

### スタート条件とストップ条件

スタート条件はSCLを“H”に保ったままSDAを“H”から“L”に遷移させて発生させます。スタート条件になった後はバスはビジーであるとみなされます。データ転送が終了すると、SCLが“H”的間にSDAを“L”から“H”に遷移させてストップ条件を発生させます。ストップ条件後一定時間が経過するとバスは再度解放されます。スタート条件とストップ条件は常にマスタが発生させます。

バスが使用されているとき、ストップ条件の代わりにリピート・スタート(Sr)条件を発生させると、バスはビジー状態に留まります。リピート・スタート(Sr)条件は機能的にスタート(S)条件と同じです。

### データ転送

スタート条件の後、I<sup>2</sup>Cバスはビジー状態になり、マスターとスレーブの間にデータ転送が設定されます。データは9ビット(1バイト)のグループ単位でI<sup>2</sup>Cを介して転送され、アクノリッジ・ビットがそれに続くので、各グループは9 SCLサイクルを要します。トランスマッタはアクノリッジ・クロック・パルスの間SDAラインを解放し、レシーバはSDAを“L”に引き下げてアクノリッジ(ACK)を返すか、またはSDAを“H”的ままでノット・アクノリッジ(NACK)条件を示します。データの状態はSCLが“L”的間だけ変化させることができます。

2483 F02

図2. I<sup>2</sup>Cバスの高速/標準モード・デバイスのタイミングの定義

## アプリケーション情報

### LTC2483のデータ・フォーマット

スタート条件の後、マスタは7ビットのアドレスを送り、次いで読み出し/書き込み(R/W)ビットを送ります。R/Wビットは読み出しリクエストの場合1、書き込みリクエストの場合0です。7ビットのアドレスがLTC2483のアドレスと一致すれば、そのデバイスが選択されます。デバイスが変換中はリクエストを受け付けず、SDAラインを“H”のままにしてノット・アクノリッジ(NACK)を発行します。NACK信号は書き込み動作によっても生成されます。変換が完了すると、デバイスはSDAを“L”にしてアクノリッジ(ACK)を発行します。

出力レジスタには最後の変換結果が格納されています。各変換が完了した後、デバイスは自動的にスリープ状態に入り、消費電流が $1\mu\text{A}$ に減少します。LTC2483は読み出し動作のために呼び出されると、SDAを“L”に下げてアクノリッジし、トランスマッタとして機能します。マスタおよびレシーバはLTC2483から最大3バイトを読み出すことができます。読み出し動作をすべて(3バイト)終えると、出力レジスタは空になり、新しい変換が開始され、それに続く同じ出力フェーズ内の読み出しリクエストはアクノリッジされません。LTC2483の出力データ・ストリームは24ビット長で、SCLの立ち下がりエッジでシフトアウトされます。最初のビットは変換結果の符号ビット(SIG)です(表1と表2を参照)。このビットは $V_{IN} \geq 0$ であれば“H”、 $V_{IN} < 0$ であれば“L”です。2番目のビットは結果の最上位ビット(MSB)で

す。最初の2ビット(SIGとMSB)を使ってオーバーレンジ状態を表示することができます。両方のビットが“H”だと、差動入力電圧が $+FS$ を超えており、続く16ビットが“L”に設定されてオーバーレンジ状態を表示します。両方のビットが“L”だと、入力電圧が $-FS$ より低く、続く16ビットが“H”に設定されてアンダーレンジ状態を表示します。これら2ビットの機能を表1にまとめます。次の16ビットには変換結果が2の補数のバイナリ・フォーマットで含まれています。残りの6ビットは“L”です。

表1. LTC2483のステータス・ビット

| 入力範囲                                  | ビット23<br>符号 | ビット22<br>MSB |

|---------------------------------------|-------------|--------------|

| $V_{IN} \geq 0.5 \cdot V_{REF}$       | 1           | 1            |

| $0V \leq V_{IN} < 0.5 \cdot V_{REF}$  | 1           | 0            |

| $-0.5 \cdot V_{REF} \leq V_{IN} < 0V$ | 0           | 1            |

| $V_{IN} < -0.5 \cdot V_{REF}$         | 0           | 0            |

IN<sup>+</sup>ピンとIN<sup>-</sup>ピンの電圧が $-0.3V \sim (V_{CC} + 0.3V)$ の絶対最大動作範囲内に維持されている限り、 $-FS = -0.5 \cdot V_{REF}$ から $+FS = 0.5 \cdot V_{REF}$ までの任意の差動入力電圧 $V_{IN}$ に対して変換結果が生成されます。差動入力電圧が $+FS$ より高い場合、変換結果は $+FS + 1LSB$ に相当する値にクランプされます。差動入力電圧が $-FS$ より低い場合、変換結果は $-FS - 1LSB$ に相当する値にクランプされます。

表2. LTC2483の出力データのフォーマット

| 差動入力電圧 $V_{IN}^*$            | ビット23<br>符号 | ビット22<br>MSB | ビット21 | ビット20 | ビット19 | … | ビット6 |

|------------------------------|-------------|--------------|-------|-------|-------|---|------|

| $V_{IN}^* \geq FS^{**}$      | 1           | 1            | 0     | 0     | 0     | … | 0    |

| $FS^{**} - 1 LSB$            | 1           | 0            | 1     | 1     | 1     | … | 1    |

| $0.5 \cdot FS^{**}$          | 1           | 0            | 1     | 0     | 0     | … | 0    |

| $0.5 \cdot FS^{**} - 1 LSB$  | 1           | 0            | 0     | 1     | 1     | … | 1    |

| 0                            | 1           | 0            | 0     | 0     | 0     | … | 0    |

| $-1 LSB$                     | 0           | 1            | 1     | 1     | 1     | … | 1    |

| $-0.5 \cdot FS^{**}$         | 0           | 1            | 1     | 0     | 0     | … | 0    |

| $-0.5 \cdot FS^{**} - 1 LSB$ | 0           | 1            | 0     | 1     | 1     | … | 1    |

| $-FS^{**}$                   | 0           | 1            | 0     | 0     | 0     | … | 0    |

| $V_{IN}^* < -FS^{**}$        | 0           | 0            | 1     | 1     | 1     | … | 1    |

\*差動入力電圧 $V_{IN} = IN^+ - IN^-$ 。 \*\*フルスケール電圧 $FS = 0.5 \cdot V_{REF}$ 。

## アプリケーション情報

### 新しい変換の開始

LTC2483は変換を終了すると自動的にスリープ状態に入ります。スリープ状態になると、デバイスは読み出し動作の準備が整います。デバイスが読み出しリクエストをアクノリッジした後、デバイスはスリープ状態から出て、データ出力状態に入れます。データ出力状態が完了し、マスタによってストップ条件が発行されるか、または24ビットすべてのデータがデバイスから読み出されると、LTC2483は新しい変換を開始します。

データ読み出しサイクルの間に新しい変換を開始し、データの転送を中止するため、マスタ・コントローラはストップ命令を出すことができます。このストップ命令は、バスが解放されているときバイト読み出しの9番目のクロック・サイクル(ACK/NACKサイクル)の間に出す必要があります。

### LTC2483のアドレス

LTC2483は2つのアドレス・ピンを備えており、表3に示されているように設定可能な6つのアドレスの1つをイネーブルします。

表3. LTC2483のアドレスの割り当て

| CA1  | CA0/F <sub>0</sub> * | アドレス      |

|------|----------------------|-----------|

| "L"  | "H"                  | 001 01 00 |

| "L"  | フロート                 | 001 01 01 |

| フロート | "H"                  | 001 01 11 |

| フロート | フロート                 | 010 01 00 |

| "H"  | "H"                  | 010 01 10 |

| "H"  | フロート                 | 010 01 11 |

\*CA0/F<sub>0</sub>は有効な外部クロックによってドライブされるとき"H"として扱われる。

### データ読み出し

データ読み出しシーケンスを図5に示します。変換が終了したら、読み出し動作のためにデバイスを呼び出すことができます。読み出し動作が終了すると、新たに変換が開始されます。変換サイクルの最後に、上述の方法を使って次の結果を読み出すことができます。変換サイクルが終了していないのに有効なアドレスによってデバイスが選択されると、LTC2483はNACK信号を生成して変換サイクルが進行中であることを知らせます。

### Easy Drive入力電流キャンセル

LTC2483は高精度デルタシグマADCを自動差動入力電流キャンセル・フロントエンドと組み合わせています。独自のフロントエンド受動サンプリング・ネットワークが透過的に差動入力電流を除去します。これにより、外部RCネットワークと高インピーダンス・センサを、外部アンプなしに、直接LTC2483にインターフェースさせることができます。残りの同相入力電流は、差動入力のインピーダンスのバランスを取るか、または同相入力を同相リファレンスに等しく設定して除去します(「自動差動入力電流キャンセル」のセクションを参照)。このユニークなアーキテクチャには内蔵バッファが不要なので、入力信号はグランドからVCCまで完全に振幅することができます。さらに、このキャンセル機能はオフセットとフルスケールの透過的な自動較正を妨げないので、外部RCネットワークが付加されても、絶対精度(フルスケール+オフセット+直線性)が維持されます。

### 変換クロック

デルタシグマ・コンバータが従来型のコンバータよりも優れている点は(一般にSINC(同期)フィルタまたはComb(櫛形)フィルタとして実装される)デジタル・フィルタを内蔵していることです。高分解能で低周波数のアプリケーションの場合、このフィルタは一般に50Hzと60Hzのライン周波数およびそれらの高調波を除去するように設計されます。フィルタの除去性能はコンバータのシステム・クロックの精度に直接関係します。LTC2483には高精度の発振器が内蔵されています。したがって、水晶発振子や発振器などの外部で周波数を設定する部品は不要です。

## アプリケーション情報

### 周波数除去の選択(CA0/F<sub>0</sub>)

LTC2483の内部発振器は、50Hzおよび60Hzのライン周波数と48Hz～62.4Hzの(255次までの)すべての高調波において87dBを上回る通常モード除去比を達成します。

50Hzまたは60Hz以外の基本除去周波数が要求される場合、またはコンバータを外部ソースに同期させる必要がある場合、外部の変換クロックを使ってLTC2483を動作させることができます。

できます。コンバータはCA0/F<sub>0</sub>ピンに外部クロック信号が与えられていることを自動的に検知し、内部発振器をオフします。CA0のチップ・アドレスは内部で“H”に設定されています。外部信号が検出されるには、その周波数f<sub>EOSC</sub>は10kHz以上でなければなりません。外部クロック信号のデューティ・サイクルは、“H”と“L”的期間(t<sub>THEO</sub>とt<sub>LEO</sub>)の最小と最大の規定値が守られる限り重要ではありません。

図3. LTC2483からの読み出しのタイミング図

2483 F03

図4. LTC2483の変換シーケンス

2483 F04

図5. 同じ構成設定を使った連続読み出し

2483 F05

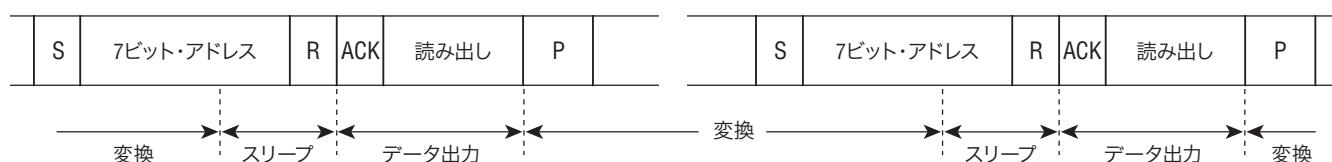

## アプリケーション情報

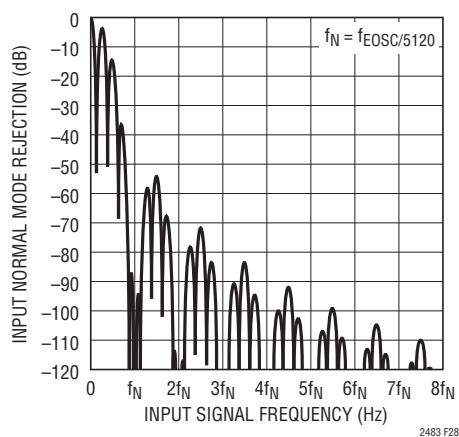

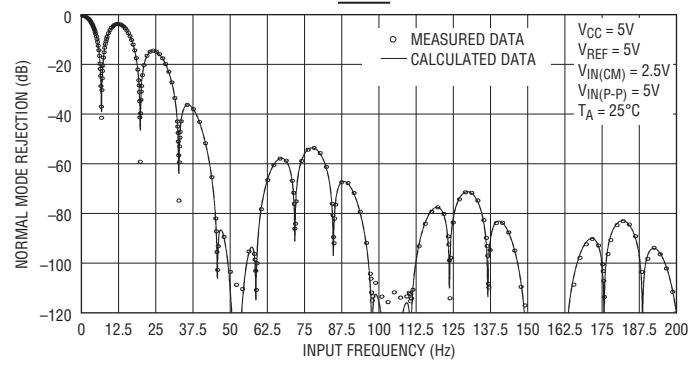

周波数が $f_{EOSC}$ の外部変換クロックを使って動作しているとき、 $f_{EOSC}/5120 \pm 4\%$ の周波数範囲およびその高調波に対し、LTC2483は110dBを超える通常モードの除去比を与えます。 $f_{EOSC}/5120$ からの入力周波数の偏差の関数としての通常モードの除去比を図6に示します。

図6. 外部発振器使用時のLTC2483の通常モード除去比

CA0/F<sub>0</sub>ピンに外部クロックが与えられていないとき、コンバータは内部発振器を自動的に起動して、内部変換クロック・モードに入ります。CA0/F<sub>0</sub>は、チップ・アドレスを設定するために、“H”に接続するか、またはフロートさせたままにすることができます。コンバータが外部のシリアル・クロックを使っているとき、スリープ状態またはデータ出力状態の間に変換クロック・ソースが変更されても、LTC2483の動作は乱されません。変換状態の間に変更されると、進行中の変換結果が仕様から外れることがあります。その後の変換は影響を受けません。

$f_{EOSC}$ の関数としての各状態の変換状態の持続時間と実現可能な出力データ・レートを表4にまとめます。

表4. LTC2483の状態の持続時間

| 状態 | 動作モード | 持続時間                                                                                                                                                |

|----|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| 変換 | 内部発振器 | 50Hz/60Hzの除去<br>147ms、出力データ・レート $\leq 6.8$ 読み取り/秒                                                                                                   |

|    | 外部発振器 | $CA0/F_0 = \text{周波数が } f_{EOSC} (\text{Hz}) \text{ の外部発振器}$<br>( $f_{EOSC}/5120$ の除去)<br>$41036/f_{EOSC}$ 、出力データ・レート $\leq f_{EOSC}/41036$ の読み取り/秒 |

## 使いやすさ

LTC2483のデータ出力には、待ち時間、フィルタのセトリング遅延、または変換サイクルに関連する冗長データがありません。変換と出力データの間には1対1対応の関係があります。したがって、複数のアナログ電圧の多重化は簡単です。

LTC2483は変換サイクルごとにオフセットとフルスケールの較正を行います。この較正はユーザーからは見えず、上述のサイクル動作には影響を与えません。連続較正の利点は、時間経過、電源電圧の変化、および温度ドリフトに対してオフセットとフルスケールの測定値がきわめて安定していることです。

## パワーアップ・シーケンス

LTC2483は電源電圧V<sub>CC</sub>が約2Vより下がると自動的に内部リセット状態になります。この機能により、変換結果の完全性が保証されます。

V<sub>CC</sub>電圧がこの臨界スレッショルドを超えると、コンバータは約4msの長さの内部パワーオン・リセット(POR)信号を生成します。このPOR信号により、すべての内部レジスタがクリアされます。POR信号に続いてLTC2483は通常の変換サイクルを開始し、図1に示されている一連の状態が発生します。POR後の最初の変換結果の精度は、PORの期間が終了する前に電源電圧が動作範囲(2.7V～5.5V)内に回復していれば、デバイスの仕様を満たします。

## アプリケーション情報

### リファレンス電圧範囲

LTC2483の外部リファレンスの電圧範囲は0.1V～V<sub>CC</sub>です。コンバータの出力ノイズはフロントエンド回路の熱ノイズによって決まるので、ナノボルトで表したその値はリファレンス電圧に対してほぼ一定です。遷移ノイズ(600nV)は量子化ノイズ( $V_{REF}/2^{17}$ )よりもはるかに小さいので、リファレンス電圧を下げるとき、コンバータの分解能が上がります。外部変換クロック(外部F<sub>0</sub>信号)を使ってはるかに高い出力データ・レートで動作させるときは、リファレンス電圧を下げるときコンバータの性能も向上します(「出力データ・レート」のセクションを参照)。

リファレンス入力は差動です。差動リファレンス入力範囲( $V_{REF} = REF^+ - REF^-$ )は100mV～V<sub>CC</sub>で、同相リファレンス入力範囲は0V～V<sub>CC</sub>です。

### 入力電圧範囲

アナログ入力は真に差動で、IN<sup>+</sup>とIN<sup>-</sup>の入力ピンの絶対/同相範囲は(GND-0.3V)～(V<sub>CC</sub>+0.3V)です。これらのリミットの外側では、ESD保護用デバイスがオンし始め、入力リーク電流による誤差が急速に増加します。これらのリミット内では、LTC2483は-FS～+FS(ここで、FS = 0.5 • V<sub>REF</sub>)のバイポーラ差動入力信号( $V_{IN} = IN^+ - IN^-$ )を変換します。この範囲の外側では、コンバータは固有の出力コードを使ってオーバーレンジまたはアンダーレンジの状態を示します。差動入力電流のキャンセルは内蔵バッファに依存しないので、DC性能とともに電流のキャンセルもレール・トゥ・レールで維持されます。

IN<sup>+</sup>ピンとIN<sup>-</sup>ピンに与えられる入力信号は、グランドより300mV下およびV<sub>CC</sub>より300mV上まで達することができます。あらゆるフォールト電流を制限するために、デバイスの性能に影響を与えることなく、最大5kの抵抗をIN<sup>+</sup>ピンとIN<sup>-</sup>ピンに直列に追加することができます。コンバータの精度に対する直列抵抗の影響は、「入力電流/リファレンス電流」のセクションに示されている曲線から評価することができます。さらに、直列抵抗は入力リーク電流により、温度に依存するオフセット誤差を生じます。V<sub>REF</sub> = 5Vのとき、1nAの入力リーク電流により、5kの抵抗には1ppmのオフセット誤差が生じます。この誤差は温度に大きく依存します。

### 入力とリファレンスのドライブ

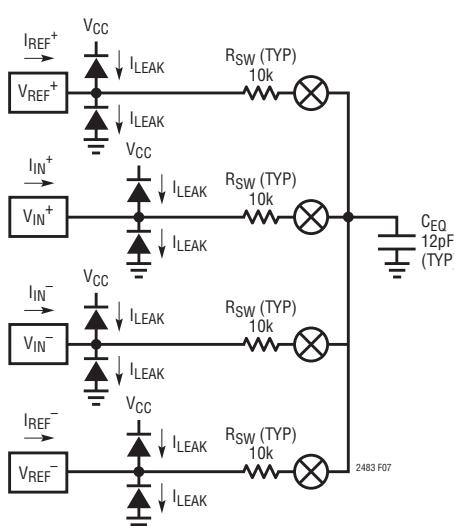

LTC2483コンバータの入力ピンとリファレンス・ピンはサンプリング・コンデンサのネットワークに直接接続されています。差動入力電圧と差動リファレンス電圧の関係に応じて、これらのコンデンサはこれらの4つのピンの間で切り替わり、その過程で少量の電荷を転送します。簡略化した等価回路を図7に示します。

スイッチング周波数

$f_{SW} = 123\text{kHz}$  (内部発振器)

$f_{SW} = 0.4 \cdot f_{EOSC}$  (外部発振器)

$$\begin{aligned} I(IN^+)_{AVG} &= I(IN^-)_{AVG} = \frac{V_{IN(CM)} - V_{REF(CM)}}{0.5 \cdot R_{EQ}} \\ I(REF^+)_{AVG} &= \frac{1.5 \cdot V_{REF} - V_{INCM} + V_{REFCM}}{0.5 \cdot R_{EQ}} - \frac{V_{IN}^2}{V_{REF} \cdot R_{EQ}} - \frac{0.5 \cdot V_{REF} \cdot D_T}{R_{EQ}} \equiv \frac{1.5V_{REF} + (V_{REF(CM)} - V_{IN(CM)})}{0.5 \cdot R_{EQ}} - \frac{V_{IN}^2}{V_{REF} \cdot R_{EQ}} \end{aligned}$$

where:

$$V_{REFCM} = \left( \frac{REF^+ + REF^-}{2} \right), V_{REF} = REF^+ - REF^-$$

$$V_{IN} = IN^+ - IN^-$$

$$V_{INCM} = \left( \frac{IN^+ + IN^-}{2} \right)$$

$$R_{EQ} = 2.98\text{M}\Omega \text{ (内部発振器)}$$

$$R_{EQ} = (0.833 \cdot 10^{12}) / f_{EOSC} \text{ (外部発振器)}$$

D<sub>T</sub>は変調器の出力のデジタル遷移密度 (REFは内部でGNDに接続されている)

図7. LTC2483の等価アナログ入力回路

## アプリケーション情報

簡単な近似法として、アナログ入力ピン( $\text{IN}^+$ 、 $\text{IN}^-$ 、 $\text{REF}^+$ または $\text{REF}^-$ )をドライブするソース・インピーダンス $R_S$ は( $R_{\text{SW}}$ および $C_{\text{EQ}}$ (図7を参照)と一緒に)時定数 $\tau = (R_S + R_{\text{SW}}) \cdot C_{\text{EQ}}$ の1次パッシブ・ネットワークを形成していると考えることができます。コンバータは、サンプリング期間が入力回路の時定数 $\tau$ よりも少なくとも14倍以上長ければ、入力信号を1ppmより高い精度でサンプリングすることができます。4つの入力アナログ・ピンのサンプリング過程はほぼ独立しているので、各時定数は個別に考える必要があり、ワーストケースの状況では、それらの誤差が合算されることがあります。

内部発振器を使っているとき、LTC2483のフロントエンド・スイッチトキャパシタ・ネットワークは8.1μsのサンプリング周期に相当する123kHzのクロックで駆動されます。したがって、セトリング誤差を1ppm未満にするには、 $\tau \leq 8.1\mu\text{s}/14 = 580\text{ns}$ となるようにドライブ・ソースのインピーダンスを選択します。周波数が $f_{\text{EOSC}}$ の外部発振器を使うと、サンプリング周期は $2.5/f_{\text{EOSC}}$ で、1ppm未満のセトリング誤差の場合、 $\tau \leq 0.178/f_{\text{EOSC}}$ です。

### 自動差動入力電流キャンセル

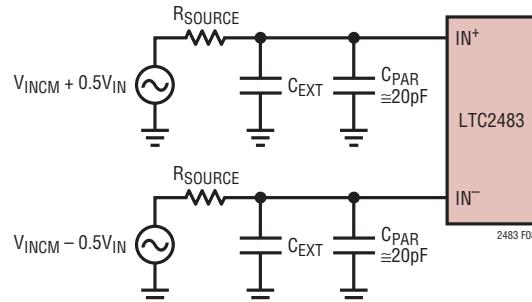

センサの出力インピーダンスが低い(外部バイパス・コンデンサなしで最大10kΩ、または0.001μFのバイパス付きで最大500Ω)アプリケーションでは、入力は完全にセトリングします。この場合、誤差は発生しないので、センサを直接デジタル化することができます。

多くのアプリケーションでは、センサの出力インピーダンスは外部バイパス・コンデンサと結合して1ppmの精度に必要な580nsをはるかに超えるRC時定数を生じます。たとえば、0.1μFのバイパス・コンデンサをドライブする10kΩのブリッジでは、必要な最大値より1桁大きい時定数になります。従来、セトリングの問題はバッファを使って解決されてきました。これらのバッファは、ノイズの増加、DC性能(オフセット/ドリフト)の低下、入力/出力振幅の制限(グランドまたは $V_{\text{CC}}$ に近い信号をデジタル変換できない)、システムのコストと電力の増加を引き起こしました。LTC2483は独自のスイッチング・アルゴリズムを使って、外部のセトリング誤差とは無関係に、平均差動入力電流をゼロに強制します。これにより、バッファがなくても高インピーダンスのセンサを精确に直接デジタル化できます(図8～図10)。整合していないリーク電流によって生じる追加誤差も考慮に入れる必要があります。

図8.  $\text{IN}^+$ と $\text{IN}^-$ のRCネットワーク

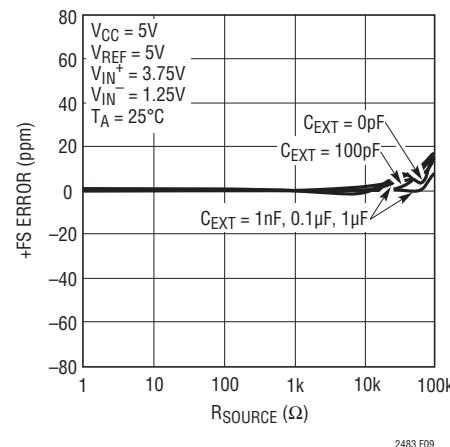

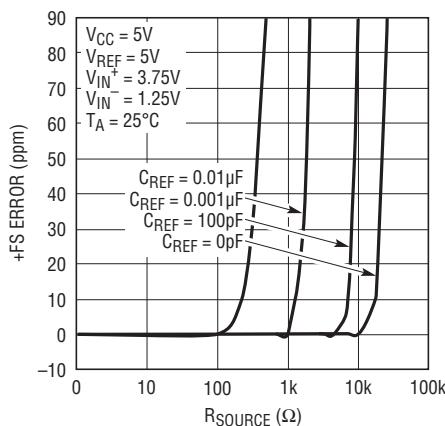

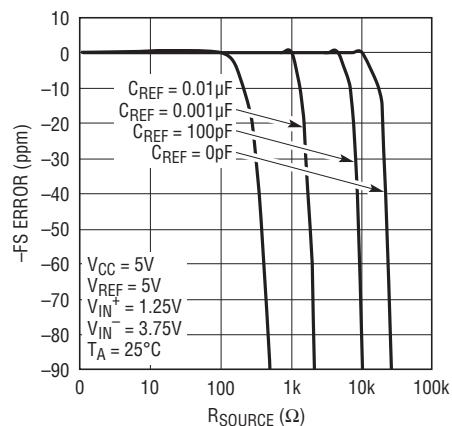

図9. +FS誤差と $\text{IN}^+$ および $\text{IN}^-$ の $\text{R}_{\text{SOURCE}}$

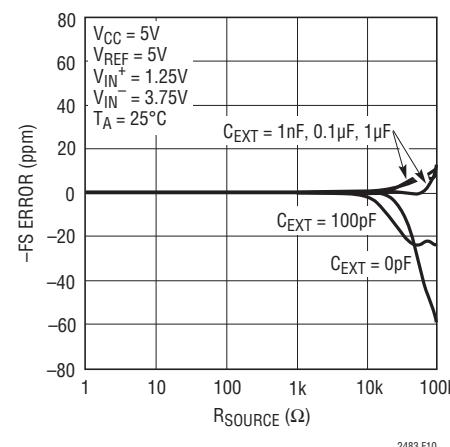

図10. -FS誤差と $\text{IN}^+$ および $\text{IN}^-$ の $\text{R}_{\text{SOURCE}}$

## アプリケーション情報

このスイッチング・アルゴリズムは、正入力( $I_{IN^+}$ )の平均入力電流を負入力( $I_{IN^-}$ )の平均入力電流に等しくなるように強制します。変換サイクル全体にわたって、平均差動入力電流( $I_{IN^+} - I_{IN^-}$ )はゼロになります。差動入力電流はゼロですが、同相入力電流( $I_{IN^+} + I_{IN^-}$ )/2は同相入力電圧( $V_{INCM}$ )と同相リファレンス電圧( $V_{REFCM}$ )の差に比例します。

バランス・ブリッジ型のアプリケーションのように、入力同相電圧がリファレンス同相電圧に等しいアプリケーションでは、差動と同相の両方の入力電流がゼロになります。コンバータの精度はセトリング誤差による影響を受けません。 $I_{IN^+}$ と $I_{IN^-}$ のソース・インピーダンスの不整合も精度に影響を与えません。

入力同相電圧が一定だがリファレンス同相電圧とは異なるアプリケーションでは、差動入力電流はゼロに保たれますが、同相入力電流は $V_{INCM}$ と $V_{REFCM}$ の差に比例します。リファレンス同相電圧が2.5Vで、入力同相電圧が1.5Vの場合、同相入力電流は約0.74 $\mu$ Aです。この同相入力電流は、 $I_{IN^+}$ と $I_{IN^-}$ に接続された外部ソースのインピーダンスが整合していれば、精度に影響を与えません。これらのソース・インピーダンスが整合していないと、固定オフセット誤差が生じますが、直線性やフルスケールの読み取りには影響を与えません。1kのソース抵抗の1%の不整合により、オフセット電圧が15ppm(74 $\mu$ V)シフトします。

同相入力電圧が入力信号レベルに応じて変化するアプリケーション(シングルエンド入力、RTD、半ブリッジ、電流センサなど)では、同相入力電流は入力電圧に比例して変化します。バランスのとれた入力インピーダンスの場合、同相入力電流の影響はLTC2483の大きなCMRRによって除去され、精度はほとんど低下しません。ソース・インピーダンスが整合していないと、同相入力電圧と同相リファレンス電圧の差に比例した利得誤差が生じます。1kのソース抵抗の1%の不整合により、(リファレンス同相電圧と入力同相電圧の差が1Vの場合)約15ppmつまり1 LSBのワーストケース利得誤差が生じます。整合していないソース・インピーダンスと、リファレンス/入力の同相電圧の差の影響を表5にまとめます。

表5. LTC2483の推奨入力構成

|                                | バランスのとれた入力抵抗                                                             | バランスのとれていない入力抵抗                                                                                   |

|--------------------------------|--------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|

| $V_{IN(CM)} - V_{REF(CM)}$ が一定 | $I_{IN^+}$ と $I_{IN^-}$ の両方で $C_{EXT} > 1nF$ 。大きなソース抵抗を取りることができ、誤差は無視できる | $I_{IN^+}$ と $I_{IN^-}$ の両方で $C_{EXT} > 1nF$ 。大きなソース抵抗を取り取ることができる。バランスのとれていない抵抗によりオフセットが生じるが、較正可能 |

| $V_{IN(CM)} - V_{REF(CM)}$ が変化 | $I_{IN^+}$ と $I_{IN^-}$ の両方で $C_{EXT} > 1nF$ 。大きなソース抵抗を取りことができ、誤差は無視できる  | $I_{IN^+}$ と $I_{IN^-}$ のコンデンサを最小にして大きなソース・インピーダンスを避ける(< 5kを推奨)                                   |

ダイナミック入力電流の大きさは、非常に安定した内部サンプリング・コンデンサのサイズとコンバータのサンプリング・クロックの精度に依存します。内部クロックの精度は、全温度範囲と全電源範囲にわたり標準で0.5%より良好です。この仕様は外部クロックでも簡単に実現できます。比較的安定した(50ppm/ $^{\circ}$ C)抵抗が $I_{IN^+}$ と $I_{IN^-}$ から見た外部ソース・インピーダンスに使われると、ダイナミック電流の予想ドリフトとオフセットは無視できるほど小さくなります(全温度範囲と全電圧範囲でそれぞれの値の約1%)。要求の非常に厳しいアプリケーションでも、一度較正しておけば十分でしょう。

入力サンプリング電荷に加えて、入力ESD保護ダイオードには温度に依存したリーク電流が流れます。公称1nA(最大 $\pm 10nA$ )のこの電流により、オフセットがわずかにシフトします。1kのソース抵抗により、標準1 $\mu$ V、最大10 $\mu$ Vのオフセット電圧が生じます。

### リファレンス電流

同様に、LTC2483は差動リファレンス・ピン( $REF^+$ と $REF^-$ )をサンプリングして、少量の電荷を外部のドライブ回路とやり取りするので、ダイナミックなリファレンス電流が生じます。この電流によりコンバータのオフセットは変化しませんが、利得とINL性能が低下することがあります。この電流の影響は2つの異なる状況に関して分析することができます。

外部リファレンス・コンデンサの値が比較的小ないと( $C_{REF} < 1nF$ )、サンプリング・コンデンサの電圧はほぼ完全にセトリングし、ソース・インピーダンスの値が比較的大きくても、小さな誤差が生じるだけです。 $C_{REF}$ がこのような値では、リファレンス・フィルタの大きな利点は得られず、コンバータのオフセットと利得性能が低下するので、ユーザーはこのような値を避けた方が良いでしょう。

## アプリケーション情報

特定の構成では、リファレンス・フィルタとしてもっと大きな値 ( $C_{REF} > 1nF$ ) のリファレンス・コンデンサが必要になることがあります。このようなコンデンサはリファレンス・サンプリング電荷を平均化するので、外部ソース抵抗から見たリファレンスの差動インピーダンスはほぼ一定になります。

以下の説明では、入力同相電圧とリファレンス同相電圧が等しいと仮定します。内部発振器を使うと、関連する差動抵抗は  $1.1M\Omega$  なので、フルスケール誤差は REF<sup>+</sup> ピンと REF<sup>-</sup> ピンをド

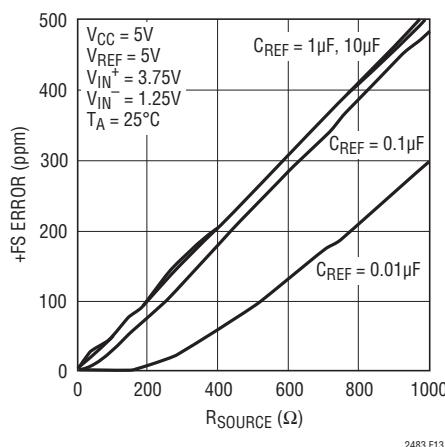

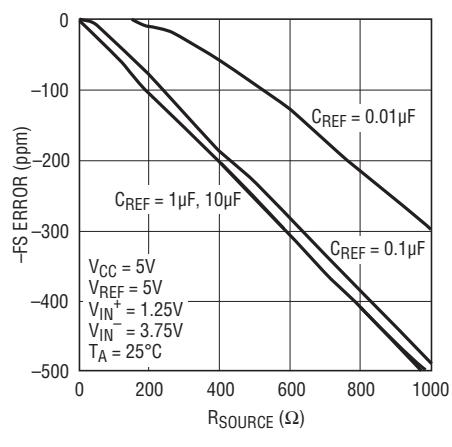

ライブしているソース抵抗  $1\Omega$  ごとに  $0.46ppm$  になります。周波数が  $f_{EOSC}$  の外部発振器によって  $CA0/F_0$  がドライブされるとき (外部変換クロック動作)、標準的な差動リファレンス抵抗は  $0.30 \cdot 10^{12}/f_{EOSC}\Omega$  であり、REF<sup>+</sup> ピンまたはREF<sup>-</sup> ピンをドライブしているソース抵抗  $1\Omega$  ごとに  $1.67 \cdot 10^{-6} \cdot f_{EOSC} ppm$  の利得誤差を生じます。REF<sup>+</sup> ピンまたはREF<sup>-</sup> ピンから見たソース抵抗とそのピンに接続された外部容量の種々の組み合わせごとに標準の +FS 誤差と -FS 誤差を図11～図14に示します。

図11. +FS誤差とREF<sup>+</sup>またはREF<sup>-</sup>のR<sub>SOURCE</sub>(小さなC<sub>REF</sub>)

図12. -FS誤差とREF<sup>+</sup>またはREF<sup>-</sup>のR<sub>SOURCE</sub>(小さなC<sub>REF</sub>)

図13. +FS誤差とREF<sup>+</sup>またはREF<sup>-</sup>のR<sub>SOURCE</sub>(大きなC<sub>REF</sub>)

図14. -FS誤差とREF<sup>+</sup>またはREF<sup>-</sup>のR<sub>SOURCE</sub>(大きなC<sub>REF</sub>)

## アプリケーション情報

この利得誤差に加えて、コンバータのINL性能はリファレンスのソース・インピーダンスによって低下します。INLは、図7に示されているリファレンス・ピンの電流の式の、入力に依存する $-V_{IN}^2/(V_{REF} \cdot R_{EQ}) - (0.5 \cdot V_{REF} \cdot D_T)/R_{EQ}$ の項によって生じます。内部発振器を使うと、リファレンス・ソース抵抗の $100\Omega$ ごとに約0.61ppmのINL誤差が追加されます。周波数が $f_{EOSC}$ の外部発振器によってCA0/ $F_0$ がドライブされるとき、 $REF^+$ または $REF^-$ ピンをドライブしているソース抵抗の $100\Omega$ ごとに約 $2.18 \cdot 10^{-6} \cdot f_{EOSC}$ (ppm)のINL誤差が追加されます。大きな $C_{REF}$ 値が使われるとき $REF^+$ ピンまたは $REF^-$ ピンをドライブしているソース抵抗によって生じる標準的なINL誤差を図15に示します。 $REF^+$ ピンと $REF^-$ ピンをドライブするソース・インピーダンスを最小にすることを推奨します。

リファレンス同相電圧と入力同相電圧が異なるアプリケーションでは、余分な誤差が生じます。リファレンス同相電圧と入力同相電圧の差( $V_{REFCM} - V_{INCM}$ )の1Vごとに、リファレンスのソース抵抗の各 $1\Omega$ により、追加の $(V_{REFCM} - V_{INCM}) / (V_{REF} \cdot R_{EQ})$ のフルスケール利得誤差が生じます。この利得誤差は、内部発振器の使用時は0.067ppmになります。外部

クロックを使うと、対応する追加の利得誤差は $0.24 \cdot 10^{-6} \cdot f_{EOSC}$ ppmです。

ダイナミック・リファレンス電流の大きさは、非常に安定した内部サンプリング・コンデンサのサイズとコンバータのサンプリング・クロックの精度に依存します。内部クロックの精度は、全温度範囲と全電源範囲にわたり標準で0.5%より良好です。この仕様は外部クロックでも簡単に実現できます。比較的安定した(50ppm/ $^{\circ}\text{C}$ )抵抗が $REF^+$ と $REF^-$ から見た外部ソース・インピーダンスに使われると、ダイナミック電流の利得誤差の予想ドリフトは無視できるほど小さくなります(全温度範囲と全電圧範囲でその値の約1%)。要求の非常に厳しいアプリケーションであっても、一度較正しておけば十分でしょう。

リファレンス・サンプリング電荷に加えて、リファレンス・ピンのESD保護ダイオードには温度に依存したリーク電流が流れます。公称1nA(最大 $\pm 10$ nA)のこのリーク電流により小さな利得誤差が生じます。100 $\Omega$ のソース抵抗により、標準0.05 $\mu\text{V}$ 、最大0.5 $\mu\text{V}$ のフルスケール誤差が生じます。

図15. INLと差動入力電圧および

リファレンスのソース抵抗( $C_{REF} > 1\mu\text{F}$ )

## アプリケーション情報

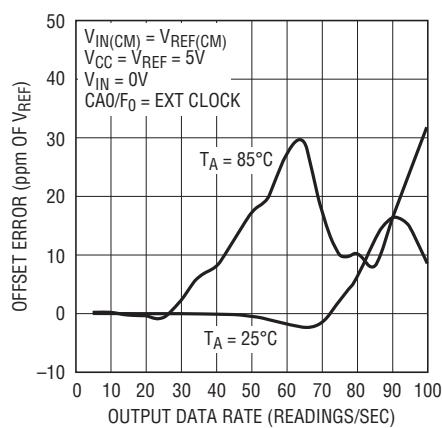

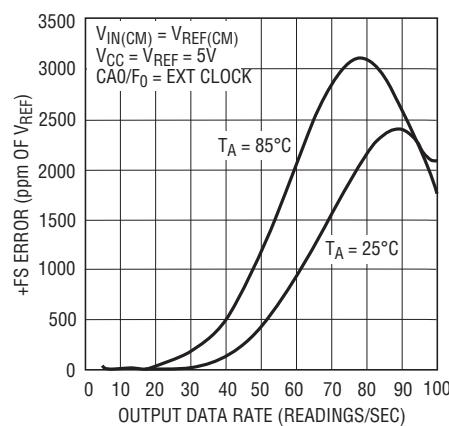

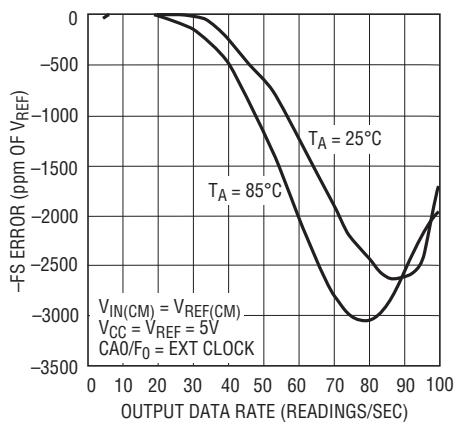

### 出力データ・レート

内部発振器の使用時、LTC2483の出力データ・レートは50Hz/60Hzの同時除去モードでは6.82/秒となります。実際の出力データ・レートはスリープ・フェーズとデータ出力フェーズの長さに依存しますが、これらは無視できるほど短く制御することができます。外部変換クロックを使って動作させるととき(CA0/F<sub>0</sub>を外部発振器に接続)、LTC2483の出力データ・レートを望むように増加させることができます。変換フェーズの持続時間は41036/fEOSCです。fEOSC = 307.2kHzならば、コンバータのノッチ周波数は60Hzに設定されます。

2483 F16

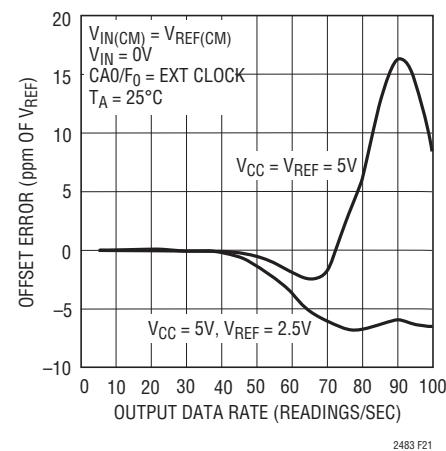

図16. オフセット誤差と出力データ・レートおよび温度

fEOSCを公称307.2kHzを超えて増加させると、最大出力データ・レートが比例して増加します。ただし、出力レートの増加は3つの潜在的影響を伴うので、それについて慎重に検討する必要があります。

第一に、fEOSCが変化すると、内部のノッチの位置が比例して変化し、コンバータの電源ライン周波数の差動モード除去が減少します。多くのアプリケーションで、その結果生じる性能低下は、LTC2483の並外れた同相除去に依存することにより、また入力回路の同相モードから差動モードへ変換される要素を慎重に除去することにより、大きく減らすことができます。ユーザーはシングルエンド入力フィルタを避けて、IN<sup>+</sup>ピンとIN<sup>-</sup>ピンをドライブする回路内で非常に高い整合性と対称性を維持してください。

2483 F17

図17. +FS誤差と出力データ・レートおよび温度

2483 F18

図18. -FS誤差と出力データ・レートおよび温度

2483 F19

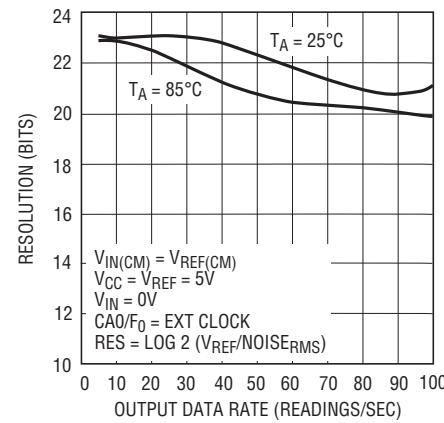

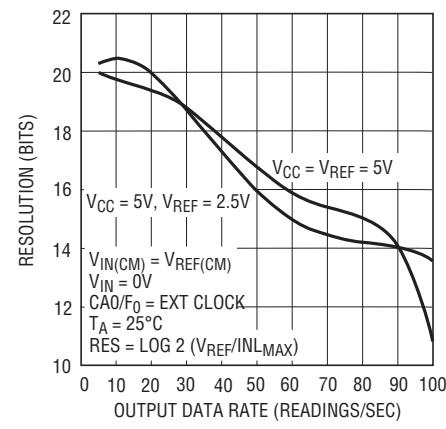

図19. 分解能( $Noise_{RMS} \leq 1\text{LSB}$ )と出力データ・レートおよび温度

## アプリケーション情報

第二に、クロック周波数が増加すると、入力ピンとリファレンス・ピンを介して転送されるサンプリング電荷の量が比例して増加します。大きな外部入力コンデンサやリファレンス・コンデンサ( $C_{IN}$ ,  $C_{REF}$ )が使われる場合、 $f_{EOSC}$ の任意の値でのコンバータの性能に対するソース抵抗の影響を評価するための式が前のセクションで与えられています。小さな外部入力コンデンサやリファレンス・コンデンサ( $C_{IN}$ ,  $C_{REF}$ )を使用する場合、LTC2483の標準的性能に対する外部ソース抵抗の影響を図9～図12から推測することができます。これらの図で、横軸のスケールは $307200/f_{EOSC}$ で調整されています。

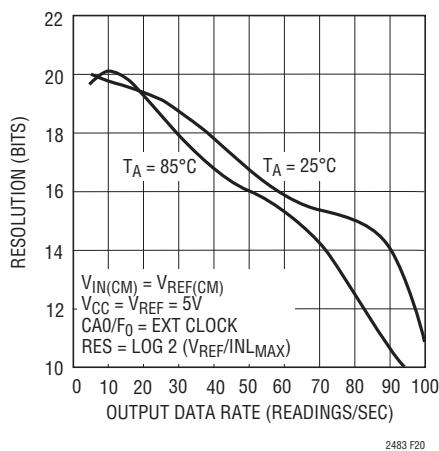

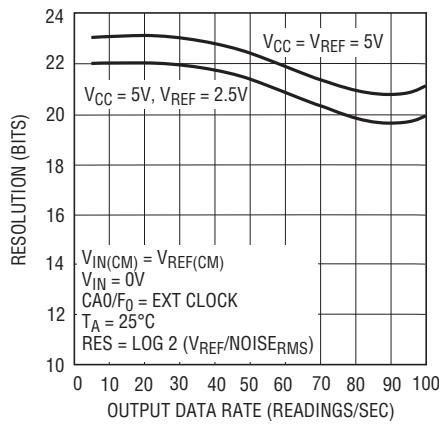

第三に、外部発振器の周波数が1MHzを超えて増加すると(出力データ・レートが3倍以上に増加)、内部の自動較正回路の有効性が低下し始めます。このため、コンバータの精度と直線性が次第に低下します。1秒当たりの読み取りが最大100回までの出力データ・レートの標準的な測定性能曲線を図16～図23に示します。1秒当たりの読み取りが20回を超える出力データ・レートで、このコンバータで可能な最高レベルの精度を得るには、使用する電源電圧を最大にし、最高周囲動作温度を制限することを推奨します。状況によっては、差動リファレンス電圧を下げる場合があります。

図20. 分解能( $INL_{MAX} \leq 1\text{LSB}$ )と

出力データ・レートおよび温度

図21. オフセット誤差と

出力データ・レートおよびリファレンス電圧

図22. 分解能( $Noise_{RMS} \leq 1\text{LSB}$ )と

出力データ・レートおよびリファレンス電圧

図23. 分解能( $INL_{MAX} \leq 1\text{LSB}$ )と

出力データ・レートおよびリファレンス電圧

## アプリケーション情報

### 入力帯域幅

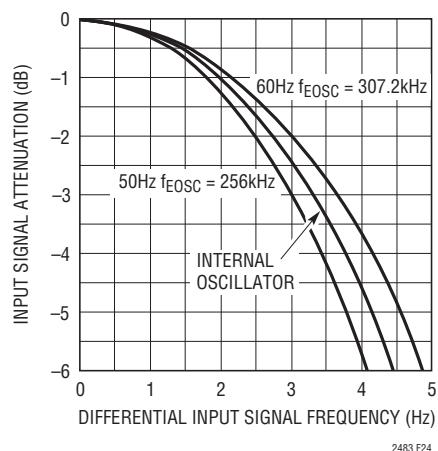

内部SINC<sup>4</sup>デジタル・フィルタとアナログおよびデジタルの自動較正回路を組み合わせた効果により、LTC2483の入力帯域幅が決まります。内部発振器を使うと、3dB入力帯域幅は3.3Hzになります。周波数がf<sub>EOSC</sub>の外部変換クロック発生器をCA0/F<sub>0</sub>ピンに接続すると、3dB入力帯域幅は $11.8 \cdot 10^{-6} \cdot f_{EOSC}$ になります。

複雑なフィルタ処理と較正アルゴリズムが採用されているため、コンバータの入力帯域幅はポールが3dB周波数に位置する1次フィルタではありません正確にモデル化されません。内部発振器が使われる場合のLTC2483の入力帯域幅の形を図24に示します。周波数がf<sub>EOSC</sub>の外部発振器が使われる場合のLTC2483の入力帯域幅の形は、図24から得ることができます。この図の横軸のスケールはf<sub>EOSC</sub>/279.2kHzで調整されています。

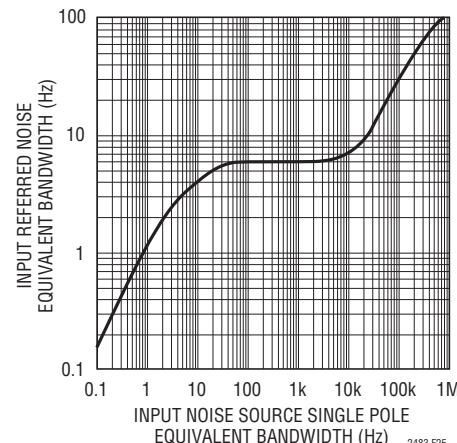

変換ノイズ(V<sub>REF</sub> = 5Vでは標準600nVRMS)は、ノイズの無いコンバータの入力に接続されたホワイトノイズ源によりモデル化することができます。帯域幅が無限のノイズ源のノイズ・スペクトル密度は47nV $\sqrt{\text{Hz}}$ 、0.5MHzの単一ポールのノイズ源では64nV $\sqrt{\text{Hz}}$ です。これらの数字から、外部増幅回路の設計に特に注意を要することは明らかです。このような回路では、出力を基準にしたノイズを減らすための非常に低い帯域幅(わずか数Hz)と、入力のスイッチトキャパシタ・ネットワークをドライブするのに必要な比較的高い帯域幅(少なくとも500kHz)の両方が要件になります。考えられる解決法は、高利得で低帯域幅のアンプ段の後ろに高帯域幅のユニティゲインのバッファを置くことです。

外部のアンプがLTC2483をドライブする場合、ADCの入力を基準にしたシステム・ノイズの計算は、図25を使うと簡単になります。LTC2483の入力ピンをドライブするアンプのノイズは帯域を制限されたホワイトノイズ源としてモデル化することができます。その帯域幅はコーナー周波数がf<sub>i</sub>の単一ポール・ローパス・フィルタの帯域幅によって近似することができます。アンプのノイズ・スペクトル密度はn<sub>i</sub>です。図25から、x軸の値の選択にf<sub>i</sub>を使って、入力をドライブするアンプのノイズに相当する帯域幅freq<sub>i</sub>をy軸上に見つけることができます。この帯域幅には、ADCの内部較正とフィルタ処理の帯域制限効果が

含まれています。これらすべての効果を含む、コンバータの入力を基準にしたドライブ用アンプのノイズは、 $N = n_i \cdot \sqrt{f_{req_i}}$ として計算することができます。このように、LTC2483の入力を基準にした全システム・ノイズは、ADCの入力を基準にする3つのノイズ源(LTC2483の内部ノイズ、IN<sup>+</sup>ドライブ用アンプのノイズ、IN<sup>-</sup>ドライブ用アンプのノイズ)の2乗の和の平方根として合算して求めることができます。

周波数がf<sub>EOSC</sub>の外部発振器でCA0/F<sub>0</sub>ピンをドライブする場合、x軸のスケールがf<sub>EOSC</sub>/307200で調整されていれば、ノイズの計算に図25をそのまま使うことができます。f<sub>EOSC</sub>/307200の比の値が大きくなると、図25のプロットの精度が低下し始めますが、同時に、LTC2483のノイズフロアが上がる所以、ドライブ用アンプのノイズの影響は重要ではなくなります。

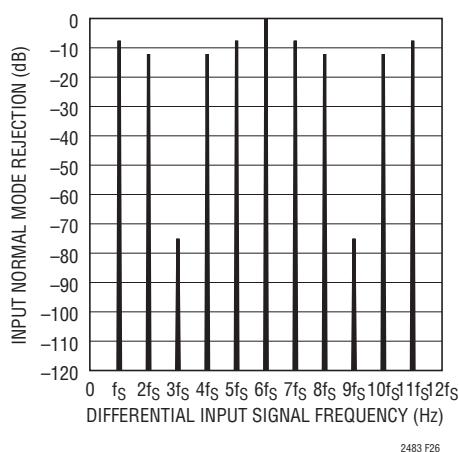

### 通常モードの除去比とアンチエイリアシング

デルタシグマADCが従来のADCよりも優れている点の1つは、デジタル・フィルタを内蔵していることです。大きなオーバーサンプリング比と組み合わせると、LTC2483はアンチエイリアシング・フィルタの要件は大幅に簡素化されます。さらに、LTC2483の入力電流キャンセル機能により、デバイスのDC性能を下げることなく、外部ローパス・フィルタを利用できます。

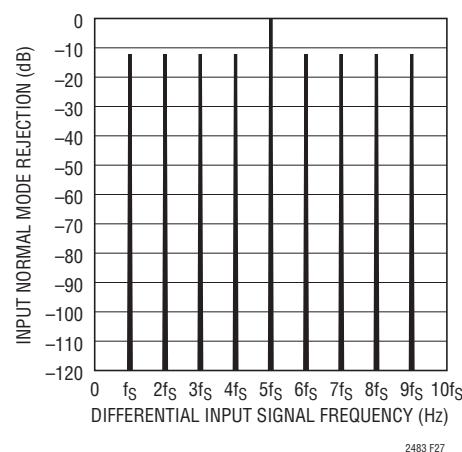

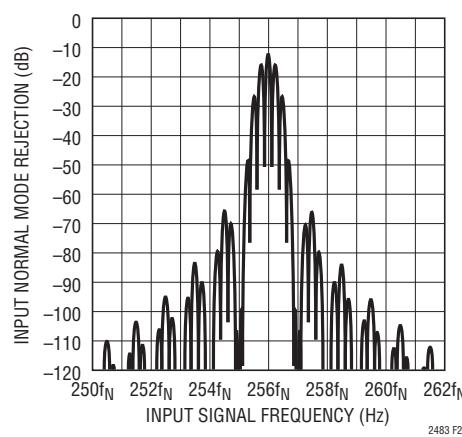

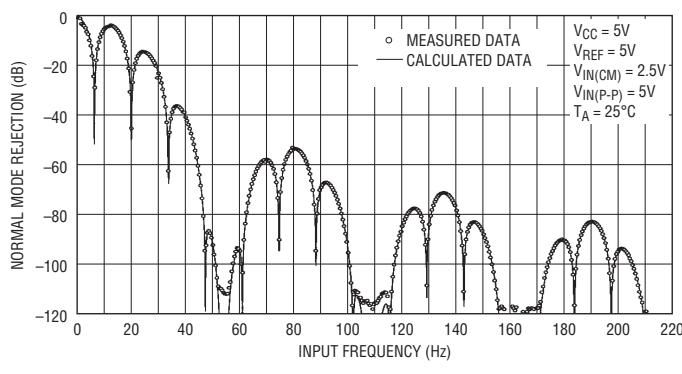

SINC<sup>4</sup>デジタル・フィルタにより、DCと変調器のサンプリング周波数(f<sub>S</sub>)の整数倍を除くすべての周波数で通常モードの除去が120dBを超えます。LTC2483の自動較正回路は、アナログとデジタルの両方の領域で通常モードでの信号フィルタ処理を追加することにより、アンチエイリアシングの要件をさらに簡素化します。動作モードにかかわらず、f<sub>S</sub> = 256 • f<sub>N</sub> = 2048 • f<sub>OUT(MAX)</sub>です。ここで、f<sub>N</sub>はノッチ周波数、f<sub>OUT(MAX)</sub>は最大出力データ・レートです。内部発振器モードでは、f<sub>S</sub> = 13960Hzです。外部発振器モードではf<sub>S</sub> = f<sub>EOSC</sub>/20です。通常モードの除去性能を図26と図27に示します。

f<sub>S</sub>の整数倍で生じる低除去領域の帯域幅は非常に狭くなります。通常モードの除去比曲線の細部を拡大したものを図28(DCの近くでの除去比)と図29(f<sub>S</sub> = 256f<sub>N</sub>での除去比)に示します。ここで、f<sub>N</sub>はノッチ周波数を表します。これらの曲線は外部発振器モードで得たものですが、それらはf<sub>N</sub>の値を適切に選択することによりすべての動作モードで使えます。

## アプリケーション情報

図24. 内部発振器を使ったときの入力信号

図25. 入力を基準にしたノイズに等価な、

入力に接続されたホワイトノイズ源の帯域幅図26. 入力通常モードの除去比、

外部発振器( $f_{EOSC} = 256\text{kHz}$ )で50Hz除去図27. DCでの入力通常モードの除去比

(内部発振器)

図28. DCでの入力通常モードの除去比

図29.  $f_s = 256f_N$ での入力通常モードの除去比

2483fc

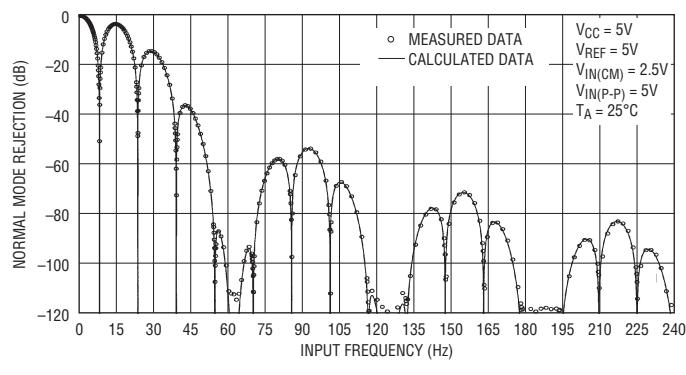

## アプリケーション情報

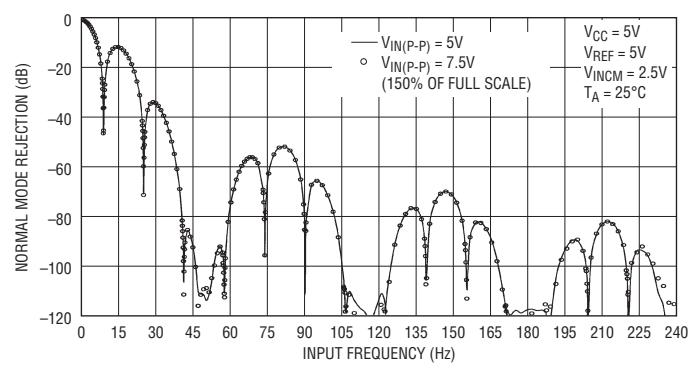

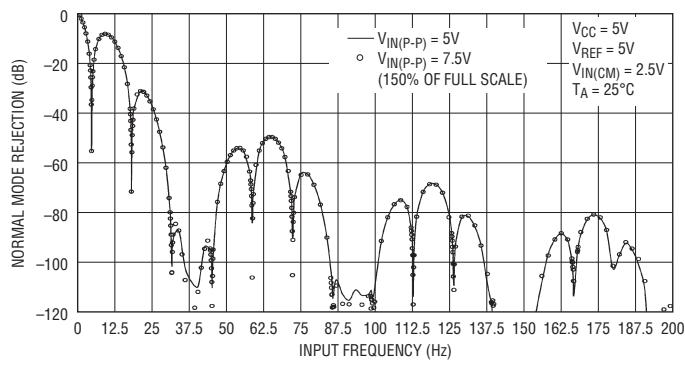

図30、図31および図32に示されているように、ユーザーは内部発振器を使ってこの性能レベルの実現を期待することができます。外部発振器を使い、60Hzのノッチ設定で動作しているLTC2483の通常モードの除去比の標準的測定値を、計算された理論曲線に重ね合わせて図30に示します。同様に、50Hz除去モード( $f_{EOSC} = 256\text{kHz}$ )と50Hz/60Hz除去モード(内部発振器)での、LTC2483の通常モード除去比の測定値を図31と図32に示します。

これらの並外れた通常モードの仕様のおかげで、LTC2483の前段のアンチエイリアシングのフィルタ処理は(もし必要だとしても)最小のもので十分です。LTC2483の前にRC受動部品を置く場合、入力のダイナミック電流について検討します(「入力電流」のセクションを参照)。この場合、LTC2483の差動入力電流キャンセル機能により、DC性能を大幅に低下させることなく、外部RCネットワークを使うことができます。

従来の高次デルタシグマ変調器は非常に優れた直線性と分解能を与えますが、大きな入力信号レベルでは潜在的に不安定です。LTC2483の3次変調器に使われている独自アーキテク

チャはこの問題を解決し、最大150%のフルスケールの入力信号レベルで予測可能な安定動作を保証します。多くの産業用アプリケーションでは、ボルト・レベルの乱れに重ねられたマイクロボルト・レベルの信号を測定しなければならないことが珍しくありませんが、LTC2483は並外れてこのような課題に適しています。乱れが差動のとき、気になる仕様は大きな入力信号レベルに対する通常モードの除去比です。リファレンス電圧  $V_{REF} = 5\text{V}$  のとき、LTC2483のフルスケール差動入力範囲は5Vピーク・トゥ・ピークです。5Vピーク・トゥ・ピーク(フルスケール)入力信号を使って得られた従来の通常モードの除去比の結果に重ね合わせた、7.5Vピーク・トゥ・ピーク(フルスケールの150%)入力信号を使った、LTC2483の通常モードの除去比の測定結果を図33と図34に示します。図33では、LTC2483はノッチを60Hzに設定して外部発振器を使い、図34では、ノッチを50Hzに設定して外部発振器を使っています。LTC2483の除去性能はこの極端な状況でも低下せずに保たれていることが明らかです。大きな入力信号レベルで動作しているとき、ユーザーはこのような信号がデバイスの絶対最大定格を超えないよう注意する必要があります。

## アプリケーション情報

図30. 100%フルスケールの入力の乱れを伴う入力通常モードの除去比と入力周波数(60Hzのノッチ、 $f_{EOSC} = 307.2\text{kHz}$ )

図31. 100%フルスケールの入力の乱れを伴う入力通常モードの除去比と入力周波数(50Hzのノッチ、 $f_{EOSC} = 256\text{kHz}$ )

図32. 100%フルスケールの入力の乱れを伴う入力通常モードの除去比と入力周波数(内部発振器)

図33. 150%フルスケールの入力の乱れを伴う測定された入力通常モードの除去比と入力周波数(60Hzのノッチ、 $f_{EOSC} = 307.2\text{kHz}$ )

図34. 150%フルスケールの入力の乱れを伴う測定された入力通常モードの除去比と入力周波数(50Hzのノッチ、 $f_{EOSC} = 256\text{kHz}$ )

# LTC2483

---

## アプリケーション情報

```

/*

LTC248X.h

Processor setup and

Lots of useful defines for configuring the LTC2481, LTC2483, and LTC2485.

*/

#include <16F73.h>                                // Device

#define _CLOCK_6MHZ                                // 6MHz clock

//#fuses NOWDT,HS, PUT, NOPROTECT, NOBROWNOUT    // Configuration fuses

#define FUSES_NOWDT_HSENABLED                        // Equivalent and more reliable fuse config.

#define I2C(master, sda=PIN_C5, scl=PIN_C3, SLOW)// Set up i2c port

#include "PCM73A.h"                                // Various defines

#include "lcd.c"                                    // LCD driver functions

#define READ      0x01      // bitwise OR with address for read or write

#define WRITE     0x00

#define LTC248XADDR 0b01001000 // The one and only LTC248X in this circuit,

// with both address lines floating.

// Useful defines for the LTC2481 and LTC2485 - OR them together to make the

// 8 bit config word.

// These do NOT apply to the LTC2483.

// Select gain - 1 to 256 (also depends on speed setting)

// Does NOT apply to LTC2485.

#define GAIN1   0b00000000 // G = 1   (SPD = 0), G = 1   (SPD = 1)

#define GAIN2   0b00100000 // G = 4   (SPD = 0), G = 2   (SPD = 1)

#define GAIN3   0b01000000 // G = 8   (SPD = 0), G = 4   (SPD = 1)

#define GAIN4   0b01100000 // G = 16  (SPD = 0), G = 8   (SPD = 1)

#define GAIN5   0b10000000 // G = 32  (SPD = 0), G = 16  (SPD = 1)

#define GAIN6   0b10100000 // G = 64  (SPD = 0), G = 32  (SPD = 1)

#define GAIN7   0b11000000 // G = 128 (SPD = 0), G = 64  (SPD = 1)

#define GAIN8   0b11100000 // G = 256 (SPD = 0), G = 128 (SPD = 1)

// Select ADC source - differential input or PTAT circuit

#define VIN     0b00000000

#define PTAT    0b00001000

// Select rejection frequency - 50, 55, or 60Hz

#define R50    0b00000010

#define R55    0b00000000

#define R60    0b00000100

// Select speed mode

#define SLOW   0b00000000 // slow output rate with autozero

#define FAST   0b00000001 // fast output rate with no autozero

```

## アプリケーション情報

```

/*

LTC2483.c

Basic voltmeter test program for LTC2483

Reads LTC2483, converts result to volts,

and prints voltage to a 2 line by 16 character LCD display.

```

Mark Thoren

Linear Technology Corporation

June 23, 2005

Written for CCS PCM compiler, Version 3.182

\*/

```

#include "LTC248X.h"

/** read_LTC2483() ****

This is the function that actually does all the work of talking to the LTC2483.

```

Arguments: addr - device address

Returns: zero if conversion is in progress,

32 bit signed integer with lower 8 bits clear, 24 bit LTC2483

output word in the upper 24 bits. Data is left-justified for

compatibility with the 24 bit LTC2485.

the i2c\_xxxx() functions do the following:

```

void i2c_start(void): generate an i2c start or repeat start condition

void i2c_stop(void): generate an i2c stop condition

char i2c_read(boolean): return 8 bit i2c data while generating an ack or nack

boolean i2c_write(): send 8 bit i2c data and return ack or nack from slave device

```

These functions are very compiler specific, and can use either a hardware i2c port or software emulation of an i2c port. This example uses software emulation.

A good starting point when porting to other processors is to write your own i2c functions. Note that each processor has its own way of configuring the i2c port, and different compilers may or may not have built-in functions for the i2c port.

When in doubt, you can always write a "bit bang" function for troubleshooting purposes.

The "fourbytes" structure allows byte access to the 32 bit return value:

```

struct fourbytes // Define structure of four consecutive bytes

{

// To allow byte access to a 32 bit int or float.

int8 te0;      //

int8 te1;      // The make32() function in this compiler will

int8 te2;      // also work, but a union of 4 bytes and a 32 bit int

int8 te3;      // is probably more portable.

};

signed int32 read_LTC2483(char addr)

{

struct fourbytes // Define structure of four consecutive bytes

{

// To allow byte access to a 32 bit int or float.

int8 te0;      //

int8 te1;      // The make32() function in this compiler will

int8 te2;      // also work, but a union of 4 bytes and a 32 bit int

int8 te3;      // is probably more portable.

};

}*****

```

# LTC2483

---

## アプリケーション情報

```

union

{

signed int32 bits32;           // adc_code.bits32      all 32 bits

struct fourbytes by;

{ adc_code; }                 // adc_code.by.te0      byte 0

// adc_code.by.te1      byte 1

// adc_code.by.te2      byte 2

// adc_code.by.te3      byte 3

}

// Start communication with LTC2483:

i2c_start();

if(i2c_write(addr | READ))// If no acknowledge, return zero

{

i2c_stop();

return 0;

}

adc_code.by.te3 = i2c_read();

adc_code.by.te2 = i2c_read();

adc_code.by.te1 = i2c_read();

adc_code.by.te0 = 0;

i2c_stop();

return adc_code.bits32;

} // End of read_LTC2483()

/***

* initialize() *****

* Basic hardware initialization of controller and LCD, send Hello message to LCD

*/

void initialize(void)

{

// General initialization stuff.

setup_adc_ports(NO_ANALOGS);

setup_adc(ADC_OFF);

setup_counters(RTCC_INTERNAL,RTCC_DIV_1);

setup_timer_1(T1_DISABLED);

setup_timer_2(T2_DISABLED,0,1);

// This is the important part - configuring the SPI port

setup_spi(SPI_MASTER|SPI_L_TO_H|SPI_CLK_DIV_16|SPI_SS_DISABLED); // fast SPI clock

CKP = 0; // Set up clock edges - clock idles low, data changes on

CKE = 1; // falling edges, valid on rising edges.

lcd_init(); // Initialize LCD

delay_ms(6);

printf(lcd_putc, "Hello!"); // Obligatory hello message

delay_ms(500); // for half a second

} // End of initialize()

/***

* main() *****

* Main program initializes microcontroller registers, then reads the LTC2483

* repeatedly

*/

void main()

{

signed int32 x; // Integer result from LTC2481

float voltage; // Variable for floating point math

int16 timeout;

initialize(); // Hardware initialization

while(1)

{

delay_ms(1); // Pace the main loop to something more than 1 ms

}

// This is a basic error detection scheme. The LTC2483 will never take more than

// 149.9ms to complete a conversion in the 55Hz

// rejection mode.

}

```

2483fc

## アプリケーション情報

```

// If read_LTC2483() does not return non-zero within this time period, something

// is wrong, such as an incorrect i2c address or bus conflict.

if((x = read_LTC2483(LTC248XADDR)) != 0)

{

// No timeout, everything is okay

timeout = 0;                      // reset timer

x ^= 0x80000000;                  // Invert MSB, result is 2's complement

voltage = (float) x;               // convert to float

voltage = voltage * 5.0 / 2147483648.0; // Multiply by Vref, divide by 2^31

lcd_putc('\f');                   // Clear screen

lcd_gotoxy(1,1);                 // Goto home position

printf(lcd_putc, "V %01.4f", voltage); // Display voltage

}

else

{

++timeout;

}

if(timeout > 200)

{

timeout = 200;      // Prevent rollover

lcd_gotoxy(1,1);

printf(lcd_putc, "ERROR - TIMEOUT");

delay_ms(500);

}

} // End of main loop

} // End of main()

```

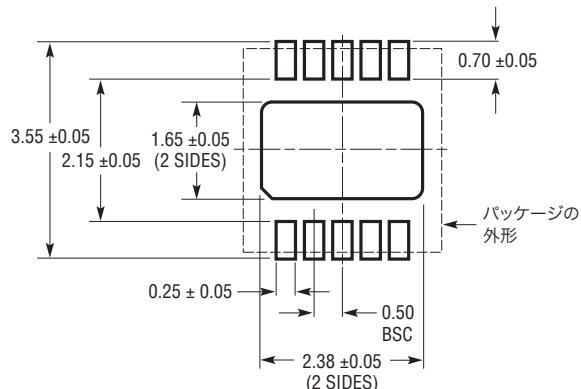

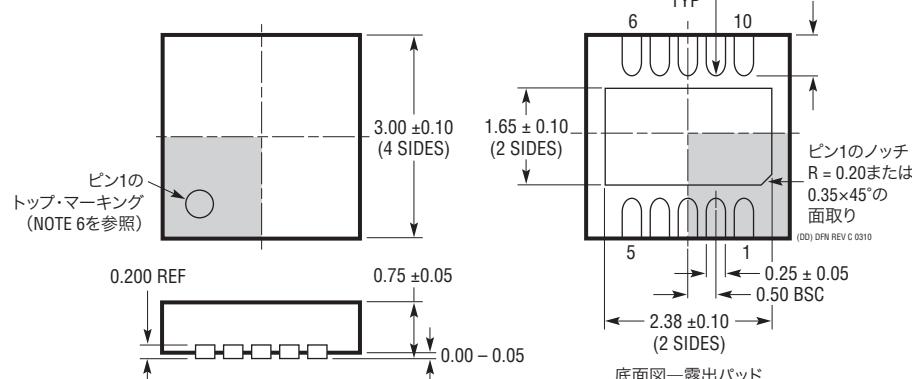

## パッケージ

**DDパッケージ

10ピン・プラスチックDFN(3mm×3mm)

(Reference LTC DWG # 05-08-1699 Rev C)**

推薦する半田パッドのピッチと寸法

NOTE:

1. 図はJEDECパッケージ・アウトラインMO-229のバリエーション(WEED-2)になる予定

バリエーションの指定の現状についてはLTCのWebサイトのデータシートを参照

2. 図は実寸とは異なる

3. すべての寸法はミリメートル

4. パッケージ底面の露出パッドの寸法にはモールドのバリを含まない

モールドのバリは(もしあれば)各サイドで0.15mmを超えないこと

5. 露出パッドは半田メッキとする

6. 網掛けの部分はパッケージの上面と底面のピン1の位置の参考に過ぎない

## 改訂履歴 (Rev Cよりスタート)

| Rev | 日付   | 概要                                                           | ページ番号   |

|-----|------|--------------------------------------------------------------|---------|

| C   | 7/10 | 「標準的応用例」の図を改訂<br>「I <sup>2</sup> Cインターフェース」のセクションの最初の段落に文を追加 | 1<br>11 |

# LTC2483

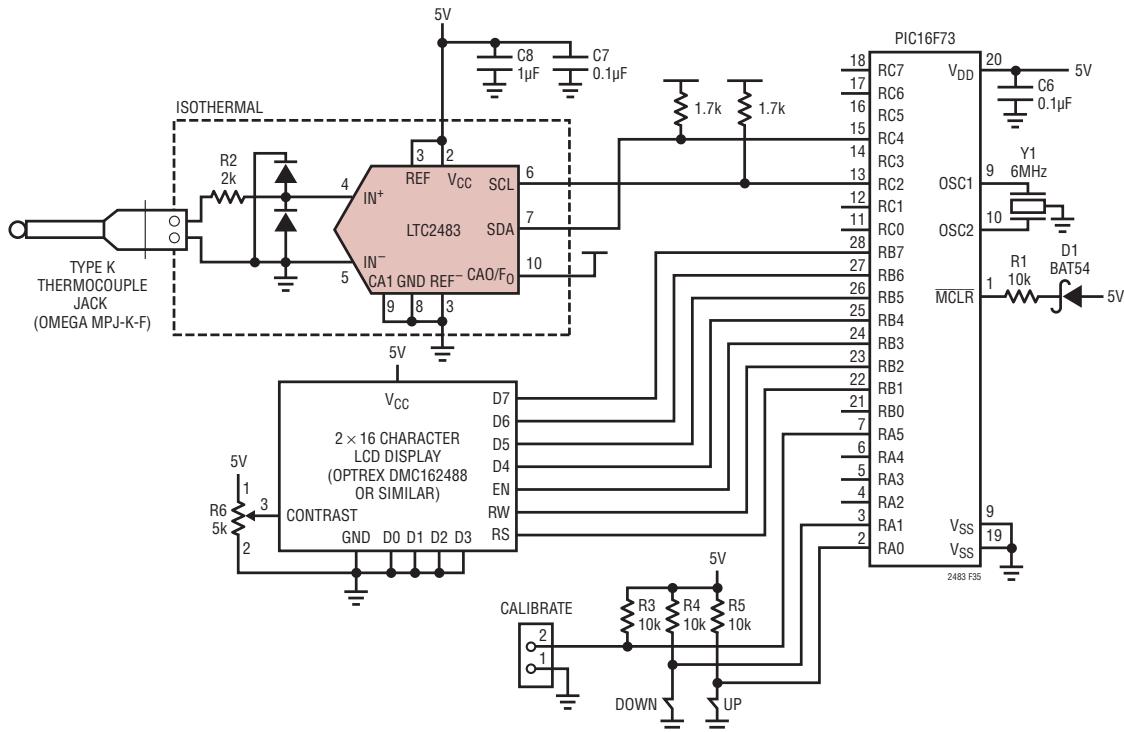

## 標準的応用例

図35. 電圧測定回路

## 関連製品

| 製品番号                  | 説明                                                                                  | 注釈                                              |

|-----------------------|-------------------------------------------------------------------------------------|-------------------------------------------------|

| LT1236A-5             | 高精度バンドギャップ・リファレンス、5V                                                                | 初期精度:最大0.05%、ドリフト:5ppm/°C                       |

| LT1460                | マイクロパワー・シリーズのリファレンス                                                                 | 初期精度:最大0.075%、ドリフト:最大10ppm/°C                   |

| LT1790                | マイクロパワーSOT-23低損失リファレンス・ファミリ                                                         | 初期精度:最大0.05%、ドリフト:最大10ppm/°C                    |

| LTC2400               | SO-8パッケージの24ビットNo Latency ΔΣ ADC、                                                   | ノイズ:0.3ppm、INL:4ppm、全未調整誤差:10ppm、200μA          |

| LTC2410               | 24ビットNo Latency ΔΣ ADC、差動入力付き                                                       | ノイズ:0.8μVRMS、INL:2ppm                           |

| LTC2411/LTC2411-1     | MSOPパッケージの24ビットNo Latency ΔΣ ADC、差動入力付き                                             | ノイズ:1.45μVRMS、INL:2ppm、50Hz/60Hz同時除去(LTC2411-1) |

| LTC2413               | 24ビットNo Latency ΔΣ ADC、差動入力付き                                                       | 50Hz/60Hz同時除去、ノイズ:800nVRMS                      |

| LTC2415/<br>LTC2415-1 | 24ビットNo Latency ΔΣ ADC、15Hzの出力レート                                                   | LTC2410とピン互換                                    |

| LTC2414/LTC2418       | 8チャネル/16チャネル、24ビットNo Latency ΔΣ ADC                                                 | ノイズ:0.2ppm、INL:2ppm、全未調整誤差:3ppm、200μA           |

| LTC2440               | 高速、低ノイズの24ビットΔΣ ADC                                                                 | 出力レート:3.5kHz、ノイズ:200nVRMS、ENOB:24.6             |

| LTC2480               | 16ビットΔΣ ADC、Easy Drive入力付き、ノイズ:600nVRMS、プログラム可能な利得、温度センサ内蔵                          | LTC2482/LTC2484とピン互換                            |

| LTC2481               | 16ビットΔΣ ADC、Easy Drive入力付き、ノイズ:600nVRMS、I <sup>2</sup> Cインターフェース、プログラム可能な利得、温度センサ内蔵 | LTC2483/LTC2485とピン互換                            |

| LTC2482               | 16ビットΔΣ ADC、Easy Drive入力付き                                                          | LTC2480/LTC2484とピン互換                            |

| LTC2484               | 24ビットΔΣ ADC、Easy Drive入力付き                                                          | LTC2480/LTC2482とピン互換                            |

| LTC2485               | 24ビットΔΣ ADC、Easy Drive入力、I <sup>2</sup> Cインターフェースおよび温度センサ付き                         | LTC2481/LTC2483とピン互換                            |

2483fc