208sps/833spsを選択可能で

最大10ppm/°Cの高精度リファレンスを

内蔵した16ビットI<sup>2</sup>C ΔΣ A/Dコンバータ

## 特長

- 16ビット分解能

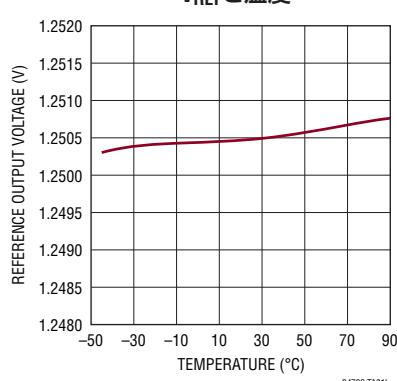

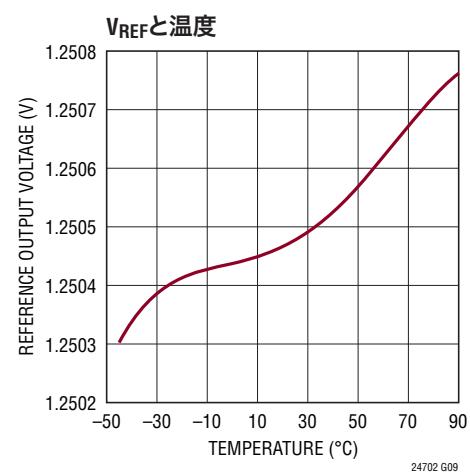

- 高精度リファレンスを内蔵 – 10ppm/°C(最大)

- シングルエンド(LTC2470)または差動(LTC2472)

- 出力レートを選択可能:208sps/833sps

- オフセット誤差:1mV

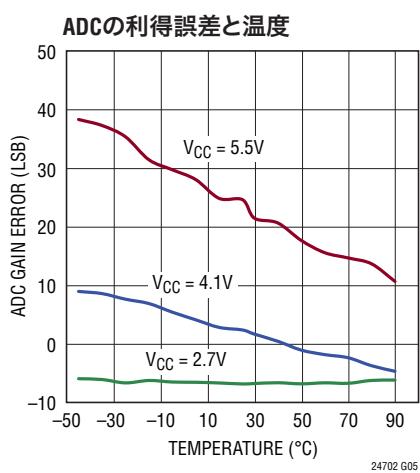

- 利得誤差:0.01%

- 単一の変換セッティング時間により、

多重化アプリケーションを簡素化

- 自動シャットダウン機能を備えた單一サイクル動作

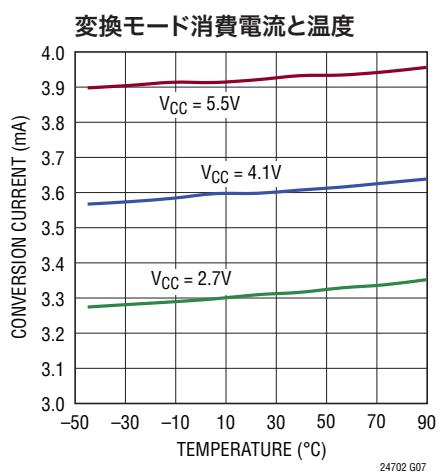

- 電源電流:3.5mA(標準)

- スリープ電流:2μA(最大)

- 発振器内蔵 – 外付け部品不要

- SPIインターフェース

- 3mm×3mmの12ピン小型DFNパッケージおよび

MSOPパッケージ

## アプリケーション

- システム・モニタ

- 環境モニタ

- 直接の温度測定

- 計測機器

- 産業用プロセス制御

- データ収集

- 組み込みA/Dコンバータのアップグレード

LT、LT、LTC、LTM、Linear TechnologyおよびLinearのロゴはリニアテクノロジーの登録商標です。No Latency ΔΣはリニアテクノロジーの商標です。その他すべての商標の所有権は、それぞれの所有者に帰属します。6208279、6411242、7088280、7164378を含む米国特許によって保護されています。

## 概要

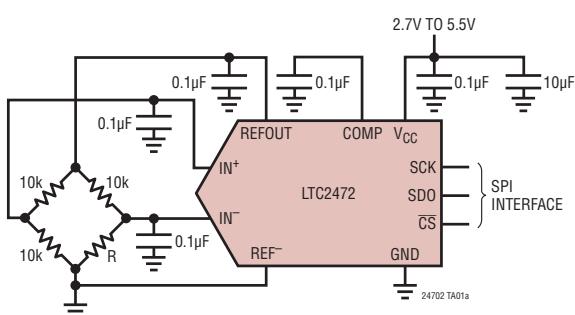

LTC®2470/LTC2472は、高精度リファレンスを内蔵し、208spsまたは833spsの出力レートを選択できる小型の16ビットA/Dコンバータです。これらのデバイスは2.7V～5.5Vの単電源を使用し、SPIインターフェースを介して通信します。LTC2470は入力範囲が0V～V<sub>REF</sub>のシングルエンド入力であり、LTC2472は入力範囲が±V<sub>REF</sub>の差動入力です。どちらのA/Dコンバータもドリフト性能が2ppm/°Cで初期精度が0.1%の1.25Vリファレンスを内蔵しています。これらのA/Dコンバータは3mm×3mmの12ピンDFNパッケージまたはMSOP-12パッケージで供給されます。発振器を内蔵しており、変換実行時の待ち時間がないので、多重化アプリケーションに対応できます。LTC2470/LTC2472は従来のデルタシグマ・コンバータと比べて平均入力電流が数桁少ない独自の入力サンプリング手法を採用しています。

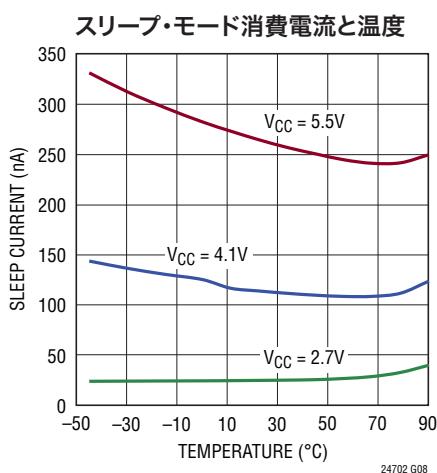

LTC2470/LTC2472は1回の変換ごとにコンバータの電源を自動的に遮断します。また、リファレンスの電源を遮断するよう設定することもできます。A/Dコンバータとリファレンスの両方の電源が遮断されると、電源電流は200nAまで減少します。

LTC2470/LTC2472では、208spsまたは833spsの出力レートをユーザが選択可能であり、オーバーサンプリング率が大きい(208spsで8,192、833spsで2,048)ので、アンチエイリアシングの要件が緩和されます。

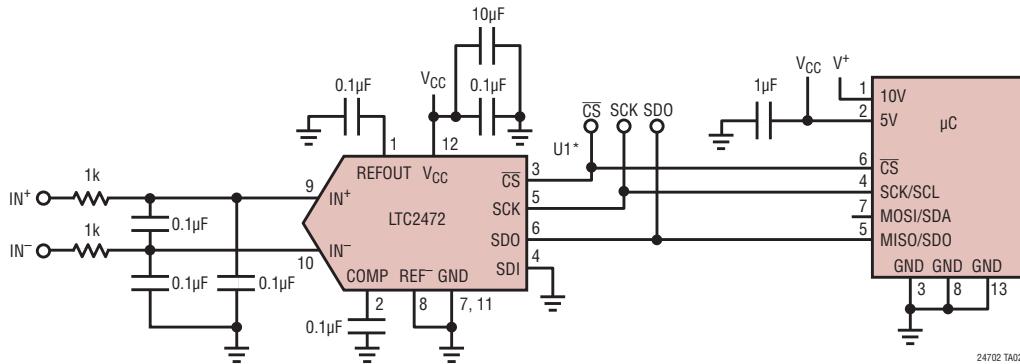

## 標準的応用例

24702fb

# LTC2470/LTC2472

## 絶対最大定格

(Note 1,2)

|                                                                                     |                         |

|-------------------------------------------------------------------------------------|-------------------------|

| 電源電圧 ( $V_{CC}$ )                                                                   | -0.3V~6V                |

| アナログ入力電圧<br>( $V_{IN^+}, V_{IN^-}, V_{IN}, V_{REF^-}$ ,<br>$V_{COMP}, V_{REFOUT}$ ) | -0.3V~( $V_{CC}+0.3V$ ) |

| デジタル電圧<br>( $V_{SDI}, V_{SDO}, V_{SCK}, V_{CS}$ )                                   | -0.3V~( $V_{CC}+0.3V$ ) |

|                   |             |

|-------------------|-------------|

| 保存温度範囲            | -65°C~150°C |

| 動作温度範囲            |             |

| LTC2470C/LTC2472C | 0°C~70°C    |

| LTC2470I/LTC2472I | -40°C~85°C  |

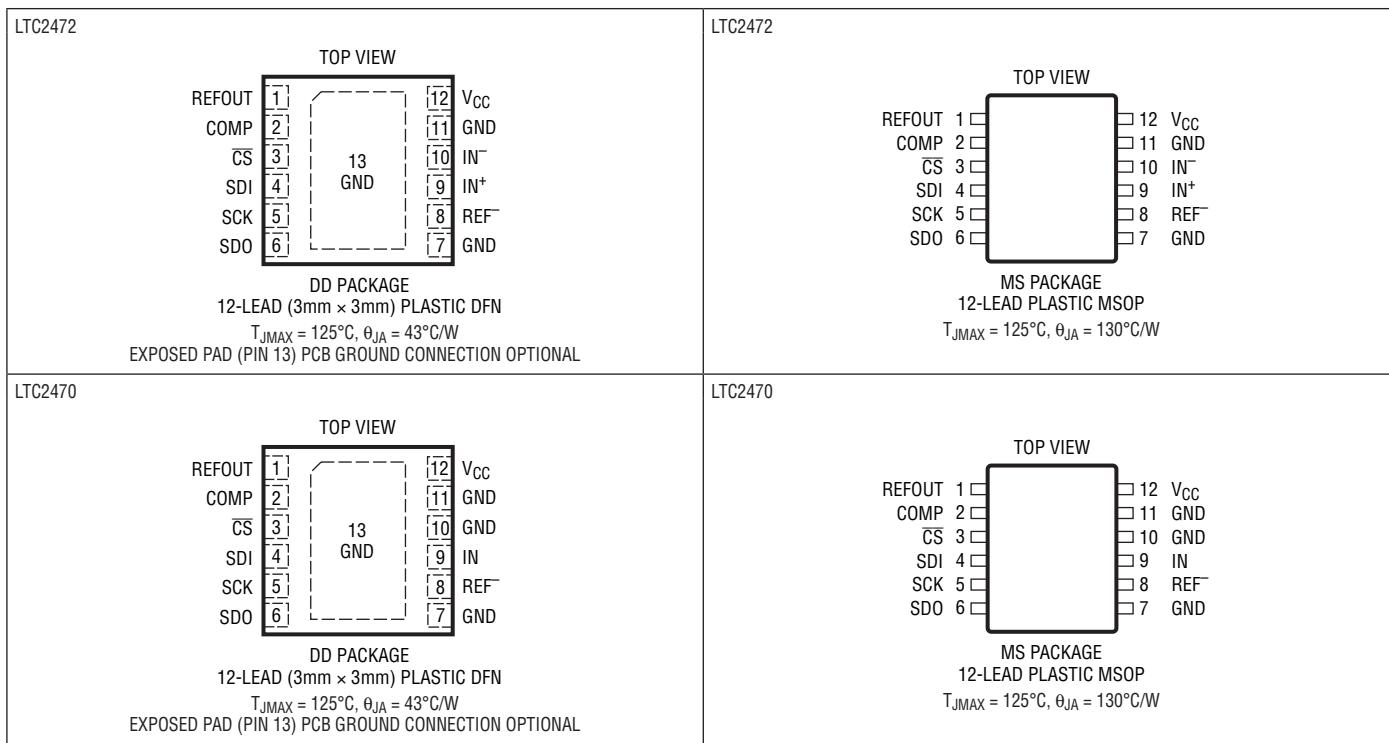

## ピン配置

## 発注情報

| 鉛フリー仕様         | テープ・アンド・リール      | 製品マーキング* | パッケージ                           | 温度範囲          |

|----------------|------------------|----------|---------------------------------|---------------|

| LTC2470CDD#PBF | LTC2470CDD#TRPBF | LFPV     | 12-Lead Plastic (3mm × 3mm) DFN | 0°C to 70°C   |

| LTC2470IDD#PBF | LTC2470IDD#TRPBF | LFPV     | 12-Lead Plastic (3mm × 3mm) DFN | -40°C to 85°C |

| LTC2470CMS#PBF | LTC2470CMS#TRPBF | 2470     | 12-Lead Plastic MSOP            | 0°C to 70°C   |

| LTC2470IMS#PBF | LTC2470IMS#TRPBF | 2470     | 12-Lead Plastic MSOP            | -40°C to 85°C |

| LTC2472CDD#PBF | LTC2472CDD#TRPBF | LFGV     | 12-Lead Plastic (3mm × 3mm) DFN | 0°C to 70°C   |

| LTC2472IDD#PBF | LTC2472IDD#TRPBF | LFGV     | 12-Lead Plastic (3mm × 3mm) DFN | -40°C to 85°C |

| LTC2472CMS#PBF | LTC2472CMS#TRPBF | 2472     | 12-Lead Plastic MSOP            | 0°C to 70°C   |

| LTC2472IMS#PBF | LTC2472IMS#TRPBF | 2472     | 12-Lead Plastic MSOP            | -40°C to 85°C |

さらに広い動作温度範囲で規定されるデバイスについては、弊社または弊社代理店にお問い合わせください。 \*温度グレードは出荷時のコンテナのラベルで識別されます。

非標準の鉛ベース仕様の製品の詳細については、弊社または弊社代理店にお問い合わせください。

鉛フリー仕様の製品マーキングの詳細については、<http://www.linear-tech.co.jp/leadfree/> をご覧ください。

テープアンドリールの仕様の詳細については、<http://www.linear-tech.co.jp/tapeandreel/> をご覧ください。

24702fb

## 電気的特性

●は全動作温度範囲の規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ 。(Note 2)

| PARAMETER                     | CONDITIONS                                                 | MIN    | TYP        | MAX        | UNITS                      |

|-------------------------------|------------------------------------------------------------|--------|------------|------------|----------------------------|

| Resolution (No Missing Codes) | (Note 3)                                                   | ●      | 16         |            | Bits                       |

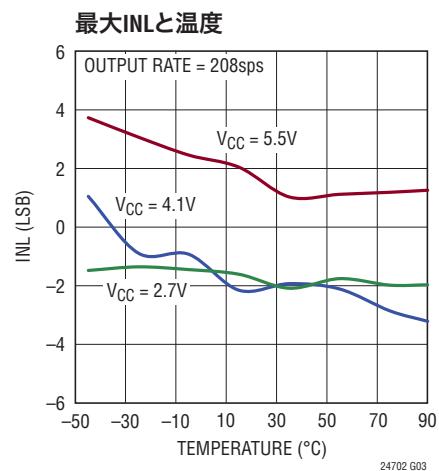

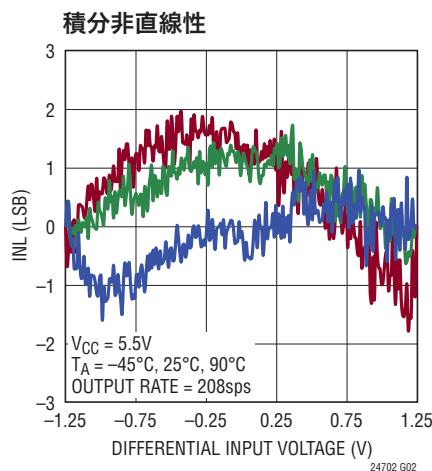

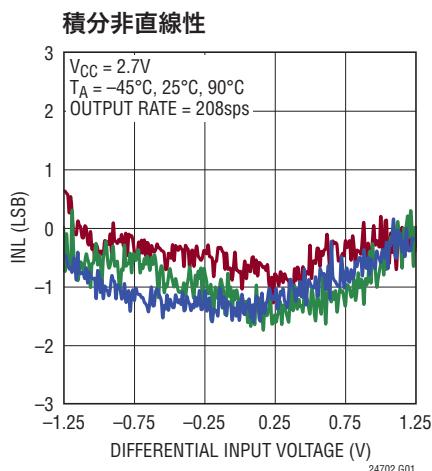

| Integral Nonlinearity         | Output Rate 208sps (Note 4)<br>Output Rate 833sps (Note 4) | ●<br>● | 2<br>8     | 8.5<br>16  | LSB<br>LSB                 |

| Offset Error                  |                                                            | ●      | $\pm 1$    | $\pm 2.5$  | mV                         |

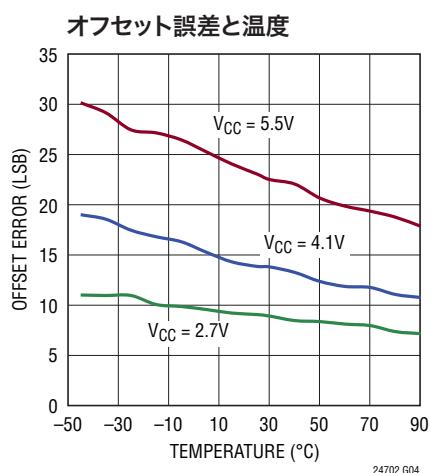

| Offset Error Drift            |                                                            |        | 0.05       |            | LSB/ $^\circ\text{C}$      |

| Gain Error                    |                                                            | ●      | $\pm 0.01$ | $\pm 0.25$ | % of FS                    |

| Gain Error Drift              |                                                            | ●      | 0.15       |            | LSB/ $^\circ\text{C}$      |

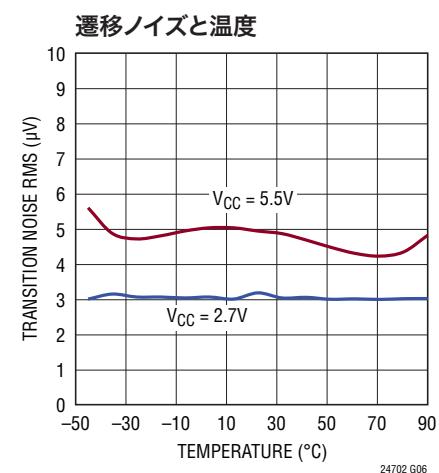

| Transition Noise              |                                                            |        | 3          |            | $\mu\text{V}_{\text{RMS}}$ |

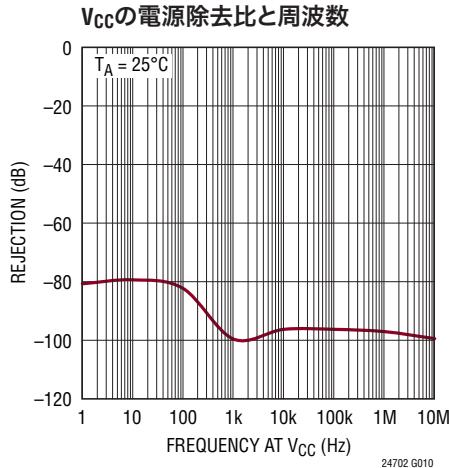

| Power Supply Rejection DC     |                                                            |        | 80         |            | dB                         |

## アナログ入力

●は全動作温度範囲の規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。

| SYMBOL                                                     | PARAMETER                                                                                         | CONDITIONS                                                                                        | MIN    | TYP        | MAX                | UNITS                        |                                                |

|------------------------------------------------------------|---------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|--------|------------|--------------------|------------------------------|------------------------------------------------|

| $V_{\text{IN}}^+$                                          | Positive Input Voltage Range                                                                      | LTC2472                                                                                           | ●      | 0          | $V_{\text{REF}}$   | V                            |                                                |

| $V_{\text{IN}}^-$                                          | Negative Input Voltage Range                                                                      | LTC2472                                                                                           | ●      | 0          | $V_{\text{REF}}$   | V                            |                                                |

| $V_{\text{IN}}$                                            | Input Voltage Range                                                                               | LTC2470                                                                                           | ●      | 0          | $V_{\text{REF}}$   | V                            |                                                |

| $V_{\text{OR}}^+, V_{\text{UR}}^+$                         | Overrange/Underrange Voltage, IN <sup>+</sup>                                                     | $V_{\text{IN}}^- = 0.625\text{V}$                                                                 |        | 8          |                    | LSB                          |                                                |

| $V_{\text{OR}}^-, V_{\text{UR}}^-$                         | Overrange/Underrange Voltage, IN <sup>-</sup>                                                     | $V_{\text{IN}}^+ = 0.625\text{V}$                                                                 |        | 8          |                    | LSB                          |                                                |

| $C_{\text{IN}}$                                            | IN <sup>+</sup> , IN <sup>-</sup> , IN Sampling Capacitance                                       |                                                                                                   |        | 0.35       |                    | pF                           |                                                |

| $I_{\text{DC\_LEAK}}(\text{IN}^+, \text{IN}^-, \text{IN})$ | IN <sup>+</sup> , IN <sup>-</sup> DC Leakage Current (LTC2472)<br>IN DC Leakage Current (LTC2470) | $V_{\text{IN}} = \text{GND}$ (Note 5)<br>$V_{\text{IN}} = V_{\text{CC}}$ (Note 5)                 | ●<br>● | -10<br>-10 | $\pm 1$<br>$\pm 1$ | 10<br>10                     | nA<br>nA                                       |

| $I_{\text{CONV}}$                                          | Input Sampling Current (Note 8)                                                                   |                                                                                                   |        | 50         |                    | nA                           |                                                |

| $V_{\text{REF}}$                                           | Reference Output Voltage                                                                          |                                                                                                   | ●      | 1.247      | 1.25               | 1.253                        | V                                              |

|                                                            | Reference Voltage Coefficient                                                                     | (Note 9)<br>C-Grade<br>I-Grade                                                                    | ●      |            | $\pm 2$<br>$\pm 5$ | $\pm 10$                     | ppm/ $^\circ\text{C}$<br>ppm/ $^\circ\text{C}$ |

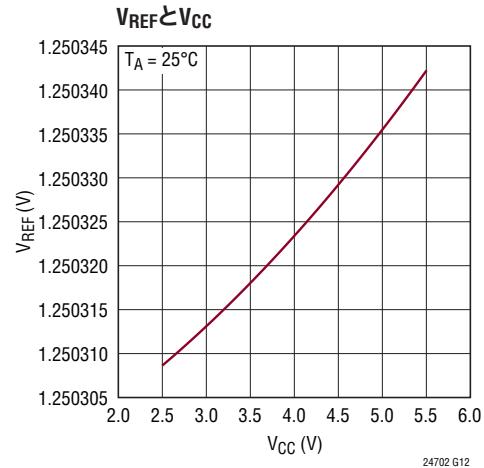

|                                                            | Reference Line Regulation                                                                         | $2.7\text{V} \leq V_{\text{CC}} \leq 5.5\text{V}$                                                 |        |            | -90                |                              | dB                                             |

|                                                            | Reference Short Circuit Current                                                                   | $V_{\text{CC}} = 5.5$ , Forcing Output to GND                                                     | ●      |            | 35                 | mA                           |                                                |

|                                                            | COMP Pin Short Circuit Current                                                                    | $V_{\text{CC}} = 5.5$ , Forcing Output to GND                                                     | ●      |            | 200                | $\mu\text{A}$                |                                                |

|                                                            | Reference Load Regulation                                                                         | $2.7\text{V} \leq V_{\text{CC}} \leq 5.5\text{V}$ , $I_{\text{OUT}} = 100\mu\text{A}$ Sourcing    |        |            | 3.5                | mV/mA                        |                                                |

|                                                            | Reference Output Noise Density                                                                    | $C_{\text{COMP}} = 0.1\mu\text{F}$ , $C_{\text{REFOUT}} = 0.1\mu\text{F}$ , At $f = 1\text{ksps}$ |        |            | 30                 | $\text{nV}/\sqrt{\text{Hz}}$ |                                                |

## 電源要件

●は全動作温度範囲の規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。

| SYMBOL          | PARAMETER                                                  | CONDITIONS                                                                                                                                                                             | MIN              | TYP                      | MAX                 | UNITS                                                            |

|-----------------|------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|--------------------------|---------------------|------------------------------------------------------------------|

| $V_{\text{CC}}$ | Supply Voltage                                             |                                                                                                                                                                                        | ●                | 2.7                      | 5.5                 | V                                                                |

| $I_{\text{CC}}$ | Supply Current<br>Conversion<br>Conversion<br>Nap<br>Sleep | $\overline{CS} = \text{GND}$ (Note 6) LTC2472<br>$\overline{CS} = \text{GND}$ (Note 6) LTC2470<br>$\overline{CS} = V_{\text{CC}}$ (Note 6)<br>$\overline{CS} = V_{\text{CC}}$ (Note 6) | ●<br>●<br>●<br>● | 3.5<br>2.5<br>800<br>0.2 | 5<br>4<br>1500<br>2 | $\mu\text{A}$<br>$\mu\text{A}$<br>$\mu\text{A}$<br>$\mu\text{A}$ |

# LTC2470/LTC2472

## デジタル入力とデジタル出力

●は全動作温度範囲の規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。(Note 2)

| SYMBOL   | PARAMETER                   | CONDITIONS              | MIN | TYP            | MAX | UNITS         |

|----------|-----------------------------|-------------------------|-----|----------------|-----|---------------|

| $V_{IH}$ | High Level Input Voltage    |                         | ●   | $V_{CC} - 0.3$ |     | V             |

| $V_{IL}$ | Low Level Input Voltage     |                         | ●   |                | 0.3 | V             |

| $I_{IN}$ | Digital Input Current       |                         | ●   | -10            | 10  | $\mu\text{A}$ |

| $C_{IN}$ | Digital Input Capacitance   |                         |     |                | 10  | pF            |

| $V_{OH}$ | High Level Output Voltage   | $I_0 = -800\mu\text{A}$ | ●   | $V_{CC} - 0.5$ |     | V             |

| $V_{OL}$ | Low Level Output Voltage    | $I_0 = 1.6\text{mA}$    | ●   |                | 0.4 | V             |

| $I_{OZ}$ | Hi-Z Output Leakage Current |                         | ●   | -10            | 10  | $\mu\text{A}$ |

## タイミング特性

●は全動作温度範囲の規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。

| SYMBOL      | PARAMETER                                   | CONDITIONS   | MIN | TYP | MAX | UNITS |

|-------------|---------------------------------------------|--------------|-----|-----|-----|-------|

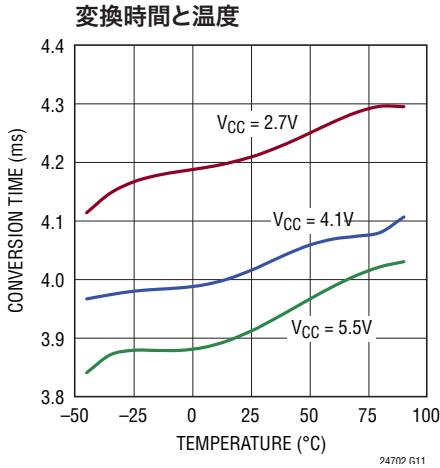

| $t_{CONV1}$ | Conversion Time                             | $SPD = 0$    | ●   | 3.2 | 4   | 4.8   |

| $t_{CONV2}$ | Conversion Time                             | $SPD = 1$    | ●   | 0.8 | 1   | 1.2   |

| $f_{SCK}$   | SCK Frequency Range                         |              | ●   |     | 2   | MHz   |

| $t_{ISCK}$  | SCK Low Period                              | (Note 7)     | ●   | 250 |     | ns    |

| $t_{HSCK}$  | SCK High Period                             | (Note 7)     | ●   | 250 |     | ns    |

| $t_1$       | $\bar{CS}$ Falling Edge to SDO Low Z        | (Note 7)     | ●   | 0   | 100 | ns    |

| $t_2$       | $\bar{CS}$ Rising Edge to SDO High Z        | (Note 7)     | ●   | 0   | 100 | ns    |

| $t_3$       | $\bar{CS}$ Falling Edge to SCK Falling Edge | (Note 7)     | ●   | 100 |     | ns    |

| $t_4$       | SDI Setup Before SCK↑                       | (Notes 3, 7) | ●   | 100 |     | ns    |

| $t_5$       | SDI Hold After SCK↑                         | (Notes 3, 7) | ●   | 100 |     | ns    |

| $t_{KQ}$    | SCK Falling Edge to SDO Valid               | (Note 7)     | ●   | 0   | 100 | ns    |

Note 1: 絶対最大定格に記載された値を超えるストレスはデバイスに永続的損傷を与える可能性がある。長期にわたって絶対最大定格条件下にさらすと、デバイスの信頼性と寿命に悪影響を与える可能性がある。

Note 2: 全ての電圧値はGNDを基準にしている。注記がない限り、 $V_{CC} = 2.7\text{V} \sim 5.5\text{V}$ 。

$$V_{REFCM} = V_{REF}/2, FS = V_{REF}, -V_{REF} \leq V_{IN} \leq V_{REF}$$

$$V_{IN} = V_{IN}^+ - V_{IN}^-, V_{INCM} = (V_{IN}^+ + V_{IN}^-)/2. (LTC2472)$$

Note 3: 設計によって保証されているが、テストされない。

Note 4: 積分非直線性は、実際の伝達曲線のエンドポイントを通る直線からのコードの偏差として定義されている。

Note 5:  $\bar{CS} = V_{CC}$ 。正の電流はDUTピンへ流れ込む。

Note 6: SCK =  $V_{CC}$ またはGND。SDOは高インピーダンスである。

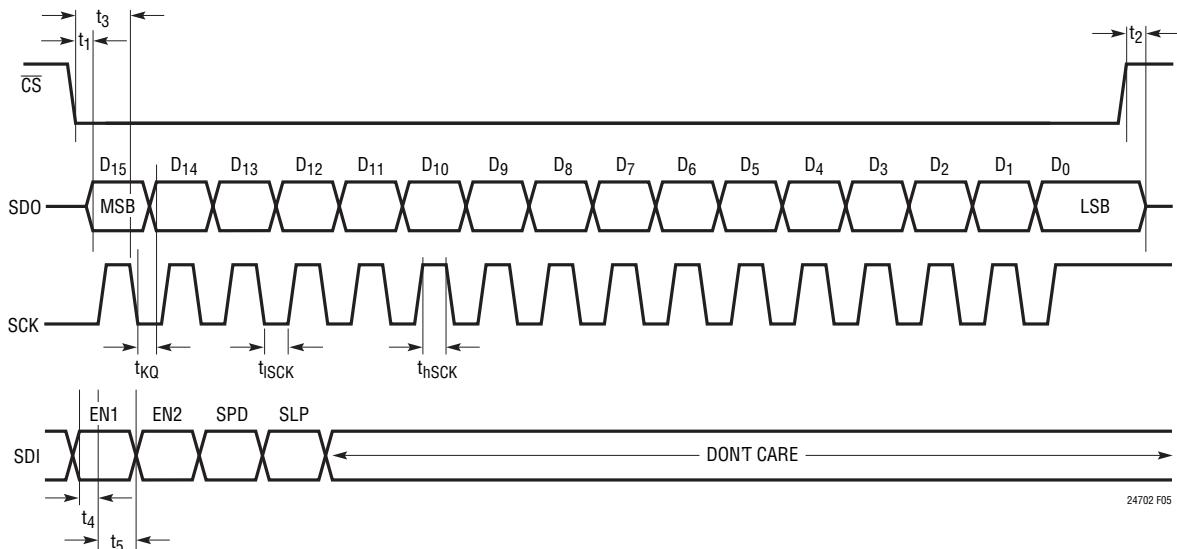

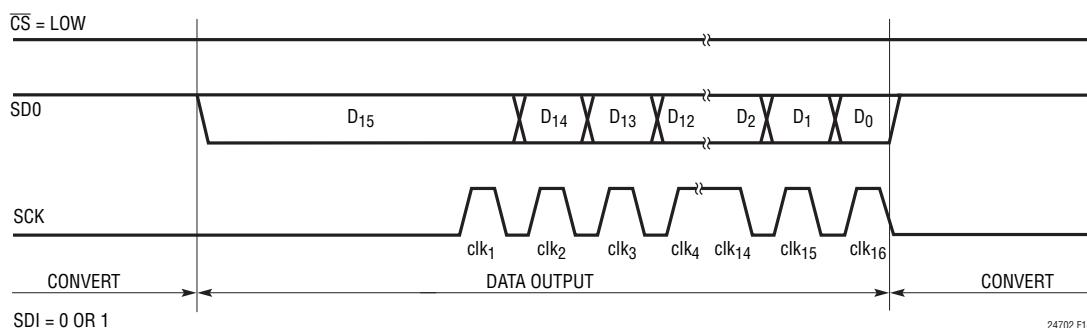

Note 7: 図5を参照。

Note 8: 入力サンプリング電流は、LTC2470/LTC2472がアクティブに入力をサンプリングしているとき入力サンプリング・ネットワークから流れる平均入力電流である。

Note 9: 温度係数は出力電圧の最大変化を規定温度範囲で割って計算される。

## 標準的性能特性 (注記がない限り $T_A = 25^\circ\text{C}$ )

24702fb

## 標準的性能特性 (注記がない限り $T_A = 25^\circ\text{C}$ )

## ピン機能

**REFOUT(ピン1)**: リファレンス出力ピン。公称1.25Vで、この電圧はADCのフルスケール入力範囲を設定します。ノイズとリファレンスの安定性のため、0.1μFのコンデンサでGNDに接続します。このコンデンサの値は、リファレンス補償ピン(COMP)に接続するコンデンサの値以下にしなければなりません。REFOUTを外部リファレンスでオーバードライブすることはできません。

**COMP(ピン2)**: 内部リファレンス補償ピン。ノイズとリファレンスの安定性のため、0.1μFのコンデンサでGNDに接続します。

**CS(ピン3)**: チップセレクト(アクティブ“L”)デジタル入力。このピンを“L”にするとSDO出力がイネーブルされます。このピンを“H”にするとSDO出力ピンが高インピーダンス状態になり、SDIおよびSCKのどんな入力も無視されます。

**SDI(ピン4)**: シリアル・データ入力ピン。このピンは、スリープ・モードおよび208sps/833spsの出力レートをプログラムするのに使われます。

**SCK(ピン5)**: シリアル・クロック入力。SCKはシリアル・データ入力/出力の同期をとります。変換が完了すると、各SCKの立ち下がりエッジで新しいデータ・ビットがSDOピンに出力されます。データはSCKの各立ち上がりエッジでSDIピンにシフトされます。

**SDO(ピン6)**: スリーステートのシリアル・データ出力。SDOはデータ入力/出力ステートの間シリアル・データ出力に使われます。このピンはCSが“H”的とき高インピーダンスになります。

**GND(ピン7、11、ピン13露出パッドーDFNパッケージ)**: グランド。低インピーダンス接続を介してグランド・プレーンに直接接続します。

**REF-(ピン8)**: ADCへの負リファレンス入力。このピンの電圧がADCへのゼロ入力を設定します。このピンは、グランドまたは入力センサのグランド・センスに直接接続します。

**IN<sup>+</sup>(LTC2472)、IN(LTC2470)(ピン9)**: LTC2472差動デバイスの正入力電圧。LTC2470シングルエンド・デバイスのADC入力。

**IN-(LTC2472)、GND(LTC2470)(ピン10)**: LTC2472差動デバイスの負入力電圧。LTC2470シングルエンド・デバイスのGND。

**V<sub>CC</sub>(ピン12)**: 正電源電圧。10μFコンデンサと低直列インダクタンスの0.1μFコンデンサを並列にしてデバイスのできるだけ近くに配置し、GNDにバイパスします。

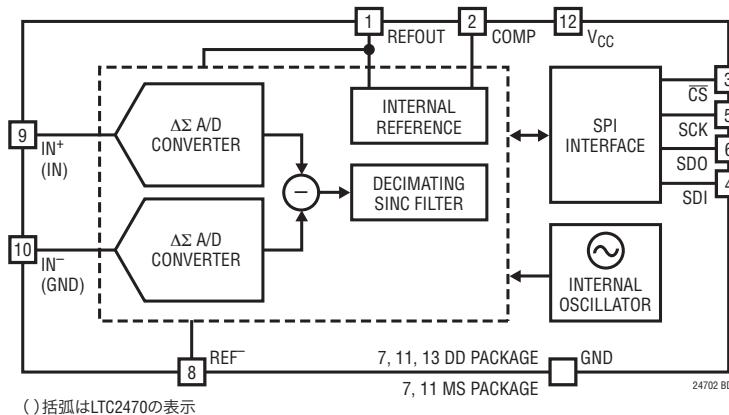

## ブロック図

図1. 機能ブロック図

## アプリケーション情報

### コンバータの動作

#### コンバータの動作サイクル

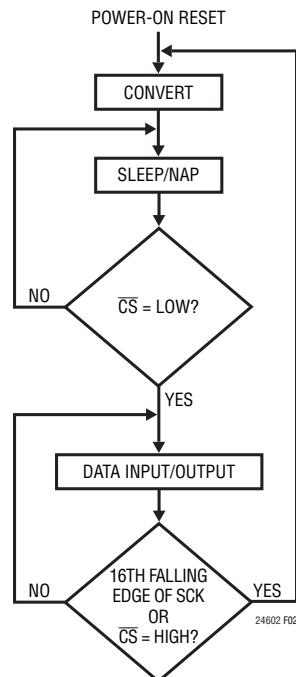

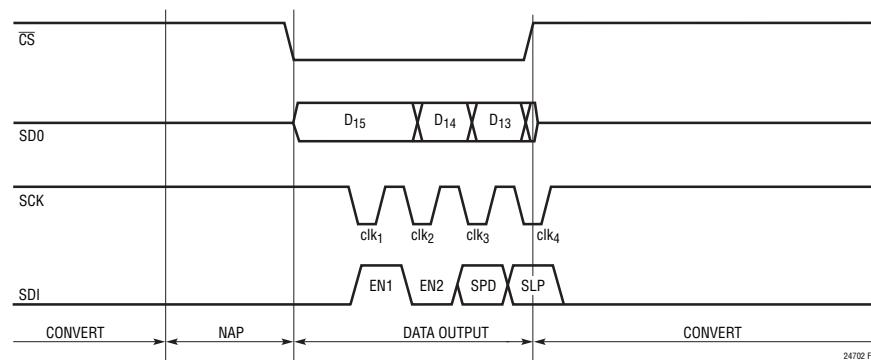

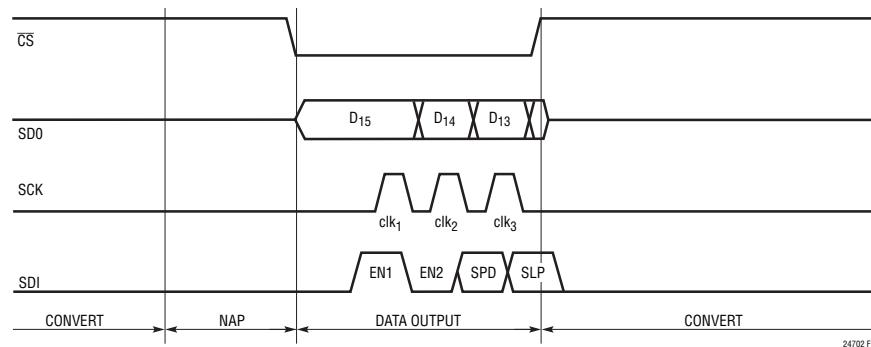

LTC2470/LTC2472は低消費電力のデルタシグマA/Dコンバータで、シンプルなSPIインターフェースと選択可能な208sps/833sps出力レートを備えています(図1を参照)。LTC2472は完全な差動入力を備えており、LTC2470はシングルエンドです。これらはピン互換およびソフトウェア互換です。動作は3つのステート(変換、スリープ/ナップ、データ入力/出力)で構成されています。動作は変換ステートから開始されます(図2を参照)。変換が終了すると、コンバータは自動的にパワーダウンします(ナップ)。または、ユーザの制御のもとに、コンバータとリファレンスの両方をパワーダウンすることができます(スリープ)。デバイスがこのステートの間、変換結果はスタティック・レジスタに保持されます。サイクルはデータ入力/出力ステートで完了します。16ビット全てが読み出される、または中断されると、デバイスは新しい変換を開始します。

変換ステート期間はLTC2470/LTC2472の変換時間(選択された出力レートにより公称4msまたは1ms)で決まります。この動作は一旦開始すると、内部パワーオン・リセット信号を発生する低電源電圧状態( $V_{CC}<2.1V$ )以外では、中止することはできません。

変換完了後、LTC2470/LTC2472はスリープ/ナップ・ステートに入り、チップセレクトが“L”( $\overline{CS} = "L"$ )になるまでそのステートに留まります。このステートに続いて、ADCはデータ入力/出力ステートに移行します。

図2. LTC2470/LTC2472のステート移行図

スリープ/ナップ・ステートの間、チップセレクト入力が“H”( $\overline{CS} = "H"$ )で、LTC2470/LTC2472のコンバータがパワーダウンします。パワーダウンによって、消費電流が約70%減少します。ナップ・ステートの間、リファレンスはパワーアップ状態のままでです。データ入力/出力ステップの間にスリープ・モードをイネーブルすることで、コンバータとリファレンスの両方をパワーダウンできます。

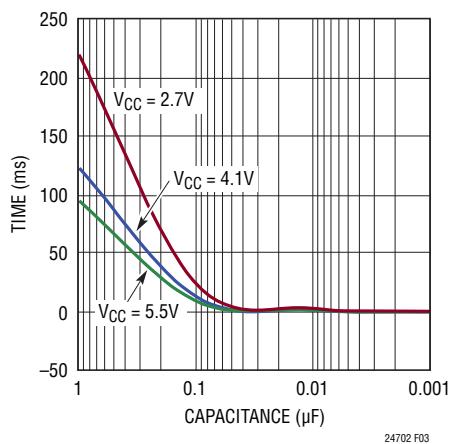

## アプリケーション情報

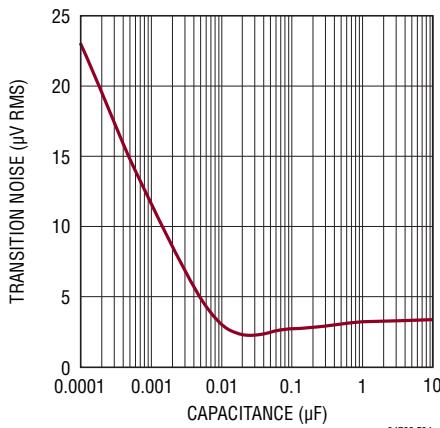

次の変換が完了すると、スリープ・ステートに入り電力は $2\mu\text{A}$ 以下に減少します。リファレンスは $\overline{\text{CS}}$ を“L”にするとパワーアップします。リファレンスの起動時間は12msです(リファレンスおよび補償コンデンサの値が両方とも $0.1\mu\text{F}$ の場合)。リファレンスおよび補償コンデンサの値を小さくすると起動時間は短くなります(図3参照)、遷移ノイズは増加します(図4参照)。

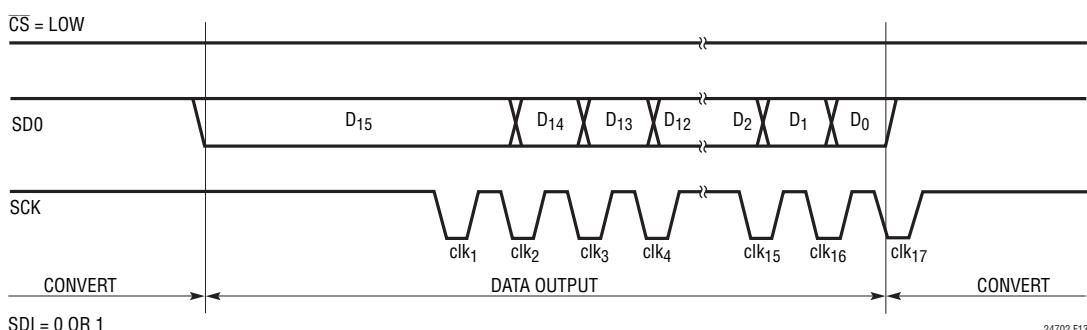

データ入力/出力ステートに入ると、SDOは変換結果の符号(D15)を出力します。このステートの間、ADCはSCK入力ピンの制御下で、SDO出力ピンを通して変換結果をシリアルにシフトして出力します。このデータが発生するまでの待ち時間はなく、その変換結果は直前に完了した変換に対応しています。データの新しいビットは、SCK入力ピンで検出される各立ち上がりエッジに追従してSDOピンに現れ、MSBからLSBへと進みます。このデータは、SCKピンをドライブしている外部シリアル・クロック信号の各立ち上がりエッジで確実にラッピングされます。

図3. リファレンス起動時間と $V_{REF}$

および補償容量

図4. RMS遷移ノイズとCOMP

およびリファレンス容量

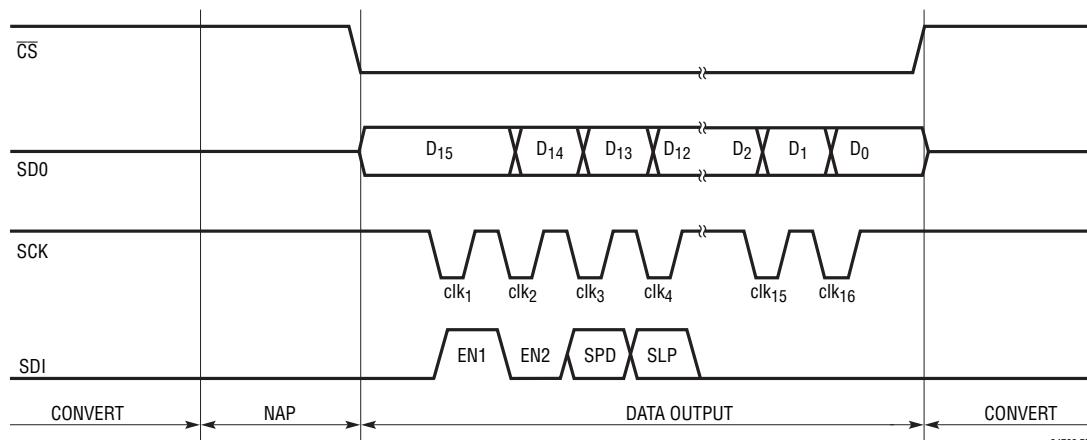

データ入力/出力ステートの間に、LTC2470/LTC2472をスリープまたはナップ(デフォルト)にプログラムすることができます。また出力レートも更新することができます。データはSCKの立ち上がりエッジで、SDIピンを通してデバイスにシフトされます。入力ワードは4ビットです。第1ビットEN1 = 1、第2ビットEN2 = 0であれば、デバイスはプログラミングのためにイネーブルされます。続く2つのビット(SPDとSLP)がデバイスに書き込まれます。SPDは出力レートを選択するために使われます。出力レートはSPD = 0(デフォルト)ならば208sps、SPD = 1ならば833spsに設定されます。次のビット(SLP)はスリープまたはナップ・モードをイネーブルします。SLP = 0(デフォルト)であれば、各変換サイクルの終了時にリファレンスはパワーアップしたままです。SLP = 1であれば、リファレンスは次の変換サイクルでパワーダウンします。SDI入力の残りの12ビットは無視されます(ドントケア)。

ユーザ・インターフェースをシンプルにするため、SDIはGNDまたは $V_{DD}$ に直接接続することもできます。SDIが“L”に接続されると出力レートは208spsになり、SDIが“H”に接続されると出力レートは833spsになります。SDIがGNDまたは $V_{DD}$ に接続されていると、リファレンス・スリープ・モードがディスエーブルされます。

データ入力/出力ステートは2つの異なった方法のどちらかで終了します。まず、16データ・ビットが全てシフトアウトされ、クロックが“L”になるとデータ入力/出力ステート動作が終了します。これはSCKの16番目の立ち下がりエッジに該当します。また、 $\overline{\text{CS}}$ 入力を“L”から“H”へ遷移させて、データ入力/出力ステートをいつでも中止することができます。これら2つのアクションのどちらかの直後にLTC2470/LTC2472は変換ステートに入り、新しい変換サイクルを開始します。

### パワーアップ・シーケンス

コンバータに与えられる電源電圧( $V_{CC}$ )が約 $2.1\text{V}$ を下回ると、ADCはパワーオン・リセットを実行します。この機能により変換結果の信号品質が保証されます。

$V_{CC}$ がこの臨界スレッショルド以上に上昇すると、コンバータは約 $0.5\text{ms}$ の内部パワーオン・リセット(POR)信号を発生します。適切な動作のためには、 $V_{DD}$ はPORサイクルが完了する以前に規定の動作範囲( $2.7\text{V} \sim 5.5\text{V}$ )に復帰する必要があります。

## アプリケーション情報

POR信号は、全ての内部レジスタをクリアします。POR信号を受けてLTC2470/LTC2472は変換サイクルを開始し、図2に示されている一連のステートに進みます。PORに続くリファレンスの起動時間は12msです( $C_{COMP} = C_{REFOUT} = 0.1\mu F$ )。パワーアップに続く最初の変換は、リファレンス電圧が完全にセトリングしていないので無効の可能性があります。パワーアップの直後の最初の変換は、データ破棄命令を使うか、または単に読んで無視することによって破棄することができます。選択した $C_{COMP}$ と $C_{REFOUT}$ の値に依存して、リファレンスの起動時間は1変換期間より長くなる場合があります(図3参照)。起動時間が1.2ms(出力レート833sps)または4.8ms(出力レート208sps)より短い場合、最初の期間の直後の変換はデバイスの規定値どおり正確です。起動時間が1.2msまたは4.8msを超える場合、必要な時間待機するか、セトリングしていない期間内の結果を無視することによって、固定した変換時間を起動タイマとして利用することができます。リファレンスが安定すると、それに続くすべての変換結果は有効です。デバイスをスリープ・モード(SLP = 1、リファレンス・パワーダウン)にしている場合、リファレンスは $C_{COMP}$ と $C_{REFOUT}$ の値(図3参照)に比例した起動時間を必要とします。

### 使いやすい仕様

LTC2470/LTC2472のデータ出力には、待ち時間、フィルタの安定遅延、または変換サイクルに関連した余分な結果はありません。変換と出力データの間には1対1対応の関係があります。したがって、複数のアナログ入力電圧の多重化に特別な処置は不要です。

LTC2470/LTC2472は従来のデルタシグマ・アーキテクチャと比べて、平均入力電流が数桁少ない独自の入力サンプリング手法を採用しています。これにより、外部フィルタ・ネットワークを直接LTC2470/LTC2472にインターフェースすることができます。平均入力サンプリング電流が50nAなので、1kΩと0.1μFを使った外部RCローパス・フィルタによる追加誤差は1LSB未満です。さらに、 $IN^+$ と $IN^-$ の間のリーク電流は無視できます(LTC2472に関して)。

### 入力電圧範囲(LTC2470)

オフセットおよびフルスケール誤差を無視すれば、LTC2470は理論的には入力がグランド(ゼロスケール入力)のとき「オールゼロ」のデジタルの結果を出力し、 $V_{REF}(V_{REFOUT} = 1.25V)$ 以上のとき「オール1」のデジタルの結果を出力します。アンダーレンジ状態(ゼロスケールより下のすべての入力電圧)では、コンバータは出力コード0を発生します。オーバーレンジ状態( $V_{REF}$ を超える全ての入力電圧)では、コンバータは出力コード65535を発生します。

### 入力電圧範囲(LTC2472)

「出力データのフォーマット」のセクションで詳細に述べられているように、出力コードは $32768 \cdot (V_{IN^+} - V_{IN^-}) / V_{REF} + 32768$ として与えられます。 $(V_{IN^+} - V_{IN^-}) \geq V_{REF}$ では、出力コードは65535(オール1)にクランプされます。 $(V_{IN^+} - V_{IN^-}) \leq -V_{REF}$ では、出力コードは0(オール0)にクランプされます。

### 出力データ・フォーマット

LTC2470/LTC2472は16ビットを直接バイナリ・エンコードした結果を発生します。それは、SCK入力ピンの制御のもとに、SDO出力ピンを通して、16ビットのシリアル・ストリームとして与えられます(図5参照)。

LTC2472(差動入力)の出力コードは $32768 \cdot (V_{IN^+} - V_{IN^-}) / V_{REF} + 32768$ によって与えられます。LTC2472からの最初のビット出力であるD15はMSBであり、これは $V_{IN^+} \geq V_{IN^-}$ では1、 $V_{IN^+} < V_{IN^-}$ では0です。 LSBがLTC2472から出力されるまで、このビットから順に下位ビット(D14, D13, ...)が続きます(表1参照)。

LTC2470(シングルエンド入力)の出力コードは、直接バイナリ・エンコードした結果です(表1参照)。

データ出力動作の間、 $\overline{CS}$ 入力ピンは“L”( $\overline{CS} = “L”$ )でなければなりません。データの出力プロセスは、 $\overline{CS}$ が“L”になり、変換結果の最上位ビットがSDO出力ピン(SDO = D15)に現れると開始されます。新しいデータ・ビットは、SCK入力ピンで検出される各立ち下がりエッジの後、SDO出力ピンに現れます。出力データは、SCKの立ち上がりエッジで確実にラッチされます。

# LTC2470/LTC2472

## アプリケーション情報

図5. データ入力/出力タイミング

表1. LTC2470/LTC2472出力データ・フォーマット

| シングルエンド入力<br>$V_{IN}$ (LTC2470) | 差動入力電圧<br>$V_{IN}^+ - V_{IN}^-$ (LTC2472) | D15<br>(MSB) | D14 | D13 | D12...D2 | D1 | D0<br>(LSB) | 対応する十進値 |

|---------------------------------|-------------------------------------------|--------------|-----|-----|----------|----|-------------|---------|

| $\geq V_{REF}$                  | $\geq V_{REF}$                            | 1            | 1   | 1   | 1        | 1  | 1           | 65535   |

| $V_{REF} - 1LSB$                | $V_{REF} - 1LSB$                          | 1            | 1   | 1   | 1        | 1  | 0           | 65534   |

| $0.75 \cdot V_{REF}$            | $0.5 \cdot V_{REF}$                       | 1            | 1   | 0   | 0        | 0  | 0           | 49152   |

| $0.75 \cdot V_{REF} - 1LSB$     | $0.5 \cdot V_{REF} - 1LSB$                | 1            | 0   | 1   | 1        | 1  | 1           | 49151   |

| $0.5 \cdot V_{REF}$             | 0                                         | 1            | 0   | 0   | 0        | 0  | 0           | 32768   |

| $0.5 \cdot V_{REF} - 1LSB$      | -1LSB                                     | 0            | 1   | 1   | 1        | 1  | 1           | 32767   |

| $0.25 \cdot V_{REF}$            | $-0.5 \cdot V_{REF}$                      | 0            | 1   | 0   | 0        | 0  | 0           | 16384   |

| $0.25 \cdot V_{REF} - 1LSB$     | $-0.5 \cdot V_{REF} - 1LSB$               | 0            | 0   | 1   | 1        | 1  | 1           | 16383   |

| 0                               | $\leq -V_{REF}$                           | 0            | 0   | 0   | 0        | 0  | 0           | 0       |

### データ入力フォーマット

データ入力ワードは4ビット長で、2つのイネーブル・ビット(EN1とEN2)および2つのプログラミング・ビット(SPDとSLP)で構成されています(表2参照)。EN1は変換完了後のSCKの最初の立ち上がりエッジで与えます。プログラミングはEN1 = 1およびEN2 = 0に設定することによりイネーブルされます。

### 表2. 入力データ・フォーマット

| ビット名 | 機能                                                                       |

|------|--------------------------------------------------------------------------|

| EN   | プログラム・モードをイネーブルするには“H”(EN1 = 1)                                          |

| EN2  | プログラム・モードをイネーブルするには“L”(EN2 = 0)                                          |

| SPD  | 出力レートは“L”(SPD = 0、デフォルト)で208sps、“H”(SPD = 1)で833sps                      |

| SLP  | “L”(SLP = 0、デフォルト)でナップ・モード、“H”(SLP = 1)でリファレンスとコンバータの両方がパワーダウンするスリープ・モード |

\*SDIは、出力レートを208spsに設定するためにGNDに直接接続、または出力レートを833spsに設定するために $V_{DD}$ に直接接続してもよい。SDIをGNDか $V_{DD}$ に接続すると、スリープ・モードはディスエーブルされる。

## アプリケーション情報

スピード・ビット(SPD)は出力レートを決定し、SPD=0(デフォルト)で208sps、SPD=1で833spsの出力レートです。内蔵リファレンスをパワーダウンするにはスリープ・ビット(SLP)を使います。デフォルト・モードでは、各変換サイクルの終了時にADCが自動的にパワーダウンしても、リファレンスはパワーアップしたままであります。SLPビットが“H”に設定された場合、次の変換サイクルが完了すれば、リファレンスとADCはパワーダウンします。 $\overline{CS}$ を“L”にすれば、リファレンスとADCは再びパワーアップします。リファレンスが起動する前に次の変換が開始されると、続く変換は無効です(補償コンデンサとリファレンス・コンデンサの関数である、リファレンス起動時間に関しては図3を参照)。

スリープ・モードが不要な場合は、ユーザ・インターフェースをシンプルにするためにSPDをGNDまたはV<sub>DD</sub>に接続することができます。SDIをGNDに接続すると出力レートは208spsに設定され、SDIをV<sub>DD</sub>に接続すると出力レートは833spsに設定されることに注意してください。

## シリアル・インターフェース

LTC2470/LTC2472は2線、3線または4線の同期式インターフェースを介して、変換結果を送信し、変換開始コマンドを受信します。このインターフェースを使って、データ出力ステートの間に変換結果を読み出し、スリープとスピード・モードをプログラミし、新しい変換をトリガすることができます。

### シリアル・インターフェース動作モード

動作モードは以下のようにまとめることができます。

- 1) LTC2470/LTC2472はSCKを“H”にアイドリングさせるか(一般にCPOL = 1として知られている)、または“L”にアイドリングさせた(一般にCPOL = 0として知られている)状態で機能します。

- 2) 16番目のビットが読み出された後、 $\overline{CS}$ を“H”、またはSCKを“L”にすると、新しい変換が開始されます。

- 3) データ出力ステートの間のどんなタイミングでも $\overline{CS}$ を“H”にすると、デバイスはI/Oステートから抜け出して出力を中止し、新しい変換を開始します。

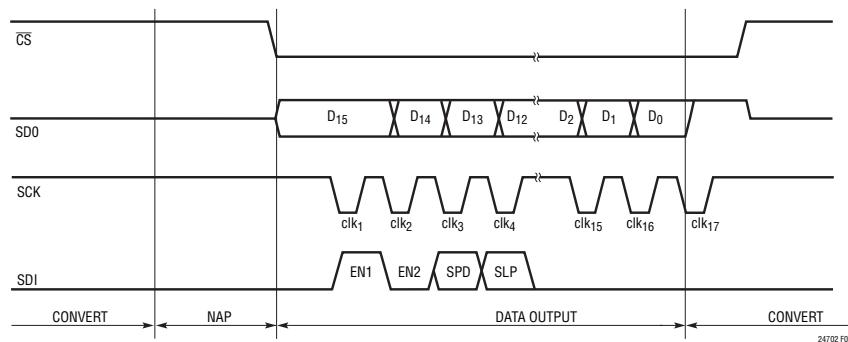

### シリアル・クロックがアイドリング“H”(CPOL = 1)の例

図6では、LTC2470/LTC2472は変換サイクルに続いて、自動的にADCがパワーダウンしたナップ・モードに入ります。ADCのリファレンスは、完了したばかりの変換の前にSLPビットが“H”にセットされていて、 $\overline{CS}$ が“H”であればパワーダウンします。 $\overline{CS}$ を“L”にすると、リファレンスとADCの両方がパワーアップします。

変換が完了すると、16クロック・サイクルを与えて結果を転送します。そして $\overline{CS}$ の立ち上がりエッジを使って新しい変換を開始します。

図7の動作例は、新しい変換サイクルがシリアル・クロック(SCK)の立ち下がりエッジでトリガされること以外は図6と同じです。

図6. アイドリング“H”(CPOL = 1)シリアル・クロック動作の例。

$\overline{CS}$ の立ち上がりエッジにより変換が開始される

## アプリケーション情報

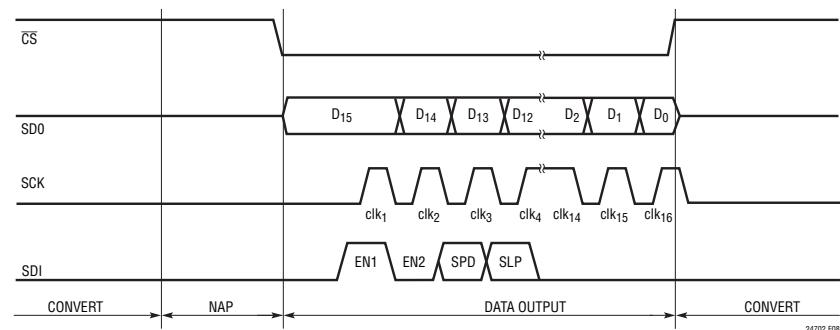

### “L”でアイドリングするシリアル・クロックの例(CPOL = 0)

図8では、LTC2470/LTC2472は各変換サイクルに続いて自動的にナップ状態になります。完了したばかりの変換の前にSLPビットが“H”にセットされていて、 $\overline{CS}$ が“H”であれば、デバイスのリファレンスはパワーダウンします。 $\overline{CS}$ を“L”にするとリファレンスはパワーアップします。外部タイミングに基づいて、データを利用できるかどうか(および変換の終了)を判断します。そして $\overline{CS}$ を“L”にして( $\overline{CS} = \downarrow$ )、16クロック・サイクルを使って結果を転送します。クロックの16番目の立ち上がりエッジの直後に $\overline{CS}$ を“H”にすると( $\overline{CS} = \uparrow$ )新しい変換がトリガれます。

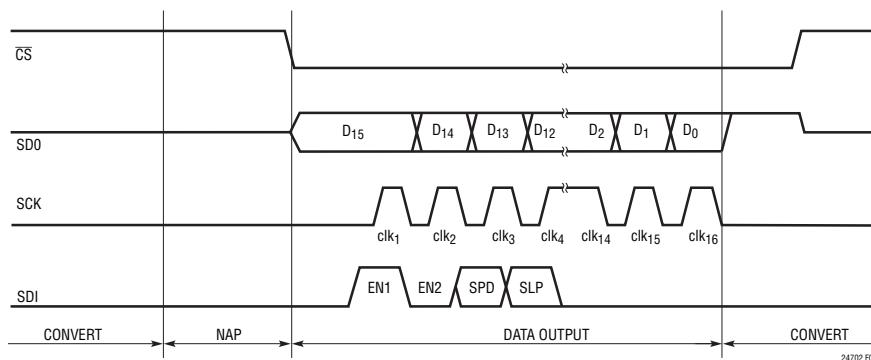

図9のタイミング図は、この場合SCKによって新しい変換がトリガされること以外は、図8と同じです。SCKの16番目の立ち下がりエッジが新しい変換サイクルをトリガし、続いて $\overline{CS}$ 信号を“H”にします。

### $\overline{CS}$ を使ったサイクル中止の例

アプリケーションによっては、I/Oサイクルを中止して新たに変換を開始したいことがあります。LTC2470/LTC2472がデータ入力/出力ステートの場合、 $\overline{CS}$ の立ち上がりエッジが、残りの

データ・ビットをレジスタから消去し、出力サイクルを中止し新しい変換をトリガします。アイドリング“H”(CPOL = 1)の状態でI/Oを中止する例を図10に示し、アイドリング“L”(CPOL = 0)の状態でI/Oを中止する例を図11に示します。

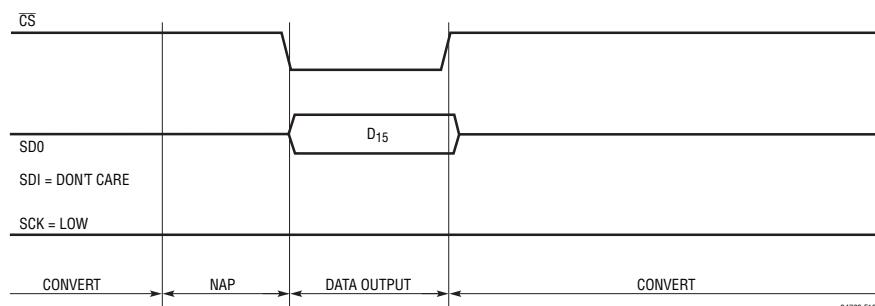

図12に示されているように、全くシリアル・クロック・パルスを発生させることなしに、 $\overline{CS}$ 信号を使って新しい変換サイクルをトリガすることができます。変換サイクル終了後、SCKを“L”ロジック・レベルに維持した場合、 $\overline{CS}$ を“L”にしてから続いて“H”にすることにより、新しい変換をトリガすることができます。 $\overline{CS}$ を“L”にすると( $\overline{CS} = “L”$ )、SDOは完了したばかりの変換結果の符号(D15)を出力します。SCKピンがロジック・レベル“L”的状態で、続いて $\overline{CS}$ を“H”にすると( $\overline{CS} = “H”$ )、結果の残り15ビット(D14～D0)が破棄され、新しい変換サイクルが開始されます。

I/Oを中止した後、変換ステートで追加のクロック・パルスを与えてもかまいませんが、SCKの過度な信号遷移は変換の間にADCにノイズを発生させる可能性があり、それが変換精度に悪影響を与えることがあります。

図7. アイドリング“H”(CPOL = 1)クロック動作の例。

新しい変換サイクルをトリガするには17番目のクロック・パルスを使う

図8. アイドリング“L”(CPOL = 0)クロック。 $\overline{CS}$ が新しい変換をトリガする

24702fb

## アプリケーション情報

図9. アイドリング“L”(CPOL = 0)クロック。SCKの16番目の立ち下がりエッジが新しい変換をトリガする

図10. アイドリング“H”(CPOL = 1)クロックおよび中止されたI/Oの例

図11. アイドリング“L”(CPOL = 0)クロックおよび中止されたI/Oの例

図12. アイドリング“L”(CPOL = 0)クロックおよび最小データ出力長の例

24702fb

## アプリケーション情報

### 2線式動作

2線式動作モードでは必要な制御信号の数が減りますが、LTC2470/LTC2472の低消費電力スリープ機能を必要としない場合にのみ使います。さらに、シリアル・データ転送を中止するオプションも利用できません。2線式動作では $\overline{CS}$ をGNDに配線します。出力レートはSDIを“L”にすると208sps、SDIを“H”にすると833spsになります。

アイドリング“H”(CPOL = 1)のシリアル・クロック信号を使う2線式動作のシーケンスを図13に示します。変換サイクルに続いて、ADCはデータ出力ステートに入り、SDO出力は“H”から“L”に遷移します。続いて、16ビットの結果をシリアルにシフトするため、16クロック・パルスがSCKに入力に与えられます。最後に、新しい変換サイクルをトリガるために17番目のパルスがSCK入力に与えられます。

アイドリング“L”(CPOL = 0)のシリアル・クロック信号を使う2線式動作のシーケンスを図14に示します。変換サイクルに続いて、LTC2470/LTC2472はデータ出力状態になります。この時点でのSDOピンは変換結果の符号(D15)を出力します。変換終了と結果の有効性を判断するのに外部タイミングを使

わなければなりません。続いて、16ビットの結果をシリアルにシフトするため、16クロック・パルスがSCKに与えられます。クロックの16番目の立ち下がりエッジが新しい変換をトリガします。出力レートはSDIを“L”にすると208sps、SDIを“H”にすると833spsになります。

### コンバータ精度の維持

LTC2470/LTC2472は、デバイスのデカップリング、PCBレイアウト、アンチエイリアシング回路、ラインや周波数の乱れなどによる変換結果への影響が最小になるように設計されています。それでもなお、このデバイスの高精度な能力を維持するには、いくつかのシンプルな予防策をとることが望まれます。

### デジタル信号レベル

CMOSロジックの性質により、入力デジタル信号をGNDまたはV<sub>CC</sub>の近くに保つことを推奨します。0.5V～(V<sub>CC</sub>-0.5V)の範囲の電圧は、デバイスからの電流リークを増大させます。アンダーシュートやオーバーシュートも、特にデバイスが変換を行っているとき、最小に抑える必要があります。したがって、エッジレートを約10nsに保ち、オーバーシュートとアンダーシュートを0.3V以下に制限するのが効果的です。

図13. 2線式、アイドリング“H”(CPOL = 1)シリアル・クロック動作の例

図14. 2線式、アイドリング“L”(CPOL = 0)シリアル・クロック動作の例

24702fb

## アプリケーション情報

ノイズが多い外部回路は、2線式動作では潜在的に出力に影響を与えます。特に、SCKパルスが失われたりノイズが余計なSCKパルスをトリガすると、LTC2470/LTC2472が未知の状態に陥る可能性があります。この状況では、 $SDO = 1$ （変換中を示す）と有効な「1」のデータ・ビットを区別することは不可能です。こういった状況を防ぐ方法は、各サイクルで16ビットではなく32ビットを読み込み、終わりの16データ・ビットを無視します。ノイズの多いバスでSCKクロック数が規定数から外れる場合、付加的な16 SCKクロック・パルスは新しい変換を強制し、デバイスを既知の状態にします。

### $V_{CC}$ とGNDのドライブ

$V_{CC}$ ピンとGNDピンに対して、LTC2470/LTC2472は内部の高周波デカップリングを減衰素子と組み合わせて、PCBレイアウトや外部部品がADCの性能に与える影響を少なくしています。それでもなお、このコンバータの非常に高い精度を最良に維持するためには、電源の低周波および高周波の注意深いデカップリングが必要です。

10μFの低ESRセラミック・コンデンサと並列にした高品質の0.1μFセラミック・コンデンサを、できるだけパッケージに近づけて、 $V_{CC}$ ピンとGNDピンの間に接続します。0.1μFのコンデンサをADCのパッケージに最も近く配置します。また、コンバータの $V_{CC}$ ピンから始まり、これら2個のデカップリング・コンデンサを通り、コンバータのGNDピンに戻ってくる経路にはビアの使用を極力避けてください。この経路によって囲まれる面積と経路長を最小にします。

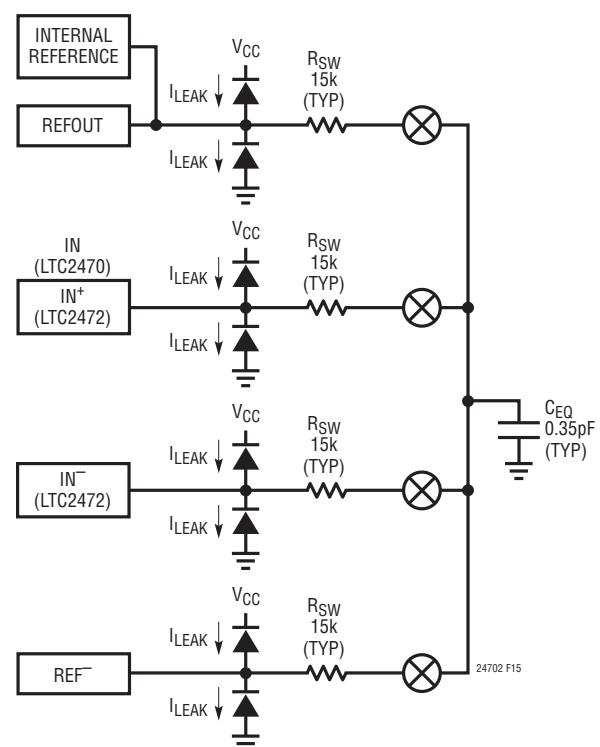

図15に示されているように、 $REF^-$ はADCへの負リファレンス電圧入力として使われています。このピンは直接グランドに接続するか、センサのグランドにケルビン接続することができます。 $REF^-$ がセンサ入力として使われる場合、10μFの低ESRセラミック・コンデンサと並列に0.1μFのセラミック・コンデンサでグランドにバイパスします。

インピーダンスが非常に低いグランドと電力プレーン、および $V_{CC}$ ピンとGNDピンの両方での星形結線が望ましいグランド接続です。 $V_{CC}$ ピンは2つの異なる接続をもちます。一方は前述したデカップリング・コンデンサに接続し、他方は電源電圧源のグランド・リターンに接続します。

### REFOUTとCOMP

内蔵1.25Vリファレンスは内部でコンバータのリファレンス入力に接続されており、REFOUTピンに出力されます。0.1μFのコンデンサをREFOUTピンに接続する必要があります。このコンデンサをもっと小さくすることはできますが、遷移ノイズが増加します（図4参照）。0.1μFのコンデンサをCOMPピンにも接続する必要があります。このピンはリファレンスの内部ポイントに接続されており、安定性を高めるために使われます。

図15. LTC2470/LTC2472のアナログ入力/リファレンスの等価回路

## アプリケーション情報

リファレンスを安定状態に保つため、COMPピンに接続されるコンデンサはREFOUTピンに接続されるコンデンサと等しいか、それより大きくしなければなりません。REFOUTピンに外部電圧を強制することはできません。

内部リファレンスの起動時間はREFOUTピンとCOMPピンに接続されるコンデンサの大きさに依存します。0.1 $\mu$ Fのコンデンサが使われるとき、この起動時間は標準で12msです。パワーアップに続く最初の変換は、データ中止命令を使うか、単純に読み出し、無視して破棄します。選択したC<sub>COMP</sub>とC<sub>REFOUT</sub>の値によっては、リファレンスの起動に1変換期間以上かかることがあります(図3を参照)。起動時間が1.2ms(出力レート833sps)または4.8ms(出力レート208sps)以下の場合、最初の期間に続く変換は正確にデバイスの仕様を満たします。起動時間が1.2msまたは4.8msを超える場合は、必要な時間待機するか、セトリングしていない期間内の結果を無視することによって、固定した変換期間を起動タイマとして使うことができます。リファレンスがセトリングすると、すべてのそれに続く変換結果は有効です。デバイスをスリープ・モード(SLP=1、リファレンスはパワーダウン)についていた場合、リファレンスはC<sub>COMP</sub>とC<sub>REFOUT</sub>の値に比例した起動時間を必要とします(図3を参照)。

リファレンスをスリープ状態(SLP = 1および $\overline{CS}$  = 1にプログラム)にすると、リファレンスは次の変換の後にパワーダウンします。この直前の変換結果は有効です。 $\overline{CS}$ の立ち下がりエッジで、リファレンスは再度パワーアップします。次の変換の前にリファレンス出力を確実にセトリングさせるために、 $\overline{CS}$ の立ち下がりエッジの後データの読み出しを遅らせることにより、パワーアップ時間を延ばすことができます。デバイスから16ビットが全て読み出されるか、 $\overline{CS}$ を”H”にすると、次の変換が自動的に開始されます。デフォルト動作では、変換サイクルの終了時にリファレンスはパワーアップしたままでです。

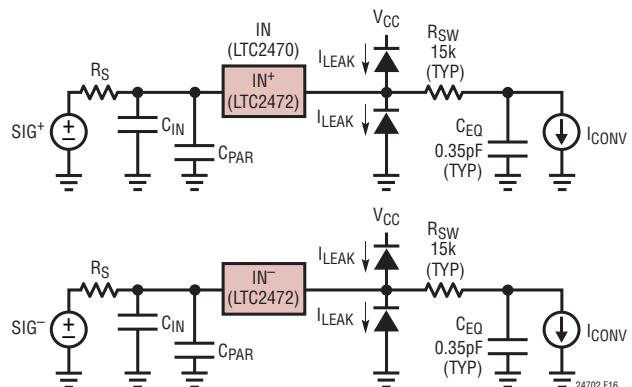

### $V_{IN^+}$ と $V_{IN^-}$ のドライブ

入力ドライブの要件は、図16の等価回路を使うと適確に分析を行うことができます。入力信号 $V_{SIG}$ は等価ソース抵抗 $R_S$ を通してADCの入力ピン( $IN^+$ および $IN^-$ )に接続されます。この抵抗には実際のジェネレータのソース抵抗と、入力ピンに接続されたすべての追加のオプション抵抗の両方が含まれます。オプションの入力コンデンサ $C_{IN}$ もADCの入力ピンに接続

されます。このコンデンサは入力寄生容量 $C_{PAR}$ に並列に配置されています。この寄生容量はPCBとADCの入力ピンに関連した成分を含みます。PCBのレイアウトに依存して、 $C_{PAR}$ の標準的値は2pF～15pFになります。さらに、図16の等価回路には、コンバータの等価内部抵抗 $R_{SW}$ とサンプリング・コンデンサ $C_{EQ}$ が含まれています。

図16. LTC2470/LTC2472の入力ドライブの等価回路

完全な回路解析をしなくとも、 $R_S$ と $C_{IN}$ には明らかにいくつかのトレードオフがあります。 $R_S$ と $C_{IN}$ を大きくすると以下の利点が得られます。

- 1) LTC2470/LTC2472の入力サンプリング・アルゴリズムにより、変換サイクルの間 $IN^+$ または $IN^-$ に流れる入力電流は標準で50nAです。 $R_S \cdot C_{IN}$ の値が大きいと入力電流の高周波成分が減衰し、1kΩまでの $R_S$ 値では1LSB未満の誤差になります。

- 2)  $V_{SIG}$ の帯域幅が入力ピン( $IN^+$ 、 $IN^-$ または $IN$ )で減少します。この帯域幅の減少によりADCが高周波信号から絶縁され、簡単なアンチエイリアス効果が得られ、入力ノイズが減少します。

- 3) ADCによって生じるスイッチング過渡は、信号源に戻る前に減衰します。

## アプリケーション情報

- 4) 大きな  $C_{IN}$  は入力ピンに良好な AC グランドを与え、信号源への反射を減らす手助けをします。

- 5)  $R_S$  を大きくすると、電源レール範囲を外れるフォールト状態の間電流が制限され、ADC が保護されます。

特定のアプリケーションで  $R_S \cdot C_{IN}$  をどのくらい大きくできるかには限界があります。所定のポイントを超えて  $R_S$  を増加させると、重大な測定誤差が生じるポイントまで入力電流による  $R_S$  両端の電圧降下が増加します。さらに、アプリケーションによっては、 $R_S \cdot C_{IN}$  の積を大きくしすぎると、目的の周波数で許容できないほど信号が減衰する可能性があります。

ほとんどのアプリケーションでは、 $C_{IN}$  は高品質の  $0.1\mu F$  セラミック・コンデンサ、 $R_S$  は  $1k$  以下の設定が望まれます。このコンデンサは実際のパッケージの  $IN^+$ 、 $IN^-$ 、 $IN$  ピンにできるだけ近づけます。さらに、この回路経路によって囲まれる領域と経路長を最小にします。

リモート地点で接地されていない 2 線式センサの場合、 $R_S$  を分割して、星形結線トポロジーを使って ADC の GND に接続するセンサのグランド・リターンとともに、ADC の入力ラインに直列抵抗を配置することが望れます。

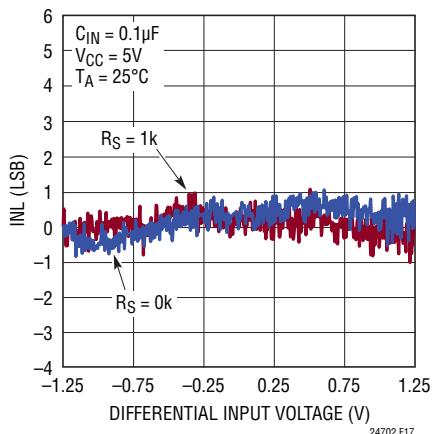

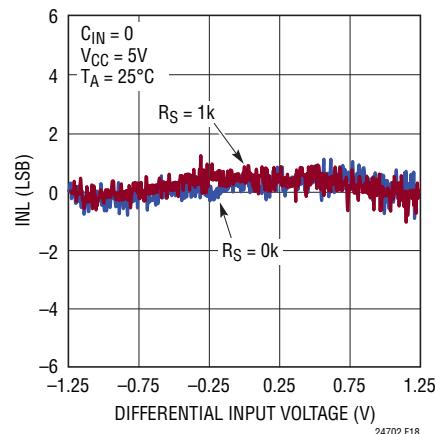

図17は、入力コンデンサ  $C_{IN}$  が  $0.1\mu F$  のときの  $R_S$  値の関数としての、LTC2472 の「INL の測定値と入力電圧」を示しています。

場合によっては、 $R_S$  をこれらのガイドラインより大きくすることができます。ADC がスリープ・モードまたは I/O モードのどちらかのとき入力電流はゼロです。したがって、入力 RC 回路の時定数  $\tau = R_S \cdot C_{IN}$  が実際の変換の間の時間と同程度か、またはそれより長い場合は、入力電流がそれに応じて減少する考えることができます。

これらの検討事項は入力信号の帯域幅とバランスをとる必要があります。 $3dB$  帯域幅は約  $1/(2\pi R_S C_{IN})$  です。

最後に、 $C_{IN}$  の推奨値が特定のアプリケーションで許容できない場合、代わりの方策として、 $C_{IN}$  を取り去って  $C_{PAR}$  と  $R_S$  を最小にします。実際には、この構成は最短トレースで直接 ADC に

接続された低インピーダンスのセンサに相当します。実際のアプリケーションとして、小さな値のセンス抵抗を使った電流測定、温度測定、低インピーダンス電圧源モニタなどがあります。図18は、その結果得られる「INL と  $V_{IN}$ 」です。図18の測定には、最小にしたレイアウト・パッドと長さが約 1 インチの最小幅入力トレースに相当するコンデンサ  $C_{PAR}$  を含みます。

### 信号帯域幅、遷移ノイズおよびノイズ等価入力帯域幅

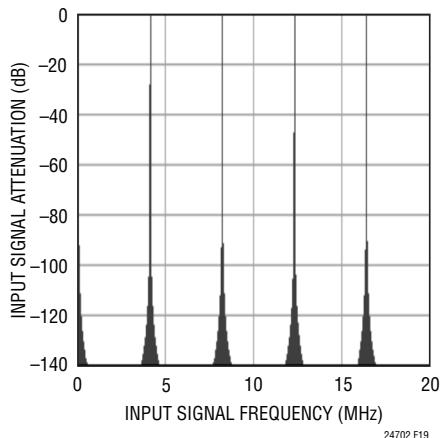

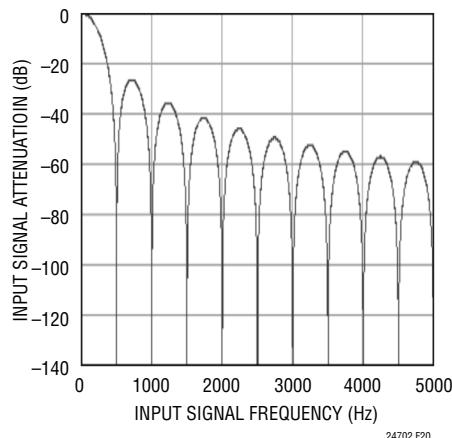

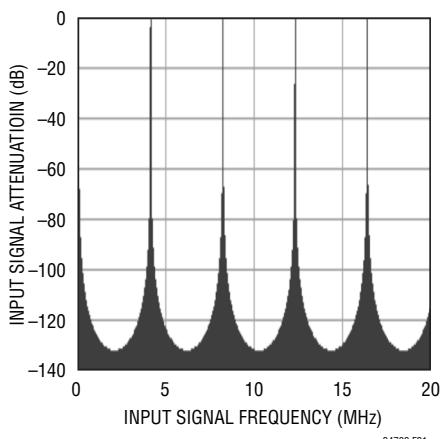

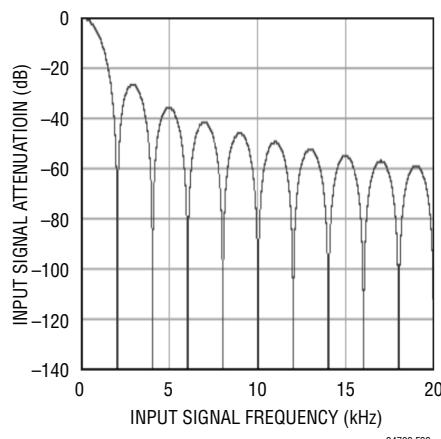

LTC2470/LTC2472 は sinc<sup>2</sup> タイプのデジタル・フィルタを備えています。208sps の出力レートが選択されている場合、第 1 ノッチは 416kHz で、833sps の出力レートでは 1666Hz です。広い周波数範囲にわたる「計算上の入力信号減衰と周波数」を図19に示します。低い周波数での「計算上の入力信号減衰と周波数」を図20に示します。コンバータのノイズ・レベルは約  $3\mu V_{RMS}$  で、ノイズの無いコンバータの入力に接続されたホワイトノイズ源によってモデル化することができます。

関連する注記として、LTC2472 は 2 つの別個の A/D コンバータを使って正入力と負入力をデジタル化します。これらの A/D コンバータのそれぞれの遷移ノイズは  $3\mu V_{RMS}$  です。一方の入力電圧がこの小さな遷移ノイズ変動幅以内だと、他方の入力電圧の値には関係なく、出力は 1 ビット変動します。両方の入力電圧がそれらの遷移ノイズ変動幅以内だと、出力が 2 ビット変動することができます。

システム・ノイズのシンプルな解析のために、 $V_{IN}$  ドライブ回路を、ポールの位置  $f_i$  とノイズ・スペクトラム密度  $n_i$  によって特徴づけられる単一ポール等価回路としてモデル化することができます。もしコンバータが無限の帯域幅または少なくとも  $f_i$  より十分に大きな帯域幅をもっていれば、外部ドライブ回路の合計ノイズの寄与は以下のようになります。

$$V_n = n_i \sqrt{\pi / 2 \cdot f_i}$$

その結果、システムの合計ノイズ・レベルは、 $(V_n^2)$  と LTC2470/LTC2472 のノイズフロアの 2 乗の和の平方根として見積もることができます。

# LTC2470/LTC2472

## アプリケーション情報

図17. 測定されたINLと入力電圧

図18. 測定されたINLと入力電圧

図19. LTC2472の入力信号の減衰と周波数

(208spsモード)

図20. LTC2472の入力信号の減衰と周波数

(208spsモード)

図21. LTC2472の入力信号の減衰と周波数

(833spsモード)

図22. LTC2472の入力信号の減衰と周波数

(833spsモード)

24702fb

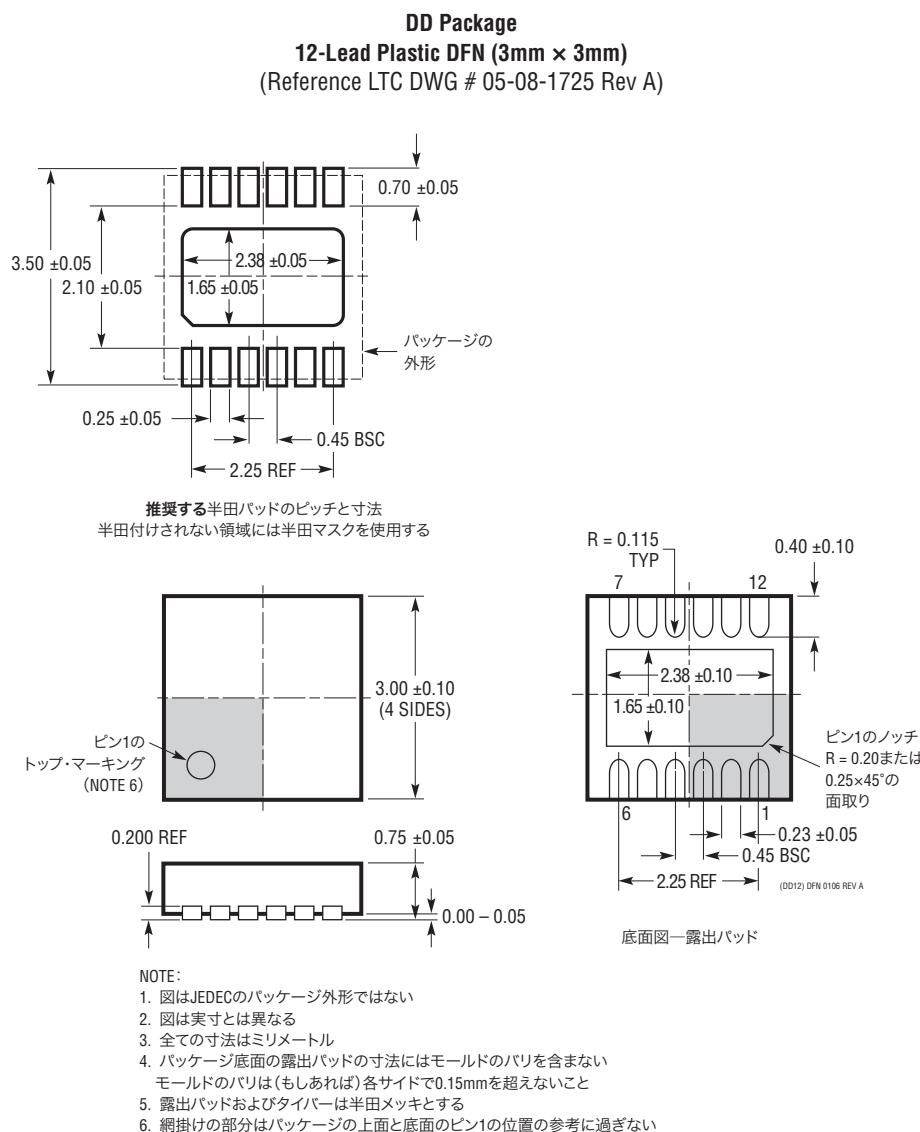

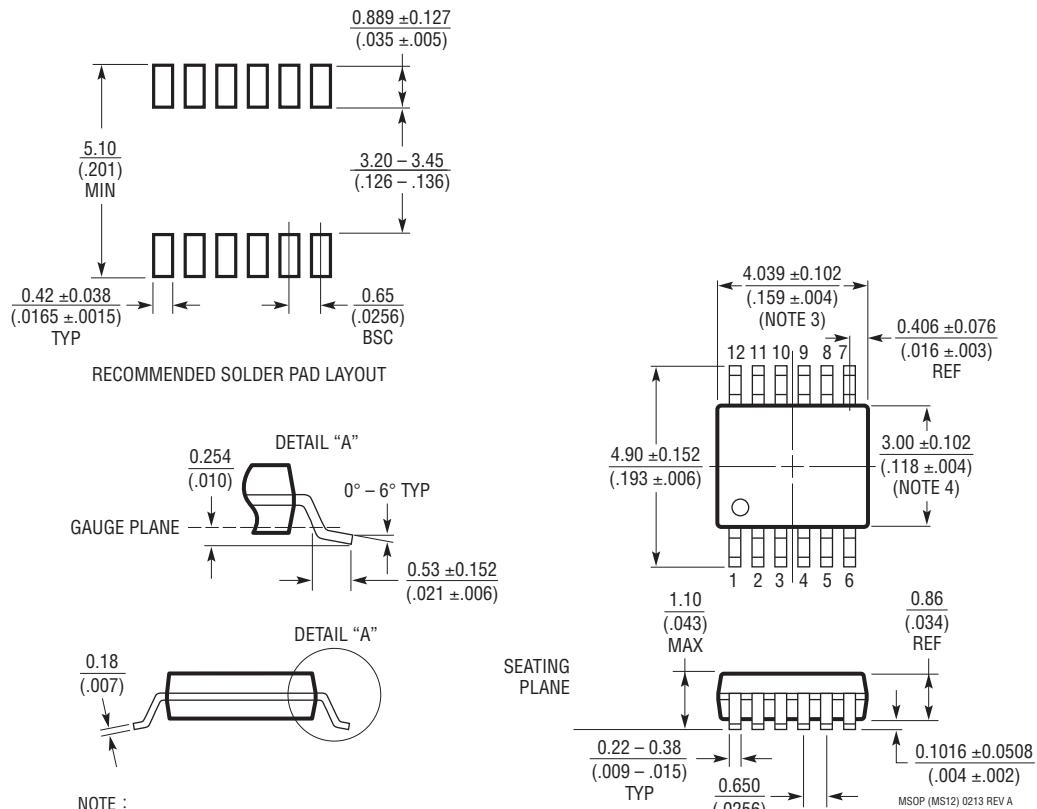

## パッケージ

最新のパッケージ図面については、<http://www.linear-tech.co.jp/designtools/packaging>をご覧ください。

# LTC2470/LTC2472

## パッケージ

最新のパッケージ図面については、<http://www.linear-tech.co.jp/designtools/packaging/>をご覧ください。

**MS Package

12-Lead Plastic MSOP**

(Reference LTC DWG # 05-08-1668 Rev A)

## 改訂履歴

| REV | 日付   | 概要                           | ページ番号 |

|-----|------|------------------------------|-------|

| A   | 9/13 | 最大動作出力レートを208sps/833spsに明確化。 | 全ページ  |

| B   | 1/14 | 「欠落コードなし」を削除。                | 1、3   |

24702fb

リニアテクノロジー・コーポレーションがここで提供する情報は正確かつ信頼できるものと考えておりますが、その使用に関する責務は一切負いません。また、ここに記載された回路結線と既存特許とのいかなる関連についても一切関知いたしません。なお、日本語の資料はあくまでも参考資料です。訂正、変更、改版に追従していない場合があります。最終的な確認は必ず最新の英語版データシートでお願いいたします。

21

# LTC2470/LTC2472

## 標準的応用例

24702 TA02

## 関連製品

| 製品番号              | 説明                                                        | 注釈                                                                      |

|-------------------|-----------------------------------------------------------|-------------------------------------------------------------------------|

| LTC1860/LTC1861   | 12ビット、5V、1ch/2ch 250ksps SAR ADC、MSOP                     | 250kspsで850µA、1kspsで2µA、SO-8およびMSOPパッケージ                                |

| LTC1860L/LTC1861L | 12ビット、3V、1ch/2ch、150ksps SAR ADC                          | 150kspsで450µA、1kspsで10µA、SO-8およびMSOPパッケージ                               |

| LTC1864/LTC1865   | 16ビット、5V、1ch/2ch 250ksps SAR ADC、MSOP                     | 250kspsで850µA、1kspsで2µA、SO-8およびMSOPパッケージ                                |

| LTC1864L/LTC1865L | 16ビット、3V、1ch/2chチャネル、150ksps SAR ADC                      | 150kspsで450µA、1kspsで10µA、SO-8およびMSOPパッケージ                               |

| LTC2360           | 12ビット、100ksps SAR ADC                                     | 3V電源、100kspsで1.5mW、TSOT 6ピン/8ピン・パッケージ                                   |

| LTC2440           | 24ビット、No Latency ΔΣ™ ADC                                  | 200nVRMSノイズ、出力レート:4kHz、15ppm INL                                        |

| LTC2480           | 16ビット、差動入力、No Latency ΔΣ ADC、PGA、温度センサ、SPI付き              | Easy Drive入力電流キャンセル、600nVRMSノイズ、小型10ピンDFNパッケージ                          |

| LTC2481           | 16ビット、差動入力、No Latency ΔΣ ADC、PGA、温度センサ、I <sup>2</sup> C付き | Easy Drive入力電流キャンセル、600nVRMSノイズ、小型10ピンDFNパッケージ                          |

| LTC2482           | 16ビット、差動入力、No Latency ΔΣ ADC、SPI                          | Easy Drive入力電流キャンセル、600nVRMSノイズ、小型10ピンDFNパッケージ                          |

| LTC2483           | 16ビット、差動入力、No Latency ΔΣ ADC、I <sup>2</sup> C             | Easy Drive入力電流キャンセル、600nVRMSノイズ、小型10ピンDFNパッケージ                          |

| LTC2484           | 24ビット、差動入力、No Latency ΔΣ ADC、SPI、温度センサ付き                  | Easy Drive入力電流キャンセル、600nVRMSノイズ、小型10ピンDFNパッケージ                          |

| LTC2485           | 24ビット、差動入力、No Latency ΔΣ ADC、I <sup>2</sup> C、温度センサ付き     | Easy Drive入力電流キャンセル、600nVRMSノイズ、小型10ピンDFNパッケージ                          |

| LTC6241           | デュアル、18MHz、低ノイズ、レール・トゥ・レール・オペアンプ                          | 550nVP-Pノイズ、オフセット:最大125µV                                               |

| LTC2450           | 使いやすい、超小型16ビットADC、SPI、0V~5.5Vの入力範囲                        | INL:2LSB、スリーブ電流:50nA、小型2mm×2mm DFN-6パッケージ、出力レート:30Hz                    |

| LTC2450-1         | 使いやすい、超小型16ビットADC、SPI、0V~5.5Vの入力範囲                        | INL:2LSB、スリーブ電流:50nA、小型2mm×2mm DFN-6パッケージ、出力レート:60Hz                    |

| LTC2451           | 使いやすい、超小型16ビットADC、I <sup>2</sup> C、0V~5.5Vの入力範囲           | INL:2LSB、スリーブ電流:50nA、小型3mm×2mm DFN-8またはTSOTパッケージ、プログラム可能な30Hz/60Hz出力レート |

| LTC2452           | 使いやすい、超小型16ビット差動ADC、SPI、±5.5Vの入力範囲                        | INL:2LSB、スリーブ電流:50nA、小型3mm×2mm DFN-8またはTSOTパッケージ                        |

| LTC2453           | 使いやすい、超小型16ビット差動ADC、I <sup>2</sup> C、±5.5Vの入力範囲           | INL:2LSB、スリーブ電流:50nA、小型3mm×2mm DFN-8またはTSOTパッケージ                        |

| LTC2460           | 超小型16ビット、ΔΣ ADC、10ppmリファレンス                               | LTC2470とピン&ソフトウェア互換、出力レート60Hz                                           |

| LTC2462           | 超小型16ビット、ΔΣ ADC、10ppmリファレンス                               | LTC2472とピン&ソフトウェア互換、出力レート60Hz                                           |

24702fb