## 特長

- $\pm V_{CC}$ の差動入力範囲

- (符号を含む)16ビット分解能、ミッシングコードなし

- オフセット誤差:2LSB

- フルスケール誤差:4LSB

- 1秒あたり変換回数:60回

- 多重化アプリケーションに対応する

单一変換セッティング時間

- 自動シャットダウン付き1サイクル動作

- 消費電流:800μA

- スリープ電流:0.2μA

- 内部発振器 - 外付け部品不要

- 2線I<sup>2</sup>Cインターフェース

- 超小型8ピン3mm×2mm DFNおよびTSOT23/パッケージ

## アプリケーション

- システム・モニタ

- 環境モニタ

- 直接温度測定

- 計測

- 産業用プロセス制御

- データ収集

- 組み込みADCのアップグレード

、LT、LTC、LTM、Linear Technology およびLinearのロゴはリニアテクノロジー社の登録商標です。No Latency ΔΣはリニアテクノロジー社の商標です。その他すべての商標の所有権は、それぞれの所有者に帰属します。6208279、6411242、7088280、7164378を含む米国特許によって保護されています。

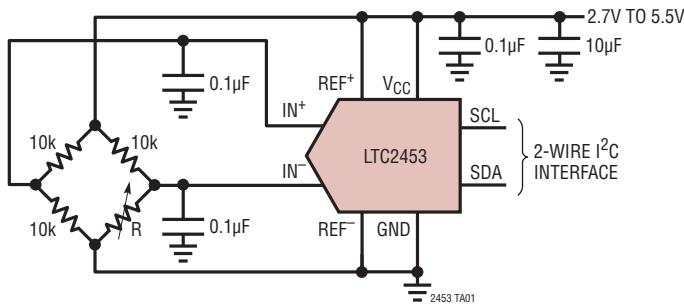

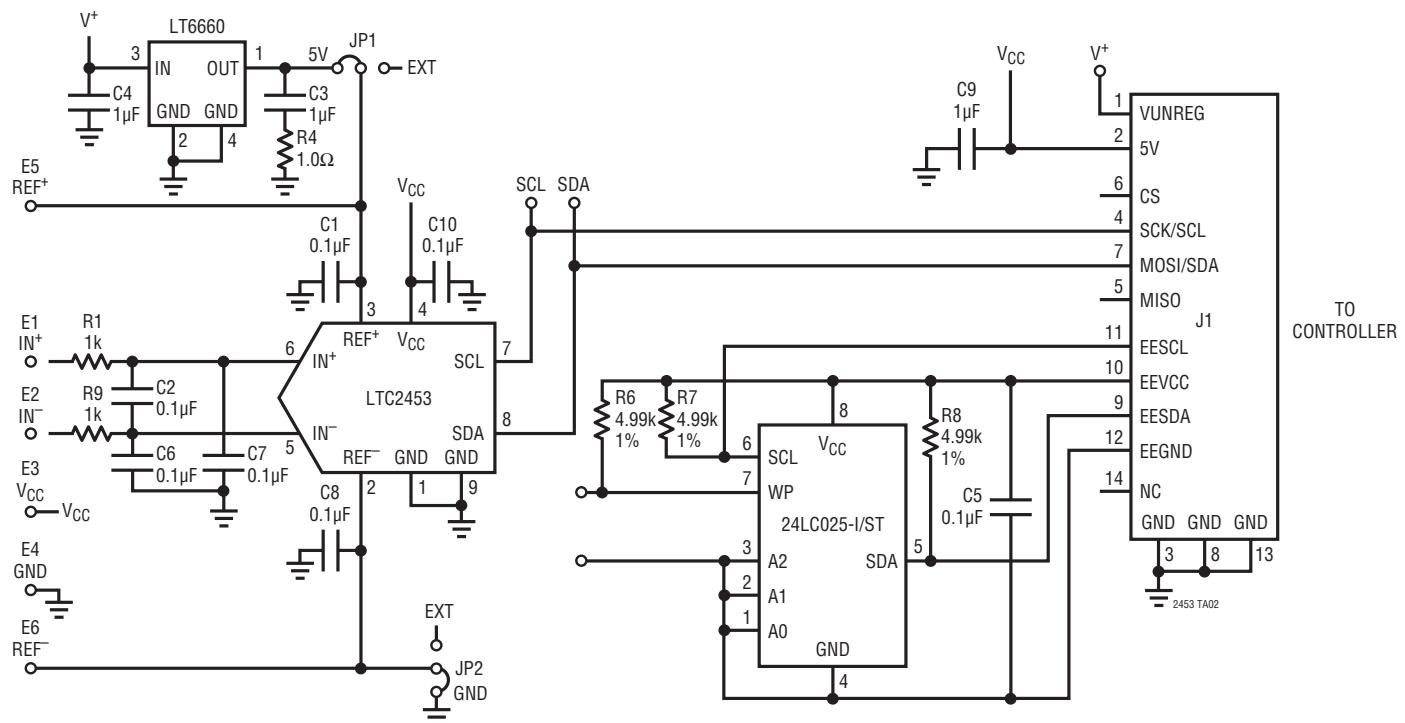

## 標準的応用例

## 概要

LTC<sup>®</sup>2453は超小型の完全差動16ビット・アナログデジタル・コンバータです。LTC2453は2.7V～5.5V単一電源を使用し、I<sup>2</sup>Cインターフェースを介して通信します。このADCは、8ピン3mm×2mm DFNパッケージと8ピン3mm×3mm TSOTパッケージで供給されます。このデバイスは外付け部品を必要としない発振器を内蔵しています。コンバータ・コアとしてデルタシグマ変調器を使用し、待ち時間がないので、多重化アプリケーションに対応できます。LTC2453は、従来のデルタシグマ・コンバータと比べて平均入力サンプリング電流が数桁少ない独自の入力サンプリング手法を採用しています。また、このアキテクチャにより、入力ピン間の電流リークは無視できるほどわずかです。

LTC2453は1秒当たり60回の変換でサンプリング可能で、この非常に大きなオーバーサンプリング率により、アンチエイリアシングの要件が大幅に緩和されています。LTC2453は、ユーザからは見えない内部のオフセットとフルスケールの連続較正アルゴリズムを採用しているので、時間の経過および動作温度範囲において高精度が保証されます。このコンバータはREF<sup>+</sup>およびREF<sup>-</sup>の外部ピンを備えており、差動入力電圧範囲は $\pm(V_{REF}^+ - V_{REF}^-)$ です。

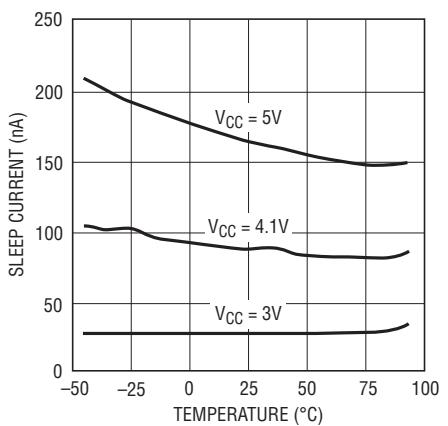

1回の変換の後、LTC2453は自動的にスリープモードになり、消費電流が0.2μA未満に減少します。ユーザが毎秒1回ADCを読み出す場合、LTC2453が2.7Vの電源から消費するのは平均50μW以下です。

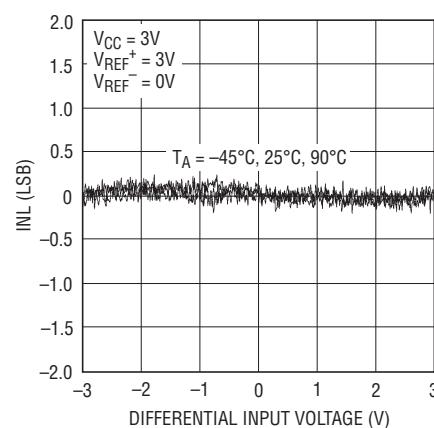

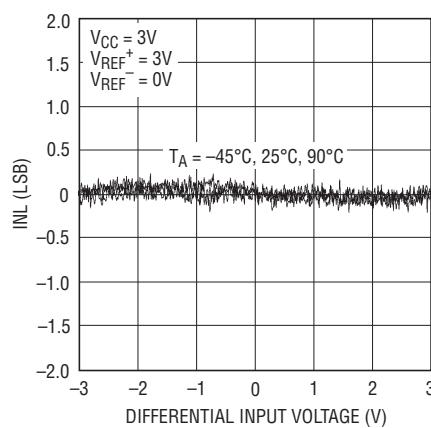

積分非直線性 ( $V_{CC} = 3V$ )

# LTC2453

## 絶対最大定格

(Notes 1,2)

|                                    |                         |          |             |

|------------------------------------|-------------------------|----------|-------------|

| 電源電圧( $V_{CC}$ )                   | -0.3V~6V                | 保存温度範囲   | -65°C~150°C |

| アナログ入力電圧( $V_{IN^+}, V_{IN^-}$ )   | -0.3V~( $V_{CC}+0.3V$ ) | 動作温度範囲   |             |

| リファレンス電圧( $V_{REF^+}, V_{REF^-}$ ) | -0.3V~( $V_{CC}+0.3V$ ) | LTC2453C | 0°C~70°C    |

| デジタル電圧(SDA、SCL)                    | -0.3V~( $V_{CC}+0.3V$ ) | LTC2453I | -40°C~85°C  |

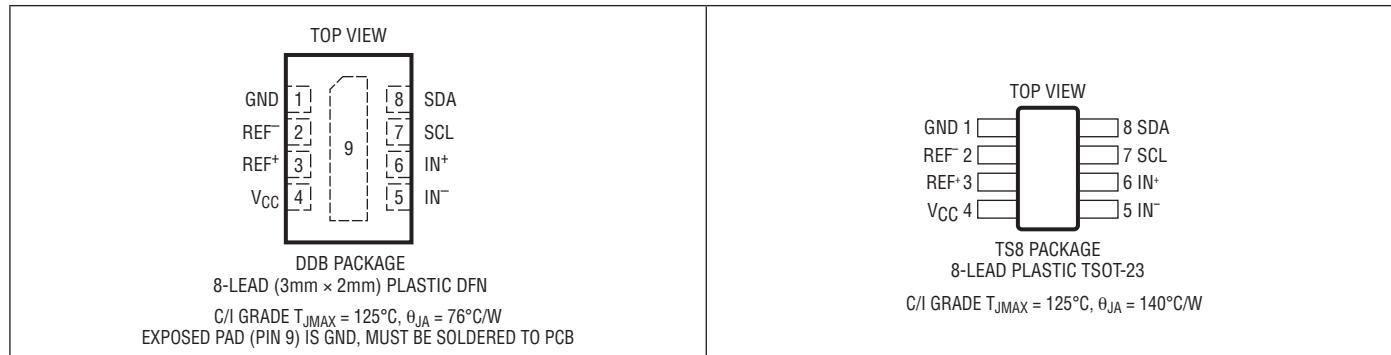

## ピン配置

## 発注情報

### 鉛フリー仕様

| テープアンドリール(ミニ)      | テープアンドリール         | 製品マーキング* | パッケージ                          | 温度範囲          |

|--------------------|-------------------|----------|--------------------------------|---------------|

| LTC2453CDDB#TRMPBF | LTC2453CDB#TRPBF  | LDBQ     | 8-Lead Plastic (3mm × 2mm) DFN | 0°C to 70°C   |

| LTC2453IDDB#TRMPBF | LTC2453IDDB#TRPBF | LDBQ     | 8-Lead Plastic (3mm × 2mm) DFN | -40°C to 85°C |

| LTC2453CTS8#TRMPBF | LTC2453CTS8#TRPBF | LTDCG    | 8-Lead Plastic TSOT-23         | 0°C to 70°C   |

| LTC2453ITS8#TRMPBF | LTC2453ITS8#TRPBF | LTDCG    | 8-Lead Plastic TSOT-23         | -40°C to 85°C |

TRM = 500個。\*温度グレードは出荷時のコンテナのラベルで識別されます。

さらに広い動作温度範囲で規定されるデバイスについては、弊社および弊社代理店にお問い合わせください。

鉛ベース仕様の製品の詳細については、弊社および弊社代理店にお問い合わせください。

鉛フリー仕様の製品マーキングの詳細については、<http://www.linear-tech.co.jp/leadfree/> をご覧ください。

テープアンドリールの仕様については、<http://www.linear-tech.co.jp/tapeandreel/> をご覧ください。

## 電気的特性

●は全動作温度範囲の規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。(Note 2)

| PARAMETER                     | CONDITIONS | MIN | TYP  | MAX  | UNITS             |

|-------------------------------|------------|-----|------|------|-------------------|

| Resolution (No Missing Codes) | (Note 3)   | ●   | 16   |      | Bits              |

| Integral Nonlinearity         | (Note 4)   | ●   | 2    | 10   | LSB               |

| Offset Error                  |            | ●   | 2    | 10   | LSB               |

| Offset Error Drift            |            |     | 0.02 |      | LSB/°C            |

| Gain Error                    |            | ●   | 0.01 | 0.02 | % of FS           |

| Gain Error Drift              |            |     | 0.02 |      | LSB/°C            |

| Transition Noise              |            |     | 1.4  |      | μV <sub>RMS</sub> |

| Power Supply Rejection DC     |            |     | 80   |      | dB                |

2453fc

## アナログ入力とリファレンス

●は全動作温度範囲の規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。

| SYMBOL                       | PARAMETER                              | CONDITIONS                                                   | MIN    | TYP            | MAX            | UNITS    |          |

|------------------------------|----------------------------------------|--------------------------------------------------------------|--------|----------------|----------------|----------|----------|

| $V_{IN^+}$                   | Positive Input Voltage Range           |                                                              | ●      | 0              | $V_{CC}$       | V        |          |

| $V_{IN^-}$                   | Negative Input Voltage Range           |                                                              | ●      | 0              | $V_{CC}$       | V        |          |

| $V_{REF^+}$                  | Positive Reference Voltage Range       | $V_{REF^+} - V_{REF^-} \geq 2.5\text{V}$                     | ●      | $V_{CC} - 2.5$ | $V_{CC}$       | V        |          |

| $V_{REF^-}$                  | Negative Reference Voltage Range       | $V_{REF^+} - V_{REF^-} \geq 2.5\text{V}$                     | ●      | 0              | $V_{CC} - 2.5$ | V        |          |

| $V_{OR^+} + V_{UR^+}$        | Overrange + Underrange Voltage, $IN^+$ | $V_{REF} = 5\text{V}, V_{IN^-} = 2.5\text{V}$ (See Figure 2) |        | 31             |                | LSB      |          |

| $V_{OR^-} + V_{UR^-}$        | Overrange + Underrange Voltage, $IN^-$ | $V_{REF} = 5\text{V}, V_{IN^+} = 2.5\text{V}$ (See Figure 2) |        | 31             |                | LSB      |          |

| $C_{IN}$                     | $IN^+, IN^-$ Sampling Capacitance      |                                                              |        | 0.35           |                | pF       |          |

| $I_{DC\_LEAK}(IN^+)$         | $IN^+$ DC Leakage Current              | $V_{IN} = \text{GND}$ (Note 8)<br>$V_{IN} = V_{CC}$ (Note 8) | ●<br>● | -10<br>-10     | 1<br>1         | 10<br>10 | nA<br>nA |

| $I_{DC\_LEAK}(IN^-)$         | $IN^-$ DC Leakage Current              | $V_{IN} = \text{GND}$ (Note 8)<br>$V_{IN} = V_{CC}$ (Note 8) | ●<br>● | -10<br>-10     | 1<br>1         | 10<br>10 | nA<br>nA |

| $I_{DC\_LEAK}(REF^+, REF^-)$ | $REF^+, REF^-$ DC Leakage Current      | $V_{REF} = 3\text{V}$ (Note 8)                               | ●      | -10            | 1              | 10       | nA       |

| $I_{CONV}$                   | Input Sampling Current (Note 5)        |                                                              |        | 50             |                |          | nA       |

## 電源要件

●は全動作温度範囲の規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。

| SYMBOL   | PARAMETER                             | CONDITIONS | MIN    | TYP        | MAX         | UNITS                          |

|----------|---------------------------------------|------------|--------|------------|-------------|--------------------------------|

| $V_{CC}$ | Supply Voltage                        |            | ●      | 2.7        | 5.5         | V                              |

| $I_{CC}$ | Supply Current<br>Conversion<br>Sleep |            | ●<br>● | 800<br>0.2 | 1200<br>0.6 | $\mu\text{A}$<br>$\mu\text{A}$ |

## I<sup>2</sup>Cの入力と出力

●は全動作温度範囲の規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。(Note 2、7)

| SYMBOL    | PARAMETER                            | CONDITIONS                             | MIN | TYP           | MAX          | UNITS         |

|-----------|--------------------------------------|----------------------------------------|-----|---------------|--------------|---------------|

| $V_{IH}$  | High Level Input Voltage             |                                        | ●   | 0.7 $V_{CC}$  |              | V             |

| $V_{IL}$  | Low Level Input Voltage              |                                        | ●   |               | 0.3 $V_{CC}$ | V             |

| $I_I$     | Digital Input Current                |                                        | ●   | -10           | 10           | $\mu\text{A}$ |

| $V_{HYS}$ | Hysteresis of Schmidt Trigger Inputs | (Note 3)                               | ●   | 0.05 $V_{CC}$ |              | V             |

| $V_{OL}$  | Low Level Output Voltage (SDA)       | $I = 3\text{mA}$                       | ●   |               | 0.4          | V             |

| $I_{IN}$  | Input Leakage                        | $0.1V_{CC} \leq V_{IN} \leq 0.9V_{CC}$ | ●   |               | 1            | $\mu\text{A}$ |

| $C_I$     | Capacitance for Each I/O Pin         |                                        | ●   | 10            |              | pF            |

| $C_B$     | Capacitance Load for Each Bus Line   |                                        | ●   |               | 400          | pF            |

## I<sup>2</sup>Cのタイミング特性

●は全動作温度範囲の規格値を意味する。それ以外はT<sub>A</sub> = 25°Cでの値。(Note 2, 7)

| SYMBOL               | PARAMETER                                            | CONDITIONS                                     | MIN | TYP                    | MAX  | UNITS |    |

|----------------------|------------------------------------------------------|------------------------------------------------|-----|------------------------|------|-------|----|

| t <sub>CONV</sub>    | Conversion Time                                      |                                                | ●   | 13                     | 16.6 | 23    | ms |

| f <sub>SCL</sub>     | SCL Clock Frequency                                  |                                                | ●   | 0                      | 400  | kHz   |    |

| t <sub>HD(SDA)</sub> | Hold Time (Repeated) START Condition                 |                                                | ●   | 0.6                    |      | μs    |    |

| t <sub>LOW</sub>     | LOW Period of the SCL Pin                            |                                                | ●   | 1.3                    |      | μs    |    |

| t <sub>HIGH</sub>    | HIGH Period of the SCL Pin                           |                                                | ●   | 0.6                    |      | μs    |    |

| t <sub>SU(STA)</sub> | Set-Up Time for a Repeated START Condition           |                                                | ●   | 0.6                    |      | μs    |    |

| t <sub>HD(DAT)</sub> | Data Hold Time                                       |                                                | ●   | 0                      | 0.9  | μs    |    |

| t <sub>SU(DAT)</sub> | Data Set-Up Time                                     |                                                | ●   | 100                    |      | ns    |    |

| t <sub>r</sub>       | Rise Time for SDA, SCL Signals                       | (Note 6)                                       | ●   | 20 + 0.1C <sub>B</sub> | 300  | ns    |    |

| t <sub>f</sub>       | Fall Time for SDA, SCL Signals                       | (Note 6)                                       | ●   | 20 + 0.1C <sub>B</sub> | 300  | ns    |    |

| t <sub>SU(STO)</sub> | Set-Up Time for STOP Condition                       |                                                | ●   | 0.6                    |      | μs    |    |

| t <sub>BUF</sub>     | Bus Free Time Between a Stop and Start Condition     |                                                | ●   | 1.3                    |      | μs    |    |

| t <sub>OF</sub>      | Output Fall Time V <sub>IHM</sub> to V <sub>IL</sub> | Bus Load C <sub>B</sub> 10pF to 400pF (Note 6) | ●   | 20 + 0.1C <sub>B</sub> | 250  | ns    |    |

| t <sub>SP</sub>      | Input Spike Suppression                              |                                                | ●   |                        | 50   | ns    |    |

**Note 1:**絶対最大格に記載された値を超えるストレスはデバイスに永続的損傷を与える可能性がある。長期にわたって絶対最大格条件に曝すと、デバイスの信頼性と寿命に悪影響を与える可能性がある。

**Note 2:**全ての電圧値はGNDを基準にしている。注記がない限り、V<sub>CC</sub> = 2.7V~5.5V。

$$V_{REF} = V_{REF^+} - V_{REF^-}, V_{REFCM} = (V_{REF^+} + V_{REF^-})/2, FS = V_{REF^+} - V_{REF^-};$$

$$V_{IN} = V_{IN^+} - V_{IN^-}, -V_{REF} \leq V_{IN} \leq V_{REF}; V_{INCM} = (V_{IN^+} + V_{IN^-})/2.$$

**Note 3:**設計によって保証されているが、テストされない。

**Note 4:**積分非直線性は、実際の伝達曲線のエンドポイントを通る直線からのコードの偏差として定義されている。設計およびテストとの相関により保証されている。

**Note 5:**入力サンプリング電流は、LTC2453が変換中に入力サンプリング・ネットワークから流れる平均入力電流である。

**Note 6:**C<sub>B</sub> = 1本のバスラインの容量(pF)。

**Note 7:**全ての値はV<sub>IH</sub>(MIN)とV<sub>IL</sub>(MAX)のレベルを基準にしている。

**Note 8:**正電流はDUTピンへ流れ込む。

## 標準的性能特性 (注記がない限り、T<sub>A</sub> = 25°C)

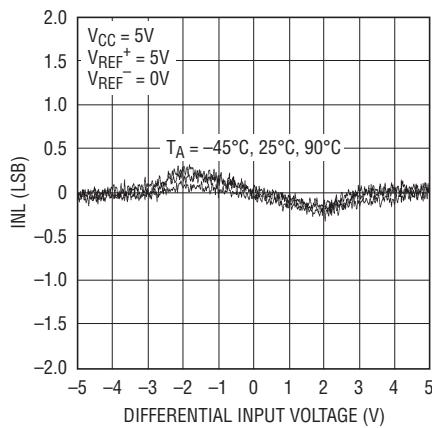

積分非直線性 (V<sub>CC</sub> = 5V)

積分非直線性 (V<sub>CC</sub> = 3V)

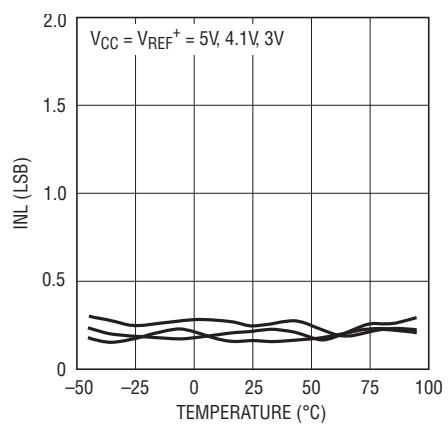

最大INLと温度

標準的性能特性 (注記がない限り、 $T_A = 25^\circ\text{C}$ )

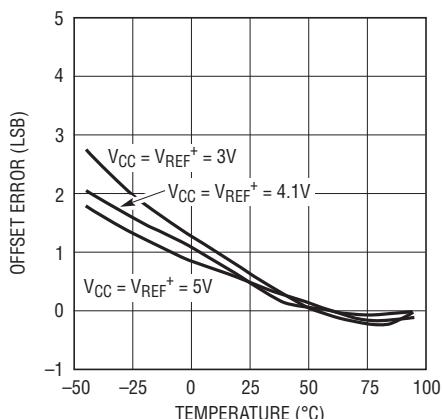

オフセット誤差と温度

2453 G04

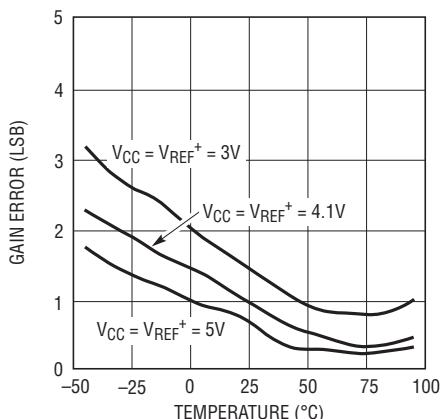

利得誤差と温度

2453 G05

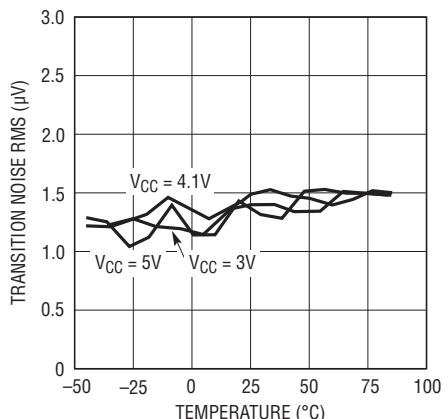

遷移ノイズと温度

2453 G06

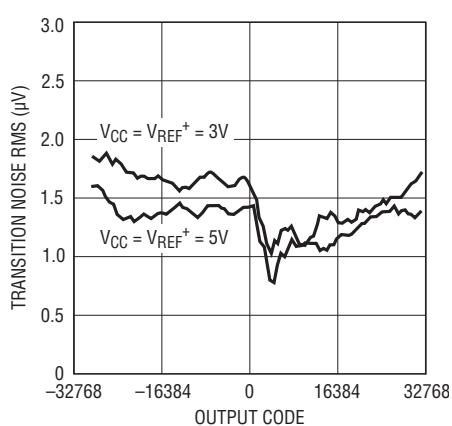

遷移ノイズと出力コード

2453 G07

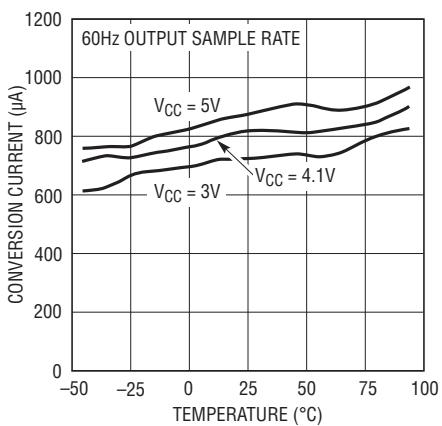

変換モードの消費電流と温度

2453 G08

スリープ・モードの消費電流と温度

2453 G09

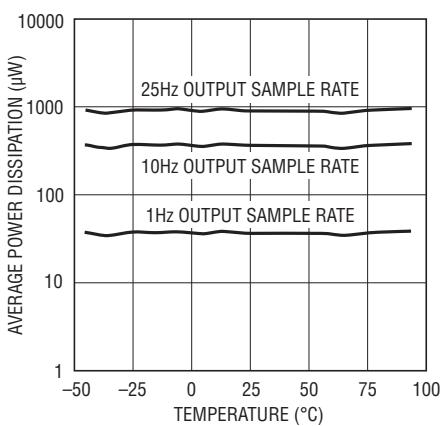

平均消費電力と温度( $V_{CC} = 3\text{V}$ )

2453 G10

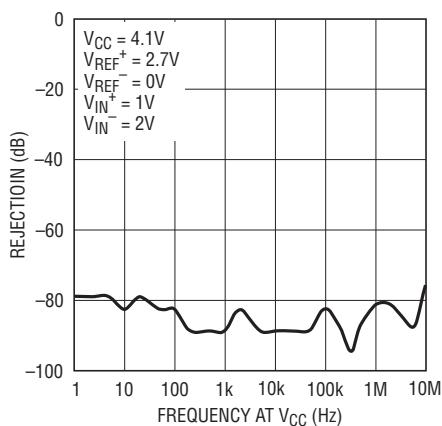

$V_{CC}$ での電源除去比と周波数

2453 G11

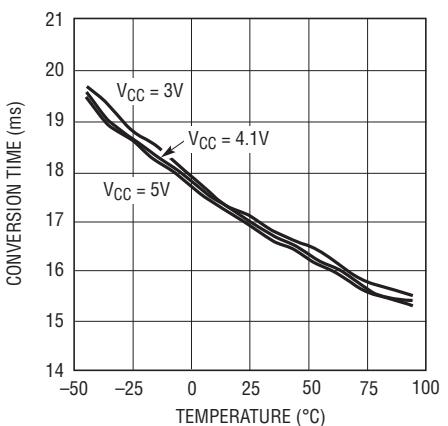

変換時間と温度

2453 G12

# LTC2453

## ピン機能

**GND(ピン1)**: グランド。低インピーダンス接続を使ってグランド・プレーンに接続します。

**REF<sup>-</sup>(ピン2)、REF<sup>+</sup>(ピン3)**: 差動リファレンス入力。これらのピンの電圧は、リファレンスの正入力(REF<sup>+</sup>)がリファレンスの負入力(REF<sup>-</sup>)より少なくとも2.5V高く保たれる限り、GND ~V<sub>CC</sub>の任意の電圧することができます。差動リファレンス電圧( $V_{REF} = REF^+ - REF^-$ )によりフルスケール・レンジが設定されます。

**V<sub>CC</sub>(ピン4)**: 正電源電圧。デバイスのできるだけ近くに配置した10μFコンデンサと直列インダクタンスの低い0.1μFコンデンサを並列に使って、GND(ピン1)にバイパスします。

**IN<sup>-</sup>(ピン5)、IN<sup>+</sup>(ピン6)**: 差動アナログ入力。

**SCL(ピン7)**: I<sup>2</sup>Cインターフェースのシリアル・クロック入力。LTC2453はスレーブとして機能することができますが、SCLピンは外部シリアル・クロックを受け入れるだけです。データはSCLの立ち上がりエッジでシフトされてSDAピンに入力され、SCLの立ち下がりエッジでSDAピンを通して出力されます。

**SDA(ピン8)**: I<sup>2</sup>Cインターフェースの双方向シリアル・データ・ライン。変換結果はSDAピンを通して出力されます。LTC2453がデータ出力モードでない限り、このピンは高インピーダンスです。LTC2453がデータ出力モードの間SDAはオープン・ドラインのプルダウンです(そのためV<sub>CC</sub>への外部1.7kプルアップ抵抗が必要です)。

**露出パッド(ピン9、DFNのみ)**: グランド。PCBグランドに半田付けする必要があります。

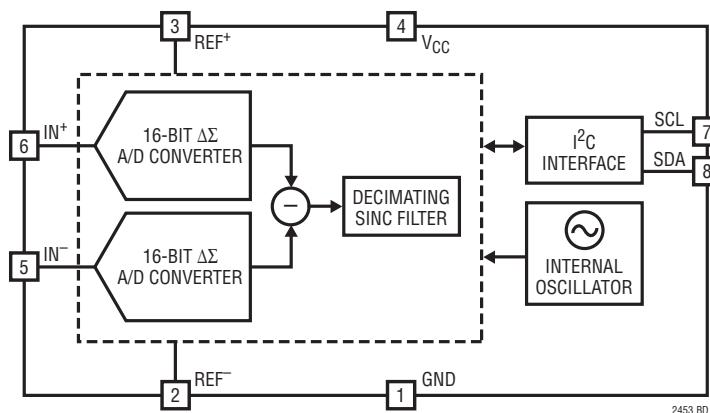

## ブロック図

## アプリケーション情報

### コンバータの動作

#### コンバータの動作サイクル

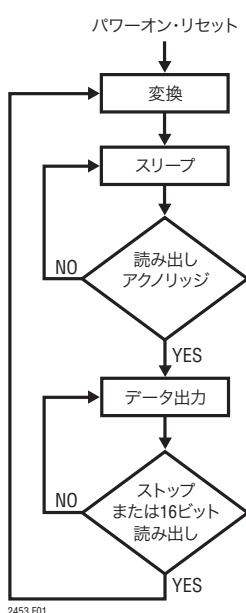

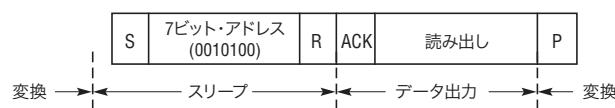

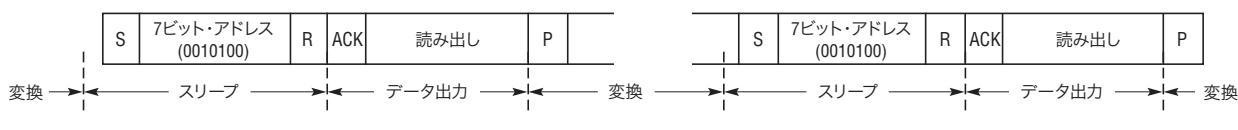

LTC2453は低消費電力の完全差動のデルタシグマ・アナログ-デジタル・コンバータで、I<sup>2</sup>Cインターフェースを備えています。その動作は、図1に示されているように、連続する3つのステート(状態)で構成されています。変換、スリープおよびデータ出力です。

LTC2453は最初に(起動時に)変換を行います。変換が完了すると、デバイスはスリープ・ステートに入ります。このスリープ・ステートの間、電力消費は数桁減少します。読み出し動作のために呼び出されない限り、デバイスはスリープ・ステートに留まります。デバイスがスリープ・ステートの間、変換結果は無期限にスタティック・シフトレジスタ内に保存されます。

図1. LTC2453の状態図

変換ステートの間、デバイスは外部からのリクエストに対してアクノリッジを返しません。変換終了後は、デバイスは読み出しのリクエストを受け入れる用意ができます。LTC2453のアドレスは0010100にハードウェイで設定されています。読み出し動作のためにLTC2453が呼び出されると、デバイスはシリアル・クロック(SCL)の制御下に変換結果の出力を開始します。変換結果には待ち時間はありません。このデータ出力は

16ビット長で、15ビットおよび符号からなる変換結果が含まれています。データはSCLの立ち下がりエッジによって更新されるので、ユーザーはSCLの立ち上がりエッジを使って確実にデータをラッチすることができます。有効な書き込み動作に続くストップ条件によって、またはデータ読み出しサイクルが完了する(全16ビットがデバイスから読み出される)と新しい変換が開始されます。

#### パワーアップ・シーケンス

コンバータに加えられる電源電圧(V<sub>CC</sub>)が約2.1Vより低いとき、ADCはパワーオン・リセットを行います。この機能により、変換結果が損なわれないことが保証されます。

V<sub>CC</sub>がこのスレッショルドを超えて上昇すると、コンバータは約0.5msの内部パワーオン・リセット(POR)信号を発生します。このPOR信号により、全ての内部レジスタがクリアされます。POR信号に続き、LTC2453は変換サイクルを開始し、図1に示されている状態が継起します。PORに続く最初の変換結果の精度は、PORの時間間隔が経過する前に電源電圧V<sub>CC</sub>が動作範囲(2.7V~5.5V)内に回復していれば、デバイスの仕様を満たします。

#### 使いやすさ

LTC2453のデータ出力には、待ち時間、フィルタのセトリング遅延、または変換サイクルに関連した冗長な結果はありません。変換と出力データの間には1対1対応の関係があります。したがって、複数のアナログ入力電圧の多重化に特別な操作は不要です。

LTC2453は変換ごとにオフセットを較正します。この較正はユーザーからは見えず、前述のサイクル動作には影響を与えません。連続較正の利点は、時間経過と温度に対してADCの性能が極めて安定していることです。

LTC2453は、従来のデルタシグマ・アーキテクチャに比べて、平均入力電流を数桁低減する独自の入力サンプリング方式を採用しています。これにより、外部フィルタ・ネットワークを直接LTC2453にインターフェースすることができます。平均入力サンプリング電流が50nAなので、1kΩと0.1μFを使った外部RCローパス・フィルタによる追加の誤差は1 LSB未満になります。さらに、IN<sup>+</sup>とIN<sup>-</sup>の間のリーク電流は無視できます。

## アプリケーション情報

### リファレンス電圧範囲

このコンバータは真に差動の外部リファレンス電圧を受け取ります。REF<sup>+</sup>ピンとREF<sup>-</sup>ピンの絶対/同相電圧範囲はデバイスの全動作範囲(GND~V<sub>CC</sub>)を含みます。コンバータを正しく動作させるには、V<sub>REF</sub><sup>+</sup>は(2.5V+V<sub>REF</sub><sup>-</sup>)より大きくなればなりません。

LTC2453の差動リファレンスの入力範囲は2.5V~V<sub>CC</sub>です。最も簡単に動作させるには、REF<sup>+</sup>をV<sub>CC</sub>に短絡し、REF<sup>-</sup>をGNDに短絡することができます。

### 入力電圧範囲

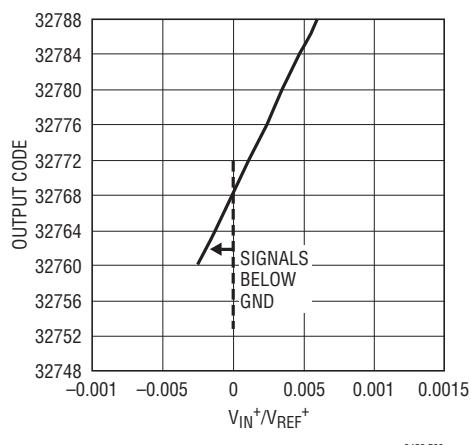

ほとんどのアプリケーションでは、V<sub>REF</sub><sup>-</sup> ≤ (V<sub>IN</sub><sup>+</sup>, V<sub>IN</sub><sup>-</sup>) ≤ V<sub>REF</sub><sup>+</sup>です。これらの条件では、出力コードは32768 • (V<sub>IN</sub><sup>+</sup> - V<sub>IN</sub><sup>-</sup>)/(V<sub>REF</sub><sup>+</sup> - V<sub>REF</sub><sup>-</sup>) + 32768として与えられます(「データのフォーマット」を参照)。LTC2453の出力は0の最小値と65535の最大値でクランプされます。

LTC2453には独自のシステムが含まれており、LTC2453の出力がクランプされていなければ、一般にV<sub>REF</sub><sup>+</sup>より8LSB上までおよびV<sub>REF</sub><sup>-</sup>より8LSB下までの各入力を正しくデジタル化することができます。一例として(図2)、ユーザーがグランドよりわずかに下の信号を測定しようと望むなら、ユーザーはV<sub>IN</sub><sup>-</sup> = V<sub>REF</sub><sup>-</sup> = GND、およびV<sub>REF</sub><sup>+</sup> = 5Vに設定することができます。V<sub>IN</sub><sup>+</sup> = GNDであれば、出力コードは約32768になります。V<sub>IN</sub><sup>+</sup> = GND - 8LSB = -1.22 mVであれば、出力コードは約32760になります。

オーバーレンジ能力とアンダーレンジ能力の合計は、所定のデバイスで標準31 LSBです。31 LSBの合計値はオーバーレン

図2. 出力コードとV<sub>IN</sub><sup>+</sup>(V<sub>IN</sub><sup>-</sup> = 0およびV<sub>REF</sub><sup>-</sup> = 0)

ジ能力とアンダーレンジ能力の間で分配されます。例えば、アンダーレンジ能力が8LSBの場合は、オーバーレンジ能力は通常31-8 = 23LSBとなります。

### I<sup>2</sup>Cインターフェース

LTC2453はI<sup>2</sup>Cインターフェースを通して通信を行います。I<sup>2</sup>Cインターフェースは2線式オープン・ドレイン・インターフェースで、複数のデバイスとマスタを单一バスでサポートします。接続されているデバイスはシリアル・データ・ライン(SDA)を“L”に引き下げることができるだけで、“H”にドライブすることはできません。SDAは外部でプルアップ抵抗を通して電源に接続する必要があります。データ・ラインが解放されているとき、データ・ラインは“H”になります。I<sup>2</sup>Cバスのデータは標準モードでは最大100kbps、高速モードでは400kbpsのレートで転送することができます。内部ESD保護ダイオードを介してI<sup>2</sup>Cバスラインに負荷がかかるのを避けるため、I<sup>2</sup>CバスがアクティブなときはV<sub>CC</sub>の電源をデバイスから取り去らないで下さい。

I<sup>2</sup>Cバス上の各デバイスはデバイスに保存されている固有アドレスで識別され、デバイスの機能に依存して、トランスマッタまたはレシーバのどちらかとして動作することができます。トランスマッタとレシーバに加えて、デバイスはデータ転送時にマスタまたはスレーブとみなすことができます。マスタはバス上でデータ転送を開始するデバイスで、転送を可能にするクロック信号を発生します。マスタによって呼び出されたデバイスはスレーブとみなされます。LTC2453のアドレスは0010100です。

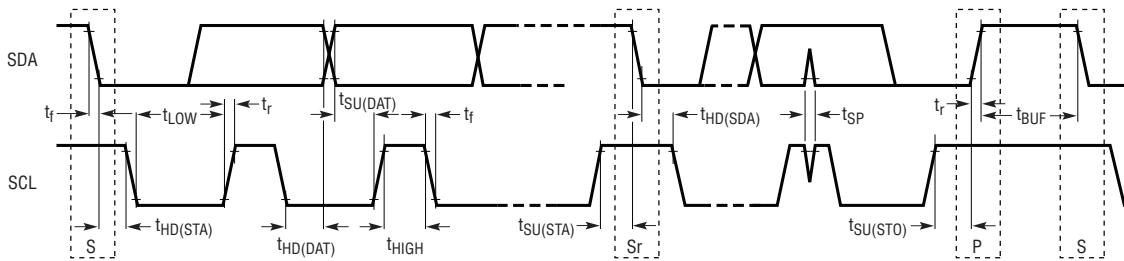

LTC2453はスレーブとして呼び出せることができます。最後の変換結果を転送することだけができます。シリアル・クロック・ライン(SCL)は常にLTC2453への入力で、シリアル・データ・ライン(SDA)は双方向です。I<sup>2</sup>Cのタイミングの定義を図3に示します。

### スタート条件とストップ条件

スタート(S)条件はSCLを“H”に保ったままSDAを“H”から“L”に遷移させて発生させます。スタート条件になった後はバスはビジーであるとみなされます。データ転送が終了すると、SCLを“H”に保ったままSDAを“L”から“H”に遷移させてストップ(P)条件を発生させます。ストップが発生した後はバスはフリーになります。スタート条件とストップ条件は常にマスタが発生させます。

バスが使用されているとき、ストップ条件の代わりにリピート・スタート(Sr)を発生させると、バスはビジー状態に留まります。

## アプリケーション情報

図3. I<sup>2</sup>Cバス上の高速/標準モード・デバイスのタイミングの定義

リピート・スタートのタイミングは機能的にスタートと同じで、新しい変換を開始する前にデバイスから読み出すのに使います。

### データ転送

スタート条件の後、I<sup>2</sup>Cバスはビジーになり、マスタと呼び出されたスレーブの間でデータ転送を開始することができます。データは9ビット(1バイトの後にアクノリッジ(ACK)の1ビットが続く)のグループでバス上を転送されます。マスタは9番目のクロック・サイクルの間SDAラインを解放します。スレーブ・デバイスはSDAを“L”に引き下げてACKを発信するか、またはSDAラインを高インピーダンスのままにして非アクノリッジ(NAK)を発信します(外部プルアップ抵抗がラインを“H”に保ちます)。クロック・ライン(SCL)が“L”的きだけデータが変化します。

### データのフォーマット

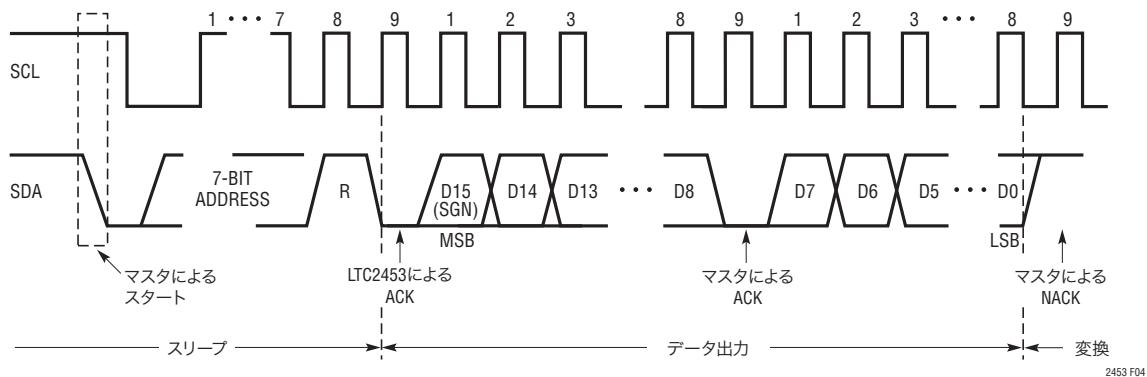

スタート条件の後、マスタは7ビットのアドレスを送り、読み出しリクエスト(R)ビットがそれに続きます。読み出しリクエストの場合、ビットRは1です。7ビットのアドレスがLTC2453のアドレス(0010100にハードウェイで設定されている)に合致すると、ADCが選択されます。変換ステートの途中にデバイスが呼び出されると、そのリクエストを受け入れないで、SDAラインを“H”的ままでNAKを発信します。変換が完了していると、LTC2453はSDAラインを“L”に引き下げてACKを発信します。

ACKに続いて、LTC2453はデータを出力することができます。データの出力ストリームは16ビット長で、SCLの立ち下がりエッジでシフトされて出力されます(図4を参照)。LTC2453から出力される最初のビット(MSB)は符号であり、これは $V_{IN}^+ \geq V_{IN}^-$ では1、 $V_{IN}^+ < V_{IN}^-$ では0です(表1を参照)。MSB(D15)の後には順に下がっていく下位ビットが続き(D14、D13、…), 最後にLSBがLTC2453から出力されます。このシーケンスを図5に示します。

### 動作シーケンス

#### 連続読み出し

LTC2453による変換は連続して読み出すことができます(図6)。読み出し動作が終了すると、新しい変換が自動的に開始されます。変換サイクルの最後に、上述の方法を使って次の結果を読み出すことができます。変換サイクルが完了していないのに有効なアドレスによってデバイスが選択されると、LTC2453はNAK信号を発生して変換サイクルが進行中であることを知らせます。

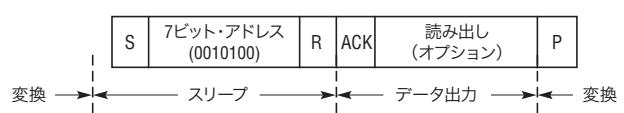

#### 変換結果の破棄と新しい変換の開始

図7に示されているように、前の結果を読み出ことなく新しい変換を開始することができます。有効な7ビット・アドレス、読み出しリクエスト(R)ビット、および有効なACKに続いて、ストップ・コマンドを与えると新しい変換が開始されます。

#### コンバータの精度の維持

デバイスのデカッピング、PCBのレイアウト、アンチエイリアシング回路、およびラインや周波数の乱れに対する、変換結果の感度が大幅に減少するようにLTC2453は設計されています。とはいえ、このデバイスの高い精度を維持するには、いくつかの配慮をしておくのが賢明です。

#### デジタル信号レベル

CMOSロジックの性質により、入力デジタル信号をGNDまたはV<sub>CC</sub>の近くに保つことを推奨します。0.5V~(V<sub>CC</sub>-0.5V)の範囲の電圧はデバイスからの追加電流リークを生じます。

# LTC2453

## アプリケーション情報

図4. 読み出しシーケンスのタイミング図

表1. LTC2453の出力データのフォーマット。 $FS = V_{REF}^+ - V_{REF}^-$ 。

| 差動入力電圧<br>$V_{IN}^+ - V_{IN}^-$ | D15<br>(MSB) | D14 | D13 | D12 ... D2 | D1 | D0<br>(LSB) | 対応する<br>10進数値 |

|---------------------------------|--------------|-----|-----|------------|----|-------------|---------------|

| $\geq FS$                       | 1            | 1   | 1   | 1          | 1  | 1           | 65535         |

| $FS - 1LSB$                     | 1            | 1   | 1   | 1          | 1  | 0           | 65534         |

| $0.5 \cdot FS$                  | 1            | 1   | 0   | 0          | 0  | 0           | 49152         |

| $0.5 \cdot FS - 1LSB$           | 1            | 0   | 1   | 1          | 1  | 1           | 49151         |

| 0                               | 1            | 0   | 0   | 0          | 0  | 0           | 32768         |

| -1LSB                           | 0            | 1   | 1   | 1          | 1  | 1           | 32767         |

| -0.5 • FS                       | 0            | 1   | 0   | 0          | 0  | 0           | 16384         |

| -0.5 • FS - 1LSB                | 0            | 0   | 1   | 1          | 1  | 1           | 16383         |

| $\leq -FS$                      | 0            | 0   | 0   | 0          | 0  | 0           | 0             |

図5. LTC2453の変換シーケンス

図6. 同じ構成設定を使った連続読み出し

図7. 前の変換結果を読み出すことなく新しい変換を開始

## アプリケーション情報

### V<sub>CC</sub>とGNDのドライブ

V<sub>CC</sub>ピンとGNDピンとの関係で、LTC2453は内部の高周波デカップリングを減衰素子と組み合わせて、ADCの性能がPCBレイアウトや外部部品による影響を受けにくくしています。にもかかわらず、このコンバータの非常に高い精度は、電源の低周波数および高周波数の注意深いデカップリングによって最も良く維持されます。

10μFセラミック・コンデンサに並列に接続された高品質のセラミック・コンデンサを、できるだけパッケージに近づけて、V<sub>CC</sub>ピンとGNDピンの間に接続します。0.1μFのコンデンサをADCパッケージの一番近くに配置します。コンバータのV<sub>CC</sub>ピンを出発して、これら2個のデカップリング・コンデンサを通り、コンバータのGNDピンに戻ってくる回路経路ではビアを使わない方が良いでしょう。この回路経路によって囲まれる領域と経路長を最小にします。

V<sub>CC</sub>ピンとGNDピンの両方で、インピーダンスの非常に低いグランドと電力プレーンおよびスター接続が望ましいといえます。V<sub>CC</sub>ピンには3つの区別された接続を行います。1番目は上

述のデカップリング・コンデンサ、2番目は入力信号源のグランド・リターン、3番目は電源電圧源のグランド・リターンです。

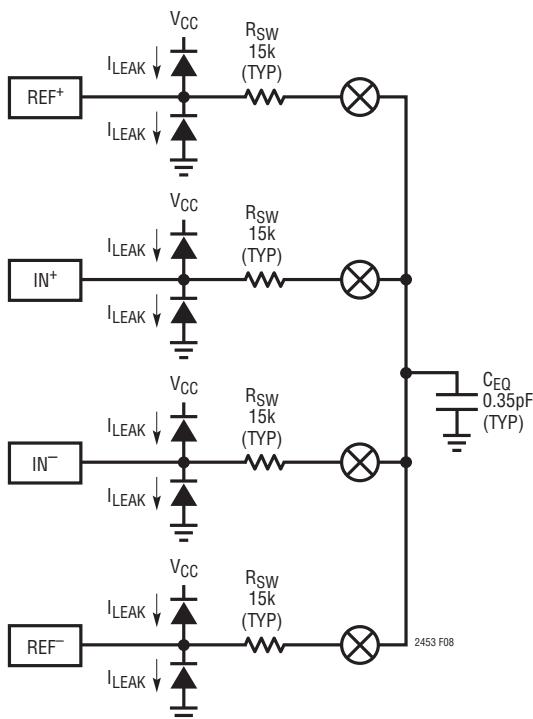

### REF<sup>+</sup>とREF<sup>-</sup>のドライブ

REF<sup>+</sup>とREF<sup>-</sup>の簡略化された等価回路を図8に示します。他の全てのA/Dコンバータと同様、LTC2453の精度は使用するリファレンスの精度に制約されます。したがって、電源の低周波数と高周波数のデカップリングを注意深く行って、リファレンス・ラインを静穏に保つことが重要です。

LTC2453のREF<sup>+</sup>ピンのドライブにはLT6660リファレンスが最適です。LT6660は2mm×2mm DFNパッケージで供給され、2.5V、3V、3.3Vおよび5Vのオプションがあります。

10μFのセラミック・コンデンサに並列に接続された0.1μFの高品質のセラミック・コンデンサを、できるだけパッケージに近づけて、REF<sup>+</sup>/REF<sup>-</sup>ピンとGNDピンの間に接続します。0.1μFのコンデンサをADCの一番近くに配置します。

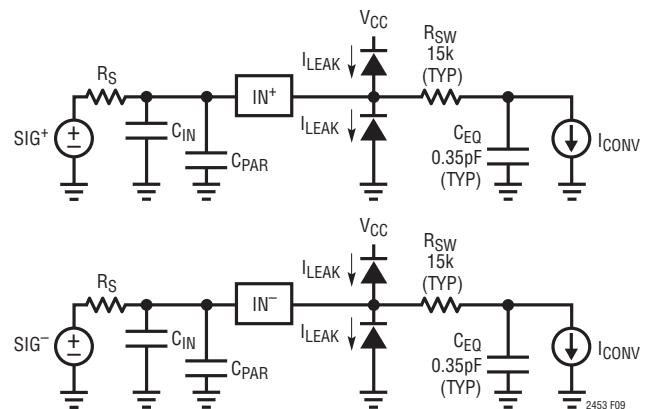

### V<sub>IN</sub><sup>+</sup>とV<sub>IN</sub><sup>-</sup>のドライブ

入力ドライブの要件は、図9の等価回路を使うと最良の分析を行うことができます。入力信号VSIGは等価ソース抵抗R<sub>S</sub>を通してADCの入力ピン(IN<sup>+</sup>およびIN<sup>-</sup>)に接続されます。この抵抗にはジェネレータの実際のソース抵抗と入力ピンに接続された追加のオプションの抵抗の両方が含まれます。オプションの入力コンデンサC<sub>IN</sub>もADCの入力ピンに接続されます。

図8. LTC2453のアナログ入力/リファレンスの等価回路

図9. LTC2453の入力ドライブの等価回路

## アプリケーション情報

のコンデンサはADCの入力の寄生容量 $C_{PAR}$ に並列に配置されます。 $C_{PAR}$ の標準的値は、PCBのレイアウトに依存して、 $2\text{pF} \sim 15\text{pF}$ です。さらに、図9の等価回路には、コンバータの等価内部抵抗 $R_{SW}$ とサンプリング・コンデンサ $C_{EQ}$ が含まれています。

完全な回路解析を必要とすることなく、 $R_S$ と $C_{IN}$ には明らかなトレードオフがいくつかあります。 $R_S$ と $C_{IN}$ を大きくすると以下の利点が得られます。

- 1) LTC2453の入力サンプリング・アルゴリズムにより、変換サイクルの間 $V_{IN^+}$ または $V_{IN^-}$ に流れる入力電流は $50\text{nA}$ です。高い $R_S \cdot C_{IN}$ は入力電流の高周波成分を減衰させ、最大 $1\text{k}\Omega$ までの $R_S$ 値では1LSB未満の誤差となります。

- 2)  $V_{SIG}$ からの帯域幅は入力ピン( $IN^+$ ,  $IN^-$ )で減少します。この帯域幅の減少により、ADCが高周波信号から遮断されるので、簡単なアンチエイリアス機能が生じ、入力ノイズが減少します。

- 3) ADCによって生じるスイッチング過渡は信号源に戻る前に減衰します。

- 4) 大きな $C_{IN}$ は入力ピンに良好なACグランドを与え、信号源への反射を減らすのに役立ちます。

- 5)  $R_S$ を大きくすると、電源レールの範囲を外れるフォールト状態の間電流が制限され、ADCを保護します。

与えられたアプリケーションで $R_S \cdot C_{IN}$ をどのくらい大きくするかには限界があります。あるポイントを超えて $R_S$ を増加させると、大きな測定誤差が生じるポイントまで入力電流による $R_S$ 両端の電圧降下が増加します。さらに、アプリケーションによっては、 $R_S \cdot C_{IN}$ の積を大きくしすぎると、目的の周波数で信号が許容できないほど減衰することがあります。

ほとんどのアプリケーションでは、高品質の $0.1\mu\text{F}$ セラミック・コンデンサと $1\text{k}$ 以下の中 $R_S$ で $C_{IN}$ を実装するのが望ましいでしょう。このコンデンサはパッケージの $V_{IN}$ ピンにできるだけ近づけます。さらに、この回路経路によって囲まれる領域と経路長を最小にします。

リモート端で接地されていない2線式センサの場合、 $R_S$ を分割して、センサのグランド・リターンとADCの入力ラインに直列抵抗を配置するのが望ましいでしょう。センサのグランド・リターン・ラインはスター接続トポロジーを使ってADCのGNDピンに接続します。

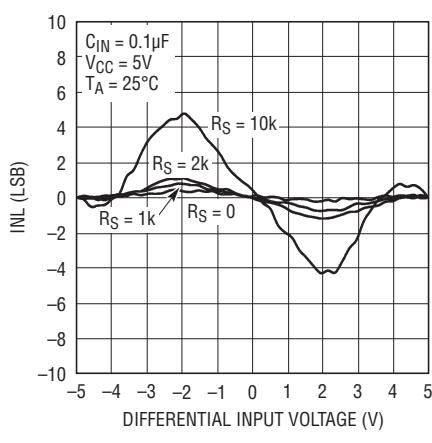

入力コンデンサ $C_{IN} = 0.1\mu\text{F}$ を使ったときの $R_S$ 値の関数として、LTC2453のINLの測定値と入力電圧を図10に示します。

場合によっては、 $R_S$ をこれらのガイドラインより大きくすることができます。ADCがスリープ・モードまたはI/Oモードのどちらかのとき、入力電流はゼロです。したがって、入力RC回路の時定数 $\tau = R_S \cdot C_{IN}$ が実際の変換と変換の間の時間と同程度か、またはそれより長ければ、それに応じて入力電流が減少するとみなすことができます。

図10. INLの測定値と入力電圧、

$C_{IN} = 0.1\mu\text{F}$ ,  $V_{CC} = 5\text{V}$ ,  $T_A = 25^\circ\text{C}$

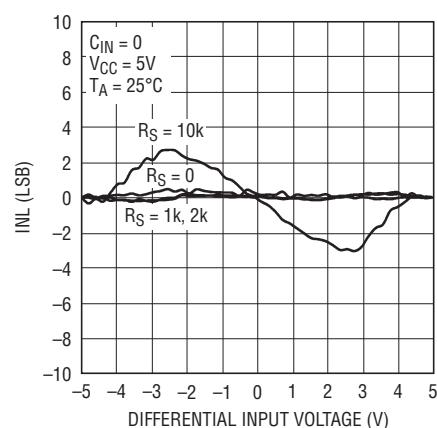

図11. INLの測定値と入力電圧、

$C_{IN} = 0$ ,  $V_{CC} = 5\text{V}$ ,  $T_A = 25^\circ\text{C}$

## アプリケーション情報

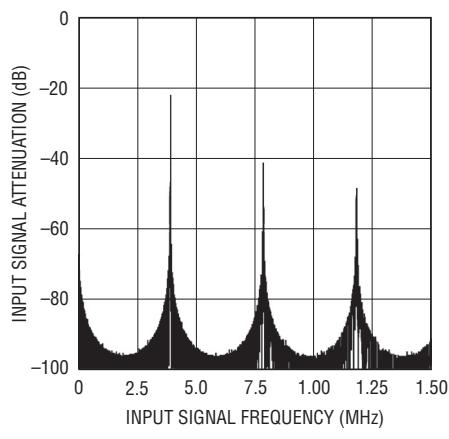

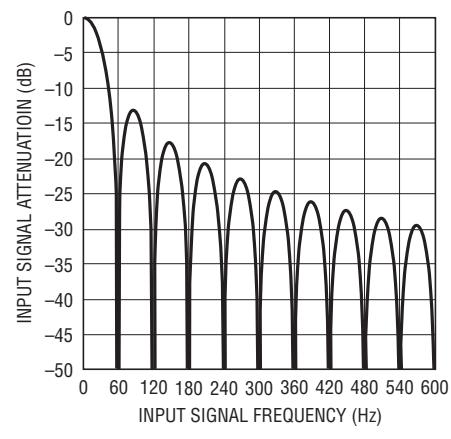

図12. LTC2453の入力信号の減衰と周波数

これらの検討事項は入力信号の帯域幅とバランスをとる必要があります。3dB帯域幅は約 $1/(2\pi \cdot R_S \cdot C_{IN})$ です。

最後に、推奨されている $C_{IN}$ の値がユーザーの特定のアプリケーションには受け入れられない場合、別の戦略として、 $C_{IN}$ を取り去って $C_{PAR}$ と $R_S$ を最小にします。要するに、この構成は最短トレースを使って直接ADCに接続された低インピーダンスのセンサに対応します。実際のアプリケーションには、値の小さなセンス抵抗を使った電流測定、温度測定、低インピーダンスの電圧源モニタなどが含まれます。その結果得られる「INLとVIN」を図11に示します。図11の測定には最小サイズのレイアウト・パッドと長さ約1インチの入力トレースの最小幅に相当するコンデンサ $C_{PAR}$ が含まれています。

### 信号帯域幅、遷移ノイズおよびノイズ等価入力帯域幅

LTC2453には最初のノッチが $f_0 = 60\text{Hz}$ に位置するsinc<sup>1</sup>タイプのデジタル・フィルタが備わっています。そのままで3dB入力信号帯域幅は26.54Hzです。広い周波数範囲にわたる計算されたLTC2453の入力信号の減衰と周波数の関係を図12に示します。低い周波数での計算されたLTC2453の入力信号の減衰と周波数の関係を図13に示します。コンバータのノイズ・レベルは約 $1.4\mu\text{VRMS}$ であり、ノイズのないコンバータの入力に接続された白色ノイズ源によってモデル化することができます。

図13. LTC2453の入力信号の減衰と周波数(低周波数)

関連した注記として、LTC2453は2つの別個のA/Dコンバータを使って正入力と負入力をデジタル化します。これらのA/Dコンバータのそれぞれの遷移ノイズは $1.4\mu\text{VRMS}$ です。一方の入力電圧がこの小さな遷移ノイズ帯域幅に入っていると、他方の入力電圧の値には関係なく、出力が1ビット変動します。両方の入力電圧がそれらの遷移ノイズ帯域幅に入っていると、出力が2ビット変動することがあります。

システム・ノイズの簡単な解析では、 $V_{IN}$ ドライブ回路を、ポールの位置 $f_i$ とノイズのスペクトル密度 $n_i$ によって特徴づけられる単一ポール等価回路としてモデル化することができます。もしコンバータが無限の帯域幅または少なくとも $f_i$ よりもはるかに大きな帯域幅をもつていれば、外部ドライブ回路の合計ノイズの寄与は次のようにになるでしょう。

$$V_n = n_i \sqrt{\pi / 2 \cdot f_i}$$

そうすれば、システムの合計ノイズ・レベルは、 $(V_n^2)$ と LTC2453のノイズフロア(約 $1.4\mu\text{V}^2$ )の2乗和の平方根として見積ることができます。

LTC2453

## 標準的應用例

## DC1266Aデモ用ボードの回路図

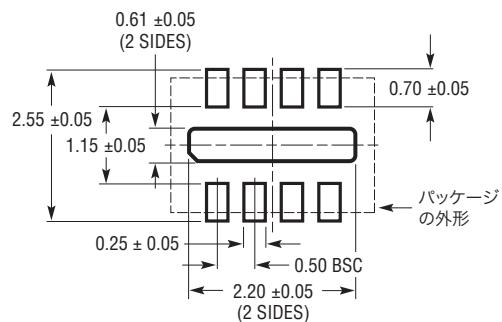

## パッケージ

**DDB パッケージ**

**8 ピン・プラスチックDFN (3mm×2mm)**

(Reference LTC DWG # 05-08-1702 Rev B)

推奨する半田パッドのピッチと寸法

## NOTE:

1. 図面はJEDECのパッケージ外形MO-229のバージョン(WECD-1)に適合

2. 図は実寸とは異なる

3. 全ての寸法はミリメートル

4. パッケージ底面の露出パッドの寸法にはモールドのバリを含まない

モールドのバリは(もしあれば)各サイドで0.15mmを超えないこと

5. 露出パッドは半田メッキとする

6. 線掛けの部分はパッケージの上面と底面のPin1の位置の参考に過ぎない

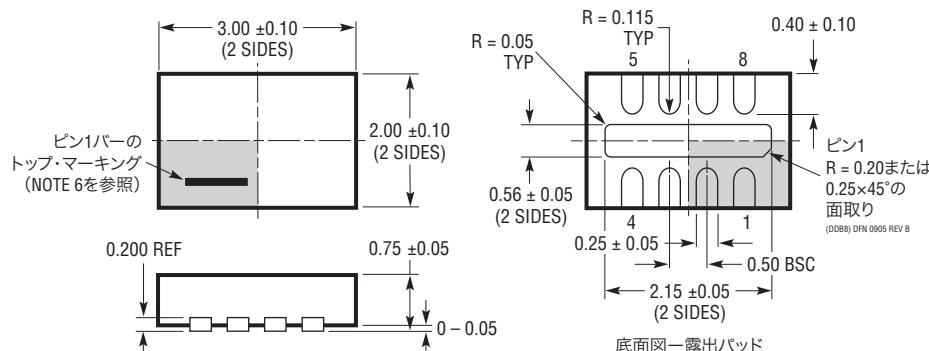

## パッケージ

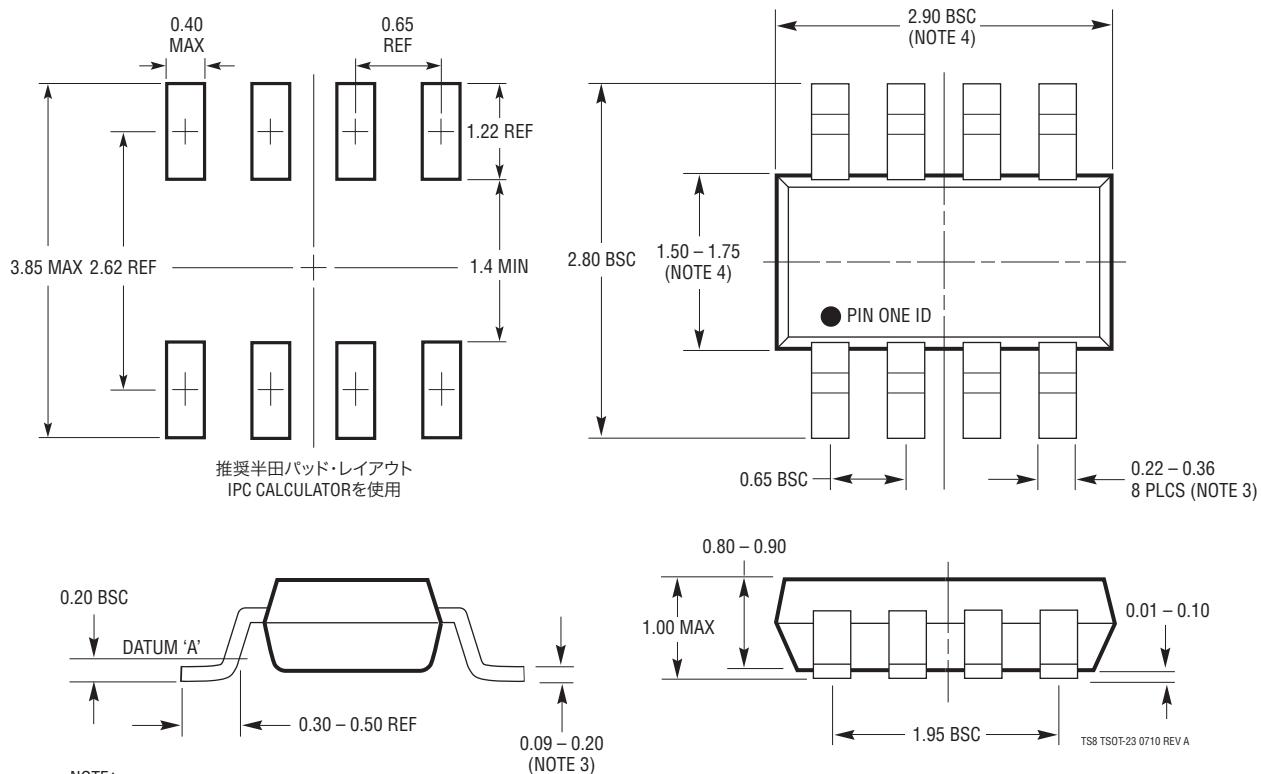

TSOT パッケージ

8 ピン・プラスチック TSOT

(Reference LTC TS8 # 05-08-1637)

## 改訂履歴 (改訂履歴はRev Bから開始)

| REV | 日付   | 概要                                             | ページ番号  |

|-----|------|------------------------------------------------|--------|

| B   | 6/10 | 「I <sup>2</sup> Cインターフェース」のセクションにテキストを追加       | 8      |

| C   | 3/11 | 「アナログ入力とリファレンス」セクションを更新<br>「入力電圧範囲」セクションに文章を追加 | 3<br>8 |

# LTC2453

## 関連製品

| 製品番号              | 説明                                                                    | 注釈                                                                                                      |

|-------------------|-----------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|

| LTC1236A-5        | 高精度バンドギャップ・リファレンス、5V                                                  | 精度:最大0.05%、ドリフト:5ppm/ $^{\circ}\text{C}$                                                                |

| LT1461            | マイクロパワー・シリーズ・リファレンス、2.5V                                              | 最大0.04%、ドリフト:3ppm/ $^{\circ}\text{C}$                                                                   |

| LT1790            | TSOT-23-6パッケージのマイクロパワー高精度リファレンス                                       | 消費電流:最大60 $\mu\text{A}$ 、ドリフト:最大10ppm/ $^{\circ}\text{C}$ 、1.25V、2.048V、2.5V、3V、3.3V、4.096Vおよび5Vの各オプション |

| LTC1860/LTC1861   | 12ビット、5V、1/2チャネル250ksps SAR ADC、MSOP                                  | 250kspsで850 $\mu\text{A}$ 、1kspsで2 $\mu\text{A}$ 、SO-8およびMSOPパッケージ                                      |

| LTC1860L/LTC1861L | 12ビット、3V、1/2チャネル、150ksps SAR ADC                                      | 150kspsで450 $\mu\text{A}$ 、1kspsで10 $\mu\text{A}$ 、SO-8およびMSOPパッケージ                                     |

| LTC1864/LTC1865   | 16ビット、5V、1/2チャネル250ksps SAR ADC、MSOP                                  | 250kspsで850 $\mu\text{A}$ 、1kspsで2 $\mu\text{A}$ 、SO-8およびMSOPパッケージ                                      |

| LTC1864L/LTC1865L | 16ビット、3V、1/2チャネル、150ksps SAR ADC                                      | 150kspsで450 $\mu\text{A}$ 、1kspsで10 $\mu\text{A}$ 、SO-8およびMSOPパッケージ                                     |

| LTC2440           | 24ビットNo Latency $\Delta\Sigma^{\text{TM}}$ ADC                        | 200nVRMSノイズ、出力レート:8kHz、INL:15ppm                                                                        |

| LTC2480           | 16ビット、差動入力、No Latency $\Delta\Sigma$ ADC、PGA、温度センサ、SPI付き              | Easy Drive入力電流キャンセル、600nVRMSノイズ、小型10ピンDFNパッケージ                                                          |

| LTC2481           | 16ビット、差動入力、No Latency $\Delta\Sigma$ ADC、PGA、温度センサ、I <sup>2</sup> C付き | Easy Drive入力電流キャンセル、600nVRMSノイズ、小型10ピンDFNパッケージ                                                          |

| LTC2482           | 16ビット、差動入力、No Latency $\Delta\Sigma$ ADC、SPI                          | Easy Drive入力電流キャンセル、600nVRMSノイズ、小型10ピンDFNパッケージ                                                          |

| LTC2483           | 16ビット、差動入力、No Latency $\Delta\Sigma$ ADC、I <sup>2</sup> C             | Easy Drive入力電流キャンセル、600nVRMSノイズ、小型10ピンDFNパッケージ                                                          |

| LTC2484           | 24ビット、差動入力、No Latency $\Delta\Sigma$ ADC、SPI                          | Easy Drive入力電流キャンセル、600nVRMSノイズ、小型10ピンDFNパッケージ                                                          |

| LTC2485           | 24ビット、差動入力、No Latency $\Delta\Sigma$ ADC、I <sup>2</sup> C             | Easy Drive入力電流キャンセル、600nVRMSノイズ、小型10ピンDFNパッケージ                                                          |

| LTC6241           | デュアル、18MHz、低ノイズ、レール・トゥ・レール・オペアンプ                                      | 550nVP-Pノイズ、オフセット:最大125 $\mu\text{V}$                                                                   |

| LT6660            | マイクロパワー・リファレンス、2mm×2mm DFNパッケージ、2.5V、3V、3.3V、5V                       | ドリフト:最大20ppm/ $^{\circ}\text{C}$ 、最大0.2%                                                                |

| LTC2450           | 使いやすい超小型16ビットADC                                                      | INL:2LSB、スリープ電流:50nA、小型2mm×2mm DFN-6パッケージ、出力レート:30Hz                                                    |

| LTC2450-1         | 使いやすい超小型16ビットADC                                                      | INL:2LSB、スリープ電流:50nA、小型2mm×2mm DFN-6パッケージ、出力レート:60Hz                                                    |

2453fc