8 チャネル/16 チャネル

24 ビット No Latency  $\Delta\Sigma^{\text{TM}}$  A/D コンバータ

**特長**

- 8チャネル/16チャネル・シングルエンド入力または4チャネル/8チャネル差動入力(LTC2414/LTC2418)

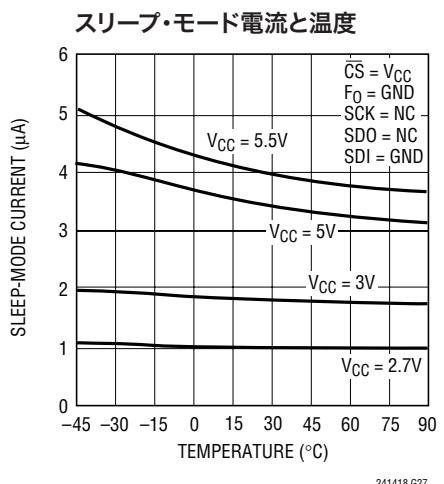

- 低電源電流(動作時  $200\mu\text{A}$ 、オースリーブ時  $4\mu\text{A}$ )

- GND～ $V_{CC}$ の同相範囲をもつ差動入力および差動リファレンス

- INL 2ppm、欠落コードなし

- 2.5ppm のフルスケール誤差と 0.5ppm のオフセット

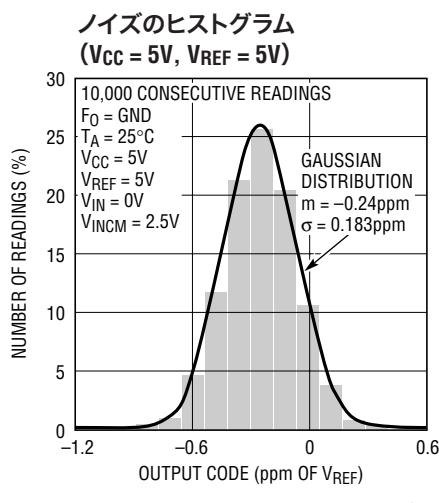

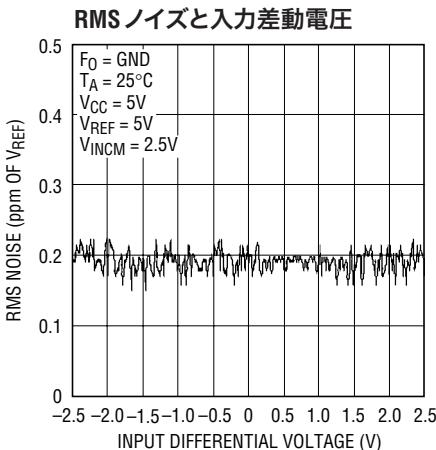

- ノイズ: 0.2ppm

- 待ち時間なし: デジタル・フィルタが単一サイクルで安定、新しいチャネルを選択した後も各変換は正確

- 2.7V～5.5V の単一電源動作

- 内部発振器—外付け部品が不要

- 最小  $110\text{dB}$ 、50Hz/60Hz のノッチ・フィルタ

**アプリケーション**

- ダイレクト・センサ・デジタイザ

- 秤

- 直接温度測定

- ガス分析器

- 歪みゲージ・トランスジューサ

- 計測器

- データ収集

- 産業用プロセス制御

**概要**

LTC®2414/LTC2418は、8チャネル/16チャネル(4チャネル/8チャネル差動)マイクロパワー24ビット $\Delta\Sigma$ アナログ/デジタル・コンバータです。発振器を内蔵し、INL 2ppm、RMS ノイズ 0.2ppm、2.7V～5.5Vで動作します。デルタシグマ技法を採用し、多重化アプリケーションに対応する1サイクルのセトリング時間を実現します。LTC2414/LTC2418は、1本のピンにより、50Hz または  $60\text{Hz} \pm 2\%$  で  $110\text{dB}$ 超の差動モード除去比を達成するように構成できます。また、ユーザー一定義の除去周波数に合わせて外部発振器で駆動することもできます。内部発振器には、周波数設定用の部品を外付けする必要はありません。

LTC2414/LTC2418は、0.1V～ $V_{CC}$ のあらゆる外部差動リファレンス電圧を使用できるので、レシオメトリックおよびリモート検出測定アプリケーションに柔軟に対応できます。また、4/8 差動チャネルまたは8/16シングルエンド・チャネルを使用するように構成可能です。フルスケールの両極性入力電圧範囲は、 $-0.5V_{REF}$ ～ $0.5V_{REF}$ です。リファレンス同相電圧  $V_{REFCM}$  と入力同相電圧  $V_{INCM}$  は、GND～ $V_{CC}$ の範囲で個別に設定可能です。DC 同相入力除去比は  $140\text{dB}$  より優れています。

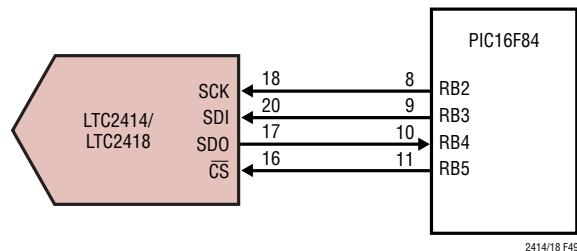

LTC2414/LTC2418は、SPI および MICROWIRE™ プロトコル互換の柔軟な4線デジタル・インターフェースを介して通信します。

□、LTC および LT はリニアテクノロジー社の登録商標です。No Latency  $\Delta\Sigma$  はリニアテクノロジー社の商標です。その他すべての商標の所有権は、それぞれの所有者に帰属します。

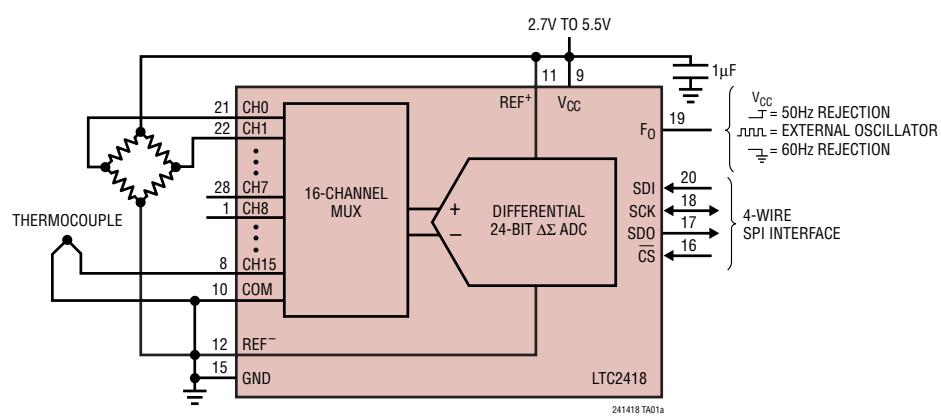

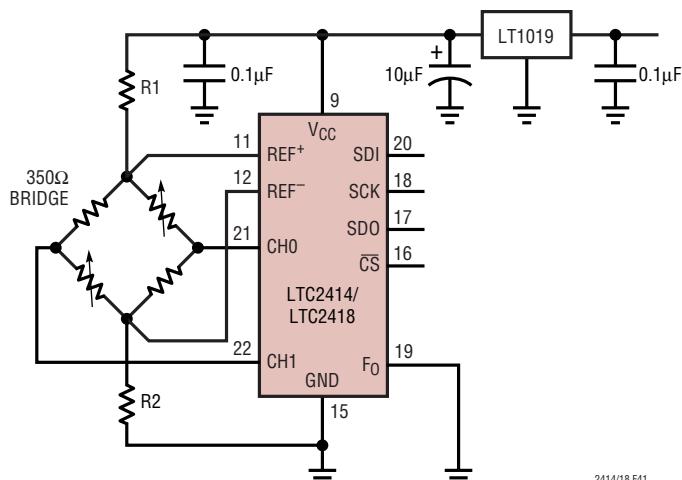

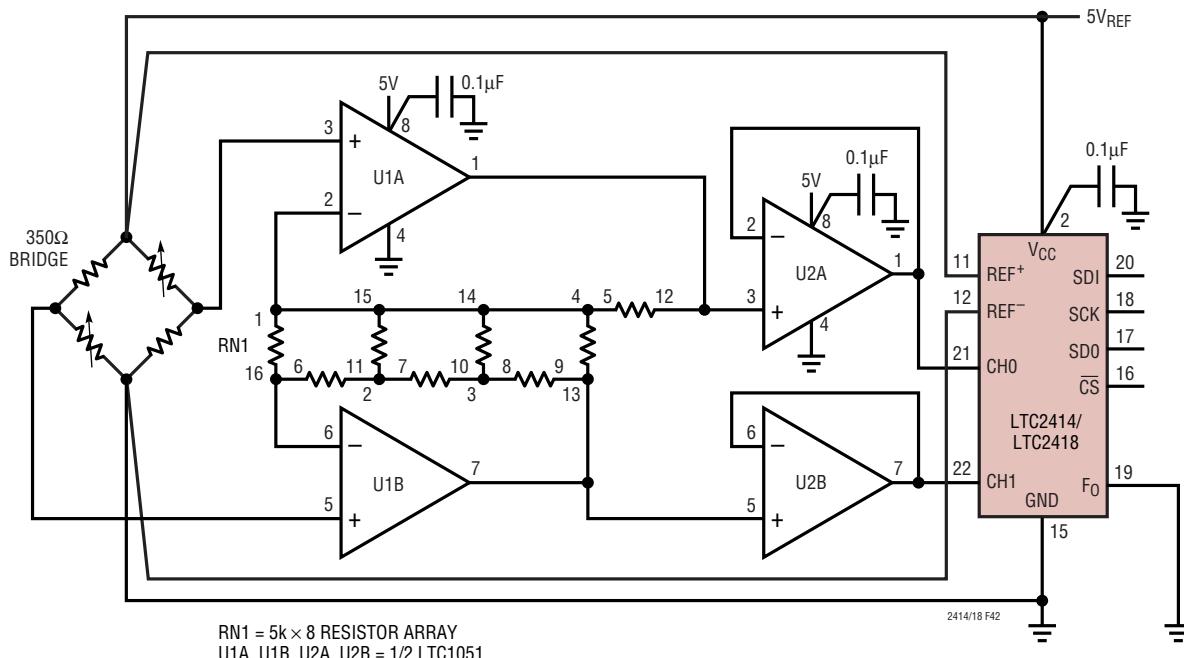

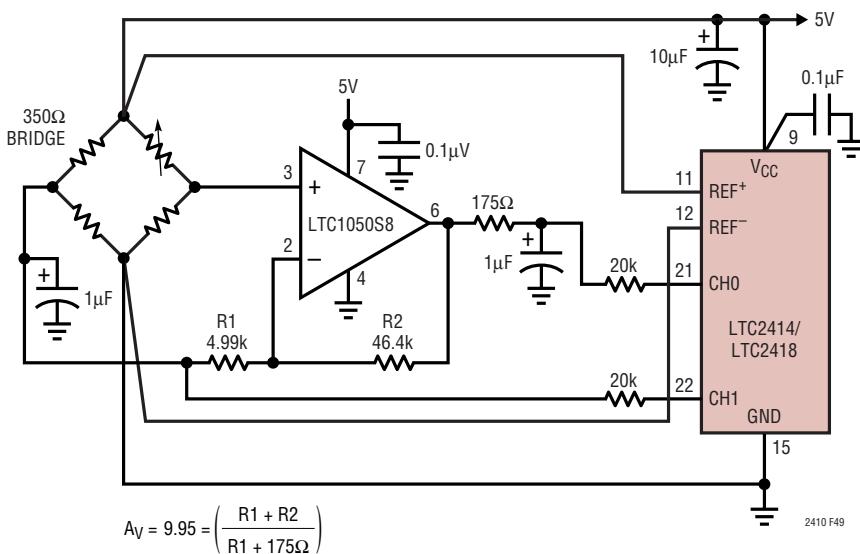

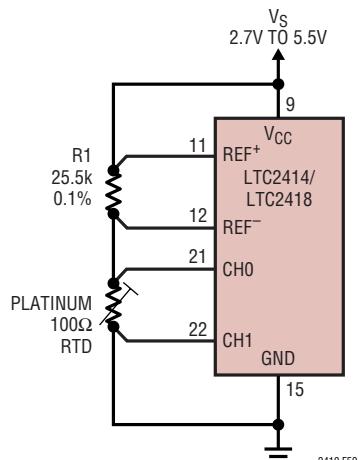

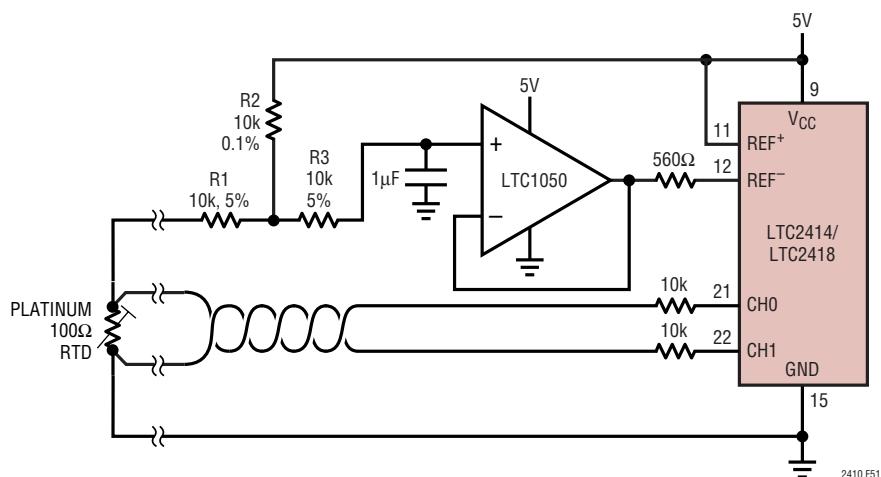

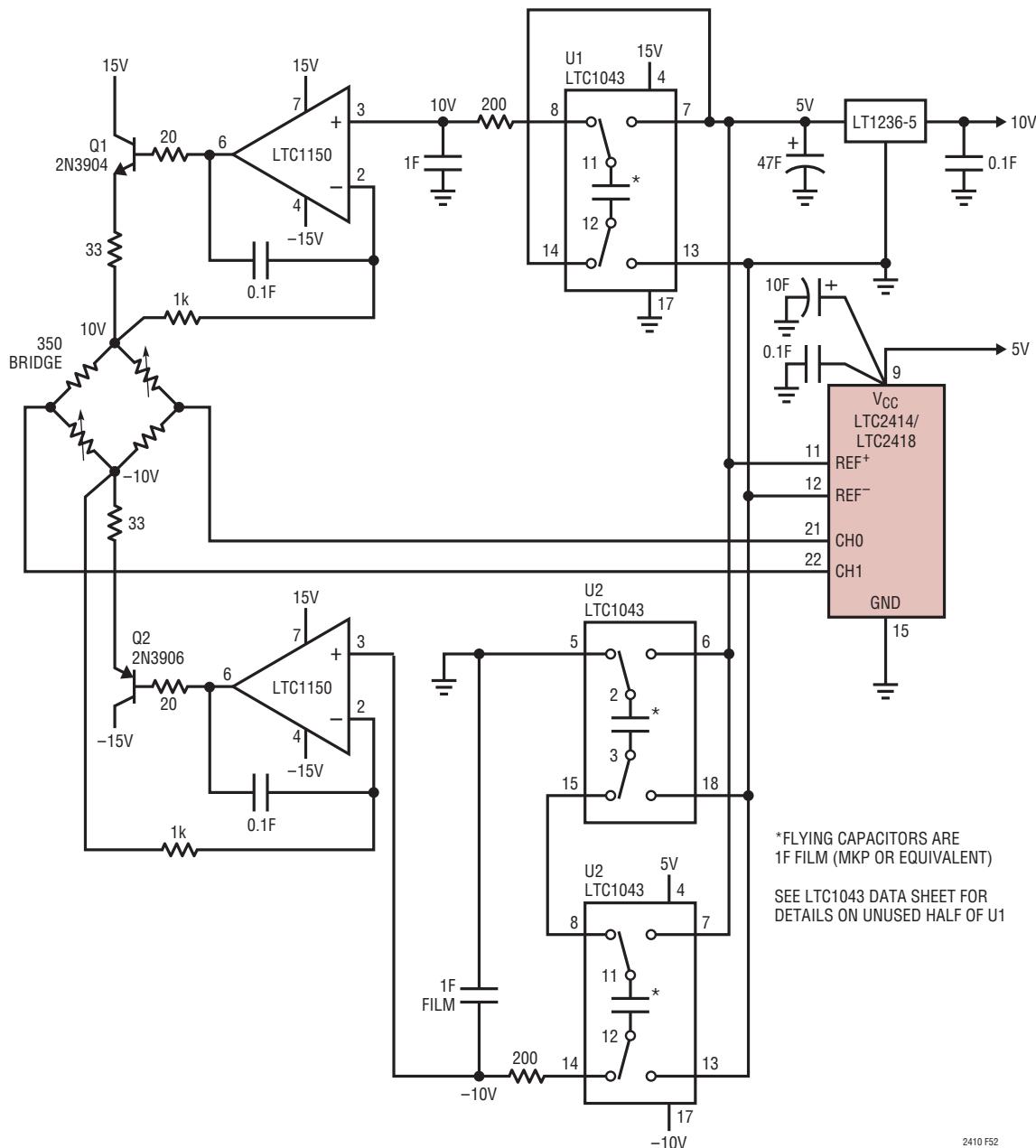

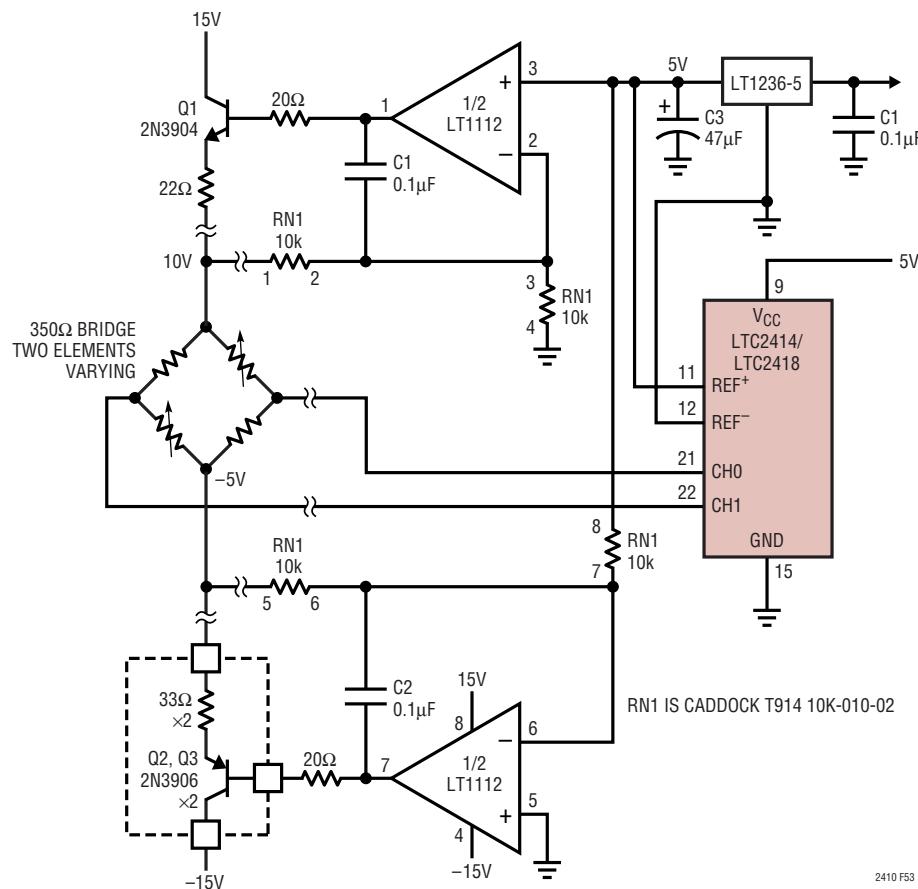

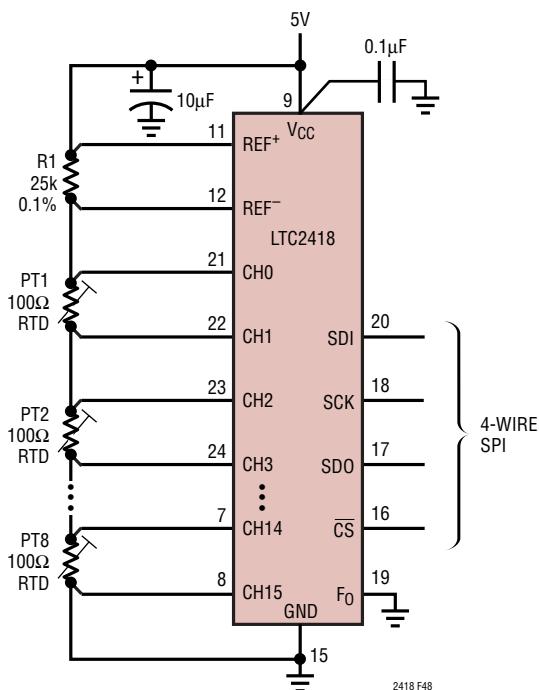

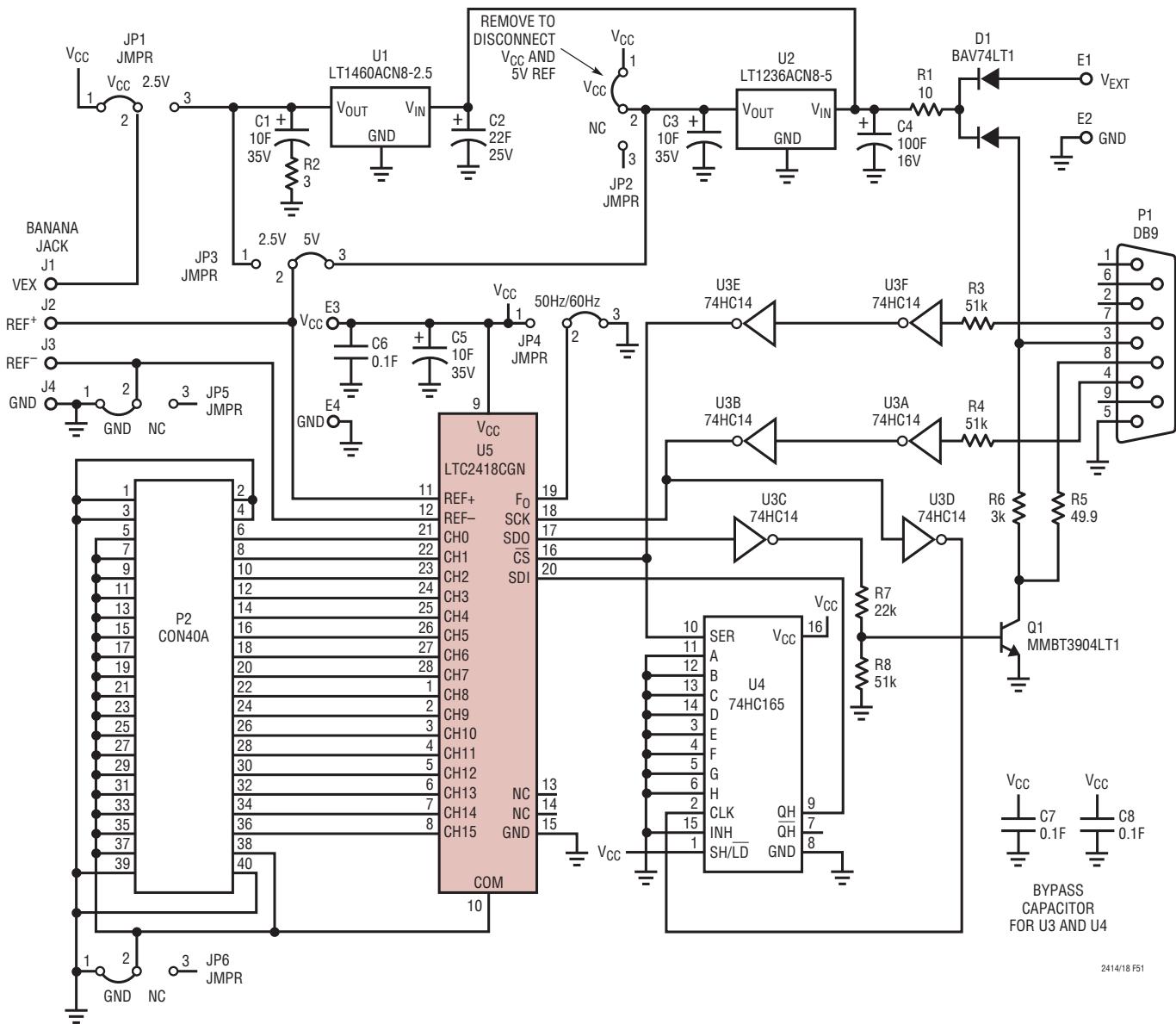

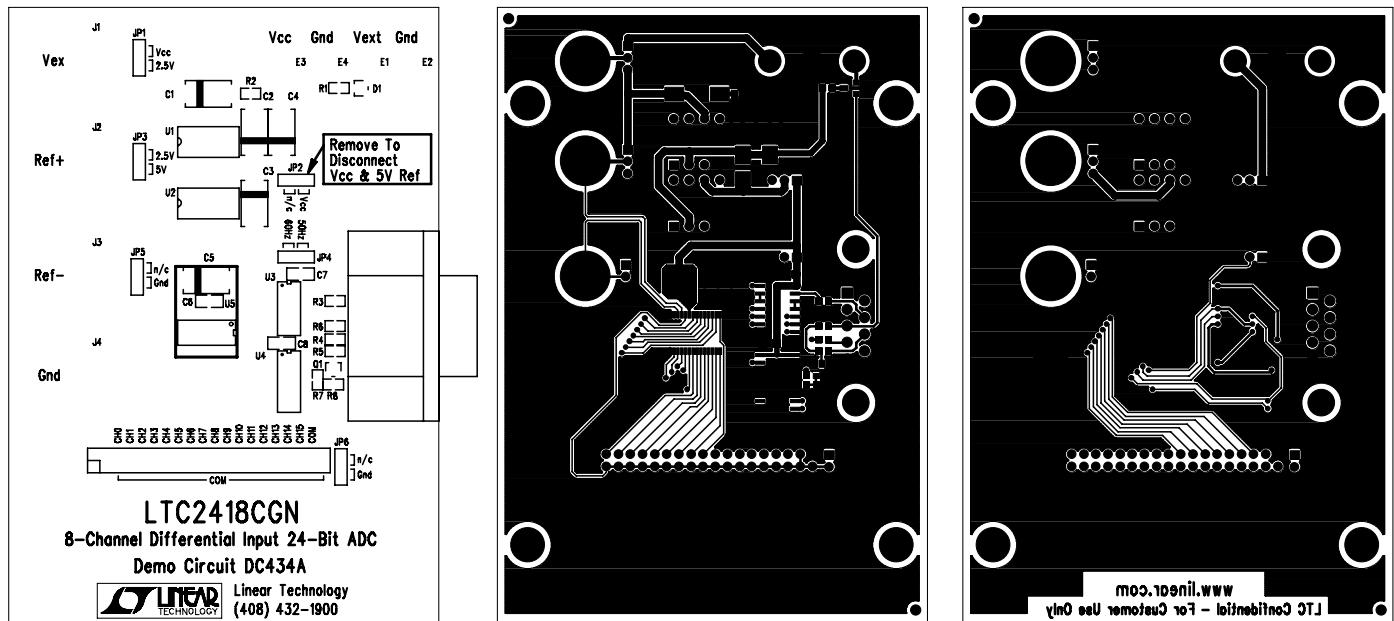

**標準的応用例**

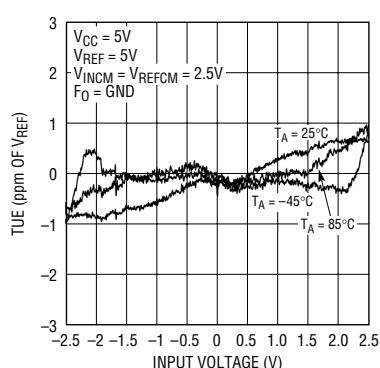

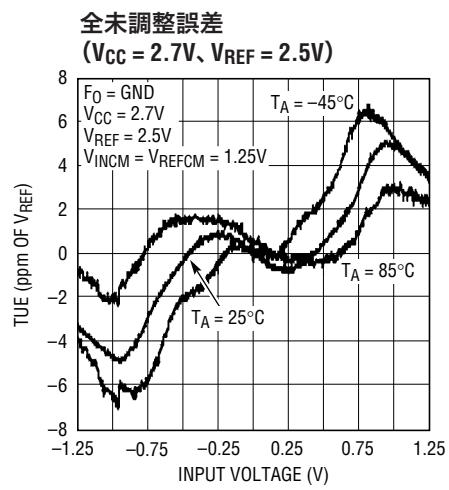

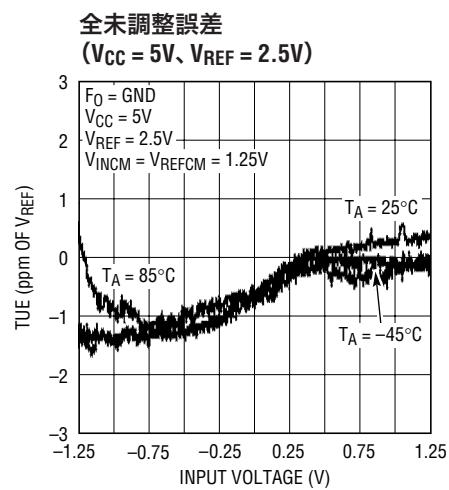

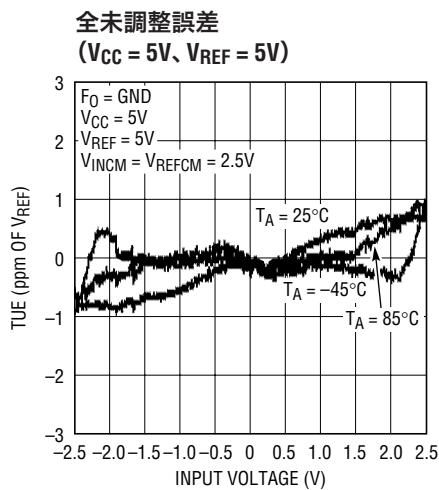

**全未調整誤差と入力電圧**

241418 TA01b

241418fa

# LTC2414/LTC2418

## 絶対最大定格 (Note 1, 2)

電源電圧 ( $V_{CC}$ ) 対 GND ..... -0.3V ~ 7V

アナログ入力電圧(対 GND) ..... -0.3V ~ ( $V_{CC} + 0.3V$ )

リファレンス入力電圧(対 GND) ..... -0.3V ~ ( $V_{CC} + 0.3V$ )

デジタル入力電圧(対 GND) ..... -0.3V ~ ( $V_{CC} + 0.3V$ )

デジタル出力電圧(対 GND) ..... -0.3V ~ ( $V_{CC} + 0.3V$ )

## 動作温度範囲

LTC2414/LTC2418C ..... 0°C ~ 70°C

LTC2414/LTC2418I ..... -40°C ~ 85°C

保存温度範囲 ..... -65°C ~ 150°C

リード温度(半田付け、10秒) ..... 300°C

## パッケージ/発注情報

| TOP VIEW         |    | TOP VIEW |            |

|------------------|----|----------|------------|

| NC               | 1  | 28       | CH7        |

| NC               | 2  | 27       | CH6        |

| NC               | 3  | 26       | CH5        |

| NC               | 4  | 25       | CH4        |

| NC               | 5  | 24       | CH3        |

| NC               | 6  | 23       | CH2        |

| NC               | 7  | 22       | CH1        |

| NC               | 8  | 21       | CH0        |

| $V_{CC}$         | 9  | 20       | SDI        |

| COM              | 10 | 19       | $F_0$      |

| REF <sup>+</sup> | 11 | 18       | SCK        |

| REF <sup>-</sup> | 12 | 17       | SDO        |

| NC               | 13 | 16       | $\bar{CS}$ |

| NC               | 14 | 15       | GND        |

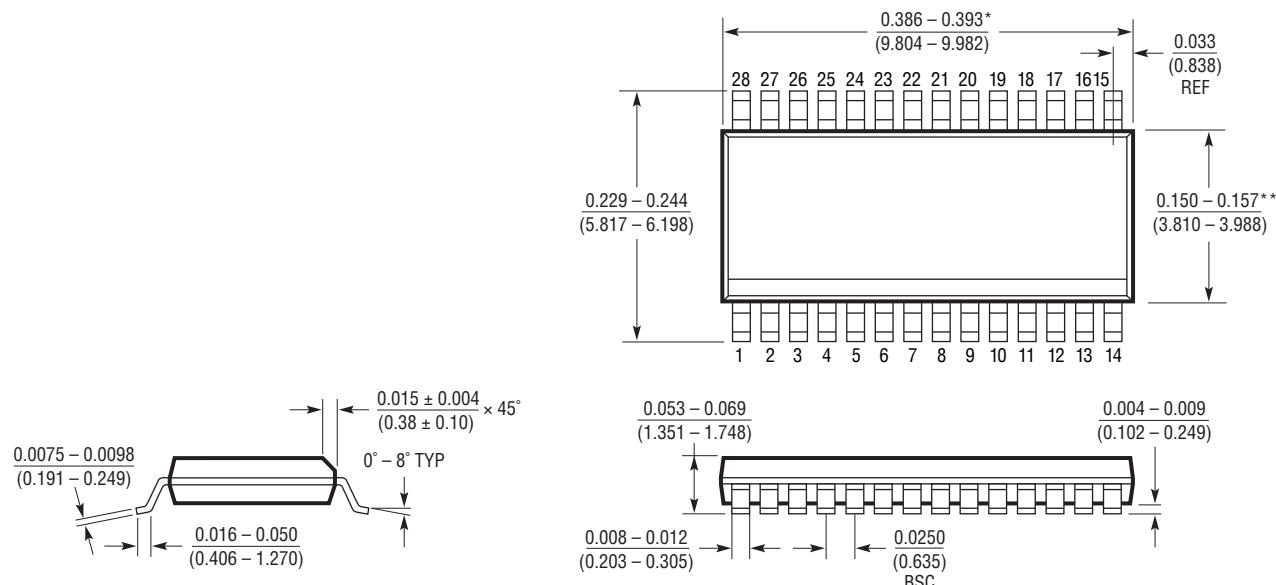

GN PACKAGE

28-LEAD PLASTIC SSOP

$T_{JMAX} = 125^{\circ}\text{C}$ ,  $\theta_{JA} = 110^{\circ}\text{C/W}$

GN PACKAGE

28-LEAD PLASTIC SSOP

$T_{JMAX} = 125^{\circ}\text{C}$ ,  $\theta_{JA} = 110^{\circ}\text{C/W}$

| ORDER PART NUMBER | PART MARKING | ORDER PART NUMBER | PART MARKING |

|-------------------|--------------|-------------------|--------------|

| LTC2414CGN        |              | LTC2418CGN        |              |

| LTC2414IGN        |              | LTC2418IGN        |              |

**発注情報** テープアンドリール:#TRを付加

無鉛仕上げ:#PBFを付加 無鉛仕上げのテープアンドリール:#TRPBFを付加

無鉛仕上げの製品マーキング:<http://www.linear-tech.co.jp/leadfree/>

\* 温度グレードは出荷時のコンテナのラベルで識別されます。さらに広い動作温度範囲で規定されるデバイスについては、弊社または弊社代理店にお問い合わせください。

## 電気的特性

●は全動作温度範囲での規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値(Note 3、4)。

| PARAMETER                       | CONDITIONS                                                                                                                                                                                                                                                                                                                      | MIN | TYP         | MAX | UNITS                                                                         |

|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------------|-----|-------------------------------------------------------------------------------|

| Resolution (No Missing Codes)   | $0.1V \leq V_{\text{REF}} \leq V_{\text{CC}}, -0.5 \cdot V_{\text{REF}} \leq V_{\text{IN}} \leq 0.5 \cdot V_{\text{REF}}$ (Note 5)                                                                                                                                                                                              | ●   | 24          |     | Bits                                                                          |

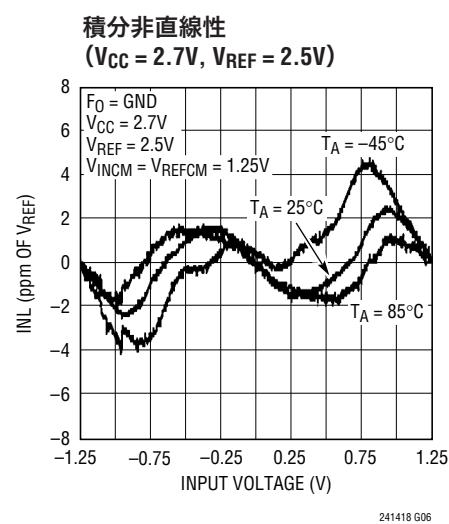

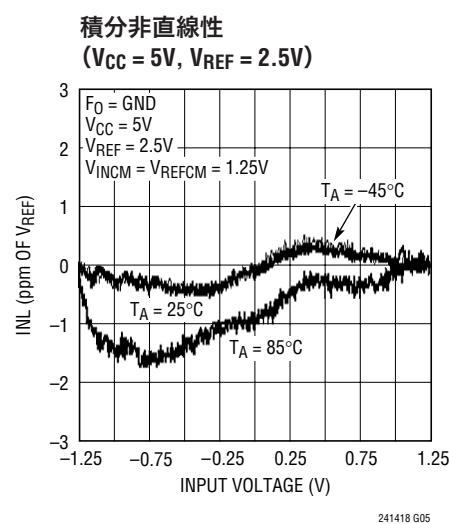

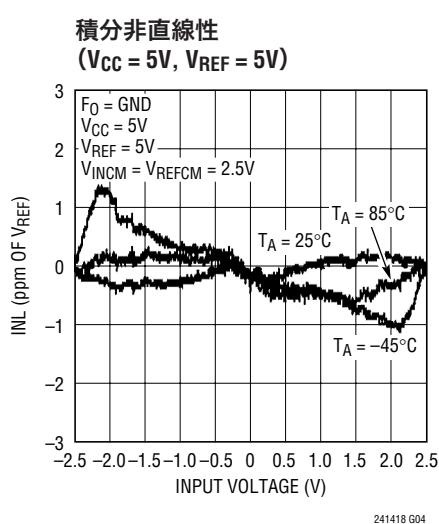

| Integral Nonlinearity           | $4.5V \leq V_{\text{CC}} \leq 5.5V, \text{REF}^+ = 2.5V, \text{REF}^- = \text{GND}, V_{\text{INCM}} = 1.25V$ (Note 6)<br>$5V \leq V_{\text{CC}} \leq 5.5V, \text{REF}^+ = 5V, \text{REF}^- = \text{GND}, V_{\text{INCM}} = 2.5V$ (Note 6)<br>$\text{REF}^+ = 2.5V, \text{REF}^- = \text{GND}, V_{\text{INCM}} = 1.25V$ (Note 6) | ●   | 1<br>2<br>5 | 14  | ppm of $V_{\text{REF}}$<br>ppm of $V_{\text{REF}}$<br>ppm of $V_{\text{REF}}$ |

| Offset Error                    | $2.5V \leq \text{REF}^+ \leq V_{\text{CC}}, \text{REF}^- = \text{GND}, GND \leq \text{IN}^+ = \text{IN}^- \leq V_{\text{CC}}$ (Note 14)                                                                                                                                                                                         | ●   | 2.5         | 10  | $\mu\text{V}$                                                                 |

| Offset Error Drift              | $2.5V \leq \text{REF}^+ \leq V_{\text{CC}}, \text{REF}^- = \text{GND}, GND \leq \text{IN}^+ = \text{IN}^- \leq V_{\text{CC}}$                                                                                                                                                                                                   |     | 20          |     | $\text{nV}/^\circ\text{C}$                                                    |

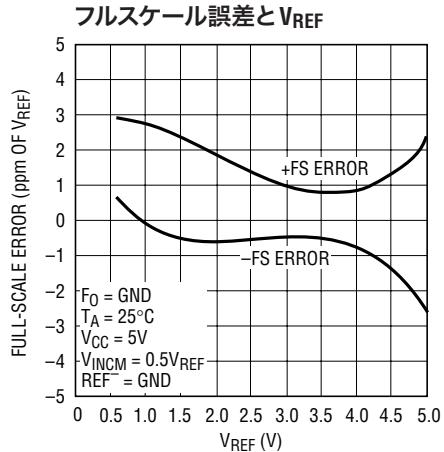

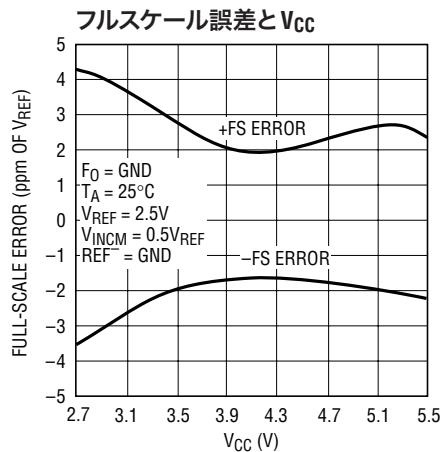

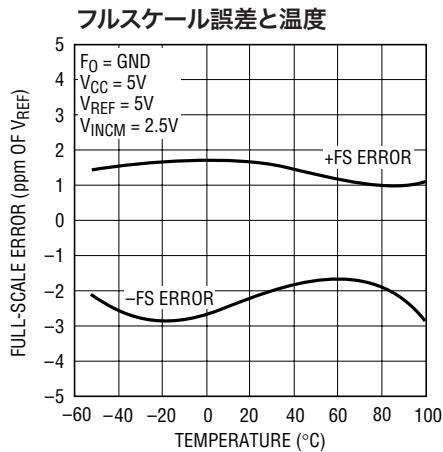

| Positive Full-Scale Error       | $2.5V \leq \text{REF}^+ \leq V_{\text{CC}}, \text{REF}^- = \text{GND}, \text{IN}^+ = 0.75 \cdot \text{REF}^+, \text{IN}^- = 0.25 \cdot \text{REF}^+$                                                                                                                                                                            | ●   | 2.5         | 12  | ppm of $V_{\text{REF}}$                                                       |

| Positive Full-Scale Error Drift | $2.5V \leq \text{REF}^+ \leq V_{\text{CC}}, \text{REF}^- = \text{GND}, \text{IN}^+ = 0.75 \cdot \text{REF}^+, \text{IN}^- = 0.25 \cdot \text{REF}^+$                                                                                                                                                                            |     | 0.03        |     | ppm of $V_{\text{REF}}/^\circ\text{C}$                                        |

| Negative Full-Scale Error       | $2.5V \leq \text{REF}^+ \leq V_{\text{CC}}, \text{REF}^- = \text{GND}, \text{IN}^+ = 0.25 \cdot \text{REF}^+, \text{IN}^- = 0.75 \cdot \text{REF}^+$                                                                                                                                                                            | ●   | 2.5         | 12  | ppm of $V_{\text{REF}}$                                                       |

| Negative Full-Scale Error Drift | $2.5V \leq \text{REF}^+ \leq V_{\text{CC}}, \text{REF}^- = \text{GND}, \text{IN}^+ = 0.25 \cdot \text{REF}^+, \text{IN}^- = 0.75 \cdot \text{REF}^+$                                                                                                                                                                            |     | 0.03        |     | ppm of $V_{\text{REF}}/^\circ\text{C}$                                        |

| Total Unadjusted Error          | $4.5V \leq V_{\text{CC}} \leq 5.5V, \text{REF}^+ = 2.5V, \text{REF}^- = \text{GND}, V_{\text{INCM}} = 1.25V$<br>$5V \leq V_{\text{CC}} \leq 5.5V, \text{REF}^+ = 5V, \text{REF}^- = \text{GND}, V_{\text{INCM}} = 2.5V$<br>$\text{REF}^+ = 2.5V, \text{REF}^- = \text{GND}, V_{\text{INCM}} = 1.25V$                            |     | 3<br>3<br>6 |     | ppm of $V_{\text{REF}}$<br>ppm of $V_{\text{REF}}$<br>ppm of $V_{\text{REF}}$ |

| Output Noise                    | $5V \leq V_{\text{CC}} \leq 5.5V, \text{REF}^+ = 5V, V_{\text{REF}^-} = \text{GND}, GND \leq \text{IN}^- = \text{IN}^+ \leq 5V$ (Note 13)                                                                                                                                                                                       |     | 1           |     | $\mu\text{VRMS}$                                                              |

## コンバータ特性

●は全動作温度範囲での規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値(Note 3、4)。

| PARAMETER                                  | CONDITIONS                                                                                                                                                  | MIN | TYP | MAX | UNITS |

|--------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|-------|

| Input Common Mode Rejection DC             | $2.5V \leq \text{REF}^+ \leq V_{\text{CC}}, \text{REF}^- = \text{GND}, GND \leq \text{IN}^- = \text{IN}^+ \leq 5V$ (Note 5)                                 | ●   | 130 | 140 | dB    |

| Input Common Mode Rejection 60Hz $\pm 2\%$ | $2.5V \leq \text{REF}^+ \leq V_{\text{CC}}, \text{REF}^- = \text{GND}, GND \leq \text{IN}^- = \text{IN}^+ \leq 5V$ (Notes 5, 7)                             | ●   | 140 |     | dB    |

| Input Common Mode Rejection 50Hz $\pm 2\%$ | $2.5V \leq \text{REF}^+ \leq V_{\text{CC}}, \text{REF}^- = \text{GND}, GND \leq \text{IN}^- = \text{IN}^+ \leq 5V$ (Notes 5, 8)                             | ●   | 140 |     | dB    |

| Input Normal Mode Rejection 60Hz $\pm 2\%$ | (Notes 5, 7)                                                                                                                                                | ●   | 110 | 140 | dB    |

| Input Normal Mode Rejection 50Hz $\pm 2\%$ | (Notes 5, 8)                                                                                                                                                | ●   | 110 | 140 | dB    |

| Reference Common Mode Rejection DC         | $2.5V \leq \text{REF}^+ \leq V_{\text{CC}}, \text{GND} \leq \text{REF}^- \leq 2.5V, V_{\text{REF}} = 2.5V, \text{IN}^- = \text{IN}^+ = \text{GND}$ (Note 5) | ●   | 130 | 140 | dB    |

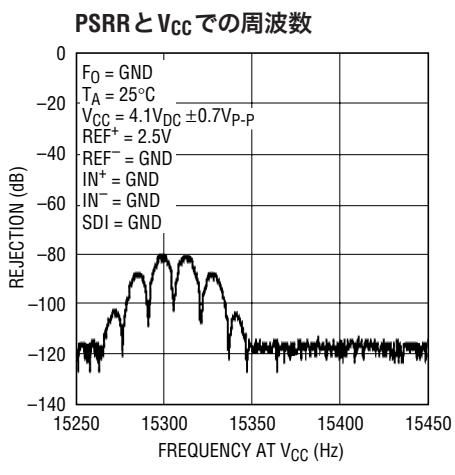

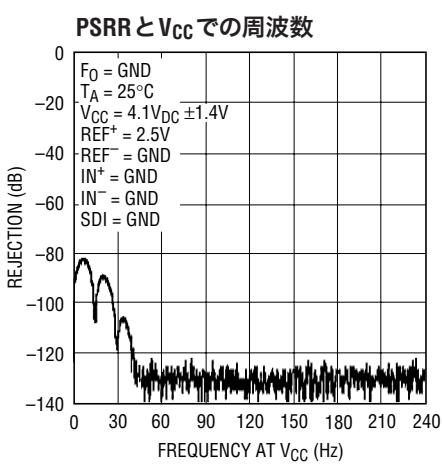

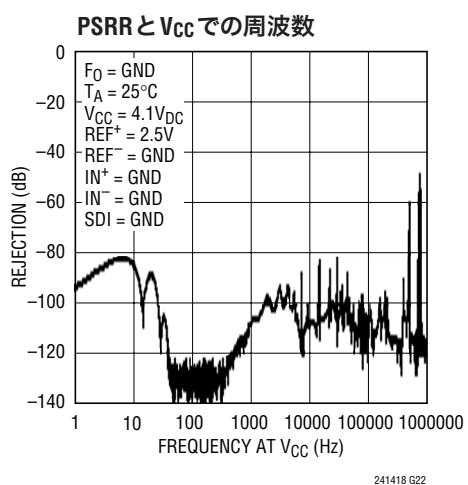

| Power Supply Rejection, DC                 | $\text{REF}^+ = 2.5V, \text{REF}^- = \text{GND}, \text{IN}^- = \text{IN}^+ = \text{GND}$                                                                    |     | 110 |     | dB    |

| Power Supply Rejection, 60Hz $\pm 2\%$     | $\text{REF}^+ = 2.5V, \text{REF}^- = \text{GND}, \text{IN}^- = \text{IN}^+ = \text{GND}$ (Note 7)                                                           |     | 120 |     | dB    |

| Power Supply Rejection, 50Hz $\pm 2\%$     | $\text{REF}^+ = 2.5V, \text{REF}^- = \text{GND}, \text{IN}^- = \text{IN}^+ = \text{GND}$ (Note 8)                                                           |     | 120 |     | dB    |

# LTC2414/LTC2418

## アナログ入力およびリファレンス

●は全動作温度範囲での規格値を意味する。それ以外は  $T_A = 25^\circ\text{C}$  での値(Note 3)。

| SYMBOL                                   | PARAMETER                                                                   | CONDITIONS                                          | MIN | TYP                  | MAX                   | UNITS          |    |

|------------------------------------------|-----------------------------------------------------------------------------|-----------------------------------------------------|-----|----------------------|-----------------------|----------------|----|

| IN <sup>+</sup>                          | Absolute/Common Mode IN <sup>+</sup> Voltage                                |                                                     | ●   | GND - 0.3            | V <sub>CC</sub> + 0.3 | V              |    |

| IN <sup>-</sup>                          | Absolute/Common Mode IN <sup>-</sup> Voltage                                |                                                     | ●   | GND - 0.3            | V <sub>CC</sub> + 0.3 | V              |    |

| V <sub>IN</sub>                          | Input Differential Voltage Range (IN <sup>+</sup> - IN <sup>-</sup> )       |                                                     | ●   | -V <sub>REF</sub> /2 | V <sub>REF</sub> /2   | V              |    |

| REF <sup>+</sup>                         | Absolute/Common Mode REF <sup>+</sup> Voltage                               |                                                     | ●   | 0.1                  | V <sub>CC</sub>       | V              |    |

| REF <sup>-</sup>                         | Absolute/Common Mode REF <sup>-</sup> Voltage                               |                                                     | ●   | GND                  | V <sub>CC</sub> - 0.1 | V              |    |

| V <sub>REF</sub>                         | Reference Differential Voltage Range (REF <sup>+</sup> - REF <sup>-</sup> ) |                                                     | ●   | 0.1                  | V <sub>CC</sub>       | V              |    |

| C <sub>S</sub> (IN <sup>+</sup> )        | IN <sup>+</sup> Sampling Capacitance                                        |                                                     |     |                      | 18                    | pF             |    |

| C <sub>S</sub> (IN <sup>-</sup> )        | IN <sup>-</sup> Sampling Capacitance                                        |                                                     |     |                      | 18                    | pF             |    |

| C <sub>S</sub> (REF <sup>+</sup> )       | REF <sup>+</sup> Sampling Capacitance                                       |                                                     |     |                      | 18                    | pF             |    |

| C <sub>S</sub> (REF <sup>-</sup> )       | REF <sup>-</sup> Sampling Capacitance                                       |                                                     |     |                      | 18                    | pF             |    |

| I <sub>DC_LEAK</sub> (IN <sup>+</sup> )  | IN <sup>+</sup> DC Leakage Current                                          | CS = V <sub>CC</sub> = 5.5V, IN <sup>+</sup> = GND  | ●   | -10                  | 1                     | 10             | nA |

| I <sub>DC_LEAK</sub> (IN <sup>-</sup> )  | IN <sup>-</sup> DC Leakage Current                                          | CS = V <sub>CC</sub> = 5.5V, IN <sup>-</sup> = 5V   | ●   | -10                  | 1                     | 10             | nA |

| I <sub>DC_LEAK</sub> (REF <sup>+</sup> ) | REF <sup>+</sup> DC Leakage Current                                         | CS = V <sub>CC</sub> = 5.5V, REF <sup>+</sup> = 5V  | ●   | -10                  | 1                     | 10             | nA |

| I <sub>DC_LEAK</sub> (REF <sup>-</sup> ) | REF <sup>-</sup> DC Leakage Current                                         | CS = V <sub>CC</sub> = 5.5V, REF <sup>-</sup> = GND | ●   | -10                  | 1                     | 10             | nA |

|                                          | Off Channel to In Channel Isolation (R <sub>IN</sub> = 100Ω)                | DC<br>1Hz<br>f <sub>S</sub> = 15,3600Hz             |     |                      | 140<br>140<br>140     | dB<br>dB<br>dB |    |

| t <sub>OPEN</sub>                        | MUX Break-Before-Make Interval                                              | 2.7V ≤ V <sub>CC</sub> ≤ 5.5V                       |     | 70                   | 100                   | 300            | ns |

| I <sub>S(OFF)</sub>                      | Channel Off Leakage Current                                                 | Channel at V <sub>CC</sub> and GND                  | ●   | -10                  | 1                     | 10             | nA |

## デジタル入力およびデジタル出力

●は全動作温度範囲での規格値を意味する。それ以外は  $T_A = 25^\circ\text{C}$  での値(Note 3)。

| SYMBOL          | PARAMETER                                          | CONDITIONS                                                                       | MIN | TYP                   | MAX        | UNITS  |

|-----------------|----------------------------------------------------|----------------------------------------------------------------------------------|-----|-----------------------|------------|--------|

| V <sub>IH</sub> | High Level Input Voltage CS, F <sub>O</sub> , SDI  | 2.7V ≤ V <sub>CC</sub> ≤ 5.5V<br>2.7V ≤ V <sub>CC</sub> ≤ 3.3V                   | ●   | 2.5<br>2.0            |            | V<br>V |

| V <sub>IL</sub> | Low Level Input Voltage CS, F <sub>O</sub> , SDI   | 4.5V ≤ V <sub>CC</sub> ≤ 5.5V<br>2.7V ≤ V <sub>CC</sub> ≤ 5.5V                   | ●   |                       | 0.8<br>0.6 | V<br>V |

| V <sub>IH</sub> | High Level Input Voltage SCK                       | 2.7V ≤ V <sub>CC</sub> ≤ 5.5V (Note 9)<br>2.7V ≤ V <sub>CC</sub> ≤ 3.3V (Note 9) | ●   | 2.5<br>2.0            |            | V<br>V |

| V <sub>IL</sub> | Low Level Input Voltage SCK                        | 4.5V ≤ V <sub>CC</sub> ≤ 5.5V (Note 9)<br>2.7V ≤ V <sub>CC</sub> ≤ 5.5V (Note 9) | ●   |                       | 0.8<br>0.6 | V<br>V |

| I <sub>IN</sub> | Digital Input Current CS, F <sub>O</sub> , SDI     | 0V ≤ V <sub>IN</sub> ≤ V <sub>CC</sub>                                           | ●   | -10                   | 10         | μA     |

| I <sub>IN</sub> | Digital Input Current SCK                          | 0V ≤ V <sub>IN</sub> ≤ V <sub>CC</sub> (Note 9)                                  | ●   | -10                   | 10         | μA     |

| C <sub>IN</sub> | Digital Input Capacitance CS, F <sub>O</sub> , SDI |                                                                                  |     |                       | 10         | pF     |

| C <sub>IN</sub> | Digital Input Capacitance SCK                      | (Note 9)                                                                         |     |                       | 10         | pF     |

| V <sub>OH</sub> | High Level Output Voltage SDO                      | I <sub>O</sub> = -800μA                                                          | ●   | V <sub>CC</sub> - 0.5 |            | V      |

## デジタル入力およびデジタル出力

●は全動作温度範囲での規格値を意味する。それ以外は  $T_A = 25^\circ\text{C}$  での値(Note 3)。

| SYMBOL   | PARAMETER                        | CONDITIONS                        |   | MIN            | TYP | MAX | UNITS         |

|----------|----------------------------------|-----------------------------------|---|----------------|-----|-----|---------------|

| $V_{OL}$ | Low Level Output Voltage<br>SDO  | $I_0 = 1.6\text{mA}$              | ● |                |     | 0.4 | V             |

| $V_{OH}$ | High Level Output Voltage<br>SCK | $I_0 = -800\mu\text{A}$ (Note 10) | ● | $V_{CC} - 0.5$ |     |     | V             |

| $V_{OL}$ | Low Level Output Voltage<br>SCK  | $I_0 = 1.6\text{mA}$ (Note 10)    | ● |                |     | 0.4 | V             |

| $I_{OZ}$ | Hi-Z Output Leakage<br>SDO       |                                   | ● | -10            |     | 10  | $\mu\text{A}$ |

## 電源要件

●は全動作温度範囲での規格値を意味する。それ以外は  $T_A = 25^\circ\text{C}$  での値(Note 3)。

| SYMBOL   | PARAMETER                                                     | CONDITIONS                                                                                                                 |             | MIN           | TYP             | MAX           | UNITS |

|----------|---------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|-------------|---------------|-----------------|---------------|-------|

| $V_{CC}$ | Supply Voltage                                                |                                                                                                                            | ●           | 2.7           |                 | 5.5           | V     |

| $I_{CC}$ | Supply Current<br>Conversion Mode<br>Sleep Mode<br>Sleep Mode | $CS = 0\text{V}$ (Note 12)<br>$CS = V_{CC}$ (Note 12)<br>$CS = V_{CC}, 2.7\text{V} \leq V_{CC} \leq 3.3\text{V}$ (Note 12) | ●<br>●<br>● | 200<br>4<br>2 | 300<br>10<br>μA | 200<br>4<br>2 | μA    |

## タイミング特性

●は全動作温度範囲での規格値を意味する。それ以外は  $T_A = 25^\circ\text{C}$  での値(Note 3)。

| SYMBOL           | PARAMETER                            | CONDITIONS                                                               |             | MIN                                            | TYP                        | MAX    | UNITS          |

|------------------|--------------------------------------|--------------------------------------------------------------------------|-------------|------------------------------------------------|----------------------------|--------|----------------|

| $f_{EOSC}$       | External Oscillator Frequency Range  |                                                                          | ●           | 2.56                                           |                            | 2000   | kHz            |

| $t_{HEO}$        | External Oscillator High Period      |                                                                          | ●           | 0.25                                           |                            | 390    | μs             |

| $t_{LEO}$        | External Oscillator Low Period       |                                                                          | ●           | 0.25                                           |                            | 390    | μs             |

| $t_{CONV}$       | Conversion Time                      | $F_0 = 0\text{V}$<br>$F_0 = V_{CC}$<br>External Oscillator (Note 11)     | ●<br>●<br>● | 130.86<br>157.03<br>20510/ $f_{EOSC}$ (in kHz) | 133.53<br>160.23<br>163.44 | 136.20 | ms<br>ms<br>ms |

| $f_{ISCK}$       | Internal SCK Frequency               | Internal Oscillator (Note 10)<br>External Oscillator (Notes 10, 11)      |             |                                                | 19.2<br>$f_{EOSC}/8$       |        | kHz<br>kHz     |

| $D_{ISCK}$       | Internal SCK Duty Cycle              | (Note 10)                                                                | ●           | 45                                             |                            | 55     | %              |

| $f_{ESCK}$       | External SCK Frequency Range         | (Note 9)                                                                 | ●           |                                                |                            | 2000   | kHz            |

| $t_{LESCK}$      | External SCK Low Period              | (Note 9)                                                                 | ●           | 250                                            |                            |        | ns             |

| $t_{HESCK}$      | External SCK High Period             | (Note 9)                                                                 | ●           | 250                                            |                            |        | ns             |

| $t_{DOUT\_ISCK}$ | Internal SCK 32-Bit Data Output Time | Internal Oscillator (Notes 10, 12)<br>External Oscillator (Notes 10, 11) | ●<br>●      | 1.64<br>256/ $f_{EOSC}$ (in kHz)               | 1.67<br>1.70               |        | ms<br>ms       |

| $t_{DOUT\_ESCK}$ | External SCK 32-Bit Data Output Time | (Note 9)                                                                 | ●           |                                                | 32/ $f_{ESCK}$ (in kHz)    |        | ms             |

## タイミング特性

●は全動作温度範囲での規格値を意味する。それ以外は  $T_A = 25^\circ\text{C}$  での値(Note 3)。

| SYMBOL             | PARAMETER                                             | CONDITIONS | MIN | TYP | MAX | UNITS |

|--------------------|-------------------------------------------------------|------------|-----|-----|-----|-------|

| $t_1$              | $\overline{\text{CS}} \downarrow$ to SDO Low          |            | ●   | 0   | 200 | ns    |

| $t_2$              | $\overline{\text{CS}} \uparrow$ to SDO High Z         |            | ●   | 0   | 200 | ns    |

| $t_3$              | $\overline{\text{CS}} \downarrow$ to SCK $\downarrow$ | (Note 10)  | ●   | 0   | 200 | ns    |

| $t_4$              | $\overline{\text{CS}} \downarrow$ to SCK $\uparrow$   | (Note 9)   | ●   | 50  |     | ns    |

| $t_{\text{KQMAX}}$ | SCK $\downarrow$ to SDO Valid                         |            | ●   |     | 220 | ns    |

| $t_{\text{KQMIN}}$ | SDO Hold After SCK $\downarrow$                       | (Note 5)   | ●   | 15  |     | ns    |

| $t_5$              | SCK Set-Up Before $\overline{\text{CS}} \downarrow$   |            | ●   | 50  |     | ns    |

| $t_6$              | SCK Hold After $\overline{\text{CS}} \downarrow$      |            | ●   |     | 50  | ns    |

| $t_7$              | SDI Setup Before SCK $\uparrow$                       | (Note 5)   | ●   | 100 |     | ns    |

| $t_8$              | SDI Hold After SCK $\uparrow$                         | (Note 5)   | ●   | 100 |     | ns    |

Note 1: 絶対最大定格は、それを超えるとデバイスの寿命に悪影響を与える恐れがある値。

Note 2: すべての電圧値は GND を基準にしている。

Note 3: 注記がない限り、 $V_{\text{CC}} = 2.7\text{V} \sim 5.5\text{V}$ 。 $V_{\text{REF}} = \text{REF}^+ - \text{REF}^-$ 、 $V_{\text{REFCM}} = (\text{REF}^+ + \text{REF}^-)/2$ 。 $V_{\text{IN}} = \text{IN}^+ - \text{IN}^-$ 、 $V_{\text{INCM}} = (\text{IN}^+ + \text{IN}^-)/2$ 、 $\text{IN}^+$  および  $\text{IN}^-$  は、それぞれ選択された正および負の入力として定義される。

Note 4: 注記がない限り、 $F_0$  ピンの接続先は GND または  $V_{\text{CC}}$  または外部変換クロック信号源 ( $f_{\text{EOSC}} = 153600\text{Hz}$ )。

Note 5: 設計によって保証されているが、テストされない。

Note 6: 積分非直線性は、実際の伝達曲線の端点を通る直線からのコードの偏差として定義されている。偏差は量子化幅の中心から測定される。

Note 7:  $F_0 = 0\text{V}$  (内部発振器) または  $f_{\text{EOSC}} = 153600\text{Hz} \pm 2\%$  (外部発振器)。

Note 8:  $F_0 = V_{\text{CC}}$  (内部発振器) または  $f_{\text{EOSC}} = 128000\text{Hz} \pm 2\%$  (外部発振器)。

Note 9: コンバータは SCK ピンをデジタル入力として使用する外部 SCK 動作モードである。データの出力時に SCK を駆動するクロック信号の周波数は  $f_{\text{SCK}}$  で、kHz 単位で表される。

Note 10: コンバータは SCK ピンをデジタル出力として使用する内部 SCK 動作モードである。この動作モードでは、SCK ピンの全等価負荷容量  $C_{\text{LOAD}} = 20\text{pF}$  となる。

Note 11: 外部発振器は  $F_0$  ピンに接続される。外部発振器の周波数は  $f_{\text{EOSC}}$  で、kHz 単位で表される。

Note 12: コンバータは内部発振器を使用する。 $F_0 = 0\text{V}$  または  $F_0 = V_{\text{CC}}$ 。

Note 13: 出力ノイズには内部の較正動作に関わる部分が含まれる。

Note 14: 設計およびテストとの相関により保証されている。

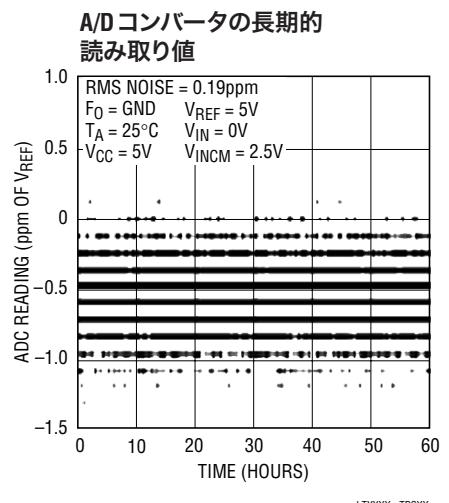

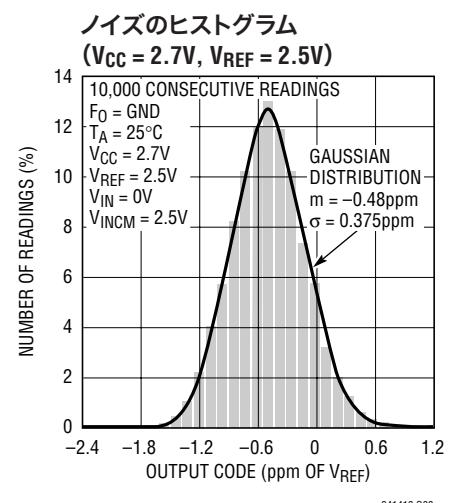

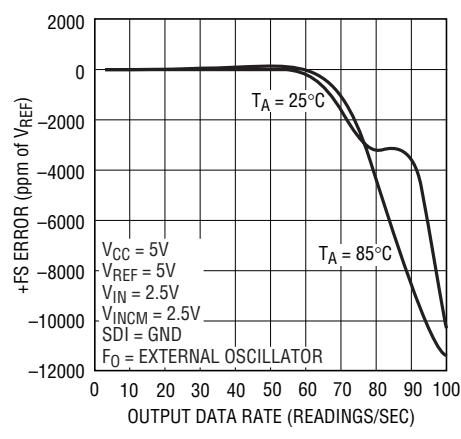

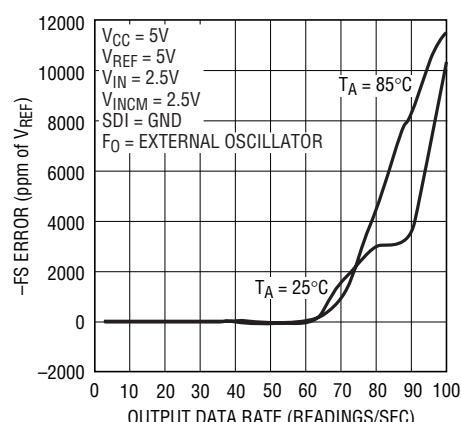

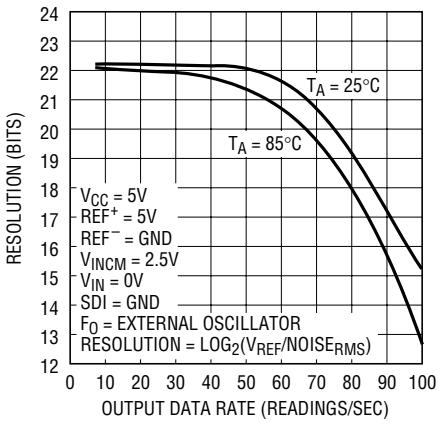

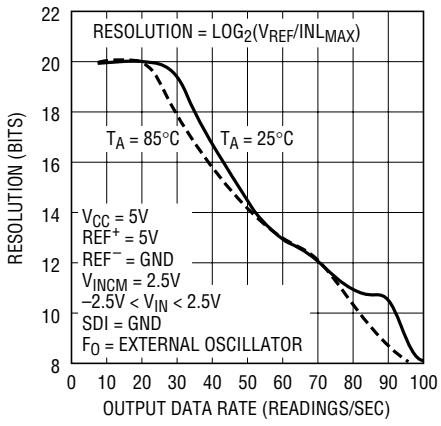

## 標準的性能特性

## 標準的性能特性

241418 G10

241418 G11

241418 G12

241418 G13

241418 G14

241418 G15

241418 G16

241418 G17

241418 G18

## 標準的性能特性

## ピン機能

**CH0～CH15 (ピン21～ピン28およびピン1～ピン8)**: アナログ入力。シングルエンド・モードまたは差動モードにプログラムすることができます。CH8～CH15 (ピン1～ピン8) は、LTC2414 では何も接続されていません。

**V<sub>CC</sub> (ピン9)**: 正の電源電圧。10μFのタンタル・コンデンサと0.1μFのセラミック・コンデンサをデバイスにできるだけ近づけて並列に接続し、GND (ピン15) にバイパスします。

**COM (ピン10)**: すべてのシングルエンド・マルチプレクサ構成の共通の負入力 (IN<sup>-</sup>)。チャネル0～15ピンおよびCOM入力ピンの電圧は、GND - 0.3V から V<sub>CC</sub> + 0.3Vまでの任意の値をとることができます。これらの制限範囲内では、選択された2つの入力 (IN<sup>+</sup> および IN<sup>-</sup>) の入力範囲は両極性 (V<sub>IN</sub> = IN<sup>+</sup> - IN<sup>-</sup>) で、-0.5 • V<sub>REF</sub> から 0.5 • V<sub>REF</sub> までとなります。この入力範囲外では、コンバータは独自のオーバーレンジ出力コードおよびアンダーレンジ出力コードを生成します。

**REF<sup>+</sup> (ピン11)、REF<sup>-</sup> (ピン12)**: 差動リファレンス入力。これらのピンの値は、正のリファレンス入力 (REF<sup>+</sup>) を負のリファレンス入力 (REF<sup>-</sup>) より 0.1V 以上高い電圧に維持する限り、GND から V<sub>CC</sub> までの任意の値にすることができます。

**GND (ピン15)**: グランド。このピンは低インピーダンスの接続点を介してグランド・プレーンに接続します。

**CS (ピン16)**: アクティブ“L”的デジタル入力。このピンを“L”にすると SDO デジタル出力がイネーブルされ、A/D コンバータが起動します。A/D コンバータは各変換後に自動的にスリープ・モードに入り、CS が“H”である限り、この低消費電力状態のままでです。データ出力伝送時に CS が“L”から“H”に切り替わると、データ伝送は中止され、新しい変換が始まります。

**SDO (ピン17)**: スリーステートのデジタル出力。データ出力期間中、このピンはシリアル・データ出力として使用されます。チップ選択 CS が“H” (CS = V<sub>CC</sub>) のとき、SDO ピンは高イン

ピーダンス状態です。変換期間中およびスリープ期間中、このピンは変換ステータス出力として使用されます。変換ステータスは CS を“L”にすれば確認できます。

**SCK (ピン18)**: 双方向のデジタル・クロック・ピン。内部シリアル・クロック動作モードでは、データ出力期間の間、内部シリアル・インターフェース・クロックのデジタル出力として SCK を使用します。外部シリアル・クロック動作モードでは、データ出力期間の間、外部シリアル・インターフェース・クロックのデジタル入力として SCK を使用します。内部シリアル・クロック動作モードでは、弱い内部プルアップが自動的に作動します。シリアル・クロック動作モードは、電源投入時または CS の直近の立ち上がりエッジのときに SCK に加わったロジック・レベルによって決まります。

**F<sub>0</sub> (ピン19)**: 周波数制御ピン。A/D コンバータのノッチ周波数および変換時間を制御するデジタル入力。F<sub>0</sub> ピンを V<sub>CC</sub> に接続すると (F<sub>0</sub> = V<sub>CC</sub>)、コンバータはその内部発振器を使用し、デジタル・フィルタの最初のヌルは 50Hz になります。F<sub>0</sub> ピンを GND に接続すると (F<sub>0</sub> = 0V)、コンバータはその内部発振器を使用し、デジタル・フィルタの最初のヌルは 60Hz になります。周波数が f<sub>EOSC</sub> の外部クロック信号で F<sub>0</sub> を駆動すると、コンバータはこの信号をコンバータのシステム・クロックとして使用し、デジタル・フィルタの最初のヌルの周波数は f<sub>EOSC</sub>/2560 になります。

**SDI (ピン20)**: シリアル・デジタル・データ入力。データ出力期間中、このピンは、SCK の最初の立ち上がりエッジから始まるマルチプレクサ・アドレスのシフト入力に使用されます。変換期間中およびスリープ期間中、このピンはドントケア状態になります。ただし、ドントケア・モードでは SDI の“H”または“L”的ロジック・レベルを維持して、SDI 入力バッファの電流が過剰にならないようにしてください。

**NC ピン**: 接続しないでください。

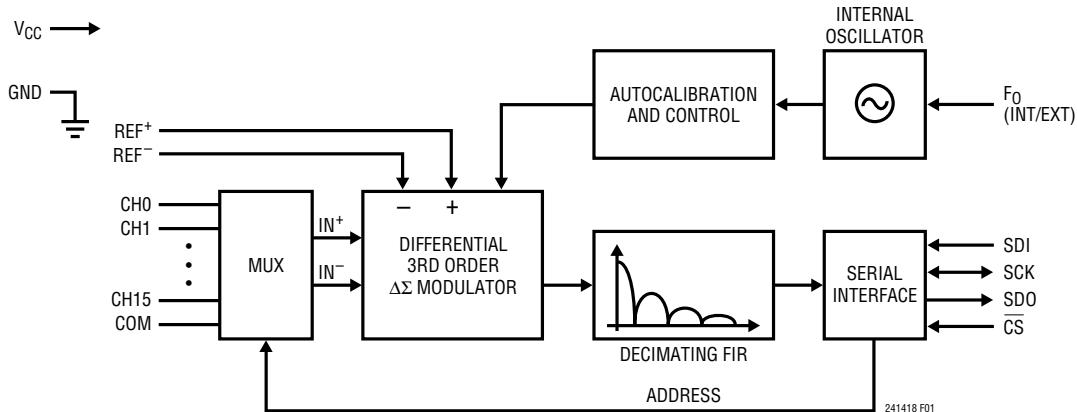

## 機能ブロック図

図1

## テスト回路

## アプリケーション情報

### コンバータの動作

### コンバータの動作サイクル

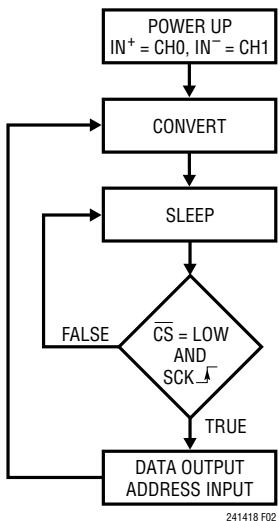

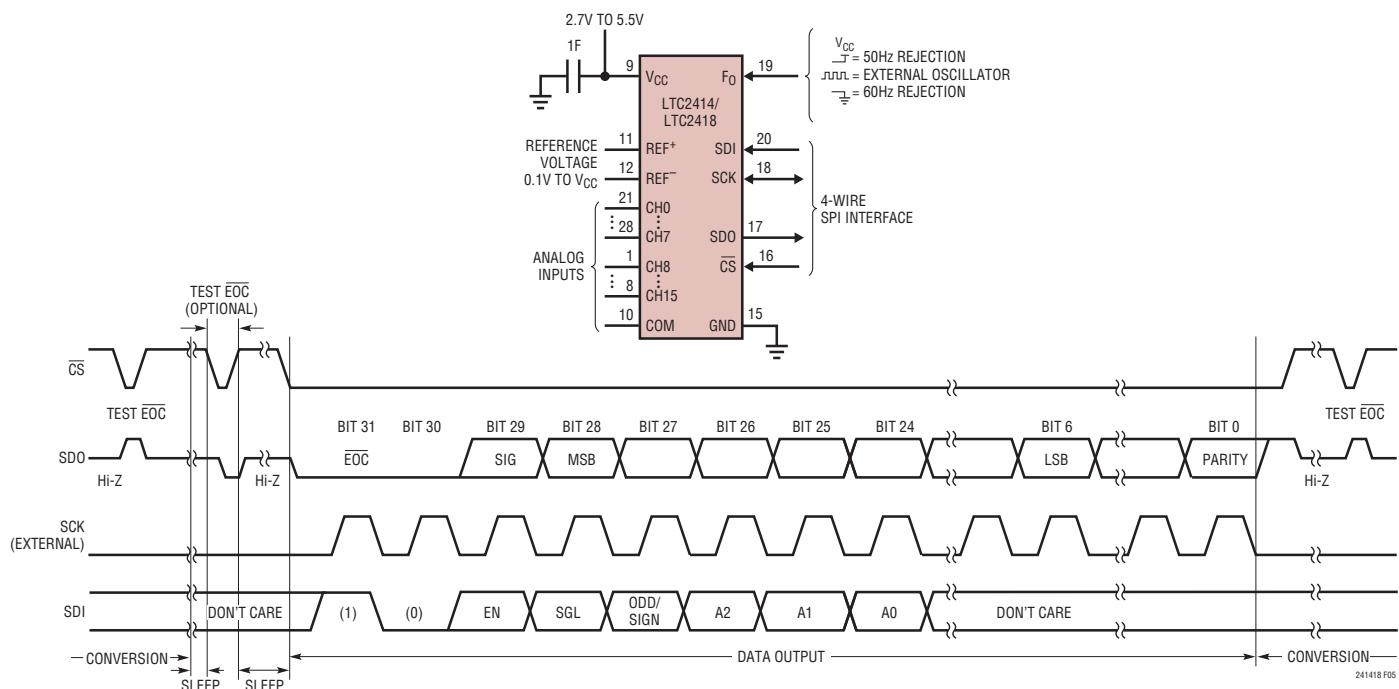

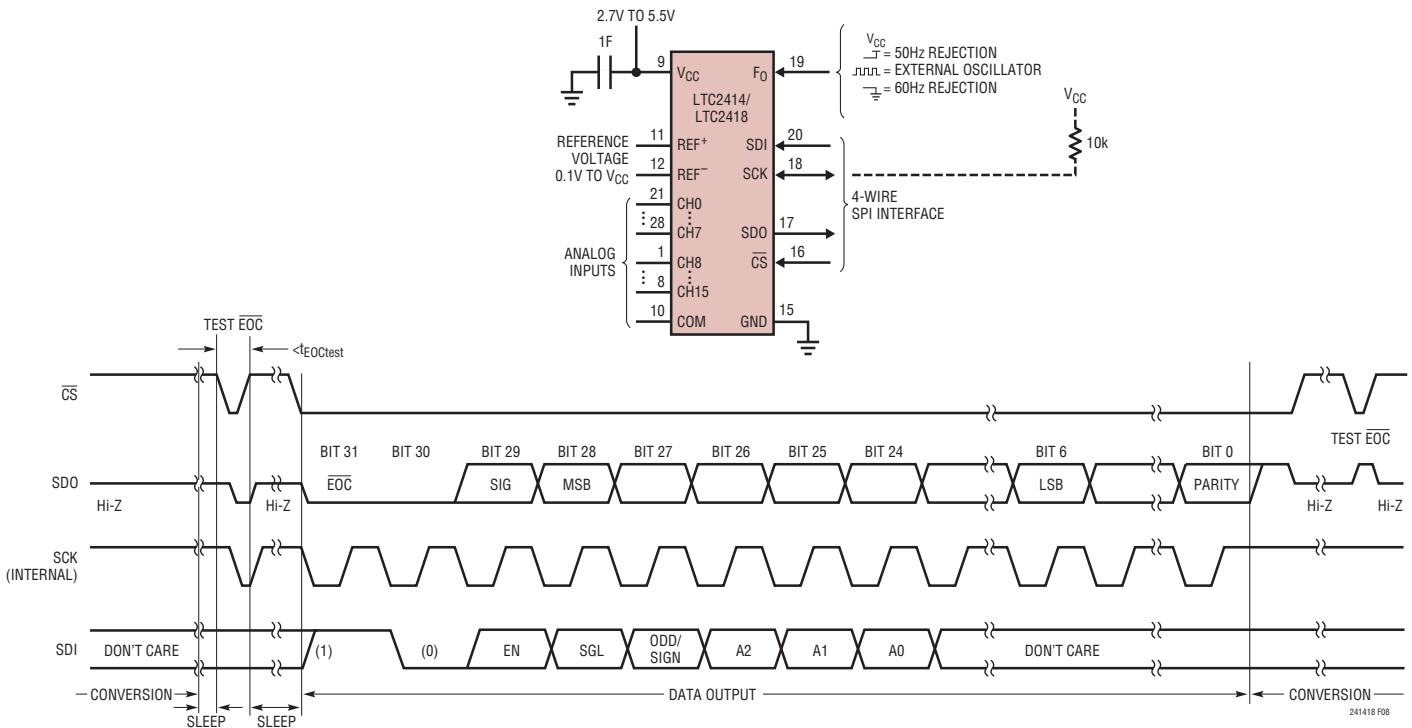

LTC2414/LTC2418は、使いやすい4線式シリアル・インターフェースを備えた多チャネル、低消費電力の $\Delta\Sigma$ アナログ/デジタル・コンバータです(図1を参照)。A/Dコンバータの動作は3つの状態からなります。コンバータの動作サイクルは変換から始まり、次に低消費電力のスリープ状態になり、データの入力/出力で終了します(図2を参照)。4線式インターフェースは、シリアル・データ入力(SDI)、シリアル・データ出力(SDO)、シリアル・クロック(SCK)、およびチップ選択( $\overline{CS}$ )で構成されています。

最初に、LTC2414またはLTC2418は変換を実行します。変換が完了すると、デバイスはスリープ状態になります。 $\overline{CS}$ が“H”

である限り、デバイスはスリープ状態のままでです。スリープ状態のとき、消費電力は2桁近く減ります。コンバータがスリープ状態のとき、変換結果は静的シフト・レジスタに無期限に保持されます。

いったん $\overline{CS}$ が“L”になると、デバイスは低消費電力モードを終了し、データ出力状態になります。SCKの最初の立ち上がりエッジの前に $\overline{CS}$ が“H”になると、デバイスは低消費電力のスリープ・モードに戻り、変換結果は内部の静的シフト・レジスタで引き続き保持されます。SCKの最初の立ち上がりエッジ後に $\overline{CS}$ が“L”的ままである場合、デバイスは変換結果の出力とチャネル選択制御ビットの入力を開始します。この時点で $\overline{CS}$ が“H”になると、データ出力状態は終了し、新しい変換が開始されます。チャネル選択制御ビットは、SCKの最初の立ち上がりエッジからSDIを介してシフトして入力されます。また、コンバ

241418fa

## アプリケーション情報

図2. LTC2414/LTC2418の状態遷移図

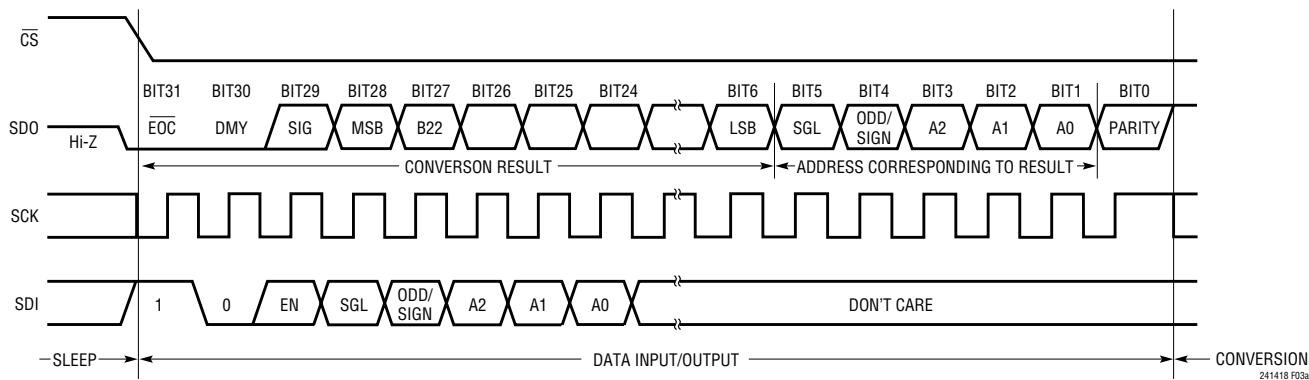

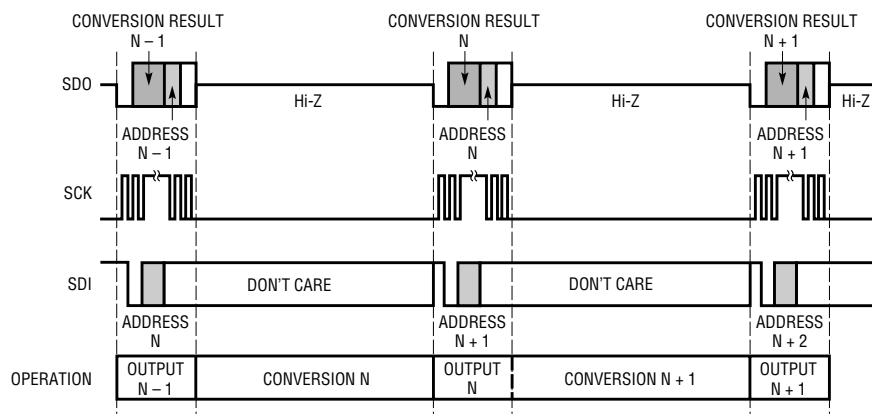

タは、制御ビットによってはそのチャネル選択を直ちに更新し、その選択は次の変換に対して有効です。チャネル選択制御ビットの詳細については、「入力データ・モード」のセクションで説明します。出力データは、シリアル・クロック(SCK)の制御により、SDOピンからシフトして出力されます。出力データはSCKの立ち下がりエッジで更新されるので、ユーザーはSCKの立ち上がりエッジでデータを確実にラッチできます(図3を参照)。A/Dコンバータから32ビットが読み出されるか、 $\overline{CS}$ が“H”になると、データ出力状態は終了します。デバイスは自動的に新しい変換を開始し、サイクルが繰り返されます。

LTC2414/LTC2418は、 $\overline{CS}$ ピンおよびSCKピンのタイミング制御により、いくつかの柔軟な動作モード(内部SCKモードまたは外部SCKモードおよび自走変換モード)を備えています。これらのさまざまなモードでは、プログラミング構成レジスタが不要です。その上、前述した周期的動作が乱されることはありません。これらの動作モードについては、「シリアル・インターフェースのタイミング・モード」のセクションで詳細に説明します。

### 変換クロック

$\Delta\Sigma$ コンバータが従来型のコンバータと比べて有利な主な点は、(一般にSincフィルタまたはくし形フィルタとして実装されている)内蔵のデジタル・フィルタです。高分解能で低周波数のアプリケーションの場合、このフィルタは通常、50Hzまたは60Hzの電源周波数とその高調波を除去する目的で設計

されます。フィルタ除去性能は、コンバータのシステム・クロックの精度に直接関係します。LTC2414/LTC2418は、高精度の発振器を内蔵しています。これにより、水晶発振子や発振器などの外部周波数設定部品が不要になります。LTC2414/LTC2418では、内蔵発振器がクロックを生成するので、電源周波数(50Hzまたは60Hz  $\pm 2\%$ )で110dB以上の除去比を実現します。

### 使いやすさ

LTC2414/LTC2418のデータ出力には、待ち時間、フィルタ設定遅延時間、変換サイクルに付随する冗長データのいずれも存在しません。変換データと出力データは1対1で対応しています。したがって、複数のアナログ電圧の多重化が容易です。

LTC2414/LTC2418は、オフセットとフルスケールの較正を変換サイクルごとに実行します。この較正はユーザーが認識することなく、前述した周期的動作には影響しません。連続的較正の利点は、オフセットとフルスケールの読み取り値が、時間、電源電圧変動、および温度ドリフトに対してきわめて安定していることです。

### 起動シーケンス

電源電圧V<sub>CC</sub>が約2Vより低くなると、LTC2414/LTC2418は自動的に内部リセット状態に入ります。この機能により、変換結果とシリアル・インターフェース・モード選択の完全性が保証されます。(「シリアル・インターフェースのタイミング・モード」のセクションの3線I/Oの部分を参照してください。)

V<sub>CC</sub>の電圧がこの臨界しきい値より高くなると、コンバータは標準周期が1msのパワーオン・リセット(POR)信号を生成します。POR信号はすべての内部レジスタをクリアします。LTC2414/LTC2418は、POR信号の後に通常の変換サイクルを開始し、その後、前述した一連の状態が続きます。PORの期間が終了する前に電源電圧が動作範囲(2.7V～5.5V)内に戻る場合、POR後の最初の変換結果はデバイスの規格範囲内で正確です。

### リファレンス電圧範囲

LTC2414/LTC2418は、完全に差動の外部リファレンス電圧を使用できます。REF<sup>+</sup>ピンとREF<sup>-</sup>ピンの絶対電圧/同相電圧規格は、GNDからV<sub>CC</sub>までの全範囲を網羅します。正確なコンバータ動作を確保するため、REF<sup>+</sup>ピンの電圧はREF<sup>-</sup>ピンの電圧より常に高い必要があります。

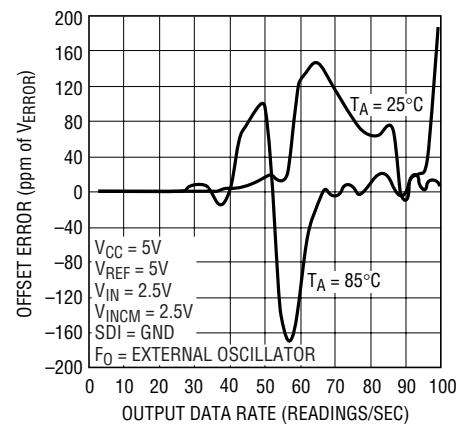

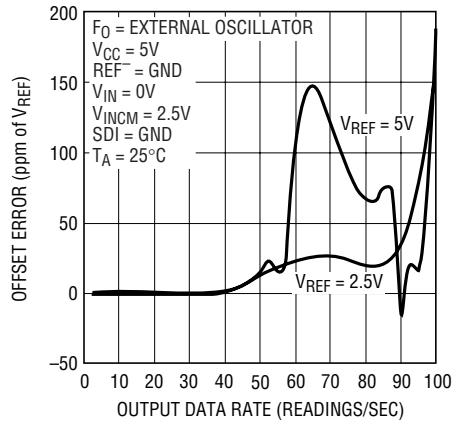

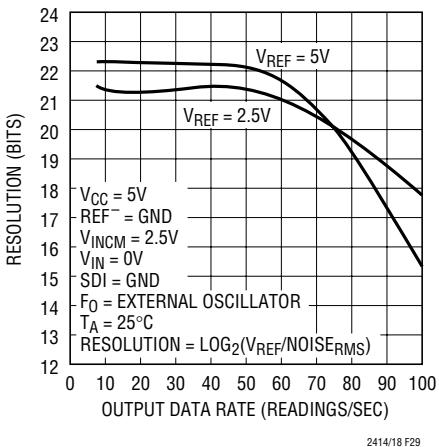

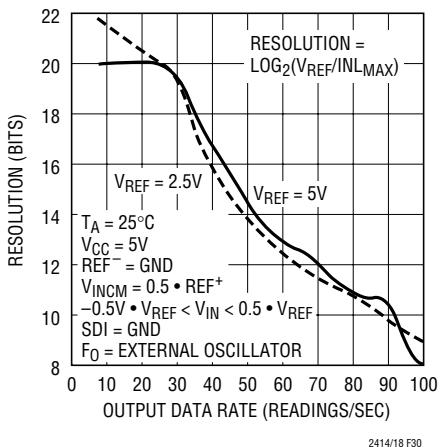

## アプリケーション情報

LTC2414/LTC2418は、0.1VからV<sub>CC</sub>までの差動リファレンス電圧を使用できます。コンバータの出力ノイズはフロントエンド回路の熱ノイズによって決まるので、その値(単位:nV)はリファレンス電圧によらずほぼ一定です。リファレンス電圧を低くしても、コンバータの実効分解能が大幅に向上することはありません。これに反して、リファレンス電圧が低いとコンバータの全体的なINL性能は向上します。また、出力データ・レートが相当高いときに外部変換クロック(外部F<sub>O</sub>信号)を使用して動作させた場合にも、リファレンス電圧が低いとコンバータの性能が向上します。

### 入力電圧範囲

2つの選択ピンはIN<sup>+</sup>およびIN<sup>-</sup>と表記されます(表1および表2を参照)。(差動モードまたはシングルエンド多重化モードで)選択した場合、アナログ入力は入力ピンIN<sup>+</sup>とIN<sup>-</sup>の同相範囲がGND - 0.3VからV<sub>CC</sub> + 0.3Vまでの差動になります。これらの限界を超えると、ESD保護デバイスが導通し始め、入力漏れ電流に起因する誤差が急速に増加します。これらの限界の範囲内では、LTC2414/LTC2418は両極性の差動入力信号V<sub>IN</sub> = IN<sup>+</sup> - IN<sup>-</sup>を-FS = -0.5 • V<sub>REF</sub>から+FS = 0.5 • V<sub>REF</sub>までの範囲で変換します。ここで、V<sub>REF</sub> = REF<sup>+</sup> - REF<sup>-</sup>です。この範囲外では、コンバータは特異な出力コードを使用してオーバーレンジ状態またはアンダーレンジ状態を示します。

IN<sup>+</sup>ピンとIN<sup>-</sup>ピンに加える入力信号は、グランドより300mV低いかV<sub>CC</sub>より300mV高い値まで広げることができます。フォルト電流を制限するため、デバイスの性能に影響を与えることなく、最大5kの抵抗をIN<sup>+</sup>ピンまたはIN<sup>-</sup>ピンと直列に追加することができます。物理的なレイアウトでは、これらの直列抵抗と対応するピンの間の接続の寄生容量をできるだけ低く抑えることが重要です。したがって、抵抗は可能な限りピンに近づけて配置します。さらに、直列抵抗により、入力漏れ電流に起因する温度依存性オフセット誤差が発生します。V<sub>REF</sub> = 5Vの場合、1nAの入力漏れ電流によって5kの抵抗に1ppmのオフセット誤差が生じます。この誤差には非常に強い温度依存性があります。

### 入力データ形式

LTC2414/LTC2418を起動すると、最初の変換で使用するデフォルトの選択はIN<sup>+</sup> = CH0およびIN<sup>-</sup> = CH1(アドレス = 00000)です。最初の変換後のデータ入力/出力モードでは、8ビット・ワードを使用してチャネル選択を更新できます。LTC2414/LTC2418のシリアル入力データはSDIピンに入り、SCKの立ち上がりエッジでクロックに同期します(図3を参照)。入力は8ビット・ワードで構成されており、先頭の3ビットは制御ビットとして、残りの5ビットはチャネル・アドレス・ビットとして機能します。

先頭の2ビットは、正常な更新動作のため、常に10です。第3ビットはENです。EN = 1の場合、後続の5ビットを使用して入力チャネル選択を更新します。EN = 0の場合、直前のチャネル選択が保持され、後続のビットは無視されます。したがって、3つの制御ビットが101のときはアドレスが更新され、100のときは保持されます。代わりに、3つの制御ビットをすべて0にして前のアドレスを保持することもできます。この代替案の目的はSDIインターフェースの簡略化であり、更新が不要な場合はSDIをグランドにそのまま接続することができます。3つの制御ビットの組み合わせを101、100、および000以外にするのは避けてください。

更新動作を設定した場合(101)、それ以降の5ビットはチャネル・アドレスです。先頭ビットSGLは、差動選択モード(SGL = 0)とシングルエンド選択モード(SGL = 1)のどちらを使用するかを決定します。SGL = 0の場合は、2つの隣接チャネルを選択して差動入力を形成できます。SGL = 1の場合、LTC2414では8チャネル(CH0 ~ CH7)のいずれかを、LTC2418では16チャネル(CH0 ~ CH15)のいずれかを正の入力として選択し、COMピンを負の入力として使用します。LTC2414では、下半分のチャネル(CH0 ~ CH7)を使用し、チャネル・アドレス・ビットA2は常に0にします。表1を参照してください。これに対してLTC2418では、16チャネルすべてを使用するので、対応する選択表(表2)のサイズはLTC2414の場合(表1)の倍になります。ある特定のチャネルの選択の場合は、表1または表2の選択行でIN<sup>+</sup>およびIN<sup>-</sup>によって表示された2つのチャネル間の電圧をコンバータが測定します。

# LTC2414/LTC2418

## アプリケーション情報

図3a. 入力/出力データのタイミング

図3b. 標準的な動作シーケンス

表1. LTC2414のチャネル選択(ビットA2は常時0)

| マルチプレクサのアドレス |          |    |       | チャネル選択          |                 |                 |                 |                 |                 |                 |                 |                 |

|--------------|----------|----|-------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|

| SGL          | ODD/SIGN | A2 | A1 A0 | 0               | 1               | 2               | 3               | 4               | 5               | 6               | 7               | COM             |

| *0           | 0        | 0  | 0 0   | IN <sup>+</sup> | IN <sup>-</sup> |                 |                 |                 |                 |                 |                 |                 |

| 0            | 0        | 0  | 0 1   |                 |                 | IN <sup>+</sup> | IN <sup>-</sup> |                 |                 |                 |                 |                 |

| 0            | 0        | 0  | 1 0   |                 |                 |                 |                 | IN <sup>+</sup> | IN <sup>-</sup> |                 |                 |                 |

| 0            | 0        | 0  | 1 1   |                 |                 |                 |                 |                 |                 | IN <sup>+</sup> | IN <sup>-</sup> |                 |

| 0            | 1        | 0  | 0 0   | IN <sup>-</sup> | IN <sup>+</sup> |                 |                 |                 |                 |                 |                 |                 |

| 0            | 1        | 0  | 0 1   |                 |                 | IN <sup>-</sup> | IN <sup>+</sup> |                 |                 |                 |                 |                 |

| 0            | 1        | 0  | 1 0   |                 |                 |                 |                 | IN <sup>-</sup> | IN <sup>+</sup> |                 |                 |                 |

| 0            | 1        | 0  | 1 1   |                 |                 |                 |                 |                 |                 | IN <sup>-</sup> | IN <sup>+</sup> |                 |

| 1            | 0        | 0  | 0 0   | IN <sup>+</sup> |                 |                 |                 |                 |                 |                 |                 | IN <sup>-</sup> |

| 1            | 0        | 0  | 0 1   |                 |                 | IN <sup>+</sup> |                 |                 |                 |                 |                 | IN <sup>-</sup> |

| 1            | 0        | 0  | 1 0   |                 |                 |                 |                 | IN <sup>+</sup> |                 |                 |                 | IN <sup>-</sup> |

| 1            | 0        | 0  | 1 1   |                 |                 |                 |                 |                 |                 | IN <sup>+</sup> |                 | IN <sup>-</sup> |

| 1            | 1        | 0  | 0 0   |                 | IN <sup>+</sup> |                 |                 |                 |                 |                 |                 | IN <sup>-</sup> |

| 1            | 1        | 0  | 0 1   |                 |                 |                 | IN <sup>+</sup> |                 |                 |                 |                 | IN <sup>-</sup> |

| 1            | 1        | 0  | 1 0   |                 |                 |                 |                 |                 | IN <sup>+</sup> |                 |                 | IN <sup>-</sup> |

| 1            | 1        | 0  | 1 1   |                 |                 |                 |                 |                 |                 |                 | IN <sup>+</sup> | IN <sup>-</sup> |

\* 電源投入時のデフォルト

241418fa

## アプリケーション情報

表2. LTC2418のチャネル選択

| マルチプレクサのアドレス |          |    |    |    | チャネル選択          |                 |                 |                 |                 |                 |                 |                 |                 |                 |                 |                 |                 |                 |                 |                 |                 |

|--------------|----------|----|----|----|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|

| SGL          | ODD/SIGN | A2 | A1 | A0 | 0               | 1               | 2               | 3               | 4               | 5               | 6               | 7               | 8               | 9               | 10              | 11              | 12              | 13              | 14              | 15              | COM             |

| *0           | 0        | 0  | 0  | 0  | IN <sup>+</sup> | IN <sup>-</sup> |                 |                 |                 |                 |                 |                 |                 |                 |                 |                 |                 |                 |                 |                 |                 |

| 0            | 0        | 0  | 0  | 1  |                 |                 | IN <sup>+</sup> | IN <sup>-</sup> |                 |                 |                 |                 |                 |                 |                 |                 |                 |                 |                 |                 |                 |

| 0            | 0        | 0  | 1  | 0  |                 |                 |                 |                 | IN <sup>+</sup> | IN <sup>-</sup> |                 |                 |                 |                 |                 |                 |                 |                 |                 |                 |                 |

| 0            | 0        | 0  | 1  | 1  |                 |                 |                 |                 |                 |                 | IN <sup>+</sup> | IN <sup>-</sup> |                 |                 |                 |                 |                 |                 |                 |                 |                 |

| 0            | 0        | 1  | 0  | 0  |                 |                 |                 |                 |                 |                 |                 | IN <sup>+</sup> | IN <sup>-</sup> |                 |                 |                 |                 |                 |                 |                 |                 |

| 0            | 0        | 1  | 0  | 1  |                 |                 |                 |                 |                 |                 |                 |                 |                 | IN <sup>+</sup> | IN <sup>-</sup> |                 |                 |                 |                 |                 |                 |

| 0            | 0        | 1  | 1  | 0  |                 |                 |                 |                 |                 |                 |                 |                 |                 |                 |                 | IN <sup>+</sup> | IN <sup>-</sup> |                 |                 |                 |                 |

| 0            | 0        | 1  | 1  | 1  |                 |                 |                 |                 |                 |                 |                 |                 |                 |                 |                 |                 |                 | IN <sup>+</sup> | IN <sup>-</sup> |                 |                 |

| 0            | 1        | 0  | 0  | 0  | IN <sup>-</sup> | IN <sup>+</sup> |                 |                 |                 |                 |                 |                 |                 |                 |                 |                 |                 |                 |                 |                 |                 |

| 0            | 1        | 0  | 0  | 1  |                 |                 | IN <sup>-</sup> | IN <sup>+</sup> |                 |                 |                 |                 |                 |                 |                 |                 |                 |                 |                 |                 |                 |

| 0            | 1        | 0  | 1  | 0  |                 |                 |                 |                 | IN <sup>-</sup> | IN <sup>+</sup> |                 |                 |                 |                 |                 |                 |                 |                 |                 |                 |                 |

| 0            | 1        | 0  | 1  | 1  |                 |                 |                 |                 |                 | IN <sup>-</sup> | IN <sup>+</sup> |                 |                 |                 |                 |                 |                 |                 |                 |                 |                 |

| 0            | 1        | 1  | 0  | 0  |                 |                 |                 |                 |                 |                 | IN <sup>-</sup> | IN <sup>+</sup> |                 |                 |                 |                 |                 |                 |                 |                 |                 |

| 0            | 1        | 1  | 0  | 1  |                 |                 |                 |                 |                 |                 |                 | IN <sup>-</sup> | IN <sup>+</sup> |                 |                 |                 |                 |                 |                 |                 |                 |

| 0            | 1        | 1  | 1  | 0  |                 |                 |                 |                 |                 |                 |                 |                 | IN <sup>-</sup> | IN <sup>+</sup> |                 |                 |                 |                 |                 |                 |                 |

| 0            | 1        | 1  | 1  | 1  |                 |                 |                 |                 |                 |                 |                 |                 |                 |                 |                 | IN <sup>-</sup> | IN <sup>+</sup> |                 |                 |                 |                 |

| 1            | 0        | 0  | 0  | 0  | IN <sup>+</sup> |                 |                 |                 |                 |                 |                 |                 |                 |                 |                 |                 |                 |                 |                 |                 | IN <sup>-</sup> |

| 1            | 0        | 0  | 0  | 1  |                 | IN <sup>+</sup> |                 |                 |                 |                 |                 |                 |                 |                 |                 |                 |                 |                 |                 |                 | IN <sup>-</sup> |

| 1            | 0        | 0  | 1  | 0  |                 |                 |                 |                 | IN <sup>+</sup> |                 |                 |                 |                 |                 |                 |                 |                 |                 |                 |                 | IN <sup>-</sup> |

| 1            | 0        | 0  | 1  | 1  |                 |                 |                 |                 |                 | IN <sup>+</sup> |                 |                 |                 |                 |                 |                 |                 |                 |                 |                 | IN <sup>-</sup> |

| 1            | 0        | 1  | 0  | 0  |                 |                 |                 |                 |                 |                 | IN <sup>+</sup> |                 |                 |                 |                 |                 |                 |                 |                 |                 | IN <sup>-</sup> |

| 1            | 0        | 1  | 0  | 1  |                 |                 |                 |                 |                 |                 |                 | IN <sup>+</sup> |                 |                 |                 |                 |                 |                 |                 |                 | IN <sup>-</sup> |

| 1            | 0        | 1  | 1  | 0  |                 |                 |                 |                 |                 |                 |                 |                 | IN <sup>+</sup> |                 |                 |                 |                 |                 |                 |                 | IN <sup>-</sup> |

| 1            | 0        | 1  | 1  | 1  |                 |                 |                 |                 |                 |                 |                 |                 |                 |                 |                 |                 |                 | IN <sup>+</sup> |                 | IN <sup>-</sup> |                 |

| 1            | 1        | 0  | 0  | 0  | IN <sup>+</sup> |                 |                 |                 |                 |                 |                 |                 |                 |                 |                 |                 |                 |                 |                 |                 | IN <sup>-</sup> |

| 1            | 1        | 0  | 0  | 1  |                 |                 | IN <sup>+</sup> |                 |                 |                 |                 |                 |                 |                 |                 |                 |                 |                 |                 |                 | IN <sup>-</sup> |

| 1            | 1        | 0  | 1  | 0  |                 |                 |                 |                 |                 | IN <sup>+</sup> |                 |                 |                 |                 |                 |                 |                 |                 |                 |                 | IN <sup>-</sup> |

| 1            | 1        | 0  | 1  | 1  |                 |                 |                 |                 |                 |                 | IN <sup>+</sup> |                 |                 |                 |                 |                 |                 |                 |                 |                 | IN <sup>-</sup> |

| 1            | 1        | 1  | 0  | 0  |                 |                 |                 |                 |                 |                 |                 | IN <sup>+</sup> |                 |                 |                 |                 |                 |                 |                 |                 | IN <sup>-</sup> |

| 1            | 1        | 1  | 0  | 1  |                 |                 |                 |                 |                 |                 |                 |                 | IN <sup>+</sup> |                 |                 |                 |                 |                 |                 |                 | IN <sup>-</sup> |

| 1            | 1        | 1  | 1  | 0  |                 |                 |                 |                 |                 |                 |                 |                 |                 |                 |                 |                 | IN <sup>+</sup> |                 |                 | IN <sup>-</sup> |                 |

| 1            | 1        | 1  | 1  | 1  |                 |                 |                 |                 |                 |                 |                 |                 |                 |                 |                 |                 |                 | IN <sup>+</sup> |                 | IN <sup>-</sup> |                 |

\* 電源投入時のデフォルト

## 出力データ形式

LTC2414/LTC2418のシリアル出力データ・ストリームは、32ビット長です。先頭の3ビットはステータス情報を表し、符号と変換状態を示します。次の23ビットは変換結果で、MSBが先頭です。その次の5ビット(ビット5～ビット1)は、変換が実

行された直後のチャネルのうち、どのチャネルが選択されたかを示します。このデータ出力段階でプログラムされたアドレス・ビットが、次のサイクルの入力チャネルを選択します。これらのアドレス・ビットは、図3bに示すように、後続のデータ読み取り時に出力されます。最終ビットは、直前の31ビットのパリティ

## アプリケーション情報

を表すパリティ・ビットです。パリティ・ビットは、特に出力データを一定の距離送信する場合、出力データの完全性を検査するのに役立ちます。また、3番目と4番目のビットは、アンダーレンジ条件(差動入力電圧が-FSより低い)またはオーバーレンジ条件(差動入力電圧が+FSより高い)を示す目的でも一緒に使用されます。

ビット31(最初の出力ビット)は、変換の終了( $\overline{\text{EOC}}$ )インジケータです。このビットは、 $\overline{\text{CS}}$ ピンが“L”的ときは必ず、変換中およびスリープ状態時にSDOピンで使用可能です。このビットは変換中は“H”になり、変換が完了すると“L”になります。

ビット30(2番目の出力ビット)はダミー・ビット(DMY)であり、常に“L”です。

ビット29(3番目の出力ビット)は変換結果の符号インジケータ(SIG)です。 $V_{IN}$ が0より高い場合、このビットは“H”です。 $V_{IN}$ が0より低い場合、このビットは“L”です。

ビット28(4番目の出力ビット)は、結果の最上位ビット(MSB)です。このビットとビット29を組み合わせた場合にも、アンダーレンジまたはオーバーレンジを示すことができます。ビット29とビット28が両方とも“H”である場合、差動入力電圧は+FSより高くなっています。ビット29とビット28が両方とも“L”である場合、差動入力電圧は-FSより低くなっています。

これらのビットの機能を表3にまとめています。

表3. LTC2414/LTC2418のステータス・ビット

| 入力範囲                                  | ビット31<br>$\overline{\text{EOC}}$ | ビット30<br>DMY | ビット29<br>SIG | ビット28<br>MSB |

|---------------------------------------|----------------------------------|--------------|--------------|--------------|

| $V_{IN} \geq 0.5 \cdot V_{REF}$       | 0                                | 0            | 1            | 1            |

| $0V \leq V_{IN} < 0.5 \cdot V_{REF}$  | 0                                | 0            | 1            | 0            |

| $-0.5 \cdot V_{REF} \leq V_{IN} < 0V$ | 0                                | 0            | 0            | 1            |

| $V_{IN} < -0.5 \cdot V_{REF}$         | 0                                | 0            | 0            | 0            |

ビット28～6は、23ビットの変換結果で、MSBが先頭になっています。

ビット6は最下位ビット(LSB)です。

ビット5～1は、図3に示すように、ビットSGLの出力を先頭にした場合の現在の変換結果に対応するチャネル選択ビットです。

ビット0は、直前の31ビットのパリティを表すパリティ・ビットです。パリティ・ビットを含めて、出力データでの1の数の合計と0の数の合計は常に同じです。

データは、シリアル・クロック(SCK)の制御により、SDOピンからシフトして出力されます。図3を参照してください。 $\overline{\text{CS}}$ が“H”的とき、SDOは常に高インピーダンスのままであり、外部で生成されたSCKクロック・パルスが入力された場合でも、内部データ出力のシフト・レジスタによって無視されます。

変換結果をデバイスからシフトするため、 $\overline{\text{CS}}$ は最初に“L”にする必要があります。 $\overline{\text{CS}}$ が“L”になると、デバイスのSDOピンに $\overline{\text{EOC}}$ が現れます。 $\overline{\text{EOC}}$ は、変換の完了時にリアルタイムで“H”から“L”に変化します。この信号は外部マイクロコントローラの割り込みとして使用できます。ビット31( $\overline{\text{EOC}}$ )はSCKの最初の立ち上がりエッジで捕捉できます。ビット30はSCKの最初の立ち下がりエッジでデバイスからシフトして出力されます。最終データ・ビット(ビット0)は、SCKの31番目の立ち下がりエッジでシフトして出力されます。また、このビットはSCKパルスの32番目の立ち上がりエッジでラッチされる場合があります。SCKパルスの32番目の立ち下がりエッジでは、SDOが“H”になり、新しい変換サイクルの開始を示します。このビットは次の変換サイクルの $\overline{\text{EOC}}$ (ビット31)として機能します。出力データ形式の要約を表4に示します。

すべてのチャネル(CH0～CH15、COM)に印加されている電圧が $-0.3V \sim (V_{CC} + 0.3V)$ の絶対最大動作範囲内に維持されている限り、 $-FS = -0.5 \cdot V_{REF}$ から $+FS = 0.5 \cdot V_{REF}$ までのすべての差動入力電圧 $V_{IN}$ に対して変換結果が生成されます。差動入力電圧が $+FS$ より高い場合、変換結果は $+FS + 1LSB$ に対応する値にクランプされます。差動入力電圧が $-FS$ より低い場合、変換結果は $-FS - 1LSB$ に対応する値にクランプされます。

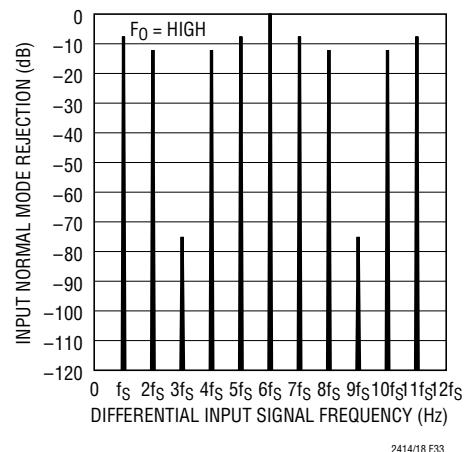

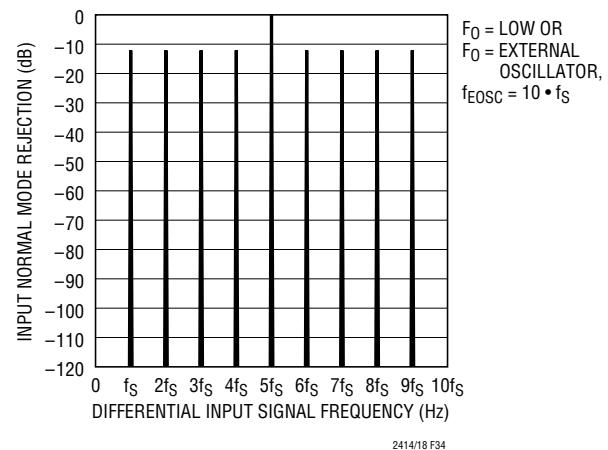

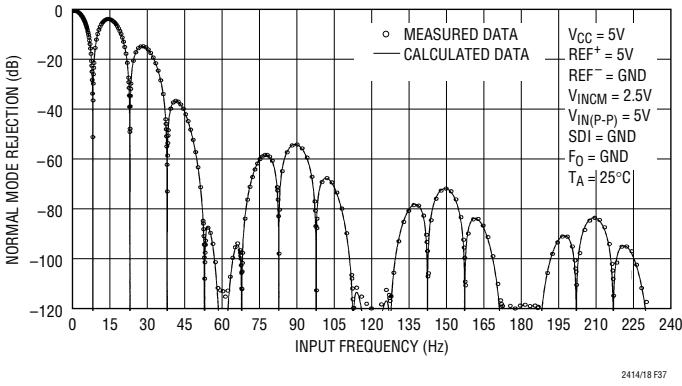

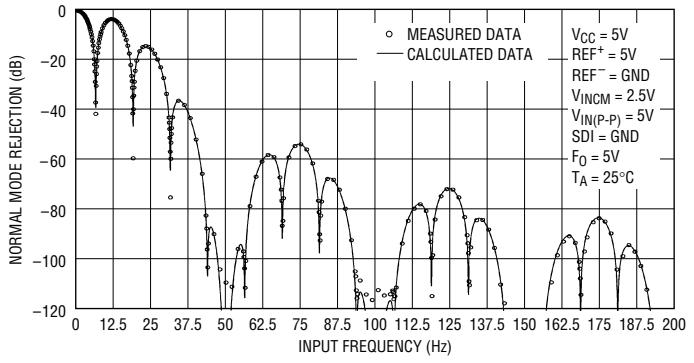

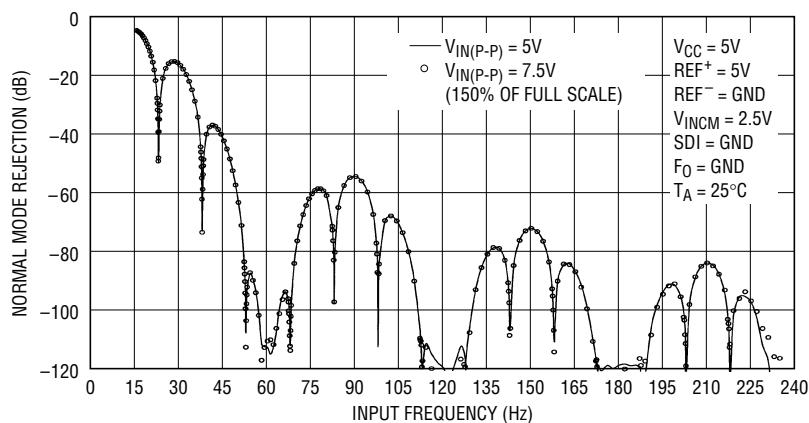

### 除去周波数の選択( $F_0$ )

LTC2414/LTC2418の内部発振器は、 $50\text{Hz} \pm 2\%$ または $60\text{Hz} \pm 2\%$ の電源周波数およびそのすべての高調波において、110dBより優れたノーマル・モード除去比を実現します。60Hzを除去する場合は $F_0$ ピンをGNDに接続しますが、50Hzを除去する場合は $F_0$ ピンを $V_{CC}$ に接続します。

50Hzまたは60Hzのどちらを除去するかは、 $F_0$ を該当のロジック・レベルに駆動して選択することもできます。スリープ状態またはデータ出力状態時に選択を変更しても、コンバータの動作に支障はありません。変換状態時に選択を行うと、進行中の変換の結果が規格外になることがあります。後続の変換は影響を受けません。

## アプリケーション情報

表4. LTC2414/LTC2418の出力データ形式

| 差動入力電圧 $V_{IN}^*$                      | ビット31<br>EOC | ビット30<br>DMY | ビット29<br>SIG | ビット28<br>MSB | ビット27 | ビット26 | ビット25 | … | ビット6<br>LSB |

|----------------------------------------|--------------|--------------|--------------|--------------|-------|-------|-------|---|-------------|

| $V_{IN}^* \geq 0.5 \cdot V_{REF}^{**}$ | 0            | 0            | 1            | 1            | 0     | 0     | 0     | … | 0           |

| $0.5 \cdot V_{REF}^{**} - 1LSB$        | 0            | 0            | 1            | 0            | 1     | 1     | 1     | … | 1           |

| $0.25 \cdot V_{REF}^{**}$              | 0            | 0            | 1            | 0            | 1     | 0     | 0     | … | 0           |

| $0.25 \cdot V_{REF}^{**} - 1LSB$       | 0            | 0            | 1            | 0            | 0     | 1     | 1     | … | 1           |

| 0                                      | 0            | 0            | 1            | 0            | 0     | 0     | 0     | … | 0           |

| -1LSB                                  | 0            | 0            | 0            | 1            | 1     | 1     | 1     | … | 1           |

| $-0.25 \cdot V_{REF}^{**}$             | 0            | 0            | 0            | 1            | 1     | 0     | 0     | … | 0           |

| $-0.25 \cdot V_{REF}^{**} - 1LSB$      | 0            | 0            | 0            | 1            | 0     | 1     | 1     | … | 1           |

| $-0.5 \cdot V_{REF}^{**}$              | 0            | 0            | 0            | 1            | 0     | 0     | 0     | … | 0           |

| $V_{IN}^* < -0.5 \cdot V_{REF}^{**}$   | 0            | 0            | 0            | 0            | 1     | 1     | 1     | … | 1           |

\* 差動入力電圧  $V_{IN} = IN^+ - IN^-$ 。\*\* 差動リファレンス電圧  $V_{REF} = REF^+ - REF^-$ 。

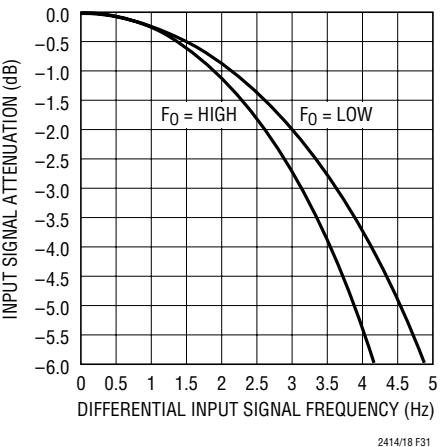

50Hzまたは60Hzとは異なる基本除去周波数が必要な場合、あるいはコンバータが外部信号源と同期する必要がある場合、LTC2414/LTC2418は外部変換クロックを使用して動作することができます。コンバータは  $F_O$  ピンで外部クロック信号の存在を自動的に検出し、内部発振器を停止します。検出する外部信号の周波数  $f_{EOSC}$  は、2560Hz(ノッチ周波数: 1Hz)以上にする必要があります。外部クロック信号のデューティ・サイクルは、“H”と“L”的周期の最小規格および最大規格  $t_{HEO}$  および  $t_{LEO}$  が守られている限り、重要ではありません。

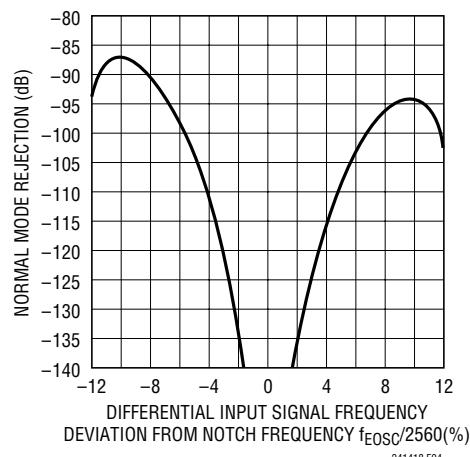

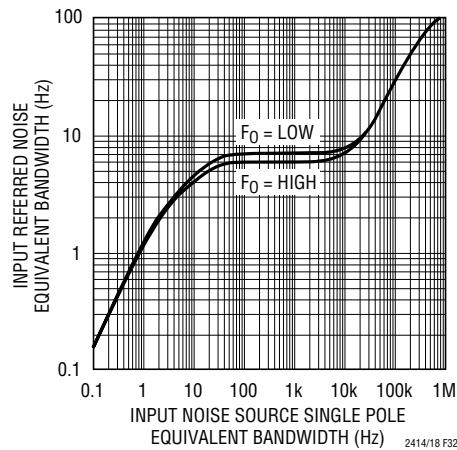

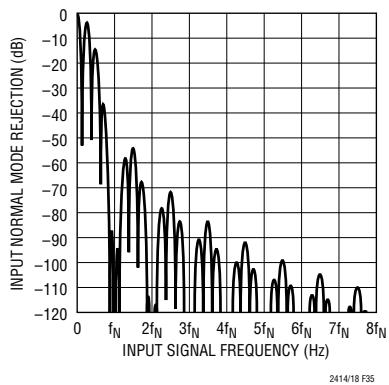

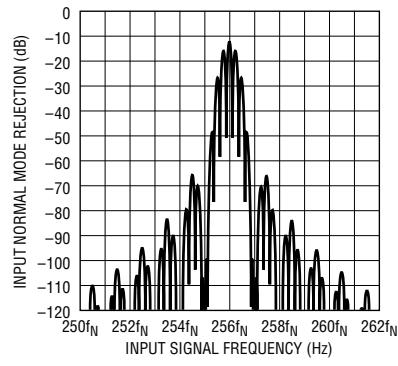

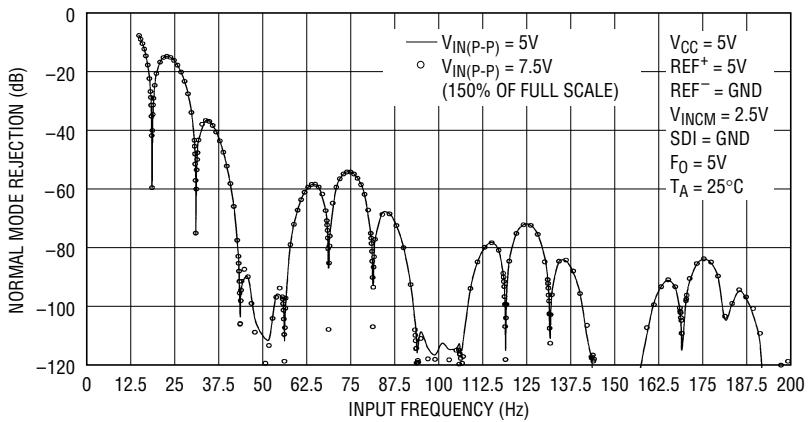

コンバータは、周波数が  $f_{EOSC}$  の外部変換クロックを使用して動作する場合、周波数範囲  $f_{EOSC}/2560 \pm 4\%$  およびその高調波においては、110dBより優れたノーマル・モード除去比を実現します。 $f_{EOSC}/2560$  からの入力周波数偏移の関数として表したノーマル・モード除去比特性を図4に示します。

$F_O$  ピンに外部クロックが存在しない場合、コンバータは必ずその内部発振器を自動的に起動し、内部変換クロック・モードに入ります。コンバータが外部シリアル・クロックを使用しているとき、スリープ状態時またはデータ出力状態時に変換クロック信号源が変更された場合でも、コンバータの動作に支障はありません。変換状態時に変更が生じると、進行中の変換の結果が規格外になることがあります。後続の変換は影響を受けません。データ出力状態時に変更が発生し、コンバータが内部SCKモードに入っている場合、シリアル・クロックのデューティ・サイクルが影響を受けることがあります。シリアル・データ・ストリームは有効のまま推移します。

図4. 周波数  $f_{EOSC}$  の外部発振器を使用した場合の LTC2414/LTC2418 のノーマル・モード除去比

$F_O$  に応じた各状態の持続時間および達成可能な出力データ・レートの要約を表5に示します。

## シリアル・インターフェース・ピン

LTC2414/LTC2418は、同期4線式インターフェースを介して変換結果を送信し、変換開始コマンドを受信します。変換状態およびスリープ状態の間は、このインターフェースを使用してコンバータのステータスにアクセスすることができます。また、データ入力/出力状態の間は、このインターフェースを使用して変換結果の読み取りとチャネル選択ビットへの書き込みを行います。

## アプリケーション情報

表5. LTC2414/LTC2418の状態持続時間

| 状態    | 動作モード                                  |                                                                                          | 持続時間                                                                                                      |

|-------|----------------------------------------|------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|

| 変換    | 内部発振器                                  | $f_0 = "L"$ (60Hzを除去)                                                                    | 133ms、出力データ・レート $\leq 7.5$ 回/秒の読み取り                                                                       |

|       |                                        | $f_0 = "H"$ (50Hzを除去)                                                                    | 160ms、出力データ・レート $\leq 6.2$ 回/秒の読み取り                                                                       |

|       | 外部発振器                                  | $f_0 = \text{周波数が } f_{\text{EOSC}} \text{ kHz の外部発振器}$<br>( $f_{\text{EOSC}}/2560$ を除去) | $20510/f_{\text{EOSC}}$ 秒、出力データ・レート $\leq f_{\text{EOSC}}/20510$ 回/秒の読み取り                                 |

| スリープ  |                                        |                                                                                          | $\overline{\text{CS}} = "L"$ で SCK が $\overline{\text{SCK}}$ になるまでは、 $\overline{\text{CS}} = "H"$ である限り持続 |

| データ出力 | 内部シリアル・クロック                            | $f_0 = "L"/"H"$ (内部発振器)                                                                  | $\overline{\text{CS}} = "L"$ である限り持続。<br>ただし、1.67ms (SCK 32 サイクル) は超えない                                   |

|       |                                        | $f_0 = \text{周波数が } f_{\text{EOSC}} \text{ kHz の外部発振器}$                                  | $\overline{\text{CS}} = "L"$ である限り持続。<br>ただし、 $256/f_{\text{EOSC}}$ ms (SCK 32 サイクル) は超えない                |

|       | 周波数が $f_{\text{SCK}}$ kHz の外部シリアル・クロック |                                                                                          | $\overline{\text{CS}} = "L"$ である限り持続。<br>ただし、 $32/f_{\text{SCK}}$ ms (SCK 32 サイクル) は超えない                  |

### シリアル・クロック入力/出力(SCK)

SCK(ピン18)にあるシリアル・クロック信号は、データ伝送を同期するために使用します。データの各ビットは、シリアル・クロックの立ち下がりエッジで SDO ピンからシフトして出力され、各入力ビットは、シリアル・クロックの立ち上がりエッジで SDI ピンにシフトして入力されます。

内部 SCK 動作モードでは、SCK ピンは出力であり、LTC2414/LTC2418 は、内部変換クロックを 8 分周することにより、デバイス固有のシリアル・クロックを生成します。外部 SCK 動作モードでは、SCK ピンは入力として使用されます。起動時に内部または外部 SCK モードが選択され、その後、 $\overline{\text{CS}}$  ピンで “H” から “L” への遷移が検出されるたびにモードは再選択されます。起動時またはこの遷移時に SCK が “H” であるかフロート状態である場合、コンバータは内部 SCK モードに入ります。起動時またはこの遷移時に SCK が “L” である場合、コンバータは外部 SCK モードに入ります。

### シリアル・データ入力(SDI)

シリアル・データ入力ピン(SDI、ピン20)を使用するのは、データ出力状態時にチャネル制御ビットにシフトして入力し、後続の変換のチャネル選択に備える場合です。

$\overline{\text{CS}}$  (ピン16) が “H” のとき、またはコンバータが変換状態のとき、SDI 入力は無視され、“H” または “L” のどちらにも駆動される可能性があります。 $\overline{\text{CS}}$  が “L” になって変換が完了すると、SDO は “L” になり、SDI は SCK の立ち上がりエッジでビットのシフト入力を開始します。

### シリアル・データ出力(SDO)

シリアル・データ出力ピン(SDO、ピン17)は、データ出力状態時に最後の変換の結果をシリアル・ビット・ストリーム(MSB が先頭)として出力します。さらに、SDO ピンは、変換状態時およびスリープ状態時に変換終了インジケータとして使用されます。

$\overline{\text{CS}}$  (ピン16) が “H” のとき、SDO ドライバは高インピーダンス状態に切り換わります。これにより、シリアル・インターフェースを他のデバイスと共有することができます。変換状態時またはスリープ状態時に  $\overline{\text{CS}}$  が “L” の場合、SDO は  $\overline{\text{EOC}}$  を出力します。変換段階時に  $\overline{\text{CS}}$  が “L” の場合は、 $\overline{\text{EOC}}$  ビットが “H” になって SDO ピンに現れます。変換が完了すると、 $\overline{\text{EOC}}$  は “L” になります。 $\overline{\text{CS}} = "L"$  の間に SCK の最初の立ち上がりエッジが現れるまで、デバイスはスリープ状態にとどまります。

### チップ選択入力( $\overline{\text{CS}}$ )

アクティブ “L” のチップ選択( $\overline{\text{CS}}$ 、ピン16)を使用するのは、前のセクションで説明したように、変換ステータスをテストし、データの入力/出力伝送を可能にするためです。

さらに、 $\overline{\text{CS}}$  信号を使用して新しい変換サイクルを起動してから、シリアル・データ伝送全体を完了させることもできます。LTC2414/LTC2418 は、データ入力/出力状態に入った後に(つまり、 $\overline{\text{CS}} = "L"$  のときに SCK の最初の立ち上がりエッジが現れた後に)、 $\overline{\text{CS}}$  ピンで “L” から “H” への遷移を検出すると、進行中のすべてのシリアル・データ伝送を中止して、新しい変換サイクルを開始します。 $\overline{\text{CS}}$  が “H” になっている間にデバイスが

## アプリケーション情報

SDIの最後の入力ビットA0の読み込みを終了しなかった場合、アドレス情報は破棄され、直前のアドレスが保持されます。

最後に、 $\overline{CS}$ を使用して自走動作モードを制御することができます。「シリアル・インターフェースのタイミング・モード」のセクションを参照してください。 $\overline{CS}$ を接地すると、A/Dコンバータによる連続変換が、 $F_O$ によって選択された最大出力レートで強制的に行われます。

### シリアル・インターフェースのタイミング・モード

LTC2414/LTC2418の4線式インターフェースは、SPIおよびMICROWIRE互換です。このインターフェースは、いくつかの柔軟な動作モードを備えています。動作モードには、内部/外部

シリアル・クロック、3線または4線入出力、单一サイクル変換などがあります。以下のセクションでは、これらのシリアル・インターフェースのタイミング・モードのそれぞれについて詳細に説明します。これらの場合には、コンバータは内部発振器( $F_O = "L"$ または $F_O = "H"$ )または $F_O$ ピンに接続されている外部発振器を使用できます。要約については表6を参照してください。

### 外部シリアル・クロック、单一サイクル動作 (SPI/MICROWIRE互換)

このタイミング・モードでは、外部シリアル・クロックを使用して変換結果と $\overline{CS}$ 信号をシフトして出力し、変換サイクルの状態をモニタして制御することができます。図5を参照してください。

表6. LTC2414/LTC2418のインターフェースのタイミング・モード

| 構成                | SCK信号源 | 変換サイクル制御                   | データ出力制御                    | 接続および波形 |

|-------------------|--------|----------------------------|----------------------------|---------|

| 外部SCK、単一サイクル変換    | 外部     | $\overline{CS}$ およびSCK     | $\overline{CS}$ およびSCK     | 図5、図6   |

| 外部SCK、3線式入出力      | 外部     | SCK                        | SCK                        | 図7      |

| 内部SCK、単一サイクル変換    | 内部     | $\overline{CS} \downarrow$ | $\overline{CS} \downarrow$ | 図8、図9   |

| 内部SCK、3線式入出力、連続変換 | 内部     | 連続                         | 内部                         | 図10     |

図5. 外部シリアル・クロック、单一サイクル動作

## アプリケーション情報

シリアル・クロック・モードは、 $\overline{CS}$ の立ち下がりエッジで選択されます。外部シリアル・クロック・モードを選択するには、 $\overline{CS}$ の立ち下がりエッジ時にシリアル・クロック・ピン(SCK)を毎回“L”にしておく必要があります。

シリアル・データ出力ピン(SDO)は、 $\overline{CS}$ が“H”である限り、高インピーダンスです。コンバータの状態をモニタするため、変換サイクル中は随時、 $\overline{CS}$ を“L”にすることができます。 $\overline{CS}$ が“L”的ときは、 $\overline{EOC}$ がSDOピンに出力されます。変換が進行中のときは $\overline{EOC} = 1$ であり、デバイスがスリープ状態の場合は $\overline{EOC} = 0$ です。変換が完了すると、 $\overline{CS}$ とは無関係に、デバイスは自動的に低消費電力のスリープ状態に入ります。

デバイスがスリープ状態のとき、その変換結果は内部の静的シフト・レジスタに保持されます。 $\overline{CS}$ が“L”的間にSCKの最初の立ち上がりエッジが現れるまで、デバイスはスリープ状態にとどまります。その後、入力データはSCKの(最初の立ち上がりエッジを含む)立ち上がりエッジで、SDIピンを介してシフトして入力されます。また、出力データはSCKの立ち下がりエッジごとにSDOピンからシフトして出力されます。これにより、外部回路はSCKの立ち上がりエッジで出力をラッチすることができます。 $\overline{EOC}$ はSCKの最初の立ち上がりエッジでラッチすることができます。また、変換結果の最後のビットはSCKの32

番目の立ち上がりエッジでラッチすることができます。SCKの32番目の立ち上がりエッジでは、デバイスが新しい変換を開始します。SDOは“H”( $\overline{EOC} = 1$ )になり、変換が進行中であることを示します。

データ・サイクルの終わりには、 $\overline{CS}$ を“L”的ままにして、 $\overline{EOC}$ を変換終了割り込みとしてモニタすることができます。あるいは、 $\overline{CS}$ を“H”にしてSDOを高インピーダンスに設定することもできます。前述したように、変換ステータスをモニタするため、 $\overline{CS}$ は随時“L”的することができます。

通常、 $\overline{CS}$ はデータ出力状態の間“L”的ままでです。ただし、SCKの最初の立ち上がりエッジから32番目の立ち下がりエッジまでの間であれば、 $\overline{CS}$ を“H”にすることにより、データ出力状態は随時中断できます。図6を参照してください。デバイスは $\overline{CS}$ の立ち上がりエッジでデータ出力状態を中断し、新しい変換を直ちに開始します。 $\overline{CS}$ が“H”になっている間にデバイスがSDIの最後の入力ビットA0の読み込みを終了しなかった場合、アドレス情報は破棄され、直前のアドレスが保持されます。これが役立つのは、必ずしも32ビットすべての出力データが必要ではないシステム、無効な変換サイクルを中断するシステム、または変換開始を同期するシステムです。

図6. 外部シリアル・クロック、短縮データ出力長

241418fa

## アプリケーション情報

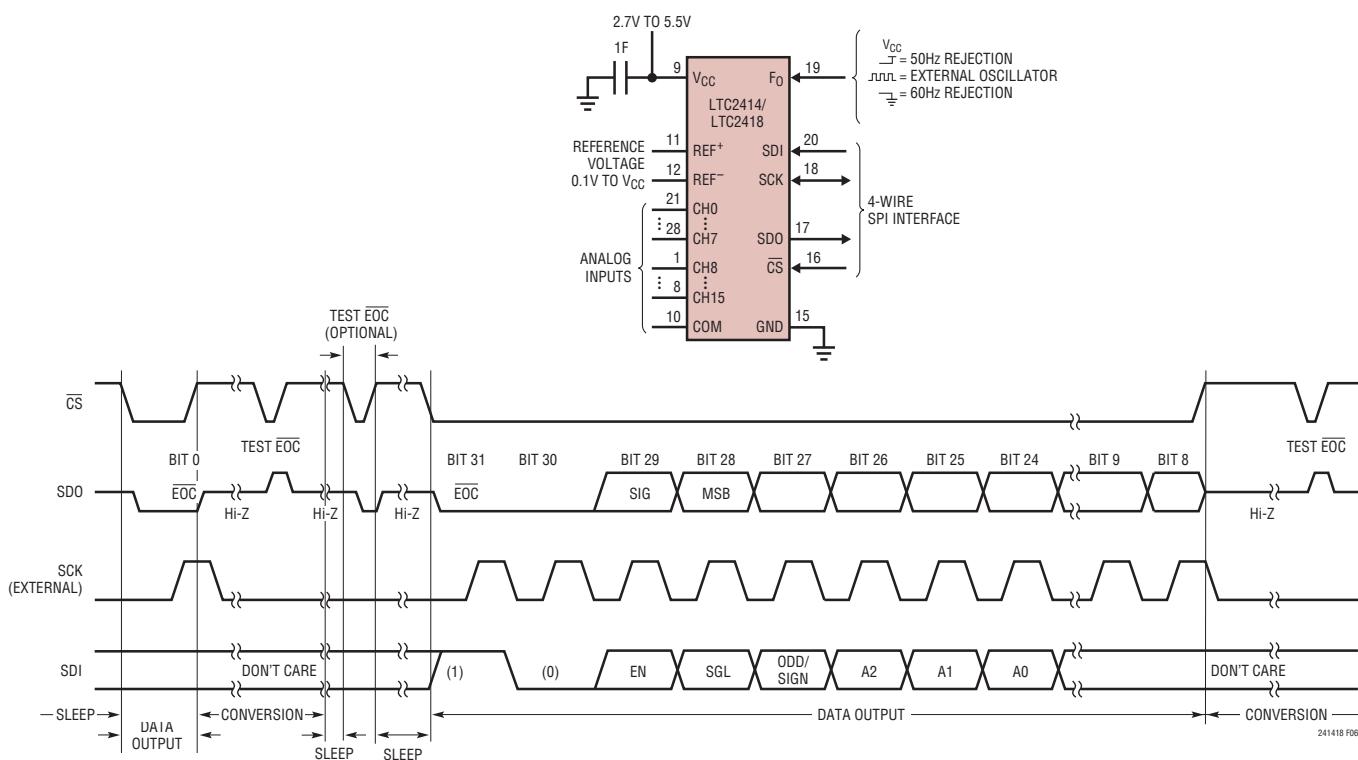

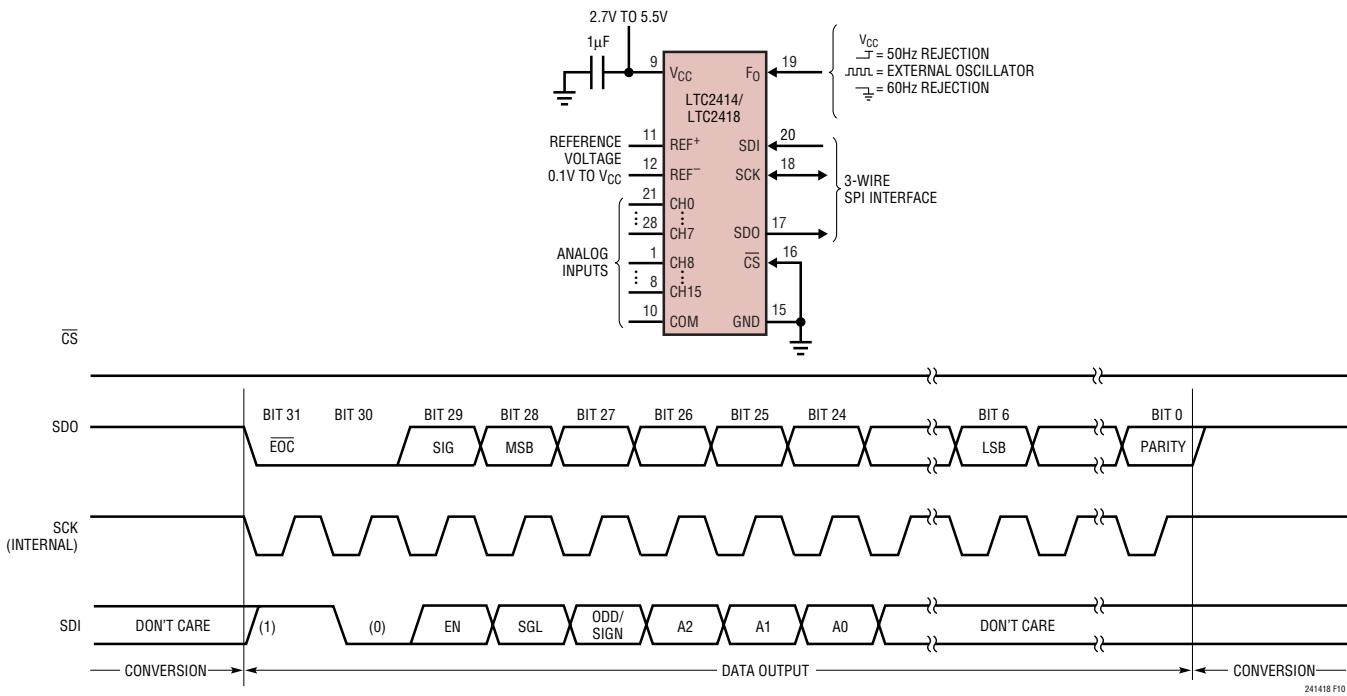

### 外部シリアル・クロック、3線式入出力

このタイミング・モードでは、3線式シリアル入出力インターフェースを使用します。変換結果は、外部で生成されたシリアル・クロック(SCK)信号により、デバイスからシフトして出力されます。図7を参照してください。 $\overline{CS}$ を永続的にグランドに接続して、ユーザー・インターフェースまたは絶縁障壁を簡略化することができます。

外部シリアル・クロック・モードは、パワーオン・リセット(POR)サイクルの最後に選択されます。PORサイクルは、 $V_{CC}$ が約2Vを超えてから標準で1ms後に終了します。この時点でSCKに印加されるレベルにより、SCKが内部であるか外部であるかを判別します。外部シリアル・クロック・タイミング・モードに入るためには、PORが終了する前にSCKを“L”にする必要があります。

$\overline{CS}$ は“L”に接続しているので、変換状態およびスリープ状態の間は、変換終了( $\overline{EOC}$ )をSDOピンで継続的にモニタすることができます。 $\overline{EOC}$ は外部コントローラに対する割り込みとして使用して、変換結果が準備できていることを示すことができます。変換が進行中のときは $\overline{EOC} = 1$ であり、変換が終了すると $\overline{EOC} = 0$ になります。 $\overline{EOC}$ の立ち下がりエッジで、変換結果は内部の静的シフト・レジスタに読み込まれます。その後、入力データはSCKの(最初の立ち上がりエッジを含む)立ち上がりエッジで、SDIピンを介してシフトして入力されます。また、出力データはSCKの立ち下がりエッジごとにSDOピンからシフトし

て出力されます。 $\overline{EOC}$ はSCKの最初の立ち上がりエッジでラッチできます。SCKの32番目の立ち上がりエッジでは、SDOが“H”になり( $\overline{EOC} = 1$ )、新しい変換が始まったことを示します。

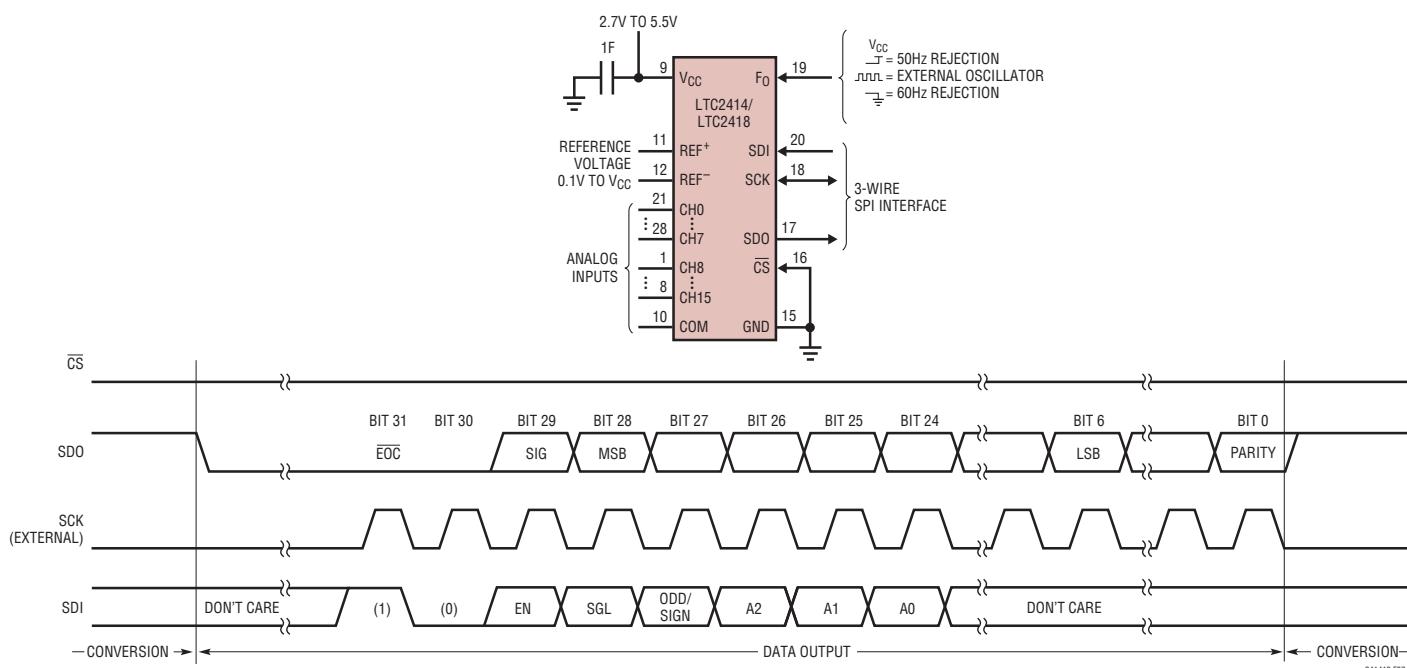

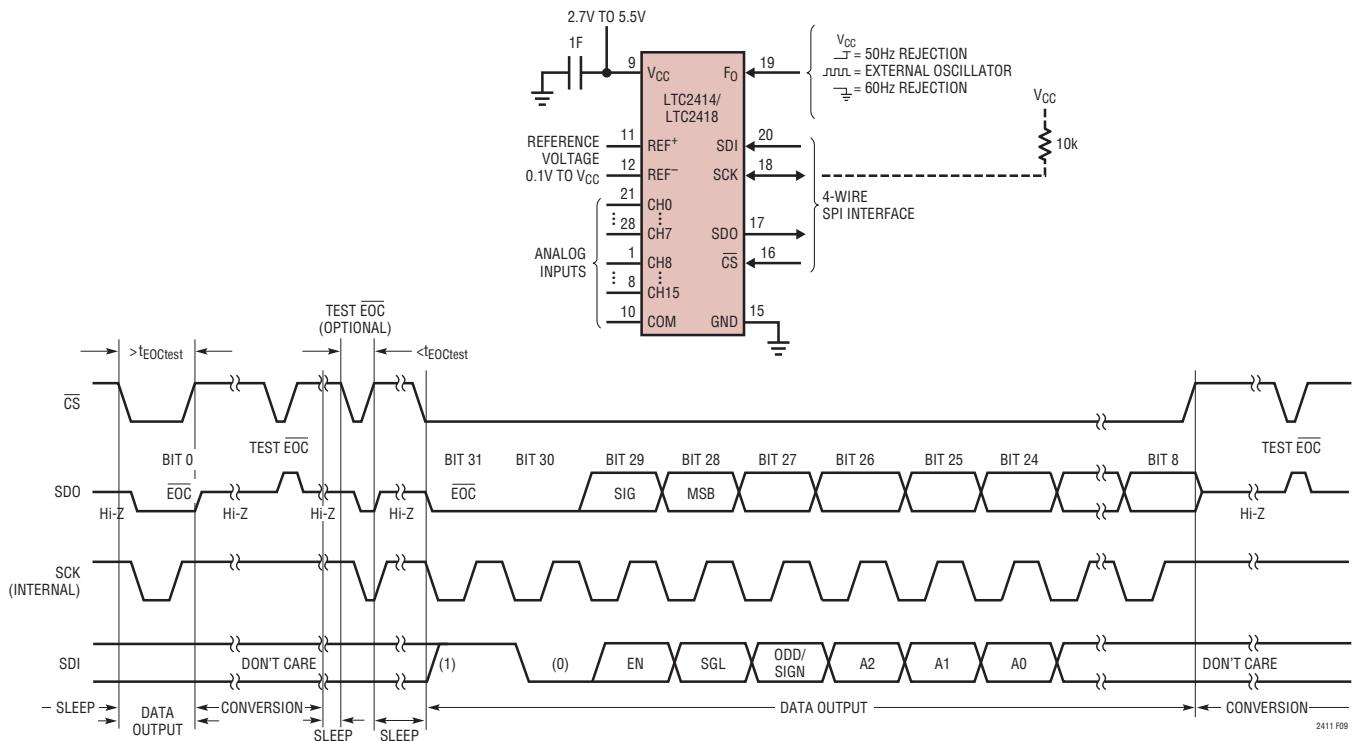

### 内部シリアル・クロック、単一サイクル動作

このタイミング・モードでは、内部シリアル・クロックを使用して変換結果と $\overline{CS}$ 信号をシフトして出力し、変換サイクルの状態をモニタして制御することができます。図8を参照してください。

内部シリアル・クロック・タイミング・モードを選択するには、 $\overline{CS}$ の立ち下がりエッジの前に、シリアル・クロック・ピン(SCK)をフロート(高インピーダンス)状態にするか“H”にする必要があります。 $\overline{CS}$ の立ち下がりエッジでSCKが“L”になっている場合、デバイスは内部シリアル・クロック・タイミング・モードには入りません。 $\overline{CS}$ の立ち下がりエッジの間は、内部の弱いプルアップ抵抗がSCKピンで導通します。このため、SCKを外部で駆動しなかった場合は、内部シリアル・クロック・タイミング・モードが自動的に選択されます。

シリアル・データ出力ピン(SDO)は、 $\overline{CS}$ が“H”である限り、高インピーダンスです。コンバータの状態をモニタするため、変換サイクル中は隨時、 $\overline{CS}$ を“L”することができます。 $\overline{CS}$ を“L”になると、SCKが“L”になり、 $\overline{EOC}$ はSDOピンに出力されます。変換が進行中のときは $\overline{EOC} = 1$ であり、デバイスがスリープ状態の場合は $\overline{EOC} = 0$ です。

図7. 外部シリアル・クロック、 $\overline{CS} = 0$ 動作

241418 F07

# LTC2414/LTC2418

## アプリケーション情報

図8. 内部シリアル・クロック、単一サイクル動作

$\overline{EOC}$ をテストしているときに変換が完了した場合( $\overline{EOC} = 0$ )、デバイスは $\overline{EOC}$ のテスト中に低消費電力モードを終了します。デバイスが低消費電力のスリープ状態に戻ることができるようになります。SCKの最初の立ち上がりエッジより前に $\overline{CS}$ を“H”にしておく必要があります。内部SCKタイミング・モードでは、SCKは“H”になり、デバイスは次の時間にデータの出力を開始します。 $\overline{EOC} = 0$ の場合は $\overline{CS}$ の立ち下がりエッジ後の時間 $t_{EOCtest}$ であり、 $\overline{EOC}$ の立ち下がりエッジの間 $\overline{CS}$ が“L”的場合は $\overline{EOC}$ が“L”になった後の時間 $t_{EOCtest}$ です。デバイスが内部発振器を使用している場合、 $t_{EOCtest}$ の値は $23\mu s$ です( $F_0$ はロジック“L”または“H”)。 $F_0$ を周波数 $f_{EOSC}$ の外部発振器で駆動する場合、 $t_{EOCtest}$ は $3.6/f_{EOSC}$ です。時間 $t_{EOCtest}$ よりも前に $\overline{CS}$ が“H”になると、デバイスはスリープ状態に戻り、変換結果は内部の静的シフト・レジスタで保持されます。

$\overline{CS}$ が $t_{EOCtest}$ より長い時間“L”的ままである場合、SCKの最初の立ち上がりエッジが現れ、変換結果はSDOピンから順次シフトして出力されます。データ入出力サイクルは、32番目の立ち上がりエッジ後に終了します。その後、入力データはSCKの(最初の立ち上がりエッジを含む)立ち上がりエッジで、SDIピンを介してシフトして入力されます。また、出力データはSCKの立ち下がりエッジごとにSDOピンからシフトして

出力されます。内部で生成されたシリアル・クロックは、SCKピンに出力されます。この信号を使用して、変換結果を外部回路にシフトすることができます。 $EOC$ はSCKの最初の立ち上がりエッジでラッチすることができます。また、変換結果の最後のビットはSCKの32番目の立ち上がりエッジでラッチすることができます。32番目の立ち上がりエッジの後、SDOは“H”になります( $\overline{EOC} = 1$ )、SCKは“H”のまま維持され、新しい変換が始まります。

通常、 $\overline{CS}$ はデータ出力状態の間“L”的ままであります。ただし、SCKの最初の立ち上がりエッジから32番目の立ち上がりエッジまでの間であれば、 $\overline{CS}$ を“H”にすることにより、データ出力状態は随時中断できます。図9を参照してください。デバイスは $\overline{CS}$ の立ち上がりエッジでデータ出力状態を中断し、新しい変換を直ちに開始します。 $\overline{CS}$ が“H”になっている間にデバイスがSDIの最後の入力ビットA0の読み込みを終了しなかった場合、アドレス情報は破棄され、直前のアドレスが引き続き保持されます。これが役立つのは、必ずしも32ビットすべての出力データが必要ではないシステム、無効な変換サイクルを中断するシステム、または変換開始を同期するシステムです。コンバータがSCKを“L”に駆動しているときに $\overline{CS}$ が“H”になった場合、内部プルアップ抵抗は導通せず、SCKはロジック“H”状

## アプリケーション情報

図9. 内部シリアル・クロック、短縮データ出力長

態に戻りません。これにより、デバイスは $\overline{CS}$ の次の立ち下がりエッジで内部シリアル・クロック・モードを終了します。これを防止するには、10kの外付けプルアップ抵抗をSCKピンに追加するか、SCKが“L”的 경우에는 $\overline{CS}$ が絶対に“H”にならないようにします。

SCKが“L”になると、LTC2414/LTC2418のSCKピンにある内部プルアップ抵抗は必ずディスエーブルされます。デバイスが内部SCKタイミング・モードになっている場合、通常はSCKが外部から駆動されることはありません。ただし、アプリケーションによってはSCKに外部ドライバが必要なことがあります。このドライバが“L”信号の出力後に高インピーダンスになると、LTC2414/LTC2418の内部プルアップ抵抗はディスエーブル状態のまま推移します。したがって、SCKは“L”的ままであります。 $\overline{CS}$ の次の立ち下がりエッジで、デバイスは外部SCKタイミング・モードに切り替わります。10kの外付けプルアップ抵抗をSCKに追加することにより、外部ドライバが高インピーダンスになればSCKは“H”になります。これにより、 $\overline{CS}$ の次の立ち下がりエッジでは、デバイスは内部SCKタイミング・モードを保持します。

変換状態をテストするために $\overline{CS}$ に“H”“L”“H”的順にパルスを加えると、スリープ状態のときに同様な状況が発生すること

があります。デバイスがスリープ状態である場合( $\overline{EOC} = 0$ )、SCKは“L”になります。 $\overline{CS}$ が( $t_{EOCtest}$ として前に定義した期間内に)“H”になると、内部プルアップ抵抗が導通します。SCKピンの容量性負荷が重い場合、 $\overline{CS}$ が再度“L”になる前にSCKを“H”に戻すには、内部プルアップ抵抗では不適当なことがあります。このことは、 $\overline{EOC} = 0$ の検出後に $\overline{CS}$ が“L”的ままである通常の条件では問題ありません。この状況は、10kの外付けプルアップ抵抗をSCKピンに追加することにより、容易に打開できます。

## 内部シリアル・クロック、3線式入出力、連続変換

このタイミング・モードでは、3線式インターフェースを使用します。変換結果は、内部で生成されたシリアル・クロック(SCK)信号により、デバイスからシフトして出力されます。図10を参照してください。 $\overline{CS}$ を永続的にグランドに接続して、ユーザー・インターフェースまたは絶縁障壁を簡略化することができます。

内部シリアル・クロック・モードは、パワーオン・リセット(POR)サイクルの最後に選択されます。PORサイクルは、VCCが $>2V$ を超えてから約1ms後に終了します。PORサイクルの間は、内部の弱いプルアップ抵抗が導通します。このため、SCKを外部で“L”に駆動しなかった場合は、内部シリアル・クロック・タイ

## アプリケーション情報

図10. 内部シリアル・クロック、 $\overline{CS} = 0$ 連続動作

241418 F10

ング・モードが自動的に選択されます(SCKに負荷がかかっているために、内部プルアップ抵抗がSCKピンを“H”に引き上げることができない場合は、外部SCKモードが選択されます)。

変換中、SCKおよびシリアル・データ出力ピン(SDO)は“H”( $\overline{EOC} = 1$ )です。いったん変換が完了すると、SCKおよびSDOは“L”( $\overline{EOC} = 0$ )になり、変換が終了したことと、デバイスが低消費電力のスリープ・モードに入ったことを示します。デバイスがスリープ状態にとどまる時間は最小限(内部SCK周期の1/2)に抑えられており、その後速やかにデータを出力し始めます。データの入力/出力サイクルはSCKの最初の立ち上がりエッジで始まり、32番目の立ち上がりエッジ後に終わります。その後、入力データはSCKの(最初の立ち上がりエッジを含む)立ち上がりエッジで、SDIピンを通してシフトして入力されます。また、出力データはSCKの立ち下がりエッジごとにSDOピンからシフトして出力されます。内部で生成されたシリアル・クロックは、SCKピンに出力されます。この信号を使用して、変換結果を外部回路にシフトすることができます。 $\overline{EOC}$ はSCKの最初の立ち上がりエッジでラッチすることができます。また、変換結果の最後のビットはSCKの32番目の立ち上がりエッジでラッチすることができます。32番目の立ち上がりエッジ後、SDOは“H”( $\overline{EOC} = 1$ )になり、新しい変換が進行中であることを示します。変換中、SCKは“H”的ままです。

## コンバータ精度の維持

LTC2414/LTC2418は、デバイスのデカッピング、PCBレイアウト、アンチエイリアシング回路、電源周波数、外乱などに対する変換結果の感度をできるだけ下げるよう設計されています。それにもかかわらず、このデバイスの超高精度の能力を維持するために、いくつかの簡単な予防措置をとることが望まれます。

## デジタル信号レベル

LTC2414/LTC2418のデジタル・インターフェースは、使い方が簡単です。そのデジタル入力(SDI、 $F_O$ 、 $\overline{CS}$ 、および外部SCK動作モードでのSCK)には、標準のTTL/CMOSロジック・レベルを入力可能であり、ヒステリシス内蔵のレシーバは100 $\mu$ s程度の低速エッジ・レートに対応できます。ただし、このコンバータの並外れた精度と低電源電流を活用するには、いくつかの検討が必要です。

デジタル出力信号(SDOおよび内部SCK動作モードでのSCK)は、変換状態の間は通常アクティブではないので、あまり問題はありません。

デジタル入力信号の範囲が0.5V～( $V_{CC} - 0.5V$ )のとき、CMOS入力レシーバでは、電源から流れる電流が増えます。

241418fa

## アプリケーション情報

デジタル入力信号(SDI、 $F_O$ 、CS、および外部SCK動作モードでのSCK)のいずれかがこの範囲内にある場合は、対象の信号が有効なロジック・レベルである場合でも、電源電流が増加する可能性があることに注意してください。マイクロパワー動作の場合は、すべてのデジタル入力信号を完全なCMOSレベル[ $V_{IL} < 0.4V$  および  $V_{OH} > (V_{CC} - 0.4V)$ ]まで駆動することを推奨します。

変換期間の間は、ピンに接続される高速デジタル信号のアンダーシュートやオーバーシュートによって、アナログ/デジタル変換処理が大きく乱されることがあります。アンダーシュートやオーバーシュートが発生するのは、外部制御信号の遷移時間が、ドライバからLTC2414/LTC2418までの伝播遅延時間の2倍より短いときに、コンバータのピンでインピーダンスの不整合が生じるからです。参考までに、正規のFR-4基板の場合、信号の伝播速度は内部トレースでは約183ps/インチであり、表面トレースでは170ps/インチです。したがって、最小遷移時間が1nsの制御信号を生成するドライバを、2.5インチより短いトレースを通じてコンバータのピンに接続する必要があります。この問題は、共用制御線を使用する場合に特に難しくなり、複数の反射が発生することがあります。解決策は、すべての伝送線を慎重に終端して、その特性インピーダンスに近づけることです。

LTC2414/LTC2418のピンの近くで並列に終端すると、この問題は解消しますが、ドライバの電力損失が増加します。27Ωから56Ωまでの直列抵抗をドライバの近くかLTC2414/LTC2418のピンの近くに配置すれば、電力損失を増やさずにこの問題を解消できます。実際の抵抗値は、トレースのインピーダンスと接続形態によって異なります。

別の解決策は、制御信号のエッジ・レートを低減する方法です。非常に低速なエッジを使用すると、遷移時間中にコンバータの電源電流が増加することに注意してください。差動入力および差動リファレンスのアーキテクチャにより、グランド電流に対するコンバータの感度は大幅に低下します。

LTC2414/LTC2418を外部の変換クロックと組み合わせて使用する場合には、 $F_O$ 信号の接続に対して特に注意する必要があります。このクロックは変換時間中に作動しており、内部デジタル・フィルタによって得られるノーマル・モード除去比は、この周波数ではありません。この周波数のノーマル・モード信号をコンバータのリファレンス端子に入力すると、DC利得とINLの誤差が生じることがあります。この周波

数のノーマル・モード信号をコンバータの入力端子に入力すると、DCオフセット誤差が生じることがあります。こうした外乱が生じる原因は、 $F_O$ 信号トレースとコンバータ入力トレースまたはリファレンス接続トレース(あるいはその両方)との間の非対称の容量結合と考えられます。直接の解決策は、 $F_O$ 信号トレースと入力/リファレンス信号との間隔を可能な最大の距離に維持することです。 $F_O$ 信号をコンバータの近くで並列に終端すると、 $F_O$ 接続トレース、終端、およびグランド帰還路によって形成されたループに相当なAC電流が流れます。このため、外乱信号がコンバータ入力やリファレンスに誘導結合される可能性があります。この状況では、ユーザーが $F_O$ 信号の最小ループ面積だけでなく、差動入力とリファレンスの接続箇所のループ面積も減らす必要があります。

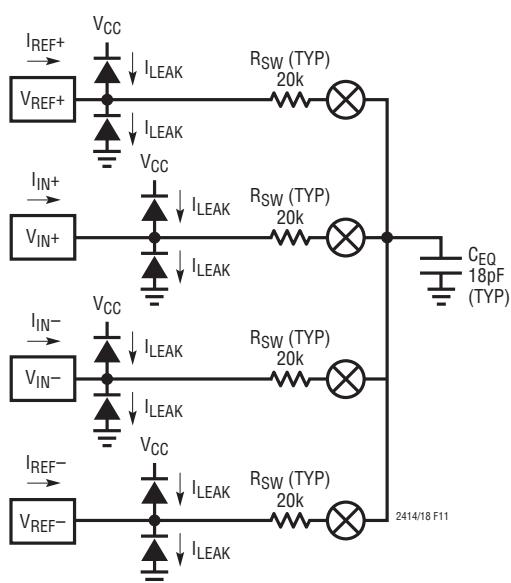

## 入力およびリファレンスの駆動

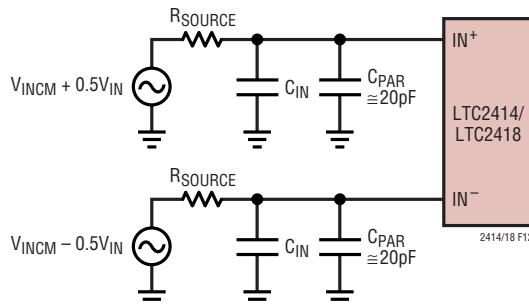

LTC2414/LTC2418コンバータの入力ピンとリファレンス・ピンは、サンプリング・コンデンサの回路網に直接接続されます。差動入力電圧と差動リファレンス電圧の間の関係によっては、これらのコンデンサはこれら4つのピンの間で切り替わり、その過程で少量の電荷を移動します。簡略等価回路図を図11に示します。

単純近似では、アナログ入力ピン( $IN^+$ 、 $IN^-$ 、 $REF^+$ 、または $REF^-$ )を駆動する信号源インピーダンス $R_S$ を考慮し、 $R_{SW}$ および $C_{EQ}$ とともに(図11を参照)、時定数 $\tau = (R_S + R_{SW}) \cdot C_{EQ}$ を持つ1次の受動回路網を形成することができます。サンプリング周期が入力回路の時定数 $\tau$ より14倍以上長い場合、コンバータは、1ppmより優れた精度で入力信号をサンプリングすることができます。4つの入力アナログ・ピンでのサンプリング・プロセスはそれぞれがほぼ独立しているので、各時定数は単独で考えます。また、ワーストケースの環境では、誤差が加わる可能性があります。

内部発振器を使用する場合( $F_O = "L"$ または $"H"$ )、LTC2414/LTC2418の先端部のスイッチト・キャパシタ回路網のクロック周波数は、13μsのサンプリング周期に対応する76800Hzになります。したがって、セトリング誤差を1ppm未満にするには、 $\tau \leq 13\mu s / 14 = 920\text{ns}$ となるように駆動信号源インピーダンスを選択します。周波数が $f_{EOSC}$ の外部発振器を使用する場合、サンプリング周期は $2/f_{EOSC}$ であり、セトリング誤差を1ppm未満にするには、 $\tau \leq 0.14/f_{EOSC}$ となるようにします。

## アプリケーション情報

### 入力電流

入力で完全なセトリングが行われる場合は、変換結果が動的入力電流による影響を受けなくなります。入力信号サンプリング・プロセスのセトリングが不完全である場合、利得誤差とオフセット誤差が発生することがあります。コンバータのINL性能は低下しません。かなりの期間(内部クロック・サイクルの64倍より長い期間)にわたって積分した場合、サンプリング電荷が移動した結果としてIN<sup>+</sup>ピンおよびIN<sup>-</sup>ピンを流れる平均バイアス電流の式を図11に示します。

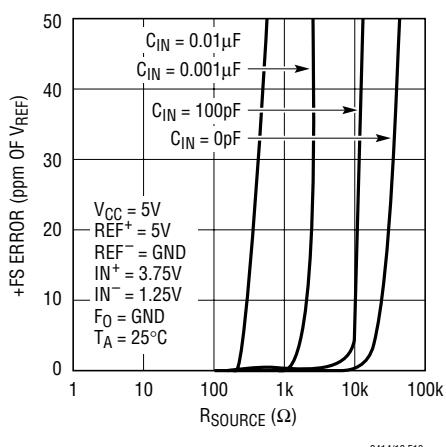

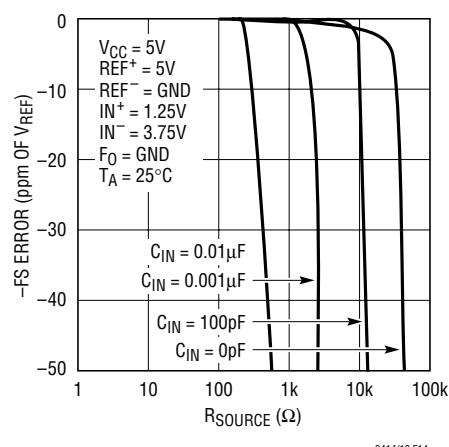

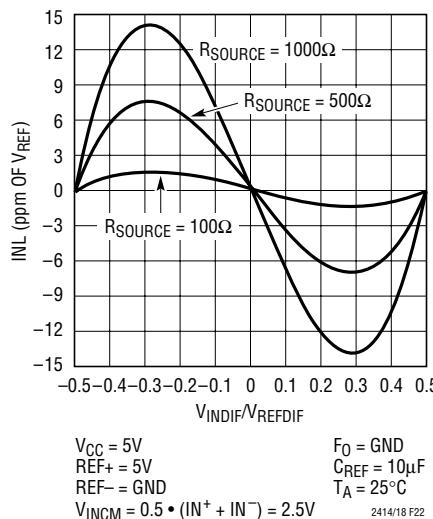

この動的入力電流の影響は、図12のテスト回路を使用して解析できます。コンデンサC<sub>PAR</sub>には、LTC2414/LTC2418のピン容量(標準5pF)と、図13および14に示す結果を得るために使用されるテスト治具の容量が含まれます。慎重に実装することにより、全入力容量(C<sub>IN</sub> + C<sub>PAR</sub>)を5pFに近づけることができる、図13および14で予測される性能より優れた性能を達成できます。説明を簡単にするため、2つの特異な状況について考えます。

入力容量の値が比較的小さい場合(C<sub>IN</sub> < 0.01μF)は、サンプリング・コンデンサの電圧がほぼ完全に安定状態になり、信号源インピーダンスの値が比較的大きい場合は誤差が少な

くて済みます。C<sub>IN</sub>をこのような値にすると、コンバータのオフセット性能と利得性能が低下し、信号フィルタリング上さほど大きな利点はないので、回避することを推奨します。それにもかかわらず、入力マルチプレクサ、電線、コネクタ、またはセンサの寄生容量として小さな値のC<sub>IN</sub>が存在することが避けられない場合、LTC2414/LTC2418はその並外れた高精度を維持できる上に、図13および14に示すように、比較的高い値の信号源抵抗で動作することができます。これらの測定結果は、前述した1次近似とはわずかに異なる場合があります。その理由は、これらの結果には、実際の2次入力回路網の影響に加えて、入力アンプの非線形のセトリング処理が含まれるからです。C<sub>IN</sub>の値が小さい場合、IN<sup>+</sup>およびIN<sup>-</sup>でのセトリングはほとんど別個に行われ、2つのピンの信号源インピーダンスを整合する利点はほとんどありません。

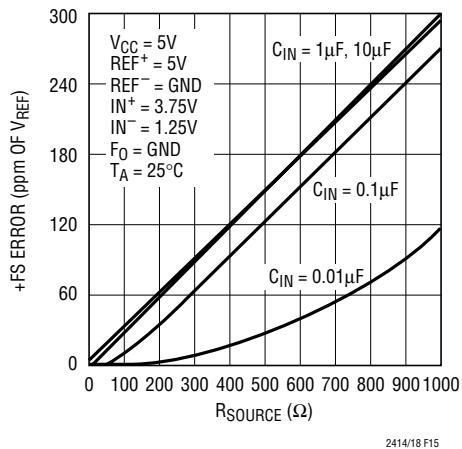

アンチエイリアシングや一般的な入力信号フィルタリングの場合、特定の構成では大きな値の入力コンデンサ(C<sub>IN</sub> > 0.01μF)が必要なことがあります。こうしたコンデンサによって入力サンプリング電荷が平均化されるので、外部信号源抵抗から見ると準一定の入力差動インピーダンスになります。F<sub>0</sub>が“L”(内部発振器および60Hzノッチ)の場合、標準的な差

SWITCHING FREQUENCY

$f_{SW} = 76800\text{Hz}$  INTERNAL OSCILLATOR ( $F_0 = \text{LOW OR HIGH}$ )

$f_{SW} = 0.5 \cdot f_{EOSC}$  EXTERNAL OSCILLATOR

$$I_{(\text{IN}^+)}_{\text{AVG}} = \frac{V_{IN} + V_{INCM} - V_{REFCM}}{0.5 \cdot R_{EQ}}$$

$$I_{(\text{IN}^-)}_{\text{AVG}} = \frac{-V_{IN} + V_{INCM} - V_{REFCM}}{0.5 \cdot R_{EQ}}$$

$$I_{(\text{REF}^+)}_{\text{AVG}} = \frac{1.5 \cdot V_{REF} - V_{INCM} + V_{REFCM}}{0.5 \cdot R_{EQ}} - \frac{V_{IN}^2}{V_{REF} \cdot R_{EQ}}$$

$$I_{(\text{REF}^-)}_{\text{AVG}} = \frac{-1.5 \cdot V_{REF} - V_{INCM} + V_{REFCM}}{0.5 \cdot R_{EQ}} + \frac{V_{IN}^2}{V_{REF} \cdot R_{EQ}}$$

where:

$$V_{REF} = \text{REF}^+ - \text{REF}^-$$

$$V_{REFCM} = \left( \frac{\text{REF}^+ + \text{REF}^-}{2} \right)$$

$$V_{IN} = \text{IN}^+ - \text{IN}^-$$

$$V_{INCM} = \left( \frac{\text{IN}^+ - \text{IN}^-}{2} \right)$$

$$R_{EQ} = 3.61\text{M}\Omega \text{ INTERNAL OSCILLATOR } 60\text{Hz Notch } (F_0 = \text{LOW})$$

$$R_{EQ} = 4.32\text{M}\Omega \text{ INTERNAL OSCILLATOR } 50\text{Hz Notch } (F_0 = \text{HIGH})$$

$$R_{EQ} = \left( 0.555 \cdot 10^{12} \right) / f_{EOSC} \text{ EXTERNAL OSCILLATOR}$$

図11. LTC2414/LTC2418のアナログ入力等価回路

## アプリケーション情報

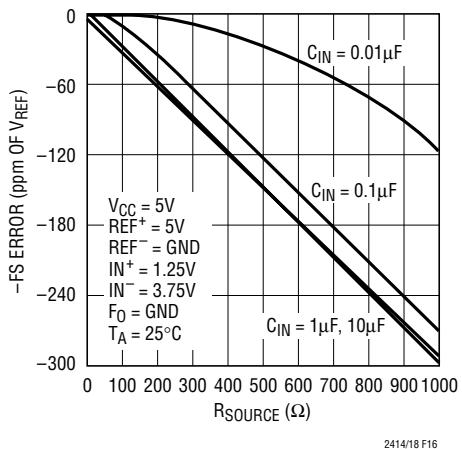

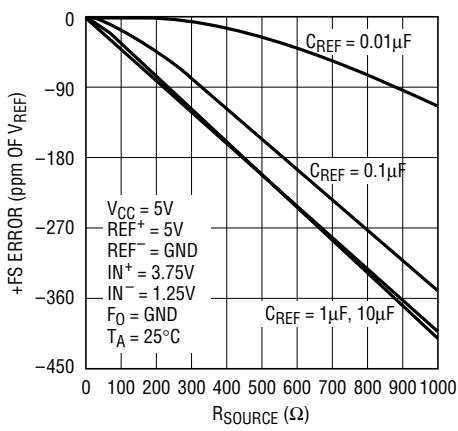

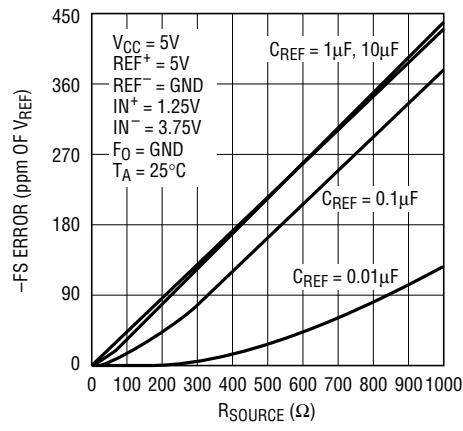

図12. IN<sup>+</sup>およびIN<sup>-</sup>でのRC回路網図13. +FS 誤差とIN<sup>+</sup>またはIN<sup>-</sup>でのR<sub>SOURCE</sub>(C<sub>IN</sub>が小さい場合)

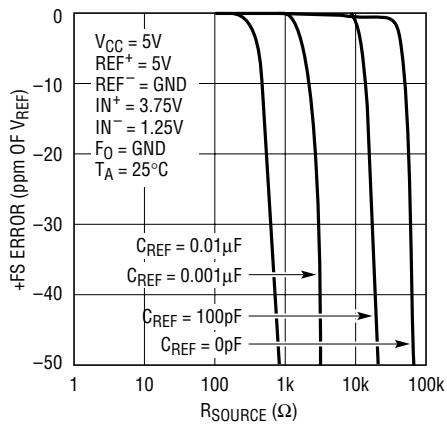

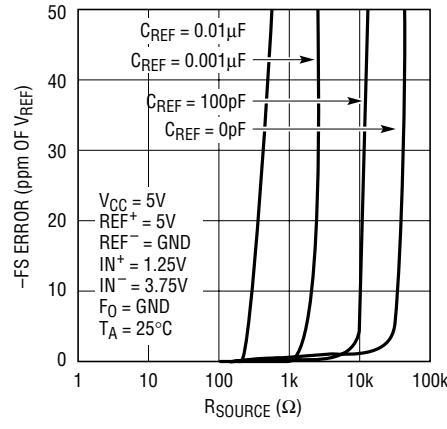

動入力抵抗は $1.8\text{M}\Omega$ であり、IN<sup>+</sup>またはIN<sup>-</sup>を駆動する信号源抵抗 $1\Omega$ につき約0.28ppmの利得誤差が発生します。F<sub>O</sub>が“H”(内部発振器および50Hzノッチ)の場合、標準的な差動入力抵抗は $2.16\text{M}\Omega$ であり、IN<sup>+</sup>またはIN<sup>-</sup>を駆動する信号源抵抗 $1\Omega$ につき約0.23ppmの利得誤差が発生します。周波数がf<sub>EOSC</sub>(外部変換クロック動作)の外部発振器でF<sub>O</sub>を駆動する場合、標準的な差動入力抵抗は $0.28 \cdot 10^{12}/f_{EOSC}\Omega$ であり、IN<sup>+</sup>またはIN<sup>-</sup>を駆動する信号源抵抗 $1\Omega$ につき $1.78 \cdot 10^{-6} \cdot f_{EOSC}$ ppmの利得誤差が発生します。2つの入力ピンでの信号源抵抗の影響は、この利得誤差に関して増加の方向に作用します。C<sub>IN</sub>の値が大きいIN<sup>+</sup>およびIN<sup>-</sup>から見た信号源抵抗の合計の関数として表した、標準的な+FS誤差および-FS誤差を図15および16に示します。

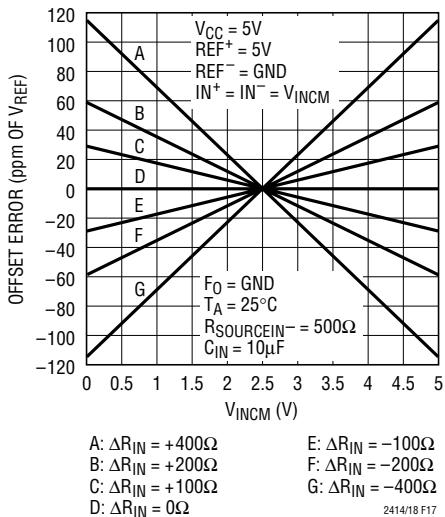

また、この利得誤差の他に、オフセット誤差の項が現れることもあります。オフセット誤差は、2つの入力ピンIN<sup>+</sup>およびIN<sup>-</sup>を駆動する信号源インピーダンス間の不整合と、入力同相電圧とリファレンス同相電圧との差に比例します。入力駆動回路

図14. -FS 誤差とIN<sup>+</sup>またはIN<sup>-</sup>でのR<sub>SOURCE</sub>(C<sub>IN</sub>が小さい場合)

にゼロではない信号源インピーダンスが存在し、これにコンバータの平均入力電流が流れてもINL性能は低下しませんが、入力信号の同相成分によるオフセット誤差の変化が原因で、間接的な歪みが発生する可能性があります。したがって、大きな値のC<sub>IN</sub>コンデンサを使用する場合は、IN<sup>+</sup>ピンとIN<sup>-</sup>ピンから見た信号源インピーダンスを慎重に整合させることを推奨します。F<sub>O</sub>が“L”(内部発振器および60Hzノッチ)の場合、信号源インピーダンスに生じた不整合 $1\Omega$ につき、フルスケールの同相入力信号が0.28ppmの差動入力信号に変換されます。F<sub>O</sub>が“H”(内部発振器および50Hzノッチ)の場合、信号源インピーダンスに生じた不整合 $1\Omega$ につき、フルスケールの同相入力信号が0.23ppmの差動入力信号に変換されます。周波数がf<sub>EOSC</sub>の外部発振器でF<sub>O</sub>を駆動する場合、信号源インピーダンスに生じた不整合 $1\Omega$ につき、フルスケールの同相入力信号が $1.78 \cdot 10^{-6} \cdot f_{EOSC}$ ppmの差動入力信号に変換されます。大きな値のC<sub>IN</sub>を使用している場合、入力同相電圧に起因する標準的なオフセット誤差を図17に示します。IN<sup>+</sup>

## アプリケーション情報

図15. +FS 誤差と IN<sup>+</sup> または IN<sup>-</sup> での R<sub>SOURCE</sub> (C<sub>IN</sub> が大きい場合)

図16. -FS 誤差と IN<sup>+</sup> または IN<sup>-</sup> での R<sub>SOURCE</sub> (C<sub>IN</sub> が大きい場合)

図17. C<sub>IN</sub> の値が大きい (C<sub>IN</sub> ≥ 1μF) 場合のオフセット誤差と

同相電圧 (V<sub>INCM</sub> = IN<sup>+</sup> = IN<sup>-</sup>) および入力信号源抵抗の不均衡度

(ΔR<sub>IN</sub> = R<sub>SOURCEIN+</sub> - R<sub>SOURCEIN-</sub>)

ピンと IN<sup>-</sup> ピンの間に存在する信号源抵抗のさまざまな値の不均衡度をパラメータとしています。

可能な場合は、対称ブリッジのレシオメトリック測定の場合と同様に、リファレンス信号同相電圧に非常に近い入力信号同相電圧を使用して動作させることを推奨します。この構成では、信号源インピーダンスの不整合に起因するオフセット誤差を取り除くことができます。