## 特長

- SO-8パッケージの24ビットADC

- INL 4ppm、ミッシング・コードなし

- フルスケール誤差：4ppm

- 多重化アプリケーションに対応する単一変換セティング時間

- オフセット：0.5ppm

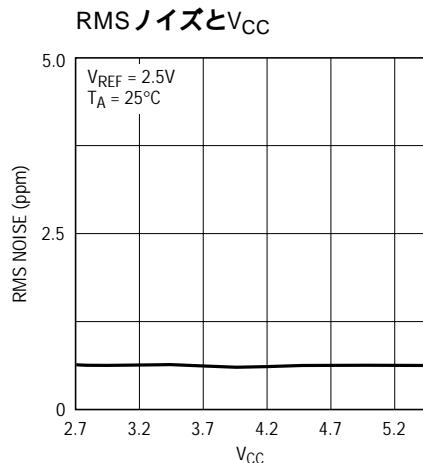

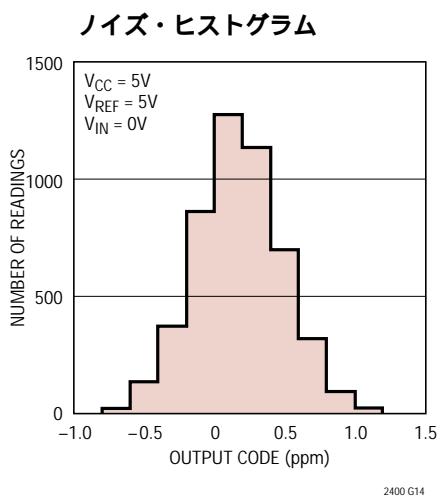

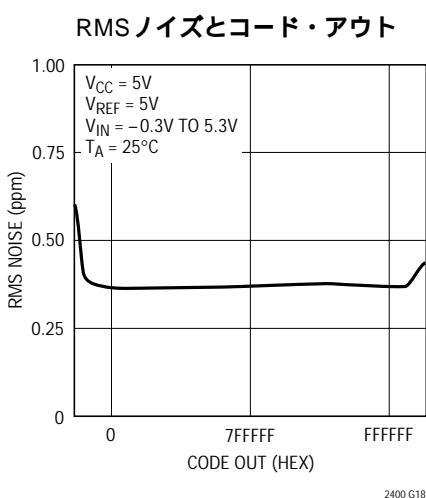

- ノイズ：0.3ppm

- 内部発振器 - 外付け部品不要

- 最小110dB、50Hz/60Hzノッチ・フィルタ

- リファレンス入力電圧：0.1V ~ V<sub>CC</sub>

- ライブ・ゼロ - 拡張入力範囲により12.5%のオーバーレンジおよびアンダーレンジに対応可能

- 2.7V ~ 5.5V単一電源動作

- 低電源電流(200 $\mu$ A)および自動シャットダウン

## アプリケーション

- 秤

- 直接温度測定

- ガス分析器

- 歪みゲージ・トランスデューサ

- 計測

- データ収集

- 産業用プロセス・コントロール

- 6桁DVM

## 概要

LTC<sup>®</sup>2400は、発振器を内蔵しINL 4ppm、RMSノイズ0.3ppm、2.7V ~ 5.5Vで動作するマイクロパワー24ビット・コンバータです。デルタ-シグマ技術を用い、多重化アプリケーションに対して単一サイクル・セトリング時間を提供します。LTC2400は1本のピンにより、50Hzまたは60Hz±2%において110dB以上の除去を達成するように構成できます。あるいは、外部発振器によってユーザが定義した除去周波数を1Hz ~ 120Hzの範囲でドライブすることができます。内部発振器には、周波数設定用の部品を外付けする必要はありません。

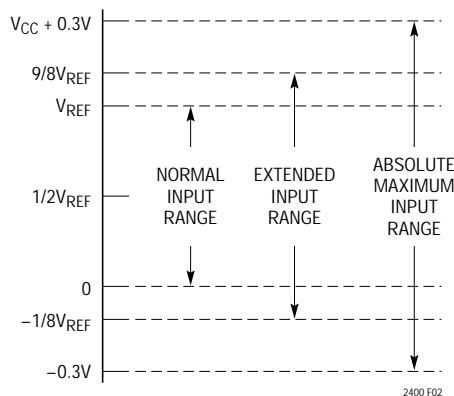

このコンバータは0.1V ~ V<sub>CC</sub>の範囲のどの外部リファレンス電圧でも受け入れます。LTC2400は-12.5% • V<sub>REF</sub> ~ 112.5% • V<sub>REF</sub>の拡張入力変換範囲を備えており、従来のセンサまたは信号処理回路で見られたオフセットやオーバーレンジの問題を円滑に解決します。

LTC2400はSPIおよびMICROWIRE<sup>TM</sup>プロトコルに適合する柔軟な3線式デジタル・インターフェースを通して通信します。

LTC、LTはリニアテクノロジー社の登録商標です。

No Latency  $\Delta\Sigma$ は、リニアテクノロジー社の商標です。

MICROWIREは、ナショナル・セミコンダクター社の商標です。

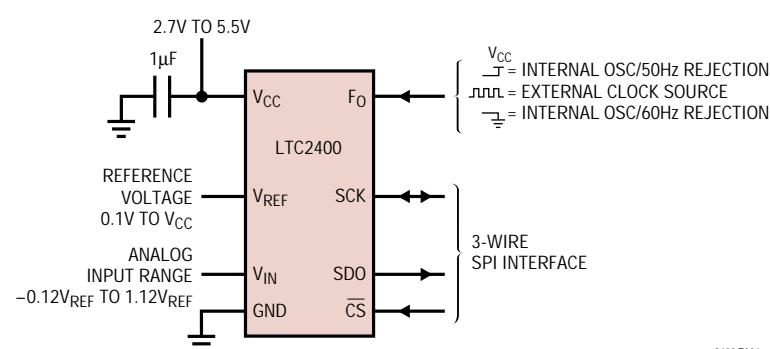

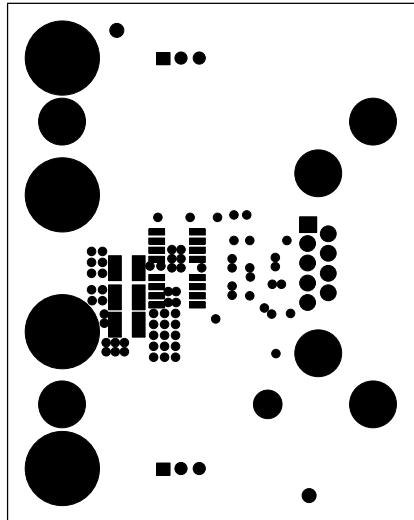

## 標準的応用例

2400 TA01

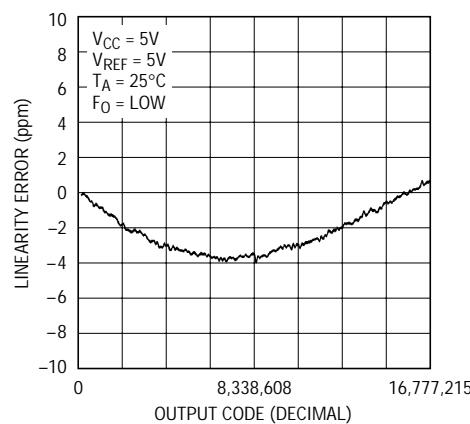

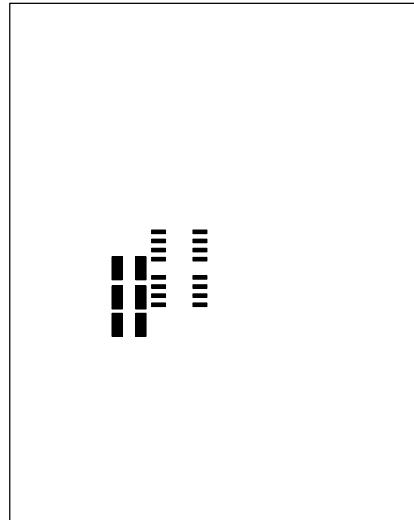

## 全未調整誤差と出力コード

2400 TA02

## 絶対最大定格

(Notes 1、2)

GNDに対する電源電圧( $V_{CC}$ ) ..... - 0.3V ~ 7V

GNDに対するアナログ入力電圧 ... - 0.3V ~ ( $V_{CC} + 0.3V$ )

GNDに対するリファレンス入力電圧 .... - 0.3V ~ ( $V_{CC} + 0.3V$ )

GNDに対するデジタル入力電圧 ... - 0.3V ~ ( $V_{CC} + 0.3V$ )

GNDに対するデジタル出力電圧 ... - 0.3V ~ ( $V_{CC} + 0.3V$ )

動作温度範囲

LTC2400C ..... 0 ~ 70

LTC2400I ..... - 40 ~ 85

保存温度範囲 ..... - 65 ~ 150

リード温度(半田付け、10秒) ..... 300

## パッケージ/発注情報

| TOP VIEW                                             | ORDER PART NUMBER        |

|------------------------------------------------------|--------------------------|

|                                                      | LTC2400CS8<br>LTC2400IS8 |

| S8 PACKAGE<br>8-LEAD PLASTIC SO                      | S8 PART MARKING          |

| T <sub>JMAX</sub> = 125°C, θ <sub>JA</sub> = 130°C/W | 2400<br>2400I            |

ミリタリ・グレードに関してはお問い合わせください。

## コンバータ特性

●は全動作温度範囲の規格値を意味する。それ以外は $T_A = 25$  での値。(Note 3、4)

| PARAMETER                        | CONDITIONS                                           | MIN    | TYP     | MAX      | UNITS                                |

|----------------------------------|------------------------------------------------------|--------|---------|----------|--------------------------------------|

| Resolution (No Missing Codes)    | $0.1V \leq V_{REF} \leq V_{CC}$ , (Note 5)           | ●      | 24      |          | Bits                                 |

| Integral Nonlinearity            | $V_{REF} = 2.5V$ (Note 6)<br>$V_{REF} = 5V$ (Note 6) | ●<br>● | 2<br>4  | 10<br>15 | ppm of $V_{REF}$<br>ppm of $V_{REF}$ |

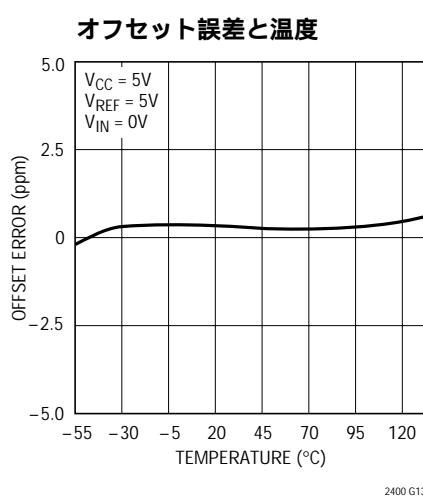

| Offset Error                     | $2.5V \leq V_{REF} \leq V_{CC}$                      | ●      | 0.5     | 2        | ppm of $V_{REF}$                     |

| Offset Error Drift               | $2.5V \leq V_{REF} \leq V_{CC}$                      |        | 0.01    |          | ppm of $V_{REF}/^{\circ}C$           |

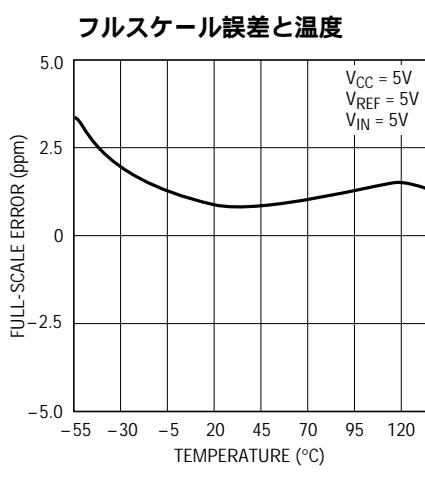

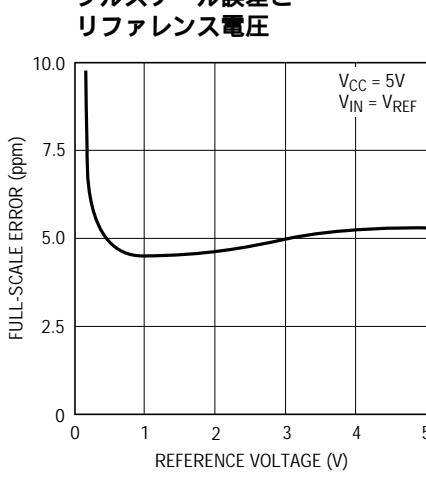

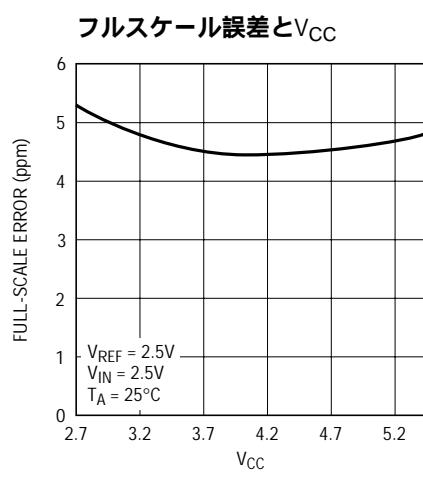

| Full-Scale Error                 | $2.5V \leq V_{REF} \leq V_{CC}$                      | ●      | 4       | 10       | ppm of $V_{REF}$                     |

| Full-Scale Error Drift           | $2.5V \leq V_{REF} \leq V_{CC}$                      |        | 0.02    |          | ppm of $V_{REF}/^{\circ}C$           |

| Total Unadjusted Error           | $V_{REF} = 2.5V$<br>$V_{REF} = 5V$                   |        | 5<br>10 |          | ppm of $V_{REF}$<br>ppm of $V_{REF}$ |

| Output Noise                     | $V_{IN} = 0V$ (Note 13)                              |        | 1.5     |          | $\mu V_{RMS}$                        |

| Normal Mode Rejection 60Hz ±2%   | (Note 7)                                             | ●      | 110     | 130      | dB                                   |

| Normal Mode Rejection 50Hz ±2%   | (Note 8)                                             | ●      | 110     | 130      | dB                                   |

| Power Supply Rejection, DC       | $V_{REF} = 2.5V$ , $V_{IN} = 0V$                     |        | 100     |          | dB                                   |

| Power Supply Rejection, 60Hz ±2% | $V_{REF} = 2.5V$ , $V_{IN} = 0V$ , (Notes 7, 15)     |        | 110     |          | dB                                   |

| Power Supply Rejection, 50Hz ±2% | $V_{REF} = 2.5V$ , $V_{IN} = 0V$ , (Notes 8, 15)     |        | 110     |          | dB                                   |

## アナログ入力およびリファレンス

●は全動作温度範囲の規格値を意味する。それ以外は $T_A = 25$  での値。(Note 3)

| SYMBOL          | PARAMETER                      | CONDITIONS                                  | MIN | TYP                | MAX               | UNITS |    |

|-----------------|--------------------------------|---------------------------------------------|-----|--------------------|-------------------|-------|----|

| $V_{IN}$        | Input Voltage Range            | (Note 14)                                   | ●   | -0.125 • $V_{REF}$ | 1.125 • $V_{REF}$ | V     |    |

| $V_{REF}$       | Reference Voltage Range        |                                             | ●   | 0.1                | $V_{CC}$          | V     |    |

| $C_{S(IN)}$     | Input Sampling Capacitance     |                                             |     | 10                 |                   | pF    |    |

| $C_{S(REF)}$    | Reference Sampling Capacitance |                                             |     | 15                 |                   | pF    |    |

| $I_{IN(LEAK)}$  | Input Leakage Current          | $\overline{CS} = V_{CC}$                    | ●   | -10                | 1                 | 10    | nA |

| $I_{REF(LEAK)}$ | Reference Leakage Current      | $V_{REF} = 2.5V$ , $\overline{CS} = V_{CC}$ | ●   | -10                | 1                 | 10    | nA |

## デジタル入力とデジタル出力

● は全動作温度範囲の規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。(Note 3)

| SYMBOL   | PARAMETER                                         | CONDITIONS                                                                     |   | MIN             | TYP | MAX  | UNITS         |

|----------|---------------------------------------------------|--------------------------------------------------------------------------------|---|-----------------|-----|------|---------------|

| $V_{IH}$ | High Level Input Voltage<br>$\overline{CS}, F_0$  | $2.7V \leq V_{CC} \leq 5.5V$<br>$2.7V \leq V_{CC} \leq 3.3V$                   | ● | 2.5             |     |      | V             |

| $V_{IL}$ | Low Level Input Voltage<br>$\overline{CS}, F_0$   | $4.5V \leq V_{CC} \leq 5.5V$<br>$2.7V \leq V_{CC} \leq 5.5V$                   | ● |                 | 0.8 | 0.6  | V             |

| $V_{IH}$ | High Level Input Voltage<br>SCK                   | $2.7V \leq V_{CC} \leq 5.5V$ (Note 9)<br>$2.7V \leq V_{CC} \leq 3.3V$ (Note 9) | ● | 2.5             |     |      | V             |

| $V_{IL}$ | Low Level Input Voltage<br>SCK                    | $4.5V \leq V_{CC} \leq 5.5V$ (Note 9)<br>$2.7V \leq V_{CC} \leq 5.5V$ (Note 9) | ● |                 | 0.8 | 0.6  | V             |

| $I_{IN}$ | Digital Input Current<br>$\overline{CS}, F_0$     | $0V \leq V_{IN} \leq V_{CC}$                                                   | ● | -10             |     | 10   | $\mu\text{A}$ |

| $I_{IN}$ | Digital Input Current<br>SCK                      | $0V \leq V_{IN} \leq V_{CC}$ (Note 9)                                          | ● | -10             |     | 10   | $\mu\text{A}$ |

| $C_{IN}$ | Digital Input Capacitance<br>$\overline{CS}, F_0$ |                                                                                |   |                 | 10  |      | $\text{pF}$   |

| $C_{IN}$ | Digital Input Capacitance<br>SCK                  | (Note 9)                                                                       |   |                 | 10  |      | $\text{pF}$   |

| $V_{OH}$ | High Level Output Voltage<br>SDO                  | $I_O = -800\mu\text{A}$                                                        | ● | $V_{CC} - 0.5V$ |     |      | V             |

| $V_{OL}$ | Low Level Output Voltage<br>SDO                   | $I_O = 1.6\text{mA}$                                                           | ● |                 |     | 0.4V | V             |

| $V_{OH}$ | High Level Output Voltage<br>SCK                  | $I_O = -800\mu\text{A}$ (Note 10)                                              | ● | $V_{CC} - 0.5V$ |     |      | V             |

| $V_{OL}$ | Low Level Output Voltage<br>SCK                   | $I_O = 1.6\text{mA}$ (Note 10)                                                 | ● |                 |     | 0.4V | V             |

| $I_{OZ}$ | High-Z Output Leakage<br>SDO                      |                                                                                | ● | -10             |     | 10   | $\mu\text{A}$ |

## 電源条件

● は全動作温度範囲の規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。(Note 3)

| SYMBOL   | PARAMETER                                       | CONDITIONS                                                           |        | MIN | TYP       | MAX       | UNITS         |

|----------|-------------------------------------------------|----------------------------------------------------------------------|--------|-----|-----------|-----------|---------------|

| $V_{CC}$ | Supply Voltage                                  |                                                                      | ●      | 2.7 |           | 5.5       | V             |

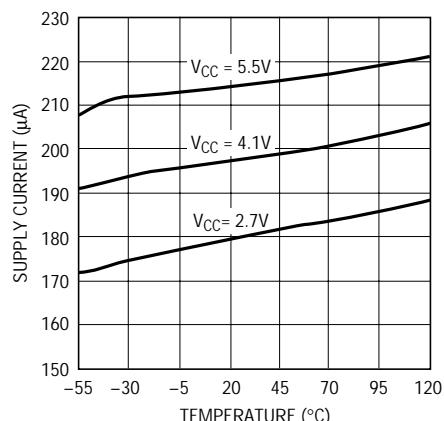

| $I_{CC}$ | Supply Current<br>Conversion Mode<br>Sleep Mode | $\overline{CS} = 0V$ (Note 12)<br>$\overline{CS} = V_{CC}$ (Note 12) | ●<br>● |     | 200<br>20 | 300<br>30 | $\mu\text{A}$ |

## タイミング特性

●は全動作温度範囲の規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。(Note 3)

| SYMBOL          | PARAMETER                                             | CONDITIONS                                                               | MIN         | TYP                                            | MAX                     | UNITS          |

|-----------------|-------------------------------------------------------|--------------------------------------------------------------------------|-------------|------------------------------------------------|-------------------------|----------------|

| $f_{EOSC}$      | External Oscillator Frequency Range                   |                                                                          | ●           | 2.56                                           | 307.2                   | kHz            |

| $t_{HEO}$       | External Oscillator High Period                       |                                                                          | ●           | 0.5                                            | 390                     | $\mu\text{s}$  |

| $t_{LEO}$       | External Oscillator Low Period                        |                                                                          | ●           | 0.5                                            | 390                     | $\mu\text{s}$  |

| $t_{CONV}$      | Conversion Time                                       | $F_O = 0\text{V}$<br>$F_O = V_{CC}$<br>External Oscillator (Note 11)     | ●<br>●<br>● | 130.66<br>156.80<br>20480/ $f_{EOSC}$ (in kHz) | 133.33<br>160<br>163.20 | ms<br>ms<br>ms |

| $f_{ISCK}$      | Internal SCK Frequency                                | Internal Oscillator (Note 10)<br>External Oscillator (Notes 10, 11)      |             | 19.2<br>$f_{EOSC}/8$                           |                         | kHz<br>kHz     |

| $D_{ISCK}$      | Internal SCK Duty Cycle                               | (Note 10)                                                                | ●           | 45                                             | 55                      | %              |

| $f_{ESCK}$      | External SCK Frequency Range                          | (Note 9)                                                                 | ●           |                                                | 2000                    | kHz            |

| $t_{LESCK}$     | External SCK Low Period                               | (Note 9)                                                                 | ●           | 250                                            |                         | ns             |

| $t_{HESCK}$     | External SCK High Period                              | (Note 9)                                                                 | ●           | 250                                            |                         | ns             |

| $t_{DOUT_ISCK}$ | Internal SCK 32-Bit Data Output Time                  | Internal Oscillator (Notes 10, 12)<br>External Oscillator (Notes 10, 11) | ●<br>●      | 1.64<br>256/ $f_{EOSC}$ (in kHz)               | 1.67<br>1.70            | ms<br>ms       |

| $t_{DOUT_ESCK}$ | External SCK 32-Bit Data Output Time                  | (Note 9)                                                                 | ●           | 32/ $f_{ESCK}$ (in kHz)                        |                         | ms             |

| $t_1$           | $\overline{\text{CS}} \downarrow$ to SDO Low Z        |                                                                          | ●           | 0                                              | 150                     | ns             |

| $t_2$           | $\overline{\text{CS}} \uparrow$ to SDO High Z         |                                                                          | ●           | 0                                              | 150                     | ns             |

| $t_3$           | $\overline{\text{CS}} \downarrow$ to SCK $\downarrow$ | (Note 10)                                                                | ●           | 0                                              | 150                     | ns             |

| $t_4$           | $\overline{\text{CS}} \downarrow$ to SCK $\uparrow$   | (Note 9)                                                                 | ●           | 50                                             |                         | ns             |

| $t_{KOMAX}$     | SCK $\downarrow$ to SDO Valid                         |                                                                          | ●           |                                                | 200                     | ns             |

| $t_{KOMIN}$     | SDO Hold After SCK $\downarrow$                       | (Note 5)                                                                 | ●           | 15                                             |                         | ns             |

| $t_5$           | SCK Set-Up Before $\overline{\text{CS}}$ $\downarrow$ |                                                                          | ●           | 50                                             |                         | ns             |

| $t_6$           | SCK Hold After $\overline{\text{CS}}$ $\downarrow$    |                                                                          | ●           |                                                | 50                      | ns             |

Note 1 : 絶対最大定格はそれを超えるとデバイスの寿命が損なわれる可能性がある値。

Note 2 : すべての電圧値はGNDを基準とする。

Note 3 : 注記がない限り、 $V_{CC} = 2.7\text{V} \sim 5.5\text{V}$

Note 4 : 注記がない限り、 $F_O$ ピンをGNDまたは $V_{CC}$ 、または $f_{EOSC} = 153600\text{Hz}$ の外部変換クロック・ソースに接続した状態の内部変換クロック・ソース。

Note 5 : 設計で保証されているが、テストされていない。

Note 6 : 積分非直線性は伝達曲線の実際のエンドポイントを通過する直線からのコードの偏差として定義される。偏差は量子化幅の中心から測定される。

Note 7 :  $F_O = 0\text{V}$  (内部発振器) または  $f_{EOSC} = 153600\text{Hz} \pm 2\%$  (外部発振器)。

Note 8 :  $F_O = V_{CC}$  (内部発振器) または  $f_{EOSC} = 128000\text{Hz} \pm 2\%$  (外部発振器)。

Note 9 : コンバータはSCKピンをデジタル入力として使用する外部SCK動作モード。データを出力している間、SCKをドライブしているクロック信号の周波数は $f_{ESCK}$ で、単位はkHz。

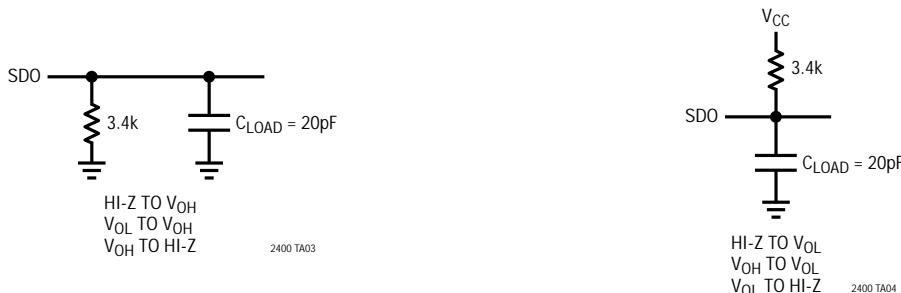

Note 10 : コンバータはSCKピンをデジタル出力として使用する内部SCK動作モード。この動作モードにおいて、SCKピンの全等化負荷容量 $C_{LOAD}$ は20pF。

Note 11 : 外部発振器は $F_O$ ピンに接続する。外部発振器周波数 $f_{EOSC}$ の単位はkHz

Note 12 : コンバータは内部発振器を使用する。 $F_O = 0\text{V}$ または $F_O = V_{CC}$

Note 13 : 出力ノイズは内部較正動作に付随する部分が含まれる。

Note 14 : リファレンス電圧値 $V_{REF} > 2.5\text{V}$ の場合、 $-0.125 \cdot V_{REF} \sim 1.125 \cdot V_{REF}$ の拡張入力は、アナログ入力電圧ピン(ピン3)の絶対最大定格によって制限される。 $2.5\text{V} < V_{REF} \leq 0.267\text{V} + 0.89 \cdot V_{CC}$ の場合、入力電圧範囲は $-0.3\text{V} \sim 1.125 \cdot V_{REF}$ である。 $0.267\text{V} + 0.89 \cdot V_{CC} < V_{REF} \leq V_{CC}$ の場合、入力電圧範囲は $-0.3\text{V} \sim V_{CC} + 0.3\text{V}$ である。

Note 15 :  $V_{CC} = 4.1\text{V}$ でのDC電圧、および $V_{CC}$ に印加されるAC電圧は $2.8\text{V}_{\text{P-P}}$ である。

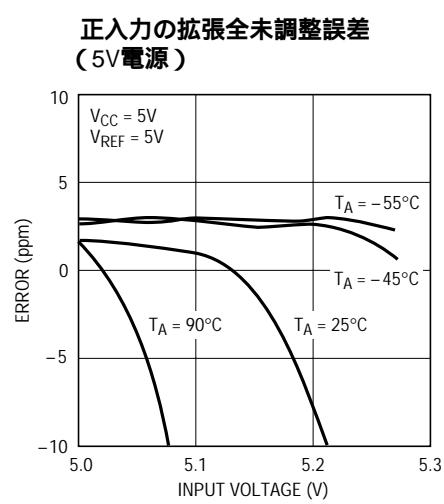

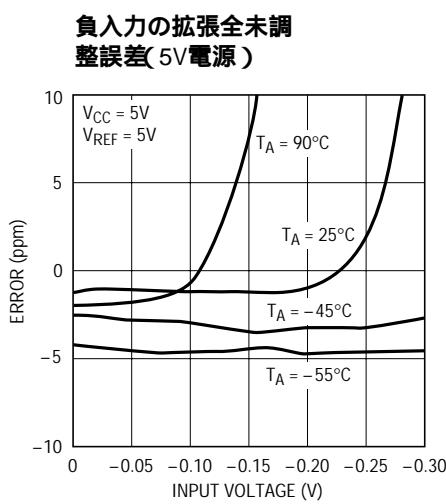

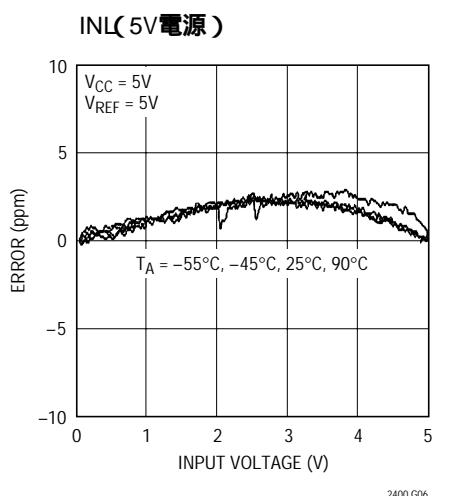

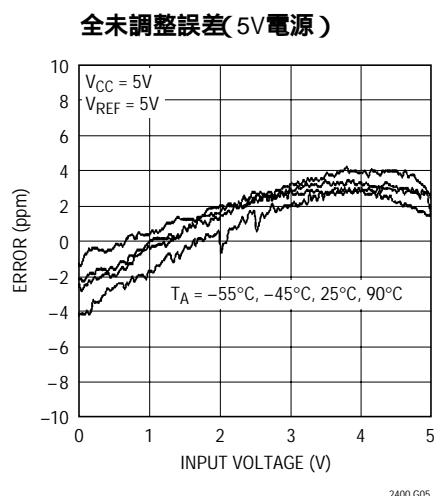

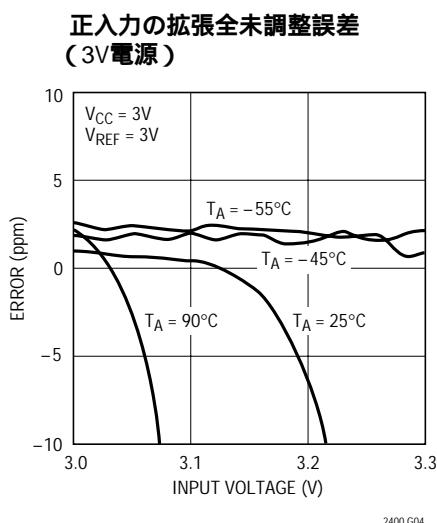

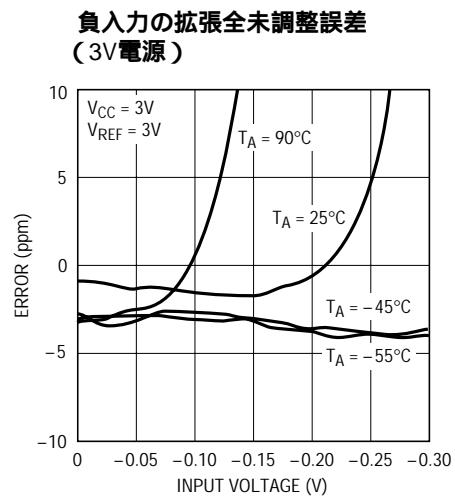

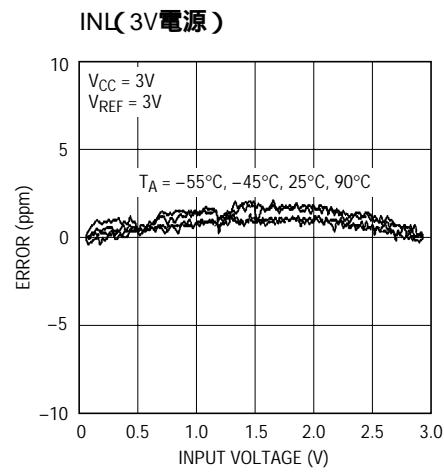

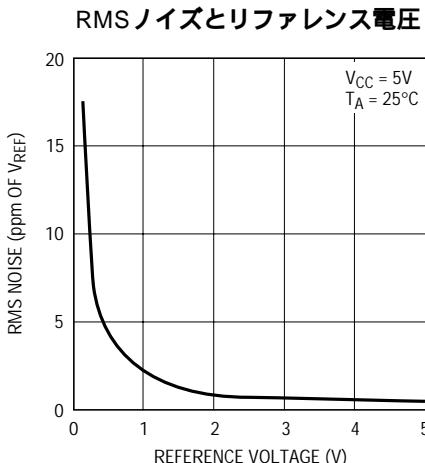

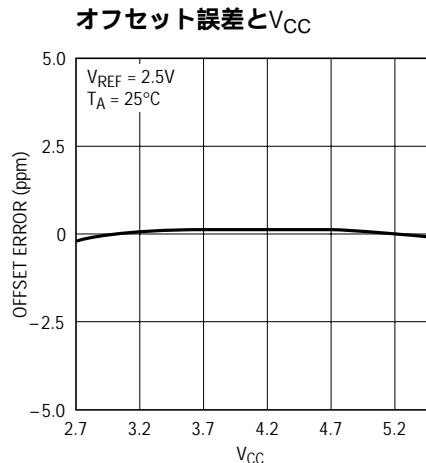

## 標準的性能特性

## 標準的性能特性

2400 G10

2400 G11

2400 G12

2400 G14

2400 G18

2400 G13

2400 G15

2400 G16

2400 G17

## 標準的性能特性

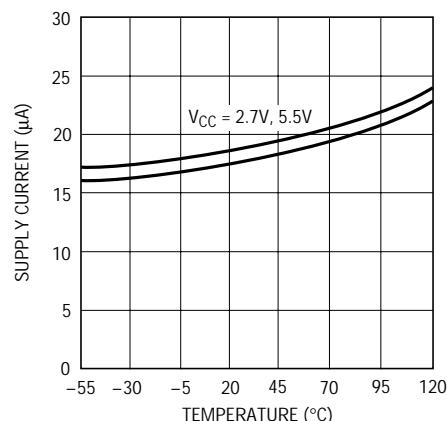

変換電流と温度

2400 G19

スリーブ電流と温度

2400 G20

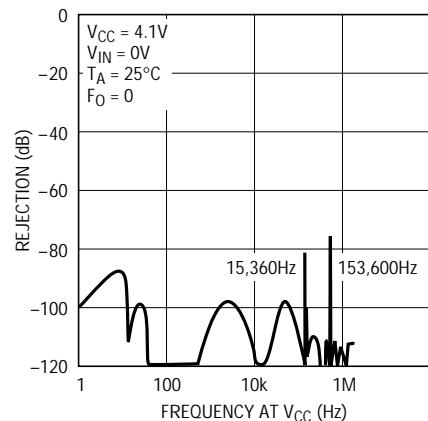

PSRRと $V_{CC}$ での周波数

2400 G23

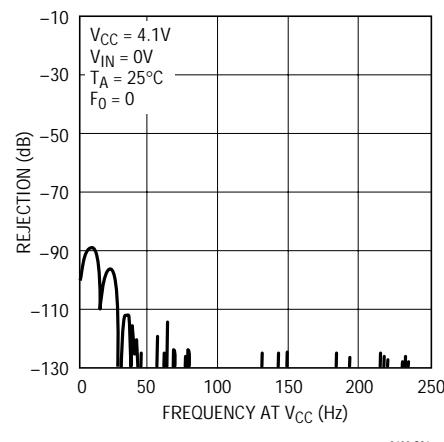

PSRRと $V_{CC}$ での周波数

2400 G21

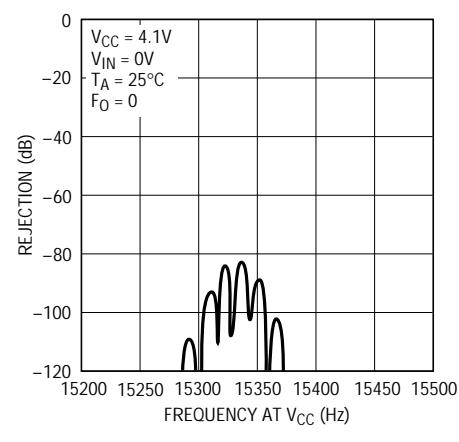

PSRRと $V_{CC}$ での周波数

1635 G22

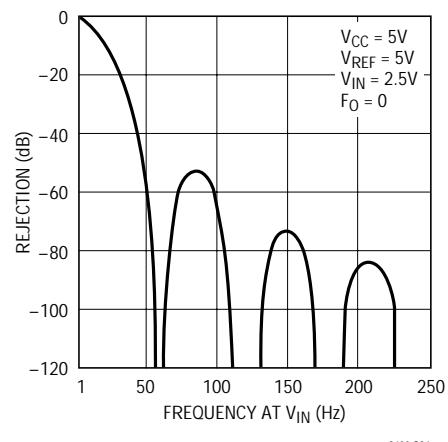

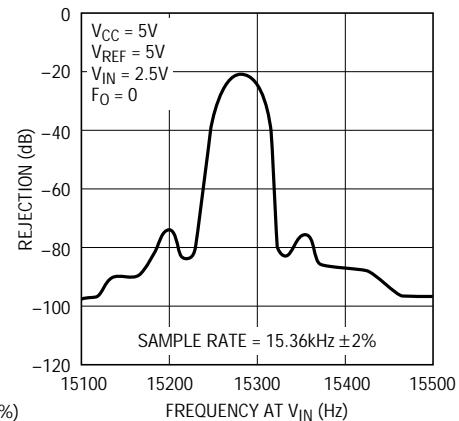

除去と $V_{IN}$ での周波数

2400 G24

除去と $V_{IN}$ での周波数

2400 G25

除去と $V_{IN}$ での周波数

2400 G26

除去と $V_{IN}$ での周波数

2400 F26

## 標準的性能特性

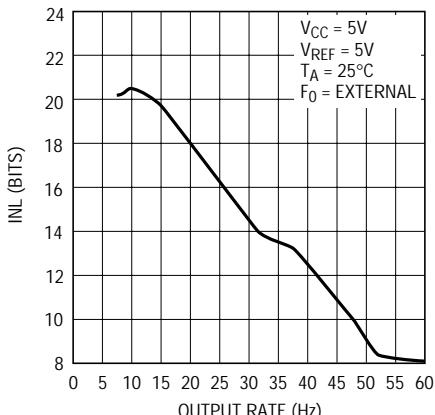

INLと出力レート

2400 G27

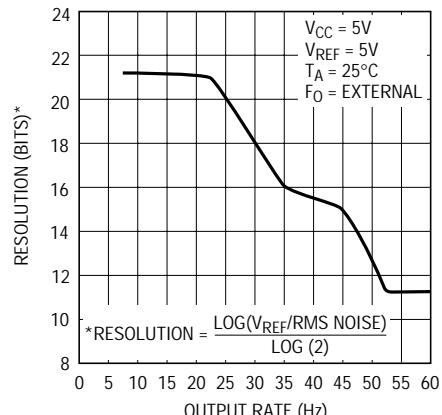

分解能と出力レート

2400 G28

## ピン機能

$V_{CC}$ ( ピン1 ): 正電源電圧。10 $\mu$ Fのタンタル・コンデンサと0.1 $\mu$ Fのセラミック・コンデンサを並列にしてGND( ピン4 )に最短でバイパスしてください。

$V_{REF}$ ( ピン2 ): リファレンス入力。リファレンス電圧範囲は0.1V ~  $V_{CC}$ です。

$V_{IN}$ ( ピン3 ): アナログ入力。入力電圧範囲は - 0.125 •  $V_{REF}$  ~ 1.125 •  $V_{REF}$ です。 $V_{REF} > 2.5$ Vの場合、入力電圧範囲はピンの絶対最大定格 - 0.3V ~  $V_{CC}$  + 0.3Vによって制限されます。

GND( ピン4 ): グランド。アナログ・グランド、デジタル・グランド、リファレンス・グランド、および信号グランドのための共用のピン。最短のトレースでグランド・プレーンに直接接続するか、シングルポイント・グランド・システムで一点接地を行ってください。

$\overline{CS}$ ( ピン5 ): アクティブ" L "デジタル入力。このピンが" L "のときは、SDOデジタル出力をイネーブルし、ADCをウェイクアップします。各変換に続いてADCは自動的にスリープモードになり、 $\overline{CS}$ ピンが" H "になっている間はこの低消費電力状態に留まります。 $\overline{CS}$ ピンを" L "にするとADCは始動します。このピンが" L "から" H "に変わると、SDOデジタル出力がディスエーブルされます。データ出力転送中に $\overline{CS}$ ピンが" L "から" H "に変わると、データ転送を中断して、新しいデータ変換を開始します。

SDQ( ピン6 ):3ステート・デジタル出力。このピンはデータ出力期間中はシリアル・データ出力に使用されます。チップ・セレクト $\overline{CS}$ ピンが" H "(  $\overline{CS} = V_{CC}$  )になると、SDOピンはハイ・インピーダンス状態になります。このピンは変換およびスリープ期間中は、変換ステータス出力として使用できます。変換ステータスは $\overline{CS}$ を" L "にすると観察することができます。

SCK( ピン7 ):双方向デジタル・クロック・ピン。内部シリアル・クロック動作モードでは、SCKはデータ出力期間中は内部シリアル・インターフェース・クロックのデジタル出力として使用されます。外部シリアル・クロック動作モードでは、SCKは外部シリアル・インターフェースのデジタル入力として使用されます。内部シリアル・クロック動作モードでは、内部の微弱なブルアップが自動的にアクティブになります。シリアル・クロック・モードは、起動時および $\overline{CS}$ の立下りエッジでSCKに印加されるレベルによって決まります。

$F_O$ ( ピン8 ):周波数制御ピン。ADCのノッチ周波数と変換時間を制御するデジタル入力。 $F_O$ ピンを $V_{CC}$ に接続すると( $F_O = V_{CC}$ )コンバータは内部発振器を使用してデジタル・フィルタの最初のヌルを50Hzにします。 $F_O$ ピンをGNDに接続すると( $F_O = OV$ )コンバータは内部発振器を使用してデジタル・フィルタの最初のヌルを60Hzにします。 $F_O$ を周波数 $f_{EOSC}$ の外部クロック信号でドライブすると、コンバータはこの信号をクロックとして使用し、デジタル・フィルタの最初のヌル周波数を $f_{EOSC}/2560$ にします。

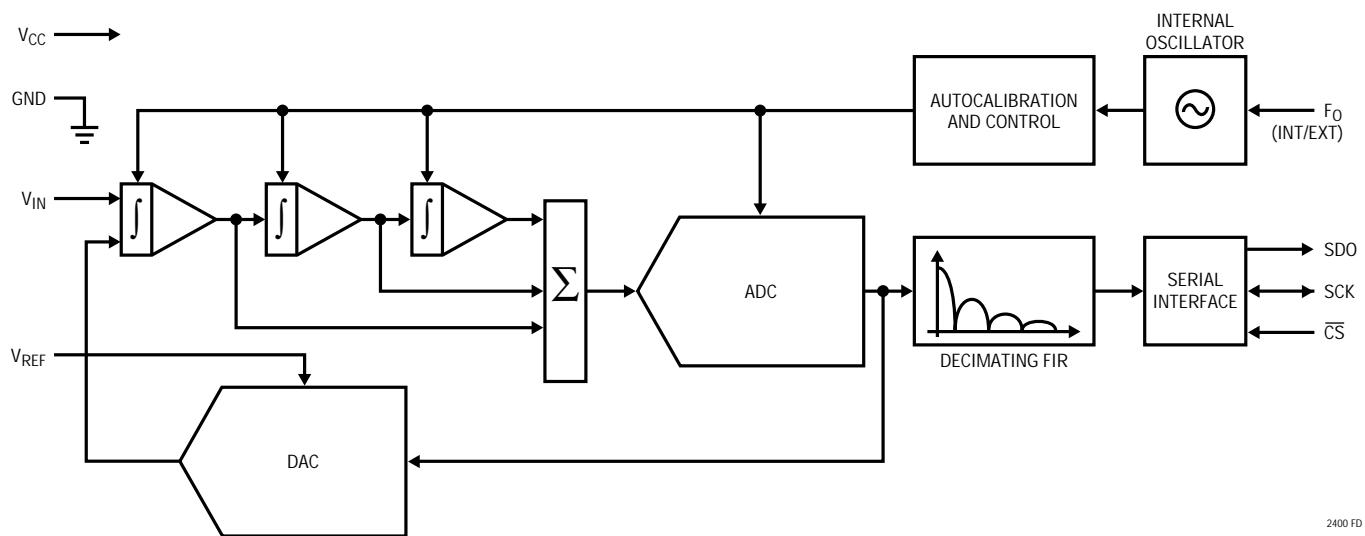

## 機能ブロック図

## テスト回路

## アプリケーション情報

### コンバータ動作サイクル

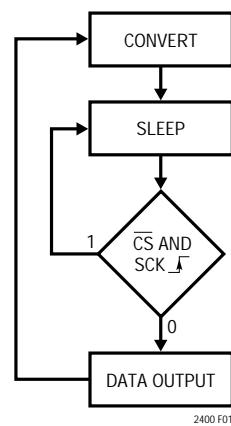

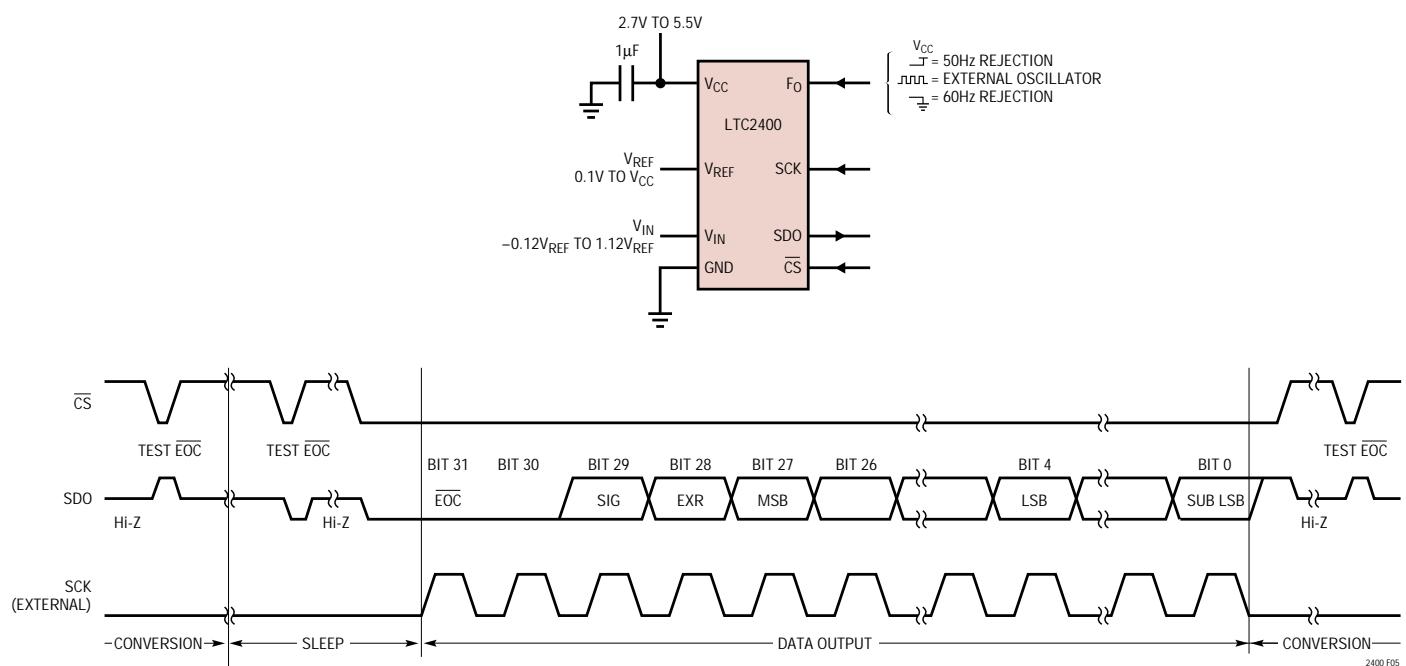

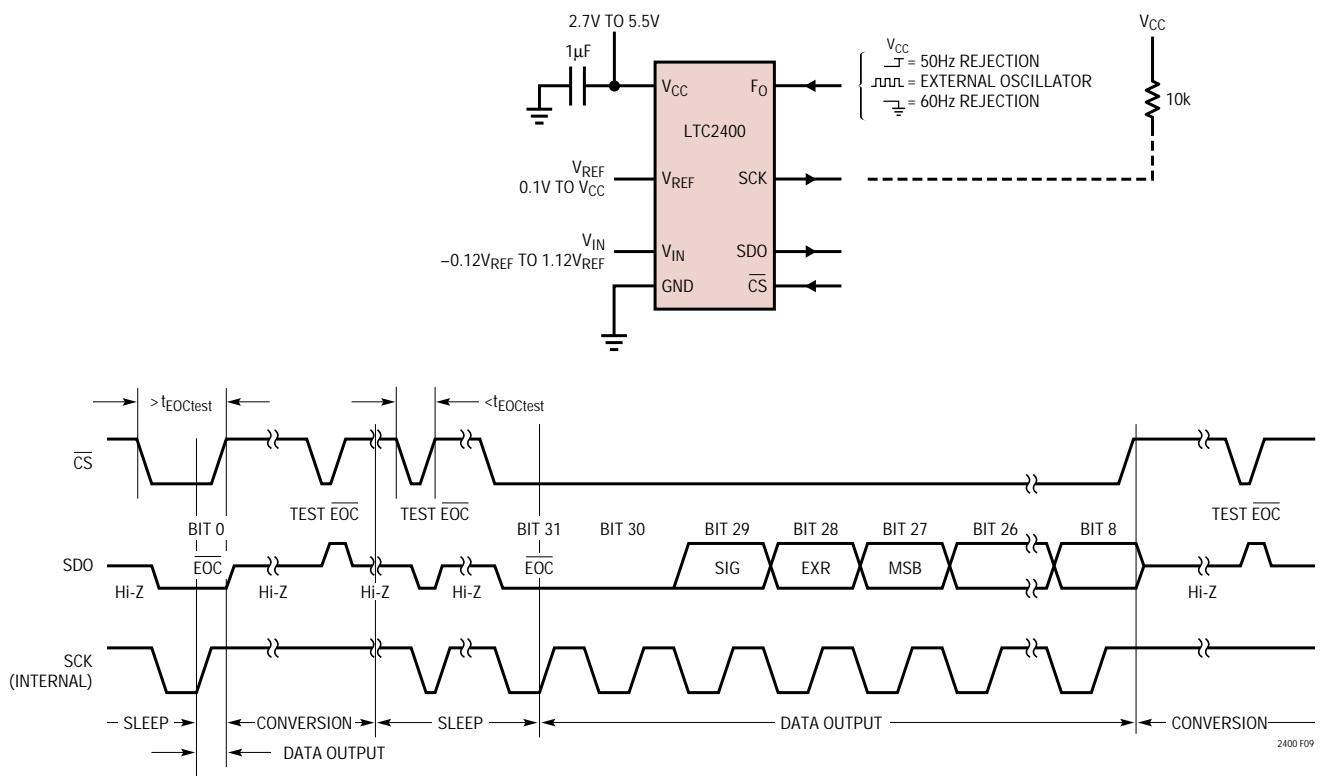

LTC2400は低消費電力のデルタ-シグマ・アナログ-デジタル・コンバータで、使いやすい3線式シリアル・インターフェースを備えています。動作は単純であり、3つの状態から構成されています。コンバータの動作サイクルは変換で始まり、低消費電力スリープ状態が続き、データ出力で終了します( 図1参照 )。3線式インターフェースは、シリアル・データ出力( SDO )、シリアル・クロック( SCK ) およびチップ・セレクト( CS )で構成されています。

最初にLTC2400は変換を実行します。変換が完了すると、デバイスはスリープ状態に入ります。このスリープ

図1. LTC2400の状態遷移図

## アプリケーション情報

状態の間は電力消費量が1桁減少します。 $\overline{CS}$ がロジック“H”の間、デバイスはスリープ状態のままでです。コンバータがスリープ状態のとき、変換結果はスタティック・シフト・レジスタに無限に保持されます。

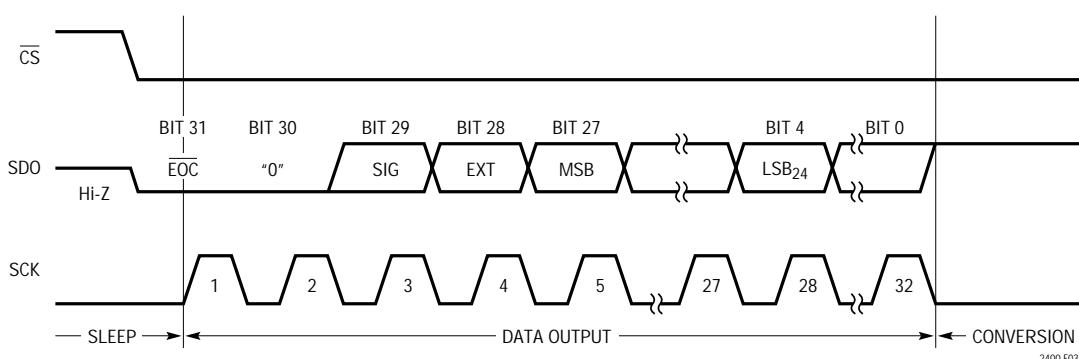

$\overline{CS}$ が“L”になると、デバイスは変換結果の出力を開始します。変換結果には待ち時間はありません。データ出力は直前に実行した変換結果に対応しています。この結果はシリアル・クロック(SCK)の制御により、シリアル・データ出力ピン( SDO )にシフトアウトされます。データはSCKの立下りエッジで更新されるので、ユーザはSCKの立上りエッジで確実にデータをラッチすることができます( 図3参照 )。ADCから32ビット・データが読み出されるか、または $\overline{CS}$ が“H”になると、データ出力状態が終了します。デバイスは自動的に新しい変換サイクルを開始し、そのサイクルが繰り返えされます。

LTC2400は $\overline{CS}$ ピンとSCKピンのタイミング制御により、いくつかの柔軟な動作モード( 内部または外部SCKモードおよび自走変換モード )を提供します。これらのモードは、構成レジスタのプログラミングを必要とせず、さらに前述のような周期的動作を妨害することもありません。これらの動作モードについては、シリアル・インターフェース・タイミング・モードのセクションで詳しく説明します。

### 変換クロック

従来型コンバータに対するデルタ-シグマ・コンバータの主な利点は、内蔵デジタル・フィルタ( 一般にSincフィルタまたはCombフィルタとして知られている )です。高分解能、低周波数アプリケーションでは、このフィルタは一般に50Hzまたは60Hzの電源周波数とそれらの高調波を除去するように設計されています。これらの周波数を110dB以上除去するには、高精度の変換クロックが必要です。LTC2400は高精度の発振器を内蔵しています。そのため水晶振動子や発振器などの外付け周波数設定部品は不要です。LTC2400は内蔵発振器からクロックが供給され、電源周波数( 50または60Hz  $\pm$  2% )を最低110dB除去します。

### 使いやすさ

LTC2400のデータ出力には、待ち時間、フィルタのセトリング、および変換サイクルに伴う冗長データはありま

せん。変換データと出力データは1対1で対応しています。したがって、アナログ入力電圧の多重化が容易です。

LTC2400は1変換サイクルごとにオフセットおよびフルスケール較正を実行します。この較正はユーザには見えず、前述の周期的動作には影響を与えません。連続較正の利点は、時間、電源電圧の変動、および温度ドリフトに対するオフセットおよびフルスケールの読取値がきわめて安定していることです。

### 起動シーケンス

電源電圧 $V_{CC}$ が約2.2V以下に低下すると、LTC2400は自動的に内部リセット状態に入ります。この機能により、変換結果および初期起動時に実行されるシリアル・インターフェース・モード選択の完全性が保証されます。( シリアル・インターフェース・タイミング・モードのセクションの2線式I/Oの項を参照 )

$V_{CC}$ 電圧がこのクリティカル・スレッショルド以上に上昇すると、コンバータは持続時間が約0.5msの内部パワーオン・リセット(POR)信号を生成します。POR信号はすべての内部レジスタをクリアします。LTC2400はPOR信号に続いて通常の変換サイクルを開始し、前述した通常の一連の状態に従います。PORに続く最初の変換結果は、デバイスの仕様に準拠して正確です。

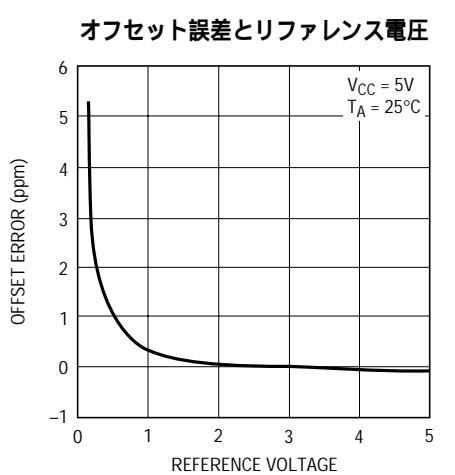

### リファレンス電圧範囲

LTC2400は、0V ~  $V_{CC}$ までのリファレンス電圧を受け入れることができます。コンバータ出力ノイズはフロントエンド回路の熱雑音によって決まるので、このマイクロボルトの値はリファレンス電圧に対しほぼ一定です。したがって、リファレンス電圧を低くしてもコンバータの有効分解能は大きくは改善されません。他方、リファレンス電圧を低くするとコンバータの全INL性能が向上します。LTC2400の電圧リファレンスの推奨範囲は100mV ~  $V_{CC}$ です。

### 入力電圧範囲

コンバータは拡張入力範囲を備えているので、システム・レベルでのオーバレンジ状況はもとより、システム・レベルのオフセットおよび利得誤差に適応することができます( 図2参照 )。LTC2400は、-0.125V •  $V_{REF}$  ~ 1.125 •  $V_{REF}$  の拡張入力範囲内で入力信号を変換します。

## アプリケーション情報

図2. LTC2400の入力範囲

$V_{REF}$ の値が大きい場合、この範囲は絶対最大電圧範囲 $-0.3V \sim (V_{CC} + 0.3V)$ に制限されます。入力がこの範囲を超えると入力ESD保護デバイスがターンオンを開始し、入力リーク電流に起因する誤差が急速に増加します。

$V_{IN}$ に印加される入力信号の範囲はグランド以下 $-300mV$ 、 $V_{CC}$ 以上 $300mV$ まで可能です。フォールト電流を制限するために、 $V_{IN}$ ピンと直列に最大 $5k$ の抵抗を追加でき、その場合にもデバイスの性能には影響ありません。物理的レイアウトでは、この直列抵抗と $V_{IN}$ ピン間の接続による寄生容量をできる限り少なくすることが重要です。したがって、抵抗は $V_{IN}$ ピンにできる限り接近して配置しなければなりません。コンバータの精度に対する直列抵抗の影響は、アナログ入力およびリファレンス電流のセクションに記載されている曲線から評価することができます。また、直列抵抗により、入力リーク電流に起因する温度依存オフセット誤差が生じます。 $V_{REF} = 5V$ の場合、 $1nA$ の入力リーク電流によって、 $5k$ の抵抗で $1ppm$ のオフセット誤差が生じます。この誤差には非常に強い温度依存関係があります。

### 出力データ・フォーマット

LTC2400のシリアル出力データ・ストリームは32ビット長です。最初の4ビットは、符号、入力範囲、および変換状態を示すステータス情報を表します。次の24ビットは変換結果で、MSBから始まります。残りの4ビットは24ビット・レベルを超えるサブLSBであり、分解能を損なうことなく、平均して算入するか切り捨てるすることができます。

ビット31(最初の出力ビット)は変換終了( $\overline{EOC}$ )インジ

ケータです。このビットは $\overline{CS}$ ピンが“L”のとき、変換およびスリープ状態の間にSDOピンから得られます。変換中はこのビットは“H”で、変換が完了すると“L”になります。

ビット30(2番目の出力ビット)はダミー・ビット(DMY)であり、常時“L”です。

ビット29(3番目の出力ビット)は、変換結果の符号インジケータ(SIG)です。 $V_{IN} > 0$ の場合、このビットは“H”です。 $V_{IN} < 0$ の場合、このビットは“L”です。符号ビットはゼロ・コード中に状態を変えます。

ビット28(4番目の出力ビット)は、拡張入力範囲(EXR)のインジケータです。入力が $0 \leq V_{IN} \leq V_{REF}$ の通常入力範囲にある場合、このビットは“L”です。入力が $V_{IN} > V_{REF}$ または $V_{IN} < 0$ の通常入力範囲外の場合、このビットは“H”です。

これらのビットの機能は表1に要約されています。

表1. LTC2400のステータス・ビット

| Input Range               | Bit 31<br>$\overline{EOC}$ | Bit 30<br>DMY | Bit 29<br>SIG | Bit 28<br>EXR |

|---------------------------|----------------------------|---------------|---------------|---------------|

| $V_{IN} > V_{REF}$        | 0                          | 0             | 1             | 1             |

| $0 < V_{IN} \leq V_{REF}$ | 0                          | 0             | 1             | 0             |

| $V_{IN} = 0^+/0^-$        | 0                          | 0             | 1/0           | 0             |

| $V_{IN} < 0$              | 0                          | 0             | 0             | 1             |

ビット27(5番目の出力ビット)は最上位ビット(MSB)です。

ビット27~4はMSBから始まる24ビットの変換結果です。

ビット4は最下位ビット(LSB)です。

ビット3~0は24ビット・レベル以下のサブLSBです。ビット3~0は分解能を損なうことなく平均して算入するか切り捨てるすることができます。

データはシリアル・クロック(SCK)の制御により、SDOピンからシフトアウトされます(図3参照)。 $\overline{CS}$ が“H”的にはいつでもSDOはハイ・インピーダンスのままで、SCKクロック・パルスはすべて内部データ出力シフト・レジスタから無視されます。

デバイスから変換結果をシフトアウトするには、最初に $\overline{CS}$ を“L”にドライブしなければなりません。 $\overline{CS}$ が“L”になると、 $\overline{EOC}$ がデバイスのSDOピンに現れます。 $\overline{EOC}$ は変換完了時にリアルタイムで“H”から“L”に変化します。この信号は外部マイクロコントローラに対する割込みに使用できます。ビット31( $\overline{EOC}$ )は、SCKの最初の立上りエッジで捕捉可能です。ビット30はSCKの最初の立下りエッジでデバイスからシフトアウトされます。最終デ-

## アプリケーション情報

タ・ビット(ビット0)は、31番目のSCKパルスの立下りエッジでシフトアウトされ、32番目のSCKパルスの立上りエッジでラッチできます。32番目のSCKパルスの立下りエッジでSDOが“H”になり、新しい変換サイクルが開始されたことを示します。このビットは、次の変換サイクルのEOC(ビット31)として働きます。表2に出力データ・フォーマットを要約します。

$V_{IN}$ ピンの電圧が $-0.3V \sim (V_{CC} + 0.3V)$ の絶対最大動作電圧範囲内に維持されている限り、 $-0.125 \cdot V_{REF}$ から $1.125 \cdot V_{REF}$ までのどの入力値に対しても変換結果が生成されます。入力電圧が $1.125 \cdot V_{REF}$ より高い場合、変換結

果は $1.125 \cdot V_{REF}$ に相当する値にクランプされます。入力電圧が $-0.125 \cdot V_{REF}$ より低い場合、変換結果は $-0.125 \cdot V_{REF}$ に相当する値にクランプされます。

### 周波数除去選択( $F_o$ ピン接続 )

LTC2400の内部発振器は、 $50Hz \pm 2\%$ または $60Hz \pm 2\%$ の電源周波数およびそのすべての高調波において $110dB$ 以上のノーマル・モード除去を提供します。60Hz除去の場合は $F_o$ (ピン8)をGND(ピン4)に接続し、50Hz除去の場合は $F_o$ ピンを $V_{CC}$ (ピン1)に接続しなればなりません。

図3. 出力データ・タイミング

表2. LTC2400の出力データ・フォーマット

| Input Voltage                 | Bit 31<br>EOC | Bit 30<br>DMY | Bit 29<br>SIG | Bit 28<br>EXR | Bit 27<br>MSB | Bit 26 | Bit 25 | Bit 24 | Bit 23 | ... | Bit 4<br>LSB | Bit 3-0<br>SUB LSBs* |

|-------------------------------|---------------|---------------|---------------|---------------|---------------|--------|--------|--------|--------|-----|--------------|----------------------|

| $V_{IN} > 9/8 \cdot V_{REF}$  | 0             | 0             | 1             | 1             | 0             | 0      | 0      | 1      | 1      | ... | 1            | X                    |

| $9/8 \cdot V_{REF}$           | 0             | 0             | 1             | 1             | 0             | 0      | 0      | 1      | 1      | ... | 1            | X                    |

| $V_{REF} + 1LSB$              | 0             | 0             | 1             | 1             | 0             | 0      | 0      | 0      | 0      | ... | 0            | X                    |

| $V_{REF}$                     | 0             | 0             | 1             | 0             | 1             | 1      | 1      | 1      | 1      | ... | 1            | X                    |

| $3/4V_{REF} + 1LSB$           | 0             | 0             | 1             | 0             | 1             | 1      | 0      | 0      | 0      | ... | 0            | X                    |

| $3/4V_{REF}$                  | 0             | 0             | 1             | 0             | 1             | 0      | 1      | 1      | 1      | ... | 1            | X                    |

| $1/2V_{REF} + 1LSB$           | 0             | 0             | 1             | 0             | 1             | 0      | 0      | 0      | 0      | ... | 0            | X                    |

| $1/2V_{REF}$                  | 0             | 0             | 1             | 0             | 0             | 1      | 1      | 1      | 1      | ... | 1            | X                    |

| $1/4V_{REF} + 1LSB$           | 0             | 0             | 1             | 0             | 0             | 1      | 0      | 0      | 0      | ... | 0            | X                    |

| $1/4V_{REF}$                  | 0             | 0             | 1             | 0             | 0             | 0      | 1      | 1      | 1      | ... | 1            | X                    |

| $0^+/0^-$                     | 0             | 0             | 1/0**         | 0             | 0             | 0      | 0      | 0      | 0      | ... | 0            | X                    |

| $-1LSB$                       | 0             | 0             | 0             | 1             | 1             | 1      | 1      | 1      | 1      | ... | 1            | X                    |

| $-1/8 \cdot V_{REF}$          | 0             | 0             | 0             | 1             | 1             | 1      | 1      | 0      | 0      | ... | 0            | X                    |

| $V_{IN} < -1/8 \cdot V_{REF}$ | 0             | 0             | 0             | 1             | 1             | 1      | 1      | 0      | 0      | ... | 0            | X                    |

\*サブ LSB は 24 ビット・レベルを超える有効な変換結果であり、分解能を損なうことなく平均して算入するか切り捨てることができる。

\*\*符号ビットはコード 0 の間に状態を変える。

## アプリケーション情報

50Hzまたは60Hz除去の選択は、 $F_0$ を適切なロジック・レベルにドライブすることにより行えます。スリープまたはデータ出力状態で選択を変更しても、コンバータ動作は妨害されません。変換状態中に選択を行った場合、実行中の変換結果は仕様を外れる可能性がありますが、以降の変換には影響ありません。

50Hzまたは60Hz以外の基本除去周波数が必要なときやコンバータを外部ソースに同期させる必要があるときは、LTC2400を外部変換クロックで動作させることができます。コンバータは、 $F_0$ ピンに外部クロック信号があることを自動的に検出し、内部発振器をターンオフします。検出されたためには外部信号の周波数 $f_{EOSC}$ は2560Hz(ノッチ周波数1Hz)以上でなければなりません。外部クロック信号のデューティ・サイクルは、“H”期間 $t_{HEO}$ と“L”期間 $t_{LEO}$ が最小仕様および最大仕様内にある限り重要ではありません。

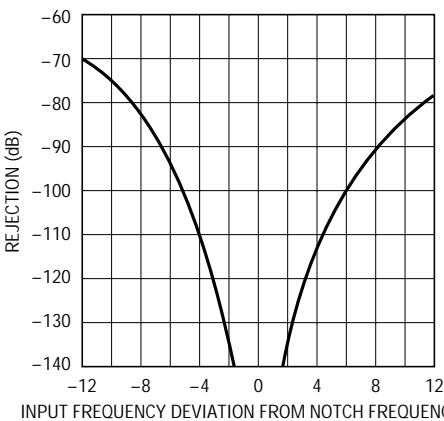

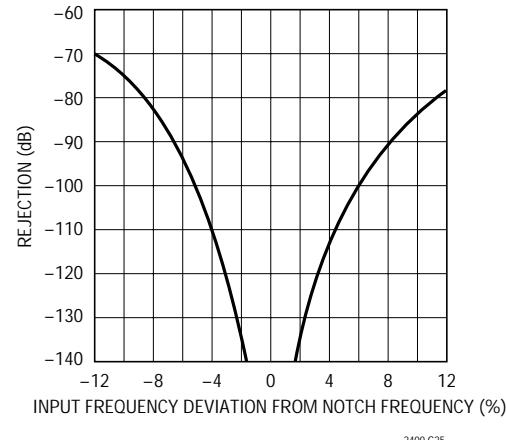

LTC2400が周波数 $f_{EOSC}$ の外部変換クロックで動作しているとき、周波数範囲 $f_{EOSC}/2560 \pm 4\%$ およびその高調波周波数のノーマル・モード除去は110dBを上回ります。入力周波数の $f_{EOSC}/2560$ からの偏差とノーマル・モード除去の相関関係を図4に示します。

$F_0$ ピンに外部クロックがないとき、コンバータは内部発振器を自動的にアクティブにして、内部変換クロック・モードに入ります。コンバータが外部シリアル・クロックを使用しているとき、スリープ状態またはデータ出力

図4. LTC2400の周波数 $f_{EOSC}$ の外部発振器を使用したノーマル・モード除去

状態において変換クロック・ソースを変更してもLTC2400の動作が影響を受けることはありません。変換状態中に変更した場合、実行中の変換結果が仕様を外れる可能性がありますが、以降の変換に影響はありません。データ出力状態でコンバータが内部SCKモードになっているときに変更されると、シリアル・クロックのデューティ・サイクルに影響を及ぼす可能性がありますが、シリアル・データ・ストリームは有効です。

表3に各状態の持続時間と $F_0$ との関係を要約します。

表3. LTC2400の状態持続時間

| State       | Operating Mode                                        |                                                                                                     | Duration                                                                                                     |

|-------------|-------------------------------------------------------|-----------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|

| CONVERT     | Internal Oscillator                                   | $F_0 = \text{LOW}$<br>(60Hz Rejection)                                                              | 133ms                                                                                                        |

|             |                                                       | $F_0 = \text{HIGH}$<br>(50Hz Rejection)                                                             | 160ms                                                                                                        |

|             | External Oscillator                                   | $F_0 = \text{External Oscillator}$<br>with Frequency $f_{EOSC}$ kHz<br>( $f_{EOSC}/2560$ Rejection) | $20480/f_{EOSC}$ s                                                                                           |

| SLEEP       |                                                       |                                                                                                     | As Long As $\overline{\text{CS}} = \text{HIGH}$ Until $\overline{\text{CS}} = 0$ and $\text{SCK} \downarrow$ |

| DATA OUTPUT | Internal Serial Clock                                 | $F_0 = \text{LOW/HIGH}$<br>(Internal Oscillator)                                                    | As Long As $\overline{\text{CS}} = \text{LOW}$ But Not Longer Than 1.67ms<br>(32 SCK cycles)                 |

|             |                                                       | $F_0 = \text{External Oscillator}$ with<br>Frequency $f_{EOSC}$ kHz                                 | As Long As $\overline{\text{CS}} = \text{LOW}$ But Not Longer Than $256/f_{EOSC}$ ms<br>(32 SCK cycles)      |

|             | External Serial Clock with<br>Frequency $f_{SCK}$ kHz |                                                                                                     | As Long As $\overline{\text{CS}} = \text{LOW}$ But Not Longer Than $32/f_{SCK}$ ms<br>(32 SCK cycles)        |

## アプリケーション情報

### シリアル・インターフェース

LTC2400は同期3線式インターフェースを通して変換結果を送信し、変換開始コマンドを受信します。変換およびスリープ状態の間、このインターフェースはコンバータ・ステータスを評価するのに使用され、データ出力状態の間は変換結果を読み出すのに使用されます。

### シリアル・クロック入力/出力( SCK )

SCK( ピン7 )上のシリアル・クロック信号は、データ転送の同期に使用されます。データの各ビットは、SDOからシリアル・クロックの立下りエッジでシフトアウトされます。

内部SCK動作モードではSCKピンは出力であり、LTC2400は内部変換クロックを8分周してLTC2400自身のシリアル・クロックを生成します。外部SCK動作モードではSCKピンは入力として使用されます。起動時に内部または外部SCKモードが選択され、その後はCSピンで“ H ”から“ L ”への遷移が検出されるたびに再選択されます。起動時またはこの遷移の間、SCKが“ H ”またはフロートの場合、コンバータは内部SCKモードに入ります。起動時またはこの遷移の間、SCKが“ L ”の場合、コンバータは外部SCKモードに入ります。

### シリアル・データ出力( SDO )

シリアル・データ出力ピンSDO( ピン6 )は、データ出力状態でシリアル・データをドライブします。また、SDOピンは変換およびスリープ状態での変換終了インジケータとして使用されます。

SDOドライバはCS( ピン5 )が“ H ”のときハイ・インピーダンス状態に切り替えられます。これにより、他のデバイスとシリアル・インターフェースを共用できるようになります。変換状態またはスリープ状態でCSが“ L ”の場合、SDOはEOCを出力します。変換フェーズでCSが“ L ”の場合、SDOピンにEOCビットが“ H ”で現れます。変換が完了する

表4. LTC2400インターフェースのタイミング・モード

| Configuration                                   | SCK Source | Conversion Cycle Control | Data Output Control | Connection and Waveforms |

|-------------------------------------------------|------------|--------------------------|---------------------|--------------------------|

| External SCK, Single Cycle Conversion           | External   | CS and SCK               | CS and SCK          | Figures 5, 6             |

| External SCK, 2-Wire I/O                        | External   | SCK                      | SCK                 | Figure 7                 |

| Internal SCK, Single Cycle Conversion           | Internal   | CS ↓                     | CS ↓                | Figures 8, 9             |

| Internal SCK, 2-Wire I/O, Continuous Conversion | Internal   | Continuous               | Internal            | Figure 10                |

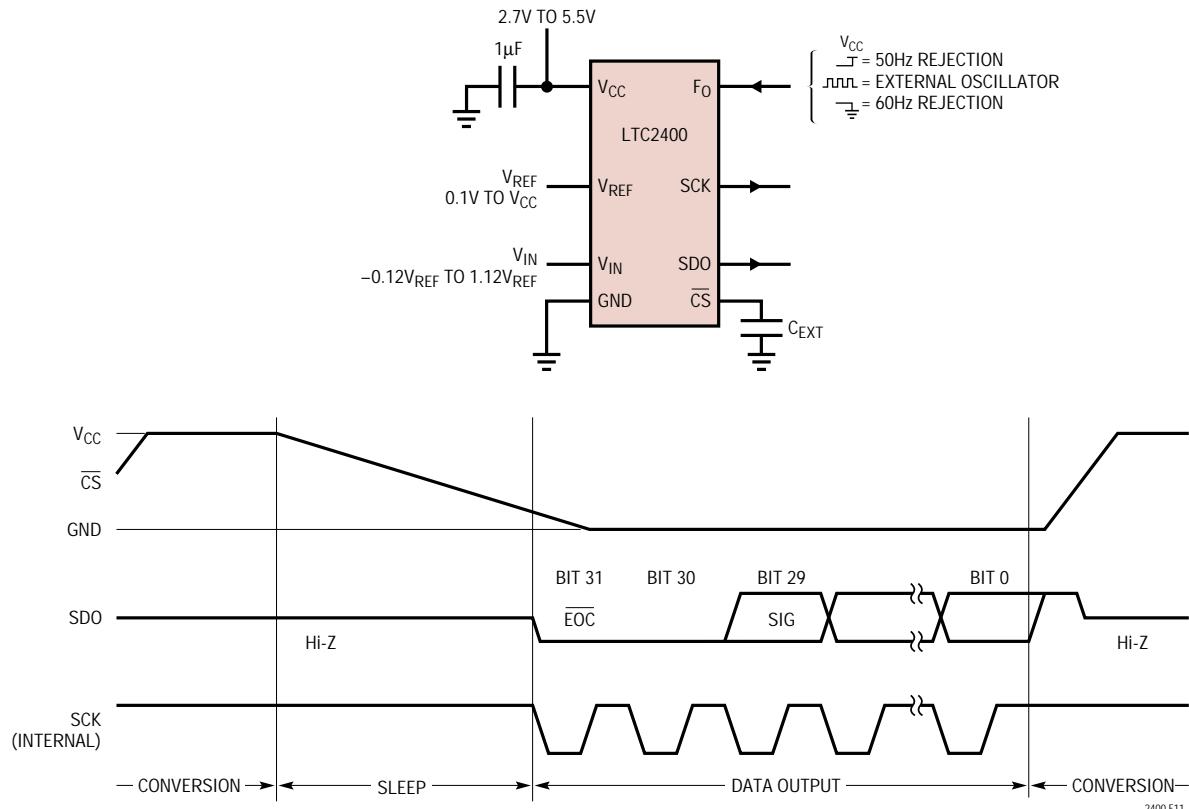

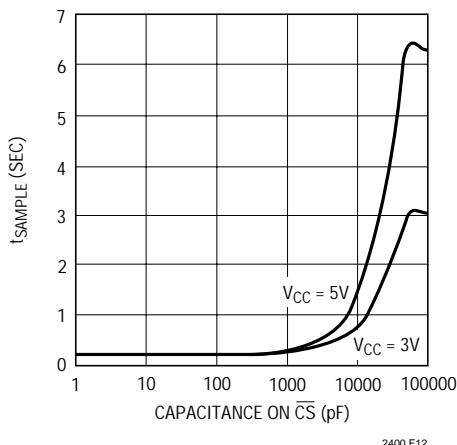

| Internal SCK, Autostart Conversion              | Internal   | C <sub>EXT</sub>         | Internal            | Figure 11                |

と、EOCは“ L ”になります。デバイスはCS = 0の間、SCKの最初の立上りエッジが発生するまでスリープ状態のままです。

### チップ・セレクト入力( CS )

前のセクションに記載したとおり、変換ステータスをテストし、データ出力転送をイネーブルするために、アクティブ“ L ”チップ・セレクトCS( ピン5 )を使用します。

さらに、CS信号を使用してシリアル・データ転送全体が完了する前に、新しい変換サイクルをトリガすることができます。LTC2400は、コンバータがデータ出力状態に入った後( すなわちCS = 0のとき )に、SCKの最初の立上りエッジが発生した後 )CSピンで“ L ”から“ H ”への遷移が検出されるといつでも、実行中のシリアル・データ転送を中断して、新しい変換サイクルを開始します。

最後に、CSを使用して自走動作モードを制御することができます( 「シリアル・インターフェース・タイミング・モード」のセクションを参照 )。CSを接地すると、ADCは強制的にF<sub>0</sub>で選択される最大出力レートで連続変換を実行します。CSにコンデンサを接続すると、コンデンサの容量に比例して出力レートと電力消費が低下します( 図12から14を参照 )。

### シリアル・インターフェースのタイミング・モード

LTC2400の3線式インターフェースは、SPIおよびMICROWIREに対応しています。このインターフェースはいくつかの柔軟な動作モードを提供します。これらの動作モードには、内部/外部シリアル・クロック、2線式または3線式I/O、単一サイクル変換、オートスタートなどがあります。以下の各セクションでは、これらのシリアル・インターフェースのタイミング・モードをそれぞれ詳しく説明します。このコンバータは、これらすべてのケースで内部発振器( F<sub>0</sub> = “ L ”またはF<sub>0</sub> = “ H ” )あるいはF<sub>0</sub>ピンに接続されている外部発振器を使用することができます。表4の要約を参照してください。

## アプリケーション情報

外部シリアル・クロック、單一サイクル動作

(SPI/MICROWIRE対応)

このタイミング・モードでは、外部シリアル・クロックを使用して変換結果をシフトアウトし、 $\overline{CS}$ 信号を使用して変換サイクルの状態をモニタし制御します(図5参照)。

シリアル・クロック・モードは $\overline{CS}$ の立下りエッジで選択されます。外部シリアル・クロック・モードを選択するには、各CSの立下りエッジの間シリアル・クロック・ピン(SCK)が“L”でなければなりません。

シリアル・データ出力ピン(SDO)は $\overline{CS}$ が“H”である限りハイ・インピーダンスです。変換サイクルのどの時点でも、 $\overline{CS}$ を“L”にしてコンバータの状態をモニタできます。 $\overline{CS}$ が“L”的とき、SDOピンにEOCが出力されます。変換実行中は EOC=1で、デバイスがスリープ状態の場合はEOC=0です。 $\overline{CS}$ の状態に関係なく、変換が完了するとデバイスは自動的に低消費電力のスリープ状態に入ります。

デバイスがスリープ状態のとき( $\overline{EOC}=0$ )、変換結果は内部スタティック・シフト・レジスタに保持されます。デバイスは、 $\overline{CS}$ が“L”的ときにSCKの最初の立上りエッジが現れるまでスリープ状態に留まります。データはSCKの各立下りエッジでSDOピンからシフトアウトさ

れます。これにより、外部回路はSCKの立上りエッジで出力をラッチできるようになります。 $\overline{EOC}$ はSCKの最初の立上りエッジでラッチでき、変換結果の最終ビットはSCKの32番目の立上りエッジでラッチできます。デバイスはSCKの32番目の立下りエッジで新しい変換を開始します。SDOが“H”( $\overline{EOC}=1$ )になって変換実行中であることを示します。

データ・サイクルの終りで $\overline{CS}$ を“L”的ままにして、EOCを変換終了割込みとしてモニタすることができます。あるいは、 $\overline{CS}$ を“H”にしてSDOをハイ・インピーダンスにすることも可能です。前述したように、 $\overline{CS}$ はいつでも“L”にして変換ステータスをモニタすることができます。

一般に、 $\overline{CS}$ はデータ出力状態の間は“L”に保持されます。ただし、SCKの最初の立上りエッジから32番目の立下りエッジまでのどの時点でも、 $\overline{CS}$ を“H”にしてデータ出力状態を中断することができます(図6参照)。 $\overline{CS}$ の立上りエッジで、デバイスはデータ出力状態を中断し、すぐに新しい変換を開始します。これは32ビットの出力データの一部しか必要としないシステムや、無効な変換サイクルを中断したり、変換開始を同期させるのに便利です。

図5. 外部シリアル・クロック、单一サイクル動作

## アプリケーション情報

図6. 外部シリアル・クロック、短縮されたデータ出力長

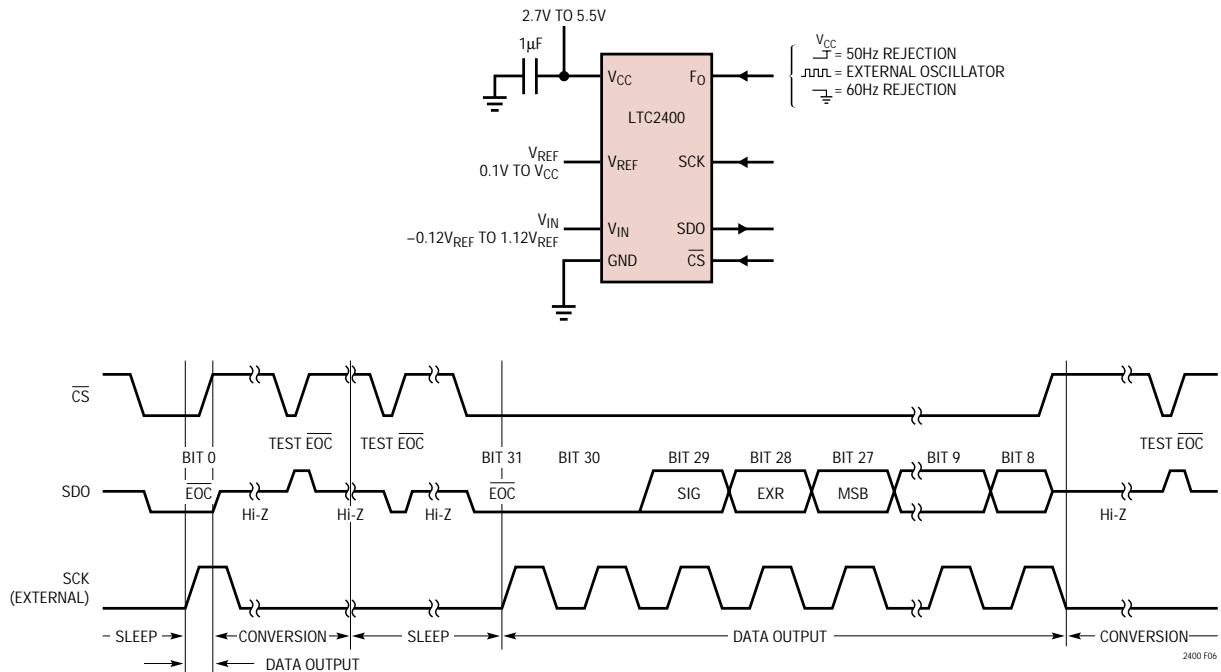

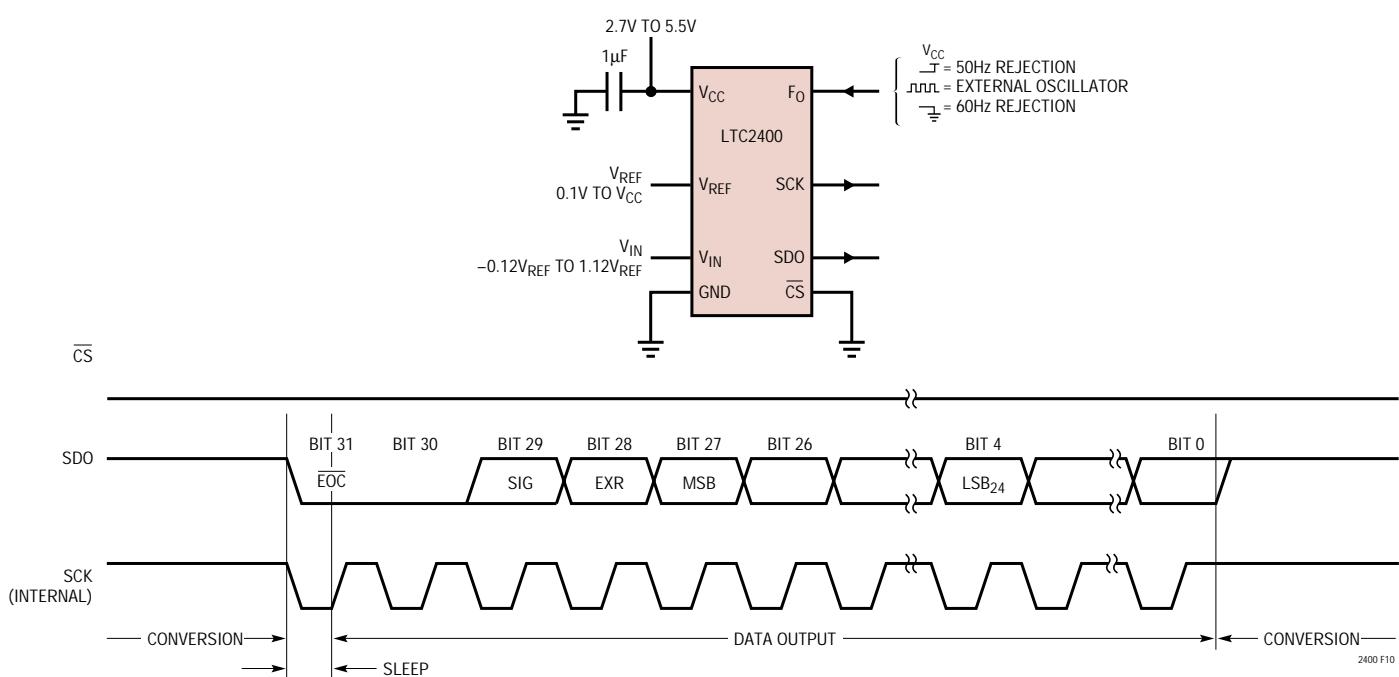

## 外部シリアル・クロック、2線式I/O

このタイミング・モードは2線式シリアルI/Oインターフェースを利用します。変換結果は、外部で生成されたシリアル・クロック(SCK)信号によりデバイスからシフトアウトされます(図7参照)。CSをグランド(ピン4)に固定接続してユーザ・インターフェースまたは絶縁バリアを単純化することができます。

外部シリアル・クロック・モードは、パワーオン・リセット(POR)サイクルの終りに選択されます。PORサイクルは $V_{CC}$ が2.2Vを超えた約0.5ms後に終了します。この時点でのSCKに印加されるレベルによってSCKが内部かまたは外部かが判定されます。外部シリアル・クロック・タイミング・モードに入るには、PORが終了する前にSCKを“L”にドライブしなければなりません。

$\overline{CS}$ は“L”に接続されているので、変換終了( $\overline{EOC}$ )は変換状態およびスリープ状態の間、SDOピンで連続的にモニタできます。 $\overline{EOC}$ は変換結果がレディになったことを示す外部コントローラへの割込みとして使用できます。変換実行中は $\overline{EOC} = 1$ で、変換が低消費電力のスリープ状態に入ると $\overline{EOC} = 0$ になります。変換結果は、 $\overline{EOC}$ の立下りエッジで内部スタティック・シフト・レジスタにロードされます。デバイスは最初のSCKの立上りエッジまでス

リープ状態になったままです。データはSCKの各立下りエッジでSDOピンからシフトアウトされ、外部回路はSCKの立上りエッジでデータをラッチできるようになります。 $\overline{EOC}$ は最初のSCKの立上りエッジでラッチされます。32番目のSCKの立下りエッジで、SDOが“H”になります( $\overline{EOC} = 1$ )新しい変換を開始したことを示します。

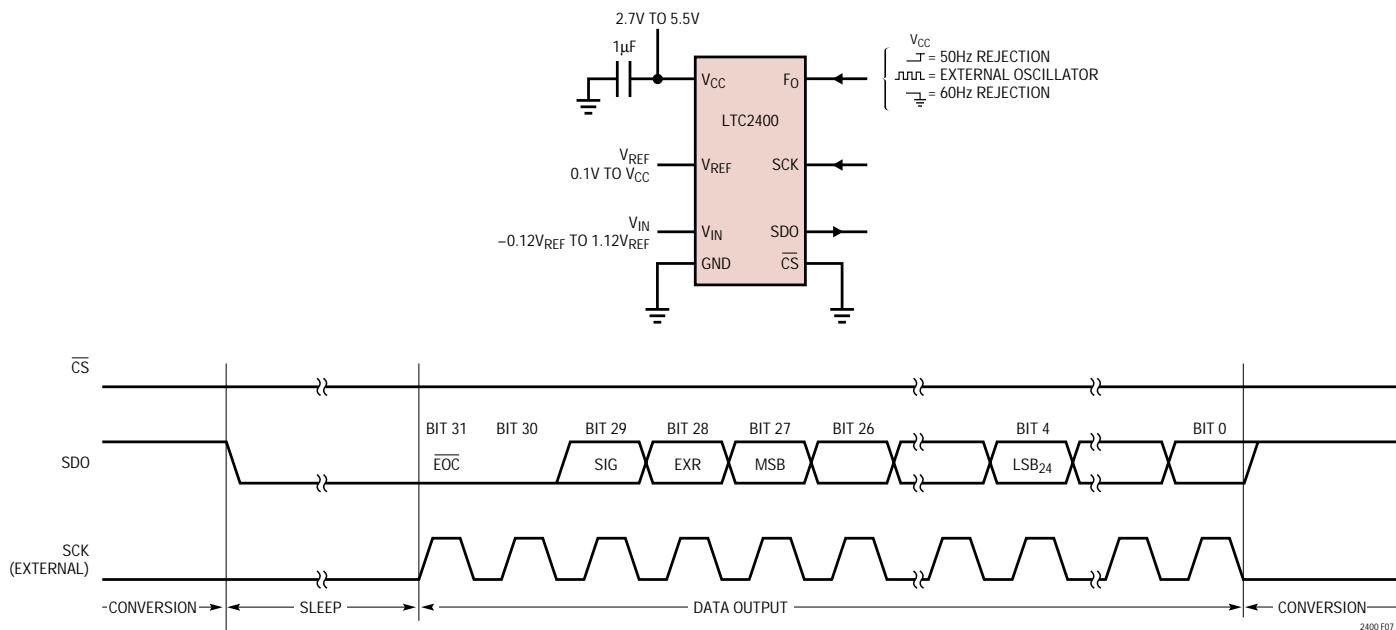

## 内部シリアル・クロック、単一サイクル動作

このタイミング・モードでは、内部シリアル・クロックを使用して変換結果をシフトアウトし、 $\overline{CS}$ 信号を使用して変換サイクルの状態をモニタし制御します(図8参照)。

内部シリアル・クロック・タイミング・モードを選択するには、シリアル・クロック・ピン(SCK)が $\overline{CS}$ の立下りエッジの前にフロート(HI-Z)状態かまたは“H”になっていなければなりません。 $\overline{CS}$ の立下りエッジでSCKが“L”にドライブされた場合、デバイスは内部シリアル・クロック・モードに入りません。 $\overline{CS}$ の立下りエッジ中に、SCKピンで内部の微弱なプルアップ抵抗がアクティブになるため、SCKが外部からドライブされない場合は、内部シリアル・クロック・タイミング・モードが自動的に選択されます。

シリアル・データ出力ピン(SDO)は $\overline{CS}$ が“H”である限りハイ・インピーダンスです。変換サイクルのどの時点でも、 $\overline{CS}$ を“L”にしてコンバータの状態をモニタできます。

## アプリケーション情報

図7. 外部シリアル・クロック、 $\bar{CS} = 0$ 動作

図8. 内部シリアル・クロック、単一サイクル動作

## アプリケーション情報

$\overline{CS}$ が“L”になるとSCKが“L”になり、 $\overline{EOC}$ がSDOピンに出力されます。変換実行中は $\overline{EOC} = 1$ で、デバイスがスリープ状態の場合は $\overline{EOC} = 0$ です。

$\overline{EOC}$ のテスト時に変換が完了した( $\overline{EOC} = 0$ )場合、 $\overline{CS}$ が“L”的ままのときにはデバイスはスリープ状態から抜け出して、データ出力状態に入ります。デバイスが低消費電力のスリープ状態から抜け出すのを防ぐには、SCKの立上りエッジの前に $\overline{CS}$ を“H”にしなければなりません。内部SCKタイミング・モードでは、SCKが“H”になり、デバイスは $\overline{CS}$ の立下りエッジの $t_{EOCtest}$ 時間後( $\overline{EOC} = 0$ の場合)または $\overline{EOC}$ が“L”になってから $t_{EOCtest}$ 時間後( $\overline{EOC}$ の立下りエッジ中に $\overline{CS}$ が“L”的場合)にデータの出力を開始します。デバイスが内部発振器を使用している( $F_0 = \text{ロジック } L$ または“H”)場合、 $t_{EOCtest}$ の値は $23\mu\text{s}$ です。 $F_0$ が周波数 $f_{EOSC}$ の外部発振器によってドライブされる場合、 $t_{EOCtest}$ は $3.6/f_{EOSC}$ です。 $t_{EOCtest}$ 時間前に $\overline{CS}$ が“H”になると、デバイスはスリープ状態に留まります。変換結果は内部スタティック・シフト・レジスタに保持されます。

$\overline{CS}$ が $t_{EOCtest}$ より長い時間“L”的ままの場合、最初のSCKの立上りエッジが発生し、変換結果はSDOピンからシリアル

にシフトアウトされます。データ出力サイクルはSCKのこの最初の立上りエッジで始まり、32番目の立上りエッジ後に終了します。データはSCKの各立下りエッジでSDOピンからシフトアウトされます。内部で生成されたシリアル・クロックがSCKピンに出力されます。この信号を使用して変換結果を外部回路にシフトすることができます。 $\overline{EOC}$ はSCKの最初の立上りエッジでラッチでき、変換結果の最終ビットはSCKの32番目の立上りエッジでラッチできます。32番目の立上りエッジの後、SDOは“H”( $\overline{EOC} = 1$ )になり、SCKは“H”に留まり、新しい変換が開始されます。

標準では、 $\overline{CS}$ はデータ出力状態の間は“L”に保持されます。ただし、最初のSCKの立上りエッジから32番目の立下りエッジまでのどの時点でも、 $\overline{CS}$ を“H”にしてデータ出力状態を中断することができます(図9参照)。 $\overline{CS}$ の立上りエッジで、デバイスはデータ出力状態を中断し、すぐに新しい変換を開始します。これは32ビットの出力データの一部しか必要ないシステムや、無効な変換サイクルを中断したり変換開始を同期させるのに便利です。コンバータがSCKを“L”にドライブしている間に $\overline{CS}$ が“H”になると、SCKを“H”に復帰させる内部プルアップは使用できません。これによって、デバイスは次の $\overline{CS}$ の立下

図9. 内部シリアル・クロック、短縮されたデータ出力長

## アプリケーション情報

リエッジで内部シリアル・クロック・モードから抜け出すことになります。これを防ぐには、SCKピンに10kの外付けプルアップ抵抗を追加するか、あるいはSCKが“L”的ときには絶対にCSを“H”にしないようにしてください。

SCKが“L”になるたびに、LTC2400のSCKピンにある内部プルアップがディスエーブルされます。通常、デバイスが内部SCKタイミング・モードにあるときには、SCKは外部からドライブされません。ただし、アプリケーションによってはSCKに外部ドライバが必要です。“L”信号の出力後にこのドライバがハイ・インピーダンスになる場合、LTC2400の内部プルアップはディスエーブルされています。したがって、SCKは“L”的ままであります。次のCSの立下りエッジで、デバイスは外部SCKタイミング・モードに切り替わります。SCKに10kの外付けプルアップ抵抗を追加すれば、このピンは外部ドライバがハイ・インピーダンスになると“H”になります。次のCSの立下りエッジでは、デバイスは内部SCKタイミング・モードのままであります。

スリープ状態で、変換ステータスをテストするためにCSにパルス“H”“L”“H”を印加したときにも同様な問題が発生する可能性があります。デバイスがスリープ状態(EOC=0)の場合、SCKは“L”になります。CSが前述の $t_{EOCtest}$ として定義した時間内で“H”になると、内部プルアップがアク

ティブになります。SCKピンの容量性負荷が重い場合、内部プルアップではCSが“L”になる前にSCKを“H”レベルに復帰させるには不十分な場合があります。これは、EOC=0を検出後CSが“L”に留まる通常の条件下では問題になりません。10kの外付けプルアップ抵抗をSCKピンに追加すれば、この状況に容易に対応できます。

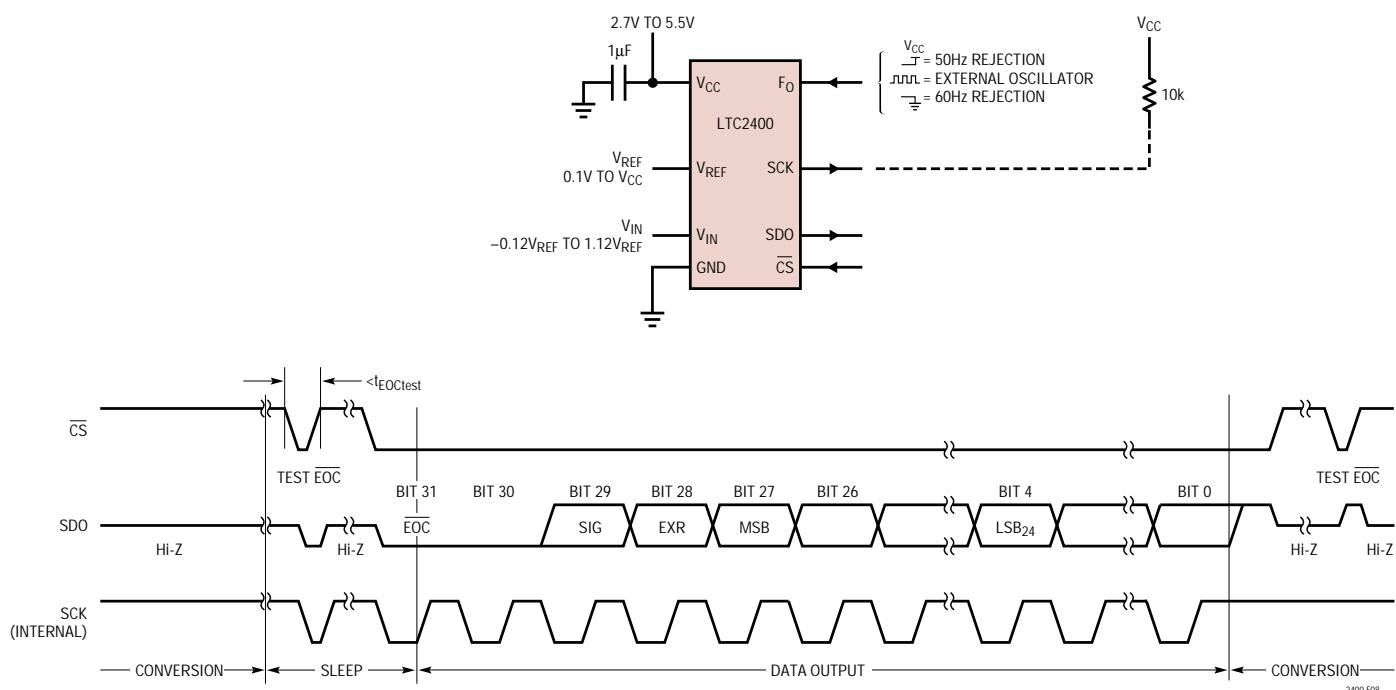

### 内部シリアル・クロック、2線式I/O、連続変換

このタイミング・モードでは、2線式の全出力(SCKおよびSDO)インターフェースを使用します。変換結果は、内部で生成されたシリアル・クロック(SCK)信号によってデバイスからシフトアウトされます(図10参照)。CSをグランド(ピン4)に固定して、ユーザ・インターフェースや絶縁バリアを単純にすることができます。

内部シリアル・クロック・モードは、パワーオン・リセット(POR)サイクルの終了時に選択されます。 $V_{CC}$ が2.2Vを超えた約0.5ms後に、PORサイクルが終了します。PORサイクル中、内部の微弱なプルアップはアクティブになっているので、SCKが外部で“L”にドライブされない場合、内部シリアル・クロック・タイミング・モードが自動的に選択されます(SCKに負荷が接続され内部プルアップがSCKピンを“H”にできない場合は、外部SCKモードが選択される)。

図10. 内部シリアル・クロック、連続動作

## アプリケーション情報

変換中、SCKおよびシリアル・データ出力ピン( SDO )は“H”( $\overline{EOC} = 1$ )です。変換が完了すると、SCKおよびSDOが“L”( $\overline{EOC} = 0$ )になり、変換が終了してデバイスが低消費電力のスリープ状態に入ったことを示します。デバイスは最短時間( 内部SCK期間の半分 )だけスリープ状態になった後、すぐにデータ出力を開始します。データ出力サイクルは、最初のSCKの立上りエッジで開始され、32番目の立上りエッジの後に終了します。データはSCKの各立下りエッジでSDOピンからシフトアウトされます。内部で生成されたシリアル・クロックがSCKピンに出力されます。この信号を使用して変換結果を外部回路にシフトすることができます。 $\overline{EOC}$ はSCKの最初の立上りエッジでラッチでき、変換結果の最終ビットはSCKの32番目の立上りエッジでラッチできます。SDOは32番目の立上りエッジの後に“H”( $\overline{EOC} = 1$ )になり、新しい変換が実行中であることを示します。SCKは変換中は“H”的ままでです。

### 内部シリアル・クロック、オートスタート変換

このタイミング・モードは内部シリアル・クロックと同じですが、前述の2線式I/Oに機能が1つ追加されています。 $\overline{CS}$ を接地する代わりに、 $\overline{CS}$ に外部タイミング・コンデンサが接続されています。

変換実行中、 $\overline{CS}$ ピンは内部の微弱なプルアップにより“H”に保持されます。変換が完了すると、デバイスは低消費電力のスリープ状態に入り、内部の25nA電流源が $\overline{CS}$ に接続されたコンデンサの放電を開始します( 図11参照 )。コンバータがスリープ状態になっている時間は、外部タイミング・コンデンサの値によって決まります( 図12および13を参照 )。 $\overline{CS}$ での電圧が内部スレッショルド電圧( 約1.4V )以下に低下すると、デバイスは自動的にデータ出力を開始します。データ出力サイクルは最初のSCKの立上りエッジで始まり、32番目の立上りエッジで終了します。データはSCKの各立下りエッジでSDOビ

図11. 内部シリアル・クロック、オートスタート動作

## アプリケーション情報

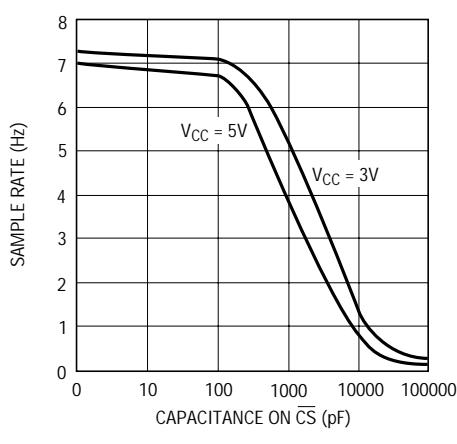

図12.  $\overline{CS}$ の容量と $t_{SAMPLE}$

図13.  $\overline{CS}$ の容量と出力レート

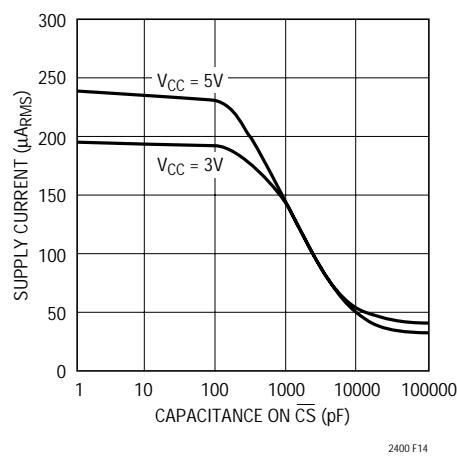

図14.  $\overline{CS}$ の容量と電源電流

ンからシフトアウトされます。内部で生成されたシリアル・クロックがSCKピンに出力されます。この信号を使用して変換結果を外部回路にシフトすることができます。32番目の立上りエッジの後で $\overline{CS}$ は“H”になり、すぐに新しい変換を開始します。これは周期的なモニタで超低電力消費が要求されるアプリケーションに役立ちます。図14に平均電源電流と $\overline{CS}$ の容量の関係を示します。

外付けコンデンサの放電電流は、スリープ状態でのコンバータの電力消費を低減するために非常に小さく維持されていることに注意してください。オートスタート・モードでは、普通のオシロスコープ・プローブを使用して $\overline{CS}$ ピンのアナログ電圧を観測すると、コンバータの動作に妨害を与えることがあります。この構成を使用するときは、リーク電流の少ない外付けコンデンサを使用し、PCB表面を正しくクリーニングして、 $\overline{CS}$ ピンの外部リーク電流を少なくすることが重要です。

$\overline{CS}$ ピンの電圧が内部スレッショルド電圧を通過するたびに、内部シリアル・クロック・モードが選択されます。 $\overline{CS}$ が放電している間、SCKピンの微弱な内部プルアップはアクティブになっているため、SCKがフロートしている場合、自動的に内部シリアル・クロック・タイミング・モードが選択されます。 $\overline{CS}$ が放電している間、SCKを“L”にする外部ドライバがないことが重要です。

### デジタル信号レベル

LTC2400のデジタル・インターフェースは使いやすくなっています。このデバイスのデジタル入力(外部SCK動作モードでの $F_O$ 、 $\overline{CS}$ 、およびSCK)は、標準TTL/CMOSロジック・レベルを受け入れます。内部ヒステリシス・レシーバは、100μsまでの低速エッジ・レートを許容できます。ただし、比類のない精度と低電源電流を活用するには若干の考慮が必要です。

デジタル出力信号(内部SCK動作モードでのSDOおよびSCK)は、変換状態では一般にアクティブではないので、それほど問題にはなりません。

LTC2400の精度を維持するために、入力やリファレンス信号と直列に生じる可能性があるグランド・バスのインピーダンスを小さくし、またこの経路を流れる電流を低減することが非常に重要です。GNDピンは最短の配線で低抵抗のグランド・プレーンに接続してください。接続抵抗を低減するために中継ホールを複数使用することを推奨します。共通グランド・ピンの抵抗分0.01Ωを流れる

## アプリケーション情報

LTC2400の電源電流によって、 $2.5\mu V$ のオフセット信号が発生します。リファレンス電圧 $V_{REF} = 2.5V$ の場合、これは1ppmのオフセット誤差になります。

あるいは別の構成では、コンバータのGNDピンはシングルポイント・グランド・システムで一点接地を行うことができます。入力信号グランド、リファレンス信号グランド、デジタル・ドライバ・グランド(通常はデジタル・グランド)および電源グランド(アナログ・グランド)は、GNDピンにできるだけ近い共通点に星状に接続してください。

変換状態での電源電流は、最小に保持してください。これはこの期間中に発生するデジタル信号の遷移数を制限することによって実現できます。

デジタル入力信号が $0.5V \sim (V_{CC} - 0.5V)$ の範囲にある場合は、電源からCMOS入力レシーバに追加電流が流れます。デジタル入力信号(外部SCK動作モードでの $F_0$ 、CS、およびSCK)のどれかがこの範囲にあるとき、問題の信号が有効なロジック・レベルであってもLTC2400の電源電流が増加する可能性があることに注意してください。マイクロパワー動作のため、また増加するグランド・ピン電流に起因する電位誤差を小さくするために、すべてのデジタル入力信号を完全なCMOSレベル[ $V_{IL} < 0.4V$ および $V_{OH} > (V_{CC} - 0.4V)$ ]でドライブすることを推奨します。

また高速デジタル入力信号のアンダーシュートによって激しいグランド・ピン電流障害も発生する可能性があります。外部制御信号の遷移時間がドライバからLTC2400への伝搬遅延の2倍以下のときに、コンバータ・ピンでインピーダンス不整合があると、アンダーシュートやオーバーシュートが発生します。参考として、通常のFR-4ボードでの信号伝搬速度は、内部配線の場合は約183ps/インチ、表面配線の場合は約170ps/インチです。したがって、最小遷移時間1nsの制御信号を生成するドライバは、2.5インチ以下の配線でコンバータ・ピンに接続しなければなりません。この問題は共用制御ラインを使用し、多重反射が発生する可能性がある場合には特に困難になります。解決策はすべての伝送ラインを特性インピーダンスに近い値で、注意深く終端することです。

LTC2400ピンの近くで並列に終端すれば、この問題が解消されますが、ドライバの消費電力が増加します。また、27 ~ 56 の直列抵抗をドライバまたはLTC2400ピンの近くに接続すれば、消費電力を増加させずにこの問題を解決できます。実際の抵抗値は配線インピーダンスと接続トポロジーによって決まります。

### 入力およびリファレンスのドライブ

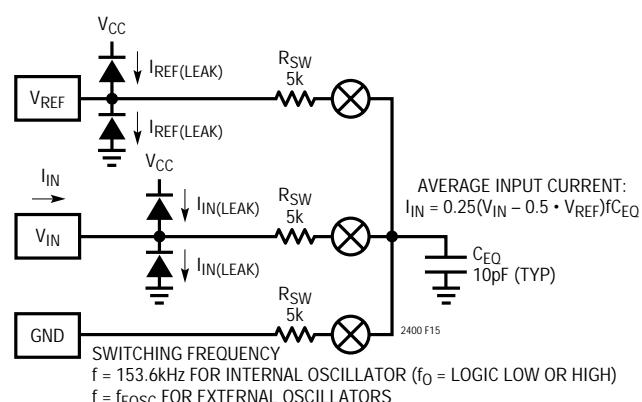

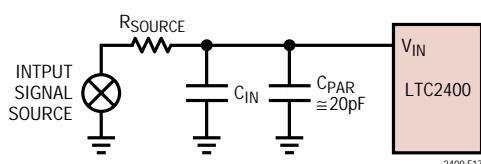

通常のデルタ-シグマ・アナログ デジタル・コンバータのアナログ入力とリファレンスはスイッチト・キャパシタ・ネットワークに接続されます。このネットワークは、アナログ入力( $V_{IN}$ ) グランド(ピン4) およびリファレンス( $V_{REF}$ )の間で切り替わるコンデンサで構成されています。その結果、 $V_{IN}$ と $V_{REF}$ の両方に小さな電流スパイクが現れます。簡略等価入力回路を図15に示します。

図15. LTC2400の等価アナログ入力回路

このダイナミック入力電流の効果を理解する鍵は、単純な1次RC時定数モデルにあります。LTC2400の内部スイッチト・キャパシタ・ネットワークは内部発振器を使用し、 $6.5\mu s$ のサンプリング周期に相当する153,600Hzでクロック駆動されます。1ppmのセトリング精度を達成するには、コンデンサが切り替わるたびに14の時定数が必要です。

したがって、1ppmの精度を達成するには、 $V_{IN}$ および $V_{REF}$ での等価時定数は $6.5\mu s/14 = 460\text{ns}$ 以下でなければなりません。

## アプリケーション情報

### 入力電流( $V_{IN}$ )

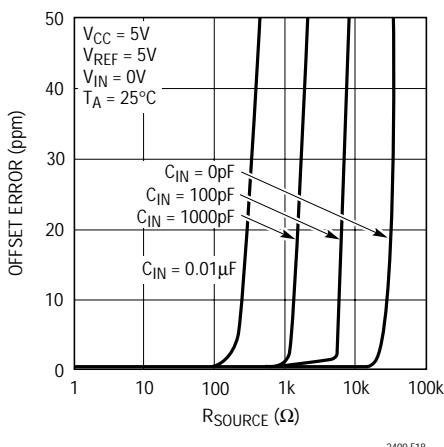

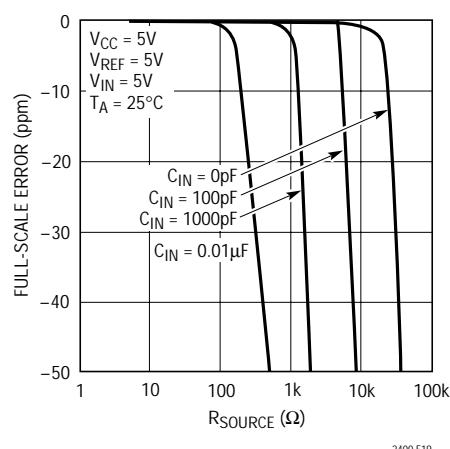

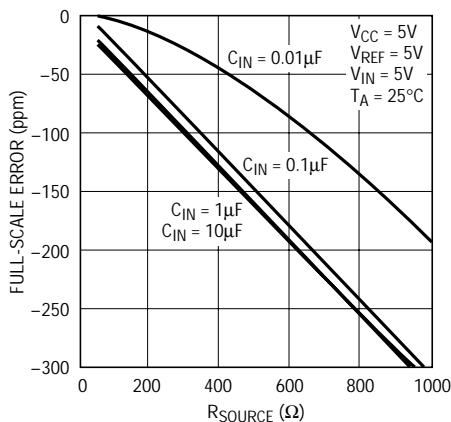

入力のセトリングが完全な場合、変換結果はダイナミック入力電流の影響を受けません。セトリングが不完全でも、デバイスの直線性性能を損なうことはありません。単にオフセット/フルスケール・シフトが生じるだけです(図16参照)。入力ダイナミック電流の解析を簡単にするために、2つの異なるケースを仮定します。すなわち、 $V_{IN}$ の容量が大きい( $C_{IN} > 0.01\mu F$ )場合と小さい( $C_{IN} < 0.01\mu F$ )場合です。

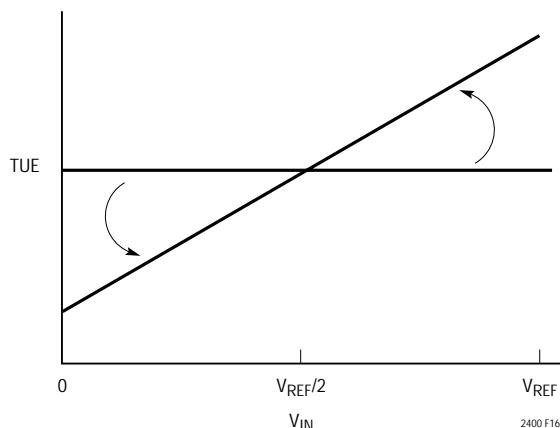

図16. オフセット/フルスケール・シフト

図17.  $V_{IN}$ のRCネットワーク

図18. オフセットと $R_{SOURCE}$ (小容量C)

$V_{IN}$ (図17参照)での全容量が小さい( $0.01\mu F$ 未満)場合は、オフセット/フルスケール誤差を生じることなく、比較的大きな外部ソース抵抗( $20pF$ の寄生容量に対し最大 $20k$ )を許容できます。図18と図19には、いくつかの小容量入力コンデンサ( $C_{IN} < 0.01\mu F$ )について、入力ソース抵抗に対するオフセット曲線およびフルスケール誤差曲線を示します。

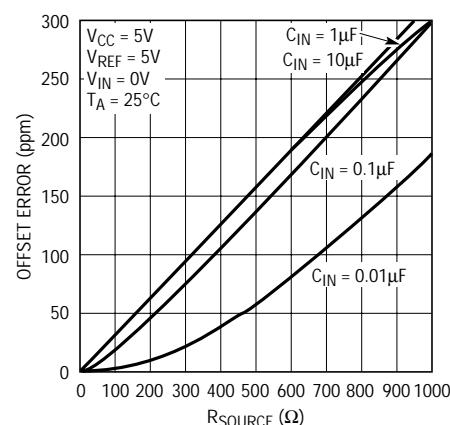

大きな入力コンデンサ値( $C_{IN} > 0.01\mu F$ )の場合、入力スパイクはコンデンサによりDC電流に平均化されます。利得シフトは、入力容量に関係なく入力ソース抵抗の線形関数になります(図20および21参照)。等価入力インピーダンスは $1.66M$ です。この結果、 $V_{IN}$ の極値( $V_{REF} = 5V$ のときには、 $V_{IN} = 0V$ および $V_{IN} = V_{REF}$ )における入力ダイナミック電流は $\pm 1.5\mu A$ となります。これは入力ソ

図19. フルスケール誤差と $R_{SOURCE}$ (小容量C)

図20. オフセットと $R_{SOURCE}$ (大容量C)

## アプリケーション情報

2400 F21

図21. フルスケール誤差とR<sub>SOURCE</sub>(大容量C)

ス抵抗1ごとのオフセットおよびフルスケールの読取り値で0.3ppmのシフトに相当します。

入力電流スパイクに加え、入力ESD保護ダイオードには温度依存リーケ電流が発生します。このリーケ電流は公称1nA(最大±10nA)で、10kのソース抵抗に対し10μV固定のオフセット・シフトが生じます。

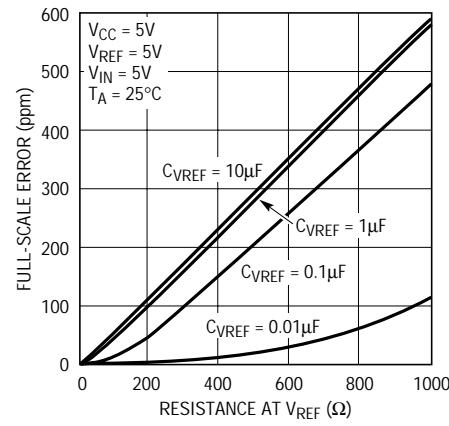

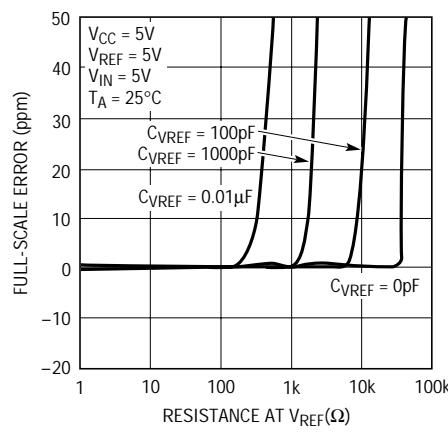

### リファレンス電流(V<sub>REF</sub>)

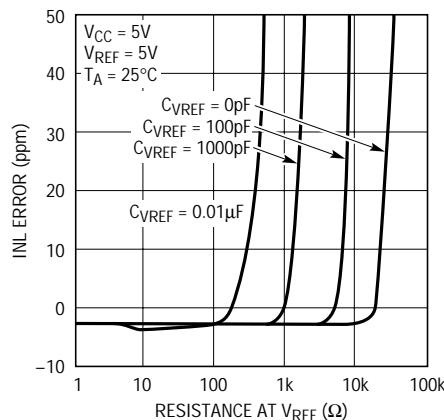

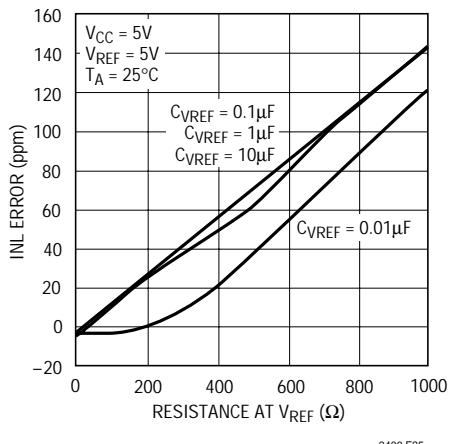

アナログ入力電流と同様、リファレンス入力にはダイナミック入力電流があります。この電流はオフセットにはほとんど影響を与えません。ただし、V<sub>IN</sub> = V<sub>REF</sub>でのリファレンス電流はフルスケールの入力電流とほぼ同じです。リファレンス容量が大きい場合(C<sub>VREF</sub> > 0.01 μF)、V<sub>REF</sub>の容量に関係なくフルスケール誤差シフトは外部リファレンス抵抗の0.3ppm/です(図22参照)。V<sub>REF</sub>に接続された容量が小さい(C<sub>VREF</sub> < 0.01 μF)場合、最大20kの入力抵抗(V<sub>REF</sub>での20pFの寄生容量)を許容できます(図23参照)。

アナログ入力とは異なり、リファレンス入力に接続された過大な外部RC時定数により、デバイスの積分非直線性が損なわれる可能性があります。V<sub>REF</sub>ノードの容量が小さい(C<sub>VREF</sub> < 0.01 μF)場合、リファレンス入力はINLが低下することなく、大きな外部抵抗を許容できます(図24参照)。外部容量が大きい(C<sub>VREF</sub> > 0.01 μF)場合、直線性はV<sub>REF</sub>の容量に関係なく0.15ppm/ずつ損なわれます(図25参照)。

2400 F22

図22. フルスケール誤差とR<sub>VREF</sub>(大容量C)

2400 F23

図23. フルスケール誤差とR<sub>VREF</sub>(小容量C)

2400 F24

図24. INL誤差とR<sub>VREF</sub>(小容量C)

## アプリケーション情報

図25. INL誤差と $R_{VREF}$ (大容量C)

ダイナミック・リファレンス電流に加え、 $V_{REF}$  ESD保護ダイオードでは温度に依存するリーク電流が発生します。このリーク電流は公称1nA(最大±10nA)であり、10kのソース抵抗に対して10μVの一一定フルスケール・シフトが発生します。

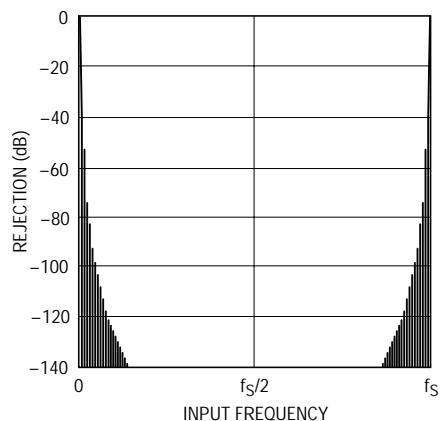

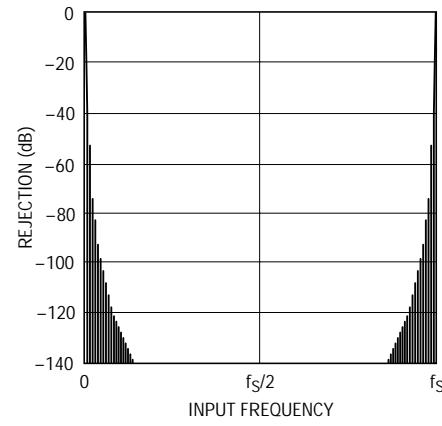

### アンチエリアシング

従来のADCに対するデルタ-シグマADCの利点の1つが内蔵デジタル・フィルタリングです。大きなオーバーサンプリング比と組み合わせると、LTC2400はアンチエリアシング・フィルタの要求条件を大幅に単純化します。

デジタル・フィルタは、変調器サンプリング周波数( $f_s$ )の整数倍以外の周波数で非常に高い除去を実現します(図26参照)。変調器サンプリング周波数は $256 \cdot F_0$ です。ここで、 $F_0$ はノッチ周波数(標準50Hzまたは60Hz)です。デジタル・フィルタで除去されない信号の帯域幅

図26.  $\text{Sinc}^4$ フィルタ除去

は、除去される周波数の帯域幅に比べて狭く(約0.2%)なります。

オーバーサンプリング比(256)とデジタル・フィルタにより、LTC2400の前段は最小の(存在する場合)アンチエリアス・フィルタリングで済みます。受動RC部品がLTC2400の前段に配置された場合、入力ダイナミック電流を検討する必要があります(入力電流のセクションを参照)。大きな実効RC時定数を使用する場合は、入力ダイナミック電流の影響を抑えるために、外部バッファ・アンプが必要になることがあります。

LTC2400の内蔵変調器は、飽和することなく大信号レベルの変動を処理できます。 $V_{REF}$ の40%までの信号レベルでは、アナログ変調器が飽和することはありません。これらの信号は入力ESD保護回路により、グランド以下300mVおよび $V_{CC}$ 以上300mVに制限されます。

## 標準的応用例

### 複数のLTC2400の同期

LTC2400の絶対精度(全未調整誤差)は10ppmなので、整合した複数のADCを利用したアプリケーションが可能です。

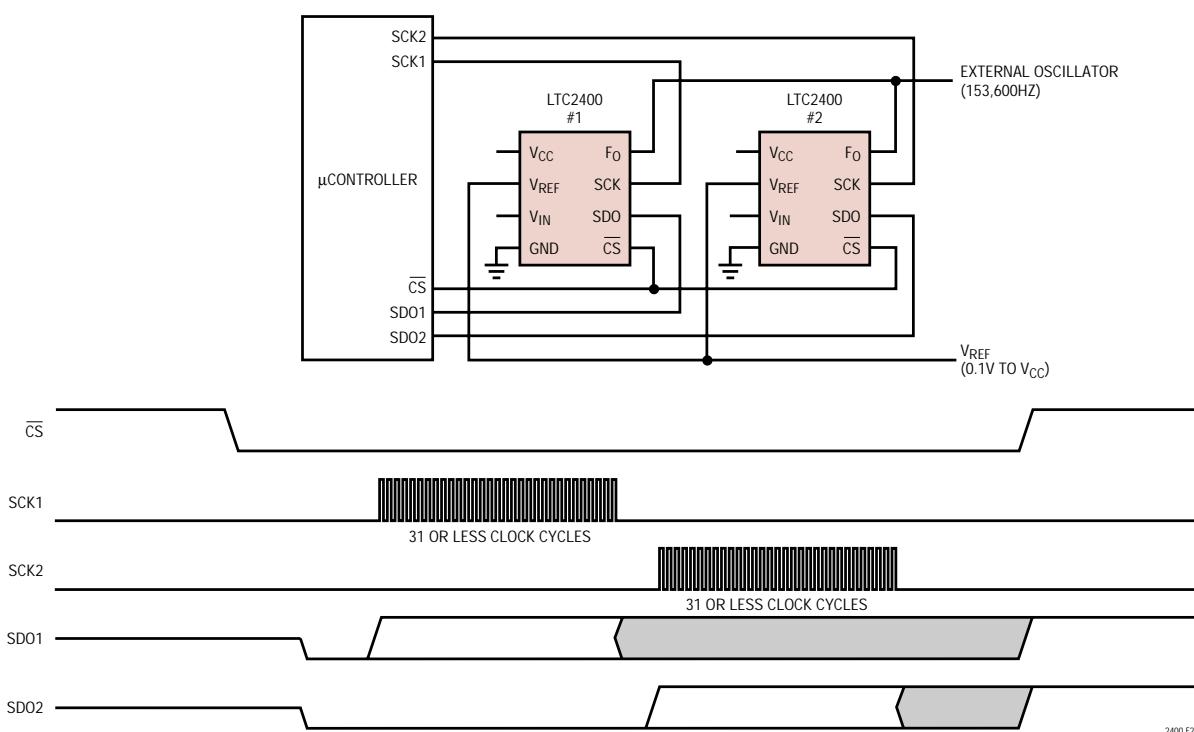

### 2個のLTC2400の同時サンプリング

このようなアプリケーションの1つが複数のLTC2400の同期化です(図27参照)。変換の開始は $\overline{CS}$ の立上りエッジに同期します。複数のLTC2400を同期させるには、 $\overline{CS}$ をすべてのADCの共通入力にしてください。データ出力の読み出し終了時に、コンバータが新しい変換をオートスタートするのを防ぐために、32番目(32番目の立下りエッジで変換が開始される)ではなく、31個以下のSCKクロック信号をLTC2400に印加します。データをソフトアウトするだけなので、SCK信号のタイミングや周波数はそれほど厳密ではありません。この場合、2個のLTC2400は $\overline{CS}$ の外部制御により変換サイクルを同時に開始および終了します。

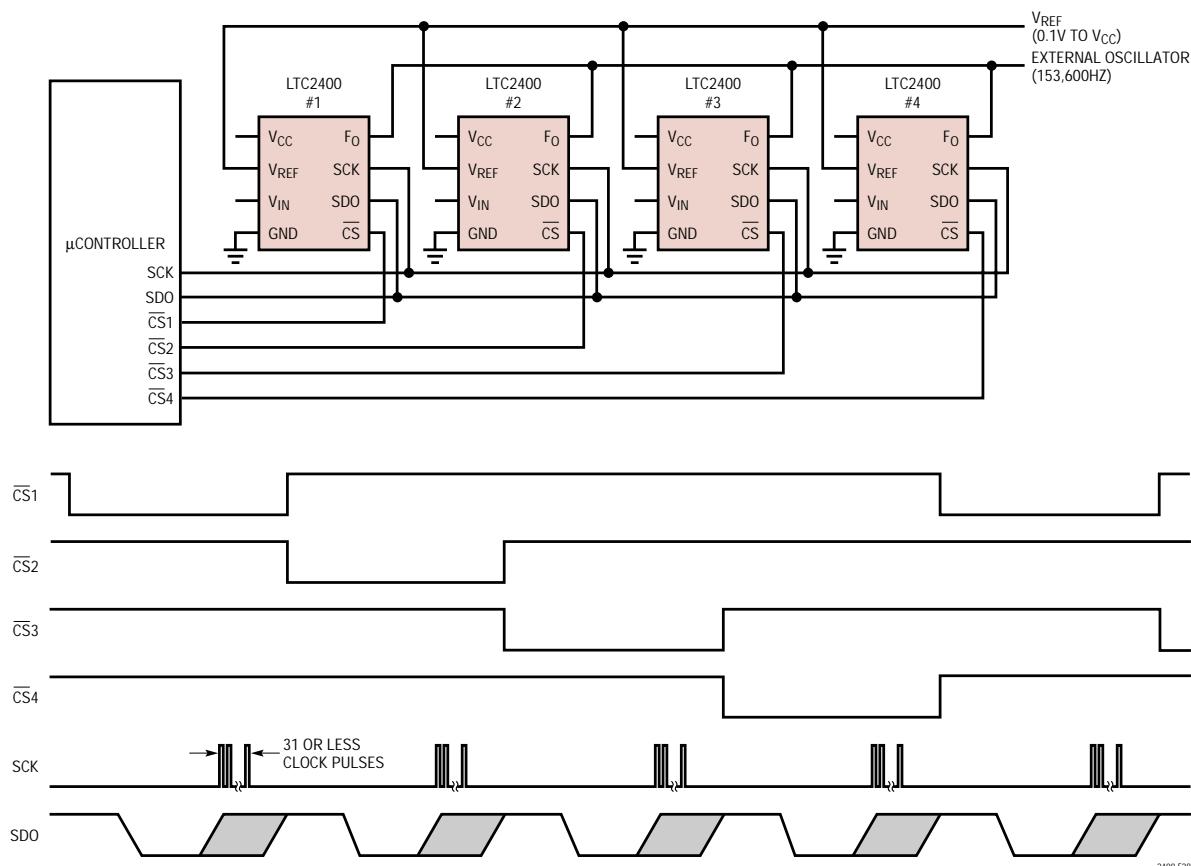

### 複数個のLTC2400による出力レートの上昇

もう1つのアプリケーションは、複数のLTC2400を使用して実効出力レートを4倍に上昇させるものです(図28参照)。この場合、4個のLTC2400は別々の $\overline{CS}$ 信号の制御によりインターブされます。これにより、実効出力レートは7.5Hzから30Hz(最大60Hz)に上昇します。加えて、ワンショット出力スペクトルが明らかになり、さらに変換結果をデジタル信号処理することができます。SCKおよびSDOは4個のLTC2400すべてに共通とすることができます。4つの $\overline{CS}$ の立上りエッジにより、LTC2400の1変換サイクルが均等に分周されます(60Hzのノッチ周波数の場合は7.5Hz)。変換開始を $\overline{CS}$ に同期させるには、各ADCに印加するSCKクロック・パルスは31個以下でなければなりません。

同期アプリケーションおよび出力レートが4倍のアプリケーションはどちらも、短縮データ出力長で外部シリアル・クロックおよび单一サイクル動作を使用します(シリアル・インターフェース・タイミング・モードのセクションと図6を参照)。サンプリング時間を同期させるために、通常は外部発振器クロックを各LTC2400の $F_o$ ピンに印加します。LTC2400の個数を増やして両方の回路を拡張することができます。

図27. 同期式変換(拡張可能)

## 標準的応用例

図28. 出力レートが4倍のLTC2400システム

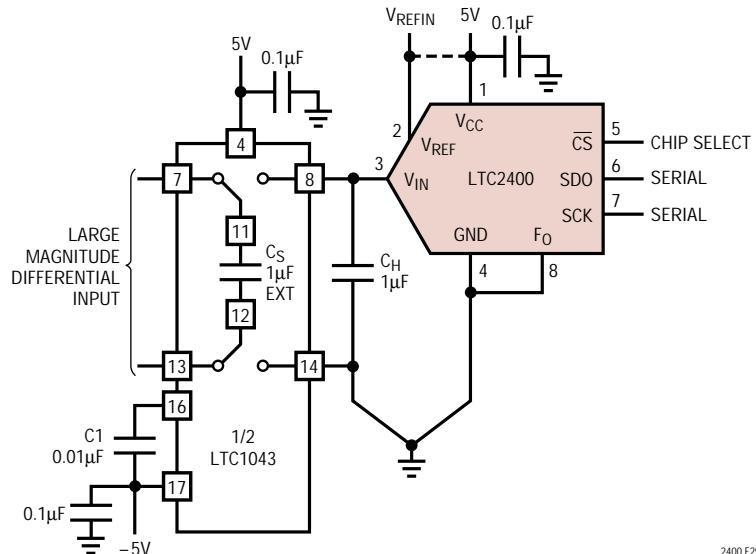

### 差動 - シングルエンド・アナログ調整

図29および図30の回路は、LTC1043デュアル高精度スイッチト・キャパシタ構成ブロックを使用しています。各回路はLTC1043の半分を使用して、電源を含む入力同相範囲にわたって差動 - シングルエンド変換を実行します。LTC1043は差動入力電圧をサンプリングし、それをC<sub>S</sub>で保持してグランド基準コンデンサC<sub>H</sub>に転送します。C<sub>H</sub>の電圧はLTC2400の入力に加えられ、デジタル値に変換されます。

LTC1043は、内部スイッチング周波数が0.01μFのコンデンサC1で設定される標準300Hzで動作し、C<sub>S</sub>とC<sub>H</sub>に1μFのコンデンサを使用しているときに、最高の差動 - シングル・エンド変換を達成します。C<sub>S</sub>とC<sub>H</sub>はマイラーやポリプロピレンのようなフィルム・タイプ・コンデンサでなければなりません。

### LTC2400用の単純な差動フロントエンド

絶対精度よりも高分解能が重要であり、大きな信号振幅と500以下の中等のソース・インピーダンスを持ち、5Vまたは±5V電源を使用するアプリケーションにおける広いダイナミック・レンジの差動信号に対しては、図29の回路が最適です。

この回路は±35ppmの非直線性(14.5ビットの直線性精度)、1.5μVRMSのノイズ、および21ビットの分解能を達成します。また、標準2.75mVのゼロ・オフセットを示します。ただし、これは単に一定値で出力コードをシフトするオフセットではありません。伝達関数のスロープを変化させる利得誤差です。利得誤差は中間スケール(V<sub>REF</sub>/2)を中心に循環します。この利得誤差は、0V入力での誤差を測定し、測定結果から補正係数を導出して、ソフトウェアで補正できます。

## 標準的应用例

図29. 単純なレール・トウ：レール回路により差動信号をシングルエンド信号に変換

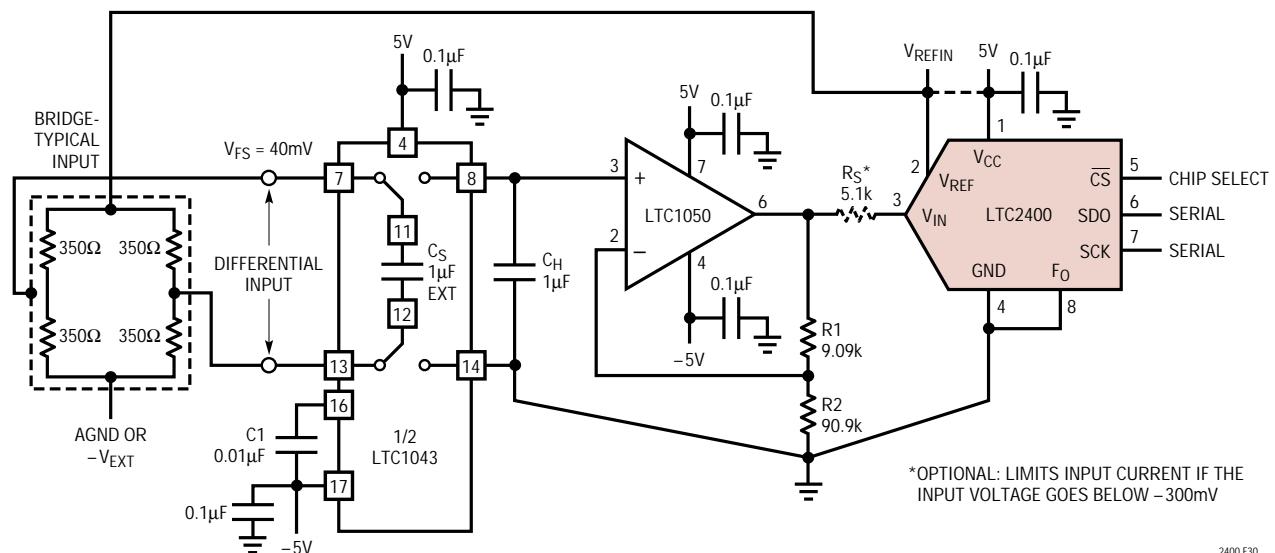

# LTC2400、±5V電源用高精度差動-シングルエンド・コンバータ

図30の回路は、 $\pm 5V$ 電源をもち較正なしで高精度を必要とするアプリケーションでの低レベル差動信号に理想的です。この回路は、LTC1043とLTC1050を入力同相範囲に電源レベルが含まれる差動 - シングルエンド・アンプとして組み合わせたものです。抵抗R1とR2でLTC1050の利得を101に設定します。

回路図にオプションの抵抗 $R_s$ を示します。この抵抗は入力が - 300mV以下になる場合に電流を制限するために、LTC2400の入力と直列に配置することができます。LTC2400の入力とグランド間に接続される浮遊容量またはその他の容量が100pF以下であれば、コンバータの性能が低下することはありません。容量が大きいほど、オフセットおよびフルスケール誤差が増大します(入力電流のセクションを参照)。

この回路はLTC1236-5高精度5Vリファレンスを使用した場合、 $\pm 1\text{ppm}$ の非直線性、 $0.05\mu\text{V}_{\text{RM}}$ の入力換算ノイズ（64サンプルの平均）、40mVのフルスケール入力に対する19.6ビットの分解能、および20ビットの全精度を実現します。

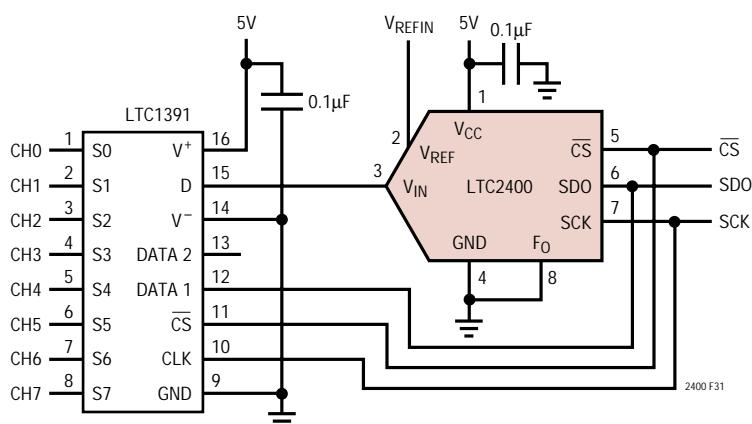

複数入力

図31に示す単純な回路は、LTC2400の单一変換セトリングを利用しています。LTC1391シリアル・プログラム・マルチプレクサにより、LTC2400の入力に接続された全容量が1000pF以下である限り、0Vから $V_{REF}$ までの入力信号に対しオフセット誤差、利得誤差、または直線性誤差を生じることなく、8チャネルのそれぞれで正確な変換が可能です。アクティブな入力チャネルの信号電圧が -300mV( 標準 )に達すると、2ppm( 標準 )の小さな誤差が発生します。グランド以下の振幅が -200mV( 標準 )より高い場合、誤差は LTC2400 の RMS ノイズ 0.3ppm より小さくなります。トップサイドでは、直線性が損なわれたりノイズが増加することなく、選択された入力信号の大きさが 5V 電源を超えることができます。図31の回路は、オーバードライブが電源電圧 +250mV より低いか、またはグランド -250mV より高い限り、変換性能を損なうことなく非選択チャネル上でのオーバードライブに耐えることができます。直線性性能は、標準的性能特性のセクションに示すものとほぼ同じです。

チャンネル間のクロストークに起因する誤差は、LTC2400の標準入力ノイズ以下です。1Hzから153.6kHz ( LTC2400の内部クロック周波数または $10f_s$  ) の周波数範囲に対してもこれが当てはまります。周波数が1.536MHz( 4V<sub>P.P.</sub> )に達すると、RMSノイズは標準的に2倍になり、直線性は30ppm( 標準 )だけ低下します。

## 標準的应用例

図30. LTC2400の高精度を維持しブリッジなどの低レベル入力に対応する差動・シングルエンド・コンバータ

図31. LTC1391による8つの信号源の多重化とLTC2400の変換精度の維持

## 標準的応用例

### LTC2400 SPIインターフェース用サンプル・ドライバ

LTC2400は、マイクロプロセッサおよびマイクロコントローラへのインターフェースが非常に容易な、きわめてシンプルなシリアル・インターフェースを備えています。図32および図34に、変換の開始とLTC2400からのデータ取込みに使用できるソース・コード例のリストを示します。

図32のリストはParallax, Inc. (916- 624-8333)がBASIC Stamp用に作成したものです。このコードは個別ポート・ラインを使用して、LTC2400の変換を制御し、32ビットの結

果を取得します。4番目のポート・ラインはLTC2400への電源供給に使用されます。これはコンバータのマイクロパワー動作を示す好例です。プログラムのメイン・シケンスは、LTC2400のシリアル・インターフェースをアクティブにし、ループを使用して32ビットの変換ビットを取得し、コンバータのインターフェースをハイ・インピーダンス状態にして、次の変換を開始します。すべてのビットは変数ADloとADhiに保持されます。これらのコードはParallax社のウェブ・サイト([www.parallaxinc.com](http://www.parallaxinc.com))に公開されています。

```

'LTC2400          Sample Driver

'03/17/99        This program is an example showing how to access the

'                 LTC2400 using the Basic Stamp2 from Parallax. Since

'                 the BS2 is based on a 16-bit architecture, only the

'                 upper 16 bits of the 24-bit result are displayed,

'                 although all 24 bits are retrieved.

ADlo  var   word      'A/D result - lower 16 bits

ADhi  var   word      'A/D result - upper 8 bits

Ctr   var   byte     'loop counter

Temp  var   bit       'temporary bit used for shift

SDO   con   0         'Serial data connected to P0

SCK   con   1         'Serial clock connected to P1

CS    con   2         'Chip Select connected to P2

Pwr   con   3         'Stamp supplies power connected to P3

'(Uses only 0.3mA!)

Init

dira = $E           'Set up data direction

Pwr, CS, and SCK are outputs

SDO is an input

outa = $0           'Initialize outputs

Pwr, CS, and SCK are low

pause 100           'Wait 100mS for I/O to settle

high Pwr            'Power up the LTC2400

pause 1              'Wait 1mS for power-on sequence

high CS              'Disable the device until we

Start

wish to read it.

pause 125           'Eight times second

low CS               'Enable the LTC2400

for Ctr = 0 to 31

high SCK            'Cycle clock 32 times

gosub ShiftL

```

## 標準的応用例

```

ADlo.bit0 = in0           'and sample data line

low SCK

next

high CS                  'Disable the LTC2400

ADhi = (ADhi<<4)+((ADlo&$F000)>>12)

debug ?ADhi              'Discard the lower eight bits

goto Start                'and display (debug command).

ShiftL

Temp = ADlo.bit15        'This routine simply

ADlo = ADlo<<1          'performs a 1 bit

ADhi = ADhi<<1          'left shift on two

ADhi.bit0 = Temp         '16 bit variables

return

```

図32. LTC2400から簡単にデータを取得可能なことを示すBASIC Stampコードの一例

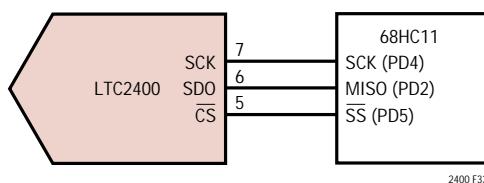

図34のリストは68HC11マイクロコントローラ用の簡単なアセンブラー・ルーチンです。PORT Dを使用して、コントローラとLTC2400間のSPIデータ転送用に構成します。図33に簡単な3線式SPI接続を示します。

コードは変数の宣言で始まり、32ビットの変換結果を格納する4つのメモリ・ロケーションを割り当てます。続いてPORT DのSPI構成を初期化します。次に、このプログラムはメイン・シーケンスに入ります。 $\overline{SS}$ 出力を“L”

に設定することによってLTC2400のシリアル・インターフェースをアクティブにし、 $\overline{CS}$ にロジック“L”を送ります。次に、データ・ラインがロジック“L”になるまでループ内で待って変換終了を通知します。ループが完結すると、4つのSPI転送が完了し、変換結果を取得します。メイン・シーケンスは $\overline{SS}$ を“H”に設定して終了します。これにより、LTC2400のシリアル・インターフェースはハイ・インピーダンス状態になり、別の変換を開始します。

図33. SPIシリアル・インターフェースを使用してLTC2400を68HC11 MCUに接続

```

*****

* This example program transfers the LTC2400's 32-bit output      *

* conversion result into four consecutive 8-bit memory locations. *

*****

```

```

*68HC11 register definition

PORTD EQU $1008 Port D data register

*           " - , - , SS*, CSK ;MOSI,MISO,TxD ,RxD"

DDRD EQU $1009 Port D data direction register

SPSR EQU $1028 SPI control register

*           "SPE,SPIE,DWOM,MSTR;SPOL,CPHA,SPR1,SPR0"

SPSR EQU $1029 SPI status register

*           "SPIF,WCOL, -,MODF; - , - , - , - "

SPDR EQU $102A SPI data register; Read-Buffer; Write-Shifter

*

* RAM variables to hold the LTC2400's 32 conversion result

```

# LTC2400

---

## 標準的応用例

```

*

DIN1 EQU $00 This memory location holds the LTC2400's bits 31 - 24

DIN2 EQU $01 This memory location holds the LTC2400's bits 23 - 16

DIN3 EQU $02 This memory location holds the LTC2400's bits 15 - 08

DIN4 EQU $03 This memory location holds the LTC2400's bits 07 - 00

*

*****

* Start GETDATA Routine *

*****

*

ORG $C000 Program start location

INIT1 LDS #$CFFF Top of C page RAM, beginning location of stack

LDAA #$2F -,1,0;1,1,1,1

*           -, -, SS*-Hi, SCK-Lo, MOSI-Hi, MISO-Hi, X, X

STAA PORTD Keeps SS* a logic high when DDRD, bit 5 is set

LDAA #$38 -,1,1;1,0,0,0

STAA DDRD SS*, SCK, MOSI are configured as Outputs

*           MISO, TxD, RxD are configured as Inputs

*DDRD's bit 5 is a 1 so that port D's SS* pin is a general output

LDAA #$50

STAA SPCR The SPI is configured as Master, CPHA = 0, CPOL = 0

*           and the clock rate is E/2

*           (This assumes an E-Clock frequency of 4MHz. For higher E-

*           Clock frequencies, change the above value of $50 to a value

*           that ensures the SCK frequency is 2MHz or less.)

GETDATA PSHX

PSHY

PSHA

LDX #$0 The X register is used as a pointer to the memory locations

*           that hold the conversion data

LDY #$1000

BCLR PORTD, Y %00100000 This sets the SS* output bit to a logic

*           low, selecting the LTC2400

TRFLP1 LDAA #$0 Load accumulator A with a null byte for SPI transfer

STAA SPDR This writes the byte in the SPI data register and starts

*           the transfer

WAIT1  LDAA SPSR This loop waits for the SPI to complete a serial

*           transfer/exchange by reading the SPI Status Register

BPL WAIT1 The SPIF (SPI transfer complete flag) bit is the SPSR's MSB

*           and is set to one at the end of an SPI transfer. The branch

*           will occur while SPIF is a zero.

LDAA SPDR Load accumulator A with the current byte of LTC2400 data

*           that was just received

STAA 0,X Transfer the LTC2400's data to memory

INX Increment the pointer

CPX #DIN4+1 Has the last byte been transferred/exchanged?

BNE TRFLP1 If the last byte has not been reached, then proceed to the

*           next byte for transfer/exchange

BSET PORTD,Y %00100000 This sets the SS* output bit to a logic high,

*           de-selecting the LTC2400

PULA Restore the A register

PULY Restore the Y register

PULX Restore the X register

RTS

```

図34. 図33に示すSPIシリアル・インタフェースでのLTC2400の変換結果

を捕捉する68HC11コードの一例

## 標準的応用例

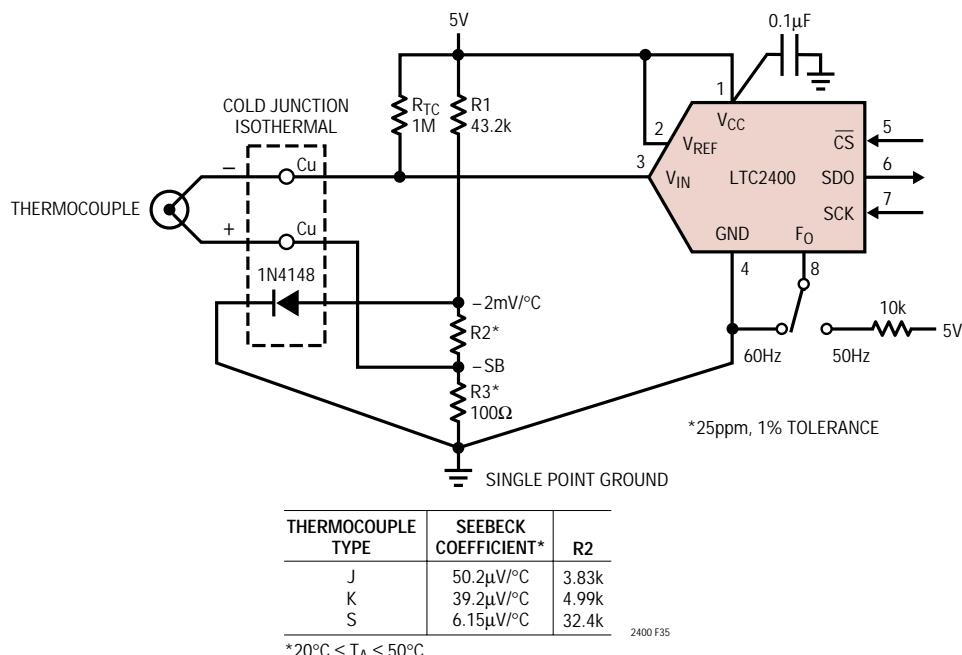

### 熱電対アプリケーション

図35に最小出力の熱電対(ここではフルスケール出力が18mVのタイプS熱電対)を使用したLTC2400への直接接続が可能な熱電対インターフェース回路を示します。

このトポロジーは熱電対センス用の最も安価なソリューションです。図に示すとおり、平均化なしで約0.25 の分解能が可能です。LTC2400は容易に判別できる量子化効果を示さないので、平均化により変化の遅いプロセスに対して大幅に分解能を向上させることができます。

この回路では、1N4148ダイオードは熱電対の正端子に冷接点で予想される全温度範囲(0 ~ 40 )にわたって、タイプS熱電対に対する平均ゼーベック係数の近似値を生成することにより、冷接点補償を行います。動作範囲が狭い場合は、予想される範囲に対してさらに良好なマッチングを行うように係数を調整することができます。選択した熱電対のタイプのゼーベック係数に合わせて抵抗の分割比を変更すれば、この基本回路を別の熱電対と組み合わせて使用することができます(表を参照)。

この回路は冷接点の基準点に1mV ~ 15mVのDCオフセットを生成します。このオフセットはソフトウェアでキャンセルしなければなりません。このDCオフセットは、ダイオードの順方向電圧から生じ、デバイス間で異なるのでユニットごとに較正しなければなりません。

1N4148ダイオードの温度係数は保証されていないので、1.7mV/ ~ 2.3mV/ の係数に対応するために調整が必要です。あるいは、TO-92トランジスタ用リティナ・クリップが付属したOmega Engineering製の熱電対回路ボード・コネクタを用い、トランジスタを物理的に冷接点に接触させて、トランジスタをセンサとして使用することができます。

図に示す1M 抵抗 $R_{TC}$ はオープン回路検出用のもので、LTC2400の入力にフルスケールを生成します。この抵抗はオフセットに影響を及ぼし、抵抗 $R_2$ や $R_3$ と同様に、TCが低くなければならないことに注意してください。R1がダイオードに順バイアスを提供するので、ダイオードの温度係数はそれほど厳密ではありません。

図35の回路はLTC2400の入力範囲のわずか12%だけを使用し、全タイプの熱電対のフルスケール出力に対応でき

図35. ダイオードの冷接点補償

## 標準的応用例

ます。一般に使用される熱電対のうち、最も出力が大きいのはEタイプ(約70mV)です。この回路は冷接点でのゼーベック効果に対する曲率補正は行いません。非常に高い精度を必要とするアプリケーションの場合、冷接点の温度はたとえばRTDを使用して、A/Dへの独立した入力を介して決定しなければなりません。冷接点補償はソフトウェアで熱電対のNBS多項曲率補正を行うことにより実現できます。(LTC2400への入力はLTC1391を使用して多重化でき、性能低下はほとんどありません。独立した温度センサを使用して冷接点をモニタする場合、熱電対からLTC2400に直接接続できます。熱電対のリードが異種金属(たとえば銅配線)に接する点で形成される接合部は温度が等しくなければならず、また冷接点センサをこの接合部に取り付けなければなりません。リード間の温度差、あるいはリードと温度センサ間に違いがあると読み取り値に誤差が生じます。

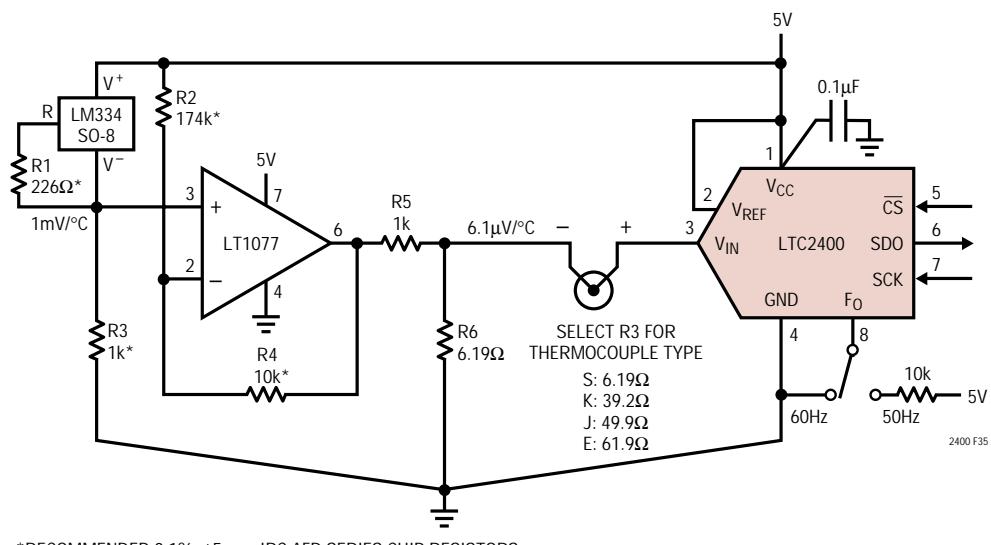

図36にDCオフセットのない安価な回路を示します。ノイズおよびオフセット誤差の影響を低減するだけでなく、必要な係数を生成するために、LT<sup>®</sup>1077の出力を減衰します。サーミスタと一緒に使用する場合は、この回路を曲率補正を生成するように変更することができます。ダイオードの順方向電圧に伴うオフセットやモノリシック温度センサの273 Kのオーバヘッドを除去すれば、熱電対後の大きな利得の使用が簡単になります。LTC1050などのチョッパ・アンプは、LTC2400のノイズ・フロアを10倍～20倍に拡張する可能性があります。LTC2400の前段で利得20をとれば、熱電対アプリケーションの分解能を0.02 以上に向上させることができます。

絶対精度が重要でない場合は、LT1028などの低ノイズ・バイポーラ・アンプを使用すれば、分解能をさらに1桁増やすことができます。

図36の回路で高精度を達成するには、回路オフセットおよび利得補正用の較正シーケンスが必要なことに注意してください。

図36. 安価なアンプによる冷接点補償の改善

## 標準的应用例

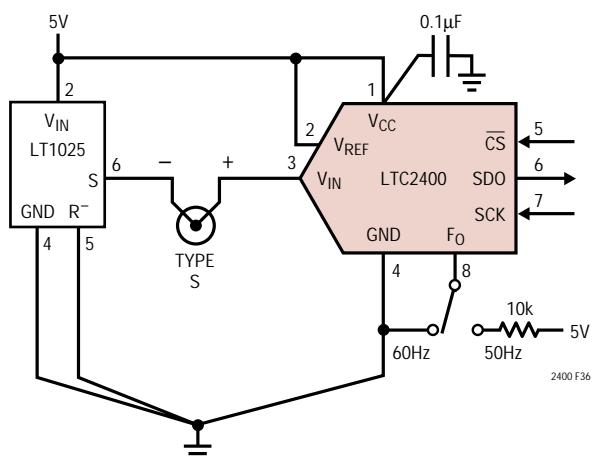

より簡単で可能性のある安価なソリューションは、図37に示すとおりLT1025を使用することです。

LT1025は温度センサ機能、曲率補正機能、5種類の熱電対に対して適切な補正を行うのに必要な高精度分割器チェーンを備えています。LT1025は冷接点に配置してください。空気の流れから保護するだけでなく、冷接点周囲のサーマル・マス(熱塊)を使用するようにしてください。

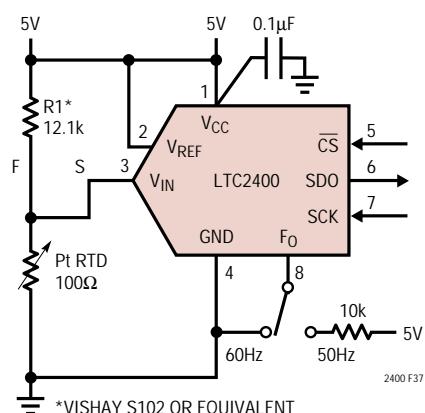

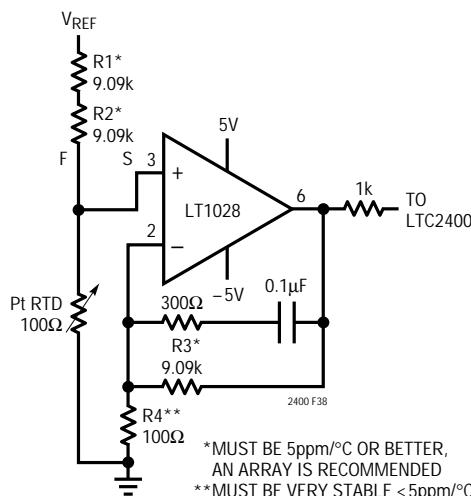

#### 簡単なプラチナRTDインターフェース

より限られた範囲で温度分解能を高くしたい場合は、図38の回路はさらに増幅することなく、約0.01 の分解能を達成できます。プラチナRTDの抵抗は、 $T_A = 25$  では約0.31 / 变化します。この回路のソース・インピーダンスは100 ~ 300 であるため、LTC2400の安定性、精度、あるいはノイズ・レベルが損なわれることはありません。

図37. LT1025の完全な冷接点ソリューション

図38. 最も簡単なプラチナRTDインターフェース

## 標準的応用例

12.1kの抵抗は、Vishay S102シリーズのような高精度抵抗か、または温度安定性の高い抵抗でなければなりません。自己発熱効果がLTC2400のノイズ・フロア付近の大部分のセンサは励起電流が十分低くなっています。

図39に示すバイポーラ・アンプ構成を使用すれば、0.001 の潜在的分解能を実現できます。

このような結果を達成するには、以下の影響を検討しなければなりません。最も難しいのは、空気の流れに起因するRTD素子の自己発熱のバラツキです。RTDが密封ガラス封止され、黒く塗られている場合、LTC2400は部屋に人が入ってきたことを検知できます。これは赤外線の熱電対センサ(サーモパイル)でも可能で、LTC2400に直結して使用できます。2個のRTDを用いたこの回路のバリエーションでは、プロセスからの熱の流入または流出を測定するための、小さな温度差を検出することができます。この回路を実現するには、アンプと抵抗の周囲温

図39. きわめて高分解能のRTDインターフェース

度を制御するか、あるいは抵抗の温度係数が非常に低くなければなりません。高精度抵抗ネットワークが常に優れた選択であり、これらはVishayまたはCaddockから入手できます。

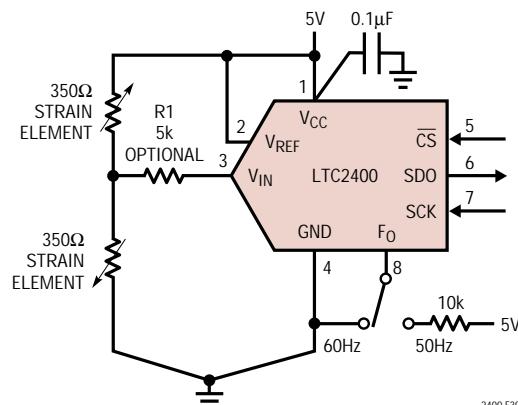

## ハーフブリッジ歪みゲージ

図40の回路は、LTC2400に直接接続された比例ハーフブリッジ回路です。2つの薄膜歪みゲージをハーフブリッジ構成で使用すれば、2mV/V出力とほぼ12ビットの分解能を実現できます。LTC2400から見た175 のソース・インピーダンスは動作に影響を与えません。

図に示すオプションの抵抗は最大5kまで可能であり、歪みゲージがLTC2400から離れて置かれている場合や歪み発生部の接地状態が悪くESDの放電が生じる可能性がある場合に、LTC2400をサージおよび過渡状態から保護します。歪みゲージの薄膜素子は、薄膜素子が接着されている歪み発

図40. 歪みゲージ用ハーフブリッジ接続

## 標準的応用例

生部への結合容量を形成します。歪み発生部から拾ったノイズがおよそ60Hzの場合、LTC2400はそのノイズを除去します。歪み発生部に問題となる高周波ノイズが存在する場合は、ノイズサプレス回路を使用できるようにバッファを追加しなければならないことがあります。

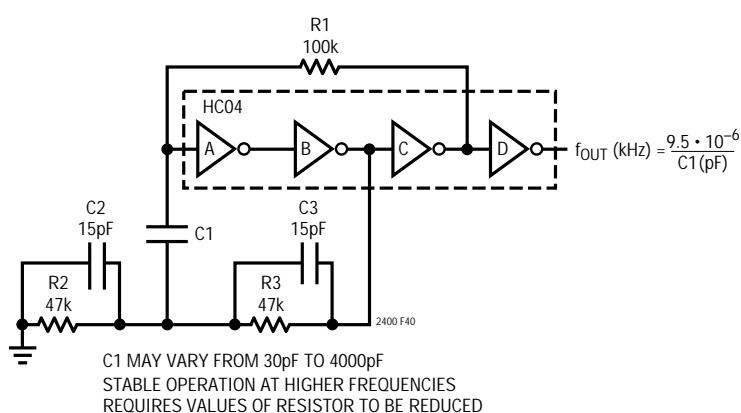

### 外部クロック用の安定したし張発振器

LTC2400のsinc<sup>4</sup>フィルタのノッチ周波数が50Hzまたは60Hz以外でなければならないアプリケーションには、外部クロックが必要です。所要周波数は $2560 \times (\text{所要ノッチ周波数})$ です。74HC14などヒステリシス付きロジック・ゲートで構成された簡単なし張発振器は、温度、電源電圧変動、デバイス間のバラツキに対して不安定です。

たとえば、遠隔重量計アプリケーションが11Hzで共振除去を必要とする場合、周波数を28.16kHzに設定しなければなりません。多くの場合、これらの周波数はフェーズ・ロック・ループまたはデジタル分周器でデジタル的に生成できますが、水晶振動子で直接生成するには低す

ぎます。ノッチが広く発振器の安定性は0.1%~1%で十分なので、一般に水晶振動子並みの安定性は必要ありません。

電源、スペース、あるいはコスト上の制限により、これらの周波数のデジタル生成が実用的でなく、4Hz~120Hzの範囲のノッチが必要な場合には、図41の回路を使用できます。

コンデンサC1の容量を4000pFから30pFの範囲で変えることにより、周波数を4Hz~120Hzの範囲で変化させることができます。図に示す抵抗値では、出力周波数(kHz)はおよそ $9.5 \times 10^{-6} \div C1(\text{pF})$ になります。この回路は、抵抗のマッチングにのみ依存する制御されたヒステリシスを生成し、入力スレッショルド付近に自己バイアスします。すべてのゲートは同一パッケージになければならず、帰還路をドライブする出力から負荷をドライブしてはなりません。予備のゲートがある場合は、ゲートBおよびDと並列に使用して帰還路のドライブを改善することができます。

図41. ノッチ同調のための安定した低消費電力し張発振器

# LTC2400

## 標準的応用例

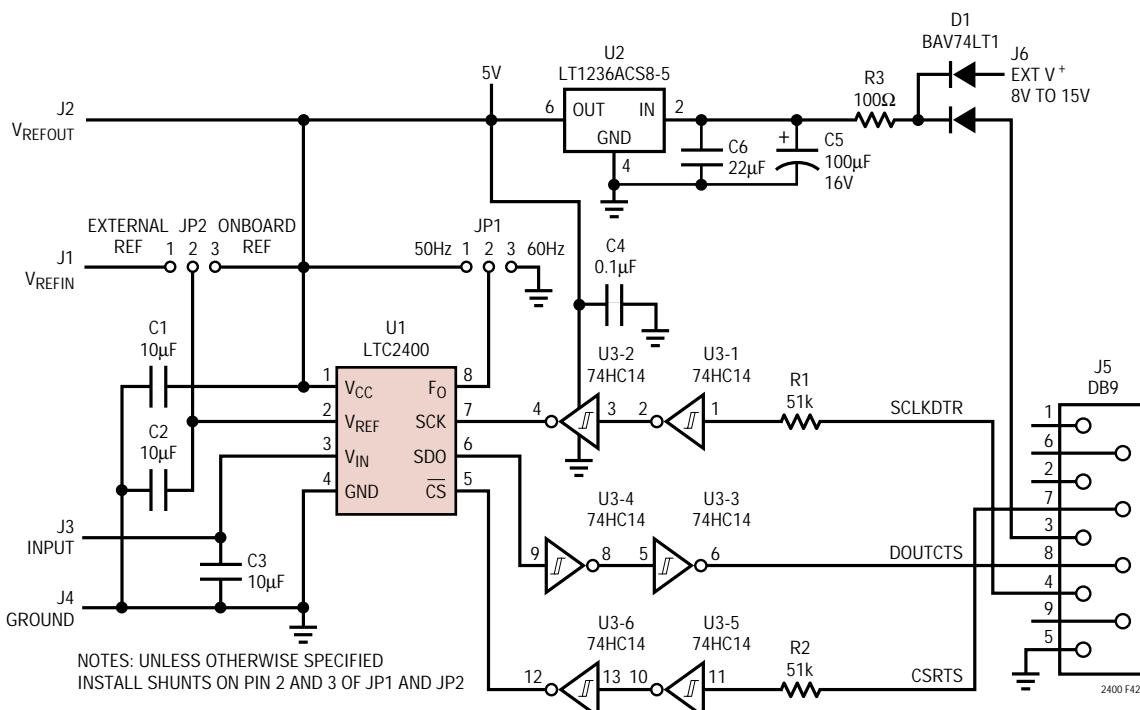

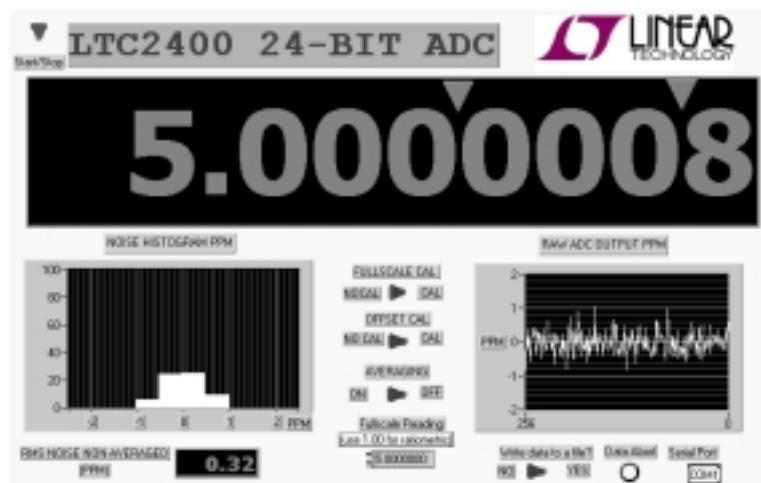

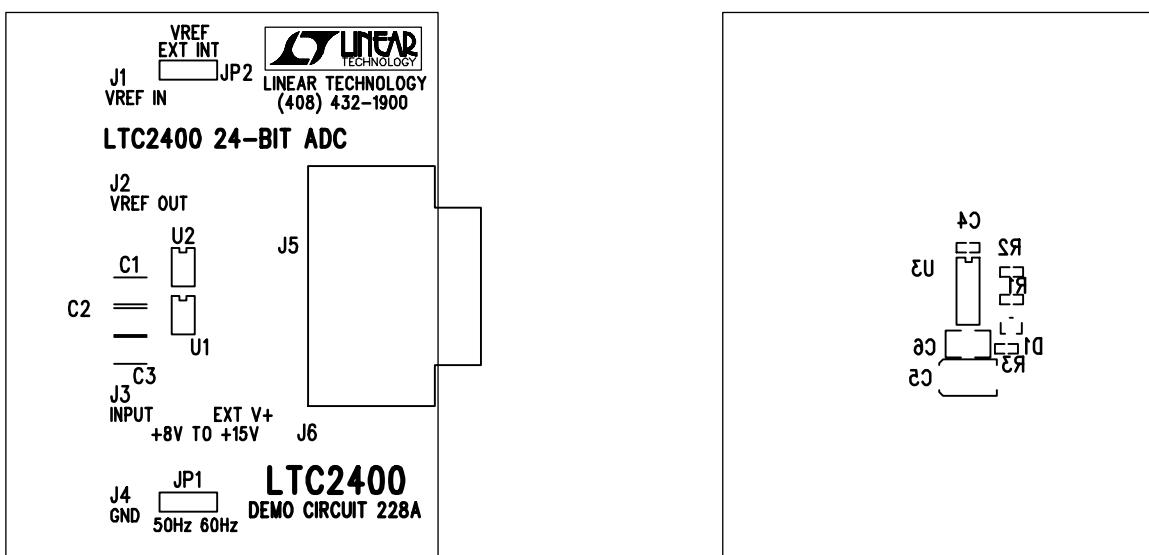

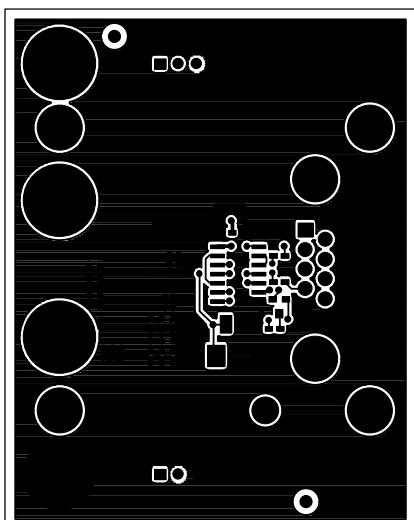

LTC2400の性能はデモ・ボードDC228により評価できます(回路図は図42を参照)。この回路はコンピュータのシリアル・ポートを使用して、電力および変換の開始と結果の読み込みに必要なSPIデジタル信号を生成します。視覚的に変換結果を捕捉するLabviewアプリケーション・ソフトウェア・プログラム(図43参照)が搭載されています。

また、ノイズ性能、安定性、そして外部ソースを使用して直線性を評価することができます。回路図で示すように、LTC2400は非常に使いやすいデバイスです。このデモ・ボードと付属のソフトウェアについては、弊社にお問い合わせください。

図42. 24ビットA/Dデモ・ボード回路図

図43. ディスプレイ・グラフィック

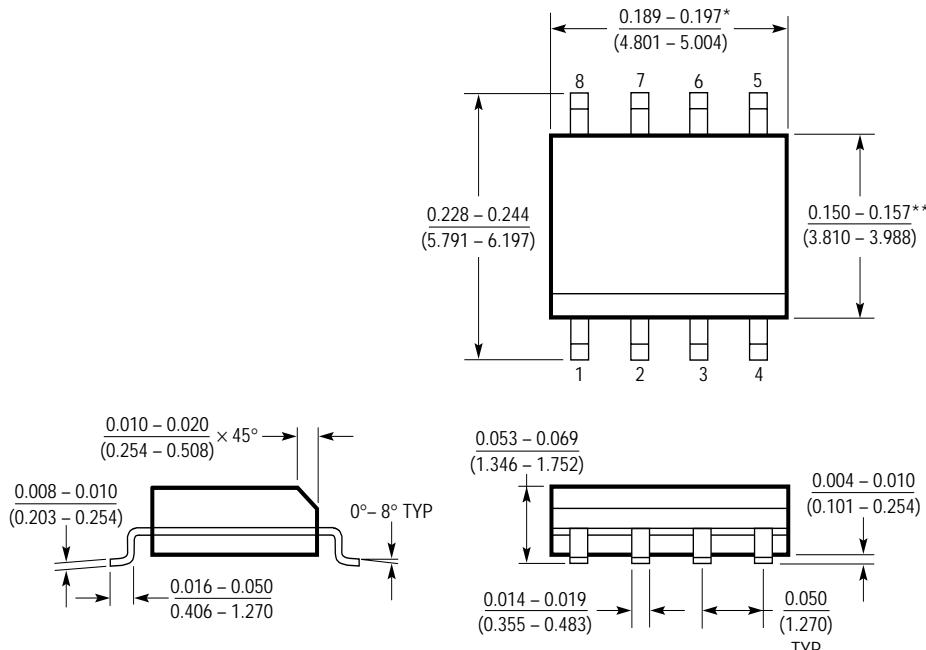

## パッケージ情報 注記がない限り、寸法はインチ( mm )

S8パッケージ

8ピン・プラスチック・スマール・アウトライン(細型0.150)

(LTC DWG # 05-08-1610 )

\* 寸法はモールドのバリを含まない。モールドのバリは各サイドで0.006" (0.152mm) を超えてはならない。

\*\* 寸法にはリード間のバリは含まれない。リード間のバリは各サイドで0.010" (0.254mm) を超えてはならない。

S08 0996

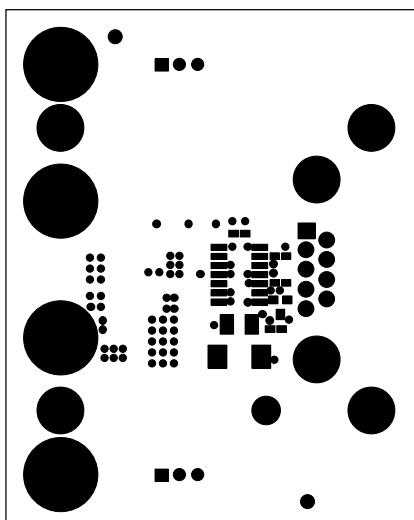

## PCBレイアウトとフィルム

部品面シルクスクリーン

半田面シルクスクリーン

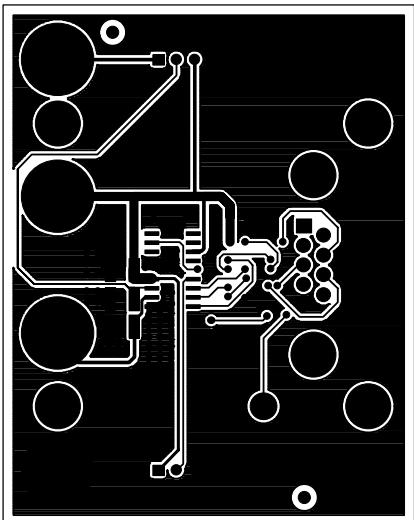

## PCBレイアウトとフィルム

部品面

部品面半田マスク

部品面ペースト・マスク

半田面

半田面半田マスク

半田面ペースト・マスク

## 関連製品

| 製品番号            | 説明                               | 注釈                                        |

|-----------------|----------------------------------|-------------------------------------------|

| LTC1019         | 高精度バンドキャップ・リファレンス、2.5V、5V        | ドリフト3ppm/、0.05%最大                         |

| LTC1025         | マイクロパワー熱電対冷接点補償器                 |                                           |

| LTC1043         | デュアル精密計装用スイッチト・キャパシタ・ビルディング・ブロック | 高精度の充電、バランスのとれたスイッチング、低消費電力               |

| LTC1050         | 高精度チョッパ安定オペアンプ                   | 外付け部品不要、オフセット5µV、ノイズ1.6µV <sub>P-P</sub>  |

| LT1236A-5       | 高精度バンドギャップ・リファレンス5V              | 0.05%最大、ドリフト5ppm/                         |

| LT1460          | マイクロパワー・シリーズ・リファレンス              | 0.075%最大、最大ドリフト10ppm/、2.5V、5V、および10Vバージョン |

| LTC2401/LTC2402 | 1チャネルおよび2チャネルの24ビットADC           | ノイズ3µV、10ピンMSOPパッケージ、グランド・センシング           |

| LTC2404/LTC2408 | 4チャネルおよび8チャネル24ビットADC            | LTC2400と同じ性能                              |

| LTC2420         | 20ビット・マイクロパワーADC                 | ノイズ6µV、LTC2400とピン・コンパチブル                  |