アナログ入力範囲をピンで

設定可能なSNRが99.8dBの

18ビット2.5MspsSARADC

## 特長

- スループット・レート: 2.5Msps

- INL:  $\pm 3$ LSB(最大)

- 欠落コードのない18ビット分解能を保証

- ピンで設定可能なアナログ入力電圧範囲:

$\pm 4.096$ V(完全差動)

0V ~  $4.096$ V(疑似差動ユニポーラ)

$\pm 2.048$ V(疑似差動バイポーラ)

- SNR(標準): 99.8dB(完全差動)/95.2dB(疑似差動)

( $f_{IN} = 2$ kHz 時)

- THD(標準): -116dB(完全差動) / -112dB(疑似差動)

( $f_{IN} = 2$ kHz 時)

- 125°Cまでの動作を保証

- 5V 単電源

- 内部リファレンス温度係数: 20ppm/°C(最大)

- リファレンス・バッファ内蔵

- 消費電力: 162.5mW(2.5Msps 時)

- パイプライン遅延なし、サイクル待ち時間なし

- I/O の電圧: 1.8V ~ 5V

- I/O インタフェース: パラレルおよびシリアル

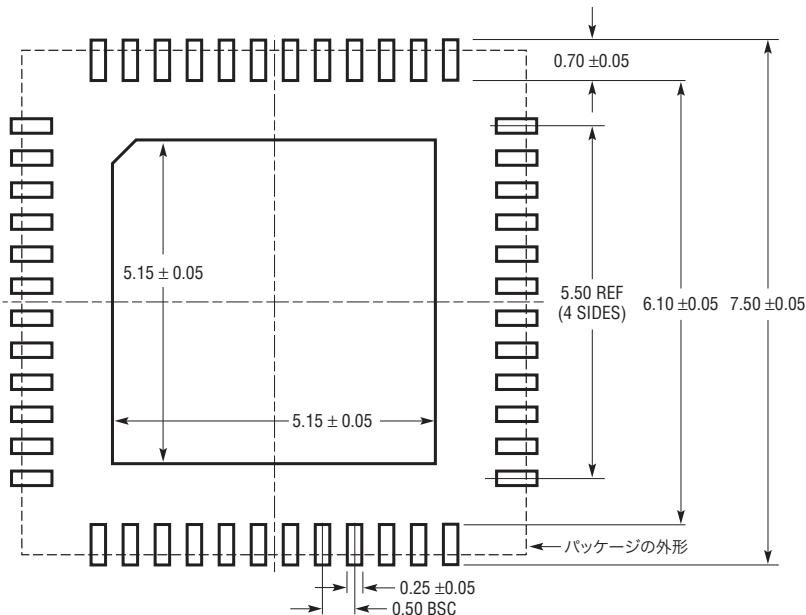

- 7mm×7mm の 48 ピン LQFP および QFN パッケージ

## アプリケーション

- 医療用画像処理

- ダイナミックレンジの広い高速データ収集

- 産業用プロセス制御

- 計測器

- ATF

## 概要

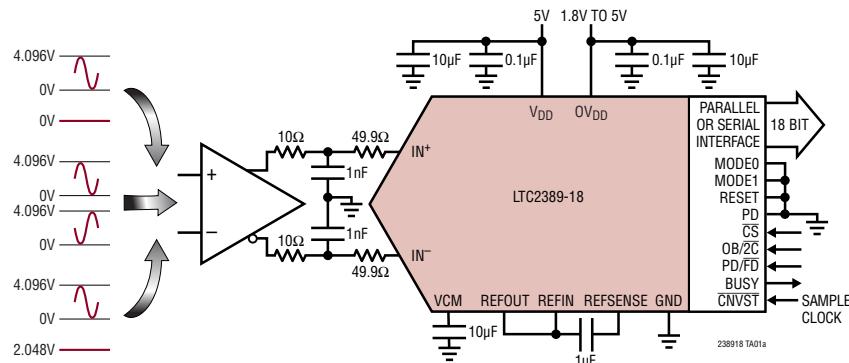

LTC<sup>®</sup>2389-18は、低ノイズの高速18ビット逐次比較レジスタ(SAR)ADCです。LTC2389-18は、5V単電源で動作し、ピンで設定可能な完全差動( $\pm 4.096\text{V}$ )、疑似差動ユニポーラ(0V～4.096V)、および疑似差動バイポーラ( $\pm 2.048\text{V}$ )のアナログ入力電圧範囲をサポートするので、追加のレベル変換または信号処理を行う必要がなく、複数の信号チェーン形式とのインターフェースを行うことができます。LTC2389-18は $\pm 3\text{LSB}$ のINL(最大)、18ビット分解能で欠落コードなし、および99.8dB(完全差動)/95.2dB(疑似差動)のSNR(標準)を実現します。

LTC2389-18は、0.5%の初期精度が保証され、 $\pm 20\text{ppm}/^\circ\text{C}$ （最大）の温度係数を持つ4.096V高精度リファレンスを内蔵しているだけでなく、リファレンス・バッファも内蔵しています。パラレル・インターフェース・モードではスループットが2.5Mspsと高速でサイクル待ち時間がないので、LTC2389-18は、さまざまな高速アプリケーションに最適です。内部発振器が変換時間を設定するので、外部のタイミングに対する配慮は少なくて済みます。LTC2389-18の2.5Msps時の消費電力はわずか162.5mWですが、ナップ・モードおよびスリープ・モードという電力節減モードが用意されているので、動作停止期間中の消費電力はさらに低減されます。

LT、LTC、LTM、Linear Technology および Linear のロゴはリニアテクノロジー社の登録商標です。SoftSpanはリニアテクノロジー社の商標です。その他すべての商標の所有権は、それぞれの所有者に帰属します。7705765を含む米国特許によって保護されています。

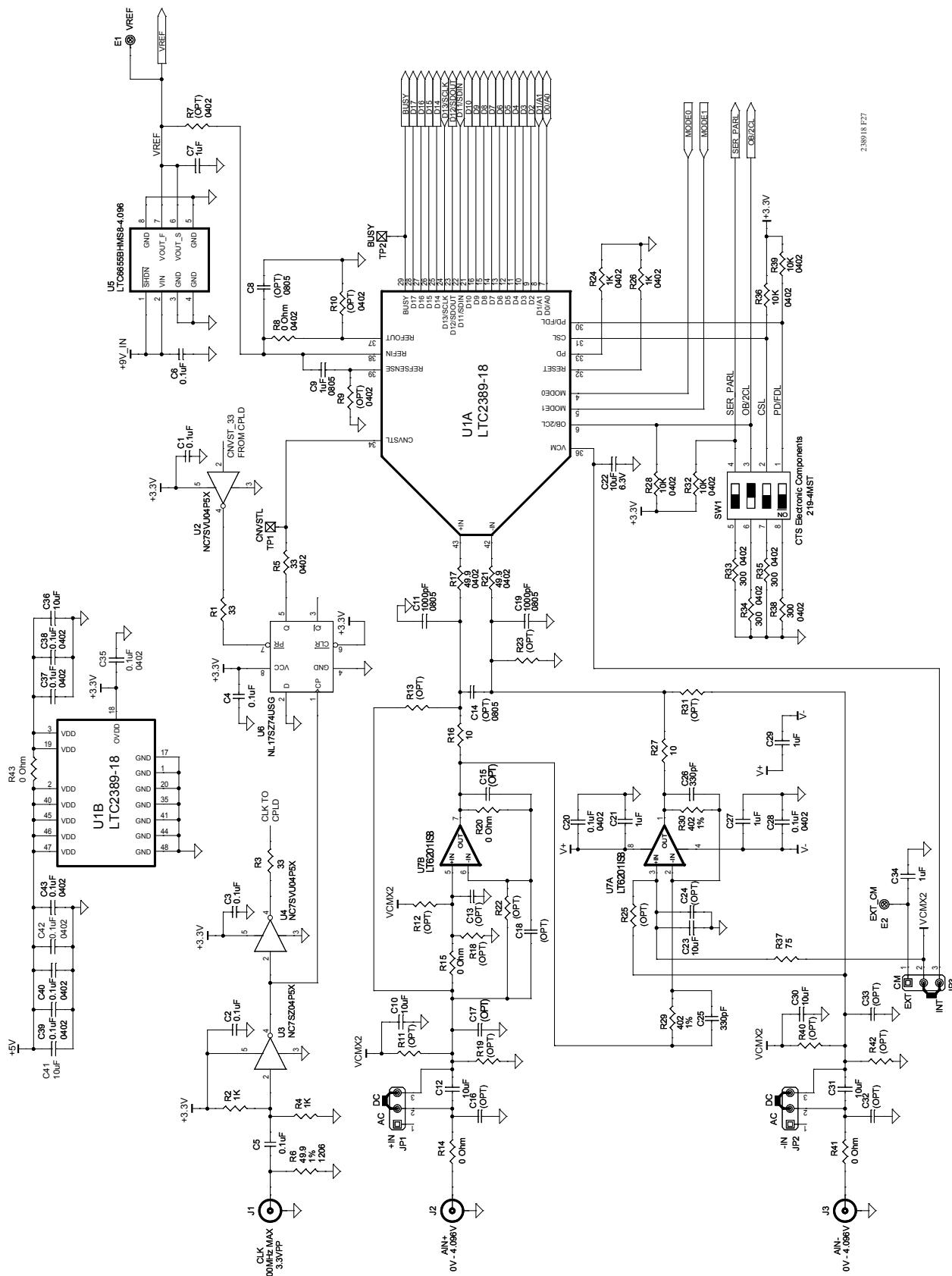

## 標準的應用例

## 絶対最大定格 (Note 1, 2)

|                                               |                                          |

|-----------------------------------------------|------------------------------------------|

| 電源電圧 (V <sub>DD</sub> 、0V <sub>DD</sub> )     | 6V                                       |

| アナログ入力電圧 (Note 3)                             |                                          |

| IN <sup>+</sup> 、IN <sup>-</sup> 、REFIN、CNVST | (GND - 0.3V) ~ (V <sub>DD</sub> + 0.3V)  |

| デジタル入力電圧                                      |                                          |

| (Note 3)                                      | (GND - 0.3V) ~ (0V <sub>DD</sub> + 0.3V) |

| デジタル出力電圧                                      |                                          |

| (Note 3)                                      | (GND - 0.3V) ~ (0V <sub>DD</sub> + 0.3V) |

| 電力損失                                          | 500mW                                    |

## 動作温度範囲

|                 |               |

|-----------------|---------------|

| LTC2389C        | 0°C ~ 70°C    |

| LTC2389I        | -40°C ~ 85°C  |

| LTC2389H        | -40°C ~ 125°C |

| 保存温度範囲          | -65°C ~ 150°C |

| リード温度(半田付け、10秒) |               |

| LXパッケージ         | 300°C         |

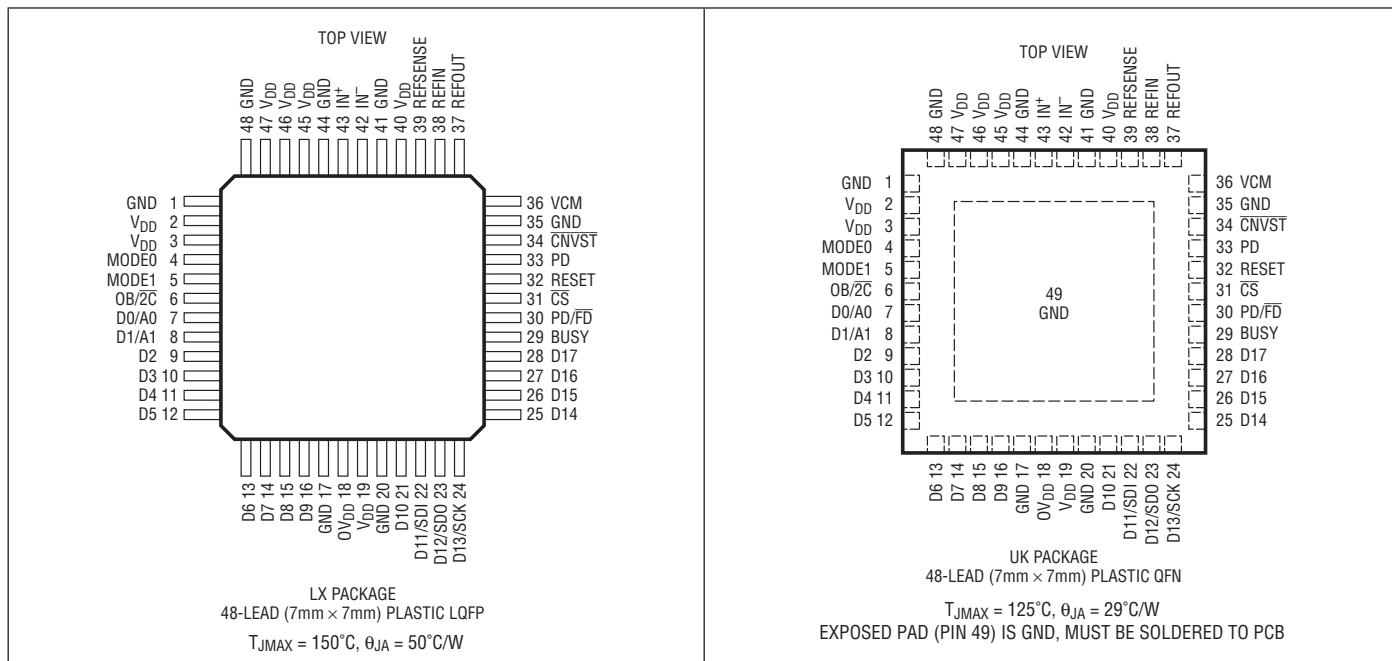

## ピン配置

## 発注情報

| 無鉛仕上げ             | テープアンドリール           | 製品マーキング*     | パッケージ                        | 温度範囲           |

|-------------------|---------------------|--------------|------------------------------|----------------|

| LTC2389CUK-18#PBF | LTC2389CUK-18#TRPBF | LTC2389UK-18 | 48-Lead 7mmx7mm Plastic QFN  | 0°C to 70°C    |

| LTC2389IUK-18#PBF | LTC2389IUK-18#TRPBF | LTC2389UK-18 | 48-Lead 7mmx7mm Plastic QFN  | -40°C ~ 85°C   |

| 無鉛仕上げ             | トレイ                 | 製品マーキング*     | パッケージ                        | 温度範囲           |

| LTC2389CLX-18#PBF | LTC2389CLX-18#PBF   | LTC2389LX-18 | 48-Lead 7mmx7mm Plastic LQFP | 0°C to 70°C    |

| LTC2389ILX-18#PBF | LTC2389ILX-18#PBF   | LTC2389LX-18 | 48-Lead 7mmx7mm Plastic LQFP | -40°C to 85°C  |

| LTC2389HLX-18#PBF | LTC2389HLX-18#PBF   | LTC2389LX-18 | 48-Lead 7mmx7mm Plastic LQFP | -40°C to 125°C |

さらに広い動作温度範囲で規定されるデバイスについては、弊社または弊社代理店にお問い合わせください。\* 温度グレードは出荷時のコンテナのラベルで識別されます。

鉛ベースの非標準仕上げの製品の詳細については、弊社または弊社代理店にお問い合わせください。

鉛フリー製品のマーキングの詳細については、<http://www.linear-tech.co.jp/leadfree/> をご覧ください。

テープアンドリールの仕様の詳細については、<http://www.linear-tech.co.jp/tapeandreel/> をご覧ください。

アナログ入力 ●は全動作温度範囲での規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。(Note 4)

| SYMBOL                | PARAMETER                         | CONDITIONS                                                                                                   |             | MIN                               | TYP                     | MAX                                         | UNITS                          |

|-----------------------|-----------------------------------|--------------------------------------------------------------------------------------------------------------|-------------|-----------------------------------|-------------------------|---------------------------------------------|--------------------------------|

| $V_{IN^+}$            | Absolute Input Range ( $IN^+$ )   | (Note 5)                                                                                                     | ●           | -0.1                              |                         | $V_{REF} + 0.1$                             | V                              |

| $V_{IN^-}$            | Absolute Input Range ( $IN^-$ )   | Fully Differential (Note 5)<br>Pseudo-Differential Unipolar (Note 5)<br>Pseudo-Differential Bipolar (Note 5) | ●<br>●<br>● | -0.1<br>-0.1<br>$V_{REF}/2 - 0.1$ | 0<br>0.1<br>$V_{REF}/2$ | $V_{REF} + 0.1$<br>0.1<br>$V_{REF}/2 + 0.1$ | V<br>V<br>V                    |

| $V_{IN^+} - V_{IN^-}$ | Input Differential Voltage Range  | Fully Differential<br>Pseudo-Differential Unipolar<br>Pseudo-Differential Bipolar                            | ●<br>●<br>● | $-V_{REF}$<br>0<br>$-V_{REF}/2$   |                         | $V_{REF}$<br>$V_{REF}$<br>$V_{REF}/2$       | V<br>V<br>V                    |

| $V_{CM}$              | Input Common Mode Voltage Range   | Fully Differential                                                                                           | ●           | $V_{REF}/2 - 0.1$                 | $V_{REF}/2$             | $V_{REF}/2 + 0.1$                           | V                              |

| $I_{IN}$              | Analog Input Leakage Current      | C- and I-Grades<br>H-Grade                                                                                   | ●<br>●      | -1<br>-2                          |                         | 1<br>2                                      | $\mu\text{A}$<br>$\mu\text{A}$ |

| $C_{IN}$              | Analog Input Capacitance          | Sample Mode<br>Hold Mode                                                                                     |             |                                   | 45<br>5                 |                                             | $\text{pF}$<br>$\text{pF}$     |

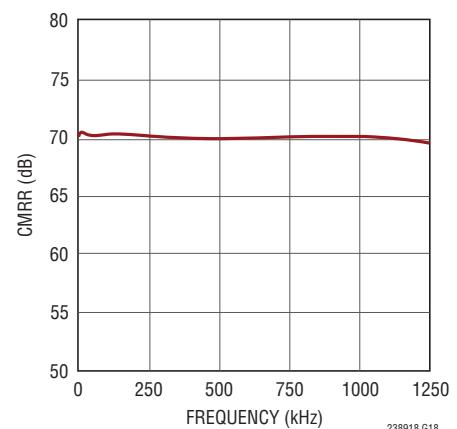

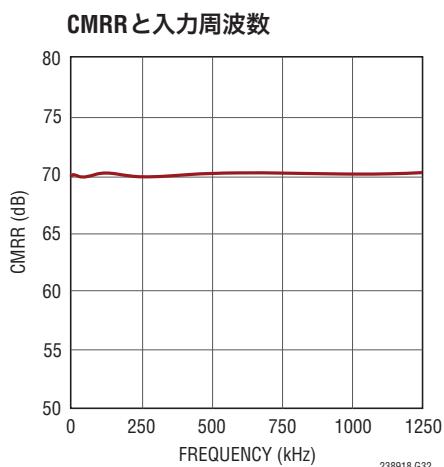

| CMRR                  | Input Common Mode Rejection Ratio |                                                                                                              |             |                                   | 70                      |                                             | dB                             |

| $V_{IHCVST}$          | CNVST High Level Input Voltage    |                                                                                                              | ●           | 1.5                               |                         |                                             | V                              |

| $V_{ILCVST}$          | CNVST Low Level Input Voltage     |                                                                                                              | ●           |                                   |                         | 0.5                                         | V                              |

| $I_{INCVST}$          | CNVST Input Current               | $V_{IN} = 0\text{V}$ to $V_{DD}$                                                                             | ●           |                                   | -25                     | -60                                         | $\mu\text{A}$                  |

コンバータ特性 ●は全動作温度範囲での規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。(Note 4)

| SYMBOL | PARAMETER                    | CONDITIONS                                                                                                   |             | MIN                  | TYP                                    | MAX               | UNITS                                                                               |

|--------|------------------------------|--------------------------------------------------------------------------------------------------------------|-------------|----------------------|----------------------------------------|-------------------|-------------------------------------------------------------------------------------|

|        | Resolution                   |                                                                                                              | ●           | 18                   |                                        |                   | Bits                                                                                |

|        | No Missing Codes             |                                                                                                              | ●           | 18                   |                                        |                   | Bits                                                                                |

|        | Transition Noise             | Fully Differential<br>Pseudo-Differential Unipolar<br>Pseudo-Differential Bipolar                            |             |                      | 0.76<br>1.5<br>1.5                     |                   | $\text{LSB}_{\text{RMS}}$<br>$\text{LSB}_{\text{RMS}}$<br>$\text{LSB}_{\text{RMS}}$ |

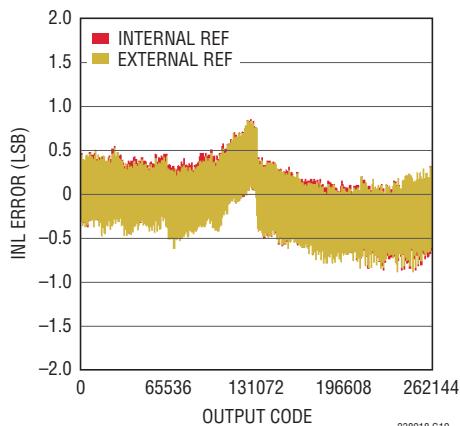

| INL    | Integral Linearity Error     | Fully Differential (Note 6)<br>Pseudo-Differential Unipolar (Note 6)<br>Pseudo-Differential Bipolar (Note 6) | ●<br>●<br>● | -3<br>-3<br>-3       | $\pm 1.25$<br>$\pm 1.25$<br>$\pm 1.25$ | 3<br>3<br>3       | LSB                                                                                 |

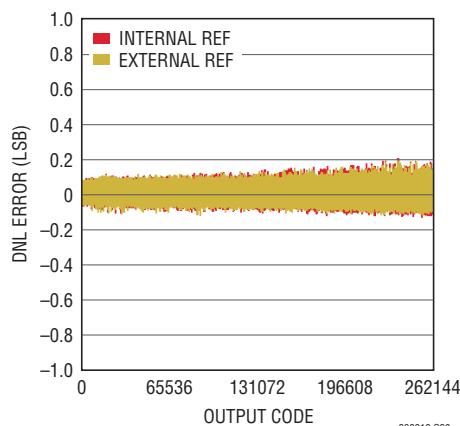

| DNL    | Differential Linearity Error | Fully Differential<br>Pseudo-Differential Unipolar<br>Pseudo-Differential Bipolar                            | ●<br>●<br>● | -0.9<br>-0.9<br>-0.9 | $\pm 0.3$<br>$\pm 0.3$<br>$\pm 0.3$    | 0.9<br>0.9<br>0.9 | LSB                                                                                 |

| ZSE    | Zero-Scale Error             | Fully Differential (Note 7)<br>Pseudo-Differential Unipolar (Note 7)<br>Pseudo-Differential Bipolar (Note 7) | ●<br>●<br>● | -10<br>-15<br>-15    | 0<br>0<br>0                            | 10<br>15<br>15    | LSB                                                                                 |

|        | Zero-Scale Error Drift       |                                                                                                              |             |                      |                                        | $\pm 0.05$        | $\text{ppm}/^\circ\text{C}$                                                         |

| FSE    | Full-Scale Error             | External Reference (Note 7)<br>Internal Reference (Note 7)                                                   | ●           |                      |                                        | 0.15<br>0.15      | %<br>%                                                                              |

|        | Full-Scale Error Drift       |                                                                                                              |             |                      |                                        | $\pm 5$           | $\text{ppm}/^\circ\text{C}$                                                         |

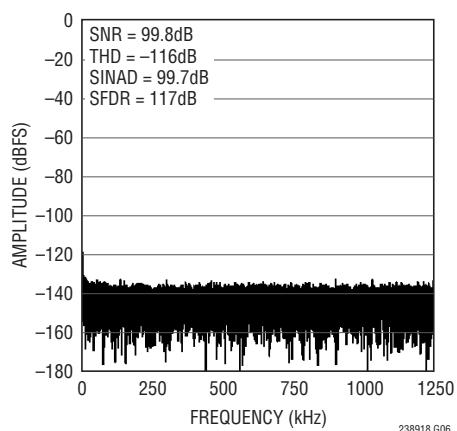

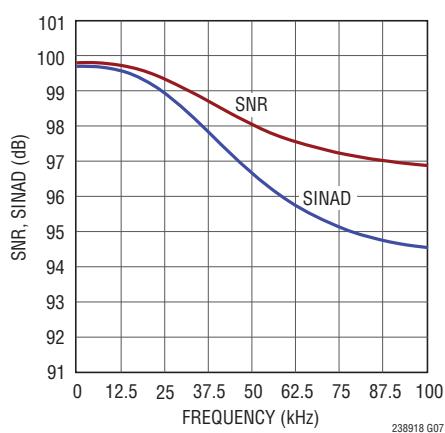

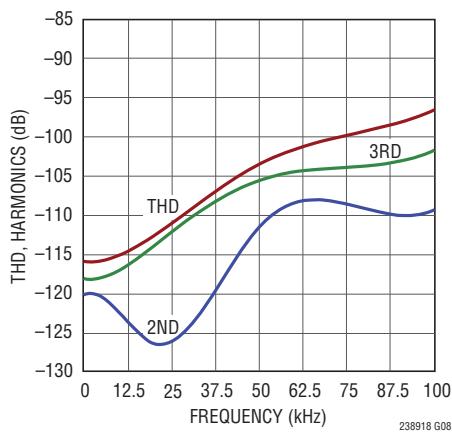

ダイナミック精度 ●は全動作温度範囲での規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。 $A_{IN} = -1\text{dBFS}$ 。(Note 4, 8)

| SYMBOL               | PARAMETER                            | CONDITIONS                                                                         | MIN | TYP  | MAX  | UNITS            |    |

|----------------------|--------------------------------------|------------------------------------------------------------------------------------|-----|------|------|------------------|----|

| SINAD                | Signal-to-(Noise + Distortion) Ratio | Fully Differential, $f_{IN} = 2\text{kHz}$                                         | ●   | 97.3 | 99.7 | dB               |    |

|                      |                                      | Pseudo-Differential Unipolar, $f_{IN} = 2\text{kHz}$                               | ●   | 92.2 | 94.5 | dB               |    |

|                      |                                      | Pseudo-Differential Bipolar, $f_{IN} = 2\text{kHz}$                                | ●   | 92.7 | 95.1 | dB               |    |

|                      |                                      | Fully Differential, $f_{IN} = 2\text{kHz}$ (H-Grade)                               | ●   | 96.6 | 99.7 | dB               |    |

|                      |                                      | Pseudo-Differential Unipolar, $f_{IN} = 2\text{kHz}$ (H-Grade)                     | ●   | 92.0 | 94.5 | dB               |    |

|                      |                                      | Pseudo-Differential Bipolar, $f_{IN} = 2\text{kHz}$ (H-Grade)                      | ●   | 92.5 | 95.1 | dB               |    |

| SNR                  | Signal-to-Noise Ratio                | Fully Differential, $f_{IN} = 2\text{kHz}$                                         | ●   | 98.1 | 99.8 | dB               |    |

|                      |                                      | Pseudo-Differential Unipolar, $f_{IN} = 2\text{kHz}$                               | ●   | 92.7 | 94.6 | dB               |    |

|                      |                                      | Pseudo-Differential Bipolar, $f_{IN} = 2\text{kHz}$                                | ●   | 93.3 | 95.2 | dB               |    |

|                      |                                      | Fully Differential, $f_{IN} = 2\text{kHz}$ (H-Grade)                               | ●   | 97.7 | 99.8 | dB               |    |

|                      |                                      | Pseudo-Differential Unipolar, $f_{IN} = 2\text{kHz}$ (H-Grade)                     | ●   | 92.5 | 94.6 | dB               |    |

|                      |                                      | Pseudo-Differential Bipolar, $f_{IN} = 2\text{kHz}$ (H-Grade)                      | ●   | 93.1 | 95.2 | dB               |    |

| THD                  | Total Harmonic Distortion            | Fully Differential, $f_{IN} = 2\text{kHz}$ , First 5 Harmonics                     | ●   |      | -116 | -105             | dB |

|                      |                                      | Pseudo-Differential Unipolar, $f_{IN} = 2\text{kHz}$ , First 5 Harmonics           | ●   |      | -112 | -102             | dB |

|                      |                                      | Pseudo-Differential Bipolar, $f_{IN} = 2\text{kHz}$ , First 5 Harmonics            | ●   |      | -111 | -102             | dB |

|                      |                                      | Fully Differential, $f_{IN} = 2\text{kHz}$ , First 5 Harmonics (H-Grade)           | ●   |      | -116 | -103             | dB |

|                      |                                      | Pseudo-Differential Unipolar, $f_{IN} = 2\text{kHz}$ , First 5 Harmonics (H-Grade) | ●   |      | -112 | -102             | dB |

|                      |                                      | Pseudo-Differential Bipolar, $f_{IN} = 2\text{kHz}$ , First 5 Harmonics (H-Grade)  | ●   |      | -111 | -102             | dB |

| SFDR                 | Spurious-Free Dynamic Range          | Fully Differential, $f_{IN} = 2\text{kHz}$                                         | ●   | 106  | 117  | dB               |    |

|                      |                                      | Pseudo-Differential Unipolar, $f_{IN} = 2\text{kHz}$                               | ●   | 102  | 113  | dB               |    |

|                      |                                      | Pseudo-Differential Bipolar, $f_{IN} = 2\text{kHz}$                                | ●   | 102  | 112  | dB               |    |

|                      |                                      | Fully Differential, $f_{IN} = 2\text{kHz}$ (H-Grade)                               | ●   | 104  | 117  | dB               |    |

|                      |                                      | Pseudo-Differential Unipolar, $f_{IN} = 2\text{kHz}$ (H-Grade)                     | ●   | 102  | 113  | dB               |    |

|                      |                                      | Pseudo-Differential Bipolar, $f_{IN} = 2\text{kHz}$ (H-Grade)                      | ●   | 102  | 112  | dB               |    |

| -3dB Input Bandwidth |                                      |                                                                                    |     |      | 50   | MHz              |    |

| Aperture Delay       |                                      |                                                                                    |     |      | 0.5  | ns               |    |

| Aperture Jitter      |                                      |                                                                                    |     |      | 1    | $\mu\text{SRMS}$ |    |

| Transient Response   |                                      |                                                                                    |     |      | 70   | ns               |    |

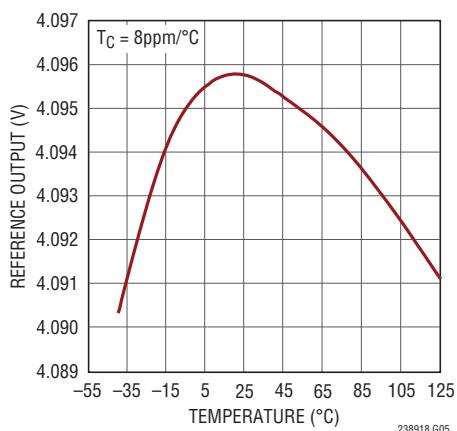

リファレンス特性 ●は全動作温度範囲での規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。(Note 4)

| SYMBOL       | PARAMETER                  | CONDITIONS                                     | MIN   | TYP      | MAX      | UNITS                      |

|--------------|----------------------------|------------------------------------------------|-------|----------|----------|----------------------------|

| $V_{REFOUT}$ | Internal Reference Voltage | REFOUT Tied to REFIN, $I_{OUT} = 0\mu\text{A}$ | 4.076 | 4.096    | 4.116    | V                          |

| $V_{REFOUT}$ | Tempco                     | $I_{OUT} = 0\mu\text{A}$ (Note 9)              | ●     | $\pm 10$ | $\pm 20$ | $\text{ppm}^\circ\text{C}$ |

|              | REFOUT Output Impedance    | $-0.1\text{mA} \leq I_{OUT} \leq 0.1\text{mA}$ |       | 2.3      |          | $\text{k}\Omega$           |

|              | REFOUT Line Regulation     | $V_{DD} = 4.75\text{V} \sim 5.25\text{V}$      |       | 0.3      |          | $\text{mV/V}$              |

| $V_{REF}$    | Converter REFIN Voltage    |                                                | 4.076 | 4.096    | 4.116    | V                          |

|              | REFIN Input Impedance      |                                                |       | 74       |          | $\text{k}\Omega$           |

|              | VCM Output Voltage         | $I_{OUT} = 0\mu\text{A}$                       |       | 2.08     |          | V                          |

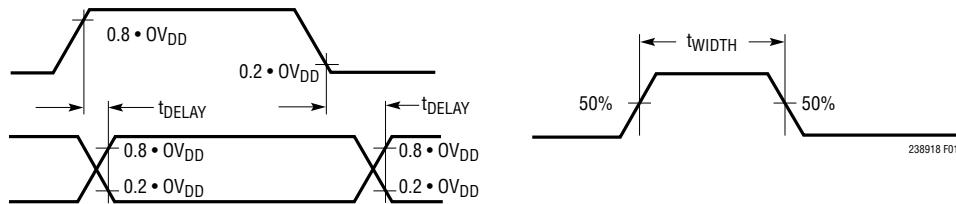

## デジタル入力とデジタル出力

●は全動作温度範囲での規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。(Note 4)

| SYMBOL       | PARAMETER                   | CONDITIONS                  | MIN | TYP             | MAX             | UNITS         |

|--------------|-----------------------------|-----------------------------|-----|-----------------|-----------------|---------------|

| $V_{IH}$     | High Level Input Voltage    |                             | ●   | 0.8 • $OV_{DD}$ |                 | V             |

| $V_{IL}$     | Low Level Input Voltage     |                             | ●   |                 | 0.2 • $OV_{DD}$ | V             |

| $I_{IN}$     | Digital Input Current       | $V_{IN} = 0V$ to $OV_{DD}$  | ●   | -10             | 10              | $\mu\text{A}$ |

| $C_{IN}$     | Digital Input Capacitance   |                             |     |                 | 5               | $\text{pF}$   |

| $V_{OH}$     | High Level Output Voltage   | $I_{OUT} = -500\mu\text{A}$ | ●   | $OV_{DD} - 0.2$ |                 | V             |

| $V_{OL}$     | Low Level Output Voltage    | $I_{OUT} = 500\mu\text{A}$  | ●   |                 | 0.2             | V             |

| $I_{OZ}$     | Hi-Z Output Leakage Current | $V_{OUT} = 0V$ to $OV_{DD}$ | ●   | -10             | 10              | $\mu\text{A}$ |

| $I_{SOURCE}$ | Output Source Current       | $V_{OUT} = 0V$              |     |                 | -10             | $\text{mA}$   |

| $I_{SINK}$   | Output Sink Current         | $V_{OUT} = OV_{DD}$         |     |                 | 10              | $\text{mA}$   |

## 電源要件

●は全動作温度範囲での規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。(Note 4)

| SYMBOL     | PARAMETER                                      | CONDITIONS                                                                                              | MIN | TYP  | MAX          | UNITS       |                              |

|------------|------------------------------------------------|---------------------------------------------------------------------------------------------------------|-----|------|--------------|-------------|------------------------------|

| $V_{DD}$   | Supply Voltage                                 |                                                                                                         | ●   | 4.75 | 5            | 5.25        | V                            |

| $OV_{DD}$  | Supply Voltage                                 |                                                                                                         | ●   | 1.71 |              | 5.25        | V                            |

| $I_{VDD}$  | Core Supply Current                            | 2.5Msps Sample Rate<br>2.5Msps Sample Rate, Internal Reference Enabled                                  | ●   |      | 32.5<br>34.1 | 36          | $\text{mA}$                  |

| $I_{OVDD}$ | I/O Supply Current                             | 2.5Msps Sample Rate ( $C_L = 15\text{pF}$ )                                                             |     |      | 1.6          |             | $\text{mA}$                  |

| $I_{PD}$   | Power Down Current<br>( $I_{VDD} + I_{OVDD}$ ) | Conversion Done, $P_D = OV_{DD}$ , Other Digital Inputs Tied to $OV_{DD}$ or GND                        | ●   |      | 15           | 250         | $\mu\text{A}$                |

| $P_D$      | Power Dissipation                              | 2.5Msps Sample Rate<br>Conversion Done, $P_D = OV_{DD}$ , Other Digital Inputs Tied to $OV_{DD}$ or GND |     |      | 162.5<br>75  | 180<br>1250 | $\text{mW}$<br>$\mu\text{W}$ |

## タイミング特性

●は全動作温度範囲での規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。(Note 4)

| SYMBOL        | PARAMETER                                   | CONDITIONS                                             | MIN    | TYP | MAX        | UNITS        |    |

|---------------|---------------------------------------------|--------------------------------------------------------|--------|-----|------------|--------------|----|

| $f_{SMPL}$    | Sampling Frequency                          | Parallel Output Modes<br>Serial Output Mode            | ●<br>● |     | 2.5<br>1.9 | Msps<br>Msps |    |

| $t_{CONV}$    | Conversion Time                             |                                                        | ●      | 245 | 280        | 310          | ns |

| $t_{ACQ}$     | Acquisition Time                            | $t_{ACQ} = t_{CYC} - t_{CONV} - t_{BUSY LH}$ (Note 10) | ●      | 77  | 110        |              | ns |

| $t_{CYC}$     | Time Between CNVST $\downarrow$             |                                                        | ●      | 400 |            |              | ns |

| $t_{CNVSTL}$  | CNVST Low Time                              |                                                        | ●      | 20  |            |              | ns |

| $t_{CNVSTH}$  | CNVST High Time                             |                                                        | ●      | 200 |            |              | ns |

| $t_{BUSY LH}$ | CNVST $\downarrow$ to BUSY Delay            | $C_L = 15\text{pF}$                                    | ●      |     | 13         |              | ns |

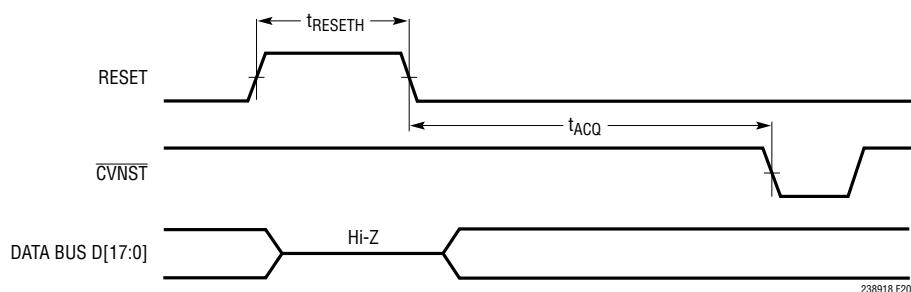

| $t_{RESETH}$  | RESET Pulse Width                           |                                                        | ●      | 200 |            |              | ns |

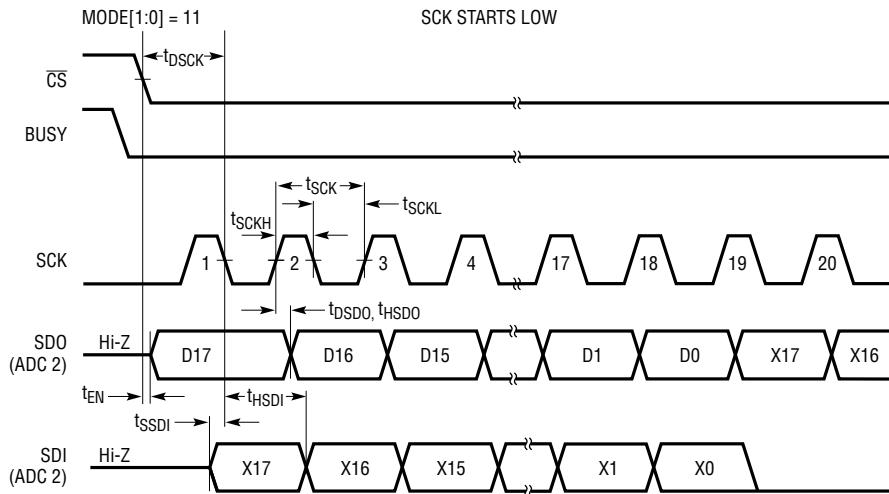

| $t_{SCK}$     | SCK Period                                  | (Note 5, 11)                                           | ●      | 10  |            |              | ns |

| $t_{SCKH}$    | SCK High Time                               |                                                        | ●      | 4   |            |              | ns |

| $t_{SCKL}$    | SCK Low Time                                |                                                        | ●      | 4   |            |              | ns |

| $t_{DSCK}$    | SCK $\downarrow$ Delay From CS $\downarrow$ |                                                        | ●      | 10  |            |              | ns |

| $t_{SSDI}$    | SDI Setup Time From SCK $\downarrow$        |                                                        | ●      | 2   |            |              | ns |

## タイミング特性 ●は全動作温度範囲での規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。(Note 4)

|               |                                                 |                     |   |   |    |    |

|---------------|-------------------------------------------------|---------------------|---|---|----|----|

| $t_{HSDI}$    | SDI Hold Time From $SCK\downarrow$              |                     | ● | 1 |    | ns |

| $t_{DSDO}$    | SDO Data Valid Delay From $SCK\uparrow$         | $C_L = 15\text{pF}$ | ● |   | 9  | ns |

| $t_{HSDO}$    | SDO Data Remains Valid Delay From $SCK\uparrow$ | $C_L = 15\text{pF}$ | ● | 1 |    | ns |

| $t_{DDBUSYL}$ | Data Valid to $BUSY\downarrow$                  | $C_L = 15\text{pF}$ | ● | 1 |    | ns |

| $t_{EN}$      | Bus Enable Time After $\bar{CS}\downarrow$      |                     | ● |   | 11 | ns |

| $t_{DDA1AO}$  | Data Valid Delay From A1 or A0 Transition       | $C_L = 15\text{pF}$ | ● |   | 8  | ns |

| $t_{DIS}$     | Bus Relinquish Time After $\bar{CS}\uparrow$    |                     | ● |   | 11 | ns |

**Note 1:** 絶対最大定格に記載された値を超えるストレスはデバイスに永続的損傷を与える可能性がある。また、長期にわたって絶対最大定格条件に曝すと、デバイスの信頼性と寿命に悪影響を与える恐れがある。

**Note 2:** すべての電圧値はグランドを基準にしている。

**Note 3:** これらのピンの電圧がグランドを下回るか、 $V_{DD}$ または $0V_{DD}$ を上回ると、内部のダイオードによってクランプされる。この製品は、GNDより低くなるか、 $V_{DD}$ または $0V_{DD}$ より高くなつた場合でも、ラッチアップを生じることなく最大100mAの入力電流を処理することができる。

**Note 4:** 注記がない限り、 $V_{DD} = 5\text{V}$ 、 $0V_{DD} = 5\text{V}$ 、 $V_{REF} = 4.096\text{V}$ 外部リファレンス、 $f_{SMPL} = 2.5\text{MHz}$ 。

**Note 5:** 推奨動作条件。

**Note 6:** 積分非直線性は、実際の伝達曲線のエンドポイントを通る直線からのコードの偏差として定義されている。偏差は量子化幅の中心から測定される。

**Note 7:** 完全差動ゼロスケール誤差は、出力コードが2の補数のフォーマットで00 0000 0000 0000 0000と11 1111 1111 1111 1111の間を行ったり来たりするとき、-0.5LSBから測定されたオフセット電圧である。ユニポーラ・ゼロスケール誤差は、出力コードが00 0000 0000 0000

0000と00 0000 0000 0000 0001の間を行ったり来たりするとき、0.5LSBから測定されたオフセット電圧である。バイポーラ・ゼロスケール誤差は、出力コードが00 0000 0000 0000と11 1111 1111 1111 1111の間を行ったり来たりするとき、-0.5LSBから測定されたオフセット電圧である。完全差動フルスケール誤差は、最初と最後のコード遷移の理想値からのワーストケースの偏差であり、オフセット誤差の影響を含む。ユニポーラ・フルスケール誤差は、最後のコード遷移の理想値からの偏差であり、オフセット誤差の影響を含む。バイポーラ・フルスケール誤差は、最初と最後のコード遷移の理想値からのワーストケースの偏差であり、オフセット誤差の影響を含む。

**Note 8:** dB表示のすべての規格値は、4.096Vのリファレンス電圧でフルスケール  $\pm 4.096\text{V}$  (完全差動)、0V～4.096V(疑似差動ユニポーラ)、または $\pm 2.048\text{V}$ (疑似差動バイポーラ)の入力を基準にしている。

**Note 9:** 温度係数は出力電圧の最大変化を規定温度範囲で割って計算される。

**Note 10:** 設計によって保証されているが、テストされない。

**Note 11:** 立ち上がりで捕捉する場合、最小10nsの $t_{SCK}$ により、最大100MHzのシフト・クロック周波数が可能である。

図1. タイミングの仕様の電圧レベル

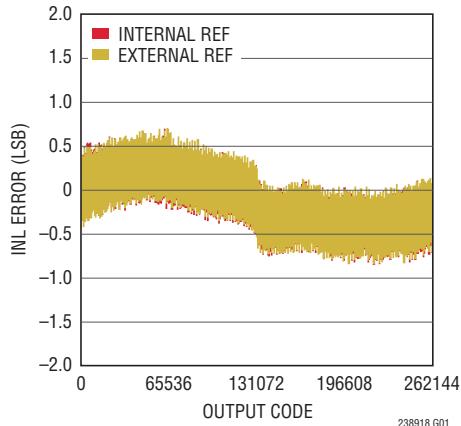

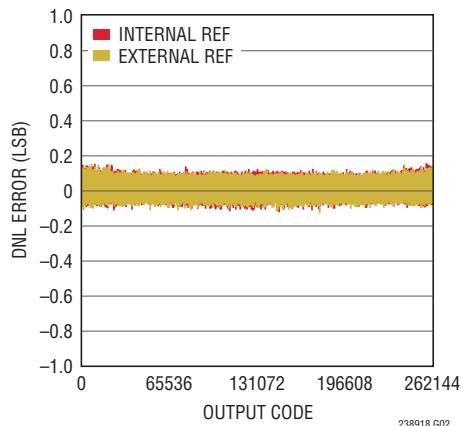

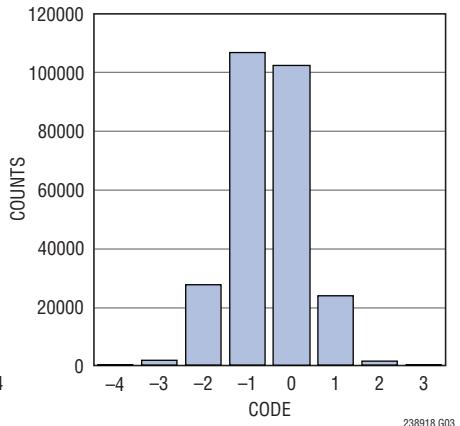

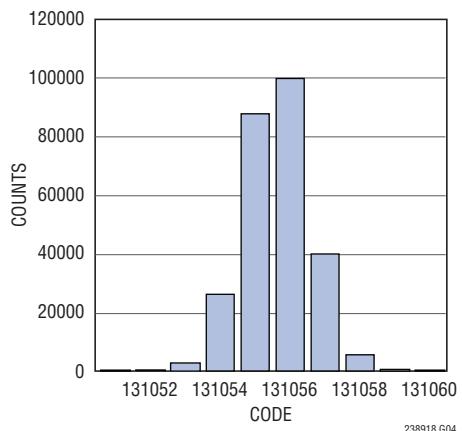

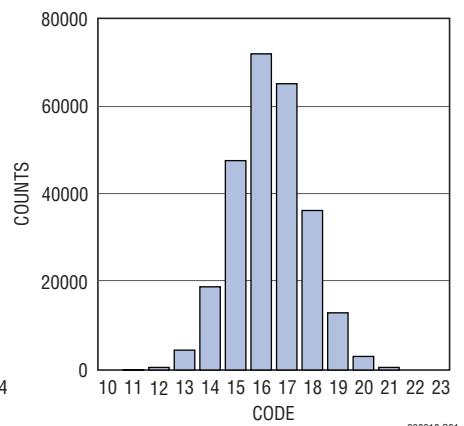

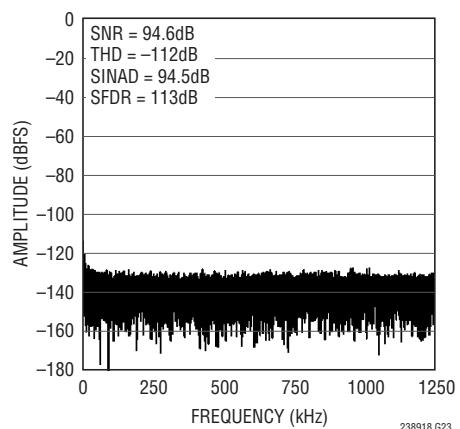

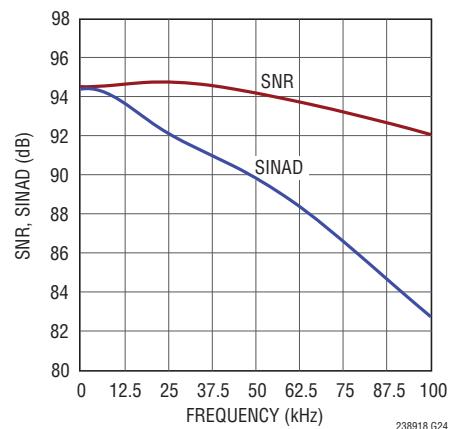

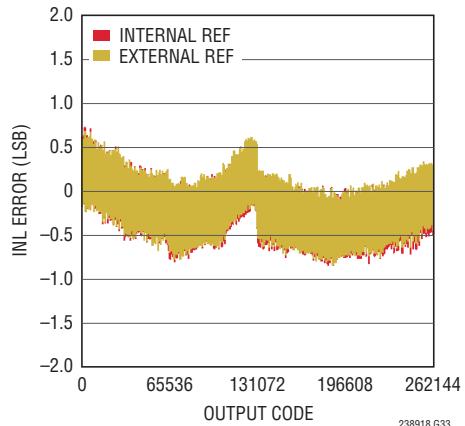

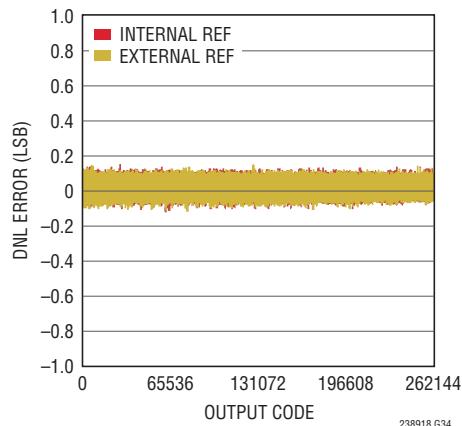

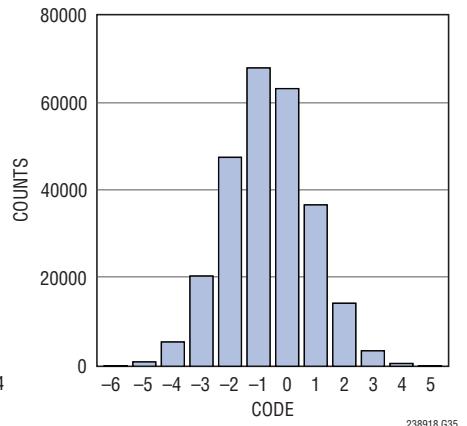

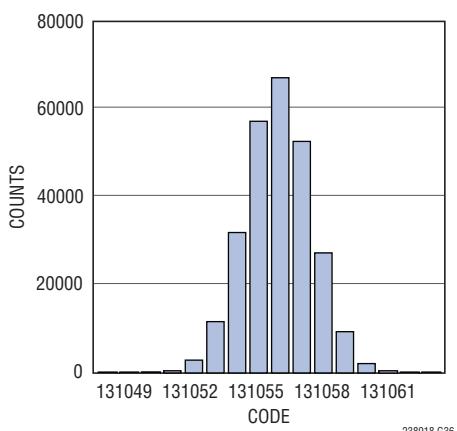

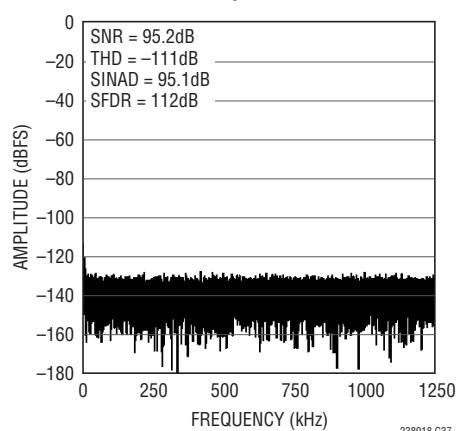

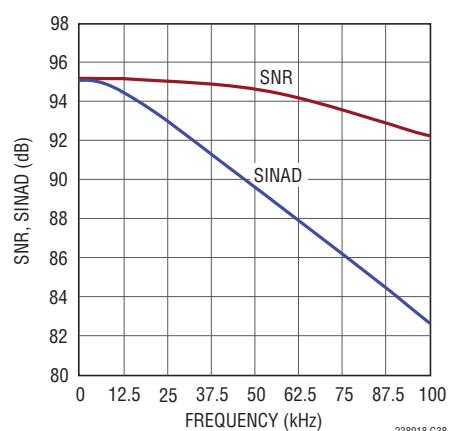

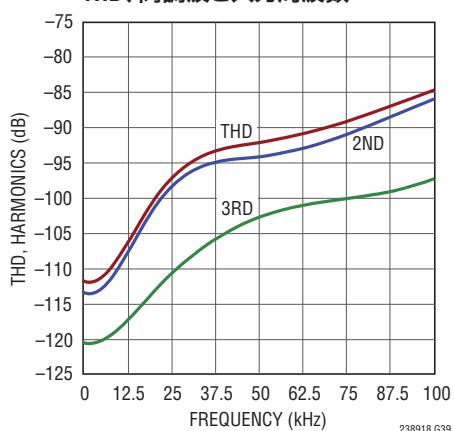

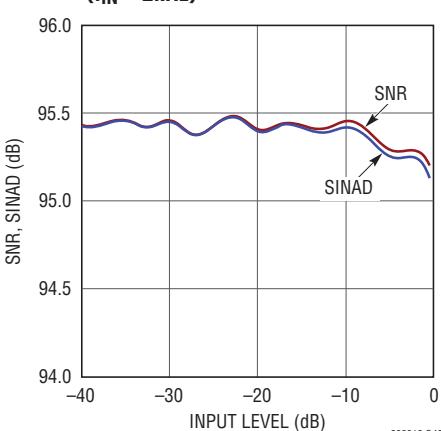

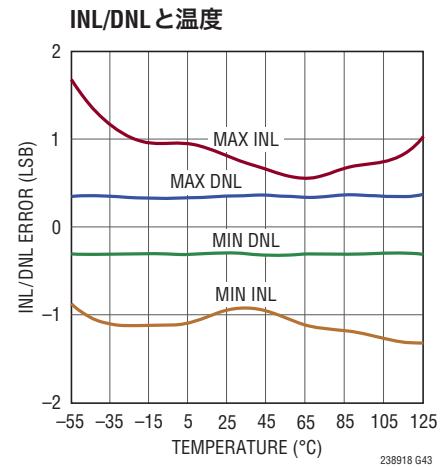

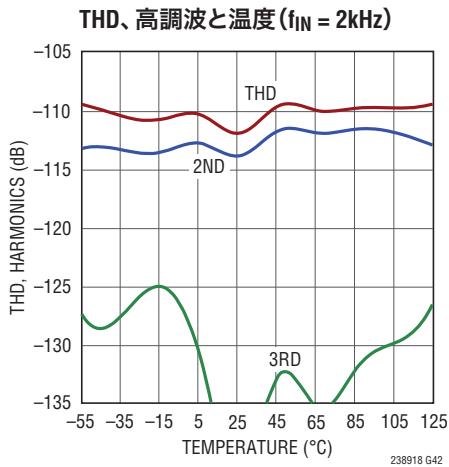

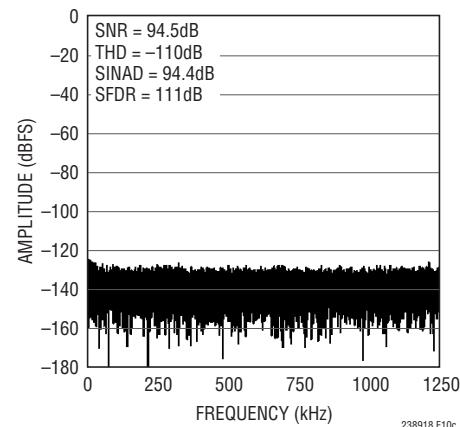

**標準的性能特性** 注記がない限り、 $T_A = 25^\circ\text{C}$ 、 $V_{DD} = 5\text{V}$ 、 $OV_{DD} = 2.5\text{V}$ 、 $V_{REF} = 4.096\text{V}$  外部リファレンス、完全差動範囲( $PD/\bar{FD} = 0\text{V}$ )、 $V_{CM} = 2.048\text{V}$ 、 $f_{SMPL} = 2.5\text{Msps}$ 。

積分非直線性と出力コード

微分非直線性と出力コード

DCヒストグラム(ゼロスケール)

DCヒストグラム(フルスケール付近)

内部リファレンス出力と温度

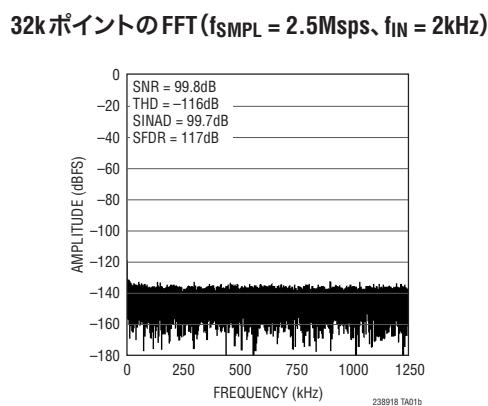

32kポイントのFFT

( $f_{SMPL} = 2.5\text{Msps}$ 、 $f_{IN} = 2\text{kHz}$ )

SNR、SINADと入力周波数

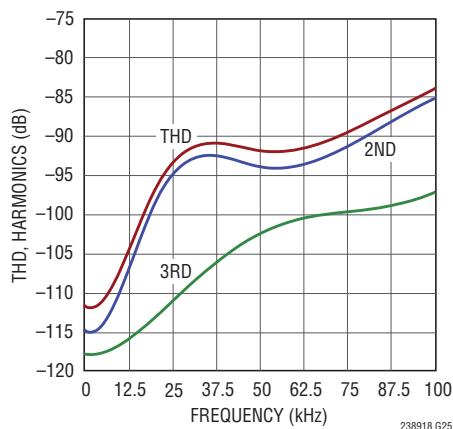

THD、高調波と入力周波数

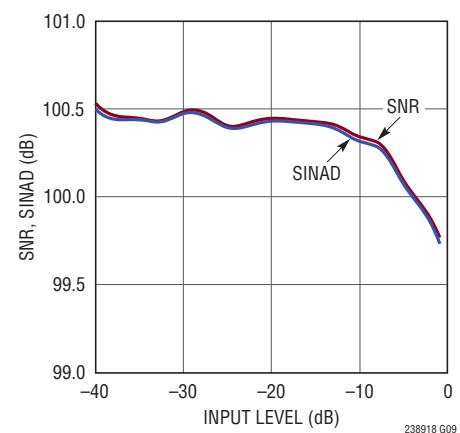

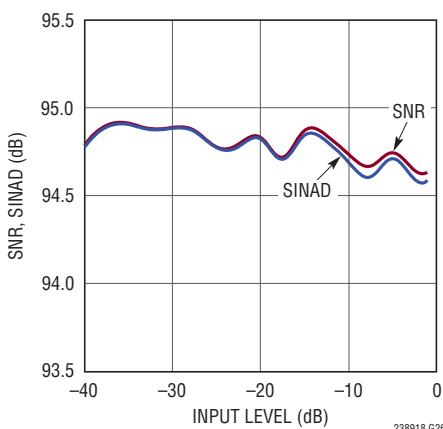

SNR、SINADと入力レベル

( $f_{IN} = 2\text{kHz}$ )

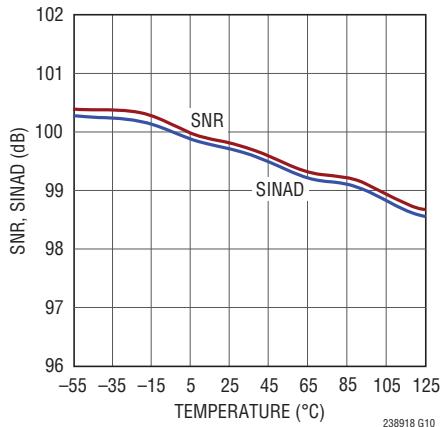

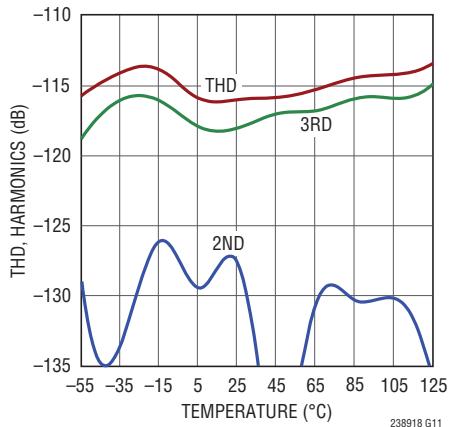

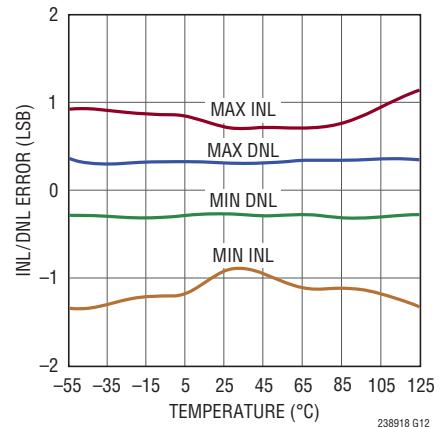

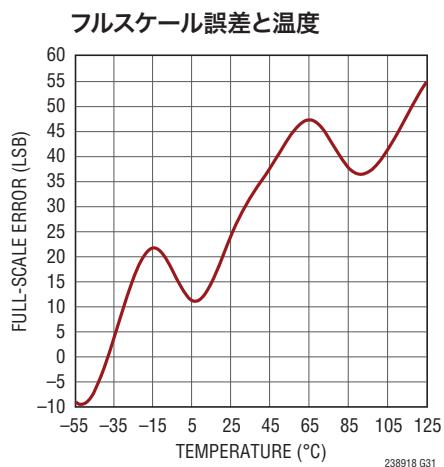

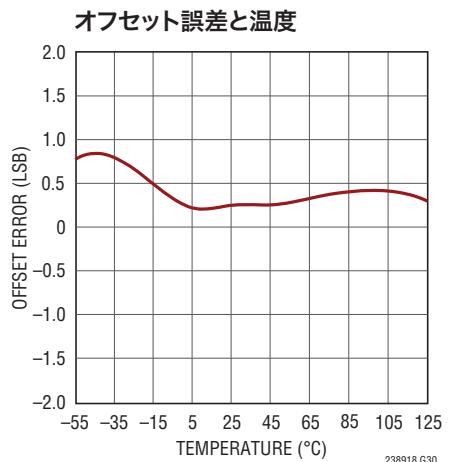

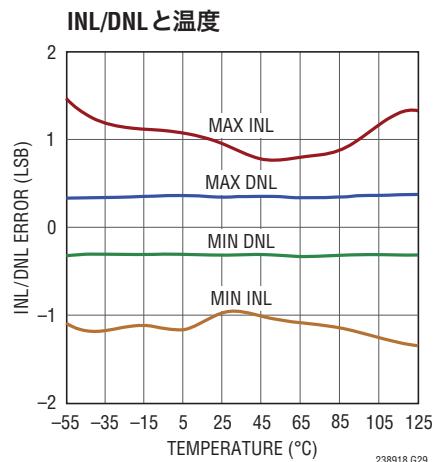

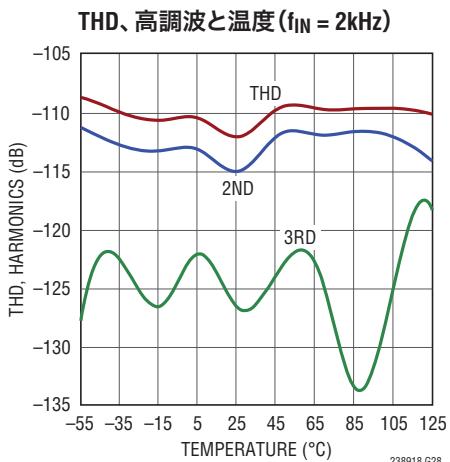

標準的性能特性 注記がない限り、 $T_A = 25^\circ\text{C}$ 、 $V_{DD} = 5\text{V}$ 、 $OV_{DD} = 2.5\text{V}$ 、 $V_{REF} = 4.096\text{V}$  外部リファレンス、完全差動範囲( $PD/FD = 0\text{V}$ )、 $V_{CM} = 2.048\text{V}$ 、 $f_{SMPL} = 2.5\text{Msps}$ 。

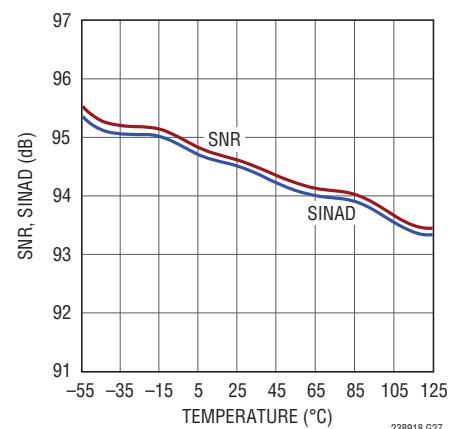

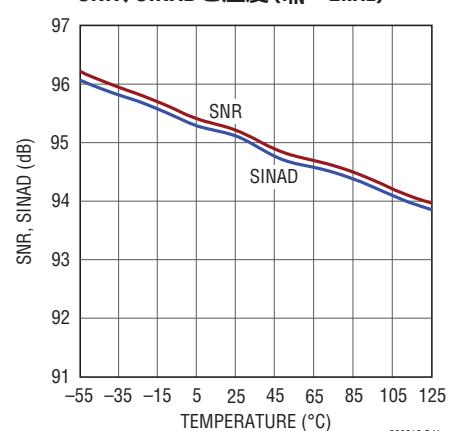

SNR、SINADと温度( $f_{IN} = 2\text{kHz}$ )

THD、高調波と温度( $f_{IN} = 2\text{kHz}$ )

INL/DNLと温度

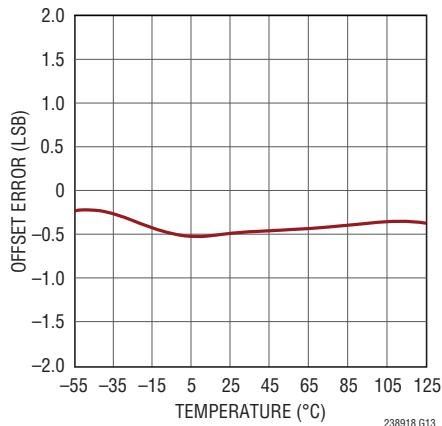

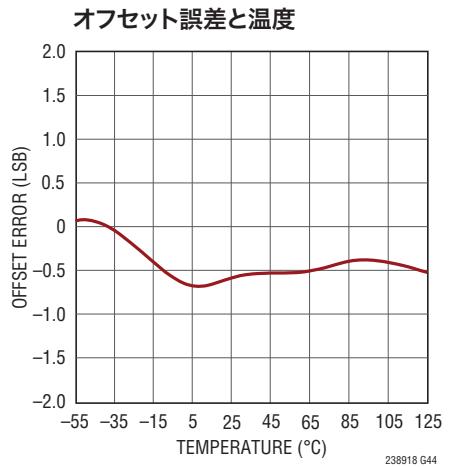

オフセット誤差と温度

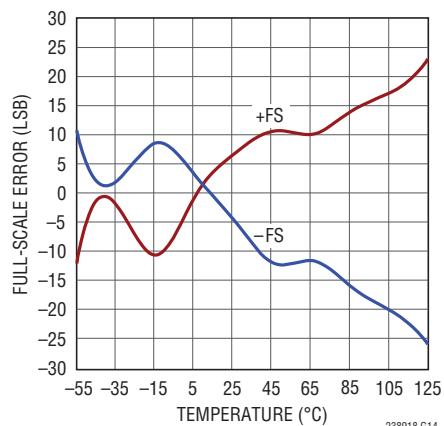

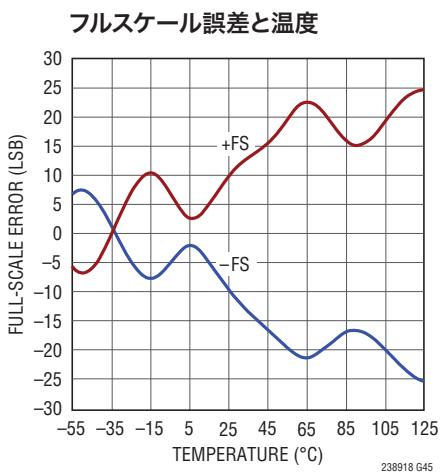

フルスケール誤差と温度

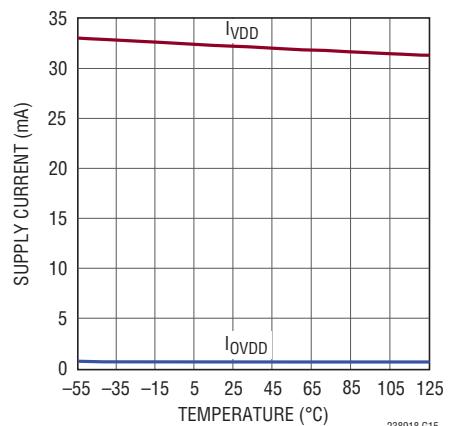

電源電流と温度

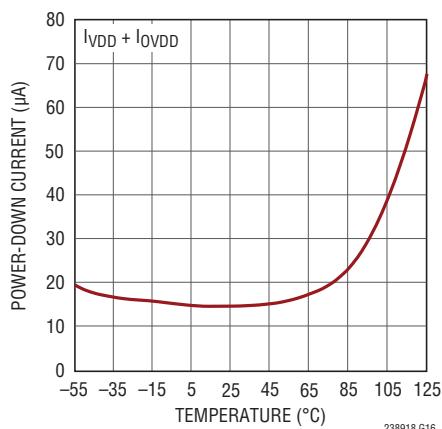

パワーダウン電流と温度

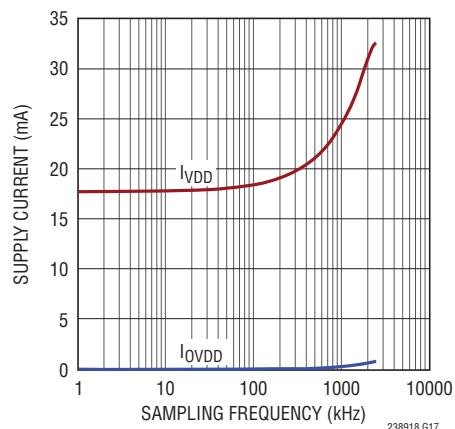

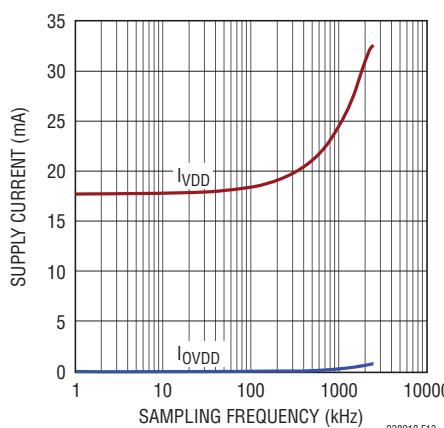

電源電流とサンプリング周波数

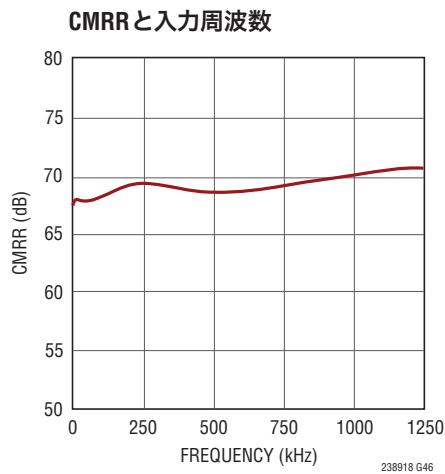

CMRRと入力周波数

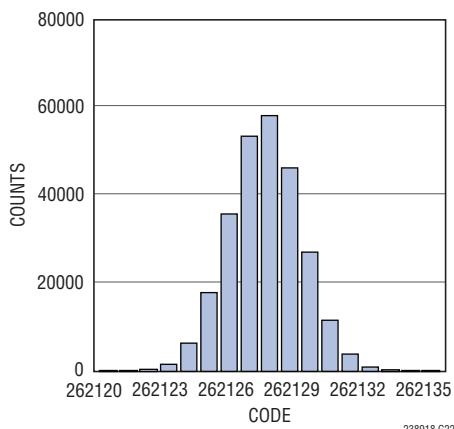

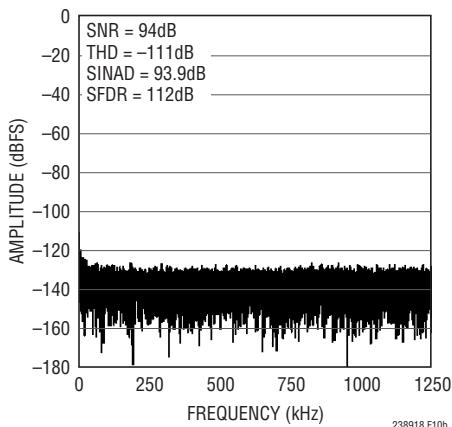

標準的性能特性 注記がない限り、 $T_A = 25^\circ\text{C}$ 、 $V_{DD} = 5\text{V}$ 、 $OV_{DD} = 2.5\text{V}$ 、 $V_{REF} = 4.096\text{V}$  外部リファレンス、疑似差動ユニポーラ範囲 ( $\text{PD}/\text{FD} = OV_{DD}$ 、 $\text{OB}/\overline{\text{OC}} = OV_{DD}$ )、 $f_{\text{SMPL}} = 2.5\text{Msps}$ 。

積分非直線性と出力コード

微分非直線性と出力コード

DCヒストグラム(ゼロスケール付近)

DCヒストグラム(フルスケール付近)

32k ポイントの FFT

( $f_{\text{SMPL}} = 2.5\text{Msps}$ ,  $f_{\text{IN}} = 2\text{kHz}$ )

SNR、SINADと入力周波数

THD、高調波と入力周波数

SNR、SINADと入力レベル

SNR、SINADと温度 ( $f_{\text{IN}} = 2\text{kHz}$ )

**標準的性能特性** 注記がない限り、 $T_A = 25^\circ\text{C}$ 、 $V_{DD} = 5\text{V}$ 、 $OV_{DD} = 2.5\text{V}$ 、 $V_{REF} = 4.096\text{V}$  外部リファレンス、疑似差動ユニポーラ範囲 ( $PD/FD = OV_{DD}$ 、 $OB/2C = OV_{DD}$ )、 $f_{SMPL} = 2.5\text{Msps}$ 。

**標準的性能特性** 注記がない限り、 $T_A = 25^\circ\text{C}$ 、 $V_{DD} = 5\text{V}$ 、 $OV_{DD} = 2.5\text{V}$ 、 $V_{REF} = 4.096\text{V}$  外部リファレンス、疑似差動バイポーラ範囲 ( $PD/FD = OV_{DD}$ 、 $OB/2C = 0\text{V}$ )、 $f_{SMPL} = 2.5\text{Msps}$ 。

積分非直線性と出力コード

微分非直線性と出力コード

DCヒストグラム(ゼロスケール)

DCヒストグラム(フルスケール付近)

32k ポイントの FFT

( $f_{SMPL} = 2.5\text{Msps}$ ,  $f_{IN} = 2\text{kHz}$ )

SNR、SINADと入力周波数

THD、高調波と入力周波数

SNR、SINADと入力レベル

SNR、SINADと温度 ( $f_{IN} = 2\text{kHz}$ )

**標準的性能特性** 注記がない限り、 $T_A = 25^\circ\text{C}$ 、 $V_{DD} = 5\text{V}$ 、 $OV_{DD} = 2.5\text{V}$ 、 $V_{REF} = 4.096\text{V}$  外部リファレンス、疑似差動バイポーラ範囲 ( $PD/FD = OV_{DD}$ 、 $OB/2C = 0\text{V}$ )、 $f_{SMPL} = 2.5\text{Msps}$ 。

## ピン機能

**GND(ピン1、17、20、35、41、44、48、露出パッド・ピン49(QFNのみ))**：グランド。GNDピンと露出パッドはすべてグランド・ブレーンに半田付けします。

**V<sub>DD</sub>(ピン2、3、19、40、45、46、47)**：5V電源。V<sub>DD</sub>の範囲は4.75V～5.25Vです。V<sub>DD</sub>ネットワークは、0.1μFのセラミック・コンデンサを各ピンの近くに置き、10μFのセラミック・コンデンサを並列に接続してGNDにバイパスします。

**MODE0、MODE1(ピン4、ピン5)**：データバス構成入力。これらのピンは、出力データ・バスの変換結果の解析と表示を制御します。MODE = MODE[1:0]の状態に基づき、バスは表1に示すように、18ビット・パラレル(MODE = 00)、16ビット・パラレル(MODE = 01)、8ビット・パラレル(MODE = 10)、またはシリアル(MODE = 11)のいずれかのデータを提供するように構成されます。特定のモードでアクティブになっていないデジタル出力は高インピーダンスになります。ロジック・レベルはOV<sub>DD</sub>によって決まります。LTC238xファミリの16ビット・バージョンとのピン互換性については、「LTC238x-16とのピン互換性」のセクションを参照してください。

**OB/2C(ピン6)**：オフセット・バイナリ／2の補数入力。このピンはピン30(PD/FD)とともに、表2に示すようにコンバータのアナログ入力範囲と変換結果のバイナリ形式を制御します。ロジック・レベルはOV<sub>DD</sub>によって決まります。

**D0/A0(ピン7)**：データ・ビット0／アドレス・ビット0。MODE = 00の時、このピンはパラレル・データ出力バスのビット0になります。MODE = 01または10の時はパラレル・アドレス入力バスのビット0で、バイナリ・アドレスA[1:0]は、表1に示すように、変換結果のどのセグメントが出力データバスの上位ビットにドライブされるかを決定します。ロジック・レベルはOV<sub>DD</sub>によって決まります。LTC238xファミリの16ビット・バージョンとのピン互換性については、「LTC238x-16とのピン互換性」のセクションを参照してください。

**D1/A1(ピン8)**：データ・ビット1／アドレス・ビット1。MODE = 00の時、このピンはパラレル・データ出力バスのビット1になります。MODE = 01または10の時はパラレル・アドレス入力バスのビット1で、バイナリ・アドレスA[1:0]は、表1に示すように、変換結果のどのセグメントが出力データバスの上位ビットにドライブされるかを決定します。ロジック・レベルはOV<sub>DD</sub>によって決まります。LTC238xファミリの16ビット・バージョンとのピン互換性については、「LTC238x-16とのピン互換性」のセクションを参照してください。

**D2(ピン9)**：データ・ビット2。表1に示すように、MODE = 00または01の時、このピンはパラレル・データ出力バスのビット2です。ロジック・レベルはOV<sub>DD</sub>によって決まります。

**D3(ピン10)**：データ・ビット3。表1に示すように、MODE = 00または01の時、このピンはパラレル・データ出力バスのビット3です。ロジック・レベルはOV<sub>DD</sub>によって決まります。

**D4(ピン11)**：データ・ビット4。表1に示すように、MODE = 00または01の時、このピンはパラレル・データ出力バスのビット4です。ロジック・レベルはOV<sub>DD</sub>によって決まります。

**D5(ピン12)**：データ・ビット5。表1に示すように、MODE = 00または01の時、このピンはパラレル・データ出力バスのビット5です。ロジック・レベルはOV<sub>DD</sub>によって決まります。

**D6(ピン13)**：データ・ビット6。表1に示すように、MODE = 00または01の時、このピンはパラレル・データ出力バスのビット6です。ロジック・レベルはOV<sub>DD</sub>によって決まります。

**D7(ピン14)**：データ・ビット7。表1に示すように、MODE = 00または01の時、このピンはパラレル・データ出力バスのビット7です。ロジック・レベルはOV<sub>DD</sub>によって決まります。

**D8(ピン15)**：データ・ビット8。表1に示すように、MODE = 00または01の時、このピンはパラレル・データ出力バスのビット8です。ロジック・レベルはOV<sub>DD</sub>によって決まります。

**D9(ピン16)**：データ・ビット9。表1に示すように、MODE = 00または01の時、このピンはパラレル・データ出力バスのビット9です。ロジック・レベルはOV<sub>DD</sub>によって決まります。

**OV<sub>DD</sub>(ピン18)**：I/Oインターフェースの電源。OV<sub>DD</sub>の範囲は1.71V～5.25Vです。OV<sub>DD</sub>は、0.1μFと10μFのセラミック・コンデンサを並列に接続して、ピンの近くでGNDにバイパスしてください。

**D10(ピン21)**：データ・ビット10。表1に示すように、MODE = 00、01、または10の時、このピンはパラレル・データ出力バスのビット10です。ロジック・レベルはOV<sub>DD</sub>によって決まります。

**D11/SDI(ピン22)**：データ・ビット11／シリアル・データ入力。表1に示すように、MODE = 00、01、または10の時、このピンはパラレル・データ出力バスのビット11です。MODE = 11の時、このピンはシリアル・データ入力で、2個以上のコンバータを1本のSDOラインでデジ털・データ・レベルはSDOの出力で、読み込みシーケンス開始後に18 SCKの遅延が生じます。ロジック・レベルはOV<sub>DD</sub>によって決まります。

## ピン機能

**D12/SD0(ピン23)**：データ・ビット12／シリアル・データ出力。表1に示すように、MODE = 00、01、または10の時、このピンはパラレル・データ出力バスのビット12です。MODE = 11の時このピンはシリアル・データ出力ラインとなり、SCKによりクロックされた最新の変換結果をシリアルに出力します。データは、SCKの立ち上がりエッジでMSBを先頭にして出力されます。データ形式は、表2に示すようにピンPD/FDおよびOB/2Cのロジック・レベルによって決まります。ロジック・レベルはOV<sub>DD</sub>によって決まります。

**D13/SCK(ピン24)**：データ・ビット13／シリアル・クロック入力。表1に示すように、MODE = 00、01、または10の時、このピンはパラレル・データ出力バスのビット13です。MODE = 11の時、このピンはシリアル・クロック入力になります。ロジック・レベルはOV<sub>DD</sub>によって決まります。

**D14(ピン25)**：データ・ビット14。表1に示すように、MODE = 00、01、または10の時、このピンはパラレル・データ出力バスのビット14です。ロジック・レベルはOV<sub>DD</sub>によって決まります。

**D15(ピン26)**：データ・ビット15。表1に示すように、MODE = 00、01、または10の時、このピンはパラレル・データ出力バスのビット15です。ロジック・レベルはOV<sub>DD</sub>によって決まります。

**D16(ピン27)**：データ・ビット16。表1に示すように、MODE = 00、01、または10の時、このピンはパラレル・データ出力バスのビット16です。ロジック・レベルはOV<sub>DD</sub>によって決まります。

**D17(ピン28)**：データ・ビット17。表1に示すように、MODE = 00、01、または10の時、このピンはパラレル・データ出力バスのビット17です。ロジック・レベルはOV<sub>DD</sub>によって決まります。

**BUSY(ピン29)**：ビジー出力。このピンは各変換の開始時に“L”から“H”に遷移して、変換が完了するまで“H”的まになります。BUSYの立ち下がりエッジは、データレディ・クロック信号として使用できます。ロジック・レベルはOV<sub>DD</sub>によって決まります。

**PD/FD(ピン30)**：疑似差動／完全差動入力。このピンはピン6(OB/2C)とともに、表2に示すようにコンバータのアナログ入力範囲と変換結果のバイナリ形式を制御します。ロジック・レベルはOV<sub>DD</sub>によって決まります。

**CS(ピン31)**：チップ・セレクト入力。データI/Oバスは、CSが“L”的時にイネーブルされ、“H”的時は高インピーダンスになります。CSは外部シフト・クロックをゲートするために使用することができます。ロジック・レベルはOV<sub>DD</sub>によって決まります。

**RESET(ピン32)**：リセット入力。このピンを“H”にすると、LTC2389-18はリセットされます。変換中にリセットが行われると変換は中断され、データバスは高インピーダンスになります。ロジック・レベルはOV<sub>DD</sub>によって決まります。

表1. データバス構成表。アプリケーションのバス幅に基づき、MODE1入力とMODE0入力を使用してバス構成を選択。16ビットおよび8ビットのパラレル構成では、D1/A1入力とD0/A0入力が、変換結果R[17:0]のデータバス・ピンD[17:2]へのマッピングを制御。網掛けされたセルは、入力として構成された双方向ピンを表わす。

| バス構成       | MODE1 | MODE0 | D[17:16]    | D[15:14] | D13 | D12    | D11         | D10         | D[9:4] | D[3:2] | D1/A1 | D0/A0       |  |  |

|------------|-------|-------|-------------|----------|-----|--------|-------------|-------------|--------|--------|-------|-------------|--|--|

| 18ビット・パラレル | 0     | 0     | R[17:0]     |          |     |        |             |             |        |        |       |             |  |  |

| 16ビット・パラレル | 0     | 1     | R[17:2]     |          |     |        | すべてゼロ       |             |        | X      | 0     |             |  |  |

|            |       |       | R[1:0]      |          |     | すべてゼロ  |             |             | R[1:0] | 0      | 1     |             |  |  |

|            |       |       | R[1:0]      | すべてゼロ    |     |        | すべてゼロ       |             |        | 1      | 1     |             |  |  |

| 8ビット・パラレル  | 1     | 0     | R[17:10]    |          |     |        | すべて高インピーダンス |             |        | 0      | 0     |             |  |  |

|            |       |       | すべてゼロ       |          |     | R[1:0] |             | すべて高インピーダンス |        | 0      | 1     |             |  |  |

|            |       |       | R[9:2]      |          |     |        | すべて高インピーダンス |             |        | 1      | 0     |             |  |  |

|            |       |       | R[1:0]      | すべてゼロ    |     |        | すべて高インピーダンス |             |        | 1      | 1     |             |  |  |

| シリアル       | 1     | 1     | すべて高インピーダンス |          | SCK | SD0    | SDI         | すべて高インピーダンス |        |        |       | すべて高インピーダンス |  |  |

## ピン機能

**PD (ピン33)**：パワーダウン入力。このピンが“H”になると LTC2389-18 はパワーダウンされ、その後の変換要求は無視されます。パワーダウンをイネーブルにする時は、事前に最後の変換の結果を読み出す必要があります。ロジック・レベルは OVDD によって決まります。

**CNVST (ピン34)**：変換開始入力。このピンの立ち下がりエッジは、内部サンプル・ホールドをホールド・モードにして変換を開始します。CNVST は CS には依存しません。ロジック・レベルは VDD によって決まります。

**VCM (ピン36)**：同相アナログ出力。このピンの出力電圧は、通常 2.08V です。10 $\mu$ F のコンデンサを使ってグランドにバイパスします。

**REFOUT (ピン37)**：内部リファレンス出力。内部リファレンスを使用する場合は、このピンを REFIN に接続すれば 4.096V の公称リファレンス電圧が得られます。外部リファレンスを使用する場合は、REFOUT をグランドに接続して内部リファレンスをパワーダウンしてください。

**REFIN (ピン38)**：リファレンス入力。内部リファレンスを使用する場合は、このピンを REFOUT に接続すれば 4.096V の公称リファレンス電圧が得られます。より正確なリファレンスが必要な場合は、外部リファレンスを REFIN に与えることができます。外部リファレンスを使用する場合は、REFOUT をグランドに接続して内部リファレンスをパワーダウンしてください。リファレンス・ノイズのフィルタリングを強化するには、1 $\mu$ F 以上のセラミック・コンデンサを使って、このピンを REFSENSE にバイパスします。

**REFSENSE (ピン39)**：リファレンス入力検出。内部リファレンスを使用する時は、REFSENSE をグランドに接続しないでください。外部リファレンスを使用する場合は、REFSENSE を外部リファレンスのグランド・ピンに接続してください。

**IN-、IN+ (ピン42、ピン43)**：正と負のアナログ入力。アナログ入力範囲は、表2に示すようにピン30 (PD/FD) とピン6 (OB/2C) に印加される電圧レベルに依存します。

表2. アナログ入力範囲および出力バイナリ形式の構成表。PD/FD と OB/2C の入力を使用して、コンバータのアナログ入力範囲と変換結果のバイナリ形式を選択。

| PD/FD | OB/2C | アナログ入力範囲  | 変換結果のバイナリ形式 |

|-------|-------|-----------|-------------|

| 0     | 0     | 完全差動      | 2の補数        |

| 0     | 1     | 完全差動      | オフセット・バイナリ  |

| 1     | 0     | 疑似差動バイポーラ | 2の補数        |

| 1     | 1     | 擬似差動ユニポーラ | ストレート・バイナリ  |

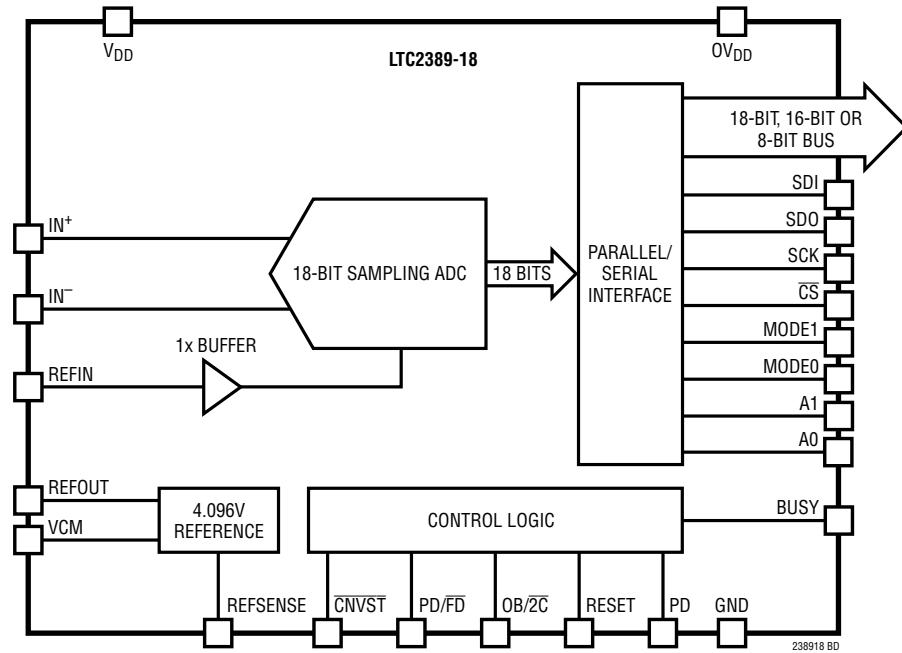

## 機能ブロック図

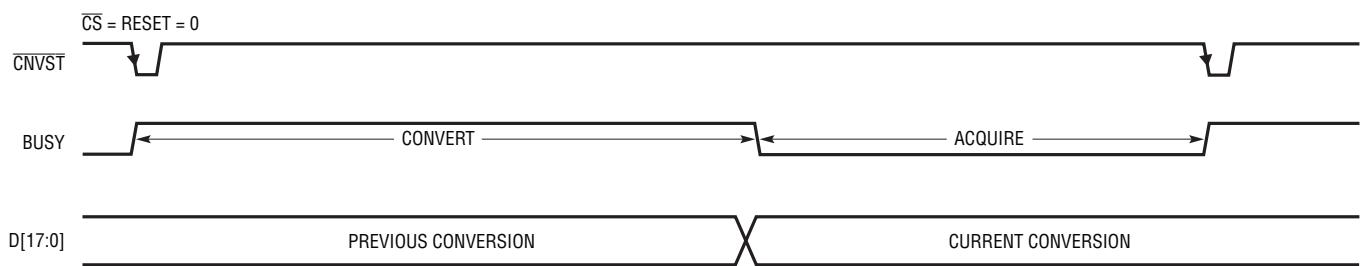

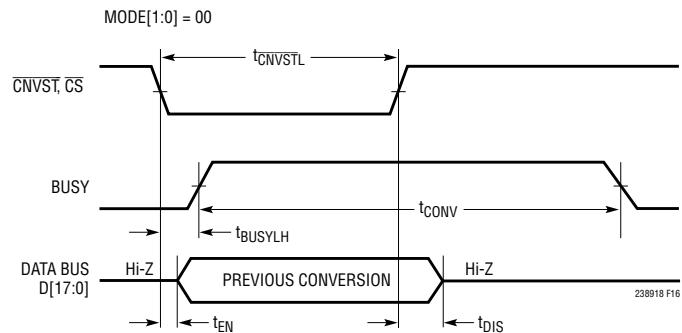

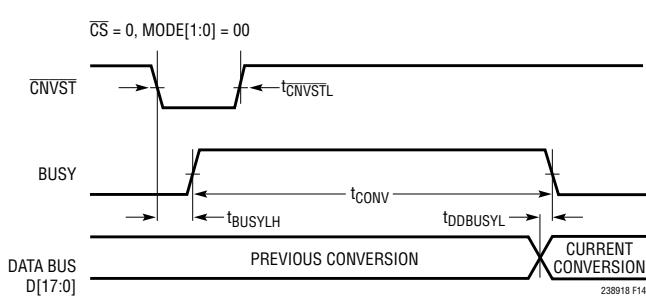

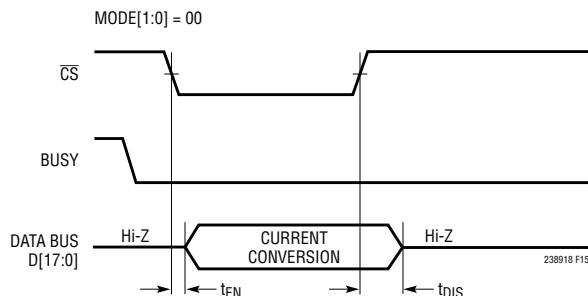

## タイミング図

## パラレル・インターフェースを使った変換のタイミング

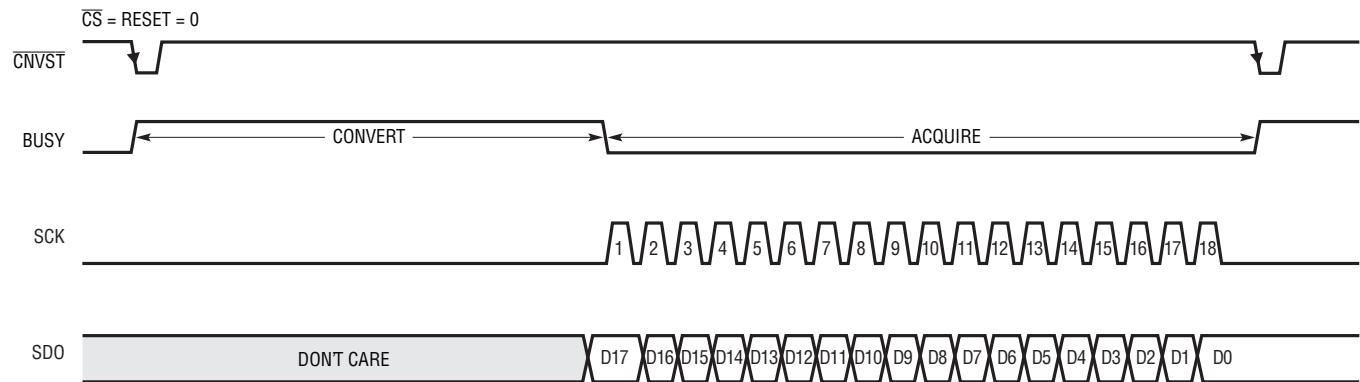

## シリアル・インターフェースを使った変換のタイミング

238918 TD01

238918f

## アプリケーション情報

### 概要

LTC2389-18は、低ノイズの高速18ビット逐次比較レジスタ(SAR)ADCです。LTC2389-18は、5V単電源で動作し、ピンで設定可能な完全差動( $\pm 4.096\text{V}$ )、疑似差動ユニポーラ(0V～ $4.096\text{V}$ )、および疑似差動バイポーラ( $\pm 2.048\text{V}$ )のアナログ入力電圧範囲をサポートするので、追加のレベル変換または信号処理を行う必要がなく、複数の信号チェーン形式とのインターフェースを行うことができます。LTC2389-18は $\pm 3\text{LSB}$ のINL(最大)、18ビット分解能で欠落コードなし、および99.8dB(完全差動)/95.2dB(疑似差動)のSNR(標準)を実現します。

LTC2389-18は、0.5%の初期精度が保証され、 $\pm 20\text{ppm}/^\circ\text{C}$ (最大)の温度係数を持つ $4.096\text{V}$ 高精度リファレンスを内蔵しているだけでなく、リファレンス・バッファも内蔵しています。パラレル・インターフェース・モードではスループットが2.5Mspsと高速でサイクル待ち時間がないので、LTC2389-18は、さまざまな高速アプリケーションに最適です。内部発振器が変換時間を設定するので、外部タイミングの問題が緩和されます。LTC2389-18の2.5Msps時の消費電力はわずか162.5mWですが、ナップ・モードおよびスリープ・モードという電力節減モードが用意されているので、動作停止期間中の消費電力はさらに低減されます。

### コンバータの動作

LTC2389-18は2段階で動作します。収集段階では、差動アナログ入力電圧をサンプリングするために、IN<sup>+</sup>ピンとIN<sup>-</sup>ピンに電荷再配分コンデンサD/Aコンバータ(CDAC)が接続されます。CNVSTピンの立ち下がりエッジにより変換が開始されます。変換段階では、18ビットCDACに対して逐次比較アルゴリズムが順番に実行され、差動コンパレータを使用してサンプリングした入力をリファレンス電圧の2進重み付け分数(例:  $\text{V}_{\text{REF}}/2$ 、 $\text{V}_{\text{REF}}/4$  ...  $\text{V}_{\text{REF}}/262144$ )と効率的に比較します。変換の最後には、CDACの出力はサンプリングされたアナログ入力に近づきます。その後、ADC制御ロジックが、パラレルまたはシリアル転送に備えて18ビット・デジタル出力コードを準備します。

### 伝達関数

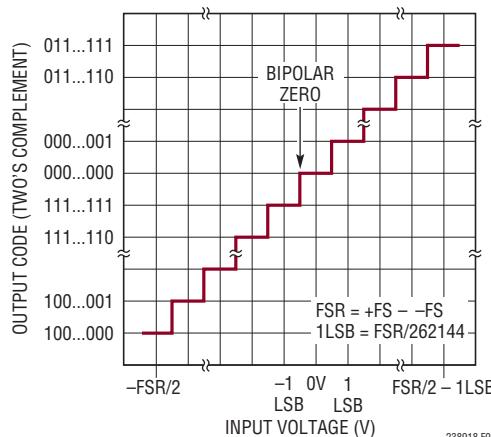

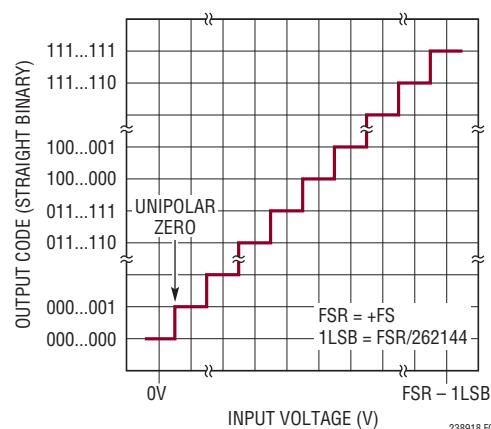

LTC2389-18は、 $2\cdot\text{V}_{\text{REF}}$ のフルスケール電圧を完全差動モードで、また、 $\text{V}_{\text{REF}}$ のフルスケール電圧を疑似差動モードで、それぞれ $2^{18}$ レベルまでデジタル化します。 $\text{V}_{\text{REF}} = 4.096\text{V}$ の場合、完全差動モードと疑似差動モードで得られるLSBサイズは、それぞれ $31.25\mu\text{V}$ と $15.625\mu\text{V}$ になります。変換結果のバイナリ形式は、表2に示すように、PD/FDピンとOB/2Cピンのロジック・レベルによって決まります。理想的な2の補数の伝達関数を図2に、理想的なストレート・バイナリ伝達関数を図3に示します。理想的なオフセット・バイナリ伝達関数は、各出力コードの最上位ビット(MSB)を反転させることによって、2の補数の伝達関数から得ることができます。

図2. LTC2389-18の2の補数の伝達関数。オフセット・バイナリ伝達関数は、各出力コードの最上位ビット(MSB)を反転させることによって得ることができます。

図3. LTC2389-18のストレート・バイナリ伝達関数

## アプリケーション情報

### アナログ入力

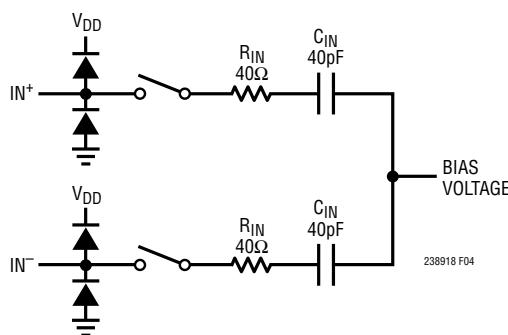

LTC2389-18のアナログ入力範囲はピンによる設定が可能で、完全差動( $\pm 4.096V$ )、疑似差動ユニポーラ( $0V \sim 4.096V$ )、疑似差動バイポーラ( $\pm 2.048V$ )の3つのうち1つを選ぶことができます。これら3つのすべての範囲において、ADCは2本のアナログ入力ピンの電圧差( $IN^+ - IN^-$ )をサンプリングしてデジタル化します。また、ADCの同相除去比(CMRR)によって、両方の入力に共通な不要信号が減少します。選択した範囲に関わらず、アナログ入力は図4に示す等価回路によってモデル化できます。入力のダイオードはESD保護機能を提供します。収集段階では、サンプリングCDACに起因する約40pF( $C_{IN}$ )と、サンプリング・スイッチのオン抵抗に起因する $40\Omega$ ( $R_{IN}$ )が各入力に直列に接続されています。収集の間に $C_{IN}$ コンデンサを充電するとき、入力には小さい電流スパイクが流れます。変換時にアナログ入力に流れるのはわずかな漏れ電流だけです。

図4. LTC2389-18の差動アナログ入力の等価回路

### 完全差動入力範囲

完全差動入力範囲は最も広い入力信号振幅を提供し、( $\pm V_{REF}$ )の幅で差動アナログ入力電圧( $IN^+ - IN^-$ )をデジタル化するようにADCを構成します。この範囲においては、同相モード電圧( $IN^+ + IN^-$ )/2付近を中心として、 $IN^+$ ピンと $IN^-$ ピンを互いに $180^\circ$ の位相差でドライブする必要があります。同相モード電圧は、( $V_{REF}/2 \pm 0.1V$ )に制限されます。 $IN^+$ ピンと $IN^-$ ピンは、ともに(GND - 0.1V)から( $V_{REF} + 0.1V$ )まで振幅できます。両方の入力に共通な不要信号は、ADCのCMRRによって減少します。

### 擬似差動ユニポーラ入力範囲

擬似差動ユニポーラ入力範囲では、ADCは、( $0V \sim V_{REF}$ )の幅で差動アナログ入力電圧( $IN^+ - IN^-$ )をデジタル化します。この範囲では、 $IN^+$ ピンにドライブされるシングルエンド・ユニポーラ入力信号は、 $IN^-$ ピンにドライブされる信号グランド・リファレンス・レベルを基準に測定されます。 $IN^+$ ピンは(GND - 0.1V)から( $V_{REF} + 0.1V$ )まで振幅可能で、 $IN^-$ ピンは(GND  $\pm 0.1V$ )に制限されます。両方の入力に共通な不要信号は、ADCのCMRRによって減少します。

### 擬似差動バイポーラ入力範囲

擬似差動バイポーラ入力範囲では、ADCは、( $\pm V_{REF}/2$ )の幅で差動アナログ入力電圧( $IN^+ - IN^-$ )をデジタル化します。この範囲では、 $IN^+$ ピンにドライブされるシングルエンド・バイポーラ入力信号は、 $IN^-$ ピンにドライブされる信号ミッドスケール・リファレンス・レベルを基準に測定されます。 $IN^+$ ピンは(GND - 0.1V)から( $V_{REF} + 0.1V$ )まで振幅可能で、 $IN^-$ ピンは( $V_{REF}/2 \pm 0.1V$ )に制限されます。両方の入力に共通な不要信号は、ADCのCMRRによって減少します。

### 入力ドライブ回路

低インピーダンスの信号源は、利得誤差を発生することなく、LTC2389-18の高インピーダンス入力を直接ドライブすることができます。高インピーダンスの信号源は、収集時のセトリング時間を最小にするととも、A/Dコンバータの歪み性能を最適化するために、バッファする必要があります。収集開始時にはADCの入力に電流スパイクが流れるので、DC信号であってもセトリング時間の最小化は重要です。

最良の性能を得るには、バッファ・アンプを使用してLTC2389-18のアナログ入力をドライブする必要があります。このアンプの出力インピーダンスは低いので、収集段階でアナログ信号の高速セトリングを可能にします。また、このアンプは、収集開始時にADCの入力に流れる電流スパイクから信号源を絶縁します。

## アプリケーション情報

### 入力フィルタ処理

バッファ・アンプやその他のサポート回路のノイズと歪みは、A/Dコンバータのノイズと歪みに上乗せされるので、これらを考慮する必要があります。ノイズ密度の低いバッファ・アンプを選択して、SNRの低下を最小限に抑えてください。フィルタ・ネットワークをバッファ出力とA/Dコンバータ入力の間に使って、バッファに対するノイズの影響を最小限に抑えると同時に、ADCサンプリングの過渡電圧によってバッファに反射される妨害電圧を減らします。多くのアプリケーションでは、簡単な1ポールのローパスRCフィルタで十分です。ただし、セトリングが不十分だとINLとTHDの性能が制限される恐れがあるので、ADCの収集時間( $t_{ACQ}$ )内にアナログ入力を18ビット分解能に完全にセトリングさせることができるように、フィルタのRC時定数を十分に小さくすることが重要です。多くのアプリケーションでは、RC時定数を10ns程度にすれば十分に高速で、収集時間内に十分な過渡セトリングが得られると同時に、ドライバの広帯域ノイズを除去することができます。

また、多くの場合、1次ローパスRCフィルタとADC入力の間に小さい直列抵抗を追加することも有効です。これらの抵抗は、ADCサンプリング・コンデンサ  $C_{IN}$  およびサンプリング・スイッチ抵抗  $R_{IN}$  とともに2次ローパスRCフィルタを形成し、高周波域のドライバのノイズをさらに制限とともに、収集開始時にアナログ入力に流れる電流スパイクを小さくします。この2次ローパス・フィルタの時定数もアナログ入力のセトリングに直

接的な影響を与えるので、小さい値に保つ必要があります。多くのアプリケーションでは、49.9Ωの直列抵抗を使用すれば、収集時の過渡セトリングを十分な値に保ちながら、広帯域ドライバ・ノイズをより効果的に除去することができます。

RCフィルタのコンデンサと抵抗は歪みを大きくする可能性があるので、これらの部品は高品質のものを使用します。NPOタイプやシルバーマイカ・タイプの誘電体コンデンサはすぐれた直線性を示します。表面実装カーボン抵抗は、自己発熱や半田工程で生じる損傷により歪みを生じることがあります。表面実装金属皮膜抵抗は、両方の問題に対してはるかに耐性があります。

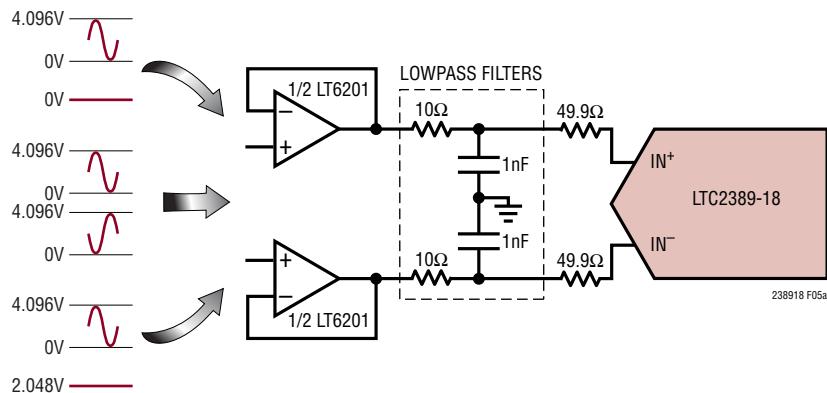

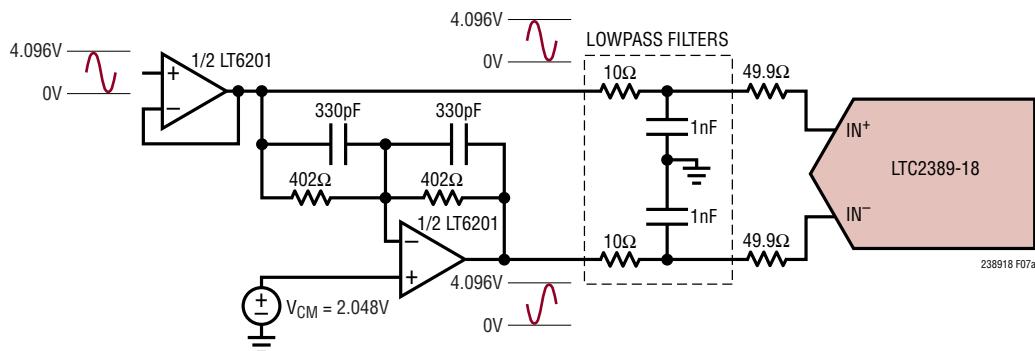

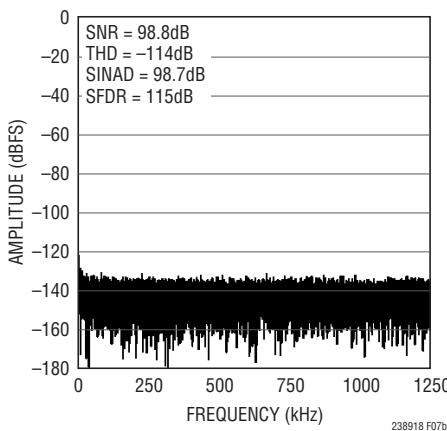

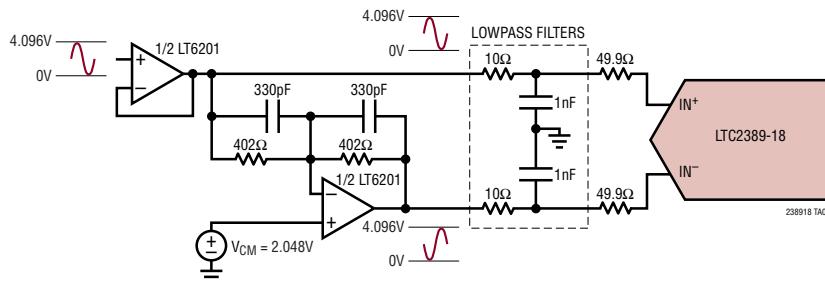

### 完全差動入力

LTC2389-18には、完全差動入力信号を直接与えることができます。ほとんどの完全差動アプリケーションにおいては、図5aに示すように、ユニティゲイン・バッファとして構成したLT6201 ADCドライバを2個使用して、LTC2389-18をドライブすることを推奨します。LT6201は、高速セトリング性と優れたDC直線性に加えて、 $0.95\text{nV}/\sqrt{\text{Hz}}$ の入力換算ノイズ密度を実現しており、図5bのFFTプロットに示すように、ADCのデータシートに示すSNRとTHDの仕様をフルに引き出すことができます。このトポロジーは、図5cと5dのFFTプロットに示すように、両方の疑似差動入力モードにおいてシングルエンド信号をバッファして、ADCのデータシートに示すSNRとTHDの仕様をフルに引き出すために使用することもできます。

## アプリケーション情報

図5a. 完全差動信号源またはシングルエンド信号源をバッファするLT6201

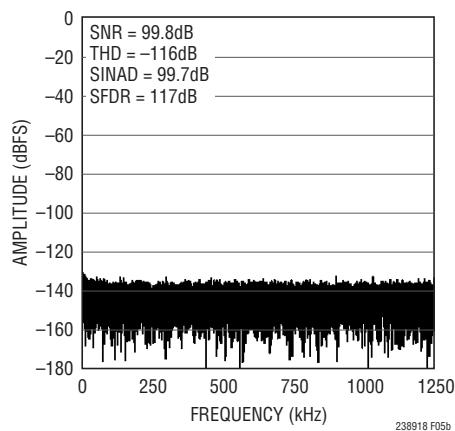

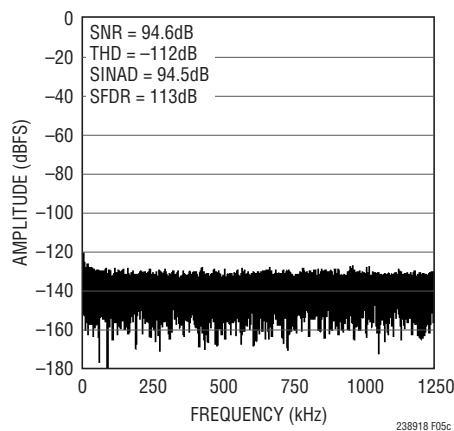

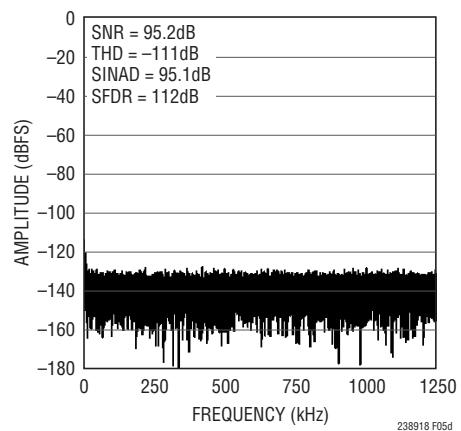

図5b. 32k ポイント FFT ( $f_{\text{SMPL}} = 2.5\text{Msps}$ 、 $f_{\text{IN}} = 2\text{kHz}$ )、図5aの回路用、完全差動入力でドライブ図5c. 32k ポイント FFT ( $f_{\text{SMPL}} = 2.5\text{Msps}$ 、 $f_{\text{IN}} = 2\text{kHz}$ )、図5aの回路用、ユニポーラ入力でドライブ図5d. 32k ポイント FFT ( $f_{\text{SMPL}} = 2.5\text{Msps}$ 、 $f_{\text{IN}} = 2\text{kHz}$ )、図5aの回路用、バイポーラ入力でドライブ

## アプリケーション情報

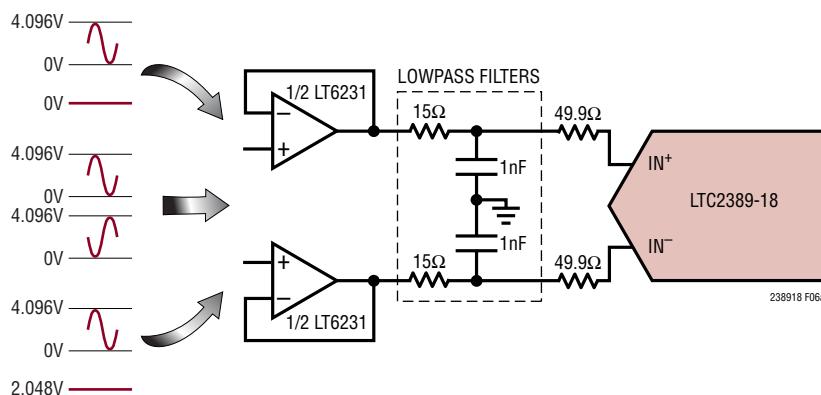

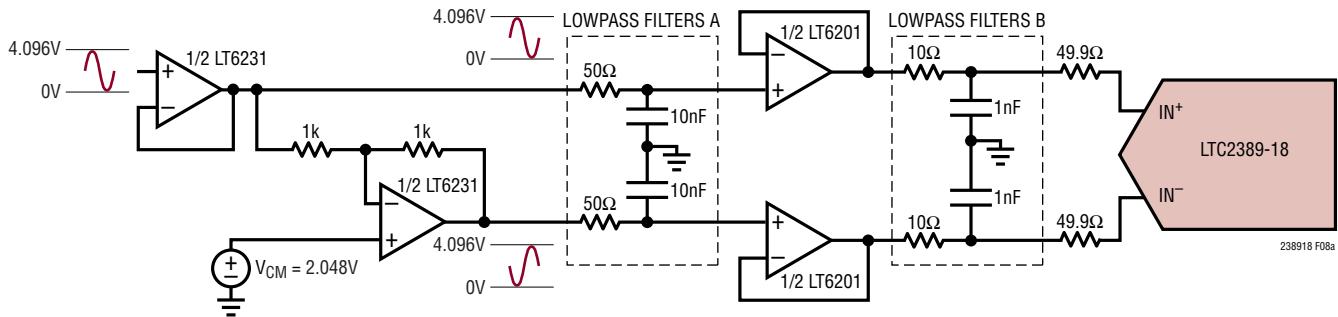

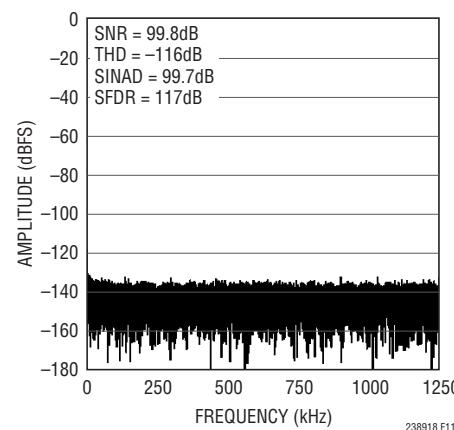

SNRとTHDの性能が多少低下しても許容できるようなアプリケーションでは、図6aに示すように、消費電力がより小さいLT6231 ADCドライバ2個をユニティゲイン・バッファとして構成し、LTC2389-18をドライブすることができます。このトポロジーにおける出力ローパス・フィルタのRC時定数は、LT6231の高周波ノイズの影響を制限するために大きくなっています。

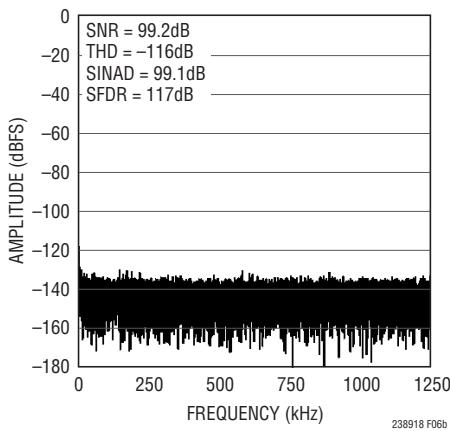

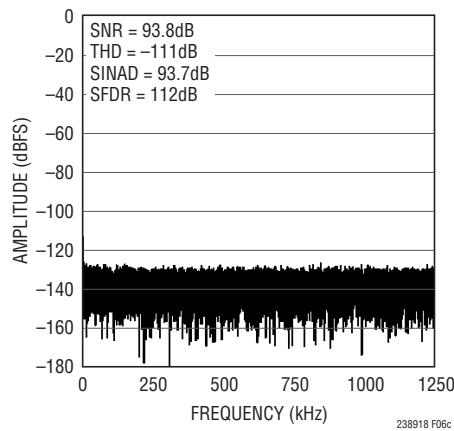

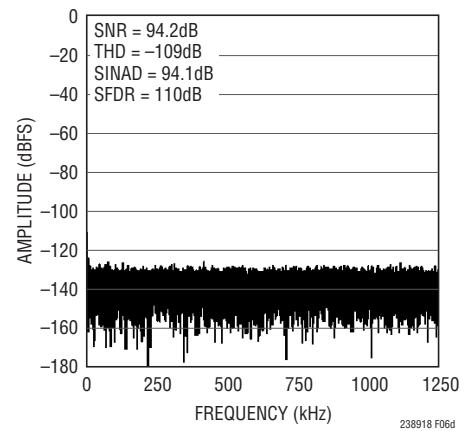

図6b～図6dのFFTプロットに示すように、この回路は完全差動入力モードで99.2dBのSNRと-116dBのTHDを、ユニポーラ入力モードで93.8dBのSNRと-111dBのTHDを、バイポーラ入力モードでは94.2dBのSNRと-109dBのTHDを実現します。

図6a. LT6231による完全差動信号源またはシングルエンド信号源のバッファリング

図6b.32kポイントFFT( $f_{\text{SMPL}} = 2.5\text{Msps}$ 、 $f_{\text{IN}} = 2\text{kHz}$ )、図6aの回路用、完全差動入力でドライブ

図6.32kポイントFFT( $f_{\text{SMPL}} = 2.5\text{Msps}$ 、 $f_{\text{IN}} = 2\text{kHz}$ )、図6aの回路用、ユニポーラ入力でドライブ

図6d.32kポイントFFT( $f_{\text{SMPL}} = 2.5\text{Msps}$ 、 $f_{\text{IN}} = 2\text{kHz}$ )、図6aの回路用、バイポーラ入力でドライブ

## アプリケーション情報

### シングルエンドから差動への変換

一部のアプリケーションでは、完全差動入力モードにおけるSNRが高いというLTC2389-18の利点を生かすため、LTC2389-18をドライブする前に、シングルエンドのユニポーラ信号やバイポーラ信号を完全差動信号に変換した方が望ましい場合があります。図7aに示すトポロジーに構成したLT6201 ADCドライバを使用すれば、0V～4.096Vのシングル

エンド入力信号を、完全差動の±4.096V出力信号に変換することができます。出力ローパス・フィルタのRC時定数は、収集時にLTC2389-18のアナログ入力が十分な過渡セトリングを得られるように選択します。フィルタ帯域幅が広く、シングルエンドから差動への変換回路の広帯域ノイズが比較的大きいので、このトポロジーにおいて実現できるSNRは、図7bに示すように98.8dBに制限されます。

図7a. 0V～4.096Vのシングルエンド信号を±4.096Vの完全差動入力信号に変換するLT6201

図7b. 32kポイントFFT( $f_{SMPL} = 2.5\text{Msps}$ 、 $f_{IN} = 2\text{kHz}$ )、

図7aの回路用

## アプリケーション情報

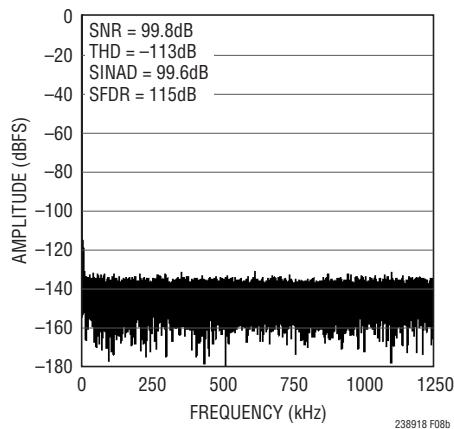

LT6231の後段にLT6201を使用した別のシングルエンド-差動変換トポロジーを図8aに示します。このトポロジーでは、ローパス・フィルタAを使用して、収集時におけるLTC2389-18の入力のセトリングに影響を与えることなく、シングルエンドー

差動変換回路の広帯域ノイズの帯域をさらに制限することができます。この回路では、図8bのFFTプロットに示すように、ADCのデータシートに示すSNR仕様をフルに引き出すことができます。

図8a. 0V～4.096Vのシングルエンド信号を±4.096Vの完全差動入力信号に変換するLT6231に、完全差動信号をバッファするLT6201を接続

図8b. 32kポイントFFT( $f_{\text{SMPL}} = 2.5\text{Msps}$ 、 $f_{\text{IN}} = 2\text{kHz}$ )、図8aの回路用

## アプリケーション情報

## シングルエンドのユニポーラ入力とバイポーラ入力

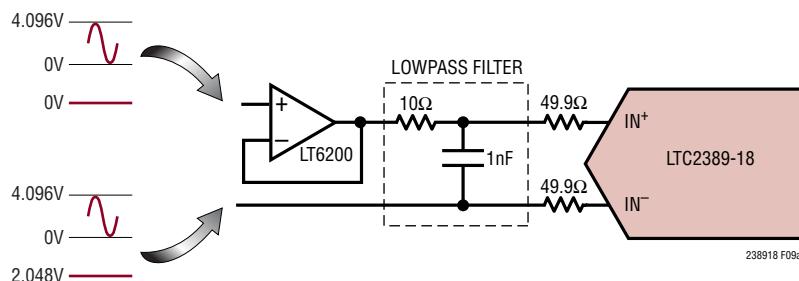

LTC2389-18には、シングルエンド・ユニポーラ入力信号とシングルエンド・バイポーラ入力信号の両方を直接与えることができます。ほとんどのシングルエンド・アプリケーションにおいては、図9aに示すように、ユニティゲイン・バッファとして構成したLT6200 ADCドライバを使用して、LTC2389-18をドライバ

ブすることを推奨します。LT6200は、高速セトリング性と優れたDC直線性に加えて、 $0.95\text{nV}/\sqrt{\text{Hz}}$ の入力換算ノイズ密度を実現しており、両方の疑似差動入力モードにおいて、図9bと図9cのFFTプロットに示すように、ADCのデータシートに示すSNRとTHDの仕様をフルに引き出すことができます。

図9a. シングルエンド信号源をバッファするLT6200

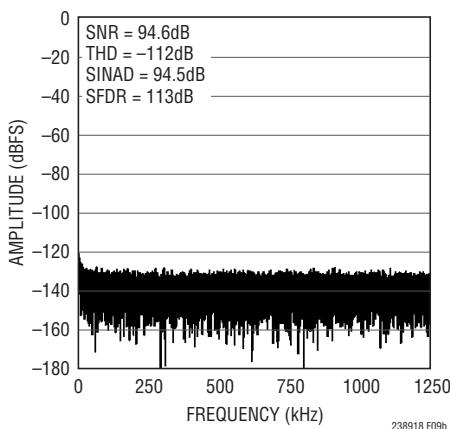

図9b.32kポイントFFT( $f_{\text{SMPL}} = 2.5\text{Msps}$ 、 $f_{\text{IN}} = 2\text{kHz}$ )、図9aの回路用、ユニポーラ入力で

ドライブ

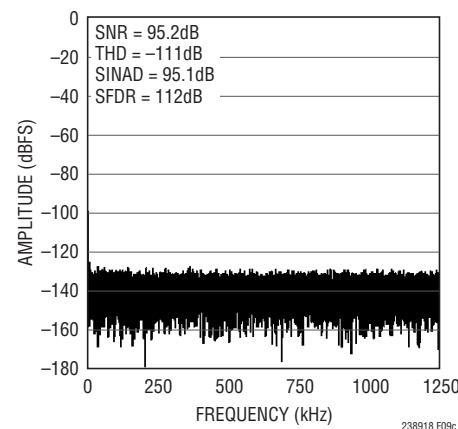

図9c.32kポイントFFT( $f_{\text{SMPL}} = 2.5\text{Msps}$ 、 $f_{\text{IN}} = 2\text{kHz}$ )、図9aの回路用、バイポーラ入力でドライブ

## アプリケーション情報

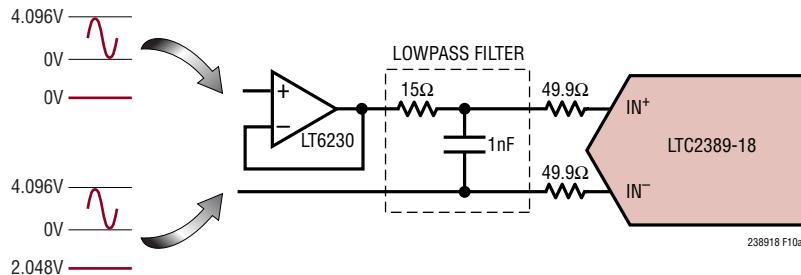

SNRとTHDの性能が多少低下しても許容できるようなアプリケーションでは、図10aに示すように、消費電力がより小さいLT6230 ADCドライバをユニティゲイン・バッファとして構成し、LTC2389-18をドライブすることができます。このトポロジーにおける出力ローパス・フィルタのRC時定数は、LT6230の高周波ノイズの影響を制限するために大きくなっています。図10bと10cのFFTプロットに示すように、この回路は、ユニポーラ入力モードで94dBのSNRと-111dBのTHDを、バイポーラ入力モードで94.5dBのSNRと-110dBのTHDを実現します。

図9aと図10aの回路では、IN-に直接与えられた信号のソース・インピーダンスが、信号収集時の入力セトリング時間に影響します。このリファレンス信号のインピーダンスが基本的に高いシングルエンド・アプリケーションでは、図5aと図6aに示すデュアル・バッファ手法を採用した方が収集時間が短くなり、ADCの歪み性能も向上します。

図10a. シングルエンド信号源をバッファするLT6230

図10b.32kポイントFFT( $f_{SMPL} = 2.5\text{Msps}$ 、 $f_{IN} = 2\text{kHz}$ )、図10aの回路用、ユニポーラ入力でドライブ

図10c.32kポイントFFT( $f_{SMPL} = 2.5\text{Msps}$ 、 $f_{IN} = 2\text{kHz}$ )、図10aの回路用、バイポーラ入力でドライブ

## アプリケーション情報

### ADCのリファレンス

このADCのデータシートで規定されている性能を完全に実現するには、低ノイズ、低温度ドリフトのリファレンスが不可欠です。LTC2389-18は、温度係数が $\pm 20\text{ppm}/^\circ\text{C}$ （最大）の優れた内部リファレンスを備えています。より高い精度が必要な場合は、外部リファレンスを使用することができます。いずれの場合にも高速低ノイズの内部リファレンス・バッファが使われ、これをバイパスすることはできません。このバッファはコンバータに対する信号依存ノイズ項に関係し、その代表的な標準偏差は次式で表されます。

$$\frac{(V_{IN+} - V_{IN-})}{V_{REF}} \cdot 16\mu V_{RMS},$$

これは、ゼロスケール入力とフルスケール入力の間の遷移ノイズの増加を考慮したものです。REFINに与えられるリファレンス電圧も同様の信号依存ノイズ項を発生させますが、その大きさは内部バッファ内の4kHz（標準）のローパス・フィルタによって制限され、ほとんどの場合、この項は無視できる程度になります。

### 内部リファレンス

内部リファレンスを使用するには、REFOUTピンとREFINピンを接続します。これによって、内部リファレンスの4.096V出力が内部リファレンス・バッファの入力に接続されます。内部リファレンスの出力インピーダンスは約 $2.3\text{k}\Omega$ で、内部リファレンス・バッファの入力インピーダンスは約 $74\text{k}\Omega$ です。REFINは、内部リファレンスの出力ノイズを除去するために、 $1\mu\text{F}$ 以上のコンデンサを使用してREFSENSEにバイパスすることを推奨します。内部リファレンスを使用する時は、REFSENSEピンをグランドに接続しないでください。

### 外部リファレンス

さらに高い性能を必要とするときは、外部リファレンスを使用することができます。LTC6655は、高精度アプリケーション向けに0.025%（最大）の初期精度と $2\text{ppm}/^\circ\text{C}$ （最大）の温度係数を実現しています。LTC6655はHグレードの温度範囲全域に対応できるよう仕様が規定されており、LTC2389-18の最大 $125^\circ\text{C}$ までの拡張温度動作を補完します。外部リファレンスを使用する時は、リファレンスの出力をREFINピンに接続してREFOUTピンをグランドに接続します。REFSENSEピンは、外部リファレンスのグランドに接続する必要があります。

### ダイナミック性能

A/Dコンバータの周波数応答、歪み、およびノイズを定格のスループットでテストするには、高速フーリエ変換(FFT)の手法を使用します。低歪みの正弦波を入力してそのデジタル出力をFFTアルゴリズムを用いて解析することにより、基本波の外側の周波数に関してA/Dコンバータのスペクトルの内容を調べることができます。LTC2389-18では、AC歪みとノイズの両方の測定値について、保証されたテスト済みの限界値を示しています。

### 信号対ノイズ+歪み比(SINAD)

信号対ノイズ+歪み比(SINAD)は、基本入力周波数のRMS振幅とA/Dコンバータ出力での他のすべての周波数成分のRMS振幅の比です。出力の帯域は、DCより高くサンプリング周波数の半分より低い周波数に制限されます。図11は、LTC2389-18が2kHzの入力、2.5MHzのサンプリング・レートで99.7dB（完全差動）の標準SINADを達成していることを示しています。

### 信号対ノイズ比(SNR)

信号対ノイズ比(SNR)は、基本入力周波数のRMS振幅と、最初の5つの高調波およびDCを除く他のすべての周波数成分のRMS振幅の比です。図11は、LTC2389-18が2kHzの入力、2.5MHzのサンプリング・レートで99.8dB（完全差動）の標準SNRを達成していることを示しています。

図11. LTC2389-18の32kポイントFFT

( $f_{SAMPL} = 2.5\text{Msps}$ ,  $f_{IN} = 2\text{kHz}$ )

## アプリケーション情報

### 全高調波歪み(THD)

全高調波歪み(THD)は、入力信号のすべての高調波のRMS値の合計と基本波のRMS値との比です。帯域外高調波は、DCからサンプリング周波数の半分( $f_{SMPL}/2$ )までの周波数帯域で折り返し歪みを生じます。THDは次のように表されます。

$$THD = 20 \log \frac{\sqrt{V_2^2 + V_3^2 + V_4^2 + \dots + V_N^2}}{V_1}$$

ここで、 $V_1$ は基本波のRMS振幅で、 $V_2 \sim V_N$ は2次～N次の高調波の振幅です。図11は、LTC2389-18が2kHzの入力、2.5MHzのサンプリング・レートで-116dB(完全差動)の標準THDを達成していることを示しています。

### 電力に関する検討事項

LTC2389-18には、5Vコア電源( $V_{DD}$ )およびデジタル入力/出力インターフェース電源( $OV_{DD}$ )という2つの電源ピンがあります。柔軟性の高い $OV_{DD}$ 電源により、LTC2389-18は、2.5Vシステムや3.3Vシステムなど、1.8V～5Vで動作する任意のデジタル・ロジックと通信できます。 $V_{DD}$ および $OV_{DD}$ 電源ネットワークは、ともに0.1 $\mu$ Fのセラミック・コンデンサを各ピンの近くに置き、10 $\mu$ Fのセラミック・コンデンサを並列に接続してGNDにバイパスする必要があります。

### 電源シーケンシング

LTC2389-18には電源シーケンシングに関する具体的な要件はありません。「絶対最大定格」のセクションに記載されている最大電圧の関係を遵守するよう注意する必要があります。LTC2389-18は内部パワーオン・リセット(POR)回路を備えています。これにより、LTC2389-18は最初の電源投入時、または電源電圧が2.5Vを下回るたびにリセットされます。電源電圧が公称電源電圧範囲に戻ると、PORはA/Dコンバータを再度初期化します。PORでは、リファレンスがセトリングするだけの十分な時間が与えられている限り、電源投入後の最初の変換結果は有効です。

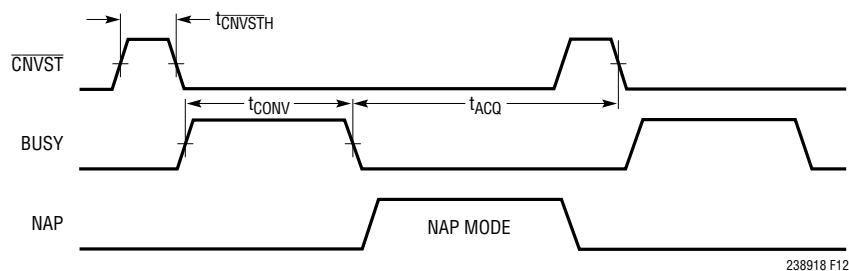

### ナップ・モード

LTC2389-18は、変換と変換の間の消費電力を減らすために、変換完了後にナップ・モードにすることができます。このモードでは、デバイスの一部の回路がオフになります。ナップ・モードは、図12に示すように、変換と変換の間に $\overline{CNVST}$ を“L”に保つことによってイネーブルされます。ナップ・モードにした後に新しい変換を開始するには、 $\overline{CNVST}$ を“H”にして少なくとも200nsその状態を保持し、次いで $\overline{CNVST}$ を再度“L”にします。

図12. LTC2389-18のナップ・モードのタイミング

## アプリケーション情報

### パワー・シャットダウン・モード

PDを“H”に接続すると、LTC2389-18はパワー・シャットダウン・モードになります。この状態では、リファレンスを含むすべての内部機能がオフされて、その後の変換要求は無視されます。パワー・シャットダウン・モードにする場合は、その前にデジタル出力データを読み出す必要があります。変換中にパワー・シャットダウン要求が行われた場合は、その変換を完了させてからデバイスがパワーダウンしますが、その変換によるデータを読み出すことができるには、パワー・シャットダウン・モードの終了後に限られます。このモードでは、消費電力の標準値が162.5mWから75μWに減少します。LTC2389-18を長時間にわたって動作停止状態にし、その間の電力損失を最小限に抑えたい場合は、このモードを使用することができます。

### パワー・シャットダウン・モードからの回復

パワー・シャットダウン・モードを終了させて内部回路を起動させるには、PDピンを“L”に戻します。内部リファレンスを使用する場合は、REFIN/REFOUTピンに接続した2.3kΩの出力インピーダンスと1μFのバイパス・コンデンサが、パワーオン回復時間の主な時定数となります。外部リファレンスを使用する場合は、通常、新しい変換を開始する前に5msの回復時間を要します。

### 電力損失とサンプリング周波数

ナップ・モードを使用すると、LTC2389-18の電力損失は、図13に示すようにサンプリング周波数の低下とともに減少します。このように平均電力損失が減少するのは、ナップ・モード

ではLTC2389-18の回路の一部がオフし、サンプリング周波数( $f_{SMPL}$ )の低下とともに休止する変換サイクル( $t_{CYC}$ )部分が増えるからです。

## タイミングと制御

### CNVSTのタイミング

LTC2389-18の変換は $\overline{CNVST}$ によって制御されます。変換プロセスは $\overline{CNVST}$ の立ち下がりエッジによって開始され、一度変換が開始されると、その変換が終了するまで変換をやり直すことはできません。最適な性能を得るには、クリーンな低ジッタの信号で $\overline{CNVST}$ をドライブし、 $\overline{CNVST}$ の立ち下がりエッジまでデータI/Oラインの遷移を避ける必要があります。コンバータの状態はBUSY出力で示され、変換の進行中はこの出力が“H”に保たれます。 $\overline{CNVST}$ が“L”になって変換が開始されたら、変換開始後40ns以内、あるいは変換完了後に“H”に戻し、デジタル化された結果にエラーが発生しないようにする必要があります。低電力ナップ・モードの動作の利点を活かすために必要な $\overline{CNVST}$ のタイミングは、「ナップ・モード」のセクションに示されています。

### 内部変換クロック

LTC2389-18は、310nsの最大変換時間を達成するように調整されている内部クロックを備えています。外部調整は不要で、77nsの最小データ収集時間の時に、パラレル出力モードで2.5Mspsのスループット性能が保証されています。

図13. 電源電流とサンプリング周波数 LTC2389-18の電力損失はサンプリング周波数の低下とともに減少

## アプリケーション情報

### デジタル・インターフェース

さまざまな特定用途向けプロセッサやFPGAのデータバス幅に対応するために、LTC2389-18の出力バスは、表1に示すように18ビット・パラレル・モード、16ビット・パラレル・モード、8ビット・パラレル・モード、またはシリアル・モードで動作するように構成することができます。柔軟性の高いOV<sub>DD</sub>電源により、LTC2389-18は、2.5Vシステムや3.3Vシステムなど、1.8V～5Vで動作する任意のデジタル・ロジックと通信できます。

#### 18ビット・パラレル・バス構成

FPGAやCPLDベースのソリューションなど、フル18ビット幅パラレル・データ・バスを使用できるアプリケーションの場合、LTC2389-18は、各変換結果R[17:0]を1つの18ビット・ワードとしてピンD[17:0]に出力できます。このバス構成を選択するには、表1に示すように、ピンMODE = MODE[1:0]をMODE = 00にドライブする必要があります。バスを共有する必要のないアプリケーションでは、図14に示すように、チップ・セレクト・ピンを $\overline{CS} = 0$ にドライブして、LTC2389-18がバスを連続的にドライブできるようにします。バスを共有しなければならないアプリケーションでは、図15および図16に示すように、他のデバイスがバスを使用する時は $\overline{CS} = 1$ にドライブしてLTC2389-18のバス・ピンを高インピーダンスにし、LTC2389-18がバスをドライブできるようにするには $\overline{CS} = 0$ にドライブします。

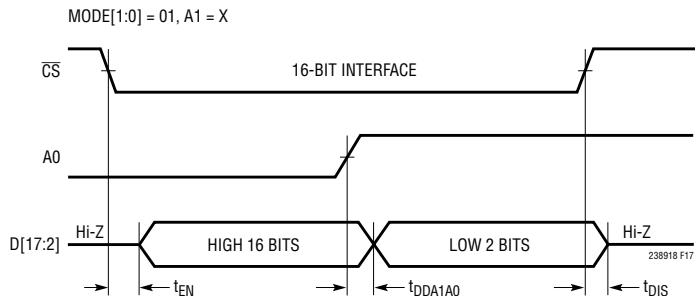

#### 16ビット・パラレル・バス構成

16ビット・マイクロコントローラ・ベースのソリューションなど、16ビット幅パラレル・データ・バスを使用できるアプリケーションの場合、LTC2389-18は、各変換結果R[17:0]を2つの16ビット・ワードとしてピンD[17:2]に出力できます。このバス構成を選択するには、表1に示すように、ピンMODE = MODE[1:0]

をMODE = 01にドライブする必要があります。この構成では、D0/A0ピンとD1/A1ピンが2ビット幅アドレス入力A[1:0]になり、これは図17に示すように、D[17:2]に変換結果の上位16ビットであるR[17:2]をドライブするか、下位2ビットであるR[1:0]をドライブするかを制御します。表1に示すように、変換結果の下位2ビットR[1:0]を出力する際には、ハードウェアやソフトウェアに関するアプリケーション固有の制約条件に対応するために、2つの形式を使用することができます。チップ・セレクト・ピン $\overline{CS}$ を使用すれば、複数のデバイス間で16ビット・パラレル・バスを共有することができます。詳細については、「18ビット・パラレル・バス構成」のセクションを参照してください。

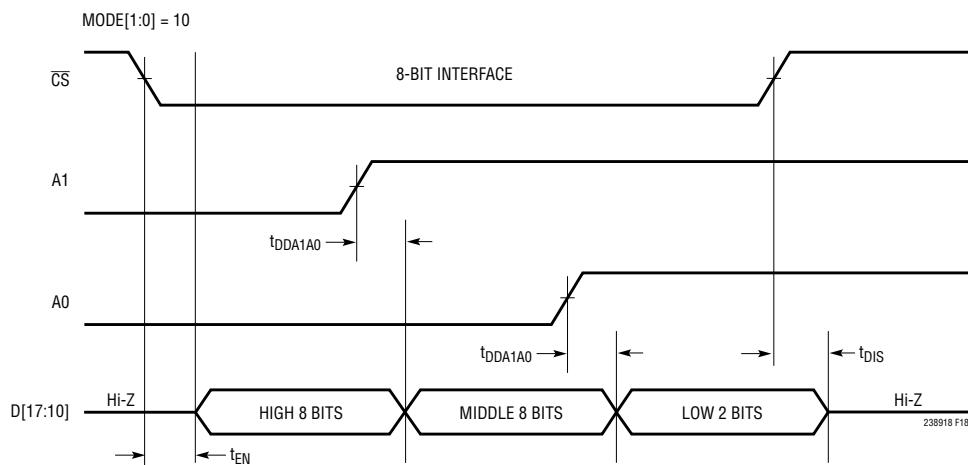

#### 8ビット・パラレル・バス構成

8ビット・マイクロコントローラ・ベースのソリューションなど、8ビット幅パラレル・データ・バスを使用できるアプリケーションの場合、LTC2389-18は、各変換結果R[17:0]を3つの8ビット・ワードとしてピンD[17:10]に出力できます。このバス構成を選択するには、表1に示すように、ピンMODE = MODE[1:0]をMODE = 10にドライブする必要があります。この構成では、D0/A0ピンとD1/A1ピンが2ビット幅アドレス入力A[1:0]になり、これは、図18に示すように、D[17:10]に変換結果の上位8ビットR[17:10]をドライブするか、中位8ビットR[9:2]をドライブするか、あるいは下位2ビットR[1:0]をドライブするかを制御します。表1に示すように、変換結果の下位2ビットR[1:0]を出力する際には、ハードウェアやソフトウェアに関するアプリケーション固有の制約条件に対応するために、2つの形式を使用することができます。チップ・セレクト・ピン $\overline{CS}$ を使用すれば、複数のデバイス間で8ビット・パラレル・バスを共有することができます。詳細については、「18ビット・パラレル・バス構成」のセクションを参照してください。

## アプリケーション情報

図14. パラレル・データを連続的に読み出す。

データ・バスは常にドライブされ、共有できない。

図16. 次の変換中にパラレル・データを読み出す

図15. 変換後にパラレル・データを読み出す

図17. A[1:0] ピンを使用する 16 ビット・パラレル・インタフェース

図18. A[1:0] ピンを使用する 8 ビット・パラレル・インタフェース

## アプリケーション情報

図19. 外部クロック使用のシリアル・インターフェース。変換後に読み出す。複数のコンバータをデイジタル・チェーン接続

## アプリケーション情報

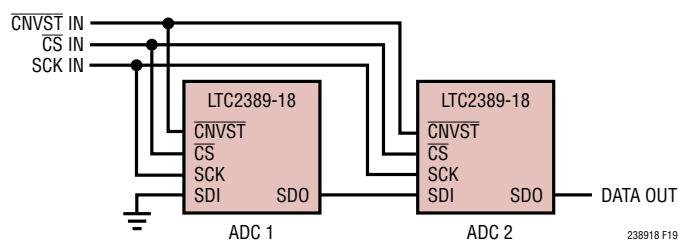

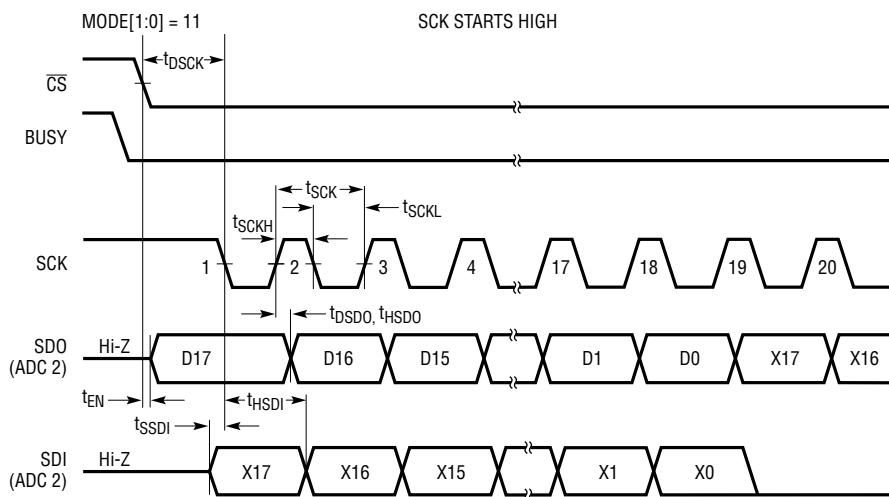

### シリアル・バスの構成

データ・バス幅を最小に抑えるためにシリアル・バスが必要とされるアプリケーションでは、LTC2389-18は、各変換結果R[17:0]をD12/SDOピンにシリアル出力できます。このバス構成を選択するには、表1に示すように、ピン MODE = MODE[1:0]を MODE = 11 にドライブする必要があります。図19に示すように、シリアル出力データは、SCKピンに与えられる外部シフト・クロック入力に応答する形で、SDOピンに出力されます。SDOのデータは、SCKの立ち上がりエッジに合わせて状態を変えます。この動作における例外は、SCKの最初の立ち下がりエッジに続く最初の立ち上がりエッジまで、D17が有効なままになるという点です。シリアル出力データをゲートするために $\overline{CS}$ を使用する場合は、 $\overline{CS}$ が“H”に戻る前にすべての変換結果を読み出す必要があります。最大限の性能を得るために、BUSYが“H”的時はシリアル・データをクロック・アウトしないでください。

SDI入力ピンを使用すると、図19に示すように複数のコンバータをデイジーチェーン接続することができます。この図では2つのデバイスがカスケード接続され、18 SCKサイクルの遅

延の後に、ADC1のMSBがADC2のシリアル出力に現れています。ADC1のシリアル出力は、SCKの立ち下がりエッジでADC2にクロック・インされます。これは、複数のコンバータとインターフェースを取るために使用できるデータラインの数が、ハードウェア上の制約によって制限されるアプリケーションに有効です。

### データ形式

変換結果のバイナリ形式は、表2に示すように、ピン PD/FD および OB/ $\overline{2C}$  の状態によって決まります。これらのピンは、パラレル・モードとシリアル・モードの両方でアクティブになります。

### リセット

図20に示すように、RESETピンが“H”になるとLTC2389-18はリセットされ、データ・バスは高インピーダンス・モードになります。変換中にリセットが行われると、その変換は直ちに中断されます。リセット中、新しい変換要求は無視されます。RESETが“L”に戻ると、LTC2389-18は収集時間経過後に新しい変換を開始できる状態になります。

図20. RESETピンのタイミング

## アプリケーション情報

## 基板のレイアウト

LTC2389-18の性能を最大限に引き出すため、プリント回路基板(PCB)を使用することを推奨します。プリント回路基板のレイアウトは、デジタル信号線とアナログ信号線をできるだけ離すようにします。特に、デジタル・クロックやデジタル信号は、アナログ信号に沿って配線したり、A/Dコンバータの下に配線したりしないように注意します。

## LTC238x-16とのピン互換性

LTC2389-18で使用することを意図した基板レイアウトを、LTC238x ファミリの 16 ビット・バージョンにも使用できるよう にするには、ピン 5 (MODE1) とピン 7 (DO/AO) をロジック “L” にドライブでき、ピン 4 (MODE0) をロジック “H” と “L” の両方にドライブできるデザインとし、さらにピン 8 (D1/A1) をロジック

ク“H”と“L”の両方に動的にドライブできるようにする必要があります。これらの制約条件は、具体的なアプリケーションに基づいて簡略化することができます。LTC238x-16デバイスの動作の詳細については、それぞれのデータシートを参照してください。

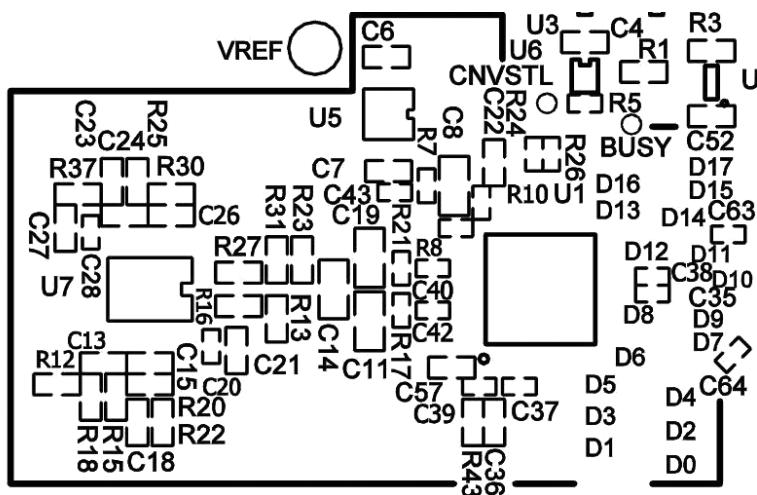

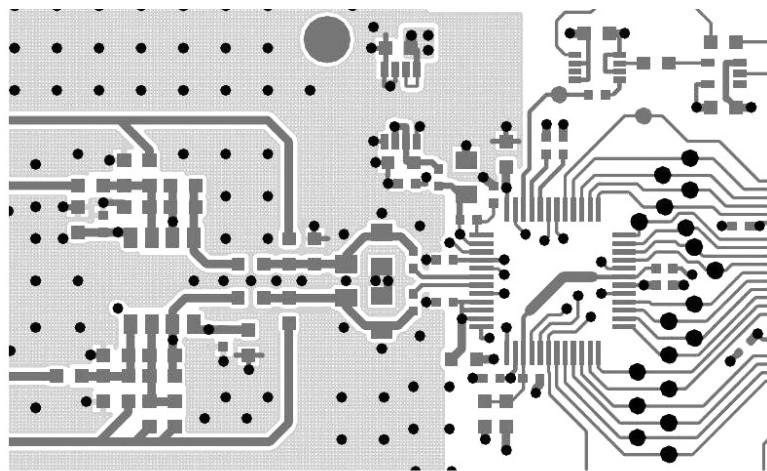

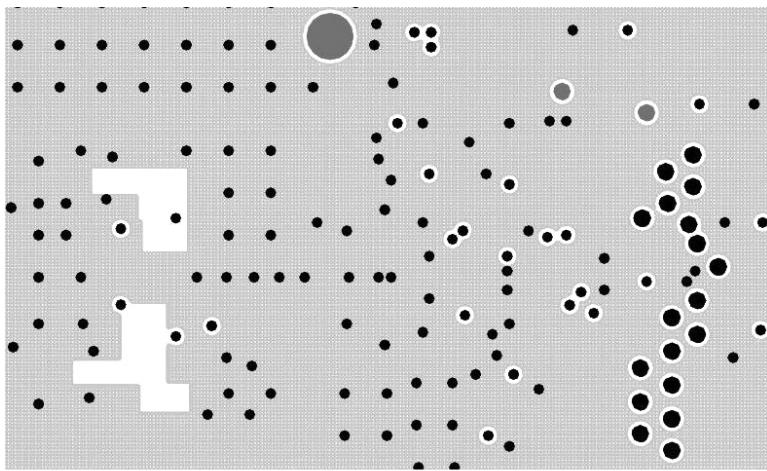

## 推奨レイアウト

以下に推奨PCBレイアウトの一例を示します。切れ目のない単一のグランド・プレーンを使用します。電源へのバイパス・コンデンサは電源ピンのできるだけ近くに配置します。A/Dコンバータを低ノイズで動作させるには、これらのバイパス・コンデンサの低インピーダンスの共同帰線が不可欠です。アナログ入力のトレースはグランドで遮蔽します。詳細については、LTC2389-18用評価キットDC1826A-Aを参照してください。

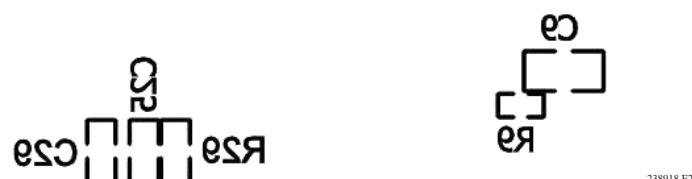

## 部品面シルク(一部)

アプリケーション情報

238918 F22

第1層、部品面(一部)

238918 F23

第2層、グランド・プレーン(一部)

## アプリケーション情報

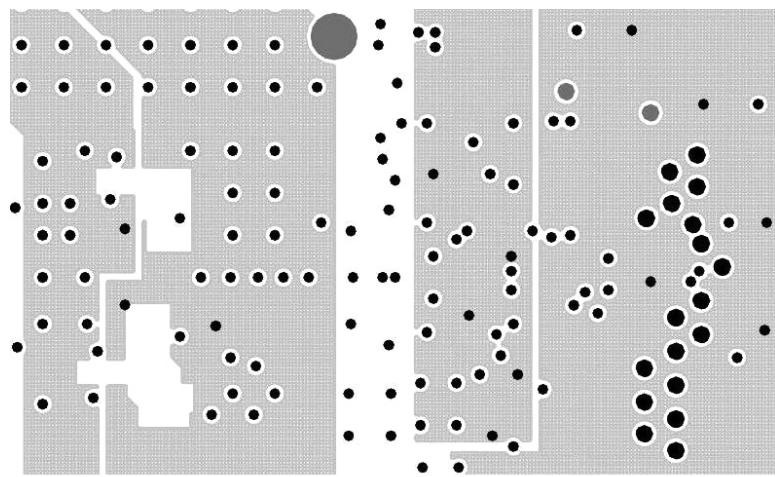

第3層、電源プレーン(一部)

第4層、最下層(一部)

半田面シルク(一部)

238918f

## アプリケーション情報

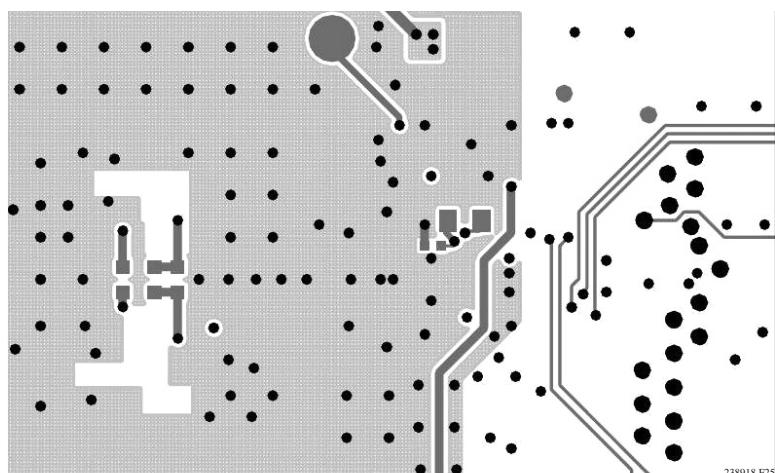

## デモボードの回路図(一部)

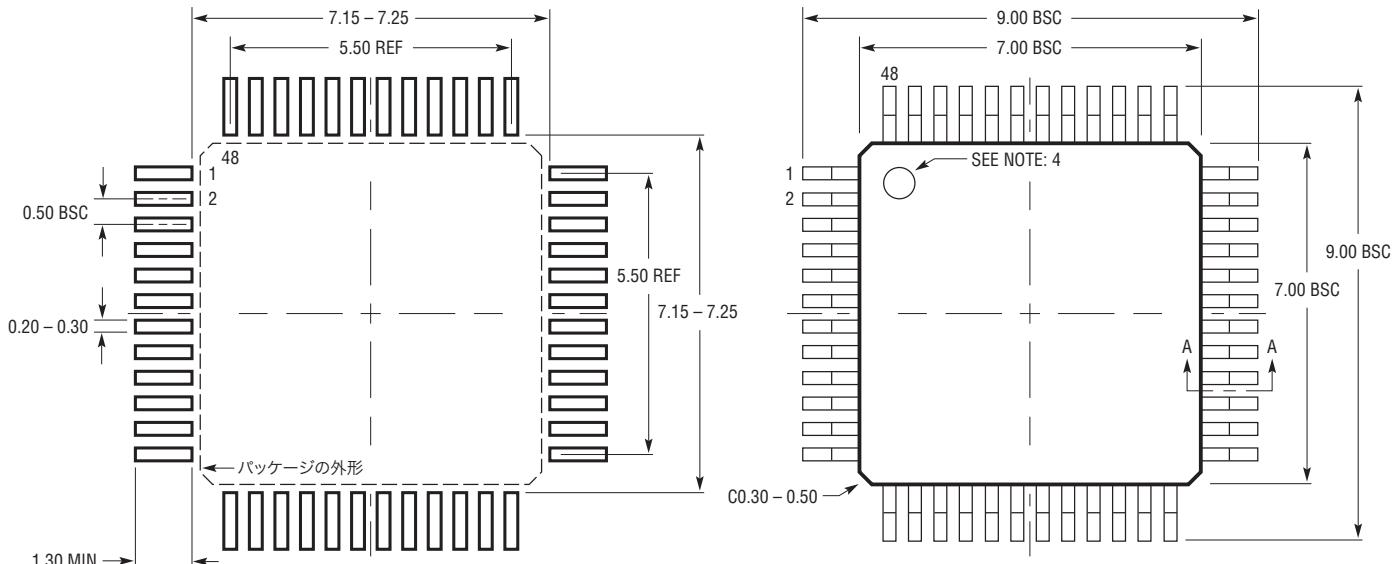

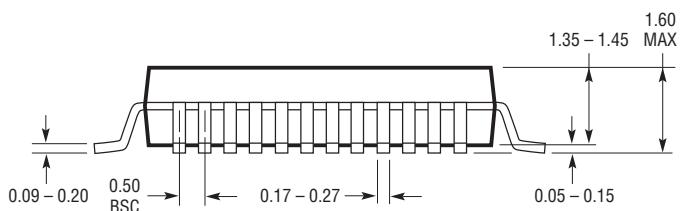

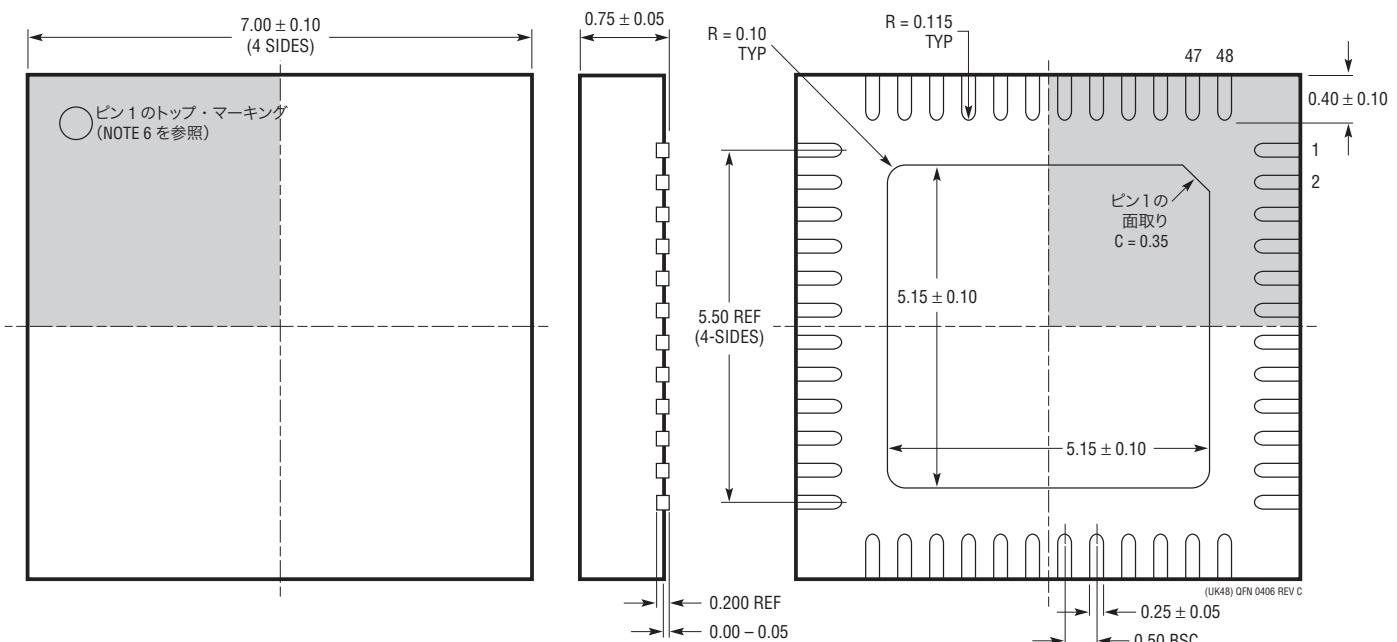

## パッケージ

最新のパッケージ図面については、<http://www.linear-tech.co.jp/designtools/packaging/> を参照してください。

**LXパッケージ

48ピン・プラスチックLQFP(7mm×7mm)**

(Reference LTC DWG # 05-08-1760 Rev Ø)

推奨半田パッド・レイアウト

半田付けされない領域には半田マスクを使用する

SECTION A-A

NOTE :

1. パッケージ寸法は JEDEC パッケージ外形 #MS-026 に適合

2. 寸法はミリメートル

3. パッケージの寸法にはモールドのバリを含まない

モールドのバリは(もしあれば)各サイドで 0.25mm を超えないこと

4. ピン1の識別マークはモールドのくぼみ、直径 0.50mm

5. 図は実寸とは異なる

LX48 LQFP 0907 REVØ

238918f

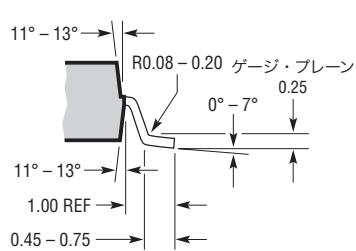

## パッケージ

最新のパッケージ図面については、<http://www.linear-tech.co.jp/designtools/packaging/> を参照してください。

**UKパッケージ

48ピン・プラスチックQFN(7mm×7mm)

(Reference LTC DWG # 05-08-1704)**

推奨する半田パッドのピッチと寸法

半田付けされない領域には半田マスクを使用する

### NOTE :

- 1. 図面は JEDEC のパッケージ外形 MO-220 バリエーション(WKKD-2)に適合

- 2. 図は実寸とは異なる

- 3. すべての寸法はミリメートル

- 4. パッケージ底面の露出パッドの寸法にはモールドのバリを含まない

モールドのバリは(もしされば)各サイドで 0.20mm を超えないこと

- 5. 露出パッドは半田メキッとする

- 6. 灰色の部分はパッケージの上面と底面のピン 1 の位置の参考に過ぎない

底面図—露出パッド

## 標準的応用例

### ADC ドライバ: シングルエンド入力から差動出力への変換

## 関連製品

| 製品番号                                         | 説明                                               | 注釈                                                                               |

|----------------------------------------------|--------------------------------------------------|----------------------------------------------------------------------------------|

| <b>ADC</b>                                   |                                                  |                                                                                  |

| LTC2379-18/LTC2378-18                        | 18ビット、1.6Msps/1Msps/500ksps/250kspsシリアル、低消費電力ADC | 2.5V電源、差動入力、SNR:101.2dB、入力範囲:±5V、DGC、MSOP-16および4mm×3mm DFN-16パッケージのピン互換ファミリ      |

| LTC2377-18/LTC2376-18                        | 16ビット、2Msps/1Msps/500ksps/250kspsシリアル、低消費電力ADC   | 2.5V電源、差動入力、SNR:96.2dB、入力範囲:±5V、DGC、MSOP-16および4mm×3mm DFN-16パッケージのピン互換ファミリ       |

| LTC2369-18/LTC2368-18/ LTC2367-18/LTC2364-18 | 18ビット、1.6Msps/1Msps/500ksps/250kspsシリアル、低消費電力ADC | 2.5V電源、疑似差動ユニポーラ入力、SNR:96.5dB、入力範囲:5V、DGC、MSOP-16および4mm×3mm DFN-16パッケージのピン互換ファミリ |

| LTC2370-16/LTC2368-16/ LTC2367-16/LTC2364-16 | 16ビット、2Msps/1Msps/500ksps/250kspsシリアル、低消費電力ADC   | 2.5V電源、疑似差動ユニポーラ入力、SNR:94dB、入力範囲:5V、DGC、MSOP-16および4mm×3mm DFN-16パッケージのピン互換ファミリ   |

| LTC2393-16/LTC2392-16/ LTC2391-16            | 16ビット、1Msps/500ksps/250kspsパラレル/シリアルADC          | 5V電源、差動入力、SNR:94dB、入力範囲:±4.096V、7mm×7mm LQFP-48およびQFN-48パッケージのピン互換ファミリ           |

| LTC2383-16/LTC2382-16/ LTC2381-16            | 16ビット、1Msps/500ksps/250kspsシリアル、低消費電力ADC         | 2.5V電源、差動入力、SNR:92dB、入力範囲:±2.5V、MSOP-16および4mm×3mm DFN-16パッケージのピン互換ファミリ           |

| LTC2302/LTC2306                              | 12ビット、500ksps、1チャネル/2チャネル、低ノイズADC                | 5V電源、500kspsで14mW、DFN-10パッケージ                                                    |

| LTC2355-14/LTC2356-14                        | 14ビット、3.5MspsシリアルADC                             | 3.3V電源、1チャネル、ユニポーラ/バイポーラ、18mW、MSOP-10パッケージ                                       |

| <b>DAC</b>                                   |                                                  |                                                                                  |

| LTC2756/LTC2757                              | 18ビット、シングル・シリアル/パラレルSoftSpan™電流出力DAC             | INL/DNL:±1LSB、7mm×7mm SSOP-28/LQFP-48パッケージ                                       |

| LTC2641                                      | 16ビット/14ビット/12ビット、シングル・シリアル電圧出力DAC               | INL/DNL:±1LSB、MSOP-8パッケージ、0V～5V出力                                                |

| LTC2751                                      | 16ビット/14ビット/12ビット、シングル・パラレル電流出力SoftSpan DAC      | INL/DNL:±1LSB、ソフトウェアで選択可能な範囲、5mm×7mm QFN-38パッケージ                                 |

| <b>リファレンス</b>                                |                                                  |                                                                                  |

| LTC6655                                      | 高精度、低ドリフト、低ノイズのバッファ付きリファレンス                      | 5V/2.5V、5ppm/°C、ピーク・トゥ・ピーク・ノイズ:0.25ppm、MSOP-8パッケージ                               |

| LTC6652                                      | 高精度、低ドリフト、低ノイズのバッファ付きリファレンス                      | 5V/2.5V、5ppm/°C、ピーク・トゥ・ピーク・ノイズ:2.1ppm、MSOP-8パッケージ                                |

| <b>アンプ</b>                                   |                                                  |                                                                                  |

| LT6200/LT6201                                | ユニティゲイン安定のシングル/デュアル165MHzオペアンプ                   | 0.95nV/√Hz(100kHz)、低歪み:-80dB(1MHz時)、TSOT23-6パッケージ                                |

| LT6230/LT6231/LT6232                         | シングル/デュアル/クワッド215MHz、レール・トゥ・レール出力、低ノイズ、低消費電力アンプ  | 1.1nV/√Hz(100kHz)、最大3.5mA、最大オフセット:350μV                                          |

| LT6202/LT6203                                | シングル/デュアル100MHz、レール・トゥ・レール入力/出力、低ノイズ、低消費電力アンプ    | 1.9nV/√Hz(100kHz)、3mA(最大)、利得帯域幅:100MHz                                           |

| LT6350                                       | 低ノイズ、シングルエンドから差動へのADCドライバ                        | レール・トゥ・レールの入力および出力、0.01%へのセトリング時間:240ns                                          |

| LTC1992                                      | 低消費電力、完全差動入出力アンプ/ドライバ・ファミリ                       | 電源電流:1mA                                                                         |