入力同相電圧範囲の広い

デュアル18ビット、666ksps/チャネルの

差動SoftSpan A/Dコンバータ

## 特長

- スループット: 666ksps/チャネル

- 2つの同時サンプリング・チャネル

- INL(最大):  $\pm 4$ LSB

- 欠落コードのない18ビット分解能を保証

- 入力同相電圧範囲の広い差動入力

- チャネル当たりのSoftSpan入力電圧範囲:

$\pm 4.096V$ 、 $0V \sim 4.096V$ 、 $\pm 2.048V$ 、 $0V \sim 2.048V$

$\pm 5V$ 、 $0V \sim 5V$ 、 $\pm 2.5V$ 、 $0V \sim 2.5V$

- 1回の変換でのSNR: 95dB(標準)

- THD(標準): -114dB( $f_{IN} = 2kHz$ )

- CMRR(標準): 105dB( $f_{IN} = 200Hz$ )

- レール・トゥ・レールの入力オーバードライブ許容範囲

- 125°Cまでの動作を保証

- 内蔵リファレンスおよびバッファ(4.096V)

- SPI CMOS(1.8V～5V)およびLVDSシリアルI/O

- 内部変換クロック、サイクル待ち時間なし

- 電力損失: 74mW(標準)

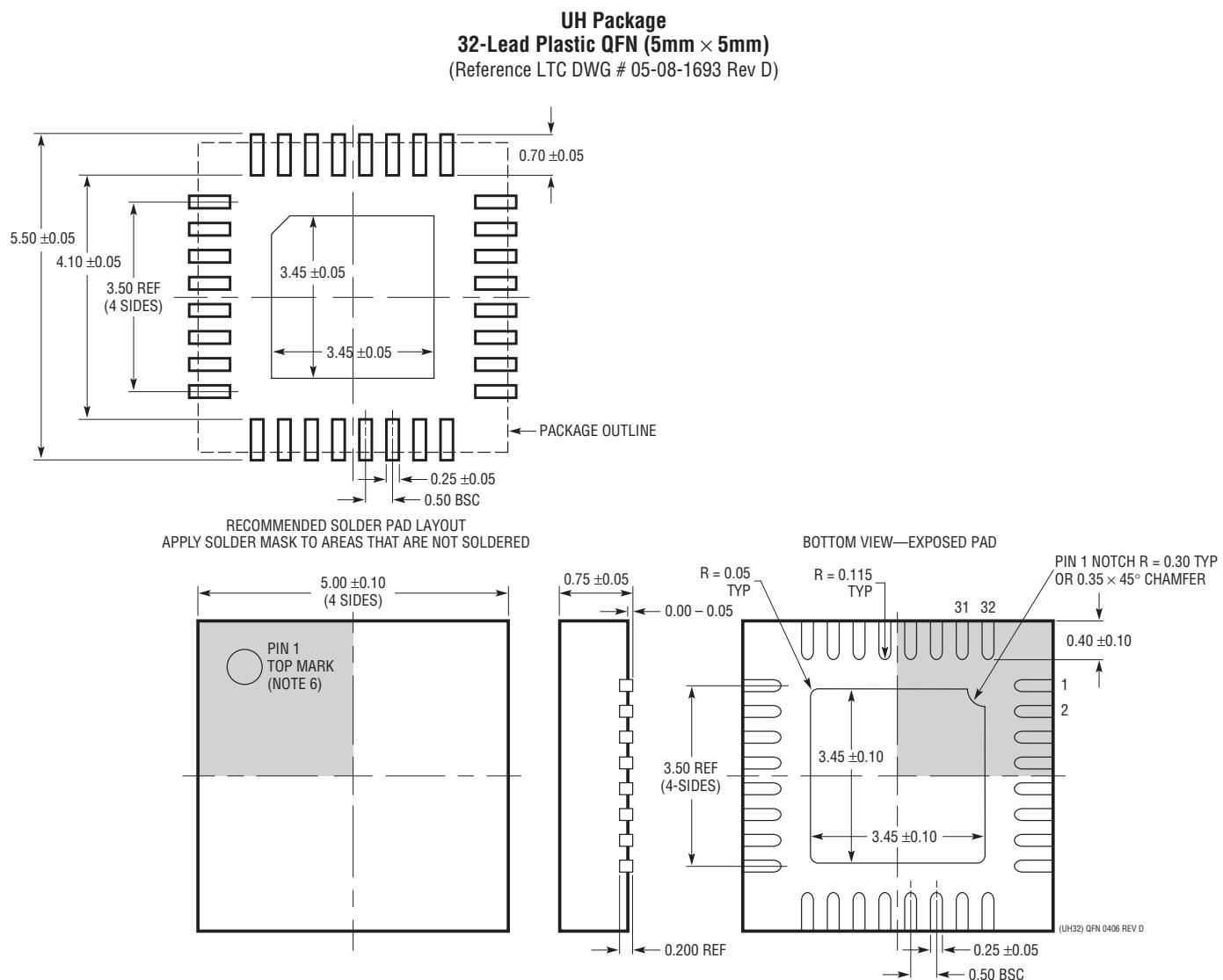

- 32ピン(5mm×5mm)QFNパッケージ

## アプリケーション

- プログラム可能なロジック・コントローラ

- 産業用プロセス制御

- 医療用画像処理

- 高速データ収集

## 概要

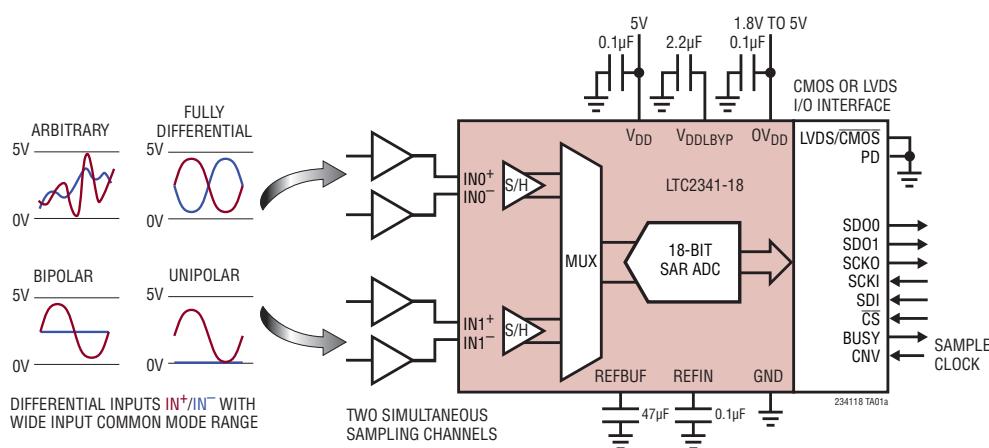

LTC<sup>®</sup>2341-18は、差動入力で入力同相電圧範囲の広い18ビット、低ノイズ、2チャネルの同時サンプリング逐次比較レジスタ(SAR)A/Dコンバータです。このSoftSpan<sup>TM</sup>A/Dコンバータは、5V電源で動作し、内部リファレンスおよびバッファを使用しており、両方のチャネルを変換ごとに独立して構成し、 $\pm 4.096V$ 、 $0V \sim 4.096V$ 、 $\pm 2.048V$ 、または $0V \sim 2.048V$ の信号を受け付けることができます。一方のチャネルをディスエーブルしてもう一方のチャネルのスループットを向上させることもできます。

LTC2341-18は、アナログ入力の入力同相電圧範囲が広く、CMRRが105dBなので、さまざまな信号を直接デジタル化して、シグナルチェーンの設計を簡略化することができます。この入力信号柔軟性と、 $\pm 4$ LSBのINL、18ビット分解能で欠落コードなし、95dBのSNRとが相まって、LTC2341-18は、広いダイナミックレンジが必要な多くのアプリケーションにとって理想的なデバイスになっています。

LTC2341-18は、ピンで選択可能なSPI CMOS(1.8V～5V)およびLVDSシリアル・インターフェースをサポートしています。CMOSモードでは1レーンまたは2レーンのデータ出力を採用することができるので、バスの幅およびスループットを最適化することができます。

**L**、**T**、**LTC**、**LTM**、**Linear Technology**およびLinearのロゴはリニアテクノロジー社の登録商標です。SoftSpanはリニアテクノロジー社の商標です。その他全ての商標の所有権は、それぞれの所有者に帰属します。7705765、7961132、8319673、9197235をはじめとする米国特許によって保護されています。

## 標準的応用例

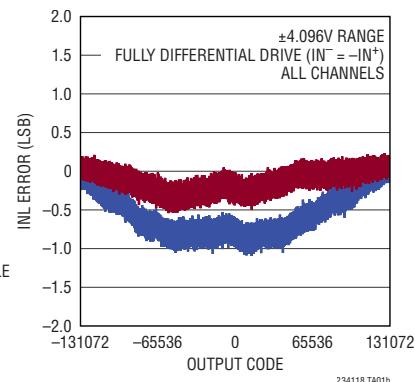

積分非直線性と

出力コードおよびチャネル

234118f

LTC2341-18

## 絶対最大定格

(Note 1, 2)

|                                                |                                |

|------------------------------------------------|--------------------------------|

| 電源電圧( $V_{DD}$ )                               | 6V                             |

| 電源電圧( $0V_{DD}$ )                              | 6V                             |

| 内部安定化電源のバイパス( $V_{DDLBYP}$ )                   | (Note 3)                       |

| アナログ入力電圧                                       |                                |

| $IN0^+$ 、 $IN1^+$ 、 $IN0^-$ 、 $IN1^-$ (Note 4) | $-0.3V \sim (V_{DD} + 0.3V)$   |

| REFIN                                          | $-0.3V \sim 2.8V$              |

| REFBUF、CNV (Note 4)                            | $-0.3V \sim (V_{DD} + 0.3V)$   |

| デジタル入力電圧 (Note 4)                              | $-0.3V \sim (0V_{DD} + 0.3V)$  |

| デジタル出力電圧 (Note 4)                              | $-0.3V \sim (0V_{DD} + 0.3V)$  |

| 電力損失                                           | 500mW                          |

| 動作温度範囲                                         |                                |

| LTC2341C                                       | $0^\circ C \sim 70^\circ C$    |

| LTC2341I                                       | $-40^\circ C \sim 85^\circ C$  |

| LTC2341H                                       | $-40^\circ C \sim 125^\circ C$ |

| 保存温度範囲                                         | $-65^\circ C \sim 150^\circ C$ |

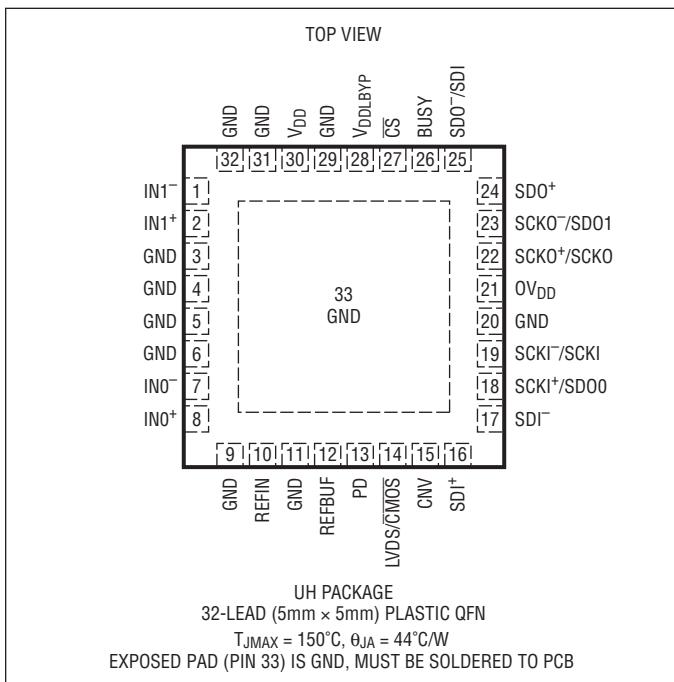

ピン配置

発注情報

<http://www.linear-tech.co.jp/product/LTC2341-18#orderinfo>

| 無鉛仕上げ             | テープ・アンド・リール         | 製品マーキング* | パッケージ                         | 温度範囲           |

|-------------------|---------------------|----------|-------------------------------|----------------|

| LTC2341CUH-18#PBF | LTC2341CUH-18#TRPBF | 234118   | 32-Lead (5mm×5mm) Plastic QFN | 0°C to 70°C    |

| LTC2341IUH-18#PBF | LTC2341IUH-18#TRPBF | 234118   | 32-Lead (5mm×5mm) Plastic QFN | -40°C to 85°C  |

| LTC2341HUH-18#PBF | LTC2341HUH-18#TRPBF | 234118   | 32-Lead (5mm×5mm) Plastic QFN | -40°C to 125°C |

更に広い動作温度範囲で規定されるデバイスについては、弊社または弊社代理店にお問い合わせください。\* 温度グレードは出荷時のコンテナのラベルで識別されます。

無鉛仕上げの製品マーキングの詳細については、<http://www.linear-tech.co.jp/leadfree/>をご覧ください。

テープ・アンド・リールの仕様の詳細については、<http://www.linear-tech.co.jp/tapeandreel/>をご覧ください。

一部のパッケージは、**#TRMPBF** 搭尾部を付けることにより、指定の販売経路を通じて 500 個入りのリールで供給可能です。

## 電気的特性

●は全動作温度範囲での規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値(Note 5)。

| SYMBOL              | PARAMETER                                    | CONDITIONS                                                                                                                                                                                                                                                                                                                                                                                  | MIN                                  | TYP                                                                                                                 | MAX                                                                                                                                                          | UNITS                           |

|---------------------|----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|---------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

| $V_{IN+}$           | Absolute Input Range ( $IN_0^+$ , $IN_1^+$ ) | (Note 6)                                                                                                                                                                                                                                                                                                                                                                                    | ●                                    | 0                                                                                                                   | $V_{DD}$                                                                                                                                                     | V                               |

| $V_{IN-}$           | Absolute Input Range ( $IN_0^-$ , $IN_1^-$ ) | (Note 6)                                                                                                                                                                                                                                                                                                                                                                                    | ●                                    | 0                                                                                                                   | $V_{DD}$                                                                                                                                                     | V                               |

| $V_{IN+} - V_{IN-}$ | Input Differential Voltage Range             | SoftSpan 7: $\pm V_{REFBUF}$ Range (Note 6)<br>SoftSpan 6: $\pm V_{REFBUF}/1.024$ Range (Note 6)<br>SoftSpan 5: 0V to $V_{REFBUF}$ Range (Note 6)<br>SoftSpan 4: 0V to $V_{REFBUF}/1.024$ Range (Note 6)<br>SoftSpan 3: $\pm 0.5 \cdot V_{REFBUF}$ Range (Note 6)<br>SoftSpan 2: $\pm 0.5 \cdot V_{REFBUF}/1.024$ Range (Note 6)<br>SoftSpan 1: 0V to $0.5 \cdot V_{REFBUF}$ Range (Note 6) | ●<br>●<br>●<br>●<br>●<br>●<br>●<br>● | - $V_{REFBUF}$<br>- $V_{REFBUF}/1.024$<br>0<br>0<br>- $0.5 \cdot V_{REFBUF}$<br>- $0.5 \cdot V_{REFBUF}/1.024$<br>0 | $V_{REFBUF}$<br>$V_{REFBUF}/1.024$<br>$V_{REFBUF}$<br>$V_{REFBUF}/1.024$<br>$0.5 \cdot V_{REFBUF}$<br>$0.5 \cdot V_{REFBUF}/1.024$<br>$0.5 \cdot V_{REFBUF}$ | V<br>V<br>V<br>V<br>V<br>V<br>V |

| $V_{CM}$            | Input Common Mode Voltage Range              | (Note 6)                                                                                                                                                                                                                                                                                                                                                                                    | ●                                    | 0                                                                                                                   | $V_{DD}$                                                                                                                                                     | V                               |

| $V_{IN+} - V_{IN-}$ | Input Differential Overdrive Tolerance       | (Note 7)                                                                                                                                                                                                                                                                                                                                                                                    | ●                                    | - $V_{DD}$                                                                                                          | $V_{DD}$                                                                                                                                                     | V                               |

| $I_{IN}$            | Analog Input Leakage Current                 |                                                                                                                                                                                                                                                                                                                                                                                             | ●                                    | -1                                                                                                                  | 1                                                                                                                                                            | $\mu\text{A}$                   |

| $C_{IN}$            | Analog Input Capacitance                     | Sample Mode<br>Hold Mode                                                                                                                                                                                                                                                                                                                                                                    |                                      |                                                                                                                     | 90<br>10                                                                                                                                                     | pF<br>pF                        |

| CMRR                | Input Common Mode Rejection Ratio            | $V_{IN+} = V_{IN-} = 3.6\text{V}_{\text{P-P}}$ 200Hz Sine                                                                                                                                                                                                                                                                                                                                   | ●                                    | 88                                                                                                                  | 105                                                                                                                                                          | dB                              |

| $V_{IHCNV}$         | CNV High Level Input Voltage                 |                                                                                                                                                                                                                                                                                                                                                                                             | ●                                    | 1.3                                                                                                                 |                                                                                                                                                              | V                               |

| $V_{ILCNV}$         | CNV Low Level Input Voltage                  |                                                                                                                                                                                                                                                                                                                                                                                             | ●                                    |                                                                                                                     | 0.5                                                                                                                                                          | V                               |

| $I_{INCNV}$         | CNV Input Current                            | $V_{IN} = 0\text{V}$ to $V_{DD}$                                                                                                                                                                                                                                                                                                                                                            | ●                                    | -10                                                                                                                 | 10                                                                                                                                                           | $\mu\text{A}$                   |

## コンバータ特性

●は全動作温度範囲での規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値(Note 8)。

| SYMBOL | PARAMETER                    | CONDITIONS                                                                                                                                                                                                                      | MIN | TYP   | MAX                      | UNITS                                                                                |                              |

|--------|------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------|--------------------------|--------------------------------------------------------------------------------------|------------------------------|

|        | Resolution                   |                                                                                                                                                                                                                                 | ●   | 18    |                          | Bits                                                                                 |                              |

|        | No Missing Codes             |                                                                                                                                                                                                                                 | ●   | 18    |                          | Bits                                                                                 |                              |

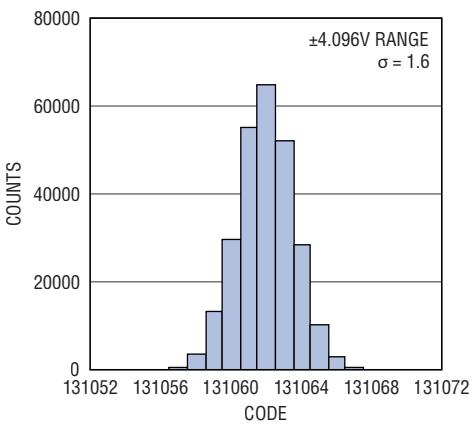

|        | Transition Noise             | SoftSpans 7 and 6: $\pm 4.096\text{V}$ and $\pm 4\text{V}$ Ranges<br>SoftSpans 5 and 4: 0V to 4.096V and 0V to 4V Ranges<br>SoftSpans 3 and 2: $\pm 2.048\text{V}$ and $\pm 2\text{V}$ Ranges<br>SoftSpan 1: 0V to 2.048V Range |     |       | 1.6<br>3.2<br>3.2<br>6.3 | LSB <sub>RMS</sub><br>LSB <sub>RMS</sub><br>LSB <sub>RMS</sub><br>LSB <sub>RMS</sub> |                              |

| INL    | Integral Linearity Error     | (Note 9)                                                                                                                                                                                                                        | ●   | -4    | $\pm 1.5$                | 4                                                                                    | LSB                          |

| DNL    | Differential Linearity Error | (Note 10)                                                                                                                                                                                                                       | ●   | -0.9  | $\pm 0.5$                | 0.9                                                                                  | LSB                          |

| ZSE    | Zero-Scale Error             | (Note 11)                                                                                                                                                                                                                       | ●   | -500  | $\pm 50$                 | 500                                                                                  | $\mu\text{V}$                |

|        | Zero-Scale Error Drift       |                                                                                                                                                                                                                                 |     |       | $\pm 2$                  |                                                                                      | $\mu\text{V}/^\circ\text{C}$ |

| FSE    | Full-Scale Error             | $V_{REFBUF} = 4.096\text{V}$ (REFBUF Overdriven) (Note 11)                                                                                                                                                                      | ●   | -0.13 | $\pm 0.025$              | 0.13                                                                                 | %FS                          |

|        | Full-Scale Error Drift       |                                                                                                                                                                                                                                 |     |       | $\pm 2.5$                |                                                                                      | ppm/ $^\circ\text{C}$        |

## ダイナミック精度

●は全動作温度範囲での規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。 $A_{IN} = -1\text{dBFS}$ 。(Note 8、12)

| SYMBOL | PARAMETER                            | CONDITIONS                                                                                                     |   | MIN  | TYP  | MAX | UNITS |

|--------|--------------------------------------|----------------------------------------------------------------------------------------------------------------|---|------|------|-----|-------|

| SINAD  | Signal-to-(Noise + Distortion) Ratio | SoftSpans 7 and 6: $\pm 4.096\text{V}$ and $\pm 4\text{V}$ Ranges, $f_{IN} = 2\text{kHz}$                      | ● | 91.0 | 95.0 |     | dB    |

|        |                                      | SoftSpans 5 and 4: 0V to 4.096V and 0V to 4V Ranges, $f_{IN} = 2\text{kHz}$                                    | ● | 85.0 | 89.1 |     | dB    |

|        |                                      | SoftSpans 3 and 2: $\pm 2.048\text{V}$ and $\pm 2\text{V}$ Ranges, $f_{IN} = 2\text{kHz}$                      | ● | 85.1 | 89.1 |     | dB    |

|        |                                      | SoftSpan 1: 0V to 2.048V Range, $f_{IN} = 2\text{kHz}$                                                         | ● | 79.3 | 83.3 |     | dB    |

| SNR    | Signal-to-Noise Ratio                | SoftSpans 7 and 6: $\pm 4.096\text{V}$ and $\pm 4\text{V}$ Ranges, $f_{IN} = 2\text{kHz}$                      | ● | 91.1 | 95.0 |     | dB    |

|        |                                      | SoftSpans 5 and 4: 0V to 4.096V and 0V to 4V Ranges, $f_{IN} = 2\text{kHz}$                                    | ● | 85.2 | 89.1 |     | dB    |

|        |                                      | SoftSpans 3 and 2: $\pm 2.048\text{V}$ and $\pm 2\text{V}$ Ranges, $f_{IN} = 2\text{kHz}$                      | ● | 85.1 | 89.1 |     | dB    |

|        |                                      | SoftSpan 1: 0V to 2.048V Range, $f_{IN} = 2\text{kHz}$                                                         | ● | 79.3 | 83.3 |     | dB    |

| THD    | Total Harmonic Distortion            | SoftSpans 7 and 6: $\pm 4.096\text{V}$ and $\pm 4\text{V}$ Ranges, $f_{IN} = 2\text{kHz}$                      | ● |      | -114 | -99 | dB    |

|        |                                      | SoftSpans 5 and 4: 0V to 4.096V and 0V to 4V Ranges, $f_{IN} = 2\text{kHz}$                                    | ● |      | -111 | -95 | dB    |

|        |                                      | SoftSpans 3 and 2: $\pm 2.048\text{V}$ and $\pm 2\text{V}$ Ranges, $f_{IN} = 2\text{kHz}$                      | ● |      | -110 | -95 | dB    |

|        |                                      | SoftSpan 1: 0V to 2.048V Range, $f_{IN} = 2\text{kHz}$                                                         | ● |      | -109 | -95 | dB    |

| SFDR   | Spurious Free Dynamic Range          | SoftSpans 7 and 6: $\pm 4.096\text{V}$ and $\pm 4\text{V}$ Ranges, $f_{IN} = 2\text{kHz}$                      | ● | 99   | 115  |     | dB    |

|        |                                      | SoftSpans 5 and 4: 0V to 4.096V and 0V to 4V Ranges, $f_{IN} = 2\text{kHz}$                                    | ● | 95   | 112  |     | dB    |

|        |                                      | SoftSpans 3 and 2: $\pm 2.048\text{V}$ and $\pm 2\text{V}$ Ranges, $f_{IN} = 2\text{kHz}$                      | ● | 95   | 111  |     | dB    |

|        |                                      | SoftSpan 1: 0V to 2.048V Range, $f_{IN} = 2\text{kHz}$                                                         | ● | 95   | 110  |     | dB    |

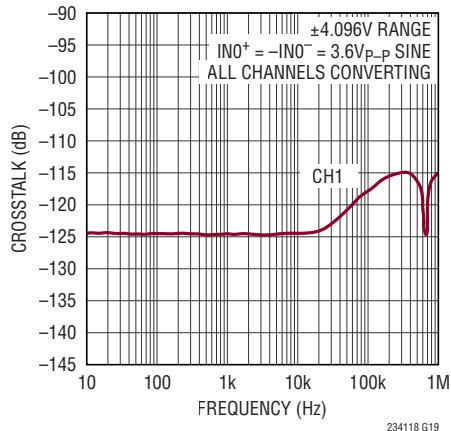

|        | Channel-to-Channel Crosstalk         | One Channel Converting 3.6V <sub>P-P</sub> 200Hz Sine in $\pm 2.048\text{V}$ Range, Crosstalk to Other Channel |   |      | -119 |     | dB    |

|        | -3dB Input Bandwidth                 |                                                                                                                |   |      | 22   |     | MHz   |

|        | Aperture Delay                       |                                                                                                                |   |      | 1    |     | ns    |

|        | Aperture Delay Matching              |                                                                                                                |   |      | 150  |     | ps    |

|        | Aperture Jitter                      |                                                                                                                |   |      | 3    |     | psRMS |

|        | Transient Response                   | Full-Scale Step, 0.005% Settling                                                                               |   |      | 210  |     | ns    |

## 内部リファレンスの特性

●は全動作温度範囲での規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値(Note 8)。

| SYMBOL      | PARAMETER                                  | CONDITIONS                                |   | MIN   | TYP   | MAX   | UNITS  |

|-------------|--------------------------------------------|-------------------------------------------|---|-------|-------|-------|--------|

| $V_{REFIN}$ | Internal Reference Output Voltage          |                                           |   | 2.043 | 2.048 | 2.053 | V      |

|             | Internal Reference Temperature Coefficient | (Note 13)                                 | ● |       | 5     | 20    | ppm/°C |

|             | Internal Reference Line Regulation         | $V_{DD} = 4.75\text{V}$ to $5.25\text{V}$ |   |       | 0.1   |       | mV/V   |

|             | Internal Reference Output Impedance        |                                           |   |       | 20    |       | kΩ     |

| $V_{REFIN}$ | REFIN Voltage Range                        | REFIN Overdriven (Note 6)                 |   | 1.25  |       | 2.2   | V      |

## リファレンス・バッファ特性

●は全動作温度範囲での規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値(Note 8)。

| SYMBOL       | PARAMETER                       | CONDITIONS                                                                                                            |   | MIN   | TYP         | MAX   | UNITS                      |

|--------------|---------------------------------|-----------------------------------------------------------------------------------------------------------------------|---|-------|-------------|-------|----------------------------|

| $V_{REFBUF}$ | Reference Buffer Output Voltage | REFIN Overdriven, $V_{REFIN} = 2.048\text{V}$                                                                         | ● | 4.091 | 4.096       | 4.101 | V                          |

|              | REFBUF Voltage Range            | REFBUF Overdriven (Notes 6, 14)                                                                                       | ● | 2.5   |             | 5     | V                          |

|              | REFBUF Input Impedance          | $V_{REFIN} = 0\text{V}$ , Buffer Disabled                                                                             |   |       | 13          |       | $\text{k}\Omega$           |

| $I_{REFBUF}$ | REFBUF Load Current             | $V_{REFBUF} = 5\text{V}$ , 2 Channels Enabled (Notes 14, 15)<br>$V_{REFBUF} = 5\text{V}$ , Acquisition Mode (Note 14) | ● |       | 1.3<br>0.35 | 1.6   | $\text{mA}$<br>$\text{mA}$ |

## デジタル入力とデジタル出力

●は全動作温度範囲での規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値(Note 8)。

| SYMBOL                 | PARAMETER                            | CONDITIONS                                                   |   | MIN             | TYP             | MAX | UNITS                 |

|------------------------|--------------------------------------|--------------------------------------------------------------|---|-----------------|-----------------|-----|-----------------------|

| <b>CMOSデジタル入力および出力</b> |                                      |                                                              |   |                 |                 |     |                       |

| $V_{IH}$               | High Level Input Voltage             |                                                              | ● | 0.8 • $0V_{DD}$ |                 |     | V                     |

| $V_{IL}$               | Low Level Input Voltage              |                                                              | ● |                 | 0.2 • $0V_{DD}$ |     | V                     |

| $I_{IN}$               | Digital Input Current                | $V_{IN} = 0\text{V}$ to $0V_{DD}$                            | ● | -10             |                 | 10  | $\mu\text{A}$         |

| $C_{IN}$               | Digital Input Capacitance            |                                                              |   |                 | 5               |     | $\text{pF}$           |

| $V_{OH}$               | High Level Output Voltage            | $I_{OUT} = -500\mu\text{A}$                                  | ● | $0V_{DD} - 0.2$ |                 |     | V                     |

| $V_{OL}$               | Low Level Output Voltage             | $I_{OUT} = 500\mu\text{A}$                                   | ● |                 | 0.2             |     | V                     |

| $I_{OZ}$               | Hi-Z Output Leakage Current          | $V_{OUT} = 0\text{V}$ to $0V_{DD}$                           | ● | -10             |                 | 10  | $\mu\text{A}$         |

| $I_{SOURCE}$           | Output Source Current                | $V_{OUT} = 0\text{V}$                                        |   |                 | -50             |     | $\text{mA}$           |

| $I_{SINK}$             | Output Sink Current                  | $V_{OUT} = 0V_{DD}$                                          |   |                 | 50              |     | $\text{mA}$           |

| <b>LVDSデジタル入力および出力</b> |                                      |                                                              |   |                 |                 |     |                       |

| $V_{ID}$               | Differential Input Voltage           |                                                              | ● | 200             | 350             | 600 | $\text{mV}$           |

| $R_{ID}$               | On-Chip Input Termination Resistance | $CS = 0\text{V}$ , $V_{ICM} = 1.2\text{V}$<br>$CS = 0V_{DD}$ | ● | 80<br>10        | 106             | 130 | $\Omega$<br>$M\Omega$ |

| $V_{ICM}$              | Common-Mode Input Voltage            |                                                              | ● | 0.3             | 1.2             | 2.2 | V                     |

| $I_{ICM}$              | Common-Mode Input Current            | $V_{IN+} = V_{IN-} = 0\text{V}$ to $0V_{DD}$                 | ● | -10             |                 | 10  | $\mu\text{A}$         |

| $V_{OD}$               | Differential Output Voltage          | $R_L = 100\Omega$ Differential Termination                   | ● | 275             | 350             | 425 | $\text{mV}$           |

| $V_{OCM}$              | Common-Mode Output Voltage           | $R_L = 100\Omega$ Differential Termination                   | ● | 1.1             | 1.2             | 1.3 | V                     |

| $I_{OZ}$               | Hi-Z Output Leakage Current          | $V_{OUT} = 0\text{V}$ to $0V_{DD}$                           | ● | -10             |                 | 10  | $\mu\text{A}$         |

## 電源要件

●は全動作温度範囲での規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値(Note 8)。

| SYMBOL              | PARAMETER         | CONDITIONS                                                                                                                                                                                                       |                       | MIN                             | TYP                               | MAX  | UNITS                                            |

|---------------------|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|---------------------------------|-----------------------------------|------|--------------------------------------------------|

| <b>CMOS I/O モード</b> |                   |                                                                                                                                                                                                                  |                       |                                 |                                   |      |                                                  |

| $V_{DD}$            | Supply Voltage    |                                                                                                                                                                                                                  | ●                     | 4.75                            | 5.00                              | 5.25 | V                                                |

| $0V_{DD}$           | Supply Voltage    |                                                                                                                                                                                                                  | ●                     | 1.71                            |                                   | 5.25 | V                                                |

| $I_{VDD}$           | Supply Current    | 666ksps Sample Rate, 2 Channels Enabled<br>666ksps Sample Rate, 2 Channels Enabled, $V_{REFBUF} = 5\text{V}$ (Note 14)<br>Acquisition Mode<br>Power Down Mode (C-Grade and I-Grade)<br>Power Down Mode (H-Grade) | ●<br>●<br>●<br>●<br>● | 13.7<br>12.3<br>1.2<br>65<br>65 | 16.0<br>14.8<br>2.0<br>225<br>500 |      | mA<br>mA<br>mA<br>$\mu\text{A}$<br>$\mu\text{A}$ |

| $I_{0VDD}$          | Supply Current    | 666ksps Sample Rate, 2 Channels Enabled ( $C_L = 25\text{pF}$ )<br>Acquisition Mode<br>Power Down Mode                                                                                                           | ●<br>●<br>●           | 2.2<br>1<br>1                   | 3.4<br>20<br>20                   |      | mA<br>$\mu\text{A}$<br>$\mu\text{A}$             |

| $P_D$               | Power Dissipation | 666ksps Sample Rate, 2 Channels Enabled<br>Acquisition Mode<br>Power Down Mode (C-Grade and I-Grade)<br>Power Down Mode (H-Grade)                                                                                | ●<br>●<br>●<br>●      | 74<br>6.0<br>0.33<br>0.33       | 89<br>10<br>1.2<br>2.6            |      | mW<br>mW<br>mW<br>mW                             |

| <b>LVDS I/O モード</b> |                   |                                                                                                                                                                                                                  |                       |                                 |                                   |      |                                                  |

| $V_{DD}$            | Supply Voltage    |                                                                                                                                                                                                                  | ●                     | 4.75                            | 5.00                              | 5.25 | V                                                |

| $0V_{DD}$           | Supply Voltage    |                                                                                                                                                                                                                  | ●                     | 2.375                           |                                   | 5.25 | V                                                |

| $I_{VDD}$           | Supply Current    | 666ksps Sample Rate, 2 Channels Enabled<br>666ksps Sample Rate, 2 Channels Enabled, $V_{REFBUF} = 5\text{V}$ (Note 14)<br>Acquisition Mode<br>Power Down Mode (C-Grade and I-Grade)<br>Power Down Mode (H-Grade) | ●<br>●<br>●<br>●<br>● | 15.7<br>14.4<br>2.7<br>65<br>65 | 18.0<br>16.8<br>3.8<br>225<br>500 |      | mA<br>mA<br>mA<br>$\mu\text{A}$<br>$\mu\text{A}$ |

| $I_{0VDD}$          | Supply Current    | 666ksps Sample Rate, 2 Channels Enabled ( $R_L = 100\Omega$ )<br>Acquisition Mode ( $R_L = 100\Omega$ )<br>Power Down Mode                                                                                       | ●<br>●<br>●           | 7.4<br>7<br>1                   | 9.5<br>8.2<br>20                  |      | mA<br>mA<br>$\mu\text{A}$                        |

| $P_D$               | Power Dissipation | 666ksps Sample Rate, 2 Channels Enabled<br>Acquisition Mode<br>Power Down Mode (C-Grade and I-Grade)<br>Power Down Mode (H-Grade)                                                                                | ●<br>●<br>●<br>●      | 97<br>31<br>0.33<br>0.33        | 114<br>40<br>1.2<br>2.6           |      | mW<br>mW<br>mW<br>mW                             |

## A/Dコンバータのタイミング特性

●は全動作温度範囲での規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値(Note 8)。

| SYMBOL     | PARAMETER                  | CONDITIONS                                                                                         |        | MIN                                          | TYP | MAX         | UNITS        |

|------------|----------------------------|----------------------------------------------------------------------------------------------------|--------|----------------------------------------------|-----|-------------|--------------|

| $f_{SMPL}$ | Maximum Sampling Frequency | 2 Channels Enabled<br>1 Channel Enabled                                                            | ●<br>● |                                              |     | 666<br>1000 | ksps<br>ksps |

| $t_{CYC}$  | Time Between Conversions   | 2 Channels Enabled, $f_{SMPL} = 666\text{ksps}$<br>1 Channel Enabled, $f_{SMPL} = 1000\text{ksps}$ | ●<br>● | 1500<br>1000                                 |     |             | ns<br>ns     |

| $t_{CONV}$ | Conversion Time            | N Channels Enabled, $1 \leq N \leq 2$                                                              | ●      | 450 • N - 40<br>500 • N - 40<br>550 • N - 40 |     |             | ns           |

**A/Dコンバータのタイミング特性**

●は全動作温度範囲での規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値(Note 8)。

| SYMBOL       | PARAMETER                                                           | CONDITIONS                                                                                         | MIN    | TYP        | MAX        | UNITS    |

|--------------|---------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|--------|------------|------------|----------|

| $t_{ACQ}$    | Acquisition Time<br>( $t_{ACQ} = t_{CYC} - t_{CONV} - t_{BUSYLH}$ ) | 2 Channels Enabled, $f_{SMPL} = 666\text{kspS}$<br>1 Channel Enabled, $f_{SMPL} = 1000\text{kspS}$ | ●<br>● | 410<br>460 | 520<br>520 | ns<br>ns |

| $t_{CNVH}$   | CNV High Time                                                       |                                                                                                    | ●      | 40         |            | ns       |

| $t_{CNVL}$   | CNV Low Time                                                        |                                                                                                    | ●      | 410        |            | ns       |

| $t_{BUSYLH}$ | CNV↑ to BUSY Delay                                                  | $C_L = 25\text{pF}$                                                                                | ●      |            | 30         | ns       |

| $t_{QUIET}$  | Digital I/O Quiet Time from CNV↑                                    |                                                                                                    | ●      | 20         |            | ns       |

| $t_{PDH}$    | PD High Time                                                        |                                                                                                    | ●      | 40         |            | ns       |

| $t_{PDL}$    | PD Low Time                                                         |                                                                                                    | ●      | 40         |            | ns       |

| $t_{WAKE}$   | REFBUF Wake-Up Time                                                 | $C_{REFBUF} = 47\text{\mu F}$ , $C_{REFIN} = 0.1\text{\mu F}$                                      |        |            | 200        | ms       |

**CMOS I/O モード**

|                 |                                                    |                               |   |        |     |    |

|-----------------|----------------------------------------------------|-------------------------------|---|--------|-----|----|

| $t_{SCKI}$      | SCKI Period                                        | (Note 16, 17)                 | ● | 10     |     | ns |

| $t_{SCKIH}$     | SCKI High Time                                     |                               | ● | 4      |     | ns |

| $t_{SCKIL}$     | SCKI Low Time                                      |                               | ● | 4      |     | ns |

| $t_{SSDISCKI}$  | SDI Setup Time from SCKI↑                          | (Note 16)                     | ● | 2      |     | ns |

| $t_{HSDISCKI}$  | SDI Hold Time from SCKI↑                           | (Note 16)                     | ● | 1      |     | ns |

| $t_{DSDOSCKI}$  | SDO Data Valid Delay from SCKI↑                    | $C_L = 25\text{pF}$ (Note 16) | ● |        | 7.5 | ns |

| $t_{HS DOSCKI}$ | SDO Remains Valid Delay from SCKI↑                 | $C_L = 25\text{pF}$ (Note 16) | ● | 1.5    |     | ns |

| $t_{SKew}$      | SDO to SCKO Skew                                   | (Note 16)                     | ● | -1 0 1 | 0 1 | ns |

| $t_{DSDOBUSYL}$ | SDO Data Valid Delay from BUSY ↓                   | $C_L = 25\text{pF}$ (Note 16) | ● | 0      |     | ns |

| $t_{EN}$        | Bus Enable Time After $\overline{CS} \downarrow$   | (Note 16)                     | ● |        | 15  | ns |

| $t_{DIS}$       | Bus Relinquish Time After $\overline{CS} \uparrow$ | (Note 16)                     | ● |        | 15  | ns |

**LVDS I/O モード**

|                 |                                                    |                |   |            |       |    |

|-----------------|----------------------------------------------------|----------------|---|------------|-------|----|

| $t_{SCKI}$      | SCKI Period                                        | (Note 18)      | ● | 4          |       | ns |

| $t_{SCKIH}$     | SCKI High Time                                     | (Note 18)      | ● | 1.5        |       | ns |

| $t_{SCKIL}$     | SCKI Low Time                                      | (Note 18)      | ● | 1.5        |       | ns |

| $t_{SSDISCKI}$  | SDI Setup Time from SCKI                           | (Notes 10, 18) | ● | 1.2        |       | ns |

| $t_{HS DISCKI}$ | SDI Hold Time from SCKI                            | (Notes 10, 18) | ● | -0.2       |       | ns |

| $t_{DSDOSCKI}$  | SDO Data Valid Delay from SCKI                     | (Notes 10, 18) | ● |            | 6     | ns |

| $t_{HS DOSCKI}$ | SDO Remains Valid Delay from SCKI                  | (Notes 10, 18) | ● | 1          |       | ns |

| $t_{SKew}$      | SDO to SCKO Skew                                   | (Note 10)      | ● | -0.4 0 0.4 | 0 0.4 | ns |

| $t_{DSDOBUSYL}$ | SDO Data Valid Delay from BUSY ↓                   | (Note 10)      | ● | 0          |       | ns |

| $t_{EN}$        | Bus Enable Time After $\overline{CS} \downarrow$   |                | ● |            | 50    | ns |

| $t_{DIS}$       | Bus Relinquish Time After $\overline{CS} \uparrow$ |                | ● |            | 15    | ns |

## A/Dコンバータのタイミング特性

**Note 1:** 絶対最大定格に記載された値を超えるストレスはデバイスに永続的損傷を与える可能性がある。また、長期にわたって絶対最大定格条件に曝すと、デバイスの信頼性と寿命に悪影響を与えるおそれがある。

**Note 2:** 全ての電圧値はグラウンドを基準にしている。

**Note 3:**  $V_{DDLBY}$  は内部電圧レギュレータの出力であり、「ピン機能」のセクションで説明するように、 $2.2\mu F$  のセラミック・コンデンサにのみ接続して、このピンを GND にバイパスする。このピンはどの外部回路にも接続しないでください。

**Note 4:** これらのピンの電圧をグラウンドより低くするか、 $V_{DD}$  ピンまたは  $0V_{DD}$  ピンの電圧より高くすると、内部のダイオードによってクランプされる。この製品は、これらのピンの電圧がグラウンドより低くなるか、 $V_{DD}$  ピンまたは  $0V_{DD}$  ピンの電圧より高くなった場合でも、ラッチアップを生じることなく最大 100mA の電流を処理できる。

**Note 5:** 特に規定がない限り、 $V_{DD} = 5V$ 。

**Note 6:** 推奨動作条件。

**Note 7:** 一方のチャネルでこれらの制限値を超えると、もう一方のチャネルの変換結果が破損することがある。デバイスの信頼性に関係するピン電圧の制限値については、「絶対最大定格」のセクションを参照。

**Note 8:** 特に規定がない限り、 $V_{DD} = 5V$ 、 $0V_{DD} = 2.5V$ 、 $f_{SMPL} = 666ksps$ 、内部リファレンスおよびバッファ、SoftSpan範囲7および6では完全差動入力信号駆動、SoftSpan範囲3および2では両極性入力信号駆動、SoftSpan範囲5、4、および1では単極性入力信号駆動。

**Note 9:** 積分非直線性は、実際の伝達曲線の端点を通る直線からのコードの偏差として定義されている。偏差は量子化幅の中心から測定される。

**Note 10:** 設計によって保証されているが、テストされない。

**Note 11:** 両極性 SoftSpan の範囲が 7、6、3、および 2 の場合、ゼロスケール誤差は、出力コードが 00 0000 0000 0000 と 11 1111 1111 1111 の間を往復しているときに、-0.5LSB から測定されたオフセット電圧である。これらの SoftSpan 範囲でのフルスケール誤差は、最初と最後のコード遷移の理想値からのワーストケース偏差であり、オフセット誤差の影響を含む。単極性 SoftSpan の範囲が 5、4、および 1 の場合、ゼロスケール誤差は、出力コードが 00 0000 0000 0000 と 00 0000 0000 0001 の間を往復しているときに、0.5LSB から測定されたオフセット電圧である。これらの SoftSpan 範囲でのフルスケール誤差は、最後のコード遷移の理想値からのワーストケース偏差であり、オフセット誤差の影響を含む。

**Note 12:** dB 単位での全ての規定値は、該当する SoftSpan 入力範囲内のフルスケール入力を基準にしている。ただし、クロストークの場合はクロストーク注入信号の振幅を基準とするので除外する。

**Note 13:** 温度係数は出力電圧の最大変化を規定温度範囲で割って計算される。

**Note 14:** REFBUF をオーバードライブする場合は、REFIN = 0V に設定して内部リファレンス・バッファをディスエーブルする必要がある。

**Note 15:**  $I_{REFBUF}$  はサンプリングレートと動作状態のチャネル数に比例して変化する。

**Note 16:** パラメータは  $V_{DD} = 1.71V$ 、 $0V_{DD} = 2.5V$ 、および  $0V_{DD} = 5.25V$  でテストされ、保証されている。

**Note 17:**  $t_{SCKI}$  周期は最小 10ns ので、立ち上がりエッジで取り込む場合は最大 100MHz のシフト・クロック周波数が可能。

**Note 18:** LVDS 差動入力対では、 $V_{ICM} = 1.2V$ 、 $V_{ID} = 350mV$ 。

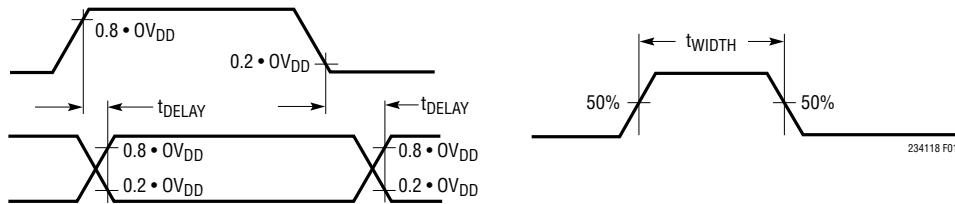

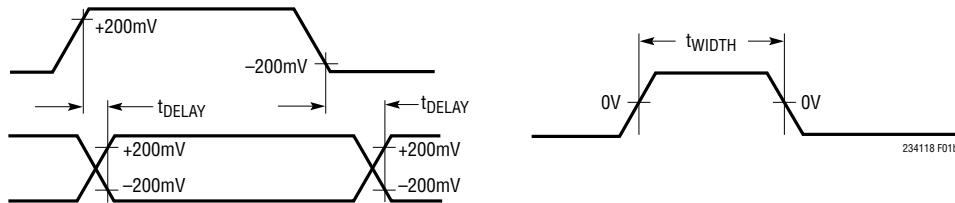

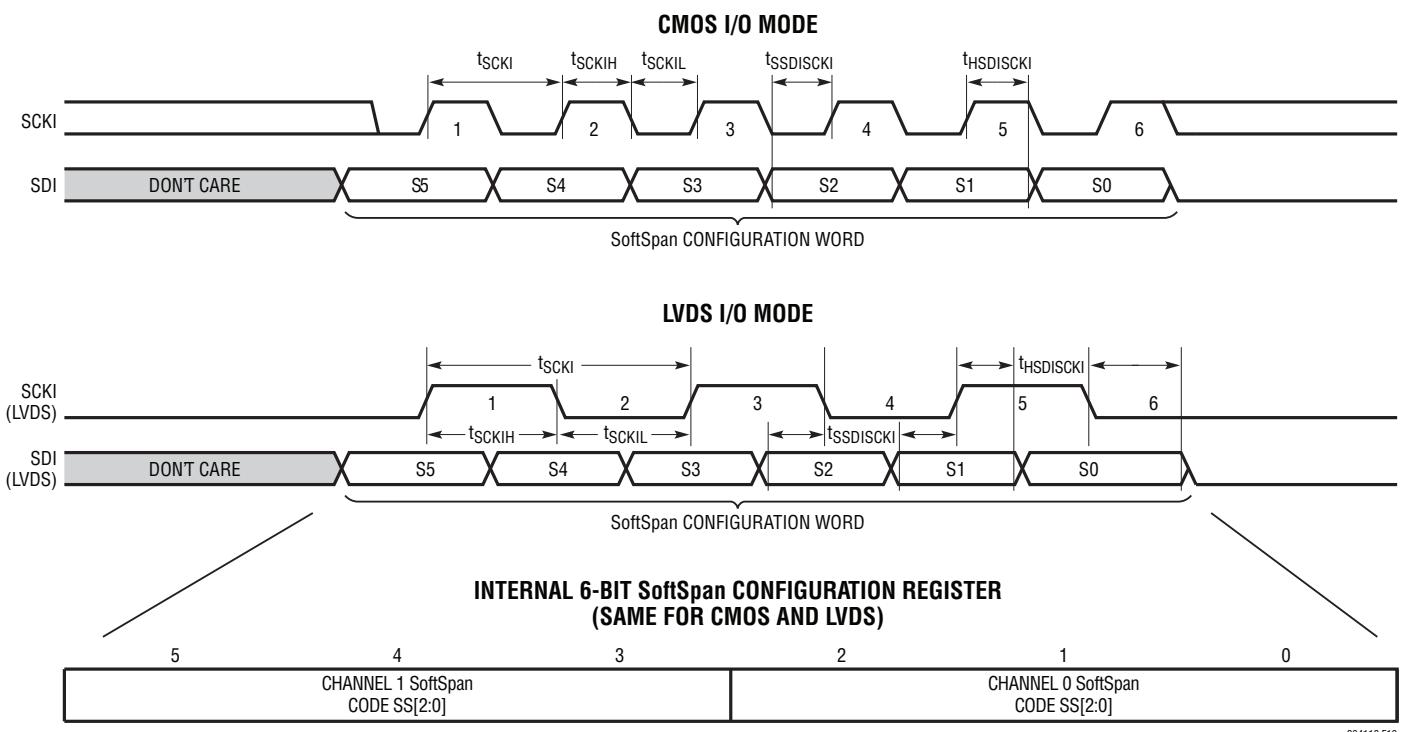

### CMOS のタイミング

### LVDS のタイミング(差動)

図1. タイミング仕様の電圧レベル

## 標準的性能特性

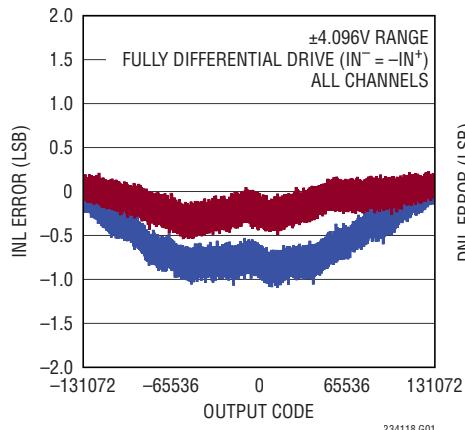

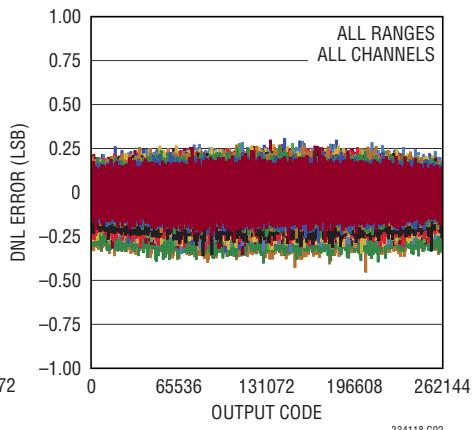

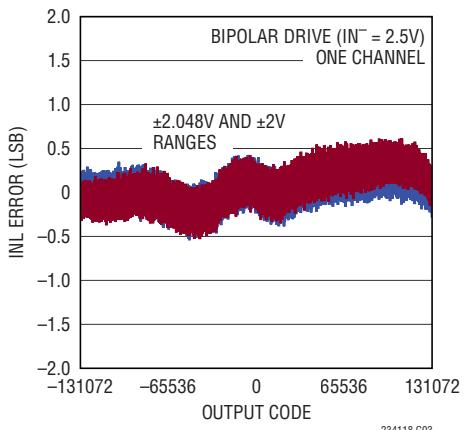

注記がない限り、 $T_A = 25^\circ\text{C}$ 、 $V_{DD} = 5\text{V}$ 、 $OV_{DD} = 2.5\text{V}$ 、内部リファレンスおよびバッファ ( $V_{REFBUF} = 4.096\text{V}$ )、 $f_{SMPL} = 666\text{kspS}$ 。

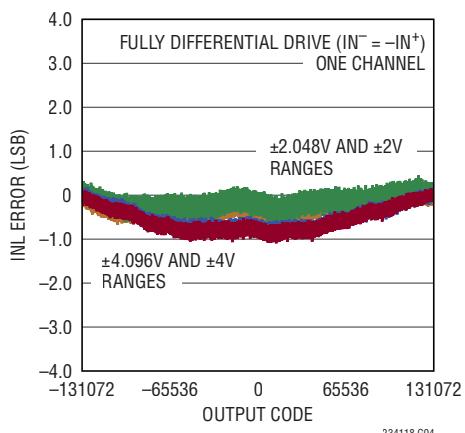

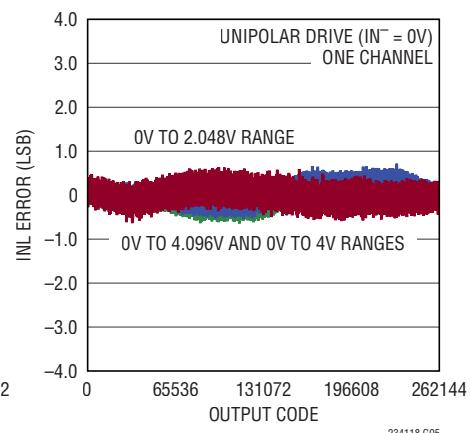

積分非直線性と

出力コードおよびチャネル

微分非直線性と

出力コードおよびチャネル

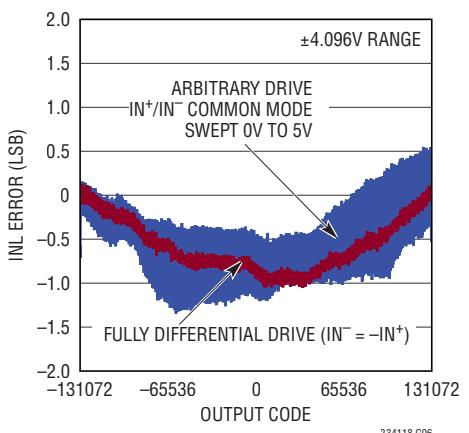

積分非直線性と

出力コードおよび範囲

積分非直線性と

出力コードおよび範囲

積分非直線性と

出力コードおよび範囲

積分非直線性と出力コード

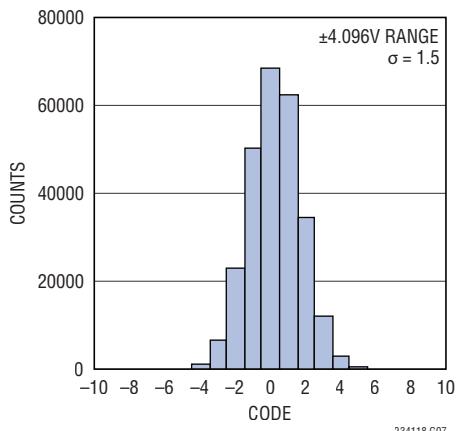

DCヒストグラム(ゼロスケール)

DCヒストグラム(フルスケール付近)

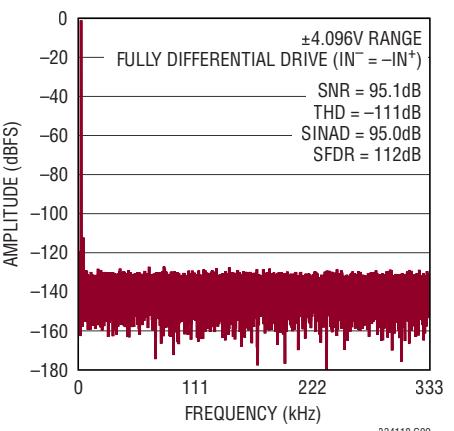

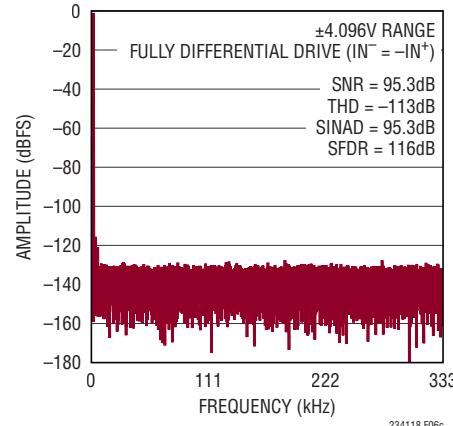

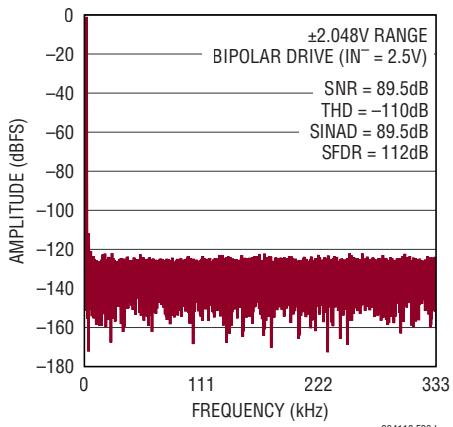

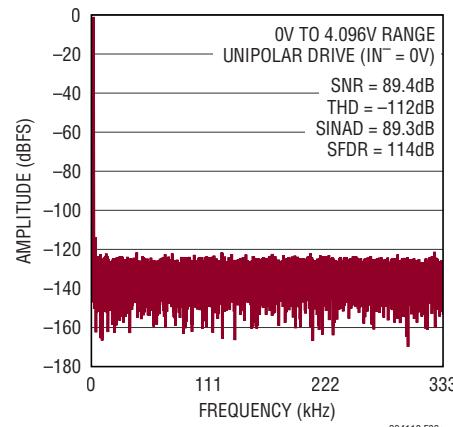

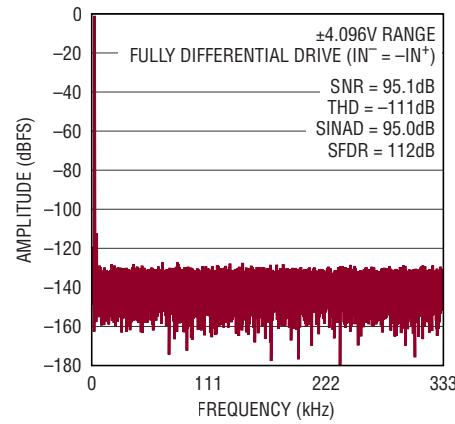

32k ポイントの FFT

( $f_{SMPL} = 666\text{kHz}$ 、 $f_{IN} = 2\text{kHz}$ )

## 標準的性能特性

注記がない限り、 $T_A = 25^\circ\text{C}$ 、 $V_{DD} = 5\text{V}$ 、 $0V_{DD} = 2.5\text{V}$ 、内部リファレンスおよびバッファ( $V_{REFBUF} = 4.096\text{V}$ )、 $f_{SMPL} = 666\text{kspS}$ 。

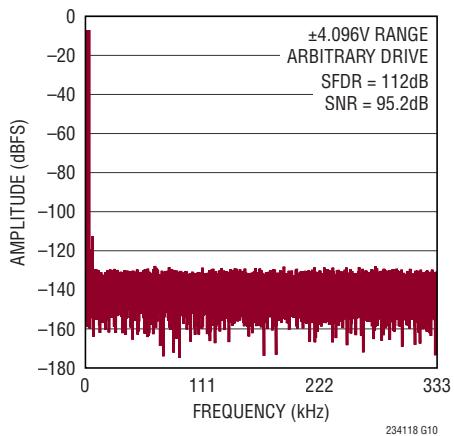

### 32kポイントの任意の2トーンFFT

( $f_{SMPL} = 666\text{kHz}$ 、 $\text{IN}^+ = -7\text{dBFS}$  2kHz

正弦波、 $\text{IN}^- = -7\text{dBFS}$  3.3kHz正弦波)

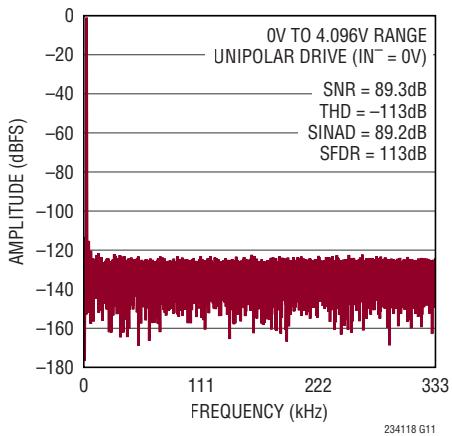

### 32kポイントのFFT

( $f_{SMPL} = 666\text{kHz}$ 、 $f_{IN} = 2\text{kHz}$ )

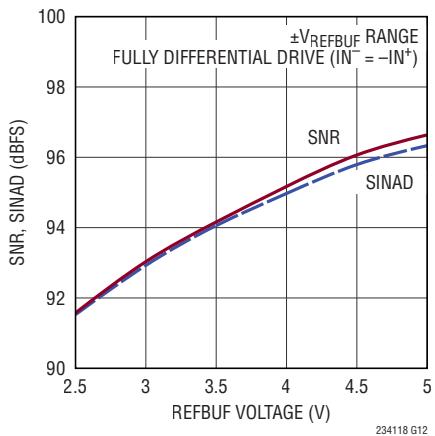

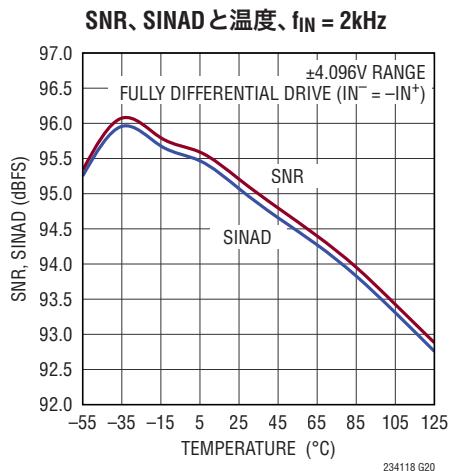

### SNR、SINADと $V_{REFBUF}$ 、 $f_{IN} = 2\text{kHz}$

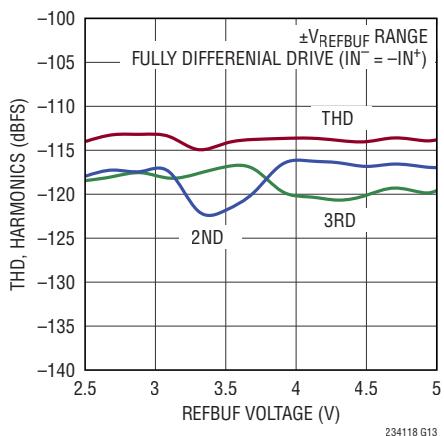

### THD、高調波と $V_{REFBUF}$ 、 $f_{IN} = 2\text{kHz}$

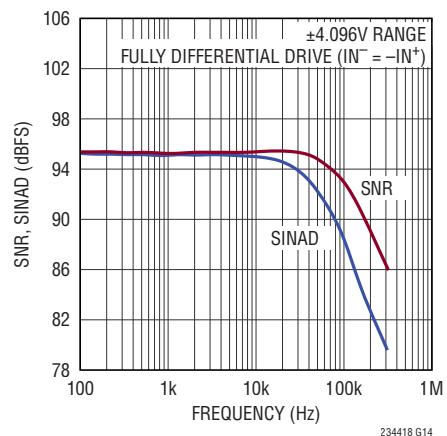

### SNR、SINADと入力周波数

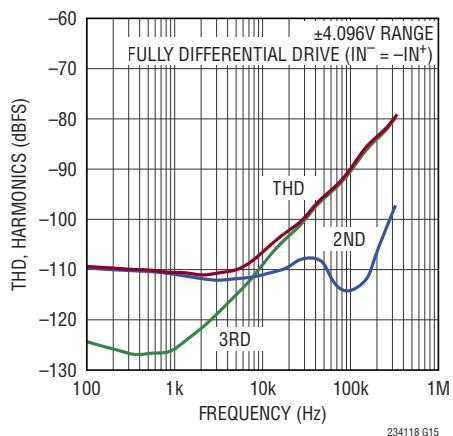

### THDおよび高調波と入力周波数

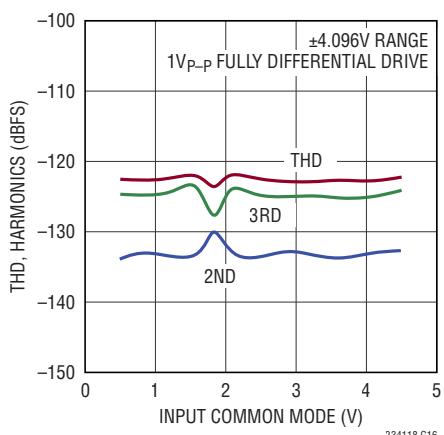

### THD、高調波と入力同相電圧、 $f_{IN} = 2\text{kHz}$

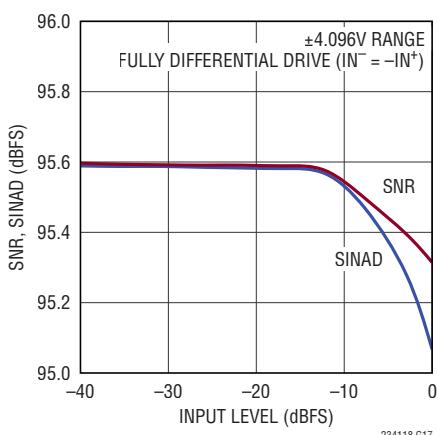

### SNR、SINADと入力レベル、 $f_{IN} = 2\text{kHz}$

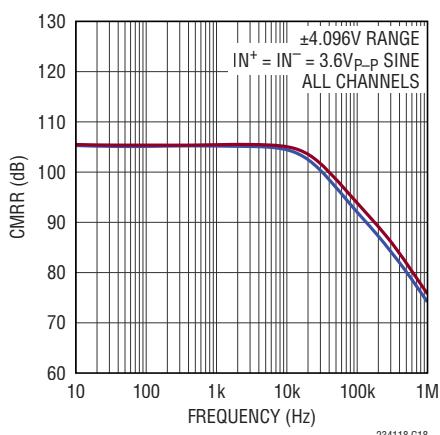

### CMRRと入力周波数およびチャネル

## 標準的性能特性

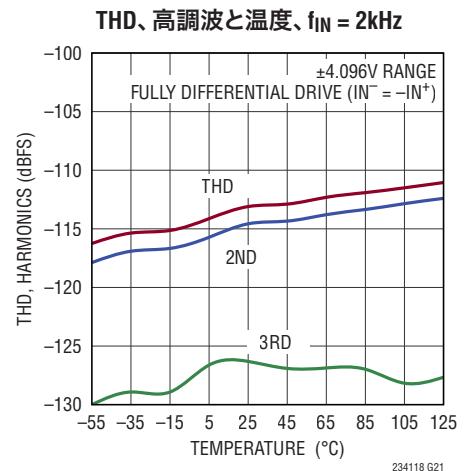

注記がない限り、 $T_A = 25^\circ\text{C}$ 、 $V_{DD} = 5\text{V}$ 、 $OV_{DD} = 2.5\text{V}$ 、内部リファレンスおよびバッファ ( $V_{REFBUF} = 4.096\text{V}$ )、 $f_{SMPL} = 666\text{kspS}$ 。

### クロストークと入力周波数およびチャネル

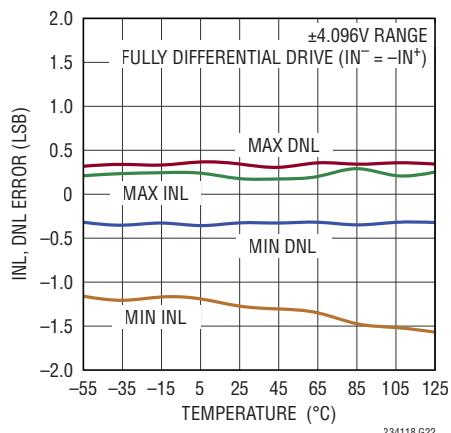

### INL、DNL と温度

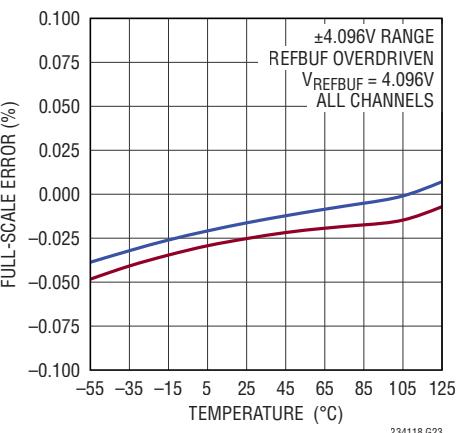

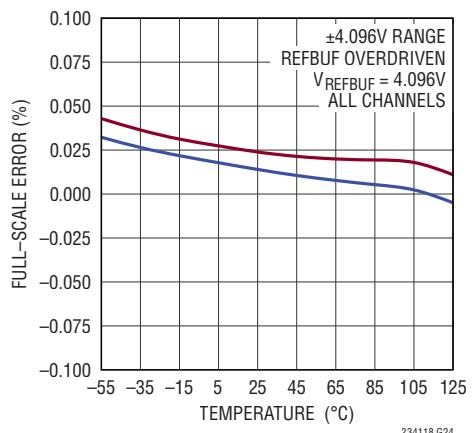

### 正のフルスケール誤差と温度およびチャネル

### 負のフルスケール誤差と温度およびチャネル

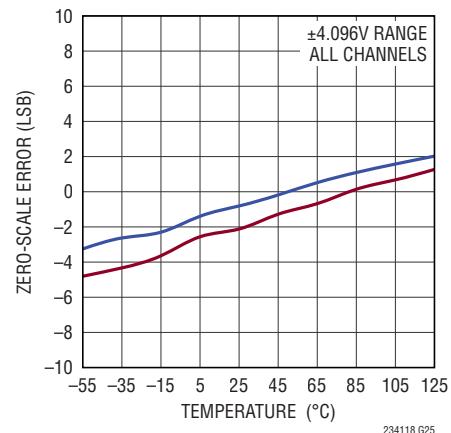

### ゼロスケール誤差と温度およびチャネル

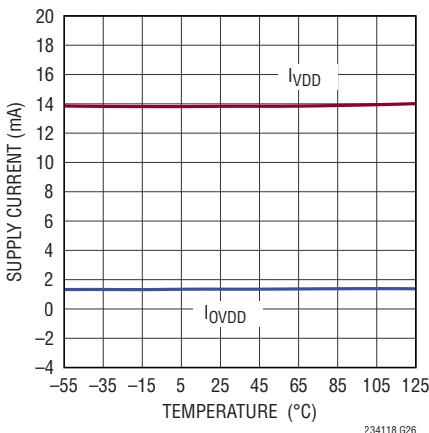

### 電源電流と温度

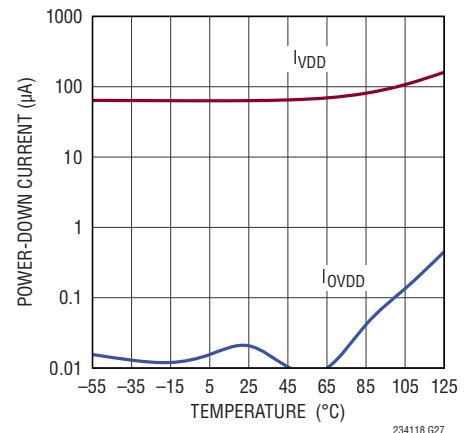

### パワーダウン電流と温度

## 標準的性能特性

注記がない限り、 $T_A = 25^\circ\text{C}$ 、 $V_{DD} = 5\text{V}$ 、 $OV_{DD} = 2.5\text{V}$ 、内部リファレンスおよびバッファ ( $V_{REFBUF} = 4.096\text{V}$ )、 $f_{SMPL} = 666\text{kspS}$ 。

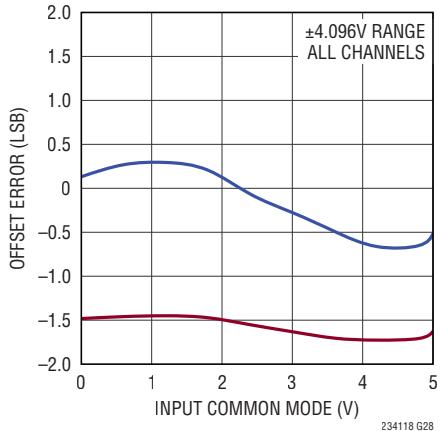

オフセット誤差と入力同相電圧

およびチャネル

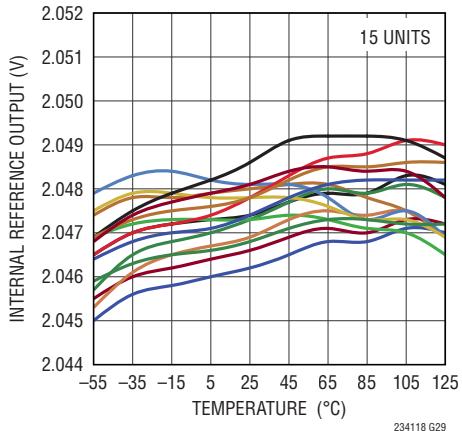

内部リファレンス出力と温度

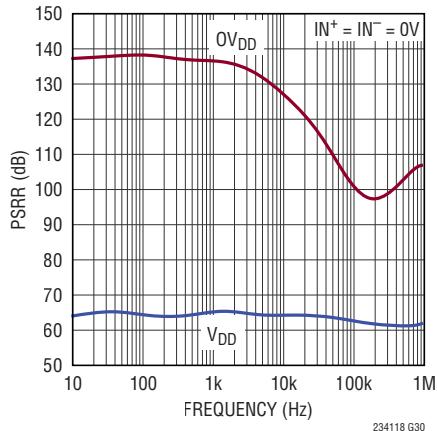

PSRR と周波数

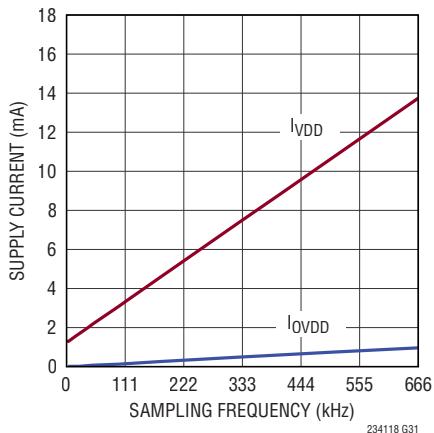

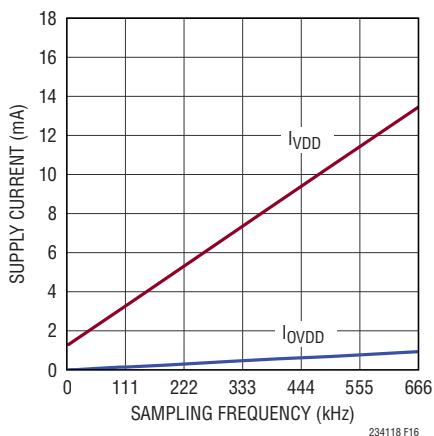

電源電流とサンプリング・レート

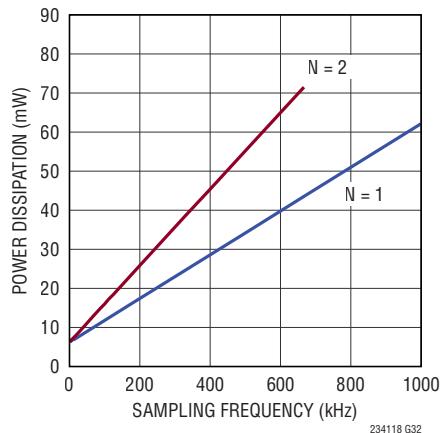

電力損失とサンプリング・レート、

N チャネルがイネーブル状態

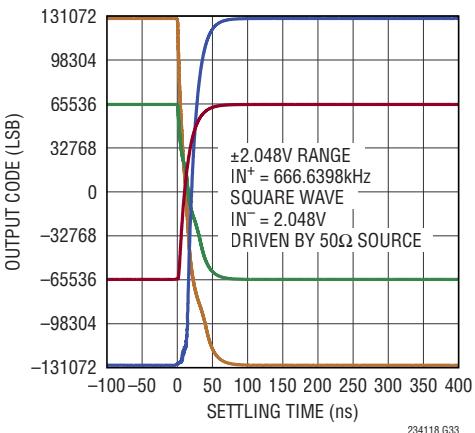

ステップ応答

(大信号のセトリング)

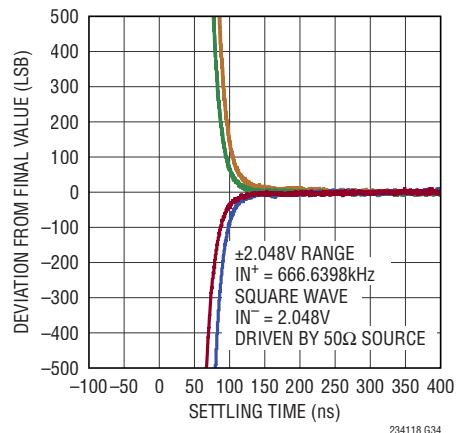

ステップ応答(細かなセトリング)

## ピン機能

**ピンは全てのデジタルI/Oモードで同一**

**IN0<sup>+</sup>/IN0<sup>-</sup>、IN1<sup>+</sup>/IN1<sup>-</sup>(ピン8/7、2/1)**: 正および負のアナログ入力、チャネル0および1。コンバータは両方のチャネルの( $V_{IN+} - V_{IN-}$ )を同時にサンプリングしてデジタル化します。同相入力電圧範囲が広く( $0V \leq V_{CM} \leq V_{DD}$ )同相電圧除去比が高いので、入力は幅広い振幅の信号を受け付けることができます。フルスケールの入力電圧範囲は、チャネルのSoftSpan構成によって決ります。

**GND(ピン3、4、5、6、9、11、20、29、31、32、33)**: グランド。全てのGNDピンを切れ目のないグランド・プレーンに半田付けします。

**REFIN(ピン10)**: バンドギャップ・リファレンス出力/リファレンス・バッファ入力。内部バンドギャップ・リファレンスはこのピンで公称2.048Vを出力します。内部リファレンス・バッファは $V_{REFIN}$ を増幅して、コンバータのマスター・リファレンス電圧 $V_{REFBUF} = 2 \cdot V_{REFIN}$ をREFBUFピンで生成します。内部リファレンスを使用する場合は、 $0.1\mu F$ のセラミック・コンデンサをREFINに近づけて接続し、このピンをGND(ピン11)にバイパスして、バンドギャップ出力ノイズを除去します。更に高い精度が必要な場合は、範囲が $1.25V \sim 2.2V$ の外部リファレンスを使用してREFINをオーバードライブします。

**REFBUF(ピン12)**: 内部リファレンス・バッファ出力。内部リファレンス・バッファは $V_{REFIN}$ を増幅して、コンバータのマスター・リファレンス電圧 $V_{REFBUF} = 2 \cdot V_{REFIN}$  (内部バンドギャップ・リファレンスを使用する場合、公称4.096V)をこのピンで生成します。 $47\mu F$ のセラミック・コンデンサをREFBUFに近づけて接続し、このピンをGND(ピン11)にバイパスします。内部リファレンス・バッファをディスエーブルするには、REFINでその入力を接地します。バッファをディスエーブルした状態では、範囲が $2.5V \sim 5V$ の外部リファレンス電圧を使用してREFBUFをオーバードライブします。内部リファレンス・バッファを使用する場合は、REFBUFに接続する外部回路の負荷を $10\mu A$ 未満に制限します。入力インピーダンスの高いアンプを使用して、外部回路に対して $V_{REFBUF}$ をバッファすることを推奨します。

**PD(ピン13)**: パワーダウン入力。このピンが"H"になると LTC2341-18はパワーダウンされ、その後の変換要求は無視されます。変換中に"H"になった場合、デバイスは変換が完了したら電源を遮断します。このピンが2回"H"になる間に変換が行われなかった場合、内部のグローバル・リセット(パワーオン・リセットと同等)が起動します。ロジック・レベルは $OV_{DD}$ によって決ります。

**LVDS/CMOS(ピン14)**: I/Oモードの選択。このピンを $OV_{DD}$ に接続してLVDS I/Oモードを選択するか、グランドに接続して CMOS I/Oモードを選択します。ロジック・レベルは $OV_{DD}$ によって決ります。

**CNV(ピン15)**: 変換開始入力。このピンの立ち上がりエッジで、内部のサンプル・アンド・ホールド回路がホールド・モードになり、新しい変換が開始されます。CNVは $\overline{CS}$ によるゲート制御が行われないので、シリアルI/Oバスの状態とは無関係に変換を開始することができます。

**BUSY(ピン26)**: ビジー出力。BUSY信号は、変換が進行中であることを示します。このピンは各変換の開始時に“L”から“H”へ遷移し、変換が完了するまで“H”的まになります。ロジック・レベルは $OV_{DD}$ によって決ります。

**V<sub>DDLYP</sub>(ピン28)**: 内蔵の2.5Vレギュレータのバイパス・ピン。このピンの電圧は、 $V_{DD}$ で動作する内部レギュレータを介して生成されます。 $2.2\mu F$ のセラミック・コンデンサをこのピンに近づけて接続し、GNDにバイパスする必要があります。このピンはどの外部回路にも接続しないでください。

**V<sub>DD</sub>(ピン30)**: 5V電源。 $V_{DD}$ の範囲は $4.75V \sim 5.25V$ です。 $0.1\mu F$ のセラミック・コンデンサをこのピンに近づけて接続し、GNDにバイパスする必要があります。

## ピン機能

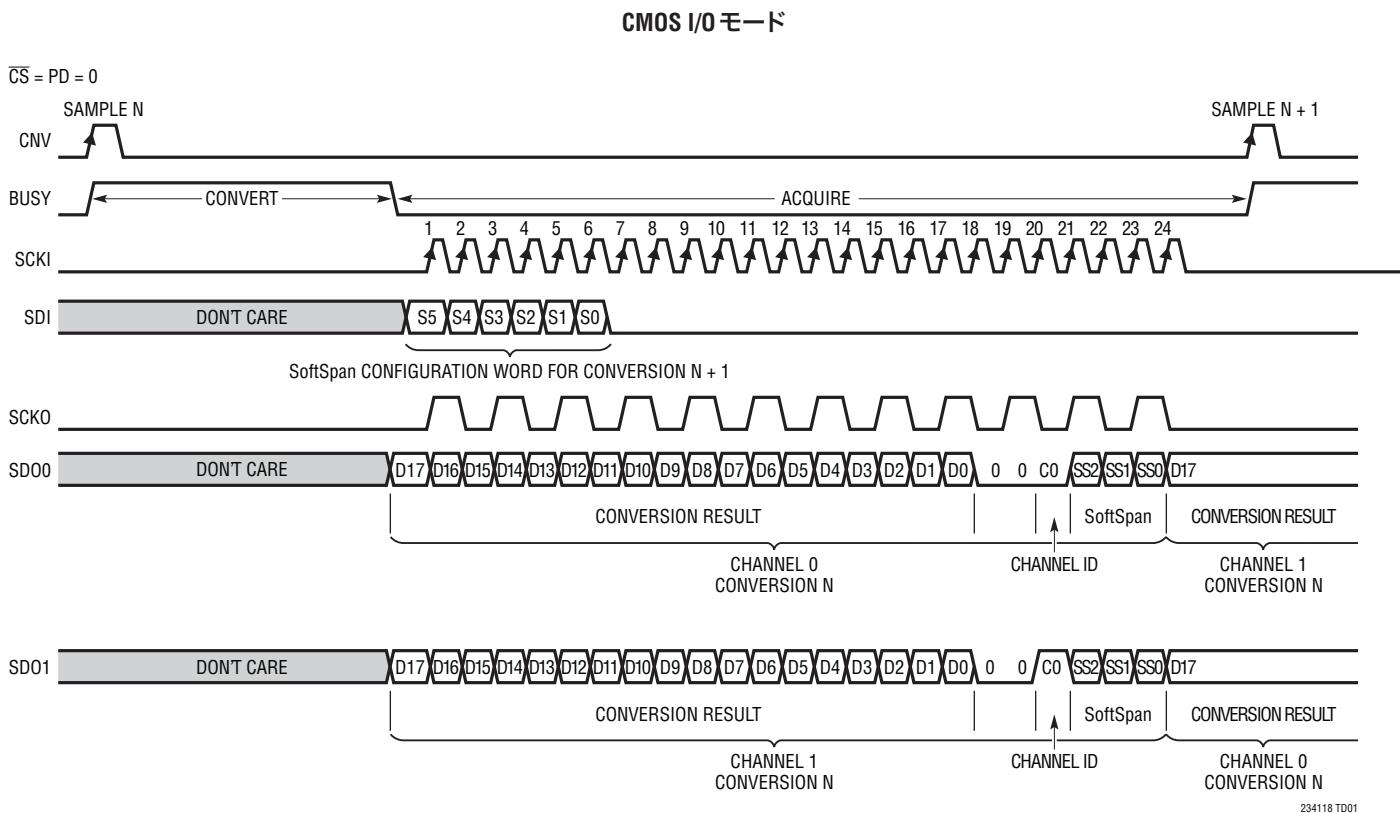

### CMOS I/Oモード

**SDI<sup>+</sup>/SDI<sup>-</sup>, SDO<sup>+</sup>(ピン16/17, 24)**: LVDSシリアル・データI/O。CMOS I/Oモードでは、これらのピンは高インピーダンスになります。

**SDO0, SDO1(ピン18, 23)**: CMOSシリアル・データ出力、チャネル0および1。最新の変換結果とチャネル構成情報の組み合わせが、SCKIの立ち上がりエッジごとにクロックと同期してSDOピンに出力されます。出力データの形式設定については、「デジタル・インターフェース」のセクションで説明します。使用しないSDO出力は、未接続のままにしておきます。ロジック・レベルはOV<sub>DD</sub>によって決まります。

**SCKI(ピン19)**: CMOSシリアル・クロック入力。SCKIはシリアルI/Oクロックを使用して駆動します。シリアル・データはSCKIの立ち上がりエッジでラッチされてSDIに入力され、クロックに同期してSDO0およびSDO1から出力されます。標準的なSPIバス動作の場合は、レシーバの出力データをSCKIの立ち上がりエッジで取り込みます。SCKIは“H”または“L”的どちらでもアイドル状態にすることができます。ロジック・レベルはOV<sub>DD</sub>によって決まります。

**OV<sub>DD</sub>(ピン21)**: I/Oインターフェースの電源。CMOS I/Oモードでは、OV<sub>DD</sub>の範囲は1.71V～5.25Vです。0.1μFのセラミック・コンデンサをOV<sub>DD</sub>に近づけて接続し、このピンをGND(ピン20)にバイパスします。

**SCKO(ピン22)**: CMOSシリアル・クロック出力。SCKIの立ち上がりエッジでSCKO信号が遷移し、この遷移はSDO0およびSDO1でのシリアル出力データ・ストリームとスキーが一致しています。得られるSCKO周波数はSCKIの半分です。SCKOの立ち上がりエッジおよび立ち下がりエッジを使用して、レシーバ(FPGA)のSDOデータをダブル・データ・レート(DDR)方式により取り込むことができます。標準的なSPIバス動作ではSCKOを使用しないので、未接続のままにします。SCKOはBUSYの立ち下がりエッジで“L”になります。ロジック・レベルはOV<sub>DD</sub>によって決まります。

**SDI(ピン25)**: CMOSシリアル・データ入力。SCKIの立ち上がりエッジでラッチされた目的の6ビットSoftSpan構成ワード(表1a参照)により、このピンを駆動します。両チャネルがSoftSpan 7でのみ動作するよう構成する場合は、SDIをOV<sub>DD</sub>に接続します。ロジック・レベルはOV<sub>DD</sub>によって決まります。

**CS(ピン27)**: チップ選択入力。シリアル・データI/OバスはCSが“L”になるとイネーブルされ、CSが“H”になるとディスエーブルされて高インピーダンスになります。また、CSも外部シフト・クロック(SCKI<sup>+/SCKI<sup>-</sup></sup>)をゲート制御します。SCKI<sup>+/SCKI<sup>-</sup></sup>およびSDI<sup>+/SDI<sup>-</sup></sup>入力対にある100Ωの内部差動終端抵抗は、CSが“H”になるとディスエーブルされます。ロジック・レベルはOV<sub>DD</sub>によって決まります。

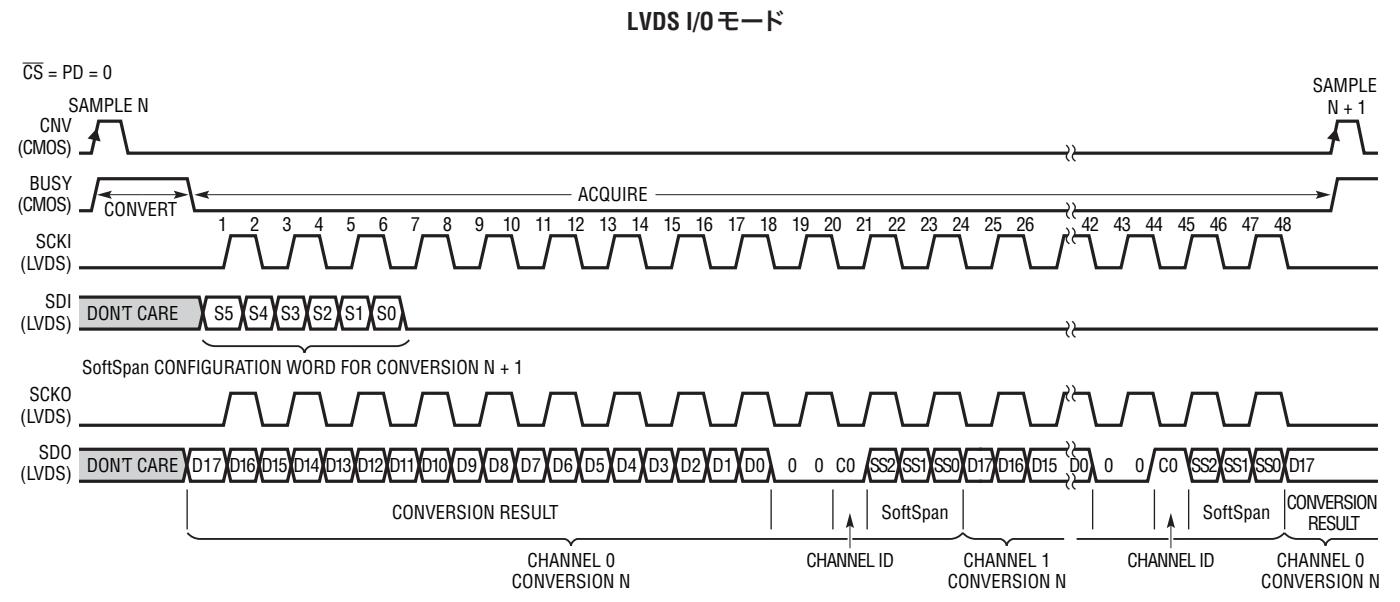

### LVDS I/Oモード

**SDI<sup>+/SDI<sup>-</sup></sup>**(ピン16/17): LVDSの正および負のシリアル・データ入力。SCKI<sup>+/SCKI<sup>-</sup></sup>の立ち上がりエッジと立ち下がりエッジの両方でラッチされた目的の6ビットSoftSpan構成ワード(表1a参照)により、SDI<sup>+/SDI<sup>-</sup></sup>を差動で駆動します。CS = 0の場合、SDI<sup>+/SDI<sup>-</sup></sup>入力対は100Ωの差動抵抗により内部で終端されます。

**SCKI<sup>+/SCKI<sup>-</sup></sup>**(ピン18/19): LVDSの正および負のシリアル・クロック入力。SCKI<sup>+/SCKI<sup>-</sup></sup>はシリアルI/Oクロックを使用して差動で駆動します。シリアル・データはSCKI<sup>+/SCKI<sup>-</sup></sup>の立ち上がりエッジでラッチされてSDI<sup>+/SDI<sup>-</sup></sup>に入力され、クロックに同期してSDO<sup>+/SDO<sup>-</sup></sup>から出力されます。SCKI<sup>+/SCKI<sup>-</sup></sup>は、CSの遷移時を含めて“L”でアイドル状態にします。CS = 0の場合、SCKI<sup>+/SCKI<sup>-</sup></sup>入力対は100Ωの差動抵抗により内部で終端されます。

**OV<sub>DD</sub>(ピン21)**: I/Oインターフェースの電源。LVDS I/Oモードでは、OV<sub>DD</sub>の範囲は2.375V～5.25Vです。0.1μFのセラミック・コンデンサをOV<sub>DD</sub>に近づけて接続し、このピンをGND(ピン20)にバイパスします。

**SCKO<sup>+/SCKO<sup>-</sup></sup>**(ピン22/23): LVDSの正および負のシリアル・クロック出力。SCKO<sup>+/SCKO<sup>-</sup></sup>は、SCKI<sup>+/SCKI<sup>-</sup></sup>で受け取った入力シリアルI/Oクロックのコピーを出力します。これは、SDO<sup>+/SDO<sup>-</sup></sup>からのシリアル出力データ・ストリームとスキーが一致しています。SCKO<sup>+/SCKO<sup>-</sup></sup>の立ち上がりエッジおよび立ち下がりエッジを使用して、SDO<sup>+/SDO<sup>-</sup></sup>のデータをレシーバ(FPGA)で取り込みます。SCKO<sup>+/SCKO<sup>-</sup></sup>出力対は、レシーバ(FPGA)に100Ωの抵抗を接続することにより、差動で終端する必要があります。

**SDO<sup>+/SDO<sup>-</sup></sup>**(ピン24/25): LVDSの正および負のシリアル・データ出力。最新の変換結果とチャネル構成情報の組み合わせが、SCKI<sup>+/SCKI<sup>-</sup></sup>の立ち上がりエッジと立ち下がりエッジの両方で、クロックと同期してチャネル0を先頭にSDO<sup>+/SDO<sup>-</sup></sup>に出力されます。SDO<sup>+/SDO<sup>-</sup></sup>出力対は、レシーバ(FPGA)に100Ωの抵抗を接続することにより、差動で終端する必要があります。

**CS(ピン27)**: チップ選択入力。シリアル・データI/OバスはCSが“L”になるとイネーブルされ、CSが“H”になるとディスエーブルされて高インピーダンスになります。また、CSも外部シフト・クロック(SCKI<sup>+/SCKI<sup>-</sup></sup>)をゲート制御します。SCKI<sup>+/SCKI<sup>-</sup></sup>およびSDI<sup>+/SDI<sup>-</sup></sup>入力対にある100Ωの内部差動終端抵抗は、CSが“H”になるとディスエーブルされます。ロジック・レベルはOV<sub>DD</sub>によって決まります。

## 構成表

表1a. SoftSpanの構成表。この表と表1bを使用し、目的とするアナログ入力電圧範囲に基づいて、独立したバイナリSoftSpanコードSS[2:0]をチャネルごとに選択します。SoftSpanコードを組み合わせて、6ビットのSoftSpan構成ワードS[5:0]を作成します。図19に示すように、シリアル・インターフェースを使用してSoftSpan構成ワードをLTC2341-18に書き込みます。

| バイナリSoftSpanコード<br>SS[2:0] | アナログ入力電圧範囲                       | フルスケール範囲                   | 変換結果の<br>バイナリ形式 |

|----------------------------|----------------------------------|----------------------------|-----------------|

| 111                        | $\pm V_{REFBUF}$                 | $2 \cdot V_{REFBUF}$       | 2の補数            |

| 110                        | $\pm V_{REFBUF}/1.024$           | $2 \cdot V_{REFBUF}/1.024$ | 2の補数            |

| 101                        | $0V \sim V_{REFBUF}$             | $V_{REFBUF}$               | ストレート・バイナリ      |

| 100                        | $0V \sim V_{REFBUF}/1.024$       | $V_{REFBUF}/1.024$         | ストレート・バイナリ      |

| 011                        | $\pm 0.5 \cdot V_{REFBUF}$       | $V_{REFBUF}$               | 2の補数            |

| 010                        | $\pm 0.5 \cdot V_{REFBUF}/1.024$ | $V_{REFBUF}/1.024$         | 2の補数            |

| 001                        | $0V \sim 0.5 \cdot V_{REFBUF}$   | $0.5 \cdot V_{REFBUF}$     | ストレート・バイナリ      |

| 000                        | チャネルはディスエーブル状態                   | チャネルはディスエーブル状態             | 全て0             |

表1b. リファレンスの構成表。LTC2341-18は3つのリファレンス構成をサポートしています。アナログ入力電圧範囲は、コンバータのマスター・リファレンス電圧  $V_{REFBUF}$  に比例します。

| リファレンスの構成                                        | $V_{REFIN}$    | $V_{REFBUF}$ | バイナリSoftSpanコード<br>SS[2:0] | アナログ入力電圧範囲       |

|--------------------------------------------------|----------------|--------------|----------------------------|------------------|

| 内部リファレンスと<br>内部バッファ                              | 2.048V         | 4.096V       | 111                        | $\pm 4.096V$     |

|                                                  |                |              | 110                        | $\pm 4V$         |

|                                                  |                |              | 101                        | $0V \sim 4.096V$ |

|                                                  |                |              | 100                        | $0V \sim 4V$     |

|                                                  |                |              | 011                        | $\pm 2.048V$     |

|                                                  |                |              | 010                        | $\pm 2V$         |

|                                                  |                |              | 001                        | $0V \sim 2.048V$ |

| 外部リファレンスと<br>内部バッファ<br>(REFINピンを外部で<br>オーバードライブ) | 1.25V<br>(最小値) | 2.5V         | 111                        | $\pm 2.5V$       |

|                                                  |                |              | 110                        | $\pm 2.441V$     |

|                                                  |                |              | 101                        | $0V \sim 2.5V$   |

|                                                  |                |              | 100                        | $0V \sim 2.441V$ |

|                                                  |                |              | 011                        | $\pm 1.25V$      |

|                                                  |                |              | 010                        | $\pm 1.221V$     |

|                                                  |                |              | 001                        | $0V \sim 1.25V$  |

|                                                  | 2.2V<br>(最大値)  | 4.4V         | 111                        | $\pm 4.4V$       |

|                                                  |                |              | 110                        | $\pm 4.297V$     |

|                                                  |                |              | 101                        | $0V \sim 4.4V$   |

|                                                  |                |              | 100                        | $0V \sim 4.297V$ |

|                                                  |                |              | 011                        | $\pm 2.2V$       |

|                                                  |                |              | 010                        | $\pm 2.148V$     |

|                                                  |                |              | 001                        | $0V \sim 2.2V$   |

## 構成表

表1b. リファレンスの構成表(続き)。LTC2341-18は3つのリファレンス構成をサポートしています。アナログ入力電圧範囲は、コンバータのマスター・リファレンス電圧  $V_{REFBUF}$  に比例します。

| リファレンスの構成                                                            | $V_{REFIN}$ | $V_{REFBUF}$  | バイナリ SoftSpan コード<br>SS[2:0] | アナログ入力電圧範囲   |

|----------------------------------------------------------------------|-------------|---------------|------------------------------|--------------|

| 外部リファレンス<br>バッファなし<br><br>(REFBUFピンは<br>外部からオーバードライブ、<br>REFINピンは接地) | 0V          | 2.5V<br>(最小値) | 111                          | $\pm 2.5V$   |

|                                                                      |             |               | 110                          | $\pm 2.441V$ |

|                                                                      |             |               | 101                          | 0V ~ 2.5V    |

|                                                                      |             |               | 100                          | 0V ~ 2.441V  |

|                                                                      |             |               | 011                          | $\pm 1.25V$  |

|                                                                      |             |               | 010                          | $\pm 1.221V$ |

|                                                                      |             |               | 001                          | 0V ~ 1.25V   |

|                                                                      | 0V          | 5V<br>(最大値)   | 111                          | $\pm 5V$     |

|                                                                      |             |               | 110                          | $\pm 4.883V$ |

|                                                                      |             |               | 101                          | 0V ~ 5V      |

|                                                                      |             |               | 100                          | 0V ~ 4.883V  |

|                                                                      |             |               | 011                          | $\pm 2.5V$   |

|                                                                      |             |               | 010                          | $\pm 2.441V$ |

|                                                                      |             |               | 001                          | 0V ~ 2.5V    |

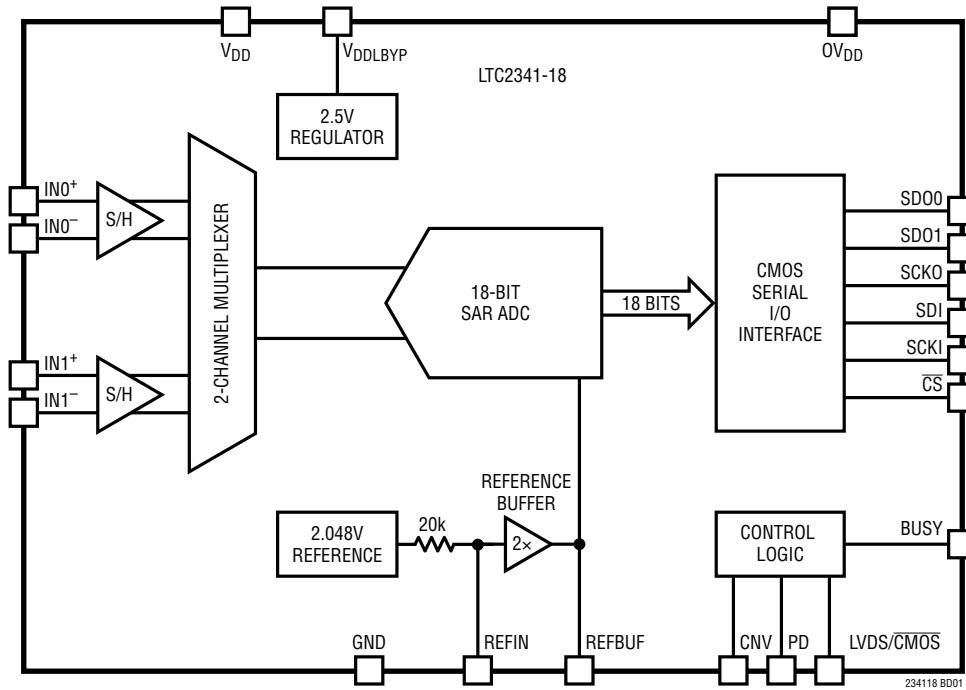

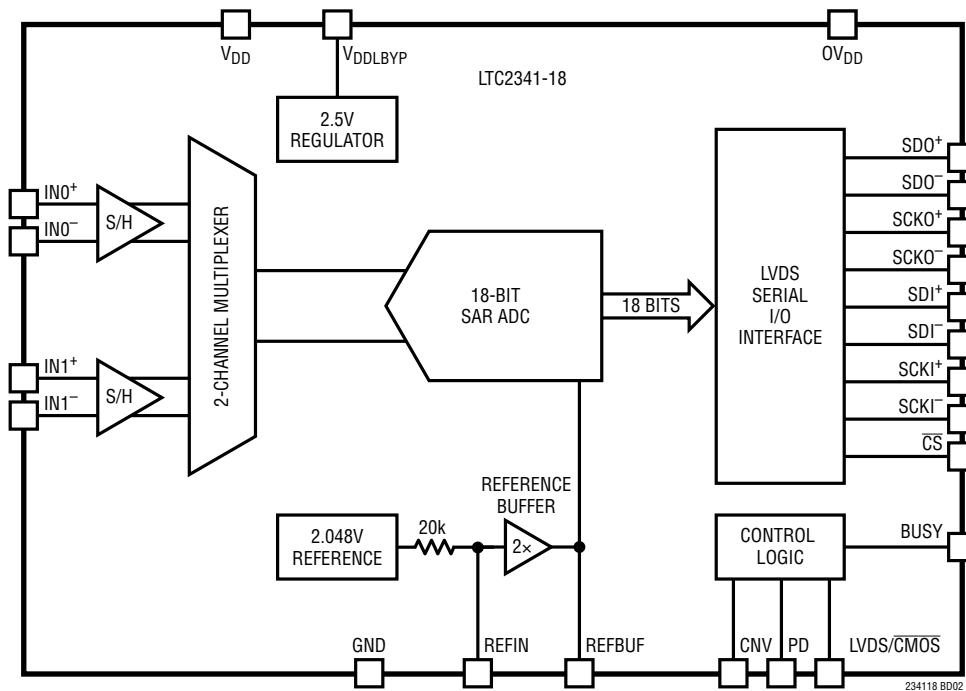

## 機能ブロック図

CMOS I/O モード

LVDS I/O モード

234118f

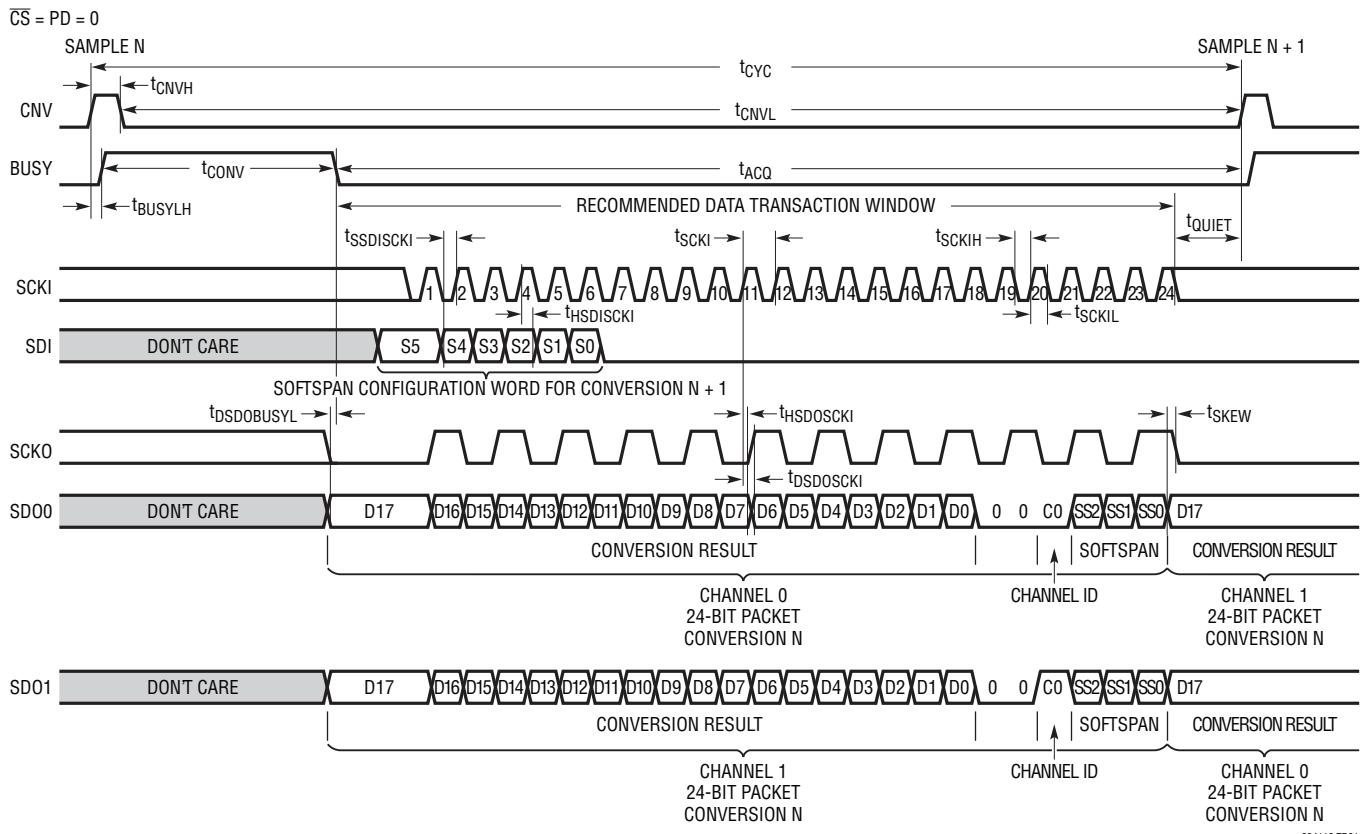

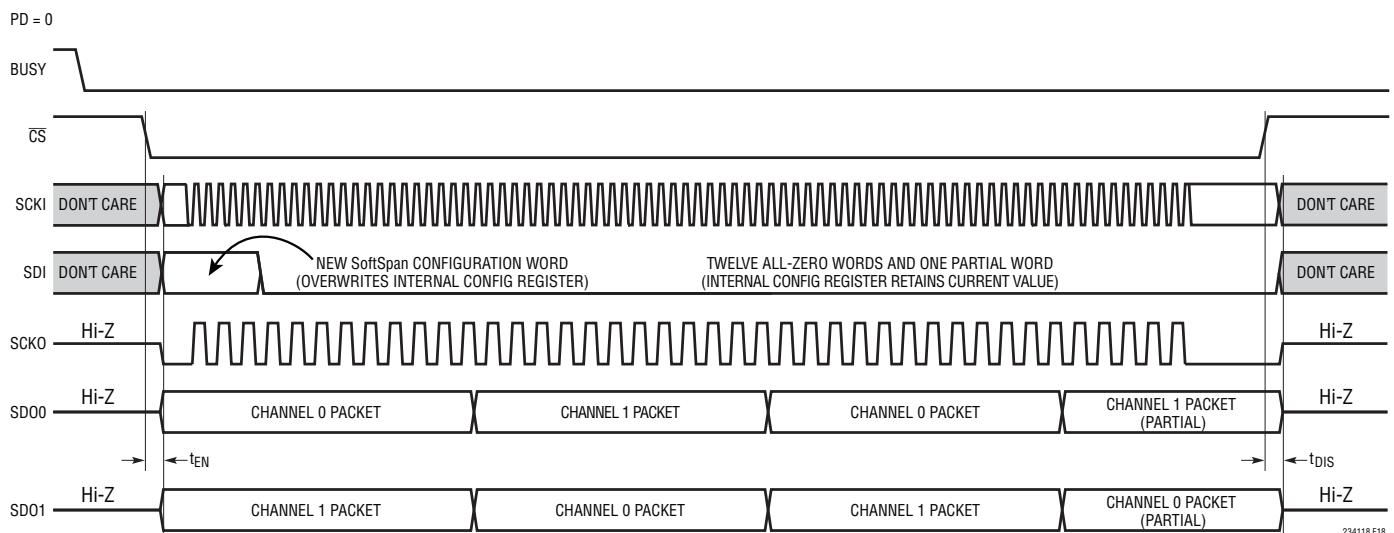

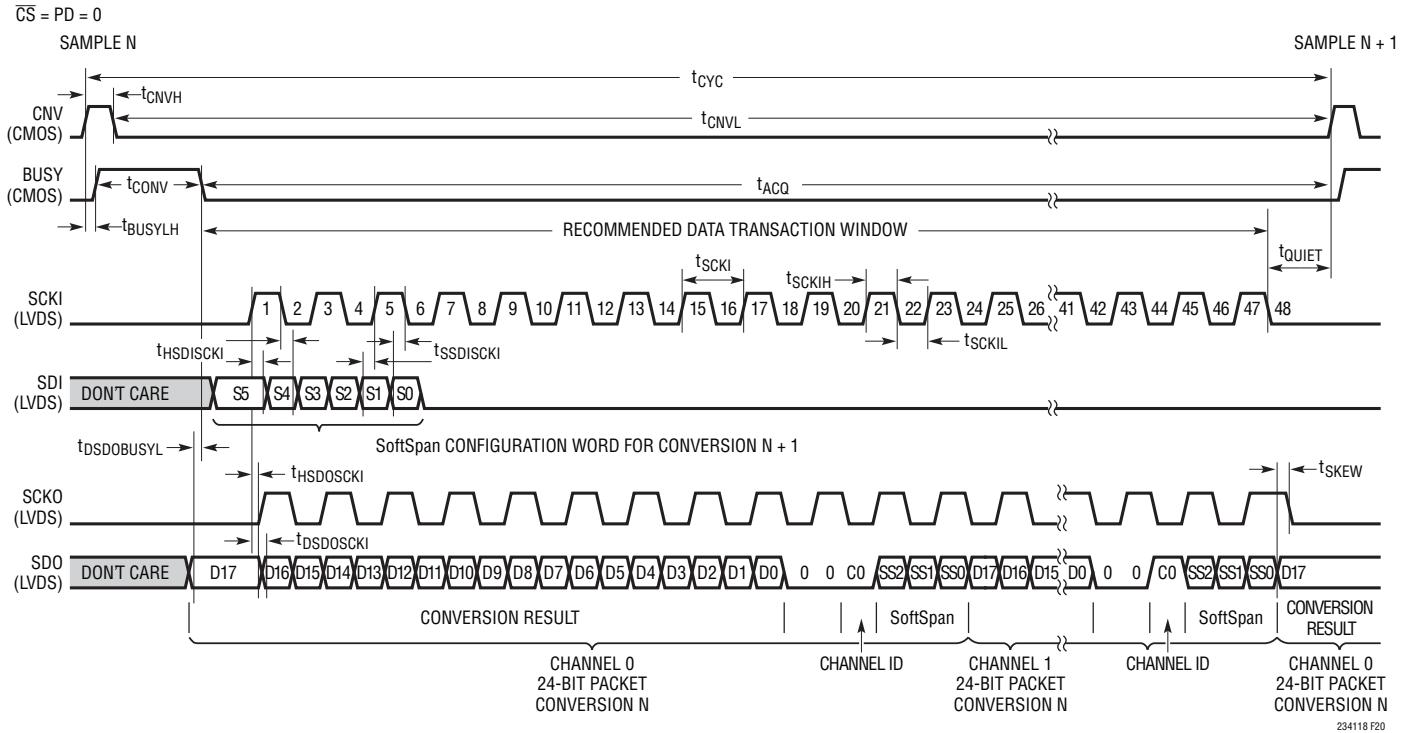

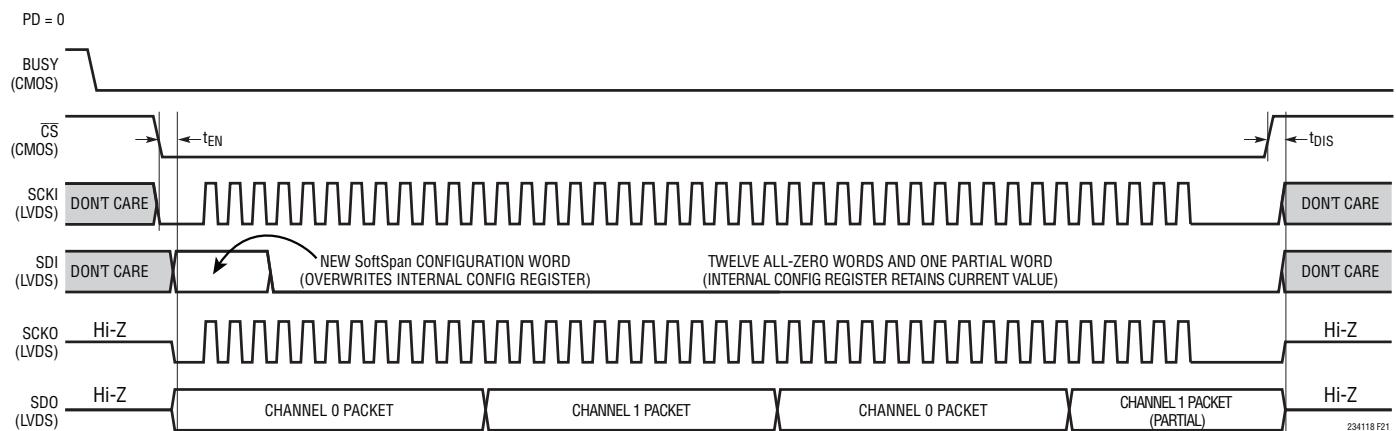

## タイミング図

234118f

## アプリケーション情報

### 概要

LTC2341-18は、差動入力で入力同相電圧範囲の広い18ビット、低ノイズ、2チャネルの同時サンプリング逐次比較レジスタ(SAR)A/Dコンバータです。このSoftSpan A/Dコンバータの2つのチャネルは、内蔵の低ドリフト・リファレンスおよびバッファ( $V_{REFBUF} = 4.096V$ 公称)を使用することにより、両方とも変換ごとに独立して構成し、 $\pm 4.096V$ 、 $0V \sim 4.096V$ 、 $\pm 2.048V$ 、または $0V \sim 2.048V$ の信号を受け付けることができます。入力信号範囲は外部の5Vリファレンスを使用して最大 $\pm 5V$ まで広げることができます。一方のチャネルをディスエーブルしてもう一方のチャネルのスループットを向上させることもできます。

LTC2341-18は、アナログ入力の入力同相電圧範囲が広く、CMRRが高い(標準105dB、 $V_{IN+} = V_{IN-} = 3.6V_{P-P}$ 、200Hz正弦波)なので、さまざまな信号を直接デジタル化して、シグナルチェーンの設計を簡略化することができます。この入力信号柔軟性と、 $\pm 4LSB$ のINL、18ビット分解能で欠落コードなし、95dBのSNRとが相まって、LTC2341-18は、広いダイナミックレンジが必要な多くのアプリケーションにとって理想的なデバイスになっています。

LTC2341-18は、ピンで選択可能なSPI CMOS(1.8V ~ 5V)シリアル・インターフェースとLVDSシリアル・インターフェースをサポートしているので、従来のマイクロコントローラと同様に最新のFPGAとも良好に通信することができます。CMOSモードでは、アプリケーションが1レーンまたは2レーンのシリアル出力データを採用することができるので、バスの幅およびデータのスループットを最適化することができます。2つのアナログ入力チャネルを666ksps/チャネルのスループットで同時に変換する場合、LTC2341-18の消費電力は標準で74mWです。オプションのパワーダウン・モードを使用して、非活動期間中の消費電力を更に節減することができます。

### コンバータの動作

LTC2341-18は2段階で動作します。収集段階では、両チャネルのサンプルアンドホールド(S/H)回路のサンプリング・コンデンサをそれぞれのアナログ入力ピンに接続して、差動アナログ入力電圧( $V_{IN+} - V_{IN-}$ )を追跡します。CNVピンの立ち上がりエッジでは、両チャネルのS/H回路がトラック・モードからホールド・モードに切り替わり、両チャネルの入力信号を同時にサンプリングして、変換を開始します。変換段階では、各チャネルのサンプリング・コンデンサが、18ビットの電荷再分配コンデンサ式D/Aコンバータ(CDAC)に一度に1チャネルずつ接続されます。CDACは逐次比較アルゴリズムによって逐次制御され、差動コンパレータを使用して、サンプリング済み入力電圧と該当チャネルのSoftSpanフルスケール範囲のバイナリ重み付け分数(例： $V_{FSR}/2$ 、 $V_{FSR}/4$  …  $V_{FSR}/262144$ )を効率的に比較します。この処理の最後には、CDACの出力が該当チャネルのサンプリング済みアナログ入力に近づきます。両方のチャネルがこのようにして変換されると、A/Dコンバータの制御ロジックは各チャネルから18ビットのデジタル出力コードを準備して、シリアル転送に備えます。

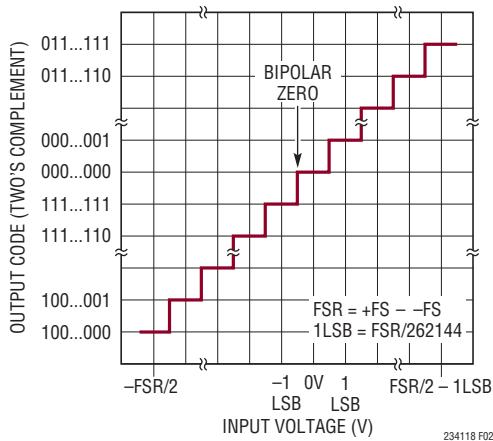

### 伝達関数

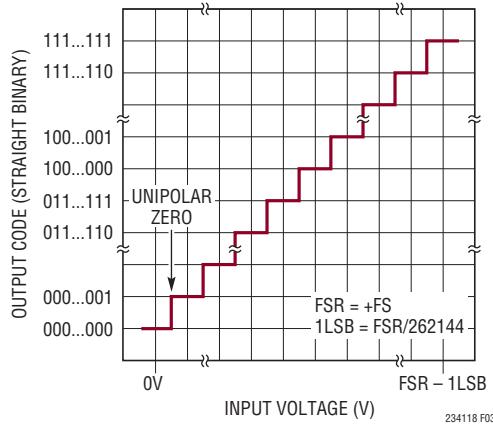

LTC2341-18は、各チャネルのフルスケール電圧範囲を $2^{18}$ レベルにデジタル化します。表1aおよび1bに示すように、A/Dコンバータのマスター・リファレンス電圧( $V_{REFBUF}$ )とチャネルのSoftSpan構成の組み合わせにより、その入力電圧範囲、フルスケール範囲、 LSB サイズ、および変換結果のバイナリ形式が決まります。例えば、内部リファレンスおよびバッファ( $V_{REFBUF} = 4.096V$ :公称)を使用して、SoftSpanを7にした場合は、 $\pm 4.096V$ のアナログ入力電圧範囲で動作するようにチャネルが構成され、これは8.192Vのフルスケール範囲と $31.25\mu V$ のLSBに対応します。他のSoftSpan構成およびリファレンス電圧を使用して、より広い範囲および狭い範囲の両極性および単極性入力電圧範囲を変換することができます。変換結果は、両極性SoftSpan範囲の場合は全て2の補数バイナリ形式で出力され、単極性SoftSpan範囲の場合は全てストレート・バイナリ形式で出力されます。理想的な2の補数伝達関数を図2に、理想的なストレート・バイナリ伝達関数を図3に示します。

## アプリケーション情報

図2. LTC2341-18の2の補数伝達関数

図3. LTC2341-18のストレート・バイナリ伝達関数

### アナログ入力

LTC2341-18の各チャネルは、アナログ入力ピン間の電圧差( $V_{IN+} - V_{IN-}$ )を広い同相入力電圧範囲にわたって同時にサンプリングしつつ、A/Dコンバータの同相信号除去比(CMRR)性能により、両方の入力ピンに共通する不要な信号を減衰します。同相入力電圧範囲が広いのに加えてCMRR

が高いので、アナログ入力 $IN^+/IN^-$ を互いに任意の関係で振ることができます。ただし、両方のピンの電圧がグランドと $V_{DD}$ の範囲内に収まることが条件です。この機能により、LTC2341-18には、疑似差動単極性、疑似差動両極性、完全差動など、従来からある種類のアナログ入力信号を含むさまざまな振幅の信号を入力できるので、シグナルチェーンの設計が簡単になります。

各チャネルのアナログ入力は、全てのSoftSpan範囲で、図4に示す等価回路によってモデル化することができます。収集の開始時には、80pFのサンプリング・コンデンサ( $C_{IN}$ )がサンプリング・スイッチを介してアナログ入力ピン $IN^+/IN^-$ に接続されます。これらのピンのオン抵抗はそれぞれ約90Ω( $R_{IN}$ )です。収集開始時の両サンプリング・コンデンサの初期電圧は、直前の変換によるサンプリング済み同相電圧( $V_{IN+} + V_{IN-}$ )/2とほぼ等しくなります。 $IN^+$ および $IN^-$ に接続されている外部回路は、サンプリング・コンデンサの電圧が収集間隔の間に初期電圧から新しい入力ピン電圧に変化して安定化するのに伴って、電荷を $R_{IN}$ を通じて流し出すか流し込む必要があります。変換中およびパワーダウン・モード時にアナログ入力に流れるのは、わずかな漏れ電流だけです。入力のダイオードはESD保護機能を果たします。

図4. 差動アナログ入力の等価回路、1チャネルのみ表示

## アプリケーション情報

### 両極性 SoftSpan 入力電圧範囲

SoftSpanの範囲を7、6、3、または2で構成したチャネルの場合、LTC2341-18は、表1aに示すように、それぞれ $\pm V_{REFBUF}$ 、 $\pm V_{REFBUF}/1.024$ 、 $\pm 0.5 \cdot V_{REFBUF}$ 、または $\pm 0.5 \cdot V_{REFBUF}/1.024$ という両極性電圧範囲で差動アナログ入力電圧( $V_{IN^+} - V_{IN^-}$ )をデジタル化します。これらのSoftSpan範囲は、 $IN^+$ と $IN^-$ が互いに相手より高い電圧にも低い電圧にも振れる入力信号をデジタル化するのに役立ちます。従来の例としては、完全差動入力信号や疑似差動両極性入力信号があります。前者では、 $IN^+$ および $IN^-$ を駆動するときに、同相電圧( $V_{IN^+} + V_{IN^-}$ )/2を中心にして互いに位相を180°ずらして駆動し、後者では $IN^-$ の電圧を基準とするリファレンス・レベルの上下に $IN^+$ の電圧が振れます。 $IN^+/IN^-$ アナログ入力は同相入力電圧範囲が広く、CMRRが高いので、選択したSoftSpan範囲に関係なく、互いに任意の関係で振ることができます。ただし、各ピンの電圧がグランドと $V_{DD}$ の範囲内に収まることが条件です。両極性SoftSpan範囲の出力データは、全て2の補数形式です。

### 単極性 SoftSpan 入力電圧範囲

SoftSpanの範囲を5、4、または1で構成したチャネルの場合、LTC2341-18は、表1aに示すように、それぞれ0V～ $V_{REFBUF}$ 、0V～ $V_{REFBUF}/1.024$ 、または0V～ $0.5 \cdot V_{REFBUF}$ という単極性電圧範囲で差動アナログ入力電圧( $V_{IN^+} - V_{IN^-}$ )をデジタル化します。これらのSoftSpan範囲は、 $IN^+$ の電圧が $IN^-$ の電圧より高い値に維持される入力信号をデジタル化するのに役立ちます。従来の例としては疑似差動単極性入力信号があります。ここでは、 $IN^-$ の電圧を基準とするグランド・リファレンス・レベルより高い電圧に $IN^+$ の電圧が振れます。 $IN^+/IN^-$ アナログ入力は同相電圧範囲が広く、CMRRが高いので、選択したSoftSpan範囲に関係なく、互いに任意の関係で振ることができます。ただし、各ピンの電圧がグランドと $V_{DD}$ の範囲内に収まることが条件です。単極性SoftSpan範囲の出力データは、全てストレート・バイナリ形式です。

### 入力駆動回路

各チャネルのサンプリング・コンデンサの収集開始時の初期電圧は、収集間隔の間に新しいピン電圧に安定化する必要があります。 $IN^+$ および $IN^-$ に接続されている外部回路は、この安定化が進行するのに応じて、 $R_{IN}$ を通じて電荷を流し出すか流し込む必要があります。LTC2341-18のサンプリング回路網のRC時定数が7.2nsであるという意味は、フ

ルスケールのステップに要する18ビットのセトリング時間が $13 \cdot (R_{IN} \cdot C_{IN}) =$ 約94nsであるということです。アナログ入力ピンに接続されている外部回路のインピーダンスおよび自己セトリング動作により、必要な全セトリング時間は長くなります。信号源が低インピーダンスの場合は、LTC2341-18の入力を直接駆動することが可能であり、利得誤差も発生しませんが、信号源が高インピーダンスの場合は、バッファ処理して収集時に十分に安定化させ、A/Dコンバータの直線性性能と歪み性能を最適化する必要があります。サンプリング・コンデンサの電圧は収集開始時のアナログ入力ピン電圧とは異なるので、入力信号がDCの場合であっても、セトリング時間は重要な考慮事項です。

ほとんどのアプリケーションでは、バッファ・アンプを使用してLTC2341-18のアナログ入力を駆動する必要があります。バッファ・アンプは出力インピーダンスが低いので、収集段階でアナログ信号の高速セトリングが可能です。また、バッファ・アンプは、収集開始時にアナログ入力での電荷の流れから信号源を切り離します。

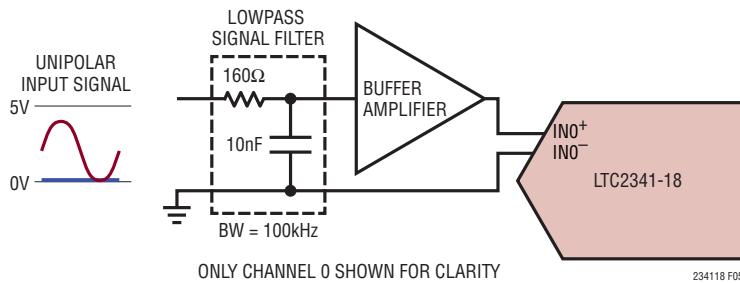

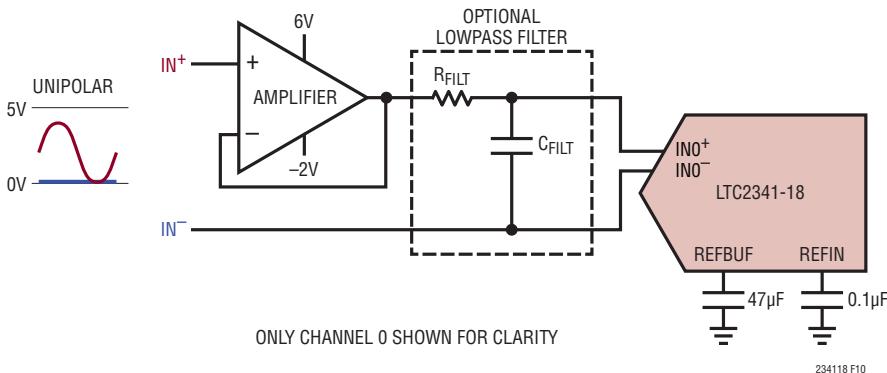

### 入力フィルタリング

入力バッファ・アンプやその他の周辺回路のノイズと歪みは、A/Dコンバータのノイズと歪みに上乗せされるので、考慮する必要があります。入力信号にノイズが多い場合は、バッファ・アンプの前段に低帯域幅のフィルタを接続してノイズを最小限に抑えます。多くのアプリケーションでは、図5に示す簡単な1ポールのRCローパス・フィルタで十分です。

バッファの出力では、サンプリング・スイッチの90Ωのオン抵抗( $R_{IN}$ )と80pFのサンプリング容量( $C_{IN}$ )で形成されるRCローパス・フィルタ回路網により、各チャネルの入力帯域幅は22MHzに制限されます。この値は、収集時に十分なトランジント・セトリング動作が可能なほど高速であると同時に、ドライバの広帯域ノイズを除去することが可能な値です。ノイズ密度の低いバッファ・アンプを選択して、この帯域幅でのSNRの低下を最小限に抑える必要があります。フィルタ回路網をバッファの出力とA/Dコンバータの入力の間に追加して、バッファに対するノイズの影響を最小限に抑え、A/Dコンバータの収集時のトランジント電圧によるバッファへの妨害電圧を低減します。多くのアプリケーションでは、簡単な1ポールのローパスRCフィルタで十分です。ただし、セトリングが不十分だとINLとTHDの性能が制限されることがあるので、A/Dコンバータの収集時間( $t_{ACQ}$ )内にアナログ入力を18ビット分解能まで完全にセトリングさせることができるように、このフィルタの

## アプリケーション情報

図5. 入力フィルタリング回路を接続した単極性シグナルチェーン

RC時定数を十分に小さくすることが重要です。また、最小収集時間は、サンプリング周波数( $f_{SMPL}$ )とイネーブル状態のチャネル数に応じて変動することにも注意してください。

RCフィルタのコンデンサと抵抗は歪みを大きくする可能性があるので、これらの部品は高品質のものを使用します。NPO/COGタイプやシルバー・マイカ・タイプの誘電体コンデンサは優れた直線性を示します。表面実装カーボン抵抗は、自己発熱や半田付け工程で生じる損傷により歪みが生じることがあります。表面実装金属皮膜抵抗は、この2つの問題に対してはるかに耐性があります。

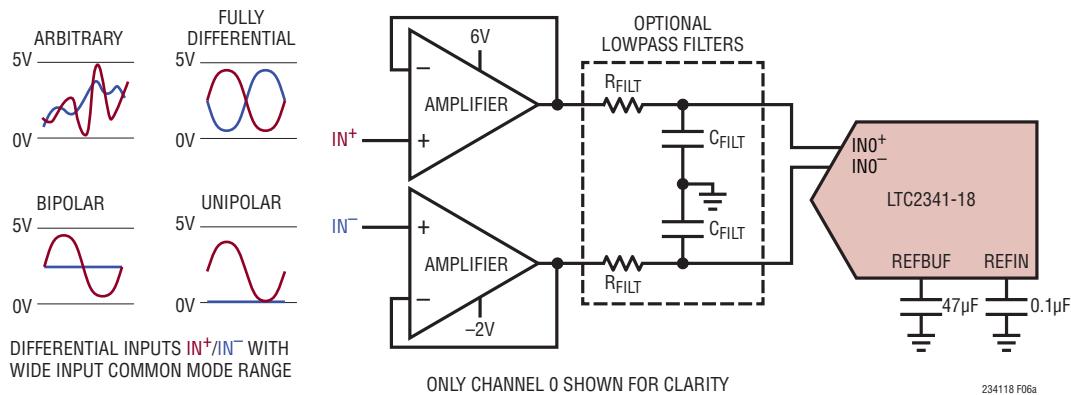

### 任意のアナログ入力信号と完全差動アナログ入力信号のバッファ処理

LTC2341-18は同相入力電圧範囲が広く、CMRRが高いので、各チャネルのIN<sup>+</sup>ピンおよびIN<sup>-</sup>ピンを互いに任意の関係で振幅させることができます。ただし、両方のピンの電圧がグランドとV<sub>DD</sub>の範囲内に収まることが条件です。この独自の機能により、LTC2341-18にはさまざまな振幅の信号を入力できるので、シグナルチェーンの設計が簡単になります。多くのアプリケーションでは、チャネルのIN<sup>+</sup>ピンとIN<sup>-</sup>ピンを既存の

シグナルチェーン回路に直接接続すると、A/Dコンバータの収集時間( $t_{ACQ}$ )内にチャネルのサンプリング回路網を18ビット分解能レベルまで安定化することができません。これらの場合には、図6aに示すように、信号源とA/Dコンバータの入力ピンの間に2つの単位利得バッファを挿入することを推奨します。この回路での使用を推奨するアンプとローパス・フィルタのいくつかの組み合わせを表2に示します。LT6237は高速セトリング特性、高い直線性、低オフセットと $1.1\text{nV}/\sqrt{\text{Hz}}$ の入力換算ノイズ密度を兼ね備えており、図6b～6eのFFTのグラフで示すように、A/Dコンバータのデータシートに示すSNRとTHDの規格値を完全に満たすことができます。SNR性能がやや劣っていても問題のないアプリケーションでは、低消費電力のLT6234を使用してLTC2341-18を駆動することができます。LT6234は高速セトリング特性、優れた直線性、低オフセットと $1.9\text{nV}/\sqrt{\text{Hz}}$ の入力換算ノイズ密度を兼ね備えており、 $24.9\Omega$ 、 $1\text{nF}$ のフィルタを採用した場合、LT6237と比べてSNRが $1.9\text{dB}$ 低下するものの、LTC2341-18を駆動することができます。表2に示すように、LT6237はローパス・フィルタなしで使用することもできますが、広帯域ノイズが増加するためにSNRが低下します(1dB以下)。

表2. 図6aおよび図9のバッファ回路でのアンプとフィルタの組み合わせ。図6aの回路を使用して測定したAC性能、完全差動入力駆動の場合は $\pm 4.096\text{V}$ の範囲、両極性入力駆動の場合は $\pm 2.048\text{V}$ の範囲

| アンプ      | R <sub>FILT</sub><br>(Ω) | C <sub>FILT</sub><br>(nF) | 入力信号の駆動方式          | SNR<br>(dB) | THD<br>(dB) | SINAD<br>(dB) | SFDR<br>(dB) |

|----------|--------------------------|---------------------------|--------------------|-------------|-------------|---------------|--------------|

| ½ LT6237 | 24.9                     | 1                         | FULLY DIFFERENTIAL | 95.2        | -114        | 95.2          | 115          |

| ½ LT6234 | 24.9                     | 1                         | FULLY DIFFERENTIAL | 93.3        | -114        | 93.3          | 115          |

| ½ LT6237 | 24.9                     | 1                         | BIPOLAR            | 89.3        | -110        | 89.3          | 111          |

| ½ LT6234 | 24.9                     | 1                         | BIPOLAR            | 87.6        | -110        | 87.6          | 111          |

| ½ LT6237 | 0                        | 0                         | BIPOLAR            | 88.6        | -110        | 88.6          | 111          |

| ½ LT6234 | 0                        | 0                         | BIPOLAR            | 83.3        | -109        | 83.3          | 111          |

## アプリケーション情報

図6a. 任意信号、完全差動信号、両極性信号、および単極性信号のバッファ処理。

アンプとフィルタの組み合わせについては、表2を参照

## 任意信号の駆動

図6b. 2トーン・テスト。 $IN^+ = -7$ dBFS、2kHzの正弦波、 $IN^- = -7$ dBFS、3.3kHzの正弦波、32kポイントのFFT、 $f_{SMPLE} = 666$ ksps。図6aに示す回路で、アンプはLT6237、 $R_{FILT} = 24.9\Omega$ 、 $C_{FILT} = 1nF$

## 完全差動信号の駆動

図6c.  $IN^+/IN^- = -1$ dBFS、2kHzの完全差動正弦波、同相電圧 = 2.5V、32kポイントのFFT、 $f_{SMPLE} = 666$ ksps。図6aに示す回路で、アンプはLT6237、 $R_{FILT} = 24.9\Omega$ 、 $C_{FILT} = 1nF$

## 両極性信号の駆動

図6d.  $IN^+ = -1$ dBFS、2kHzの両極性正弦波、 $IN^- = 2.5V$ 、32kポイントのFFT、 $f_{SMPLE} = 666$ ksps。図6aに示す回路で、アンプはLT6237、 $R_{FILT} = 24.9\Omega$ 、 $C_{FILT} = 1nF$

## 単極性信号の駆動

図6e.  $IN^+ = -1$ dBFS、2kHzの単極性正弦波、 $IN^- = 0V$ 、32kポイントのFFT、 $f_{SMPLE} = 666$ ksps。図6aに示す回路で、アンプはLT6237、 $R_{FILT} = 24.9\Omega$ 、 $C_{FILT} = 1nF$

234118f

## アプリケーション情報

図6bに示す2トーン・テストは、LTC2341-18の任意入力信号駆動能力を実証しています。このテストでは、IN<sup>+</sup>には-7dBFS、2kHzのシングルエンド正弦波を入力し、IN<sup>-</sup>には-7dBFS、3.3kHzのシングルエンド正弦波を入力して、同時に駆動します。合わせて、より一般的な任意の入力信号の場合と同様に、同相電圧と差動電圧の幅広い組み合わせにわたってこれらの信号がアナログ入力を掃引します。これらの信号には、単純なスペクトル表現もあります。同相電圧の影響を受けない理想的な差動コンバータは、この信号を2つの-7dBFSスペクトル・トーン(各正弦波周波数に1つ)としてデジタル化します。図6bのFFTのグラフは、LTC2341-18の応答がこの理想に近づいていることと、IN<sup>+</sup>に入力された3.3kHzの正弦波に対するコンバータの2次高調波歪み応答によってSFDRが114dBに制限されていることを示しています。

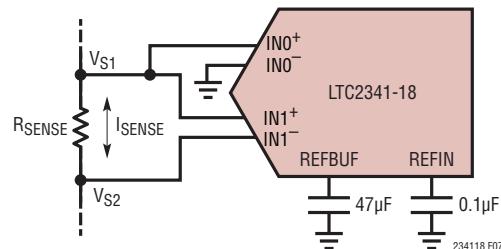

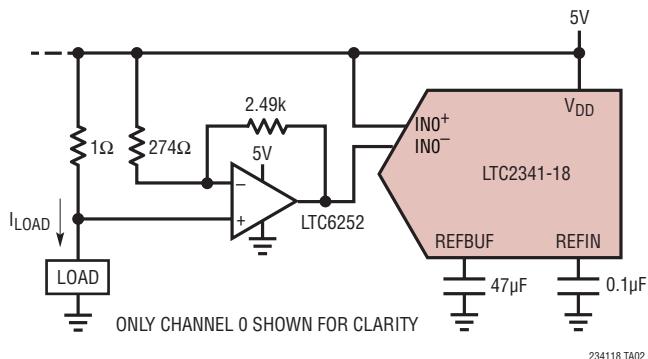

LTC2341-18は、広い入力同相電圧範囲にわたって任意の振幅の信号を入力可能で、しかもCMRRが高いので、アプリケーションの解決策を簡単にすることができます。LTC2341-18を使用してこの種類の信号をデジタル化する1つの方法を図7に示します。LTC2341-18の2つのチャネルは、検出抵抗の電圧と検出抵抗を流れる双方向の電流を広い同相電圧範囲にわたって同時に検出します。この種の多くのアプリケーションでは、外部回路のインピーダンスが十分に低いので、A/Dコンバータのサンプリング回路網は、バッファ処理なしで信号を完全に安定化することができます。

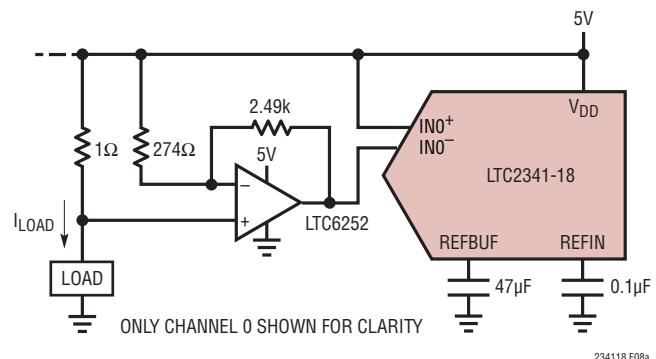

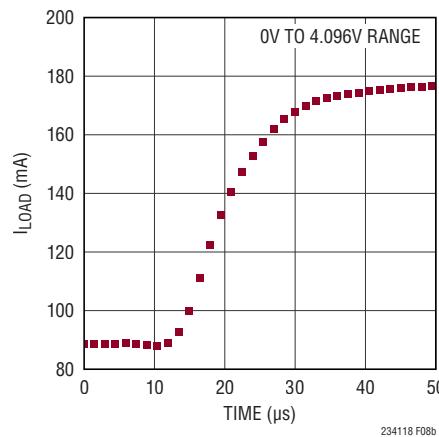

LTC2341-18の同相入力電圧範囲にはV<sub>DD</sub>が含まれているので、図8aに示す回路は、5V单電源から流れる負荷電流(I<sub>LOAD</sub>)を増幅して測定することができます。図8bには、LEDドライバ LTC3207を負荷とするトランジエント電源電流ステップの測定結果を示します。LTC6252の電源がこの回路の利用可能な電流検出範囲を50mA～450mAに制限していることに注意してください。

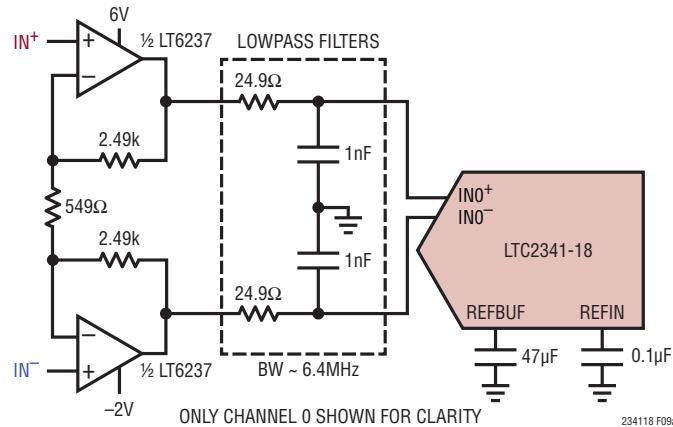

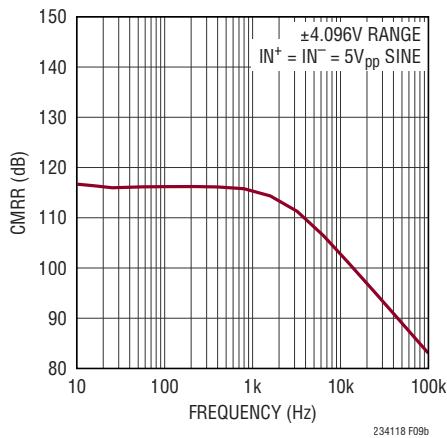

入力信号を増幅するより一般的な方法を図9aに示します。目的のセンサ信号に対する増幅段の差動利得は約10V/Vである一方、不要な同相信号はA/DコンバータのCMRRによって減衰されます。この解決策のCMRR性能の測定結果を図9bに示します。この性能は、商品化されている最高の計装アンプと比べて見劣りしません。

$$I_{SENSE} = \frac{V_{S1} - V_{S2}}{R_{SENSE}} \quad 0V \leq V_{S1} \leq 5V \quad 0V \leq V_{S2} \leq 5V$$

図7. 広い同相電圧範囲にわたって電圧(CH0)と電流(CH1)を同時に検出

図8a. 5V 単電源から流れる50mA～450mAの電流を増幅して検出

図8b. LED ドライバ LTC3207 を負荷とするトランジエント電源電流ステップ、図8aの回路を使用して測定

## アプリケーション情報

図9a. 高いCMRRを示す、差動信号のデジタル化

図9b. CMRRと入力周波数。回路は図9aに示す

## シングルエンド・アナログ入力信号のバッファ処理

図6aに示す回路はシングルエンド入力信号をバッファ処理することができますが、シングルエンド信号のリファレンス・レベルが本質的に低インピーダンスでバッファ処理が不要の場合は、図10に示す回路を推奨します。この回路では、ドライバとローパス・フィルタを1つずつ取り除いて部品数と電力損失を低減し、ドライバのノイズに起因するSNRの低下を抑えています。表2に示すドライバとフィルタの推奨の組み合わせを使用すると、この回路にシングルエンド信号を入力した場合の性能は、図6aの回路の性能と同等になります。

## A/Dコンバータのリファレンス

表1bに示すように、LTC2341-18は3つのリファレンス構成をサポートします。最初の構成では、内部バンドギャップ・リファレンスとリファレンス・バッファの両方を使用します。2番目の構成では、内部リファレンスを外部からオーバードライブしますが、内部バッファを維持して、外部リファレンスをA/D変換時のトランジメントから切り離します。この構成は、1つの高精度外部リファレンスを複数のA/Dコンバータで共有する場合に最適です。3番目の構成では、内部バッファをディスエーブルし、REFBUFピンを外部からオーバードライブします。

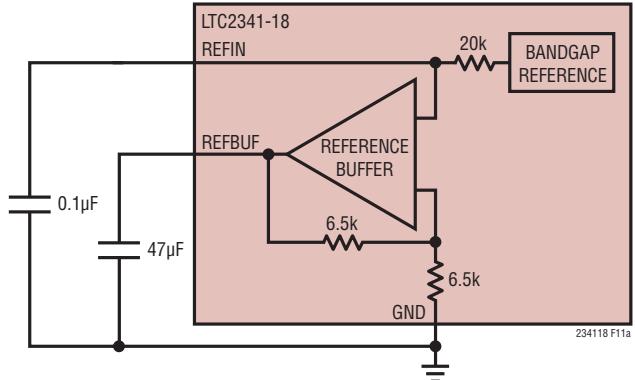

## 内部リファレンスと内部バッファ

LTC2341-18は、工場出荷時に2.048Vに調整された、低ノイズ、低ドリフト(最大20ppm/°C)の温度補償バンドギャップ・リファレンスを内蔵しています。リファレンス出力は20kΩの抵抗を介してREFINピンに接続されます。REFINピンは、図11aに示すように、内蔵リファレンス・バッファの入力として機能し

図10. シングルエンド入力信号のバッファ処理アンプとフィルタの推奨の組み合わせについては、表2を参照

## アプリケーション情報

ます。内部バンドギャップ・リファレンスを使用する場合は、 $0.1\mu F$ のセラミック・コンデンサをREFINピンに近づけて接続し、このピンをGND(ピン11)にバイパスして、広帯域ノイズを除去します。リファレンス・バッファはV<sub>REFBUF</sub>を増幅して、コンバータのマスター・リファレンス電圧 V<sub>REFBUF</sub> = 2 • V<sub>REFIN</sub> (内部バンドギャップ・リファレンスを使用する場合、公称4.096V) をREFBUFピンで生成します。47 $\mu F$ 以上のセラミック・コンデンサ(X7R、10V、1210サイズまたはX5R、10V、0805サイズ)をREFBUFピンに近づけて接続し、このピンをGND(ピン11)にバイパスして、リファレンス・バッファを補償し、変換時のトランジエント電流を吸収して、ノイズを最小限に抑えます。

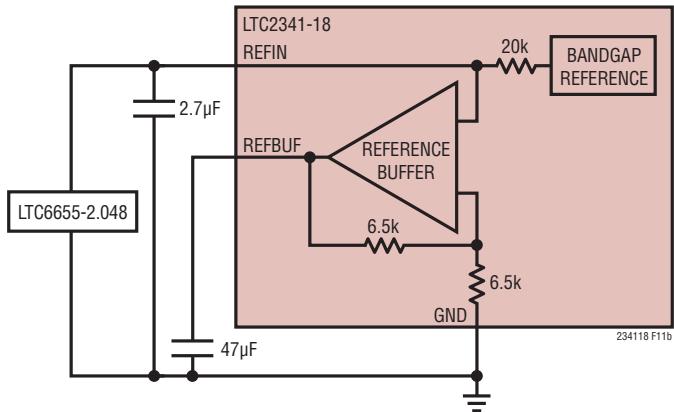

### 外部リファレンスと内部バッファ

より高い精度や低ドリフトが必要な場合は、図11bに示すように、外部リファレンスによってREFINを簡単にオーバードライブすることができます。これは、20k $\Omega$ の抵抗によって内部バンドギャップ・リファレンス出力がREFINピンを分離しているからです。REFINピンでの外部リファレンス電圧オーバードライブの有効な範囲は1.25V～2.2Vなので、コンバータのマスター・リファレンス電圧 V<sub>REFBUF</sub> は2.5V～4.4Vになります。リニアテクノロジーでは、さまざまなアプリケーションの要求を満たすように設計された高性能リファレンスを取り揃えております。LTC6655-2.048は小型、低消費電力、高精度なので、LTC2341-18と組み合わせて内部リファレンスのオーバードライブに使用するのに最適です。LTC6655-2.048は、高精度アプリケーション向けに0.025% (最大)の初期精度と2ppm/ $^{\circ}C$  (最大)の温度係数を実現しています。LTC6655-2.048はHグレードの温度範囲で完全に規定されており、LTC2341-18の広い温度範囲(最大125 $^{\circ}C$ )を補完します。2.7 $\mu F$ ～100 $\mu F$ のセラミック・コンデンサをREFINピンの近くに配置して、LTC6655-2.048をバイパスすることを推奨します。

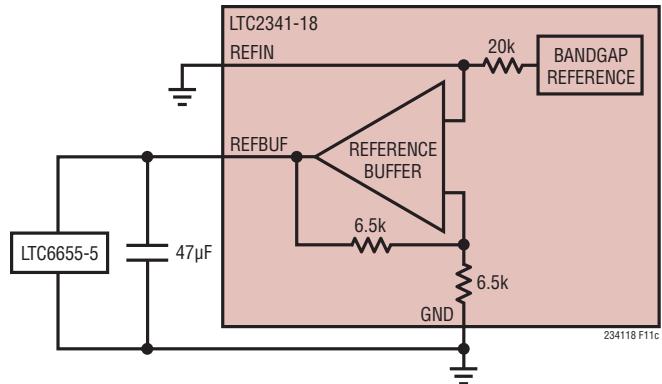

### 外部リファレンスとディスエーブル状態の内部バッファ

内部リファレンス・バッファは、V<sub>REFBUF</sub> = 4.4V (最大)をサポートします。REFINを接地すると内部バッファをディスエーブルすることができるので、図11cに示すように、2.5V～5Vの外部リファレンス電圧を使用してREFBUFをオーバードライブすることができます。入力信号の振幅とSNRを最大にするには、外部5Vリファレンスを使用してREFBUFをオーバードライブします。リファレンス・バッファをディスエーブルした場合でも、バッファの帰還抵抗により、REFBUFピンには13k $\Omega$ の負荷が加わります。LTC6655-5は、小型サイズ、精度、ドリフト、広い温度範囲の点でLTC6655-2.048と同じであり、

図11a. 内部リファレンスと内部バッファの構成

図11b. 外部リファレンスと内部バッファの構成

図11c. 外部リファレンスとディスエーブル状態の内部バッファの構成

## アプリケーション情報

LTC2341-18と併用した場合、標準で96.5dBのSNRを実現します。47 $\mu$ F以上のセラミック・コンデンサ(X7R、10V、1210サイズまたはX5R、10V、0805サイズ)をREFBUFピンに近づけて接続し、LTC6655-5をGND(ピン11)にバイパスして、変換時のトランジエント電流を吸収し、ノイズを最小限に抑えます。

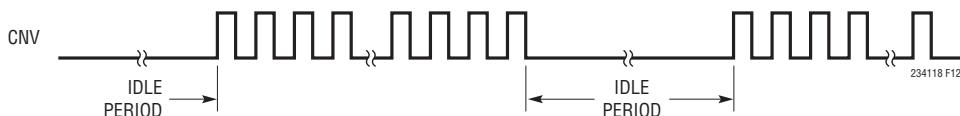

各変換サイクル中に、LTC2341-18コンバータはREFBUFピンから電荷( $Q_{CONV}$ )を流します。短時間の尺度では、この電荷の大半はREFBUFの外付けバイパス・コンデンサによって供給されますが、長時間の尺度では、全ての電荷がリファレンス・バッファによって供給されるか、内部リファレンス・バッファがディスエーブルされている場合は外部リファレンスによって供給されます。この電荷の流れは $I_{REFBUF} = Q_{CONV} \cdot f_{SMPL}$ と等価のDC電流に対応し、サンプリング・レートに比例します。図12に示すように、長時間のアイドル状態の後、集中的にサンプリングされるアプリケーションでは、 $I_{REFBUF}$ は約0.4mAから1.5mAへ急速に遷移します( $V_{REFBUF} = 5V$ 、 $f_{SMPL} = 666kHz$ )。この電流ステップが外部リファレンスのトランジエント応答のトリガとなります。 $V_{REFBUF}$ が正常値から逸脱するとコンバータの精度に影響するので、このトランジエント応答には注意が必要です。外部リファレンスを使用してREFBUFをオーバードライブする場合は、高速セトリング特性のLTC6655リファレンス・ファミリを推奨します。

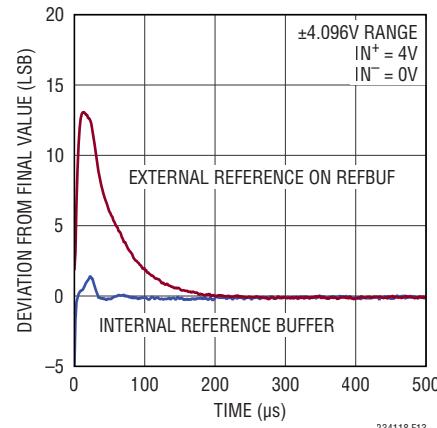

### 内部リファレンス・バッファのトランジエント応答

集中的なサンプリングを使用するアプリケーションで性能を最適化するには、外部リファレンスを内部リファレンス・バッファ構成で使用します。内部リファレンス・バッファは、休止期間後の集中的な変換に応答するときに $V_{REFBUF}$ の変化を最小限に抑える独自の設計回路を内蔵しています。図13では、LTC2341-18の集中的な変換の応答を、2つのリファレンス構成についてフルスケールに近い入力で比較しています。最初

図13. LTC2341-18の集中的なサンプリング、 $f_{SMPL} = 666\text{ksps}$

の構成では、内部リファレンス・バッファを使用し、LTC6655-2.048によって外部からREFINをオーバードライブするのに対して、2番目の構成では、内部リファレンス・バッファをディスエーブルし、外部のLTC6655-4.096を使用してREFBUFをオーバードライブしています。いずれの場合も、REFBUFは47 $\mu$ Fのセラミック・コンデンサによってGNDにバイパスされます。

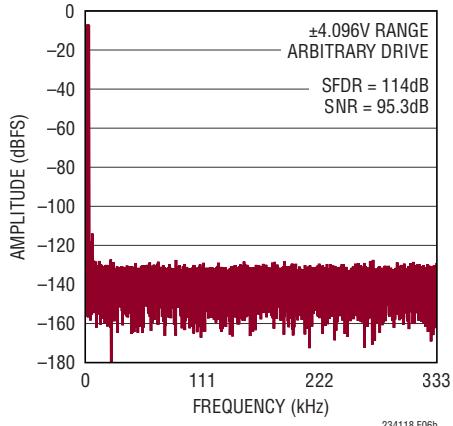

### ダイナミック性能

A/Dコンバータの周波数応答、歪み、およびノイズを定格のスループットでテストするには、高速フーリエ変換(FFT)の手法を使用します。低歪みの正弦波を入力し、そのデジタル出力をFFTアルゴリズムを使用して解析することにより、基本波の外側の周波数に関してA/Dコンバータのスペクトル成分を調べることができます。LTC2341-18では、AC歪みとノイズの測定値について、いずれも保証されたテスト済みの限界値を示しています。

図12. 集中的なサンプリングを示すCNVの波形

## アプリケーション情報

### 信号対ノイズ+歪み比(SINAD)

信号対ノイズ+歪み比(SINAD)は、基本入力周波数のRMS振幅とA/Dコンバータ出力での他の全ての周波数成分のRMS振幅の比です。出力は、サンプリング周波数の半分より低い周波数に帯域制限されますが、DCは除外されます。図14は、2kHzの完全差動入力信号を使用して、サンプリング・レートが666kHzの場合、LTC2341-18が $\pm 4.096V$ の範囲内でSINADの標準値である95.0dBを達成することを示しています。

### 信号対ノイズ比(SNR)

信号対ノイズ比(SNR)は、基本入力周波数のRMS振幅と、1次から5次までの高調波とDCを除く他の全ての周波数成分のRMS振幅の比です。図14は、2kHzの完全差動入力信号を使用して、サンプリング・レートが666kHzの場合、LTC2341-18が $\pm 4.096V$ の範囲内でSNRの標準値である95.1dBを達成することを示しています。

### 全高調波歪み(THD)

全高調波歪み(THD)は、入力信号の全ての高調波のRMS値の合計と基本波のRMS値との比です。帯域外高調波は、DCからサンプリング周波数の半分( $f_{SMPL}/2$ )までの周波数帯域で折り返し歪みを生じます。THDは次のように表されます。

$$THD = 20 \log \frac{\sqrt{V_2^2 + V_3^2 + V_4^2 + \dots + V_N^2}}{V_1}$$

ここで、 $V_1$ は基本周波数のRMS振幅で、 $V_2$ から $V_N$ まではそれぞれ2次高調波からN次高調波までの振幅です。図14は、2kHzの完全差動入力信号を使用して、サンプリング・レートが666kHzの場合、LTC2341-18が $\pm 4.096V$ の範囲内でTHDの標準値である-111dB ( $N = 6$ )を達成することを示しています。

図14. 32kポイントのFFT( $f_{SMPL} = 666\text{ksps}$ ,  $f_{IN} = 2\text{kHz}$ )

### 電源に関する検討事項

LTC2341-18は2つの電源ピンを備えています。5Vのコア電源( $V_{DD}$ )とデジタル入力/出力(I/O)インターフェースの電源( $OV_{DD}$ )です。柔軟な $OV_{DD}$ 電源により、LTC2341-18は、2.5Vや3.3Vのシステムなど、1.8V～5Vで動作するCMOSロジックと通信することができます。LVDS I/Oモードを使用する場合、 $OV_{DD}$ の範囲は2.375V～5.25Vです。

### 電源シーケンシング

LTC2341-18には電源シーケンシングに関する特別な要件はありません。「絶対最大定格」のセクションに記載されている最大電圧の関係を遵守するよう注意する必要があります。LTC2341-18は、最初の電源投入時、または $V_{DD}$ が2Vより低くなったときに必ずA/Dコンバータをリセットするパワーオン・リセット(POR)回路を内蔵しています。電源電圧が公称の電源電圧範囲内に戻ると、POR回路はA/Dコンバータを再度初期化します。初期化の期間が確実に終了するように、POR発生後少なくとも10msは変換を開始しないようにします。内部リファレンス・バッファを使用する場合は、バッファが起動してREFBUFバイパス・コンデンサを再充電するまでに200msを見込んでおきます。これらの時点より前に変換を開始すると、結果は無効になります。

## アプリケーション情報

### タイミングと制御

#### CNVのタイミング

LTC2341-18のサンプリングと変換はCNVによって制御されます。CNVの立ち上がりエッジでは、両チャネルのS/H回路がトラック・モードからホールド・モードに切り替わり、両チャネルの入力信号を同時にサンプリングして、変換を開始します。「リセットのタイミング」のセクションで説明するように、いったん変換が開始されると、A/Dコンバータをリセットしない限り、変換を途中で終了させることはできません。最適な性能を得るには、クリーンな低ジッタの信号でCNVを駆動し、CNVの立ち上がりエッジに到達するまでデータI/Oラインが遷移しないようにする必要があります。更に、チャネル間クロストークを最小限に抑えるため、CNVの立ち上がりエッジの前後100nsでは、アナログ入力のスルーレートが高くならないようになります。A/DコンバータのステータスはBUSY出力によって示されます。この出力は各変換の開始時に“L”から“H”へ遷移し、変換が完了するまで“H”的ままであります。CNVは、いったん“H”になって変換が始まったら、40ns～60ns後に“L”に戻すか、BUSYの立ち下がりエッジ後に“L”に戻して、内部変換処理中の外乱を最小限に抑える必要があります。BUSYの立ち下がりエッジ後にCNVを“L”に戻す場合は、もう一度“H”にするまでに410ns以上“L”的ままで保持します。この場合、A/Dコンバータの収集時間( $t_{ACQ}$ )はCNVが“L”的時間( $t_{CNVL}$ )によって設定されるからです。

#### 内部変換クロック

LTC2341-18はクロックを内蔵しており、Nチャネルをイネーブルしている場合、最大変換時間が $550 \cdot N - 40\text{ns}$ になるよう調整されています。2チャネルを同時に変換する場合の最小収集時間は410nsなので、外部調整なしで666kspsのスループット性能が保証されています。

#### パワーダウン・モード

PDが“H”になるとLTC2341-18の電源は遮断され、その後の変換要求は無視されます。変換中に“H”になった場合、デバイスは変換が完了したら電源を遮断します。このモードでは、デバイスに流れる電流が少量のレギュレータ・スタンバイ電流だけなので、標準的な電力損失は0.33mWになります。パワーダウン・モードを終了するには、PDピンを“L”にしてから10ms以上待機し、その後、変換を開始します。内部リファレンス・バッファを使用する場合は、バッファが起動してREFBUFバイパス・コンデンサを再充電するまでに200msを見込んでおきます。これらの時点より前に変換を開始すると、結果は無効になります。

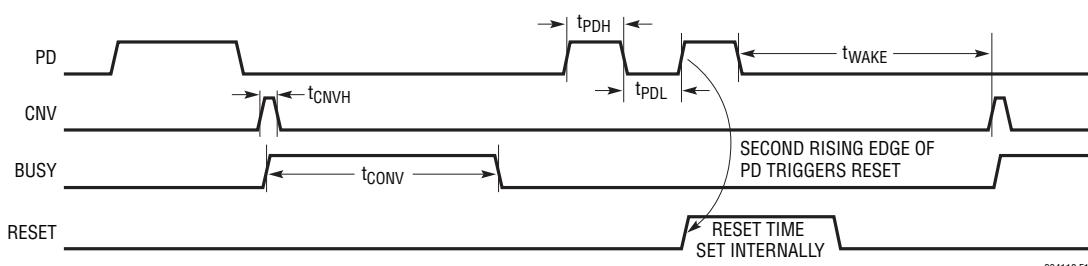

#### リセットのタイミング

LTC2341-18のグローバル・リセットは、パワーオン・リセットと同等であり、電源を入れ直さずに実行することができます。この機能が役立つのは、システム全体の状態を同期した既知の値にリセットすることが必要なシステムレベルの事態から回復する場合です。グローバル・リセットを開始するには、図15に示すように、PDを2回“H”にして、その間に変換を行わないようにします。リセットはPDの2番目の立ち上がりエッジで作動し、内部タイマに基づいて非同期で終了します。リセットによって全てのシリアル・データ出力レジスタがクリアされ、内部SoftSpan構成レジスタは両チャネルともSoftSpan 7のデフォルト状態に戻ります。変換中にリセットが作動すると、変換は直ちに停止します。PDが“H”に切り替わることに関連付けられている通常のパワーダウン動作は、リセットによる影響を受けません。PDが“L”になったら、変換を開始する前に10ms以上待機します。内部リファレンス・バッファを使用する場合は、バッファが起動してREFBUFバイパス・コンデンサを再充電するまでに200msを見込んでおきます。これらの時点より前に変換を開始すると、結果は無効になります。

図15. LTC2341-18のリセットのタイミング

## アプリケーション情報

### 自動ナップ・モード