## 特長

- スループット・レート: 2Msps

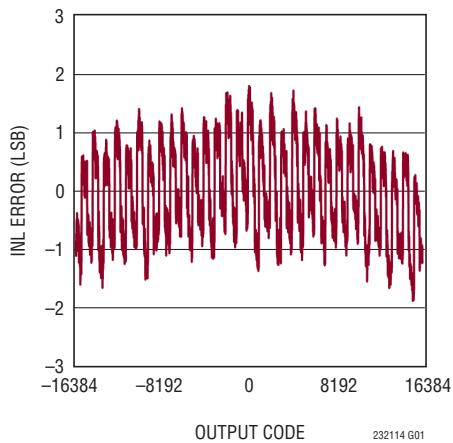

- INL(標準):  $\pm 1$  LSB

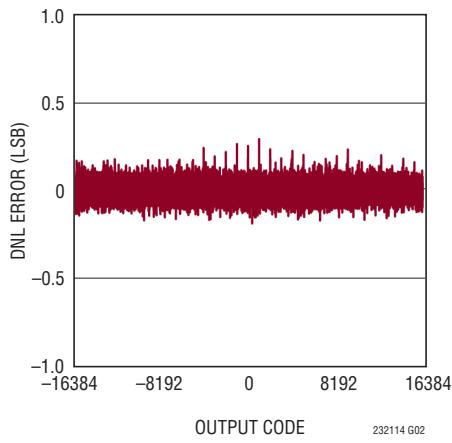

- 欠落コードのない14ビットを保証

- 入力同相範囲の広い差動入力: 8V<sub>P-P</sub>

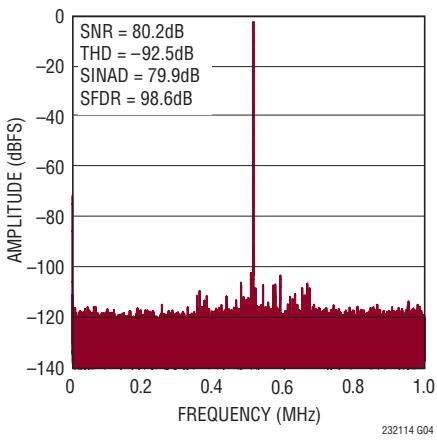

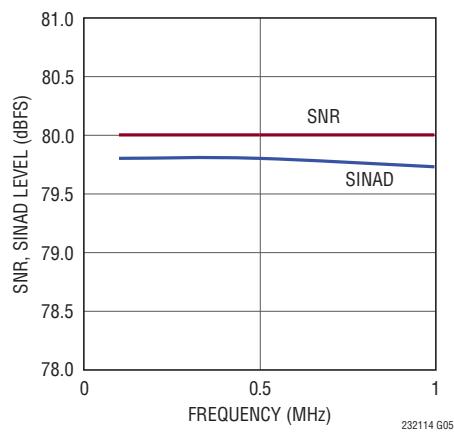

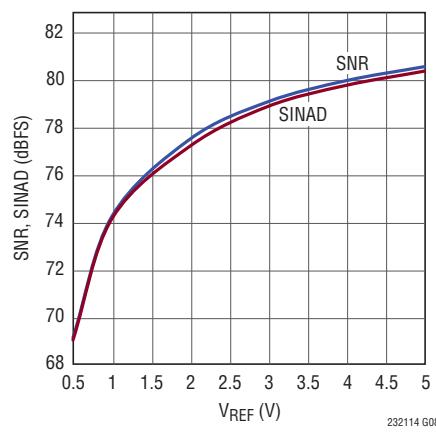

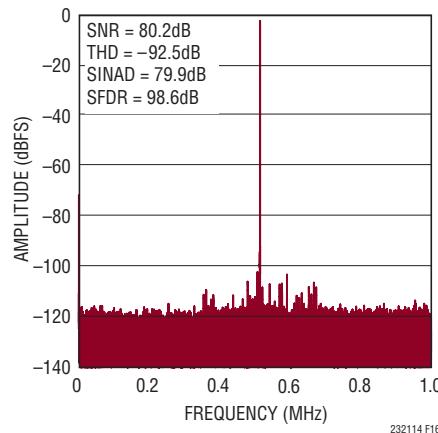

- SNR: 標準 80dB ( $f_{IN} = 500$ kHz)

- THD: 標準 -90dB ( $f_{IN} = 500$ kHz)

- サイクル待ち時間なし

- 125°Cまでの動作を保証

- 3.3Vまたは5V 単電源

- 2.048Vまたは4.096Vの低ドリフト(最大 20ppm/°C)内部リファレンス

- I/O(入出力)の電圧範囲: 1.8V ~ 2.5V

- SPI 互換シリアルI/O: CMOSまたはLVDS

- 電力損失: 33mW/チャネル(標準)

- 小型 28 ピン(4mm×5mm) QFN パッケージ

## アプリケーション

- 高速データ収集システム

- 通信機器

- リモート・データ収集

- 画像処理

- 光通信

- 自動車

- 多相モニタ制御

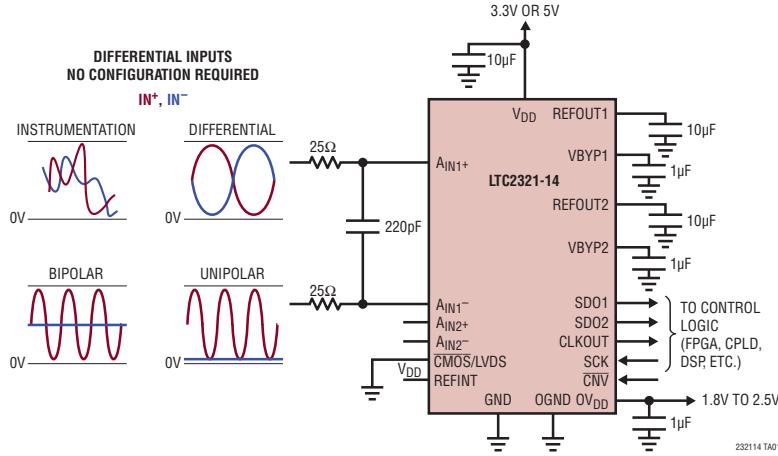

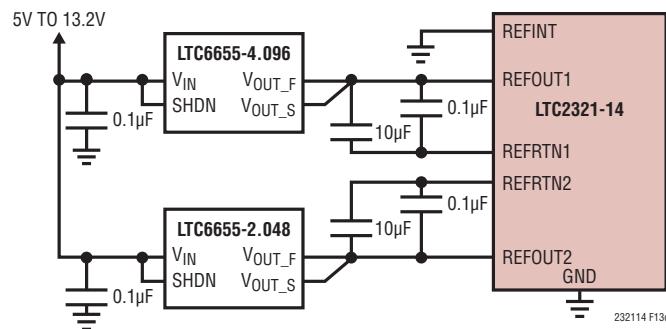

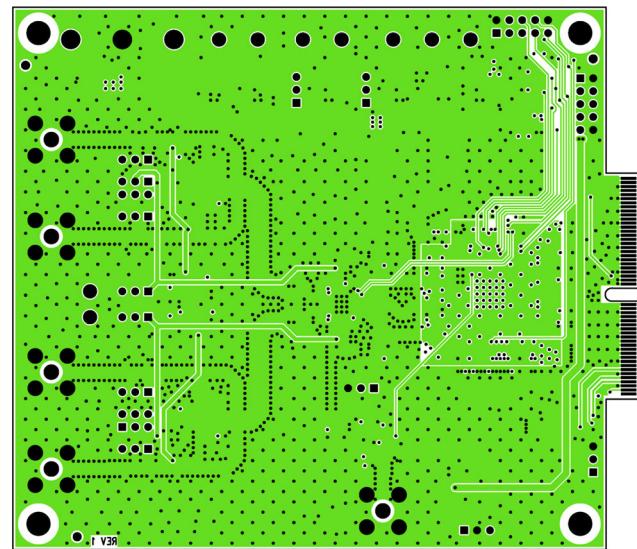

## 標準的應用例

## 絶対最大定格

(Notes 1, 2)

|                                   |                                         |

|-----------------------------------|-----------------------------------------|

| 電源電圧 ( $V_{DD}$ )                 | 6V                                      |

| 電源電圧 ( $0V_{DD}$ )                | 3V                                      |

| 電源バイパス電圧 ( $V_{BYP1}, V_{BYP2}$ ) | 3V                                      |

| アナログ入力電圧                          |                                         |

| $A_{IN+}, A_{IN-}$ (Note 3)       | -0.3V ~ ( $V_{DD} + 0.3V$ )             |

| REFOUT1, 2                        | -0.3V ~ ( $V_{DD} + 0.3V$ )             |

| CNV (Note 15)                     | -0.3V ~ ( $V_{DD} + 0.3V$ )             |

| デジタル入力電圧                          |                                         |

| (Note 3)                          | ( $GND - 0.3V$ ) ~ ( $0V_{DD} + 0.3V$ ) |

| デジタル出力電圧                          | ( $GND - 0.3V$ ) ~ ( $0V_{DD} + 0.3V$ ) |

| 電力損失                              | 200mW                                   |

| 動作温度範囲                            |                                         |

| LTC2321C                          | 0°C ~ 70°C                              |

| LTC2321I                          | -40°C ~ 85°C                            |

| LTC2321H                          | -40°C ~ 125°C                           |

| 保存温度範囲                            | -65°C ~ 150°C                           |

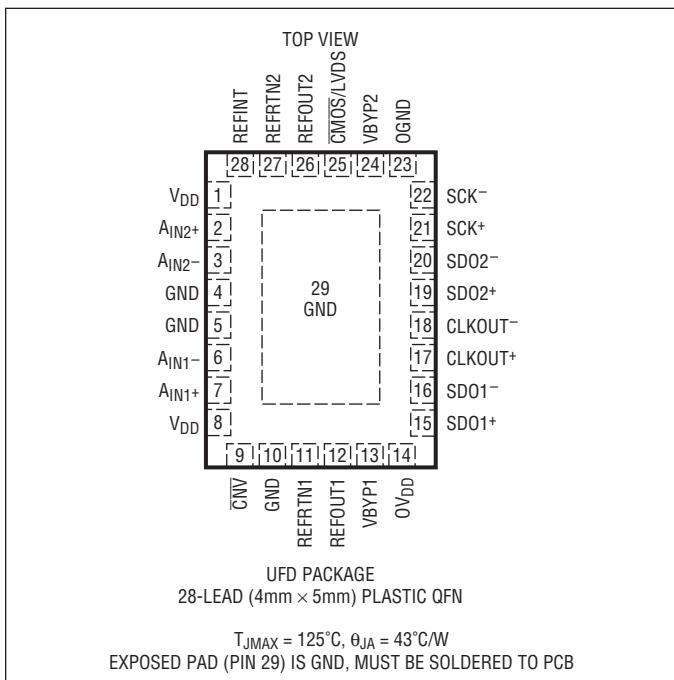

## ピン配置

## 発注情報

| 無鉛仕上げ              | テープアンドリール            | 製品マーキング* | パッケージ                           | 温度範囲           |

|--------------------|----------------------|----------|---------------------------------|----------------|

| LTC2321CUFD-14#PBF | LTC2321CUFD-14#TRPBF | 23214    | 28-Lead (4mm x 5mm) Plastic QFN | 0°C to 70°C    |

| LTC2321IUFD-14#PBF | LTC2321IUFD-14#TRPBF | 23214    | 28-Lead (4mm x 5mm) Plastic QFN | -40°C to 85°C  |

| LTC2321HUFD-14#PBF | LTC2321HUFD-14#TRPBF | 23214    | 28-Lead (4mm x 5mm) Plastic QFN | -40°C to 125°C |

さらに広い動作温度範囲で規定されるデバイスについては、弊社または弊社代理店にお問い合わせください。\* 温度グレードは出荷時のコンテナのラベルで識別されます。

無鉛仕上げの製品マーキングの詳細については、<http://www.linear-tech.co.jp/leadfree/> をご覧ください。

テープアンドリールの仕様の詳細については、<http://www.linear-tech.co.jp/tapeandreel/> をご覧ください。

## 電気的特性

●は全動作温度範囲での規格値を意味する。それ以外は  $T_A = 25^\circ\text{C}$  での値 (Note 4)。

| SYMBOL              | PARAMETER                                     | CONDITIONS                                                 | MIN | TYP        | MAX       | UNITS         |

|---------------------|-----------------------------------------------|------------------------------------------------------------|-----|------------|-----------|---------------|

| $V_{IN+}$           | Absolute Input Range ( $A_{IN1+}, A_{IN2+}$ ) | (Note 5)                                                   | ●   | 0          | $V_{DD}$  | V             |

| $V_{IN-}$           | Absolute Input Range ( $A_{IN1-}, A_{IN2-}$ ) | (Note 5)                                                   | ●   | 0          | $V_{DD}$  | V             |

| $V_{IN+} - V_{IN-}$ | Input Differential Voltage Range              | $V_{IN} = V_{IN+} - V_{IN-}$                               | ●   | -REFOUT1,2 | REFOUT1,2 | V             |

| $V_{CM}$            | Common Mode Input Range                       | $V_{IN} = (V_{IN+} + V_{IN-})/2$                           | ●   | 0          | $V_{DD}$  | V             |

| $I_{IN}$            | Analog Input DC Leakage Current               |                                                            | ●   | -1         | 1         | $\mu\text{A}$ |

| $C_{IN}$            | Analog Input Capacitance                      |                                                            |     |            | 10        | $\text{pF}$   |

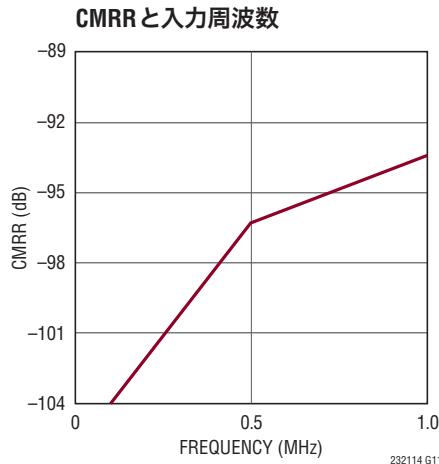

| CMRR                | Input Common Mode Rejection Ratio             | $f_{IN} = 500\text{kHz}$                                   |     |            | 85        | dB            |

| $I_{REFOUT}$        | External Reference Current                    | $\text{REFINT} = 0\text{V}, \text{REFOUT} = 4.096\text{V}$ |     |            | 310       | $\mu\text{A}$ |

232114fa

## コンバータ特性

●は全動作温度範囲での規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値(Note 4, 16)。

| SYMBOL | PARAMETER                      | CONDITIONS                                                        | MIN | TYP   | MAX       | UNITS  |        |

|--------|--------------------------------|-------------------------------------------------------------------|-----|-------|-----------|--------|--------|

|        | Resolution                     |                                                                   | ●   | 14    |           | Bits   |        |

|        | No Missing Codes               |                                                                   | ●   | 14    |           | Bits   |        |

|        | Transition Noise               |                                                                   |     | 0.5   |           | LSBRMS |        |

| INL    | Integral Linearity Error       | (Note 6)                                                          | ●   | -4    | $\pm 1$   | 4      | LSB    |

| DNL    | Differential Linearity Error   |                                                                   | ●   | -0.99 | $\pm 0.4$ | 0.99   | LSB    |

| BZE    | Bipolar Zero-Scale Error       | (Note 7)                                                          | ●   | -4    | 0         | 4      | LSB    |

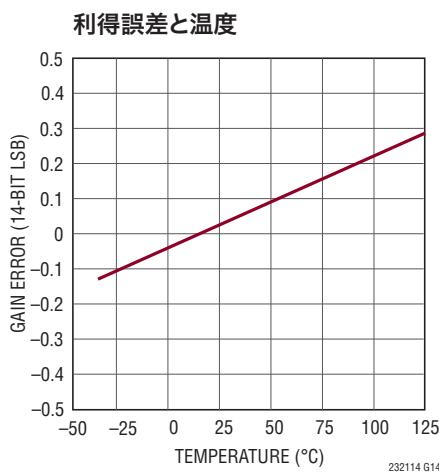

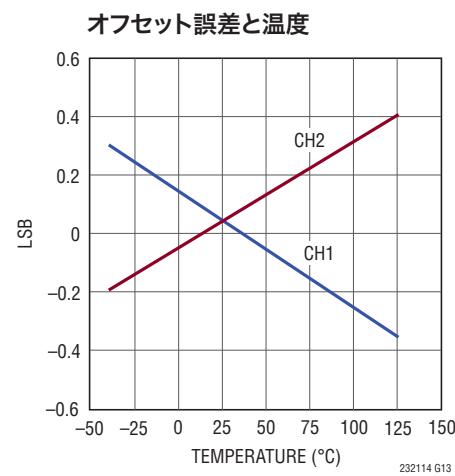

|        | Bipolar Zero-Scale Error Drift |                                                                   |     | 0.006 |           |        | LSB/°C |

| FSE    | Bipolar Full-Scale Error       | $V_{\text{REFOUT1,2}} = 4.096\text{V}$ (REFINT Grounded) (Note 7) | ●   | -25   | $\pm 3$   | 25     | LSB    |

|        | Bipolar Full-Scale Error Drift | $V_{\text{REFOUT1,2}} = 4.096\text{V}$ (REFINT Grounded)          |     | 15    |           |        | ppm/°C |

## ダイナミック精度

●は全動作温度範囲での規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。また、 $A_{\text{IN}} = -1\text{dBFS}$  (Note 4, 8)。

| SYMBOL | PARAMETER                            | CONDITIONS                                                                                    | MIN | TYP  | MAX | UNITS |

|--------|--------------------------------------|-----------------------------------------------------------------------------------------------|-----|------|-----|-------|

| SINAD  | Signal-to-(Noise + Distortion) Ratio | $f_{\text{IN}} = 500\text{kHz}$ , $V_{\text{REFOUT1,2}} = 4.096\text{V}$ , Internal Reference | ●   | 72.5 | 80  | dB    |

|        |                                      | $f_{\text{IN}} = 500\text{kHz}$ , $V_{\text{REFOUT1,2}} = 5\text{V}$ , External Reference     |     | 80   |     | dB    |

| SNR    | Signal-to-Noise Ratio                | $f_{\text{IN}} = 500\text{kHz}$ , $V_{\text{REFOUT1,2}} = 4.096\text{V}$ , Internal Reference | ●   | 73   | 80  | dB    |

|        |                                      | $f_{\text{IN}} = 500\text{kHz}$ , $V_{\text{REFOUT1,2}} = 5\text{V}$ , External Reference     |     | 80.7 |     | dB    |

| THD    | Total Harmonic Distortion            | $f_{\text{IN}} = 500\text{kHz}$ , $V_{\text{REFOUT1,2}} = 4.096\text{V}$ , Internal Reference | ●   | -90  | -80 | dB    |

|        |                                      | $f_{\text{IN}} = 500\text{kHz}$ , $V_{\text{REFOUT1,2}} = 5\text{V}$ , External Reference     |     | -84  |     | dB    |

| SFDR   | Spurious Free Dynamic Range          | $f_{\text{IN}} = 500\text{kHz}$ , $V_{\text{REFOUT1,2}} = 4.096\text{V}$ , Internal Reference | ●   | 80   | 88  | dB    |

|        |                                      | $f_{\text{IN}} = 500\text{kHz}$ , $V_{\text{REFOUT1,2}} = 5\text{V}$ , External Reference     |     | 88   |     | dB    |

|        | -3dB Input Linear Bandwidth          |                                                                                               |     | 10   |     | MHz   |

|        | Aperture Delay                       |                                                                                               |     | 500  |     | ps    |

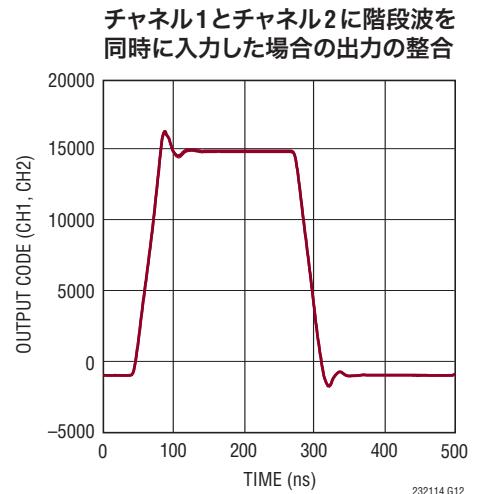

|        | Aperture Delay Matching              |                                                                                               |     | 500  |     | ps    |

|        | Aperture Jitter                      |                                                                                               |     | 1    |     | psRMS |

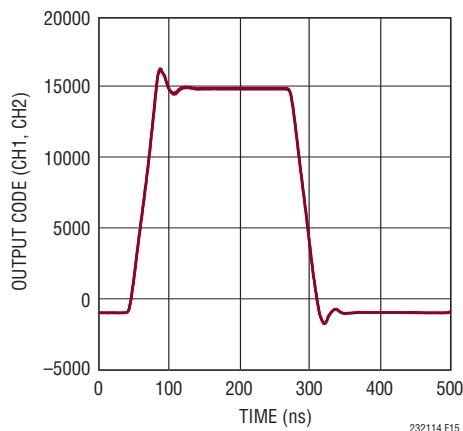

|        | Transient Response                   | Full-Scale Step                                                                               |     | 3    |     | ns    |

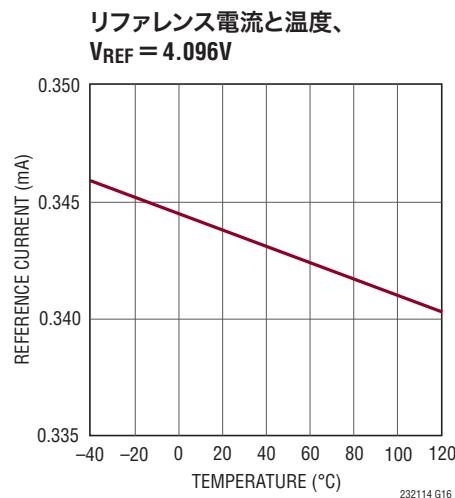

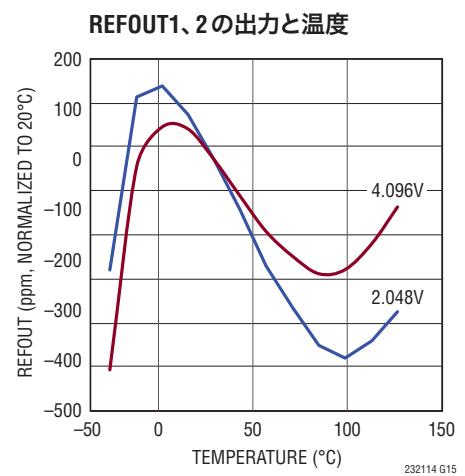

## 内部リファレンスの特性

●は全動作温度範囲での規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値(Note 4)。

| SYMBOL                 | PARAMETER                                      | CONDITIONS                                                                                     | MIN    | TYP            | MAX            | UNITS          |   |

|------------------------|------------------------------------------------|------------------------------------------------------------------------------------------------|--------|----------------|----------------|----------------|---|

| $V_{\text{REFOUT1,2}}$ | Internal Reference Output Voltage              | $4.75\text{V} < V_{\text{DD}} < 5.25\text{V}$<br>$3.13\text{V} < V_{\text{DD}} < 3.47\text{V}$ | ●<br>● | 4.088<br>2.044 | 4.096<br>2.048 | 4.106<br>2.053 | V |

|                        | $V_{\text{REFOUT1,2}}$ Temperature Coefficient | (Note 14)                                                                                      | ●      | 3              | 20             | ppm/°C         |   |

|                        | REFOUT1,2 Output Impedance                     |                                                                                                |        | 0.25           |                | Ω              |   |

|                        | $V_{\text{REFOUT1,2}}$ Line Regulation         | $V_{\text{DD}} = 4.75\text{V}$ to $5.25\text{V}$                                               |        | 0.3            |                | mV/V           |   |

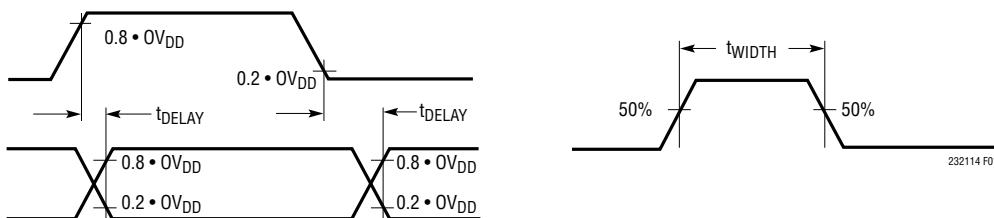

## デジタル入力とデジタル出力

●は全動作温度範囲での規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値(Note 4)。

| SYMBOL       | PARAMETER                                  | CONDITIONS                                                           | MIN                | TYP | MAX  | UNITS         |

|--------------|--------------------------------------------|----------------------------------------------------------------------|--------------------|-----|------|---------------|

| $V_{IH}$     | High Level Input Voltage                   |                                                                      | ● 0.8 • 0 $V_{DD}$ |     |      | V             |

| $V_{IL}$     | Low Level Input Voltage                    |                                                                      | ● 0.2 • 0 $V_{DD}$ |     |      | V             |

| $I_{IN}$     | Digital Input Current                      | $V_{IN} = 0\text{V}$ to $0V_{DD}$                                    | ● -10              |     | 10   | $\mu\text{A}$ |

| $C_{IN}$     | Digital Input Capacitance                  |                                                                      |                    | 5   |      | $\text{pF}$   |

| $V_{OH}$     | High Level Output Voltage                  | $I_O = 500\mu\text{A}$                                               | ● 0 $V_{DD}$ - 0.2 |     |      | V             |

| $V_{OL}$     | Low Level Output Voltage                   | $I_O = 500\mu\text{A}$                                               | ● 0.2              |     |      | V             |

| $I_{OZ}$     | Hi-Z Output Leakage Current                | $V_{OUT} = 0\text{V}$ to $0V_{DD}$                                   | ● -10              |     | 10   | $\mu\text{A}$ |

| $I_{SOURCE}$ | Output Source Current                      | $V_{OUT} = 0\text{V}$                                                |                    | -10 |      | $\text{mA}$   |

| $I_{SINK}$   | Output Sink Current                        | $V_{OUT} = 0V_{DD}$                                                  |                    | 10  |      | $\text{mA}$   |

| $V_{ID}$     | LVDS Differential Input Voltage            | 100 $\Omega$ Differential Termination $0V_{DD} = 2.5\text{V}$        | ● 240              |     | 600  | $\text{mV}$   |

| $V_{IS}$     | LVDS Common Mode Input Voltage             | 100 $\Omega$ Differential Termination $0V_{DD} = 2.5\text{V}$        | ● 1                |     | 1.45 | V             |

| $V_{OD}$     | LVDS Differential Output Voltage           | 100 $\Omega$ Differential Load, LVDS Mode<br>$0V_{DD} = 2.5\text{V}$ | ● 100              | 150 | 300  | $\text{mV}$   |

| $V_{OS}$     | LVDS Common Mode Output Voltage            | 100 $\Omega$ Differential Load, LVDS Mode<br>$0V_{DD} = 2.5\text{V}$ | ● 0.85             | 1.2 | 1.4  | V             |

| $V_{OD\_LP}$ | Low Power LVDS Differential Output Voltage | 100 $\Omega$ Differential Load, LVDS Mode<br>$0V_{DD} = 2.5\text{V}$ | ● 75               | 100 | 250  | $\text{mV}$   |

| $V_{OS\_LP}$ | Low Power LVDS Common Mode Output Voltage  | 100 $\Omega$ Differential Load, LVDS Mode<br>$0V_{DD} = 2.5\text{V}$ | ● 0.9              | 1.2 | 1.4  | V             |

## 電源要件

●は全動作温度範囲での規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値(Note 4)。

| SYMBOL        | PARAMETER          | CONDITIONS                                                                                                                                       | MIN                        | TYP        | MAX          | UNITS         |

|---------------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|------------|--------------|---------------|

| $V_{DD}$      | Supply Voltage     | 5V Operation<br>3.3V Operation                                                                                                                   | ● 4.75<br>● 3.13           |            | 5.25<br>3.47 | V             |

| $0V_{DD}$     | Supply Voltage     |                                                                                                                                                  | ● 1.71                     |            | 2.63         | V             |

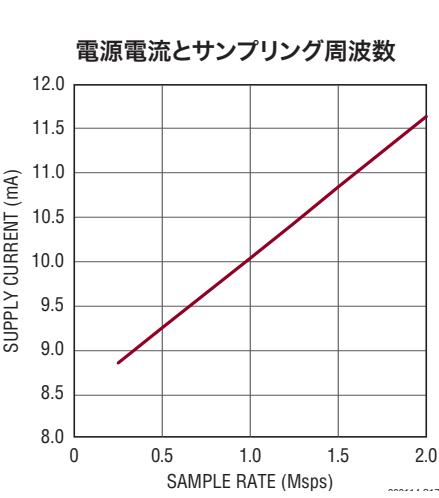

| $I_{VDD}$     | Supply Current     | 2Msps Sample Rate ( $IN^+ = IN^- = 0\text{V}$ )                                                                                                  | ● 11.8                     | 15         |              | $\text{mA}$   |

| $I_{0VDD}$    | Supply Current     | 2Msps Sample Rate ( $C_L = 5\text{pF}$ )<br>2Msps Sample Rate ( $R_L = 100\Omega$ )                                                              | ● CMOS Mode<br>● LVDS Mode | 1.8<br>7.1 | 2<br>11      | $\text{mA}$   |

| $I_{NAP}$     | Nap Mode Current   | Conversion Done ( $I_{VDD}$ )                                                                                                                    | ● 2.55                     |            | 5            | $\text{mA}$   |

| $I_{SLEEP}$   | Sleep Mode Current | Sleep Mode ( $I_{VDD} + I_{0VDD}$ )<br>Sleep Mode ( $I_{VDD} + I_{0VDD}$ )                                                                       | ● CMOS Mode<br>● LVDS Mode | 1<br>1     | 5<br>5       | $\mu\text{A}$ |

| $P_{D\_3.3V}$ | Power Dissipation  | $V_{DD} = 3.3\text{V}$ 2Msps Sample Rate ( $IN^+ = IN^- = 0\text{V}$ )<br>$V_{DD} = 3.3\text{V}$ 2Msps Sample Rate ( $IN^+ = IN^- = 0\text{V}$ ) | ● CMOS Mode<br>● LVDS Mode | 37<br>52   | 58<br>86     | $\text{mW}$   |

|               | Nap Mode           | $V_{DD} = 3.3\text{V}$ Conversion Done ( $I_{VDD} + I_{0VDD}$ )<br>$V_{DD} = 3.3\text{V}$ Conversion Done ( $I_{VDD} + I_{0VDD}$ )               | ● CMOS Mode<br>● LVDS Mode | 7.8<br>26  | 13<br>41     | $\text{mW}$   |

|               | Sleep Mode         | $V_{DD} = 3.3\text{V}$ Sleep Mode ( $I_{VDD} + I_{0VDD}$ )<br>$V_{DD} = 3.3\text{V}$ Sleep Mode ( $I_{VDD} + I_{0VDD}$ )                         | ● CMOS Mode<br>● LVDS Mode | 5<br>5     | 16.5<br>16.5 | $\mu\text{W}$ |

| $P_{D\_5V}$   | Power Dissipation  | $V_{DD} = 5\text{V}$ 2Msps Sample Rate ( $IN^+ = IN^- = 0\text{V}$ )<br>$V_{DD} = 5\text{V}$ 2Msps Sample Rate ( $IN^+ = IN^- = 0\text{V}$ )     | ● CMOS Mode<br>● LVDS Mode | 66<br>77   | 80<br>102.5  | $\text{mW}$   |

|               | Nap Mode           | $V_{DD} = 5\text{V}$ Conversion Done ( $I_{VDD} + I_{0VDD}$ )<br>$V_{DD} = 5\text{V}$ Conversion Done ( $I_{VDD} + I_{0VDD}$ )                   | ● CMOS Mode<br>● LVDS Mode | 13<br>31   | 25<br>40     | $\text{mW}$   |

|               | Sleep Mode         | $V_{DD} = 5\text{V}$ Sleep Mode ( $I_{VDD} + I_{0VDD}$ )<br>$V_{DD} = 5\text{V}$ Sleep Mode ( $I_{VDD} + I_{0VDD}$ )                             | ● CMOS Mode<br>● LVDS Mode | 5<br>5     | 25<br>25     | $\mu\text{W}$ |

232114fa

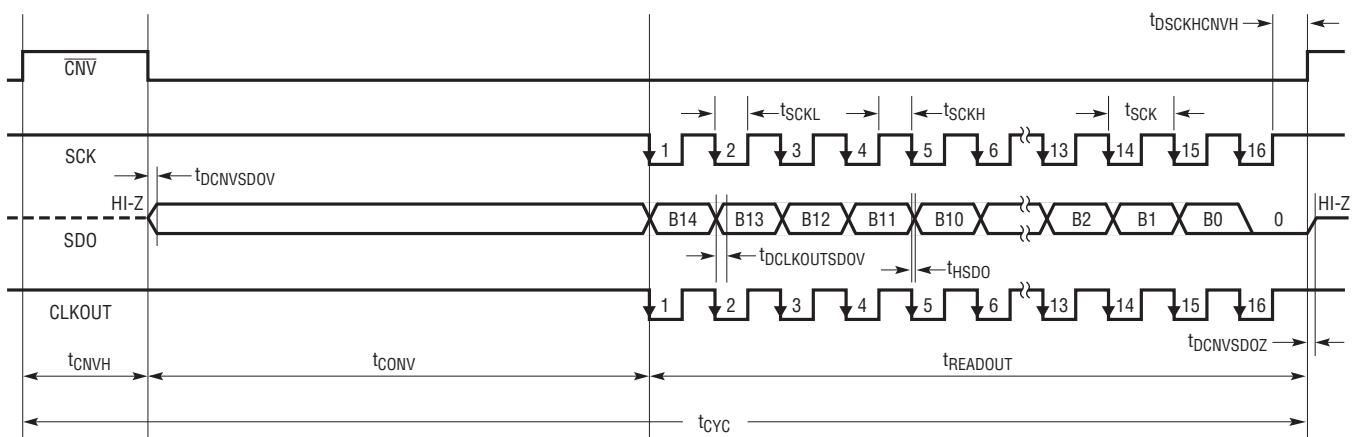

## A/Dコンバータのタイミング特性

●は全動作温度範囲での規格値を意味する。それ以外は  $T_A = 25^\circ\text{C}$  での値 (Note 4)。

| SYMBOL                   | PARAMETER                                                   | CONDITIONS                                                                          | MIN | TYP  | MAX     | UNITS |    |

|--------------------------|-------------------------------------------------------------|-------------------------------------------------------------------------------------|-----|------|---------|-------|----|

| $f_{\text{SMPL}}$        | Maximum Sampling Frequency                                  |                                                                                     |     | 2    |         | Msps  |    |

| $t_{\text{CYC}}$         | Time Between Conversions                                    | (Note 11) $t_{\text{CYC}} = t_{\text{CNVH}} + t_{\text{CONV}} + t_{\text{READOUT}}$ | ●   | 500  | 1000000 | ns    |    |

| $t_{\text{CONV}}$        | Conversion Time                                             |                                                                                     | ●   | 220  |         | ns    |    |

| $t_{\text{CNVH}}$        | $\overline{\text{CNV}}$ High Time                           |                                                                                     | ●   | 25   |         | ns    |    |

| $t_{\text{DSCKHCNVH}}$   | SCK Delay Time to $\overline{\text{CNV}}\uparrow$           | (Note 11)                                                                           | ●   | 0    |         | ns    |    |

| $t_{\text{SCK}}$         | SCK Period                                                  | (Notes 12, 13)                                                                      | ●   | 15.6 |         | ns    |    |

| $t_{\text{SCKH}}$        | SCK High Time                                               |                                                                                     | ●   | 7    |         | ns    |    |

| $t_{\text{SCKL}}$        | SCK Low Time                                                |                                                                                     | ●   | 7    |         | ns    |    |

| $t_{\text{DSCKCLKOUT}}$  | SCK to CLKOUT Delay                                         | (Note 12)                                                                           | ●   | 2.8  |         | ns    |    |

| $t_{\text{DCLKOUTSDOV}}$ | SDO Data Valid Delay from CLKOUT $\downarrow$               | $C_L = 5\text{pF}$ (Note 12)                                                        | ●   |      | 2       | ns    |    |

| $t_{\text{HSDO}}$        | SDO Data Remains Valid Delay from CLKOUT $\downarrow$       | $C_L = 5\text{pF}$ (Note 11)                                                        | ●   |      | 2       | ns    |    |

| $t_{\text{DCNVSDOV}}$    | SDO Data Valid Delay from $\overline{\text{CNV}}\downarrow$ | $C_L = 5\text{pF}$ (Note 11)                                                        | ●   |      | 2.5     | 3     | ns |

| $t_{\text{DCNVSDOZ}}$    | Bus Relinquish Time After $\overline{\text{CNV}}\uparrow$   | (Note 11)                                                                           | ●   |      | 3       | ns    |    |

| $t_{\text{WAKE}}$        | REFOUT1,2 Wakeup Time                                       | $C_{\text{REFOUT1,2}} = 10\text{pF}$                                                |     |      | 10      | ms    |    |

**Note 1:** 絶対最大定格に記載された値を超えるストレスはデバイスに永続的損傷を与える可能性がある。長期にわたって絶対最大定格条件に曝すと、デバイスの信頼性と寿命に悪影響を与える恐れがある。

**Note 2:** 全ての電圧値はグラウンドを基準にしている。

**Note 3:** これらのピンの電圧をグラウンドより低くするか、 $V_{\text{DD}}$ ピンまたは $0V_{\text{DD}}$ ピンの電圧より高くなると、内部のダイオードによってクランプされる。この製品は、これらのピンの電圧がグラウンドより低くなるか、 $V_{\text{DD}}$ ピンまたは $0V_{\text{DD}}$ ピンの電圧より高くなった場合でも、ラッチアップを生じることなく最大100mAの入力電流を処理できる。

**Note 4:**  $V_{\text{DD}} = 5\text{V}$ ,  $0V_{\text{DD}} = 2.5\text{V}$ , REFOUT1, 2 = 4.096V,  $f_{\text{SMPL}} = 2\text{MHz}$ 。

**Note 5:** 推奨動作条件。

**Note 6:** 積分非直線性は、実際の伝達曲線のエンドポイントを通る直線からのコードの偏差として定義されている。偏差は量子化幅の中心から測定される。

**Note 7:** 両極性のゼロ点誤差は、出力コードが $0000\ 0000\ 0000\ 000$ と $1111\ 1111\ 1111\ 111$ の間を往復しているときに、 $-0.5\text{LSB}$ から測定されたオフセット電圧である。フルスケールの両

極性誤差は、最初と最後の理想的なコード遷移からの $-FS$ または $+FS$ の未調整偏差の最悪値であり、オフセット誤差の影響が含まれる。

**Note 8:** dB表示のすべての規格値は、REFOUT = 4.096V での  $\pm 4.096\text{V}$  のフルスケール入力を基準にしている。

**Note 9:** REFOUT1, 2をオーバードライブする場合は、REFINT = 0V に設定して内部リファレンス・パッファをオフにしなければならない。

**Note 10:**  $f_{\text{SMPL}} = 2\text{MHz}$ 。I<sub>REFBUF</sub>はサンプル・レートに比例して変化する。

**Note 11:** 設計によって保証されているが、テストされない。

**Note 12:** パラメータは  $0V_{\text{DD}} = 1.71\text{V}$  および  $0V_{\text{DD}} = 2.5\text{V}$  でテストされ、保証されている。

**Note 13:** 立ち上がりで捕捉する場合、最大 15.6ns の  $t_{\text{SCK}}$  により最大 64MHz のシフト・クロック周波数が可能である。

**Note 14:** 温度係数は出力電圧の最大変化を規定温度範囲で割って計算される。

**Note 15:**  $\overline{\text{CNV}}$  は、低ジッタのデジタル信号源により、標準では  $0V_{\text{DD}}$  ロジック・レベルで駆動される。この入力ピンは、少量の電流が流れる TTL 方式の入力回路を内蔵している。

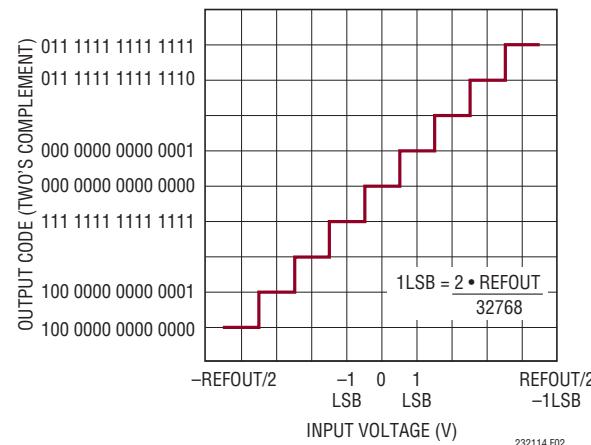

**Note 16:** 1LSB =  $2 \cdot \text{REFOUT1, 2}/2^{14}$

図1. タイミング仕様での電圧レベル

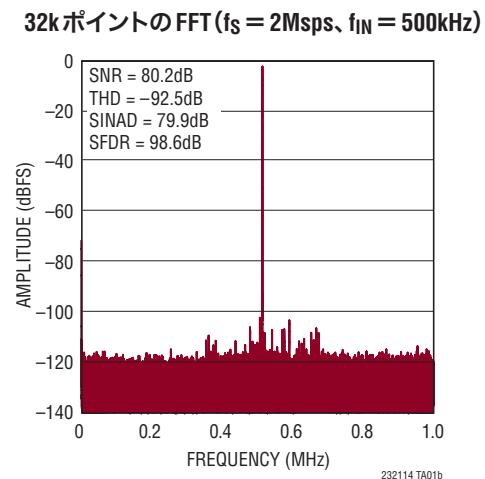

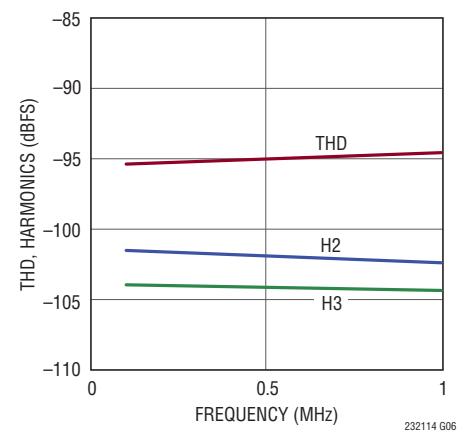

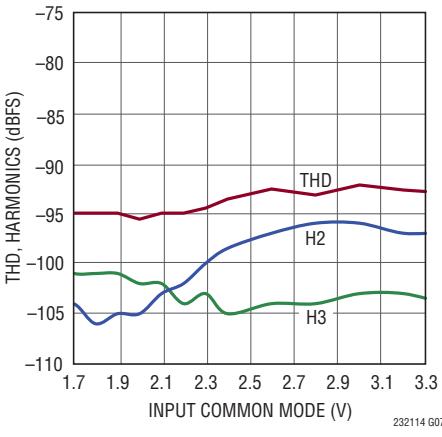

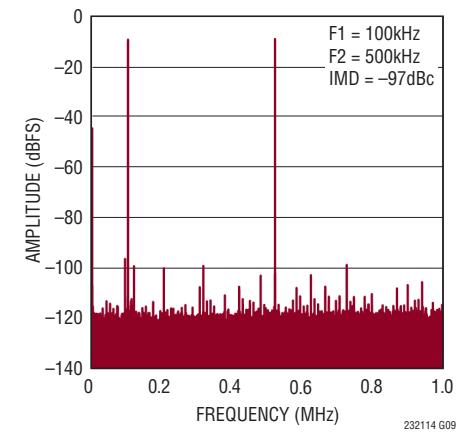

## 標準的性能特性

注記がない限り、 $T_A = 25^\circ\text{C}$ 、 $V_{DD} = 5\text{V}$ 、 $0V_{DD} = 2.5\text{V}$ 、 $\text{REFOUT1,2} = 4.096\text{V}$ 、 $f_{SMPL} = 2\text{Msps}$ 。(Note 16)

積分非直線性と出力コード

微分非直線性と出力コード

DCのヒストグラム

32kポイントのFFT

( $f_s = 2\text{Msps}$ ,  $f_{IN} = 500\text{kHz}$ )

SNR, SINADと入力周波数

(100kHz～1MHz)

THD、高調波と入力周波数

THD、高調波と入力同相電圧

(500kHz)

SNR および SINAD と  $V_{REF}$  (500kHz)

32kポイントのFFT、IMD、 $f_s = 2\text{Msps}$ 、 $V_{IN^+} = 100\text{kHz}$ 、 $V_{IN^-} = 500\text{kHz}$

## 標準的性能特性

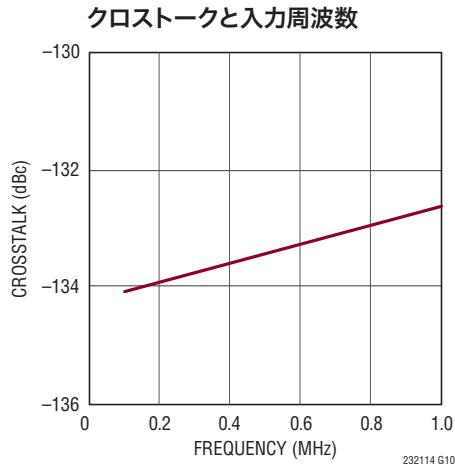

注記がない限り、 $T_A = 25^\circ\text{C}$ 、 $V_{DD} = 5\text{V}$ 、 $OV_{DD} = 2.5\text{V}$ 、 $\text{REFOUT1,2} = 4.096\text{V}$ 、 $f_{SMPL} = 2\text{Msps}$ 。(Note 16)

## ピン機能

**V<sub>DD</sub> (ピン1、8)** : 電源。V<sub>DD</sub>は10μFと0.1μFのセラミック・コンデンサをデバイスの近くに配置してGNDにバイパスします。V<sub>DD</sub>ピンは互いに短絡し、同じ電源で駆動してください。

**A<sub>IN2+</sub>、A<sub>IN2-</sub> (ピン2、3)** : アナログ差動入力ピン。フルスケール範囲(A<sub>IN2+</sub> – A<sub>IN2-</sub>)はREFOUT2の正負の電圧です。これらのピンを駆動できる電圧範囲はV<sub>DD</sub>からGNDまでです。

**GND (ピン4、5、10、29)** : グランド。これらのピンと露出パッド(29ピン)は切れ目のないグランド・プレーンに直接接続する必要があります。

**A<sub>IN1-</sub>、A<sub>IN1+</sub> (ピン6、7)** : アナログ差動入力ピン。フルスケール範囲(A<sub>IN1+</sub> – A<sub>IN1-</sub>)はREFOUT1の正負の電圧です。これらのピンを駆動できる電圧範囲はV<sub>DD</sub>からGNDまでです。

**CNV (ピン9)** : 変換入力。このピンが“H”的ときは、サンプリング段階が規定されます。このピンを“L”にすると、変換段階が開始され、出力データは変換遅延後にクロックに同期して出力されます。この入力ピンは、低ジッタのパルスにより標準でOV<sub>DD</sub>レベルに駆動されるTTL方式の入力ですが、V<sub>DD</sub>レベルに設定されます。このピンはCMOS/LVDSピンの影響は受けません。

**REFRTN1 (ピン11)** : リファレンス・バッファ1の出力帰路。REFRTN1はREFOUT1にバイパスします。REFRTN1ピンはグランド・プレーンに接続しないでください。

**REFOUT1 (ピン12)** : リファレンス・バッファ1の出力。内蔵バッファはこのピンに公称4.096Vを出力します。このピンはREFRTN1を基準にしており、0.1μF(X7R、0402サイズ)のコンデンサと10μF(X5R、0805サイズ)のセラミック・コンデンサを(ビアなしで)このピンに近づけて並列に接続してデカッピングする必要があります。このピンを駆動する内部バッファをディスエーブルするには、REFINTピンを接地します。バッファがディスエーブルされている場合、外部リファレンスは1.25V~5Vの範囲でこのピンを駆動できます。

**VBYP1 (ピン13)** : この内部電源ピンは1μFのセラミック・コンデンサを使用してグランドにバイパスします。このピンの公称出力電圧は1.6Vです。

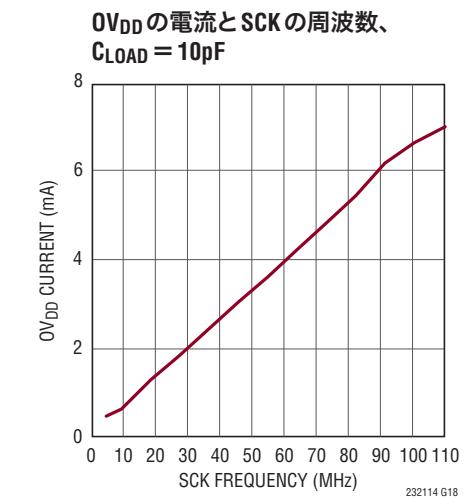

**OV<sub>DD</sub> (ピン14)** : 入力/出力インターフェースのデジタル電源。OV<sub>DD</sub>の範囲は1.71V~2.5Vです。この電源は公称値がホストのインターフェースと同じ電源電圧に設定します(CMOS:1.8Vまたは2.5V、LVDS:2.5V)。OV<sub>DD</sub>ピンは、0.1μFのコンデンサを使用してOGNDにバイパスします。

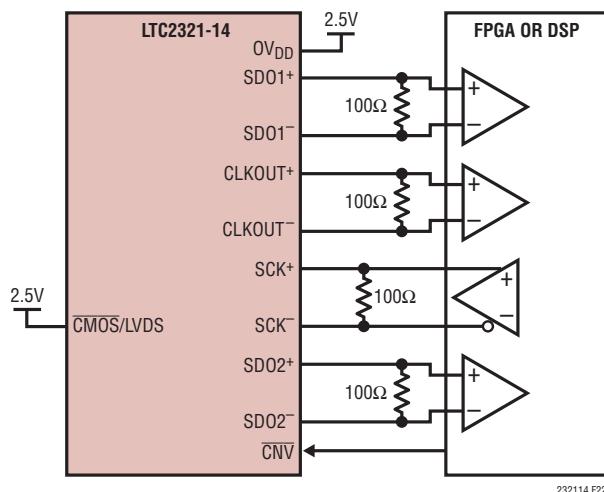

**SDO1<sup>+</sup>、SDO1<sup>-</sup> (ピン15、16)** : チャネル1のシリアル・データ出力。変換結果は、SCKの各立ち下がりエッジでMSBを先頭

にシフトして出力されます。CMOSモードでは、結果はSDO1<sup>+</sup>に出力されます。ロジック・レベルはOV<sub>DD</sub>によって決まります。SDO1<sup>-</sup>は接続しないでください。LVDSモードでは、結果はSDO1<sup>+</sup>およびSDO1<sup>-</sup>に差動で出力されます。これらのピンは、レシーバ(FPGA)に100Ωの抵抗を外付けすることによって差動で終端する必要があります。

**CLKOUT<sup>+</sup>、CLKOUT<sup>-</sup> (ピン17、18)** : シリアル・データのクロック出力。CLKOUTは、SDO出力をレシーバでラッチするために、スキーの整合したクロックを出力します。CMOSモードでは、スキーの整合したクロックはCLKOUT<sup>+</sup>に出力されます。ロジック・レベルはOV<sub>DD</sub>によって決まります。CLKOUT<sup>-</sup>は接続しないでください。SCKを使用してSDO出力をラッチする低スループットのアプリケーションでは、CLKOUT<sup>-</sup>をOV<sub>DD</sub>に接続すればCLKOUT<sup>+</sup>をディスエーブルできます。LVDSモードでは、スキーの整合したクロックはCLKOUT<sup>+</sup>およびCLKOUT<sup>-</sup>に差動で出力されます。これらのピンは、レシーバ(FPGA)に100Ωの抵抗を外付けすることによって差動で終端する必要があります。

**SDO2<sup>+</sup>、SDO2<sup>-</sup> (ピン19、20)** : チャネル2のシリアル・データ出力。変換結果は、SCKの各立ち下がりエッジでMSBを先頭にシフトして出力されます。CMOSモードでは、結果はSDO2<sup>+</sup>に出力されます。ロジック・レベルはOV<sub>DD</sub>によって決まります。SDO2<sup>-</sup>は接続しないでください。LVDSモードでは、結果はSDO2<sup>+</sup>およびSDO2<sup>-</sup>に差動で出力されます。これらのピンは、レシーバ(FPGA)に100Ωの抵抗を外付けすることによって差動で終端する必要があります。

**SCK<sup>+</sup>、SCK<sup>-</sup> (ピン21、22)** : シリアル・データ・クロック入力。このクロックの立ち下がりエッジにより、変換結果はMSBを先頭にシフトしてSDOピンに出力されます。CMOSモードでは、シングルエンドのクロックを使用してSCK<sup>+</sup>を駆動します。ロジック・レベルはOV<sub>DD</sub>によって決まります。SCK<sup>-</sup>は接続しないでください。LVDSモードでは、差動クロックを使用してSCK<sup>+</sup>およびSCK<sup>-</sup>を駆動します。これらのピンは、レシーバ(ADC)に100Ωの抵抗を外付けすることによって差動で終端する必要があります。

**OGND (ピン23)** : 入力/出力のグランド。このグランドはグランド・プレーンに一点で接続する必要があります。OV<sub>DD</sub>はこのピンにバイパスされます。

**VBYP2 (ピン24)** : この内部電源ピンは1μFのセラミック・コンデンサを使用してグランドにバイパスします。このピンの公称出力電圧は1.6Vです。

## ピン機能

**CMOS/LVDS (ピン25) :** 入力/出力のモード選択。CMOS モードをイネーブルするにはこのピンを接地し、LVDS モードをイネーブルするには OV<sub>DD</sub> に接続します。低消費電力の LVDS モードをイネーブルするには、このピンをフロート状態にします。

**REFOUT2 (ピン26) :** リファレンス・バッファ2の出力。内蔵バッファはこのピンに公称4.096Vを出力します。このピンは REFRTN2 を基準にしており、0.1 $\mu$ F (X7R, 0402 サイズ) のコンデンサと 10 $\mu$ F (X5R, 0805 サイズ) のセラミック・コンデンサを(ビアなしで)このピンに近づけて並列に接続してデカッピングする必要があります。このピンを駆動する内部バッファをディスエーブルするには、REFINT ピンを接地します。バッファがディスエーブルされている場合、外部リファレンスは 1.25V ～ V<sub>DD</sub> の範囲でこのピンを駆動できます。

**REFRTN2 (ピン27) :** リファレンス・バッファ2の出力帰路。REFRTN2 は REFOUT2 にバイパスします。REFRTN2 ピンはグランド・プレーンに接続しないでください。

**REFINT (ピン28) :** リファレンス・バッファ出力のイネーブル・ピン。内部リファレンスを使用する場合は V<sub>DD</sub> に接続します。REFOUT1 および REFOUT2 の内部バッファをディスエーブルして外部リファレンス電圧を使用するには、グランドに接続します。このピンには V<sub>DD</sub> へのプルアップ抵抗 (500k) が内蔵されています。

**露出パッド (ピン29) :** グランド。このパッドはグランドに半田付けします。

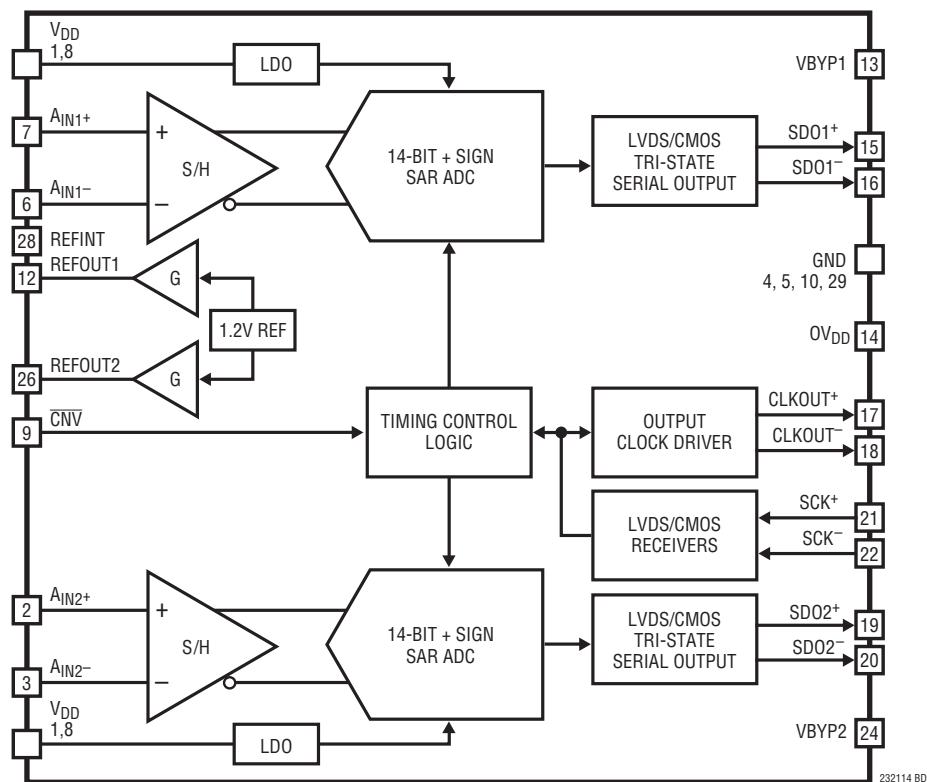

## 機能ブロック図

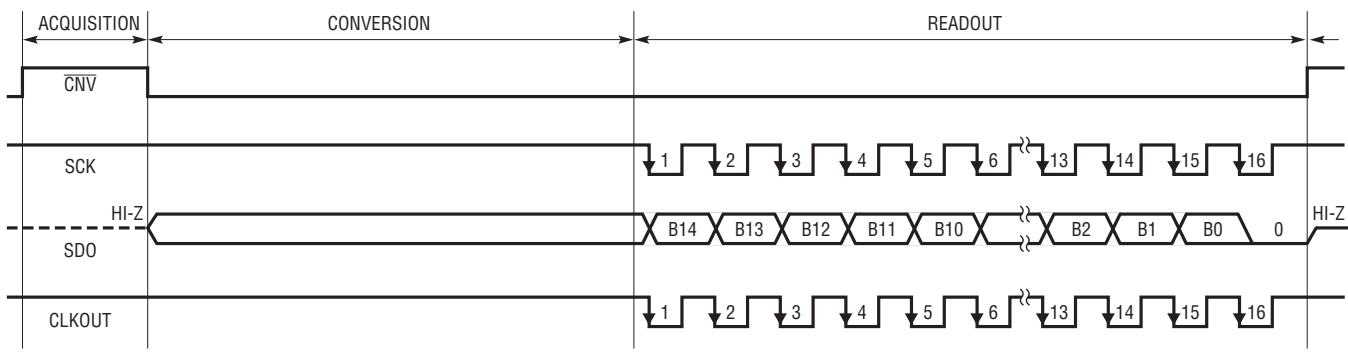

## タイミング図

## アプリケーション情報

### 概要

LTC2321-14は、差動入力で入力同相範囲の広い低ノイズ、高速14ビット+符号ビットのデュアル逐次比較レジスタ(SAR)A/Dコンバータです。アナログ入力が柔軟なので、ハードウェアを構成する必要なく、完全差動、両極性の疑似差動、単極性の疑似差動の各駆動方式をサポートします。14ビット+符号ビットの2の補数出力のMSBは、差動アナログ入力電圧の符号を表します。

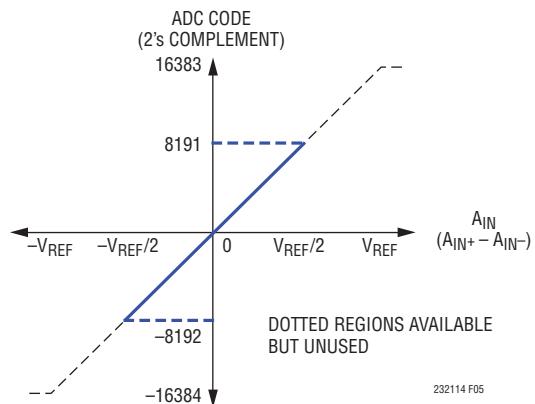

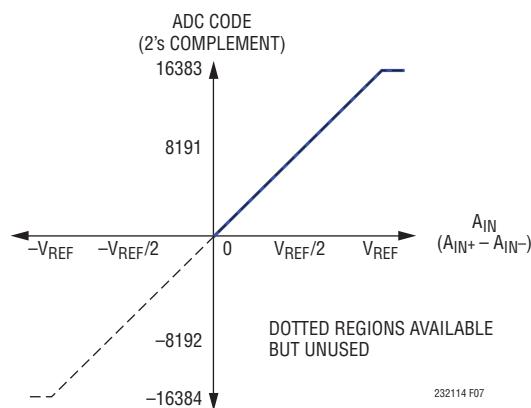

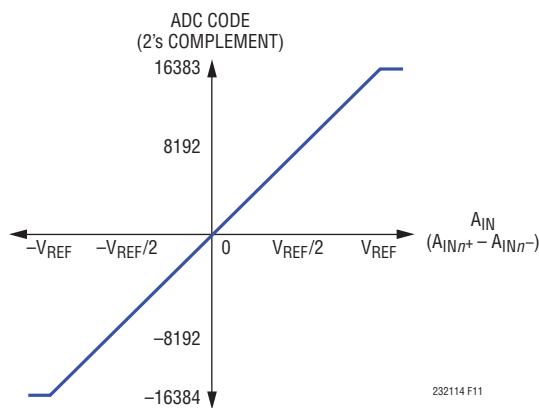

A/Dコンバータの伝達関数は、図2に示すように、2・REFOUTのフルスケール範囲にわたって15ビットの分解能を備えています。アナログ入力範囲がこのフルスケール範囲より狭い(疑似差動駆動などの)場合、A/Dコンバータはこの狭まった範囲内で14ビットの分解能を示し、表1に示すように、オーバーレンジやアンダーレンジの条件でのデジタル化という利点が加わります。この独自の機能が特に有益なのは、制御ループ・アプリケーションです。

### コンバータの動作

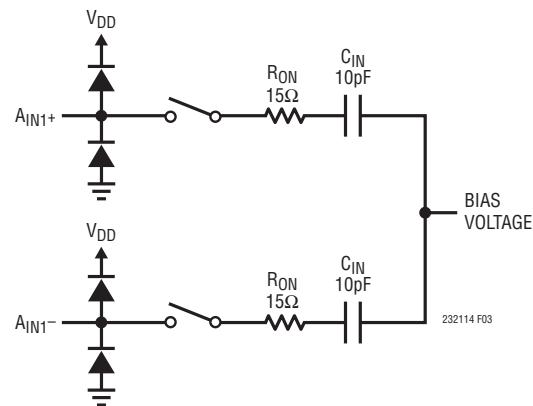

LTC2321-14は2段階で動作します。収集段階では、図3に示すようにサンプル・コンデンサがアナログ入力ピン $A_{IN+}$ および $A_{IN-}$ に接続され、差動アナログ入力電圧がサンプリングされます。 $CNV$ ピンの立ち下がりエッジにより変換が開始されます。変換段階では、15ビットのCDACが逐次比較アルゴリズムを通じて逐次制御され、差動コンパレータを使用してサンプル入力とリファレンス電圧の2進重み付け分数(例:  $V_{REFOUT}/2, V_{REFOUT}/4 \dots V_{REFOUT}/16384$ )を効率的に比較します。変換の最後には、CDACの出力はサンプリングされたアナログ入力に近づきます。その後、A/Dコンバータの制御ロジックが15ビットのデジタル出力コードを準備して、シリアル転送に備えます。データは $SCK^+$ 入力クロックの各立ち下がりエッジでクロックに同期して出力されます。

## アプリケーション情報

### 伝達関数

LTC2321-14は $2 \cdot \text{REFOUT}$ のフルスケール電圧を $2^{15}$ レベルにデジタル化するので、 $\text{REFBUF} = 4.096\text{V}$ では15ビット分解能の大きさは $250\mu\text{V}$ になります。理想的な伝達特性を図2に示します。出力データは2の補数形式です。完全差動入力で駆動した場合、伝達関数の対象範囲コード数は $2^{15}$ です。疑似差動入力で駆動した場合、伝達関数の対象範囲コード数は $2^{14}$ です。

### アナログ入力

LTC2321-14の差動入力は柔軟性が高いので、構成の必要なく幅広いアナログ信号を変換できます。LTC2321-14は、 $A_{\text{IN}+}$ ピンと $A_{\text{IN}-}$ ピンの間の差電圧をデジタル化する一方で、広い同相入力範囲をサポートしています。アナログ入力信号が $V_{\text{DD}}$ とGNDの範囲内にとどまる場合には、信号間の関係を互いに自由なものにすることができます。LTC2321-14は、単極性/双極性の疑似差動、完全差動など、種類がさらに制限されたアナログ入力信号を構成の必要なくデジタル化できます。

LTC2321-14のアナログ入力は、図3に示す等価回路でモデル化できます。入力のバック・トゥ・バック・ダイオードは、ESD保護を実現するクランプを形成します。収集段階では、サンプリング・コンデンサによる $10\text{pF}$  ( $C_{\text{IN}}$ )とサンプリング・スイッチのオン抵抗による約 $15\Omega$  ( $R_{\text{ON}}$ )が入力に直列に接続されます。両方の入力に共通する不要な信号は、ADCサンプリング回路の同相除去特性によって減少します。収集中に $C_{\text{IN}}$ コンデンサを充電するときには、ADCコアの入力に少量の電流スパイクが流れます。

図2. LTC2321-14の伝達関数

図3. LTC2321-14の差動アナログ入力の等価回路

表1. アナログ入力動作モードのコード範囲

| モード     | 範囲( $V_{\text{IN}+} \sim V_{\text{IN}-}$ ) | 最小コード              | 最大コード              |

|---------|--------------------------------------------|--------------------|--------------------|

| 完全差動    | $-\text{REFOUT} \sim +\text{REFOUT}$       | 100 0000 0000 0000 | 011 1111 1111 1111 |

| 両極性疑似差動 | $-\text{REFOUT}/2 \sim +\text{REFOUT}/2$   | 110 0000 0000 0000 | 001 1111 1111 1111 |

| 単極性疑似差動 | $0 \sim \text{REFOUT}$                     | 000 0000 0000 0000 | 011 1111 1111 1111 |

## アプリケーション情報

図4. 両極性疑似差動のアプリケーション回路

## シングルエンド信号

シングルエンド信号はLTC2321-14によって直接デジタル化できます。同相信号除去性能が向上するように、これらの信号は疑似差動式に検出します。主要なアナログ信号のリファレンス信号(例:グランド検出信号)を別のAINピンに接続することにより、2つの信号と同相のノイズまたは外乱はA/Dコンバータの高いCMRRによって除去されます。LTC2321-14は、その柔軟性により、疑似差動の単極性信号と両極性信号の両方に対応し、構成の必要はありません。入力同相範囲が広いので、アナログ入力の前段でのシグナル・コンディショニング回路の精度要件が緩和されます。

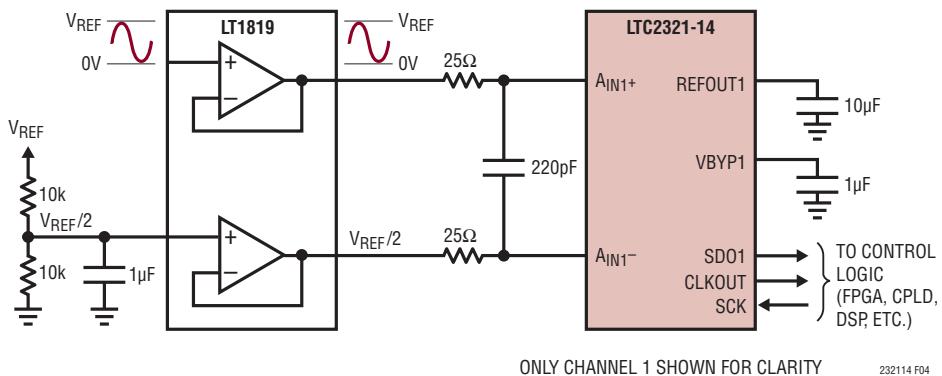

### 両極性の疑似差動入力電圧範囲

両極性の疑似差動構成とは、一方のアナログ入力を固定電圧(標準では $V_{REF}/2$ )で駆動し、信号をもう一方の $A_{IN}$ ピンに入力することを意味します。この場合、アナログ入力の振幅範囲は固定入力電圧を中心に対称となるので、A/D変換の範囲がフルスケールの半分となる両極性の2の補数出力コードが得られます。この構成を図4に示し、対応する伝達関数を図5に示します。アナログ入力ピンの固定電圧は必ずしも $V_{REF}/2$ に設定する必要はありませんが、 $V_{DD}$ レールの範囲内のいずれかの電圧に設定することにより、代替入力がこの電圧

圧を中心として対称に振れることができます。入力信号( $A_{IN+} - A_{IN-}$ )が $\pm REFOUT/2$ を超えて振れる場合、有効なコードはA/Dコンバータによって生成されるので、必要に応じてユーザがクランプする必要があります。

図5. 両極性疑似差動の伝達関数

## アプリケーション情報

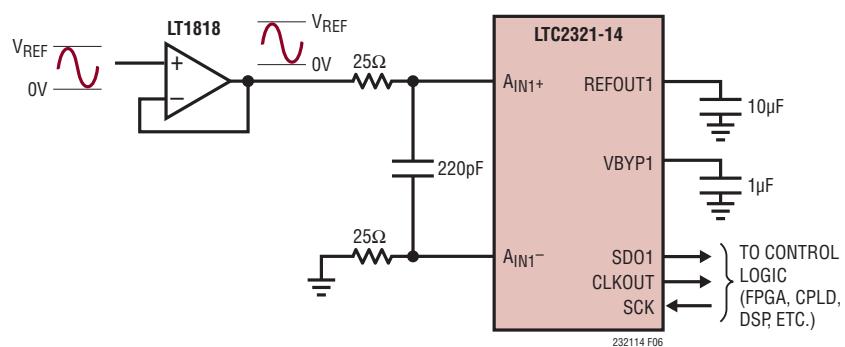

### 单極性の疑似差動入力電圧範囲

単極性の疑似差動構成とは、一方のアナログ入力をグランドで駆動し、信号をもう一方のAINピンに入力することを意味します。この場合、アナログ入力の振幅範囲はグランドとV<sub>REF</sub>の間になるので、A/D変換の範囲がフルスケールの半分となる

る単極性の2の補数出力コードが得られます。この構成を図6に示し、対応する伝達関数を図7に示します。入力信号( $A_{IN+} - A_{IN-}$ )が負側に振れる場合、有効なコードはA/Dコンバータによって生成されるので、必要に応じてユーザがクランプする必要があります。

図6. 単極性疑似差動のアプリケーション回路

図7. 単極性疑似差動の伝達関数

## アプリケーション情報

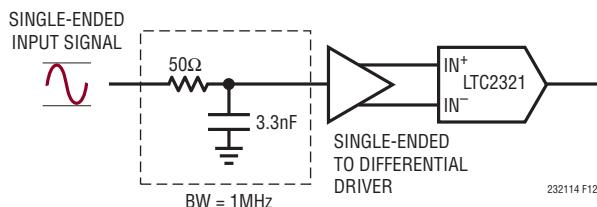

### シングルエンドから差動への変換

前述したように、シングルエンド信号は直接デジタル化できますが、より広いダイナミックレンジが求められる場合は、シングルエンドから差動への変換回路を使用することもできます。LTC2321-14の入力で差動信号を生成することにより、A/Dコンバータに入力される信号の振幅は最大になります。実現可能なSNRが高くなります。

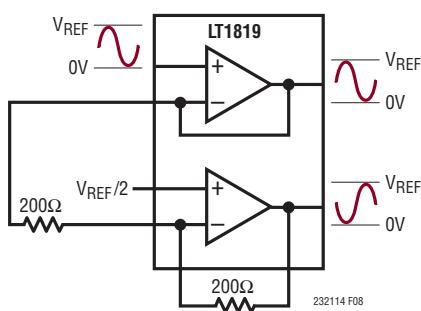

シングルエンドから差動への変換を行うには、図8に示すように、LT<sup>®</sup>1819高速デュアル・オペアンプの使用を推奨します。この場合、最初のアンプは単位利得のバッファとして構成されており、シングルエンド入力信号はこのアンプの高インピーダンス入力を直接駆動します。

### 完全差動入力

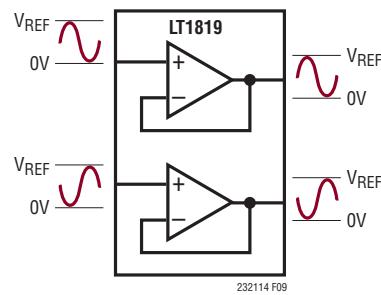

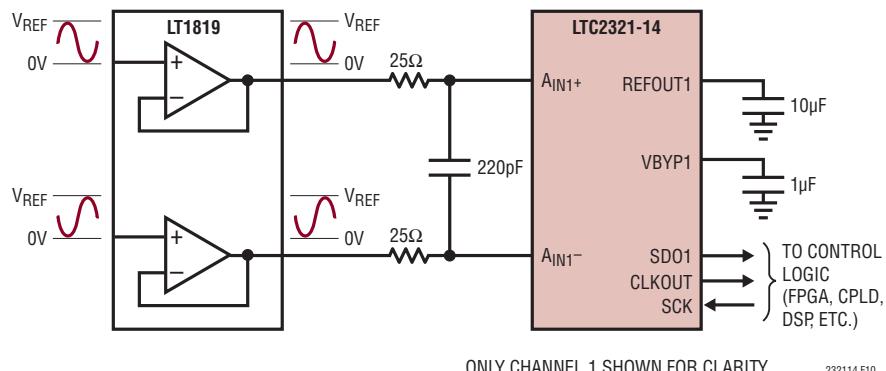

LTC2321-14の最大限の歪み性能を実現するため、図9に示すように、2つの単位利得バッファとして構成したLT1819を介して駆動する歪みの少ない完全差動信号源を使用できます。この回路により、データシートのTHD規格である-85dBを500kHz以下での入力周波数で完全に満たすことができます。高周波数領域で得られたデータシートの標準的性能曲線では、A/Dコンバータと信号源の間に高調波除去フィルタを使用して、歪みの主要な発生源としてのオペアンプを取り除きました。

図8. シングルエンド入力/差動出力ドライバ

完全差動構成では、アナログ入力電圧範囲( $A_{IN^+} - A_{IN^-}$ )が $\pm REFOU1, 2$ になります。この構成では、入力信号は各AINピンで駆動され、通常は同じ範囲で逆の極性になります。これにより、入力信号の同相電圧除去比が高くなります。アナログ入力の同相電圧は $V_{DD}$ の入力電圧範囲内であれば何Vでもかまいませんが、全範囲の入力信号のピーク振幅によって制限されます。たとえば、 $V_{DD} = 5VDC$ で内部リファレンスを使用する場合、全入力電圧範囲は $\pm 4.096V$ になります。通常は入力電圧範囲の半分が各AINピンで駆動されるので、AINピンごとに $4.096V_{P-P}$ の信号電圧範囲が得られます。これにより、同相電圧の変動許容範囲は約0.9Vになります。外部リファレンスを使用する場合は、A/Dコンバータの全範囲のコードをより狭い範囲内に圧縮することにより、同相電圧の許容範囲を広げることができます。たとえば、 $2.048V$ の外部リファレンスを $V_{DD} = 5V$ で使用する場合、全範囲は $\pm 2.048V$ になり、各AINの信号範囲は $2.048V_{P-P}$ に制限されるので、約3Vの同相電圧範囲が可能になります。入力電圧範囲を圧縮するとSNRが約2dB低下します。入力電圧範囲の圧縮が便利なのは、レール・トゥ・レールの振幅が不可能な単電源のアナログ入力ドライバを使用する場合です。完全差動構成を図10に示し、対応する伝達関数を図11に示します。

図9. 完全差動信号源のバッファとなるLT1819

## アプリケーション情報

### 入力駆動回路

信号源が低インピーダンスの場合は、利得誤差を発生することなく、LTC2321-14の高インピーダンス入力を直接駆動することができます。信号源が高インピーダンスの場合は、収集時のセトリング時間を最小にするためとA/Dコンバータの歪み性能を最適化するために、バッファを接続する必要があります。収集時にはA/Dコンバータの入力に電流スパイクが流れるので、DC入力であっても、セトリング時間の最小化が重要です。

最良の性能を得るには、バッファ・アンプを使用して LTC2321-14 のアナログ入力を駆動する必要があります。バッファ・アンプは出力インピーダンスが低いので、利得誤差を最小限に抑えることと、収集段階ではアナログ信号の高速セトリングが可能です。また、バッファ・アンプは、収集時に少量の電流スパイクが流れるA/Dコンバータの入力を信号源から切り離す役割も果たします。

図10. 完全差動のアプリケーション回路

図11. 完全差動の伝達関数

232114fa

## アプリケーション情報

### 入力フィルタリング

バッファ・アンプと信号源のノイズと歪みはA/Dコンバータのノイズと歪みに加わるので、これらについても考慮しなければなりません。入力信号にノイズが多い場合は、バッファ・アンプの入力の前に低帯域幅のフィルタを使ってノイズを最小限に抑えます。多くのアプリケーションでは、図12に示す簡単な1ポールのRCローパス・フィルタで十分です。

入力の抵抗分割器回路網、サンプリング・スイッチオン抵抗( $R_{ON}$ )、およびサンプル・コンデンサ( $C_{IN}$ )が第2のローパス・フィルタを構成し、ADCコアへの入力帯域幅を110MHzに制限します。ノイズ密度の低いバッファ・アンプを選択して、この帯域幅でのSNRの劣化を最小限に抑える必要があります。

RCフィルタのコンデンサと抵抗は歪みを大きくする可能性があるので、これらの部品は高品質のものを使用します。NPOタイプやシルバー・マイカ・タイプの誘電体コンデンサは優れた直線性を示します。表面実装型カーボン抵抗は、半田付け工程で生じる損傷および自己発熱により歪みが生じることがあります。表面実装型金属皮膜抵抗は、この2つの問題に対してはるかに耐性があります。

### A/Dコンバータのリファレンス

#### 内部リファレンス

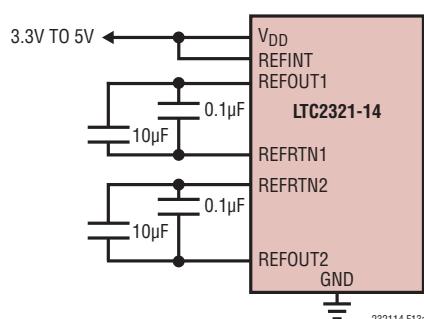

LTC2321-14は、低ノイズ、低ドリフト(最大20ppm/ $^{\circ}$ C)の温度補償バンドギャップ・リファレンスを内蔵しています。内部でバッファに接続されており、REFOUT1、2(ピン12、26)で利用できます。リファレンス・バッファにより、内部リファレンスの電圧は、電源電圧 $V_{DD}$ =5Vの場合は4.096Vになり、 $V_{DD}$ =3.3Vの場合は2.048Vになります。0.1 $\mu$ F(X7R、0402サイズ)のコンデンサと10 $\mu$ F(X5R、0805サイズ)のセラミック・コンデンサを並列に接続してREFOUT1、2をREFRTN1、2にバイパスし、リファレンス・バッファを補償してノイズを最小限に抑えます(図13a)。0.1 $\mu$ FのコンデンサはLTC2321-14のパッケージにできるだけ近づけて、配線インダクタンスを最小限に抑えます。内部リファレンス・バッファをイネーブルするにはREFINTピンを $V_{DD}$ に接続します。

表2. REFOUT1、2の電圧源および範囲と $V_{DD}$

| $V_{DD}$ | REFINTピン | REFOUT1、2ピン    | 差動電圧範囲                    |

|----------|----------|----------------|---------------------------|

| 5V       | 5V       | 内部4.096V       | $\pm 4.096V$              |

| 5V       | 0V       | 外部(1.25V~5V)   | $\pm 1.25V \sim \pm 5V$   |

| 3.3V     | 3.3V     | 内部2.048V       | $\pm 2.048V$              |

| 3.3V     | 0V       | 外部(1.25V~3.3V) | $\pm 1.25V \sim \pm 3.3V$ |

図12. 入力信号チェーン

## アプリケーション情報

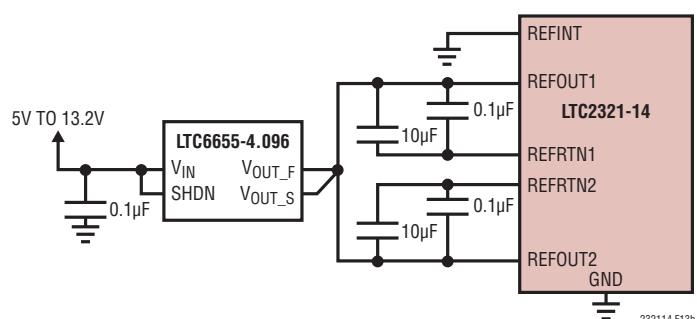

## 外部リファレンス

内部リファレンス・バッファは、図13(bおよびc)に示すように、REFOUT1、2に外部リファレンスを接続して1.25V～5Vの範囲でオーバードライブすることもできます。そのためには、REFINTを接地してリファレンス・バッファをディスエーブルする必要があります。リファレンス・バッファがディスエーブルされると、55kの内部抵抗がREFOUT1、2ピンの負荷になります。入力信号振幅と対応するSNRをできるだけ大きくするため、REFOUT1、2をオーバードライブする場合はLTC6655-5の使用を推奨します。LTC6655-5は、LTC6655-4.096と同様に小型、高精度、低ドリフトで、拡張温度範囲に対応します。5Vリファレンスを使用することにより、SNRを高くすることができます。0.1 $\mu$ F(X7R、0402サイズ)のコンデンサと10 $\mu$ F(X5R、0805サイズ)のセラミック・

コンデンサを、REFOUT1、2およびREFRTN1、2の各ピンに近づけて並列に接続し、LTC6655-5をバイパスすることを推奨します。

## 内部リファレンス・バッファのトランジエント応答

LTC2321-14のREFOUT1、2ピンには、各変換サイクルの間に外付けのバイパス・コンデンサから電荷( $Q_{CONV}$ )が引き寄せられます。内部リファレンス・バッファをオーバードライブする場合は、外部リファレンスが  $I_{REF} = Q_{CONV}/t_{CYC}$  に等しいDC電流でこの全電荷を供給する必要があります。したがって、REFOUT1、2に流れるDC電流は、サンプリング・レートと出力コードによって異なります。図14に示すように、長時間のアイドル状態の後、集中的にサンプリングされるアプリケーションでは、 $I_{REFBUR}$ は短時間で約75 $\mu$ Aから最大500 $\mu$ A

### (13a) LTC2321-14の内部リファレンス回路

### (13b) 共用の外部リファレンス回路を使用する LTC2321-14

### (13c) 異なる外部リファレンス電圧を使用する LTC2321-14

図13.

## アプリケーション情報

(REFOUT1、2 = 5V、2Msps 時)になります。このDC電流のステップにより、外部リファレンスにトランジエント応答が生じます。REFOUT1、2の電圧が正常値から逸脱すると、出力コードの精度に影響を与えるので、このトランジエント応答には配慮が必要です。外部リファレンスを使用してREFOUT1、2をオーバードライブする場合は、高速セトリング特性のLTC6655リファレンスを推奨します。

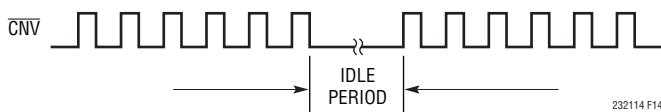

図14. 集中的なサンプリングを示すCNVの波形

図15. LTC2321-14のトランジエント応答

図16. LTC2321-14の32kポイントのFFT

232114fa

## アプリケーション情報

### 全高調波歪み(THD)

全高調波歪み(THD)は、入力信号のすべての高調波のRMS値の合計と基本波のRMS値との比です。帯域外高調波は、DCからサンプリング周波数の半分( $f_{SMPL}/2$ )までの周波数帯域で折り返し歪みを生じます。THDは次のように表されます。

$$THD = 20 \log \frac{\sqrt{V_2^2 + V_3^2 + V_4^2 + \dots + V_N^2}}{V_1}$$

ここで、 $V_1$ は基本周波数のRMS振幅で、 $V_2 \sim V_N$ は2次～ $N$ 次の高調波の振幅です。

### 電源に関する検討事項

LTC2321-14には2つの電源が必要です。1つは5V電源( $V_{DD}$ )で、もう1つはデジタル入力/出力インターフェース電源( $OV_{DD}$ )です。柔軟な $OV_{DD}$ 電源により、LTC2321-14は、1.8V～2.5Vで動作する任意のデジタル・ロジックと通信することができます。入力/出力にLVDSを使用する場合は、 $OV_{DD}$ 電源を2.5Vに設定する必要があります。

### 電源シーケンシング

LTC2321-14には電源シーケンシングに関する特別な要件はありません。「絶対最大定格」のセクションに記載されている最大電圧の関係を遵守するよう注意する必要があります。LTC2321-14は、最初の起動時、または電源電圧が2Vより低くなったとき必ずLTC2321-14をリセットするパワーオン・リセット(POR)回路を備えています。電源電圧が公称電源電圧範囲に戻ると、PORはA/Dコンバータを再度初期化します。再初期化の期間が確実に終了するように、PORイベントの10ms後までは変換を開始しないようにします。この時点より前に変換を開始すると、結果は無効になります。

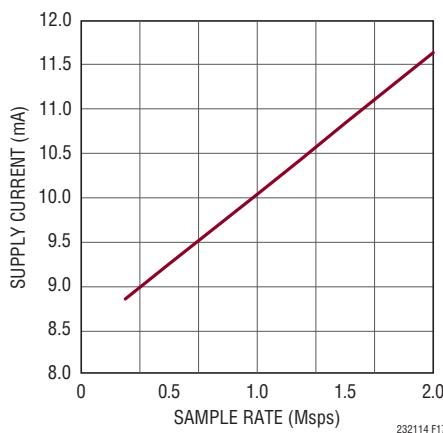

図17. LTC2321-14の電源電流とサンプリング・レート

## アプリケーション情報

### タイミングと制御

#### CNVのタイミング

LTC2321-14のサンプリングと変換は $\overline{\text{CNV}}$ によって制御されます。 $\overline{\text{CNV}}$ の立ち上がりエッジでサンプリングが開始され、立ち下がりエッジで変換と読み取り処理が開始されます。変換処理のタイミングは内部で決定されます。最適な性能を得るには、 $\overline{\text{CNV}}$ をノイズのない低ジッタの信号で駆動します。FPGAの $\overline{\text{CNV}}$ パルス発生源からの比較的大きなジッタの発生を抑制する推奨の実装回路をデータシート裏表紙の「標準的応用例」に示します。低ジッタの入力クロックは、 $\overline{\text{CNV}}$ 信号の立ち下がりエッジのタイミングを決定することに注意してください。 $\overline{\text{CNV}}$ の立ち上がりエッジのジッタは、性能にはほとんど影響しません。 $\overline{\text{CNV}}$ 信号の標準のパルス幅は、変換レートが2Mspsのとき30nsです。

#### SCKシリアル・データ・クロック入力

このクロックの立ち下がりエッジにより、変換結果はMSBを先頭にシフトしてSDOピンに出力されます。2Mspsのスループットを実現するには、64MHzの外部クロックをSCKピンに入力する必要があります。

#### CLKOUTシリアル・データ・クロック出力

CLKOUT出力は、SDO出力をレシーバでラッチするために、スキーの整合したクロックを出力します。CLKOUT出力とSDO出力のタイミング・スキーは整合します。高スループットのアプリケーションでは、SCKの代わりにCLKOUTを使用してSDO出力を取り込むと、レシーバでのタイミング要件が緩和されます。低スループットのアプリケーションでは、CLKOUTをOV<sub>DD</sub>に接続すればCLKOUT<sup>+</sup>をディスエーブルできます。

#### ナップ/スリープ・モード

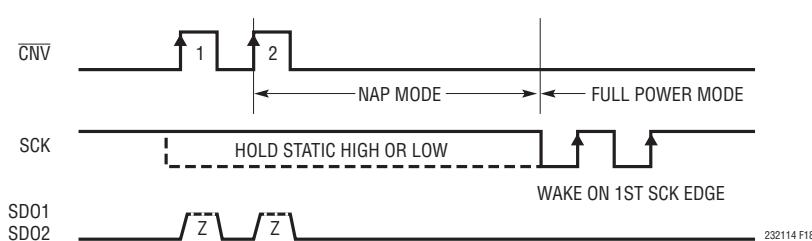

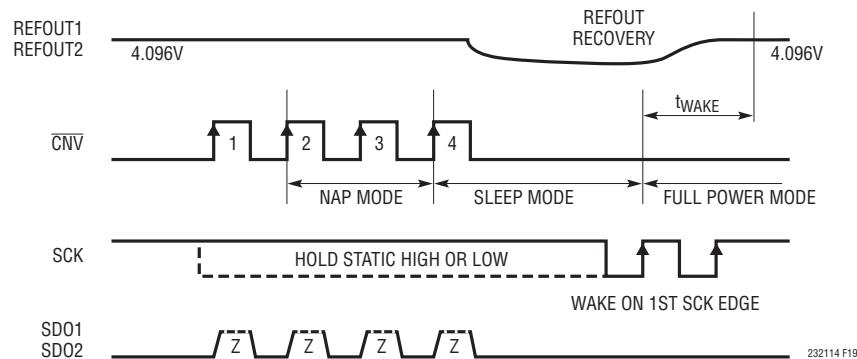

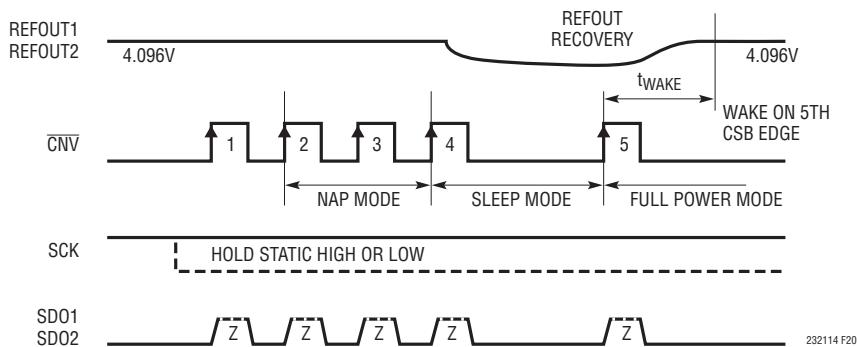

ナップ・モードは、後続の変換のために起動時の遅延を犠牲にせずに、電力を節減する方法です。スリープ・モードでは電力を大幅に節減できますが、リファレンスと電源システムを有効にするために起動時の遅延が生じます。LTC2321-14がナップ・モードに入るには、SCK信号を“H”または“L”に保持し、2つの $\overline{\text{CNV}}$ パルスを連続して入力する必要があります。これはCMOSモードとLVDSモードの両方に該当します。ナップ状態が始まるのは、 $\overline{\text{CNV}}$ の2番目の立ち上がりエッジです。SCKの立ち上がりエッジが1回入力されるか、 $\overline{\text{CNV}}$ パルスがさらに入力されるまで、ナップ状態は持続します。LTC2321-14は、SCKの立ち上がりエッジによって動作(最大電力)状態に戻ります。LTC2321-14は、ナップ・モードのときに、2つの追加パルスが入力されるとスリープ・モードになります。LTC2321-14をCMOS入出力動作に合わせて構成した場合は、SCKの立ち上がりエッジ1回で動作モードに戻ることができます。リファレンス・バッファが外付けのフィルタ・コンデンサを再充電できるようにするには、スリープ・モードの終了後に10msの遅延が必要です。LVDSモードでは、5番目の $\overline{\text{CNV}}$ パルスを入力すればスリープ・モードを終了できます。5番目のパルスによってLTC2321-14は動作モードに戻り、その後さらにSCKパルスが入ると、デバイスはナップ・モードとスリープ・モードに戻らなくなります。5番目のSCKパルスは、CMOSモードでもスリープ・モードを終了する方法として機能します。SCKパルスがない期間に $\overline{\text{CNV}}$ パルスを繰り返し入力すると、LTC2321-14は動作モード、ナップ・モード、スリープ・モードの間を無期限に循環します。

スリープ・モードとナップ・モードに関するより詳細なタイミング情報については、図18、図19、図20、および図21のタイミング図を参照してください。

図18. CMOSモードおよびLVDSモードでのSCKを使用したナップ状態および起動

## アプリケーション情報

図19. CMOSモードでのSCKを使用したスリープ状態および起動

図20. LVDSモードおよびCMOSモードでのCNVを使用したスリープ状態および起動

## アプリケーション情報

### デジタル・インターフェース

LTC2321-14は、単純明快に使えるシリアル・デジタル・インターフェースを備えています。柔軟なOV<sub>DD</sub>電源により、LTC2321-14は、1.8V～2.5Vで動作する任意のデジタル・ロジックと通信することができます。2Mspsのスループットを実現するには、64MHzの外部クロックをSCKピンに入力する必要があります。

LTC2321-14は、標準のCMOS SPIインターフェースのほかに、低ノイズのデジタル設計をサポートするオプションのLVDS SPIインターフェースを備えています。デジタル・インターフェース・モードを選択するには、CMOS/LVDSピンを使用します。

SCKの立ち下がりエッジにより、変換結果はMSBを先頭にSDOピンに出力されます。CLKOUTは、SDO出力をレシーバでラッチするために、スキーの整合したクロックを出力します。CLKOUT出力とSDO出力のタイミング・スキューは

整合します。高スループットのアプリケーションでは、SCKの代わりにCLKOUTを使用してSDO出力を取り込むと、レシーバでのタイミング要件が緩和されます。

CMOSモードでは、SDO1<sup>+</sup>、SDO2<sup>+</sup>、およびCLKOUT<sup>+</sup>ピンを出力として使用します。SCK<sup>+</sup>ピンは入力として使用します。SDO1<sup>-</sup>、SDO2<sup>-</sup>、SCK<sup>-</sup>、およびCLKOUT<sup>-</sup>ピンには、内部にOGNDへのプルダウン回路がそれぞれ存在するので、これらのピンは接続しないでください。

LVDSモードでは、SDO1<sup>+</sup>/SDO1<sup>-</sup>、SDO2<sup>+</sup>/SDO2<sup>-</sup>、およびCLKOUT<sup>+</sup>/CLKOUT<sup>-</sup>ピンを差動出力として使用します。これらのピンは、レシーバ(FPGA)に100Ωの抵抗を外付けすることによって差動で終端する必要があります。SCK<sup>+</sup>/SCK<sup>-</sup>ピンは差動入力であり、レシーバ(A/Dコンバータ)に100Ωの抵抗を外付けすることによって差動で終端する必要があります。

図21. LTC2321-14のタイミング図

232114 F21

## アプリケーション情報

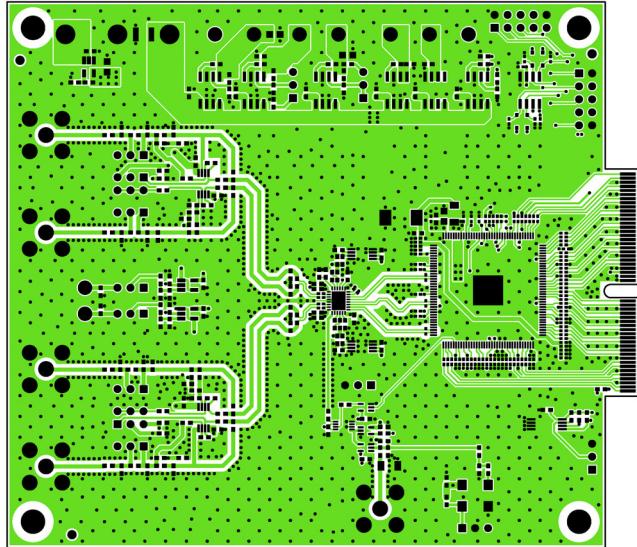

### 基板のレイアウト

LTC2321-14から最大限の性能を引き出すには、プリント回路基板を推奨します。プリント回路基板(PCB)のレイアウトでは、デジタル信号線とアナログ信号線をできるだけ離すようにします。特に、デジタル・クロックやデジタル信号は、アナログ信号に隣接して配線したり、A/Dコンバータの下に配線したりしないように注意します。

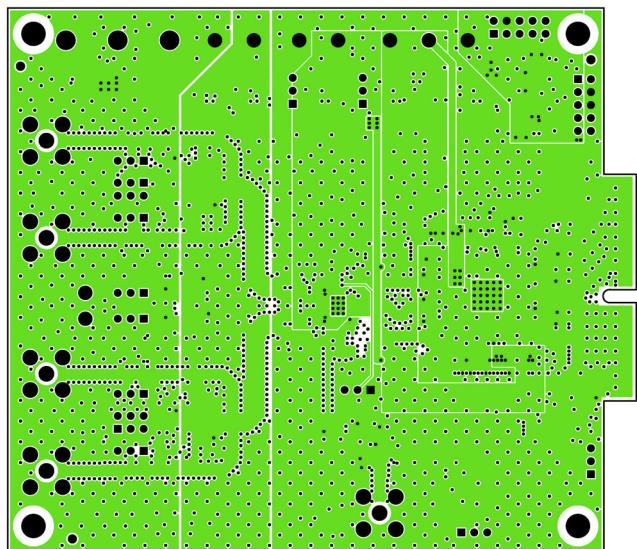

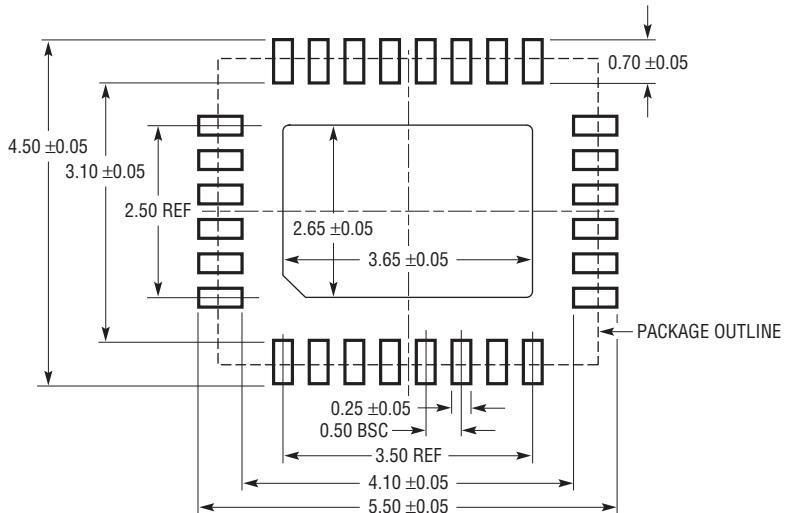

### 推奨レイアウト

推奨するPCBレイアウトの一例を以下に示します。切れ目のない単一のグランド・プレーンを使用します。電源へのバイパス・コンデンサは電源ピンのできるだけ近くに配置します。A/Dコンバータを低ノイズで動作させるには、これらのバイパス・コンデンサに低インピーダンスの共通の戻り線を使うことが不可欠です。アナログ入力のトレースはグランドで遮蔽します。詳細については、LTC2321-14用評価キットDC1996Aを参照してください。

図22. LVDSインターフェースを使用するLTC2321

図23. 第1層、トップ層

図24. 第2層、グランド・プレーン

図25. 第3層、電源プレーン

図26. 第4層、最下層

## 標準的応用例

クロックの方波整形回路/レベルシフト回路およびリタイミングのフリップフロップを使用した

RF正弦波発生器による低ジッタのクロック・タイミング回路

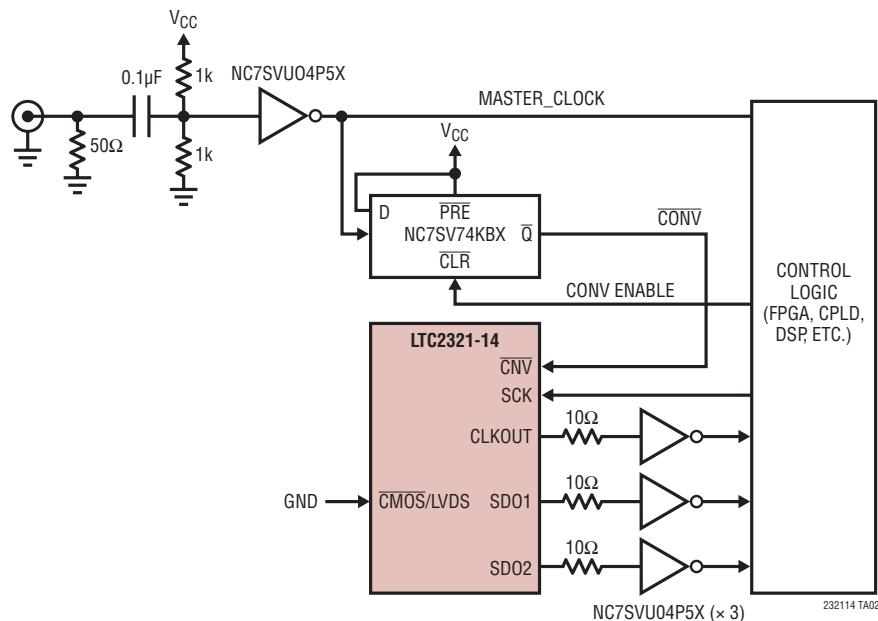

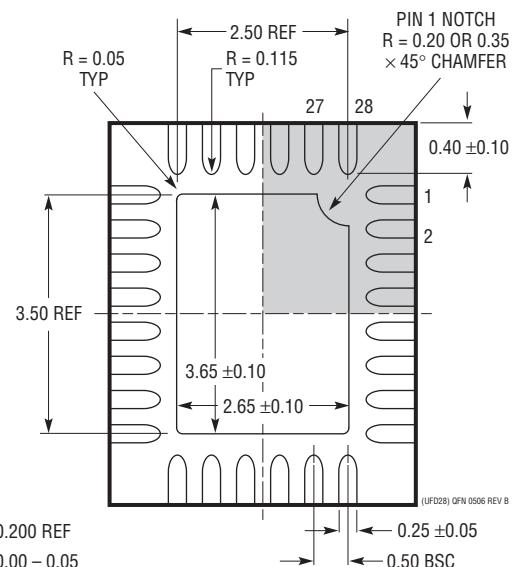

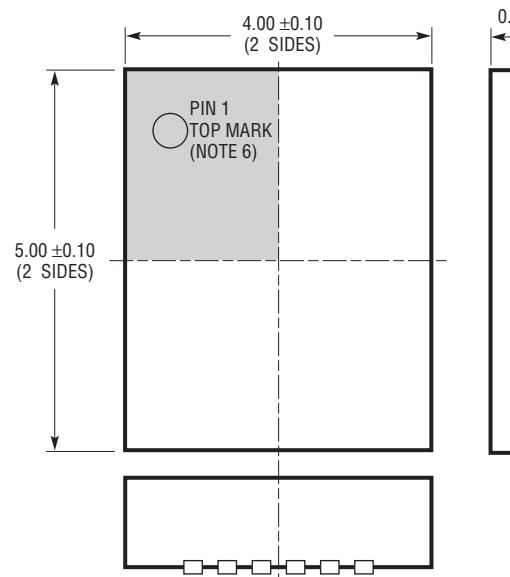

## パッケージ

最新のパッケージ図面については、<http://www.linear-tech.co.jp/designtools/packaging/> を参照してください。

**UFD Package

28-Lead Plastic QFN (4mm × 5mm)**

(Reference LTC DWG # 05-08-1712 Rev B)

RECOMMENDED SOLDER PAD PITCH AND DIMENSIONS

APPLY SOLDER MASK TO AREAS THAT ARE NOT SOLDERED

BOTTOM VIEW—EXPOSED PAD

注記:

1. 図はJEDECパッケージ外形MO-220のバリエーション(WXX-X)にするよう提案されている

2. 図は実寸とは異なる

3. すべての寸法はミリメートル

4. パッケージ底面の露出パッドの寸法にはモールドのバリを含まない

モールドのバリは(もしあれば)各サイドで0.15mmを超えないこと

5. 露出パッドは半田メッキとする

6. 網掛けの部分はパッケージの上面と底面のピン1の位置の参考に過ぎない

## 改訂履歴

| REV | 日付    | 概要              | ページ番号 |

|-----|-------|-----------------|-------|

| A   | 11/14 | タイミング特性と図21を更新。 | 5、22  |

# LTC2321-14

## 関連製品

| 製品番号                                            | 説明                                                       | 注釈                                                                                    |

|-------------------------------------------------|----------------------------------------------------------|---------------------------------------------------------------------------------------|

| <b>A/Dコンバータ</b>                                 |                                                          |                                                                                       |

| LTC2323-16/LTC2323-14/<br>LTC2323-12            | 16/14/12ビット、デュアル、5Msps、<br>同時サンプリング A/Dコンバータ             | 3.3V/5V電源、同相範囲の広い差動入力、<br>スループット:5Msps/チャネル、40mW/チャネル、<br>4mm×5mm QFN-28パッケージ         |

| LTC2321-16/LTC2321-12                           | 16/12ビット、デュアル、2Msps、<br>同時サンプリング A/Dコンバータ                | 3.3V/5V電源、入力同相範囲の広い差動入力、<br>スループット:2Msps/チャネル、33mW/チャネル、<br>4mm×5mm QFN-28パッケージ       |

| LTC2314-14                                      | 14ビット、4.5MspsシリアルA/Dコンバータ                                | 3V/5V電源、18mW/31mW、最大20ppm/°Cの内部リファレンス、<br>単極性入力、8ピンTSOT-23パッケージ                       |

| LTC2370-16/LTC2368-16<br>LTC2367-16/LTC2364-16  | 16ビット、2Msps/1Msps/500ksps/<br>250kspsシリアル、低消費電力A/Dコンバータ  | 2.5V電源、単極性の疑似差動入力、SNR:94dB、<br>入力範囲:5V、DGC、MSOP-16および<br>4mm×3mm DFN-16パッケージのピン互換ファミリ |

| LTC2380-16/LTC2378-16/<br>LTC2377-16/LTC2376-16 | 16ビット、2Msps/1Msps/500ksps/<br>250kspsシリアル、低消費電力A/Dコンバータ  | 2.5V電源、差動入力、SNR:96.2dB、入力範囲:±5V、DGC、<br>MSOP-16および4mm×3mm DFN-16パッケージの<br>ピン互換ファミリ    |

| <b>D/Aコンバータ</b>                                 |                                                          |                                                                                       |

| LTC2632                                         | 内部リファレンス使用のデュアル12/10/8ビット<br>SPI電圧出力D/Aコンバータ             | 電源電圧範囲:2.7V～5.5V、10ppm/°Cのリファレンス、<br>外部REFモード、レール・トゥ・レール出力、<br>8ピンThinSOT™パッケージ       |

| LTC2602/LTC2612/<br>LTC2622                     | 外部リファレンス使用のデュアル16/14/12ビット<br>SPI電圧出力D/Aコンバータ            | 300μA/DAC、電源電圧範囲:2.5V～5.5V、<br>レール・トゥ・レール出力、8ピンMSOPパッケージ                              |

| <b>リファレンス</b>                                   |                                                          |                                                                                       |

| LTC6655                                         | 高精度、低ドリフト、<br>低ノイズのバッファ付きリファレンス                          | 5V/4.096V/3.3V/3V/2.5V/2.048V/1.25V、5ppm/°C、<br>ピーク・トゥ・ピーク・ノイズ:0.25ppm、MSOP-8パッケージ    |

| LTC6652                                         | 高精度、低ドリフト、<br>低ノイズのバッファ付きリファレンス                          | 5V/4.096V/3.3V/3V/2.5V/2.048V/1.25V、5ppm/°C、<br>ピーク・トゥ・ピーク・ノイズ:2.1ppm、MSOP-8パッケージ     |

| <b>アンプ</b>                                      |                                                          |                                                                                       |

| LT1818/LT1819                                   | 400MHz、2500V/μs、<br>9mAシングル/デュアル・オペアンプ                   | 5MHzでの歪み:-85dBc、入力ノイズ電圧:6nV/√Hz、<br>電源電流:9mA、単位利得で安定                                  |

| LT1806                                          | 325MHz、シングル、レール・トゥ・レール入力<br>および出力、低歪み、低ノイズ、<br>高精度オペアンプ  | 5MHzでの歪み:-80dBc、入力ノイズ電圧:3.5nV/√Hz、<br>電源電流:9mA、単位利得で安定                                |

| LT6200                                          | 165MHz、レール・トゥ・レール入力および出力、<br>低ノイズ(0.95nV/√Hz)、オペアンプ・ファミリ | 低ノイズ、低歪み、単位利得で安定                                                                      |

232114fa

28

リニアテクノロジー株式会社

〒102-0094 東京都千代田区紀尾井町3-6紀尾井町パークビル8F

TEL 03-5226-7291 • FAX 03-5226-0268 • [www.linear-tech.co.jp/LTC2321-14](http://www.linear-tech.co.jp/LTC2321-14)

LT 1114 REV A • PRINTED IN JAPAN

© LINEAR TECHNOLOGY CORPORATION 2014